Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

8809 results about "Photolithography" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Photolithography, also called optical lithography or UV lithography, is a process used in microfabrication to pattern parts of a thin film or the bulk of a substrate (also called a wafer). It uses light to transfer a geometric pattern from a photomask (also called an optical mask) to a photosensitive (that is, light-sensitive) chemical photoresist on the substrate. A series of chemical treatments then either etches the exposure pattern into the material or enables deposition of a new material in the desired pattern upon the material underneath the photoresist. In complex integrated circuits, a CMOS wafer may go through the photolithographic cycle as many as 50 times.

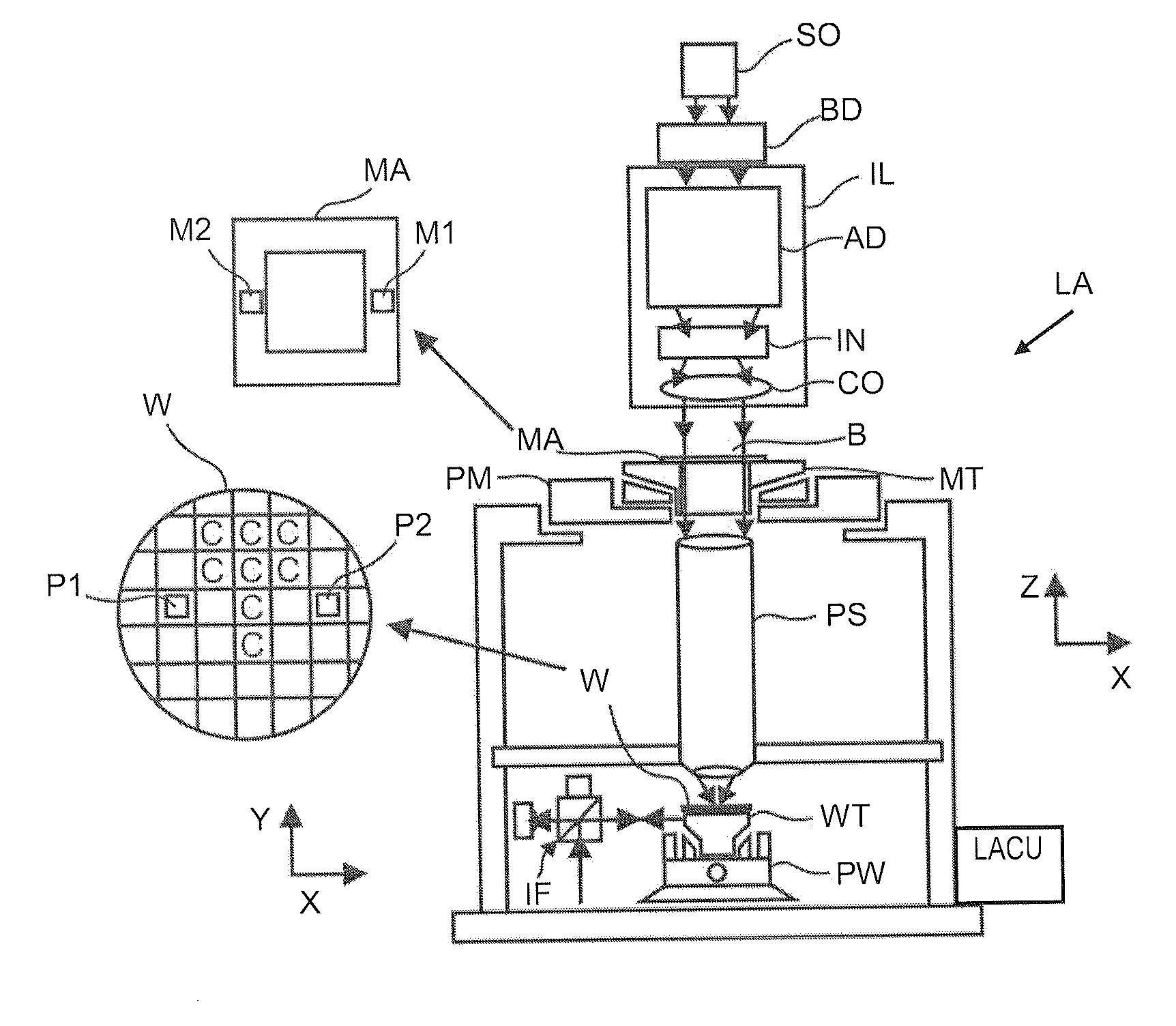

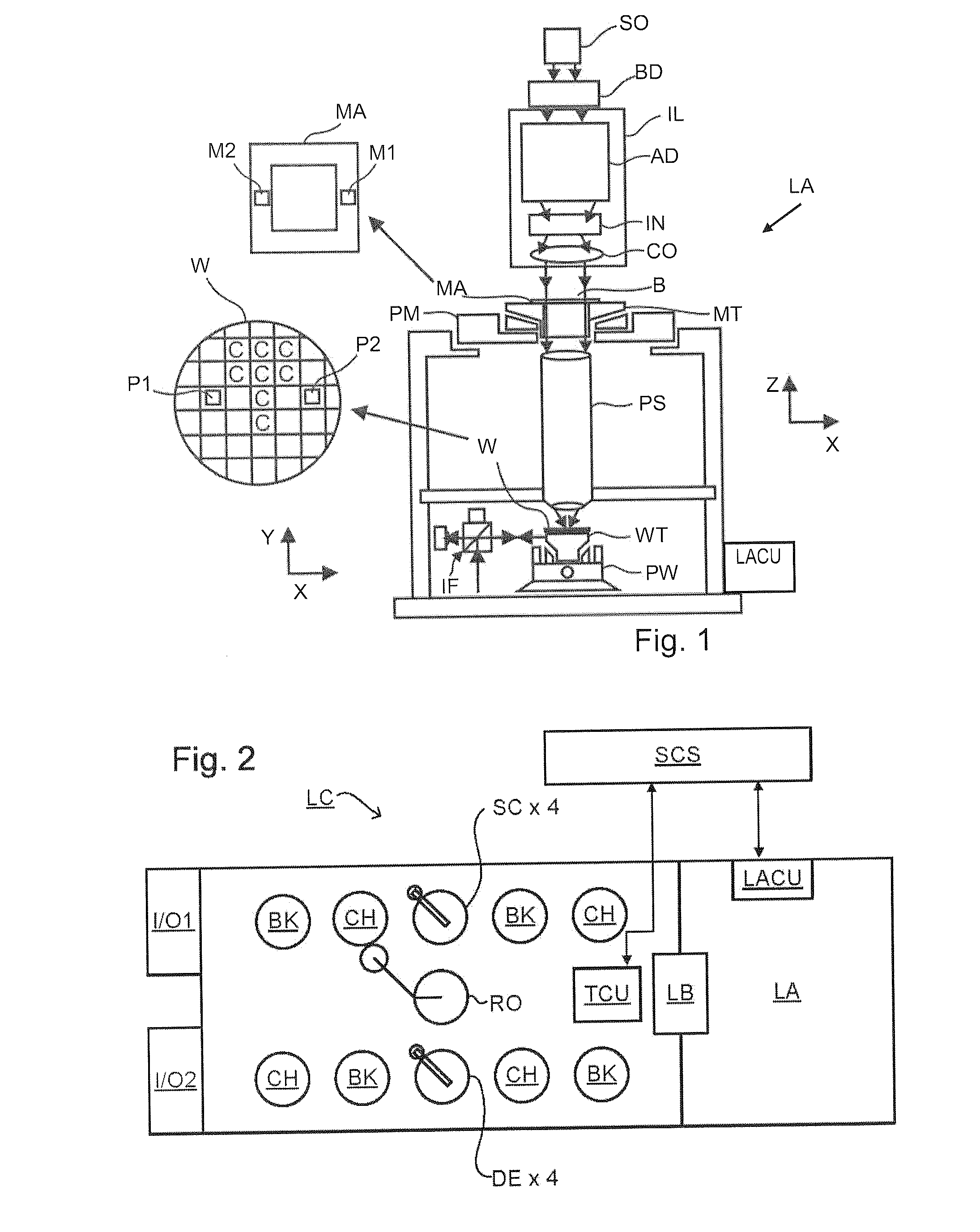

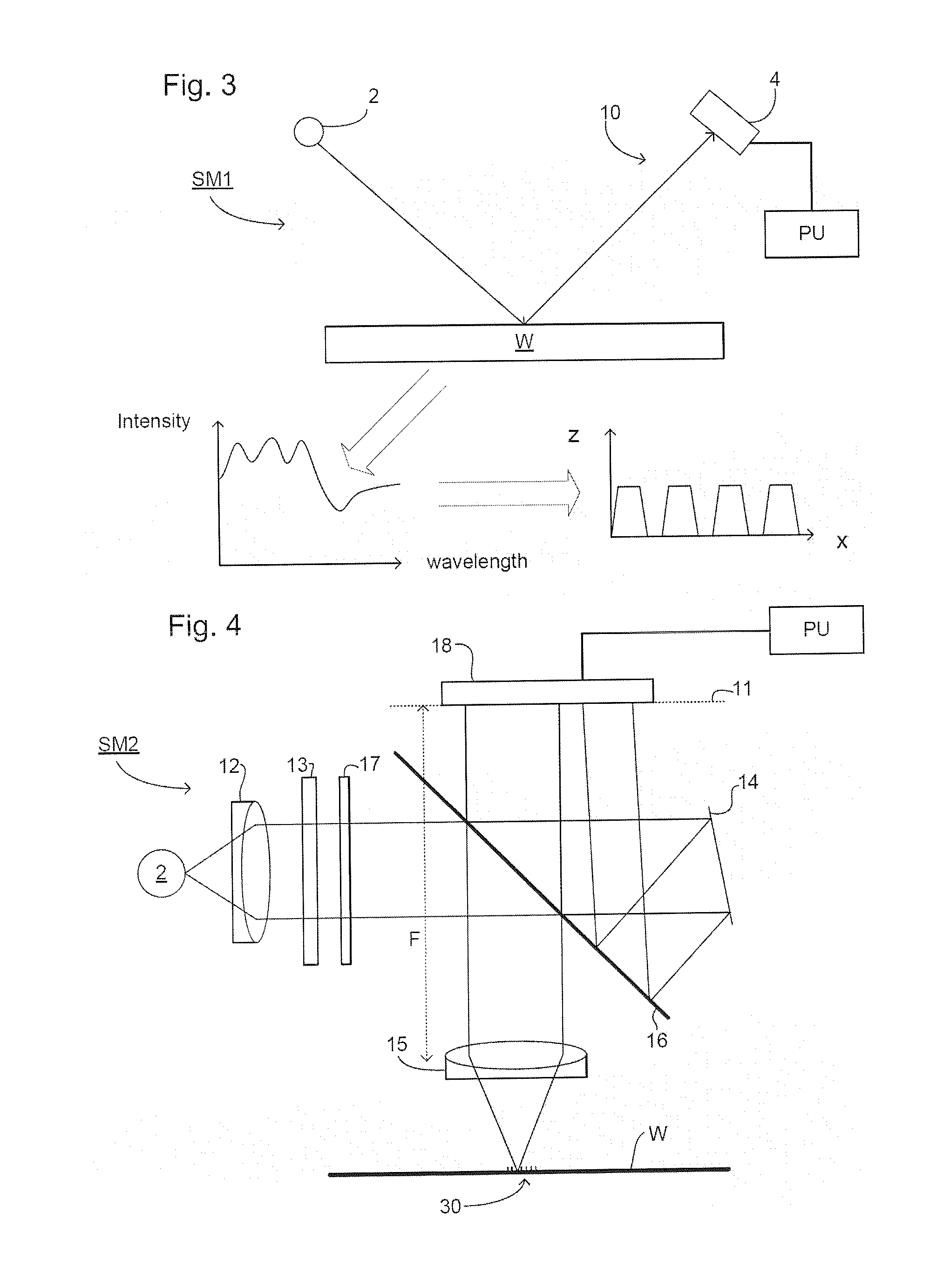

Methods and Scatterometers, Lithographic Systems, and Lithographic Processing Cells

ActiveUS20110027704A1Scattering properties measurementsSemiconductor/solid-state device manufacturingScatterometerEngineering

In a method of determining the focus of a lithographic apparatus used in a lithographic process on a substrate, the lithographic process is used to form a structure on the substrate, the structure having at least one feature which has an asymmetry in the printed profile which varies as a function of the focus of the lithographic apparatus on the substrate. A first image of the periodic structure is formed and detected while illuminating the structure with a first beam of radiation. The first image is formed using a first part of non-zero order diffracted radiation. A second image of the periodic structure is foamed and detected while illuminating the structure with a second beam of radiation. The second image is formed using a second part of the non-zero order diffracted radiation which is symmetrically opposite to the first part in a diffraction spectrum. The ratio of the intensities of the measured first and second portions of the spectra is determined and used to determine the asymmetry in the profile of the periodic structure and / or to provide an indication of the focus on the substrate. In the same instrument, an intensity variation across the detected portion is determined as a measure of process-induced variation across the structure. A region of the structure with unwanted process variation can be identified and excluded from a measurement of the structure.

Owner:ASML NETHERLANDS BV

Methods and devices to design and fabricate surfaces on contact lenses and on corneal tissue that correct the eye's optical aberrations

Methods and devices are described that are needed to design and fabricate modified surfaces on contact lenses or on corneal tissue that correct the eye's optical aberrations beyond defocus and astigmatism. The invention provides the means for: 1) measuring the eye's optical aberrations either with or without a contact lens in place on the cornea, 2) performing a mathematical analysis on the eye's optical aberrations in order to design a modified surface shape for the original contact lens or cornea that will correct the optical aberrations, 3) fabricating the aberration-correcting surface on a contact lens by diamond point turning, three dimensional contour cutting, laser ablation, thermal molding, photolithography, thin film deposition, or surface chemistry alteration, and 4) fabricating the aberration-correcting surface on a cornea by laser ablation.

Owner:BROOKFIELD OPTICAL SYST

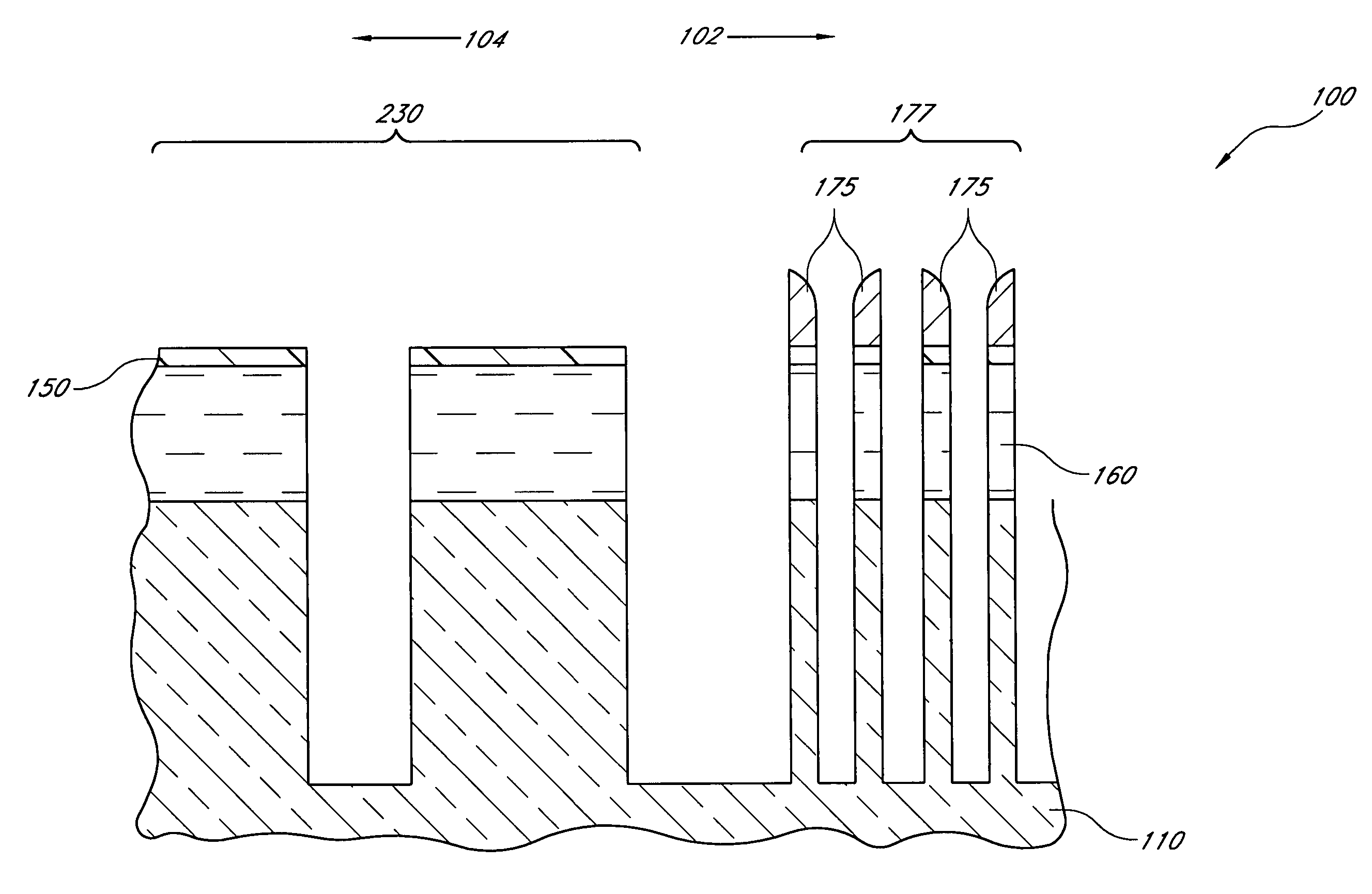

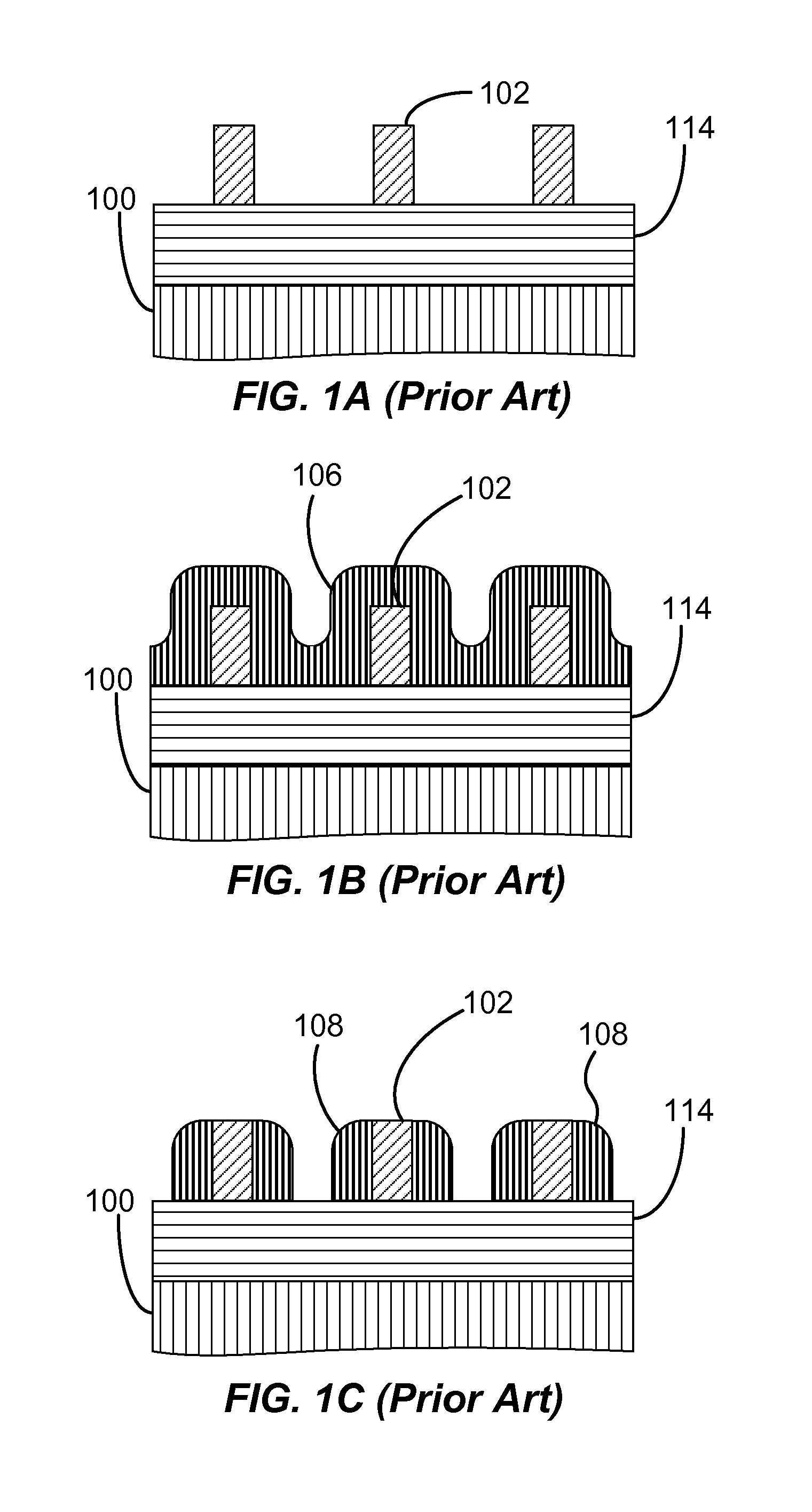

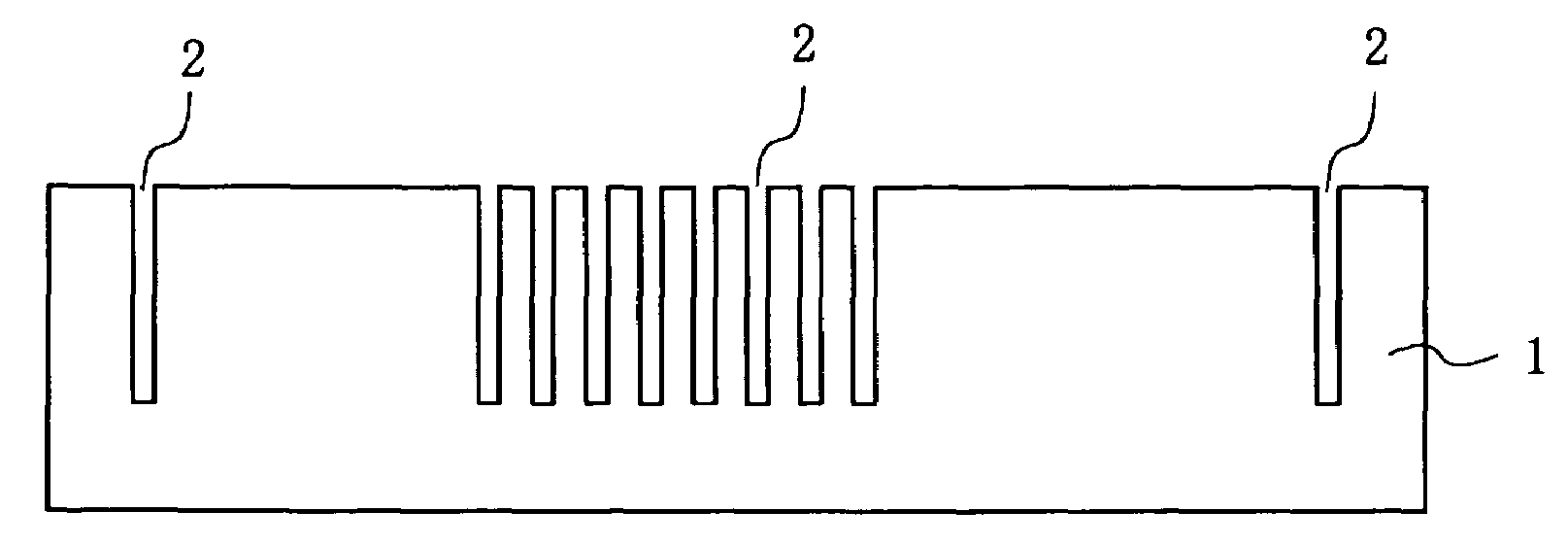

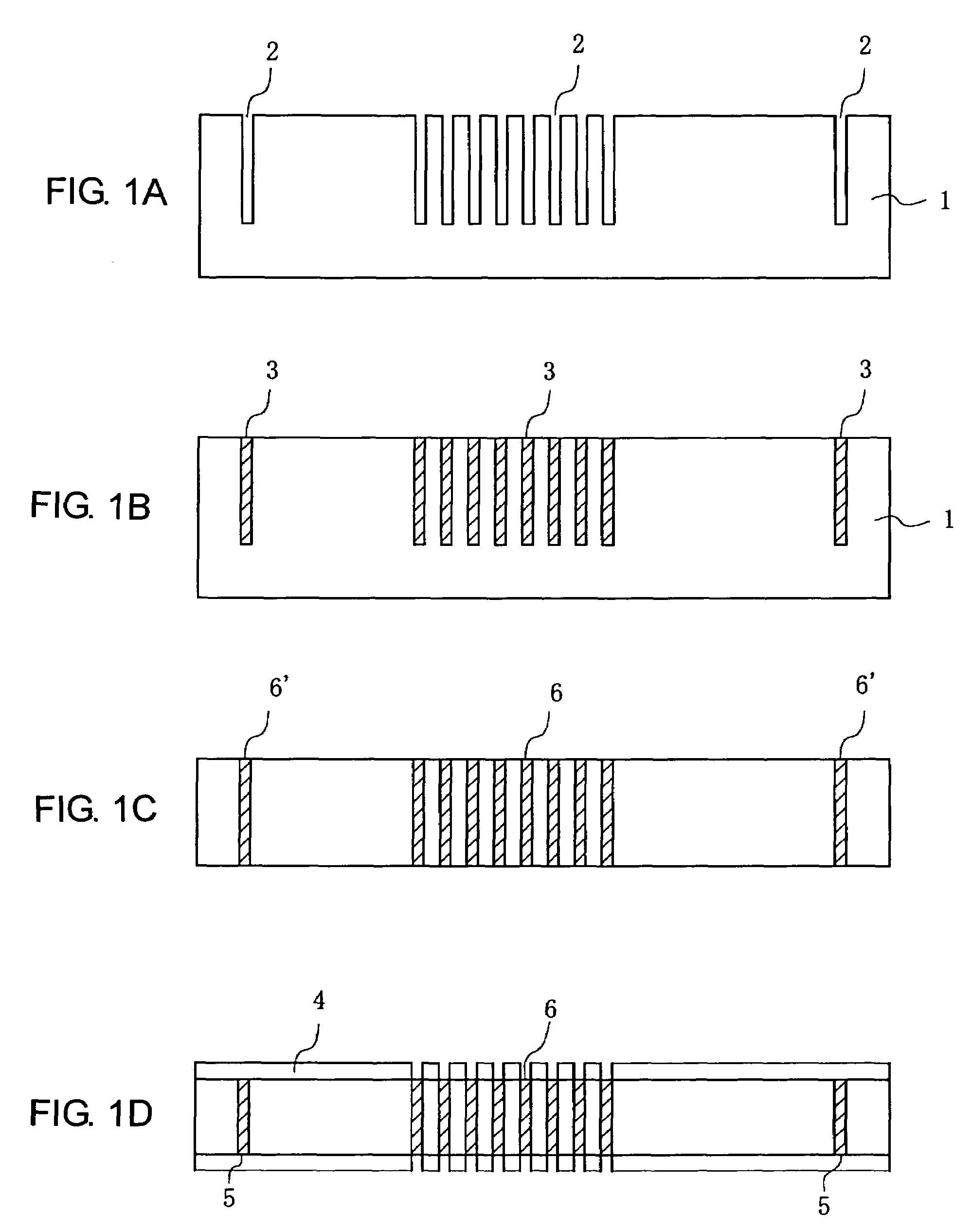

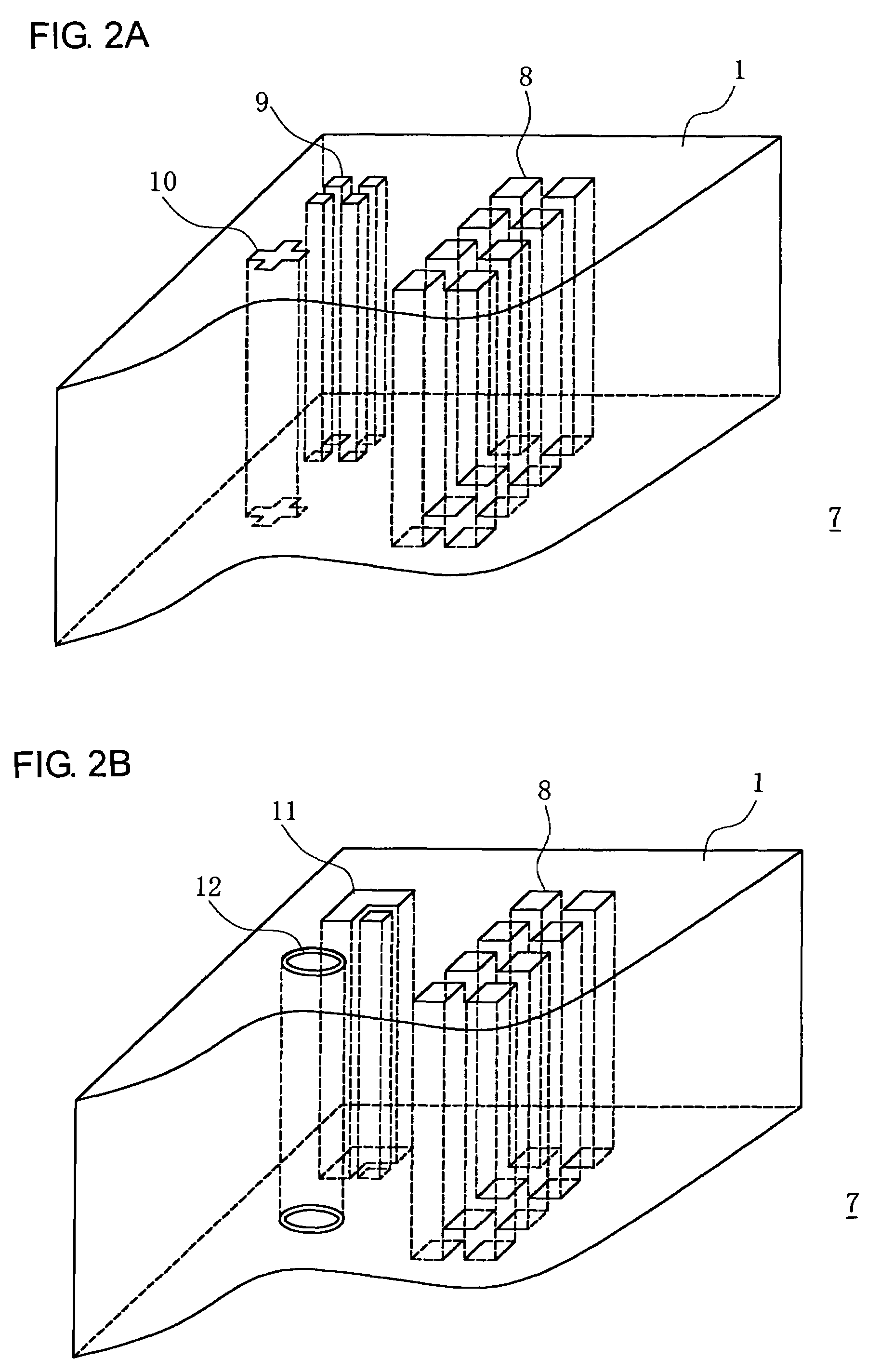

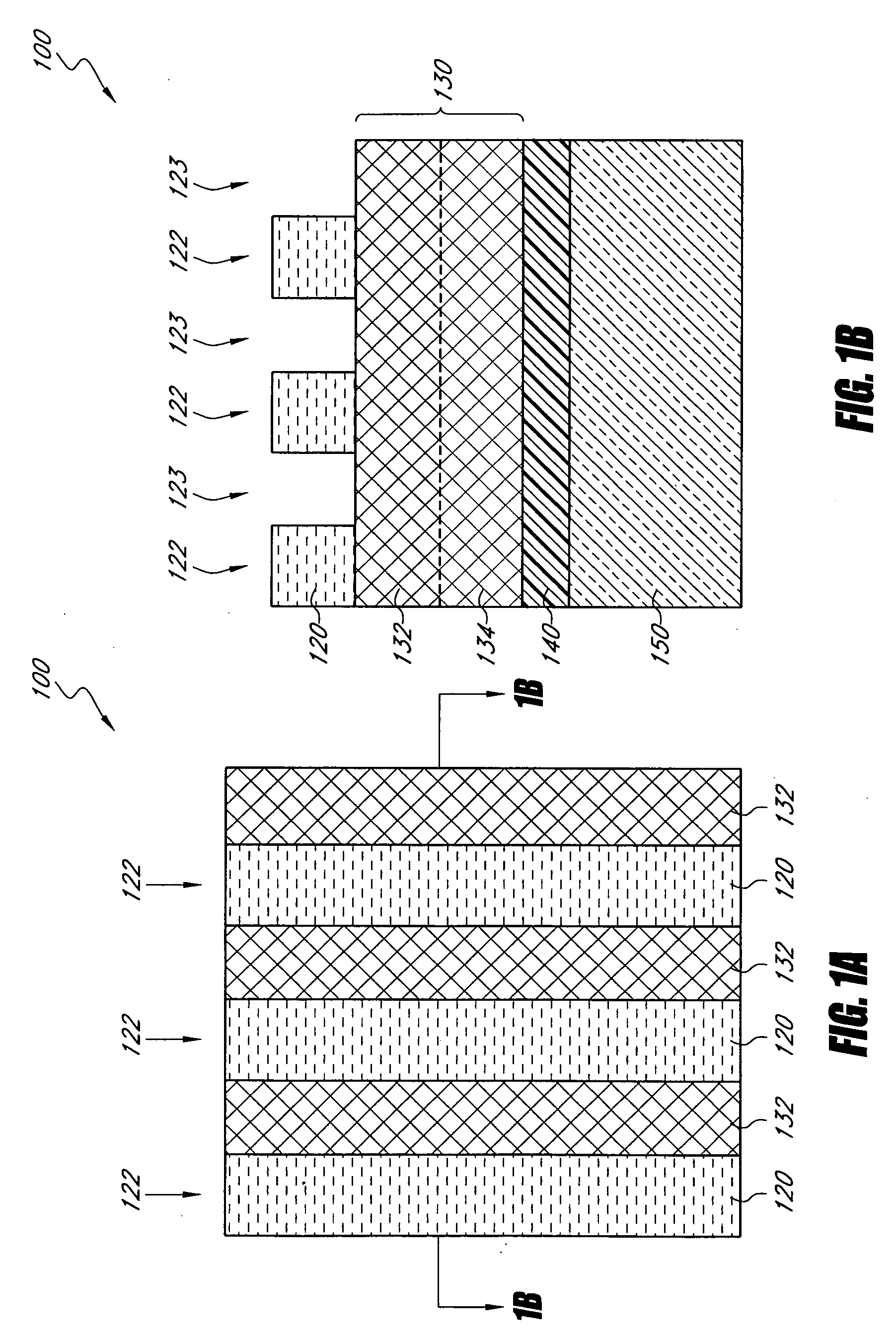

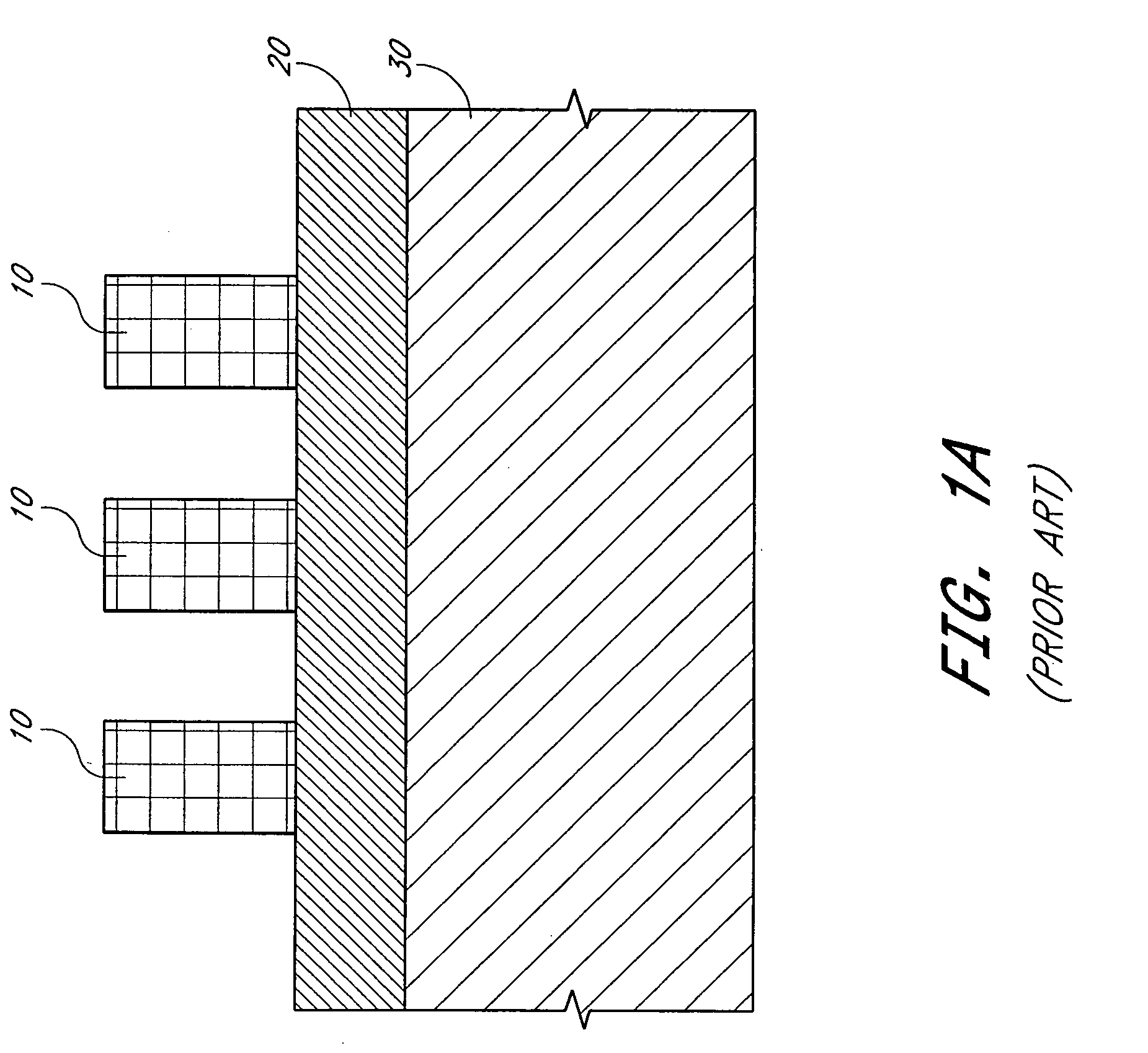

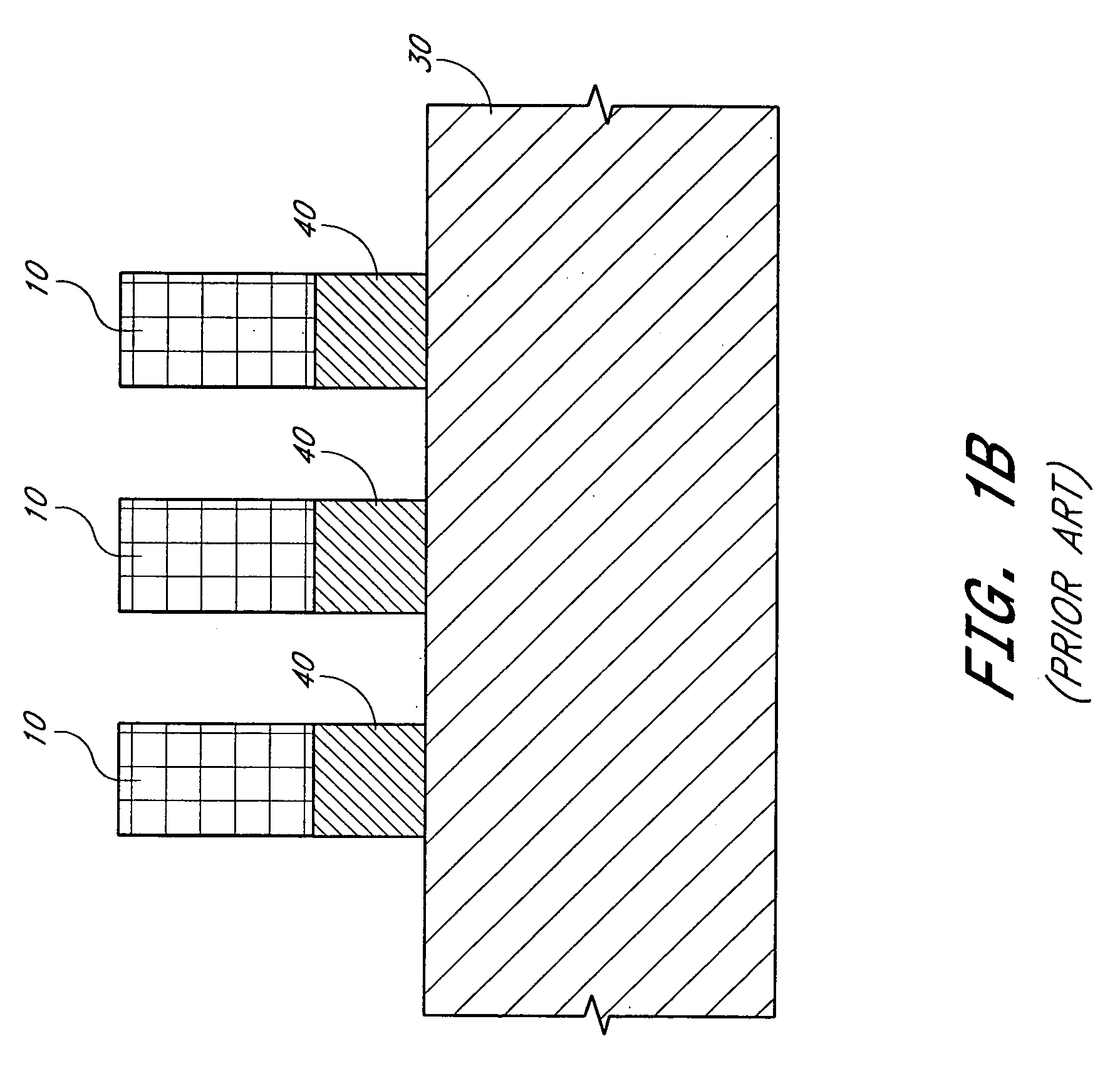

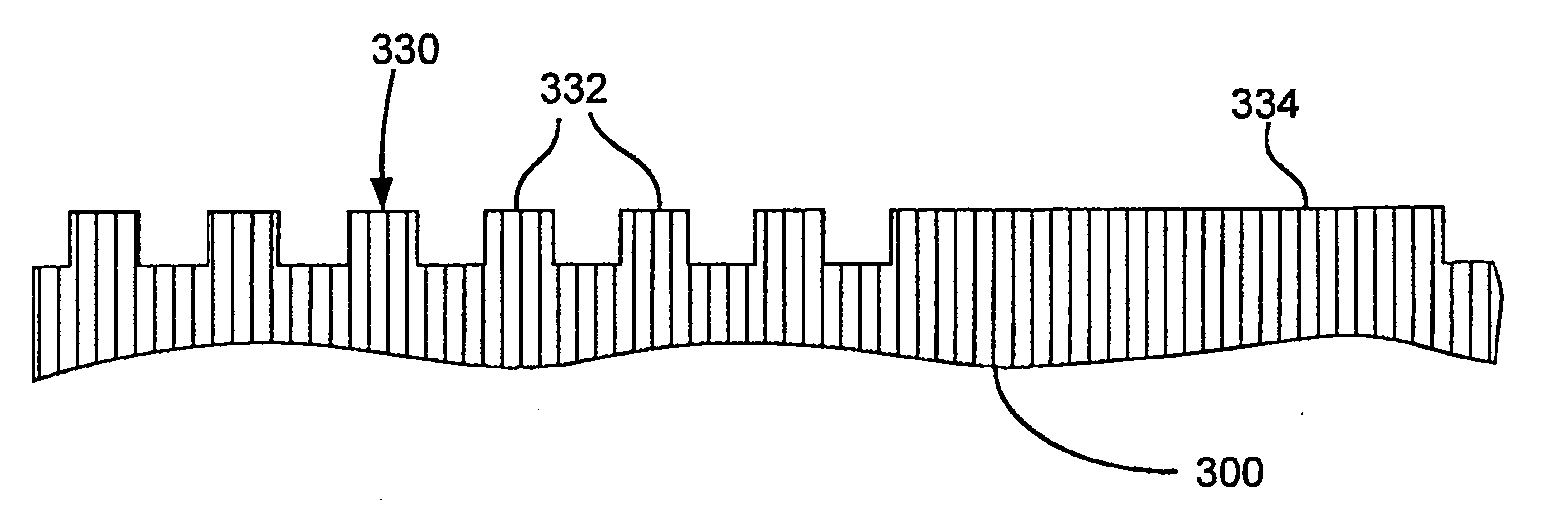

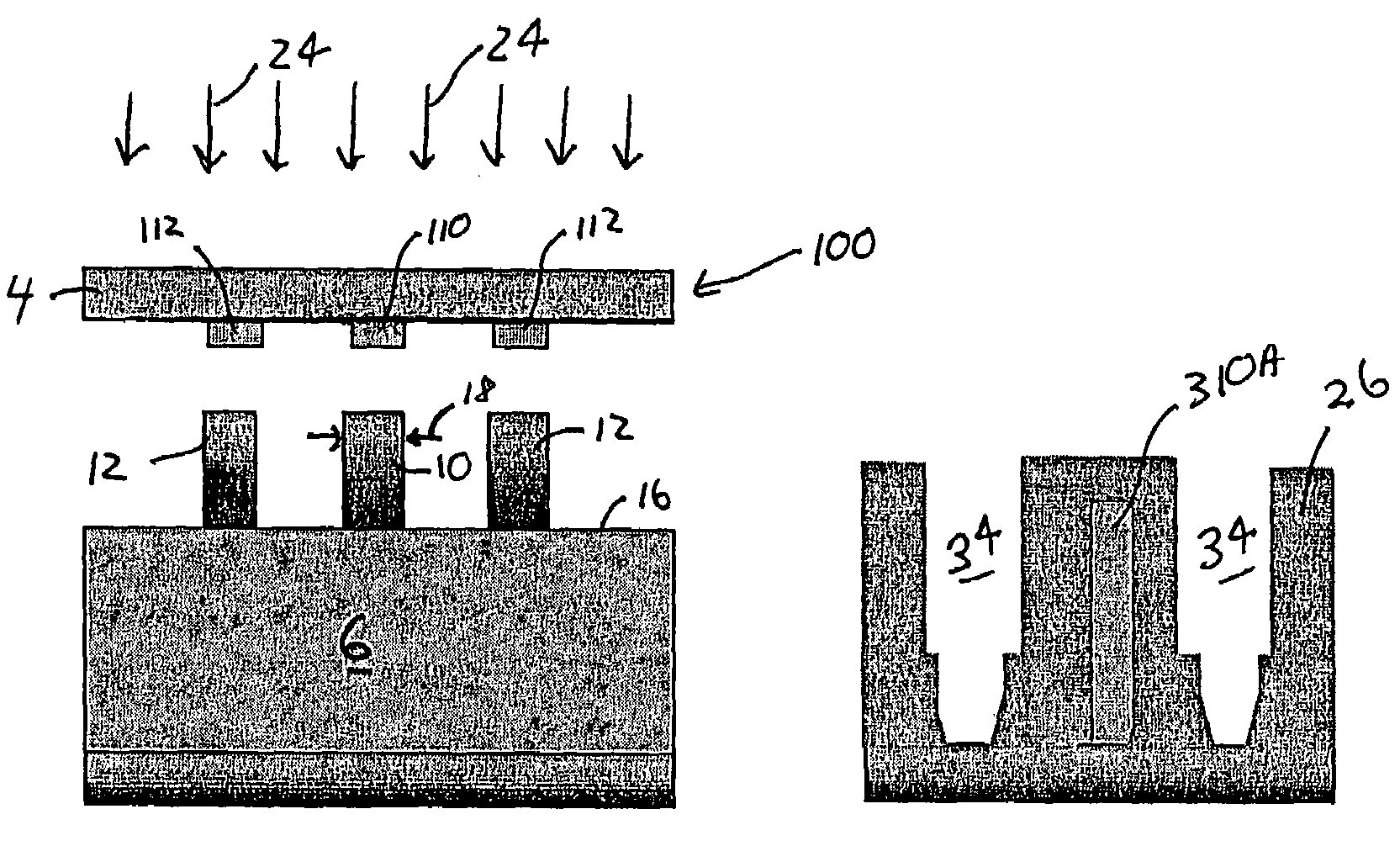

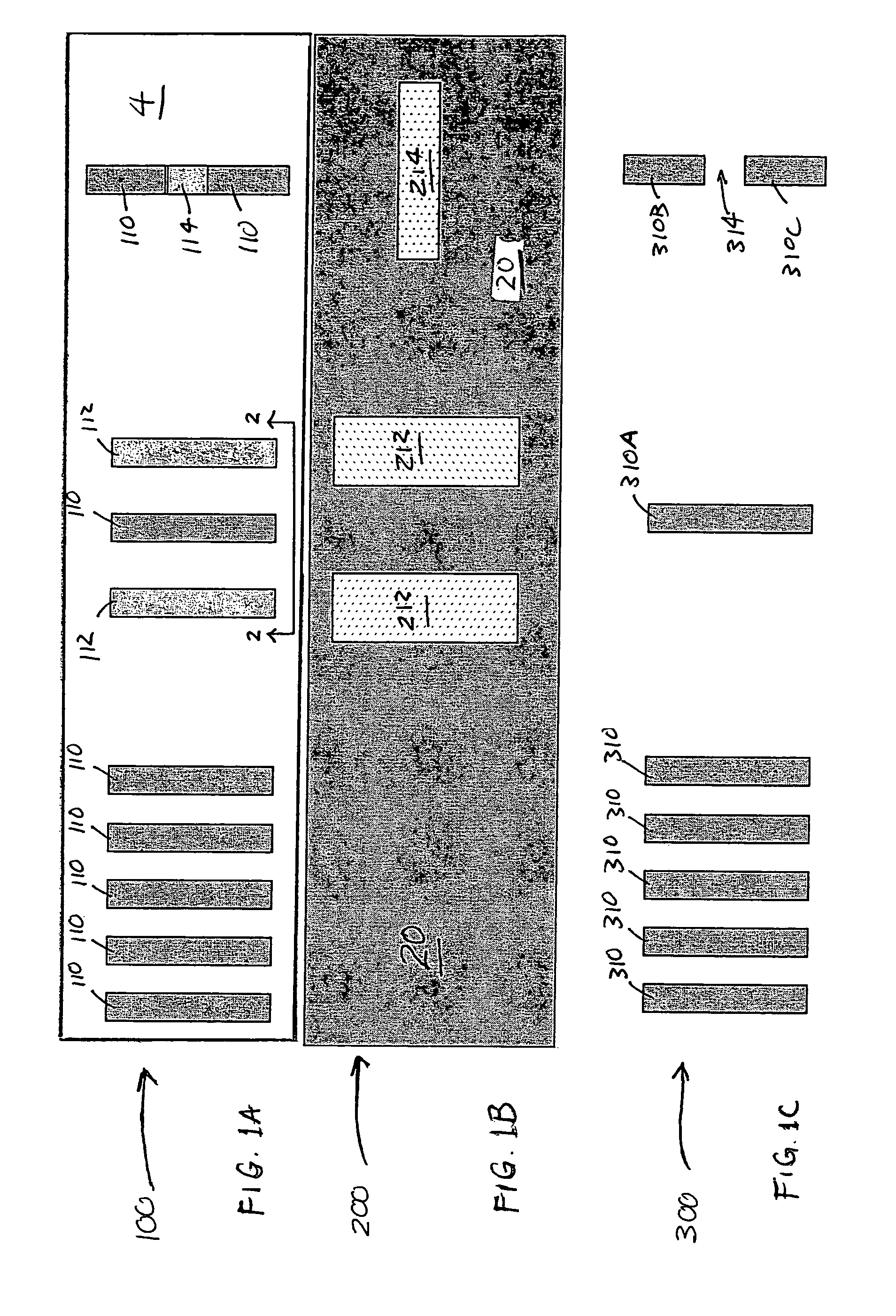

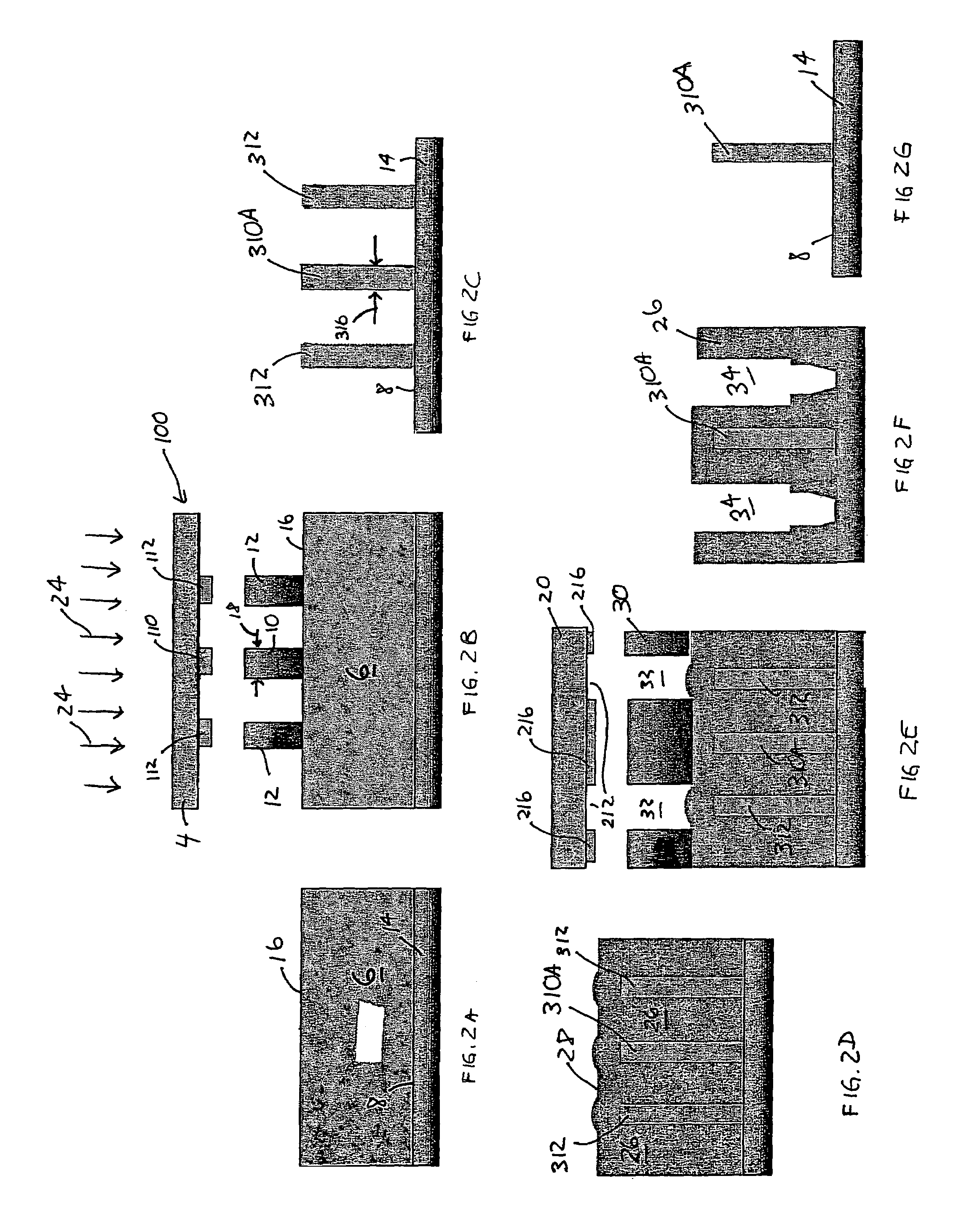

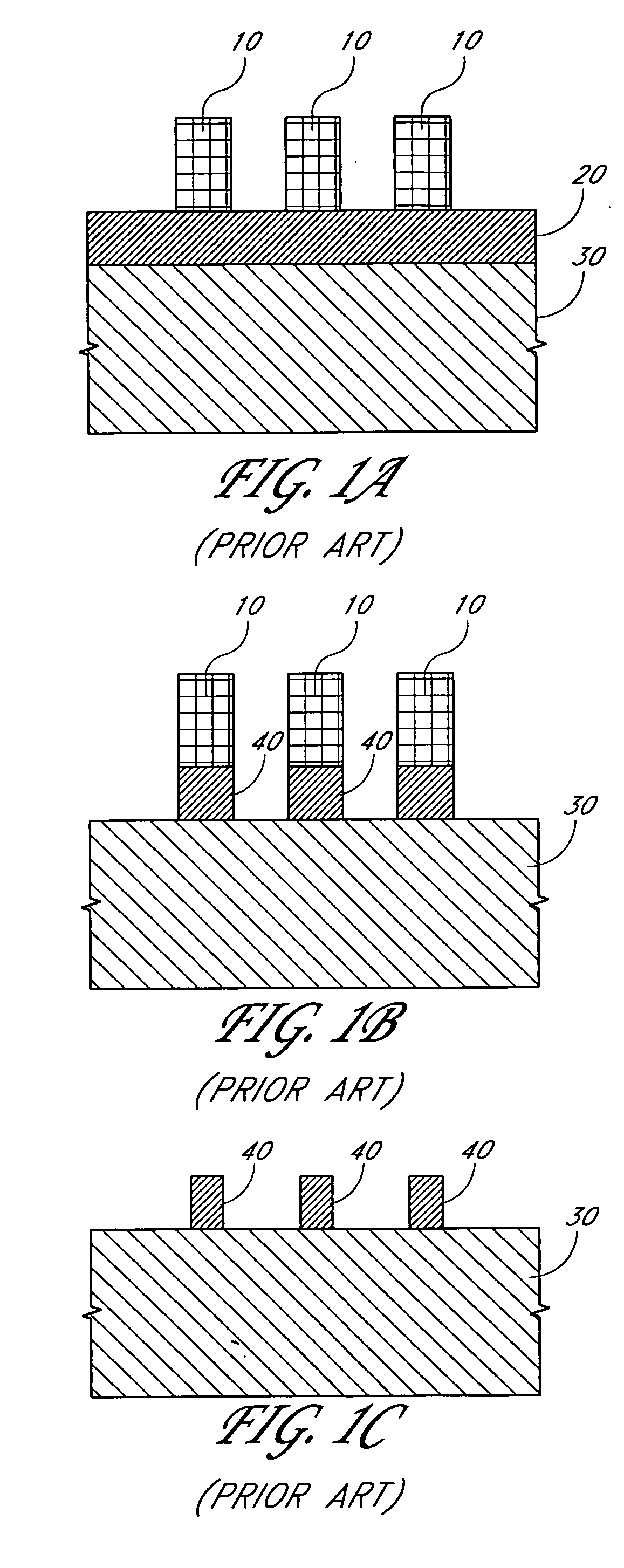

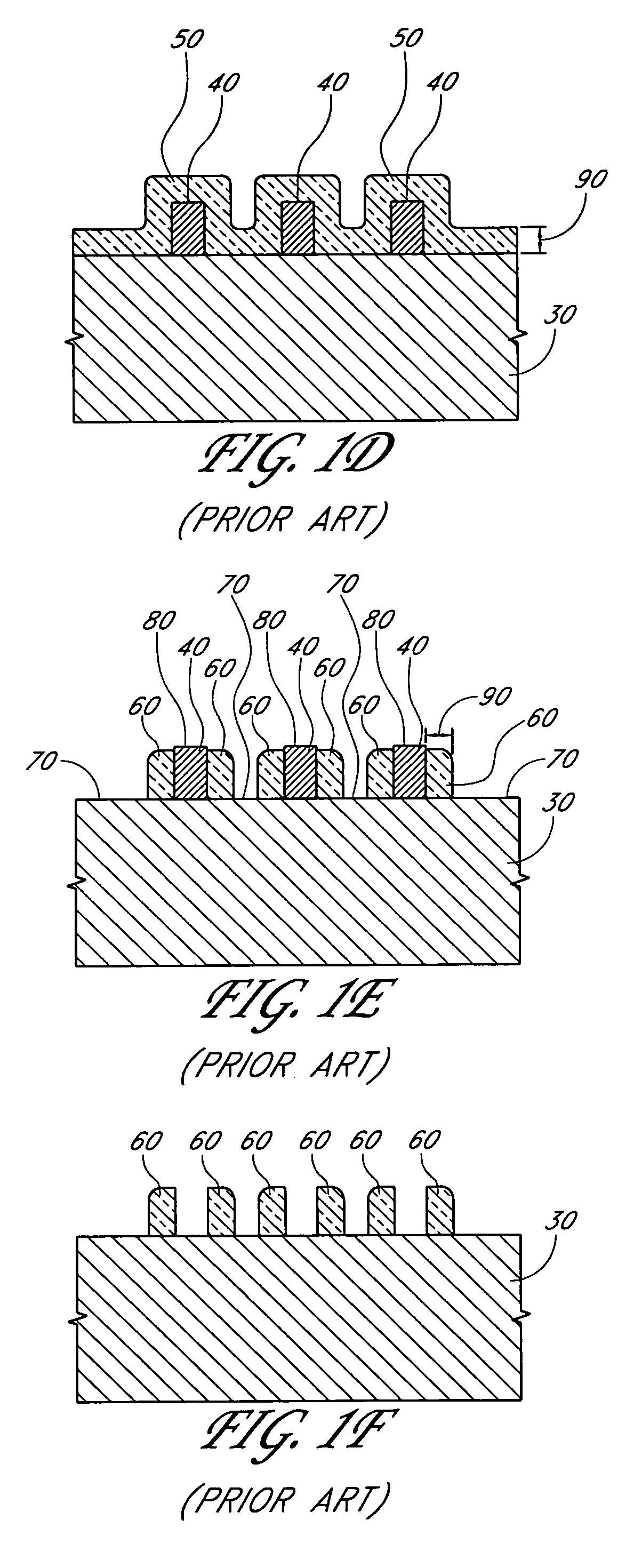

Method for integrated circuit fabrication using pitch multiplication

InactiveUS7115525B2Electric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

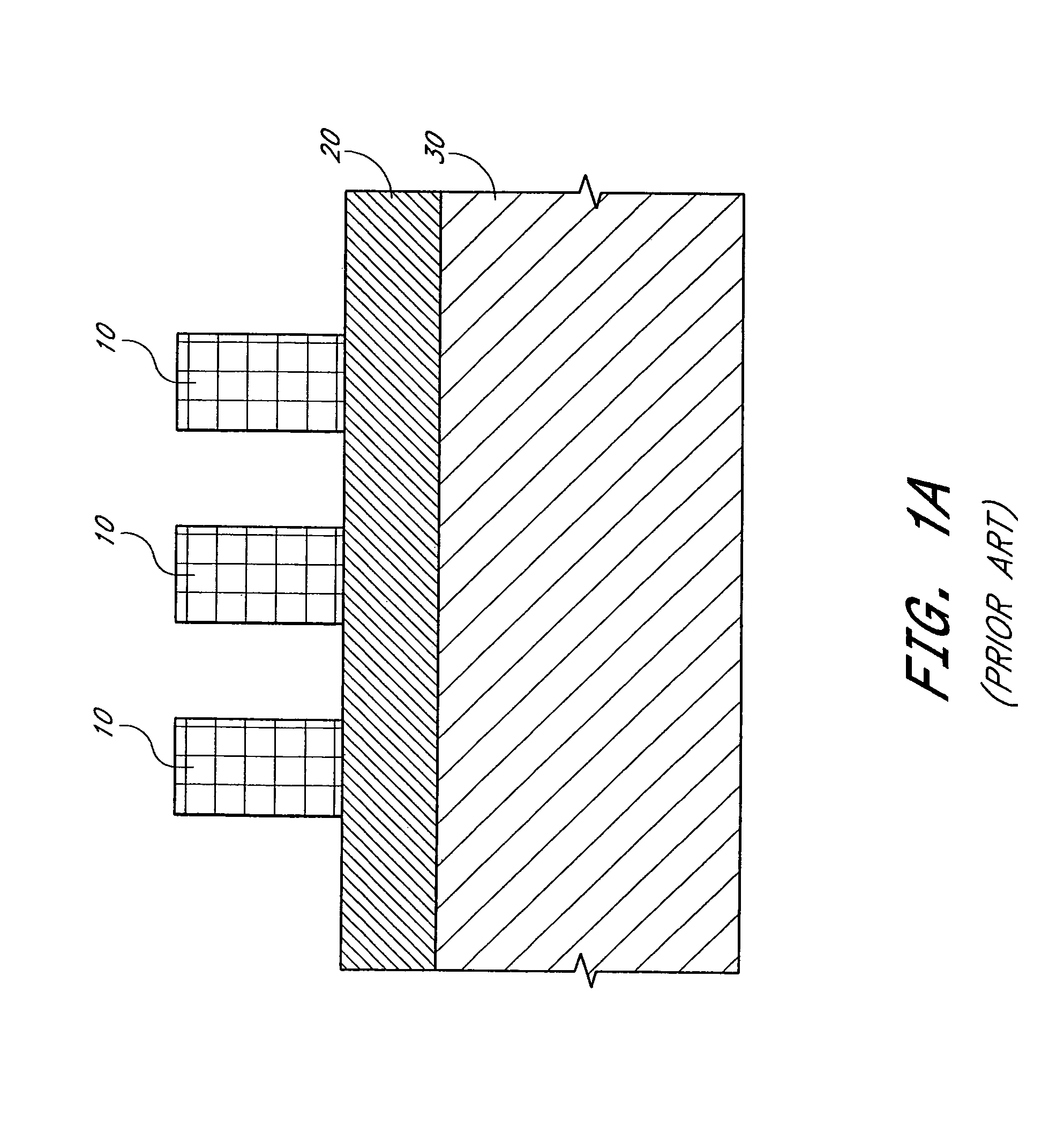

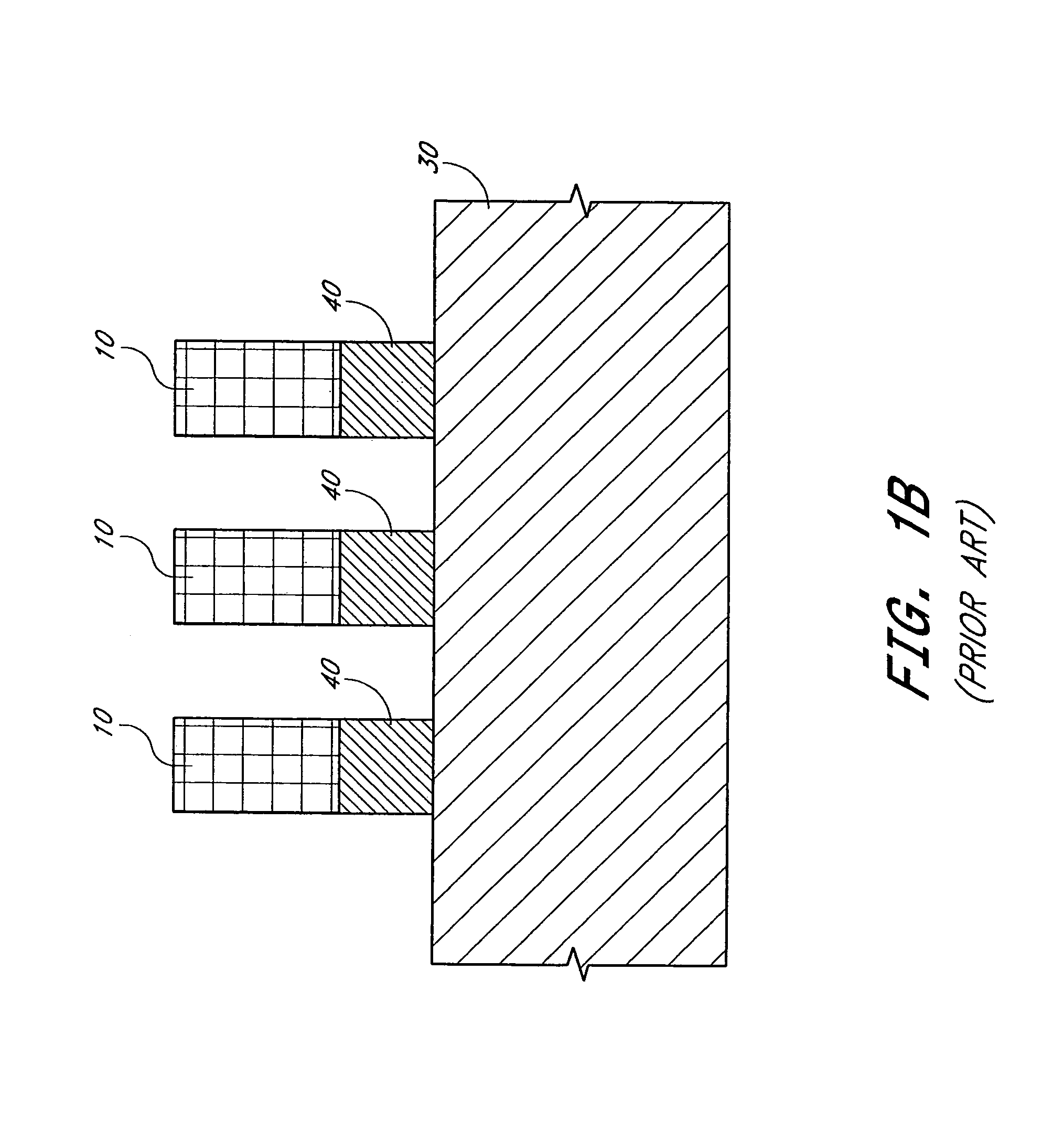

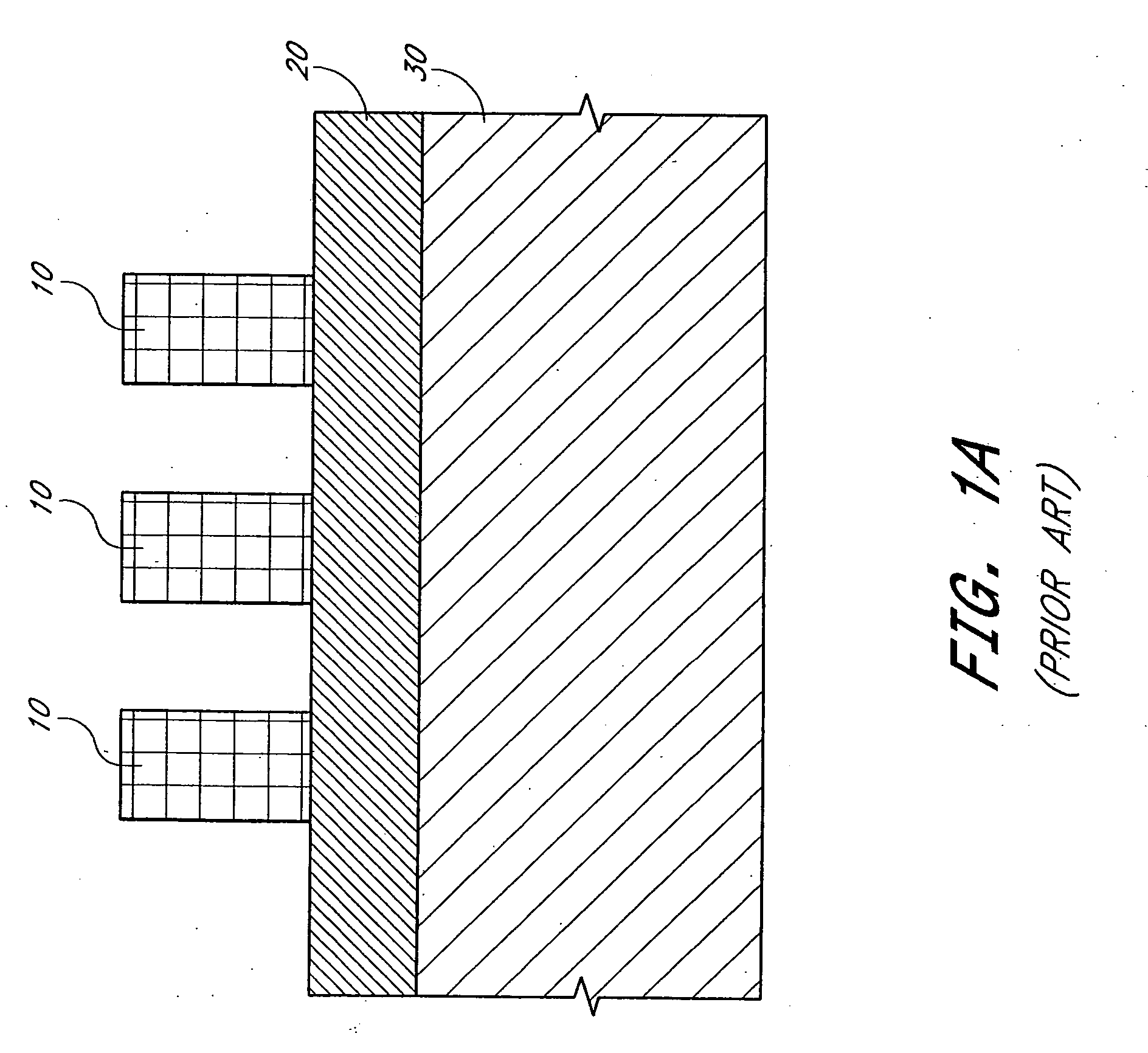

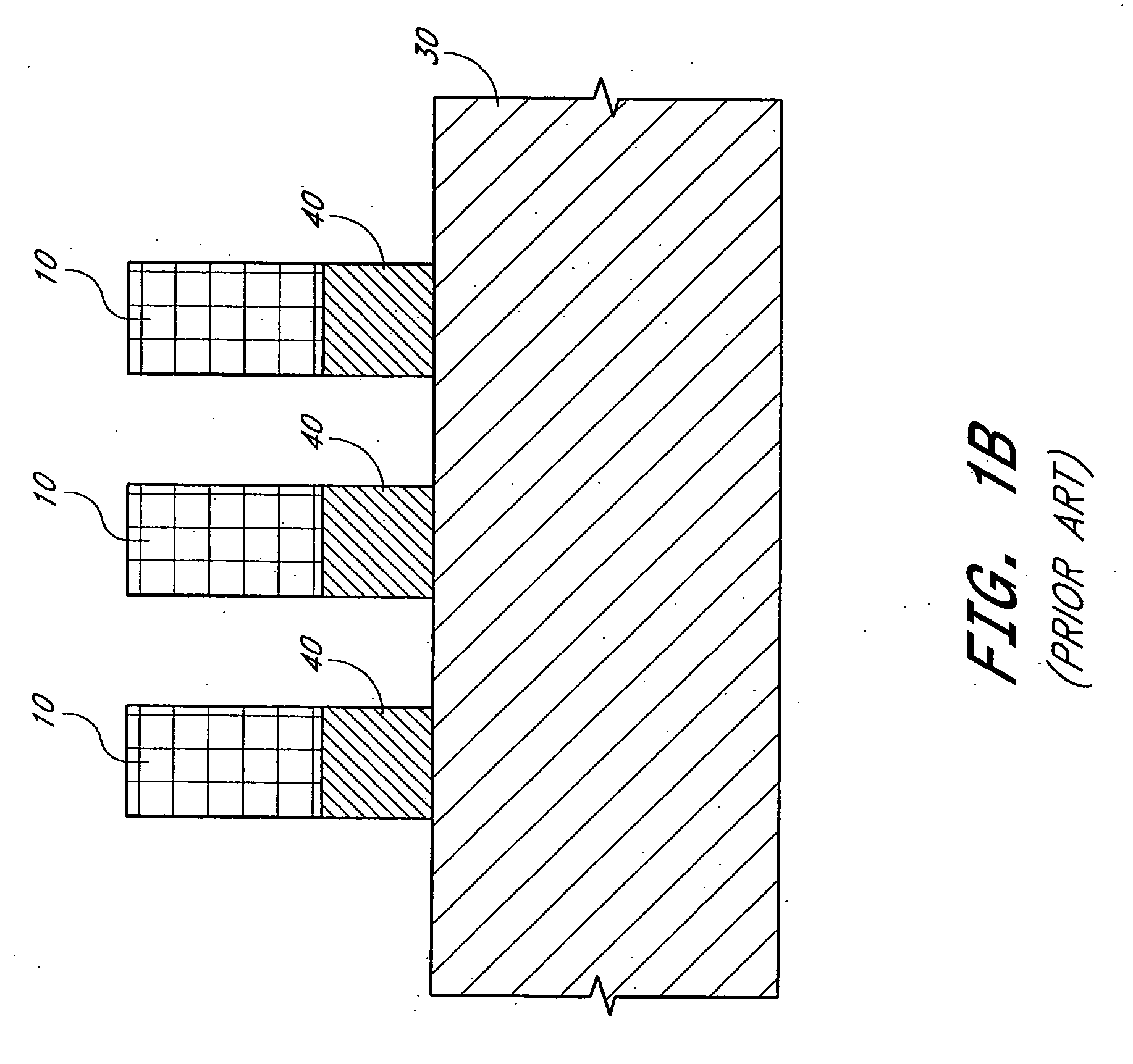

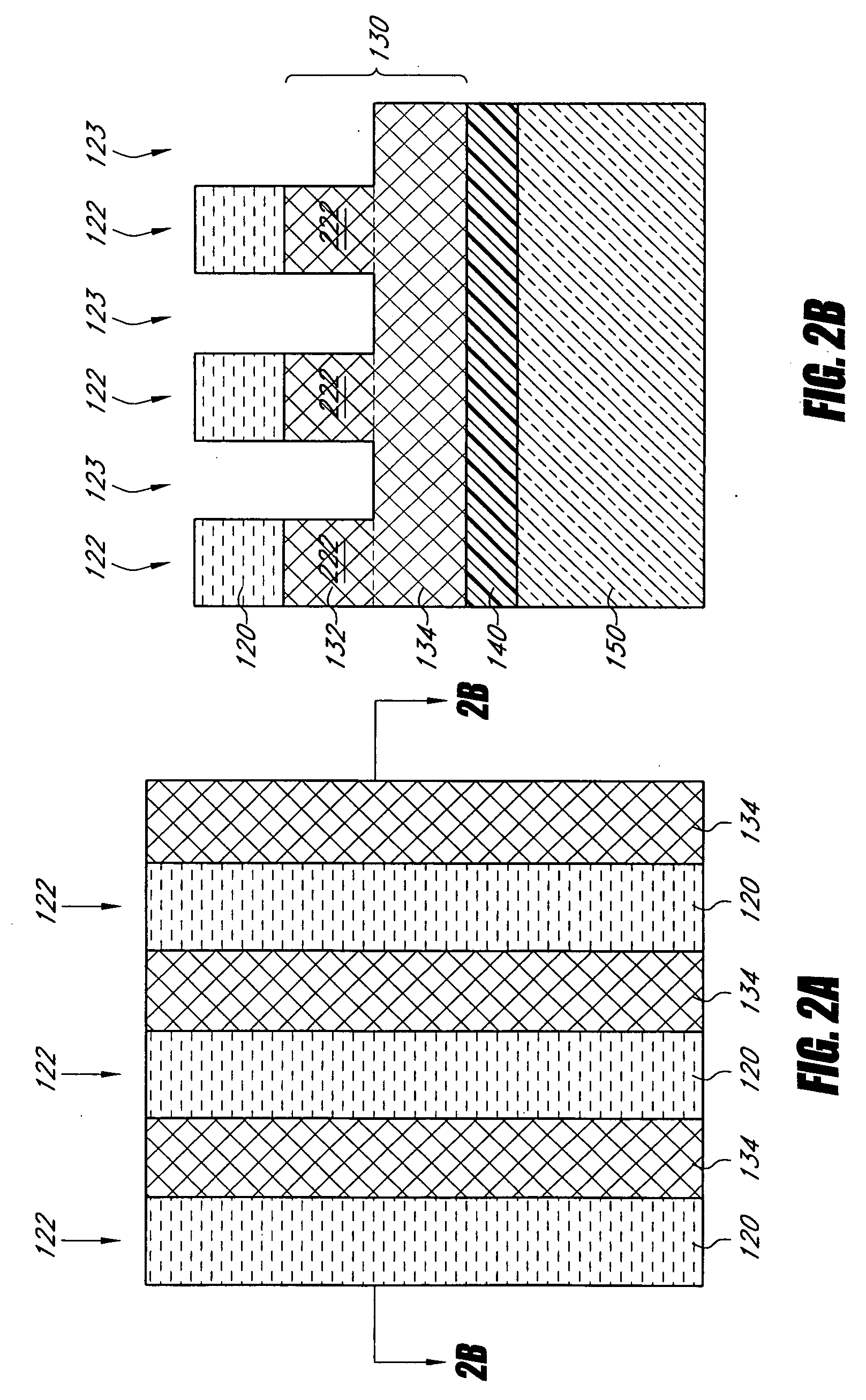

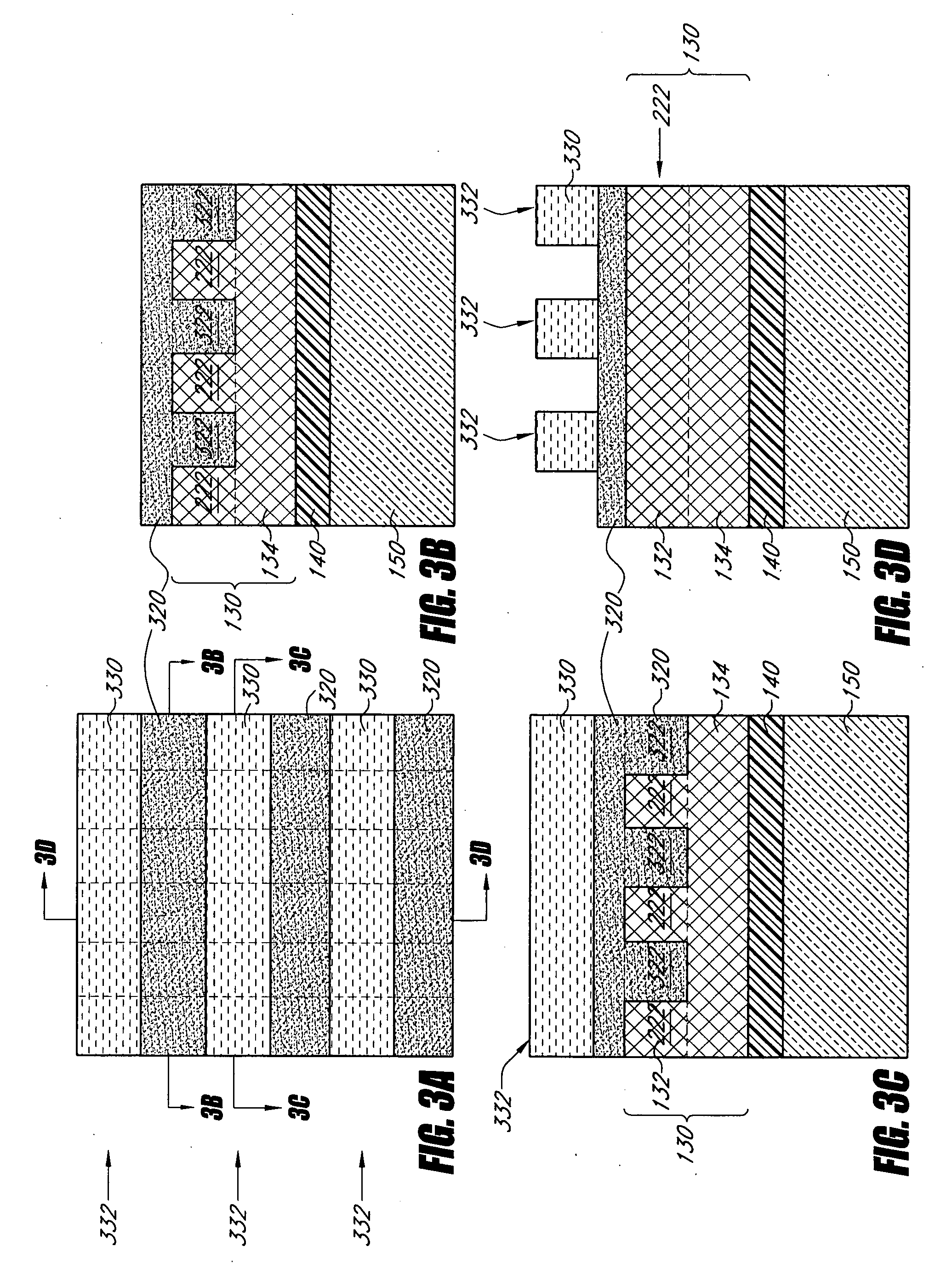

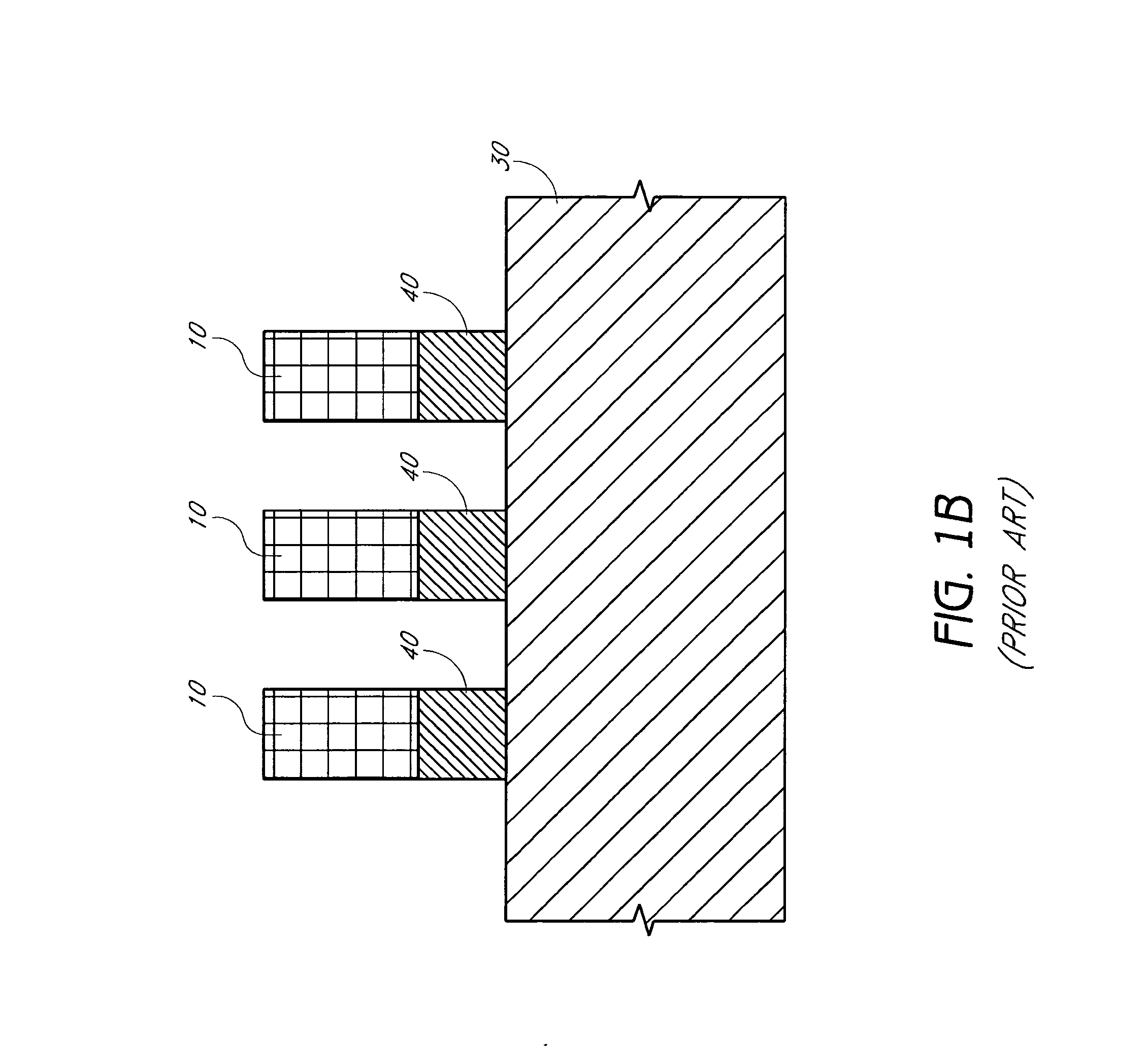

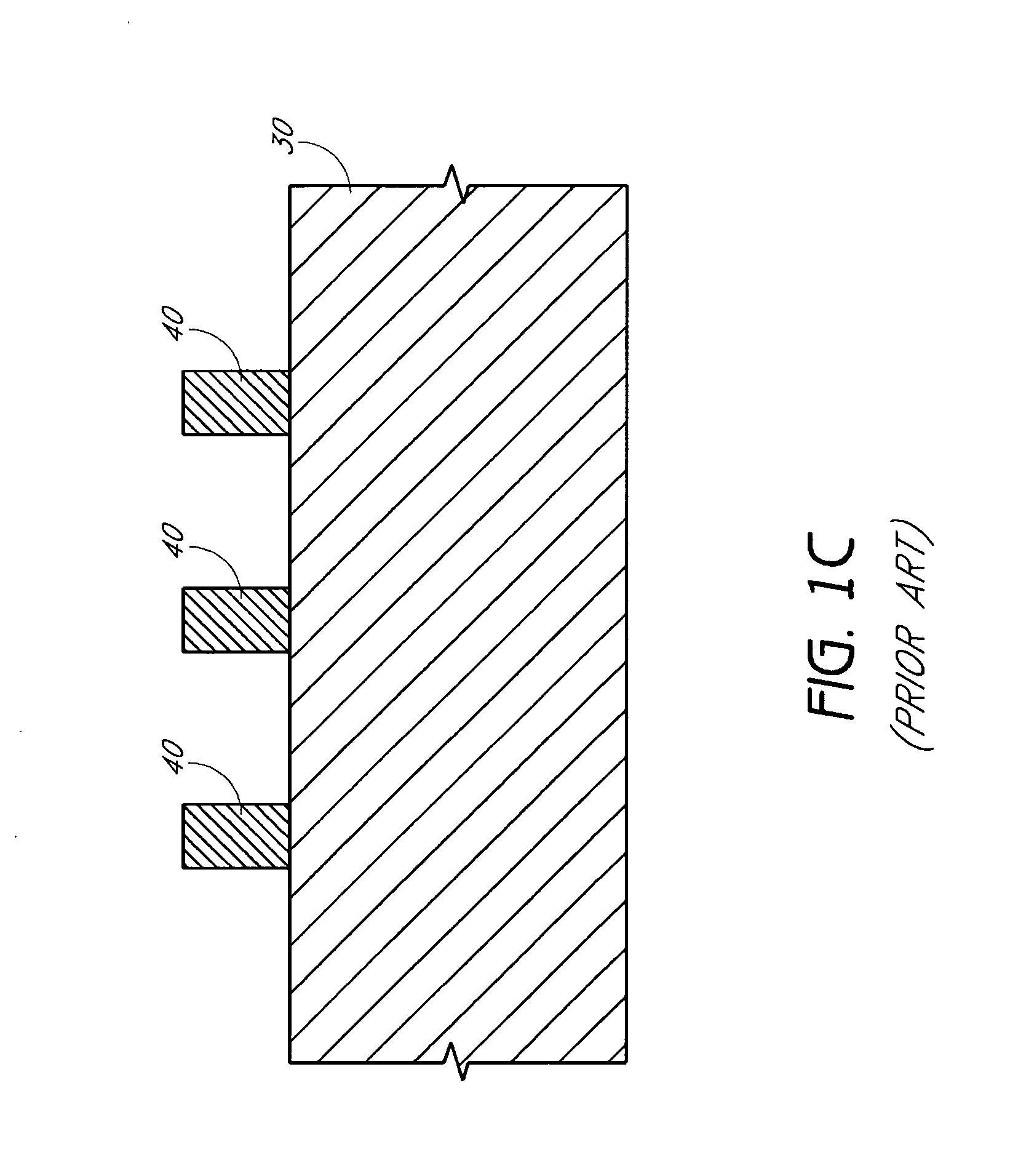

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Method for integrated circuit fabrication using pitch multiplication

InactiveUS20060046484A1Electric discharge tubesSemiconductor/solid-state device manufacturingImage resolutionDifferences size

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

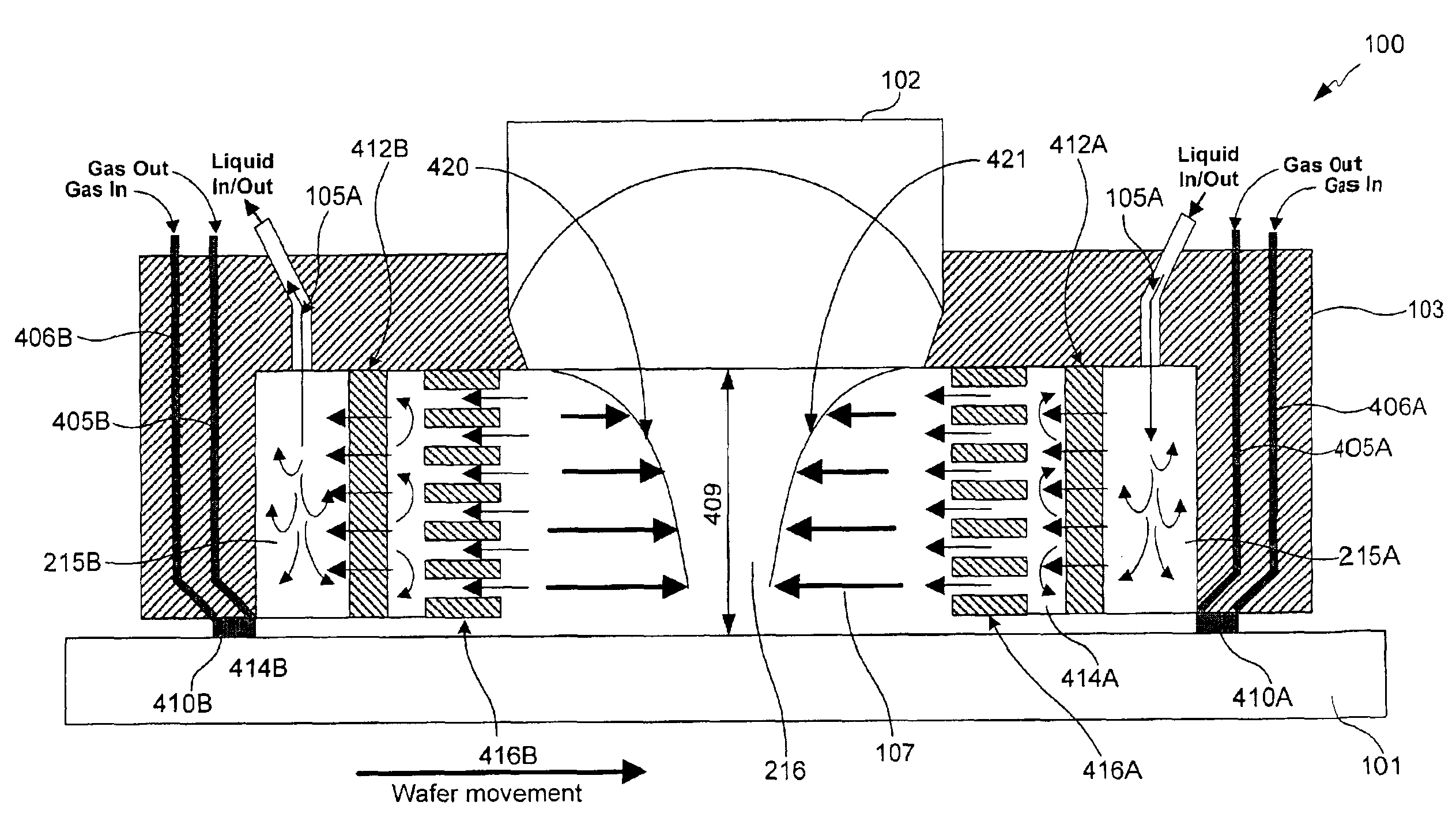

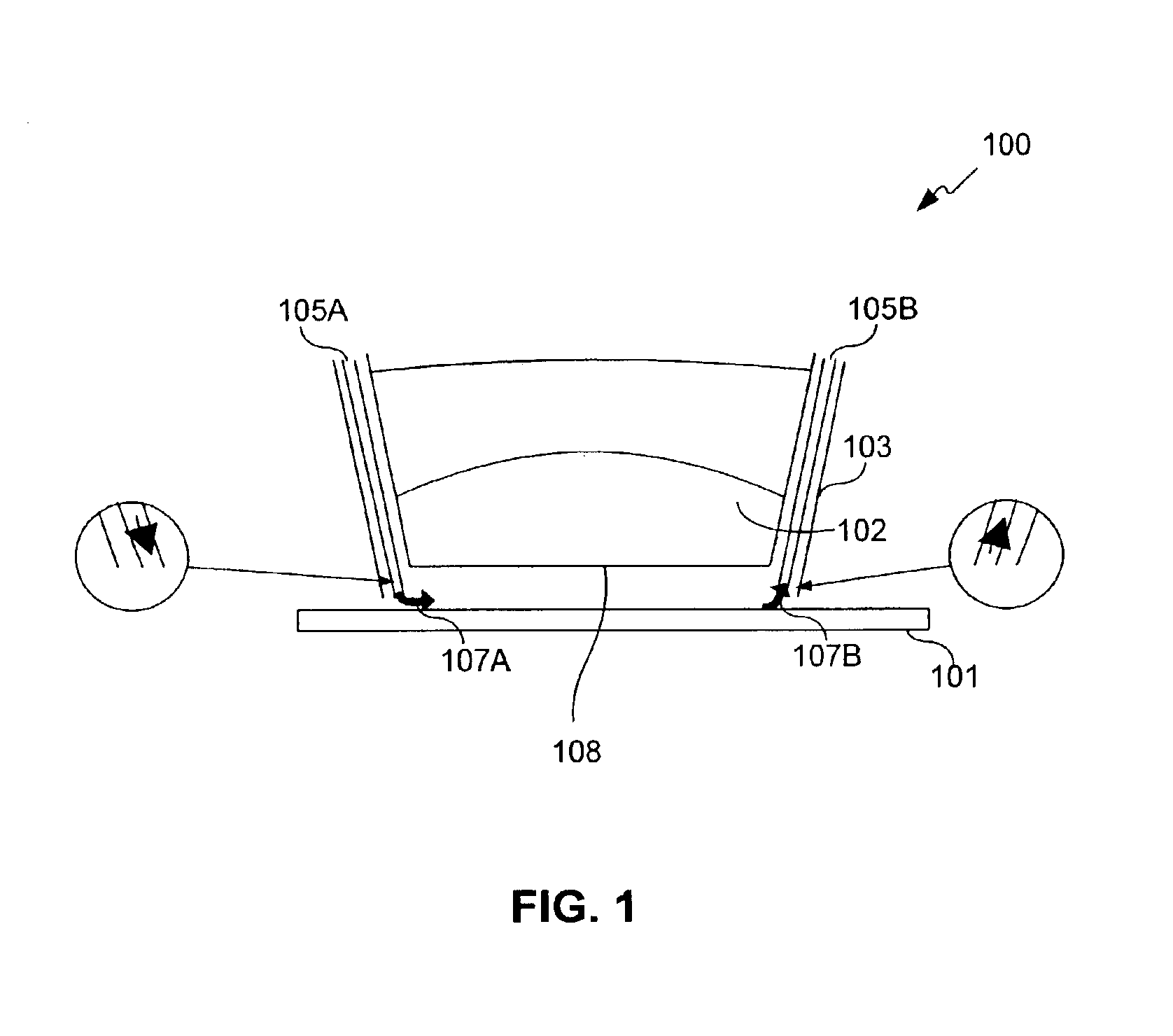

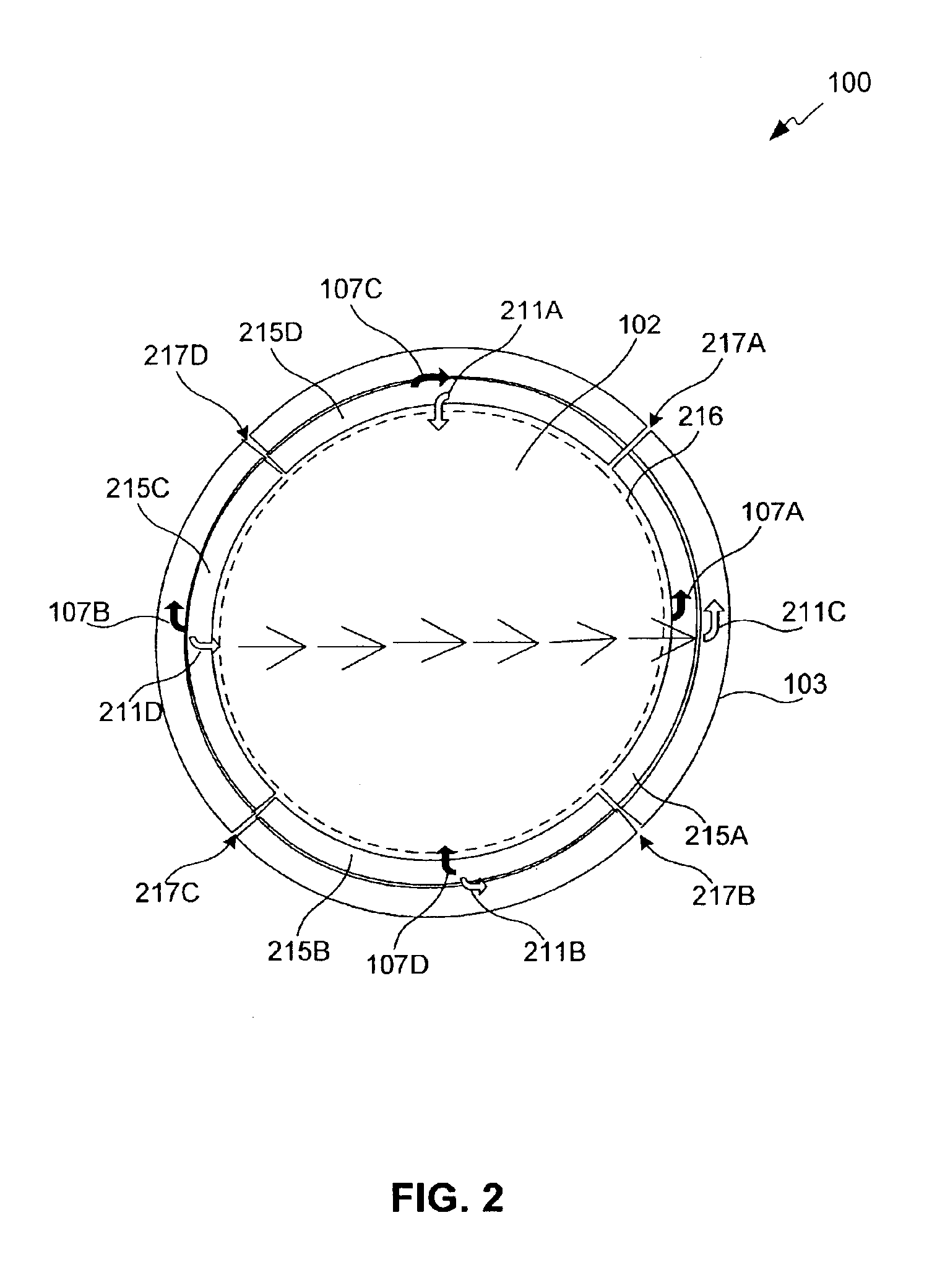

Immersion photolithography system and method using microchannel nozzles

InactiveUS6867844B2Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusElectromagnetic radiationPhotolithography

A liquid immersion photolithography system includes an exposure system that exposes a substrate with electromagnetic radiation and includes a projection optical system that focuses the electromagnetic radiation on the substrate. A liquid supply system provides liquid flow between the projection optical system and the substrate. An optional plurality of micronozzles are arranged around the periphery of one side of the projection optical system so as to provide a substantially uniform velocity distribution of the liquid flow in an area where the substrate is being exposed.

Owner:ASML HLDG NV

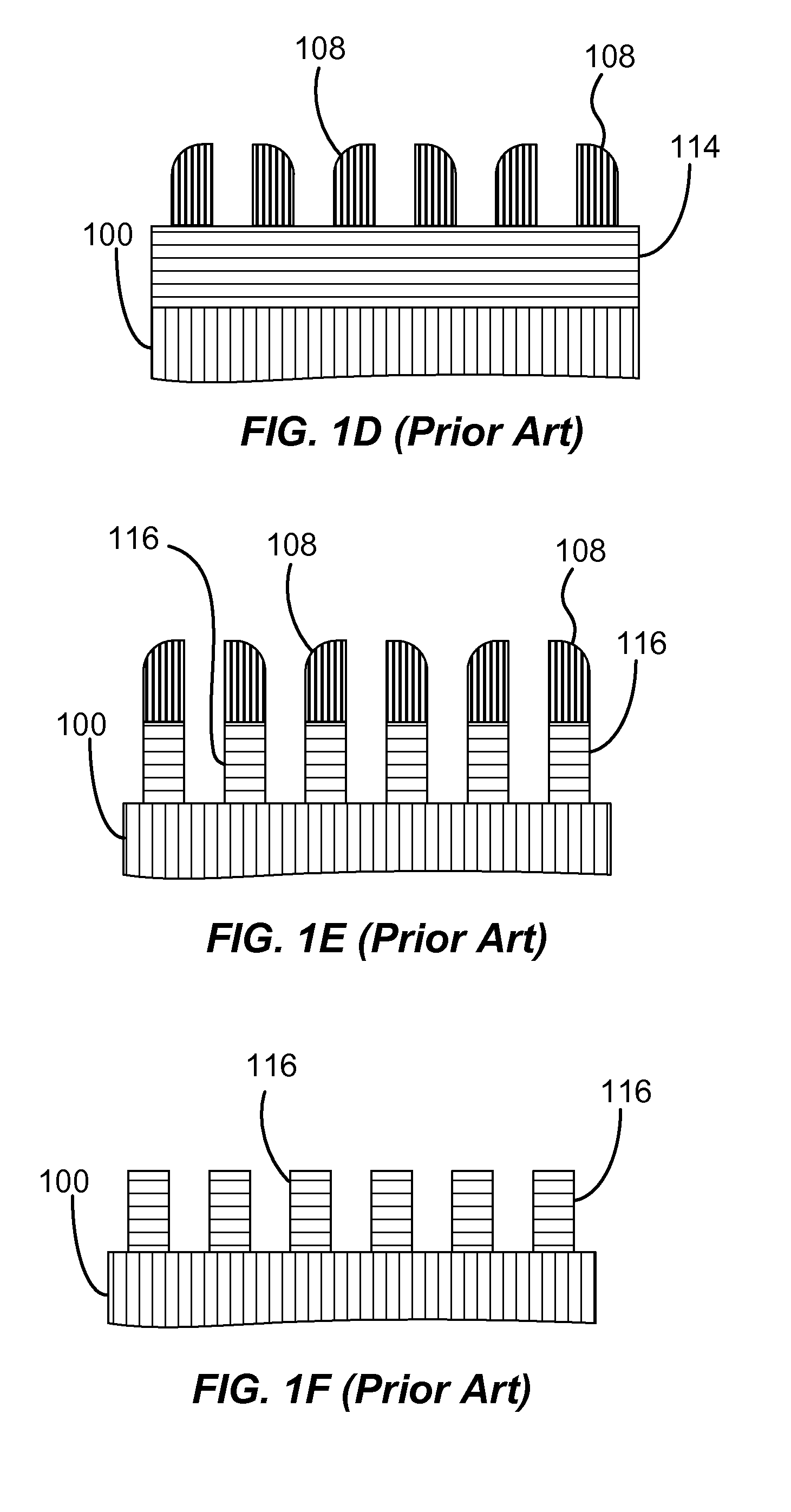

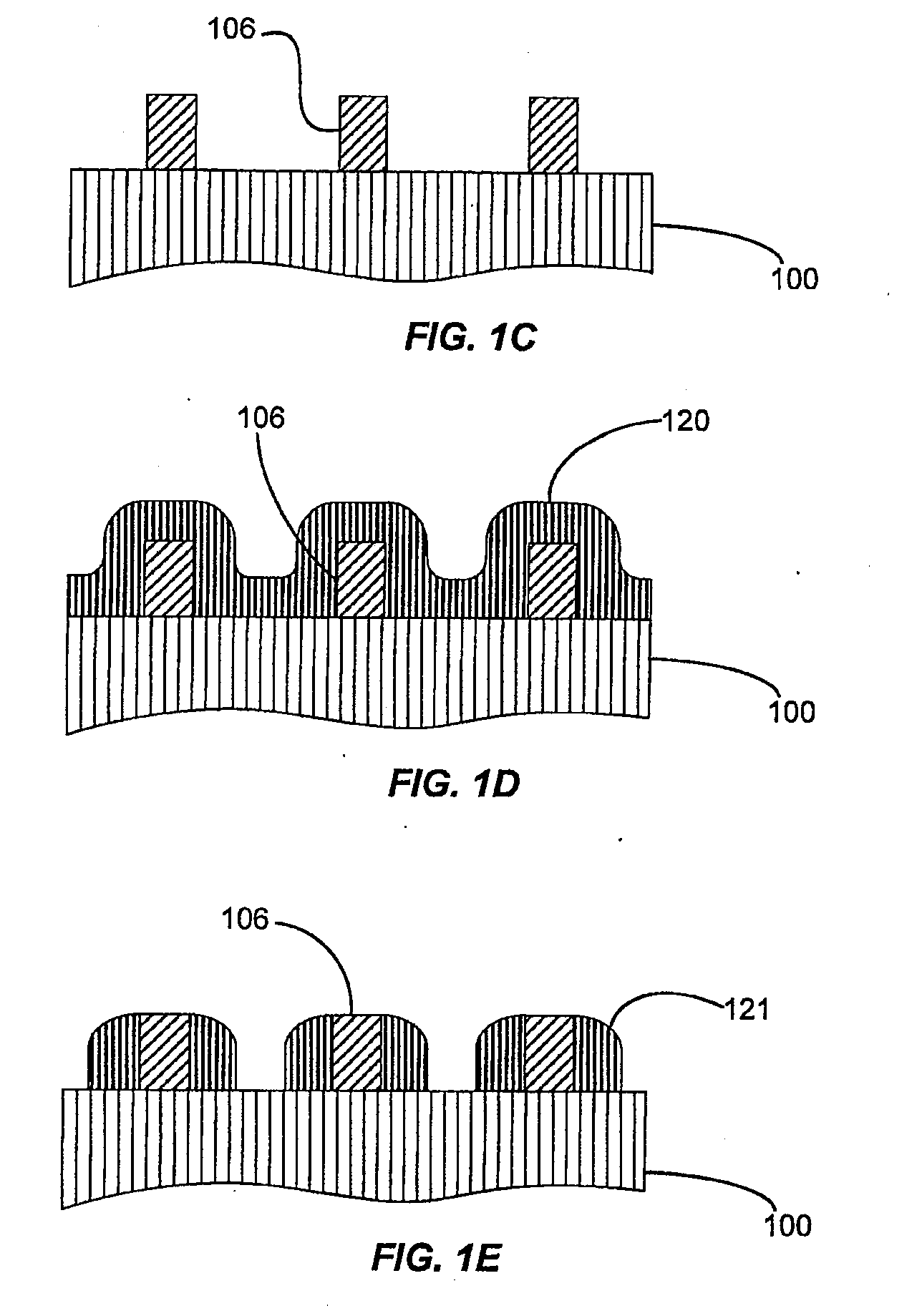

Spacer formation

ActiveUS20150287612A1Semiconductor/solid-state device manufacturingImage resolutionOptical resolution

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

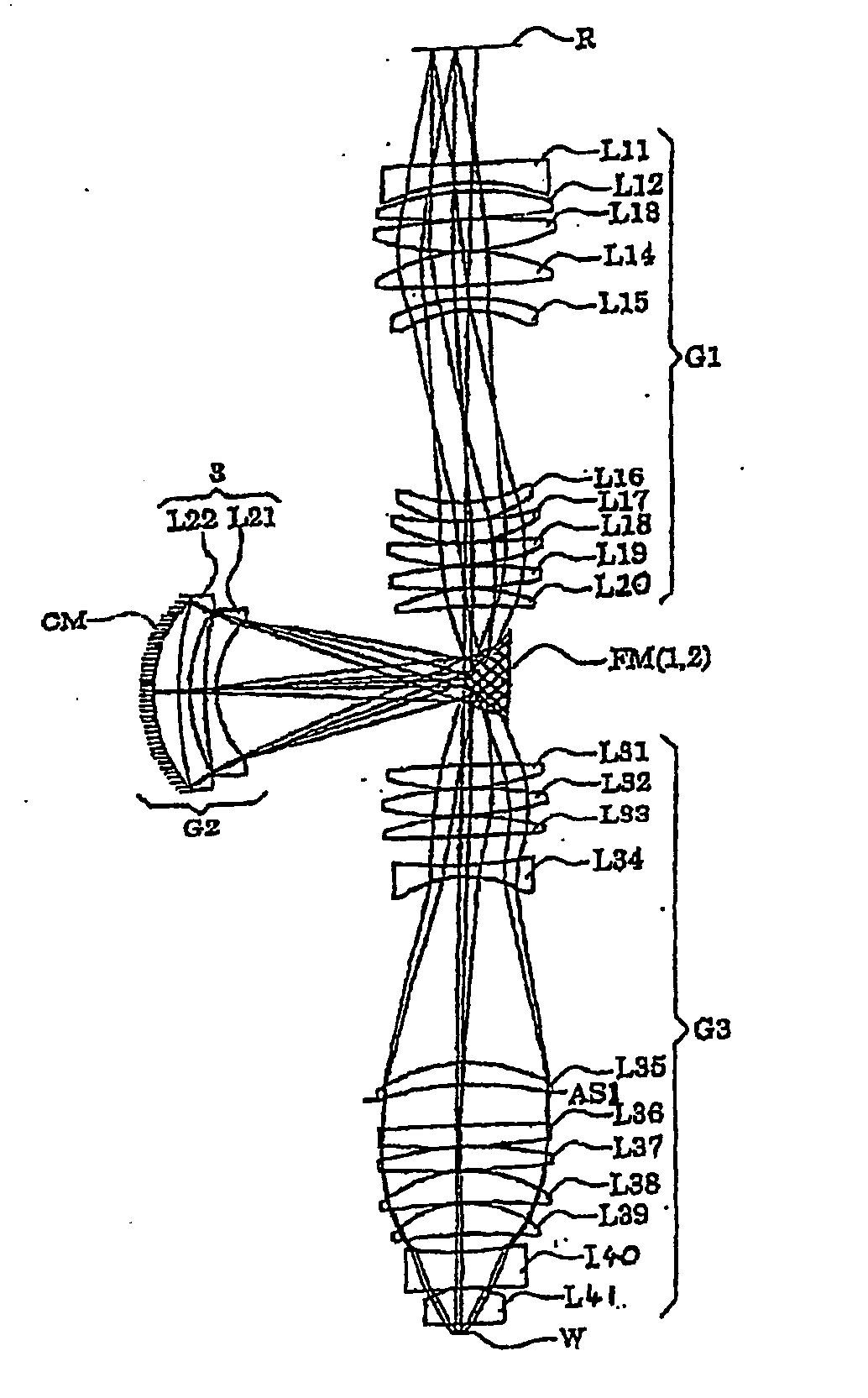

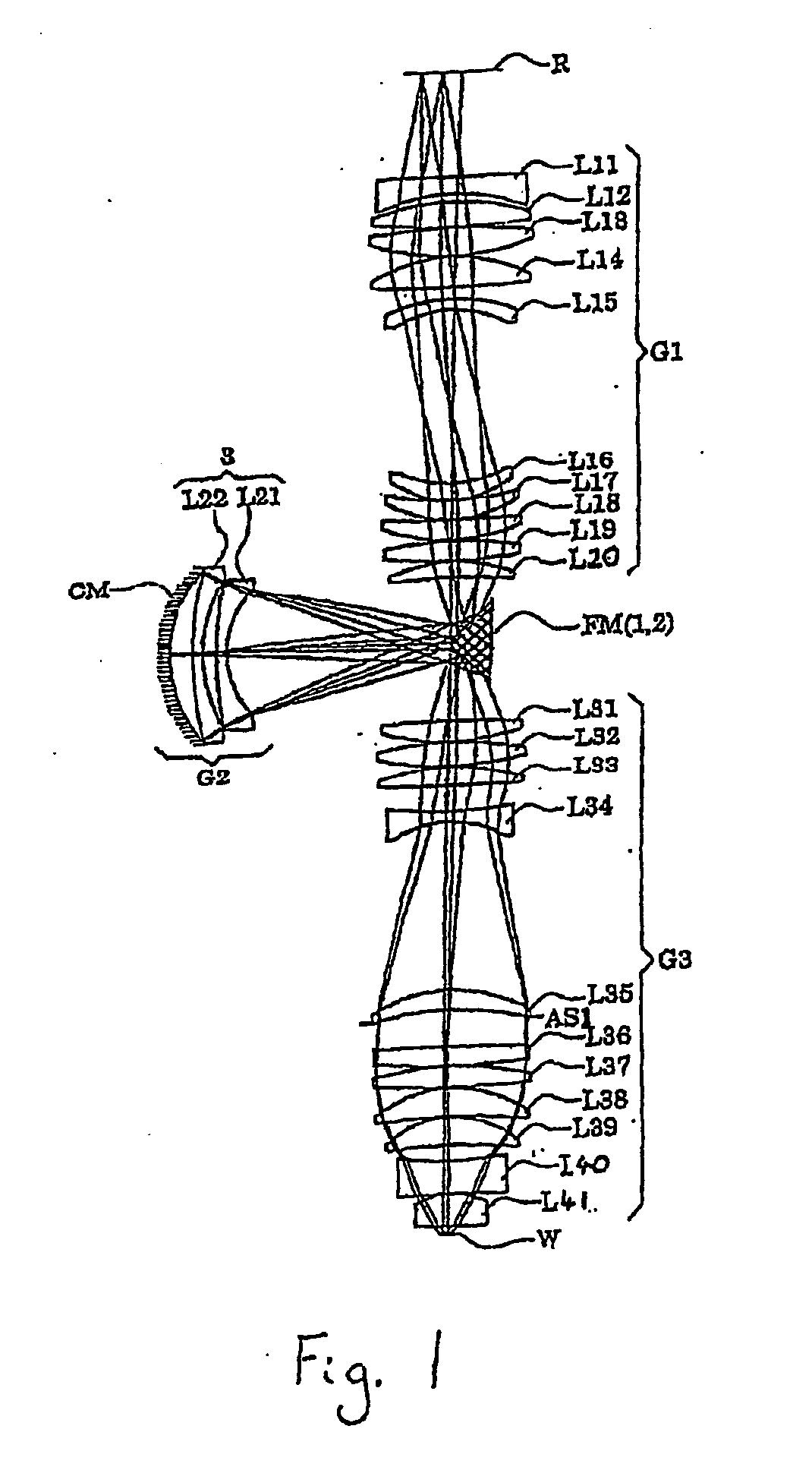

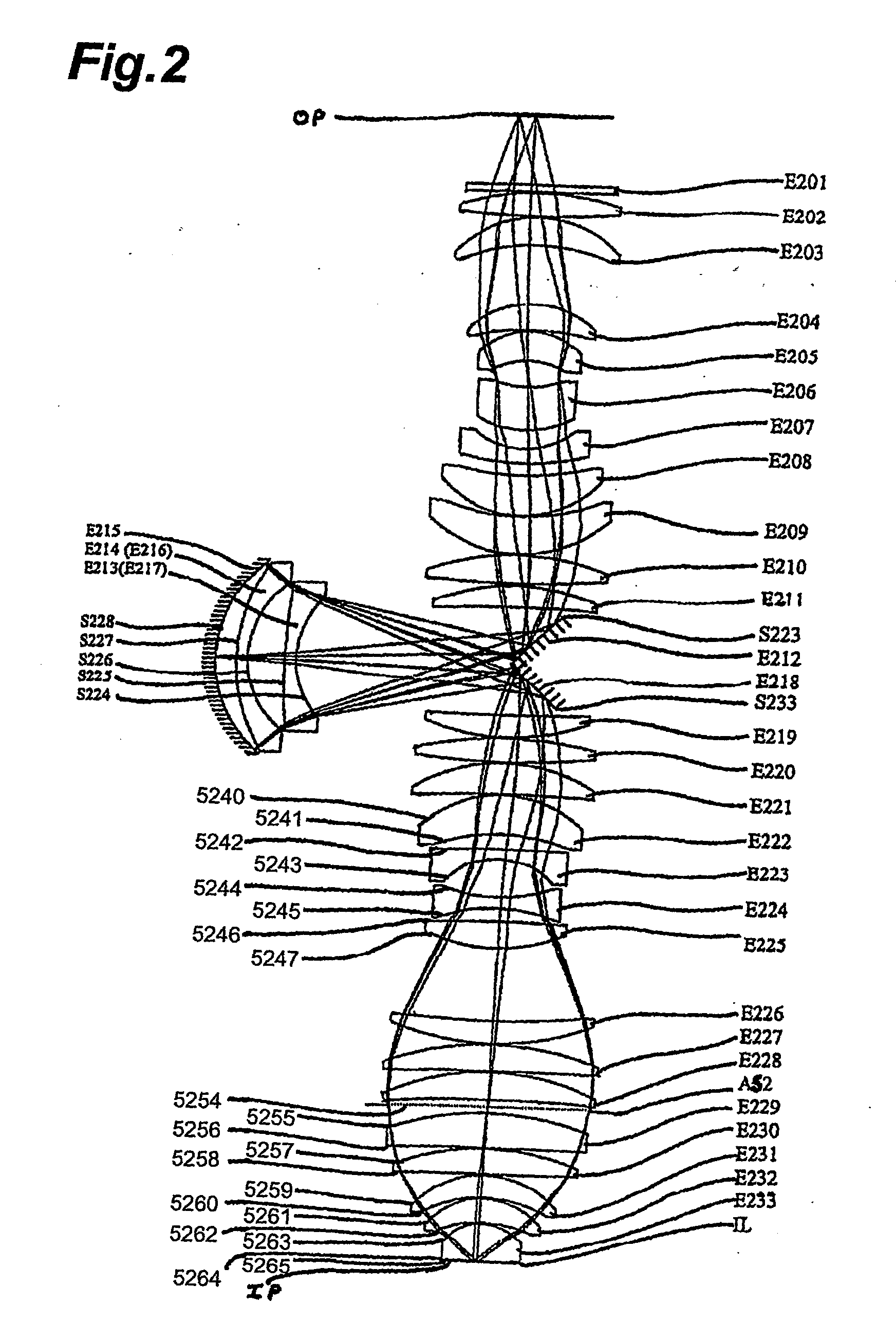

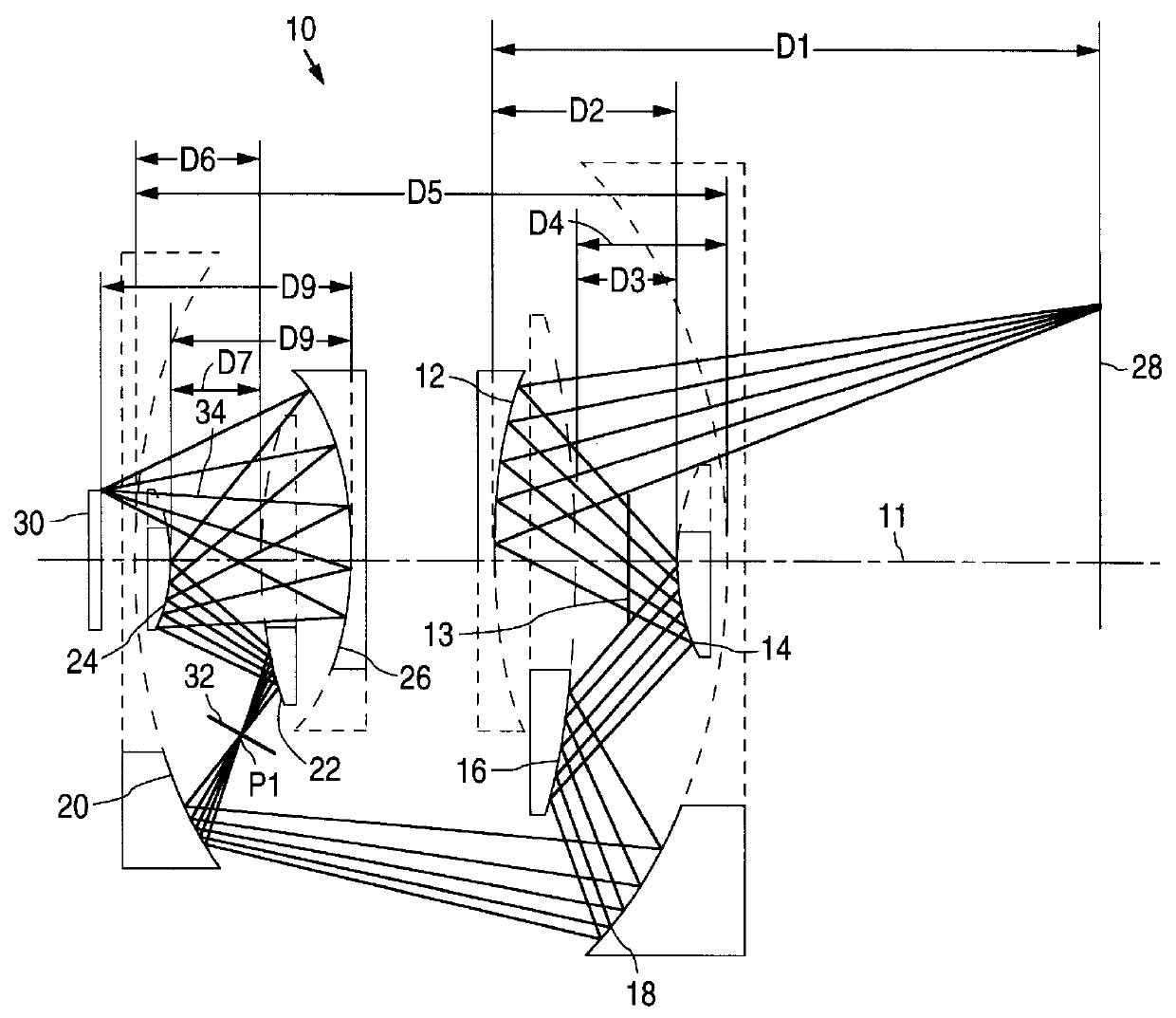

Projection optical system and method for photolithography and exposure apparatus and method using same

InactiveUS20050248856A1Large image-sideWide effective image forming areaSemiconductor/solid-state device manufacturingMicroscopesWide fieldProjection system

Optical Projection System and Method for Photolithography. A lithographic immersion projection system and method for projecting an image at high resolution over a wide field of view. The projection system and method include a final lens which decreases the marginal ray angle of the optical path before light passes into the immersion liquid to impinge on the image plane.

Owner:NIKON CORP

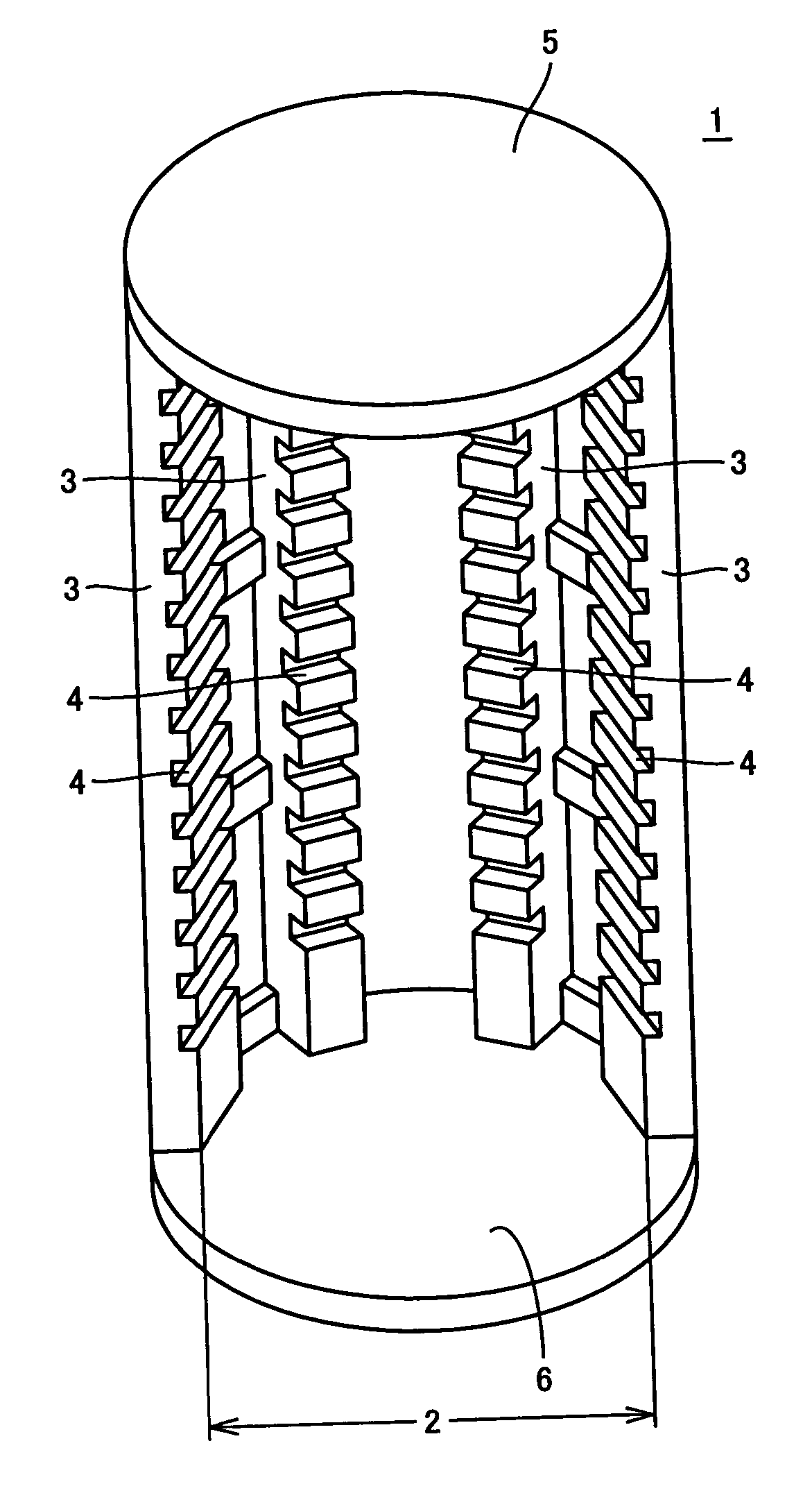

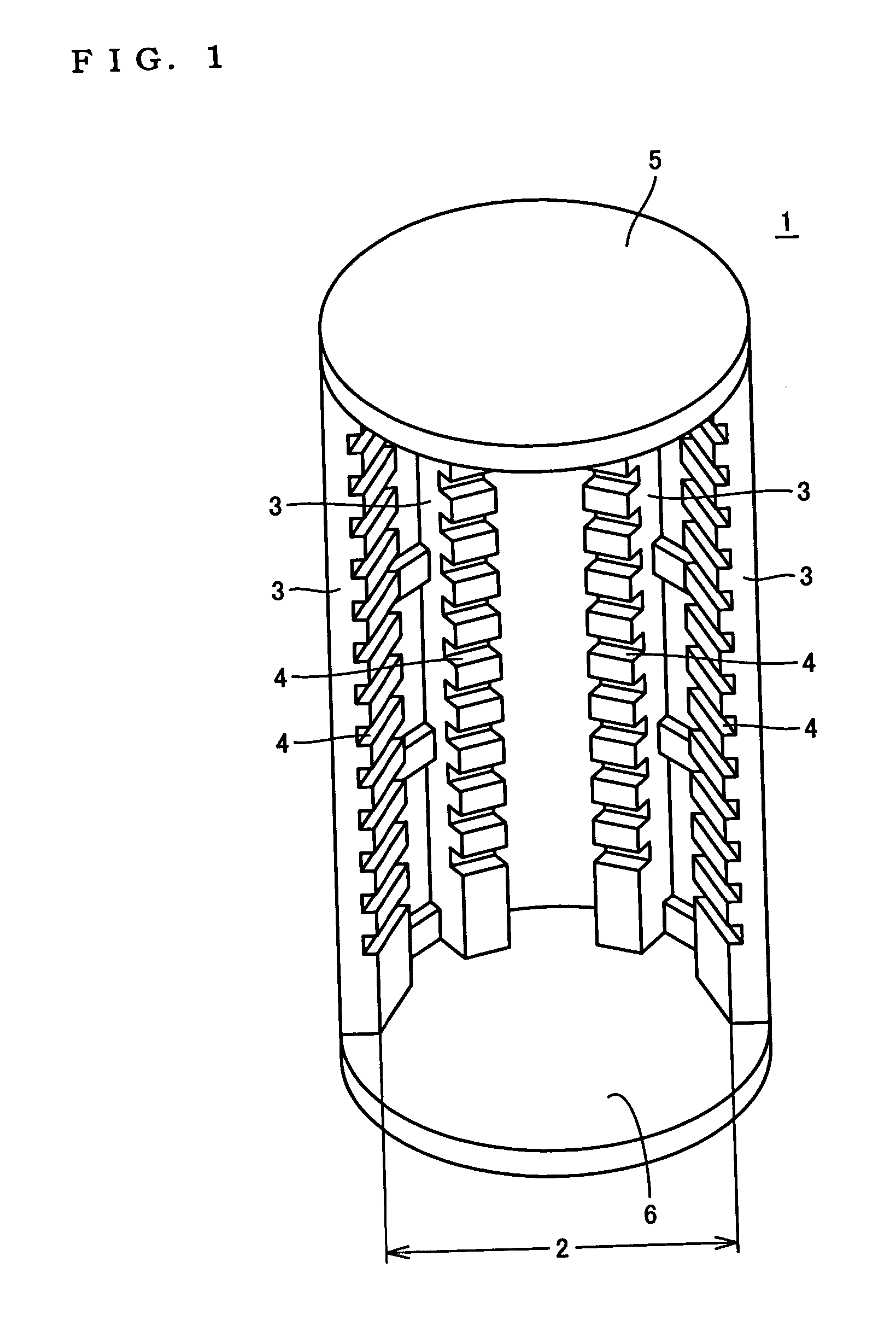

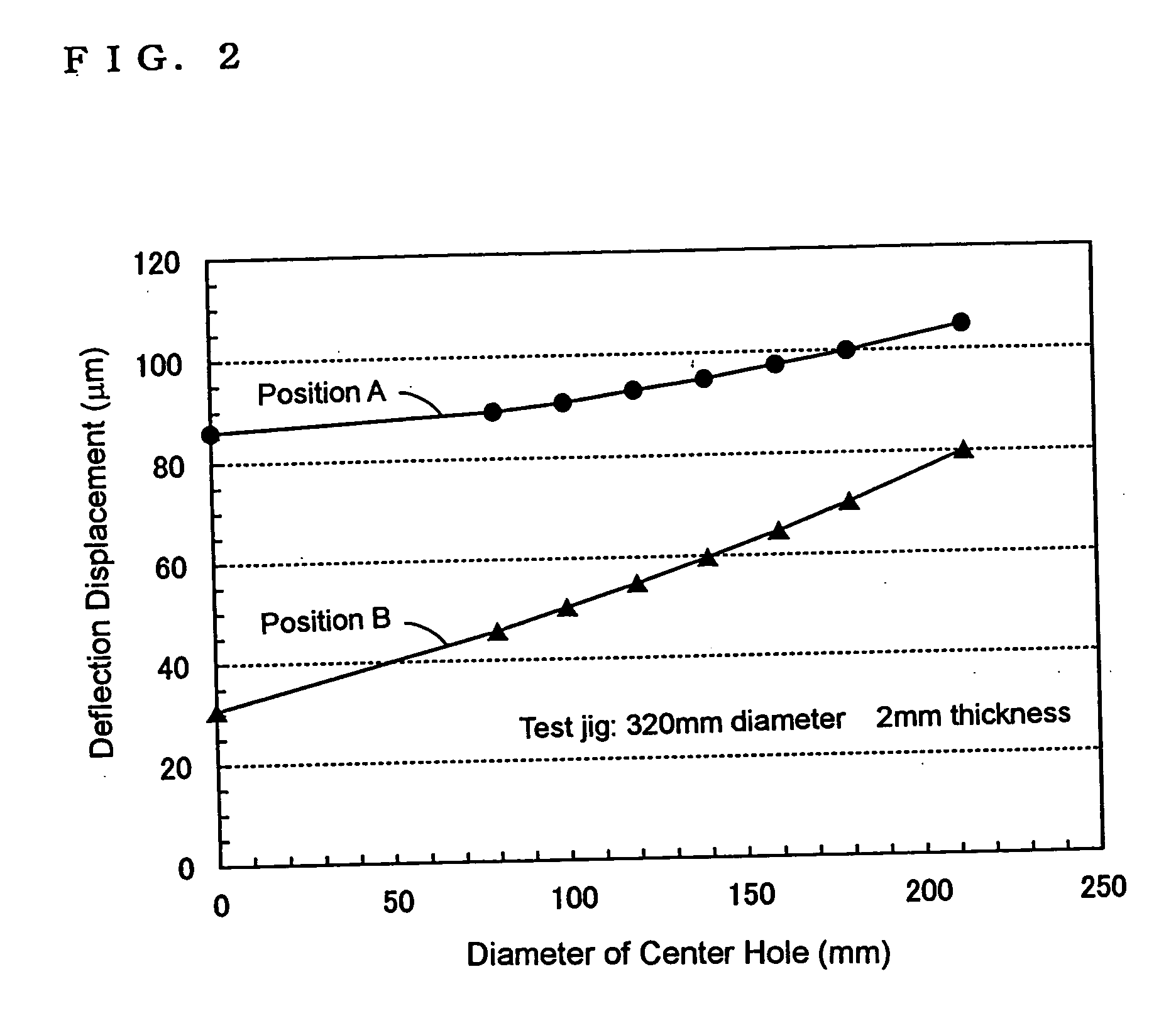

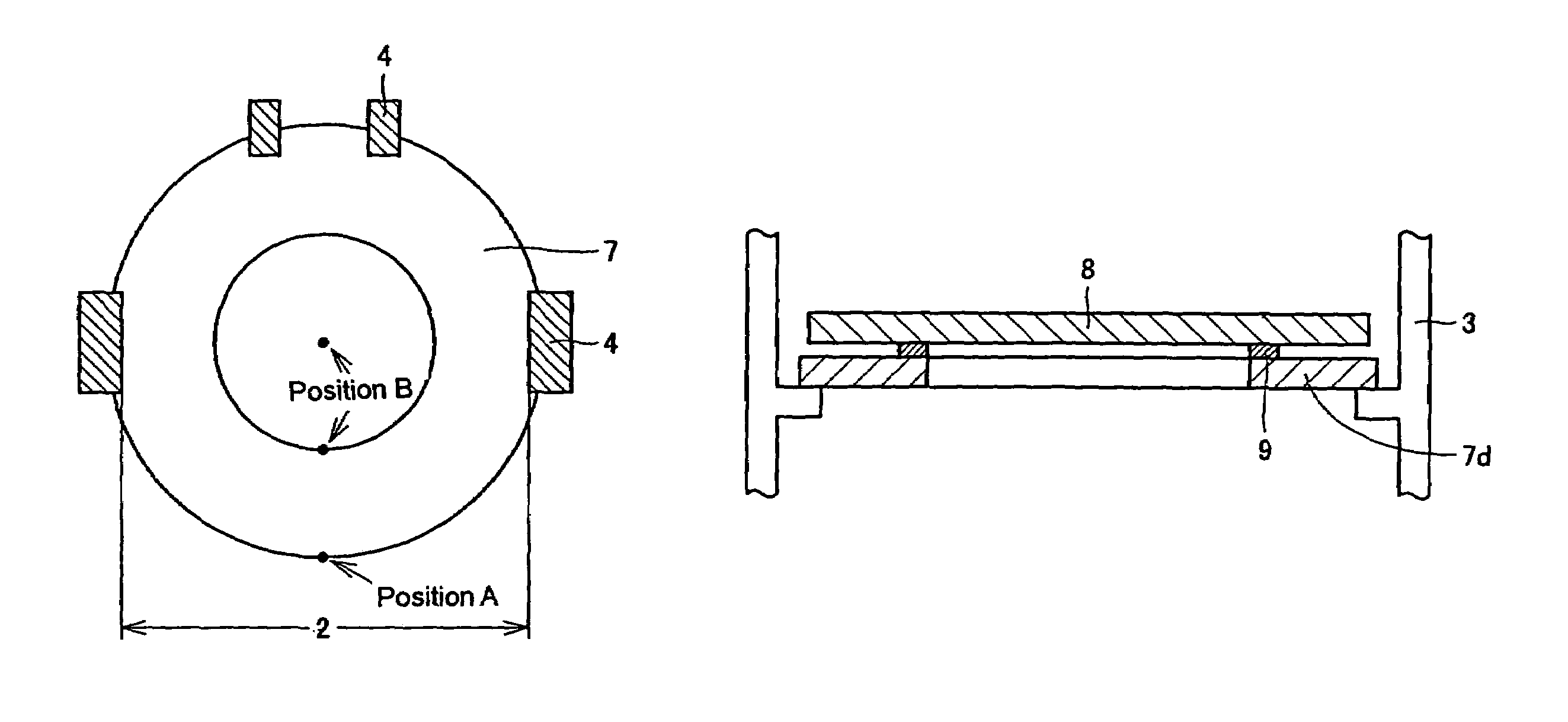

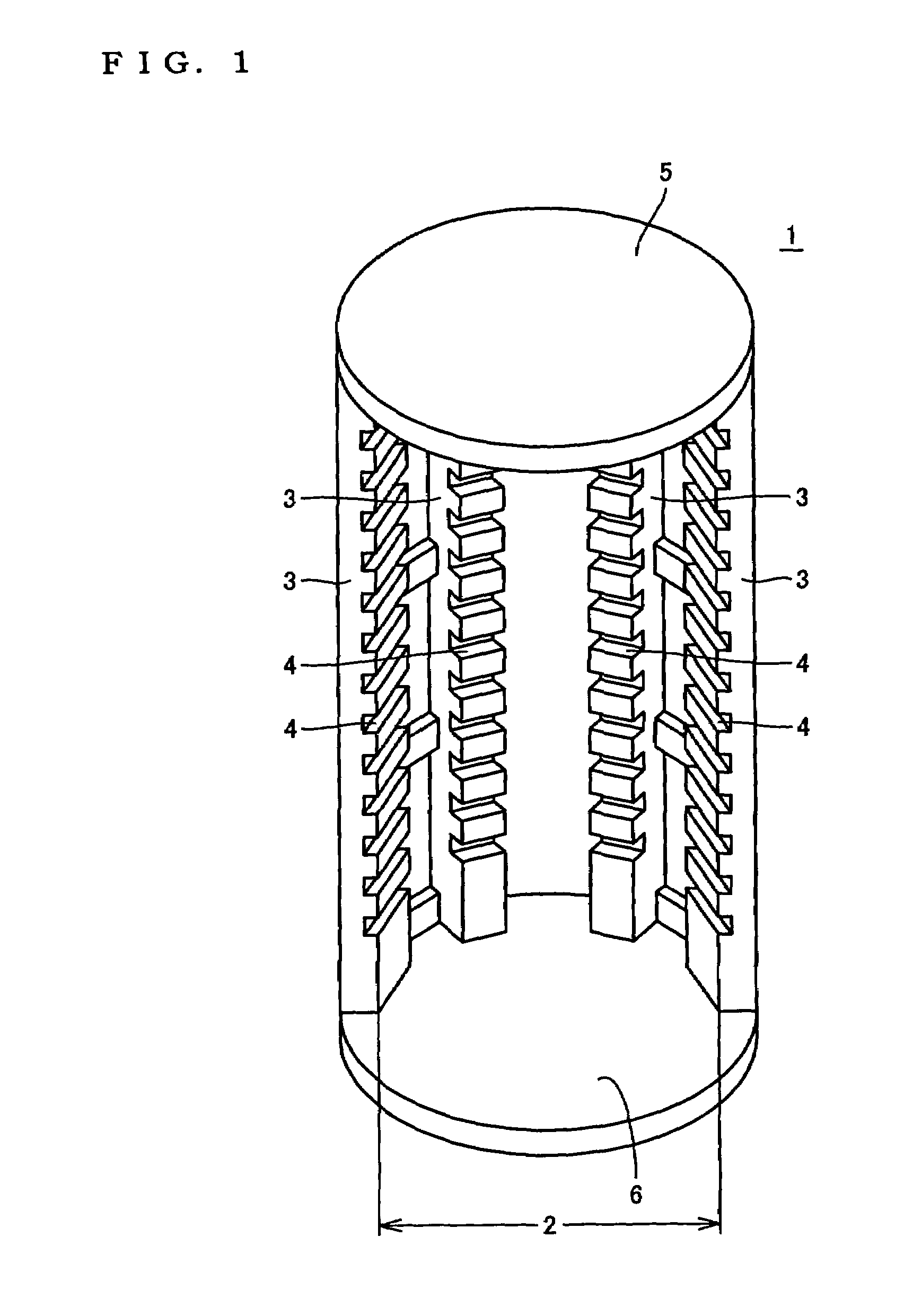

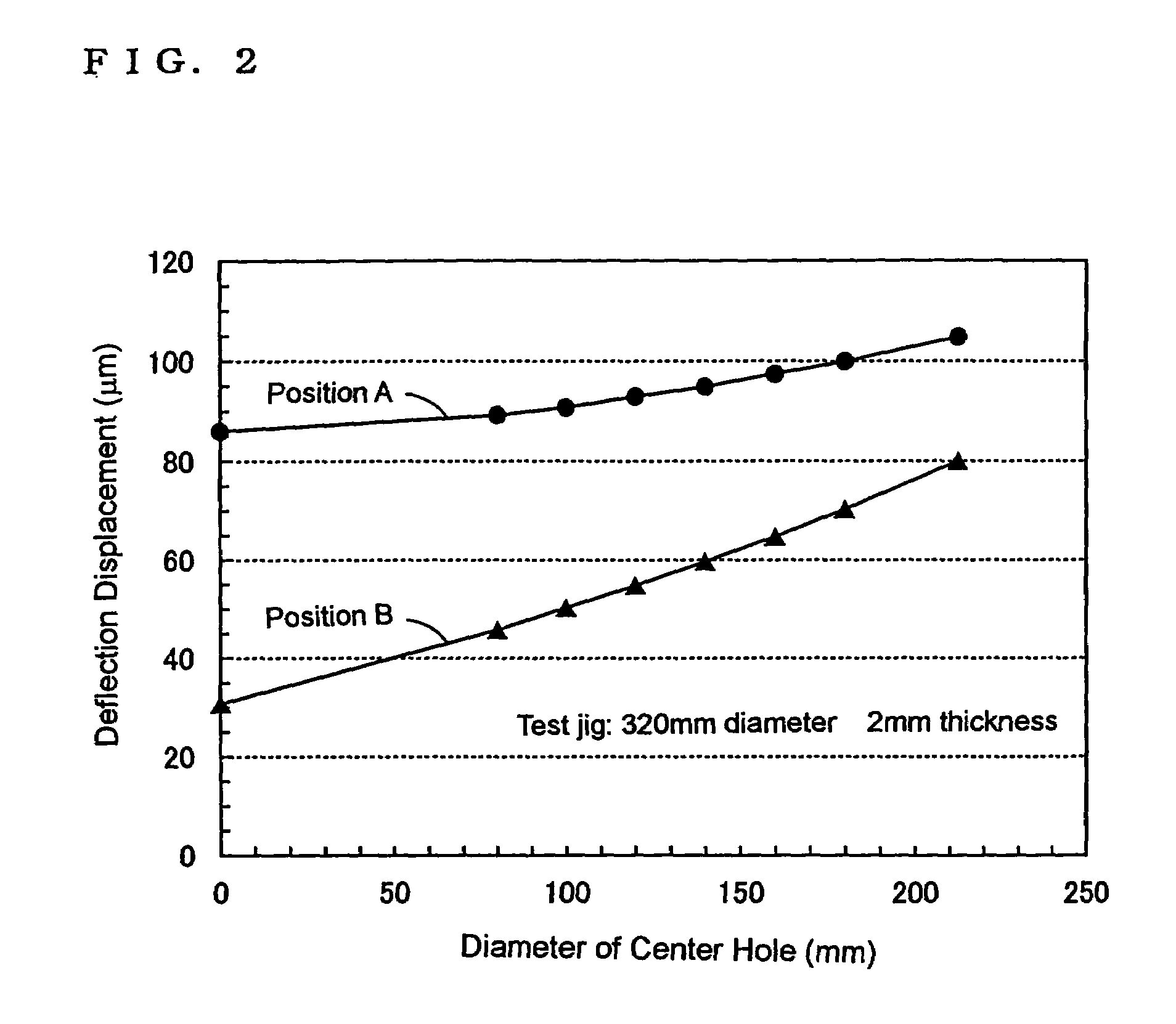

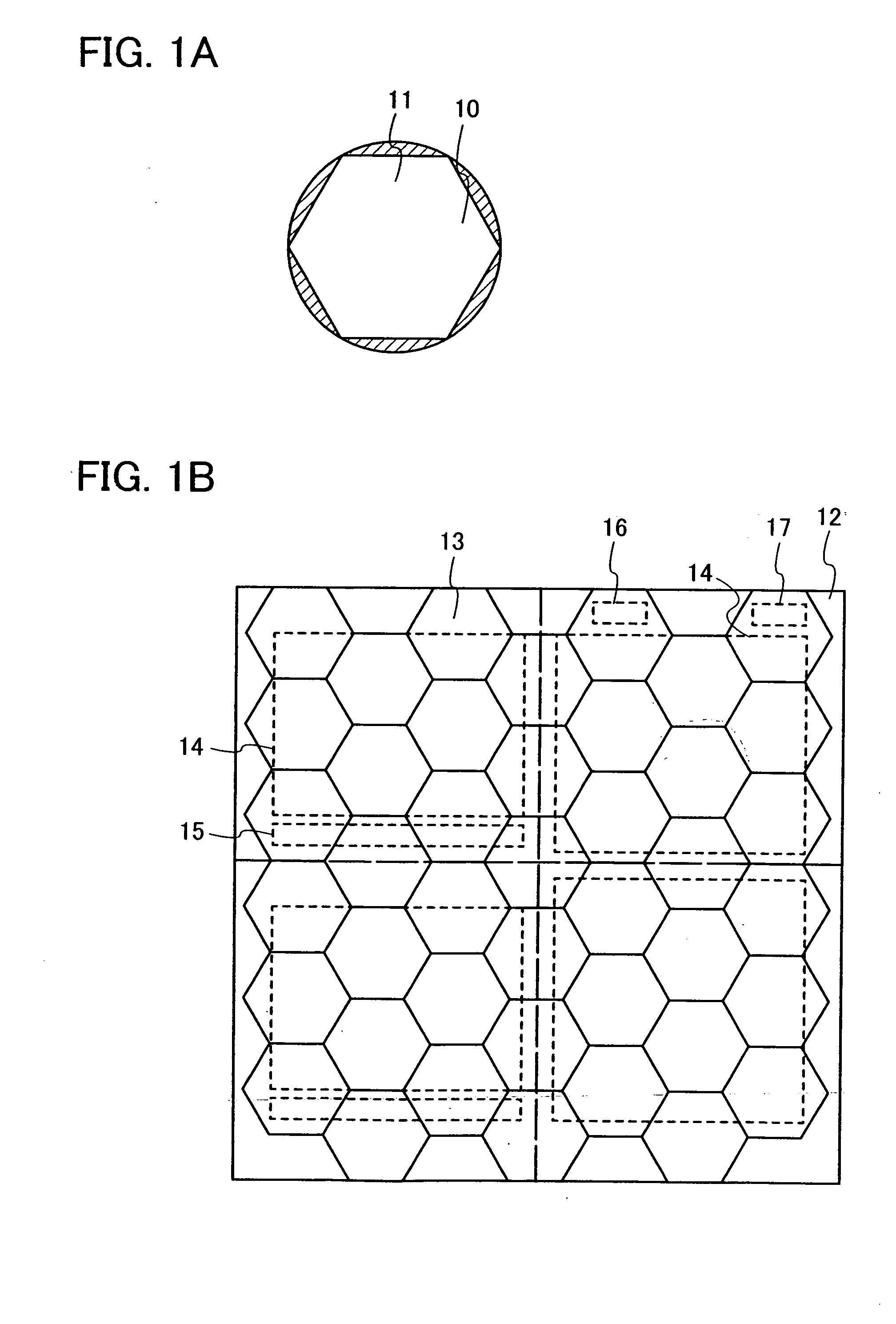

Heat treatment jig for silicon semiconductor substrate

ActiveUS20050282101A1Reduce generationDiminish surface stepCharge supportsSemiconductor/solid-state device manufacturingSurface roughnessSemiconductor

A heat treatment jig for supporting silicon semiconductor substrates by contacting, being loaded onto a heat treatment boat in a vertical heat treatment furnace, comprises; the configuration of a ring or a disc structure with the wall thickness between 1.5 and 6.0 mm; the deflection displacement of 100 μm or less at contact region in loaded condition; the outer diameter which is 65% or more of the diameter of said substrate; and the surface roughness (Ra) of between 1.0 and 100 μm at the contact region. The use of said jig enables to effectively retard the slip generation and to avoid the growth hindrance of thermally oxidized film at the back surface of said substrate, diminishing the surface steps causing the defocus in photolithography step in device fabrication process, thereby enabling to maintain high quality of silicon semiconductor substrates and to substantially enhance the device yield.

Owner:SUMITOMO MITSUBISHI SILICON CORP

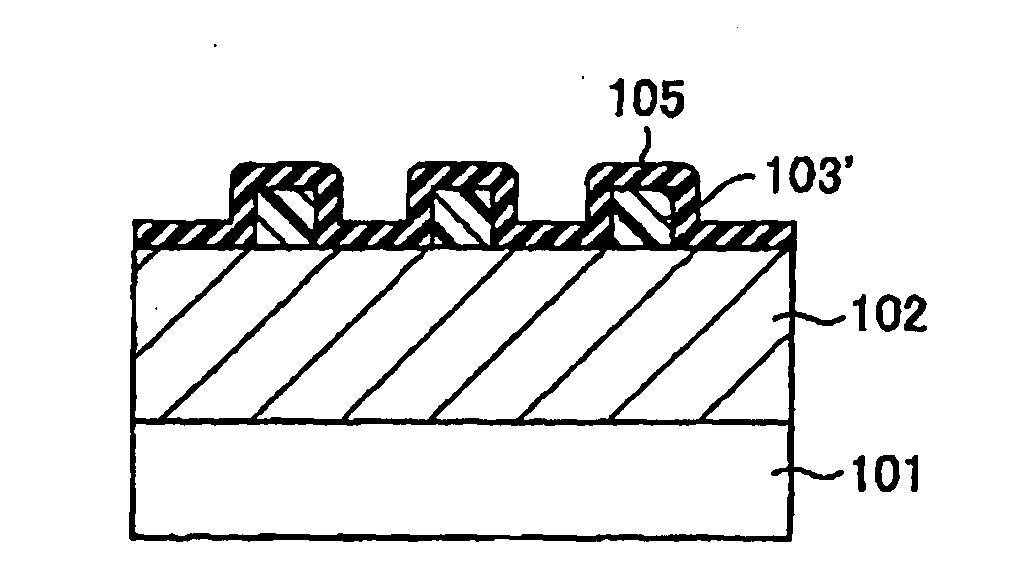

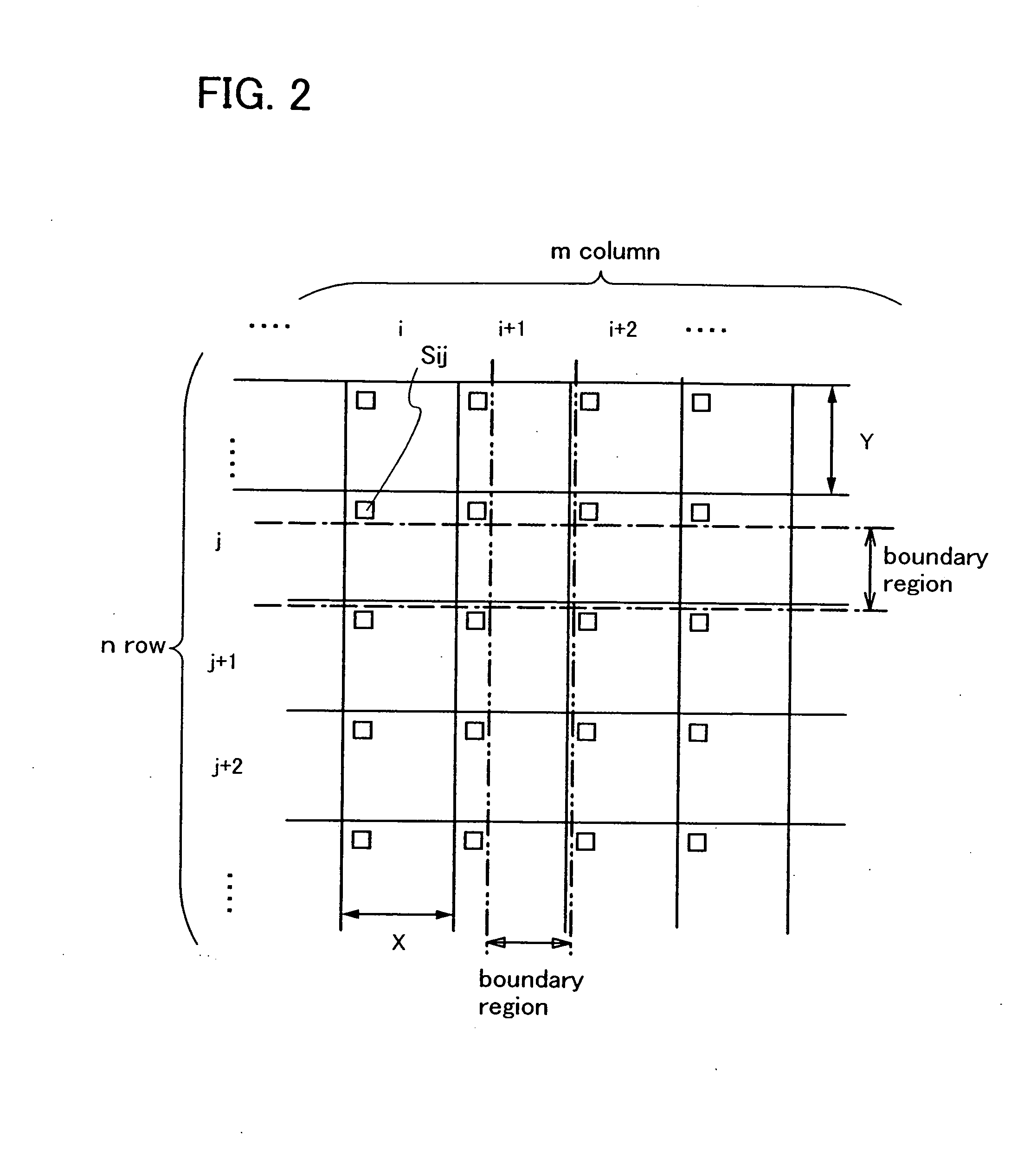

Chip and multi-chip semiconductor device using thereof and method for manufacturing same

InactiveUS7122912B2Improve alignment accuracyReduce the overall diameterSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

Owner:RENESAS ELECTRONICS CORP

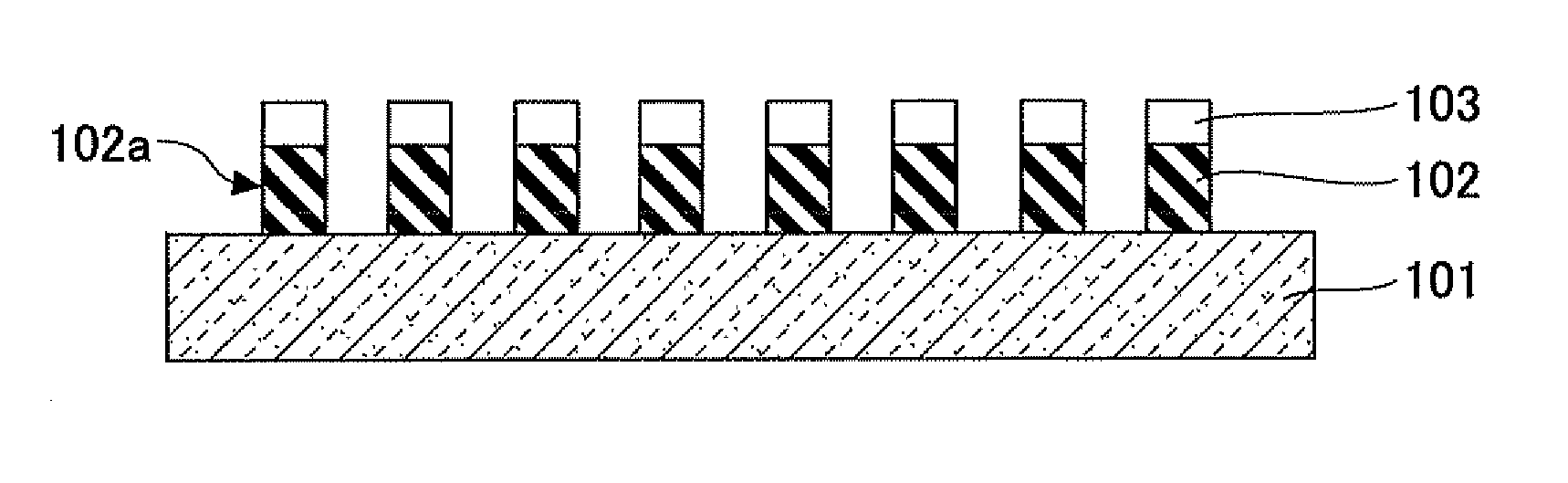

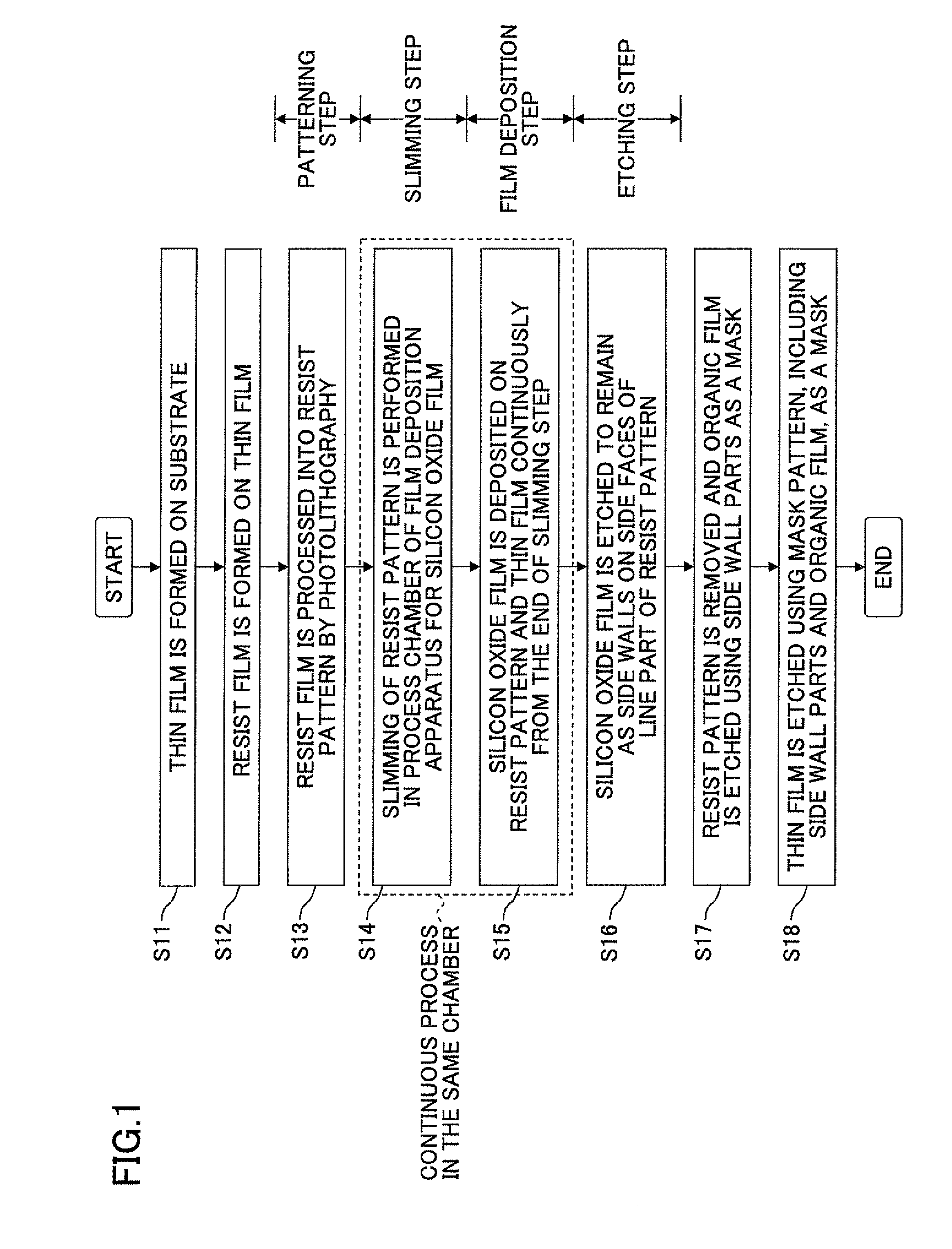

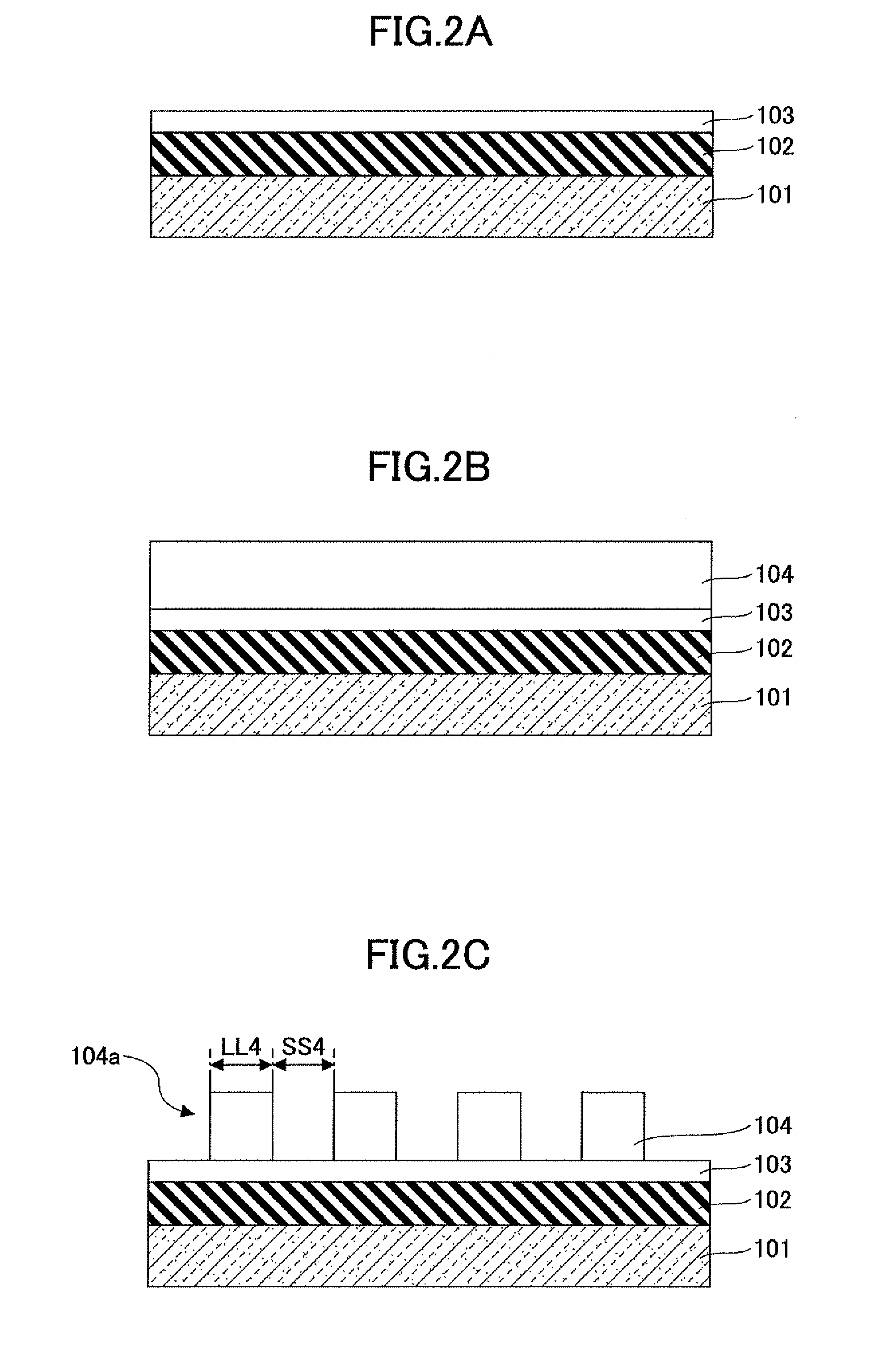

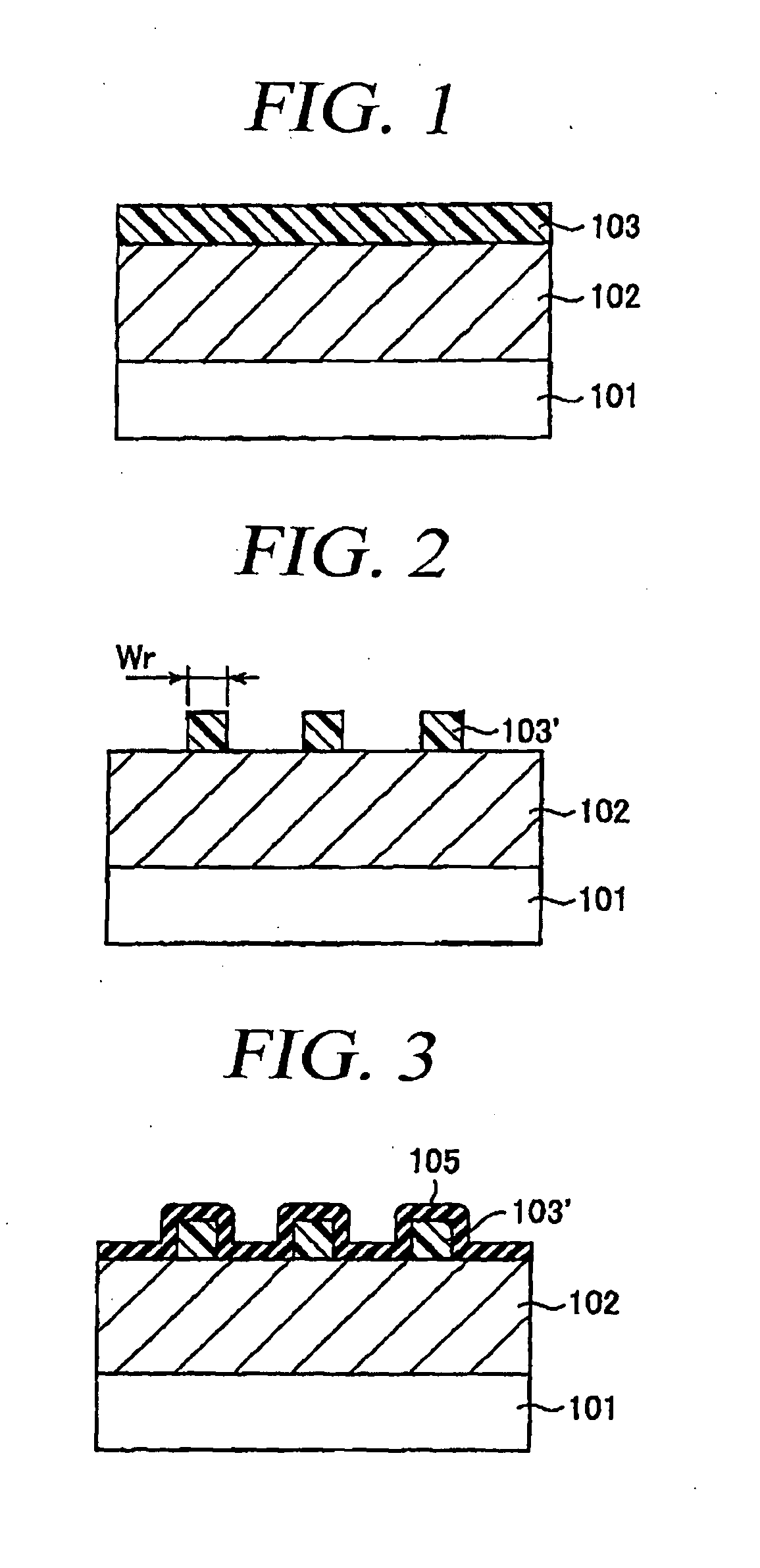

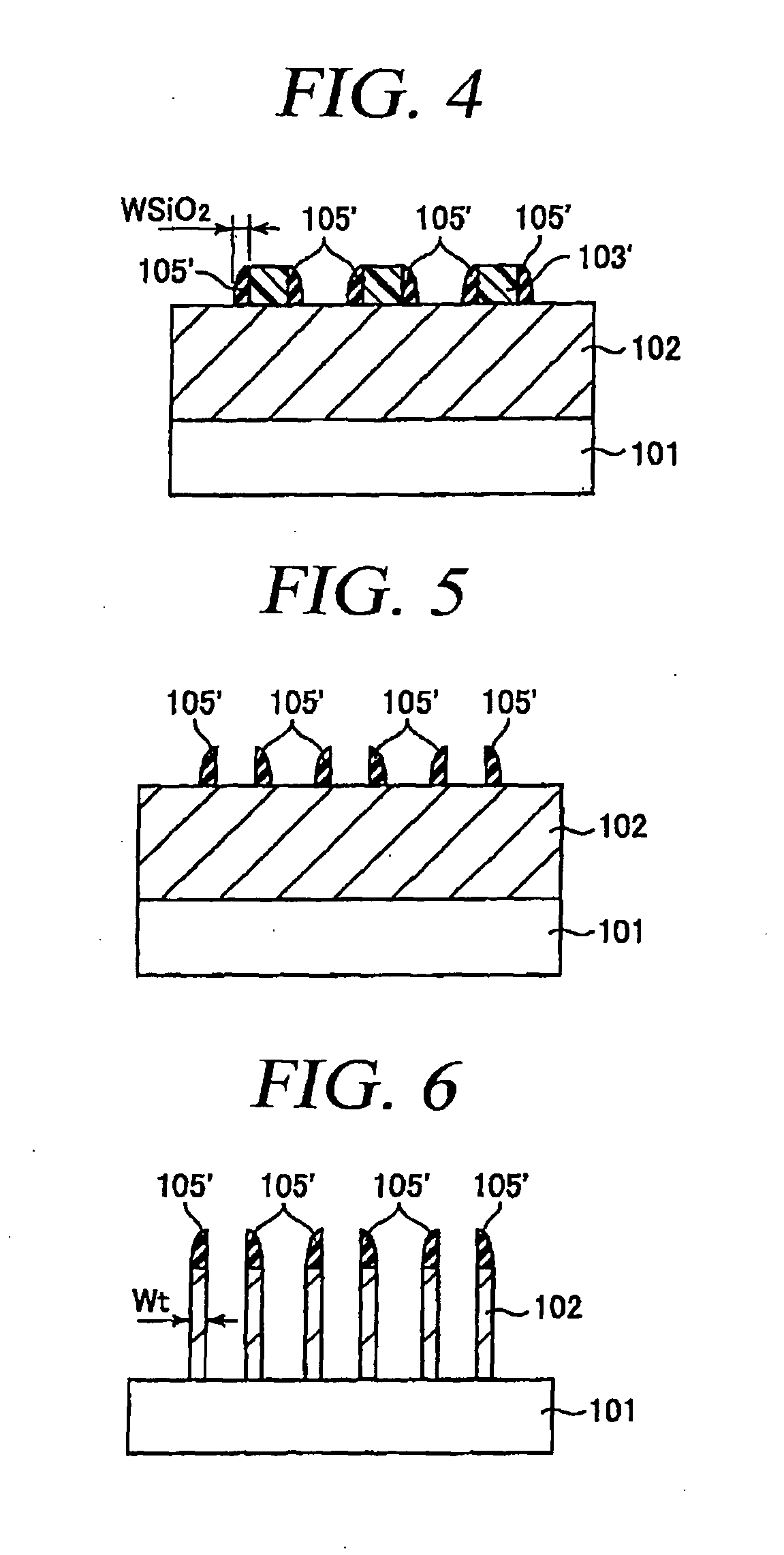

Mask pattern forming method, fine pattern forming method, and film deposition apparatus

ActiveUS20100081094A1Low costOptimizationElectric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

In a mask pattern forming method, a resist film is formed over a thin film, the resist film is processed into resist patterns having a predetermined pitch by photolithography, slimming of the resist patterns is performed, and an oxide film is formed on the thin film and the resist patterns after an end of the slimming step in a film deposition apparatus by supplying a source gas and an oxygen radical or an oxygen-containing gas. In the mask pattern forming method, the slimming and the oxide film forming are continuously performed in the film deposition apparatus.

Owner:TOKYO ELECTRON LTD

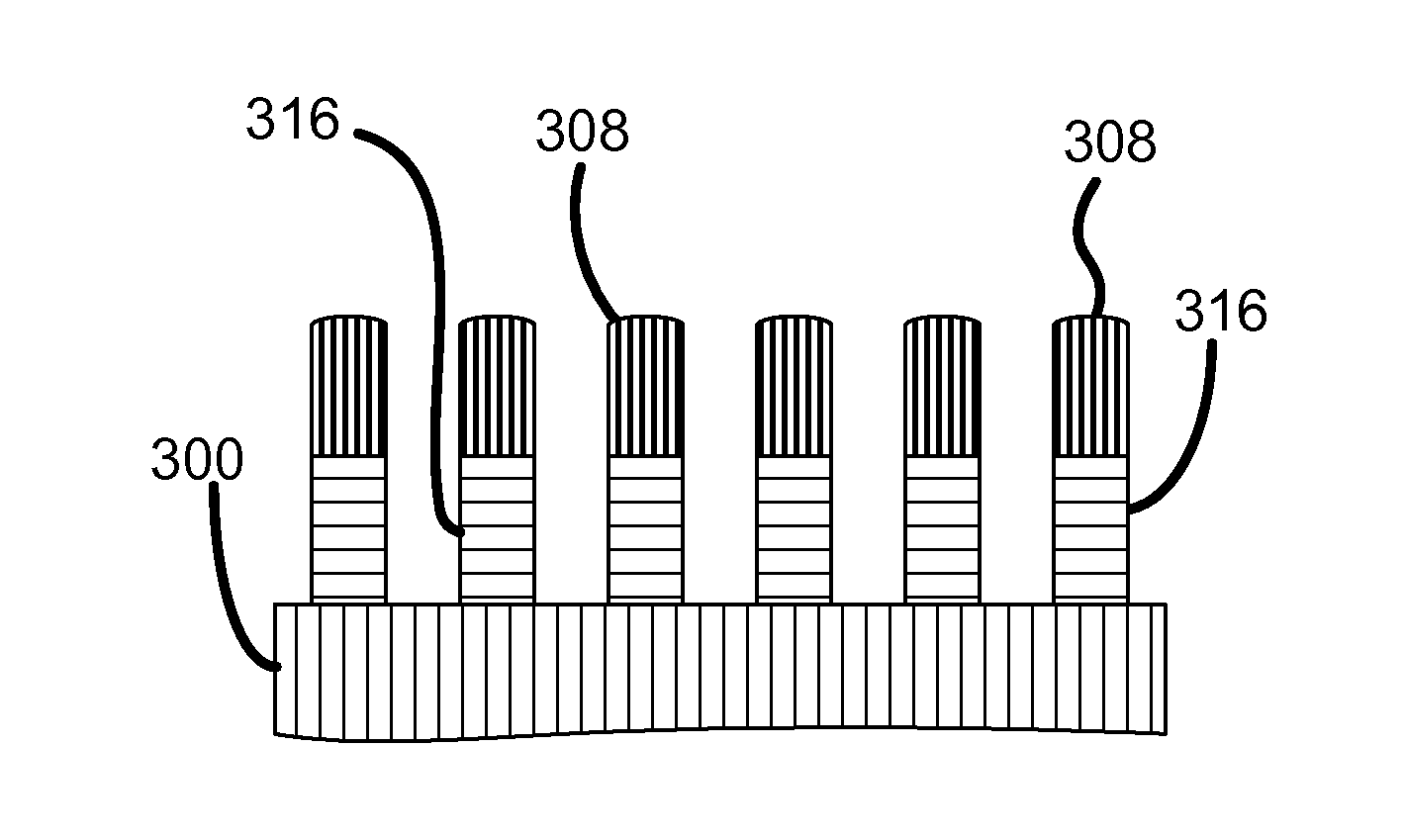

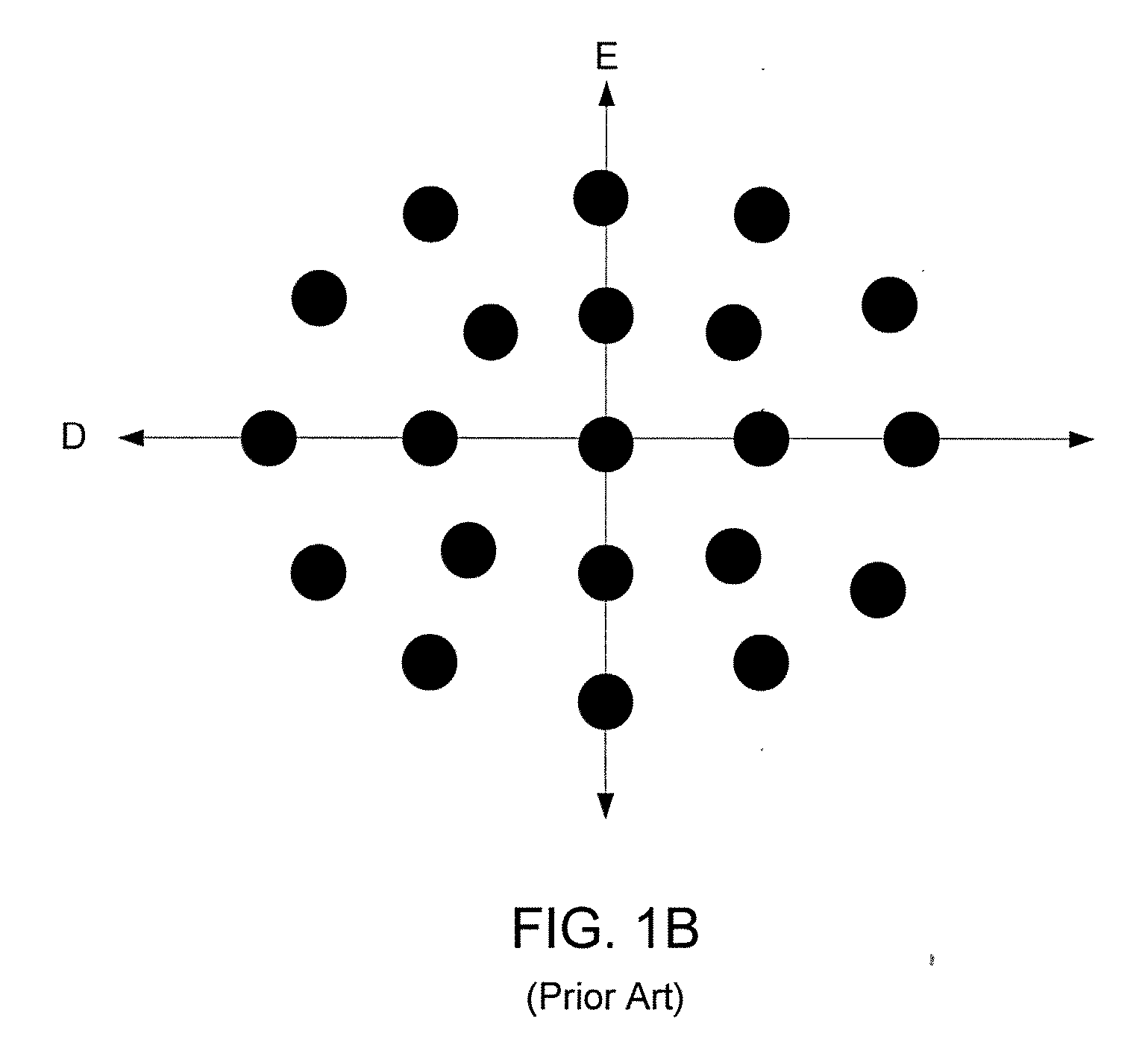

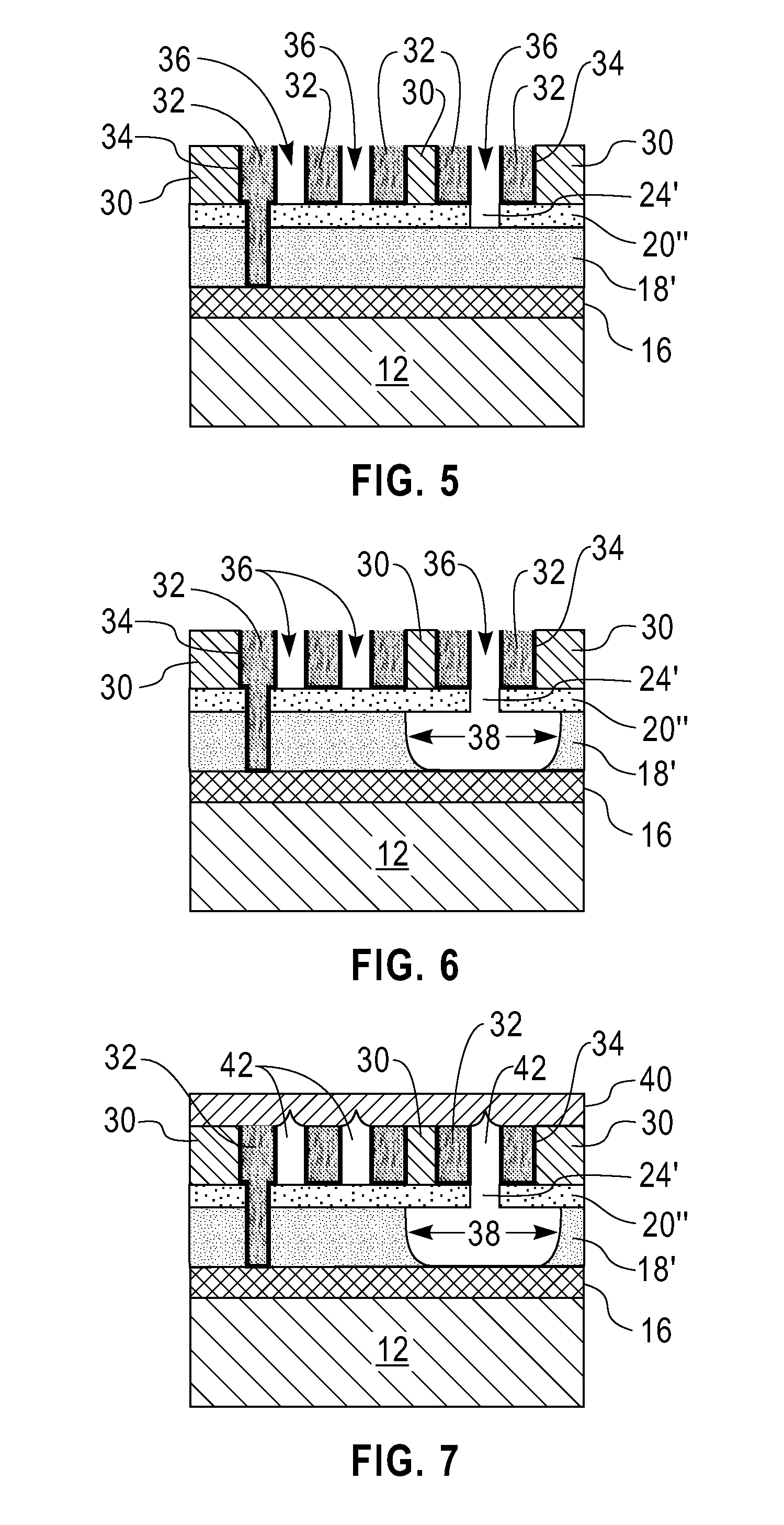

Methods for forming arrays of small, closely spaced features

Methods of forming arrays of small, densely spaced holes or pillars for use in integrated circuits are disclosed. Various pattern transfer and etching steps can be used, in combination with pitch-reduction techniques, to create densely-packed features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form superimposed patterns of crossing elongate features with pillars at the intersections. Spacers are simultaneously applied to sidewalls of both sets of crossing lines to produce a pitch-doubled grid pattern. The pillars facilitate rows of spacers bridging columns of spacers.

Owner:MICRON TECH INC

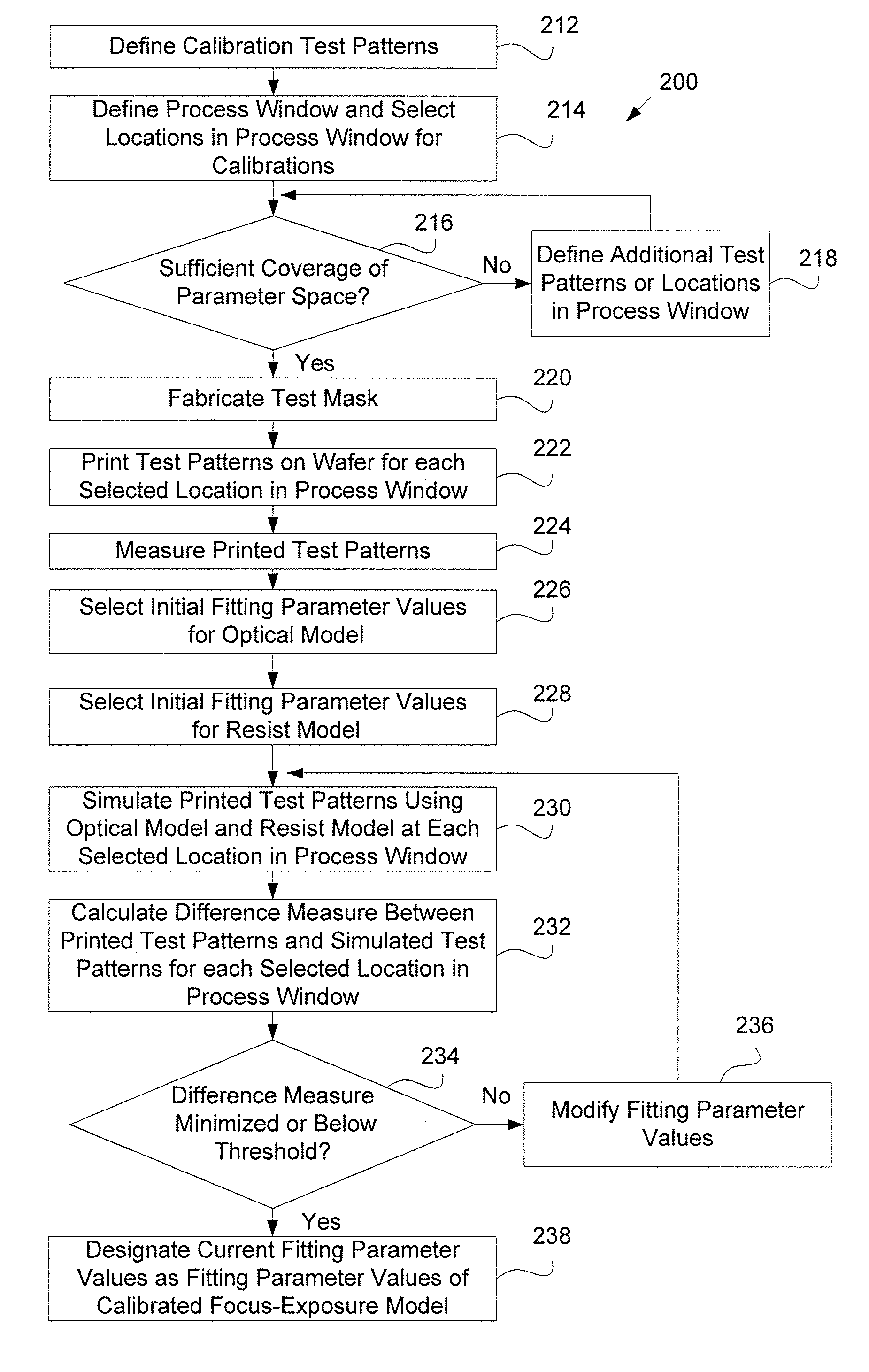

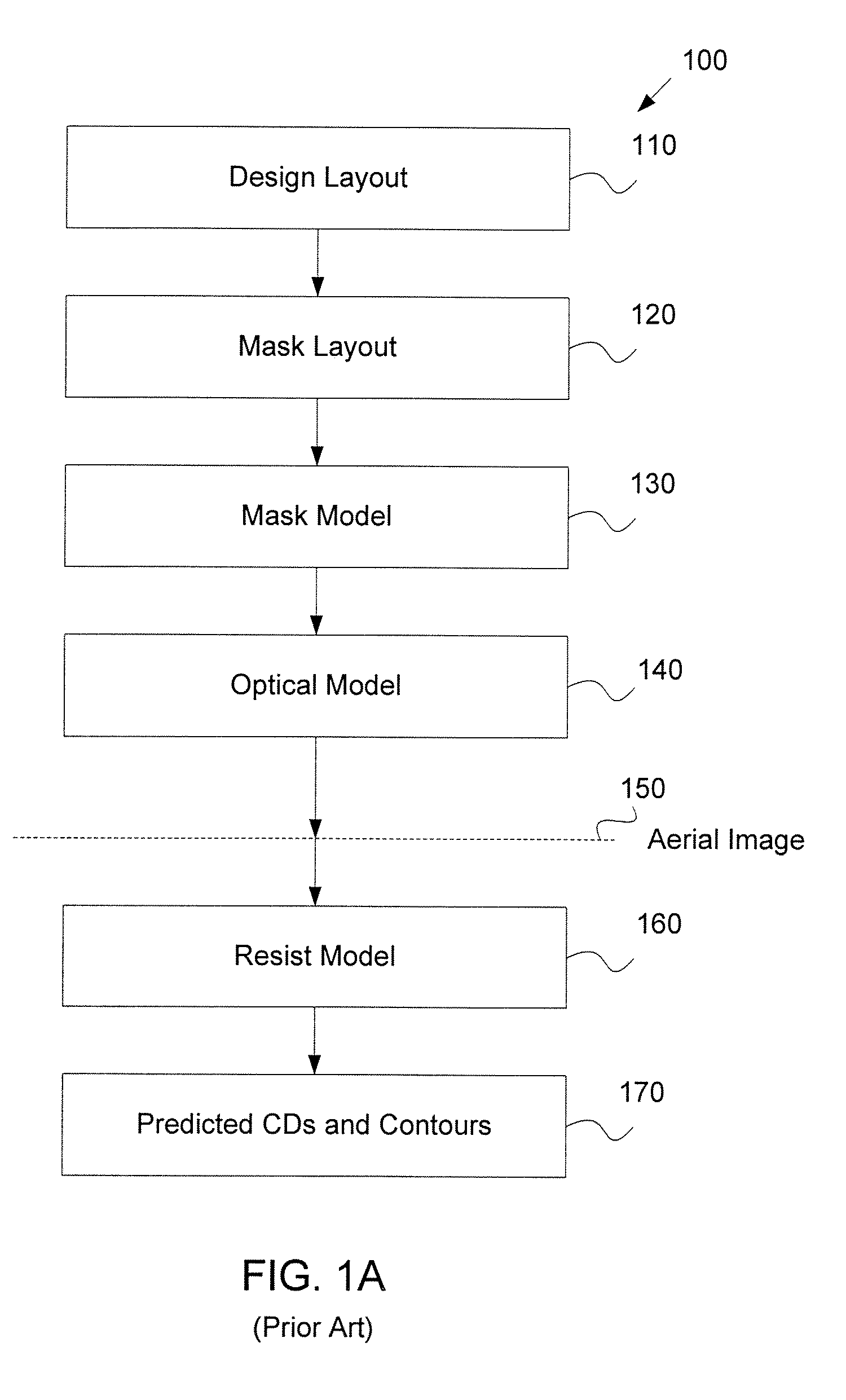

System and method for creating a focus-exposure model of a lithography process

ActiveUS20070031745A1Good accuracy and robustnessPhotomechanical apparatusOriginals for photomechanical treatmentLithography processAlgorithm

A system and a method for creating a focus-exposure model of a lithography process are disclosed. The system and the method utilize calibration data along multiple dimensions of parameter variations, in particular within an exposure-defocus process window space. The system and the method provide a unified set of model parameter values that result in better accuracy and robustness of simulations at nominal process conditions, as well as the ability to predict lithographic performance at any point continuously throughout a complete process window area without a need for recalibration at different settings. With a smaller number of measurements required than the prior-art multiple-model calibration, the focus-exposure model provides more predictive and more robust model parameter values that can be used at any location in the process window.

Owner:ASML NETHERLANDS BV

Heat treatment jig for silicon semiconductor substrate

ActiveUS7210925B2Reduce generationGenerated with easeCharge supportsSemiconductor/solid-state device manufacturingSurface roughnessSilicon

A heat treatment jig for supporting silicon semiconductor substrates by contacting, being loaded onto a heat treatment boat in a vertical heat treatment furnace, comprises; the configuration of a ring or a disc structure with the wall thickness between 1.5 and 6.0 mm; the deflection displacement of 100 μm or less at contact region in loaded condition; the outer diameter which is 65% or more of the diameter of said substrate; and the surface roughness (Ra) of between 1.0 and 100 μm at the contact region. The use of said jig enables to effectively retard the slip generation and to avoid the growth hindrance of thermally oxidized film at the back surface of said substrate, diminishing the surface steps causing the defocus in photolithography step in device fabrication process, thereby enabling to maintain high quality of silicon semiconductor substrates and to substantially enhance the device yield.

Owner:SUMITOMO MITSUBISHI SILICON CORP

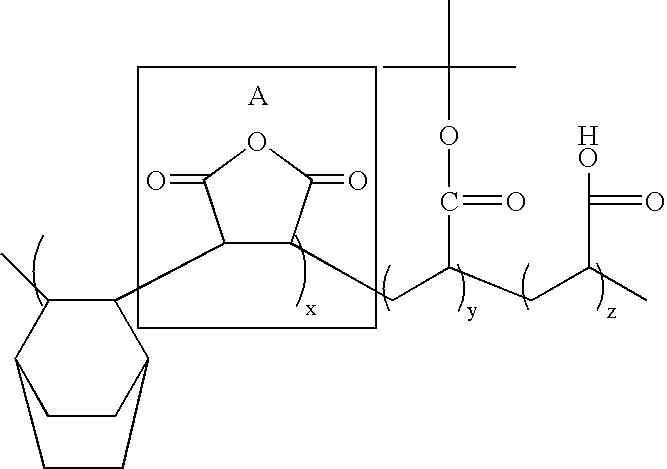

Photoresist monomers, polymers and photoresist compositions for preventing acid diffusion

Photoresist monomers, polymers thereof, photoresist compositions containing the same for preventing acid generated in the exposed area during the course of a photolithography process from being diffused to the unexposed area. The line edge roughness and slope pattern are improved when an ultrafine photoresist pattern is formed using photoresist copolymer having a multi-oxygen-containing compound as a repeating unit such as an ethyleneoxy moiety represented by Formula 1 with at least one polymerizable carbon-carbon double bond. In addition, the shape of pattern is improved by eliminating top loss and the adhesion of pattern to the substrate is improved. wherein n is an integer ranging from 1 to 5.

Owner:SK HYNIX INC +1

Patterning method

ActiveUS20100112496A1Photosensitive materialsSemiconductor/solid-state device manufacturingResistSilicon oxide

Owner:TOKYO ELECTRON LTD

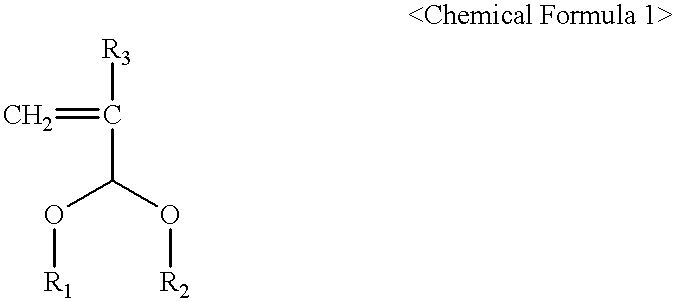

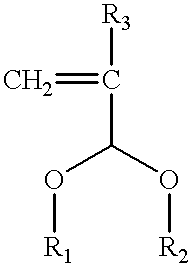

Photoresist cross-linker and photoresist composition comprising the same

InactiveUS6368773B1Enhance the imageAdequate resultOrganic chemistryPhotosensitive materialsCarboxylic acidKetone

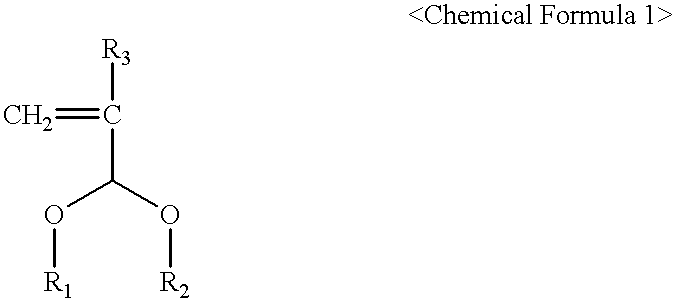

The present invention relates to a cross-linker for photoresist compositions which is suitable for a photolithography process using KrF (248 mn), ArF (193 mn), E-beam, ion beam or EUV light sources. Preferred cross-linkers, according to the present invention, comprise a copolymer of (i) a compound represented by following Chemical Formula 1 and / or (ii) one or more compound(s) selected from the group consisting of acrylic acid, methacrylic acid and maleic anhydride. ##STR1## wherein, R.sub.1 and R.sub.2 individually represent straight or branched C.sub.1-10 alkyl, straight or branched C.sub.1-10 ester, straight or branched C.sub.1-10 ketone, straight or branched C.sub.1-10 carboxylic acid, straight or branched C.sub.1-10 acetal, straight or branched C.sub.1-10 alkyl including at least one hydroxyl group, straight or branched C.sub.1-10 ester including at least one hydroxyl group, straight or branched C.sub.1-10 ketone including at least one hydroxyl group, straight or branched C.sub.1-10 carboxylic acid including at least one hydroxyl group, and straight or branched C.sub.1-10 acetal including at least one hydroxyl group; and R.sub.3 represents hydrogen or methyl.

Owner:HYUNDAI ELECTRONICS IND CO LTD

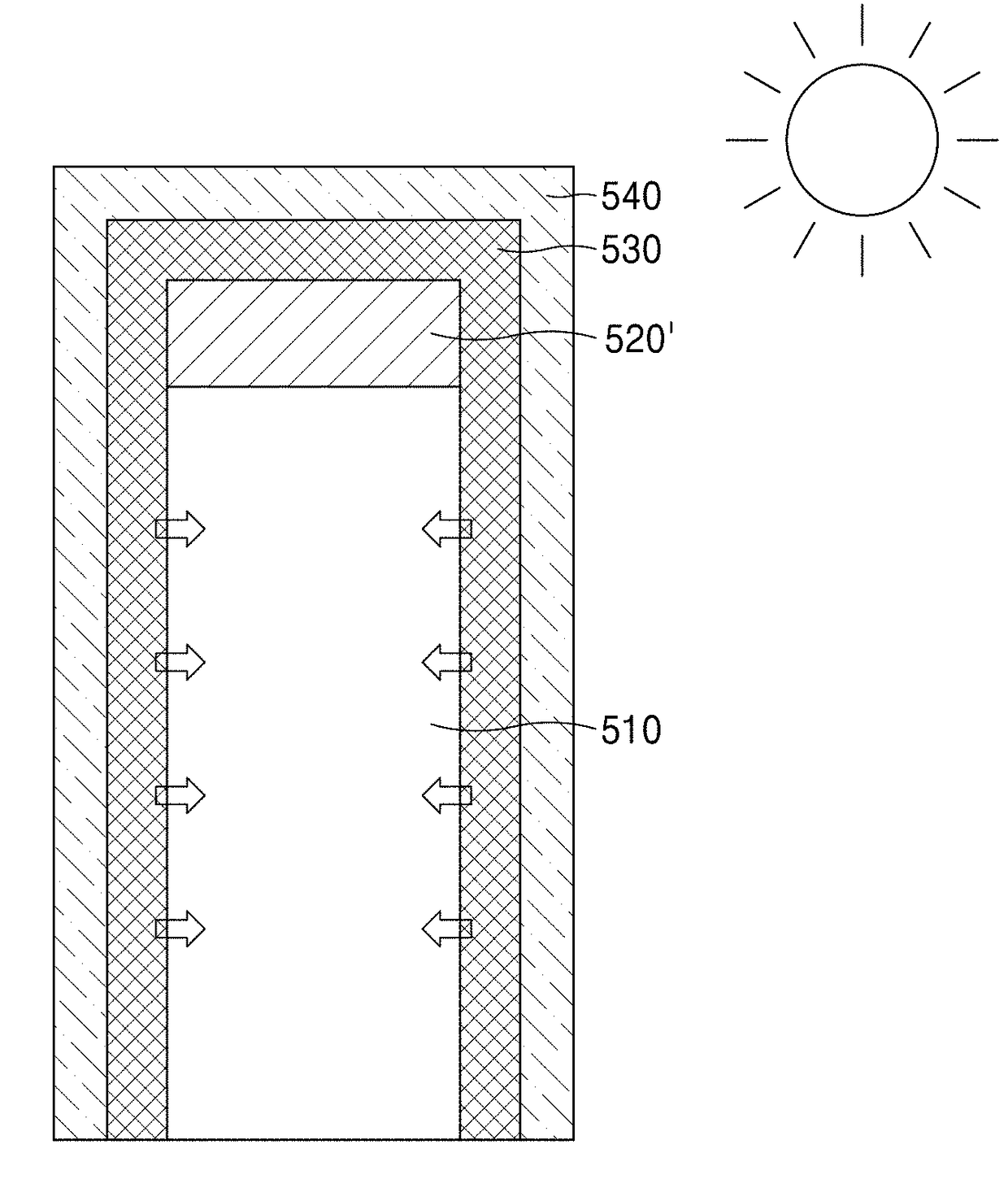

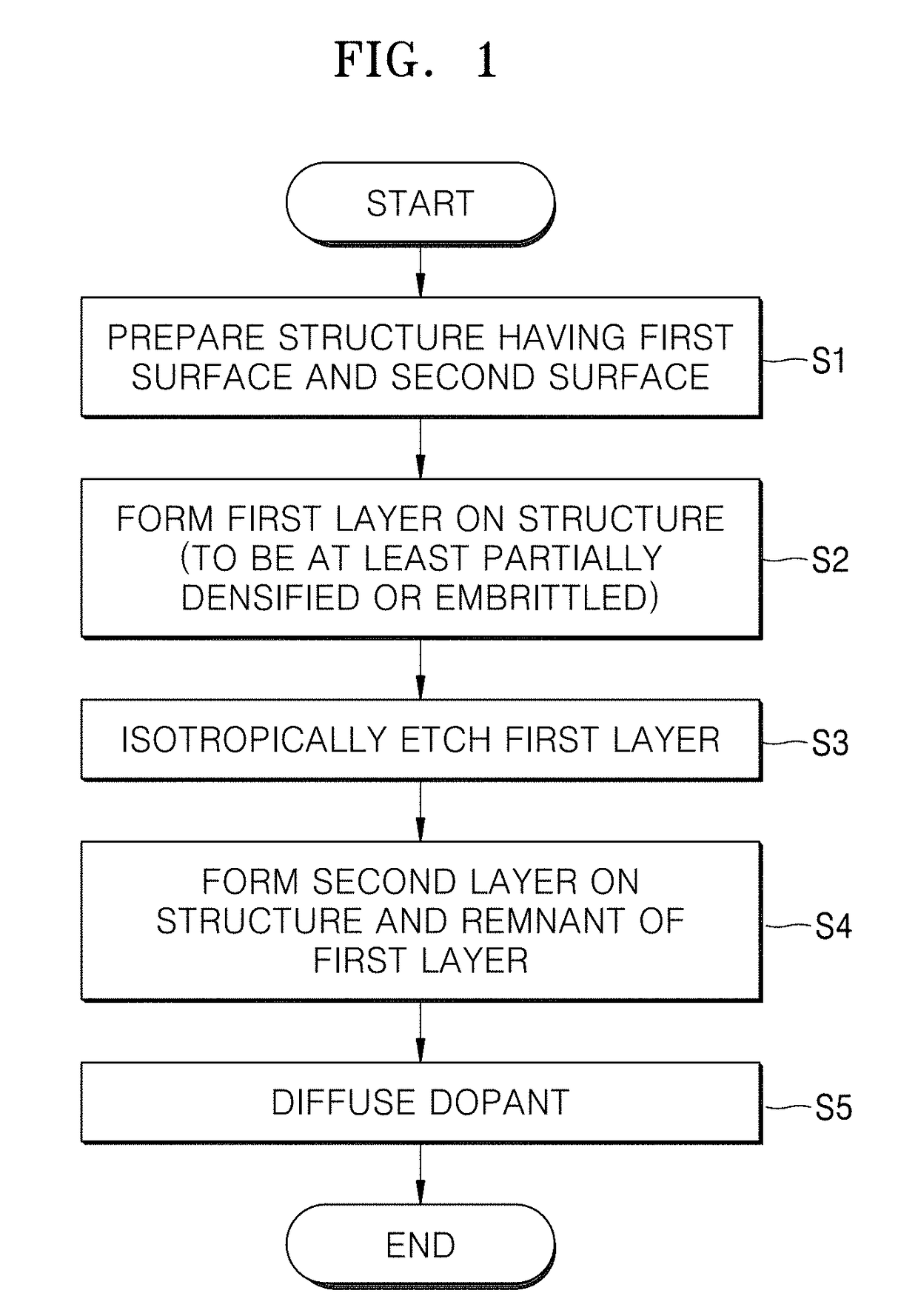

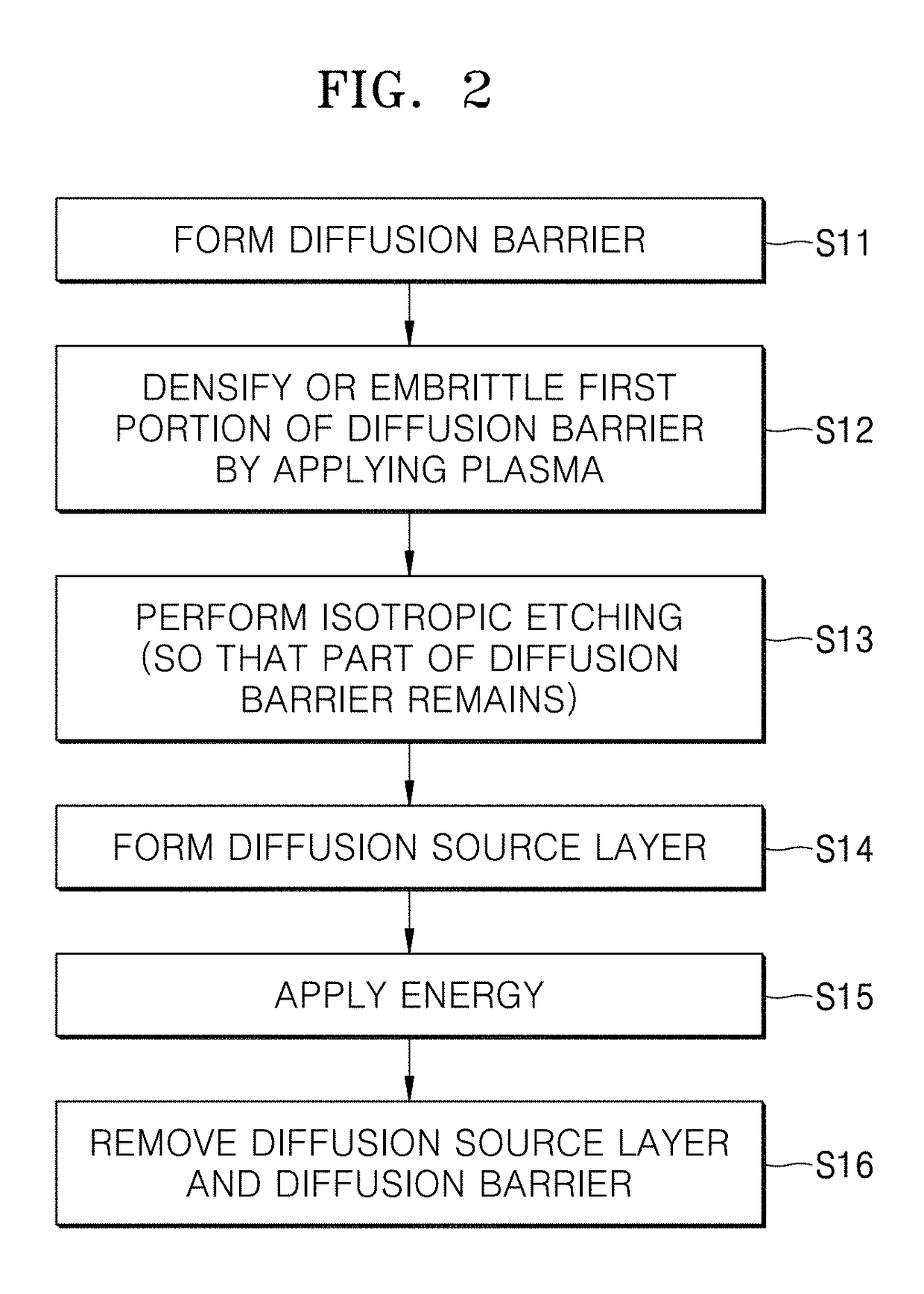

Method of processing substrate

A method of processing a substrate to enable selective doping without a photolithography process is provided. The method includes forming a diffusion barrier on the substrate having a patterned structure using plasma deposition method, removing the diffusion barrier except for part of the diffusion barrier using wet etching, forming a diffusion source layer on the patterned structure and the part of the diffusion barrier, and applying energy to the diffusion source layer.

Owner:ASM IP HLDG BV

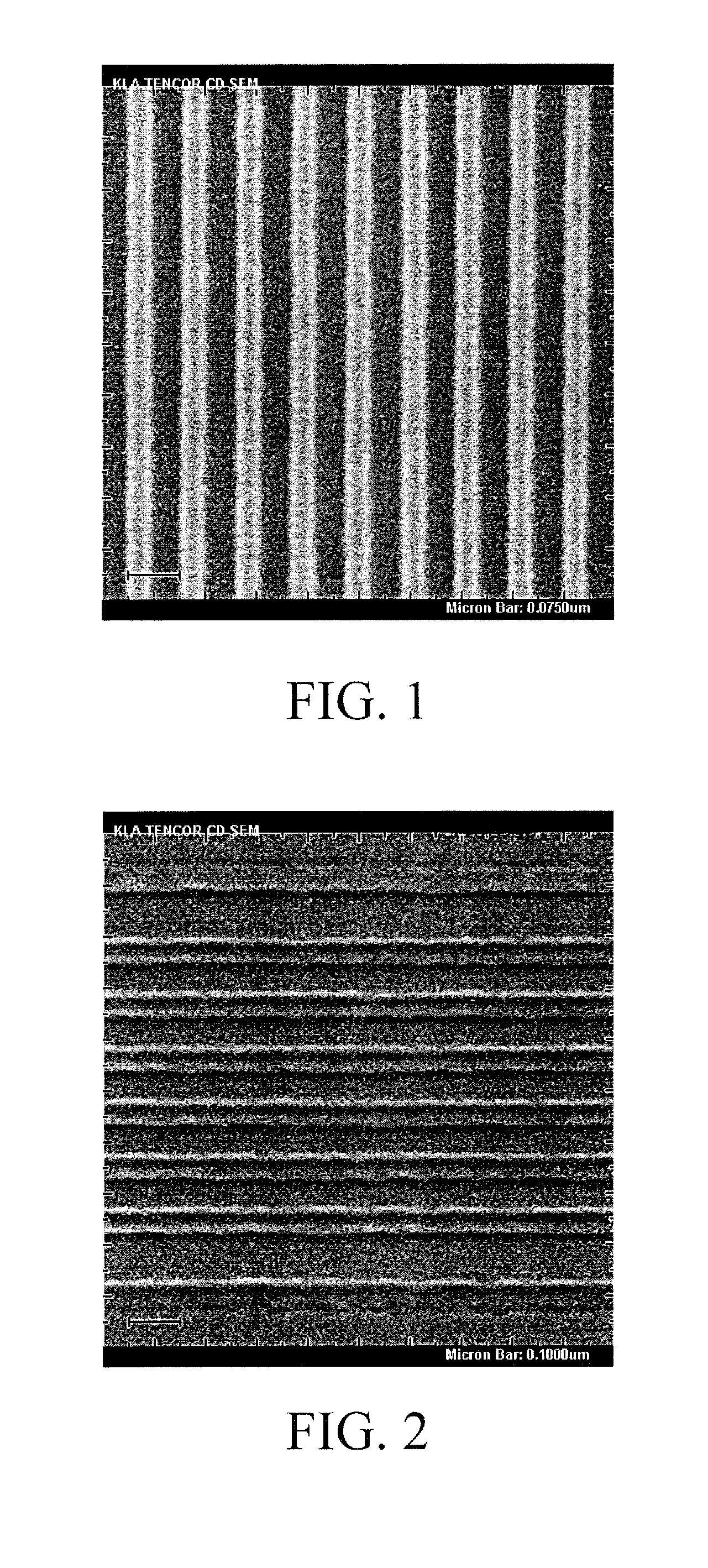

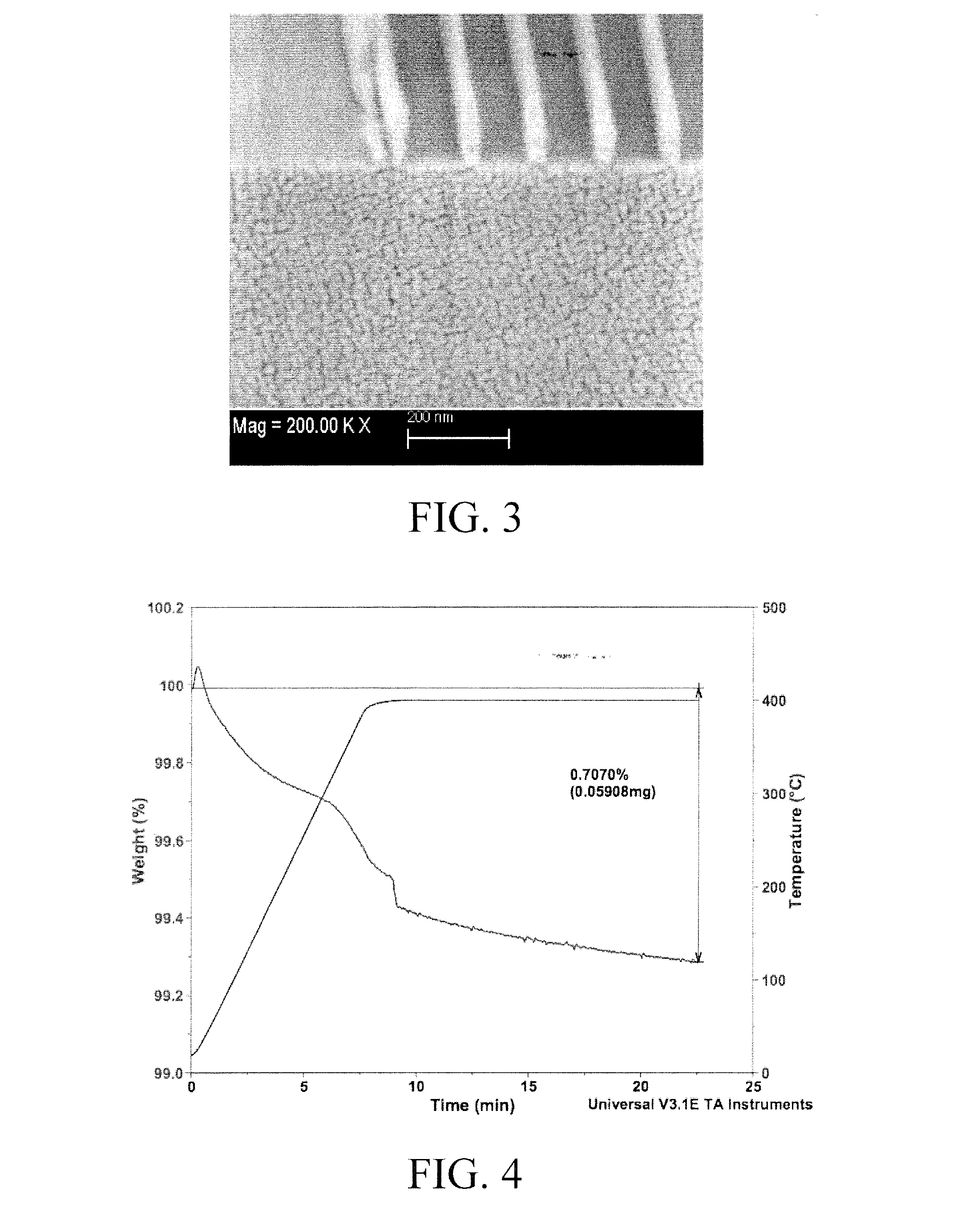

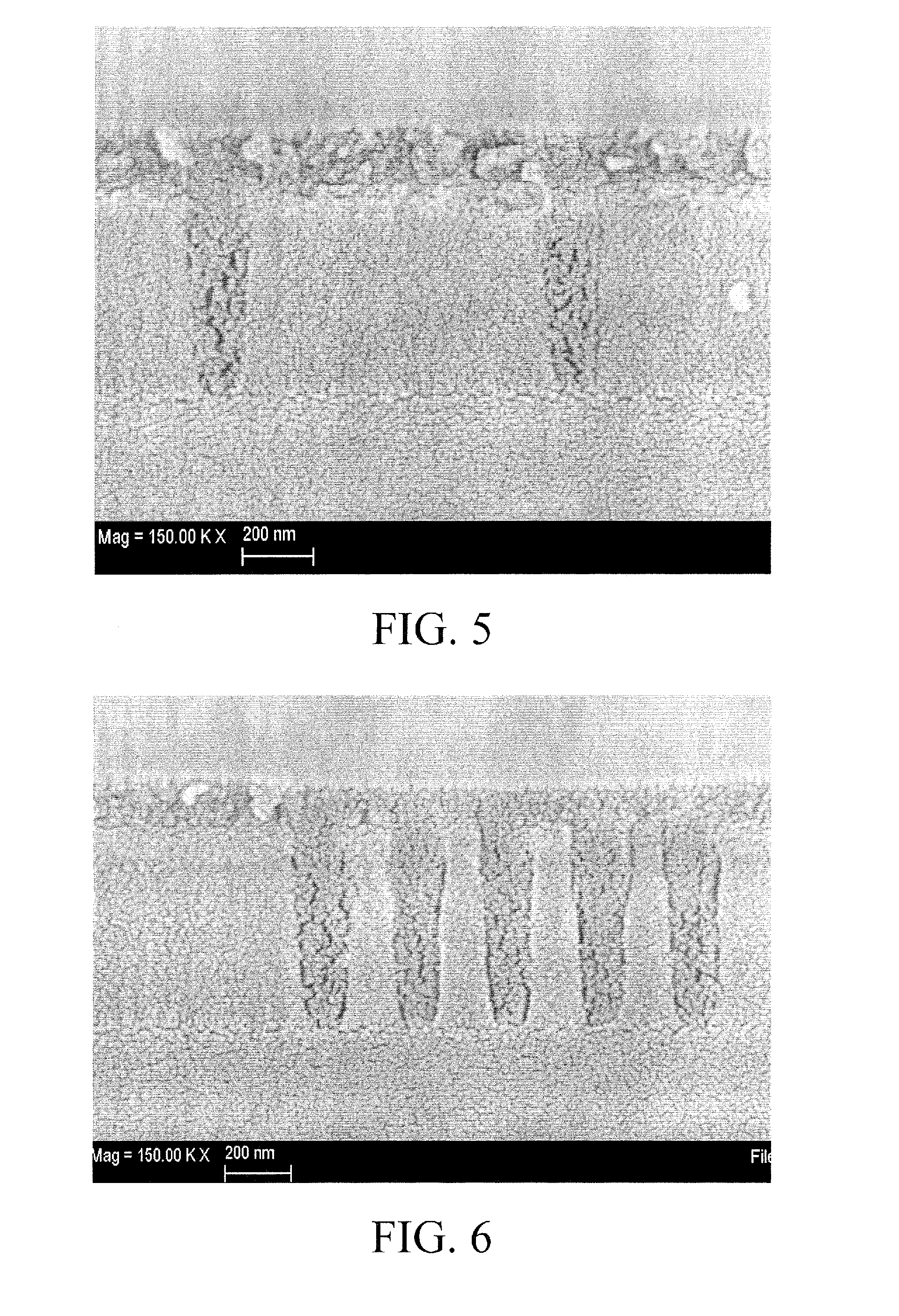

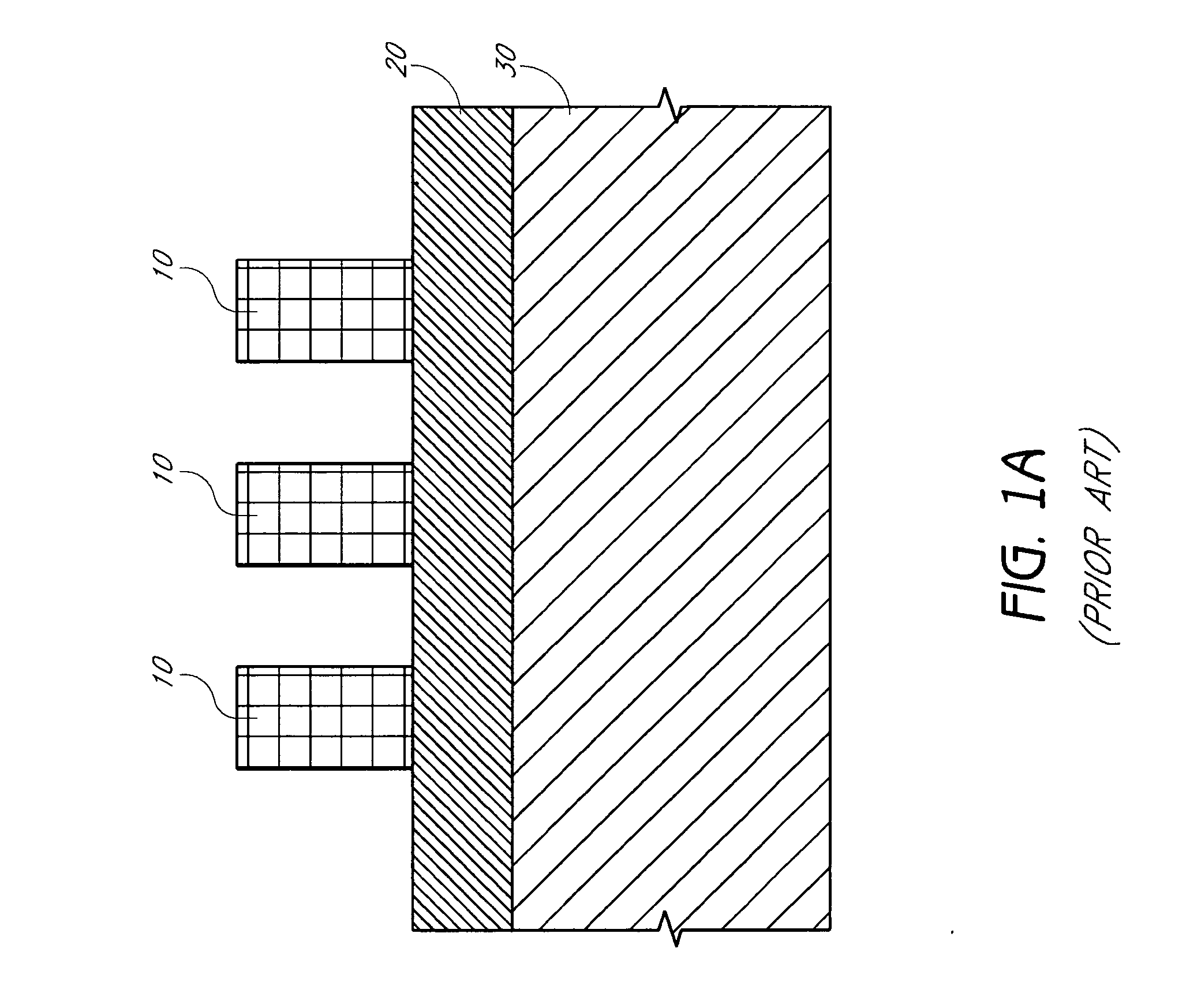

Spin-on carbon compositions for lithographic processing

The invention described herein is directed towards spin-on carbon materials comprising polyamic acid compositions and a crosslinker in a solvent system. The materials are useful in trilayer photolithography processes. Films made with the inventive compositions are not soluble in solvents commonly used in lithographic materials, such as, but not limited to PGME, PGMEA, and cyclohexanone. However, the films can be dissolved in developers commonly used in photolithography. In one embodiment, the films can be heated at high temperatures to improve the thermal stability for high temperature processing. Regardless of the embodiment, the material can be applied to a flat / planar or patterned surface. Advantageously, the material exhibits a wiggling resistance during pattern transfer to silicon substrate using fluorocarbon etch.

Owner:BREWER SCI

Methods for forming arrays of a small, closely spaced features

ActiveUS20060263699A1Solid-state devicesSemiconductor/solid-state device manufacturingCombined useEngineering

Methods of forming arrays of small, densely spaced holes or pillars for use in integrated circuits are disclosed. Various pattern transfer and etching steps can be used, in combination with pitch-reduction techniques, to create densely-packed features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form sumperimposed, pitch-reduced patterns of crossing elongate features that can be consolidated into a single layer.

Owner:MICRON TECH INC

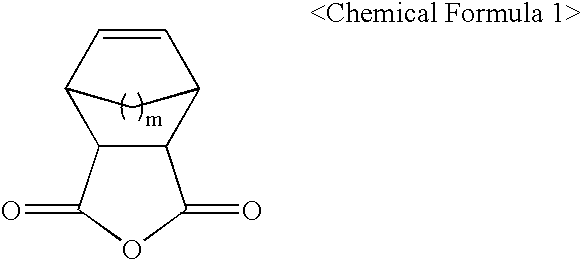

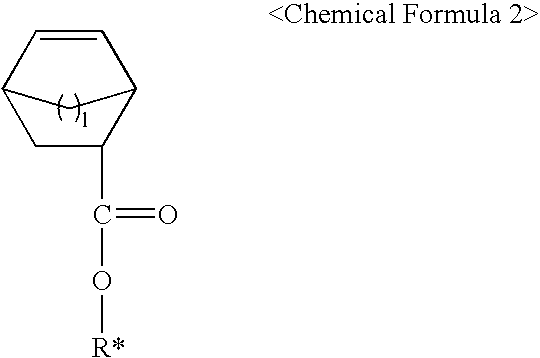

Polymers for photoresist and photoresist compositions using the same

InactiveUS6987155B2Improve the immunityExcellent etching resistance and adhesiveness and photosensitivityElectric discharge tubesPhotomechanical exposure apparatusResistX-ray

The present invention relates to photoresist monomers, polymers formed therefrom and photoresist compositions suitable for photolithography processes employing a DUV light source, such as KrF (249 nm) and ArF(193 nm); EUV; VUV; E-beam; ion-beam; and X-ray. Photoresist monomers of the present invention are represented by the following Chemical Formula 1: wherein, m is 1 or 2.Polymers of the present invention comprise repeating units derived from the comonomer of Chemical Formula 1, preferably together with monomers of the following Chemical Formula 2: wherein,R* is an acid-labile group, andl is 1 or 2.

Owner:HYUNDAI ELECTRONICS IND CO LTD

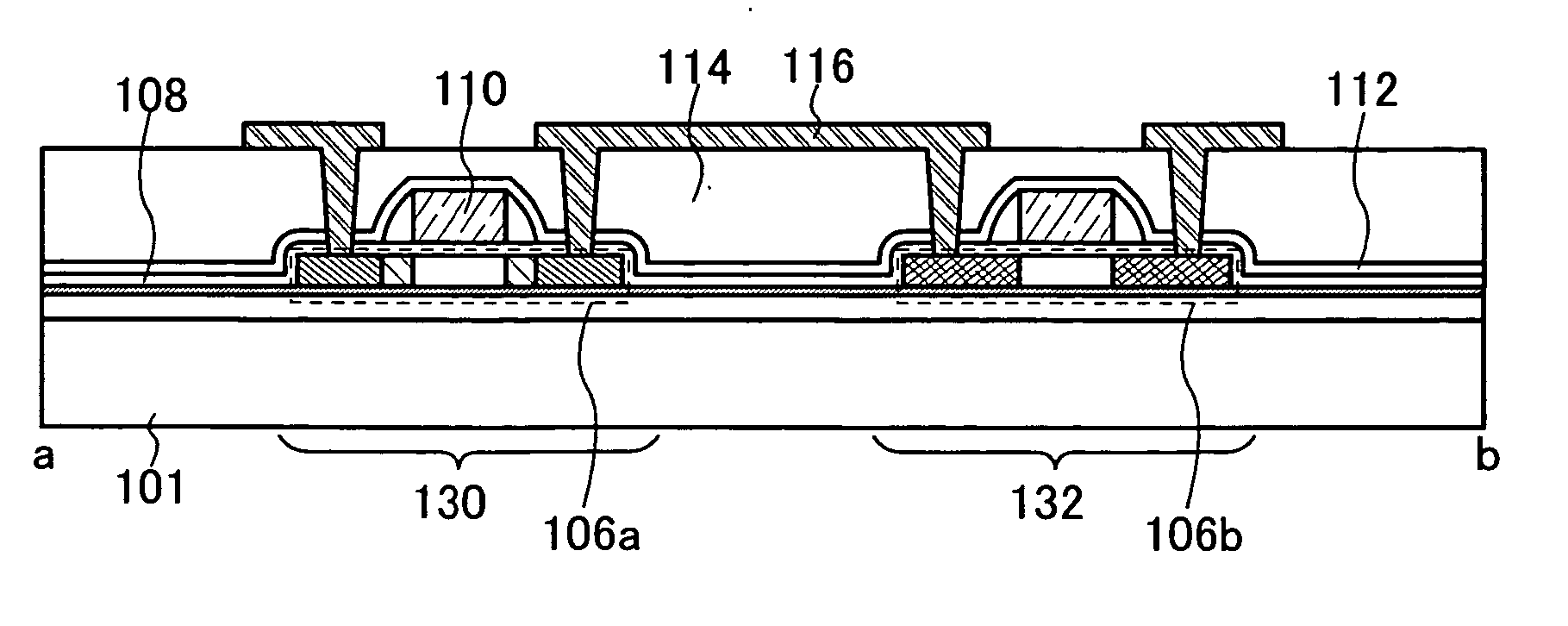

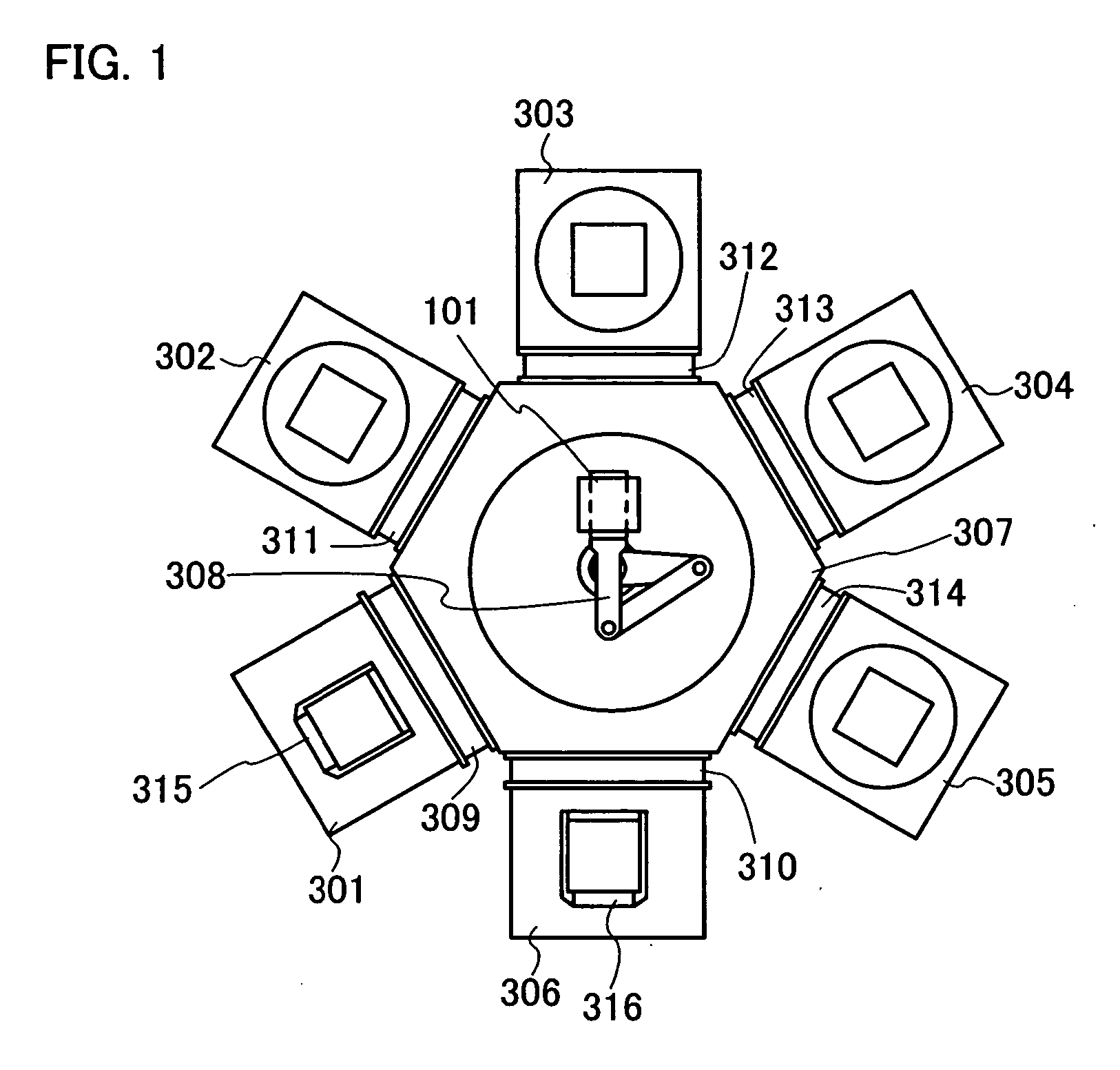

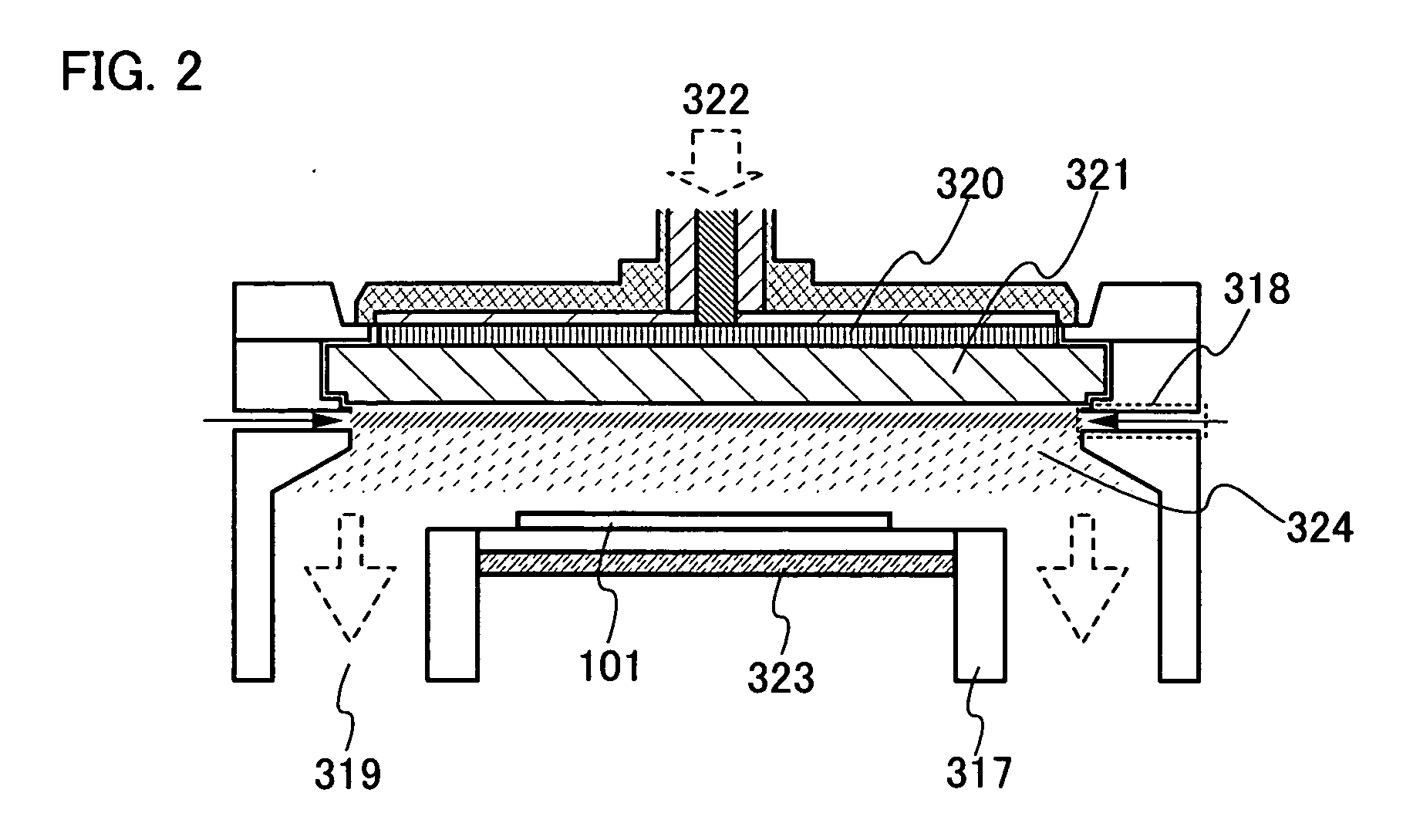

Semiconductor device and manufacturing method thereof

InactiveUS20060275710A1Reduce light intensityImprove routing densitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialContinuous wave laser beam

To provide a semiconductor device having a circuit with high operating performance and high reliability, and improve the reliability of the semiconductor device, thereby improving the reliability of an electronic device having the same. The aforementioned object is achieved by combining a step of crystallizing a semiconductor layer by irradiation with continuous wave laser beams or pulsed laser beams with a repetition rate of 10 MHz or more, while scanning in one direction; a step of photolithography with the use of a photomask or a leticle including an auxiliary pattern which is formed of a diffraction grating pattern or a semi-transmissive film having a function of reducing the light intensity; and a step of performing oxidation, nitridation, or surface-modification to the surface of the semiconductor film, an insulating film, or a conductive film, with high-density plasma with a low electron temperature.

Owner:SEMICON ENERGY LAB CO LTD

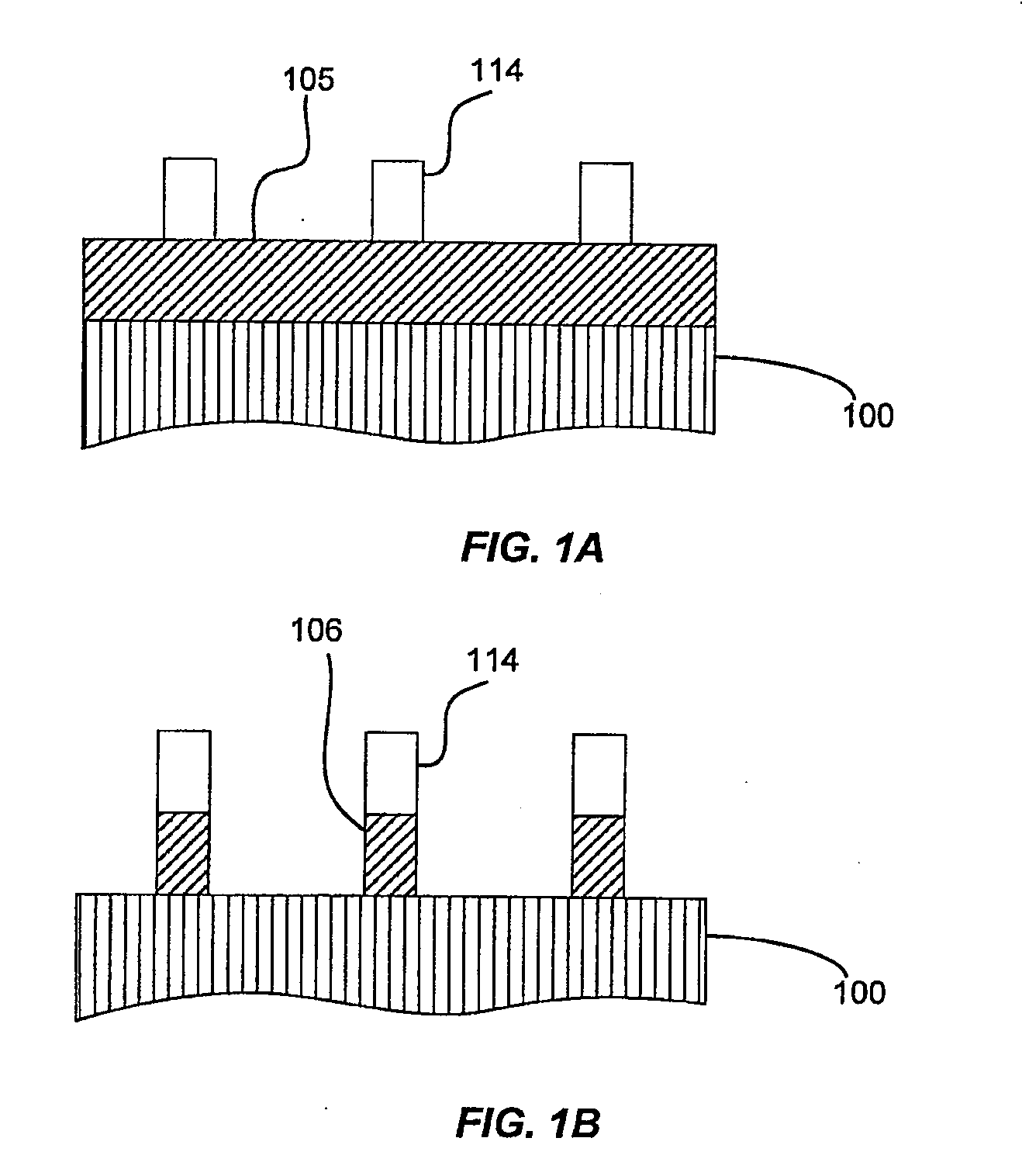

Method to align mask patterns

Alignment tolerances between narrow mask lines, for forming interconnects in the array region of an integrated circuit, and wider mask lines, for forming interconnects in the periphery of the integrated circuit, are increased. The narrow mask lines are formed by pitch multiplication and the wider mask lines are formed by photolithography. The wider mask lines and are aligned so that one side of those lines is flush with or inset from a corresponding side of the narrow lines. Being wider, the opposite sides of the wider mask lines protrude beyond the corresponding opposite sides of the narrow mask lines. The wider mask lines are formed in negative photoresist having a height less than the height of the narrow mask lines. Advantageously, the narrow mask lines can prevent expansion of the mask lines in one direction, thus increasing alignment tolerances in that direction. In the other direction, use of photolithography and a shadowing effect caused by the relative heights of the photoresist and the narrow mask lines causes the wider mask lines to be formed with a rounded corner, thus increasing alignment tolerances in that direction by increasing the distance to a neighboring narrow mask line.

Owner:MICRON TECH INC

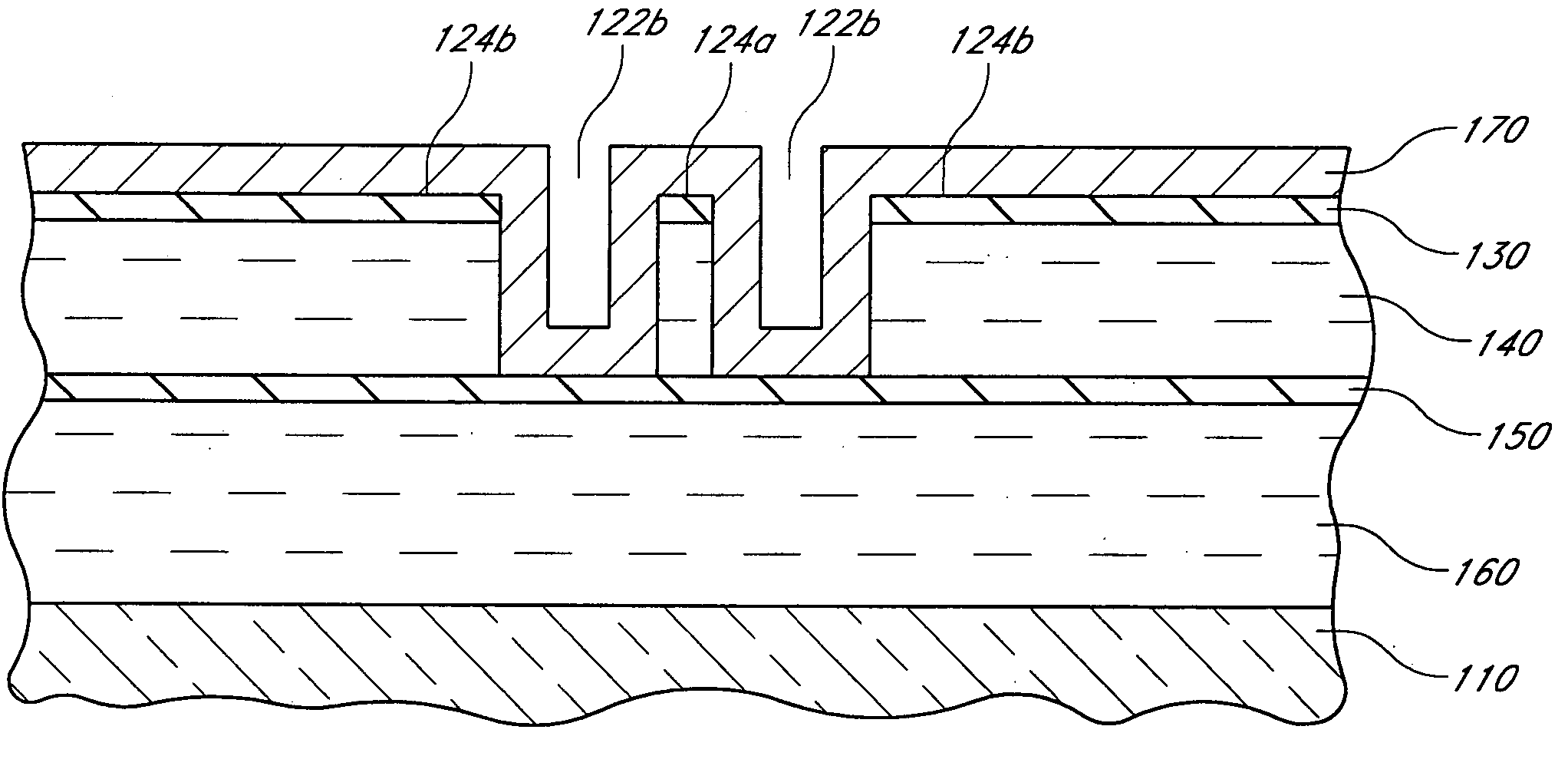

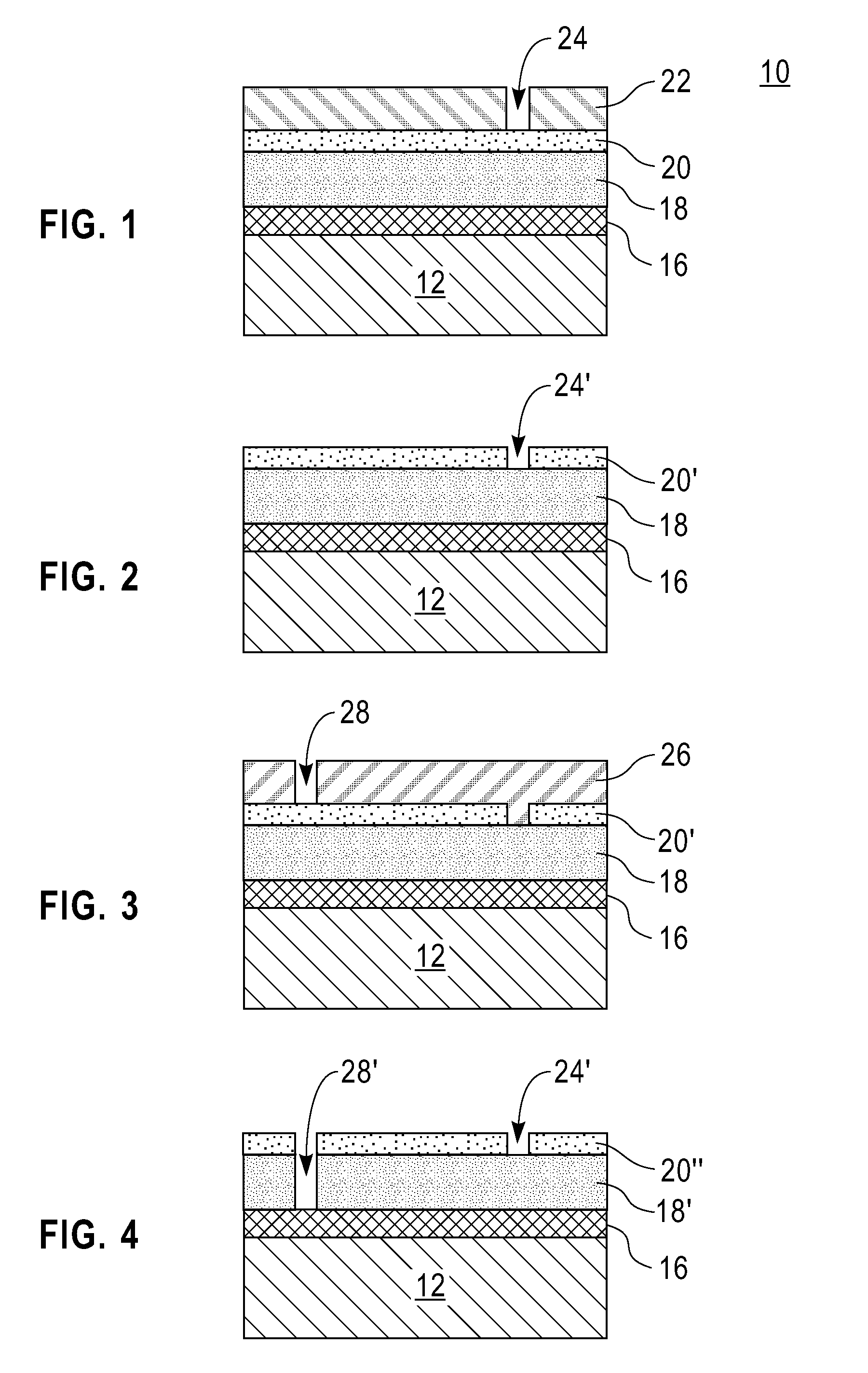

Method for air gap interconnect integration using photo-patternable low k material

ActiveUS8241992B2Stable structureSemiconductor/solid-state device detailsSolid-state devicesMetal insulatorPhotolithography

Methods for producing air gap-containing metal-insulator interconnect structures for VLSI and ULSI devices using a photo-patternable low k material as well as the air gap-containing interconnect structure that is formed are disclosed. More particularly, the methods described herein provide interconnect structures built in a photo-patternable low k material in which air gaps are defined by photolithography in the photo-patternable low k material. In the methods of the present invention, no etch step is required to form the air gaps. Since no etch step is required in forming the air gaps within the photo-patternable low k material, the methods disclosed in this invention provide highly reliable interconnect structures.

Owner:ALSEPHINA INNOVATIONS INC

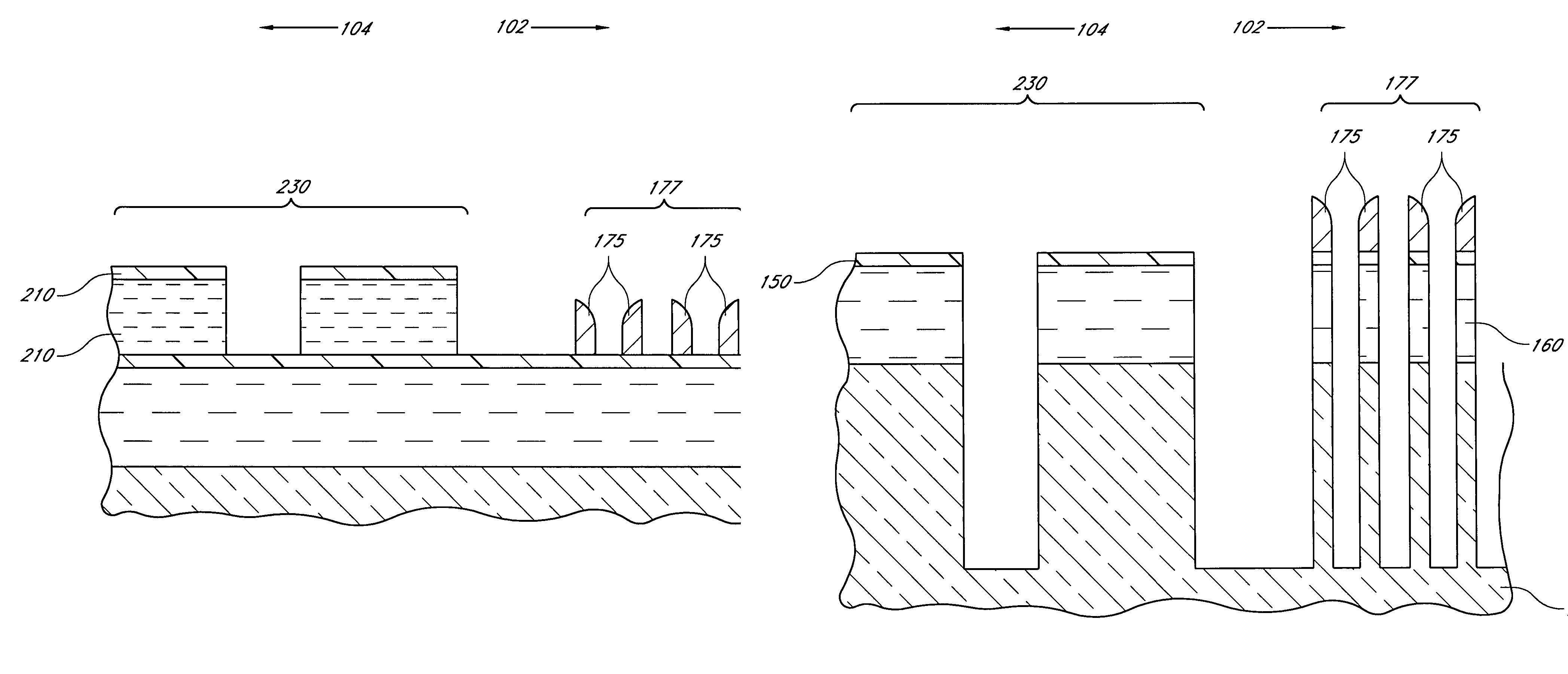

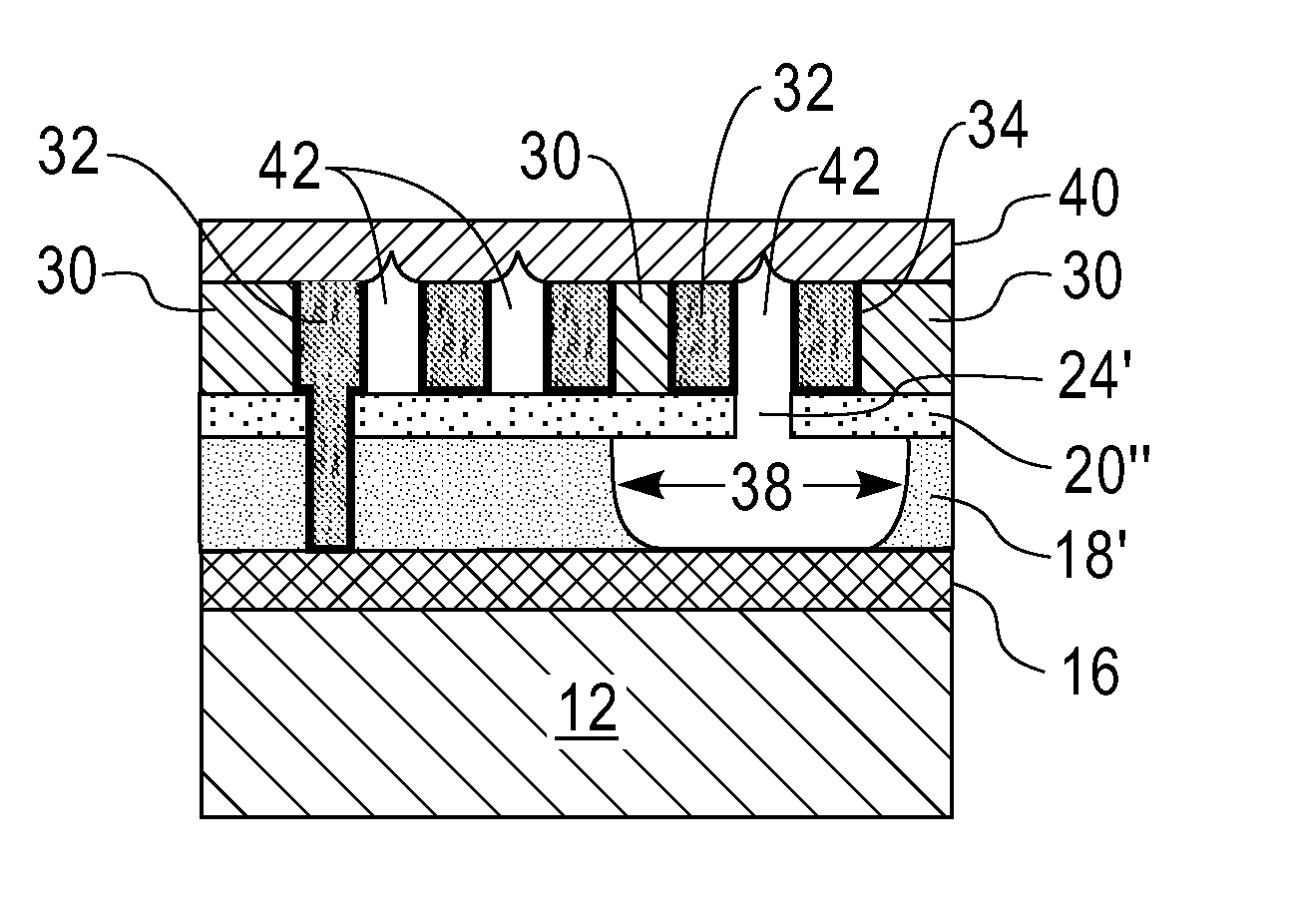

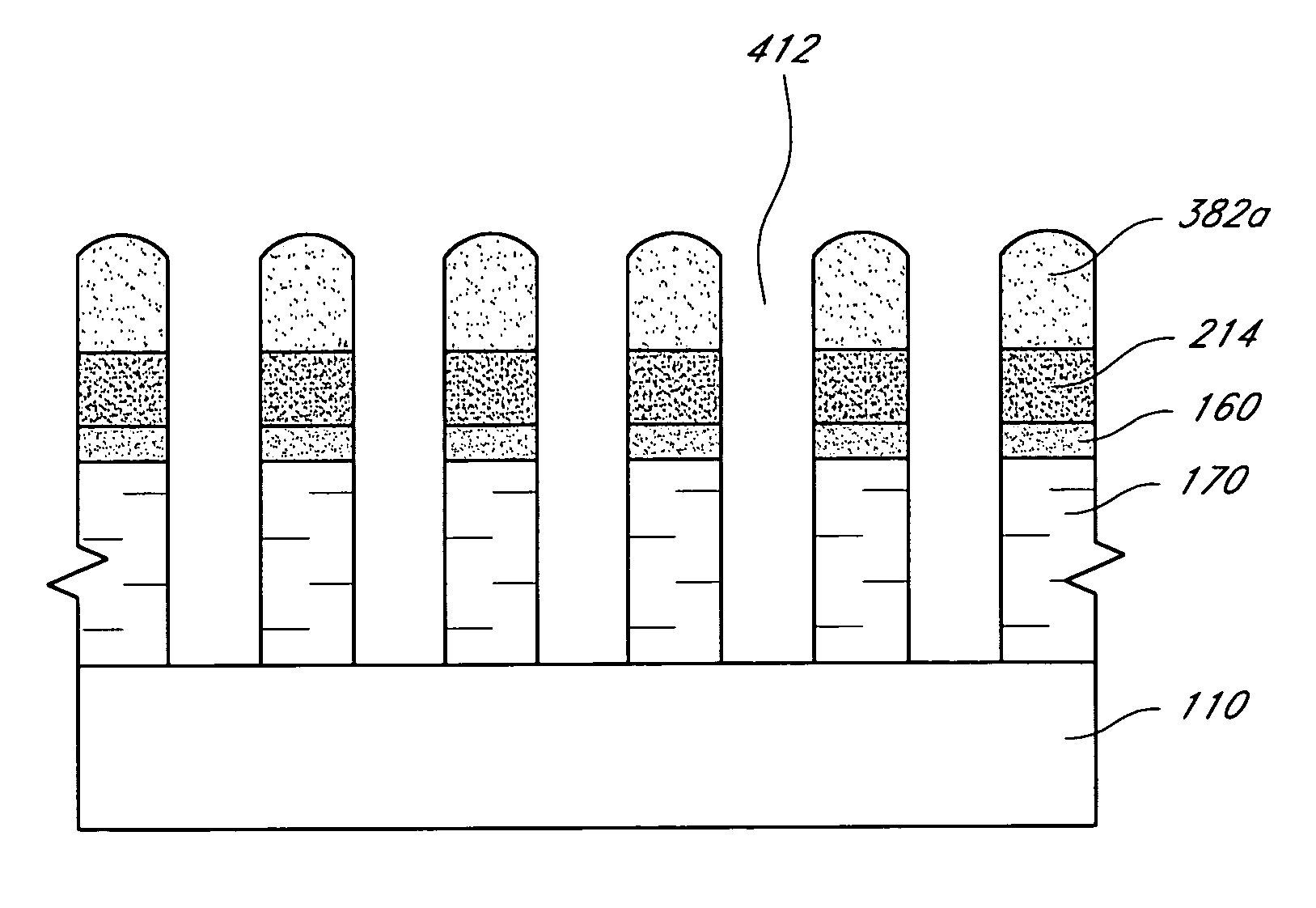

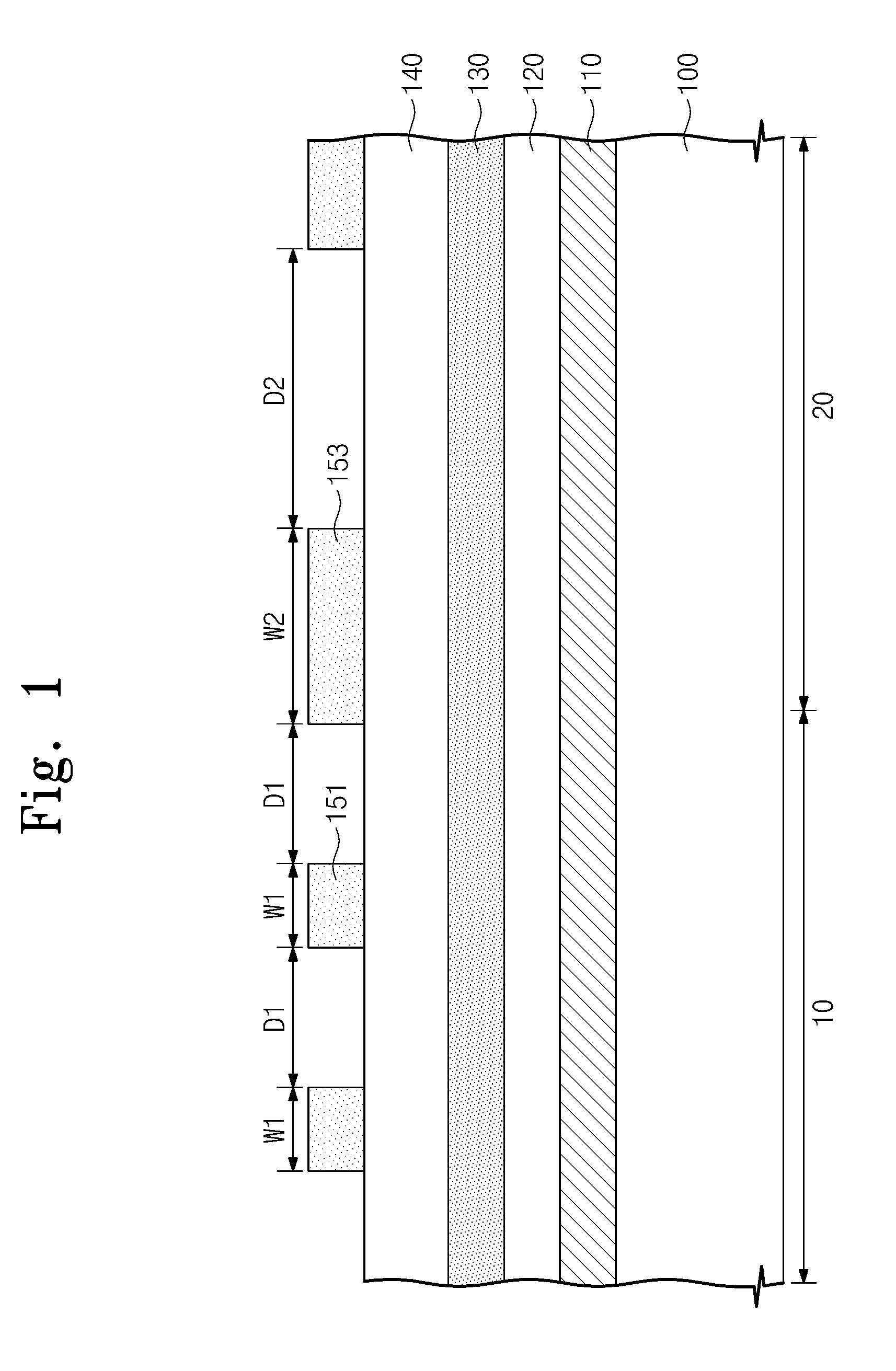

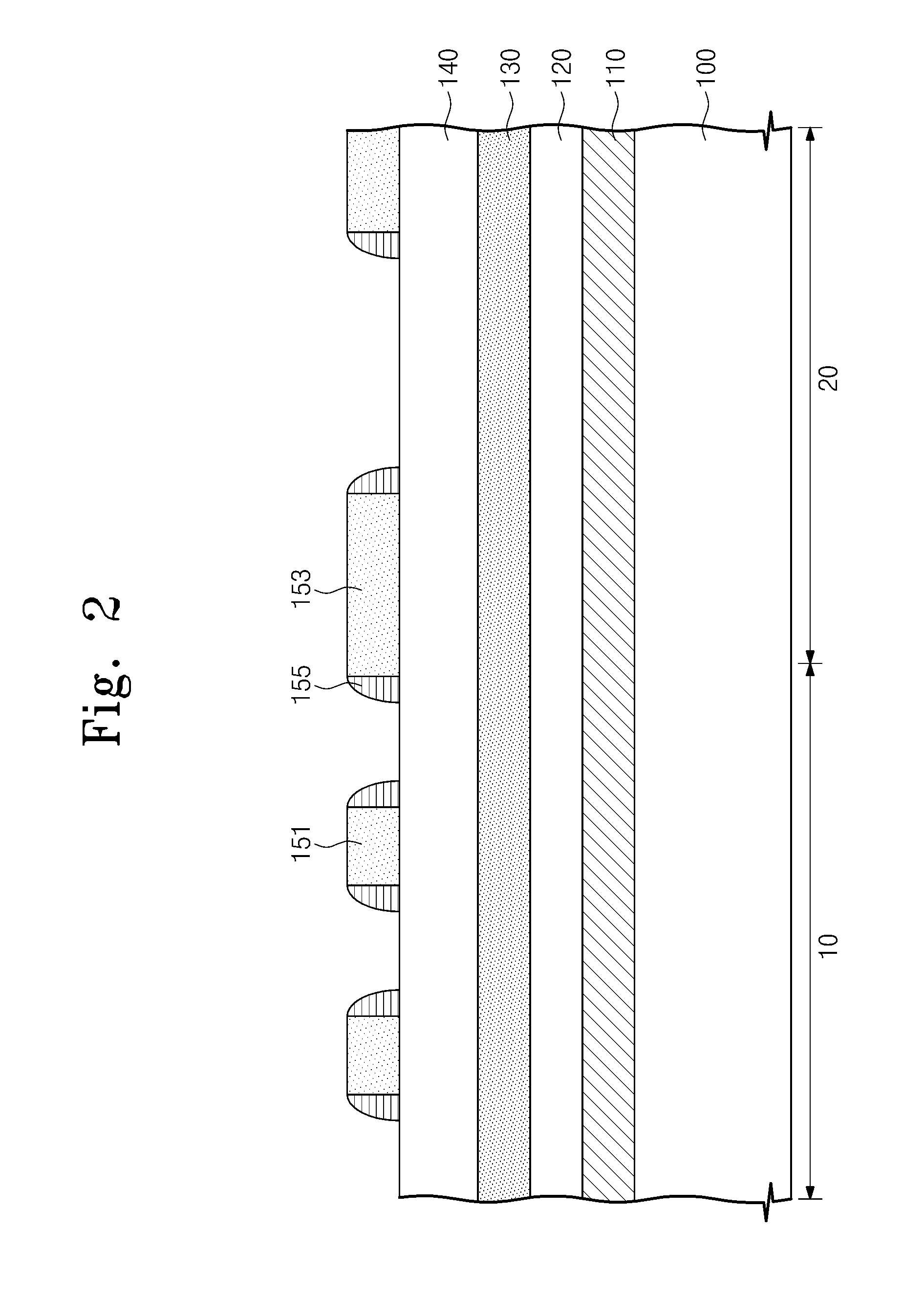

Integral patterning of large features along with array using spacer mask patterning process flow

InactiveUS20100075503A1Reduce spacingHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotolithography

Embodiments of the present invention pertain to methods of forming patterned features on a substrate having an increased density (i.e. reduced pitch) as compared to what is possible using standard photolithography processing techniques using a single high-resolution photomask while also allowing both the width of the patterned features and spacing (trench width) between the patterned features to vary within an integrated circuit.

Owner:APPLIED MATERIALS INC

Method utilizing compensation features in semiconductor processing

InactiveUS7202148B2Increased process windowReduce depthRadiation applicationsSemiconductor/solid-state device manufacturingEngineeringFlare

A photolithography and etch process sequence includes a photomask having a pattern with compensation features that alleviate patterning variations due to the proximity effect and depth of focus concerns during photolithography. The compensation features may be disposed near isolated or outermost lines of a device pattern. A photoresist pattern is formed to include the compensation features and the pattern etched to form a corresponding etched pattern including the compensation features. After etching, a protection material is formed over the layer and a trim mask is used to form a further photoresist pattern over the protection material. A subsequent etching pattern etches the protection material and removes the compensation features and results in the device lines being formed unaffected by proximity effects. Flare dummies may additionally be added to the mask pattern to increase pattern density and assist in endpoint detection. Flare dummies, like the compensation features, are subsequently removed by a photolithography and etching process sequence.

Owner:TAIWAN SEMICON MFG CO LTD

Protective coating for planarization

ActiveUS20070049032A1Reduce the overall heightReduce layeringSemiconductor/solid-state device manufacturingComputer sciencePhotolithography

Various pattern transfer and etching steps can be used to create features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form superimposed, pitch-reduced patterns of crossing elongate features that can be consolidated into a single layer. Planarizing techniques using a filler layer and a protective layer are disclosed. Portions of an integrated circuit having different heights can be etched to a common plane.

Owner:MICRON TECH INC

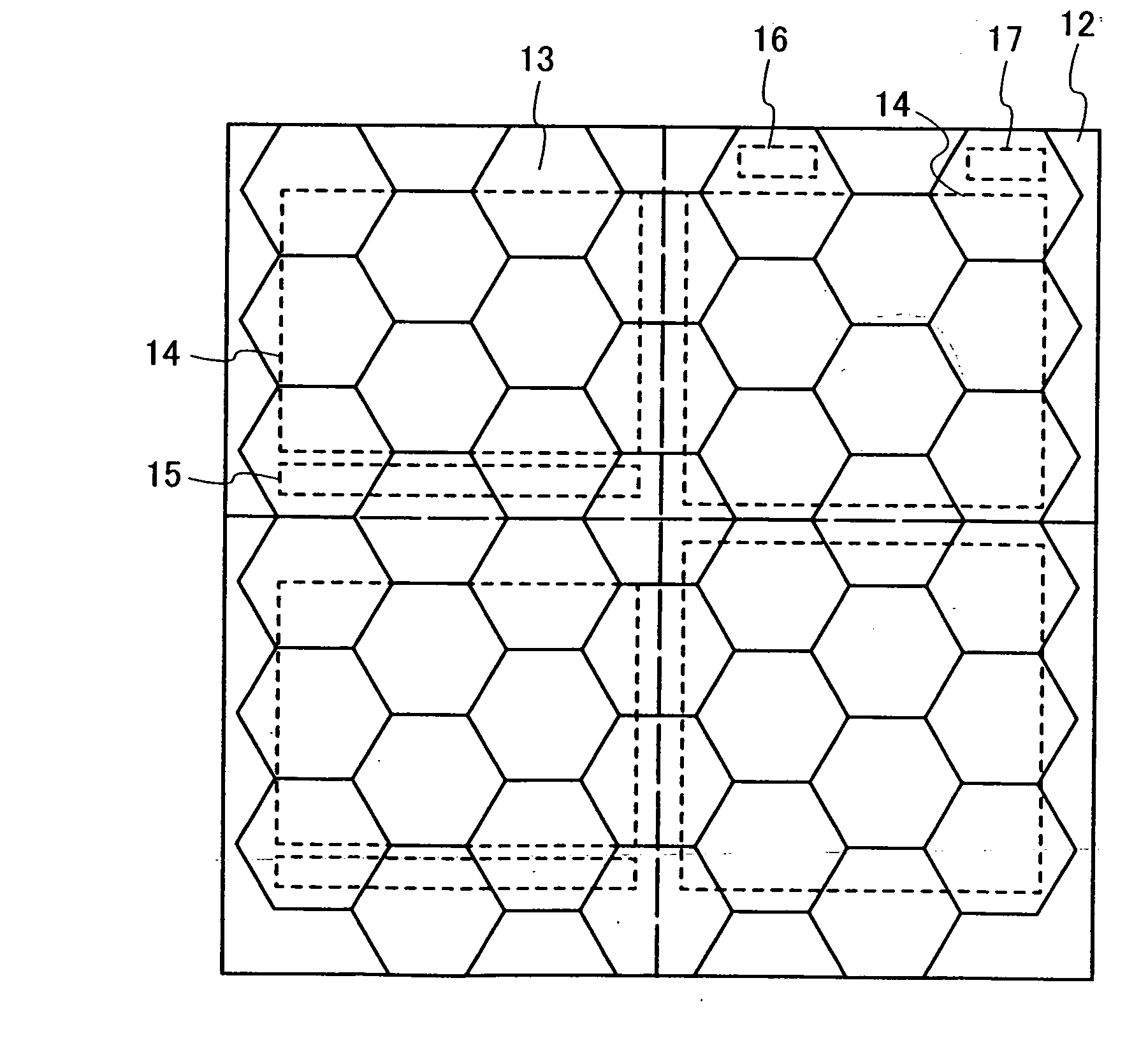

Display device and method for manufacturing the same

InactiveUS20090001469A1Increase the areaEasy to useSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A semiconductor substrate is formed into a regular hexagon or a shape similar to the regular hexagon. The semiconductor substrate is bonded to and separated from a large-area substrate. Moreover, layout is designed so that a boundary of bonded semiconductors is located in a region which is removed by etching when patterning is performed by photolithography or the like.

Owner:SEMICON ENERGY LAB CO LTD

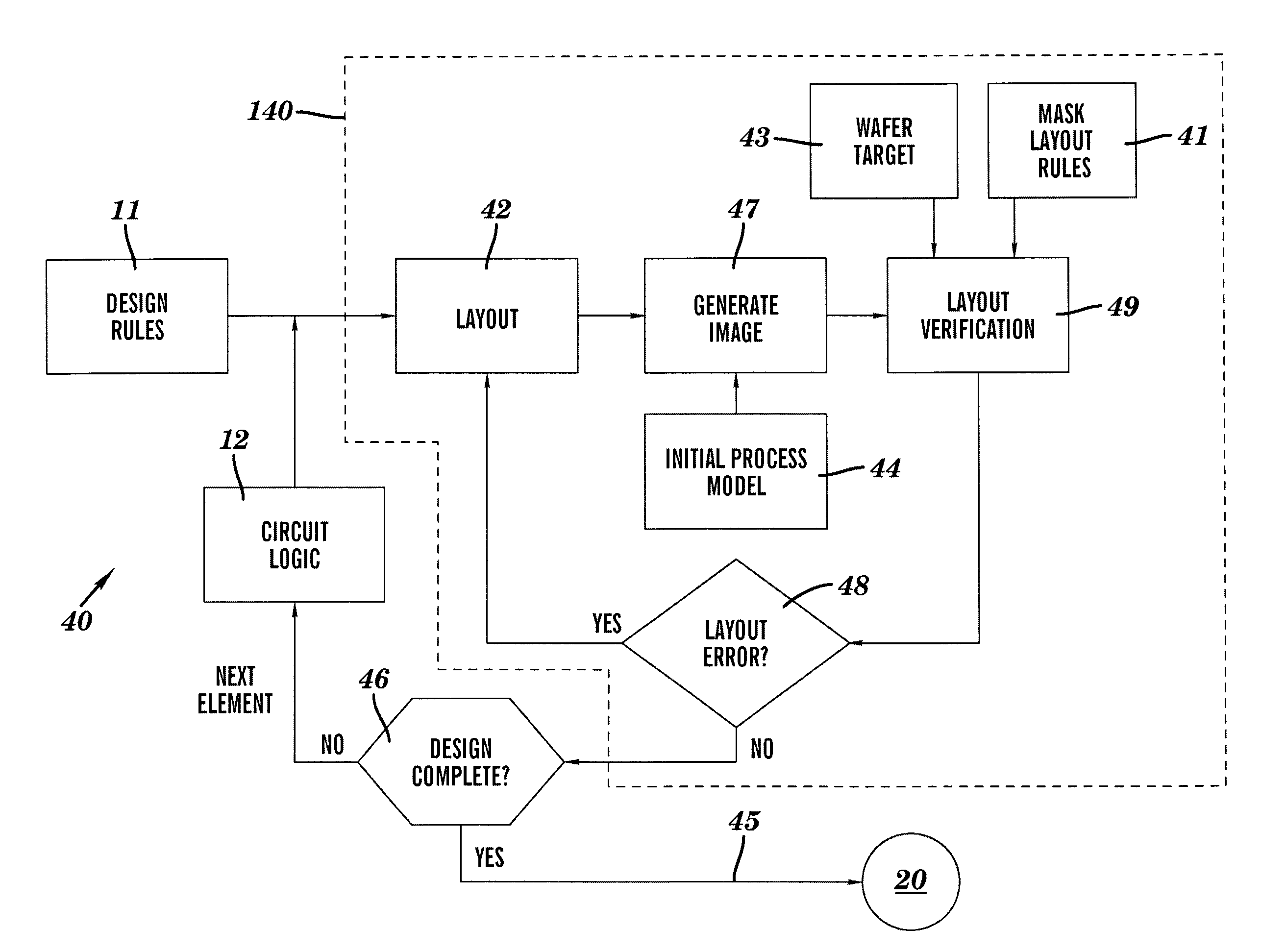

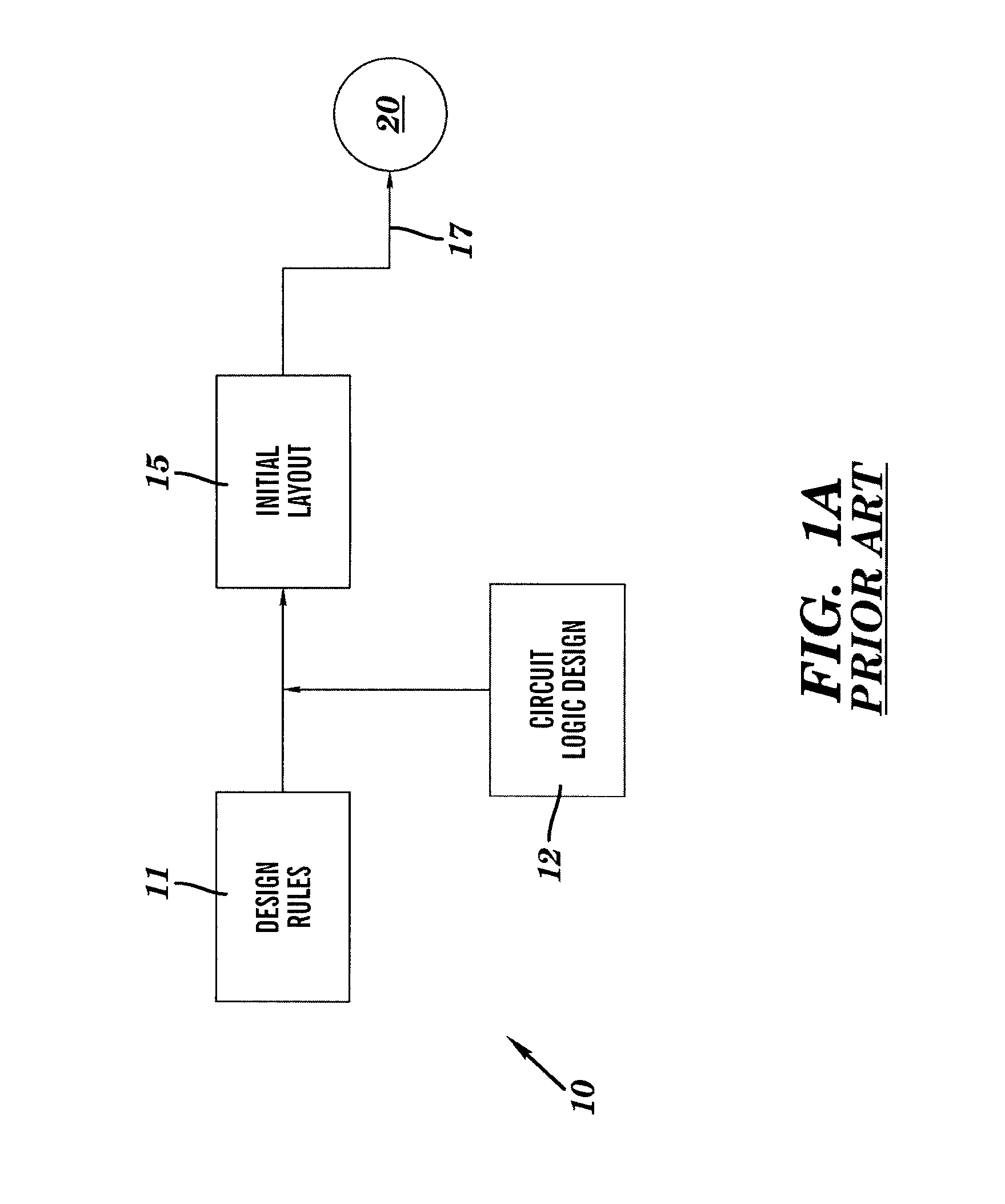

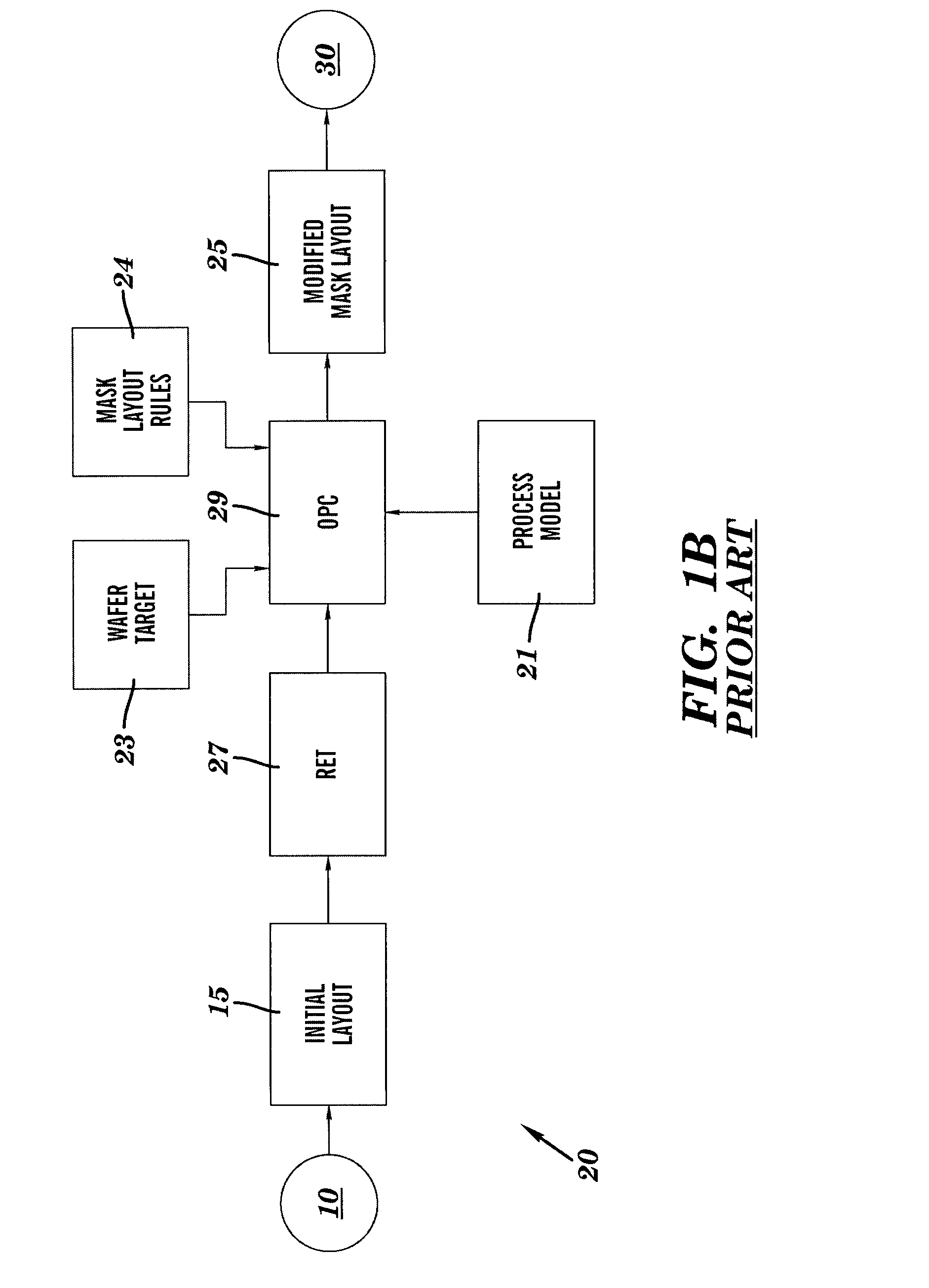

Closed-loop design for manufacturability process

InactiveUS20080127029A1Satisfy constraintsSimple methodOriginals for photomechanical treatmentSpecial data processing applicationsDesign phaseEngineering

A method of designing an integrated circuit is provided in which the design layout is optimized using a process model until the design constraints are satisfied by the image contours simulated by the process model. The process model used in the design phase need not be as accurate as the lithographic model used in preparing the lithographic mask layout during data prep. The resulting image contours are then included with the modified, optimized design layout to the data prep process, in which the mask layout is optimized using the lithographic process model, for example, including RET and OPC. The mask layout optimization matches the images simulated by the lithographic process model with the image contours generated during the design phase, which ensures that the design and manufacturability constraints specified by the designer are satisfied by the optimized mask layout.

Owner:IBM CORP

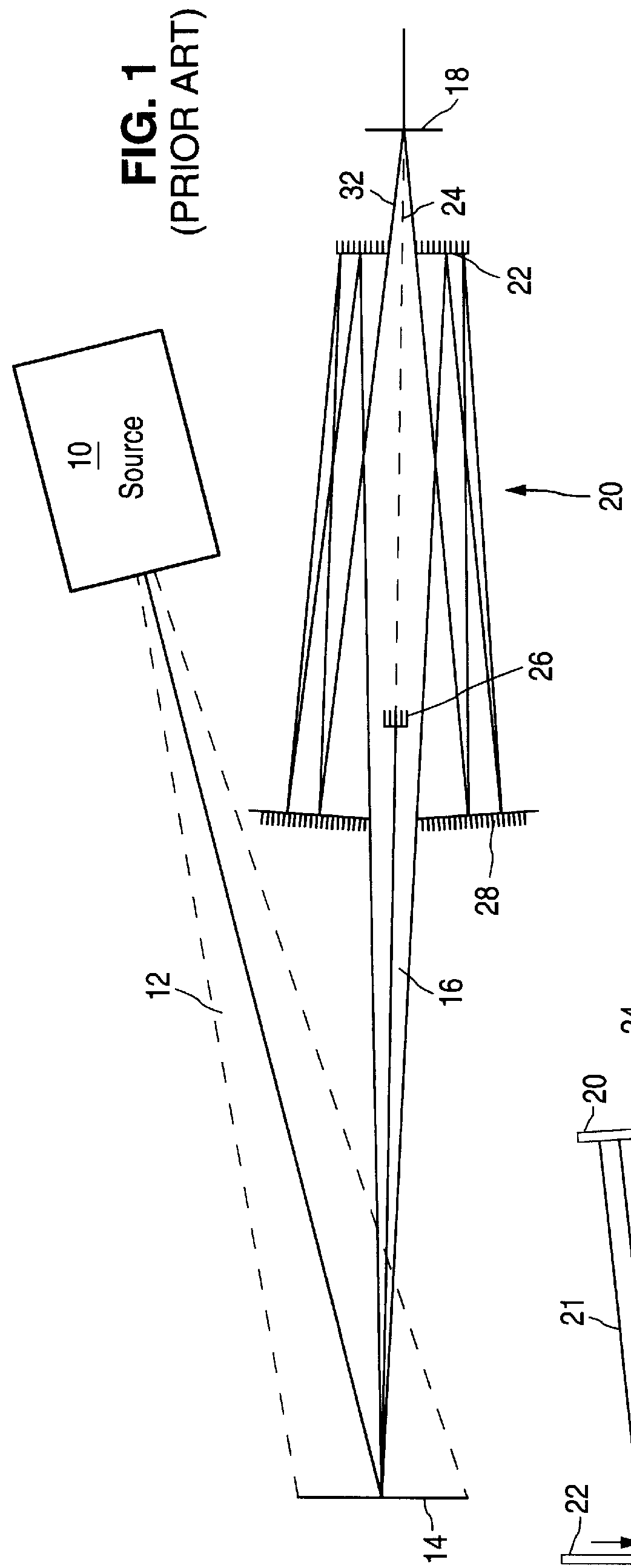

High numerical aperture ring field projection system for extreme ultraviolet lithography

An all-refelctive optical system for a projection photolithography camera has a source of EUV radiation, a wafer and a mask to be imaged on the wafer. The optical system includes a first concave mirror, a second mirror, a third convex mirror, a fourth concave mirror, a fifth convex mirror and a sixth concave mirror. The system is configured such that five of the six mirrors receives a chief ray at an incidence angle less than substantially 12 DEG , and each of the six mirrors receives a chief ray at an incidence angle of less than substantially 15 DEG . Four of the six reflecting surfaces have an aspheric departure of less than substantially 7 mu m. Five of the six reflecting surfaces have an aspheric departure of less than substantially 14 mu m. Each of the six refelecting surfaces has an aspheric departure of less than 16.0 mu m.

Owner:EUV

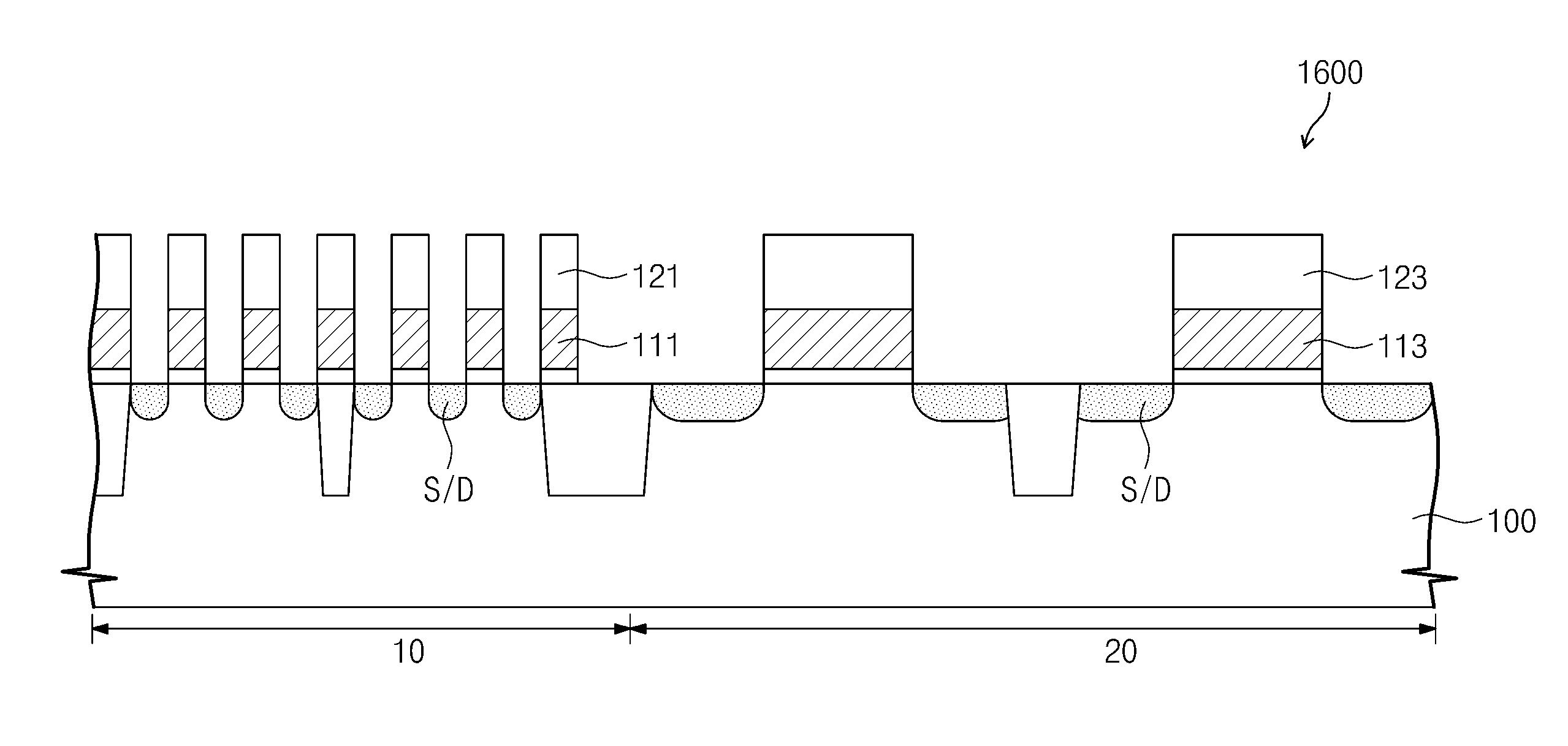

Method for forming fine patterns of a semiconductor device

ActiveUS20120208361A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialImage resolution

A method of forming fine patterns in a semiconductor device includes forming narrow-width patterns in a first region and wide-width patterns in a second region, where the widths of the narrow-width patterns are smaller than the resolution limitations in a photolithography process used to make the semiconductor device. The first and second regions may comprise cell array regions, with memory cells in the first region and peripheral circuits for operating the memory cells in the second region. The semiconductor device can be, for example, a NAND FLASH memory device. The semiconductor memory device can be variously classified according to the type of memory cells to be integrated in the cell array region, e.g., a DRAM, an SRAM, a PRAM, a RRAM, an MRAM, and a FRAM. In other embodiments, a MEMS device, an optoelectronic device, or a processor, such as CPU or DSP, may be provided on the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com