Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1287results about How to "Reduce layering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

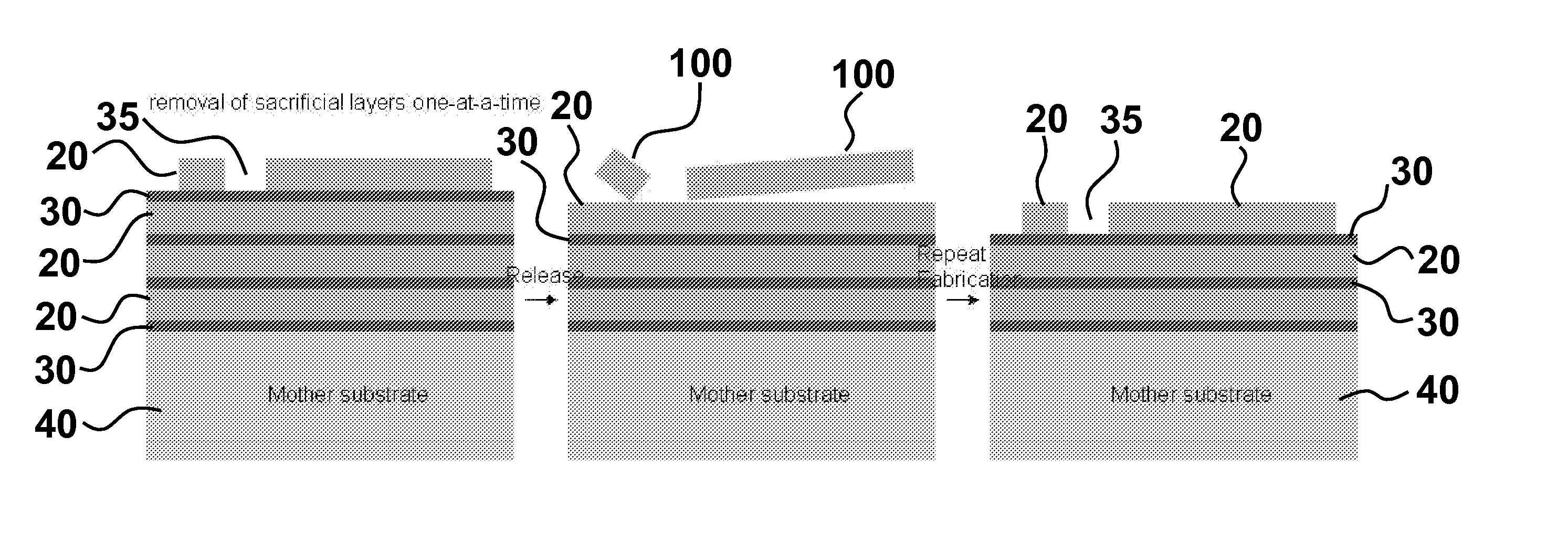

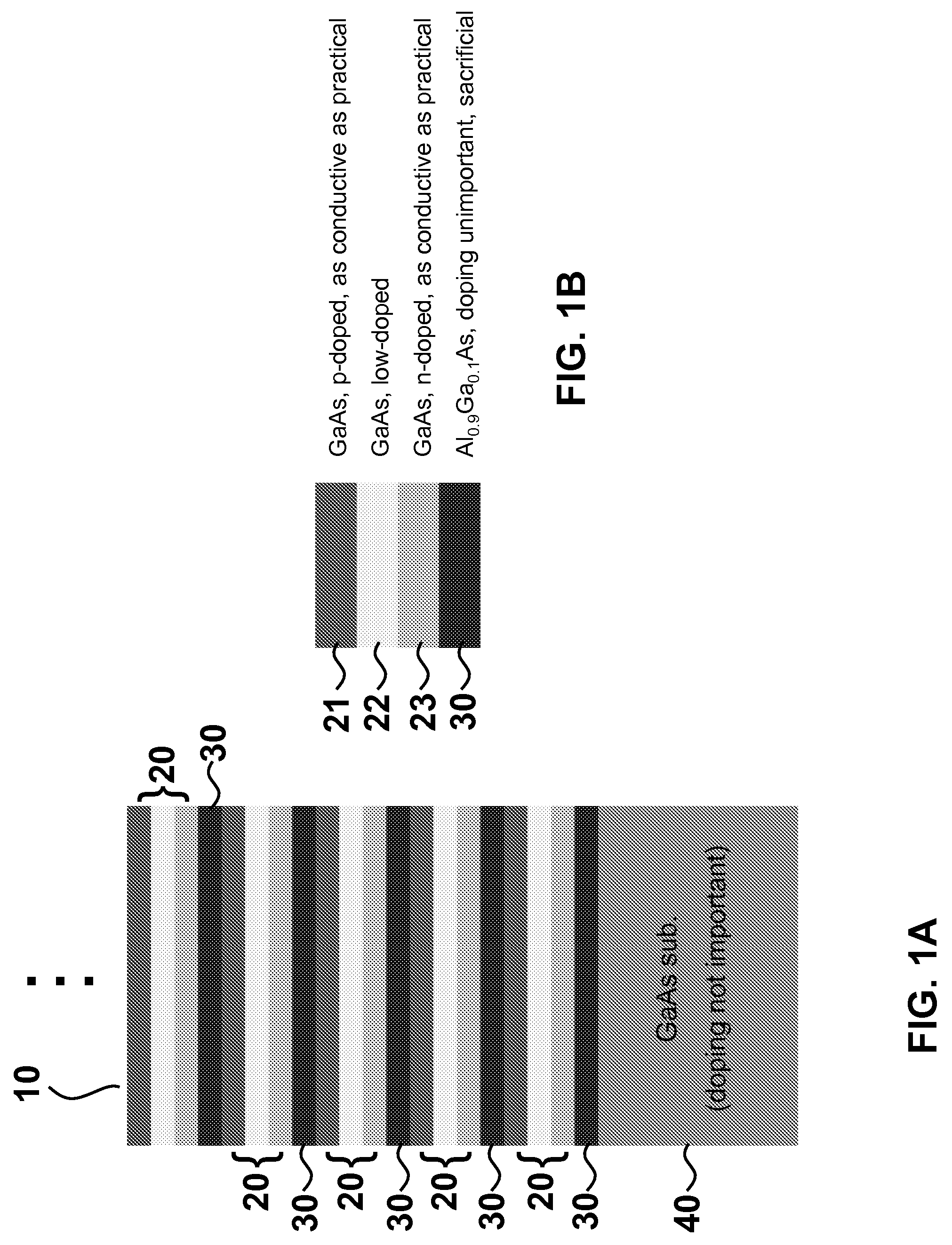

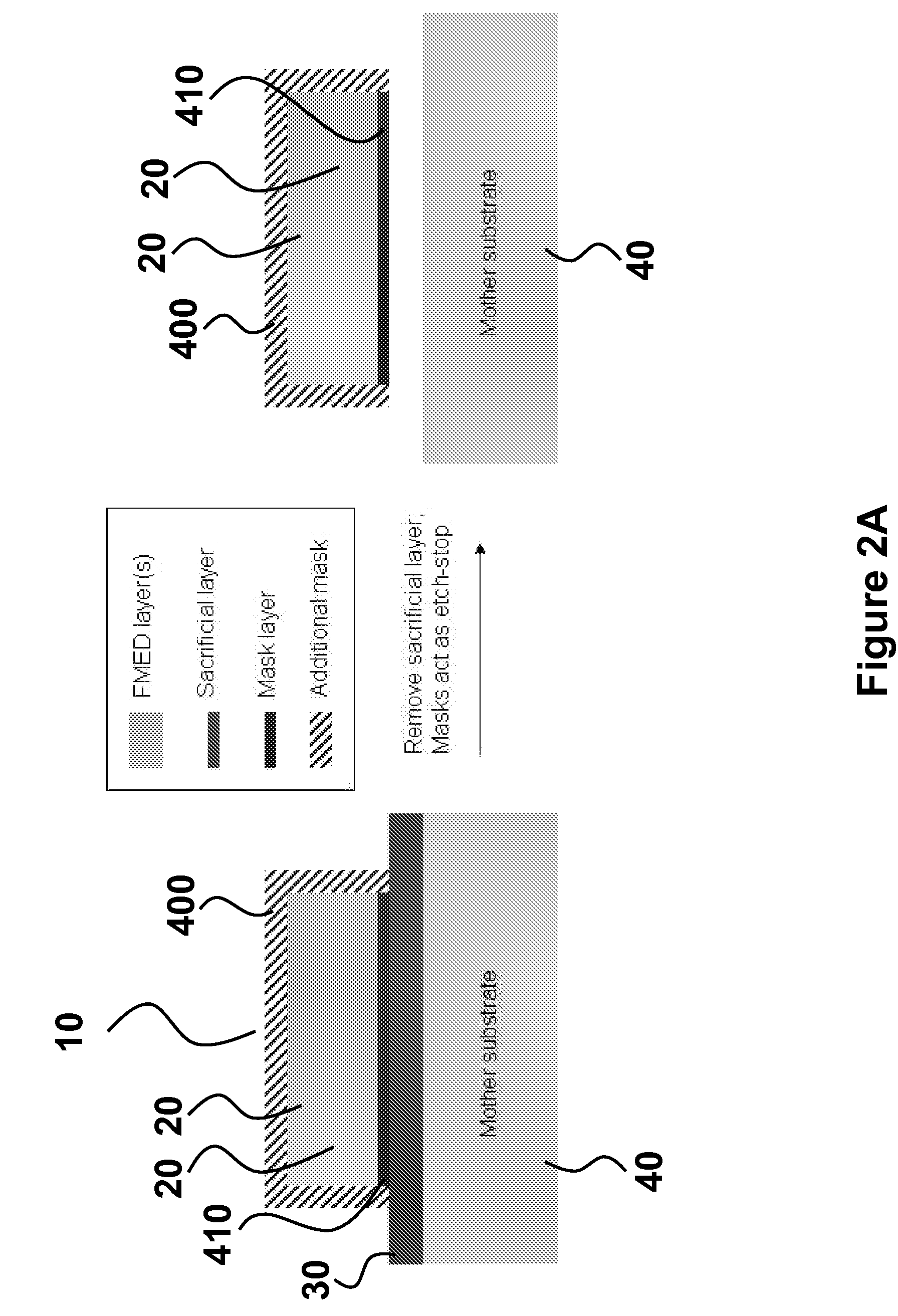

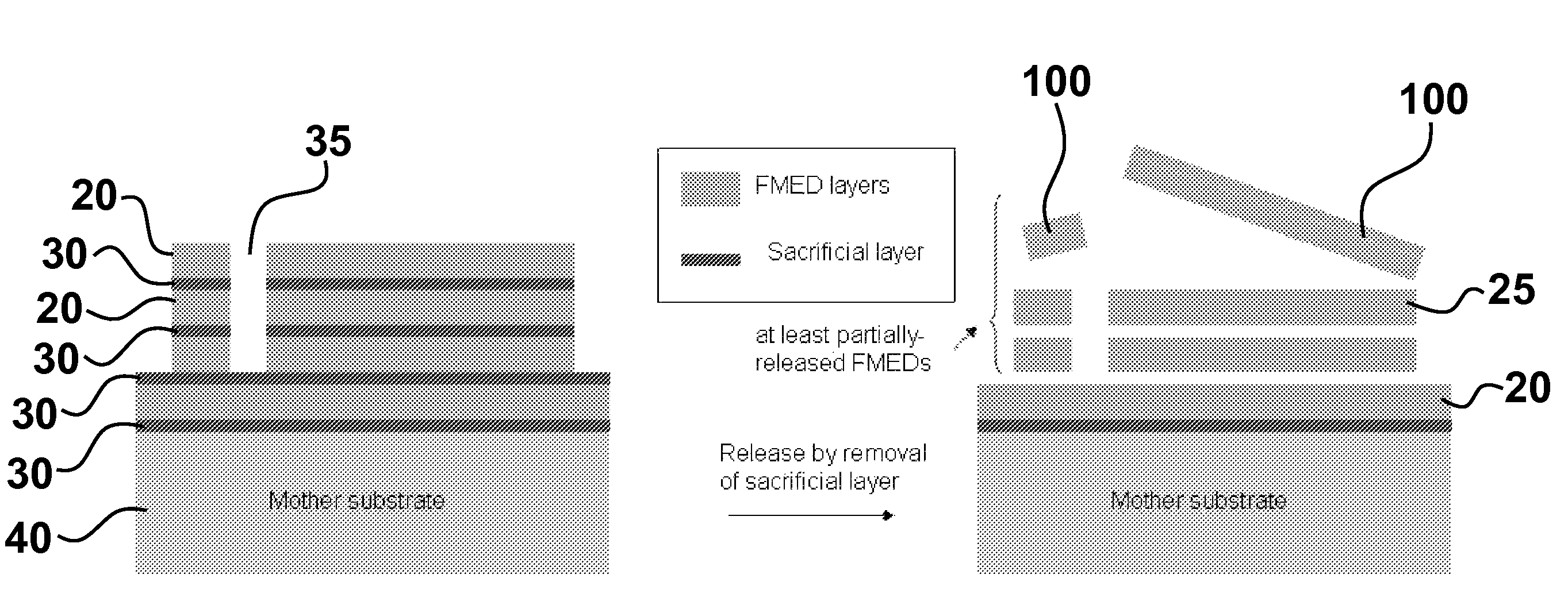

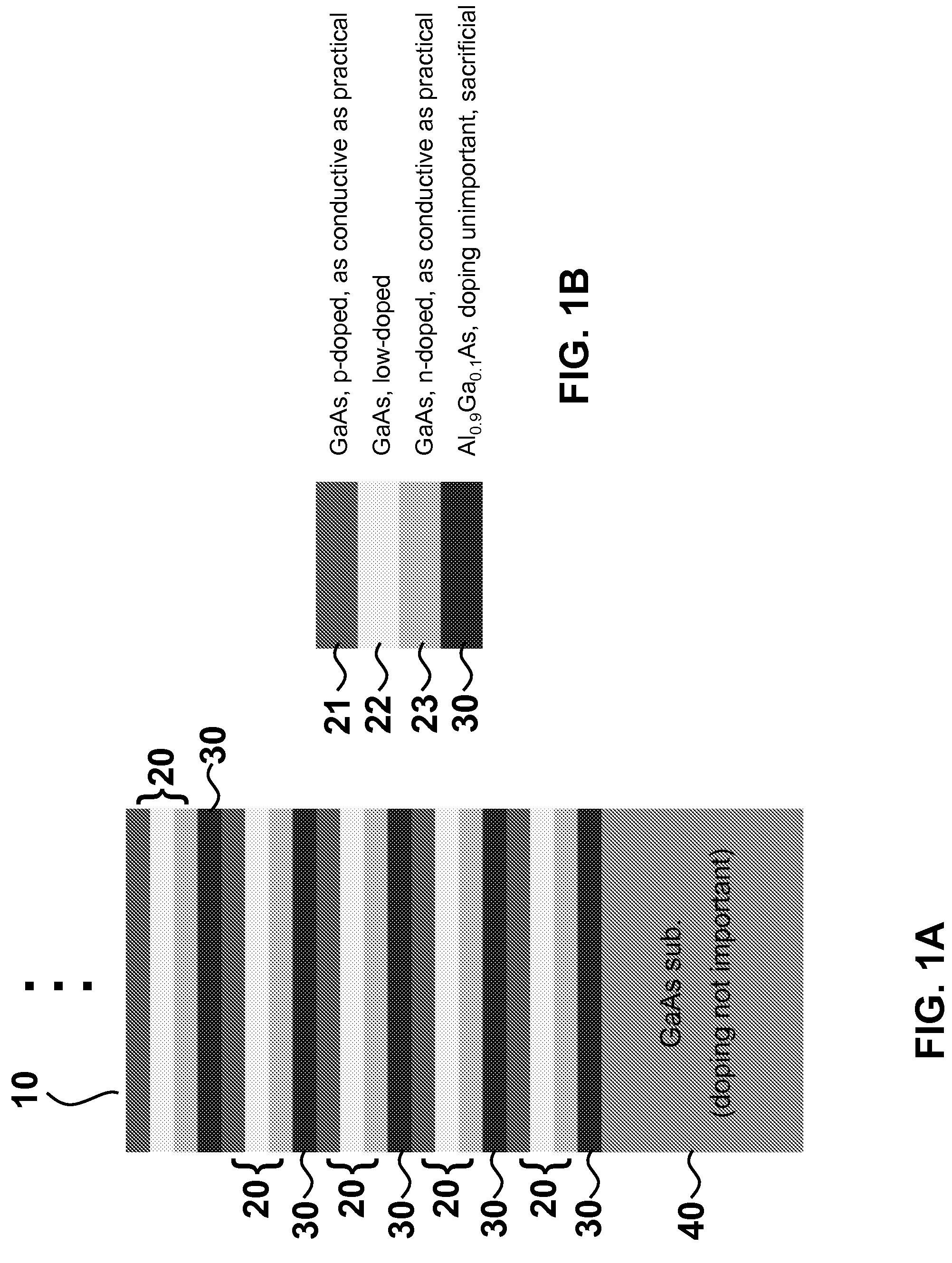

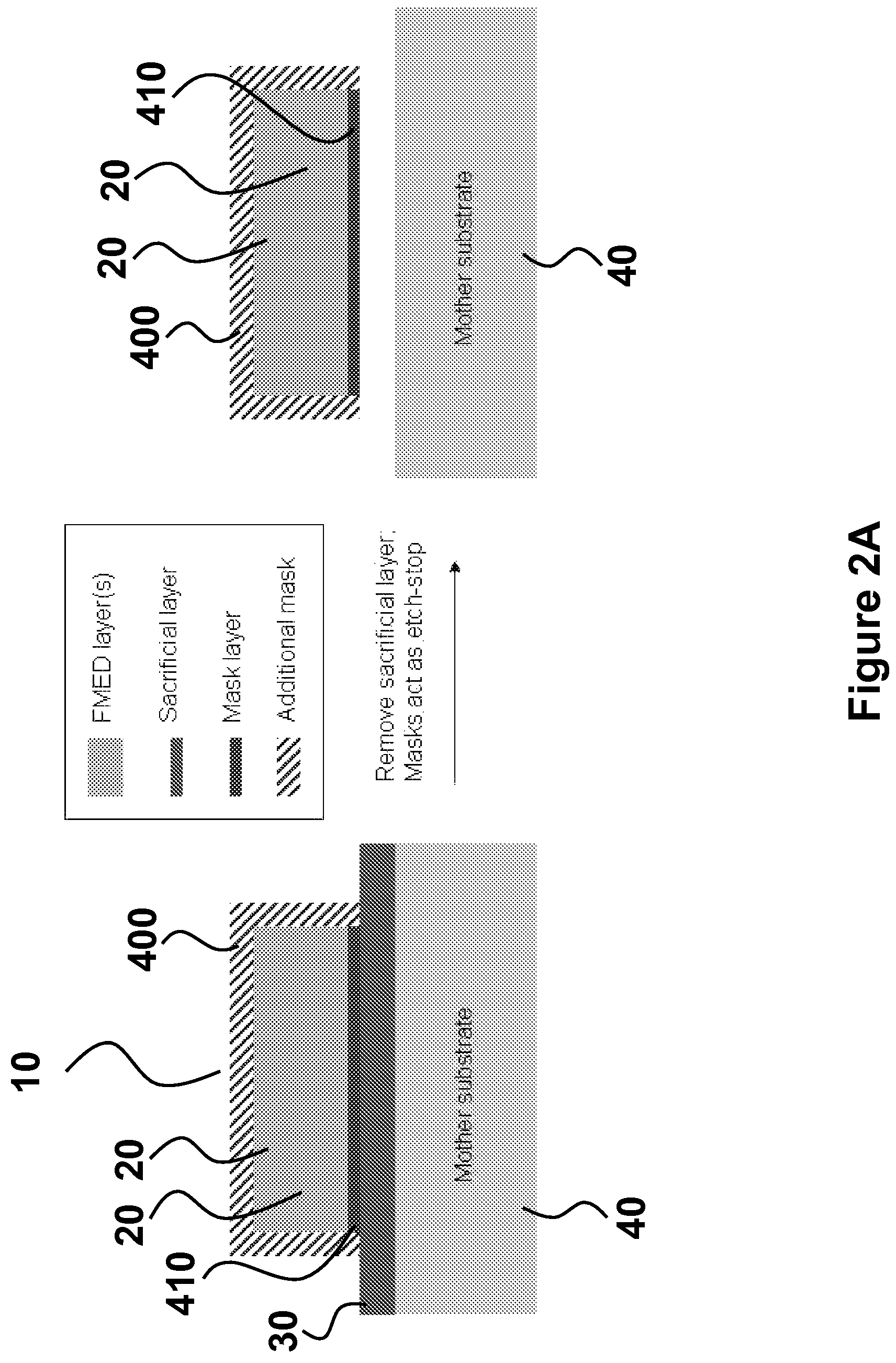

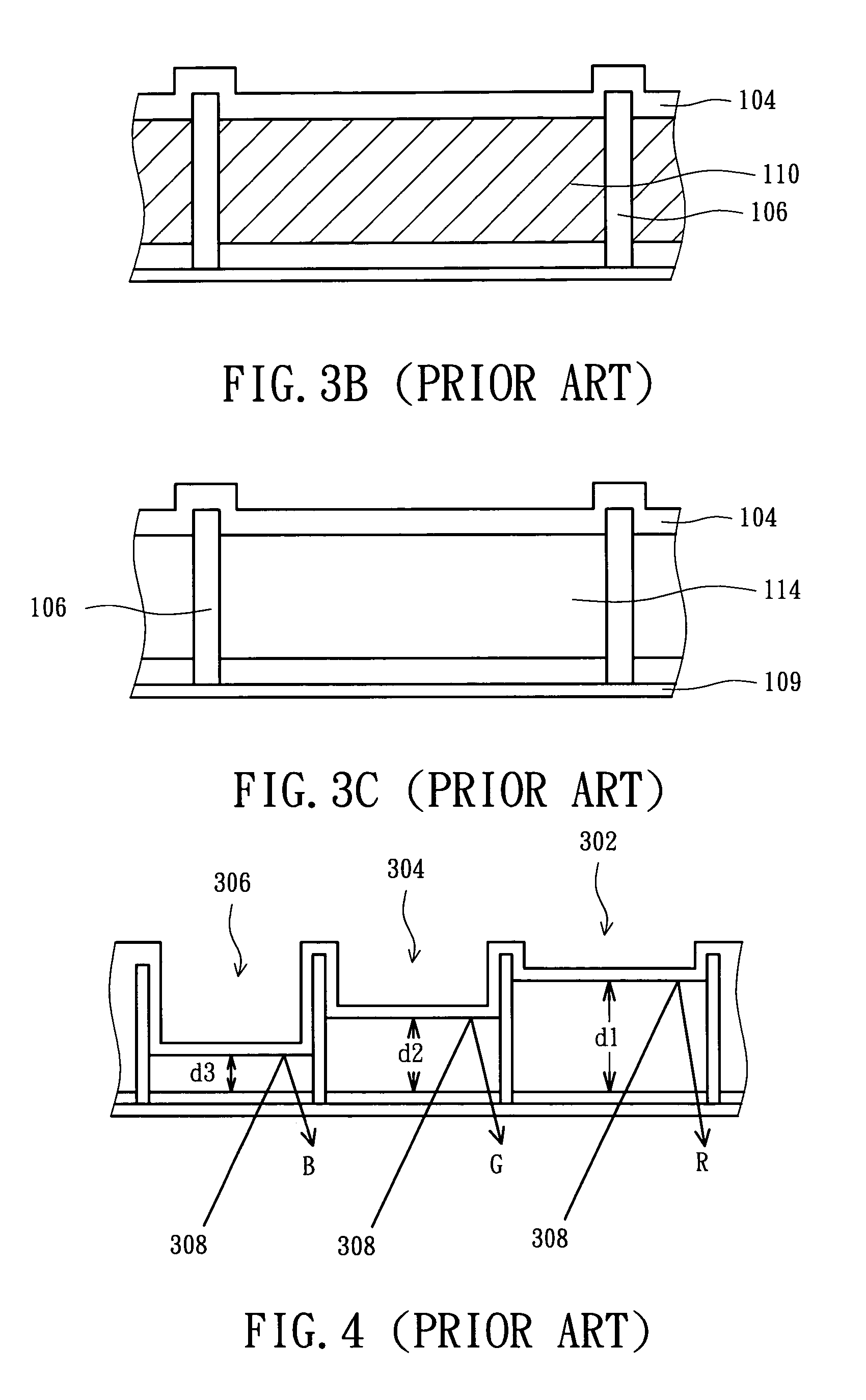

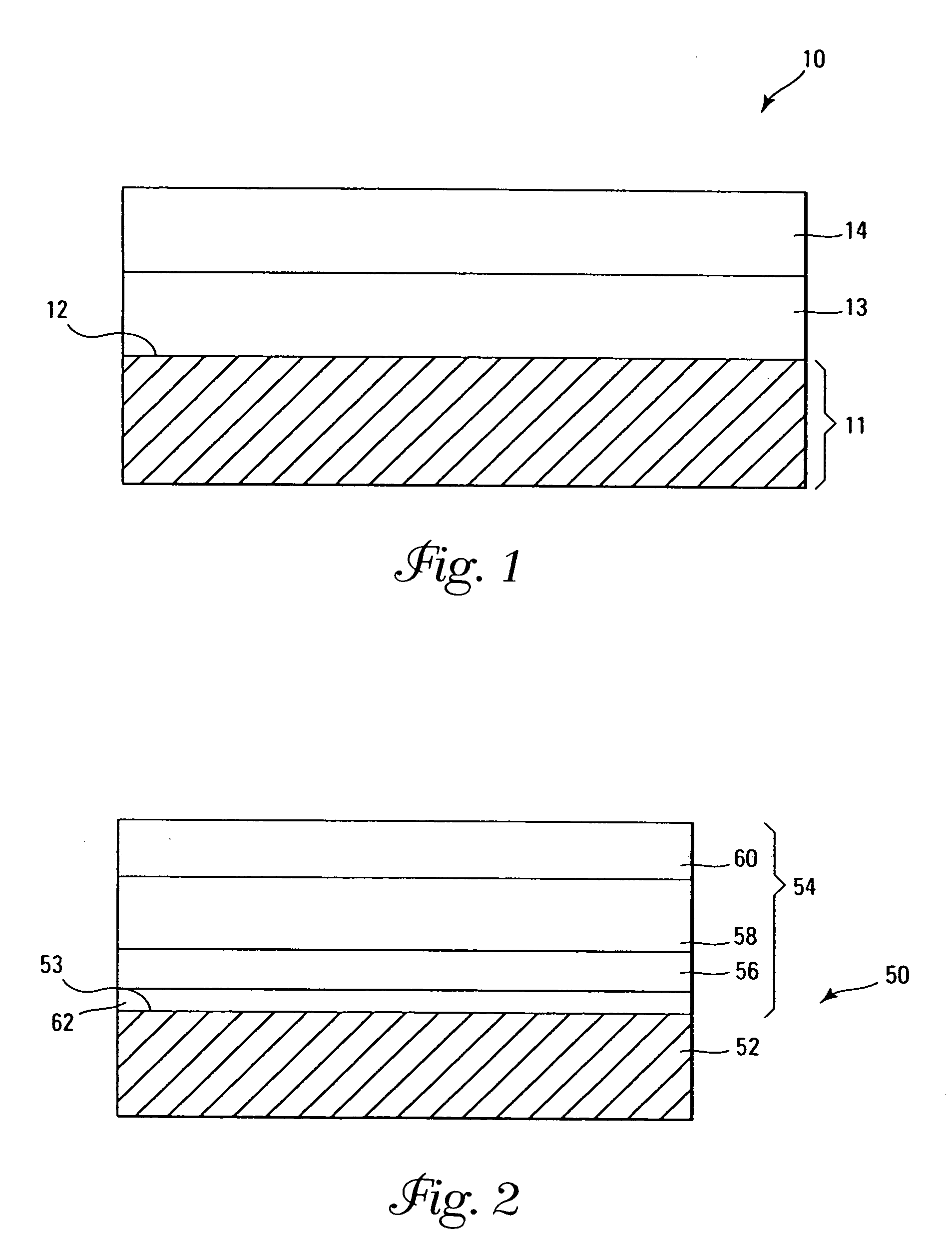

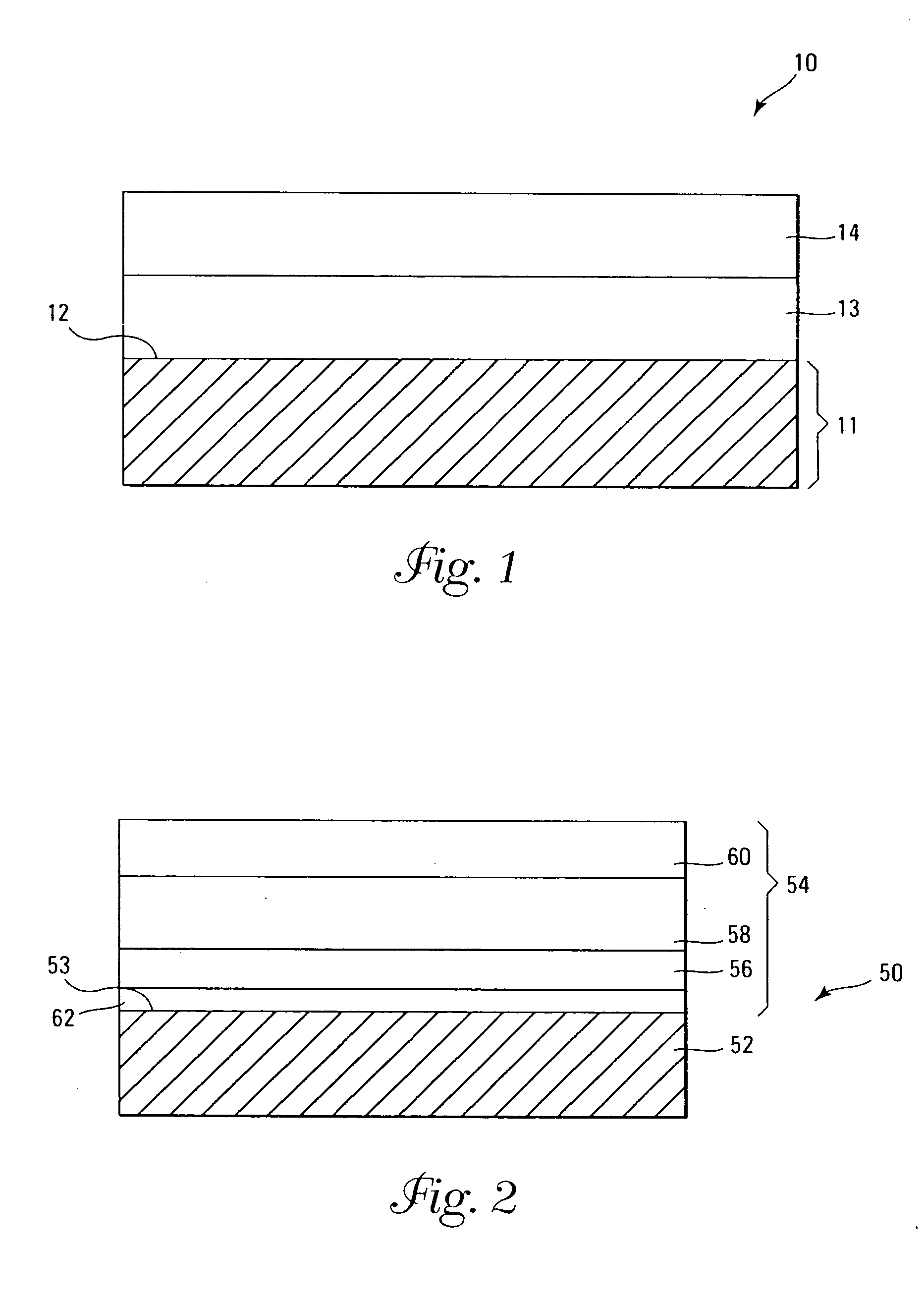

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS20080108171A1Low cost structureLow costFinal product manufactureNanoinformaticsSemiconductor structureDevice Subassembly

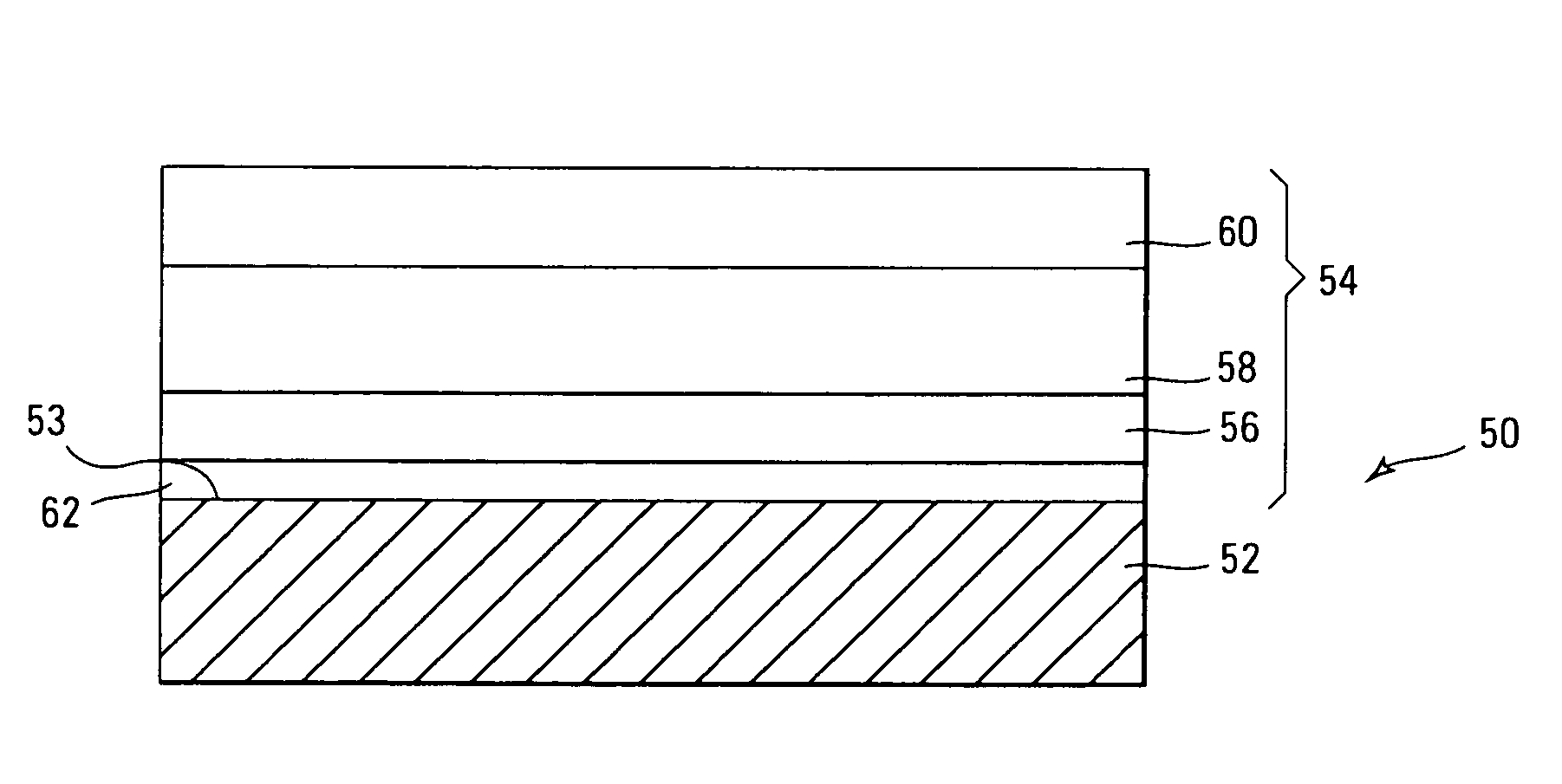

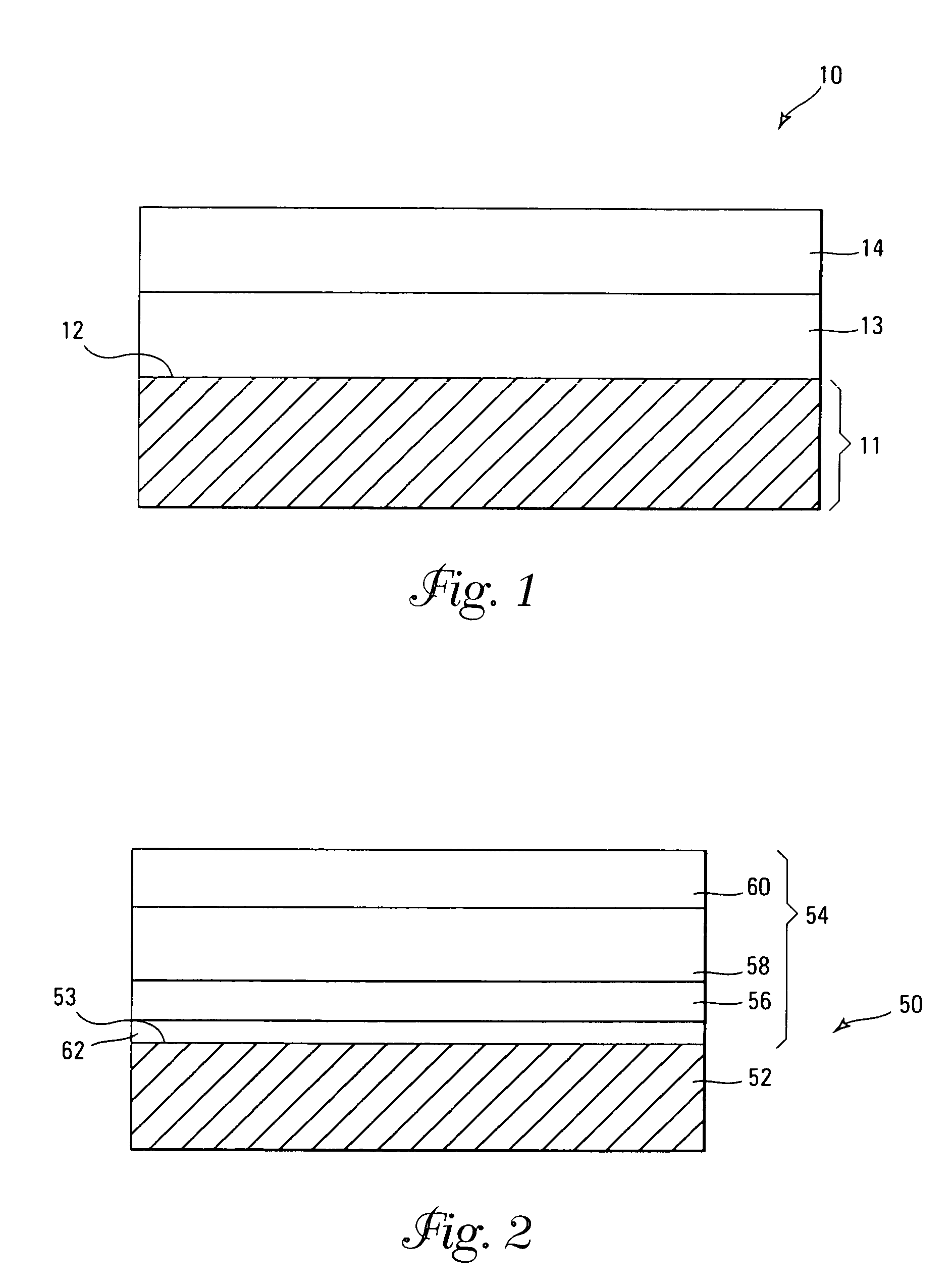

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

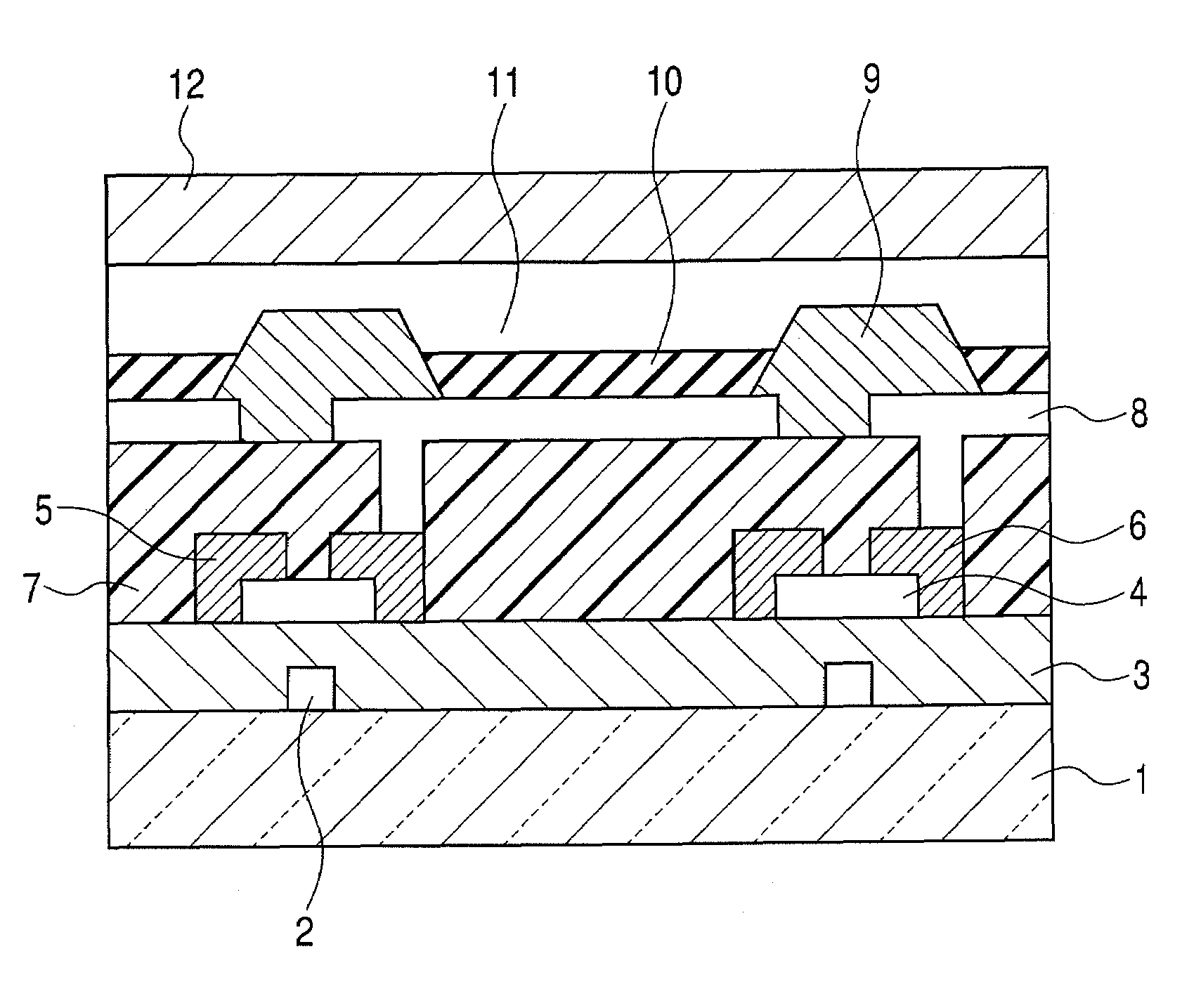

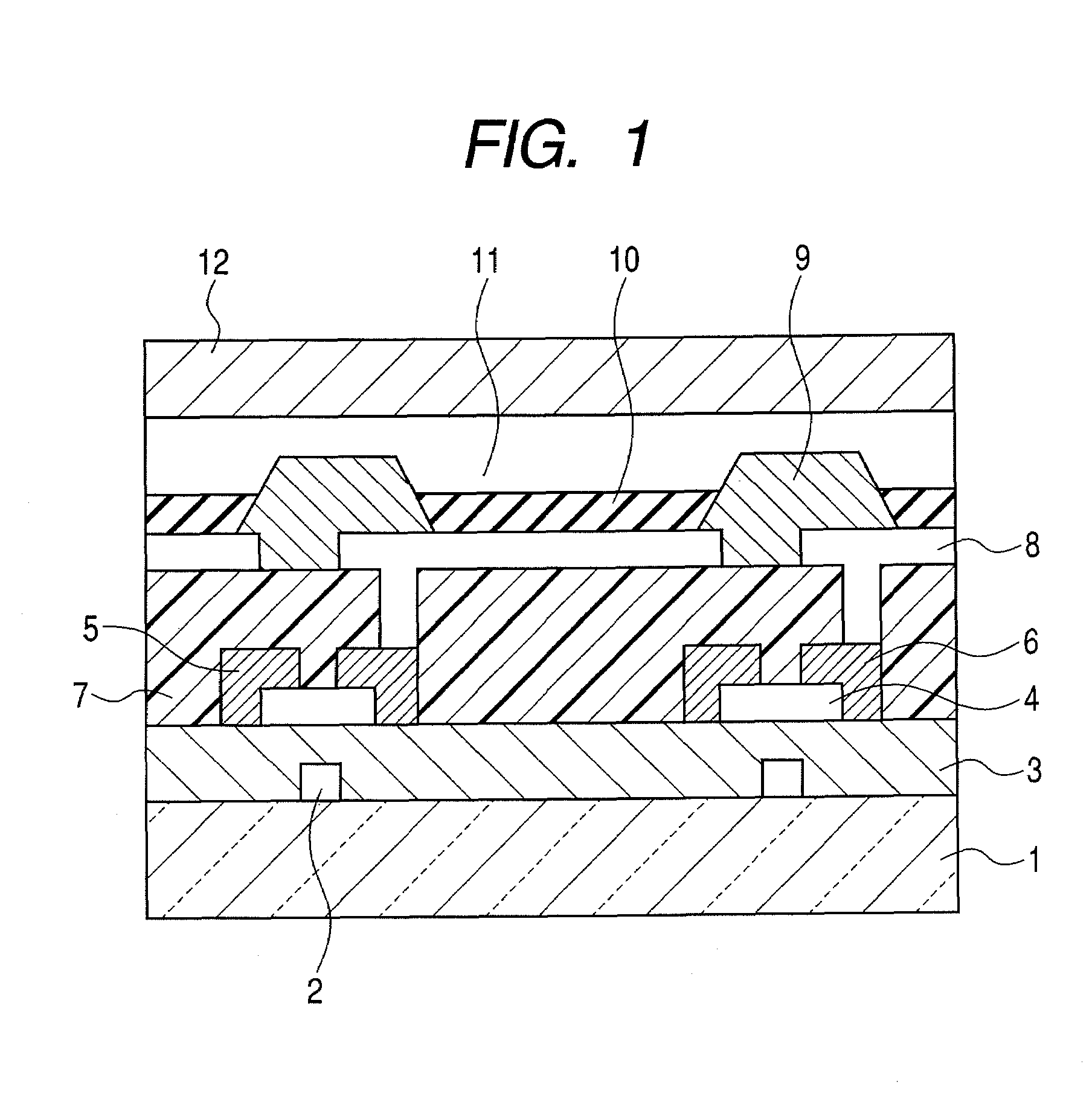

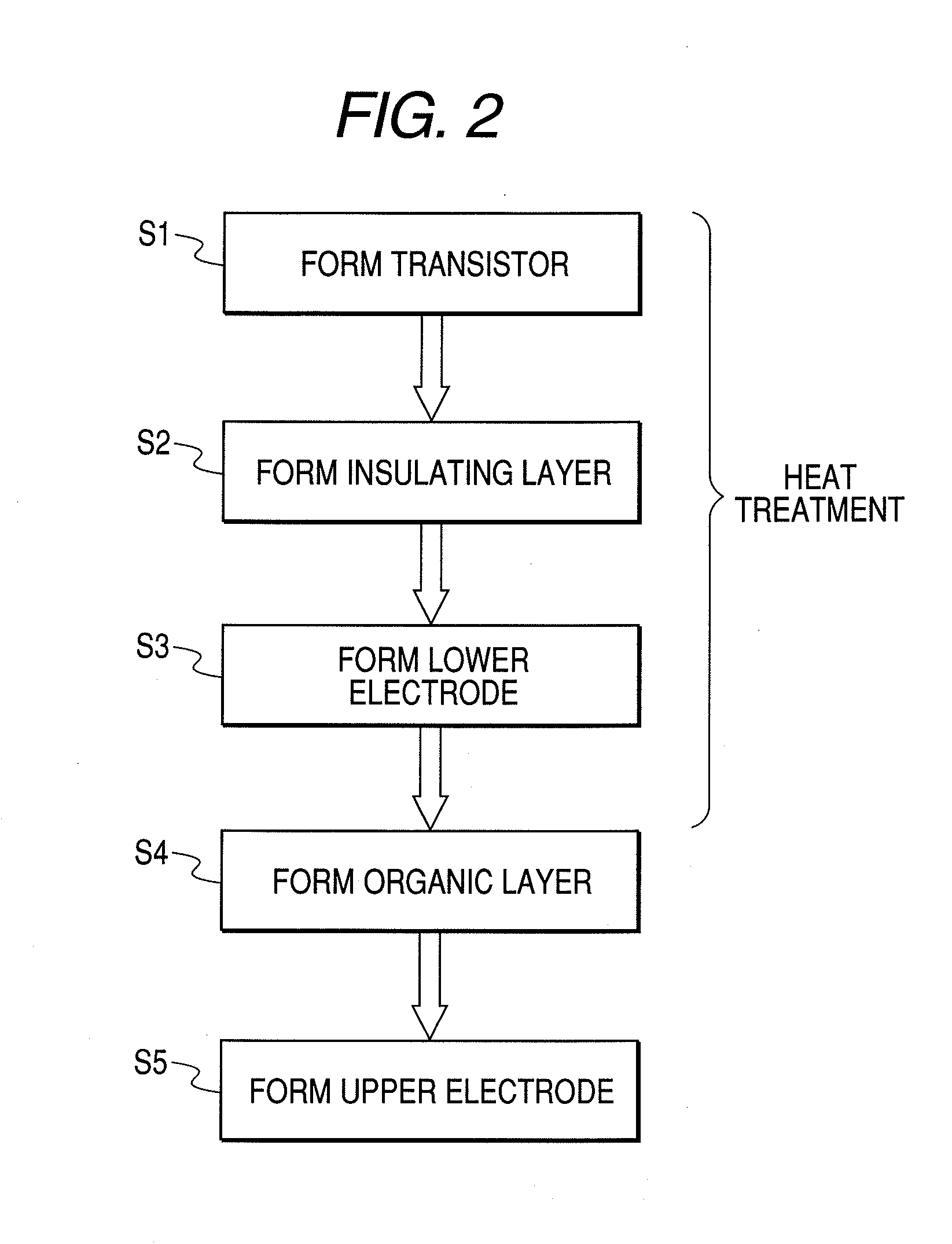

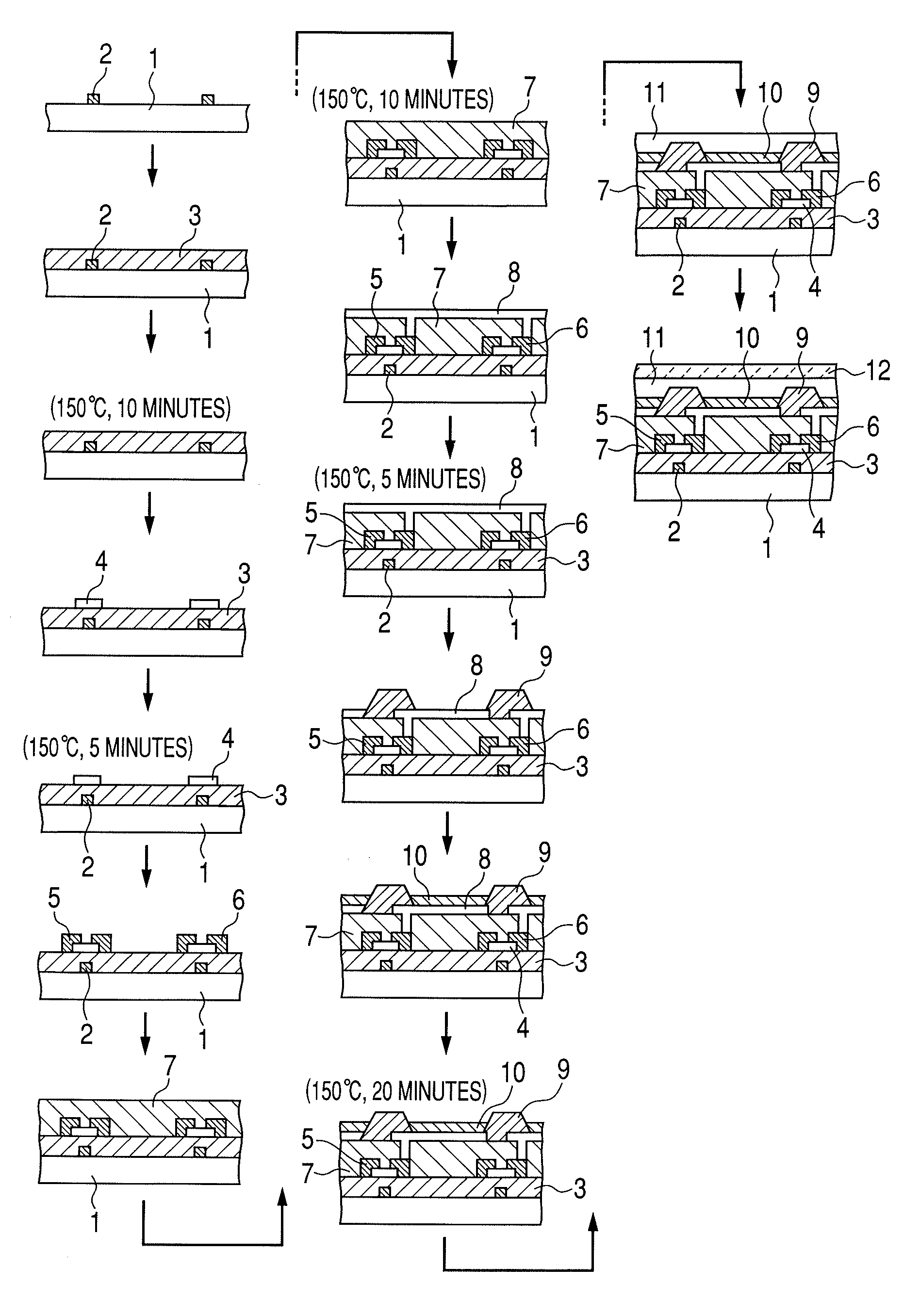

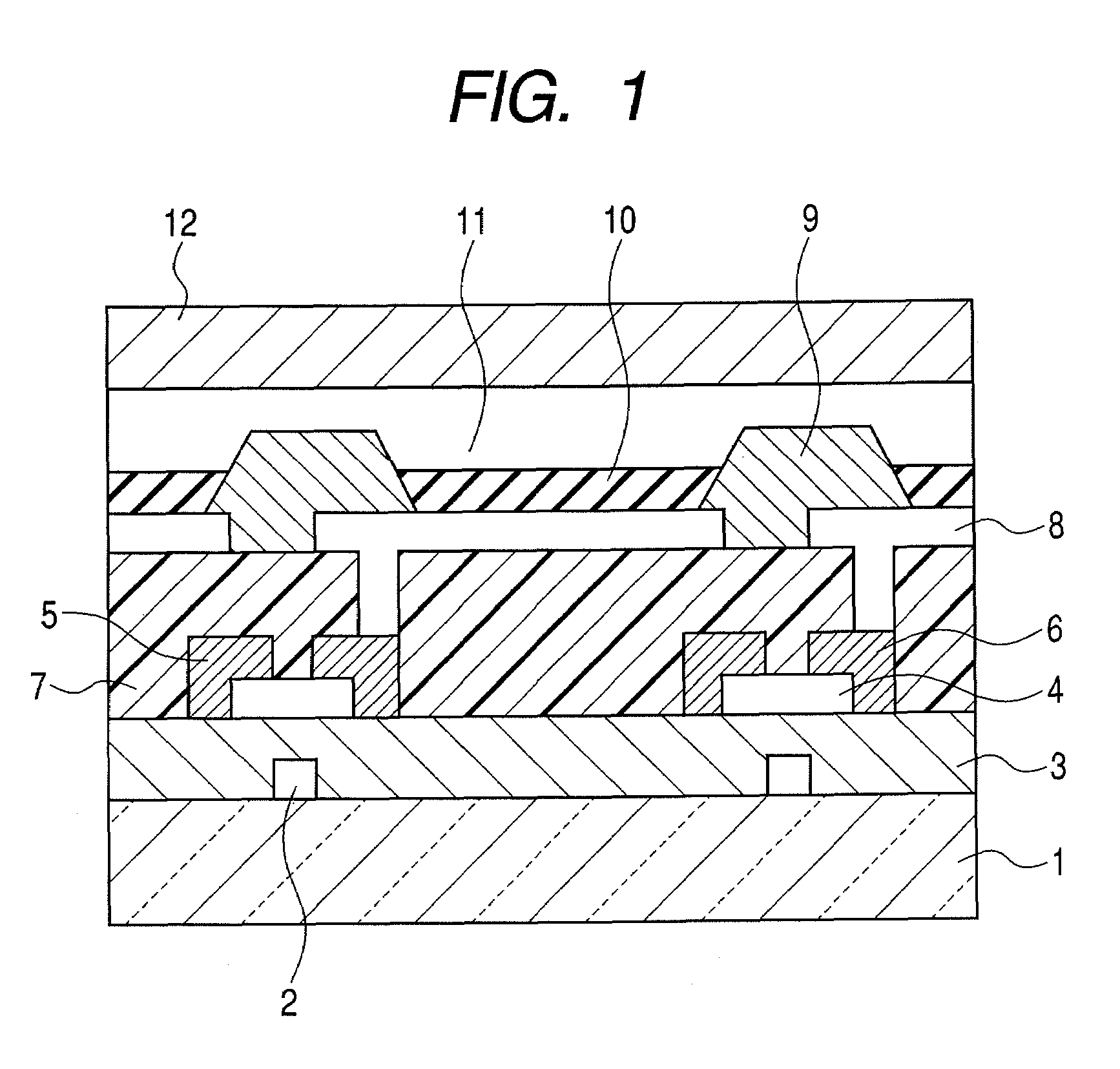

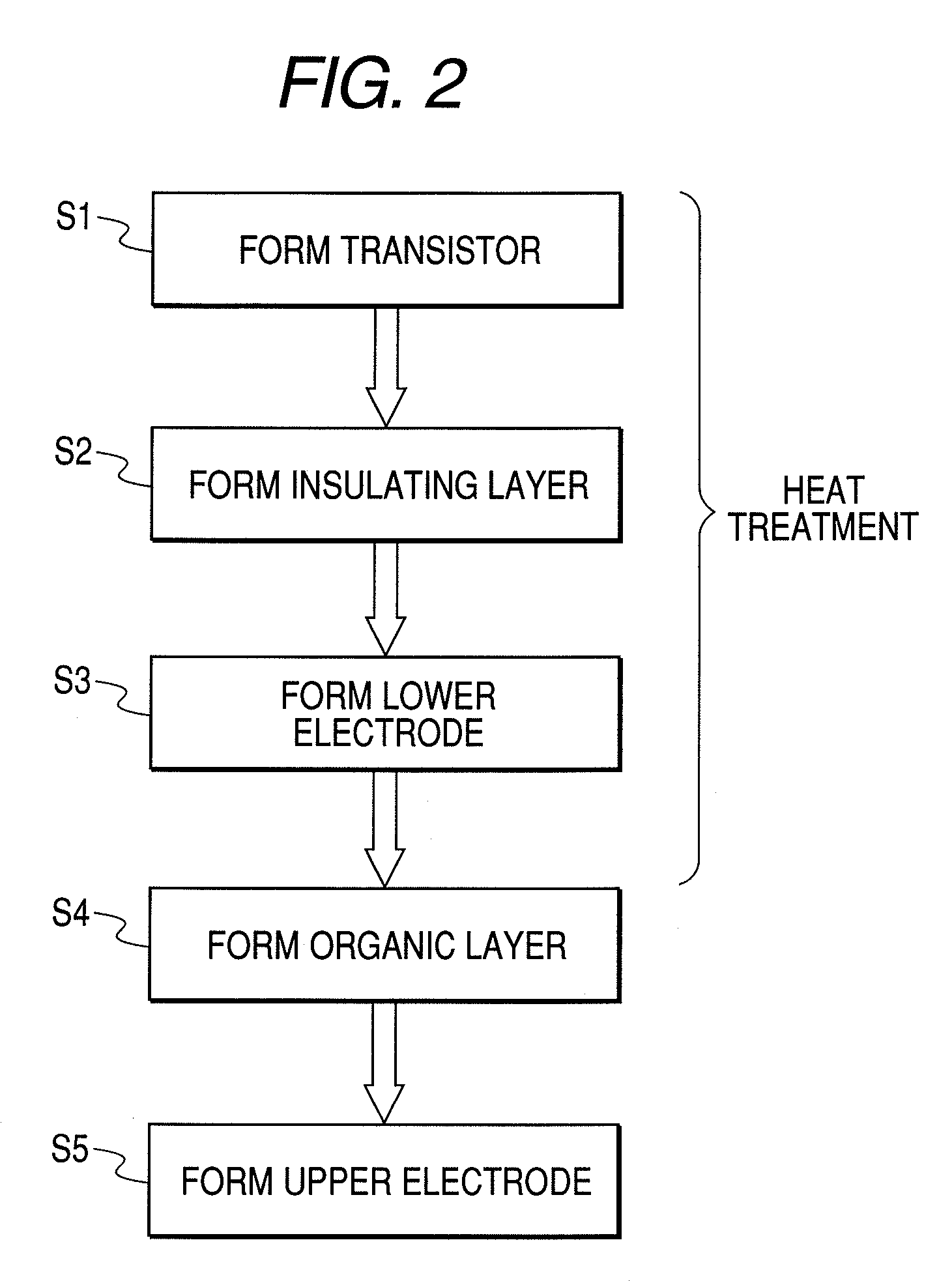

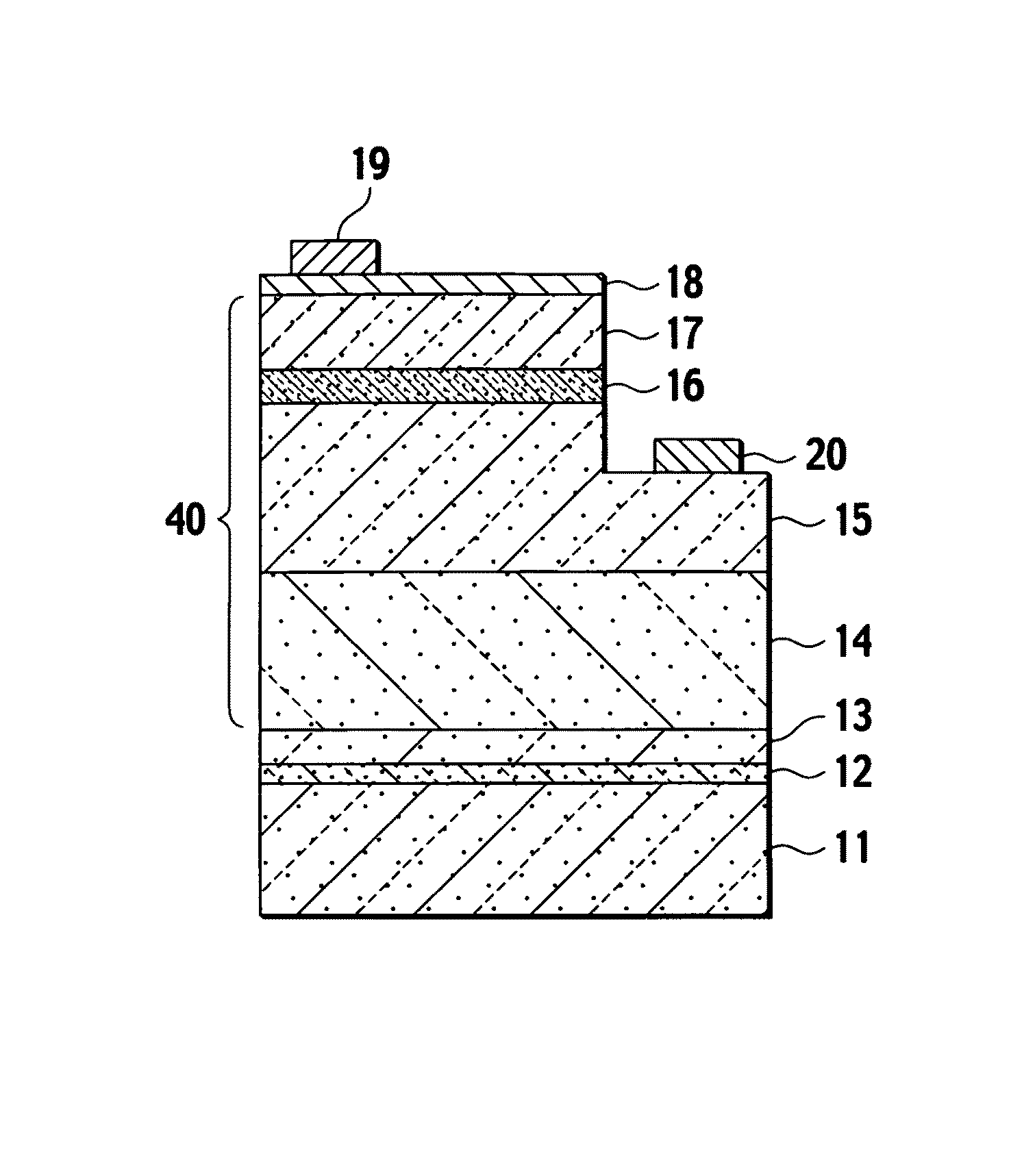

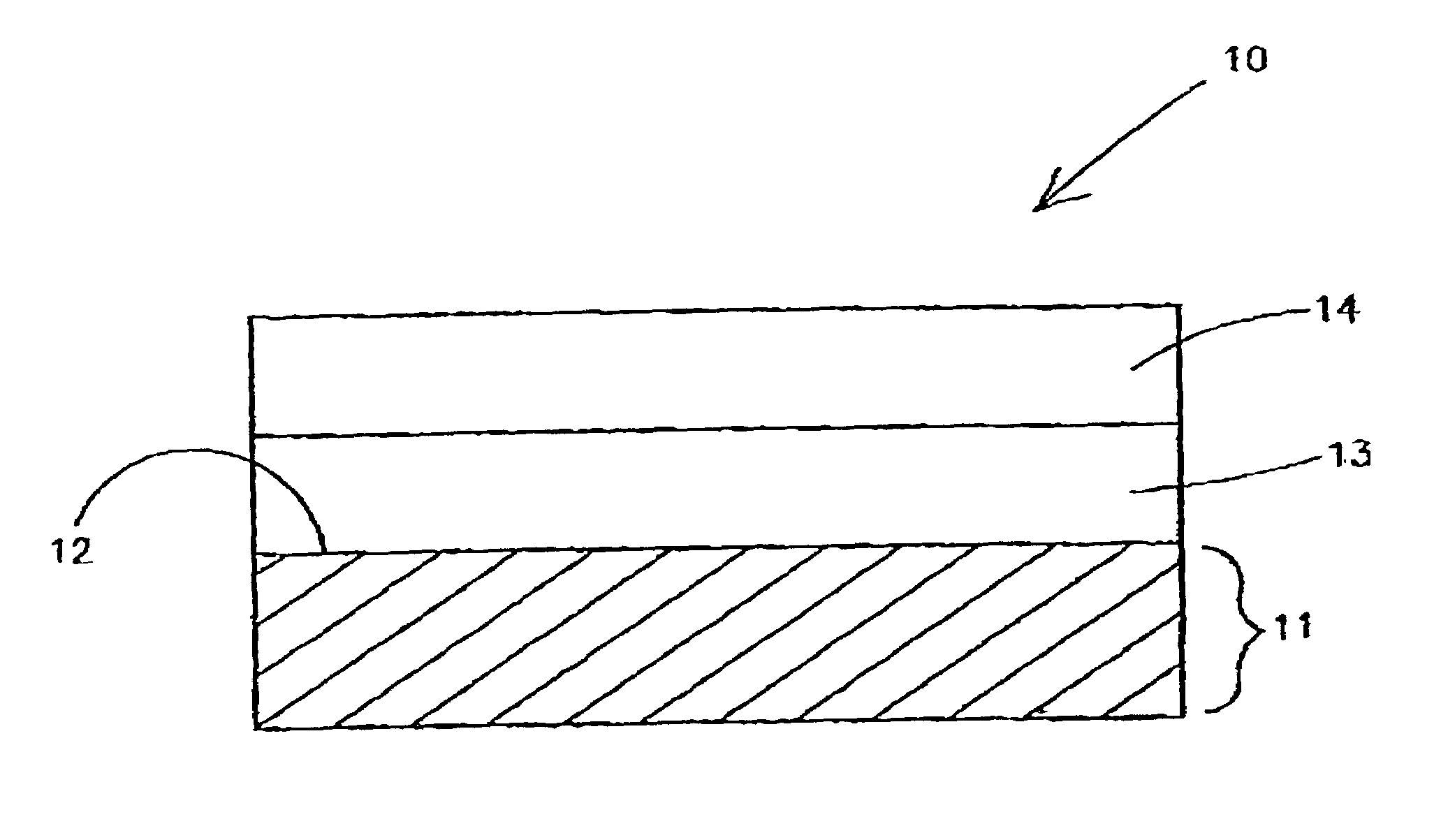

Light-emitting apparatus and production method thereof

Provided is a method of producing a light-emitting apparatus having a field effect transistor for driving an organic EL device, the field effect transistor including an oxide semiconductor containing at least one element selected from In and Zn, the method including the steps of: forming a field effect transistor on a substrate; forming an insulating layer; forming a lower electrode on the insulating layer; forming an organic layer for constituting an organic EL device on the lower electrode; forming an upper electrode on the organic layer; and after the step of forming the semiconductor layer of the field effect transistor and before the step of forming the organic layer, performing heat treatment such that an amount of a component that is desorbable as H2O from the field effect transistor during the step of forming the organic layer is less than 10−5 g / m2.

Owner:CANON KK

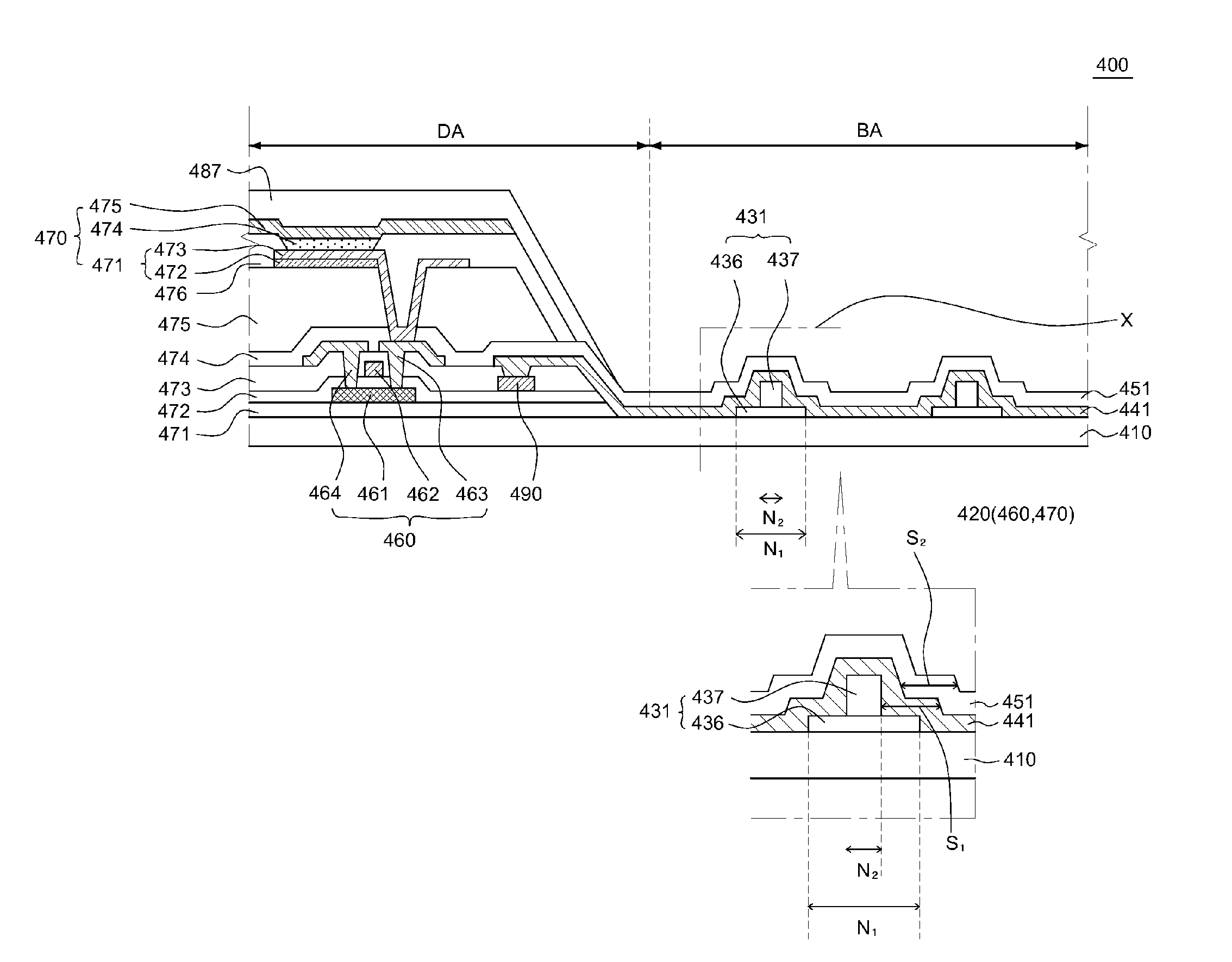

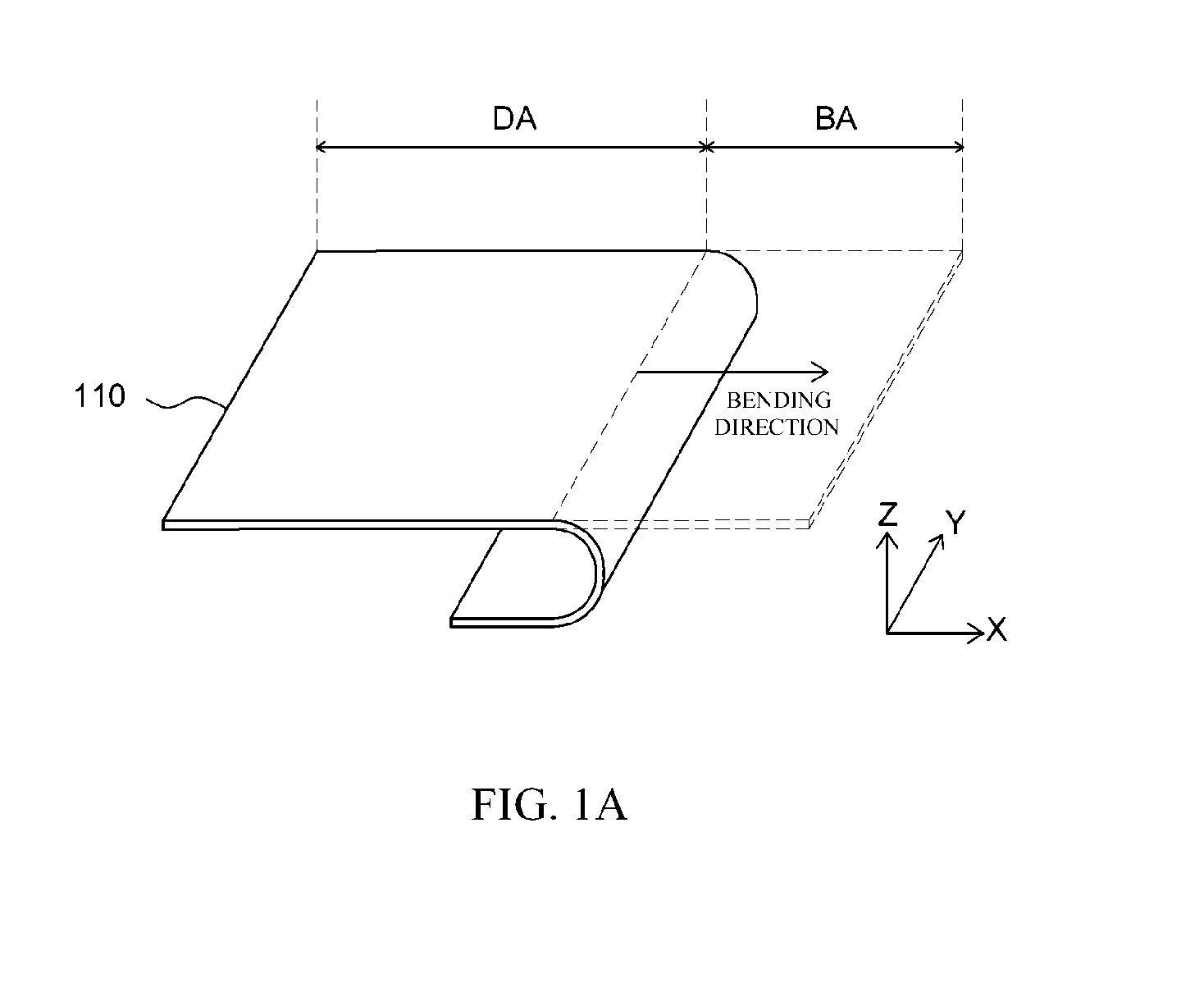

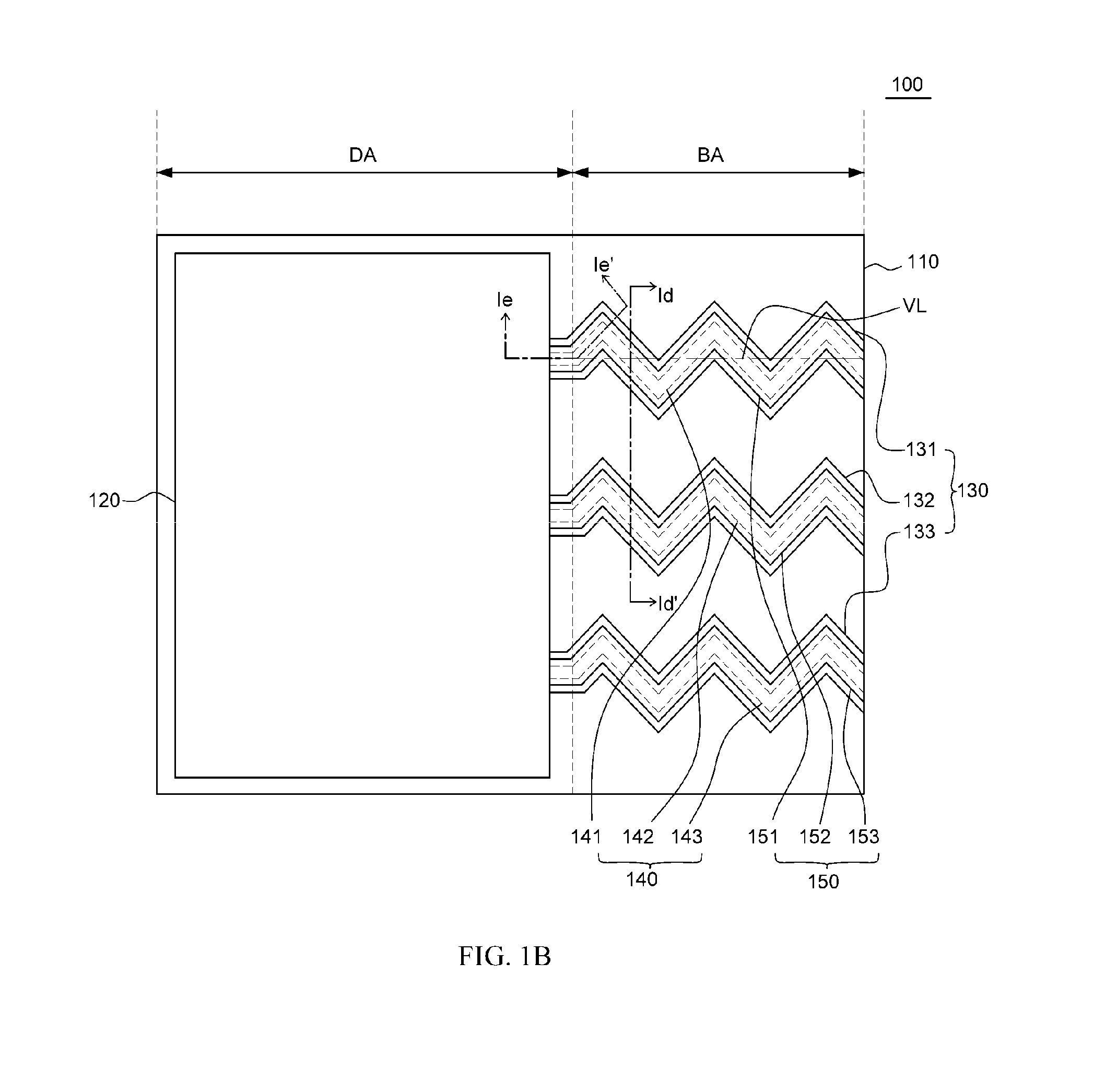

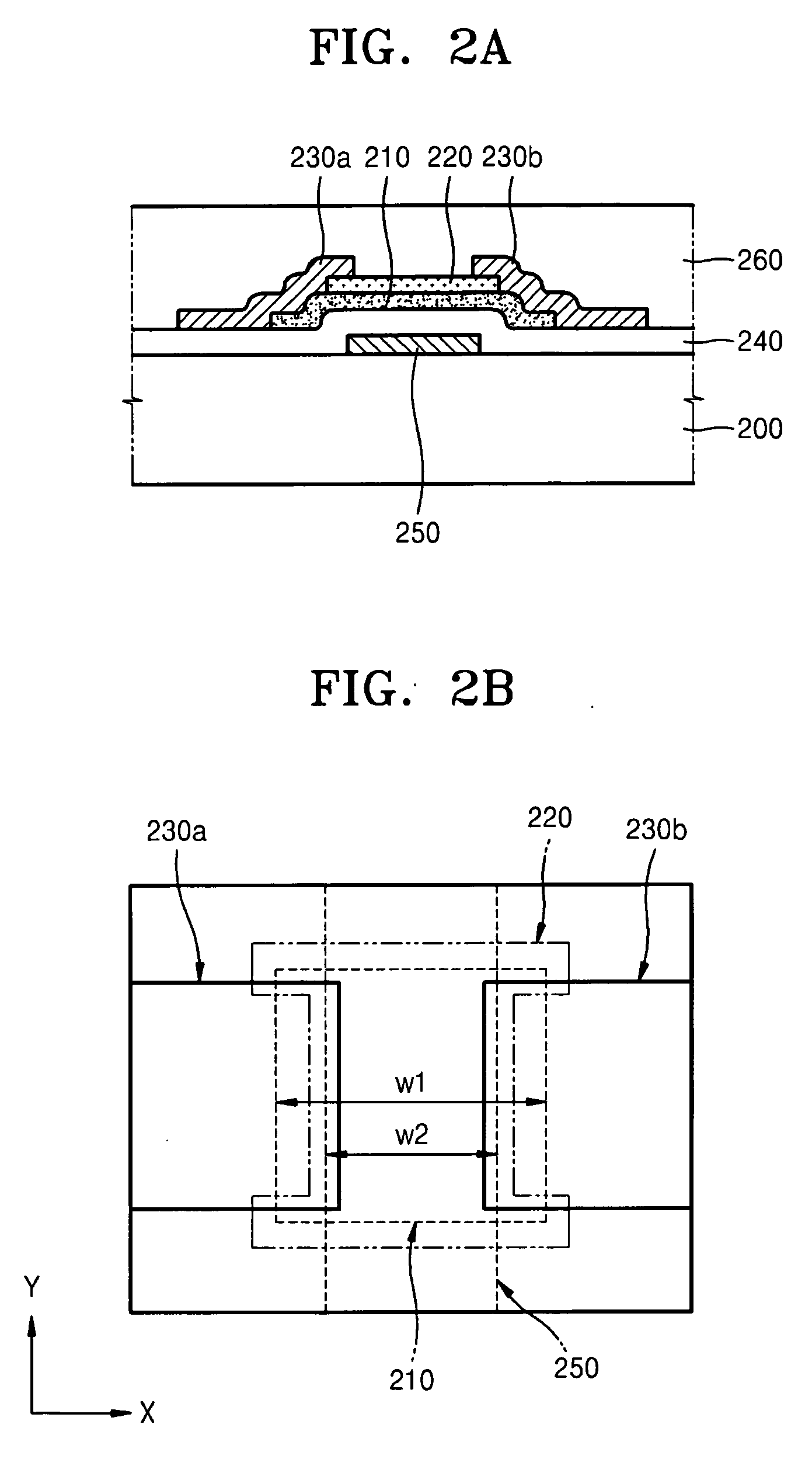

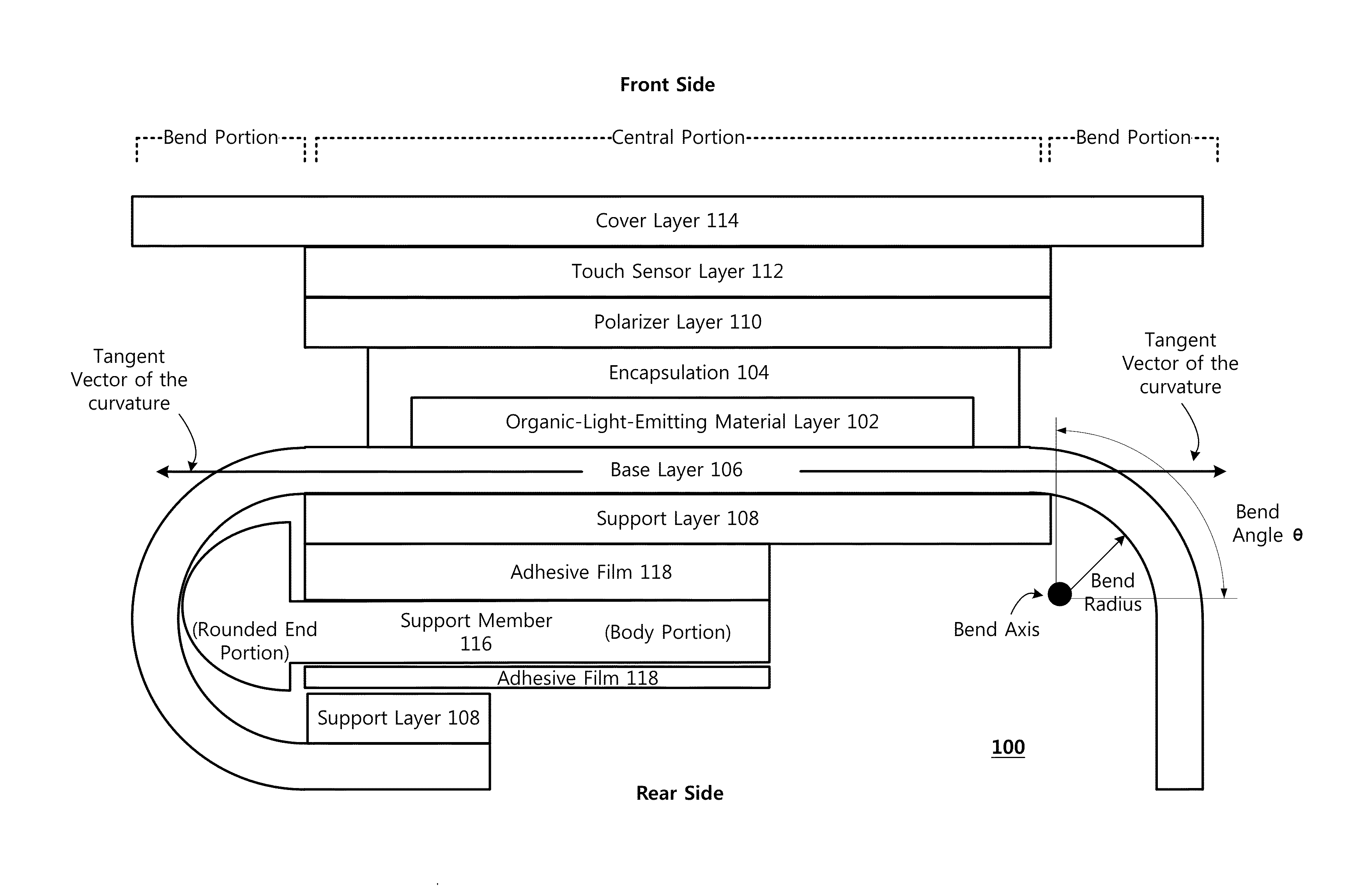

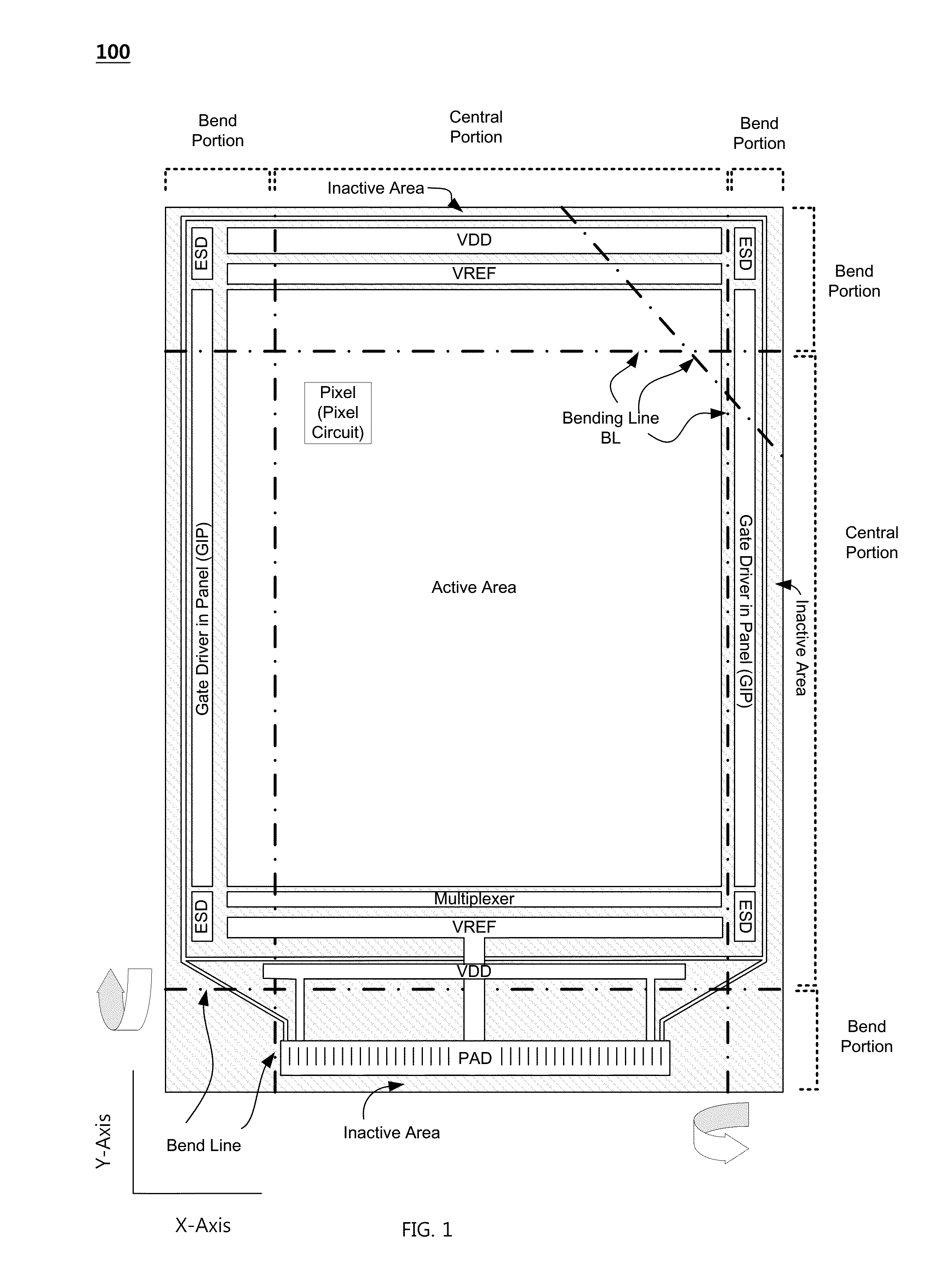

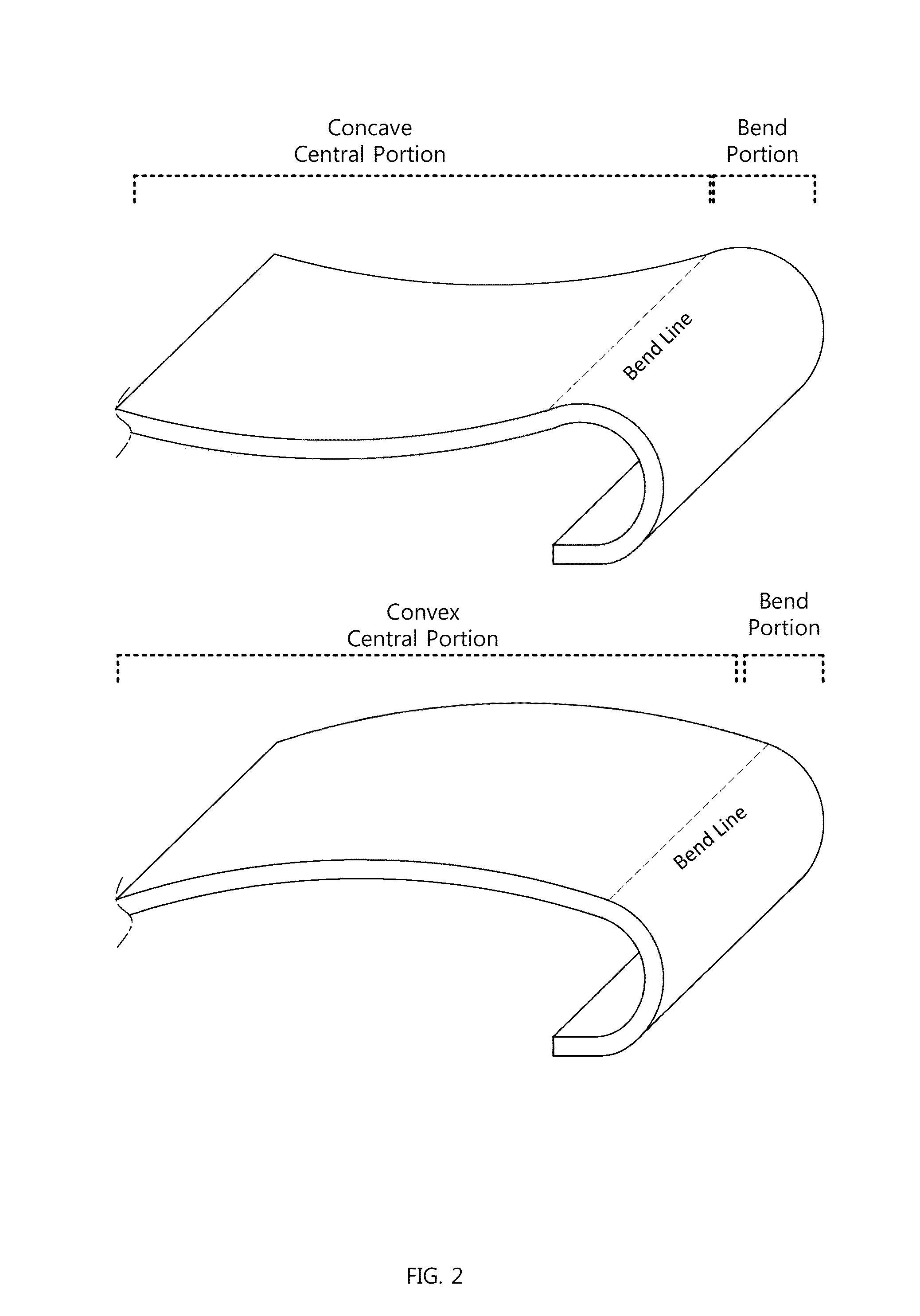

Flexible organic light emitting display device and method for manucaturing the same

ActiveUS20140232956A1Increase flexibilityReduce generationFinal product manufactureSolid-state devicesDisplay deviceEngineering

There is provided a flexible display having a new wire structure and a new insulating layer structure. A flexible display includes a flexible substrate having a first area and a second area. The second area is curved in a non-zero angle relative to the plane of the first area. The flexible display further includes a plurality of wires that extend over from the first area to the second area of the flexible substrate. Each of the wires is covered by an upper insulating pattern, which is separated from other upper insulating pattern. Each upper insulating pattern covering the wire has substantially the same trace pattern shape of the corresponding wire thereunder. Accordingly, by adopting the above-described wire structure and upper insulating layer structure, crack generation and propagation in the wires and the insulating layers from bending of the flexible display can be minimized.

Owner:LG DISPLAY CO LTD

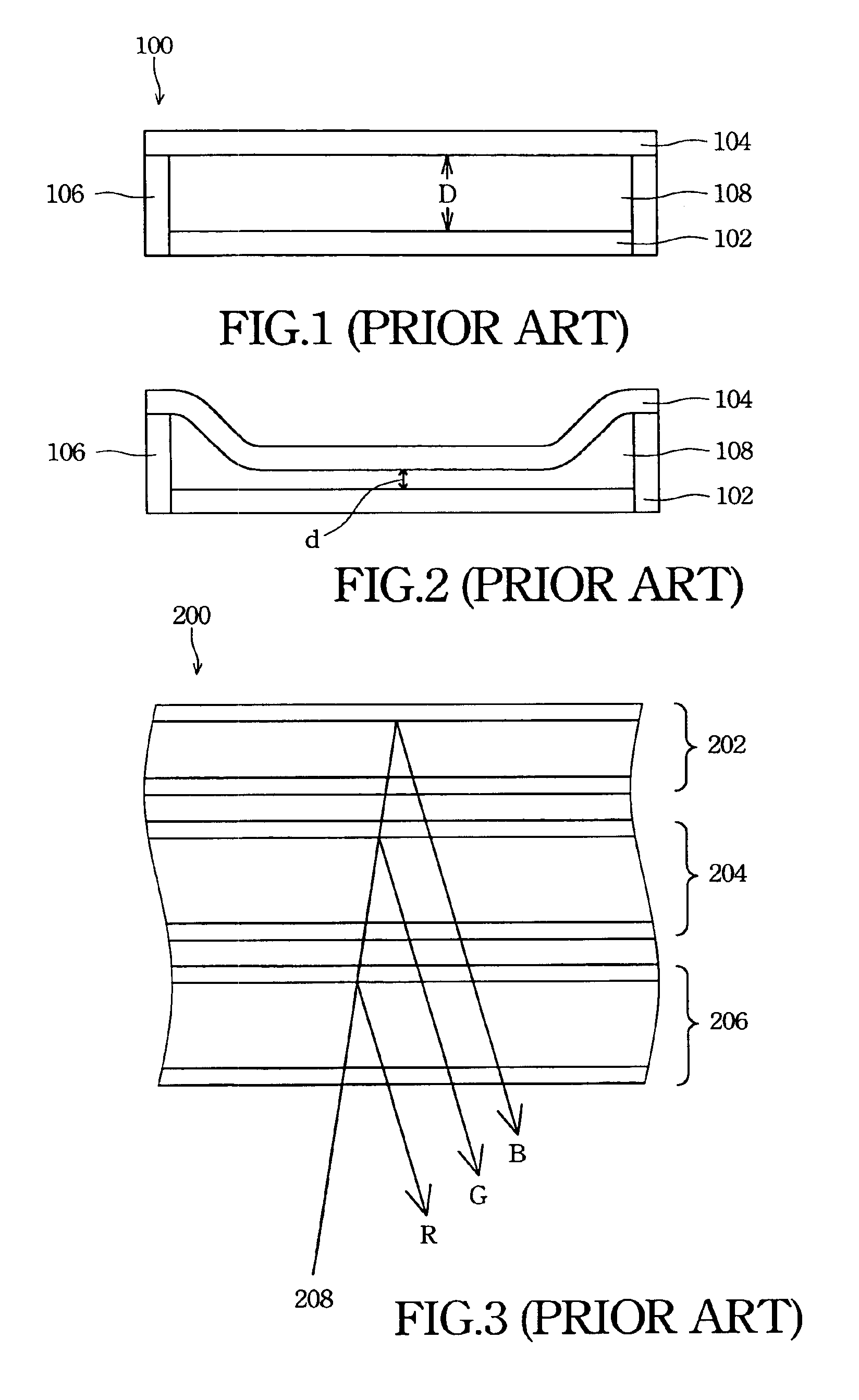

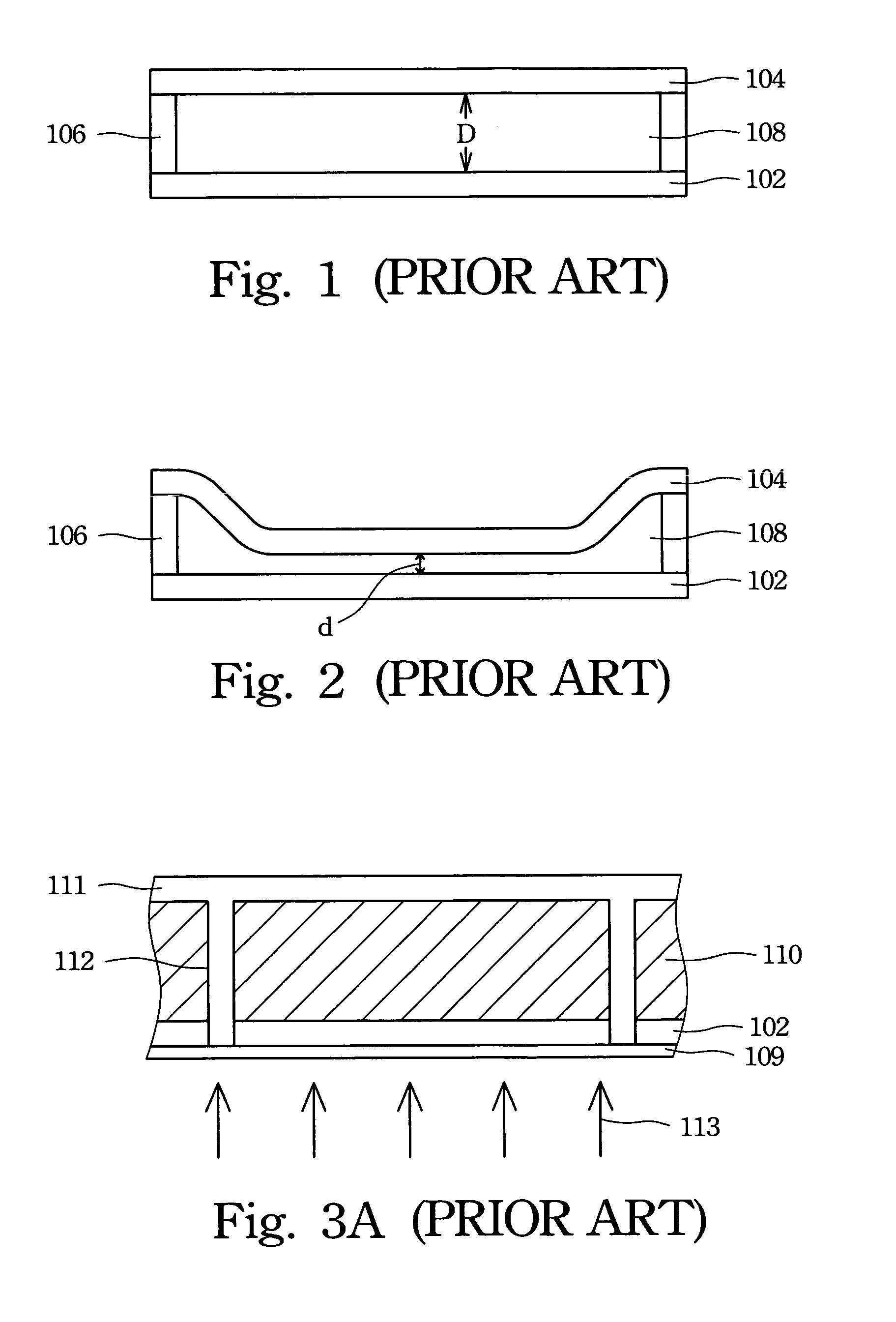

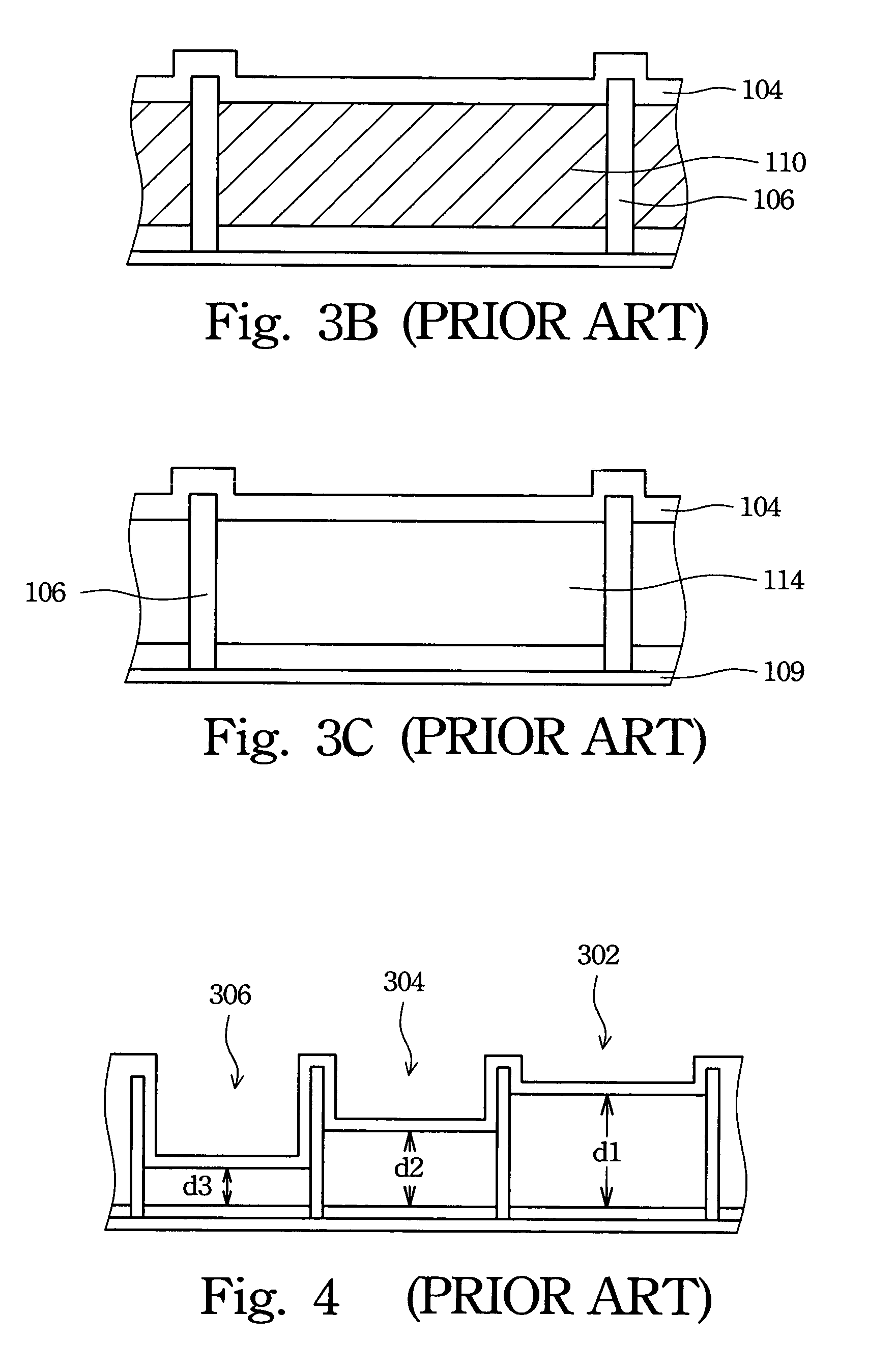

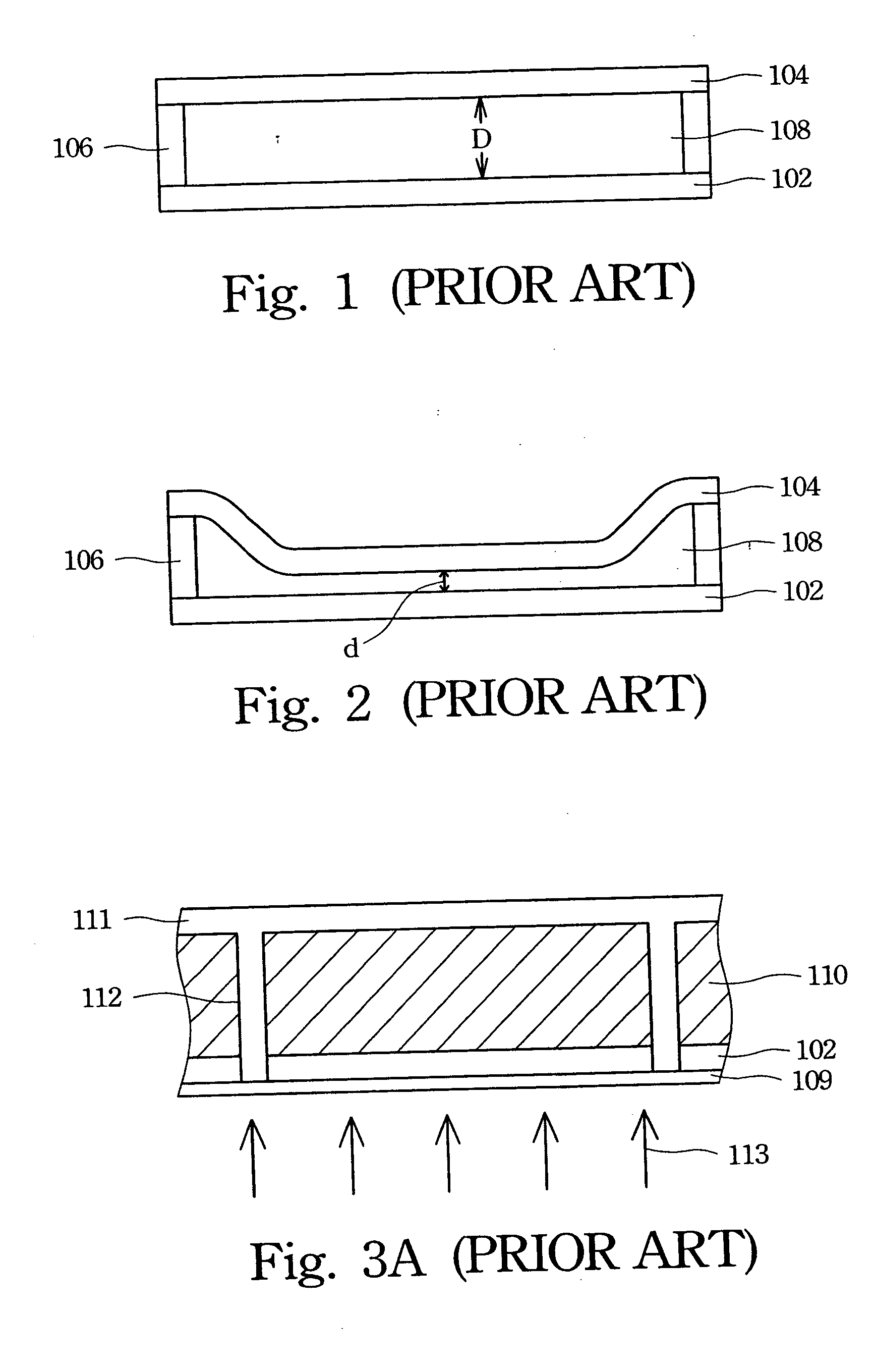

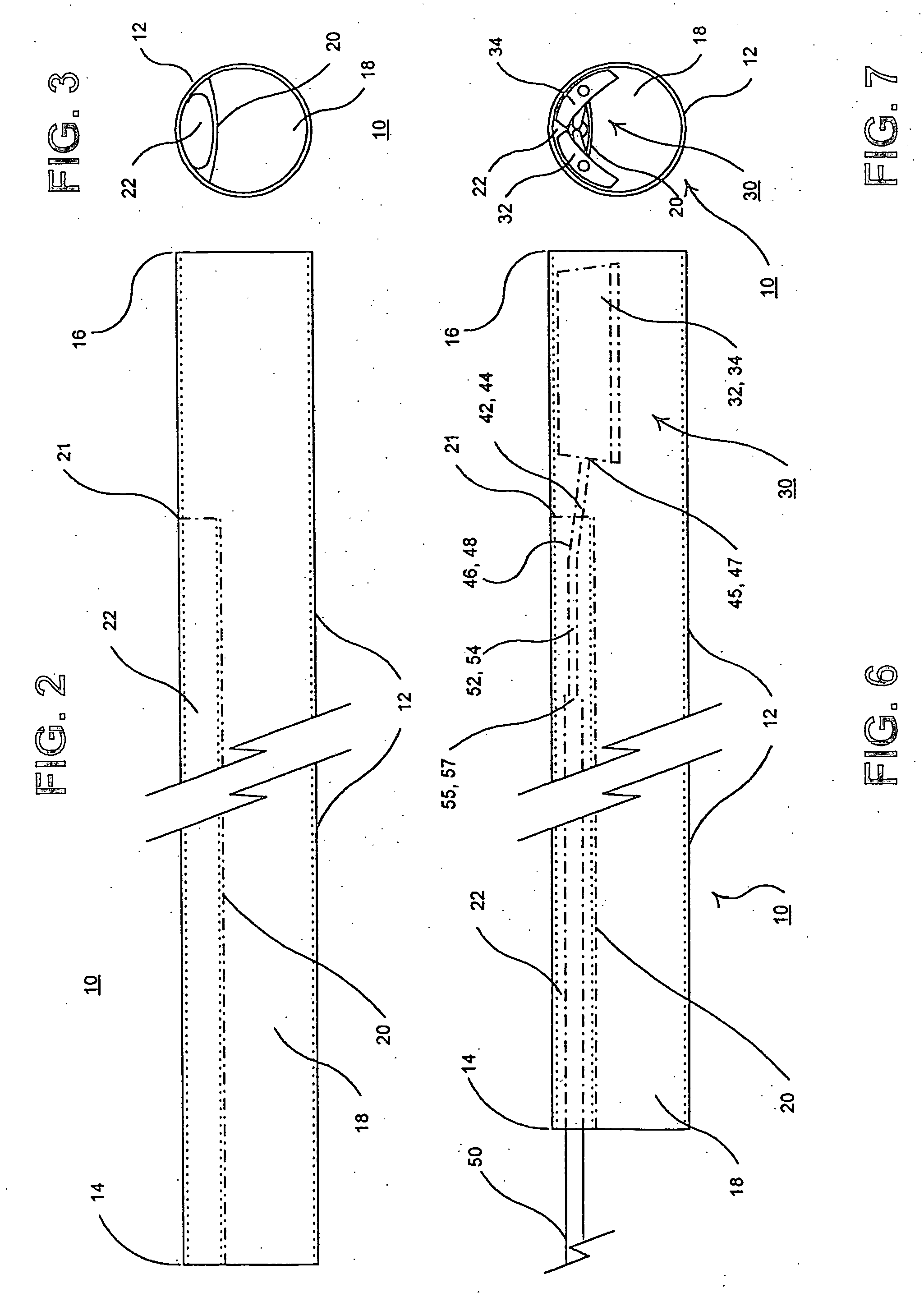

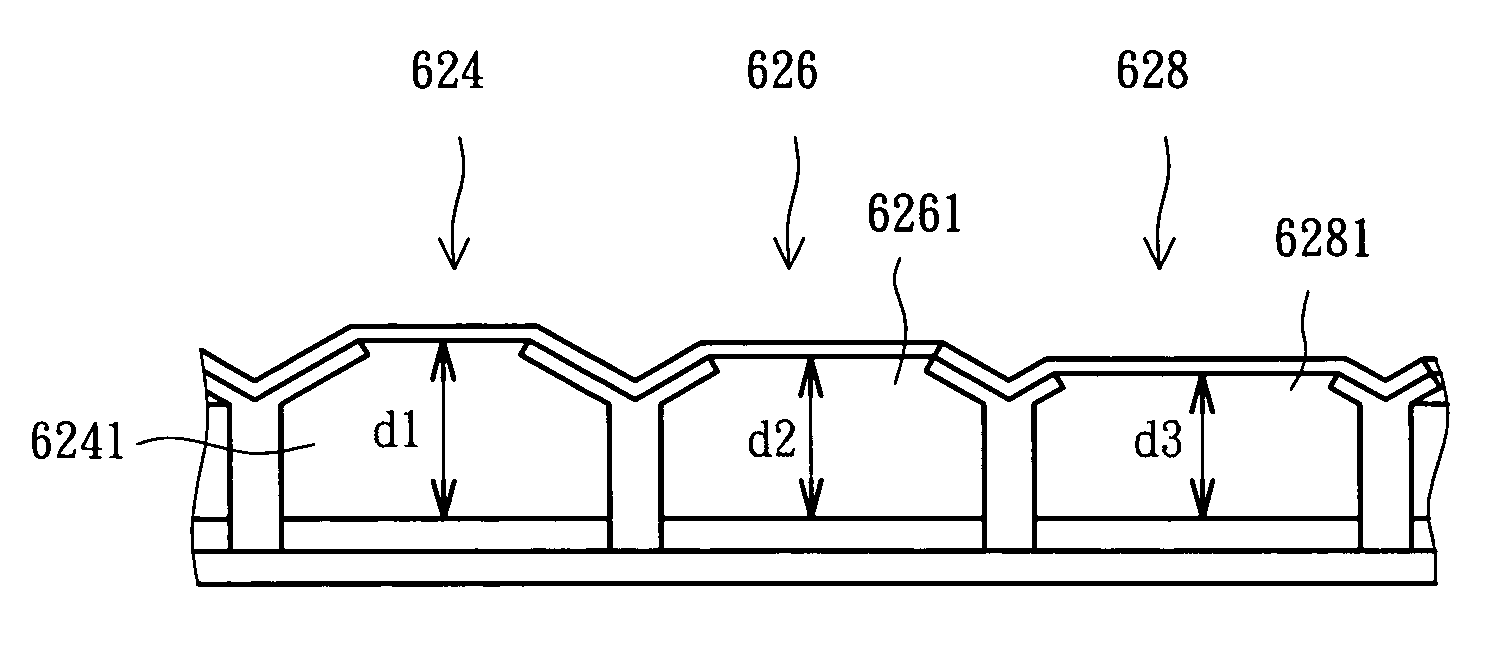

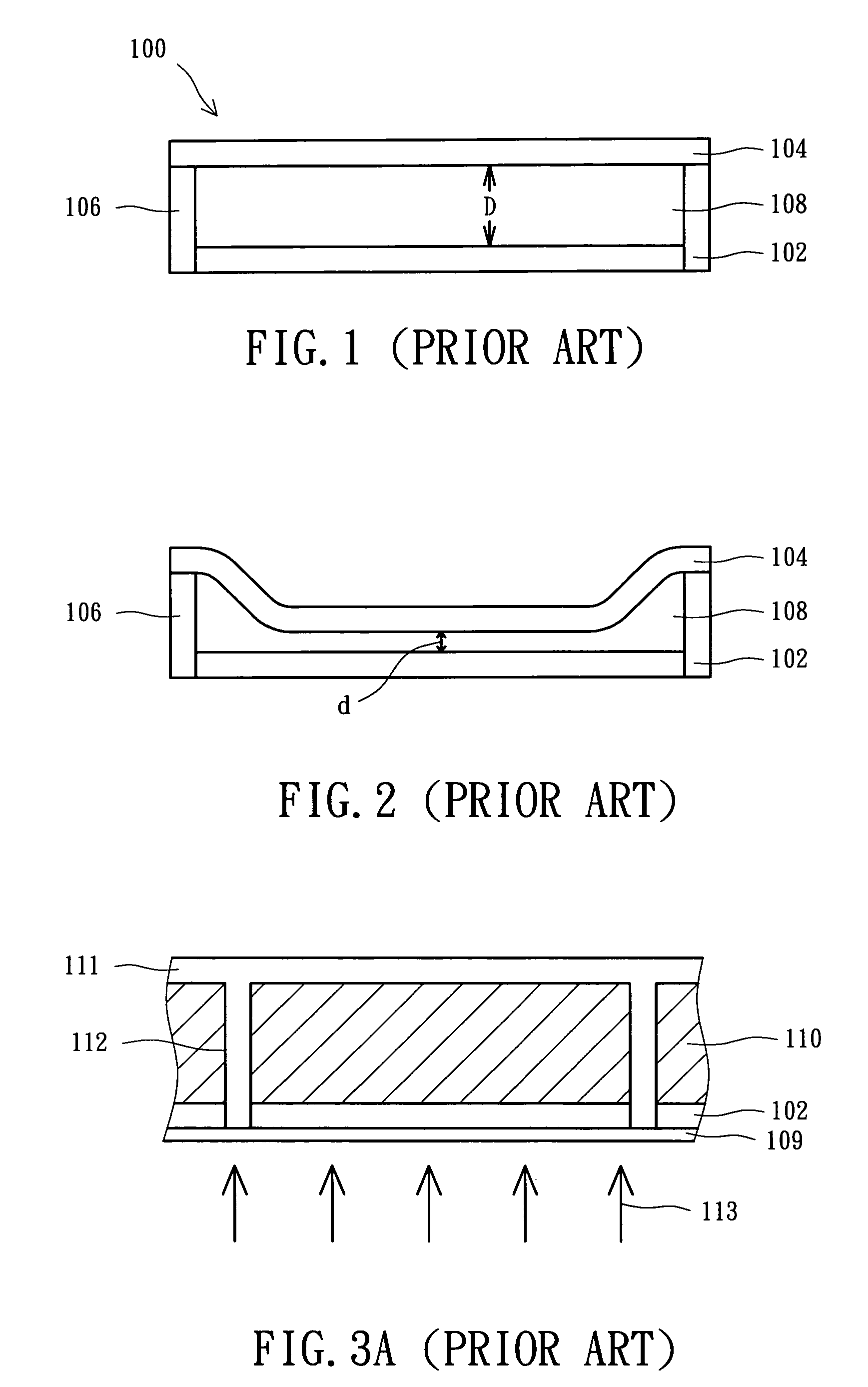

Structure of an optical interference display cell

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

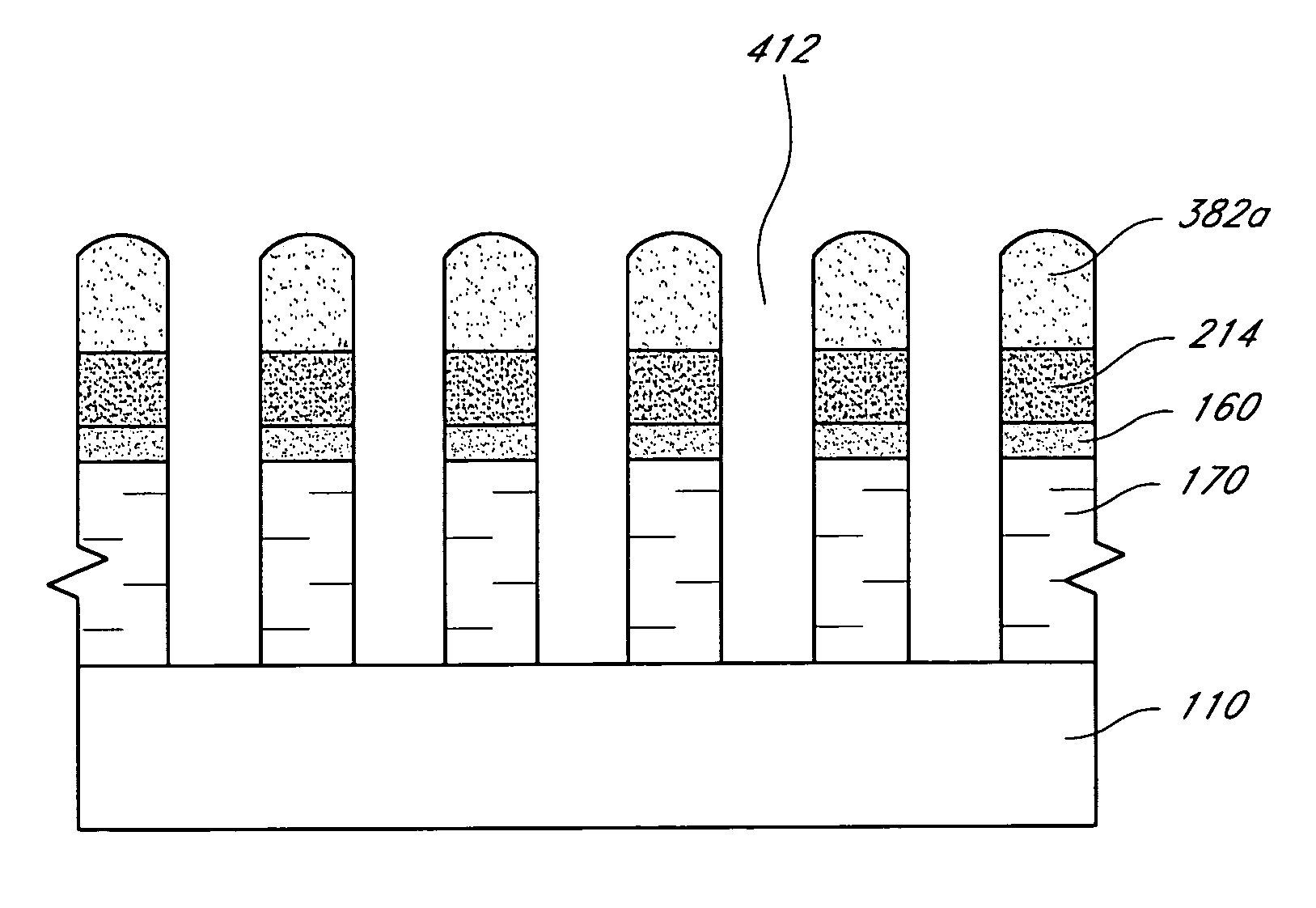

Release strategies for making transferable semiconductor structures, devices and device components

ActiveUS7932123B2Low costReduce layeringFinal product manufactureNanoinformaticsSemiconductor structureElectron

Provided are methods for making a device or device component by providing a multilayer structure having a plurality of functional layers and a plurality of release layers and releasing the functional layers from the multilayer structure by separating one or more of the release layers to generate a plurality of transferable structures. The transferable structures are printed onto a device substrate or device component supported by a device substrate. The methods and systems provide means for making high-quality and low-cost photovoltaic devices, transferable semiconductor structures, (opto-)electronic devices and device components.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

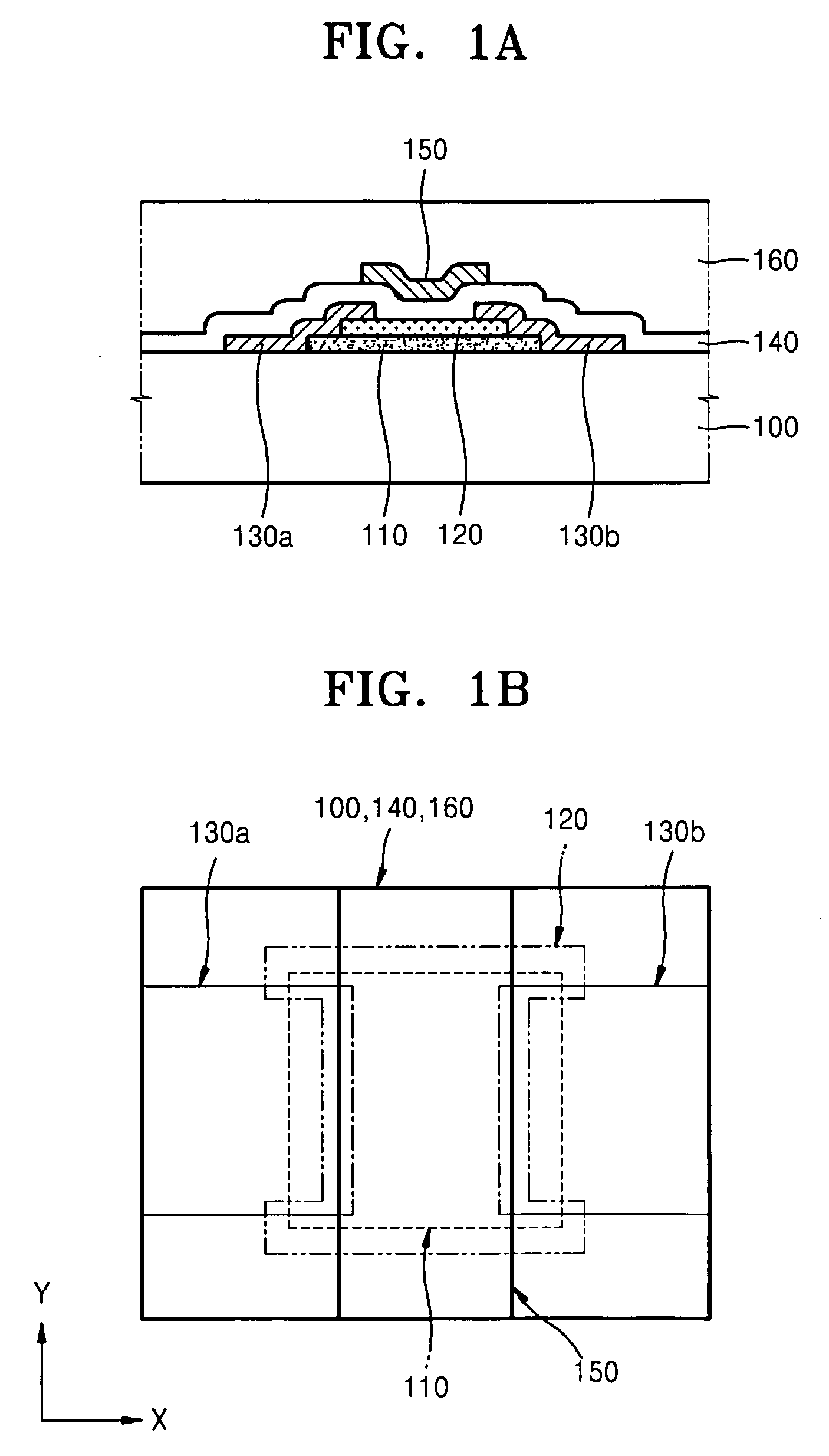

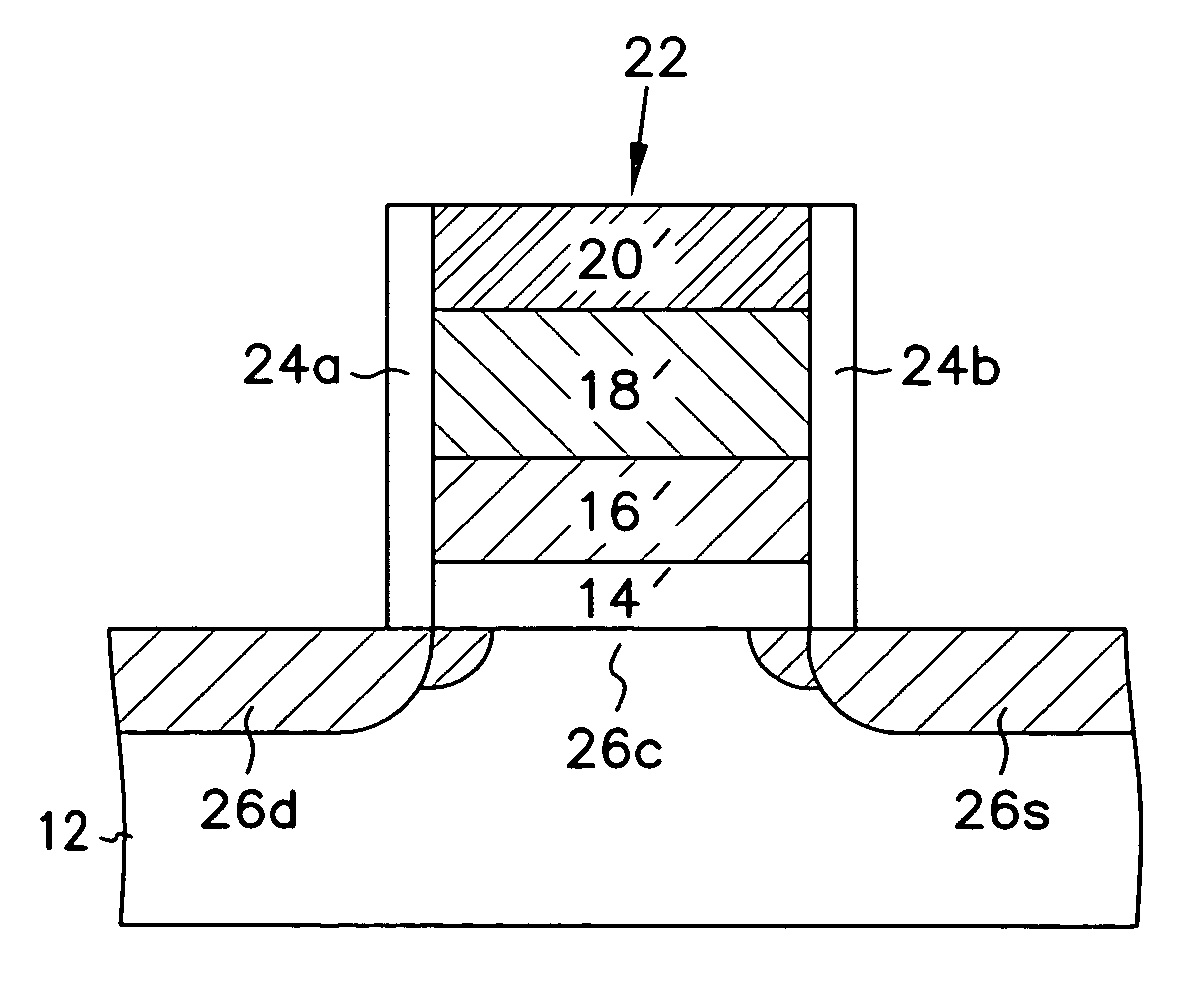

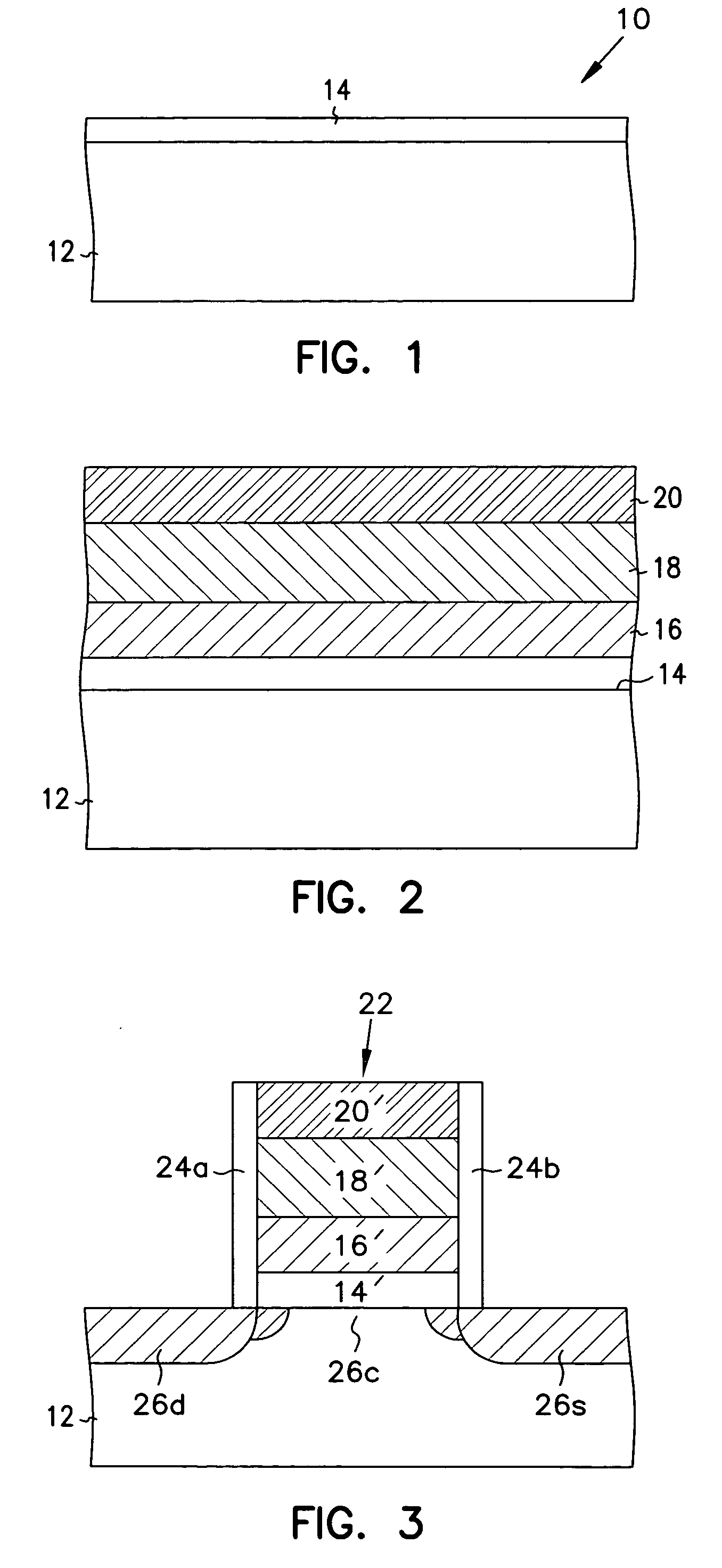

Thin film transistor and method of forming the same

ActiveUS20080197350A1Reduce layeringReduce degradationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A thin film transistor (TFT) may include a channel layer, a source electrode, a drain electrode, a protective layer, a gate electrode, and / or a gate insulating layer. The channel layer may include an oxide semiconductor material. The source electrode and the drain electrode may face each other on the channel layer. The protective layer may be under the source electrode and the drain electrode and / or may cover the channel layer. The gate electrode may be configured to apply an electric field to the channel layer. The gate insulating layer may be interposed between the gate electrode and the channel layer.

Owner:SAMSUNG ELECTRONICS CO LTD

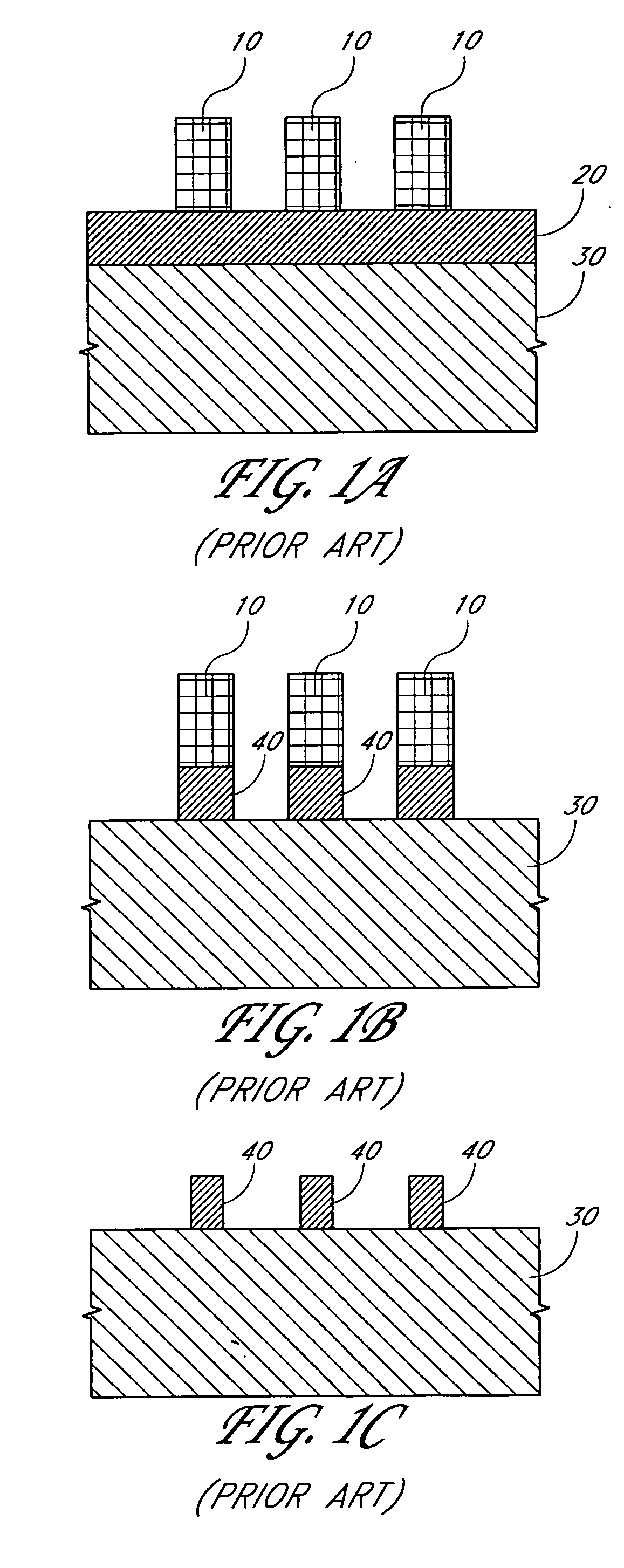

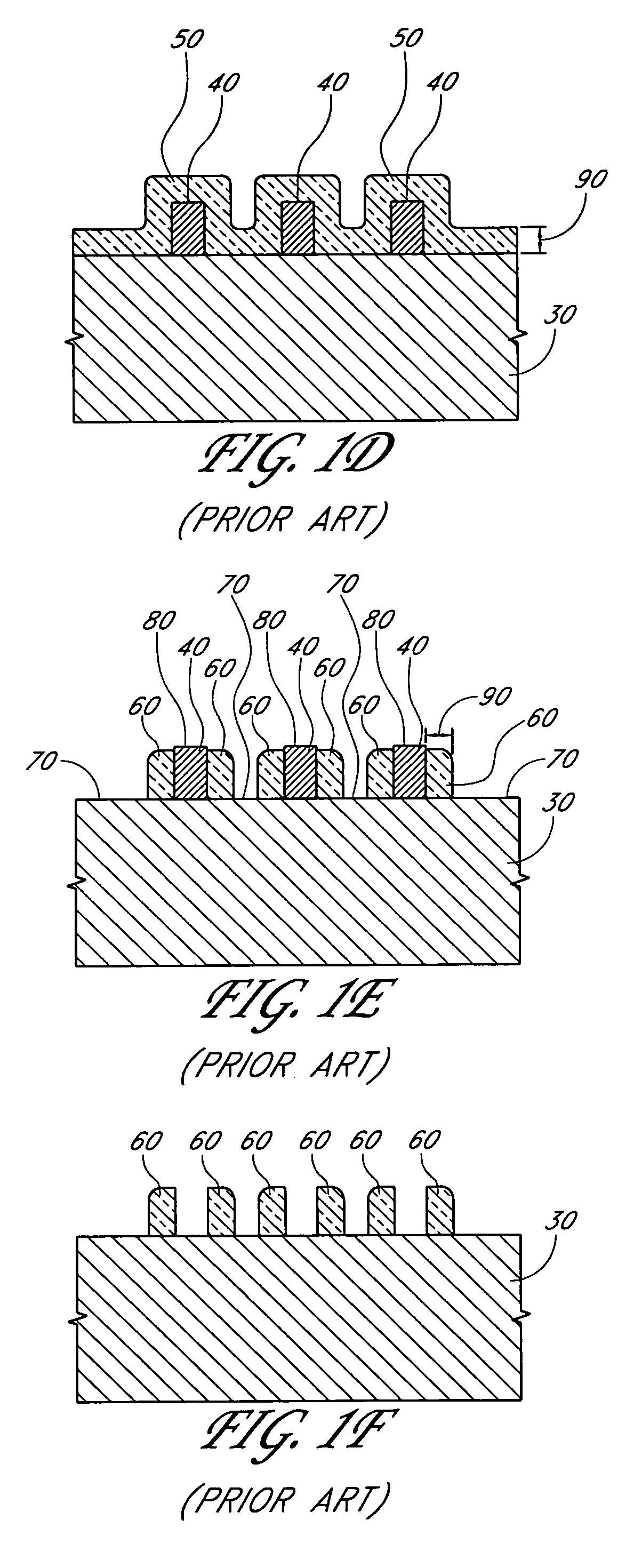

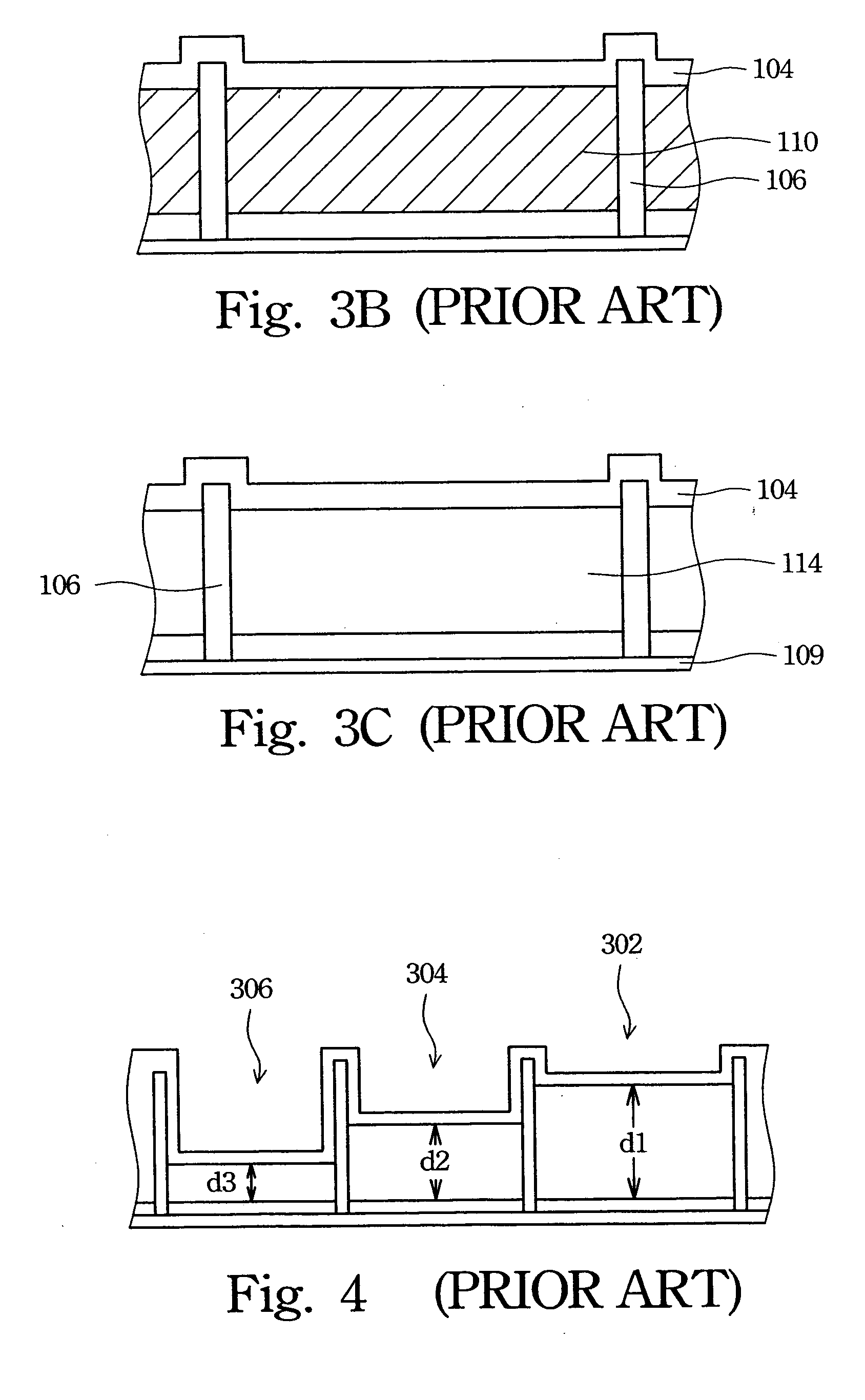

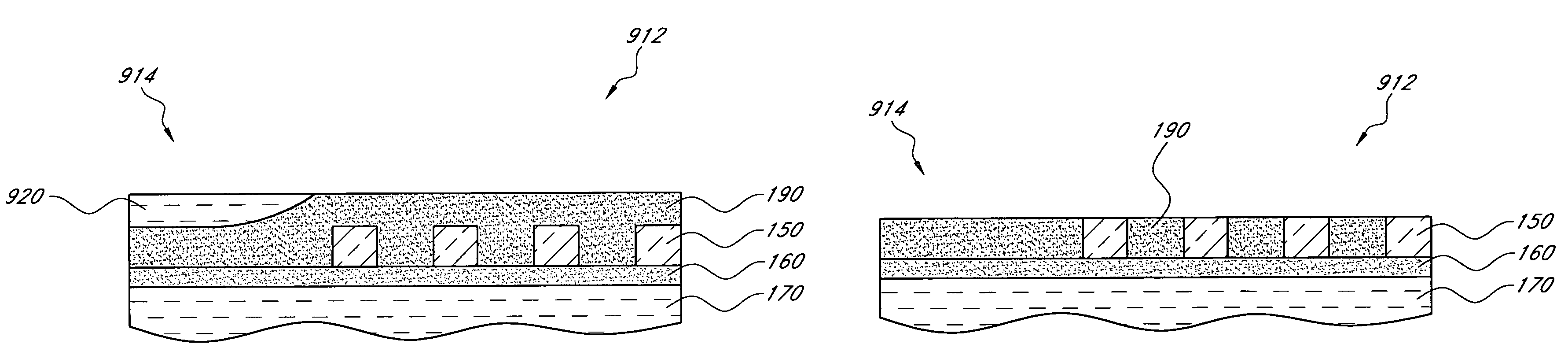

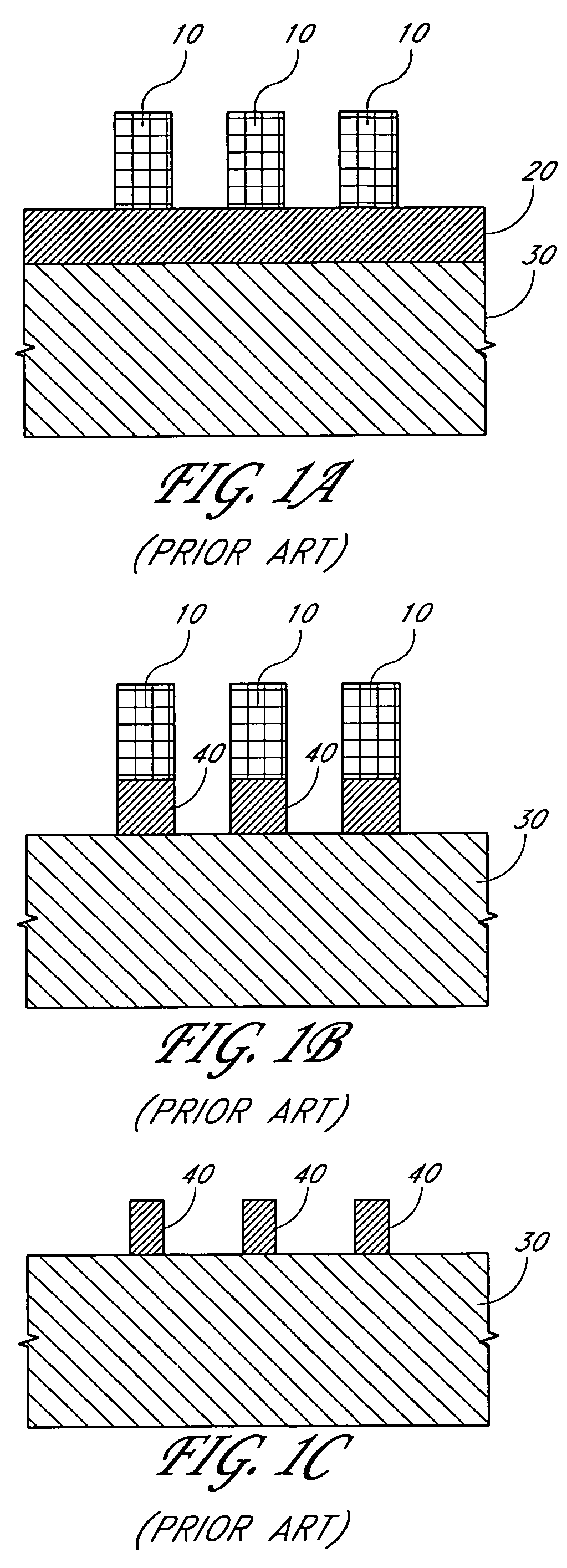

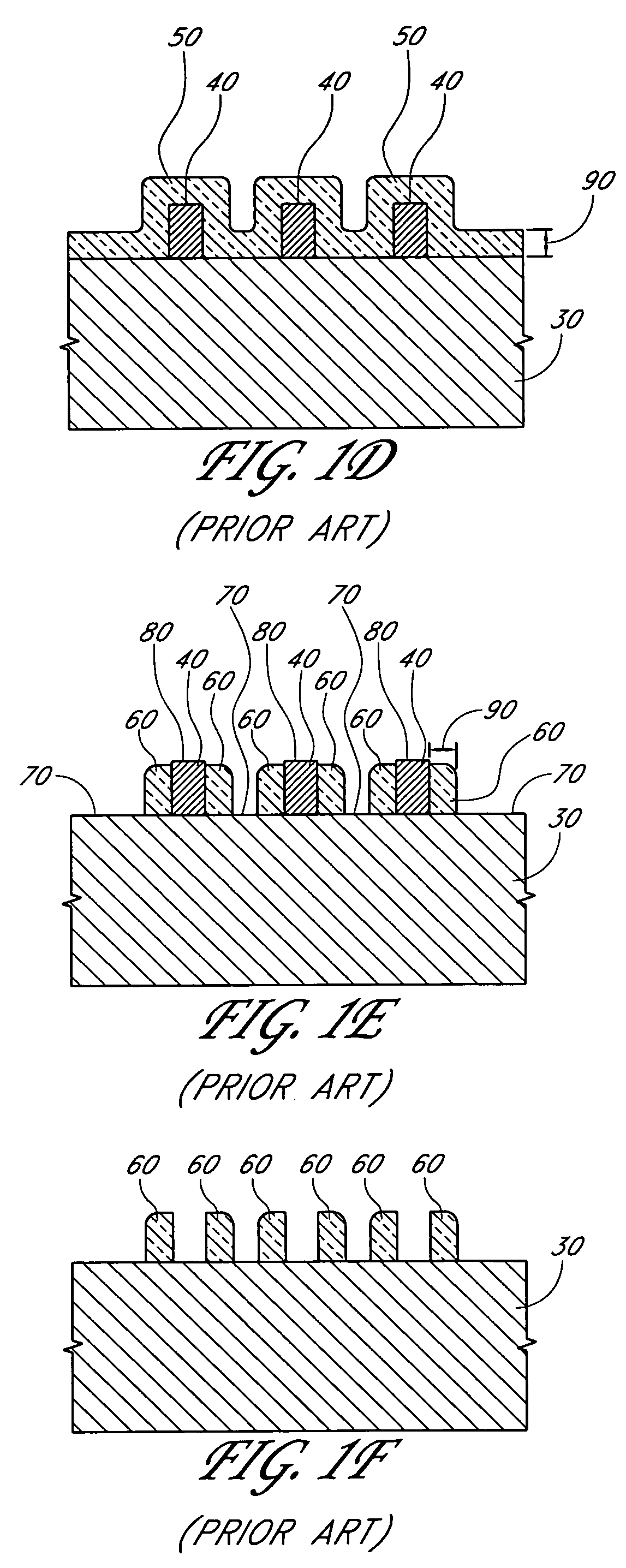

Protective coating for planarization

ActiveUS20070049032A1Reduce the overall heightReduce layeringSemiconductor/solid-state device manufacturingComputer sciencePhotolithography

Various pattern transfer and etching steps can be used to create features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form superimposed, pitch-reduced patterns of crossing elongate features that can be consolidated into a single layer. Planarizing techniques using a filler layer and a protective layer are disclosed. Portions of an integrated circuit having different heights can be etched to a common plane.

Owner:MICRON TECH INC

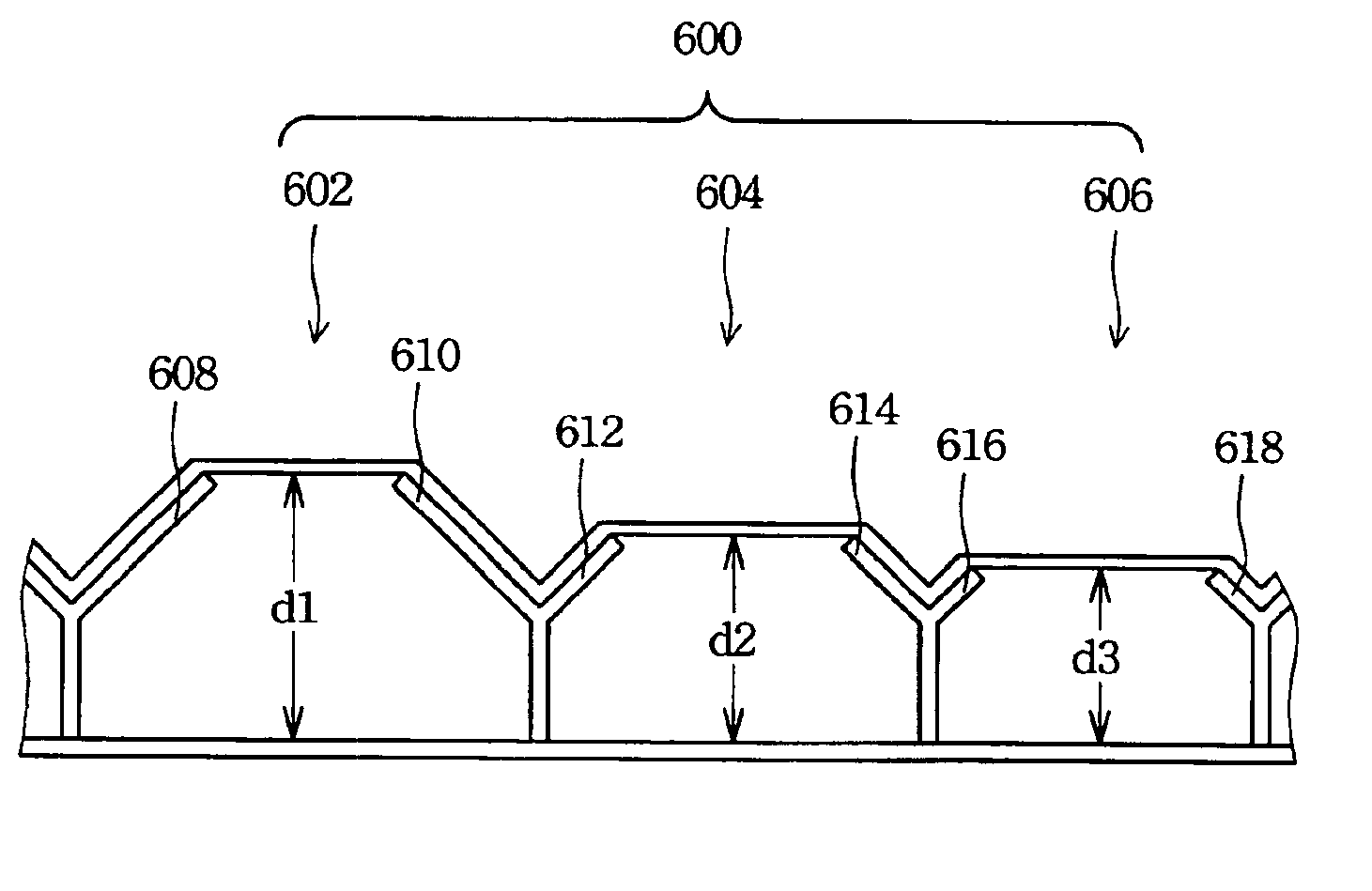

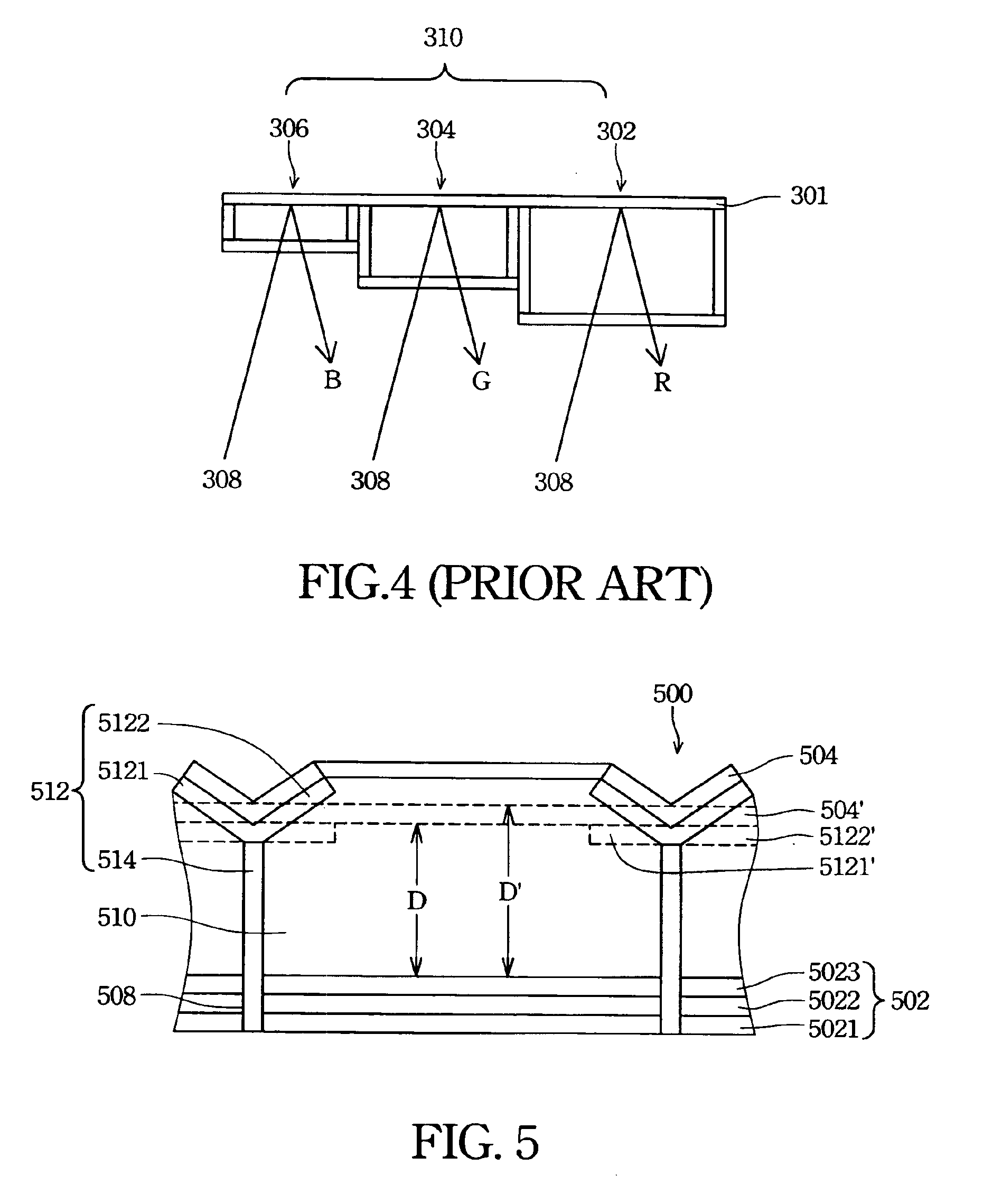

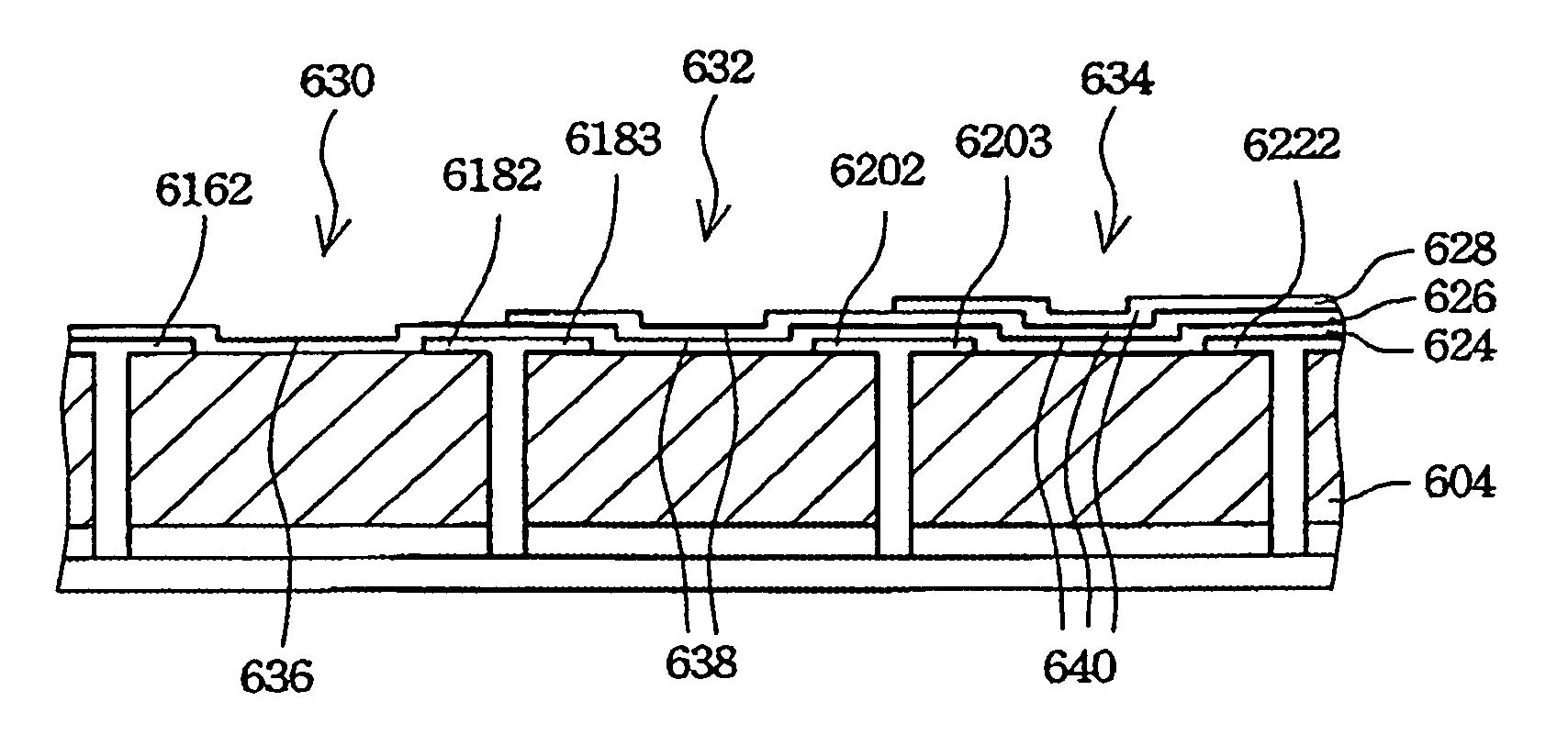

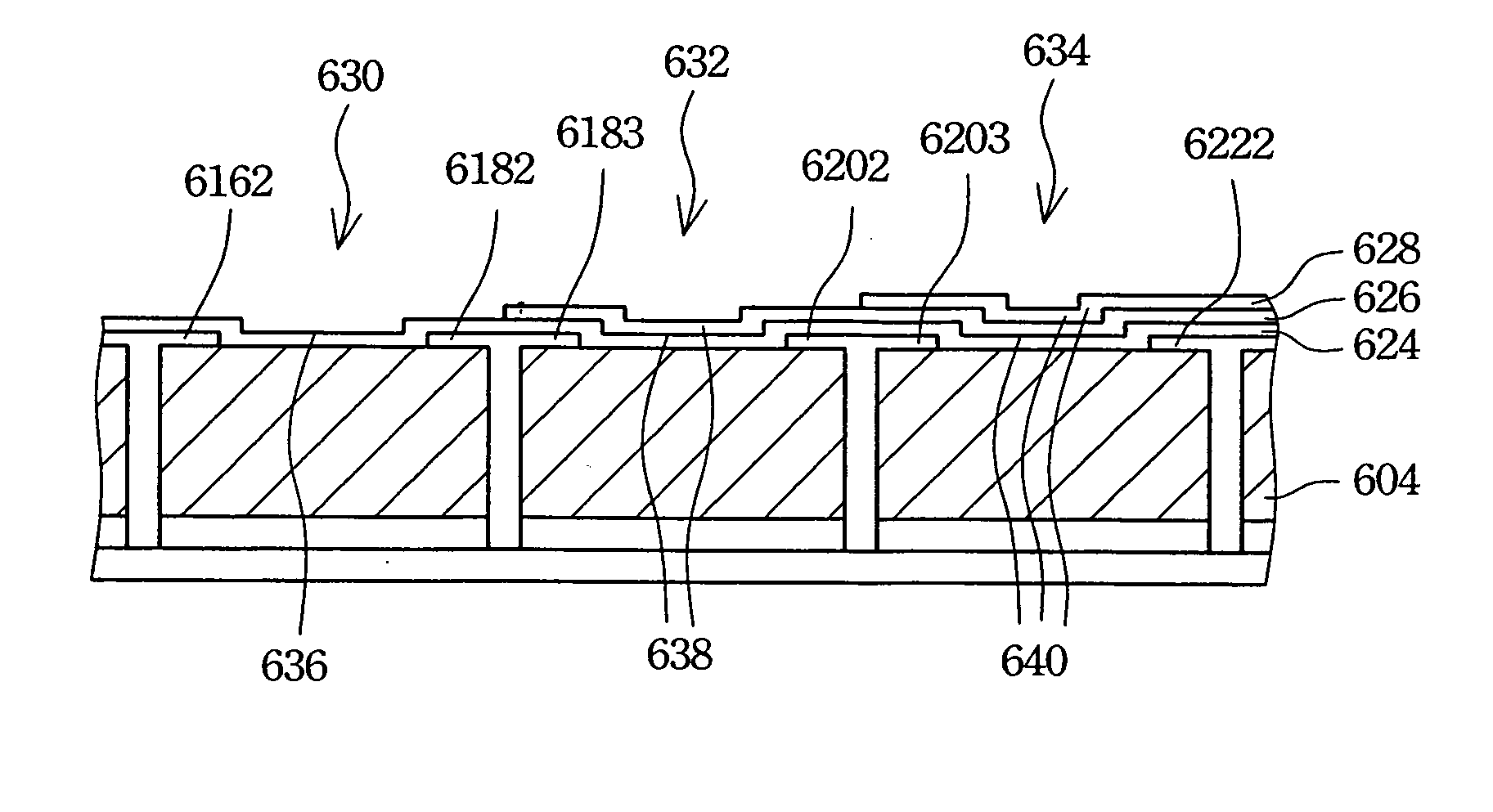

Interference display unit

InactiveUS6995890B2Increase brightnessSimple and easy manufacturing processDecorative surface effectsOptical filtersEngineeringHeat treated

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Method for fabricating an interference display unit

InactiveUS20050168849A1Increase brightnessSimple and easy manufacturing processMirrorsDecorative surface effectsEngineeringHeat treated

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

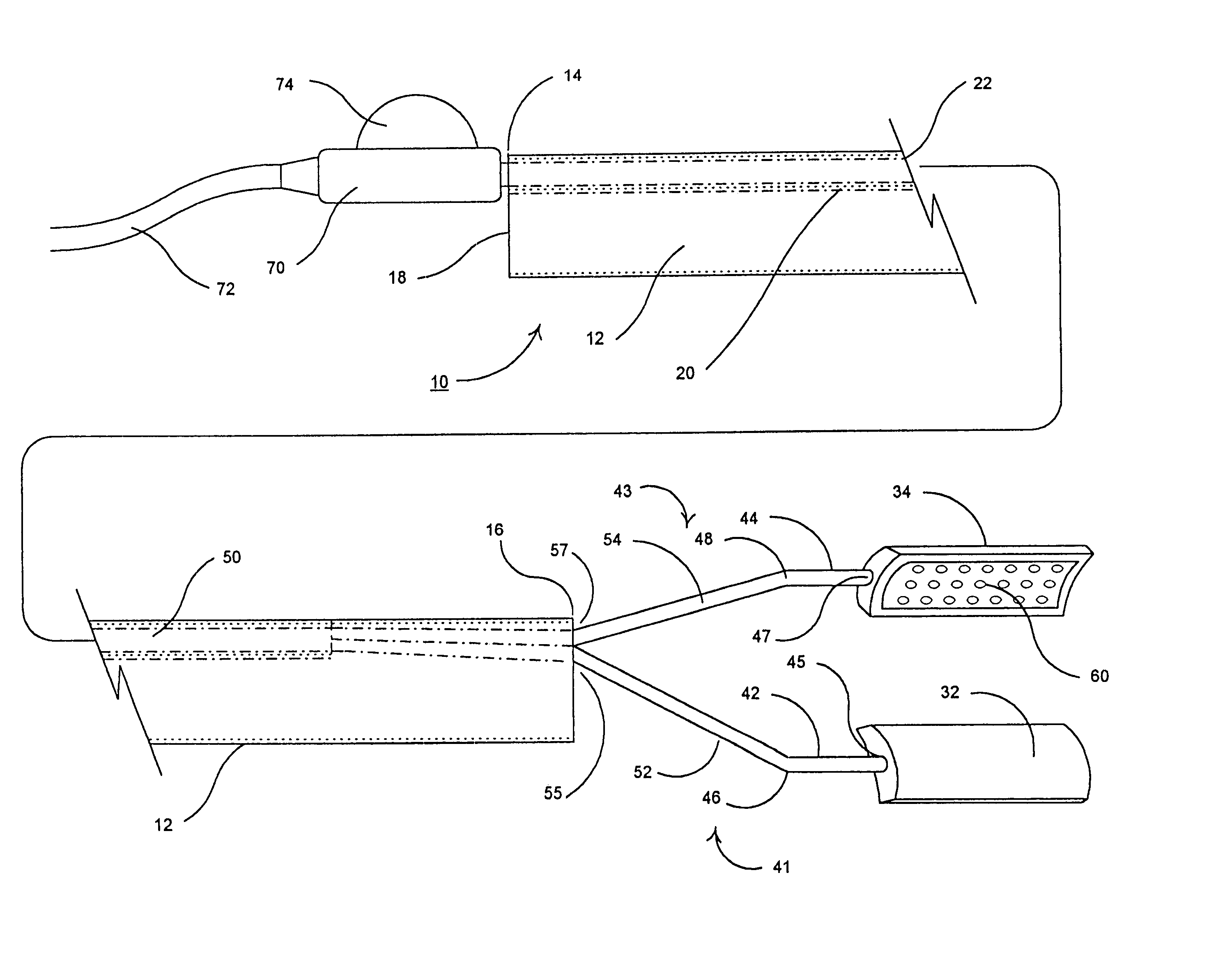

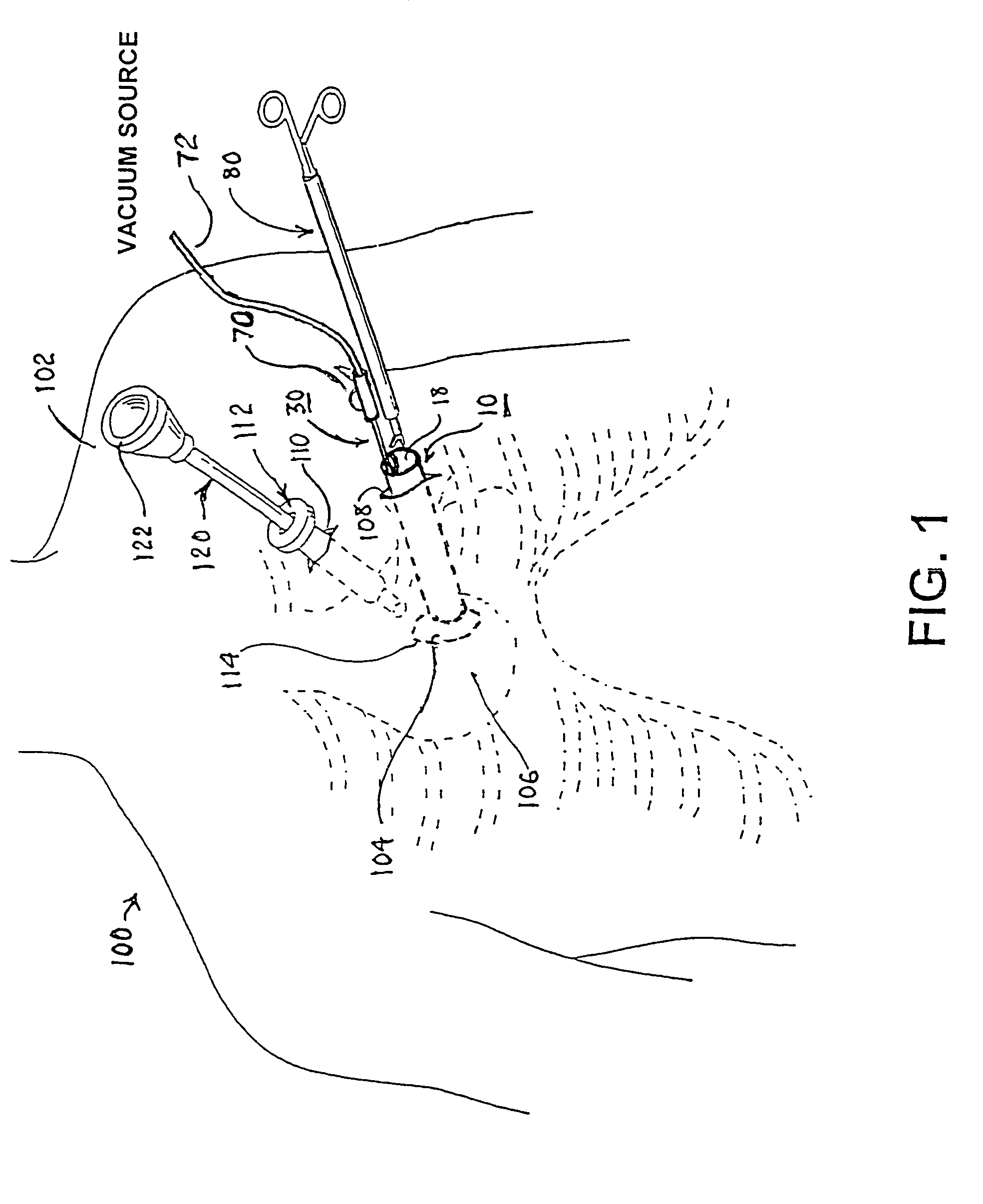

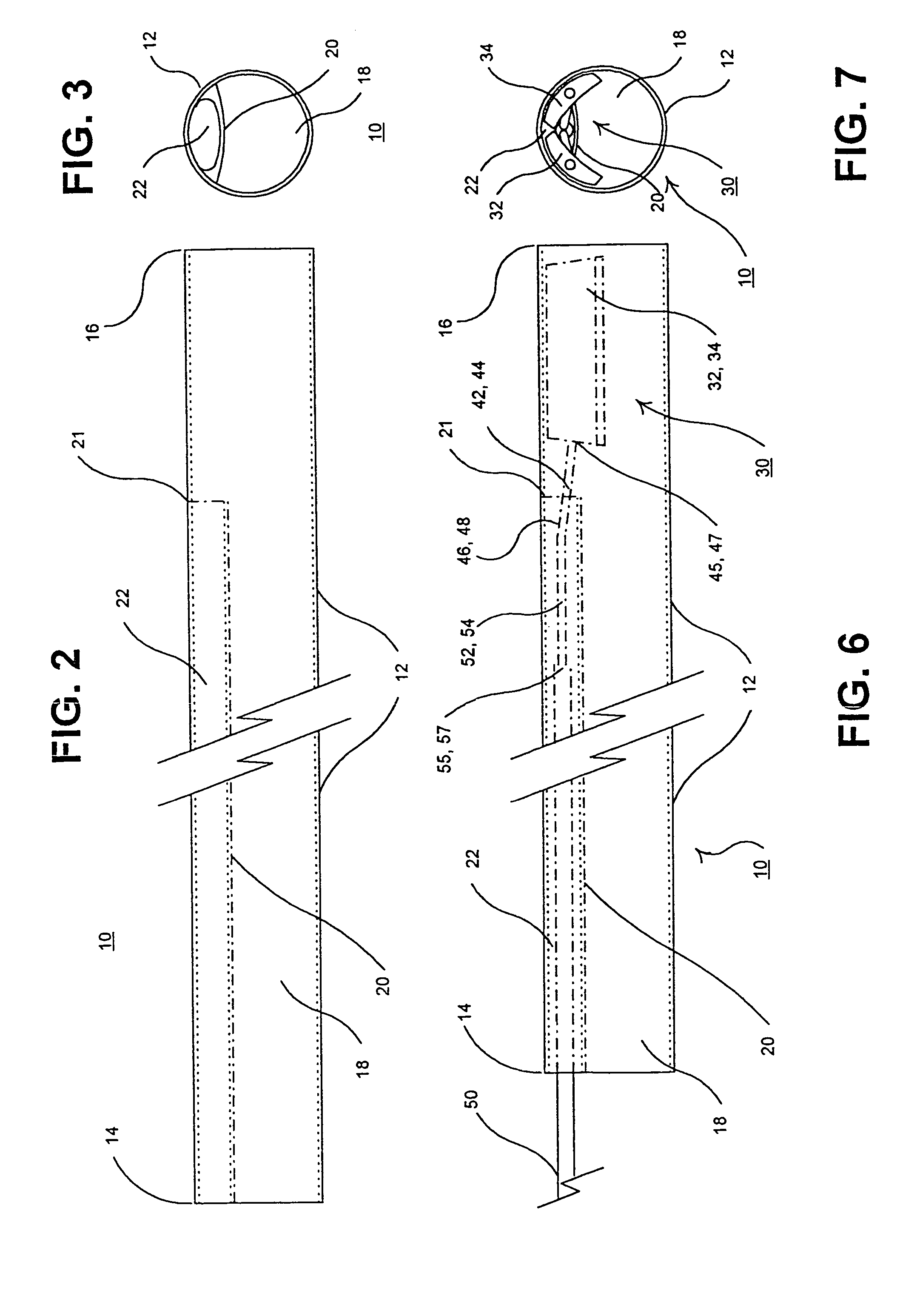

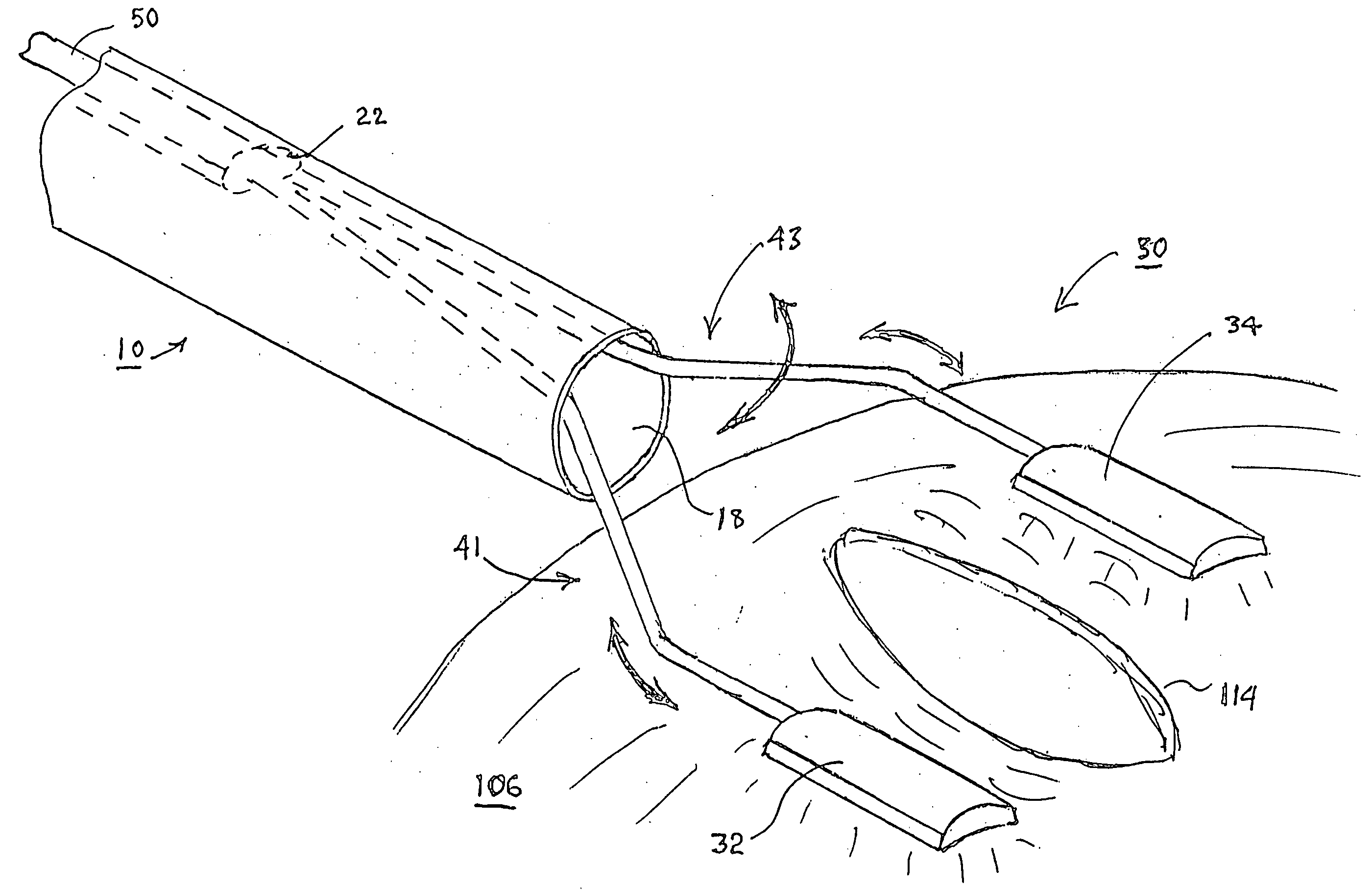

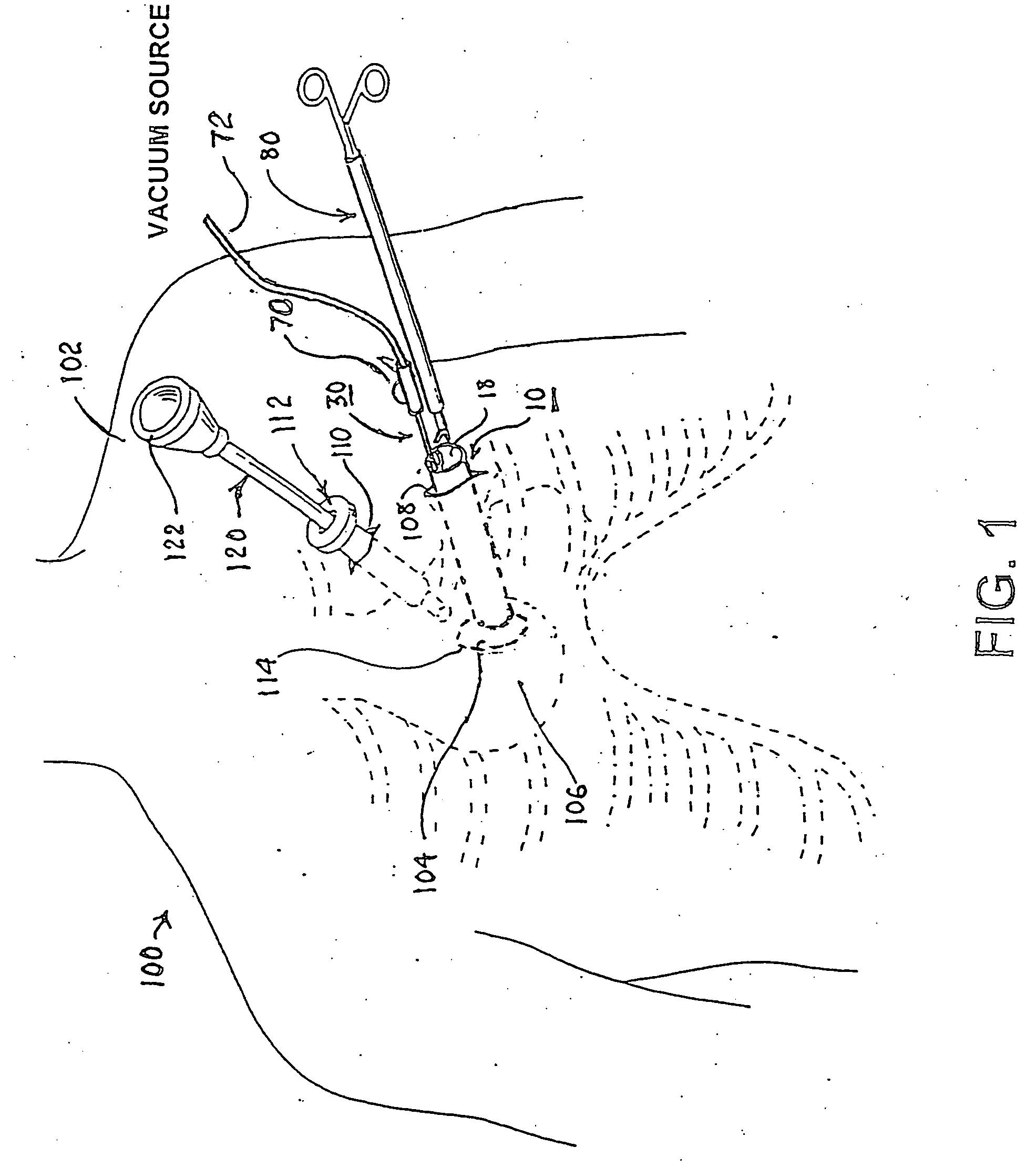

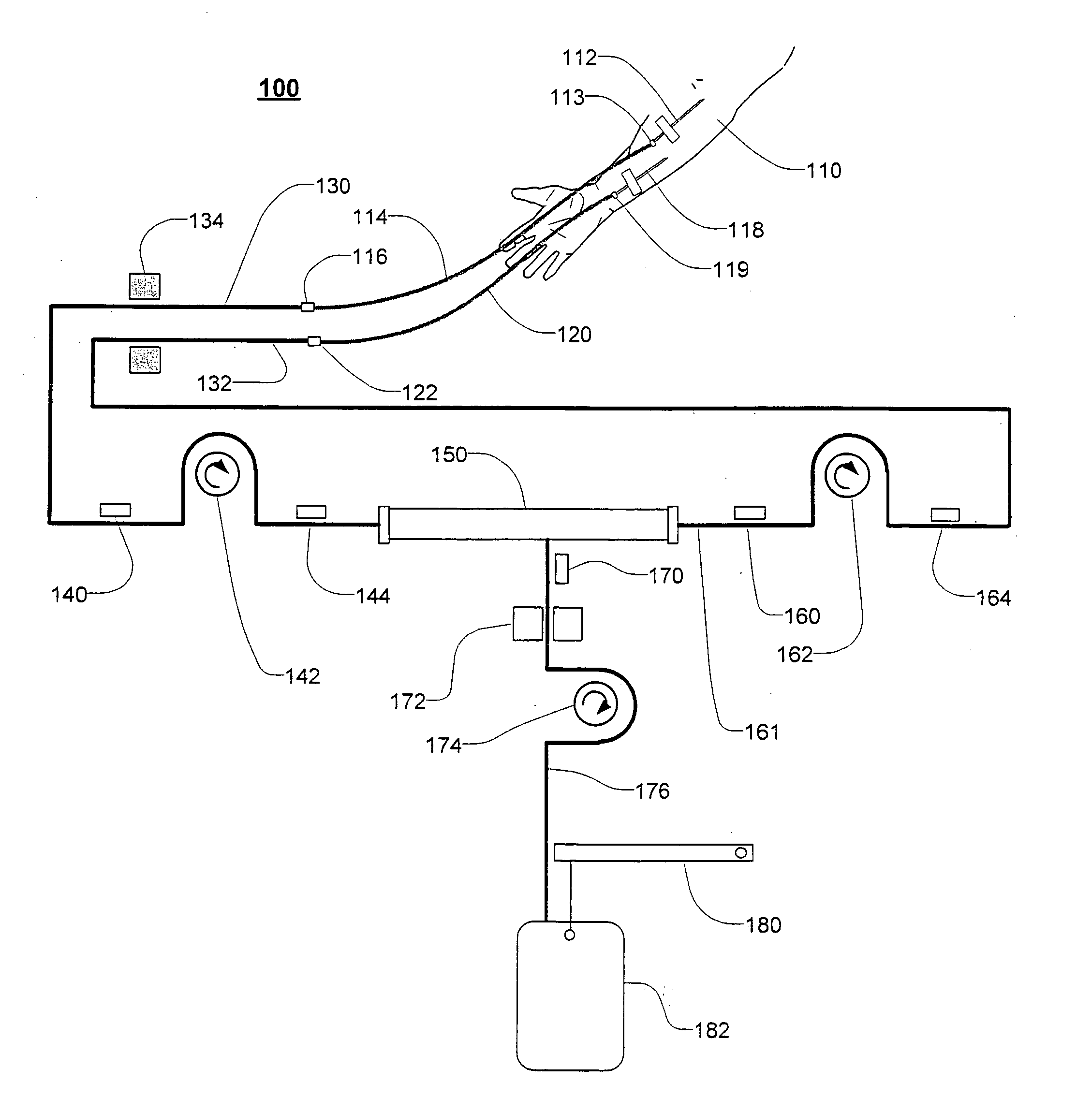

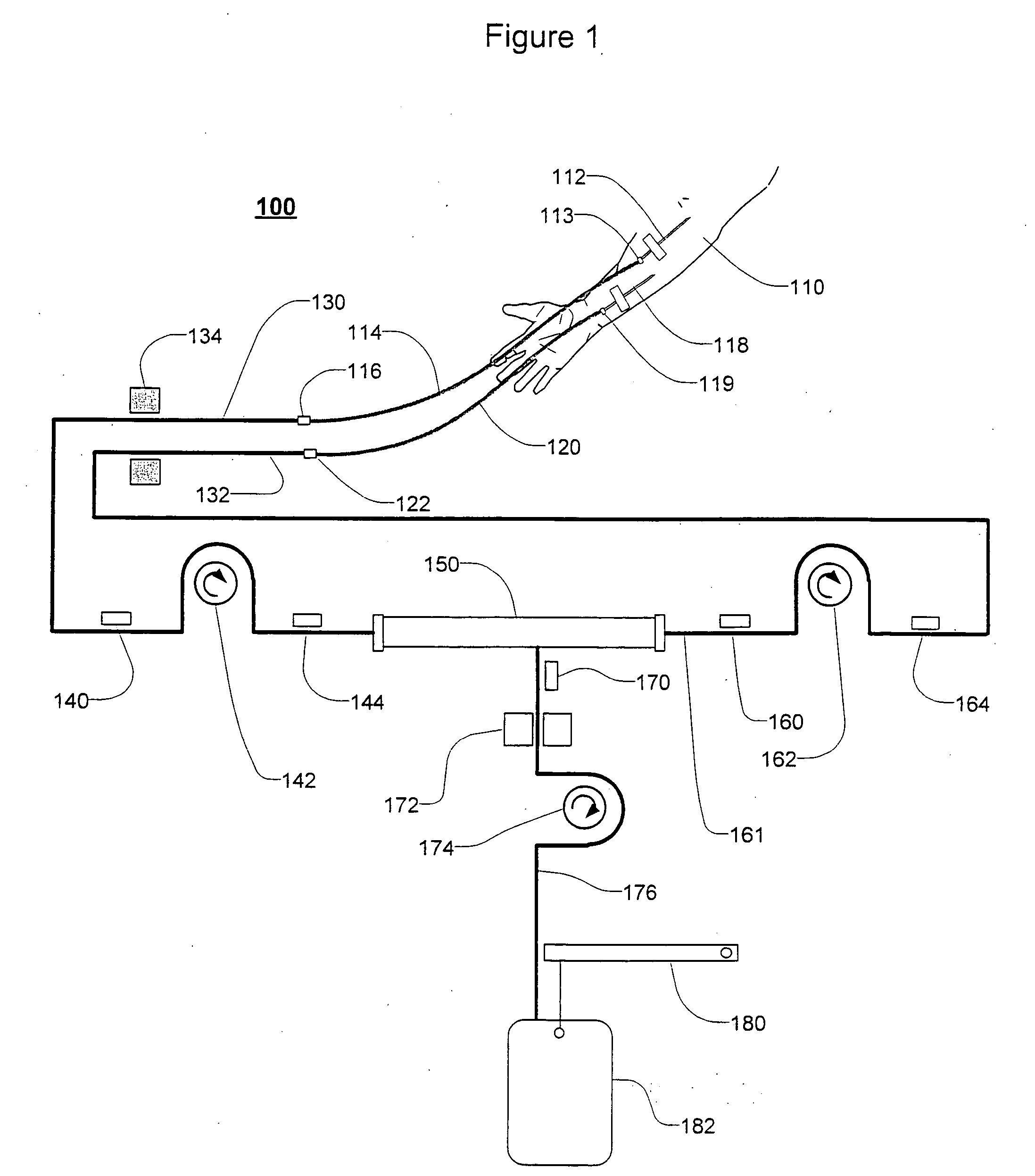

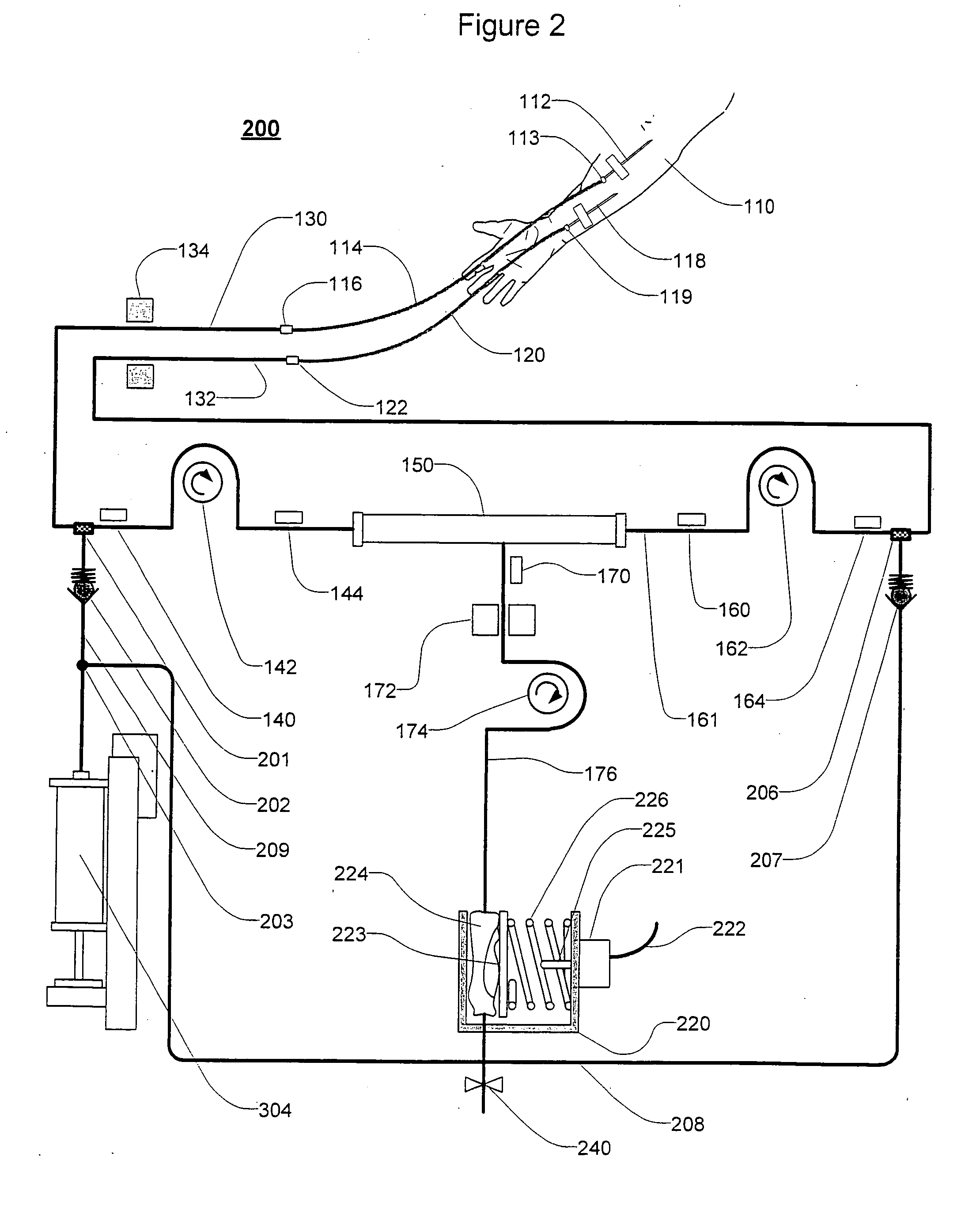

Methods and tools for accessing an anatomic space

InactiveUS7063693B2Robust fixationReduce layeringEndoscopesSurgical instrument detailsPericardial spaceAnatomic Surface

A tubular access sleeve and suction tool for accessing an anatomic surface or anatomic space and particularly the pericardium to access pericardial space and the epicardial surface of the heart in a minimally invasive manner are disclosed. A suction tool trunk extending through a suction tool lumen of the sleeve is coupled to suction pads at the ends elongated support arms. The suction pads can be retracted into a sleeve working lumen during advancement of the access sleeve through a passage and deployed from the tubular access sleeve lumen and disposed against the an outer tissue layer. Suction can be applied through suction tool lumens to suction ports of the suction pads that fix to the outer tissue layer so as to tension the outer tissue layer and / or pull the outer tissue layer away from an inner tissue layer so that the anatomic space can be accessed by instruments introduced through the working lumen to penetrate the outer tissue layer.

Owner:MEDTRONIC INC

Light-emitting apparatus and production method thereof

ActiveUS8785240B2Reduce layeringLow costTransistorSolid-state devicesEngineeringField-effect transistor

Provided is a method of producing a light-emitting apparatus having a field effect transistor for driving an organic EL device, the field effect transistor including an oxide semiconductor containing at least one element selected from In and Zn, the method including the steps of: forming a field effect transistor on a substrate; forming an insulating layer; forming a lower electrode on the insulating layer; forming an organic layer for constituting an organic EL device on the lower electrode; forming an upper electrode on the organic layer; and after the step of forming the semiconductor layer of the field effect transistor and before the step of forming the organic layer, performing heat treatment such that an amount of a component that is desorbable as H2O from the field effect transistor during the step of forming the organic layer is less than 10−5 g / m2.

Owner:CANON KK

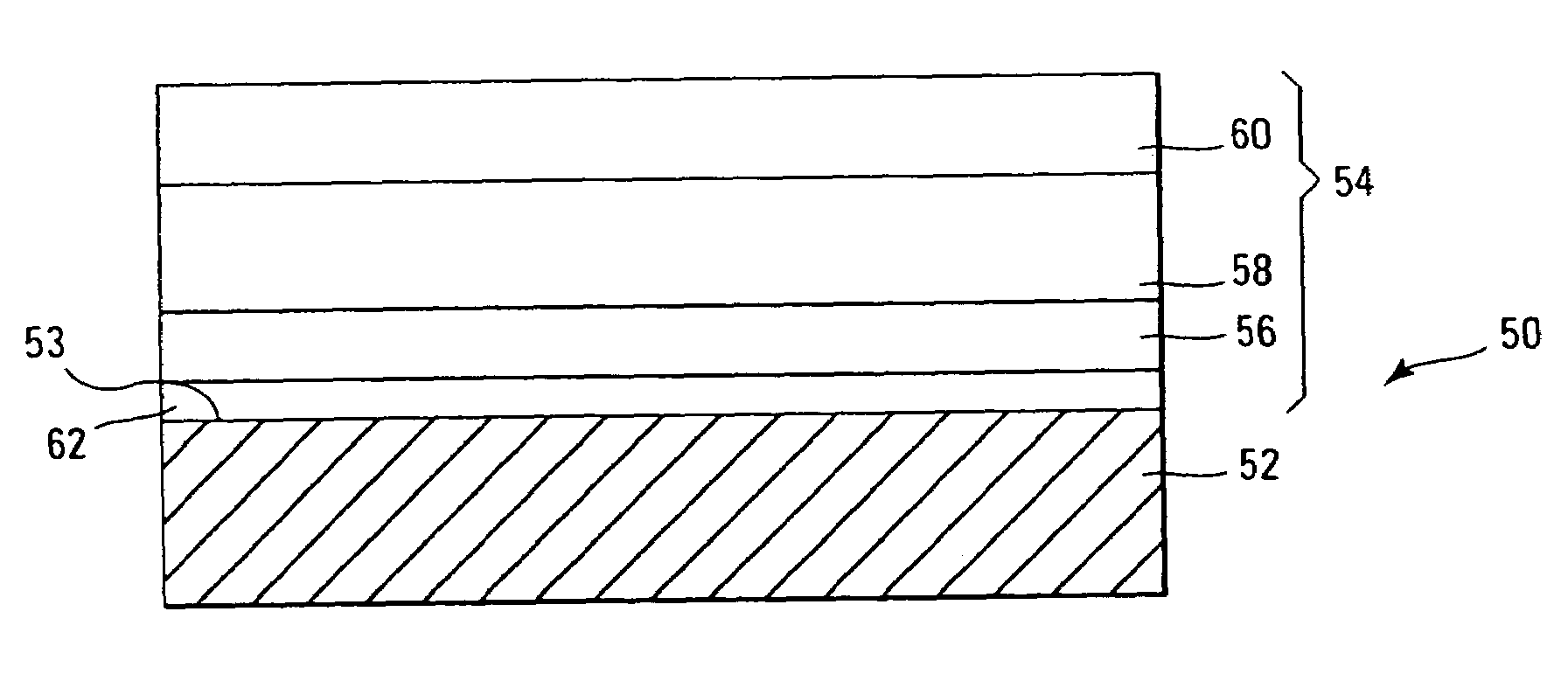

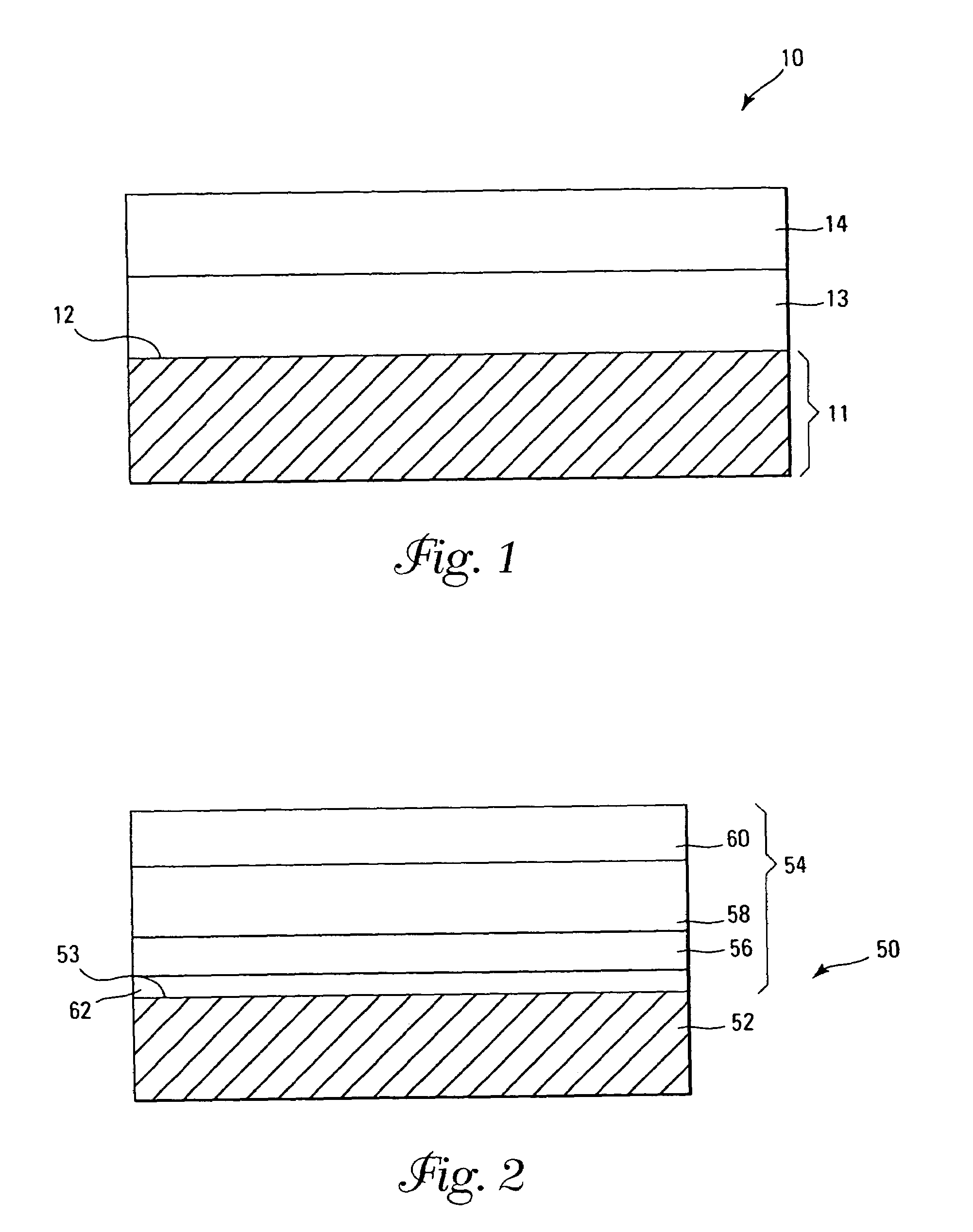

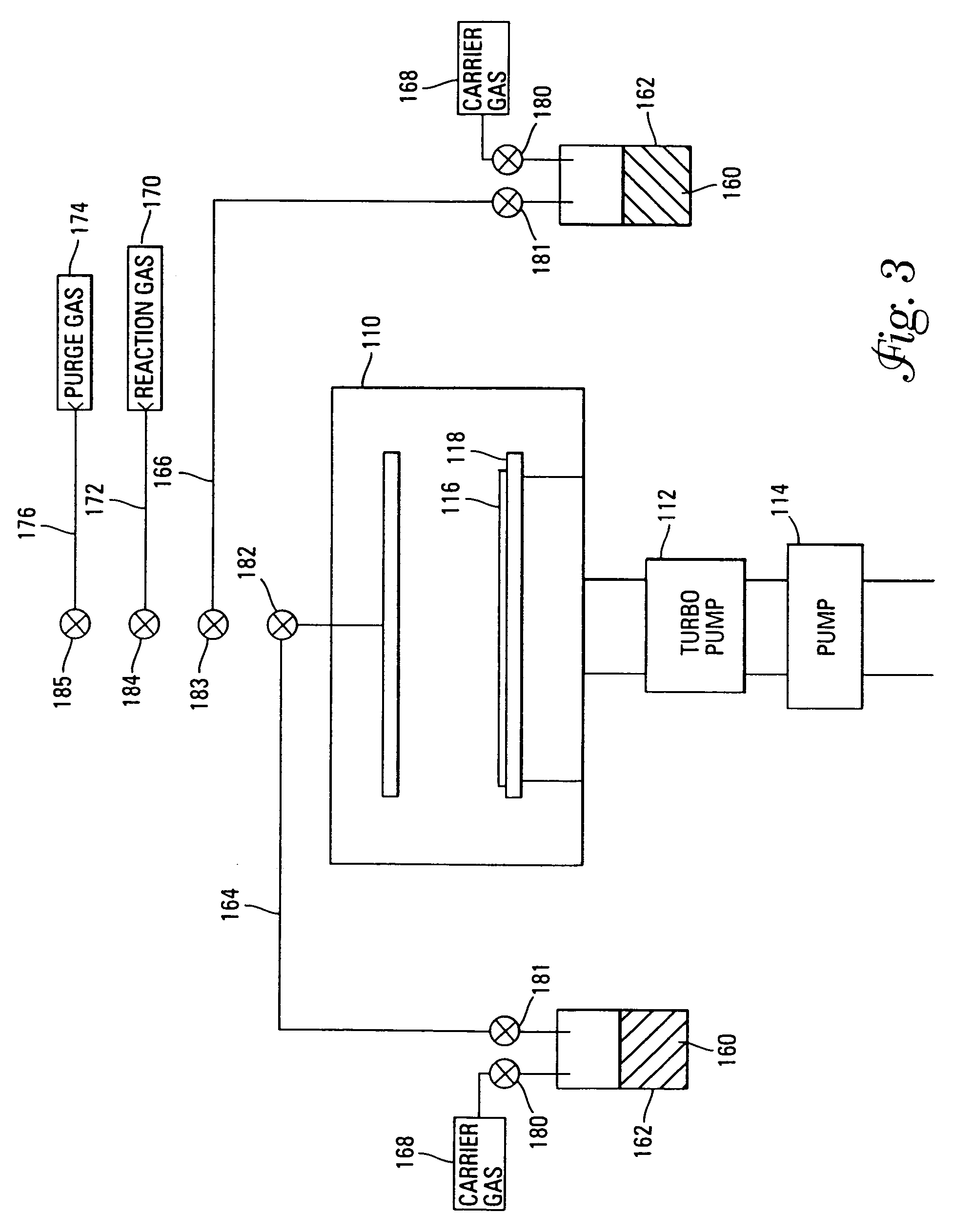

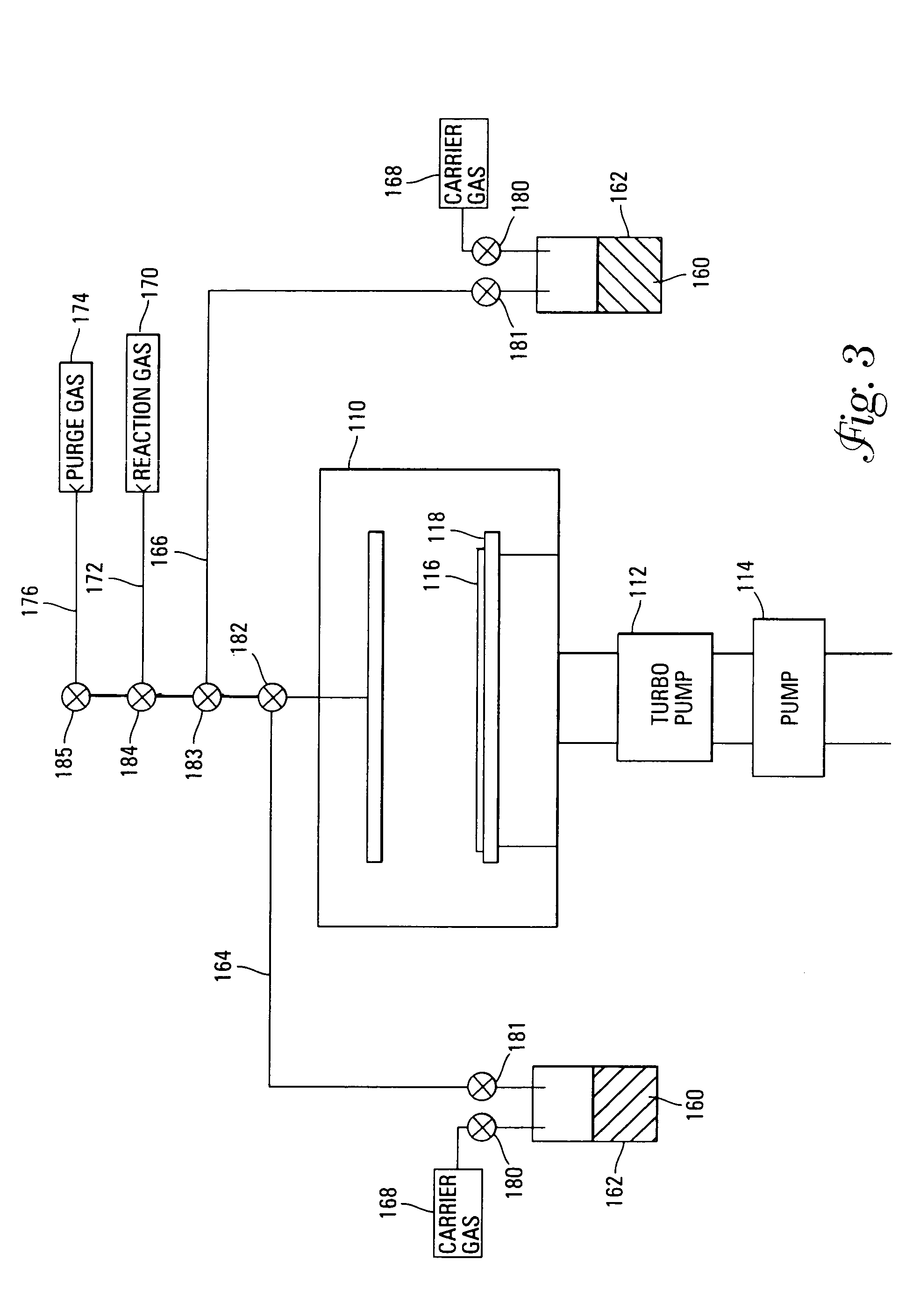

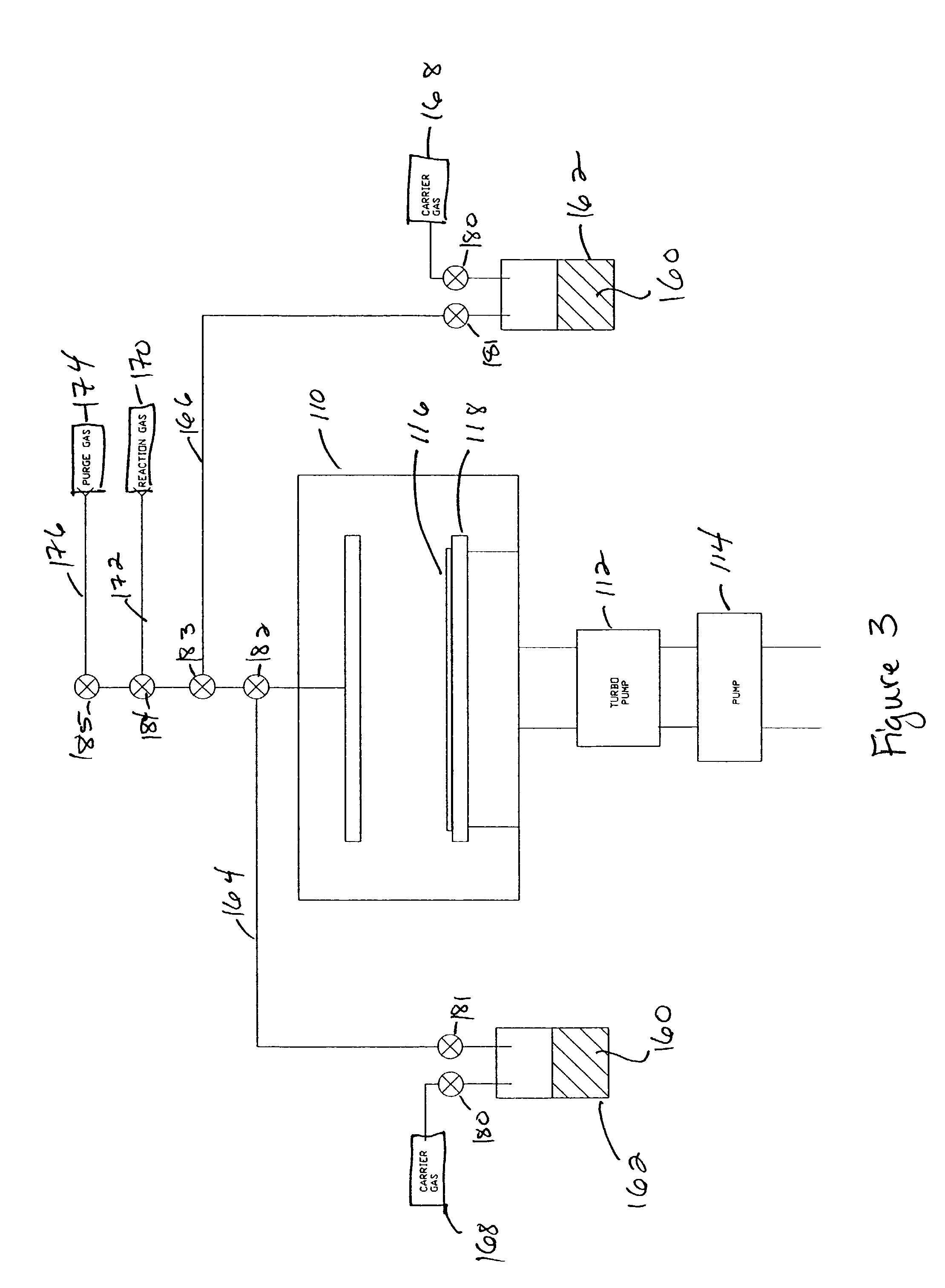

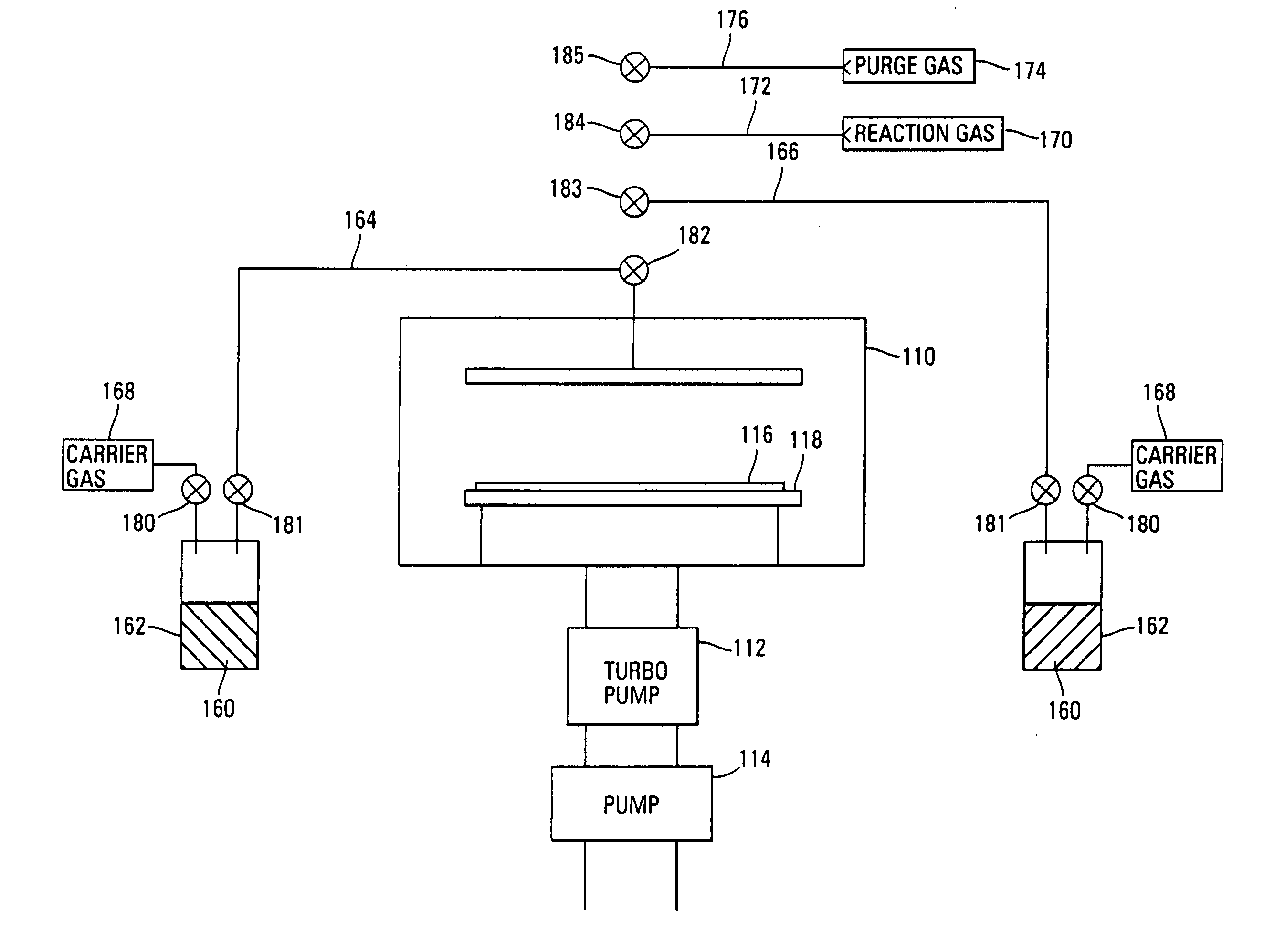

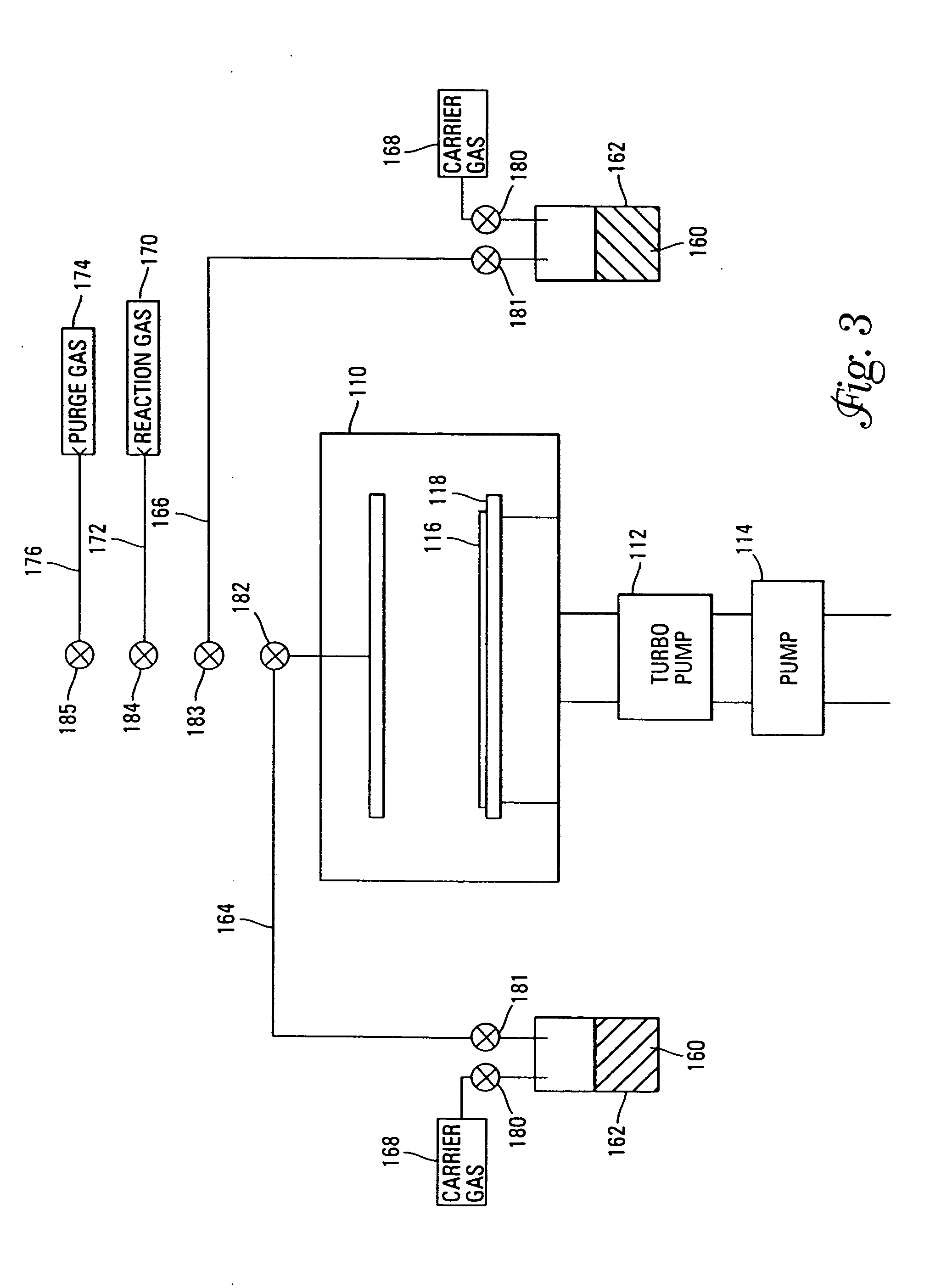

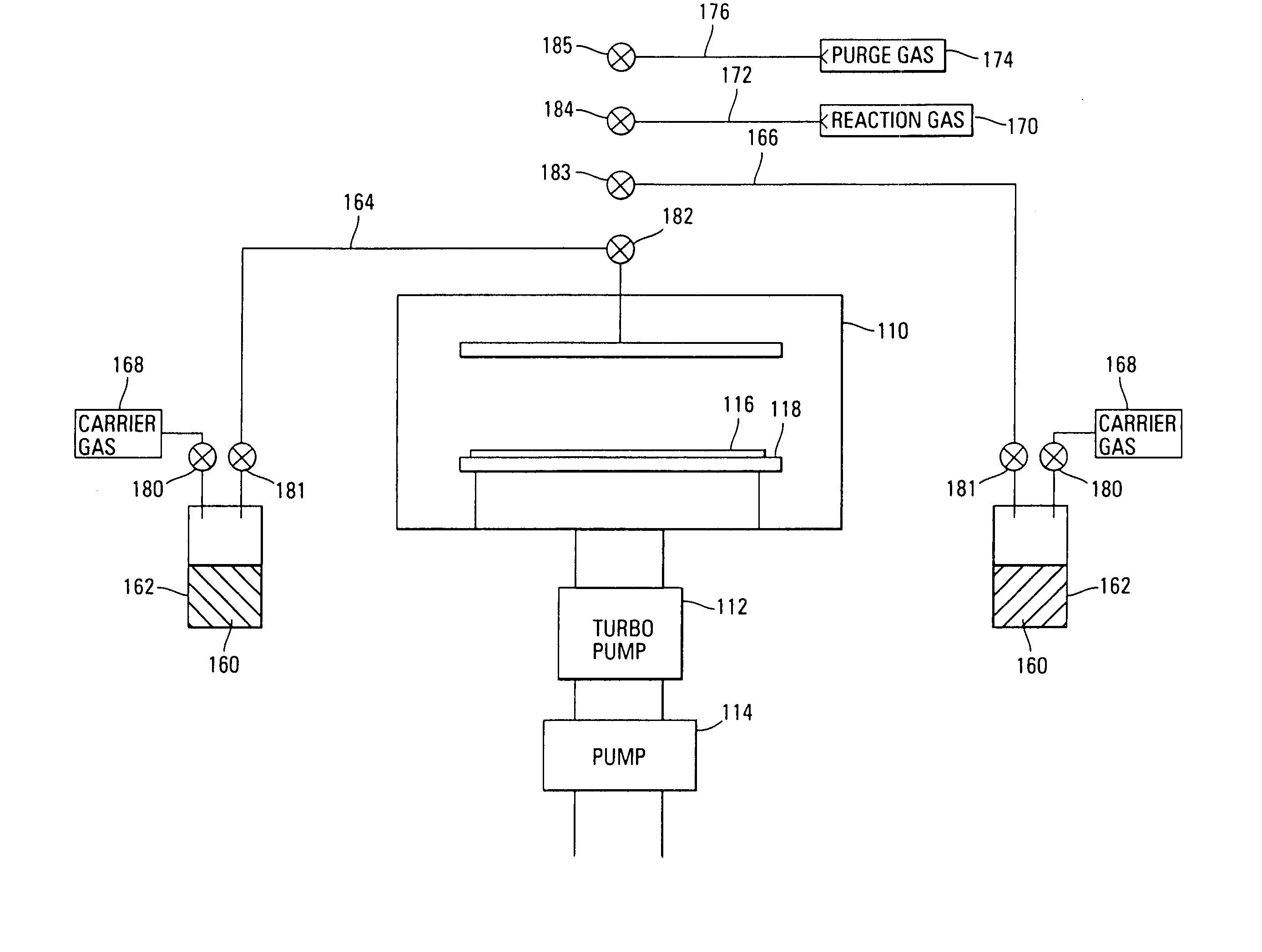

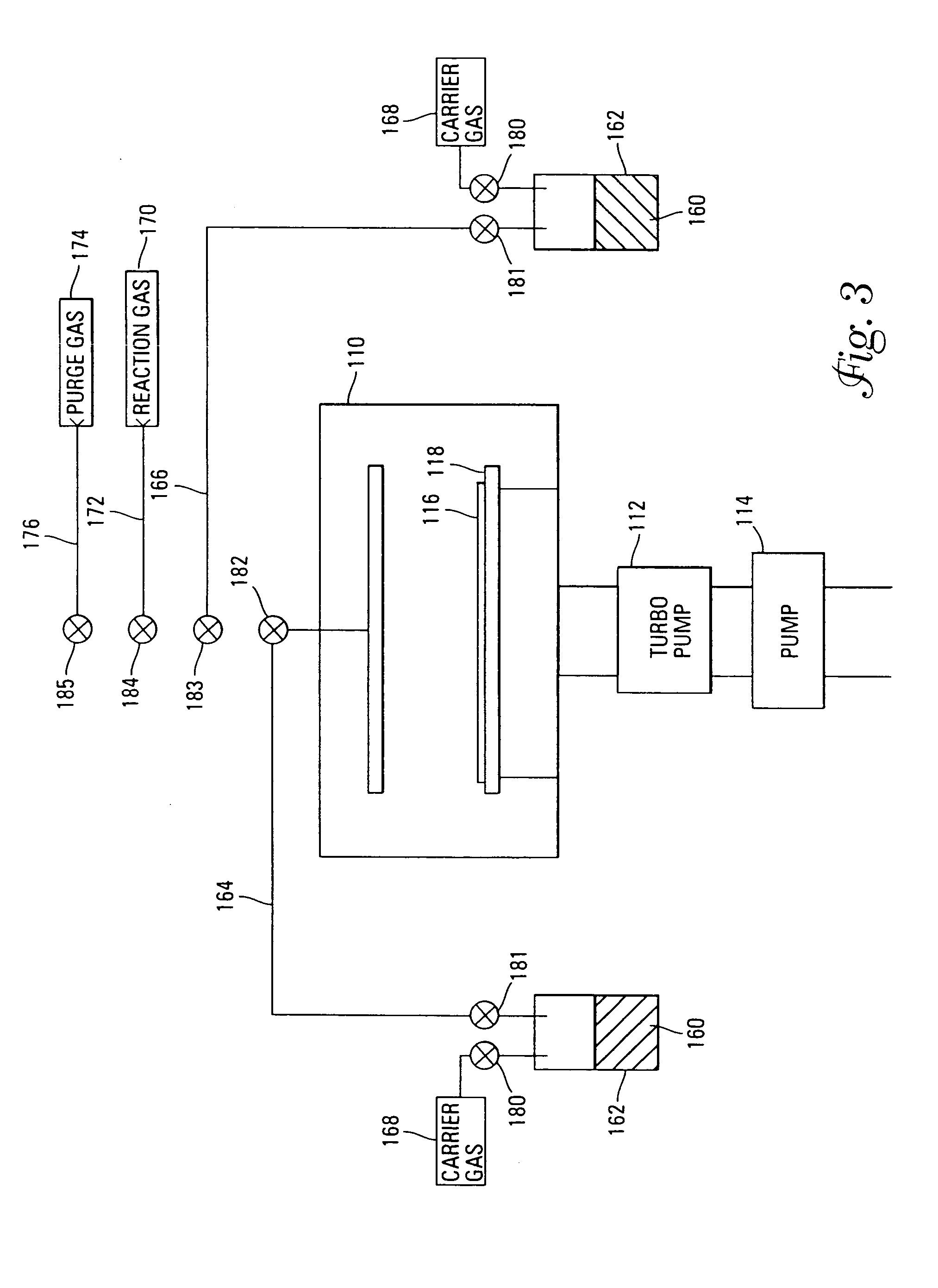

Systems and methods of forming refractory metal nitride layers using disilazanes

InactiveUS7122464B2Reduce diffuseReduce layeringSemiconductor/solid-state device manufacturingCapacitorsGas phaseDeposition process

A method of forming (and apparatus for forming) refractory metal nitride layers (including silicon nitride layers), such as a tantalum (silicon) nitride barrier layer, on a substrate by using a vapor deposition process with a refractory metal precursor compound, a disilazane, and an optional silicon precursor compound.

Owner:MICRON TECH INC

Methods and tools for accessing an anatomic space

ActiveUS20060200002A1Reduce layeringRobust fixationSurgical instrument detailsSurgical pincettesPericardial spacePericardium tissue

Owner:MEDTRONIC INC

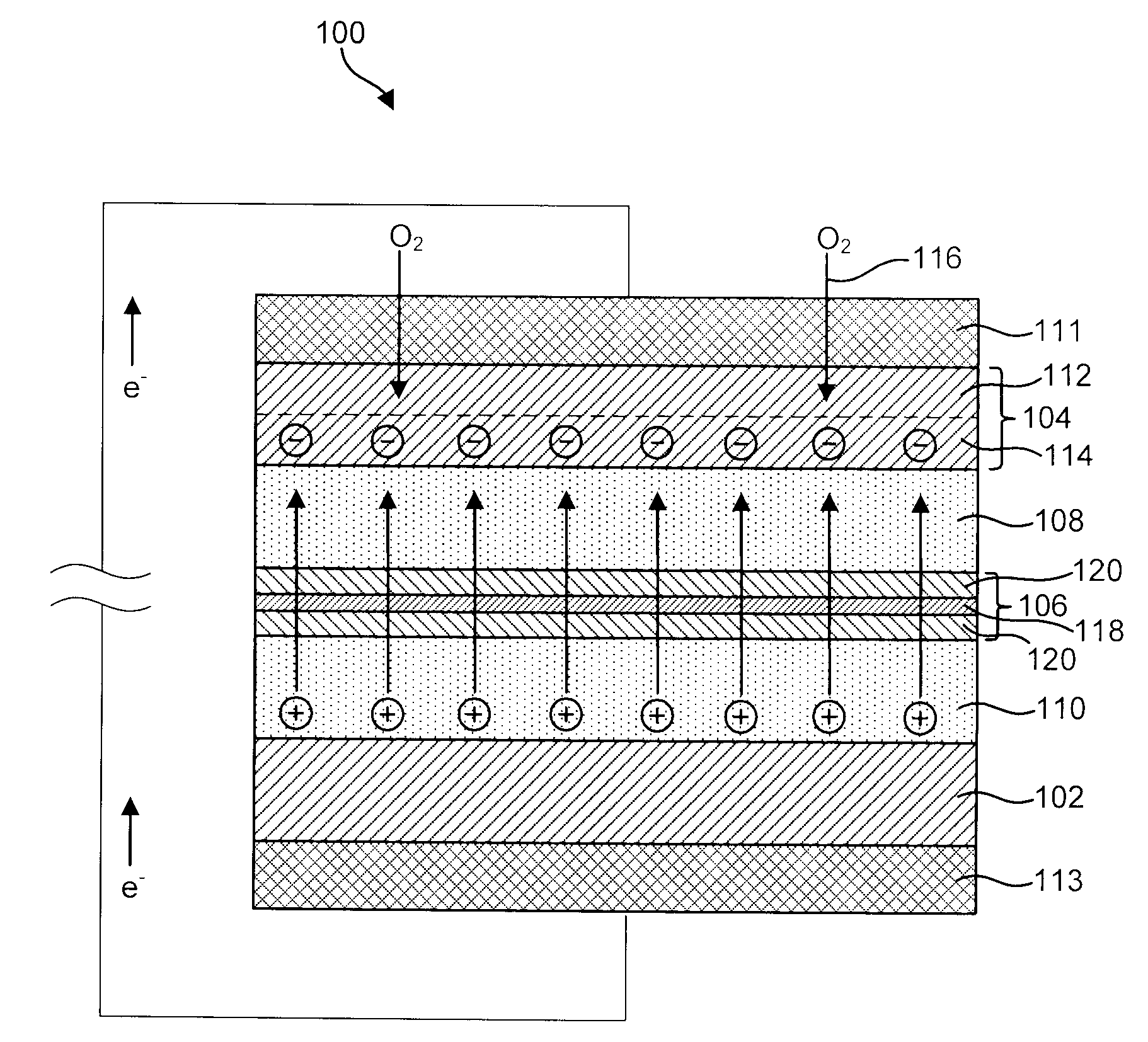

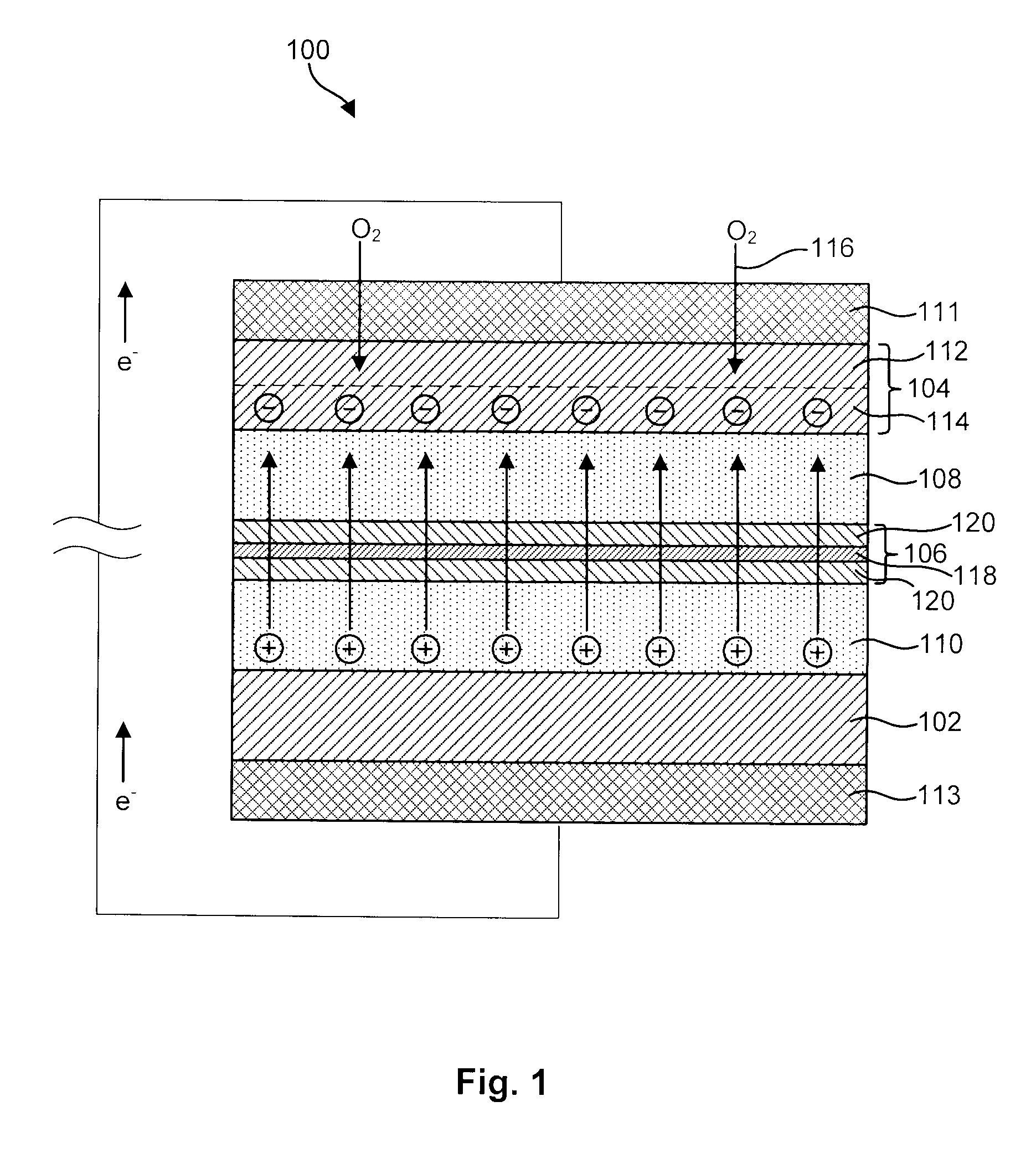

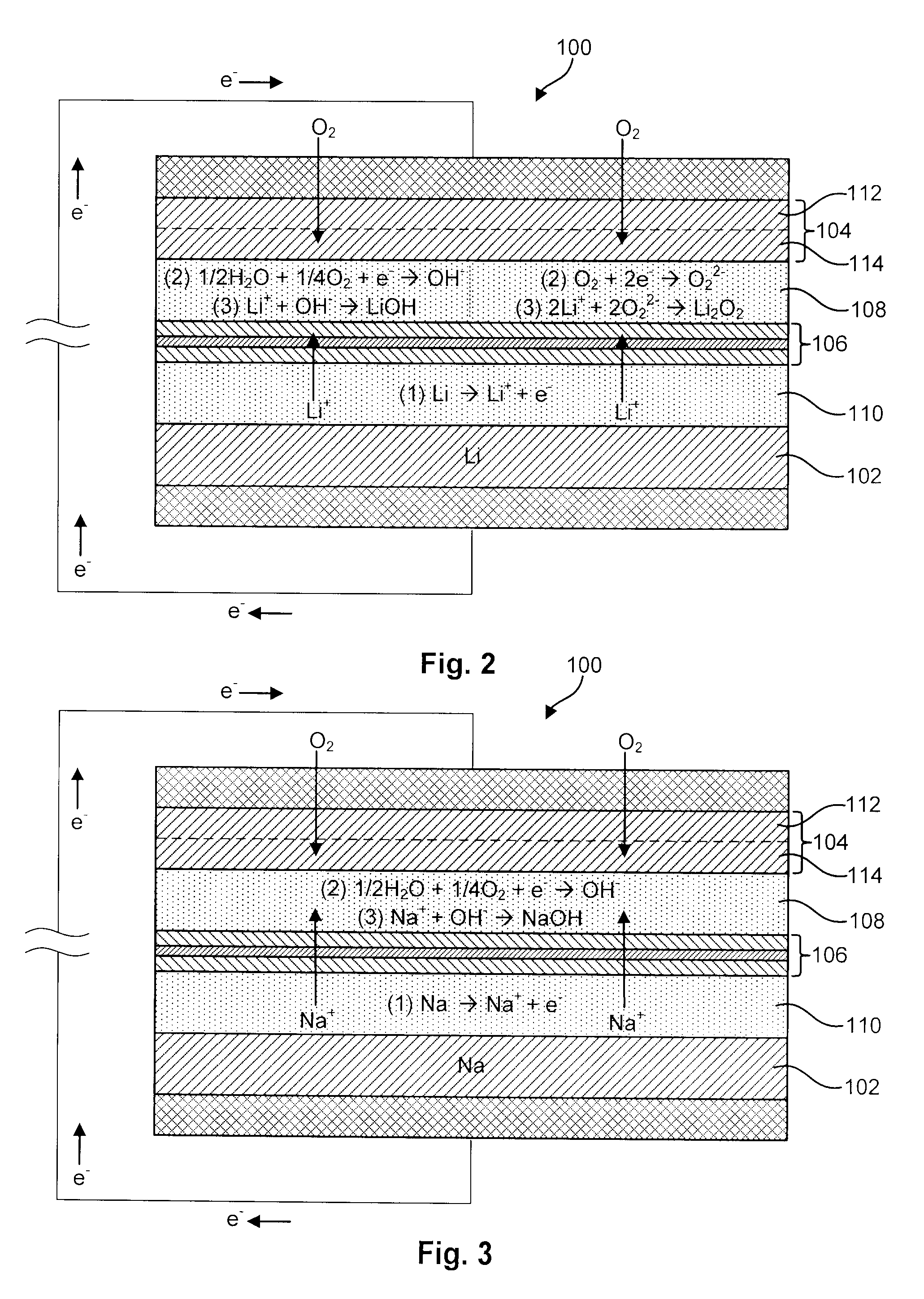

Advanced Metal-Air Battery Having a Ceramic Membrane Electrolyte Background of the Invention

ActiveUS20080268327A1Reduce oxygenReduce layeringFuel and primary cellsSolid electrolytesOxygenCeramic membrane

A metal-air battery is disclosed in one embodiment of the invention as including a cathode to reduce oxygen molecules and an alkali-metal-containing anode to oxidize the alkali metal (e.g., Li, Na, and K) contained therein to produce alkali-metal ions. An aqueous catholyte is placed in ionic communication with the cathode to store reaction products generated by reacting the alkali-metal ions with the oxygen containing anions. These reaction products are stored as solutes dissolved in the aqueous catholyte. An ion-selective membrane is interposed between the alkali-metal containing anode and the aqueous catholyte. The ion-selective membrane is designed to be conductive to the alkali-metal ions while being impermeable to the aqueous catholyte.

Owner:FIELD UPGRADING USA INC

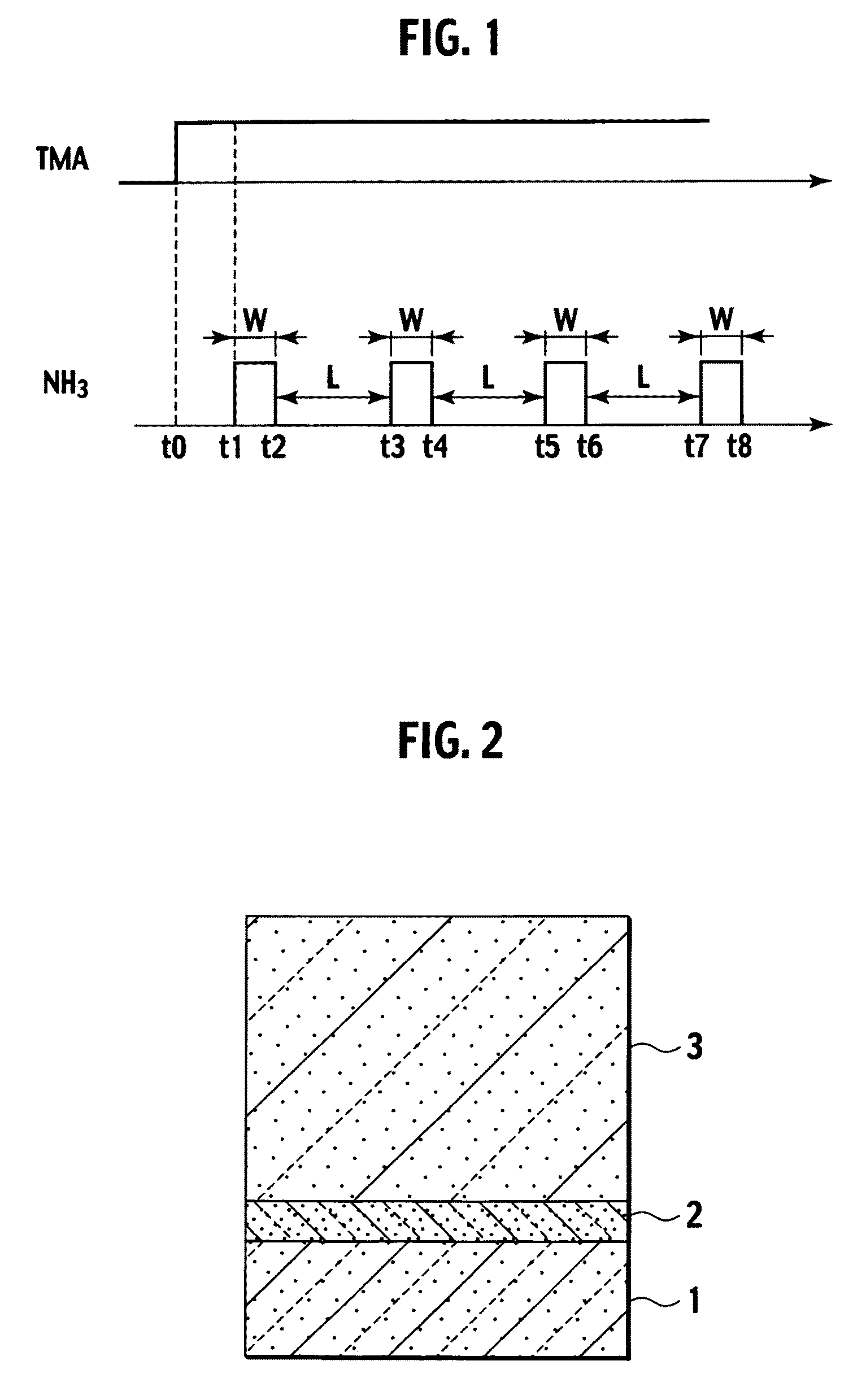

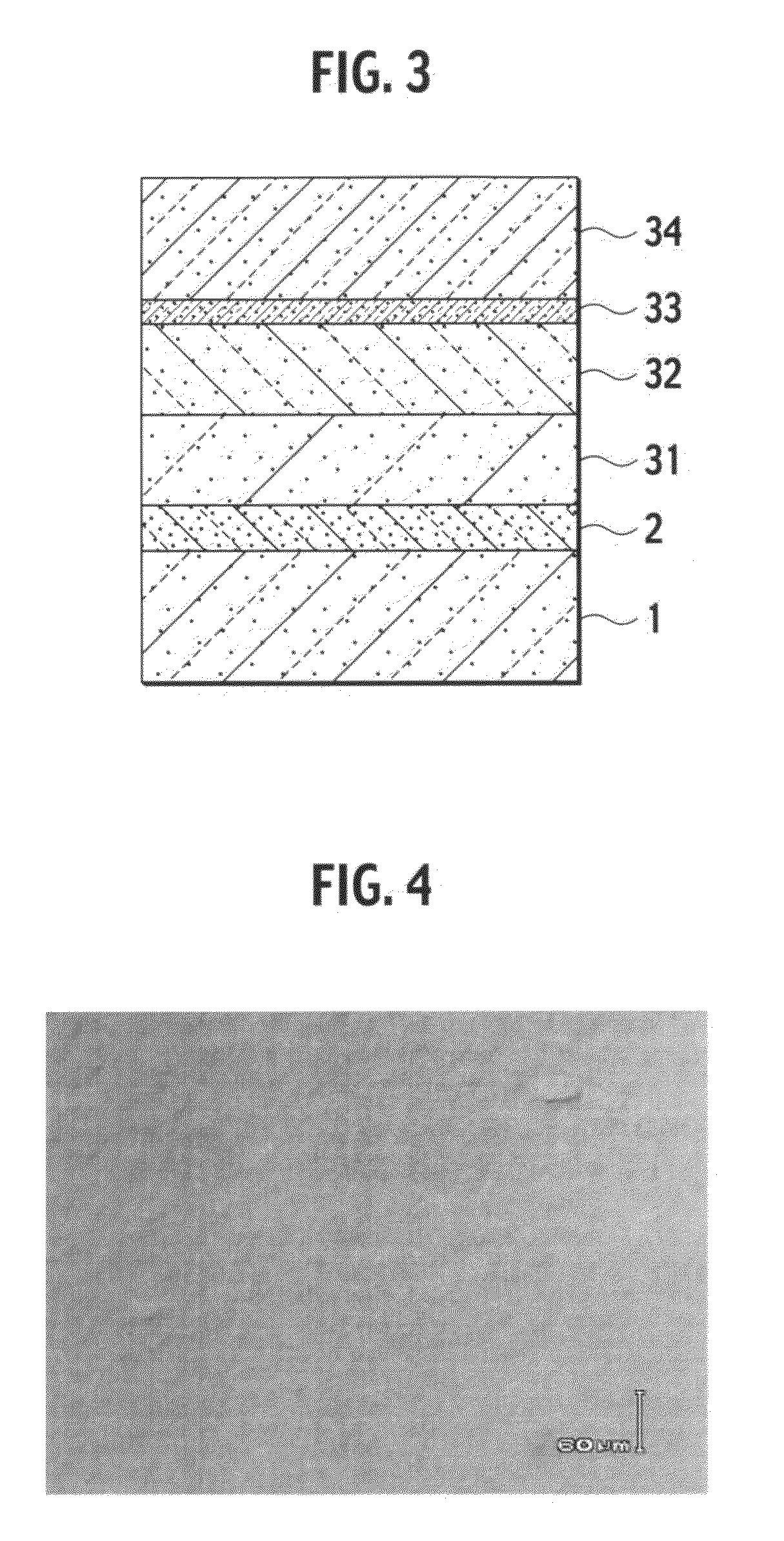

Method of manufacturing nitride semiconductor and nitride semiconductor element

ActiveUS8709843B2Improve surface morphologyReduce layeringPolycrystalline material growthSemiconductor/solid-state device manufacturingSource materialCrystallinity

The present invention provides a method of manufacturing a nitride semiconductor capable of improving the crystallinity and the surface state of the nitride semiconductor crystal formed on top of a high-temperature AlN buffer layer. An AlN buffer layer is formed on top of a growth substrate, and then nitride semiconductor crystals are grown on top of the AlN buffer layer. In a stage of manufacturing the nitride semiconductor, the crystal of the AlN buffer layer is grown at a high temperature of 900° C. or higher. In addition, an Al-source material of the AlN buffer layer is started to be supplied first to a reaction chamber and continues to be supplied without interruption, and then a N-source material is supplied intermittently.

Owner:ROHM CO LTD

Systems and methods for forming refractory metal nitride layers using organic amines

InactiveUS6967159B2Reduce diffuseReduce layeringSemiconductor/solid-state device manufacturingCapacitorsTantalum nitrideDeposition process

A method of forming (and apparatus for forming) refractory metal nitride layers (including silicon nitride layers), such as a tantalum nitride barrier layer, on a substrate by using an atomic layer deposition process (a vapor deposition process that includes a plurality of deposition cycles) with a refractory metal precursor compound, an organic amine, and an optional silicon precursor compound.

Owner:MICRON TECH INC

Method for fabricating an interference display unit

InactiveUS7198973B2Increase brightnessSimple and easy manufacturing processPhotomechanical apparatusSemiconductor/solid-state device manufacturingProcess patternsEngineering

A method for fabricating an interference display unit is provided. A first plate and a sacrificial layer are formed in order on a substrate and at least two openings are formed in the first plate and the sacrificial layer. A photoresist layer is spin-coated on the sacrificial layer and fills the openings. A photolithographic process patterns the photoresist layer to define a support with an arm. A second plate is formed on the sacrificial layer and posts. The arm's stress is released through a thermal process. The position of the arm is shifted and the distance between the first plate and the second plate is therefore defined. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Systems and methods for forming tantalum silicide layers

InactiveUS6995081B2Easy to controlMinimizing detrimental gas phase reactionSemiconductor/solid-state device manufacturingCapacitorsGas phaseNitrogen

A method of forming (and apparatus for forming) tantalum suicide layers (including tantalum silicon nitride layers), which are typically useful as diffusion barrier layers, on a substrate by using a vapor deposition process with a tantalum halide precursor compound, a silicon precursor compound, and an optional nitrogen precursor compound.

Owner:MICRON TECH INC

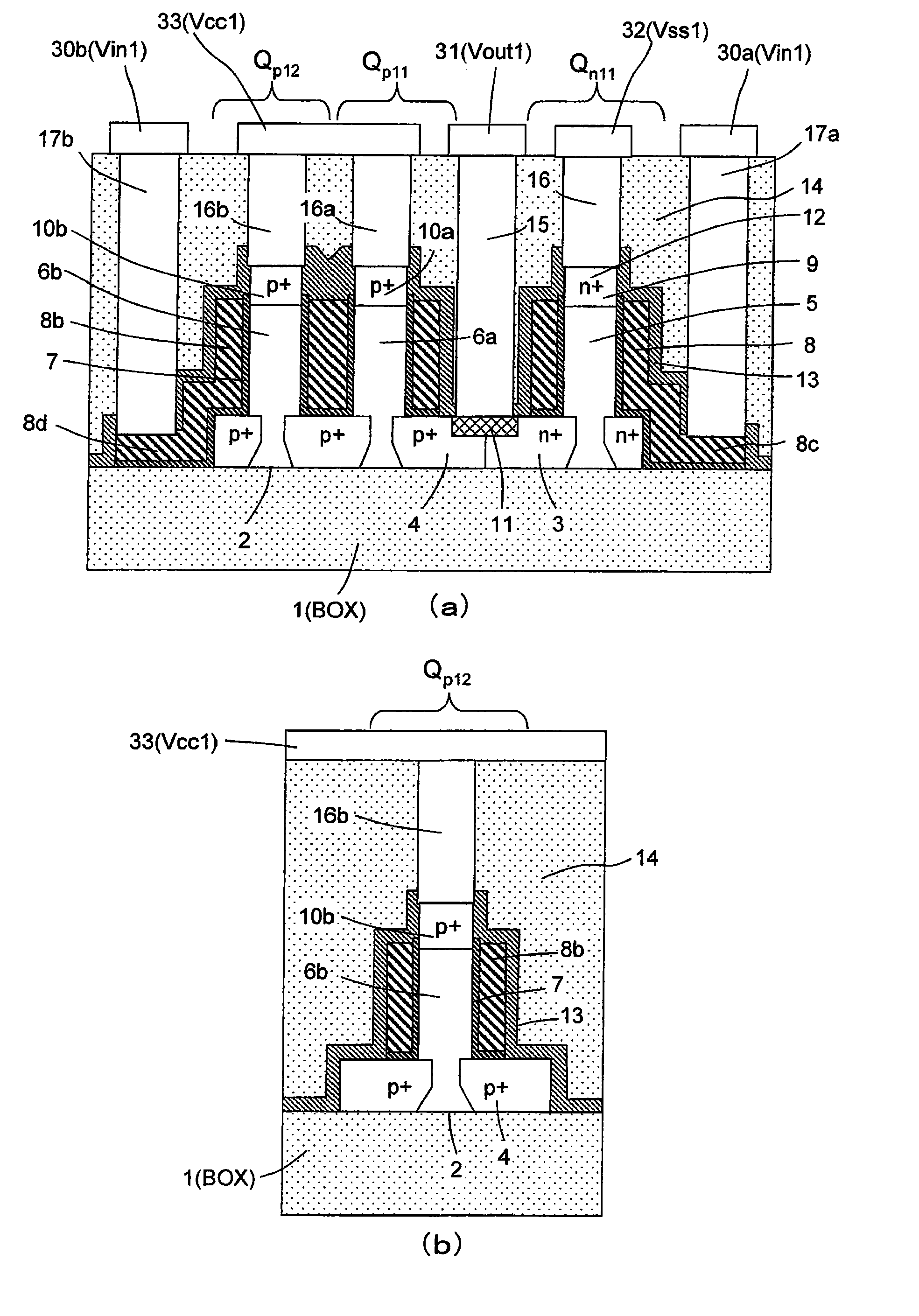

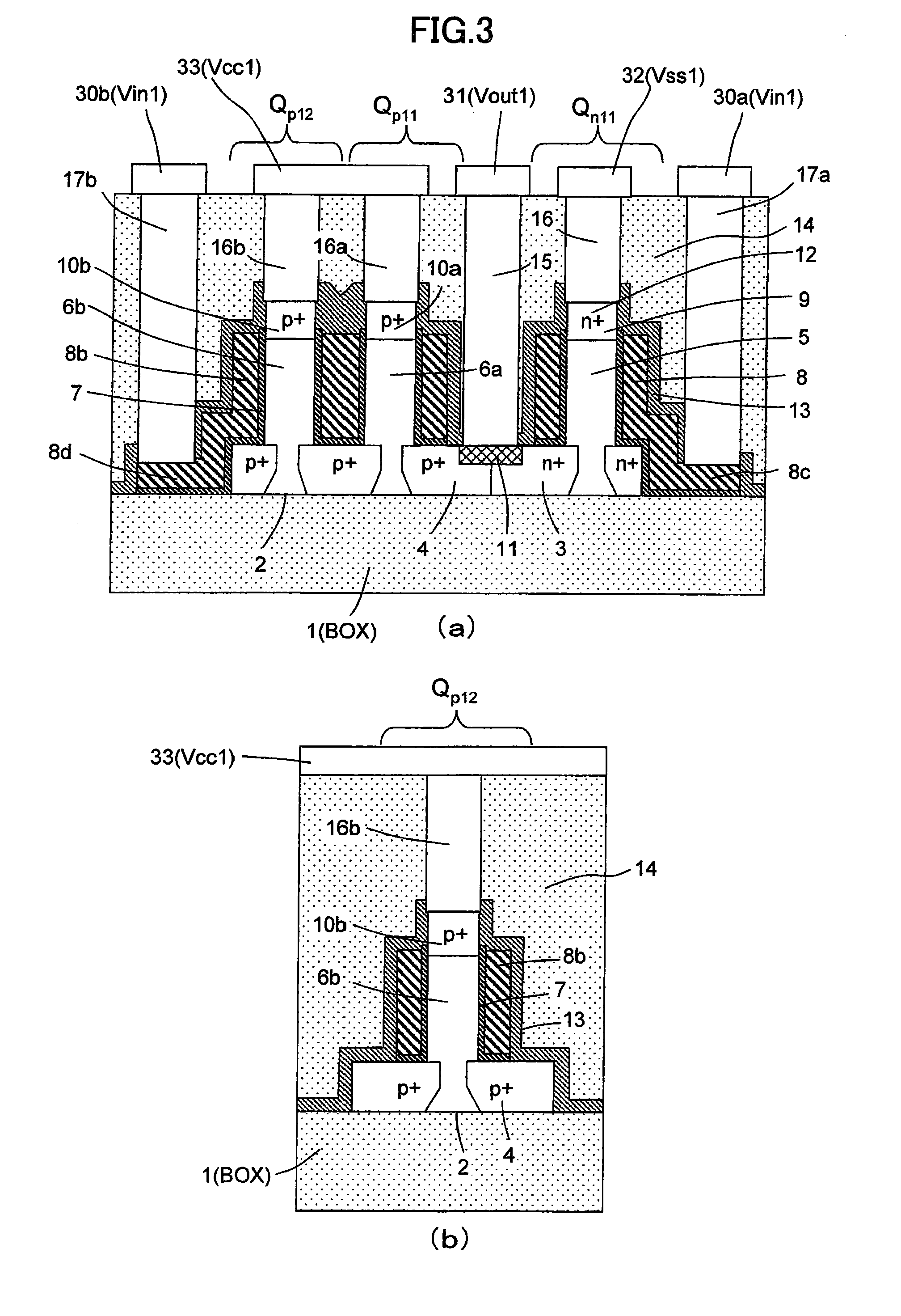

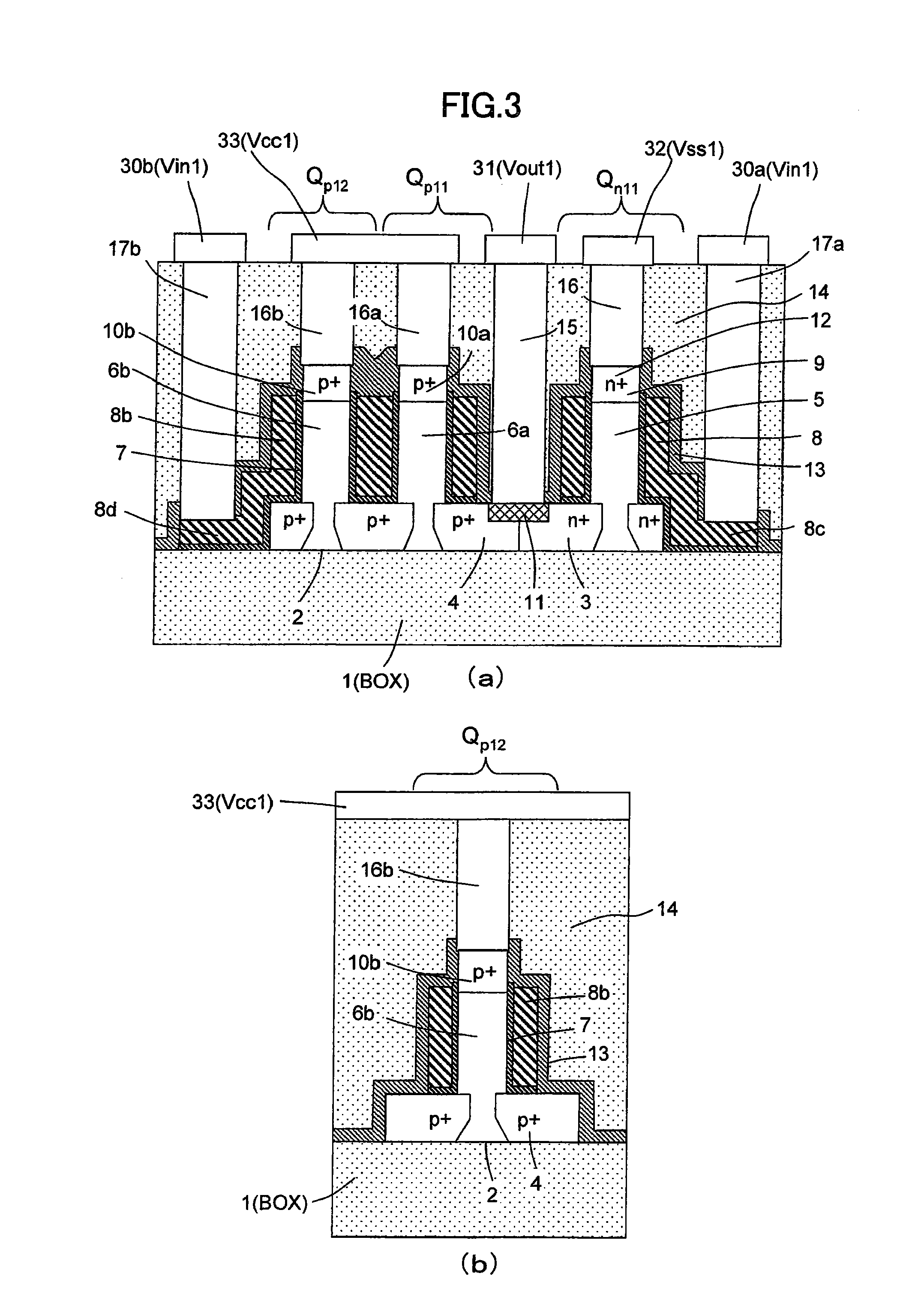

Semiconductor device and production method therefor

ActiveUS20100213539A1Reduce widthImprove area efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCondensed matter physics

It is intended to provide a semiconductor device including a MOS transistor, comprising: a semiconductor pillar; one of a drain region and a source region formed in contact with a lower part of the semiconductor pillar; a first gate formed around a sidewall of the semiconductor pillar through a first dielectric film therebetween; and an epitaxial semiconductor layer formed on a top surface of the semiconductor pillar, wherein the other of the source region and the drain region is formed so as to be at least partially in the epitaxial semiconductor layer, and wherein: the other of the source region and the drain region has a top surface having an area greater than that of the top surface of the semiconductor pillar.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

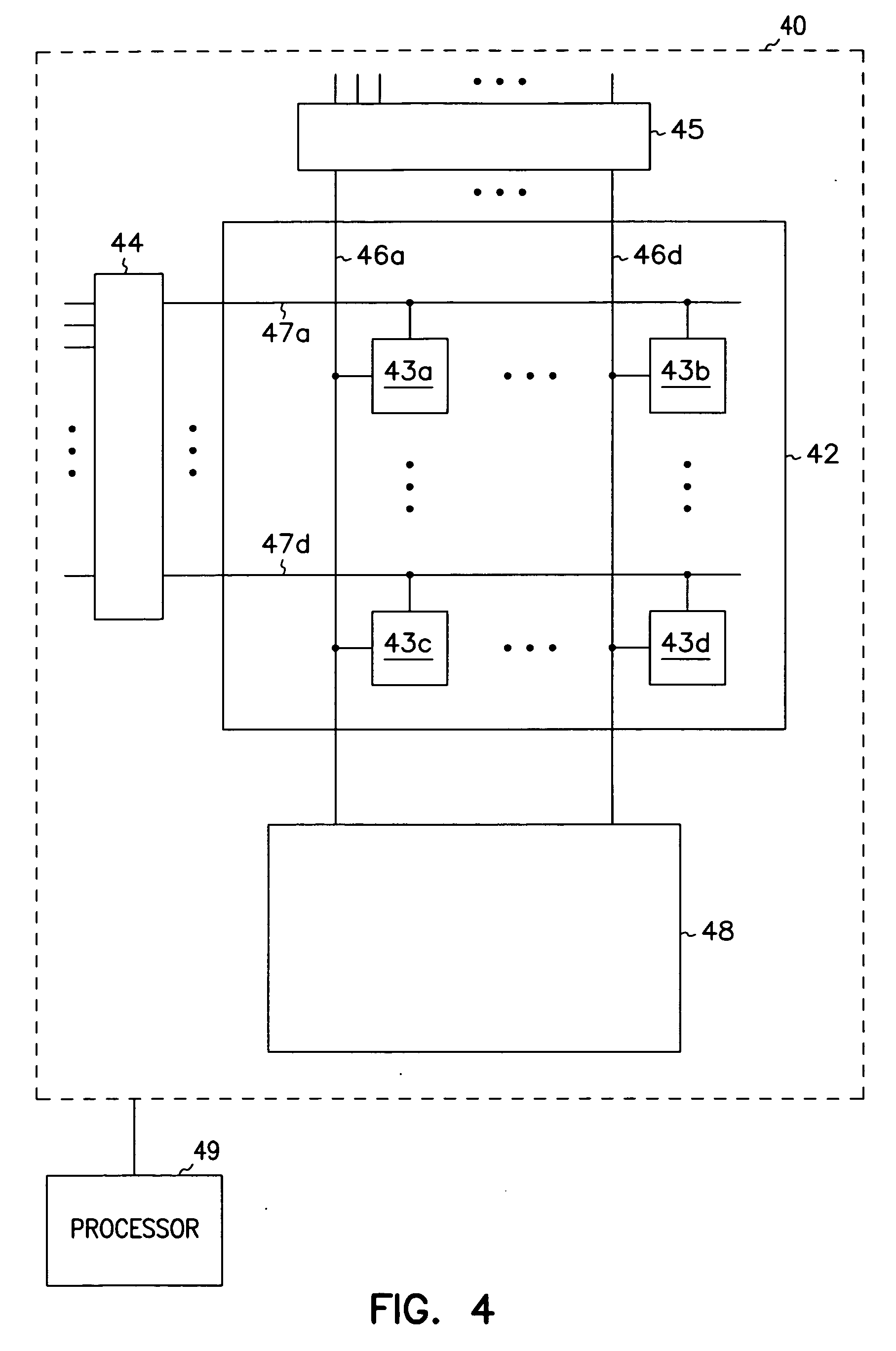

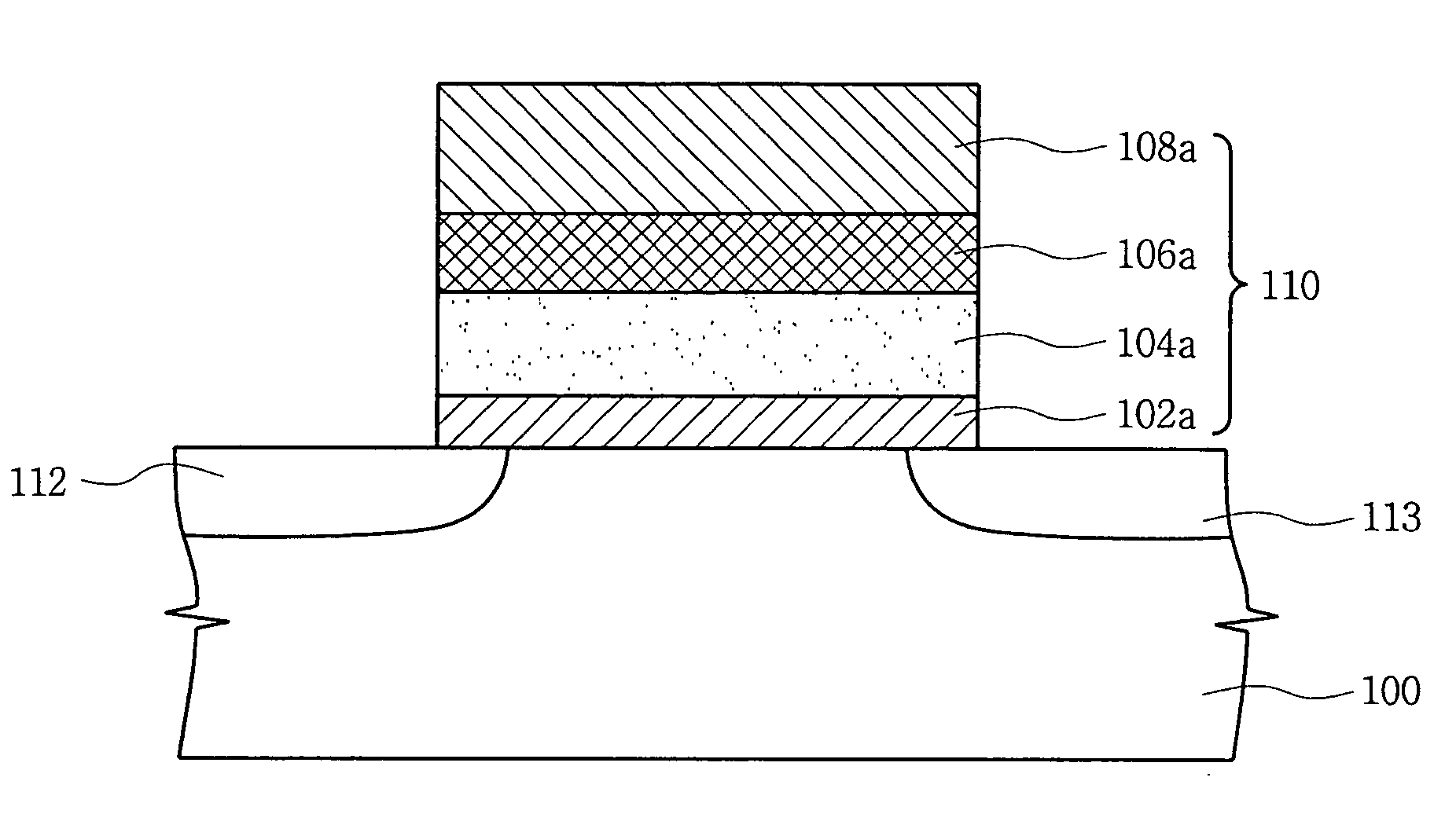

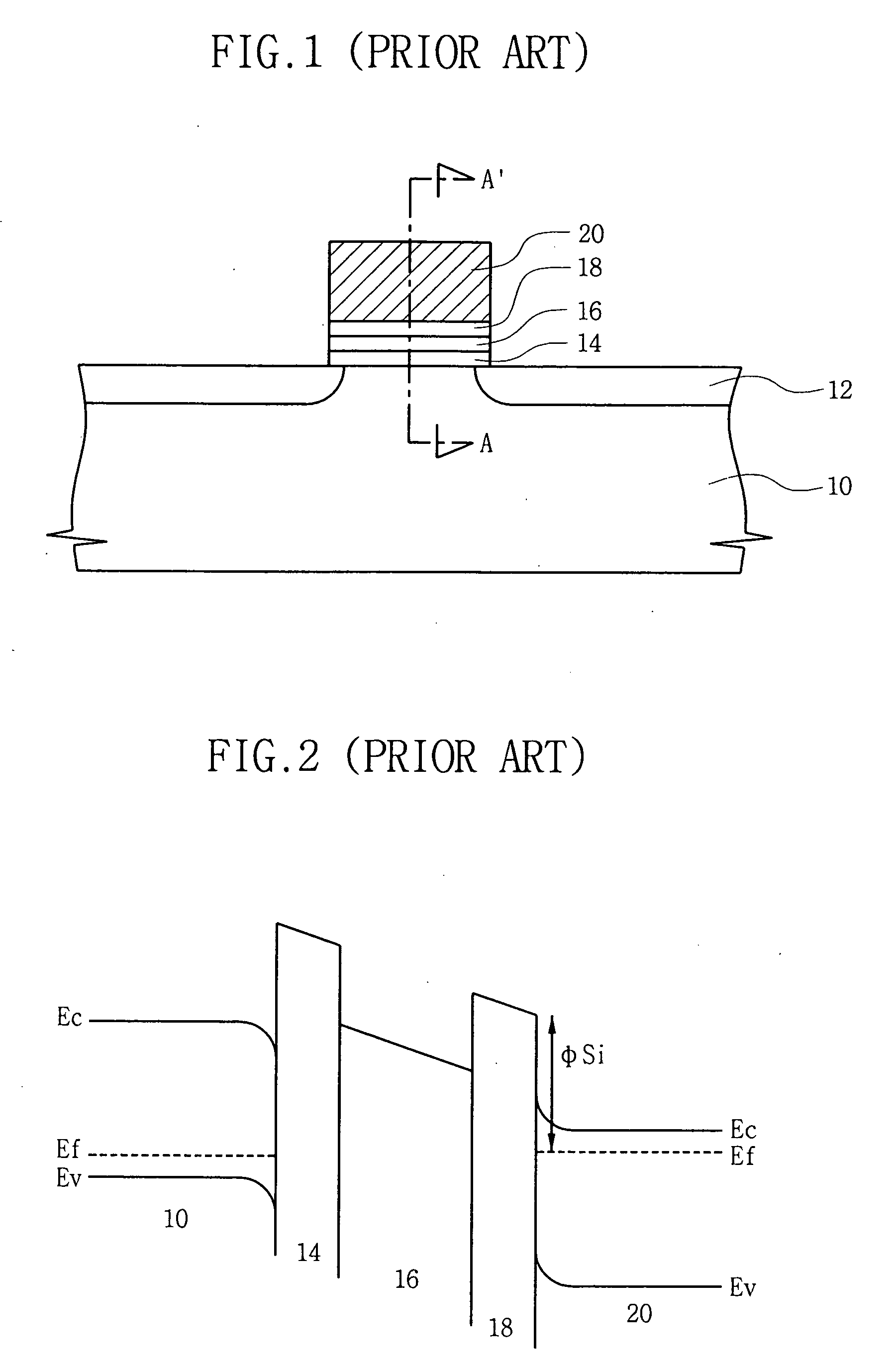

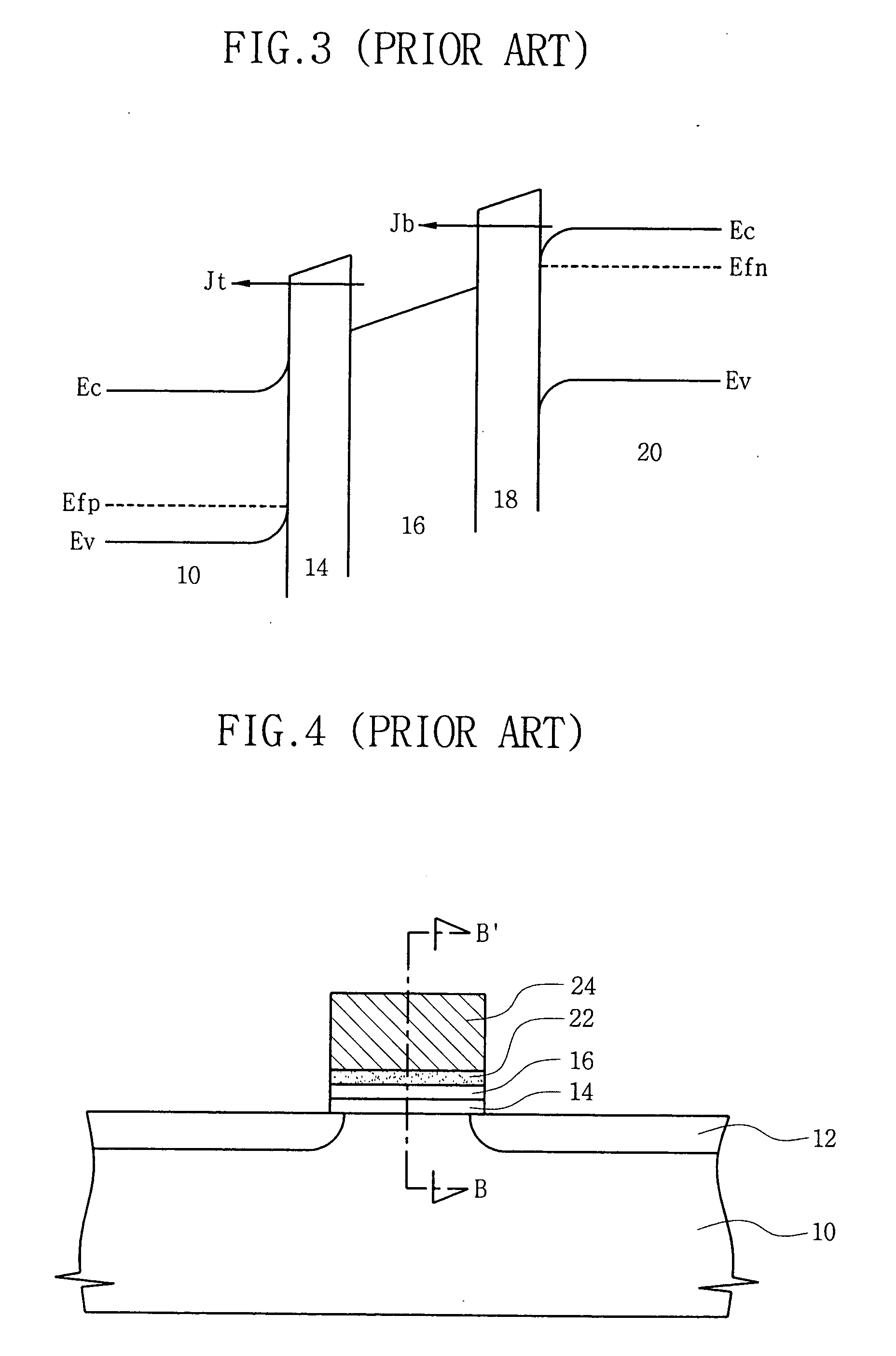

Structures, methods, and systems for ferroelectric memory transistors

InactiveUS20050030825A1Reliability can be promotedReduce layeringSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPermittivity

Integrated memory circuits, key components in thousands of electronic and computer products, have recently been made using ferroelectric memory transistors, which offer faster write cycles and lower power requirements than over conventional floating-gate transistors. One problem that hinders the continued down-scaling of conventional ferroelectric memory transistors is the vulnerability of their gate insulations to failure at thinner dimensions. Accordingly, the inventors devised unique ferroelectric gate structures, one of which includes a high-integrity silicon-oxide insulative layer, a doped titanium-oxide layer, a weak-ferroelectric layer, and a control gate. The doped titanium-oxide layer replaces a metal layer in the conventional ferroelectric gate structure, and the weak-ferroelectric layer replaces a conventional ferroelectric layer. These replacements reduce the permittivity mismatch found in conventional gate structures, and thus reduce stress on gate insulation layers, thereby improving reliability of ferroelectric memory transistors, particularly those with thinner gate insulation.

Owner:MICRON TECH INC

Flexible display device with divided power lines and manufacturing method for the same

ActiveUS20160093644A1Improve wettabilityReduce viscid dragFinal product manufactureSolid-state devicesDisplay deviceEngineering

There is provided a flexible display having a plurality of innovations configured to allow bending of a portion or portions to reduce apparent border size and / or utilize the side surface of an assembled flexible display.

Owner:LG DISPLAY CO LTD

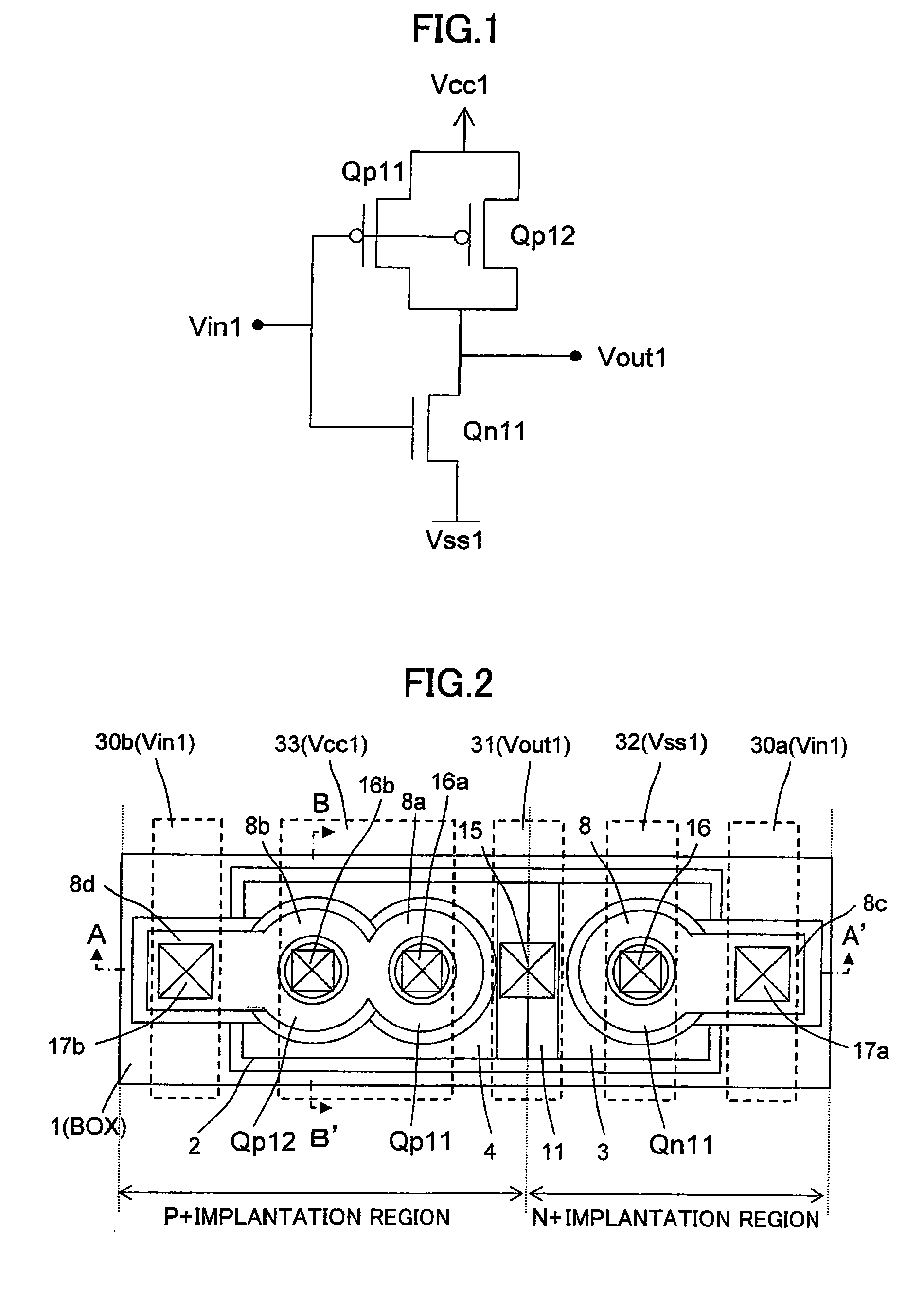

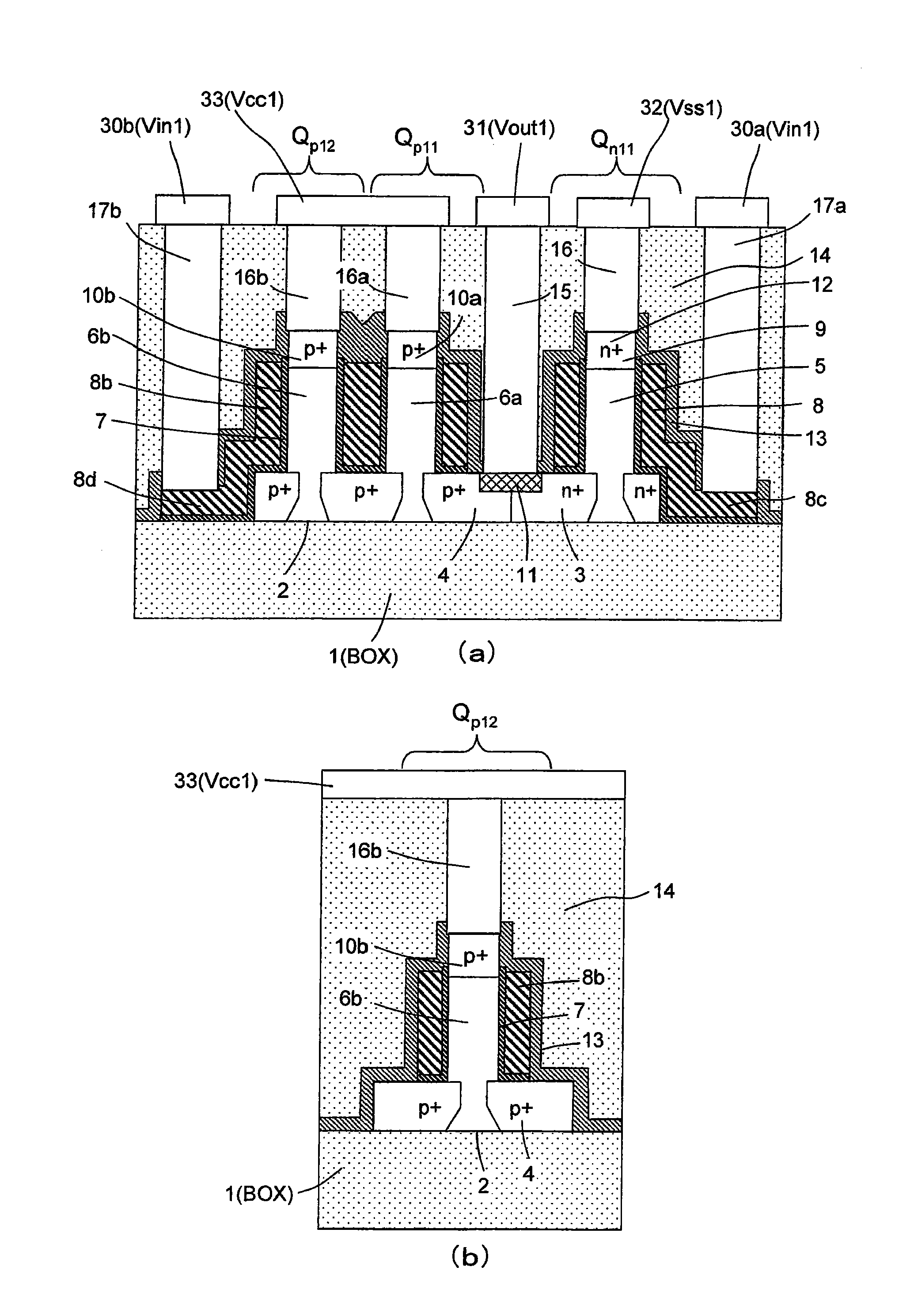

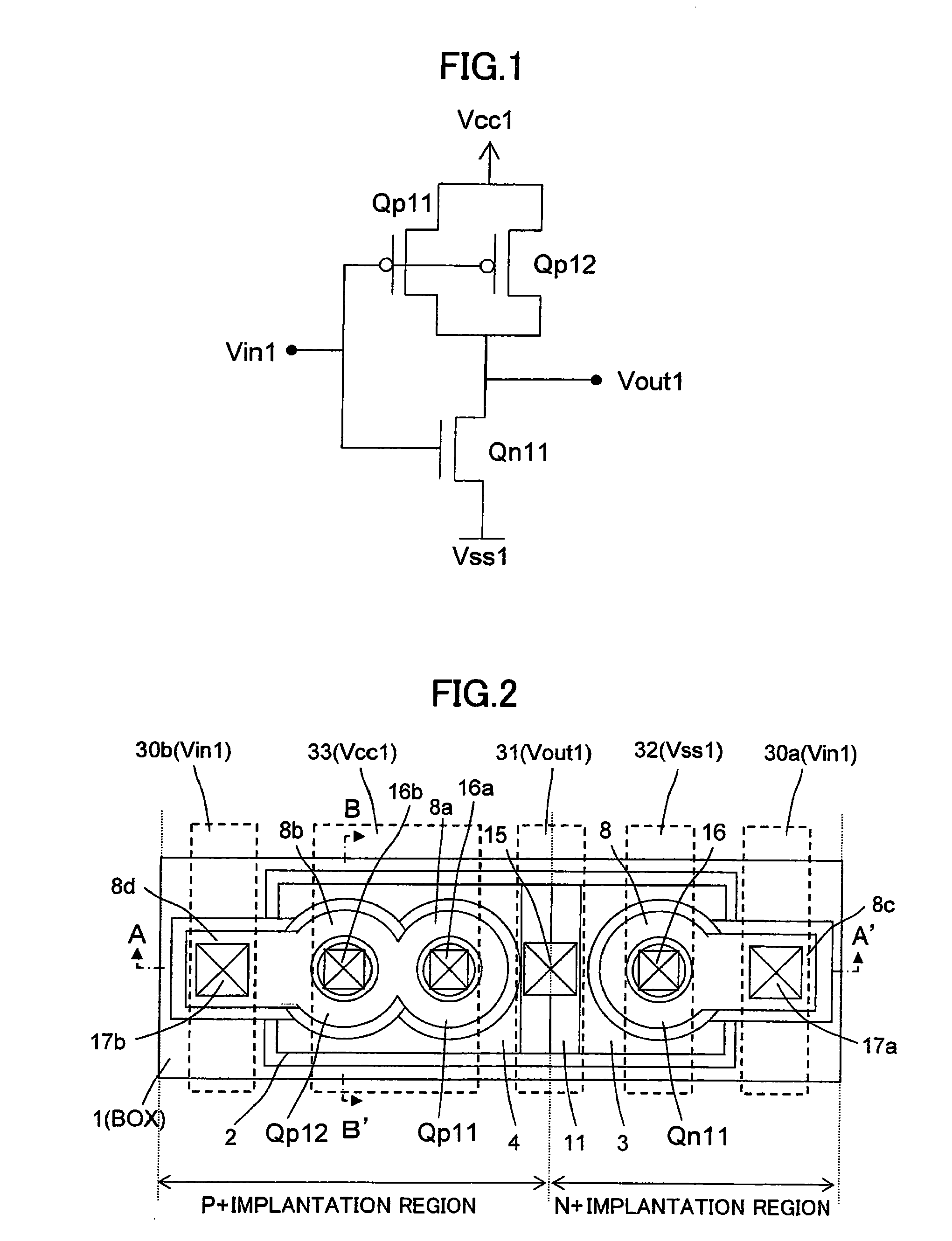

Semiconductor device and production method therefor

ActiveUS20100207201A1Reduce widthImprove area efficiencyTransistorSolid-state devicesDielectricEngineering

It is intended to provide a semiconductor device comprising a circuit which has a connection between one of a drain region and a source region of a first MOS transistor and one of a drain region and a source region of a second MOS transistor. The semiconductor device comprises: a substrate; a dielectric film on the substrate; and a planar semiconductor layer formed on the on-substrate dielectric film, wherein: the first MOS transistor includes a first drain or source region formed in the planar semiconductor layer, a first pillar-shaped semiconductor layer formed on the planar semiconductor layer, a second source or drain region formed in an upper portion of the first pillar-shaped semiconductor layer, and a first gate electrode formed in such a manner that the first gate electrode surrounds a sidewall of the first pillar-shaped semiconductor layer through a first dielectric film; and the second MOS transistor includes a third drain or source region formed in the planar semiconductor layer, a second pillar-shaped semiconductor layer formed on the planar semiconductor layer, a fourth source or drain region formed in an upper portion of the second pillar-shaped semiconductor layer, and a second gate electrode formed in such a manner that the second gate electrode surrounds a sidewall of the second pillar-shaped semiconductor layer through a second dielectric film, and wherein a first silicide layer is formed to connect at least a part of a surface of the first drain or source region and at least a part of a surface of the third drain or source region, wherein the first silicide layer is formed in an area other than an area in which a contact for at least the first drain or source region and the third drain or source region is formed.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Systems and methods of forming refractory metal nitride layers using disilazanes

InactiveUS20050028733A1Easy to controlMinimizing detrimental gas phase reactionPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseDeposition process

A method of forming (and apparatus for forming) refractory metal nitride layers (including silicon nitride layers), such as a tantalum (silicon) nitride barrier layer, on a substrate by using a vapor deposition process with a refractory metal precursor compound, a disilazane, and an optional silicon precursor compound.

Owner:MICRON TECH INC

Extracorporeal blood treatment and system having reversible blood pumps

InactiveUS20060122552A1Increase blood flowKeep for a long timeSolvent extractionOther blood circulation devicesTreatment systemBlood vessel

An extracorporeal blood treatment system including: a blood circuit having a first blood passage coupled at a first end to a first end of a blood treatment device and a second blood passage coupled at a first end to a second end of the treatment device, wherein the first and second blood passages each have a second end adapted to be coupled to a vascular system of a human patient; a first blood pump connectable to the first blood passage and a second blood pump connectable to the second blood passage, wherein said first and second blood pumps are adapted to move blood through the first and second blood passages in a first direction and in a reverse direction, and a pump controller operatively connected to the first and second blood pumps, said controller operates the blood pumps to cyclically move blood through the first and second blood passages in the first direction and the reverse direction.

Owner:GAMBRO LUNDIA AB

Systems and methods of forming tantalum silicide layers

InactiveUS20060048711A1Reduce diffuseReduce layeringSemiconductor/solid-state device manufacturingCapacitorsGas phaseNitrogen

A method of forming (and apparatus for forming) tantalum silicide layers (including tantalum silicon nitride layers), which are typically useful as diffusion barrier layers, on a substrate by using a vapor deposition process with a tantalum halide precursor compound, a silicon precursor compound, and an optional nitrogen precursor compound.

Owner:MICRON TECH INC

Protective coating for planarization

ActiveUS7393789B2Reduce the overall heightReduce layeringSemiconductor/solid-state device manufacturingComputer sciencePhotolithography

Various pattern transfer and etching steps can be used to create features. Conventional photolithography steps can be used in combination with pitch-reduction techniques to form superimposed, pitch-reduced patterns of crossing elongate features that can be consolidated into a single layer. Planarizing techniques using a filler layer and a protective layer are disclosed. Portions of an integrated circuit having different heights can be etched to a common plane.

Owner:MICRON TECH INC

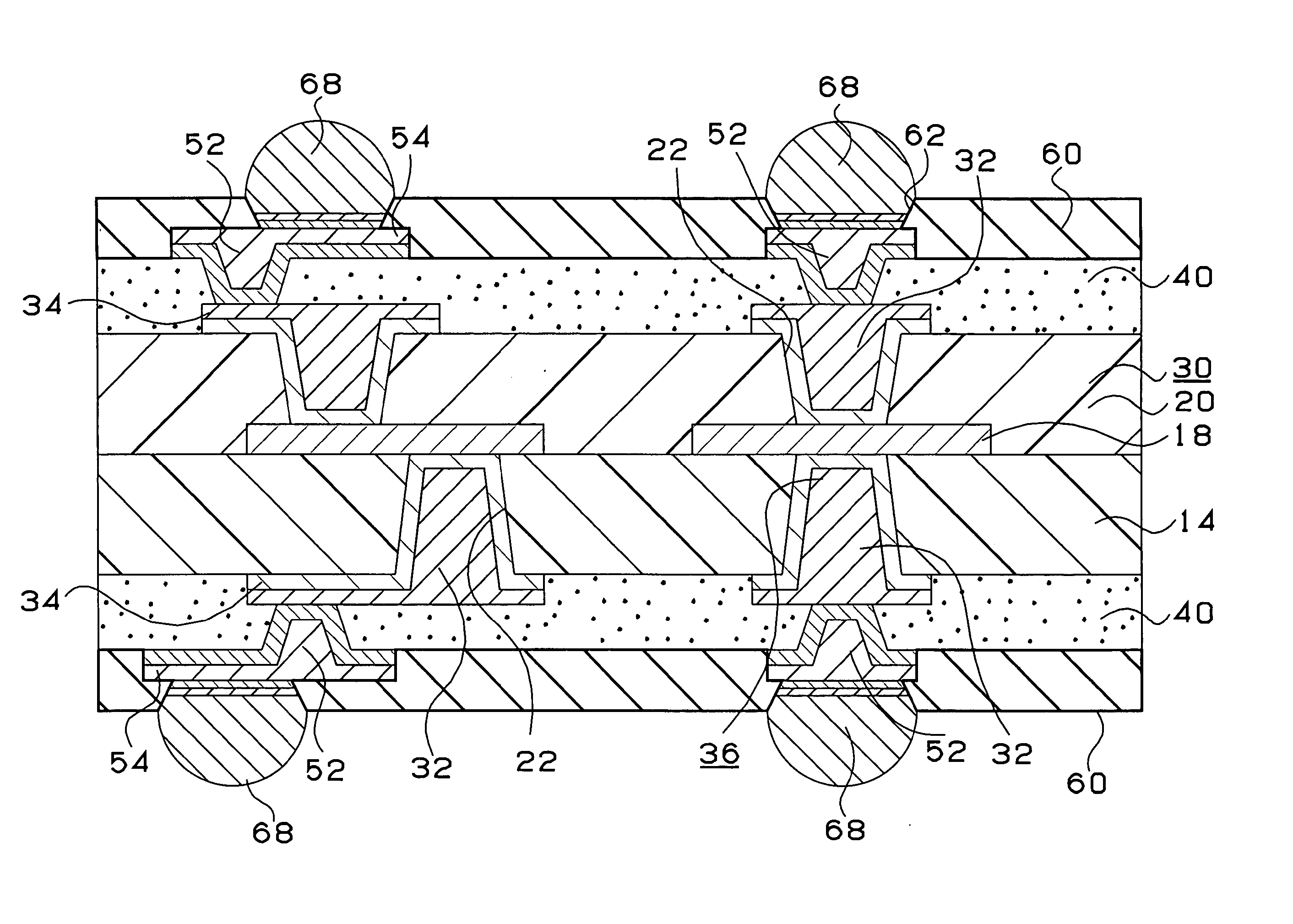

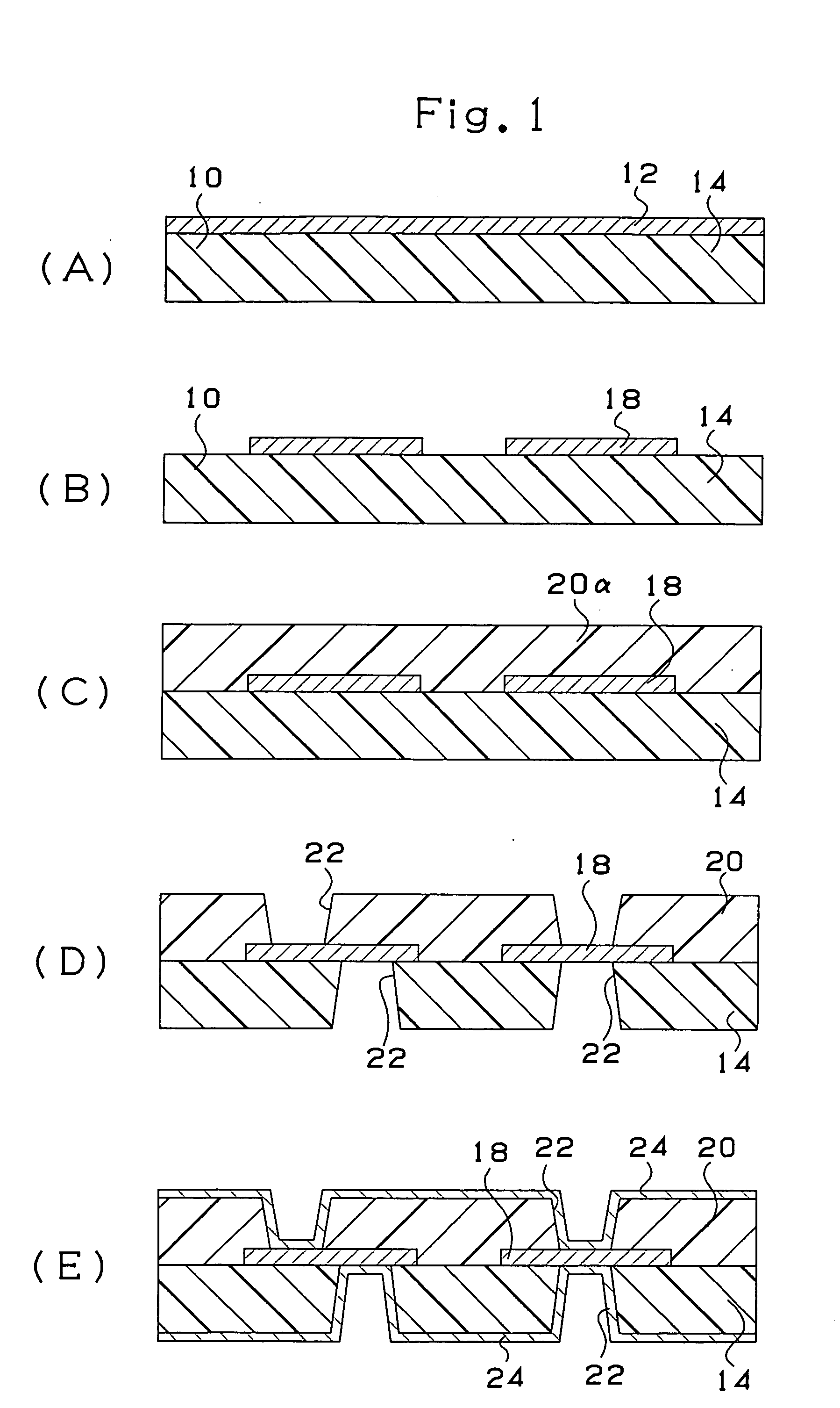

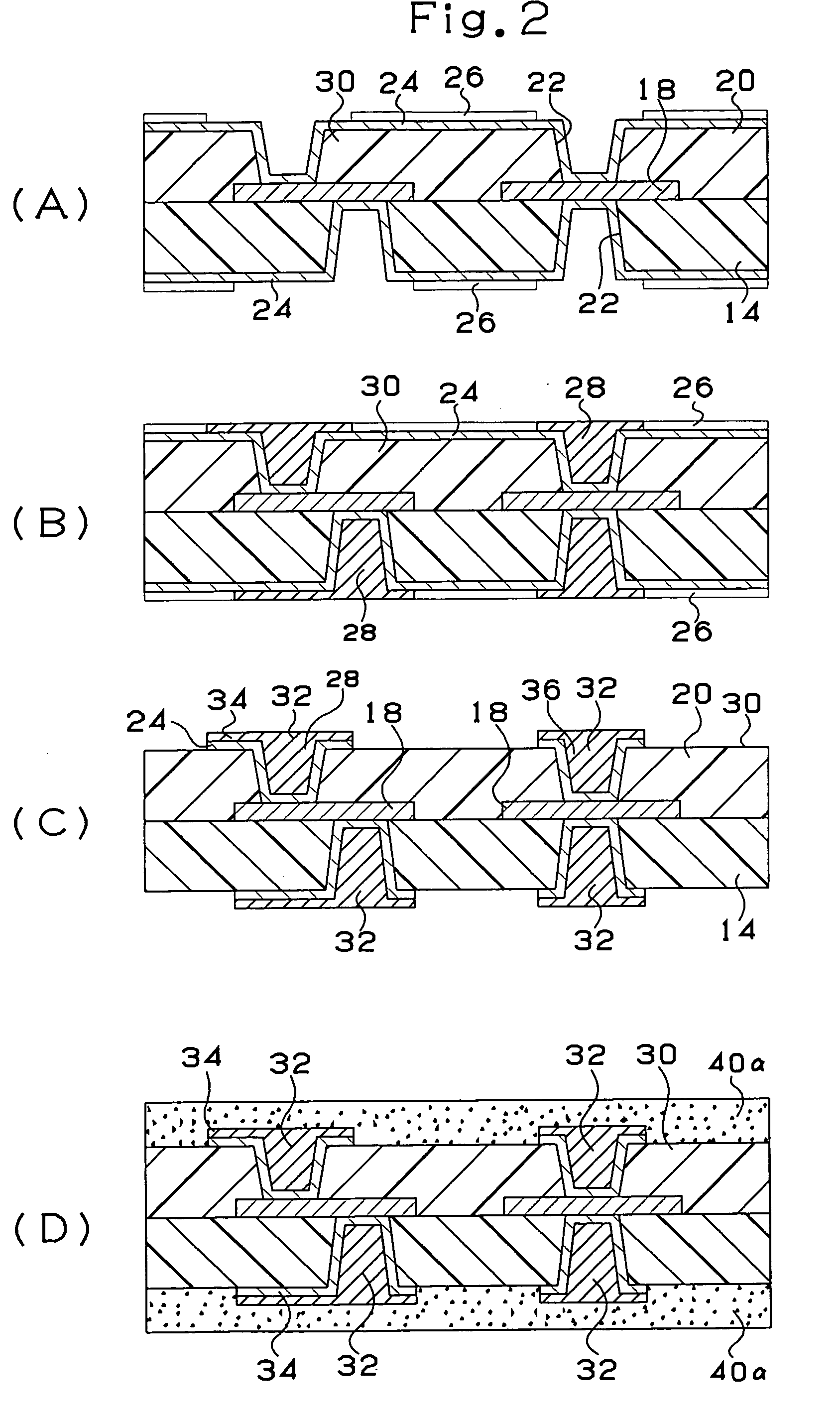

Multi-layer printed circuit board and method of manufacturing multi-layer printed circuit board

InactiveUS20050039948A1Shorten the timeSmall diameterInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringPrinted circuit board

A metal layer 18 is sandwiched between insulating layers 14 and 20 so that required strength is maintained. Hence it follows that the thickness of a core substrate 30 can be reduced and, therefore, the thickness of a multi-layer printed circuit board can be reduced. Formation of non-penetrating openings 22 which reach the metal layer 18 in the insulating layers 14 and 20 is simply required. Therefore, small non-penetrating openings 22 can easily be formed by applying laser beams. Thus, through holes 36 each having a small diameter can be formed.

Owner:IBIDEN CO LTD

Nonvolatile memory device and method of fabricating the same

There are provided a nonvolatile memory device and a method of fabricating the same. A gate region of the nonvolatile memory device is formed as a stack structure including a tunnel oxide layer, a trapping layer, a blocking layer and a control gate electrode. The trapping layer is formed of a high-k dielectric having a higher dielectric constant than that of the tunnel oxide layer. When the trapping layer is formed of high-k dielectric, an EOT in a same thickness can be reduced, and excitation of electrons of the control gate electrode to the tunnel oxide layer due to a high potential barrier relative to the tunnel oxide layer is prevented so that program and erase voltages can be further reduced. As such, a problem that the tunnel oxide layer is damaged due to the conventional high program and erase voltages can be solved by reducing the program and erase voltages, and program and erase speeds of the transistor can be further improved.

Owner:SAMSUNG ELECTRONICS CO LTD

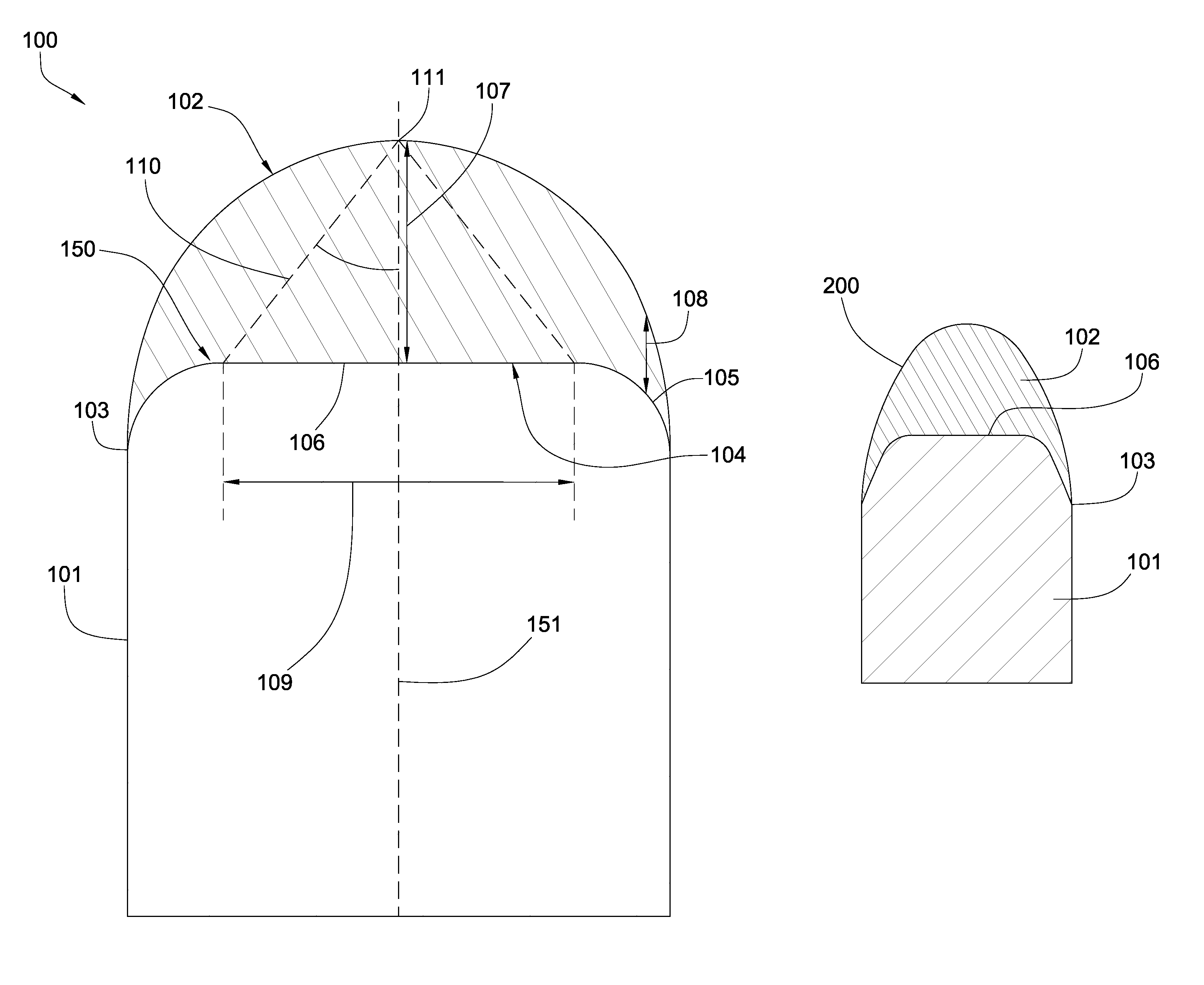

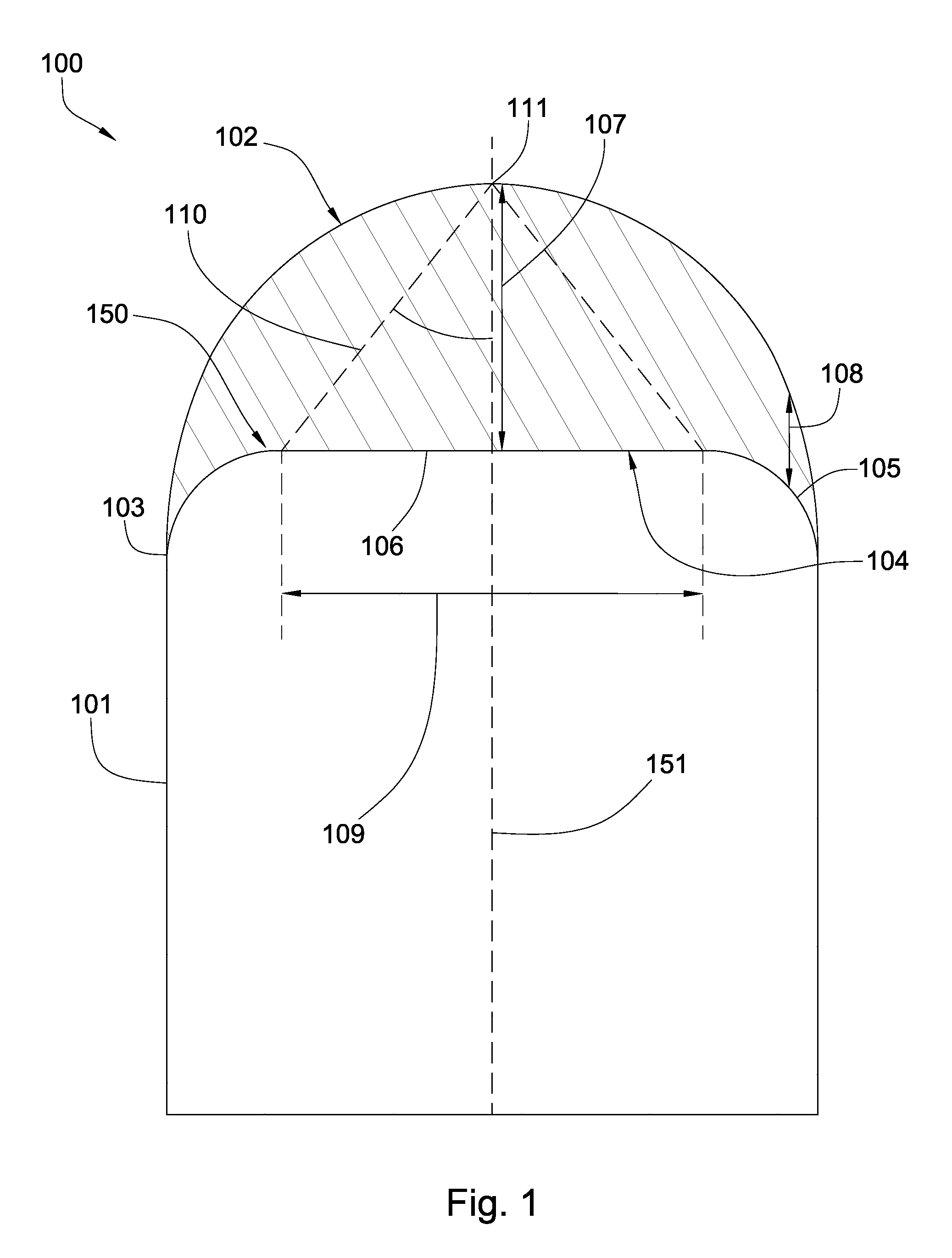

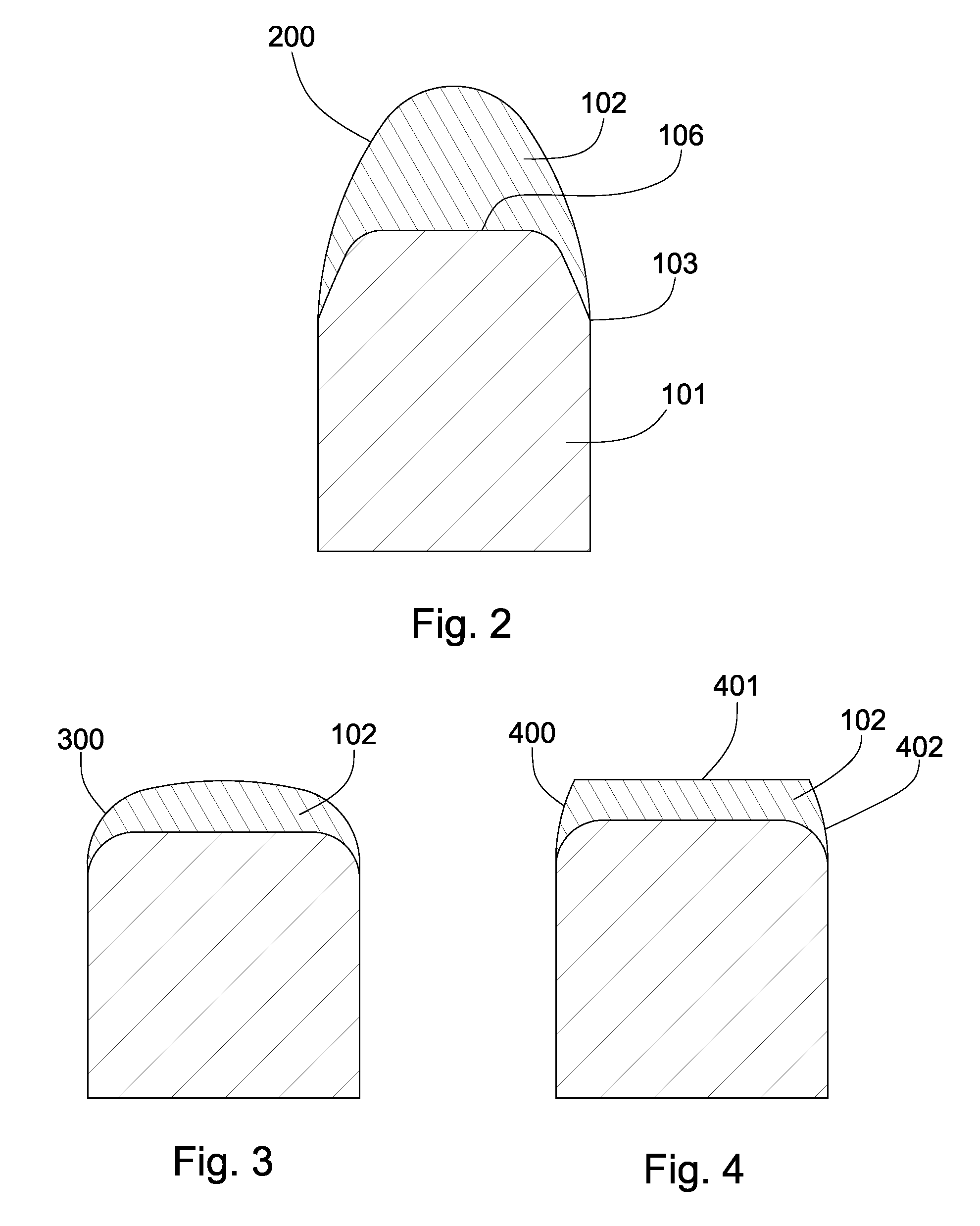

Superhard insert with an interface

In one aspect of the invention, a superhard insert has a carbide substrate bonded to ceramic layer at an interface. The substrate has a generally frusto-conical end at the interface with a tapered portion leading to a flat portion. The central section of the ceramic layer may have a first thickness immediately over the flat portion of the substrate. The peripheral section of the ceramic layer has a second thickness being less than the first thickness covering the tapered portion of the substrate. The ceramic layer may be formed using HPHT technology.

Owner:SCHLUMBERGER TECH CORP

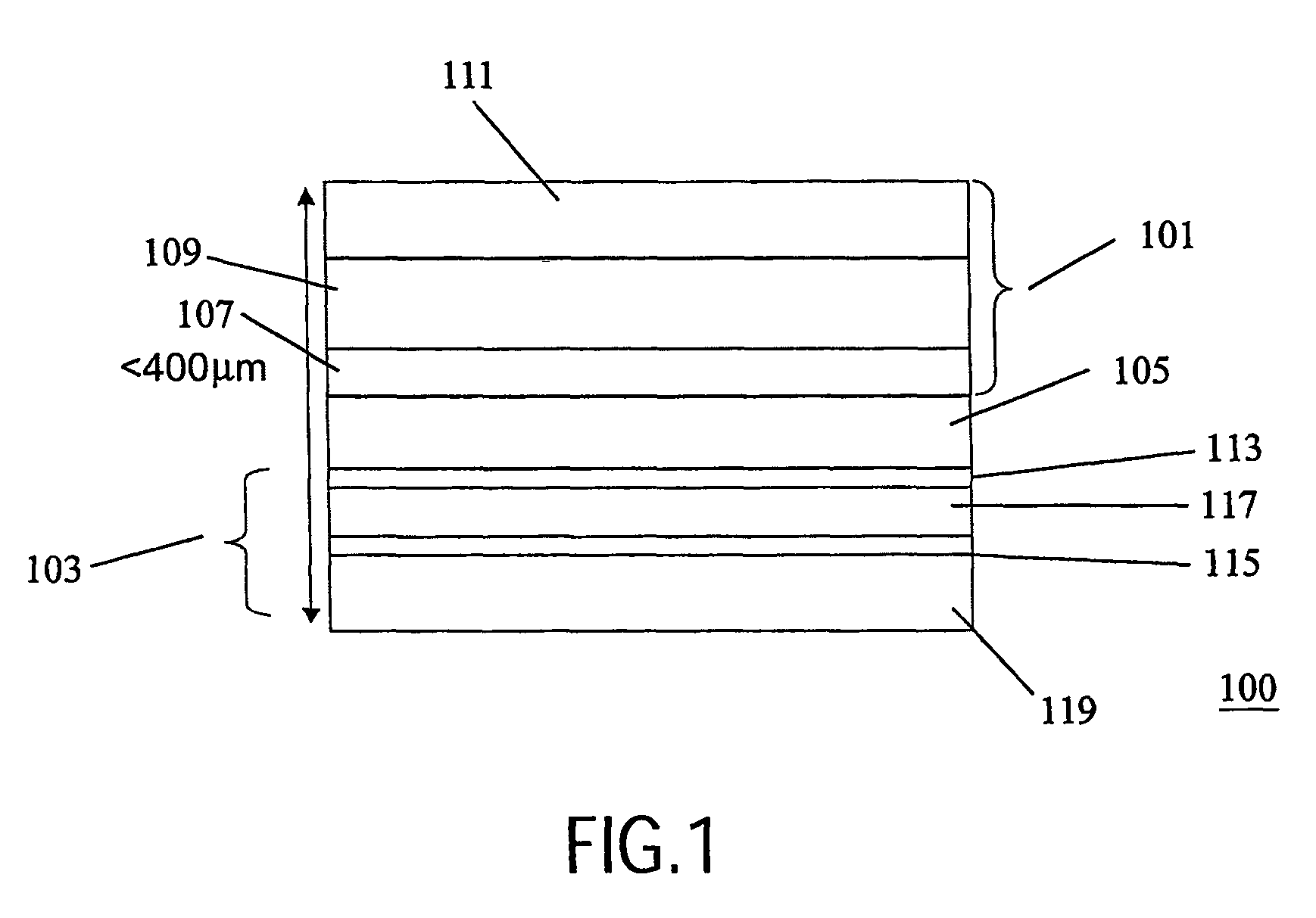

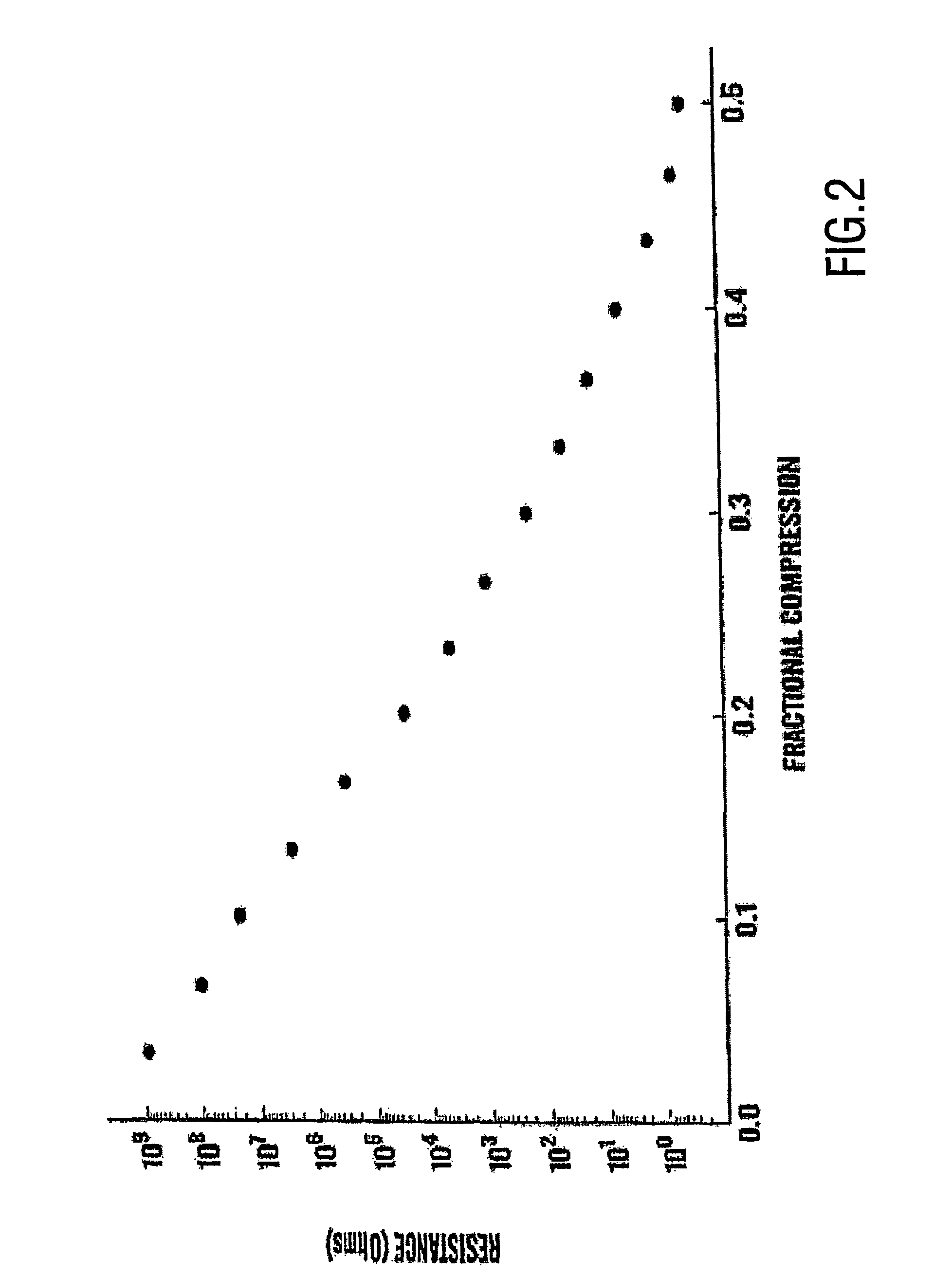

Touch sensitive display for a portable device

InactiveUS8325143B2Reduce layeringReduce sensitivityCathode-ray tube indicatorsGraph readingElectrical conductorActive matrix

A portable device is provided having a touch sensitive display (100) comprising an active matrix display element (101) and a touch sensitive element (103). The touch sensitive element (103) is disposed on the viewer distal side of the active matrix display element (101) thereby not affecting the display properties. The touch sensitive element (103) comprises a first and second conductive layer (113, 115) each having a plurality of conductors. The conductive layers (113, 115) sandwich a pressure sensitive layer (117) which modifies an electrical conductivity between two conductors of the two conductive layers (113, 115) in response to a pressure point resulting from an applied pressure. Thus, accurate position detection is achieved. The conductors may be aligned with the active matrix and the requirement for calibration may be obviated.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com