Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

25468 results about "Condensed matter physics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Condensed matter physics is the field of physics that deals with the macroscopic and microscopic physical properties of matter. In particular it is concerned with the "condensed" phases that appear whenever the number of constituents in a system is extremely large and the interactions between the constituents are strong. The most familiar examples of condensed phases are solids and liquids, which arise from the electromagnetic forces between atoms. Condensed matter physicists seek to understand the behavior of these phases by using physical laws. In particular, they include the laws of quantum mechanics, electromagnetism and statistical mechanics.

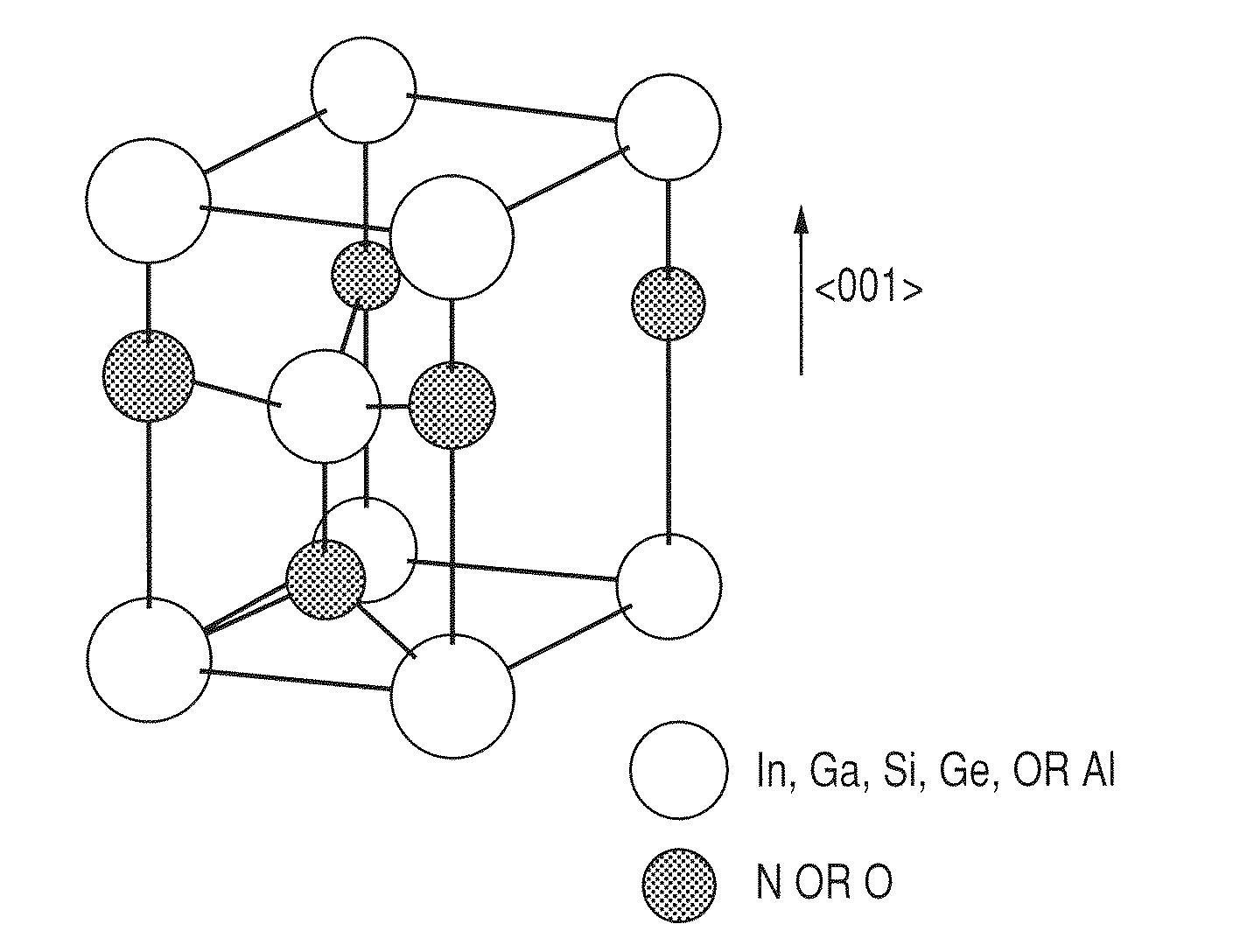

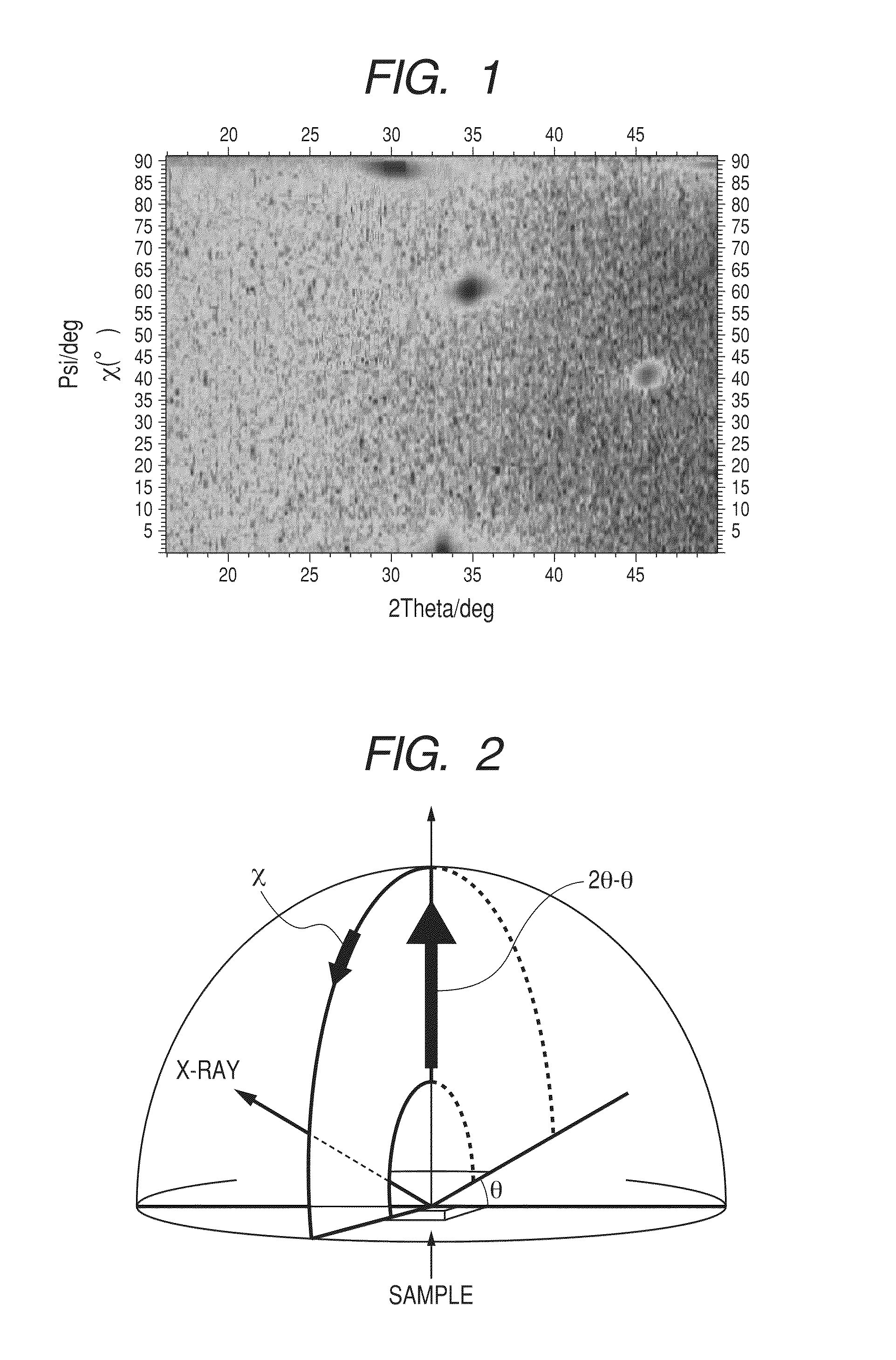

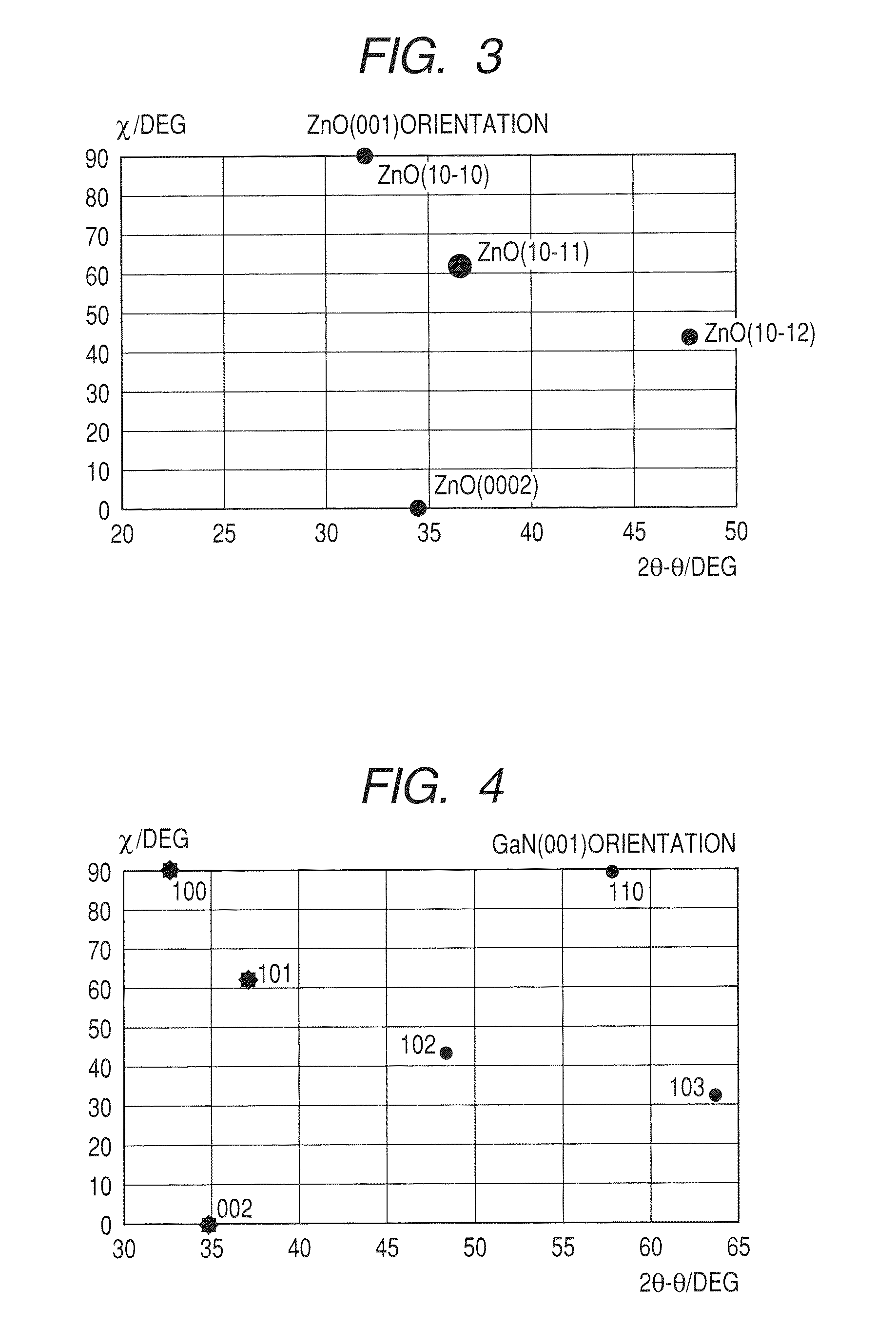

Substrate for growing wurtzite type crystal and method for manufacturing the same and semiconductor device

ActiveUS20100092800A1Low costHigh crystallinityPolycrystalline material growthVacuum evaporation coatingNitrideSemiconductor

A laminated structure comprises a first layer comprising a crystal with six-fold symmetry, and a second layer comprising a metal oxynitride crystal formed on the first layer, wherein the second layer comprises at least one element selected from the group consisting of In, Ga, Si, Ge and Al, N, O and Zn, as main elements, and wherein the second layer has in-plane orientation.

Owner:CANON KK

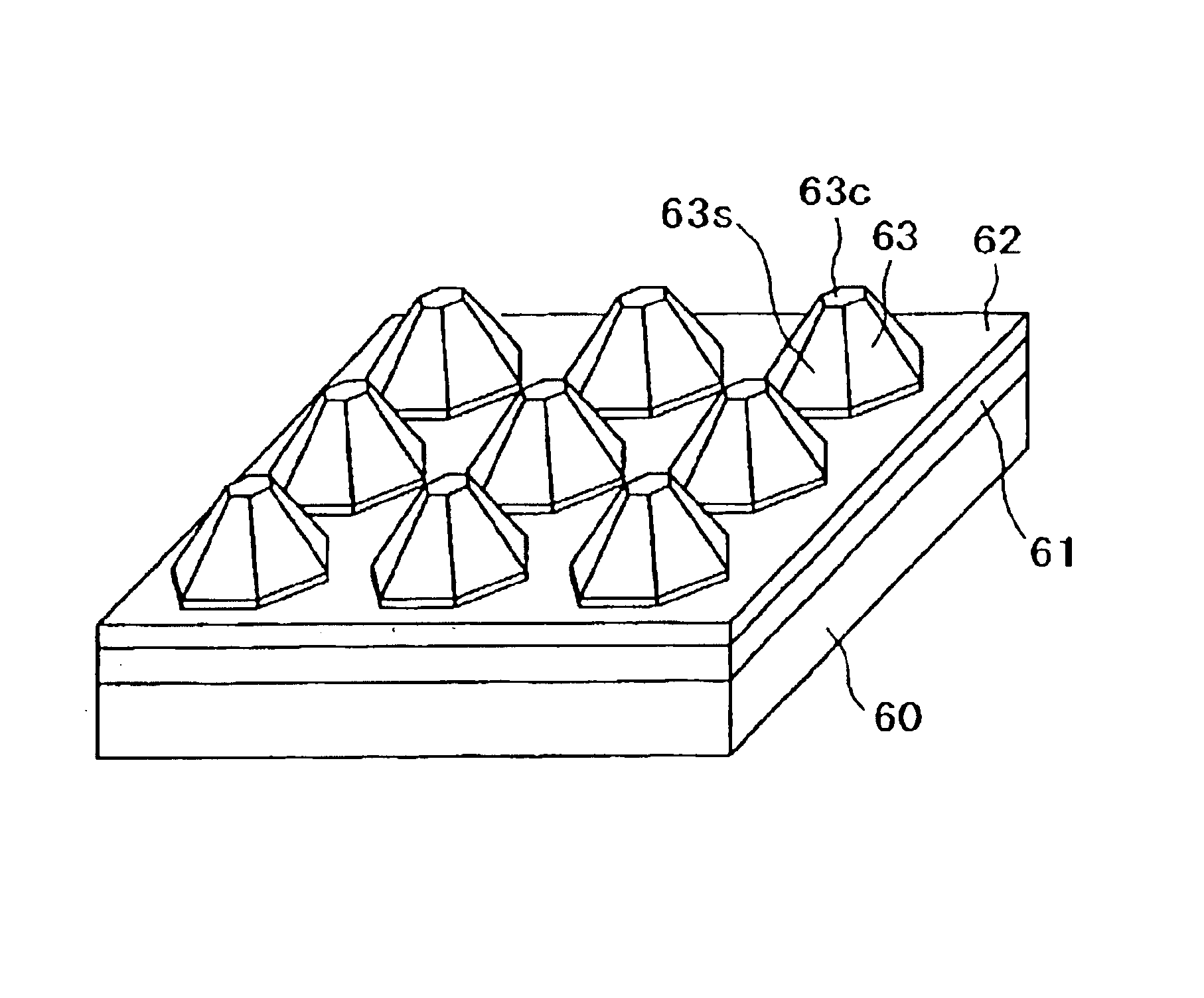

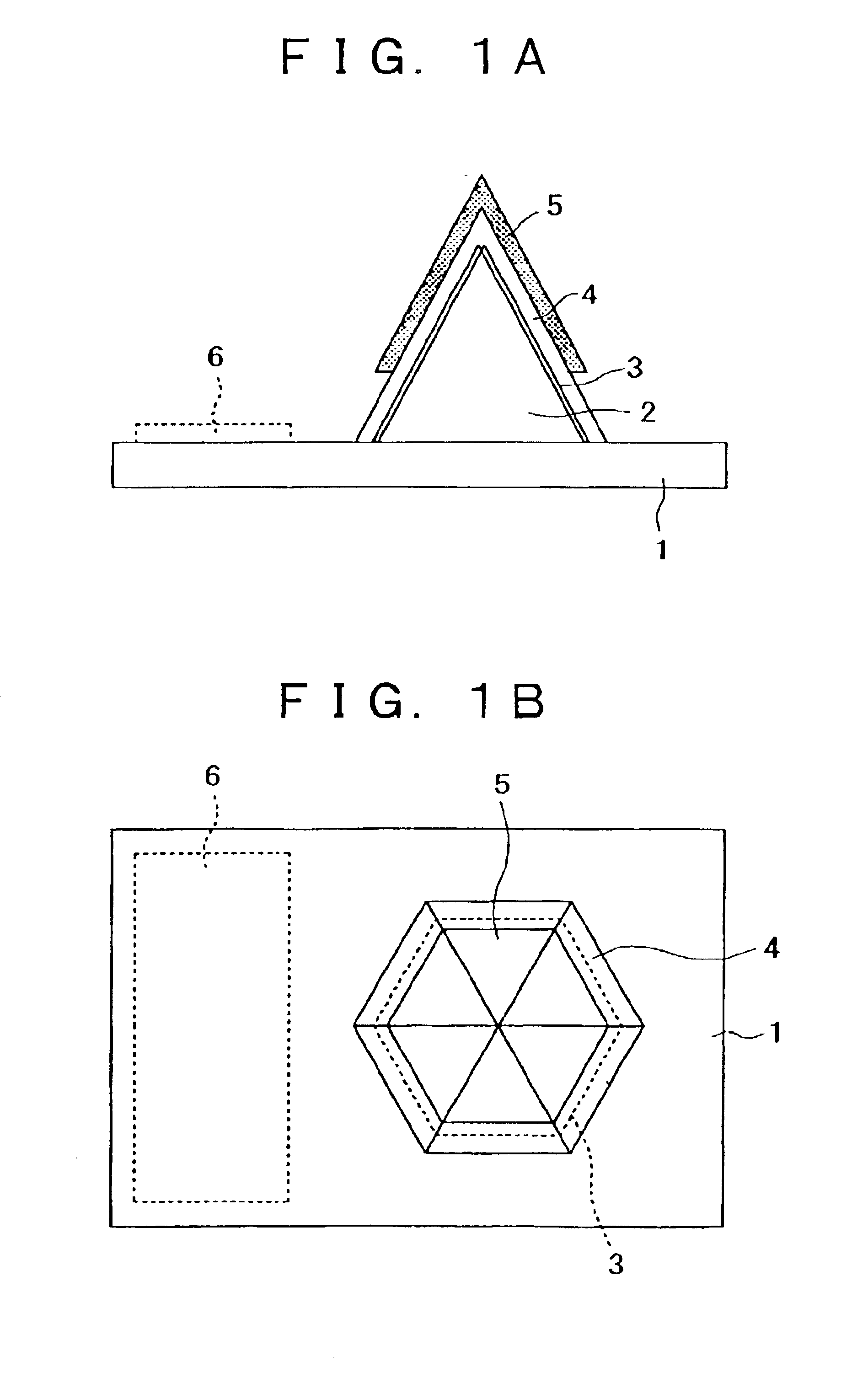

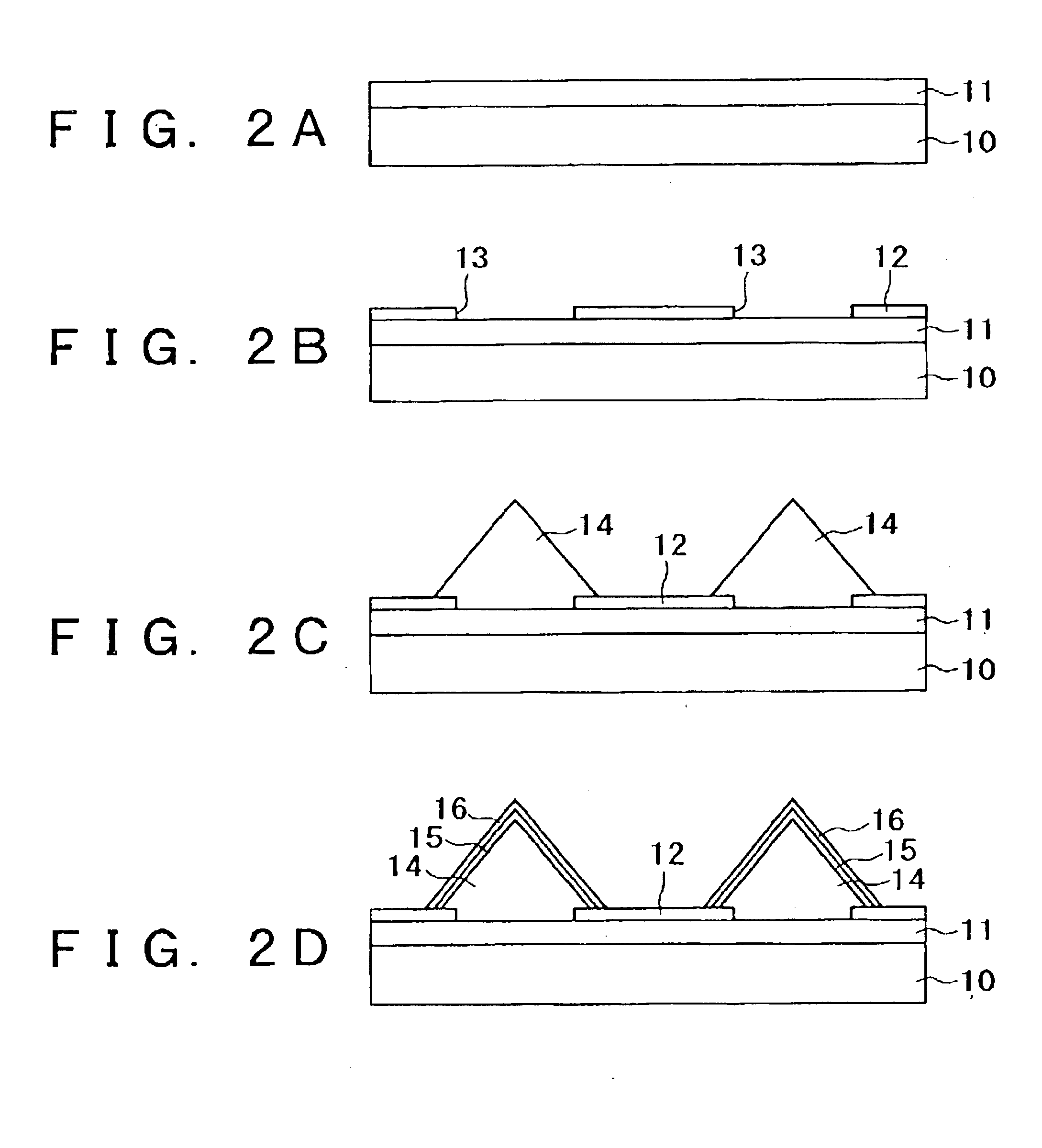

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

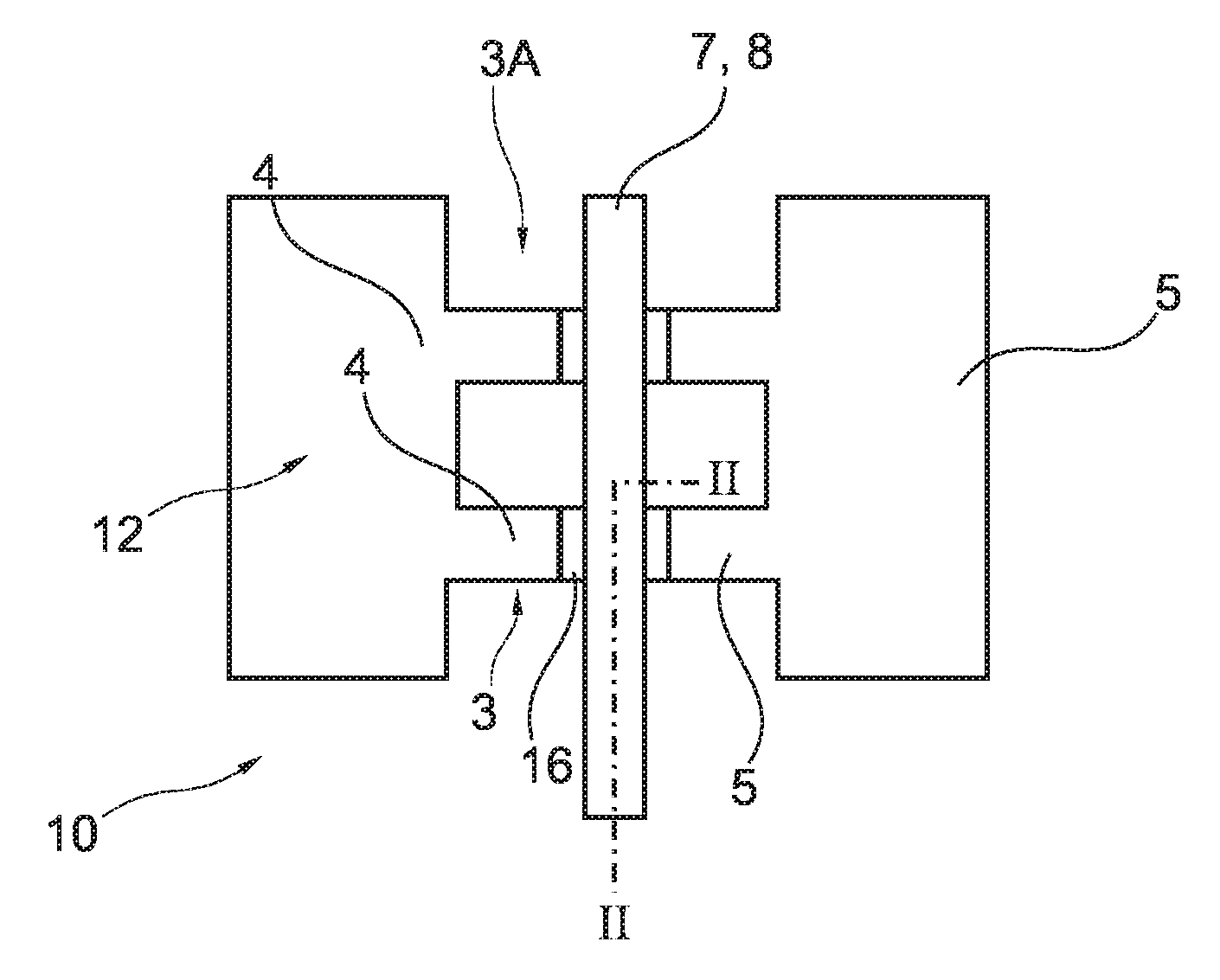

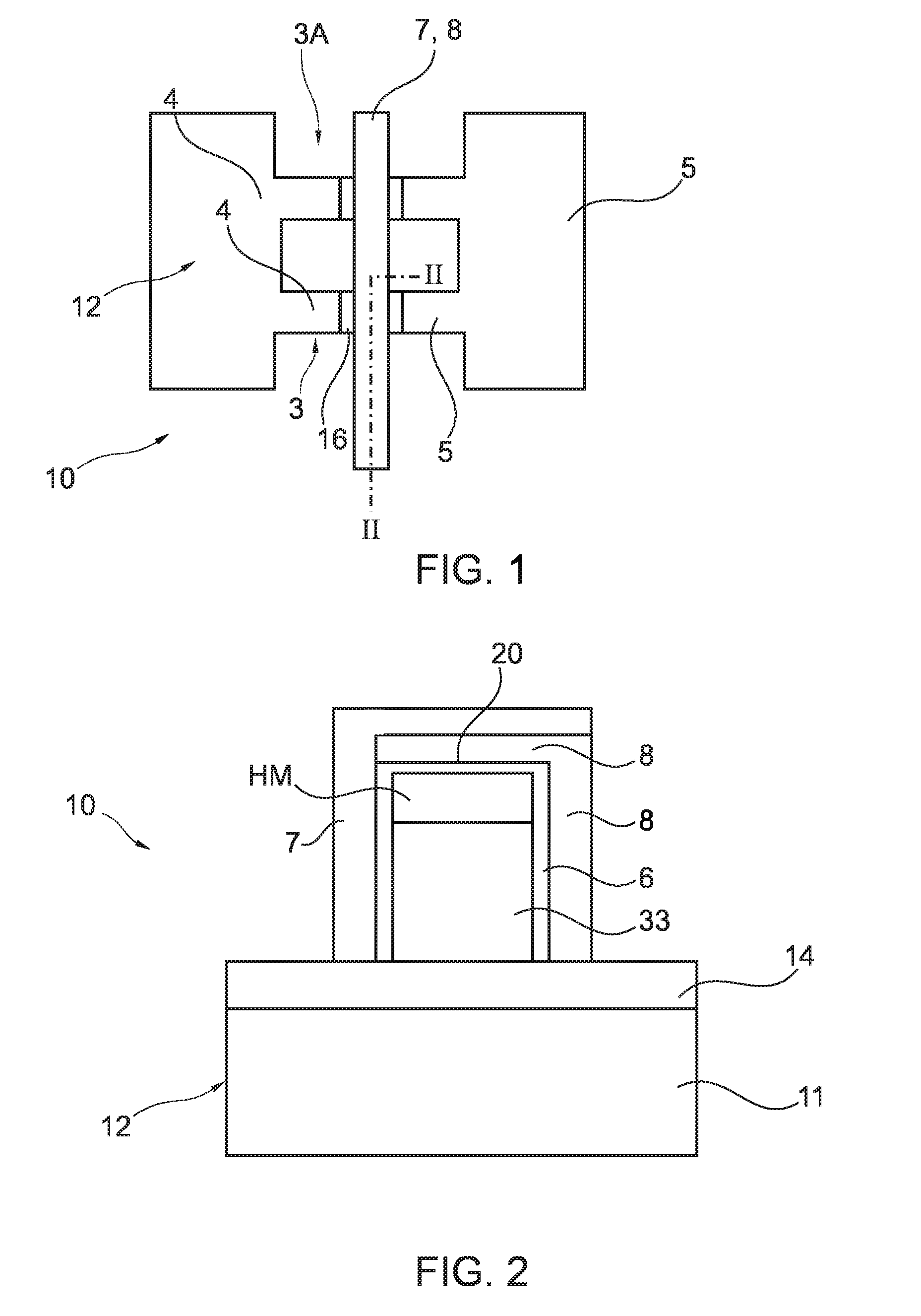

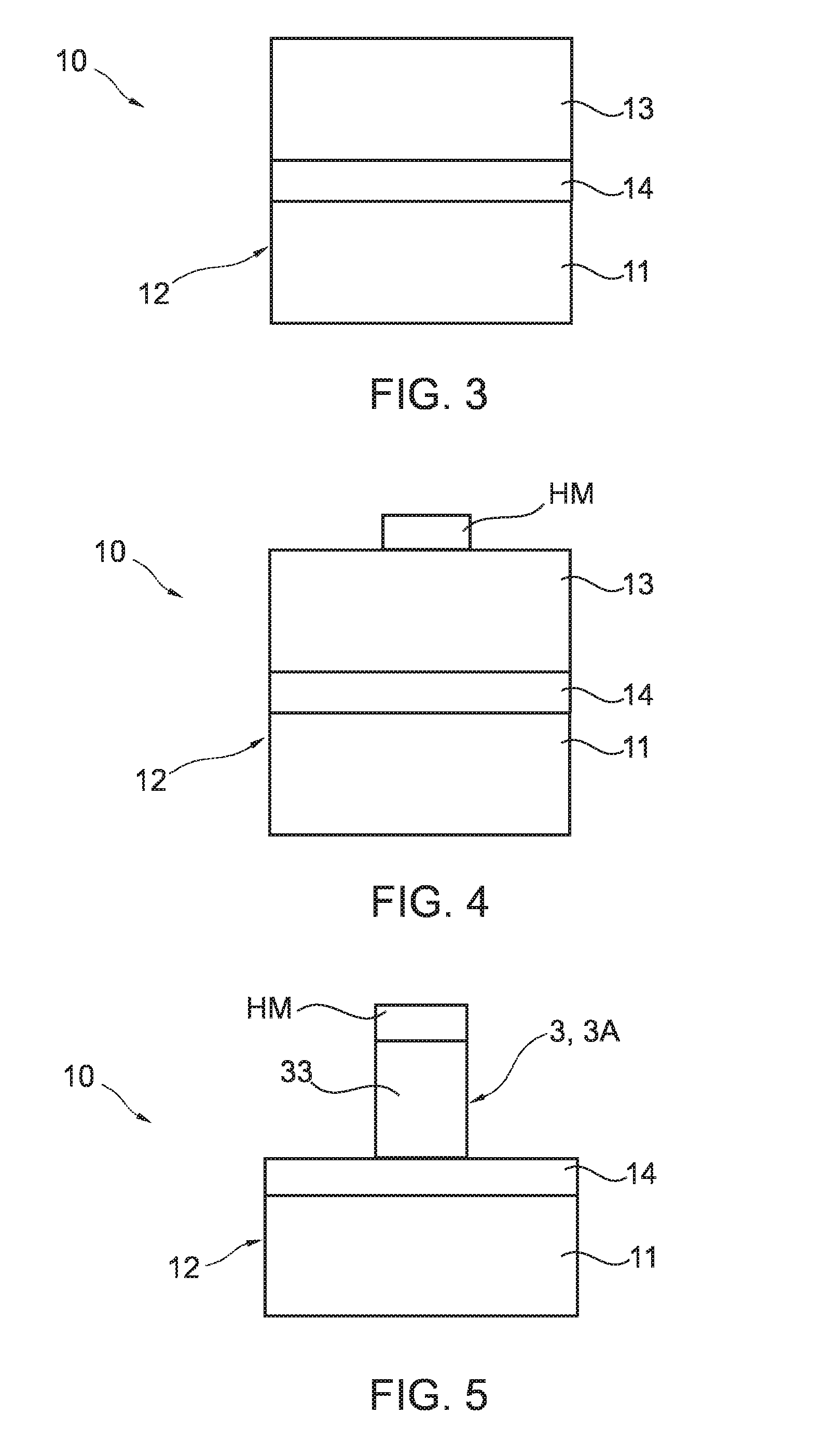

Transistor device and method of manufacturing such a transistor device

ActiveUS20100025766A1Suitable for high-scale integrationImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate insulatorEngineering

A transistor device (10), the transistor device (10) comprising a substrate (11, 14), a fin (3, 3A) aligned along a horizontal direction on the substrate (11, 14), a first source / drain region (4) of a first type of conductivity in the fin (3, 3A), a second source / drain region (5) of a second type of conductivity in the fin (3, 3A), wherein the first type of conductivity differs from the second type of conductivity, a channel region (33) in the fin (3, 3A) between the first source / drain region (4) and the second source / drain region (5), a gate insulator (6) on the channel region (33), and a gate structure (7, 8) on the gate insulator (6), wherein the sequence of the first source / drain region (4), the channel region (33) and the second source / drain region (5) is aligned along the horizontal direction.

Owner:UNITED MICROELECTRONICS CORP

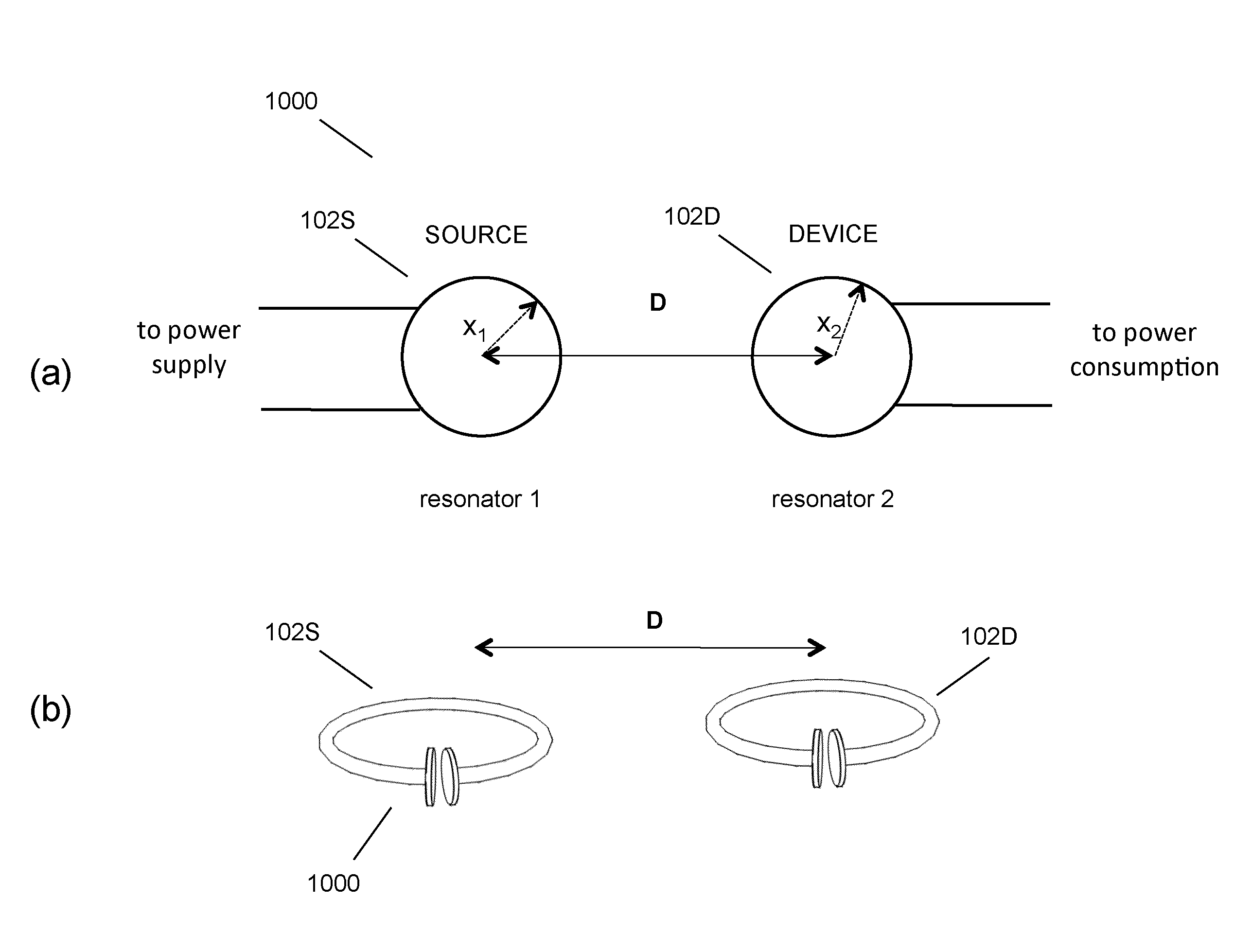

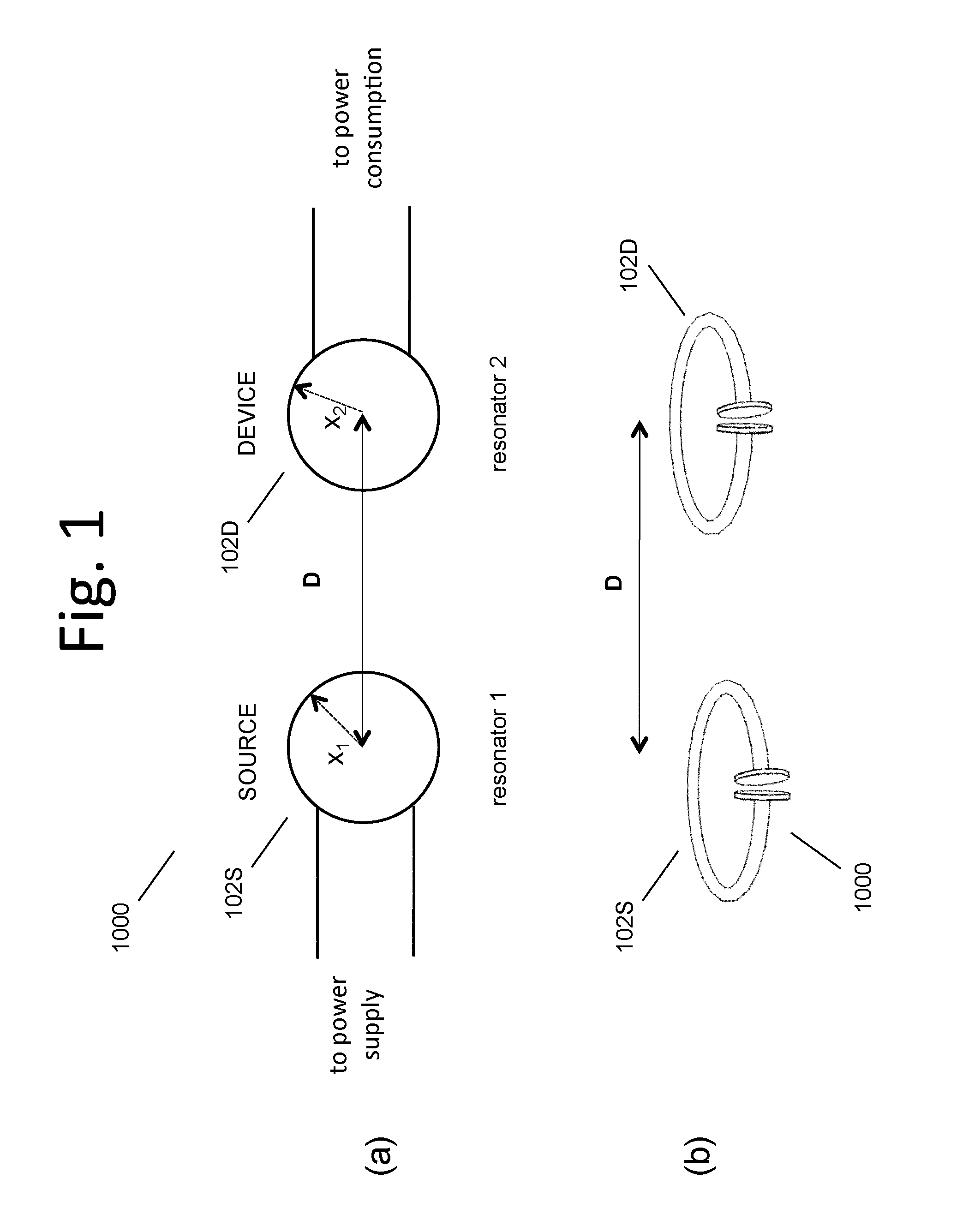

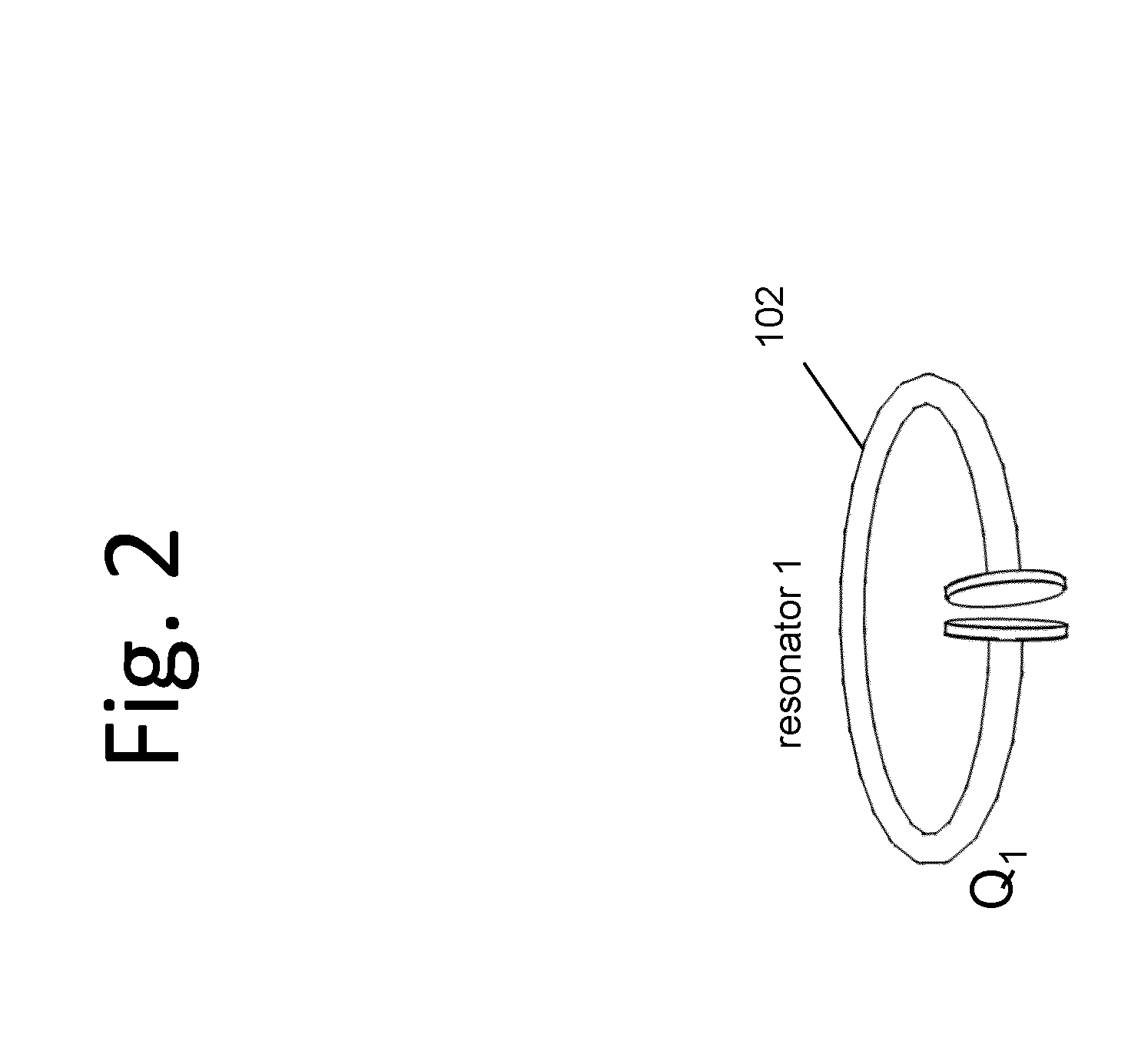

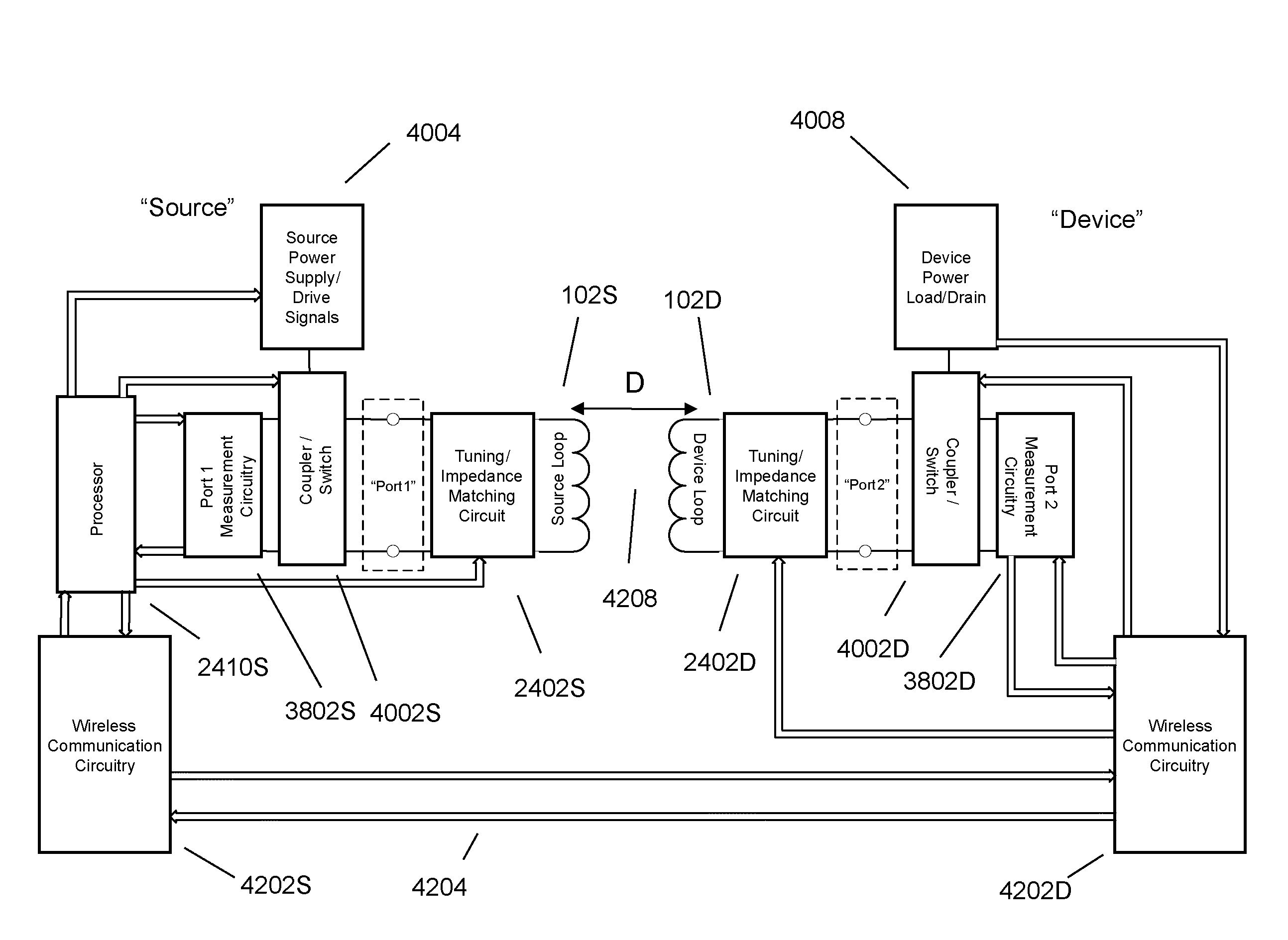

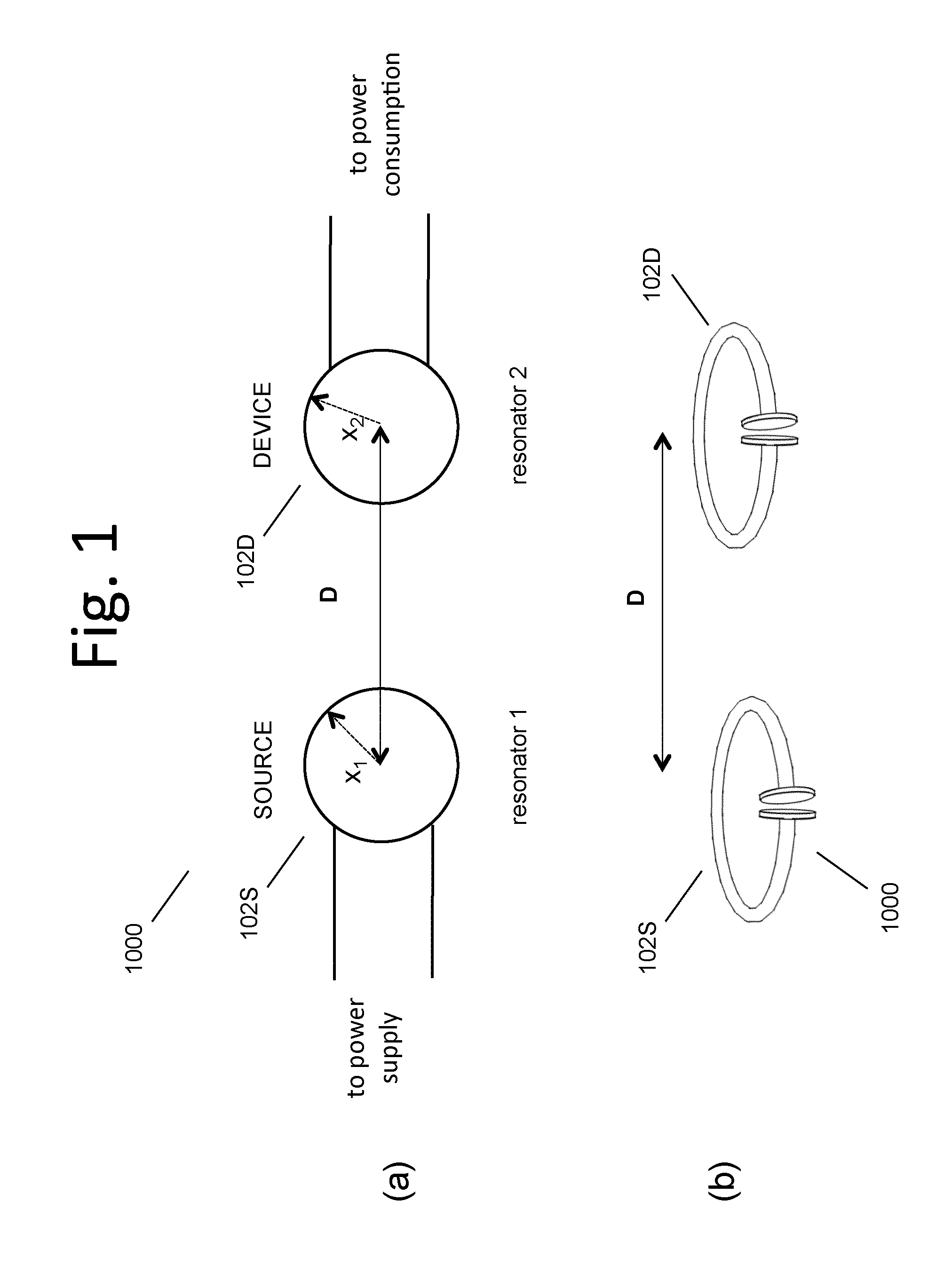

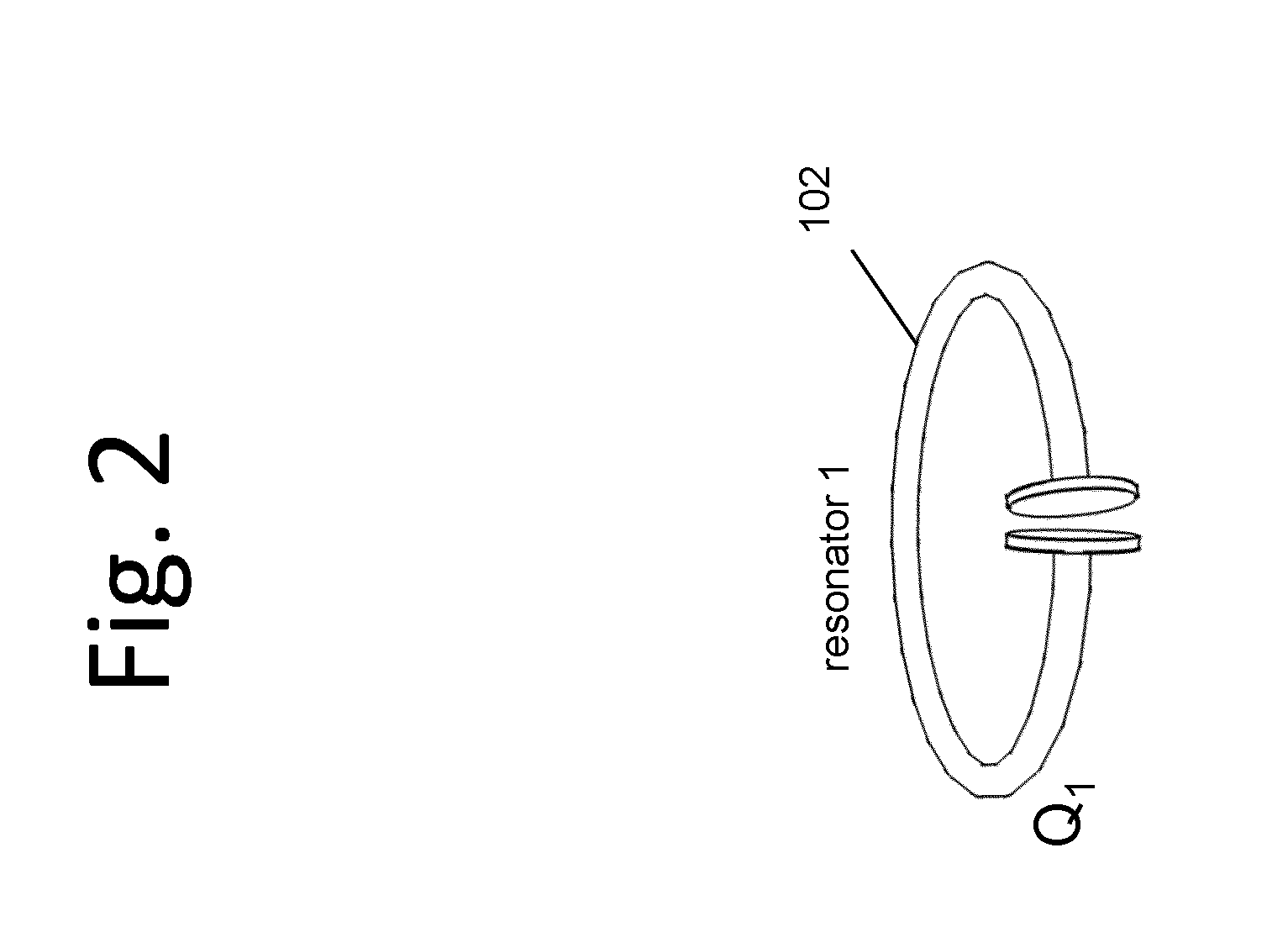

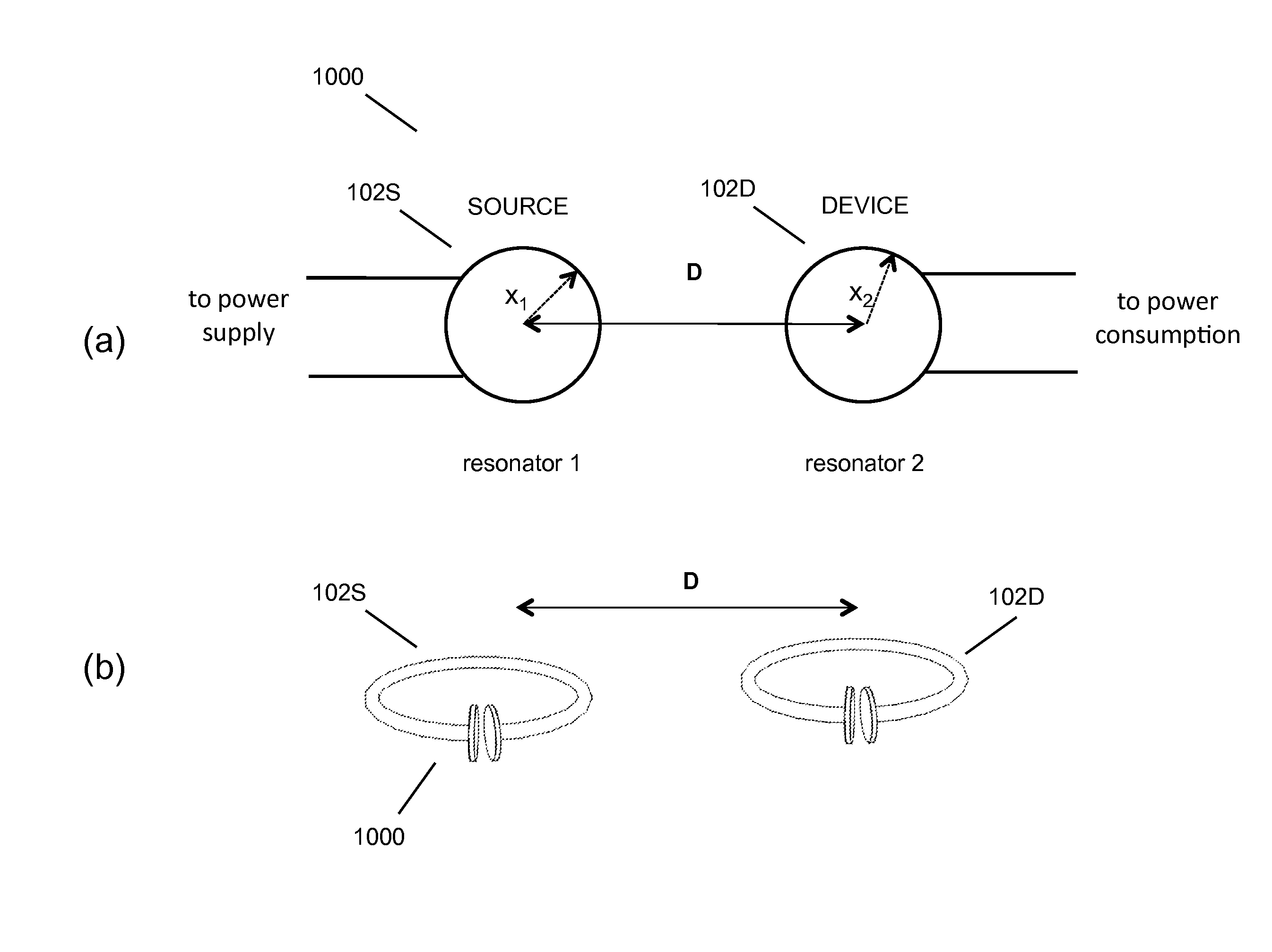

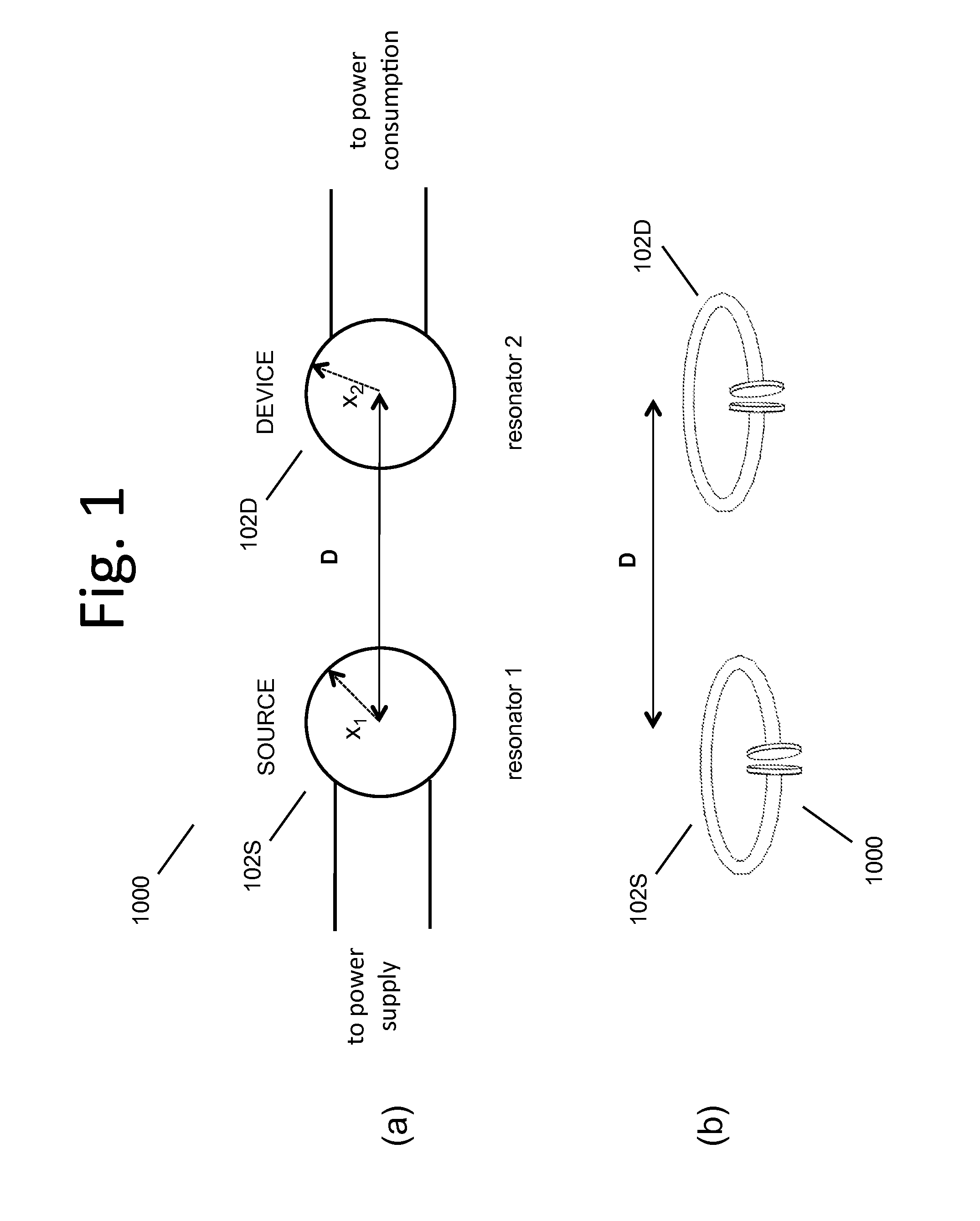

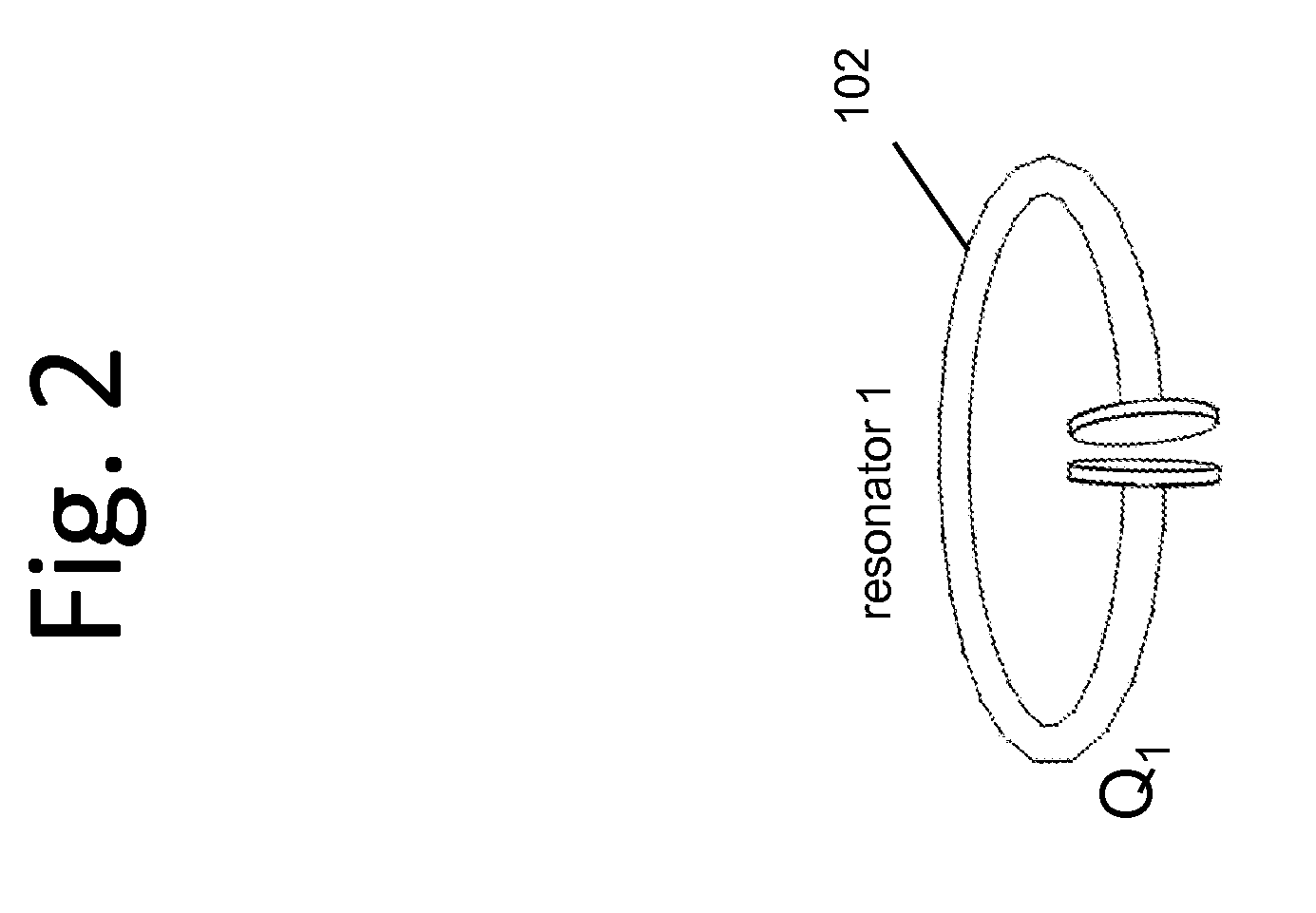

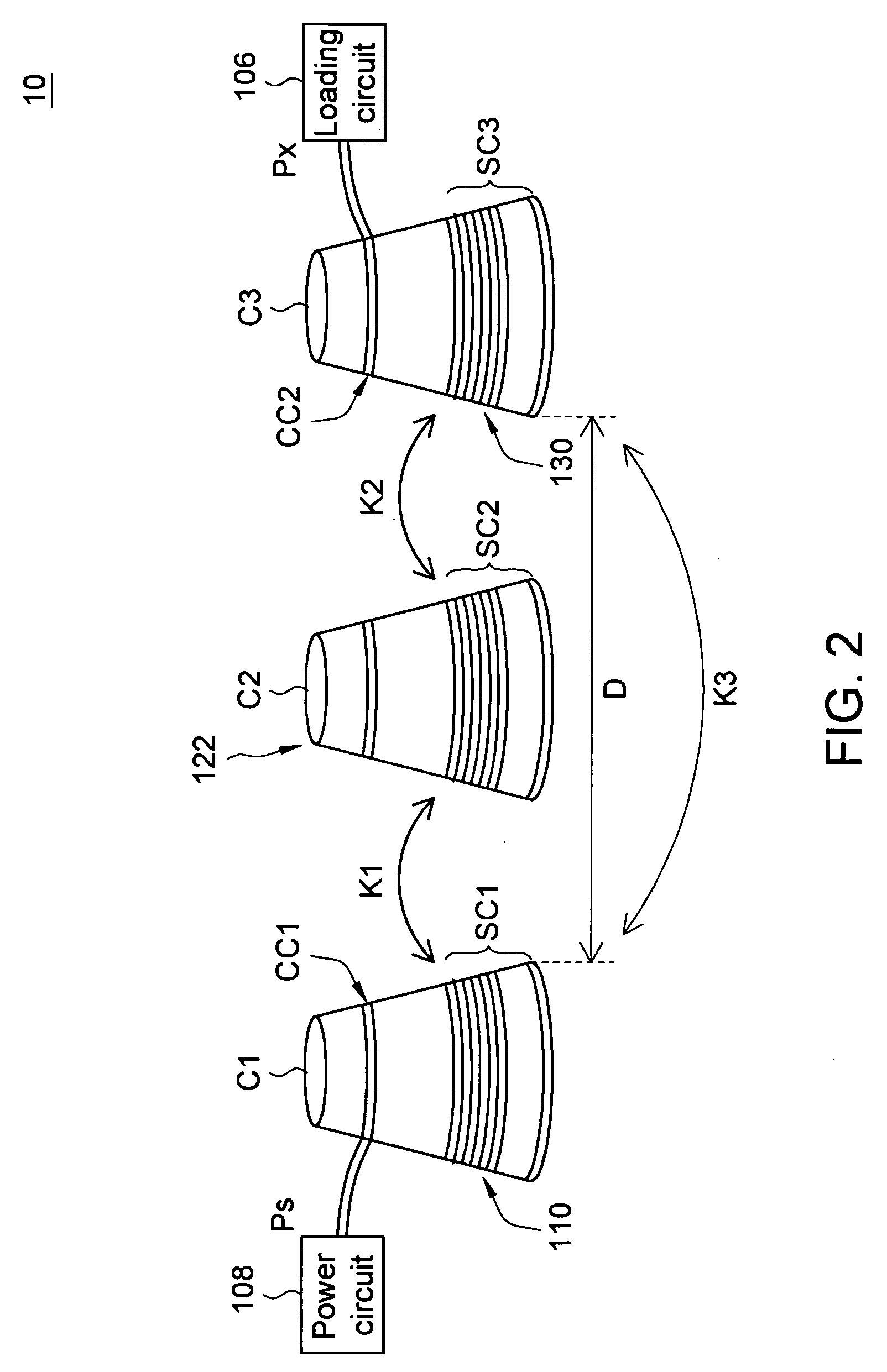

Wireless energy transfer systems

ActiveUS20100141042A1Efficient deliveryEfficient energy transferMultiple-port networksNear-field transmissionEnergy transferCondensed matter physics

Described herein are improved capabilities for a source resonator having a Q-factor Q1>100 and a characteristic size x1 coupled to an energy source, and a second resonator having a Q-factor Q2>100 and a characteristic size x2 coupled to an energy drain located a distance D from the source resonator, where the source resonator and the second resonator are coupled to exchange energy wirelessly among the source resonator and the second resonator.

Owner:WITRICITY CORP

Wireless energy transfer systems

ActiveUS20100109445A1Efficient deliveryEfficient energy transferMultiple-port networksNear-field transmissionEnergy transferCondensed matter physics

Described herein are improved capabilities for a source resonator having a Q-factor Q1>100 and a characteristic size x1 coupled to an energy source, and a second resonator having a Q-factor Q2>100 and a characteristic size x2 coupled to an energy drain located a distance D from the source resonator, where the source resonator and the second resonator are coupled to exchange energy wirelessly among the source resonator and the second resonator.

Owner:WITRICITY CORP

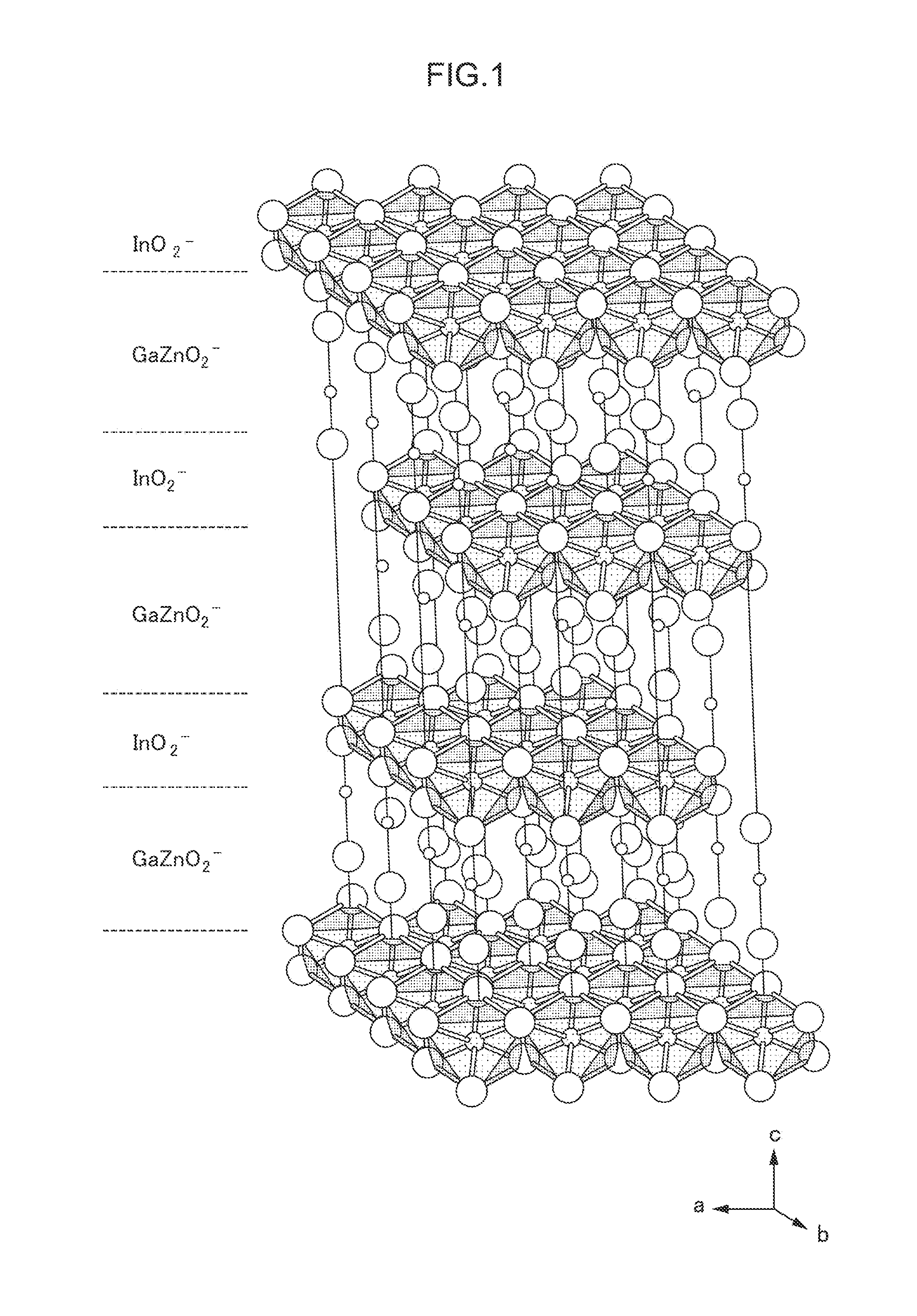

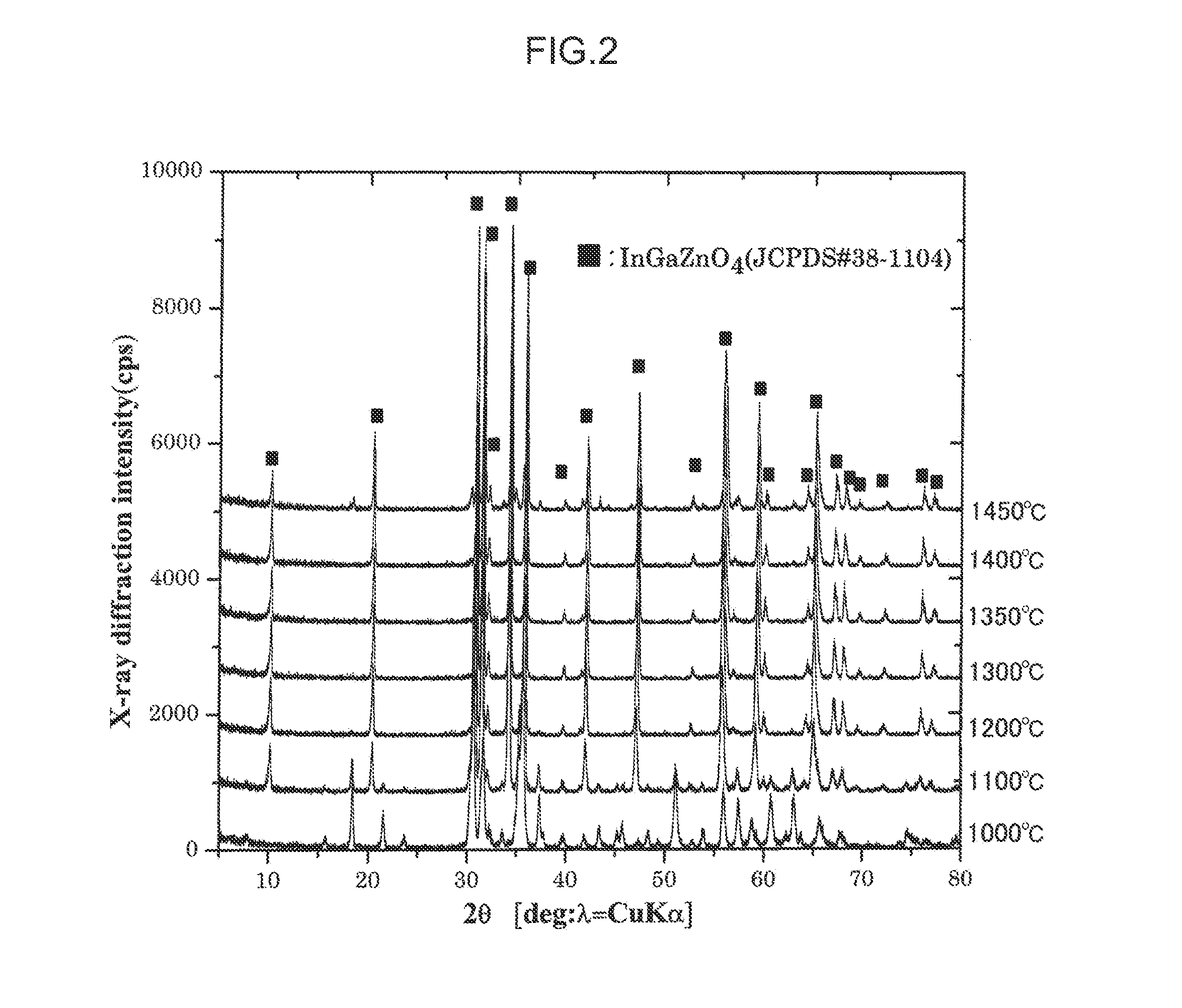

Thin film transistor and method of producing thin film transistor

ActiveUS20100320459A1TransistorSemiconductor/solid-state device manufacturingThin membraneCrystal structure

The invention provides a thin film transistor comprising an active layer, the active layer comprising an IGZO-based oxide material, the IGZO-based oxide material being represented by a composition formula of In2-xGaxZnO4-δ, where 0.75<x<1.10 and 0<δ≦1.29161×exp(−x / 0.11802)+0.00153 and being formed from a single phase of IGZO having a crystal structure of YbFe2O4, and a method of producing the thin film transistor.

Owner:SAMSUNG DISPLAY CO LTD

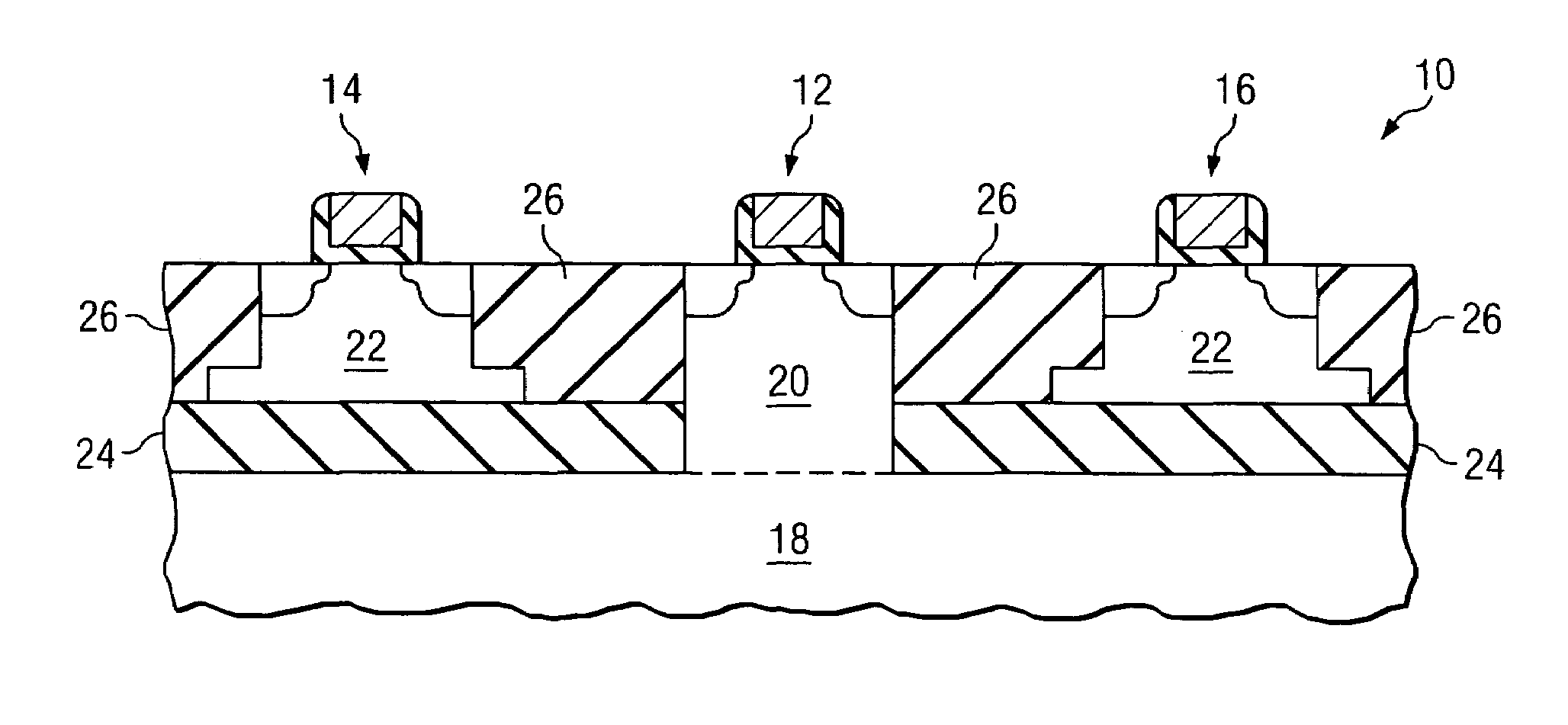

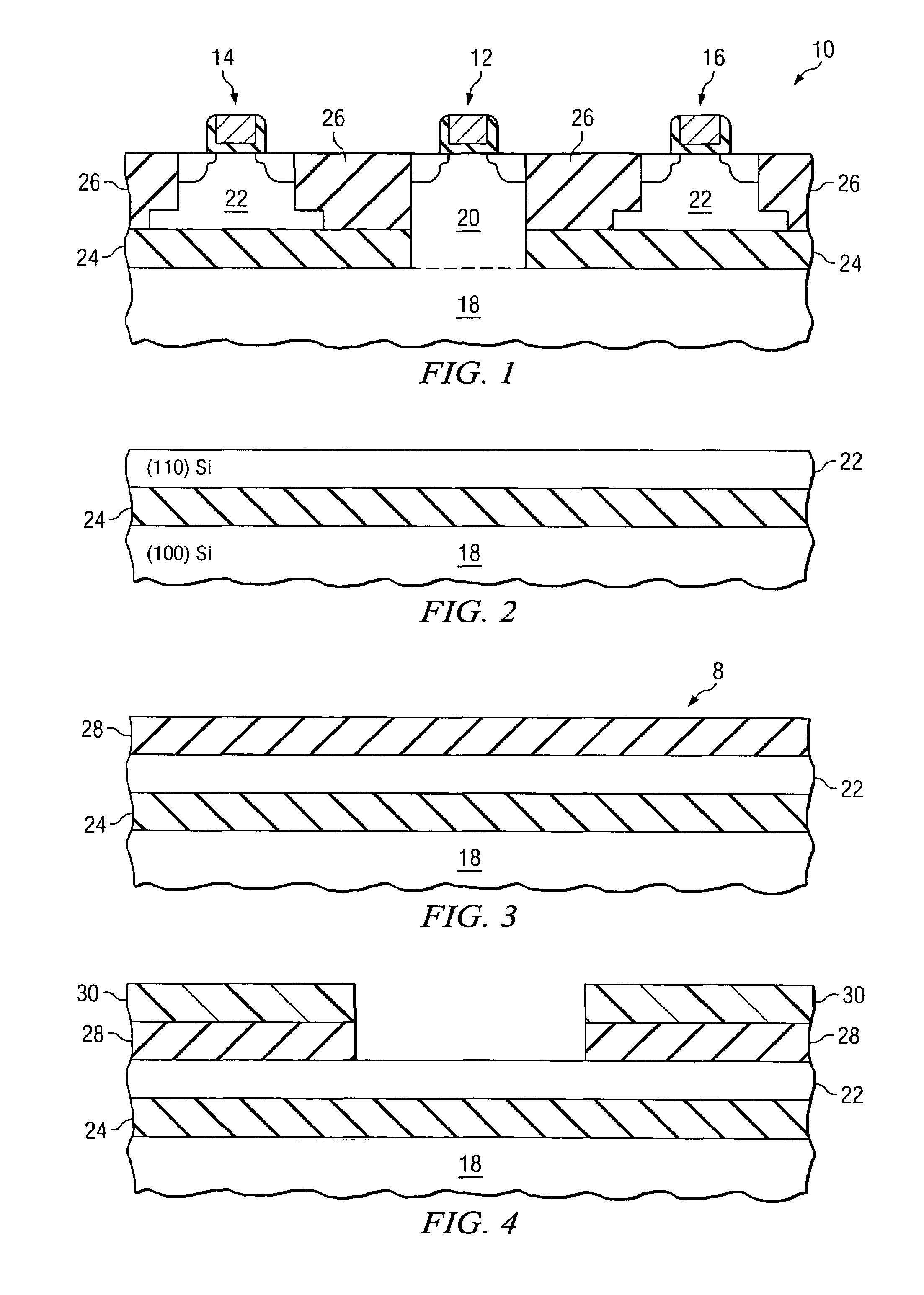

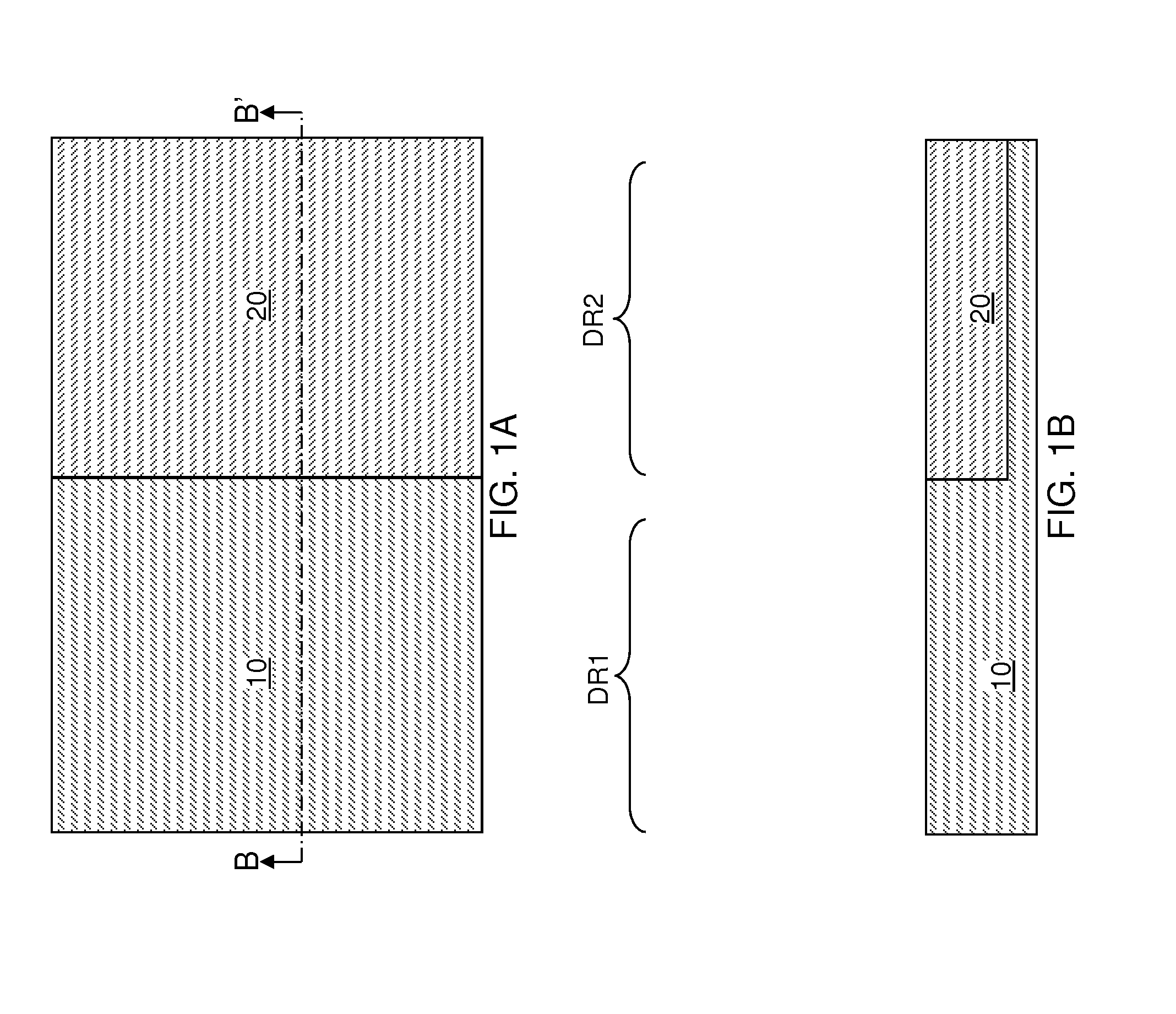

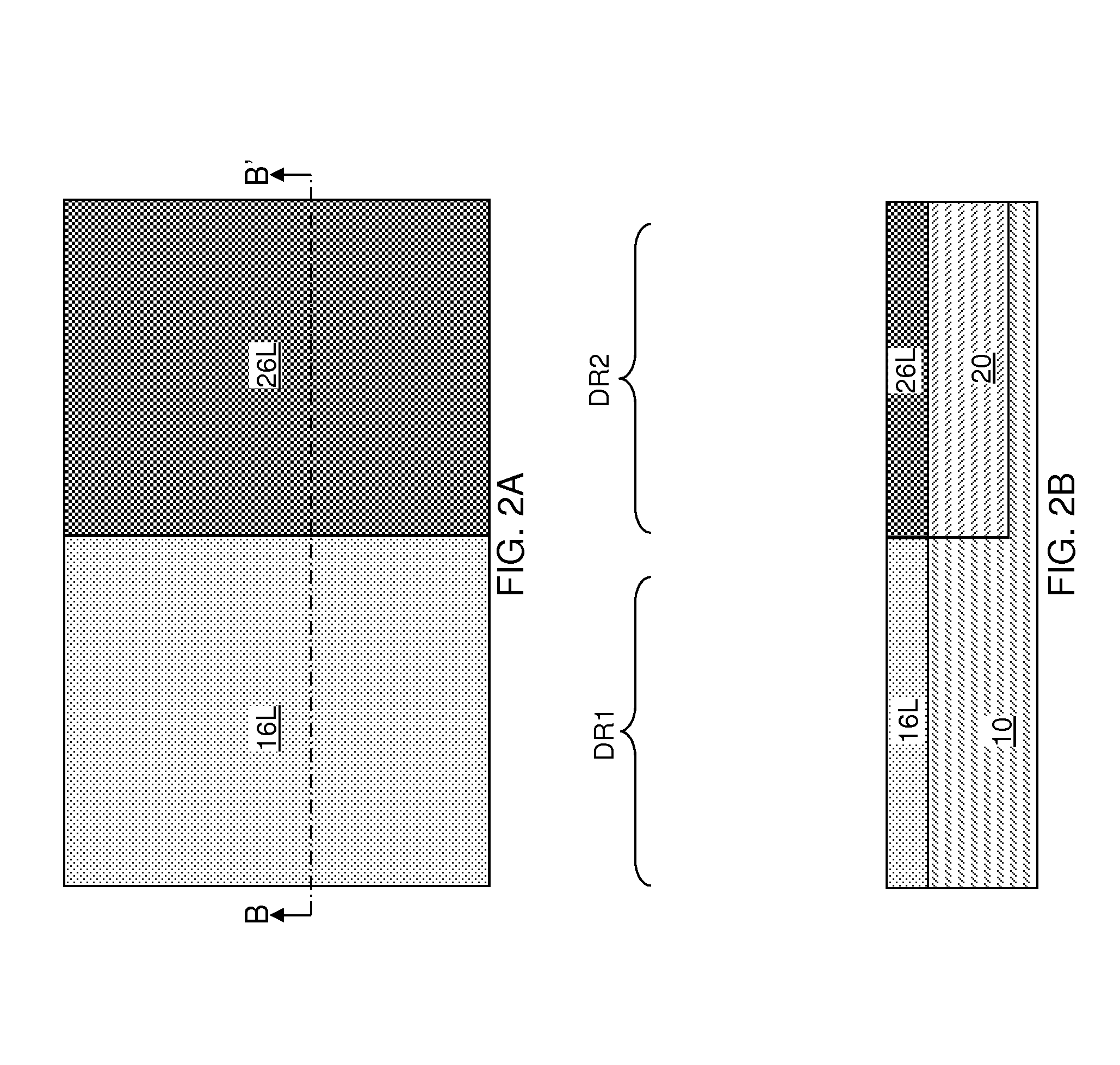

Semiconductor method and device with mixed orientation substrate

InactiveUS7298009B2Critical dimension of this mask is relaxedReduce processing stepsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsCrystal orientation

Owner:INFINEON TECH AG +1

Wireless energy transfer using field shaping to reduce loss

ActiveUS20110043047A1Efficient deliveryEfficient energy transferMultiple-port networksCircuit monitoring/indicationEnergy transferCondensed matter physics

In embodiments of the present invention improved capabilities are described for a method and system comprising a source resonator optionally coupled to an energy source and a second resonator located a distance from the source resonator, where the source resonator and the second resonator are coupled to provide near-field wireless energy transfer among the source resonator and the second resonator and where the field of at least one of the source resonator and the second resonator is shaped to avoid a loss-inducing object.

Owner:WITRICITY CORP

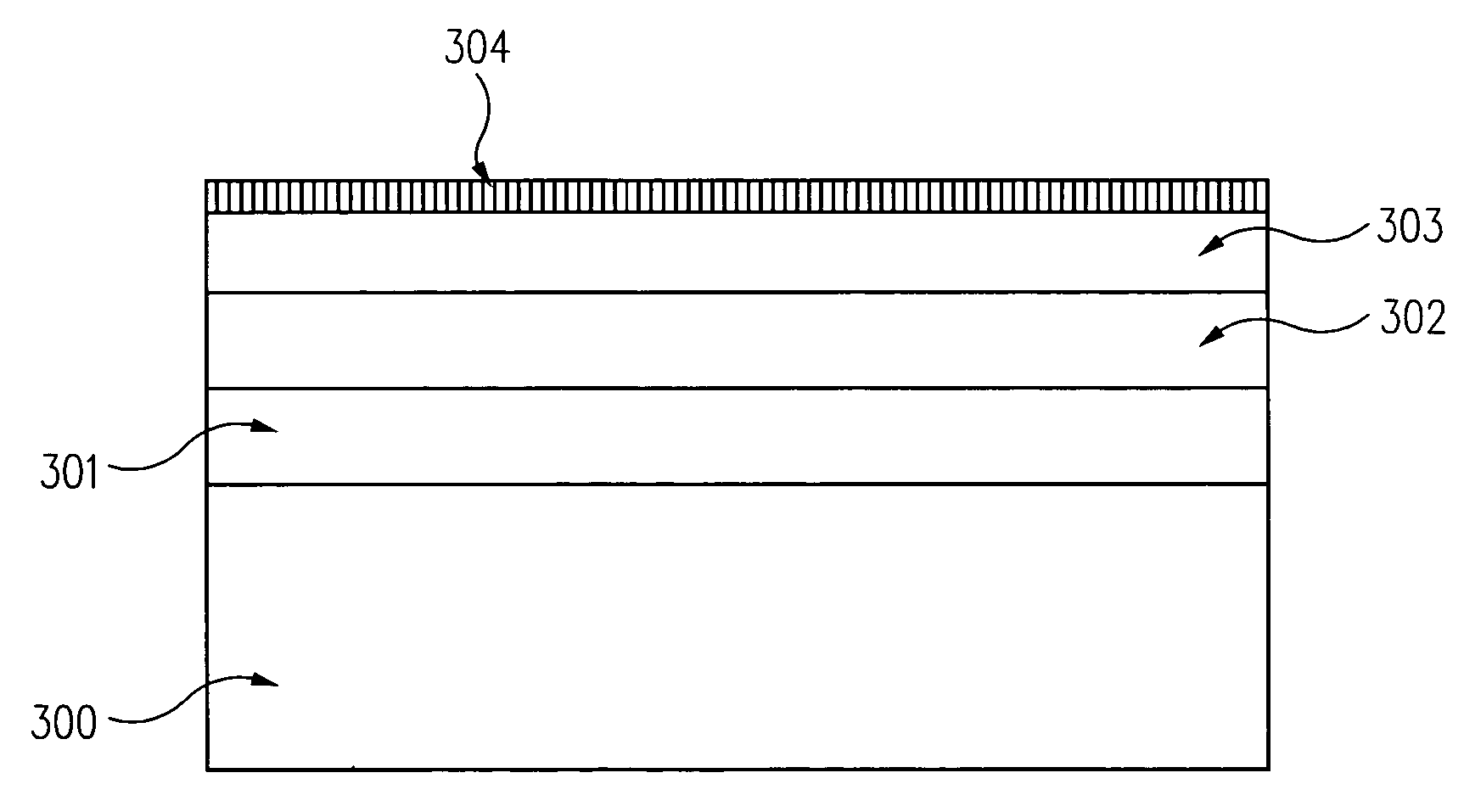

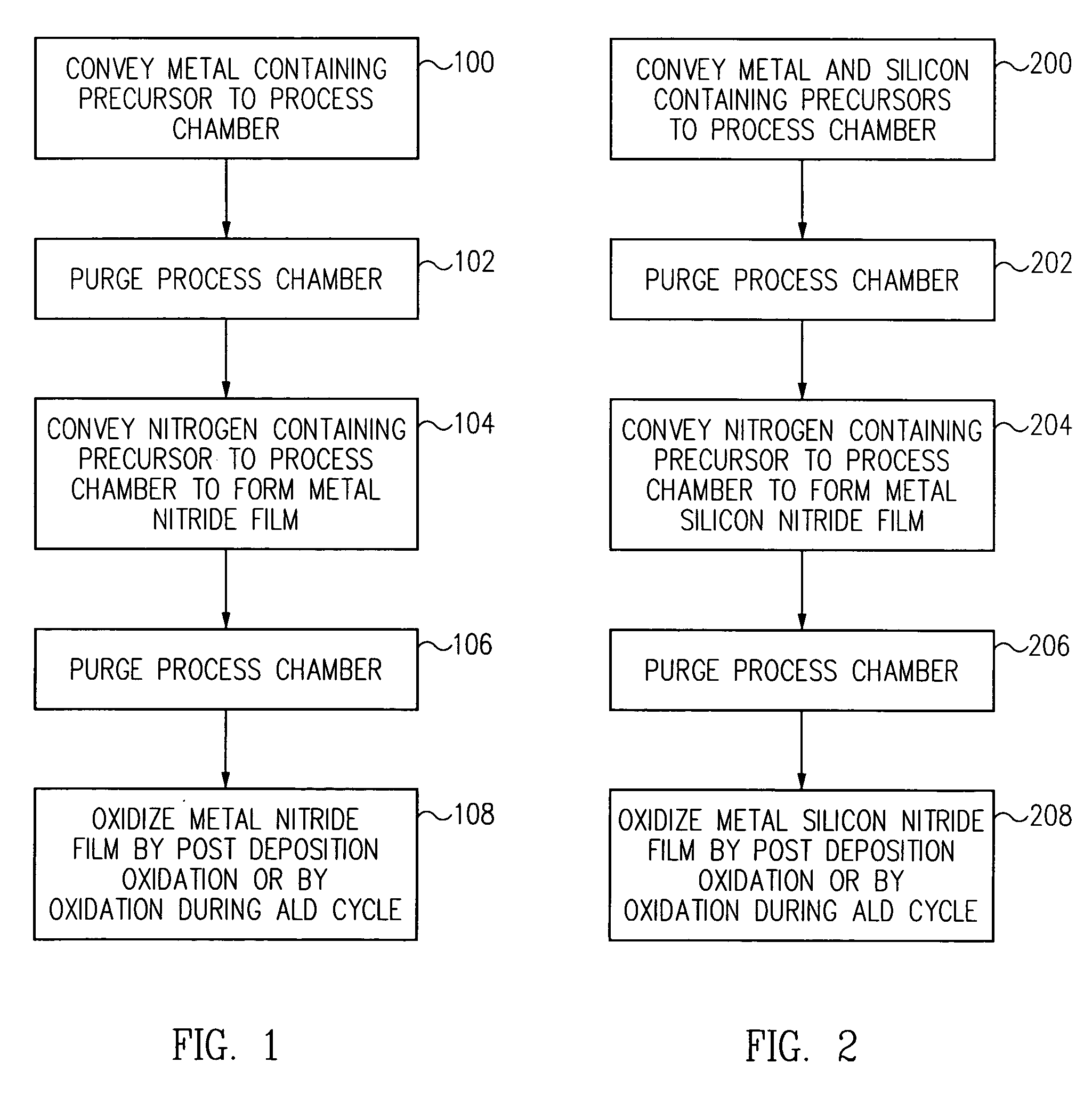

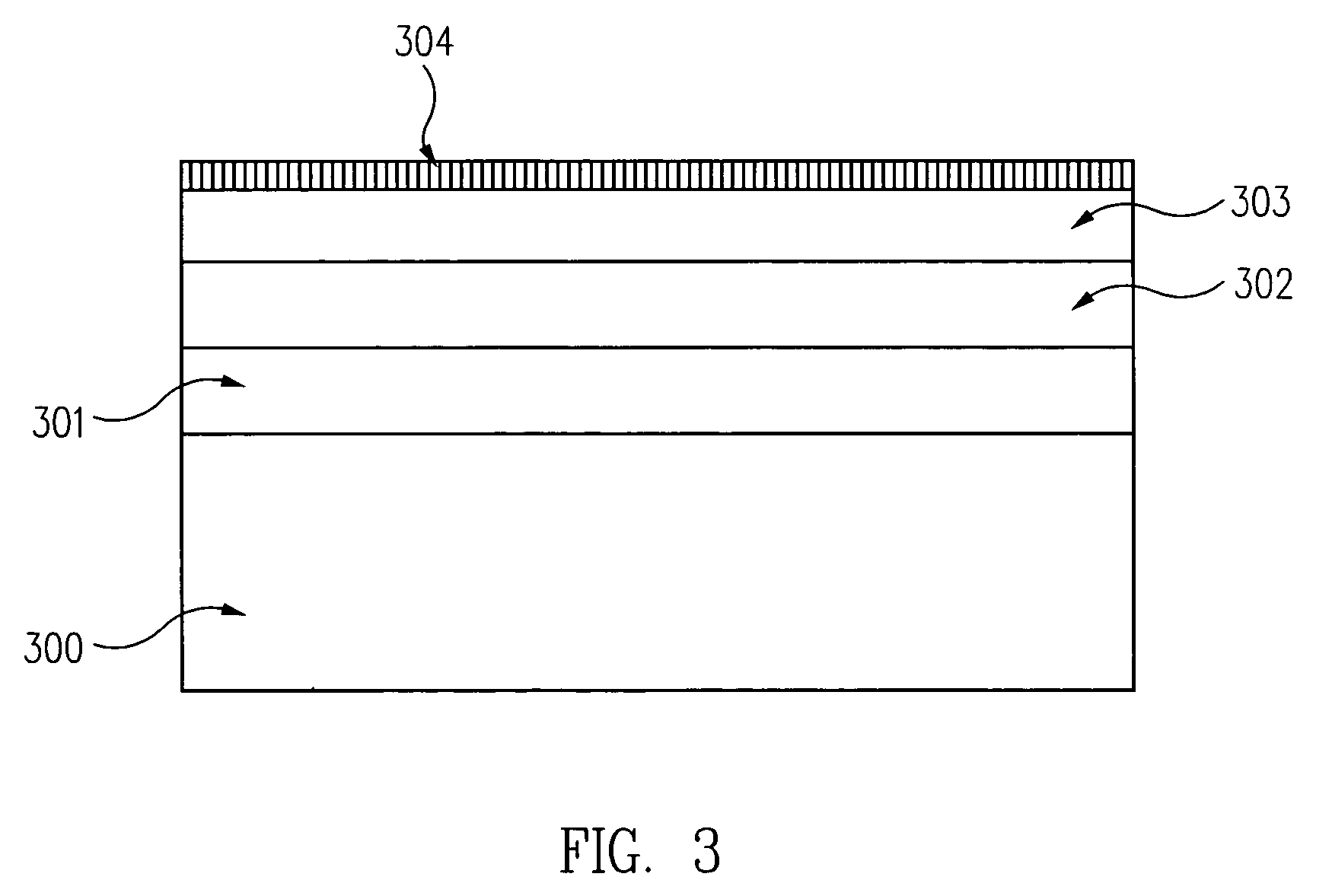

Nitridation of high-k dielectric films

InactiveUS20050153571A1Improve mobilityInterface stabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricElectricity

The present invention promotes incorporation of nitrogen (e.g., nitridation) into high-k dielectric films using a low temperature process. Further, the present invention provides an in-situ method; that is formation of the high-k dielectric film and nitridation of the film are carried out in the same process chamber during deposition of the film, as opposed to the conventional post processing techniques. In another aspect, a method for depositing a multi-layer material for use as a gate dielectric layer in semiconductor devices is provided.

Owner:AVIZA TECHNOLOGY INC

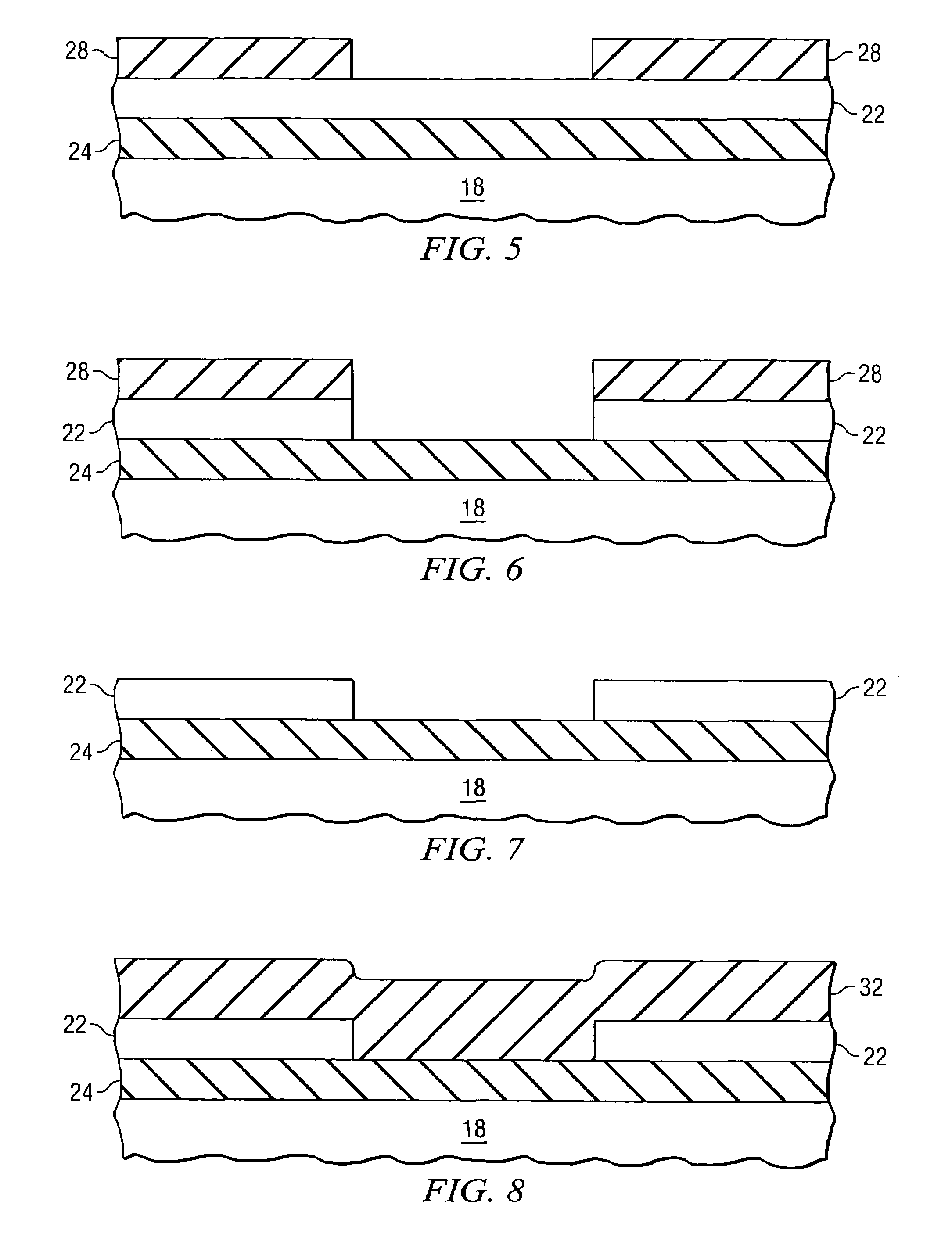

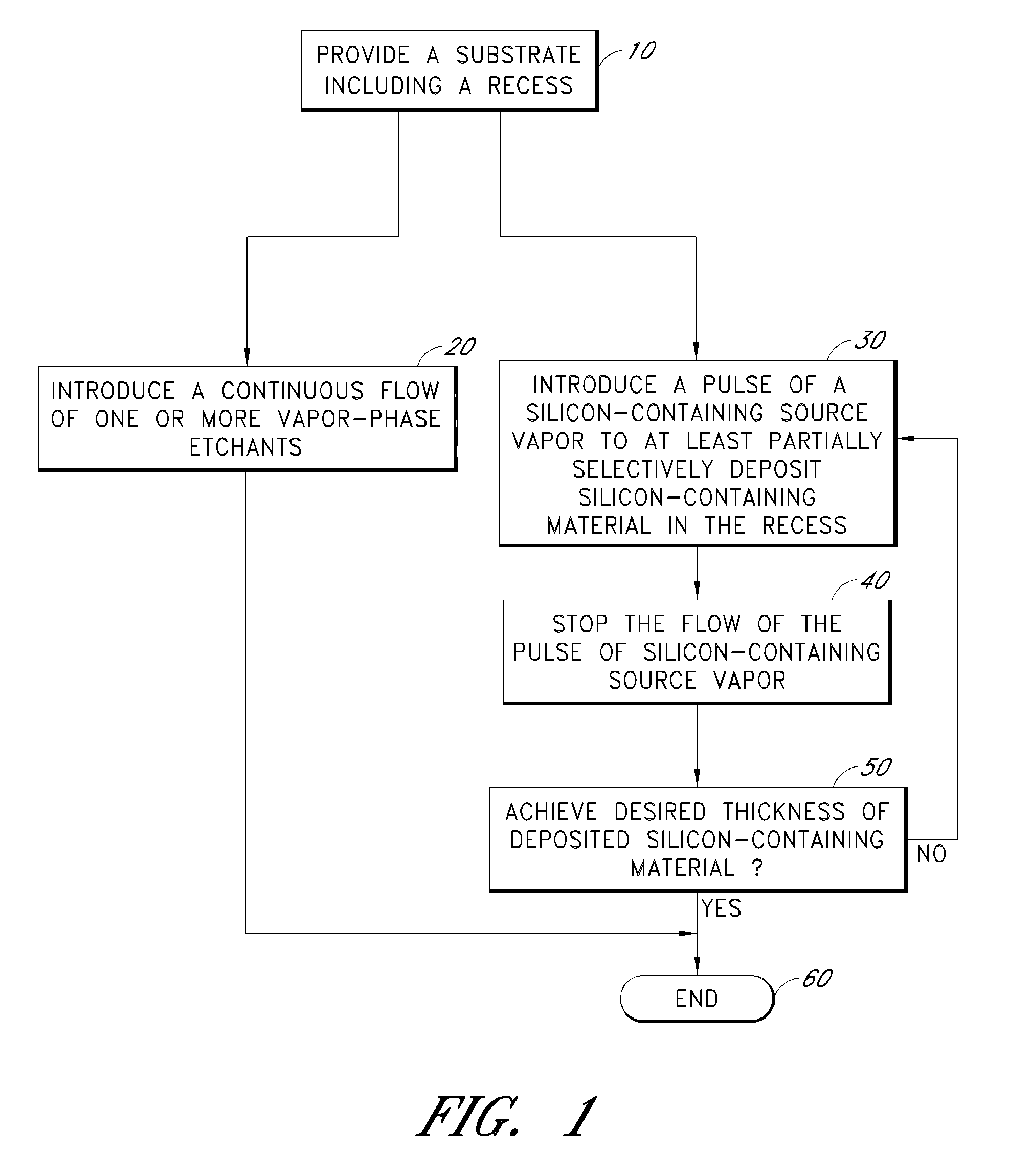

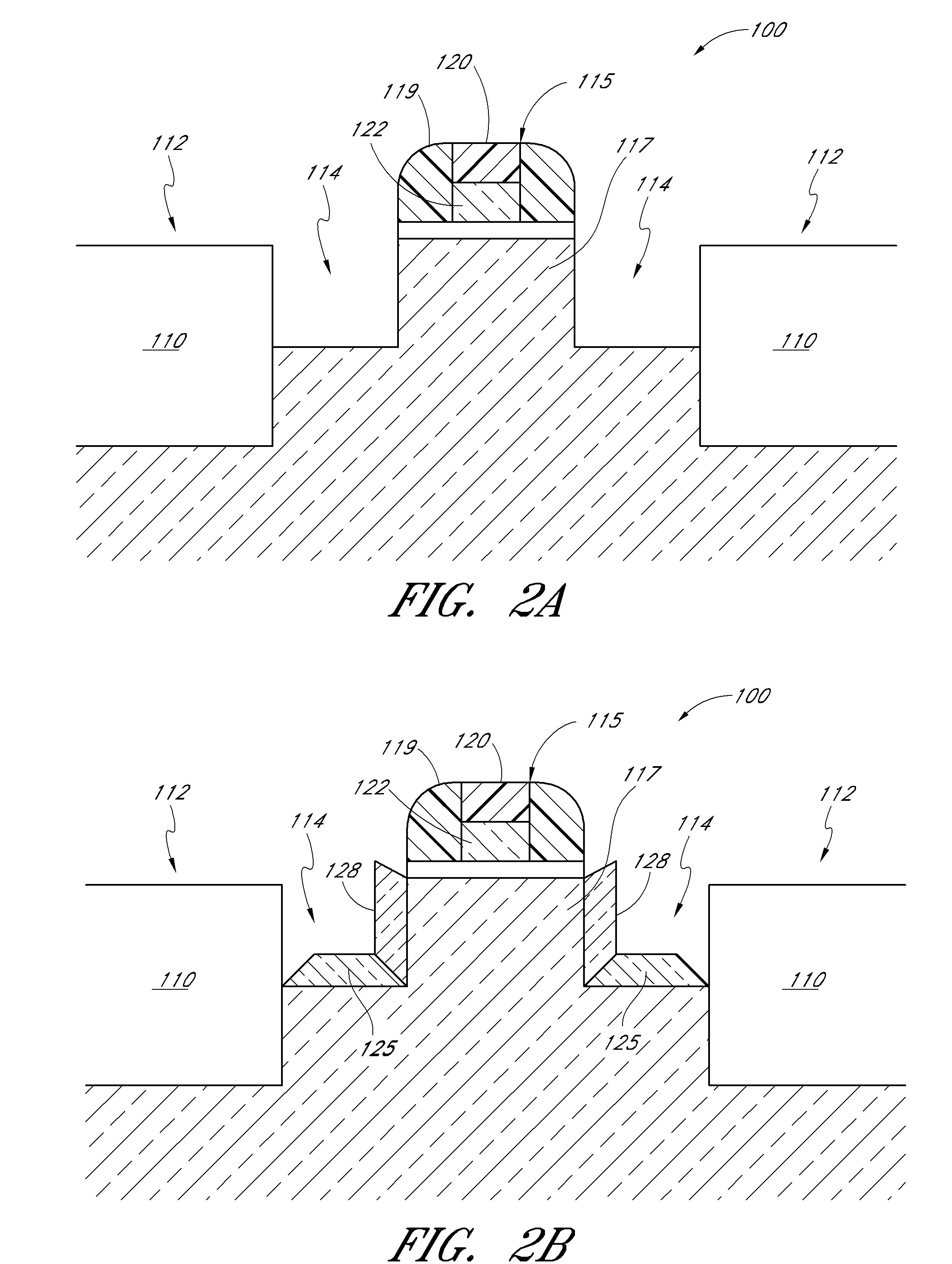

Cyclical epitaxial deposition and etch

ActiveUS20110117732A1Quality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesEpitaxial materialSemiconductor

Methods for selectively depositing high quality epitaxial material include introducing pulses of a silicon-source containing vapor while maintaining a continuous etchant flow. Epitaxial material is deposited on areas of a substrate, such as source and drain recesses. Between pulses, the etchant flow continues such that lower quality epitaxial material may be removed, as well as any non-epitaxial material that may have been deposited. The pulse of silicon-source containing vapor may be repeated until a desired thickness of epitaxial material is selectively achieved in semiconductor windows, such as recessed source / drain regions.

Owner:ASM IP HLDG BV

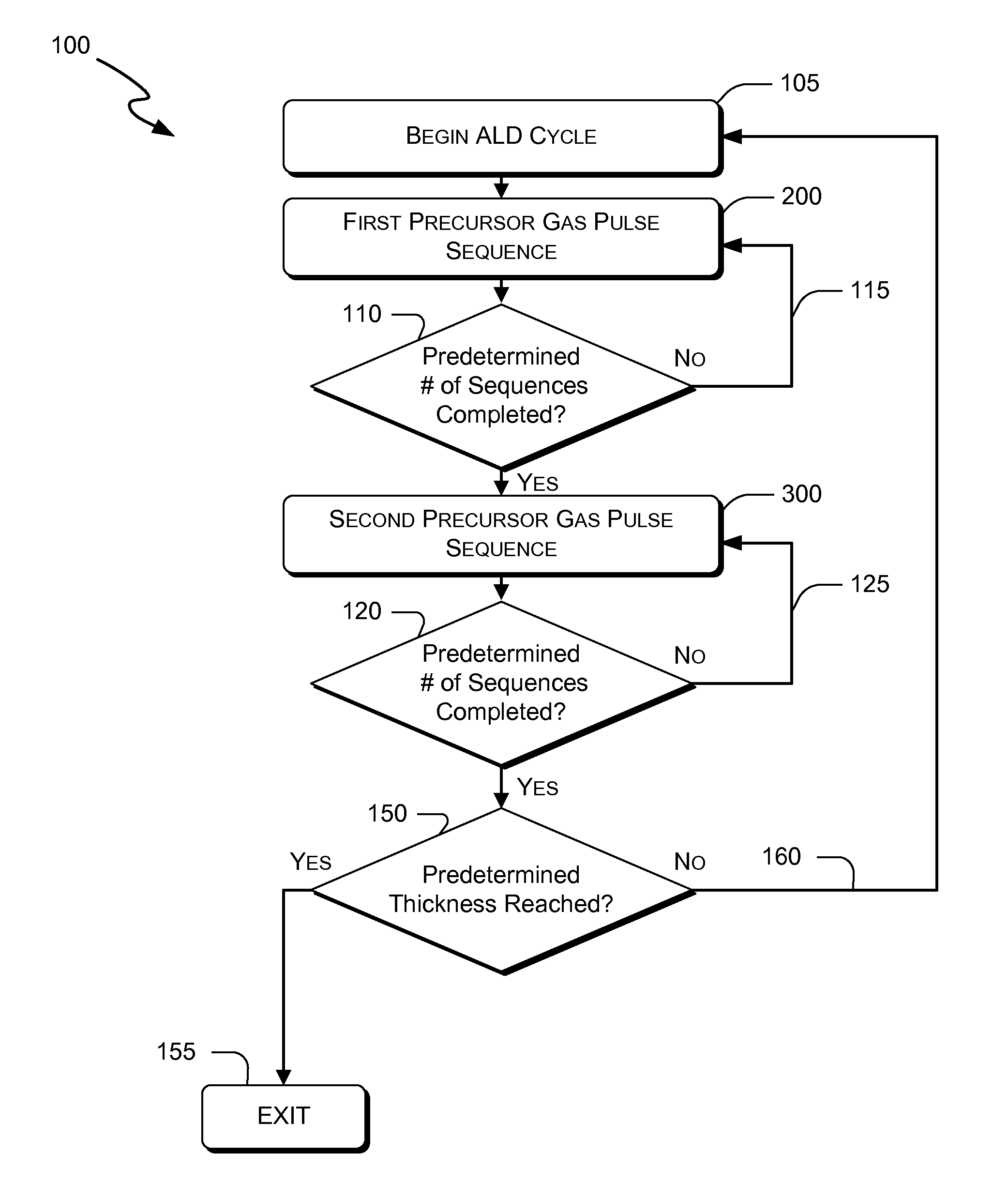

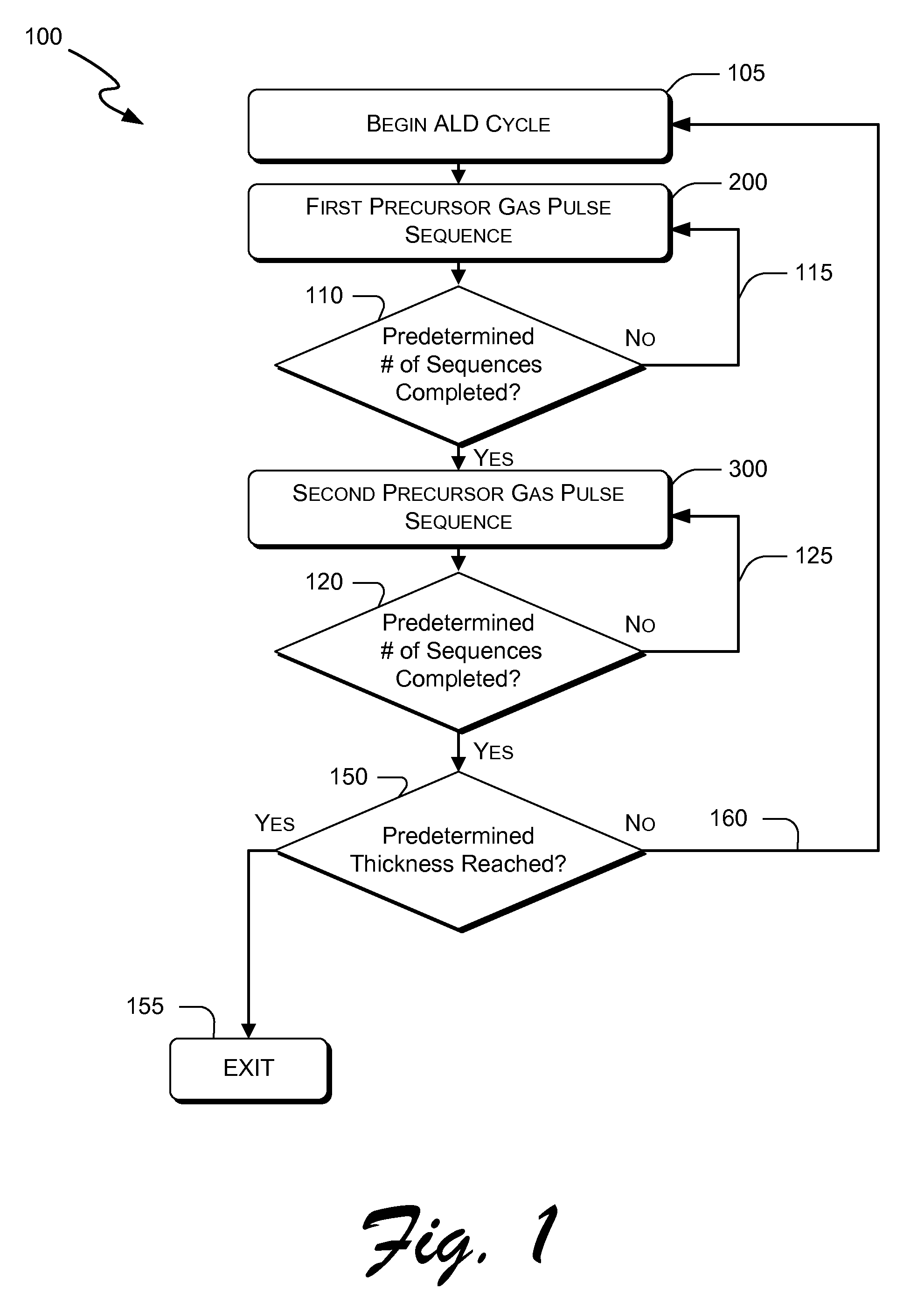

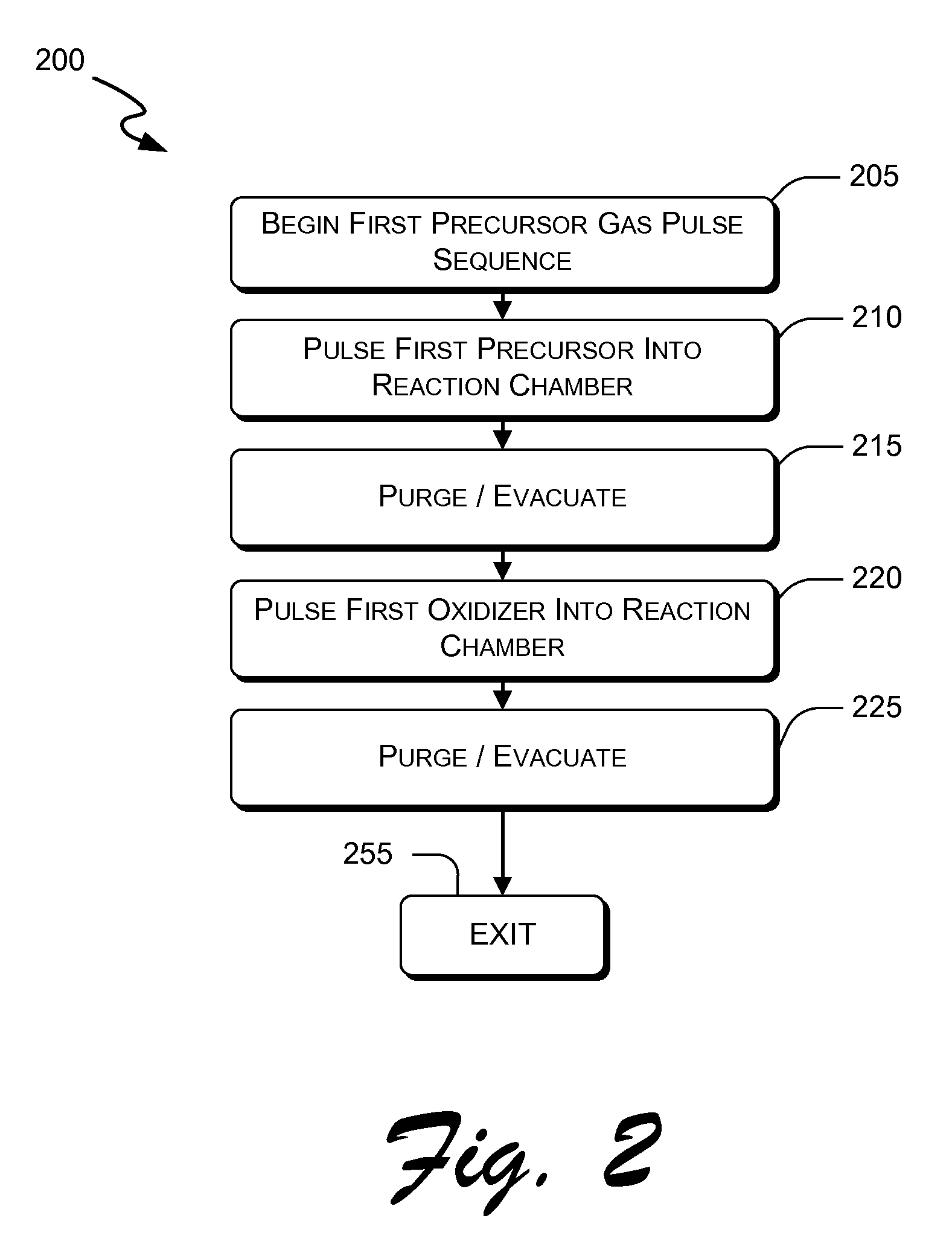

Atomic layer deposition of hafnium lanthanum oxides

There is provided an improved method for depositing thin films using precursors to deposit binary oxides by atomic layer deposition (ALD) techniques. Also disclosed is an ALD method for depositing a high-k dielectric such as hafnium lanthanum oxide (HfLaO) on a substrate. Embodiments of the present invention utilize a combination of ALD precursor elements and cycles to deposit a film with desired physical and electrical characteristics. Electronic components and systems that integrate devices fabricated with methods consistent with the present invention are also disclosed.

Owner:ASM IP HLDG BV

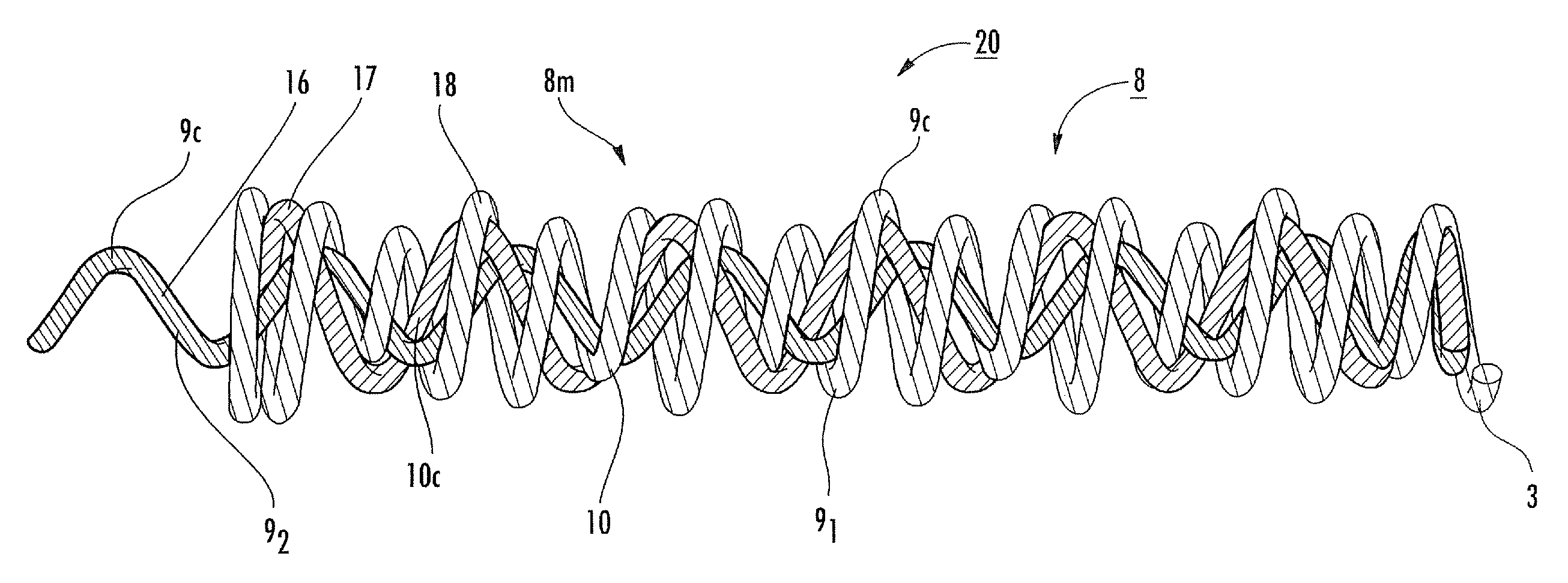

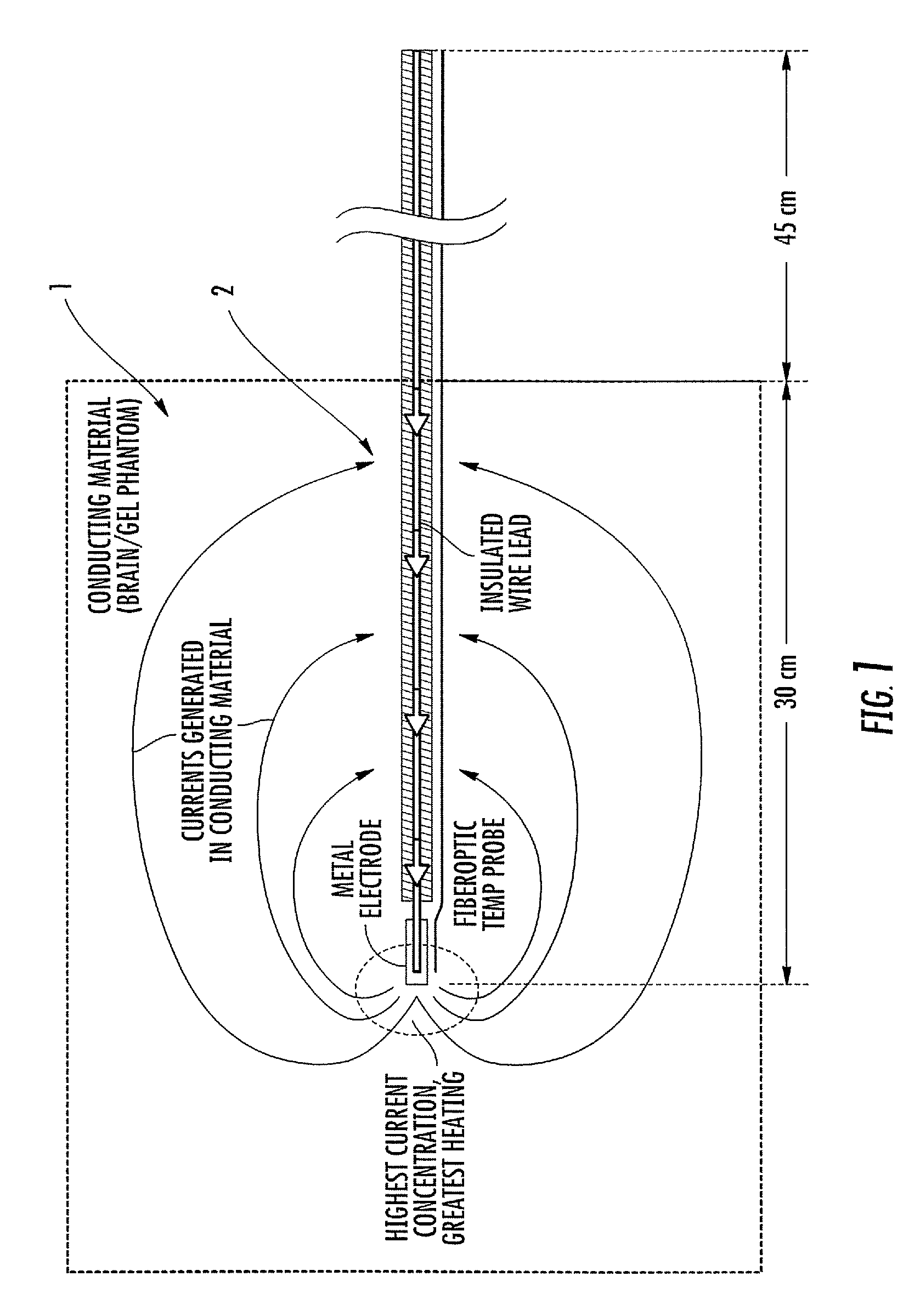

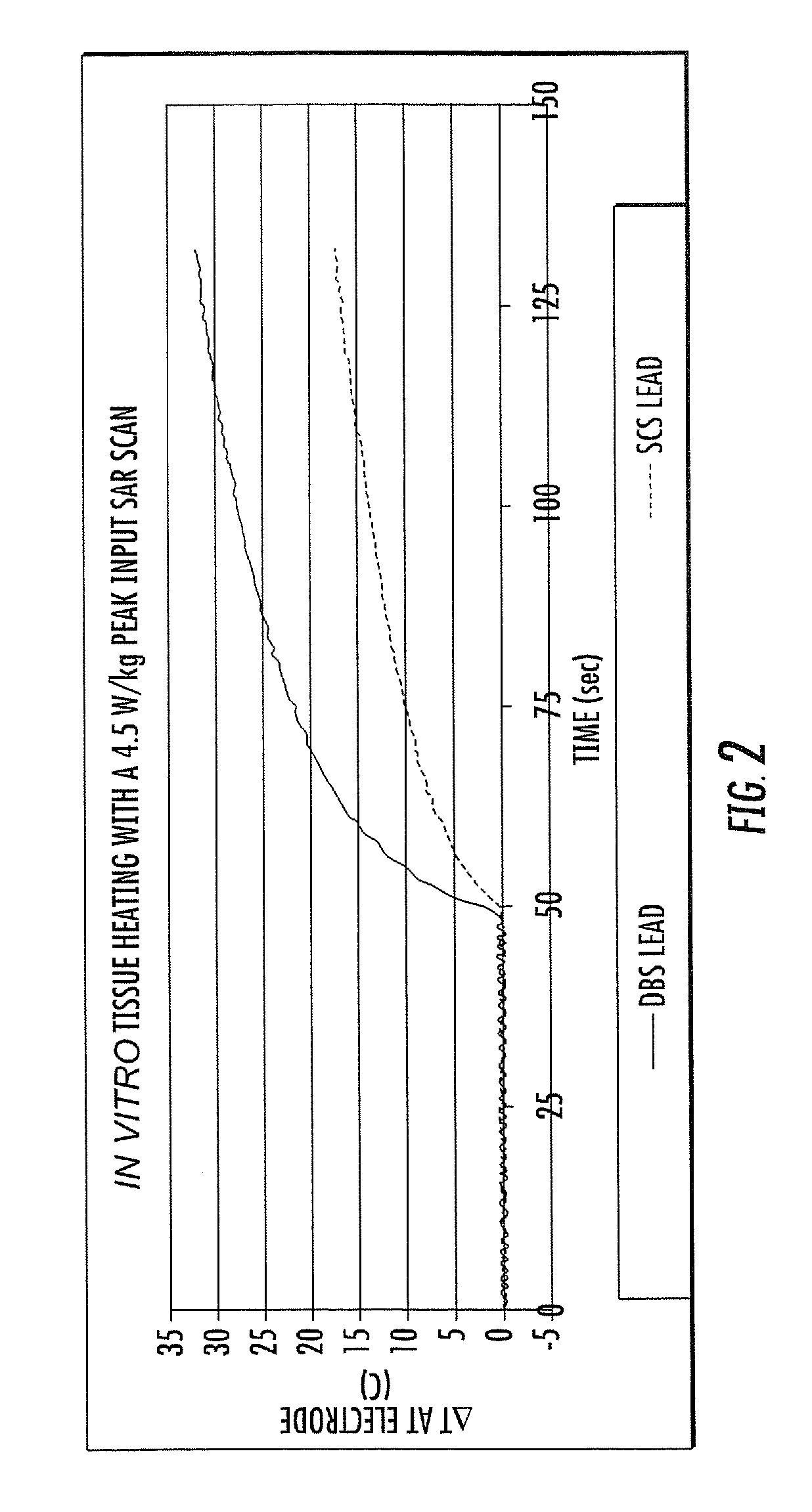

Methods and apparatus for fabricating leads with conductors and related flexible lead configurations

ActiveUS20080262584A1Prevent undesired heatingEasy to useInternal electrodesMaterial strength using steady bending forcesElectrical conductorDegree Celsius

MRI / RF compatible leads include at least one conductor, a respective conductor having at least one segment with a multi-layer stacked coil configuration. The lead can be configured so that the lead heats local tissue less than about 10 degrees Celsius (typically about 5 degrees Celsius or less) or does not heat local tissue when a patient is exposed to target RF frequencies at a peak input SAR of at least about 4 W / kg and / or a whole body average SAR of at least about 2 W / kg. Related leads and methods of fabricating leads are also described.

Owner:MRI INTERVENTIONS INC +1

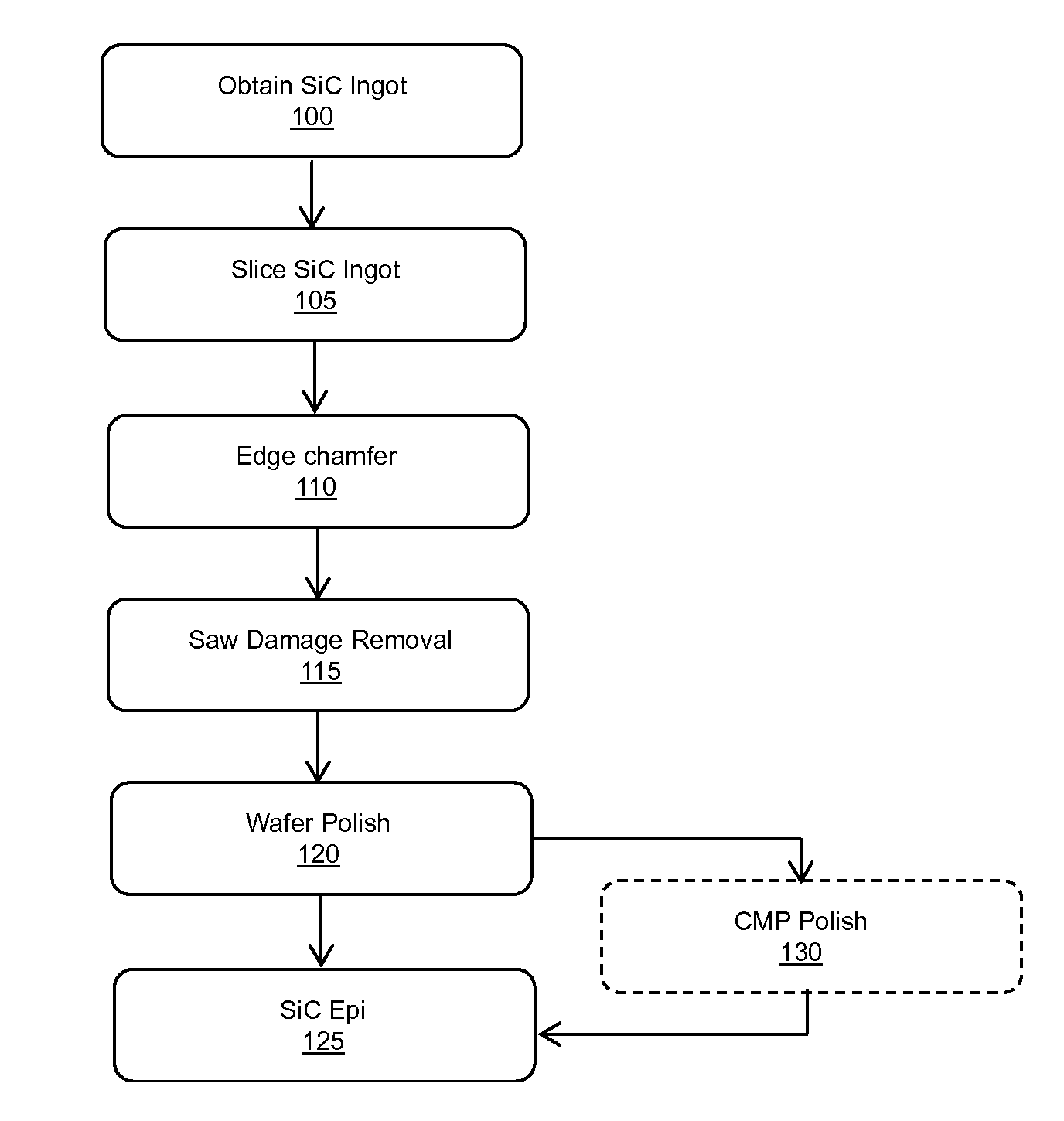

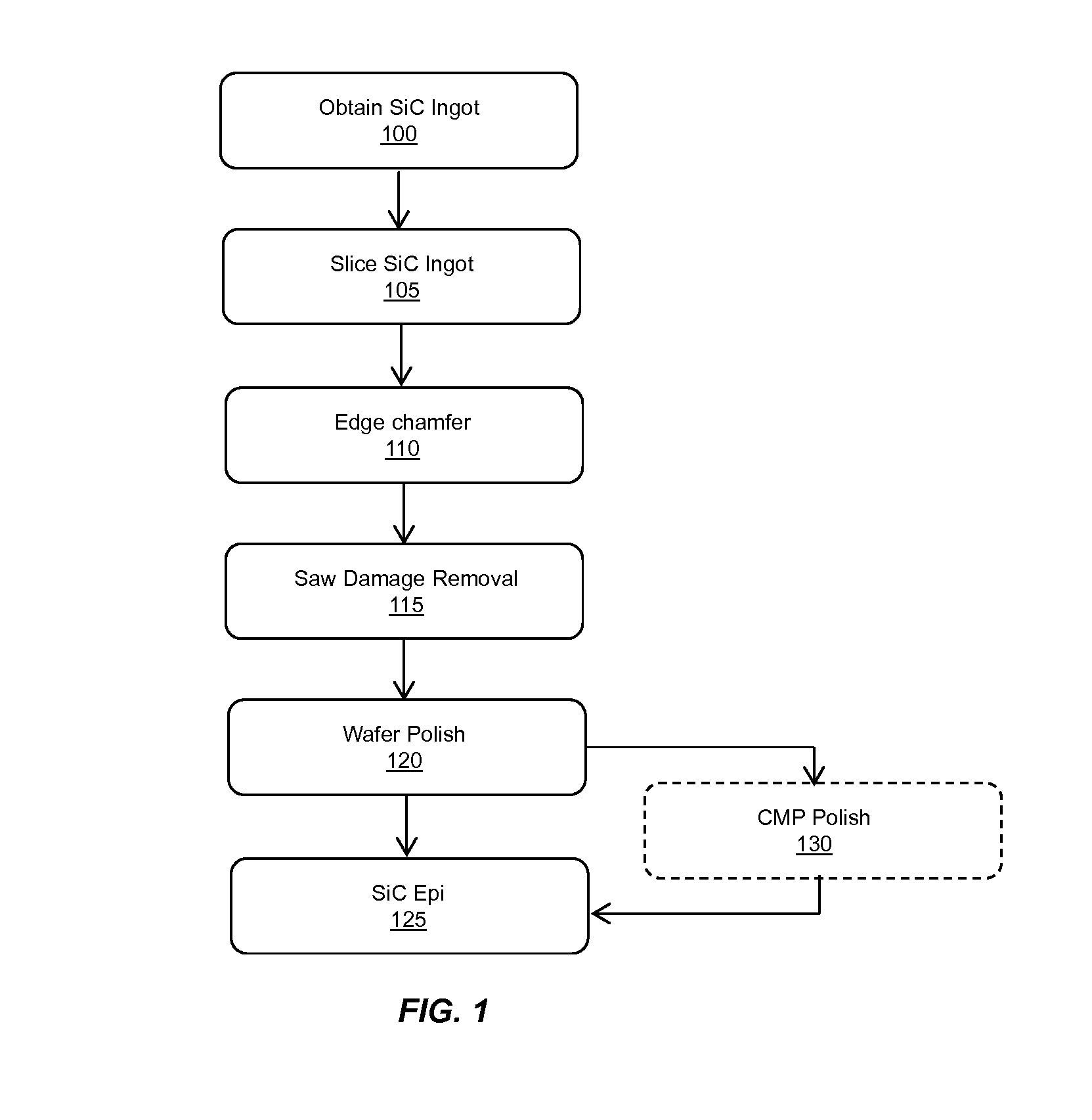

Flat sic semiconductor substrate

ActiveUS20140117380A1Efficient polishingImprove performanceEdge grinding machinesPolycrystalline material growthCrystallographyWafering

Methods for manufacturing silicon carbide wafers having superior specifications for bow, warp, total thickness variation (TTV), local thickness variation (LTV), and site front side least squares focal plane range (SFQR). The resulting SiC wafer has a mirror-like surface that is fit for epitaxial deposition of SiC. The specifications for bow, warp, total thickness variation (TTV), local thickness variation (LTV), and site front side least squares focal plane range (SFQR) of the wafer are preserved following the addition of the epitaxy layer.

Owner:SK SILTRON CSS LLC

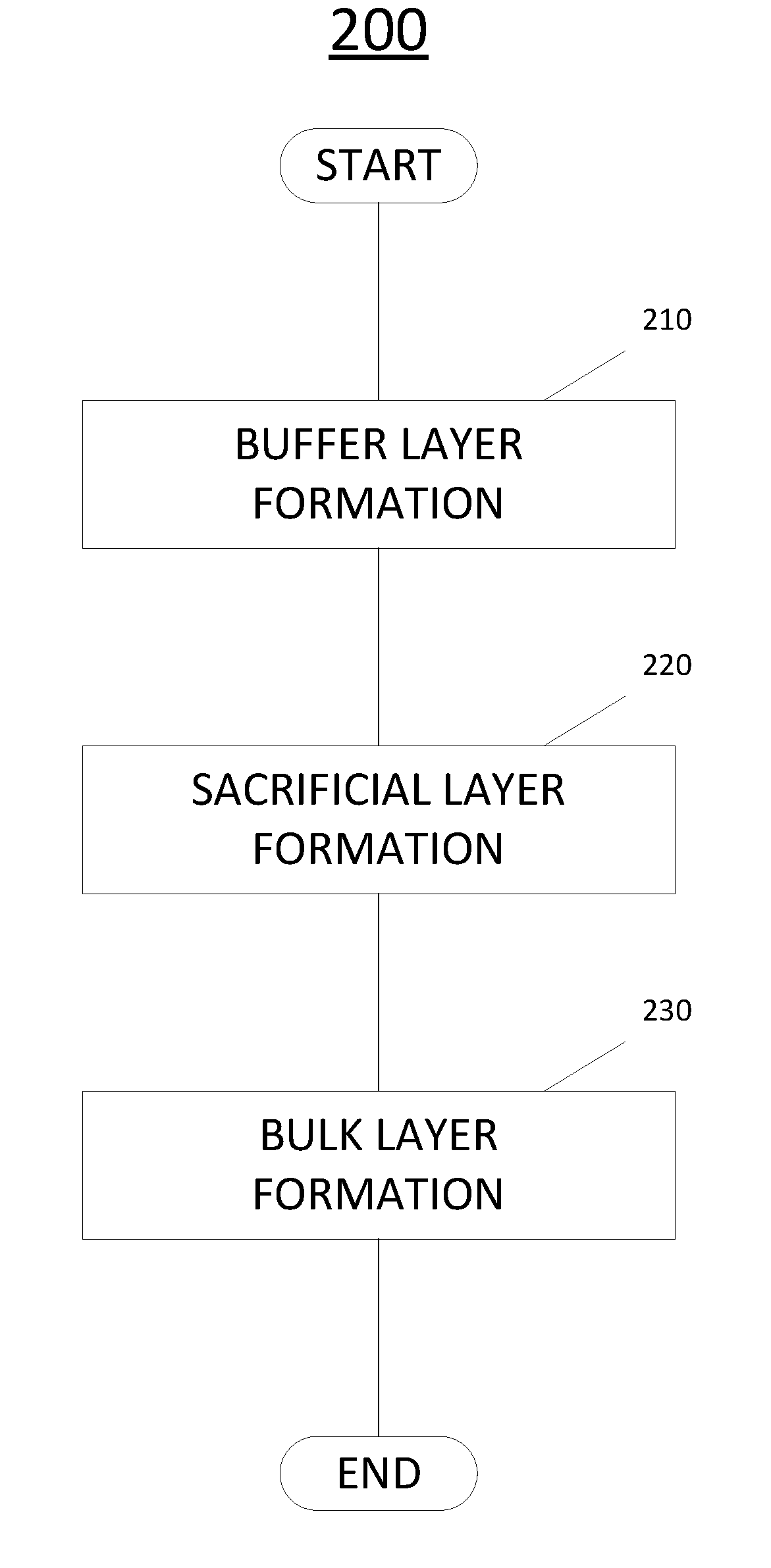

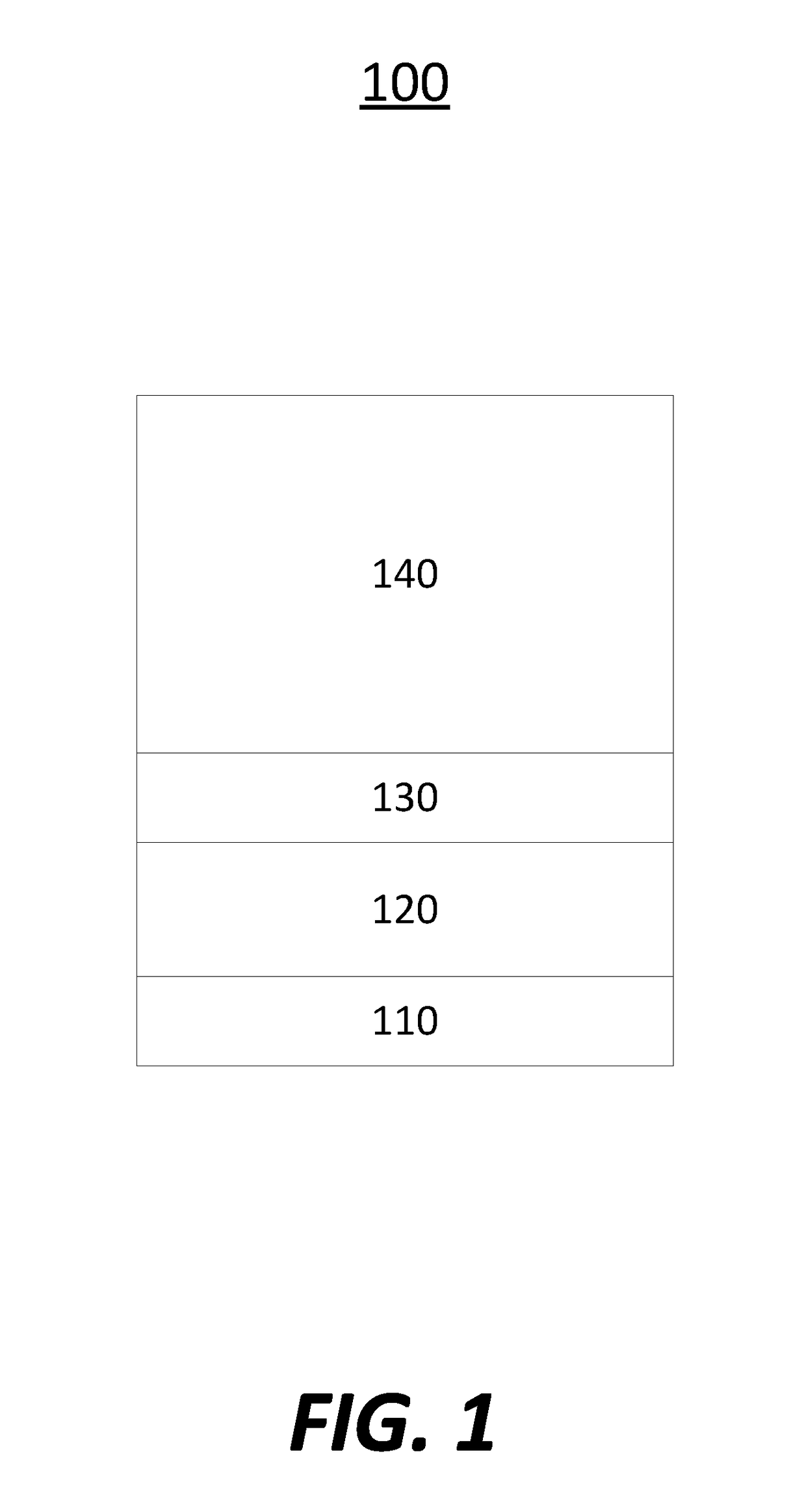

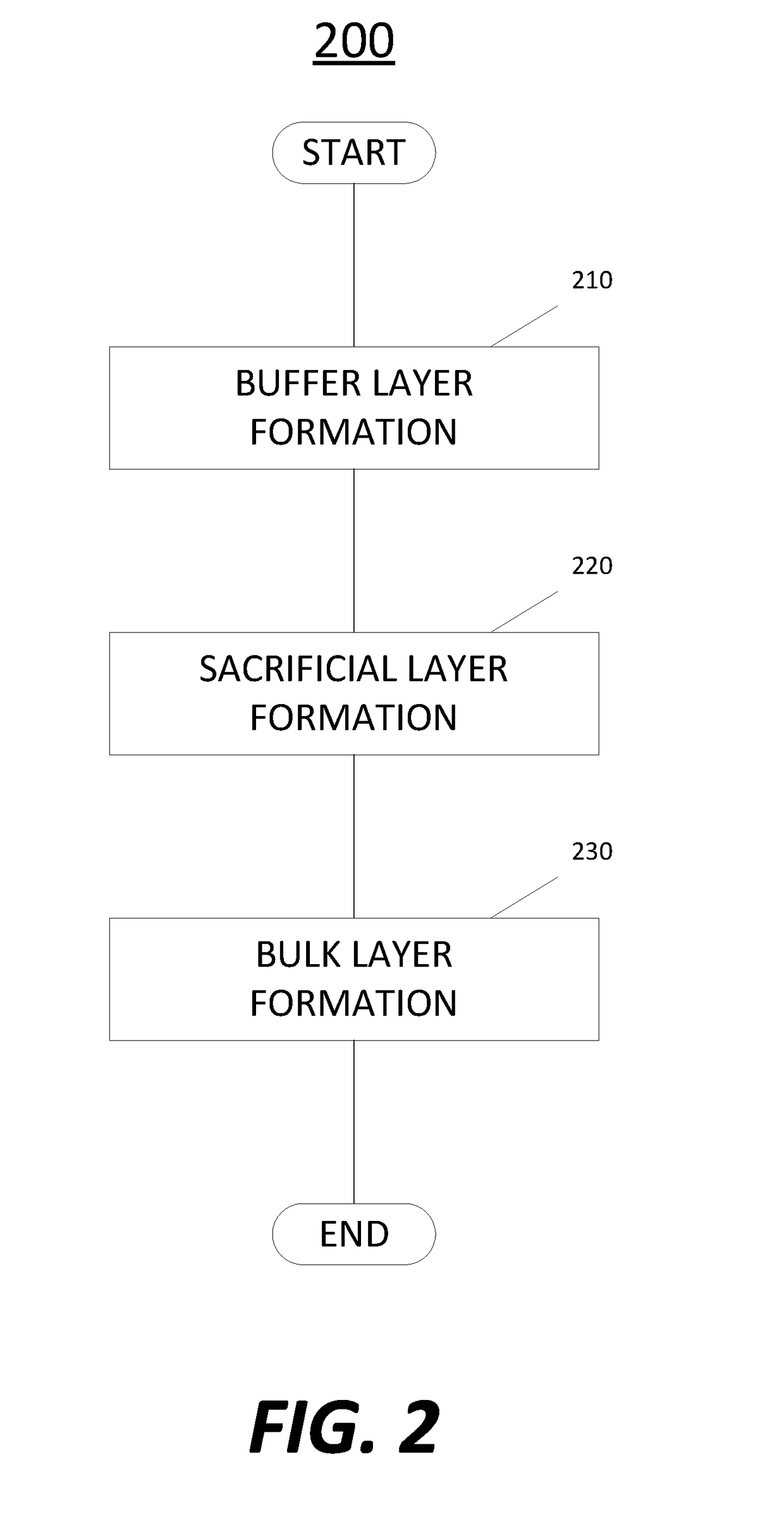

Formation of epitaxial layers via dislocation filtering

ActiveUS20170372884A1Semiconductor/solid-state device manufacturingSemiconductor devicesProcess conditionsDislocation

A process for forming a thick defect-free epitaxial layer is disclosed. The process may comprise forming a buffer layer and a sacrificial layer prior to forming the thick defect-free epitaxial layer. The sacrificial layer and the thick defect-free epitaxial layer may be formed of the same material and at the same process conditions.

Owner:ASM IP HLDG BV

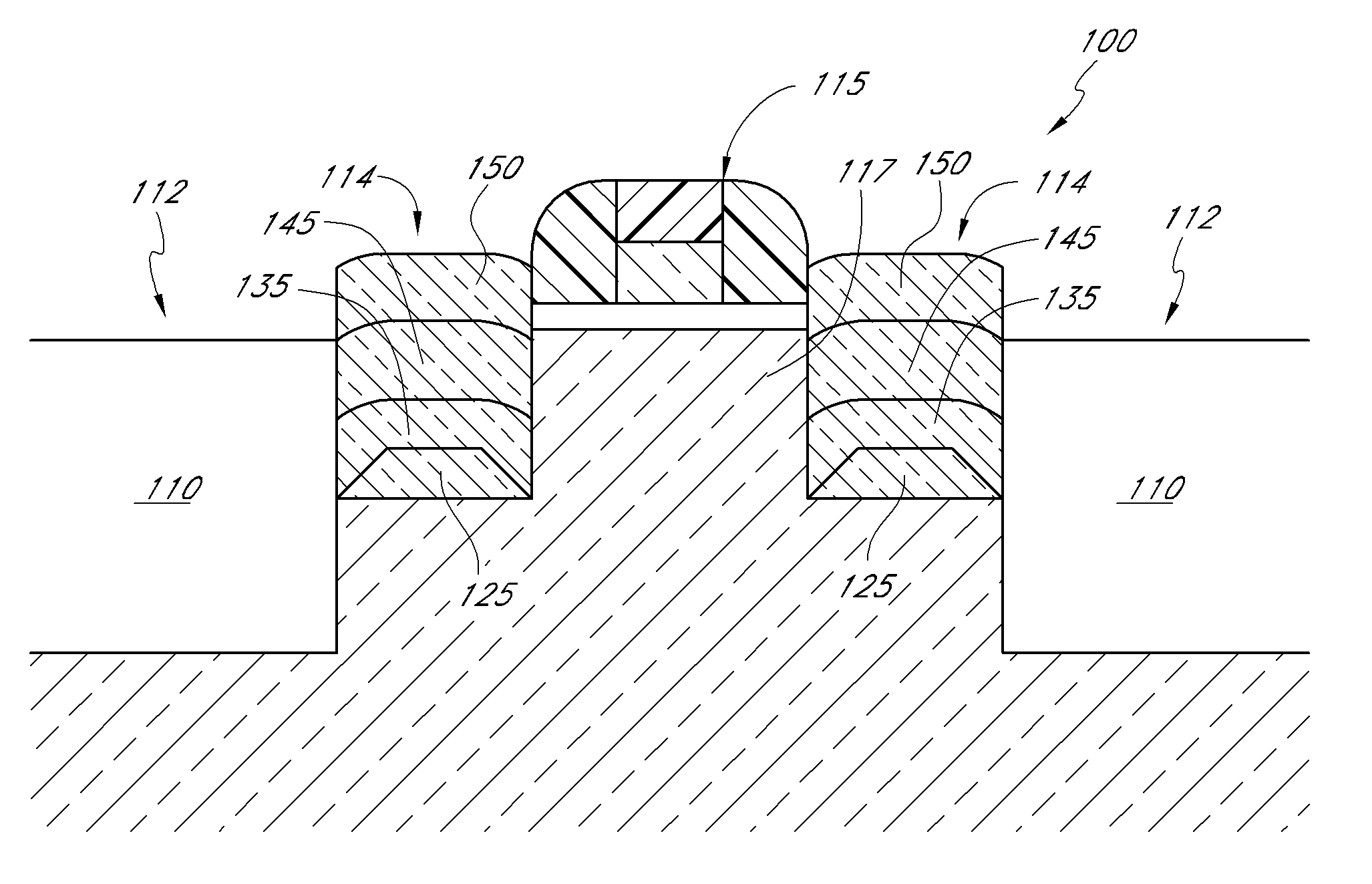

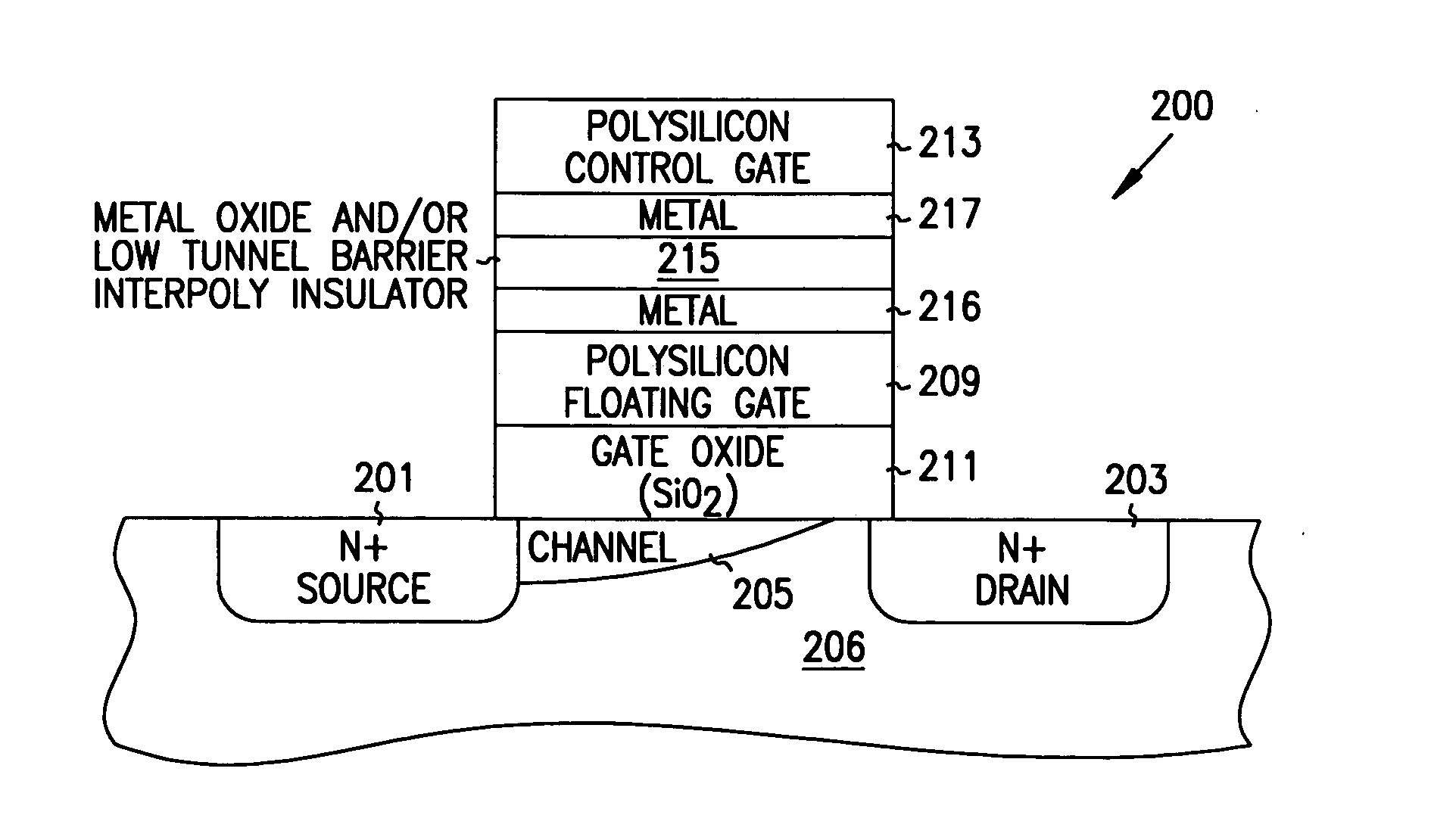

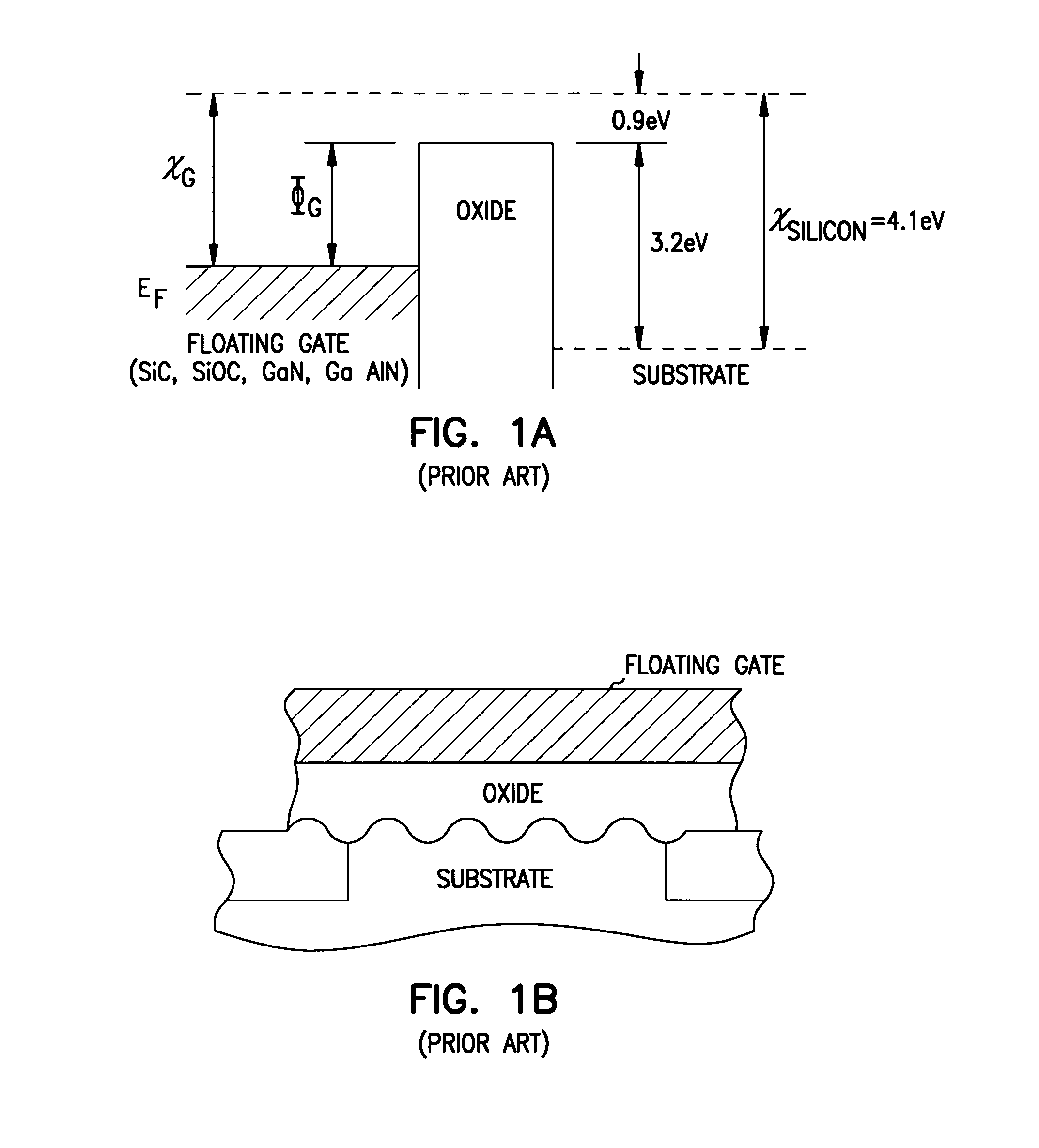

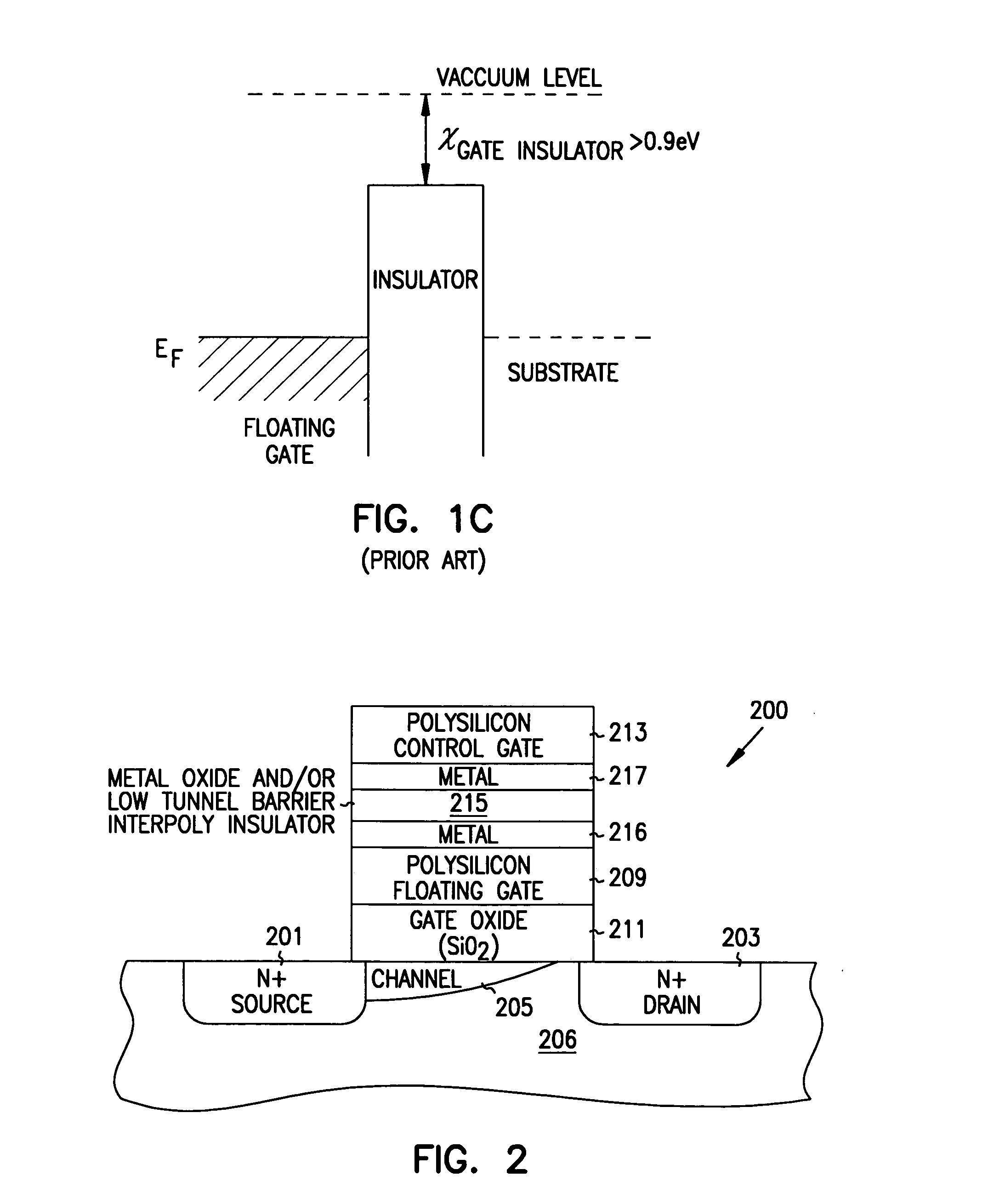

Atomic layer deposition of metal oxide and/or low asymmetrical tunnel barrier interpoly insulators

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator formed by atomic layer deposition. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3.

Owner:MICRON TECH INC

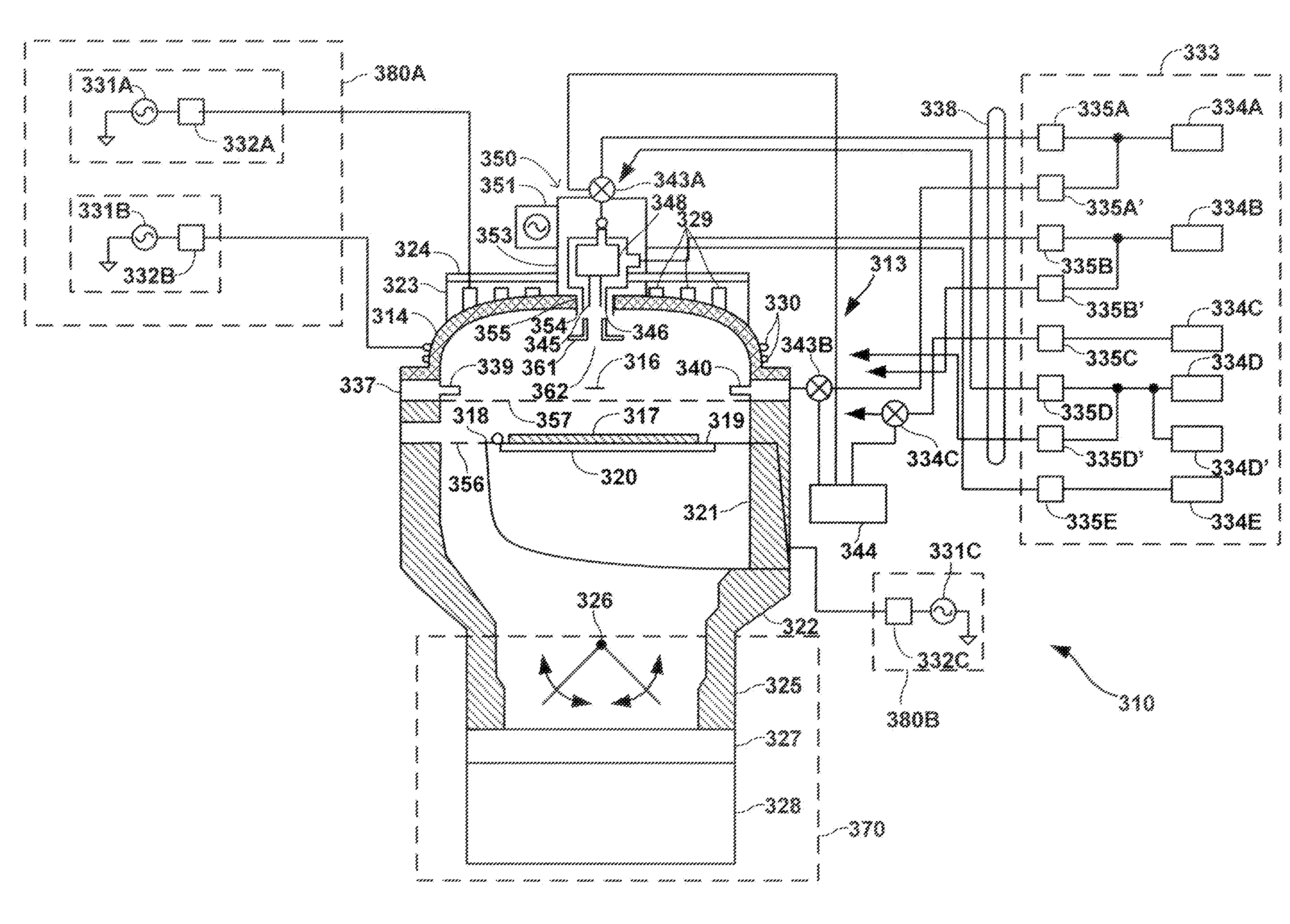

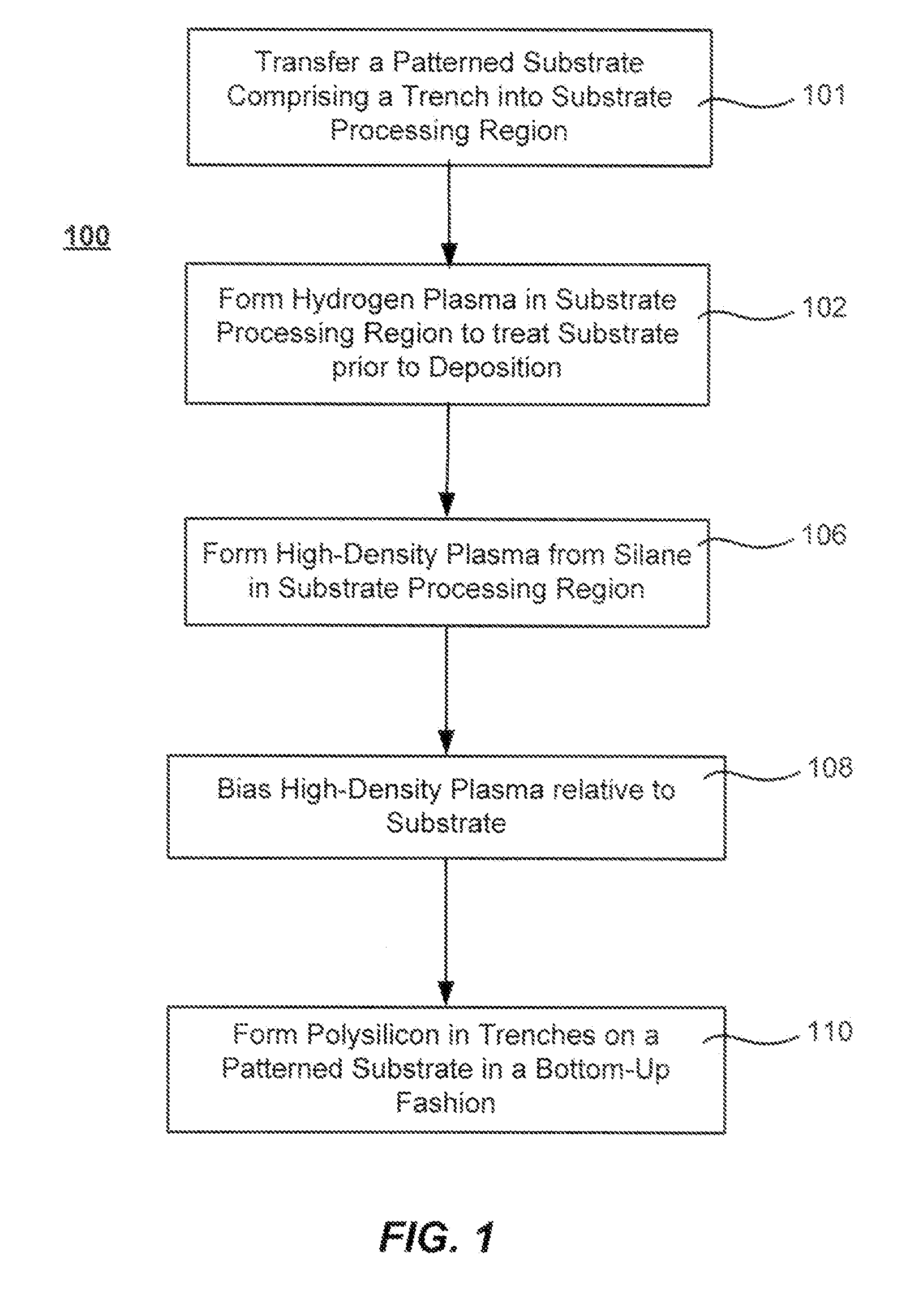

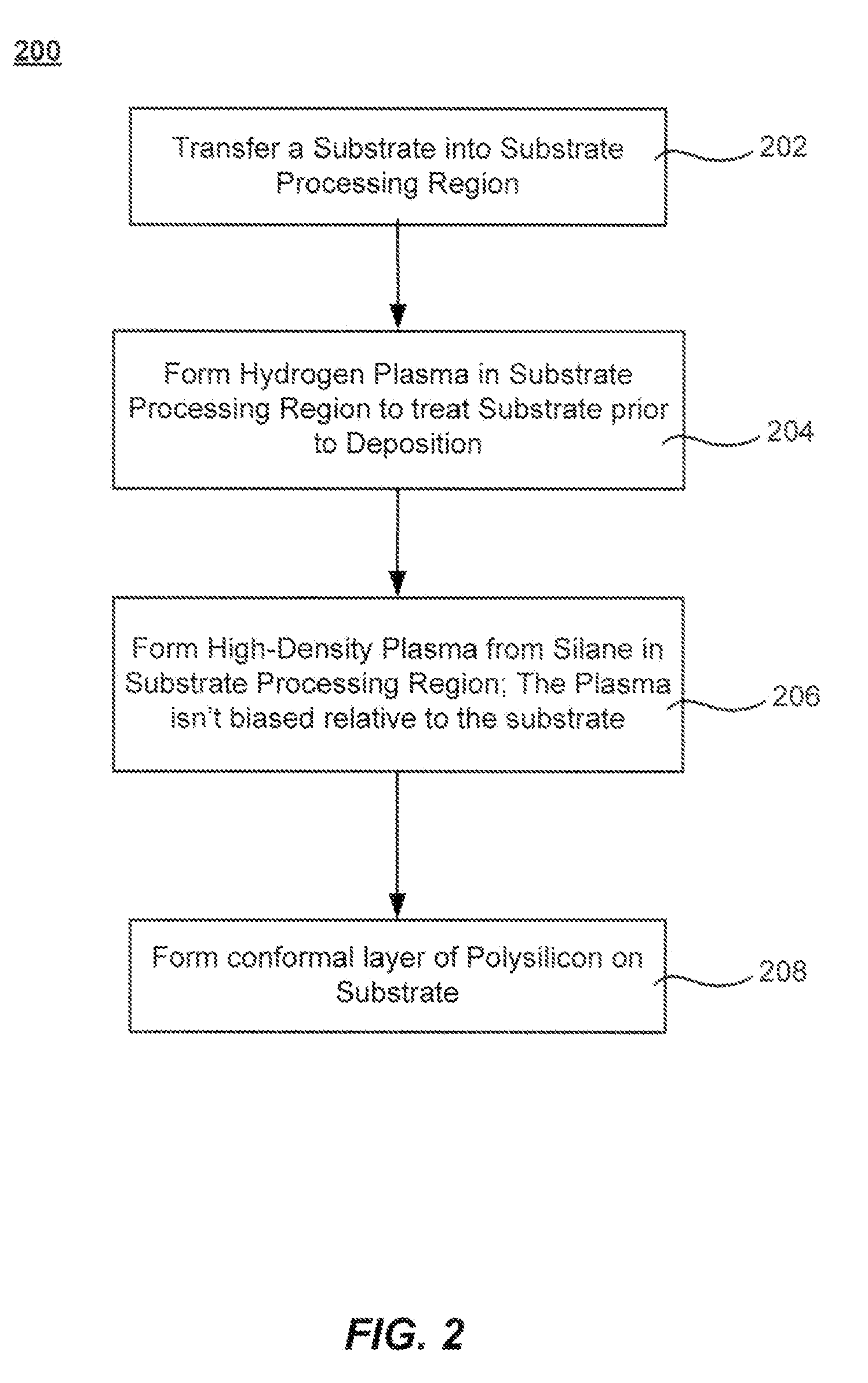

Polysilicon films by HDP-CVD

InactiveUS8450191B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDopantHigh density

Methods of forming polysilicon layers are described. The methods include forming a high-density plasma from a silicon precursor in a substrate processing region containing the deposition substrate. The described methods produce polycrystalline films at reduced substrate temperature (e.g. <500° C.) relative to prior art techniques. The availability of a bias plasma power adjustment further enables adjustment of conformality of the formed polysilicon layer. When dopants are included in the high density plasma, they may be incorporated into the polysilicon layer in such a way that they do not require a separate activation step.

Owner:APPLIED MATERIALS INC

Semiconductor fin isolation by a well trapping fin portion

ActiveUS20140252479A1Solid-state devicesSemiconductor/solid-state device manufacturingDopantSemiconductor materials

A bulk semiconductor substrate including a first semiconductor material is provided. A well trapping layer including a second semiconductor material and a dopant is formed on a top surface of the bulk semiconductor substrate. The combination of the second semiconductor material and the dopant within the well trapping layer is selected such that diffusion of the dopant is limited within the well trapping layer. A device semiconductor material layer including a third semiconductor material can be epitaxially grown on the top surface of the well trapping layer. The device semiconductor material layer, the well trapping layer, and an upper portion of the bulk semiconductor substrate are patterned to form at least one semiconductor fin. Semiconductor devices formed in each semiconductor fin can be electrically isolated from the bulk semiconductor substrate by the remaining portions of the well trapping layer.

Owner:IBM CORP

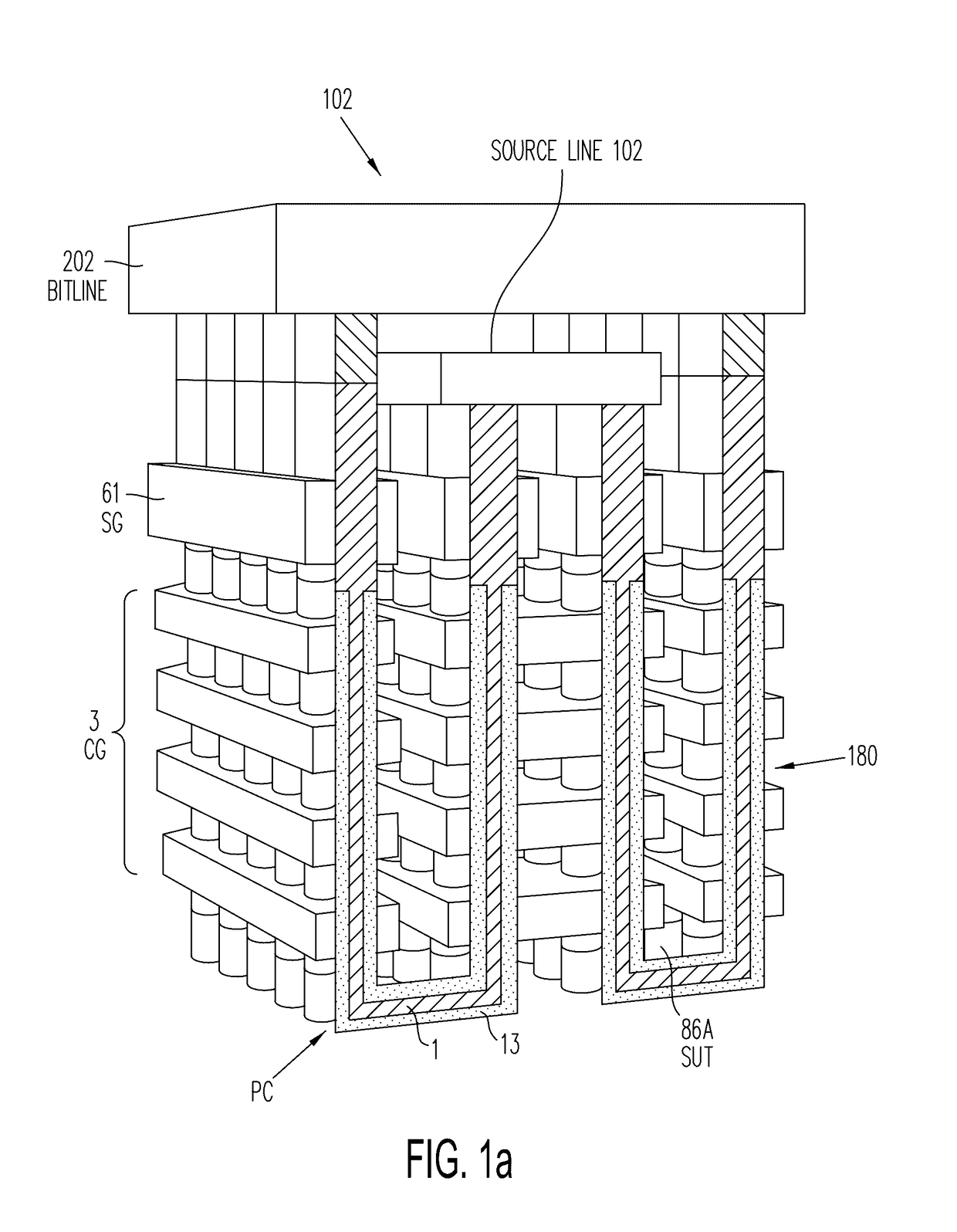

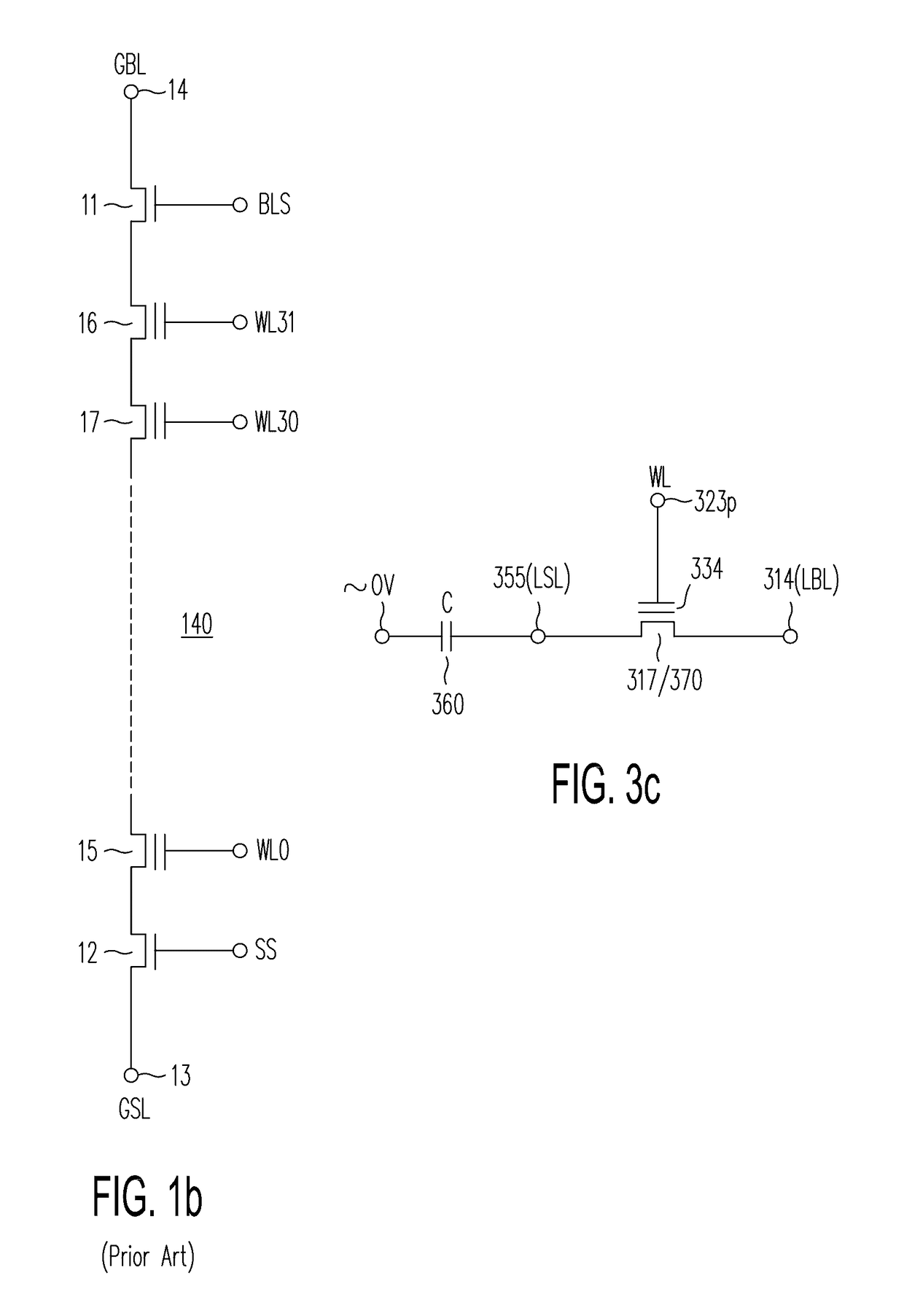

Three-dimensional vertical nor flash thin film transistor strings

ActiveUS20170148517A1Less resistanceFaster senseTransistorSemiconductor/solid-state device detailsEngineeringPolycrystalline silicon

A memory structure, includes (a) active columns of polysilicon formed above a semiconductor substrate, each active column extending vertically from the substrate and including a first heavily doped region, a second heavily doped region, and one or more lightly doped regions each adjacent both the first and second heavily doped region, wherein the active columns are arranged in a two-dimensional array extending in second and third directions parallel to the planar surface of the semiconductor substrate; (b) charge-trapping material provided over one or more surfaces of each active column; and (c) conductors each extending lengthwise along the third direction. The active columns, the charge-trapping material and the conductors together form a plurality of thin film transistors, with each thin film transistor formed by one of the conductors, a portion of the lightly doped region of an active column, the charge-trapping material between the portion of the lightly doped region and the conductor, and the first and second heavily doped regions. The thin film transistors associated with each active column are organized into one or more vertical NOR strings.

Owner:SUNRISE MEMORY CORP

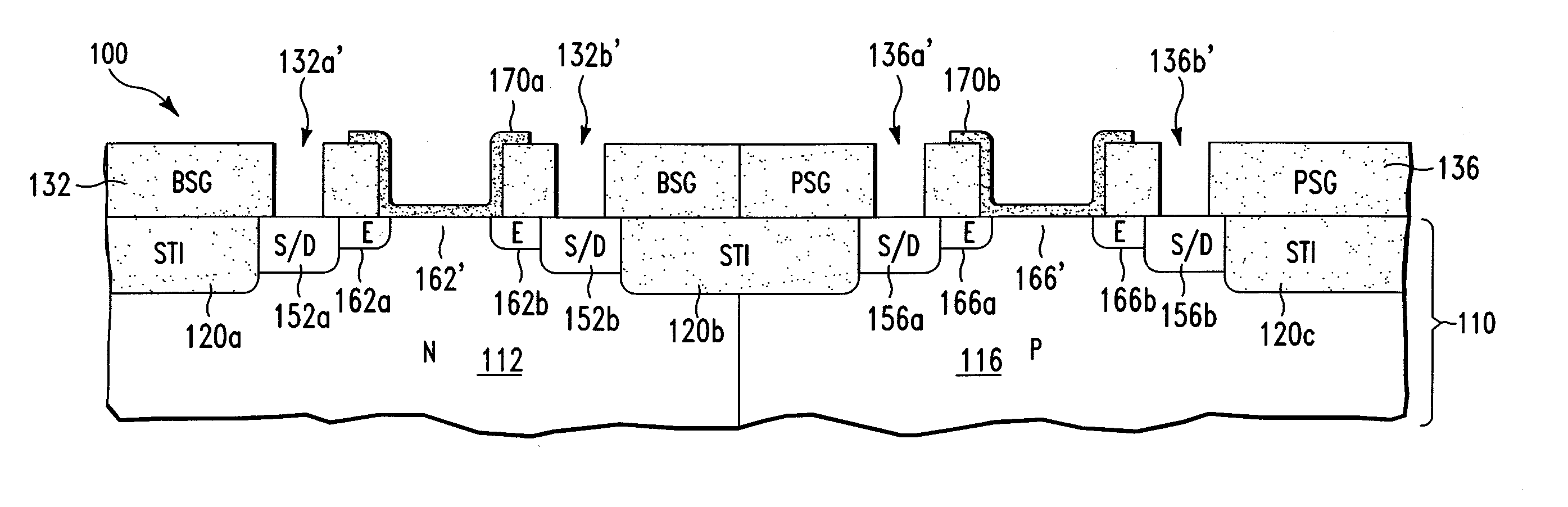

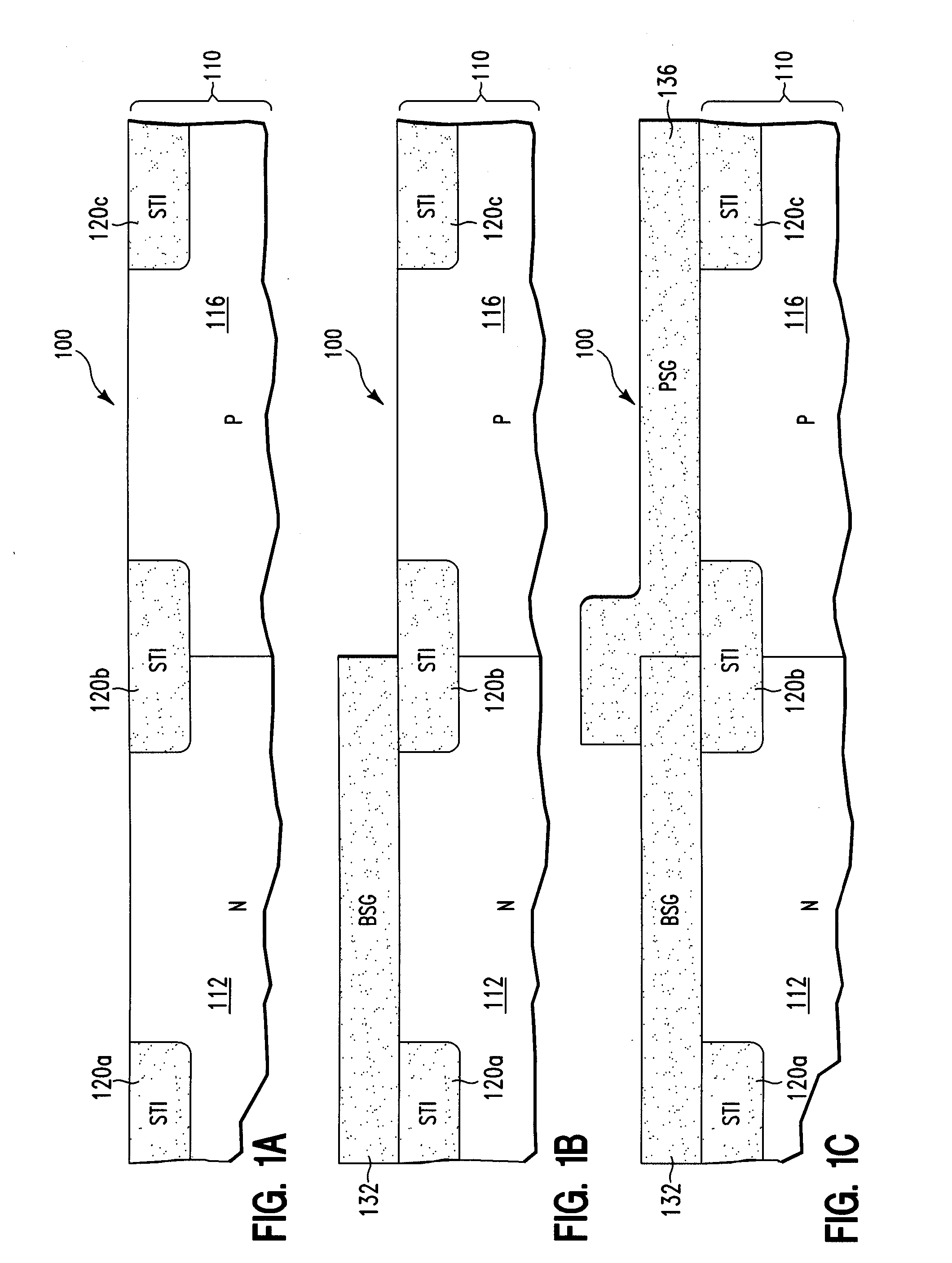

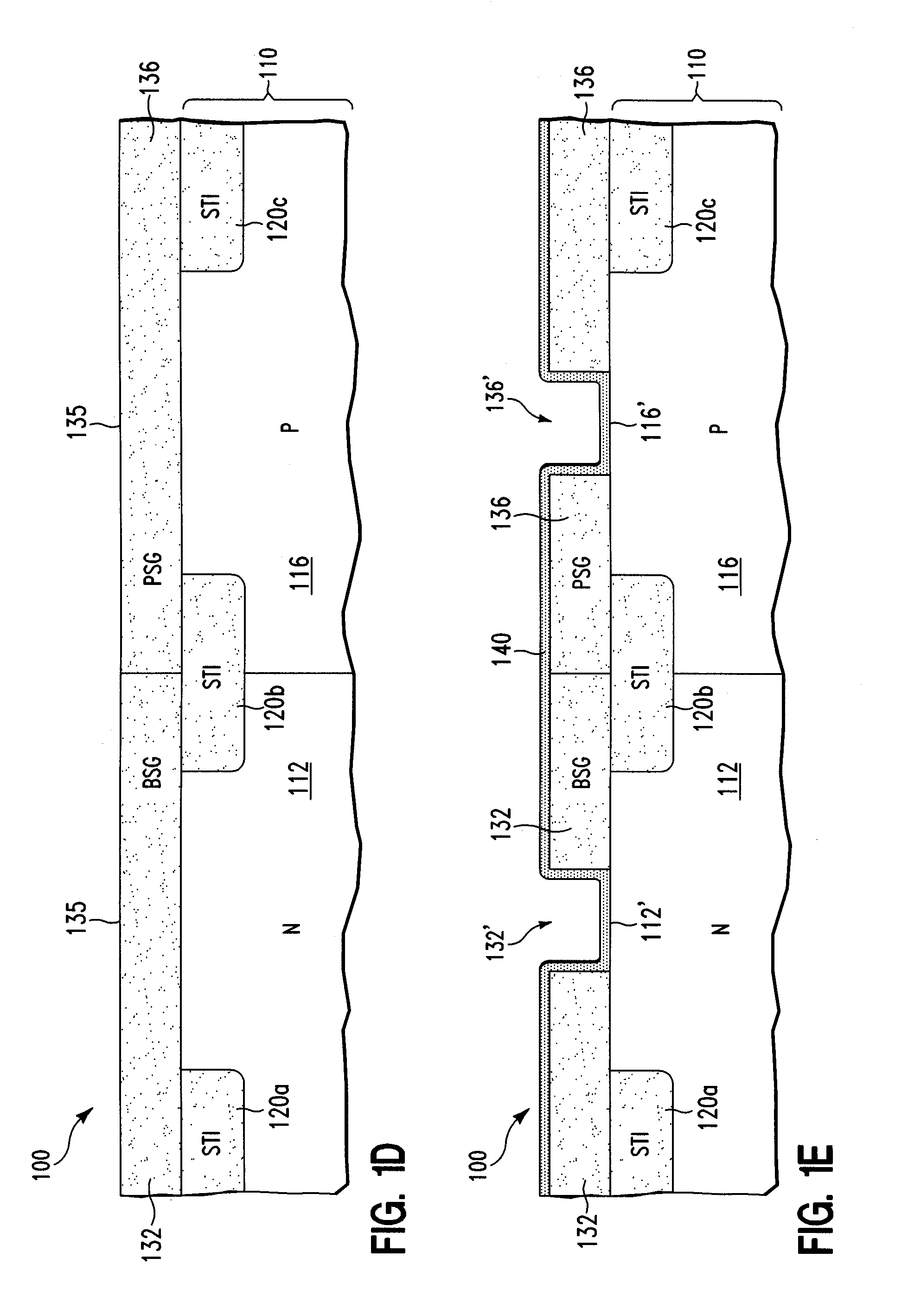

IMPROVED CMOS (Complementary Metal Oxide Semiconductor) TECHNOLOGY

InactiveUS20070020830A1Leakage problemSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCMOS

A method for forming semiconductor transistor. The method comprises providing a structure including (a) a semiconductor region, and (b) first and second dopant source regions on and in direct physical contact with the semiconductor region, wherein each region of the first and second dopant source regions comprises a dielectric material which contains dopants; causing the dopants to diffuse from the first and second dopant source regions into the semiconductor region so as to form first and second source / drain extension regions, respectively, wherein the first and second source / drain extension regions define a channel region disposed between; forming a gate dielectric region on a channel region; and forming a gate region on the gate dielectric region, wherein the gate dielectric region electrically insulates the gate region from the channel region.

Owner:IBM CORP

Method for forming nitride crystals

ActiveUS20080087919A1High dislocation densityPolycrystalline material growthNitrogen compoundsDislocationSingle crystal

A method for growing a nitride crystal and a crystalline composition selected from one of AlN, InGaN, AlGaInN, InGaN, and AlGaNInN is provided. The composition comprises a true single crystal, grown from a single nucleus, at least 1 mm in diameter, free of lateral strain and tilt boundaries, with a dislocation density less than about 104 cm−2.

Owner:SLT TECH

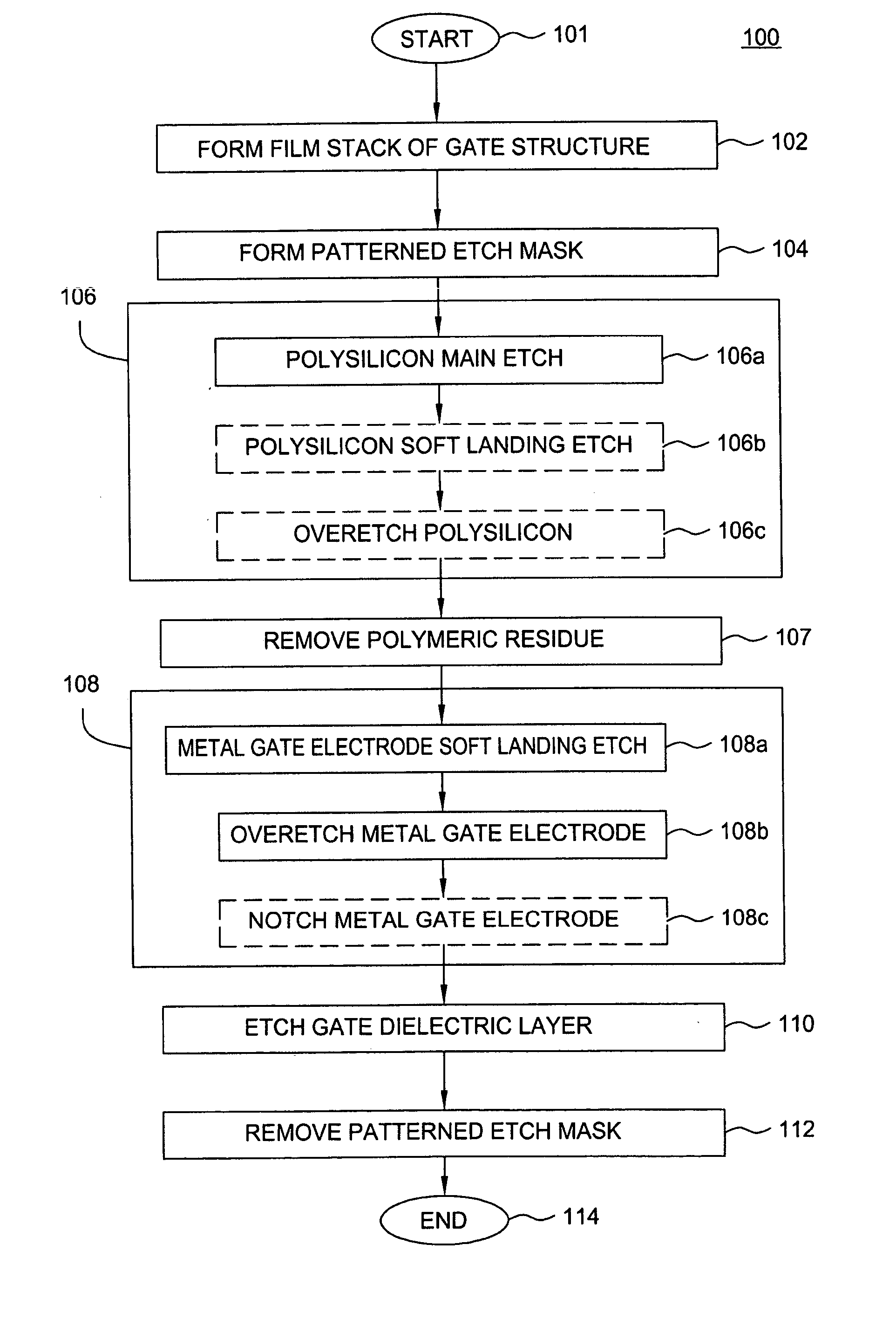

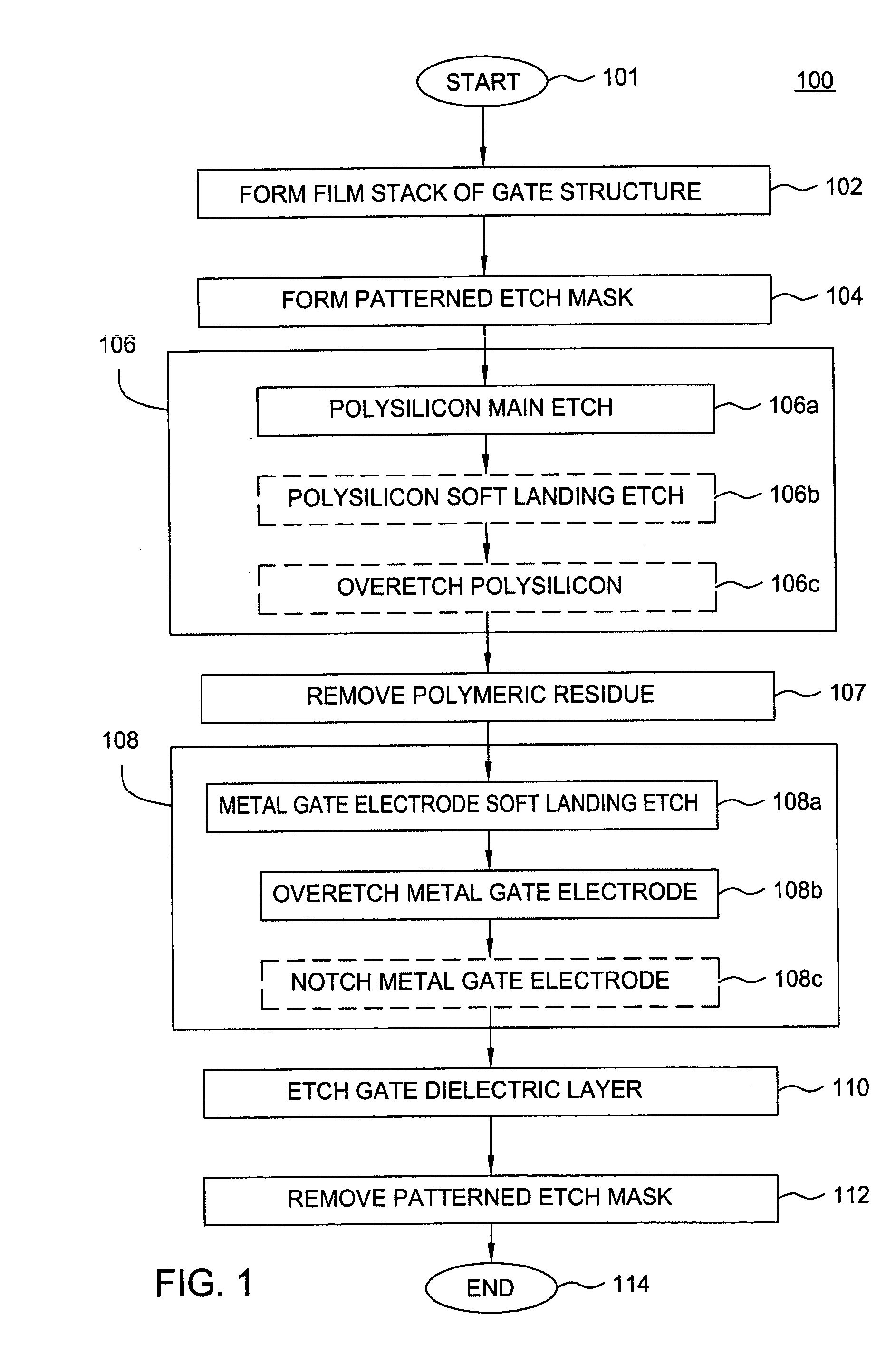

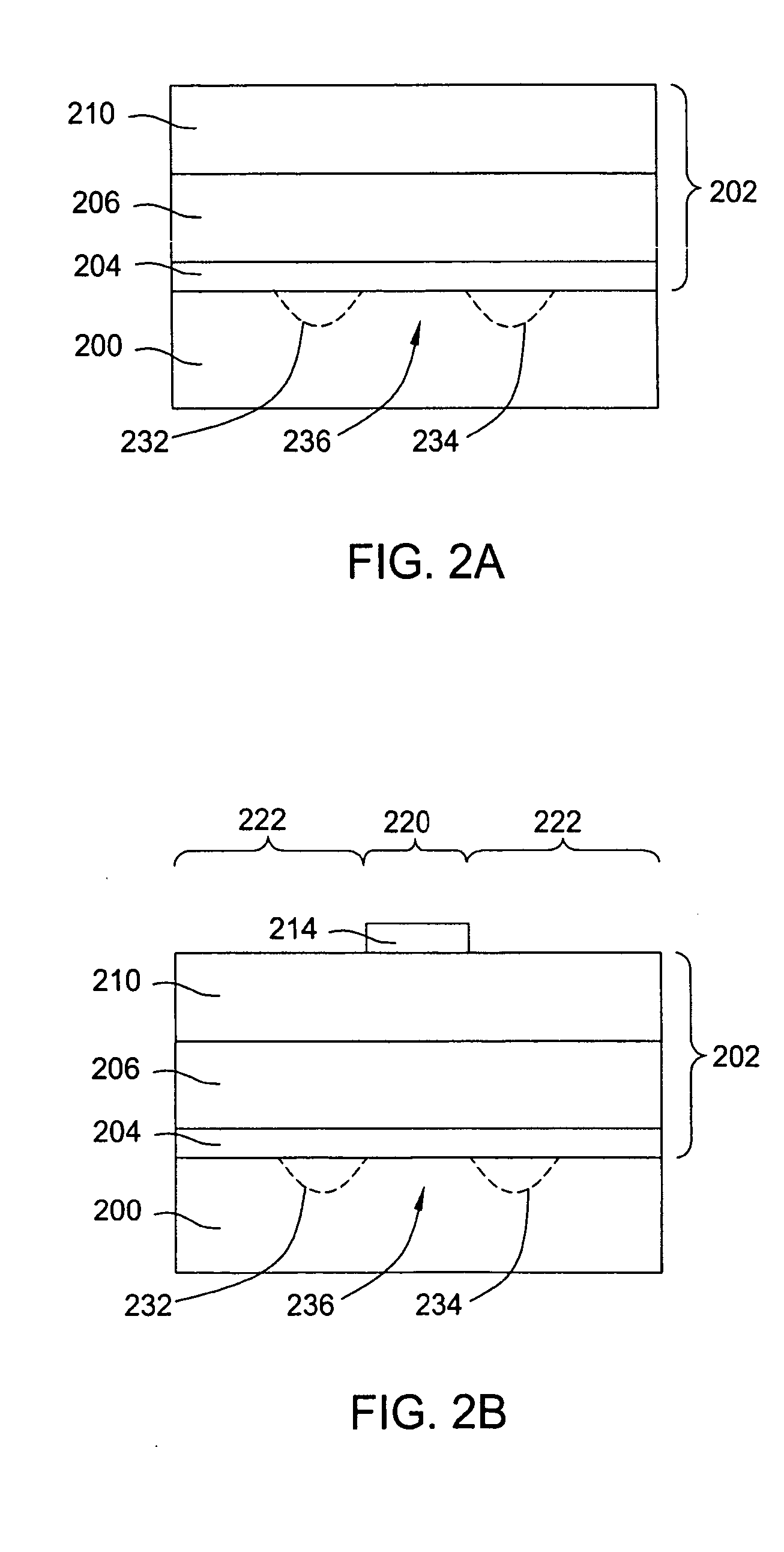

Method of fabricating a gate structure of a field effect transistor having a metal-containing gate electrode

InactiveUS20050009358A1High selectivitySemiconductor/solid-state device detailsSolid-state devicesBromineTitanium nitride

A method of etching metals and / or metal-containing compounds using a plasma comprising a bromine-containing gas. In one embodiment, the method is used during fabrication of a gate structure of a field effect transistor having a titanium nitride gate electrode, an ultra-thin (about 10 to 20 Angstroms) silicon dioxide gate dielectric, and a polysilicon upper contact. In a further embodiment, the gate electrode is selectively notched to a pre-determined width.

Owner:APPLIED MATERIALS INC

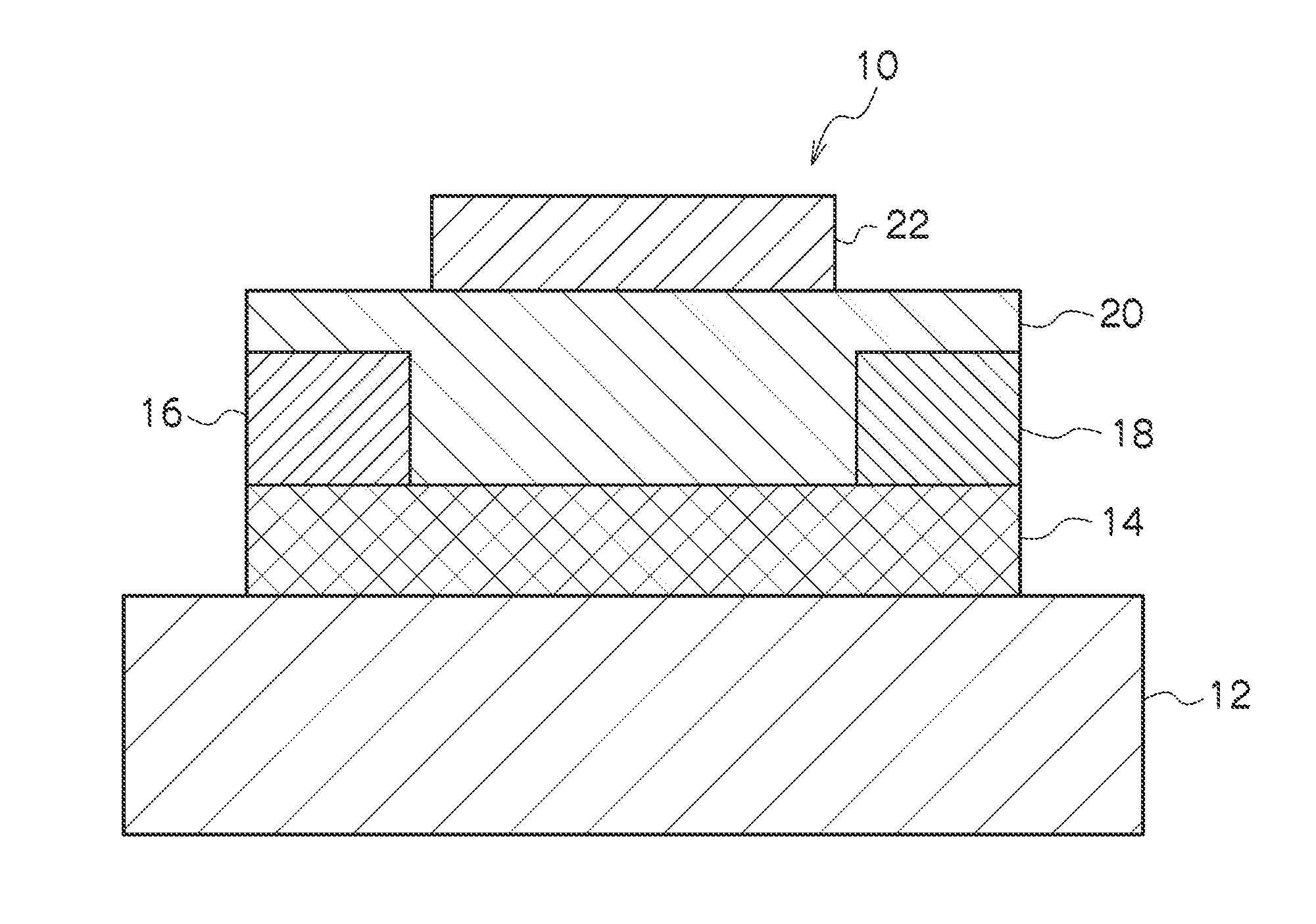

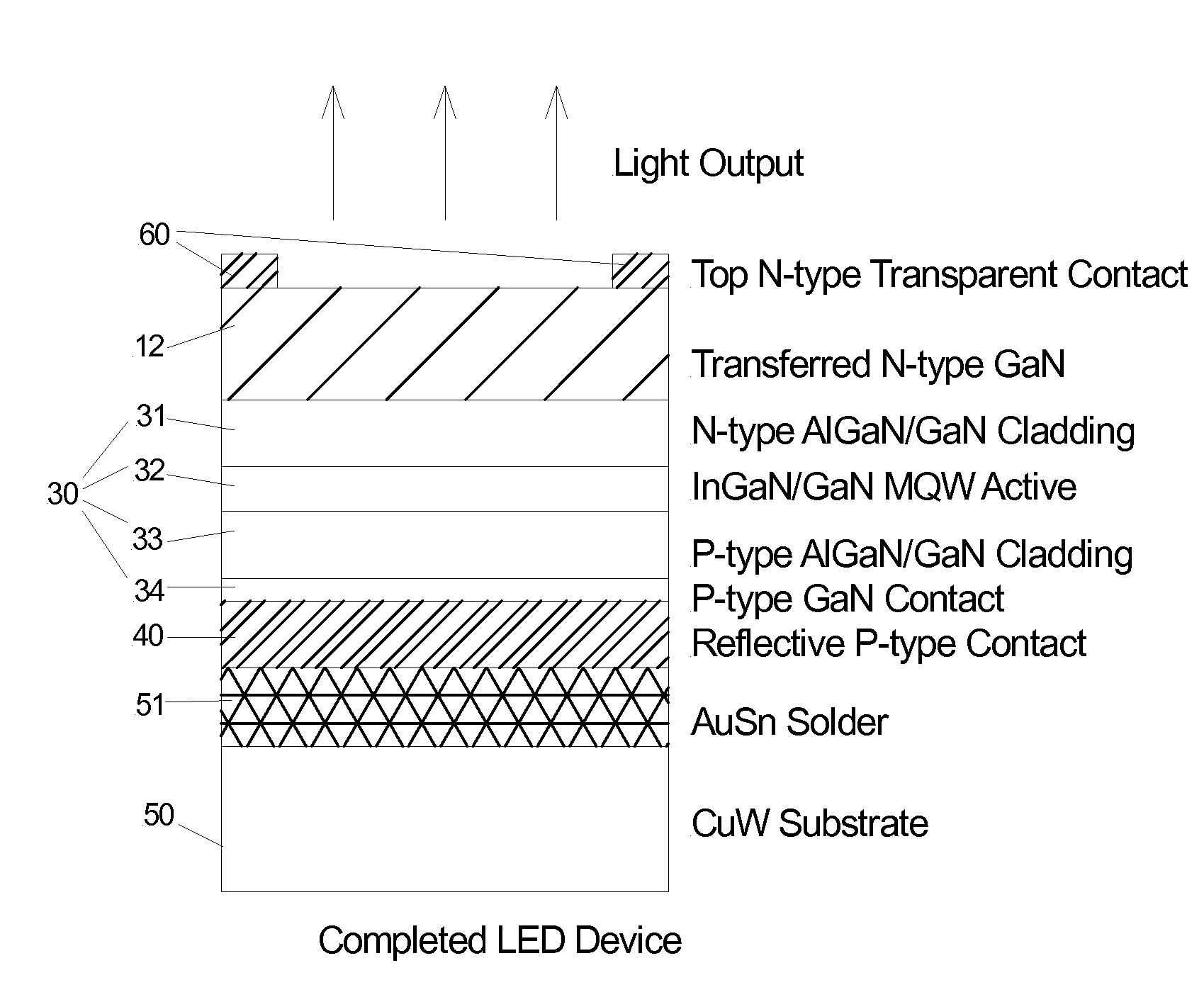

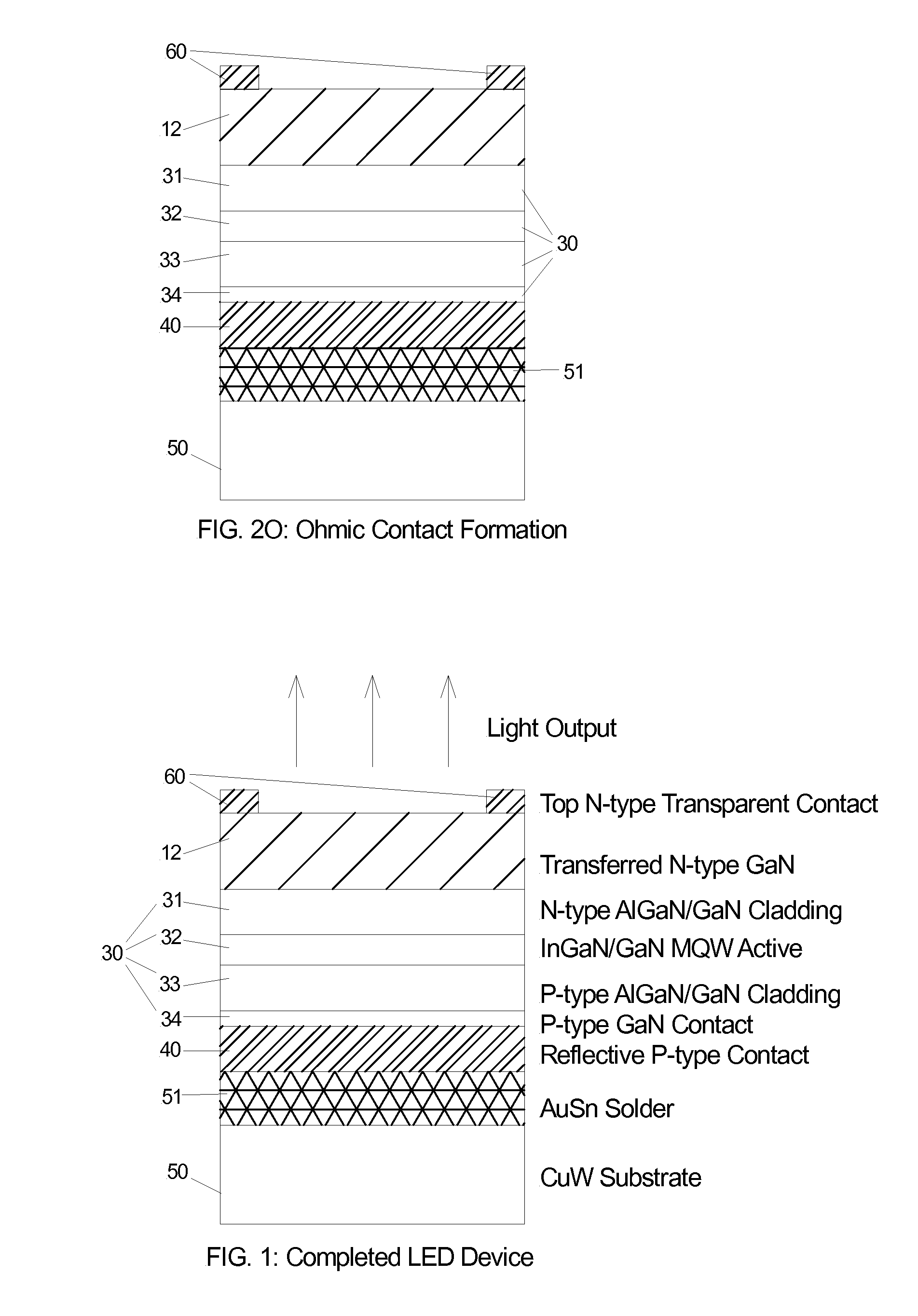

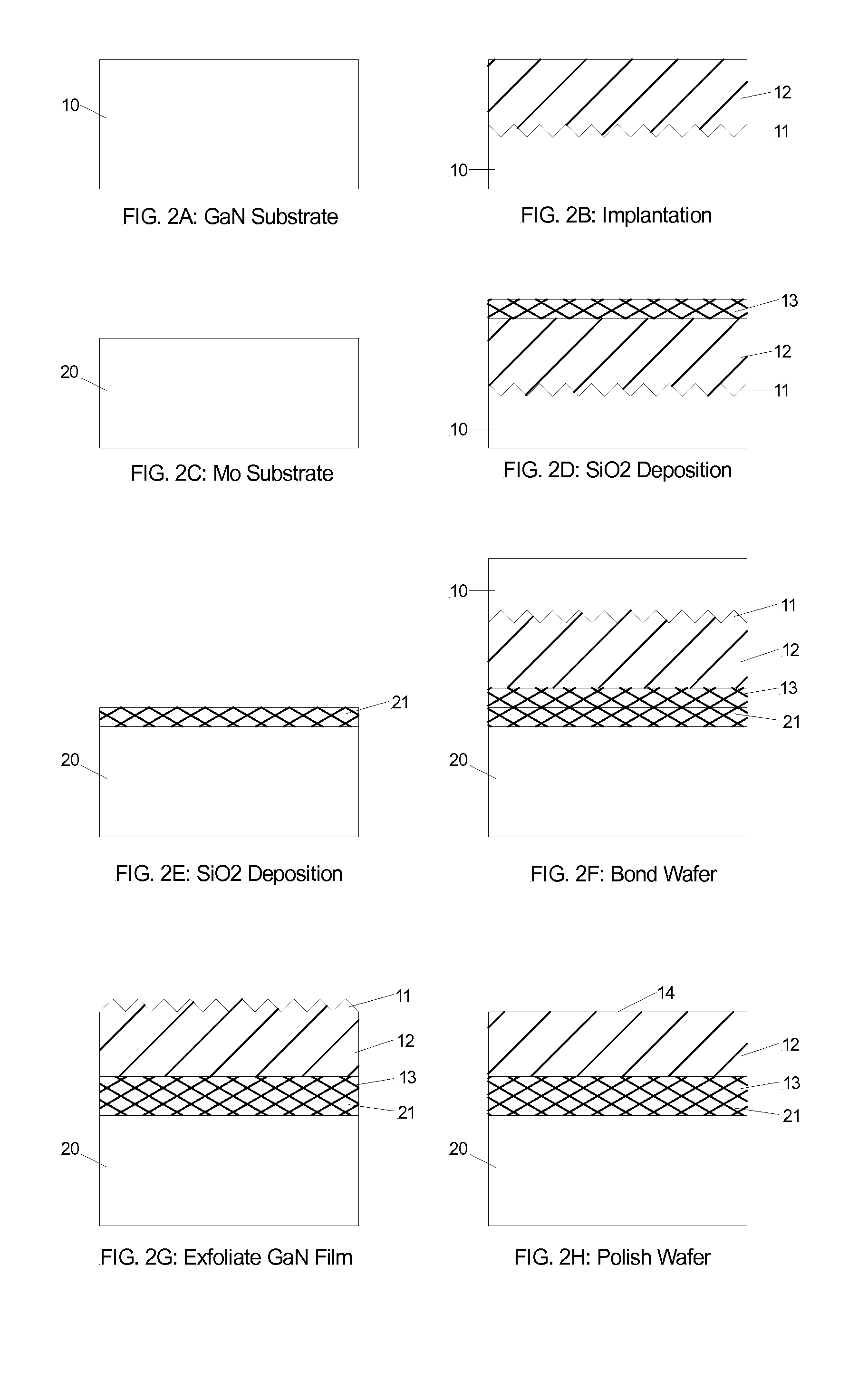

Bonded intermediate substrate and method of making same

InactiveUS20090278233A1Quality improvementSolid-state devicesSemiconductor/solid-state device manufacturingNitrideIon implantation

A method includes growing a first epitaxial layer of III-nitride material, forming a damaged region by implanting ions into an exposed surface of the first epitaxial layer, and growing a second epitaxial layer of III-nitride material on the exposed surface of the first epitaxial layer. A level of defects present in the second epitaxial layer is less than a level of defects present in the first epitaxial layer.

Owner:AMBERWAVE SYST

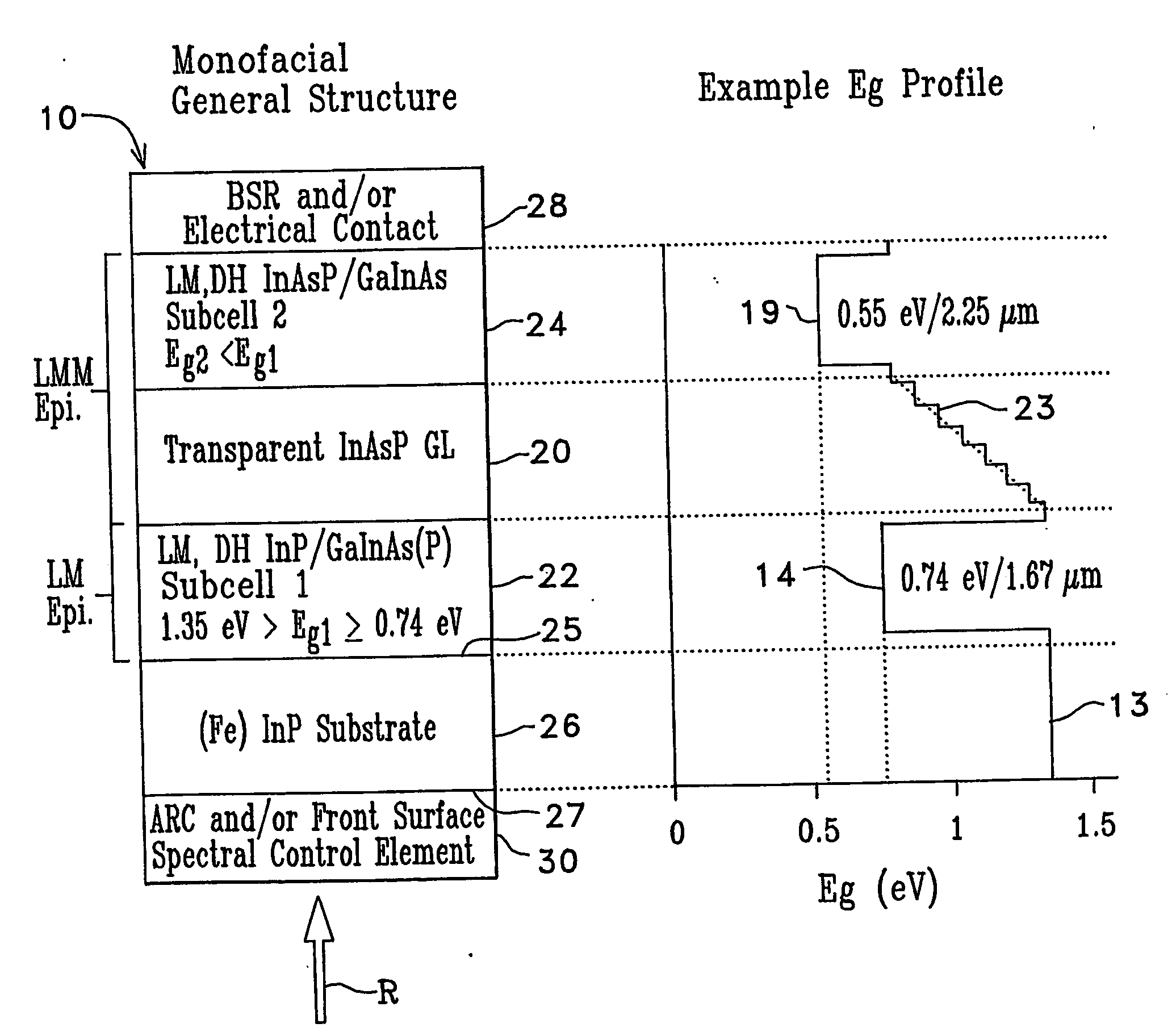

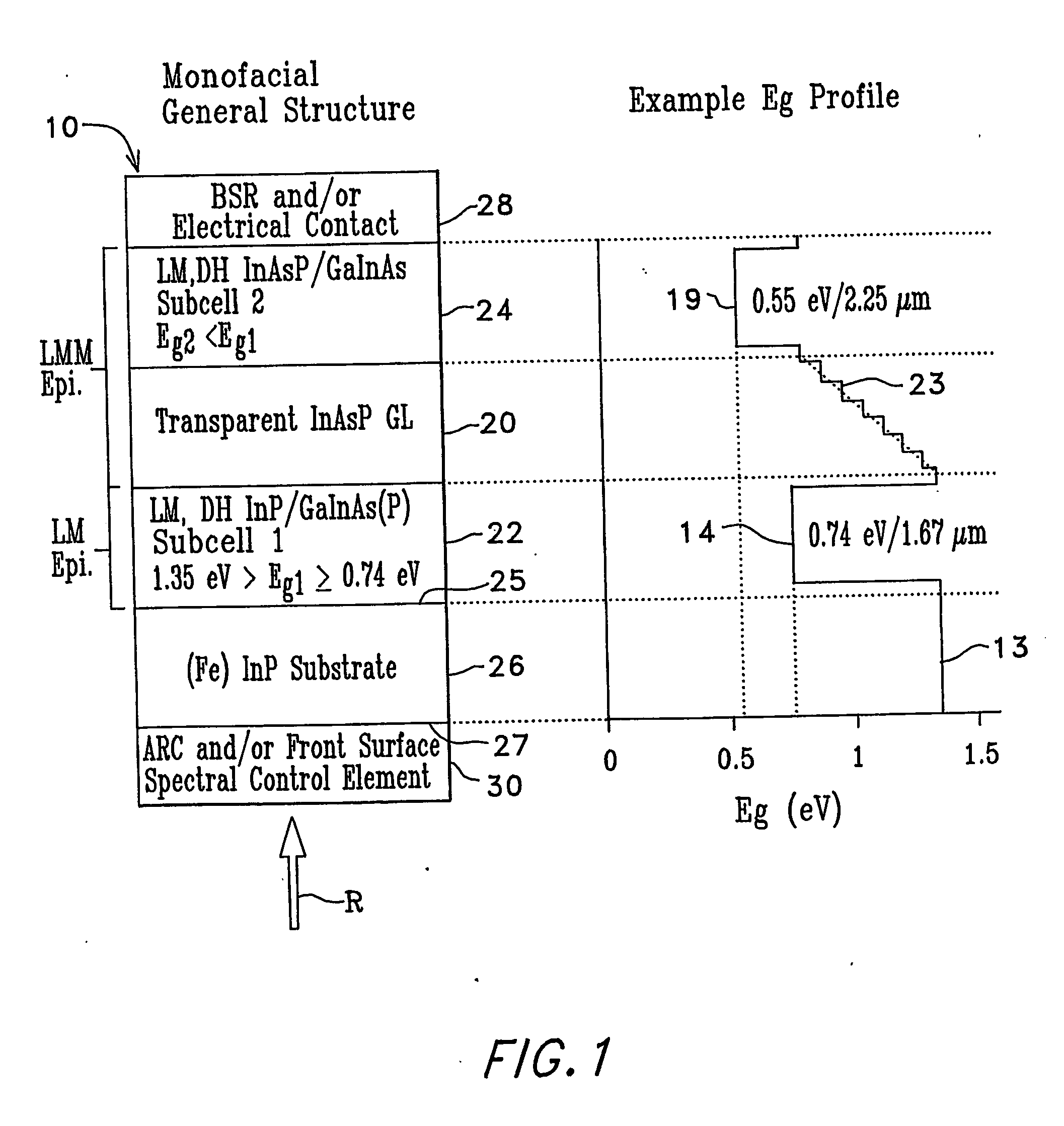

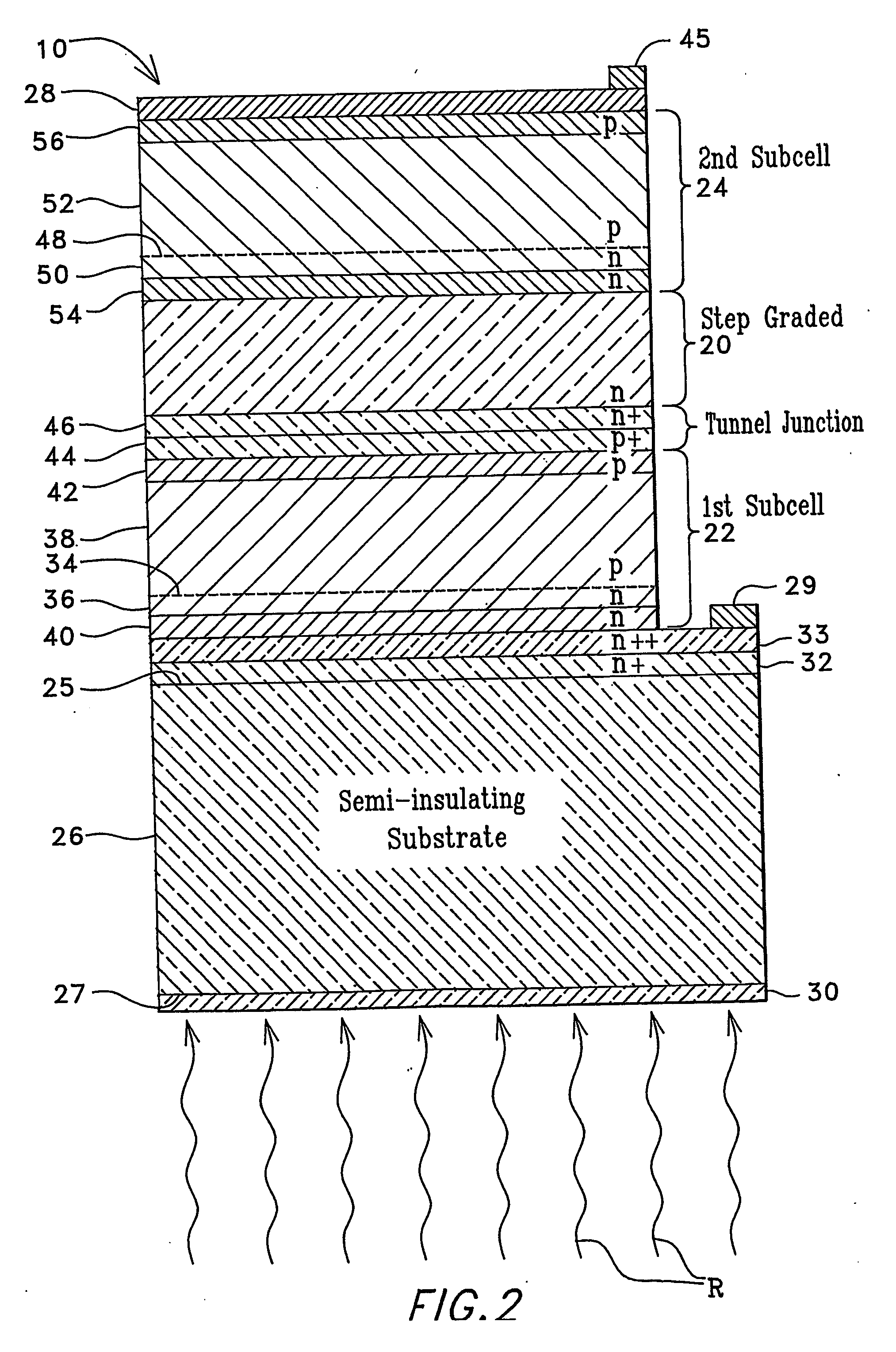

Low bandgap, monolithic, multi-bandgap, optoelectronic devices

InactiveUS20060162768A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

Low-bandgap, monolithic, multi-bandgap, optoelectronic devices (10), including PV converters, photodetectors, and LED's, have lattice-matched (LM), double-heterostructure (DH), low-bandgap GaInAs(P) subcells (22, 24) including those that are lattice-mismatched (LMM) to InP, grown on an InP substrate (26) by use of at least one graded lattice constant transition layer (20) of InAsP positioned somewhere between the InP substrate (26) and the LMM subcell(s) (22, 24). These devices are monofacial (10) or bifacial (80) and include monolithic, integrated, modules (MIMs) (190) with a plurality of voltage-matched subcell circuits (262, 264, 266, 270, 272) as well as other variations and embodiments.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

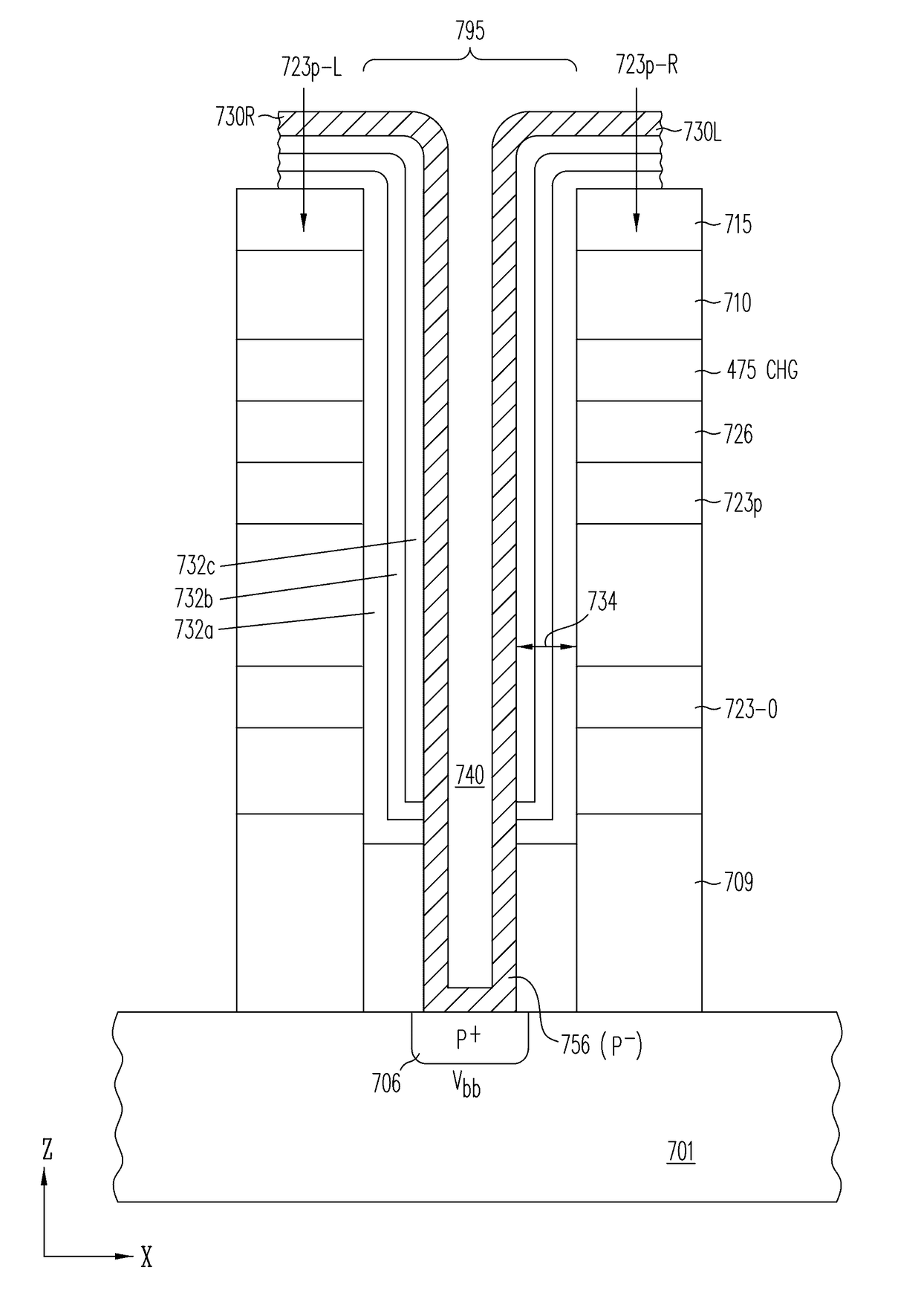

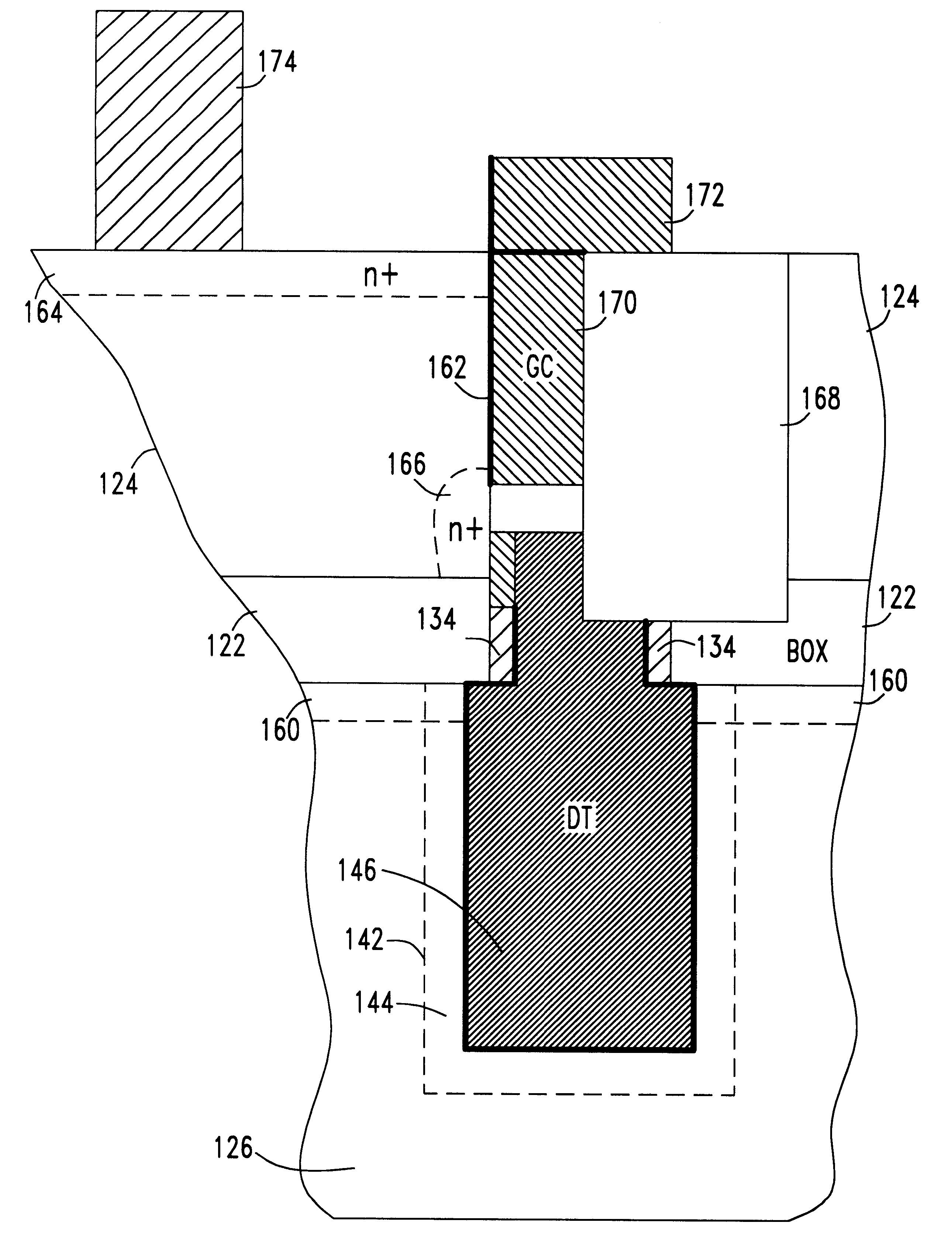

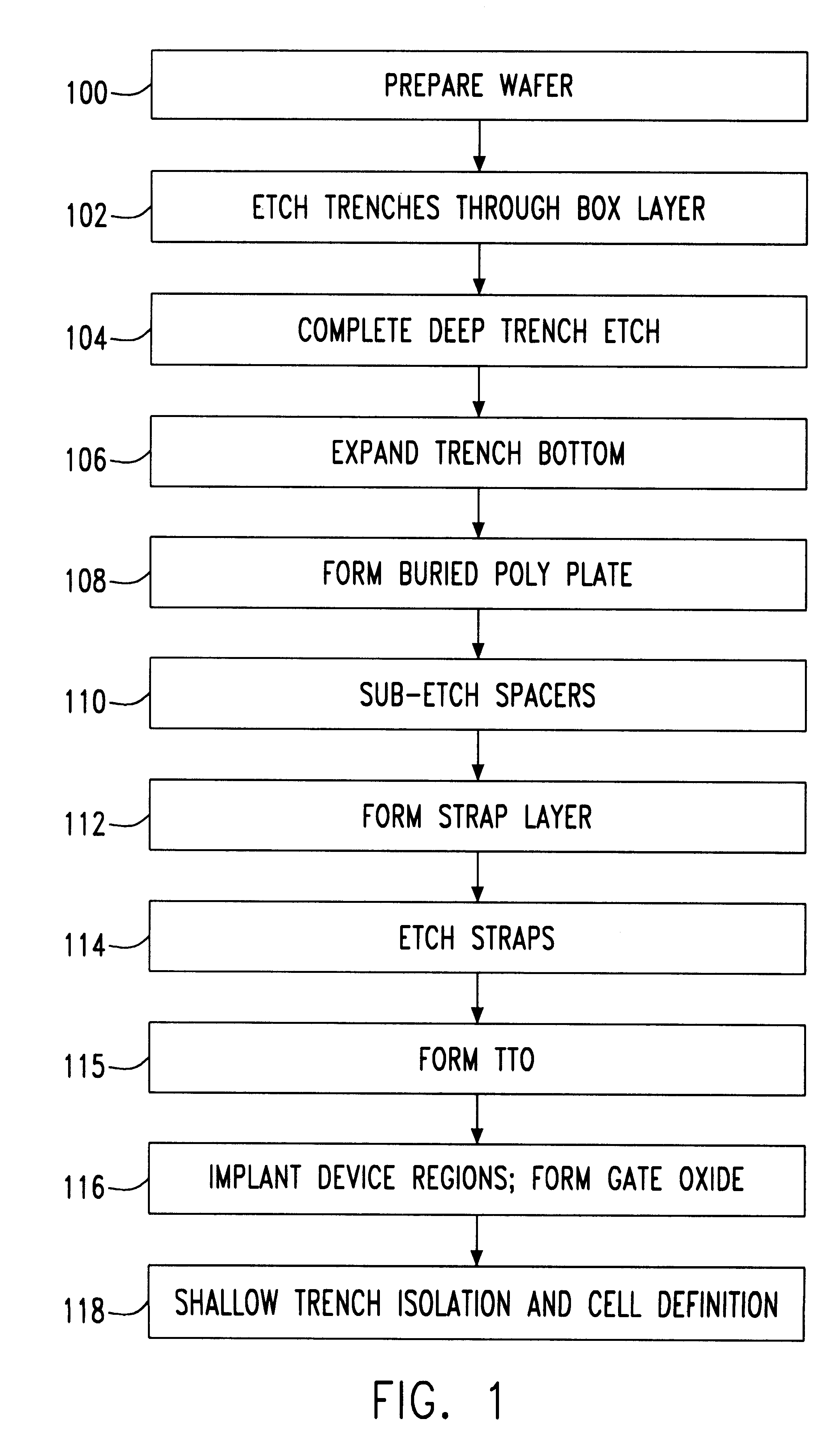

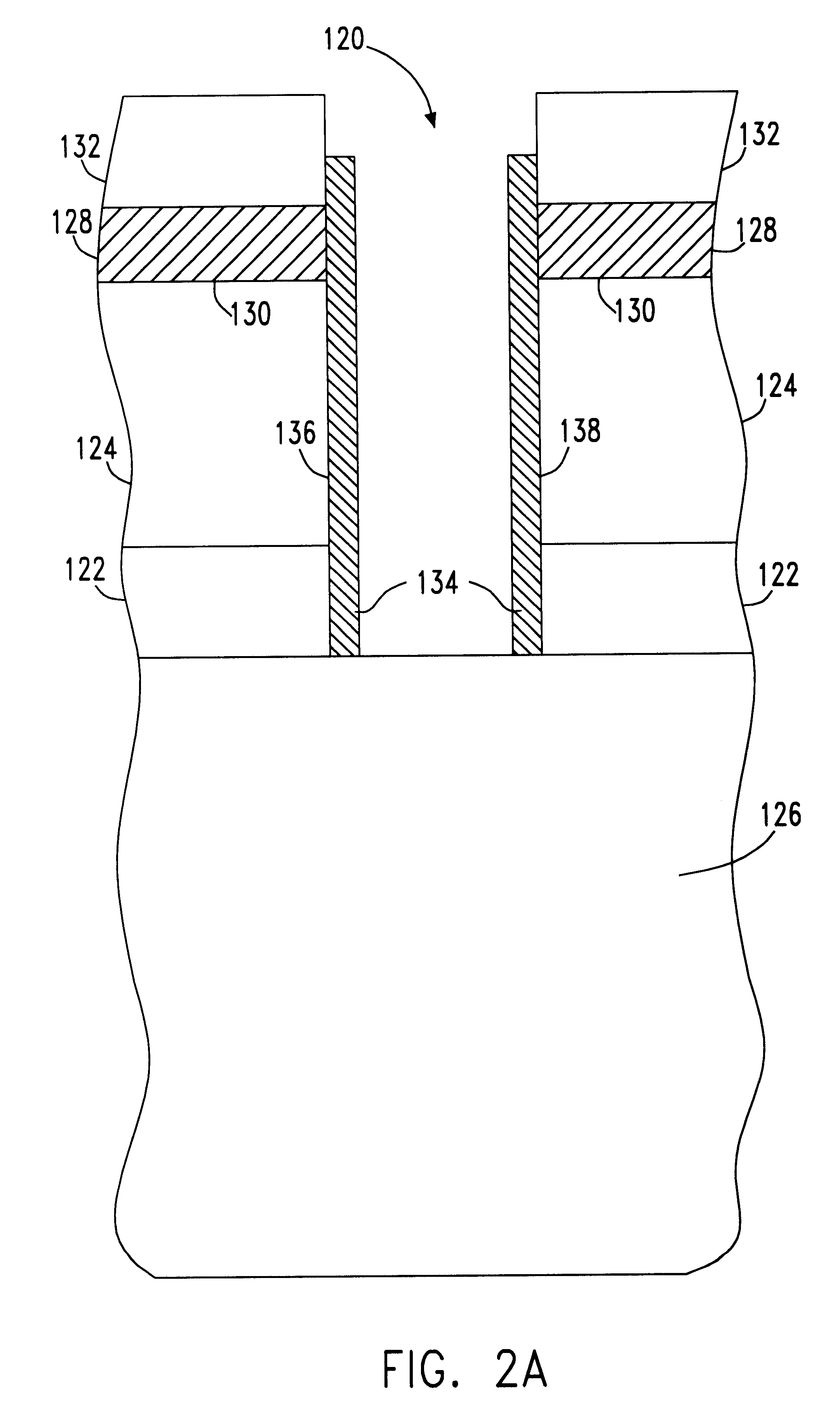

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

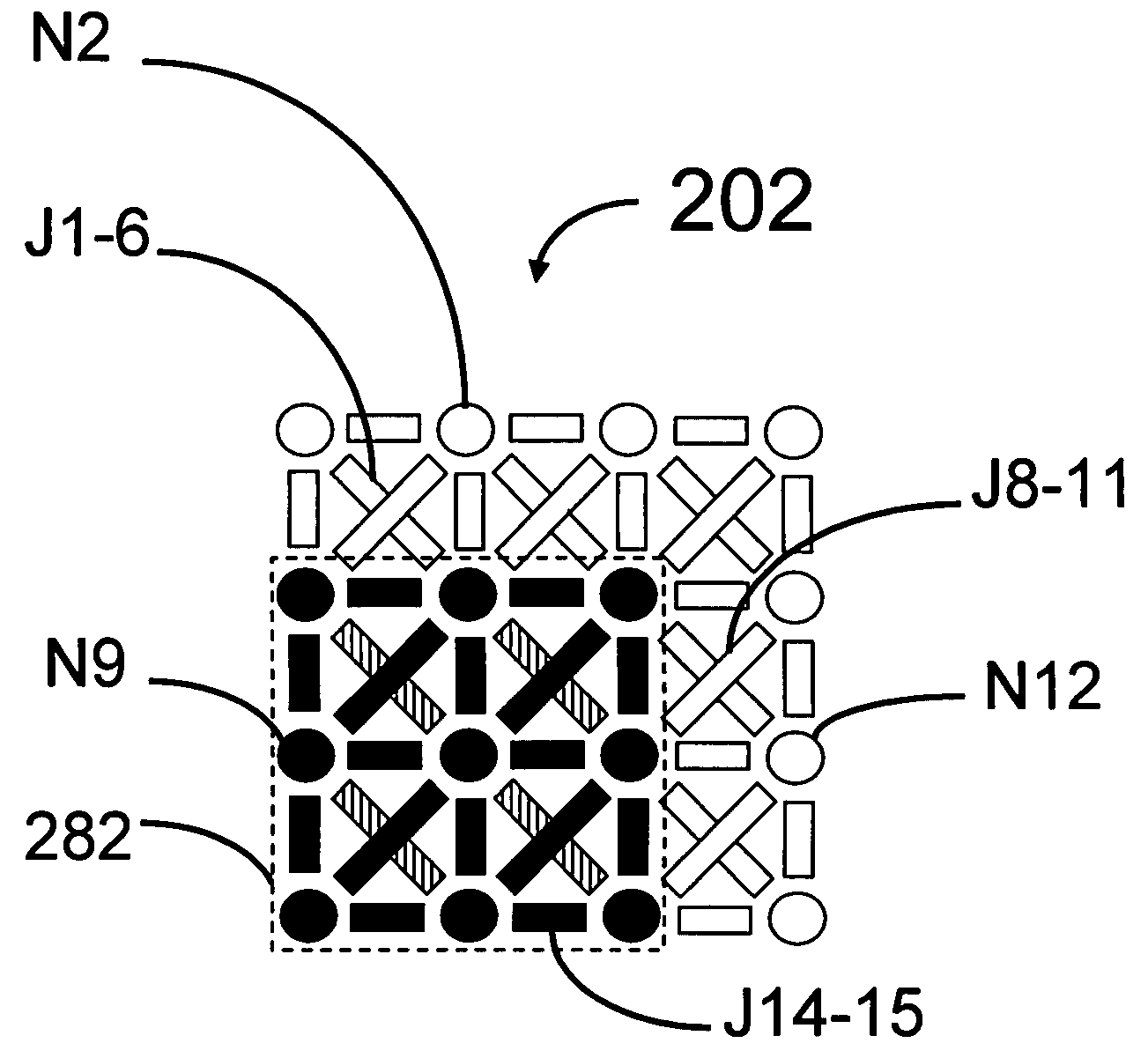

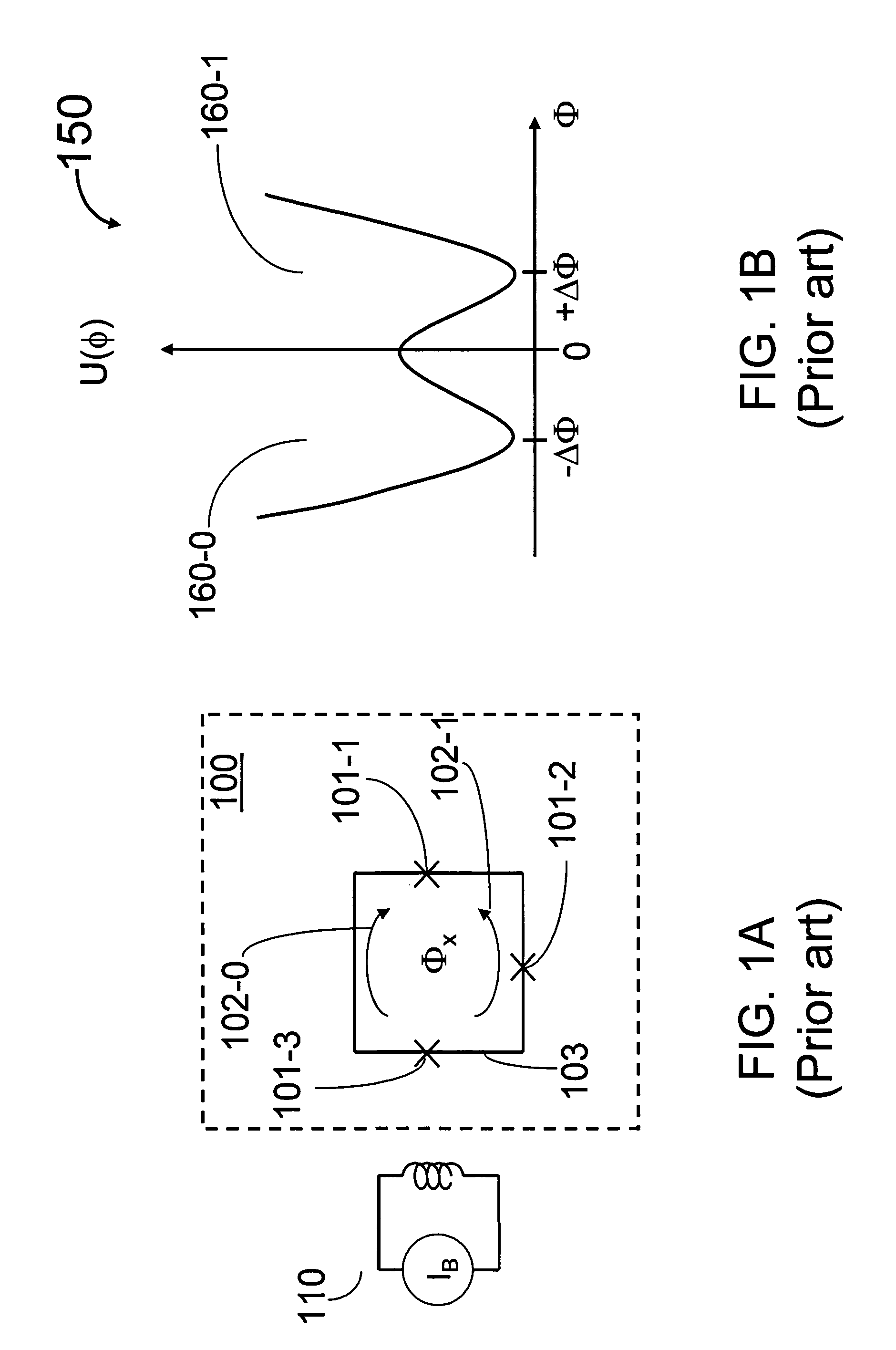

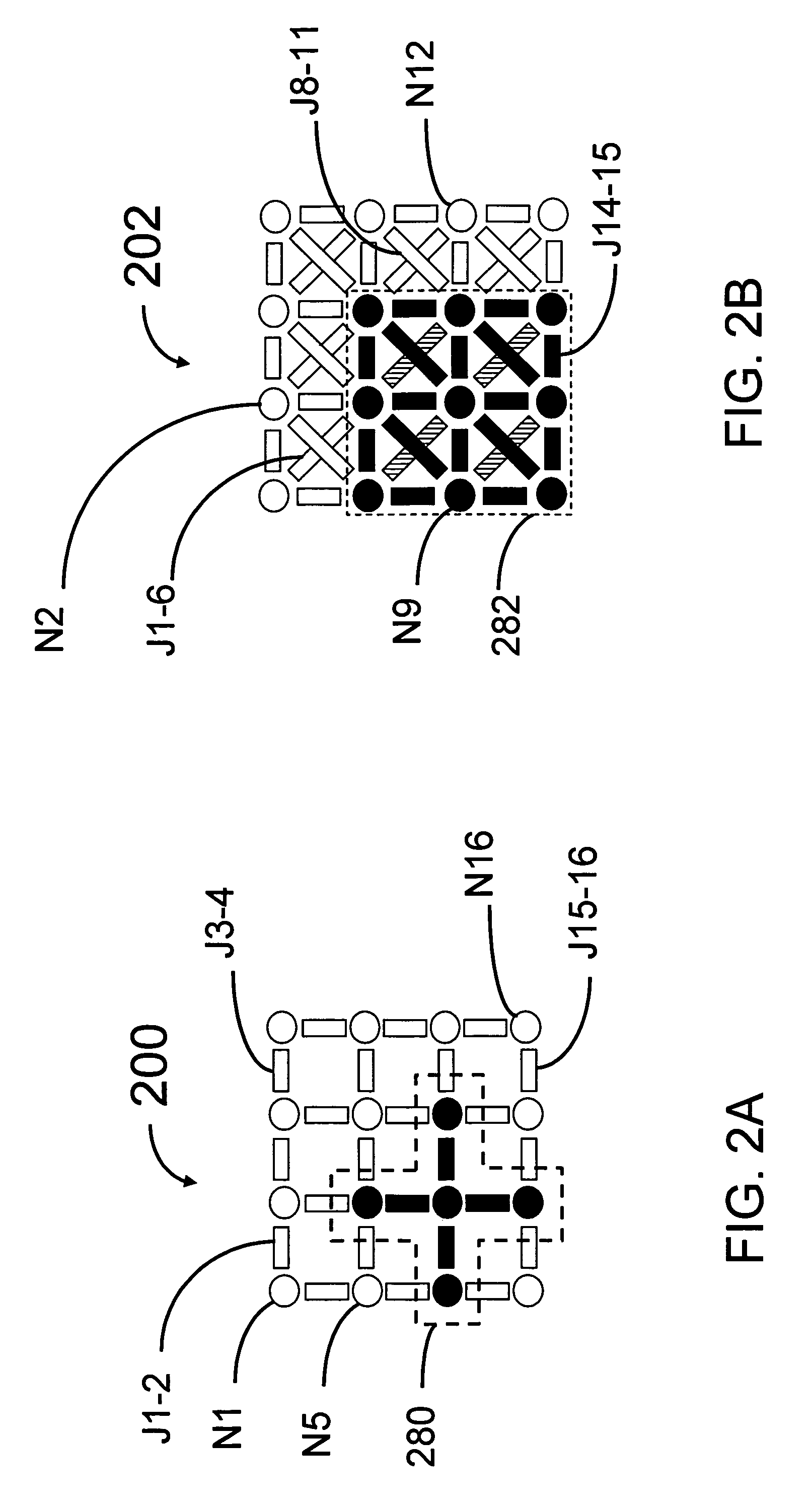

Analog processor comprising quantum devices

Owner:D WAVE SYSTEMS INC

Nonplanar semiconductor device with partially or fully wrapped around gate electrode and methods of fabrication

InactiveUS20090061572A1High densityTransistorSemiconductor/solid-state device manufacturingGate dielectricDevice material

Owner:TAHOE RES LTD

Semiconductor device including a vertical field effect transistor, having trenches, and a diode

Owner:HITACHI LTD +1

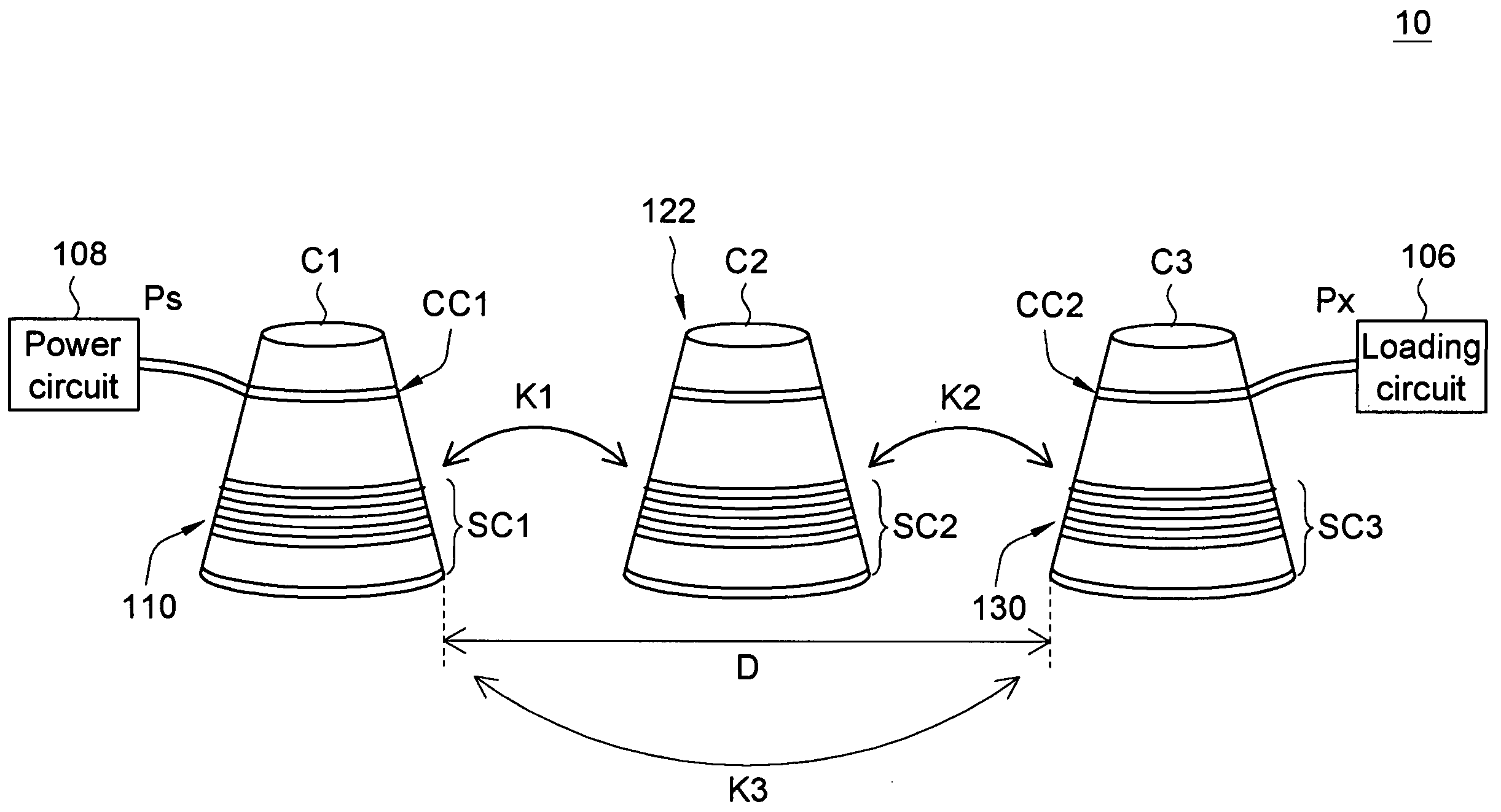

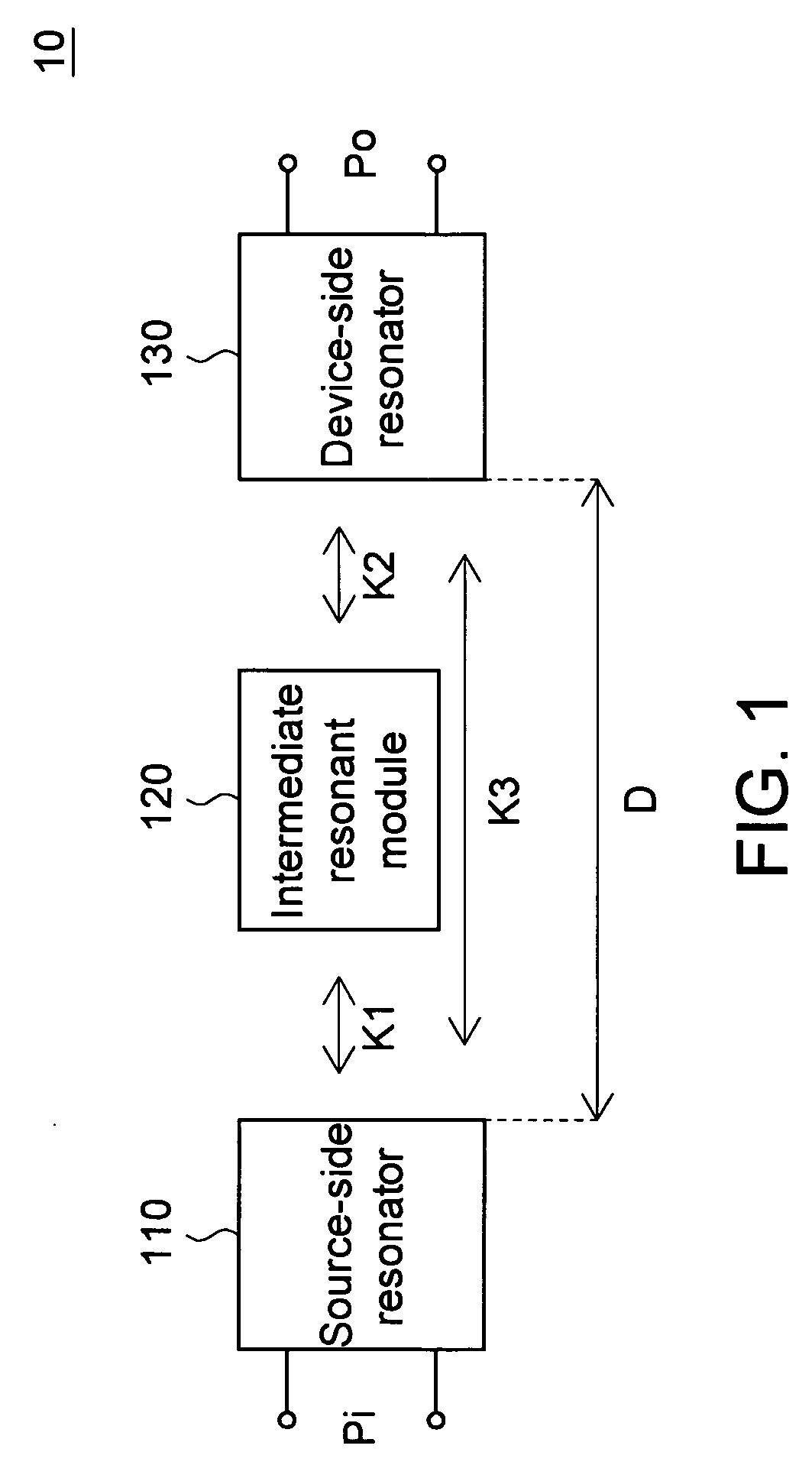

Energy transferring system and method thereof

InactiveUS20090153273A1Improve energy transfer efficiencySmall volumeMultiple-port networksTransformersEnergy transferResonance

An energy transferring system including a source-side resonator, an intermediate resonant module, and a device-side resonator is provided. The three resonators substantially have the same resonant frequency for generating resonance. The energy on the source-side resonator is coupled to the intermediate resonant module, such that non-radiative energy transfer is performed between the source-side resonator and the intermediate resonant module. The energy coupled to the intermediate resonant module is further coupled to the device-side resonator, such that non-radiative energy transfer is performed between the intermediate resonant module and the device-side resonator to achieve energy transfer between the source-side resonator and the device-side resonator. The coupling coefficient between the intermediate resonant module and its two adjacent resonators is larger than the coupling coefficient between the source-side resonator and the device-side resonator. The invention has the advantages of high transmission efficiency, small volume, low cost.

Owner:DARFON ELECTRONICS CORP

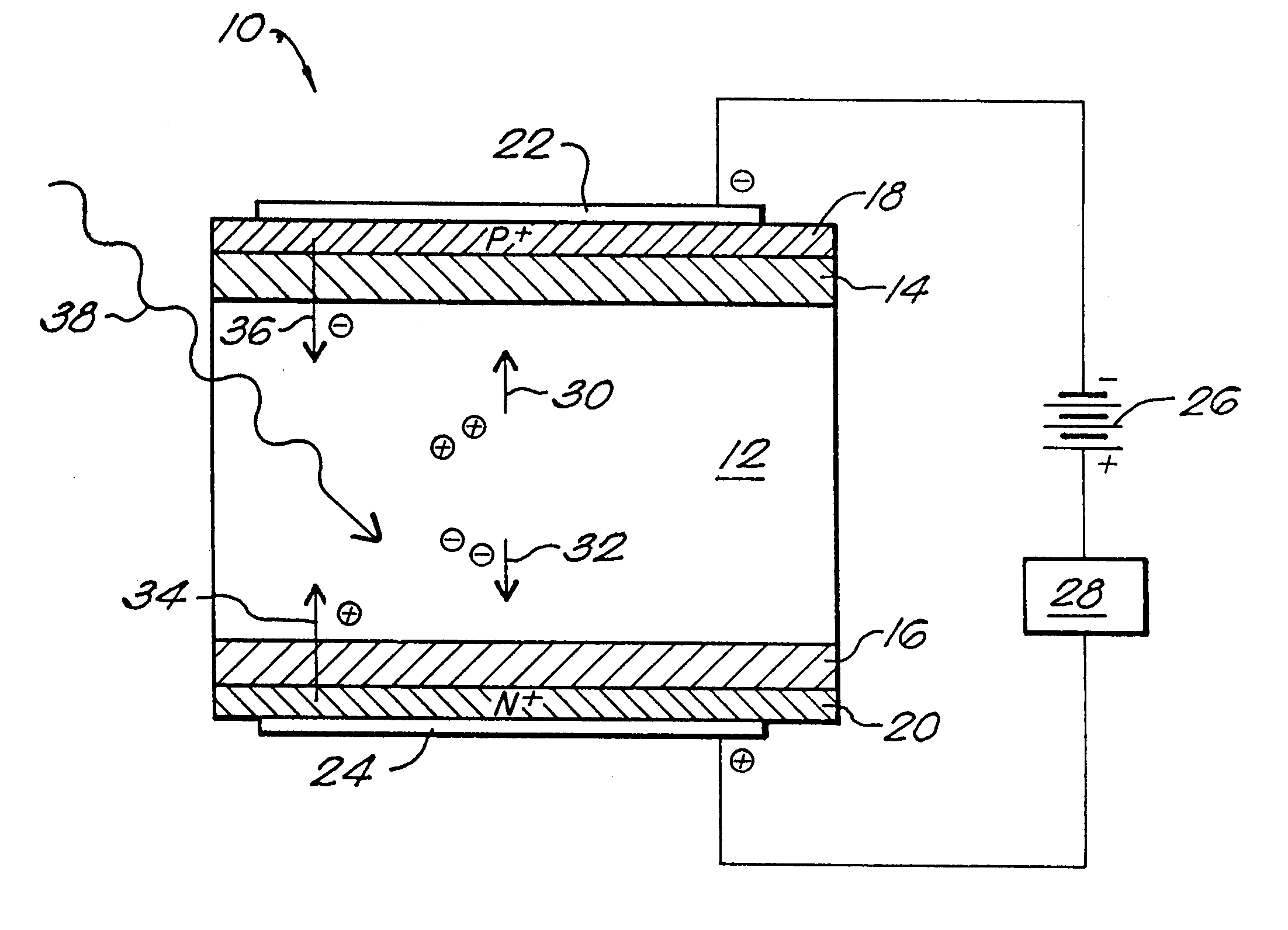

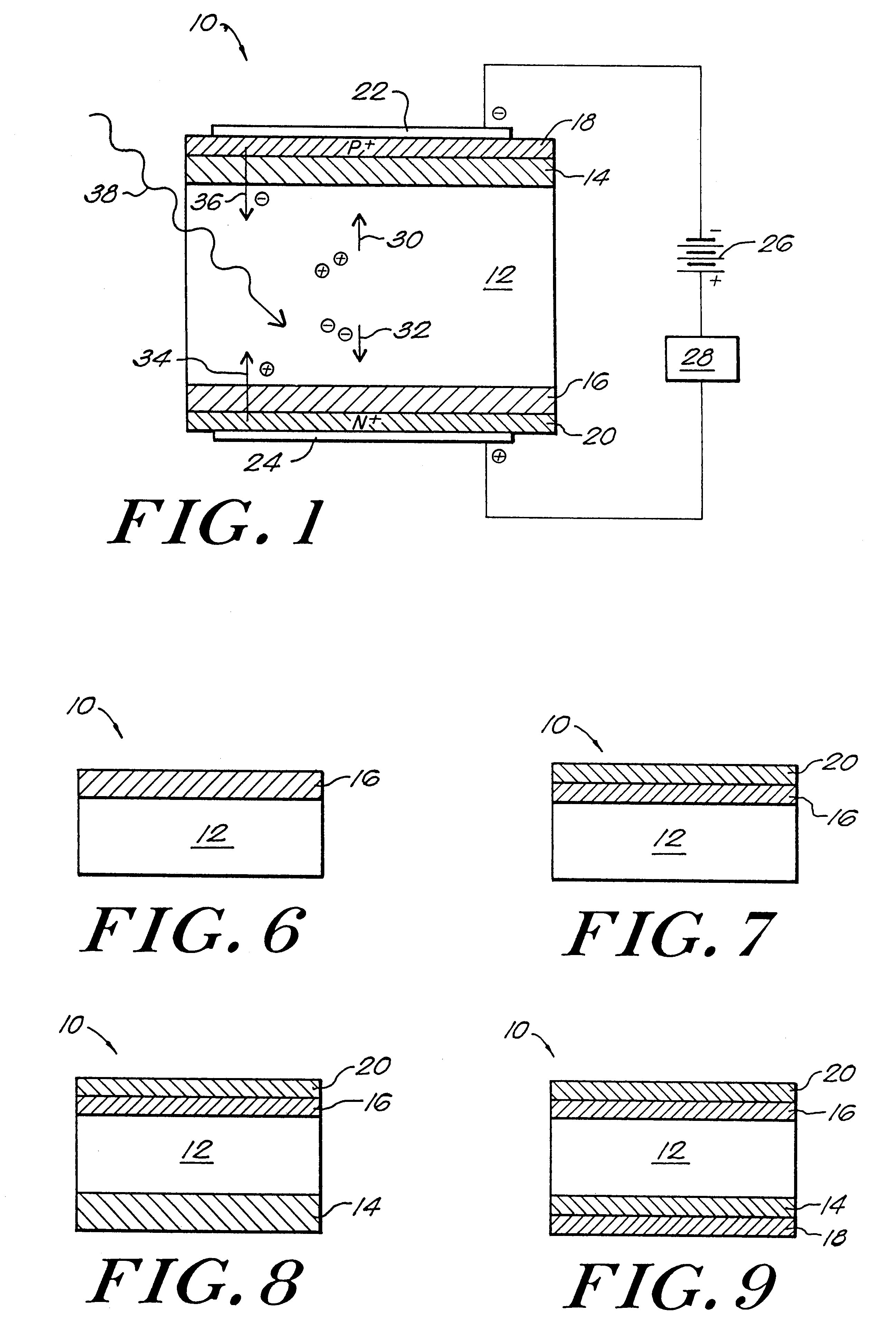

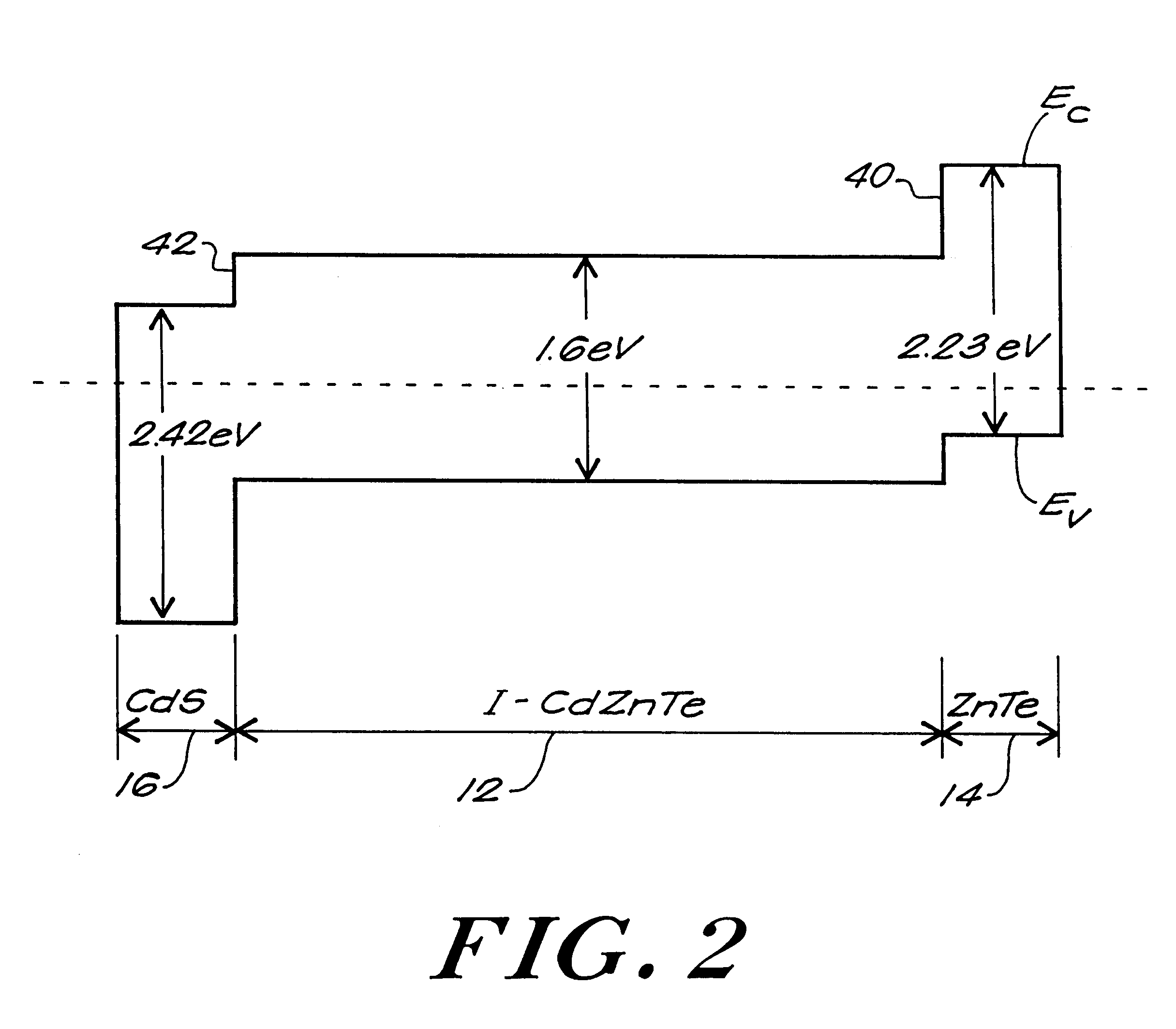

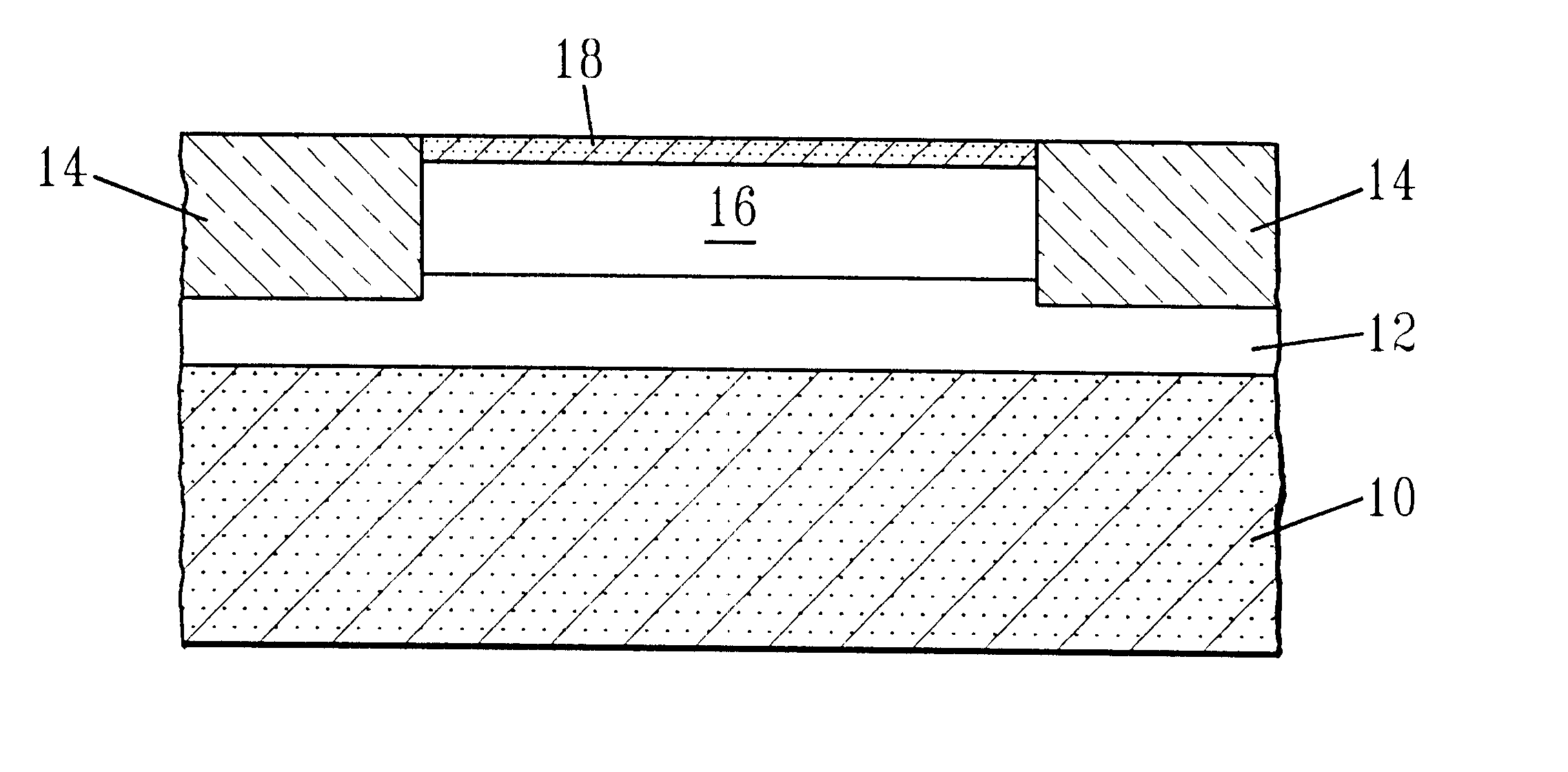

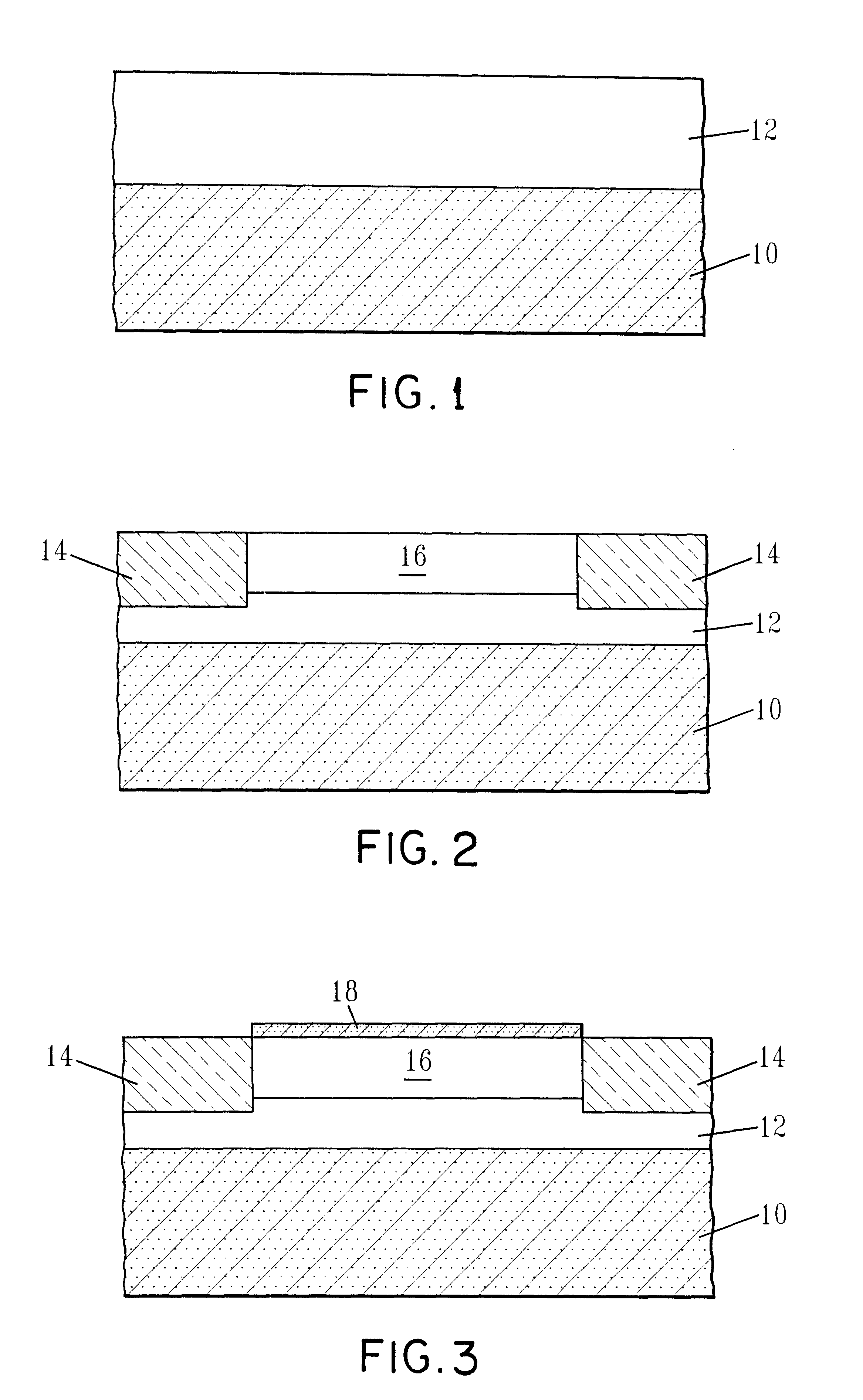

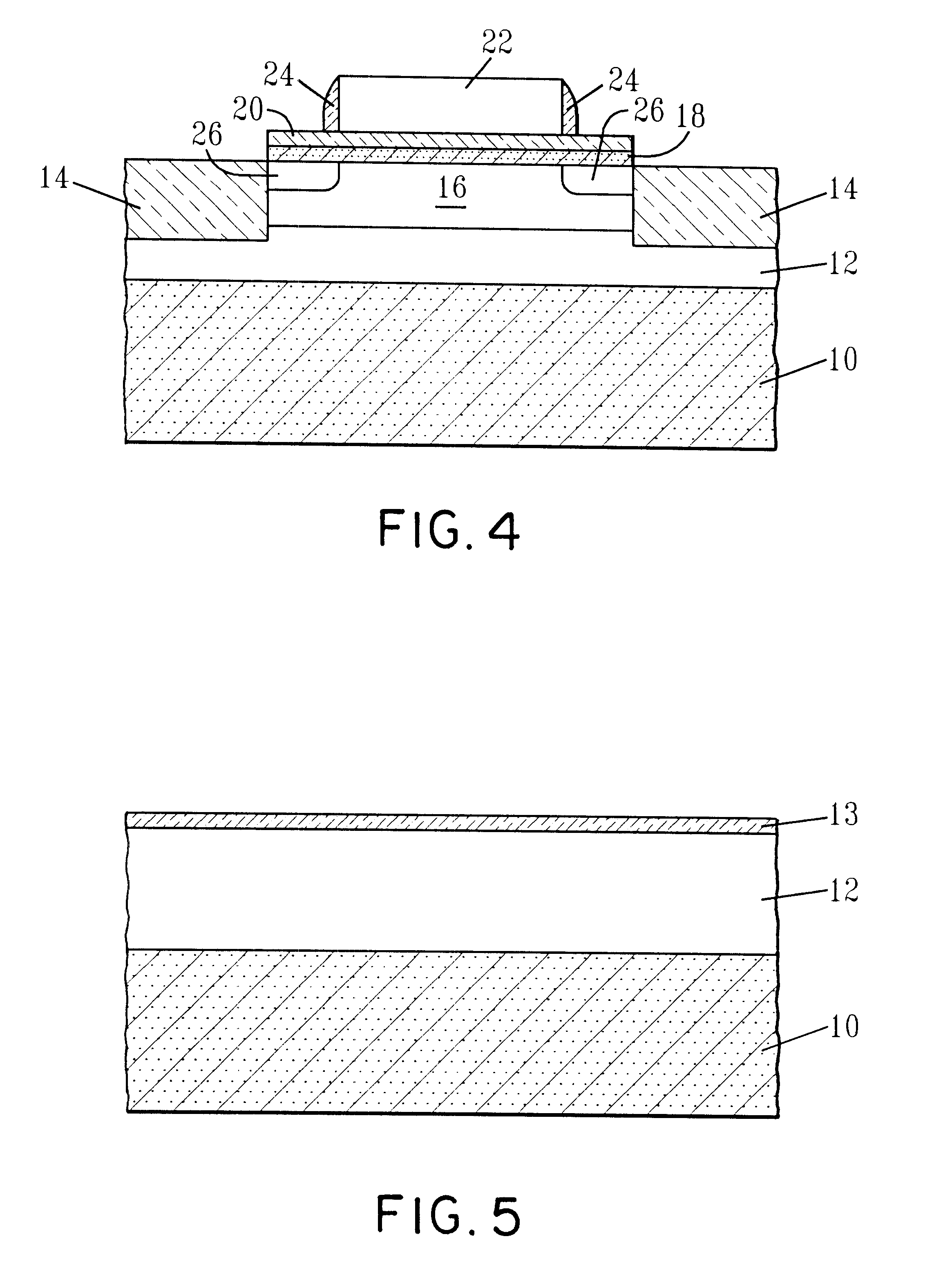

Semiconductor P-I-N detector

InactiveUS6255708B1Reduce leakage currentMitigating dopant diffusionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIndium

A semiconductor P-I-N detector including an intrinsic wafer, a P-doped layer, an N-doped layer, and a boundary layer for reducing the diffusion of dopants into the intrinsic wafer. The boundary layer is positioned between one of the doped regions and the intrinsic wafer. The intrinsic wafer can be composed of CdZnTe or CdTe, the P-doped layer can be composed of ZnTe doped with copper, and the N-doped layer can be composed of CdS doped with indium. The boundary layers is formed of an undoped semiconductor material. The boundary layer can be deposited onto the underlying intrinsic wafer. The doped regions are then typically formed by a deposition process or by doping a section of the deposited boundary layer.

Owner:MASIMO SEMICON +2

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation

InactiveUS6429061B1Thickness minimizationTransistorSemiconductor/solid-state device manufacturingCMOSMOSFET

A strained Si CMOS structure is formed by steps which include forming a relaxed SiGe layer on a surface of a substrate; forming isolation regions and well implant regions in said relaxed SiGe layer; and forming a strained Si layer on said relaxed SiGe layer. These processing steps may be used in conjunction with conventional gate processing steps in forming a strained MOSFET structure.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com