Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

144 results about "Analog processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Analog processor comprising quantum devices

Owner:D WAVE SYSTEMS INC

Analog processor comprising quantum devices

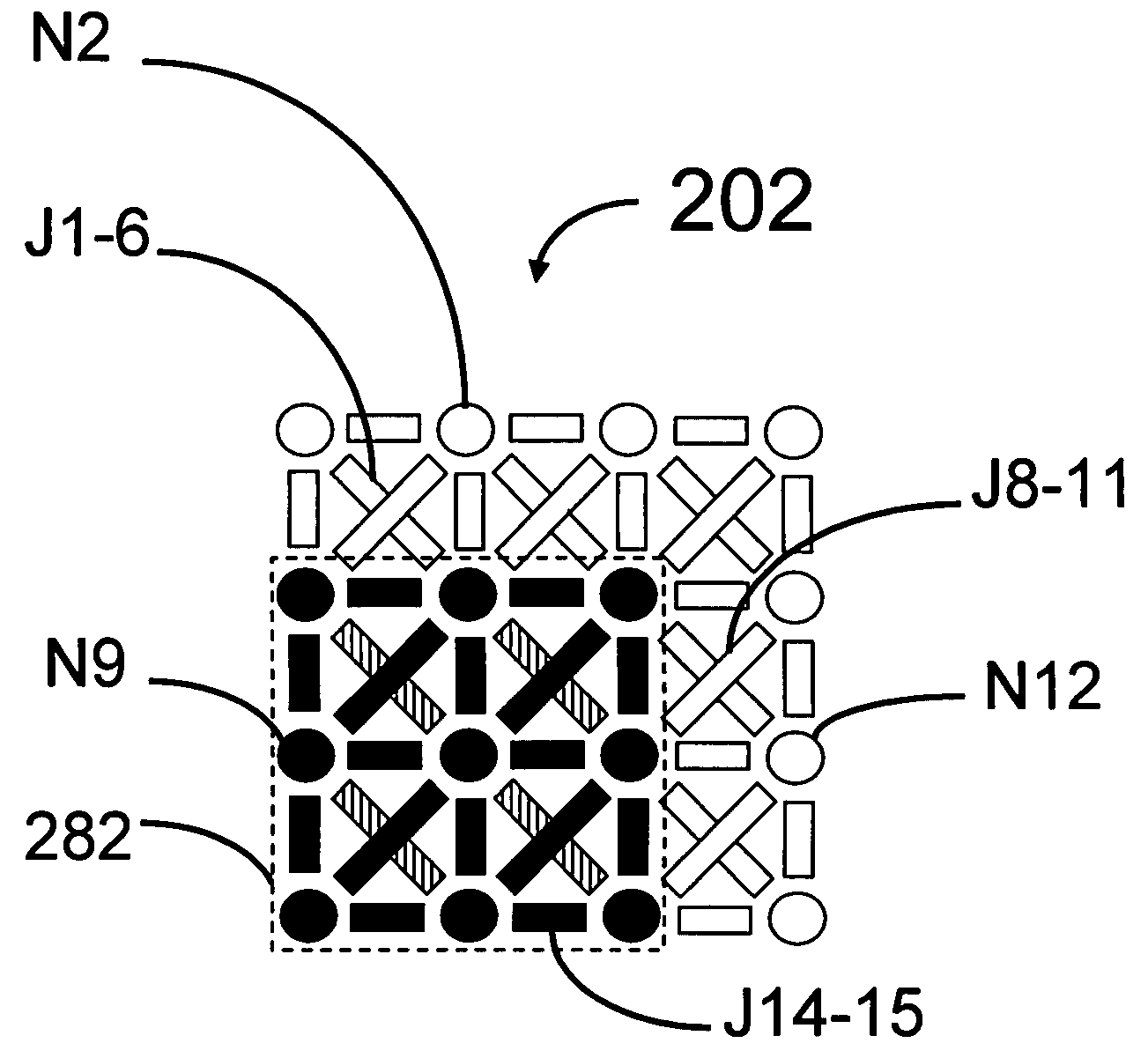

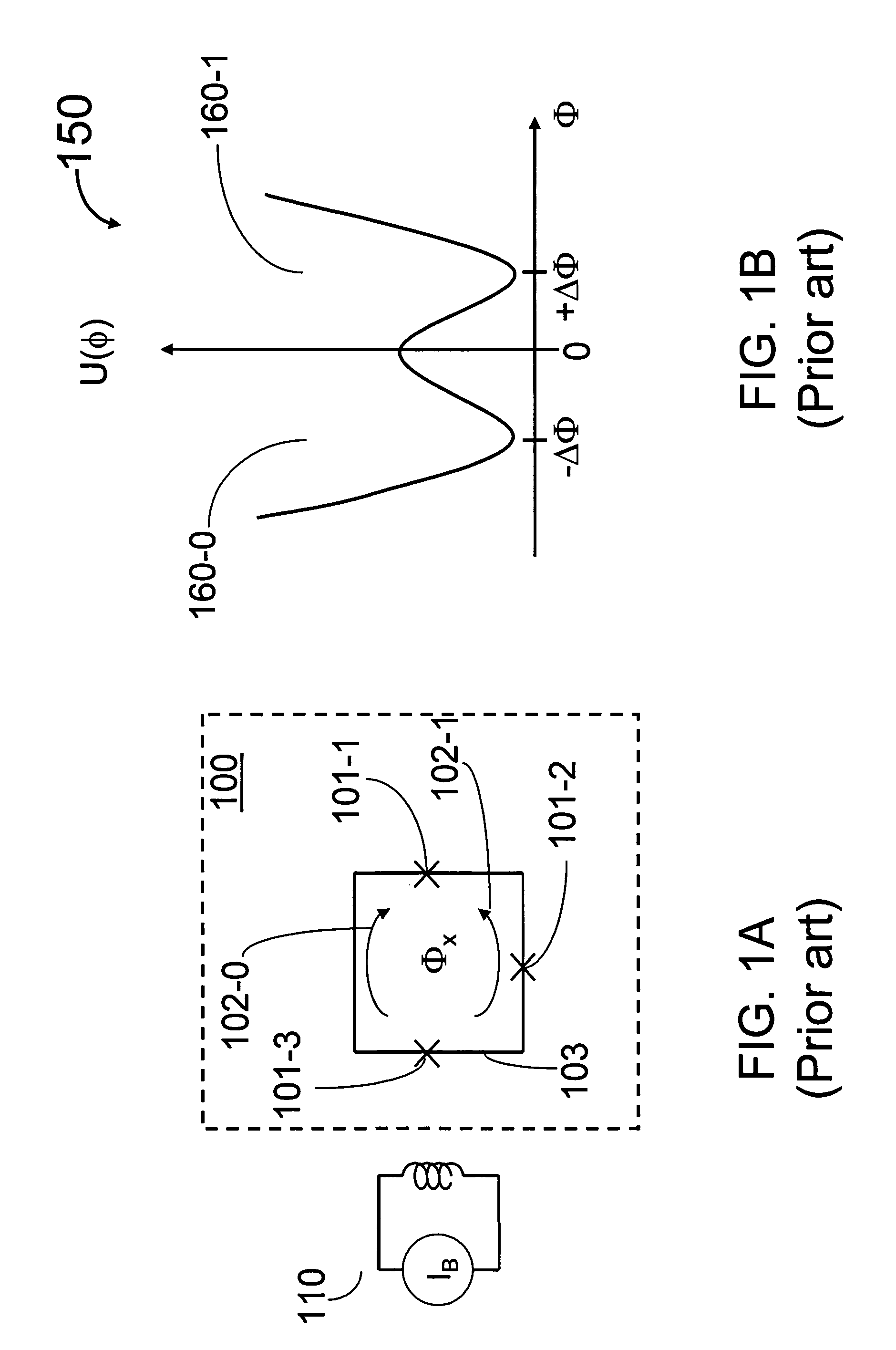

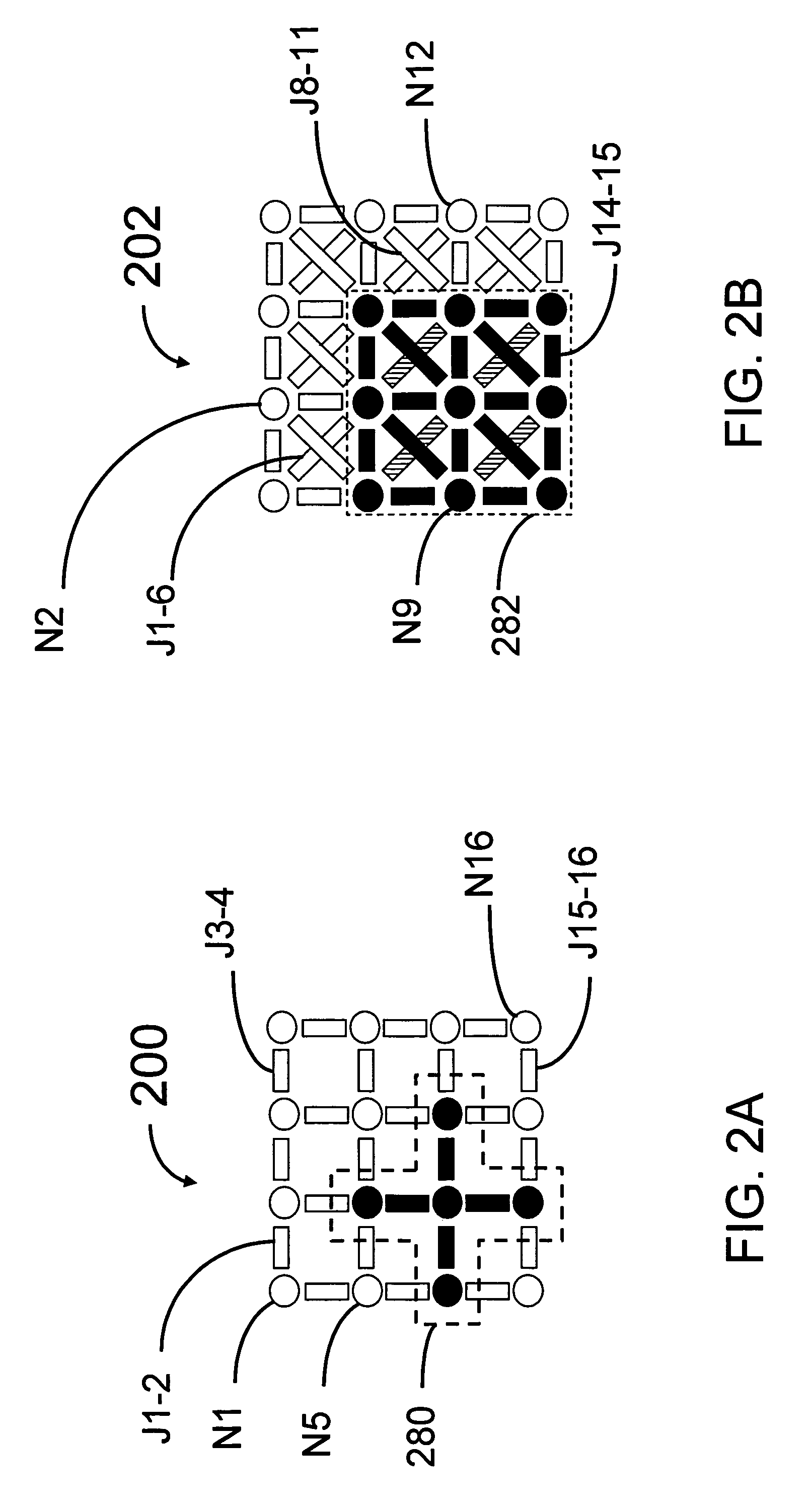

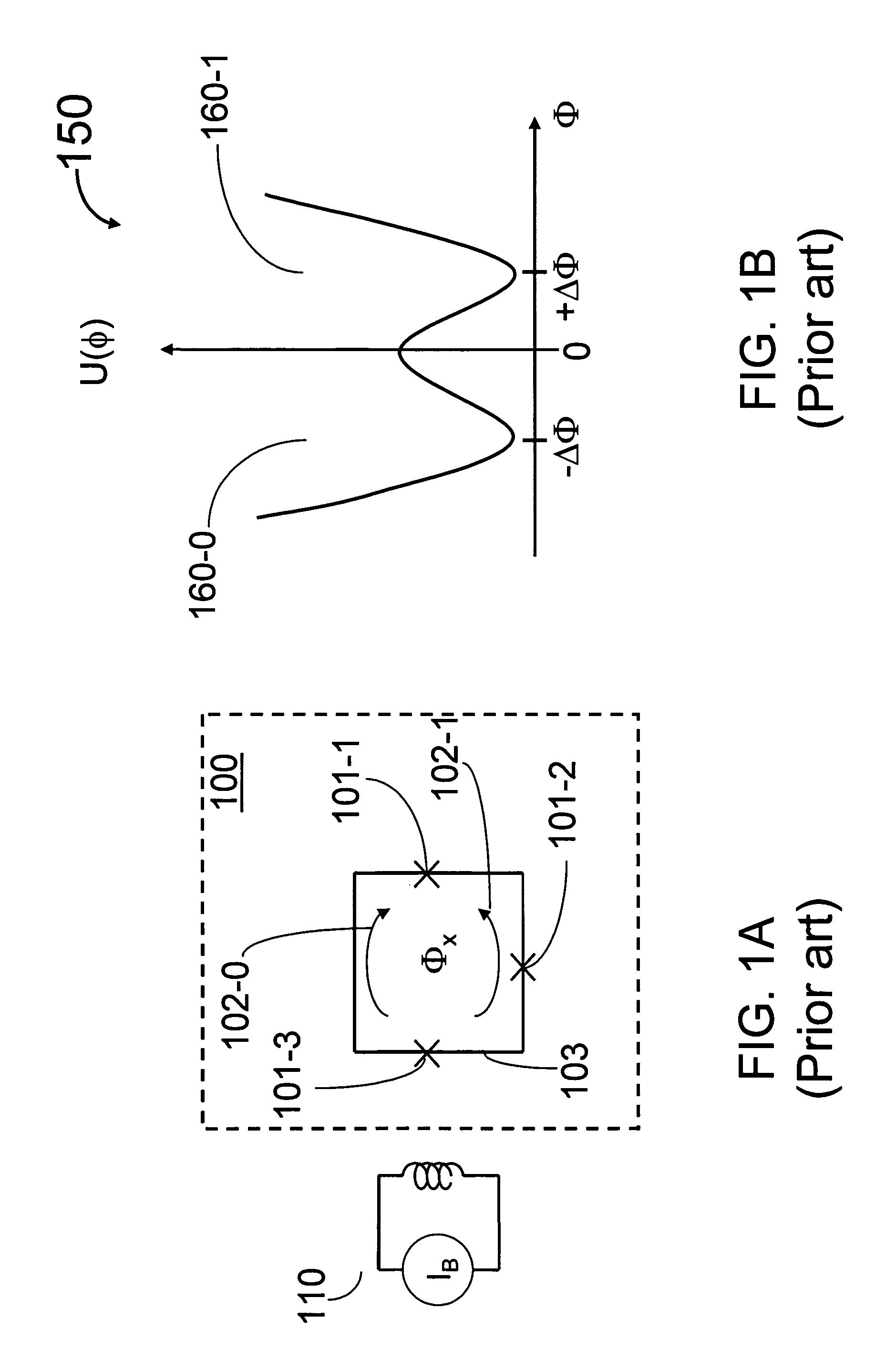

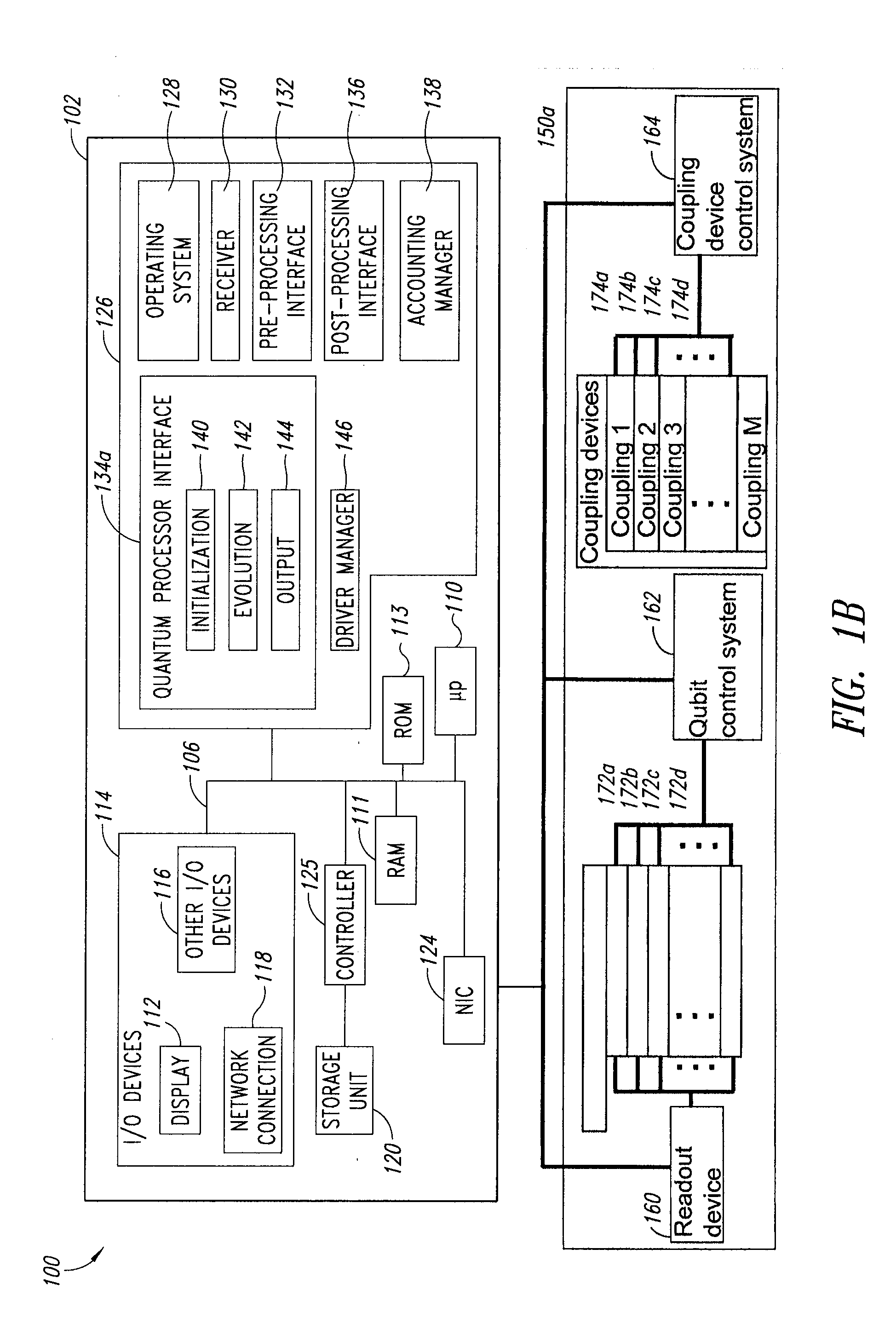

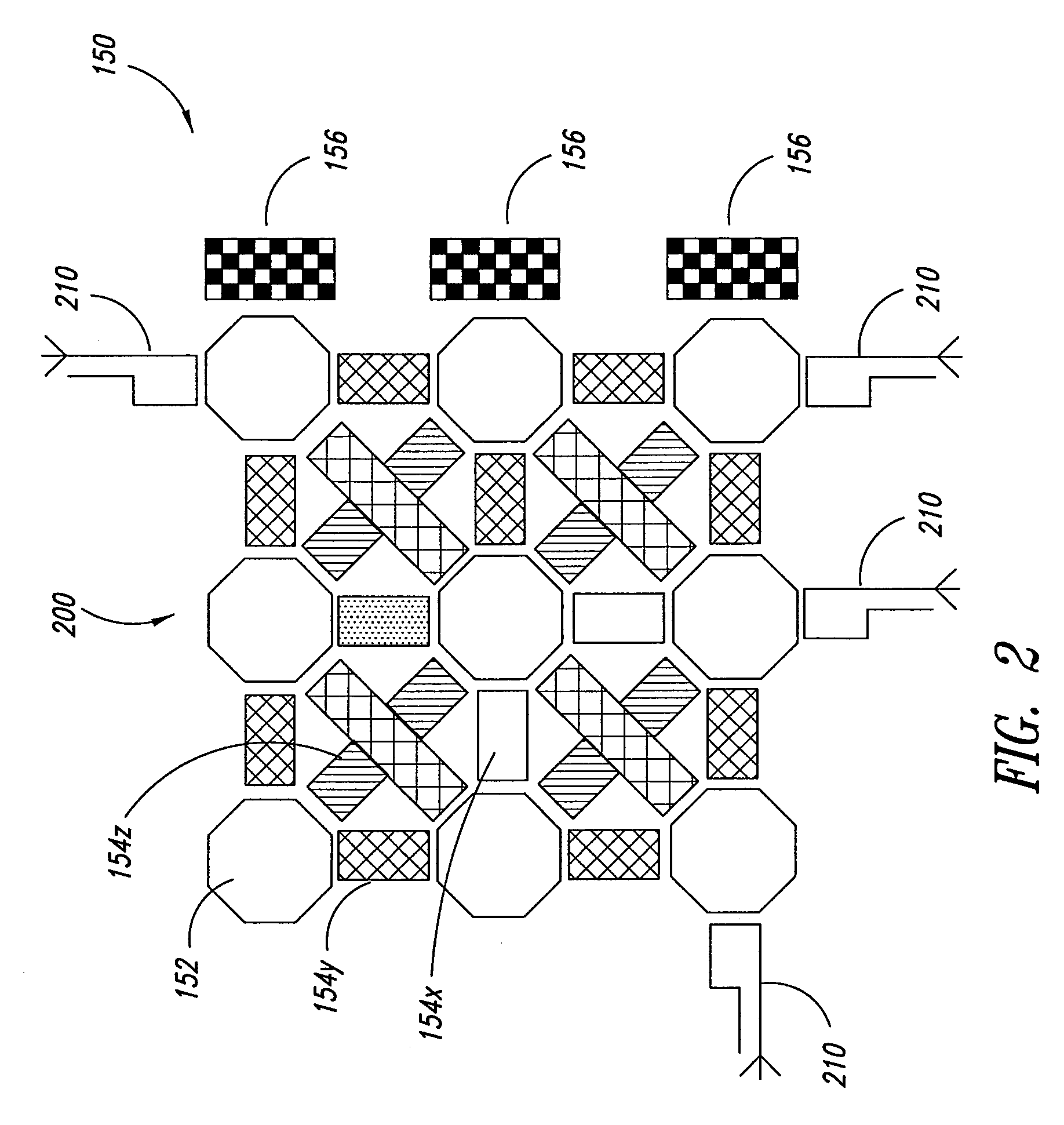

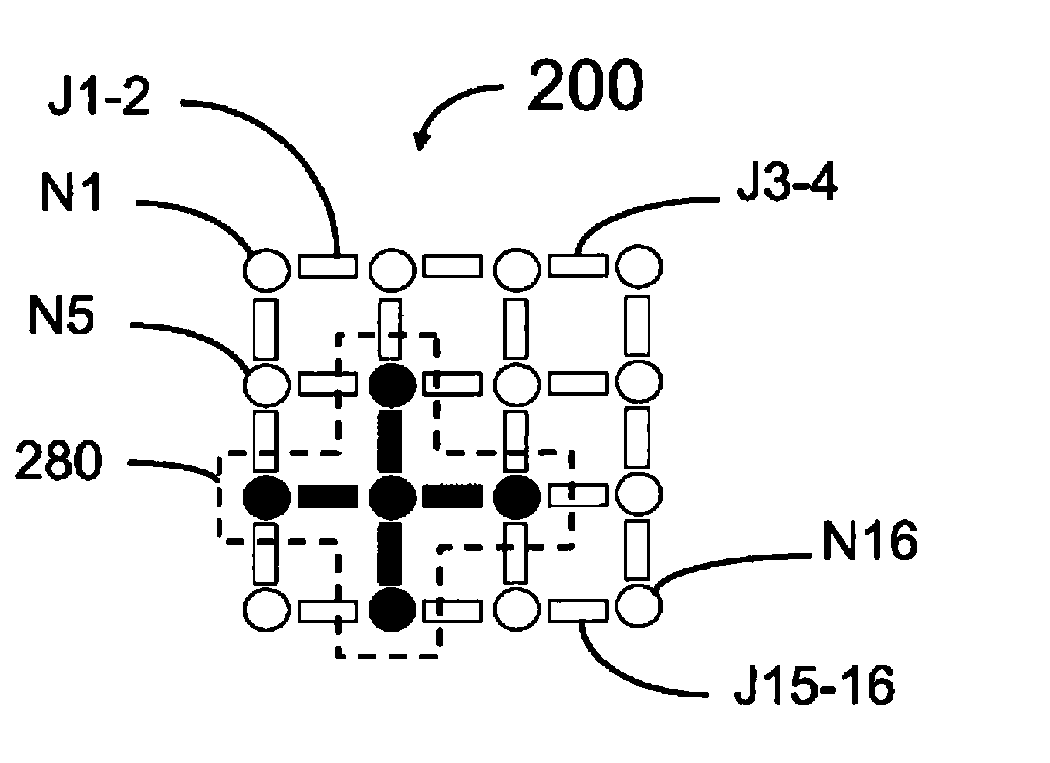

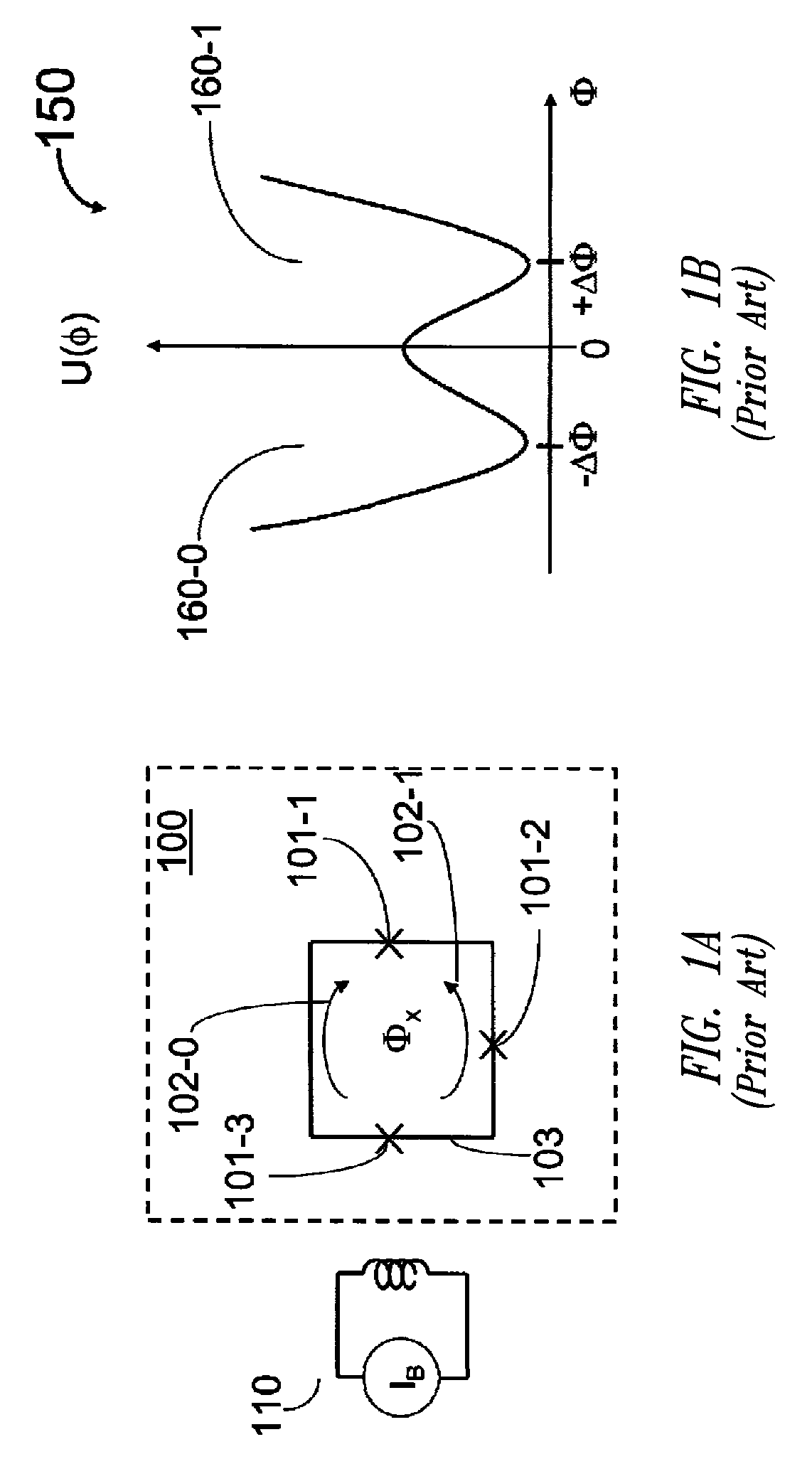

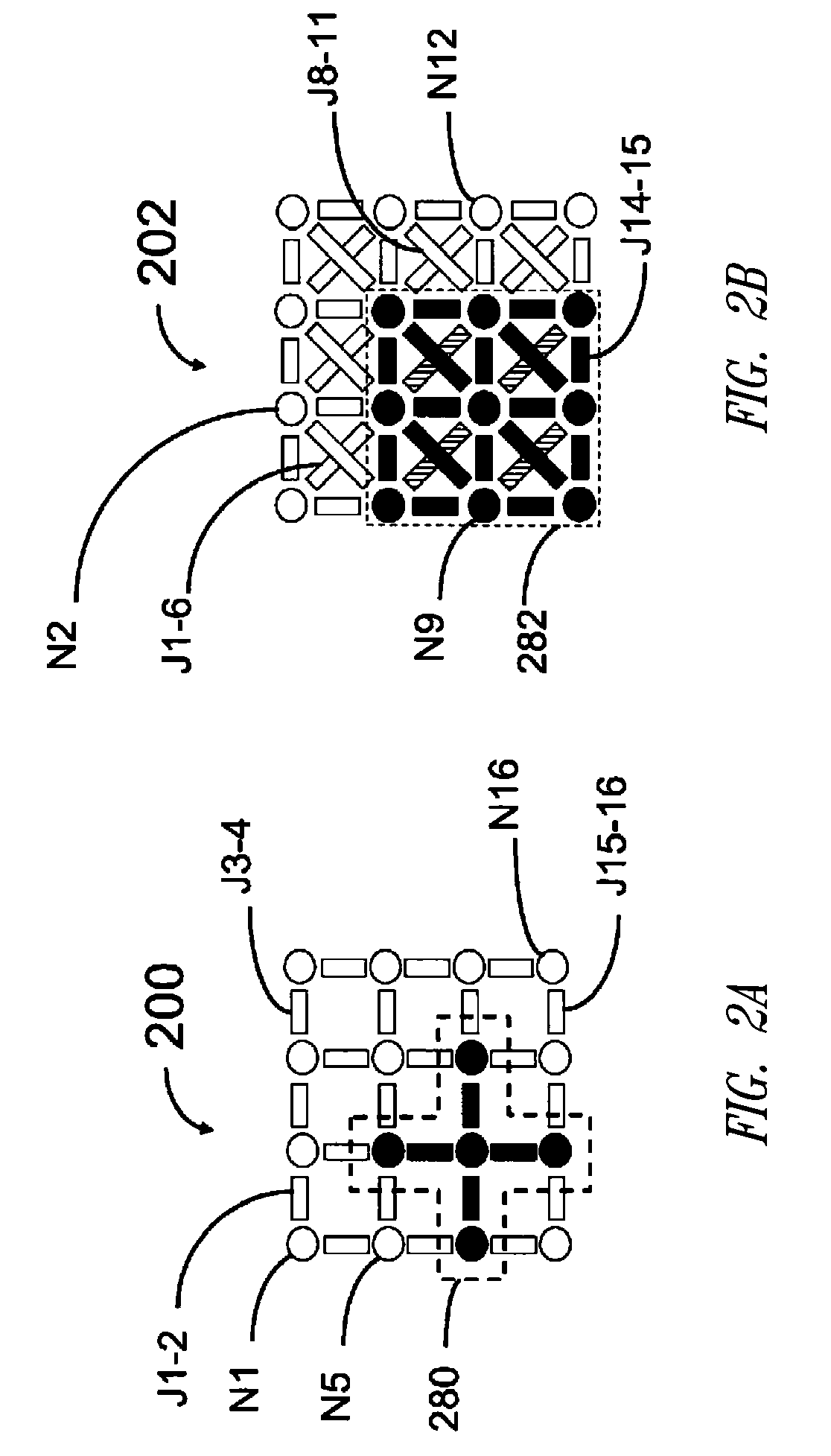

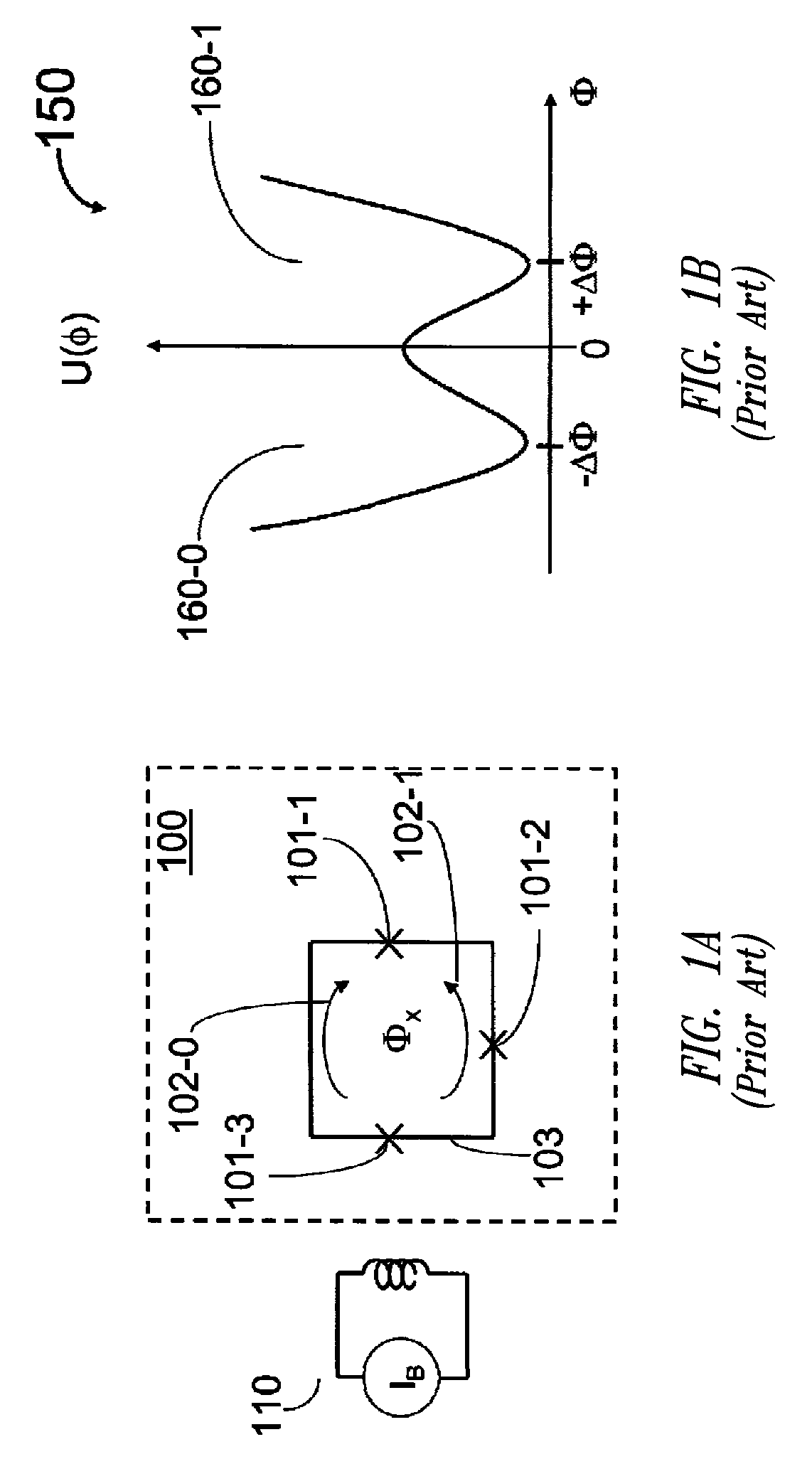

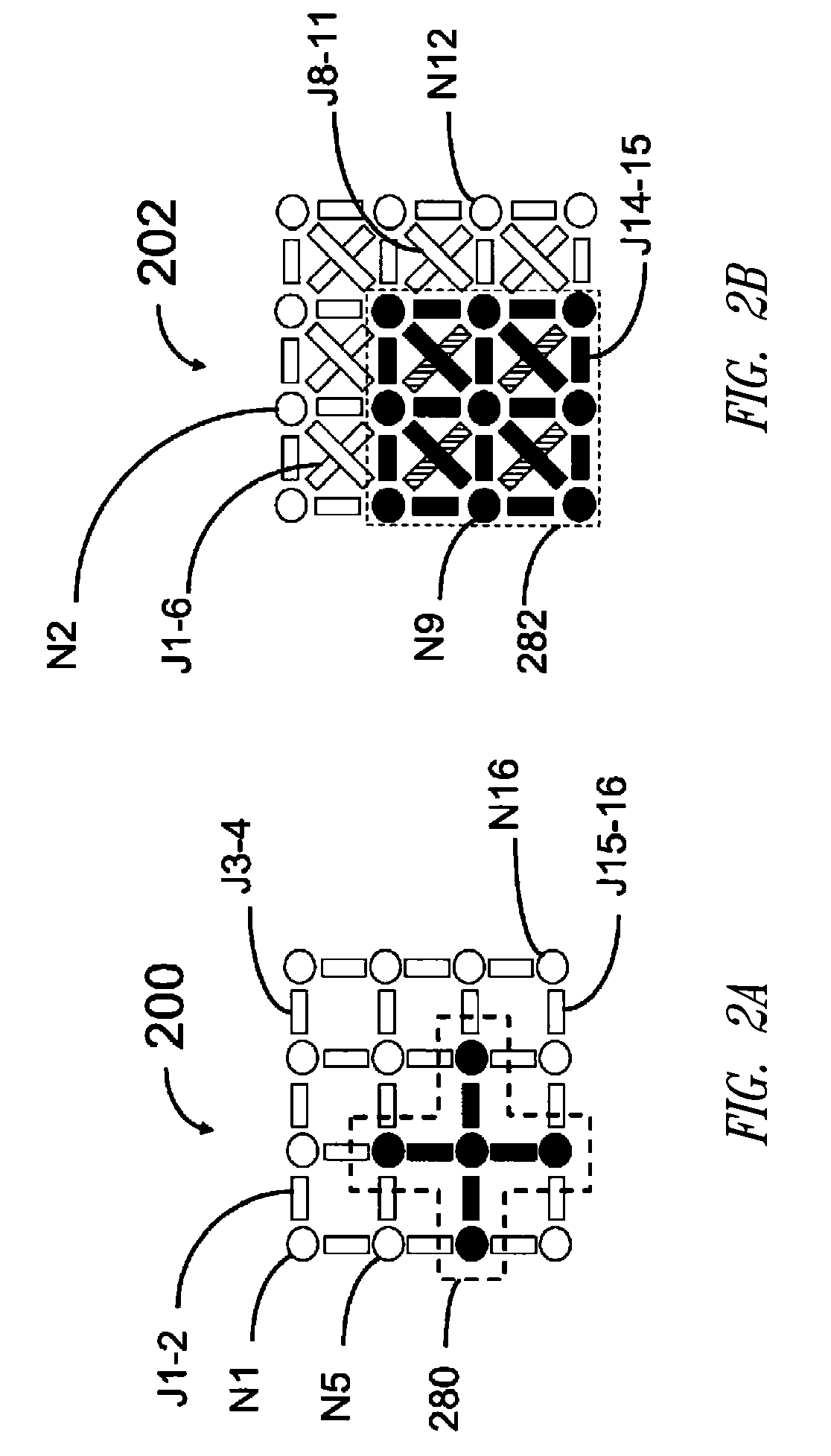

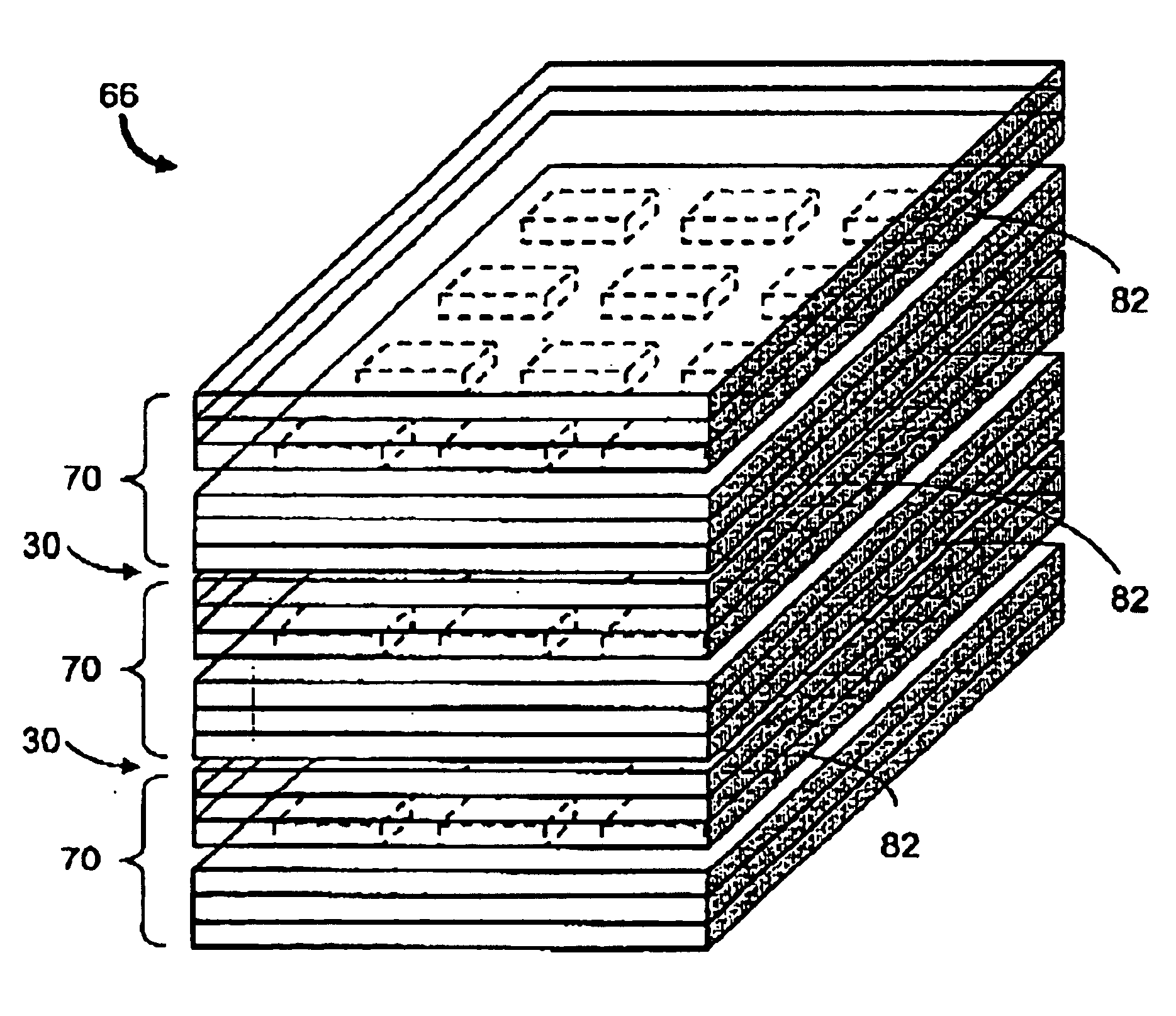

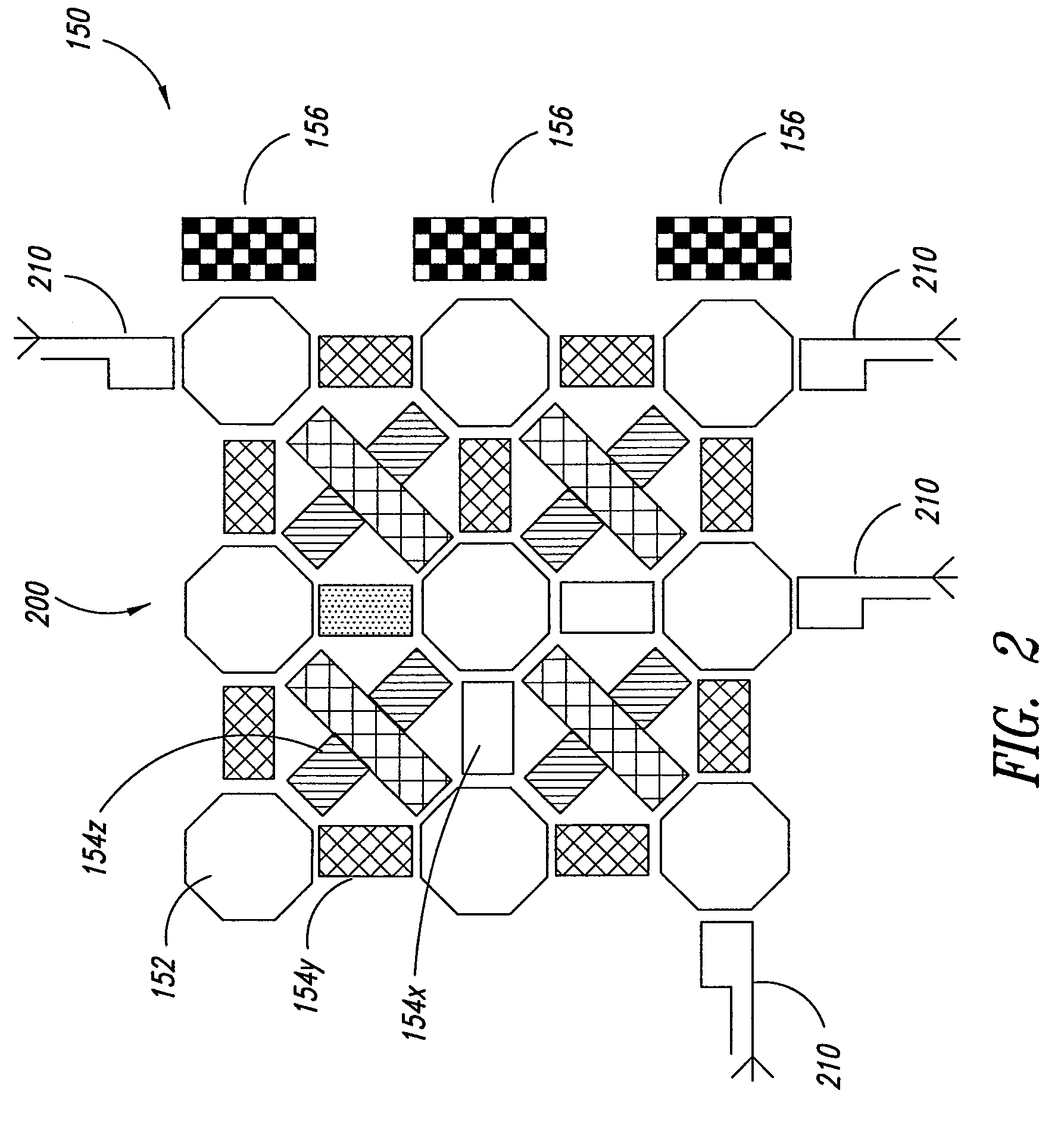

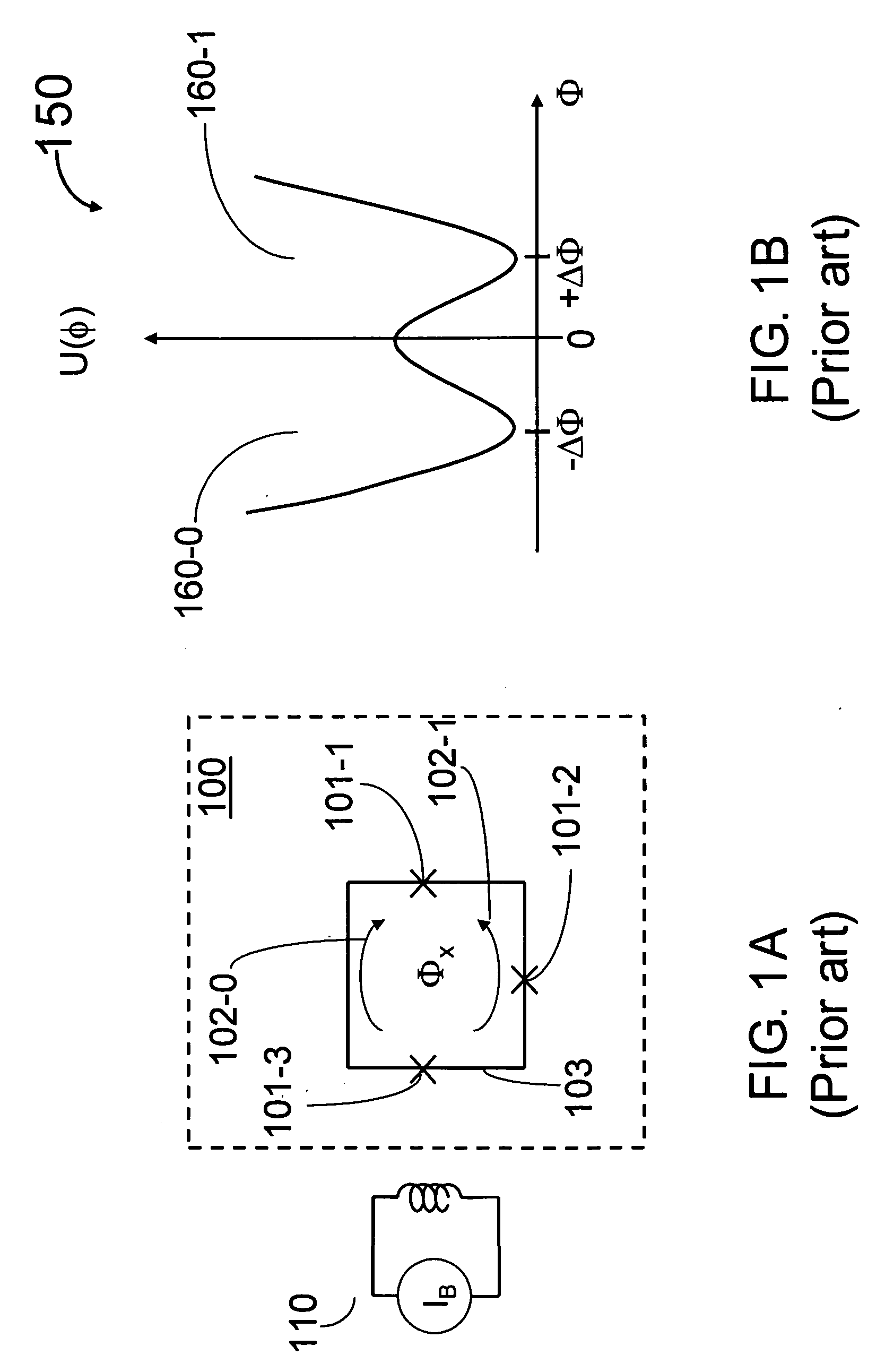

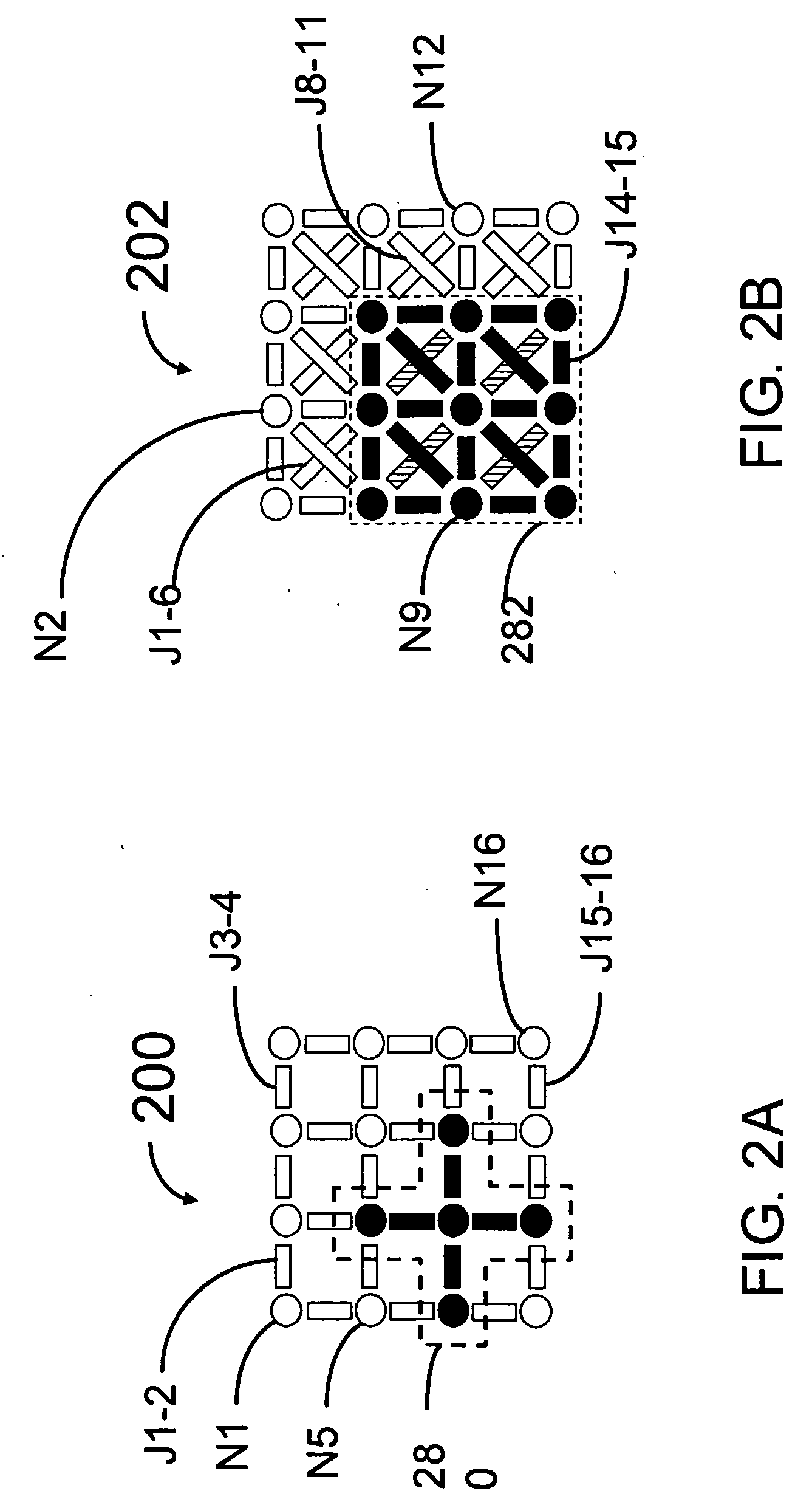

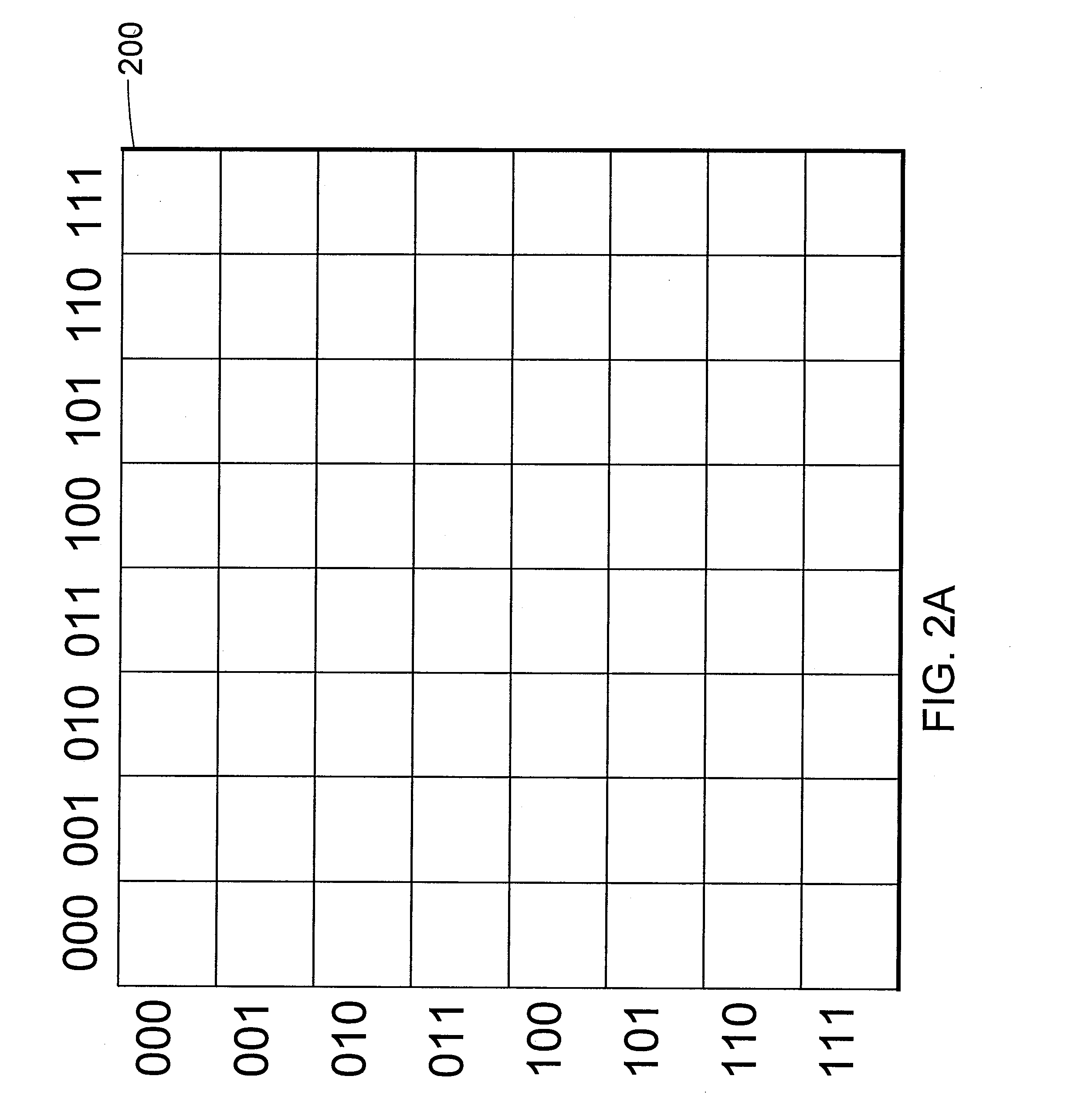

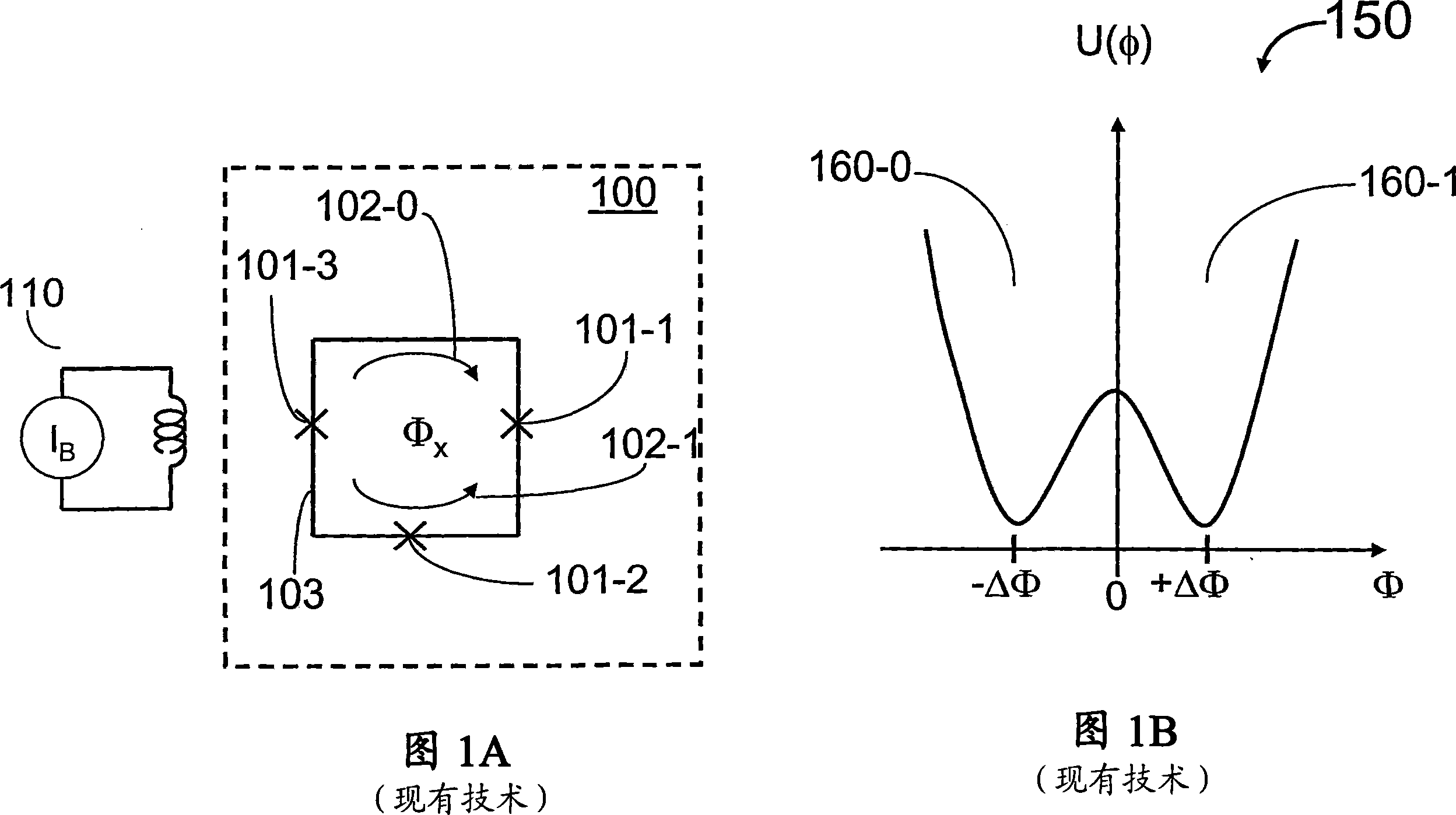

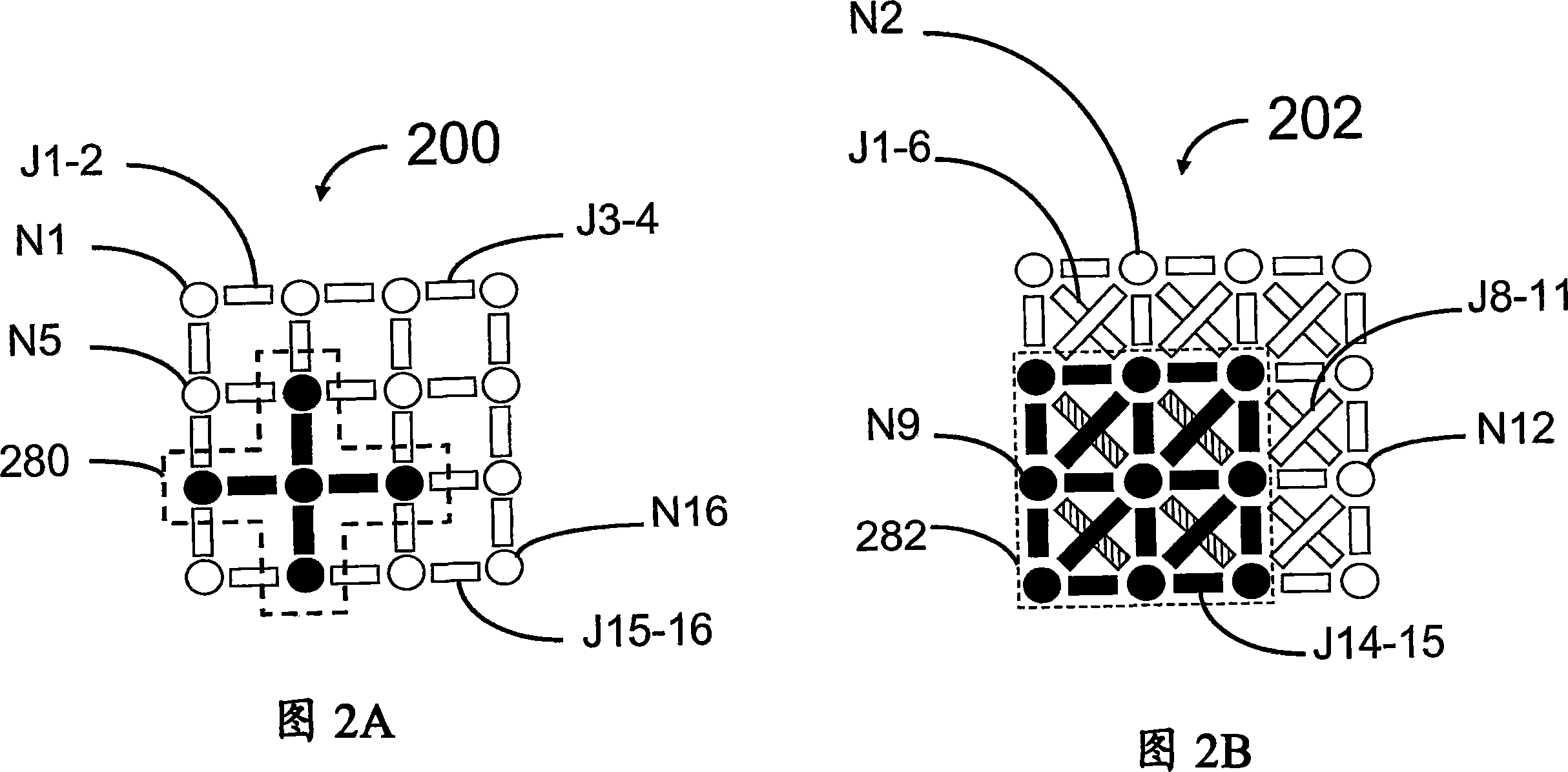

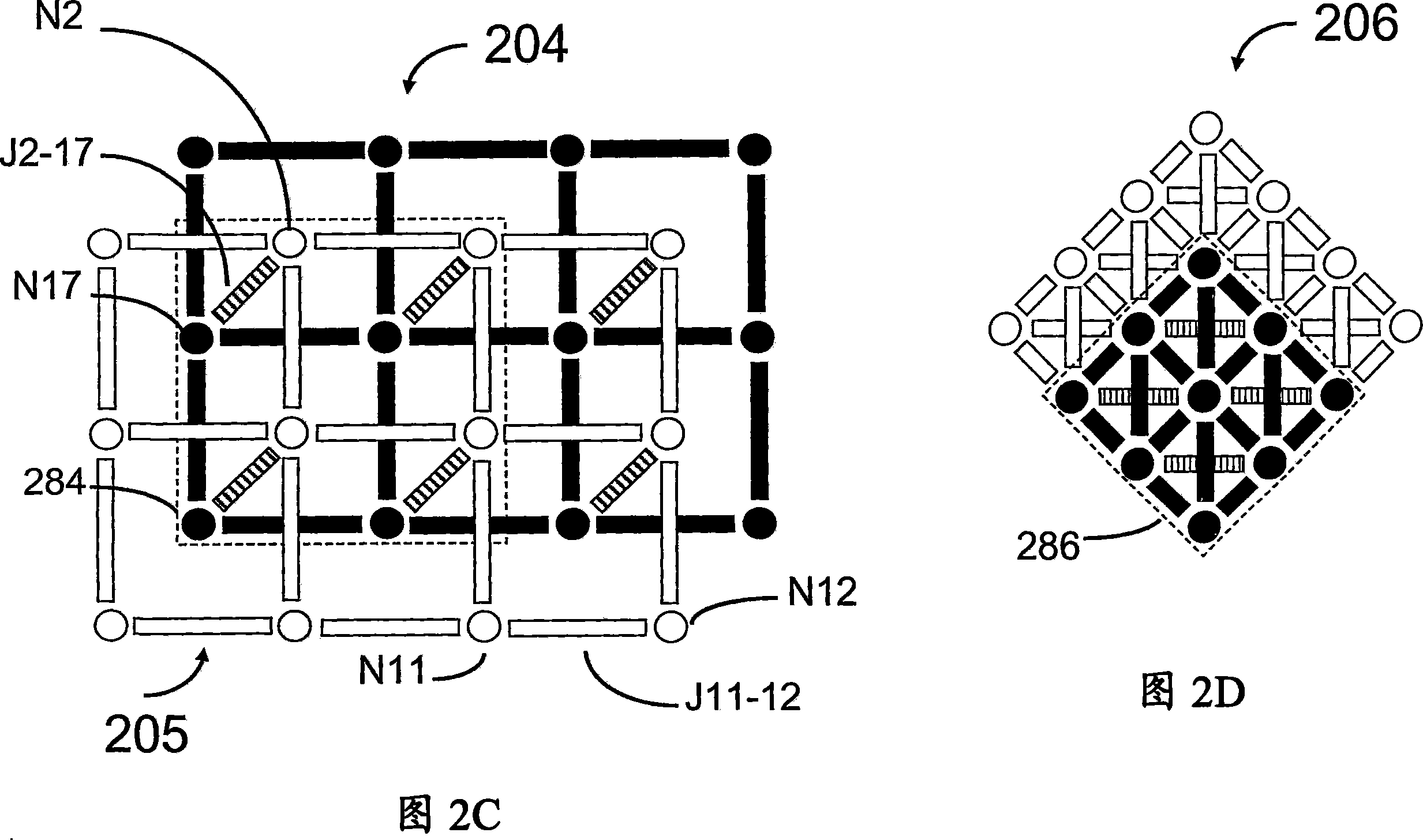

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

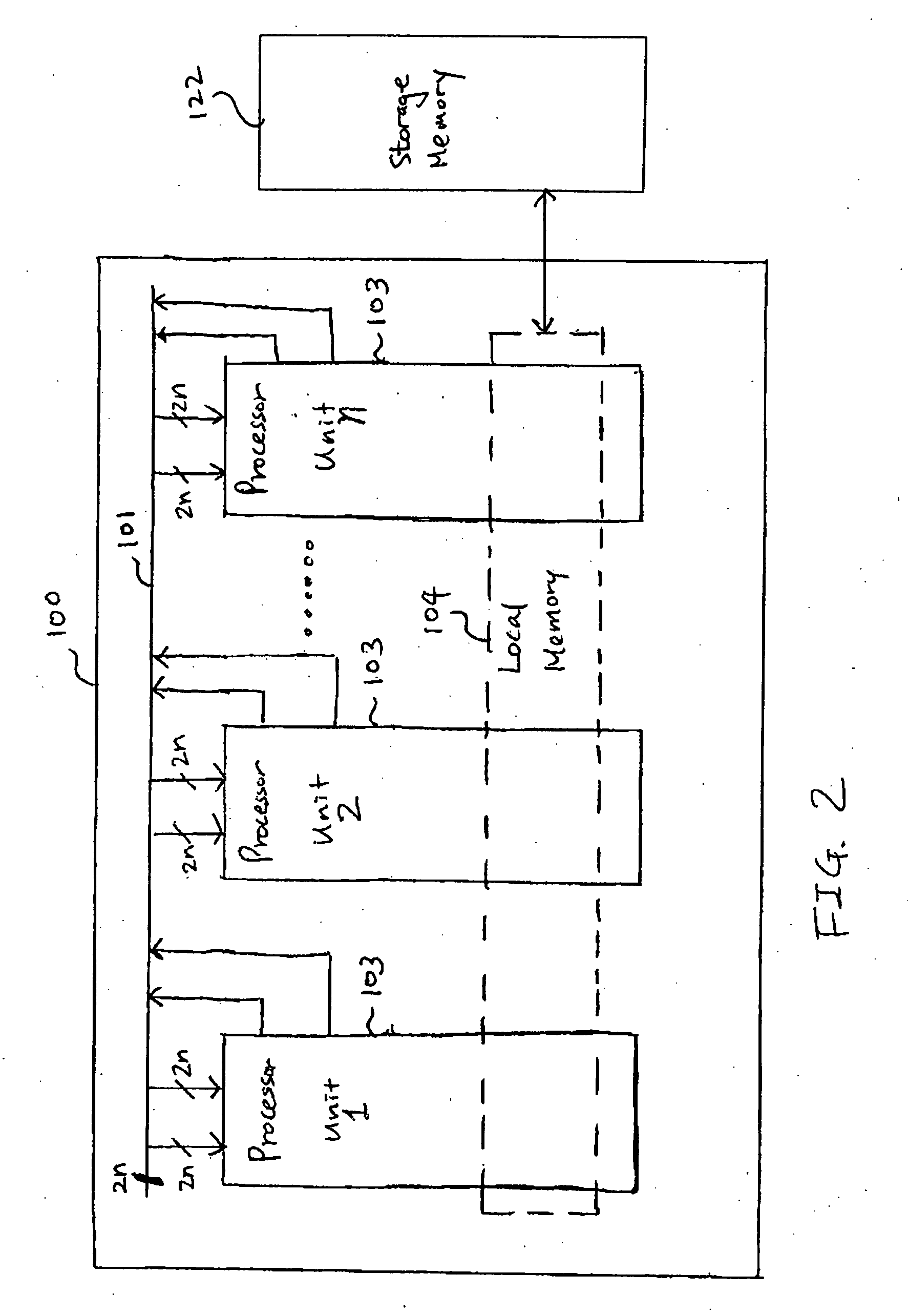

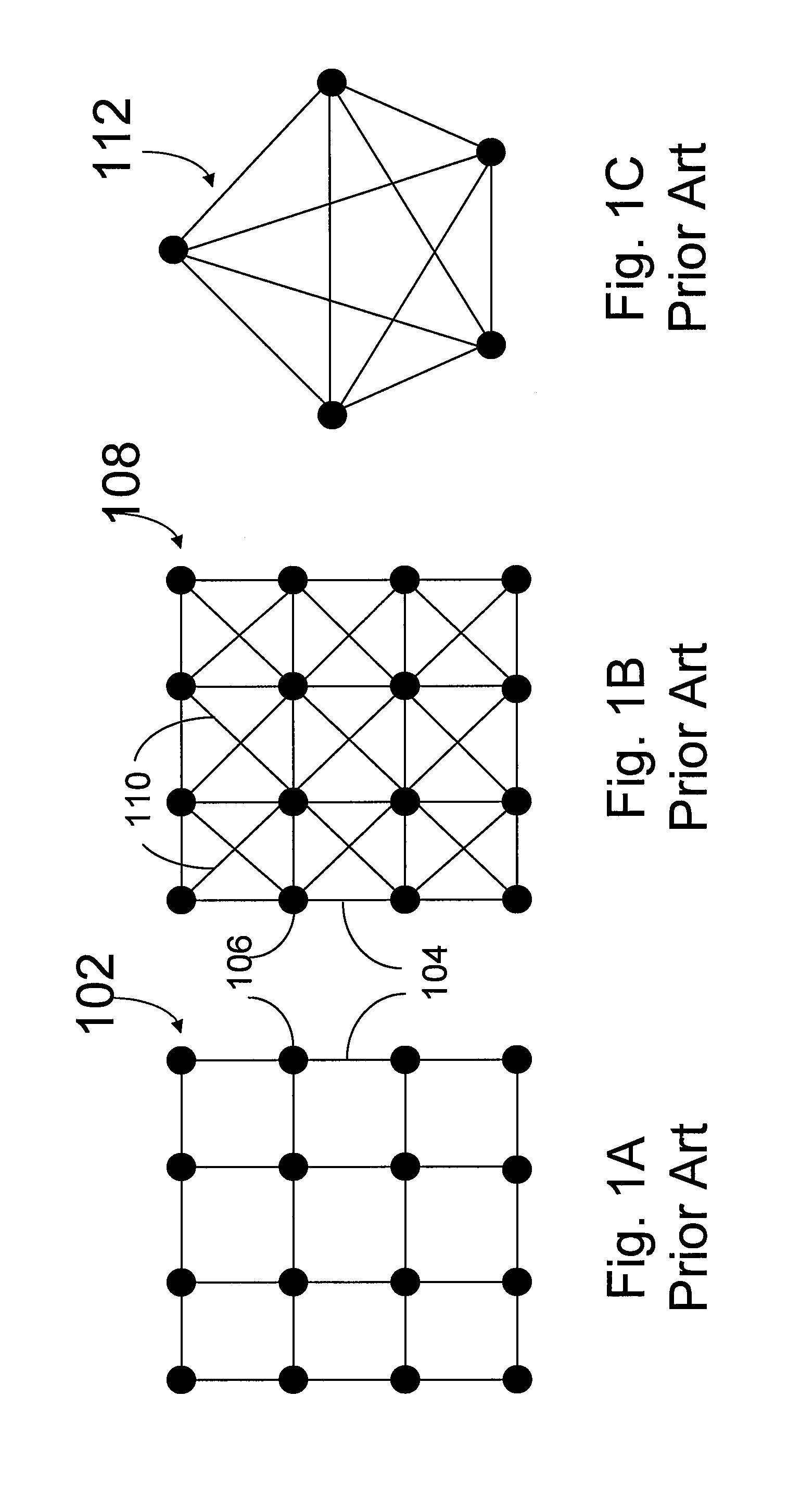

Systems, devices, and methods for interconnected processor topology

ActiveUS20080176750A1Improve legibilityQuantum computersProgram control using wired connectionsAnalog processorCoupling

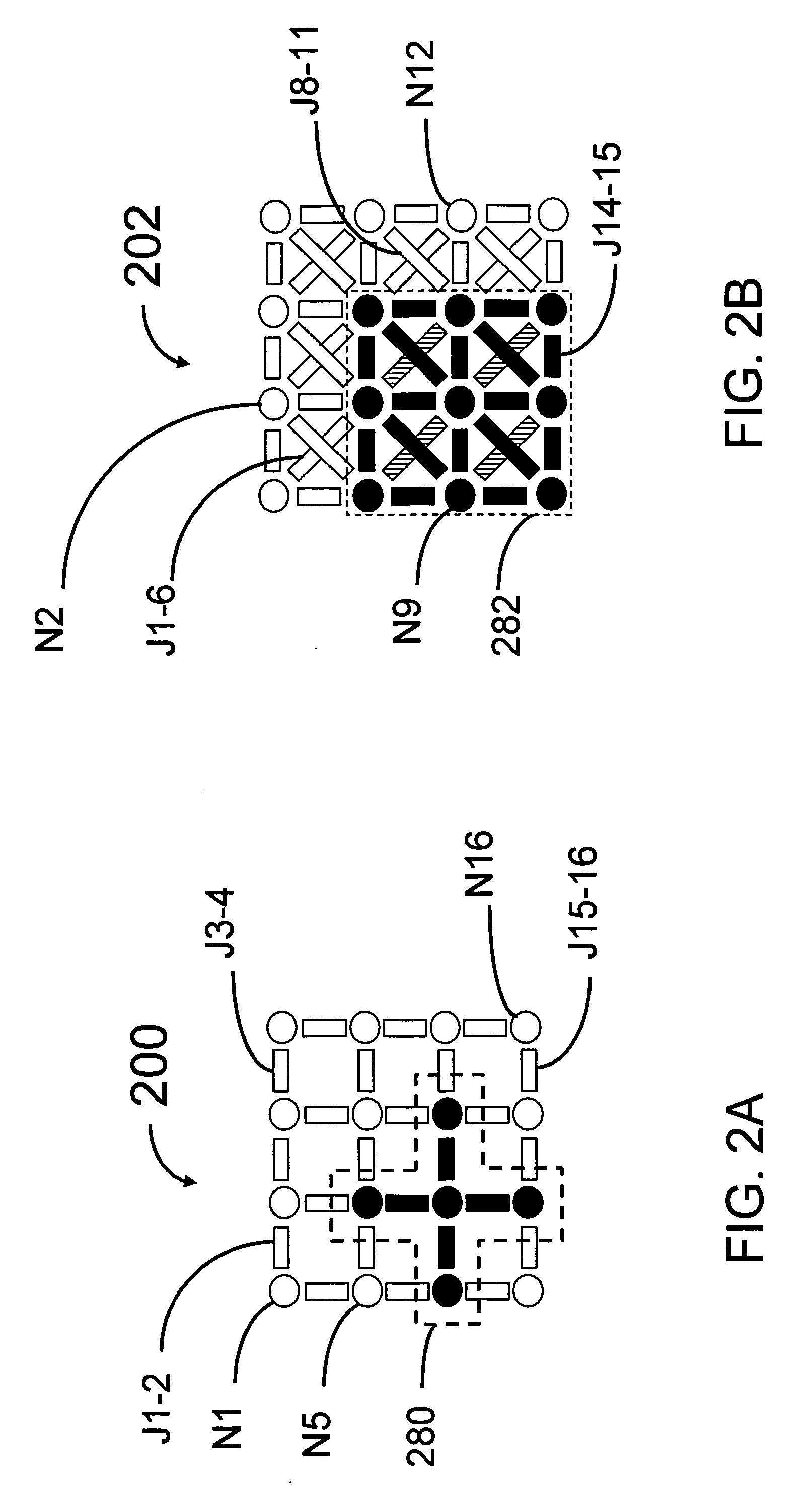

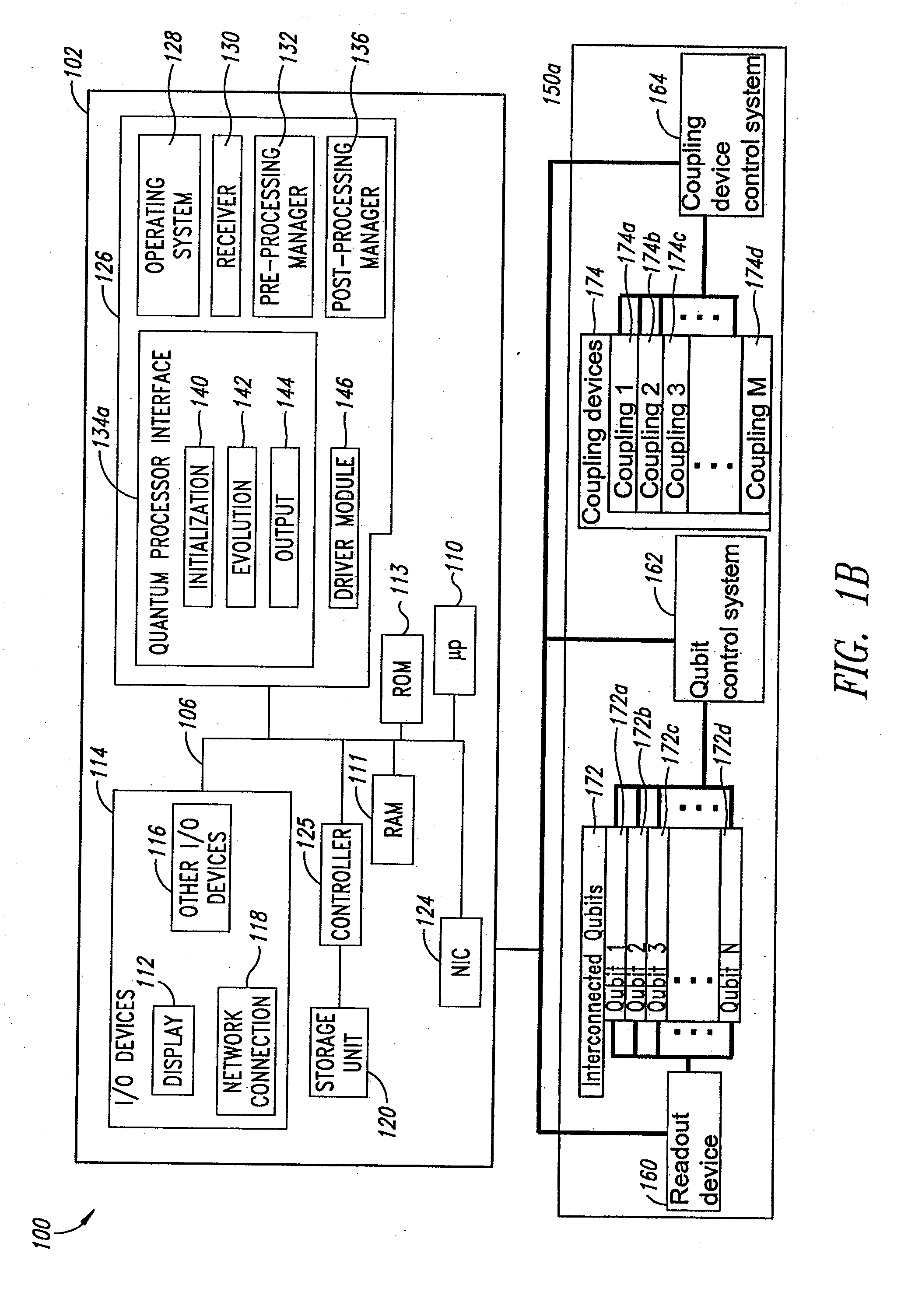

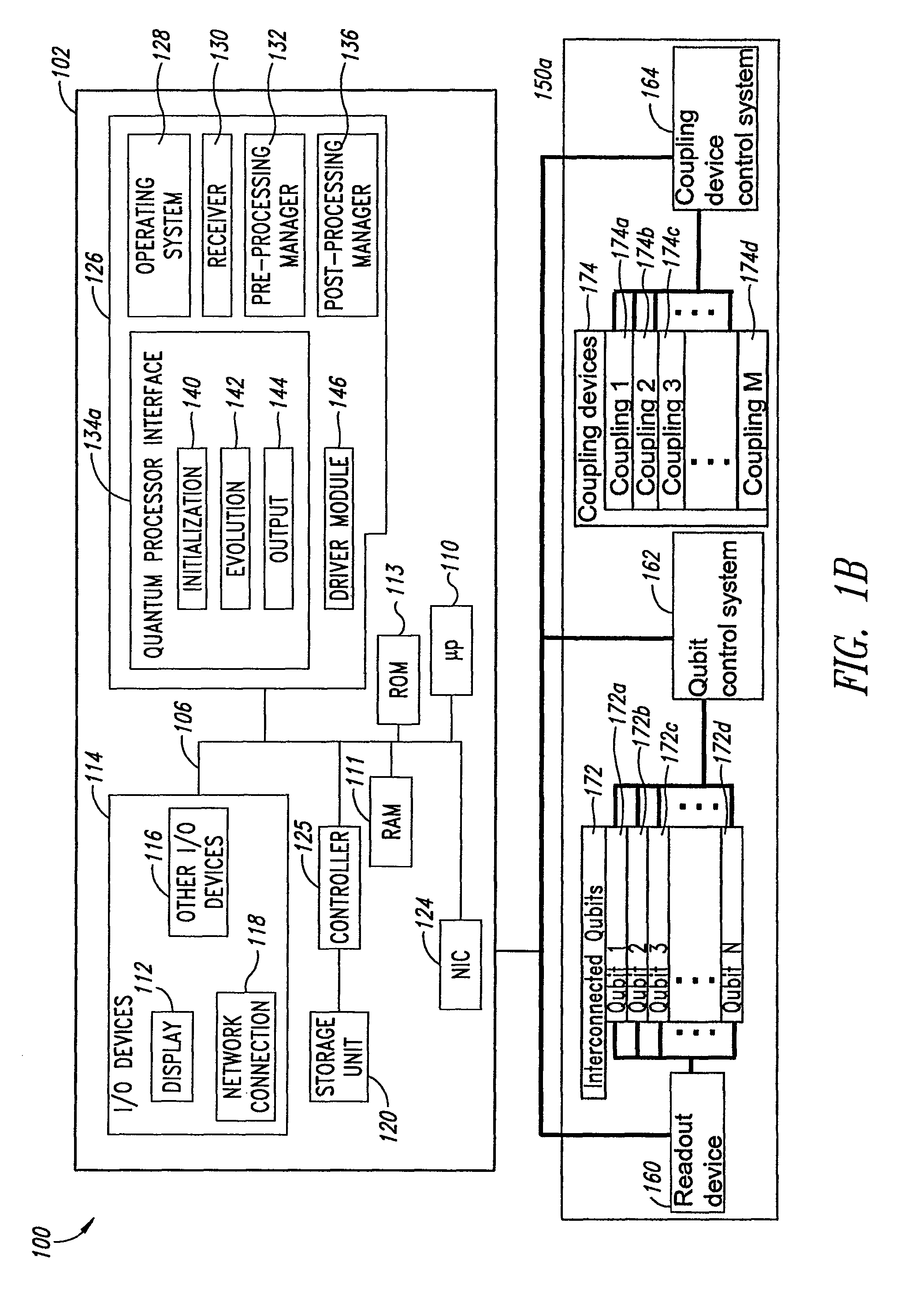

An analog processor, for example a quantum processor may include a plurality of elongated qubits that are disposed with respect to one another such that each qubit may selectively be directly coupled to each of the other qubits via a single coupling device. Such may provide a fully interconnected topology.

Owner:D WAVE SYSTEMS INC

Systems, devices, and methods for interconnected processor topology

An analog processor, for example a quantum processor may include a plurality of elongated qubits that are disposed with respect to one another such that each qubit may selectively be directly coupled to each of the other qubits via a single coupling device. Such may provide a fully interconnected topology.

Owner:D WAVE SYSTEMS INC

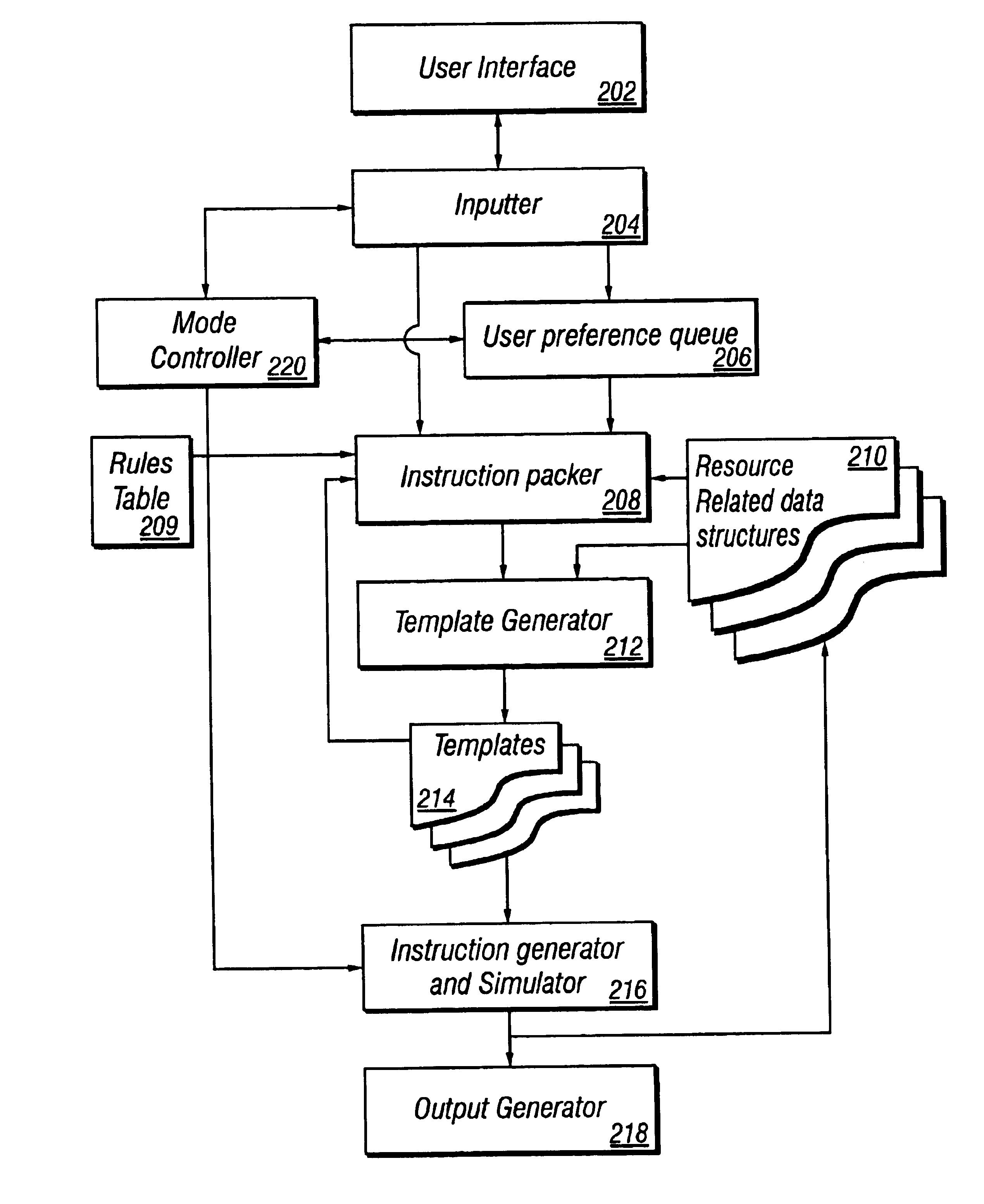

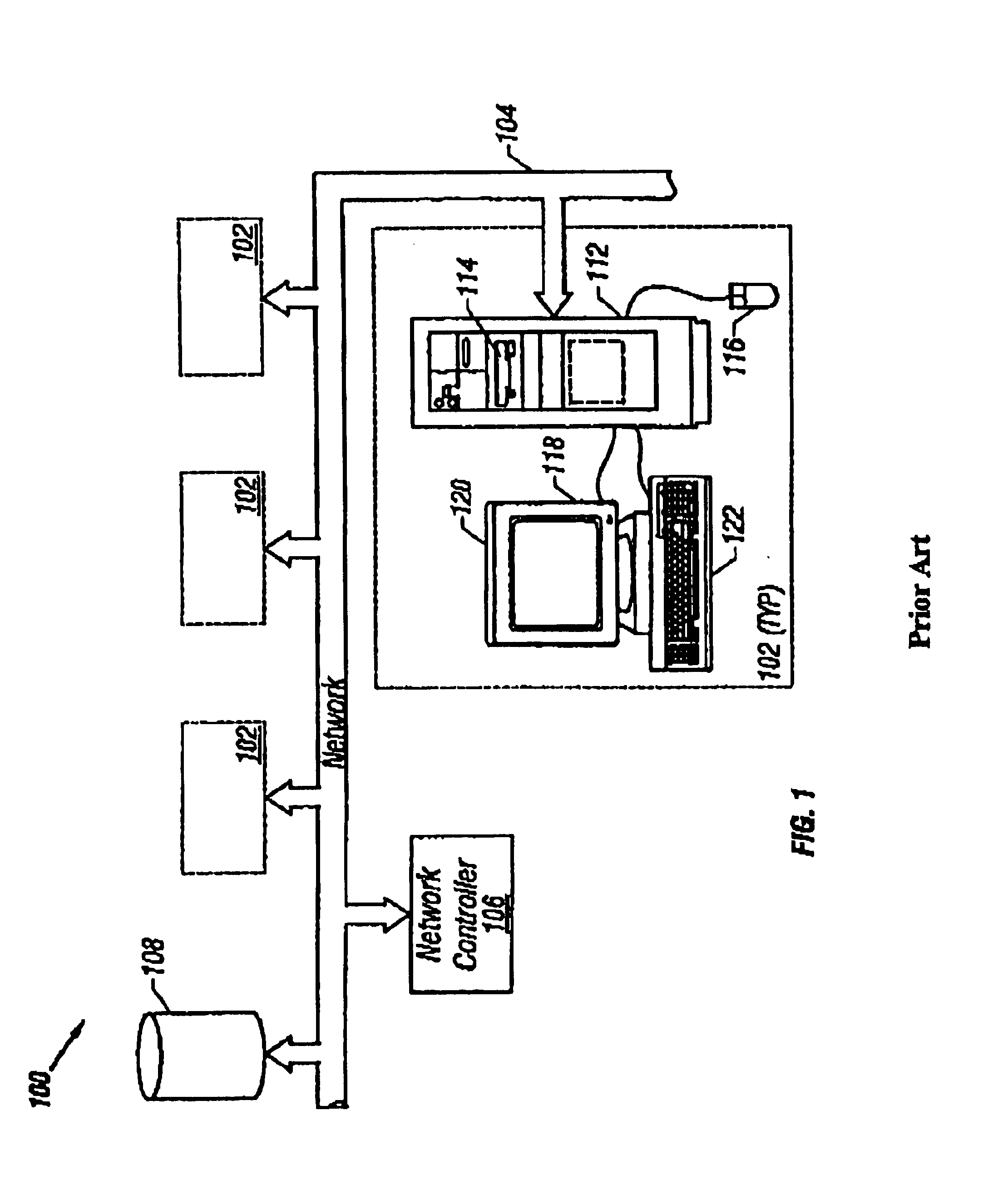

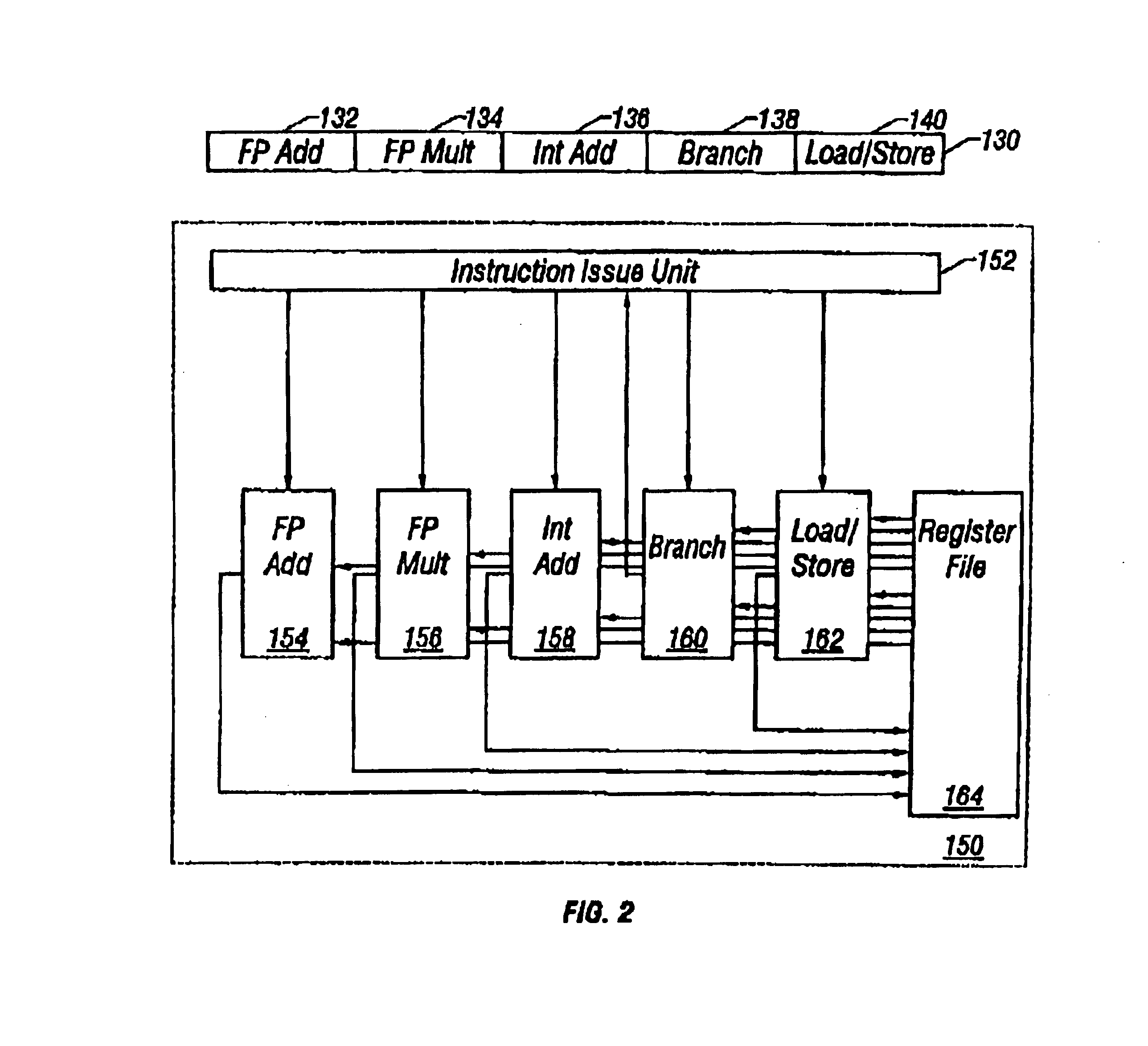

Method and apparatus that simulates the execution of paralled instructions in processor functional verification testing

InactiveUS6871298B1Properly be executeError detection/correctionDigital computer detailsAnalog processorParallel computing

A dynamic test generation method and apparatus enabling verification of the parallel instruction execution capabilities of VLIW processor systems is described. The test generator includes a user preference queue, a rules table, plurality of resource-related data structures, an instruction packer, and an instruction generator and simulator. The present invention generates a test by selecting instructions for parallel execution based upon resource availability as indicated by the resource-related data structures and the processor's instruction grouping rules, simulating the parallel execution of the instructions on a golden model, updating the resource-related data structures, and evaluating the updated architectural state of the golden model.

Owner:ARM INC

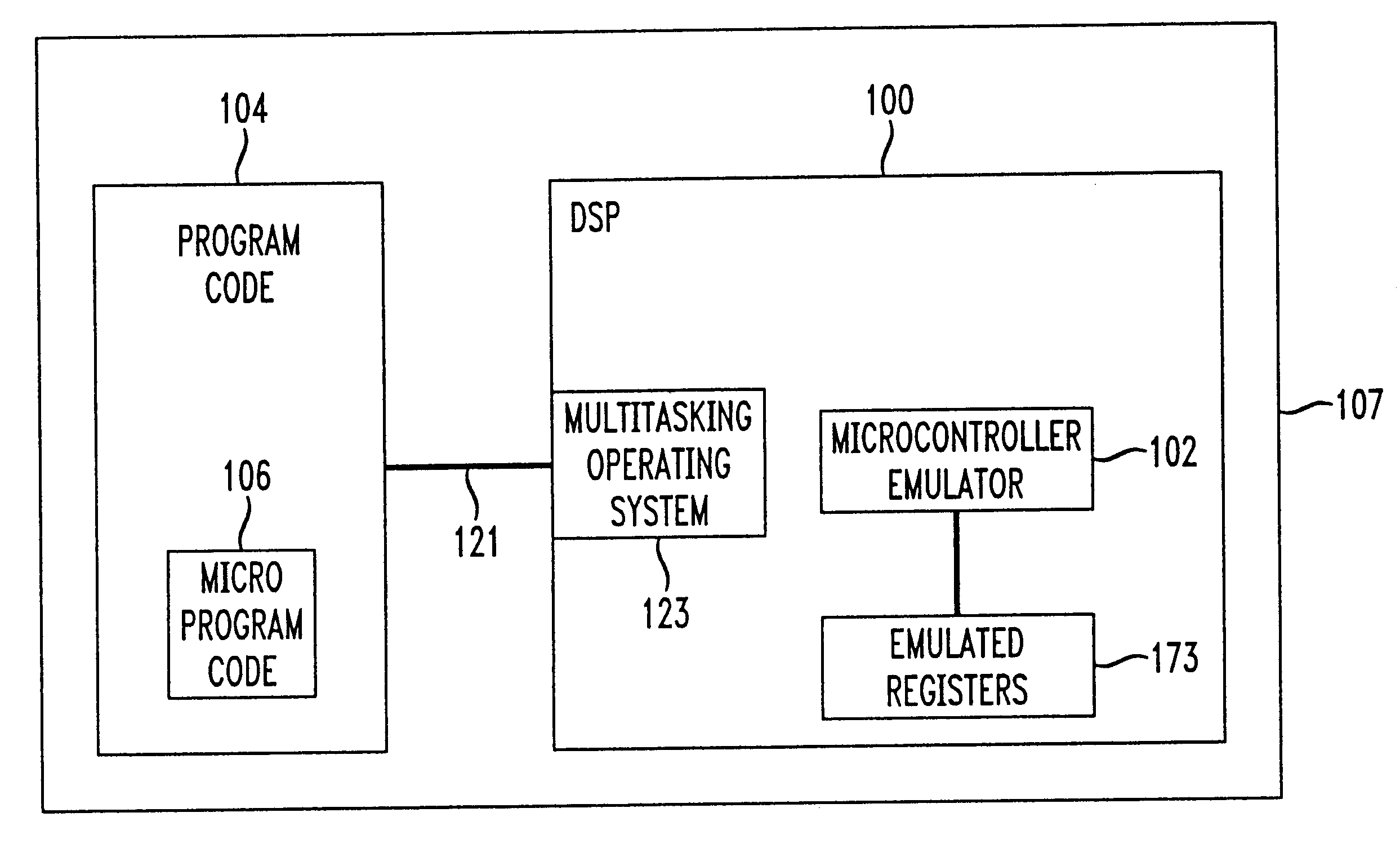

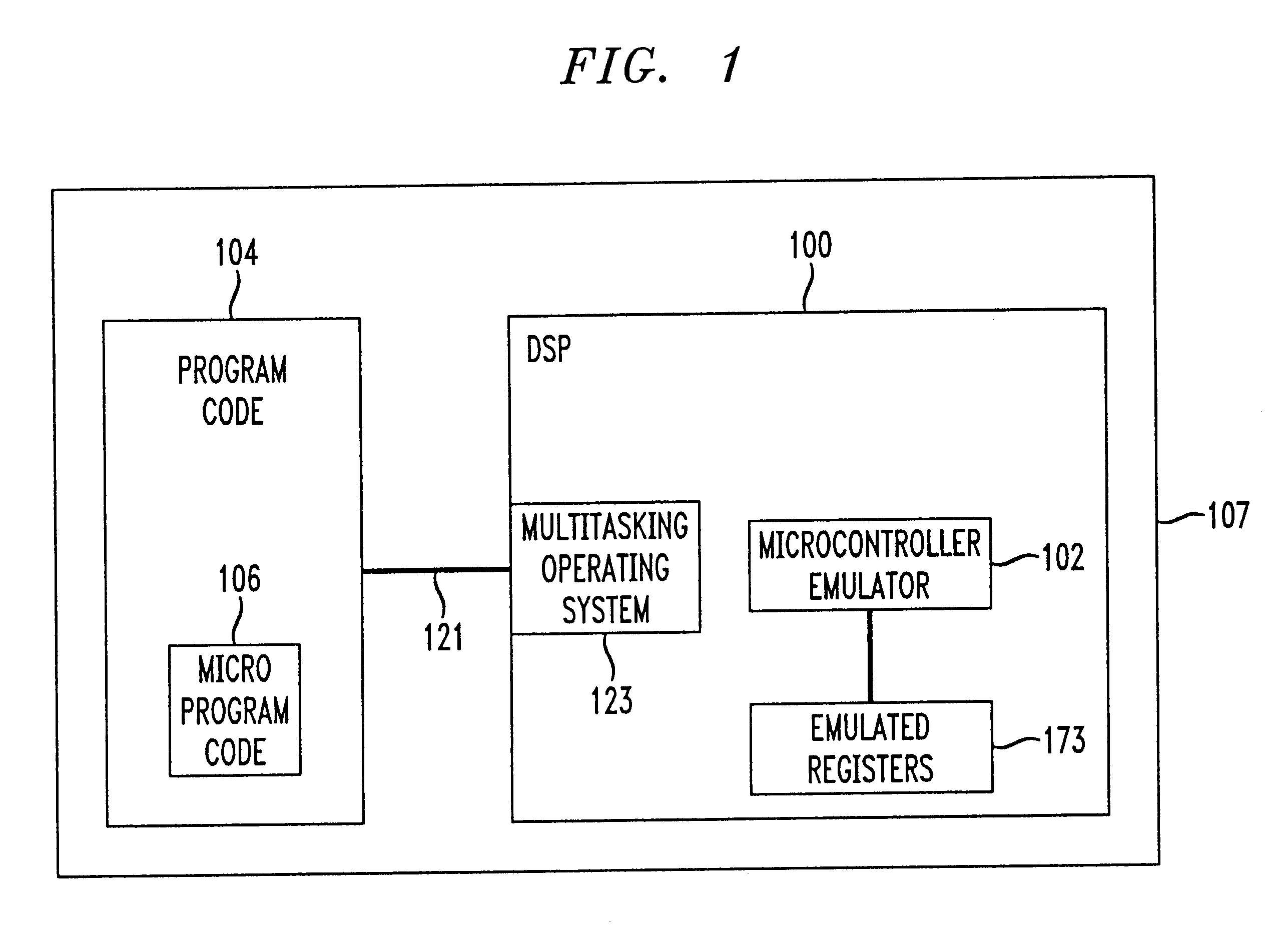

DSP emulating a microcontroller

InactiveUS6564179B1General purpose stored program computerSoftware simulation/interpretation/emulationMicrocontrollerOperational system

The present invention provides a processor device and technique having the capability of providing a two-processor solution with only one processor. In accordance with the principles of the present invention, a host processor is programmed in its native source and machine code language, and an emulated second processor is programmed in a different native source or machine code language particular to that emulated processor, to allow programming specialists in the different processors to develop common code for use on the same host processor. A multitasking operating system is included to allow time sharing operation between instructions from program code relating to the host processor (e.g., a DSP in the disclosed embodiment), and different program code relating to the emulated processor. The program code relating to the host processor (e.g., DSP) is written in program code which is native to the DSP, while the program code relating to the emulated processor (e.g., microcontroller) is written in program code which is native to the microcontroller. The SoftCore emulation module allows both DSP code and control code written for a microcontroller to execute independently on the same processor by multi-tasking resources in the faster, host processor (e.g., in the DSP), giving equal time slots of processor time to each processor (real and emulated).

Owner:LUCENT TECH INC +1

Method and system for solving integer programming and discrete optimization problems using analog processors

ActiveUS20080065573A1Improve legibilityDigital computer detailsChaos modelsAnalog processorDiscrete optimization

Discrete optimization problem are solved using an analog optimization device such as a quantum processor. Problems are solved using an objective function and at least one constraint corresponding to the discrete optimization problems. The objective function is converted into a first set of inputs and the at least one constraint is converted into a second set of inputs for the analog optimization device. A third set of inputs is generated which are indicative of at least one penalty coefficient. A final state of the analog optimization device corresponds to at least a portion of the solution to the discrete optimization problem.

Owner:D WAVE SYSTEMS INC

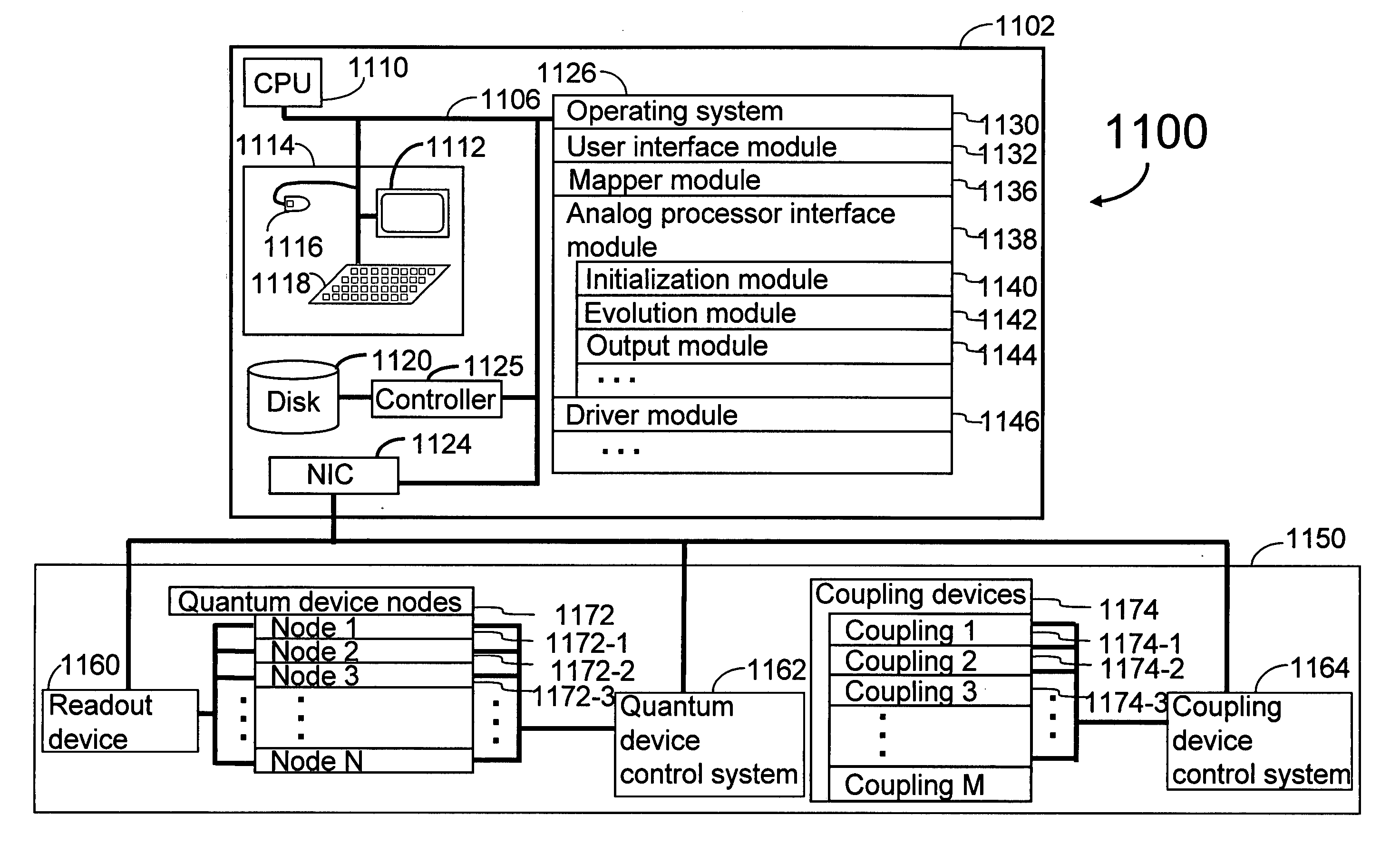

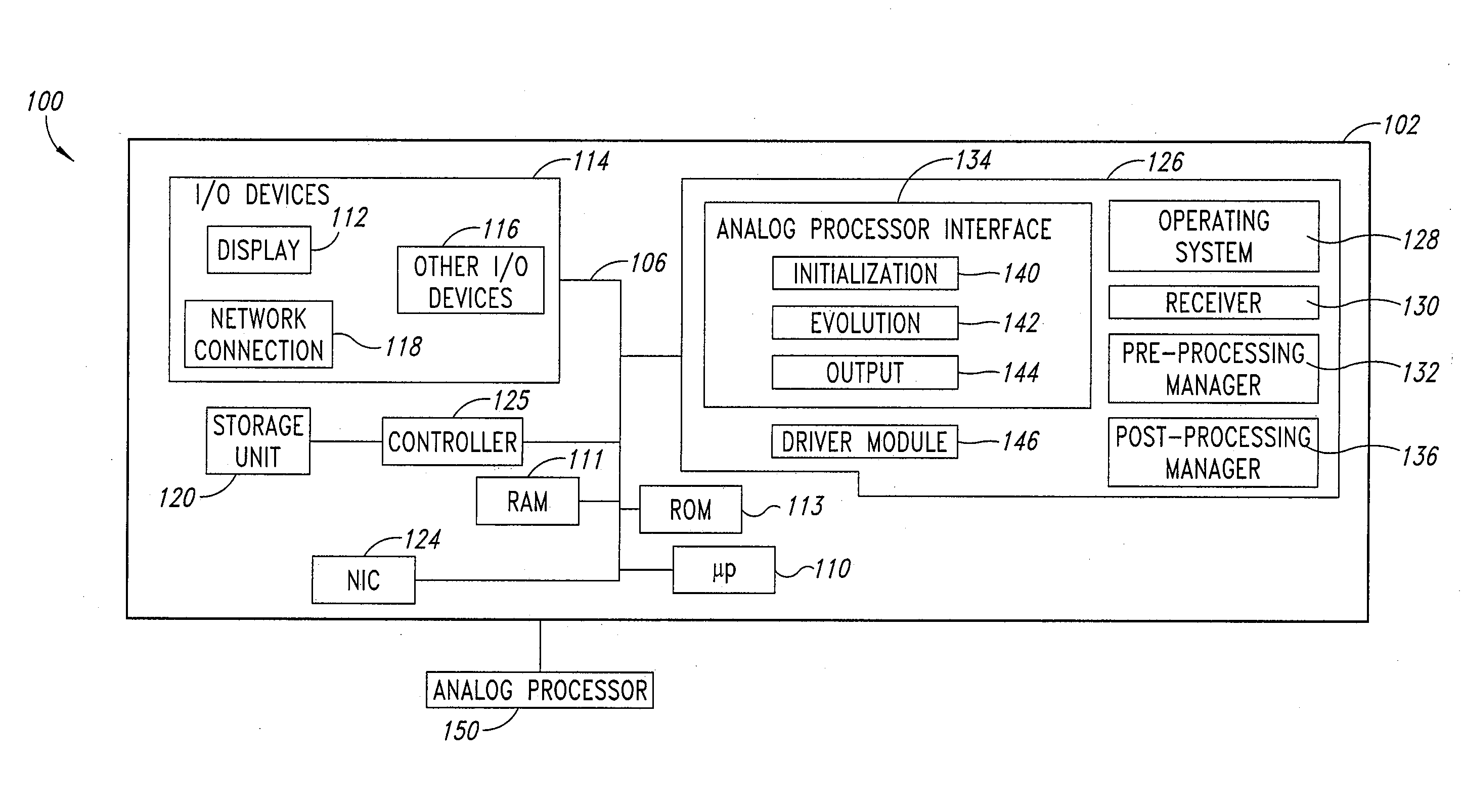

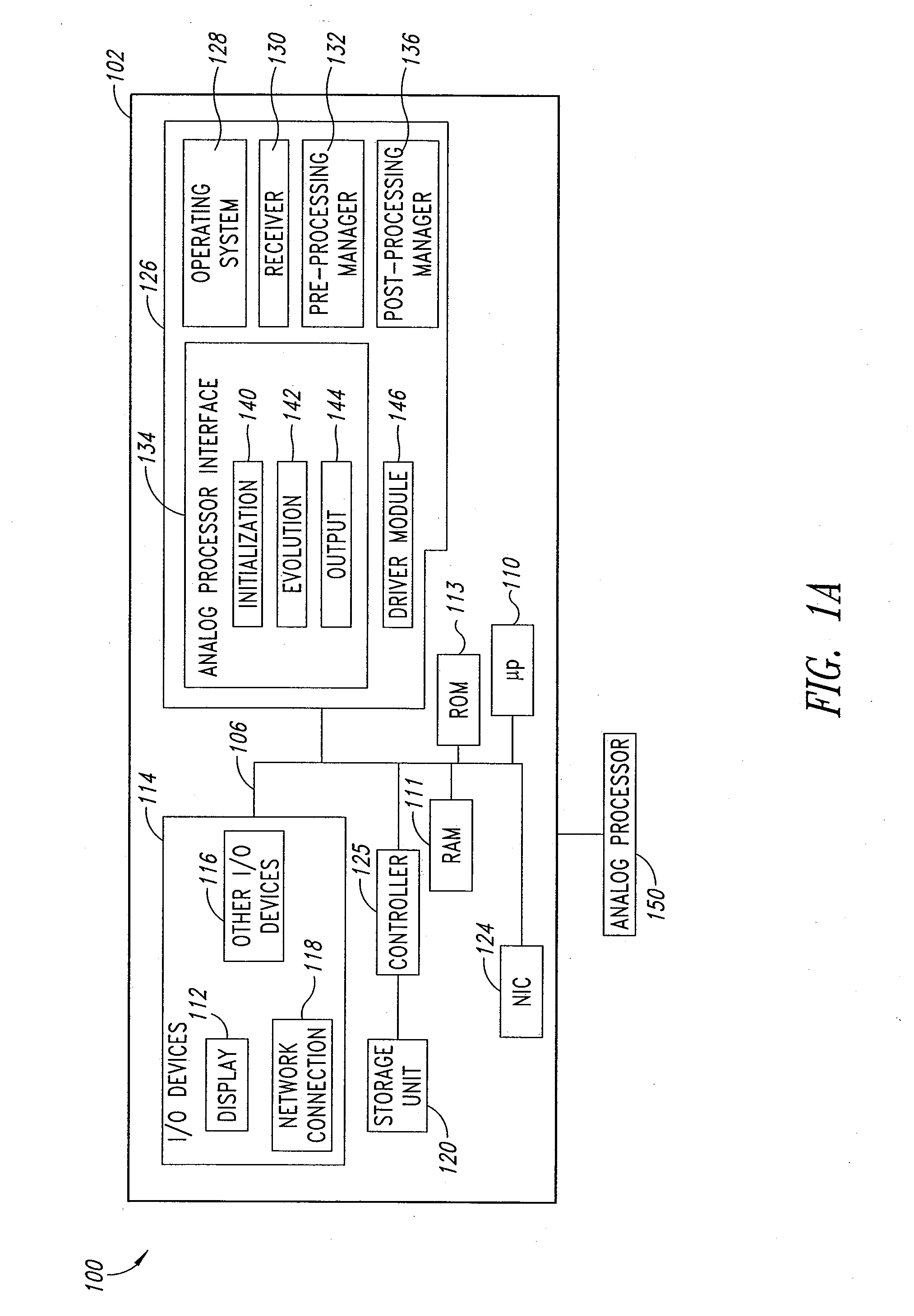

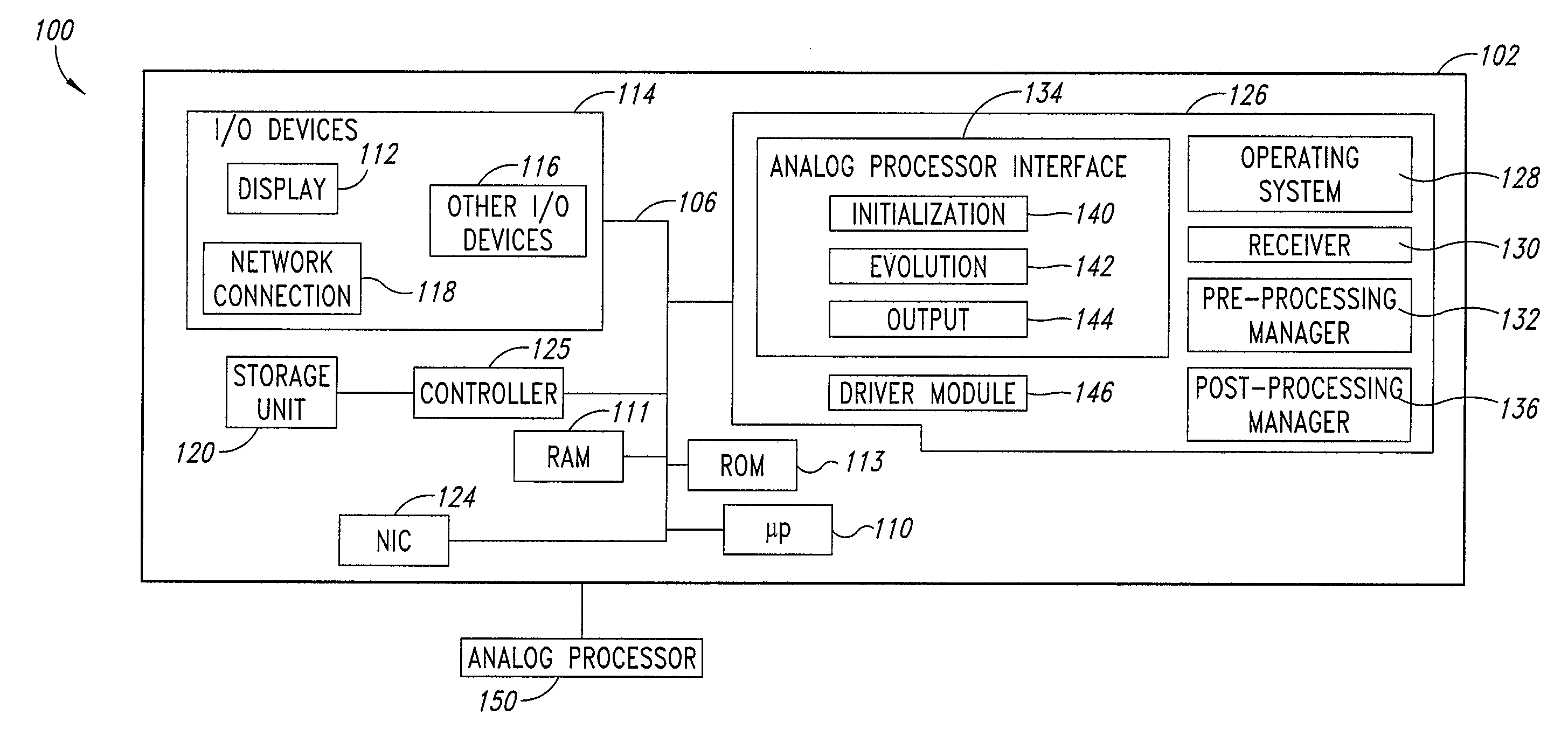

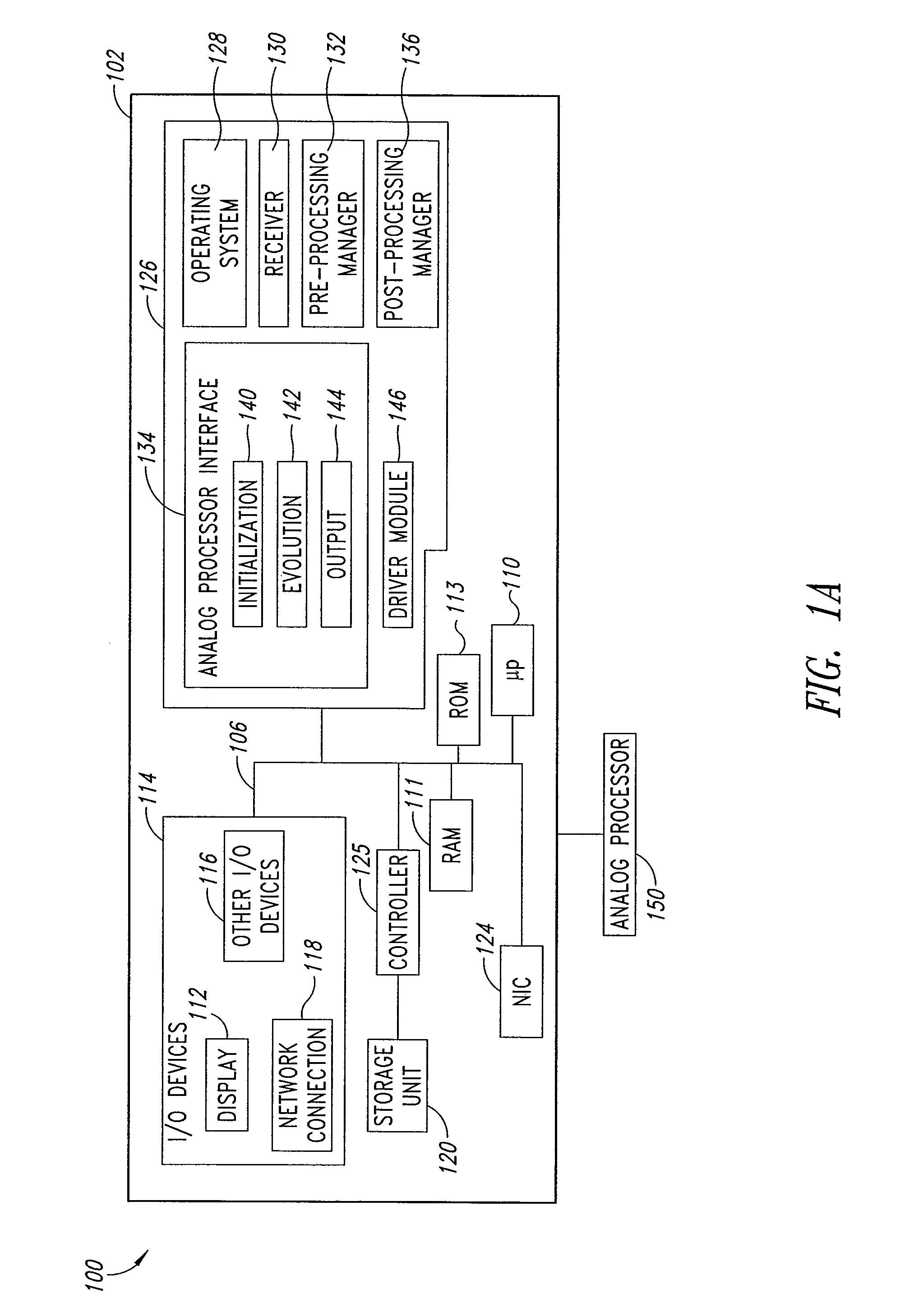

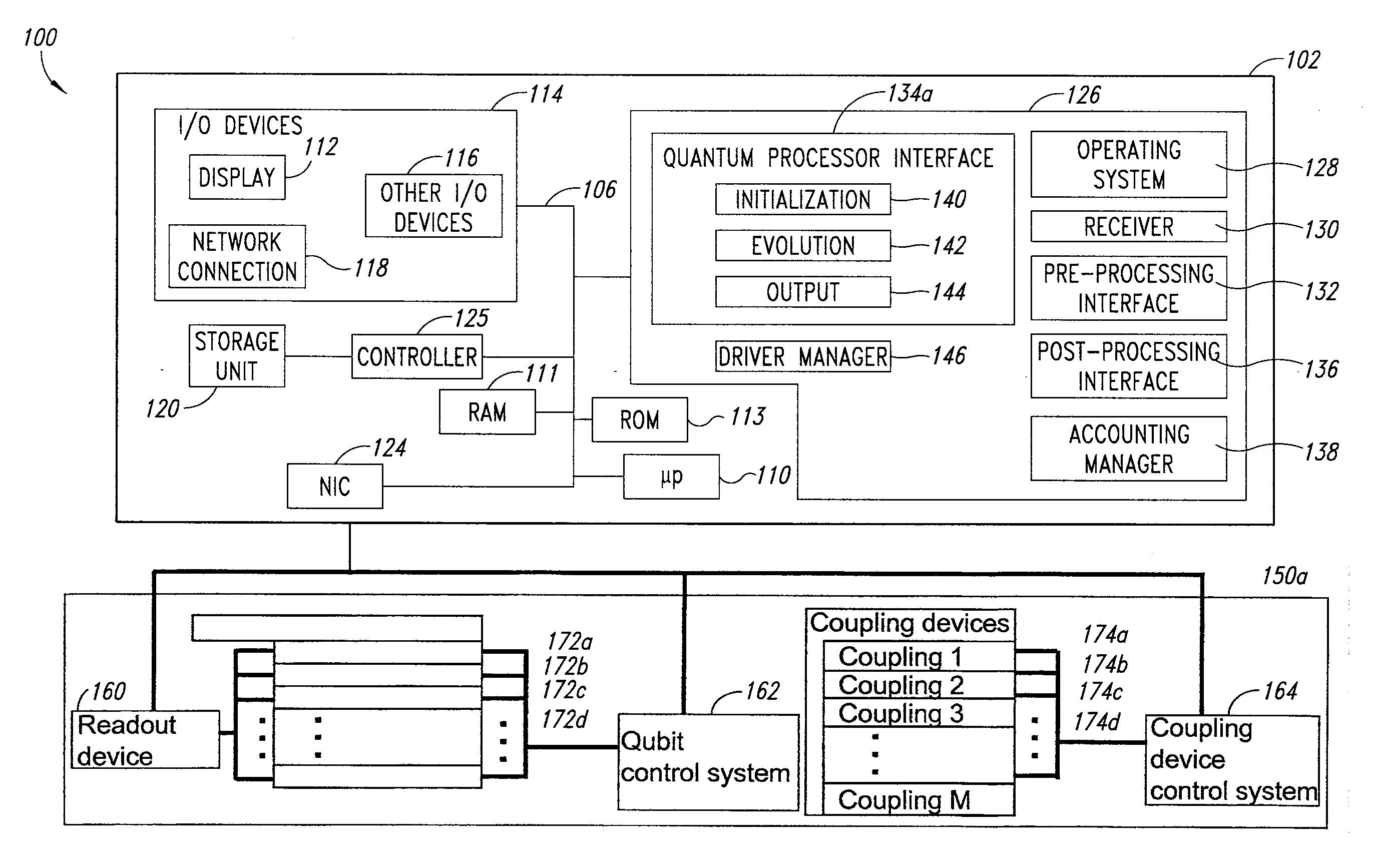

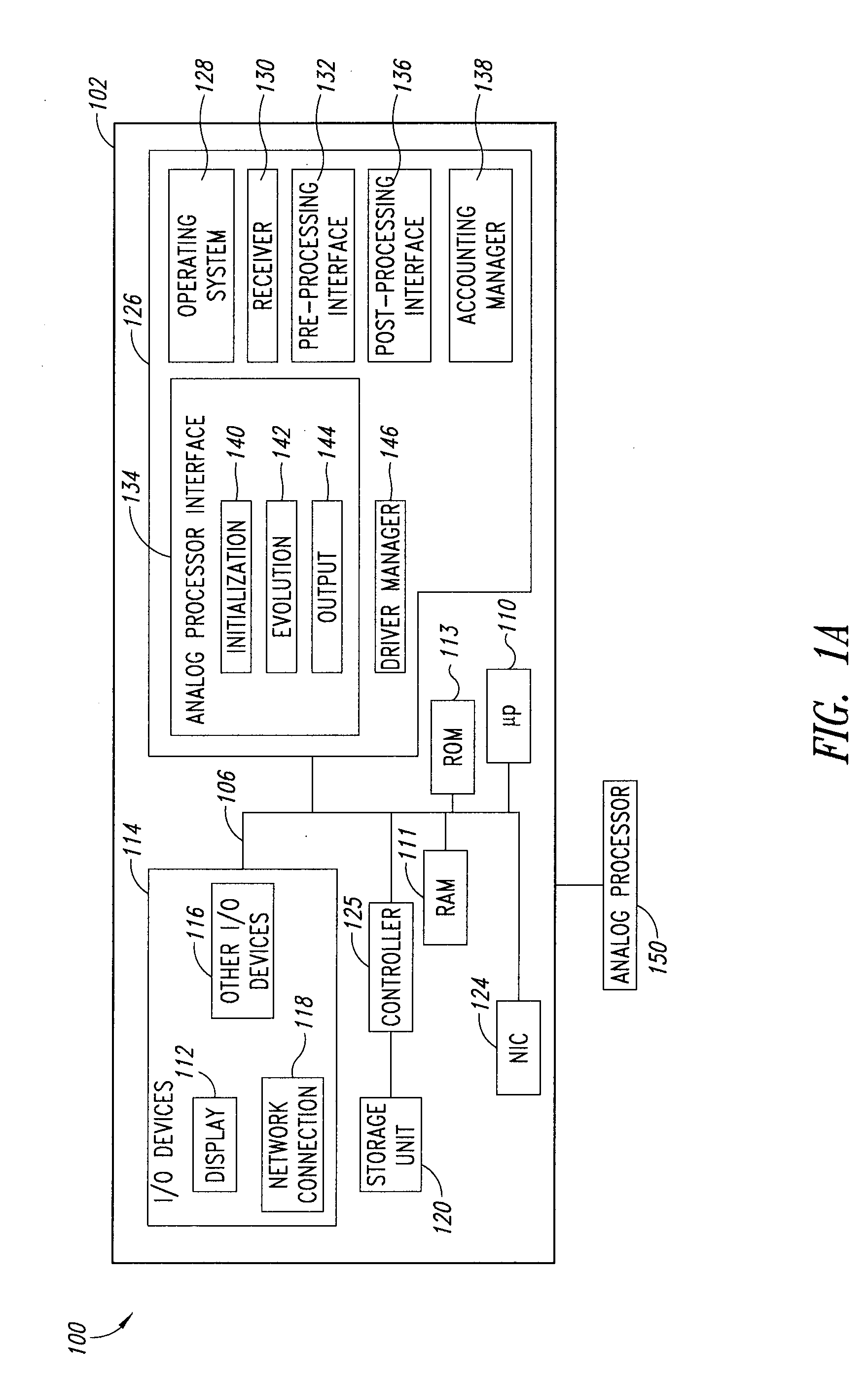

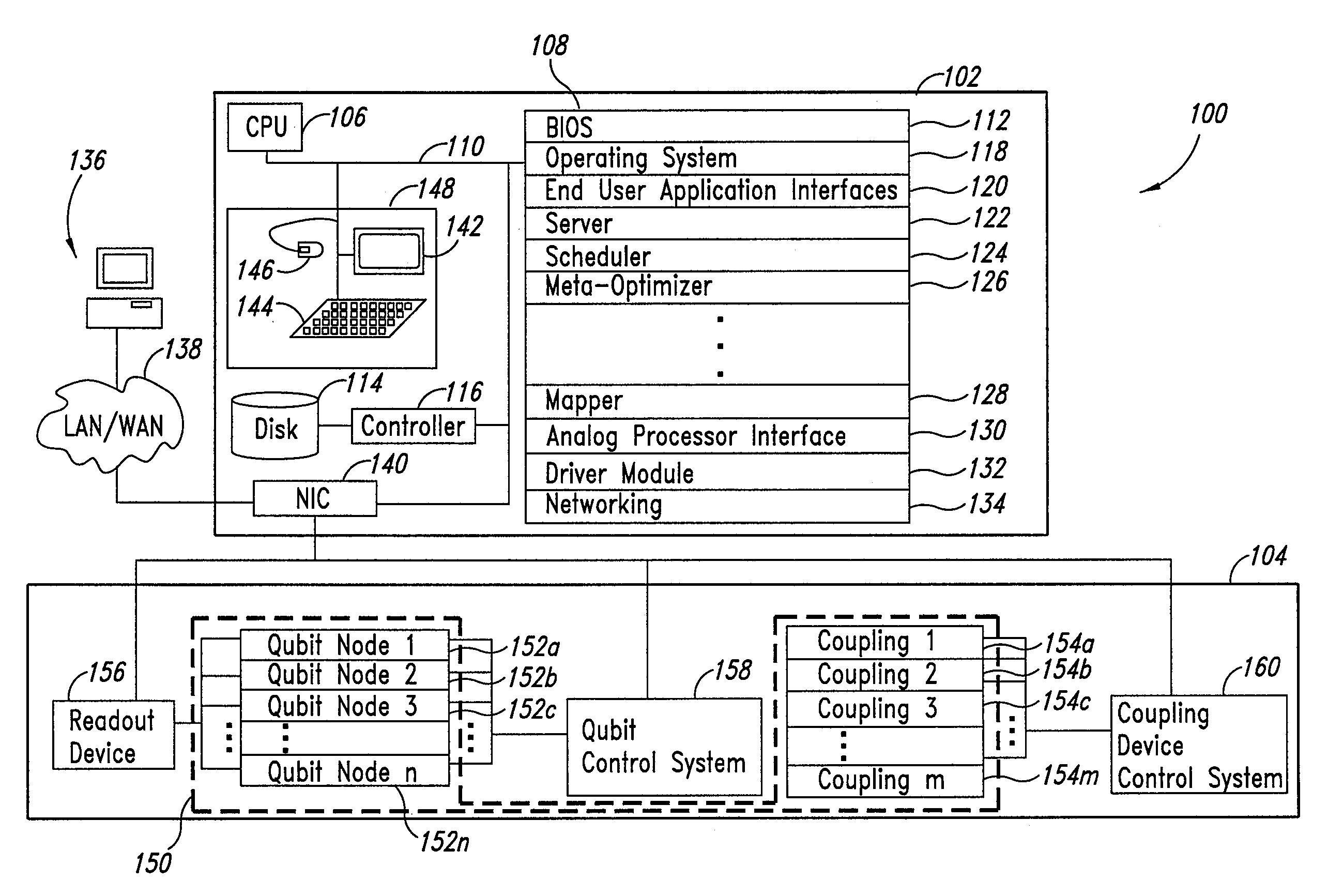

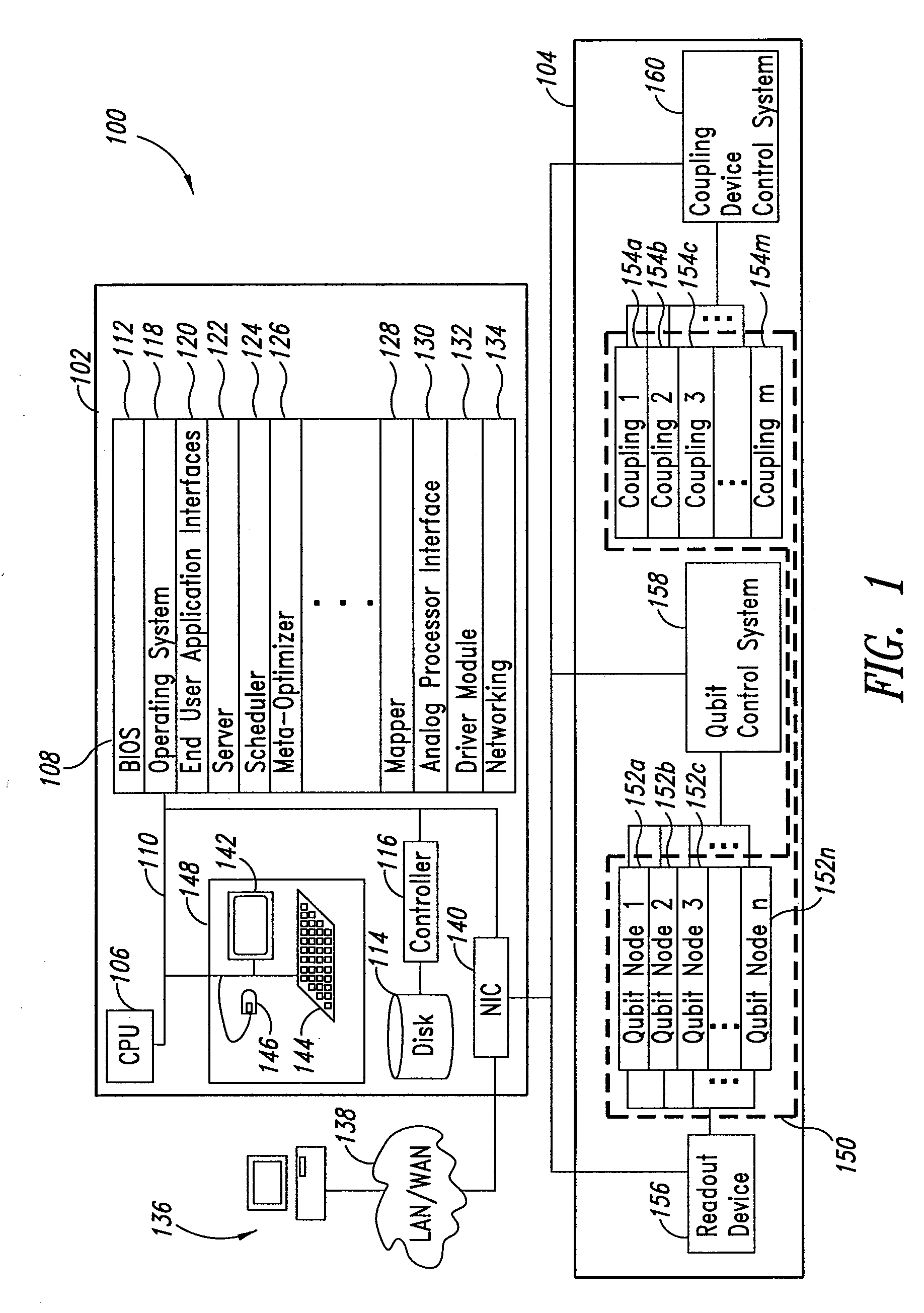

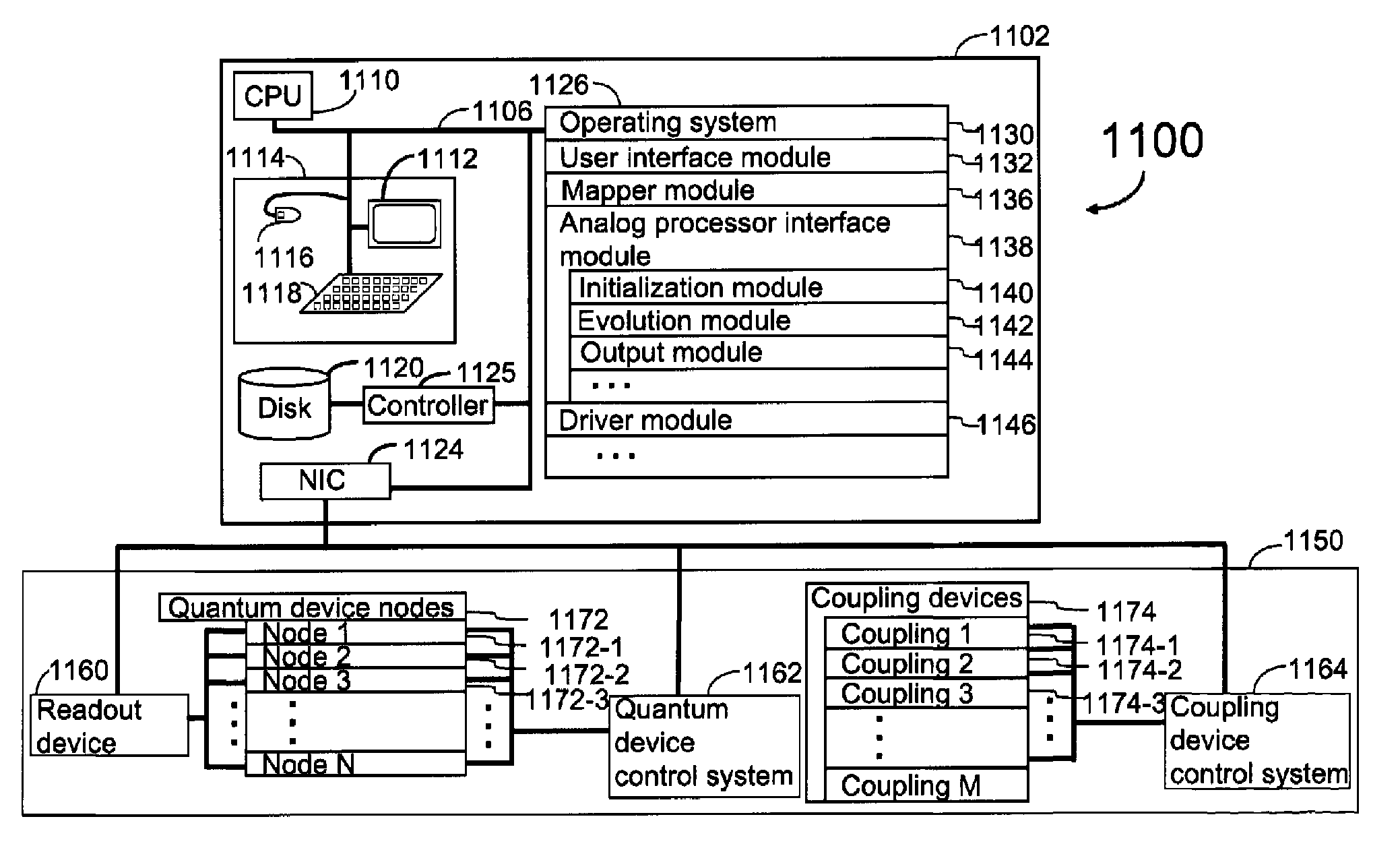

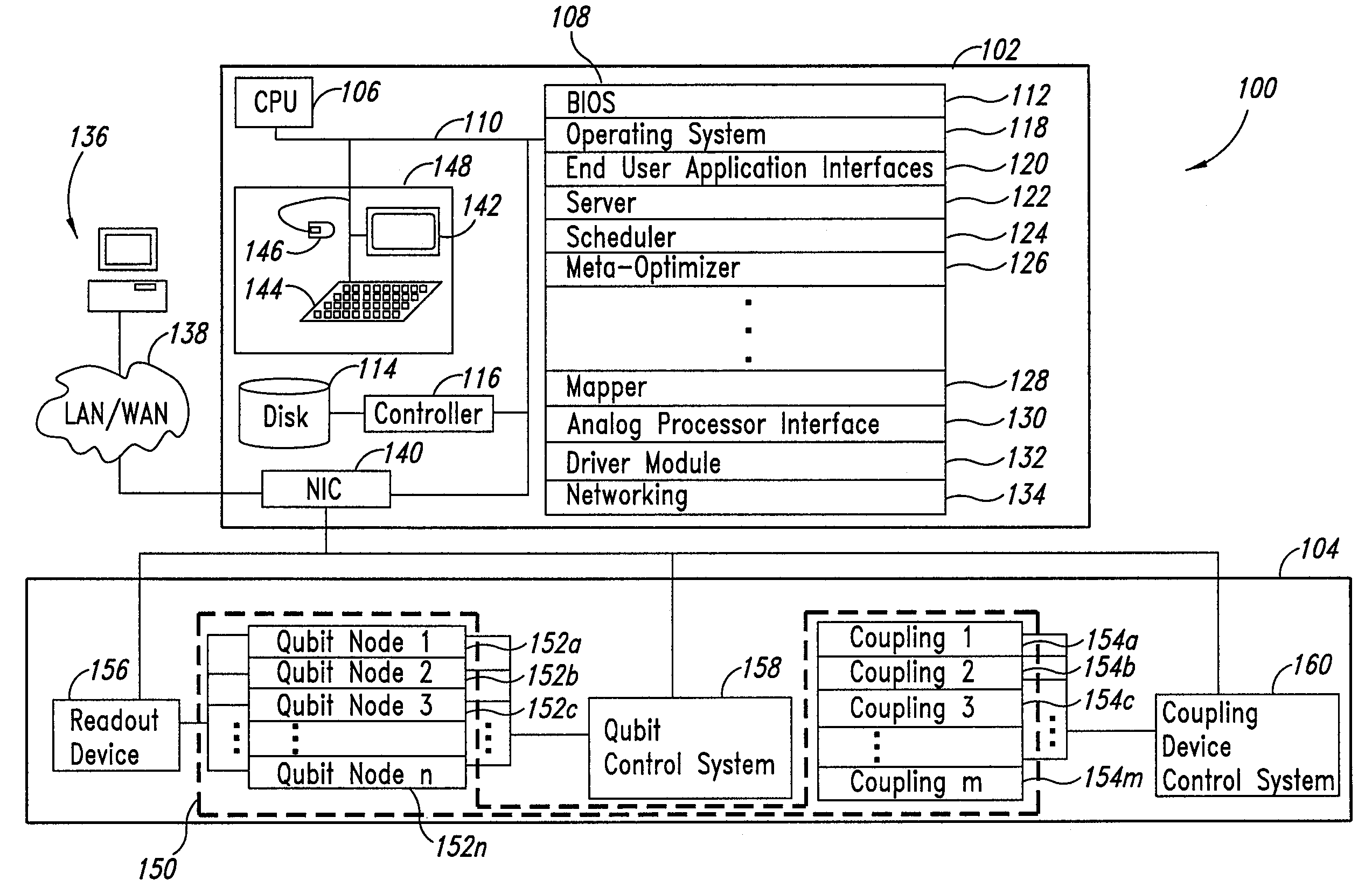

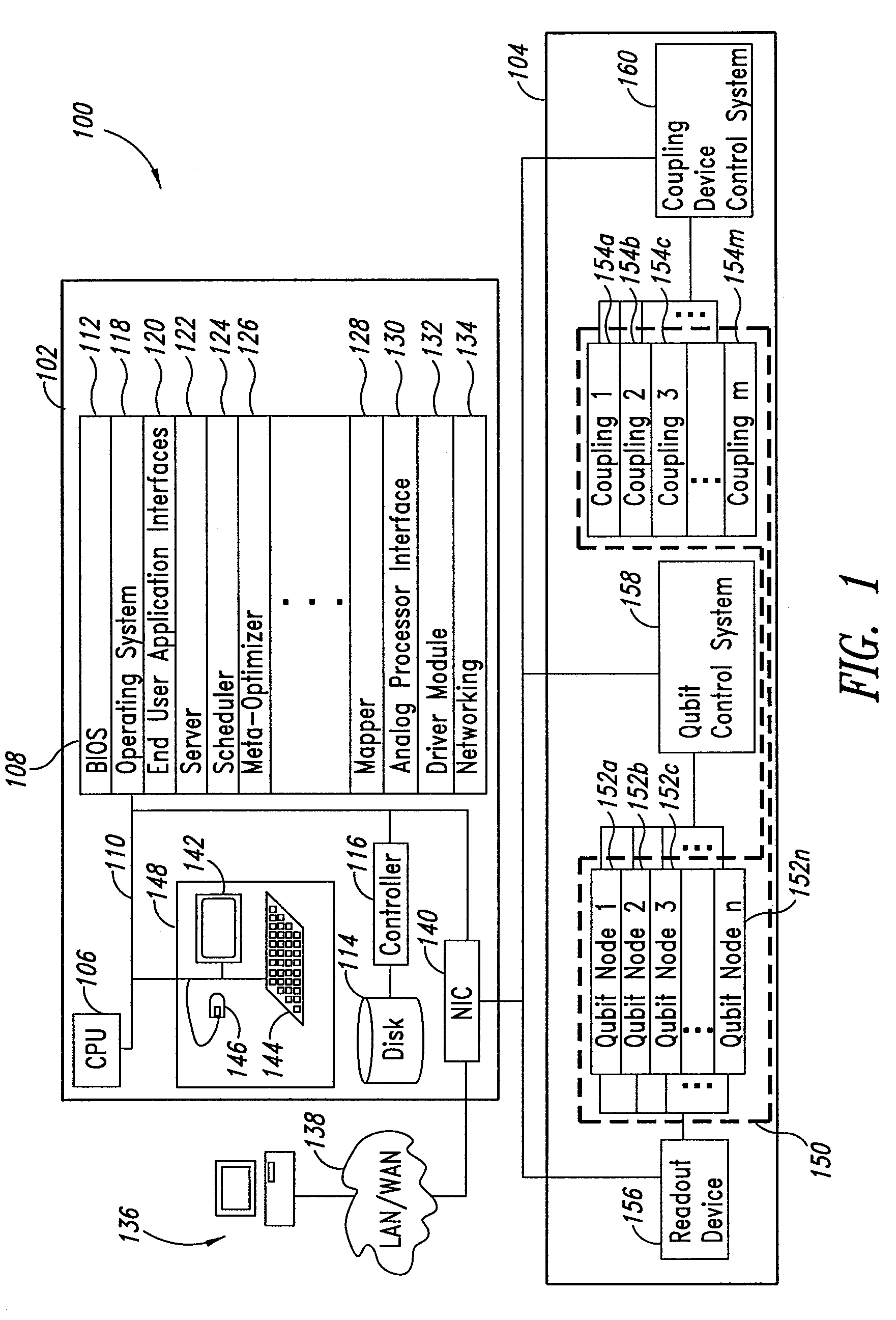

Systems, devices, and methods for solving computational problems

Systems, devices, and methods for using an analog processor to solve computational problems. A digital processor is configured to track computational problem processing requests received from a plurality of different users, and to track at least one of a status and a processing cost for each of the computational problem processing requests. An analog processor, for example a quantum processor, is operable to assist in producing one or more solutions to computational problems identified by the computational problem processing requests via a physical evolution.

Owner:D WAVE SYSTEMS INC

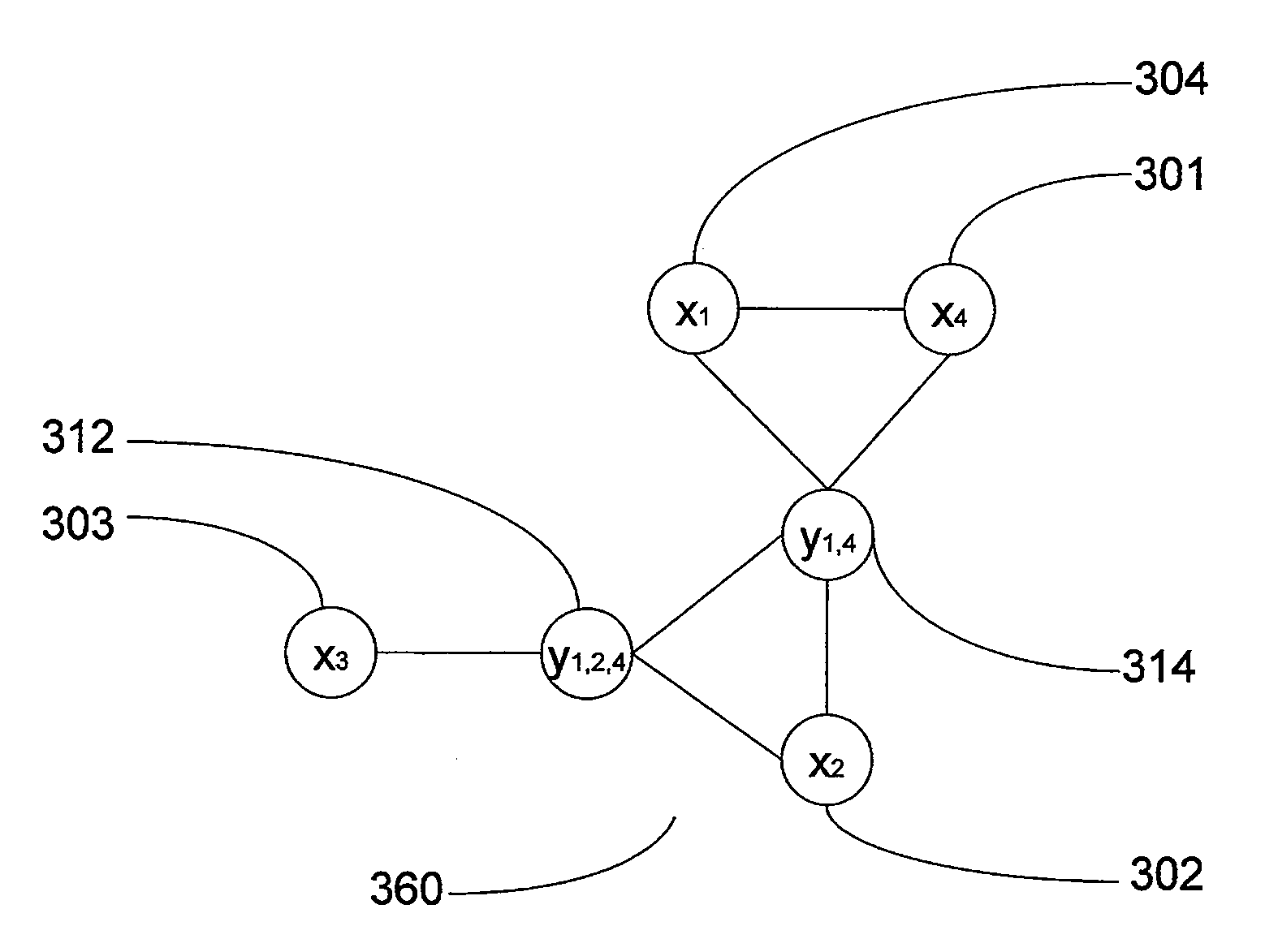

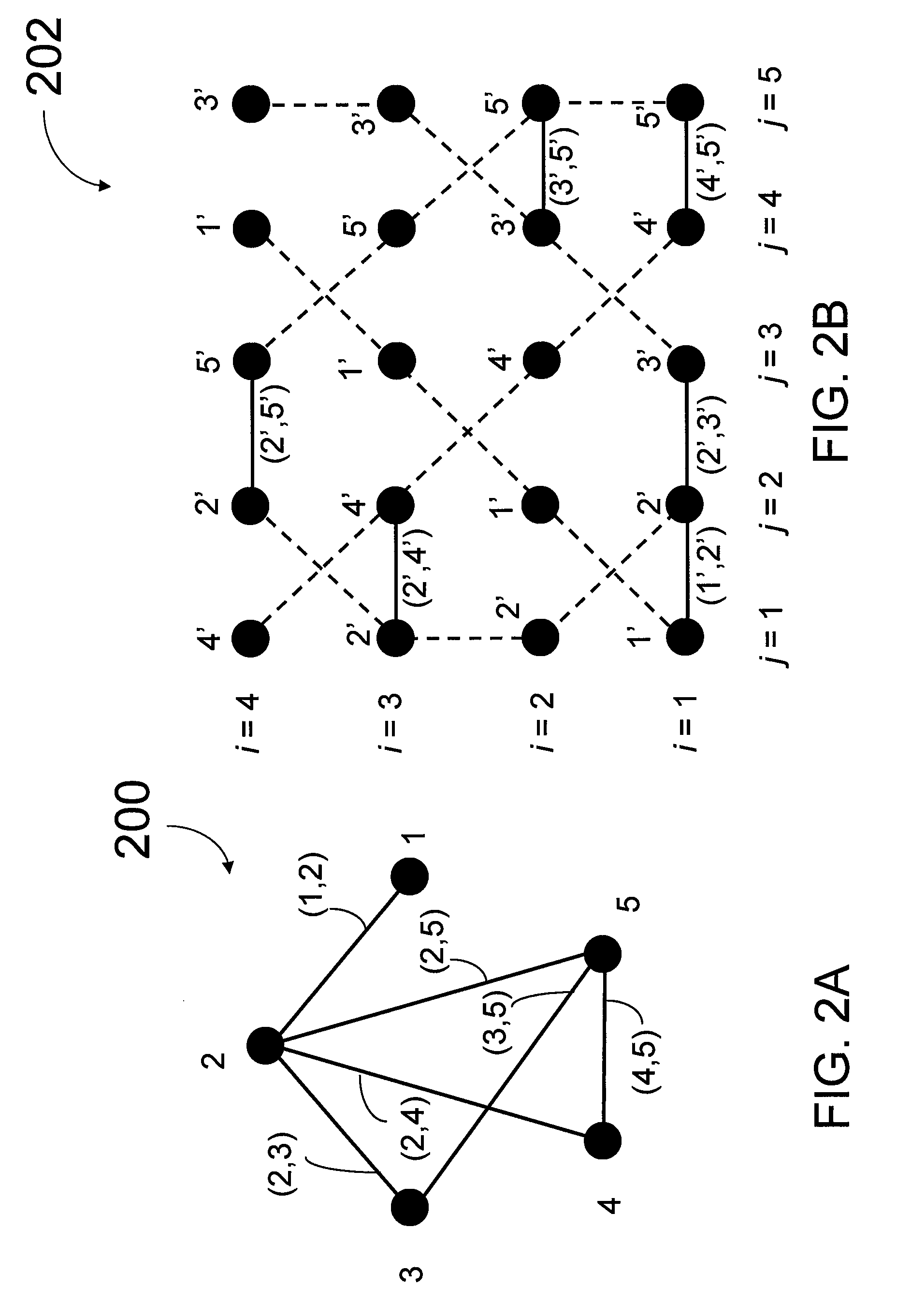

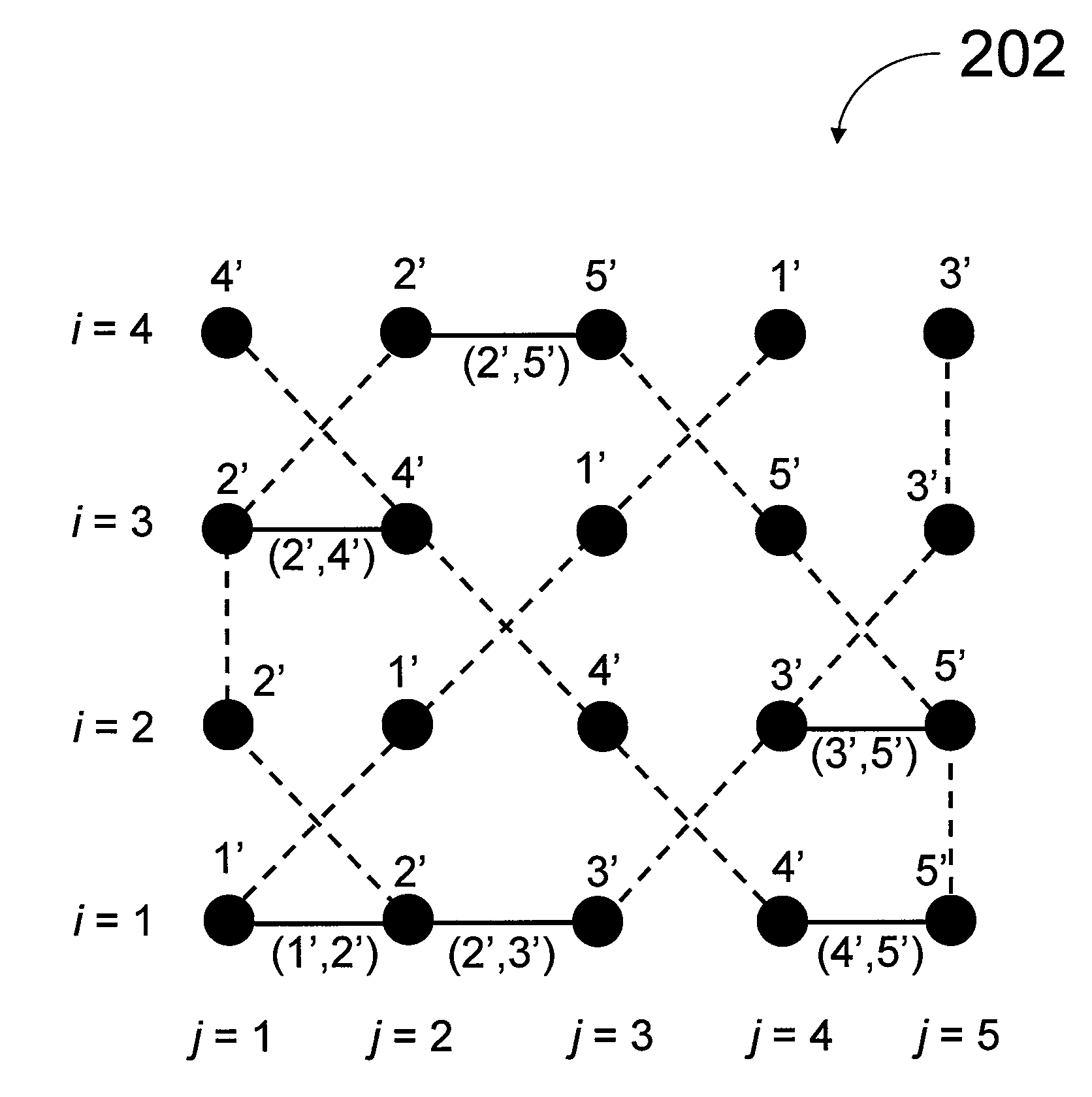

Graph embedding techniques

ActiveUS7984012B2Maximizing numberDrawing from basic elementsDigital computer detailsAnalog processorAlgorithm

Approaches to embedding source graphs into targets graphs in a computing system are disclosed. Such may be advantageously facilitate computation with computing systems that employ one or more analog processors, for example one or more quantum processors.

Owner:D WAVE SYSTEMS INC

Processing relational database problems using analog processors

Systems, methods and articles solve queries or database problems through the use of graphs. An association graph may be formed based on a query graph and a database graph. The association graph may be solved for a clique, providing the results to a query or problem and / or an indication of a level of responsiveness of the results. Thus, unlimited relaxation of constraint may be achieved. Analog processors such as quantum processors may be used to solve for the clique.

Owner:D WAVE SYSTEMS INC

Analog processor comprising quantum devices

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, for instance qubits, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D-WAVE SYSTEMS

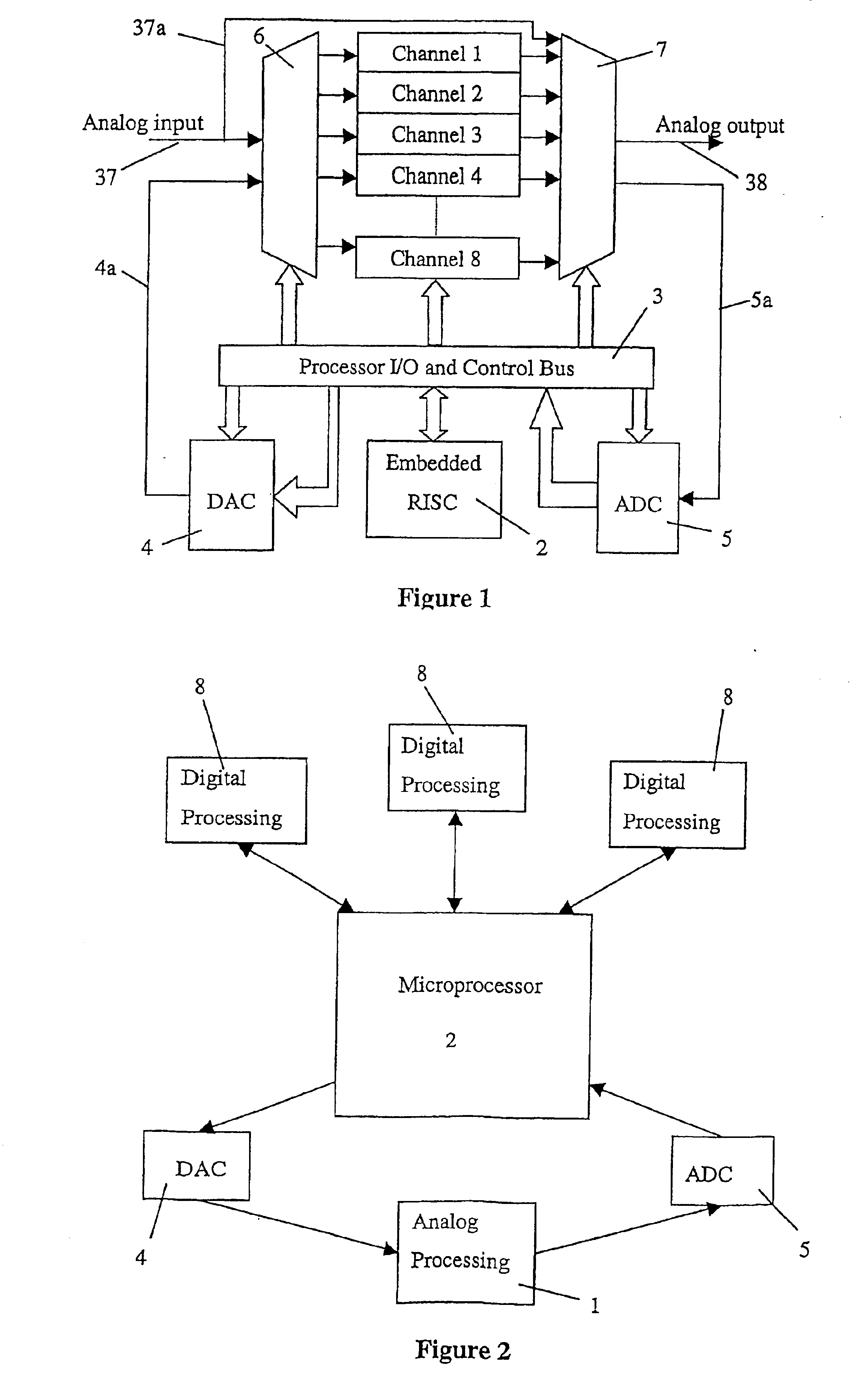

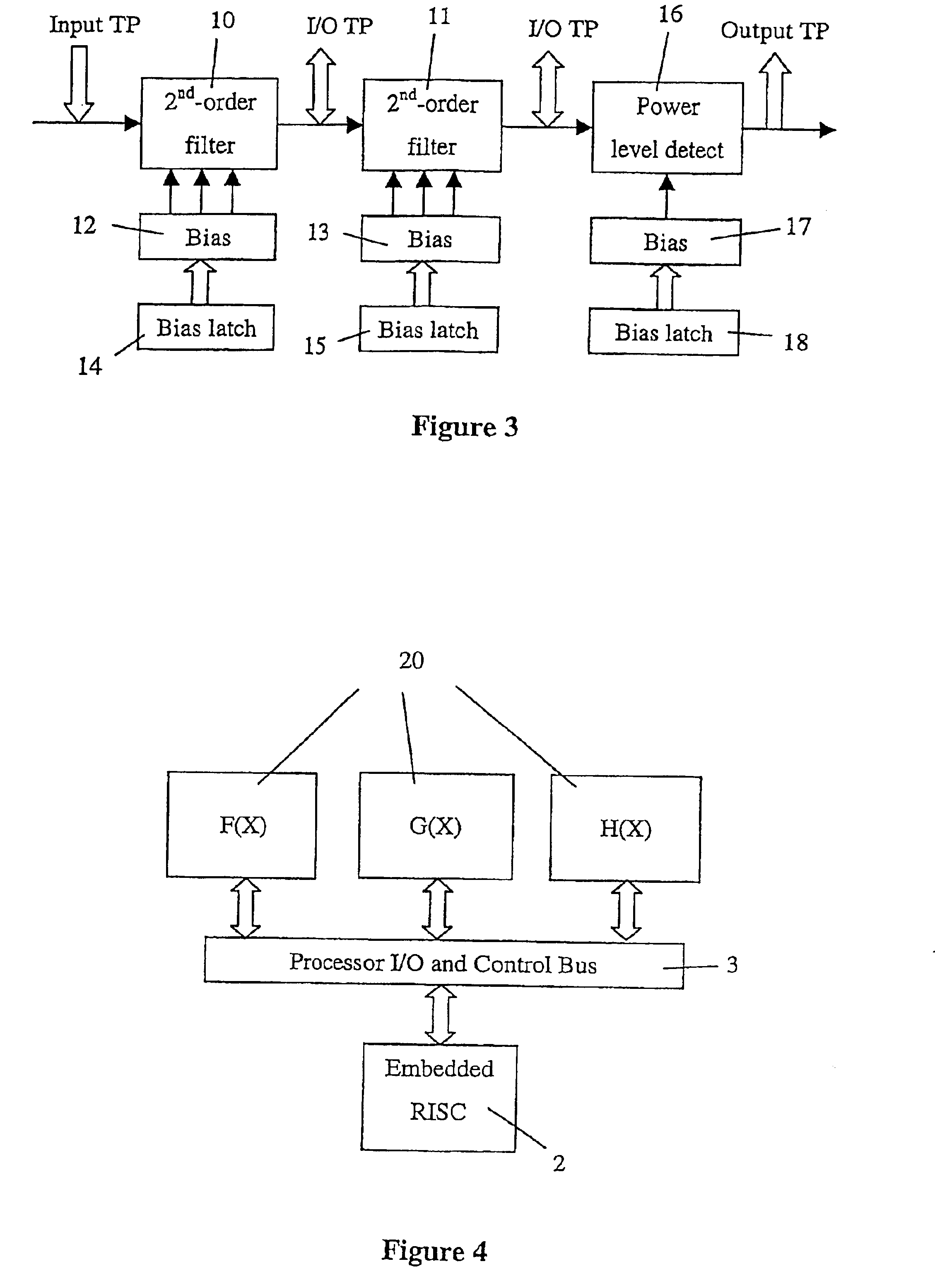

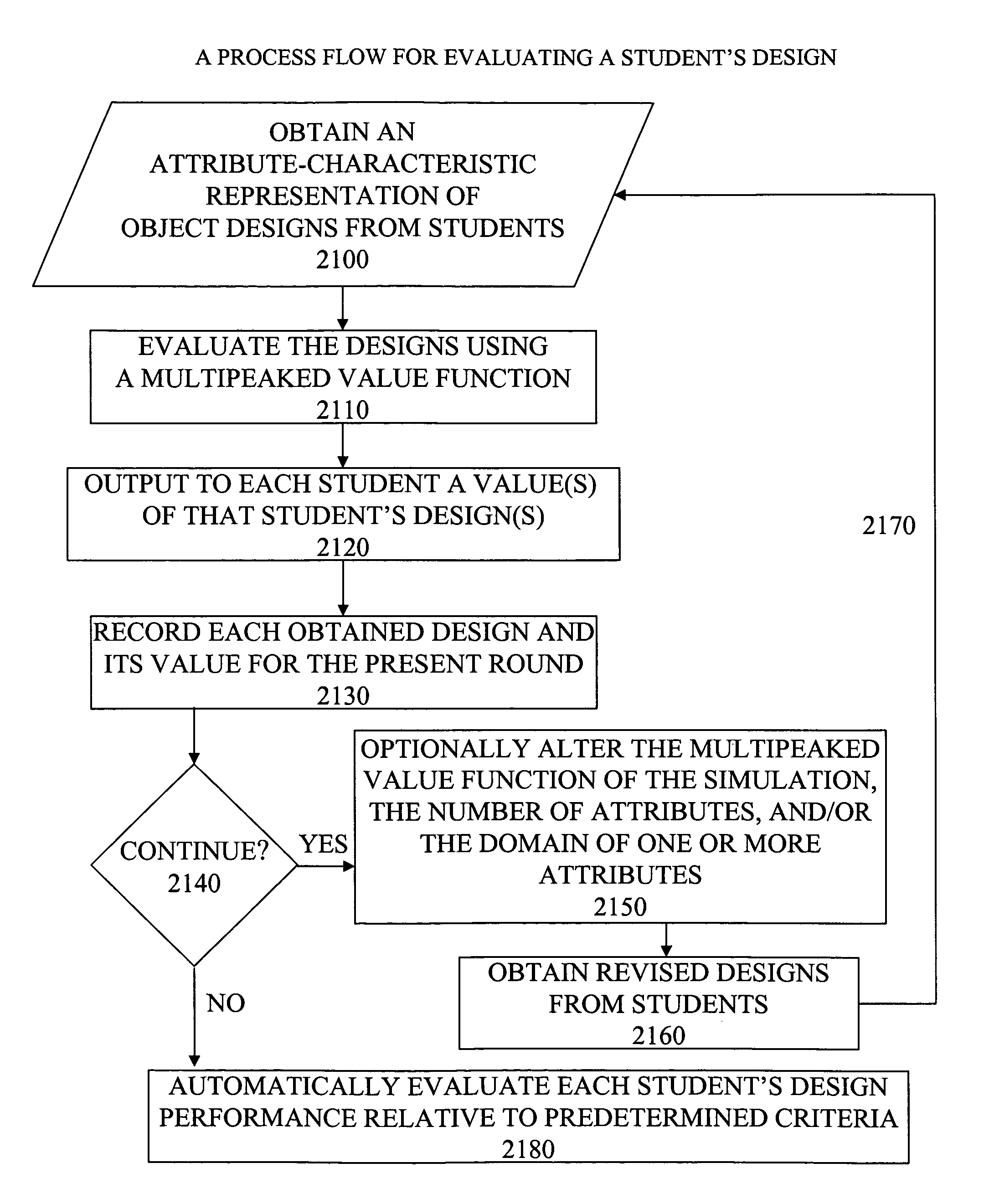

Hybrid digital/analog processing circuit

InactiveUS6954163B2Overcomes and mitigatesOvercome disadvantagesElectric signal transmission systemsDigital-analogue convertorsAnalog processorA d converter

A circuit comprising a digital processor, analogue processing means, a digital to analogue converter for converting digital values output from the digital processor into analogue values which are processed by the analogue processing means, and an analogue to digital converter for converting resulting analogue values into digital values for input to the digital processor, wherein the analogue processing means comprises one or more analogue processors, and the circuit is dynamically reconfigurable under the control of the digital processor, such that analogue values are processed according to a first function by the analogue processing means, and following reconfiguration, analogue values are processed according to a second function by the analogue processing means.

Owner:TOUMAZ TECH

Graph embedding techniques

ActiveUS20080218519A1Maximizing numberDrawing from basic elementsDigital computer detailsGraphicsAnalog processor

Approaches to embedding source graphs into targets graphs in a computing system are disclosed. Such may be advantageously facilitate computation with computing systems that employ one or more analog processors, for example one or more quantum processors.

Owner:D WAVE SYSTEMS INC

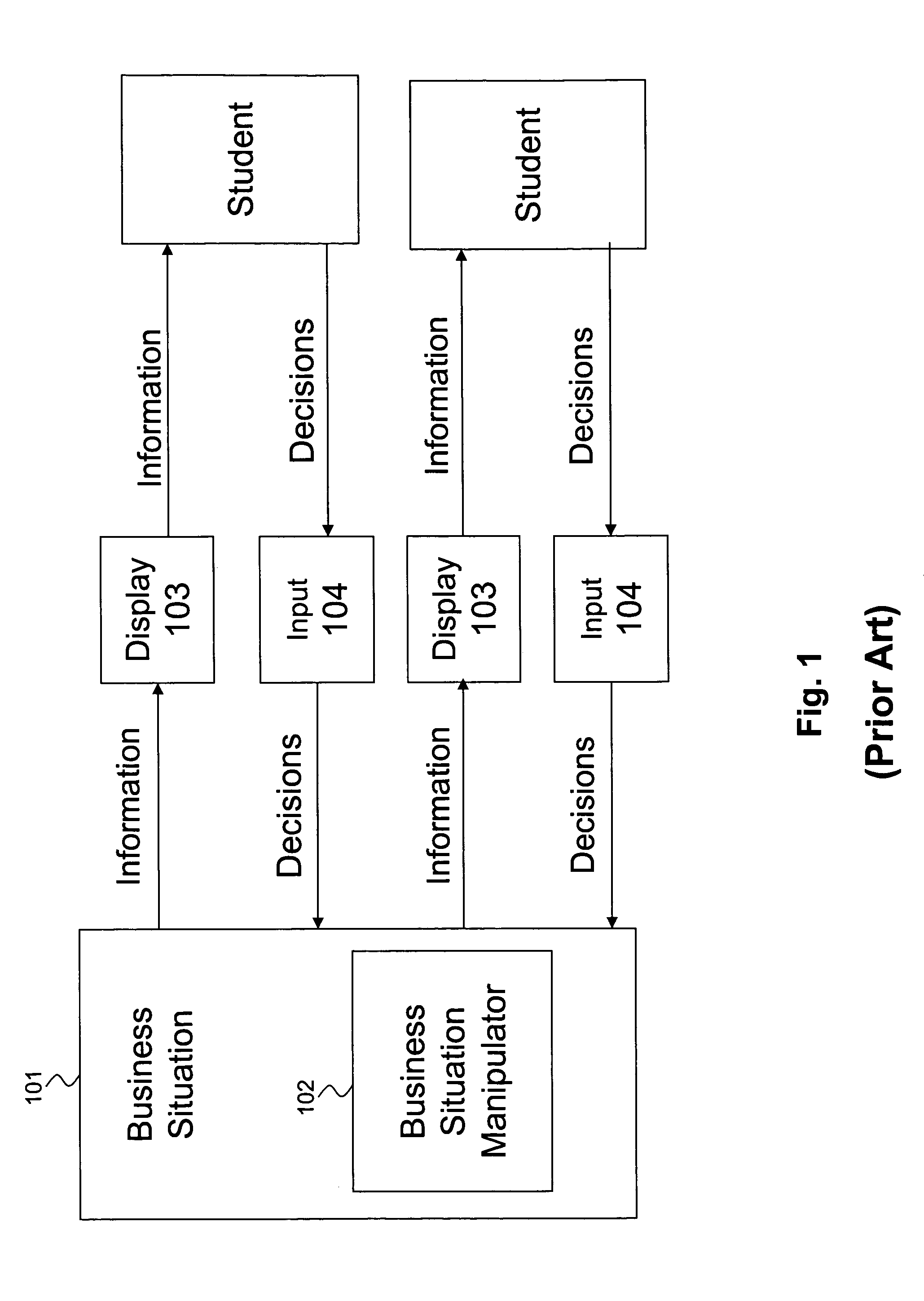

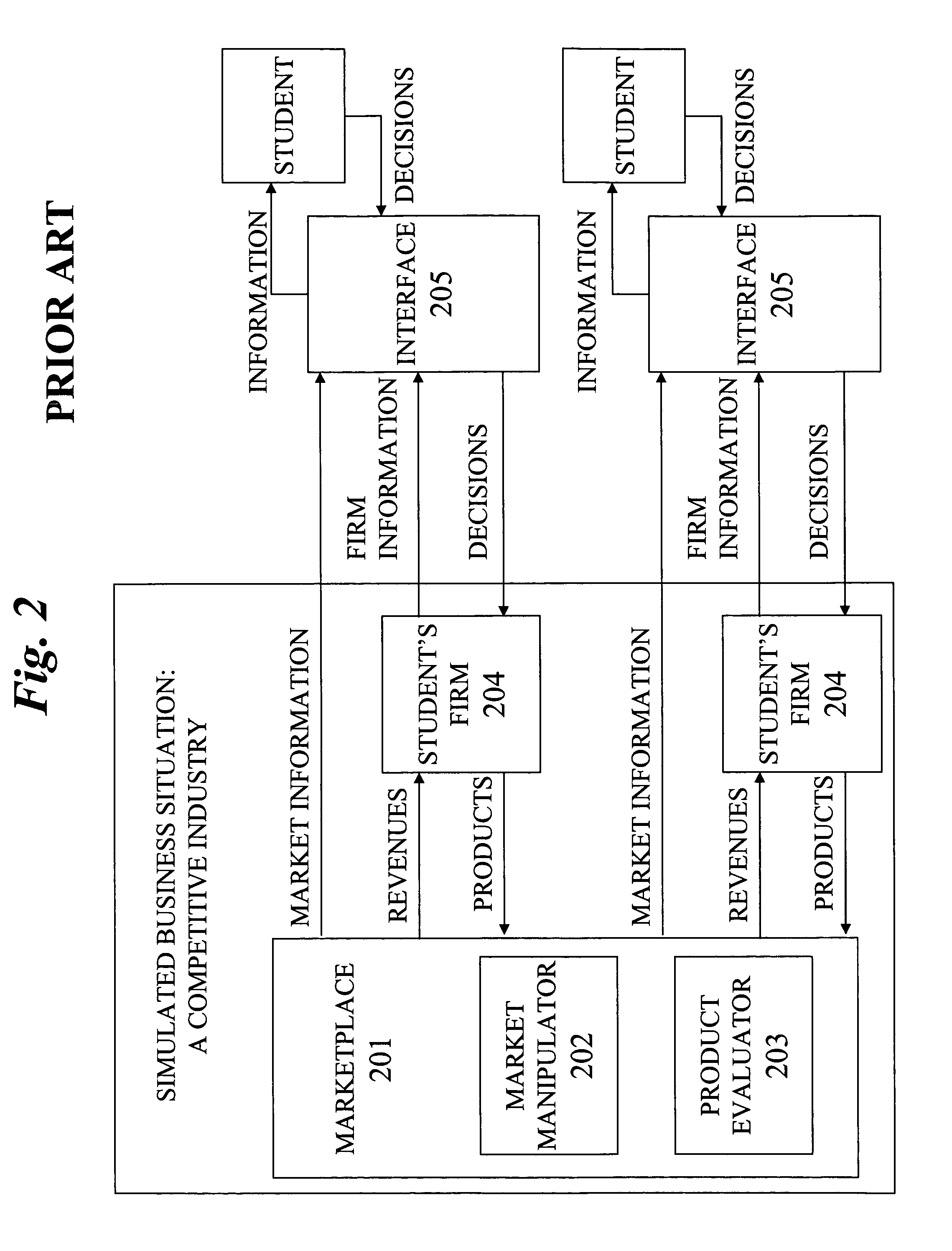

Management training simulation method and system

InactiveUS7349838B2Low production costImprove product qualityAnalogue computers for electric apparatusOffice automationTelecommunications linkAnalog processor

Developing decision-making skills of a user through practice in a simulated environment comprises defining a simulated situation to be influenced by the user including a set of objects that are represented by an attribute-characteristic representation, presenting information concerning a current state of the simulation, obtaining decisions from the user that at least partially determine object designs to be evaluated, evaluating an object design using a value function having multiple optima, updating the simulation with the results from the evaluation, and permitting continued practice by selectively repeating several of these steps. A system executes simulation software that simulates such a situation on a processor, and includes evaluation software for selecting and evaluating design objects by applying a value function having multiple optima. At least one terminal and communication links are provided for information transfer and implementation of the simulated situation. Diagnosis of the user's cognitive approach is also disclosed.

Owner:TUMBLEWEED HLDG LLC

Analog processor comprising quantum devices

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, for instance qubits, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

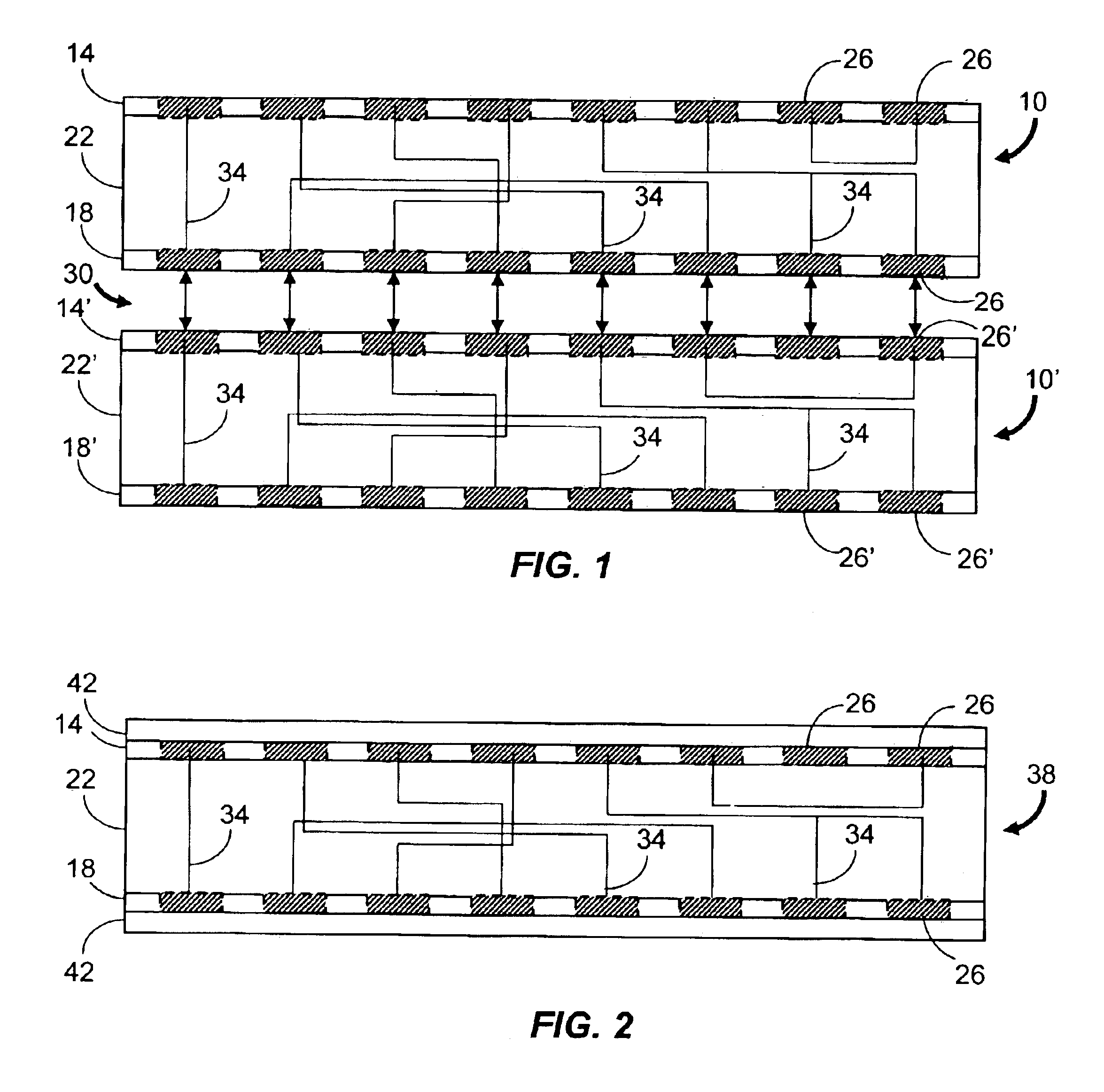

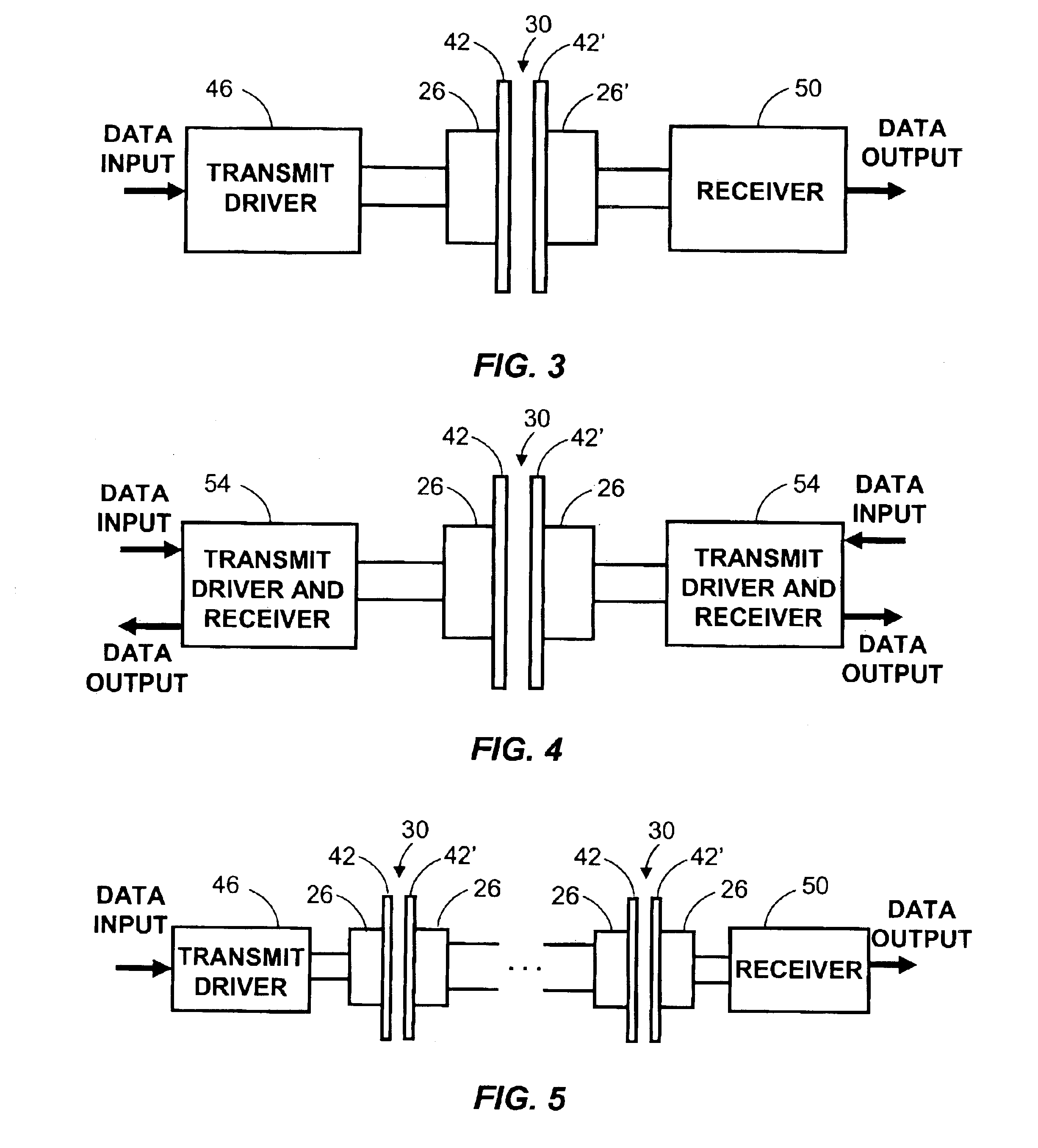

Electromagnetic coupling connector for three-dimensional electronic circuits

An electromagnetic coupling connector for three-dimensional electronic circuits is described. The coupling connector includes two coupling layers each having multiple electromagnetic coupling elements. Each coupling element can communicate through an electromagnetic path to a mating coupling element in a separate coupling connector. A routing layer is disposed between the two coupling layers and conducts an electrical signal between a coupling in one layer and at least one coupling element in the other layer. The coupling connector can also include a device layer having devices such as analog processors, memory modules and switching processor modules.

Owner:MASSACHUSETTS INST OF TECH

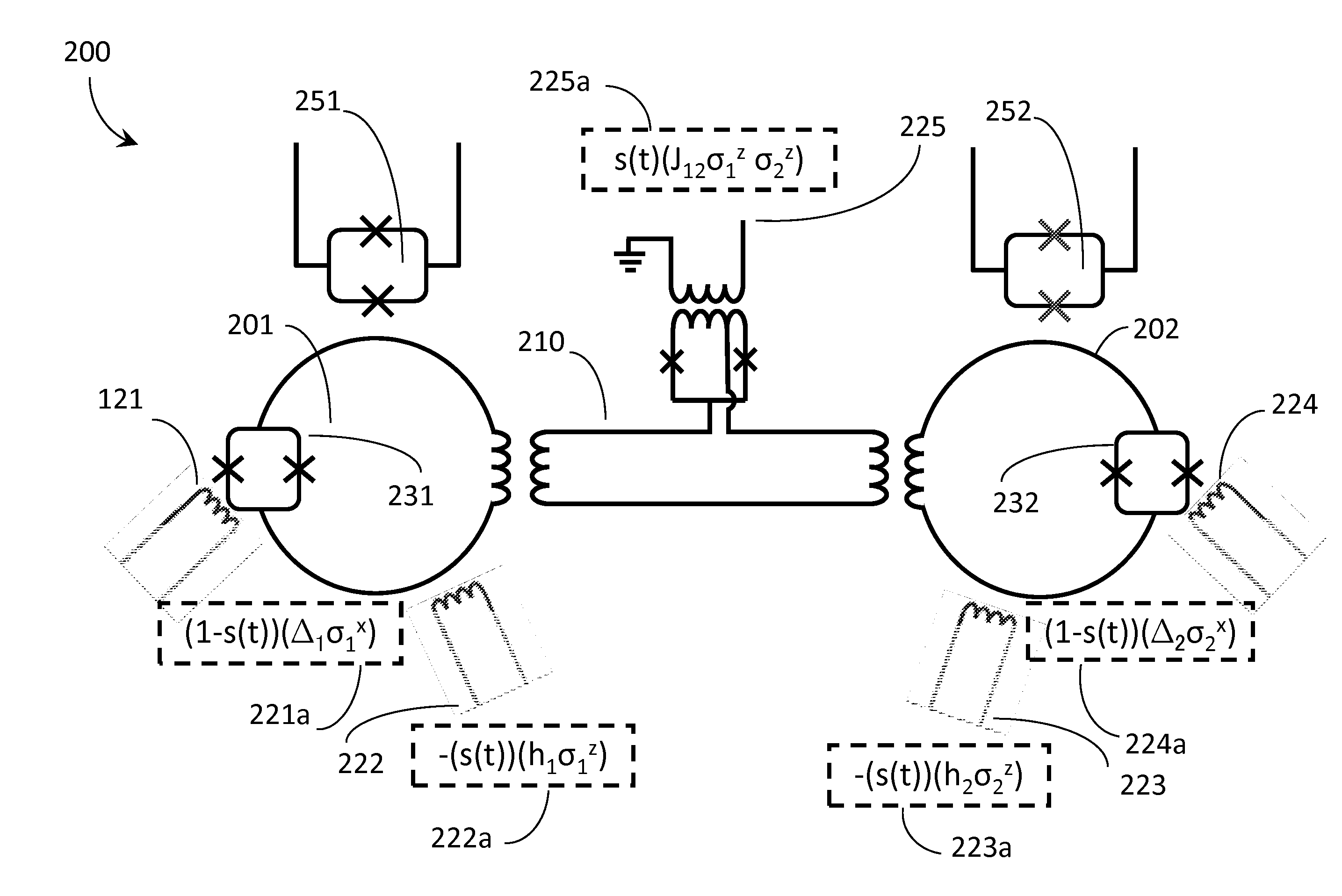

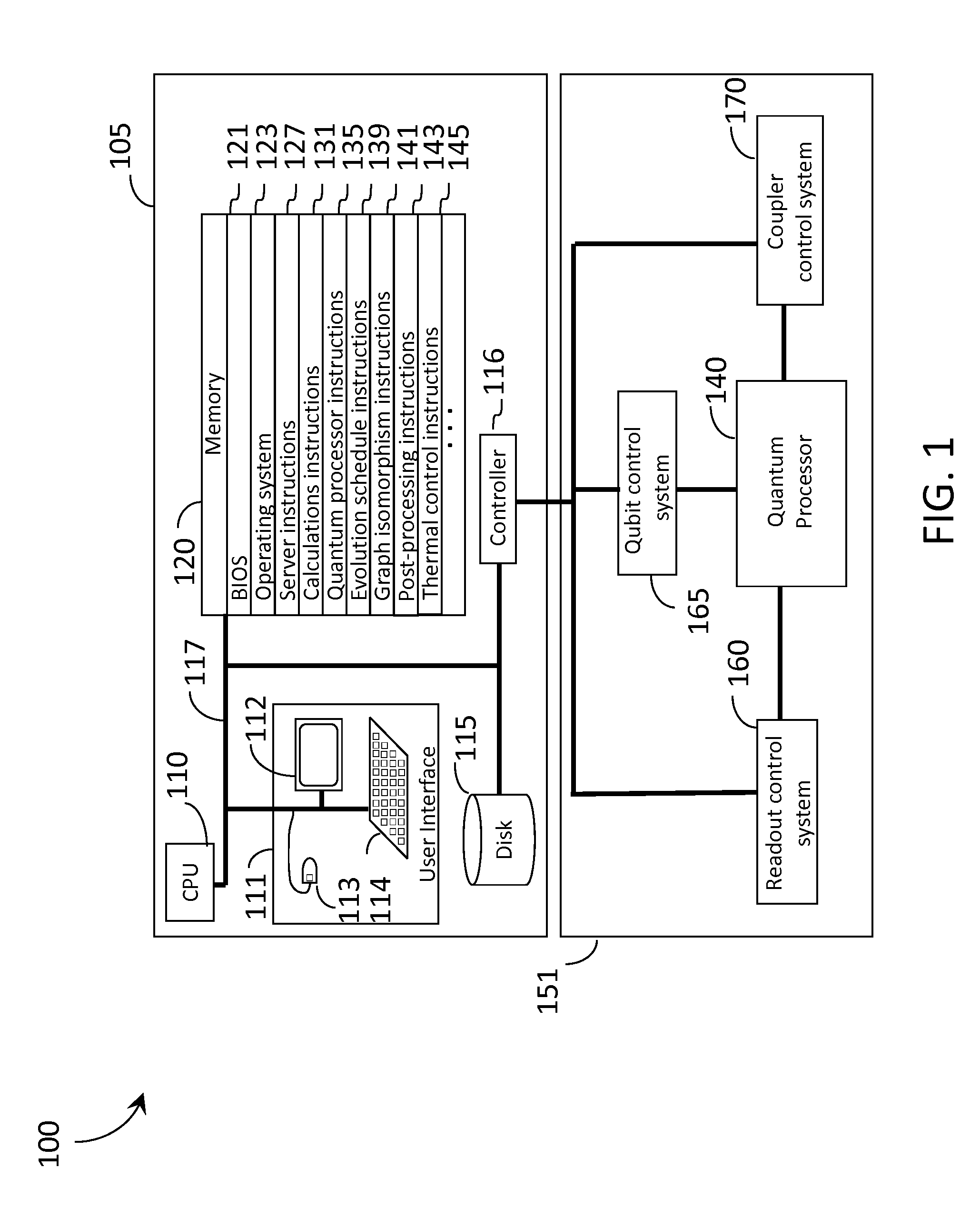

Systems and methods employing new evolution schedules in an analog computer with applications to determining isomorphic graphs and post-processing solutions

ActiveUS20150363708A1Quantum computersArchitecture with single central processing unitAnalog processorAnalog computer

A second problem Hamiltonian may replace a first problem Hamiltonian during evolution of an analog processor (e.g., quantum processor) during a first iteration in solving a first problem. This may be repeated during a second, or further successive iterations on the first problem, following re-initialization of the analog processor. An analog processor may evolve under a first non-monotonic evolution schedule during a first iteration, and second non-monotonic evolution schedule under second, or additional non-monotonic evolution schedule under even further iterations. A first graph and second graph may each be processed to extract final states versus a plurality of evolution schedules, and a determination made as to whether the first graph is isomorphic with respect to the second graph. An analog processor may evolve by decreasing a temperature of, and a set of quantum fluctuations, within the analog processor until the analog processor reaches a state preferred by a problem Hamiltonian.

Owner:D WAVE SYSTEMS INC

Processing relational database problems using analog processors

Owner:D WAVE SYSTEMS INC

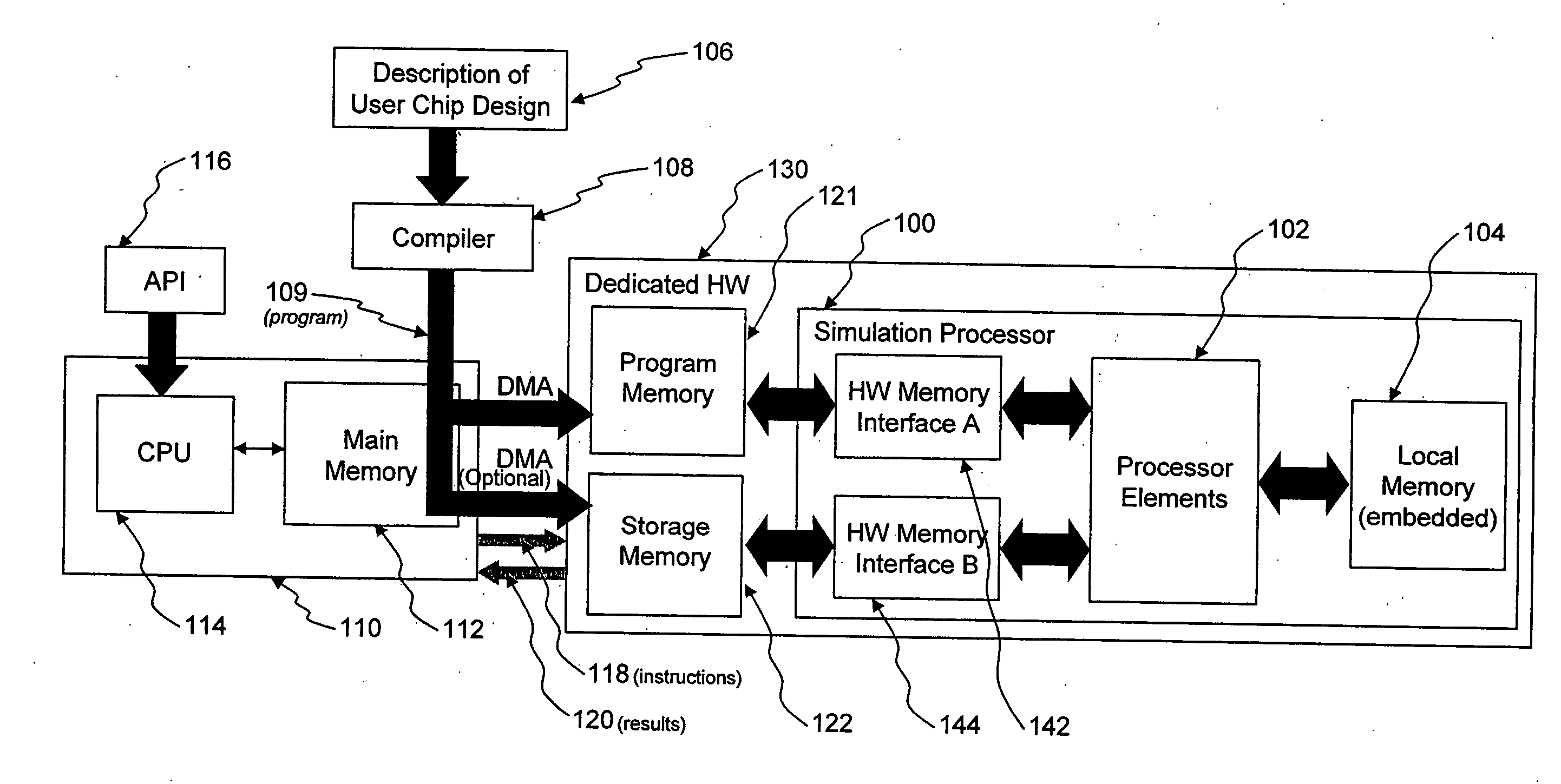

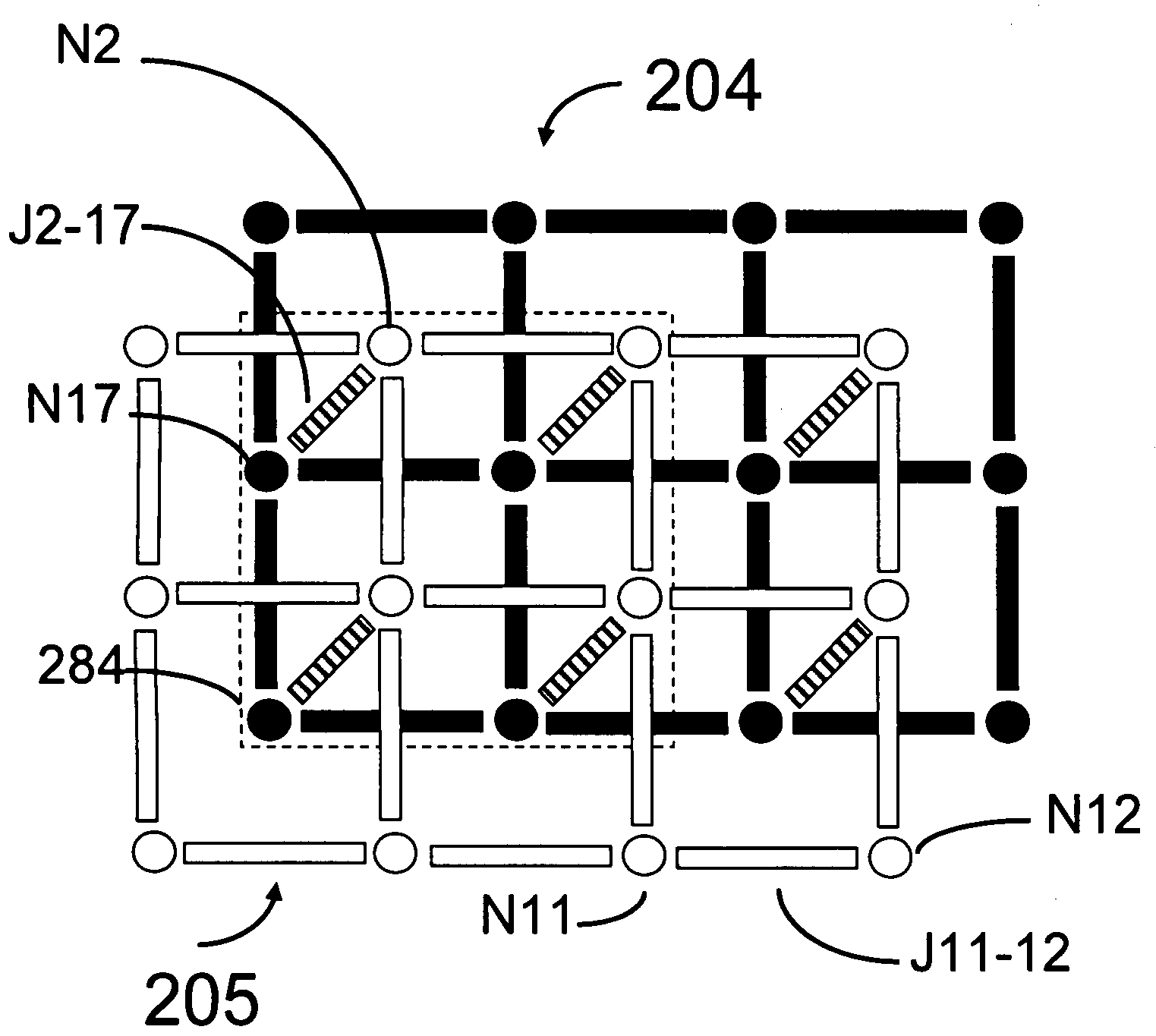

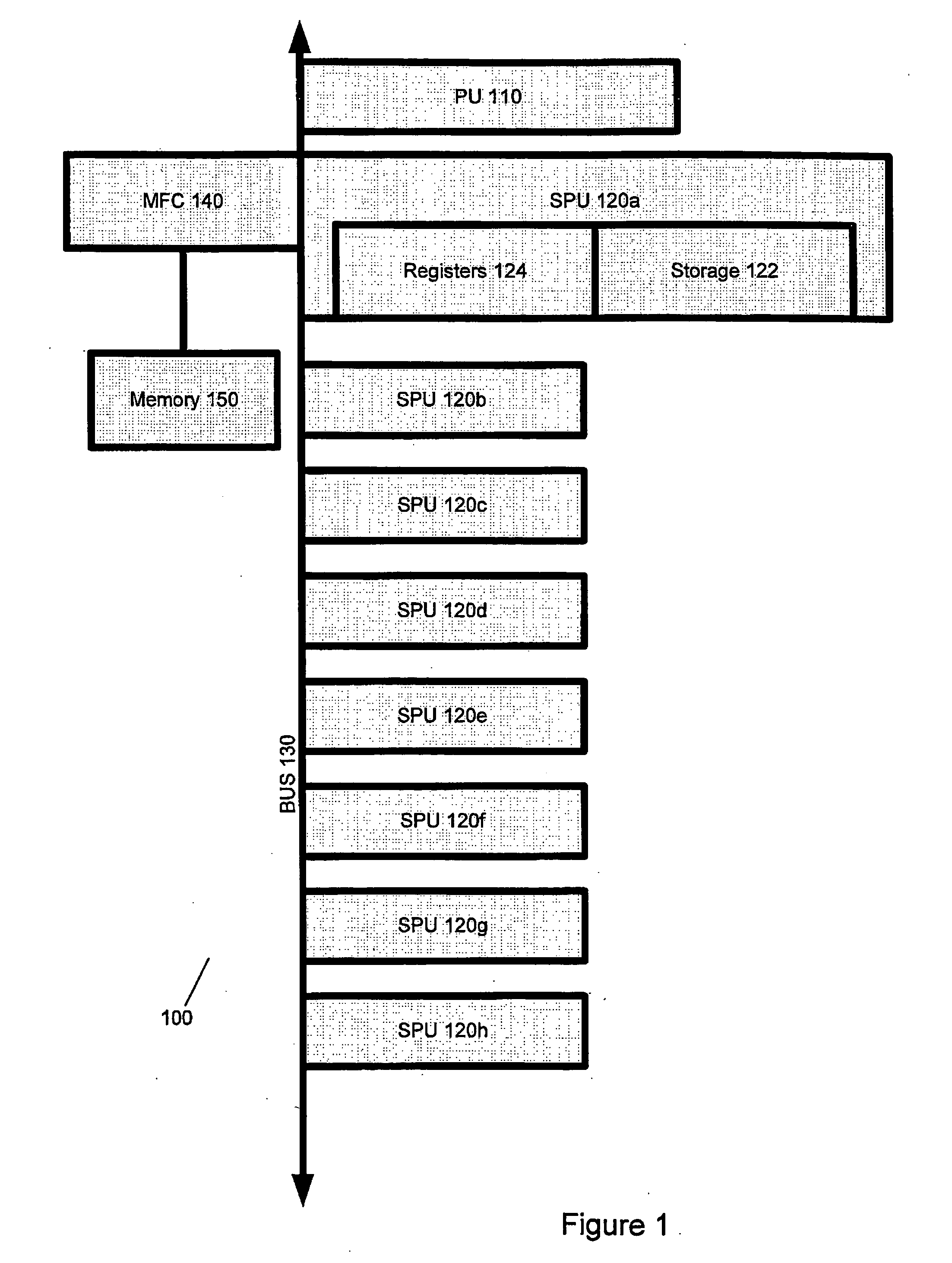

Hardware acceleration system for simulation of logic and memory

InactiveUS20070129926A1Improve simulation speedOvercome limitationsError detection/correctionCAD circuit designMemory addressAnalog processor

A hardware-accelerated simulator includes a storage memory and a program memory that are separately accessible by the simulation processor. The program memory stores instructions to be executed in order to simulate the chip. The storage memory is used to simulate the user memory. Since the program memory and storage memory are separately accessible by the simulation processor, the simulation of reads and writes to user memory does not block the transfer of instructions between the program memory and the simulation processor, thus increasing the speed of simulation. In one aspect, user memory addresses are mapped to storage memory addresses by adding a fixed, predetermined offset to the user memory address. Thus, no address translation is required at run-time.

Owner:LIGA SYST

Analog processor comprising quantum devices

ActiveUS20090167342A1Quantum computersLogic circuits characterised by logic functionComputational problemAnalog processor

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

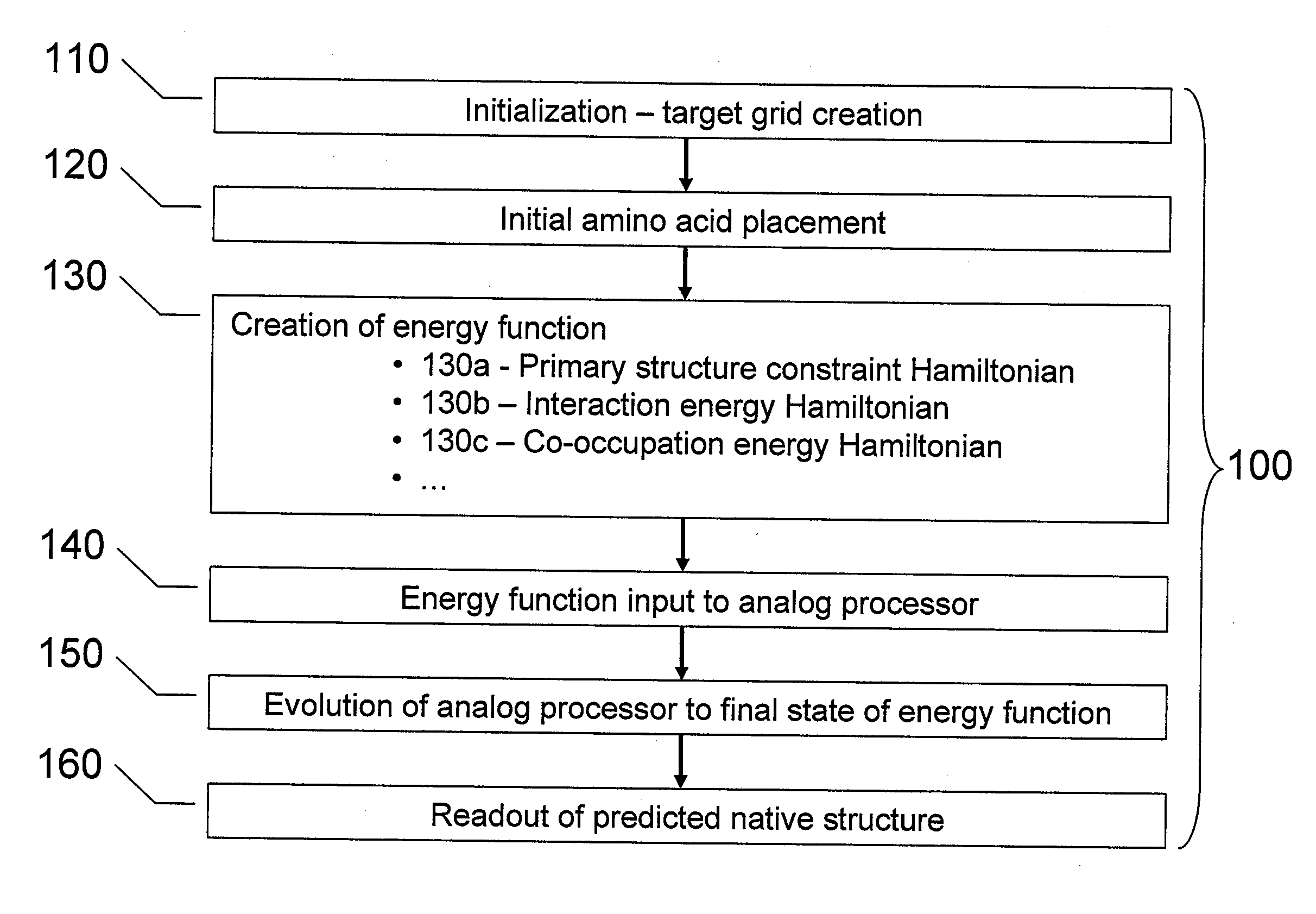

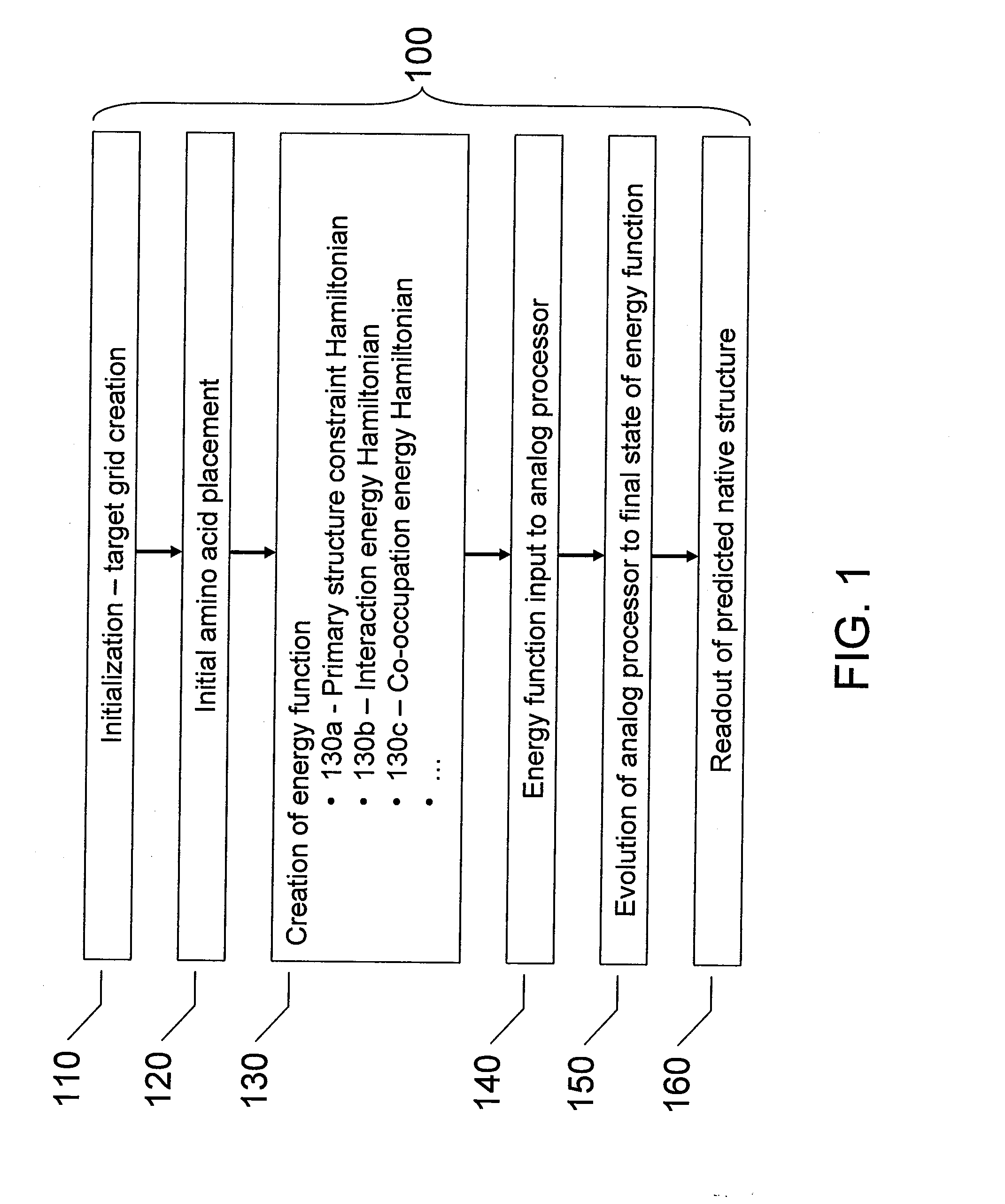

Systems, methods and apparatus for protein folding simulation

InactiveUS20080052055A1Improve legibilityAnalogue computers for chemical processesSpecial data processing applicationsNative structureAnalog processor

Analog processors such as quantum processors are employed to predict the native structures of proteins based on a primary structure of a protein. A target graph may be created of sufficient size to permit embedding of all possible native multi-dimensional topologies of the protein. At least one location in a target graph may be assigned to represent a respective amino acid forming the protein. An energy function is generated based assigned locations in the target graph. The energy function is mapped onto an analog processor, which is evolved from an initial state to a final state, the final state predicting a native structure of the protein.

Owner:D WAVE SYSTEMS INC

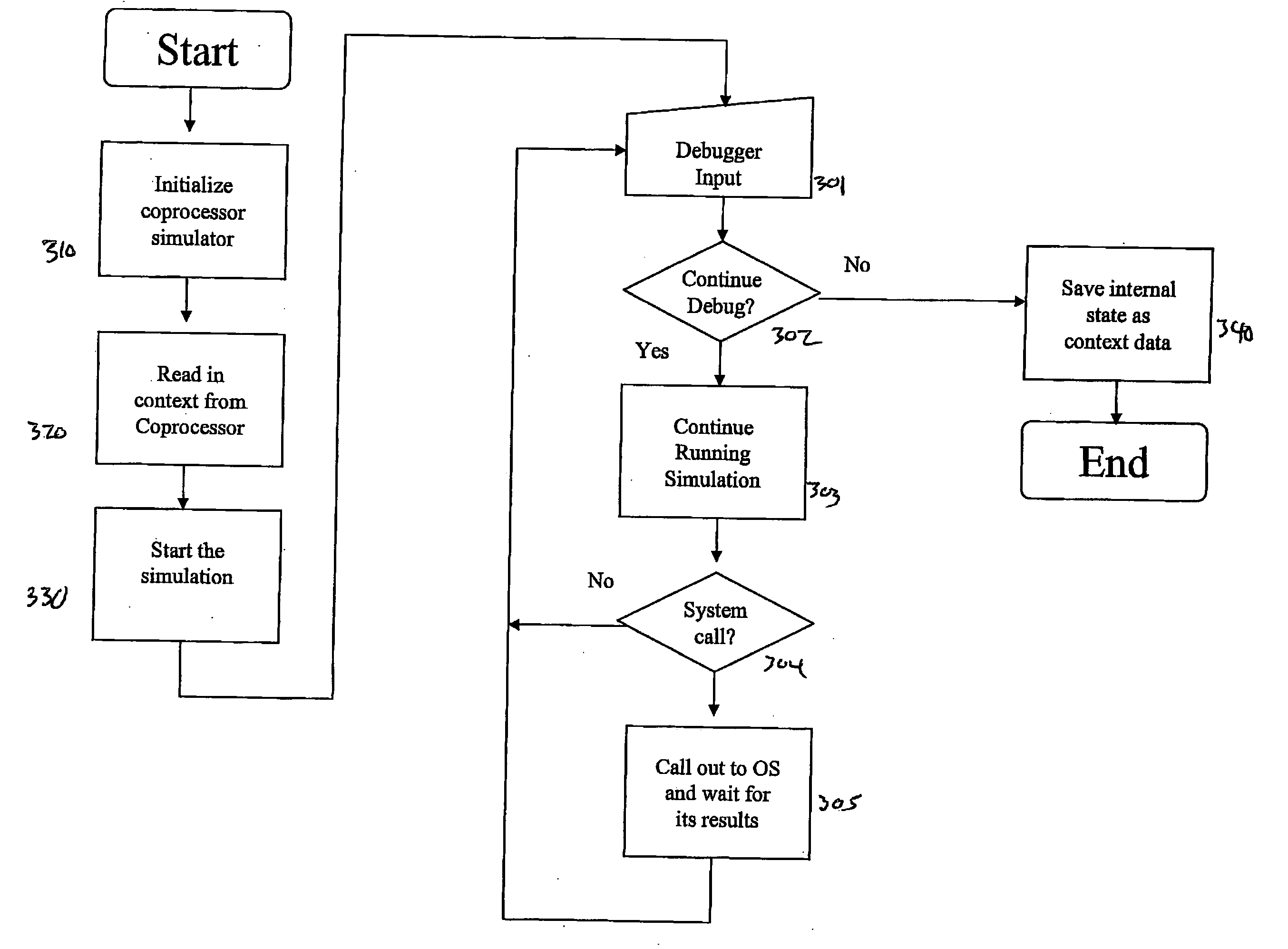

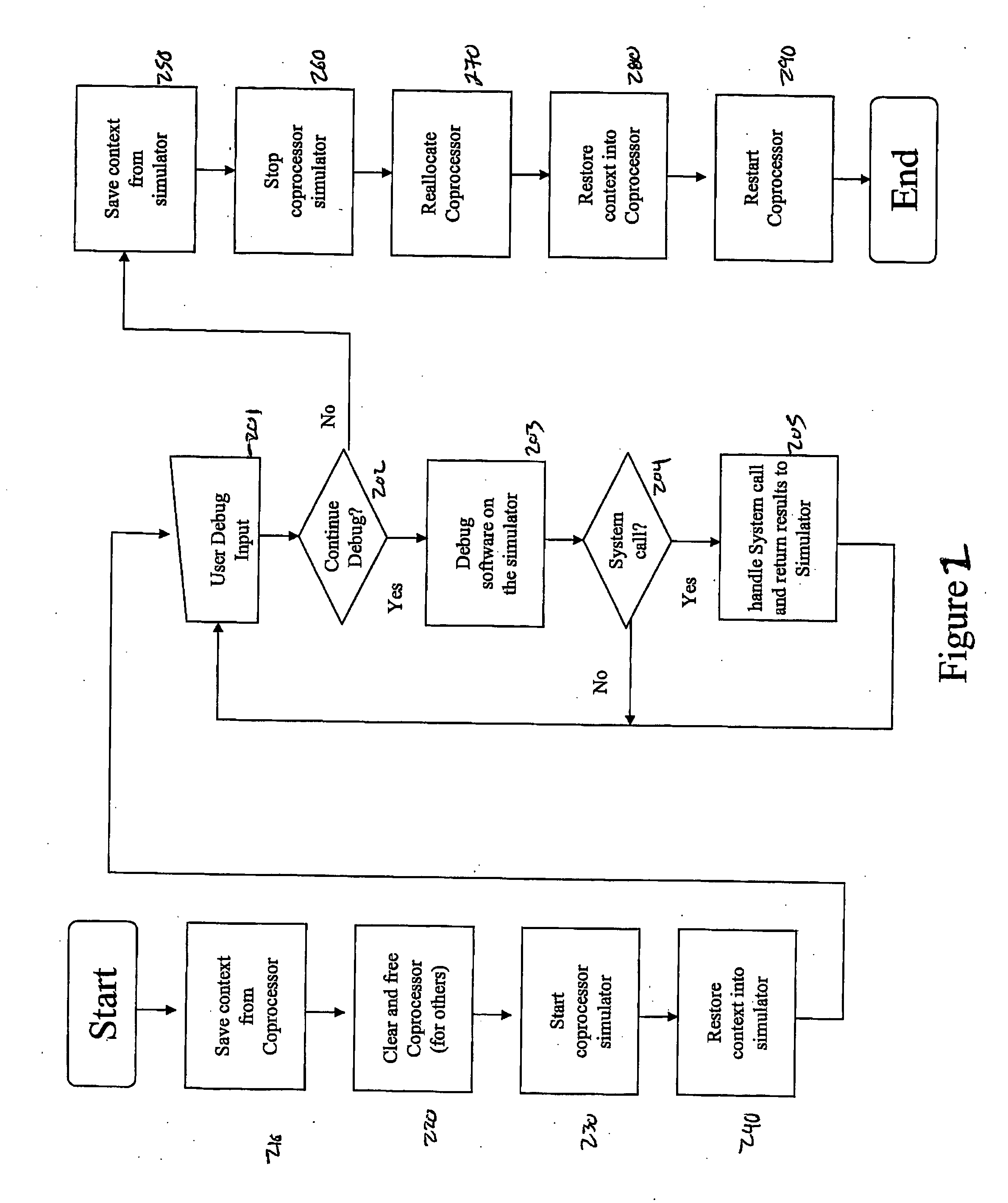

Method and system for software debugging using a simulator

Systems and methods for debugging software and / or hardware are disclosed. A processor may execute a program for a certain amount of time. The context of the processor at the end of that time may then be made available to a simulator operable to simulate the processor. The program can then be executed from that point on the simulator using the context. Additionally, a context resulting from the execution of the program on the simulator may result and be restored to the processor for continued execution.

Owner:KK TOSHIBA

Method and system for solving integer programming and discrete optimization problems using analog processors

Discrete optimization problem are solved using an analog optimization device such as a quantum processor. Problems are solved using an objective function and at least one constraint corresponding to the discrete optimization problems. The objective function is converted into a first set of inputs and the at least one constraint is converted into a second set of inputs for the analog optimization device. A third set of inputs is generated which are indicative of at least one penalty coefficient. A final state of the analog optimization device corresponds to at least a portion of the solution to the discrete optimization problem.

Owner:D WAVE SYSTEMS INC

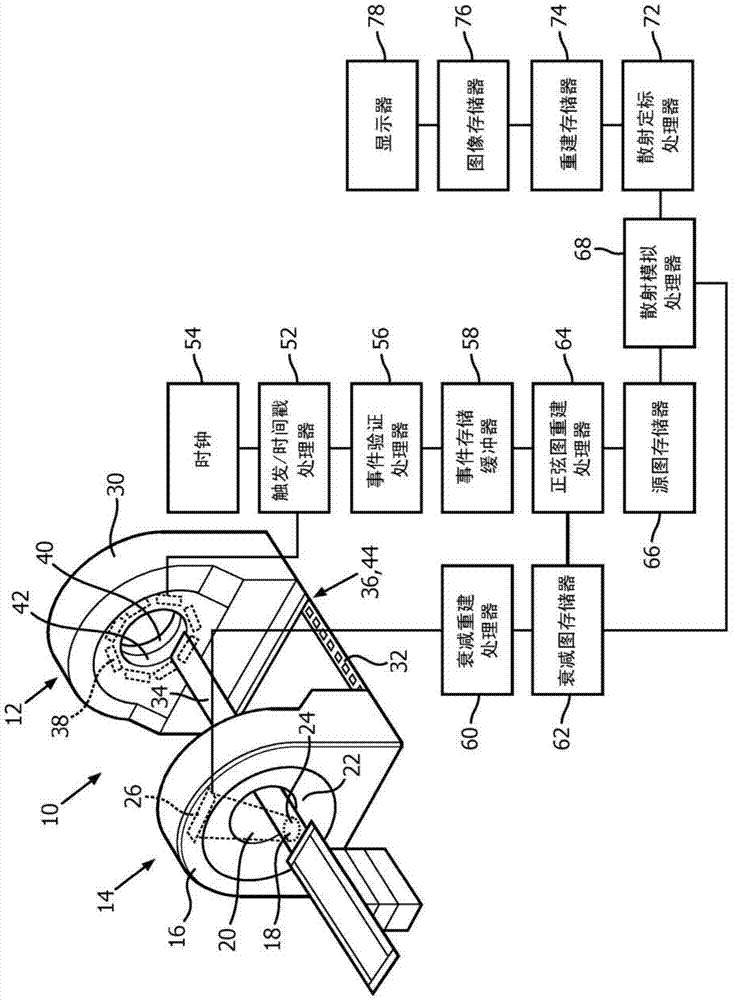

Fast scatter estimation in PET reconstruction.

ActiveCN104335247AAccurate estimateQuick estimateReconstruction from projectionImaging processingAnalog processor

An image processing apparatus includes a scatter simulation processor which processes measured sinograms generated from imaging data acquired for an imaging subject by an imaging apparatus to produce a scatter sinogram that represents a shape of scatter contribution. A scatter scaling processor utilizesa Monte Carlo simulation to determine a scatter fraction and scales the scatter sinogram to generate a scaled scatter sinogram that matches the scatter contribution in the measured sinogram. A reconstruction processor reconstructs the imaging data into an image representation using the scaled scatter sinogram for scatter correction.

Owner:KONINKLJIJKE PHILIPS NV

Graph embedding techniques

ActiveUS20110238607A1Maximizing number2D-image generationKnowledge representationAnalog processorAlgorithm

Approaches to embedding source graphs into targets graphs in a computing system are disclosed. Such may be advantageously facilitate computation with computing systems that employ one or more analog processors, for example one or more quantum processors.

Owner:D WAVE SYSTEMS INC

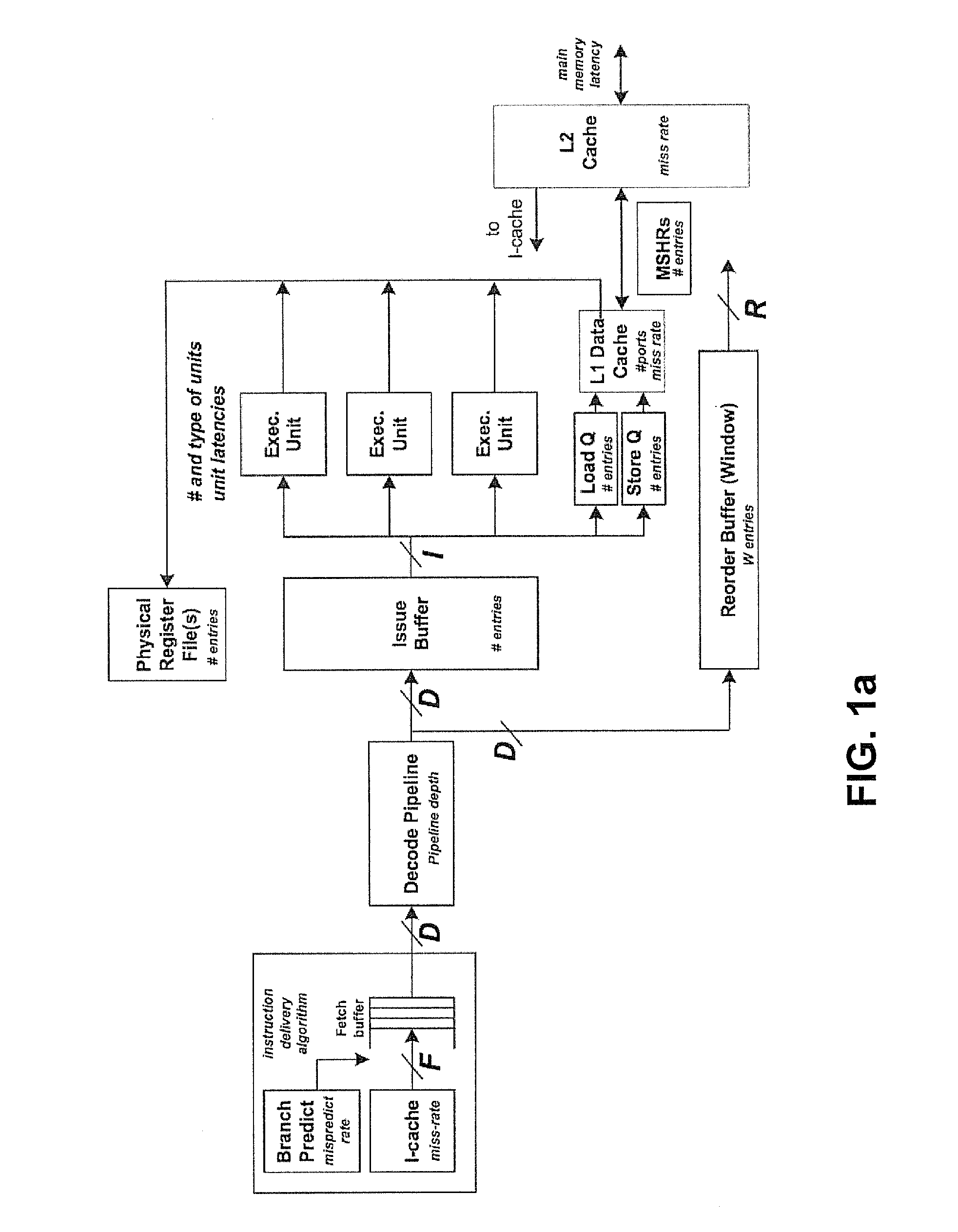

Methods and systems for simulating a processor

InactiveUS20110295587A1Accurate time informationEffective simulationError detection/correctionCAD circuit designAnalog processorParallel computing

A method is described for simulating a set of instructions to be executed on a processor. The method comprises performing a functional simulation of the processor over a number of simulation cycles. Performing the functional simulation of the processor thereby may comprise using an analytical model comprising a timing estimator and estimating during the functional simulation timing information of the processor.

Owner:UNIV GENT

Analog processor comprising quantum devices

ActiveCN101088102AComputing modelsDissimilar materials junction devicesAnalog processorComputational problem

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

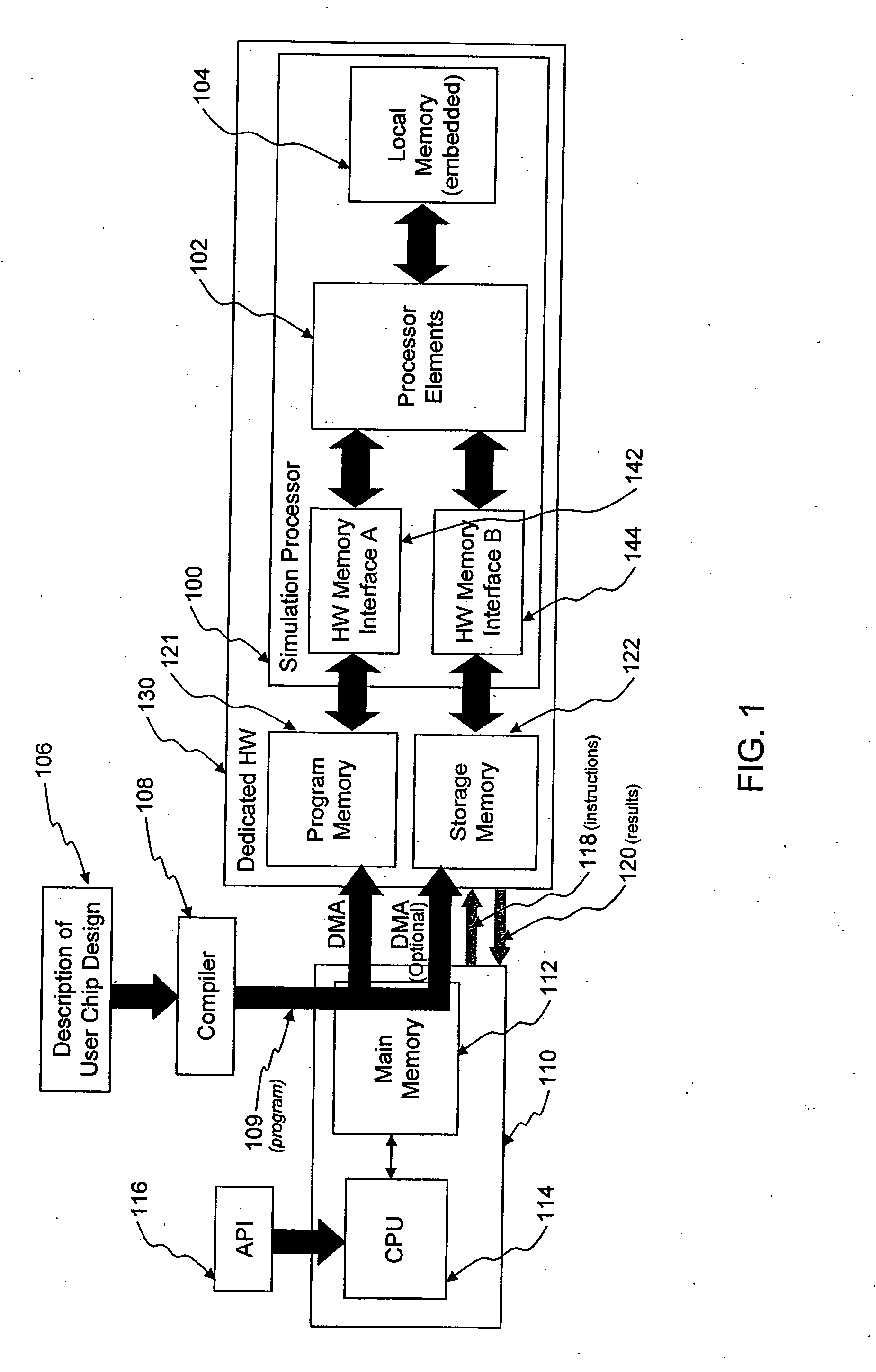

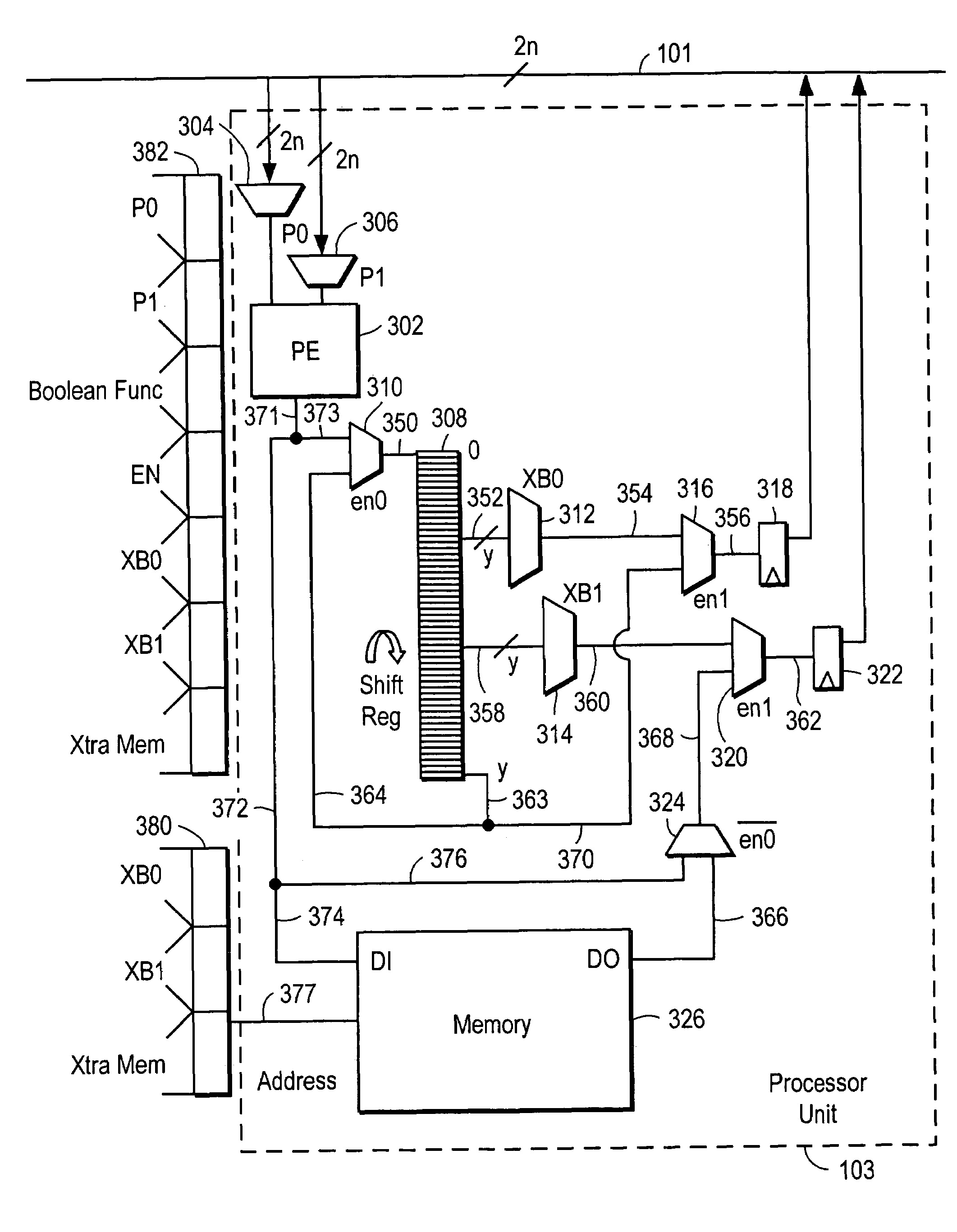

Hardware acceleration system for logic simulation using shift register as local cache

InactiveUS7444276B2Simplify hardware designShorten the lengthGeneral purpose stored program computerComputer aided designShift registerProcessor element

A logic simulation processor stores in a shift register intermediate values generated during the logic simulation. The simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic gate, and a shift register associated with the processor element. The shift register includes multiple entries to store the intermediate values, and is coupled to receive the output of the processor element. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units may further include a local memory for storing data from, and loading the data to, the simulation processor.

Owner:LIGA SYST

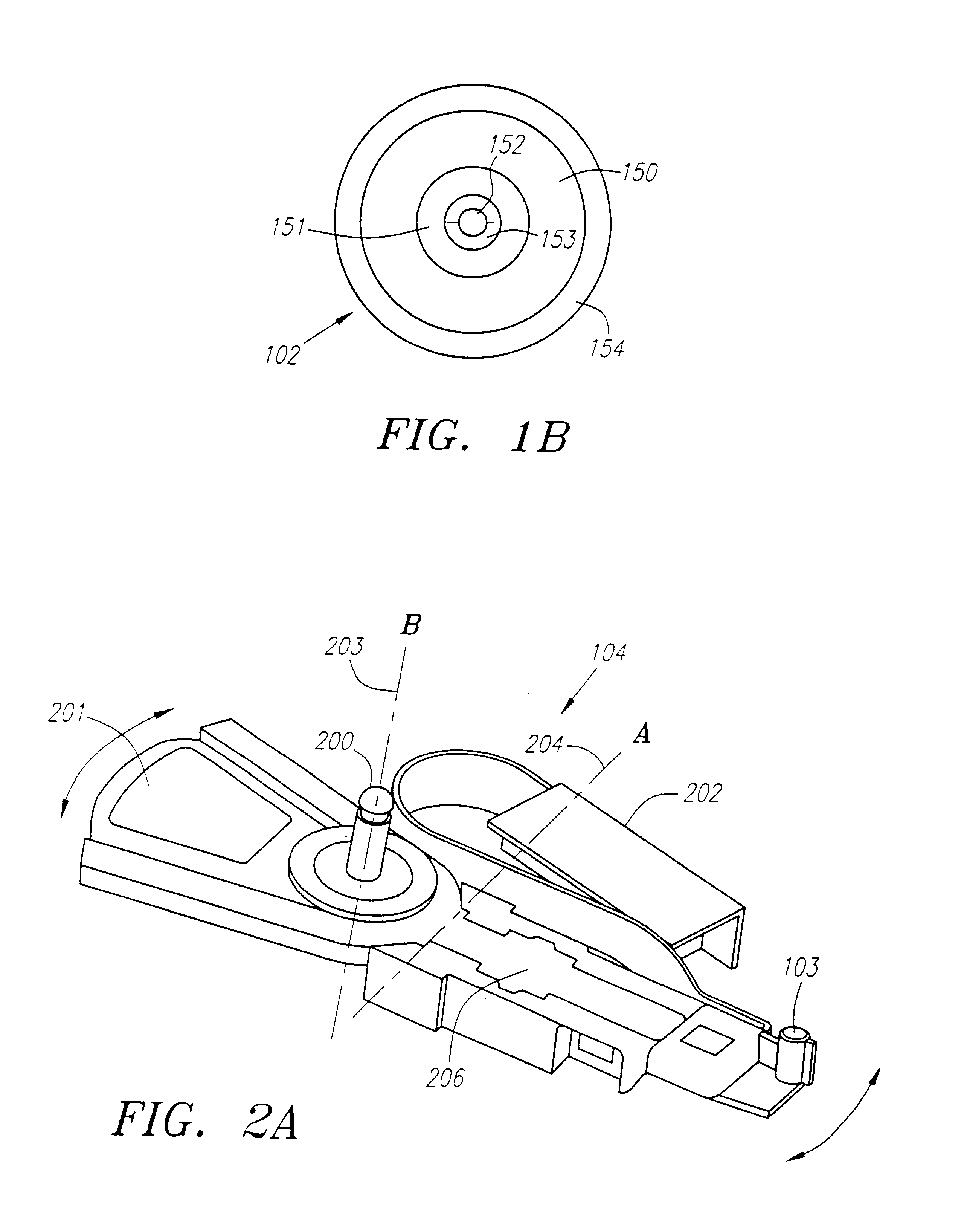

Digital focus and tracking servo system

InactiveUS6809995B2Television system detailsRecord information storageAnalog processorControl signal

A digital servo system for controlling tracking or focus in an optical disk driver is presented. A servo system according to the present invention includes an optical pick-up with detectors providing optical signals, an analog processor receiving the optical signals and providing a digital signal, and digital processors receiving the digital signal and providing a control signal that controls the position of the optical pick-up unit. The digital processor executes an algorithm that calculates an error signal, provides amplification and biasing to the error signal, provides filtering for the error signal, and computes the control signal. The error signal can be the focus error signal or the tracking error signal.

Owner:RPX CORP

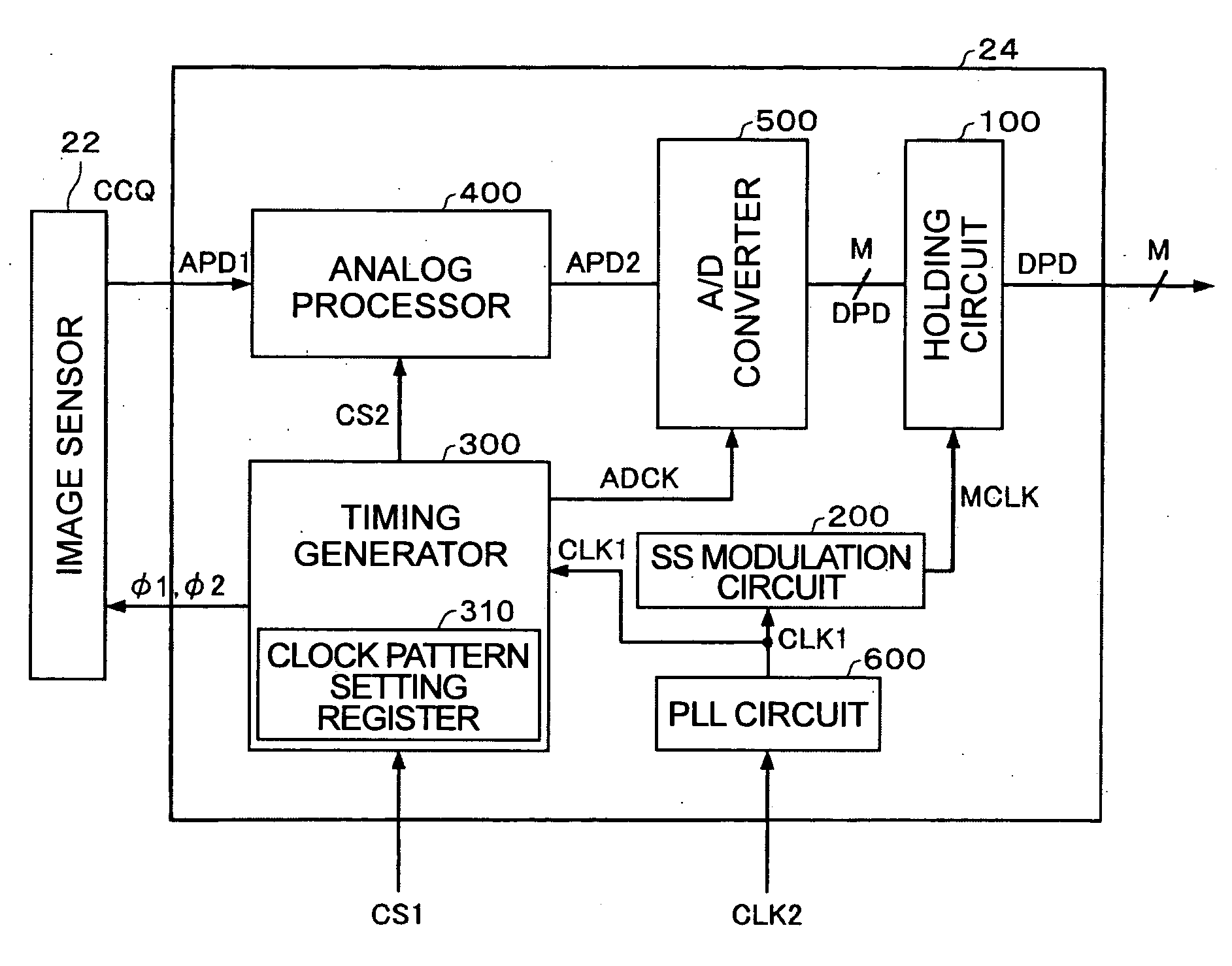

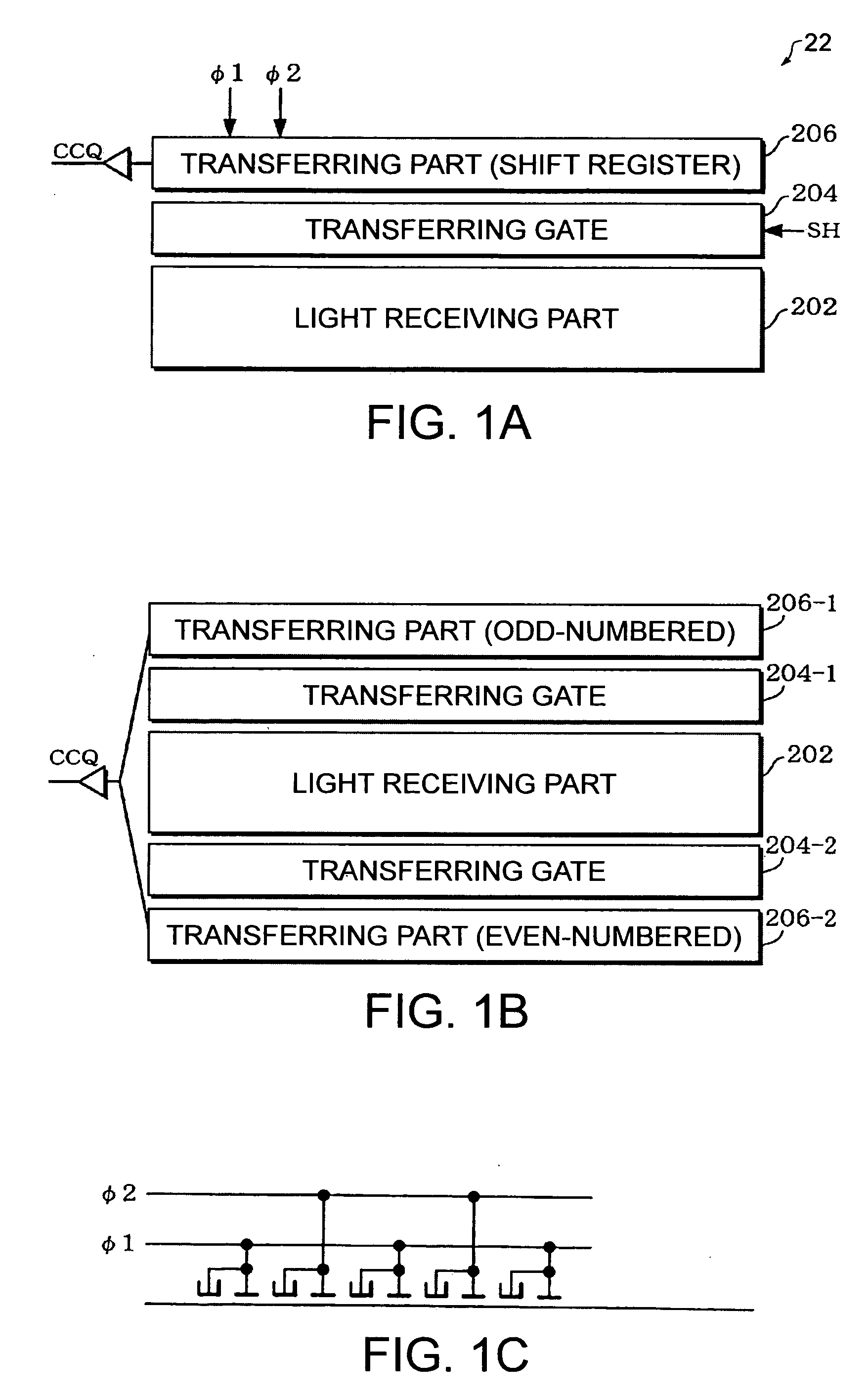

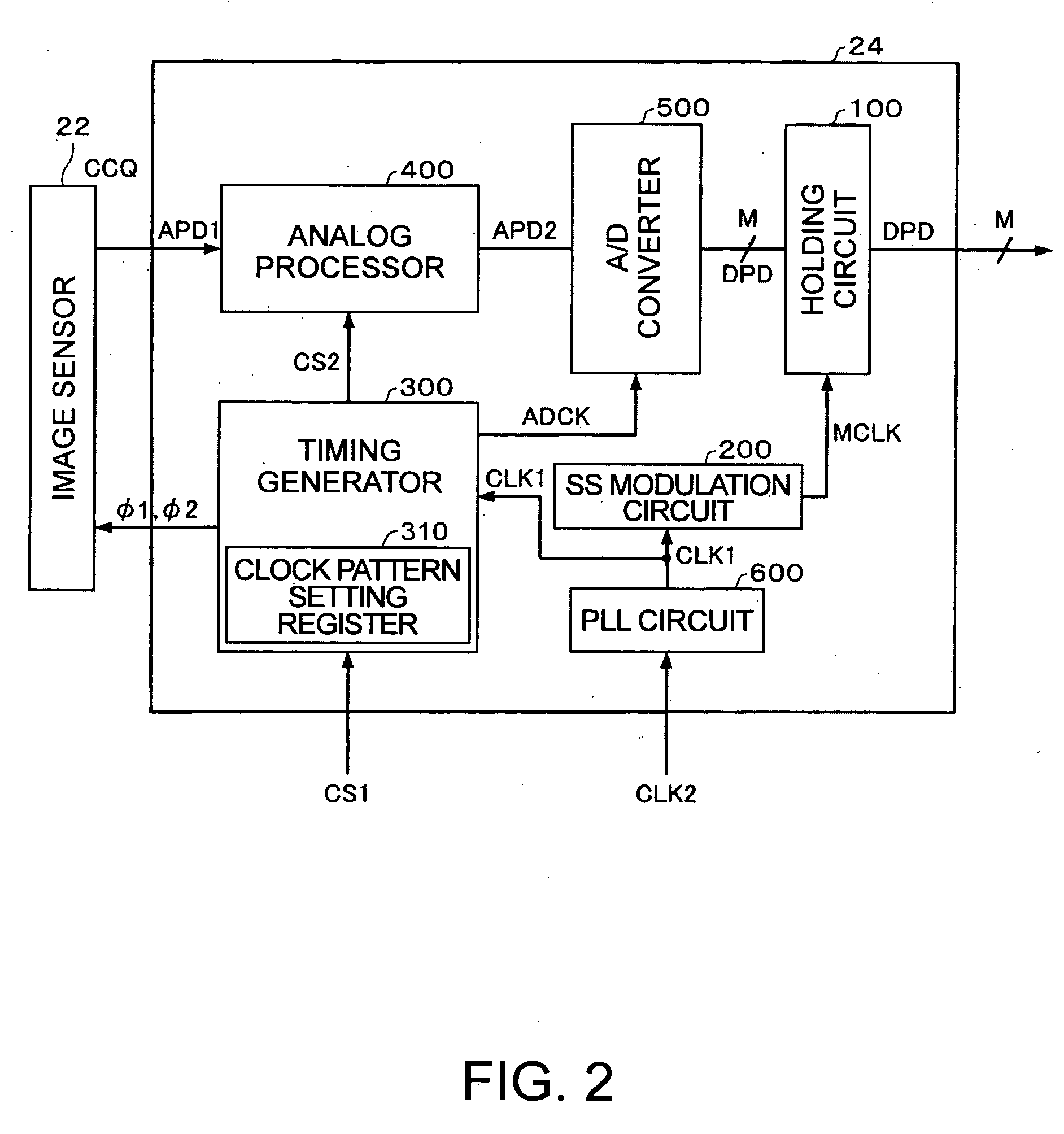

Analog front-end circuit and electronic apparatus

InactiveUS20060176525A1Reduce degradationReduce radiated noisePictoral communicationTiming generatorAnalog processor

An analog front-end circuit that controls an imaging device and processes an analog image signal output from the imaging device comprises: an analog processor that receives an analog image signal from the imaging device, provides the image signal with predetermined processing, and outputs a resultant signal; an A / D converter that performs A / D conversion with the image signal output from the analog processor; a holding circuit that holds digital image data output from the A / D converter; a timing generator that, based on a first reference clock, generates a plurality of clocks and outputs the clocks to at least one of the analog processor and the A / D converter; and a spread spectrum modulation circuit that performs spread spectrum modulation with the first reference clock and outputs a resultant clock that has been subject to the spread spectrum modulation as a modulated clock to the holding circuit; wherein the holding circuit holds the digital image data from the A / D converter based on the modulated clock output from the spread spectrum modulation circuit.

Owner:SEIKO EPSON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com