Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

479 results about "Timing generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

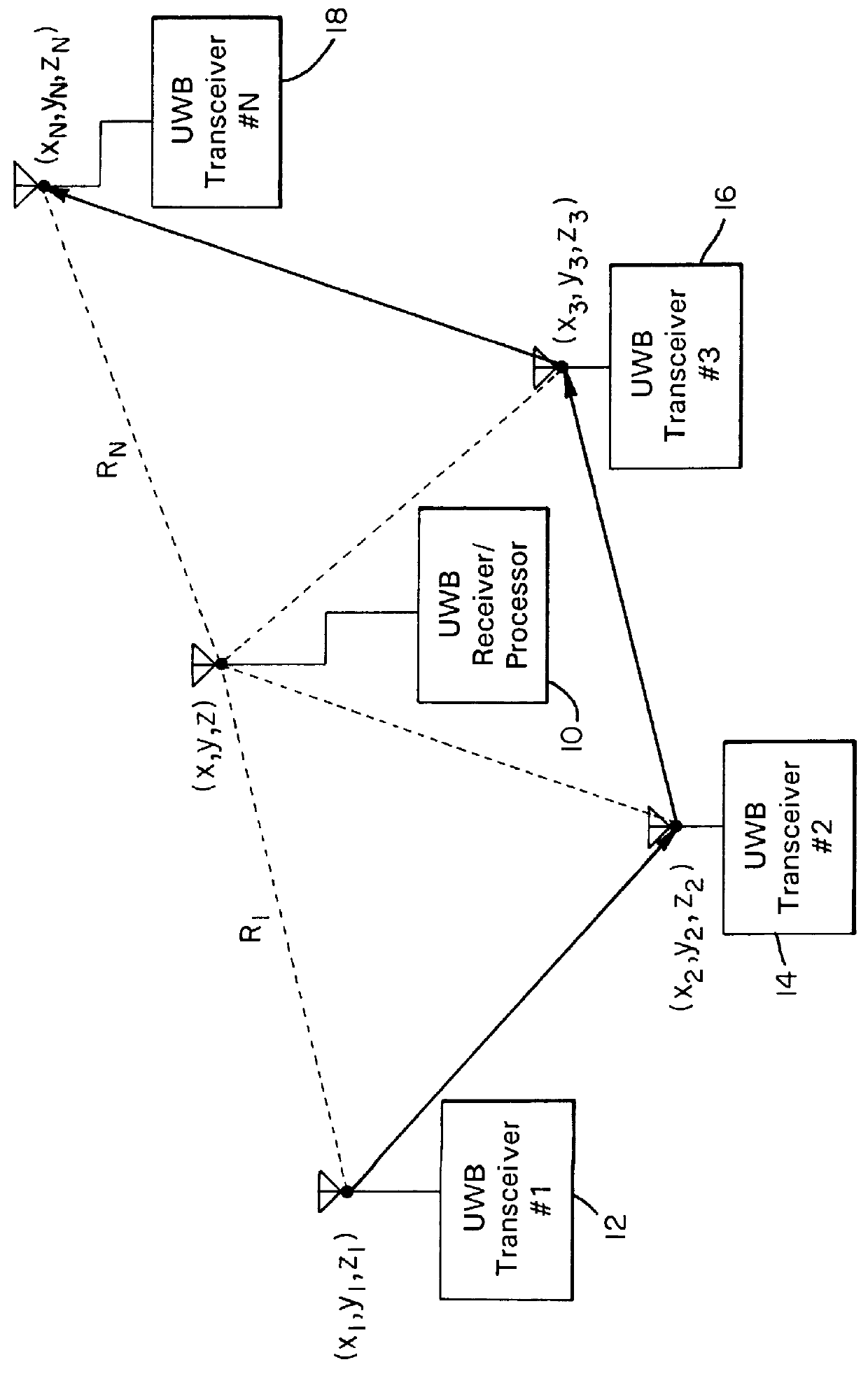

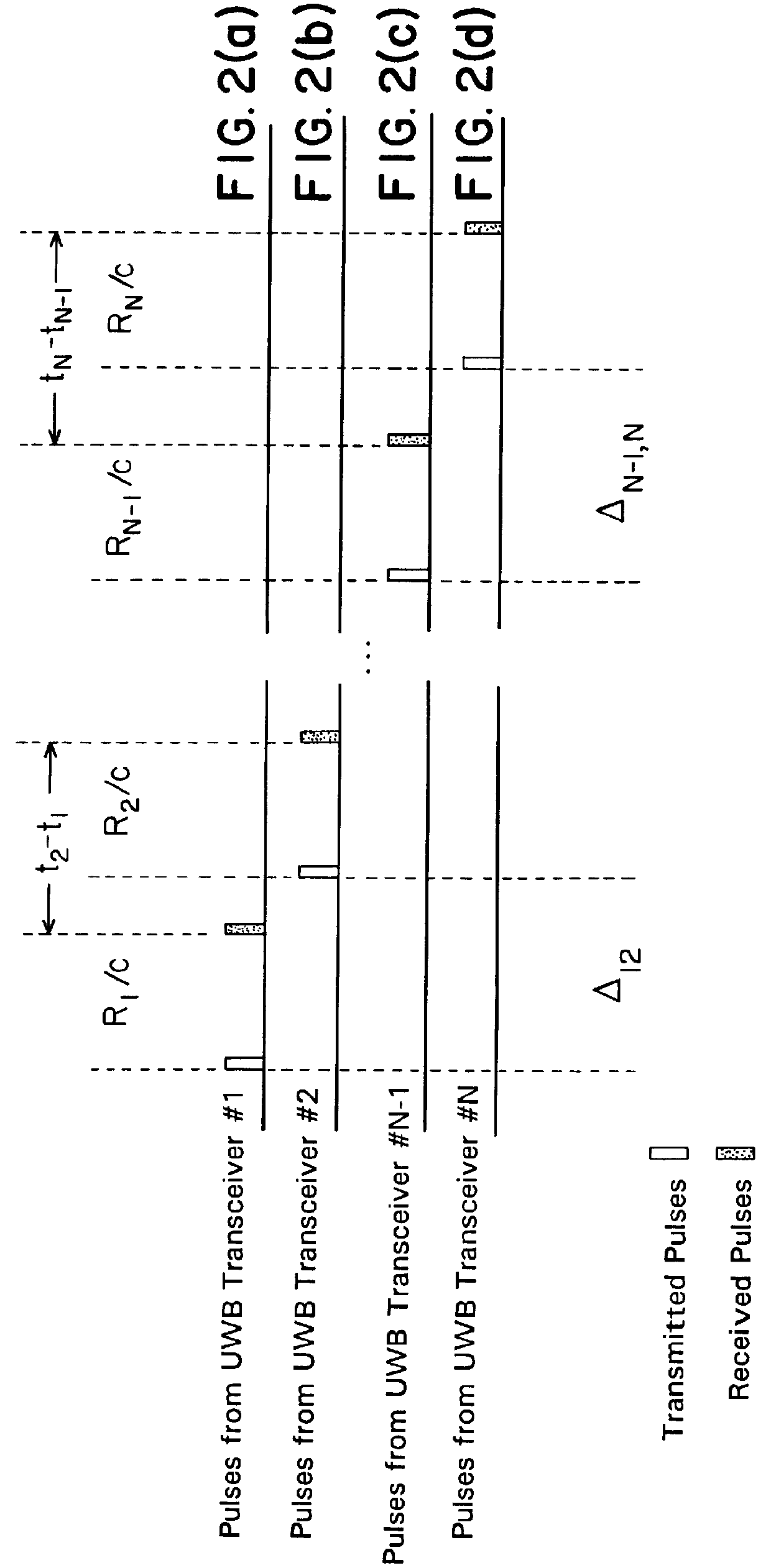

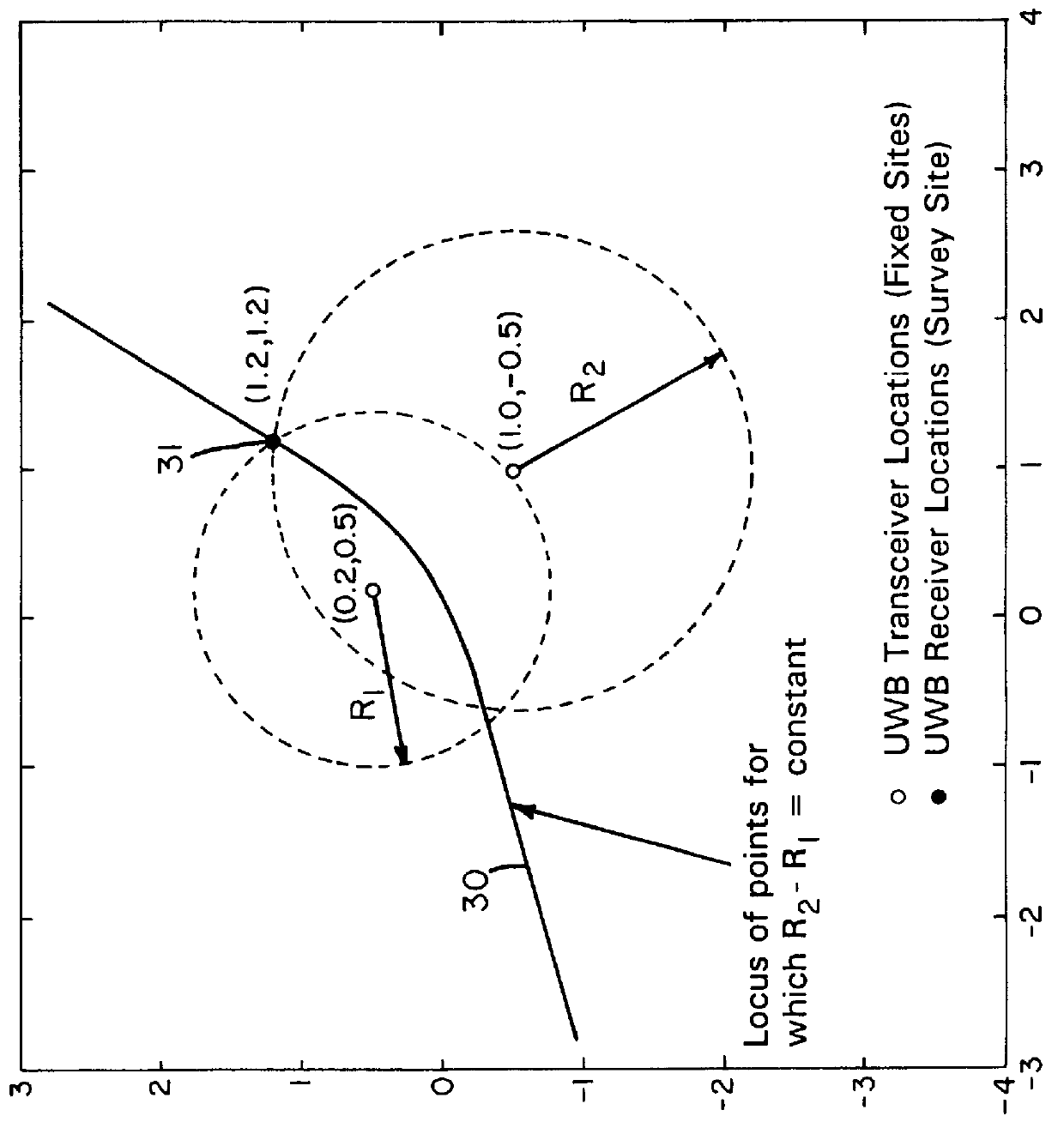

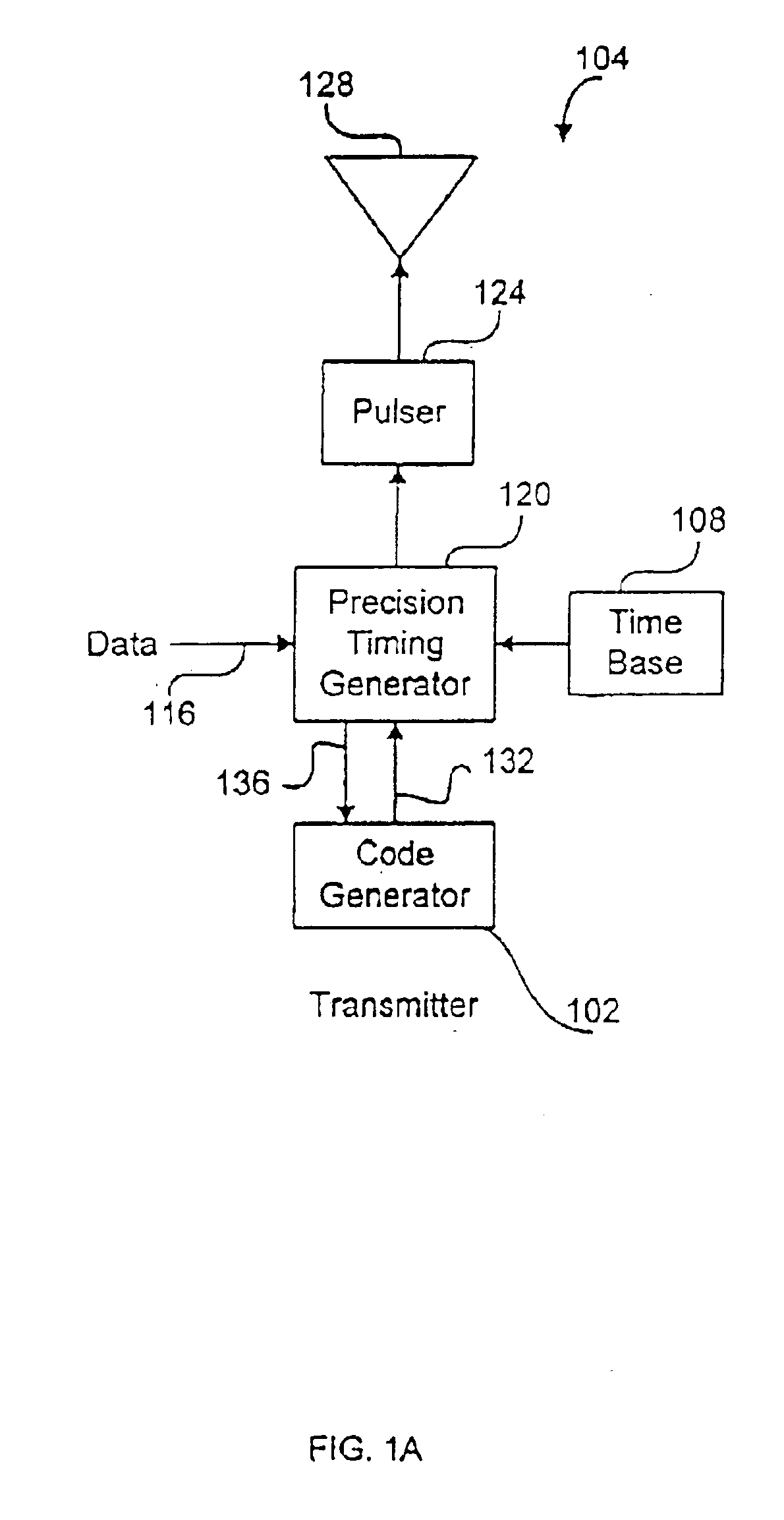

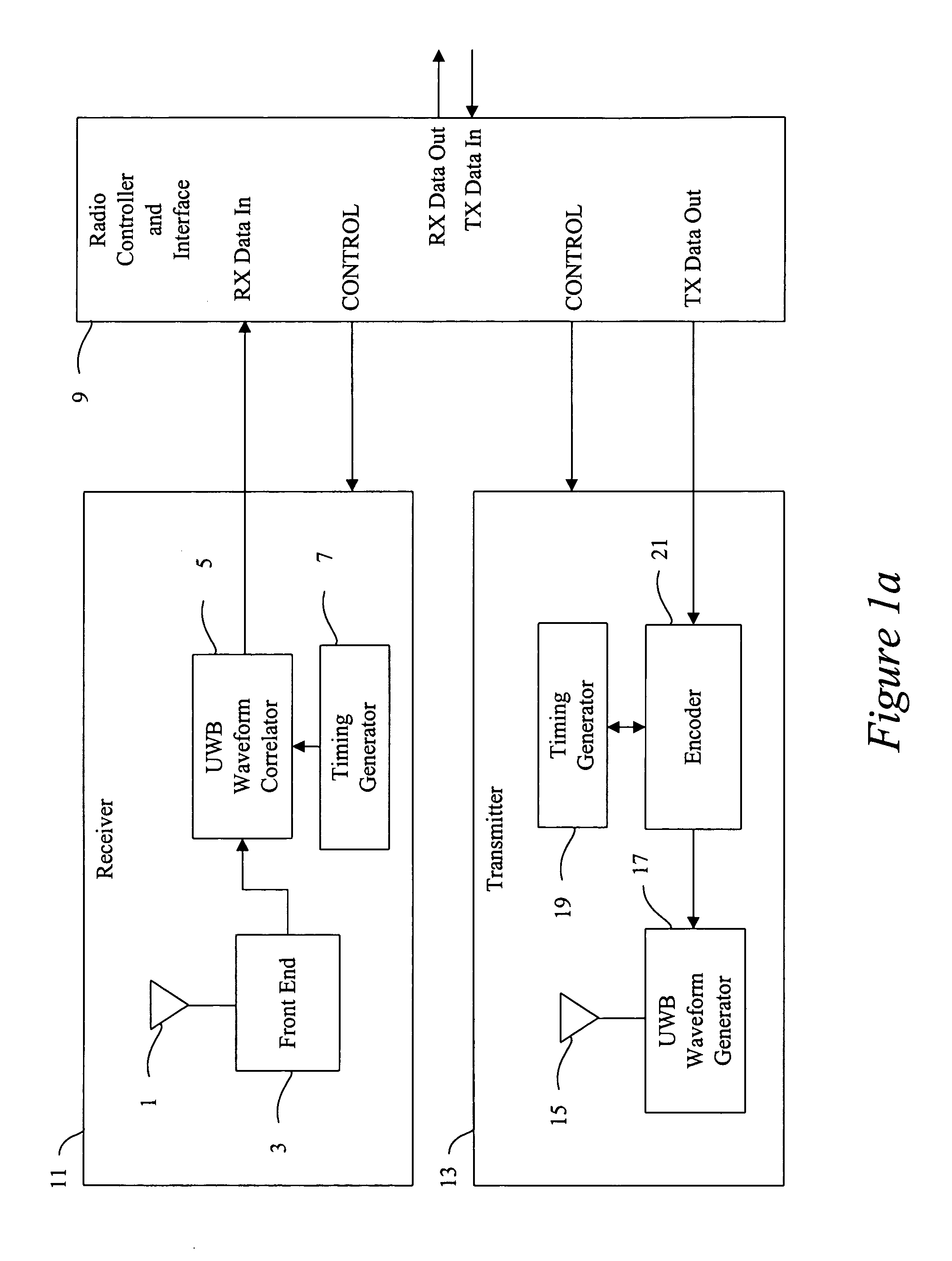

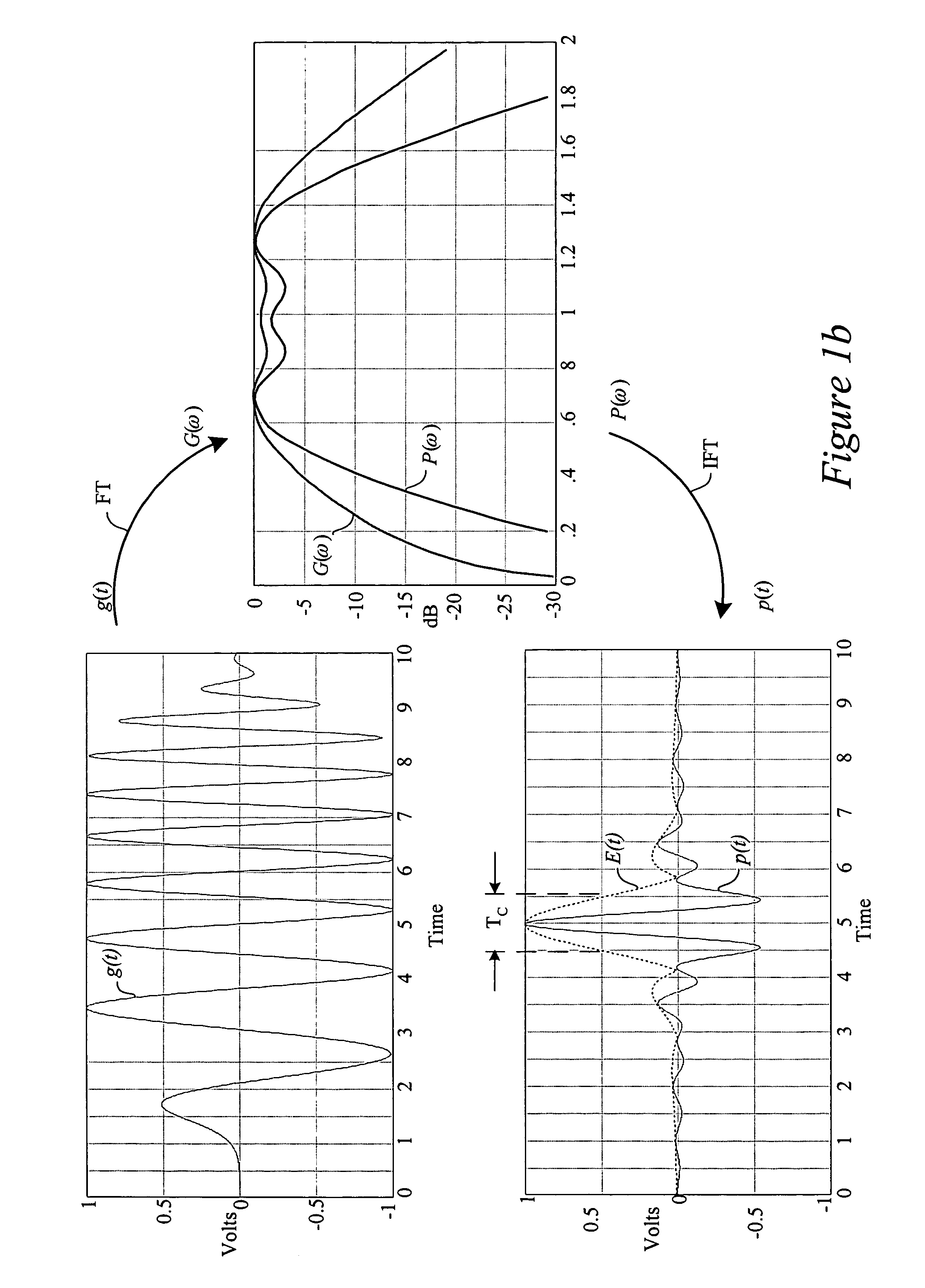

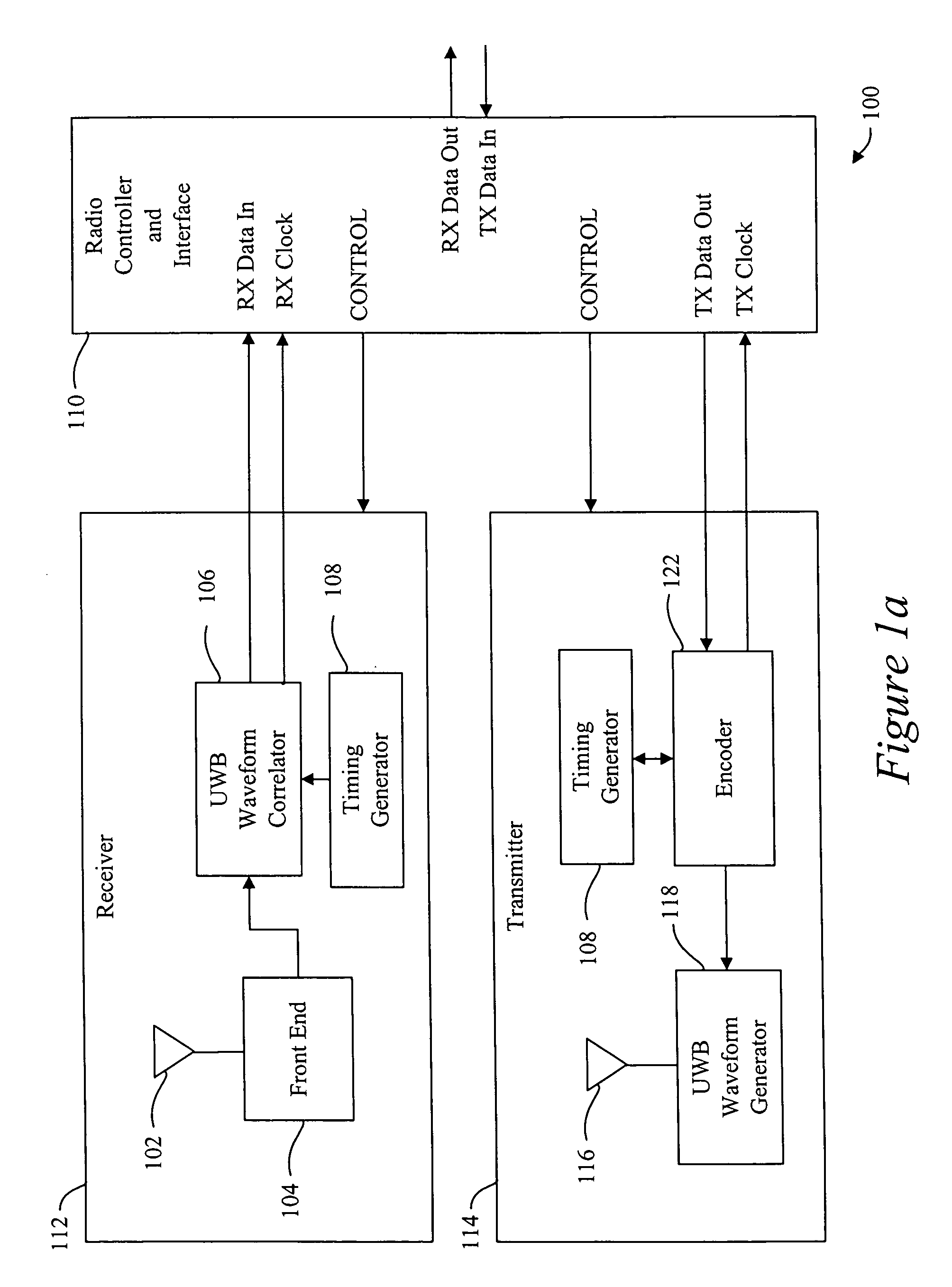

Ultra wideband precision geolocation system

InactiveUS6054950AEliminate needDirection finders using radio wavesPosition fixationUltra-widebandTransceiver

An ultra wideband (UWB) or short-pulse transmission system that enables precise tracking or geolocation of a target over distances of several kilometers. The system includes a set of N (where N>2) untethered UWB transceivers located at fixed positions, an untethered UWB receiver at the target, and a processor at the target for resolving time-of-flight measurement ambiguities of received pulses to determine precise geolocation by solving a set of equations according to time-of-flight measurements and surveyed positions of N-1 transceivers. To eliminate a clock distribution system, self-synchronizing of pulse timing is achieved by generating a start pulse at one of the untethered transceivers. Alternatively, a timing source may be provided by a GPS or other timing generator at the transceivers in order to synchronize emissions of their pulses.

Owner:ZEBRA TECH CORP

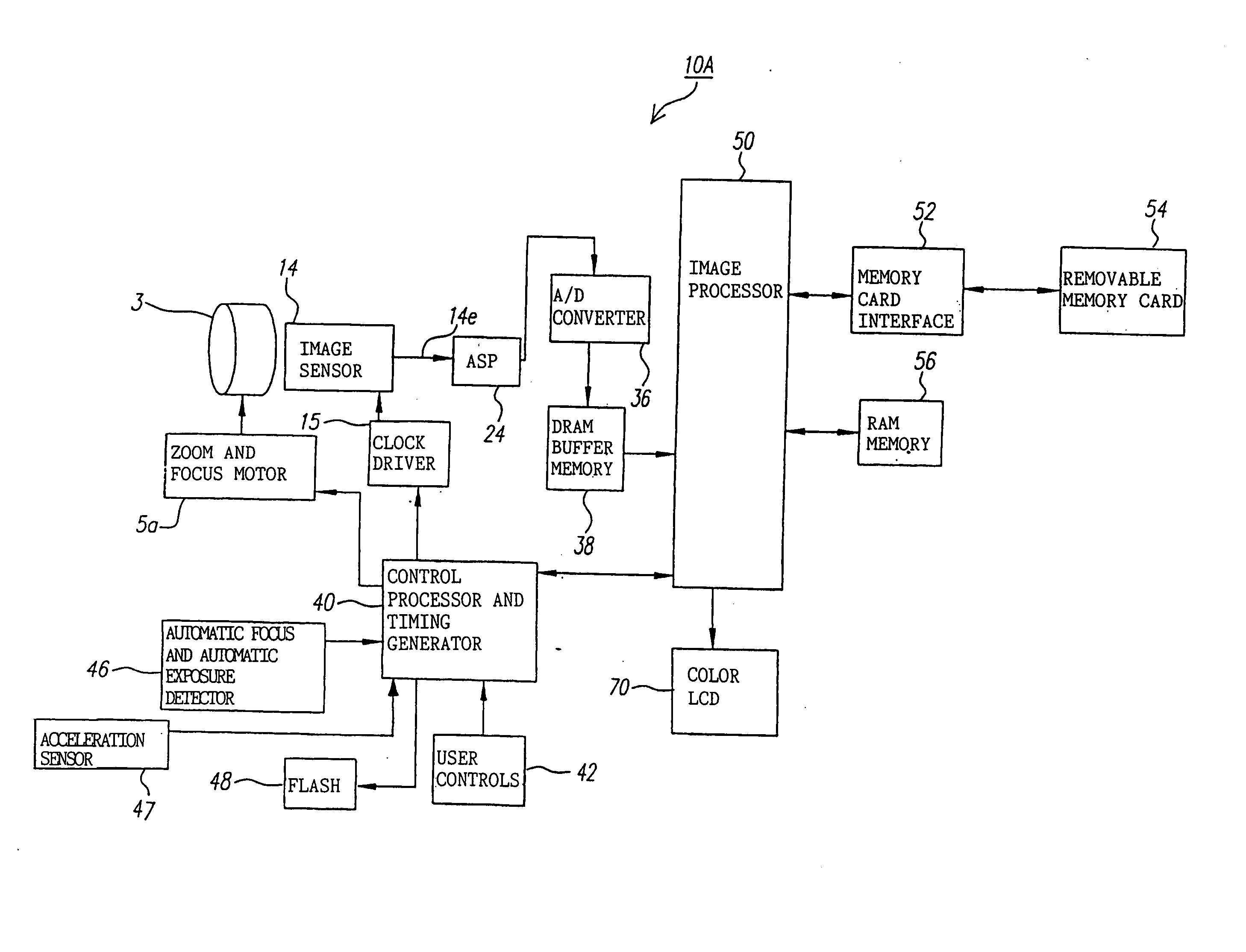

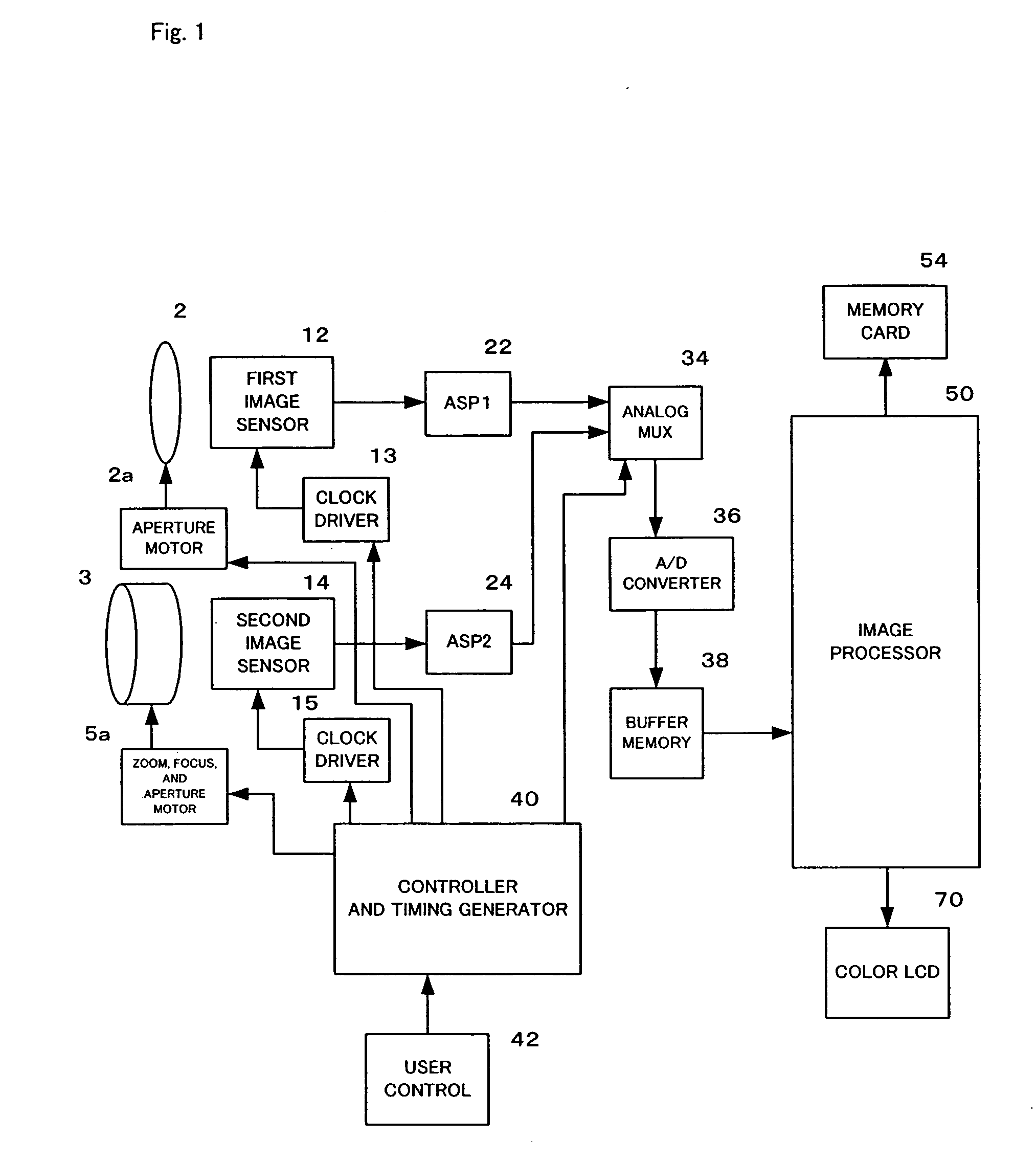

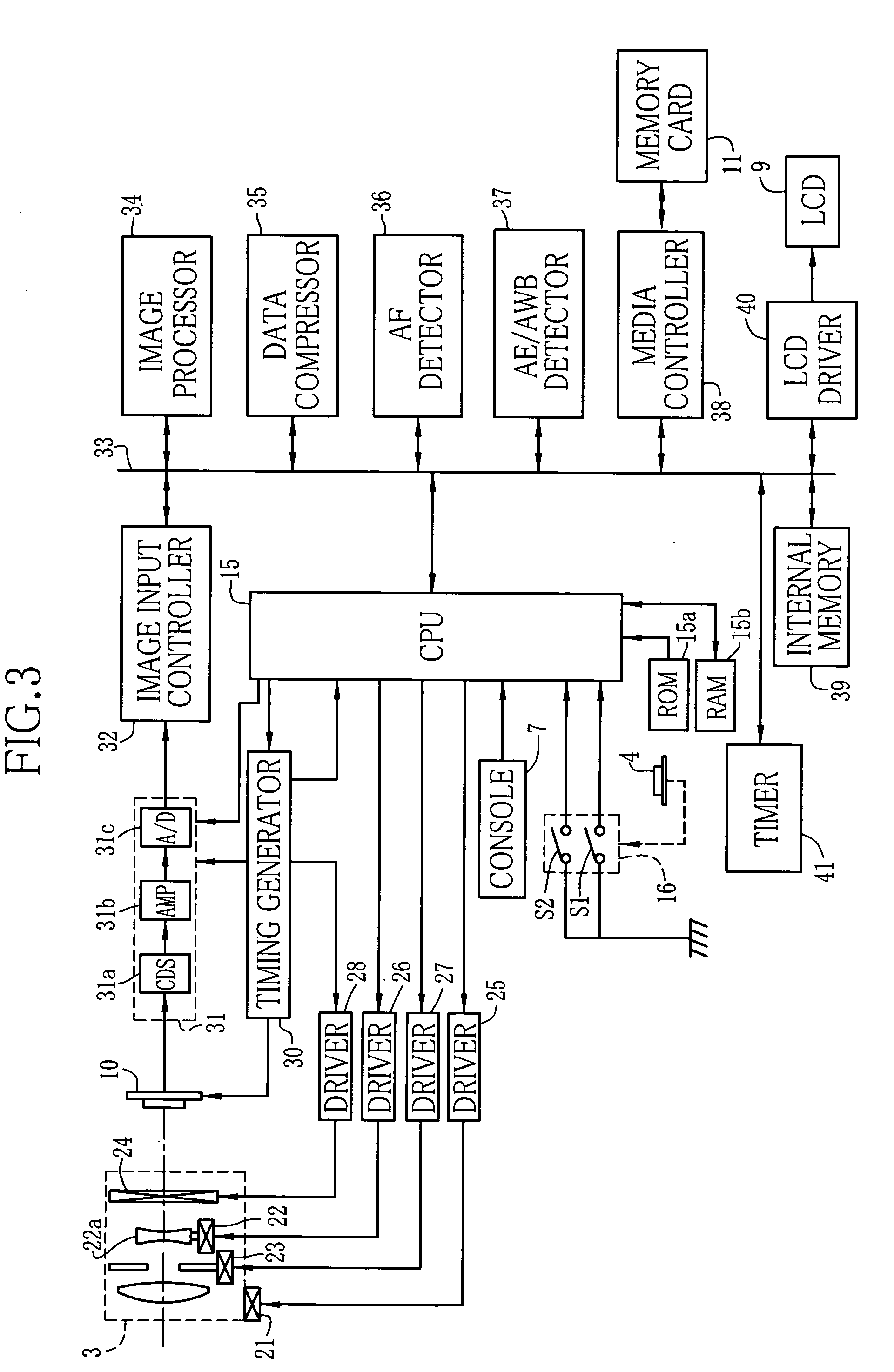

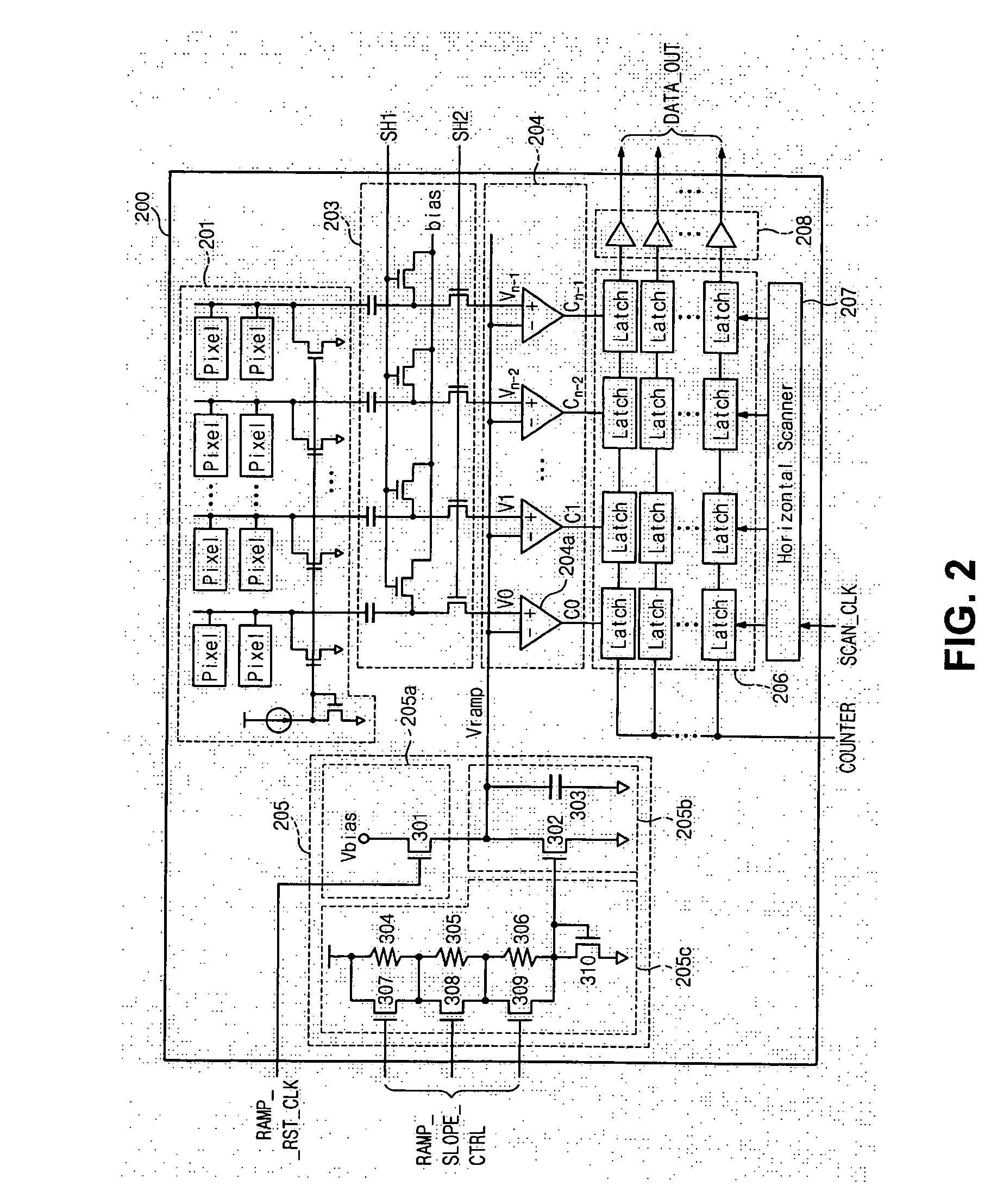

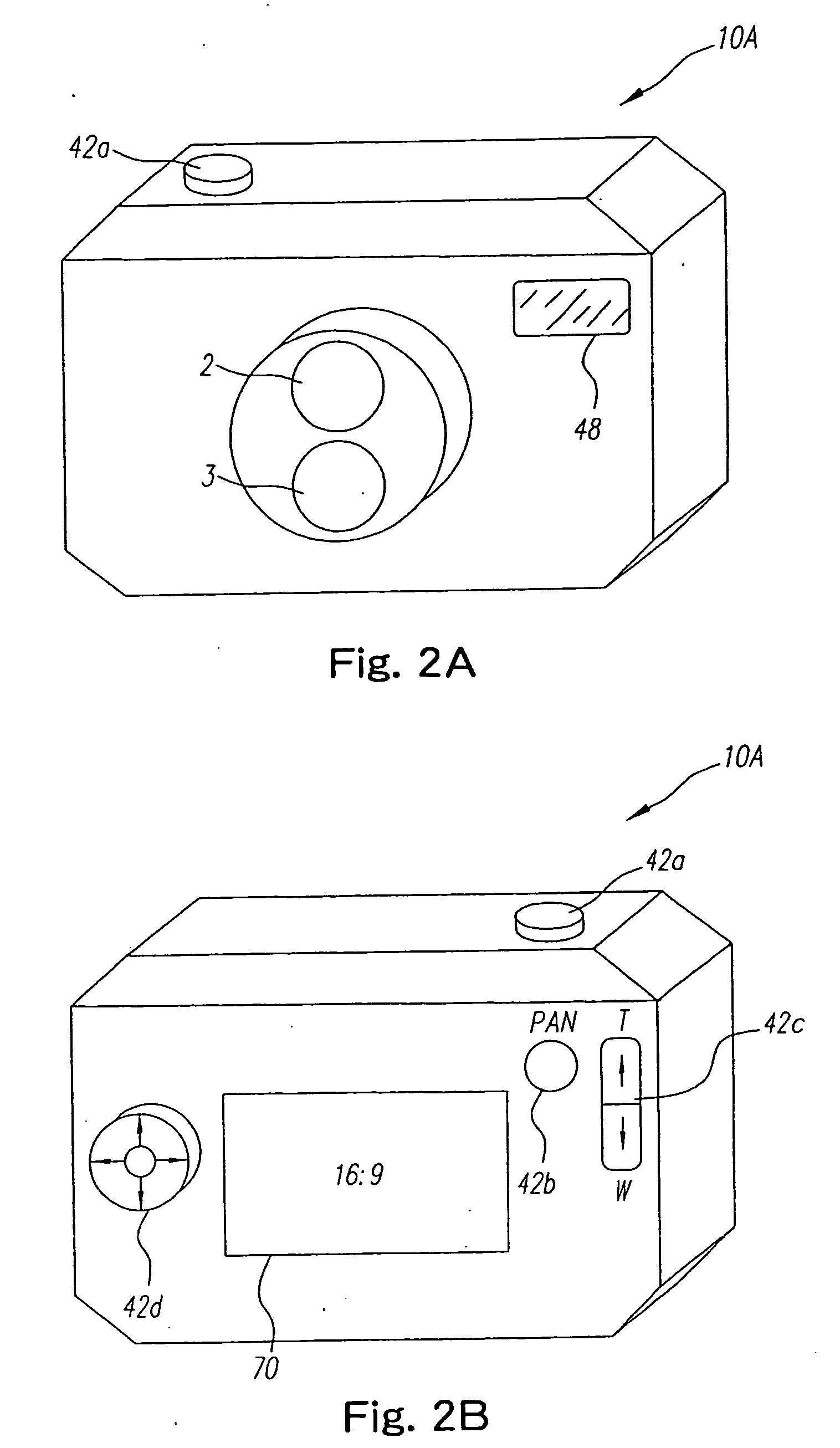

Image capturing apparatus

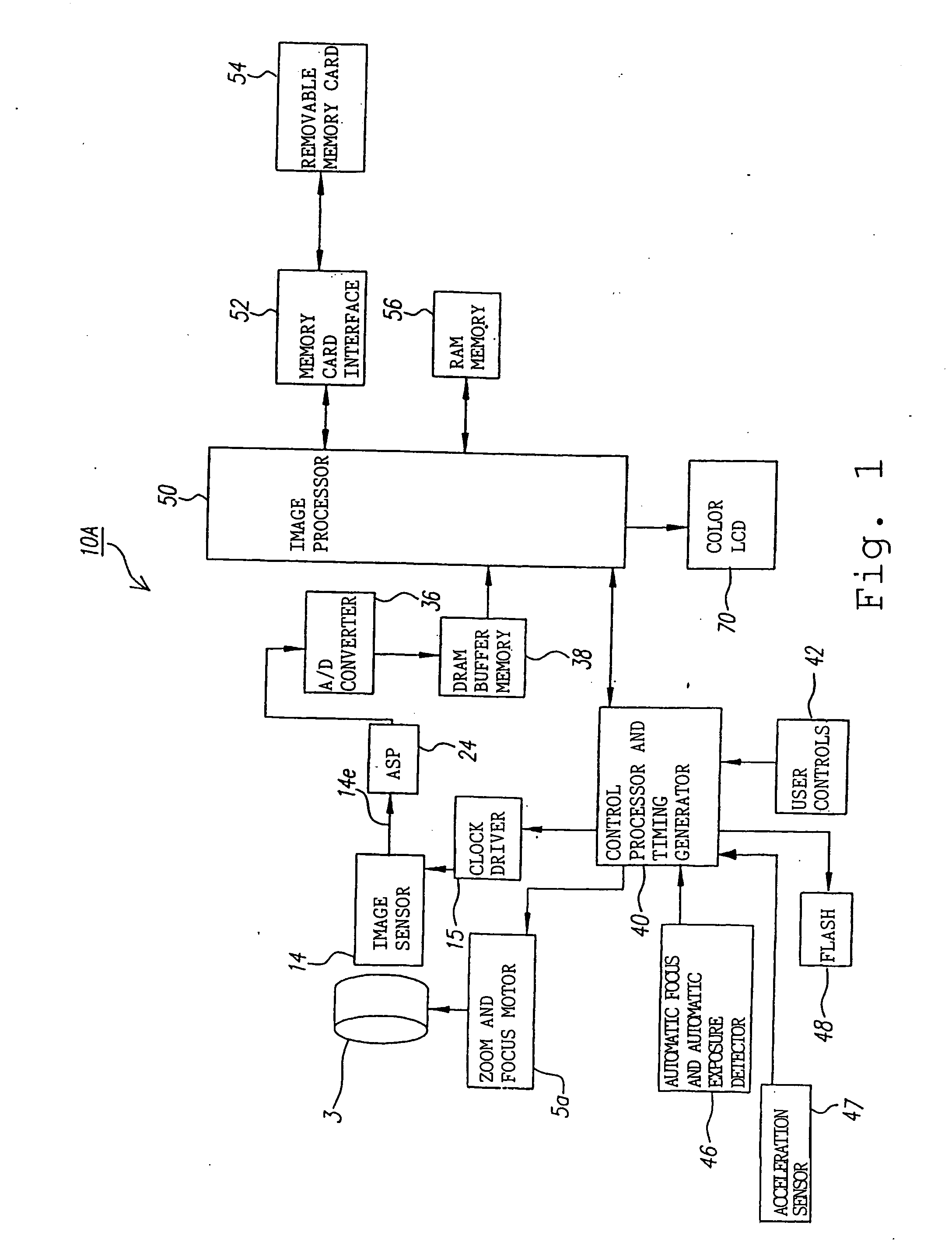

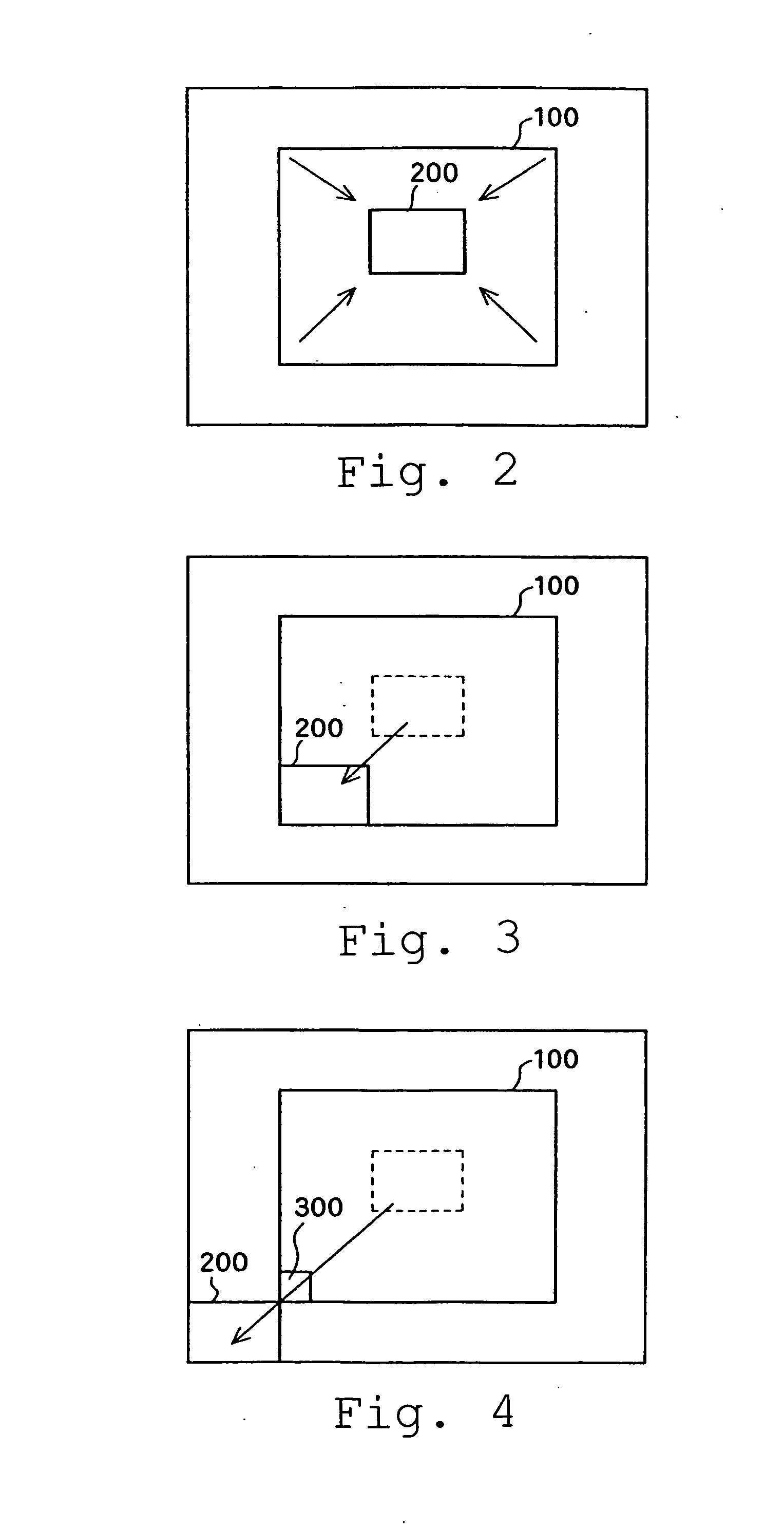

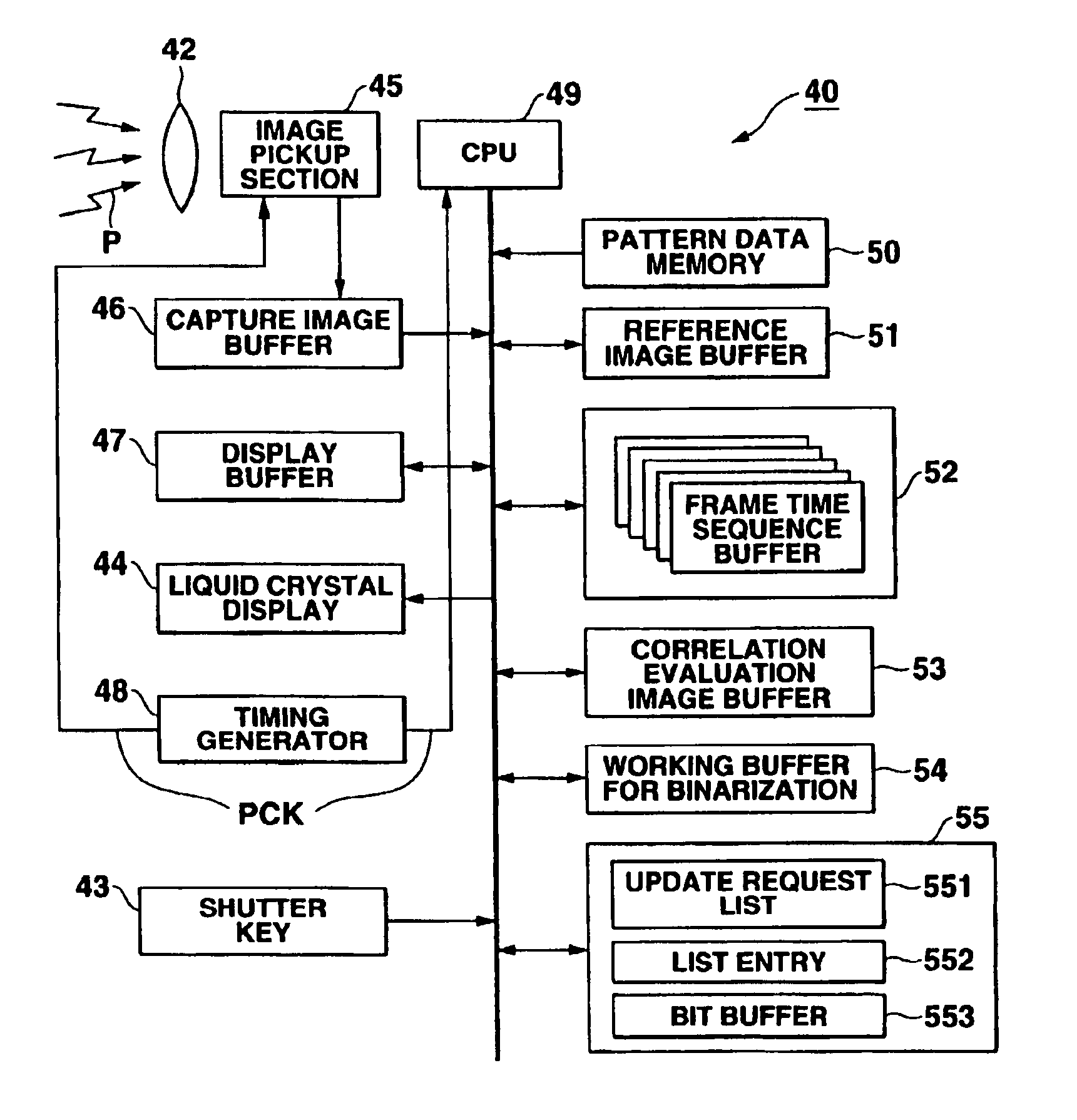

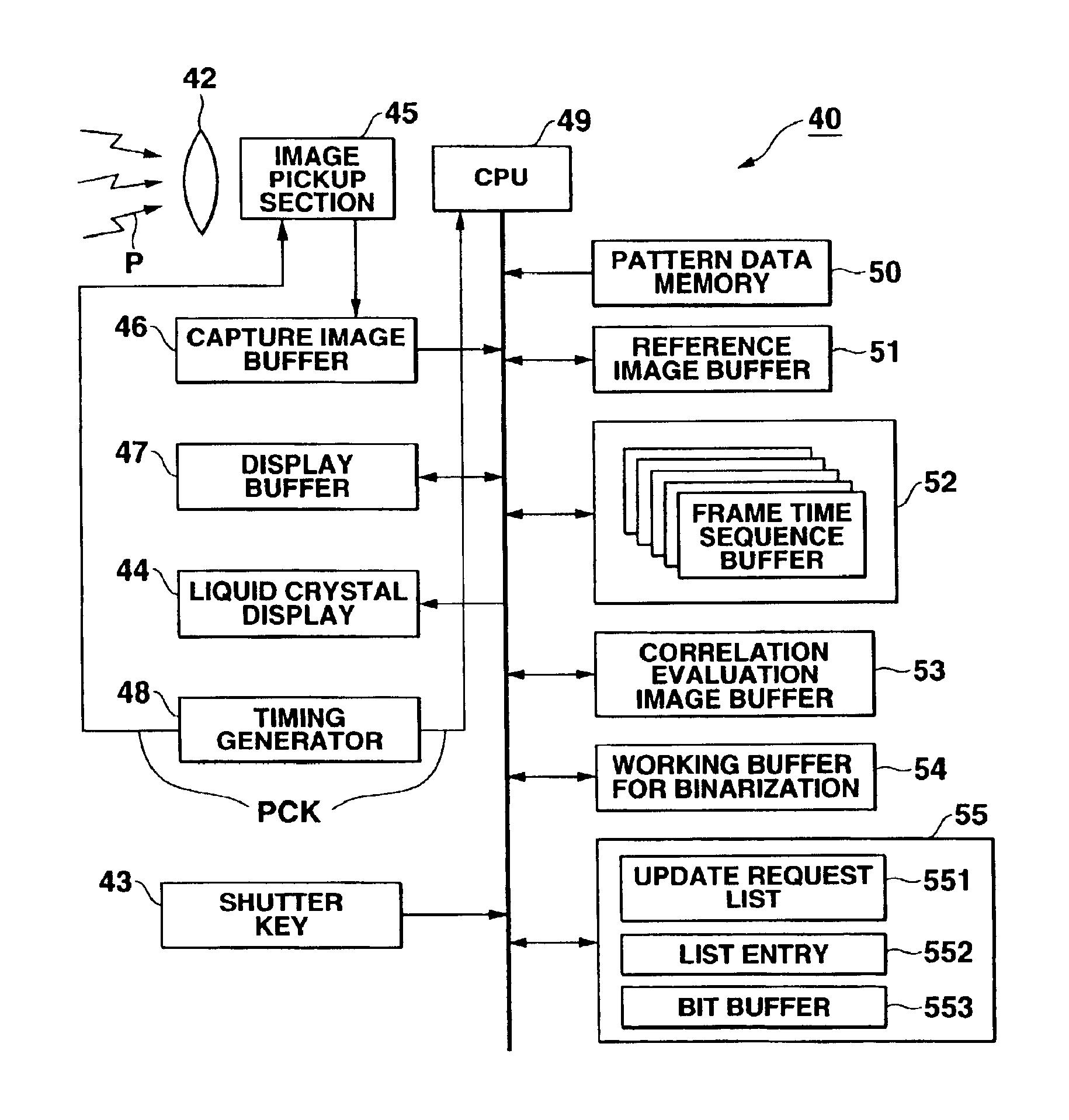

InactiveUS20070025714A1Easy to handleInappropriate exposureTelevision system detailsCamera body detailsImaging conditionTiming generator

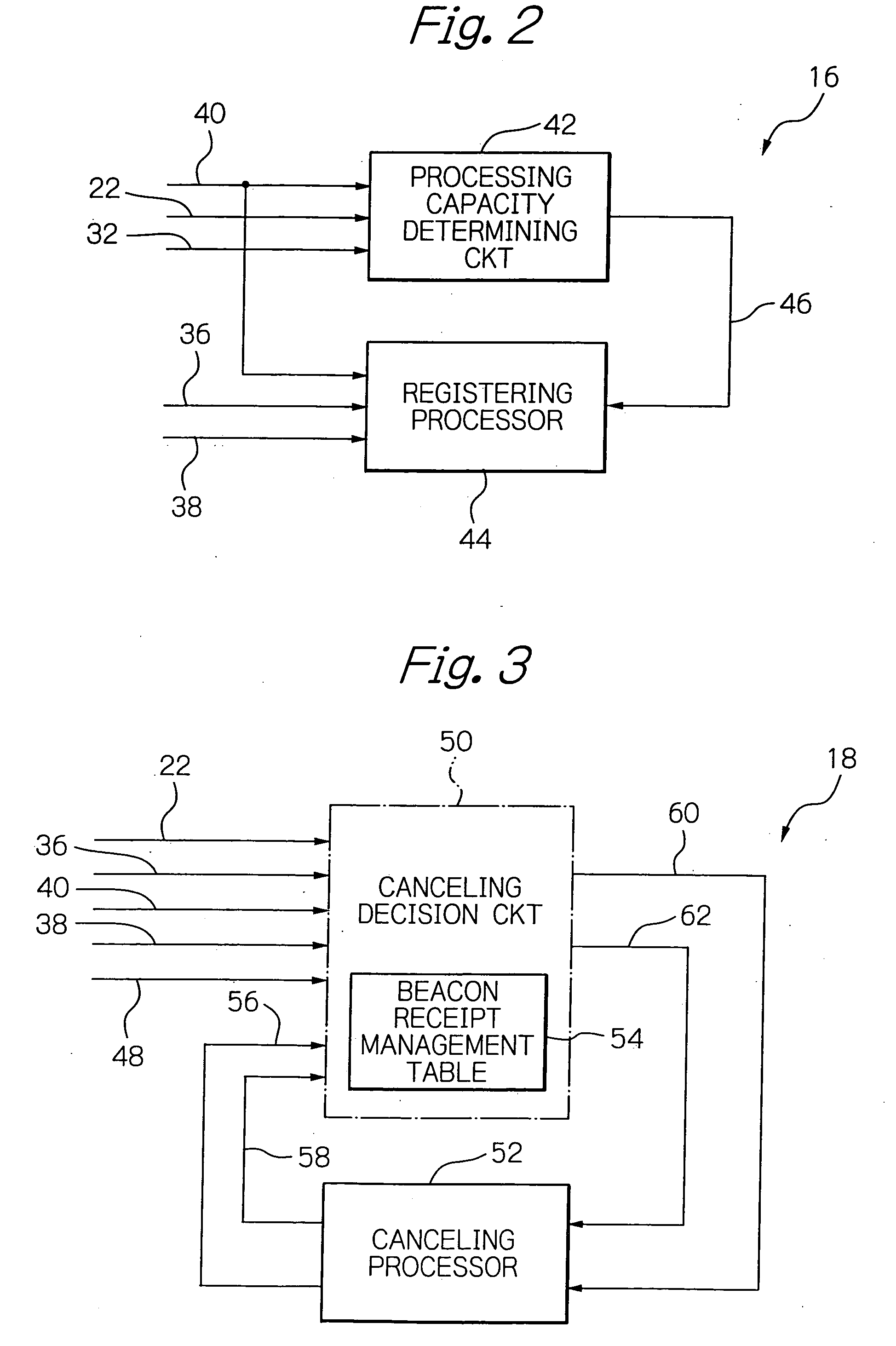

In a digital camera, control operations, such as an AF (automatic focusing) operation which is performed immediately after zooming or panning of the camera, can be performed quickly in an appropriate manner. When a zoom lens 3 is driven to zoom “up”(“in”), a control processor and timing generator 40 uses, of imaging conditions data, such as distance measuring data and photometering data, which are obtained at a wide viewing angle before zooming up, a portion of the imaging conditions data corresponding to a “tele” (telephoto) viewing angle after zooming up, to thereby perform AF, AE, and / or AWB operations after zooming up. When the user pans the camera to shift the viewing angle out of the range of the original wide viewing angle, the data of an area of the image plane of the wide viewing angle closest to the image plane of a new post-panning viewing angle is reused. In a digital camera having a plurality of image capturing optical systems which are switched in response to a zoom position, data obtained by the pre-switching image capturing optical system is reused by a selected post-switching image capturing optical system.

Owner:EASTMAN KODAK CO

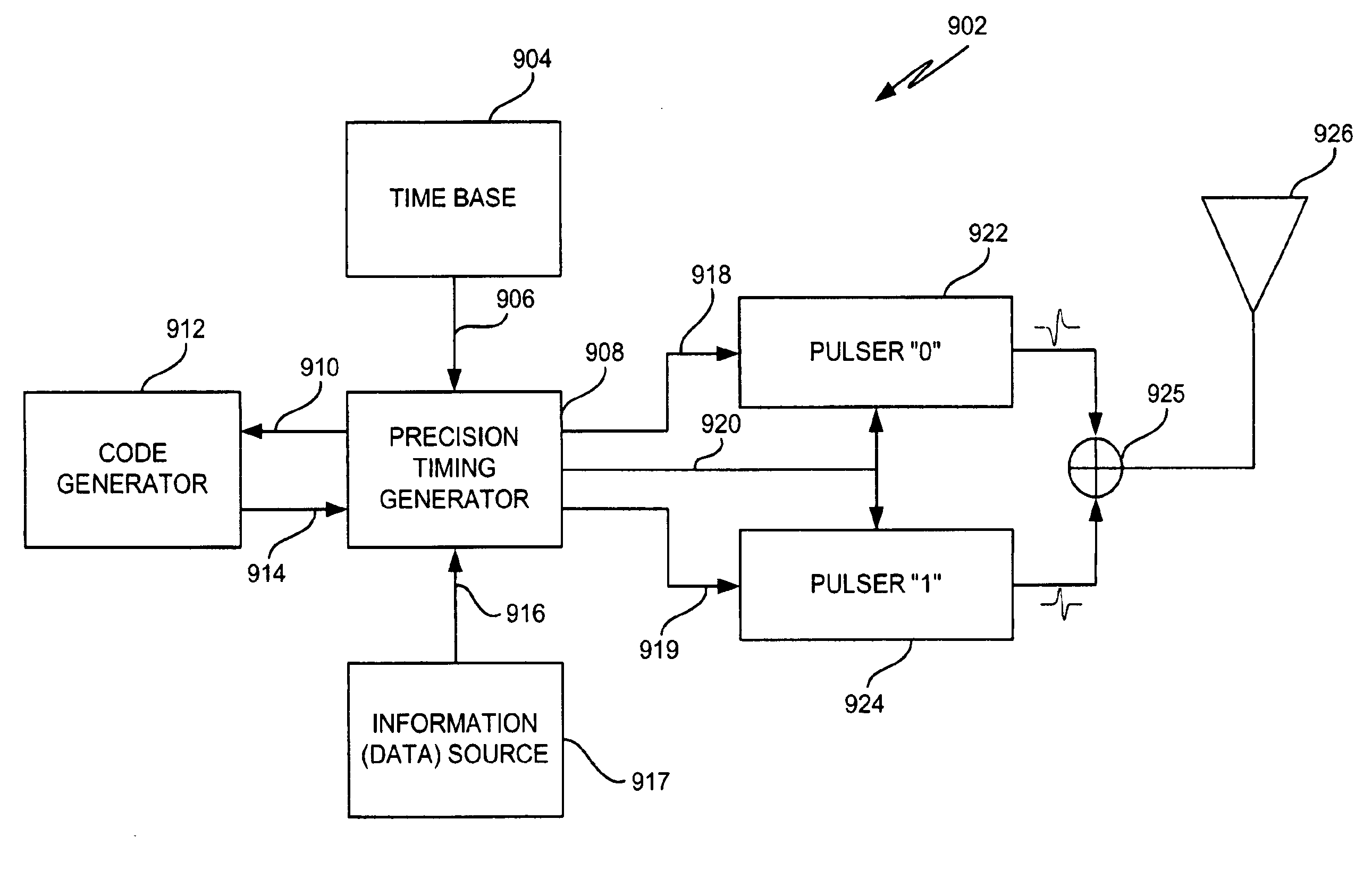

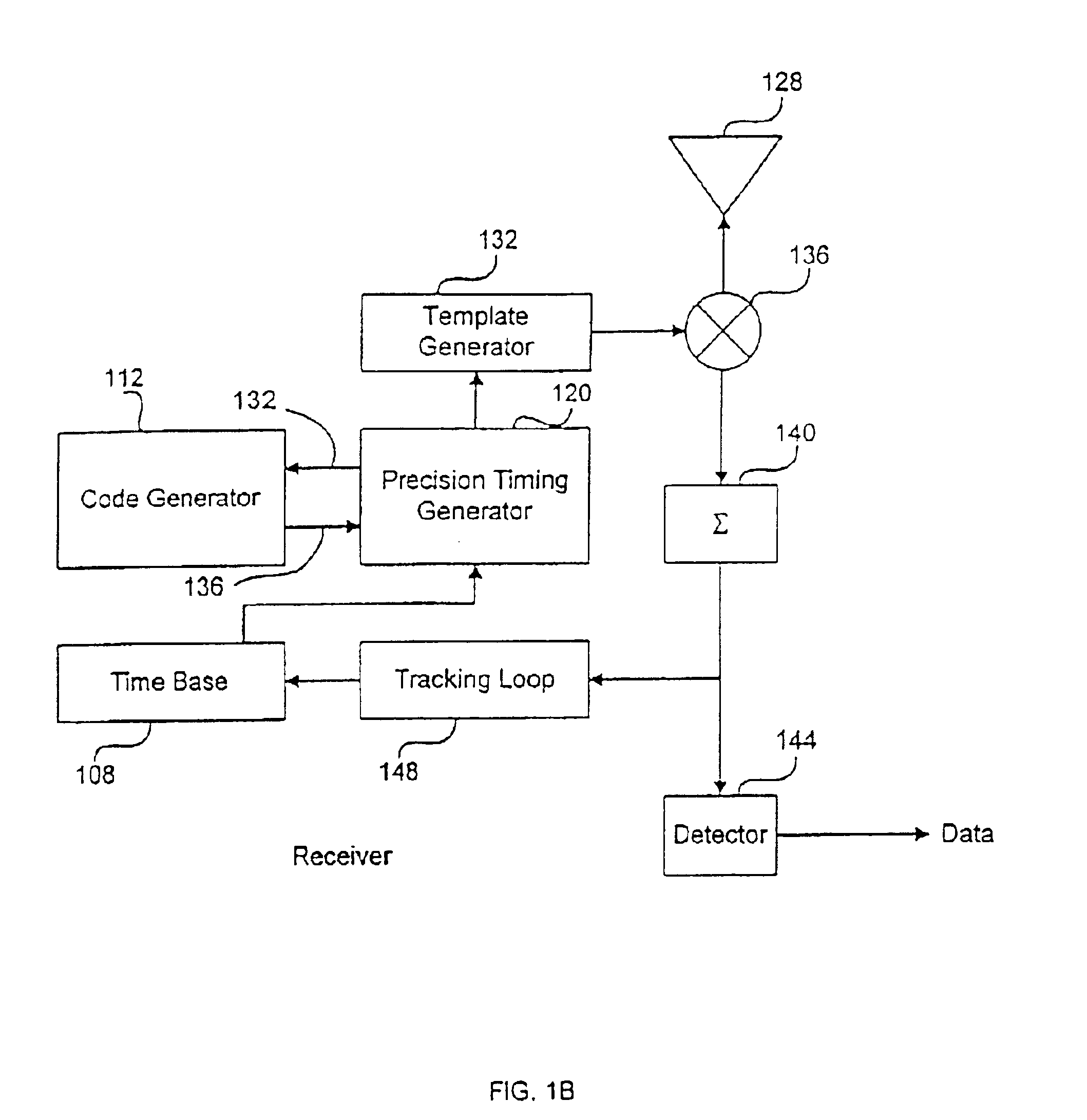

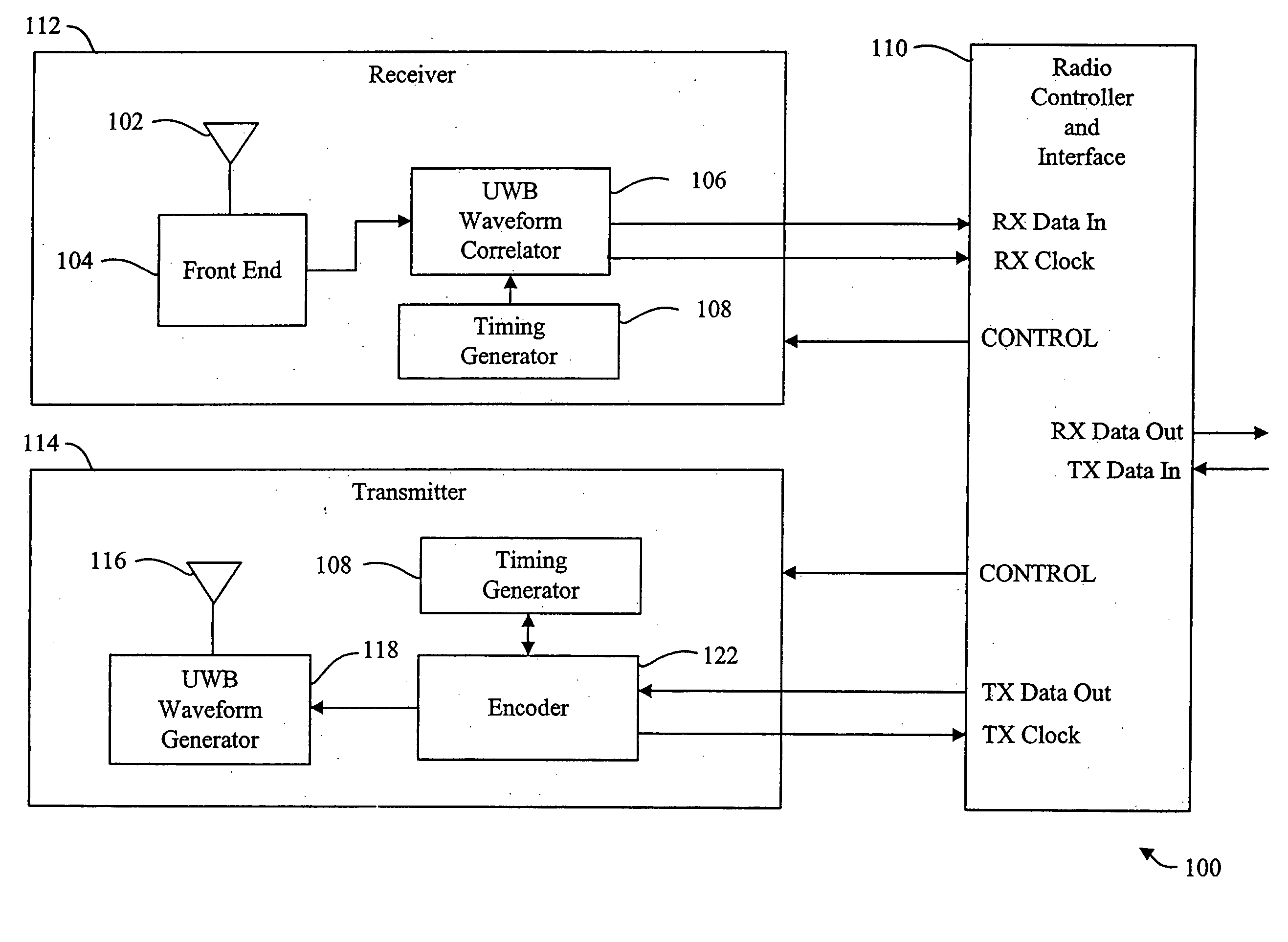

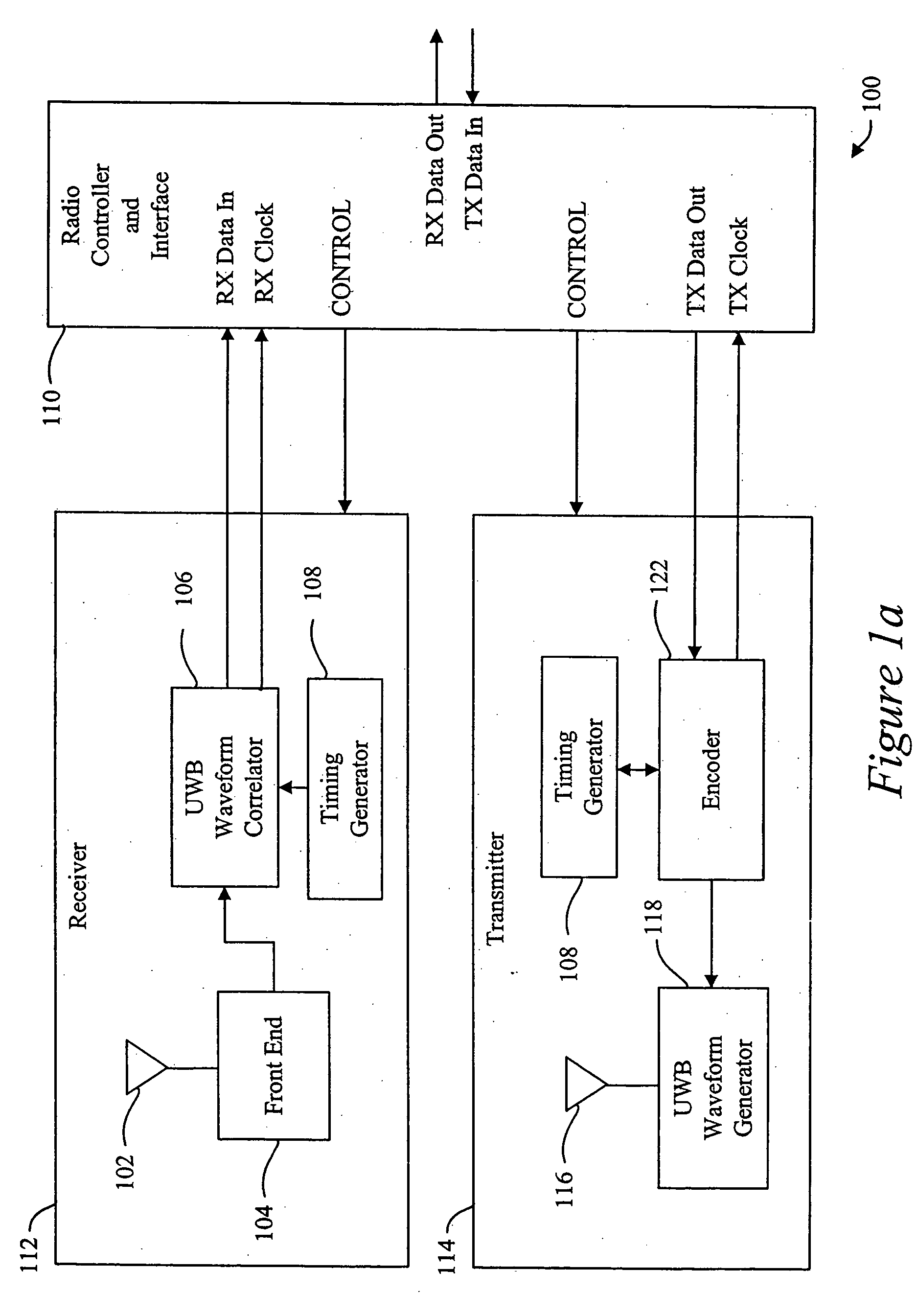

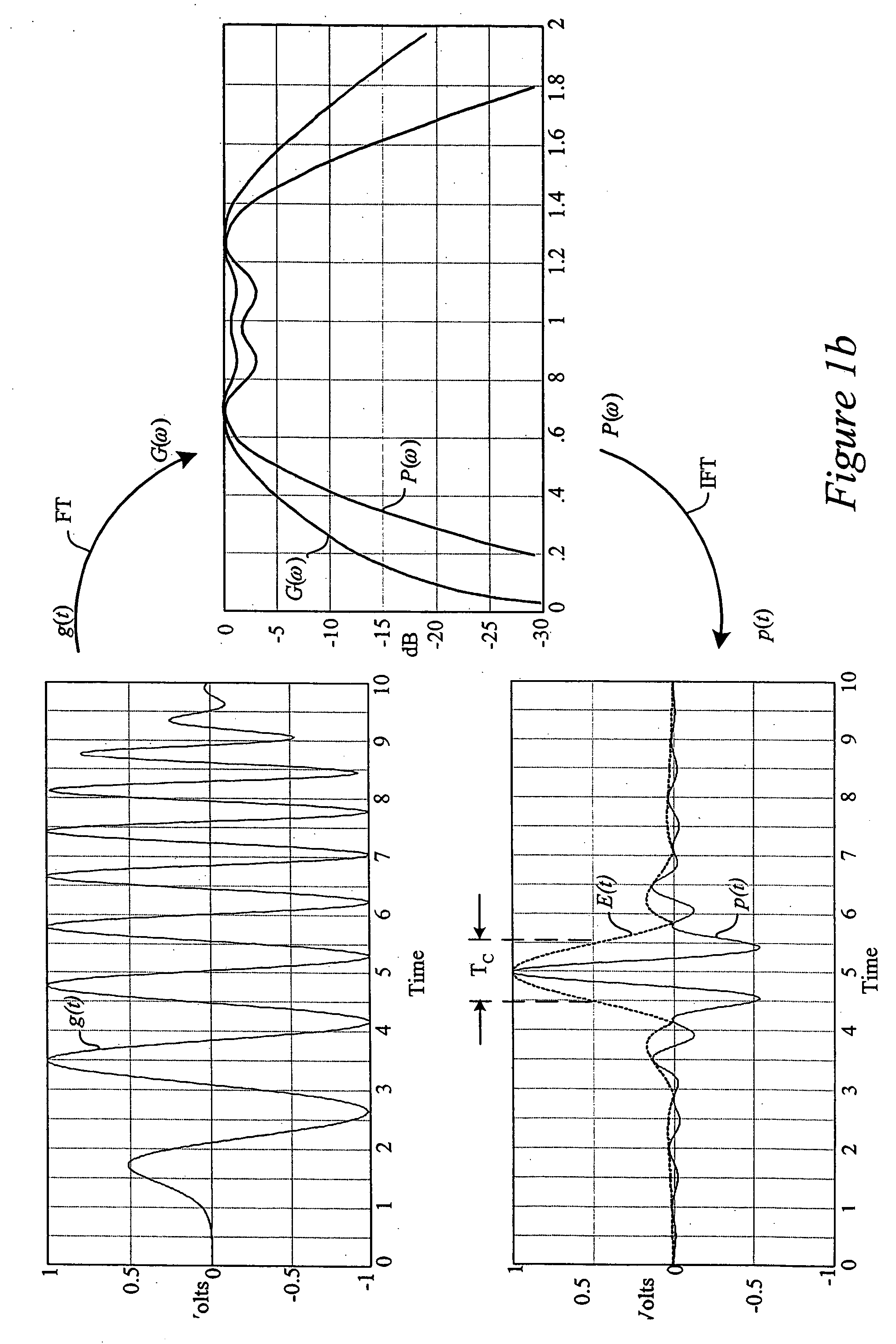

Apparatus, system and method for flip modulation in an impulse radio communications system

Apparatuses, systems and methods for transmitting and receiving modulated impulse radio signals. An impulse radio receiver includes a time base, a precision timing generator, a template generator, a delay, first and second correlators, a data detector and a time base adjustor. The time base produces a periodic timing signal that is used by the precision timing generator to produce a timing trigger signal. The template generator uses the timing trigger signal to produce a template signal. A delay receives the template signal and outputs a delayed template signal. When an impulse radio signal is received, the first correlator correlates the received impulse radio signal with the template signal to produce a first correlator output signal, and the second correlator correlates the received impulse radio signal with the delayed template signal to produce a second correlator output signal. The data detector produces a data signal based on at least the first correlator output signal. The time base adjustor produces a time base adjustment signal based on at least the second correlator output signal. The time base adjustment signal is used to synchronize the time base with the received impulse radio signal.

Owner:ALEREON

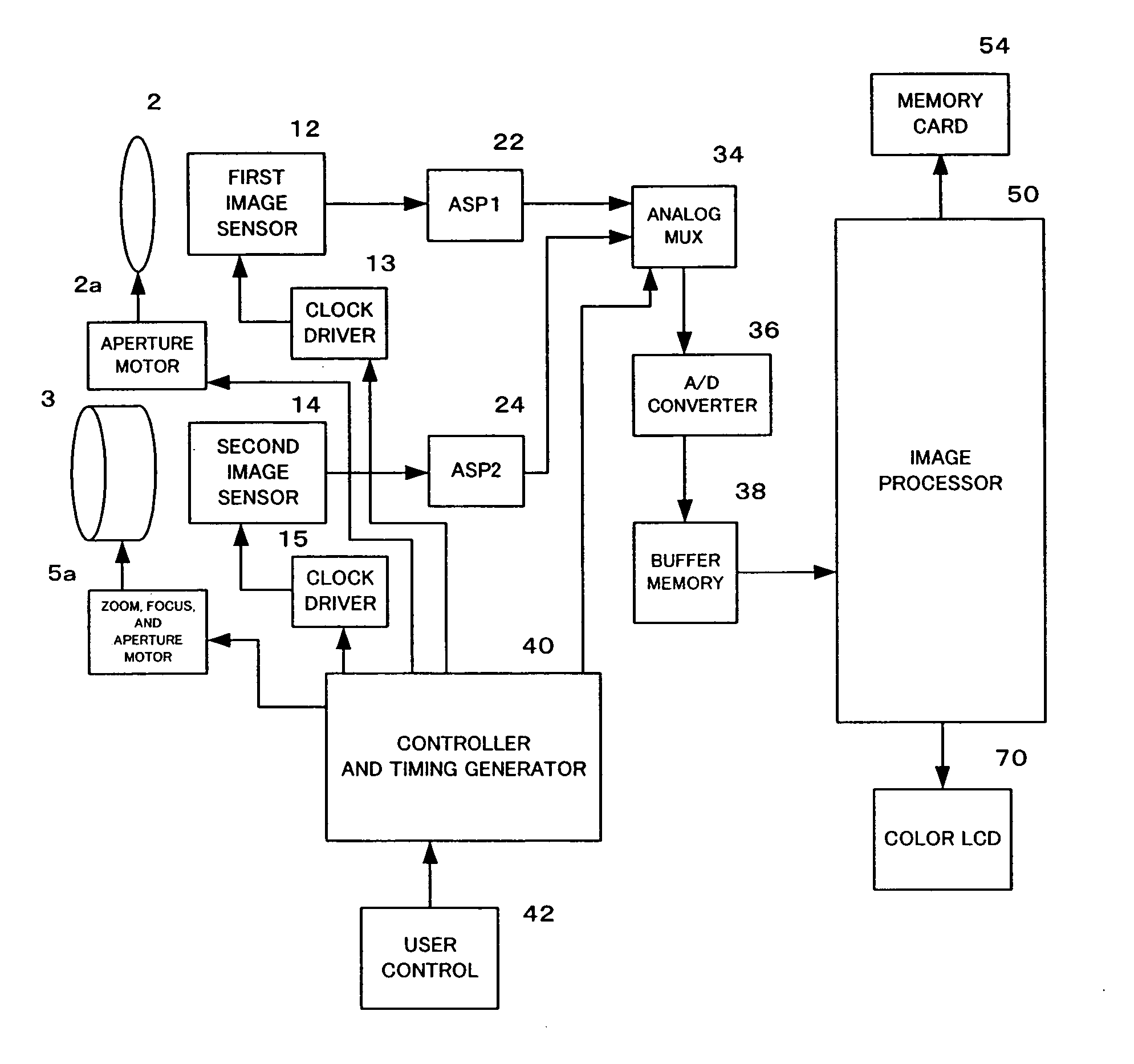

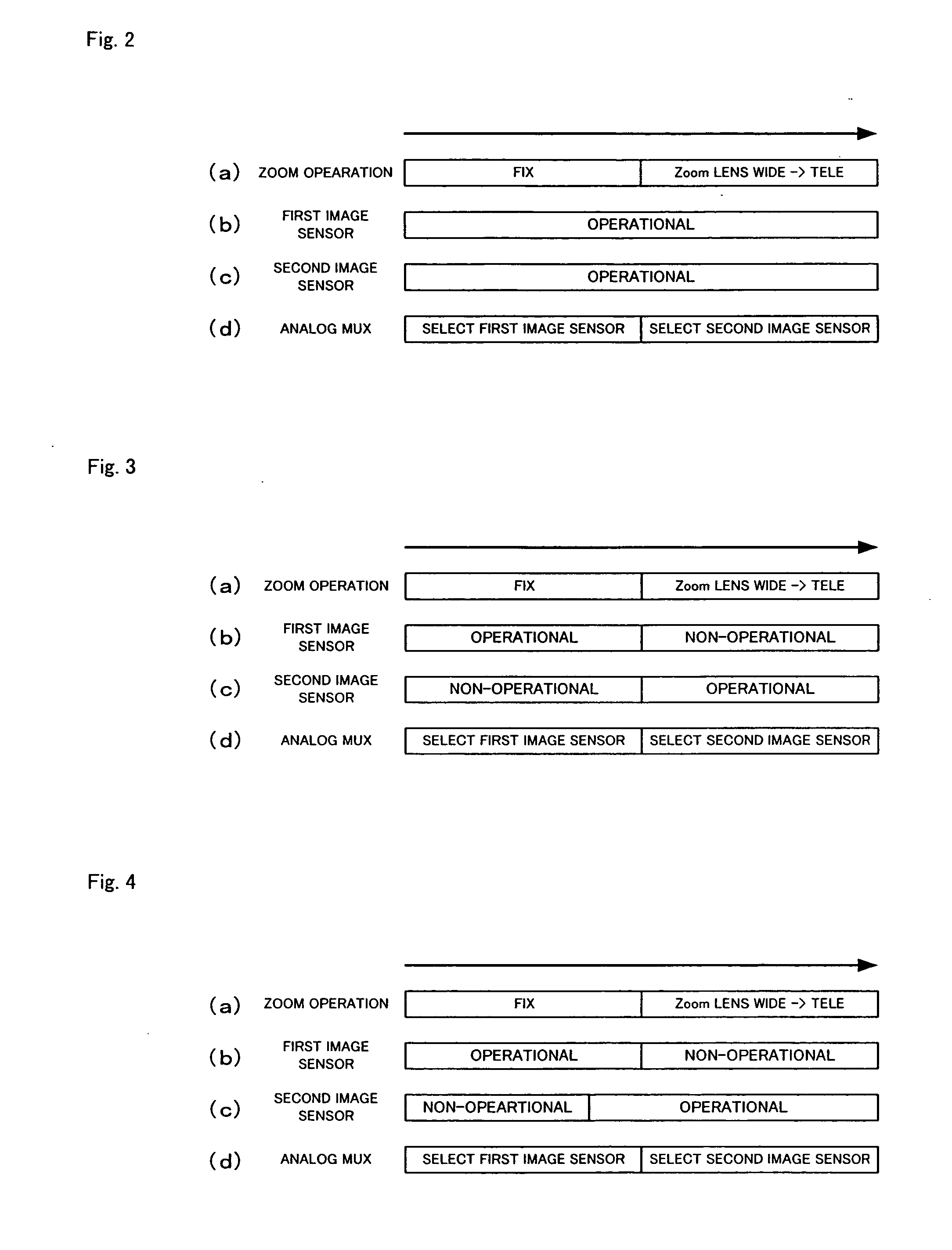

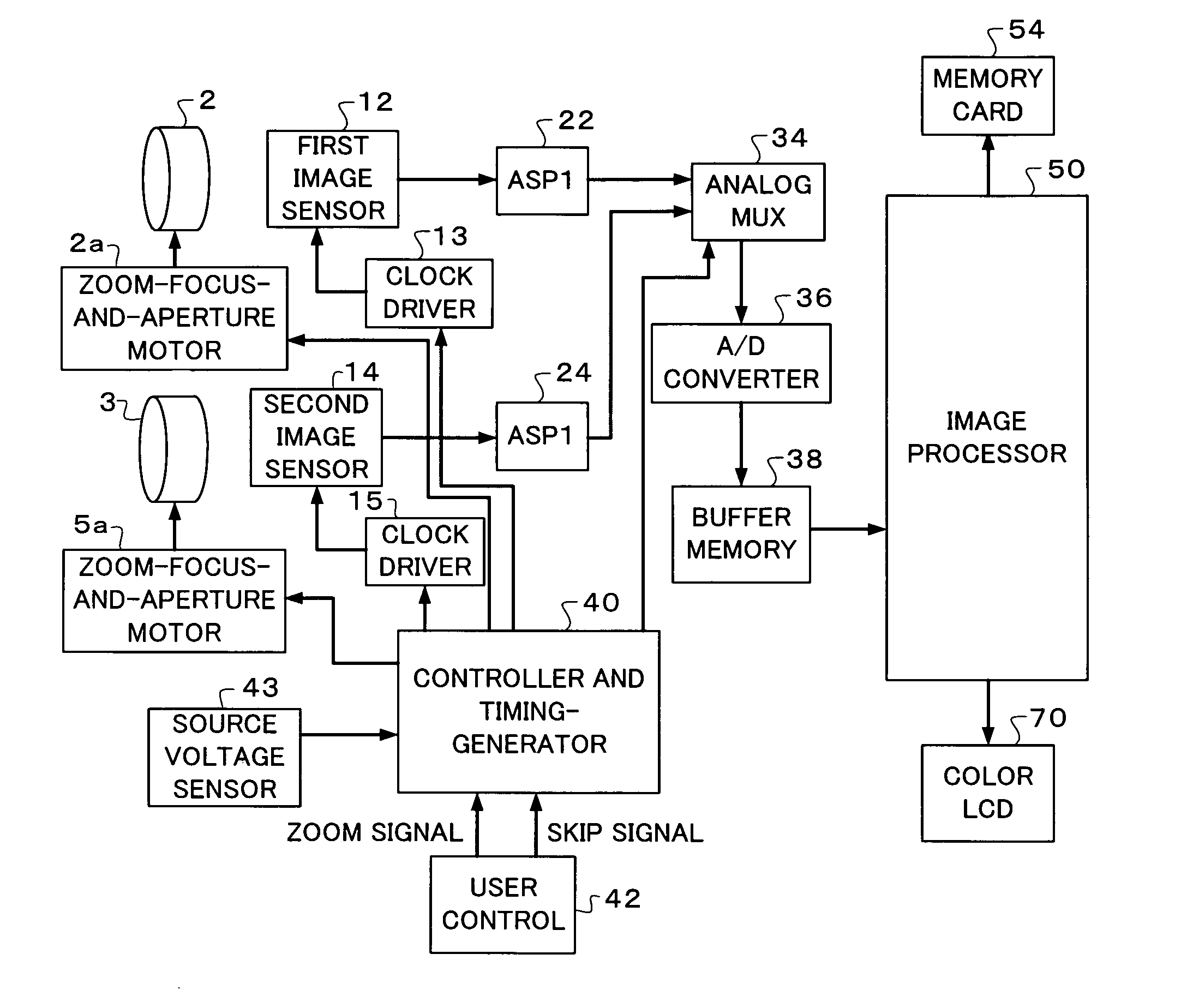

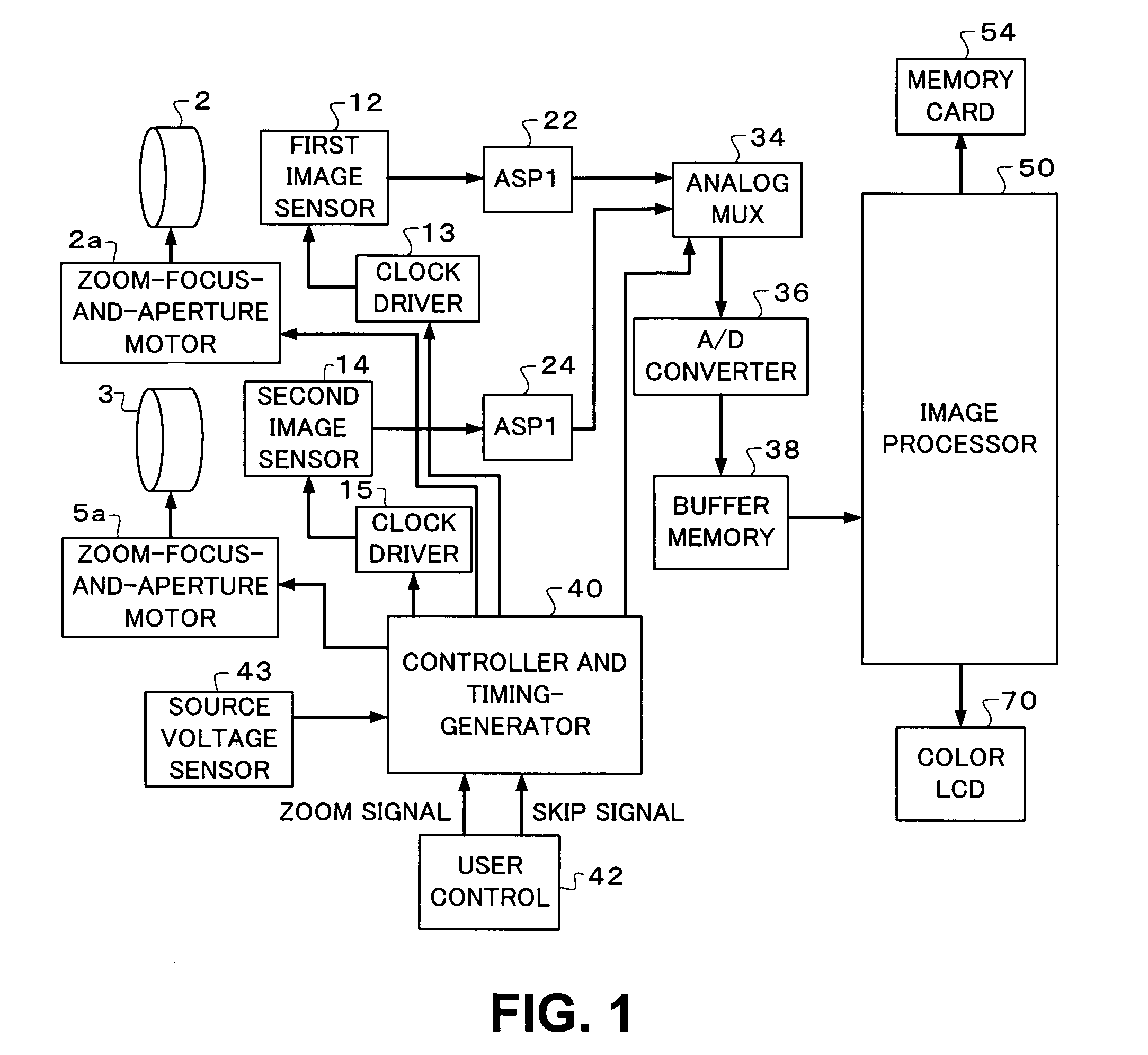

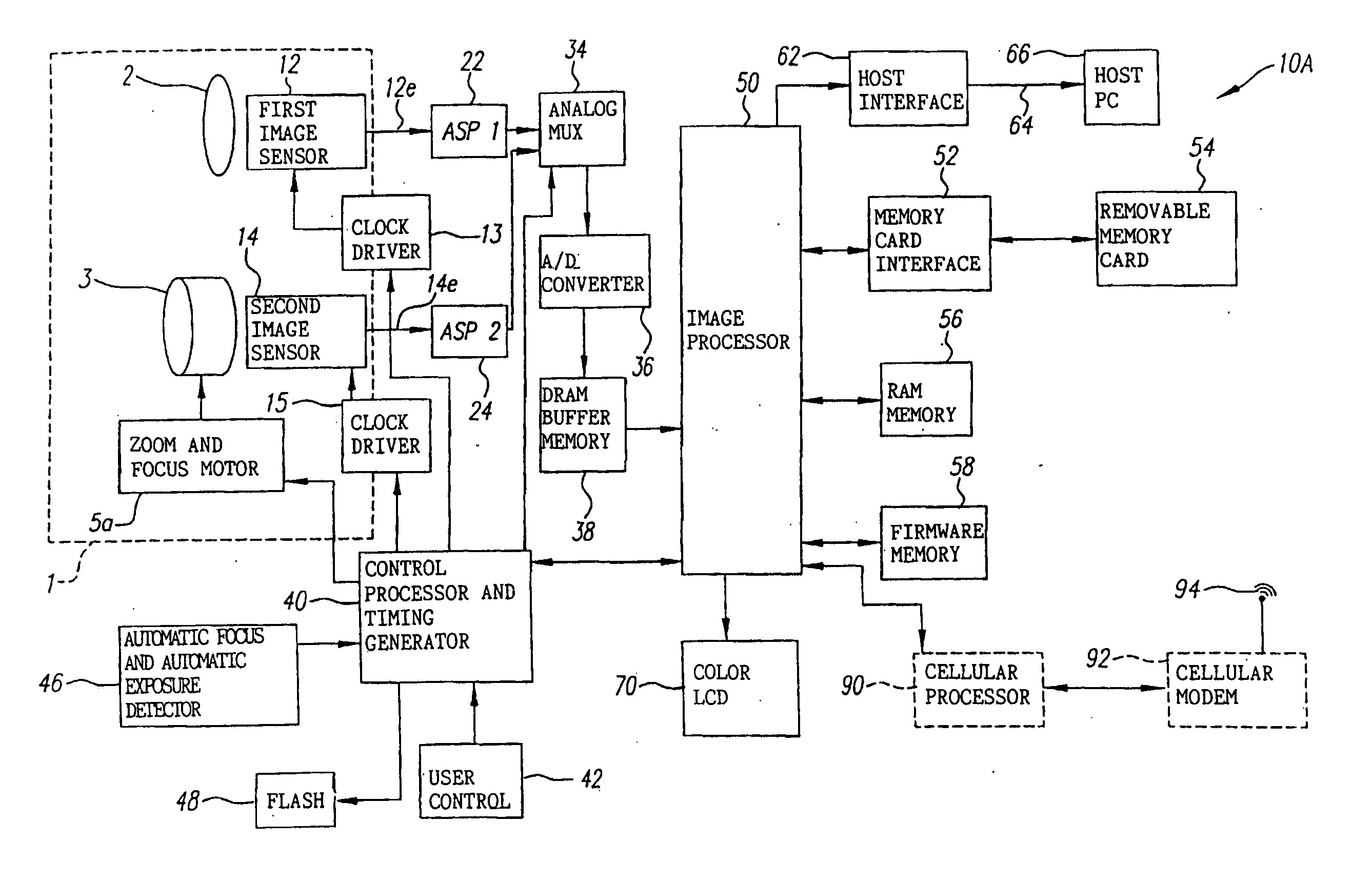

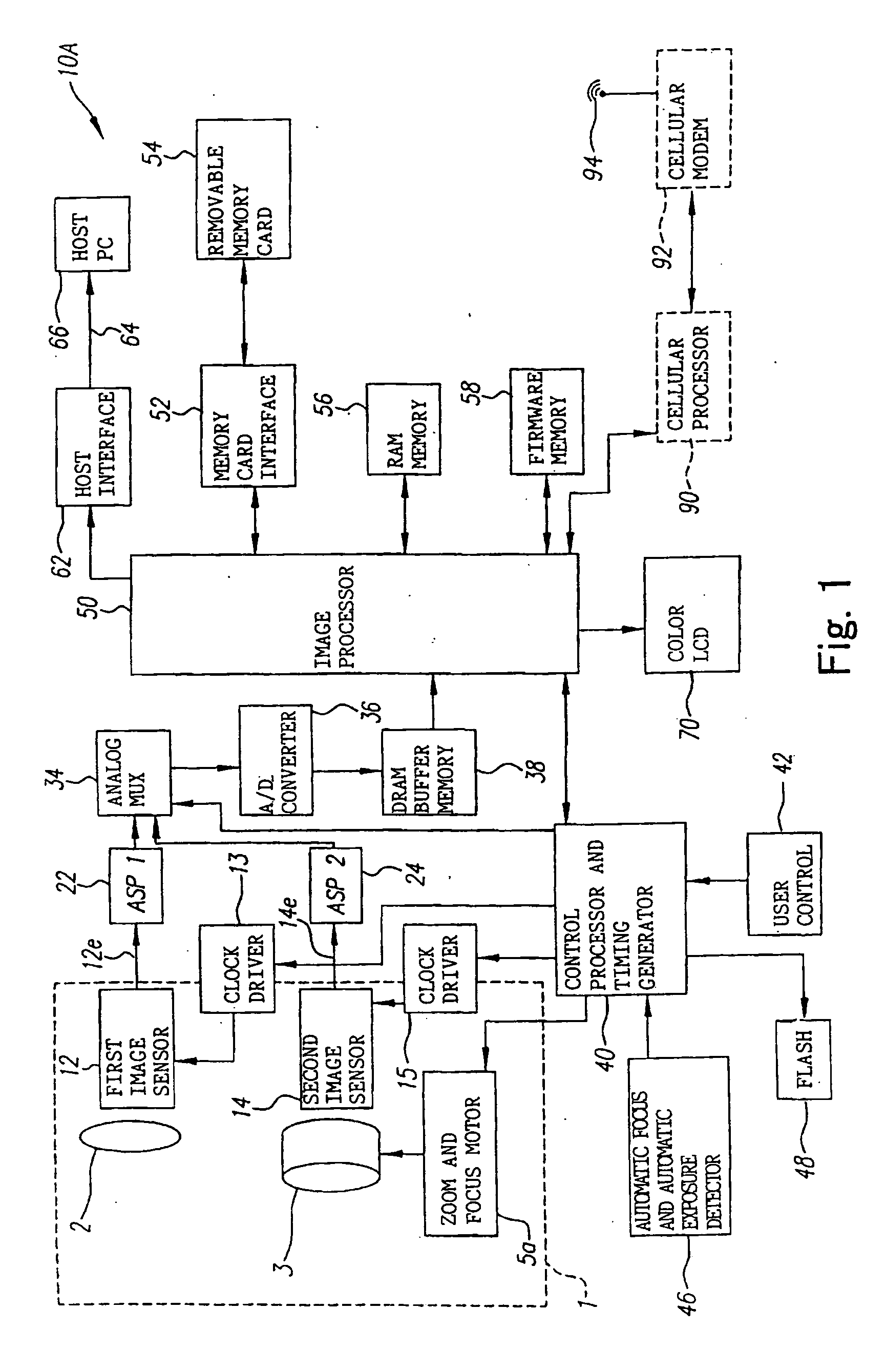

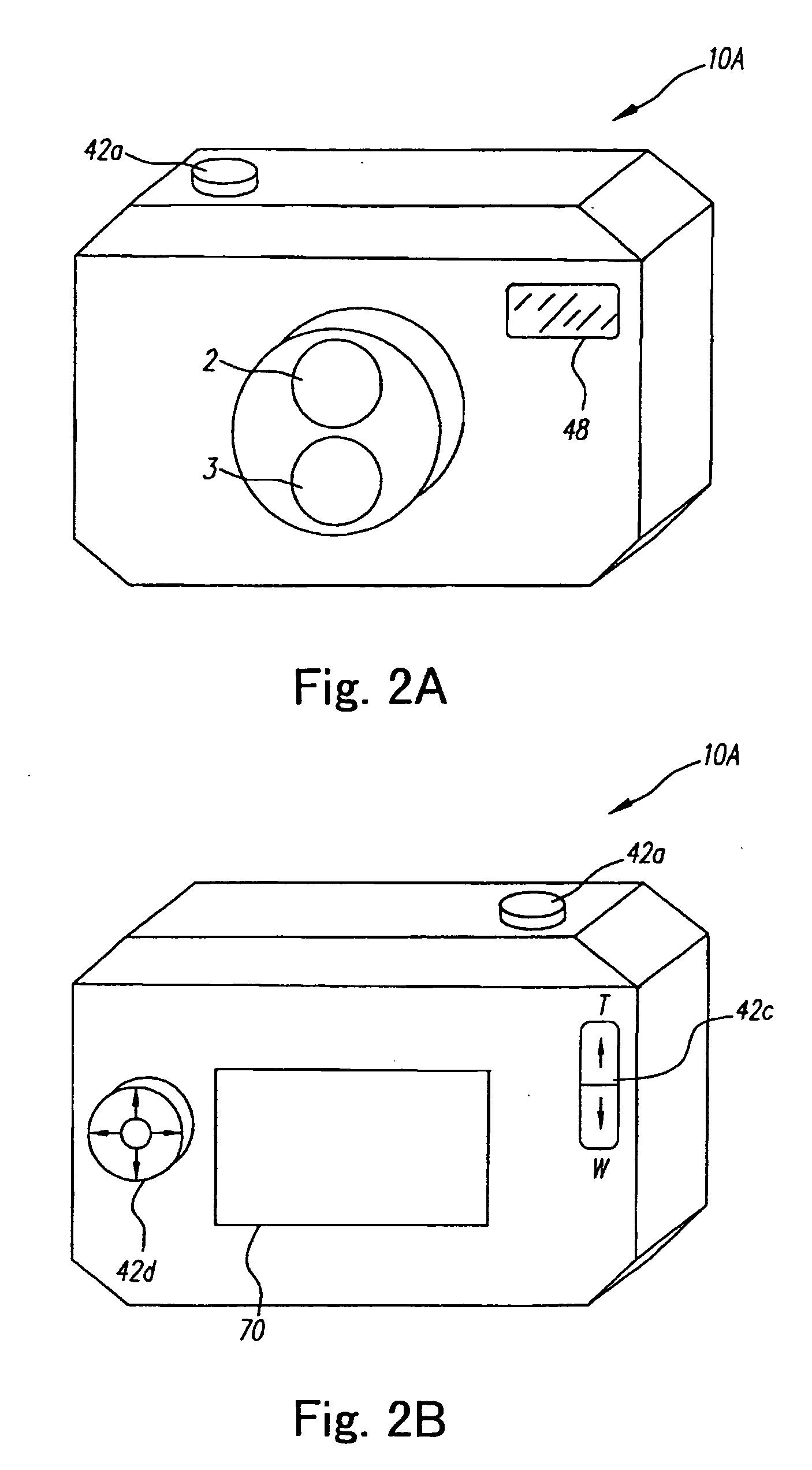

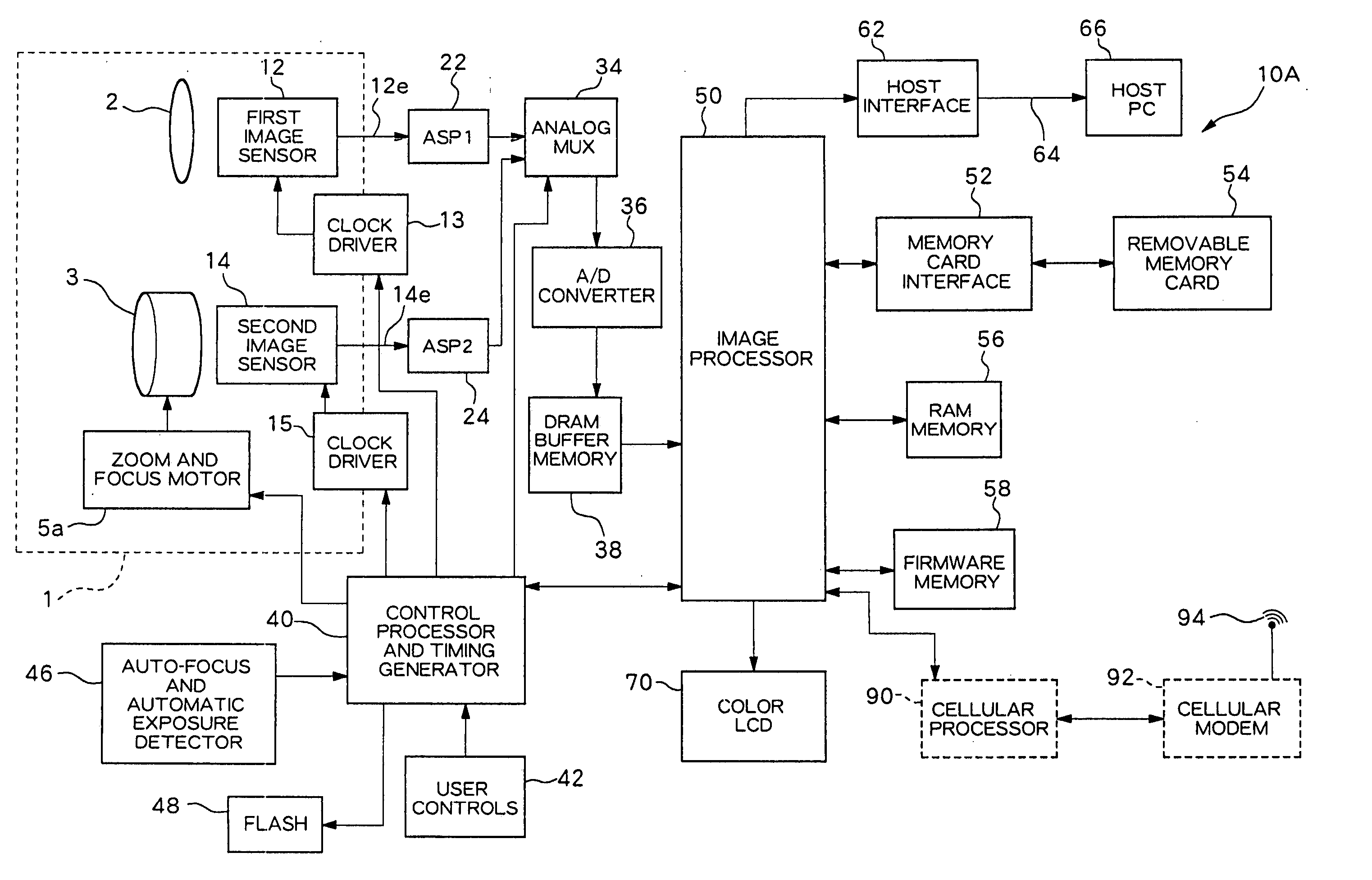

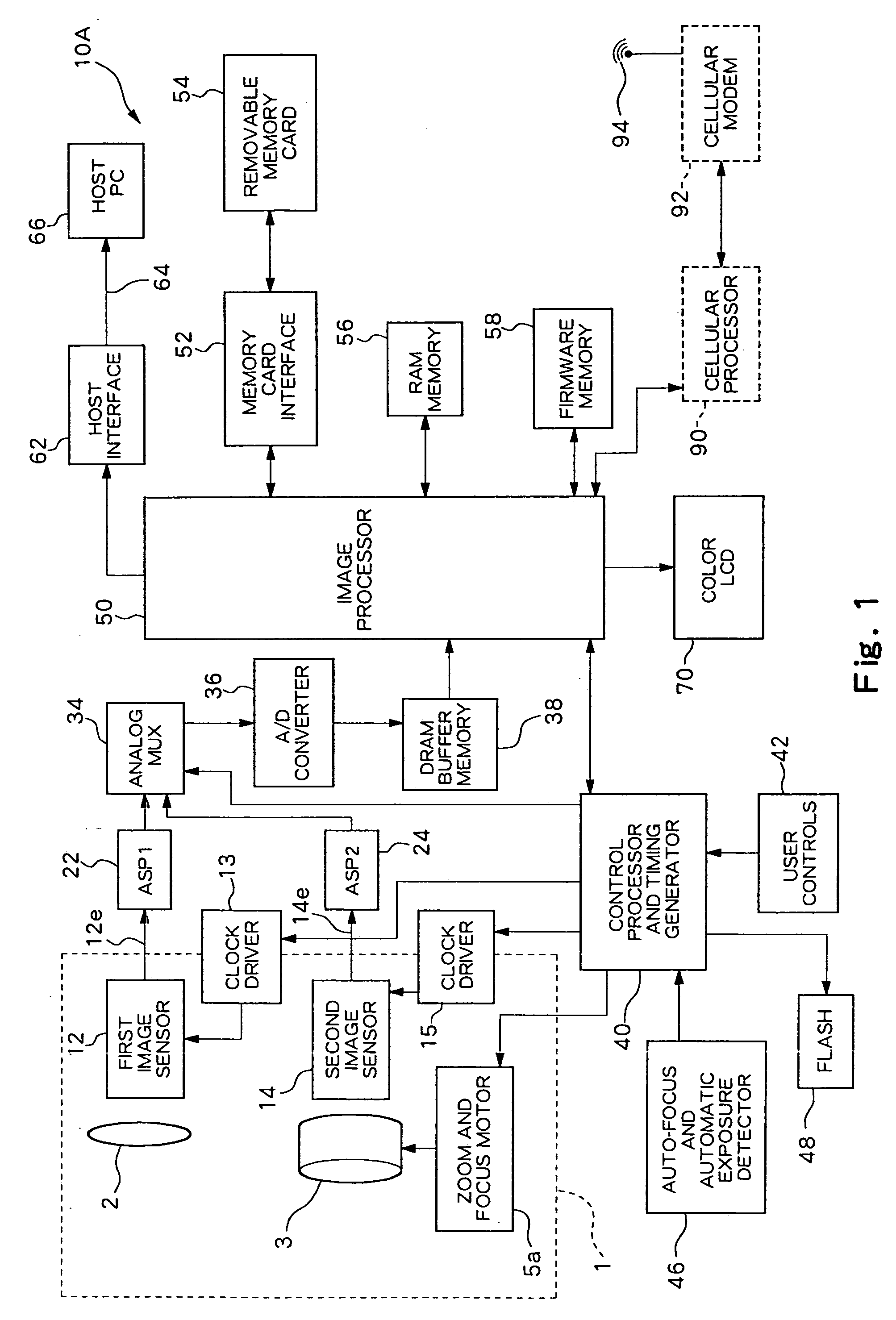

Image capturing device having multiple optical systems

InactiveUS20070024737A1Reduce power consumptionTelevision system detailsColor television detailsTiming generatorOptic system

In a digital camera having multiple optical systems, multiple image capturing elements are effectively driven to reduce power consumption. A digital camera has a first image capturing optical system having a lens and a first image sensor and a second image capturing optical system having a lens and a second image sensor. A controller and timing generator selects the image signal from the first image capturing optical system while controlling an operation or power of the second image sensor and a clock driver to be OFF when the zoom position falls within a first zoom range. When the zoom position falls within a second zoom range, the image signal from the second image capturing optical system is selected while an operation or power of the first image sensor and a clock driver is controlled to be OFF. An operation or power of the image capturing optical system which is not selected is stopped so that power consumption is reduced.

Owner:INTELLECTUAL VENTURES FUND 83 LLC

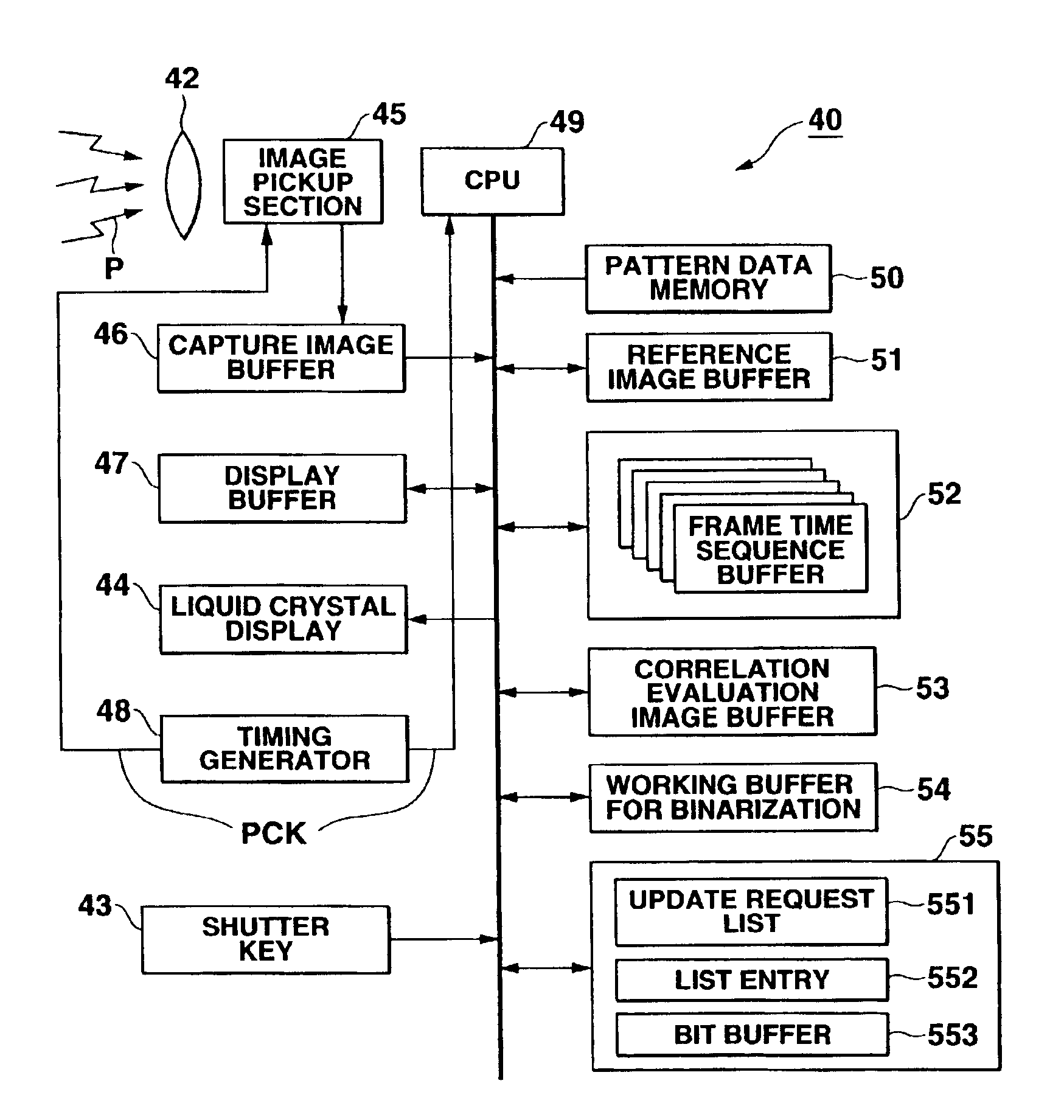

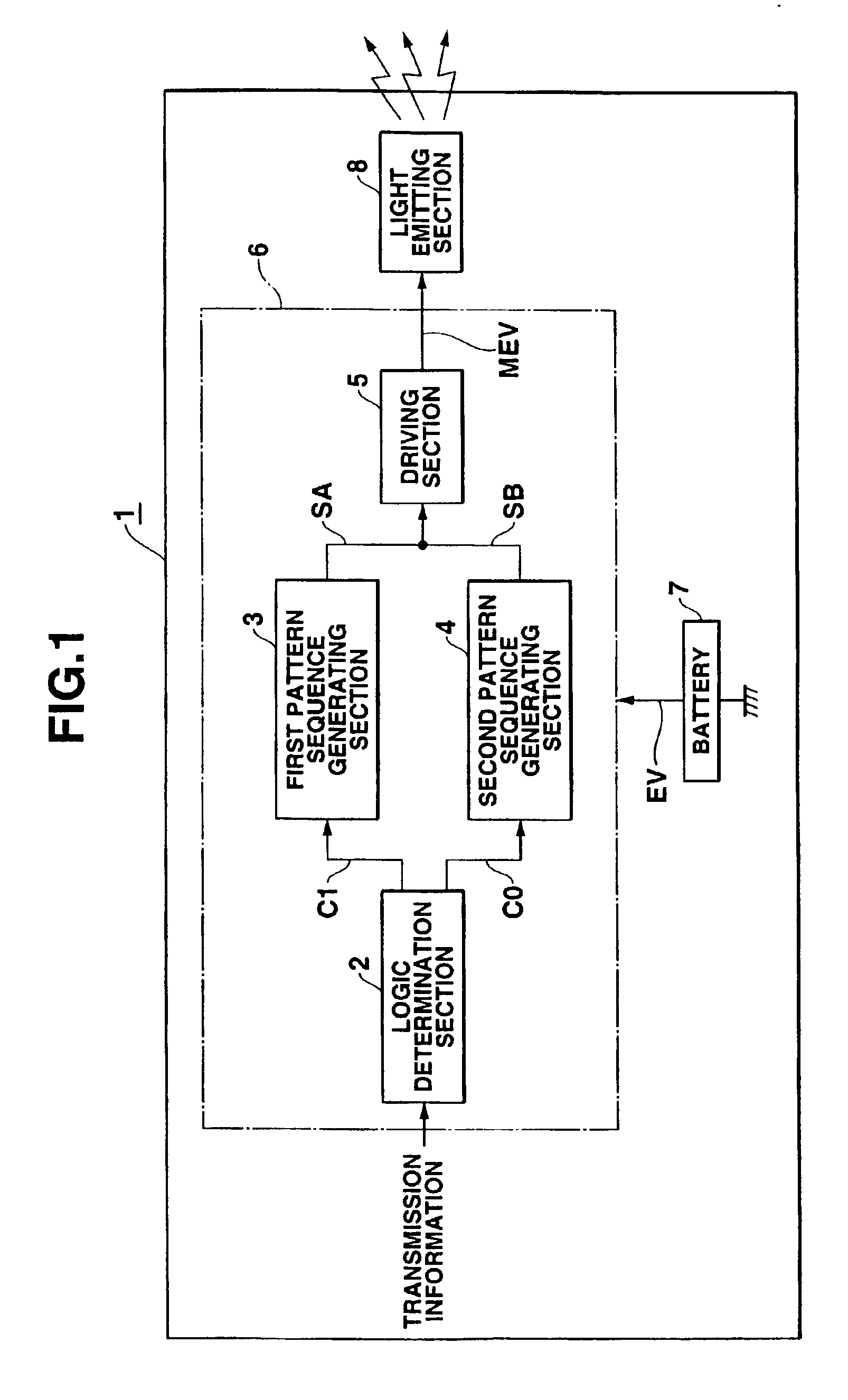

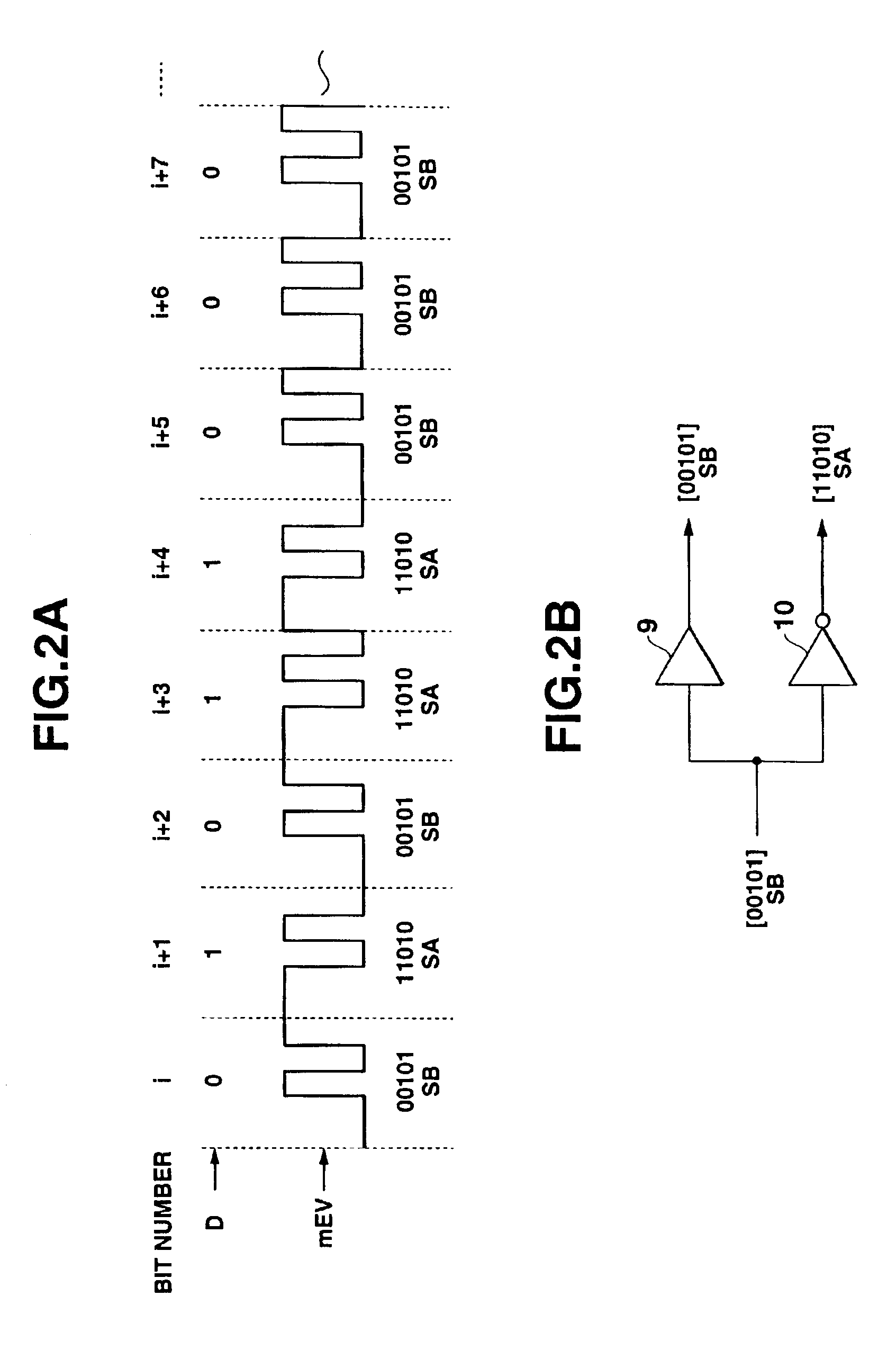

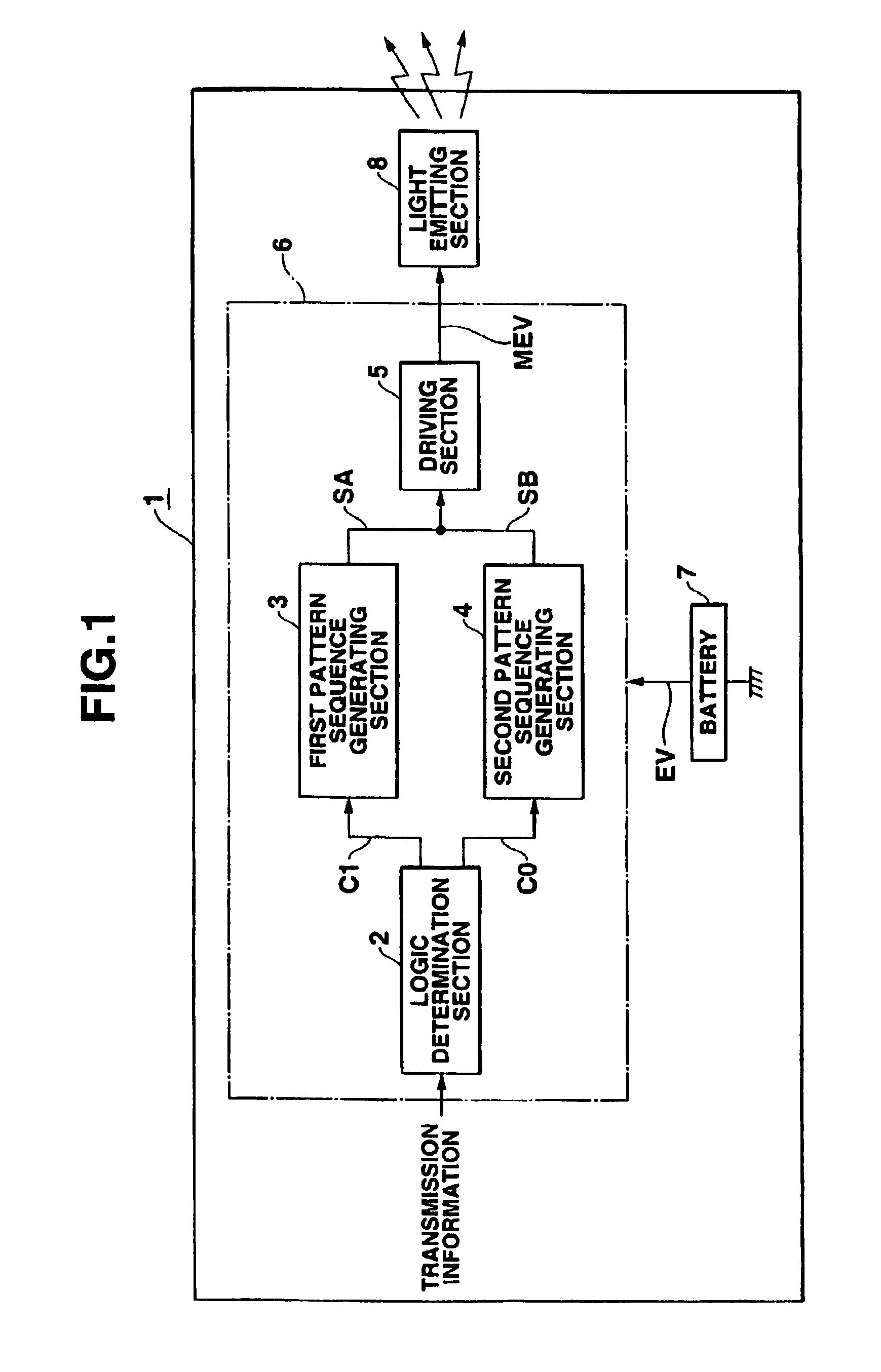

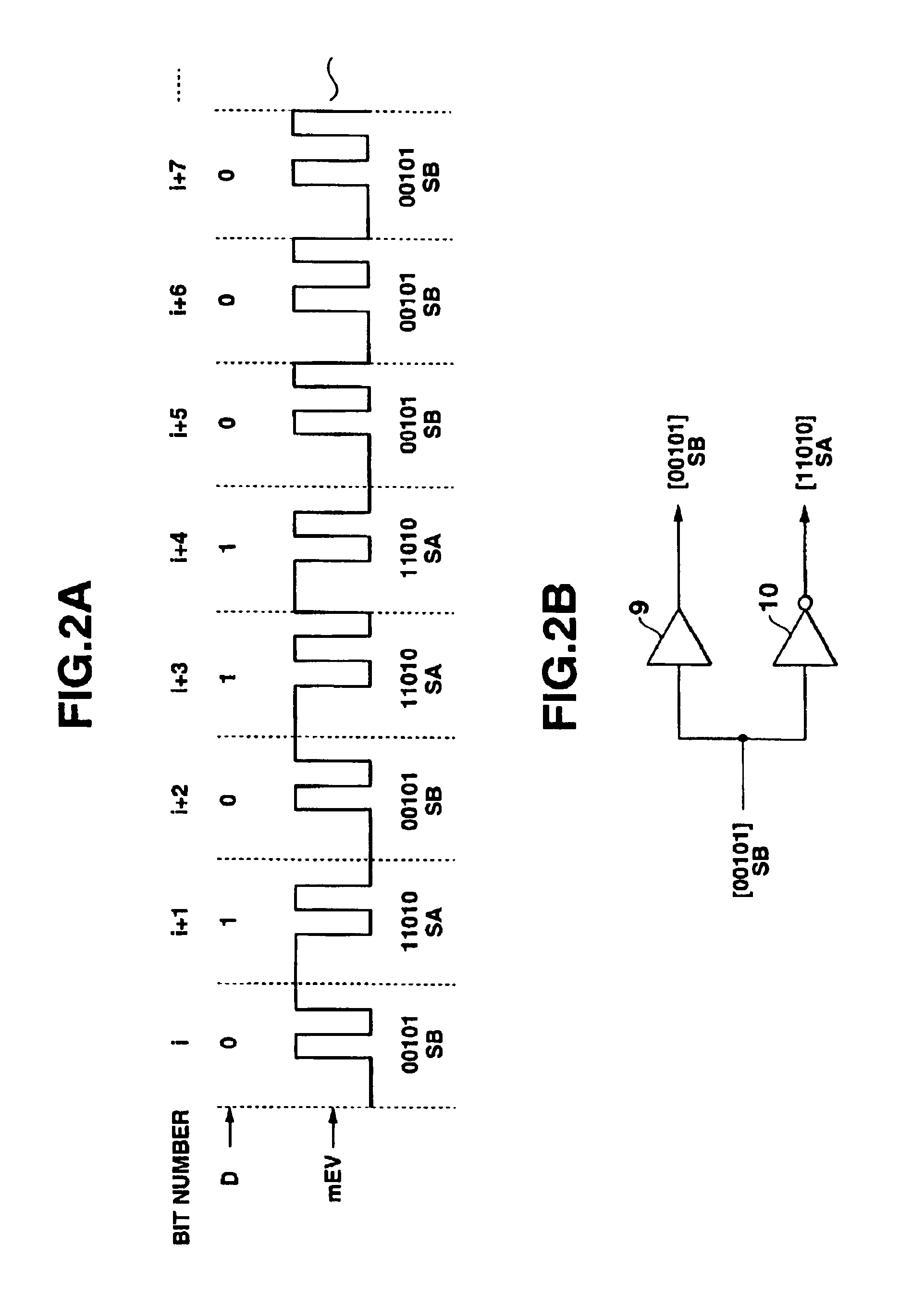

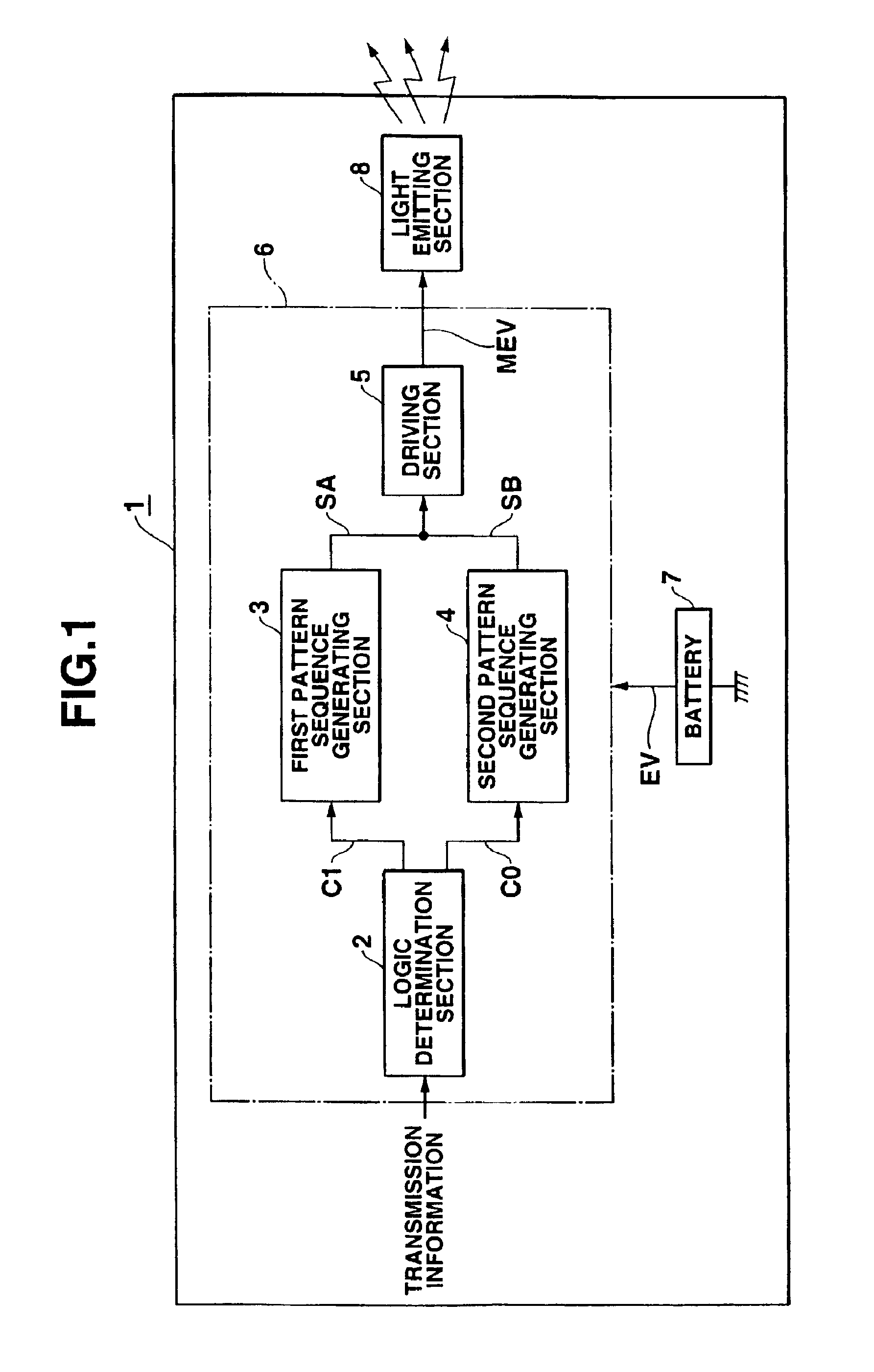

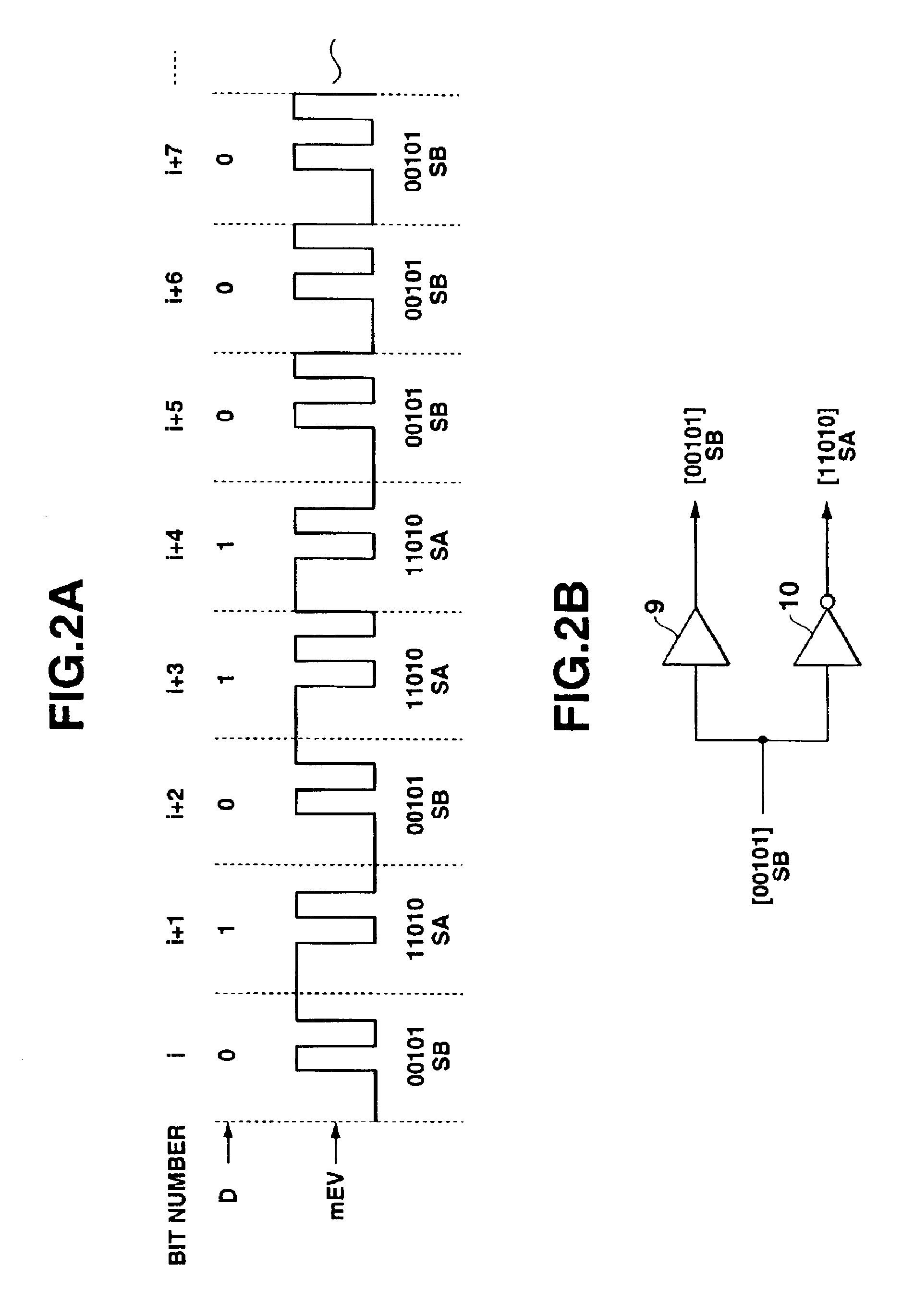

Information transmission system using light as communication medium, information transmission method, image pickup device, and computer programmed product

ActiveUS6933956B2Reduce adverse effectsTelevision system detailsAdvertisingPattern sequenceInformation transmission

A CPU 36 of a light emitting unit 30 fetches ith bit of transmission information TX stored in a transmission data memory 33 in synchronization with a clock signal CK from a timing generator 35. The CUP 36 determines the bit value and fetches a first pattern sequence SA from a pattern data memory 44 when the bit is logic signal 1, and fetches a second pattern sequence SB from a pattern data memory 34 when the bit is logic signal 0, and outputs the first pattern sequence SA and second pattern sequence SB to a light emitting section 37. While, a CPU 39 of a light receiving unit 40 extracts a pixel area with a time sequence luminance variation pattern from a frame image captured into a capture image buffer 46, and binarizes the luminance variation pattern, and performs logic determination. A liquid crystal display 44 displays information of a light emitting area to be overlapped with a subject image.

Owner:CASIO COMPUTER CO LTD

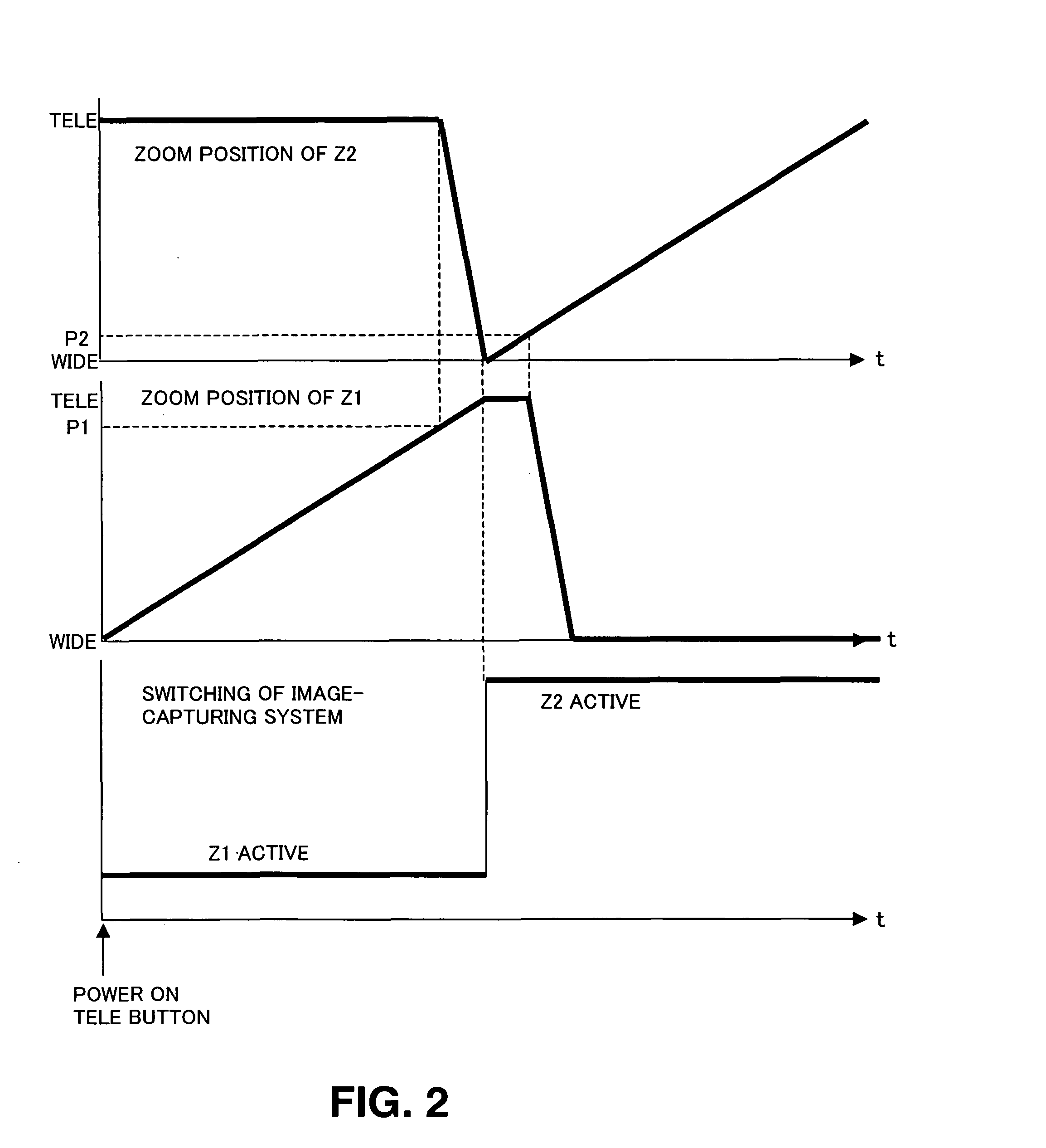

Digital camera with dual optical systems

ActiveUS7738016B2Easy to switchTelevision system detailsColor television detailsCamera lensTiming generator

A digital camera has a first optical system having a wide zoom lens and a second optical system for a telephotography zoom lens. In an initial state where power is active, a controller and timing-generator controls the wide zoom lens so as to be situated at a wide position and the telephotography zoom lens so as to be situated at a telephotograph position. When zoom-in is effected, the wide zoom lens is actuated, and the telephotography zoom lens is maintained at the telephotograph position. When a zoom position of the wide zoom lens has reached a threshold zoom position set to a wider angle of view than that achieved at the telephotograph position, the telephotography zoom lens starts being actuated toward the wide position. When the zoom lens has reached the telephotograph position, an image signal is switched from the wide zoom lens to the telephotography zoom lens, and the selected image signal is output.

Owner:APPLE INC

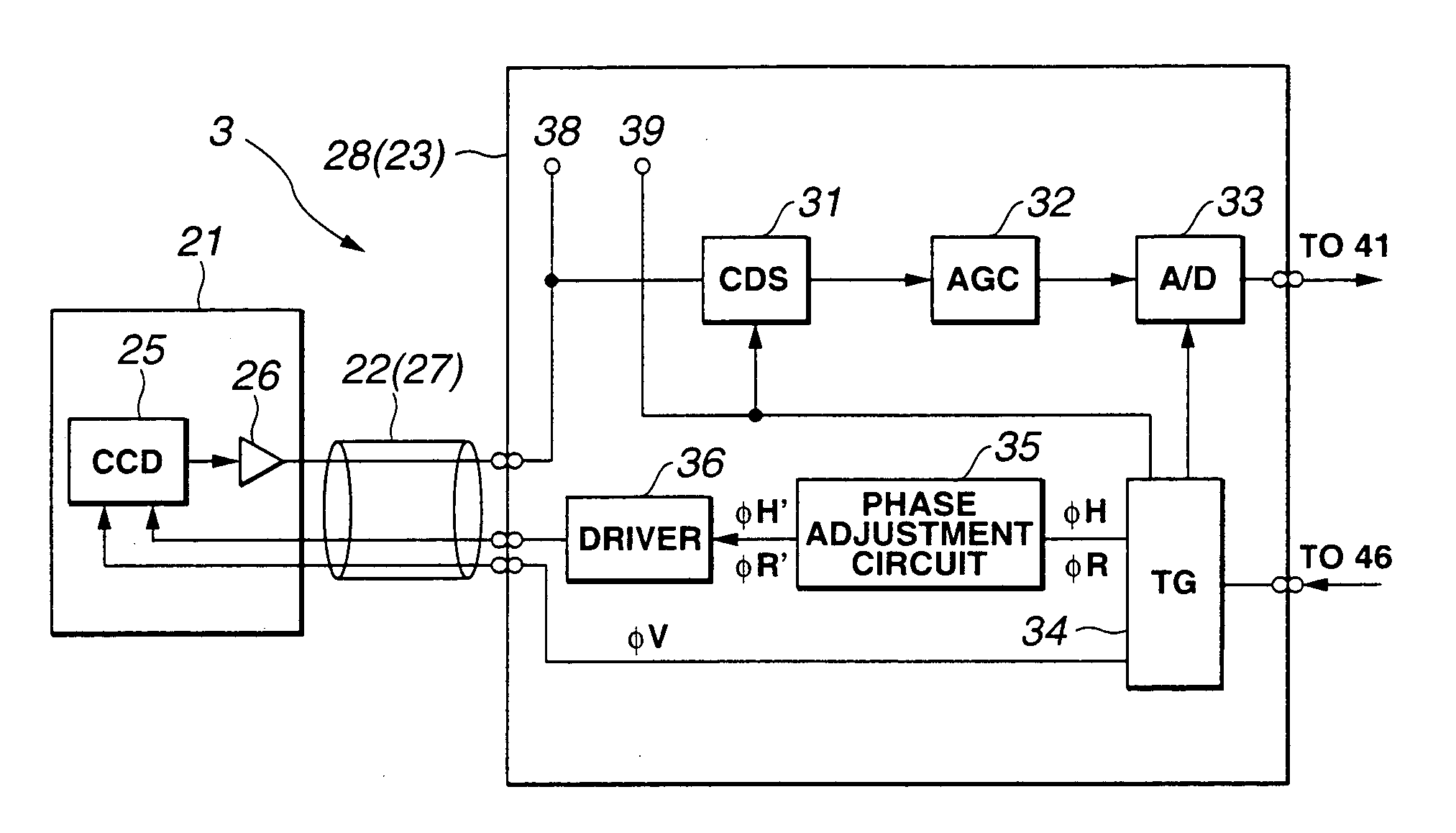

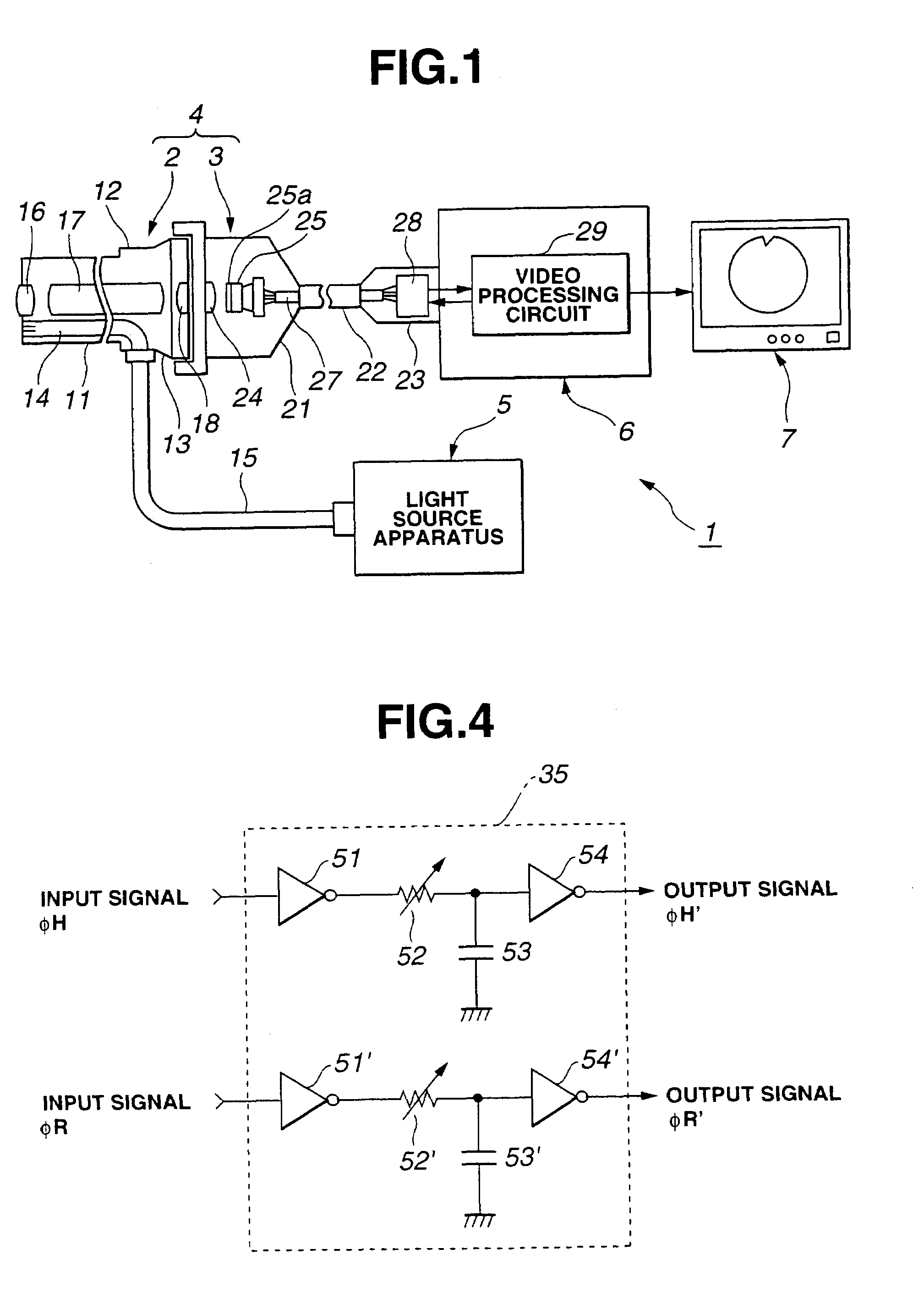

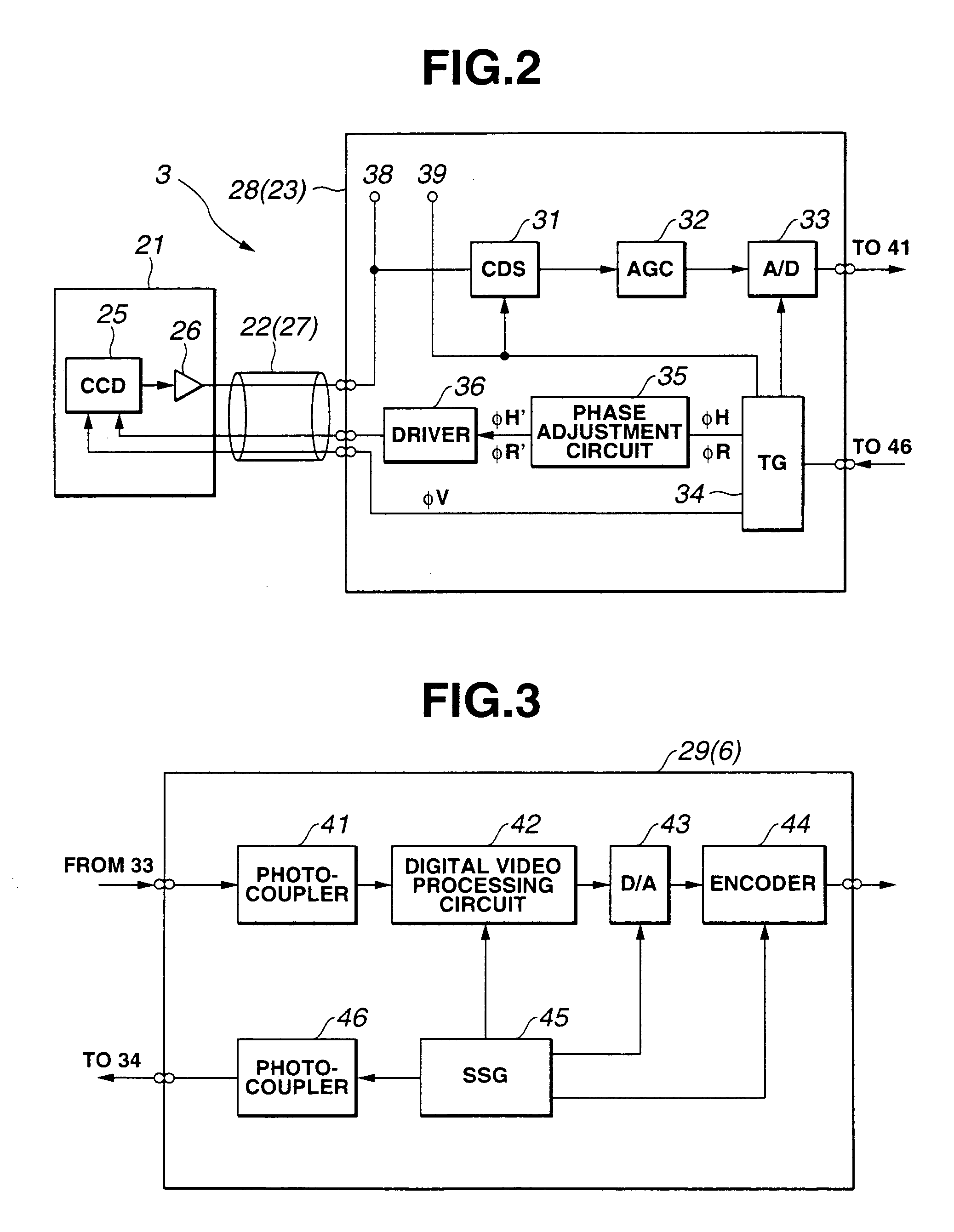

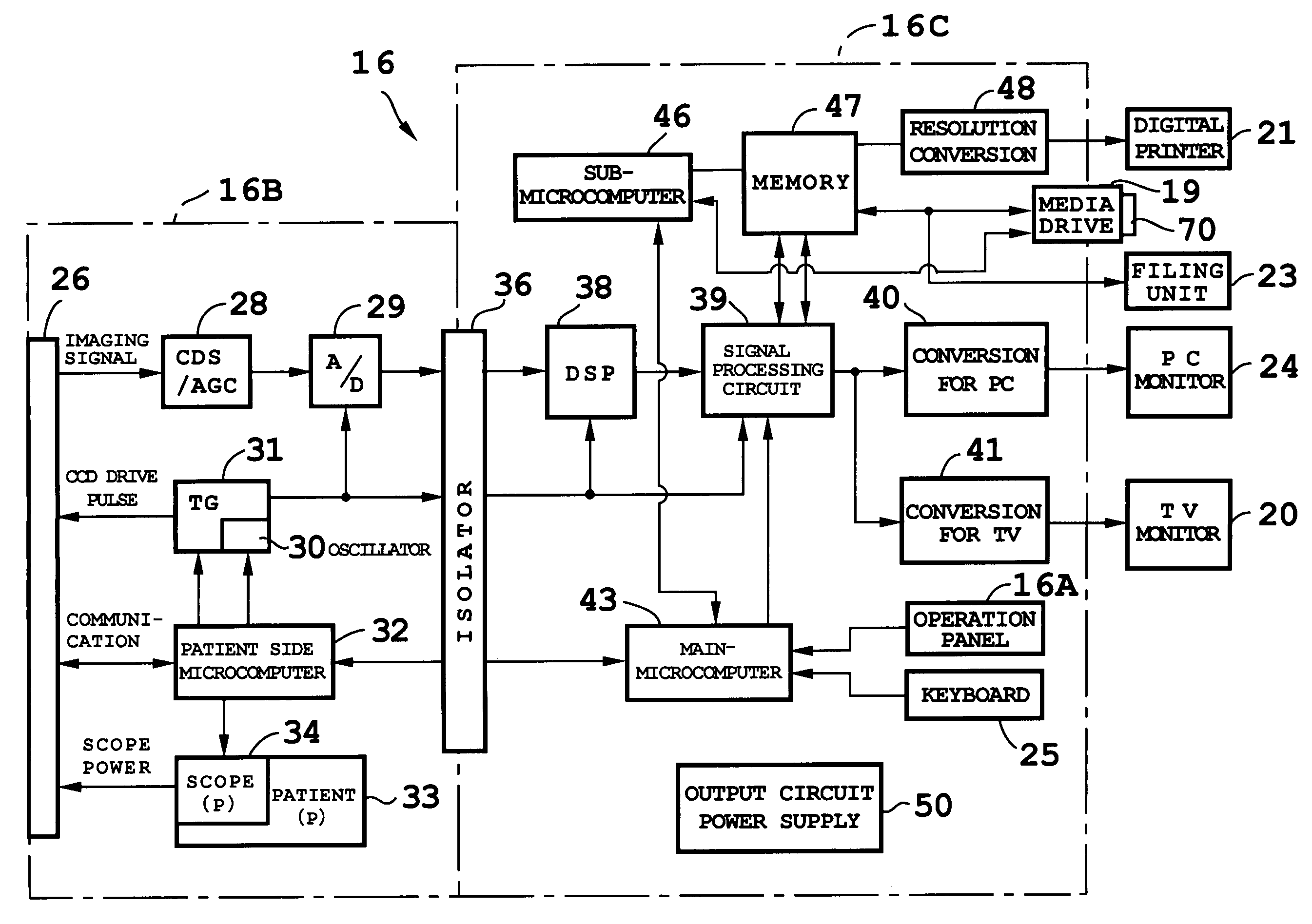

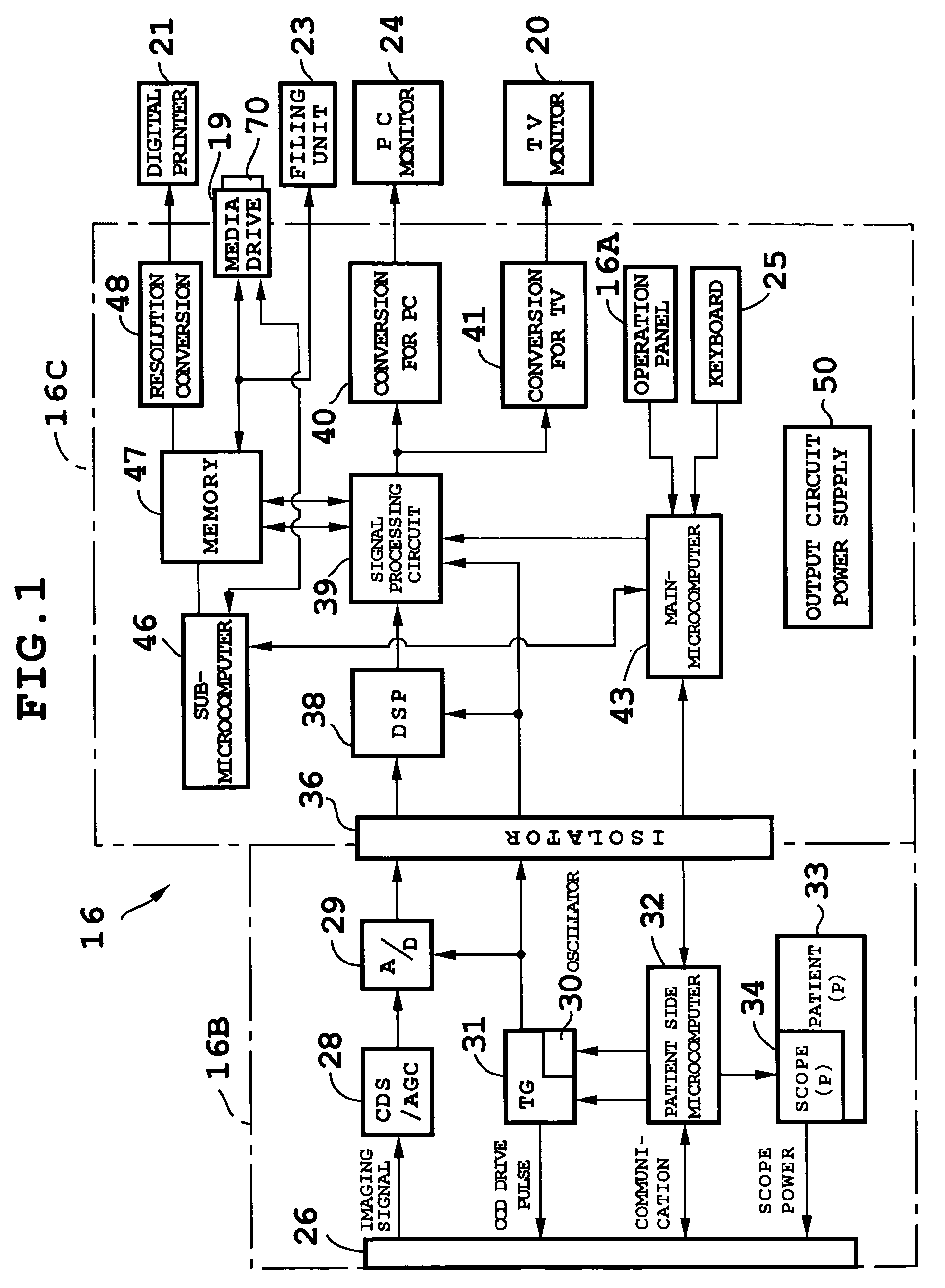

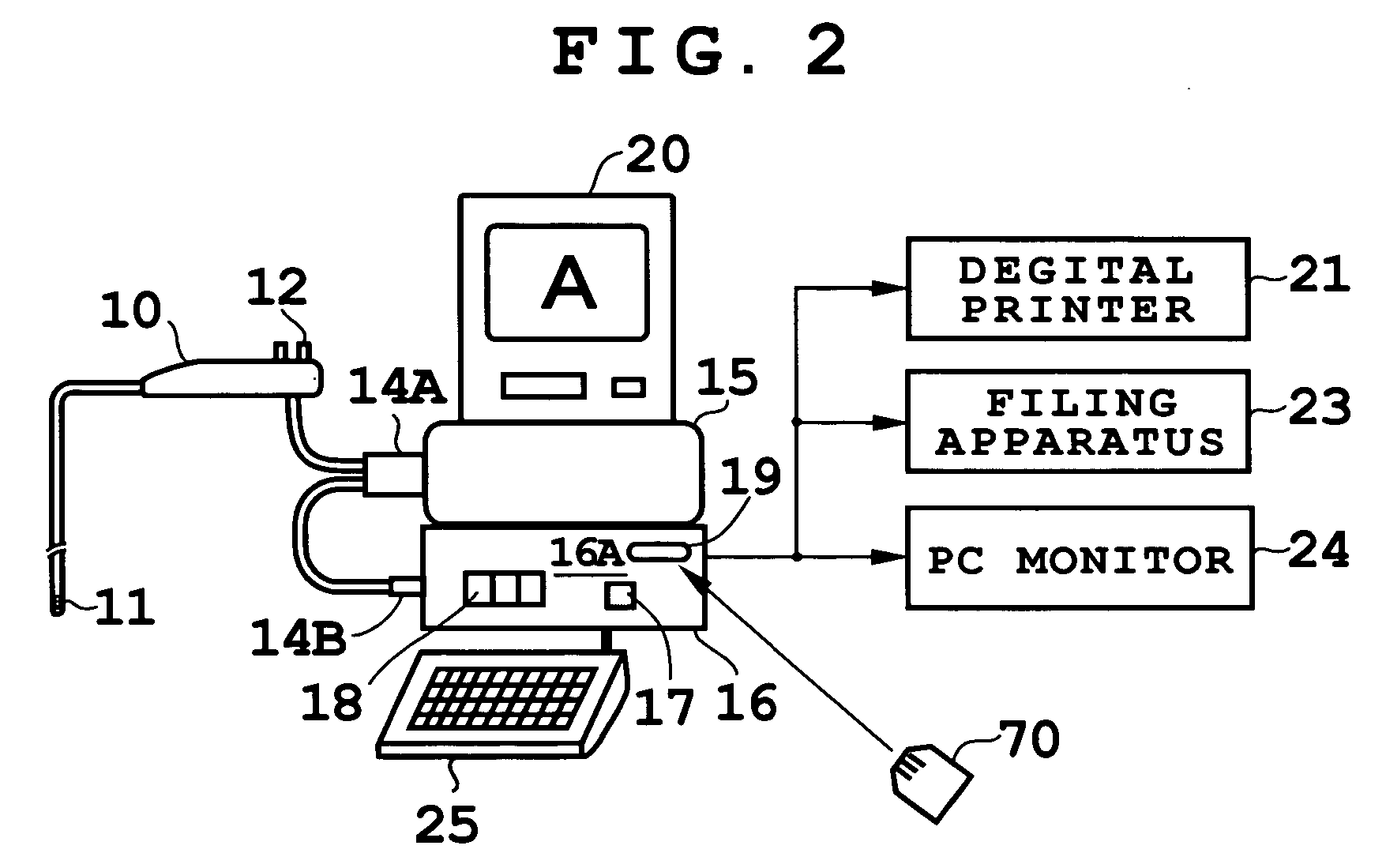

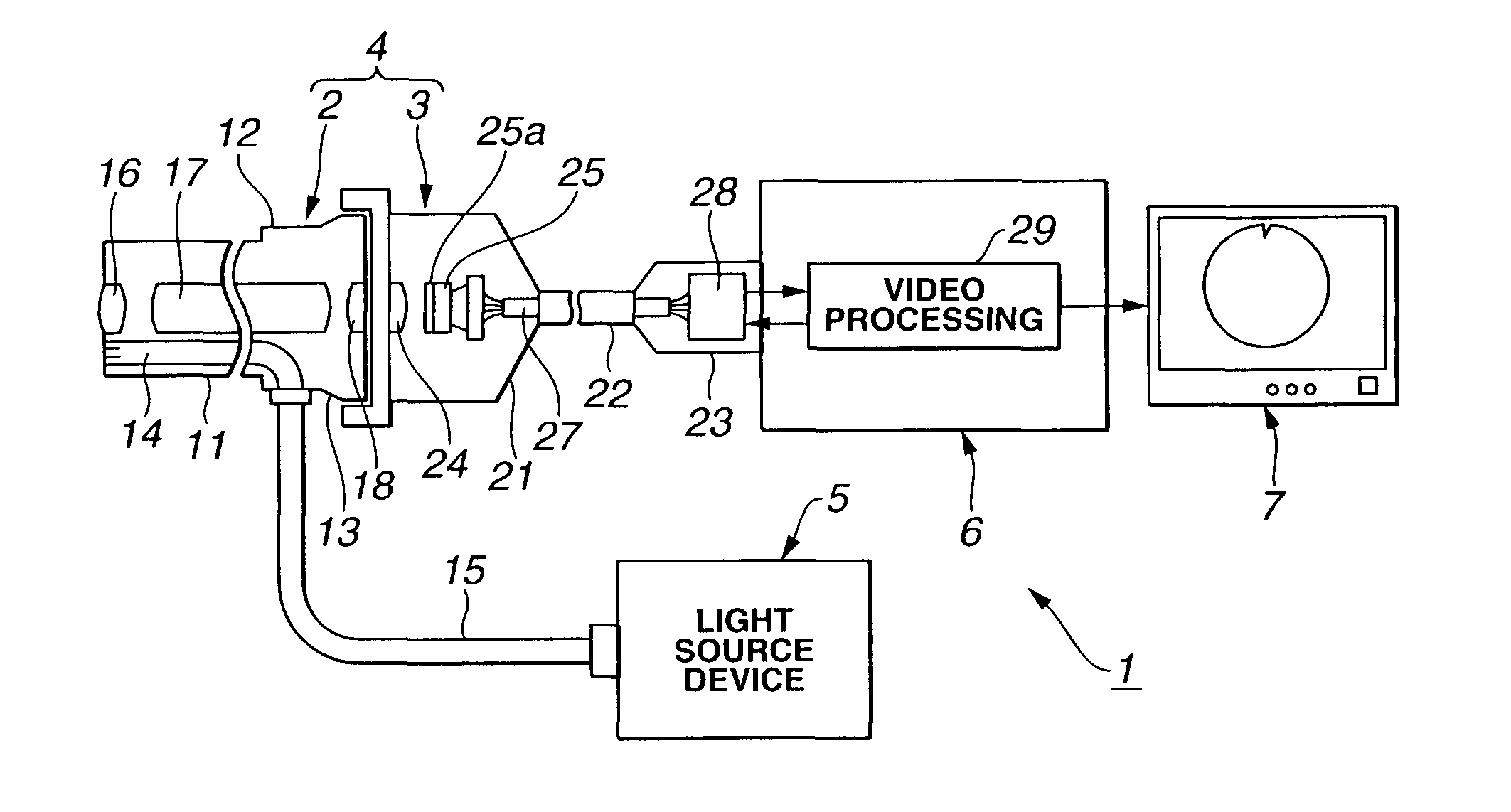

Endoscopic imaging system and endoscope system

InactiveUS7355625B1Simple configurationEasy to adjustTelevision system detailsEndoscopesTiming generatorVideo processing

An imaging apparatus having an imaging device for imaging an object in cooperation with an endoscope is connected to a video processing unit for producing a standard video signal so that it can be disconnected freely. A signal delay occurs over a signal line linking the imaging device and the video processing unit. For this reason, a timing generator and a phase adjustment circuit are incorporated in the imaging apparatus. The timing generator generates driving signals used to drive the imaging device, and the phase adjustment circuit adjusts the phases of the driving signals so that an output signal of the imaging device will be input to the video processing unit according to predetermined timing. Even when the signal line has a different length from any other or the imaging device offers a different number of pixels from any other, the difference can be readily coped with owing to the imaging apparatus. This leads to alleviation of a load incurred by the video processing unit.

Owner:OLYMPUS CORP

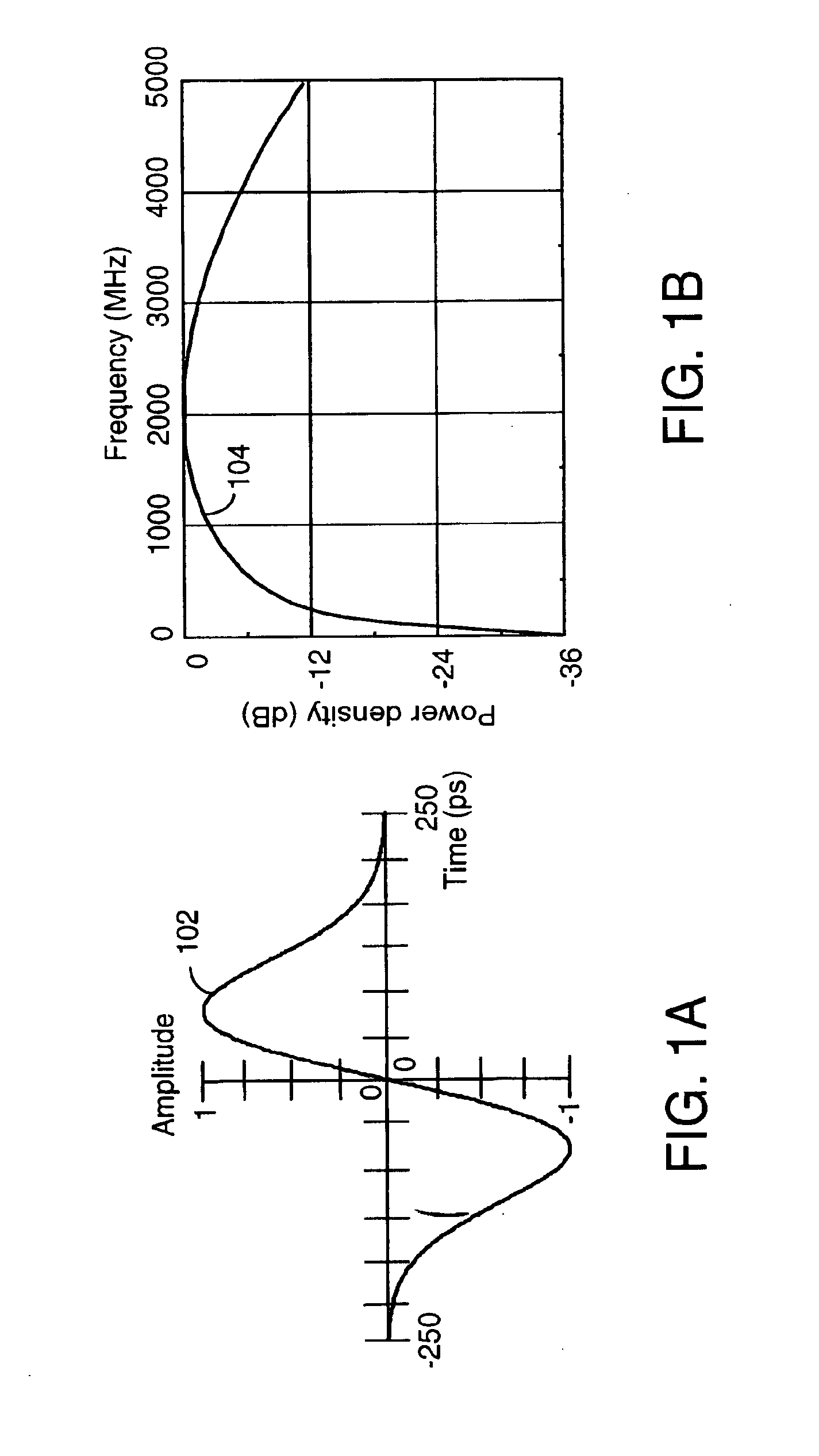

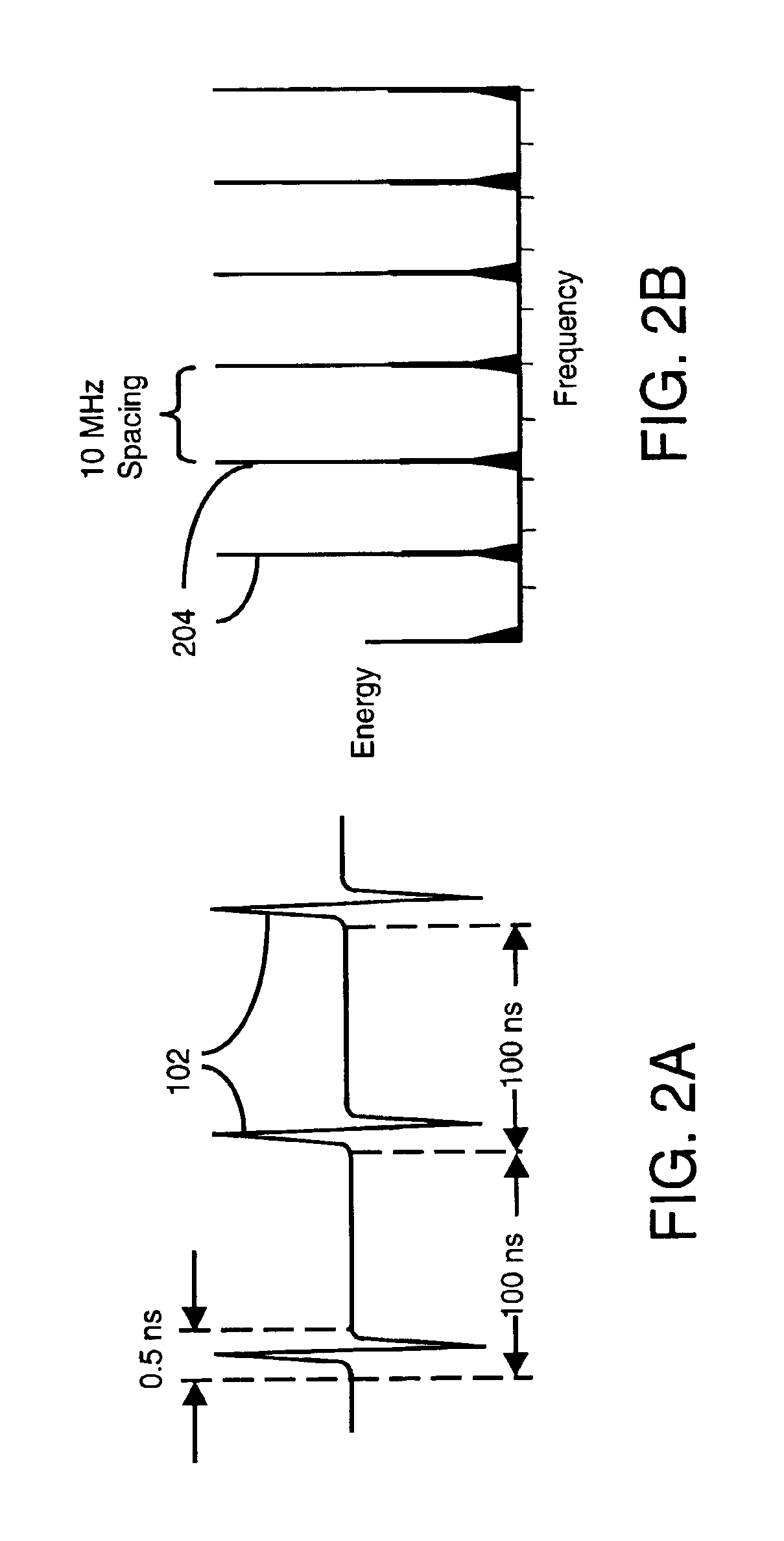

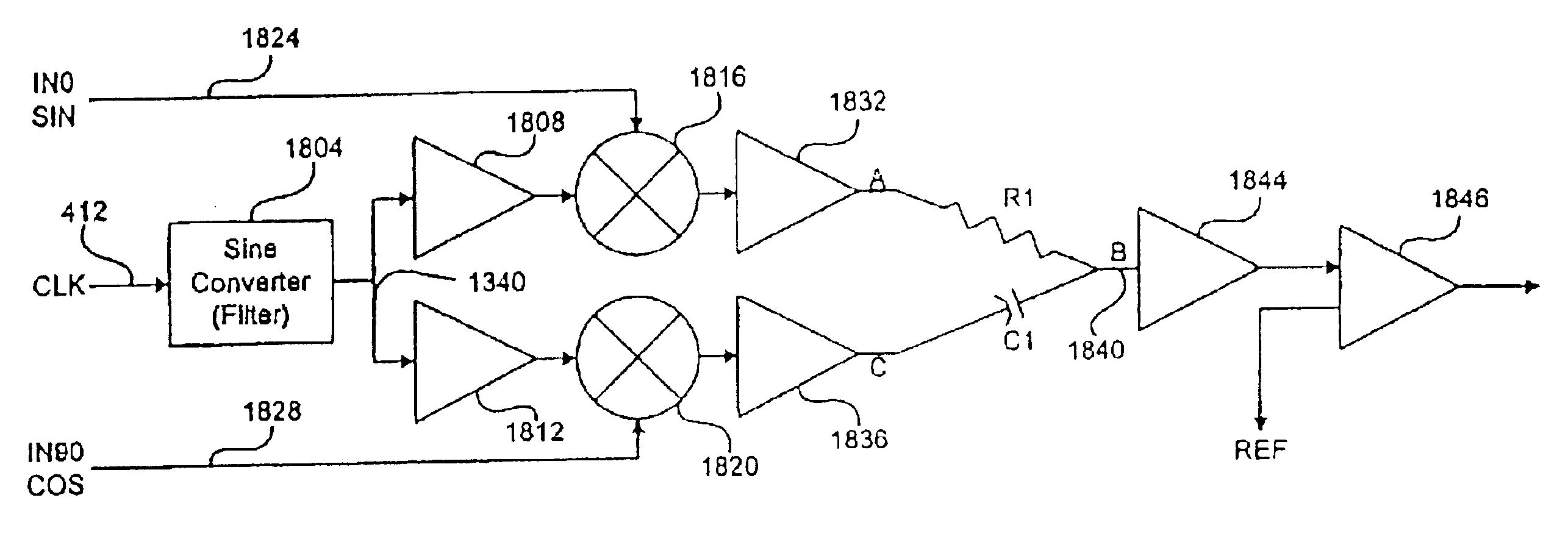

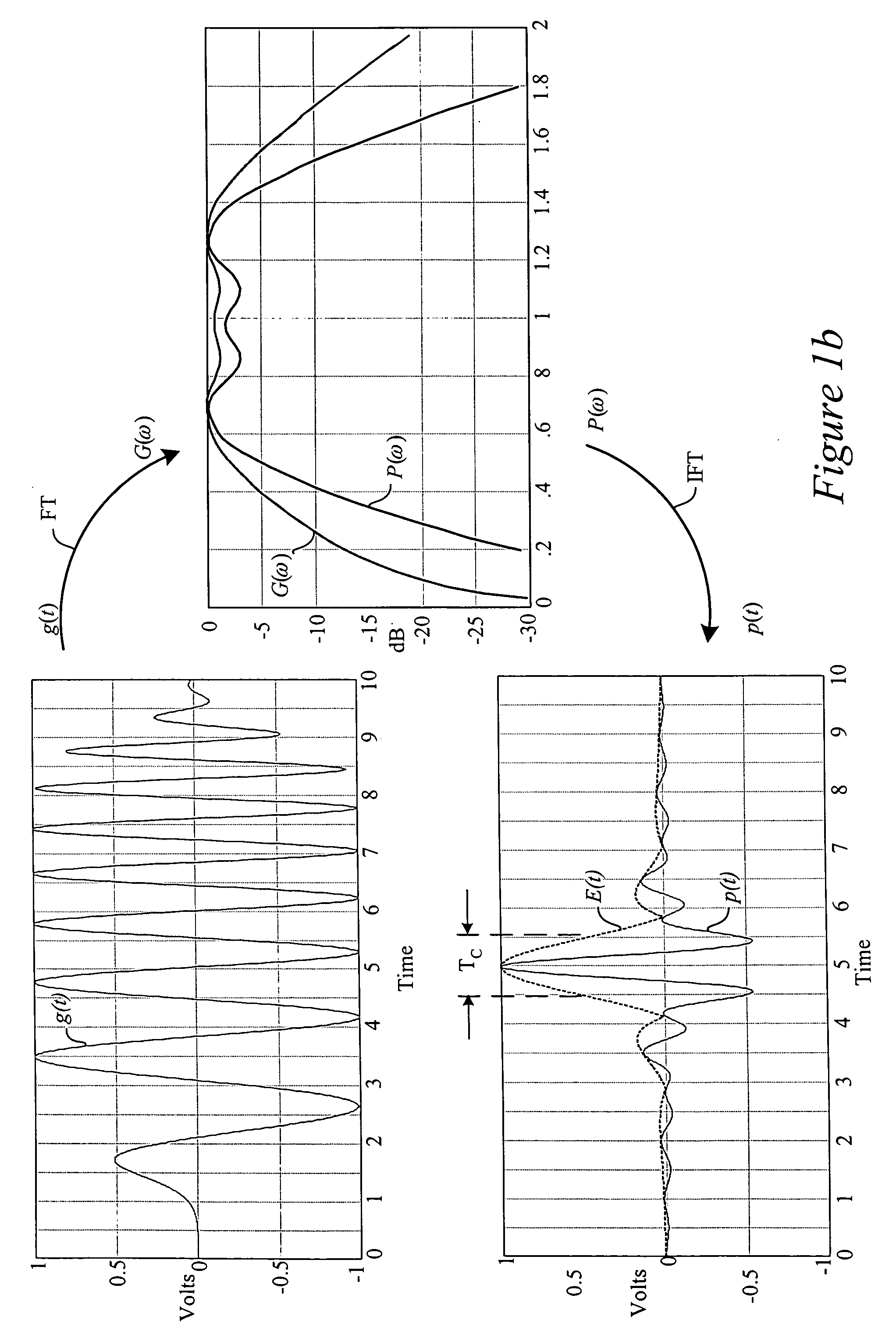

Precision timing generator apparatus and associated methods

InactiveUS6950485B2Overcome problemsPulse automatic controlTime-division multiplexTiming generatorPhase shifted

A precision timing generator includes a combiner that provides a timing signal by combining a coarse timing signal and a fine timing signal derived from a phase-shifted sinusoidal signal that has a desired phase shift. The coarse timing generator generates the coarse timing signal from a clock signal and a timing command input. The fine timing generator includes a sinusoidal-signal generator that receives the clock signal and generates a sinusoidal signal. The fine timing generator also includes a phase shifter that receives the sinusoidal signal and the timing command input and shifts the phase of the sinusoidal signal based on the timing input to generate the phase shifted sinusoidal signal.

Owner:ALEREON

Information transmission system using light as communication medium, information transmission method, image pickup device, and computer programmed product

InactiveUSRE42848E1Reduce adverse effectsTelevision system detailsAdvertisingPattern sequenceInformation transmission

A CPU 36 of a light emitting unit 30 fetches ith bit of transmission information TX stored in a transmission data memory 33 in synchronization with a clock signal CK from a timing generator 35. The CUP 36 determines the bit value and fetches a first pattern sequence SA from a pattern data memory 44 when the bit is logic signal 1, and fetches a second pattern sequence SB from a pattern data memory 34 when the bit is logic signal 0, and outputs the first pattern sequence SA and second pattern sequence SB to a light emitting section 37. While, a CPU 39 of a light receiving unit 40 extracts a pixel area with a time sequence luminance variation pattern from a frame image captured into a capture image buffer 46, and binarizes the luminance variation pattern, and performs logic determination. A liquid crystal display 44 displays information of a light emitting area to be overlapped with a subject image.

Owner:CASIO COMPUTER CO LTD

Information transmission system using light as communication medium, information transmission method, image pickup device, and computer programmed product

InactiveUSRE44004E1Reduce adverse effectsTelevision system detailsAdvertisingPattern sequenceInformation transmission

A CPU 36 of a light emitting unit 30 fetches ith bit of transmission information TX stored in a transmission data memory 33 in synchronization with a clock signal CK from a timing generator 35. The CUP 36 determines the bit value and fetches a first pattern sequence SA from a pattern data memory 44 when the bit is logic signal 1, and fetches a second pattern sequence SB from a pattern data memory 34 when the bit is logic signal 0, and outputs the first pattern sequence SA and second pattern sequence SB to a light emitting section 37. While, a CPU 39 of a light receiving unit 40 extracts a pixel area with a time sequence luminance variation pattern from a frame image captured into a capture image buffer 46, and binarizes the luminance variation pattern, and performs logic determination. A liquid crystal display 44 displays information of a light emitting area to be overlapped with a subject image.

Owner:CASIO COMPUTER CO LTD

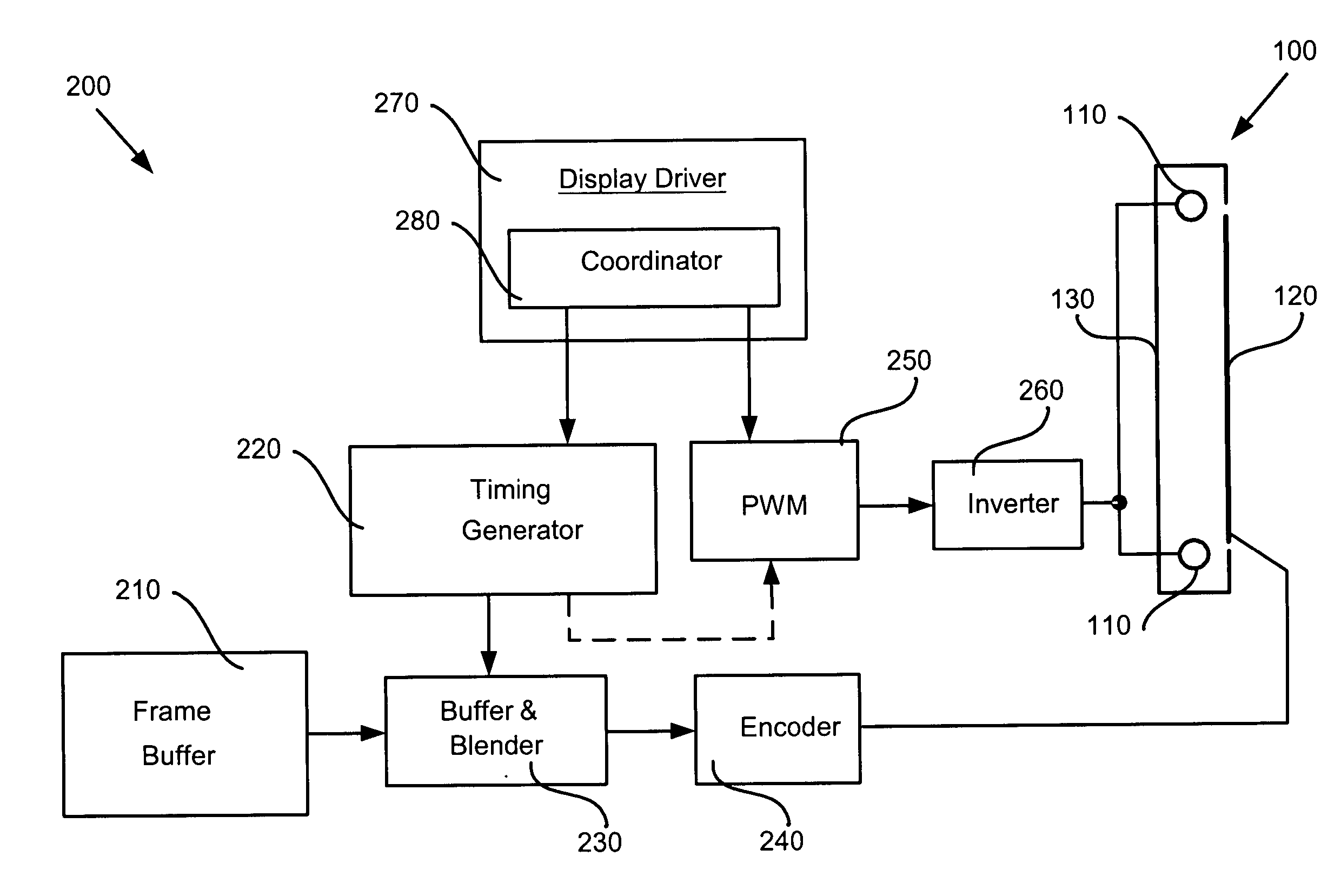

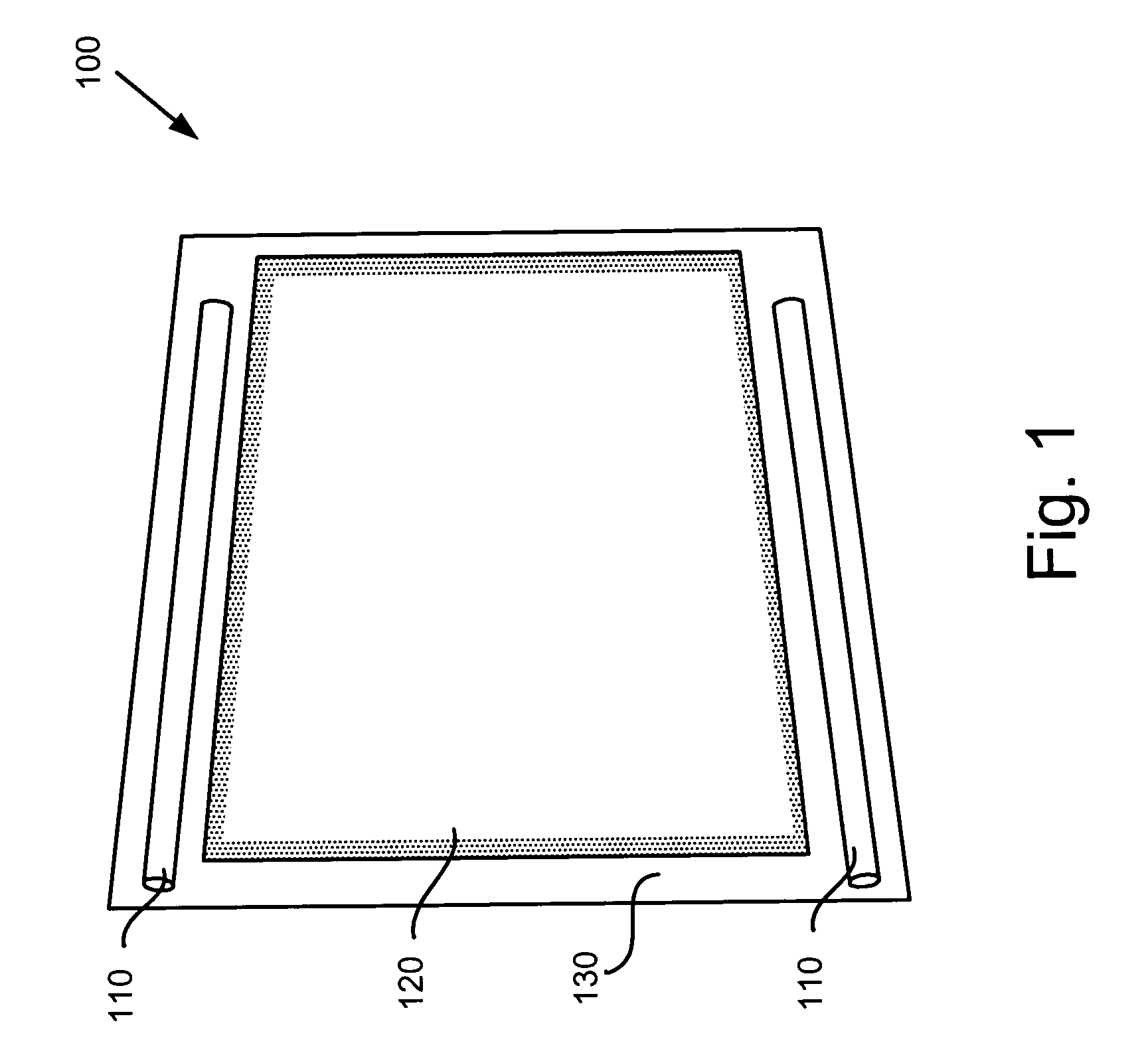

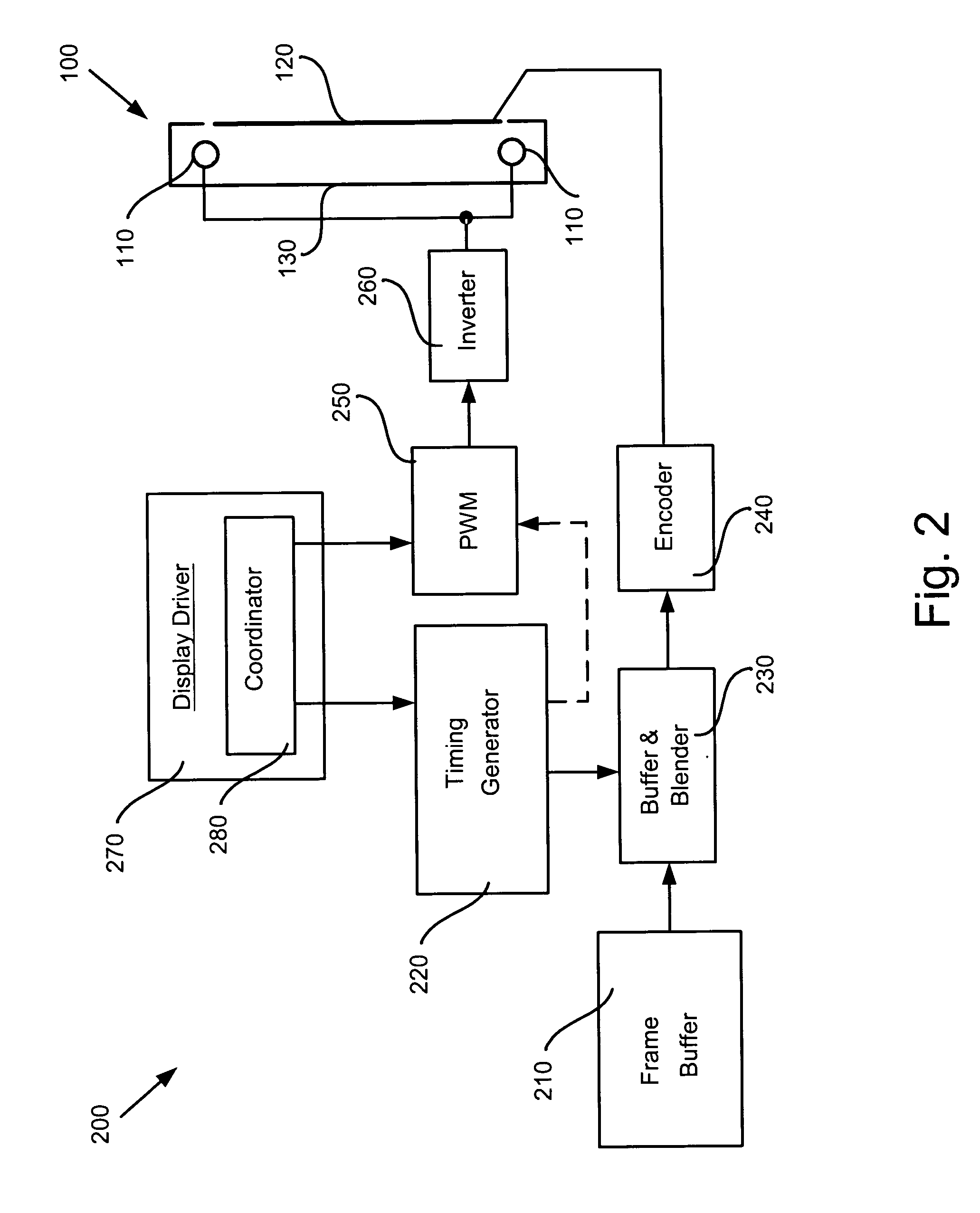

Coordinating backlight frequency and refresh rate in a panel display

ActiveUS20050068289A1Cathode-ray tube indicatorsInput/output processes for data processingTiming generatorDisplay device

A panel may be arranged to display image data, and a backlight may be arranged to illuminate a back of the panel. A timing generator may be arranged to control the refresh rate of the panel, and a modulator may be arranged to control the backlight based on an associated modulation frequency. A coordinator may be arranged to synchronize between the refresh rate and the modulation frequency when the refresh rate or the modulation frequency is changed.

Owner:TAHOE RES LTD

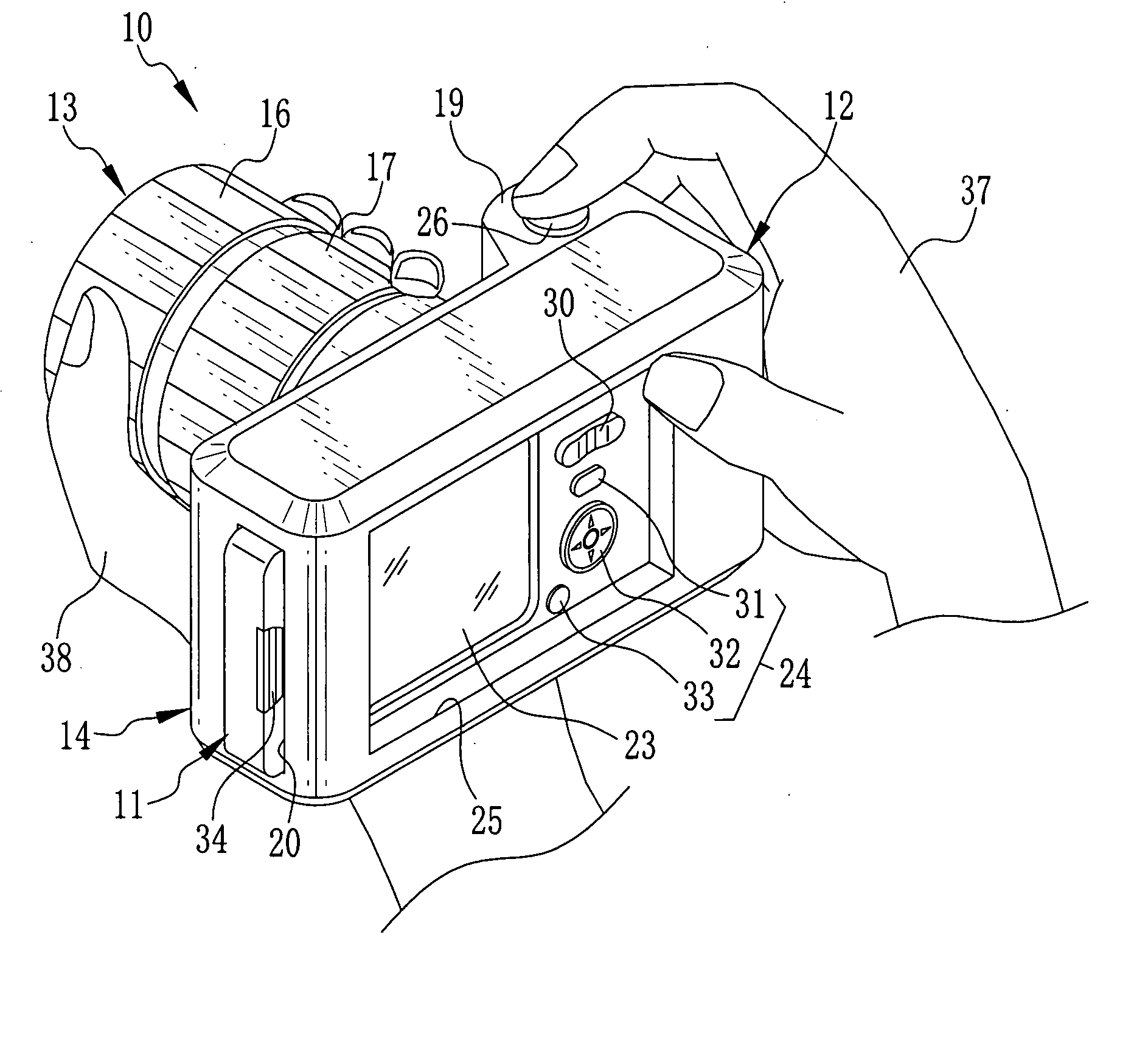

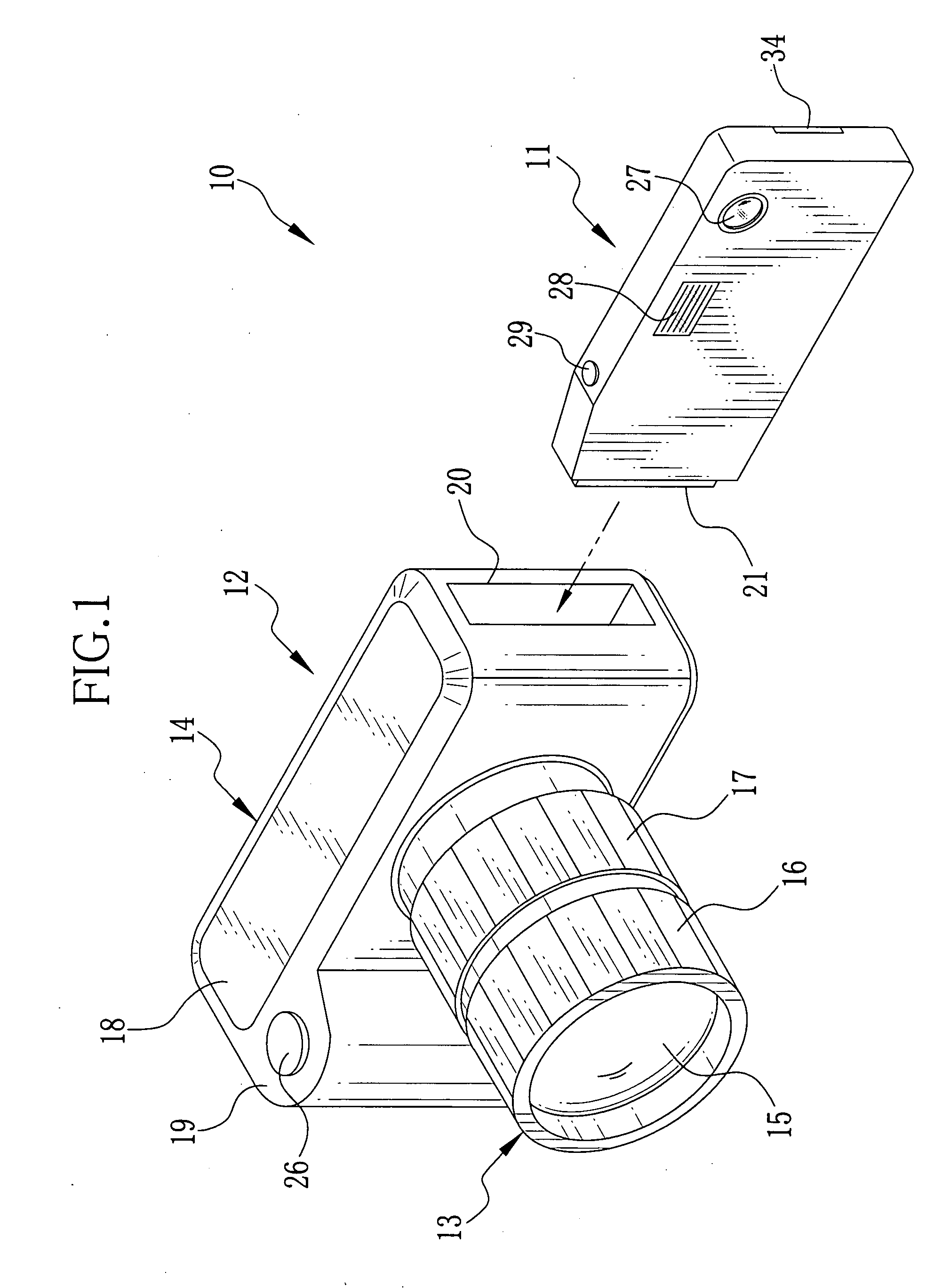

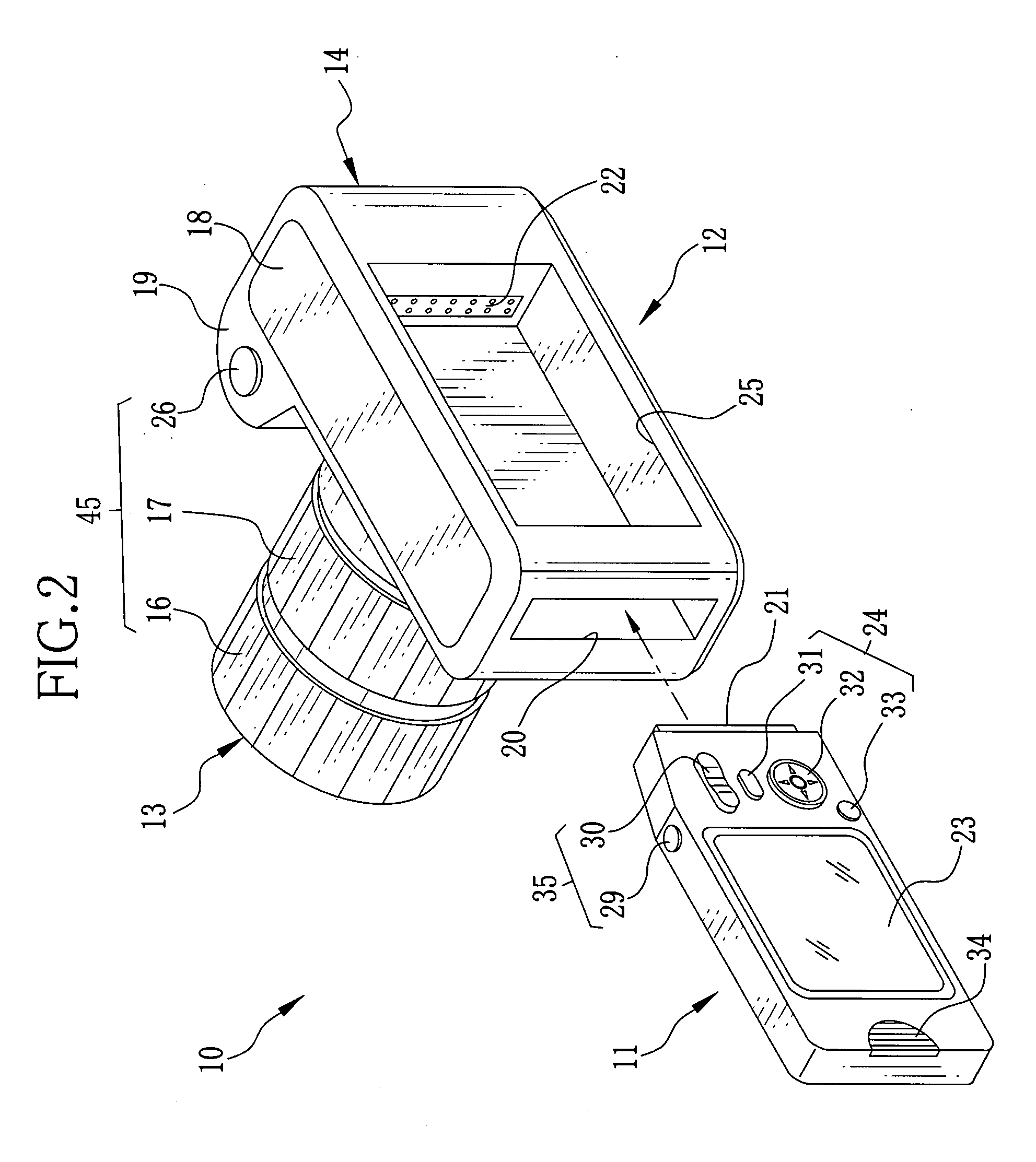

Camera and lens unit

InactiveUS20070268371A1Improve gripTelevision system detailsPicture signal generatorsDriver circuitTiming generator

A camera consists of a first unit and a second unit removably connectable to the first unit. The first unit is provided with an imaging section including an optical system and an imaging device, that enables to capture high-quality images. The first unit is formed with a grip portion for holding and handling the camera as a combination of the first unit and the second unit. The second unit is provided with a driving device including a CPU, a lens driver circuit, a stop driver circuit and a timing generator, and a second imaging section including an optical system and an imaging device, that enables to capture relatively low-quality images. While the second unit is connected to the first unit, the driving device drives the imaging section of the first unit. While the second unit is not connected to the first unit, the driving device drives the imaging section of the second unit.

Owner:FUJIFILM CORP

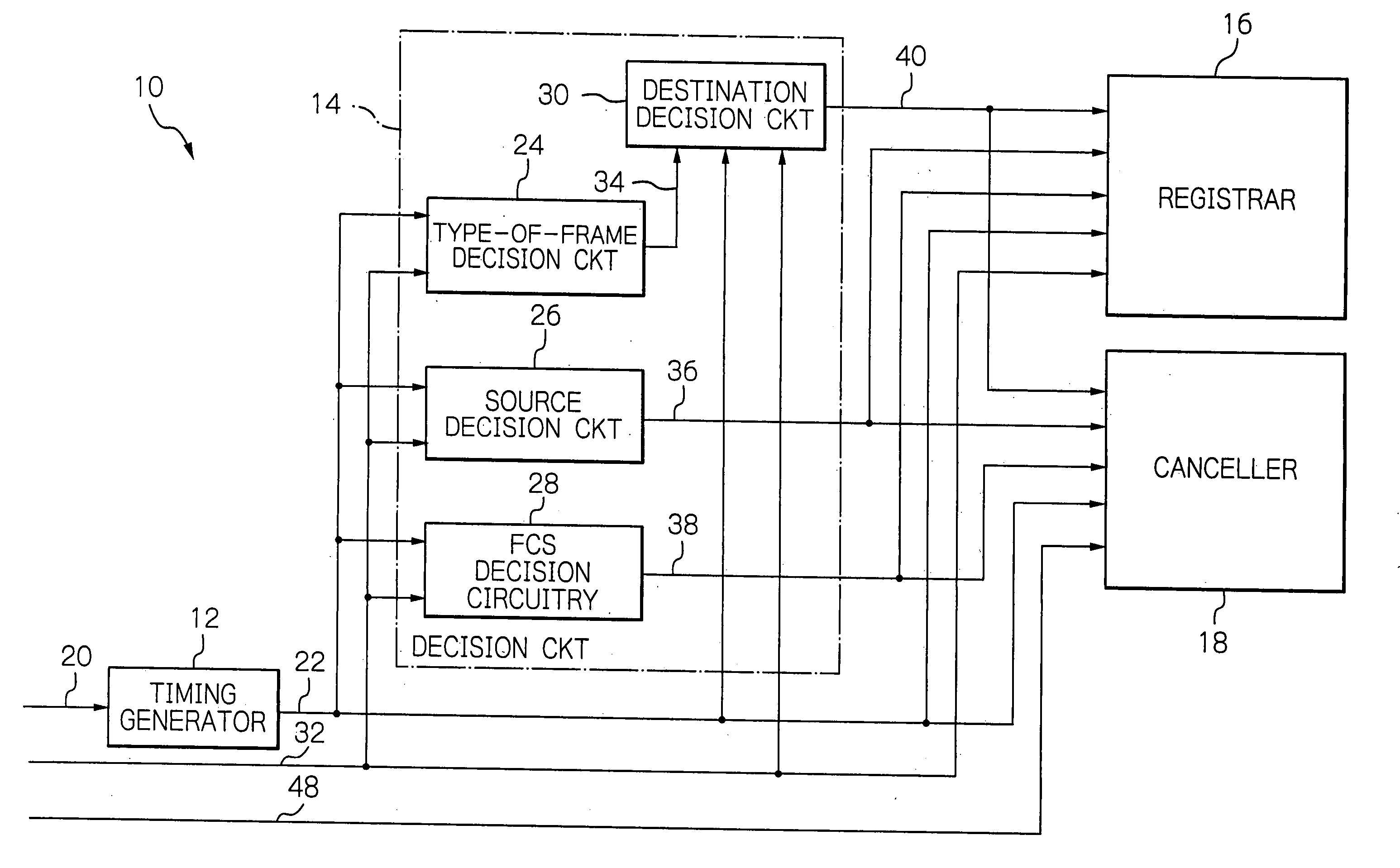

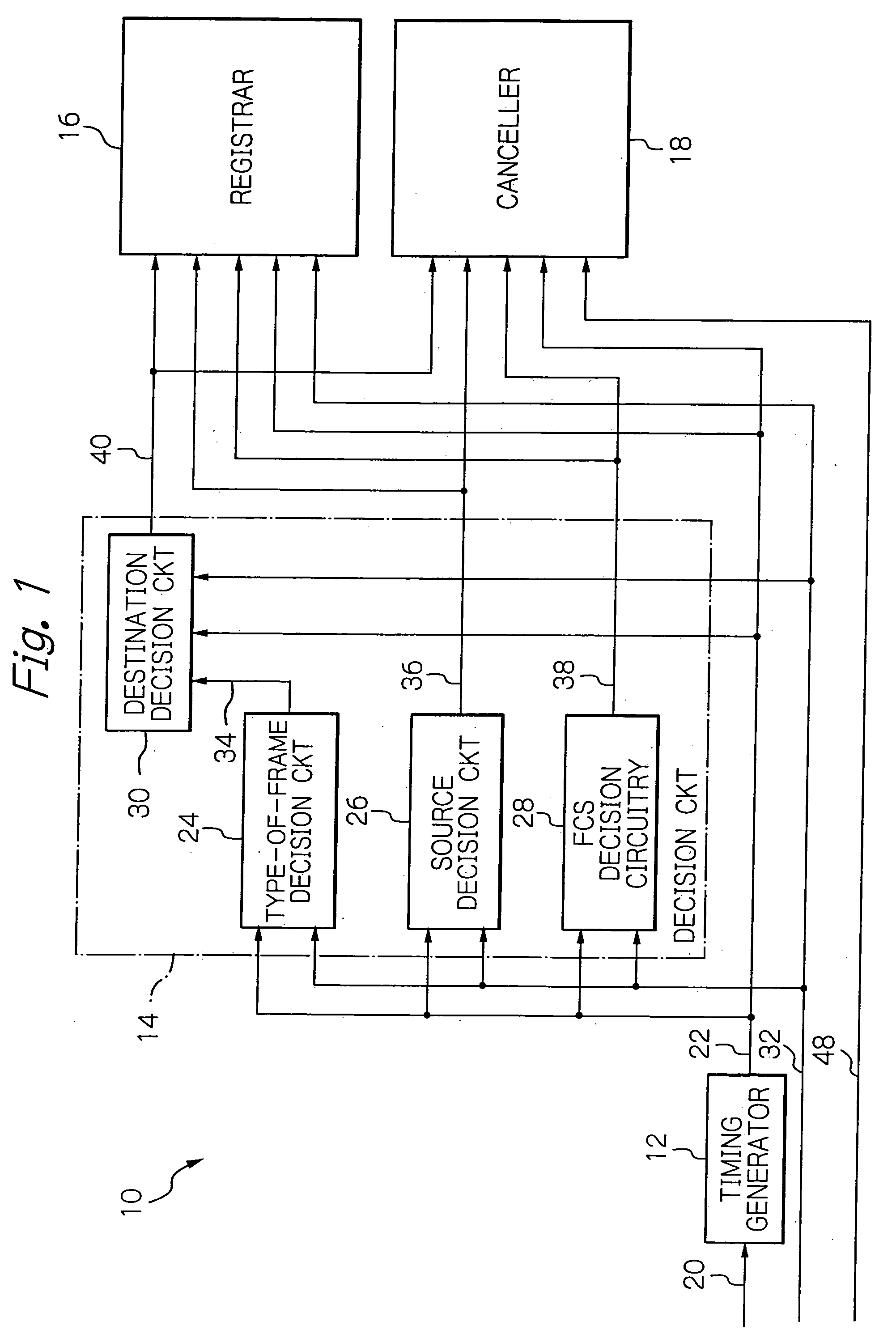

Radio apparatus joining an IBSS or ad hoc network

A radio apparatus applicable to an IBSS (Independent Basic Service Set) network includes a timing generator for generating a timing signal in accordance with the phase of a received frame. A decision circuitry acquires the source address of the received frame in response to the timing signal and received frame, and determines the type of the received frame and whether or not the received frame is addressed to the radio apparatus and correctly received. A registrar acquires information representative of the processing capability of a source from the received frame in accordance with the timing signal, signals output from the decision circuitry and source address and registers the above information and source address. A canceller determines withdrawal from an IBSS area in response to the timing signal, signals output from said decision circuitry, source address and particular information relating to the type of the received frame.

Owner:LAPIS SEMICON CO LTD

Photographic device and control method therefor

InactiveUS20050200744A1Shorten posting timeAvoid flickeringTelevision system detailsTelevision system scanning detailsElectronic shutterTiming generator

There is disclosed a photographic device that uses an image sensor and an electronic viewfinder. When a release button is pressed halfway, an aperture value, an electronic shutter speed and a photosensitivity are decided based on the present subject brightness to provide a proper exposure value for photographing a still image. So long as the release button is kept being pressed halfway, a timing generator drives the image sensor to shoot video images at a frame rate of 20 Hz, and the aperture value decided for still image photography is fixed, whereas the electronic shutter speed and the photosensitivity are adjusted according to the subject brightness by use of an aperture-priority type video program. When the release button is pressed to the full, an exposure for a still image is done with the fixed aperture value.

Owner:FUJIFILM CORP

Image-capturing device having multiple optical systems

InactiveUS20070025713A1Improve visibility and operationReduce in quantityTelevision system detailsCamera body detailsTiming generatorOptic system

A digital camera comprises a first image-capturing optical system having a fixed focal length lens 2 and an image sensor 12, and a second image-capturing optical system having a zoom lens 3 and an image sensor 14. The first image-capturing optical system has a first electronic zoom range, and the second image-capturing optical system has an optical zoom range between a predetermined minimum focal length and a maximum focal length. A tele end of the first electronic zoom range is set to be at a position nearer to the wide side than the maximum focal length of the second image-capturing optical system and to be a position nearer to a tele side than the minimum focal length of the second image-capturing optical system and a wide end of the first electronic zoom range is set at a position nearer to the wide side than a minimum focal length of the second image-capturing optical system, so that the first electronic zoom range and the optical zoom range partially overlap. A control processor and timing generator 40 switches zoom at the tele end of the first electronic zoom range from an electronic zoom of the first image-capturing optical system to the optical zoom of the second image-capturing optical system during a zoom-in process and at the wide end of the optical zoom range from the optical zoom of the second image-capturing optical system to the electronic zoom of the first image-capturing optical system during a zoom-out process.

Owner:MONUMENT PEAK VENTURES LLC

Electronic endoscope apparatus which stores image data on recording medium

InactiveUS7420586B2Process stabilityEnhance the imageTelevision system detailsSurgeryTiming generatorEndoscope

Owner:FUJI PHOTO OPTICAL CO LTD

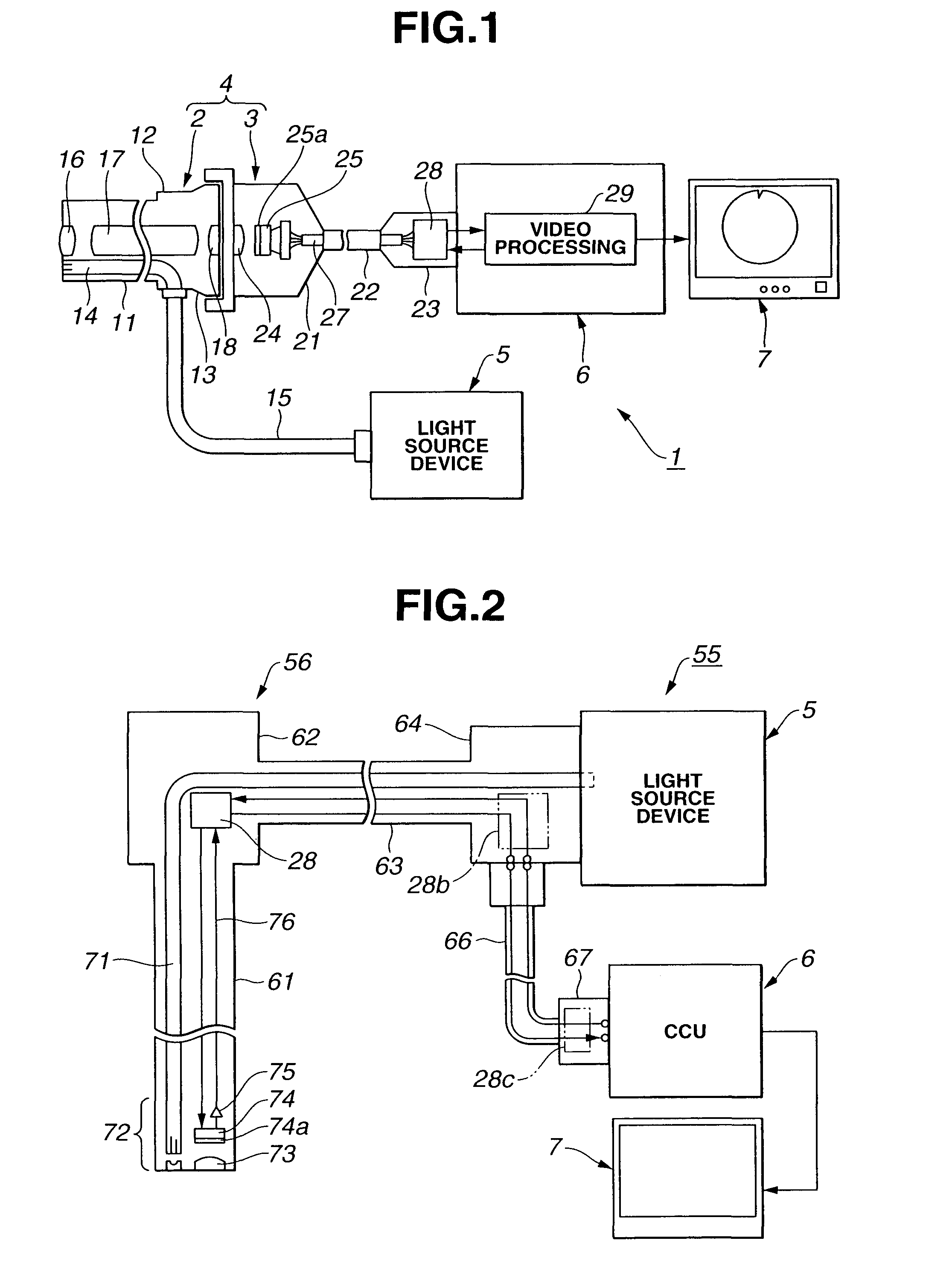

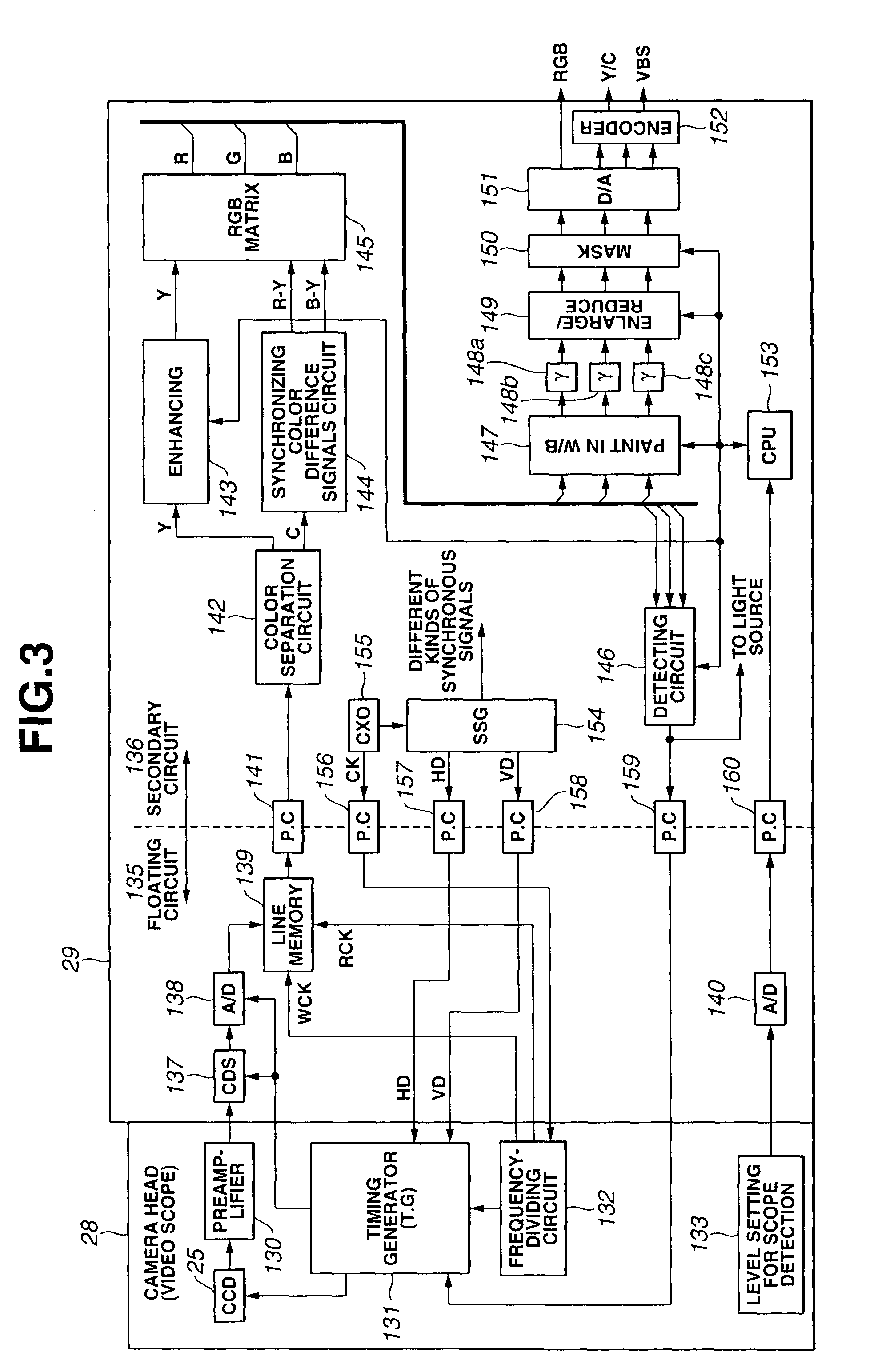

Image pickup system

To provide an image pickup system having CCDs 25 driven at different frequencies respectively which can drive each CCD 25 with a predetermined frequency if a detachable camera head (or electronic endoscope) 28 is used and also can process a signal processing clock of a video processing circuit 29 with one type of clock. A drive signal of the predetermined frequency supplied to the CCD is produced via a generating circuit CXO 155 in the video processing circuit 29, a frequency dividing circuit 132 and a timing generator (T.G.) 131. A CCD signal outputted from the CCD 25 is inputted to a line memory 139 in a floating circuit 135. As a writing clock (WCK) of the line memory 139, the one which is divided in the frequency dividing circuit 132 to a frequency in accordance with the CCD 25 to be used is used, and as a reading clock (RCK), the one of one type of frequency is used without regard to the CCD 25 to be used. Hence, it is possible to perform the signal processing of a secondary circuit 136 of the line memory 139 and following ones always with a common generating clock.

Owner:OLYMPUS CORP

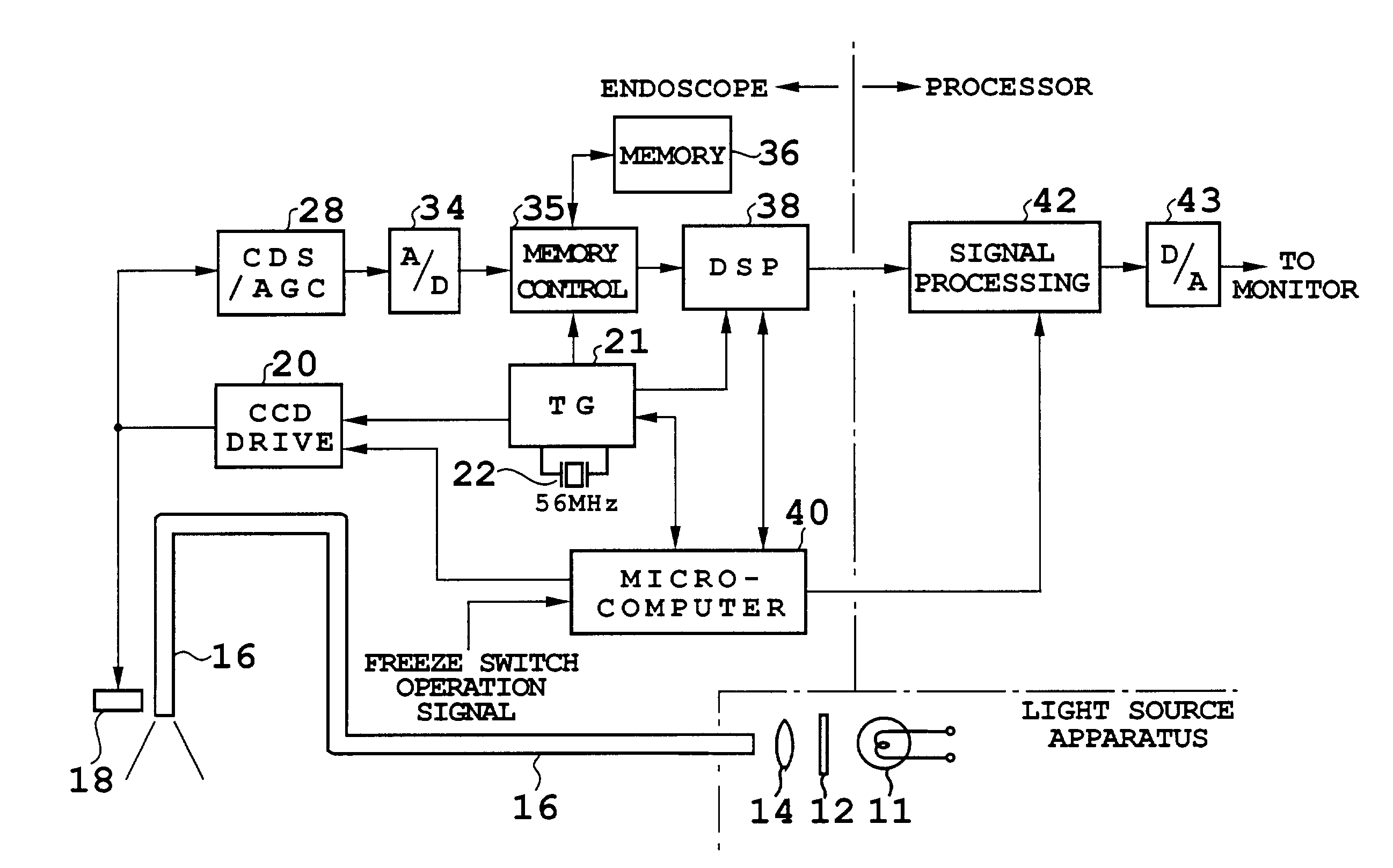

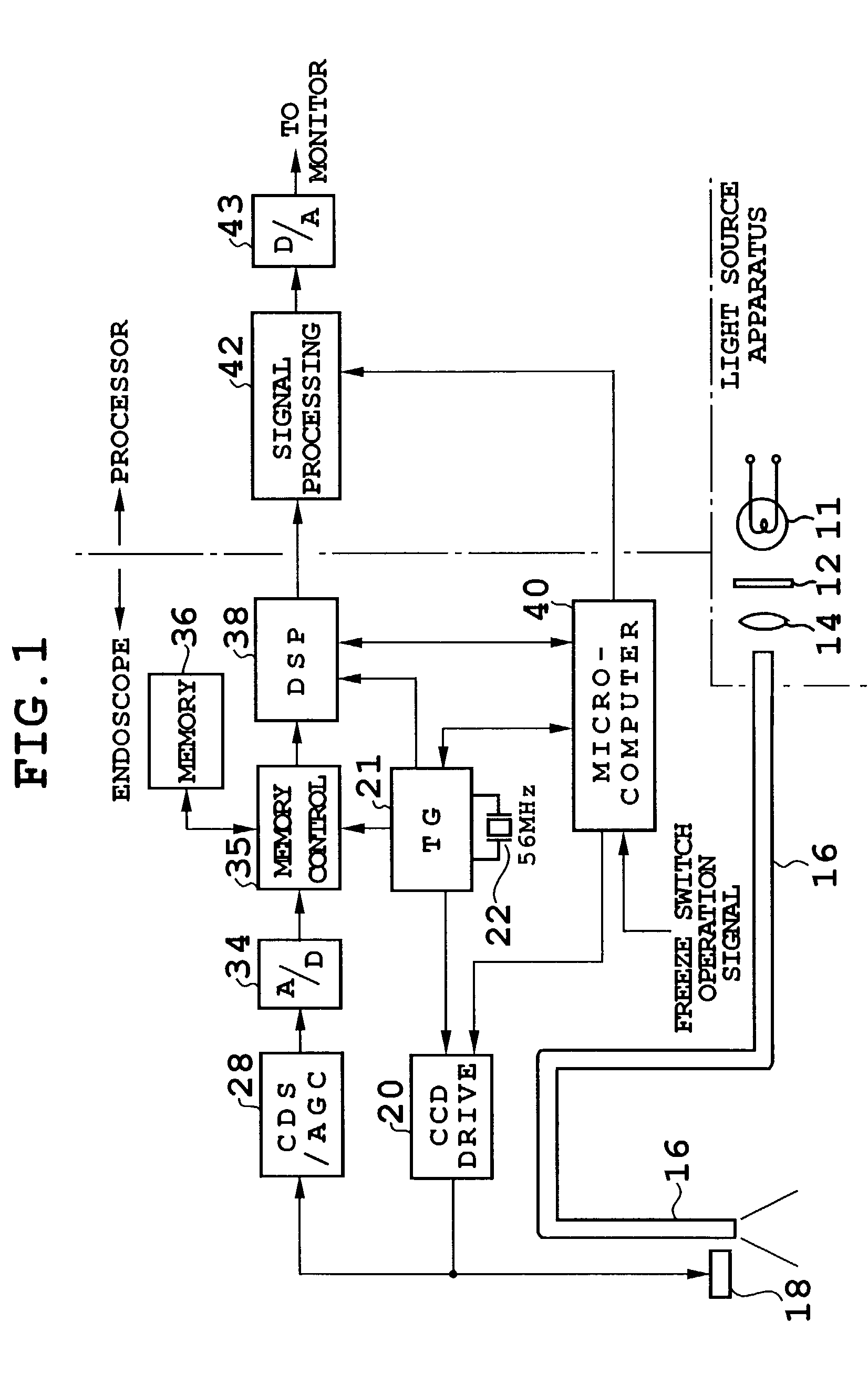

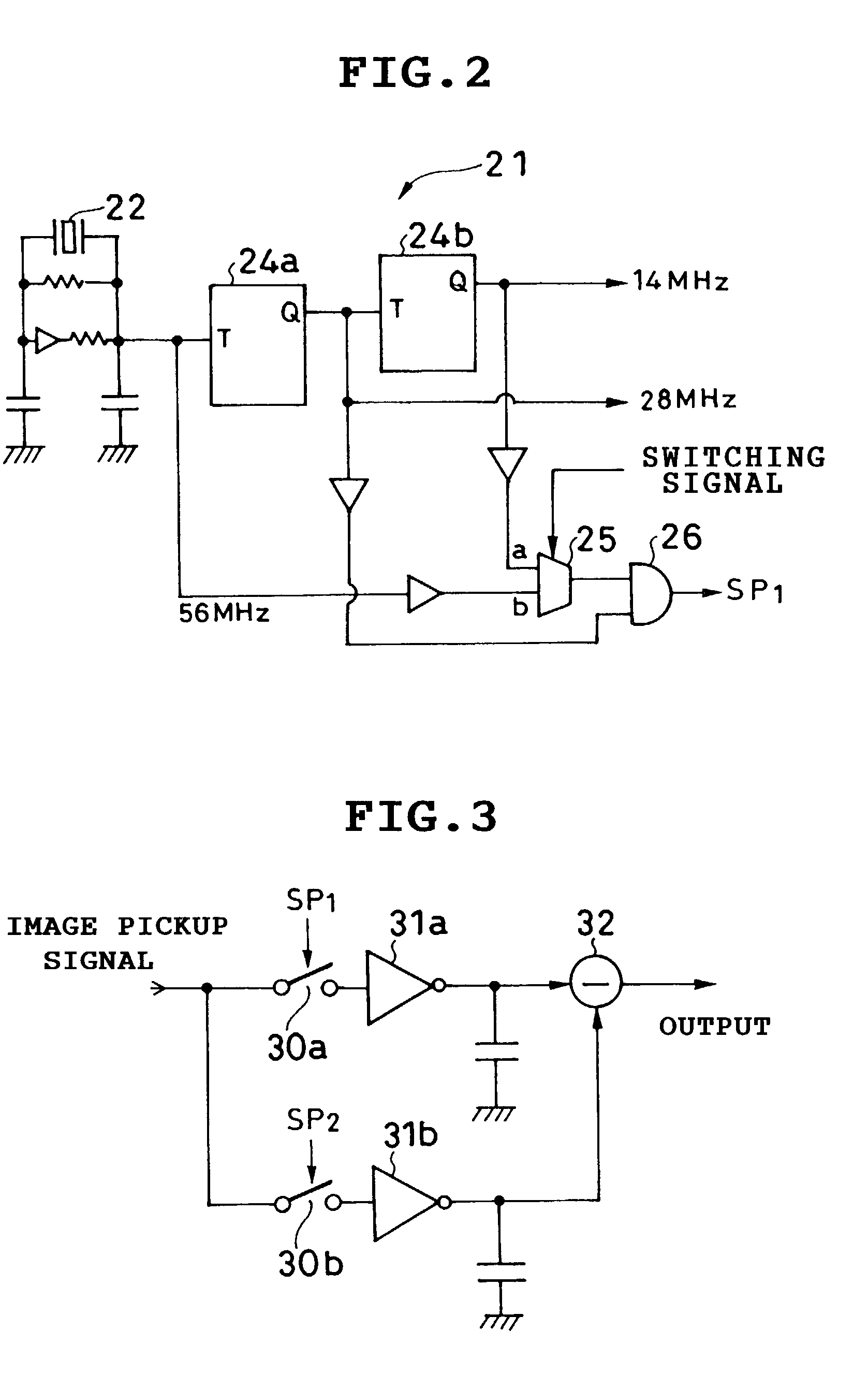

Electronic endoscope forming still image by double-speed reading

InactiveUS6995786B2Eliminate needConfiguration is complicatedTelevision system detailsEndoscopesTiming generatorEndoscope

To provide a timing generator which generates a first reference signal at a standard speed of approximately 14 MHz and a second reference signal operating at approximately 28 MHz which is double the standard speed and forms a moving image based on the first reference signal, reads, when a freeze switch is operated, an image pickup signal based on the second reference signal operating at the double speed and writes this signal into the memory 36 at the same speed. Then, by reading this still image signal from the memory at the standard speed, the still image is displayed on the monitor. Thereby, the need for setting a conventional light shielding period can be eliminated.

Owner:FUJI PHOTO OPTICAL CO LTD

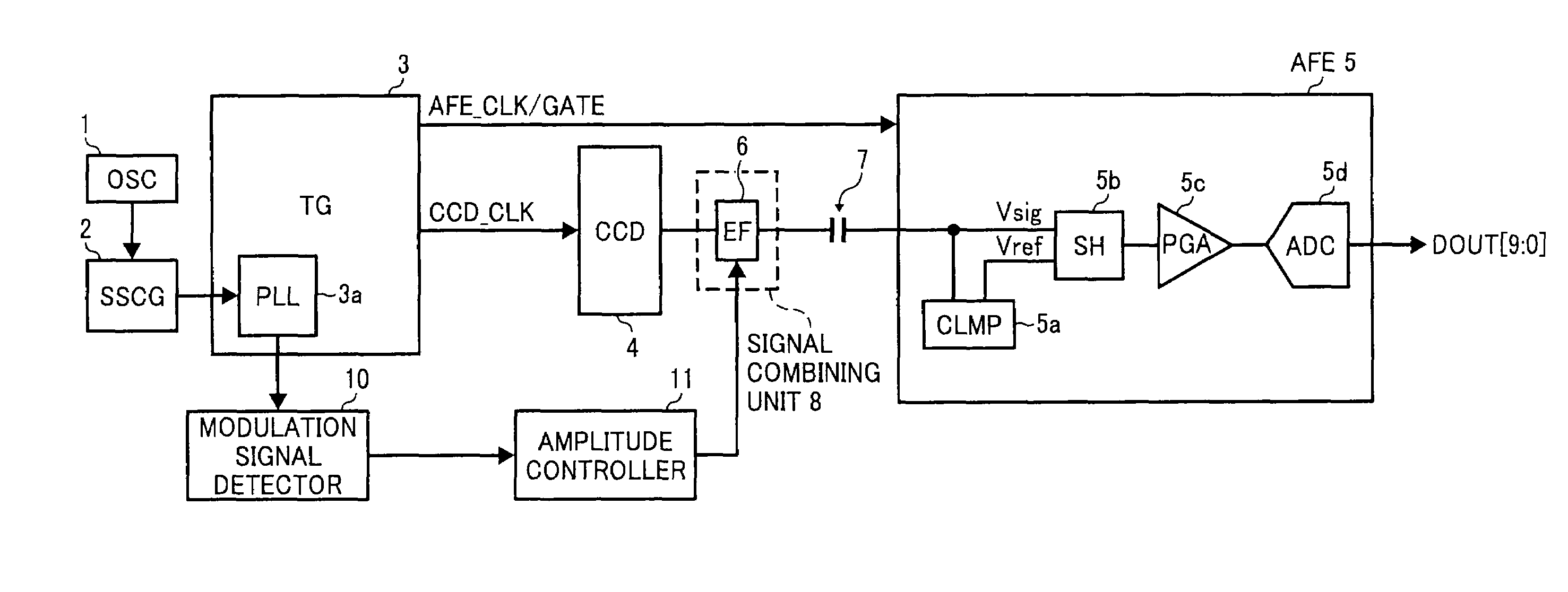

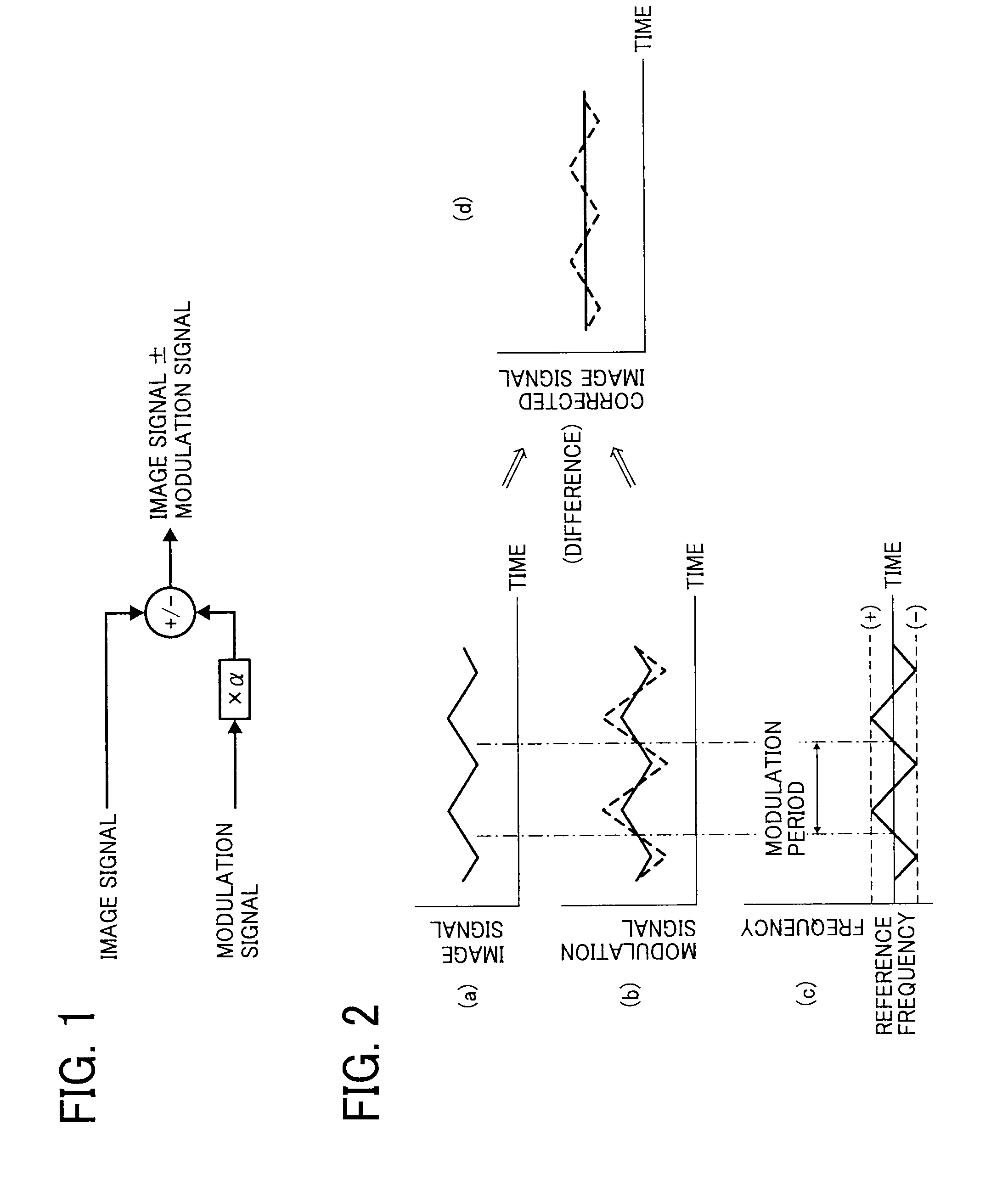

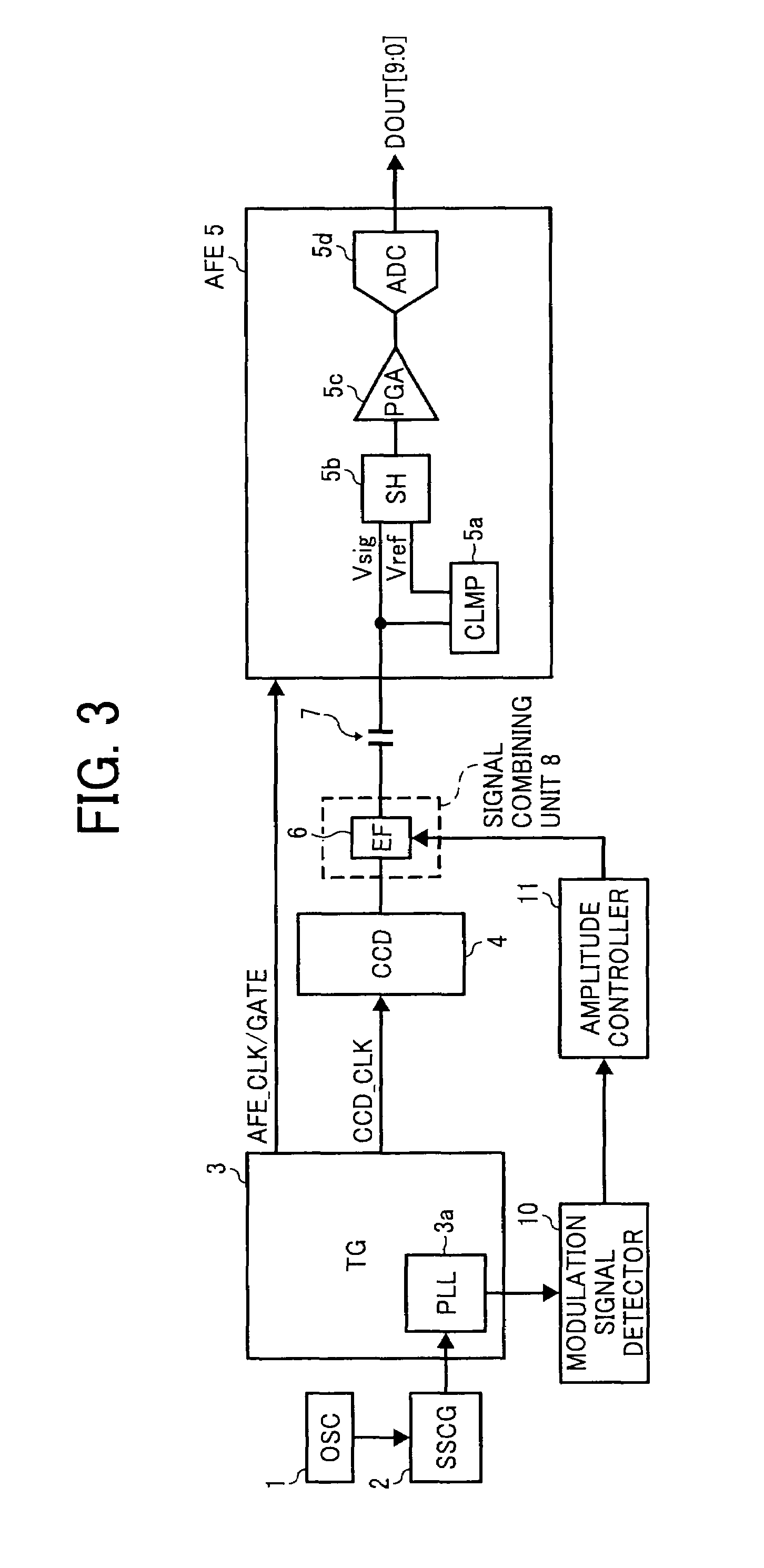

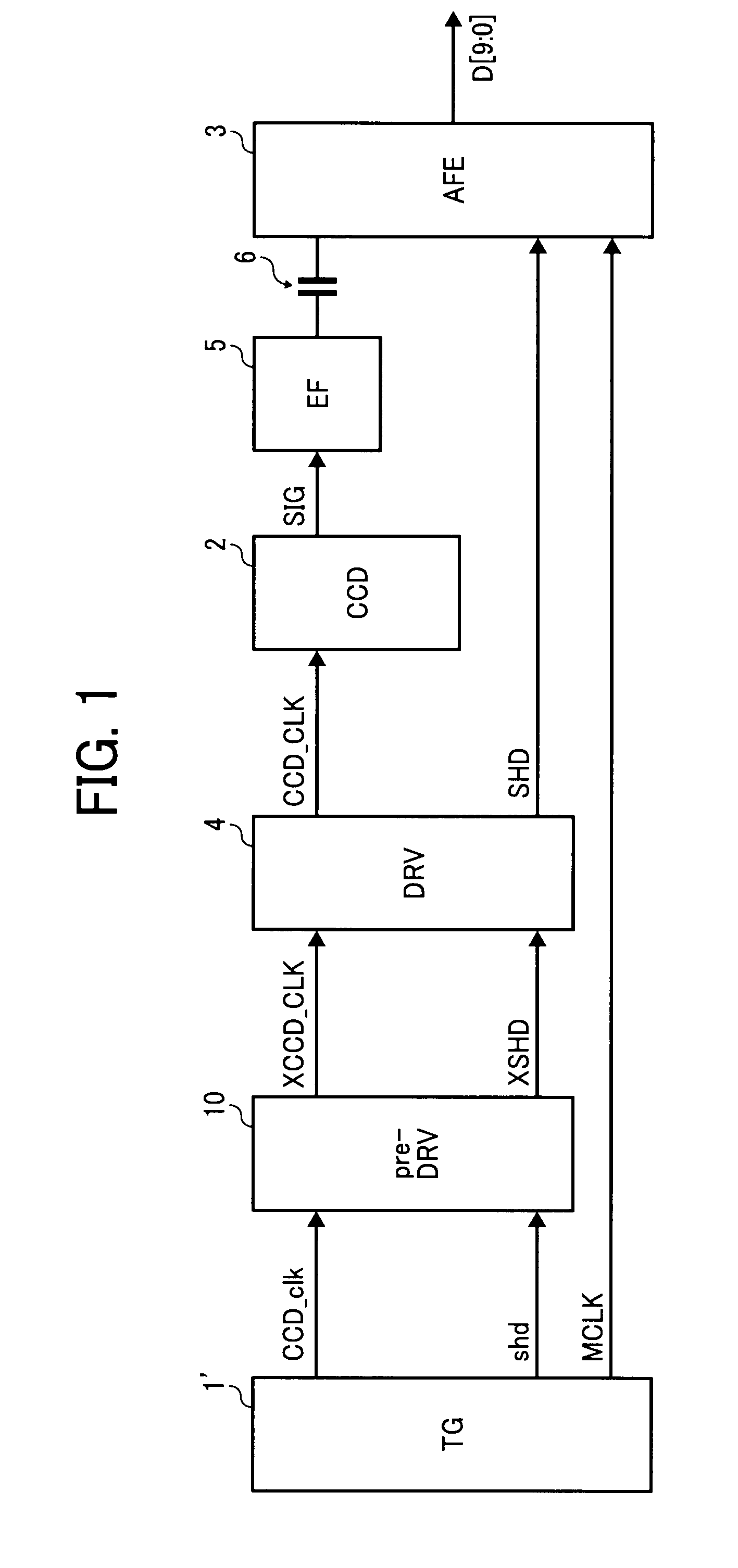

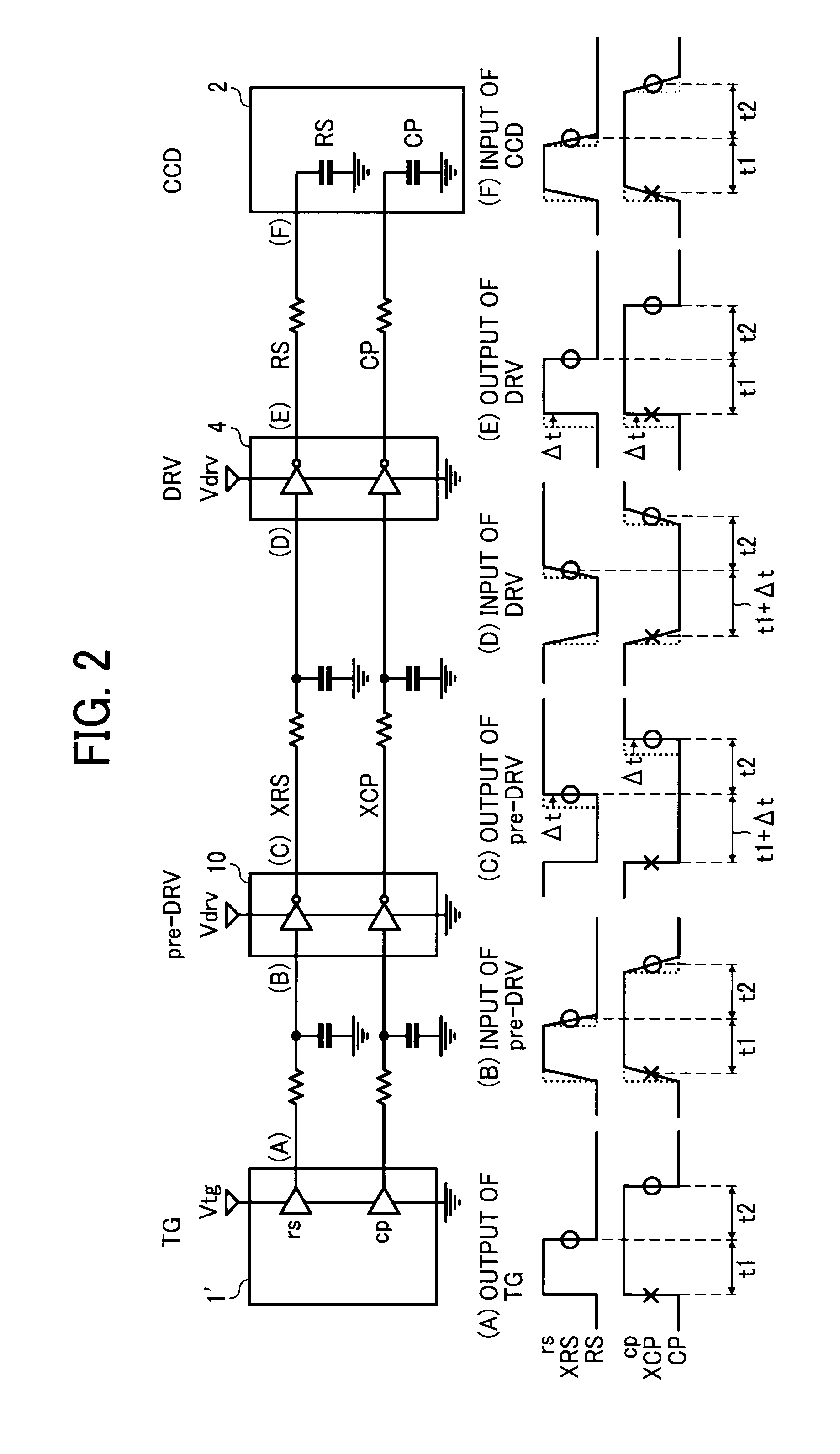

Image reading device and image forming apparatus

ActiveUS20100027061A1Solve problemsTelevision system detailsDigitally marking record carriersTiming generatorClock rate

An image reading device includes a charge-coupled device that generates and outputs an image signal, a timing generator that outputs a frequency-modulated clock, a modulation signal detector that detects a modulation signal being a signal corresponding to a change in frequency of the clock, an amplitude controller that controls an amplitude of the modulation signal, and a signal combining unit that superimposes the modulation signal after the amplitude is controlled on the image signal.

Owner:RICOH KK

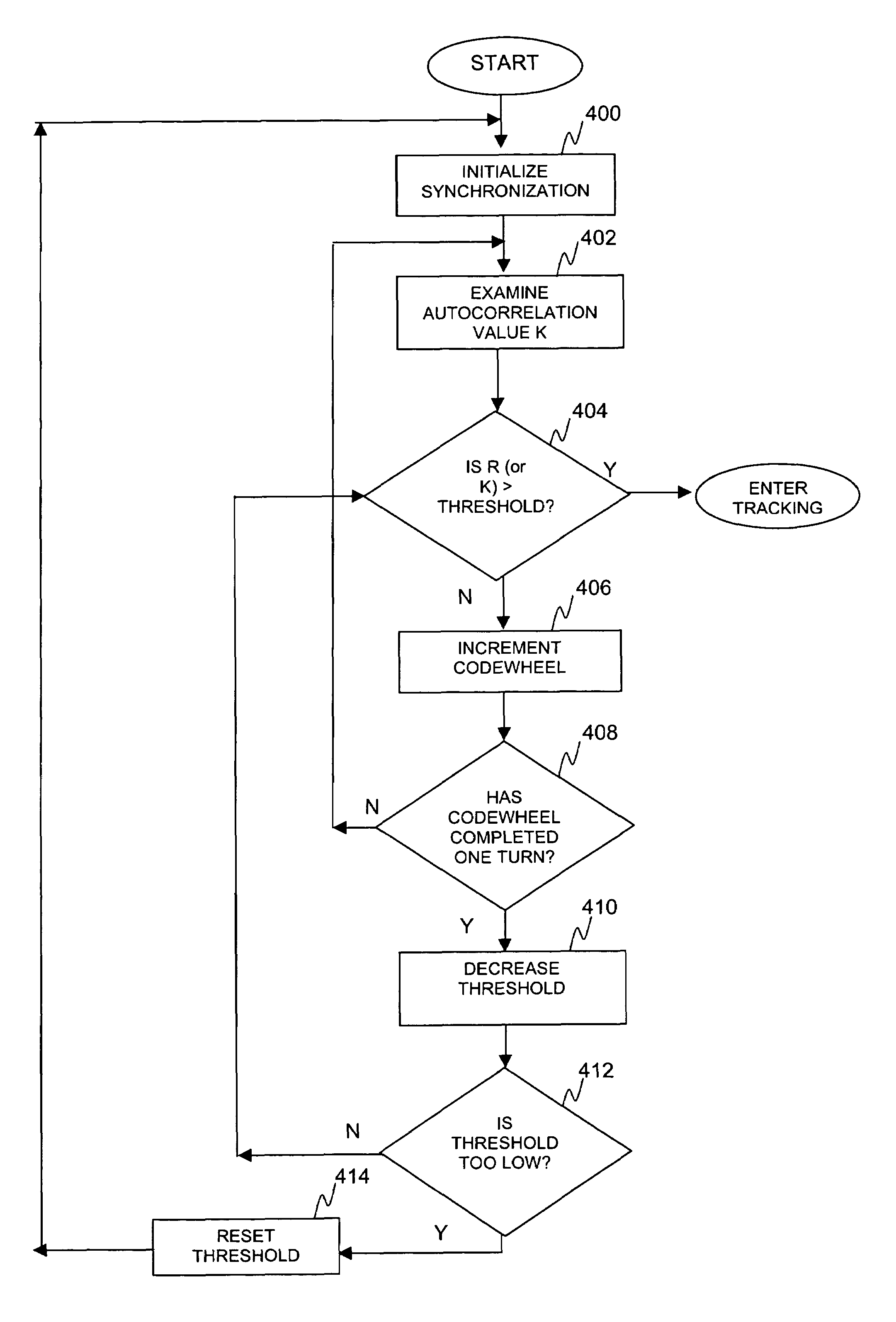

Ultrawide bandwidth system and method for fast synchronization using sub-code spins

InactiveUS6967993B1Sync fastFast recognitionModulated carrier system with waveletsRadio wave reradiation/reflectionQuality of serviceData synchronization

A UWB communication system and method for fast synchronization of one transceiver with another using the incoming UWB signal, where synchronization is achieved in less than a full code wheel spin. An exemplary embodiment includes a UWB waveform correlator, a timing generator, and a controller wherein the controller examines the correlator outputs as the code-wheel spins, and generates control signals to cause the timing generator to stop and track the incoming UWB signal whenever the incoming signal is received with sufficient SNR to provide a predetermined quality of service such as bit-error rate (BER). This embodiment will in any case determine when the receiver has been substantially synchronized with an incoming signal, yet without an exhaustive search of the entire code-wheel.

Owner:NORTH STAR INNOVATIONS

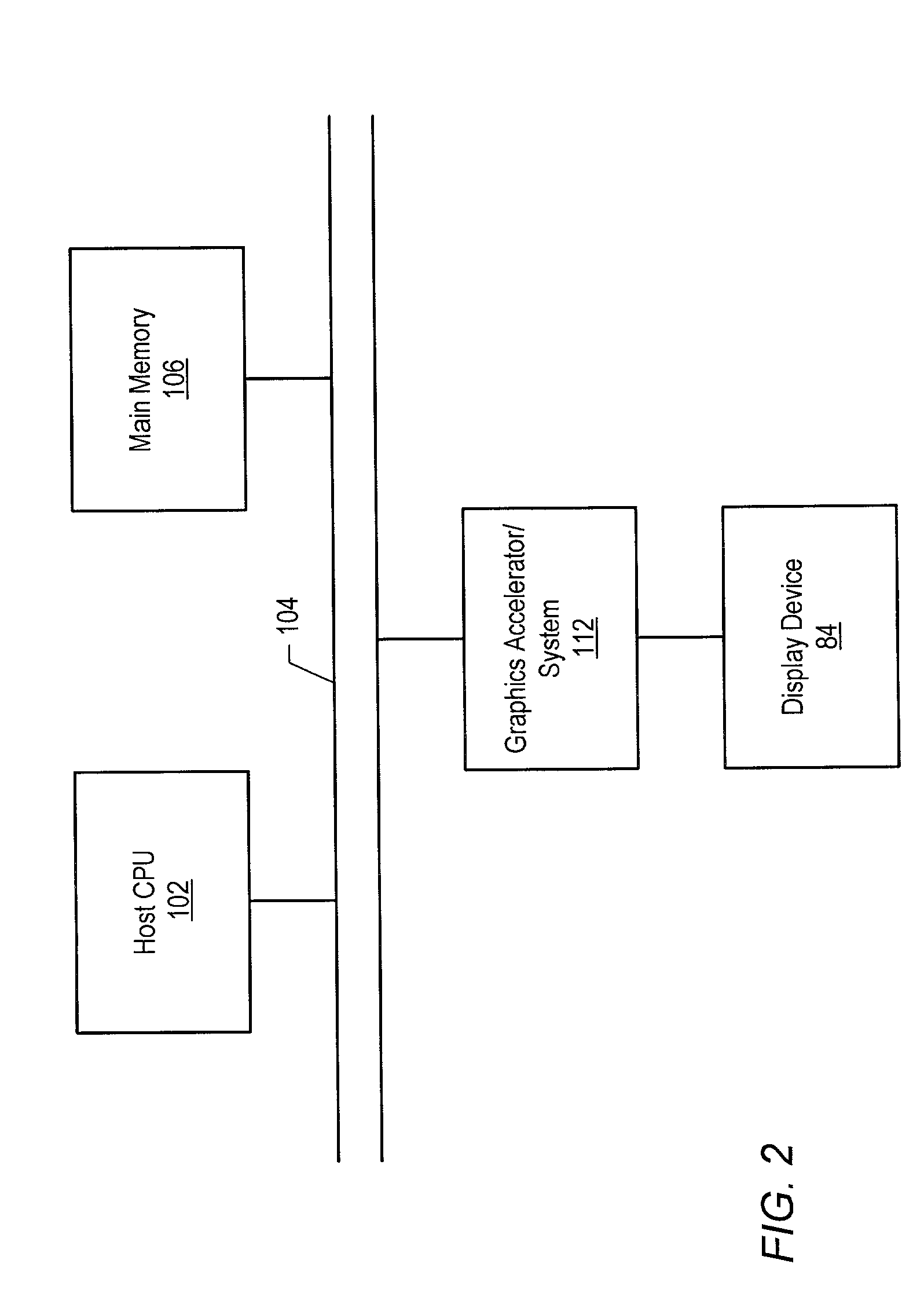

Synchronizing multiple display channels

InactiveUS20030137528A1Cathode-ray tube indicatorsDifferential synchronisation source lockingGraphicsTiming generator

A graphics system that is configured to synchronize a slave display channel to a master display channel may include a master display timing generator configured to provide a frame event indication and a slave display timing generator. The slave display timing generator may be configured to receive the frame event indication and, in response to receiving the frame event indication during its active display period, the slave display timing generator may be configured to wait until its current active display period ends and then jump to its synchronization point. Alternatively, the slave display timing generator may be configured to jump to its synchronization point immediately or after the end of the current horizontal line, and any remaining display information in an interrupted frame may be displayed during the next active display period.

Owner:ORACLE INT CORP

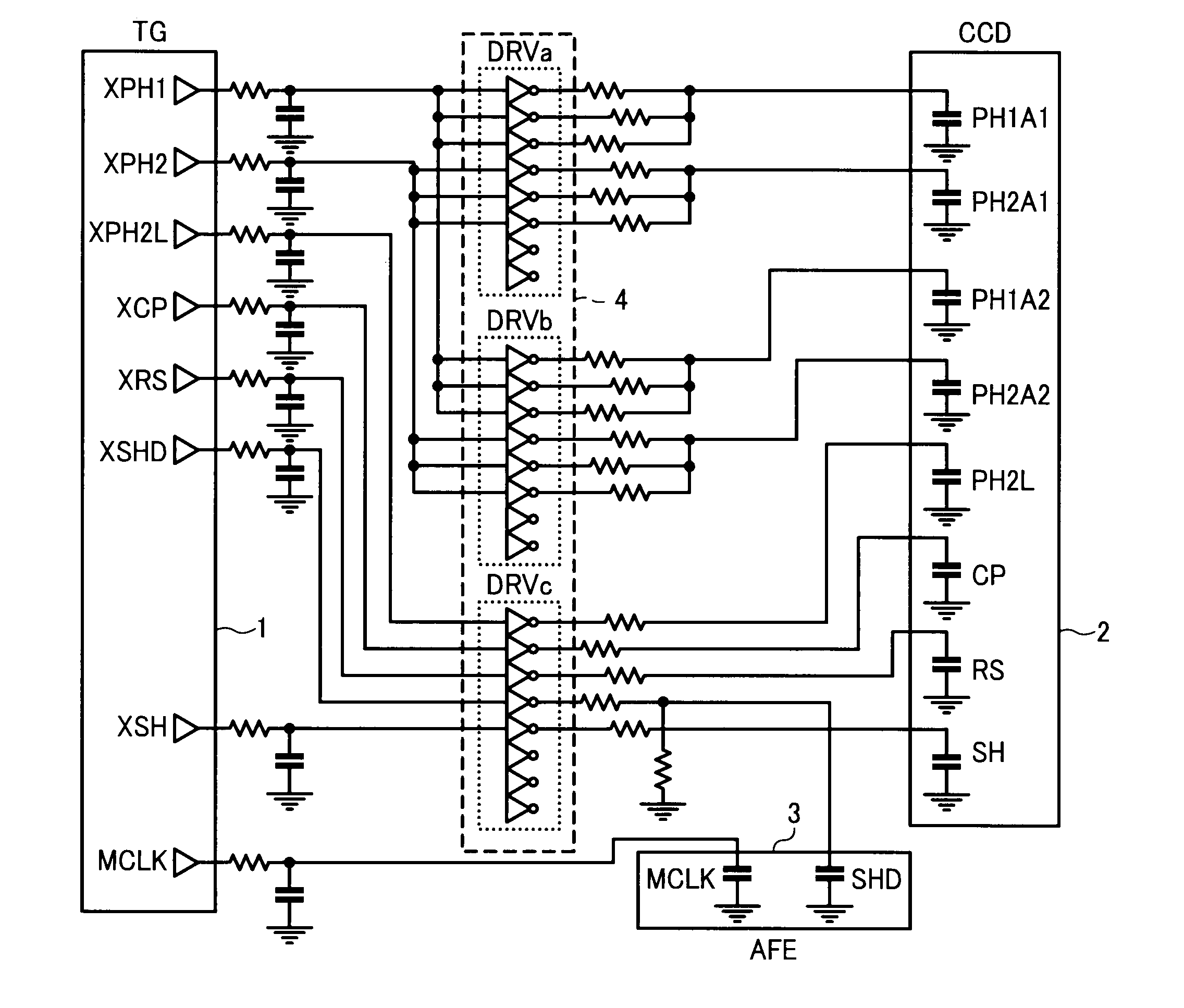

Sensor driving circuit, driver device, image reading apparatus, and image forming apparatus

ActiveUS20110063488A1Television system detailsTelevision system scanning detailsDriver circuitTiming generator

There is provided a sensor driving circuit that includes: an image sensor that converts light reflected from an original to be read into electric signals; a driver circuit that drives the image sensor; and a timing generator circuit that outputs timing signals for use in control of the image sensor. The driver circuit includes a first inverting buffer circuit and a second inverting buffer circuit that are equivalent to each other and arranged in series connection of two stages with the first inverting buffer circuit at the first stage of the two stages. The timing signal output from the timing generator circuit has the same polarity as the polarity of an input signal fed to the image sensor.

Owner:RICOH KK

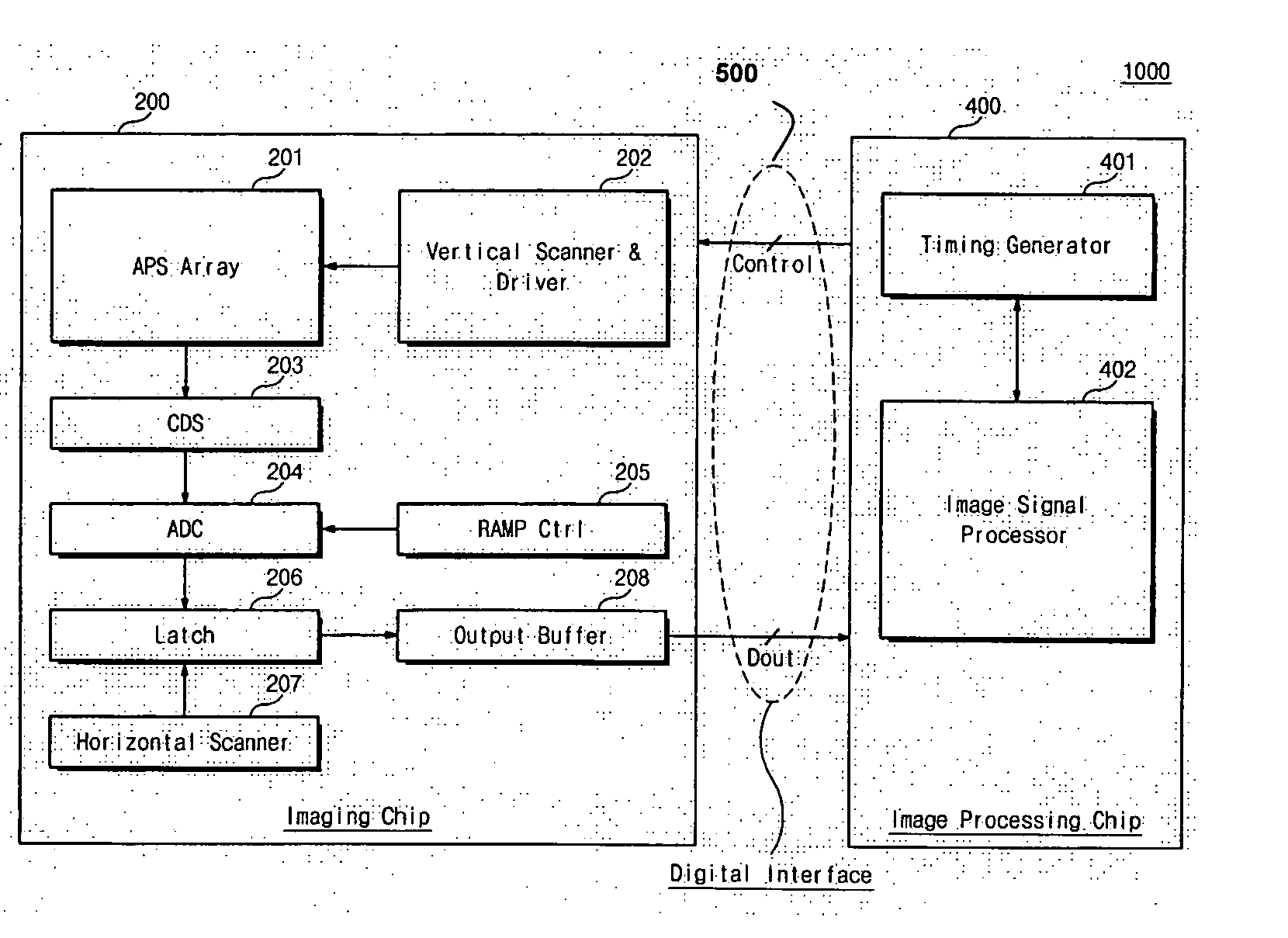

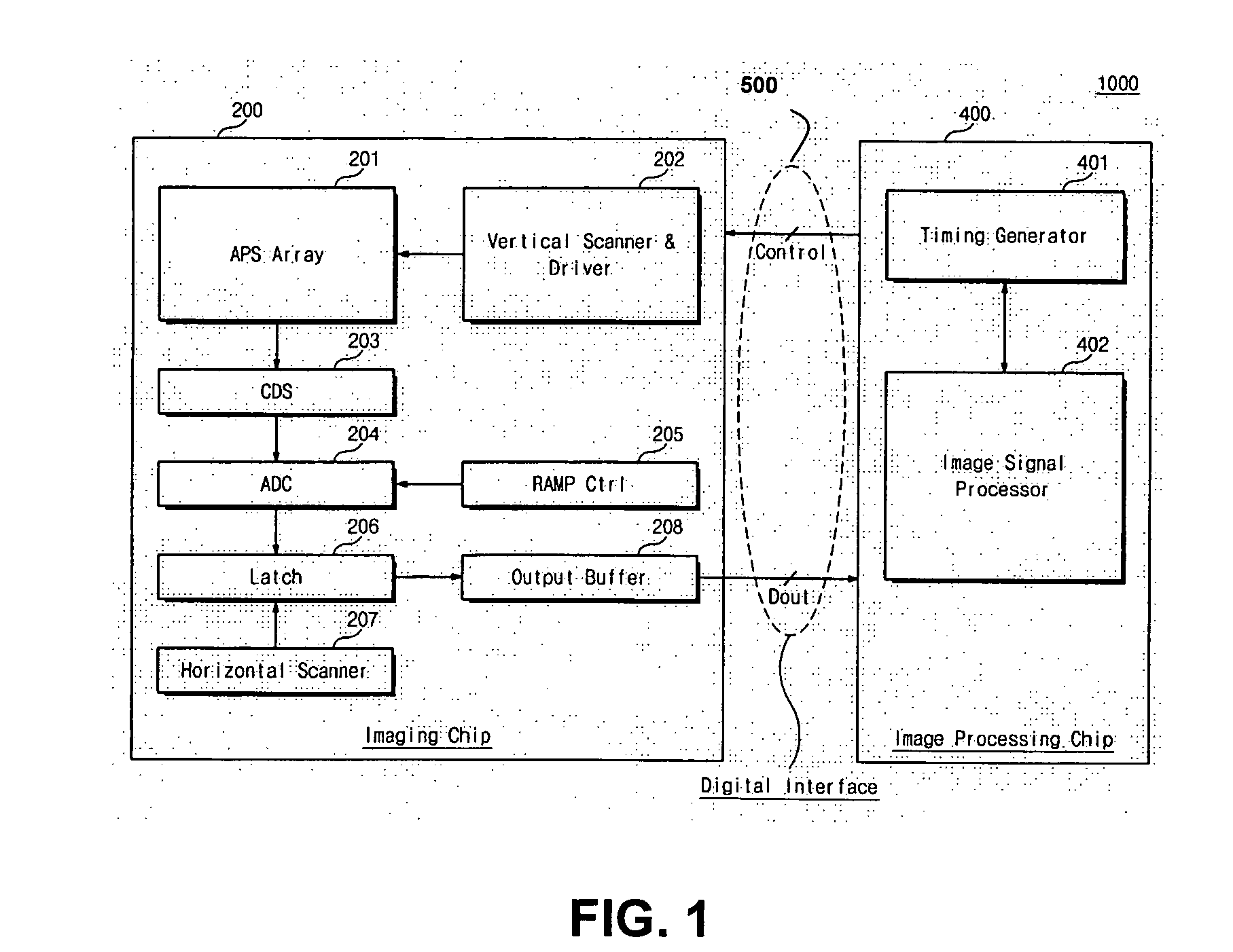

Active pixel image sensors

In one aspect, an imaging device is provided which includes first and second semiconductor chips and a digital interface. The first semiconductor chip includes an active pixel sensor, a digital input / output, and a plurality of control circuits, where transistors of the active pixel sensor are all n-type or p-type transistors, and where at least one of the controls circuits operates under control of a timing signal externally input to the digital input / output. The second semiconductor chip includes a timing generator which supplies the timing signal to the digital input / output of the first semiconductor chip. The digital interface is operatively connected between the digital input / output of first semiconductor chip and the second semiconductor chip.

Owner:SAMSUNG ELECTRONICS CO LTD

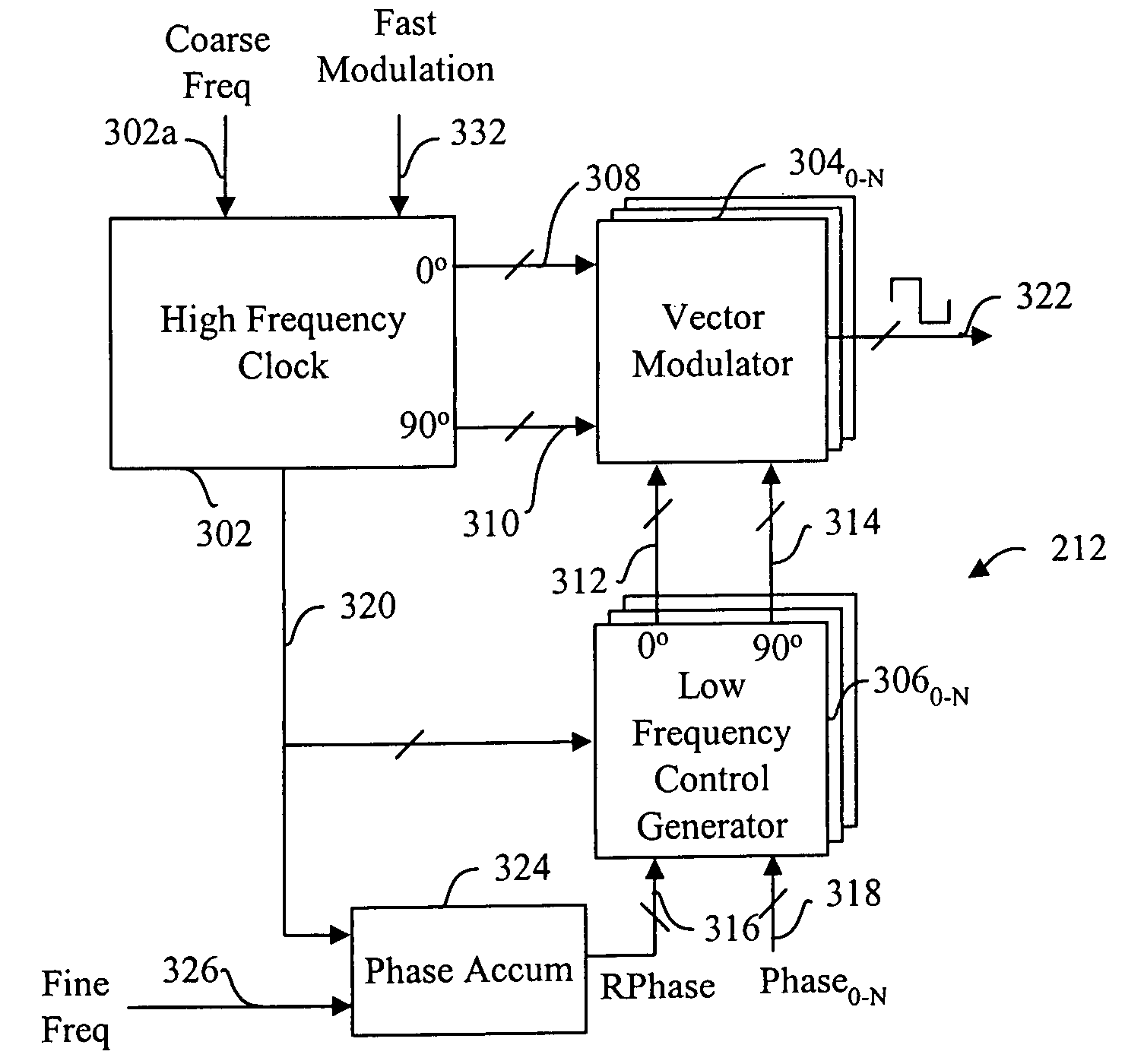

Low power, high resolution timing generator for ultra-wide bandwidth communication systems

InactiveUS20050265428A1Decreased power and part count and costImprove linearityModulated carrier system with waveletsAngle demodulation by phase difference detectionPhase noiseControl signal

An ultra wide bandwidth communications system, method and computer program product including an ultra wide bandwidth timing generator. The timing generator includes a high frequency clock generation circuit having low phase noise; a low frequency control generation circuit; and a modulation circuit coupled between the high frequency clock generation circuit and the low frequency control generation circuit. The high frequency clock generation circuit generates a plurality of high frequency clock signals. The low frequency control generation circuit generates a plurality of low frequency control signals. The modulation circuit modulates the high frequency clock signals with the low frequency control signals to produce an agile timing signal at a predetermined frequency and phase. The agile timing signal is generated at the predetermined frequency and phase by adjustments to at least one of frequency of the low frequency control signals, phase of the low frequency control signals, frequency of the high frequency clock signals, and phase of the high frequency clock signals.

Owner:NORTH STAR INNOVATIONS

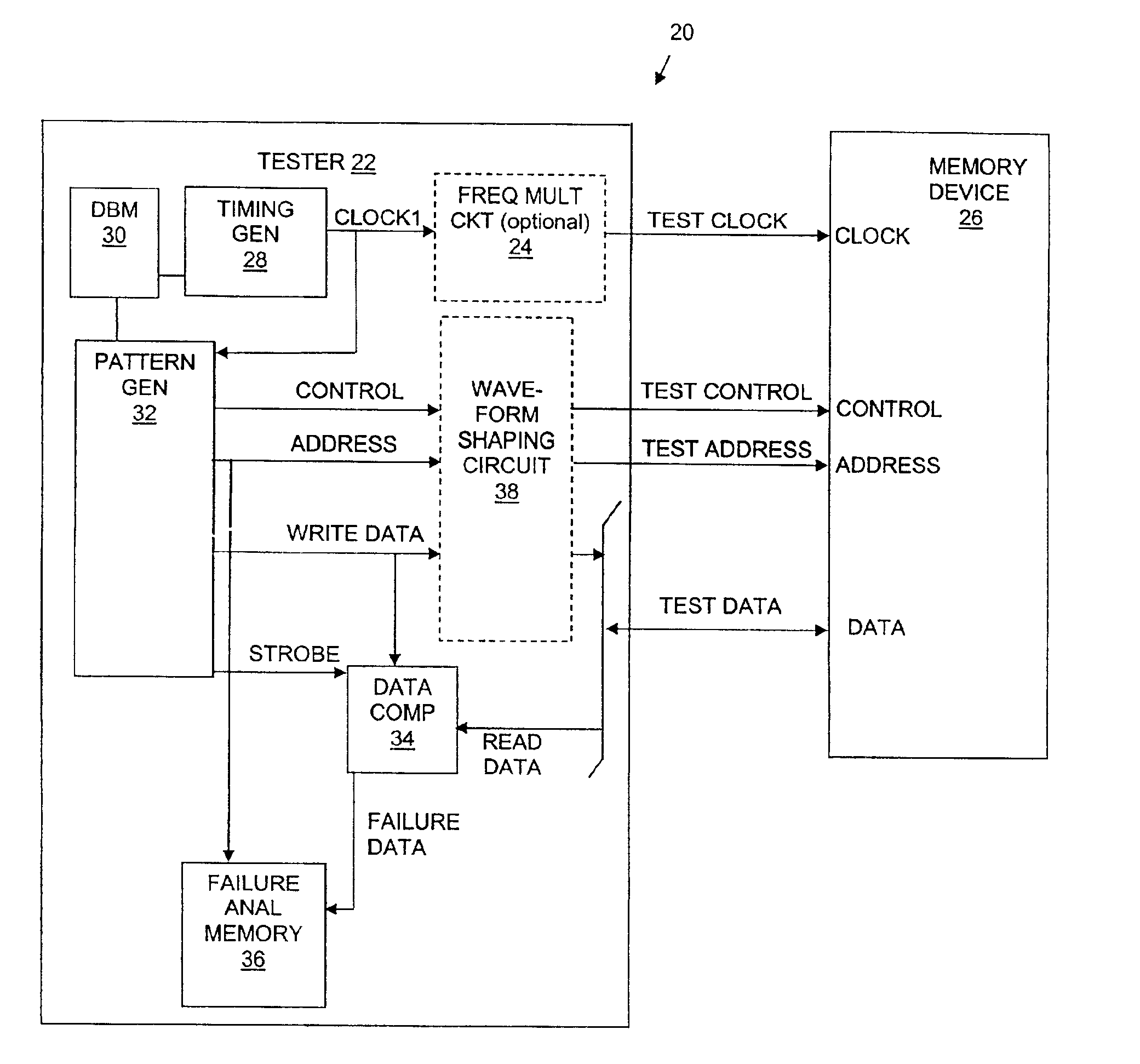

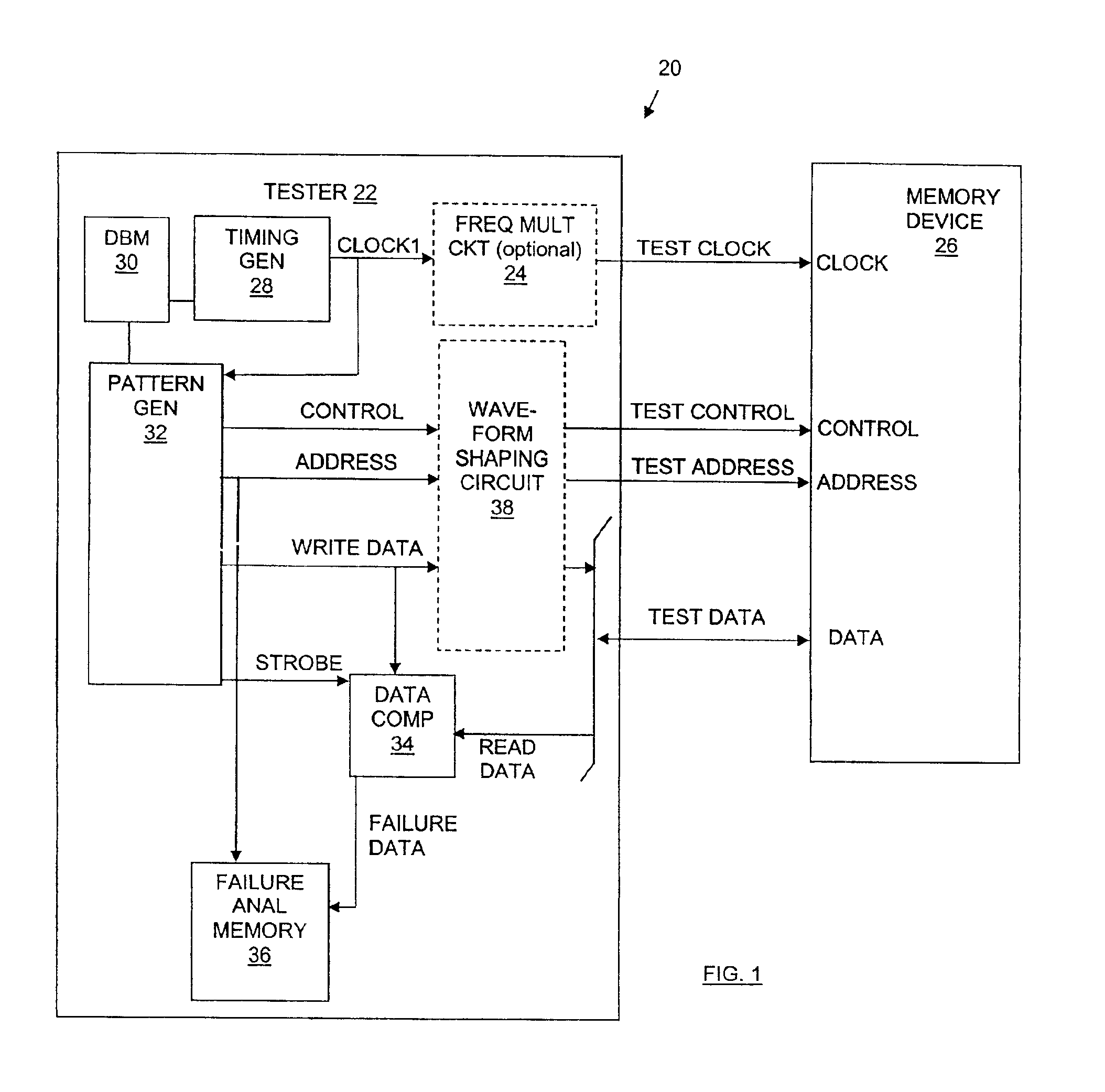

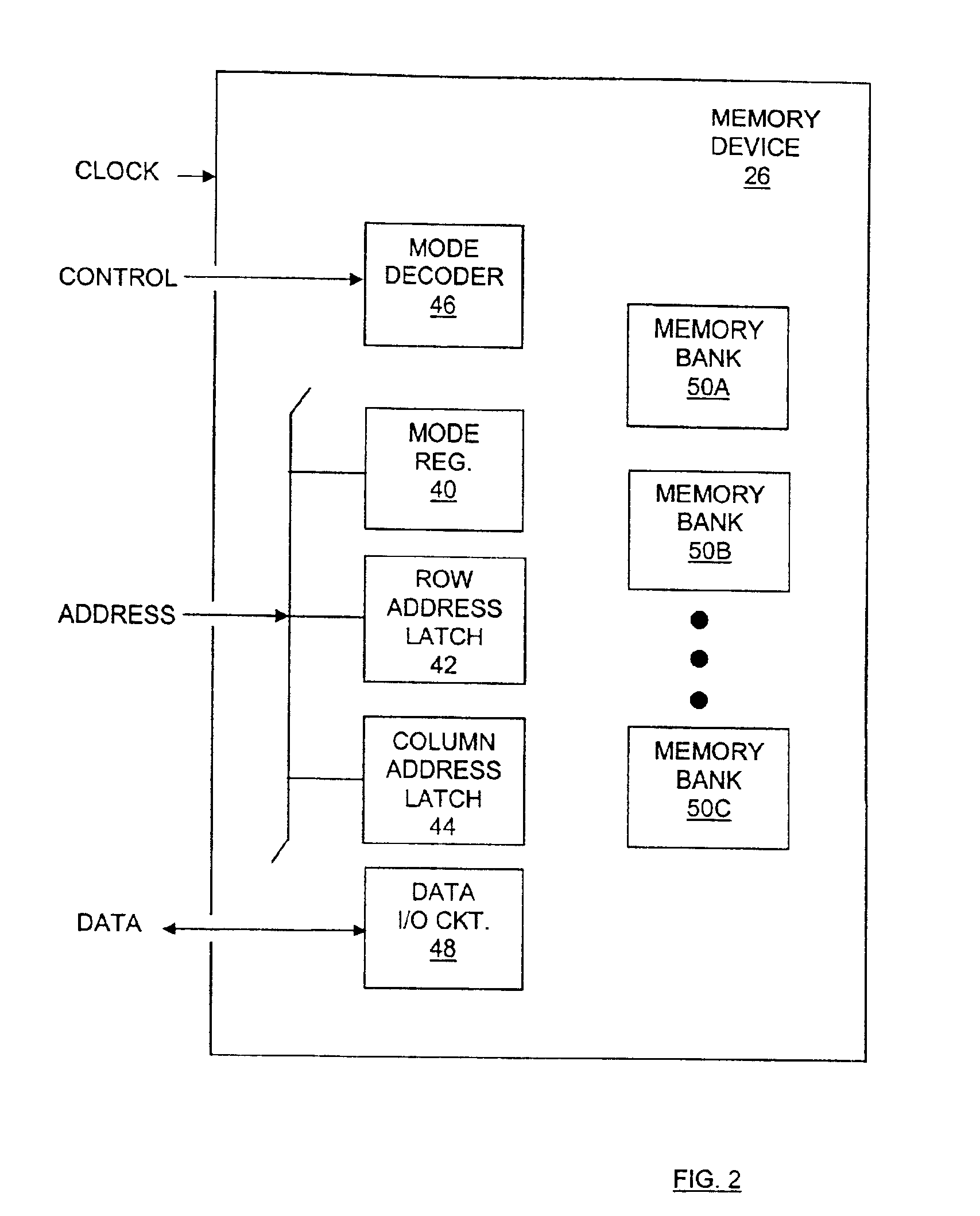

Memory device test system and method

InactiveUS6880117B2Shorten test timeStatic storageSpecial data processing applicationsTiming generatorWaveform shaping

A testing system is described for testing a memory device. The testing system includes a timing generator, an optional frequency multiplier circuit, a pattern generator, and a waveform shaping circuit. The timing generator generates a first clock signal. The frequency multiplier circuit receives the first clock signal, and uses the first clock signal to produce a second clock signal. In general, the second clock signal has a frequency greater than a frequency of the first clock signal. The frequency of the second clock signal may twice the frequency of the first clock signal. The testing system provides the second clock signal to the memory device such that operations within the memory device are synchronized to the second clock signal. The waveform shaping circuit produces an address signal synchronized to the first clock signal, and provides the address signal to the memory device when reading data from the memory device. In another embodiment, the first clock signal is not used and the address signals are synchronized to every two cycles of the second clock signal. A method for testing a memory device, which may be embodied in the testing system, is also described.

Owner:MACRONIX INT CO LTD

Imaging apparatus

ActiveUS20070120988A1Improve image qualityDeterioration of image qualityTelevision system detailsColor television detailsCamera lensTiming generator

An imaging apparatus suppresses deterioration in an image quality caused by an electronic zoom. A digital camera equipped with a plurality of optical systems includes a fixed focal distance lens and a zoom lens. When a user sets a zoom position between discrete optical zoom positions within an overlapping range of the electronic zoom range of the fixed focal distance lens and the optical zoom range of the zoom lens, a control processor and timing generator sets the electronic zoom at the user's setting zoom position. Subsequently, when the zoom position of the zoom lens passes the user's setting zoom position, a photograph is taken, and an optical zoom image is stored in a memory card.

Owner:APPLE INC

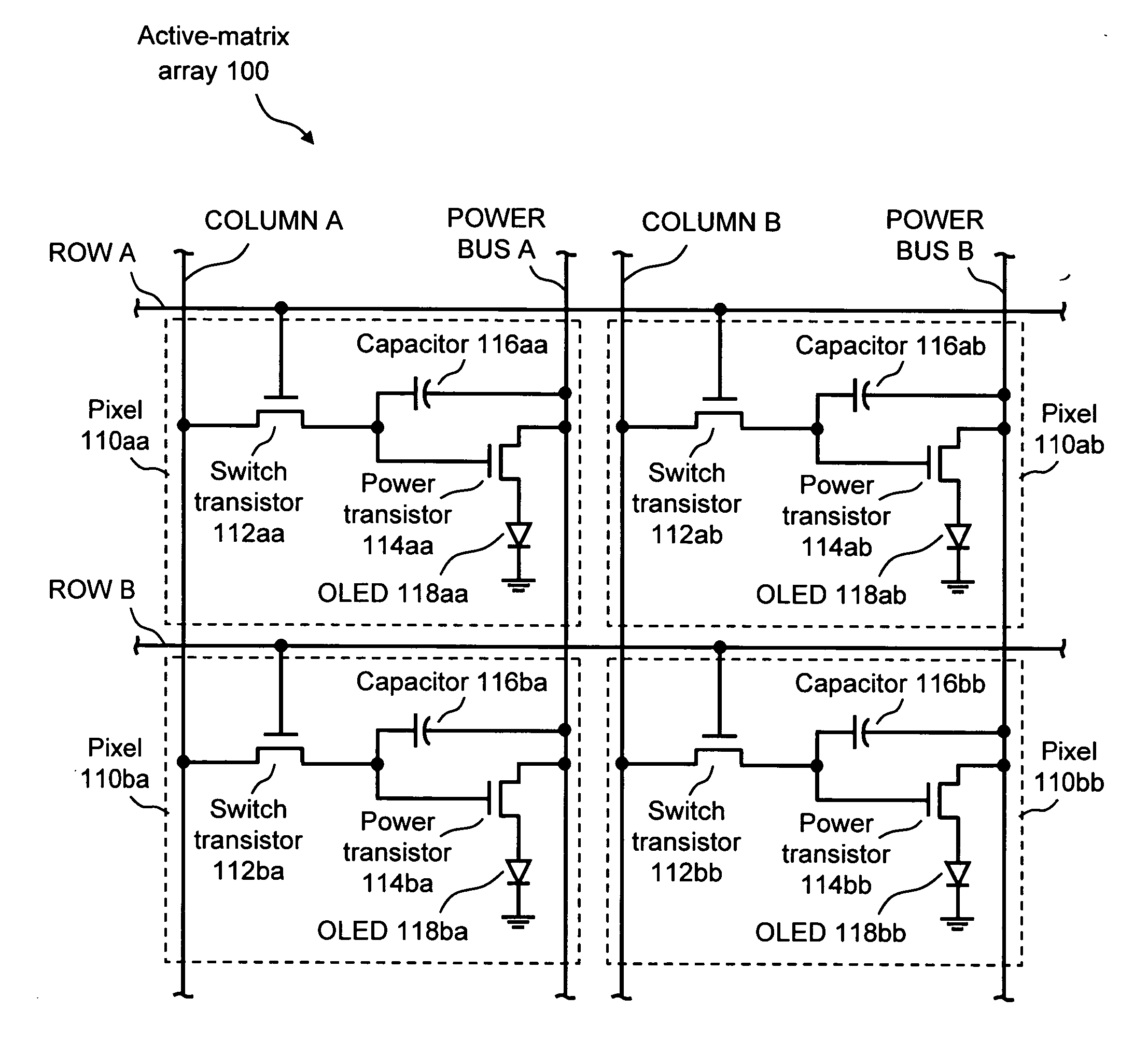

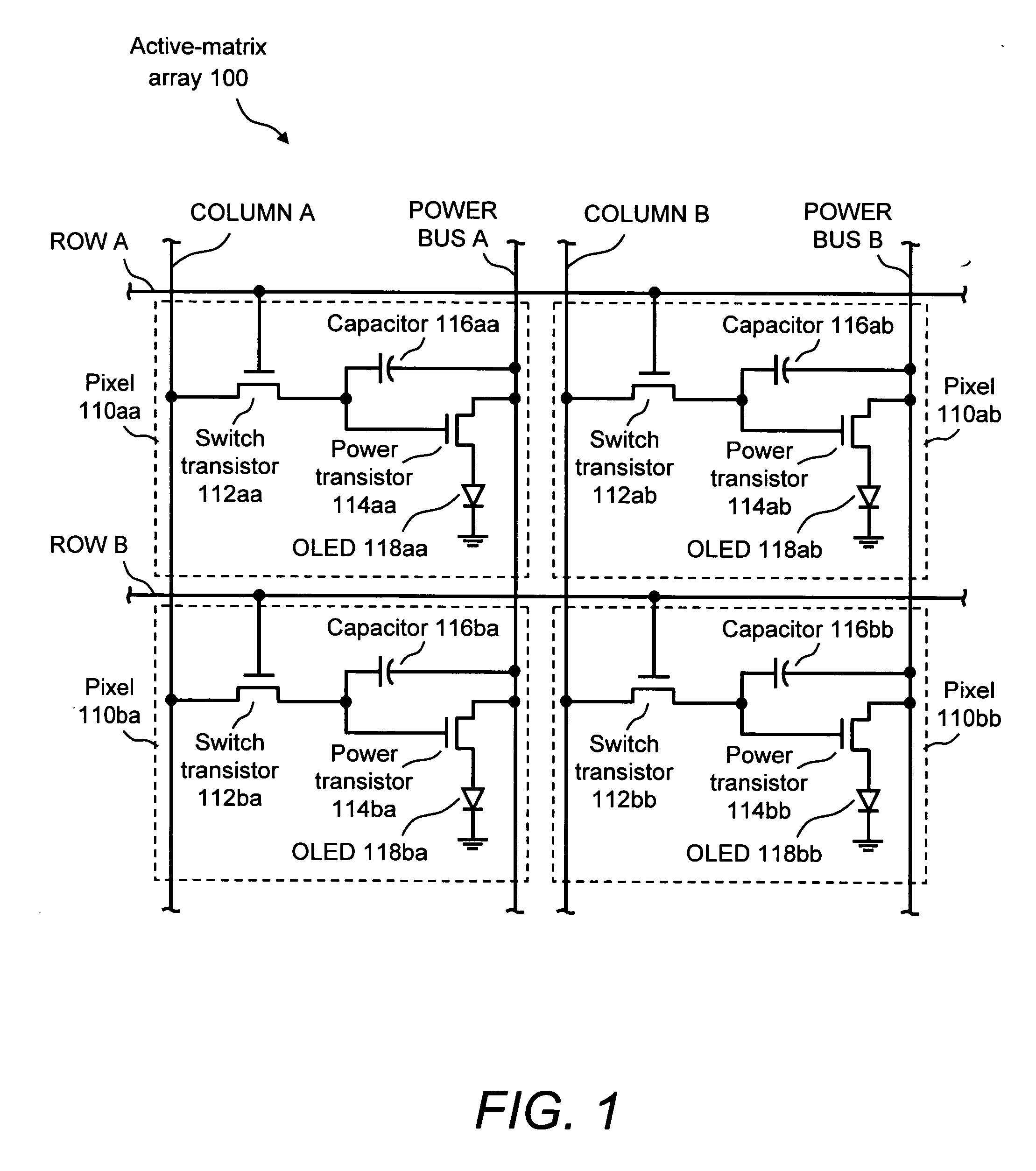

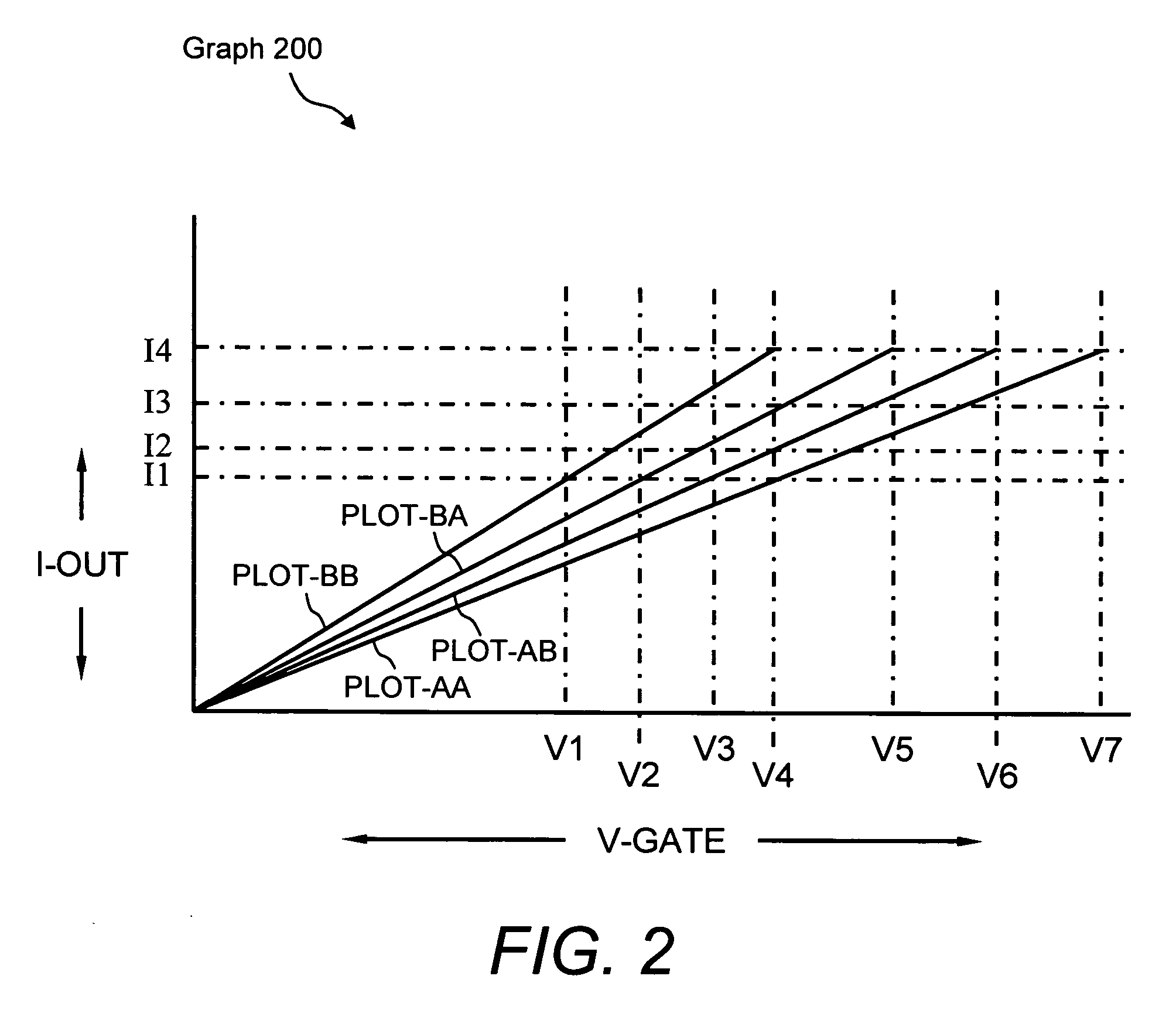

System and method for compensation of active element variations in an active-matrix organic light-emitting diode (OLED) flat-panel display

A brightness compensation system and method of providing brightness uniformity in an active-matrix organic light-emitting diode (OLED) flat-panel display. The brightness compensation system of the present invention includes a system controller, a timing generator, a test brightness generator, a pixel address generator, a video formatter, a first and second multiplexer, a memory device, a pixel adjust device, a level shifter and driver, a current sensor, an analog-to-digital converter, a DC power supply, and an active-matrix OLED display under test. The brightness compensation system and method of the present invention subjects an active-matrix OLED display to a testing operation that alternately tests every pixel, detects its output current, which is an indicator of light output level, for a given input voltage, saves the output current value in memory, then applies a corrective voltage to each pixel, so that each pixel has the same light output (output current) as its neighboring pixel.

Owner:ADVANTECH GLOBAL LTD

Low power, high resolution timing generator for ultra-wide bandwidth communication systems

An ultra wide bandwidth communications system, method and computer program product including an ultra wide bandwidth timing generator. The timing generator includes a high frequency clock generation circuit having low phase noise; a low frequency control generation circuit; and a modulation circuit coupled between the high frequency clock generation circuit and the low frequency control generation circuit. The high frequency clock generation circuit generates a plurality of high frequency clock signals. The low frequency control generation circuit generates a plurality of low frequency control signals. The modulation circuit modulates the high frequency clock signals with the low frequency control signals to produce an agile timing signal at a predetermined frequency and phase. The agile timing signal is generated at the predetermined frequency and phase by adjustments to at least one of frequency of the low frequency control signals, phase of the low frequency control signals, frequency of the high frequency clock signals, and phase of the high frequency clock signals.

Owner:NORTH STAR INNOVATIONS

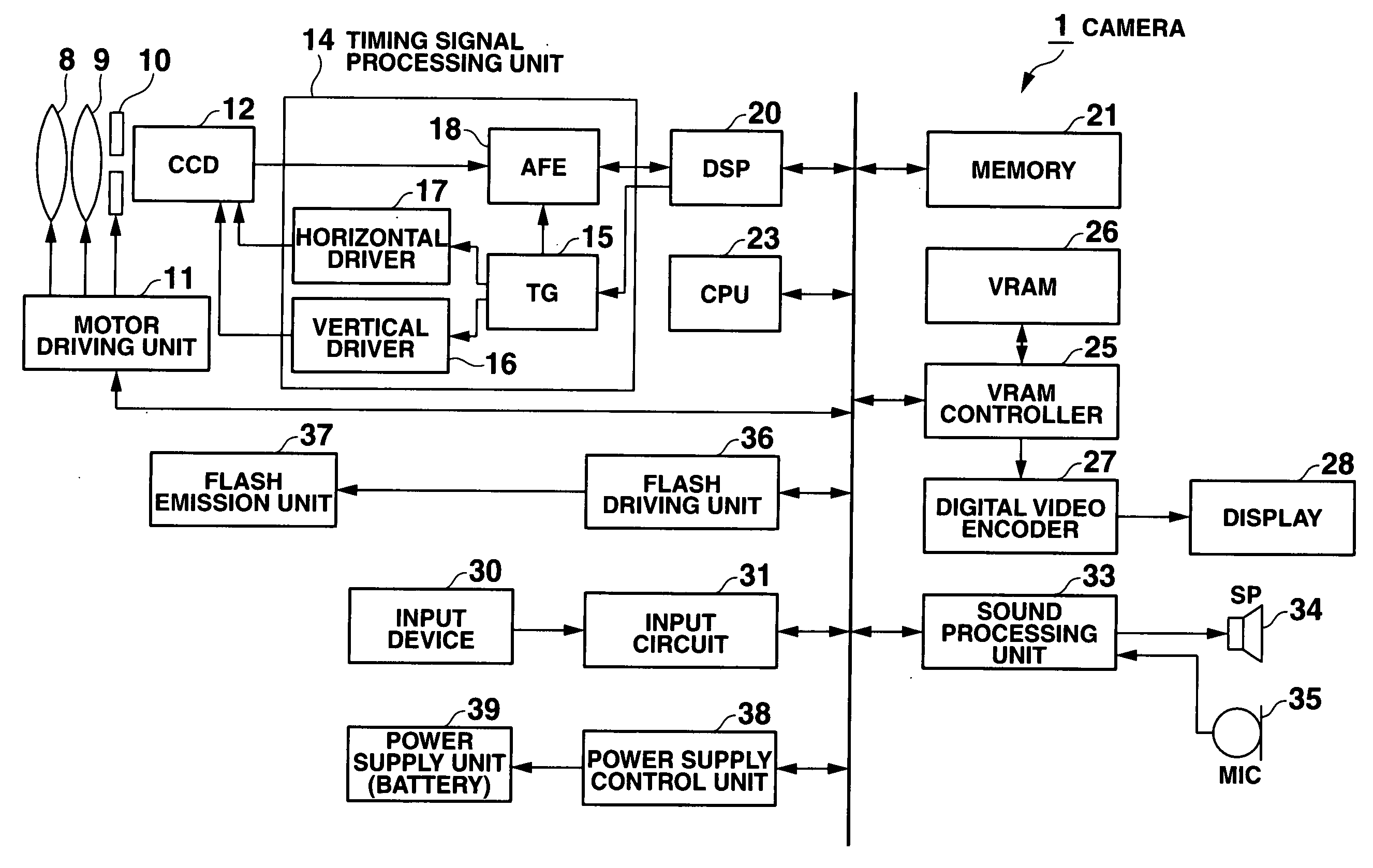

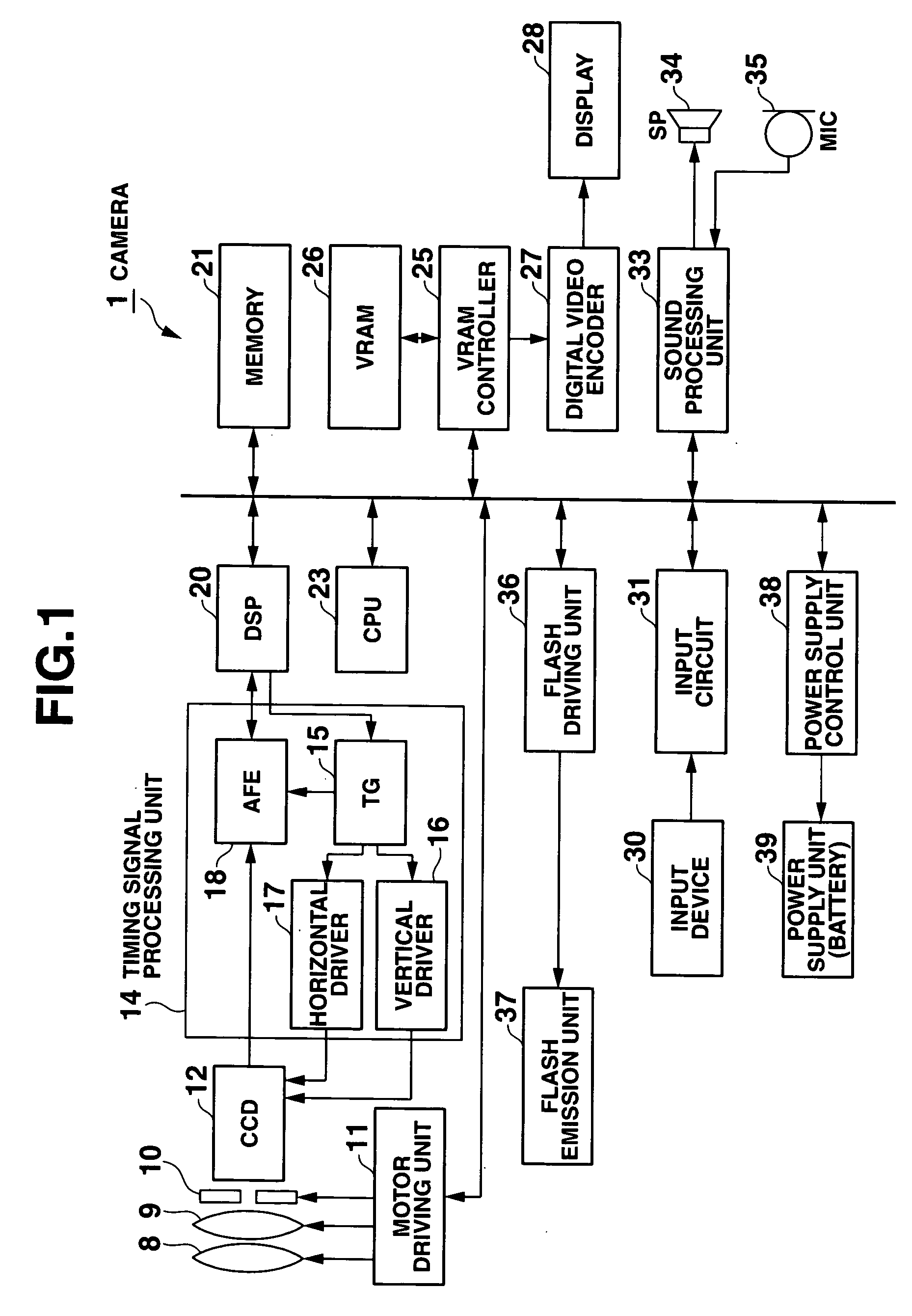

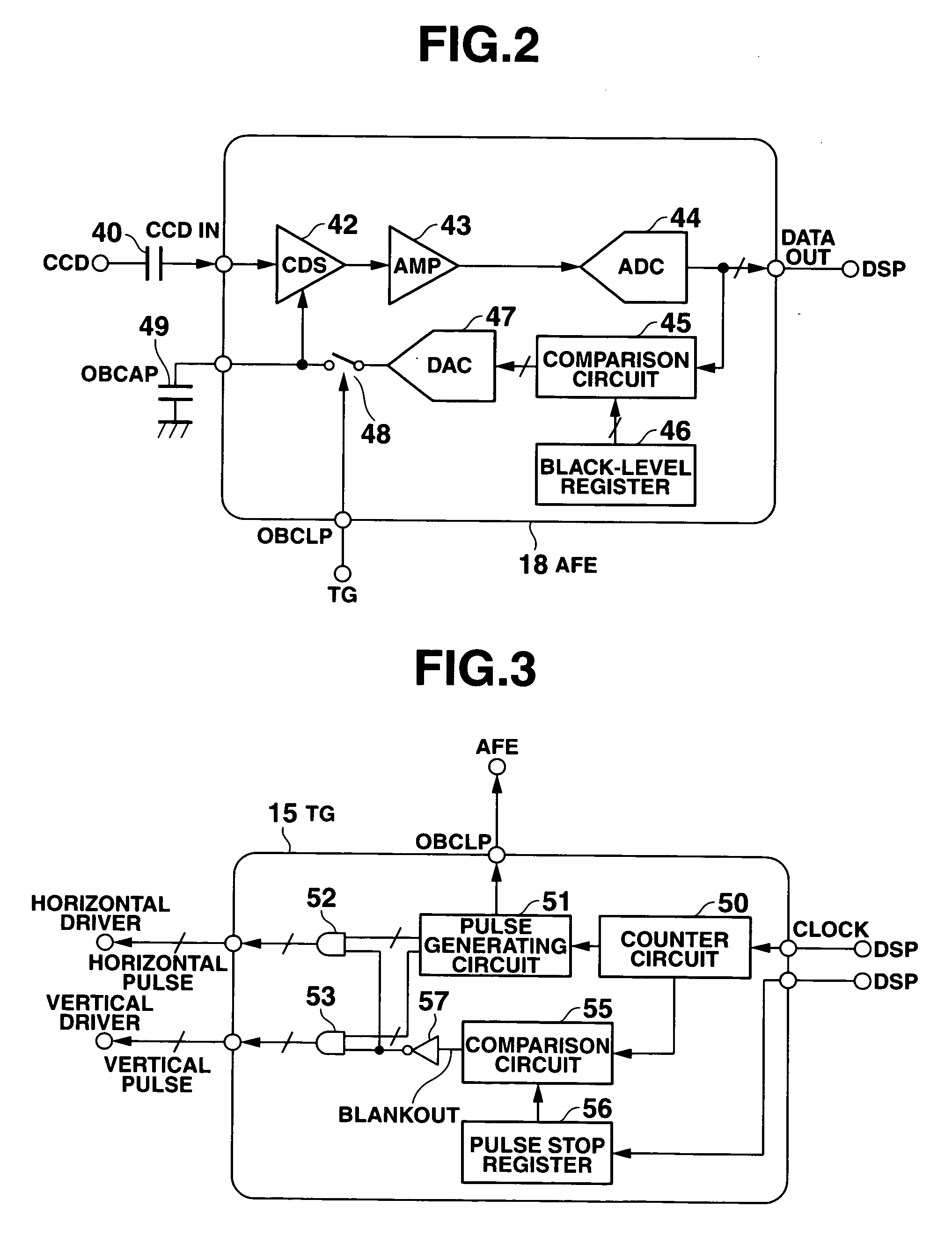

Timing signal processing apparatus for controlling driving of image-capturing element, and camera

InactiveUS20070035650A1Short timeTelevision system detailsTelevision system scanning detailsTiming generatorTime segment

A timing generator sets a 1-frame period, in which a pixel signal is read from a CCD, at a first period or a second period that is longer than the first period. The timing generator outputs specific timing signals (with optimal driving frequencies) to a vertical driver and a horizontal driver. If it is discriminated that the timing signal for a time period necessary for reading the pixel signal for one frame is output, the timing generator stops the output of the timing signal. Thereby, power saving can be achieved without deterioration of image quality, while reading of the pixel signal is being executed with an optimal driving frequency for the image-capturing element.

Owner:CASIO COMPUTER CO LTD

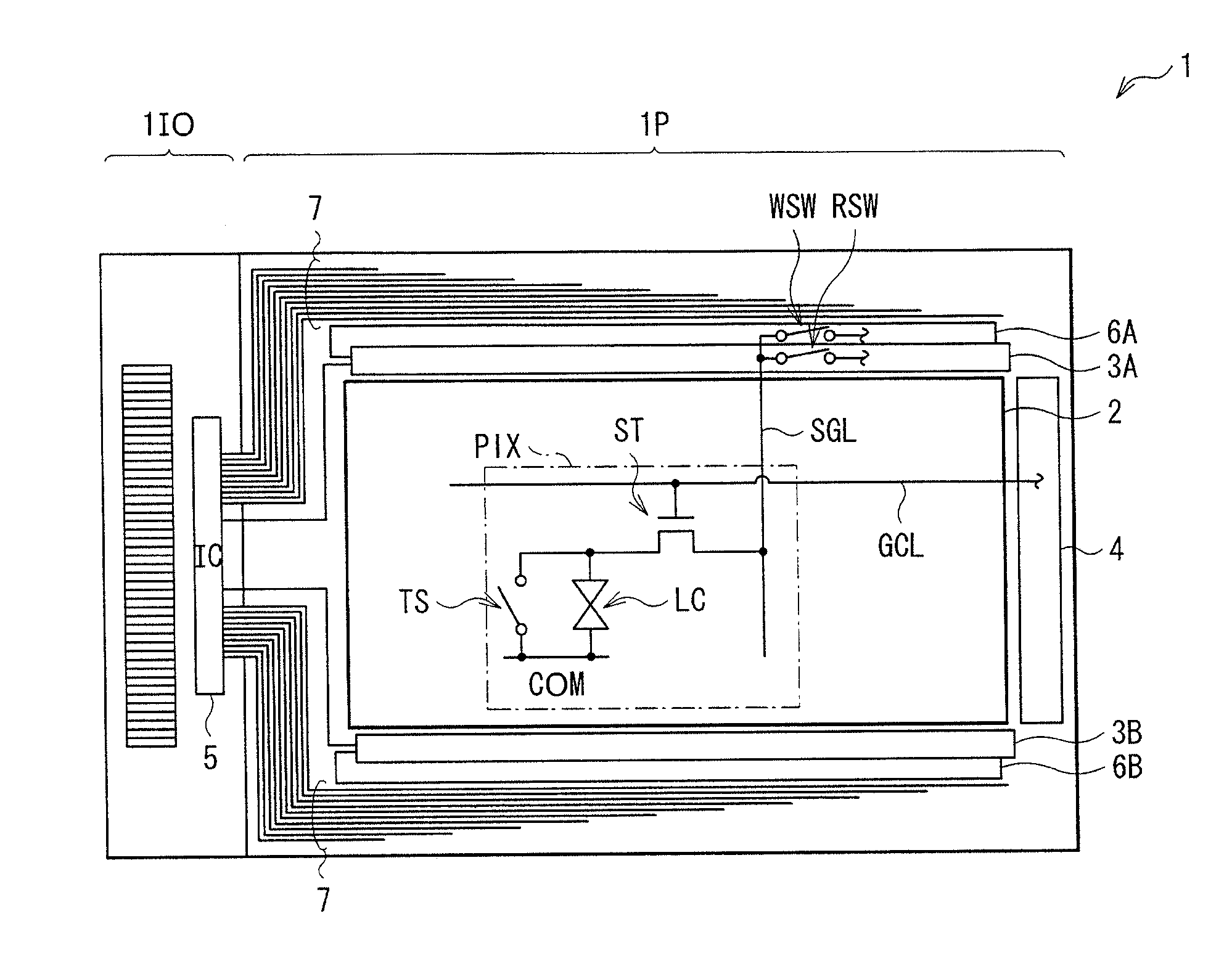

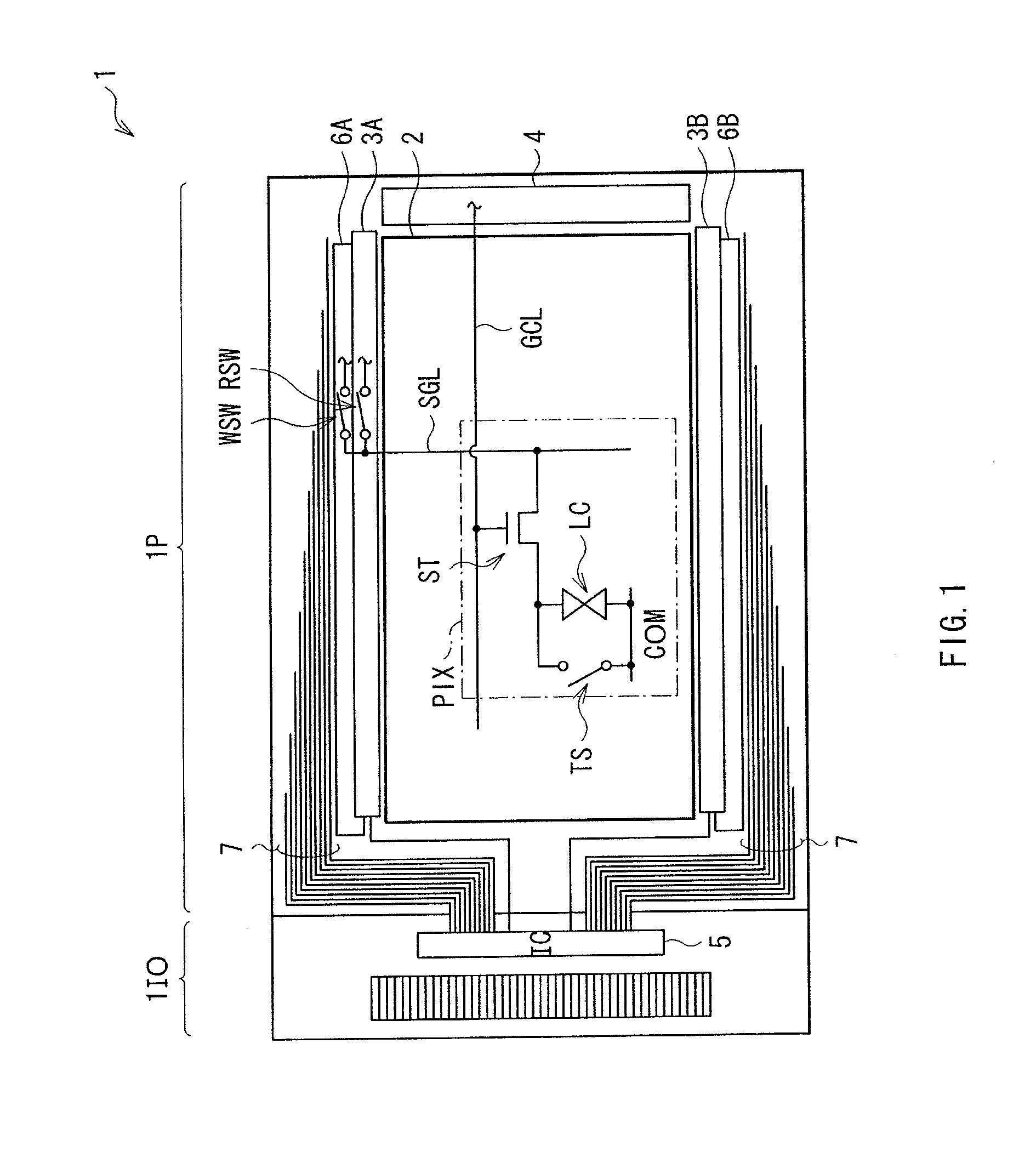

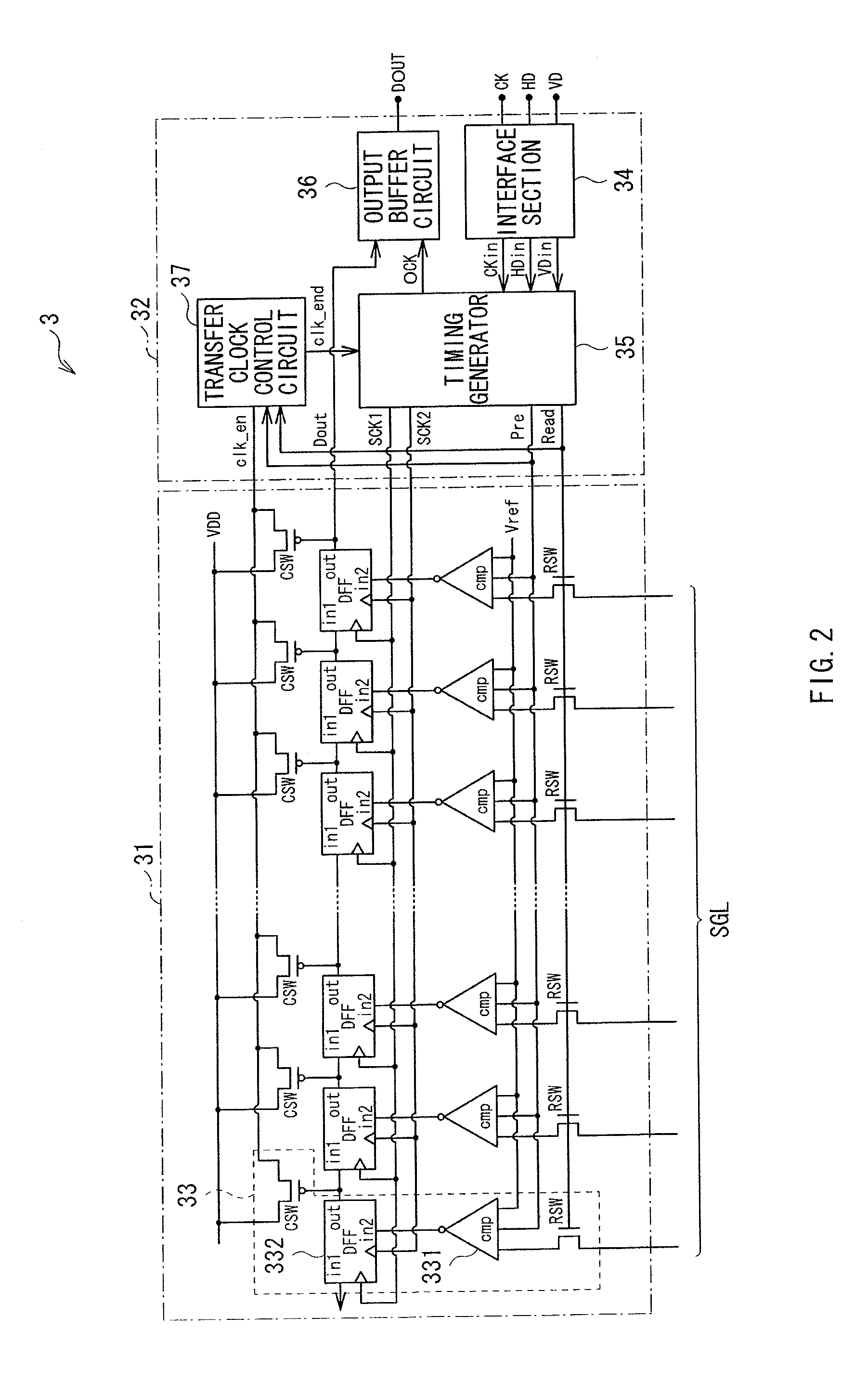

Display, touch panel and electronic device

InactiveUS20110043483A1Improve responsivenessReduce power consumptionStatic indicating devicesDigital data processing detailsTiming generatorDisplay device

A display with a touch panel allowed to achieve high response performance while reducing power consumption is obtained. The display includes a plurality of display elements performing display based on picture signals supplied to a plurality of picture signal lines, respectively, a plurality of sensor elements outputting touch signals indicating detection of an external proximity object to a plurality of sensor signal lines (SGL), respectively, a detection section (a comparator 331) detecting each of the touch signals, a transfer output section (a D-type flip-flop 332 and an output buffer circuit 36) transferring and outputting a detection result of the detection section to outside, and a control section (a transistor switch SCW, a transfer clock control circuit 37 and a timing generator 35) controlling operations of the detection section and the transfer output section, allowing the transfer output section to operate in a case where the touch signal is detected in the detection section, and suspending an operation of the transfer output section in a case where the touch signal is not detected.

Owner:JAPAN DISPLAY WEST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com