Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

862 results about "CMOS sensor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

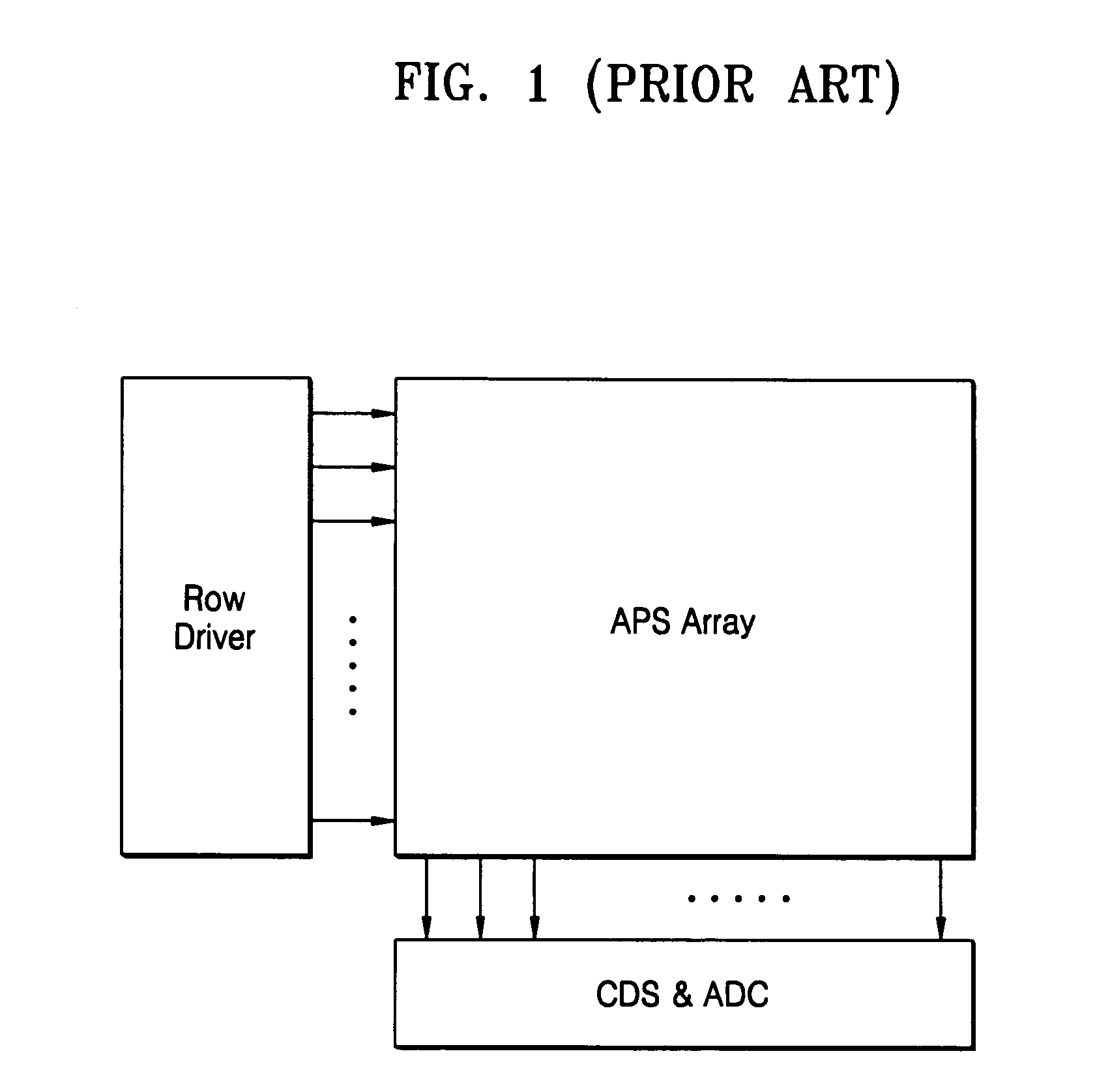

An active-pixel sensor (APS) is an image sensor where each pixel sensor unit cell has a photodetector (typically a pinned photodiode) and one or more active MOSFET (metal-oxide-semiconductor field-effect transistor) amplifiers. There are different types of integrated circuit active pixel sensors, including the complementary metal–oxide–semiconductor (CMOS) APS used most commonly in digital camera technologies such as cell phone cameras, web cameras, most modern digital pocket cameras, most digital single-lens reflex cameras (DSLRs), and mirrorless interchangeable-lens cameras (MILCs). Such an image sensor is produced using CMOS technology (and is hence also known as a CMOS sensor), which emerged as an alternative to charge-coupled device (CCD) image sensors and eventually outsold them by the mid-2000s.

Solid-state image-sensing device that compensates for brightness at edges of a display area and a driving method thereof

ActiveUS7193199B2Lower ratioImprove noiseTelevision system detailsTelevision system scanning detailsCMOS sensorControl signal

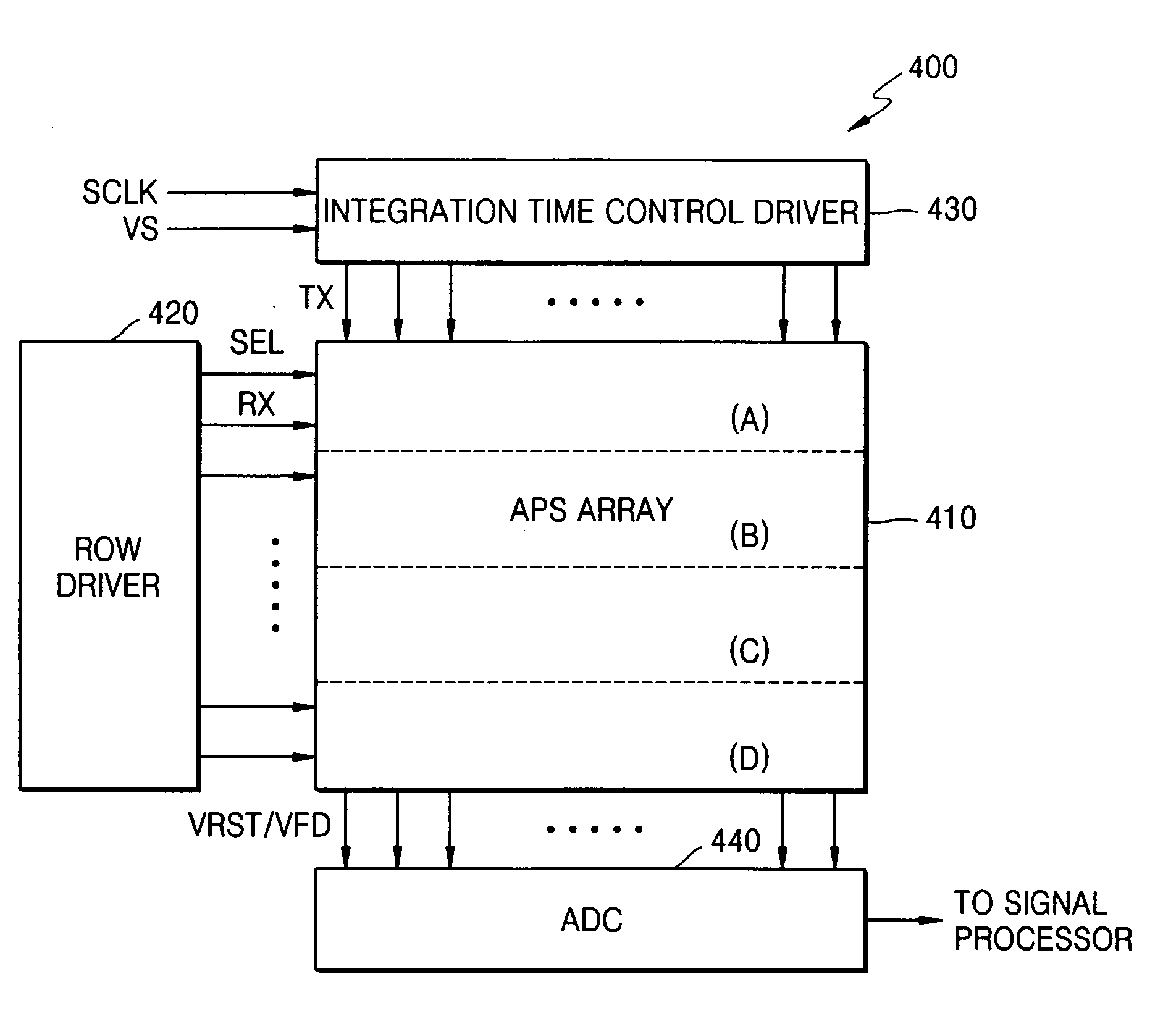

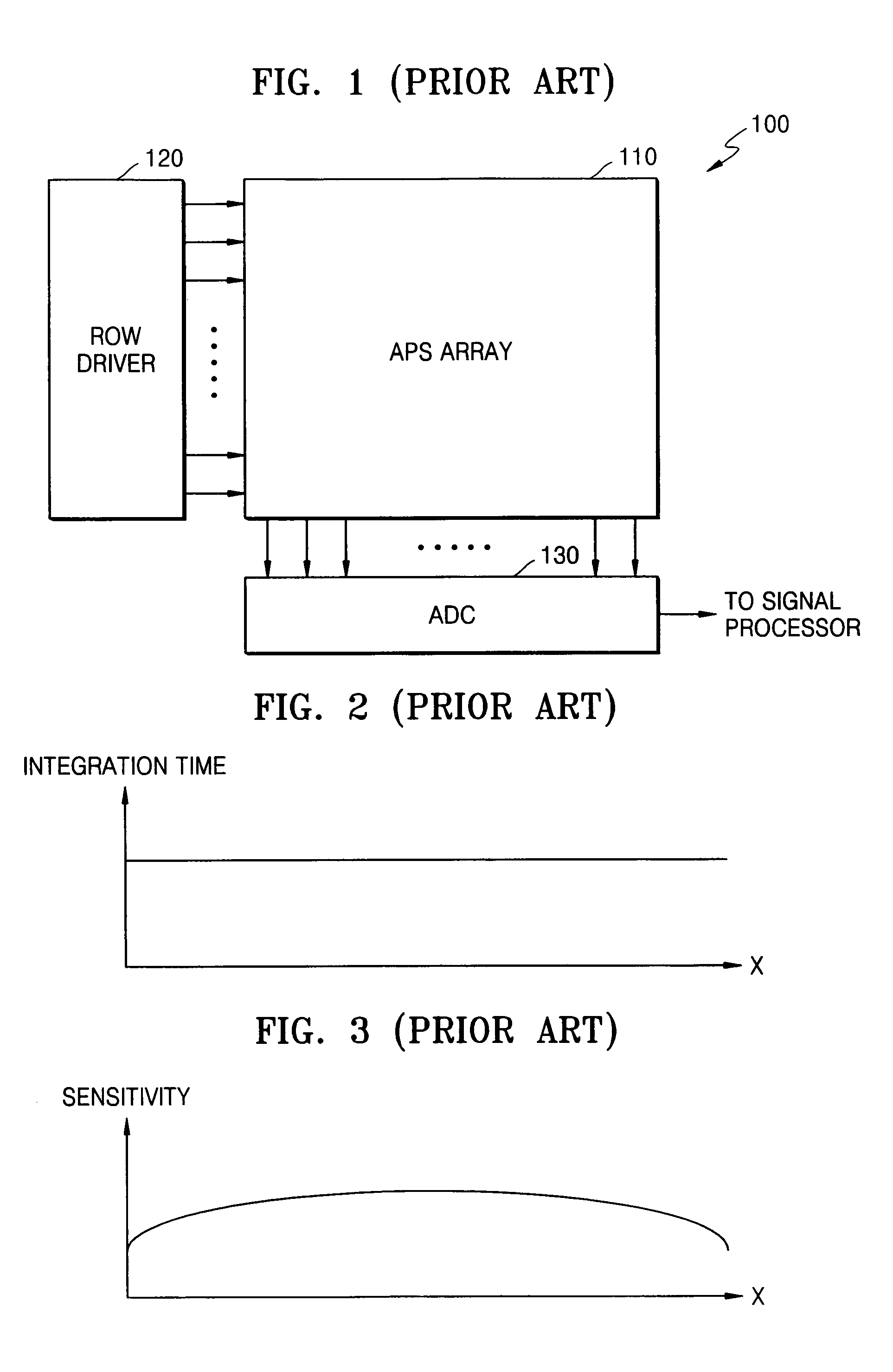

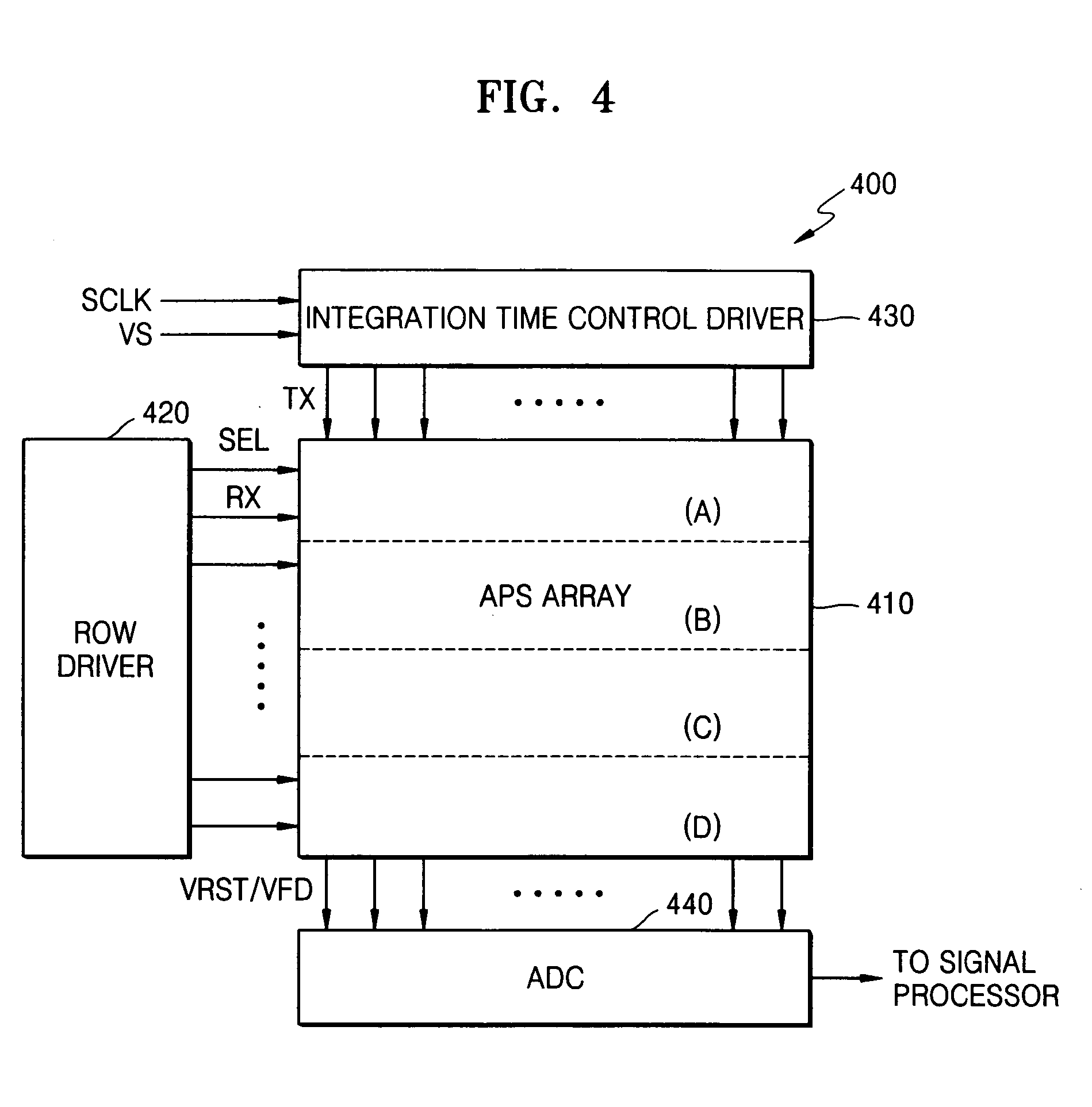

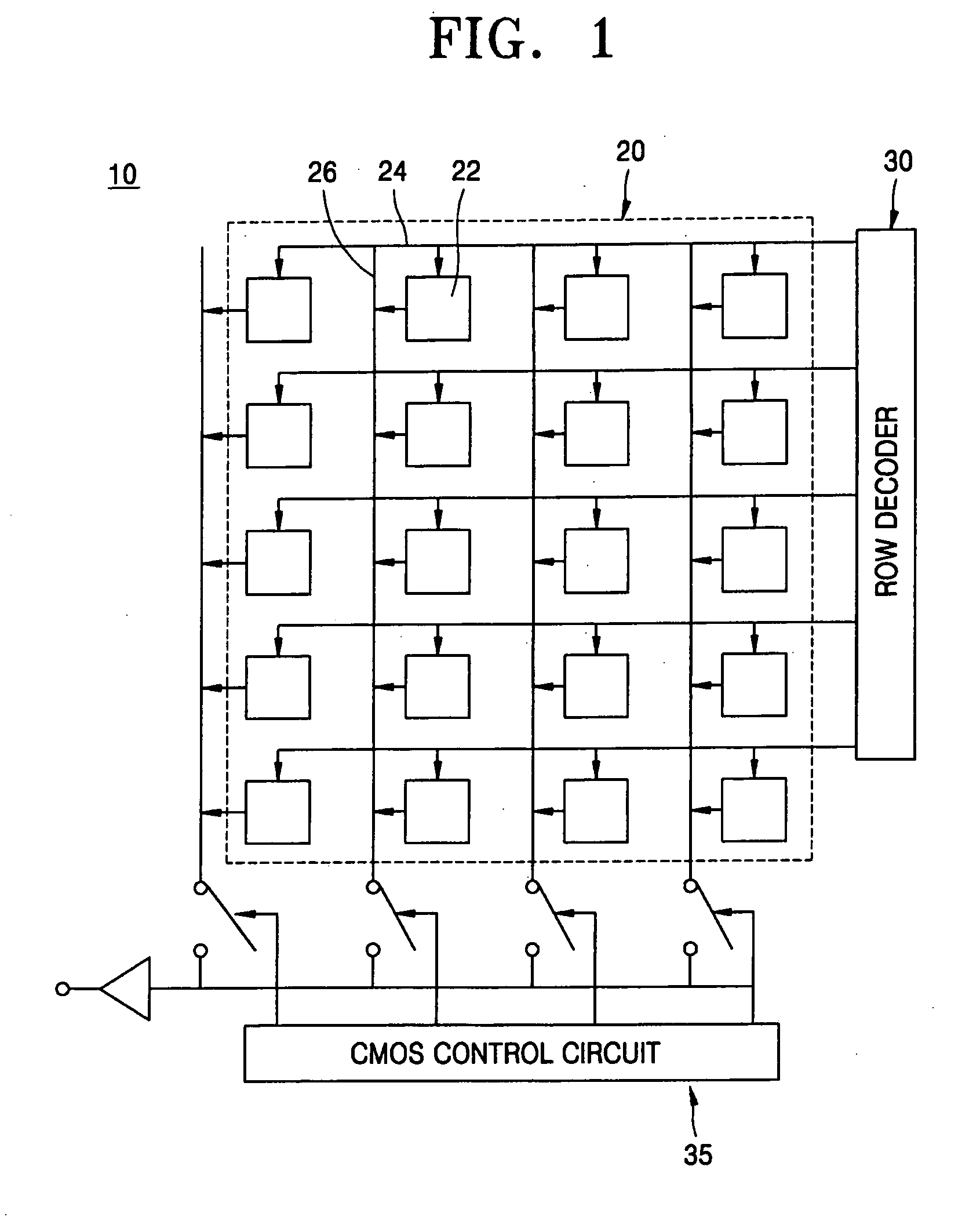

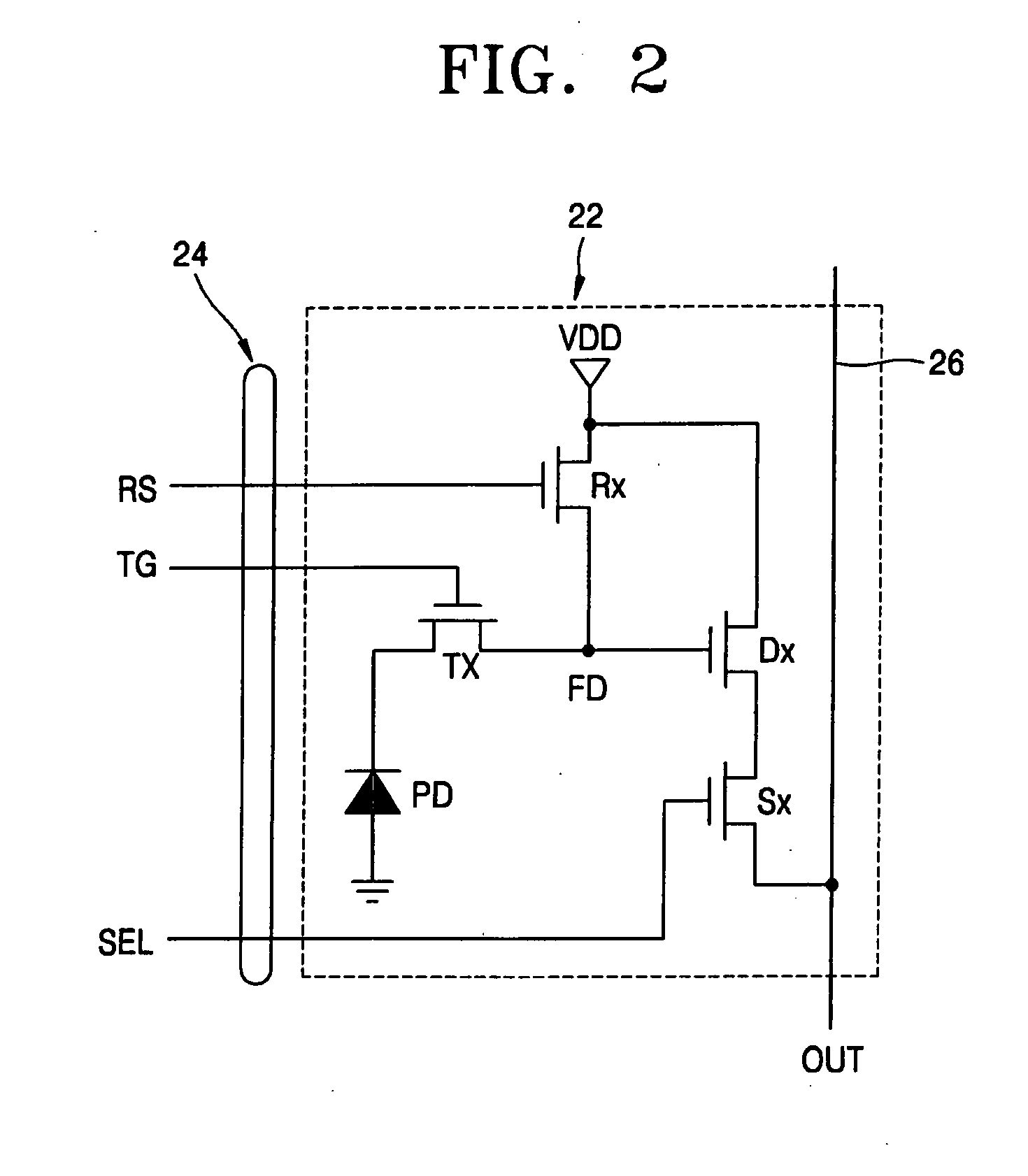

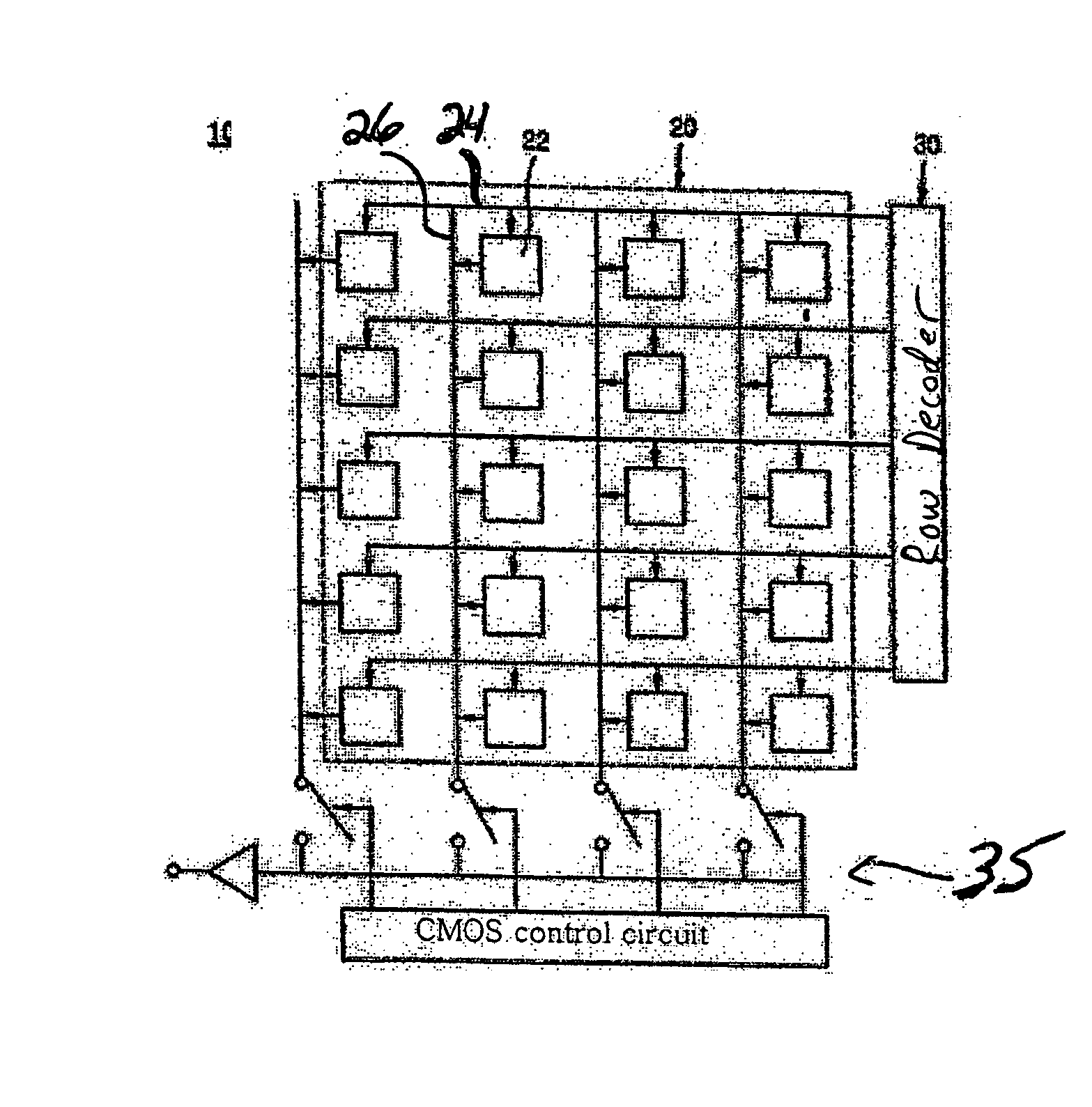

A solid-state image-sensing device that compensates for brightness at edges of a screen and a method of driving the device are provided. The solid-state image-sensing device comprises: an active pixel sensor (APS) array including pixels disposed in a two-dimensional matrix, each pixel for outputting a photoelectrically converted image signal generated by a photodiode in response to one of a plurality of transmission control signals transmitted to a selected row of the APS array, and for generating and outputting a reset signal in response to a reset control signal; a row driver for selecting a row of the APS array by generating row selection signals and for generating the reset control signal; an integration time control driver for generating the transmission control signals for setting non-uniform integration times of the photodiodes in each pixel; and an analog-digital converter for converting an analog signal corresponding to a difference between the image signal and the reset signal into a digital signal.

Owner:SAMSUNG ELECTRONICS CO LTD

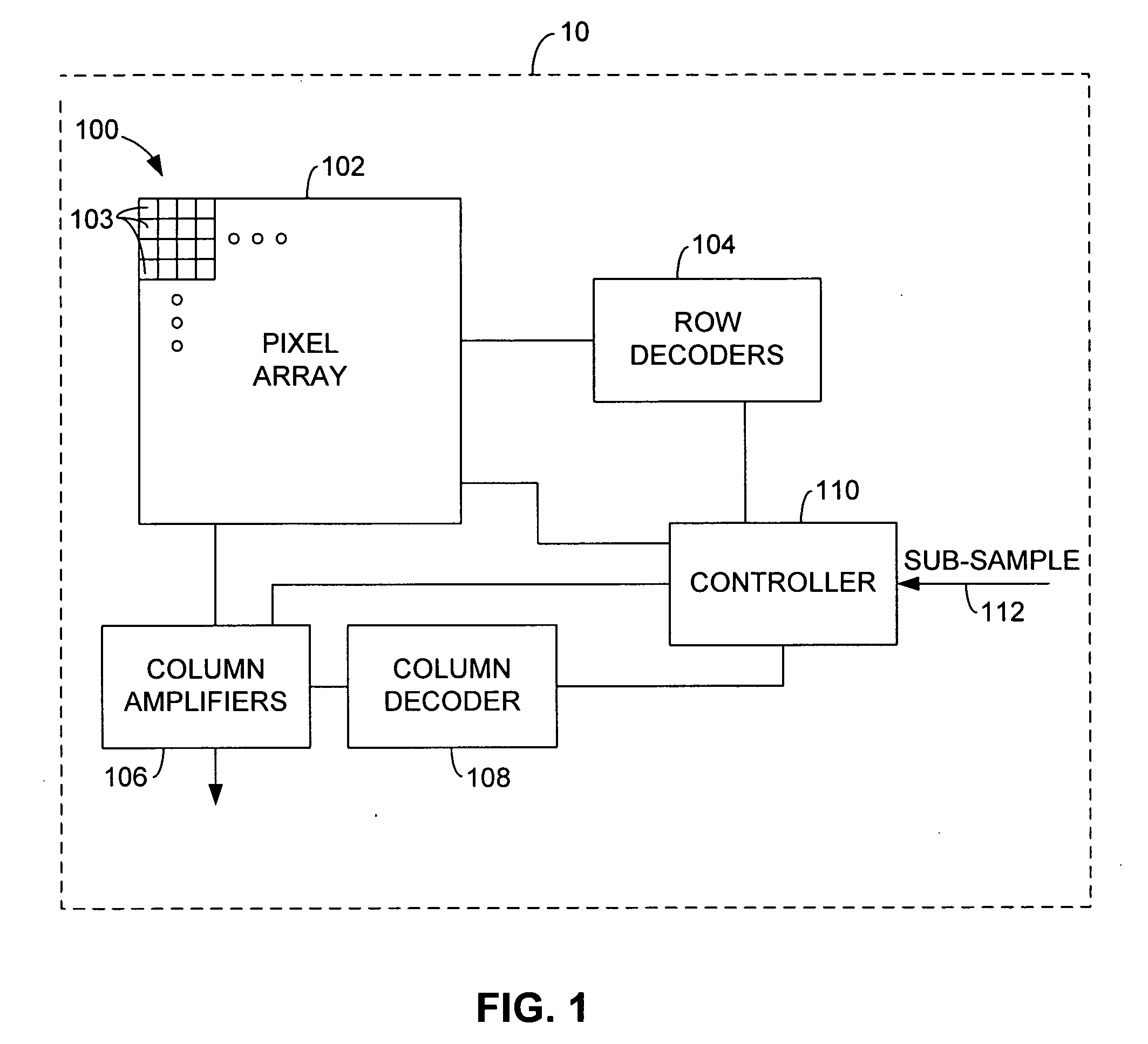

Analog vertical sub-sampling in an active pixel sensor (APS) image sensor

ActiveUS20070228256A1Television system detailsTelevision system scanning detailsCMOS sensorAudio power amplifier

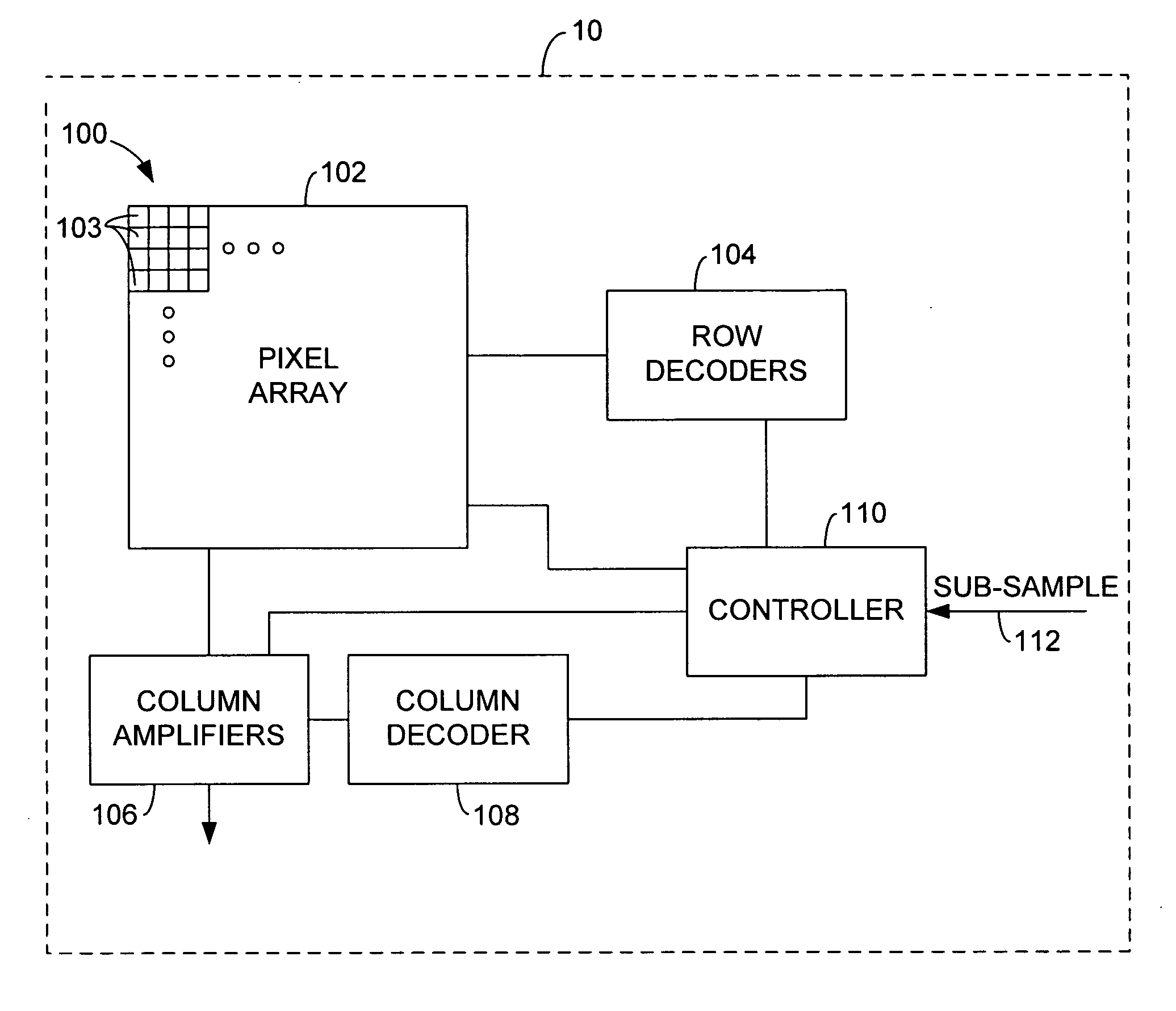

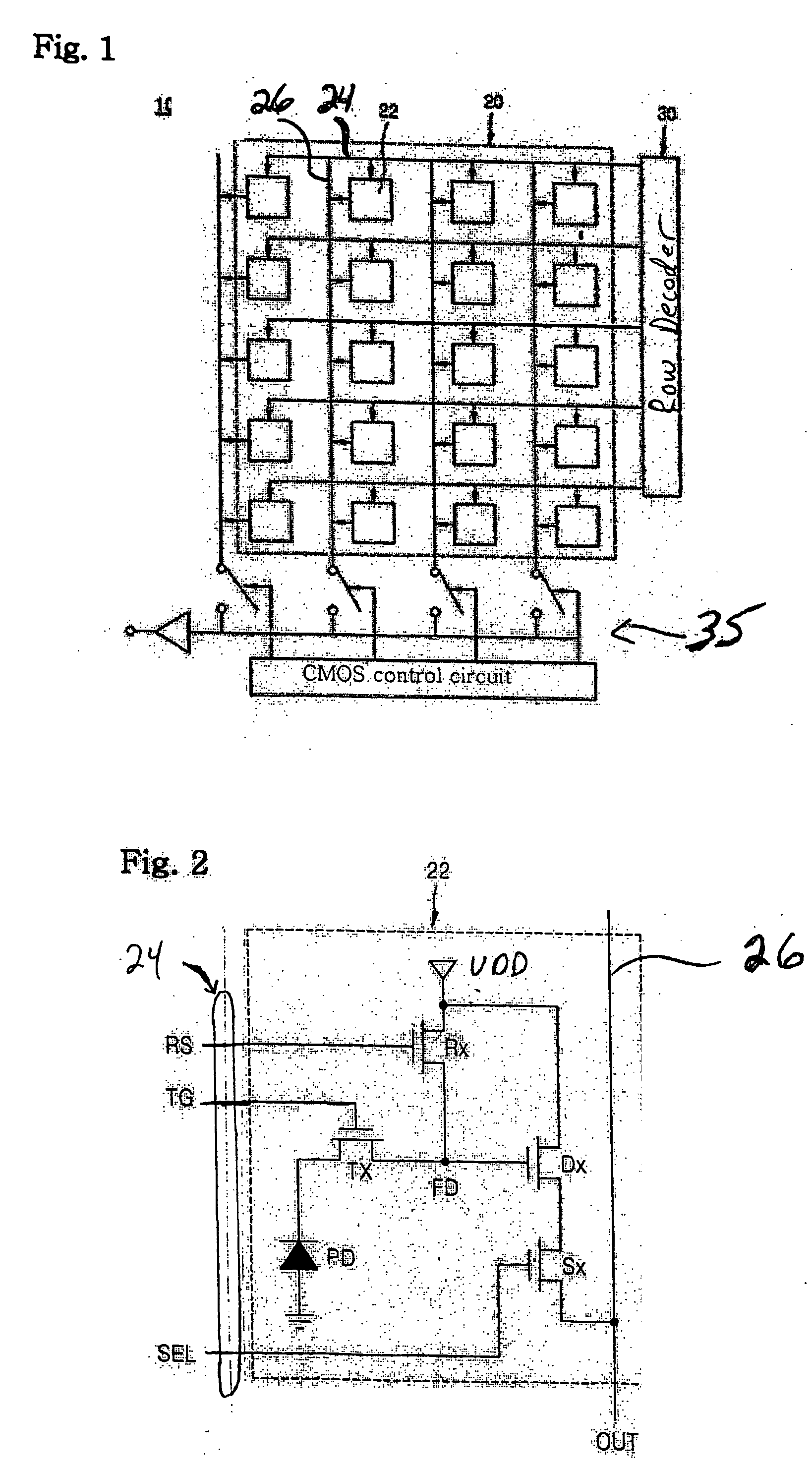

An active pixel sensor (APS) image sensor comprises an array of pixel circuits corresponding to rows and columns of pixels, a plurality of amplifiers that buffer signals output by the array of pixel circuits, and a plurality of sample and hold circuits that read the buffered signals. A routing mechanism is positioned between the array of pixel circuits and the plurality of amplifiers. A controller selects a set of the pixel circuits for sampling and is configured to control the routing mechanism to couple each pixel circuit in the set to a different one of the amplifiers during a normal mode of operation and to couple each pixel circuit of a subset of pixel circuits in a first set of pixel circuits to a different amplifier of a first subset of the amplifiers, to couple each pixel circuit of a subset of pixel circuits in a second set of pixel circuits to a different amplifier of a second subset of the amplifiers, and to connect the amplifiers of the first and second subsets of amplifiers in pairs to a common one of the sample and hold circuits during a sub-sampling mode of operation.

Owner:APTINA IMAGING CORP +1

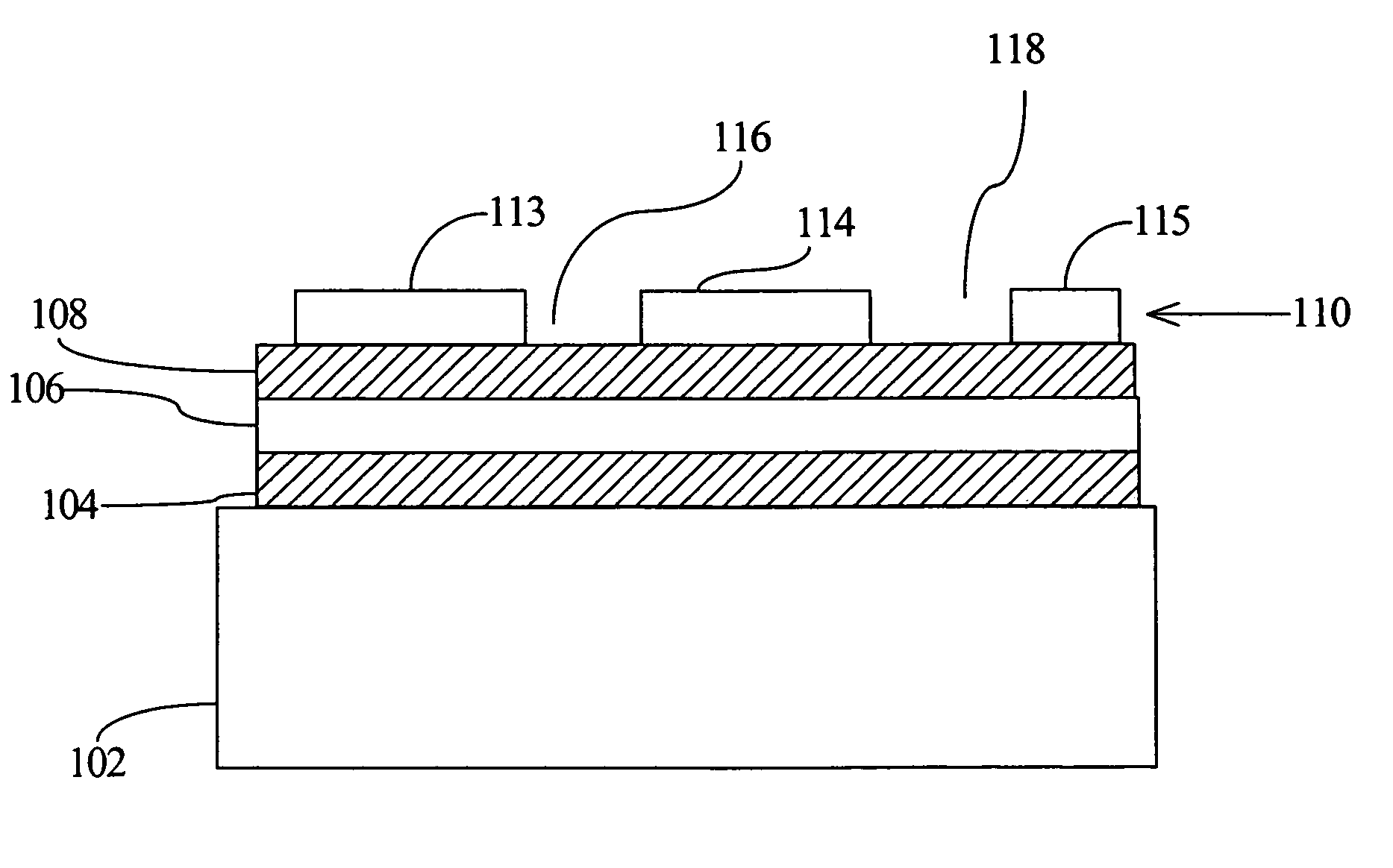

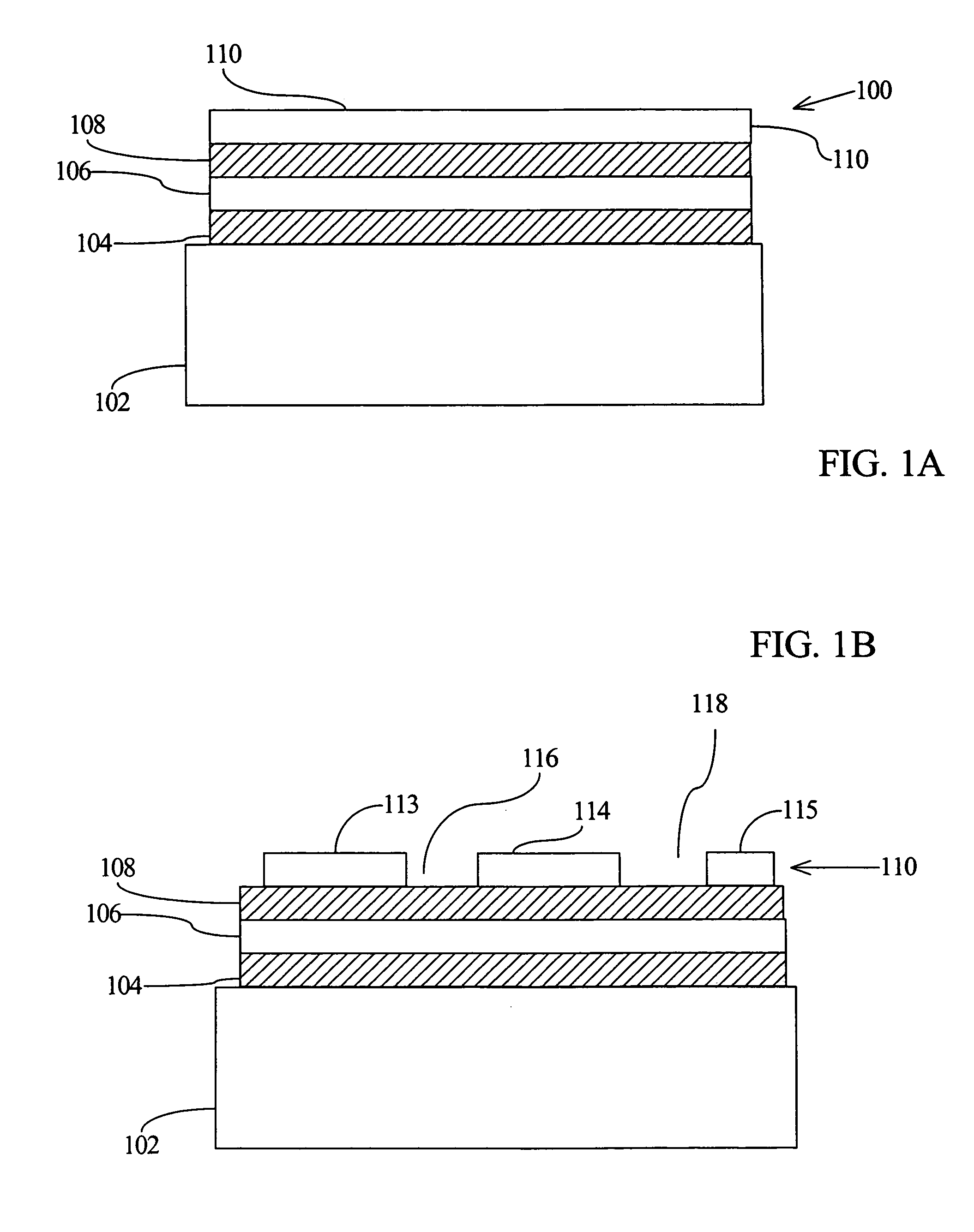

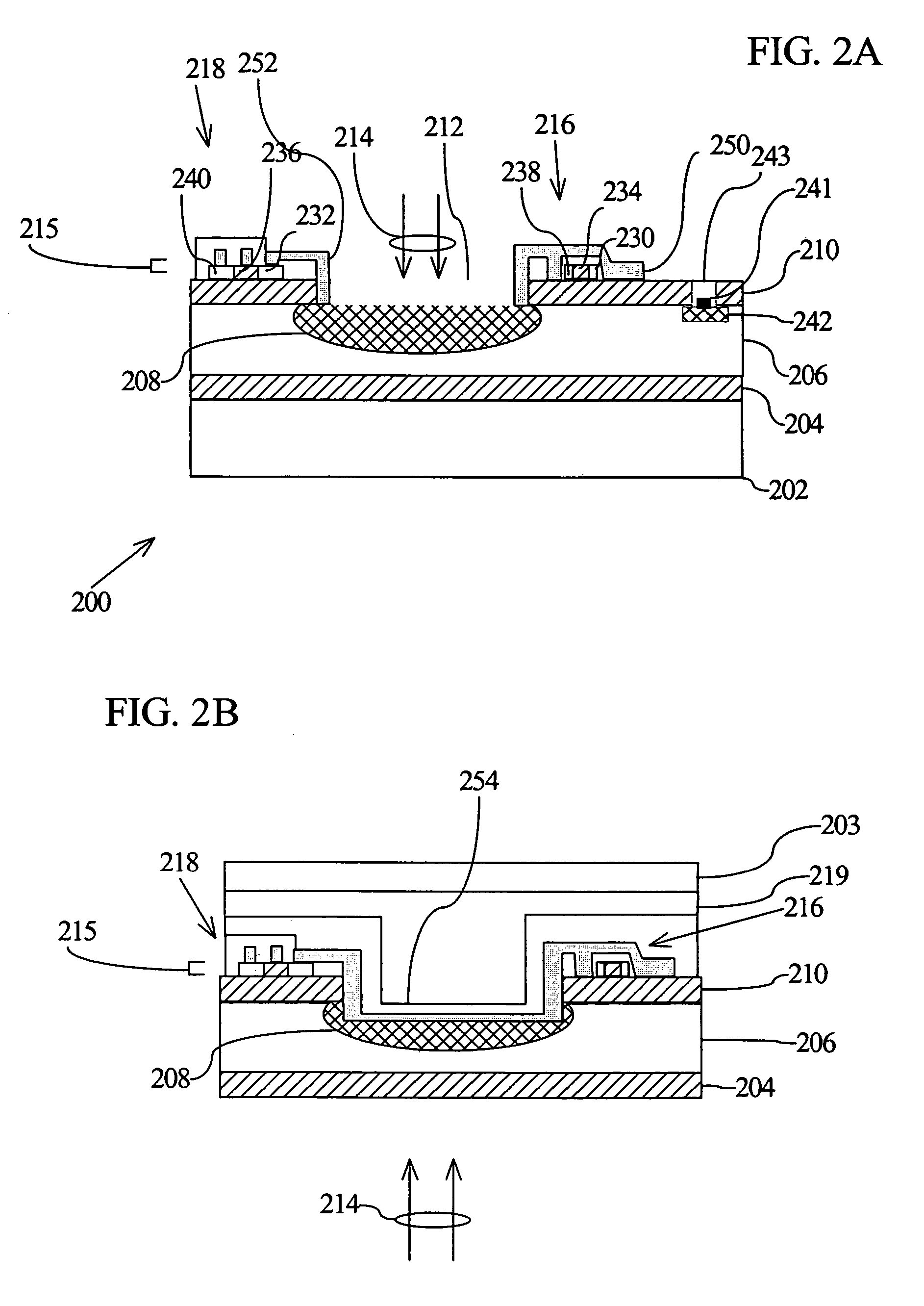

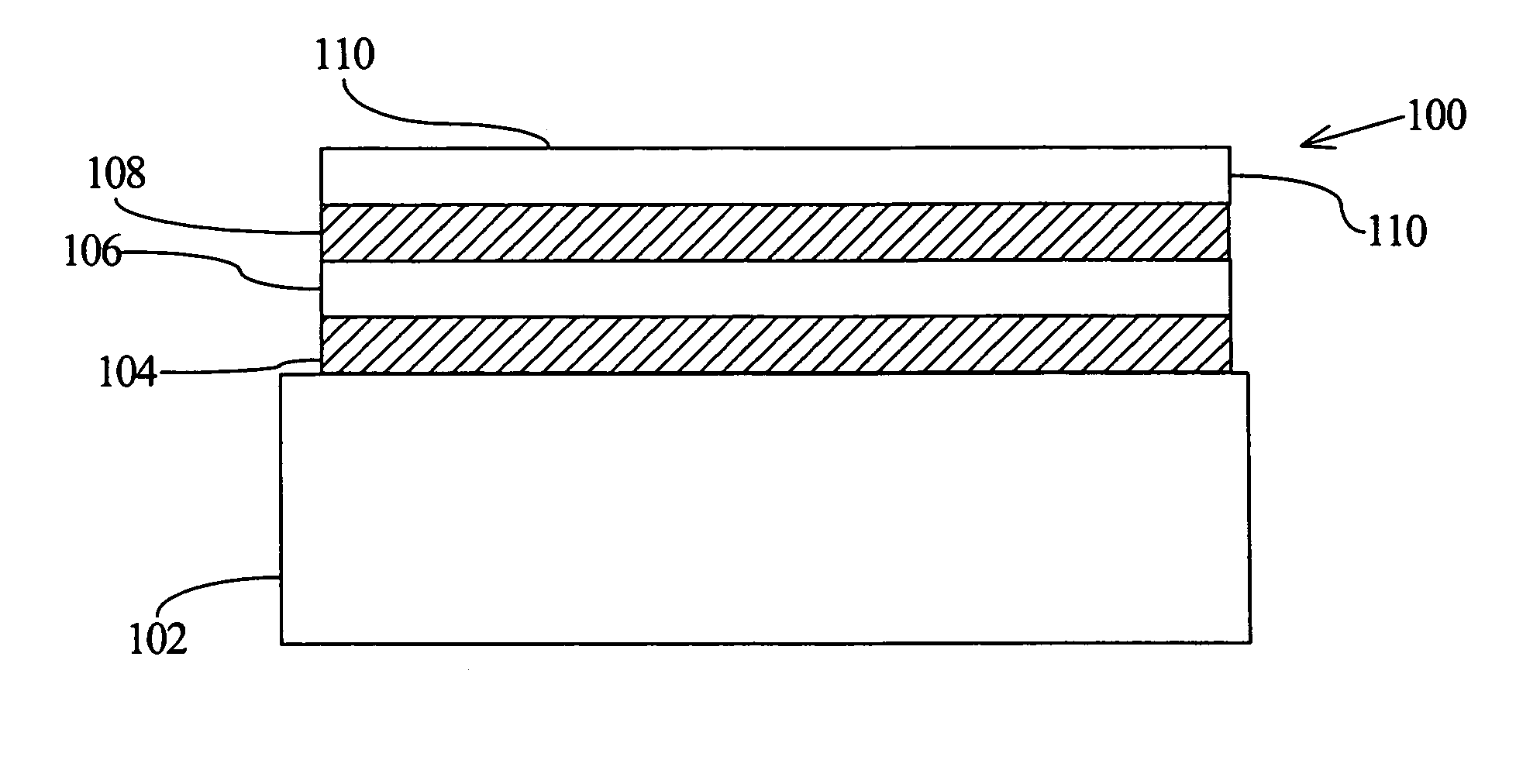

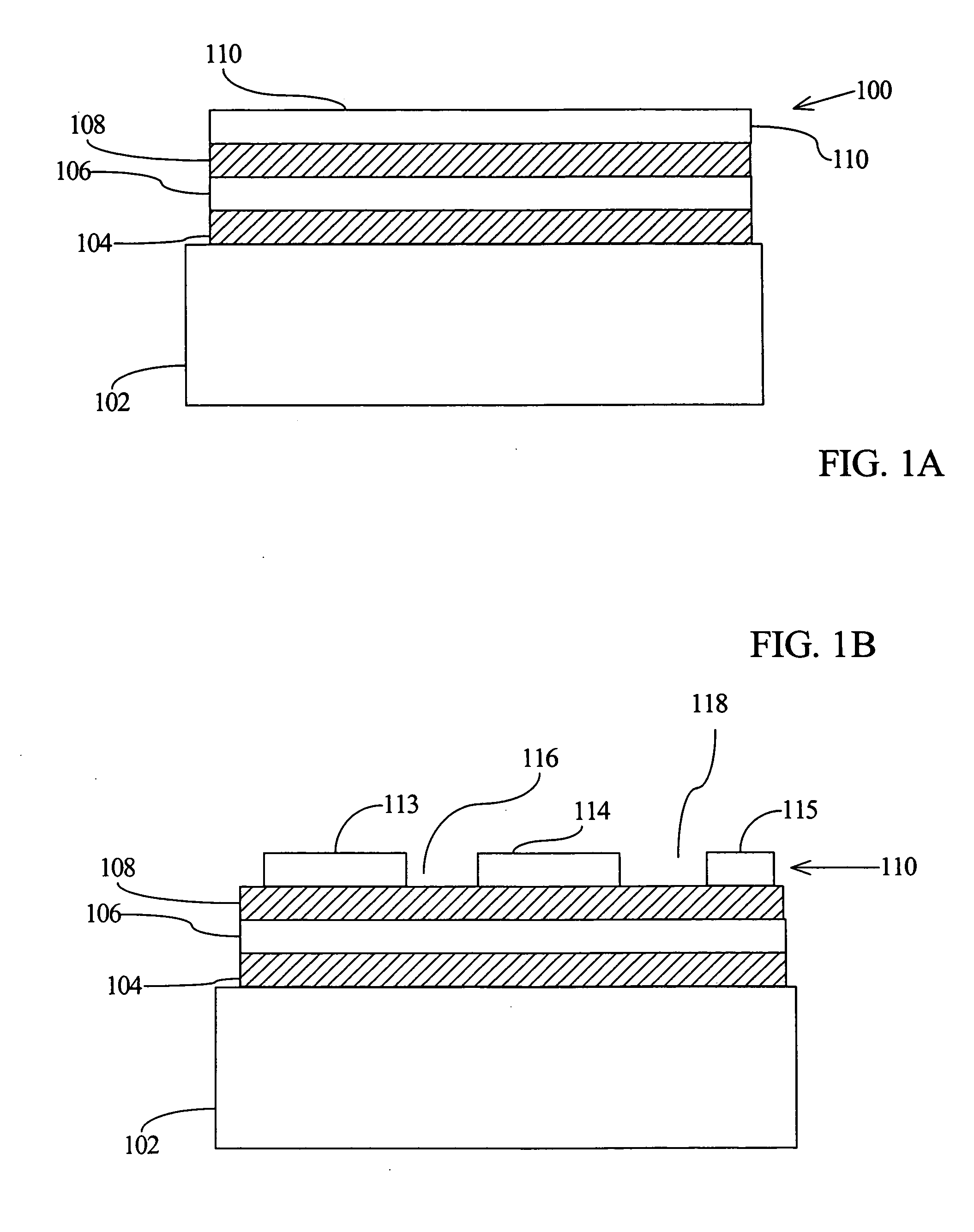

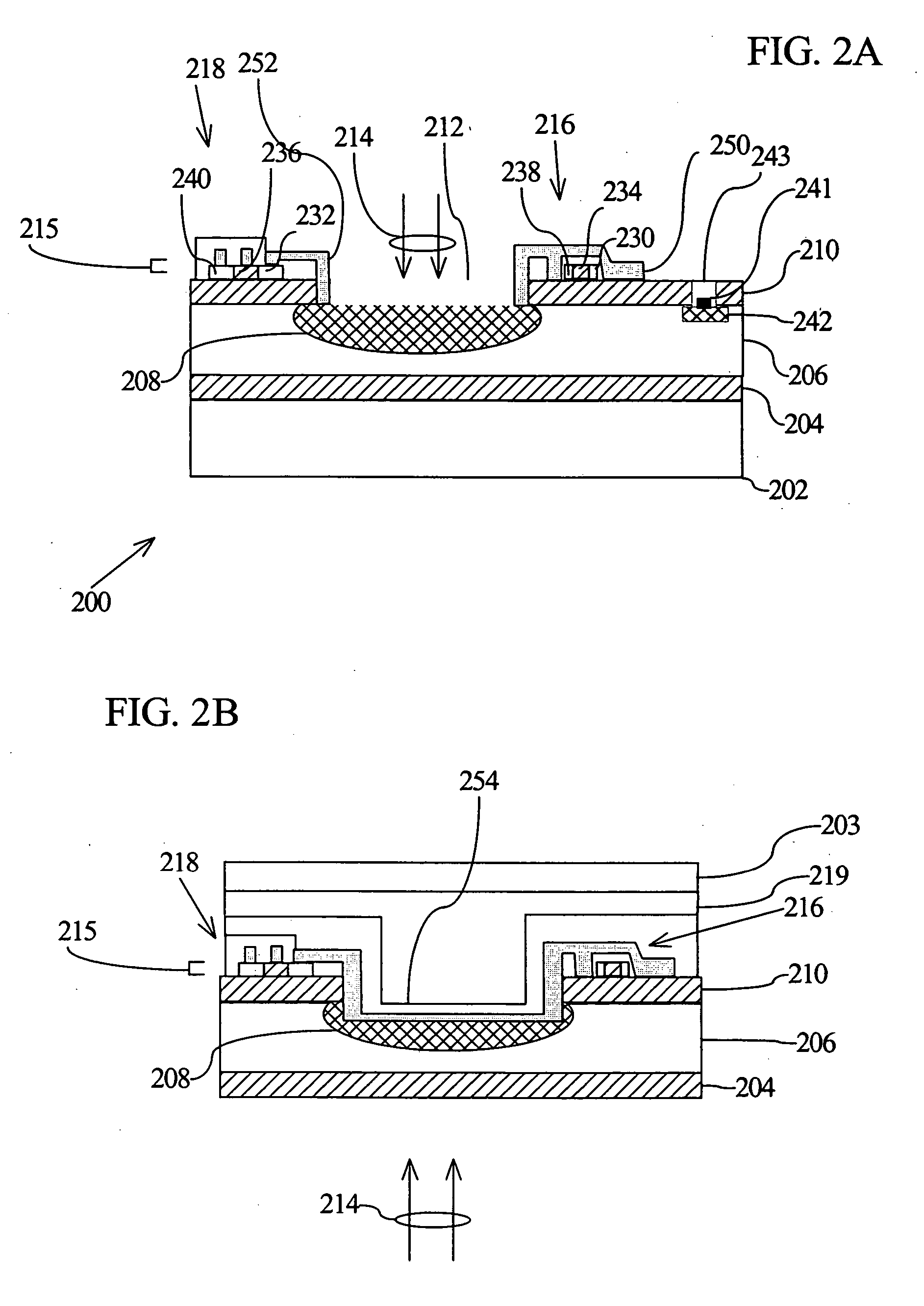

Silicon-on-insulator active pixel sensors

ActiveUS7160753B2Improve performanceEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOS sensorSoi substrate

Active pixel sensors are defined on double silicon on insulator (SOI) substrates such that a first silicon layer is selected to define radiation detection regions, and a second silicon layer is selected to define readout circuitry. The first and second silicon layers are separated by an insulator layer, typically an oxide layer, and the layers can be independently doped. Doping can be provided in the silicon layers of the SOI substrate during assembly of the SOI substrate, or later during device processing. A semiconductor substrate that supports the first and second layers can be removed for, for example, back side radiation detection, using a second insulator layer (typically an oxide layer) as an etch stop.

Owner:LADARSYST INC

Silicon-on-insulator active pixel sensors

ActiveUS20050205930A1Reduce sensitivityImprove radiation hardnessSolid-state devicesSemiconductor/solid-state device manufacturingCMOS sensorSoi substrate

Active pixel sensors are defined on double silicon on insulator (SOI) substrates such that a first silicon layer is selected to define radiation detection regions, and a second silicon layer is selected to define readout circuitry. The first and second silicon layers are separated by an insulator layer, typically an oxide layer, and the layers can be independently doped. Doping can be provided in the silicon layers of the SOI substrate during assembly of the SOI substrate, or later during device processing. A semiconductor substrate that supports the first and second layers can be removed for, for example, back side radiation detection, using a second insulator layer (typically an oxide layer) as an etch stop.

Owner:LADARSYST INC

Visible/near infrared image sensor

InactiveUS20050104089A1Improve performanceHigh sensitivityTelevision system detailsTelevision system scanning detailsLow earth orbitBeam steering

A MOS or CMOS sensor for high performance imaging in broad spectral ranges including portions of the infrared spectral band. These broad spectral ranges may also include portions or all of the visible spectrum, therefore the sensor has both daylight and night vision capabilities. The sensor includes a continuous multi-layer photodiode structure on a many pixel MOS or CMOS readout array where the photodiode structure is chosen to include responses in the near infrared spectral ranges. A preferred embodiment incorporates a microcrystalline copper indium diselenide / cadmium sulfide photodiode structure on a CMOS readout array. An alternate preferred embodiment incorporates a microcrystalline silicon germanium photodiode structure on a CMOS readout array. Each of these embodiments provides night vision with image performance that greatly surpasses the GEN III night vision technology in terms of enhanced sensitivity, pixel size and pixel count. Further advantages of the invention include low electrical bias voltages, low power consumption, compact packaging, and radiation hardness. In special preferred embodiments CMOS stitching technology is used to provide multi-million pixel focal plane array sensors. One embodiments of the invention made without stitching is a two-million pixel sensor. Other preferred embodiments available using stitching techniques include sensors with 250 million (or more) pixels fabricated on a single wafer. A particular application of these very high pixel count sensors is as a focal plane array for a rapid beam steering telescope in a low earth orbit satellite useful for tracking over a 1500-meter wide track with a resolution of 0.3 meter.

Owner:C PHOCUS

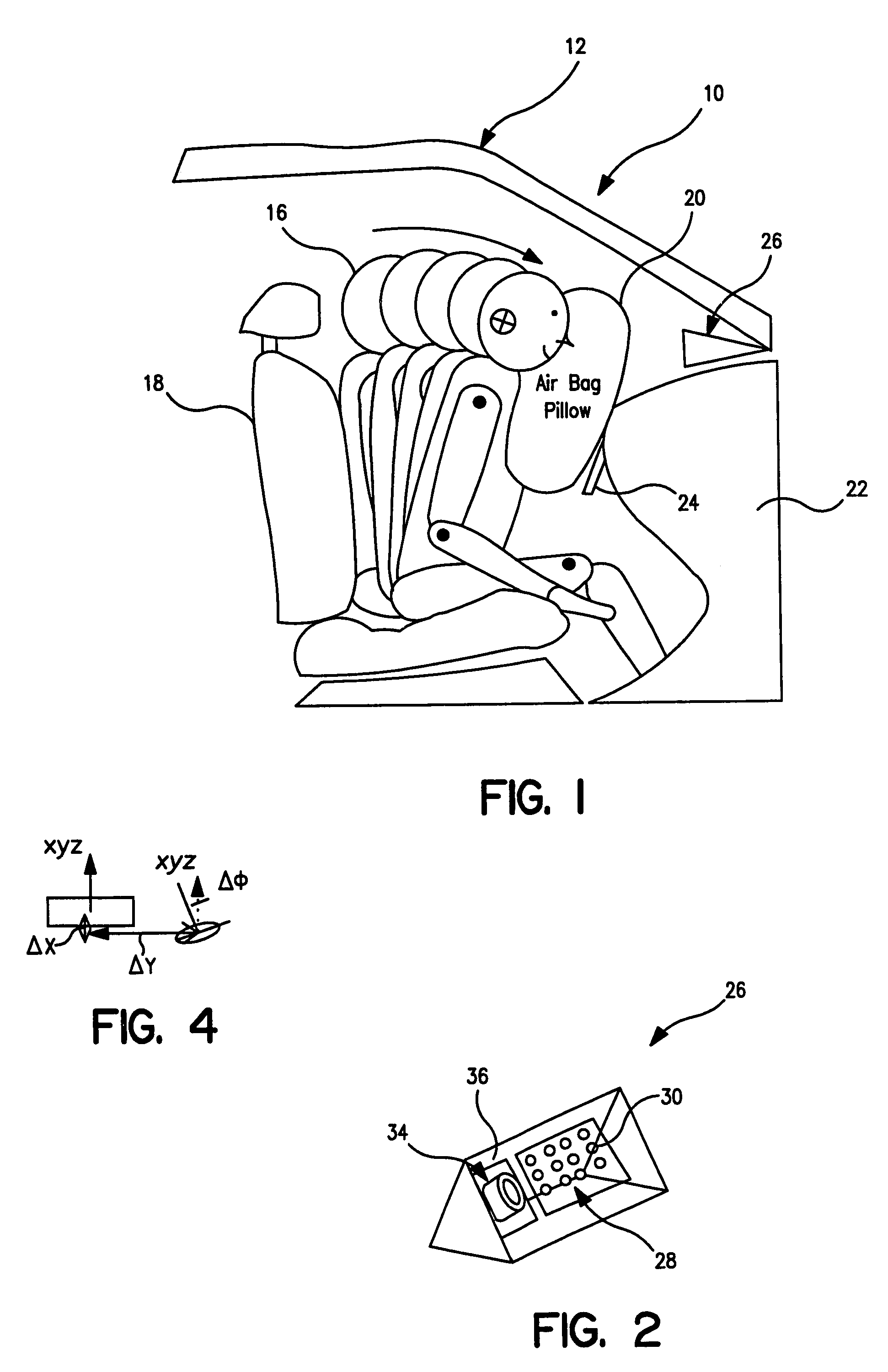

Application of human facial features recognition to automobile security and convenience

An imaging system (50) for providing vehicle security and convenience features that employs face recognition software to identify and track a person. The system (50) employs infrared emitters (30) that emit an infrared signal along a predetermined field-of-view, and an infrared sensor (34), such as a CMOS sensor used as a video signal array, that receives reflected infrared illumination from objects in the field-of-view. A processor (52) including the face recognition software, is employed to detect human faces to identify and track the person. Once a face is detected, it can be compared to a data base to identify the person. Various applications for the imaging system (50) to provide driver convenience and security include determining driver identification as the driver approaches the vehicle, determining if a potential thief is in the vehicle by face recognition, providing driver seat adjustment, rear and side mirror adjustment and steering wheel adjustment, providing vehicle speed control, automatically starting the vehicle, etc.

Owner:TRW INC

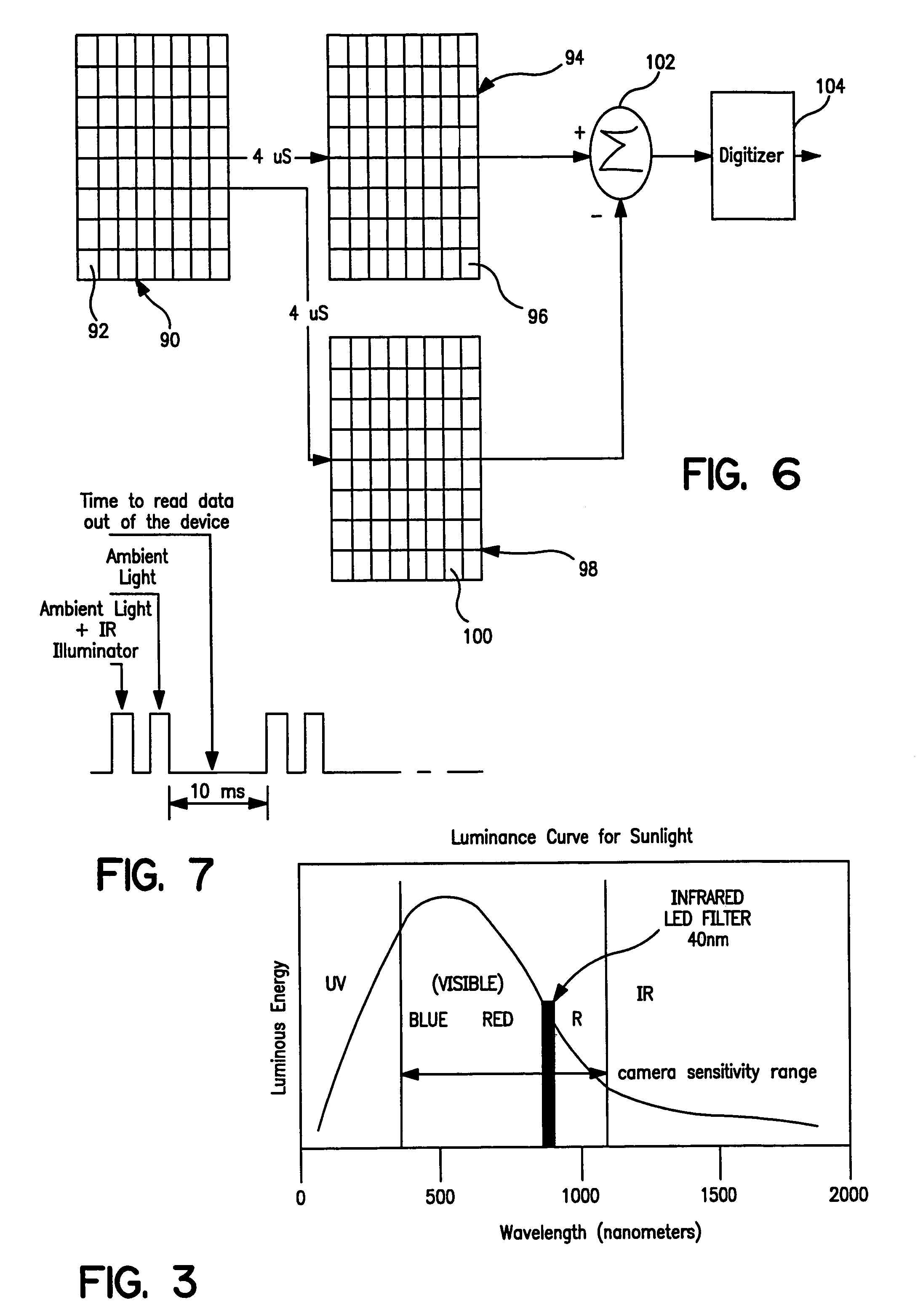

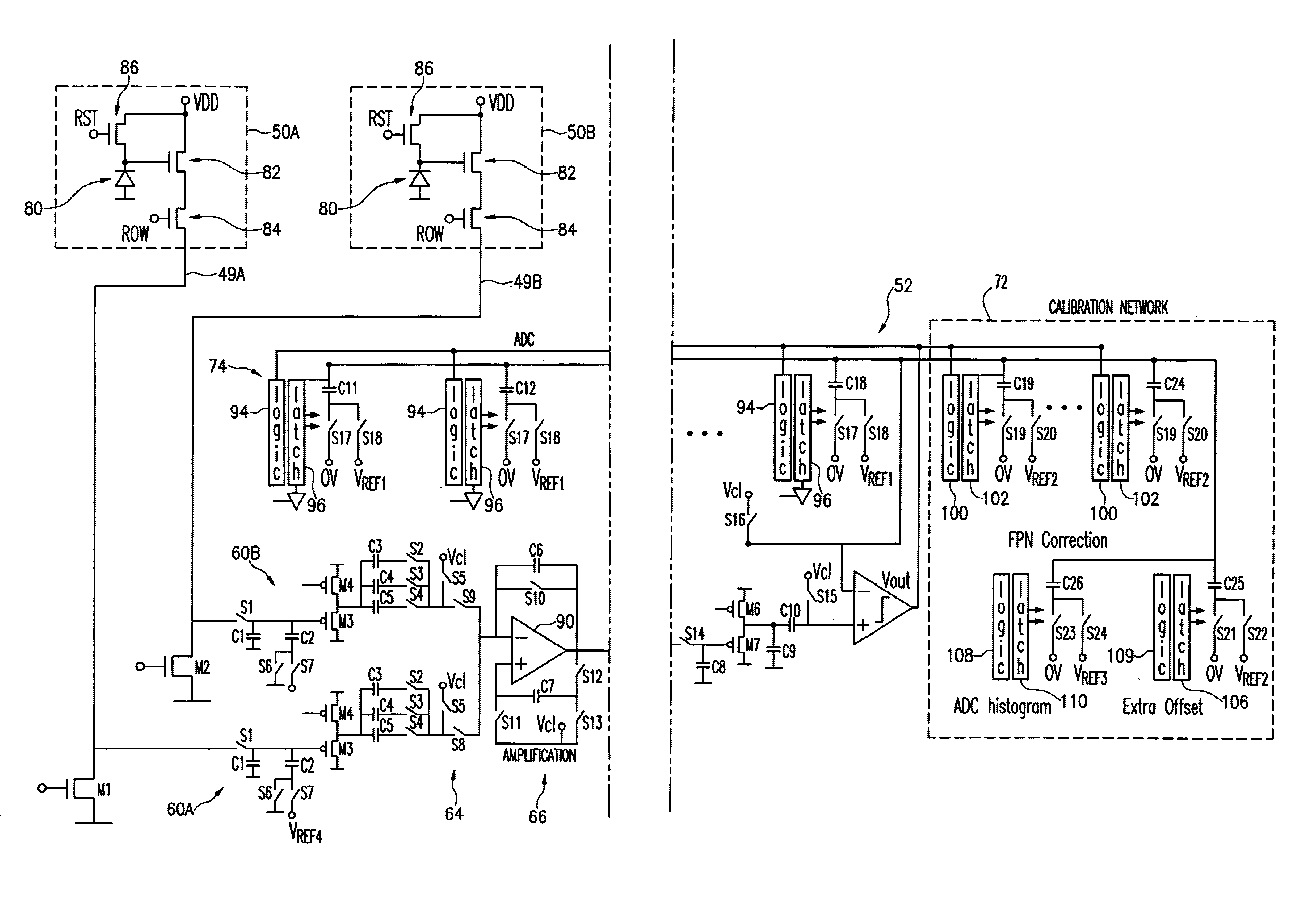

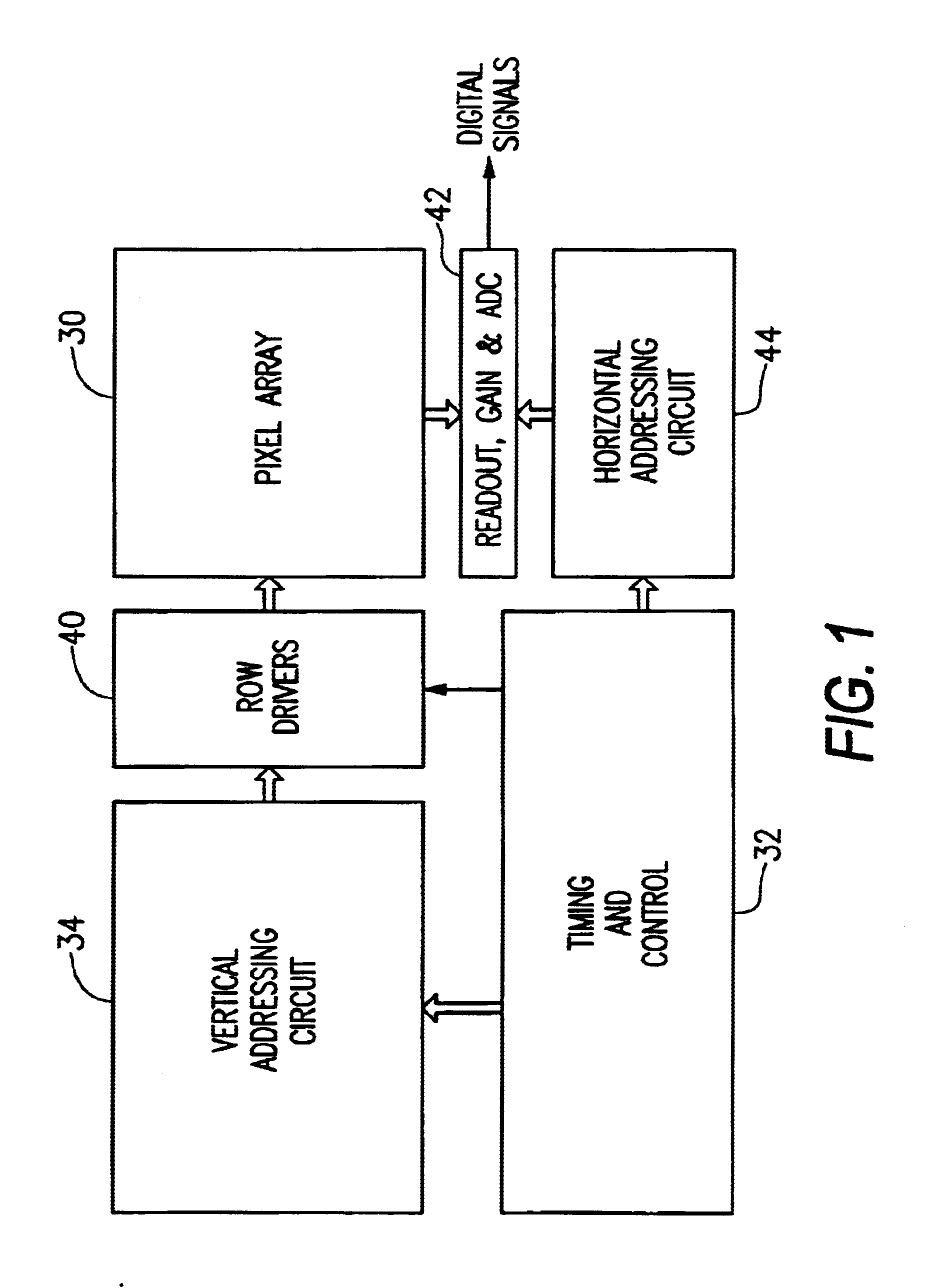

Readout circuit with gain and analog-to-digital a conversion for image sensor

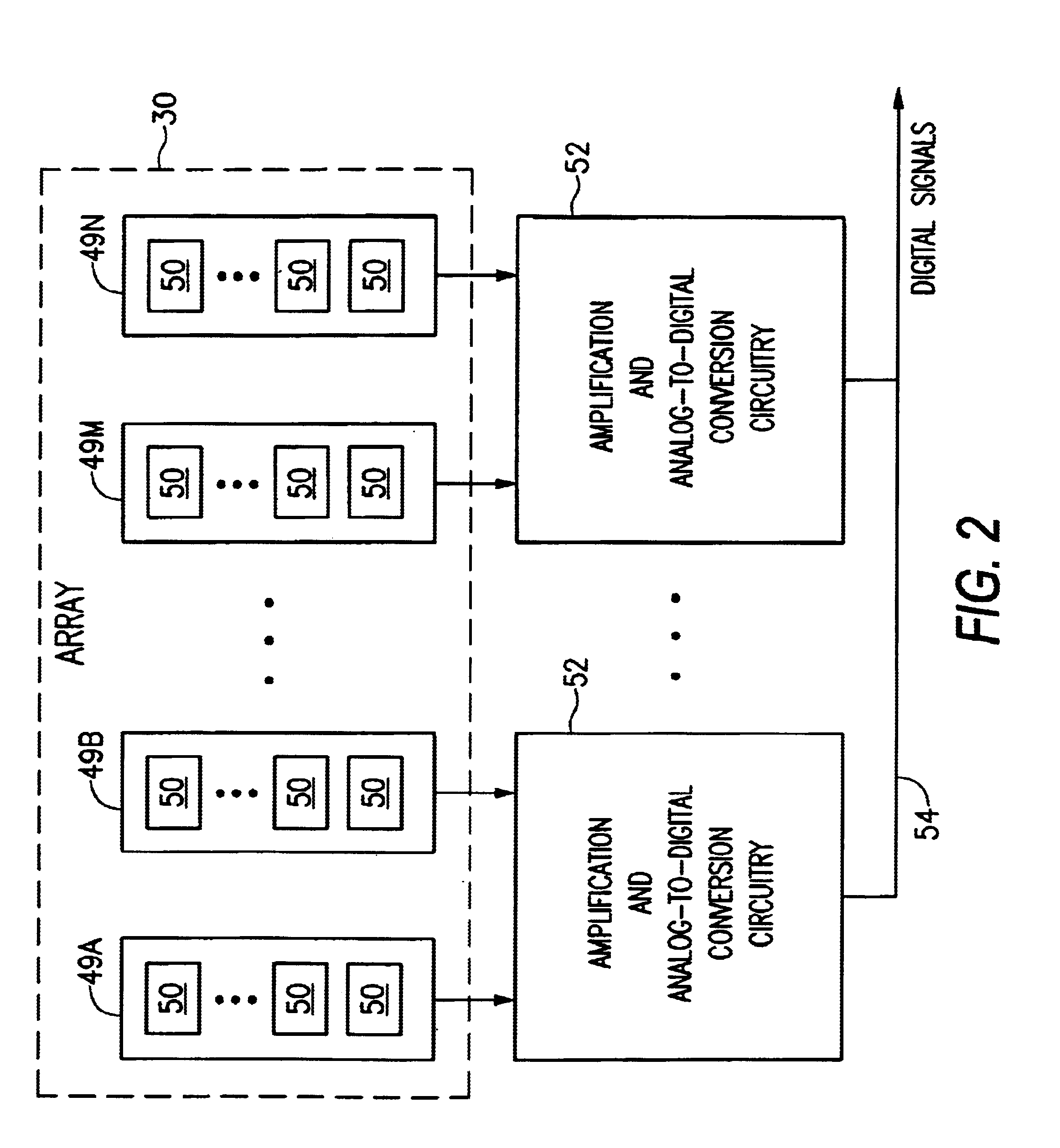

InactiveUS6885396B1Increase parallel structureAttenuation bandwidthTelevision system detailsElectric signal transmission systemsSensor arrayCMOS sensor

A CMOS imager includes an array of active pixel sensors, wherein each pixel is associated with a respective column in the array. The imager also includes multiple circuits for reading out values of pixels from the active sensor array. Each readout circuit can be associated with a respective pair of columns in the array and can include first and second sample-and-hold circuits. The first and second sample-and-hold circuits are associated, respectively, with first and second columns of pixels in the array. Each readout circuit also includes an operational amplifier-based charge sensing circuit that selectively provides an amplified differential output signal based on signals sampled either by the first sample-and-hold circuit or the second sample-and-hold circuit. The readout circuit also has an analog-to-digital converter for converting the differential output to a corresponding digital signal using a successive approximation technique. Use of the readout circuit can increase the parallel structure of the overall chip, thereby reducing the bandwidth which each readout circuit must be capable of handling.

Owner:APTINA IMAGING CORP

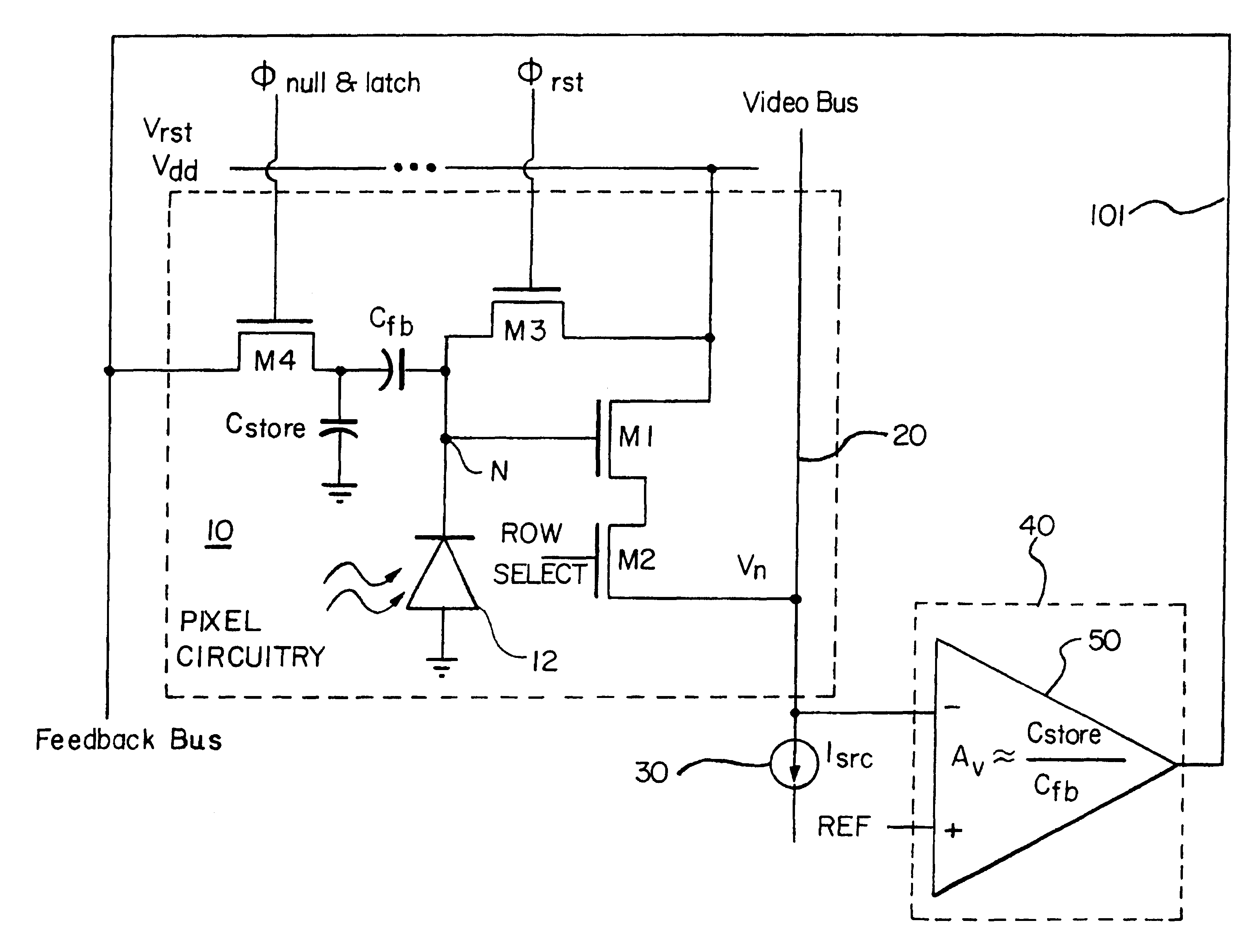

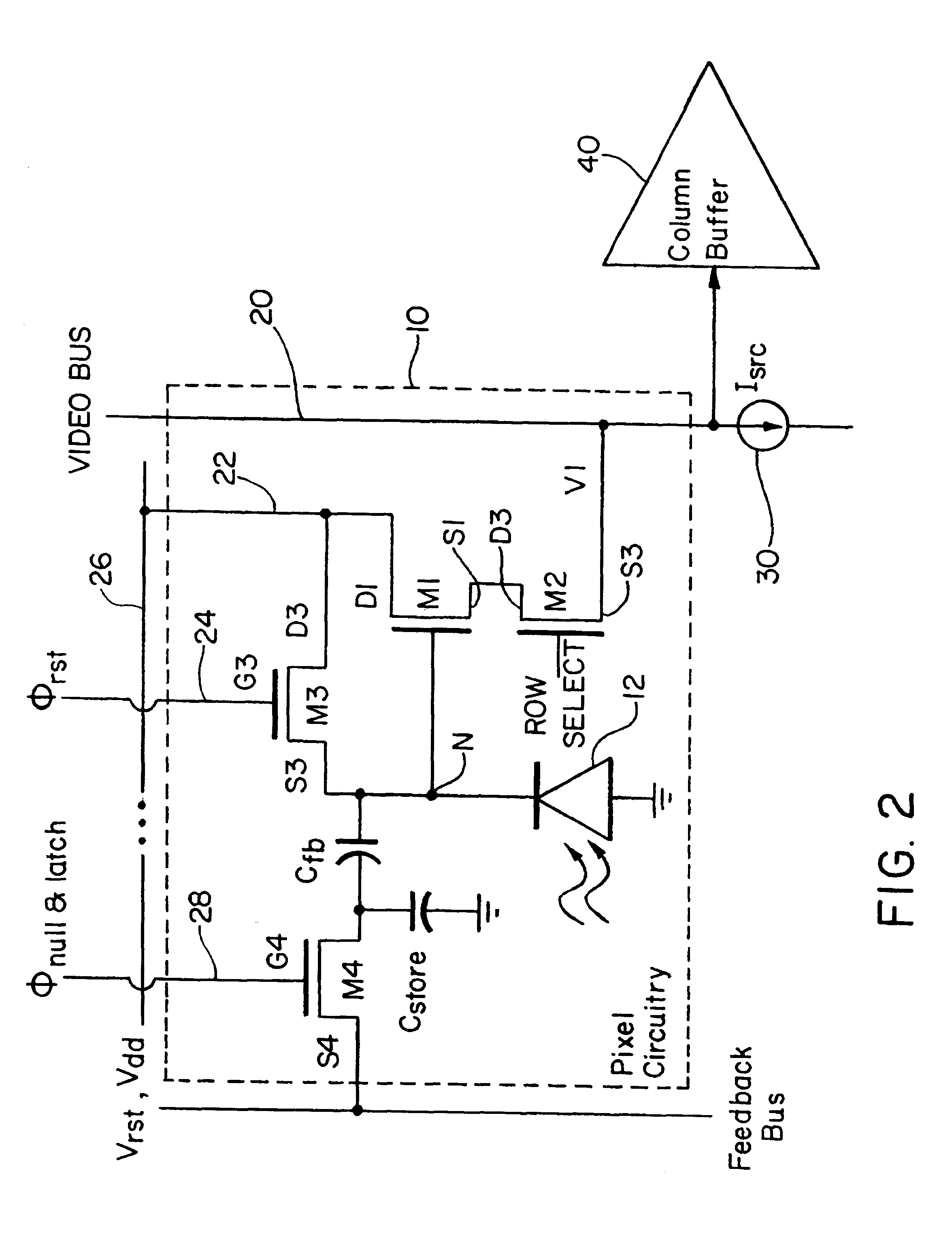

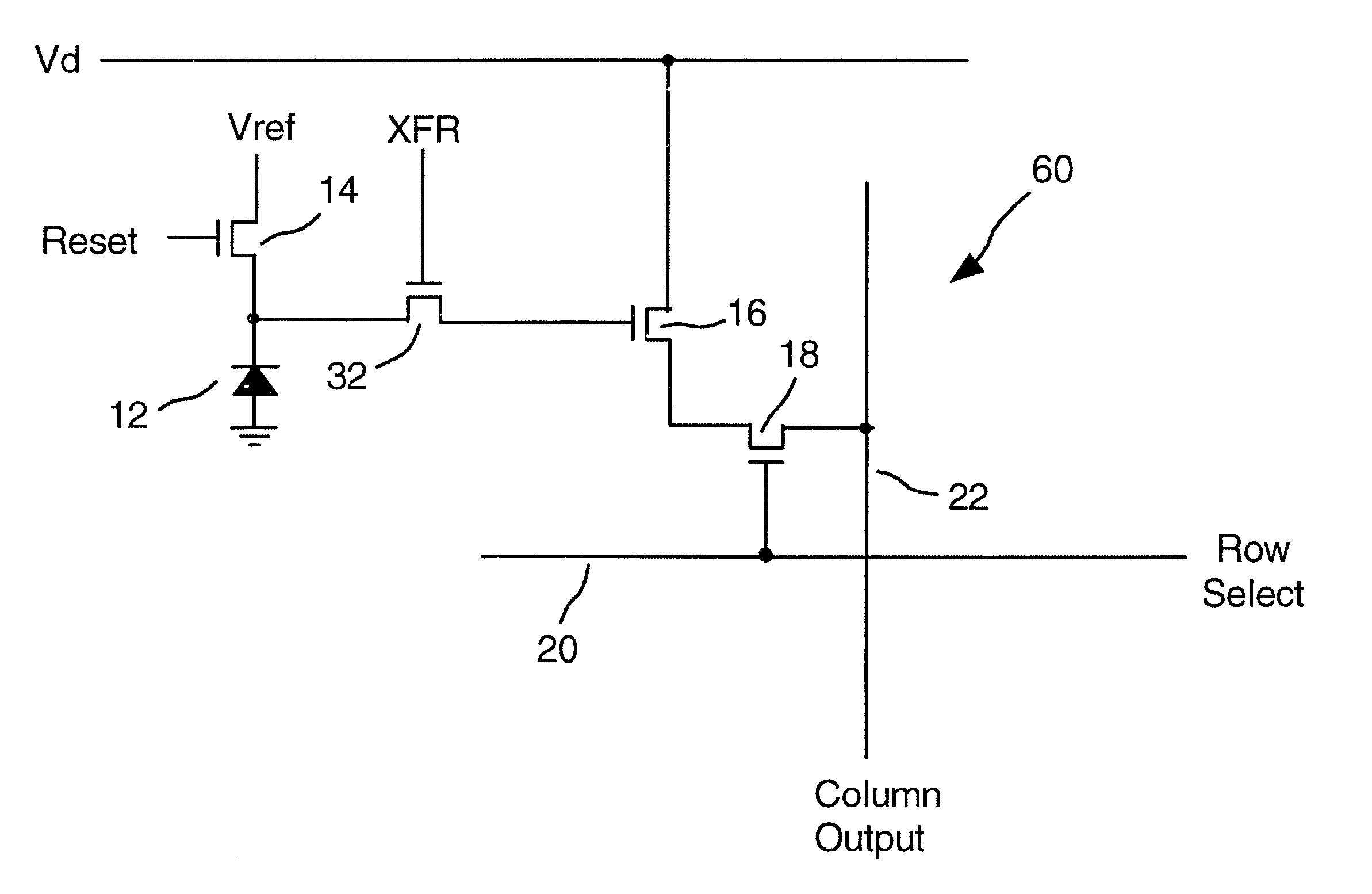

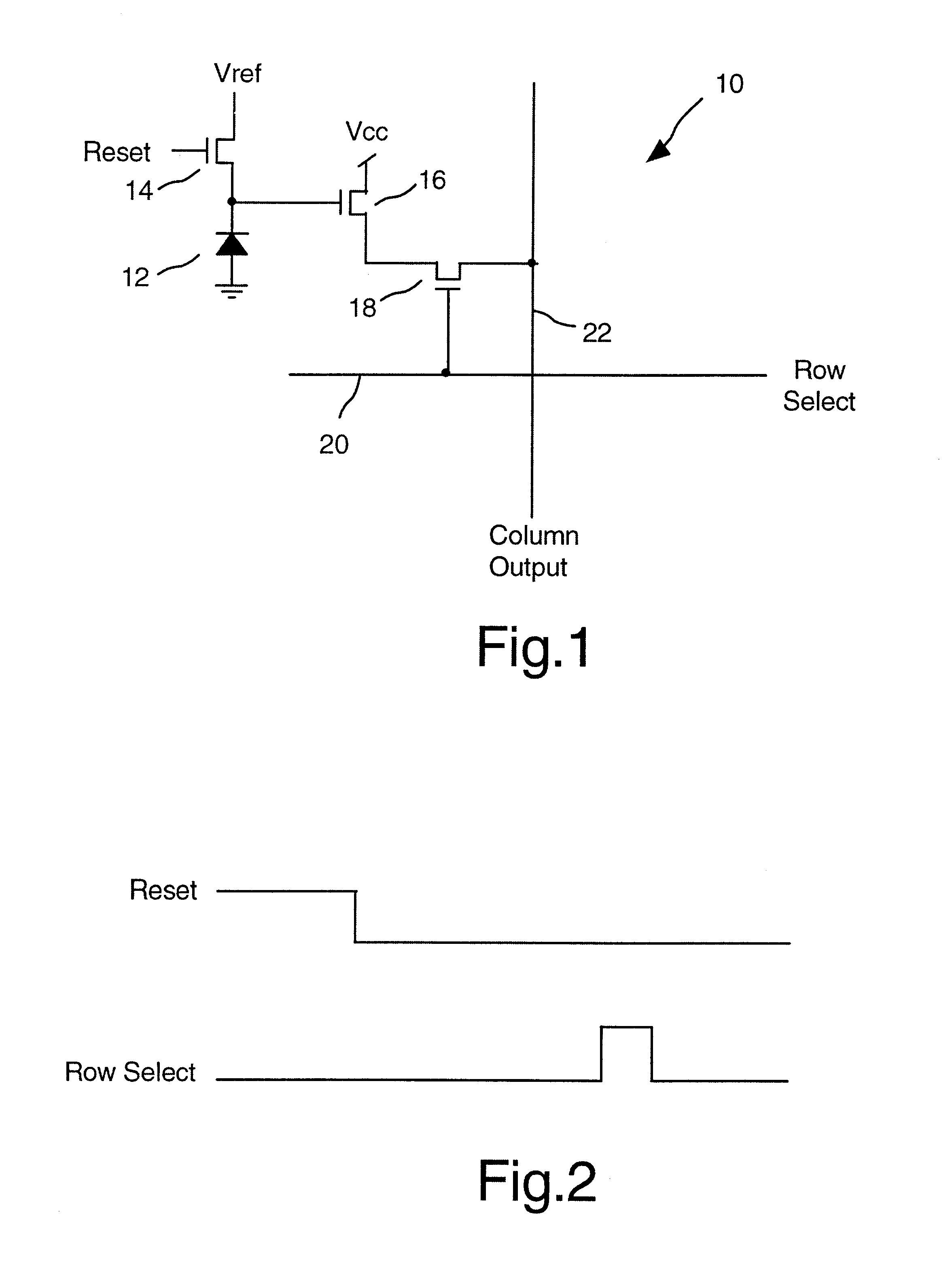

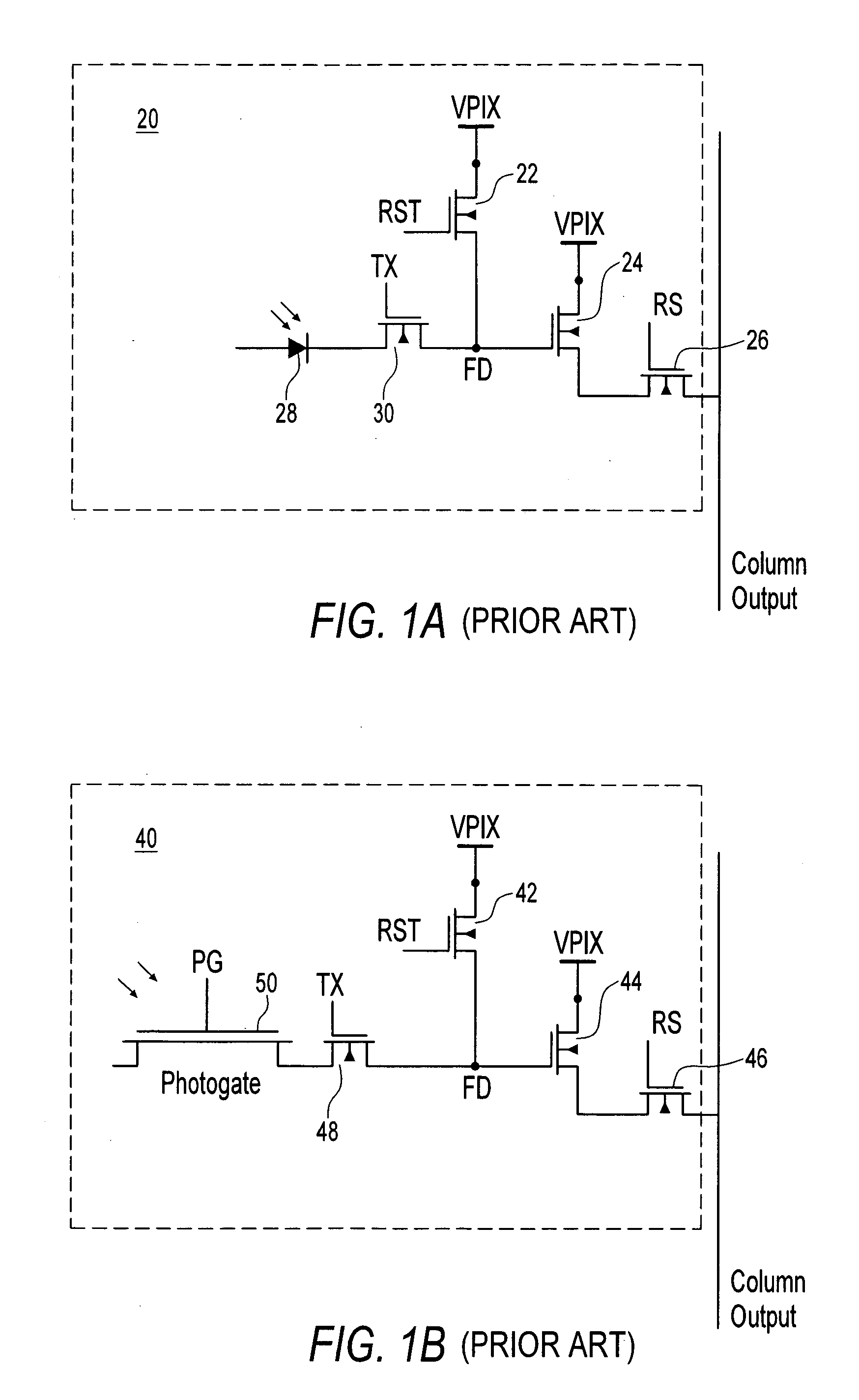

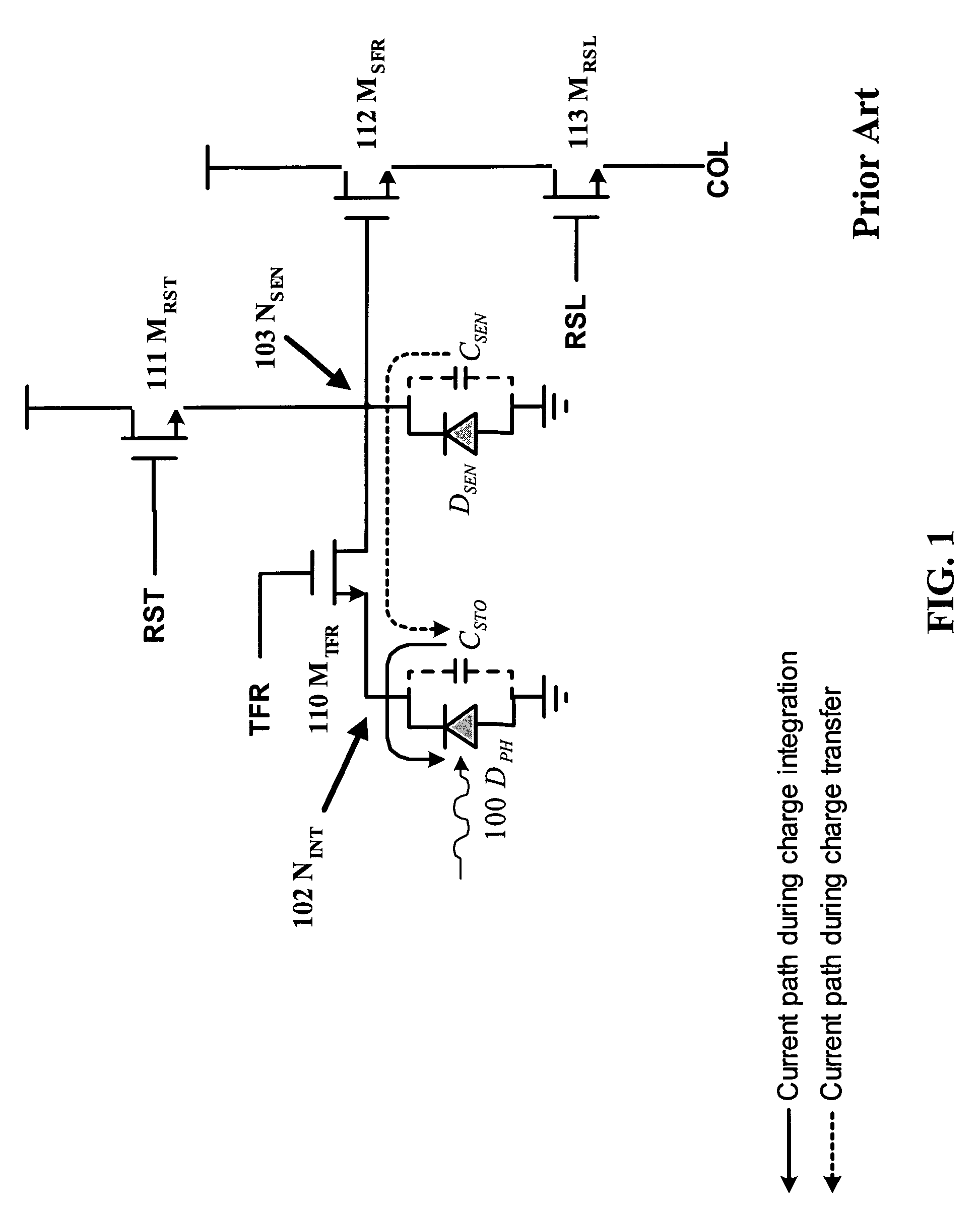

Low-noise active-pixel sensor for imaging arrays with high speed row reset

InactiveUS6532040B1Reduce noiseEasy to manufactureTelevision system detailsTelevision system scanning detailsCMOS sensorLow noise

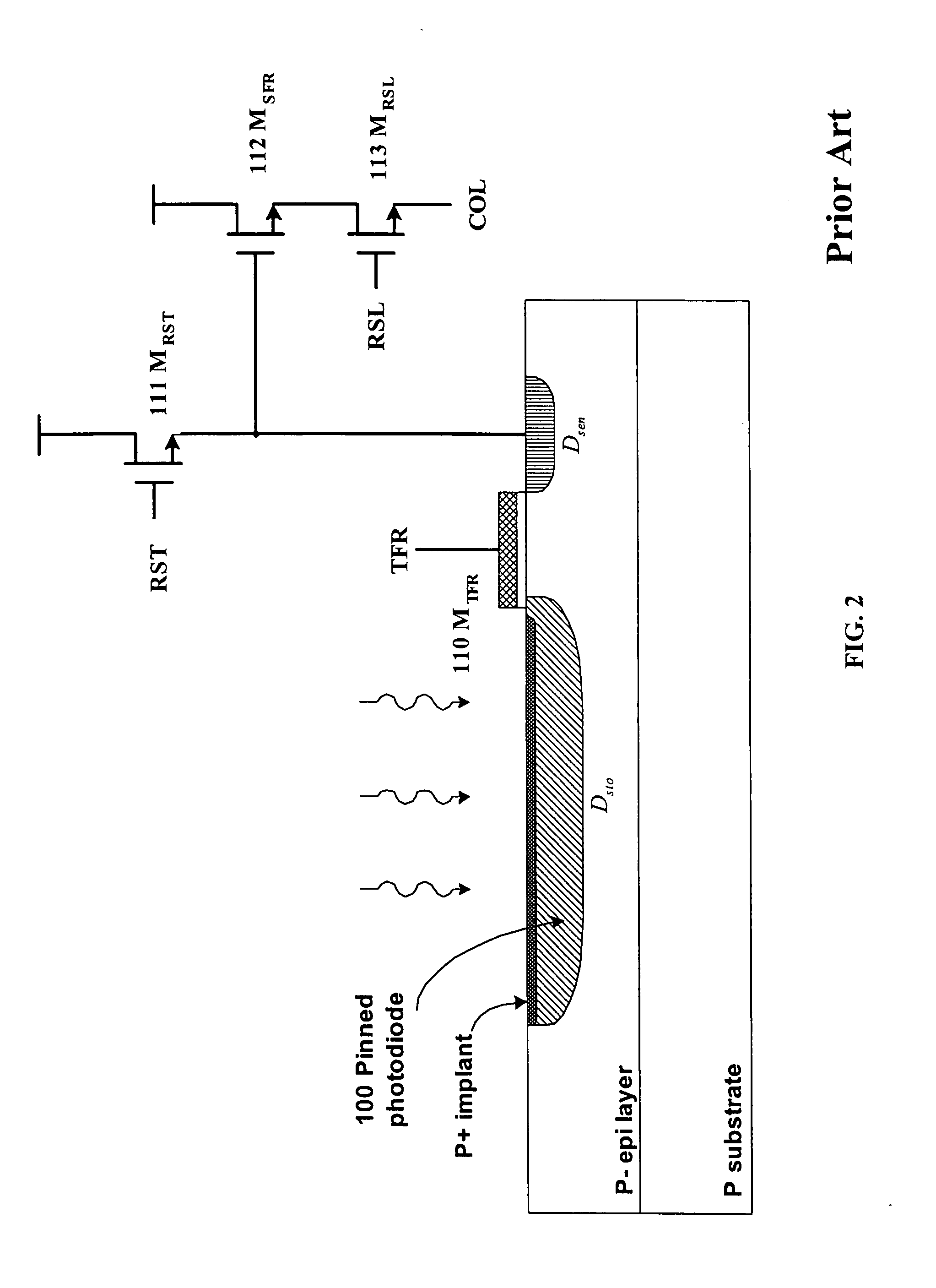

An imager pixel including a photodetector, a first MOS transistor functioning as the driver of a source follower amplifier during signal readout, a second MOS transistor serving as a pixel readout transistor, a third MOS transistor serving as a photodetector reset transistor, and a reset noise cancellation circuit including a fourth MOS transistor, first and second capacitances, and an amplifier having a gain which is the inverse of the ratio of the first to the second capacitance.

Owner:RE SECURED NETWORKS LLC +2

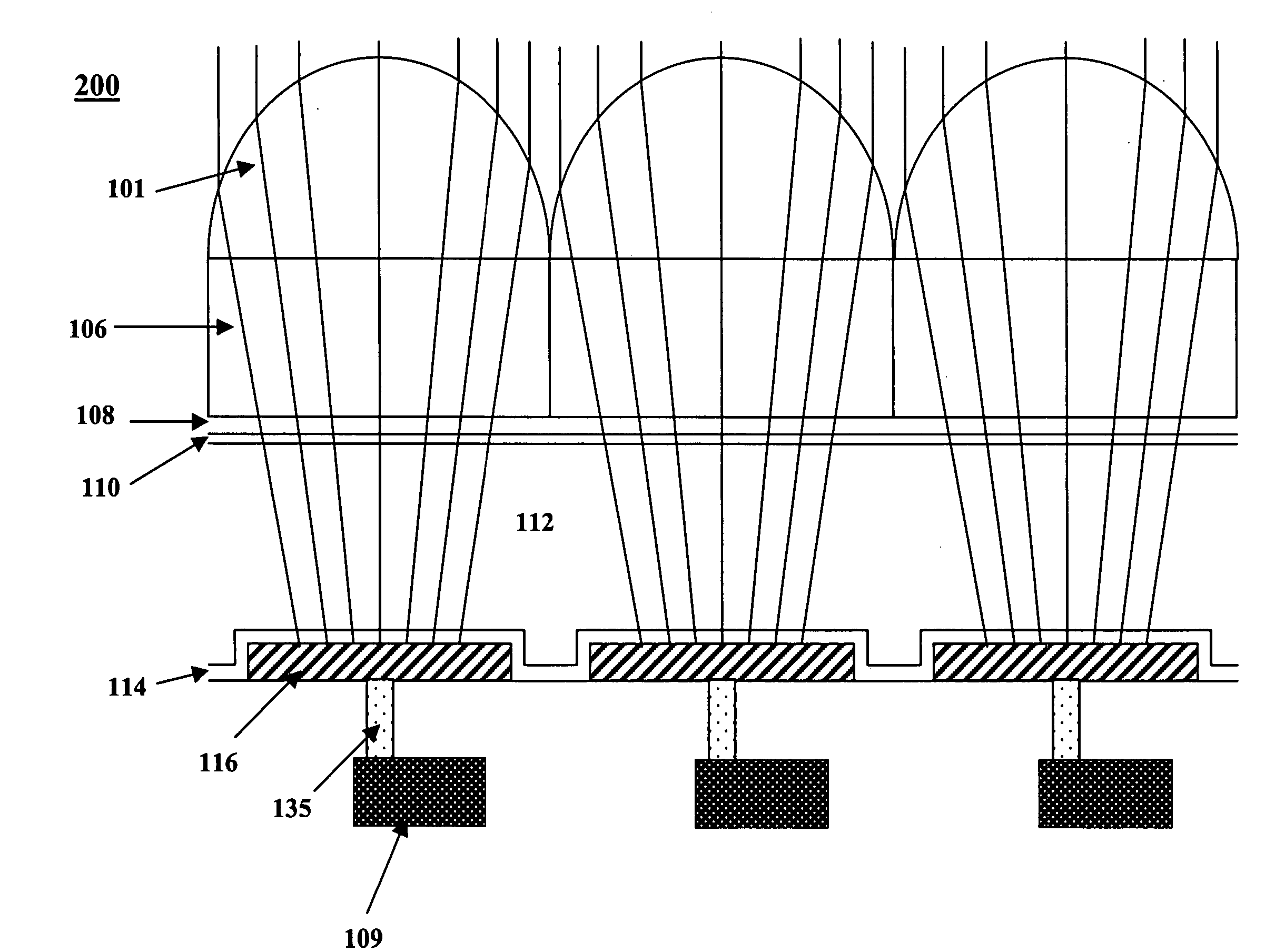

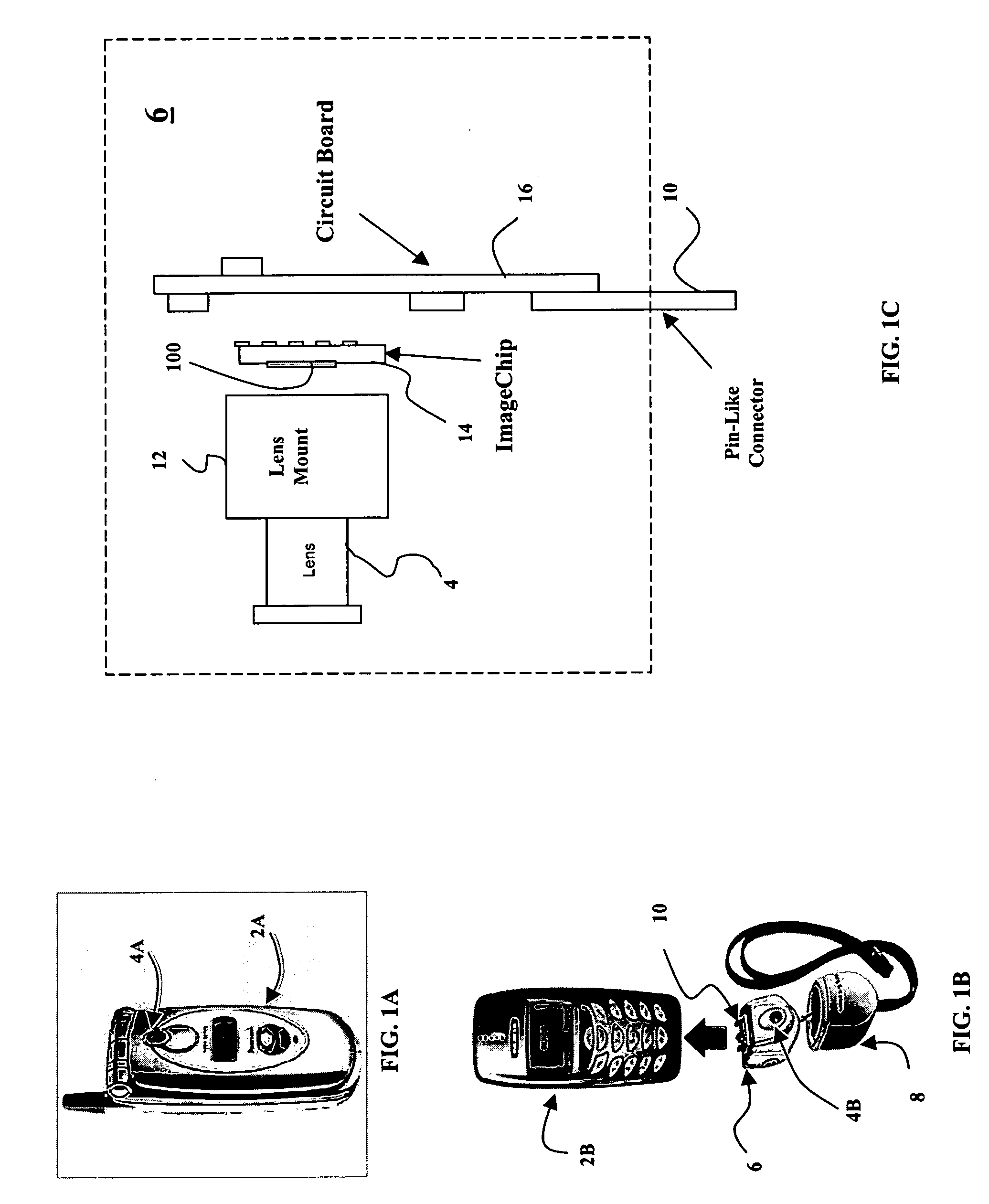

MOS or CMOS sensor with micro-lens array

InactiveUS20060249765A1Small pixelsMinimize and eliminate pixel to pixel crosstalkSolid-state devicesRadiation controlled devicesCMOS sensorHigh-definition television

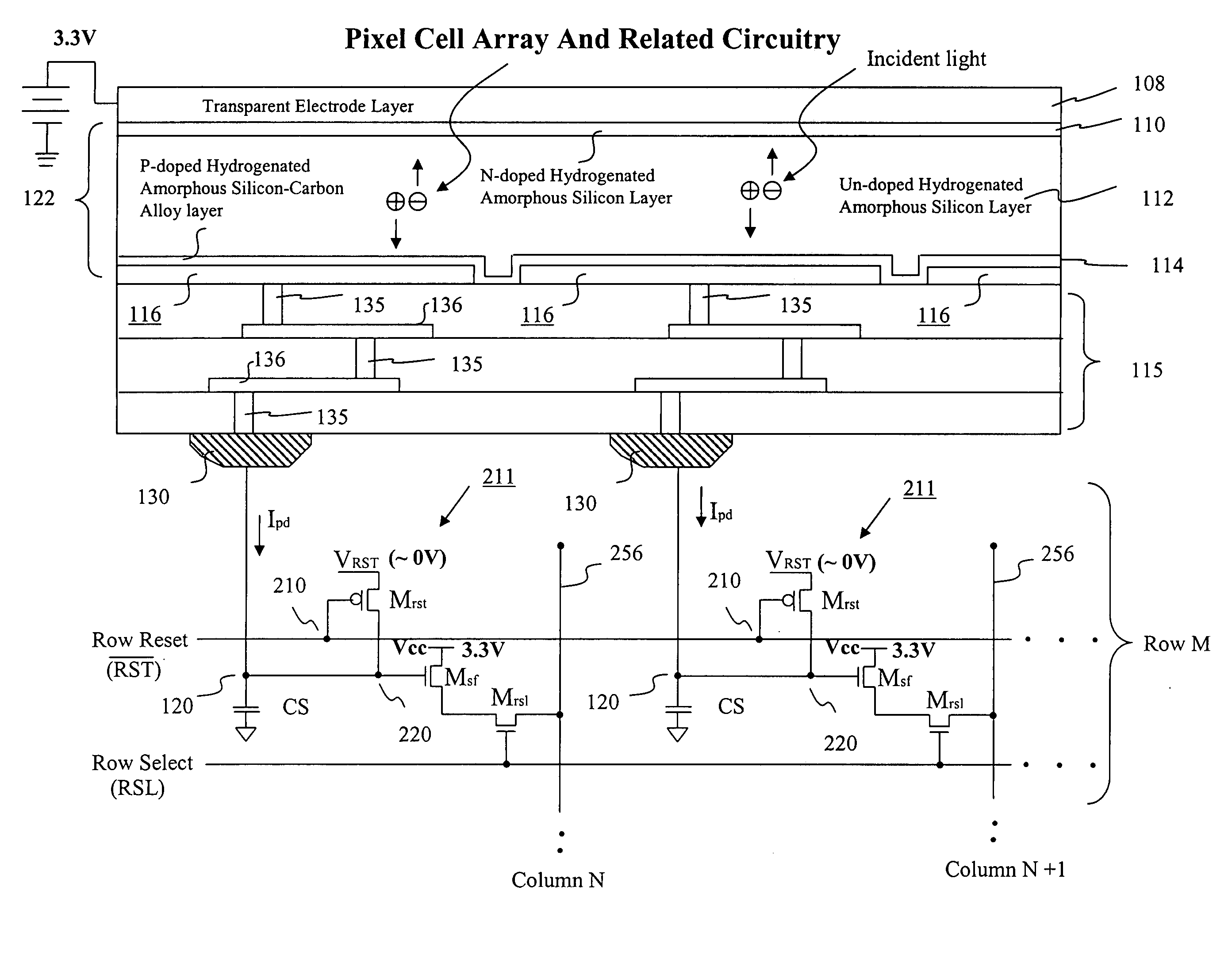

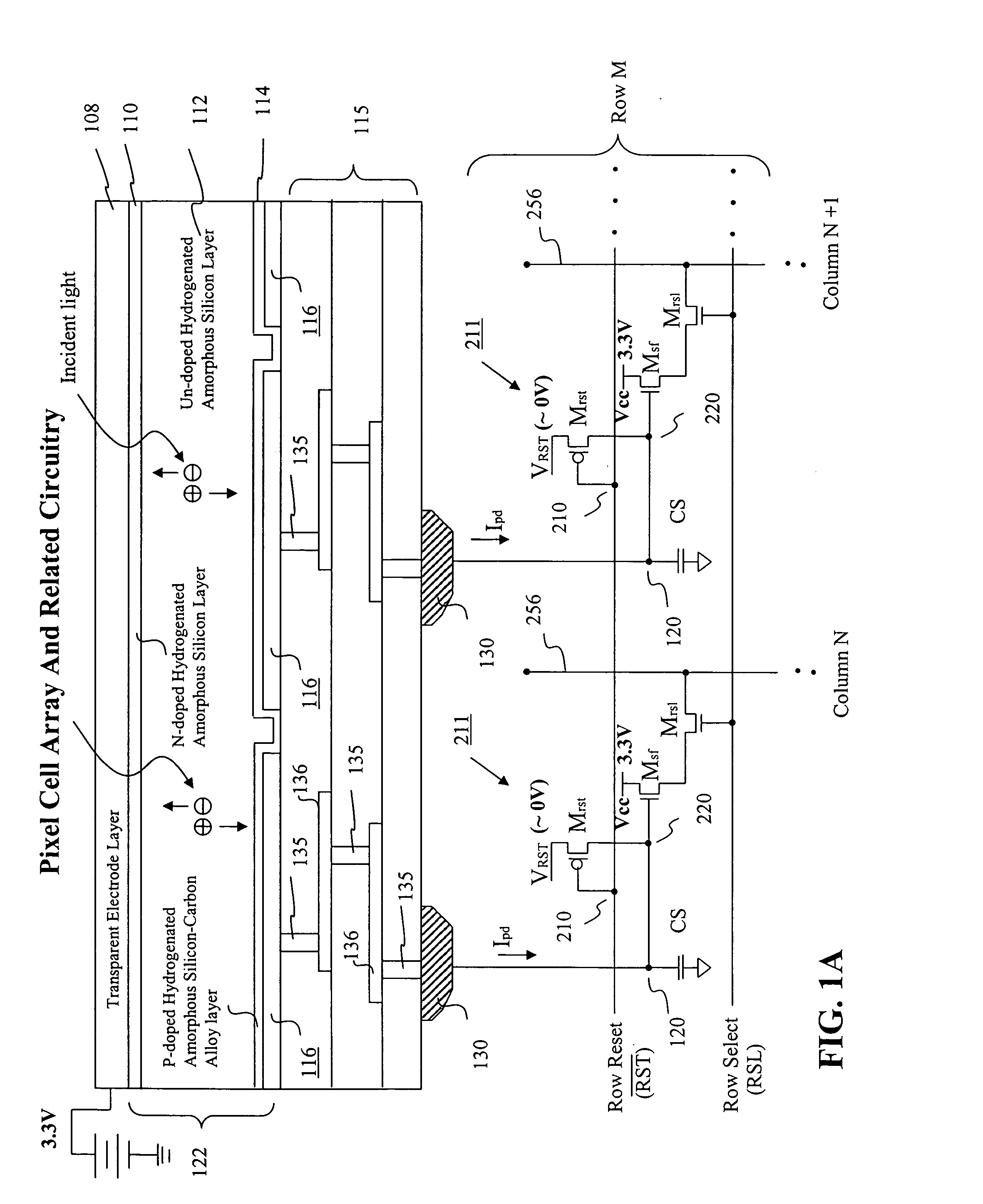

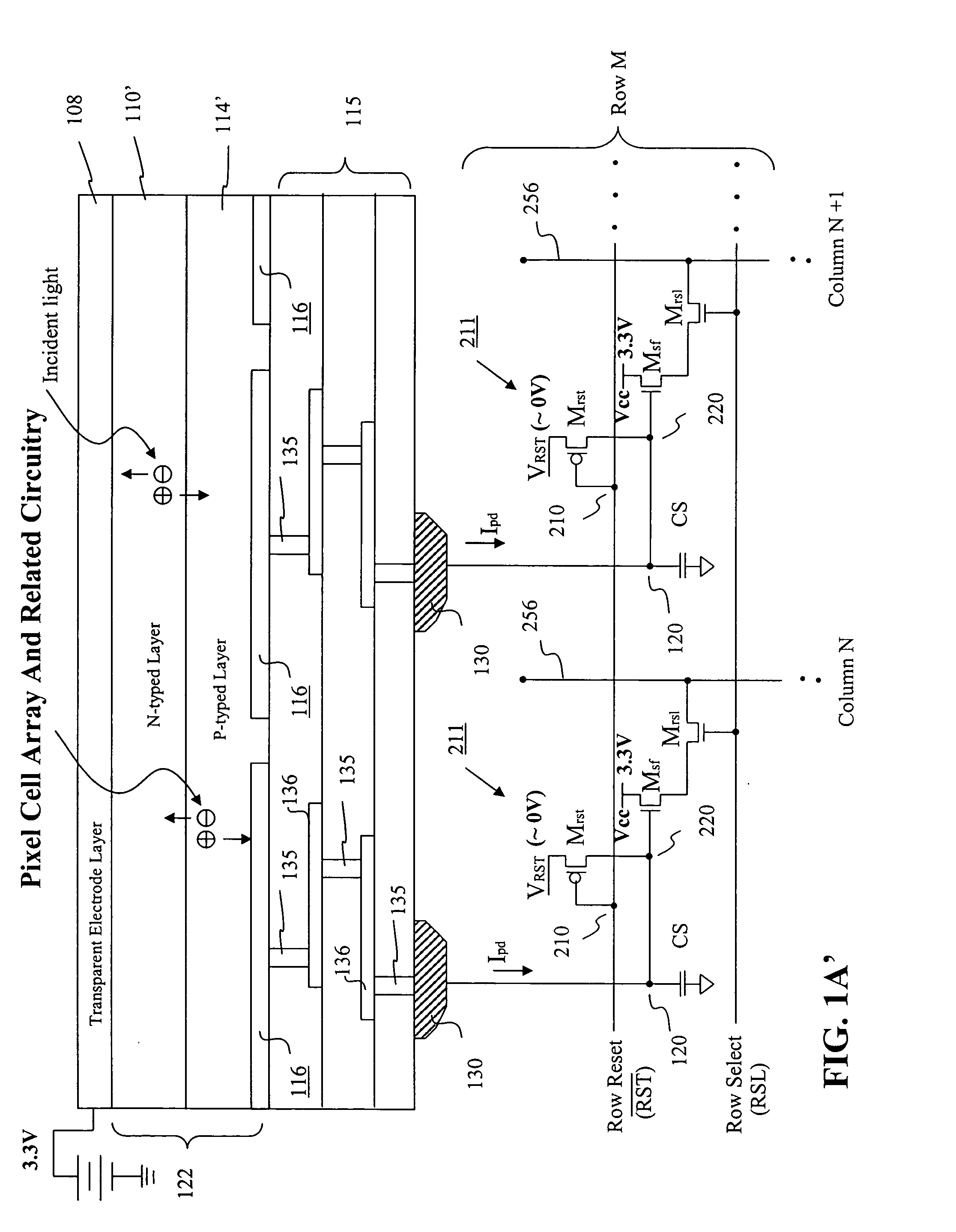

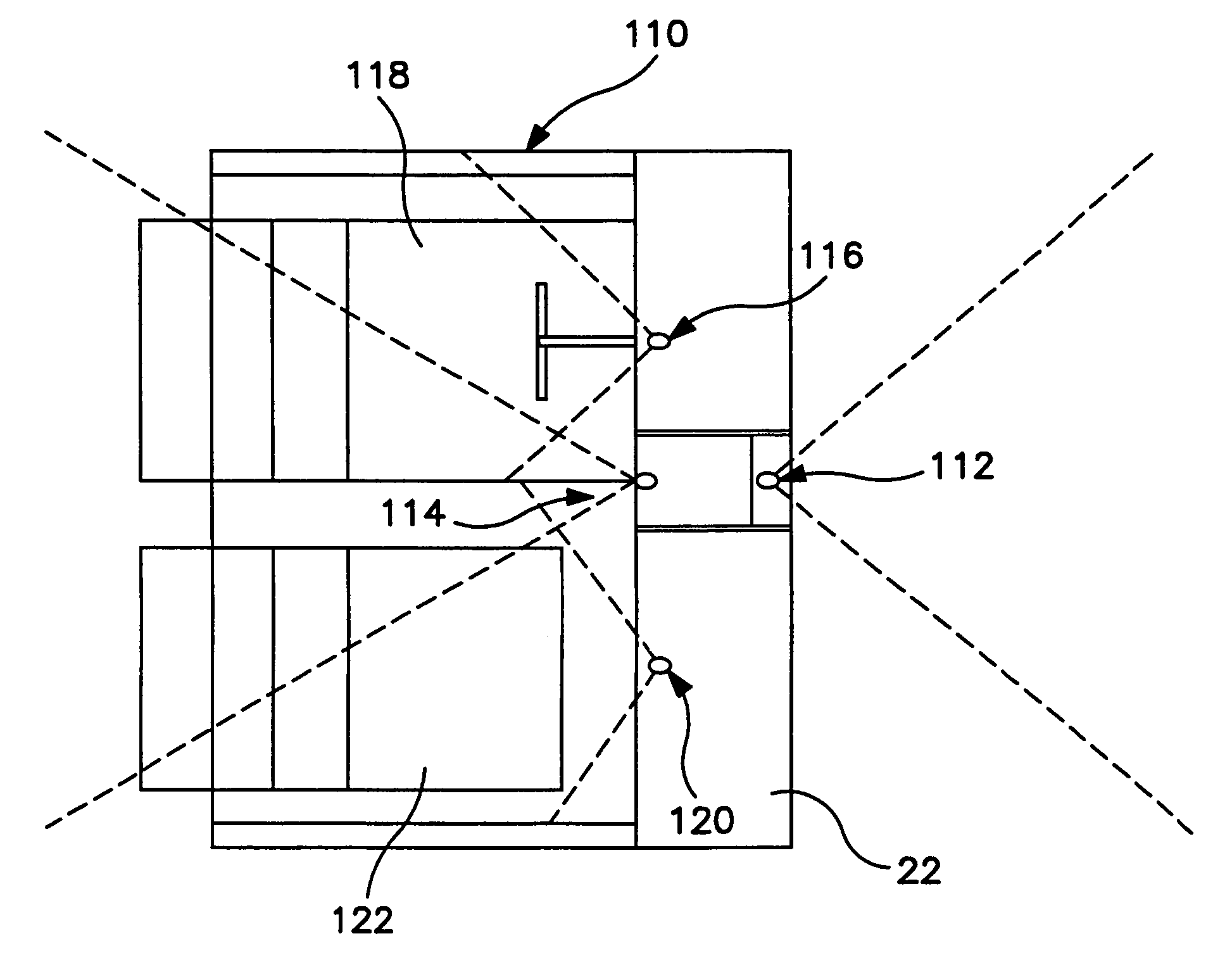

A MOS or CMOS sensor with a multi-layer photodiode layer covering an array of active pixel circuits. The multi-layer photodiode layer of each pixel is fabricated as continuous layers of charge generating material on top of the MOS and / or CMOS pixel circuits so that extremely small pixels are possible with almost 100 percent packing factors. The sensor includes special features to minimize or eliminate pixel to pixel crosstalk. A micro-lens array with a micro-lens positioned above each pixel directs light illuminating the pixel toward the central portion of the pixel and away from its edges. Also, preferably carbon is added to doped amorphous silicon N or P bottom layer of the multi-layer photodiode layer to increase the electrical resistivity in the bottom layer to further discourage crosstalk. In preferred embodiments each of the pixels define a tiny surface area equal to or larger than about 3.24 square microns and smaller than or equal to about 25 square microns. Detailed descriptions are provided for two general types of sensors. The first type has a pixel count of about 0.3 to 1.9 million pixels and are especially suited for sues such as cell phone cameras. The second type with pixel count of between about 1.9 million pixels to more than 5 million pixels is especially suited for high definition television cameras.

Owner:E PHOCUS

Active pixel sensor with bootstrap amplification and reduced leakage during readout

InactiveUS6410899B1Television system detailsTelevision system scanning detailsCMOS sensorEngineering

An integrated active pixel sensor array comprises a plurality of row select lines, each of said row select lines coupled to a source of a row-select signal; a plurality of source-follower drain row lines, each of said source-follower drain row lines coupled to a source of a source-follower drain row signal; a plurality of column output lines; a reset line coupled to a source of a reset signal; a source of reset potential; and a plurality of active pixel sensors, each pixel sensor associated with one row and one column of the array and including a photodiode having a first terminal coupled to a first reference potential and a second terminal, a Reset transistor having a gate coupled to the reset line, a drain coupled to the reset potential to reverse bias the photodiode, and a source coupled to the second terminal of the photodiode, a Source-Follower transistor having a gate coupled to the second terminal of the photodiode, a drain connected to the one of the plurality of source-follower drain row lines with which its active pixel sensor is associated, and a source, a Row-select transistor having a gate coupled to the one of the plurality of row-select lines with which its active pixel sensor is associated, a drain coupled to the source of the Source-follower transistor, and a source coupled to the one of the plurality of column output lines with which its active pixel sensor is associated.

Owner:FOVEON

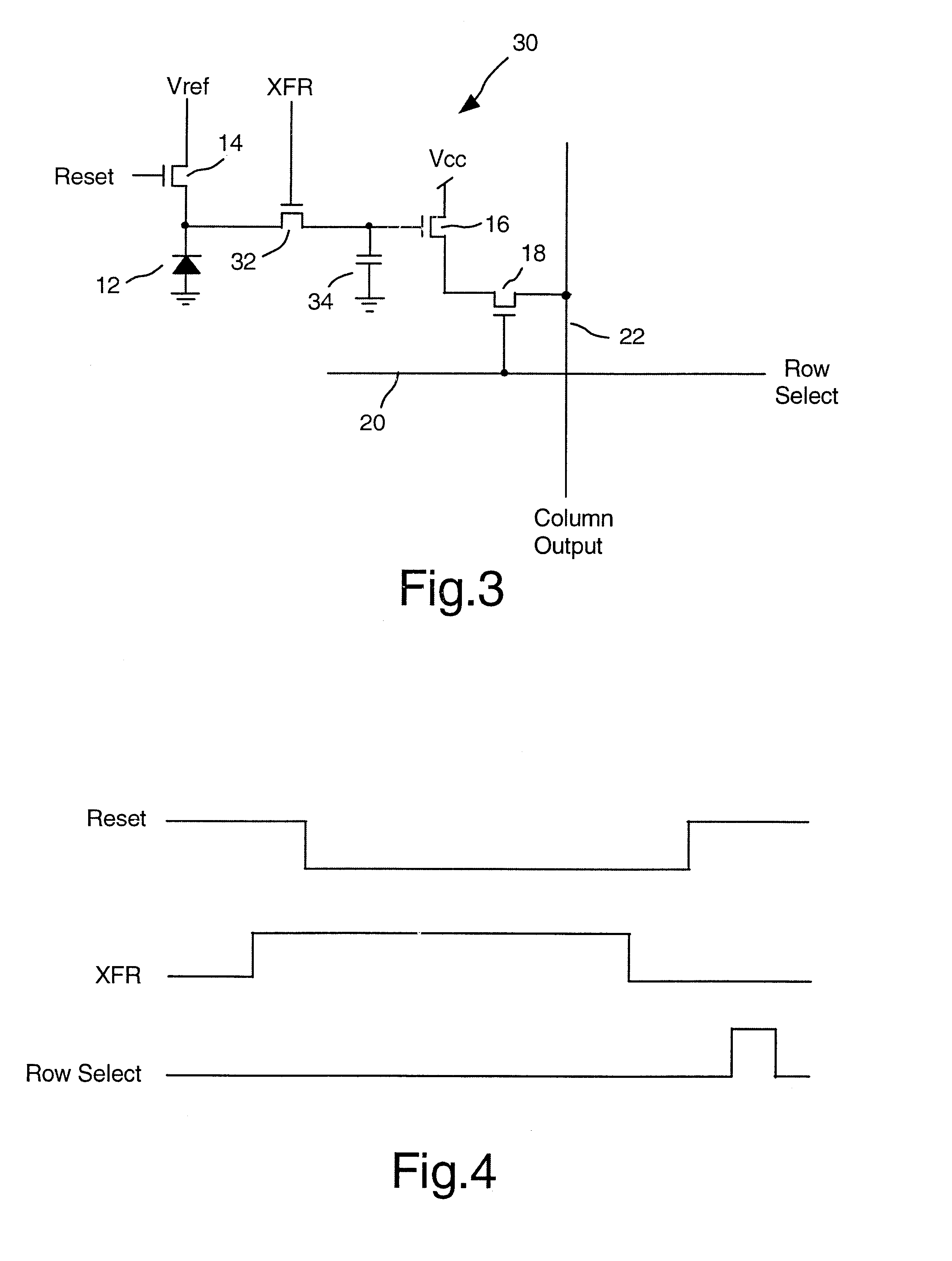

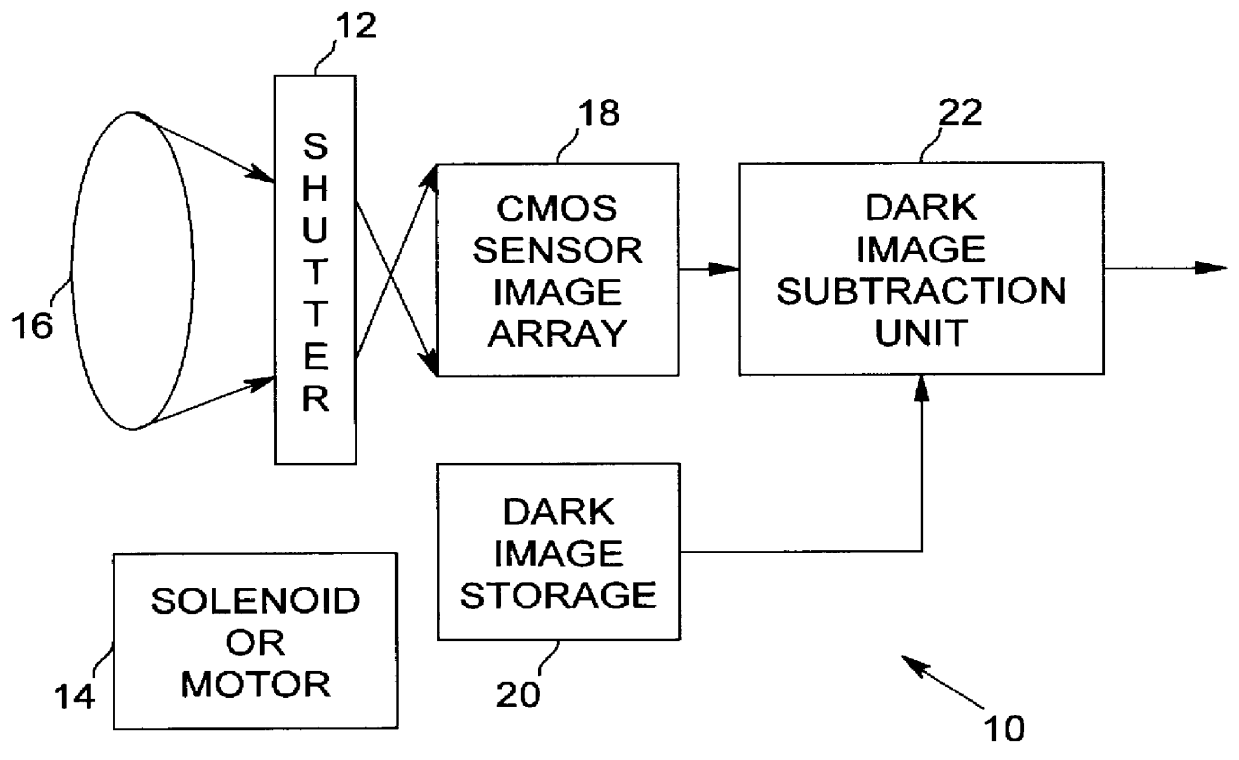

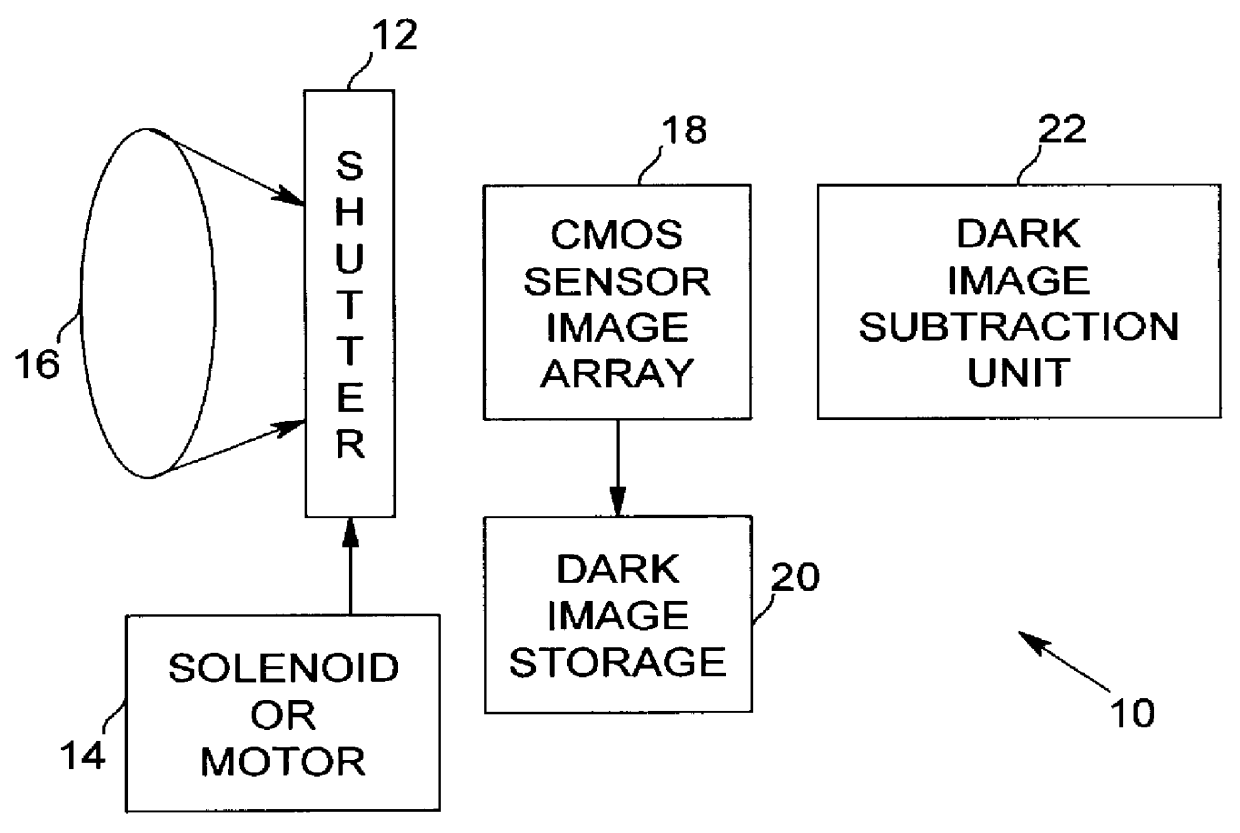

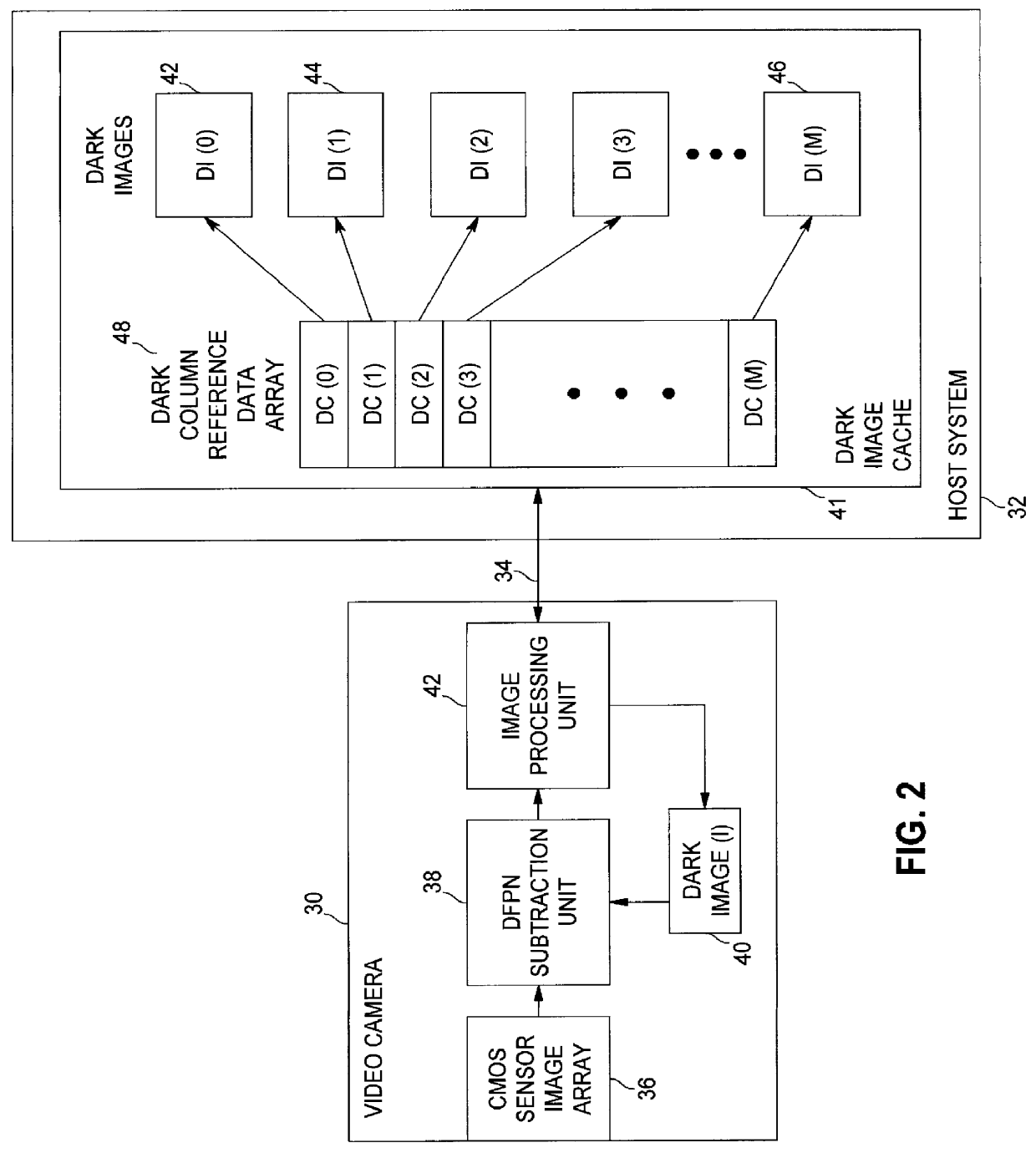

Method and apparatus for dark frame cancellation for CMOS sensor-based tethered video peripherals

Elimination of dark fixed pattern noise (DFPN) for tethered CMOS sensor-based digital video cameras is supported by supplying and maintaining a host-based dark image cache. Since the camera is tethered to a host computer system such as a PC, it takes advantage of the storage and processing capabilities of the host to manage the cache. By using a dark image cache for updating of the currently applicable dark image for DFPN cancellation processing, operation of the camera shutter for acquiring dark images is dramatically reduced, thereby using less system resources such as power, and increasing the MTBF of the electromechanical devices such as the camera shutter and associated controls. Dark images are obtained at different integration, gain, and temperature operating characteristics of the camera and stored in the cache. The cached dark images are referenced on the host according to a fixed, predetermined dark column of data in video frames generated by the CMOS sensor image array of the camera. The dark column data represents a portion of the CMOS sensor image array which is permanently and totally shadowed for use during DFPN cancellation processing.

Owner:INTEL CORP

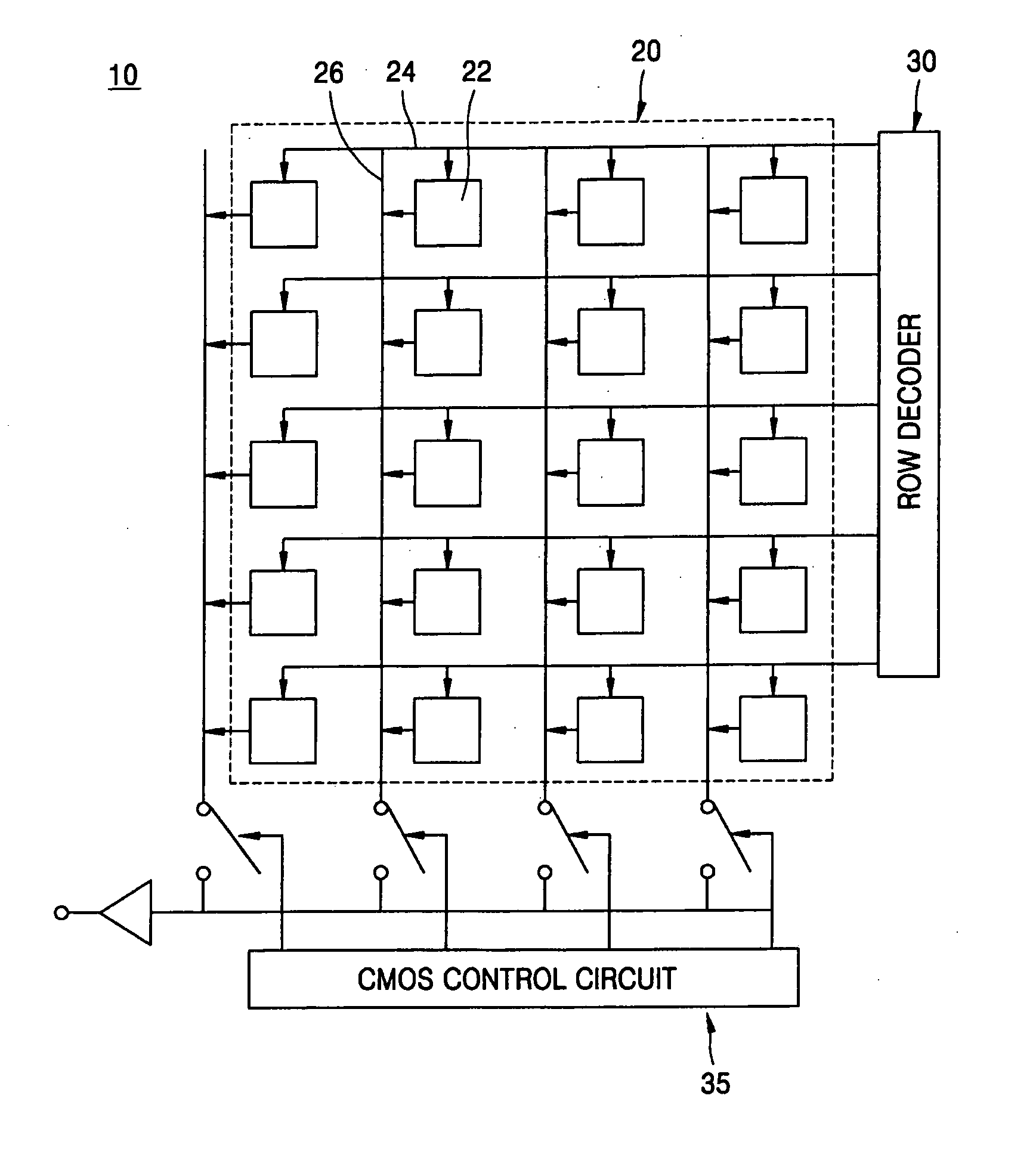

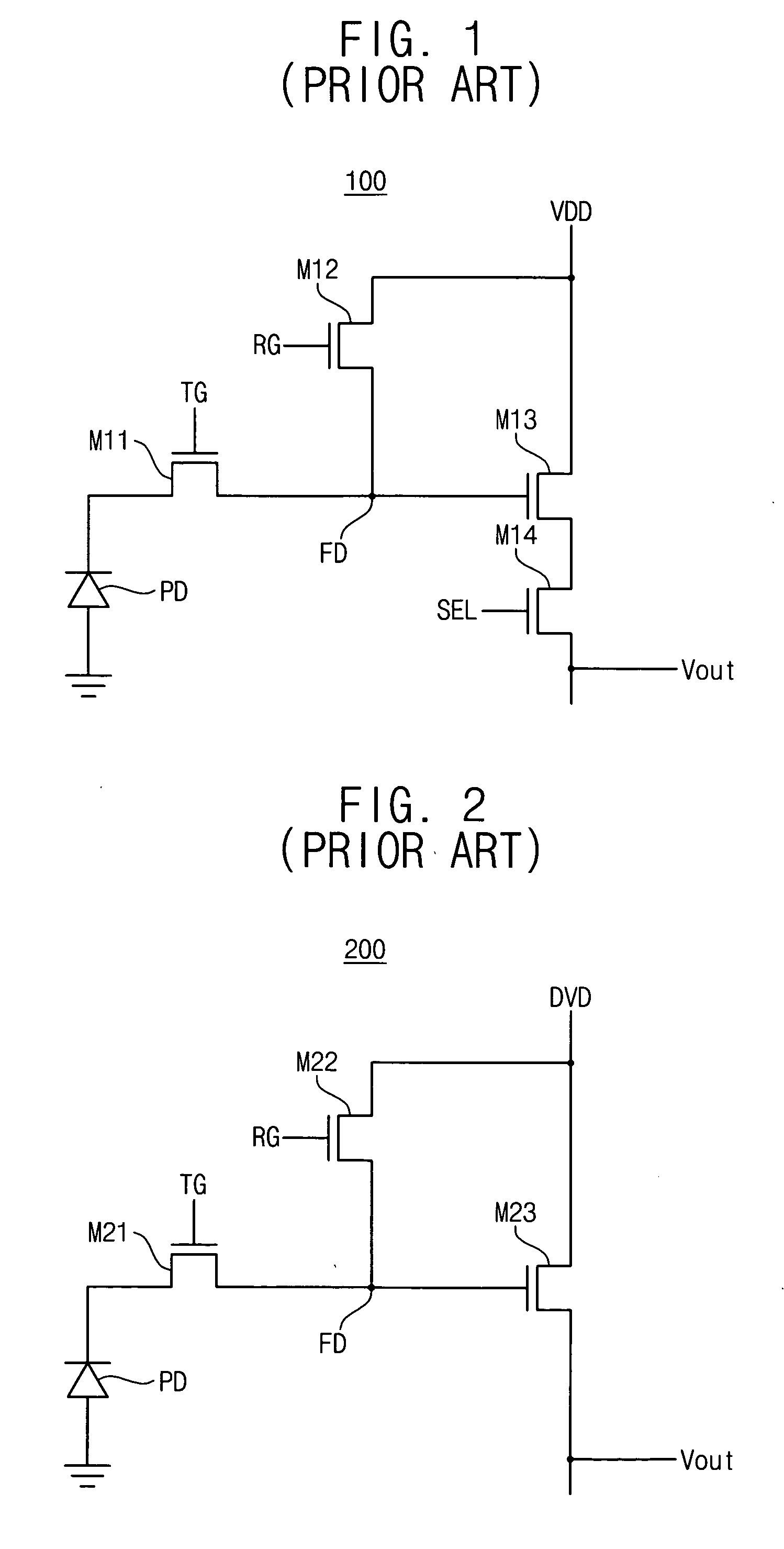

CMOS sensor array with a shared structure

Owner:SAMSUNG ELECTRONICS CO LTD

Image capturing system

ActiveUS20060028558A1Privacy protectionPrevent unauthorized image capturingTelevision system detailsColor television detailsCMOS sensorImage capture

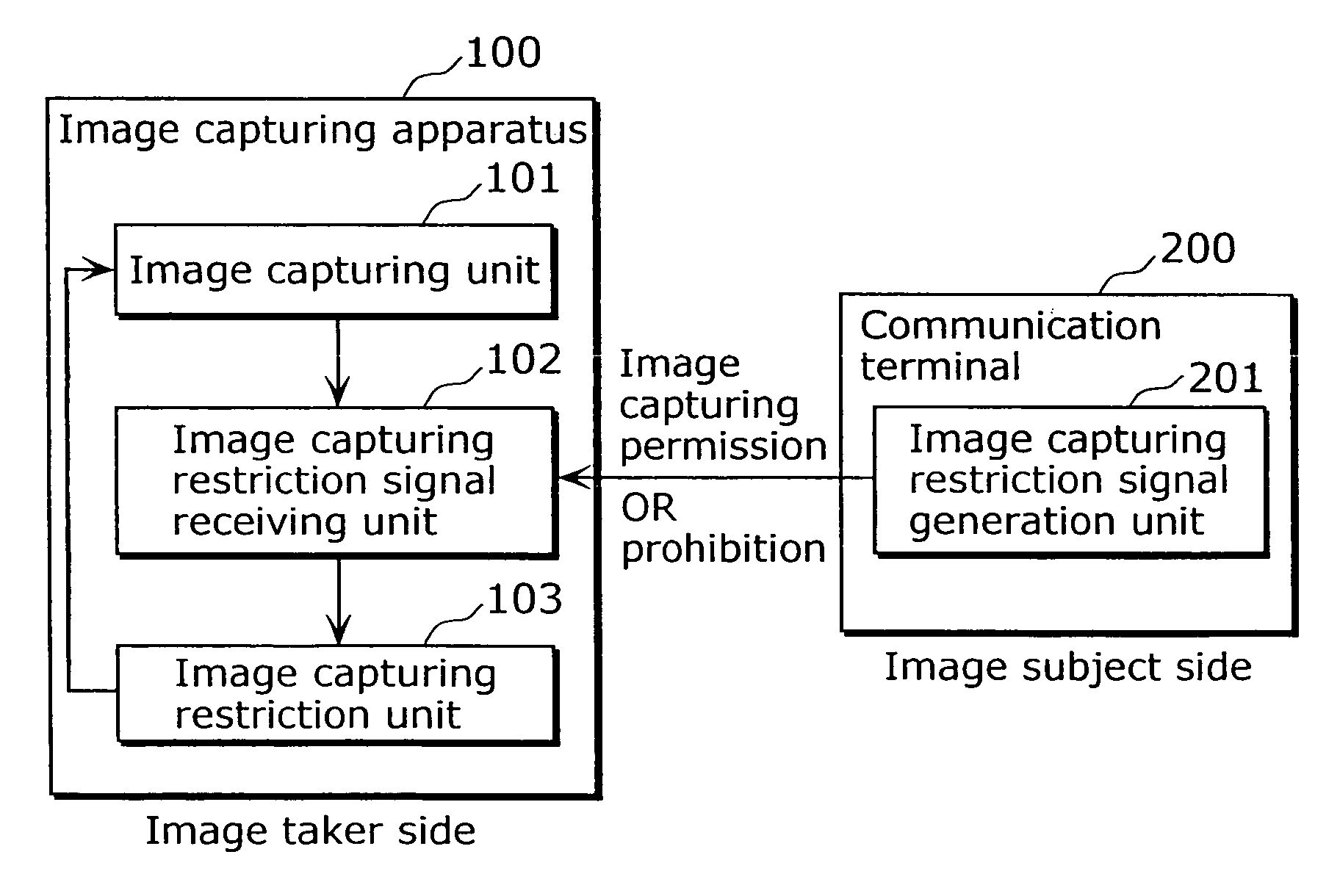

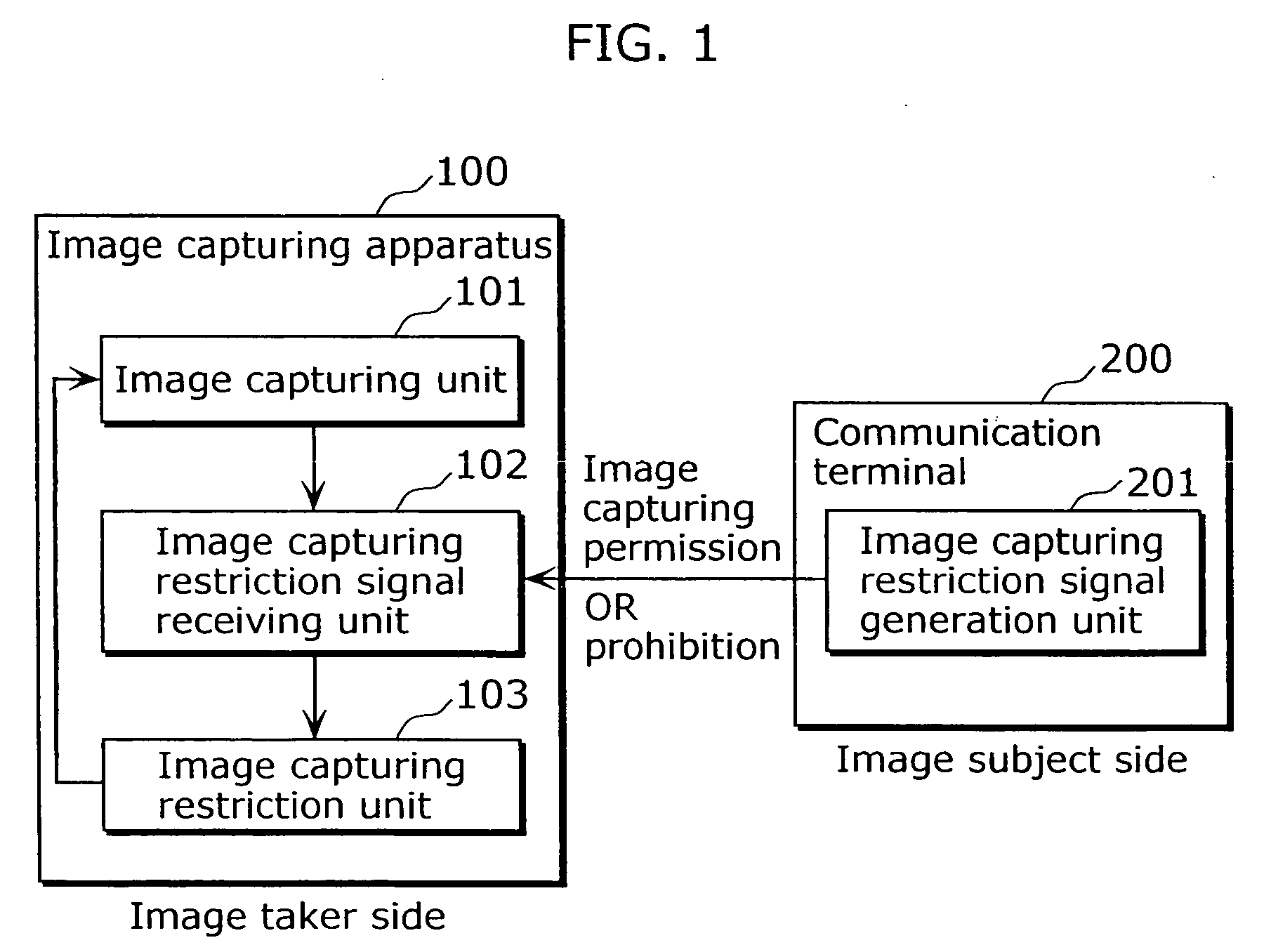

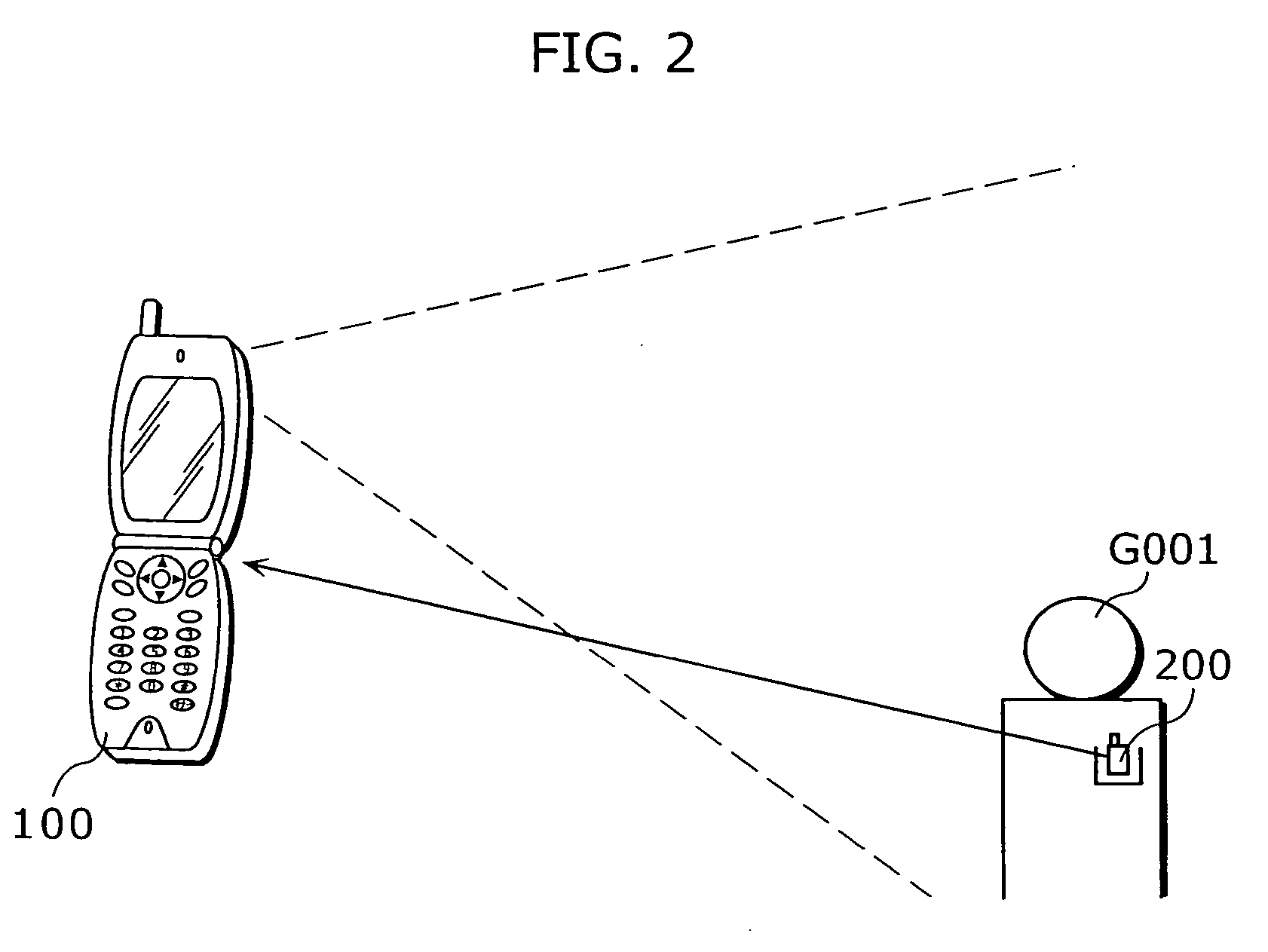

An image capturing apparatus (100) of an image taker side has an image capturing unit (101) which captures an image using a CCD sensor, a CMOS sensor and the like, an image capturing restriction signal receiving unit (102) which receives an image capturing restriction signal transmitted by a communication terminal (200), and an image capturing restriction unit (103) which restricts the image capturing performed by the image capturing unit (101) according to a request of the image capturing restriction signal. Further, the communication terminal (200) of a subject side has an image capturing restriction signal generation unit (201) which transmits the image capturing restriction signal for requesting to restrict the image capturing.

Owner:PANASONIC CORP

Low-resistivity photon-transparent window attached to photo-sensitive silicon detector

InactiveUS6025585ALow resistivityHigh resistivitySolid-state devicesMaterial analysis by optical meansCMOS sensorX-ray

The invention comprises a combination of a low resistivity, or electrically conducting, silicon layer that is transparent to long or short wavelength photons and is attached to the backside of a photon-sensitive layer of silicon, such as a silicon wafer or chip. The window is applied to photon sensitive silicon devices such as photodiodes, charge-coupled devices, active pixel sensors, low-energy x-ray sensors and other radiation detectors. The silicon window is applied to the back side of a photosensitive silicon wafer or chip so that photons can illuminate the device from the backside without interference from the circuit printed on the frontside. A voltage sufficient to fully deplete the high-resistivity photosensitive silicon volume of charge carriers is applied between the low-resistivity back window and the front, patterned, side of the device. This allows photon-induced charge created at the backside to reach the front side of the device and to be processed by any circuitry attached to the front side. Using the inventive combination, the photon sensitive silicon layer does not need to be thinned beyond standard fabrication methods in order to achieve full charge-depletion in the silicon volume. In one embodiment, the inventive backside window is applied to high resistivity silicon to allow backside illumination while maintaining charge isolation in CCD pixels.

Owner:RGT UNIV OF CALIFORNIA

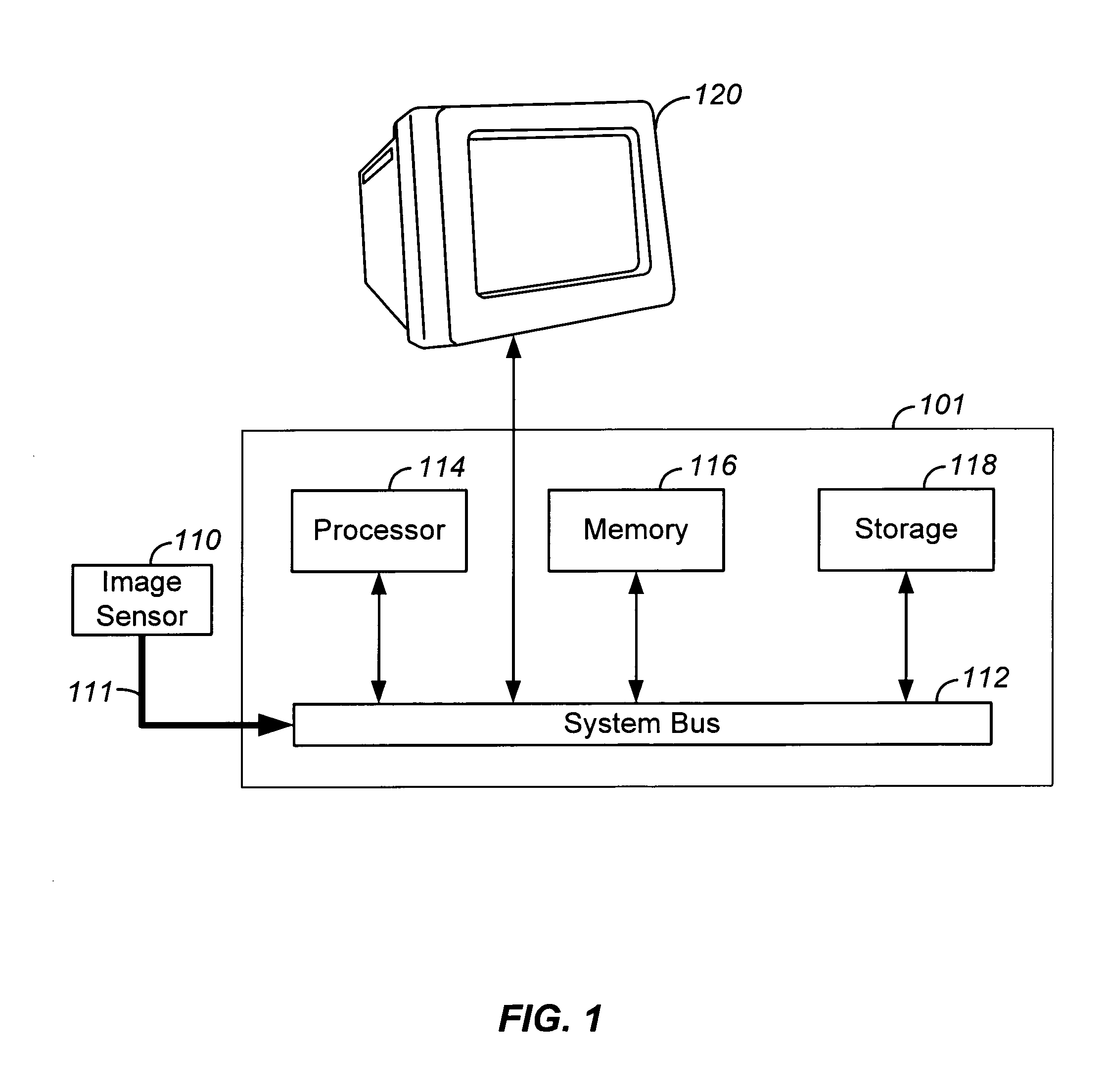

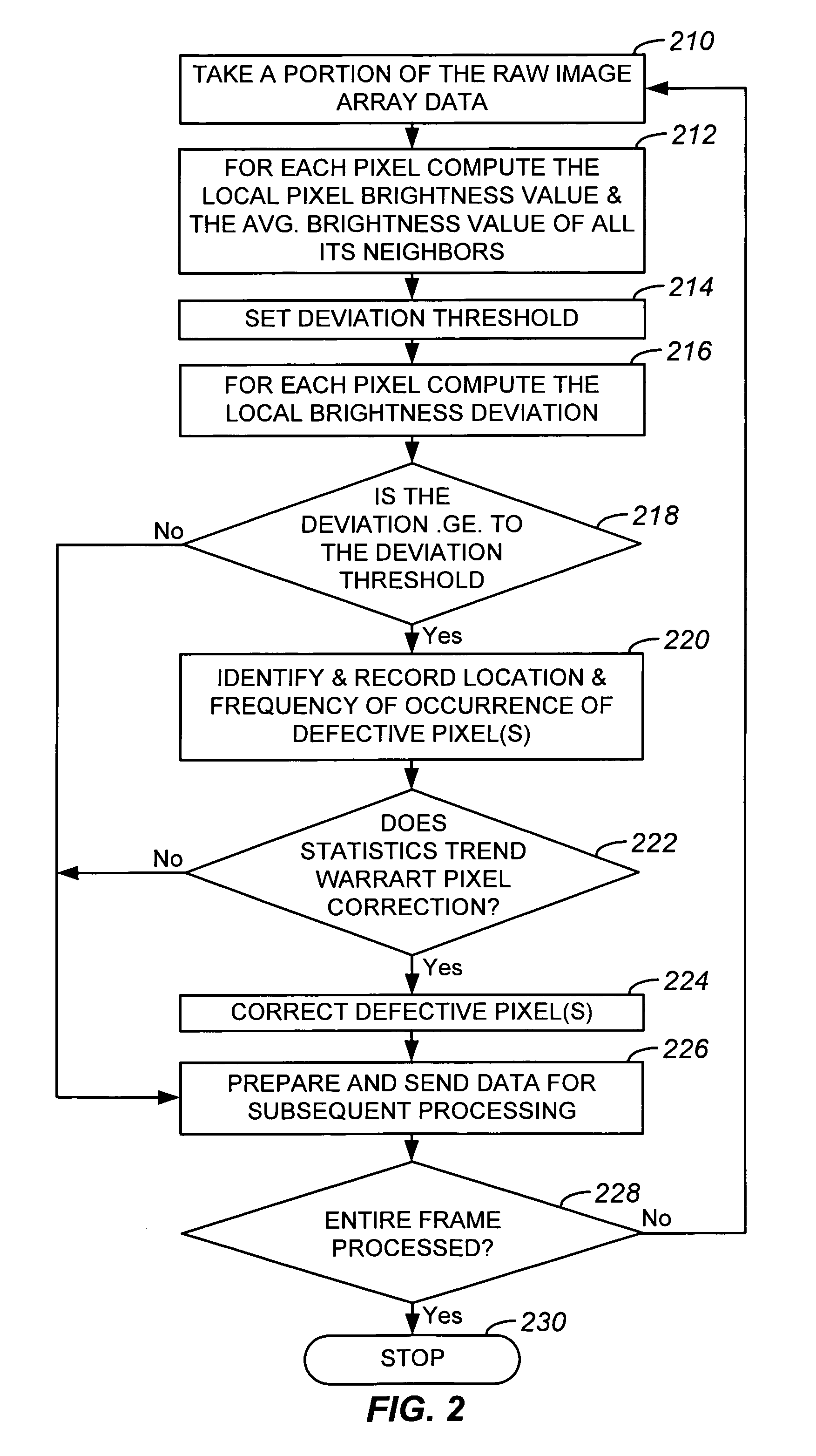

Dynamic anomalous pixel detection and correction

InactiveUS7009644B1Minimally affectedImpact rateTelevision system detailsColor signal processing circuitsPattern recognitionCMOS sensor

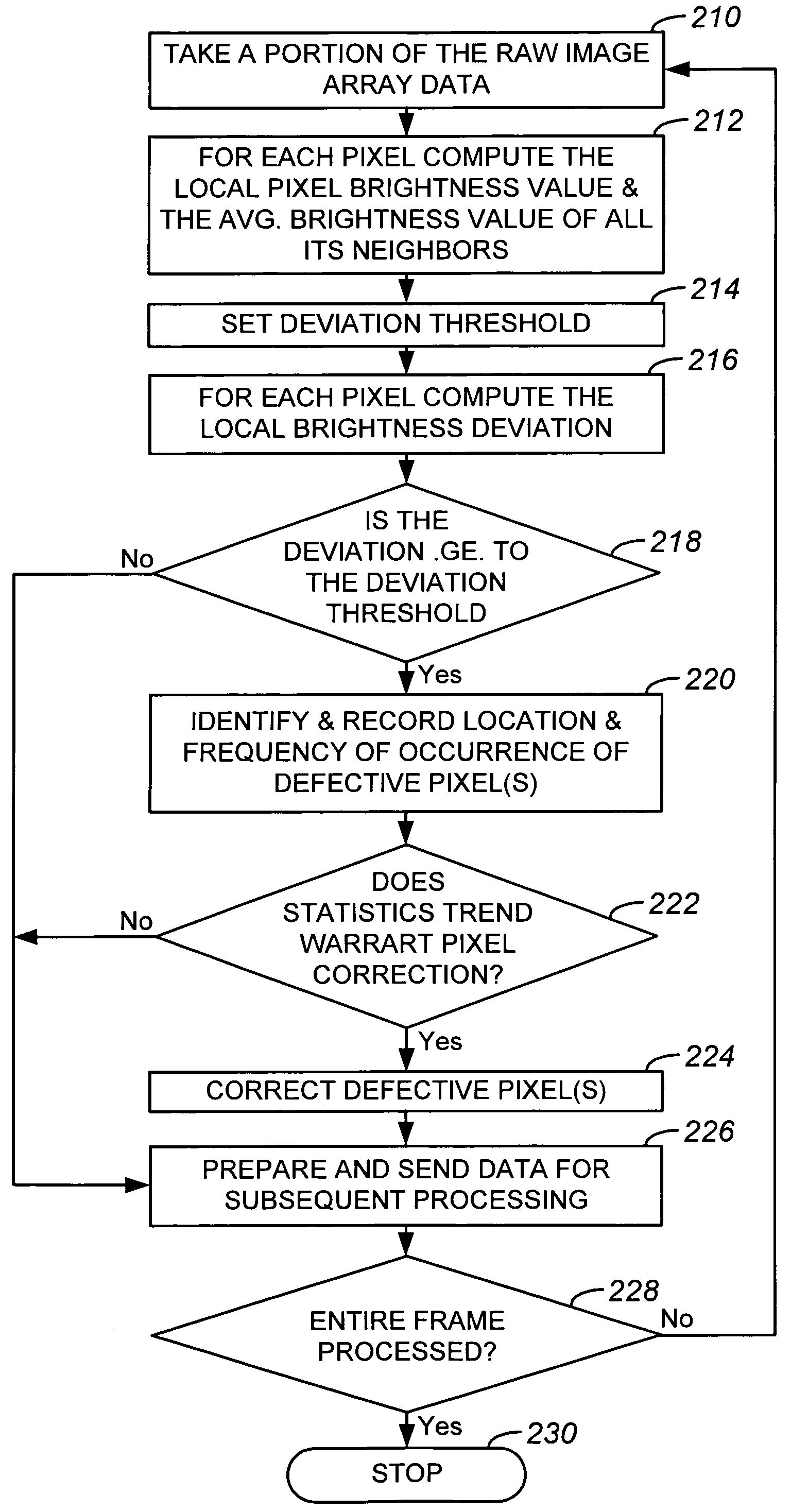

A method and a system for dynamically detecting and correcting anomalous pixels in the raw data taken from an image sensor array such as a CCD or a CMOS sensor array, thus allowing the use of dumb cameras to capture digital images for subsequent use by an intelligent host—such as being displayed on a computer monitor. This invention uses software algorithms running on an intelligent host processor to dynamically correct the anomalous pixels in the raw data taken from an image sensor array typical of those in a digital still or a video camera. Using the combination of a dumb camera which provides raw data to an intelligent host, which does all the subsequent image processing, the system works by scanning an image frame for pixels that vary more than a specified amount in their brightness value from their neighboring pixels and designating those as defective pixels. The location and frequency of the photosites sending the defective pixels are stored in a statistical database in the computer's memory. The brightness value of a defective pixel is then replaced by a local brightness value obtained from the defective pixel's neighboring pixels. The process includes video subsampling, meaning that the defective pixel detection is carried out and repeated at a pre-specified frame rate to ensure optimum detection and correction at a minimal level of scanning. A statistical database is kept so that truly anomalous pixels can over time be distinguished from false detection of true anomalies in the target image, lighting or other environmentally induced anomalies.

Owner:LOGITECH EURO SA

Method and apparatus providing dark current reduction in an active pixel sensor

An imager has one or more pixel circuits arranged to receive negatively biased control signals at one or more gates associated with charge holding regions to reduce dark current generation and flow.

Owner:MICRON TECH INC

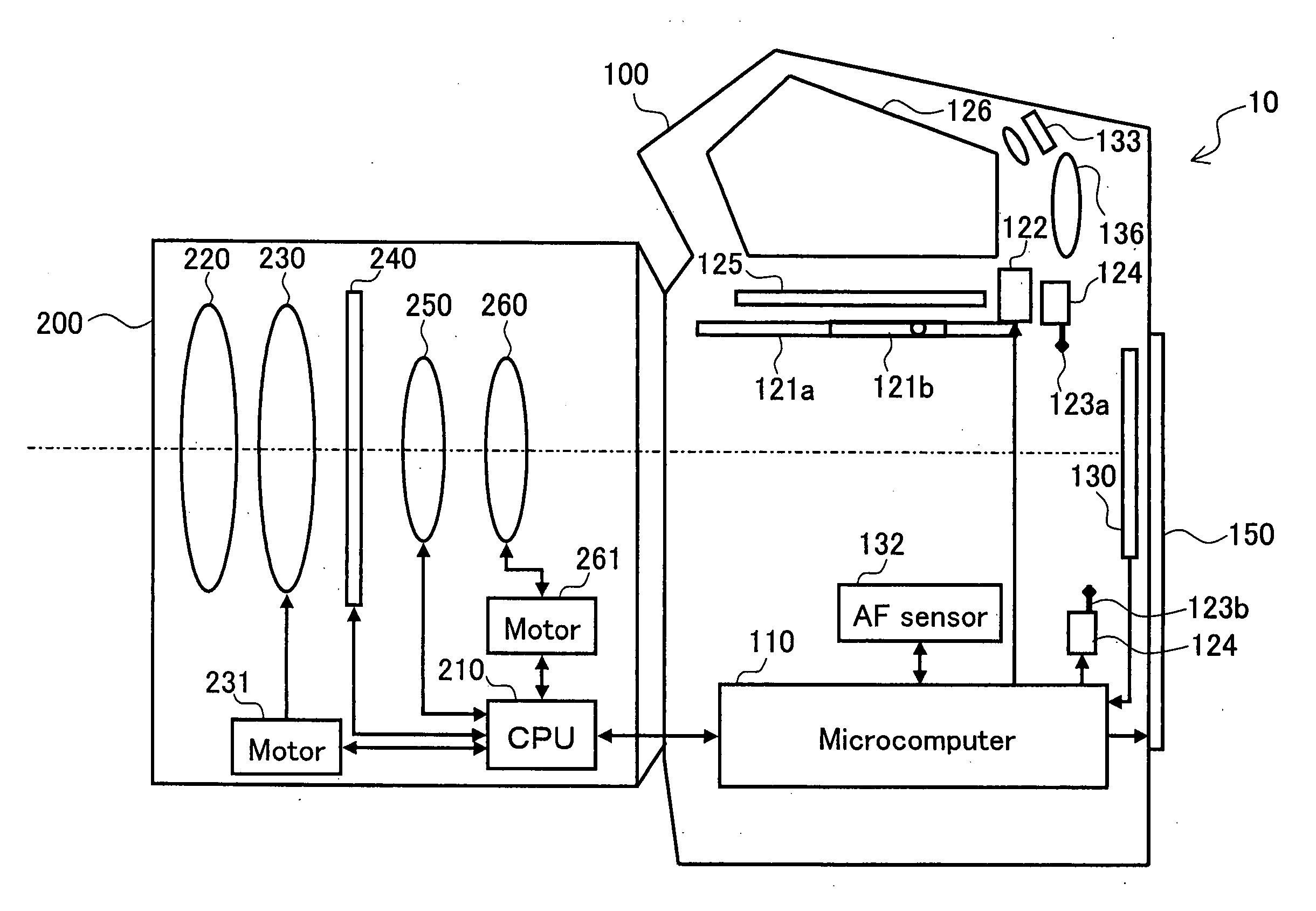

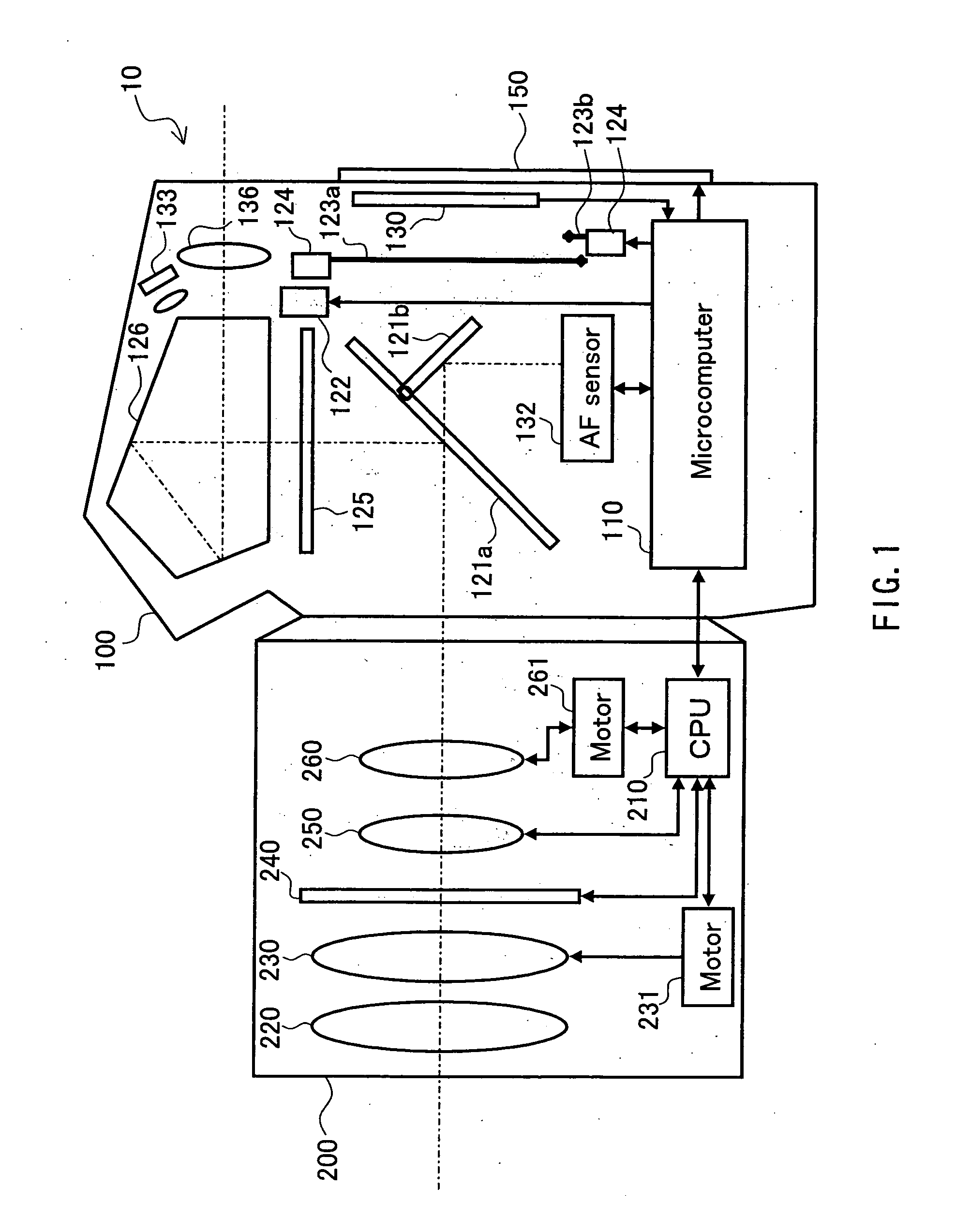

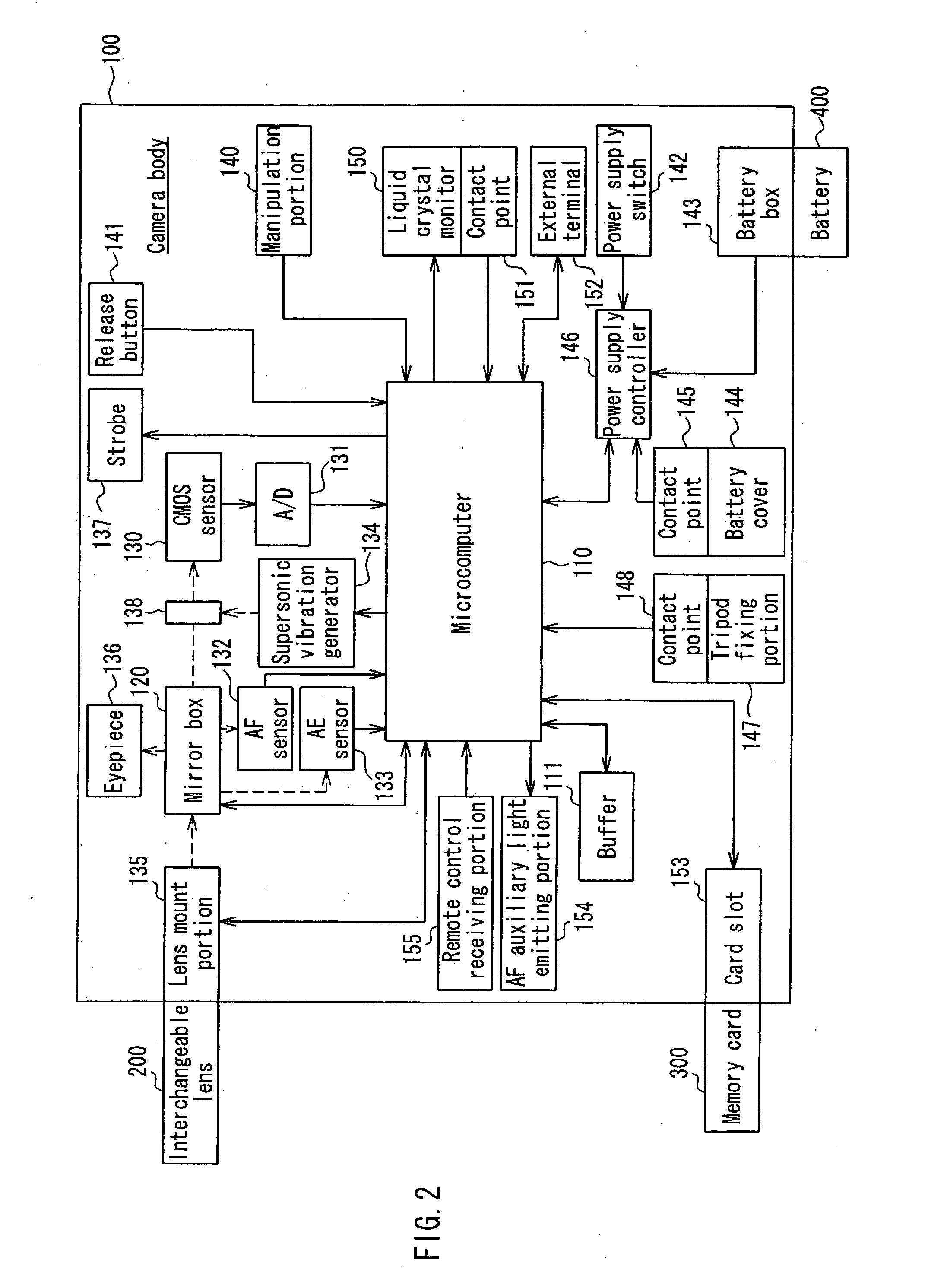

Digital camera

ActiveUS20070153112A1Easy to operateTelevision system detailsColor television detailsCMOS sensorMicrocomputer

A digital camera of the present invention includes a microcomputer 110 having a live view mode controlling so that image data generated by a CMOS sensor 130 or image data obtained by subjecting the image data generated by the CMOS sensor 130 to predetermined processing is displayed on a liquid crystal monitor 150 as a moving image in real time, and the microcomputer 110 controls so that movable mirrors 121a and 121b to enter an optical path of an image pickup optical system after the amount of light from a subject is obtained based on the image data generated by the CMOS sensor 130, a strobe 137 emits light, and measurement results of an AE sensor 133 are obtained. Due to this configuration, in a digital camera that includes a movable mirror and is capable of displaying a subject image in a live view through an electronic viewfinder, the operability thereof can be enhanced.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

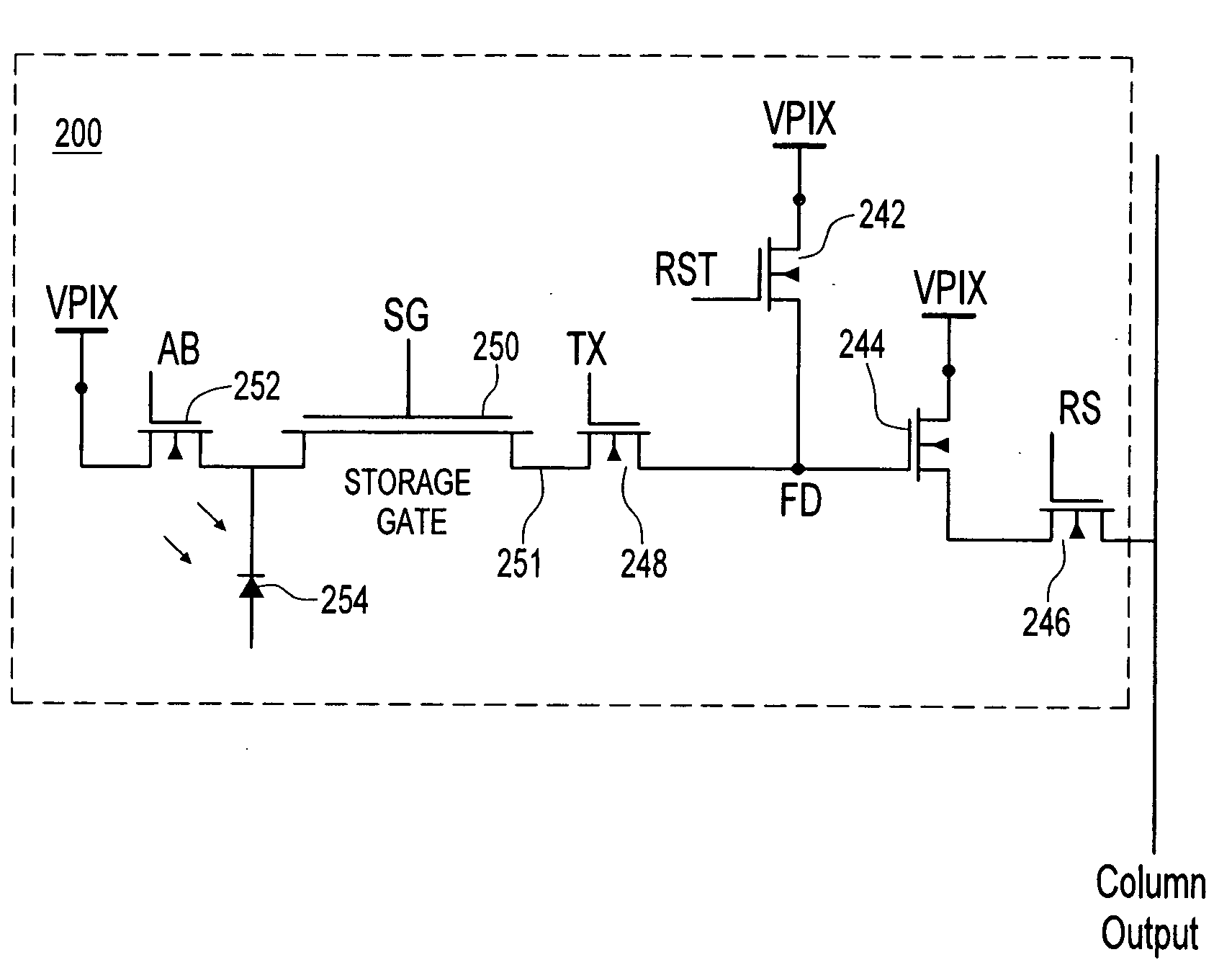

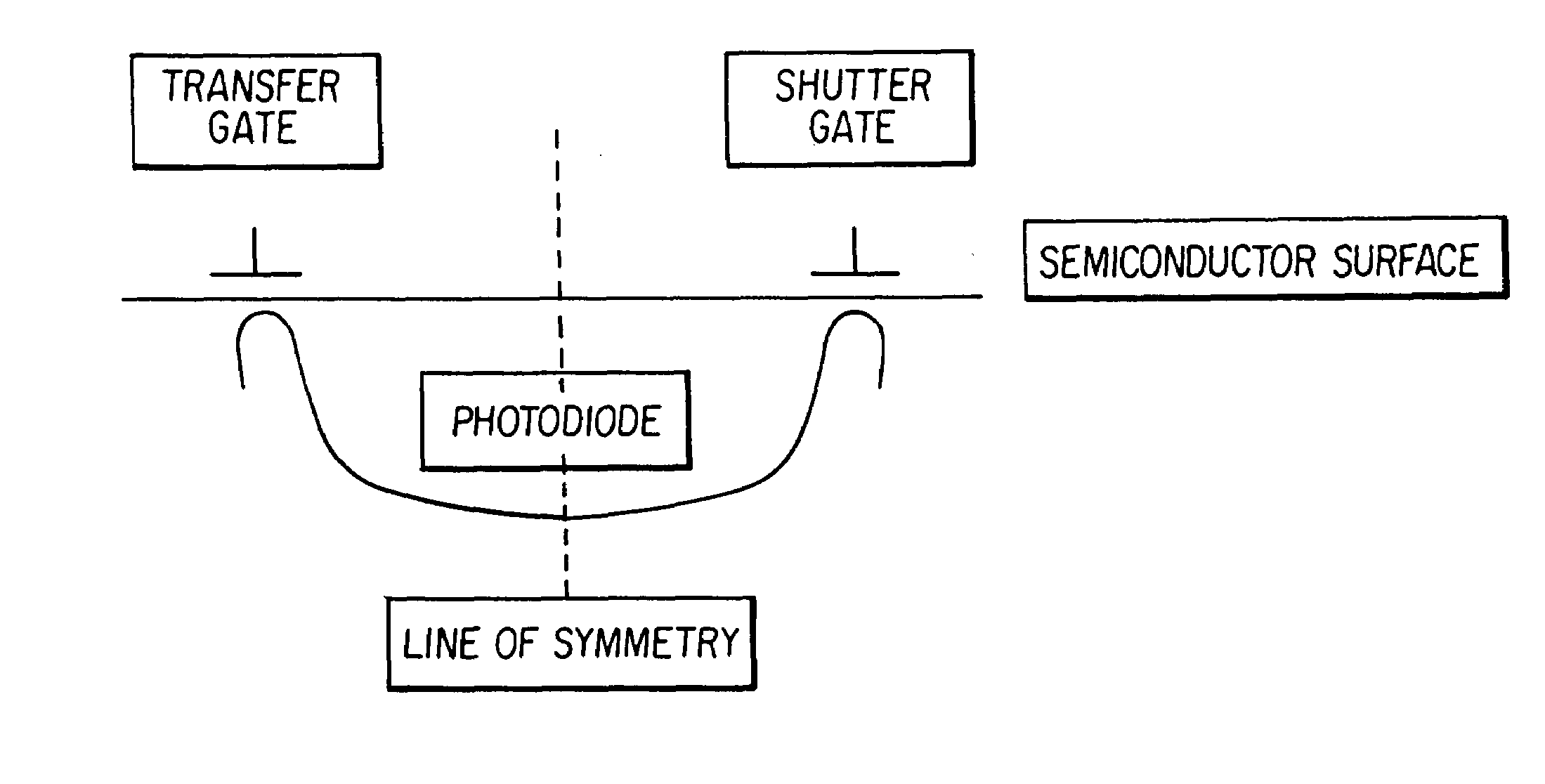

Image sensor pixel for global electronic shuttering

InactiveUS7129979B1Television system detailsTelevision system scanning detailsCMOS sensorPixel density

A pixel design for CMOS image sensors that has a high frame rate potential and, therefore, provides motion capture capabilities. The pixel is designed for global electronic shuttering so every pixel is exposed simultaneously to images incident upon the pixel array plane. The present invention has the advantages of: (1) Allowing the accommodation of changes in the pixel output groupings for different monochrome output format or CFA patterns with only changes in metal routing layers; (2) allowing true electronic shuttering to image moving scene with all the pixels having the same capture time windows; and (3) providing a symmetric global shutter gate and transfer gate to minimize pixel related fixed pattern noise. The pixel architecture provides for a CMOS based, active pixel image sensor comprising an array of pixels formed in rows and columns, with each of the pixels containing at least one active circuit element. There are a plurality of output channels formed such that each of the output channels are operatively connected to a subset of pixels wherein each of the pixel have an attribute that is the same. The pixel architecture also provides an output gate region and a shutter gate region that are symmetric about the center of the pixel. By arranging the shutter and transfer gates, a symmetric manner about the center of the pixel, a more efficient transfer of electrons to these gates is provided. A Pixel Output Bus structure allows configurable connections to column-wise signal busses that provide parallel output channels.

Owner:OMNIVISION TECH INC

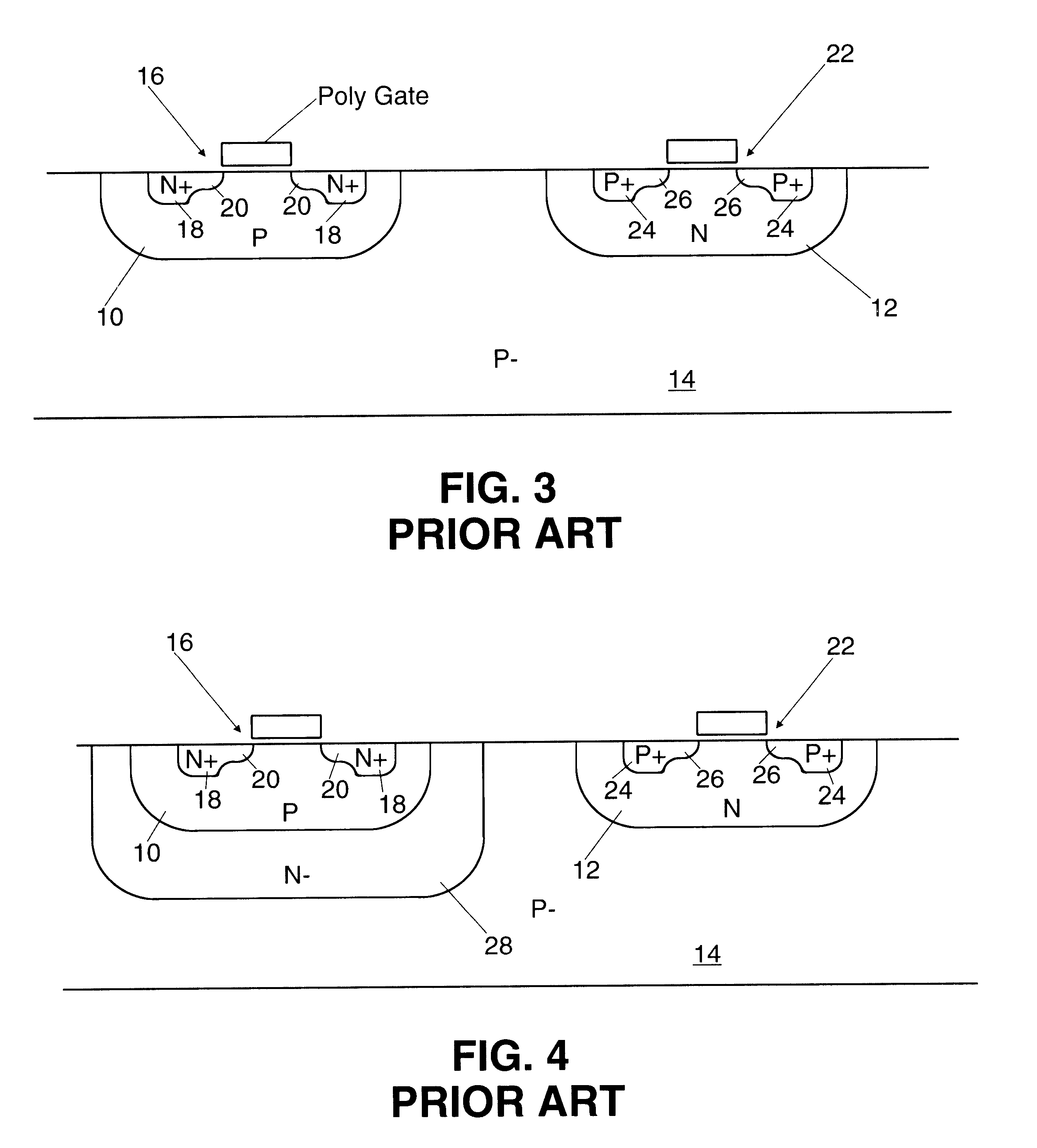

Methods for fabricating solid state image sensor devices having non-planar transistors

Methods for fabricating CMOS image sensor devices are provided, wherein active pixel sensors are constructed with non-planar transistors having vertical gate electrodes and channels, which minimize the effects of image lag and dark current.

Owner:SAMSUNG ELECTRONICS CO LTD

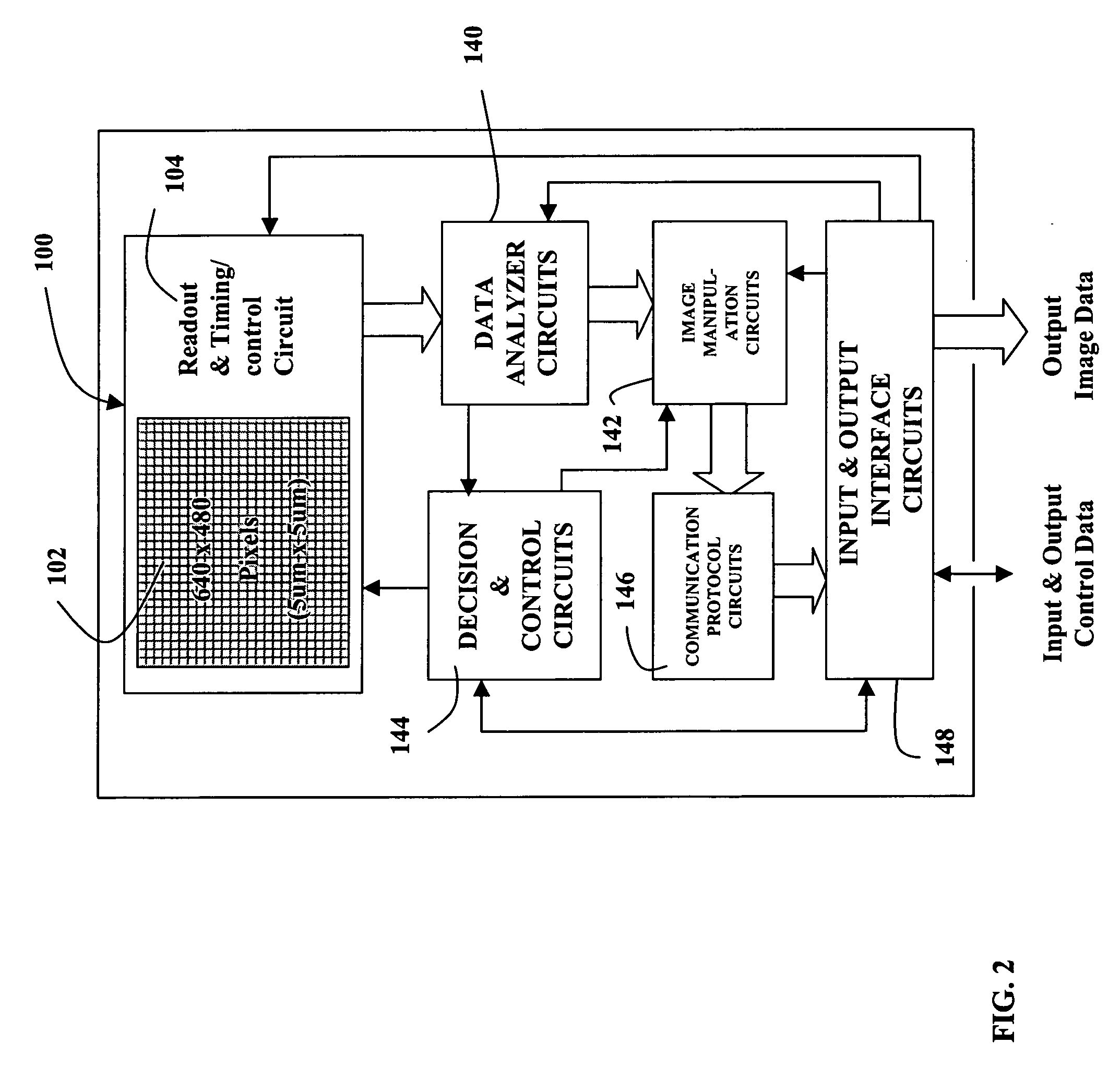

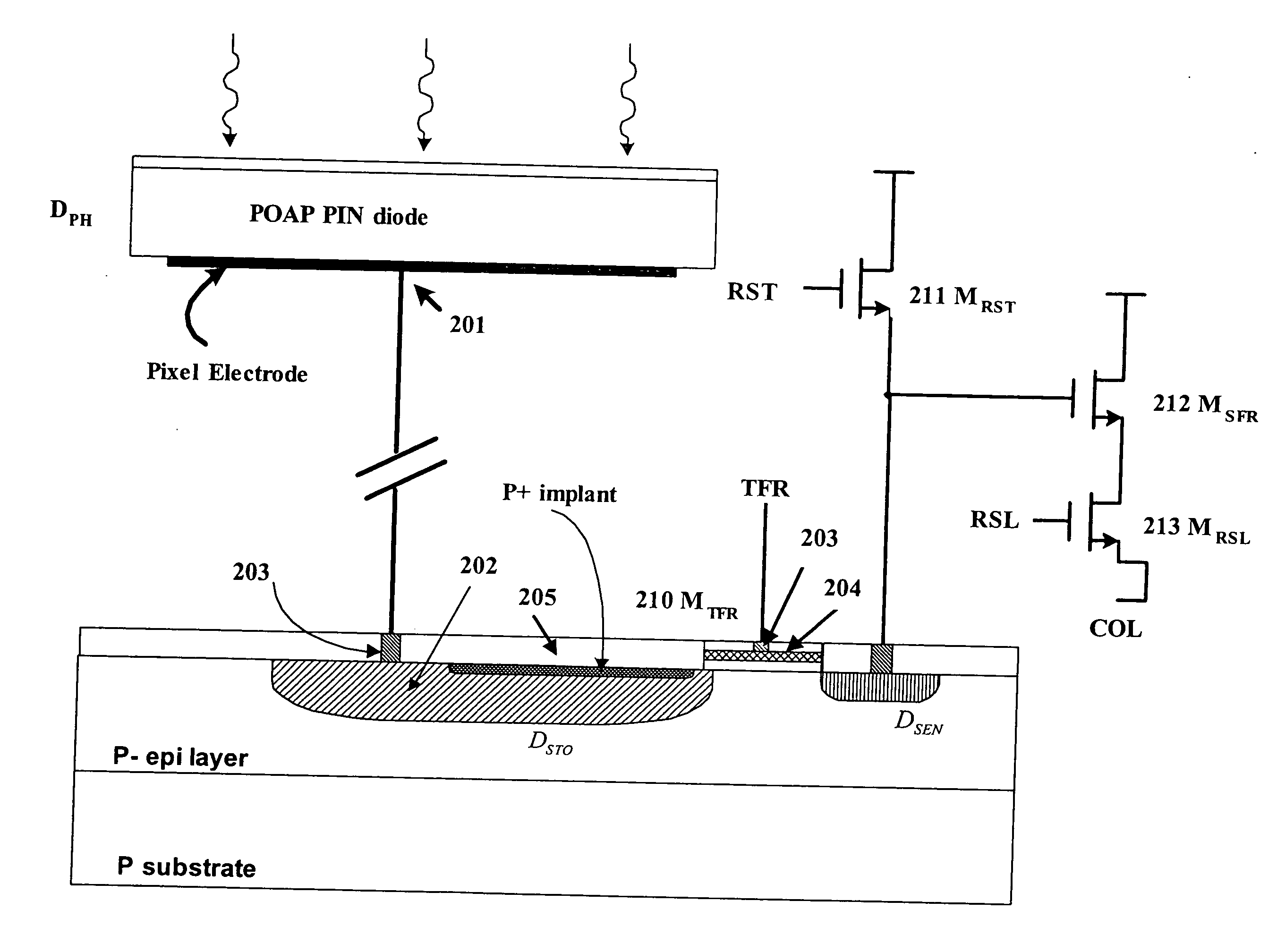

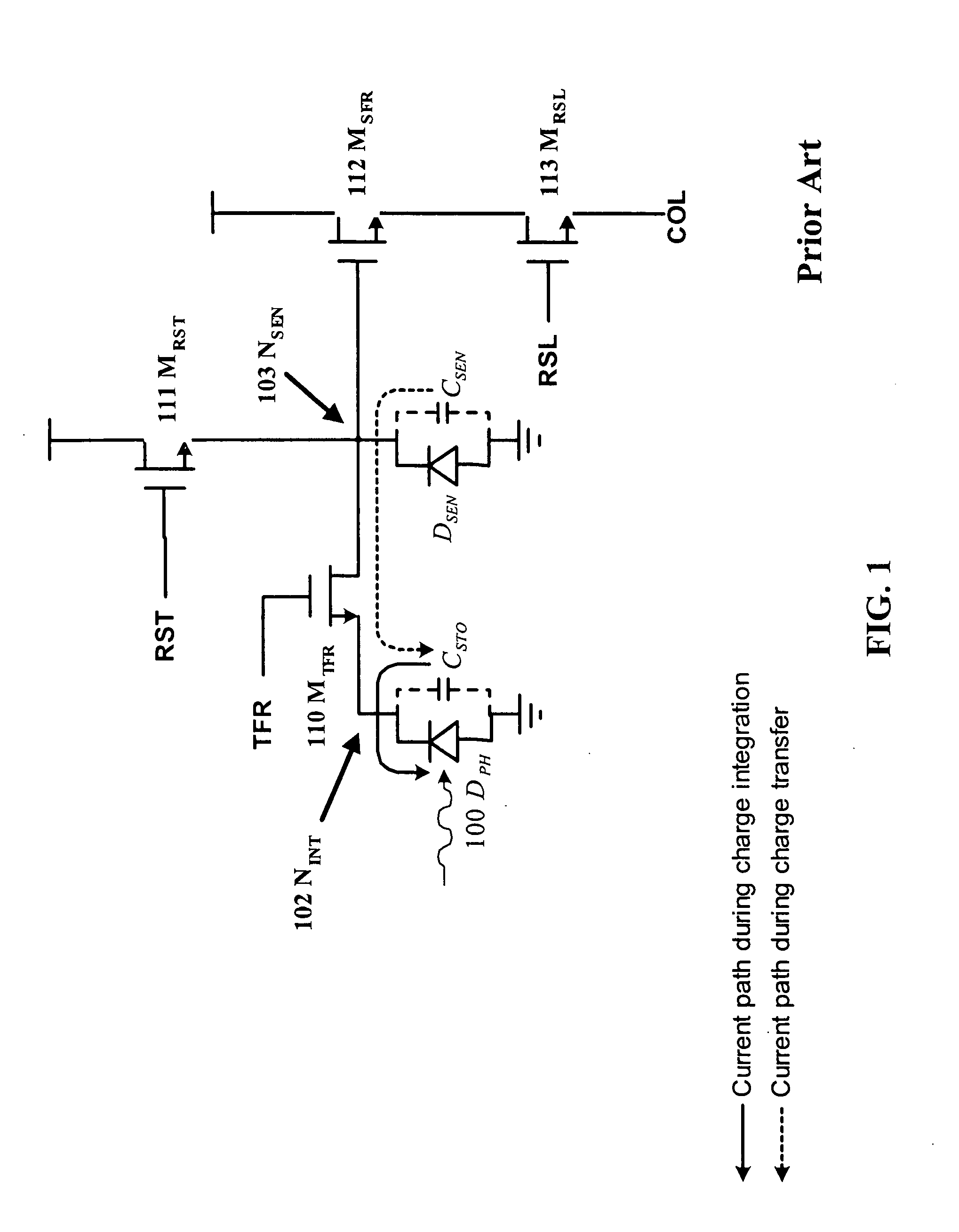

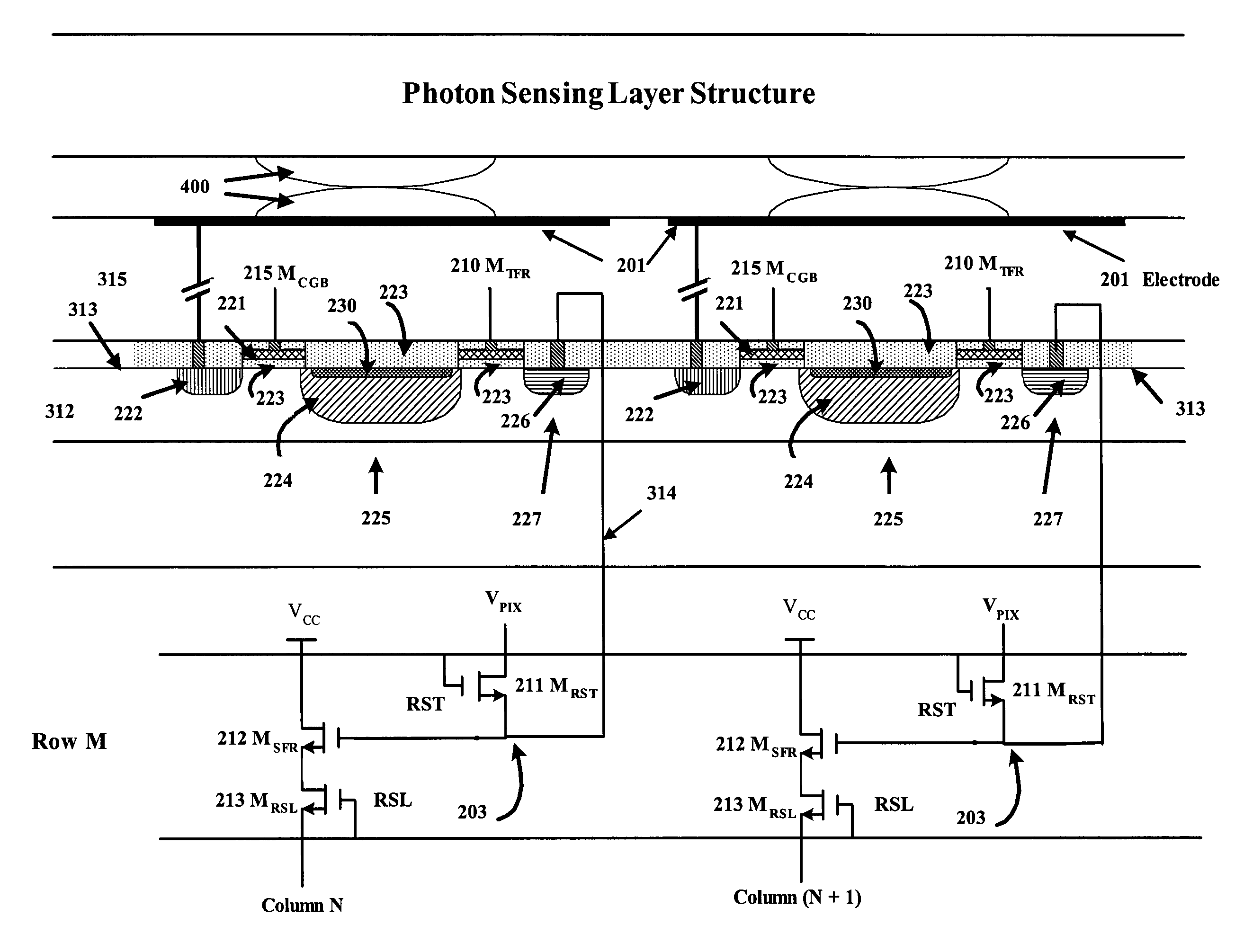

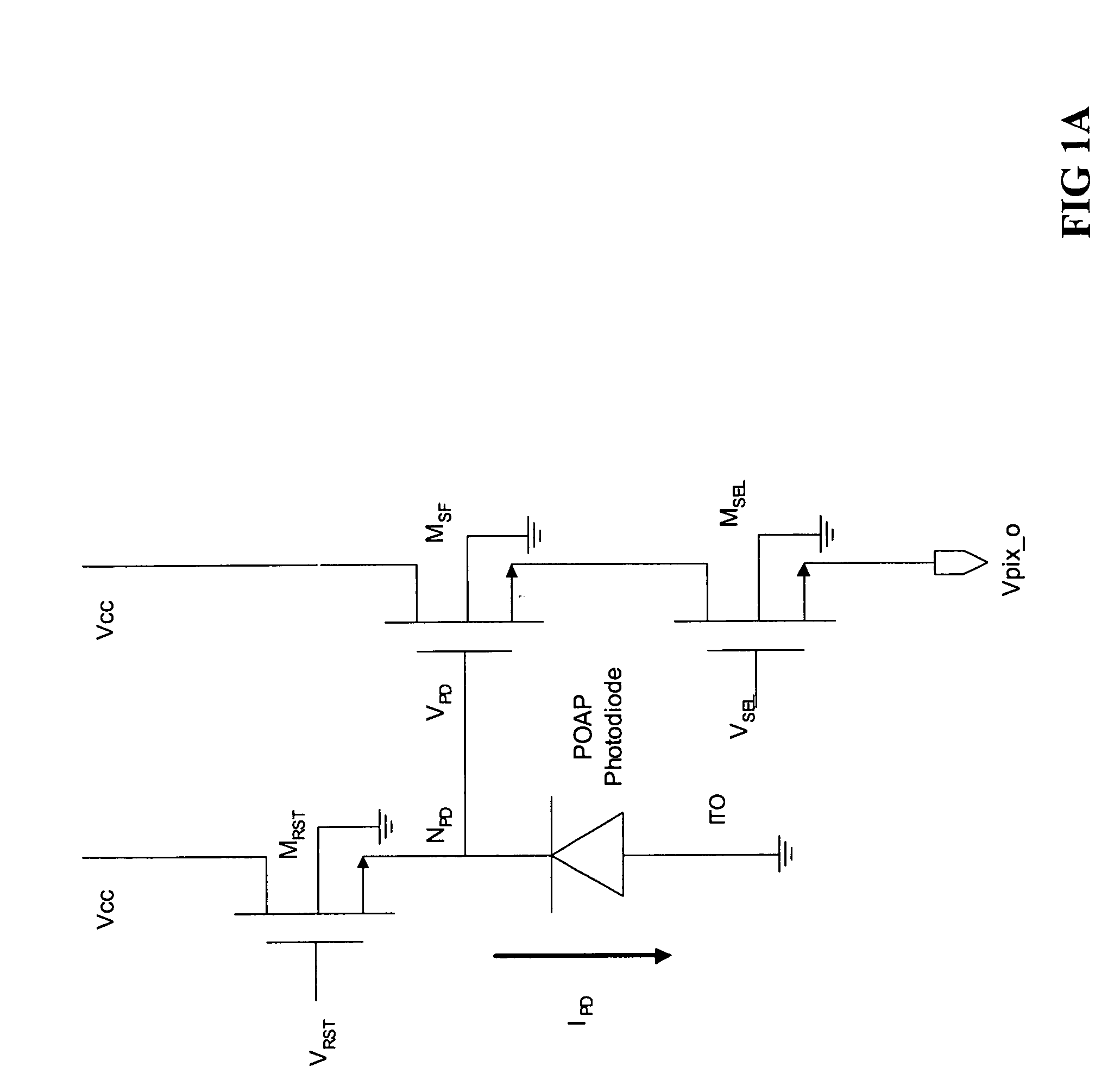

CDS capable sensor with photon sensing layer on active pixel circuit

InactiveUS20070285545A1Eliminate clock noiseFine tune overall sensor performanceTelevision system detailsTelevision system scanning detailsCapacitanceCMOS sensor

A MOS or CMOS based active pixel sensor with special sampling features to substantially eliminate clock noise. The sensor includes an array of pixels fabricated in or on a substrate, each pixel defining a charge collection node on which charges generated inside a photodiode region are collected, a charge integration node, at which charges generated in said pixel are integrated to produce pixel signals, a charge sensing node from which reset signals and the pixel signals are sensed. In preferred embodiments the sensor includes a continuous electromagnetic radiation detection structure located above the pixel circuits providing a photodiode region for each pixel. The sensor includes integrated circuit elements adapted to maintain voltage potentials of the charge integration nodes substantially constant during charge integration cycles. The sensor also includes integrated circuit elements having electrical capacitance adapted to store charges providing an electrical potential at the charge integration node. In preferred embodiments this is a pinned diode.

Owner:E PHOCUS

Solid state image sensor devices having non-planar transistors

CMOS image sensor devices are provided, wherein active pixel sensors are designed with non-planar transistors having vertical gate electrodes and channels, which minimize the effects of image lag and dark current.

Owner:SAMSUNG ELECTRONICS CO LTD +1

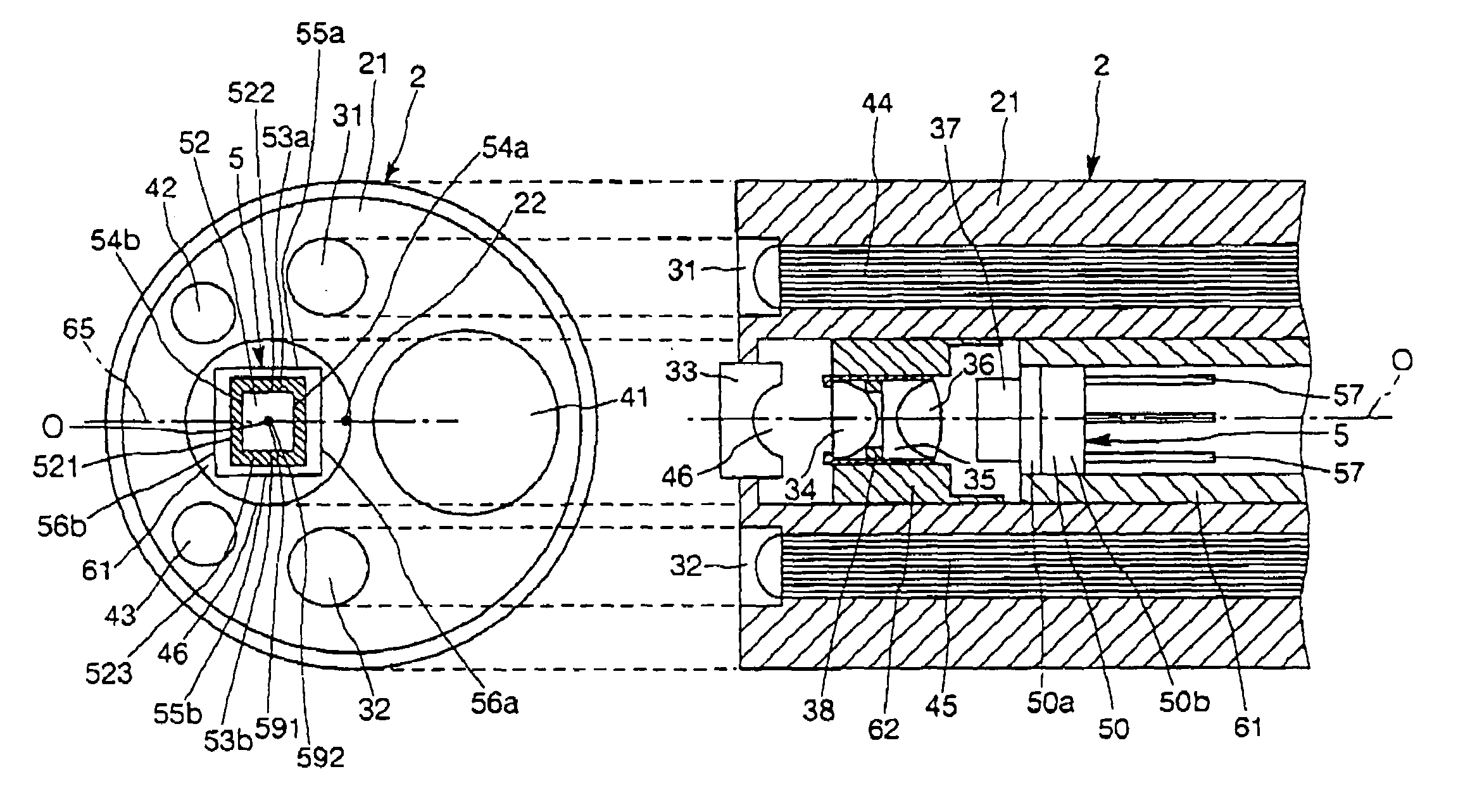

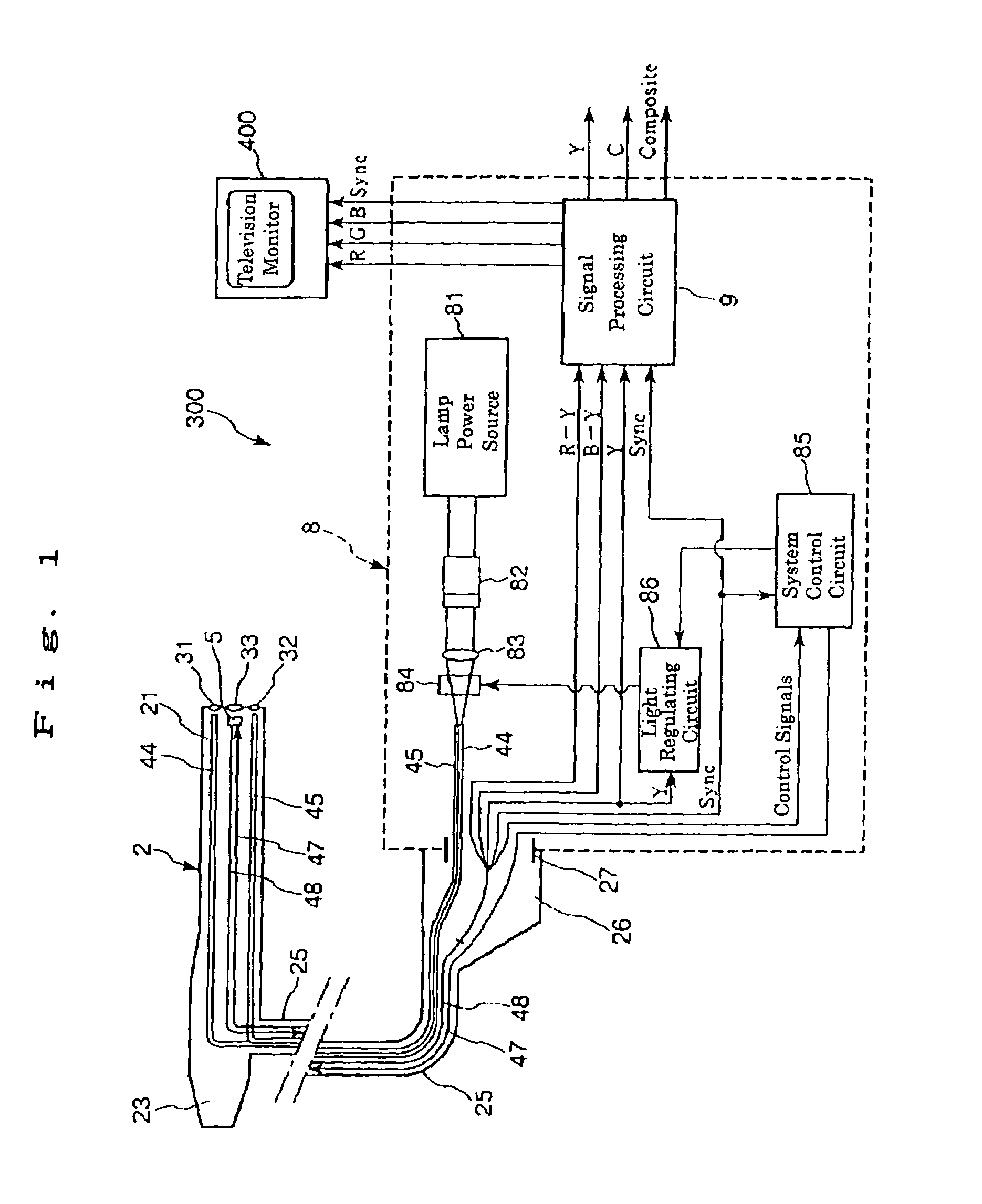

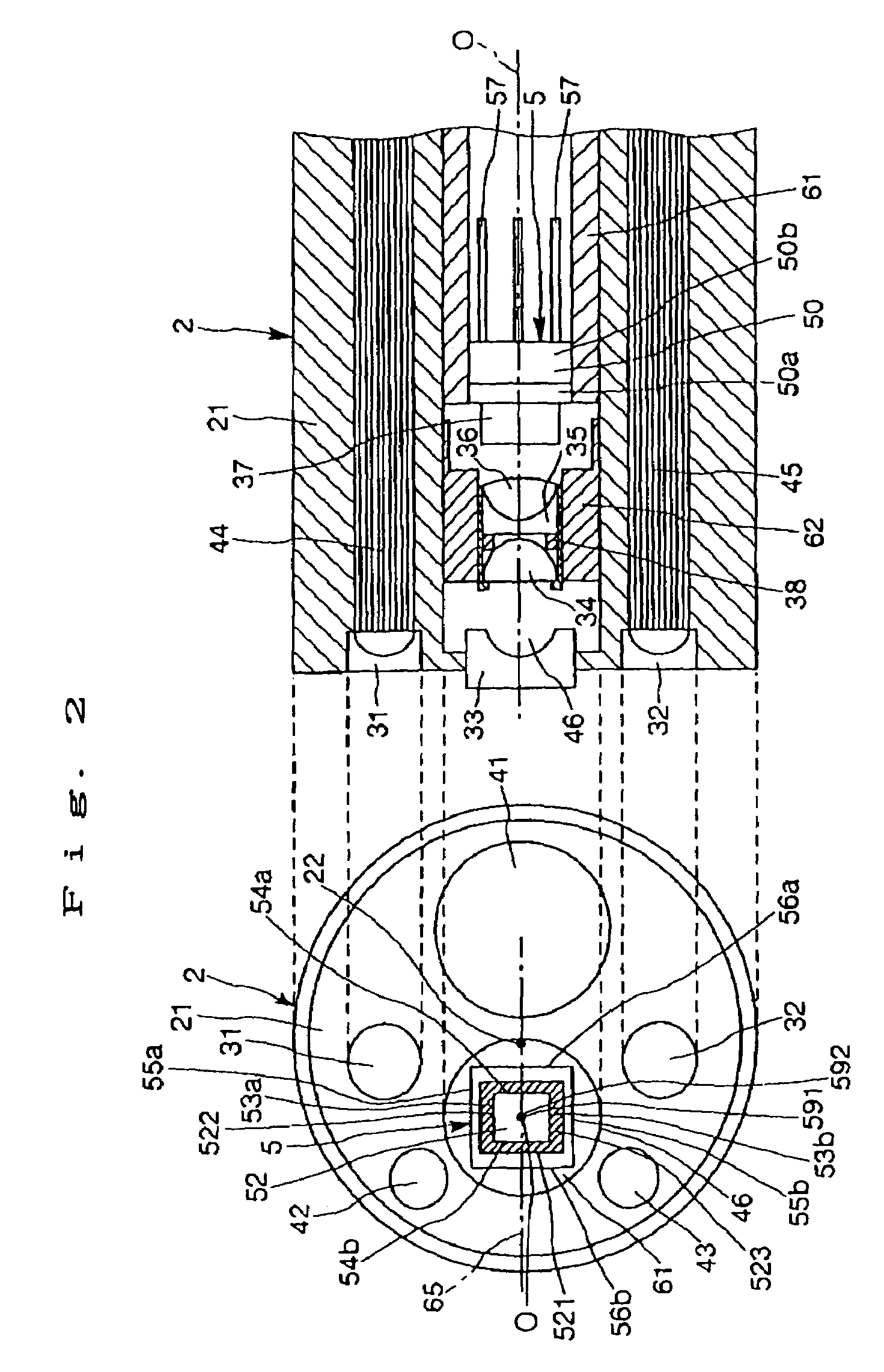

Imaging element for electronic endoscopes and electronic endoscope equipped with the imaging element

InactiveUS7042487B2Reduce the overall diameterSmall diameterTelevision system detailsSurgeryCMOS sensorSignal processing circuits

An imaging element for an electronic endoscope is disclosed. The electronic endoscope has an elongated tubular main body. At the tip end portion of the main body, there are provided an optical imaging system comprising a convex lens, a concave lens and an optical low-pass filter, a CMOS type imaging element having a CMOS sensor, and a pair of light distribution lenses. The imaging element includes the CMOS sensor, a signal processing circuit for processing a signal outputted from the CMOS sensor, and a signal control circuit for timing control for extracting a signal from the CMOS sensor. In this imaging element, the signal processing circuit and the signal control circuit are arranged along the periphery of the light-receiving surface of the CMOS sensor so that a center of the base of the sensor on the light-receiving surface is substantially aligned with a center of an effective imaging region of the image sensor.

Owner:HOYA CORP

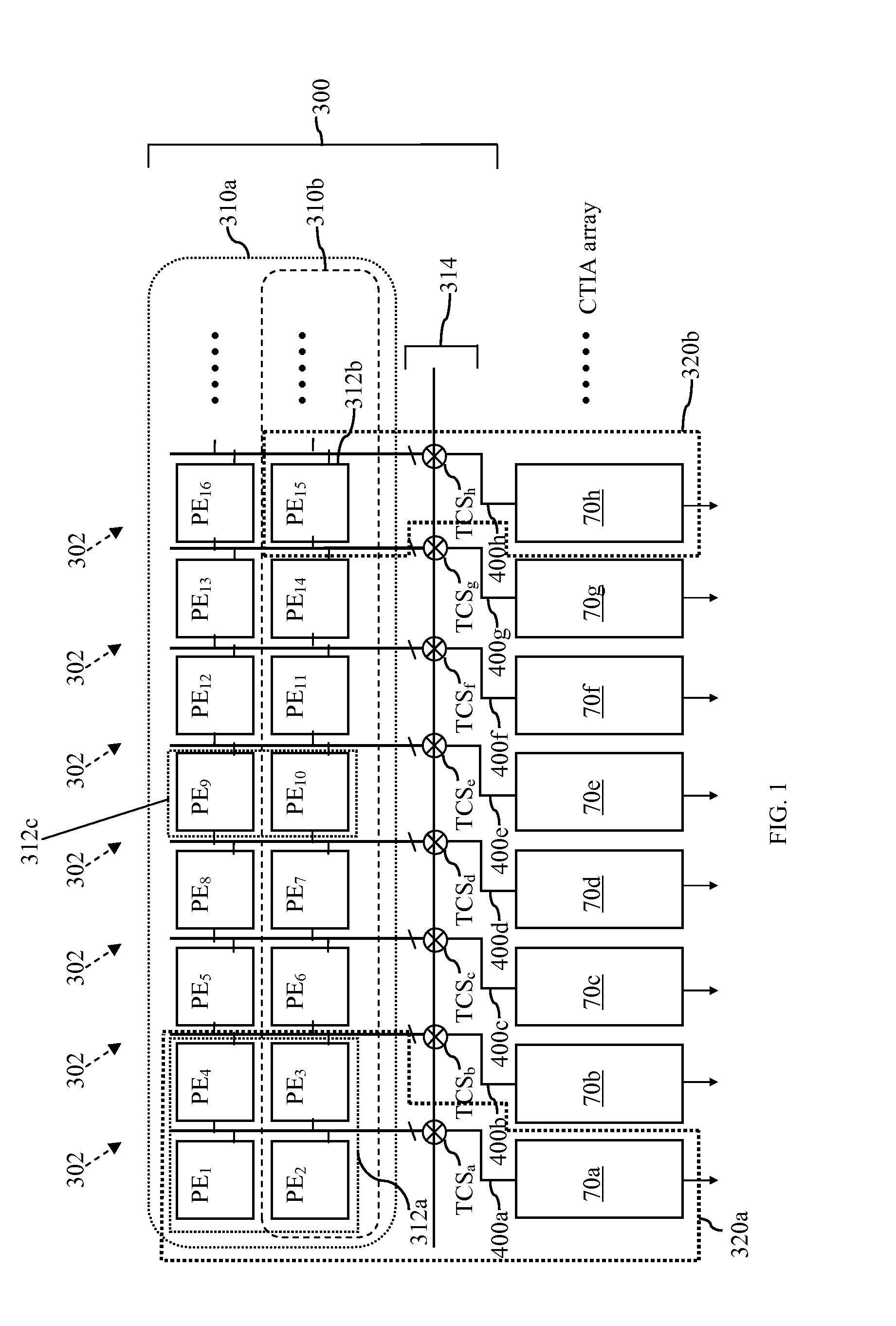

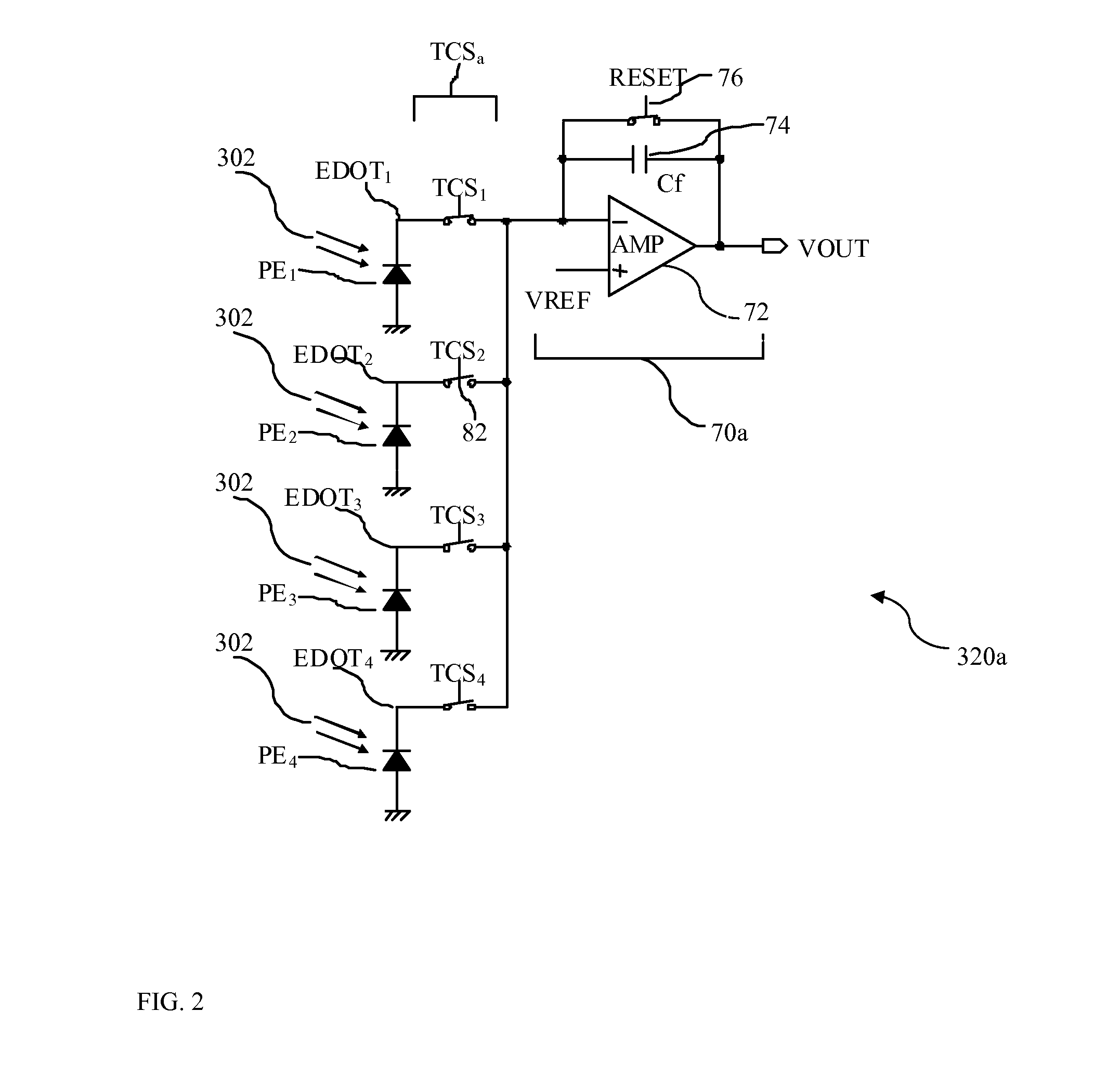

Multi-resolution Image Sensor Array with High Image Quality Pixel Readout Circuitry

InactiveUS20090091648A1Improve performanceImprove image qualityTelevision system detailsTelevision system scanning detailsSensor arrayCMOS sensor

A configurable, compact multi-resolution linear image sensor array is disclosed. The multi-resolution image sensor array employs a spatial array of photoelectric sites with each site having an image output terminal and a cluster of switched photo-detector elements. To effect a high quality snapshot operation mode for a high pixel count array, a transfer control switch is added bridging each photo-detector element and its correspondingly connected negative input terminal of an operational amplifier to form an active pixel sensor circuit. To minimize a reset kTC noise associated with numerous traditional active pixel sensor circuits, an in-pixel KTC noise-correlated correlated multiple sampling (CMS) circuitry is also proposed to replace an otherwise traditional correlated double sampling (CDS) circuitry.

Owner:CMOS SENSOR

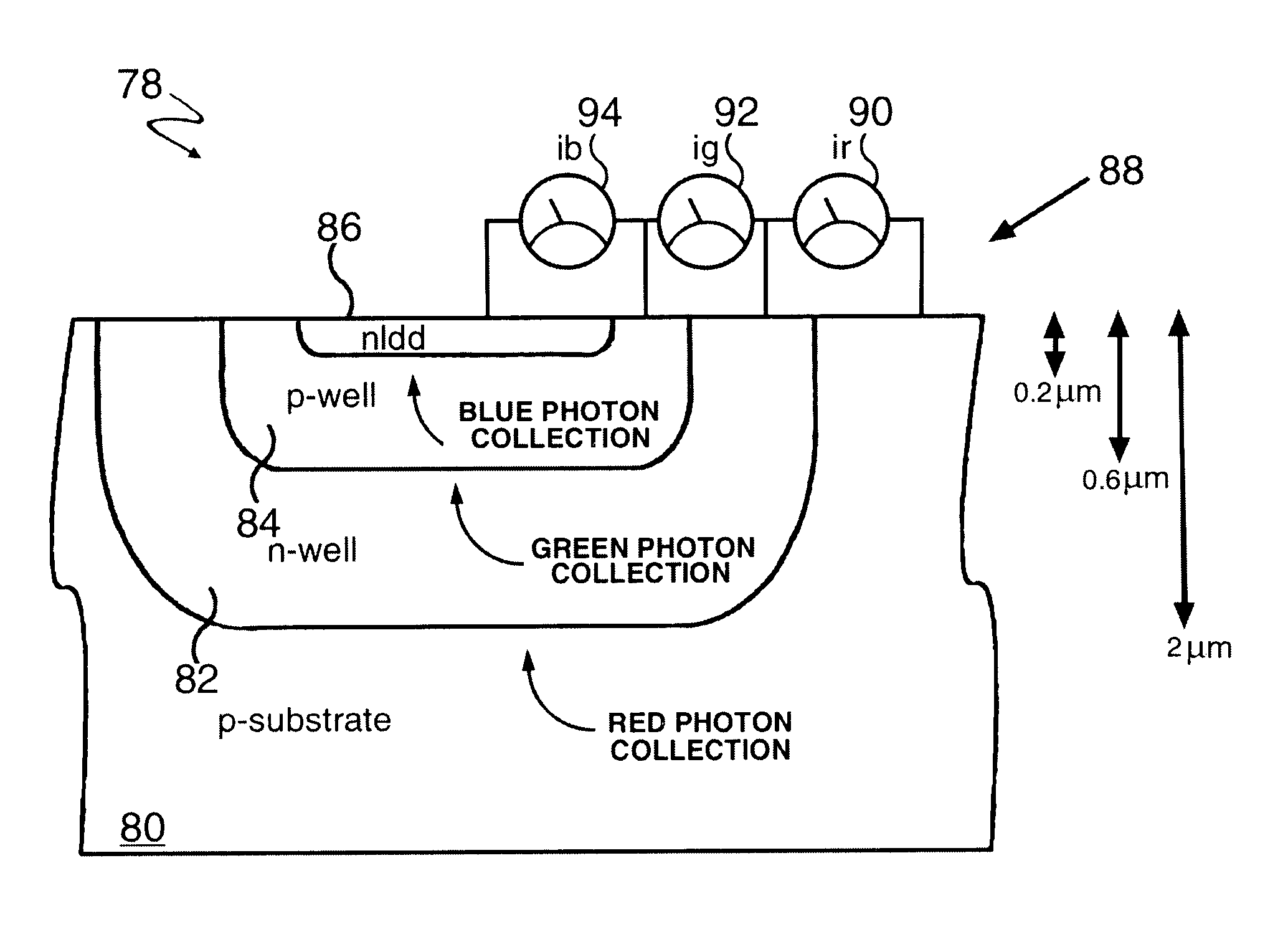

Method for storing and retrieving digital image data from an imaging array

InactiveUS6731397B1Television system detailsDigitally marking record carriersCMOS sensorDigital data

A method for storing digital information from an image sensor comprises the steps of providing an image sensor producing three-color output data at each of a plurality of pixel locations; providing a digital storage device coupled to the image sensor; sensing three-color digital output data from the image sensor; and storing said three-color output data as digital data in the digital storage device without performing any interpolation on the three-color output data. The data may be compressed prior to storage and expanded after retrieval from storage. In a preferred embodiment, the image sensor comprises a triple-junction active pixel sensor array.

Owner:FOVEON

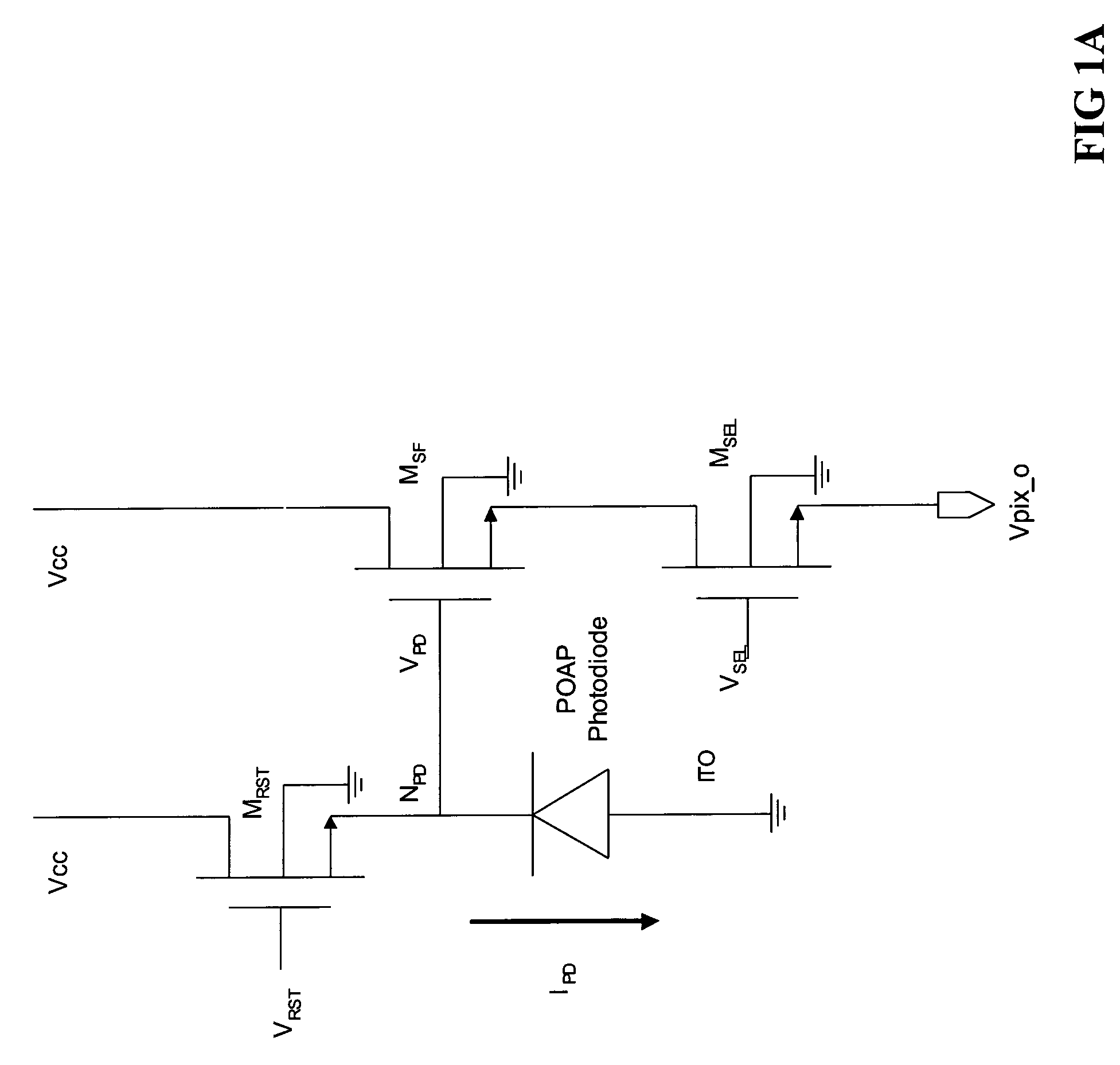

CMOS sensor with electrodes across photodetectors at approximately equal potential

InactiveUS7525168B2Minimize and eliminate currentMinimise currentTelevision system detailsTelevision system scanning detailsCMOS sensorPhotovoltaic detectors

A MOS or CMOS based active pixel sensor designed for operation with zero or close to zero potential across the pixel photodiodes to minimize or eliminate dark current. In preferred embodiments the pixel photodiodes are produced with a continuous pin or nip photodiode layer laid down over pixel electrodes of the sensor. In this preferred embodiment, the voltage potential across the pixel photodiode structures is maintained constant and close to zero, preferably less than 1.0 volts. This preferred embodiment enables the photodiode to be operated at a constant bias condition during the charge detection cycle. Setting this constant bias condition close to zero (near “short circuit” condition) assures that dark current is substantially zero.

Owner:E PHOCUS

CMOS sensor with approximately equal potential photodiodes

InactiveUS20090224351A1Minimize and eliminate dark currentReduce and eliminate clock noiseTelevision system detailsTelevision system scanning detailsCMOS sensorCharge detection

A MOS or CMOS based active pixel sensor designed for operation with zero or close to zero potential across the pixel photodiodes to minimize or eliminate dark current. In this preferred embodiment, the voltage potential across the pixel photodiode structures is maintained constant and close to zero, preferably less than 1.0 volts. This preferred embodiment enables the photodiode to be operated at a constant bias condition during the charge detection cycle. In preferred embodiments the pixel photodiodes are produced with a continuous pin or nip photodiode layer laid down over pixel electrodes of the sensor. In other preferred embodiments the pixel photodiode structures are produced beside and physically isolated from the regions where CMOS circuits are formed. In some of these preferred embodiments the isolated pixel photodiode structures are comprised of crystalline germanium deposited in cavities in a silicon substrate. This embodiment can be adapted especially for imaging at short wave infrared frequencies. Preferred embodiments are adapted for correlated double sampling.

Owner:E PHOCUS

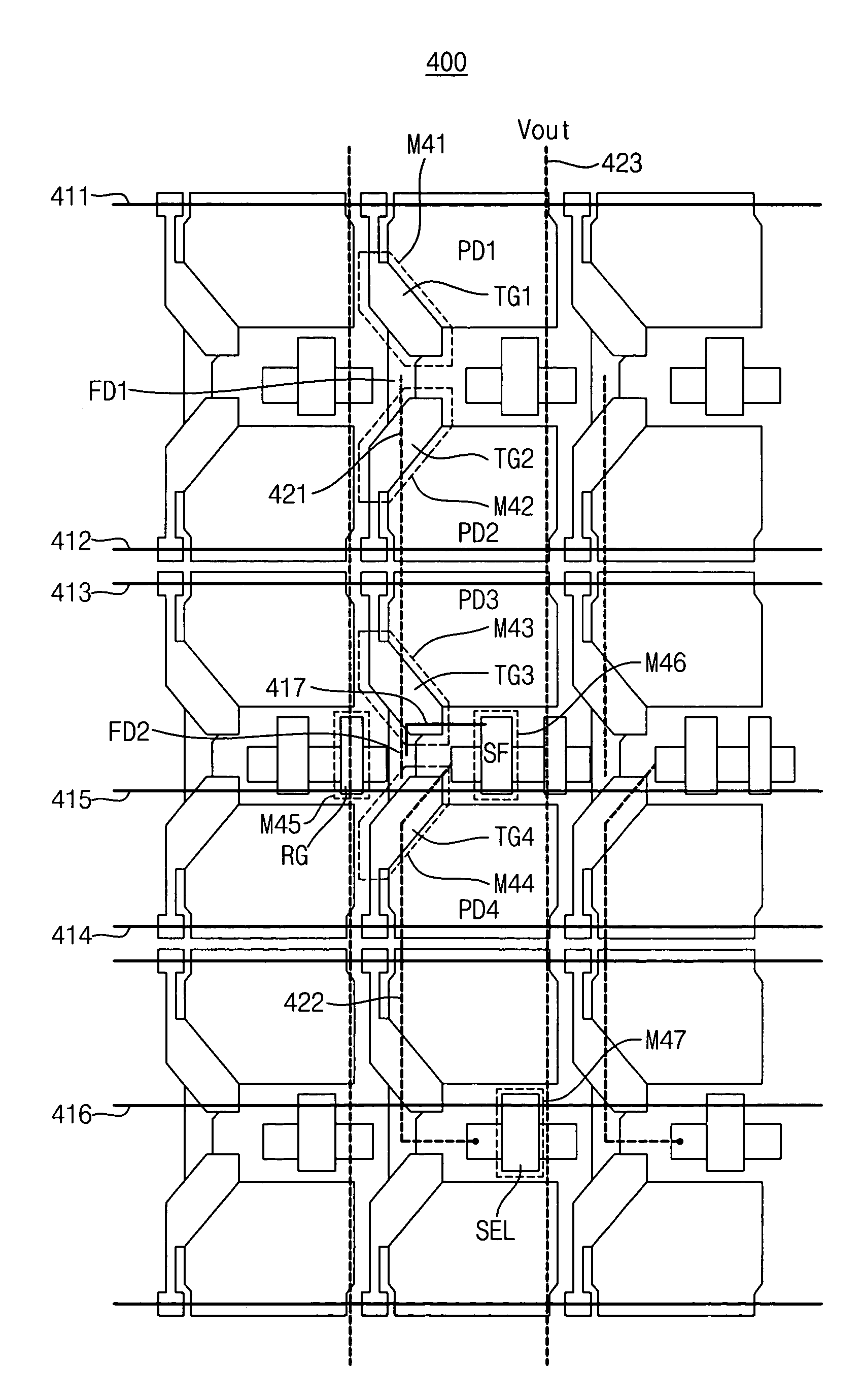

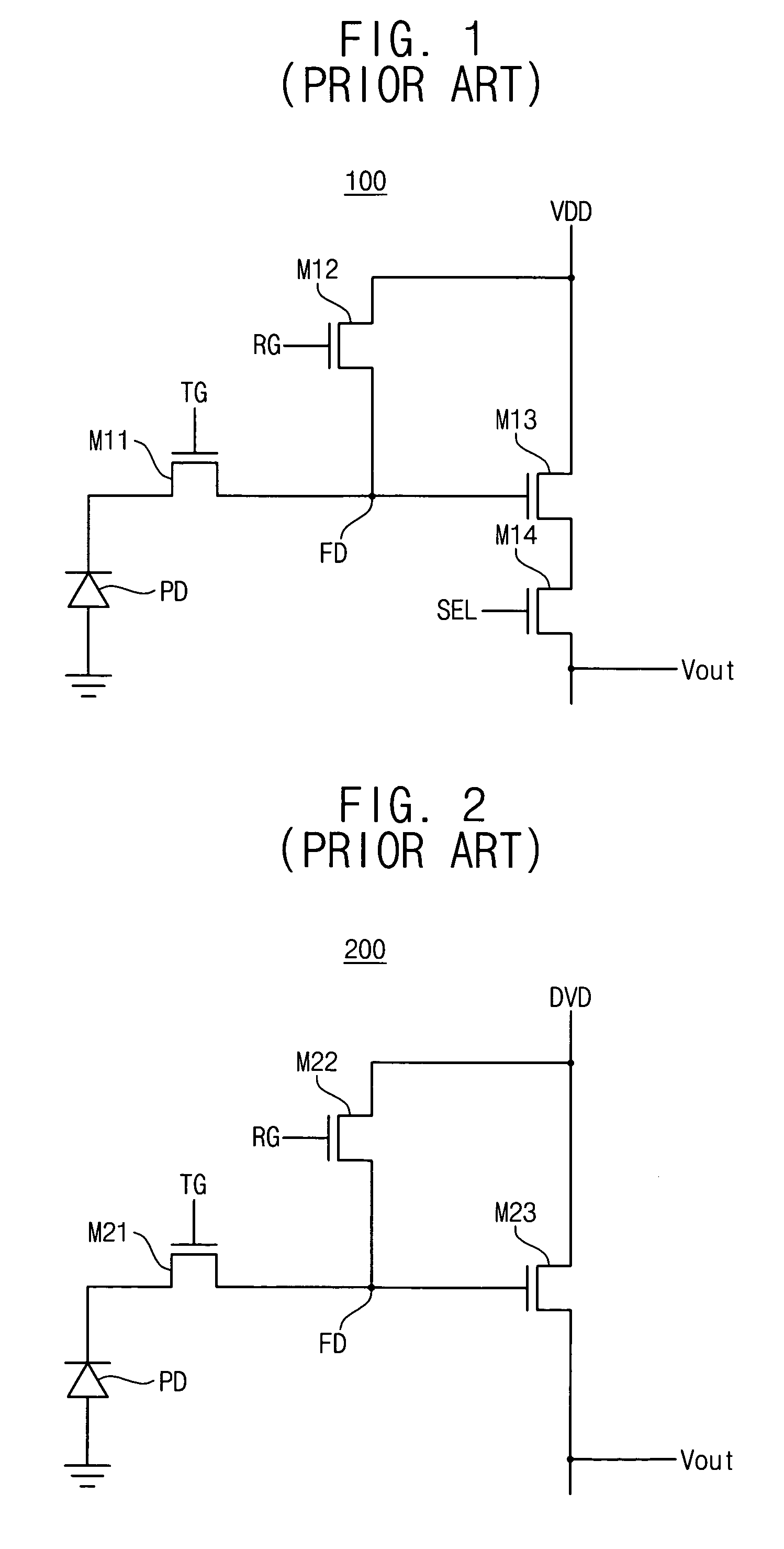

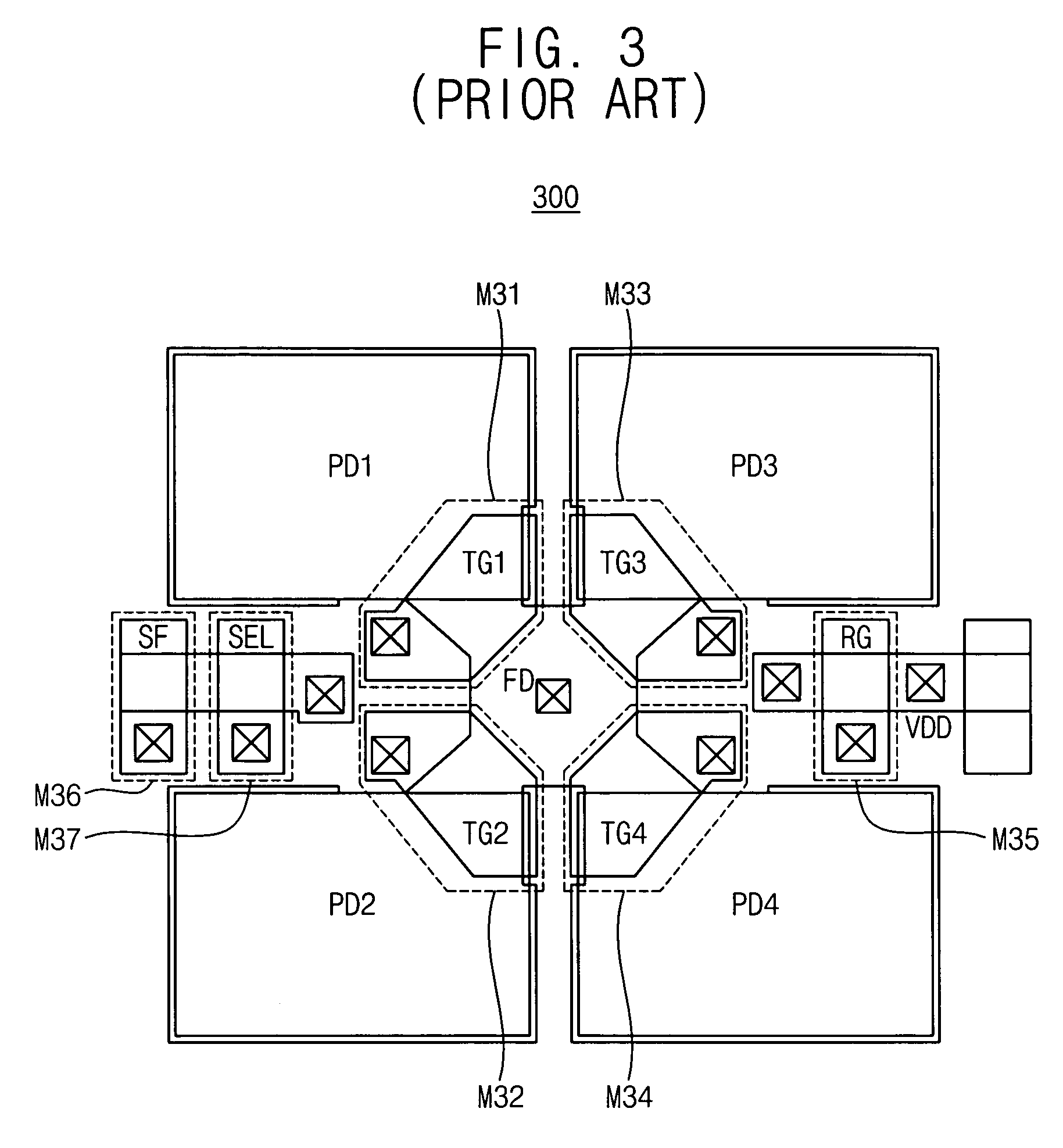

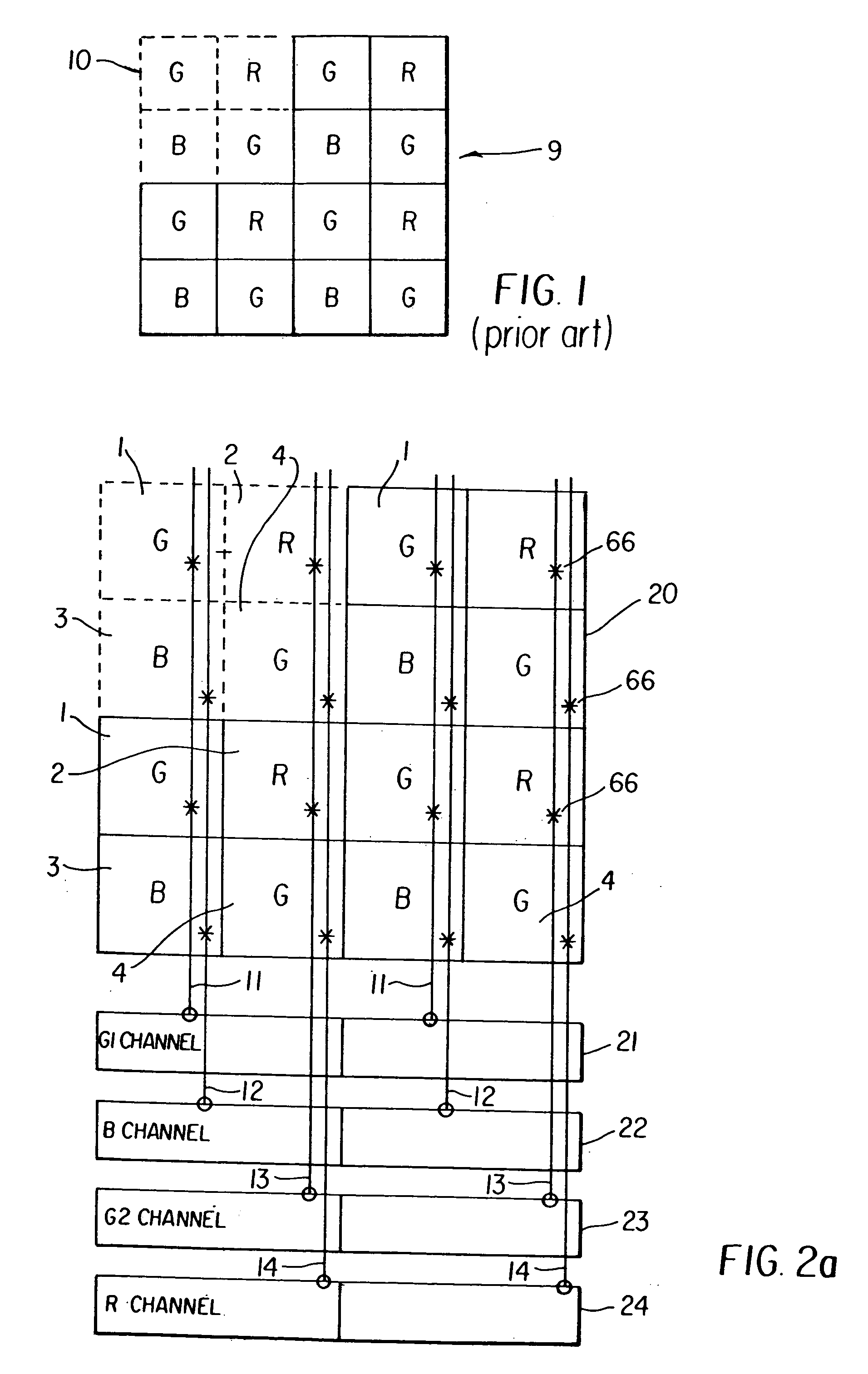

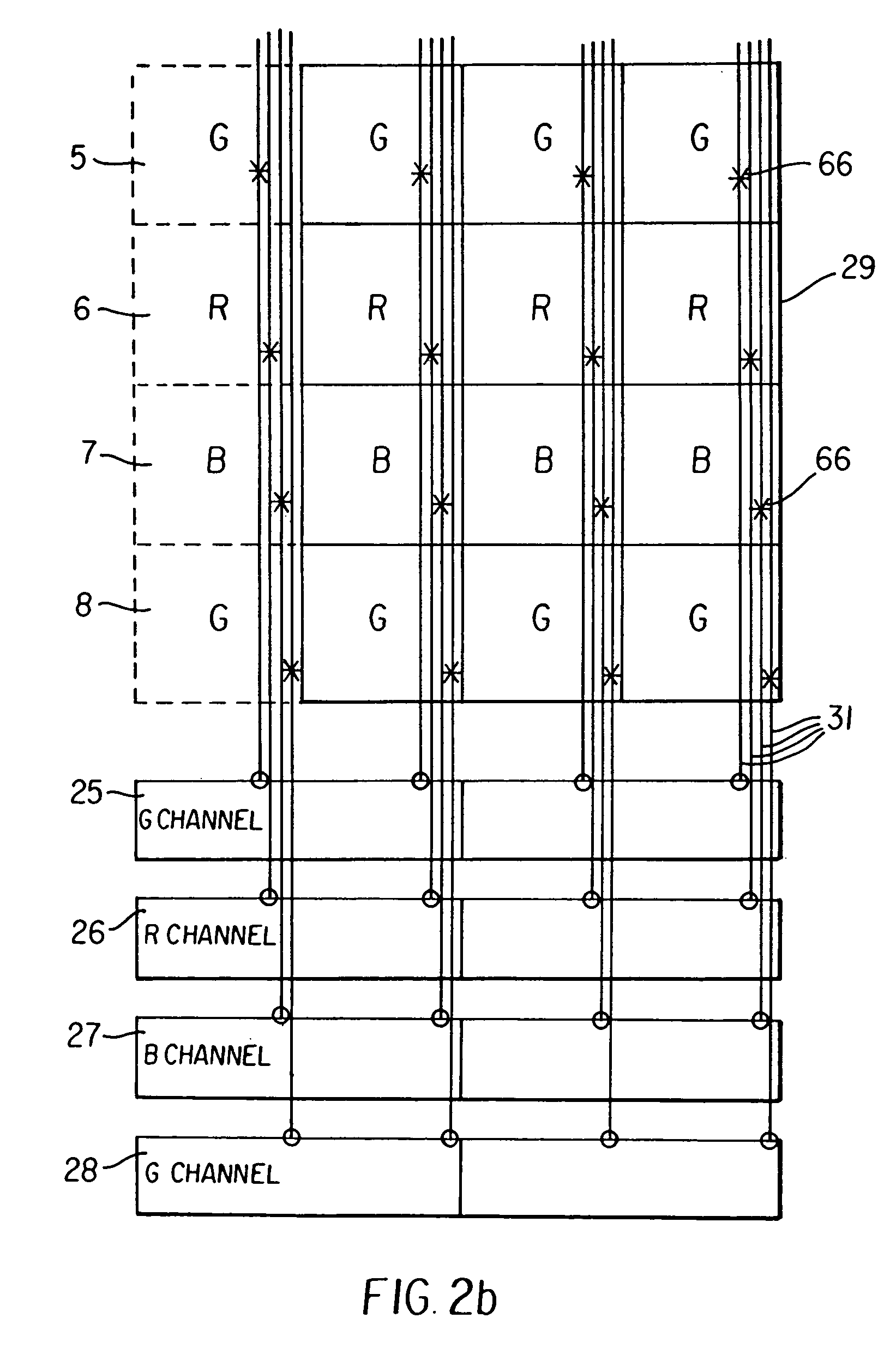

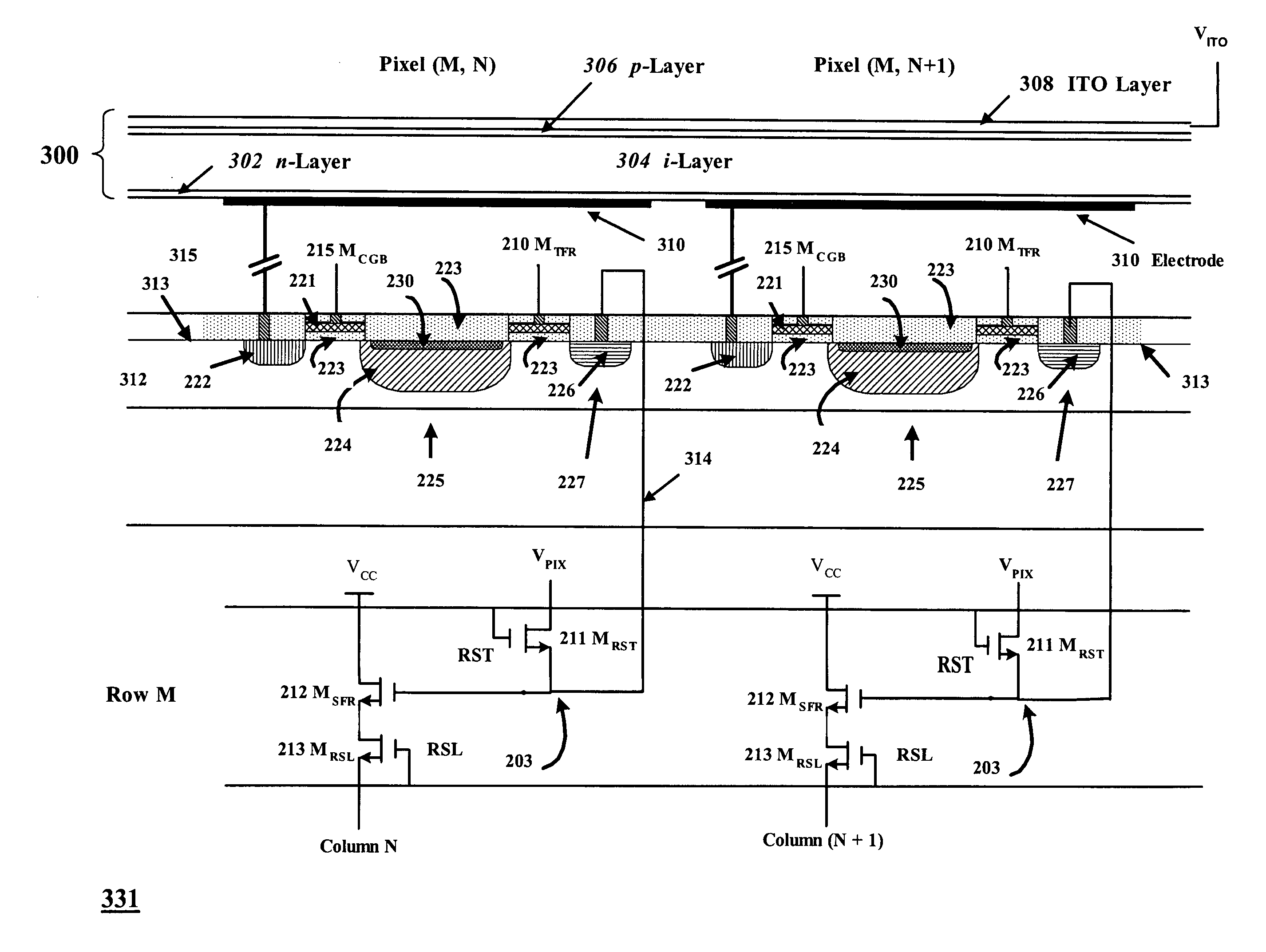

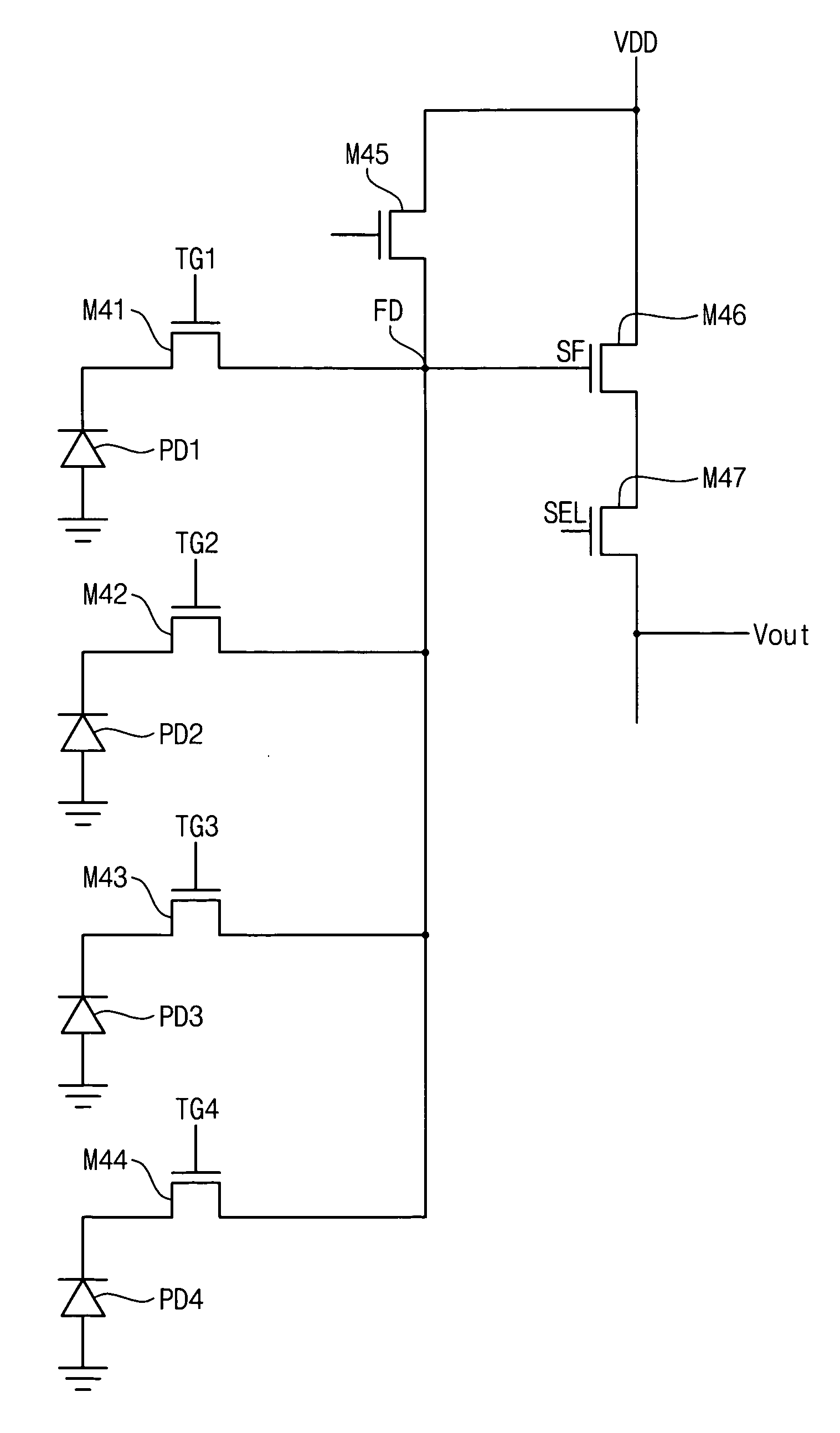

CMOS sensor array with a shared structure

ActiveUS20060175536A1Television system detailsTelevision system scanning detailsCMOS sensorSensor array

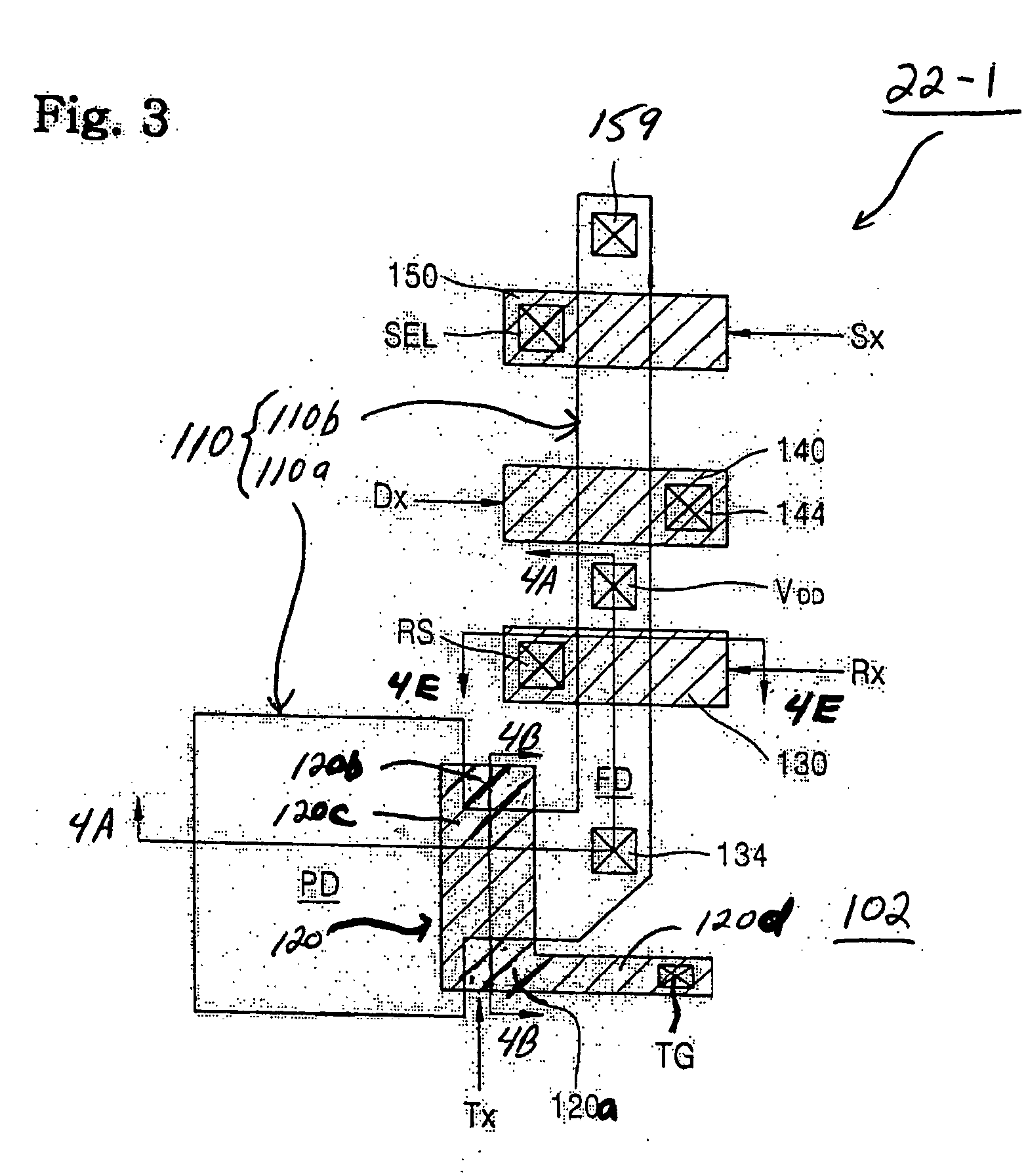

A CMOS sensor array includes a plurality of unit blocks. A unit block includes: N pairs of photo diode regions arranged in a first direction; 2N transfer transistors respectively corresponding to the photo diode regions, wherein each of the transfer transistors is formed at a corner of the corresponding photo diode region, and wherein for each pair of photo diode regions the two corresponding transfer transistors symmetrically oppose each other; N floating diffusion nodes, wherein each of the floating diffusion nodes is respectively arranged between a pair of photo diode regions, and wherein each of the floating diffusion nodes is shared by the two corresponding transfer transistors and the pair of photo diode regions; at least one metal line for coupling the floating diffusion nodes; a reset transistor for resetting a voltage of the floating diffusion nodes; a readout circuit including at least one transistor for sampling the floating diffusion node, wherein the reset transistor and the readout circuit are disposed between the pair of photo diode regions.

Owner:SAMSUNG ELECTRONICS CO LTD

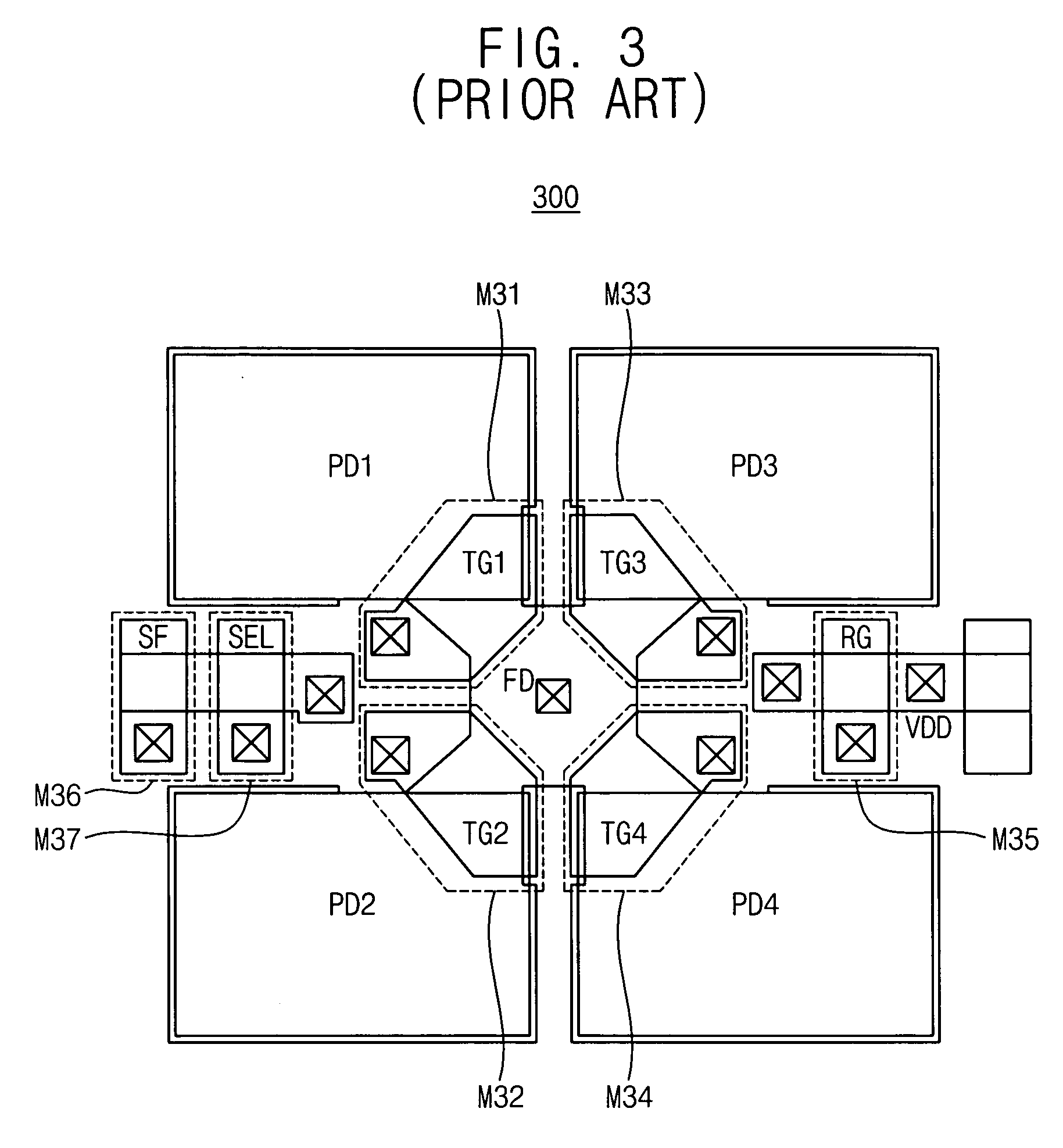

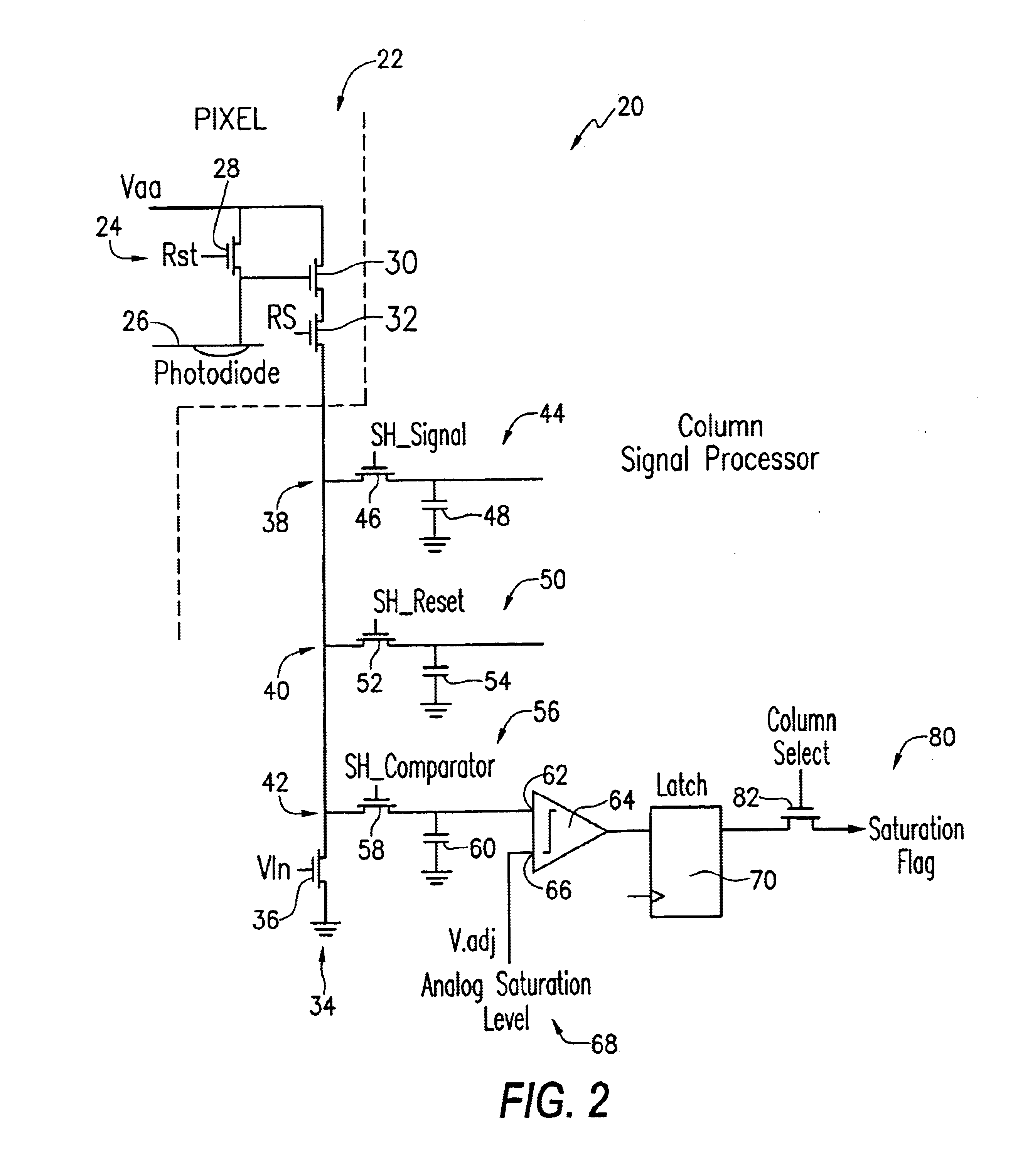

Technique for flagging oversaturated pixels

InactiveUS6873363B1Television system detailsTelevision system scanning detailsCMOS sensorPattern recognition

An active pixel sensor (APS) that includes circuitry to eliminate artifacts in digital images. The APS includes a comparator for comparing a signal level from a pixel to an adjusted saturation voltage to determine if the pixel is saturated. If the pixel is saturated, an associated saturation flag is stored and used to replace the signal from the pixel with a maximum value corresponding to a brightest pixel in the image.

Owner:APTINA IMAGING CORP

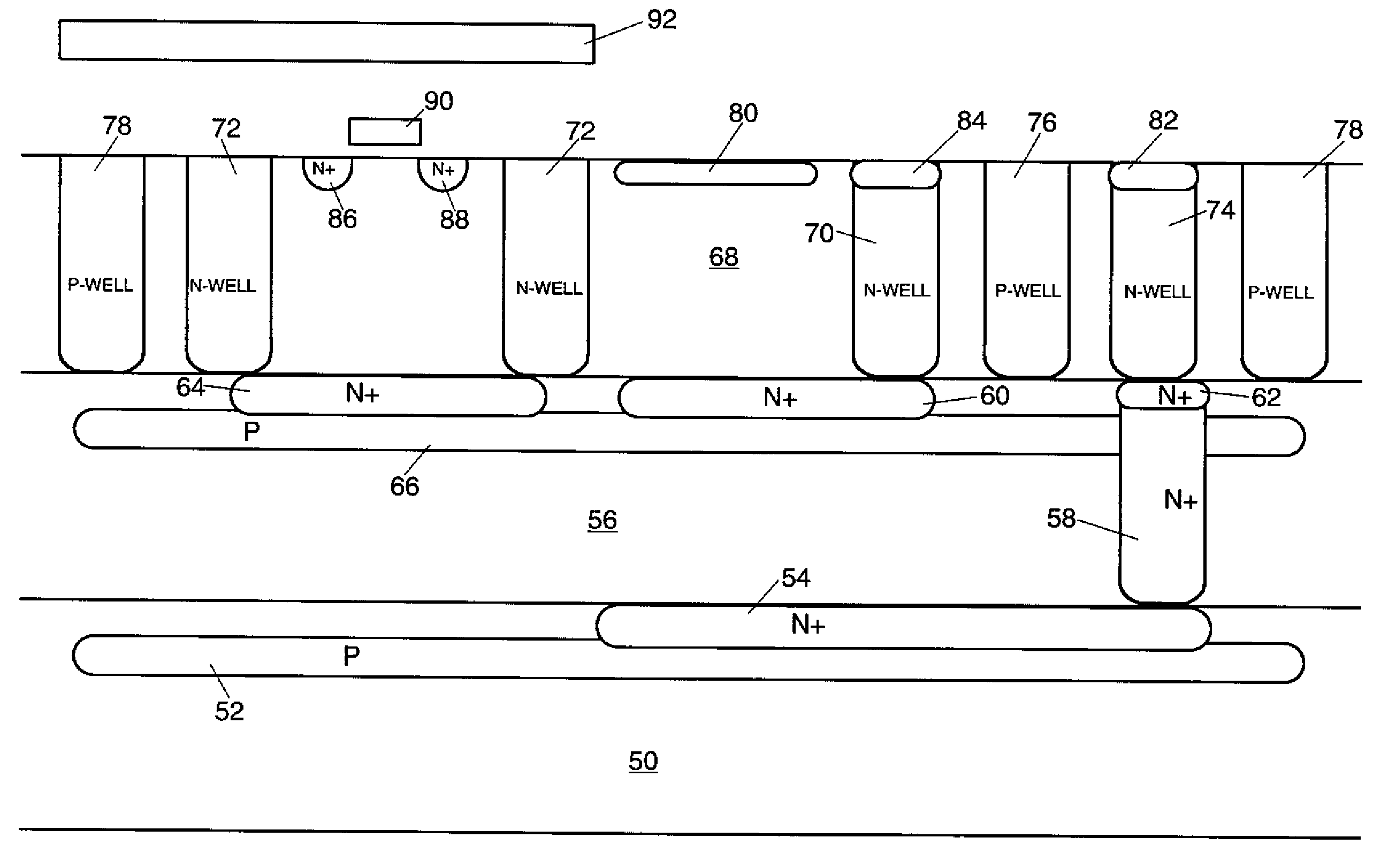

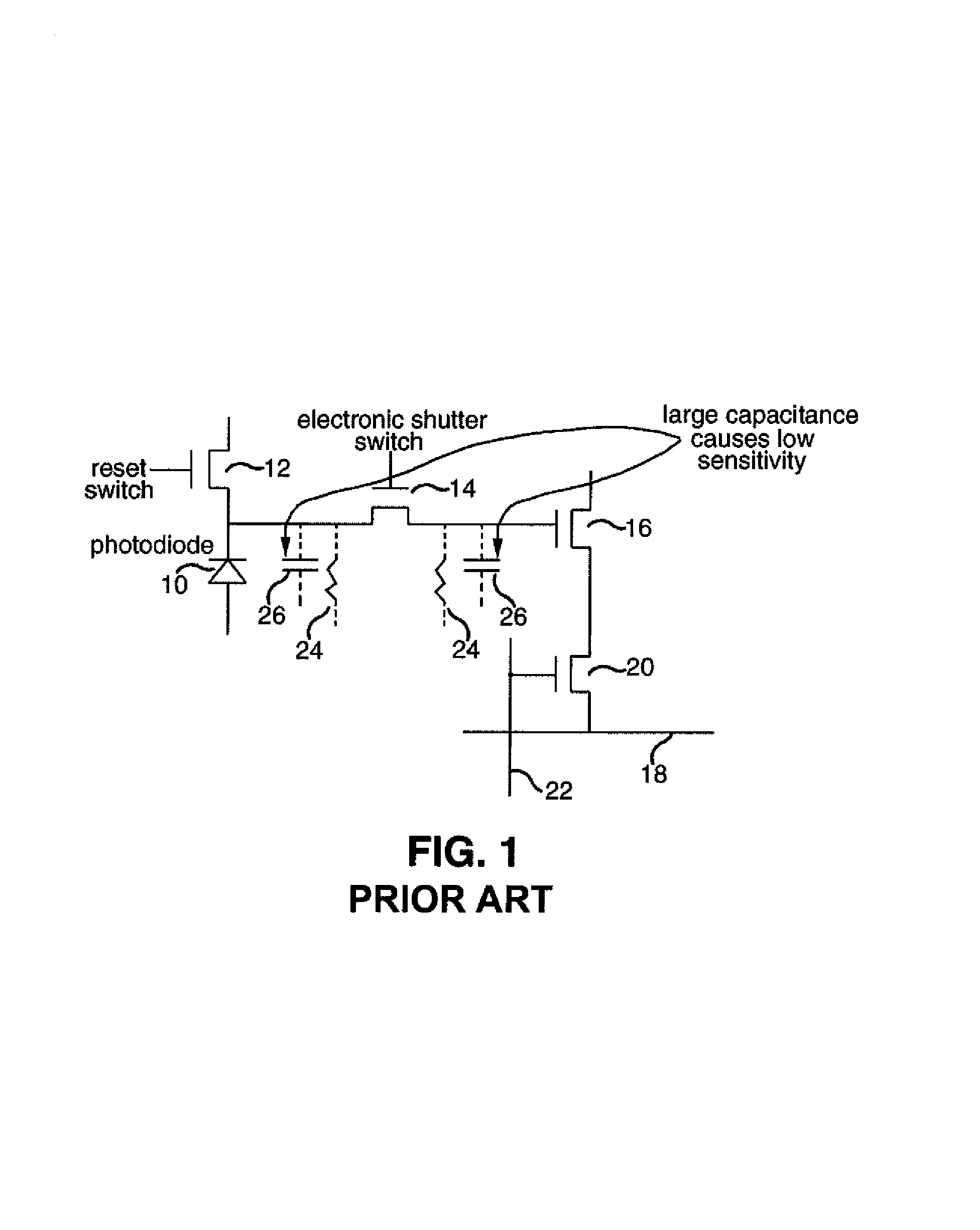

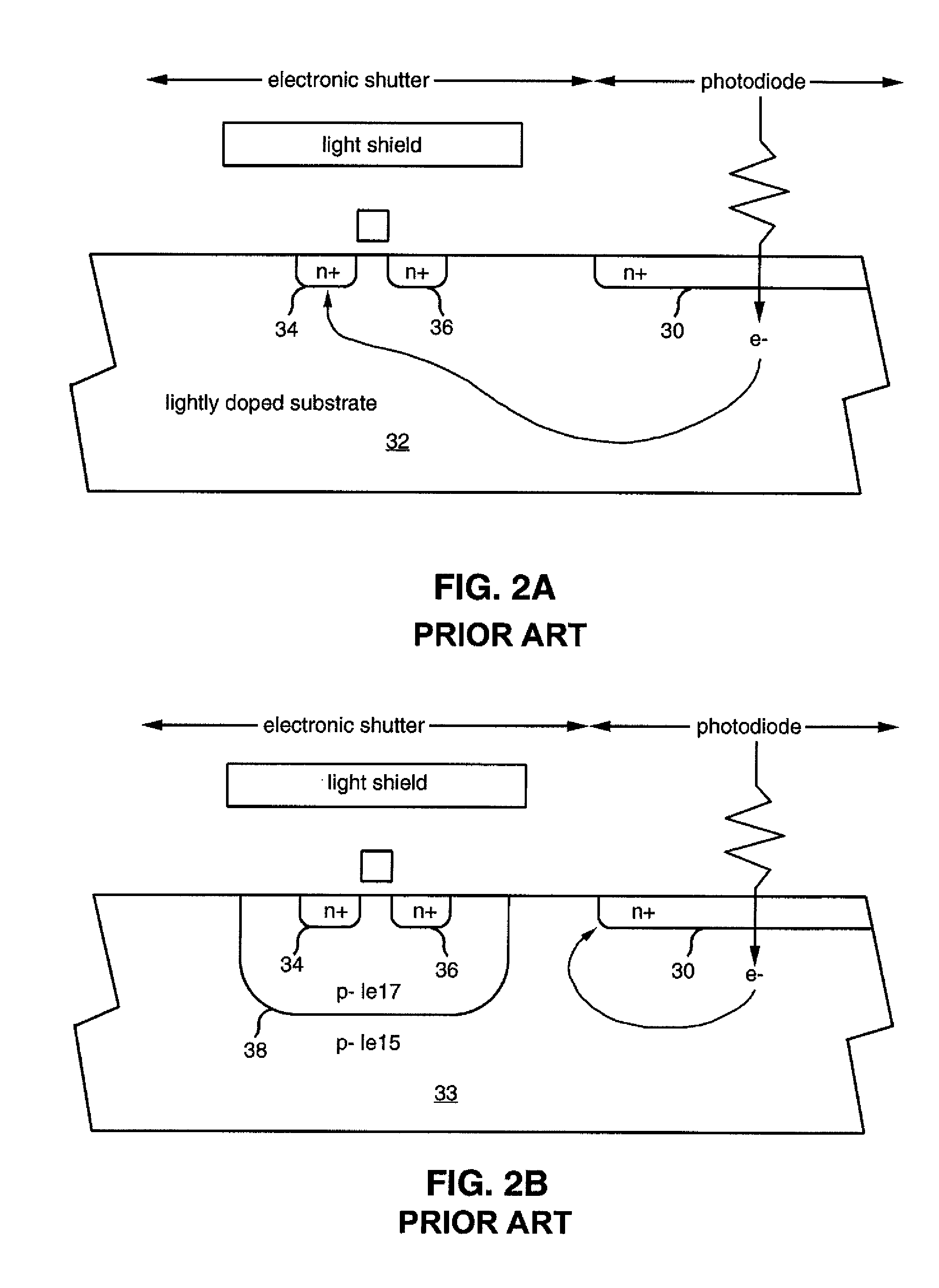

Electronic shutter using buried layers and active pixel sensor and array employing same

InactiveUS7110028B1Improved electronic shutter techniqueImprove noiseTelevision system detailsTelevision system scanning detailsCMOS sensorElectronic shutter

An electronic shutter switching transistor for a CMOS electronic is formed in a semiconductor substrate of a first conductivity type. The transistor comprises a pair of spaced apart doped regions of a second conductivity type opposite the first conductivity type disposed in the semiconductor substrate forming source / drain regions. A gate is disposed above and insulated from the semiconductor substrate and is self aligned with the pair of spaced apart doped regions. A well of the second conductivity type laterally surrounds the pair of spaced apart doped regions and extends deeper into the substrate than the doped regions. A buried layer of the second conductivity type underlies and is in contact with the well.

Owner:FOVEON

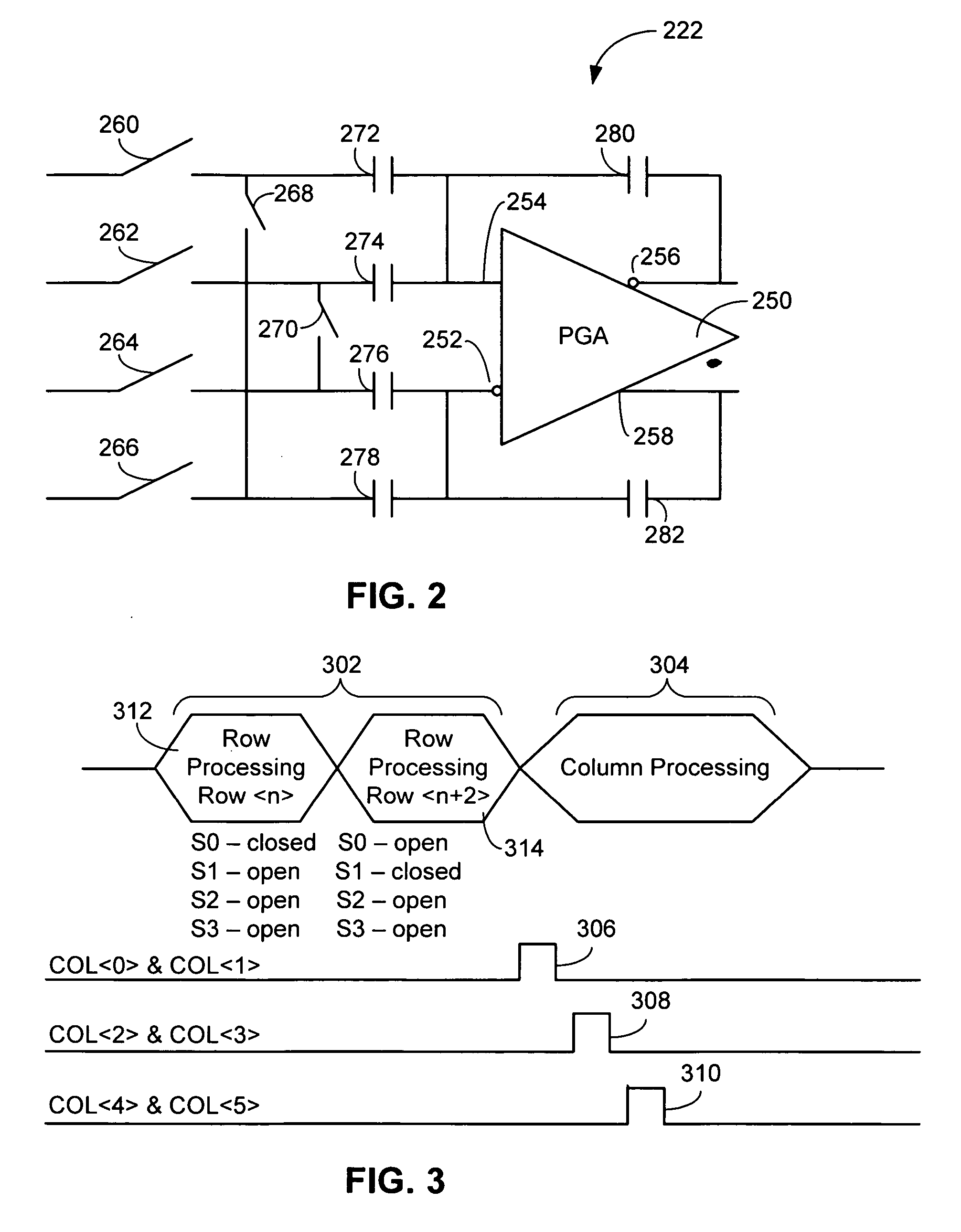

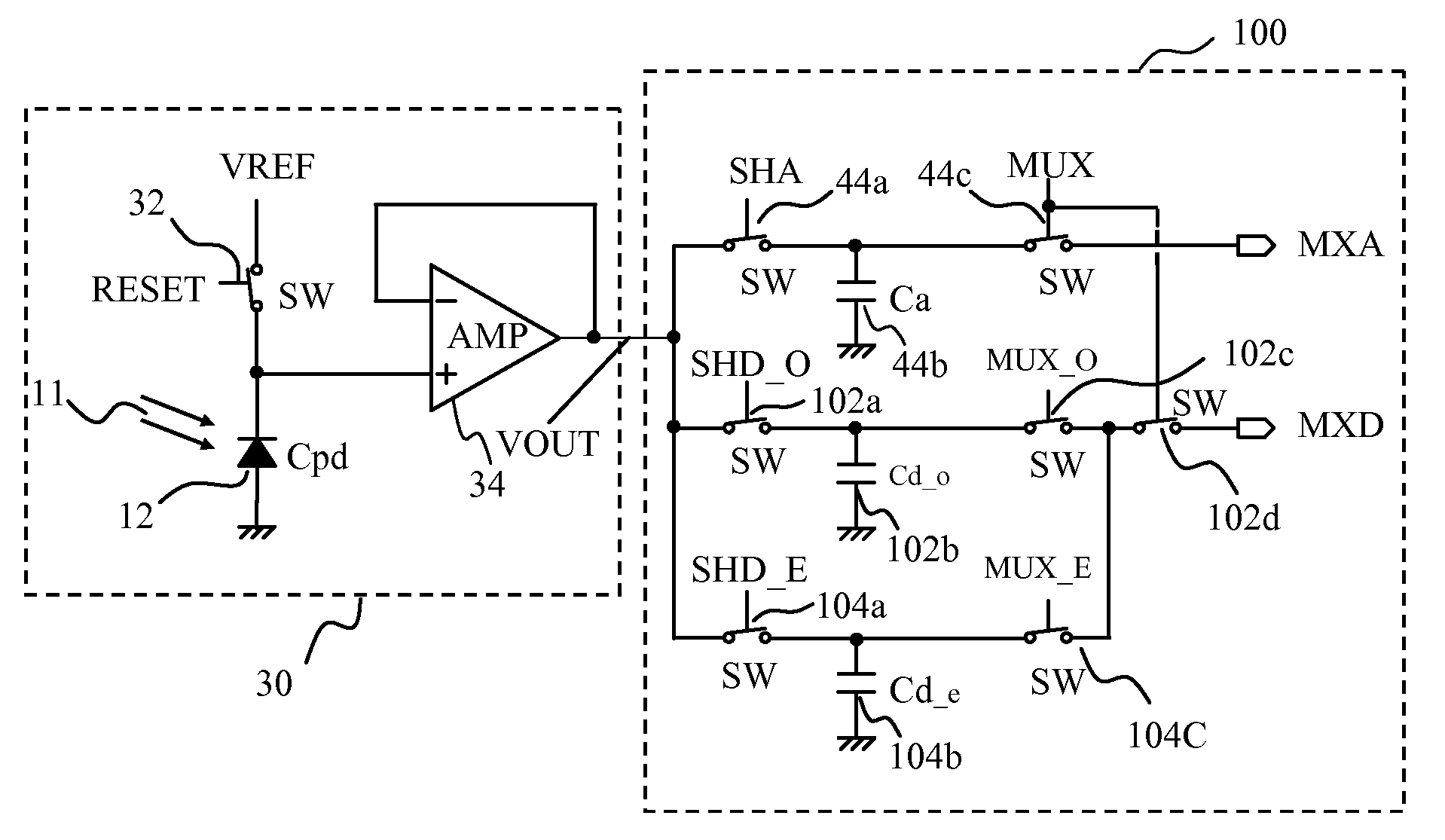

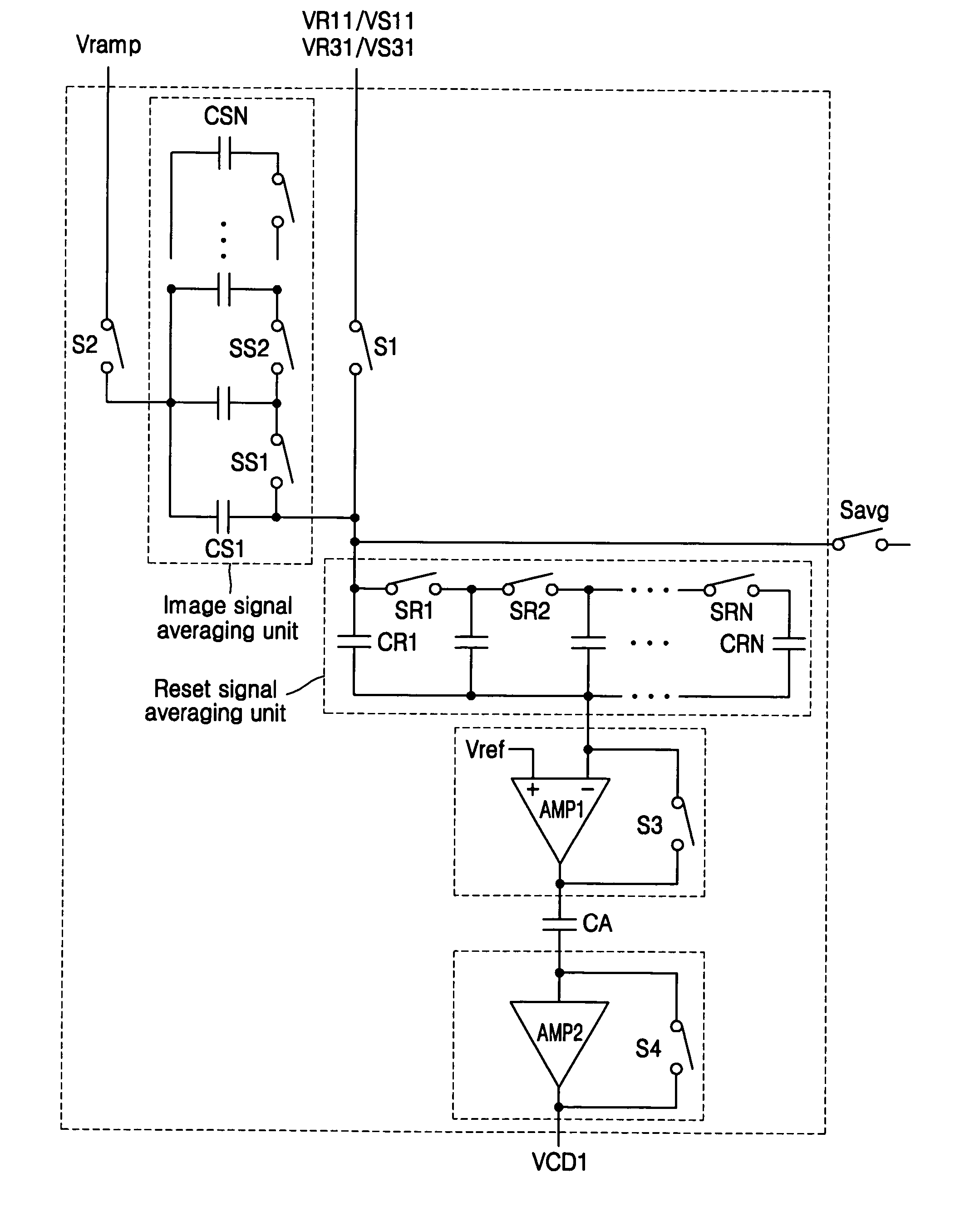

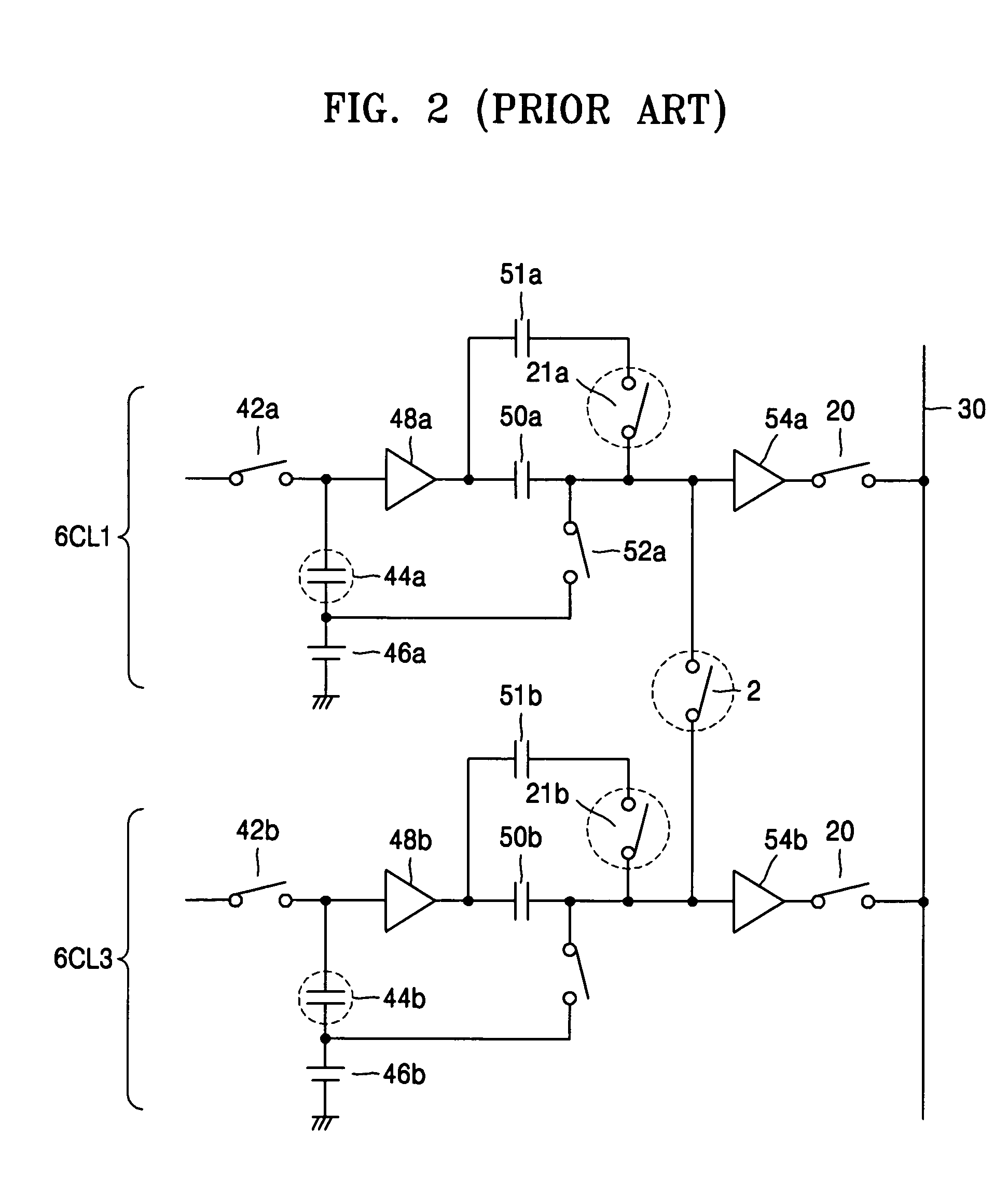

Method and circuit for performing correlated double sub-sampling (CDSS) of pixels in an active pixel sensor (APS) array

ActiveUS20050206752A1Television system detailsTelevision system scanning detailsCMOS sensorSensor array

A method and circuit for performing Correlated Double Sub-Sampling (CDSS) of pixels in an active pixel sensor (APS) array. Each pixel outputs a reset voltage and then an image signal voltage. The method and the apparatus subsamples a plurality (L2 ) of pixels by: storing L2 analog reset charges output from the L2 pixels into a first set of (N2) storage capacitors, and combining the (L2) reset charges; storing L2 analog image signal charges output from the L2 pixels into a second set of (N2) storage capacitors, and combining the (L2) image charges; and then obtaining a differential voltage (VS−VR) by subtracting (in the analog-domain) the voltage (VR) represented by the combined (L2) reset charges from the voltage (VS) represented by the combined (L2) image signal charges. When L equals one, the circuit performs conventional Correlated Double Sampling CDS upon the one pixel. When L is greater than one, the circuit performs Correlated Double Sub-Sampling (CDSS) of the L2 pixels. Dynamic selection of a subsampling ratio B (where B equals 1:L2 and L ranges from 1 up to N) is supported. Averaging units used to combine the reset and image signal charges, and analog-to-digital converters (ADCs) for converting the differential voltage to a digital pixel data, may be commonly biased by the same variable bias voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com