Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2999results about How to "High resistivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

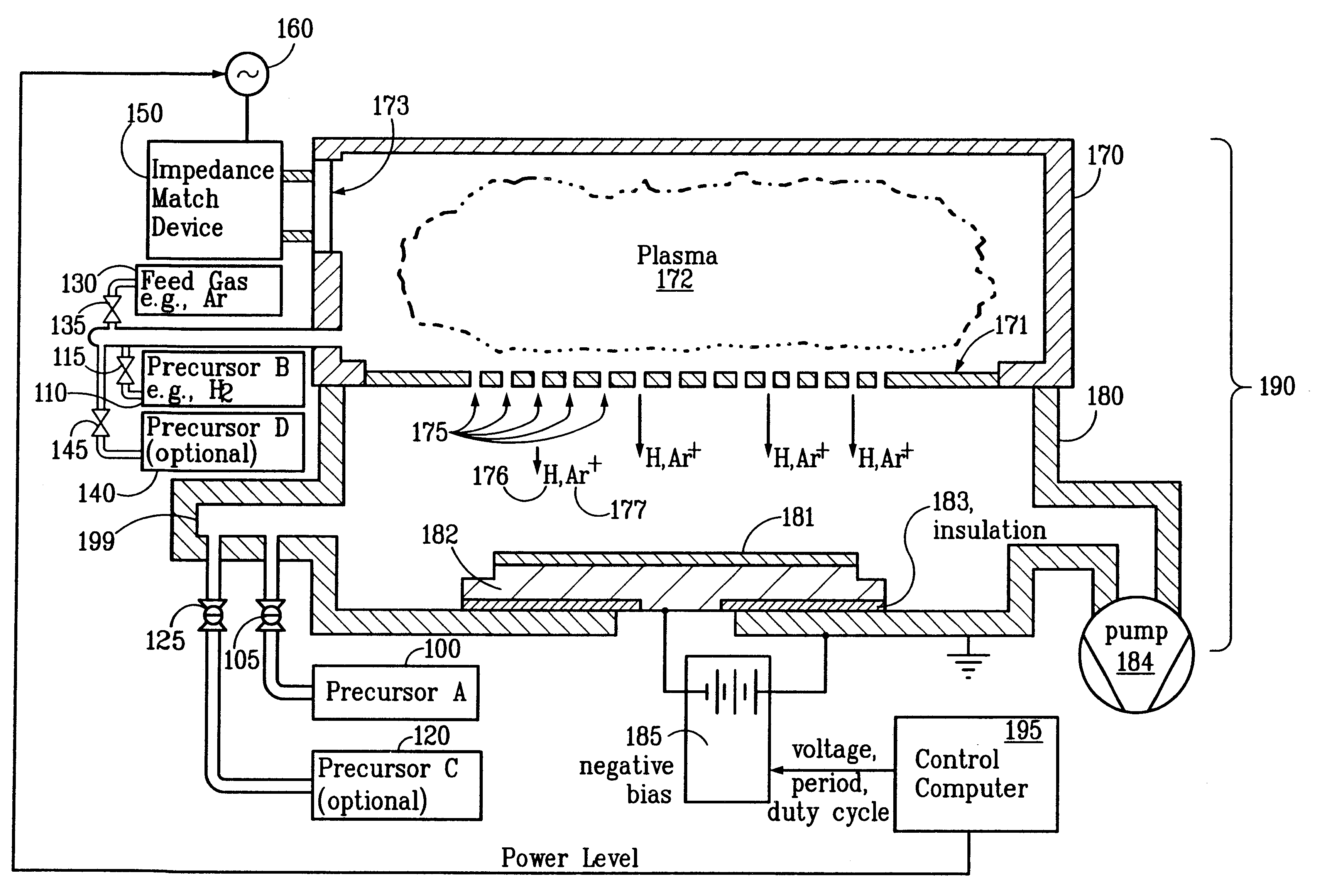

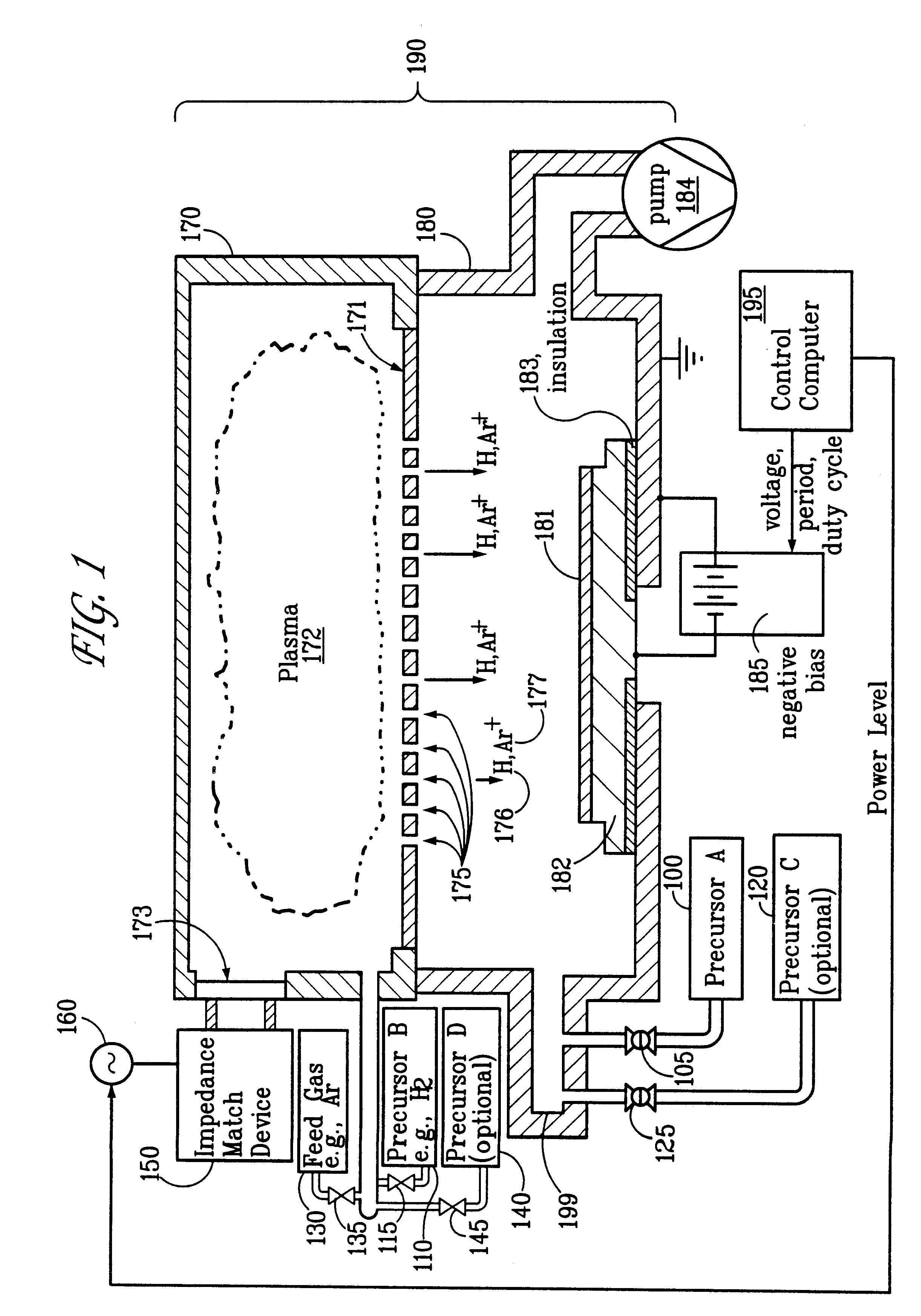

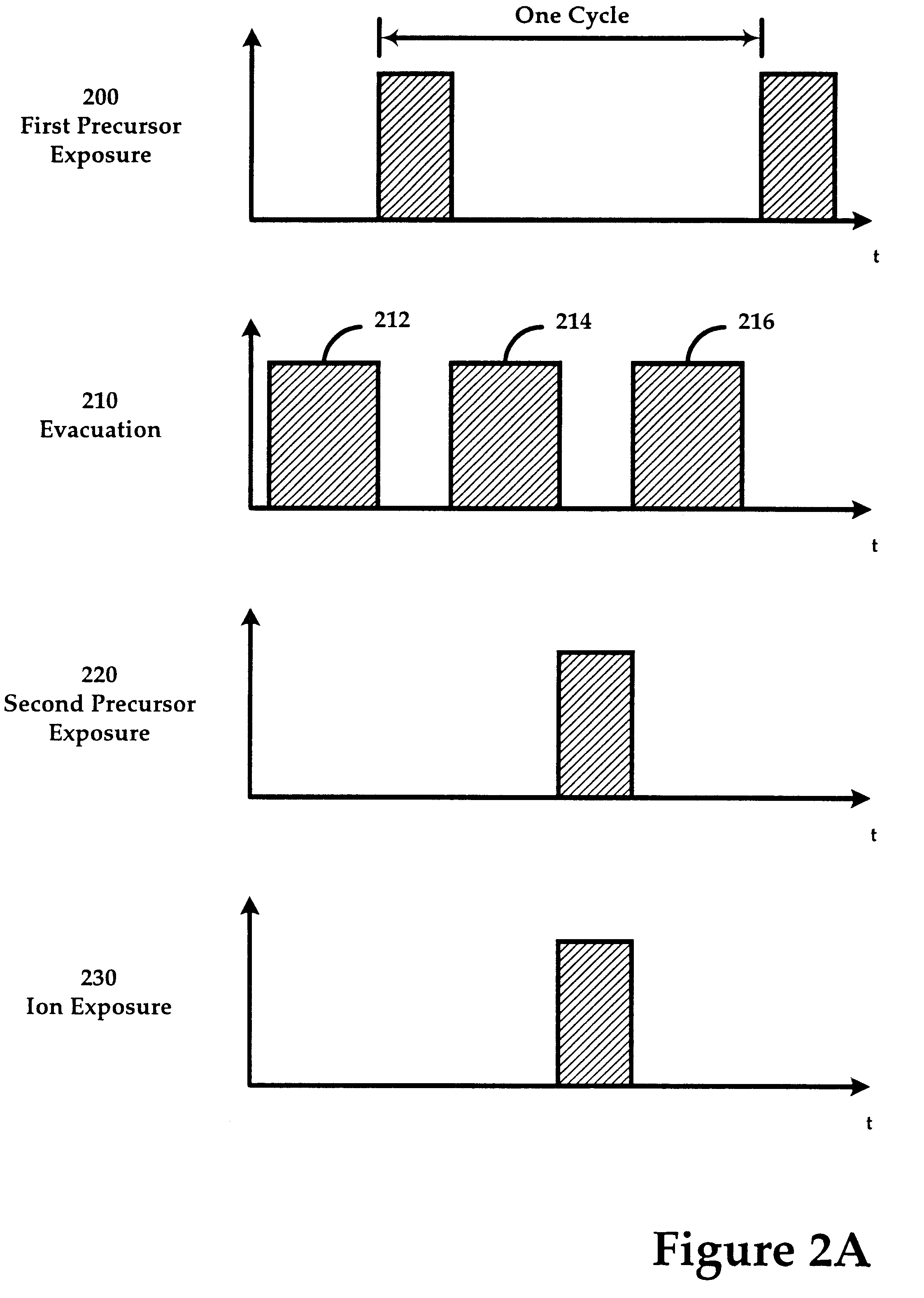

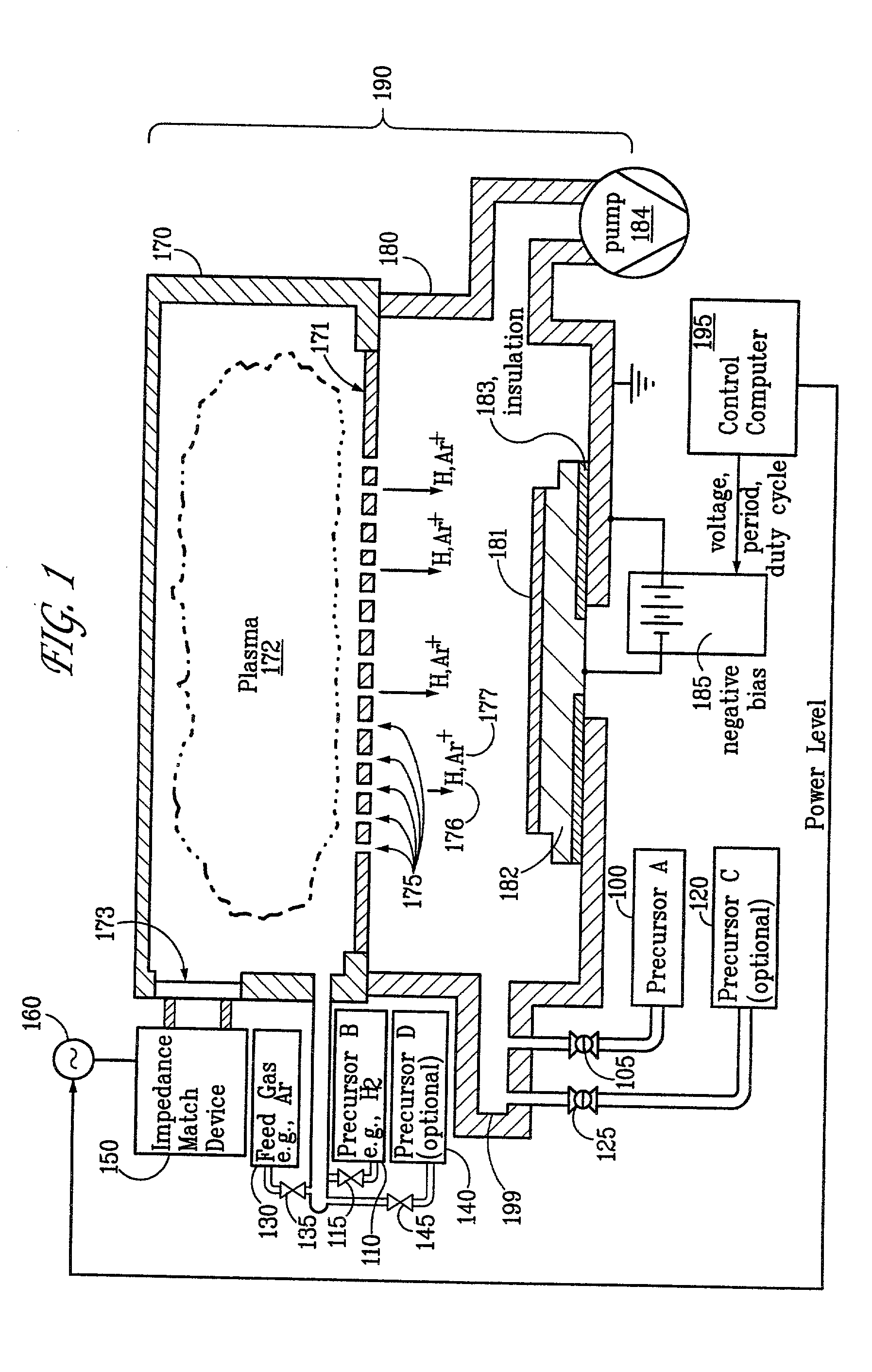

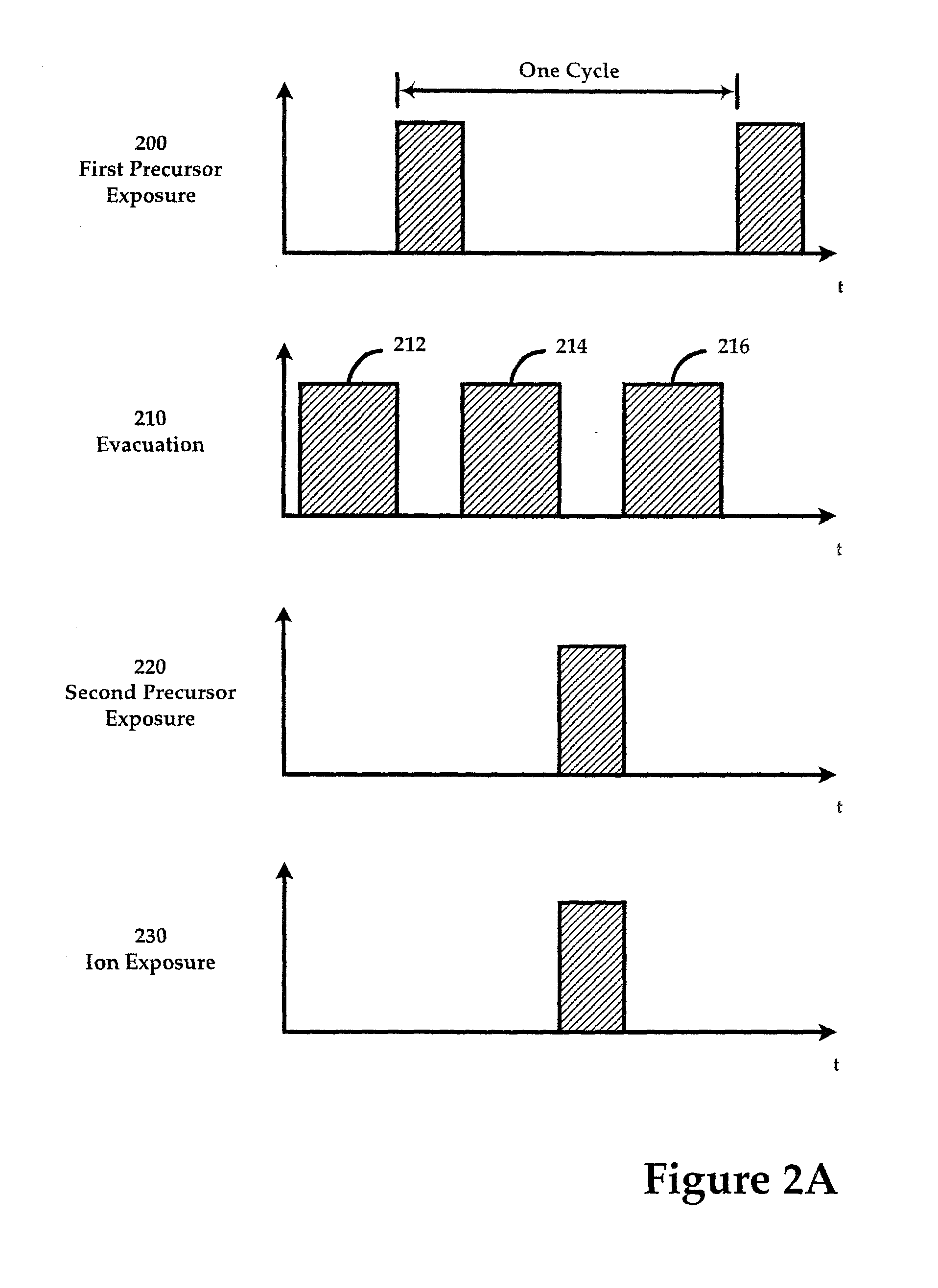

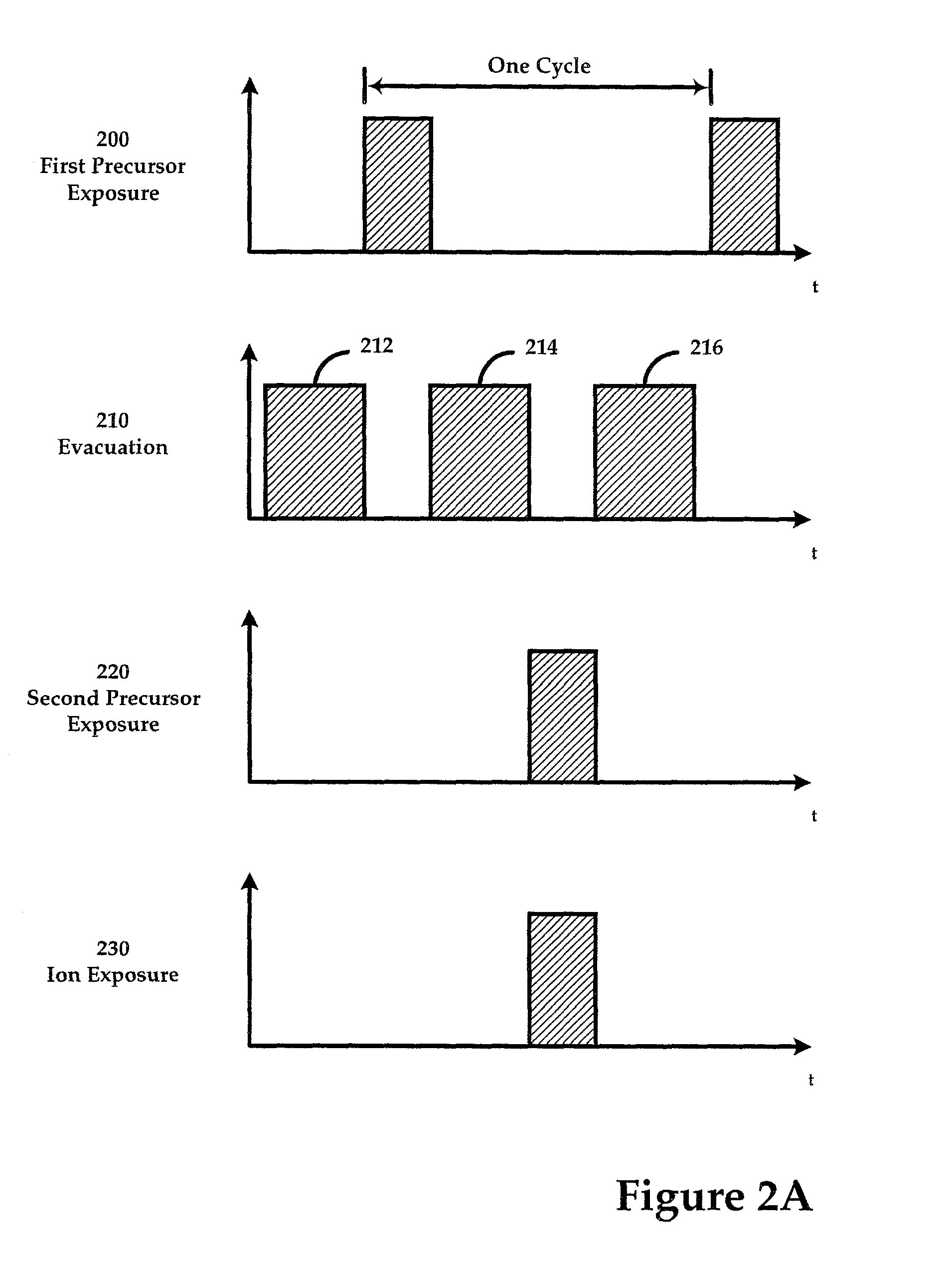

Sequential method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

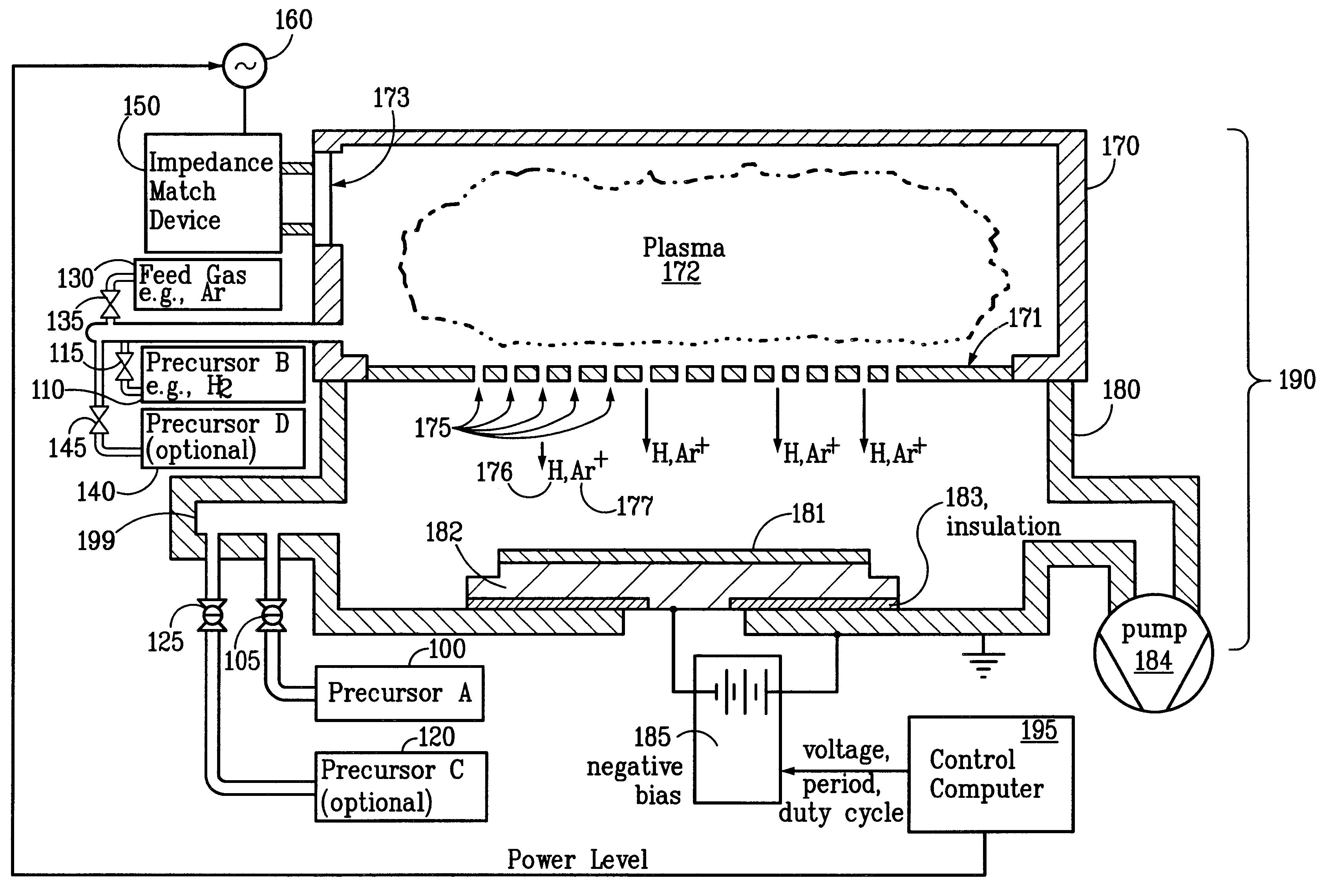

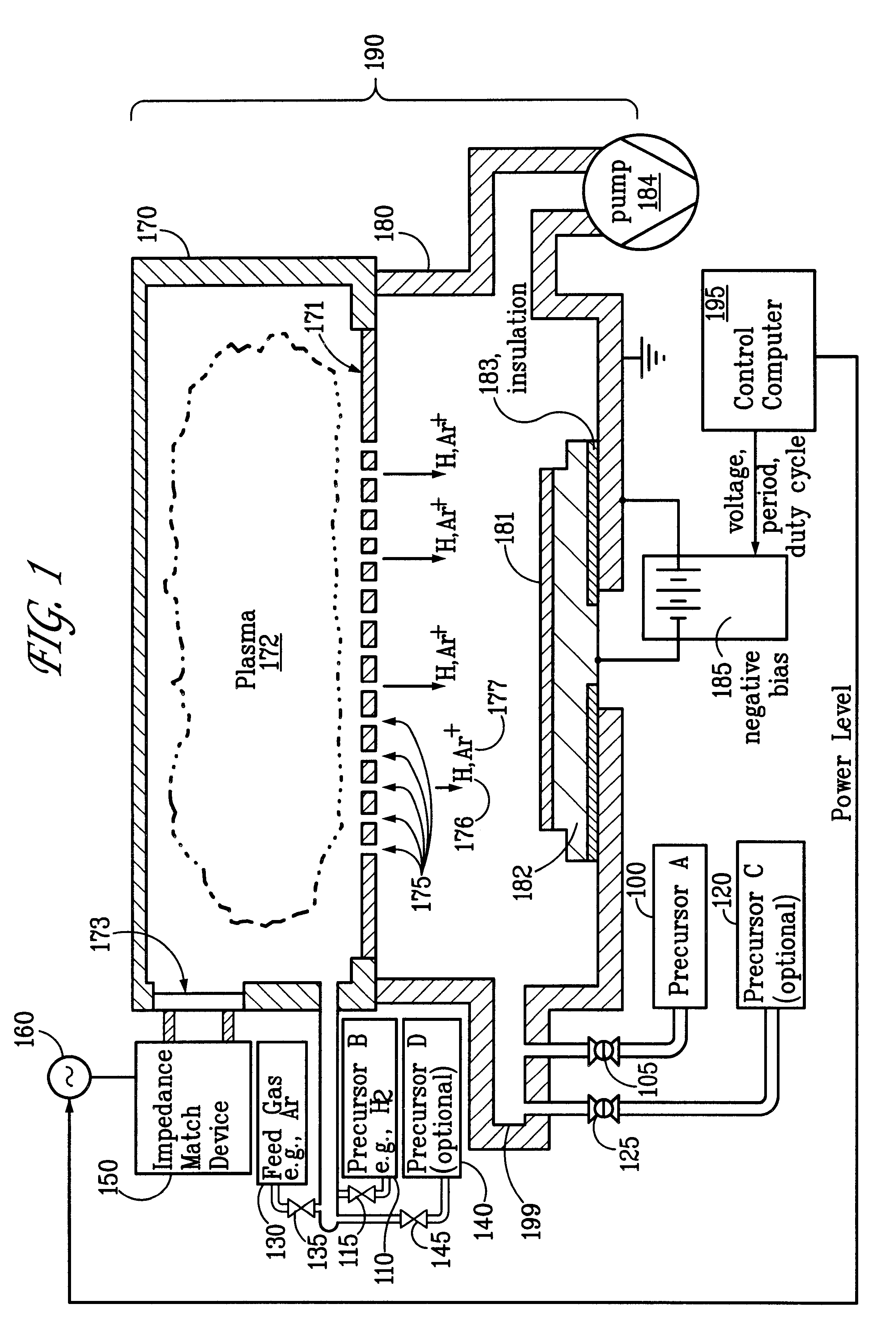

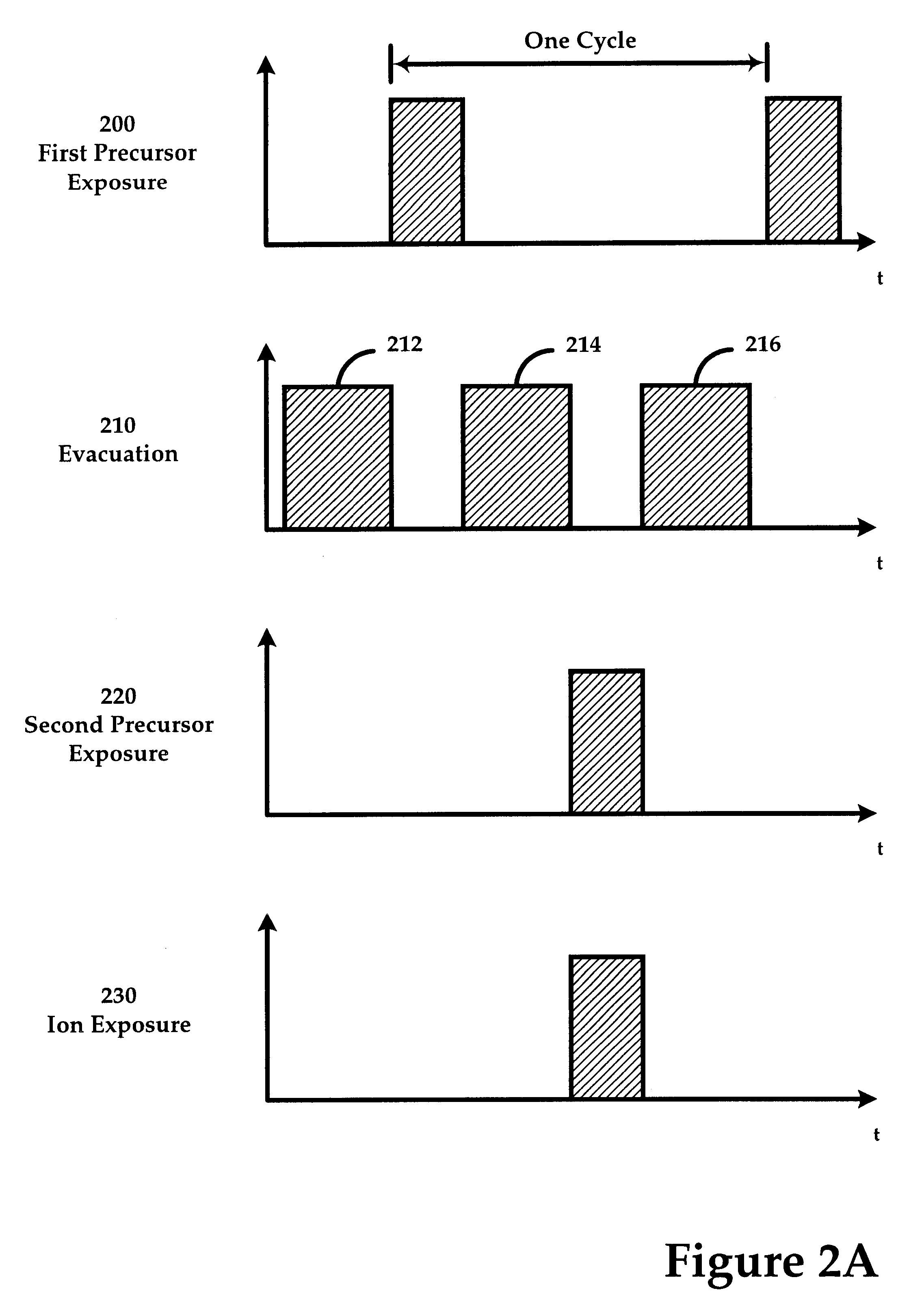

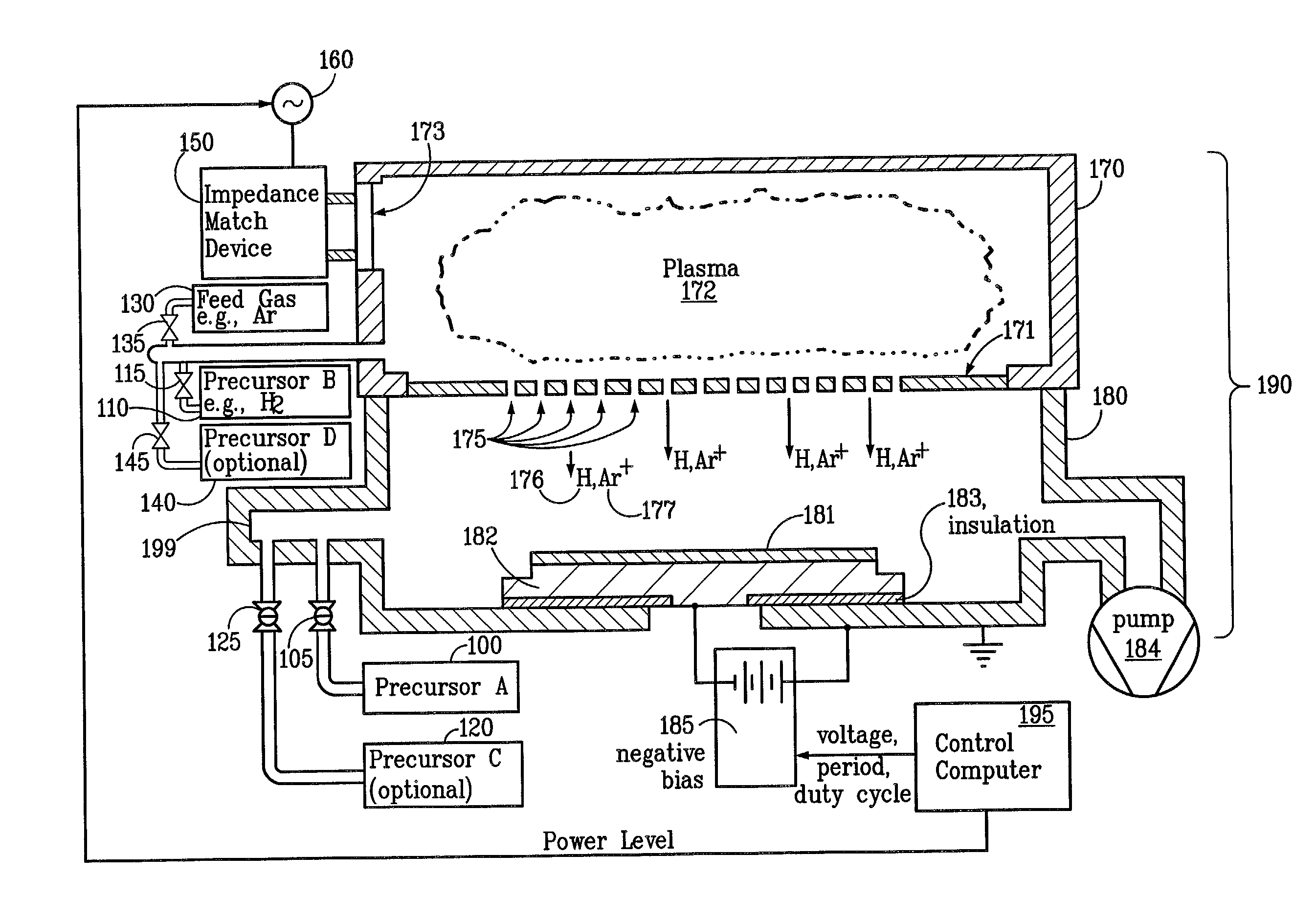

InactiveUS6428859B1Faster efficient meanSimple methodVacuum evaporation coatingSputtering coatingSequential methodHigh density

The present invention relates to an enhanced sequential atomic layer deposition (ALD) technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; and, 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:NOVELLUS SYSTEMS

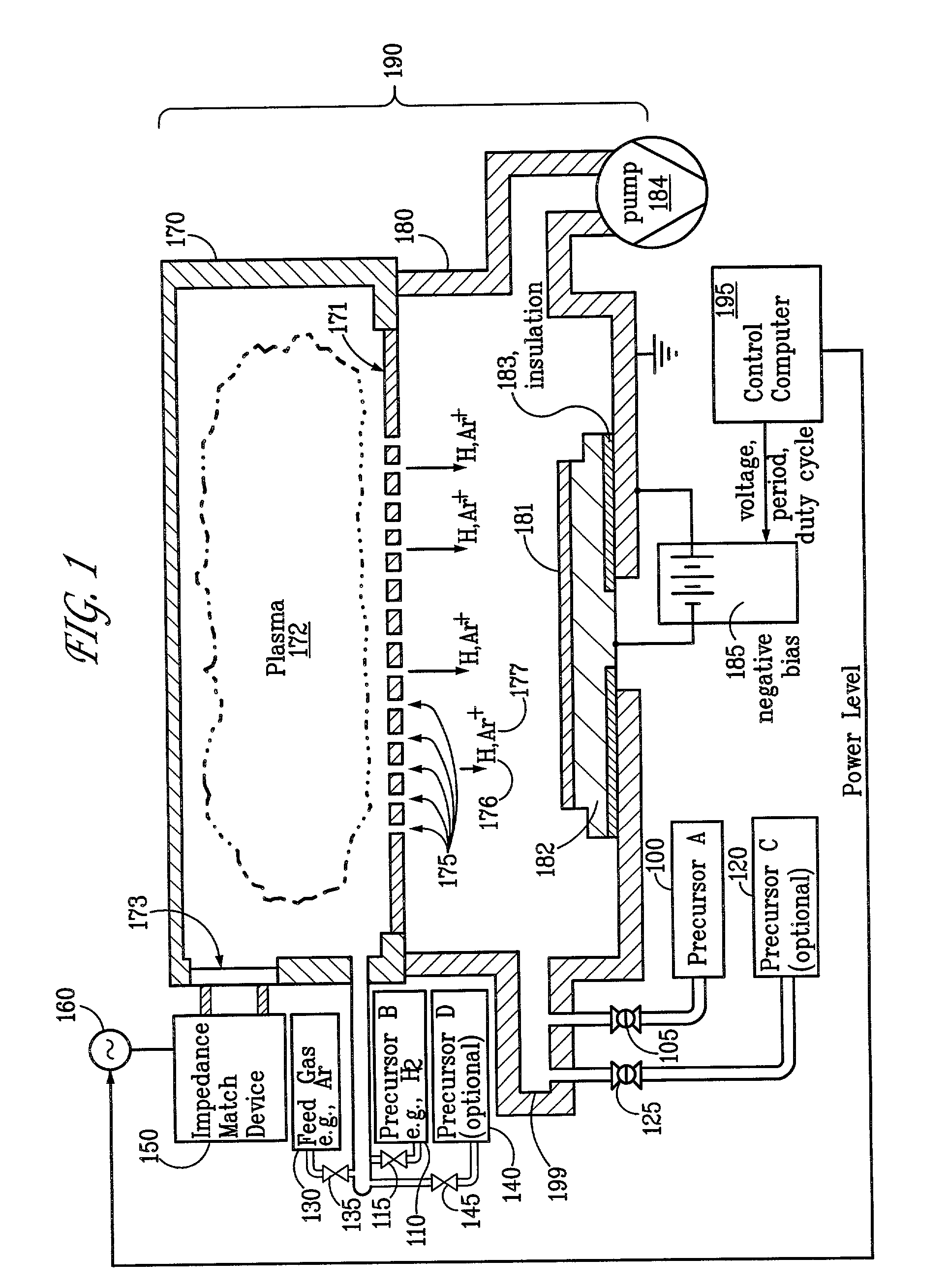

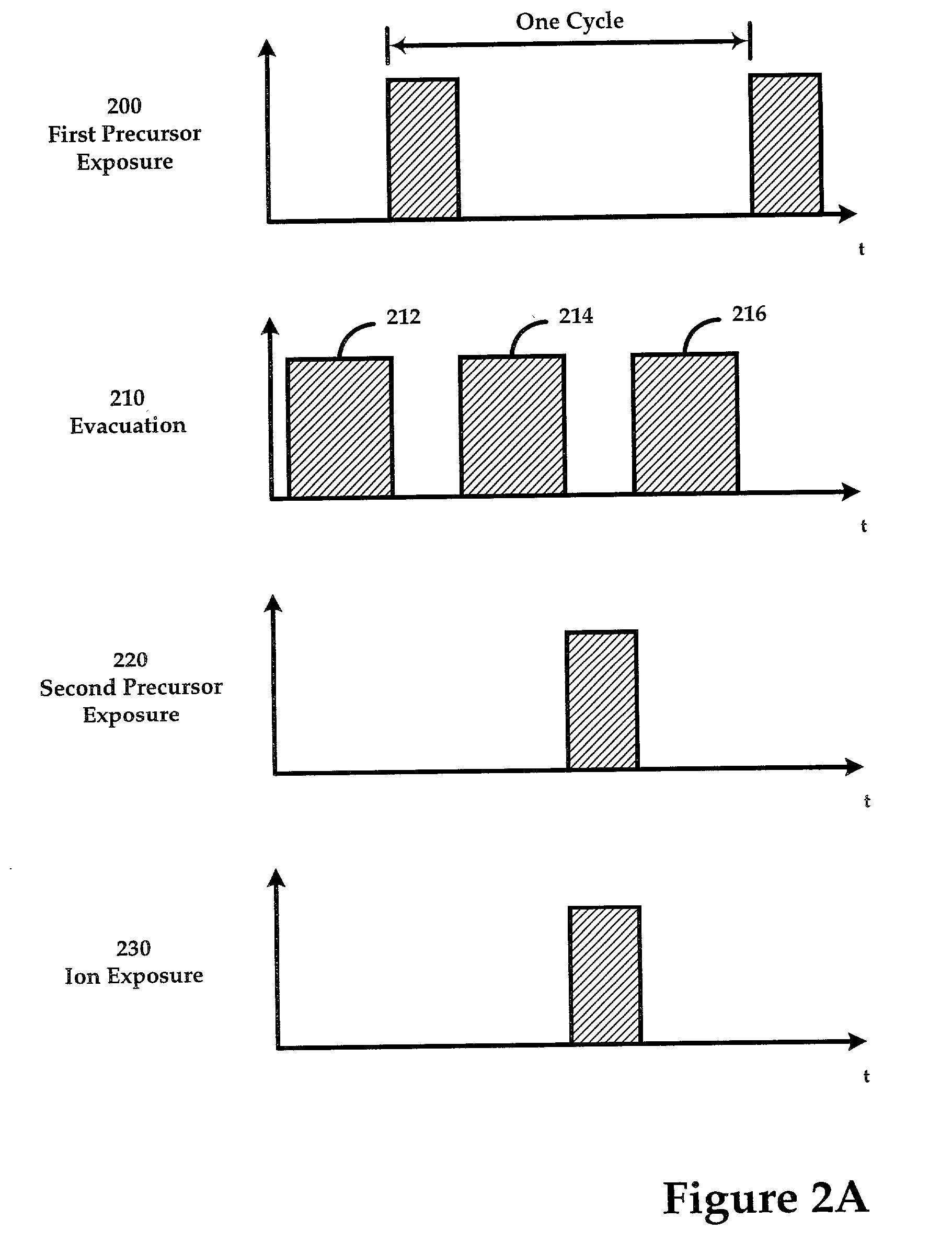

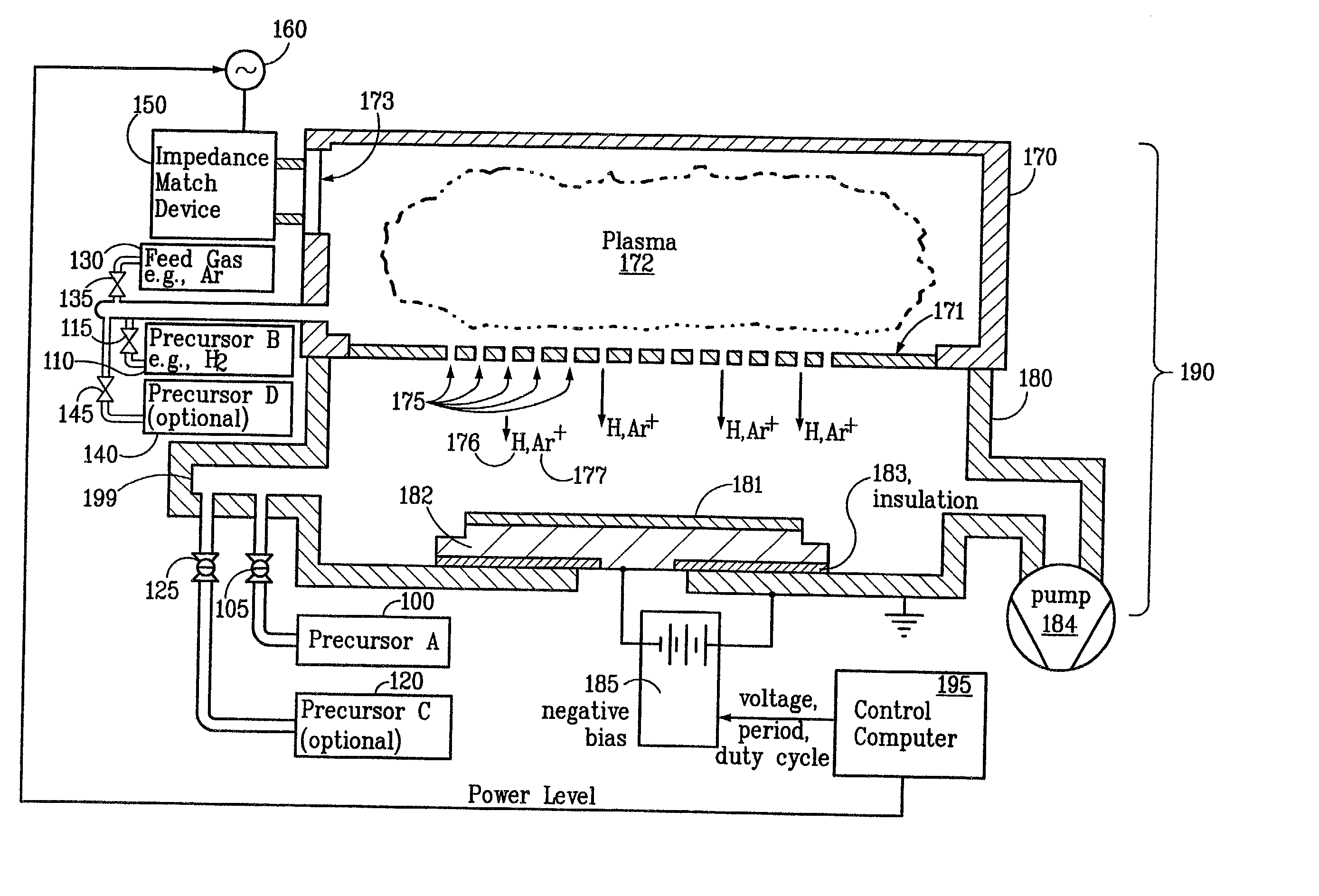

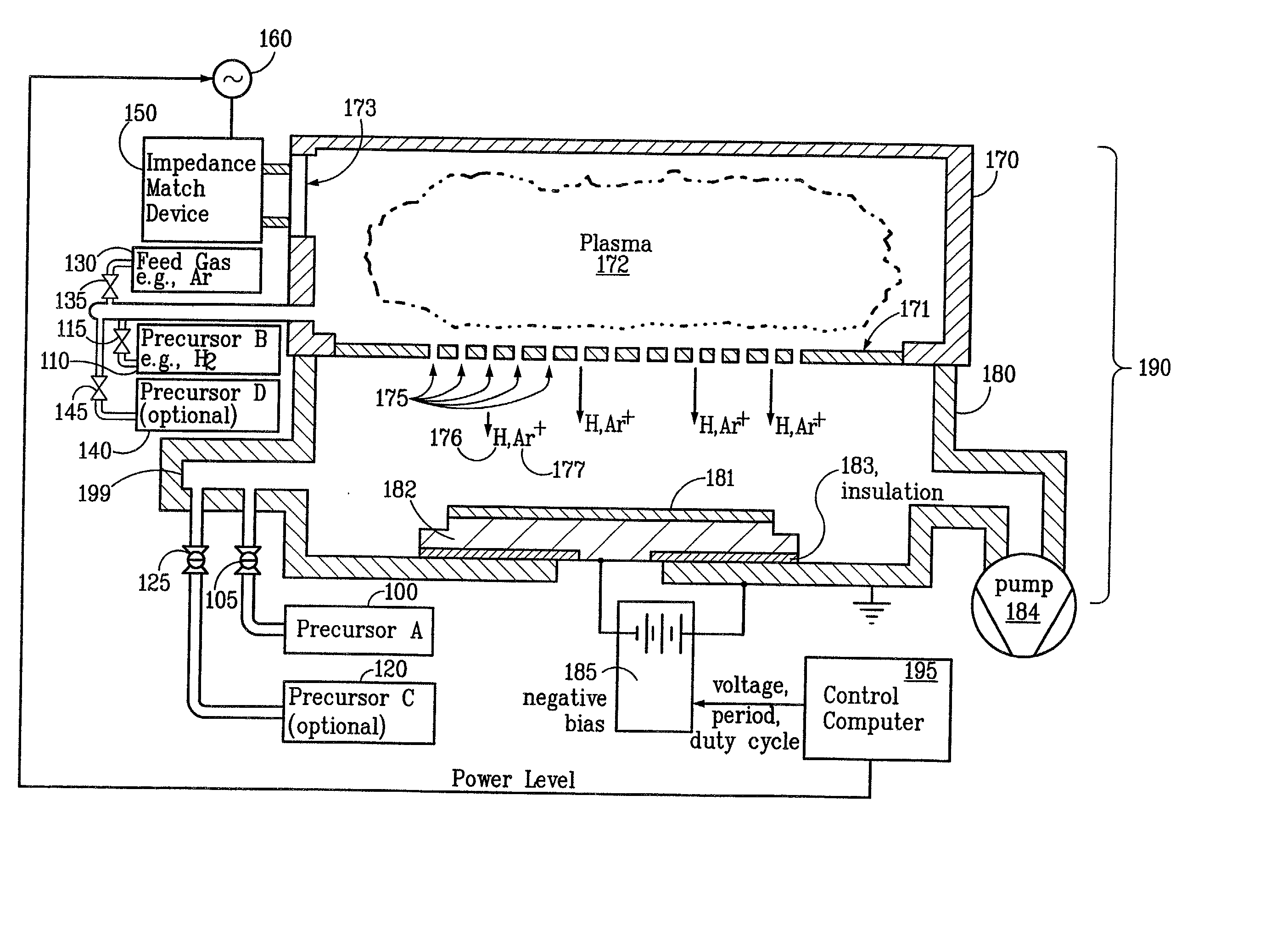

System and method for modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS20020104481A1Faster efficient meanSimple methodSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh densitySubject matter

The present invention relates to an enhanced sequential or non-sequential atomic layer deposition (ALD) apparatus and technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method; and, 4) providing a means of improved radical generation and delivery. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. [37 C.F.R. § 1.72(b)].

Owner:ANGSTRON SYST

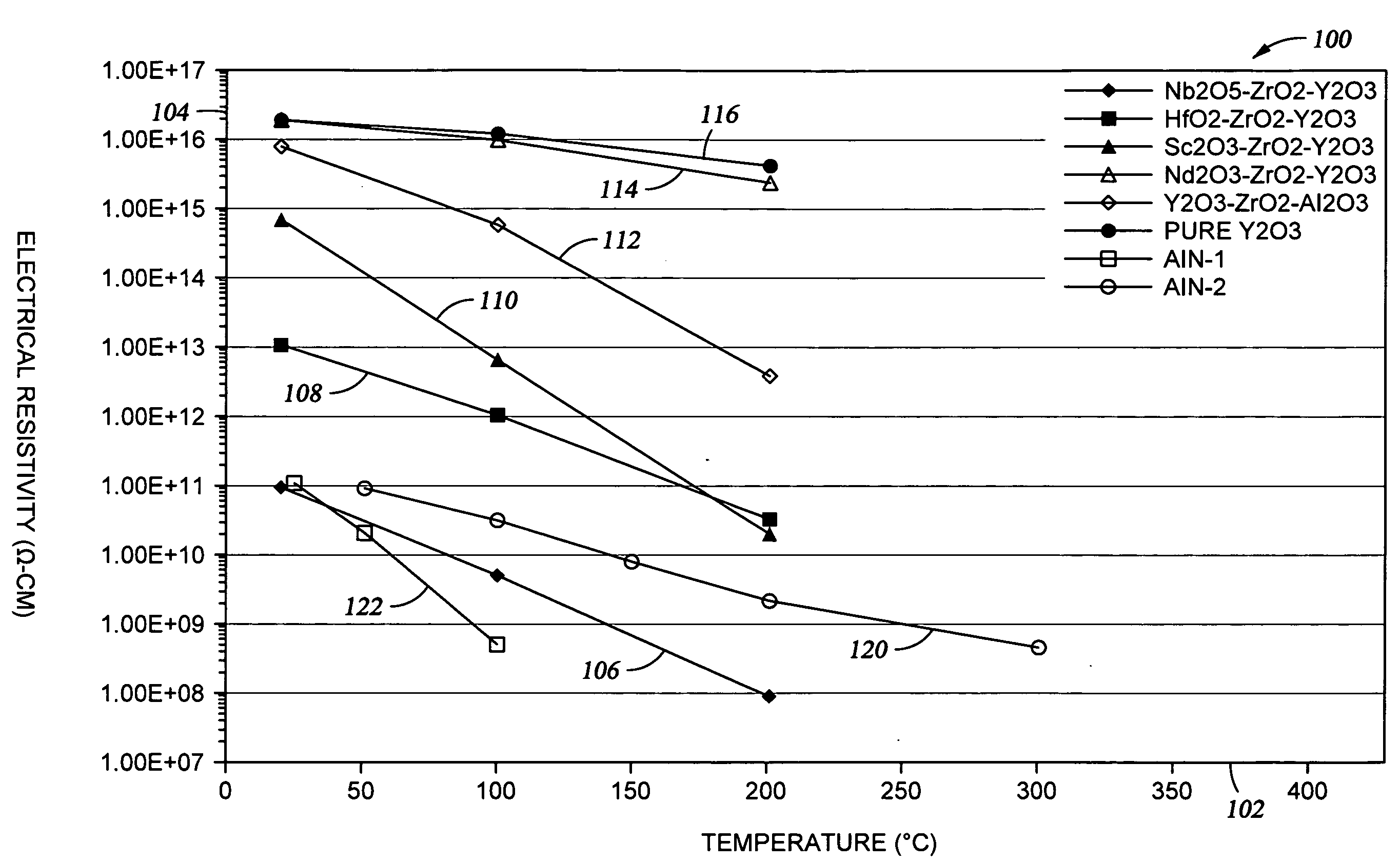

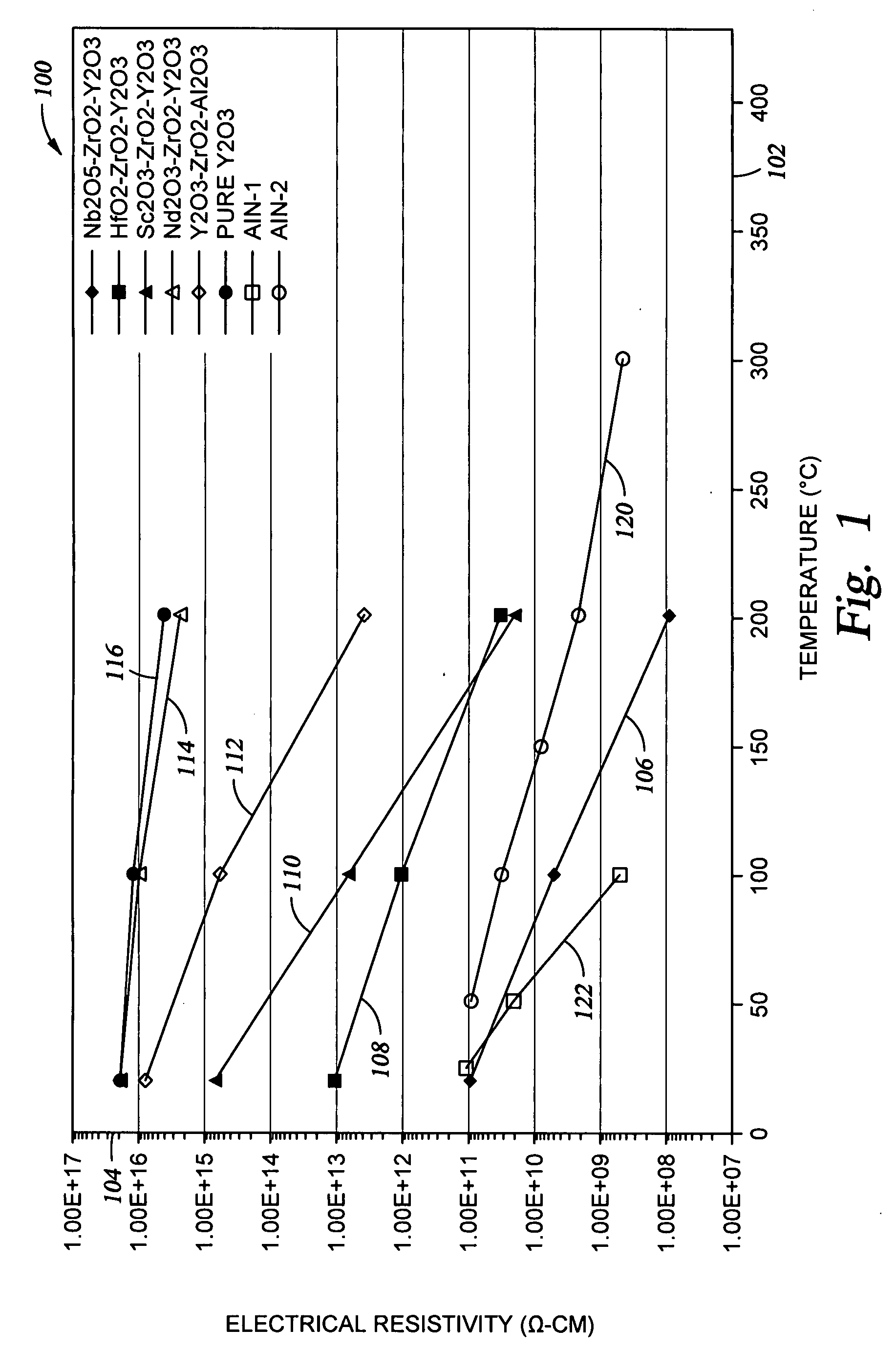

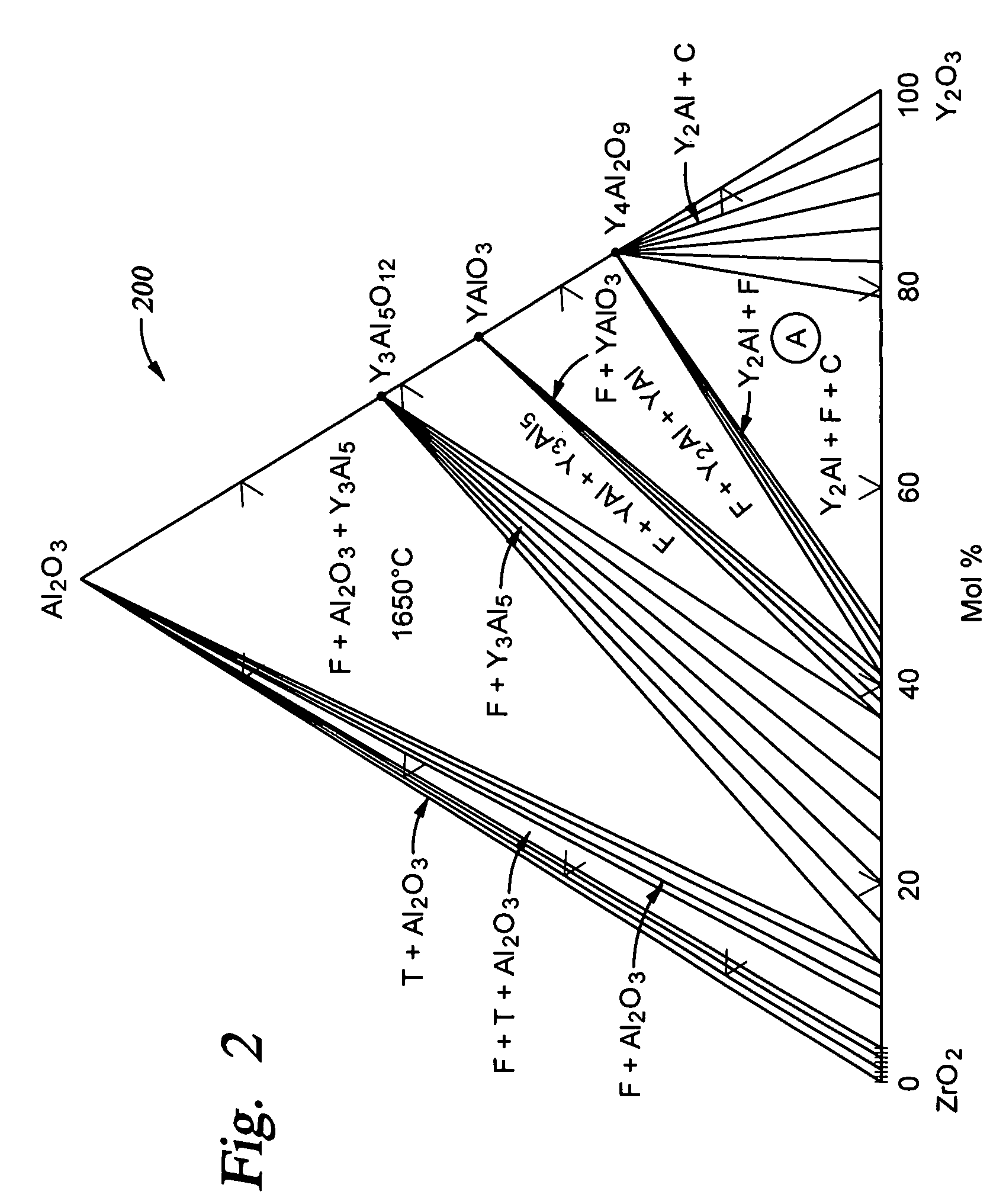

Plasma-resistant ceramics with controlled electrical resistivity

ActiveUS20090036292A1Improve plasma resistanceTailored mechanical propertiesSemiconductor/solid-state device manufacturingGlass/slag layered productsHalogenCeramic

Specialty ceramic materials which resist corrosion / erosion under semiconductor processing conditions which employ a corrosive / erosive plasma. The corrosive plasma may be a halogen-containing plasma. The specialty ceramic materials have been modified to provide a controlled electrical resistivity which suppresses plasma arcing potential.

Owner:APPLIED MATERIALS INC

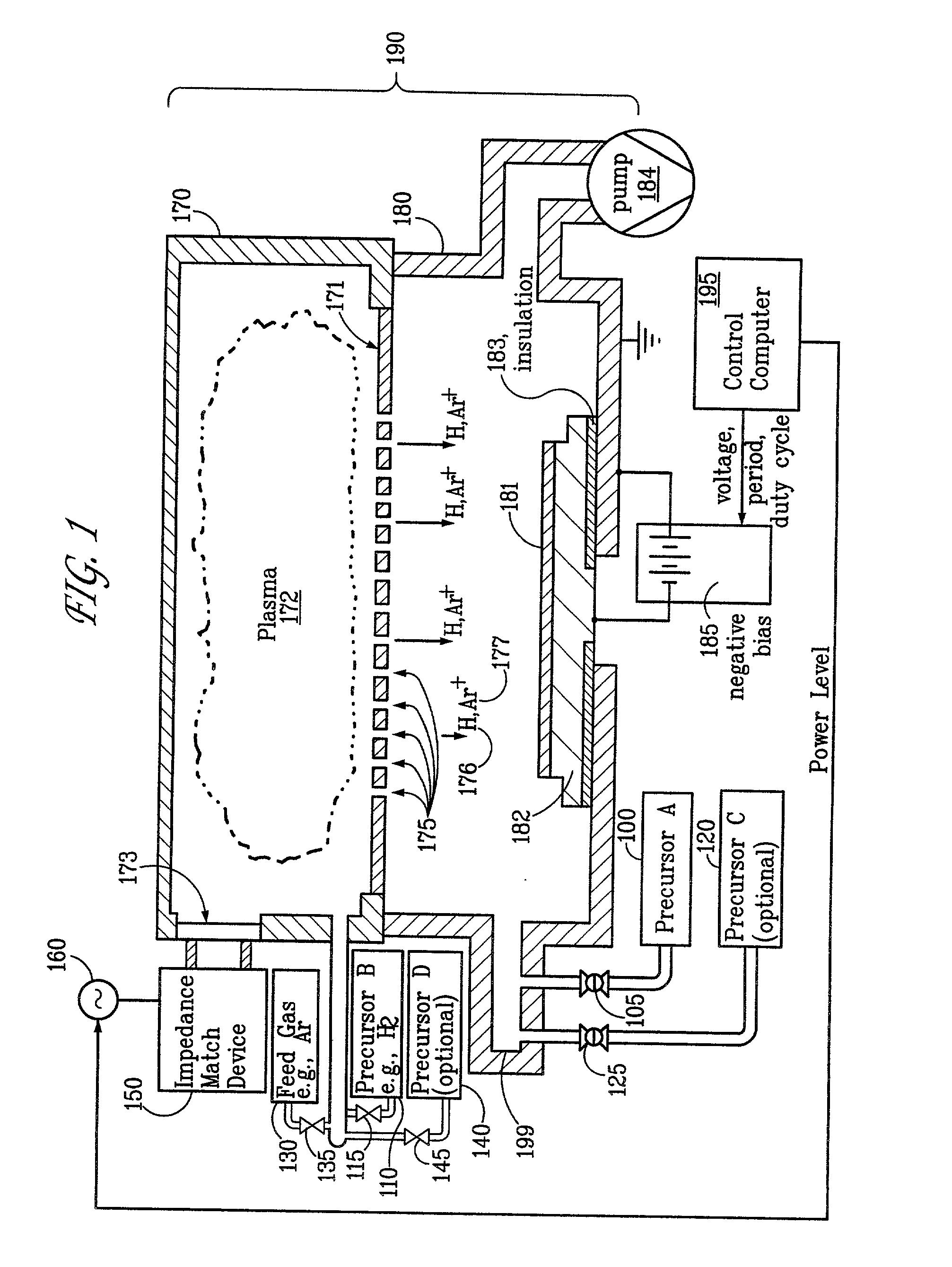

Continuous method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS6416822B1Faster efficient meanSimple methodPretreated surfacesSemiconductor/solid-state device manufacturingHigh densityVolumetric Mass Density

The present invention relates to an enhanced non-sequential atomic layer deposition (ALD) technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; and, 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method.

Owner:NOVELLUS SYSTEMS

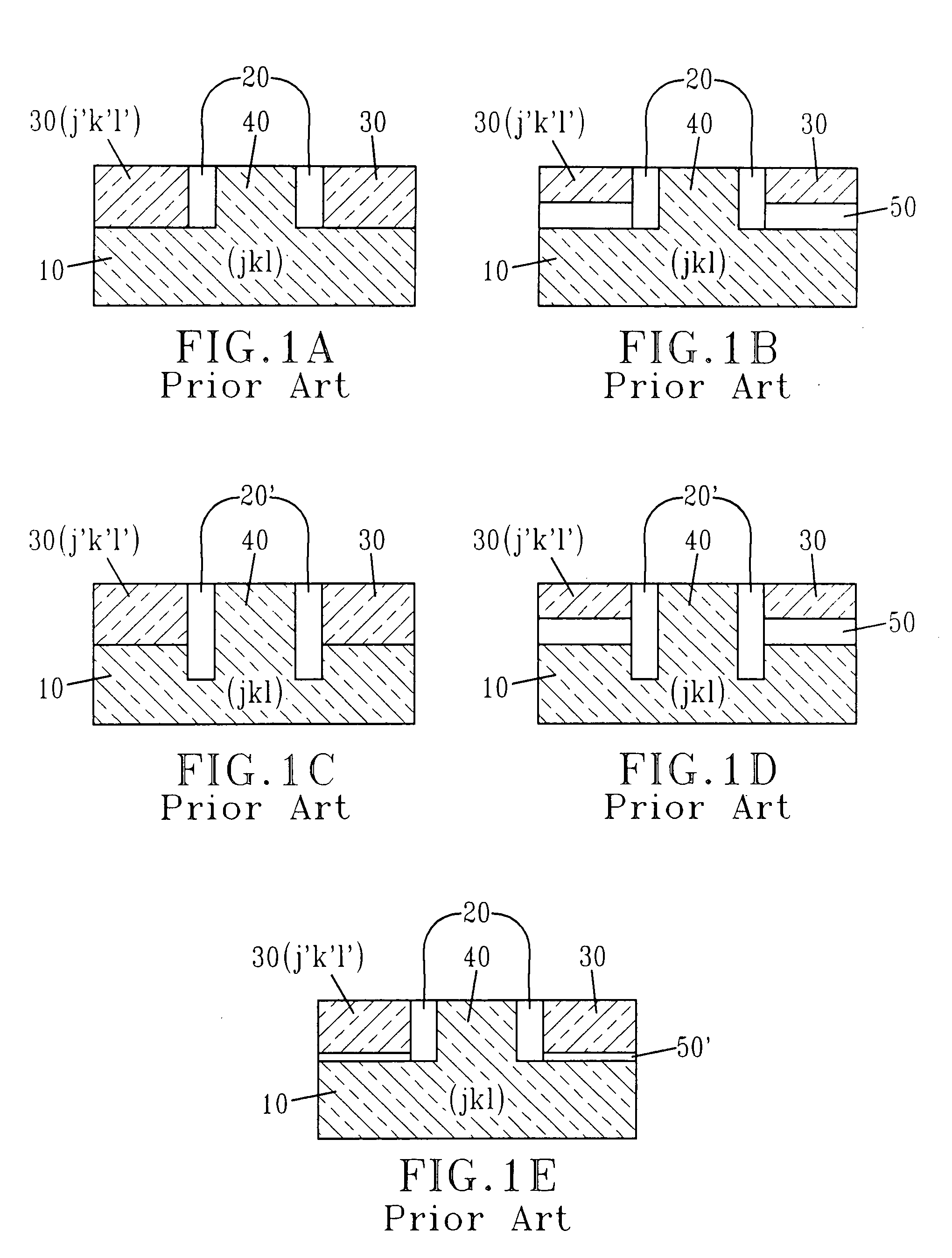

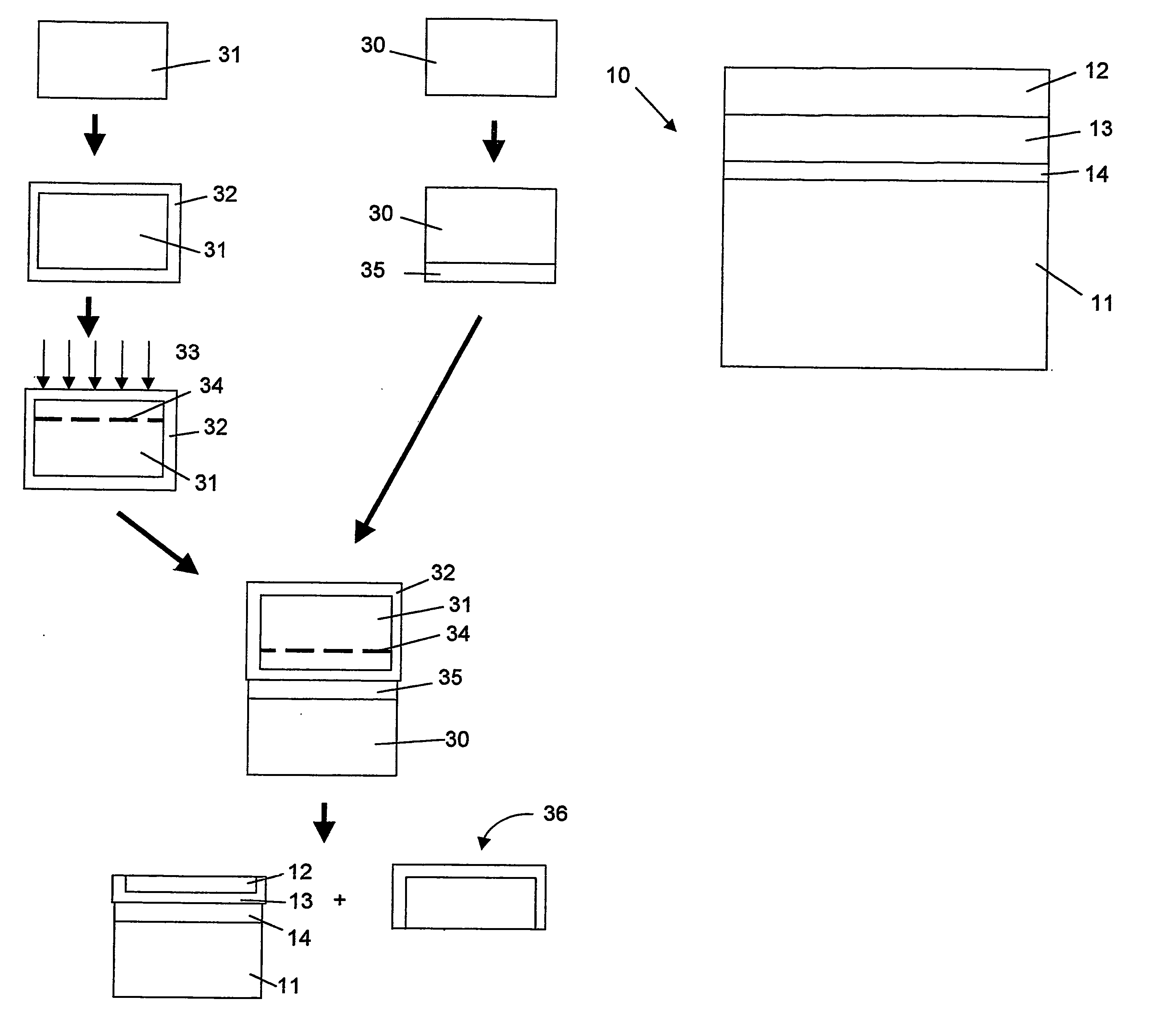

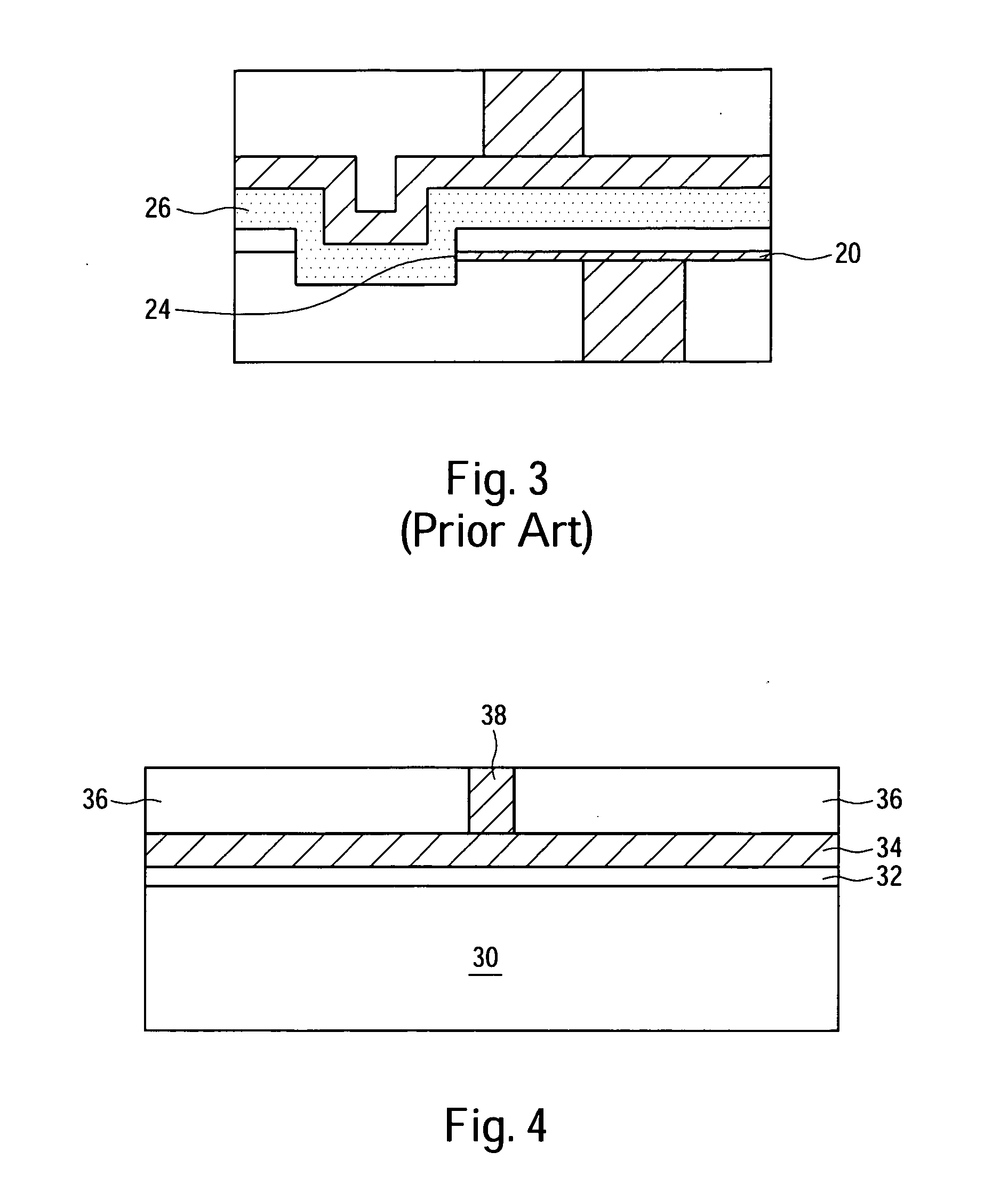

Planar substrate with selected semiconductor crystal orientations formed by localized amorphization and recrystallization of stacked template layers

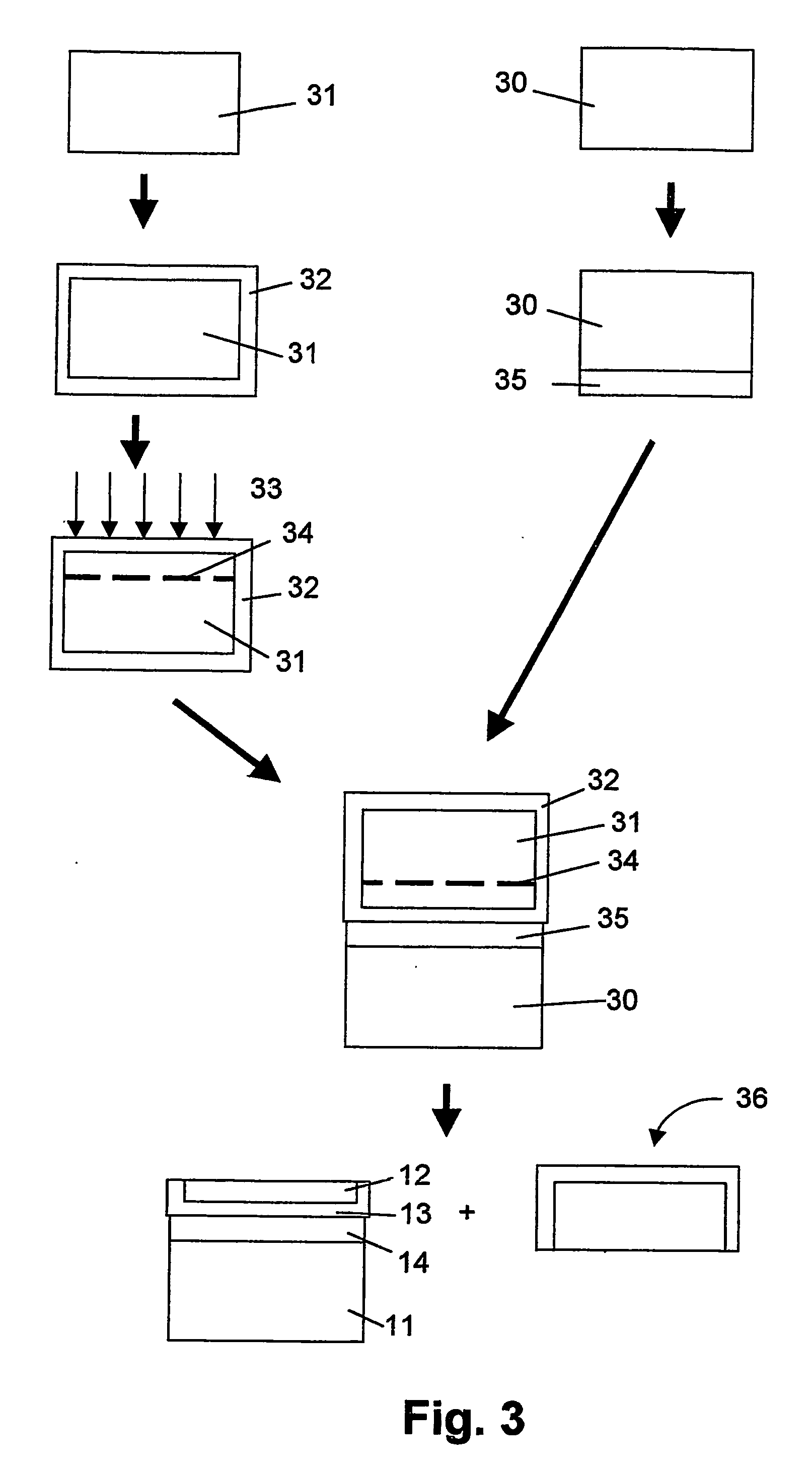

A method utilizing localized amorphization and recrystallization of stacked template layers is provided for making a planar substrate having semiconductor layers of different crystallographic orientations. Also provided are hybrid-orientation semiconductor substrate structures built with the methods of the invention, as well as such structures integrated with various CMOS circuits comprising at least two semiconductor devices disposed on different surface orientations for enhanced device performance.

Owner:GLOBALFOUNDRIES INC

Continuous method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS20020164423A1Faster efficient meanSimple methodPretreated surfacesSolid state diffusion coatingHigh densityOptoelectronics

The present invention relates to an enhanced sequential atomic layer deposition (ALD) technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; and, 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method.

Owner:NOVELLUS SYSTEMS

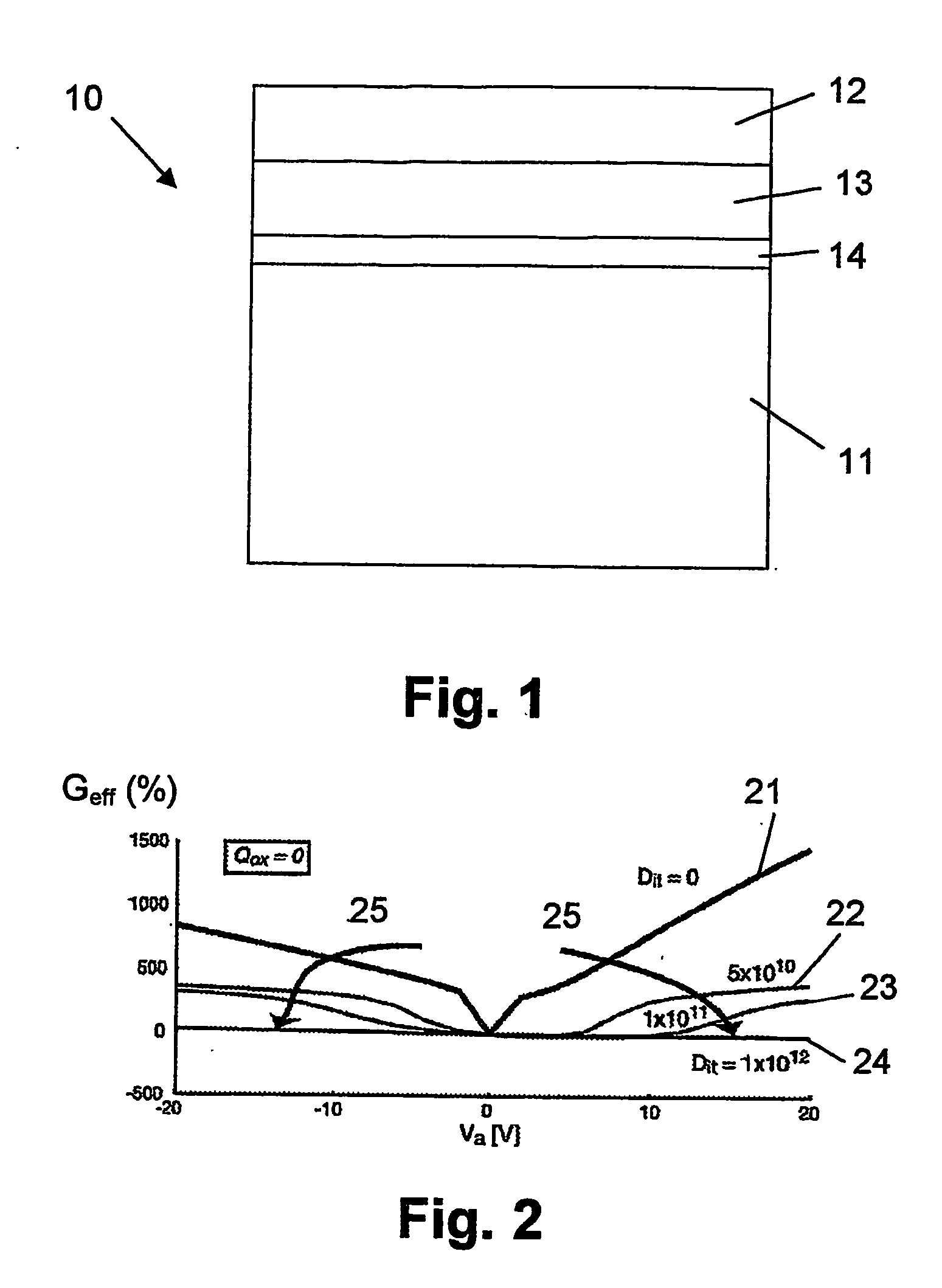

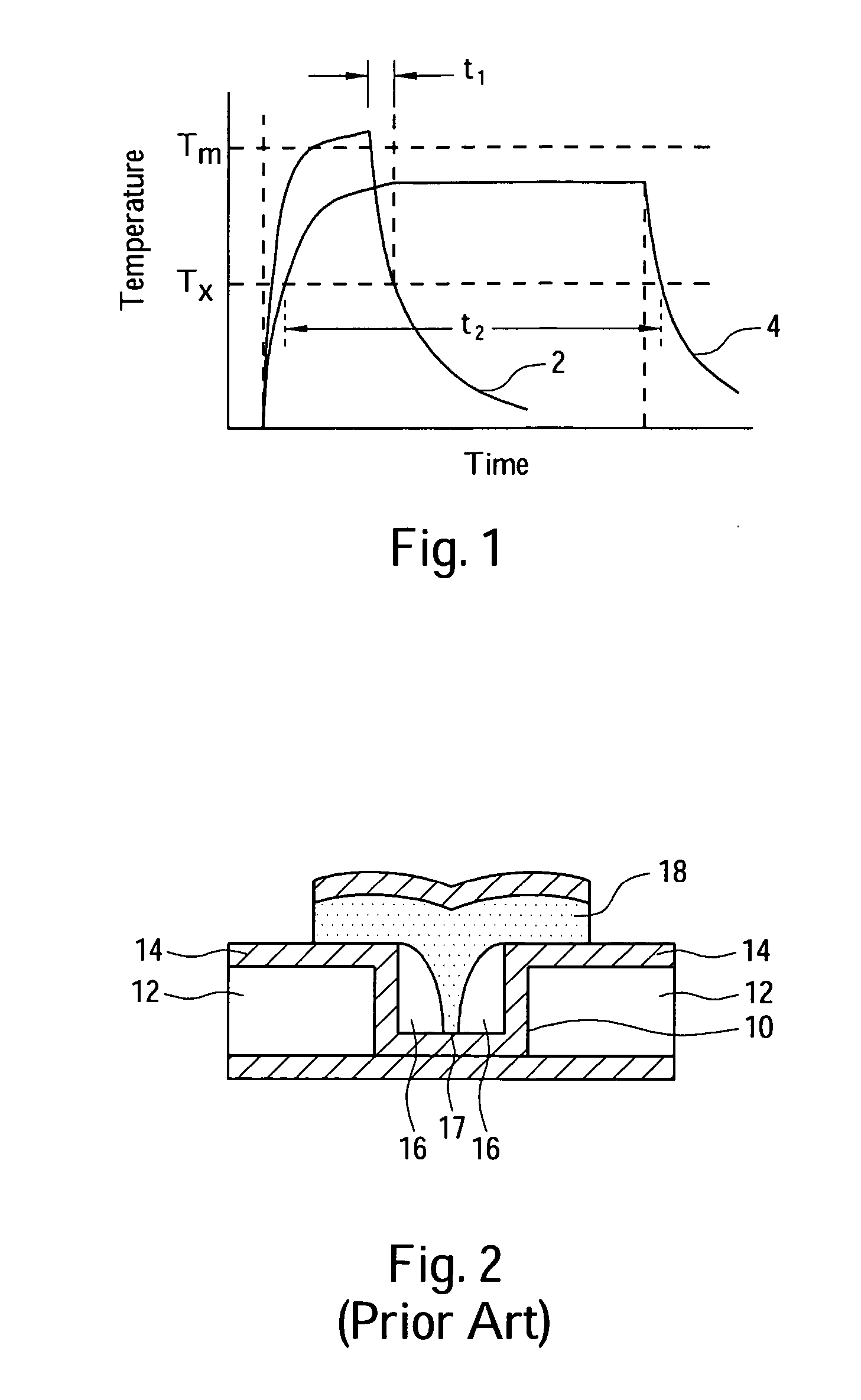

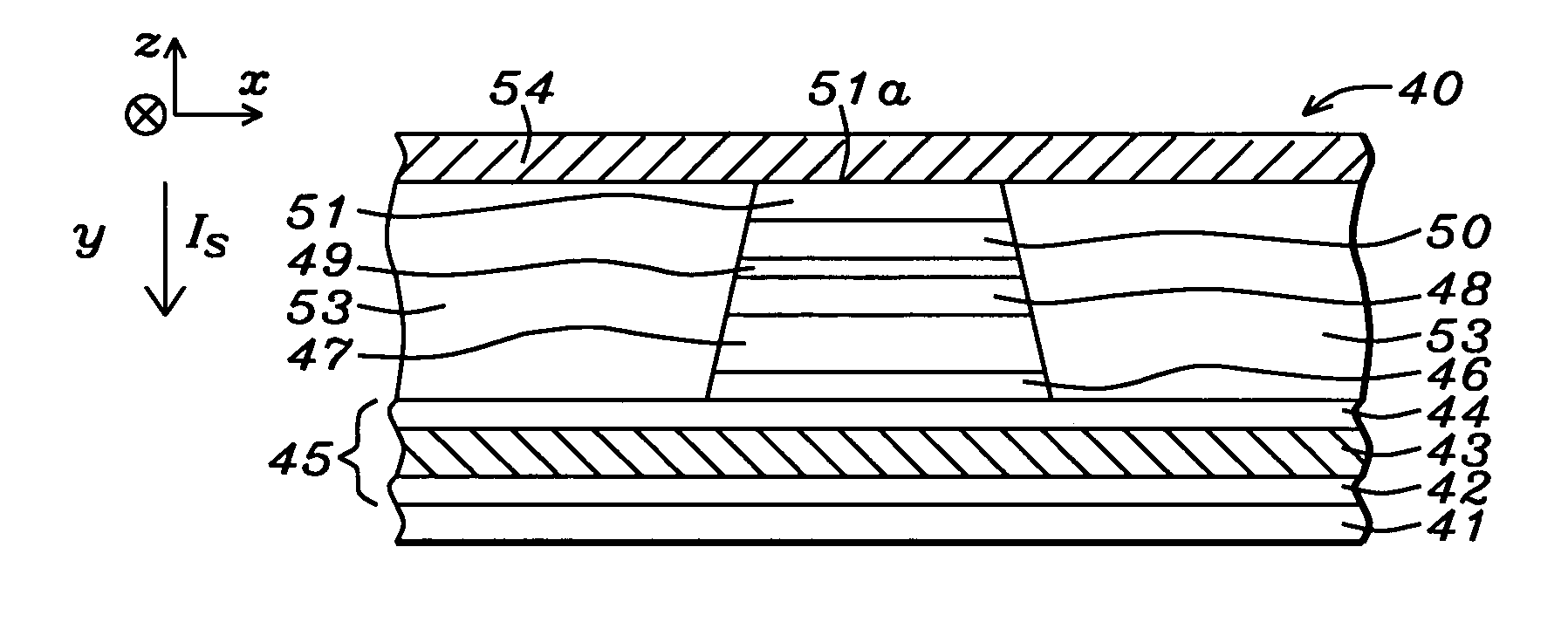

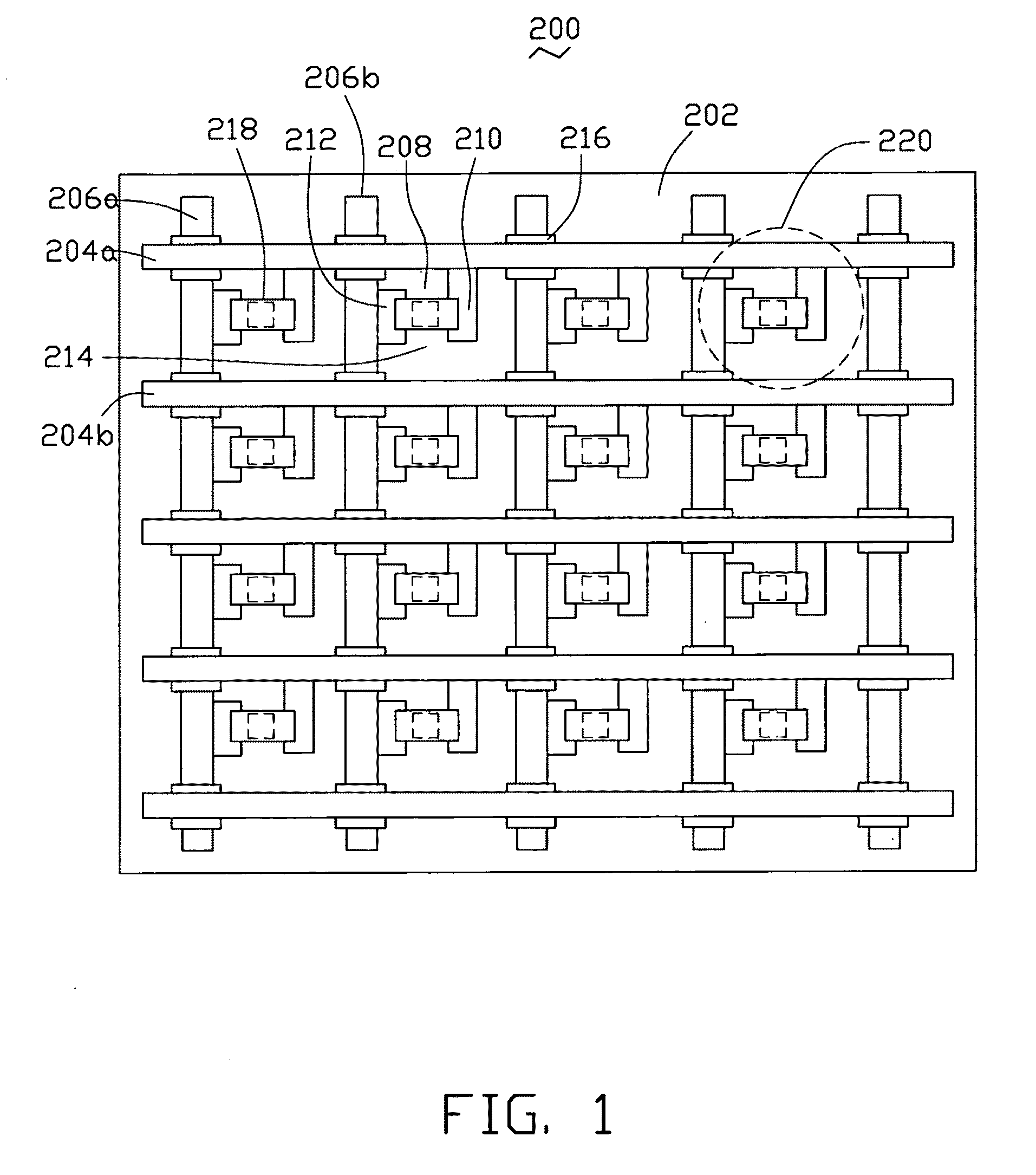

Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

InactiveUS20070032040A1Reduce and minimiseElectrical losses are reducedSolid-state devicesSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

The present invention provides a method of manufacturing a multilayer semiconductor structure featuring reduced ohmic losses with respect to standard multilayer semiconductor structures. The semiconductor structure comprises a high resistivity silicon substrate with resistivity higher than 3 KΩ.cm, an active semiconductor layer and an insulating layer in between the silicon substrate and the active semiconductor layer. The method comprises suppressing ohmic losses inside the high resistivity silicon substrate by increasing, with regard to prior art devices, charge trap density between the insulating layer and the silicon substrate. In particular this may be obtained by applying an intermediate layer in between the silicon substrate and the insulating layer, the intermediate layer comprising grains having a size, wherein the mean size of the grains of the intermediate layer is smaller than 150 nm, preferably smaller than 50 nm.

Owner:UNIV CATHOLIQUE DE LOVAIN

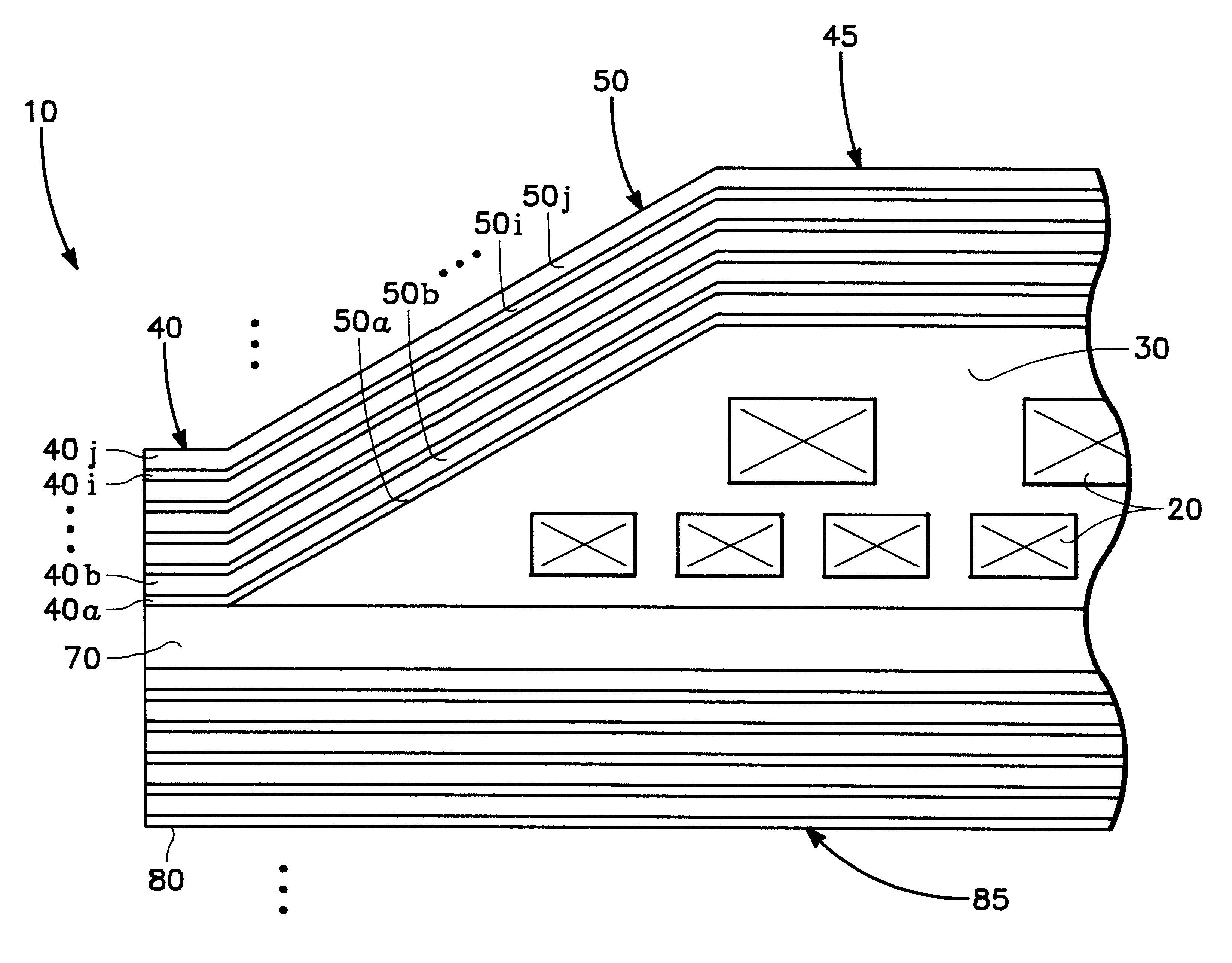

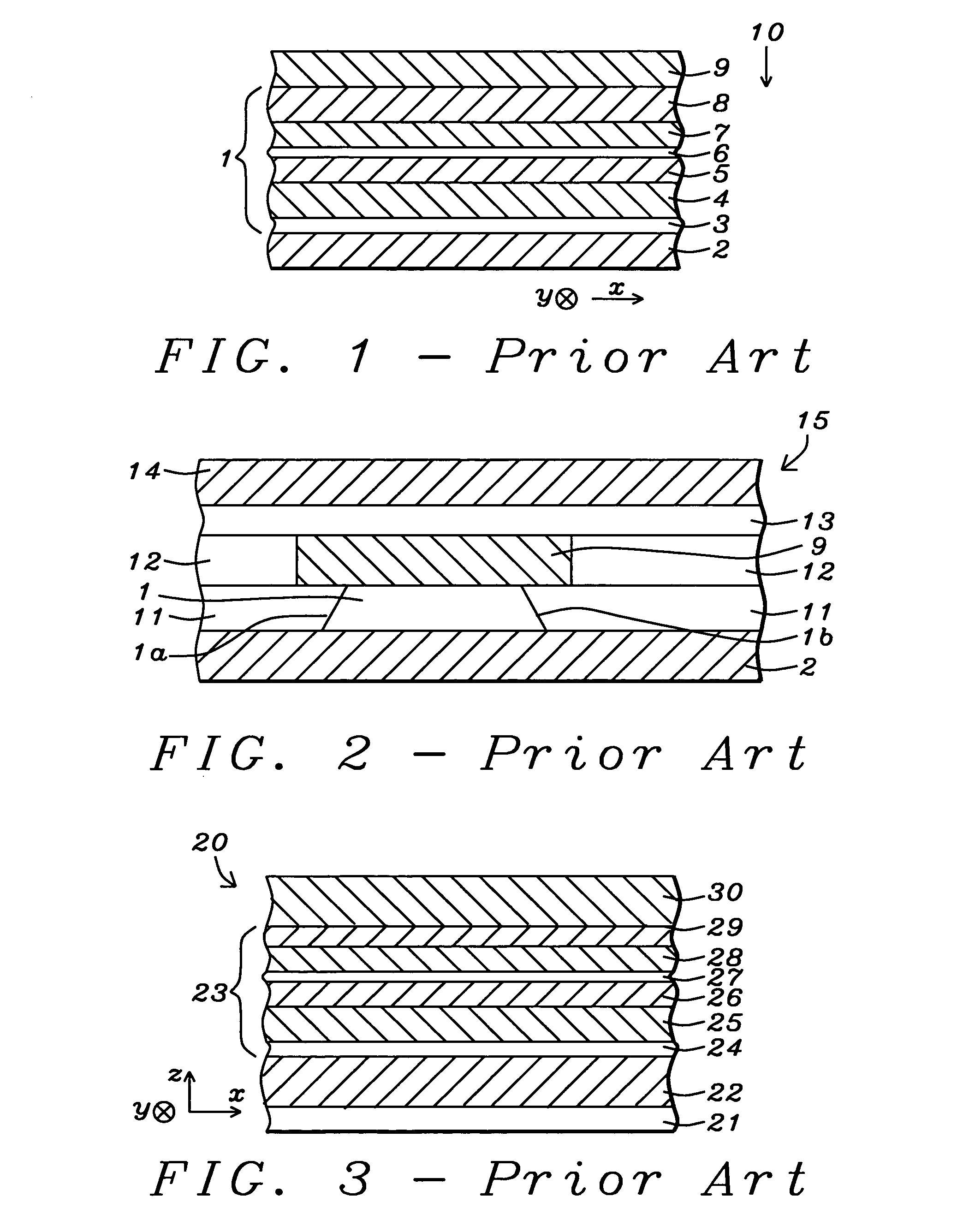

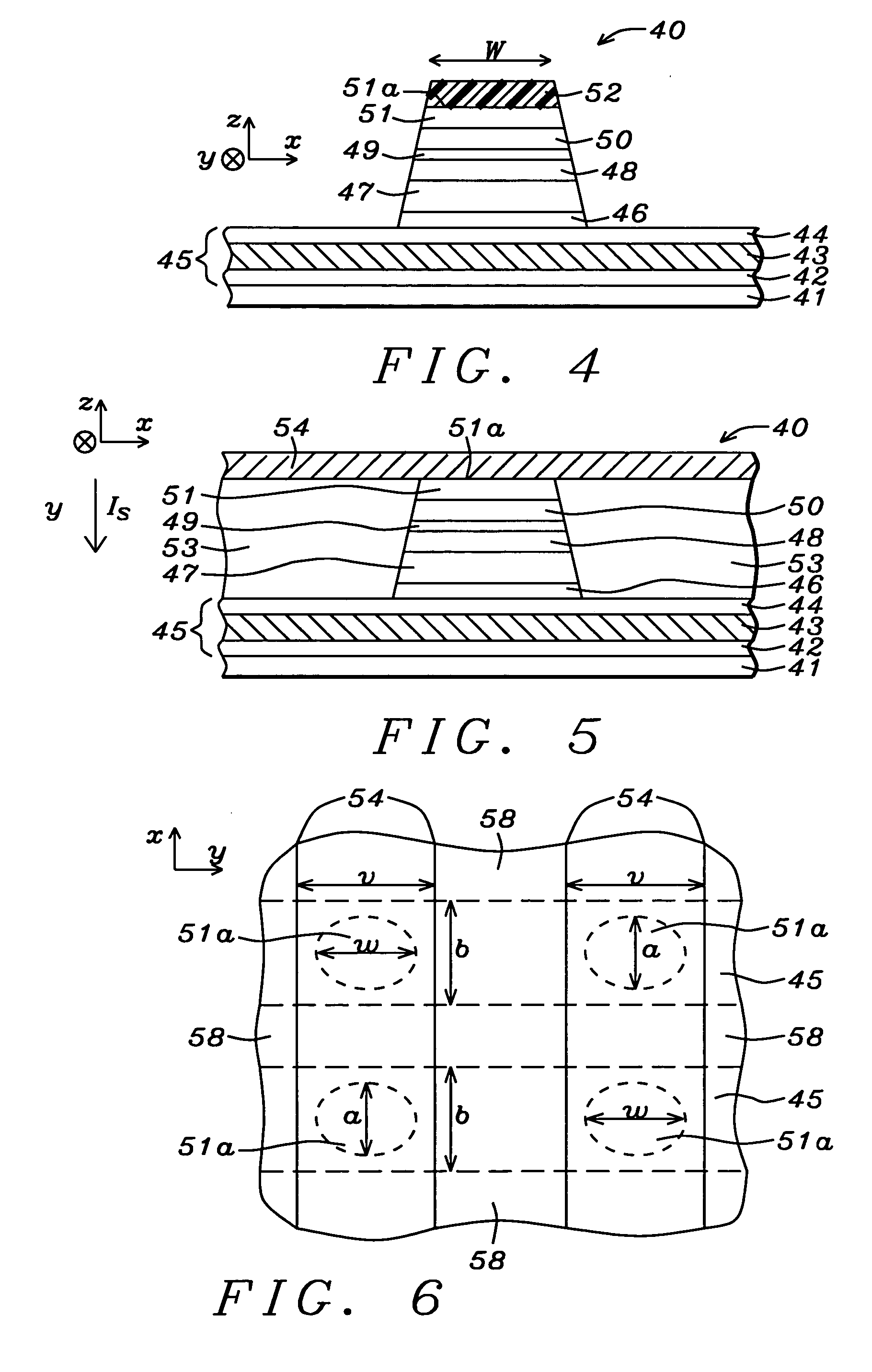

Thin film write head with improved laminated flux carrying structure and method of fabrication

InactiveUS6233116B1High resistivityExcellent soft magnetic propertiesConstruction of head windingsHeads using thin filmsLower poleHigh resistivity

The present invention provides a thin film write head having an improved laminated flux carrying structure and method of fabrication. The preferred embodiment provides laminated layers of: high moment magnetic material, and easily aligned high resistivity magnetic material. In the preferred embodiment, the easily aligned laminating layer induces uniaxial anisotropy, by exchange coupling, to improve uniaxial anisotropy in the high moment material. This allows deposition induced uniaxial anisotropy by DC magnetron sputtering and also provides improved post deposition annealing, if desired. It is preferred to laminate FeXN, such as FeRhN, or other crystalline structure material, with an amorphous alloy material, preferably Co based, such as CoZrCr. In the preferred embodiment, upper and lower pole structures may both be laminated as discussed above. Such laminated structures have higher Bs than structures with insulative laminates, and yokes and pole tips and may be integrally formed, if desired, because flux may travel along or across the laminating layers. The preferred embodiment of the present invention improves soft magnetic properties, reduces eddy currents, improves hard axis alignment while not deleteriously affecting the coercivity, permeability, and magnetostriction of the structure, thus allowing for improved high frequency operation.

Owner:WESTERN DIGITAL TECH INC +1

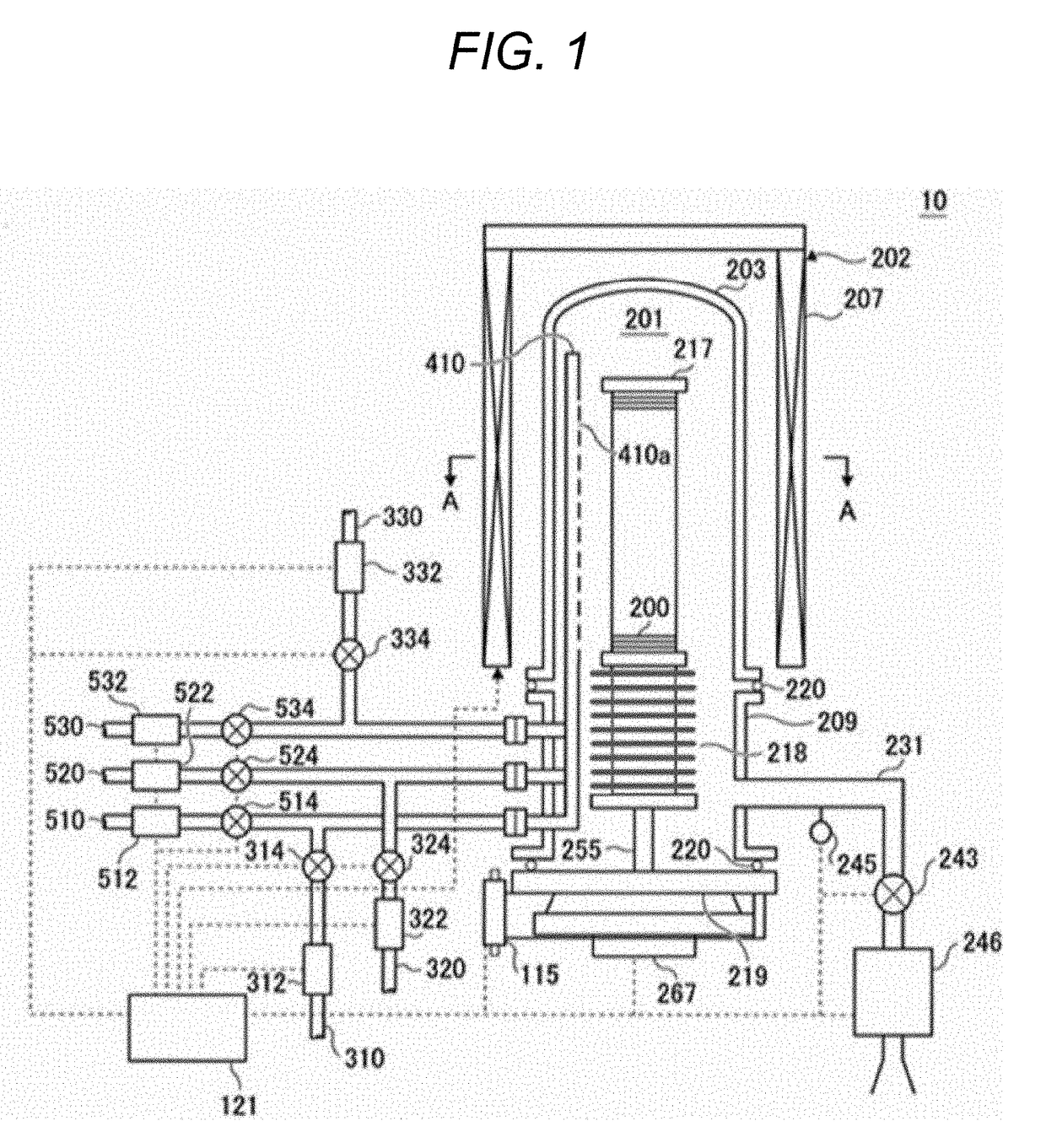

Method of manufacturing semiconductor device

PendingUS20170309490A1Reduce roughnessLow resistivitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductorAmorphous metal

A method of manufacturing a semiconductor device includes: forming an amorphous metal film on a substrate by time-divisionally conducting a cycle a predetermined number of times, the cycle including: (a) simultaneously supplying a metal-containing gas and a first reducing gas to the substrate to form a first amorphous metal layer on the substrate, and (b) forming a second amorphous metal layer on the first amorphous metal layer by time-divisionally supplying, a predetermined number of times, the metal-containing gas and a second reducing gas to the substrate on which the first amorphous metal layer is formed; and forming a crystallized metal layer on the substrate by simultaneously supplying the metal-containing gas and the first reducing gas to the substrate on which the amorphous metal film is formed.

Owner:KOKUSA ELECTRIC CO LTD

Sequential method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS20020164421A1Faster efficient meanSimple methodVacuum evaporation coatingSemiconductor/solid-state device manufacturingSequential methodHigh density

Owner:NOVELLUS SYSTEMS

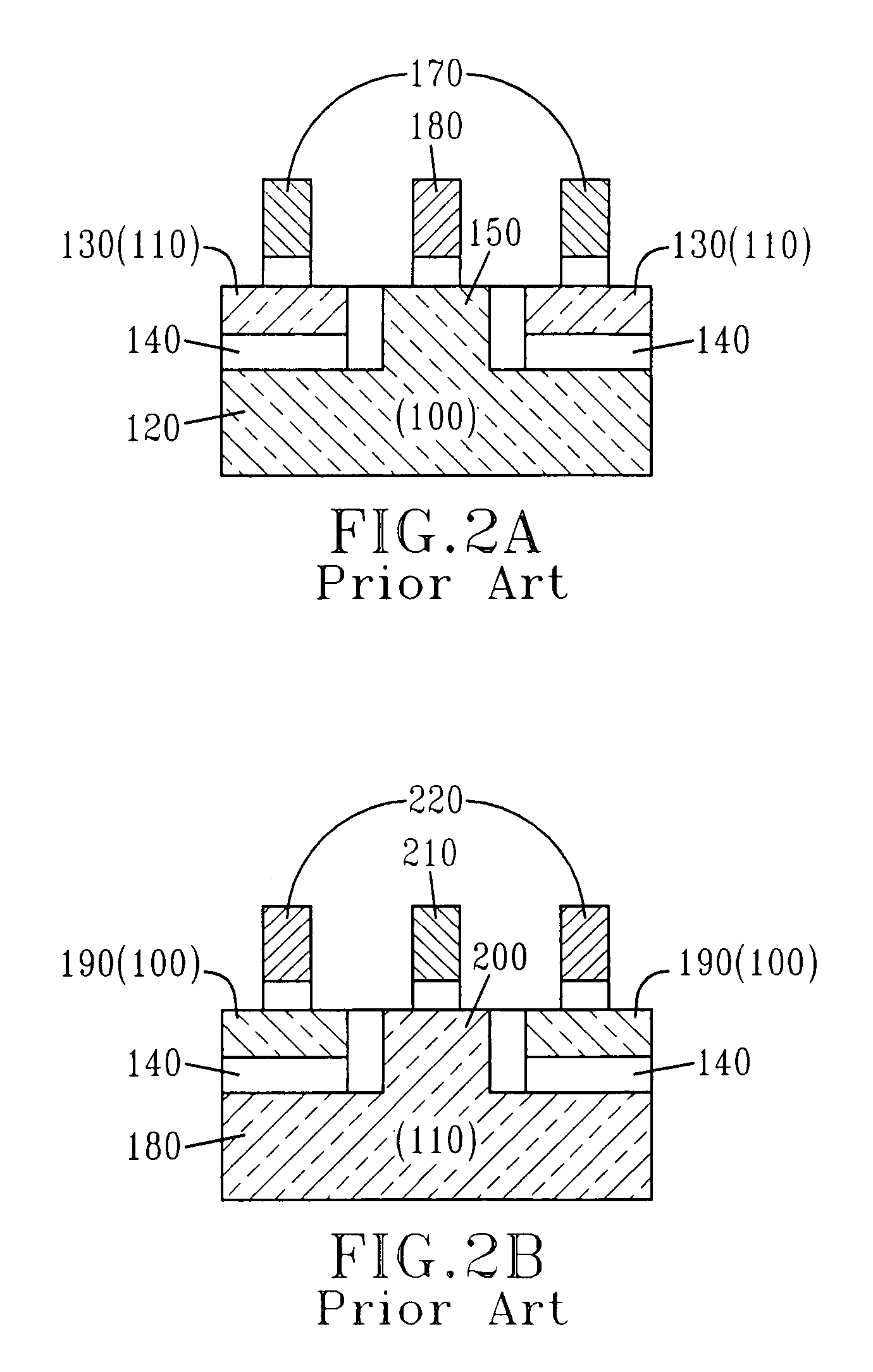

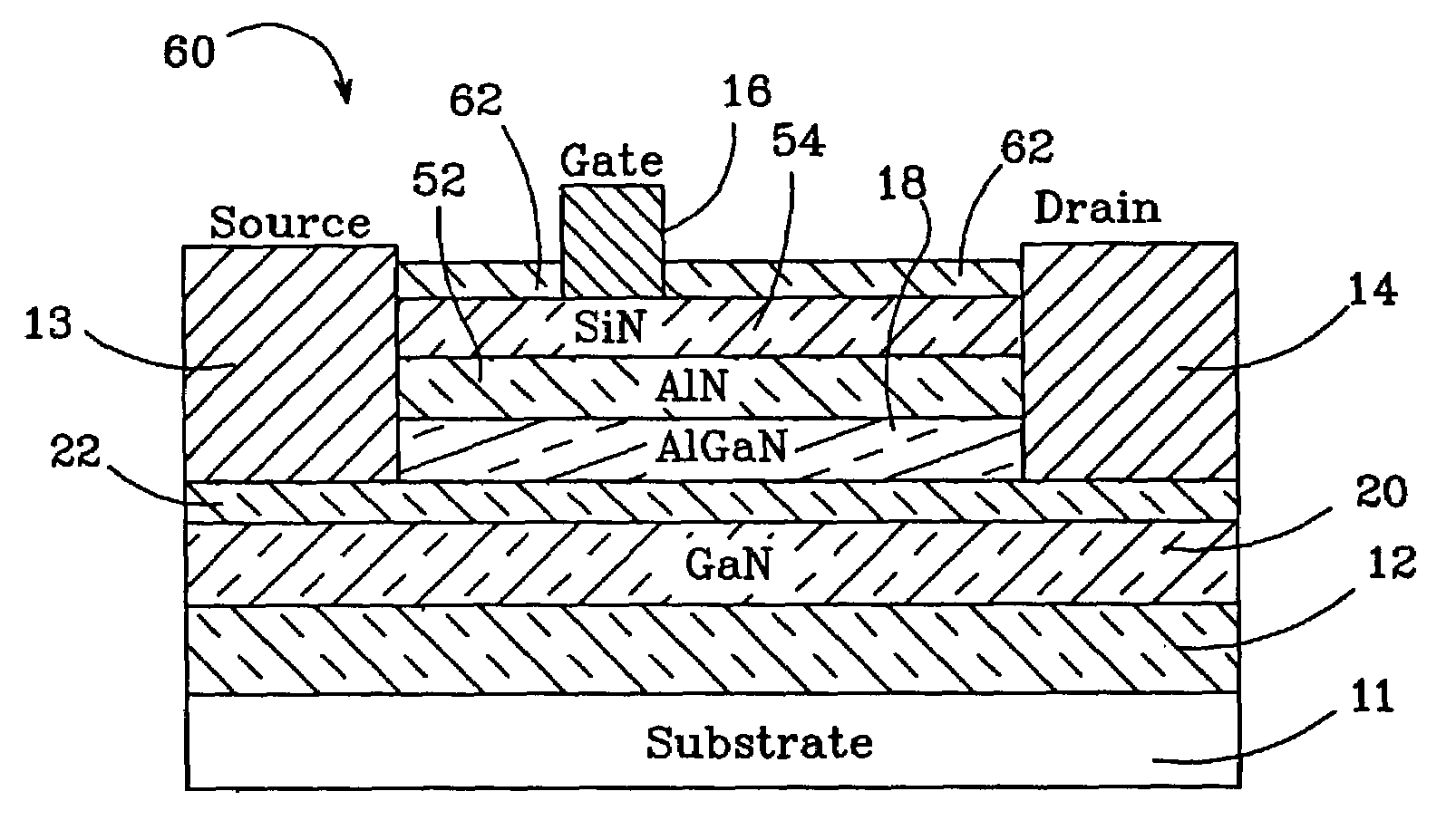

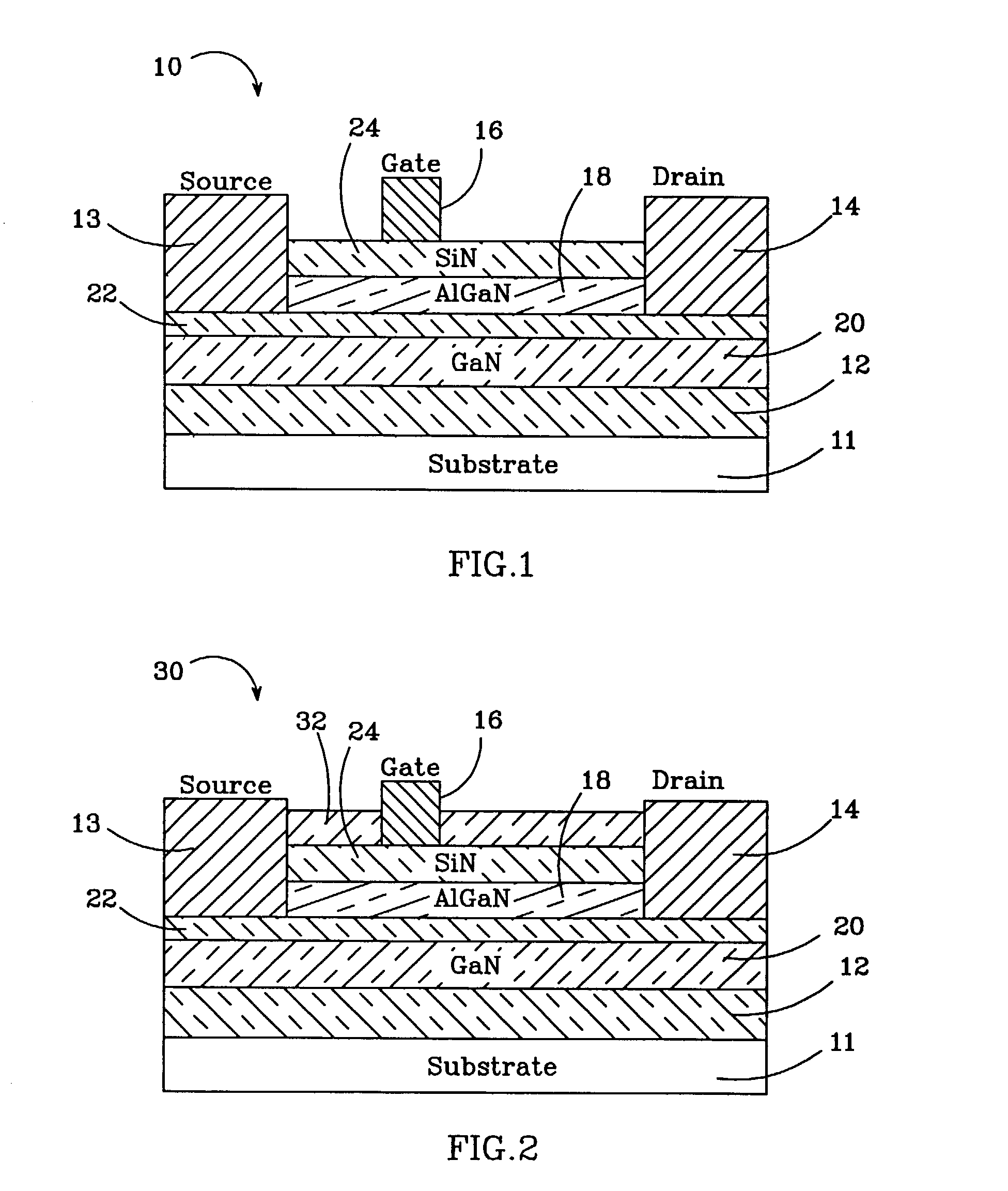

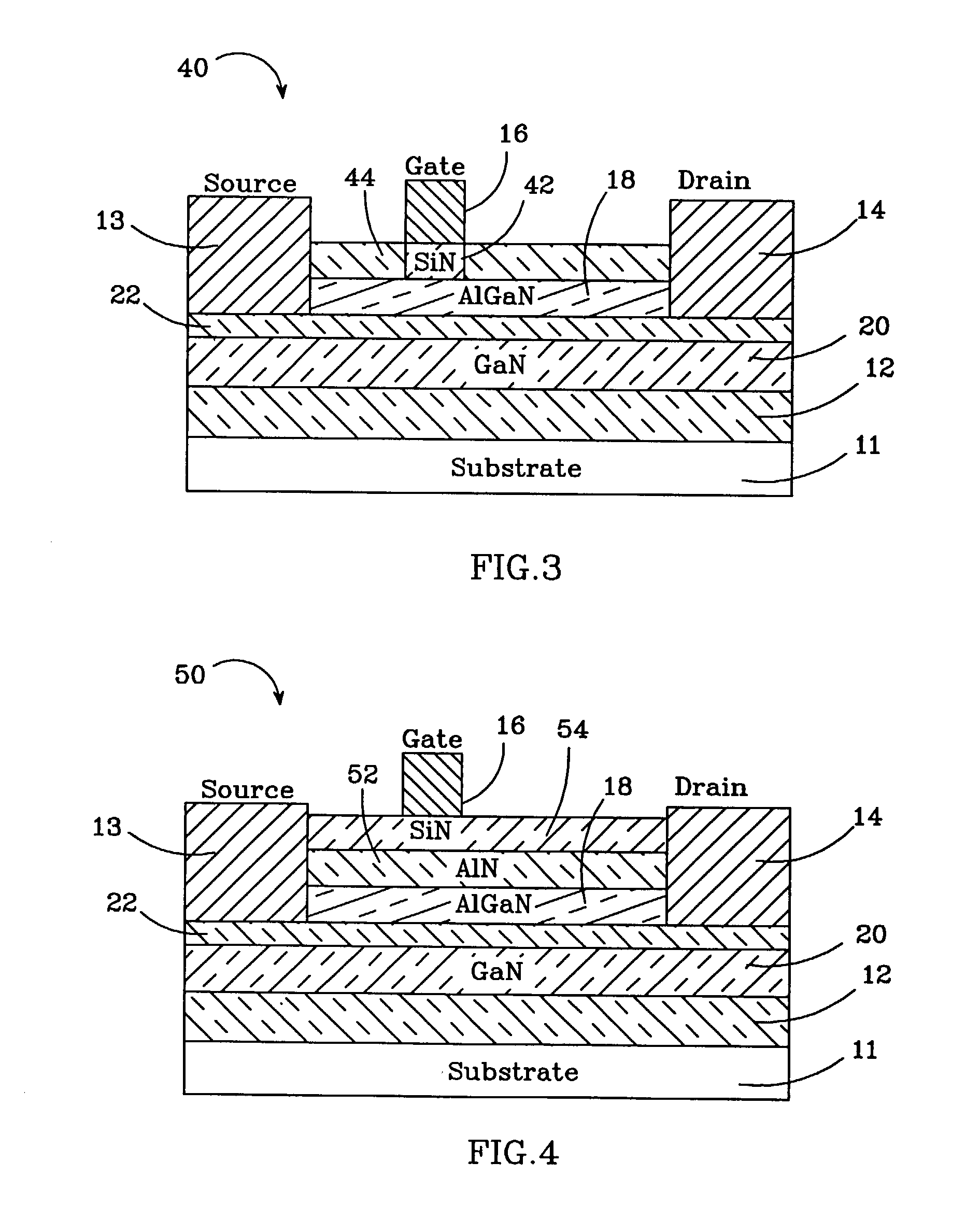

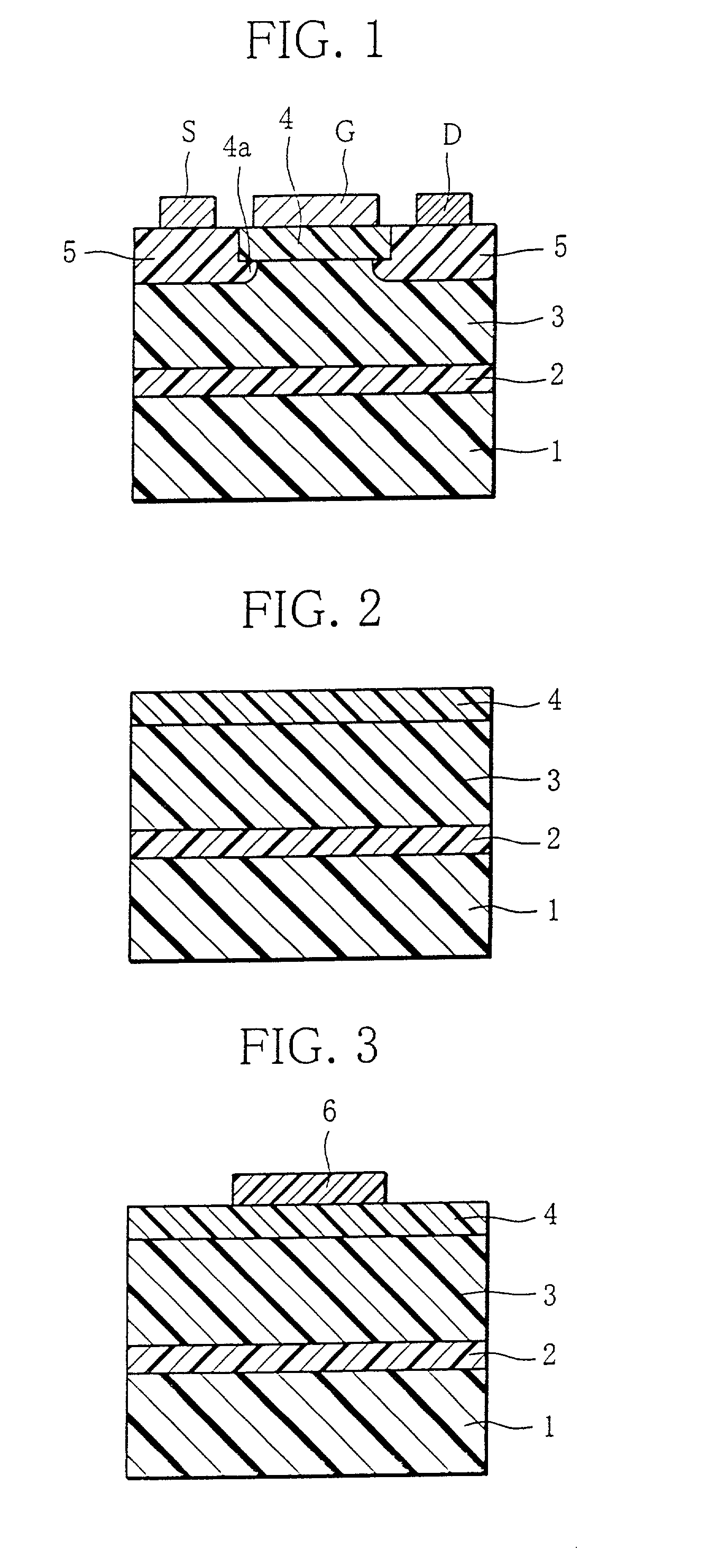

Insulating gate AlGaN/GaN HEMT

InactiveUS7230284B2Reduce trappingReduce gate leakageSemiconductor/solid-state device detailsSolid-state devicesGate leakage currentDriving current

AlGaN / GaN HEMTs are disclosed having a thin AlGaN layer to reduce trapping and also having additional layers to reduce gate leakage and increase the maximum drive current. One HEMT according to the present invention comprises a high resistivity semiconductor layer with a barrier semiconductor layer on it. The barrier layer has a wider bandgap than the high resistivity layer and a 2DEG forms between the layers. Source and drain contacts contact the barrier layer, with part of the surface of the barrier layer uncovered by the contacts. An insulating layer is included on the uncovered surface of the barrier layer and a gate contact is included on the insulating layer. The insulating layer forms a barrier to gate leakage current and also helps to increase the HEMT's maximum current drive. The invention also includes methods for fabricating HEMTs according to the present invention. In one method, the HEMT and its insulating layer are fabricated using metal-organic chemical vapor deposition (MOCVD). In another method the insulating layer is sputtered onto the top surface of the HEMT in a sputtering chamber.

Owner:CREE INC

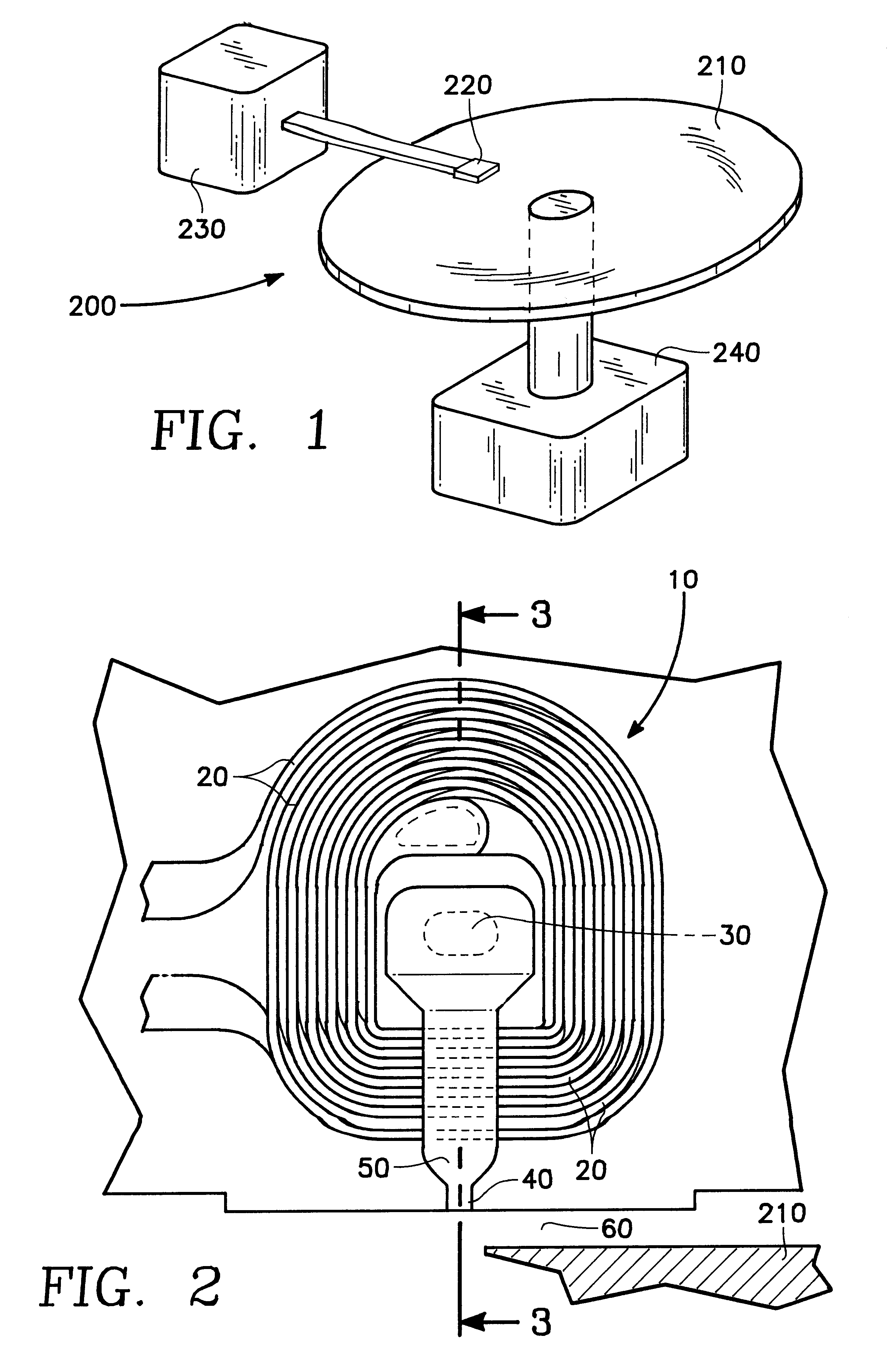

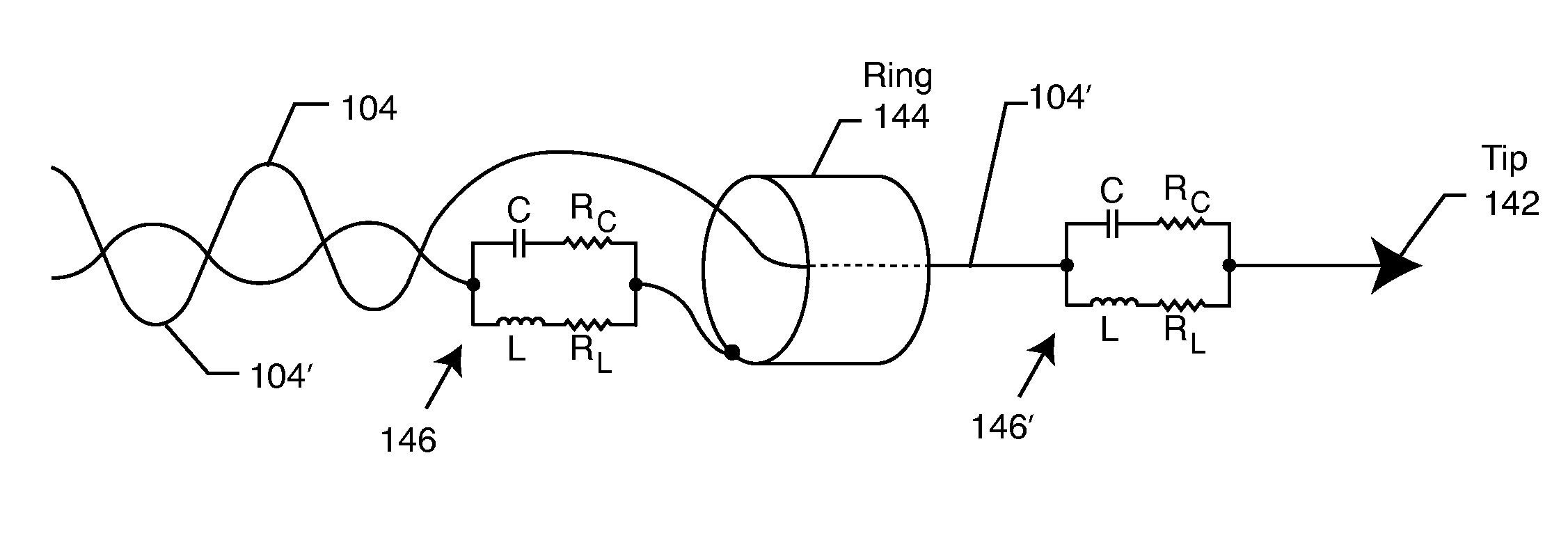

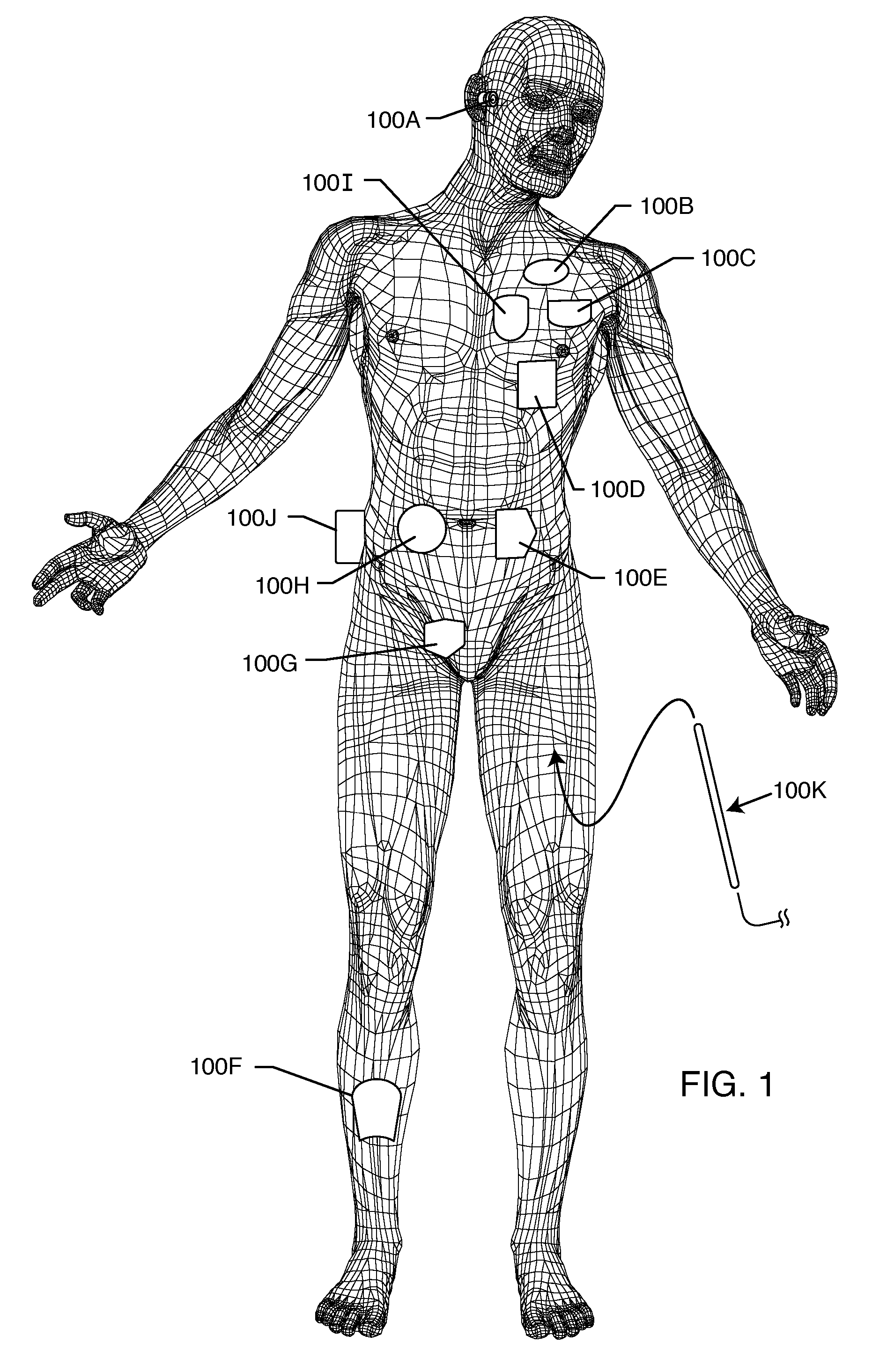

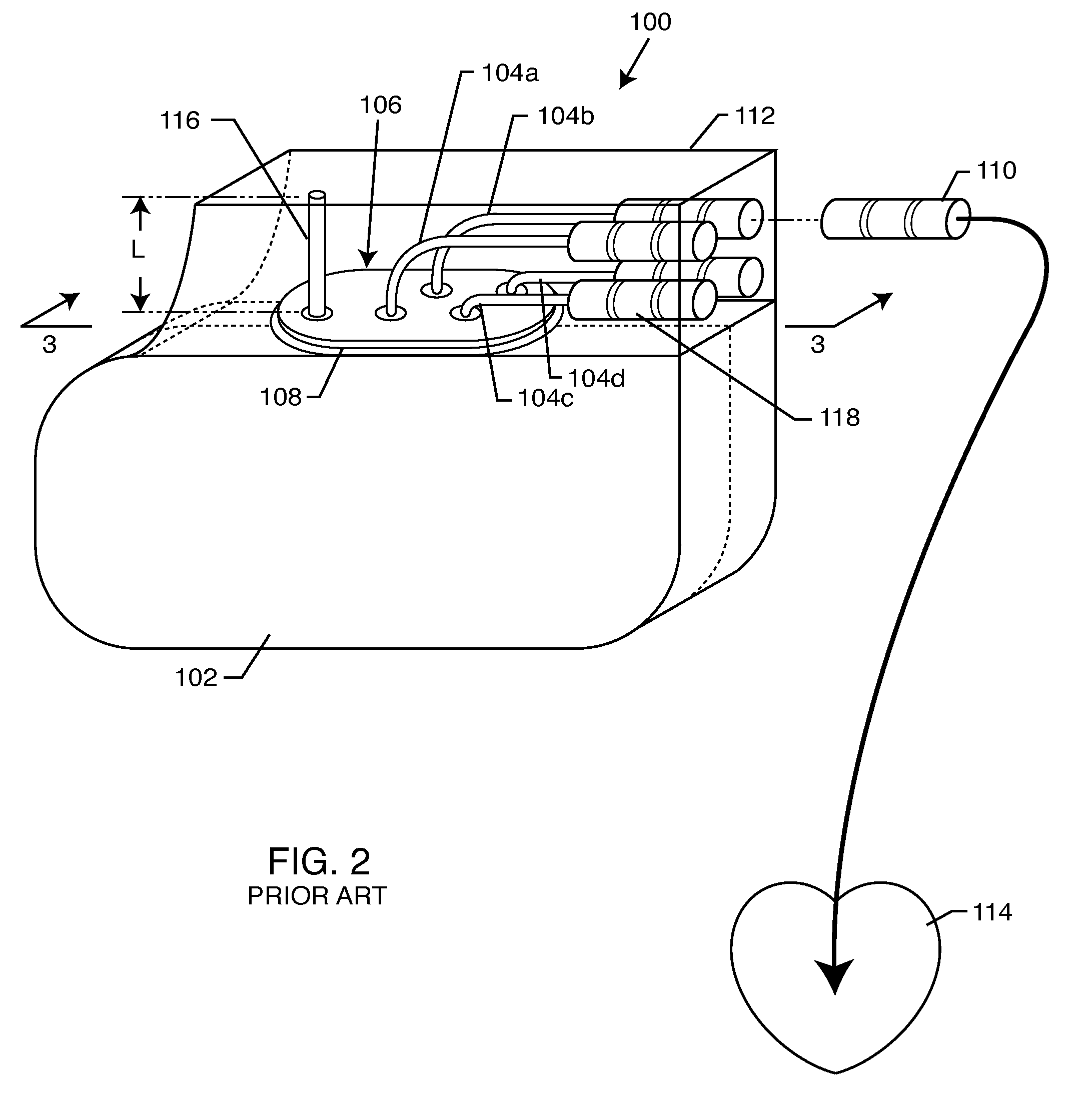

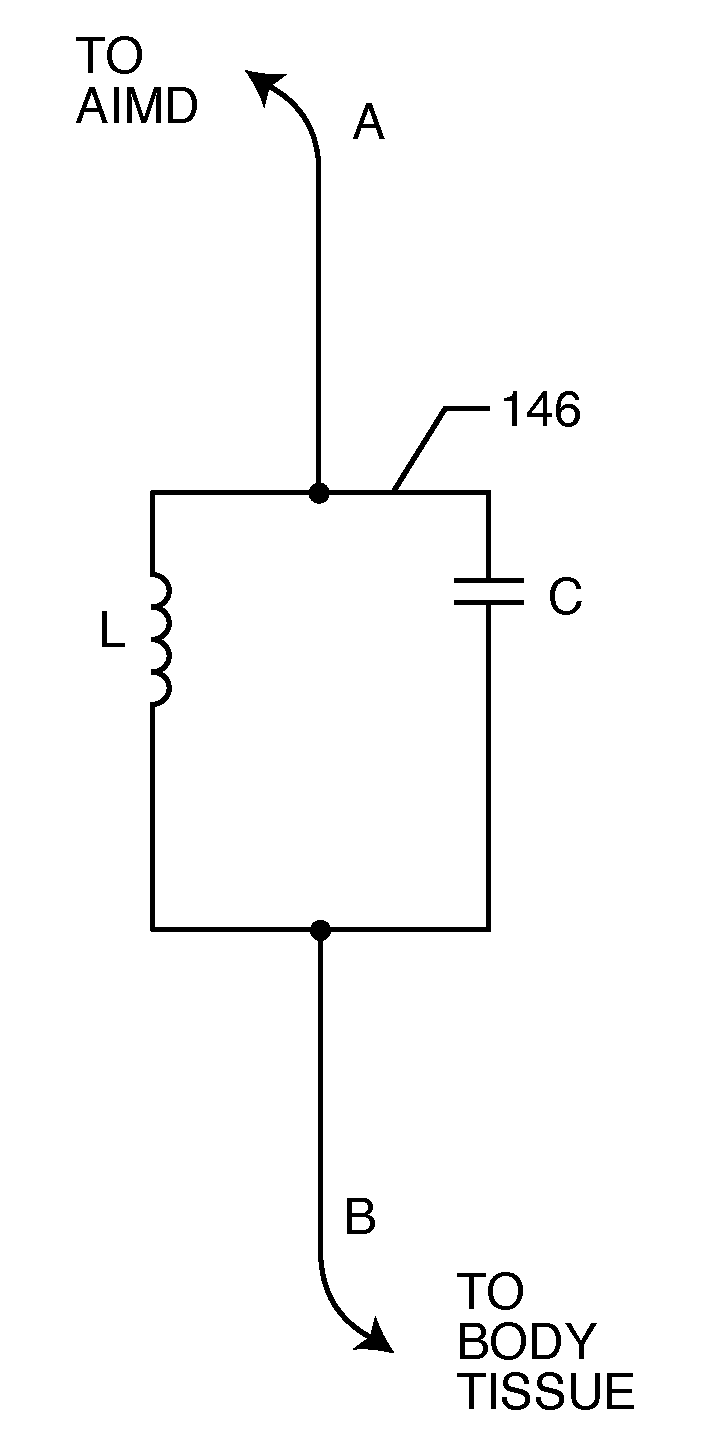

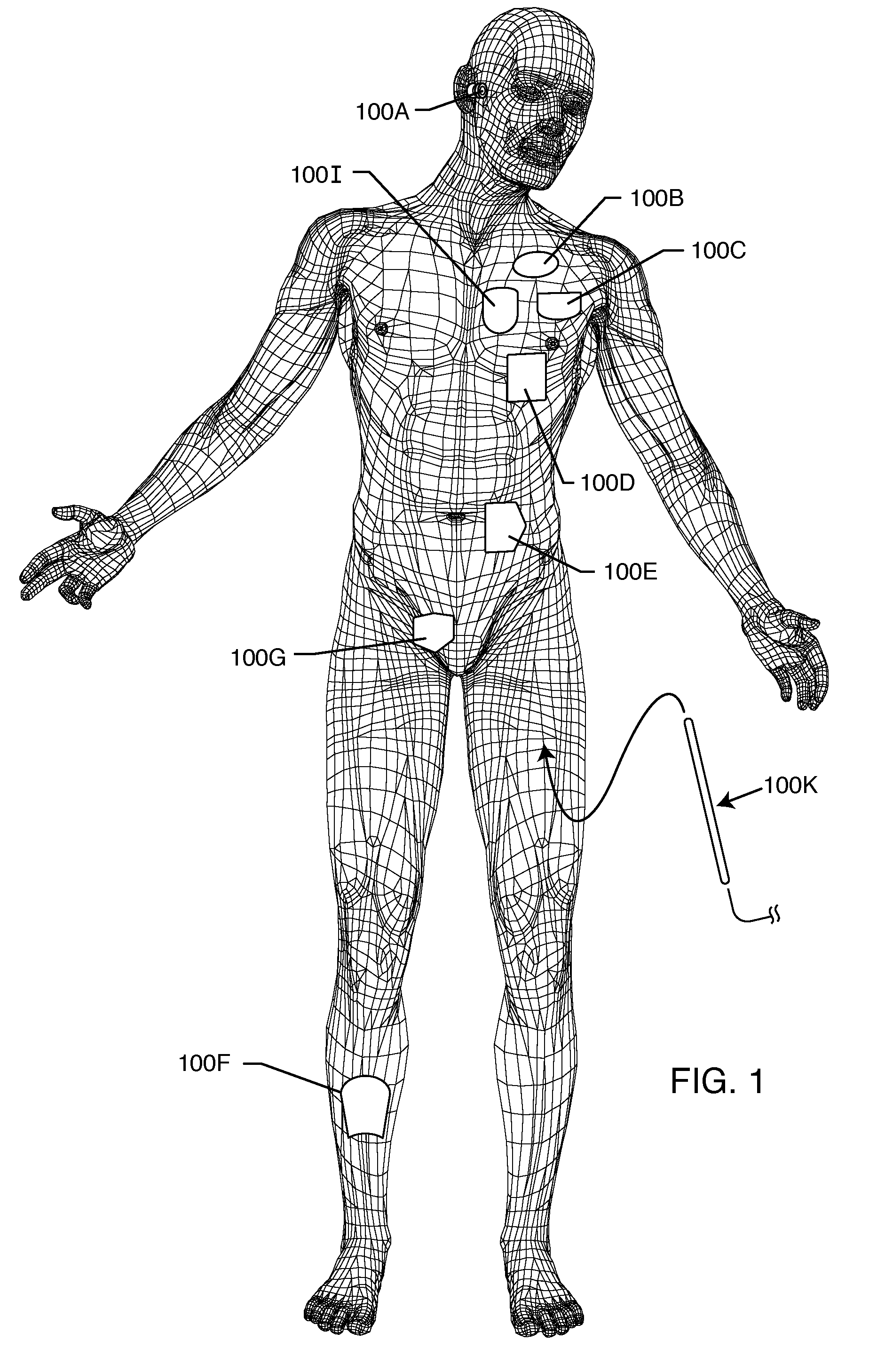

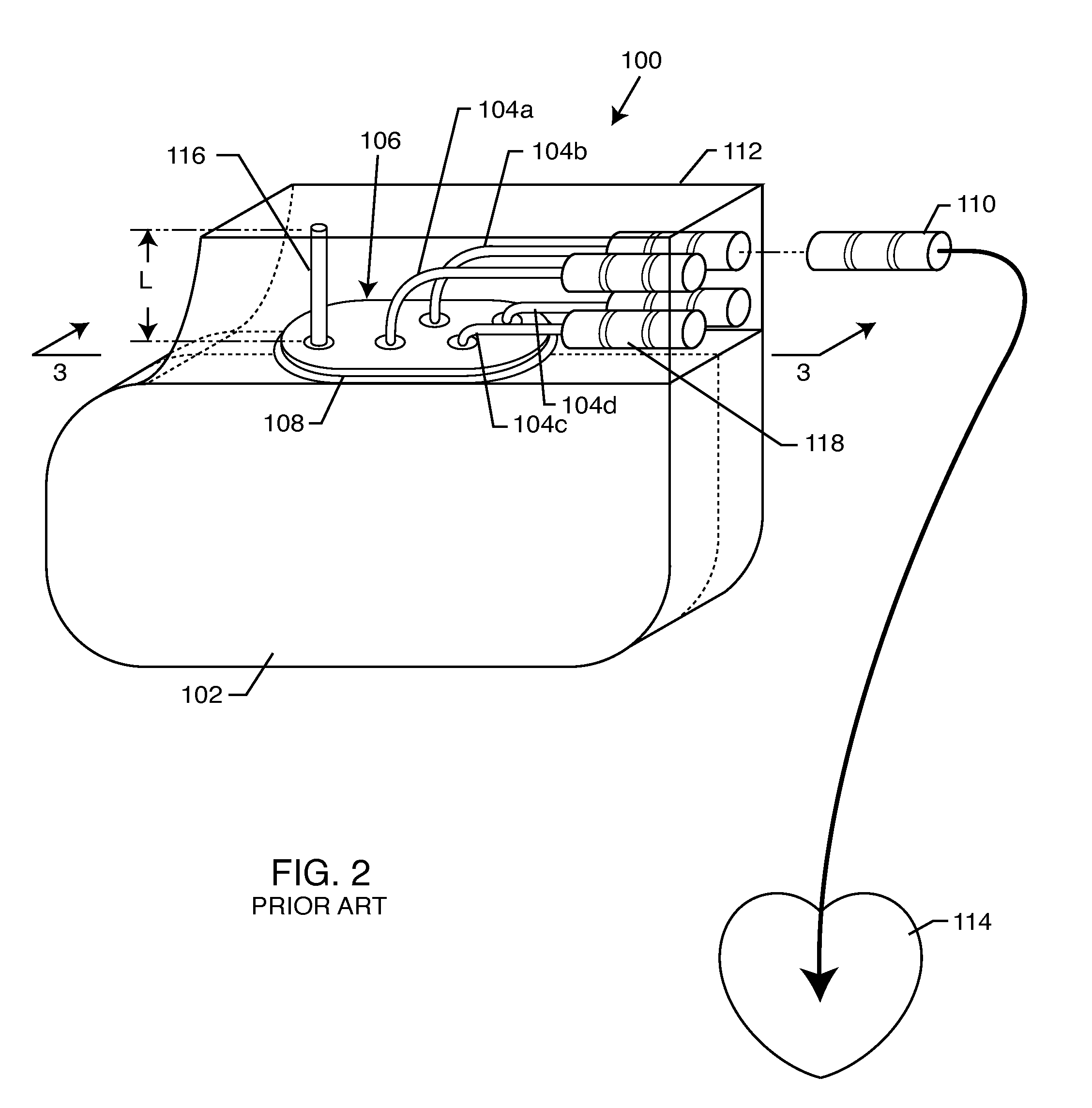

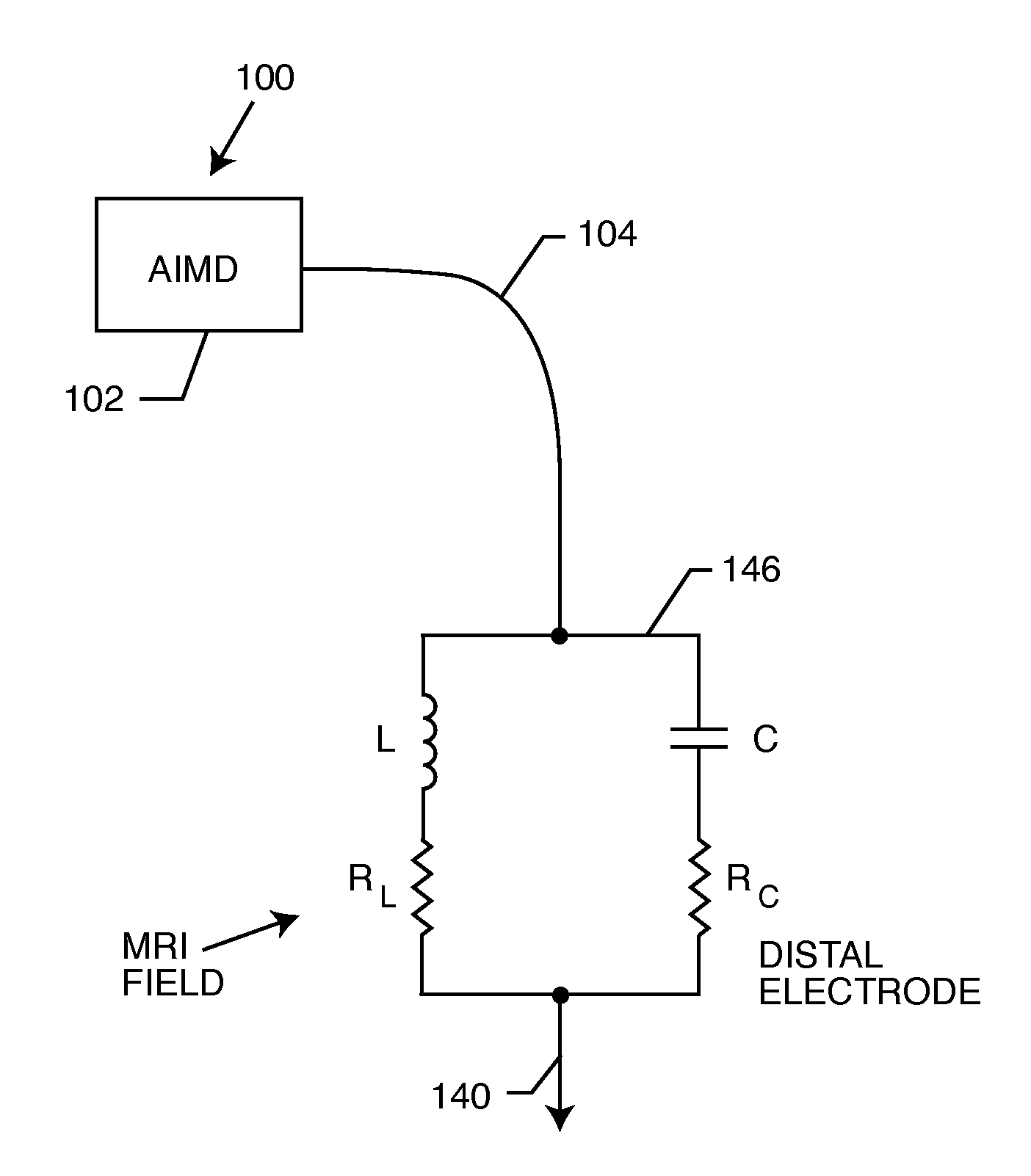

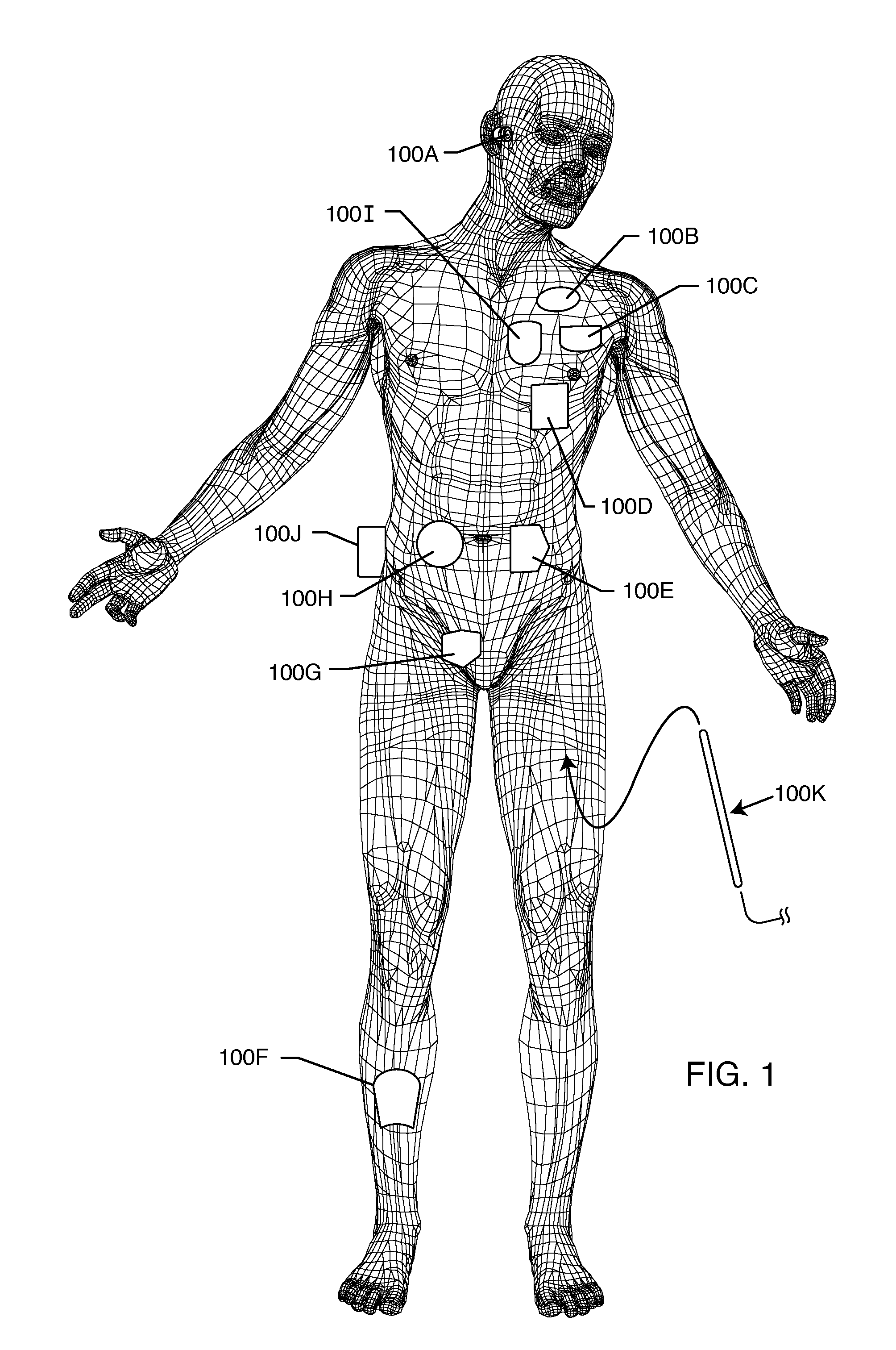

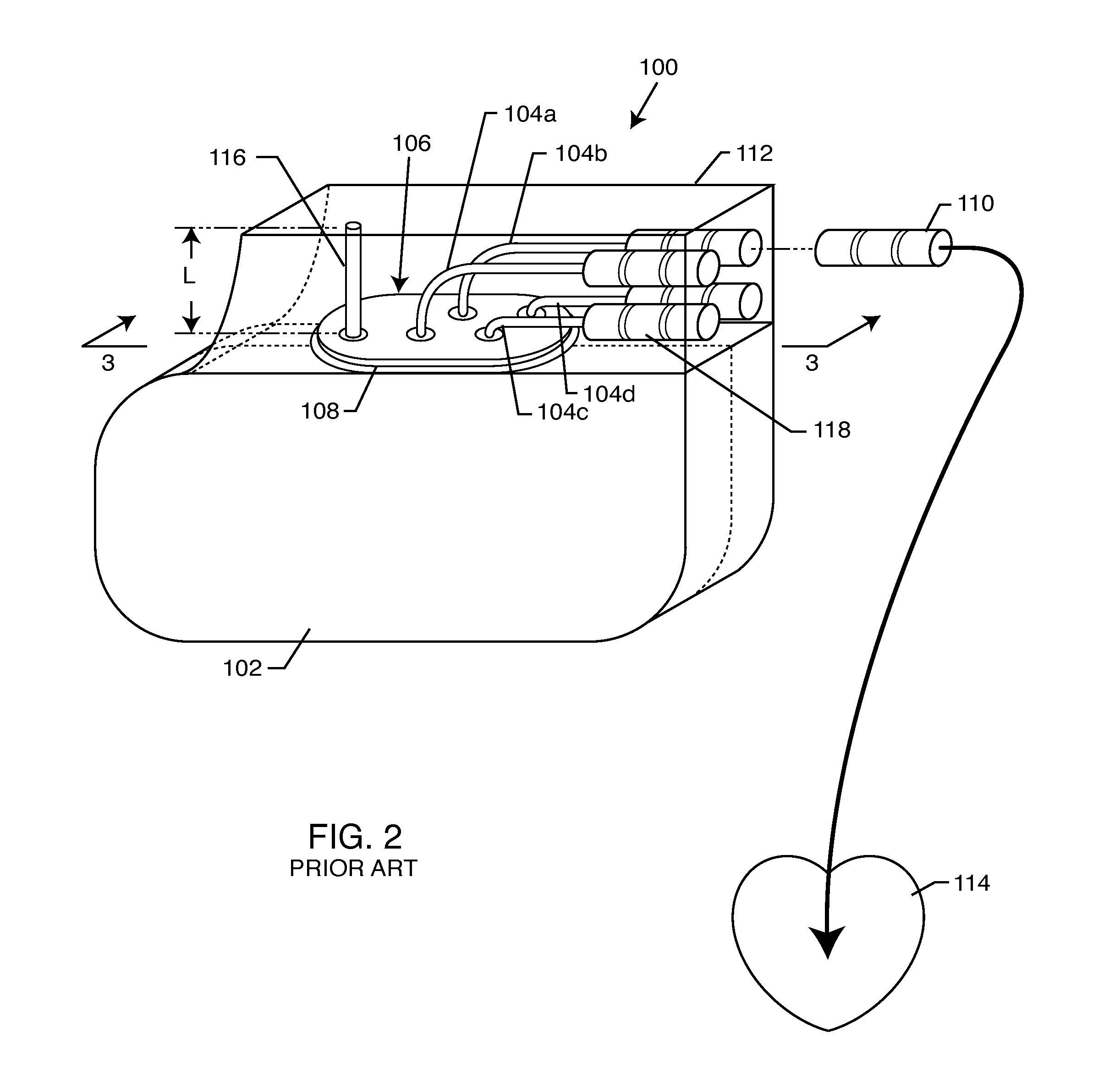

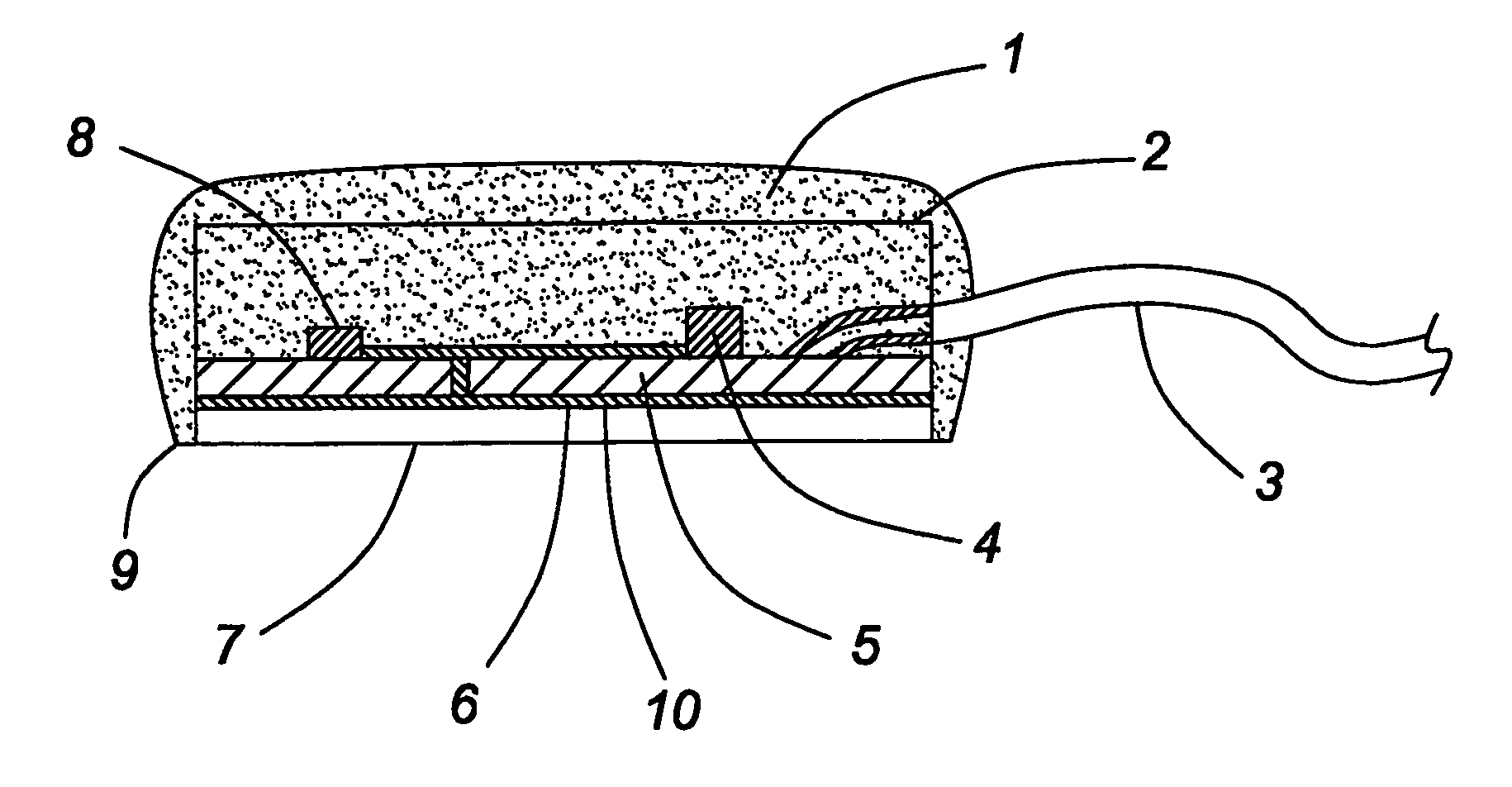

Band stop filter employing a capacitor and an inductor tank circuit to enhance MRI compatibility of active medical devices

InactiveUS20060247684A1Decrease QCapacitor is relatively minimizedMultiple-port networksInternal electrodesCapacitanceEngineering

A band stop filter is provided for a lead wire of an active medical device (AMD). The band stop filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the lead wire of the AMD, wherein values of capacitance and inductance are selected such that the band stop filter is resonant at a selected frequency. The Q of the inductor may be relatively maximized and the Q of the capacitor may be relatively minimized to reduce the overall Q of the band stop filter to attenuate current flow through the lead wire along a range of selected frequencies. In a preferred form, the band stop filter is integrated into a TIP and / or RING electrode for an active implantable medical device.

Owner:WILSON GREATBATCH LTD

Band stop filter employing a capacitor and an inductor tank circuit to enhance MRI compatibility of active implantable medical devices

InactiveUS20070288058A1Avoid flowAvoid loopsMultiple-port networksInternal electrodesCapacitanceInductor

Owner:WILSON GREATBATCH LTD

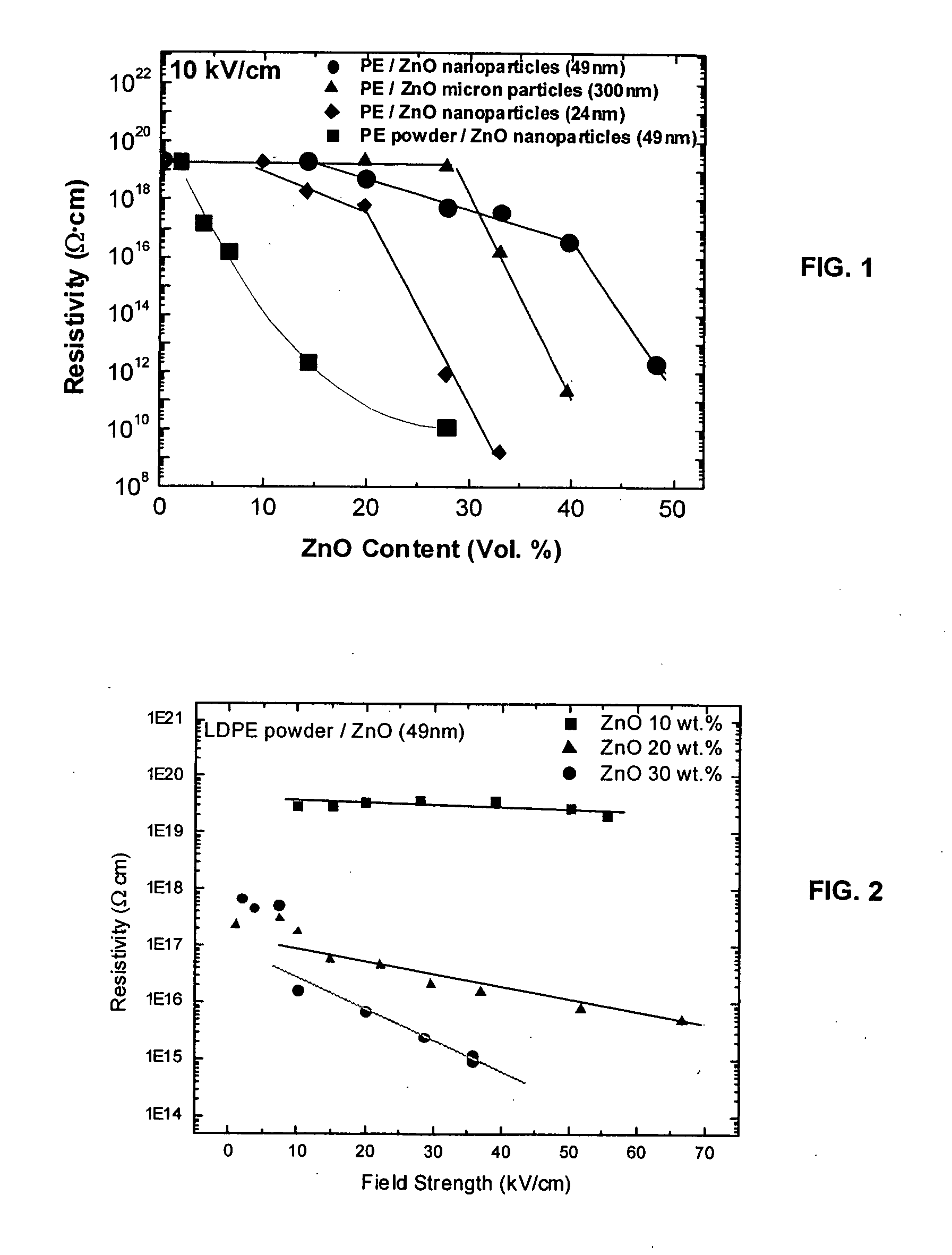

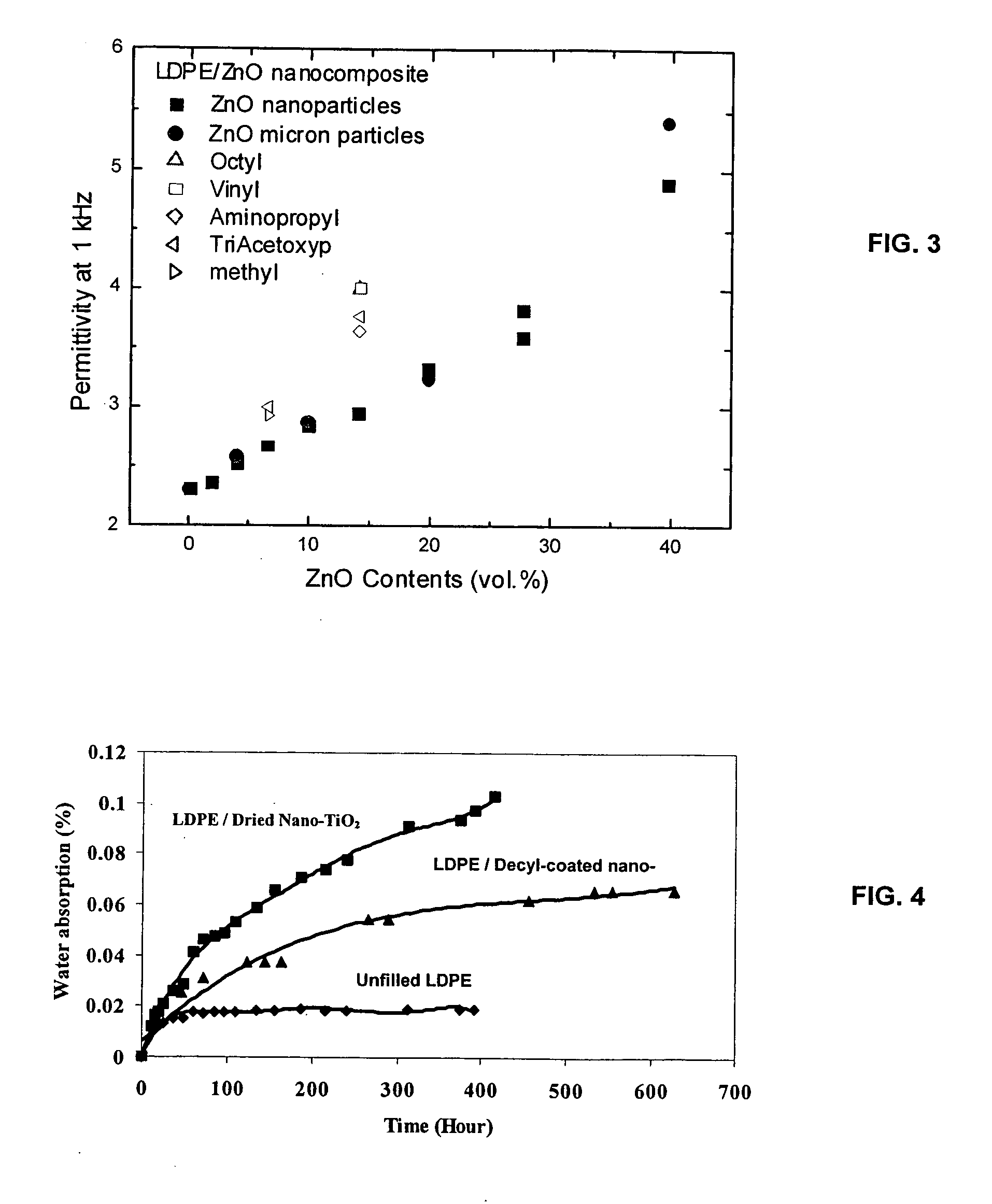

Nanocomposites With Controlled Electrical Properties

ActiveUS20070199729A1Improve permittivityImprove propertiesMaterial nanotechnologySpecial tyresNanoparticleNanometre

A field grading material includes a field grading effective amount of a nanoparticle filler distributed in a polymeric matrix, and the nanoparticle filler is heterogeneously distributed in the polymeric matrix.

Owner:RENESSELAER POLYTECHNIC INST +1

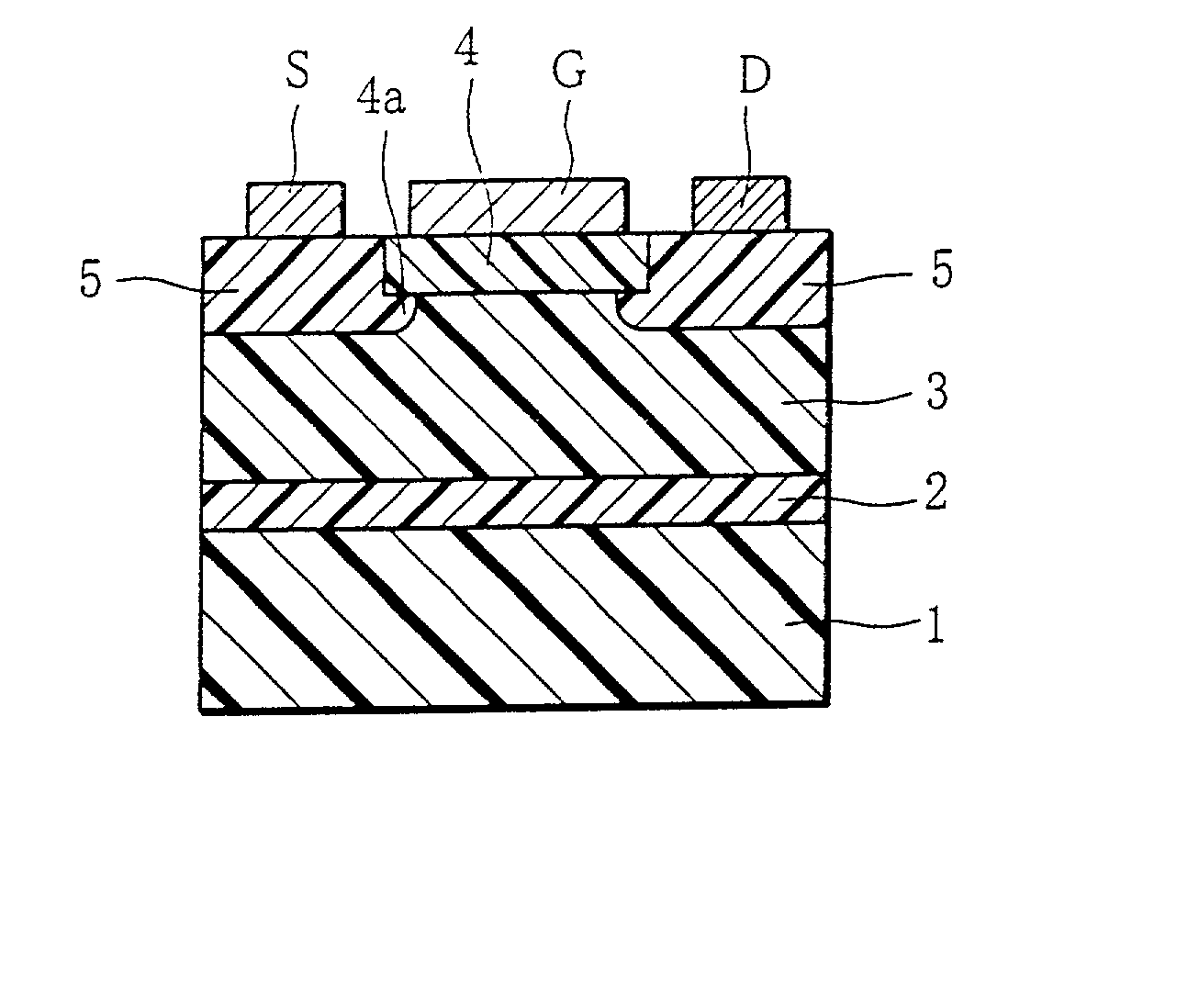

GaN-based high electron mobility transistor

InactiveUS20020079508A1Improve mobilityIncreased electrical resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectric resistivity

A GaN-based high electron mobility transistor (HEMT) has an undoped GaN layer where a two-dimensional electron gas layer is formed, the undoped GaN layer having a high electric resistivity enabling a pinch-off state to be obtained even when the gate bias voltage is 0 V. The GaN-based HEMT comprises a semi-insulating substrate on which a GaN buffer layer is formed. An undoped GaN layer is disposed on the GaN buffer layer and has an electric resistivity of not less than 1x106 OMEGA / cm2. An undoped AlGaN layer is disposed on the undoped GaN layer via a heterojunction such that an undercut portion is formed therebetween. An n-type GaN layer is further disposed in such a manner as to bury side portions of the undoped AlGaN layer and the undercut portion. The individual layers thus Ad form a layered structure. A gate electrode G is formed on the undoped AlGaN layer, and a source electrode S and a drain electrode D are formed on the n-type GaN layer.

Owner:FURUKAWA ELECTRIC CO LTD

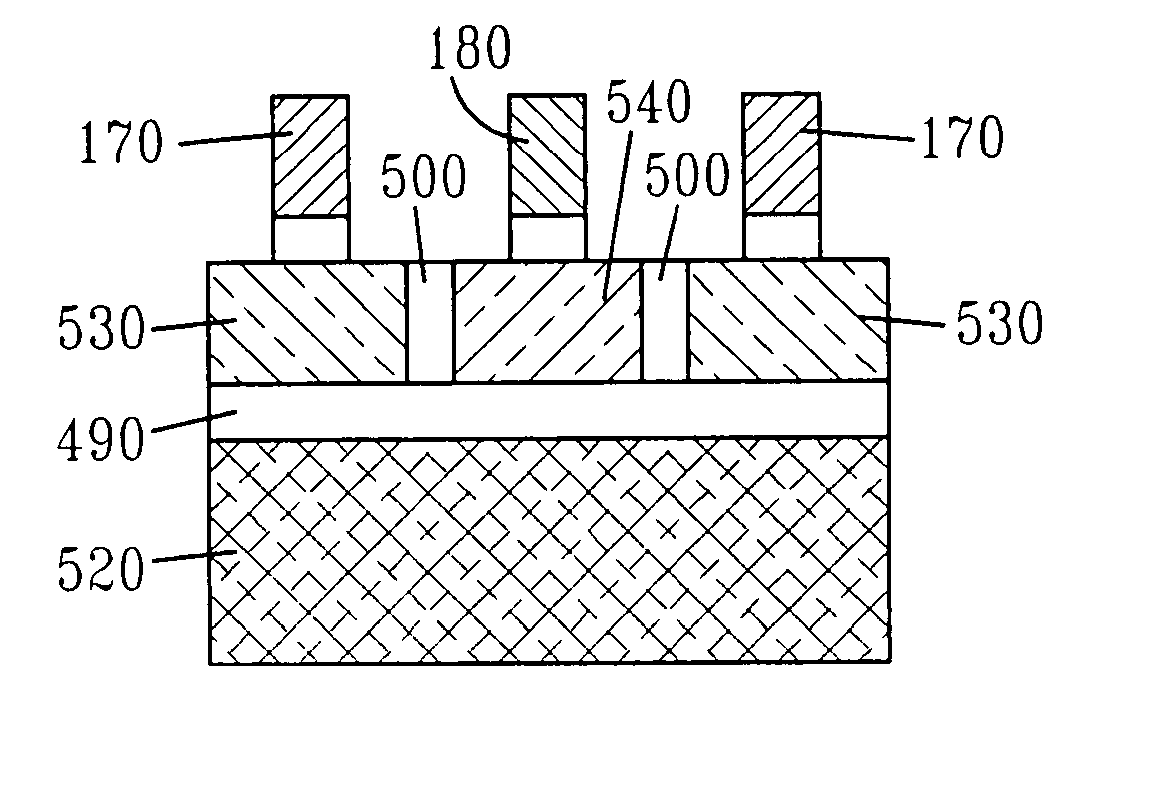

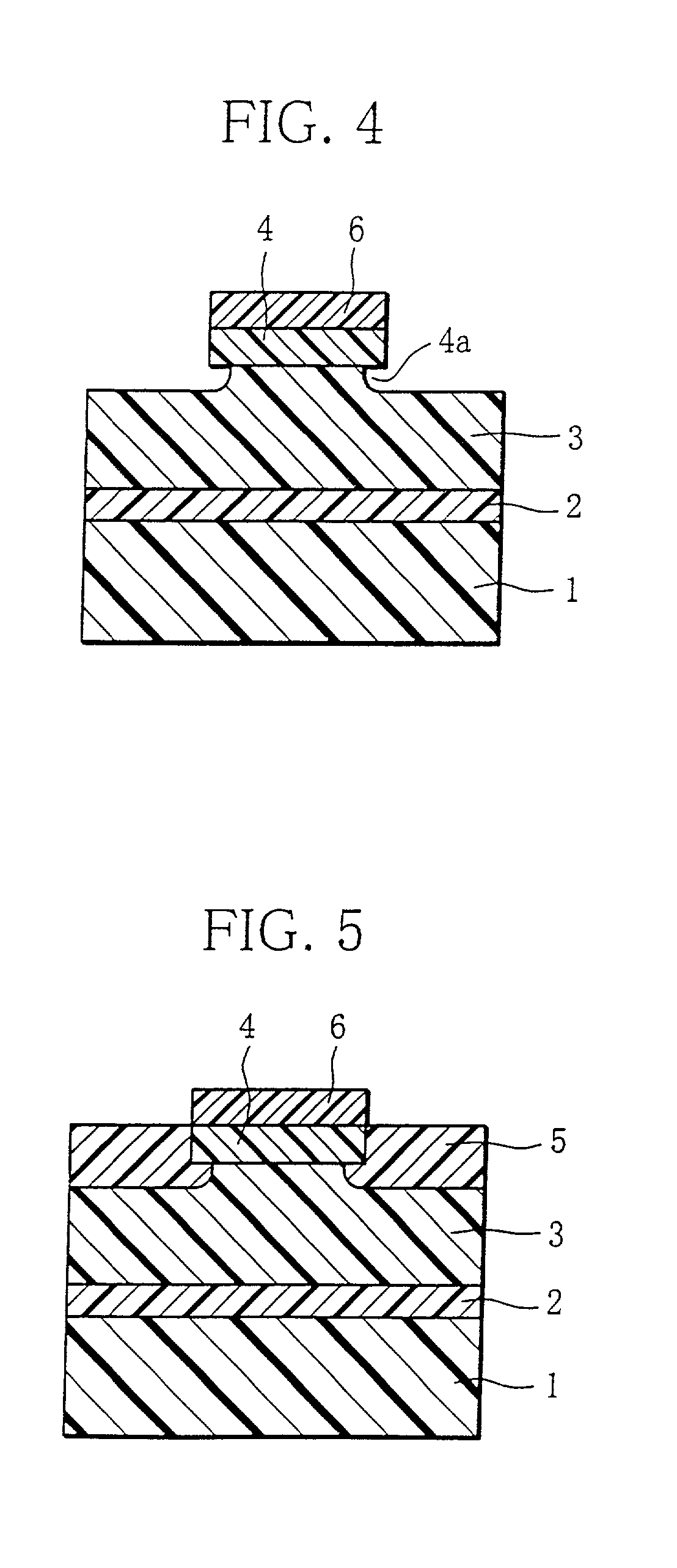

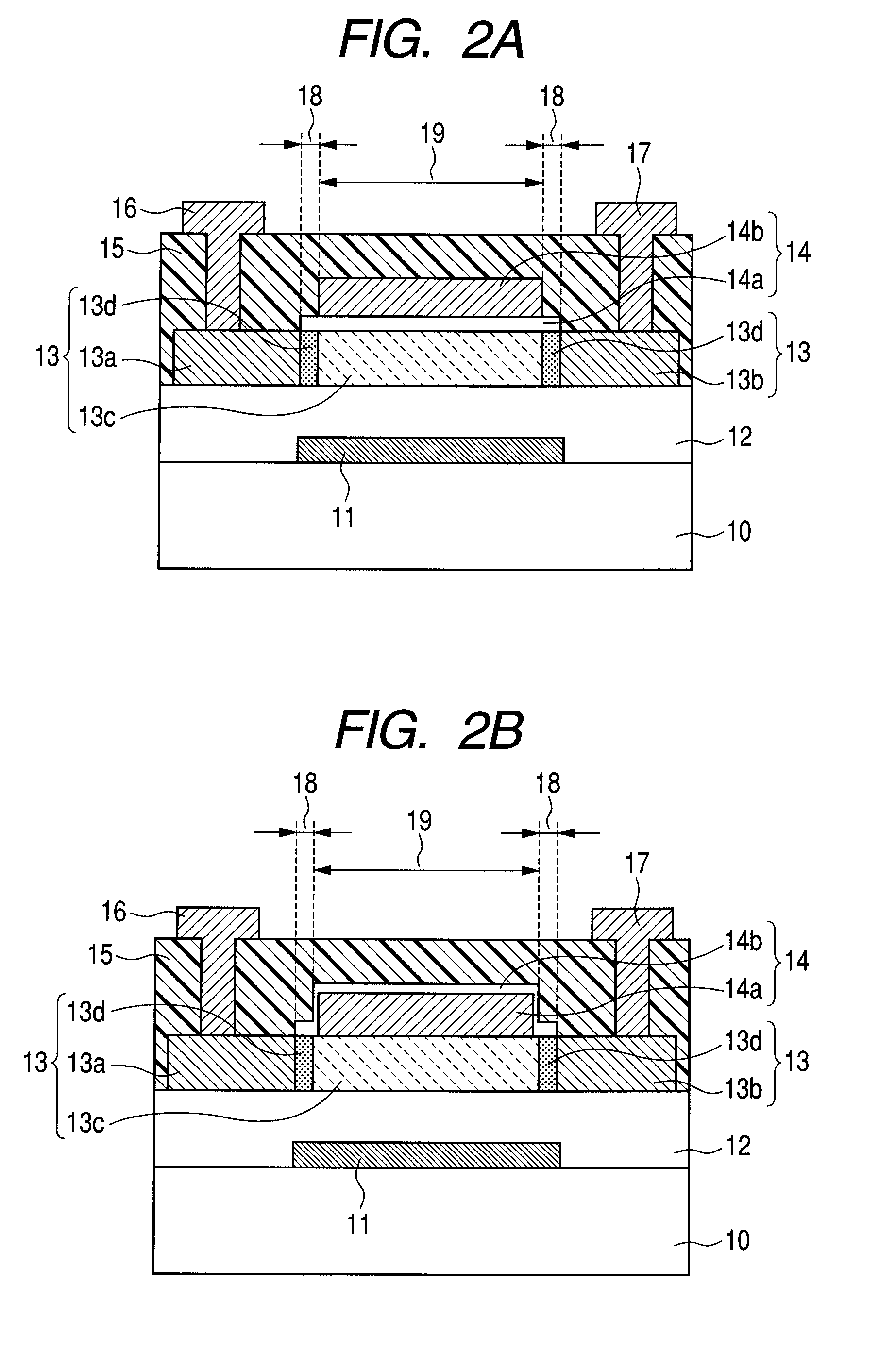

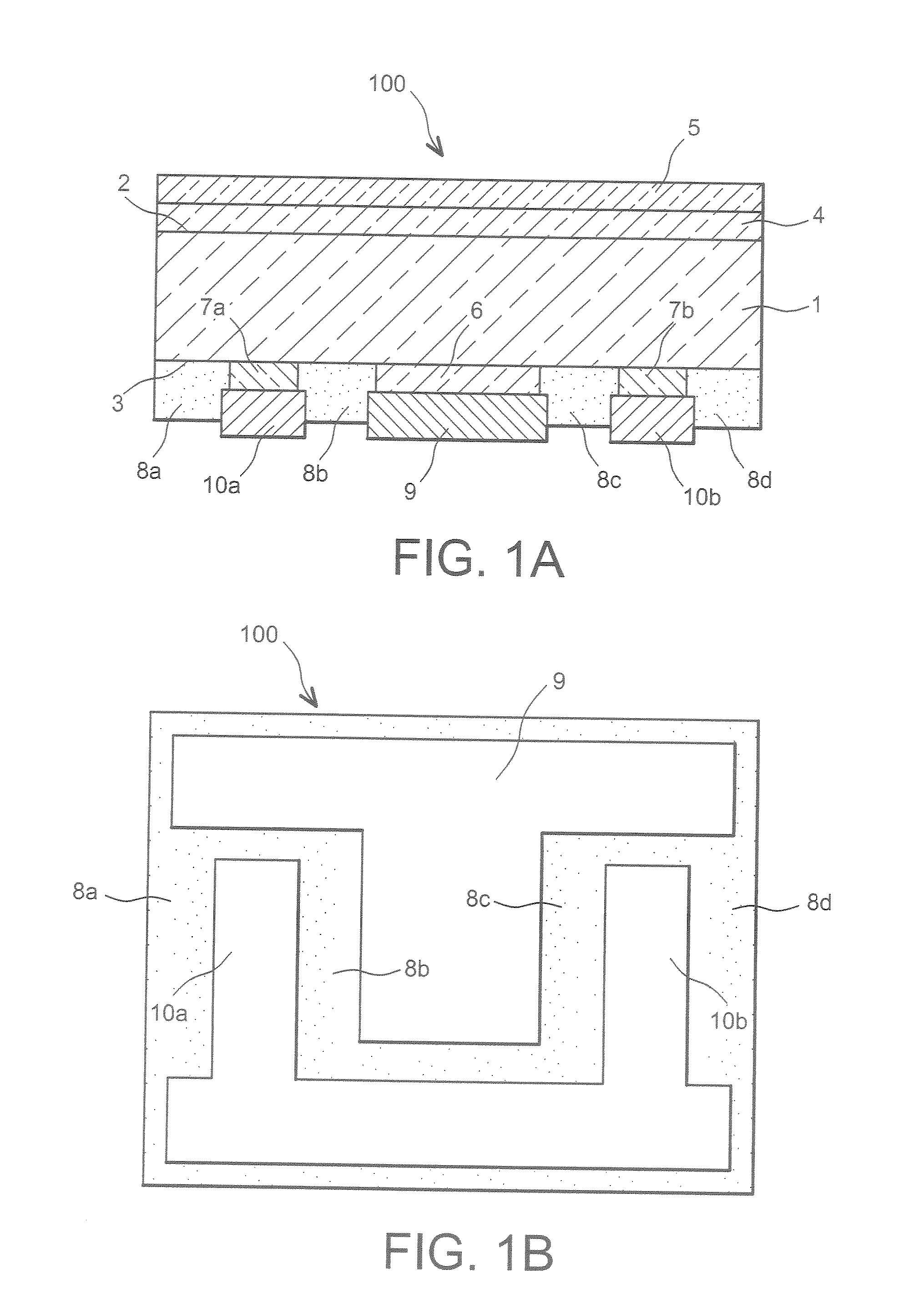

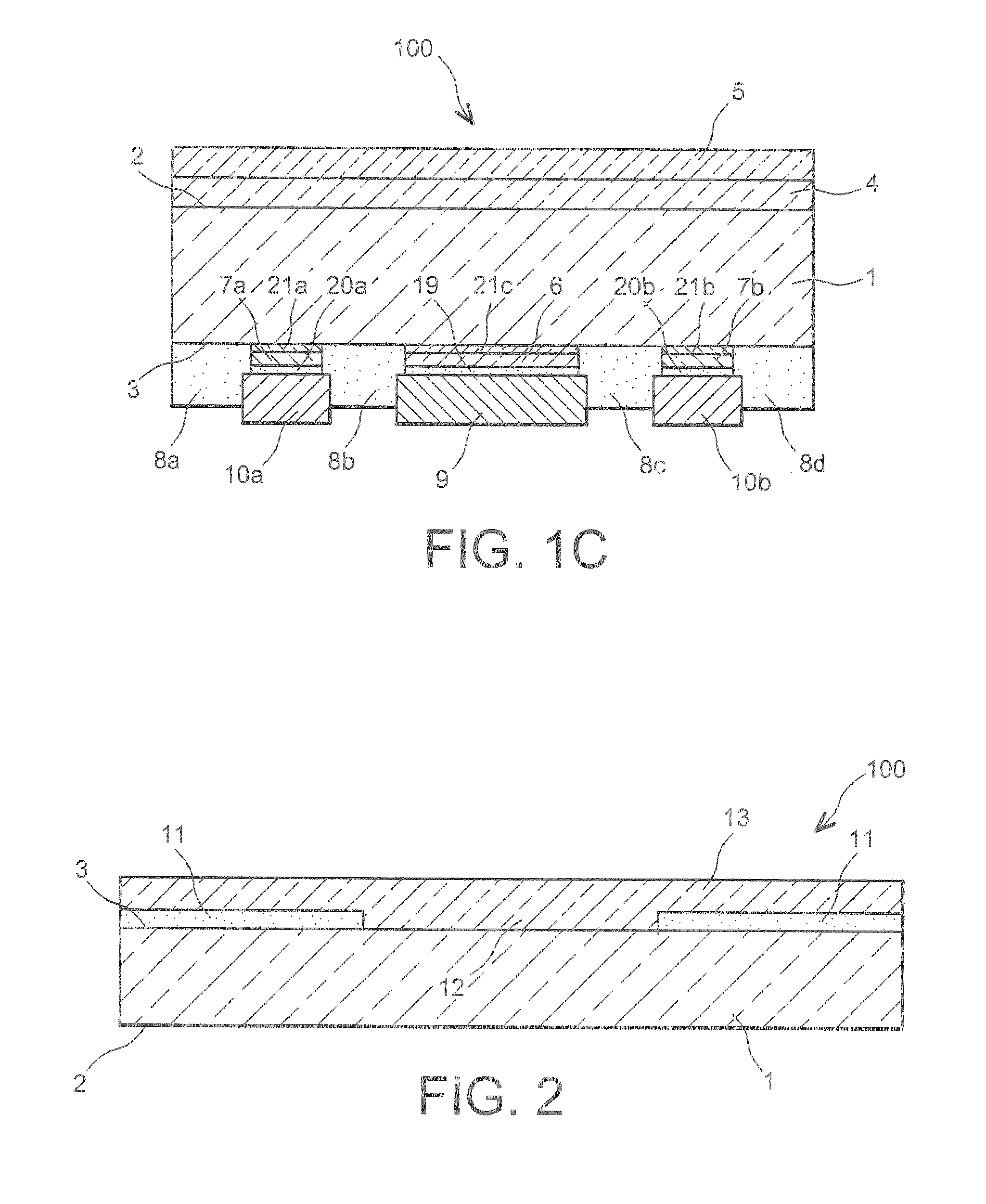

High resistivity silicon-on-insulator substrate and method of forming

ActiveUS20130168835A1High resistivityHigh materialSemiconductor/solid-state device detailsSolid-state devicesHigh resistivityPolycrystalline diamond

A semiconductor structure and a method of forming the same. In one embodiment, a method of forming a silicon-on-insulator (SOI) wafer substrate includes: providing a handle substrate; forming a high resistivity material layer over the handle substrate, the high resistivity material layer including one of an amorphous silicon carbide (SiC), a polycrystalline SiC, an amorphous diamond, or a polycrystalline diamond; forming an insulator layer over the high resistivity material layer; and bonding a donor wafer to a top surface of the insulator layer to form the SOI wafer substrate.

Owner:GLOBALFOUNDRIES US INC

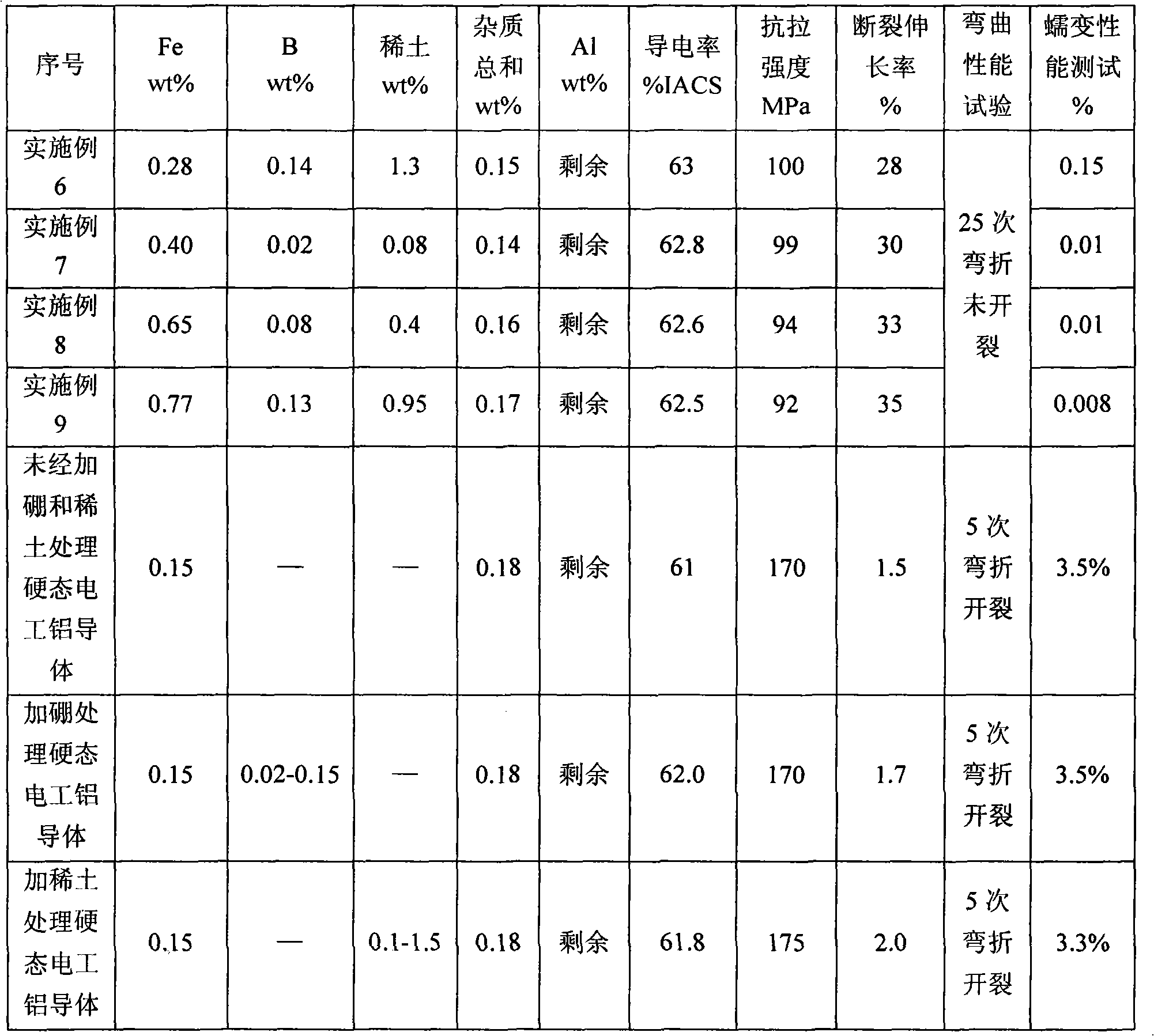

High-conductivity aluminum alloy material for cable and preparation method thereof

InactiveCN101886198ALittle impact on electrical performanceEasy to stretchMetal/alloy conductorsRare-earth elementPliability

The invention relates to a high-conductivity aluminum alloy material for a cable and a preparation method thereof. The aluminum alloy material comprises the following components in percentage by weight: 0.25-0.80 percent of iron element, 0.02-0.15 percent of boron element, 0.1-1.5 percent of rare earth element and the balance of aluminum and inevitable impurities. The aluminum alloy is formed by adding an aluminum alloy intermediate alloy, an aluminum-boron alloy and an aluminum-rare earth intermediate alloy into an aluminum ingot of which the purity is more than 99.80 percent by weight and carrying out a casting process and annealing treatment on the mixture. Compared with a common electric aluminum conductor, the prepared aluminum alloy conductor has more excellent conductive performance and the conductivity reaching or exceeding 62.5 percent IACS (International Annealed Copper Standard); the aluminum alloy conductor treated by using a special process has excellent flexibility and creep resistance; and compared with a common electric aluminum conductor, the prepared aluminum alloy material used as a cable extrusion insulating lead core is more energy-saving and safer.

Owner:ANHUI JOY SENSE CABLE

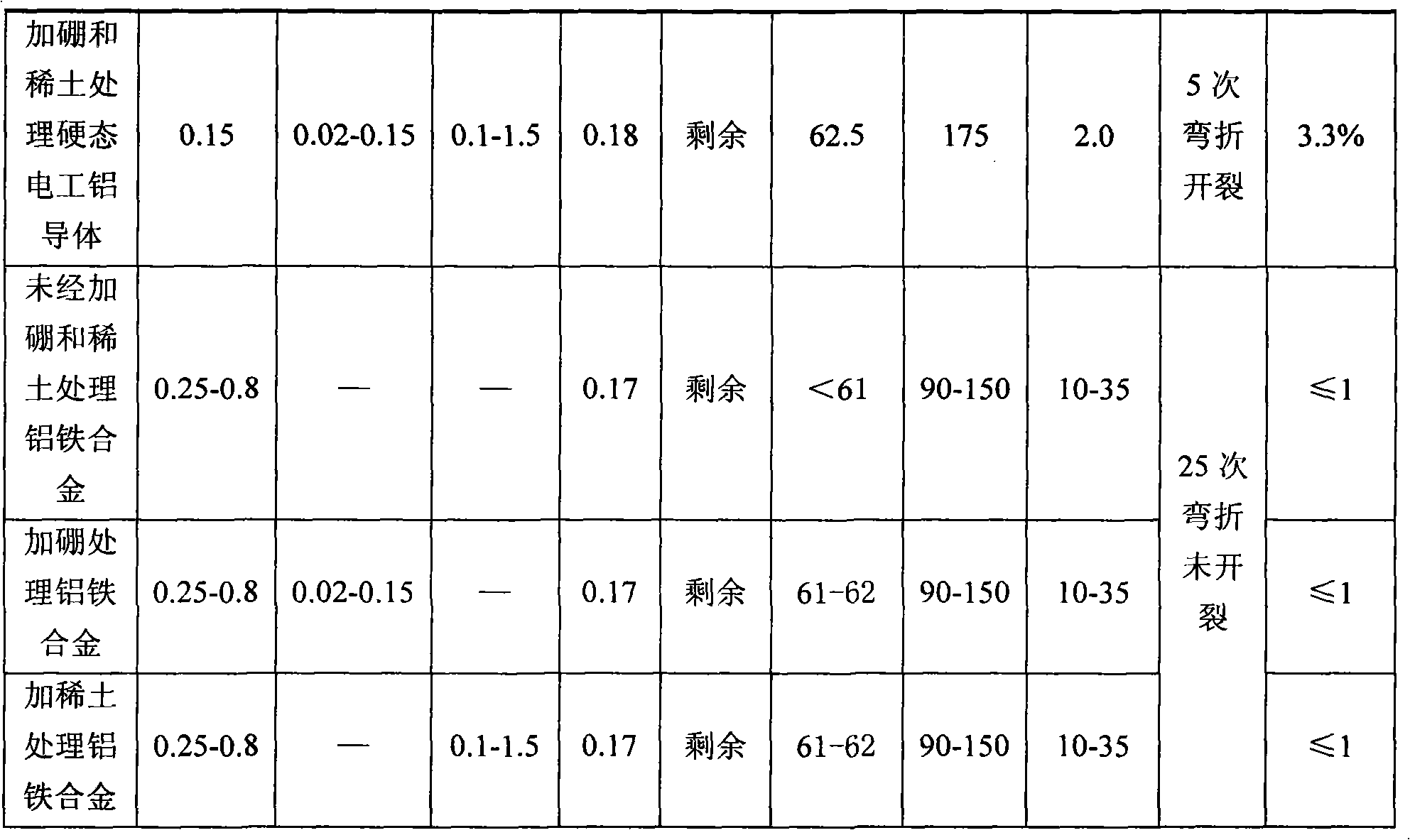

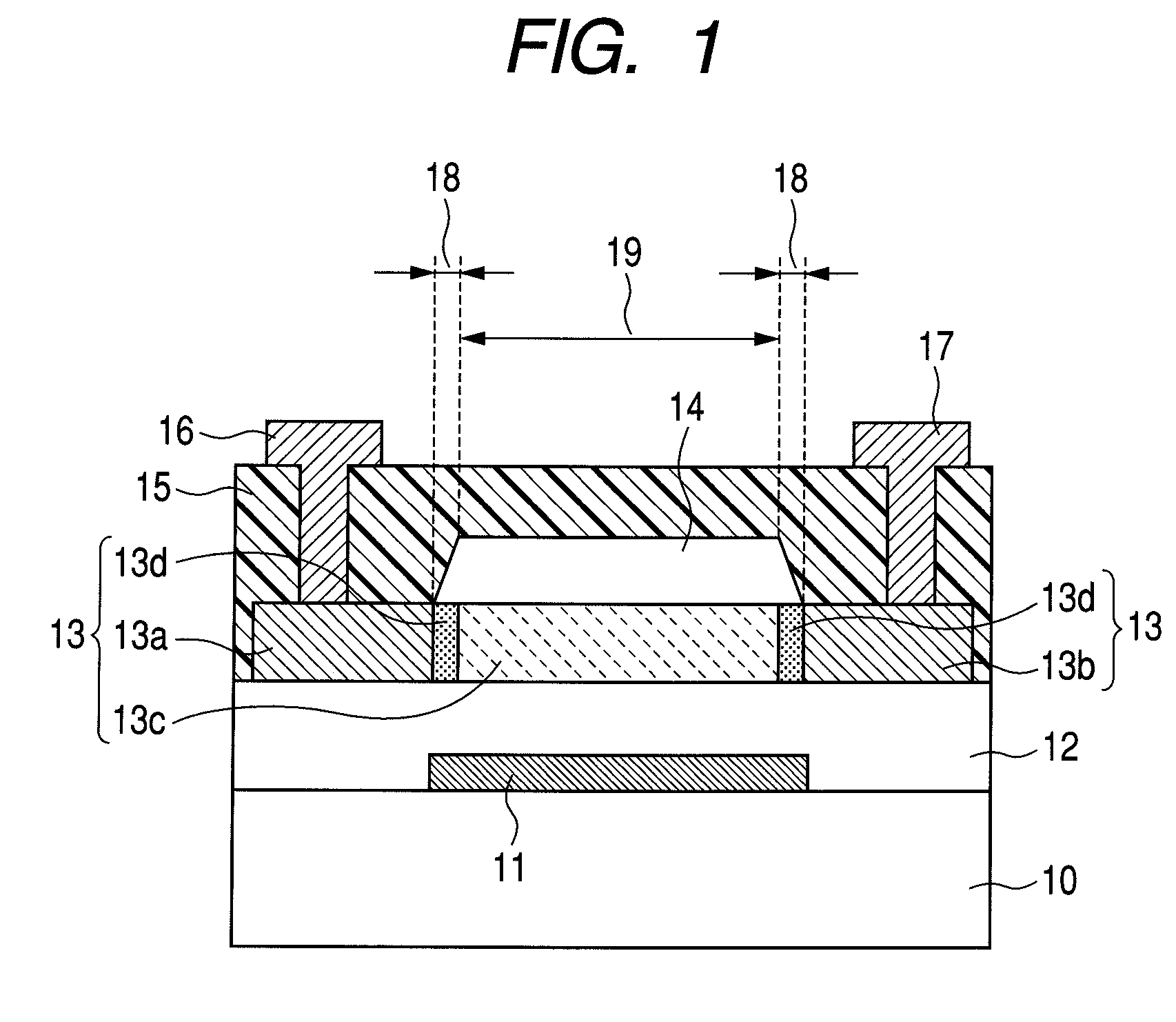

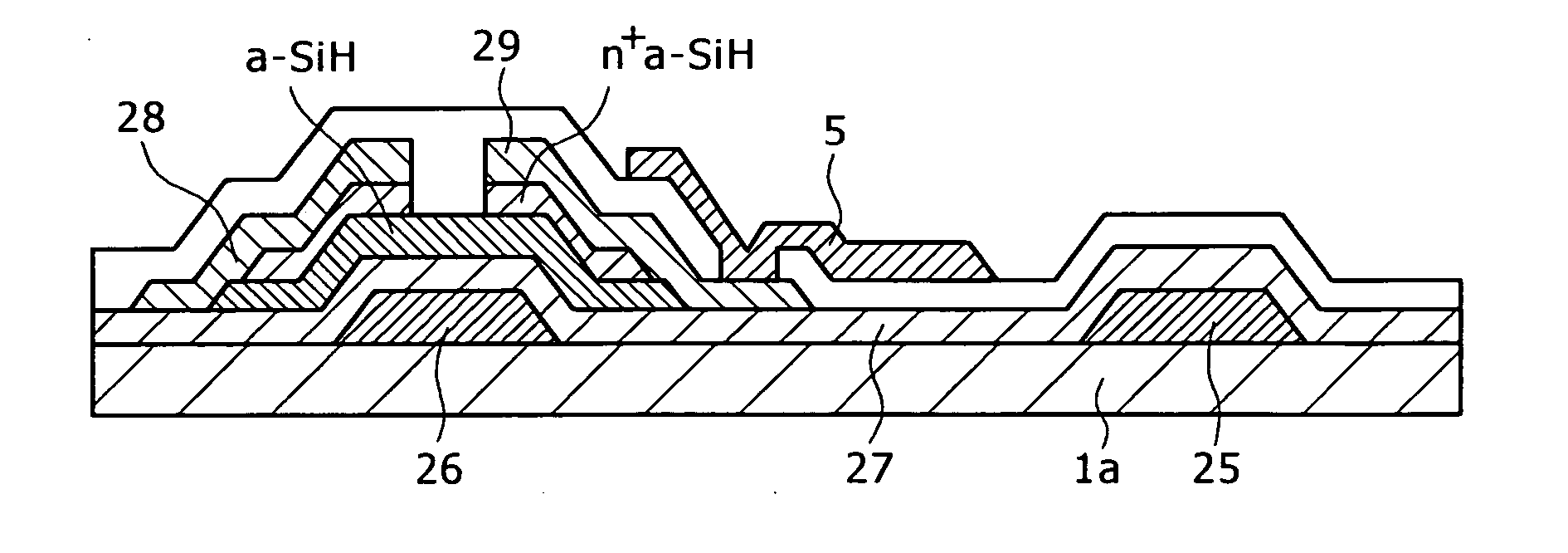

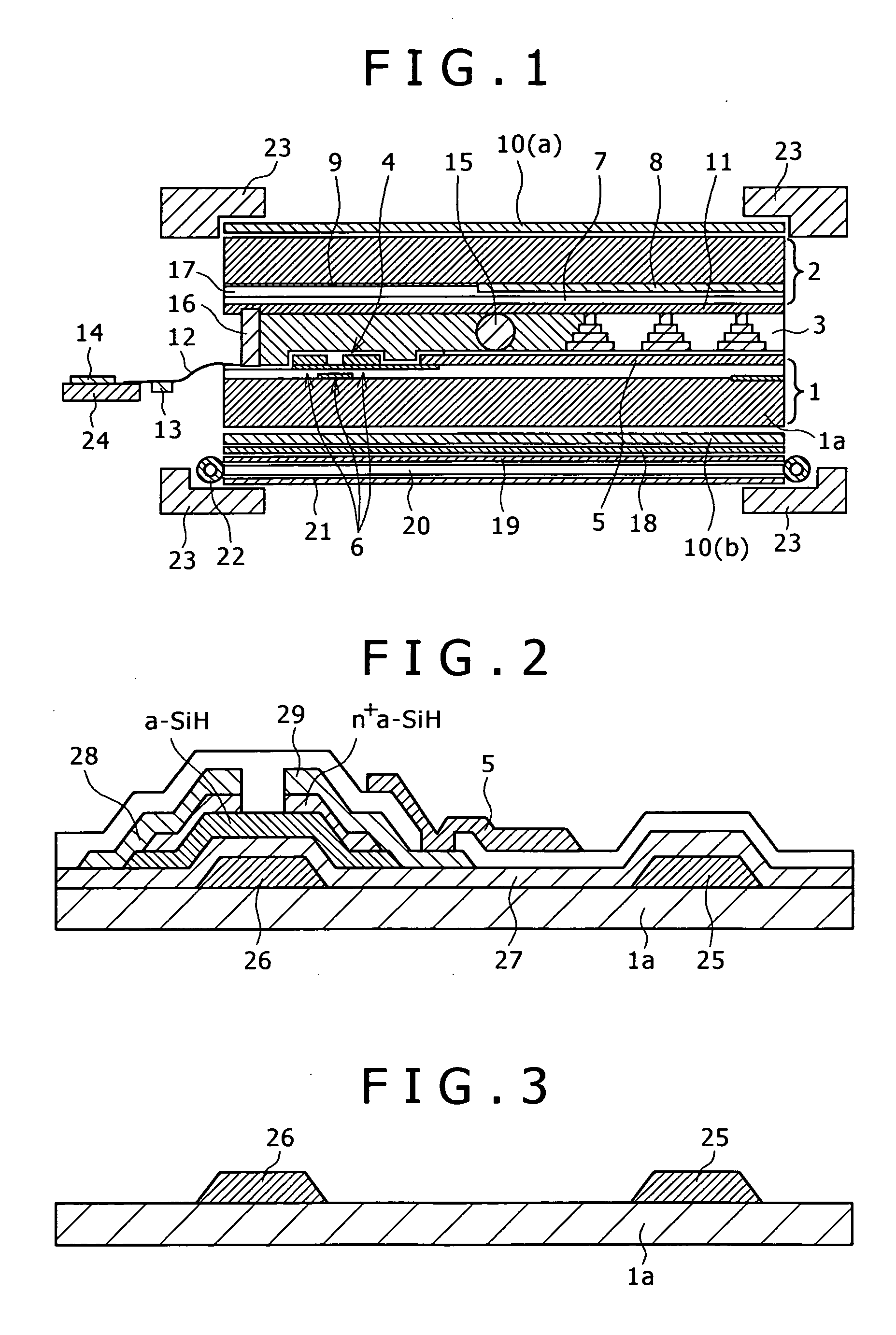

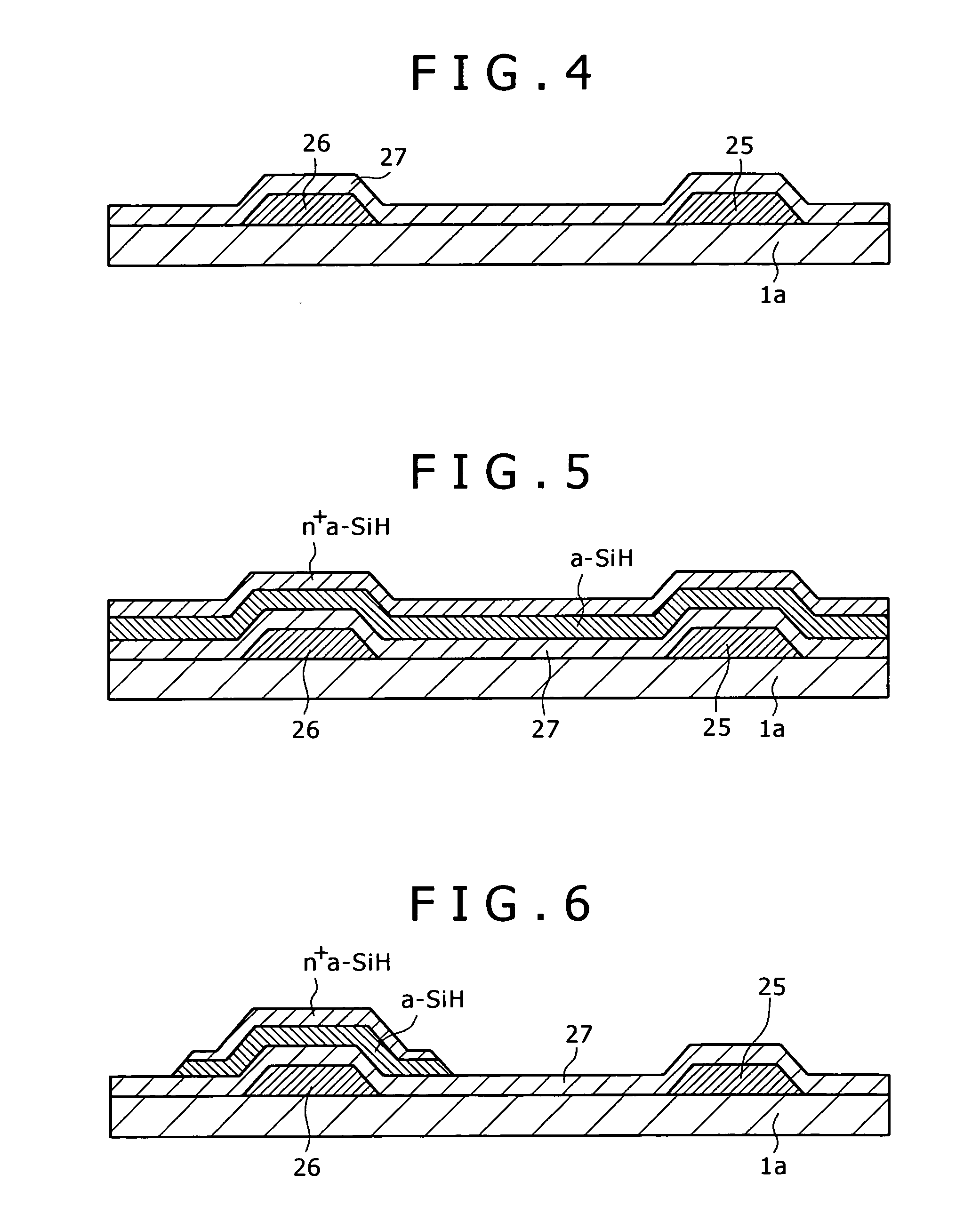

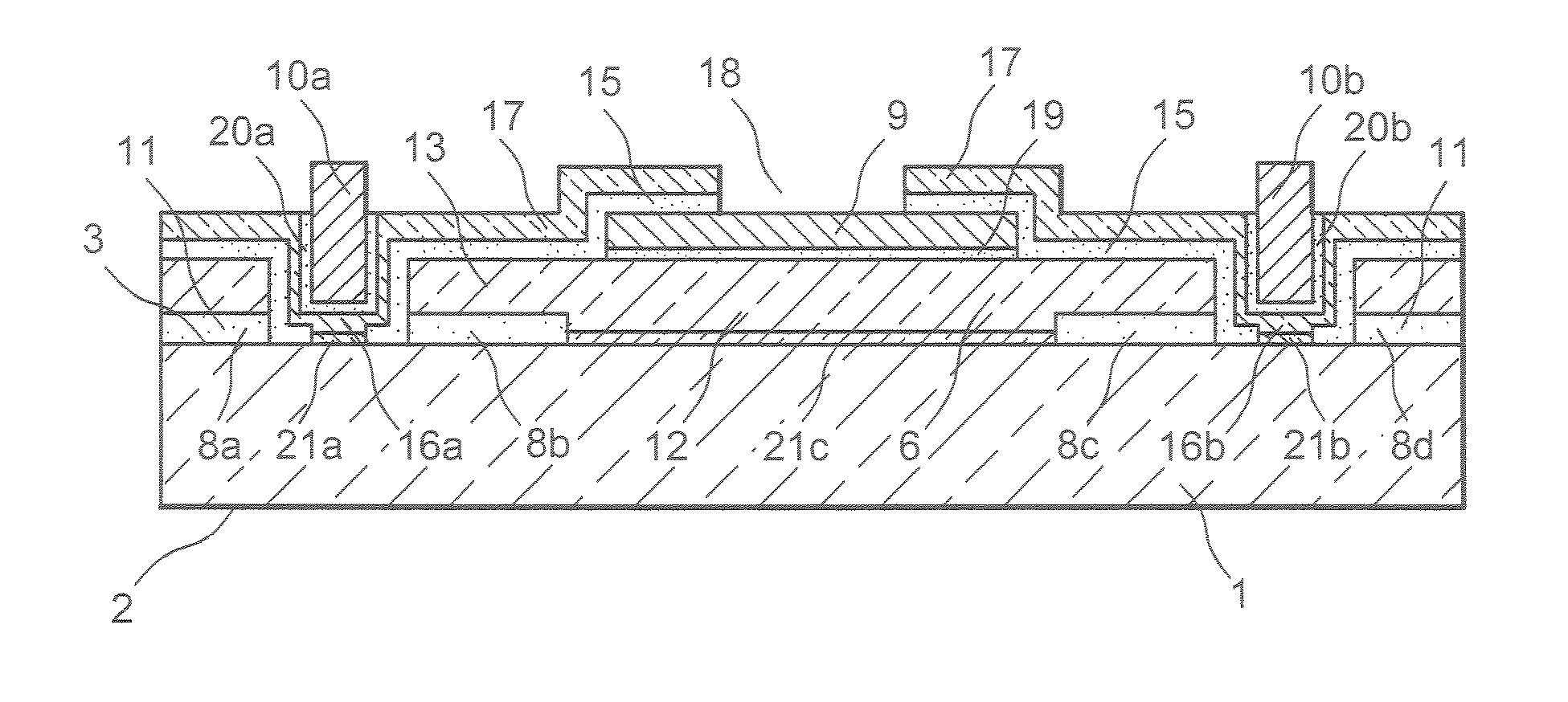

Thin film transistor and method of manufacturing the same

ActiveUS8445902B2Parasitic resistanceAvoid controlSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenEngineering

Provided are a coplanar structure thin film transistor that allows a threshold voltage to change only a little under electric stress, and a method of manufacturing the same. The thin film transistor includes on a substrate at least: a gate electrode; a gate insulating layer; an oxide semiconductor layer including a source electrode, a drain electrode, and a channel region; a channel protection layer; and an interlayer insulating layer. The channel protection layer includes one or more layers, the layer in contact with the oxide semiconductor layer among the one or more layers being made of an insulating material containing oxygen, ends of the channel protection layer are thinner than a central part of the channel protection layer, the interlayer insulating layer contains hydrogen, and regions of the oxide semiconductor layer that are in direct contact with the interlayer insulating layer form the source electrode and the drain electrode.

Owner:CANON KK

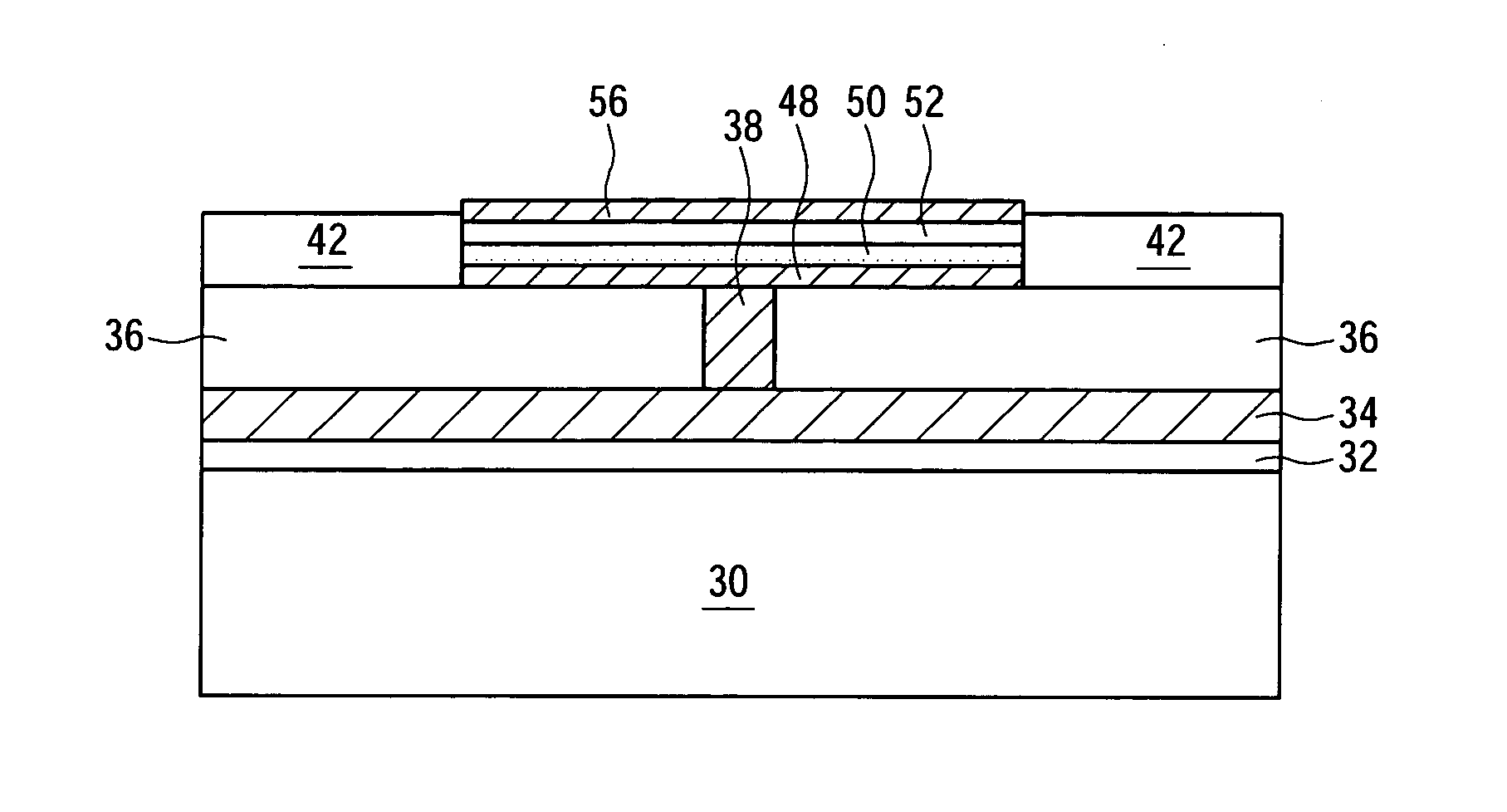

Phase change memory devices with reduced programming current

ActiveUS20070075347A1High resistivityReduce programming currentTransistorSolid-state devicesPhase-change memoryEngineering

A phase change memory device and a method of forming the same are provided. The phase change memory device includes a conducting electrode in a dielectric layer, a bottom electrode over the conducting electrode, a phase change layer over the bottom electrode, and a top electrode over the phase change layer. The phase change memory device may further include a heat sink layer between the phase change layer and the top electrode. The resistivities of the bottom electrode and the top electrode are preferably greater than the resistivity of the phase change material in the crystalline state.

Owner:TAIWAN SEMICON MFG CO LTD +1

EMI filter employing a capacitor and an inductor tank circuit having optimum component values

ActiveUS20100198312A1Fast imagingAvoid flowMultiple-port networksMagnetic measurementsCapacitancePower flow

A bandstop filter having optimum component values is provided for a lead of an active implantable medical device (AIMD). The bandstop filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the implantable lead of the AIMD, wherein values of capacitance and inductance are selected such that the bandstop filter is resonant at a selected frequency. The Q of the inductor may be relatively maximized and the Q of the capacitor may be relatively minimized to reduce the overall Q of the bandstop filter to attenuate current flow through the implantable lead along a range of selected frequencies.

Owner:WILSON GREATBATCH LTD

Method for chemical vapor deposition of silicon on to substrates for use in corrosive and vacuum environments

InactiveUS7070833B2Improve propertiesReduce outgassingPretreated surfacesSolid state diffusion coatingRoom temperatureSurface conditions

A method of passivating the surface of a substrate to protect the surface against corrosion, the surface effects on a vacuum environment, or both. The substrate surface is placed in a treatment environment and is first dehydrated and then the environment is evacuated. A silicon hydride gas is introduced into the treatment environment, which may be heated prior to the introduction of the gas. The substrate and silicon hydride gas contained therein are heated, if the treatment environment was not already heated prior to the introduction of the gas and pressurized to decompose the gas. A layer of silicon is deposited on the substrate surface. The duration of the silicon depositing step is controlled to prevent the formation of silicon dust in the treatment environment. The substrate is then cooled and held at a cooled temperature to optimize surface conditions for subsequent depositions, and the treatment environment is purged with an inert gas to remove the silicon hydride gas. The substrate is cycled through the silicon depositing step until the surface of the substrate is covered with a layer of silicon. The treatment environment is then evacuated and the substrate cooled to room temperature.

Owner:SILCOTEK CORP

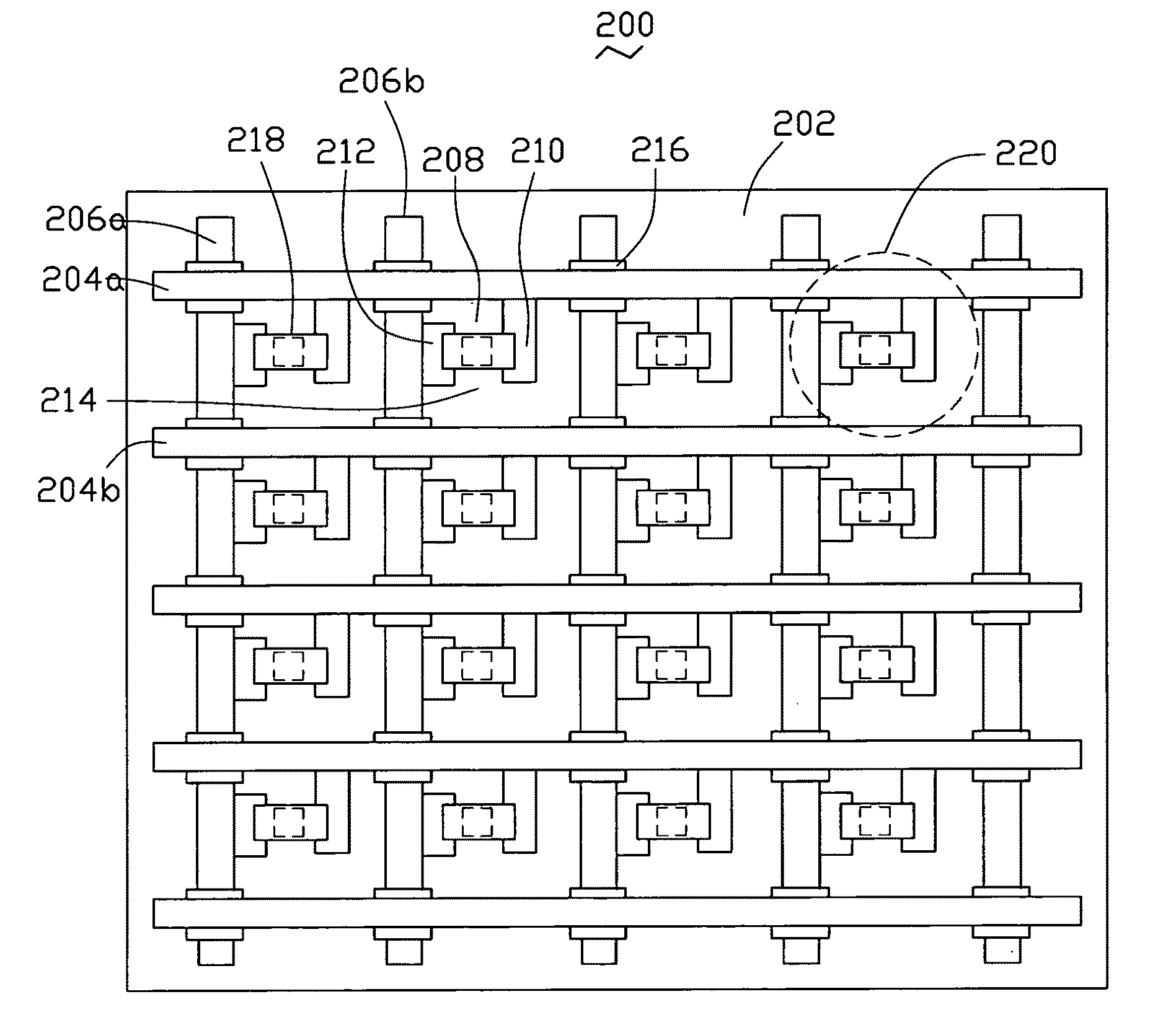

Display device

InactiveUS20060275618A1Low electrical connection resistivityImprove display qualitySolid-state devicesNatural mineral layered productsLiquid-crystal displayDisplay device

A display device in which interconnection—electrode comprising a Cu alloy film having a lower electrical resistivity than Al alloy and a transparent conductive film are directly connected not by way of a refractory metal thin film, wherein the Cu alloy film contains Zn and / or Mg in a total amount from 0.1 to 3.0 at %, or Ni and / or Mn in a total amount from 0.1 to 5 at %, thereby enabling the direct connection at low resistivity between the Cu alloy film and the transparent electrode without using a barrier metal, and giving high display quality in a case of application, for example, to a liquid crystal display.

Owner:KOBE STEEL LTD

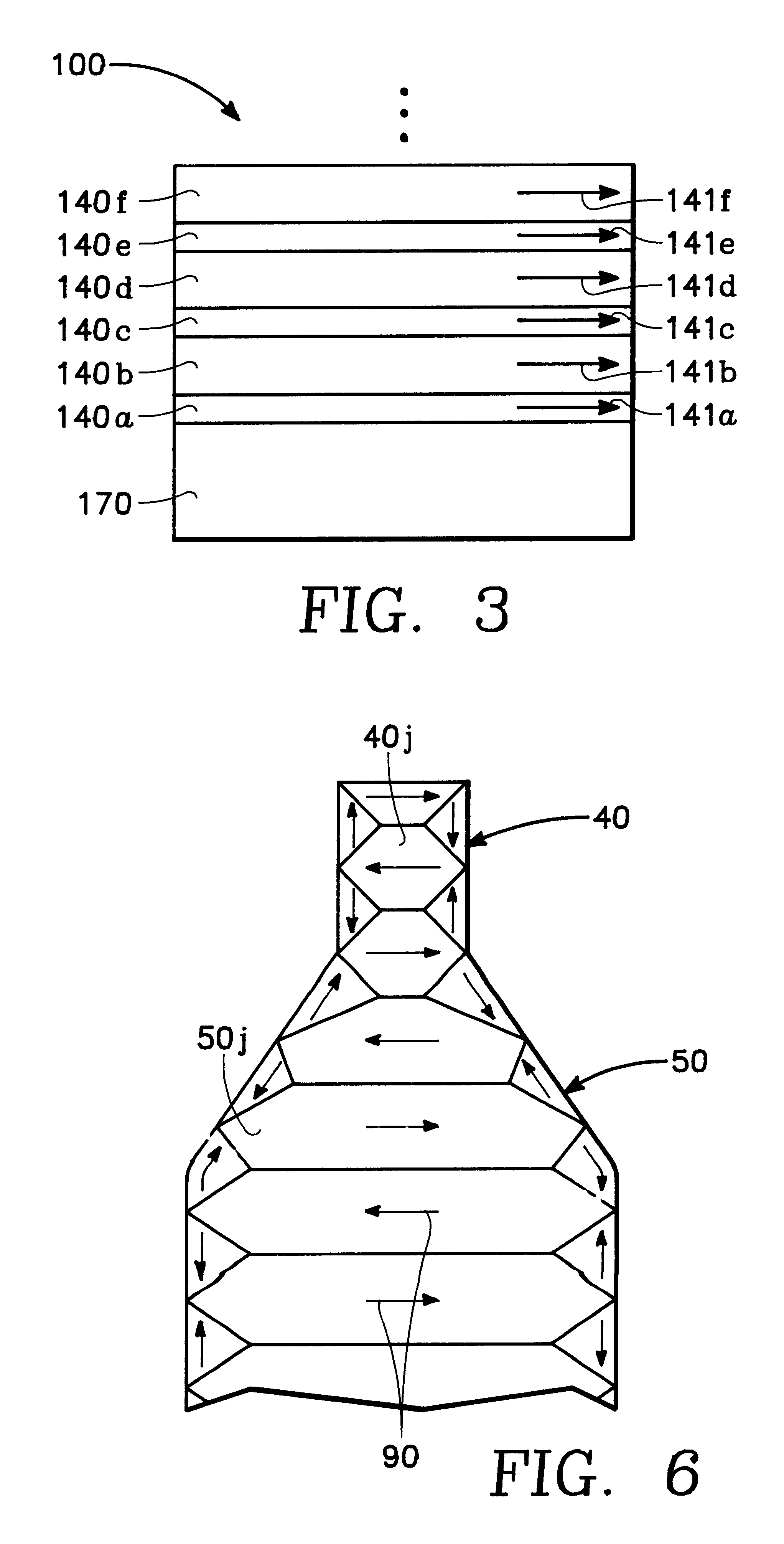

Low-resistivity photon-transparent window attached to photo-sensitive silicon detector

InactiveUS6025585ALow resistivityHigh resistivitySolid-state devicesMaterial analysis by optical meansCMOS sensorX-ray

The invention comprises a combination of a low resistivity, or electrically conducting, silicon layer that is transparent to long or short wavelength photons and is attached to the backside of a photon-sensitive layer of silicon, such as a silicon wafer or chip. The window is applied to photon sensitive silicon devices such as photodiodes, charge-coupled devices, active pixel sensors, low-energy x-ray sensors and other radiation detectors. The silicon window is applied to the back side of a photosensitive silicon wafer or chip so that photons can illuminate the device from the backside without interference from the circuit printed on the frontside. A voltage sufficient to fully deplete the high-resistivity photosensitive silicon volume of charge carriers is applied between the low-resistivity back window and the front, patterned, side of the device. This allows photon-induced charge created at the backside to reach the front side of the device and to be processed by any circuitry attached to the front side. Using the inventive combination, the photon sensitive silicon layer does not need to be thinned beyond standard fabrication methods in order to achieve full charge-depletion in the silicon volume. In one embodiment, the inventive backside window is applied to high resistivity silicon to allow backside illumination while maintaining charge isolation in CCD pixels.

Owner:RGT UNIV OF CALIFORNIA

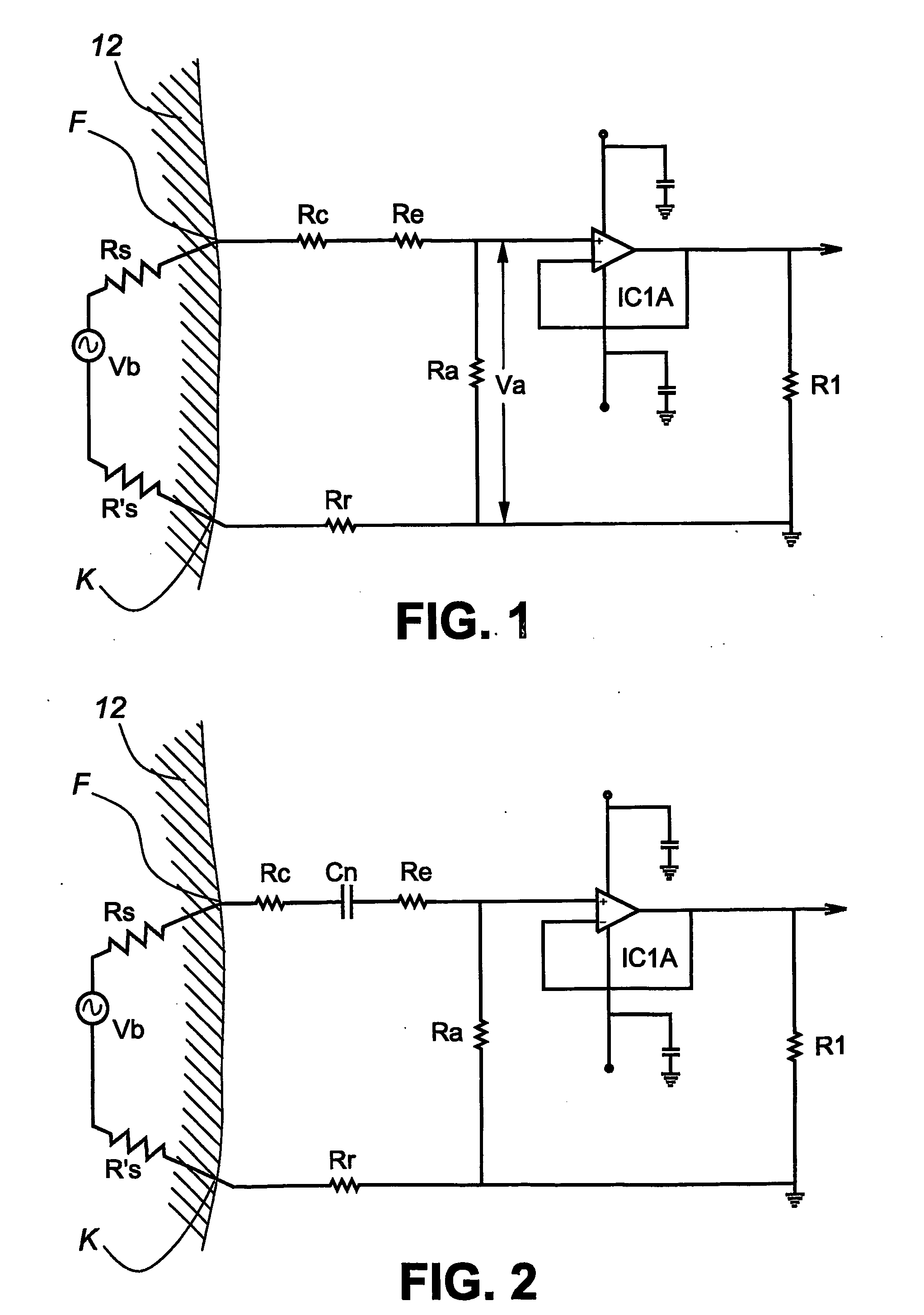

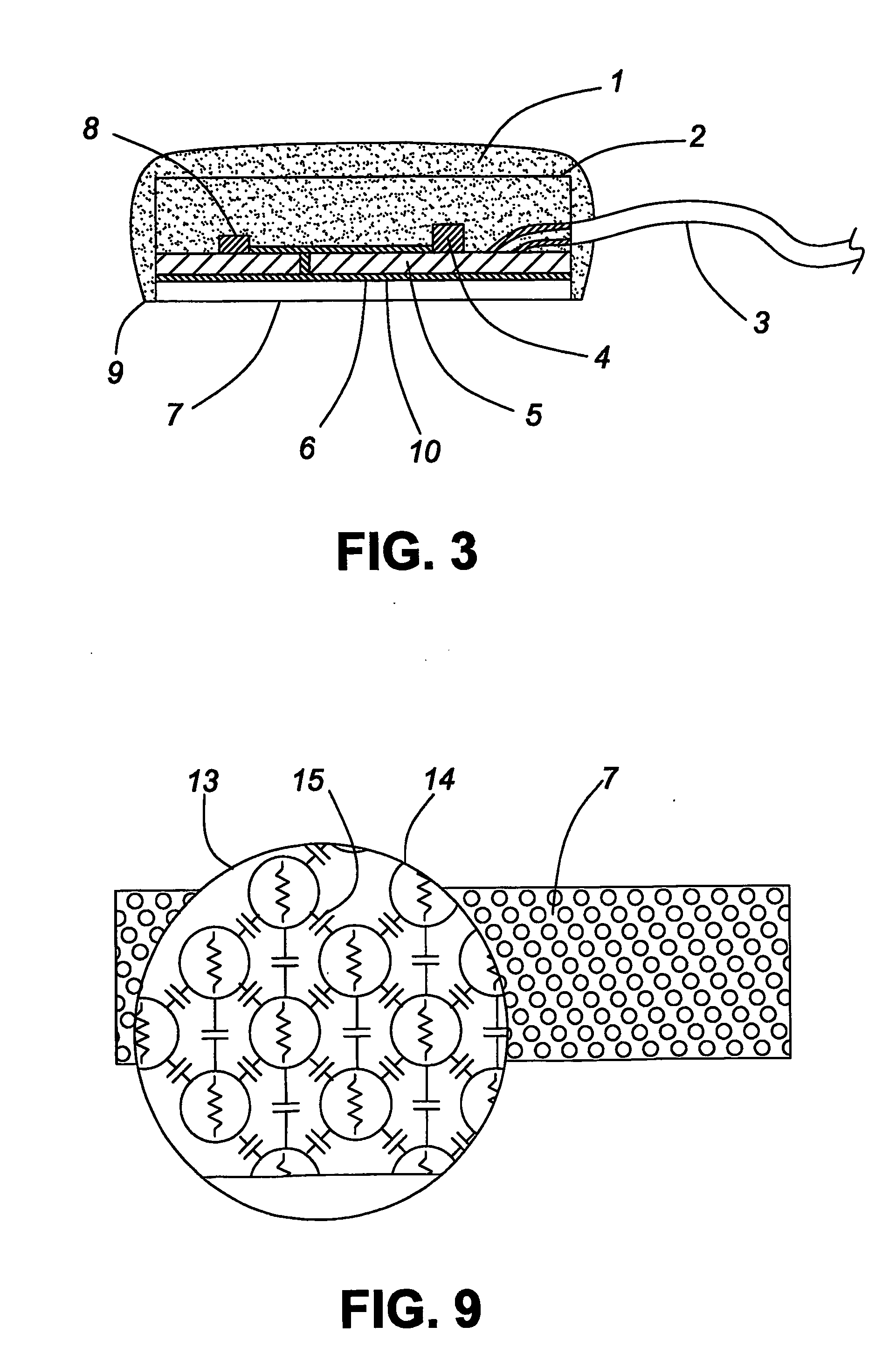

Skin impedance matched biopotential electrode

InactiveUS20050177038A1Low output impedanceHigh input impedanceElectrocardiographySensorsEngineeringElectric resistivity

A bio-electrode for detecting heart signals and the like comprises a dry electode surface having an elevated resistivity to reduce the effect of polarization noise. The electrode is combined with a circuit having an external discharge resistor across which an output signal is obtained wherein the discharge resistor has a value which reduces the time constant of polarization noise to less than one second.

Owner:ADVANCED BIOELECTRIC CORP

Novel underlayer for high performance magnetic tunneling junction MRAM

ActiveUS20060002184A1High resistivityConsistent growthNanomagnetismMagnetic measurementsOptoelectronicsHigh resistivity

An MRAM structure is disclosed in which the bottom electrode has an amorphous TaN capping layer to consistently provide smooth and dense growth for AFM, pinned, tunnel barrier, and free layers in an overlying MTJ. Unlike a conventional Ta capping layer, TaN is oxidation resistant and has high resistivity to avoid shunting of a sense current caused by redeposition of the capping layer on the sidewalls of the tunnel barrier layer. Alternatively, the α-TaN layer is the seed layer in the MTJ. Furthermore, the seed layer may be a composite layer comprised of a NiCr, NiFe, or NiFeCr layer on the α-TaN layer. An α-TaN capping layer or seed layer can also be used in a TMR read head. An MTJ formed on an α-TaN capping layer has a high MR ratio, high Vb, and a RA similar to results obtained from MTJs based on an optimized Ta capping layer.

Owner:APPLIED SPINTRONICS +1

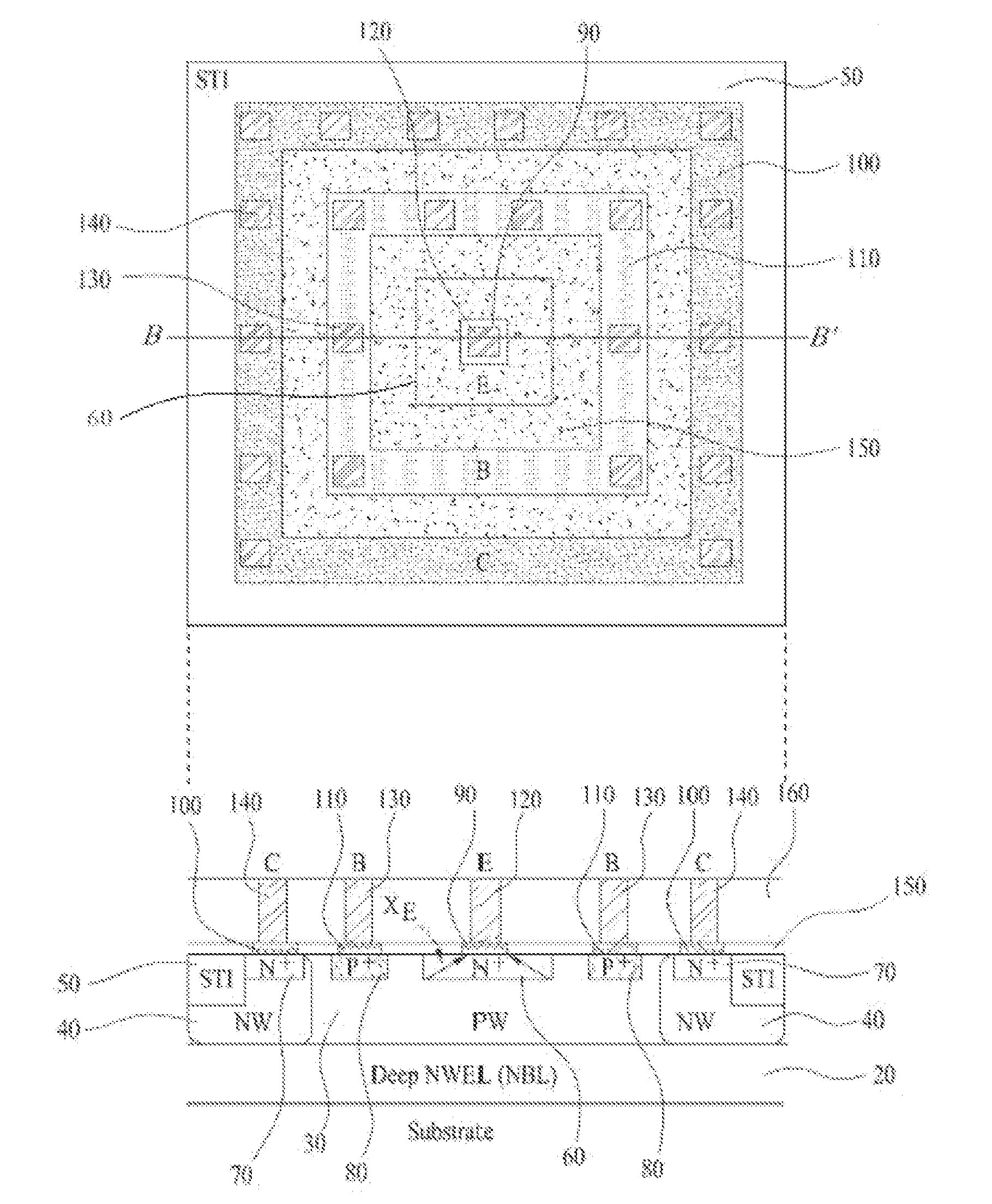

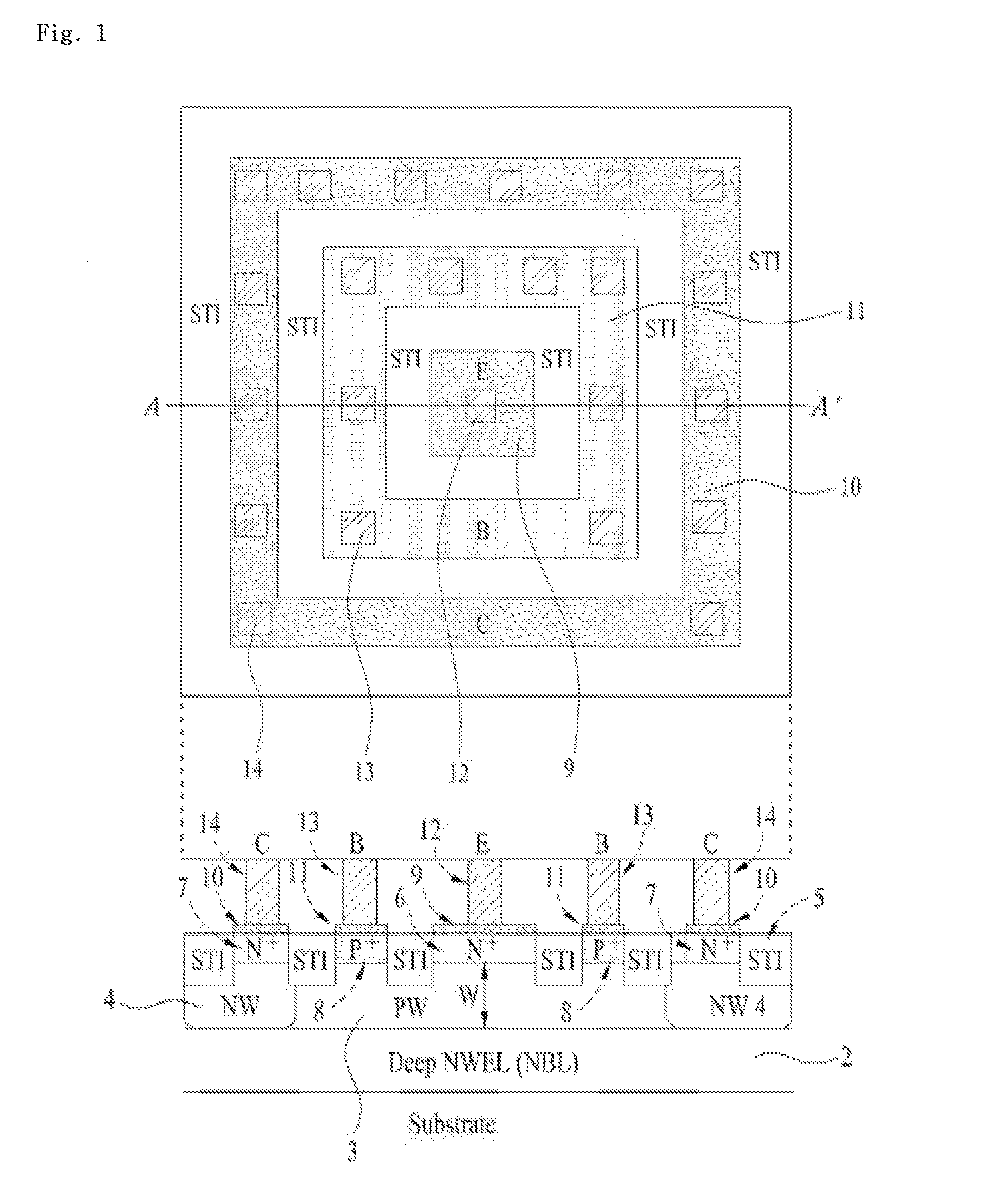

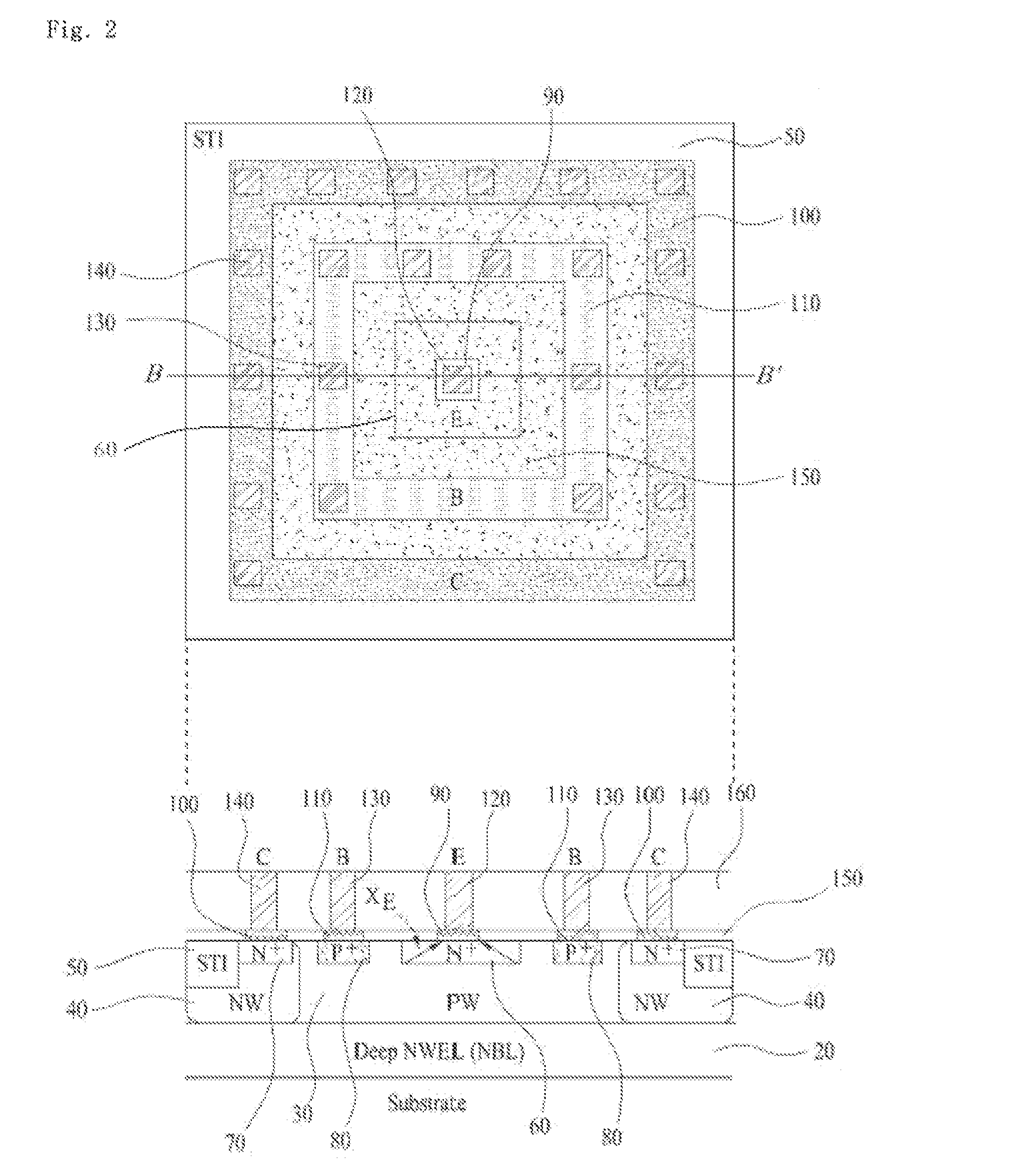

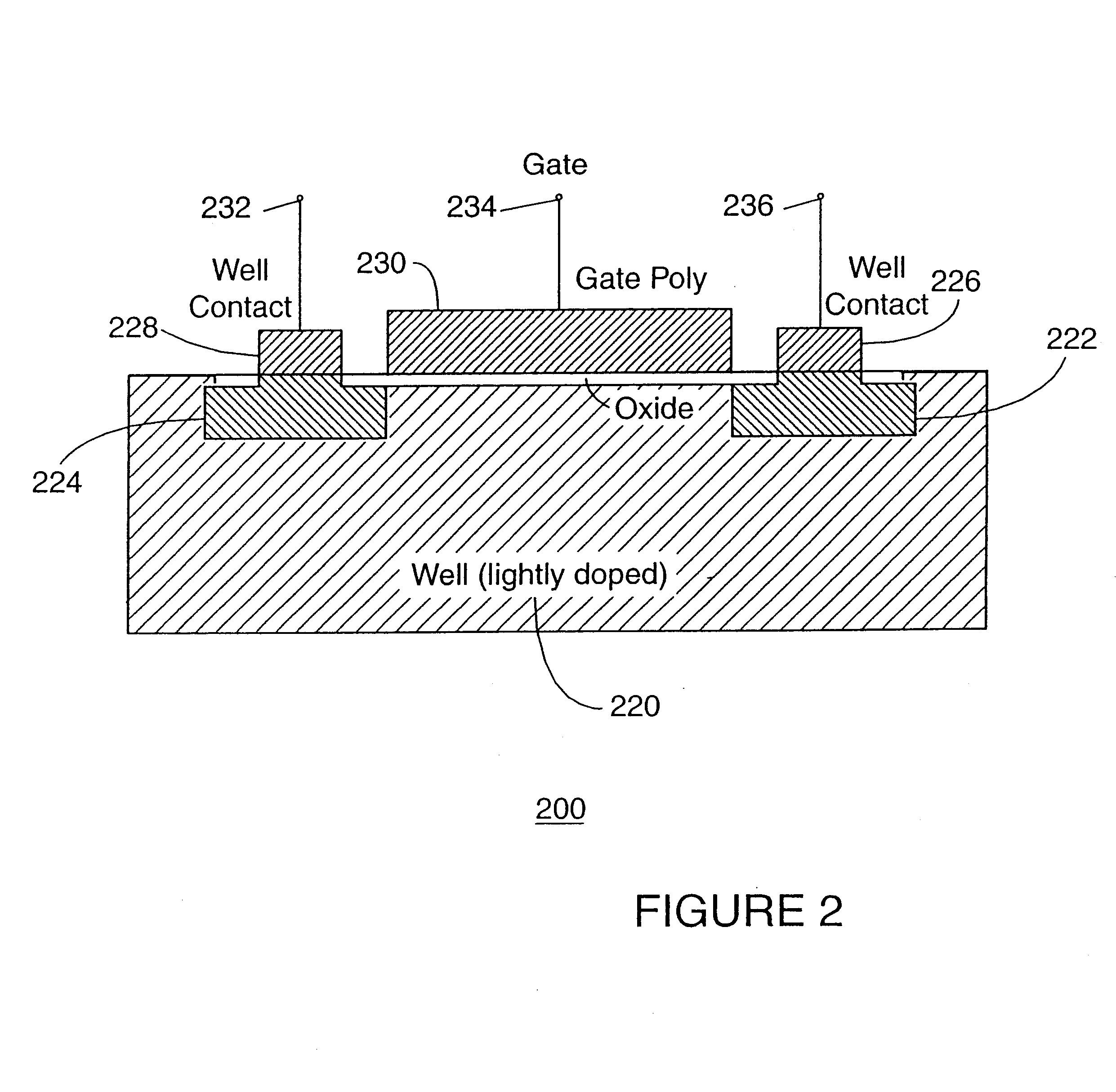

Bipolar Junction Transistor Based on CMOS Technology

InactiveUS20120032303A1Increase currentHigh base resistanceTransistorSemiconductor/solid-state device manufacturingCMOSEngineering

The present invention relates to semiconductor technologies, and more particularly to a bipolar junction transistor (BJT) in a CMOS base technology and methods of forming the same. The BJT includes a semiconductor substrate having an emitter region, a base having a first contact, and a collector having a second contact and a well plug; a first silicide film on the first contact; a second silicide film on the second contact; a first silicide blocking layer on or over the semiconductor substrate between the first and second silicide films, and a second silicide blocking layer on the semiconductor substrate between the first silicide film and the emitter region.

Owner:DONGBU HITEK CO LTD

Thermionic emission device

ActiveUS20090167136A1Reduce consumptionLimited applicationControl electrodesElectrode and associated part arrangementsThermionic emissionAtomic physics

A thermionic emission device includes an insulating substrate, and one or more grids located thereon. Each grid includes a first, second, third and fourth electrode down-leads located on the periphery thereof, and a thermionic electron emission unit therein. The first and second electrode down-leads are parallel to each other. The third and fourth electrode down-leads are parallel to each other. The first and second electrode down-leads are insulated from the third and fourth electrode down-leads. The thermionic electron emission unit includes a first electrode, a second electrode, and a thermionic electron emitter. The first electrode and the second electrode are separately located and electrically connected to the first electrode down-lead and the third electrode down-lead respectively. The insulating substrate comprises one or more recesses that further insulate the thermionic electron emitters from the substrate.

Owner:TSINGHUA UNIV +1

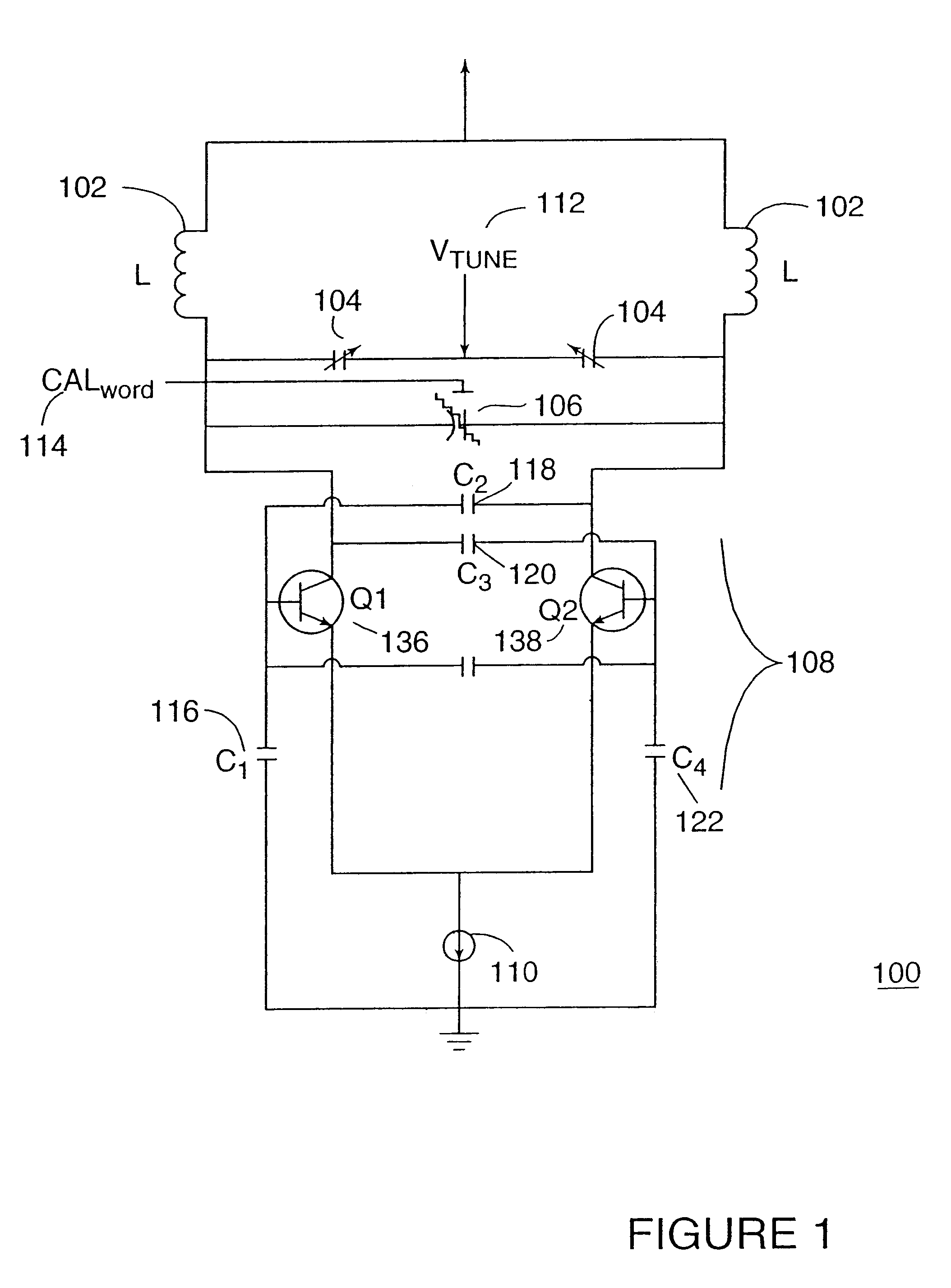

Method and apparatus for fully integrating a voltage controlled oscillator on an integrated circuit

InactiveUS6268778B1Wide tuning capacitance rangeReduce parasitic capacitanceAngle modulation by variable impedencePulse automatic controlLc resonatorSelf resonance

A method and apparatus for fully integrating a Voltage Controlled Oscillator (VCO) on an integrated circuit. The VCO is implemented using a differential-mode circuit design. The differential-mode implementation of the VCO preferably comprises a differential mode LC-resonator circuit, a digital capacitor, a differential pair amplifier, and a current source. The LC-resonator circuit includes at least one tuning varactor and two high Q inductors. The tuning varactor preferably has a wide tuning capacitance range. The tuning varactor is only used to "fine-tune" the center output frequency f0 of the VCO. The center output frequency f0 is coarsely tuned by the digital capacitor. The VCO high Q inductors comprise high gain, high self-resonance, and low loss IC inductors. The IC VCO is fabricated on a high resistivity substrate material using a trench isolated guard ring. The guard ring isolates the fully integrated VCO, and each of its component parts, from RF signals that may be introduced into the IC substrate by other devices. By virtue of the improved performance characteristics provided by the digital capacitor, the analog tuning varactor, the high Q inductor, and the trench isolated guard ring techniques, the inventive VCO is fully integrated despite process variations in IC fabrication.

Owner:CSR TECH INC

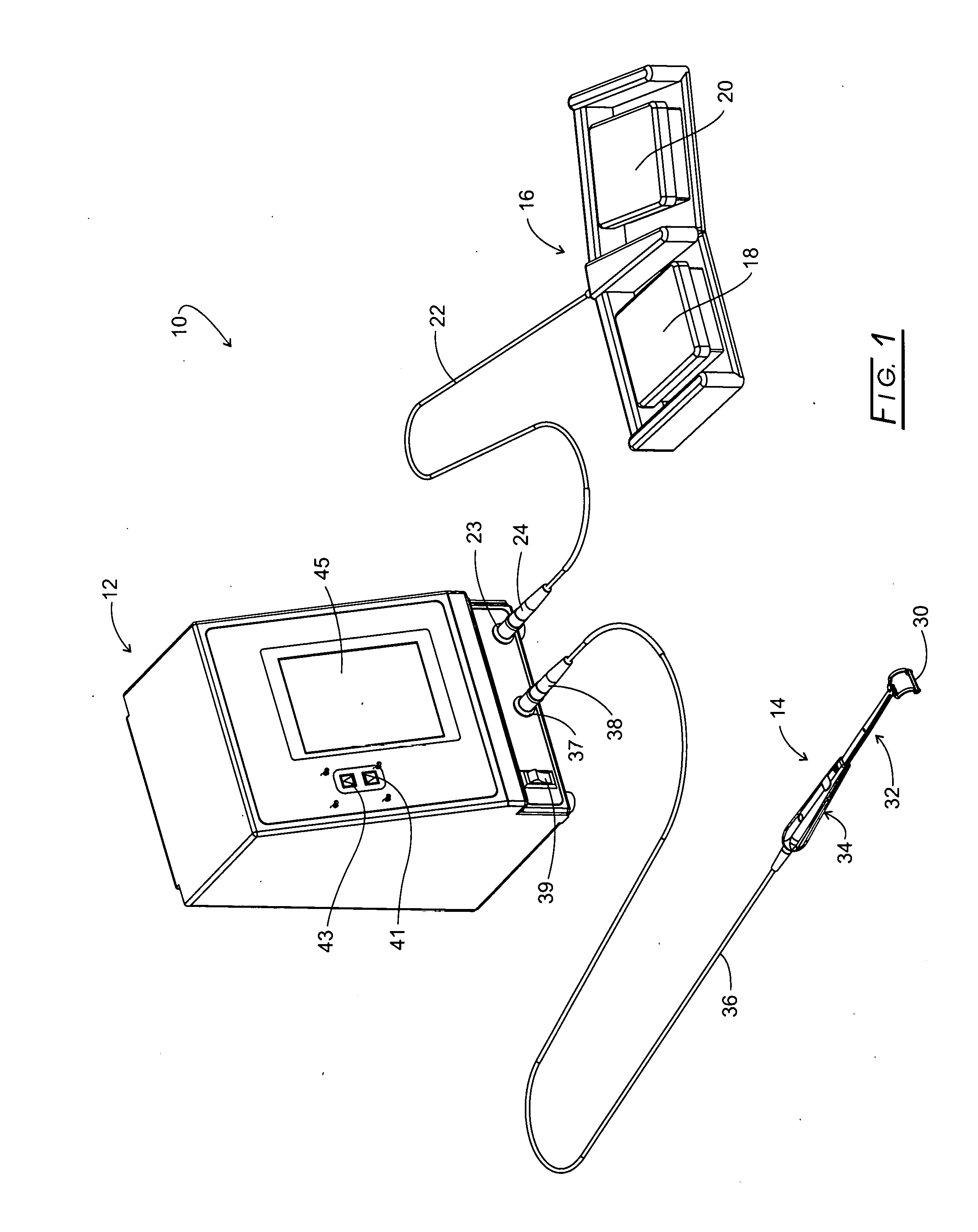

Apparatus, System and Method for Excision of Soft Tissue

InactiveUS20160242836A1Minimize heat conductionMinimize intra-operative and post-operative bleedingSurgical instruments for heatingContact padEngineering

Owner:HEMOSTATIX MEDICAL TECH

Semiconductor Device with Heterojunctions and an Inter-Finger Structure

InactiveUS20080061293A1Improve insulation performanceSimple structureFinal product manufactureSemiconductor/solid-state device manufacturingHeterojunctionDevice material

A semiconductor device including, on at least one surface of a crystalline semiconductor substrate, at least one first amorphous semiconductor region doped with a first type of conductivity. The semiconductor substrate includes, on the same at least one surface, at least one second amorphous semiconductor region doped with a second type of conductivity, opposite the first type of conductivity. The first amorphous semiconductor region, insulated for the second amorphous semiconductor region by at least ore dielectric region in the contact with the semiconductor substrate, and the second amorphous semiconductor region form an interdigitated structure.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com