Planar substrate with selected semiconductor crystal orientations formed by localized amorphization and recrystallization of stacked template layers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention, which provides planar hybrid-orientation SOI substrate structures and methods of fabricating the same, will now be described in greater detail by referring to the drawings that accompany the present application.

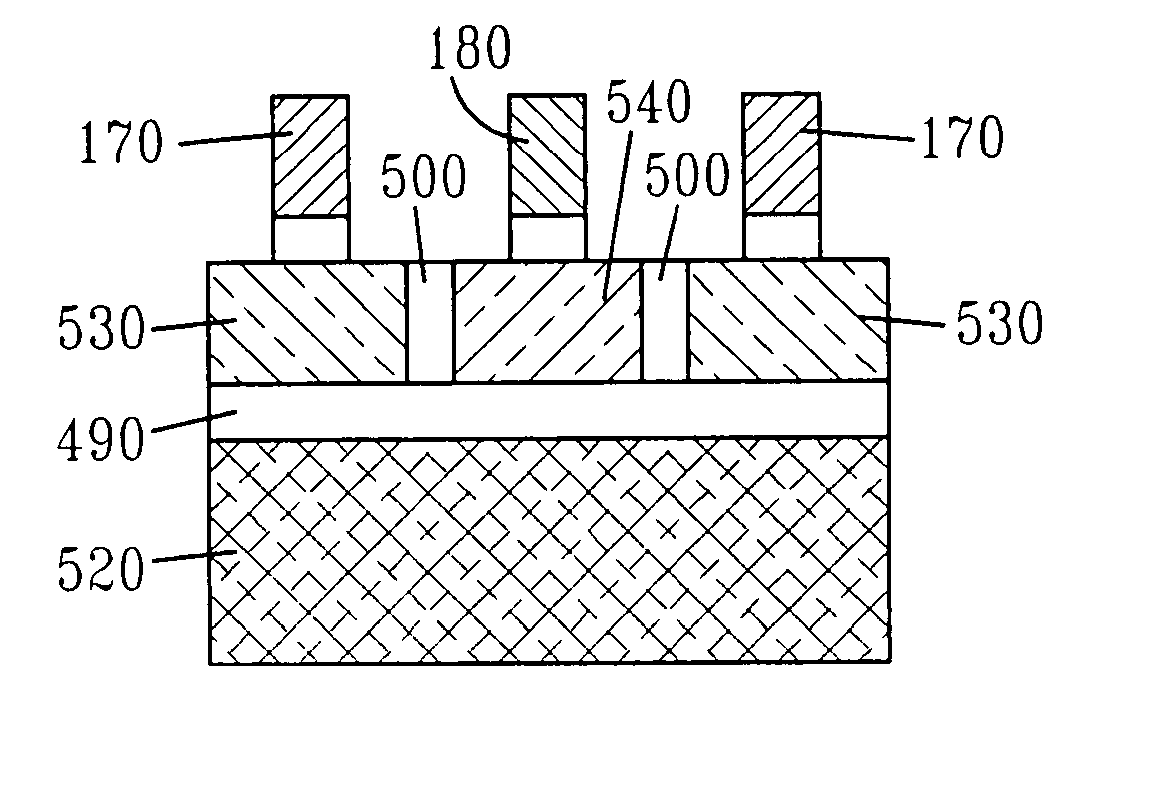

[0036]FIGS. 5A-5B show, in cross section view, two preferred embodiments of hybrid-orientation substrates that can be fabricated by the methods of the present invention. Hybrid-orientation substrate 450 of FIG. 5A and hybrid-orientation substrate 460 of FIG. 5B both comprise first single crystal semiconductor regions 470 with a first orientation, and second single crystal semiconductor regions 480 with a second orientation different from the first orientation. Semiconductor regions 470 and 480 have approximately the same thickness and are disposed on the same BOX layer 490. The term “BOX” denotes a buried oxide region. Although this terminology is specifically used here, the present invention is not limited to merely buried oxides. Instead, vari...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com