Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

204results about How to "Simplify hardware design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

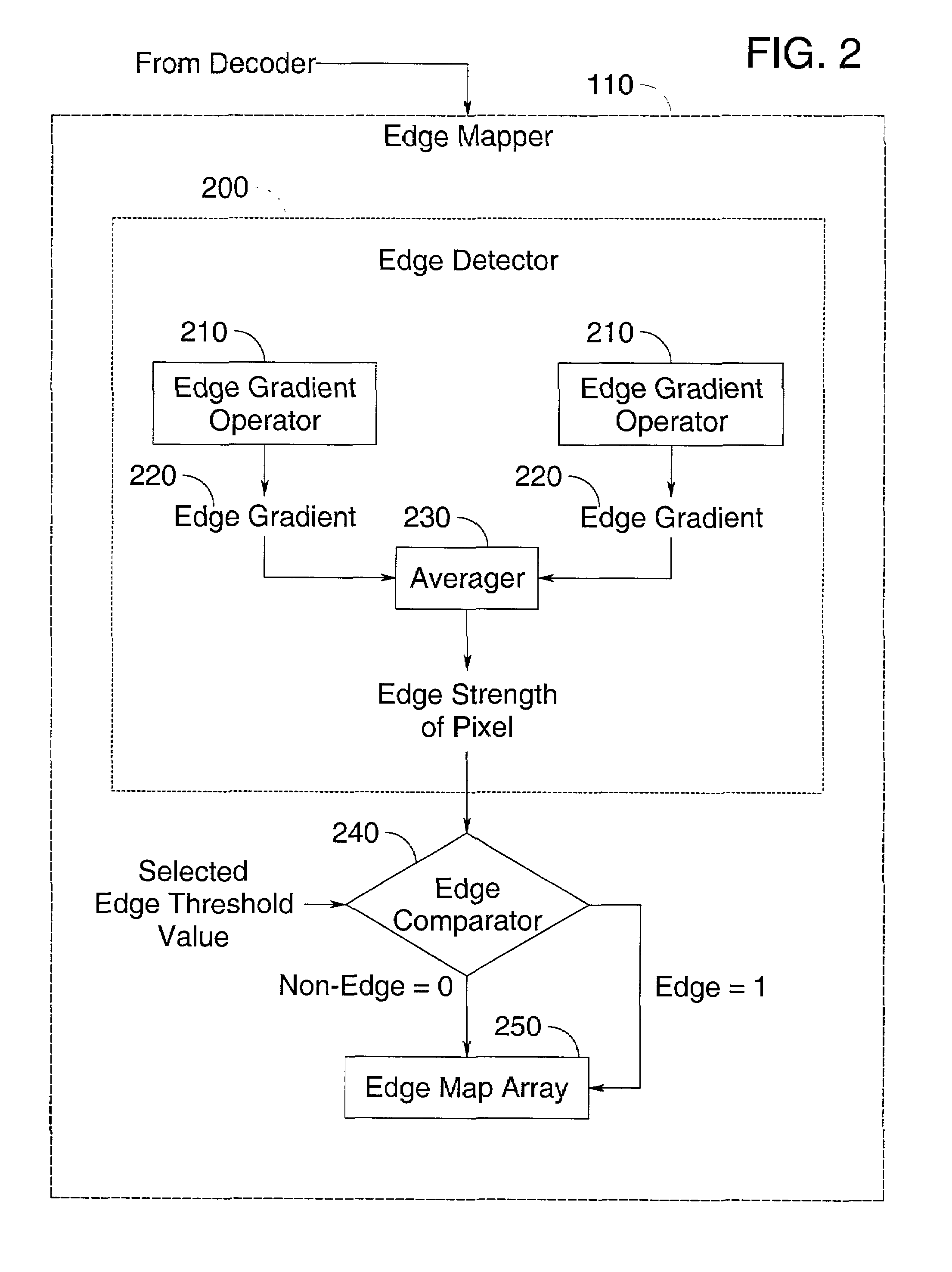

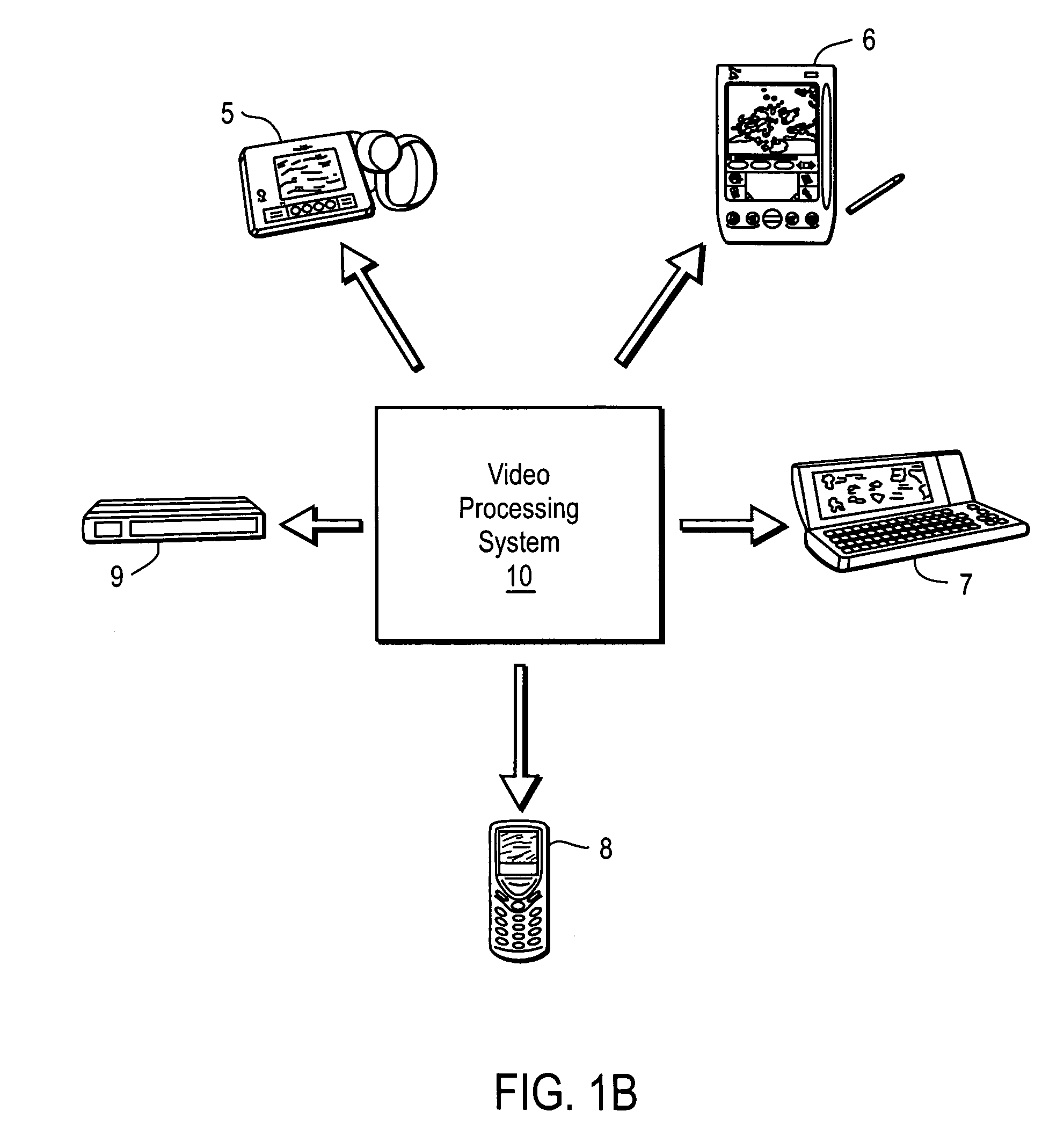

Filter for combined de-ringing and edge sharpening

InactiveUS7003173B2Reduce redundancyComputationally less-expensiveTelevision system detailsImage enhancementAdaptive filterSharpening

A filter for post-processing digital images and videos, having an edge mapper, a pixel sorter, and an adaptive filter that simultaneously performs de-ringing and edge sharpening. The combined filter is computationally simpler than known methods and can achieve removal of ringing artifacts and sharpening of true edges at the same time. The present invention also includes a preferred method of simultaneously de-ringing and edge sharpening digital images and videos.

Owner:SHARP KK

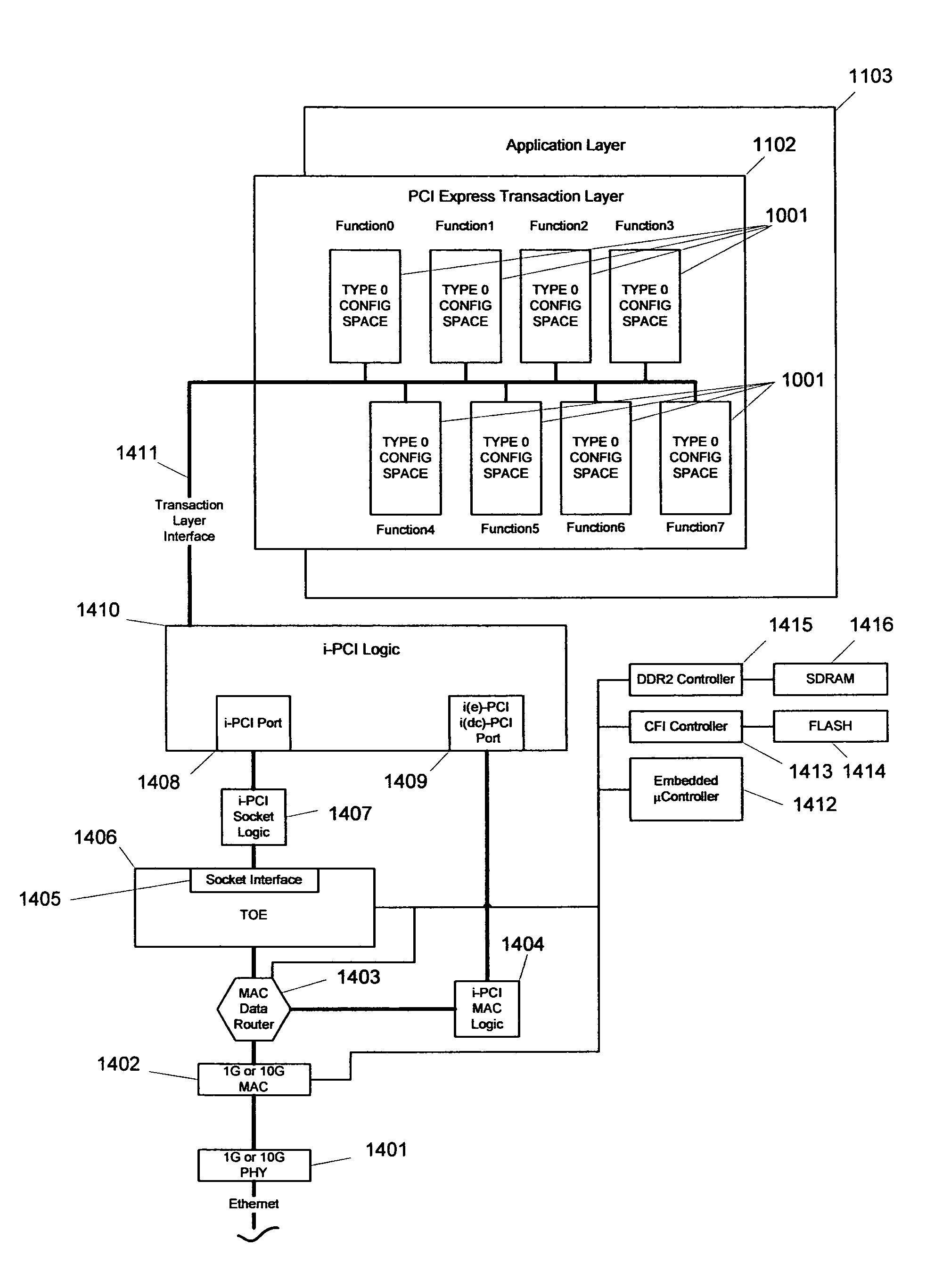

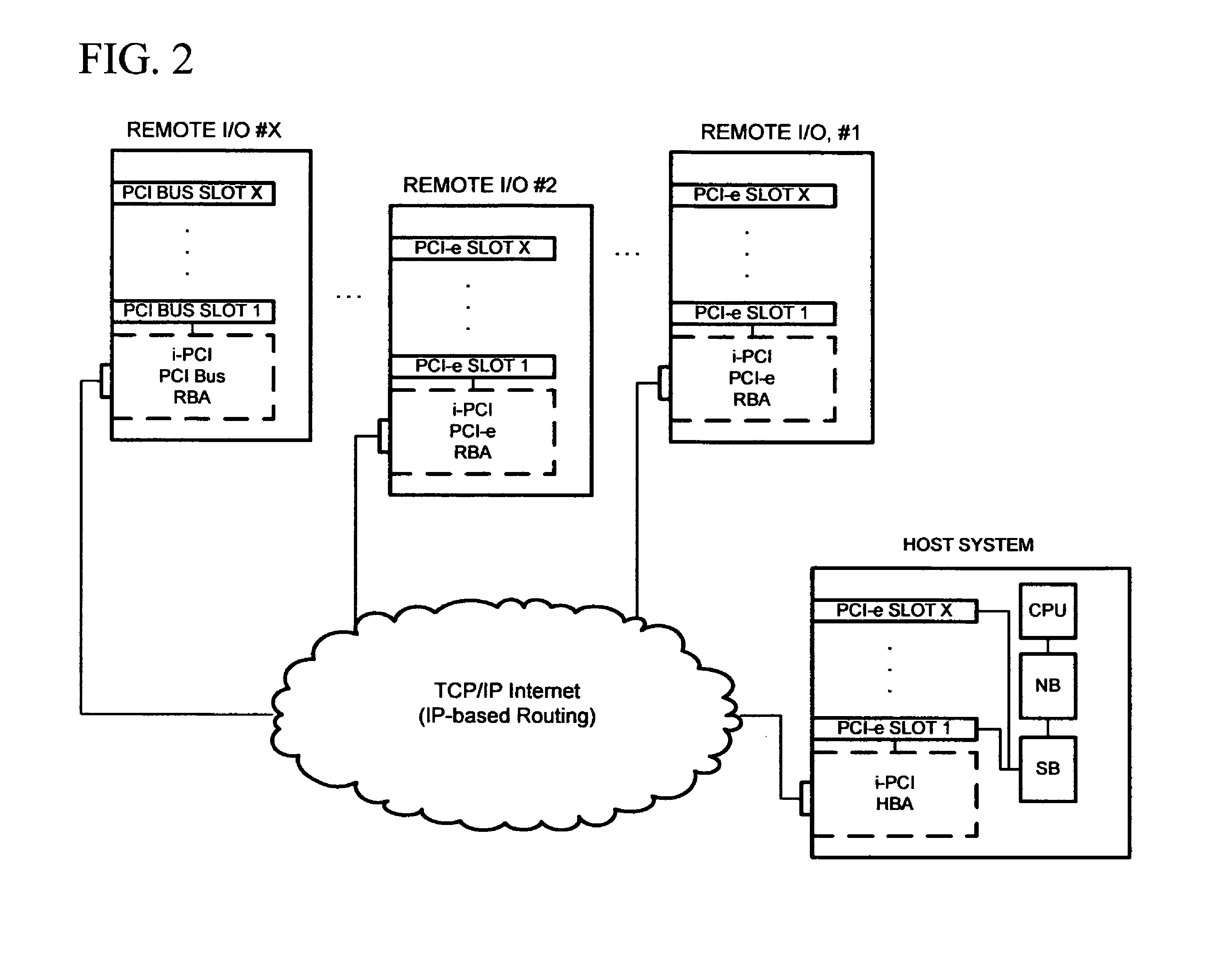

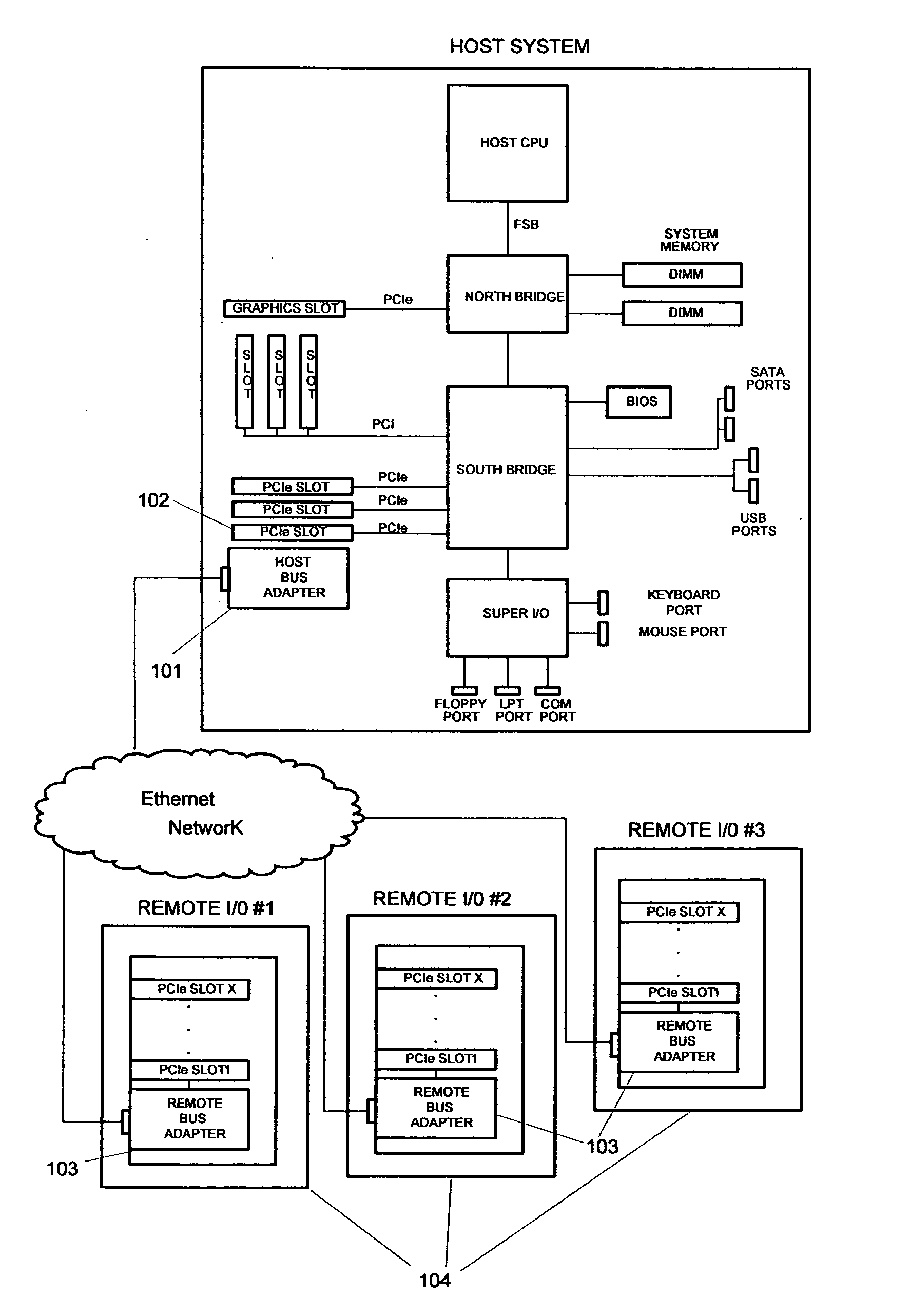

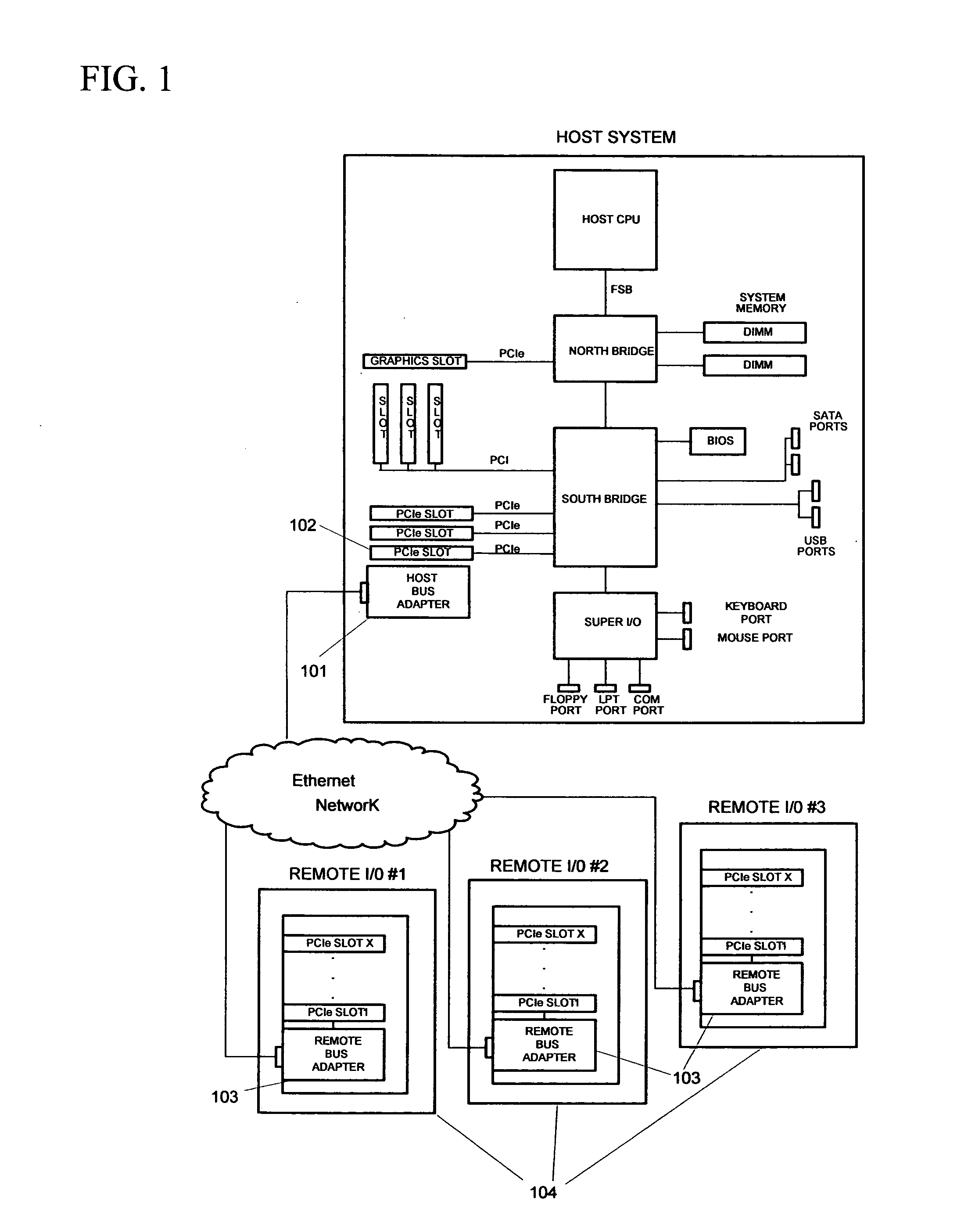

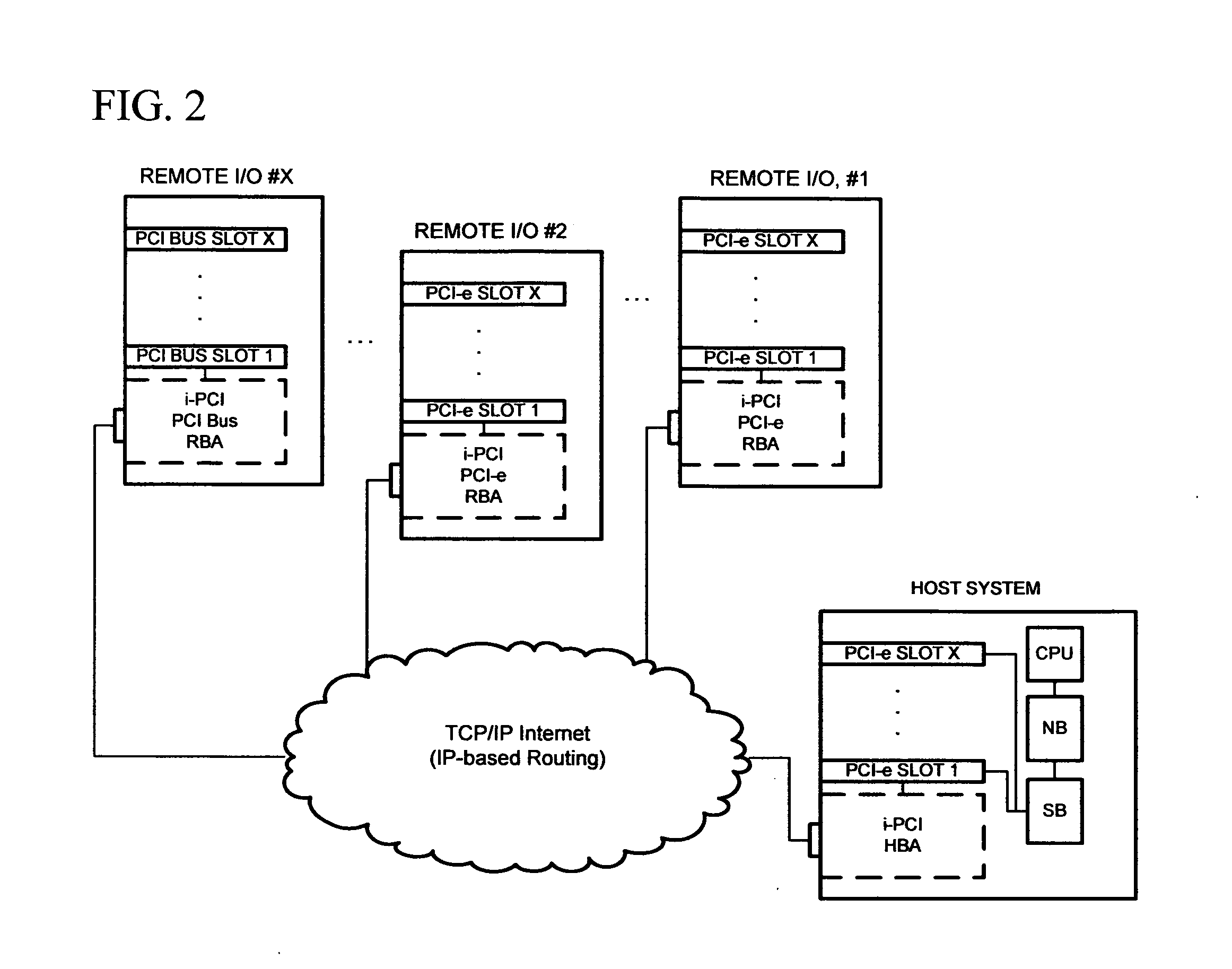

Virtualized PCI endpoint for extended systems

InactiveUS9064058B2Simple virtualizationLess powerTransmissionElectric digital data processingVirtualizationThe Internet

Owner:NUON

Virtualized PCI endpoint for extended systems

InactiveUS20100161870A1Simple virtualizationLess powerTransmissionElectric digital data processingVirtualizationThe Internet

Virtualization of a PCI Endpoint via the Internet and LANs. The invention is a solution that allows the use of low-complexity, low-cost PCI Express Endpoint Type 0 cores or custom logic for relatively simple virtualization applications. The invention combines two physically separate assemblies in such a way that they appear to the host system as one local multifunctional PCI Express Endpoint device.

Owner:NUON

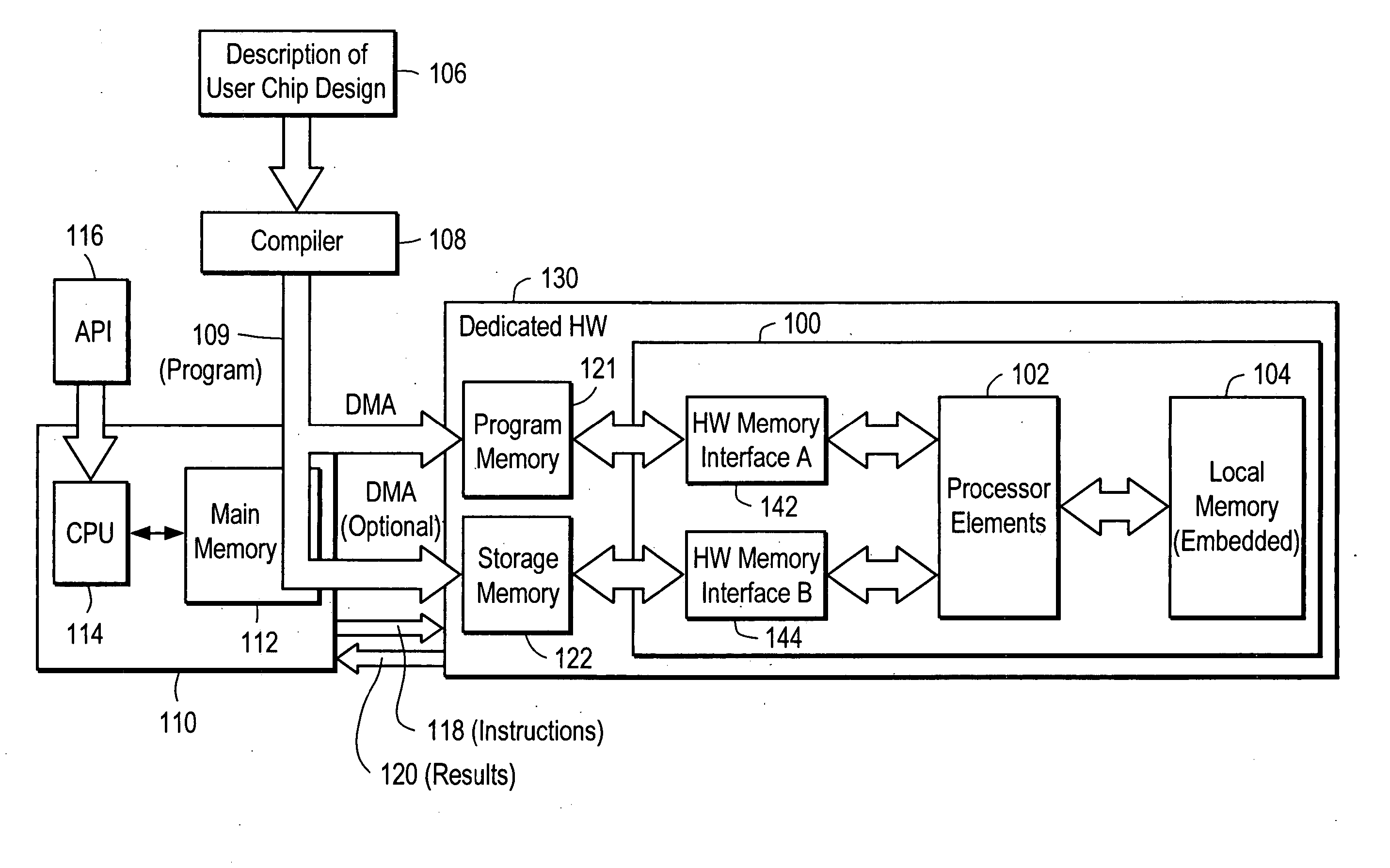

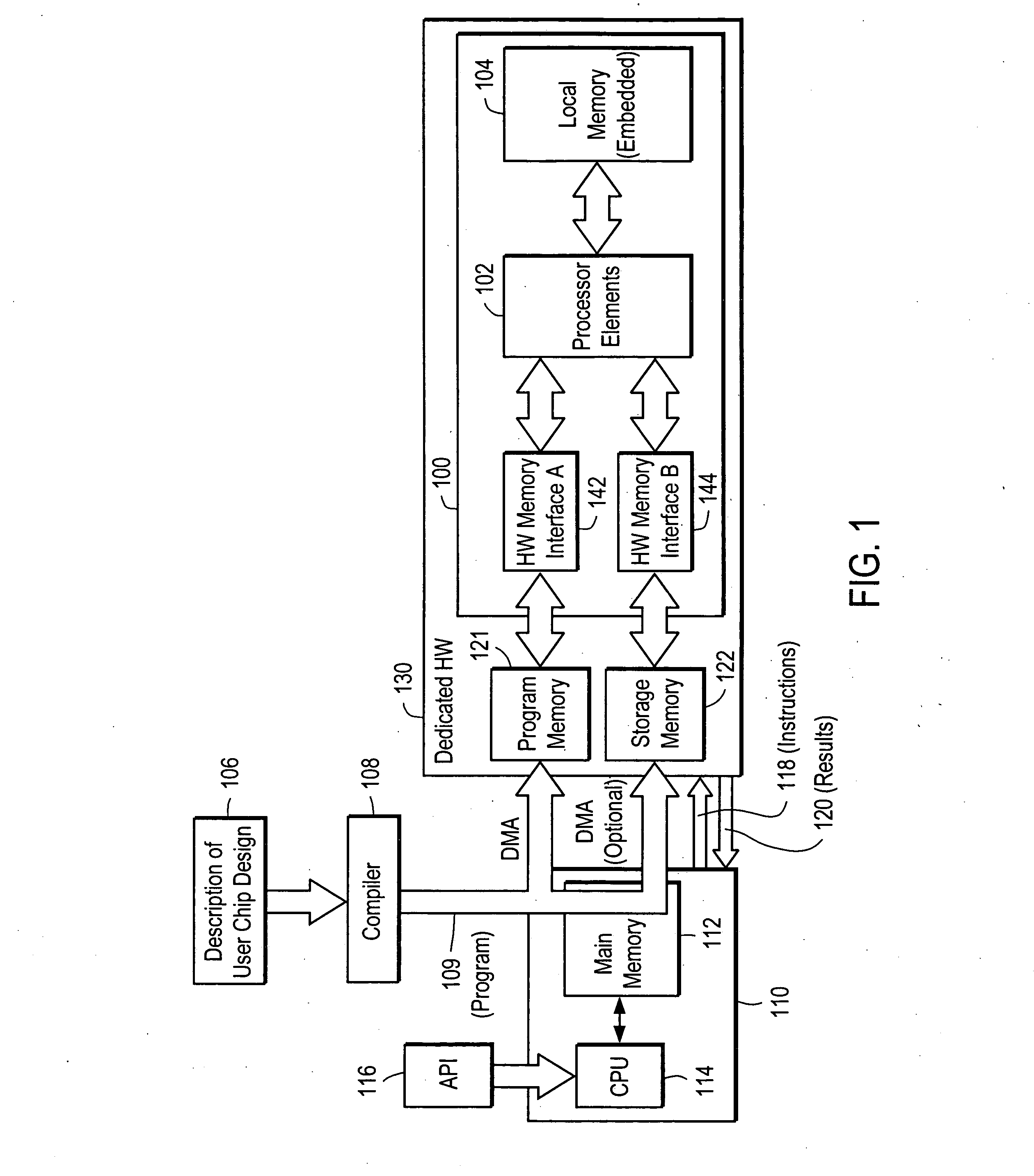

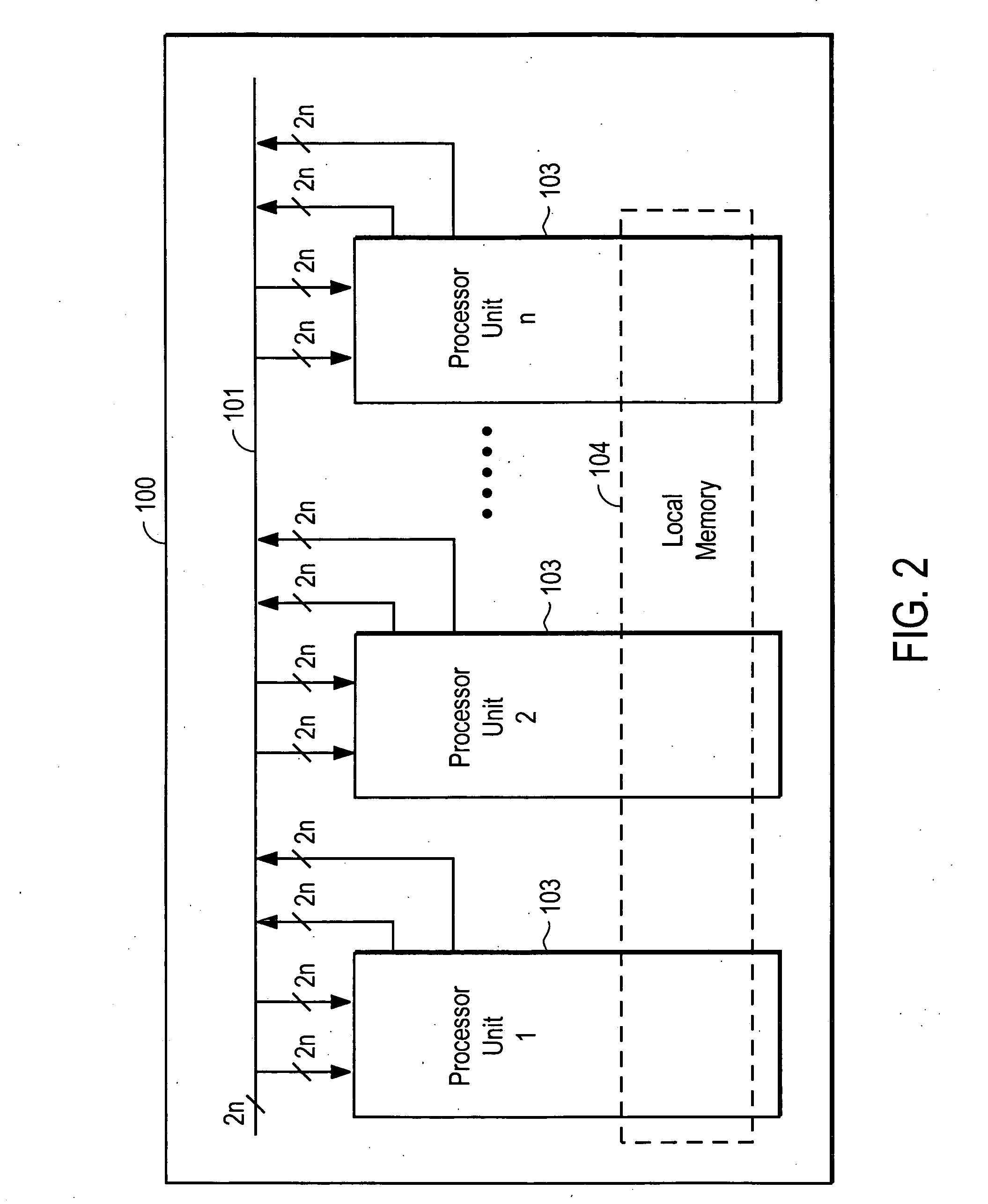

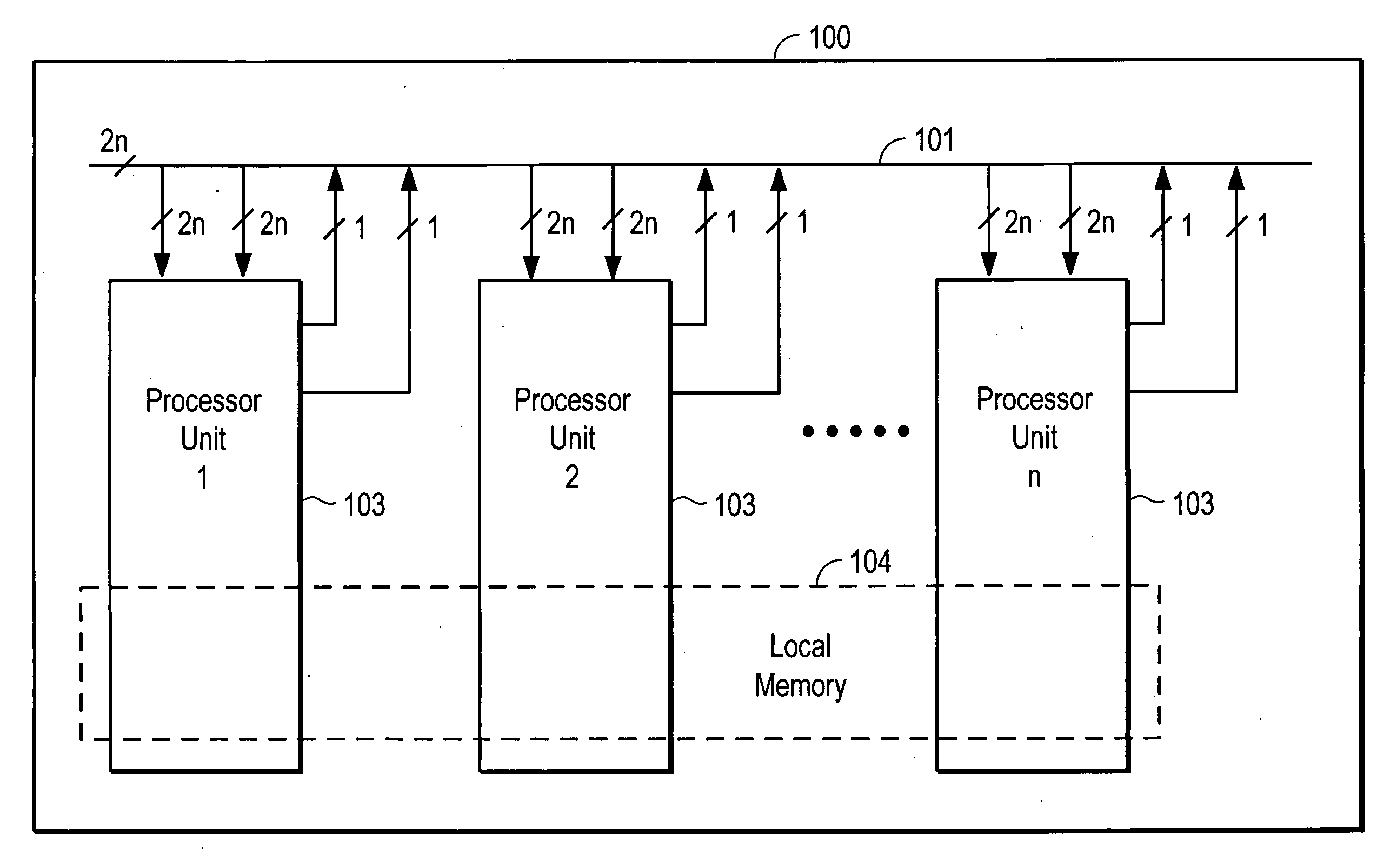

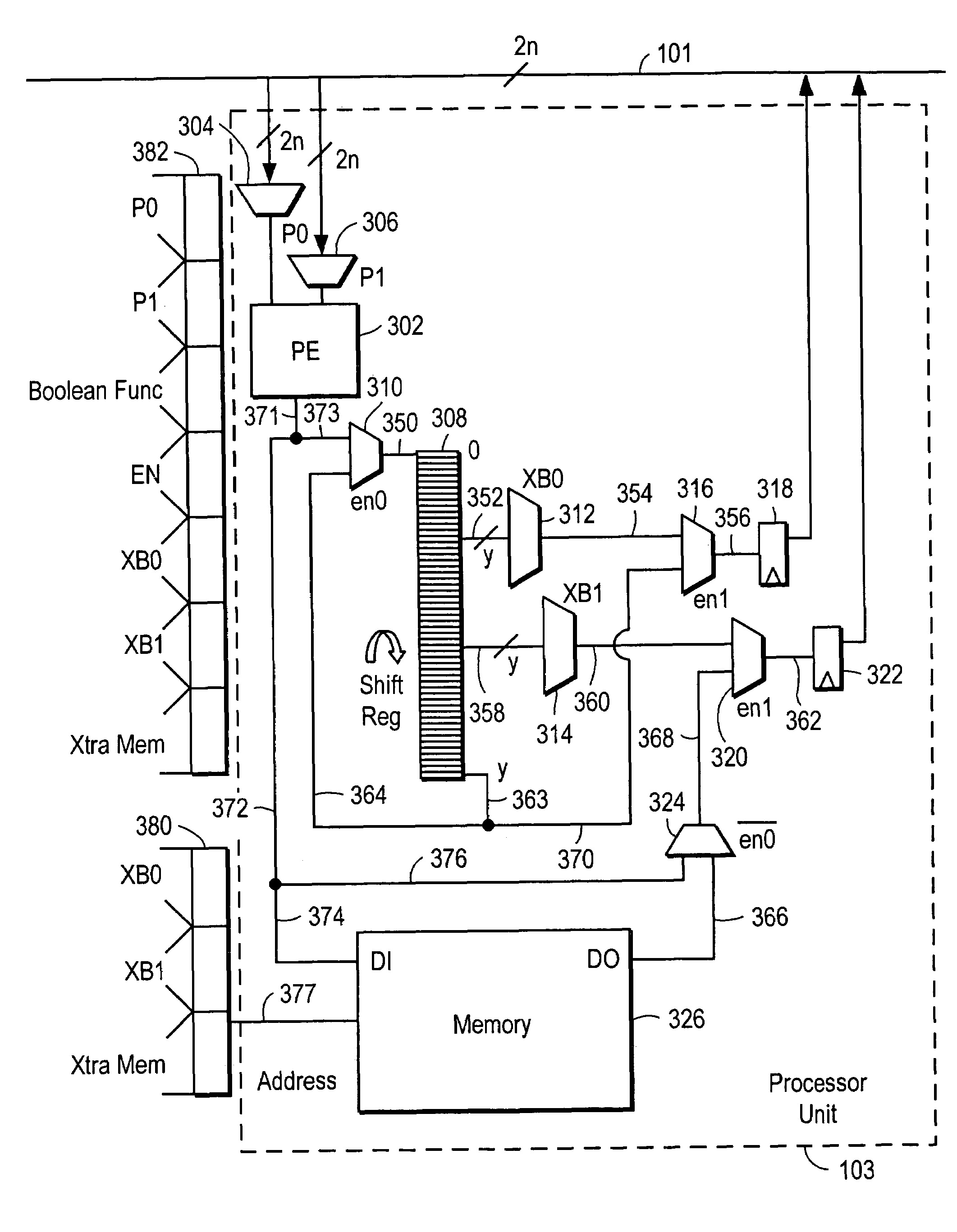

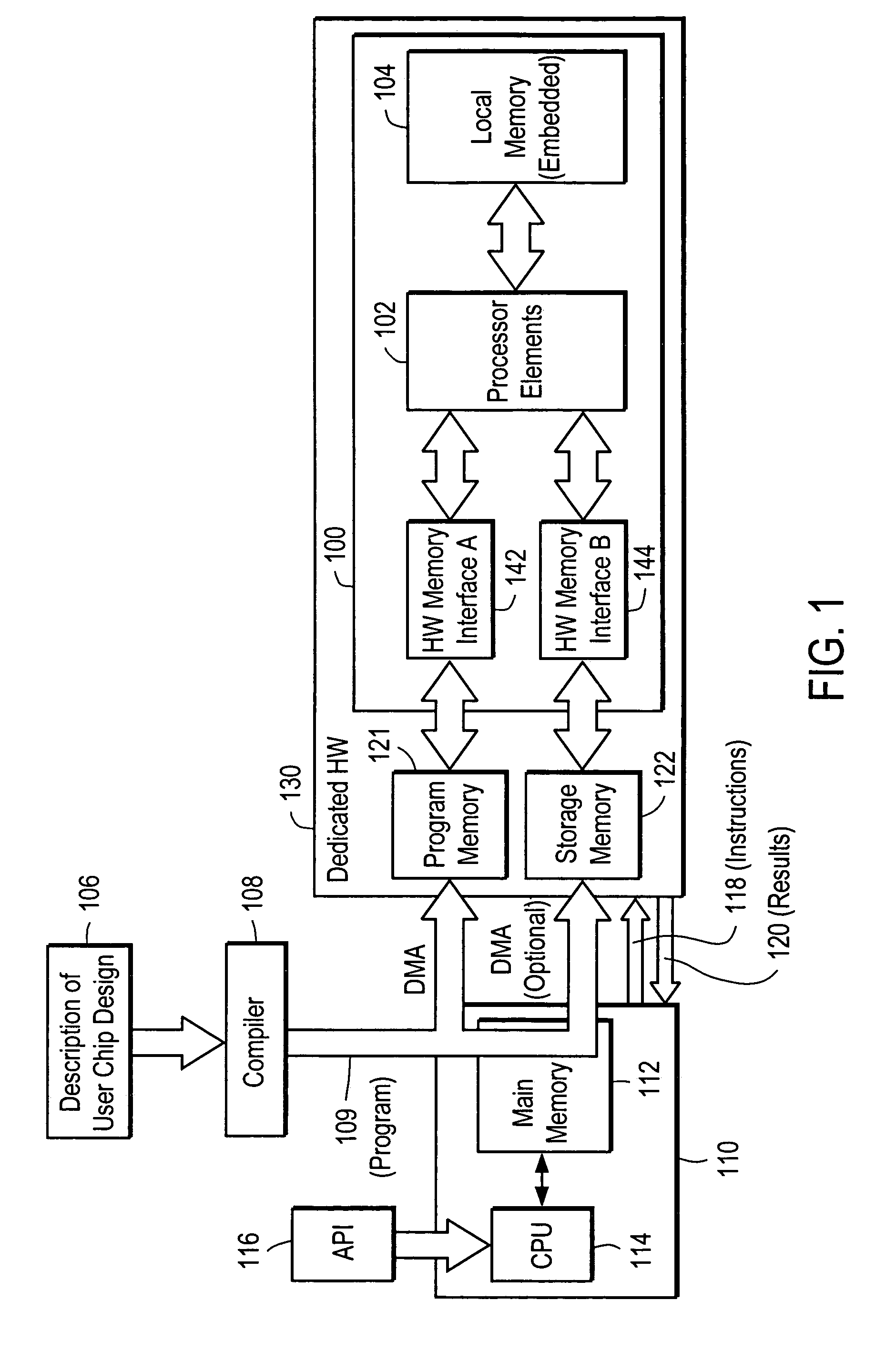

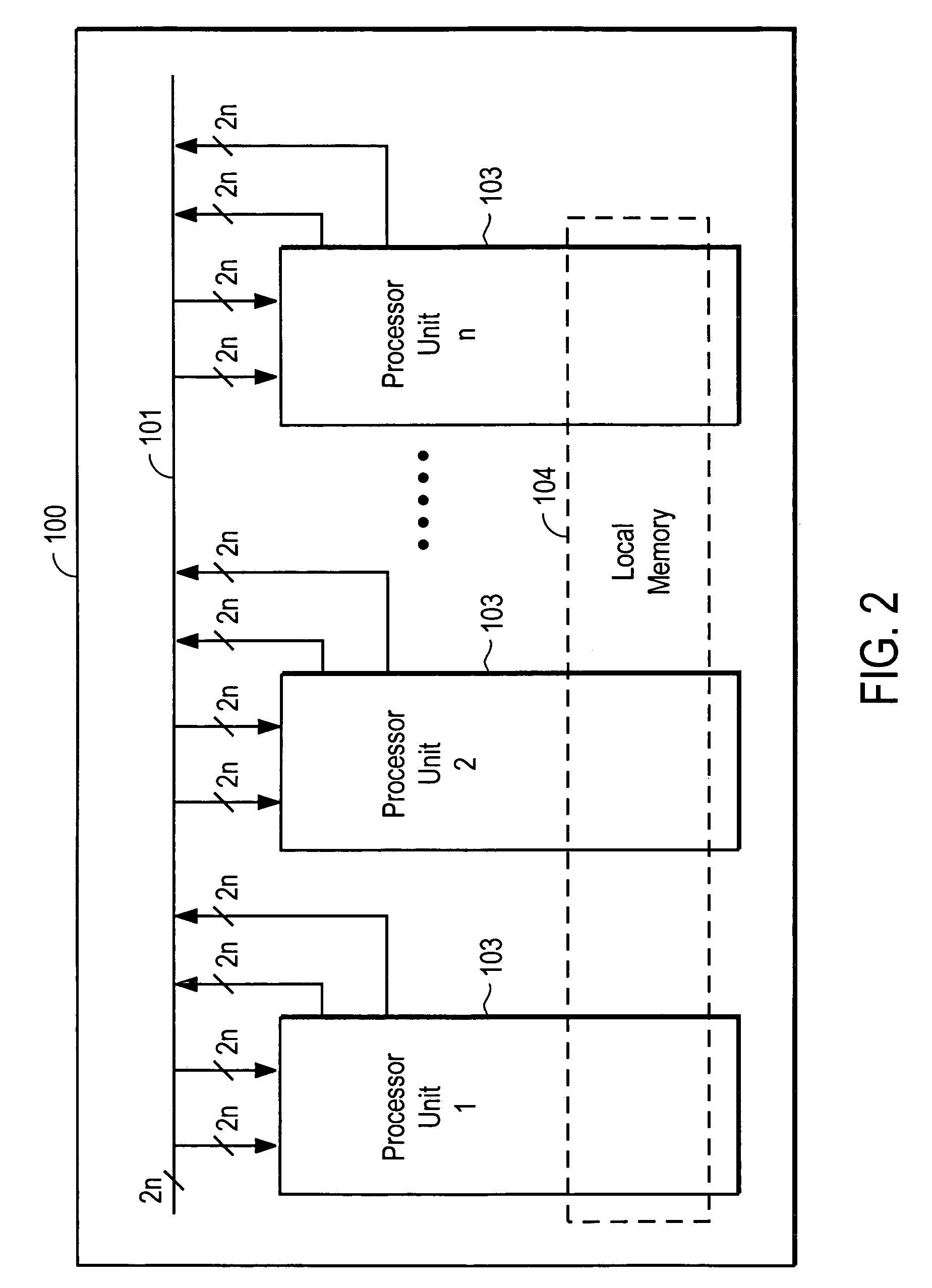

Hardware acceleration system for logic simulation using shift register as local cache

InactiveUS20070073528A1Reduces instruction lengthSimplify hardware designGeneral purpose stored program computerComputer aided designLocal memoriesHardware acceleration

A logic simulation processor stores in a shift register intermediate values generated during the logic simulation. The simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic gate, and a shift register associated with the processor element. The shift register includes multiple entries to store the intermediate values, and is coupled to receive the output of the processor element. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units may further include a local memory for storing data from, and loading the data to, the simulation processor.

Owner:LIGA SYST

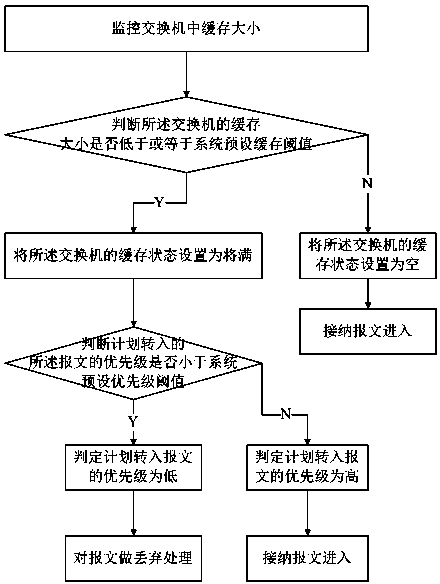

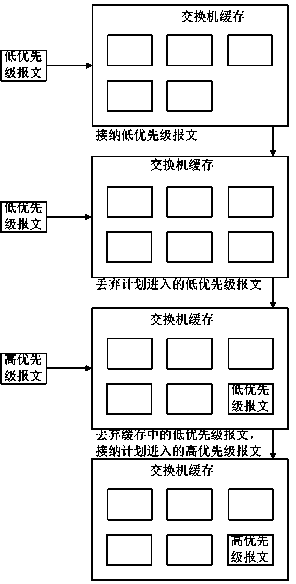

Method and device for detecting message sending rate

InactiveCN104378308AReduce forwarding delayLow costData switching networksComputer networkTime delays

The invention provides a method and device for detecting the message sending rate. The method comprises the steps that the cache size of an interchanger is monitored; whether the catch state of the interchanger is about to reach the maximum extent or not is judged according to the cache size; when the catch state of the interchanger is about to reach the maximum extent, whether the priority of a message to be forwarded is high or low is judged; the interchanger receives the message or directly discards the message according to the priority judgment on the message. According to the method, the cache size of the interchanger is monitored in real time, when the catch size reaches the preset cache threshold value of a system, the interchanger is marked, the message with high priority can occupy the cache of the interchanger at any time, a message with low priority occupies the cache space of the interchanger only when the cache of the interchanger is not used up, and therefore the forwarding time delay of the messages can be shortened in the forwarding process.

Owner:SUZHOU CENTEC COMM CO LTD

Hardware acceleration system for logic simulation using shift register as local cache with path for bypassing shift register

InactiveUS20070073999A1Reduces instruction lengthSimplify hardware designGeneral purpose stored program computerCAD circuit designShift registerProcessor element

A simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic operation, and a shift register for storing intermediate values generating during the logic simulation. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units can also include one or more bypass multiplexers coupled between the output of the processor element and the interconnect system, for providing a path for bypassing the shift register to provide the output of the processor element directly to the interconnect system.

Owner:LIGA SYST

DCT/IDCT with minimum multiplication

InactiveUS7035332B2Increase the number ofHigh precisionPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningDiscrete cosine transformLookup table

A method, apparatus, computer medium, and other embodiments for discrete cosine transform and inverse discrete cosine transform (DCT / IDCT) of image signals are described. A DCT / IDCT module includes a plurality of different cores. One embodiment of a core includes two sets of lookup tables to provide multiplication and add operations for the DCT and IDCT functions. Another embodiment of a core include one set of lookup tables, while another embodiment of a core includes no lookup table. The DCT / IDCT module provides forward DCT and IDCT functionality without the use of additional multipliers.

Owner:MICRONAS

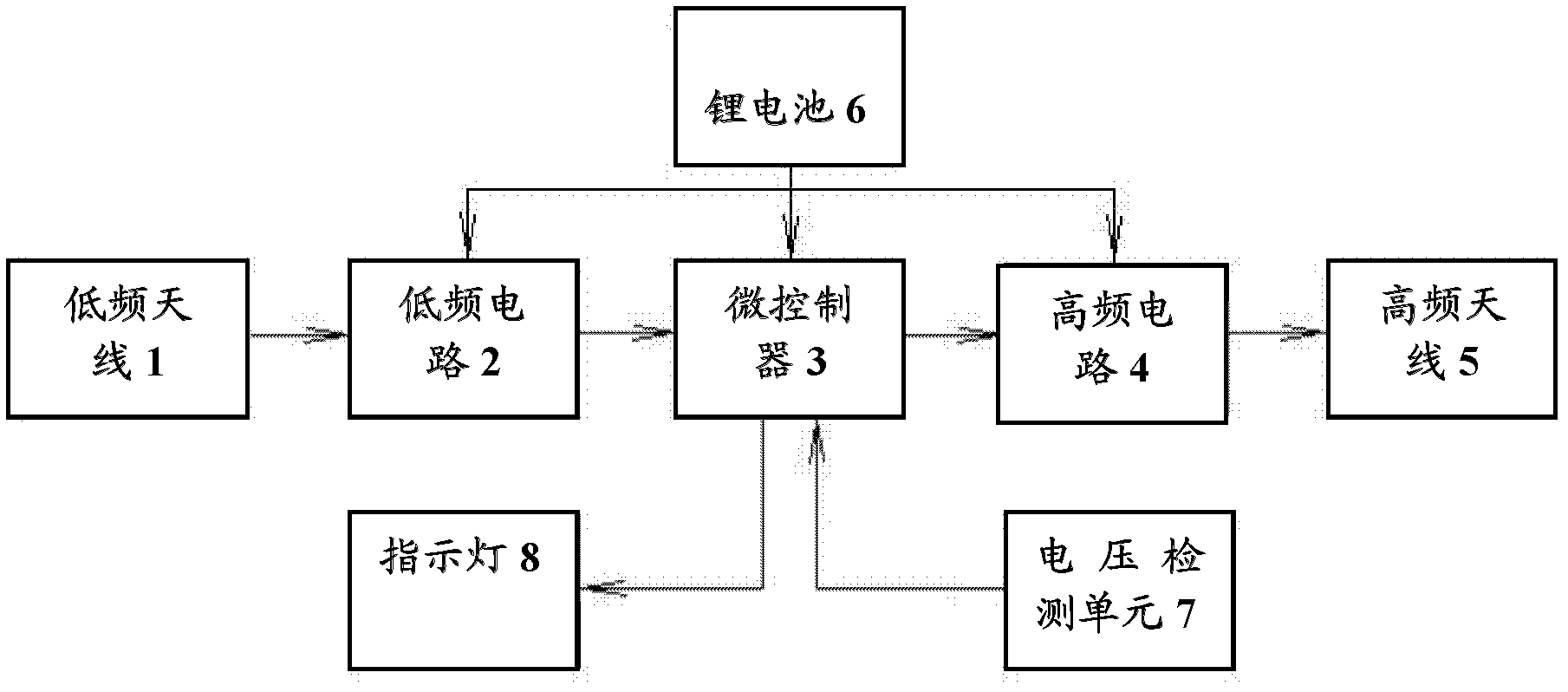

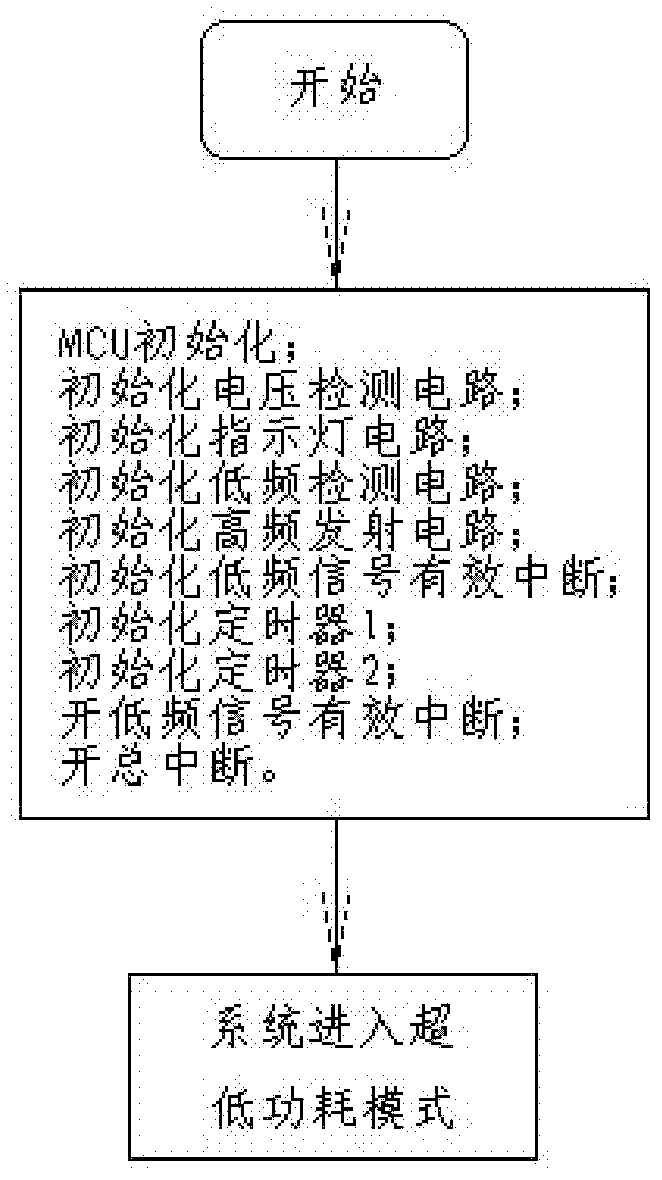

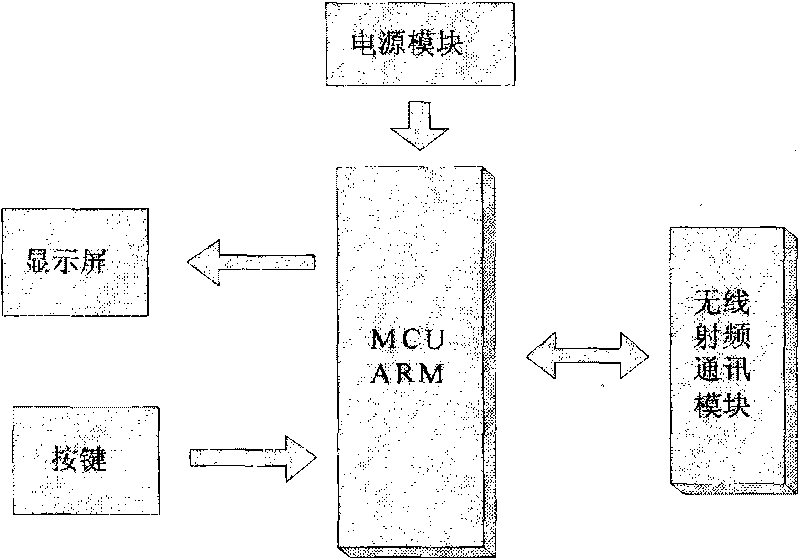

Dual-frequency radio frequency electronic tag

InactiveCN103164730AReduce power consumptionAvoid distanceRecord carriers used with machinesMicrocontrollerElectronic tagging

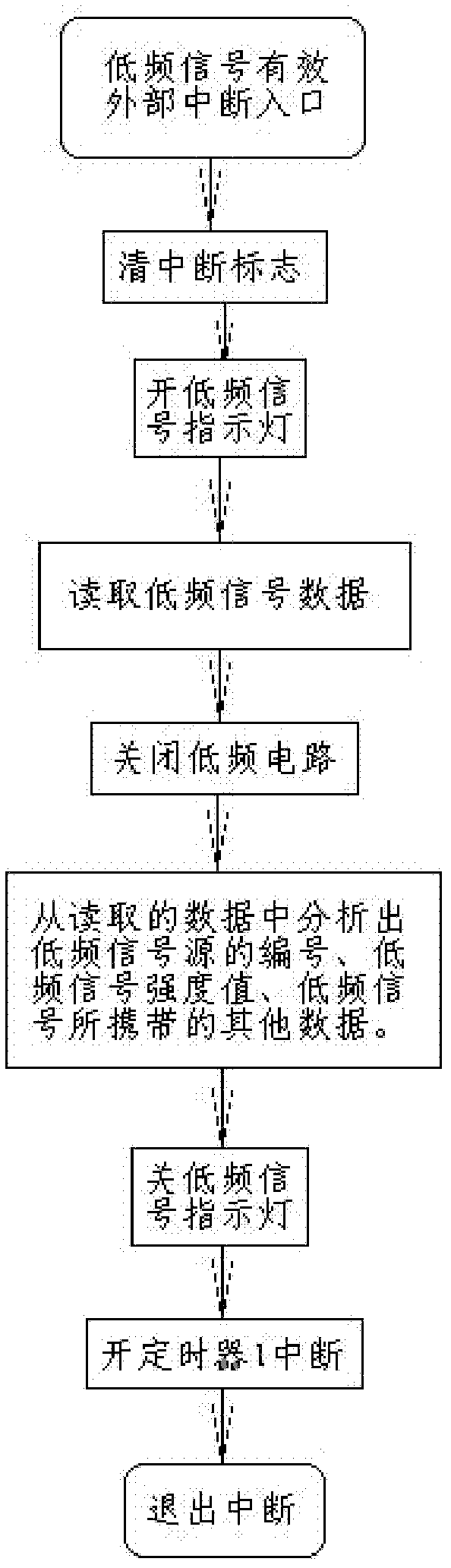

The invention discloses a dual-frequency radio frequency electronic tag which comprises a low frequency antenna used for receiving low frequency signals form an activation source, a low frequency circuit, a high frequency circuit, a high frequency antenna used for sending coded signals to space through high-frequency carrier, and a microcontroller storing identity (ID) numbers of the electronic tag. Programming of the microcontroller comprises the following steps: step one. reading lower frequency information signals and generating intensity identification signals according to intensity of the lower frequency information signals, step two. analyzing and extracting the low frequency information signals and producing signal source codes according to the low frequency information signals, step three. starting timing device interrupt in a time interval, in interrupt status, starting the high frequency circuit, closing the high frequency circuit and opening the low frequency circuit in sequence, step four. quitting the timing device interrupt when time duration achieves the time interval. Distance between the dual-frequency radio frequency electronic tag and a card reader can be measured, accurate positioning is achieved, identification distance is adjustable, and the problem that a plurality of card readers read the same electronic tag at the same time is solved.

Owner:SUZHOU MULAN ELE&TEC

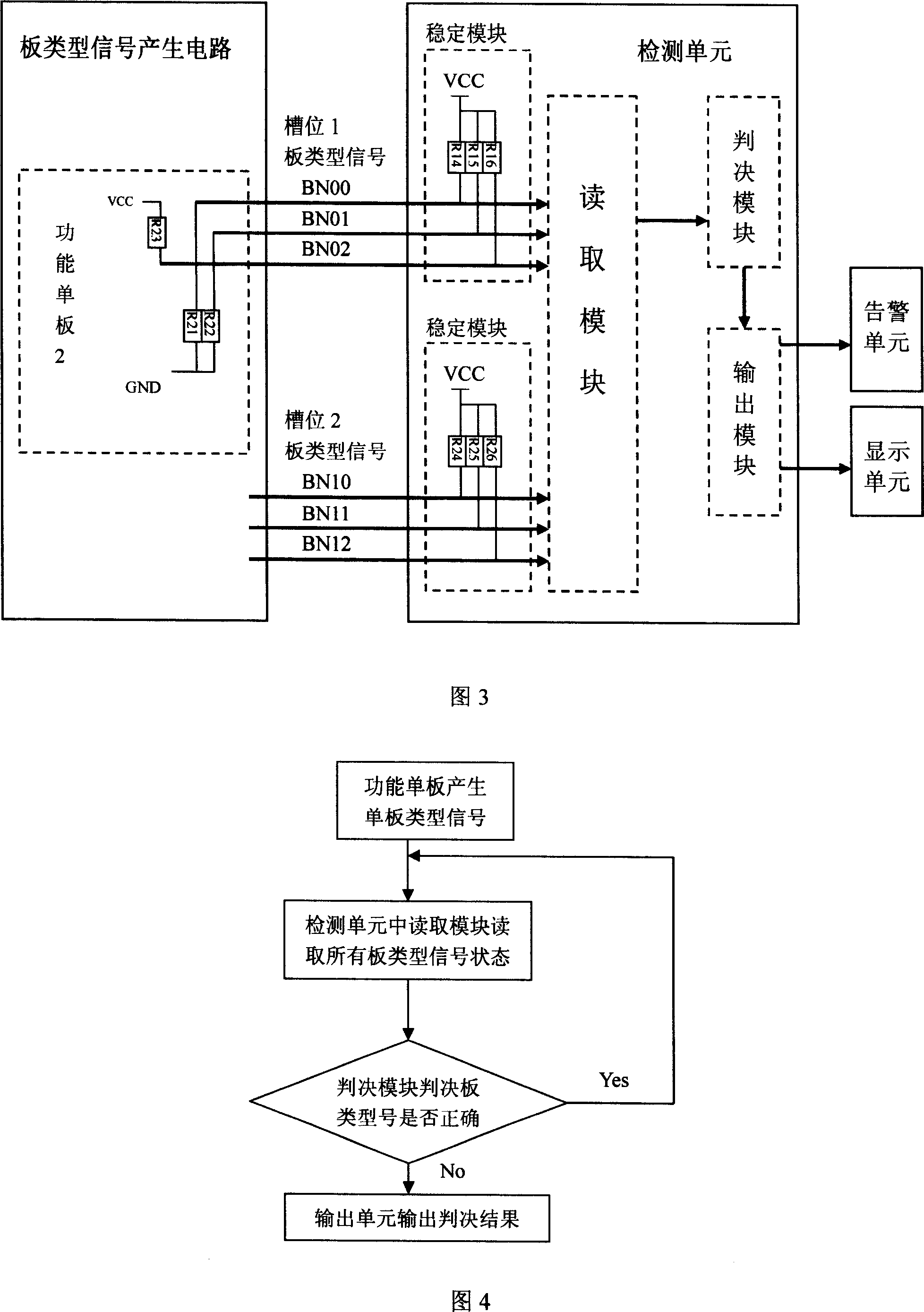

Method and system for realizing recognizing and detecting plate type of single plate

ActiveCN101097534ASimple designLow costDetecting faulty computer hardwareSingle plateEmbedded system

The invention discloses a method and system of identifying and detecting type of veneer, said system includes board type signal generating unit and detecting unit on function veneer; detecting unit which includes stabilization module, reading module, judging module and output module; function veneer generates veneer type signal; detecting unit reads board type signal state output by all function veneer; detecting unit judges whether the relationship between all function veneer type and slot is correct based on set list of relationship between all function veneer type and slot. If it is correct, continue executing. When the judging module judges the inserting of veneer is fault, result of judgment is output by output module. Hardware of the invention is easy, cost is low, and it can be used as a function sub-module of controlling veneer; user can determine relationship between veneer type and slot, application mode can be agile and changeable; position of fault and type of veneer can be positioned correctly when there is a fault inserting.

Owner:ZTE CORP

Hardware acceleration system for logic simulation using shift register as local cache

InactiveUS7444276B2Simplify hardware designShorten the lengthGeneral purpose stored program computerComputer aided designShift registerProcessor element

A logic simulation processor stores in a shift register intermediate values generated during the logic simulation. The simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic gate, and a shift register associated with the processor element. The shift register includes multiple entries to store the intermediate values, and is coupled to receive the output of the processor element. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units may further include a local memory for storing data from, and loading the data to, the simulation processor.

Owner:LIGA SYST

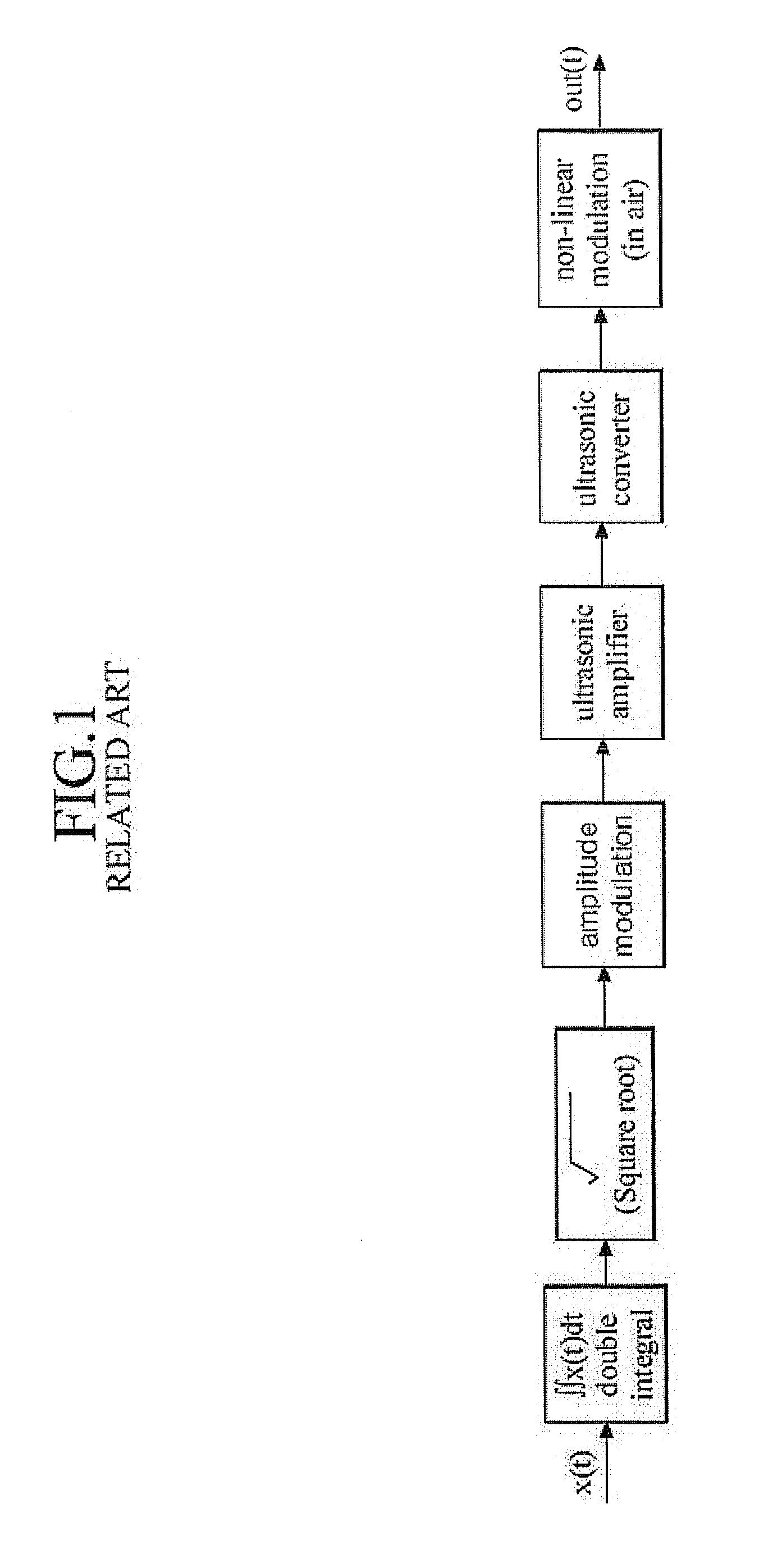

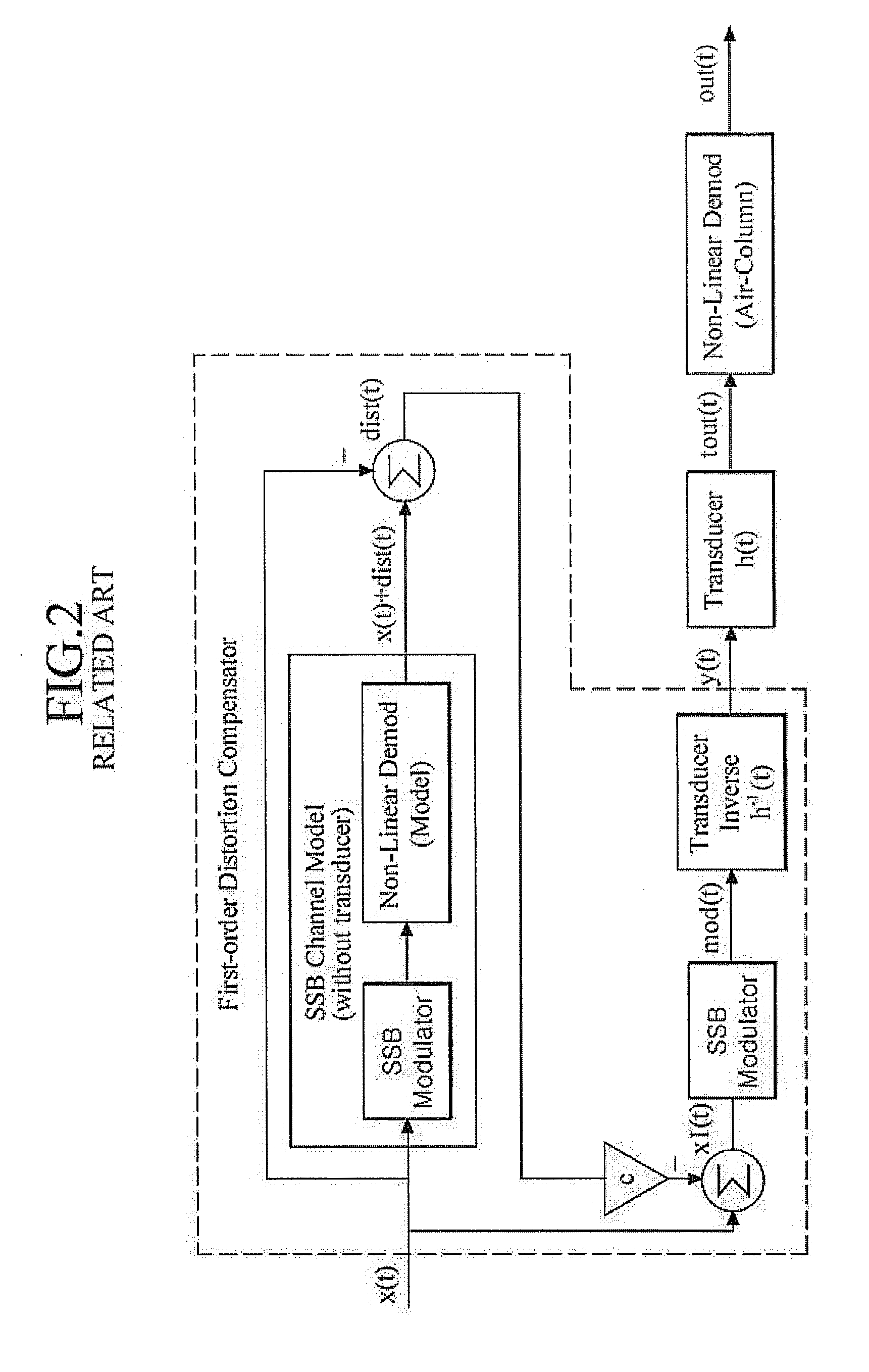

Ultra directional speaker system and signal processing method thereof

ActiveUS20070121968A1Minimize of reproducedImprove sound qualityPiezoelectric/electrostrictive transducersMagnetostrictive transducersLoudspeakerSignal processing

An ultra directional speaker system and a signal processing method thereof are disclosed. In accordance with the present invention, the pre-distortion compensation may be applied to the input signal in real time and a signal to be modulated is subjected to a VSB modulation to minimize the distortion according to a level of the signal, and a signal difference compensation according to an envelop detection of a current signal and a signal in previous stage.

Owner:SOLITONIX

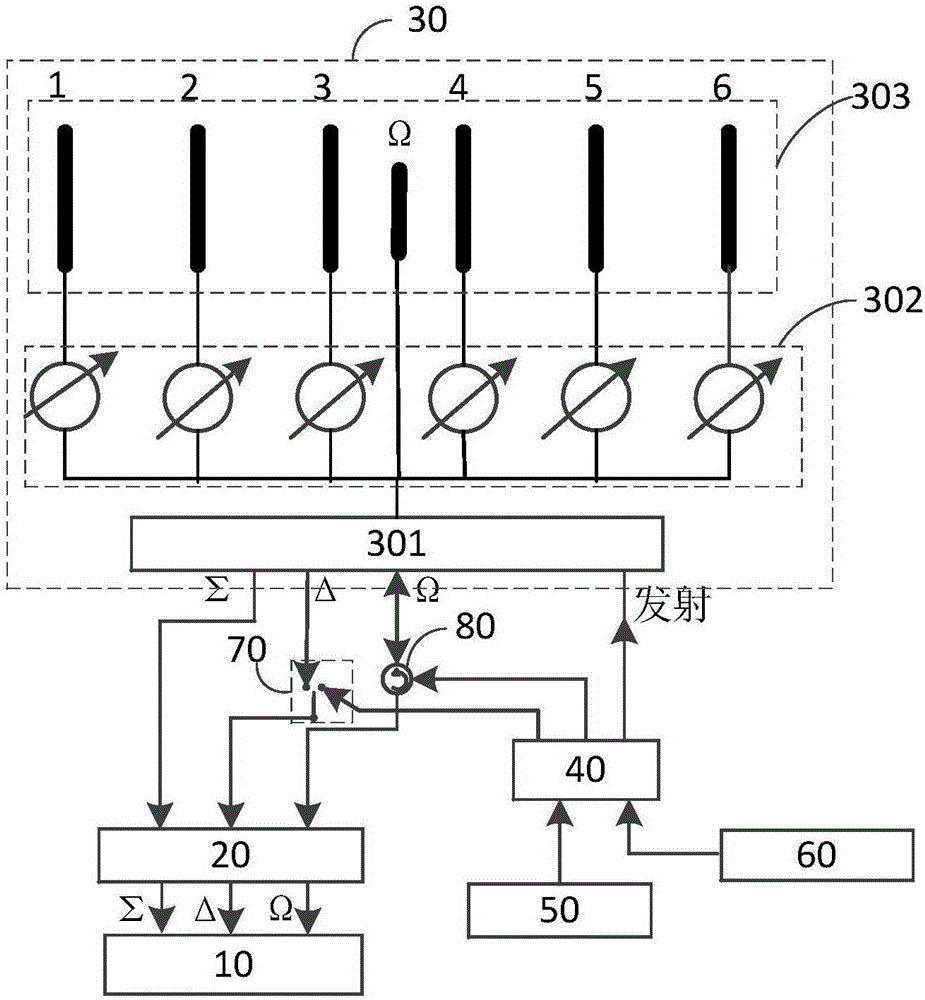

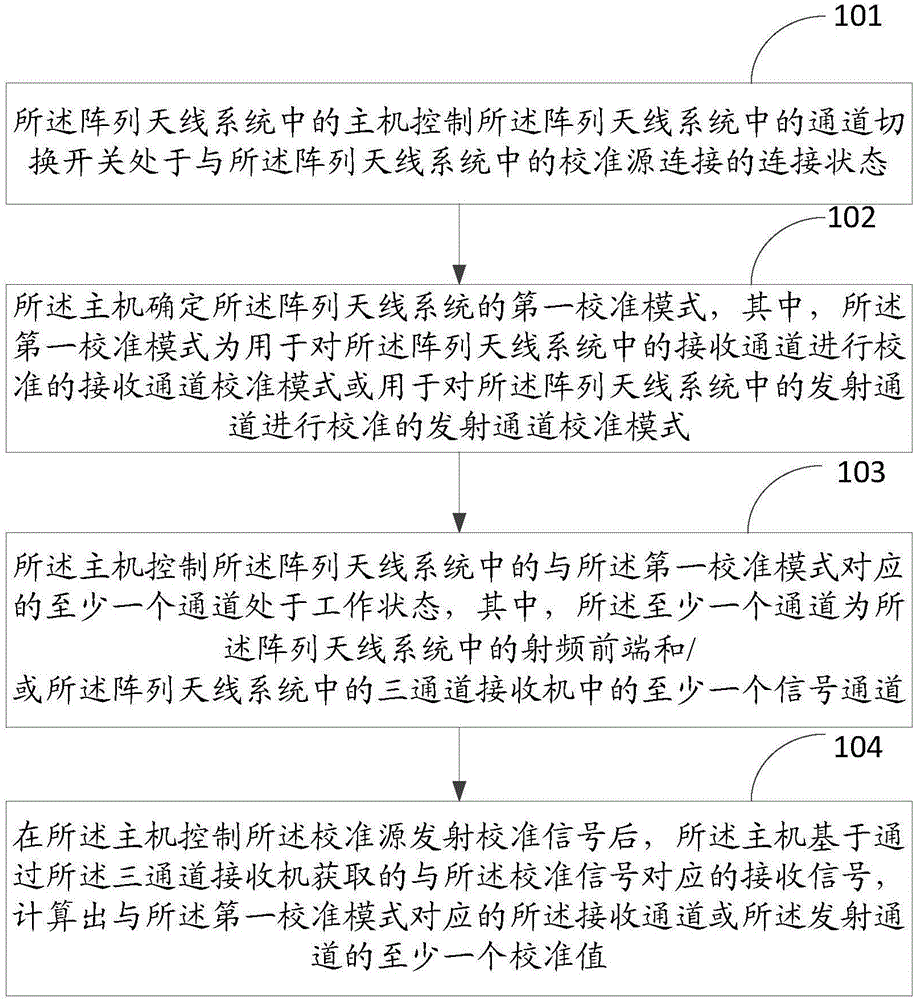

Array antenna system and calibration method of antenna

ActiveCN106450796AShorten the timeSimplify hardware designTransmitters monitoringAntenna arraysTransceiverTransmitter

The invention discloses an array antenna system and a calibration method of an antenna. The array antenna system comprises a host computer, a three-channel receiving machine, a radio frequency front end, a channel switching switch, a calibration source and a transmitter, wherein the three-channel receiving machine is connected with the host computer; the radio frequency front end is connected with the three-channel receiving machine through a transceiver channel; the first end of the channel switching switch is connected with the radio frequency front end; the calibration source is connected with the second end of the channel switching switch; and the transmitter is connected with the third end of the channel switching switch. When the host computer controls the channel switching switch to be connected with the calibration source in a connecting condition, a first calibration mode of the array antenna system is determined through the host computer, and at least one channel corresponding to the first calibration mode is controlled in a working condition; and after the host computer controls the calibration source to transmit a calibration signal, the host computer calculates at least one calibration value of the transceiver channel based on a receiving signal acquired by the three-channel receiving machine.

Owner:SICHUAN JIUZHOU ELECTRIC GROUP

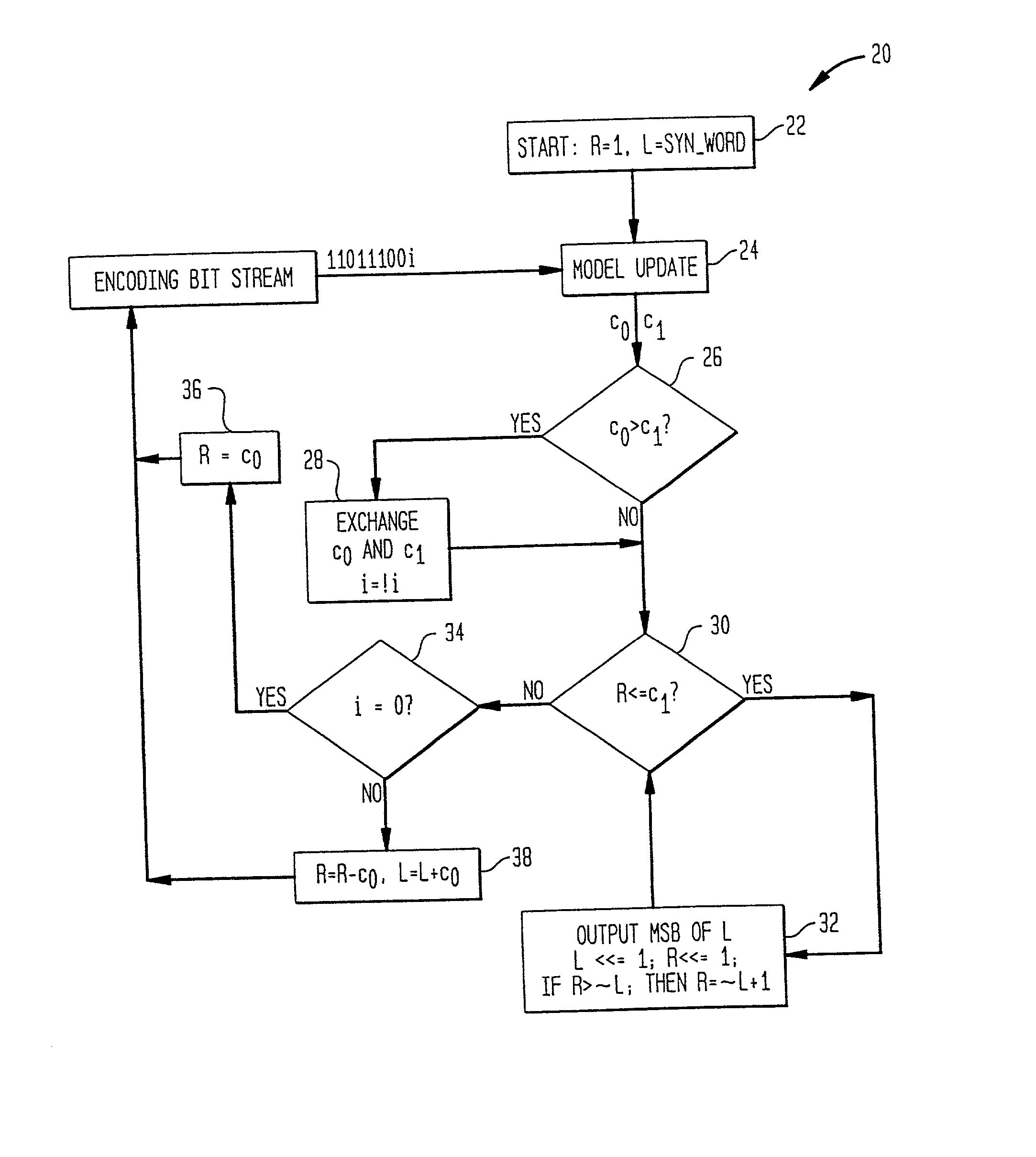

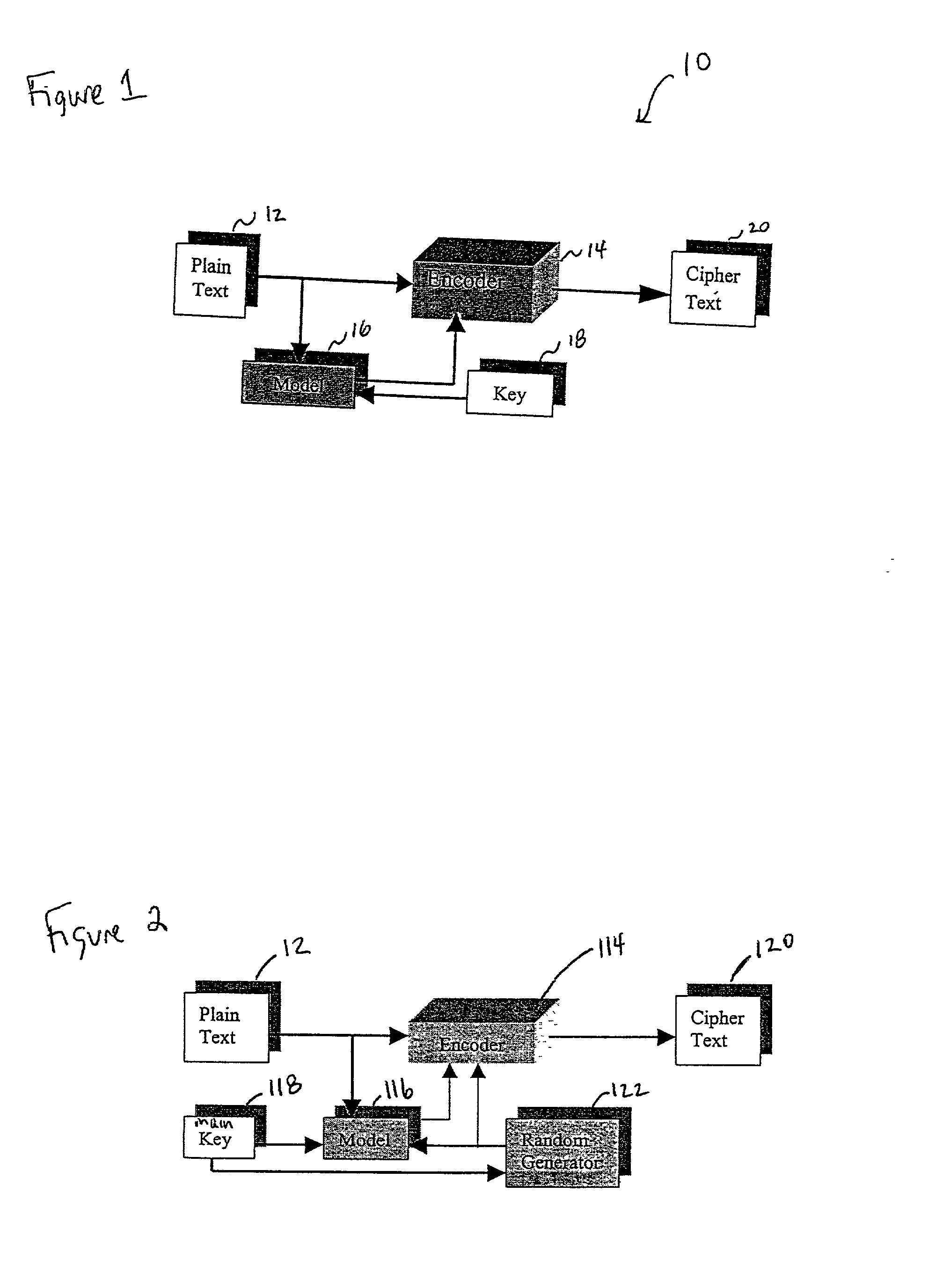

Variable size key cipher and method and device using the same

InactiveUS20020094080A1Unlimited lengthSimplify hardware designEncryption apparatus with shift registers/memoriesSecret communicationPlaintextComputer hardware

An encryption device and method and decryption device and method which implement a bit-based encryption scheme and hardware design. The encryption device includes a random number generator, receiving a main key, determining a working key using at least one random number and outputting a working key, a model, receiving the main key, the working key and plain text to be encoded and generating at least two frequency counts. The encryption device further includes an encoder, which outputs encoded text based on the working key, the plain text and the at least two frequency counts. The encryption device and method and decryption device and method progress encrypted text that is based upon a stream structure with an unlimited key length and may be compressed by 50%. The encoded text is changeable with different environments even for the same plain text and the same key. Operations of the hardware design are based on arithmetic additions and shifts, and not multiplications and divisions. As a result, the hardware design is simple and applicable to cryptography and e-commerce.

Owner:AGERE SYST INC

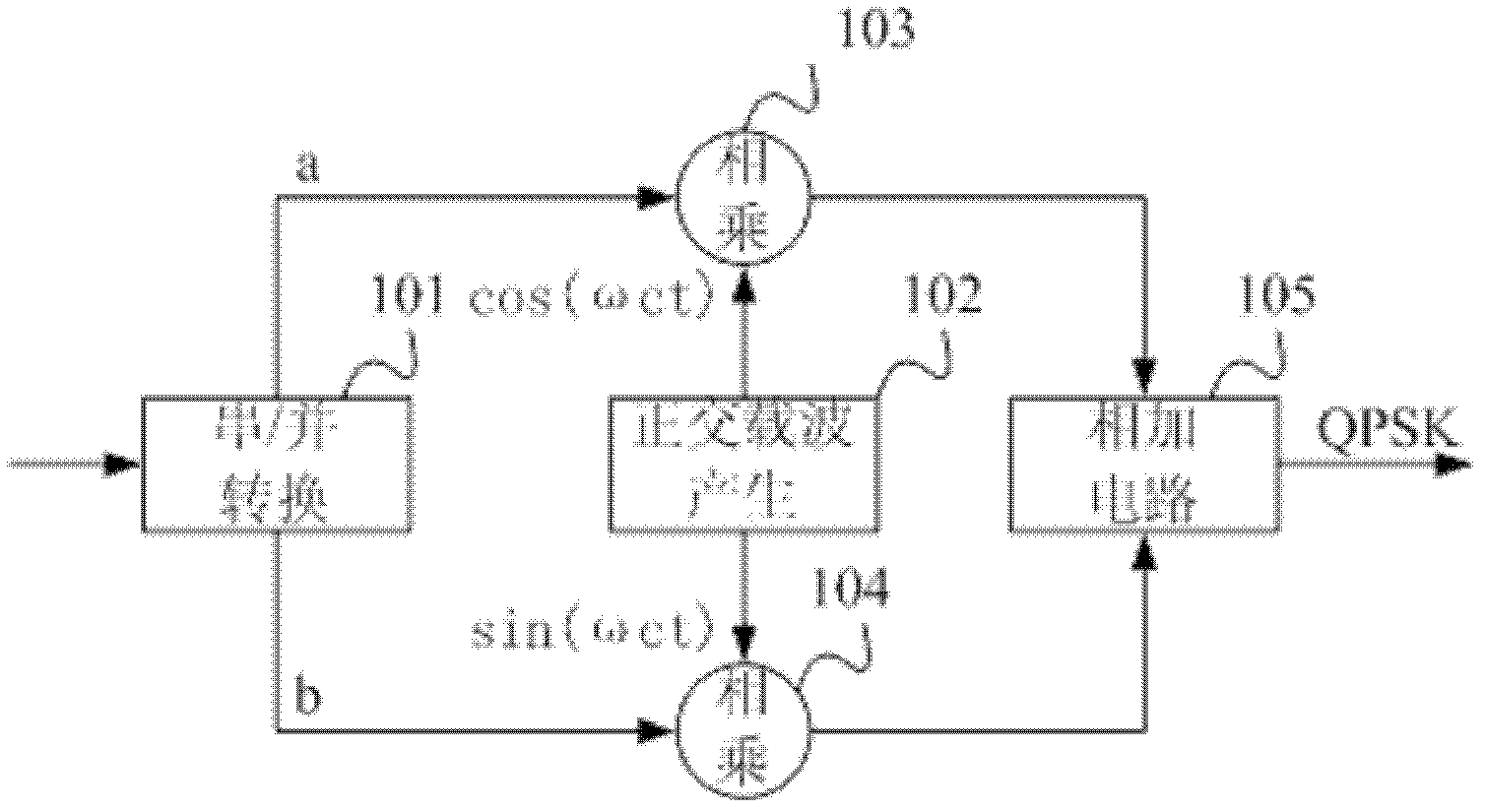

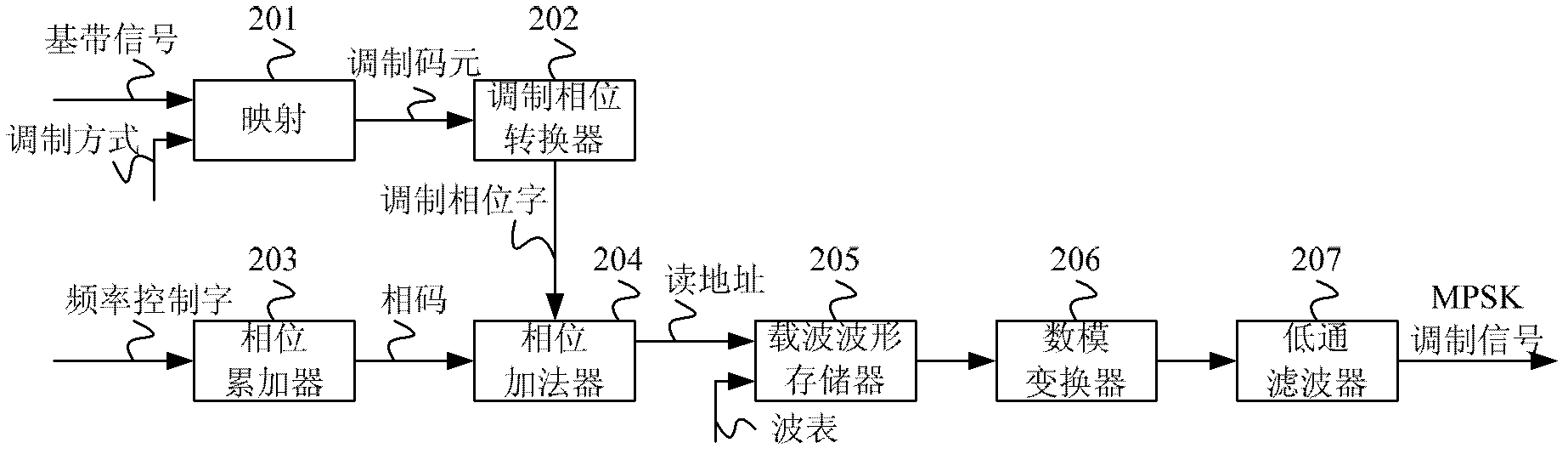

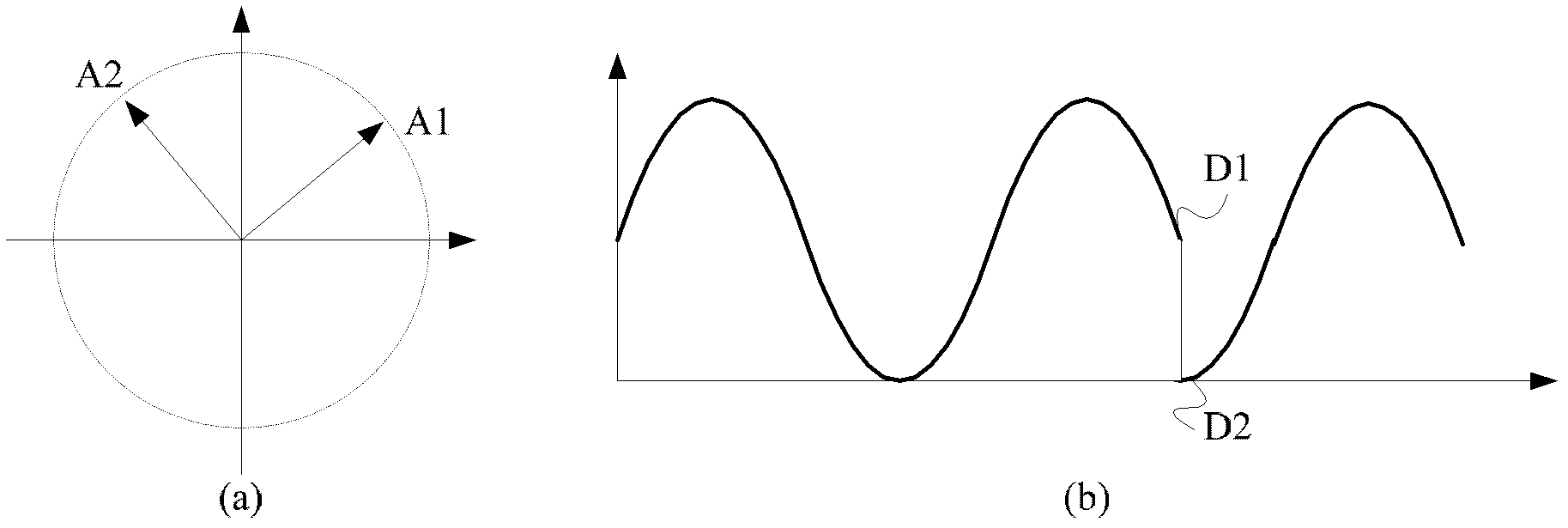

Multi-system phase shifting keying (MPSK) modulation method, MPSK modulation device and function signal generator

ActiveCN103179066ASimplify hardware designAvoid Orthogonal CarriersPhase-modulated carrier systemsData translationWave shape

An embodiment of the invention provides a multi-system phase shifting keying (MPSK) modulation method, an MPSK modulation device and a function signal generator. The MPSK modulation device comprises a mapping module used for converting serial base band signals to be modulated into modulation code elements according to the modulation mode, a modulation phase converter used for converting the modulation code elements into phase words, a phase accumulator used for accumulating frequency control words to obtain a phase code, a phase summator used for summating the phase code and the modulation phase words to obtain a reading address, a carrier wave form storage used for reading carrier wave form data stored in the storage according to the reading address and a digital-to-analog converter used for converting the carrier wave form data into MPSK modulation signals in analog form. The MPSK modulation device has the advantages of being capable of achieving full digital achieving mode, free of a multiplying unit, free of quadrature carrier, good in expandability, simple to achieve and especially suitable for the function signal generator.

Owner:RIGOL

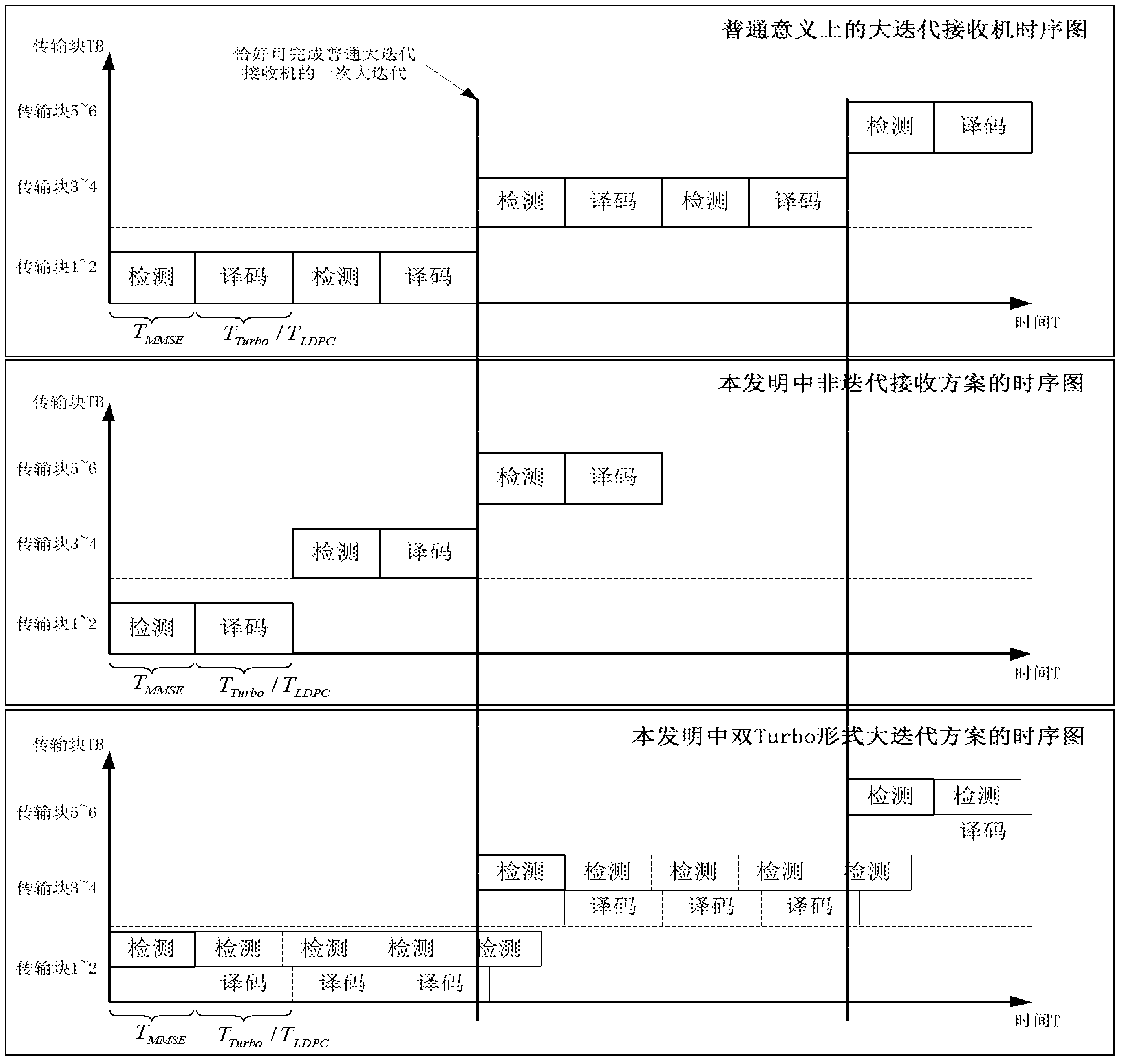

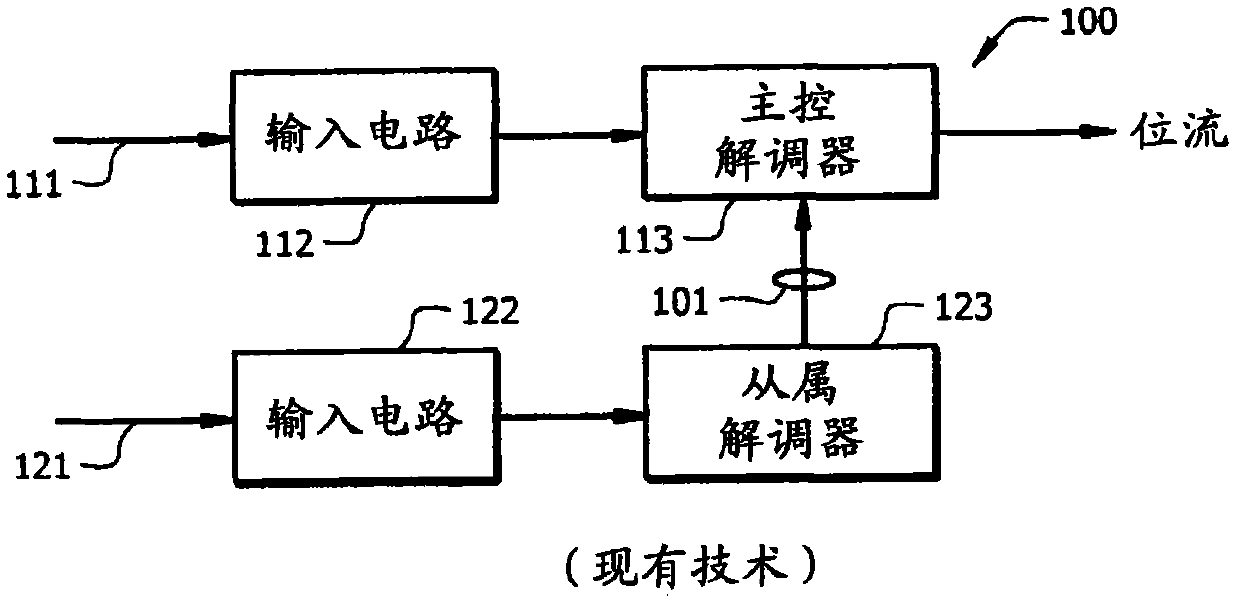

Bandwidth-adaptive big iteration receiver

InactiveCN102325001AImprove performanceIncrease profitSpatial transmit diversityError preventionCoding blockCommunications system

The invention relates to a bandwidth-adaptive big iteration receiver. For a broadband multi-antenna orthogonal frequency division multiplexing (OFDM) communication system, the traditional minimum mean square error (MMSE) receiver and a Turbo / LDPC code decoder are combined together so as to compose the big iteration receiver which can provide interference cancellation; and the receiving schemes and the iterating parameters in various OFDM application contexts with different bandwidths are subjected to adaptive adjustment so as to reach the optimal system performance. The receiver provided by the invention has the following working steps: (1) detecting parameters, such as the size of bandwidth, the length of a transmission block, the number of code block, the code rate and the like, which are allocated to a user by a receiving terminal; and (2) calculating the time required for finishing detecting and decoding according to the obtained communication parameters. If a context cannot support the big iteration receiver under the real-time requirements, a receiving scheme is adjusted to be a non-iteration form; and if the iterative reception can be adopted, an MMSE soft interference cancellation-based big iteration detecting scheme which is in a double Turbo form is selected, and the parameters required for the big iteration are further determined.

Owner:SOUTHEAST UNIV

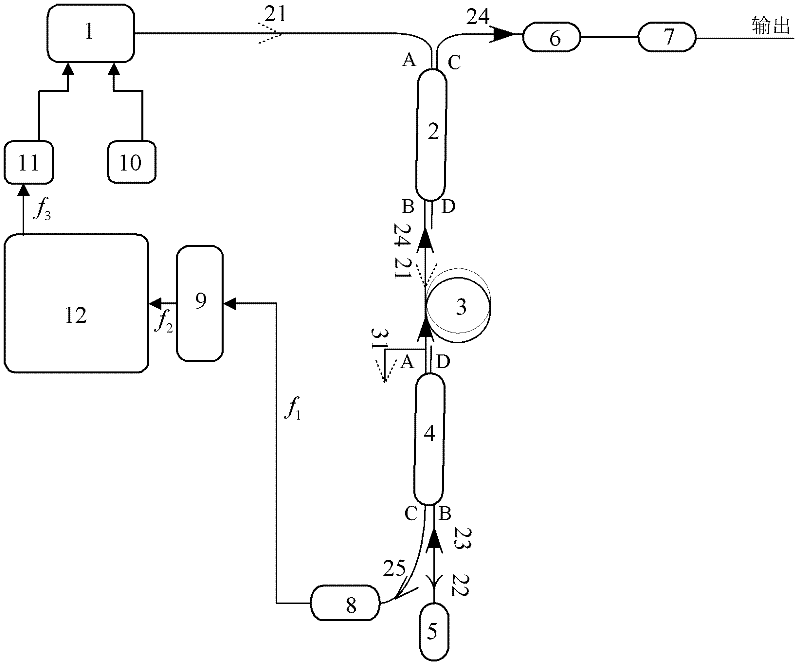

Anti-radiation wide spectrum fiber light source

ActiveCN102386553AGood radiation resistanceImprove stabilityActive medium shape and constructionLoop controlClosed loop

The invention discloses an anti-radiation wide spectrum fiber light source. 980nm pump light can be coupled in an Er-doped fiber by a wavelength division multiplexer (WDM), and mixed light is output after the light is amplified through spontaneous emission (ASE) of erbium ions; the mixed light can generate reflected light after being processed by a second WDM and a reflecting mirror; the remnant 980nm pump light output from the second WDM can be converted to a voltage signal by a 980nm monitoring detector, and the voltage signal can act on a 980nm pump light source after being processed by a microprocessor and a digital constant current source; and an automatic temperature control circuit can ensure the 980nm pump light source to work at the temperature of 25 DEG C. The wide spectrum fiber light source provided by the invention utilizes the electrical signal output by the 980nm monitoring detector as a basis of feedback regulation and regulates drive current to control the stability of power and average wavelength of the output ASE light by using the negative feedback closed loop control principle, and thus the anti-radiation problem of the wide spectrum fiber light source can be well solved by using an active protective technology under the condition of not increasing the weight of the light source system.

Owner:BEIHANG UNIV

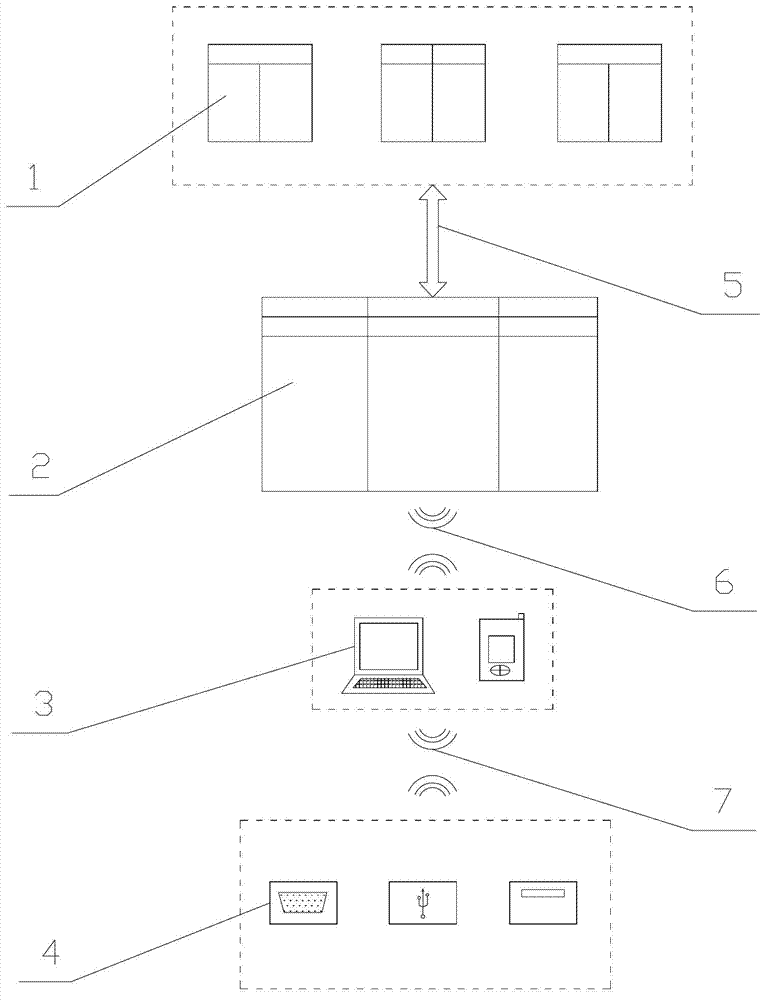

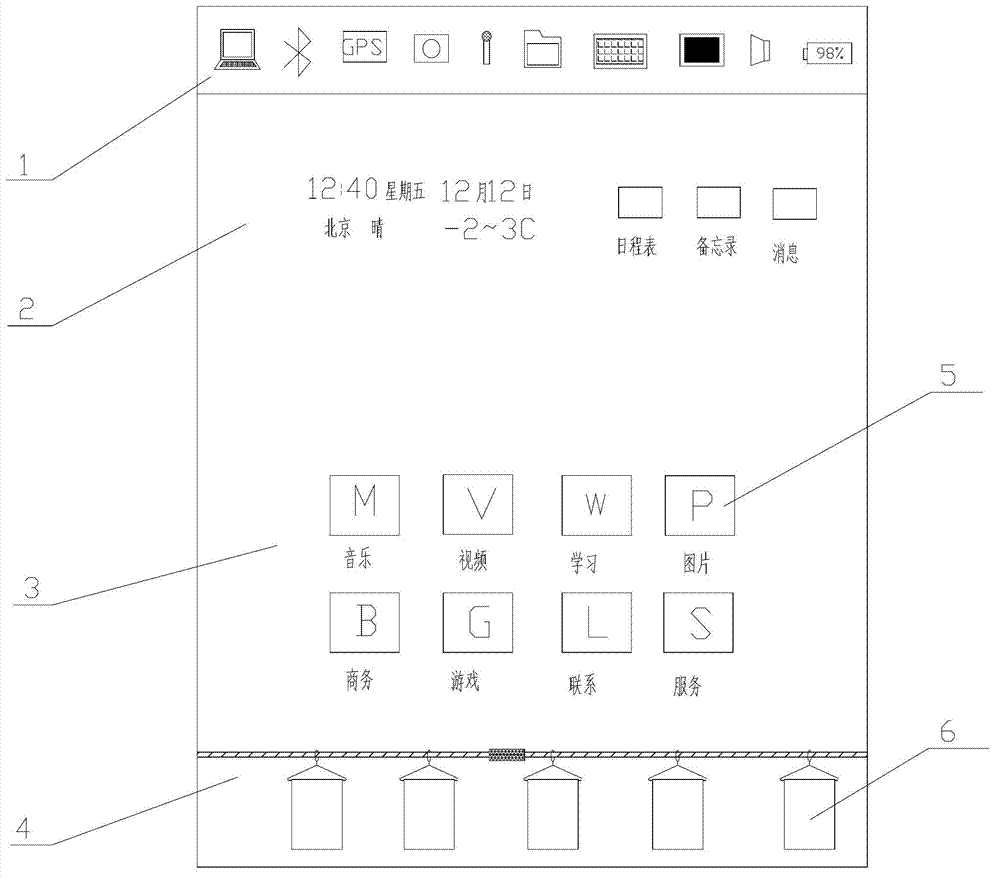

Personal information system based on cloud computing and formed by dependent special terminals

A personal information system based on the cloud computing and formed by dependent special terminals is mainly composed of a client device, a cloud end server and a corresponding connection network. The client device first needs to build connection with the cloud end server through the connection network to serve as a whole, and cannot visit other network serves alone or finish information processing and file storage tasks independently. Effect of the client device is similar to that of a browser in hardware level. The cloud end server finishes file storage and main information processing tasks of the whole system and can accept visit of client devices in different types of users as an information pivot. The whole system can respectively conduct software resource and hardware device expansion at the cloud end and the client. The system aims at resolving the problems of device performance, connection mode, file storage, information safety, manipulation experience, service provider profit, user using cost contradiction and the like in the field of personal information service.

Owner:马青川

Systems and methods for intra communication system information transfer

ActiveCN102387005AReduce transmissionReduce exchangeCriteria allocationSignal allocationCommunications systemInformation transfer

Systems and methods which provide for reduced intra communication system information transfer by providing a compressed representation of a portion of intra communication system information are shown. An embodiment operates to provide intra communication system transfer of uncompressed received information while providing intra communication system transfer of a compressed representation of information ancillary to the received information. According to embodiments, ancillary information, such as CSI, associated with other transferred information is transferred with reduced data throughput requirements through application of compression techniques with respect to the transferred ancillary information. Embodiments additionally or alternatively reduce the intra communication system information transferred by reducing the received information transferred.

Owner:ZHUORAN CO

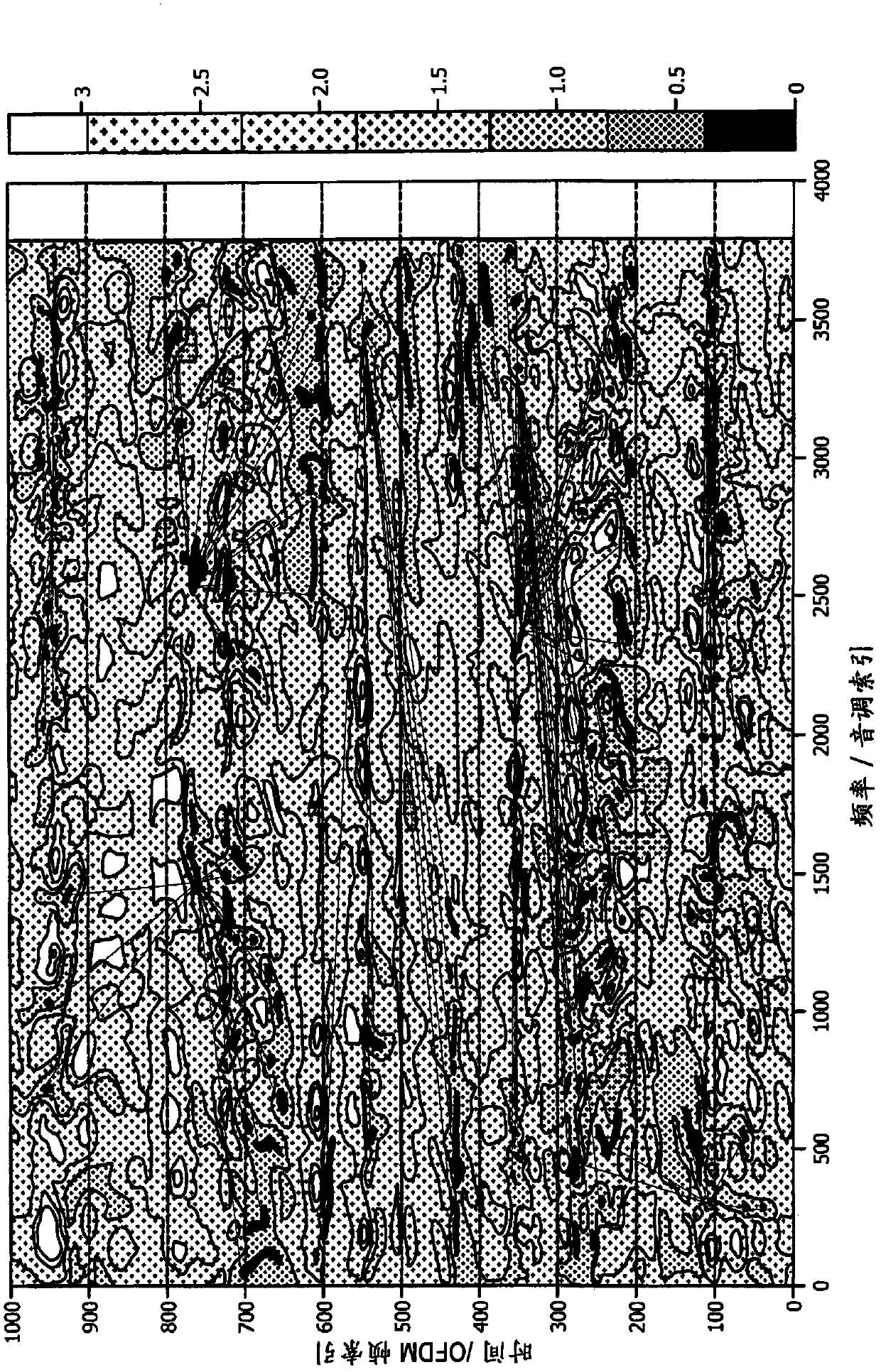

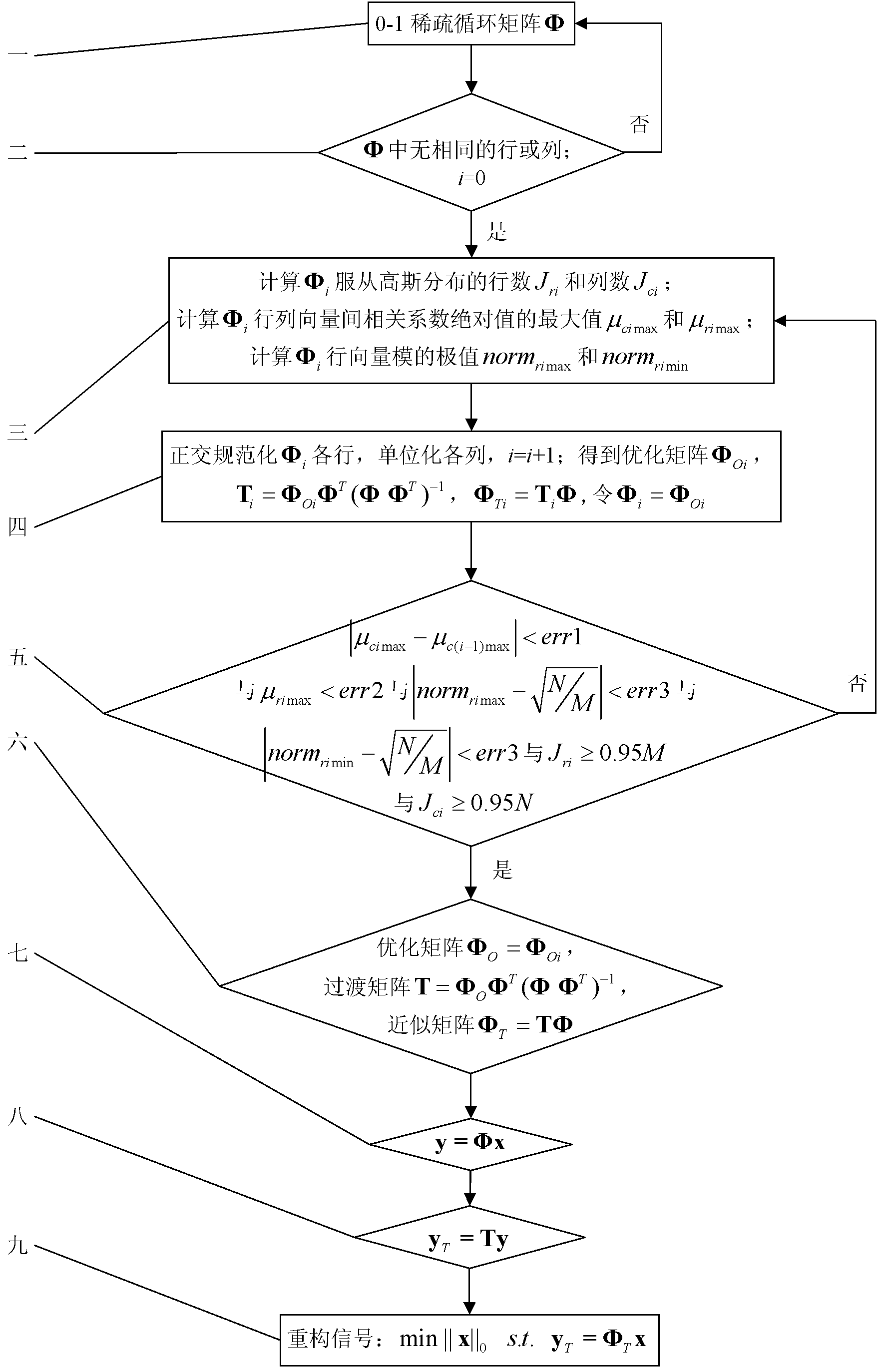

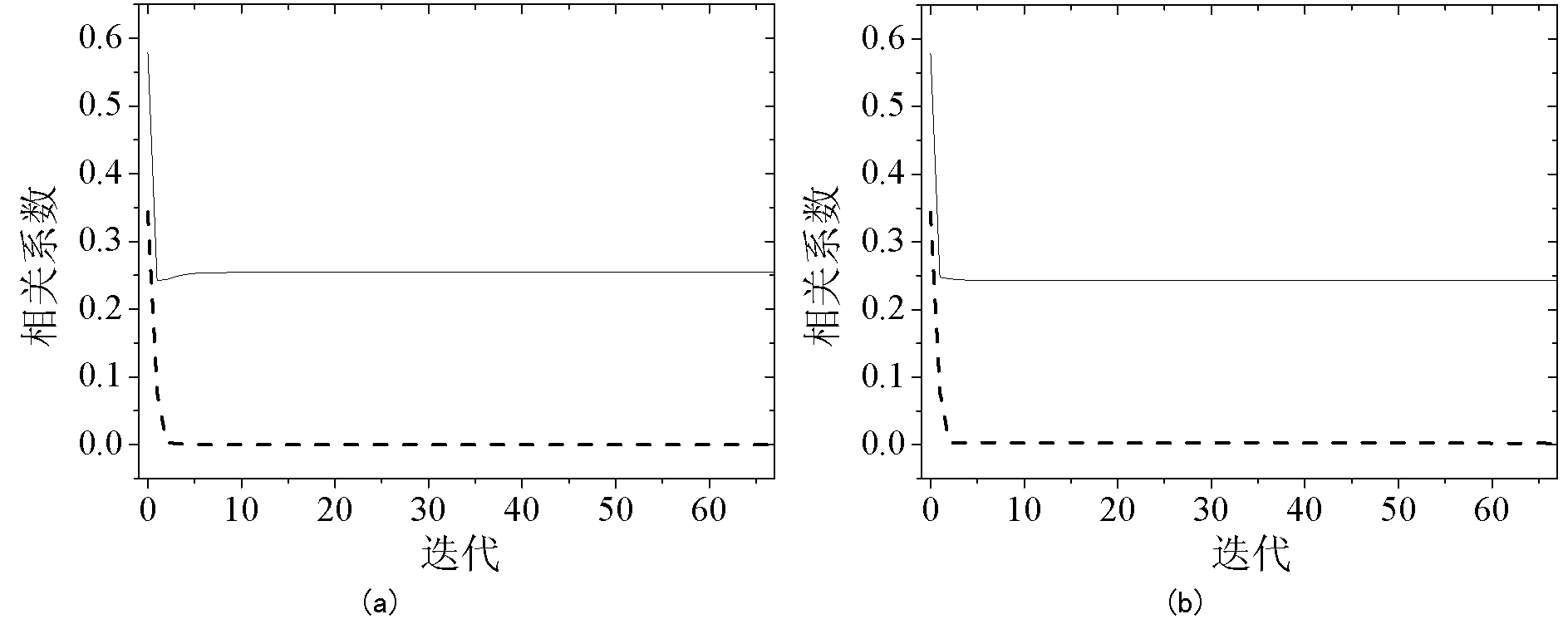

Approximation optimization and signal acquisition reconstruction method for 0-1 sparse cyclic matrix

ActiveCN102801428AUniversalSimplify hardware designCode conversionComplex mathematical operationsReconstruction methodTransition matrices

The invention discloses an approximation optimization and signal acquisition reconstruction method for a 0-1 sparse cyclic matrix, belongs to the technical field for the design and optimization of measurement matrix in compressive sensing, and provides a posteriori optimizing method which is easy to implement by hardware and can ensure signal reconstruction effect, wherein the 0-1 sparse cyclic matrix is adopted in the measurement stage, and a Gaussian matrix is adopted in the reconstruction stage. The method comprises the following steps: orthonormalizing the row vector and unitizing the column vector of the measurement matrix obtained by the i-1th iteration by the ith iteration; and optimizing the 0-1 sparse cyclic matrix by taking the maximum value of the absolute value of the correlated coefficient between each row and column vector, the convergence stability of each row vector module and the row and column number of each row and column subjected to Gaussian distribution as the criteria. The posteriori optimization of the measured data and measured matrix is completed by solving a transition matrix and an approximate matrix. The method establishes the foundation for the compressive sensing to be practical from the theoretical study.

Owner:GUANGXI UNIVERSITY OF TECHNOLOGY

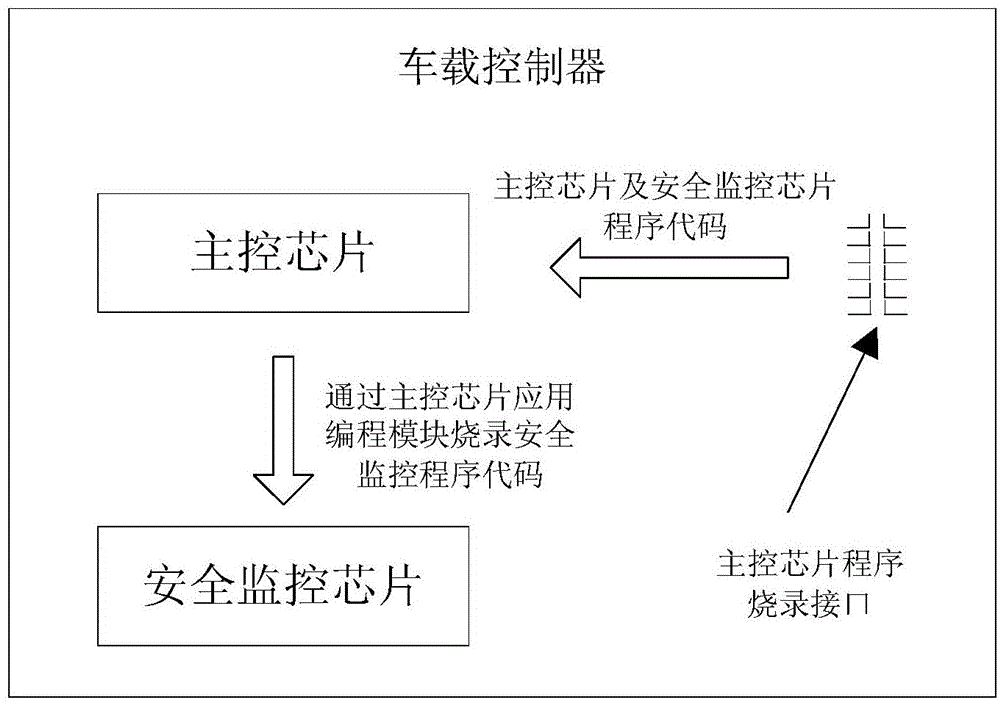

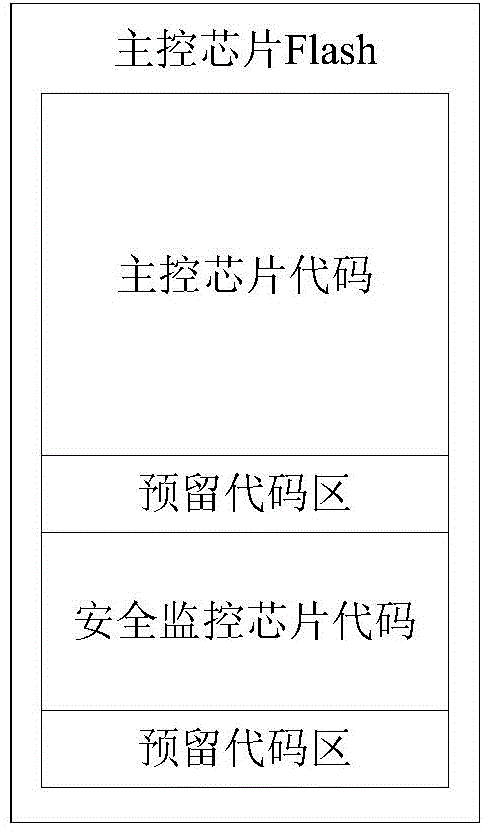

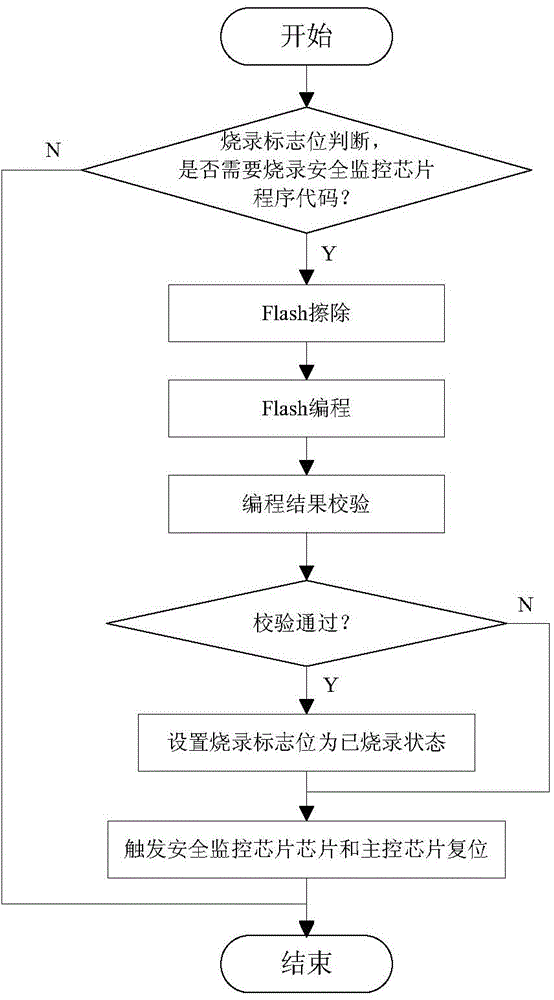

Multichip application burning method of vehicle-mounted controller

ActiveCN104657160ARealize synchronous automatic updateImprove programming efficiencyComputer security arrangementsProgram loading/initiatingEngineeringSafety monitoring

The invention discloses a multichip application burning method of a vehicle-mounted controller. The multichip application burning method comprises the division of a main control chip address space and the fragmentation of codes, the integration of the main control chip codes and safety monitoring chip codes, and burning the safety monitoring chip codes into the safety monitoring chip by use of an application burning module in the main control chip codes. The multichip application burning method is capable of completing the downloading and the updating of the codes of the main control chip and the safety monitorin through one program burning process.

Owner:LIANCHUANG AUTOMOBILE ELECTRONICS +1

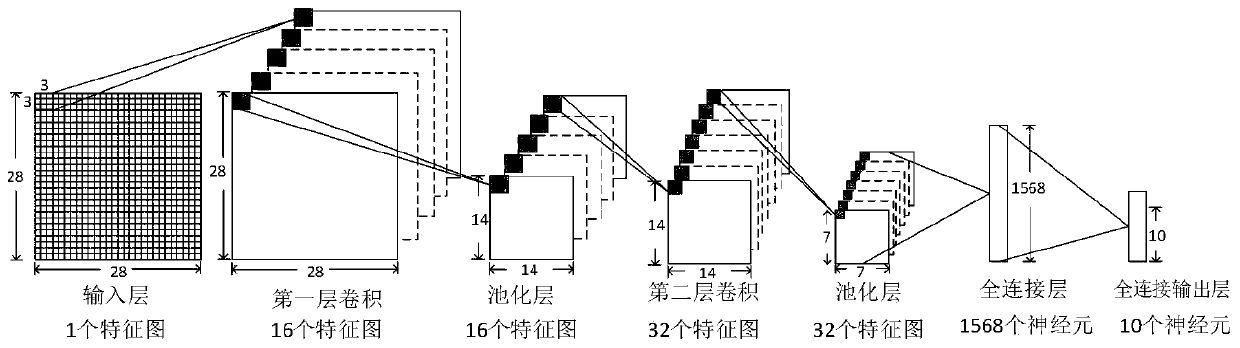

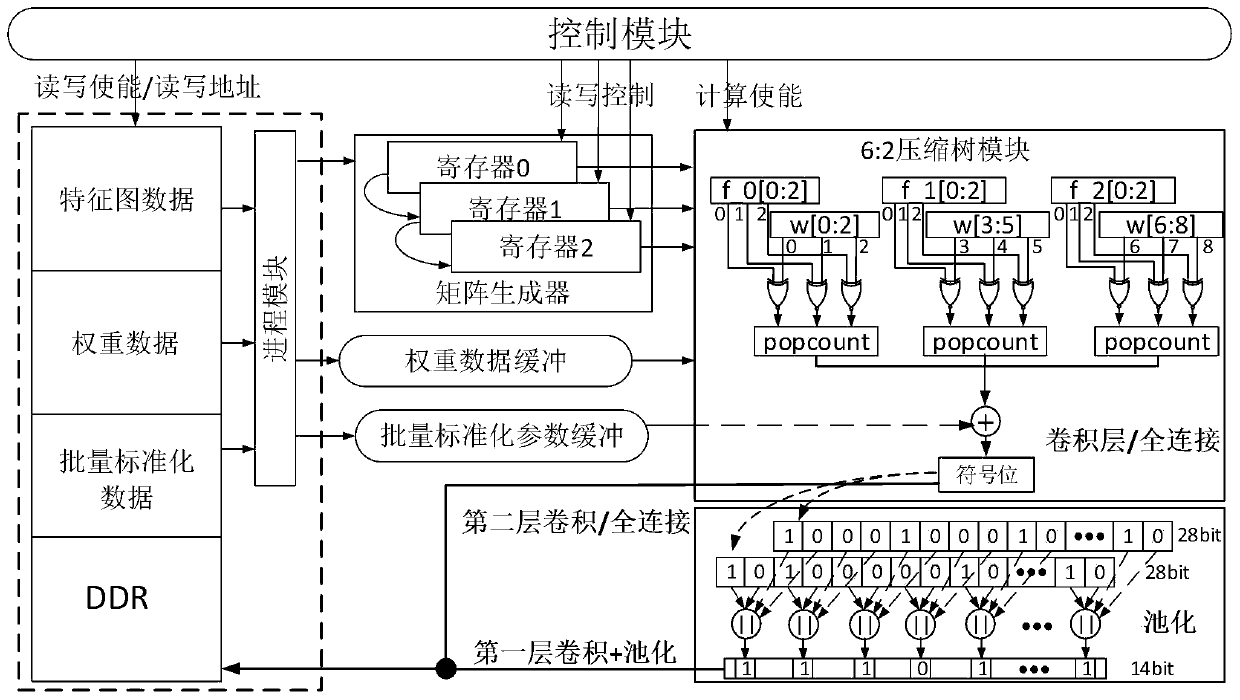

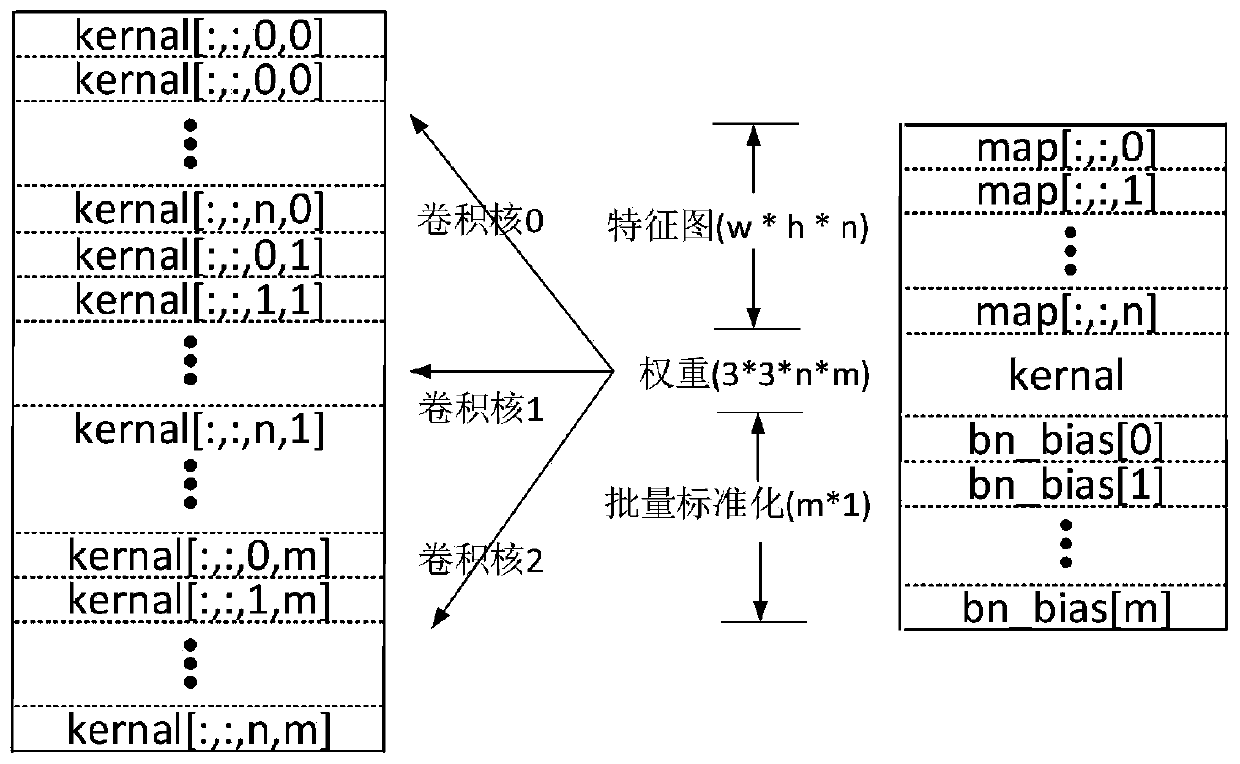

Hardware accelerator applied to binarized convolutional neural network and data processing method thereof

ActiveCN110780923AFast operationSave storage spaceRegister arrangementsNeural architecturesComputer hardwareEngineering

The invention discloses a hardware accelerator applied to a binarized convolutional neural network and a data processing method of the hardware accelerator. The hardware accelerator comprises a neuralnetwork parameter storage module, a matrix generator module, a convolution calculation array module, a pooling layer module and a global control module. A binary grayscale picture and neural networktraining parameters of each layer are pre-stored in the neural network parameter storage module; the matrix generator is responsible for preparing input data of convolution operation; the convolutioncalculation array is responsible for convolution calculation of a convolution layer; the pooling layer module is responsible for performing pooling operation on the output of the convolution layer; the global control module is responsible for controlling the whole system to work normally. The hardware accelerator aims to improve the operation speed of the convolutional neural network, reduce resources and computing resources consumed by network deployment on a hardware platform, and reduce the power consumption of network operation at the same time.

Owner:HEFEI UNIV OF TECH

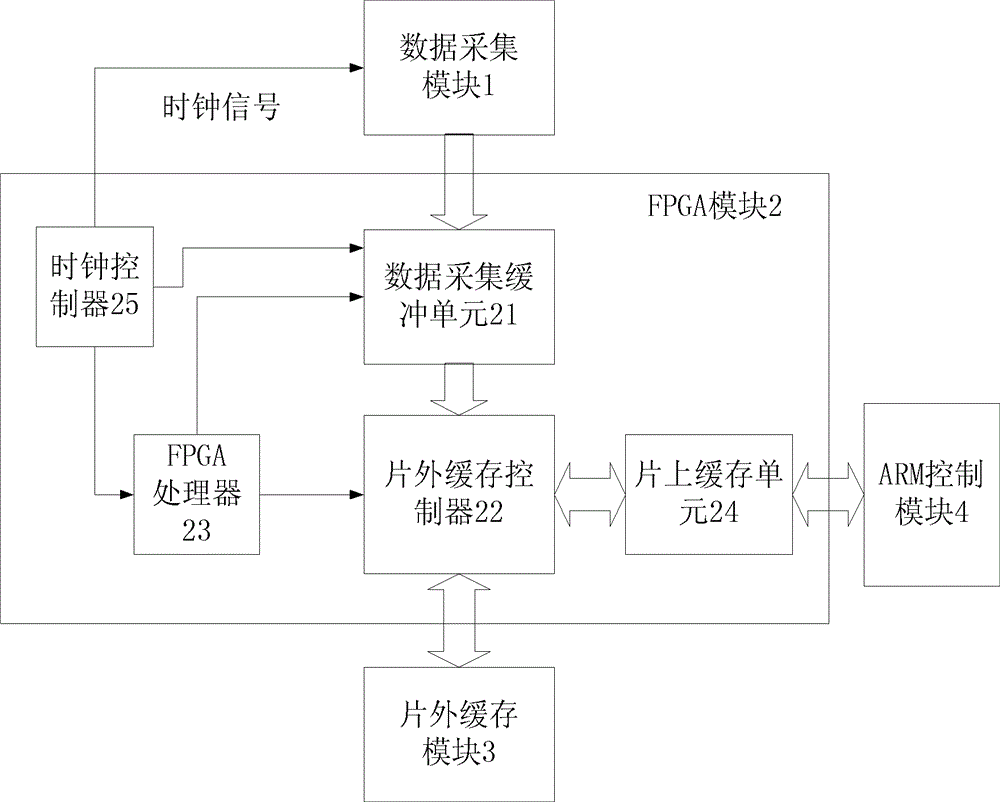

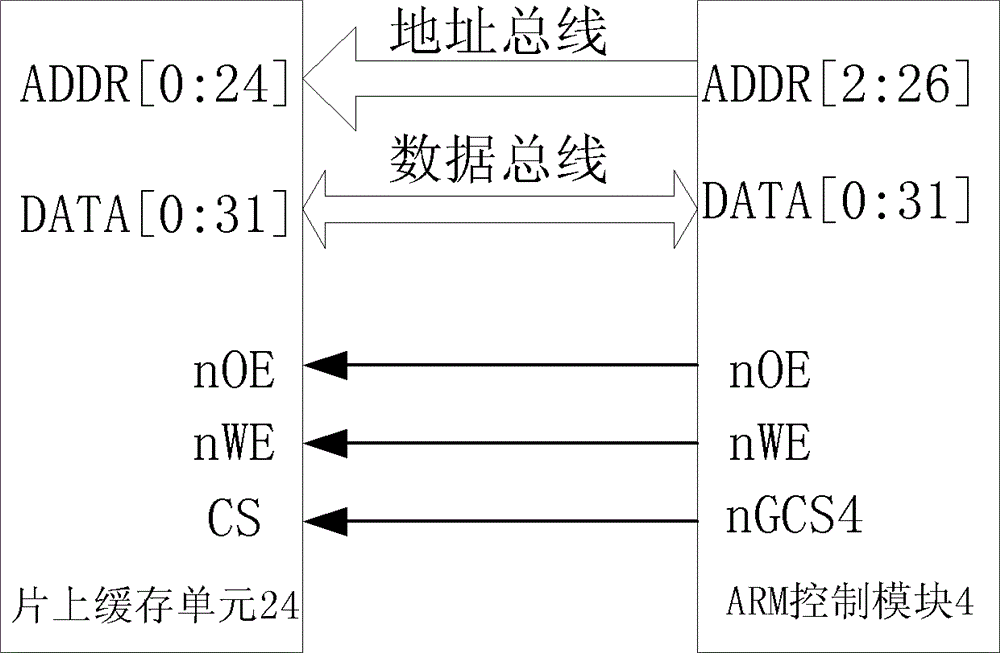

Field programmable gate array (FPGA) and advanced RISC machine (ARM)-based data transmission method and system

ActiveCN102801593AHigh speed transmissionReal-time transmissionDuplex signal operationBus networksUltra high voltageControl store

The invention relates to a field programmable gate array (FPGA) and advanced RISC machine (ARM)-based data transmission method and an FPGA and ARM-based data transmission system. According to the system, a parallel bus mechanism is used for transmitting data. The system comprises a data acquisition module, an FPGA module, an off-chip cache module and an ARM control module, wherein the FPGA module comprises an off-chip cache controller, an FPGA processor and a two-way dual-clock on-chip cache unit. The data transmission method comprises the following steps that: the data acquisition module transmits acquired data to a data acquisition and cache unit of the FPGA module; the off-chip cache controller reads the data from the data acquisition and cache unit, and transmits the data to the off-chip cache module for storage; the off-chip cache controller reads the data from the off-chip cache module, and transmits the data to the on-chip cache unit for storage; and the ARM control module reads the data from the off-chip cache module under the control of a built-in storage controller of the ARM control module to realize data communication with the FPGA module. The acquired data can be transmitted to an upper computer at high speed in real time, and the requirements of application fields of ultra high-voltage corona current source data transmission and the like are met.

Owner:CHINA ELECTRIC POWER RES INST +1

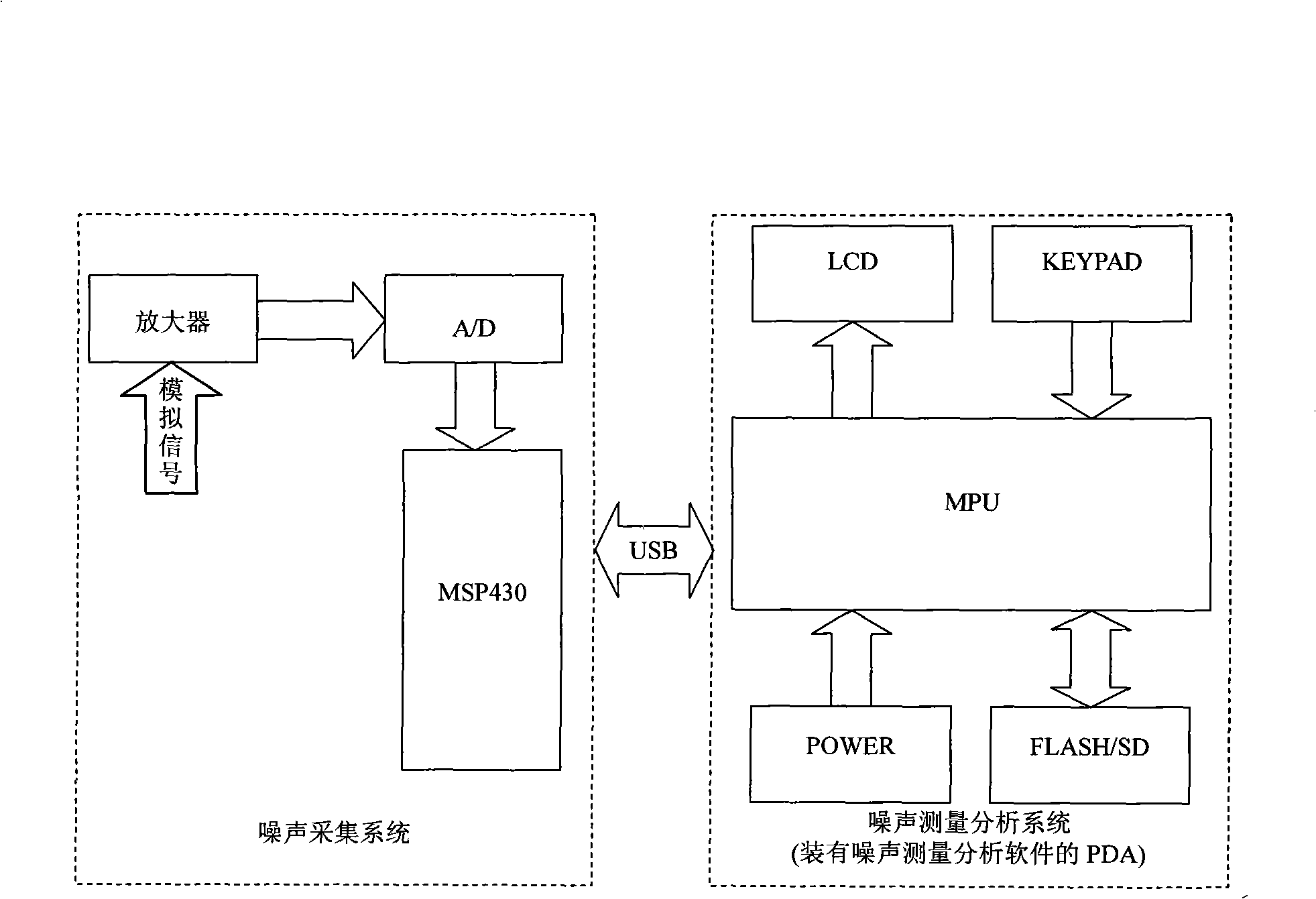

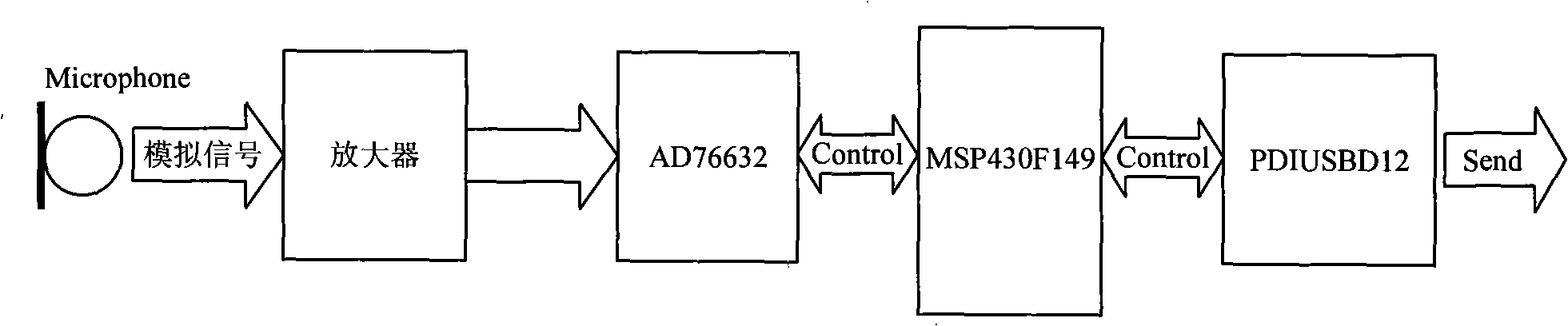

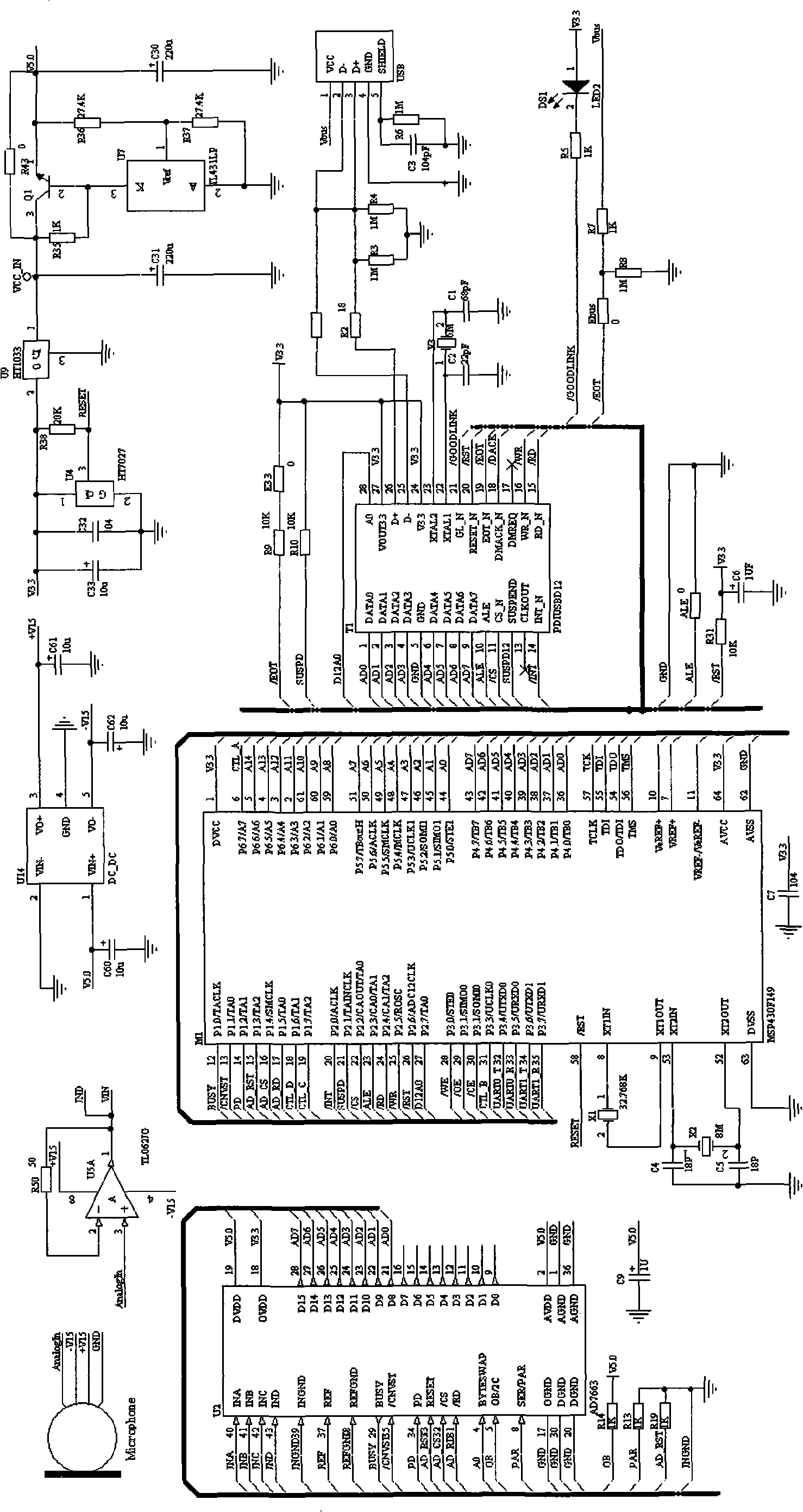

Full-digital real-time noise measurement and analysis method and system thereof

InactiveCN101539602ASimple designSimplify hardware designSpectral/fourier analysisNoise figure or signal-to-noise ratio measurementCollection systemOctave

The invention discloses a full-digital real-time noise measurement and analysis method and a system thereof. The noise measurement and analysis system provided with a noise measurement and analysis software PDA is connected with a noise collection system by a USB port. The method and system realize the digitization of frequency weighting, time weighting, octave and 1 / 3 octave processing, and can display time domain waveform and frequency domain waveform and provide system settings; and a user can select settings of sampling frequency and sampling time of the noise collection system, select L linearity, A and C types of frequency weighting and select time average, fast gear and slow gear of time weighting. In a graphic display mode, the user selects a frequency domain analysis method of signals and displays a corresponding frequency spectrogram according to needs, wherein the functions of FFT frequency spectrogram analysis, octave frequency spectrum analysis, 1 / 3 octave frequency spectrogram analysis and the like realize the measurement and analysis to real-time noise. The method and system utilize a PDA computer system to realize the full-digital real-time noise signal measurement and analysis with low cost and high quality.

Owner:ZHEJIANG SCI-TECH UNIV

Packet processor with mild programmability

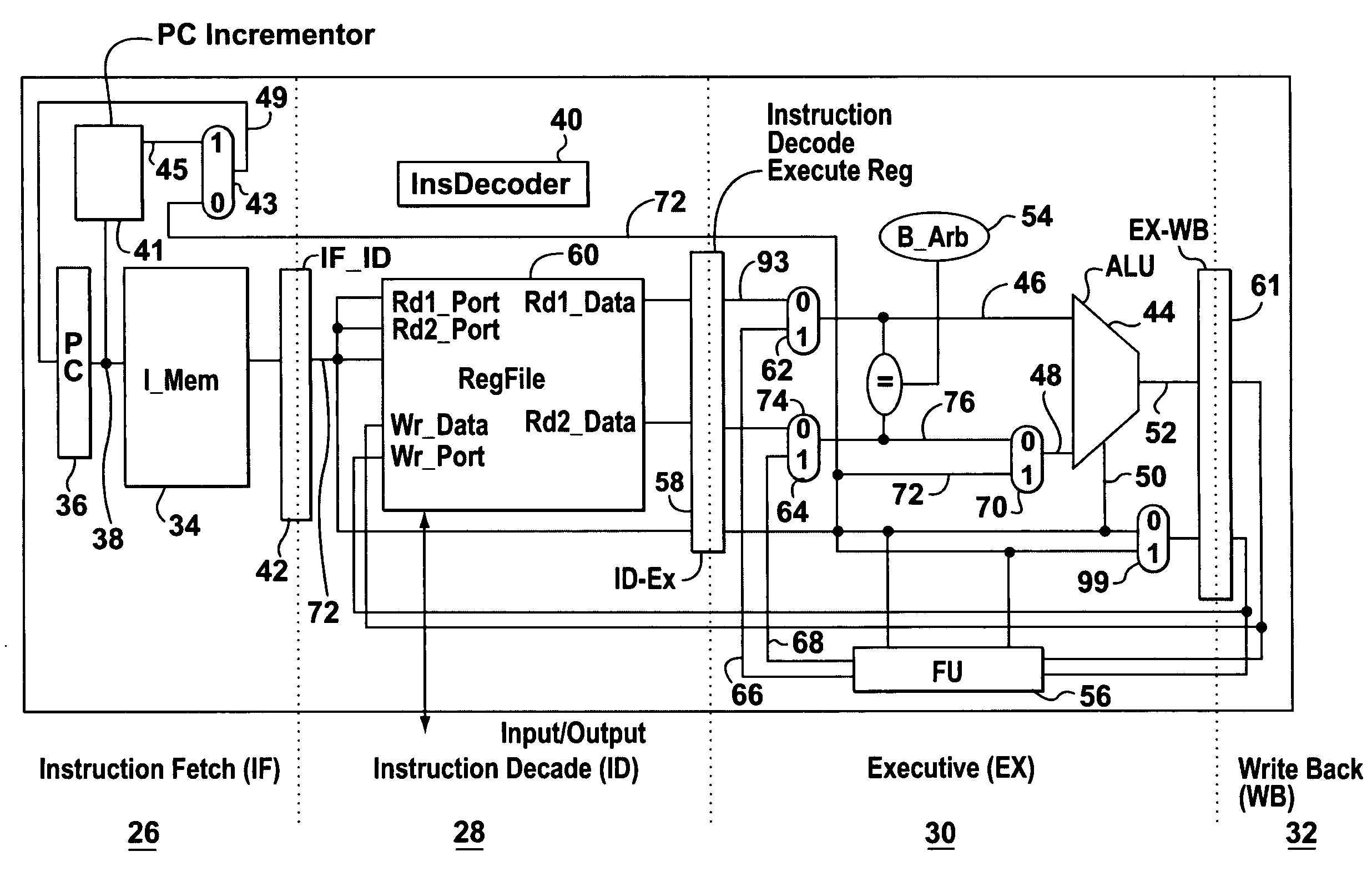

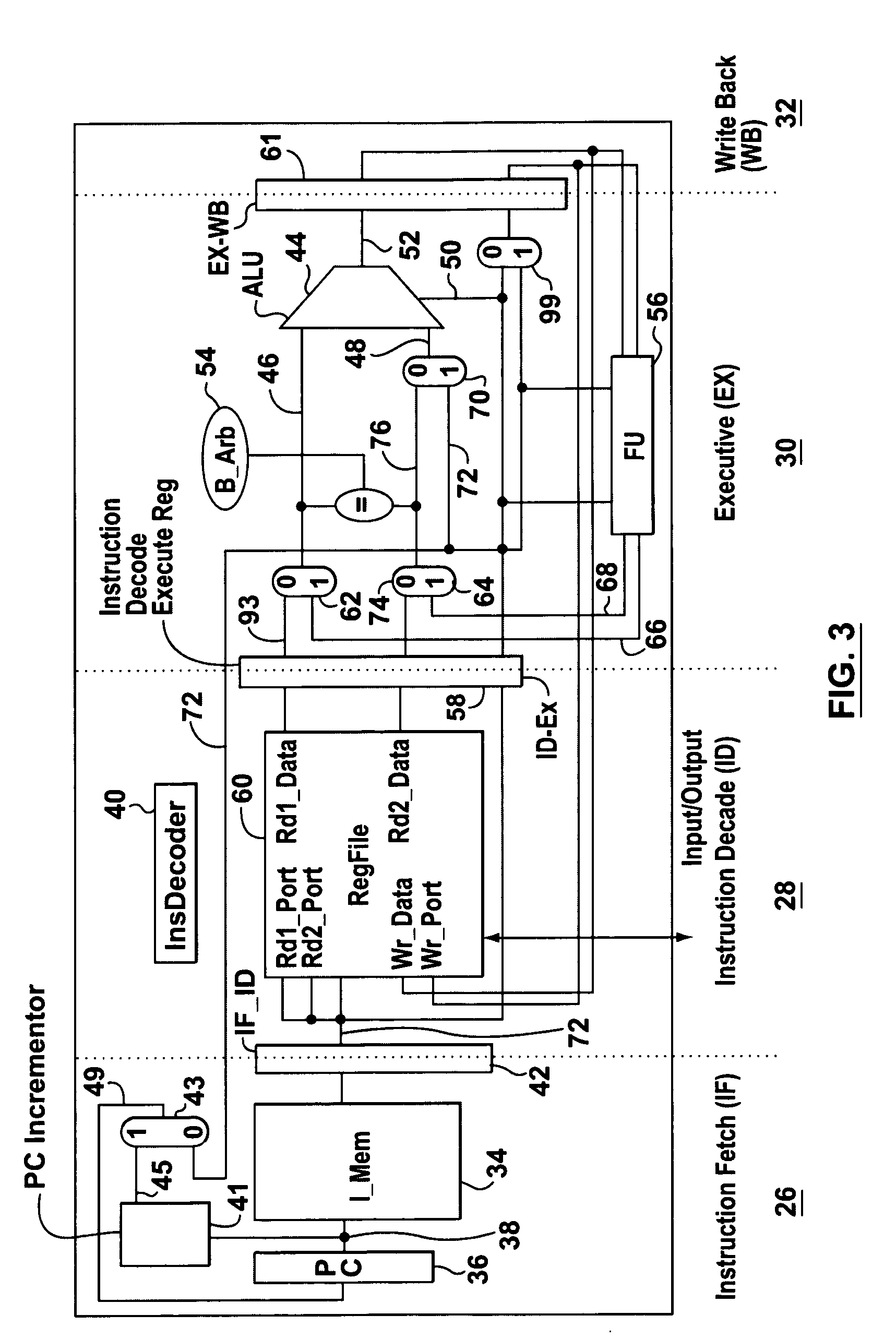

InactiveUS20050289326A1Simplify hardware designReduce complexityDigital computer detailsConcurrent instruction executionMultiplexingComputer architecture

A reduced instruction set pipelined processor having an instruction fetch stage, an instruction decode stage, an executive stage and a write back stage and programmed with a single program which is structured to implement a function performed by a finite state machine. Only read after write data hazards exist in said processor, and these data hazards are eliminated by a forwarding unit in said executive stage which does an address comparison between the executive and write back stages and decides if a data hazard exists in accordance with predetermined logic. If a data hazard exists, suitable control signals are generated to control switching by multiplexers to supply operands to said ALU from said forwarding unit so as to eliminate said data hazards. Pipeline stall control hazards are reduced by inserting useful delay-slot instructions following at least some branch instructions in said program.

Owner:THE HONG KONG UNIV OF SCI & TECH

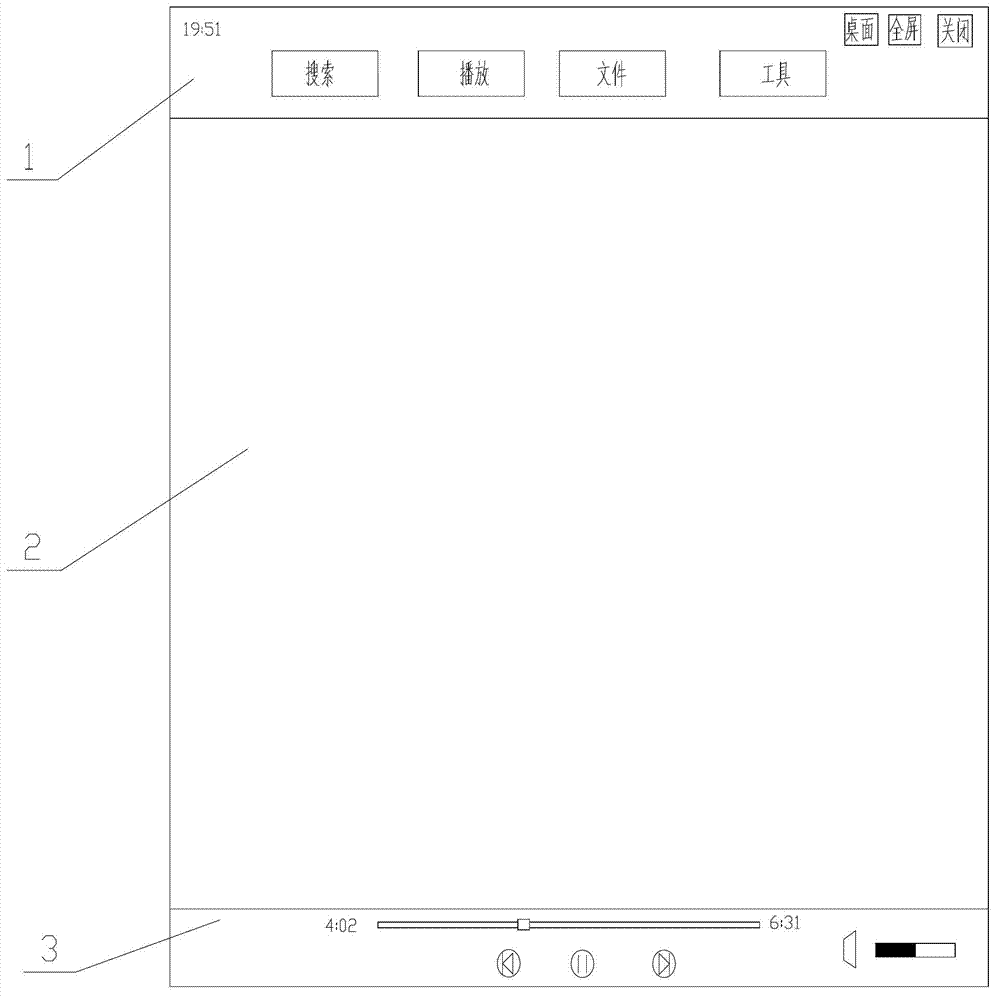

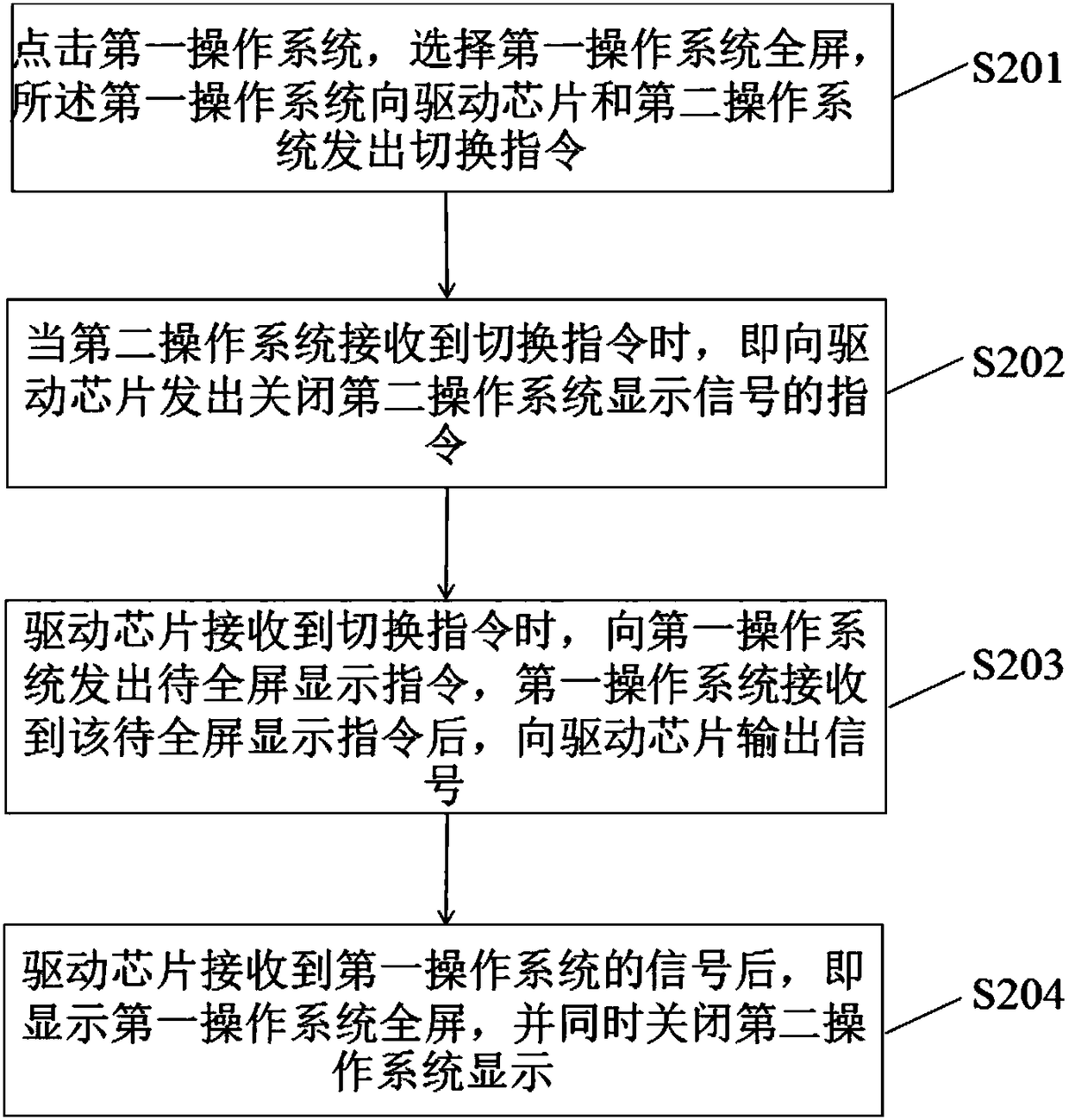

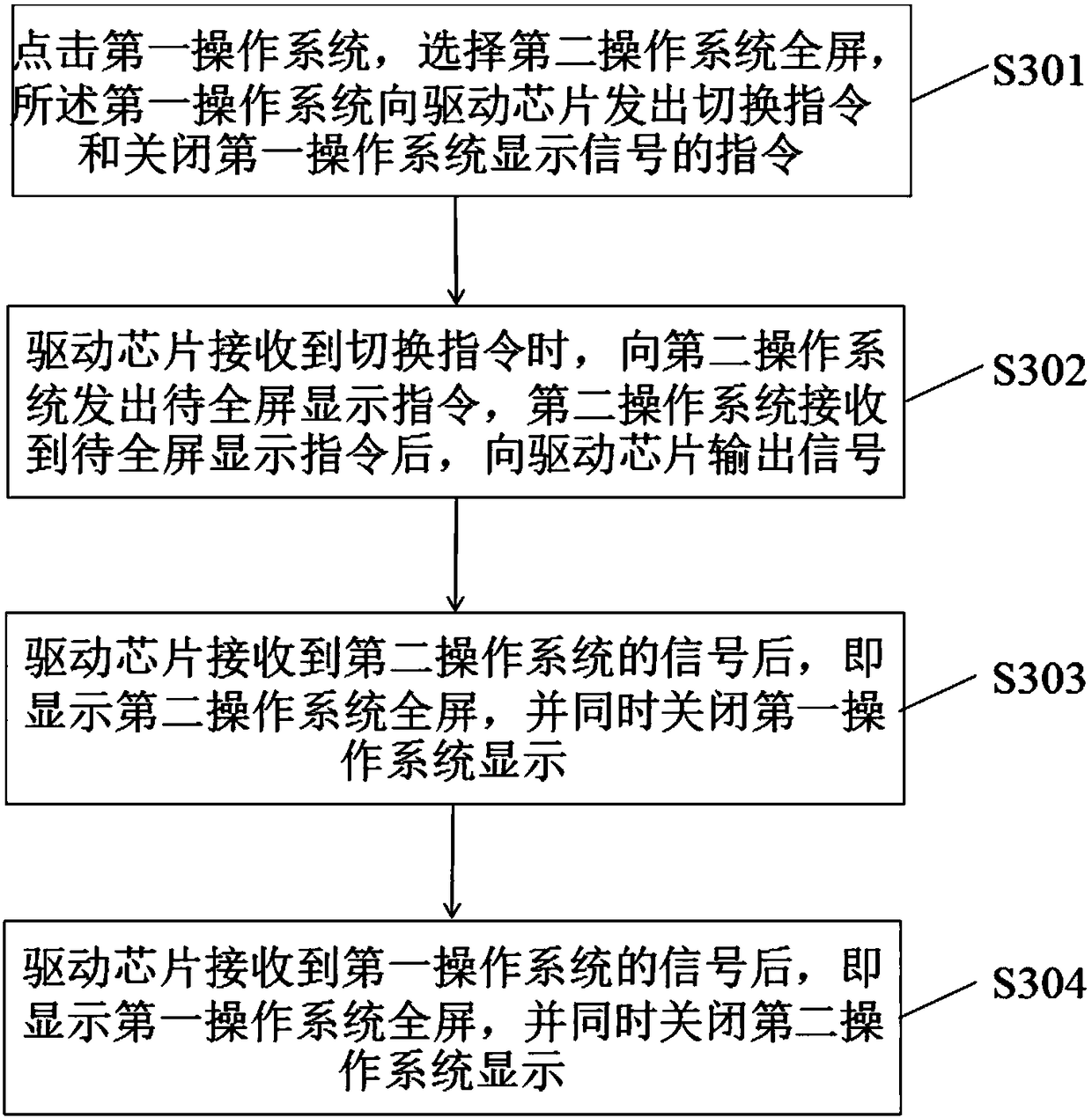

Dual-system real-time-display running method and device and dual-system integrated-machine

PendingCN108628569ASimplify hardware designReduce economic costsInput/output processes for data processingEngineeringReal time display

The application aims to provide a dual-system real-time-display running method. The method includes: turning on a power supply, and simultaneously starting a first operating system and a second operating system, wherein the first operating system and the second operating system respectively output signals to a driving chip; when the driving chip receives the signals of the two operating systems atthe same time, running a screen splitting display program to split display of a display screen into two independent display areas; issuing communication instructions of display to the two operating systems by the driving chip, and carrying out split-screen real-time-display in the display areas after the first operating system and the second operating system receive the communication instructions. According to the method, real-time dual-system split-screen running is realized, a user can be enabled to quickly experience different functions of the different operating systems, and needs of thepublic for using the different operating systems are satisfied.

Owner:上海信颐信息技术有限公司 +1

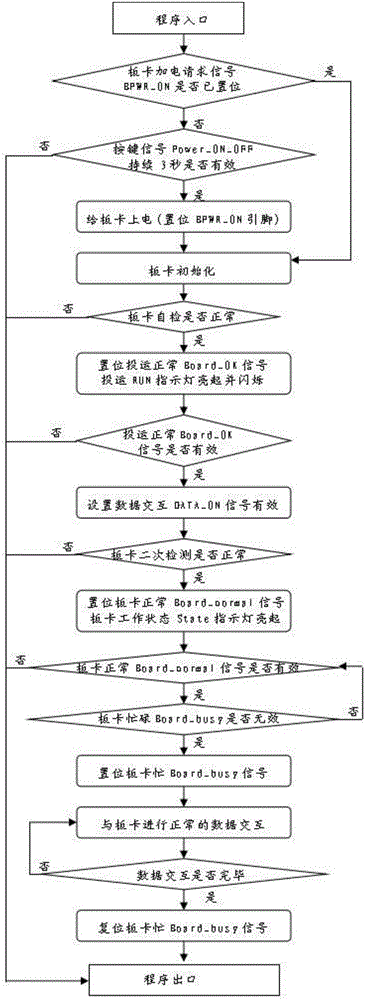

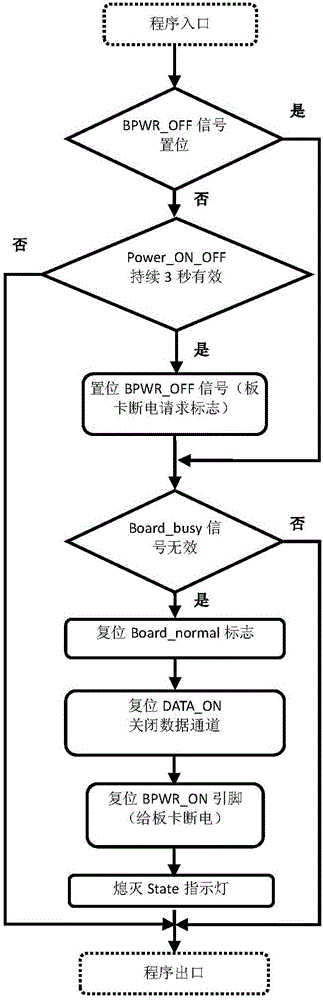

CPU (Central Processing Unit) control board capable of realizing hot plug of board card and implementation method thereof

InactiveCN106598902AImprove efficiencyImprove scalabilityHardware monitoringData interfaceHuman–computer interaction

The invention discloses a CPU (Central Processing Unit) control board capable of realizing hot plug of a board card and an implementation method thereof. The CPU control board comprises a CPU, an IO (Input Output) module, a power control module and a data interface module, and is characterized in that the CPU implements signal detection, man-machine interaction and input output indication on the board card via the IO module, supplies power to the board card via the power control module, manages the data interface module by using a data interface, and exchanges data with the board card by using a data bus and the data interface module; and a control program for realizing hot plug of the board card is stored in the CPU control board. The CPU control board and the implementation method thereof avoid the problems of hardware damage, misoperation and the like in the hot plug process of the board card, also avoid the problems of program locking and system crash caused by abnormal unplugging of the board card, and simultaneously improve the efficiency of field work.

Owner:INTEGRATED ELECTRONICS SYST LAB

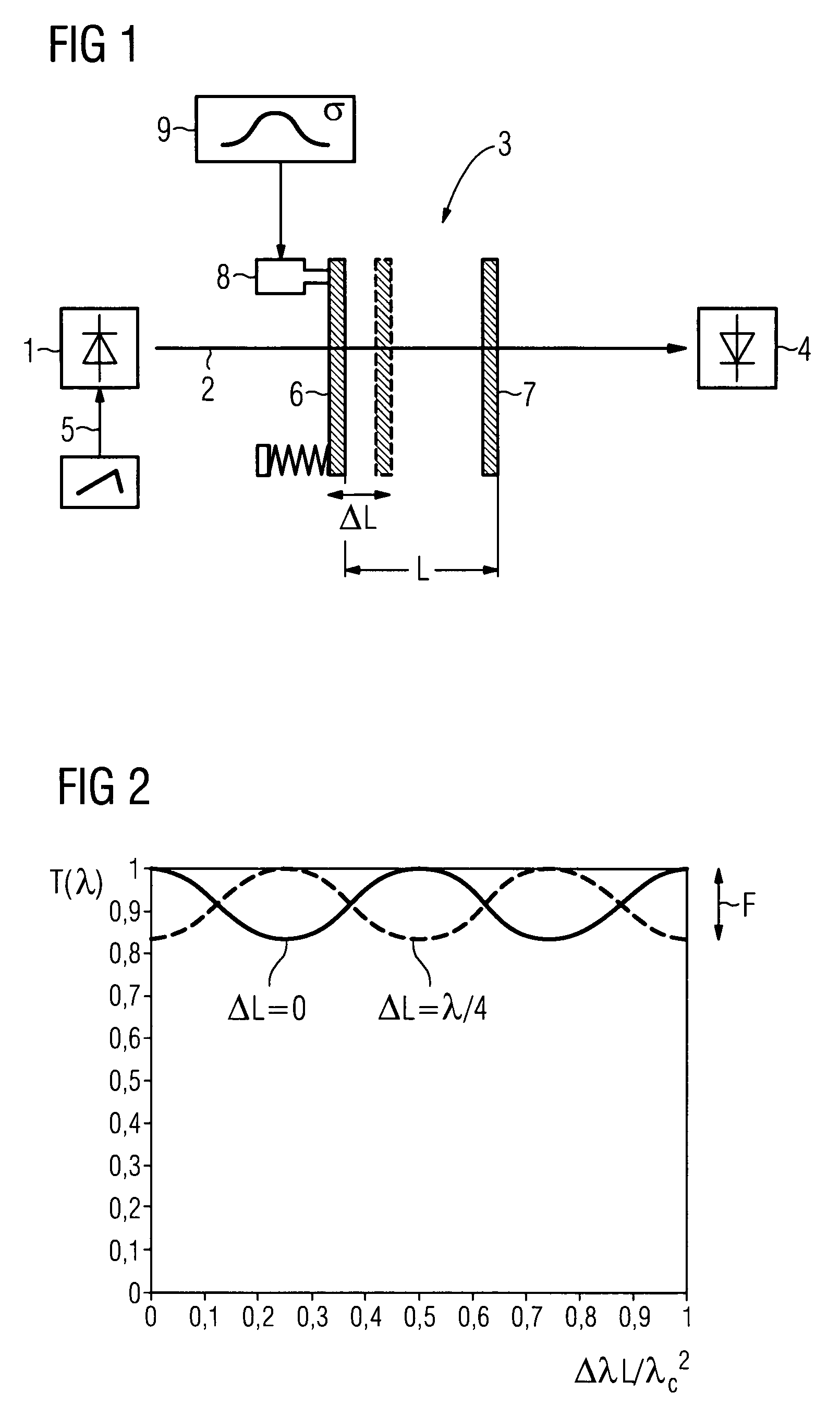

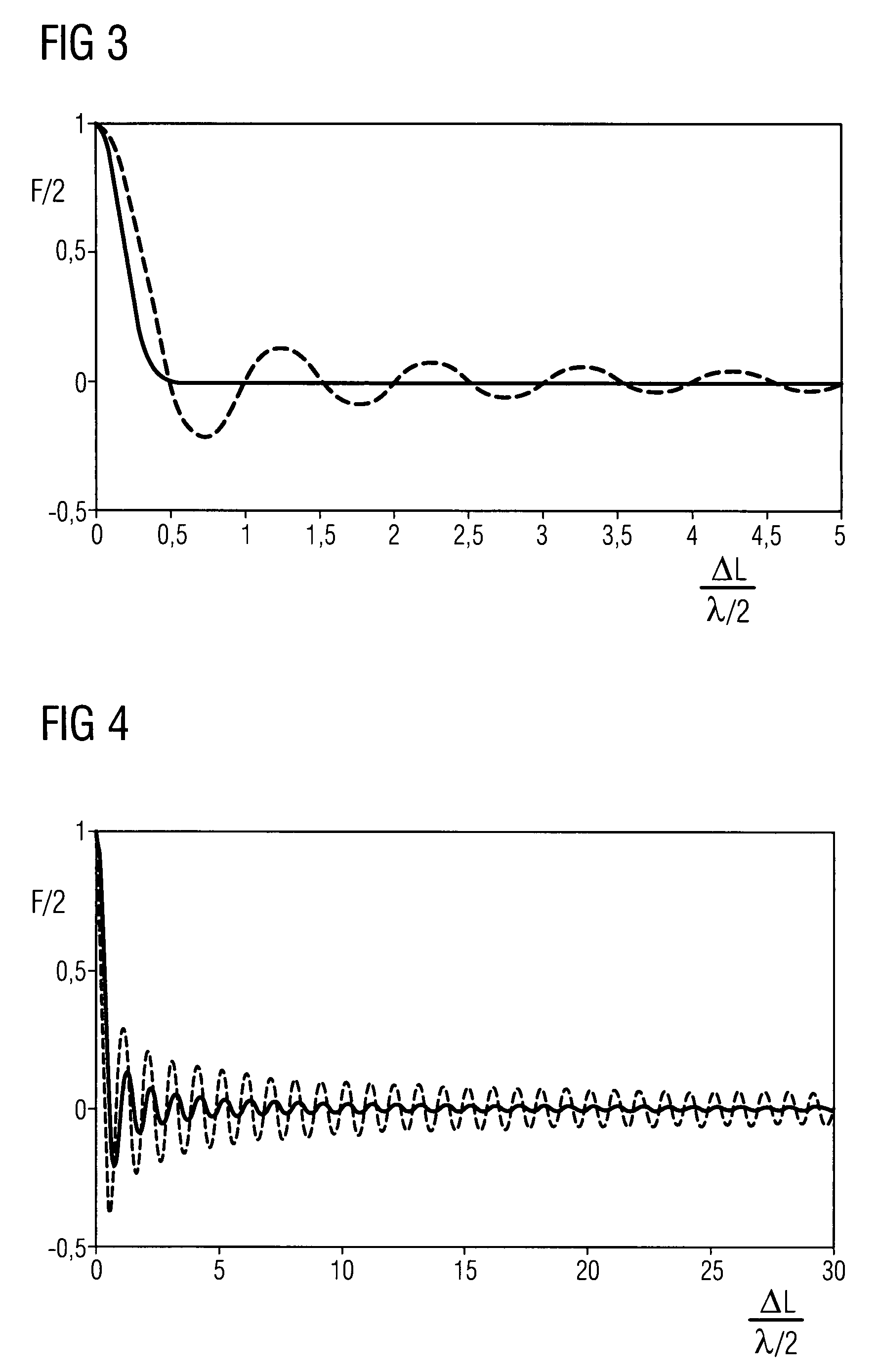

Method and apparatus for reducing fringe interference of light

ActiveUS7800764B2Reduce interferenceSimplify hardware designUsing optical meansColor/spectral properties measurementsLength waveOptical path length

A method for reducing fringe interference of light created in a passive cavity defined by partially reflecting optical surfaces, wherein the optical path length of the cavity is varied with a Gaussian distribution, where the standard deviation is at least one-quarter of the light's wavelength.

Owner:SIEMENS AG

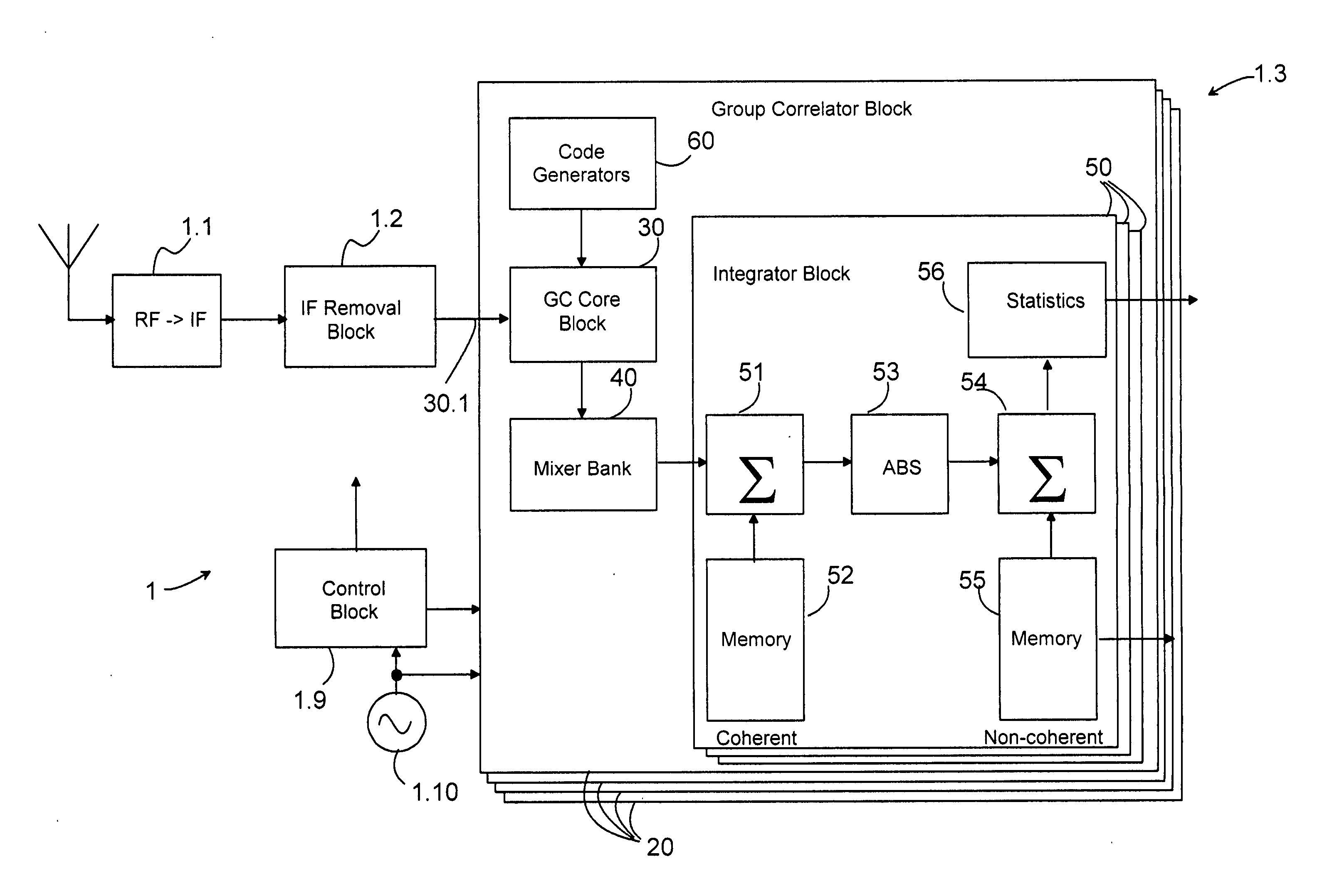

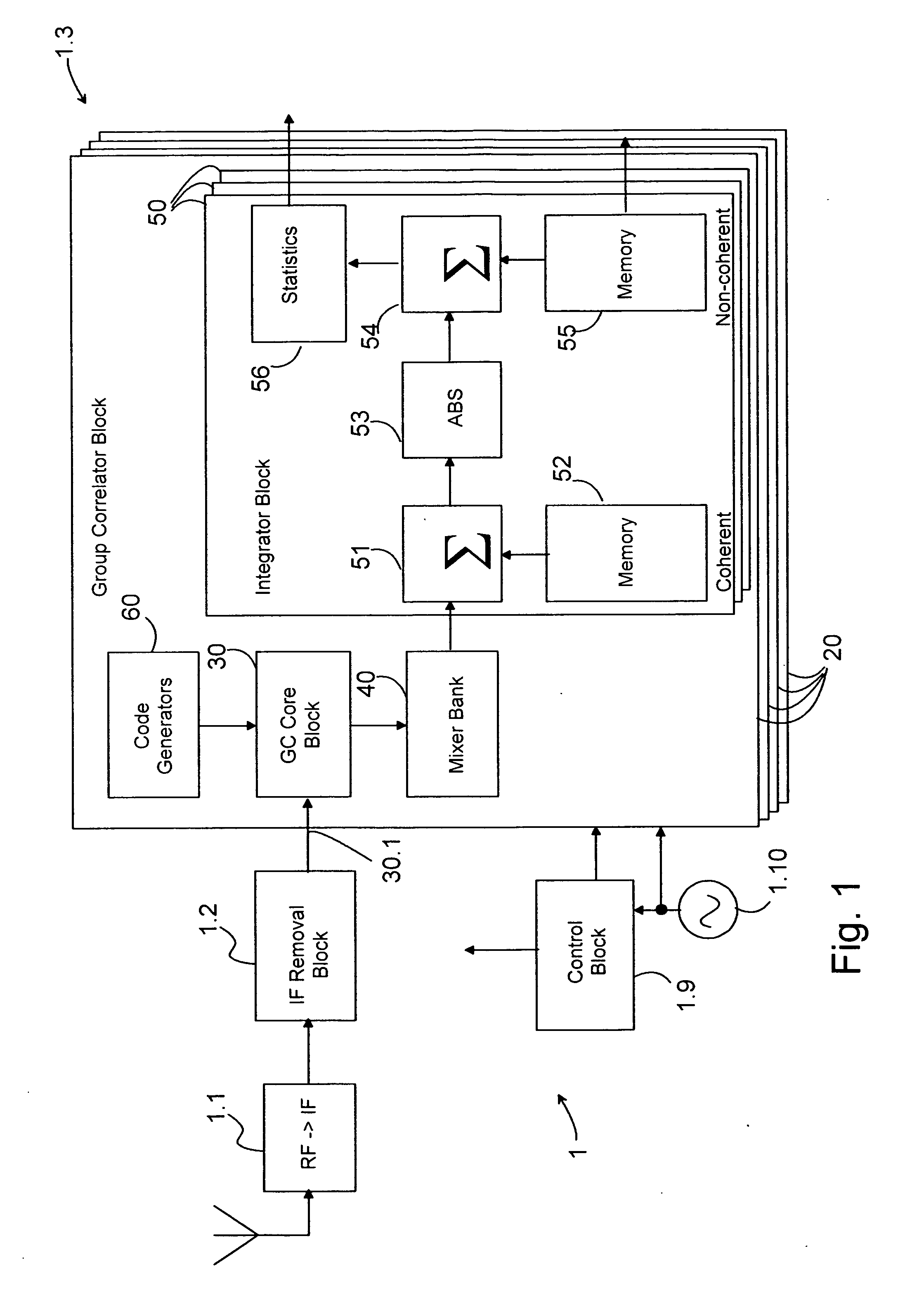

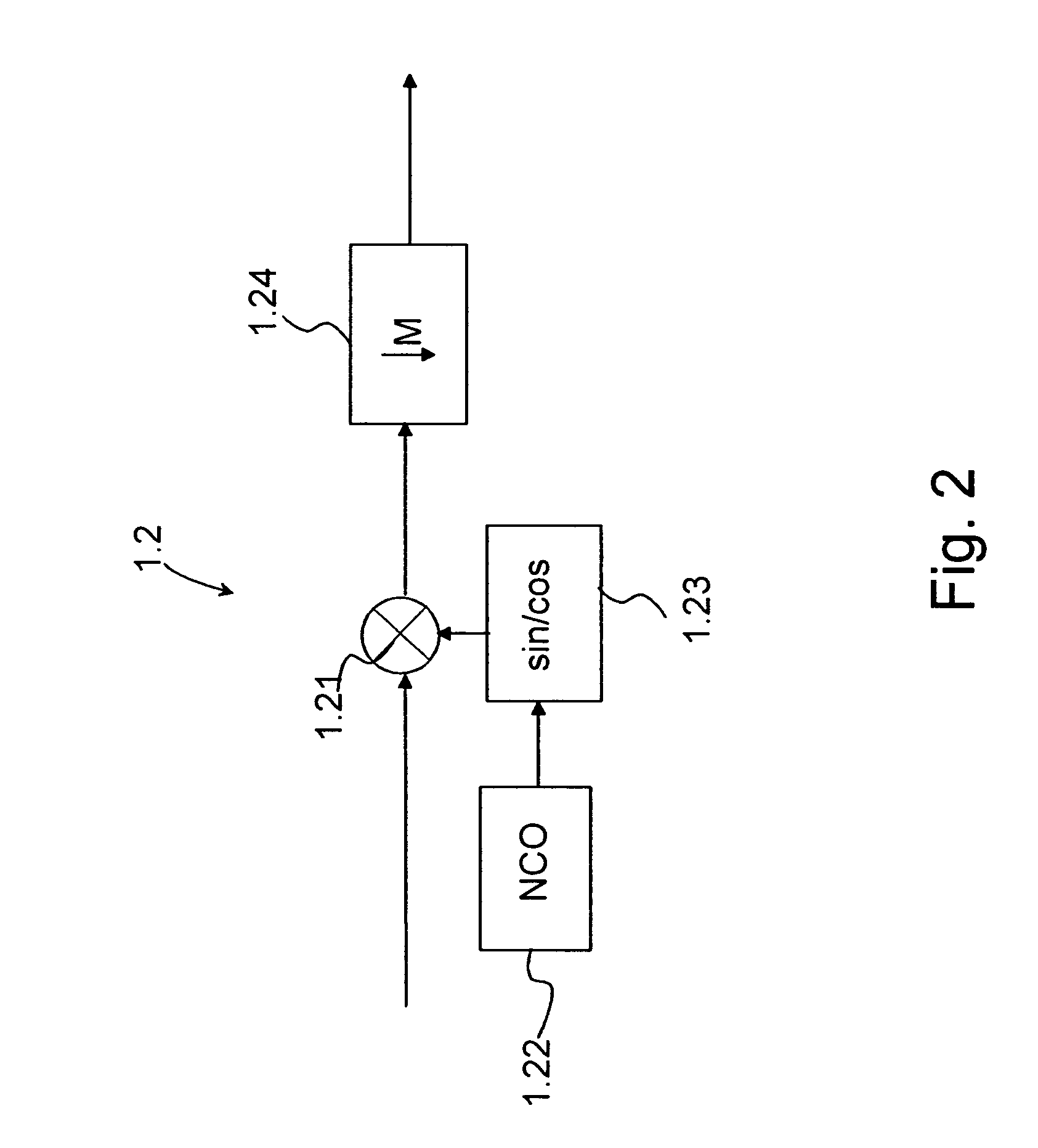

Performing a correlation in reception of a spread spectrum signal

InactiveUS20070153882A1Reduce control complexitySmall size of hardwarePosition fixationNavigation instrumentsShift registerParallel computing

A correlator (30) for performing a correlation with a received spread spectrum signal, comprising at least an input (30.1) for inputting samples of a received signal; at least one reference code input (30.2) for inputting at least one reference code, a correlator block comprising a data shift register (36) for receiving the signal samples; a number of register groups (31) comprising a code shift register (33) for receiving at least a part of at least one reference code; and a code register (34) for receiving data from the code shift register (33); configuration pathways (201, 202, 203) for arranging the connections between the code shift register and code register (33, 34) of the register groups (31) in a reconfigurable manner.

Owner:RPX CORP

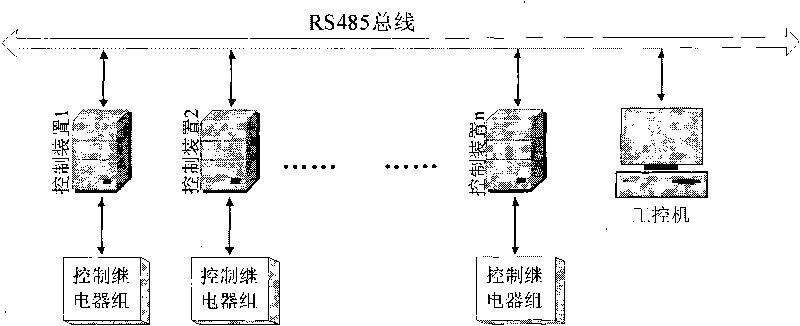

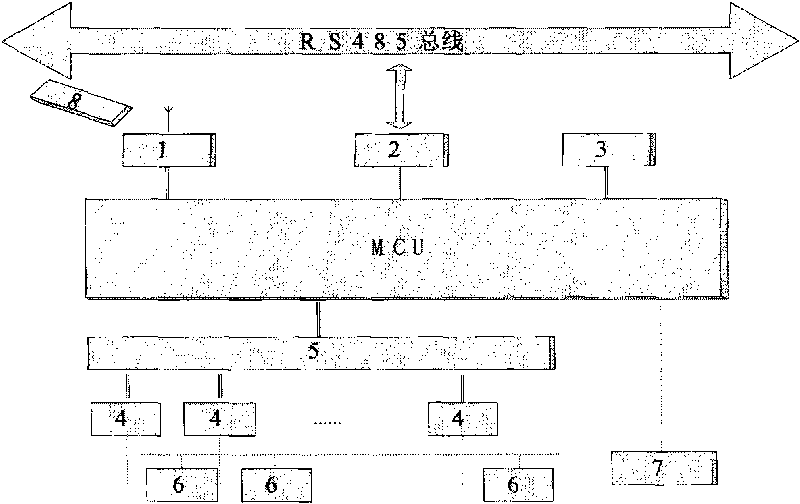

Intelligent plant building illumination control method and system

InactiveCN101742782ARealize remote controlImplement queryElectric light circuit arrangementEnergy saving control techniquesCommunication interfaceAutomatic control

The invention discloses an intelligent plant building illumination control method and an intelligent plant building illumination control system. In the invention, a plurality of intelligent control devices and a host computer form an intelligent plant building illumination control network through an RS485 bus; each intelligent control device is arranged in an illumination control box; the intelligent control device mainly comprises a central processing unit, a lamp main circuit and a handheld remote controller and the handheld remote controller controls a plurality of intelligent control devices; the central processing unit adopted has an integrated RS-485 communication interface; and all the illumination control boxes in the plant building form the network through the RS485 bus and the network is connected to an internal Ethernet network of the plant building, so lamps can be remotely controlled and inquired through a communication program of the intelligent plant building illumination control network. The method and system can realize intelligent management of the plant building illumination, reduce waste of the energy sources, reduce labor intensity of workers and realize automatic control for the plant building illumination.

Owner:CHINA NON-FERROUS METALS PROCESSING TECH CO LTD

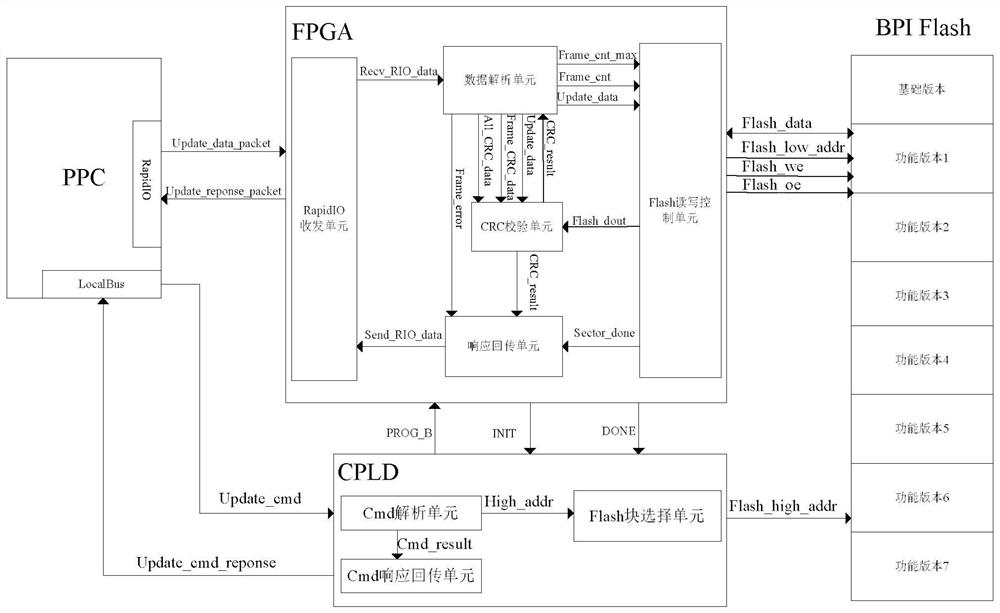

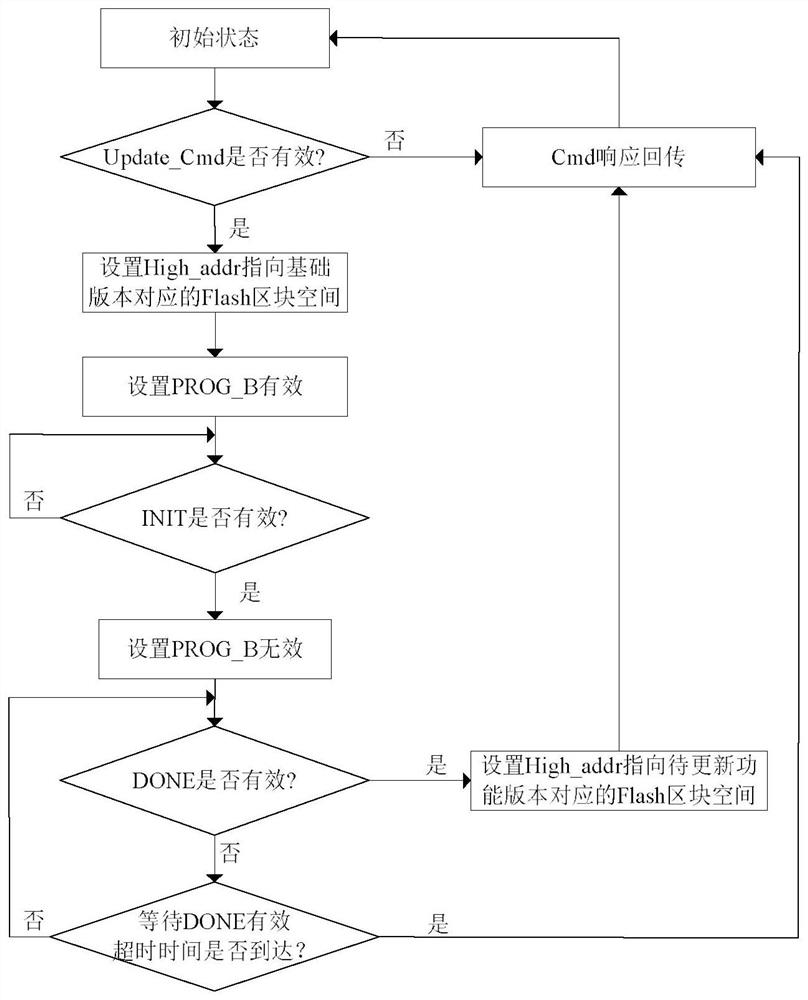

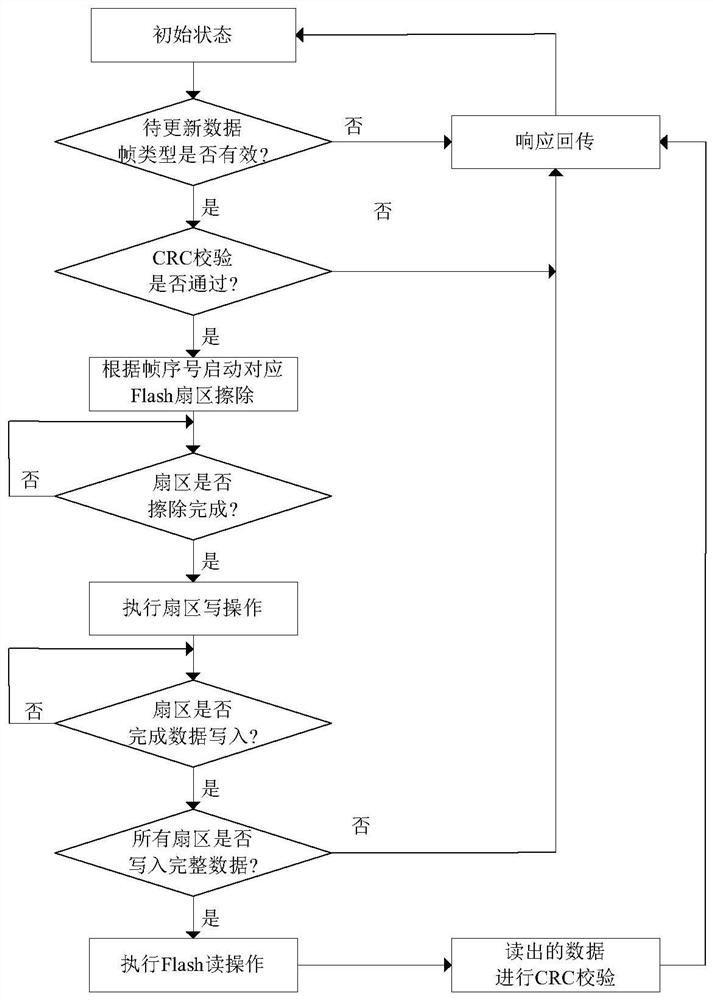

Method for remotely updating multi-version program of FPGA online

ActiveCN113434162ANo increase in design complexitySimplify hardware designVersion controlSoftware deploymentComputer architectureEngineering

According to the method for remotely updating the multi-version programs of the FPGA online, hardware is simple, the real-time processing efficiency is high, and the fault-tolerant capability is high. According to the technical scheme, a PPC processor receives an FPGA program remote updating instruction and sends the updating instruction to a CPLD, after the CPLD verifies that the updating instruction is correct, an FPGA basic version program is loaded into the FPGA from Flash to run, then a Flash high-order address is switched to point to a Flash block space corresponding to a to-be-updated function program version, the FPGA receives a to-be-updated program file from the PPC, after data frame CRC (Cyclic Redundancy Check) is recieved and all program files to be updated are written, all data updated and written by the Flash at this time are read, the data is written into a corresponding Flash address space, the previously written data are read from the Flash, and secondary CRC is carried out, and a check result is reported to the PPC.

Owner:10TH RES INST OF CETC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com