Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

10245results about "Duplex signal operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

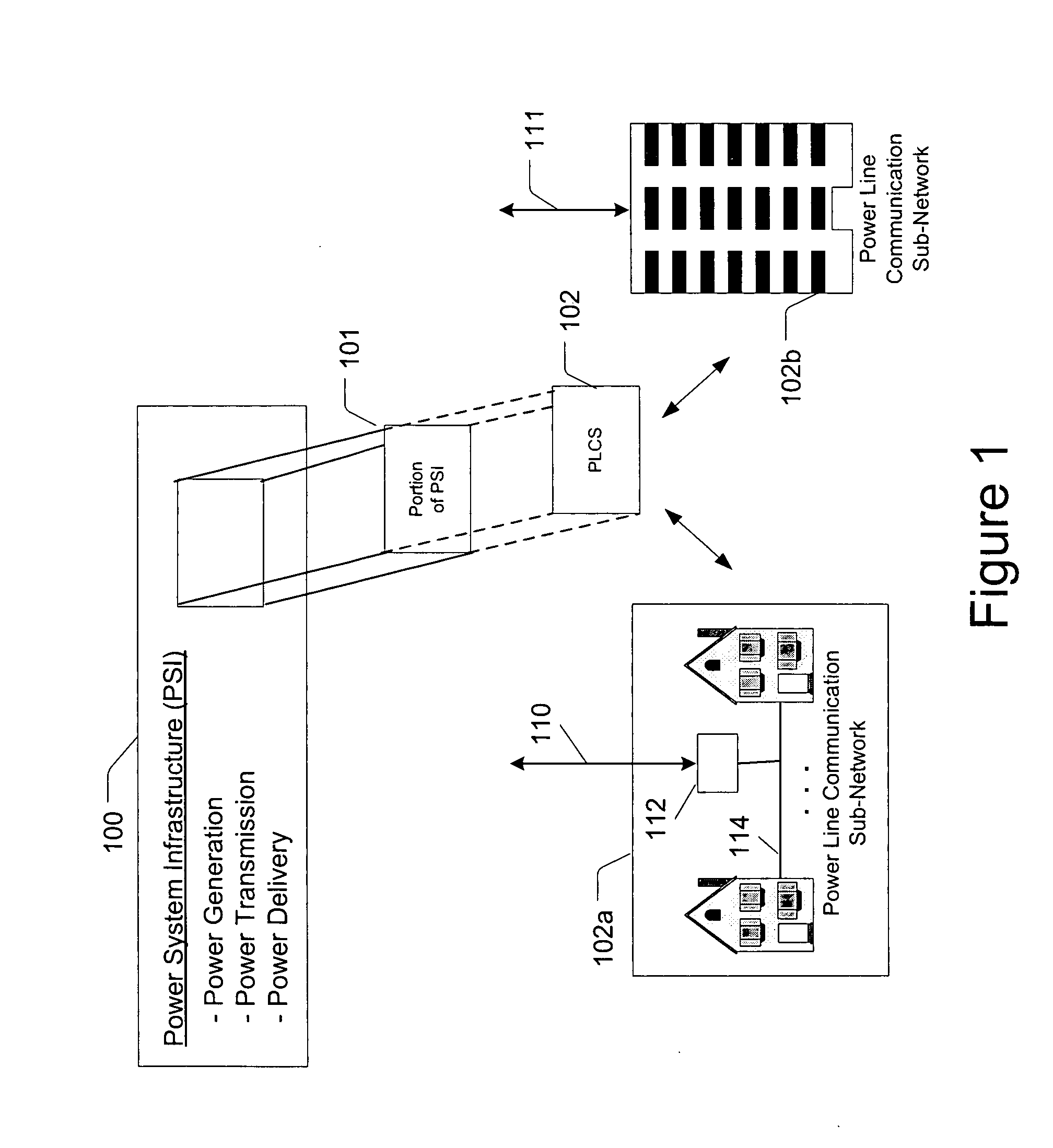

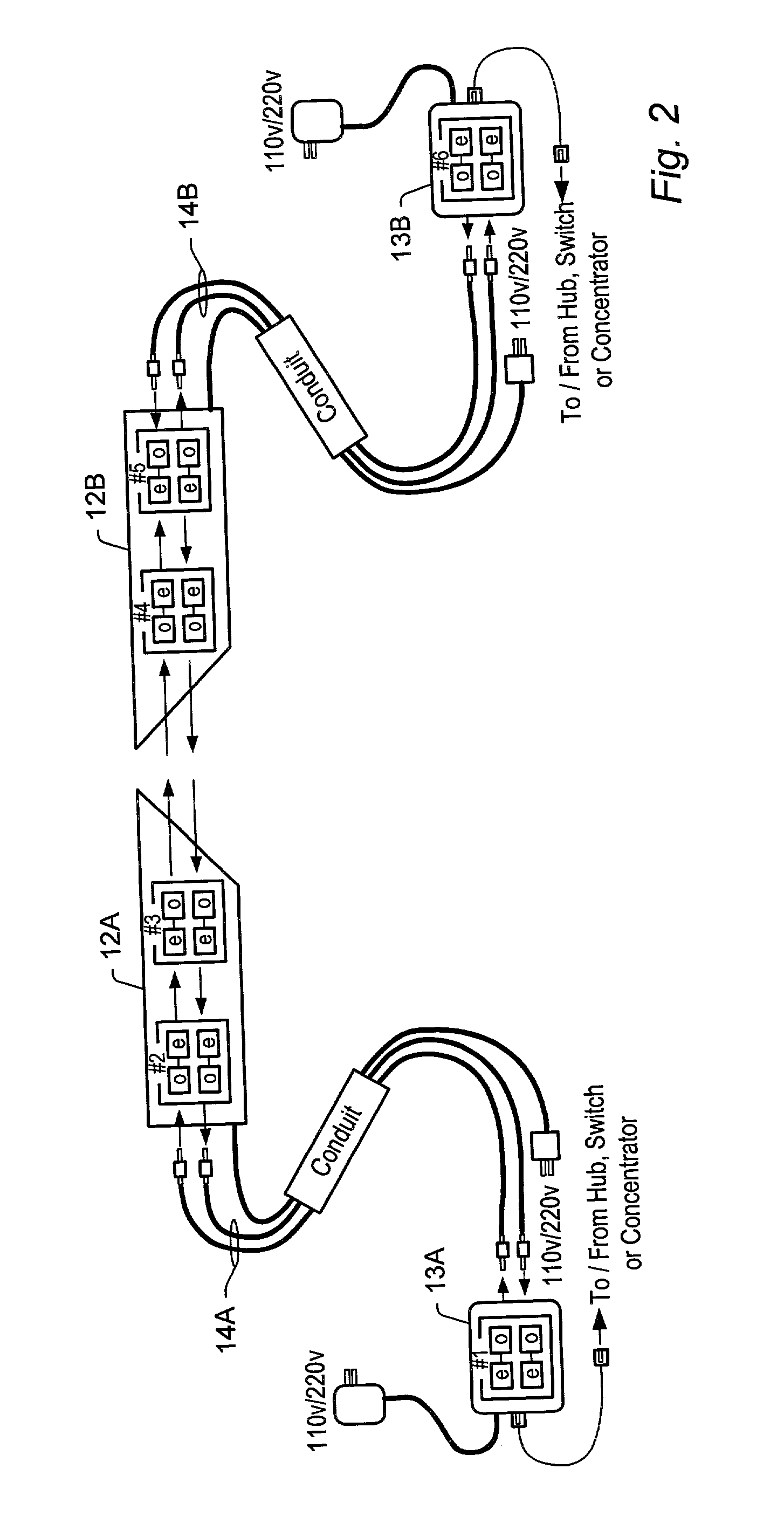

Surface wave power line communications system and method

InactiveUS20050111533A1Electric signal transmission systemsInterconnection arrangementsCommunication interfaceCommunications system

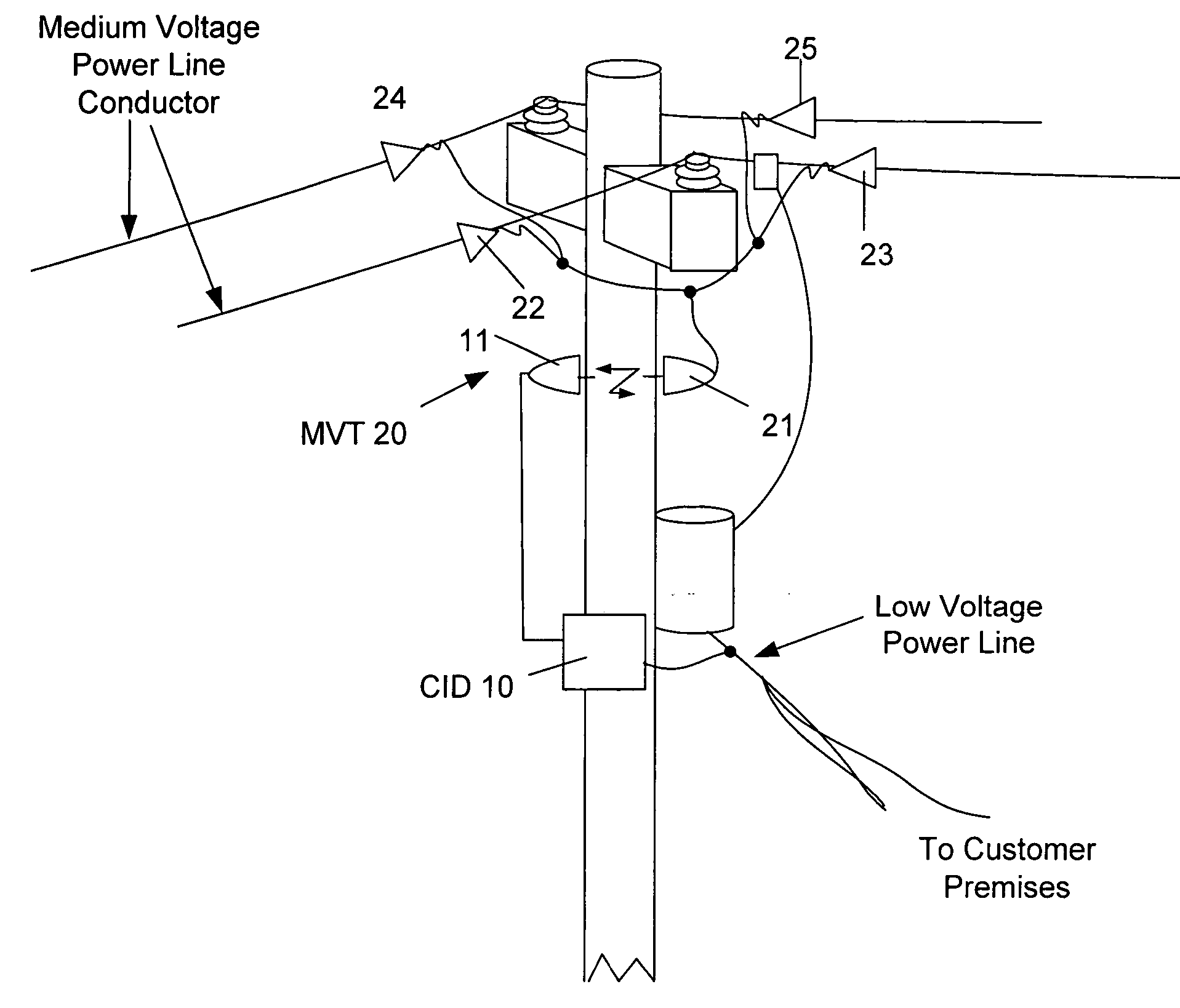

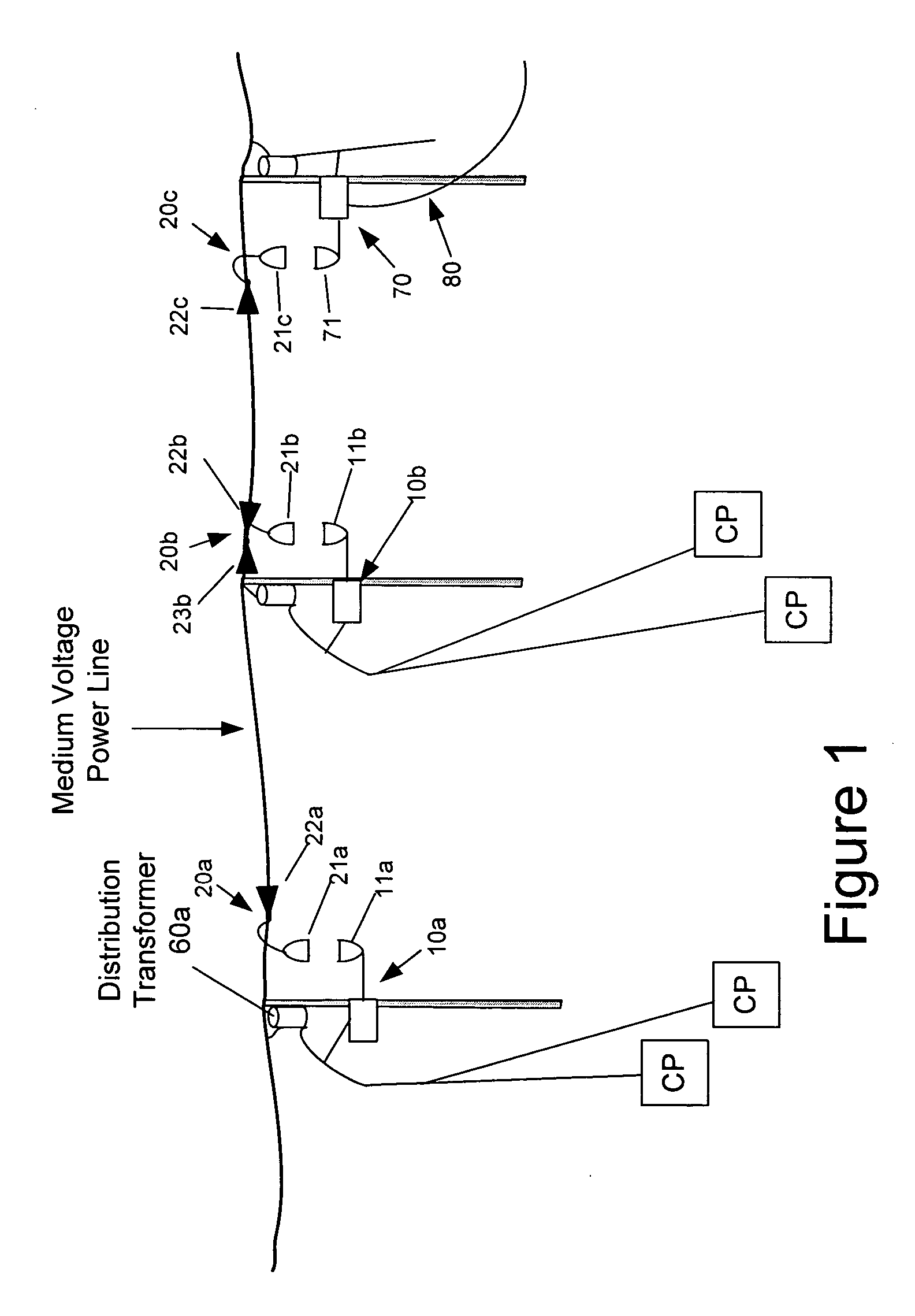

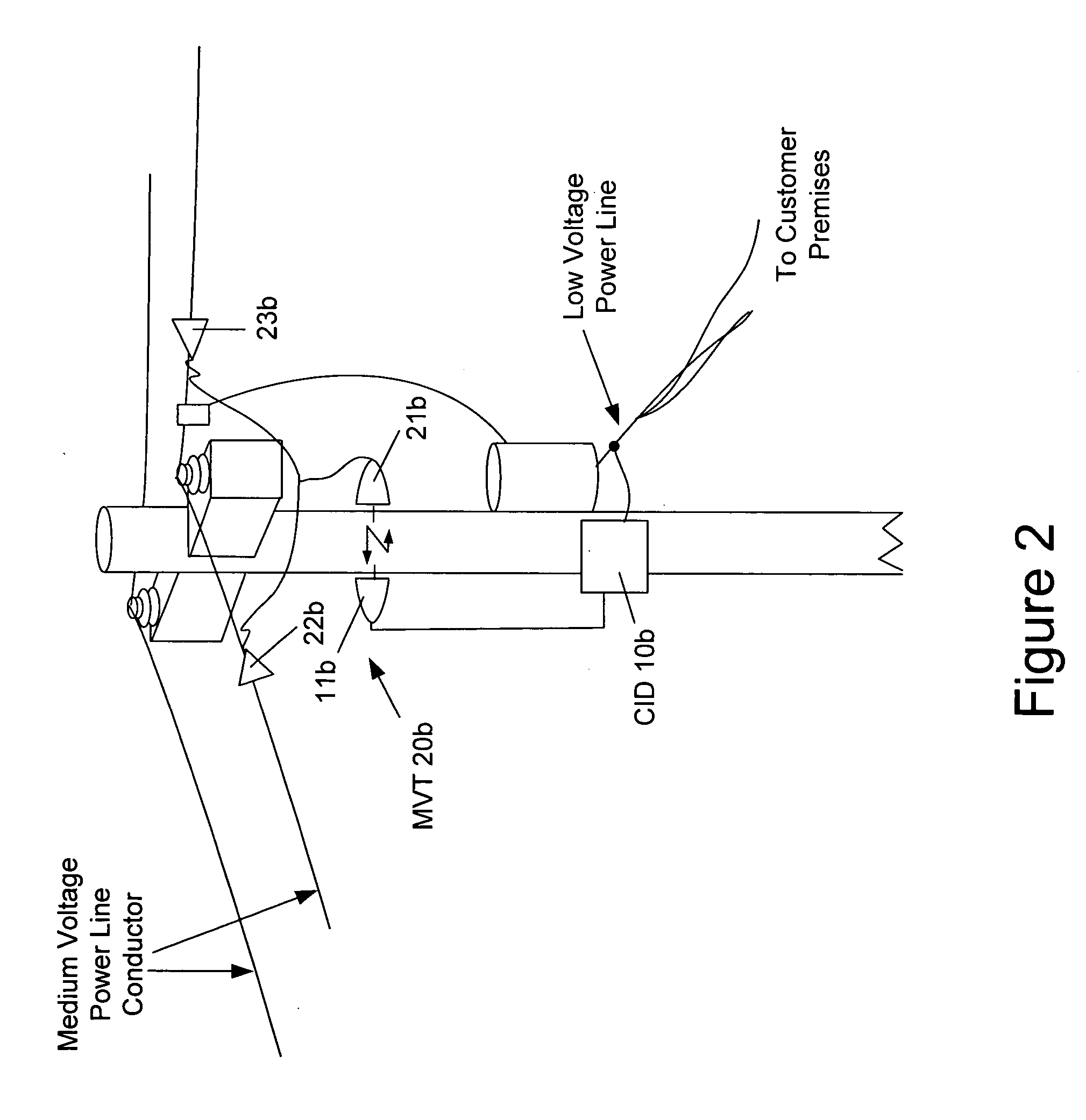

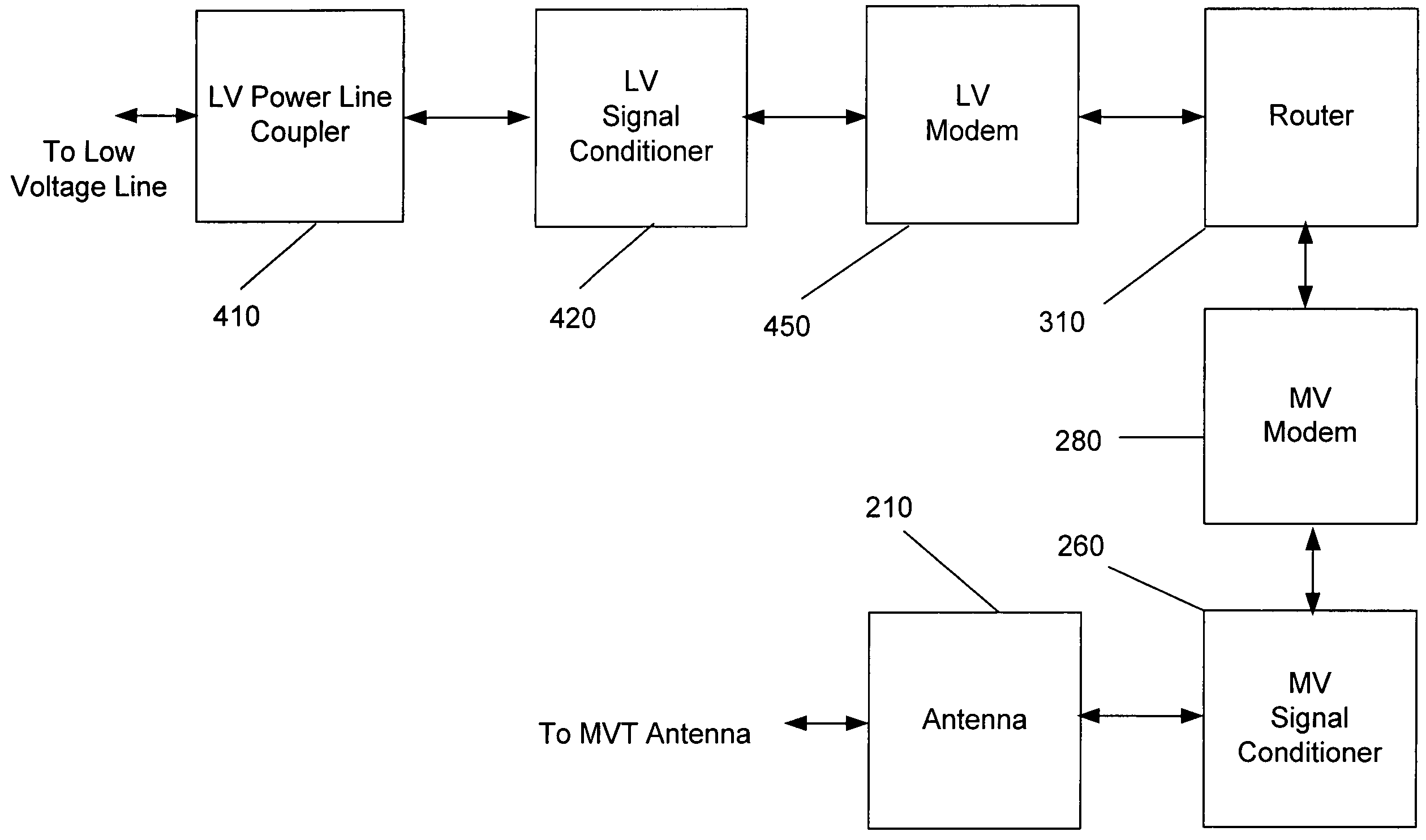

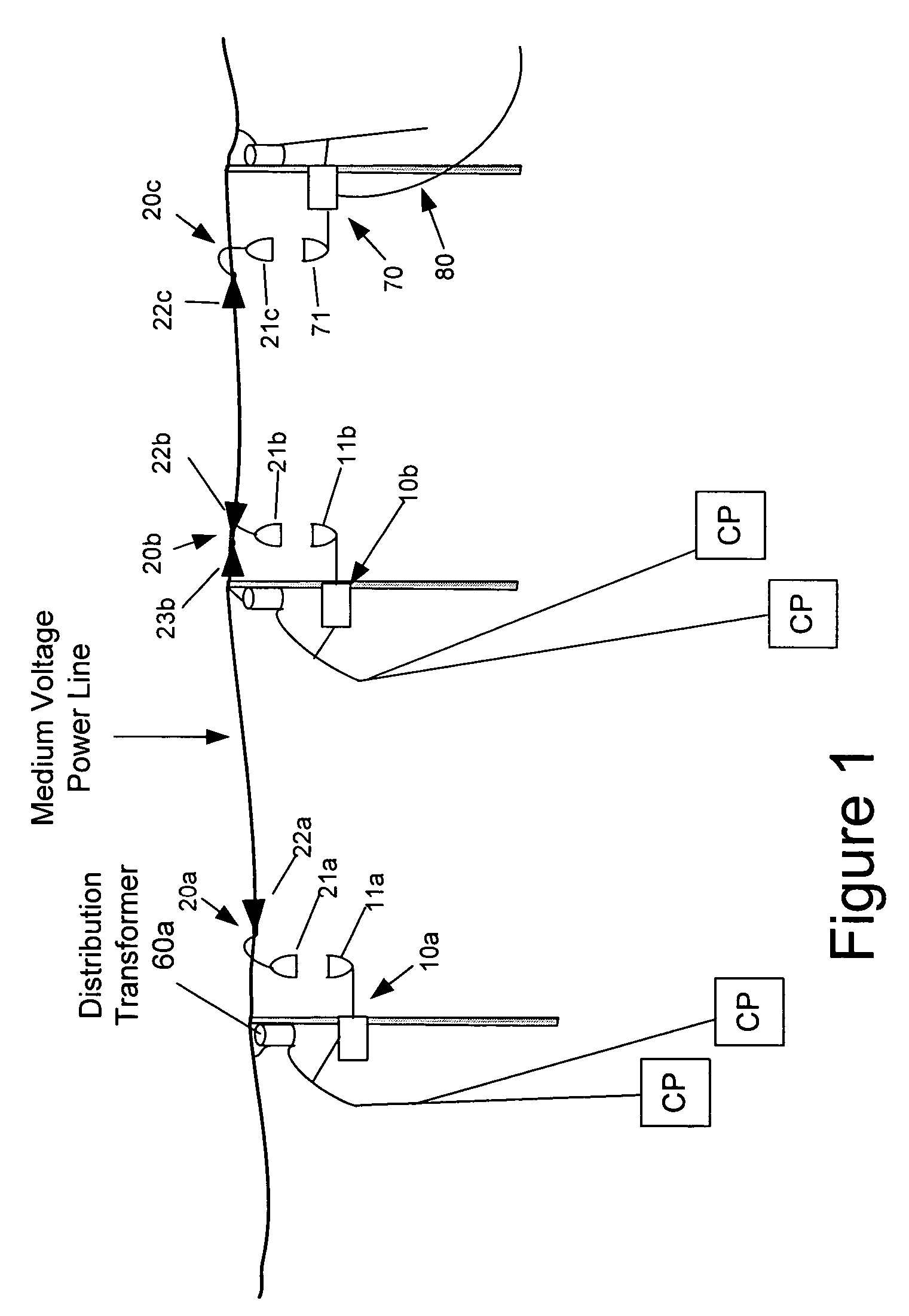

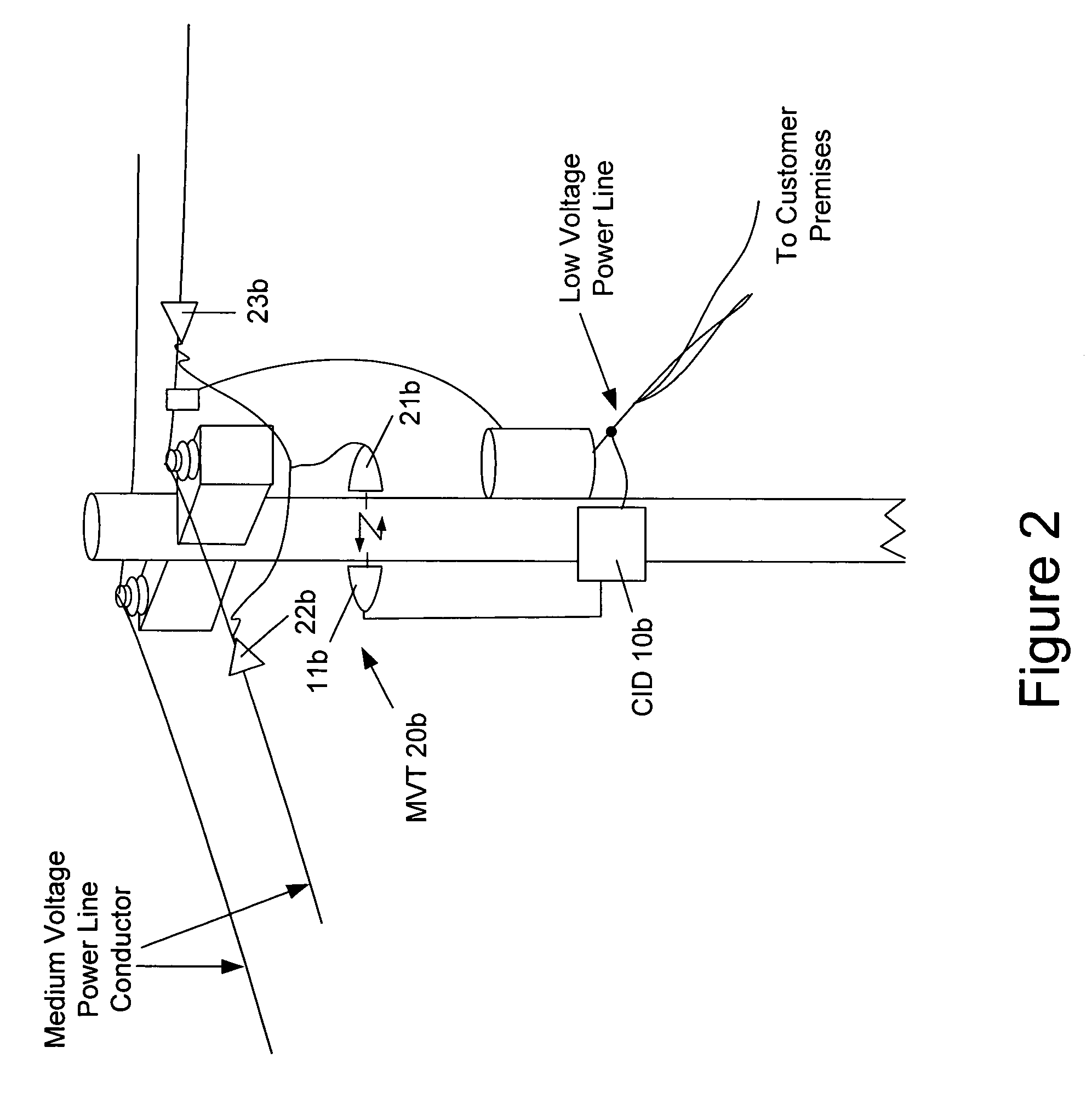

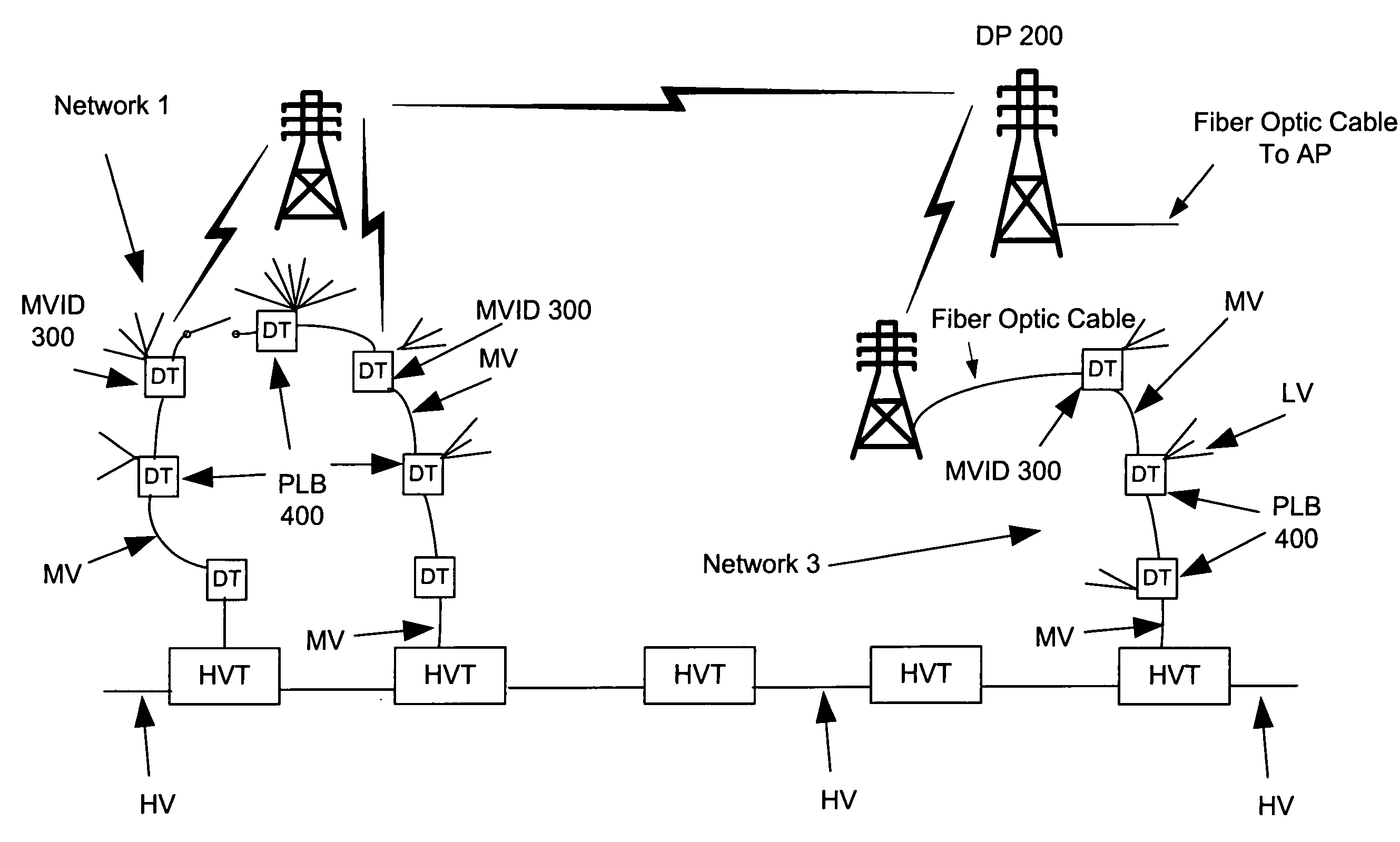

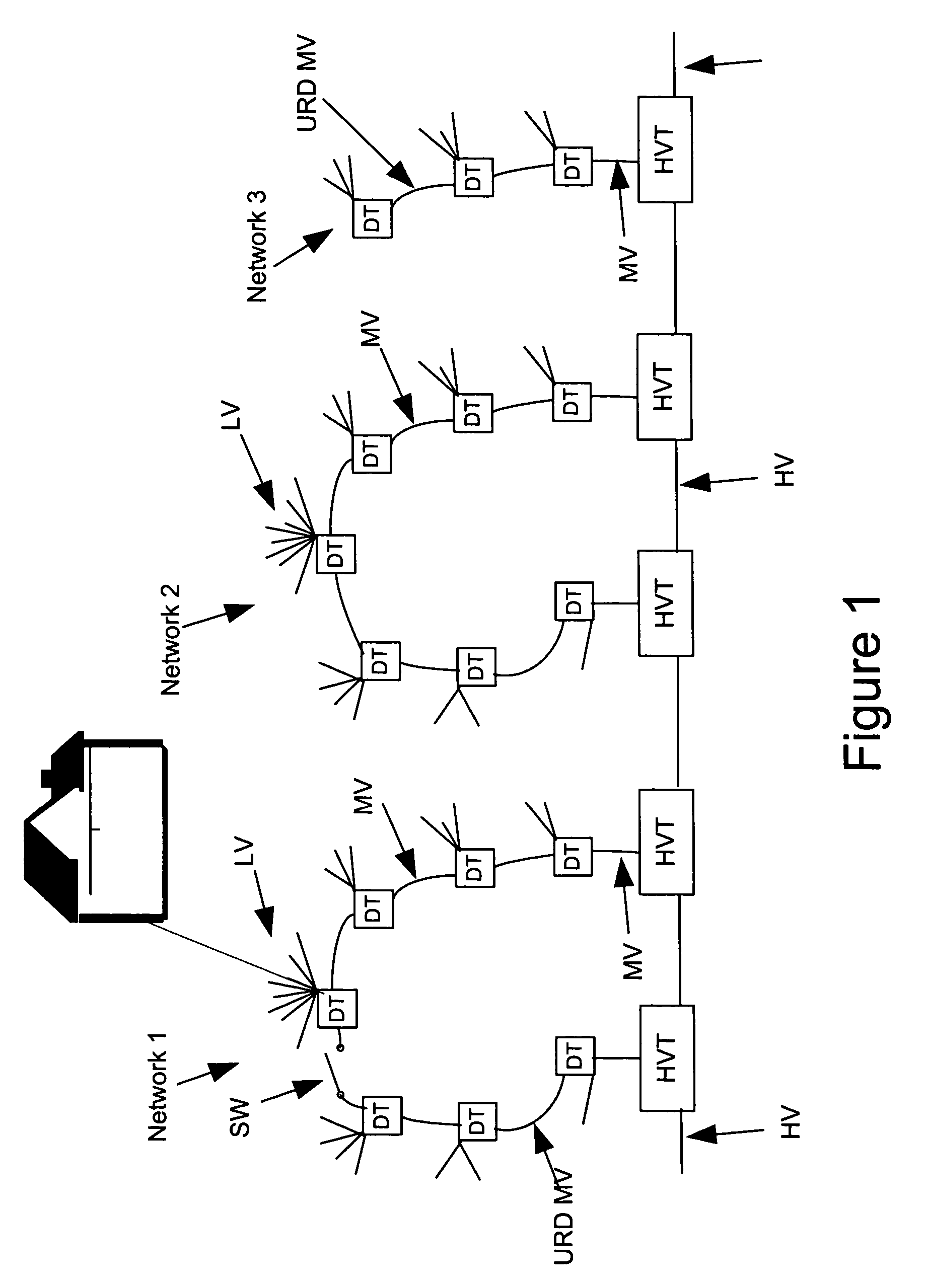

The present invention provides a system for operating a power line communications system that employs surface wave communications and conducted communications. The system is comprised of a plurality of network elements, which may take the form of repeaters, communication interface devices, backhaul devices, medium voltage transducers, distribution points, aggregation points, and others. In one embodiment, surface waves are communicated over the medium voltage power lines and the conducted communications are communicated via the low voltage power lines to and from customer premises.

Owner:CURRENT TECH

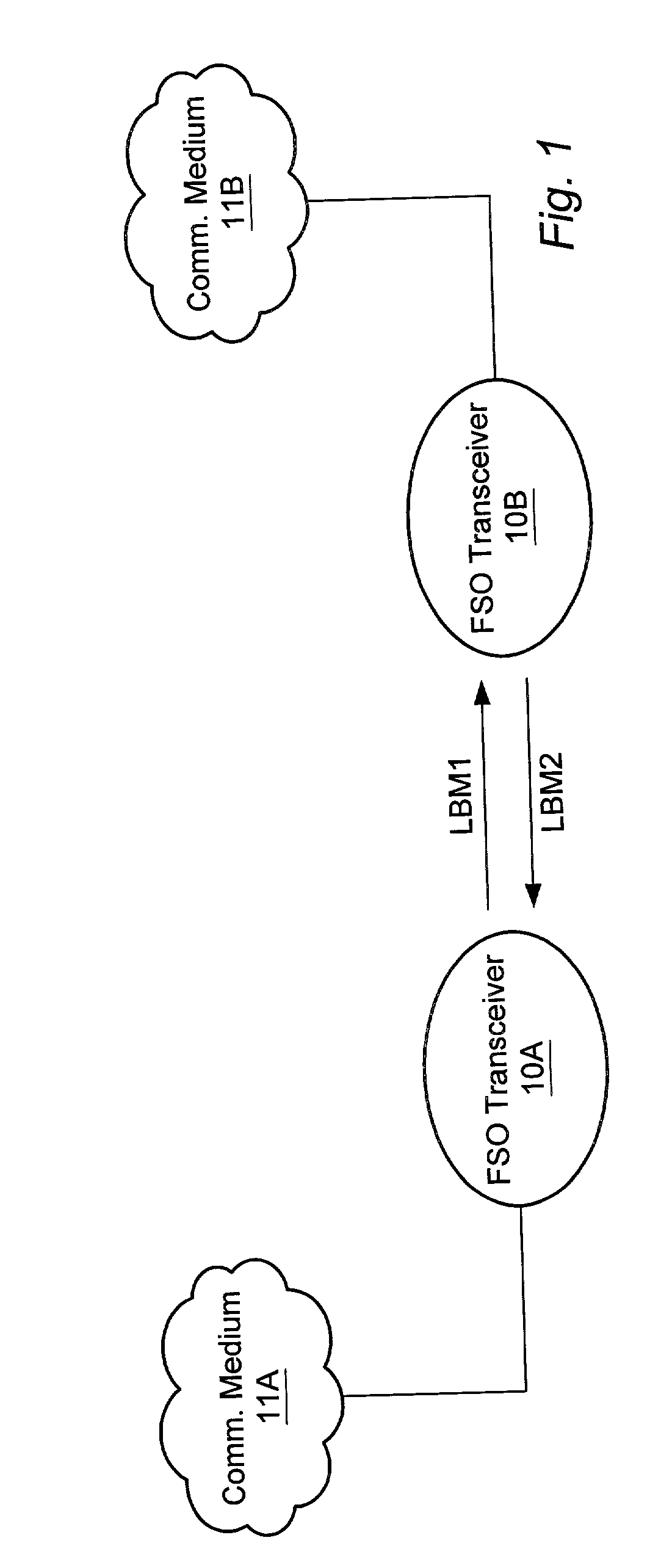

Conductive line communication apparatus and conductive line radar system and method

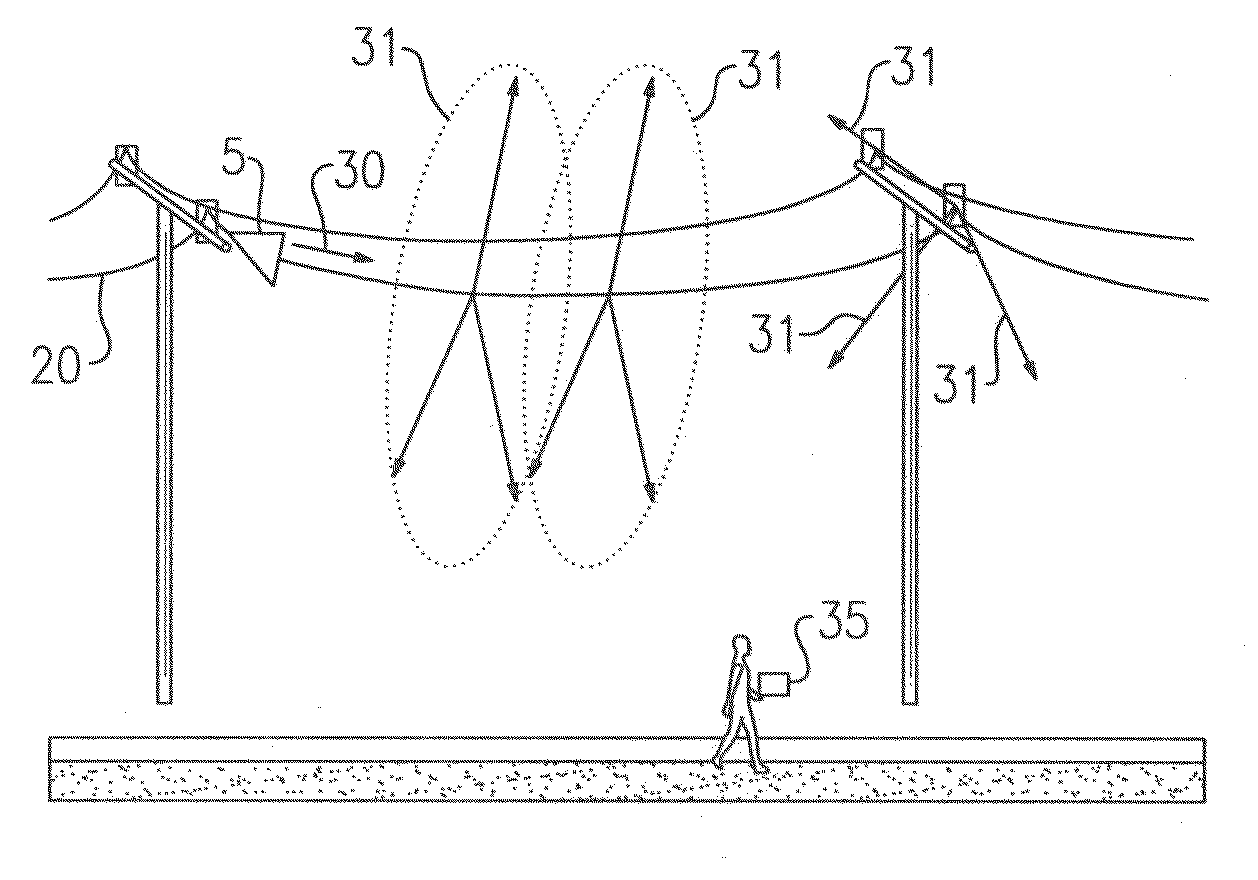

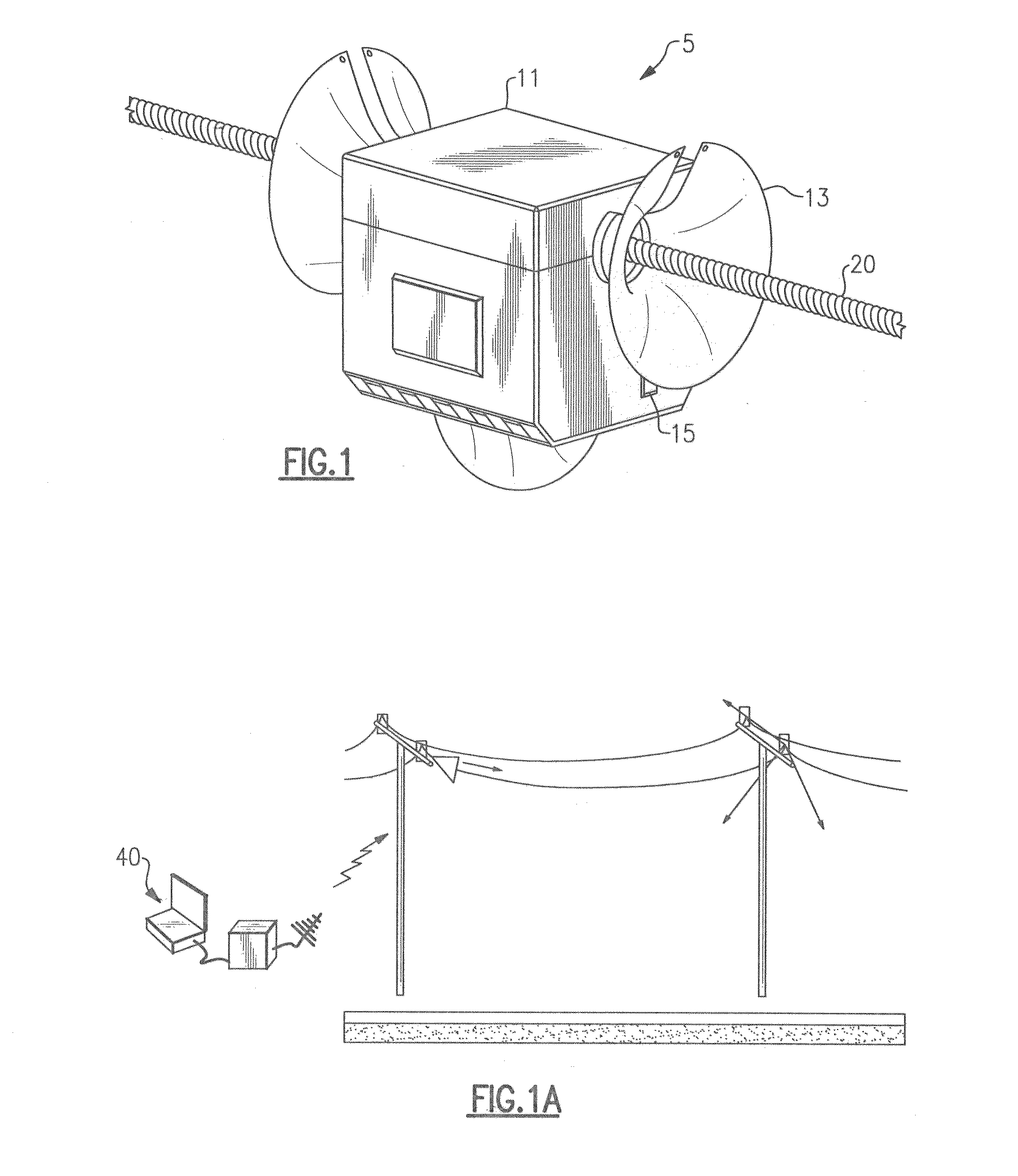

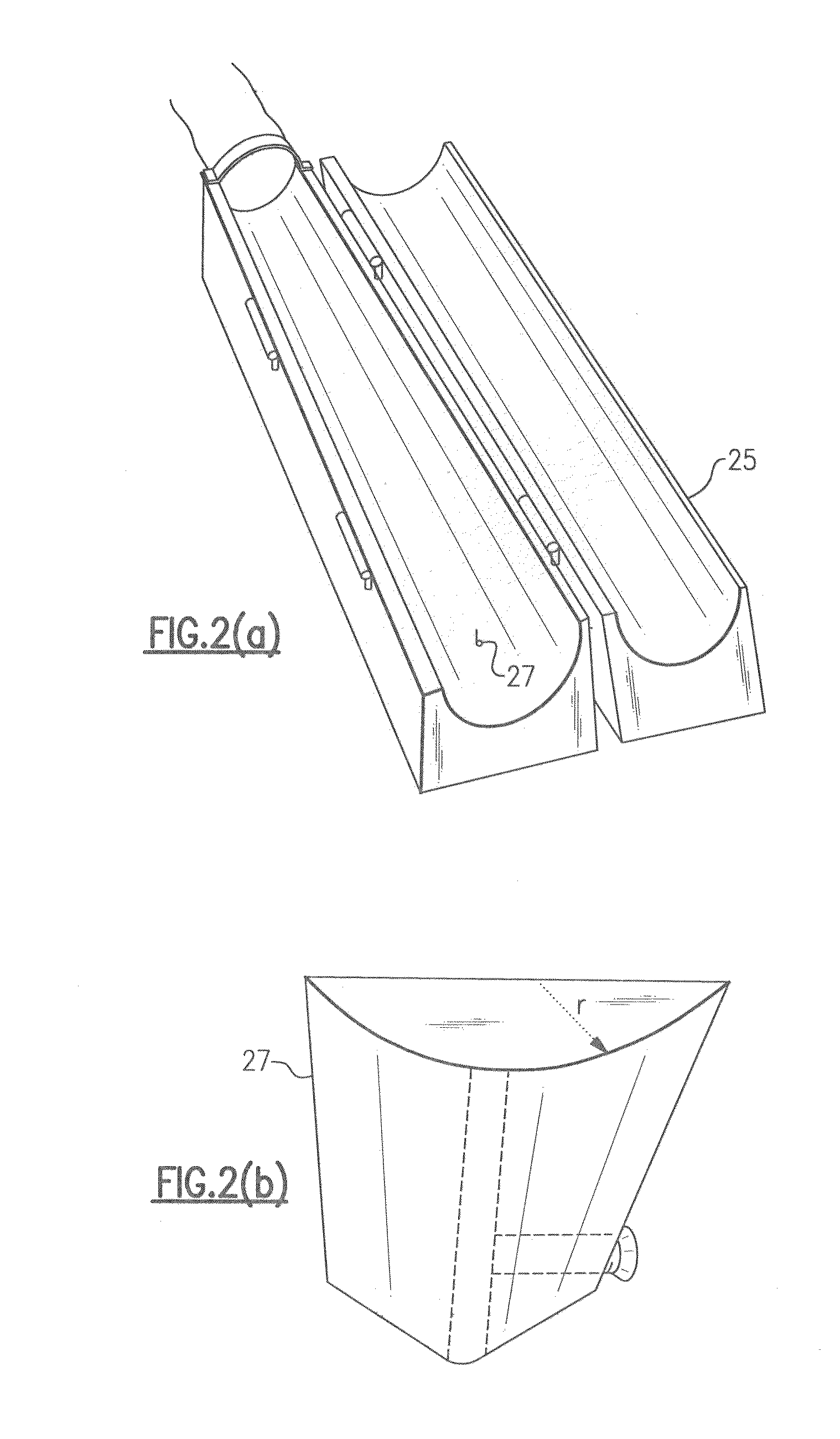

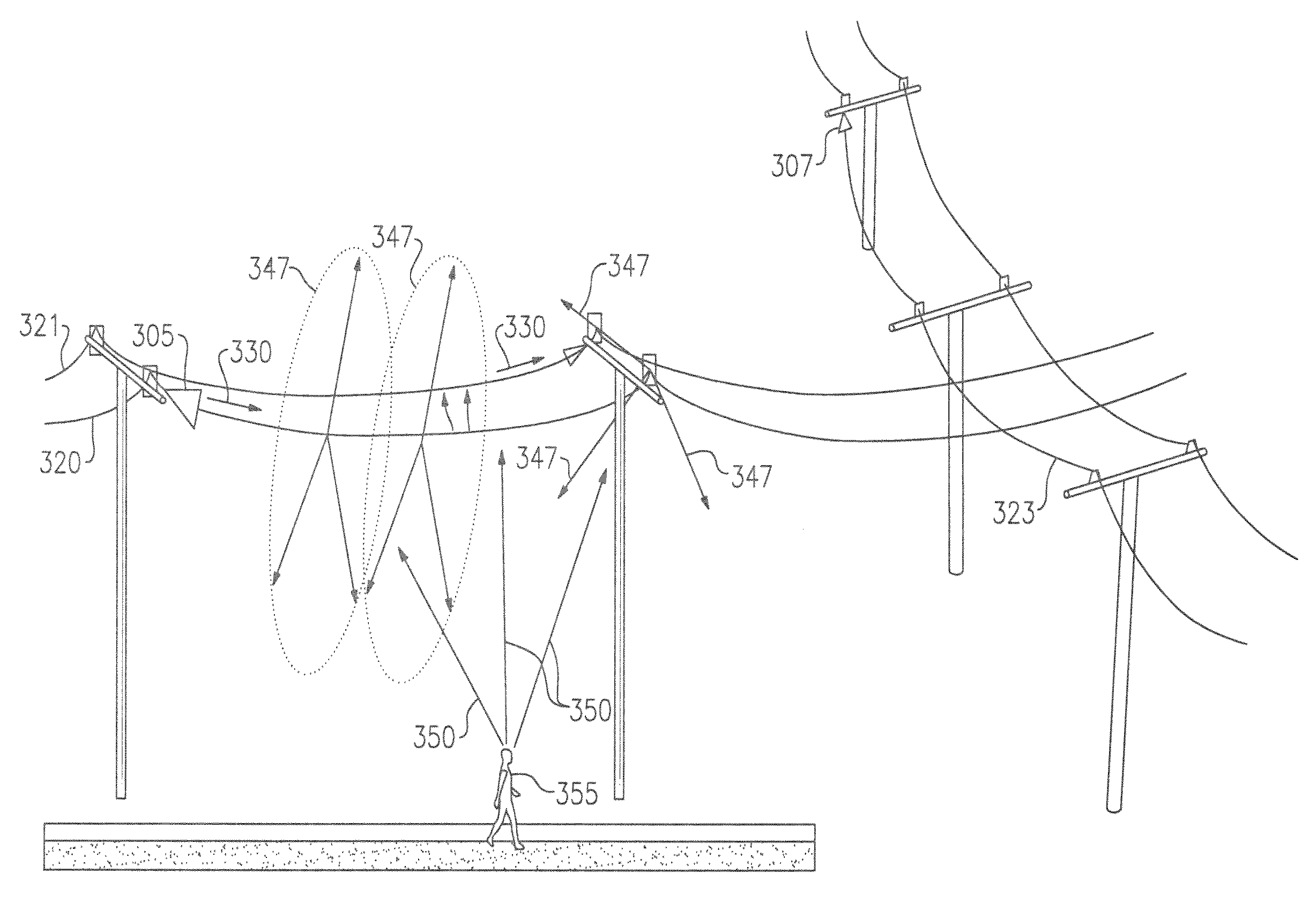

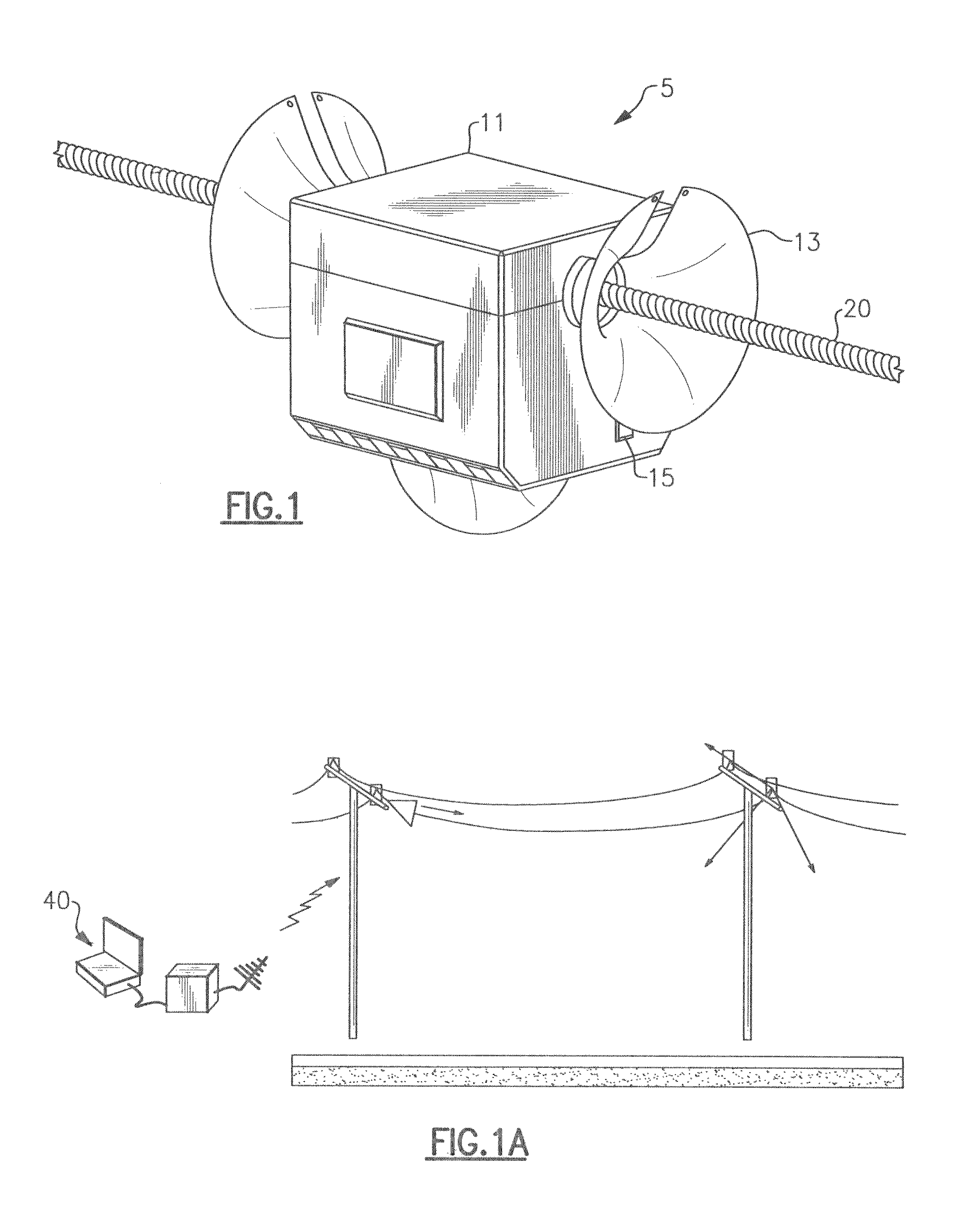

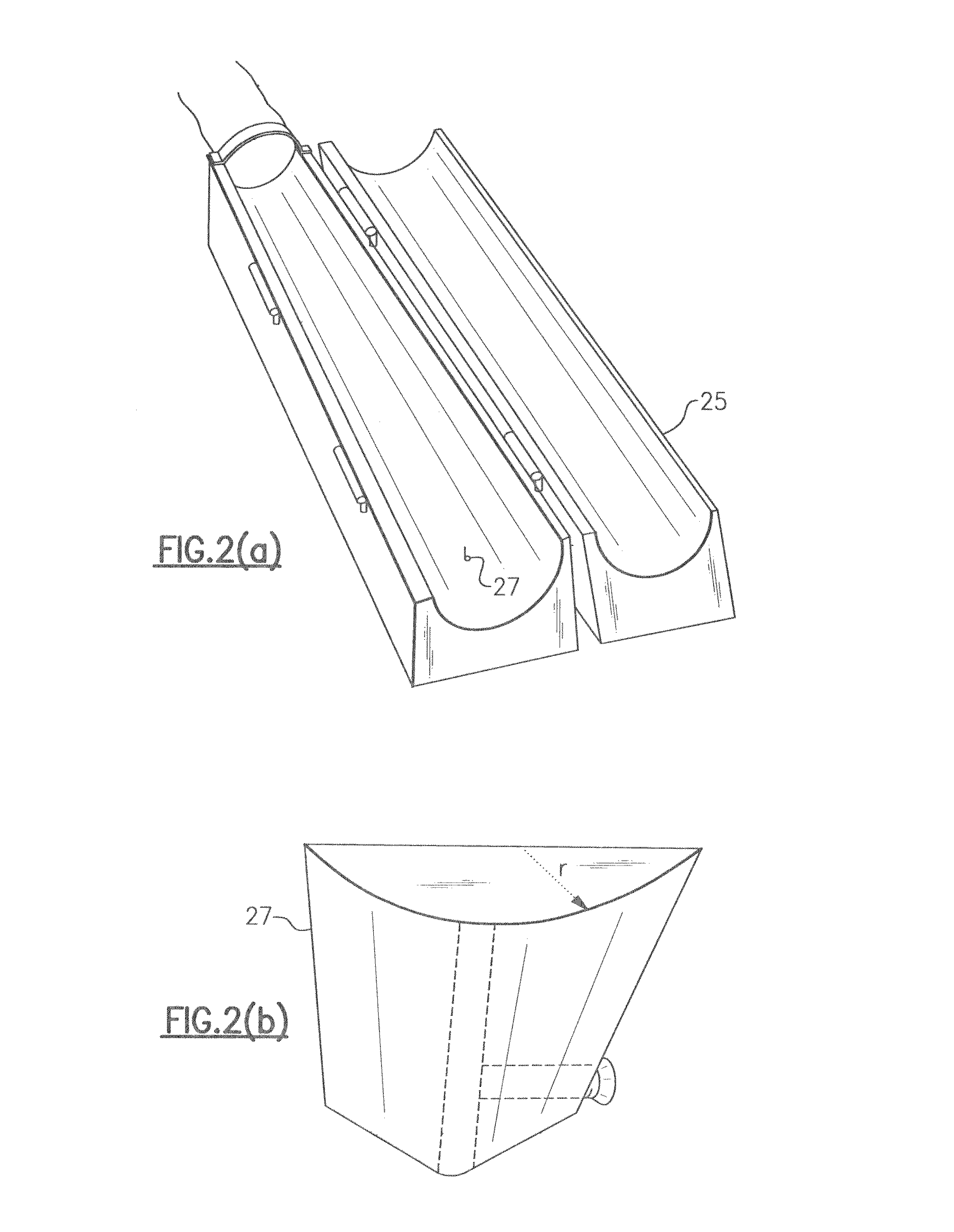

InactiveUS20110187578A1Increase heightAvoid interferenceDuplex signal operationRadio wave reradiation/reflectionRadar systemsTransceiver

A conductive line radar comprising at least one signal surface wave launcher, which comprises a signal surface wave transceiver, which is physically attached to a power line. The signal surface wave transceiver transmits a wave signal along the power line with another signal radiating from the wave signal in a plurality of directions along the power line. The at least one signal surface wave transceiver receives reflected signals from a target within a distance of the power line. The at least one signal surface wave launcher includes at least one RF communications transceiver and can be inductively powered from the power line.

Owner:SENSIS CORPORATION

Conductive line communication apparatus and conductive line radar system and method

InactiveUS8159385B2Eliminate the effects ofIncrease the areaDuplex signal operationRadio wave reradiation/reflectionTransceiverRadar systems

A conductive line radar comprising at least one signal surface wave launcher, which comprises a signal surface wave transceiver, which is physically attached to a power line. The signal surface wave transceiver transmits a wave signal along the power line with another signal radiating from the wave signal in a plurality of directions along the power line. The at least one signal surface wave transceiver receives reflected signals from a target within a distance of the power line. The at least one signal surface wave launcher includes at least one RF communications transceiver and can be inductively powered from the power line.

Owner:SENSIS CORPORATION

Surface wave power line communications system and method

InactiveUS7280033B2Electric signal transmission systemsInterconnection arrangementsCommunication interfaceCommunications system

The present invention provides a system for operating a power line communications system that employs surface wave communications and conducted communications. The system is comprised of a plurality of network elements, which may take the form of repeaters, communication interface devices, backhaul devices, medium voltage transducers, distribution points, aggregation points, and others. In one embodiment, surface waves are communicated over the medium voltage power lines and the conducted communications are communicated via the low voltage power lines to and from customer premises.

Owner:CURRENT TECH

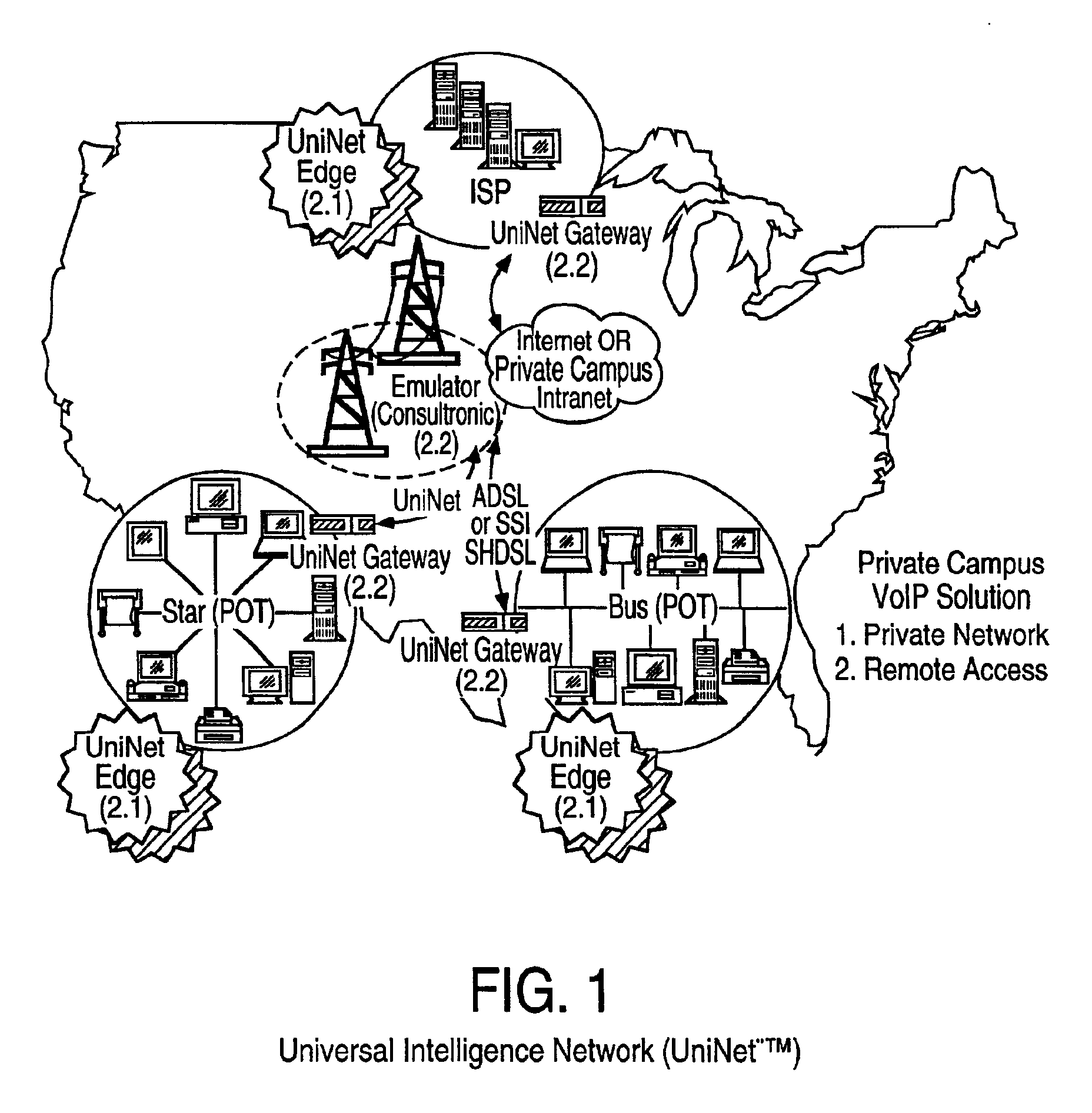

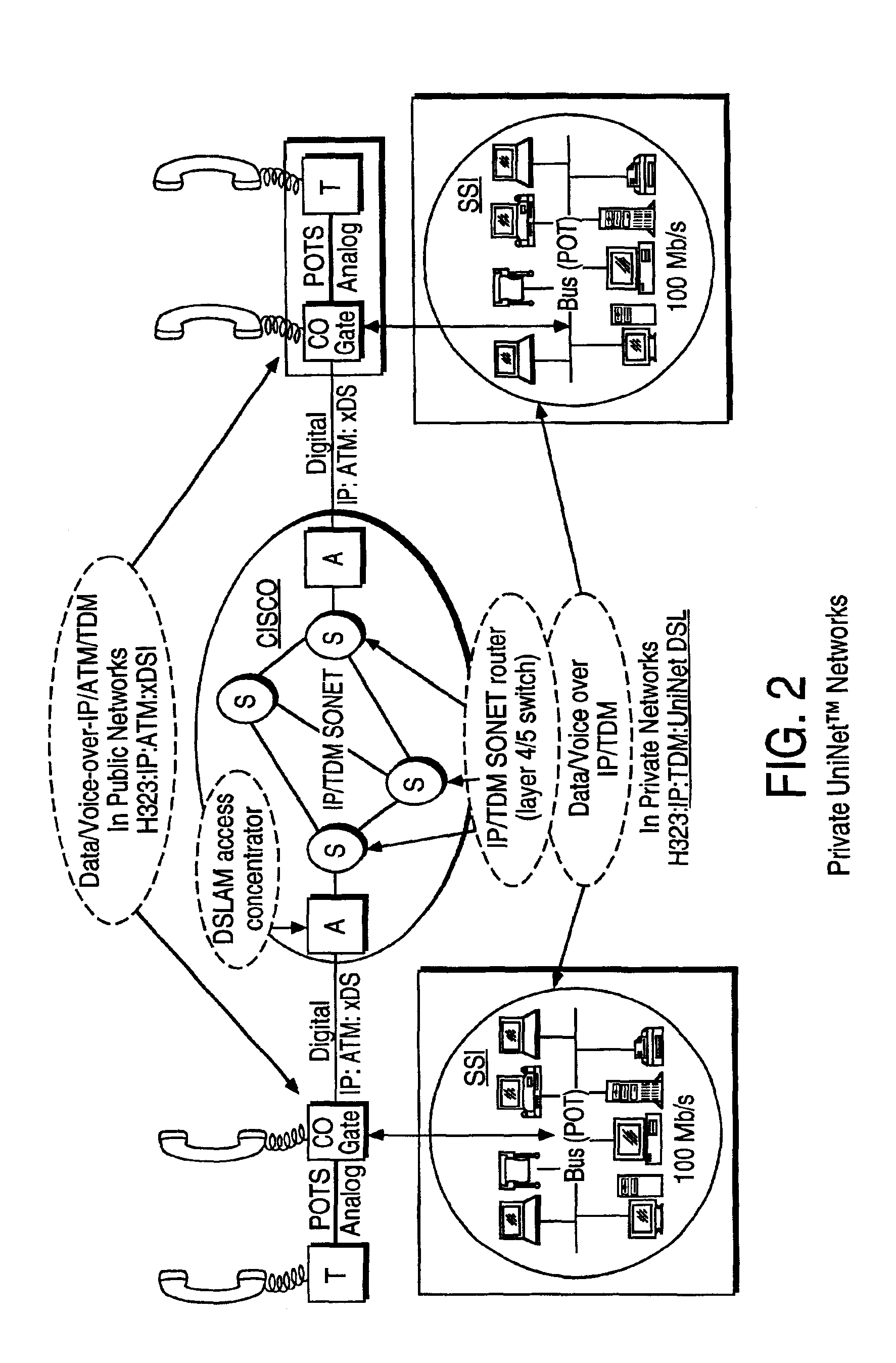

Channel equalization system and method

InactiveUS6904110B2Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsFiberEngineering

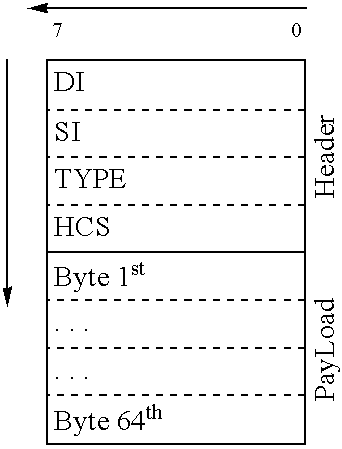

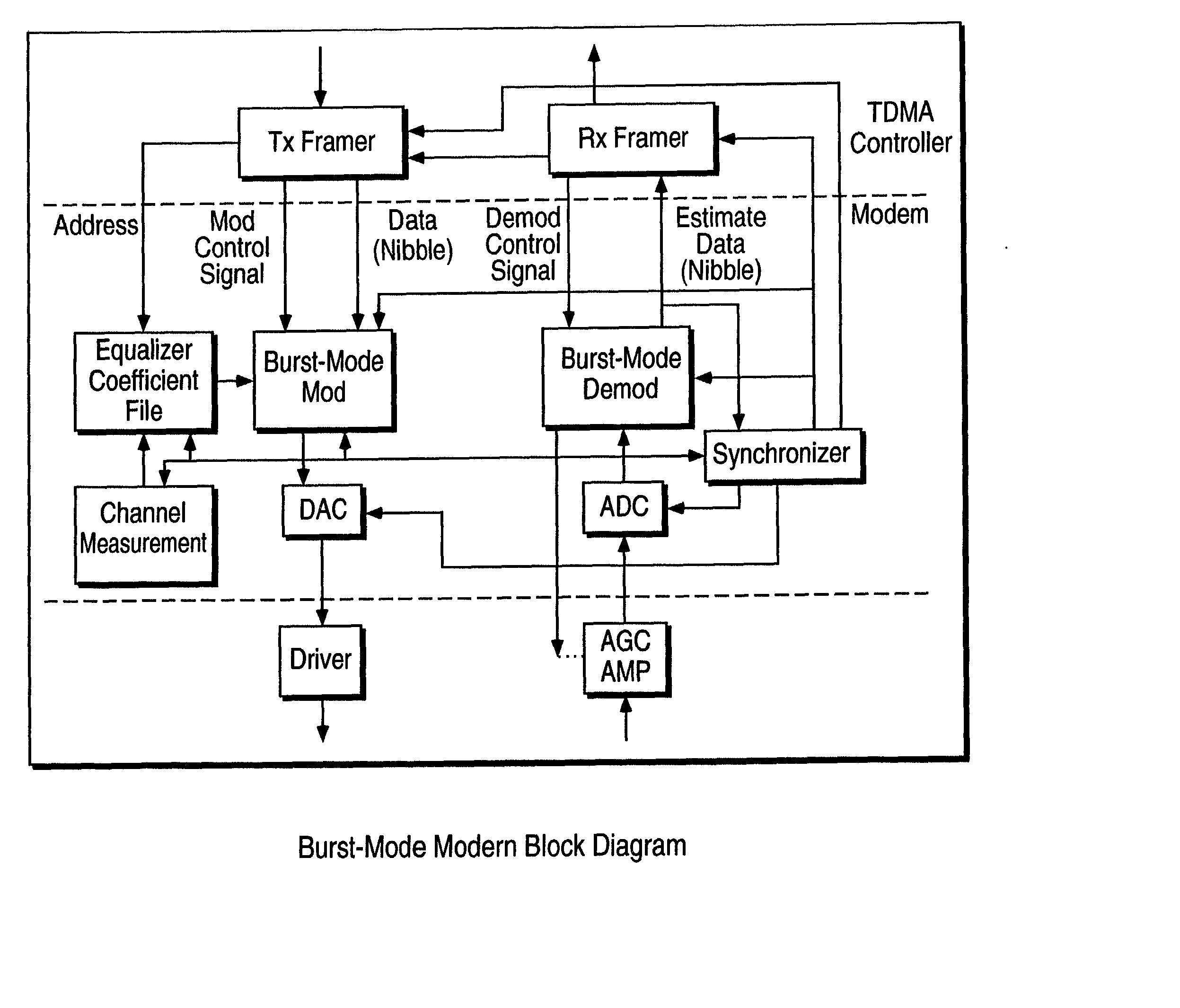

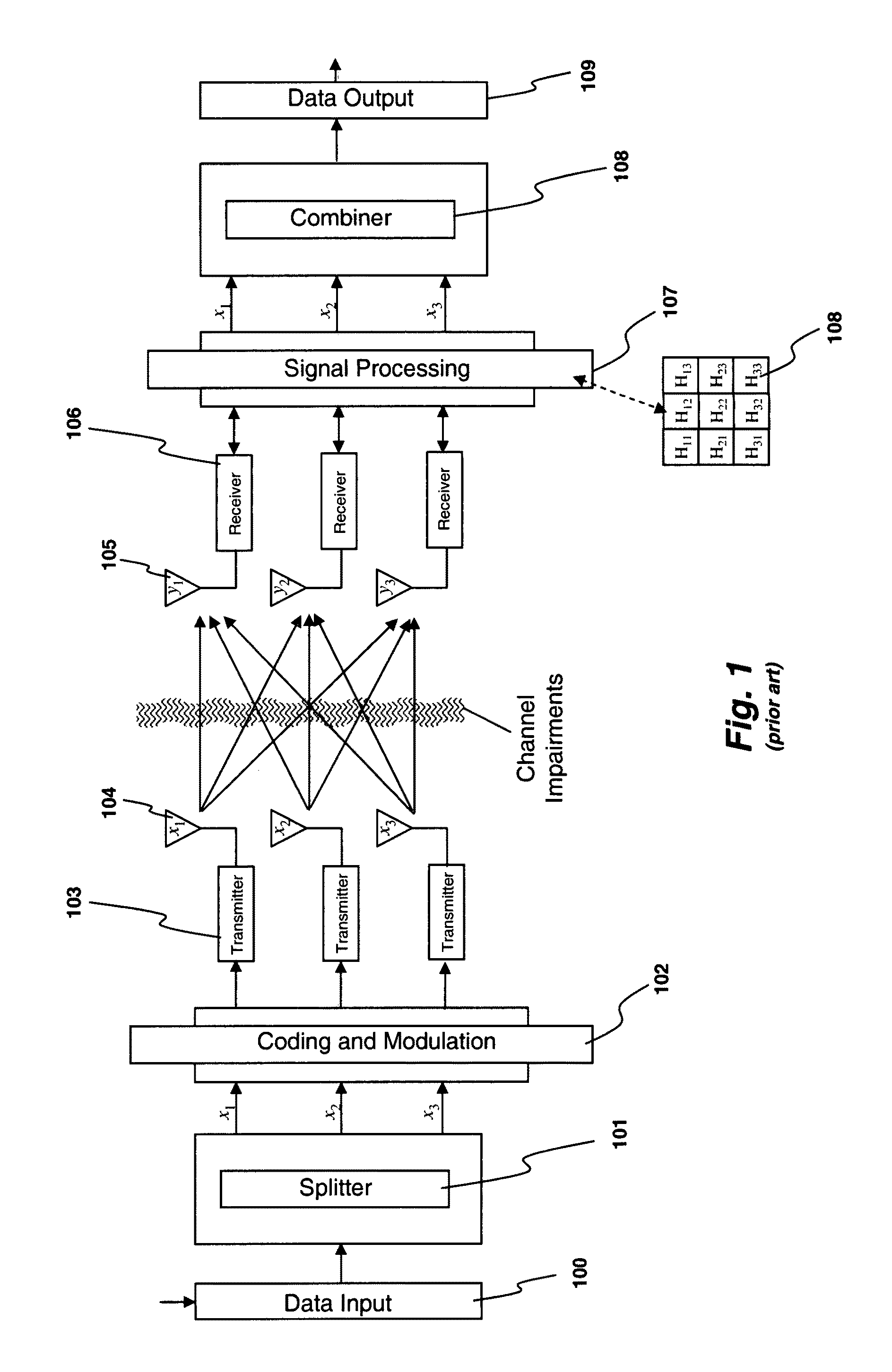

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

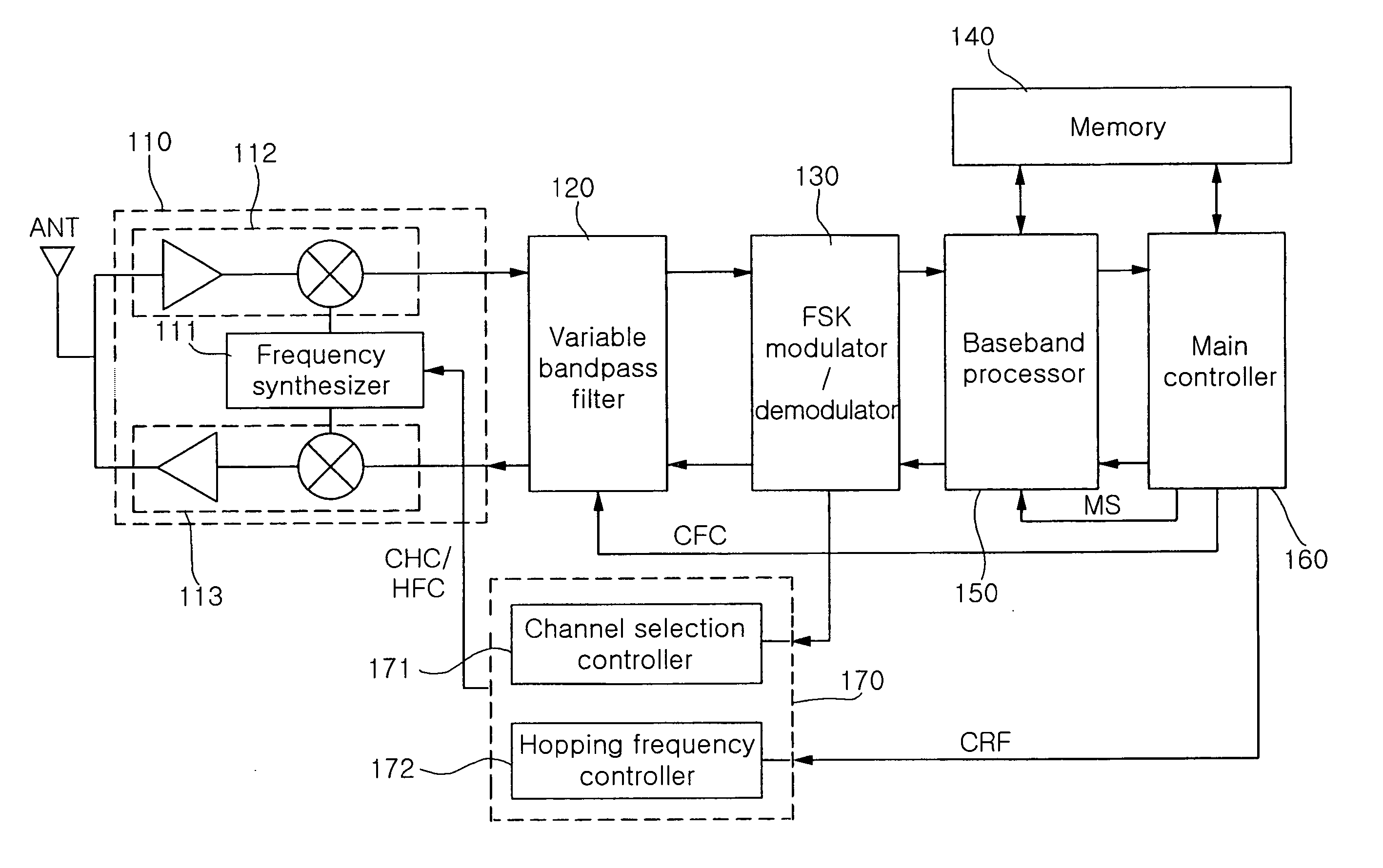

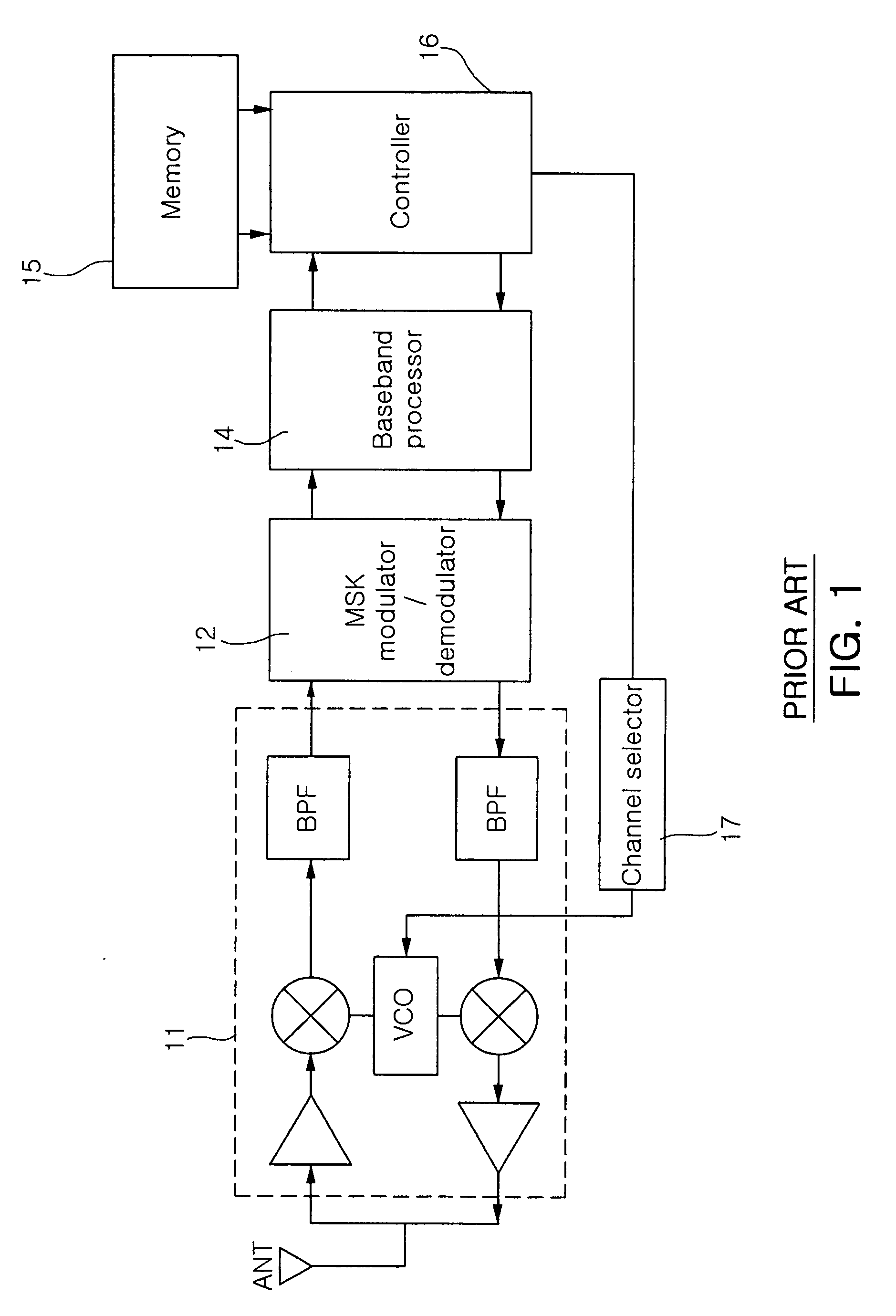

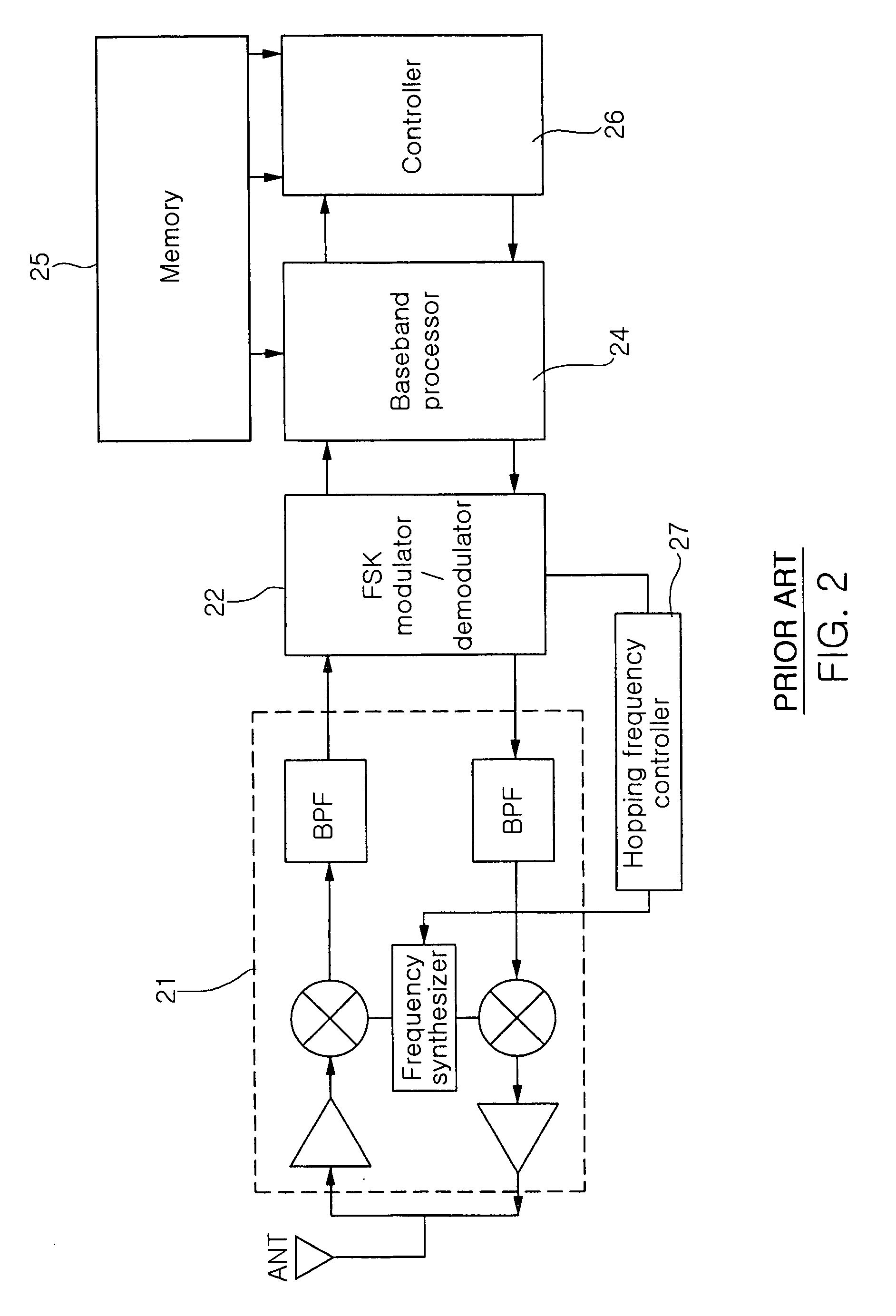

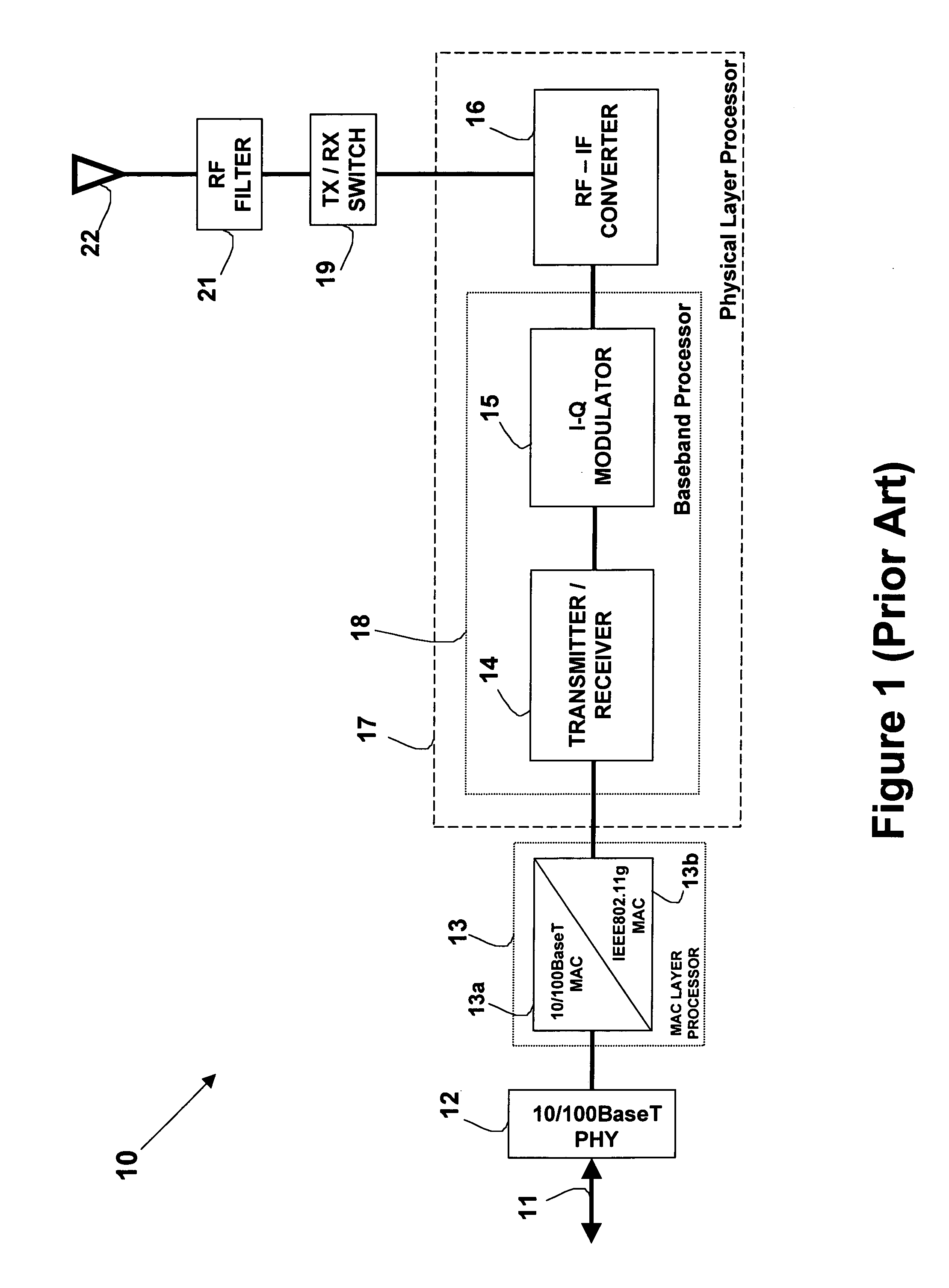

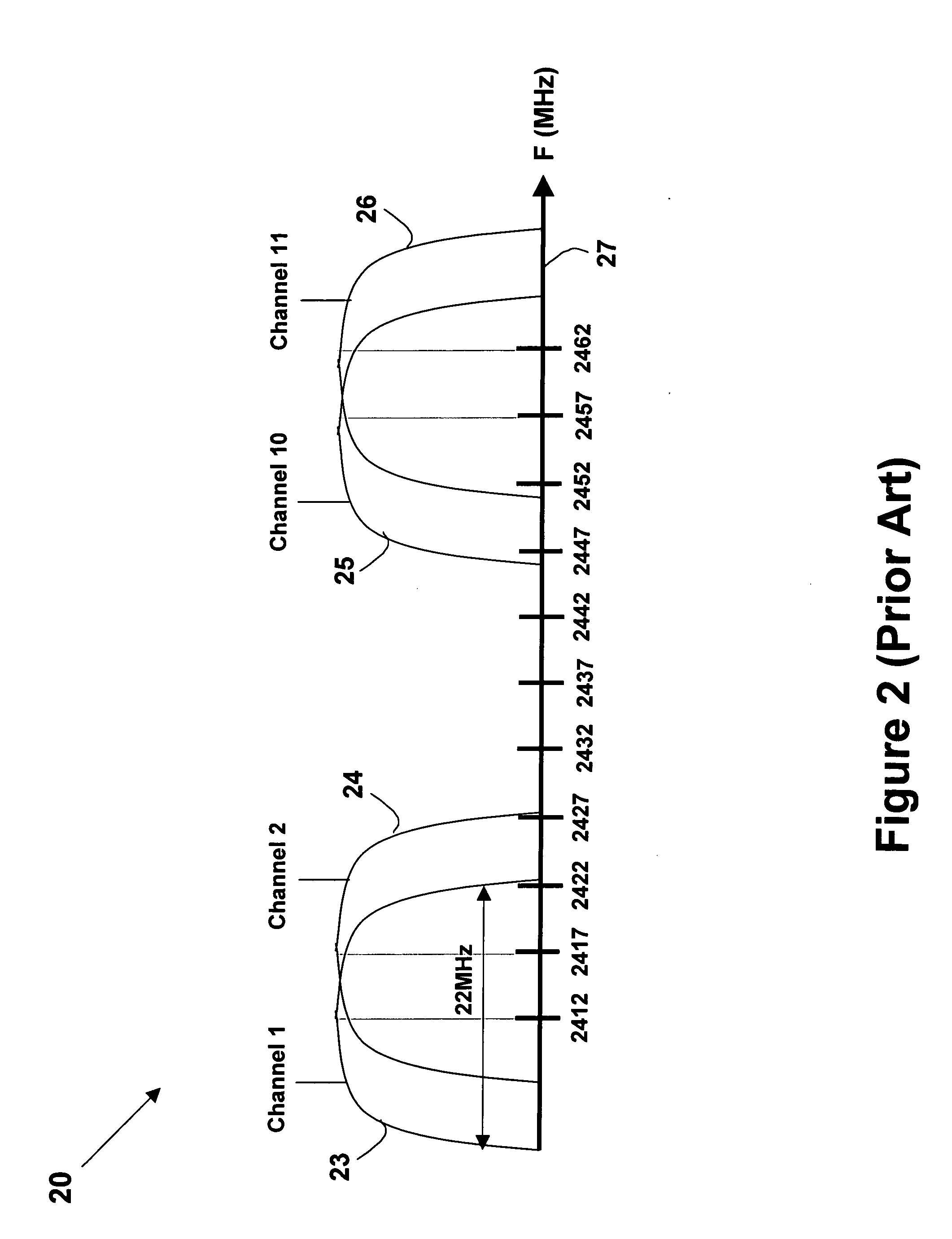

Transceiver for zigbee and bluetooth communications

InactiveUS20060193375A1Multiple modulation transmitter/receiver arrangementsSewerage structuresBandpass filteringTransceiver

The invention provides a transceiver for Zigbee and Bluetooth communications integrating a Zigbee transceiver and a Bluetooth transceiver. The transceiver includes an RF processor 110, a variable bandpass filter 120, an FSK modulator / demodulator 130, a memory 140, a baseband processor 150, a main controller 160, and a channel selection / frequency hopping controller 170. The invention integrates the Zigbee transceiver and the Bluetooth transceiver so as to partially make common use of a higher layer application and a physical layer of the Zigbee transceiver and the Bluetooth transceiver. As a result, the invention has the advantage of functioning as a transceiver for Zigbee and Bluetooth communications, without causing a significant increase in size and unit price.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

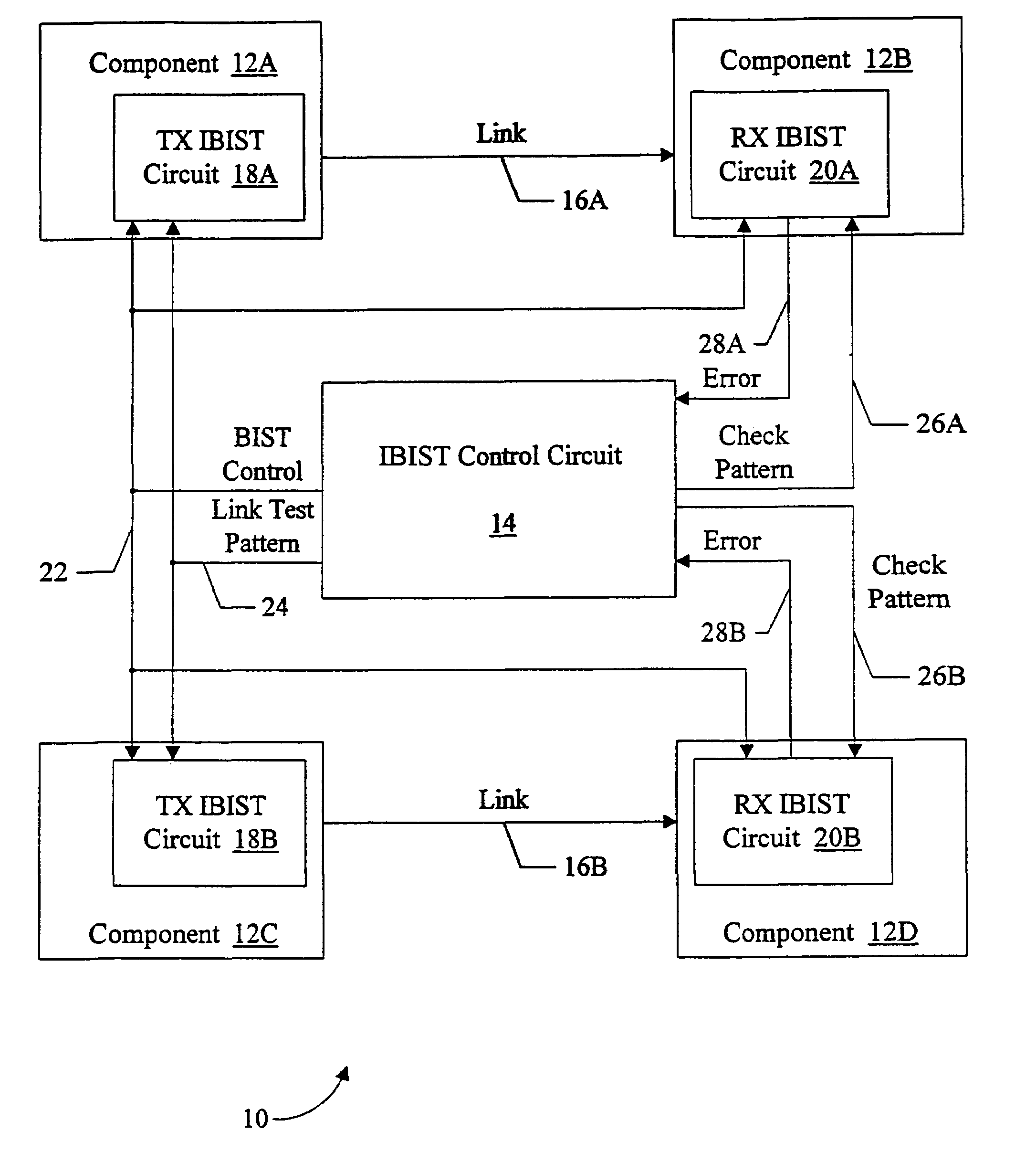

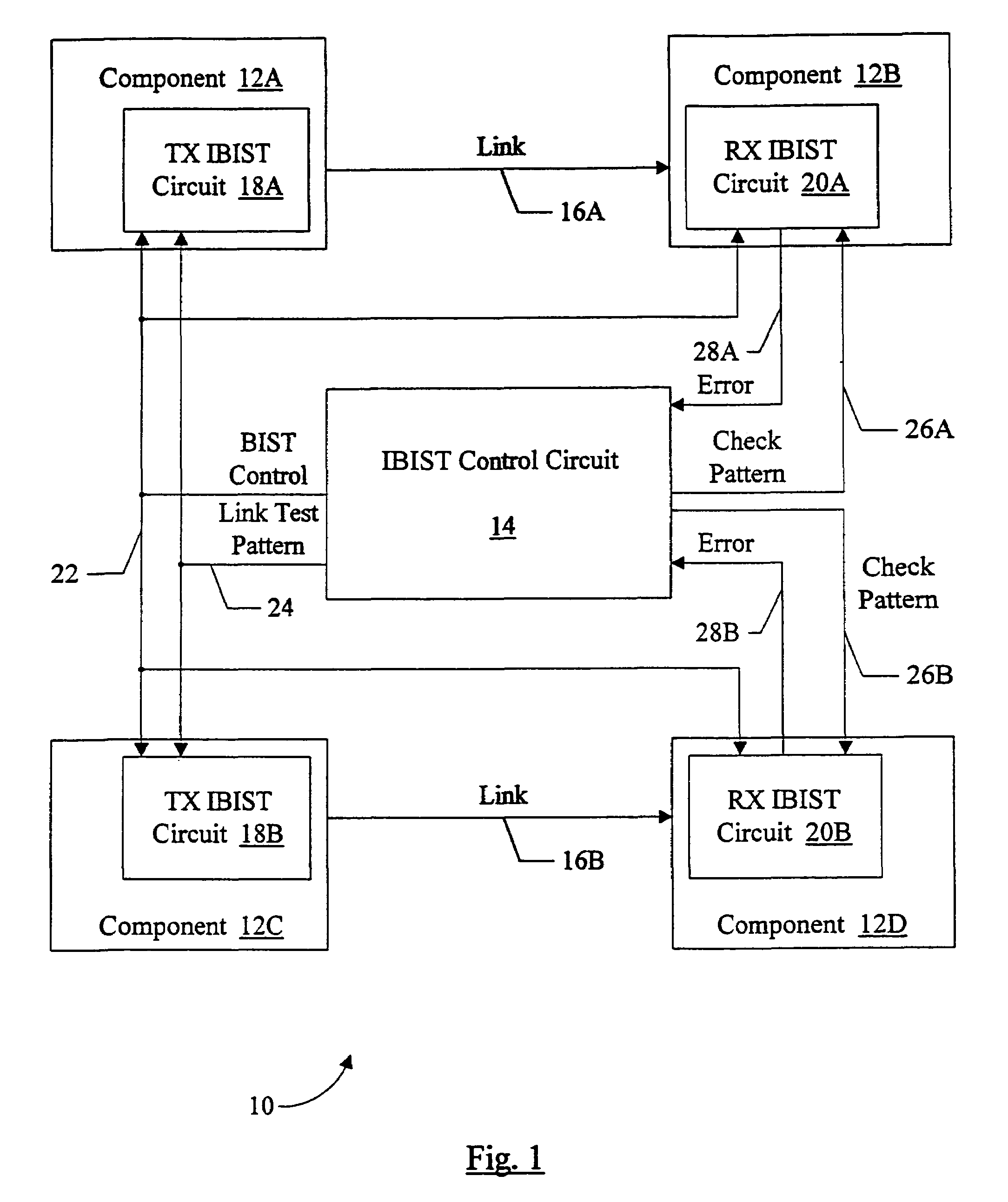

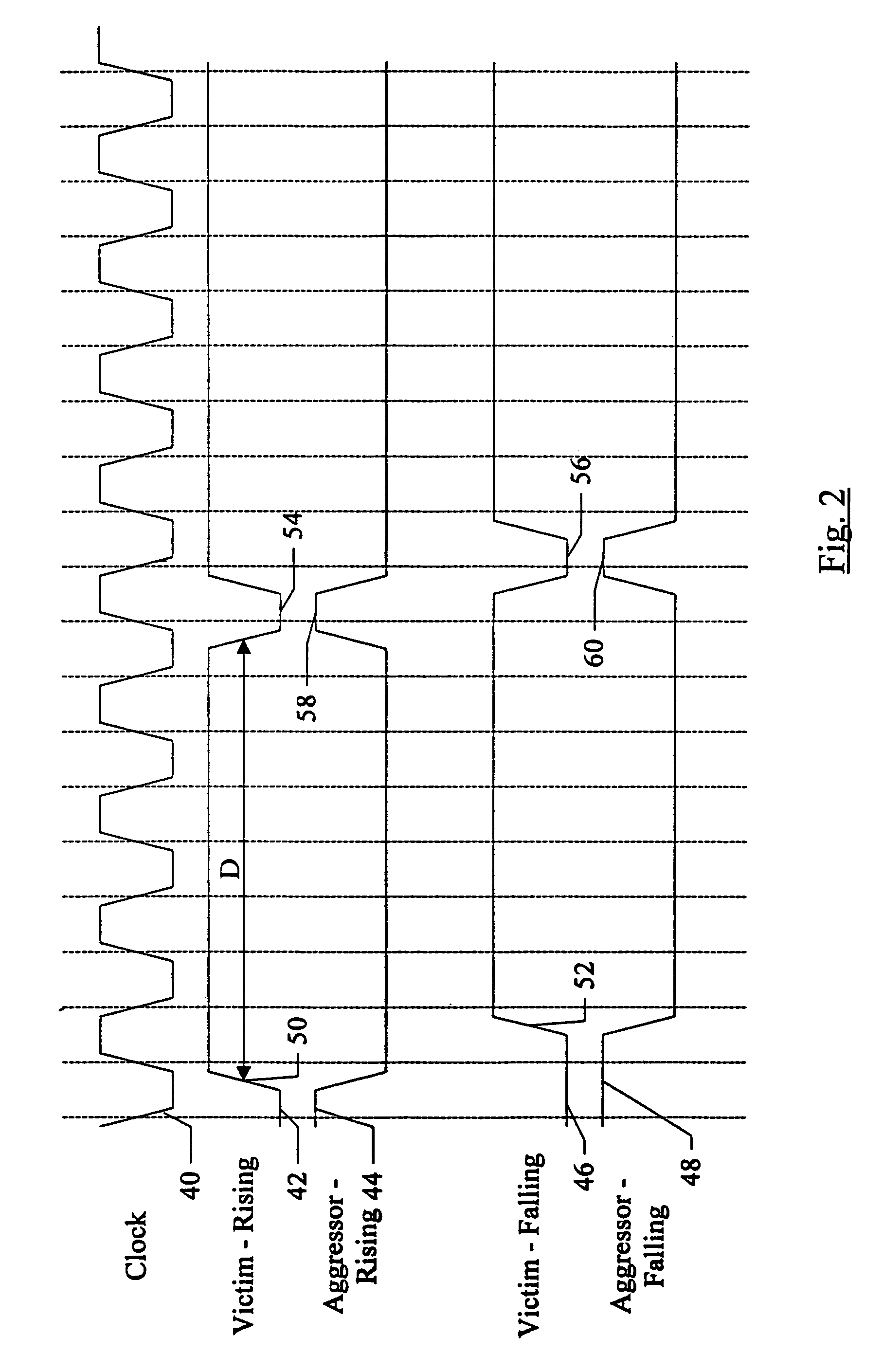

Source synchronous link integrity validation

InactiveUS6965648B1Flexible implementationCorrect operation testingElectronic circuit testingElectrical polaritySource-synchronous

A system may perform interconnect BIST (IBIST) testing on source synchronous links. The system may perform, at normal operating frequency, a source synchronous link test that tests a victim line on the source synchronous link using a transition weave pattern. The transition weave pattern causes interaction between a data transition on the victim line, previous transitions on the victim line, and transitions on the other lines of the link (the “aggressor” lines). The interaction caused may be: (i) a first crossing pulse on the victim line; (ii) a second crossing pulse of the opposite polarity on each aggressor line concurrent with the first crossing pulse on the victim line; and (iii) a reflection in the opposite direction of the first transition of the first crossing pulse, wherein the reflection results from a previous transition on the victim line.

Owner:ORACLE INT CORP

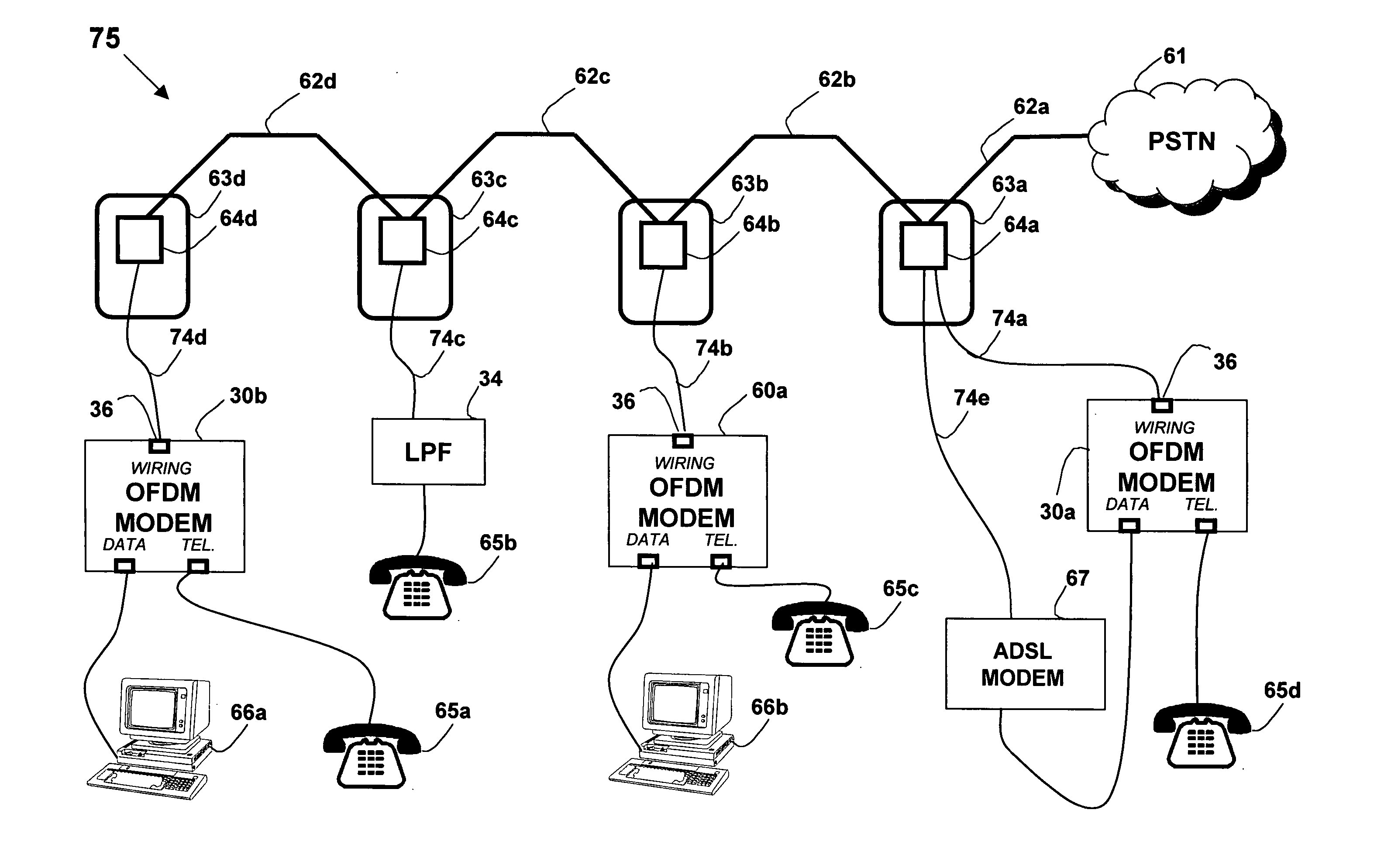

System and method for carrying a wireless based signal over wiring

InactiveUS20050249245A1Power distribution line transmissionFrequency-division multiplexData connectionModem device

A device, network and method wherein a standard wireless modem is coupled to wiring for carrying a wireless baseband signal that may be OFDM based, and may be directly generated by the wireless IF modem, or extracted from the modem RF signal. The wiring may be a building utility wiring, such as telephone, AC power or CATV wiring. The baseband signal is carried simultaneously with the utility service signal over the utility wiring using Frequency Division Multiplexing. The device may be enclosed with a data unit, a standalone dedicated enclosure, within an outlet or as a plug-in outlet adapter. Data units may couple the device by a wiring port such as standard data connector, or via wireless connection. The device may be locally powered or via a power signal carried over the wiring. This abstract is not intended to limit or construe the scope of the claims.

Owner:CORNING OPTICAL COMM WIRELESS

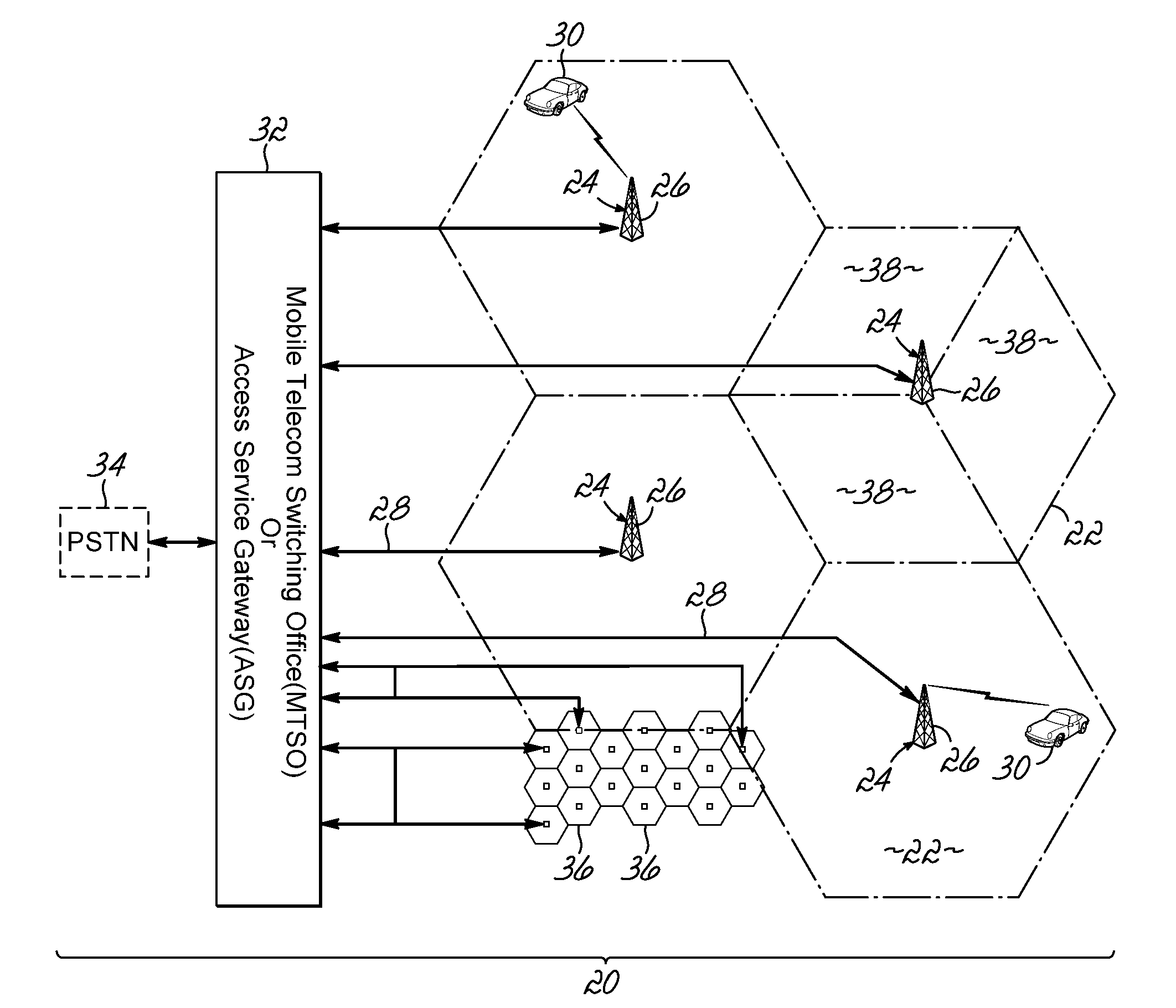

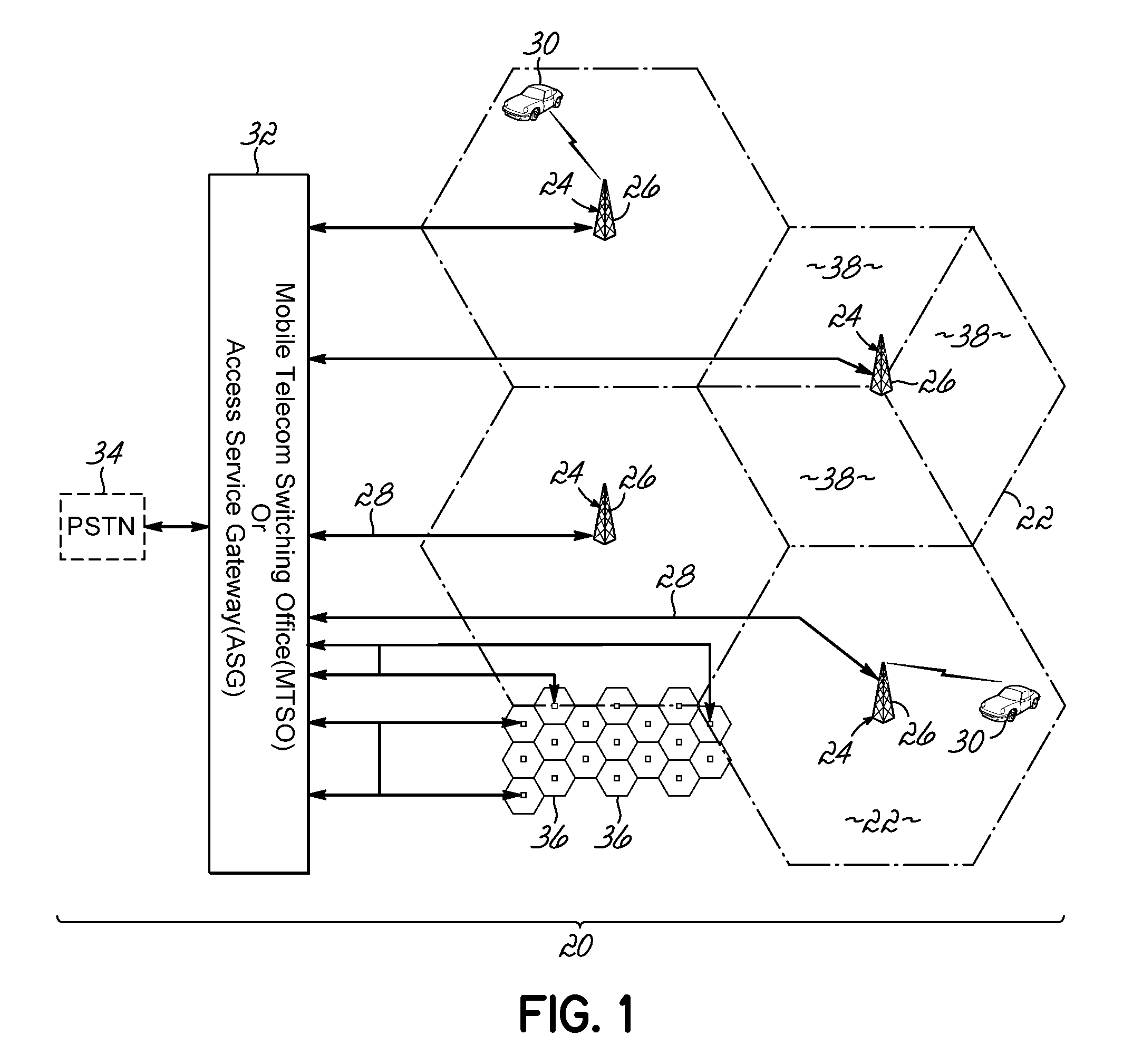

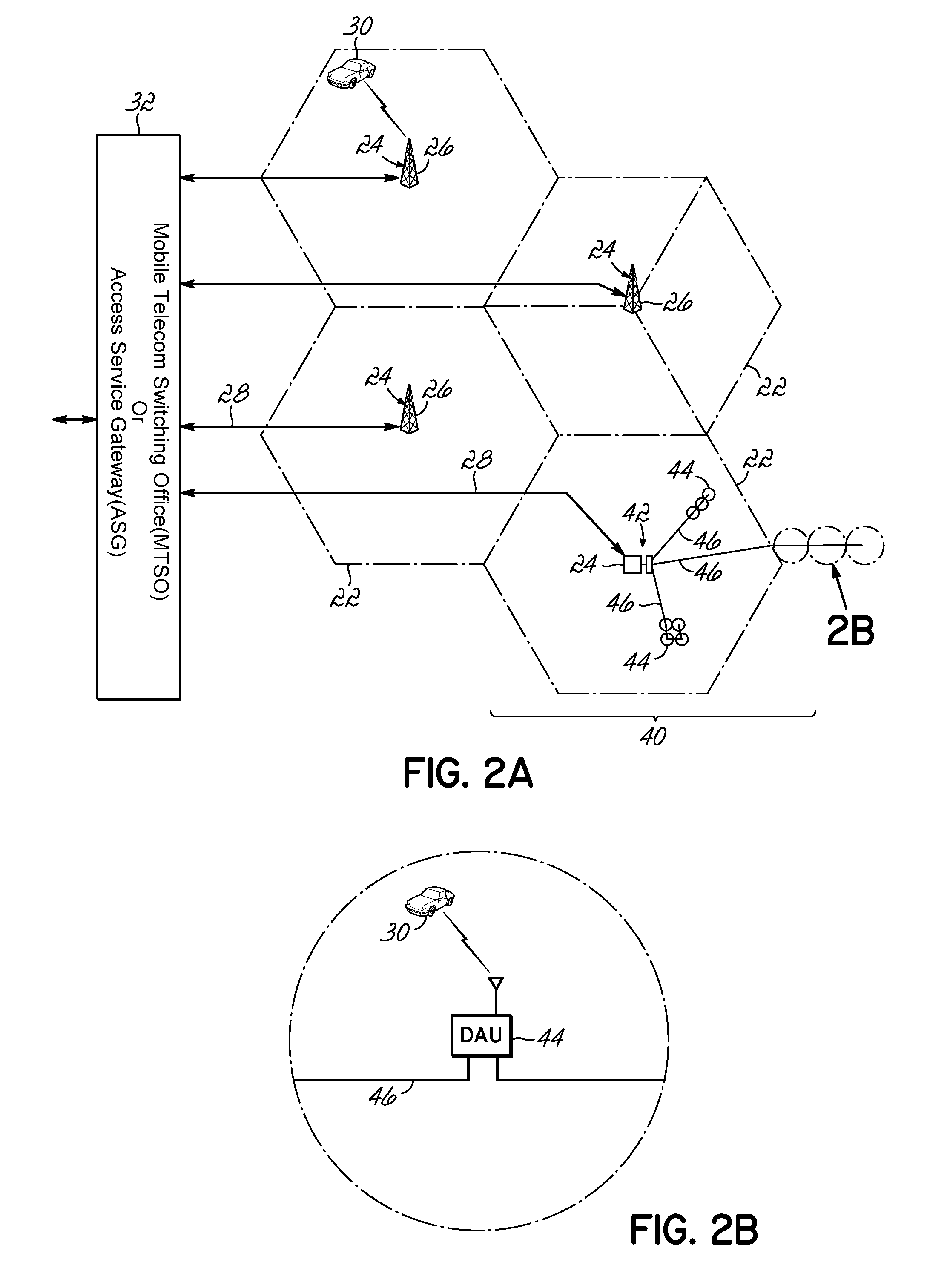

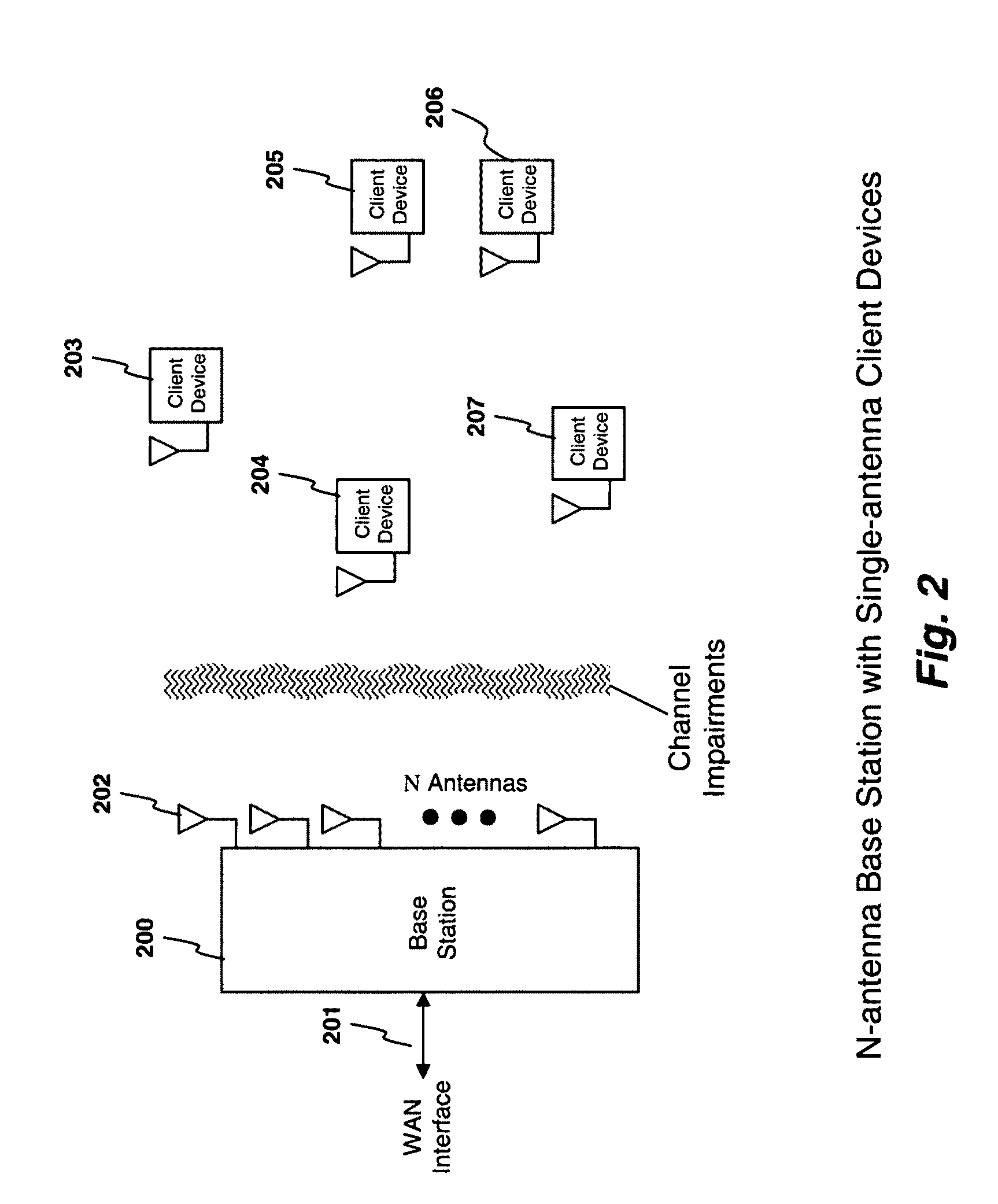

Distributed antenna system for wireless network systems

ActiveUS20100278530A1Increase capacityLarge coverage areaModulated-carrier systemsWavelength-division multiplex systemsDigital dataTransceiver

A distributed antenna system is provided for communicating with a plurality of base stations. The distributed antenna system includes a system controller and a master unit communicating with at least one of the plurality of base stations. A remote unit communicates over a high data rate media with the master unit and / or a downstream remote unit. Alternatively, the distributed antenna system includes a controller and a digital time / space crosspoint switch controlled by the controller. A digitizing transceiver is in communication with the digital time / space crosspoint switch. The crosspoint switch is configured to transmit and receive digital data through the digitizing transceiver.

Owner:COMMSCOPE TECH LLC

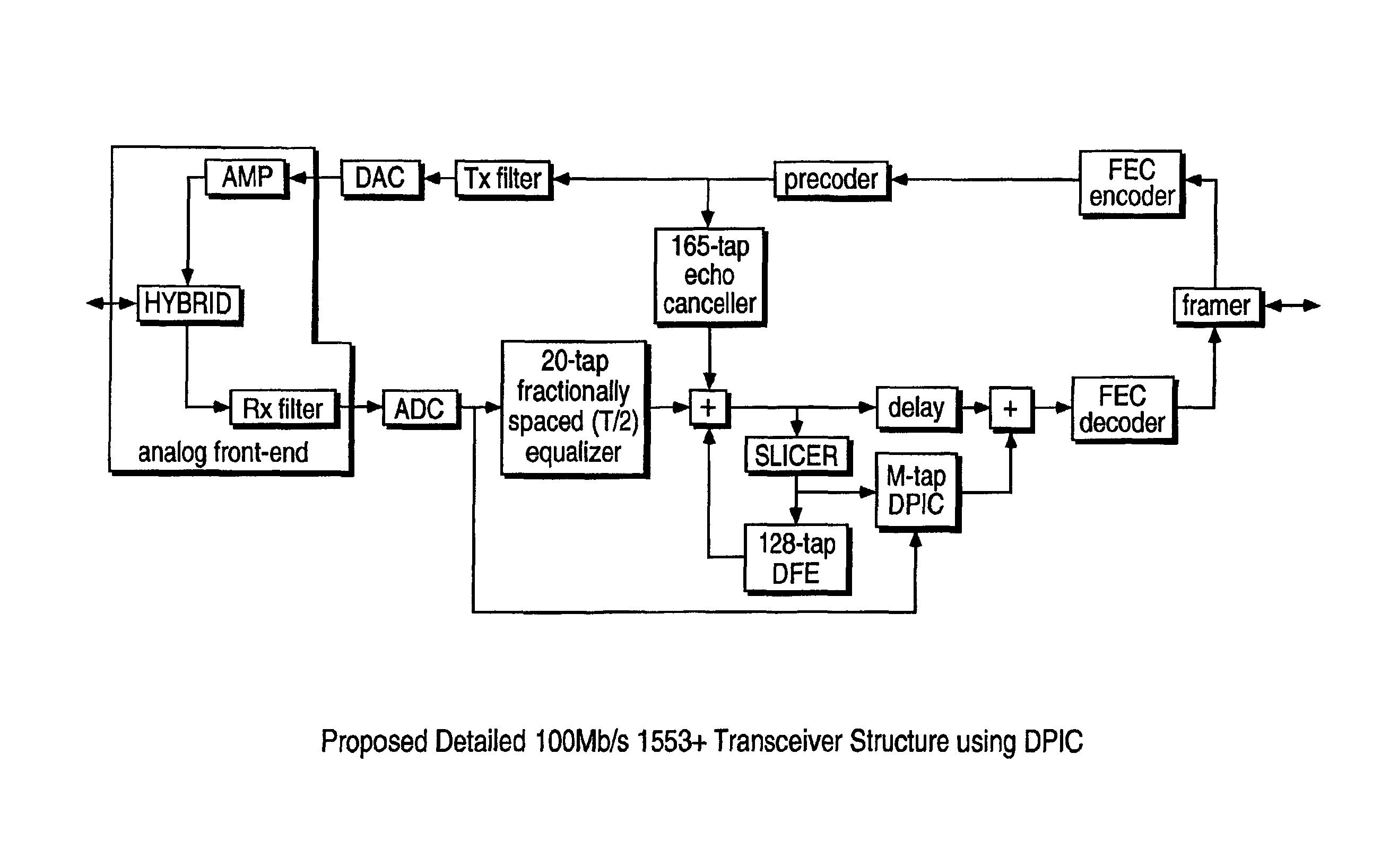

Channel adaptive equalization precoding system and method

InactiveUS20030086515A1Increase high performance and data rate capacityLow costChannel dividing arrangementsError detection/prevention using signal quality detectorPrecodingOperational system

A system and method for delivering increased speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities.

Owner:TRANS FRANCOIS +1

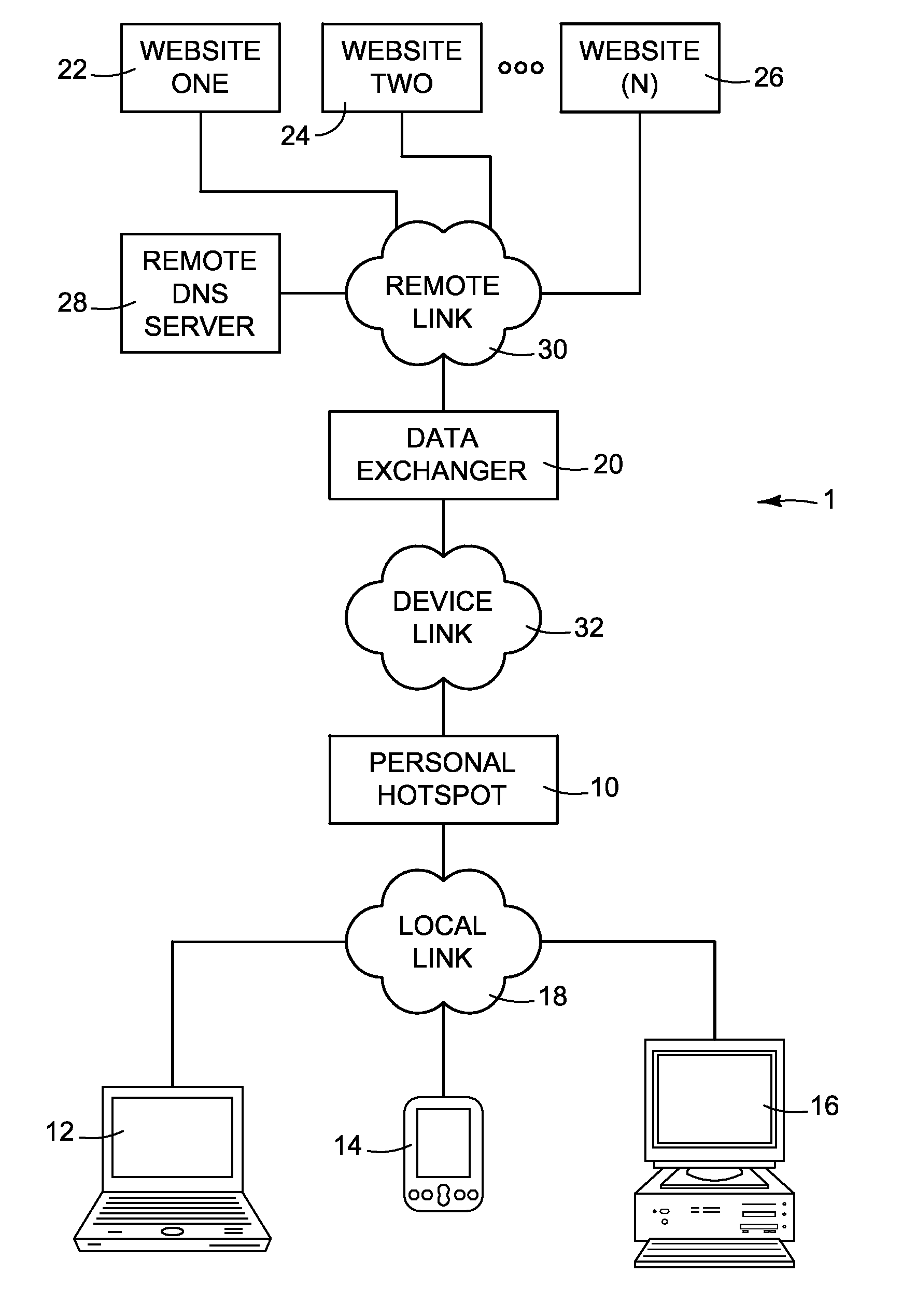

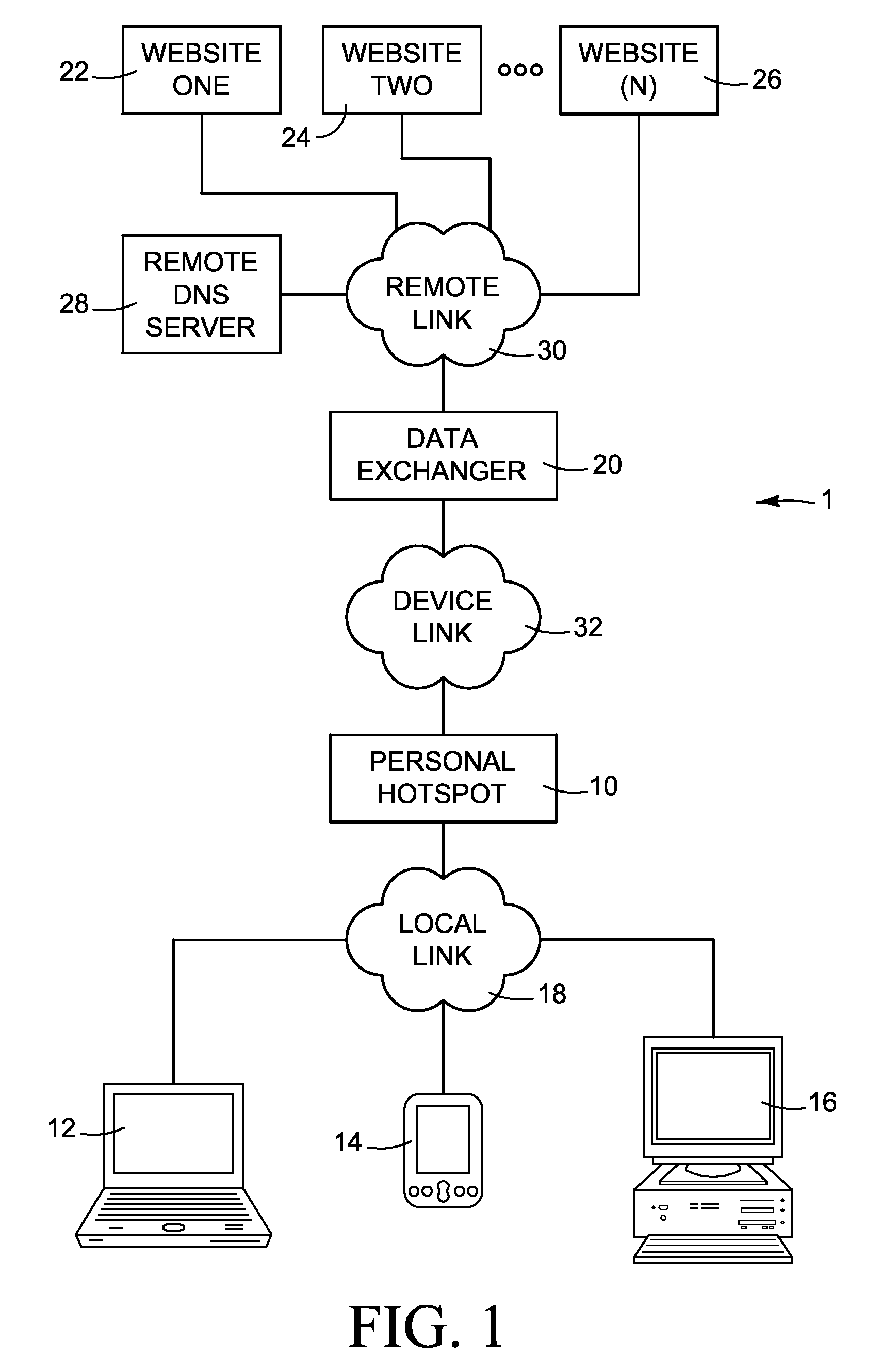

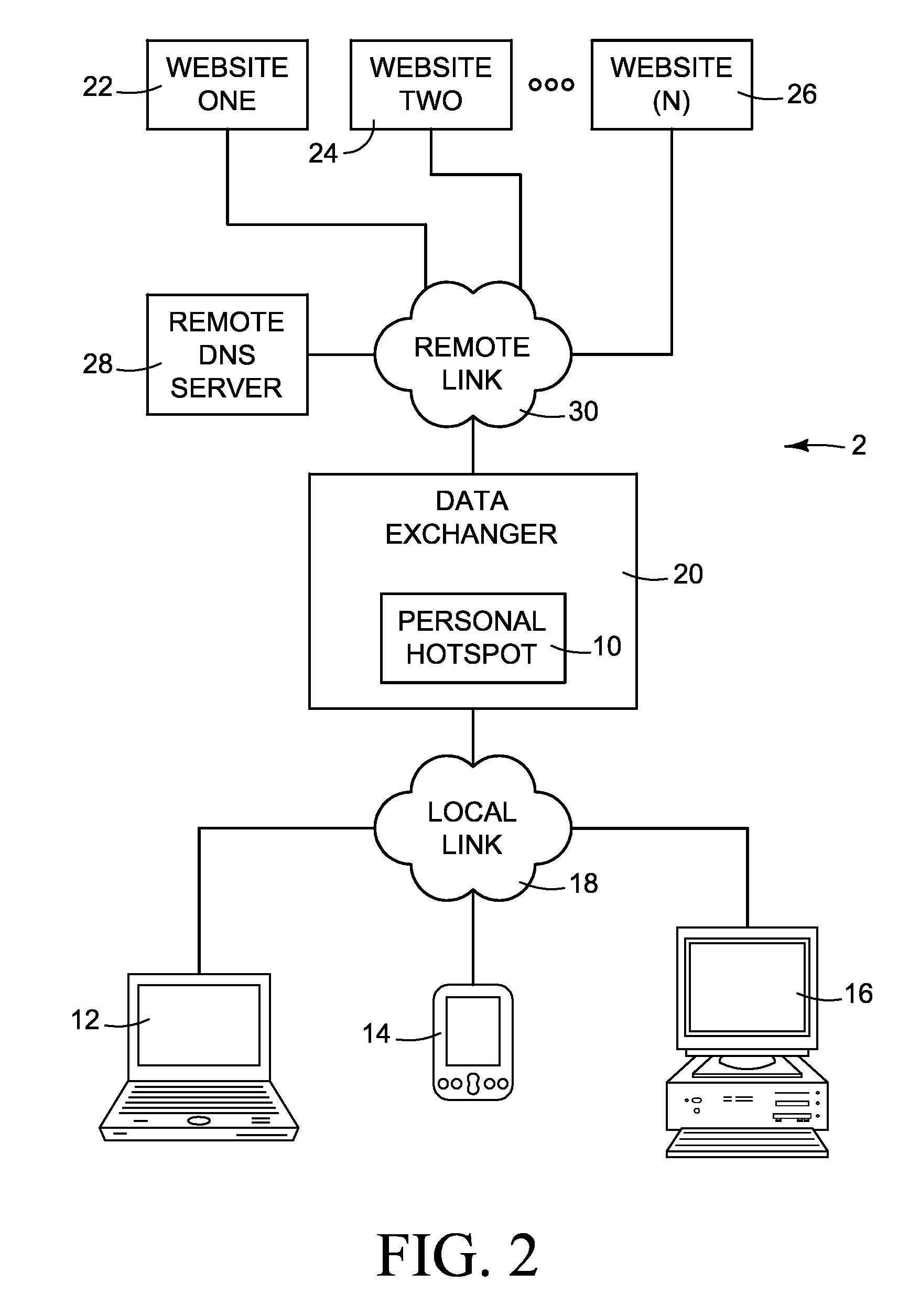

Embedded DNS

An embodiment is directed to a method for selectively routing a DNS request in which a DNS request to translate a domain name is received from a local client device. The DNS request is directed to a remote DNS server on a remote network. A link status to the remote network is identified. If the link status indicates that a connection to the remote network is not possible, the DNS request is routed to a locally embedded DNS server. If the link status indicates that a connection to the remote network is possible, the DNS request is routed to the remote DNS server on the remote network.

Owner:CRADLEPOINT

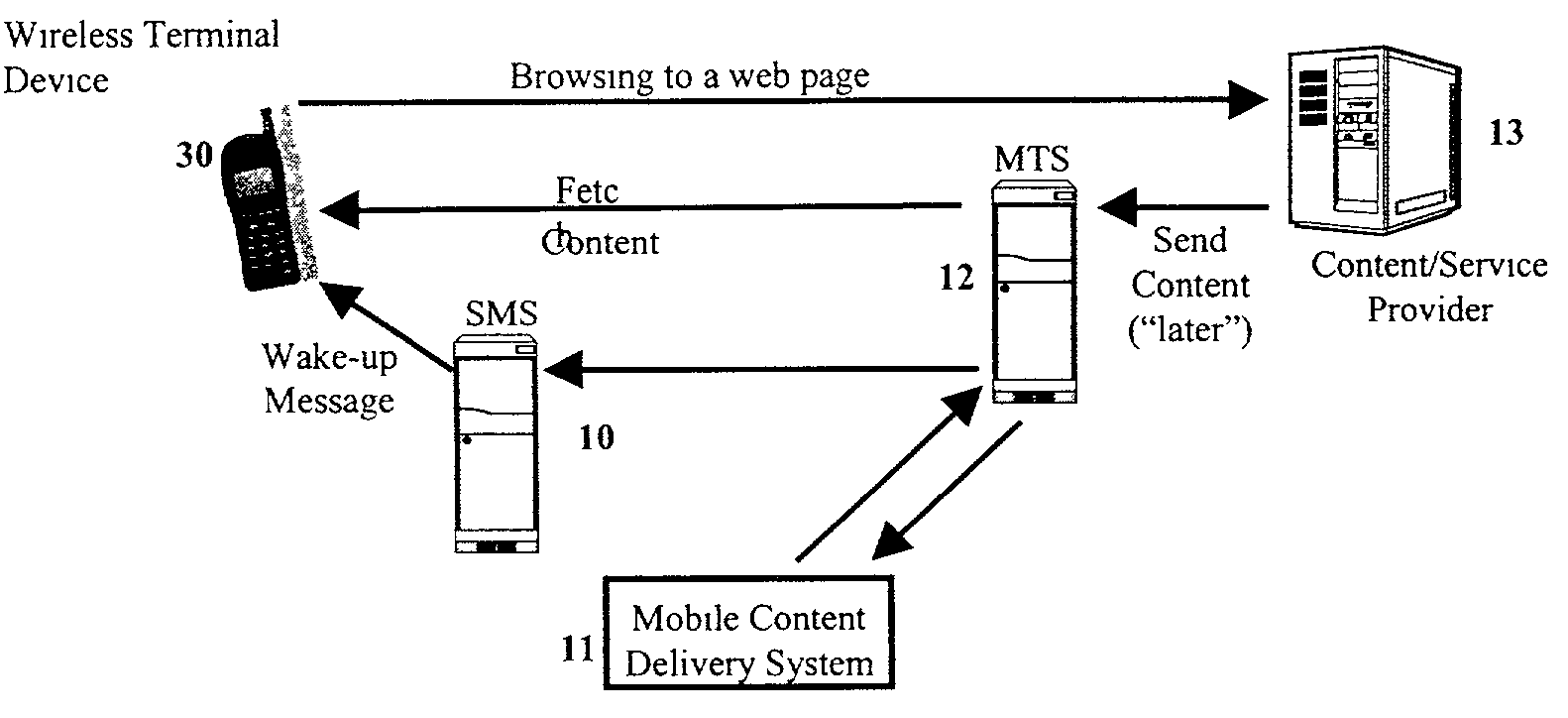

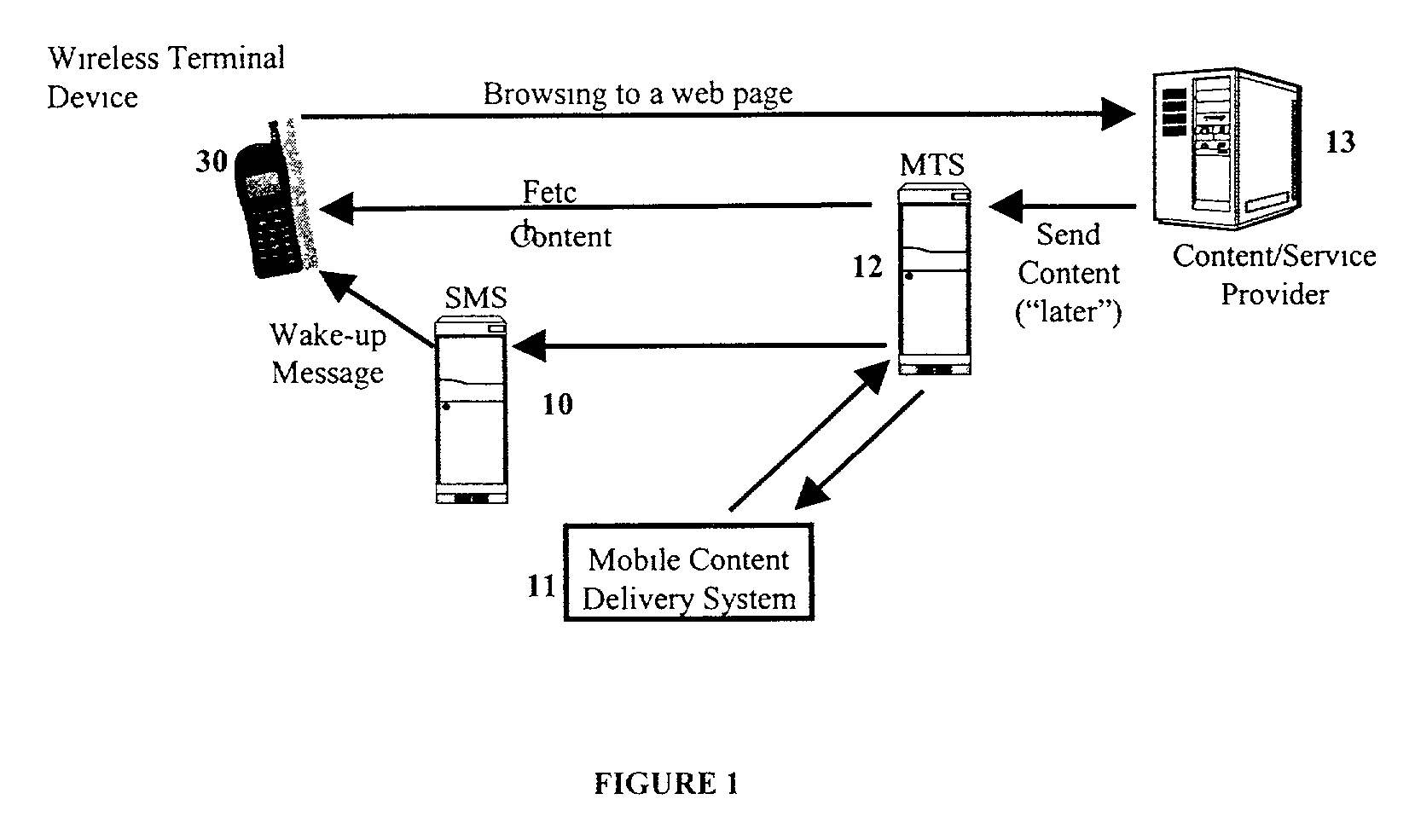

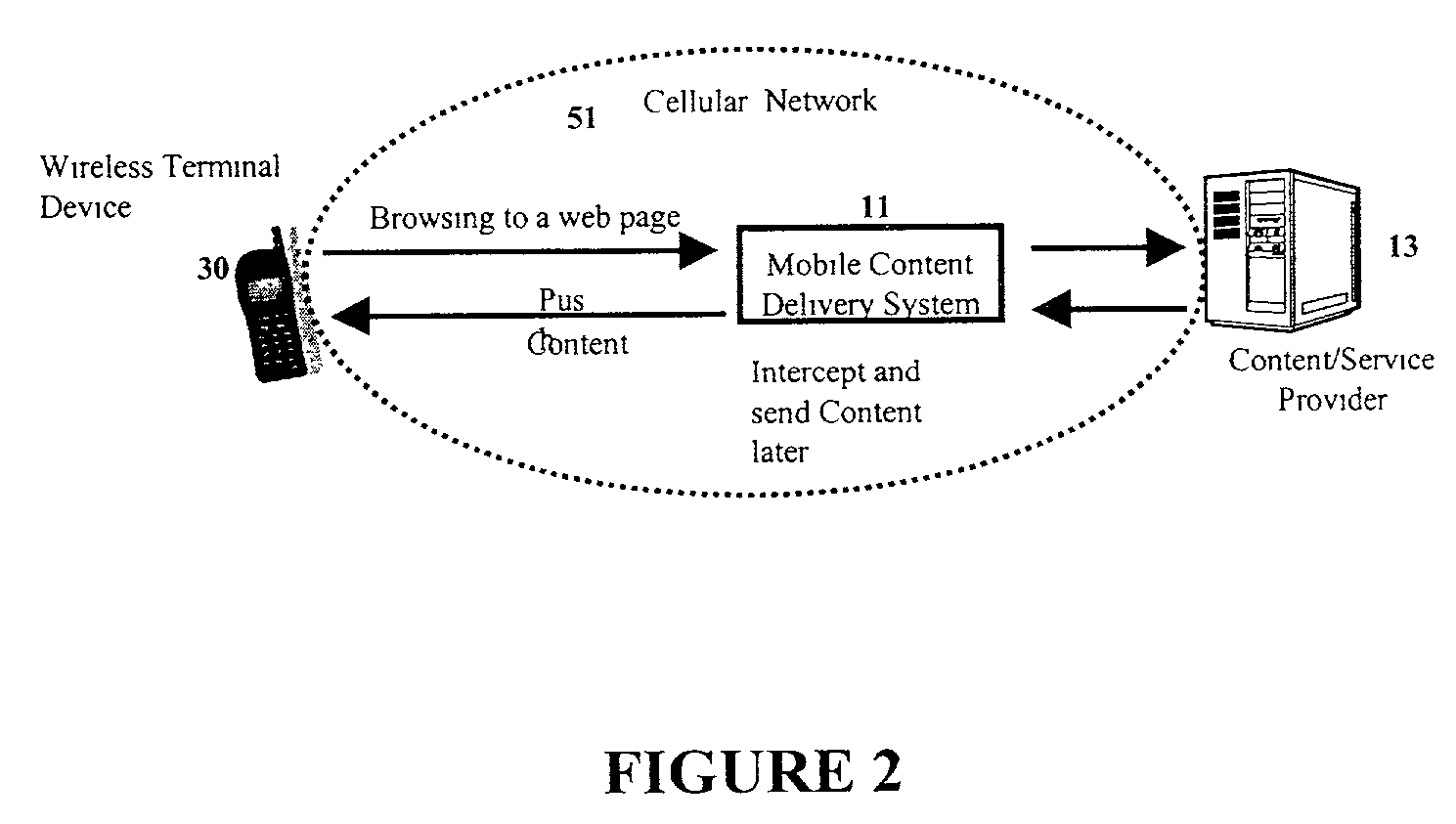

Mobile content delivery system

InactiveUS6996393B2Attracting more userImprove network throughputMetering/charging/biilling arrangementsSpecial service for subscribersRadio networksMobile content

A mobile content delivery system that optimizes the delivery of especially bandwidth-consuming content (or the flow of any peak-hour data traffic) in a way that best utilizes the free capacity in the radio network, thus enabling considerably more efficient usage of the radio capacity. It also allows new services and pricing structures to be used in the cellular network, that otherwise would not be possible. The class of delivery of message content can be selected by the user on a transaction basis, or subscription-based and pre-defined in a user profile. By choosing a scheduled delivery the user can receive the content at a fraction of the price compared to instant delivery, since the content is sent at a time when the network is least utilized.

Owner:NOKIA CORP

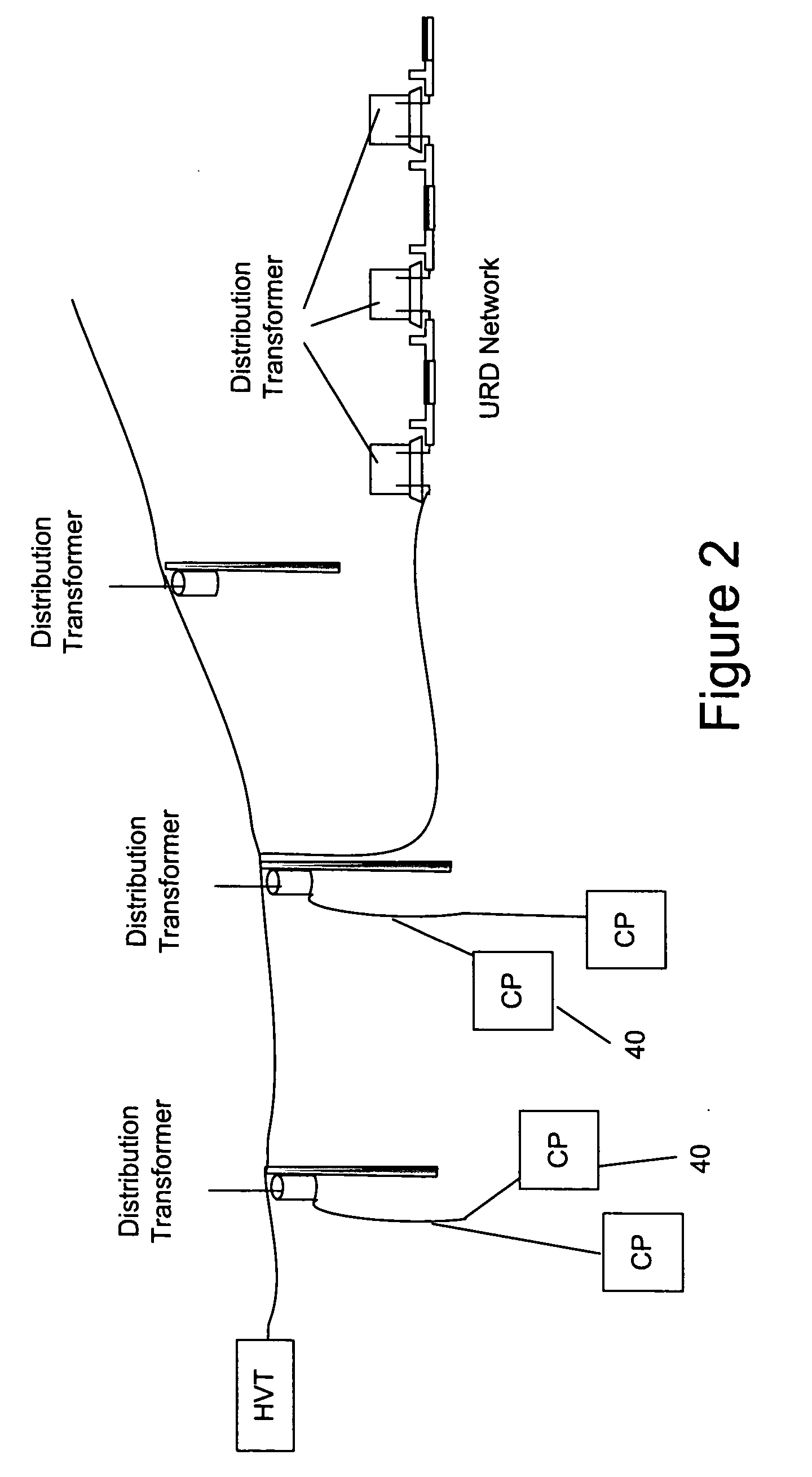

Power line communications device and method

InactiveUS20060192672A1Modulated-carrier systemsFrequency-division multiplex detailsFiberElectricity

A device and method for providing power line communications via an underground residential distribution power system is provided. One embodiment of the present invention includes a medium voltage interface device that may include a first port configured to communicate over the power line and a network interface. A first amplifier may form part of a first communication path between the first port and the network interface and be configured to amplify data signals transmitted via the first port. In addition, a second amplifier may form part of a second communication path between the first port and the network interface and be configured to amplify data signals received via the first port. In addition, the embodiment may include a diplexer forming part of the first communication path between the first amplifier and the first port and forming part of the second communication path between the second amplifier and the first port. The device may include an electro-optic converter coupled to the network interface to convert between electrical and optic data signals, wherein the network interface is configured to communicate via one or more fiber optic conductors.

Owner:CURRENT TECH

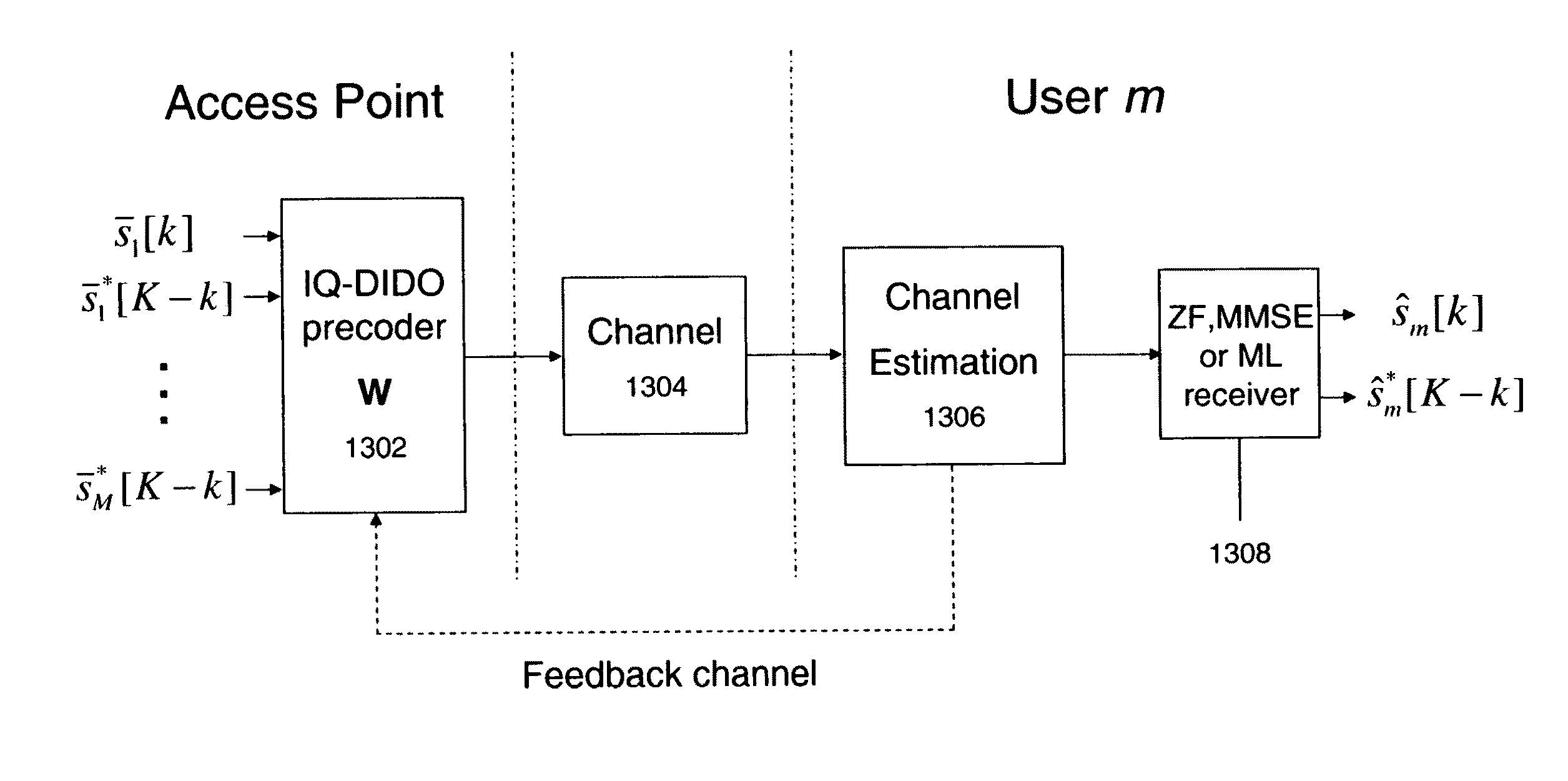

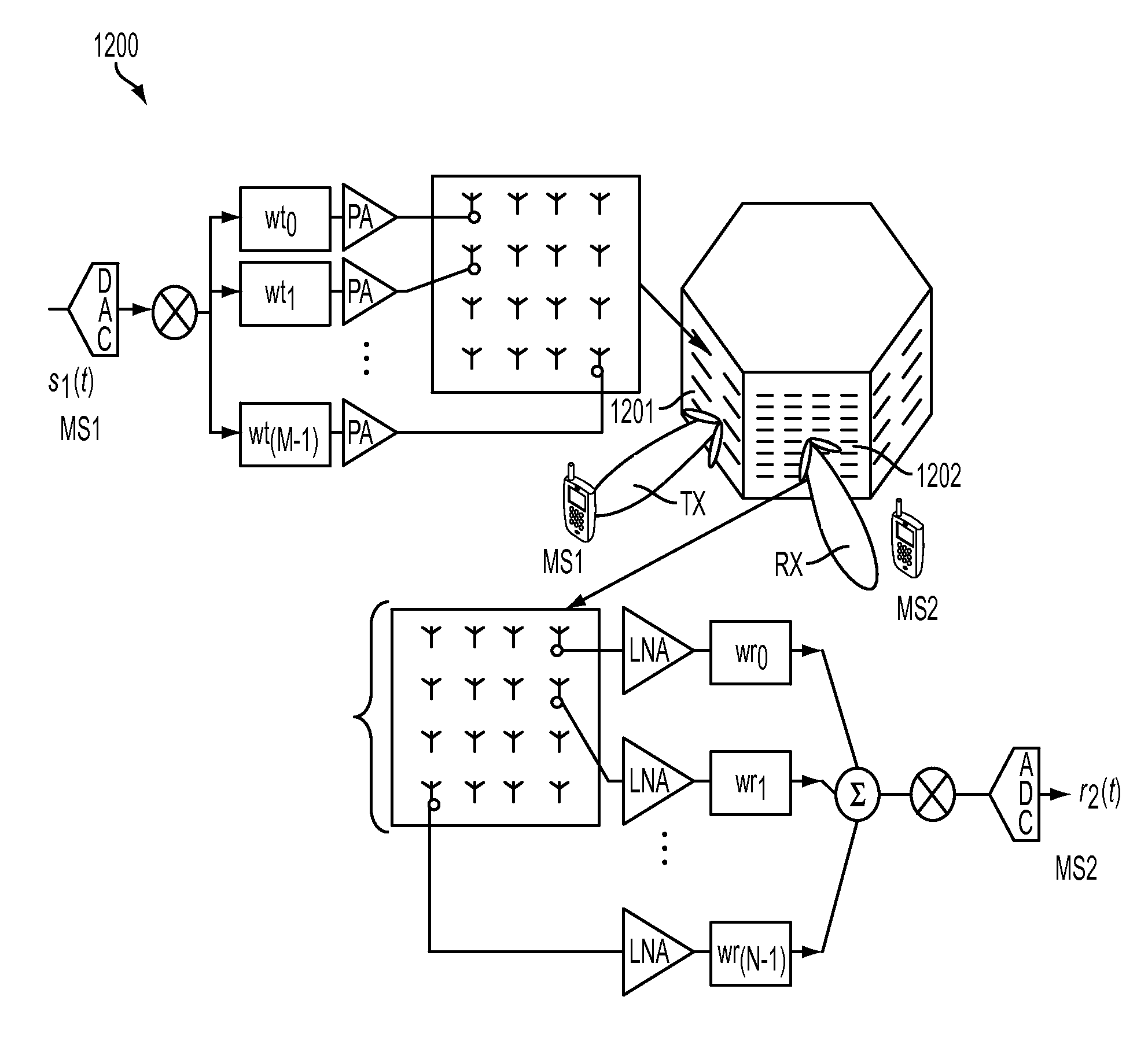

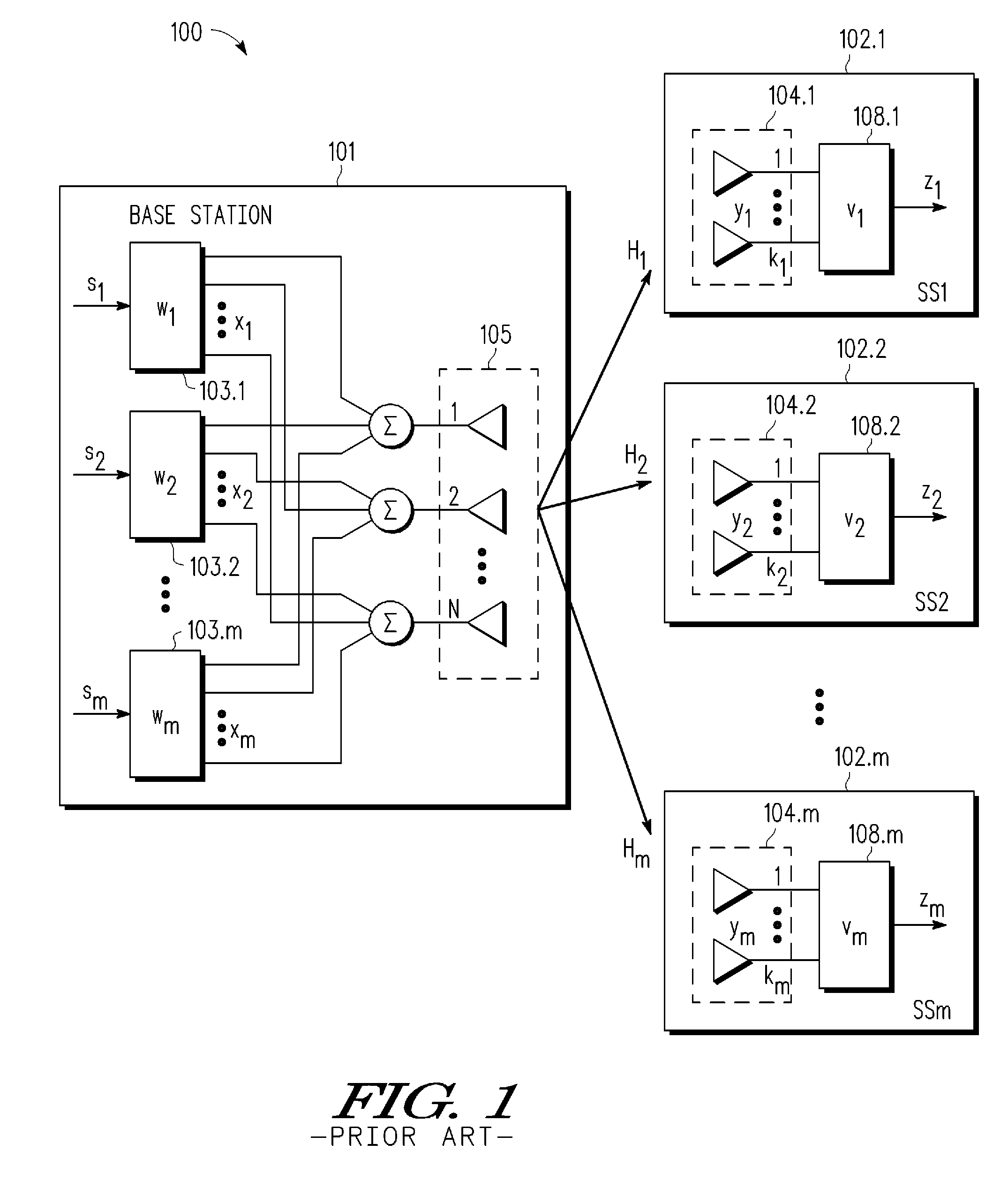

System and method for distributed input distributed output wireless communications

A system and method are described for compensating for frequency and phase offsets in a multiple antenna system (MAS) with multi-user (MU) transmissions (“MU-MAS”). For example, a method according to one embodiment of the invention comprises: transmitting a training signal from each antenna of a base station to one or each of a plurality of wireless client devices, one or each of the client devices analyzing each training signal to generate frequency offset compensation data, and receiving the frequency offset compensation data at the base station; computing MU-MAS precoder weights based on the frequency offset compensation data to pre-cancel the frequency offset at the transmitter; precoding training signal using the MU-MAS precoder weights to generate precoded training signals for each antenna of the base station; transmitting the precoded training signal from each antenna of a base station to each of a plurality of wireless client devices, each of the client devices analyzing each training signal to generate channel characterization data, and receiving the channel characterization data at the base station; computing a plurality of MU-MAS precoder weights based on the channel characterization data, the MU-MAS precoder weights calculated to pre-cancel frequency and phase offset and / or inter-user interference; precoding data using the MU-MAS precoder weights to generate precoded data signals for each antenna of the base station; and transmitting the precoded data signals through each antenna of the base station to each respective client device.

Owner:REARDEN LLC

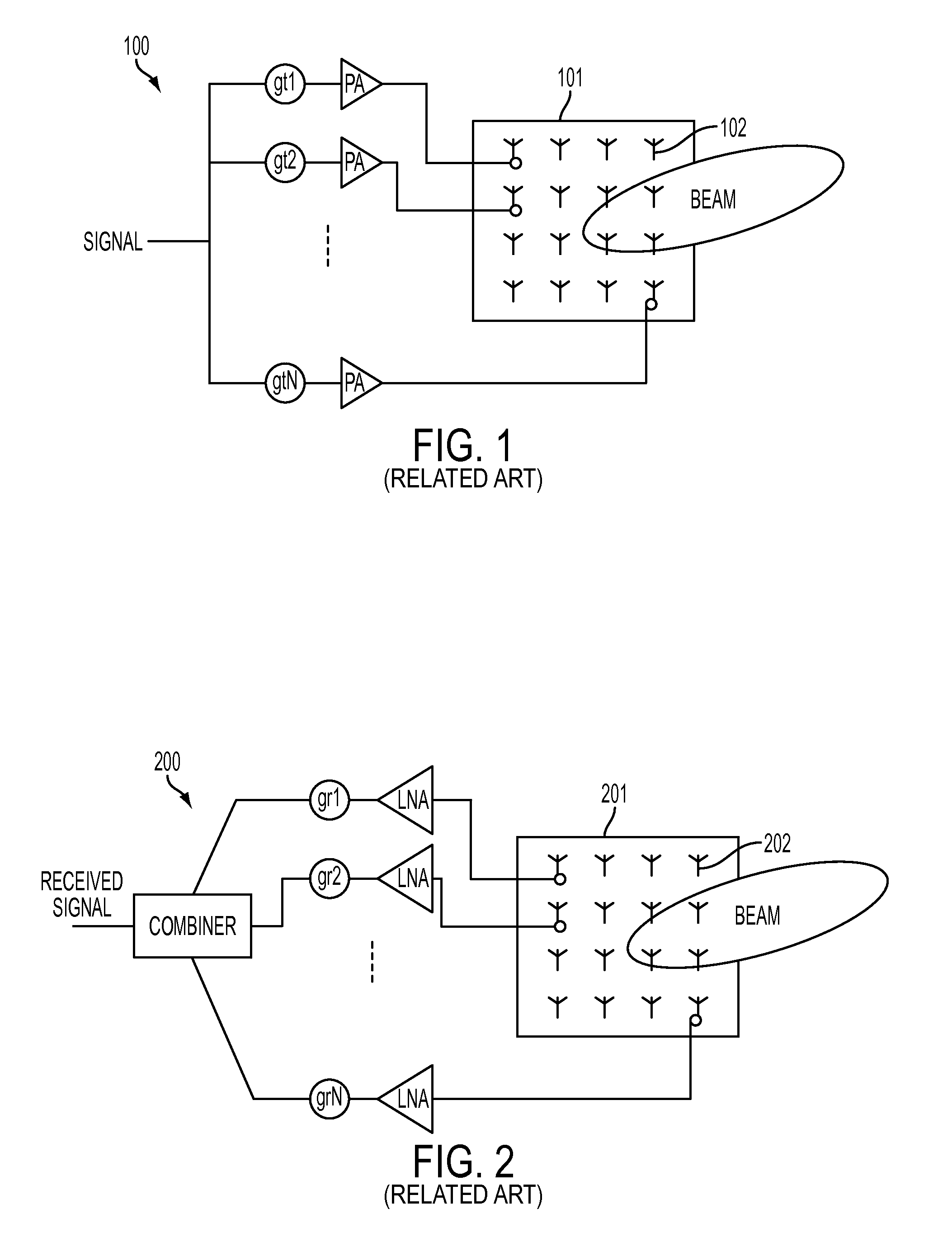

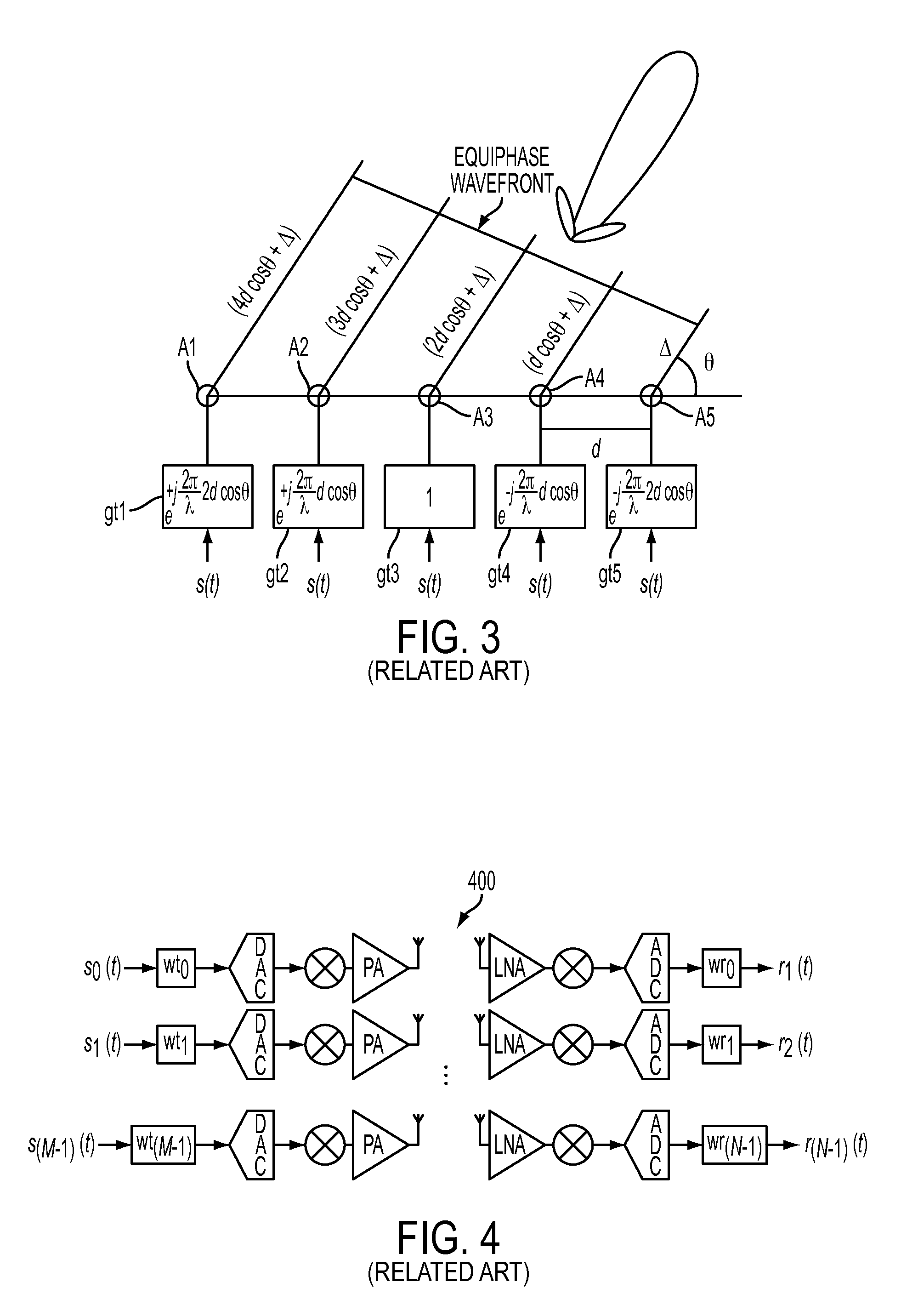

Apparatus and method for spatial division duplex (SDD) for millimeter wave communication system

ActiveUS20110243040A1Antenna arraysFrequency-division multiplex detailsMillimeter wave communication systemsMobile communication systems

An apparatus and method for full-duplex millimeter wave mobile wireless communication are provided. The apparatus includes a Spatial Division Duple (SDD) mobile communication system using millimeter waves, the SDD mobile communication system including a first wireless terminal having a first transmit antenna array having a plurality of first transmit antennas for transmitting a spatially beamformed first transmit beam, and a first receive antenna array having a plurality of first receive antennas for forming a spatially beamformed first receive beam and a second wireless terminal including a second transmit antenna array having a plurality of second transmit antennas for transmitting a spatially beamformed second transmit beam directed towards a receive beam of the first wireless terminal, and a second receive antenna array having a plurality of second receive antennas for forming a spatially beamformed second receive beam directed toward the transmit beam of the first terminal.

Owner:SAMSUNG ELECTRONICS CO LTD

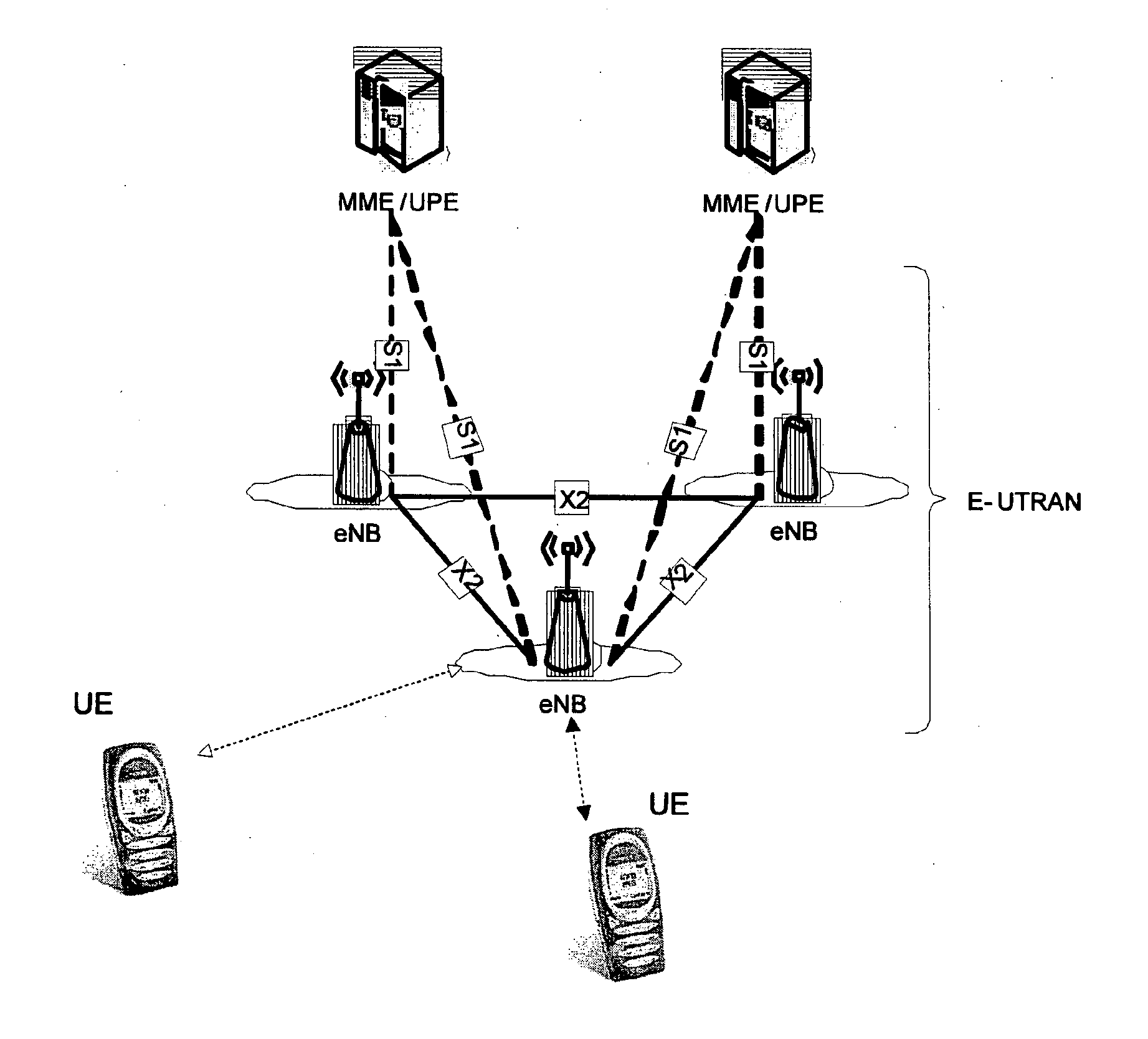

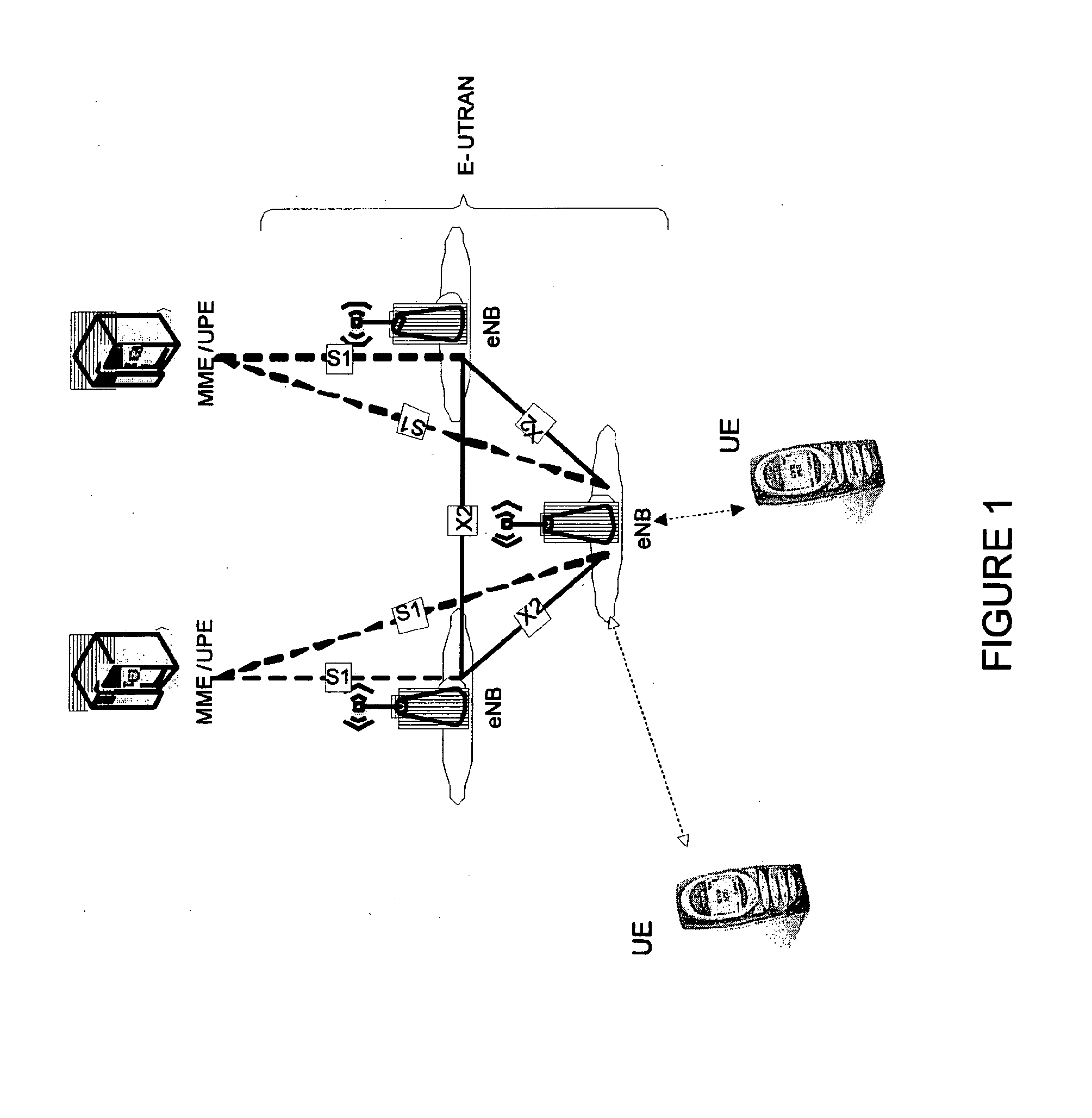

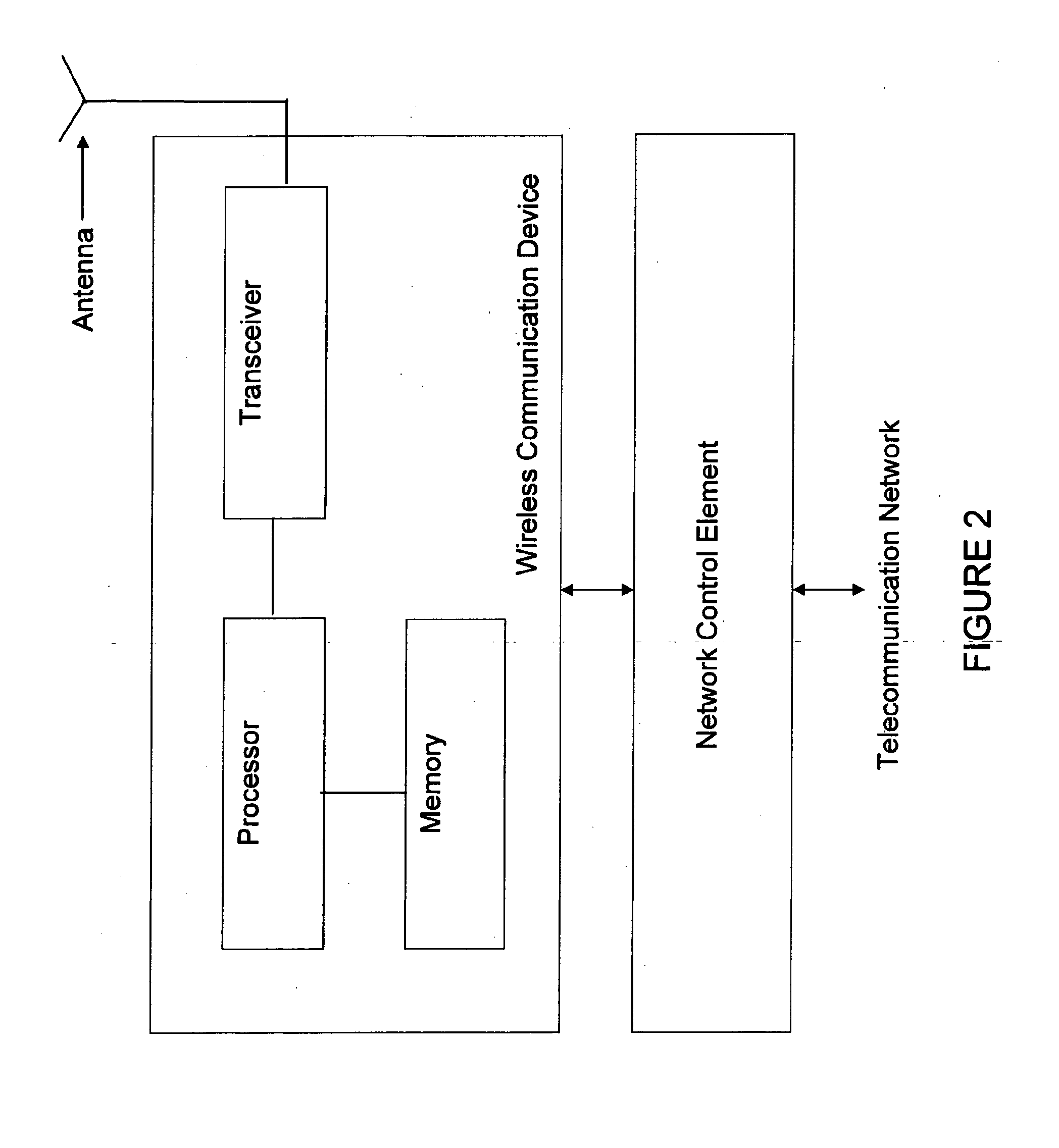

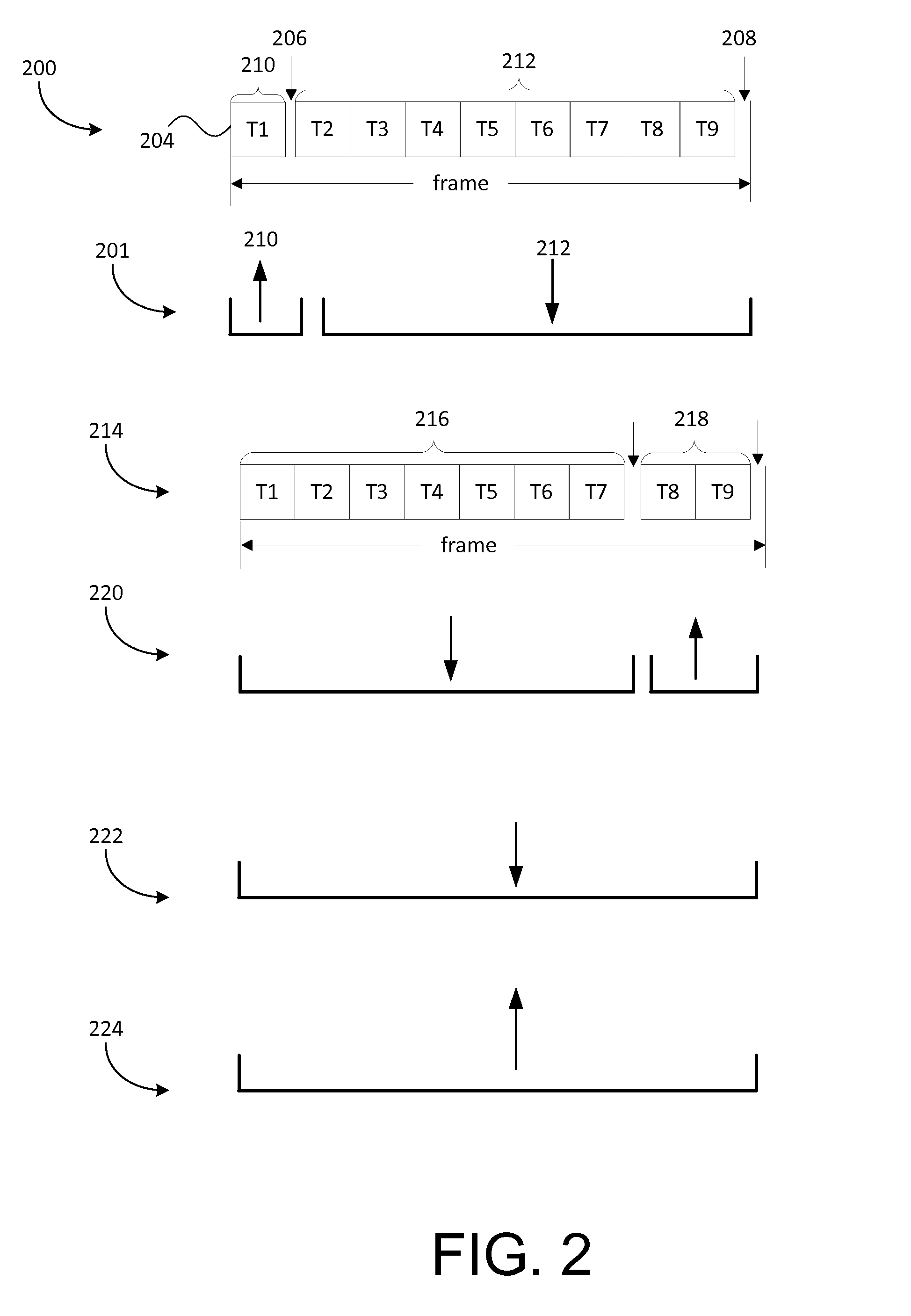

Dynamic allocation of subframe scheduling for time divison duplex operation in a packet-based wireless communication system

ActiveUS20110211503A1Easy to useError preventionTransmission path divisionCommunications systemResource based

Systems and methods for enabling the dynamic allocation of certain sub frames as downlink or uplink resources in a time division duplexed over the air communications system. A base station or eNB may allocate certain subframes within a repeating radio frame of a TDD configuration as either DL or UL subframes for communicating to user equipment or UE devices to increase efficient use of system resources based on the data to be transmitted. Methods for determining the capabilities of a selected UE and based on the determining step, dynamically allocating certain subframes are disclosed. The methods and systems are compatible with user equipment that does not support the dynamic allocation of subframes.

Owner:NOKIA TECHNOLOGLES OY

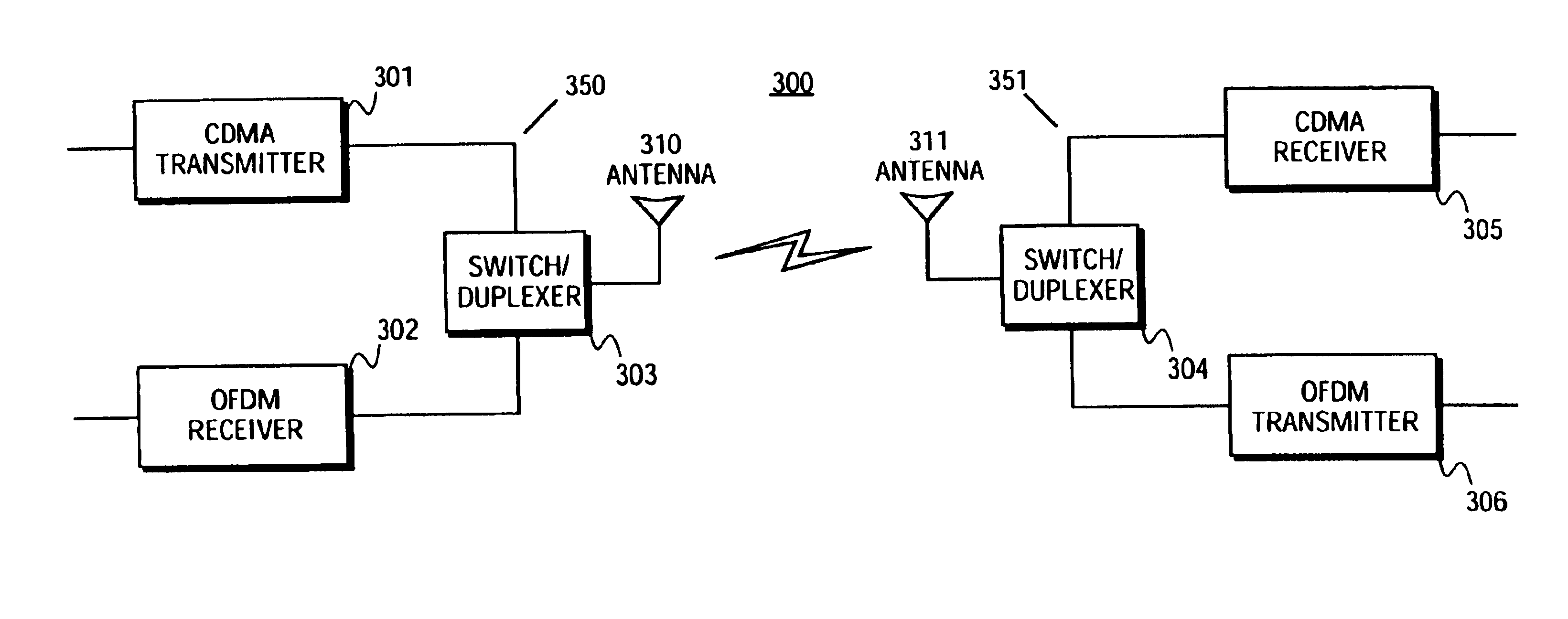

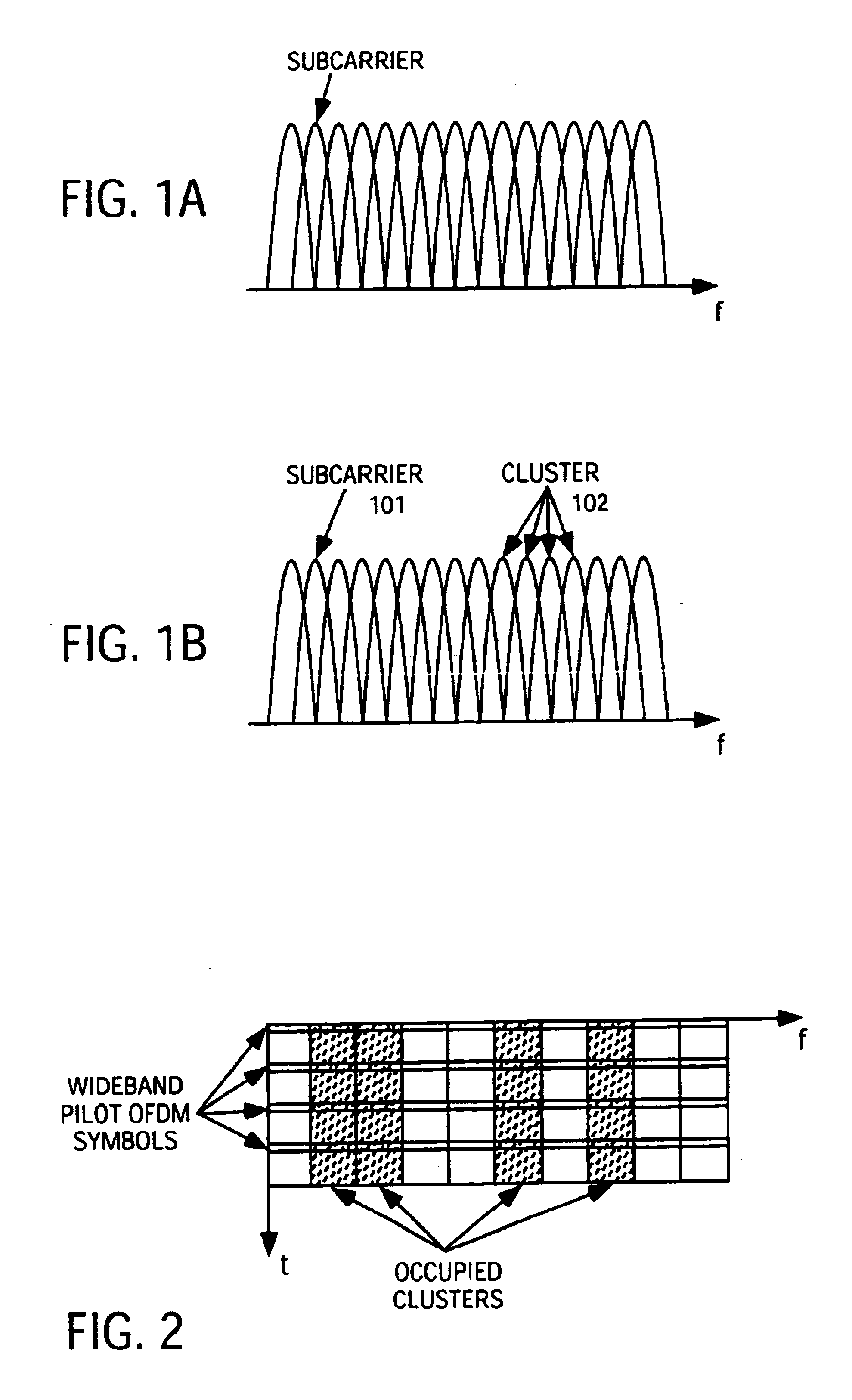

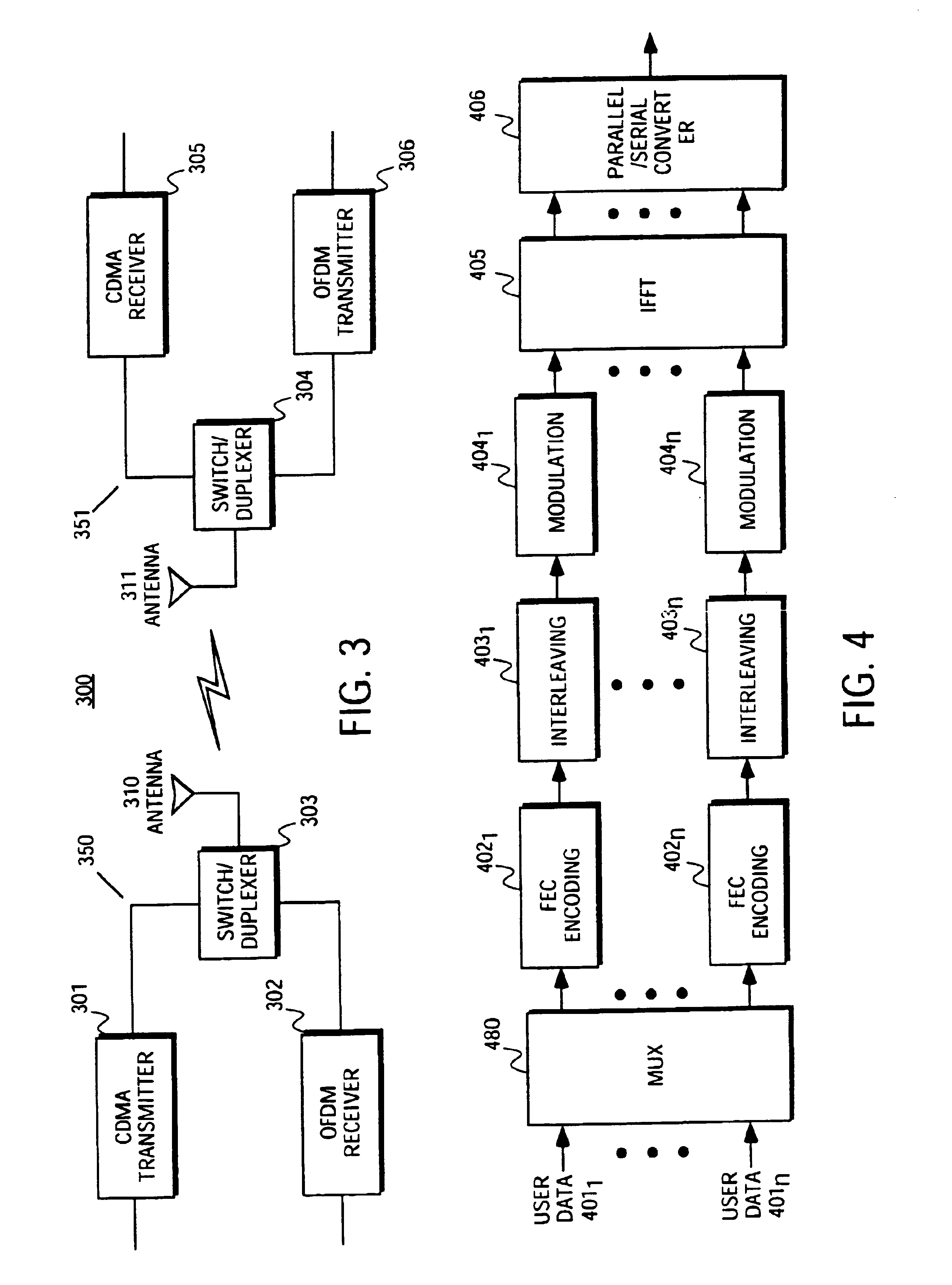

Communication system using OFDM for one direction and DSSS for another direction

InactiveUS6940827B2Power managementTransmission path divisionCommunications systemTelecommunications

A method and apparatus for wireless communication are described. In one embodiment, a method for communicating with a subscriber comprises transmitting orthogonal frequency domain multiplexing (OFDM) signals to the subscriber, and receiving direct-sequence spread spectrum (DSSS) signals from the subscriber.

Owner:ADAPTIX +1

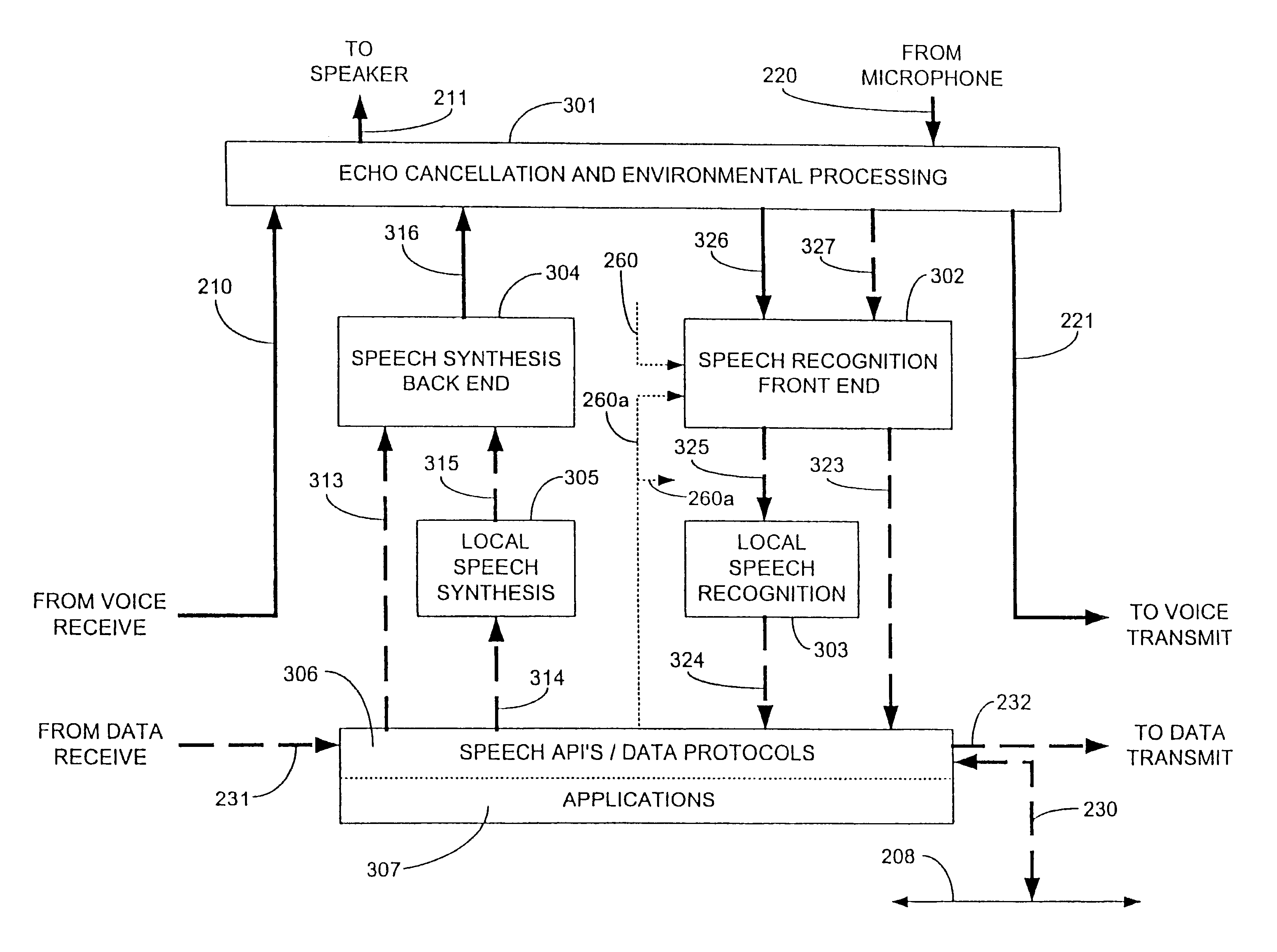

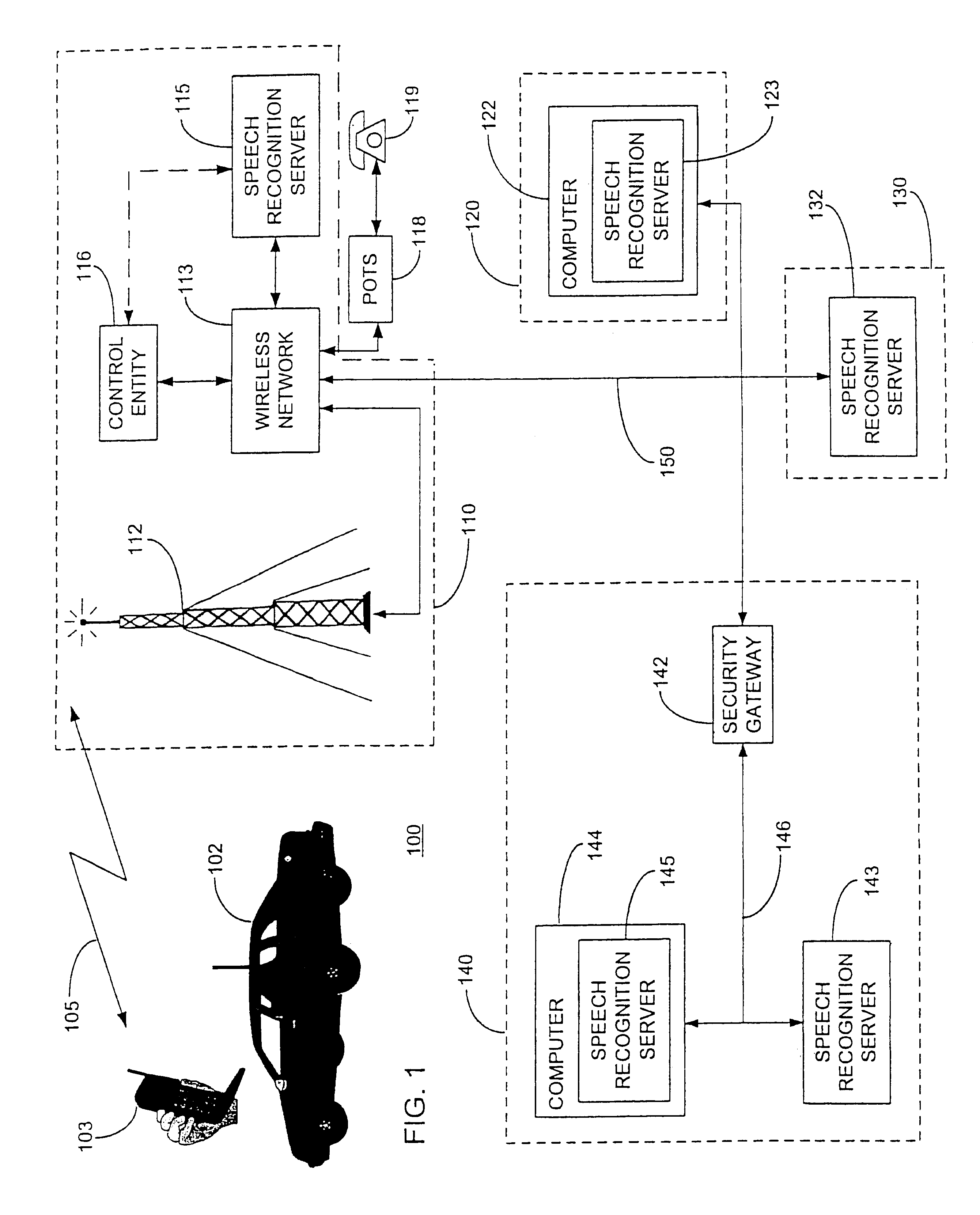

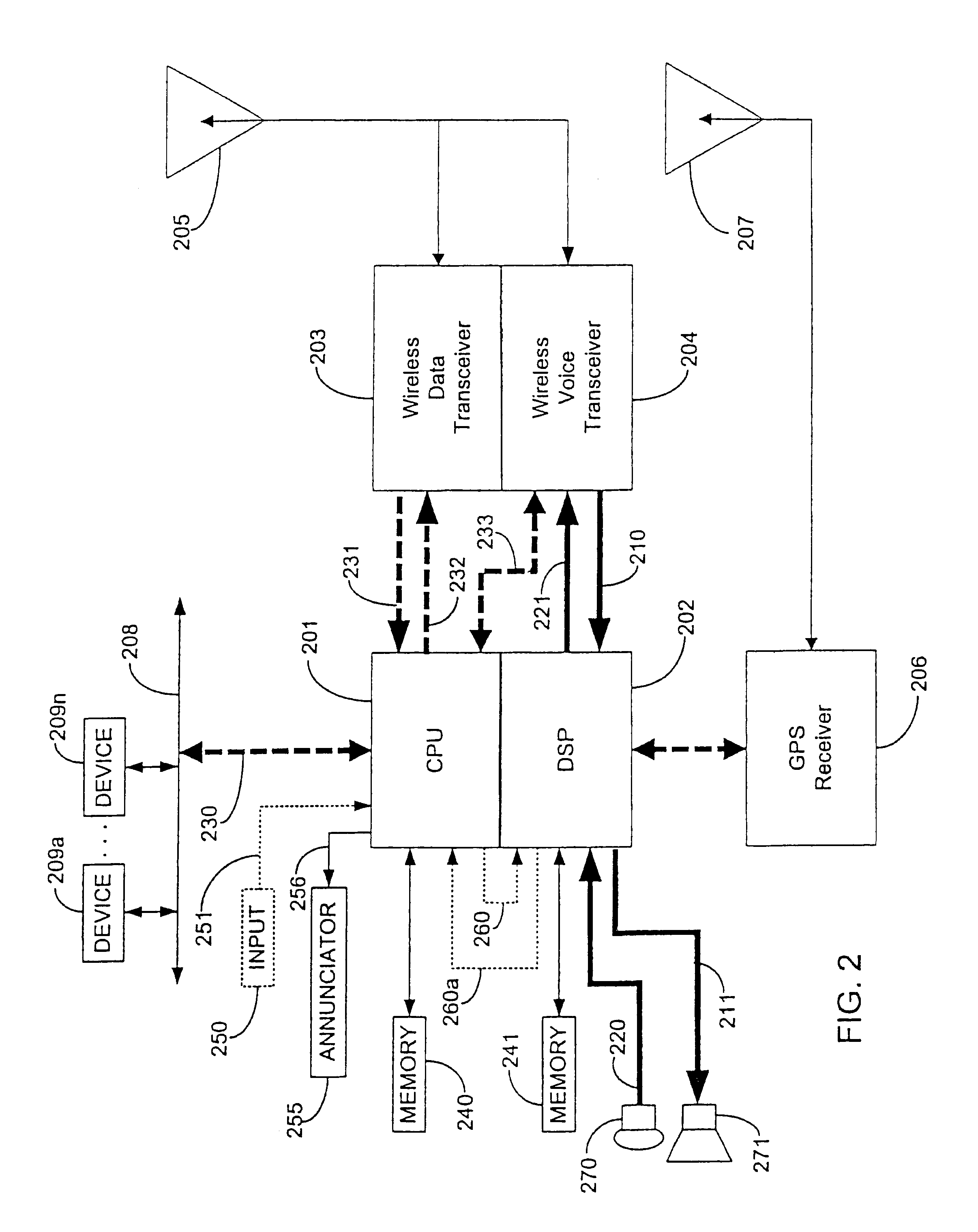

Method and apparatus for the provision of information signals based upon speech recognition

InactiveUS6868385B1Automatic call-answering/message-recording/conversation-recordingSpecial service for subscribersSpeech identificationSpeech sound

A wireless system comprises at least one subscriber unit in wireless communication with an infrastructure. Each subscriber unit implements a speech recognition client, and the infrastructure comprises a speech recognition server. A given subscriber unit takes as input an unencoded speech signal that is subsequently parameterized by the speech recognition client. The parameterized speech is then provided to the speech recognition server that, in turn, performs speech recognition analysis on the parameterized speech. Information signals, based in part upon any recognized utterances identified by the speech recognition analysis, are subsequently provided to the subscriber unit. The information signals may be used to control the subscriber unit itself; to control one or more devices coupled to the subscriber unit, or may be operated upon by the subscriber unit or devices coupled thereto.

Owner:MALIKIE INNOVATIONS LTD +1

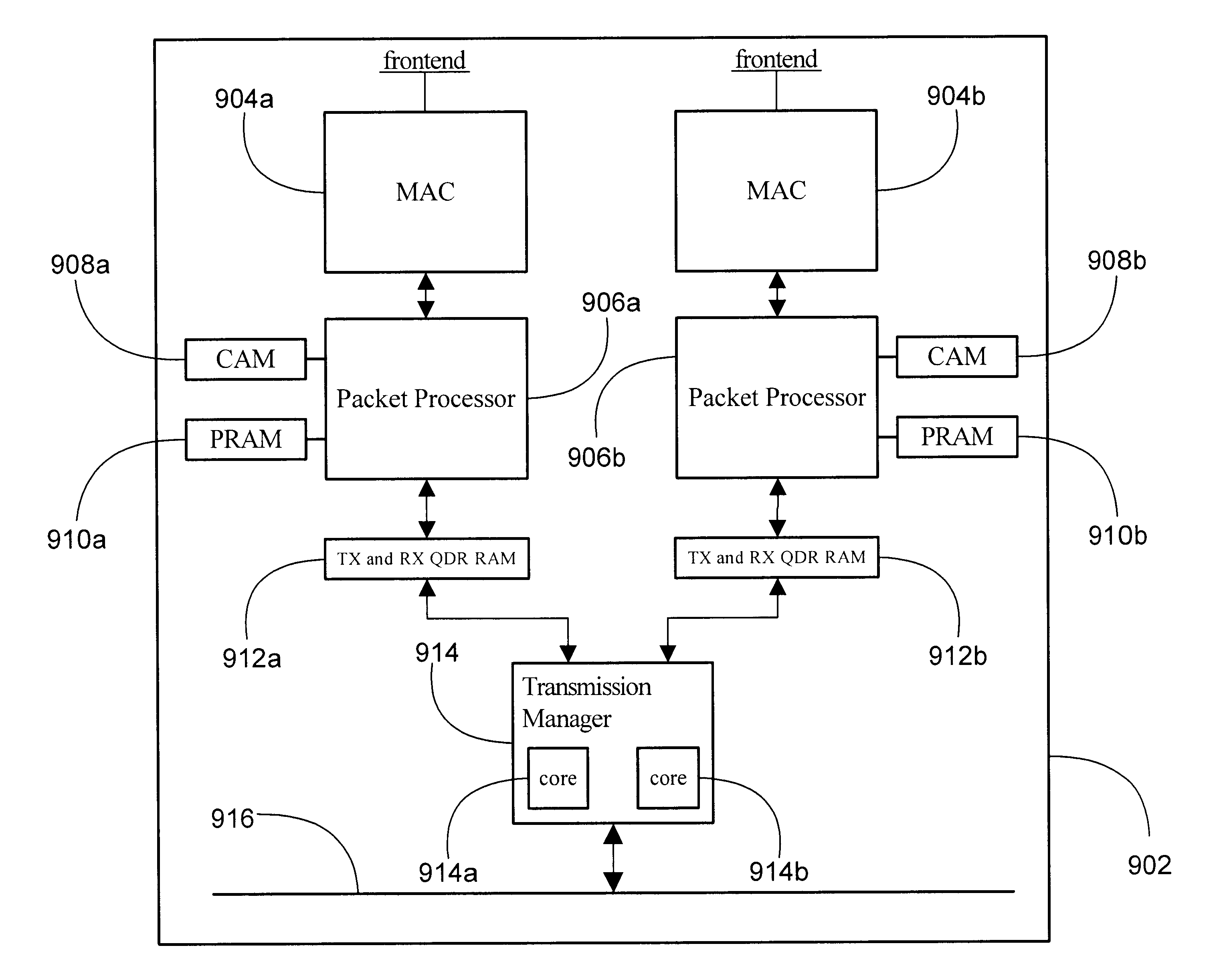

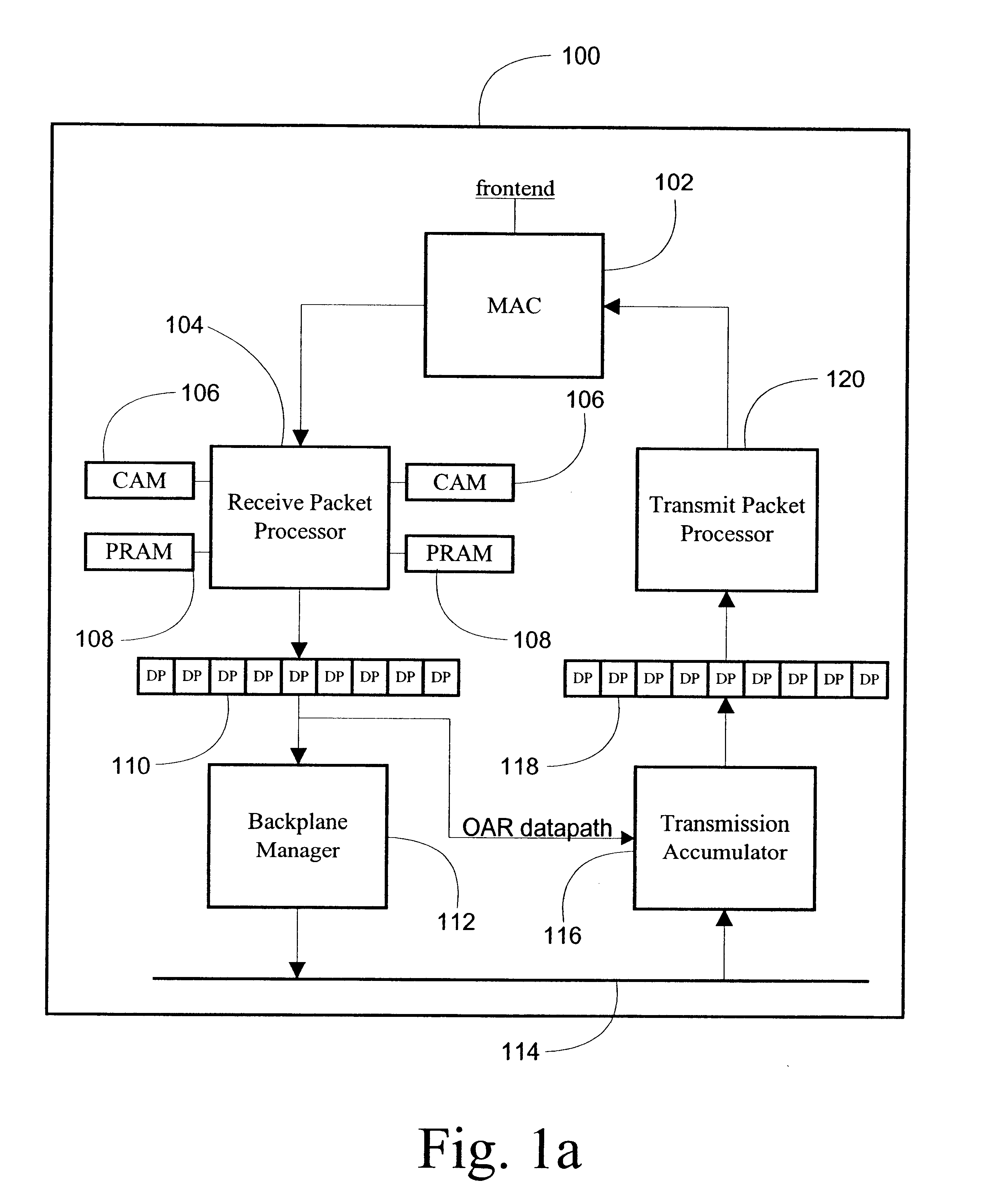

System and method for high speed packet transmission implementing dual transmit and receive pipelines

InactiveUS6901072B1Multiplex system selection arrangementsCircuit switching systemsGigabitStructure of Management Information

The present invention provides systems and methods for providing data transmission speeds at or in excess of 10 gigabits per second between one or more source devices and one or more destination devices. According to one embodiment, the system of the present invention comprises a first and second media access control (MAC) interfaces to facilitate receipt and transmission of packets over an associated set of physical interfaces. The system also contemplates a first and second field programmable gate arrays (FPGA) coupled to the MAC interfaces and an associated first and second memory structures, the first and second FPGAs are configured to perform initial processing of packets received from the first and second MAC interfaces and to schedule the transmission of packets to the first and second MAC interface for transmission to one or more destination devices. The first and second FPGAs are further operative to dispatch and retrieve packets to and from the first and second memory structures. A third FPGA, coupled to the first and second memory structures and a backplane, is operative to retrieve and dispatch packets to and from the first and second memory structures, compute appropriate destinations for packets and organize packets for transmission. The third FPGA is further operative to receive and dispatch packets to and from the backplane.

Owner:AVAGO TECH INT SALES PTE LTD

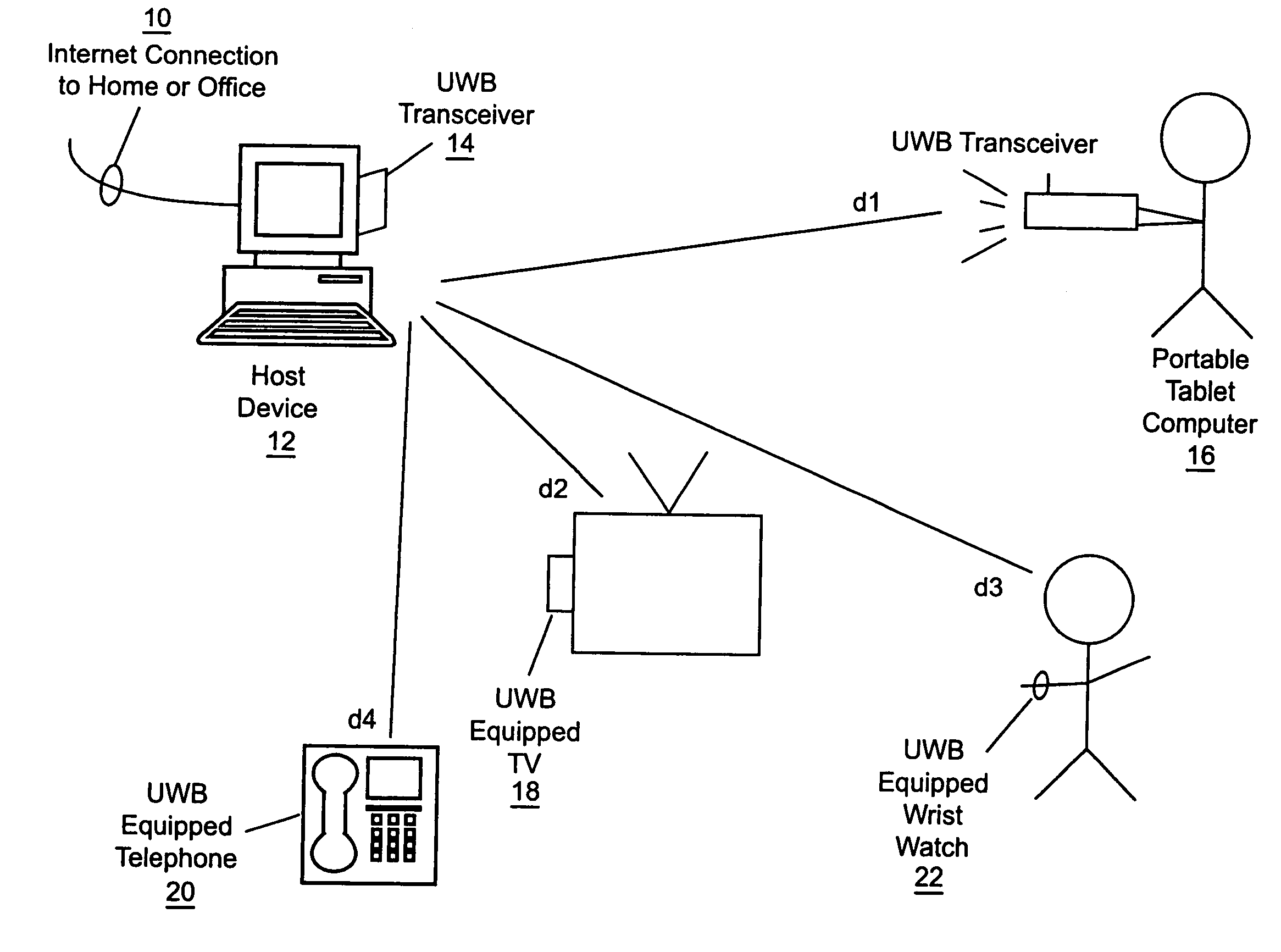

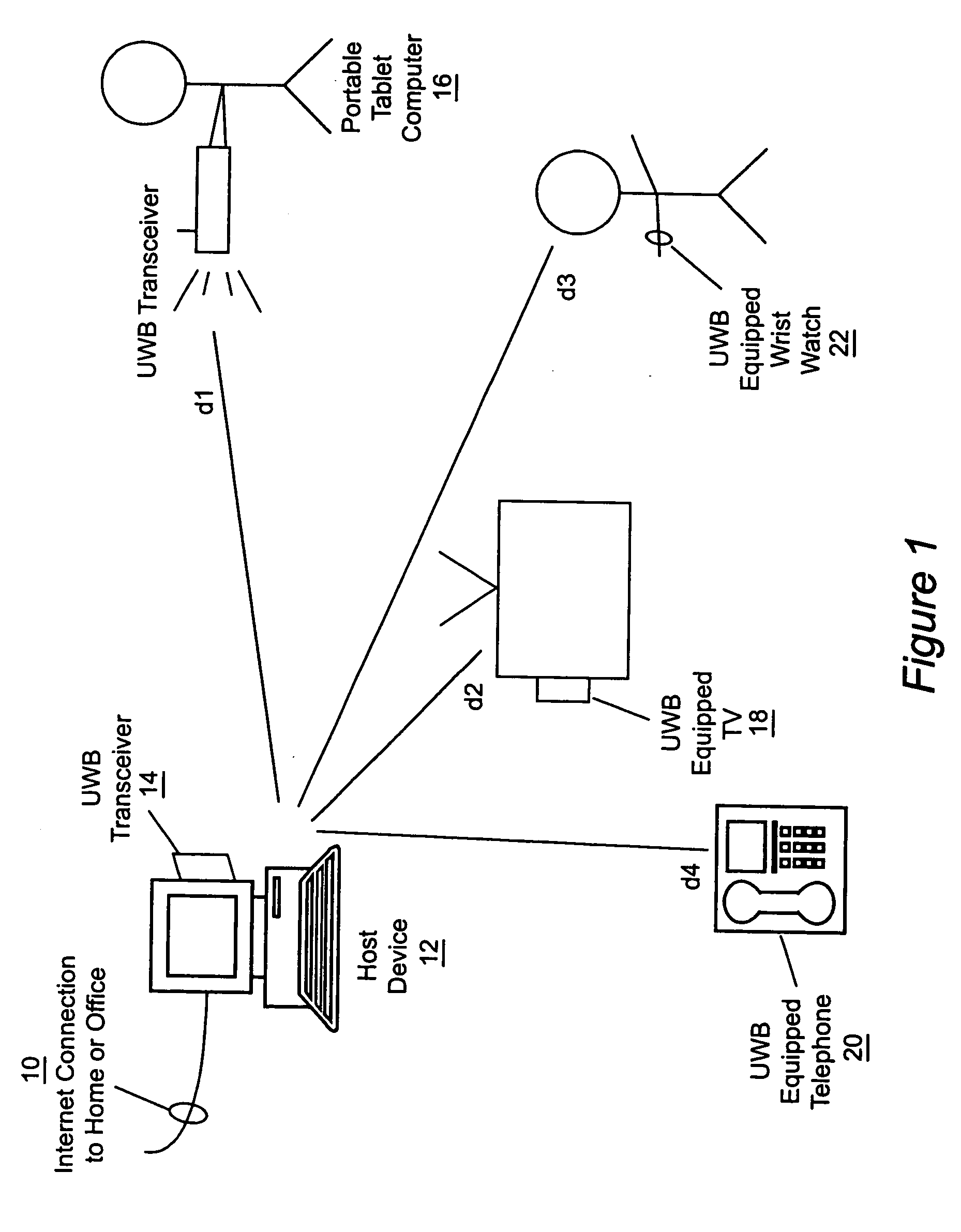

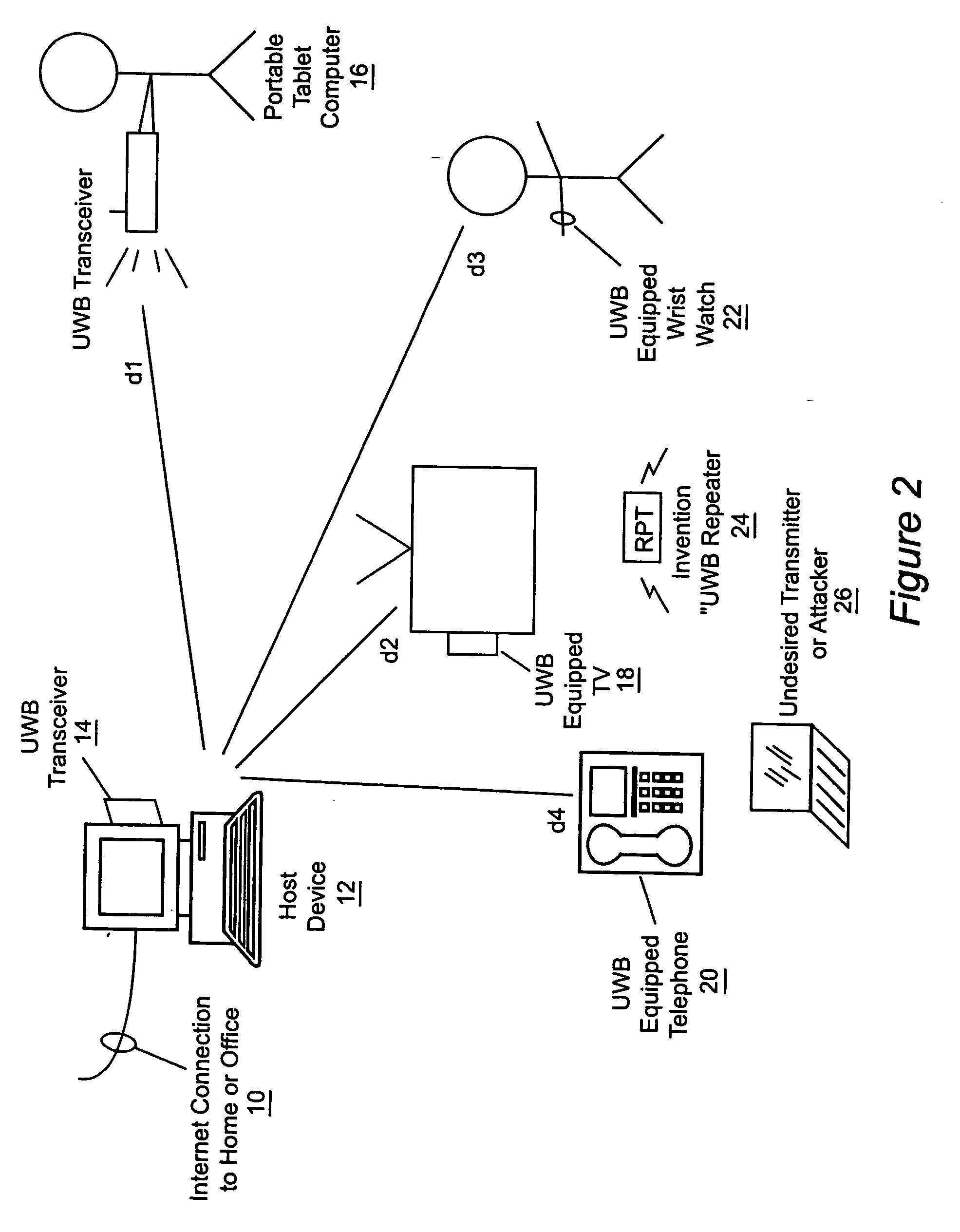

Broadband repeater with security for ultrawideband technologies

ActiveUS20050042999A1Improve wireless network performanceLow costFrequency-division multiplex detailsActive radio relay systemsTransceiverEngineering

An ultrawideband radio transceiver / repeater provides a low cost infrastructure solution that merges wireless and wired network devices while providing connection to the plant, flexible repeater capabilities, network security, traffic monitoring and provisioning, and traffic flow control for wired and wireless connectivity of devices or networks. The ultrawidebande radio transceiver / repeater can be implemented in discrete, integrated, distributed or embedded forms.

Owner:RAPPAPORT THEODORE S

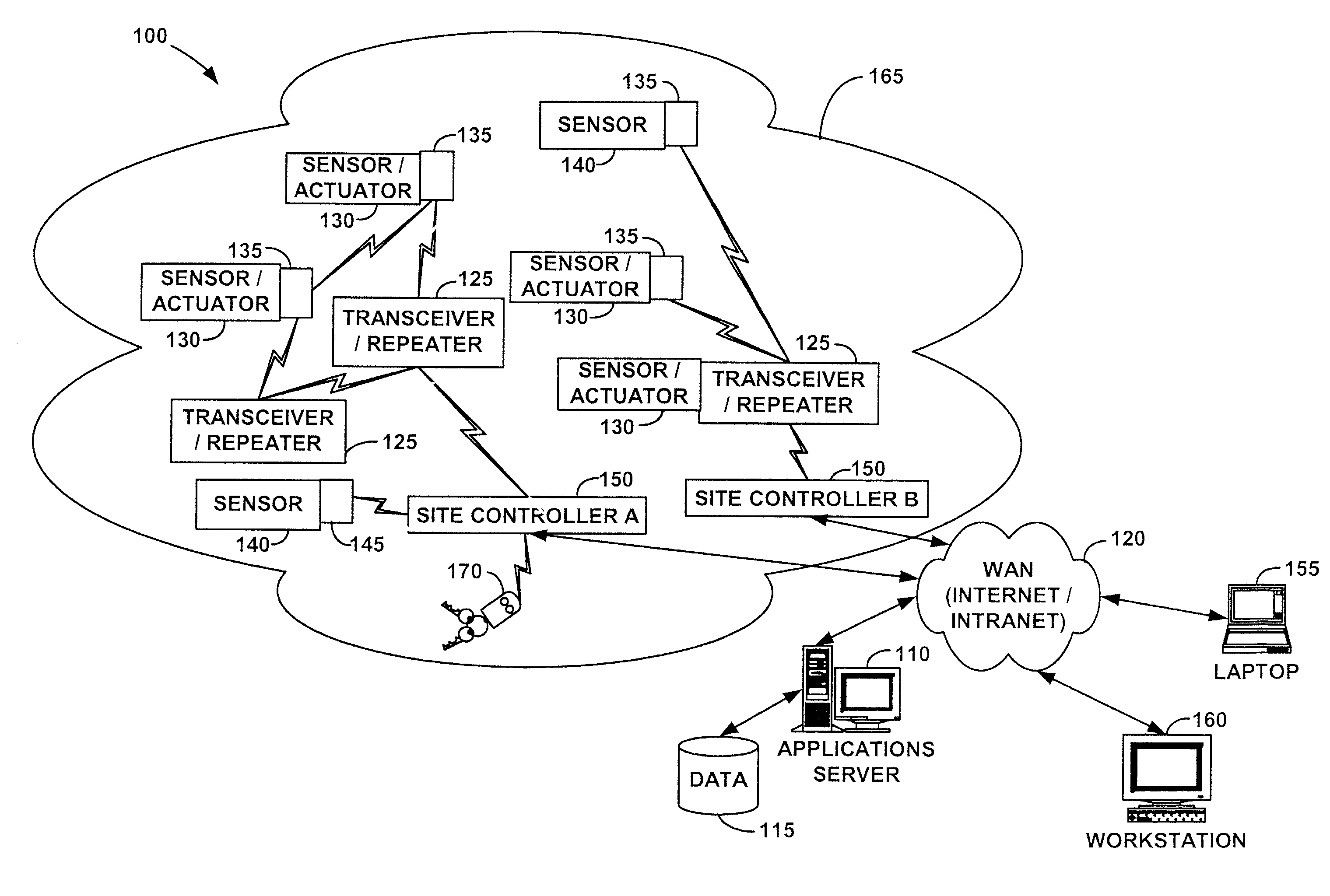

Systems and methods for enabling a mobile user to notify an automated monitoring system of an emergency situation

InactiveUS7263073B2Electric signal transmission systemsCircuit arrangementsTransceiverMonitoring system

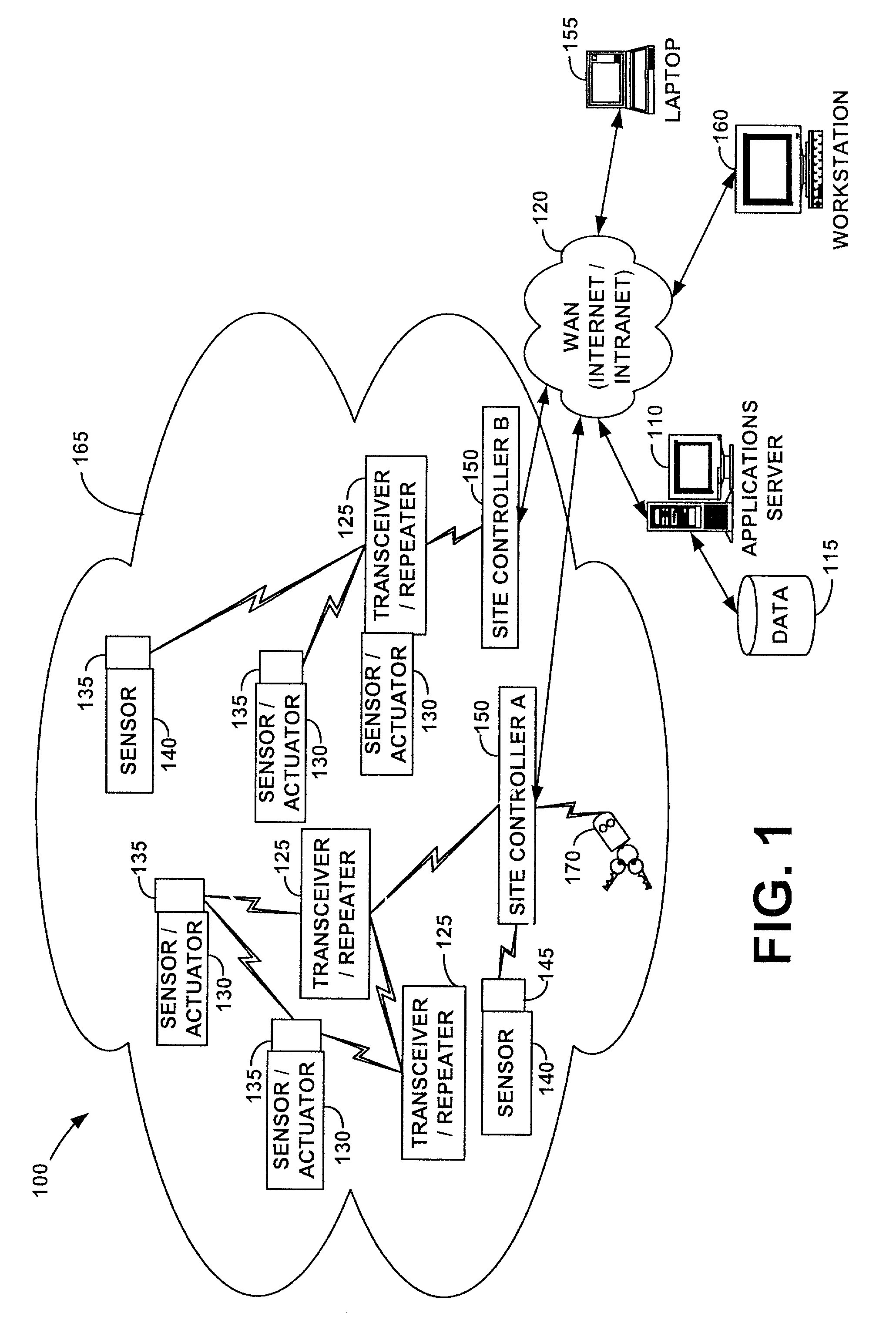

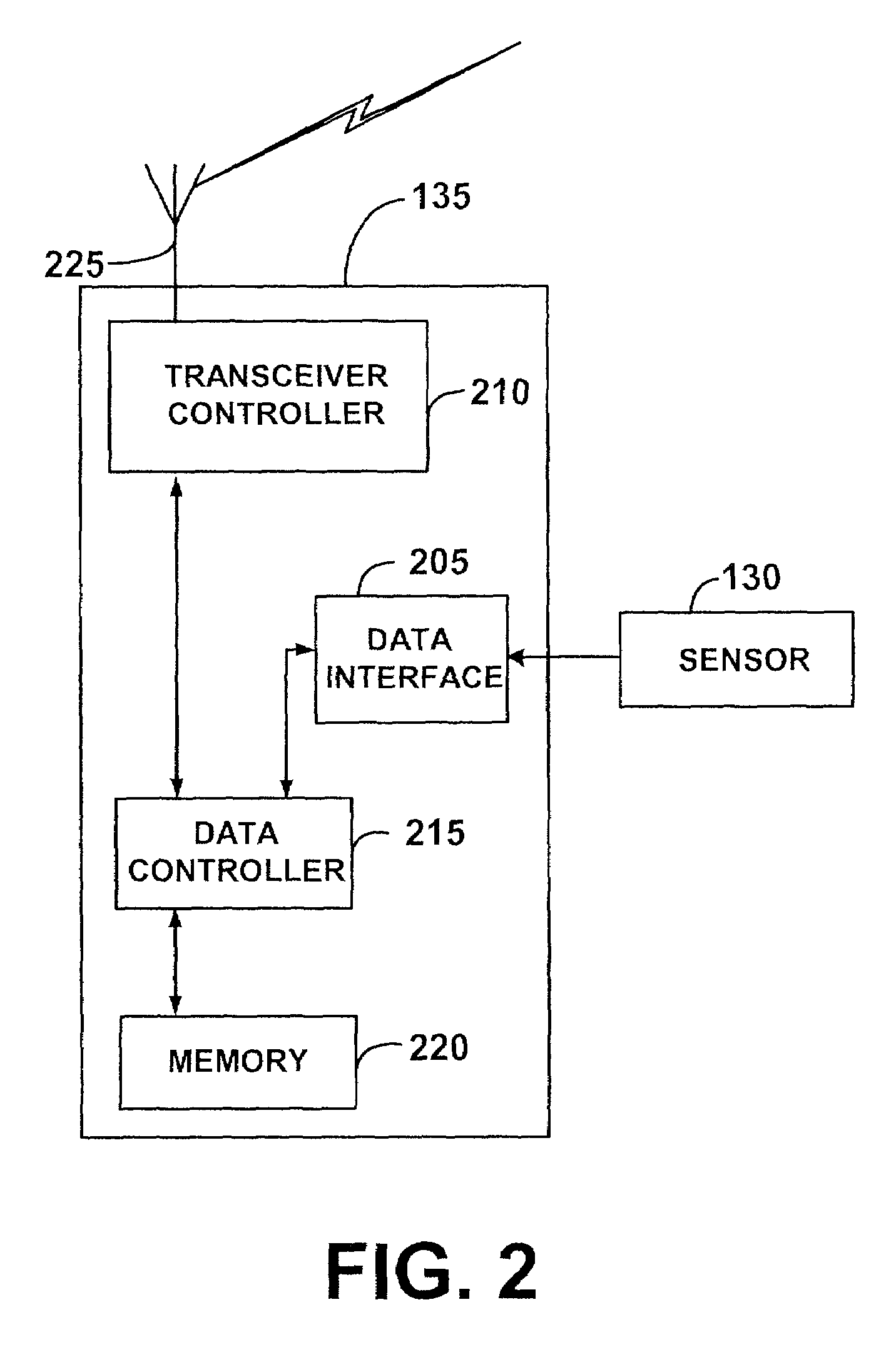

Systems and methods for enabling a mobile user to notify an automated monitoring system of an emergency situation are provided. The automated monitoring system may be configured for monitoring and controlling a plurality of remote devices and may comprise a site controller in communication with the plurality of remote devices via a plurality of transceivers defining a wireless communication network and in communication with a host computer via a wide area network. Briefly described, one such method comprises the steps of: receiving notification that the mobile user desires to initiate transmission of an emergency message to the site controller; determining the identity of the mobile user; and providing an emergency message over the wireless communication network for delivery to the site controller, the emergency message indicating the identity of the mobile user.

Owner:SIPCO

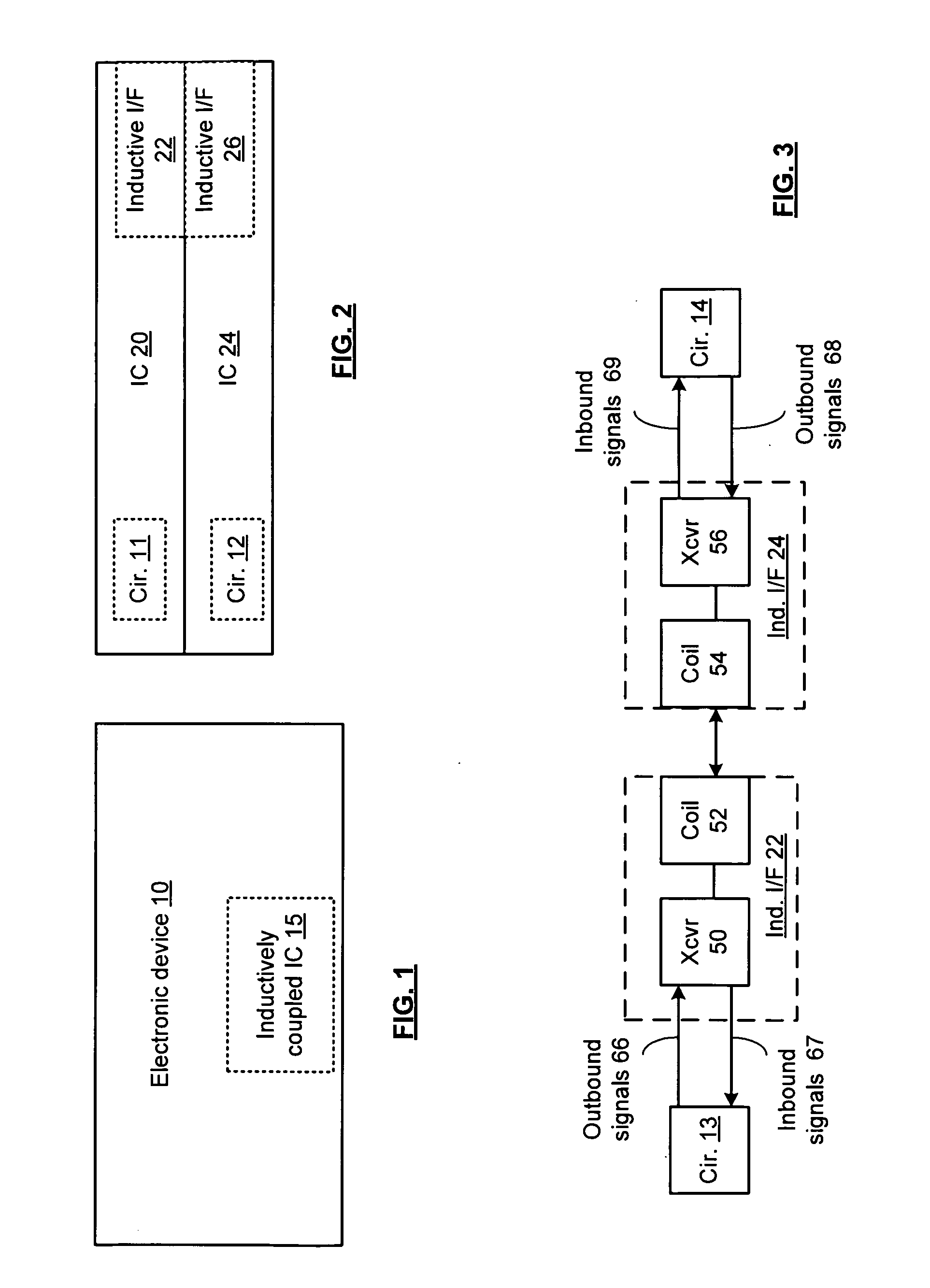

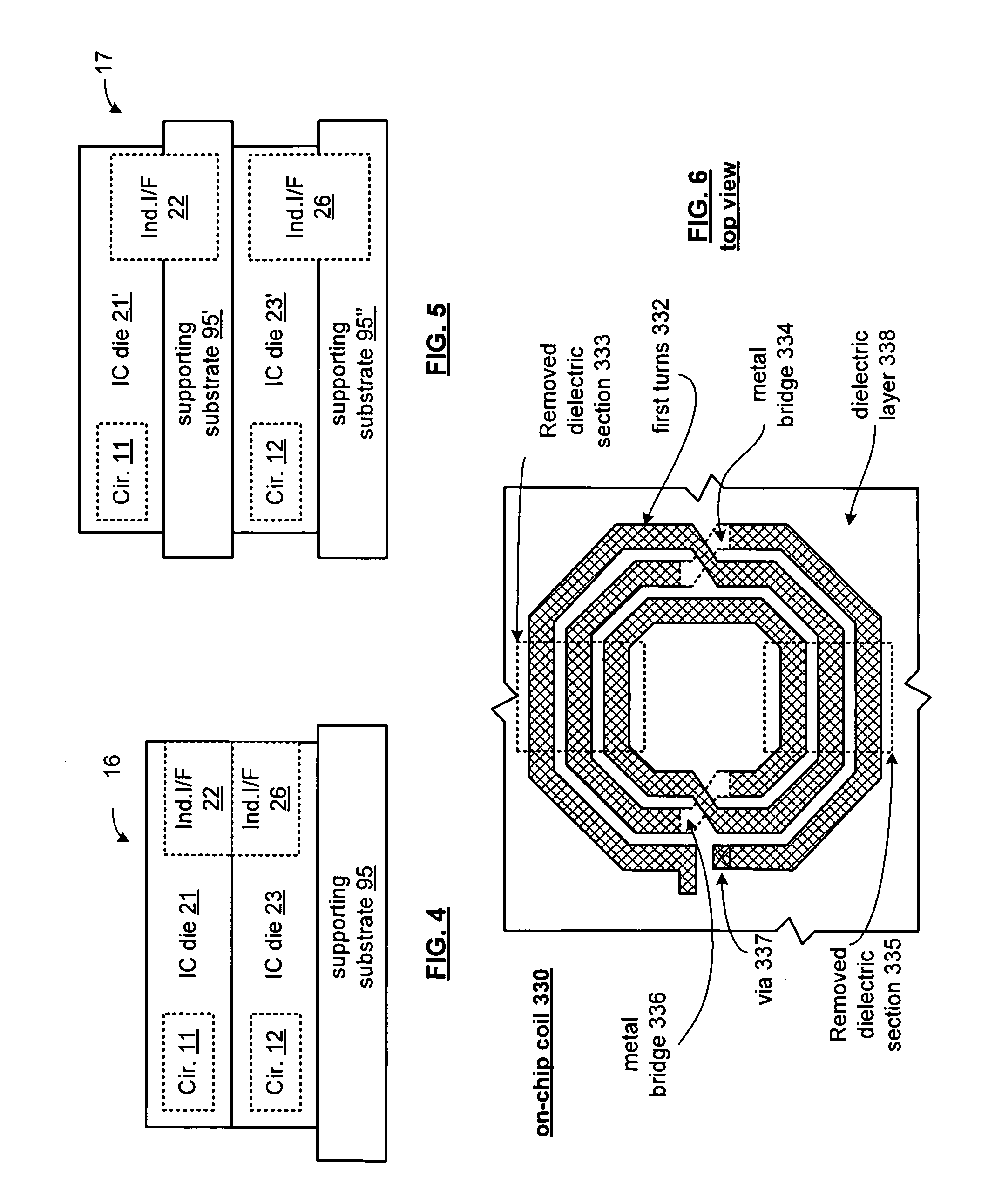

Integrated circuit with millimeter wave and inductive coupling and methods for use therewith

ActiveUS20090218407A1Near-field transmissionSemiconductor/solid-state device detailsEngineeringMillimetre wave

A circuit includes a plurality of integrated circuits or dies having corresponding circuits, the plurality of integrated circuits or dies include a first plurality of integrated circuits or dies having corresponding millimeter wave interfaces and a second plurality of integrated circuits or dies having corresponding inductive interfaces. The first plurality of integrated circuits or dies communicate first signals therebetween via the corresponding millimeter wave interfaces and the second plurality of integrated circuits or dies communicate second signals therebetween via the corresponding inductive interfaces.

Owner:AVAGO TECH INT SALES PTE LTD

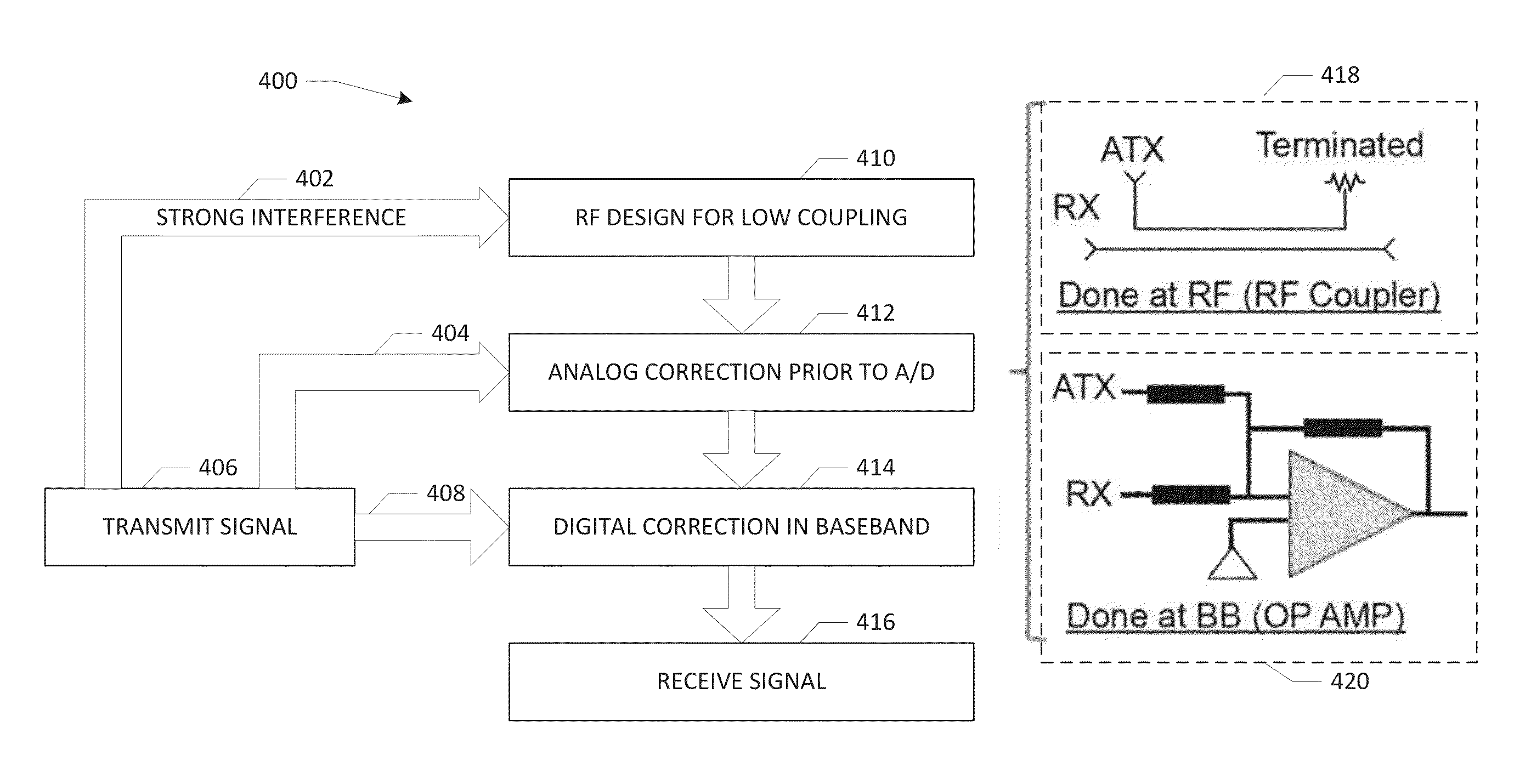

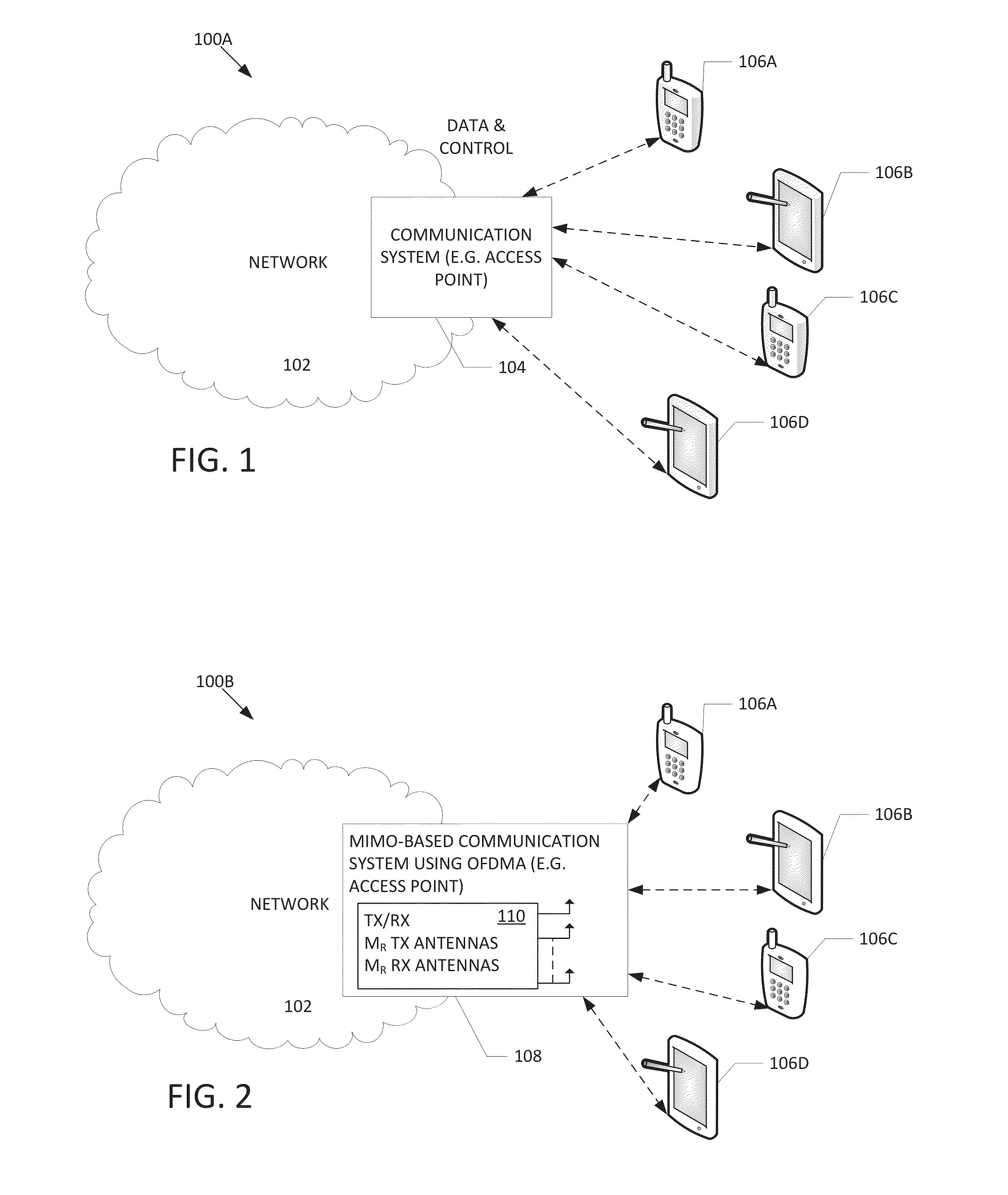

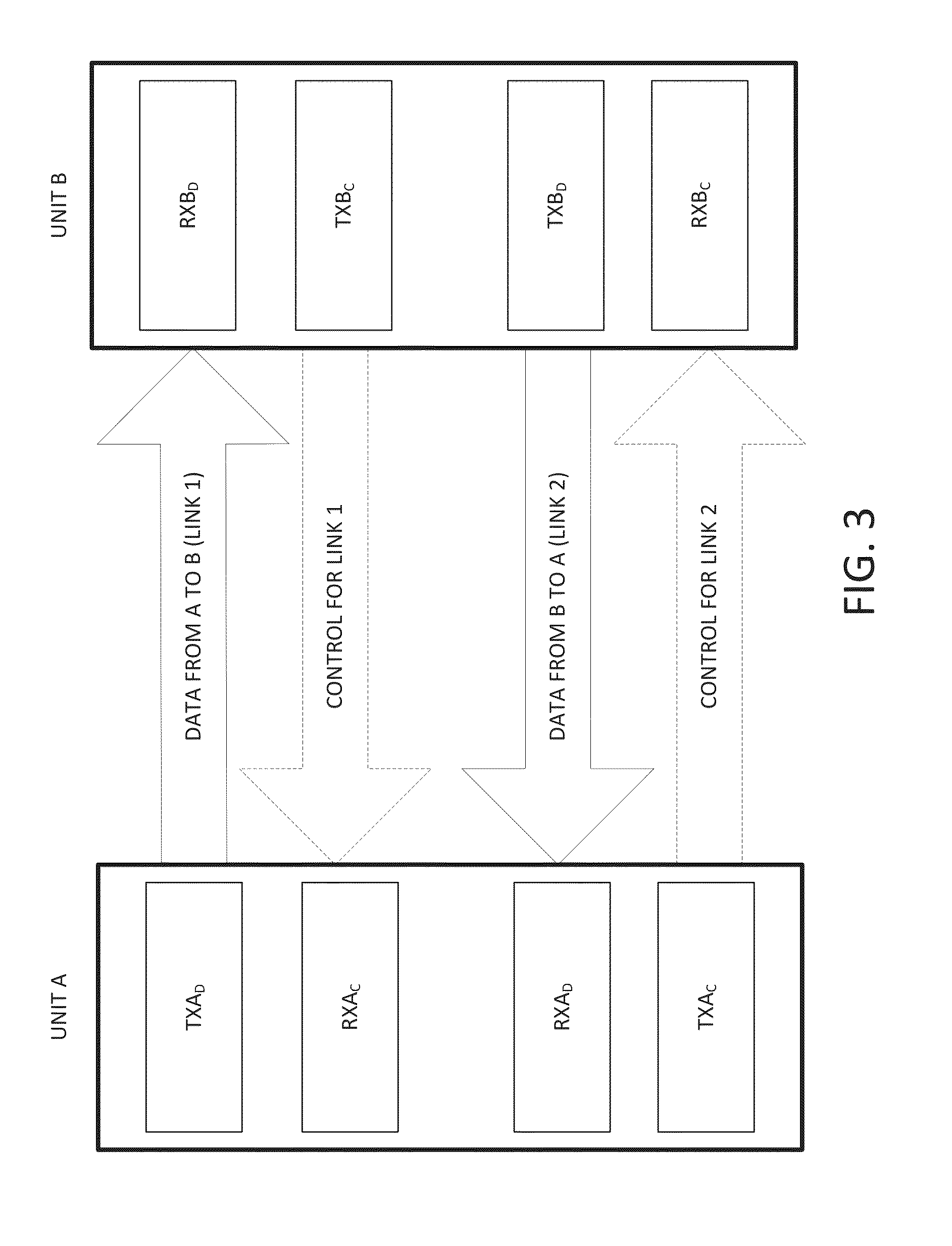

Full Duplex Wireless Transmission with Self-Interference Cancellation

ActiveUS20130301487A1Error prevention/detection by using return channelSite diversitySelf interferenceWireless transmission

Two-way (full-duplex) wireless communications. Various embodiments measure interference channels and provide for interference cancellation in both analog and digital domains to mitigate self-interference. The system supports multiple clients wherein new clients can join the network asynchronously, and also supports Multiple-Input Multiple-Output (MIMO) antennas.

Owner:KHANDANI AMIR KEYVAN

Data communication systems and methods

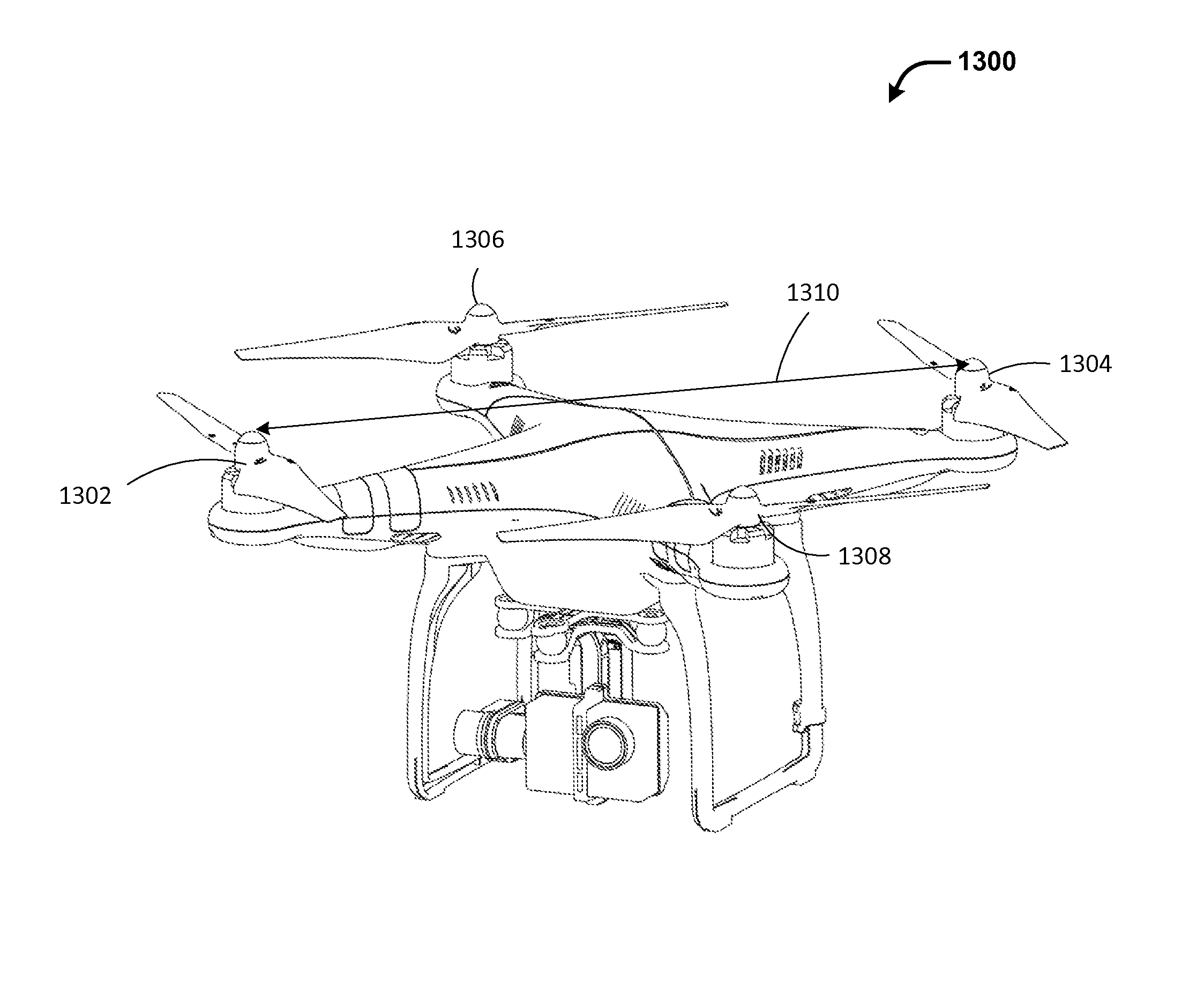

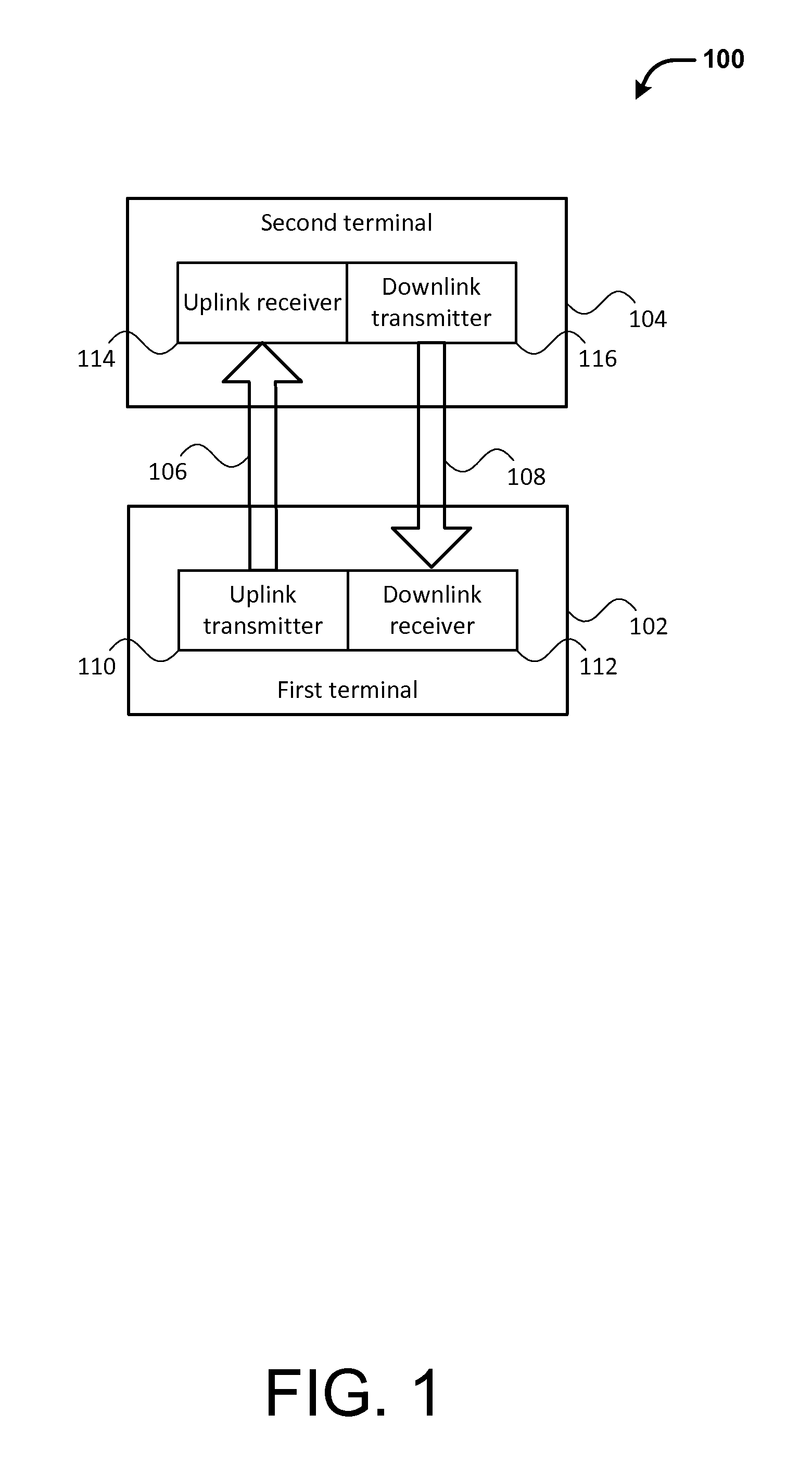

ActiveUS8908573B1Facilitate data communicationAvoid interferenceError detection/prevention using signal quality detectorCriteria allocationCommunications systemBroadband transmission

The present invention provides systems and methods for improved data communication between communication terminals such as a base station and an unmanned aerial vehicle. In some instances, the systems and methods described herein provide robust transmission uplink data such as control data and wideband transmission of downlink data such as image data or other sensor data, while avoiding interference between the uplink data transmission and the downlink transmission.

Owner:SZ DJI TECH CO LTD

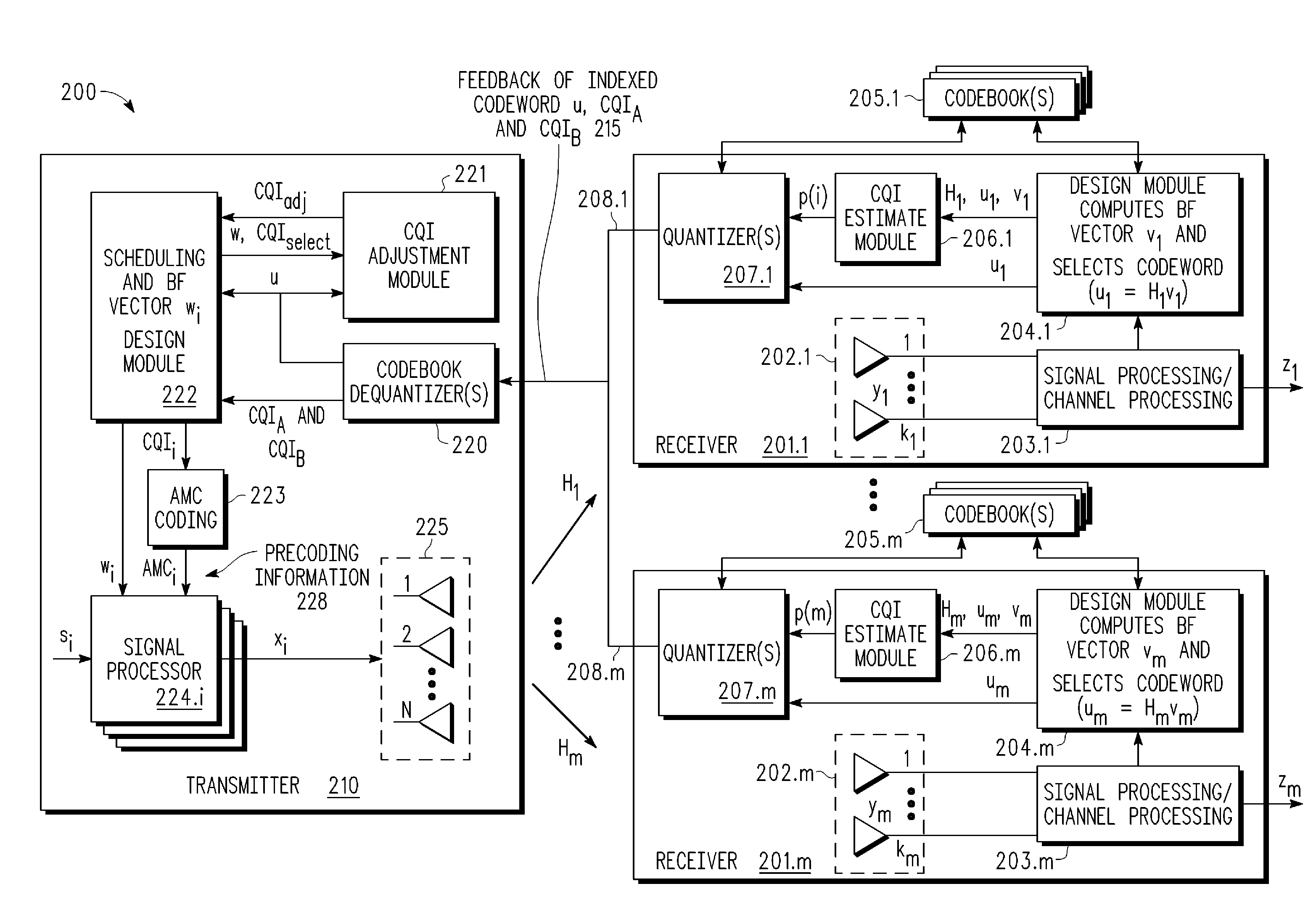

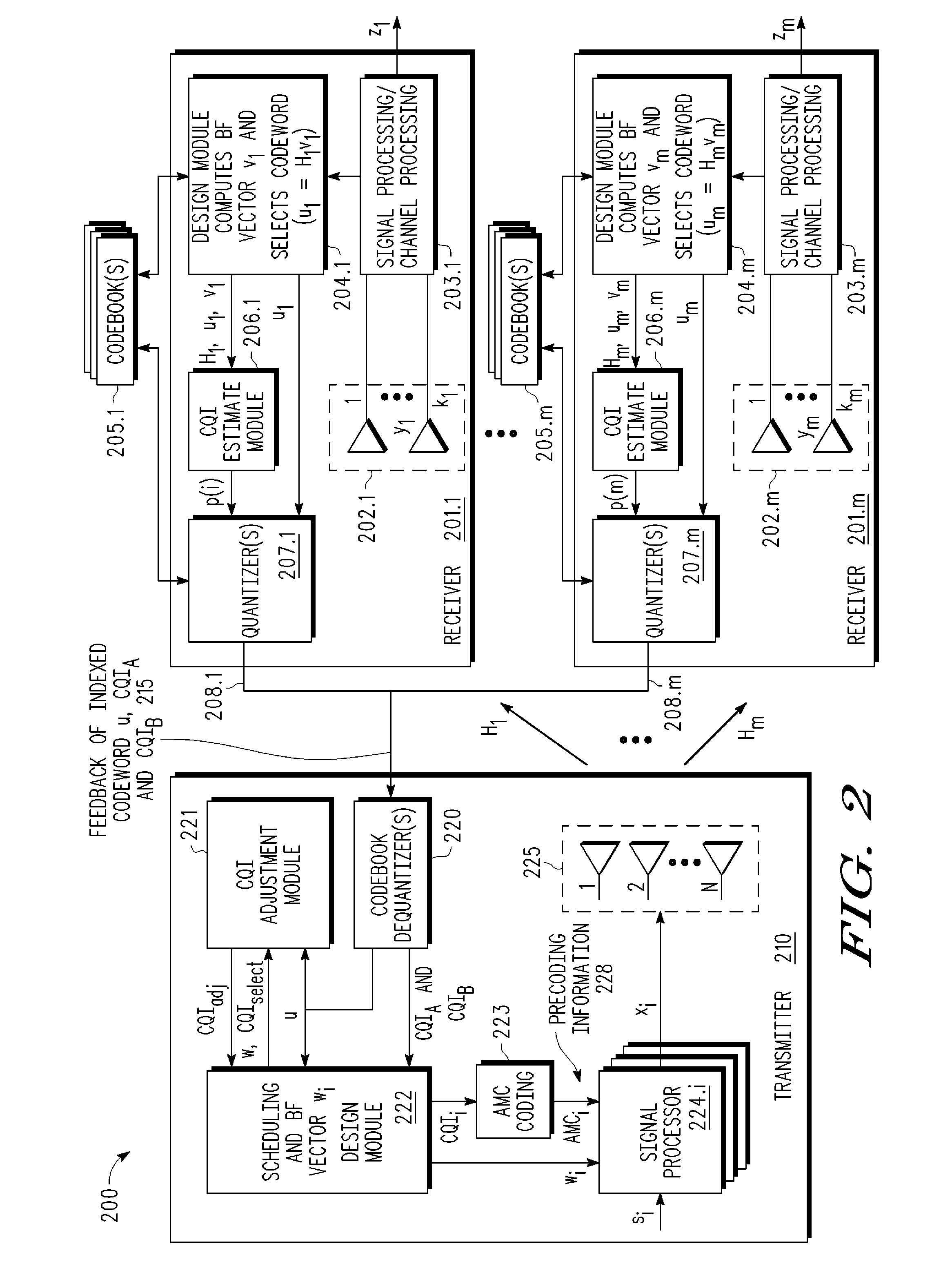

Multi-user MIMO-SDMA for finite rate feedback systems

ActiveUS20080165875A1Diversity/multi-antenna systemsSecret communicationDownlink beamformingSignal-to-noise ratio (imaging)

A multi-user MIMO downlink beamforming system with limited feedback (200) is provided to enable preceding for multi-stream transmission, where a channel codeword (ui) and one or more channel quality indicator values (CQIA, CQIB) are computed at the user equipment (201.i) on the basis of maximizing a predetermined SINR performance metric (ρi) which estimates the receive signal-to-noise-ratio (SINR) at the user equipment (201.i). The computed codeword (ui) and CQI values (or differential values related thereto) are quantized and fed back to help the base station (210) which applies a correction to the appropriate CQI value in the course of designing the transmit beamforming vectors w and determining the appropriate modulation and coding level to be used for downlink data transmission.

Owner:APPLE INC

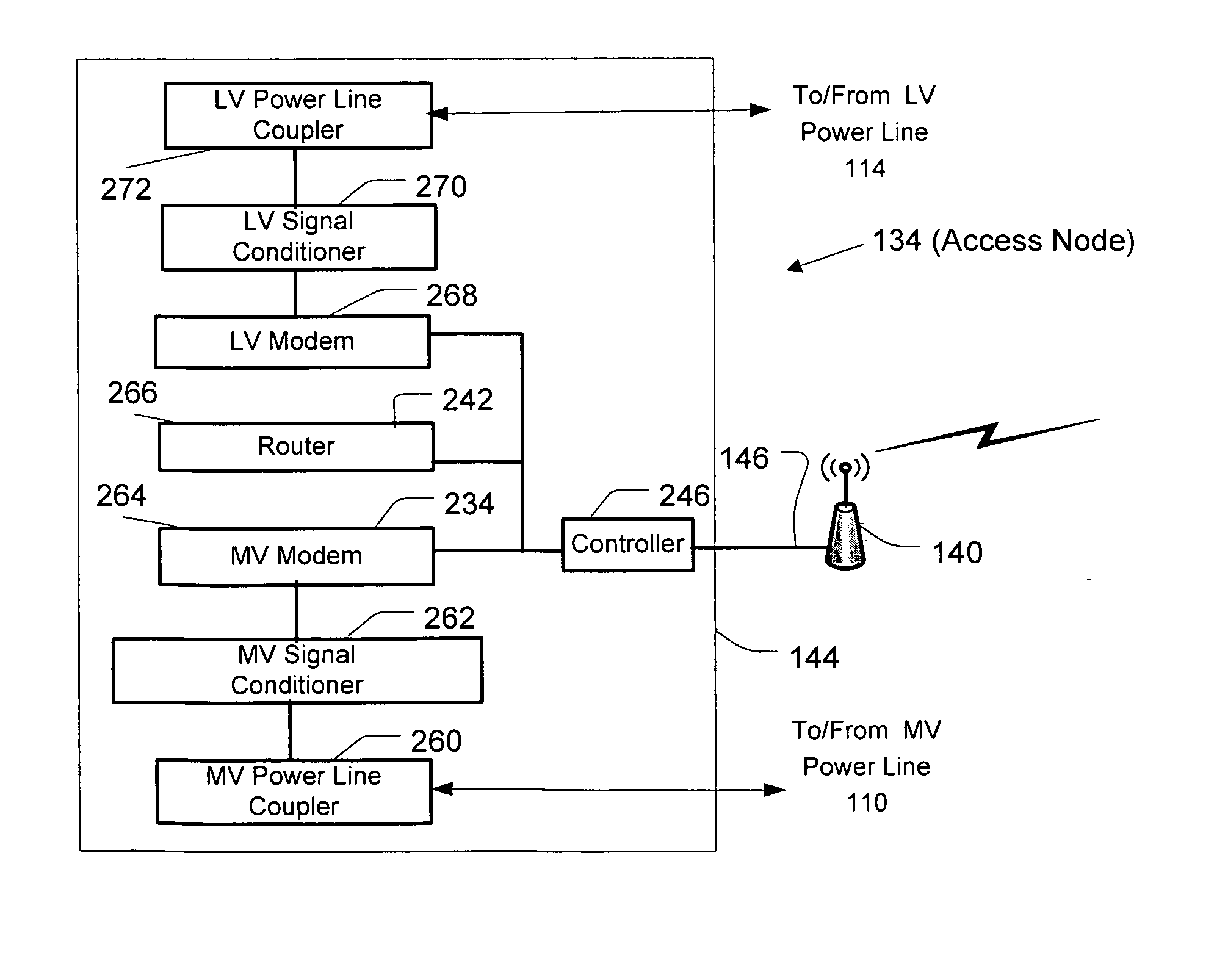

Hybrid power line wireless communication network

InactiveUS20070201540A1Wireless systems/telephoneLock network applicationsCommunications systemLow voltage

A hybrid power line wireless communication system may include an access controller and plurality of communication nodes that each may include a wireless access point coupled to a power line communication device. The wireless access points may provide wireless broadband communications to one or more user devices while the power line communication devices may provide low voltage power line broadband communications. The access controller remotely manages the wireless access points by sending control messages to the communication nodes. Control messages may traverse a power line, a non-power line medium, and / or a wireless medium. Control messages may include information relating to encryption parameters, transmission power levels, communication channels, access control, and other such parameters.

Owner:CURRENT TECH

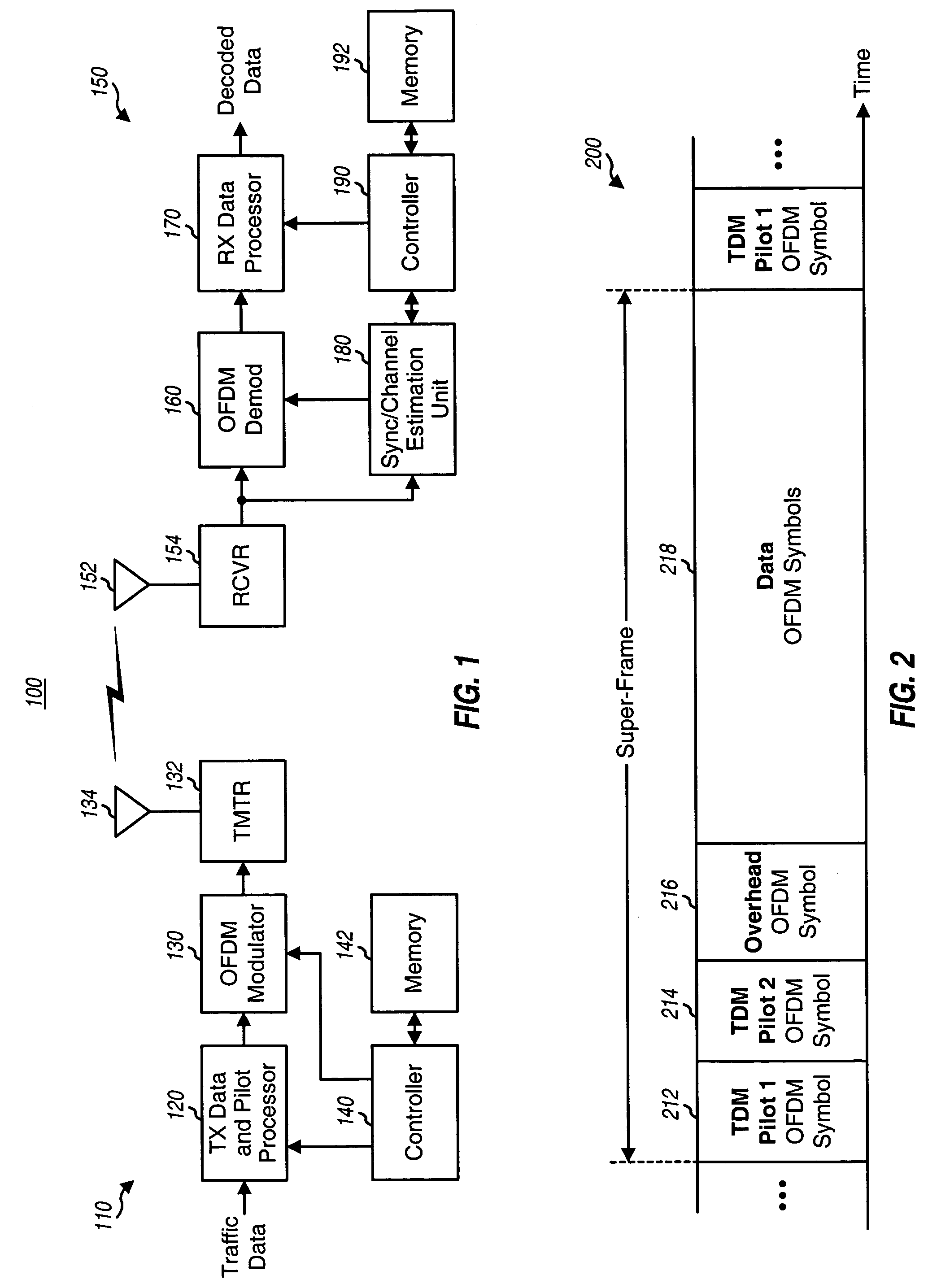

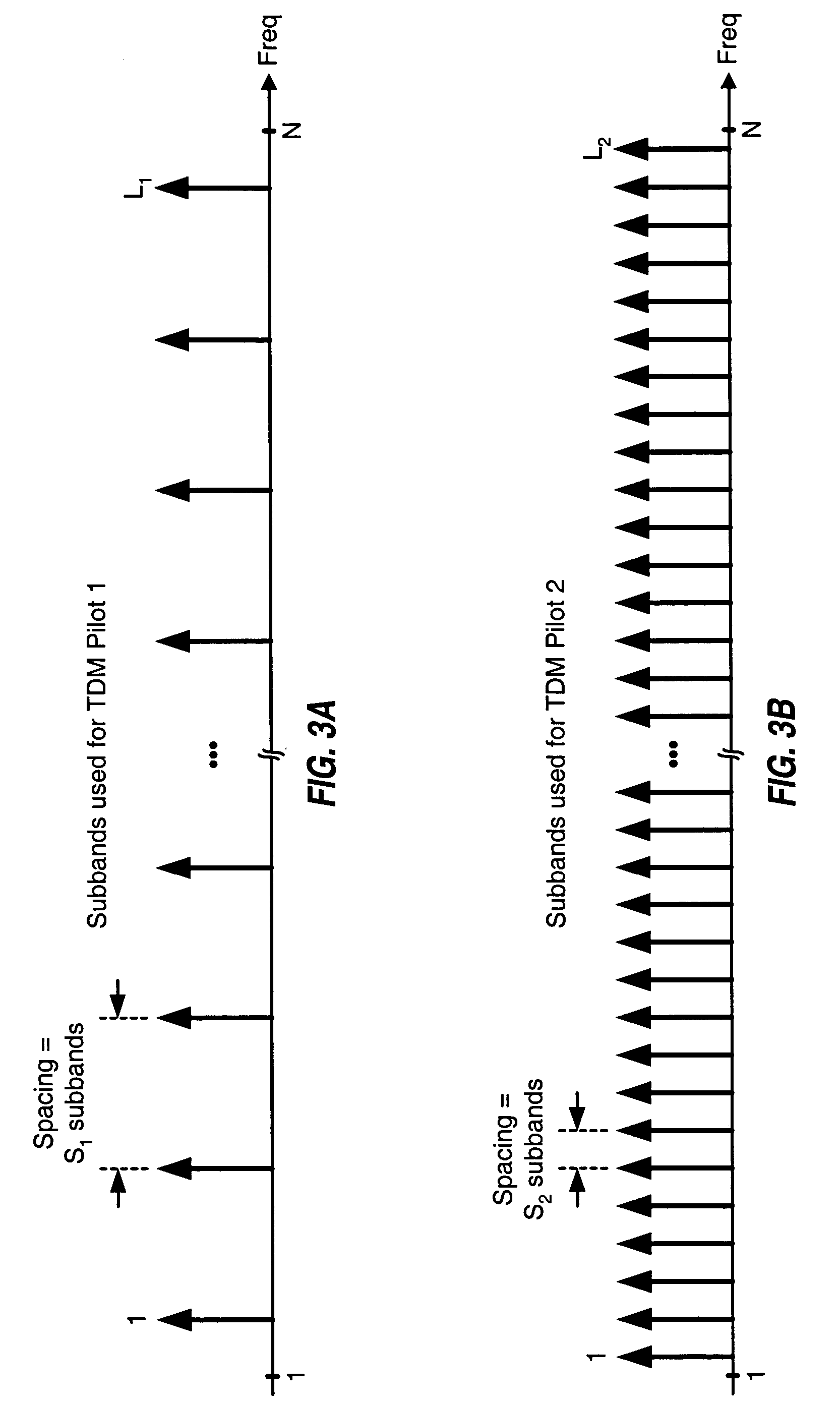

Synchronization in a broadcast OFDM system using time division multiplexed pilots

InactiveUS20050063298A1Accurate channel estimationTransmission control/equlisationFrequency-division multiplex detailsChannel impulse responseTime-division multiplexing

In an OFDM system, a transmitter broadcasts a first TDM pilot on a first set of subbands followed by a second TDM pilot on a second set of subbands in each frame. The subbands in each set are selected from among N total subbands such that (1) an OFDM symbol for the first TDM pilot contains at least S1 identical pilot-1 sequences of length L1 and (2) an OFDM symbol for the second TDM pilot contains at least S2 identical pilot-2 sequences of length L2, where L2>L1, S1·L1=N, and S2·L2=N. The transmitter may also broadcast an FDM pilot. A receiver processes the first TDM pilot to obtain frame timing (e.g., by performing correlation between different pilot-1 sequences) and further processes the second TDM pilot to obtain symbol timing (e.g., by detecting for the start of a channel impulse response estimate derived from the second TDM pilot).

Owner:QUALCOMM INC

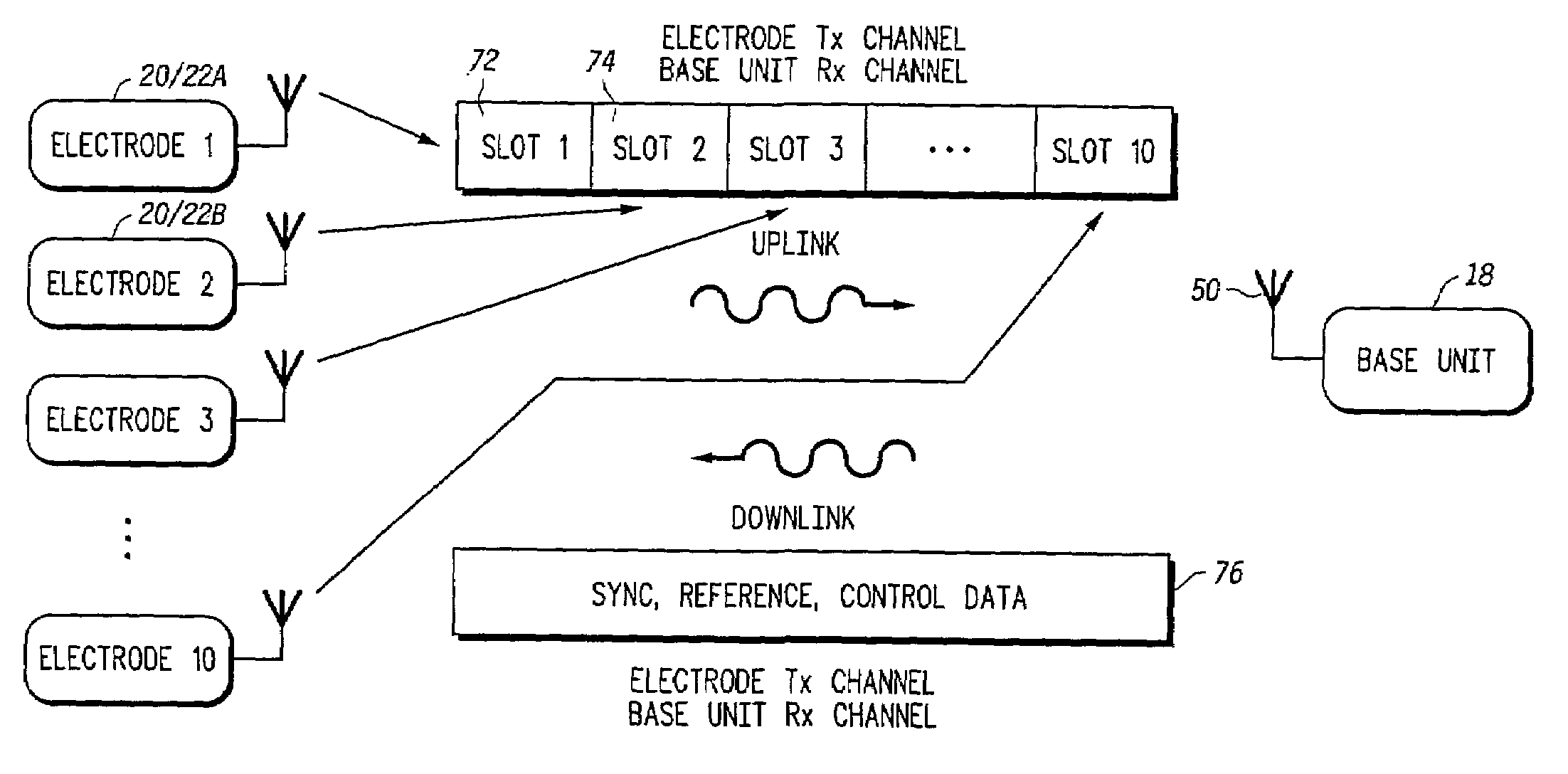

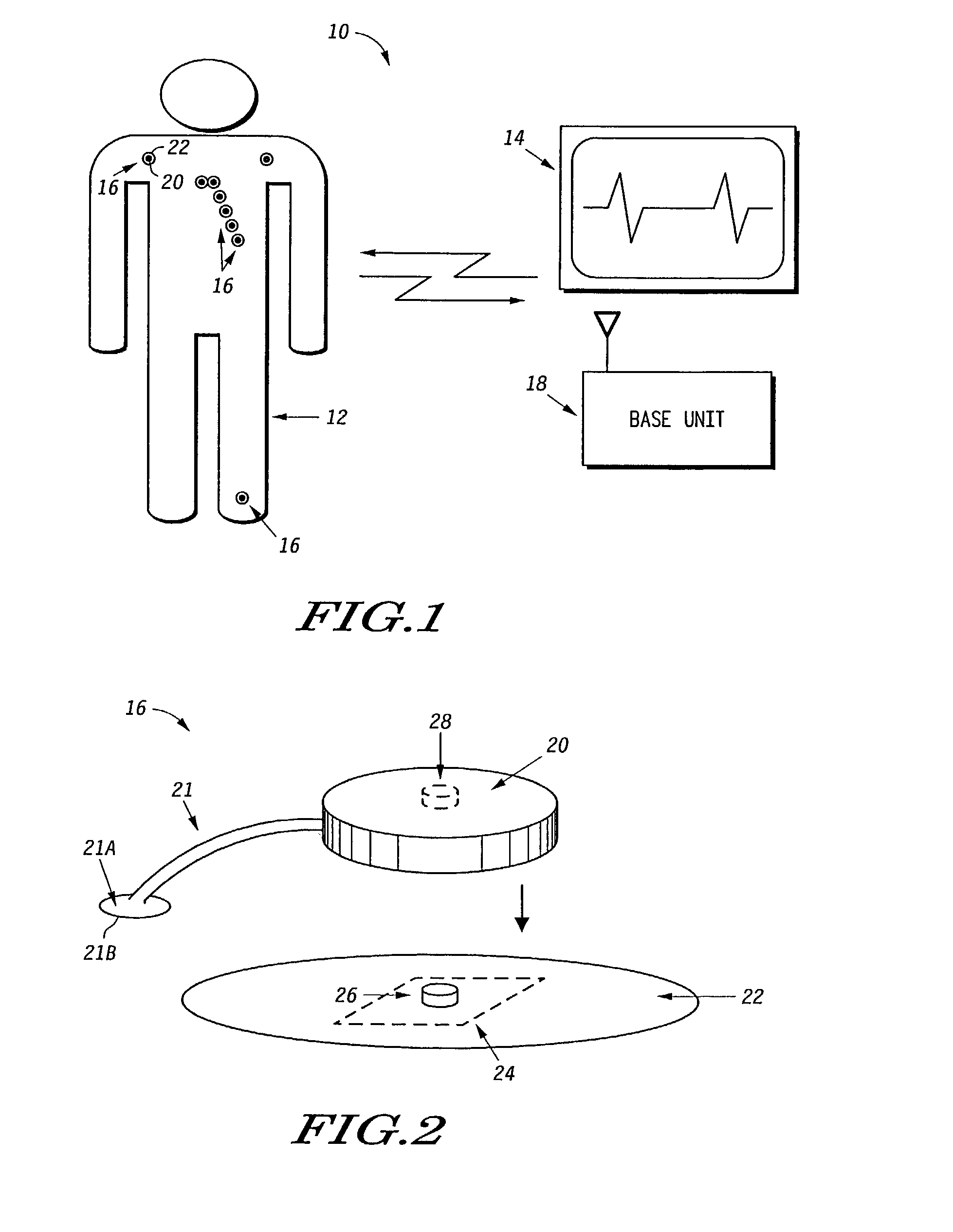

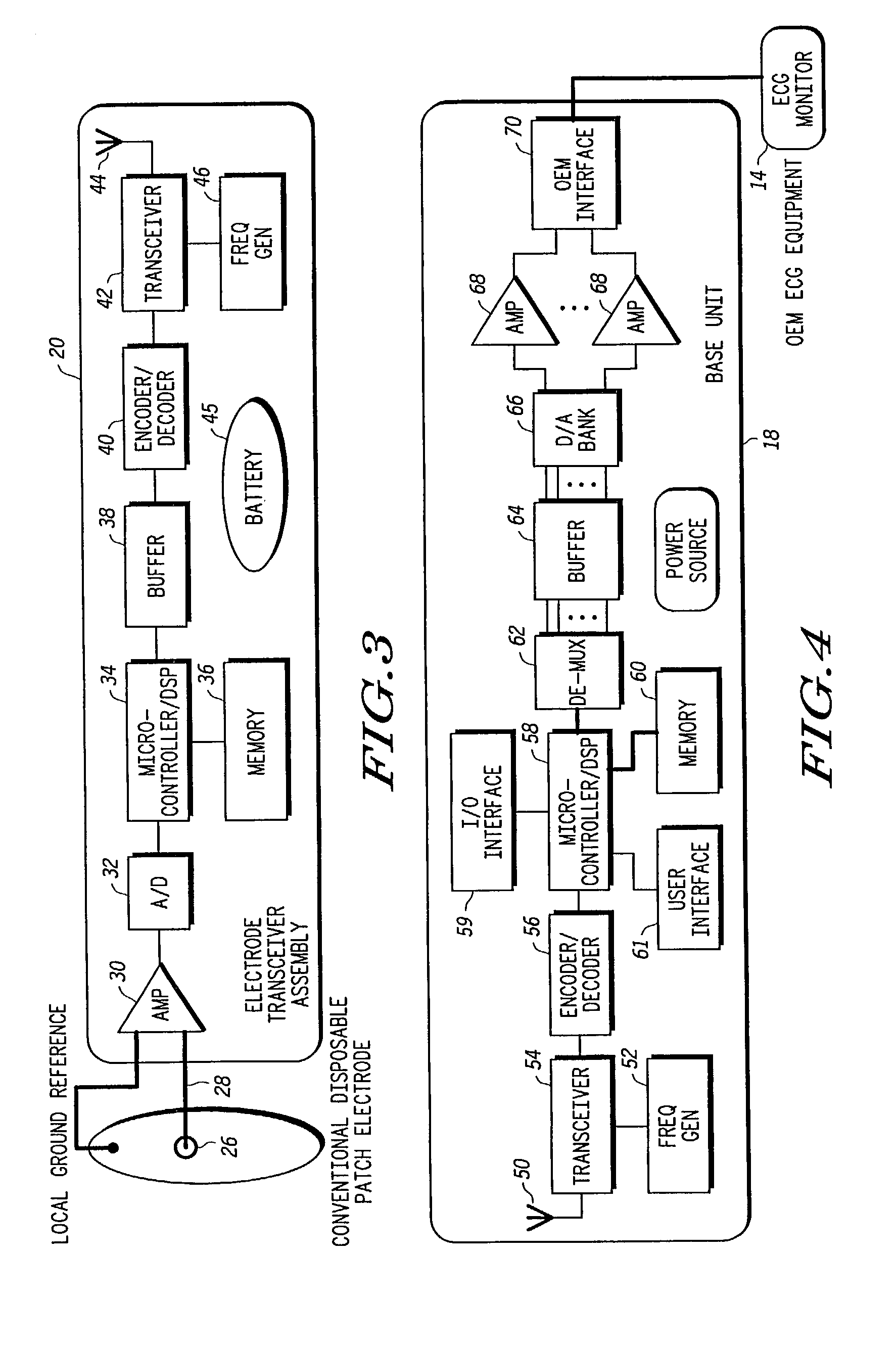

Programmable wireless electrode system for medical monitoring

InactiveUS6987965B2Consider flexibilityElectrocardiographyNetwork traffic/resource managementWireless transceiverTransceiver

A wireless, programmable system for bio-potential signal acquisition (e.g., electrocardiogram (ECG) data) includes a base unit and a plurality of individual wireless, remotely programmable transceivers that connect to patch electrodes. The base unit manages the transceivers by issuing registration, configuration, data acquisition, and transmission commands using wireless techniques. Bio-potential signals from the wireless transceivers are demultiplexed and supplied via a standard interface to a conventional monitor for display.

Owner:LIFESYNC

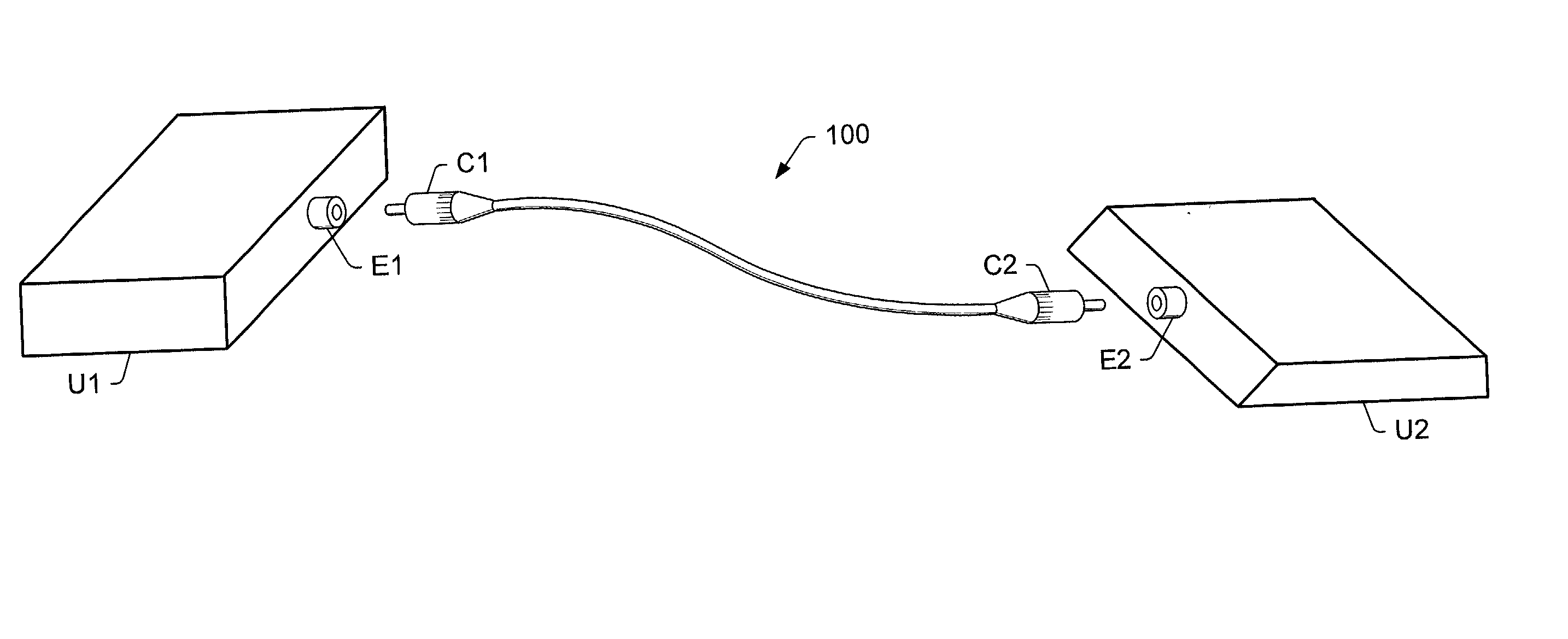

Hybrid electro-optic cable

InactiveUS20020126967A1Reduce initial system cost costReduce cost ongoing maintenance costCommunication cablesFlat/ribbon cablesElectricityFiber

A hybrid cable comprising an optical fiber, an intermediate layer surrounding the optical fiber, and an electrically insulating jacket surrounding the intermediate layer. The intermediate layers include a collection of metallic strands. The hybrid cable may be used to establish simultaneous electrical and fiber-optic connection between two communication devices. Thus, the two communication devices may simultaneously transfer optical signals through the optical fiber and perform any of various electrical functions (power transfer, eye safety control) through the metallic strands. For example, an optical transceiver may couple to an optical antenna unit through the hybrid cable. Such an optical transceiver may serve as part of a point-to-point link, a point-to-multipoint link, and / or, a link between a primary transceiver unit and an optical router.

Owner:SEAFORT INT TRADING SRL

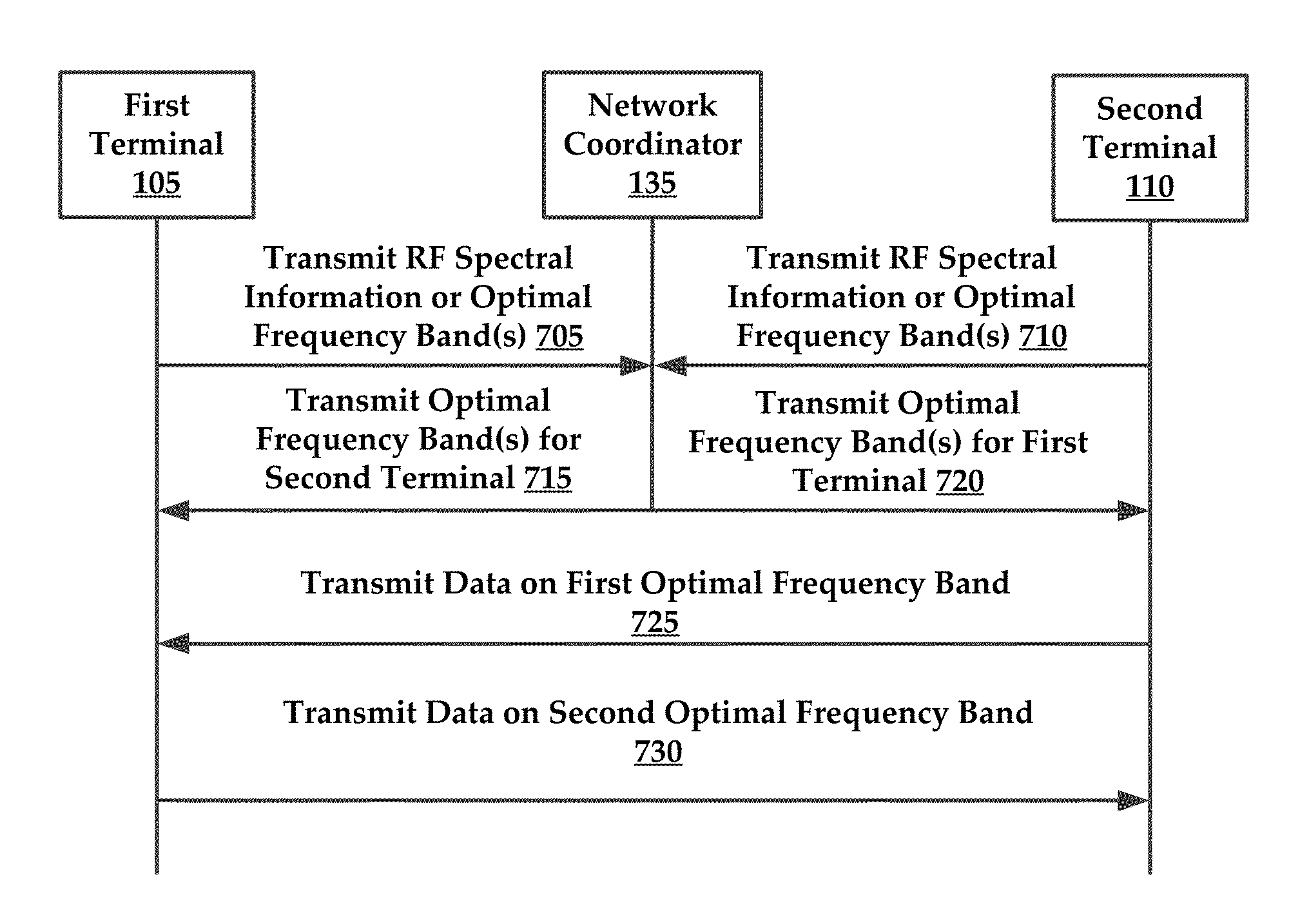

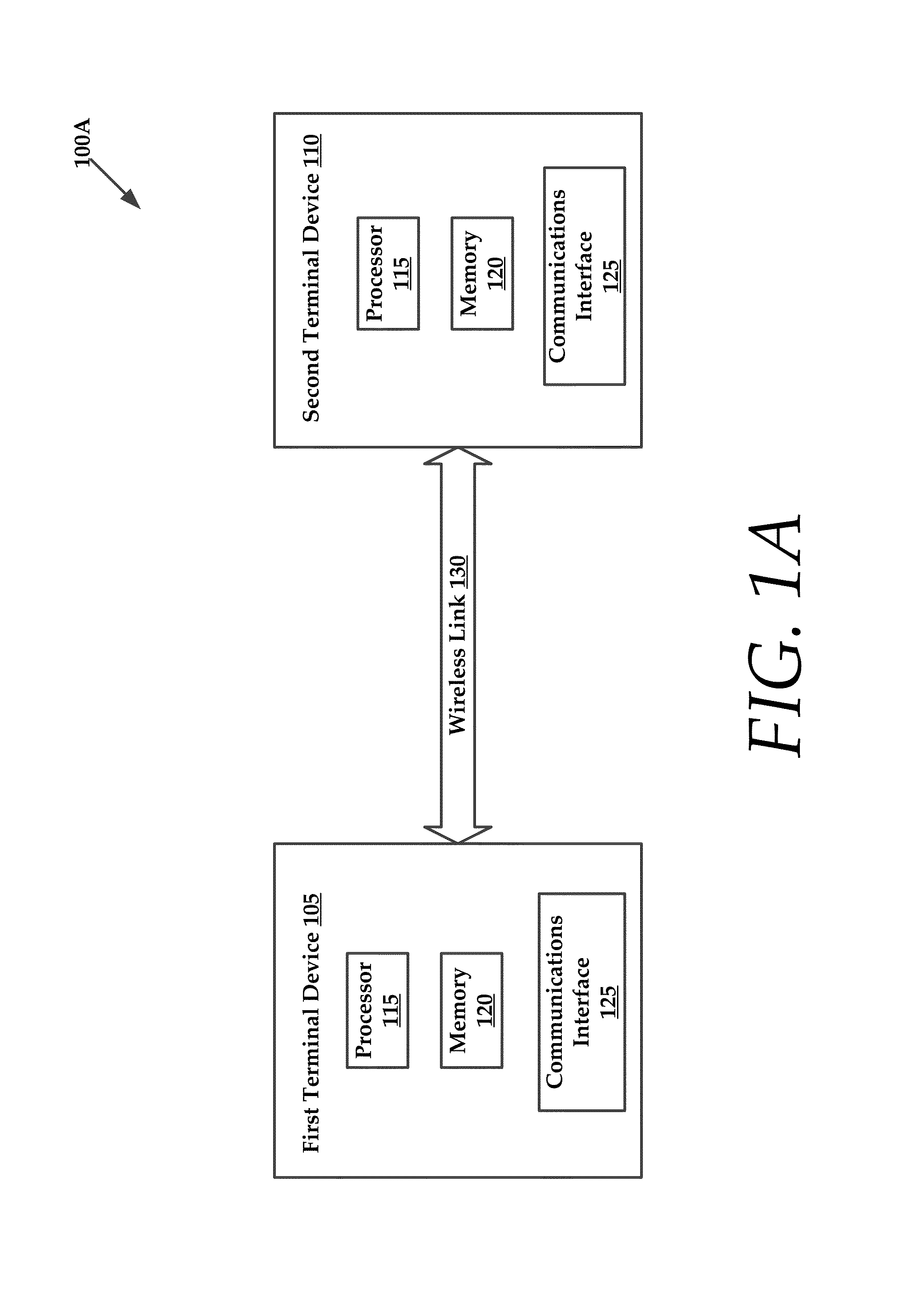

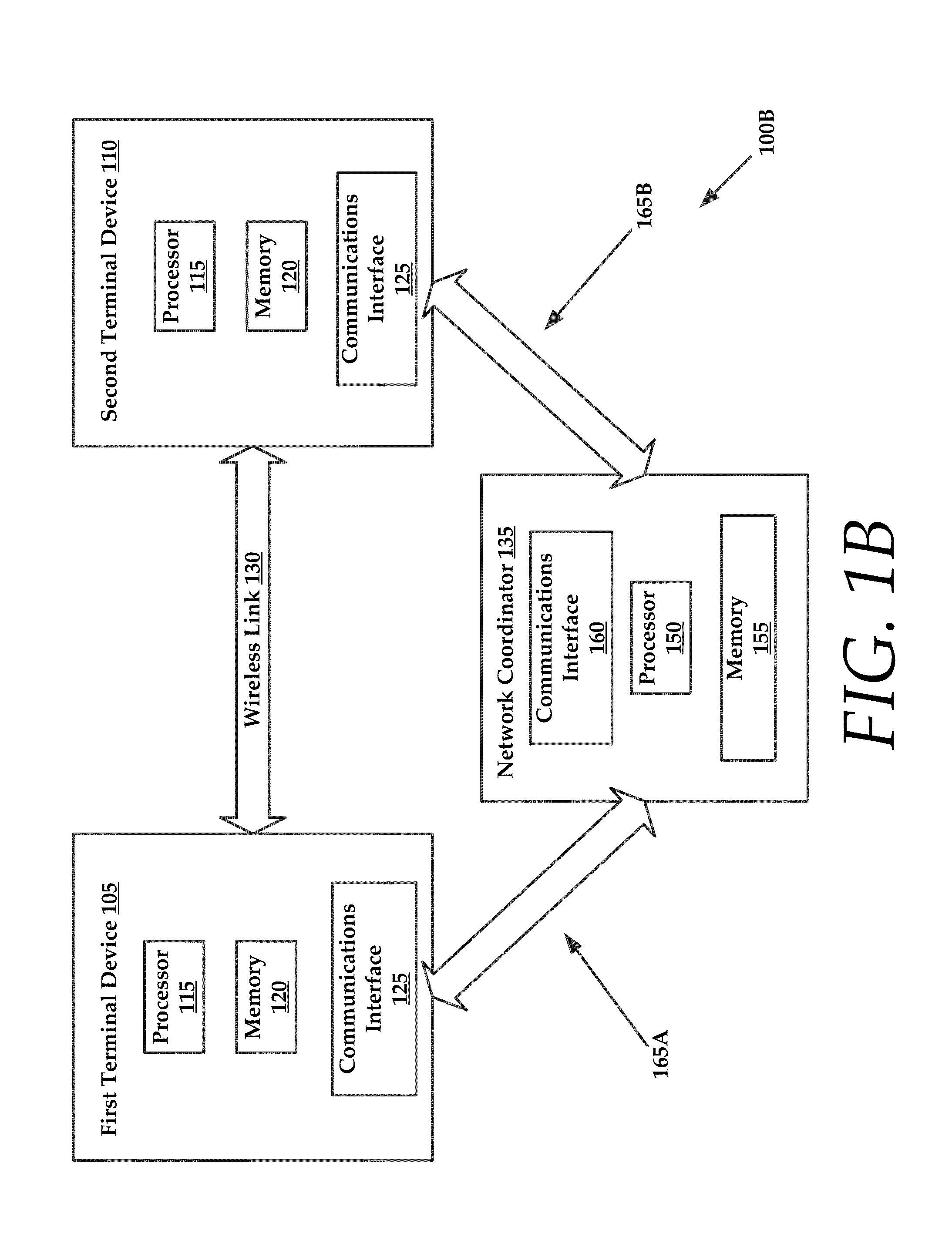

Channel optimization in half duplex communications systems

Channel Optimization in Half Duplex Communications Systems is provided herein. Methods may include obtaining at a first terminal, radio frequency (RF) spectral information local to the first terminal, analyzing at the first terminal, RF spectral information for a second terminal that is not co-located with the first terminal, transmitting data to the second terminal on a second terminal optimal frequency band, and receiving data from the second terminal on the first terminal optimal frequency band, where the first terminal optimal frequency being based upon the RF spectral information local to the first terminal.

Owner:PACIFIC WESTERN BANK AS AGENT +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com