Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1405 results about "Gigabit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The gigabit is a multiple of the unit bit for digital information or computer storage. The gigabit has the unit symbol Gbit or Gb. Using the common byte size of 8 bits, 1 Gbit is equal to 125 megabytes (MB) or approximately 119 mebibytes (MiB).

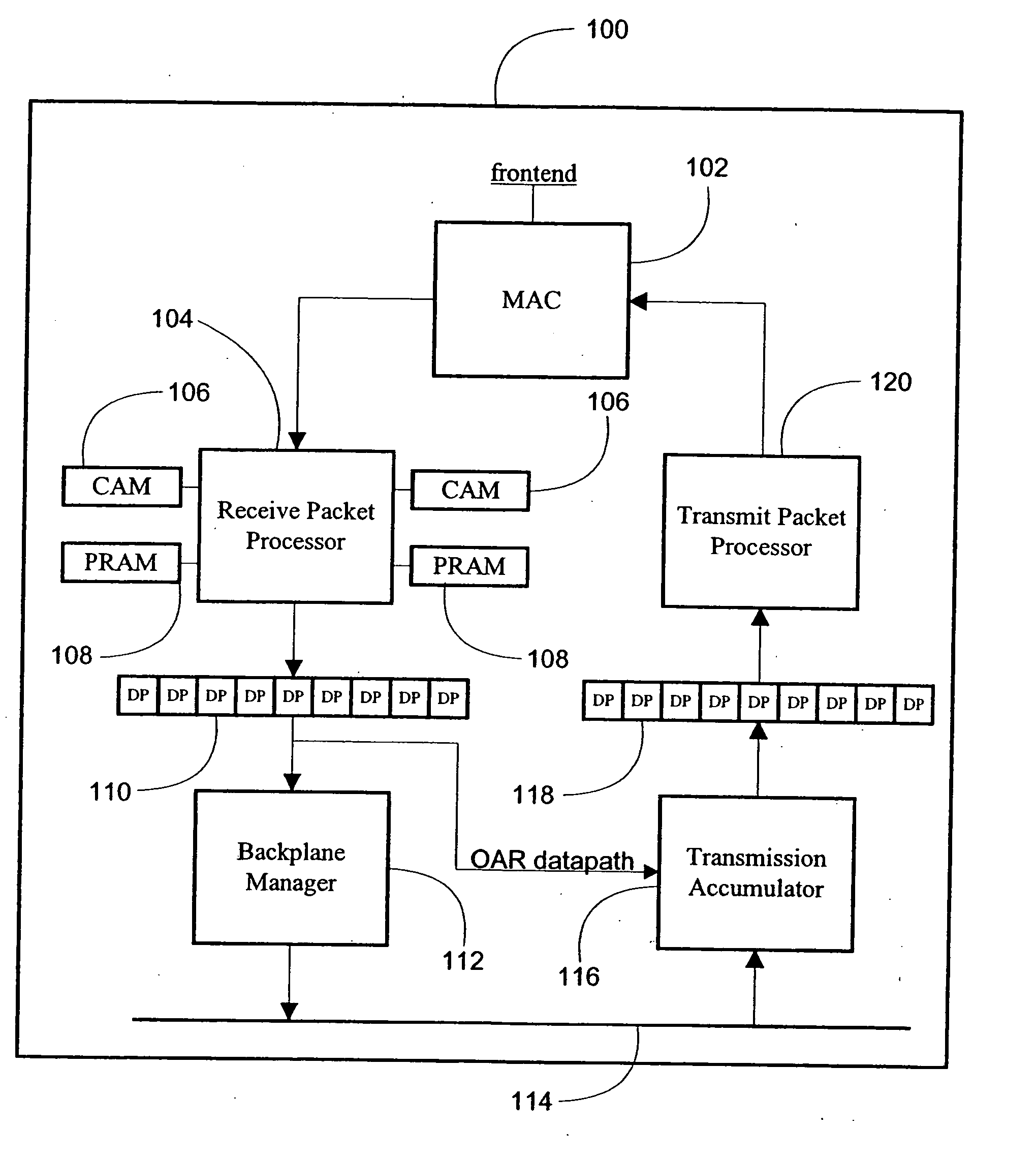

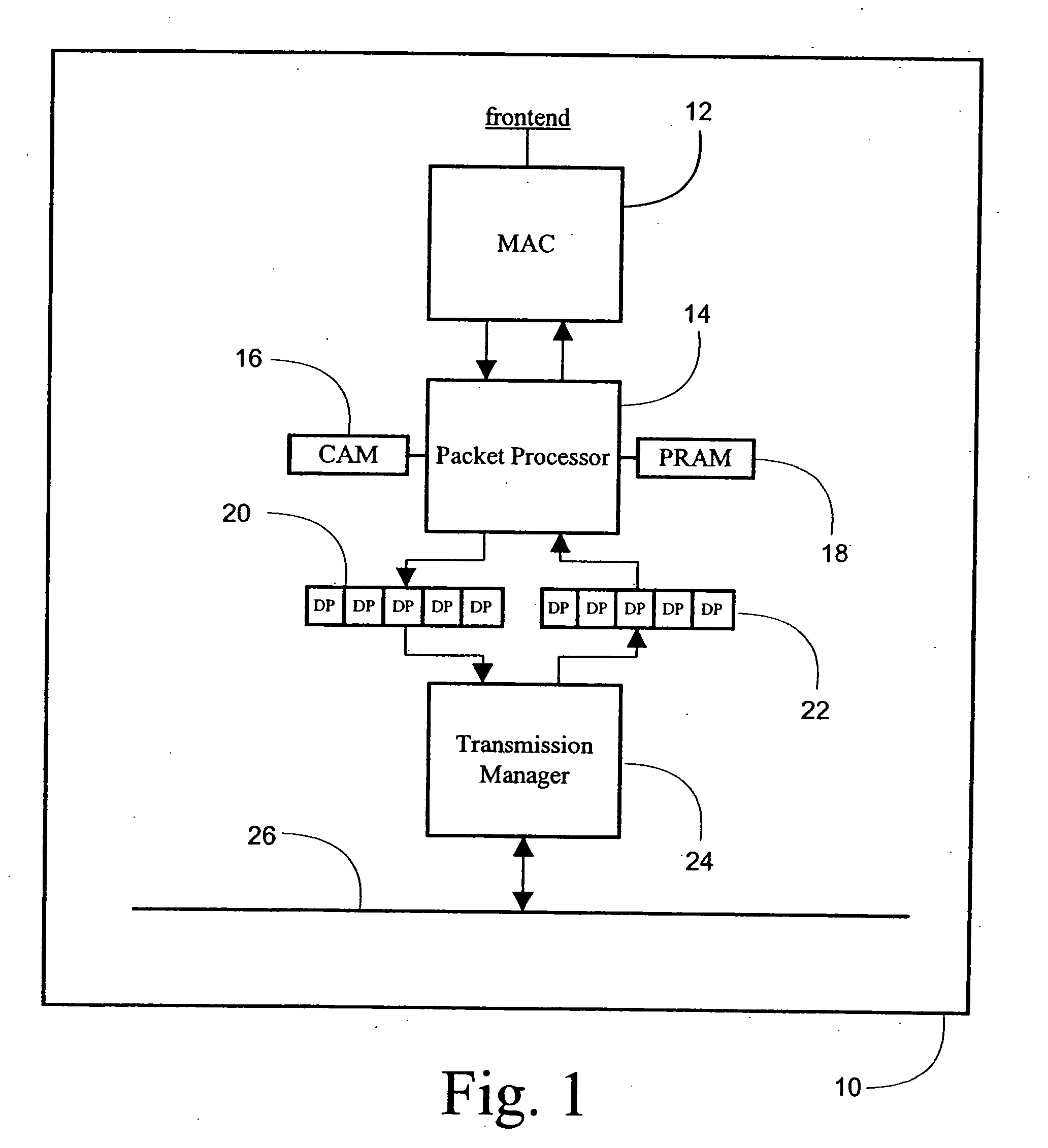

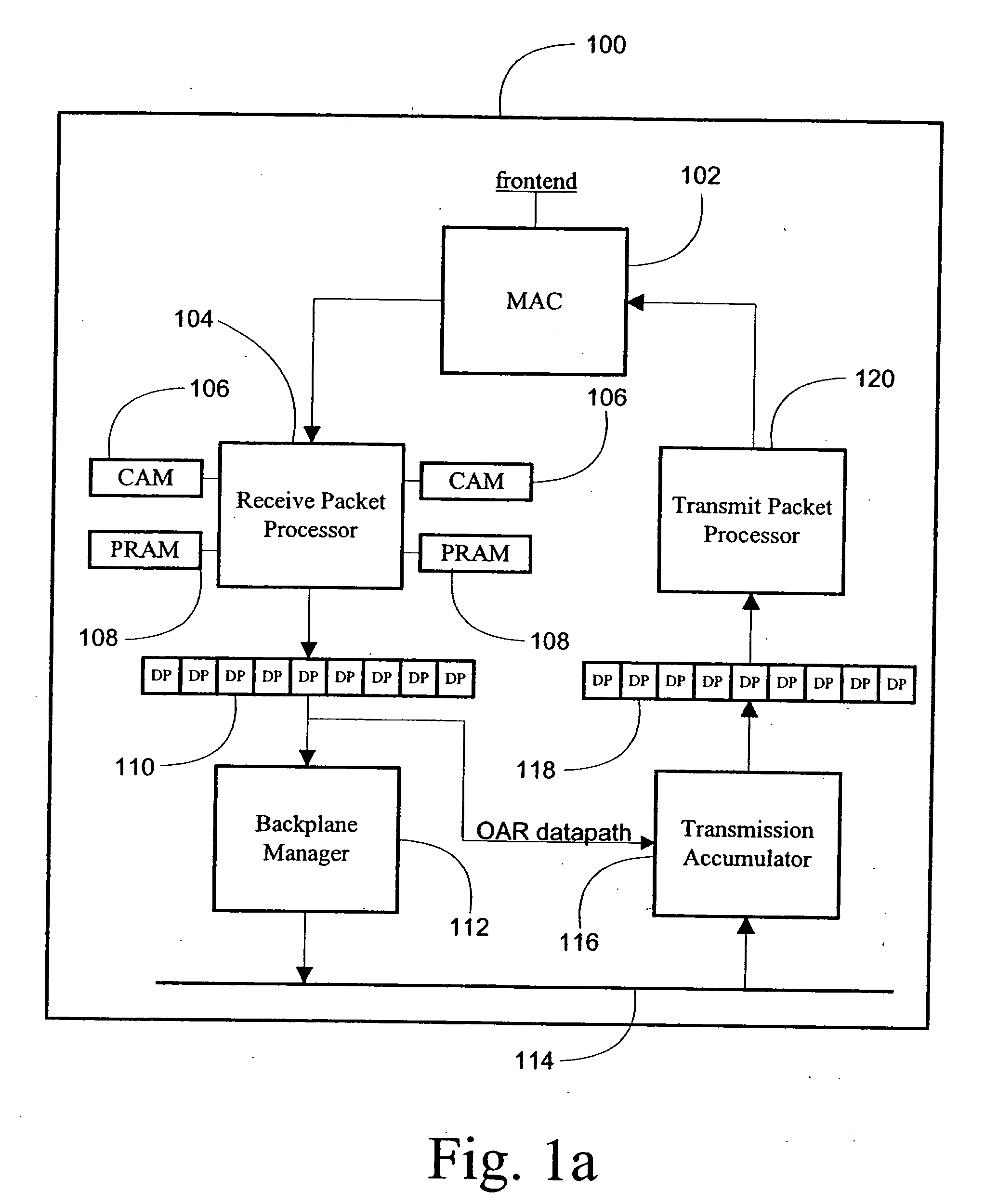

System and method for high speed packet transmission implementing dual transmit and receive pipelines

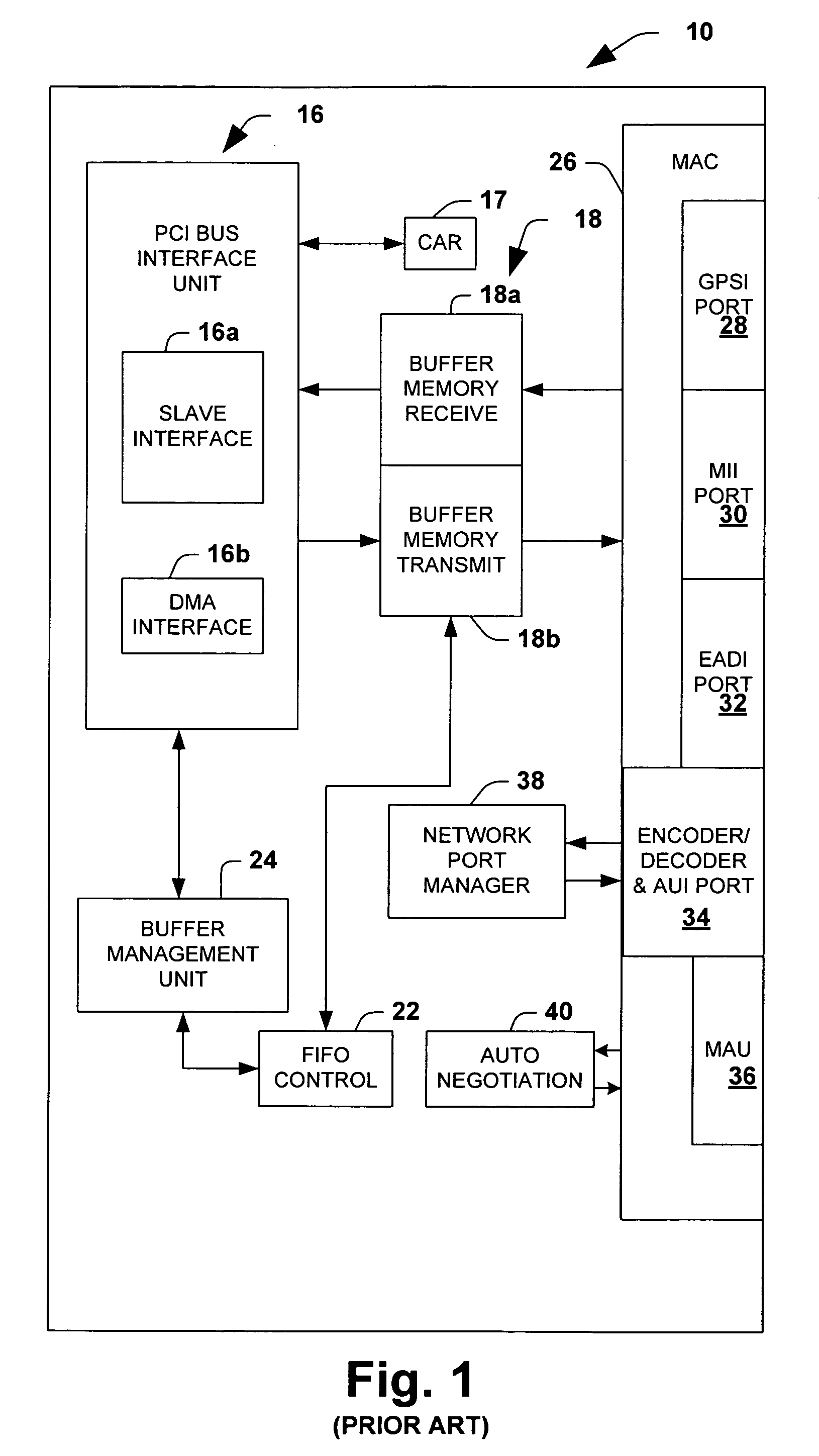

InactiveUS6901072B1Multiplex system selection arrangementsCircuit switching systemsGigabitStructure of Management Information

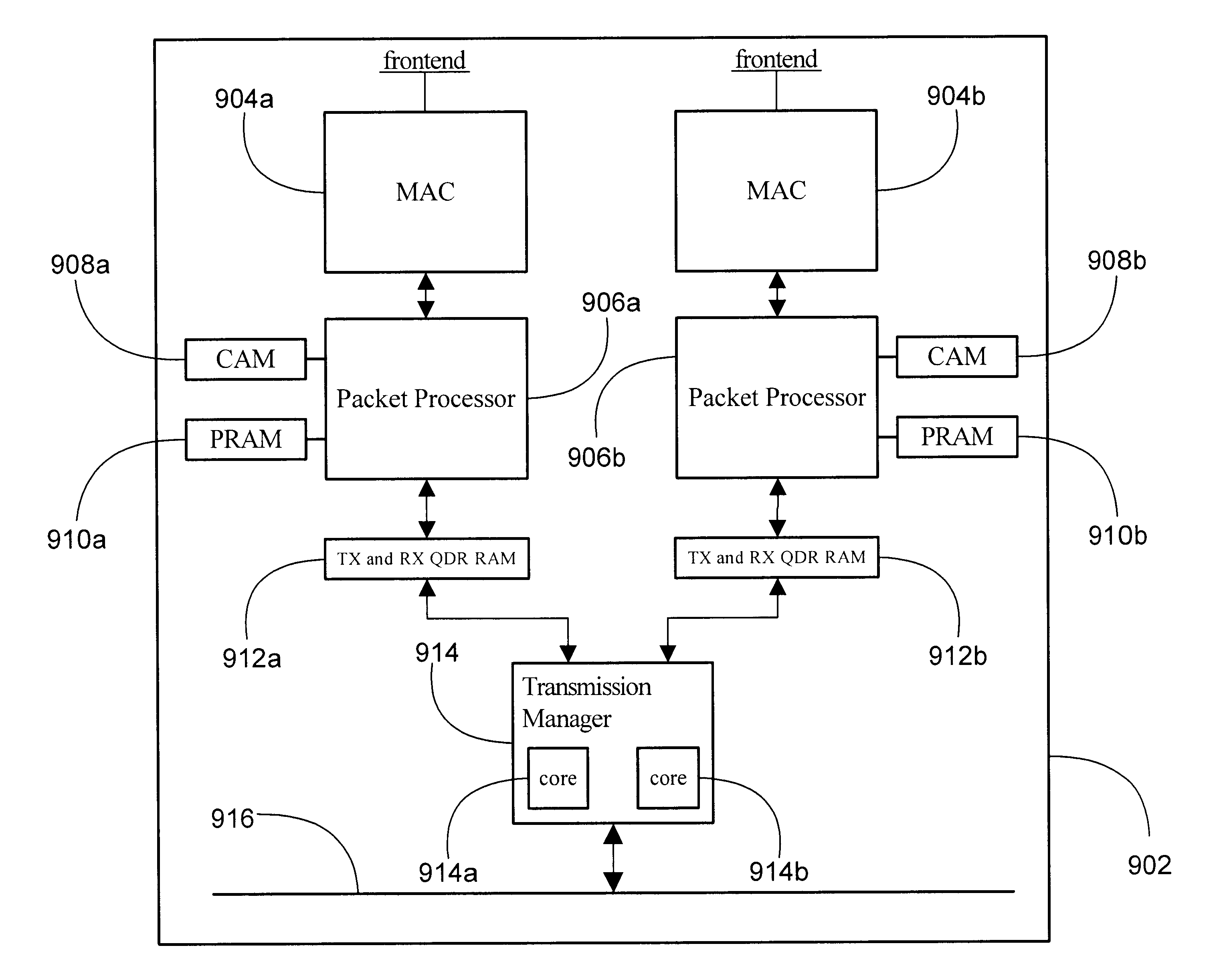

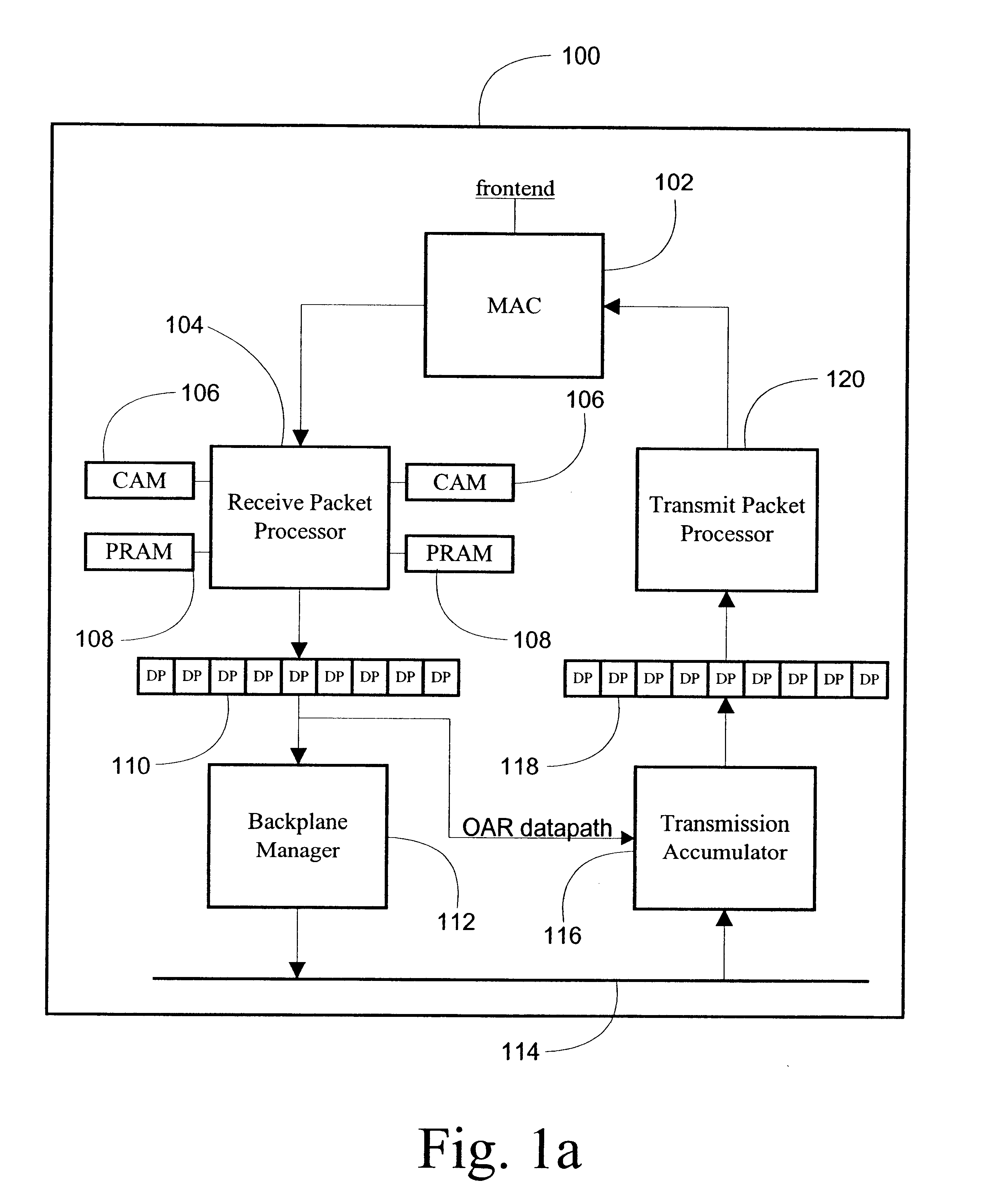

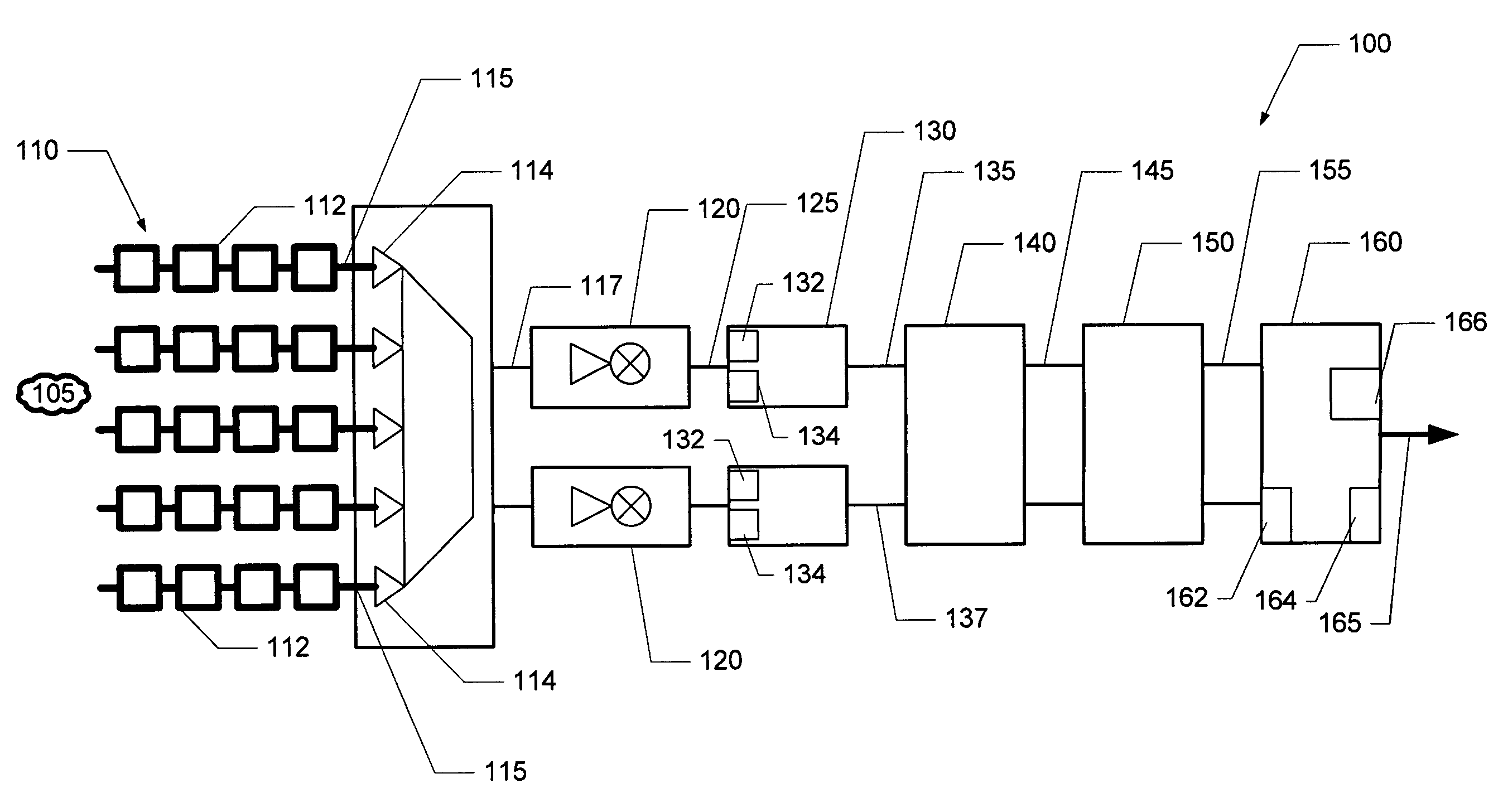

The present invention provides systems and methods for providing data transmission speeds at or in excess of 10 gigabits per second between one or more source devices and one or more destination devices. According to one embodiment, the system of the present invention comprises a first and second media access control (MAC) interfaces to facilitate receipt and transmission of packets over an associated set of physical interfaces. The system also contemplates a first and second field programmable gate arrays (FPGA) coupled to the MAC interfaces and an associated first and second memory structures, the first and second FPGAs are configured to perform initial processing of packets received from the first and second MAC interfaces and to schedule the transmission of packets to the first and second MAC interface for transmission to one or more destination devices. The first and second FPGAs are further operative to dispatch and retrieve packets to and from the first and second memory structures. A third FPGA, coupled to the first and second memory structures and a backplane, is operative to retrieve and dispatch packets to and from the first and second memory structures, compute appropriate destinations for packets and organize packets for transmission. The third FPGA is further operative to receive and dispatch packets to and from the backplane.

Owner:AVAGO TECH INT SALES PTE LTD

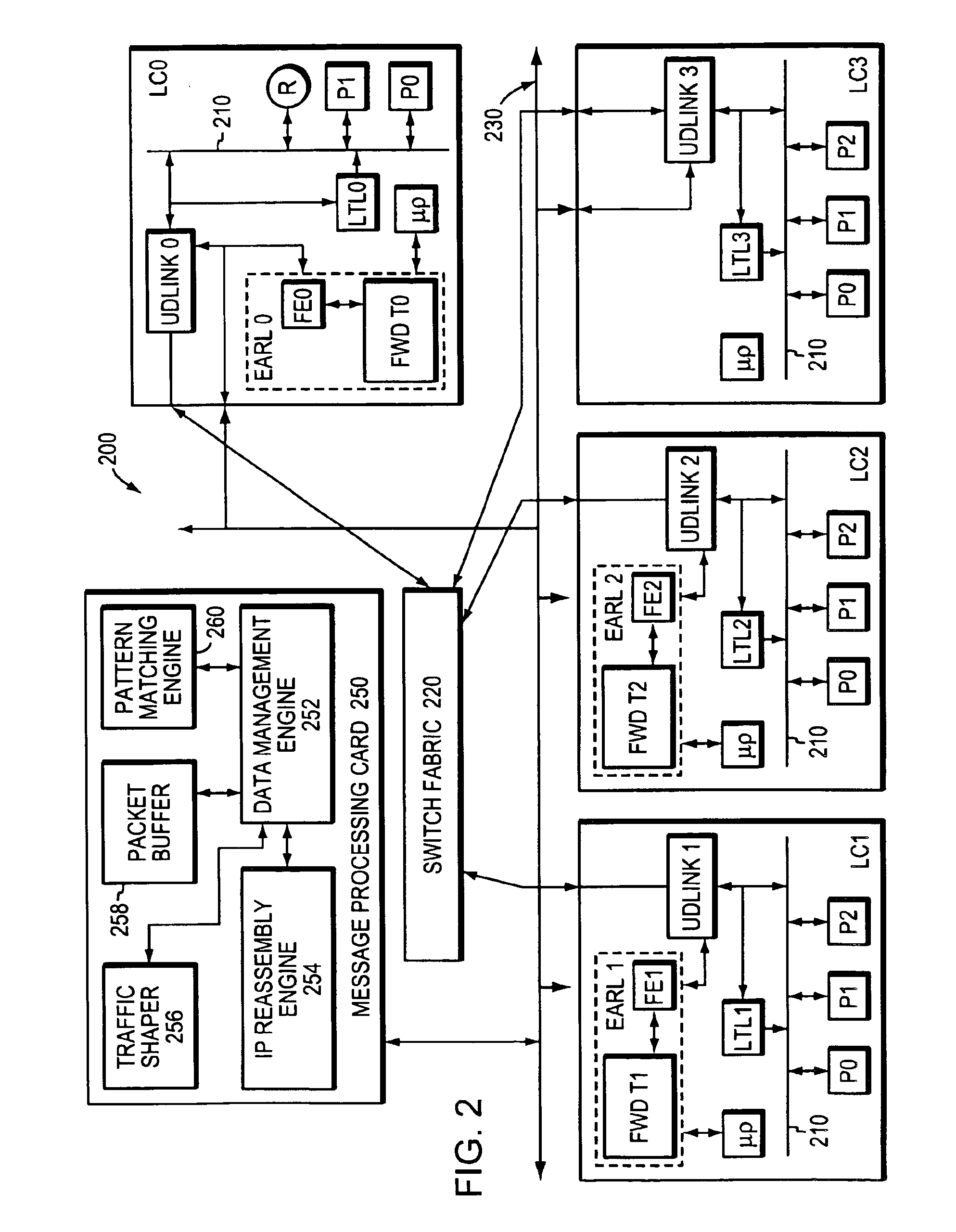

Method and apparatus for high-speed parsing of network messages

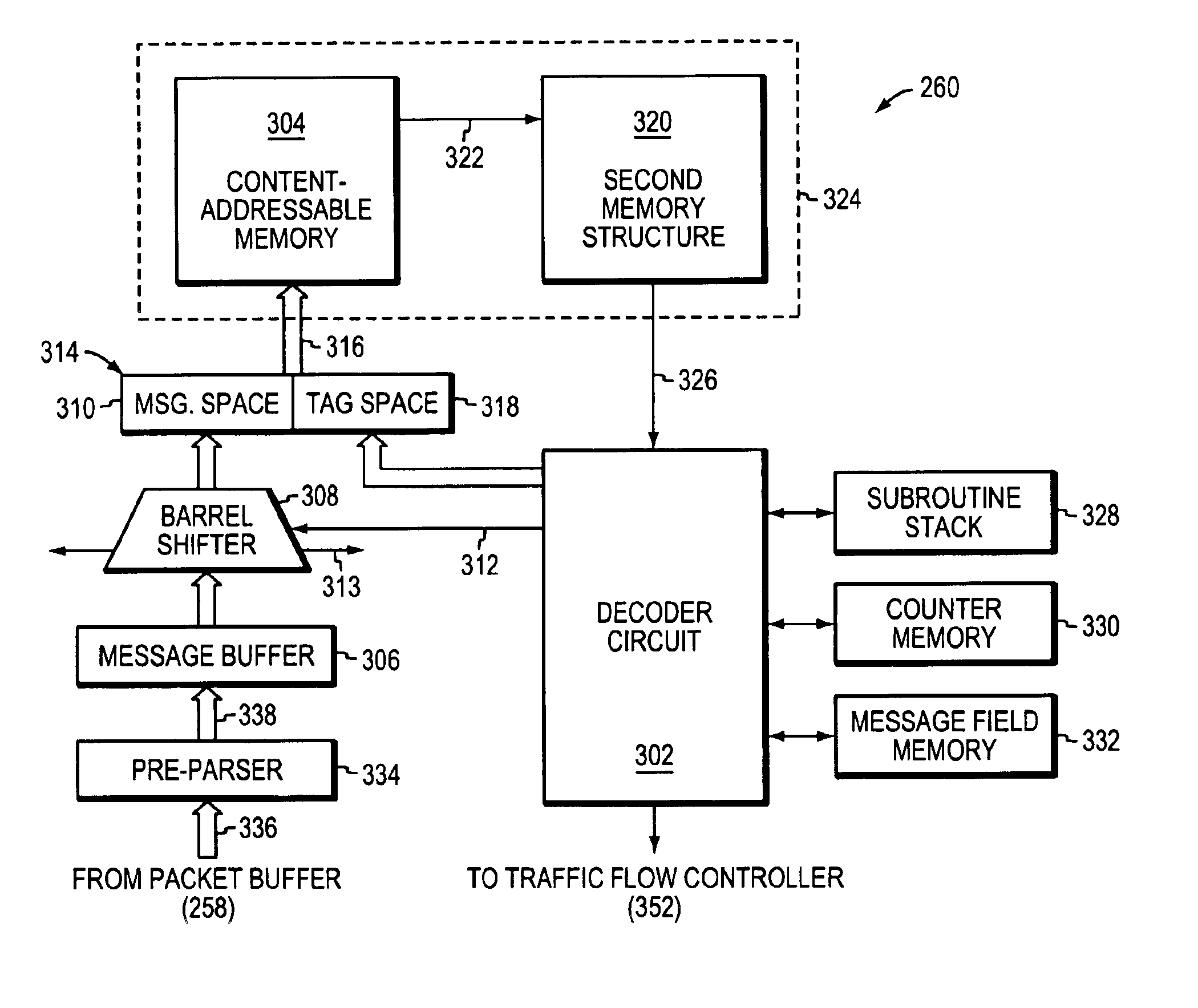

InactiveUS6892237B1Efficient analysisIncrease speedMultiple digital computer combinationsData switching networksPattern matchingRandom access memory

A programmable pattern matching engine efficiently parses the contents of network messages for regular expressions and executes pre-defined actions or treatments on those messages that match the regular expressions. The pattern matching engine is preferably a logic circuit designed to perform its pattern matching and execution functions at high speed, e.g., at multi-gigabit per second rates. It includes, among other things, a message buffer for storing the message being evaluated, a decoder circuit for decoding and executing corresponding actions or treatments, and one or more content-addressable memories (CAMs) that are programmed to store the regular expressions used to search the message. The CAM may be associated with a second memory device, such as a random access memory (RAM), as necessary, that is programmed to contain the respective actions or treatments to be applied to messages matching the corresponding CAM entries. The RAM provides its output to the decoder circuit, which, in response, decodes and executes the specified action or treatment.

Owner:CISCO TECH INC

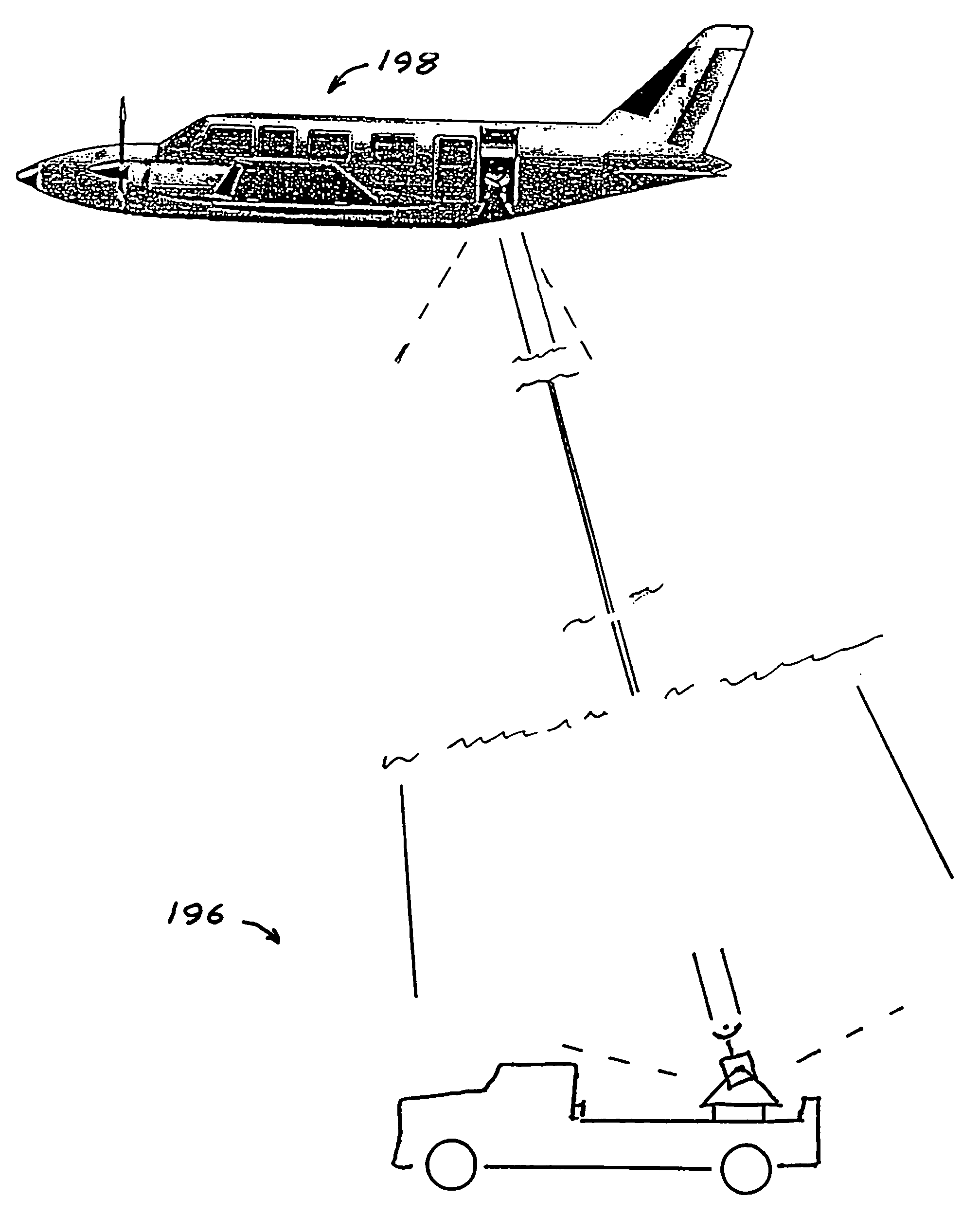

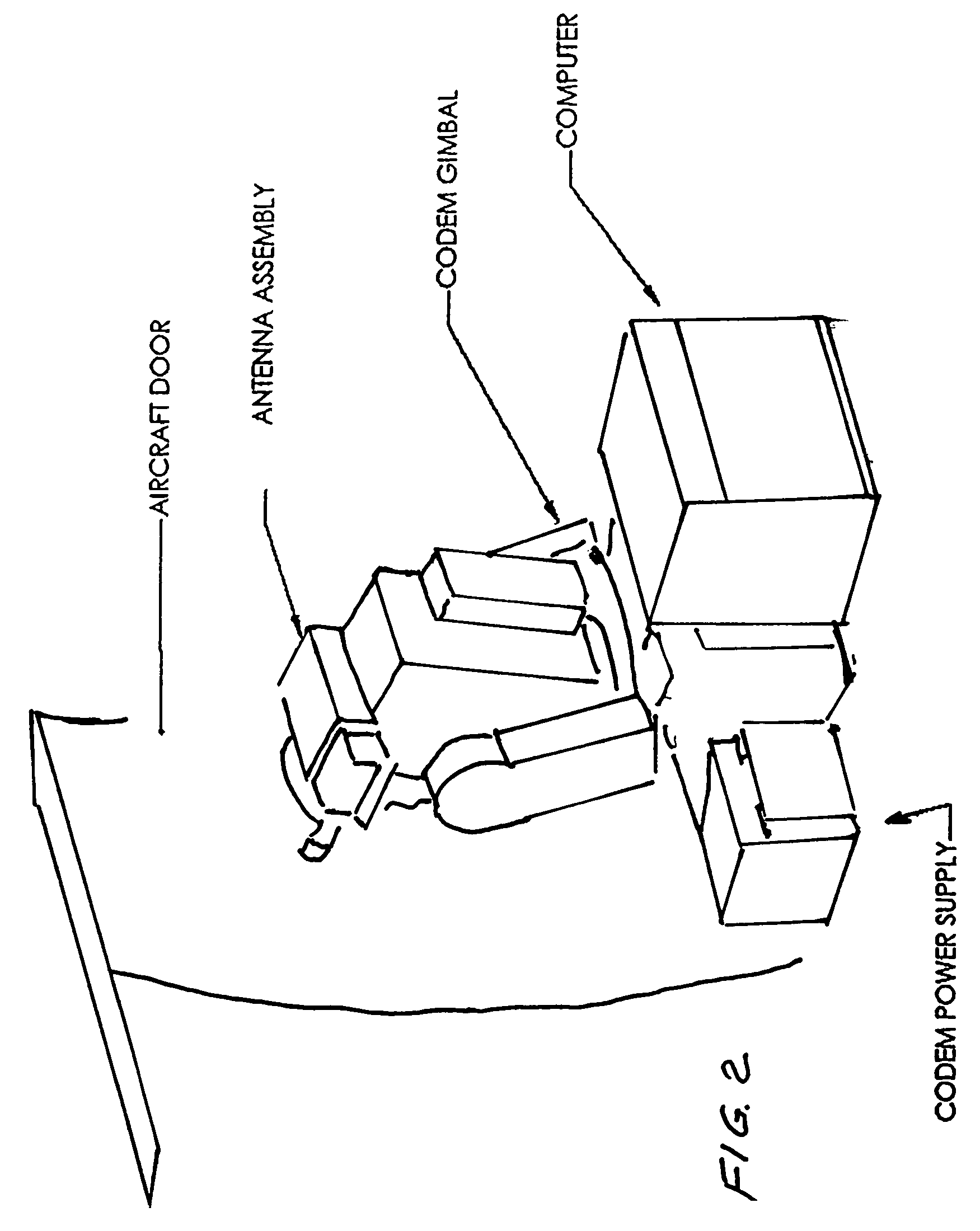

Mobile millimeter wave communication link

A point-to-point, wireless, millimeter wave communications link between two stations at least one of which is a mobile station. A millimeter wave transmitter system operating at frequencies higher than 57 GHz with a tracking antenna producing a beam having a half-power beam width of about 2 degrees or less and a millimeter wave receiver also with a tracking antenna having a half-power beam width of about 2 degrees or less. In preferred embodiments each mobile station has a global position system (GPS) and a radio transmitter and both tracking antennas are pointed utilizing GPS information from the mobile station or stations. The GPS information preferably is transmitted via a low frequency, low data rate radio. Each millimeter wave unit is capable of transmitting and / or receiving, through the atmosphere, digital information to / from the other station at rates in excess of 155 million bits per second during normal weather conditions. In preferred embodiments actually built and tested by Applicants digital information has been transmitted at rates of 1.25 gigabits per second. Preferred communication links described here are millimeter wave links operating at frequencies of 71-73 GHz and 74-76 GHz mounted on simple two-axis gimbals. Pointing information of the required accuracy is provided by GPS receivers and standard radio links which send the GPS calculated positions to the millimeter wave systems at the opposite end of the link. In these embodiments there is no need for any complicated closed loop pointing information derived from received signal intensity or phase. On moving platforms locally generated inertial attitude information is combined with the GPS positions to control pointing of the gimbaled transceivers.

Owner:TREX ENTERPRISES CORP

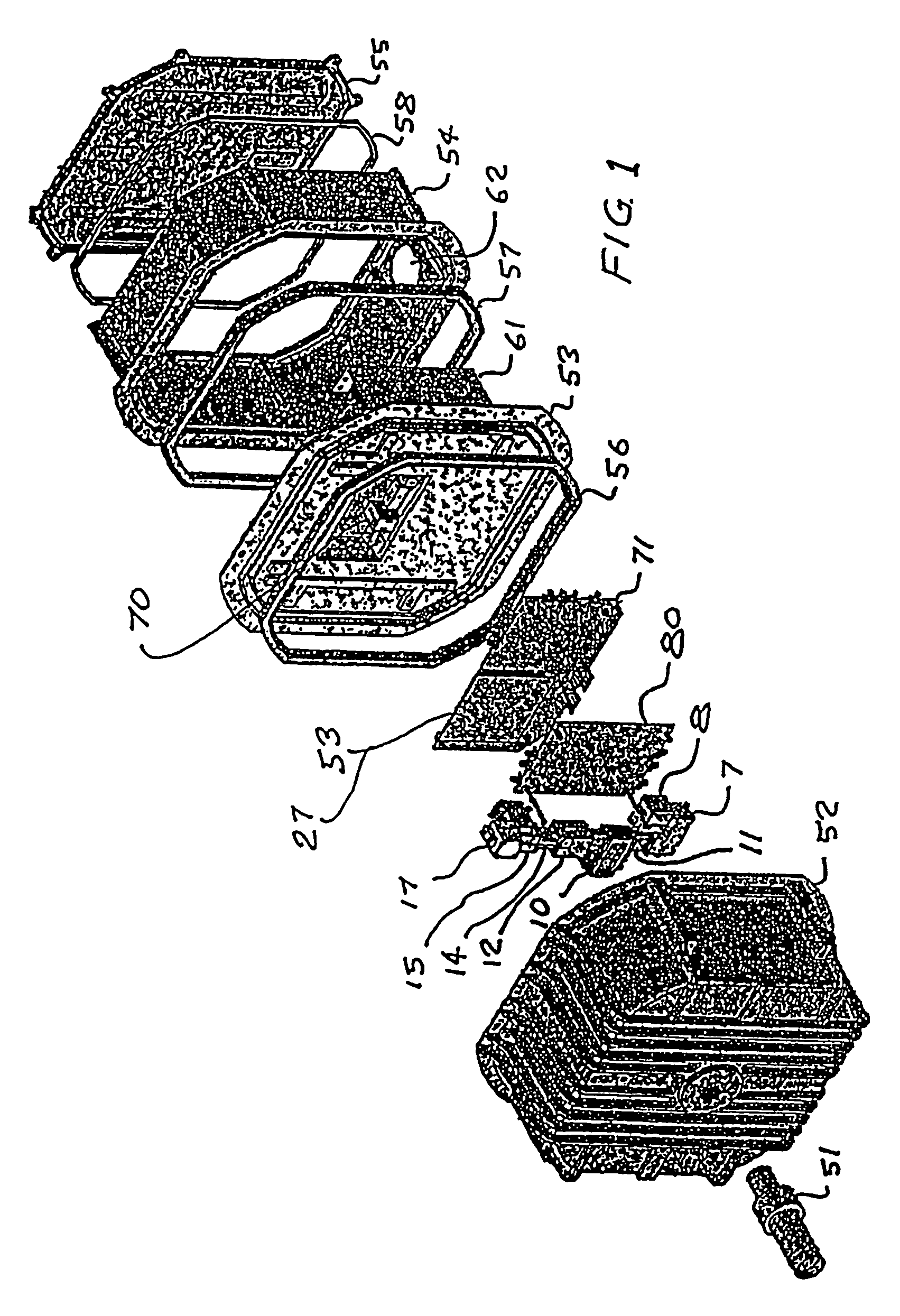

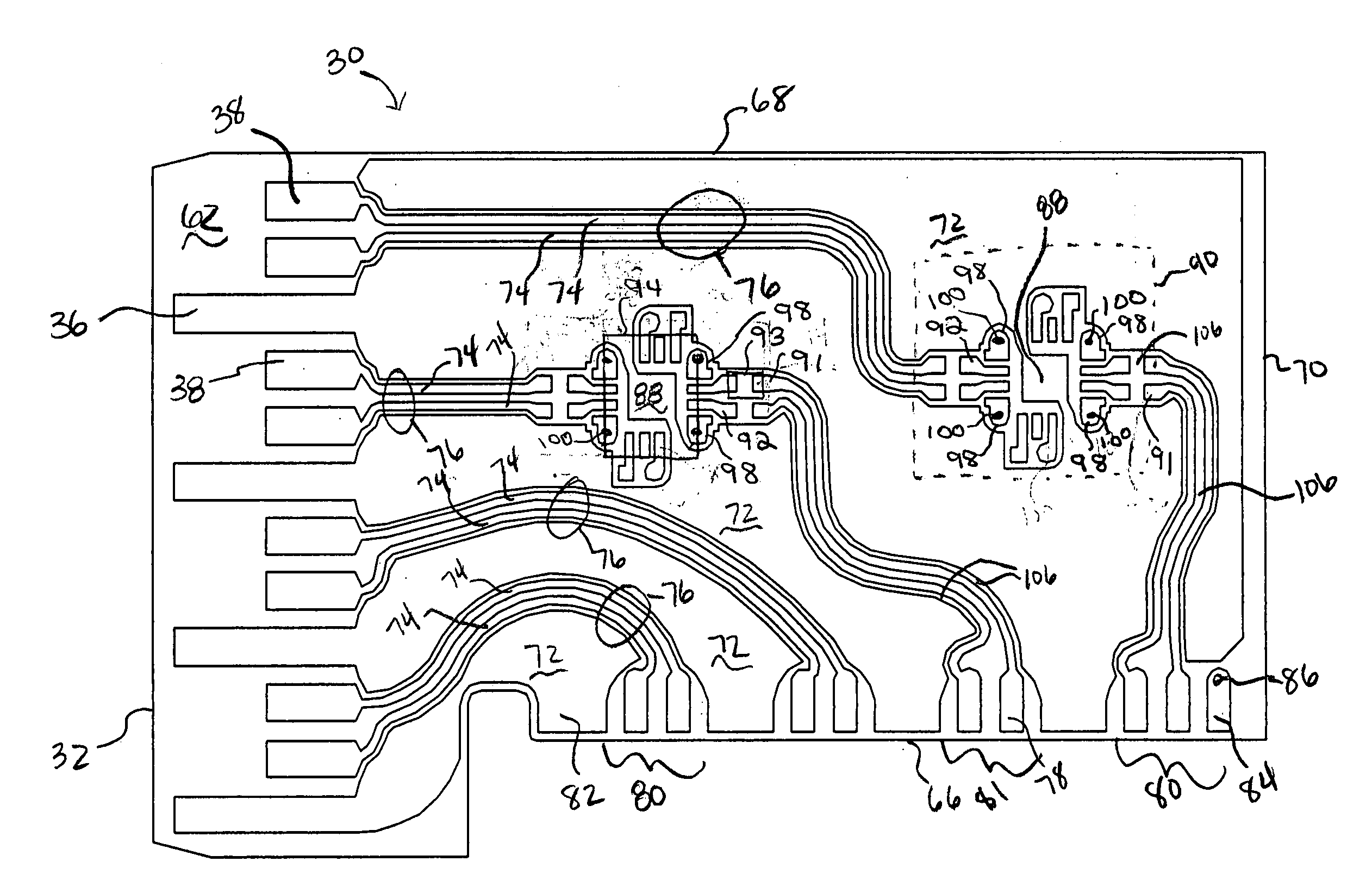

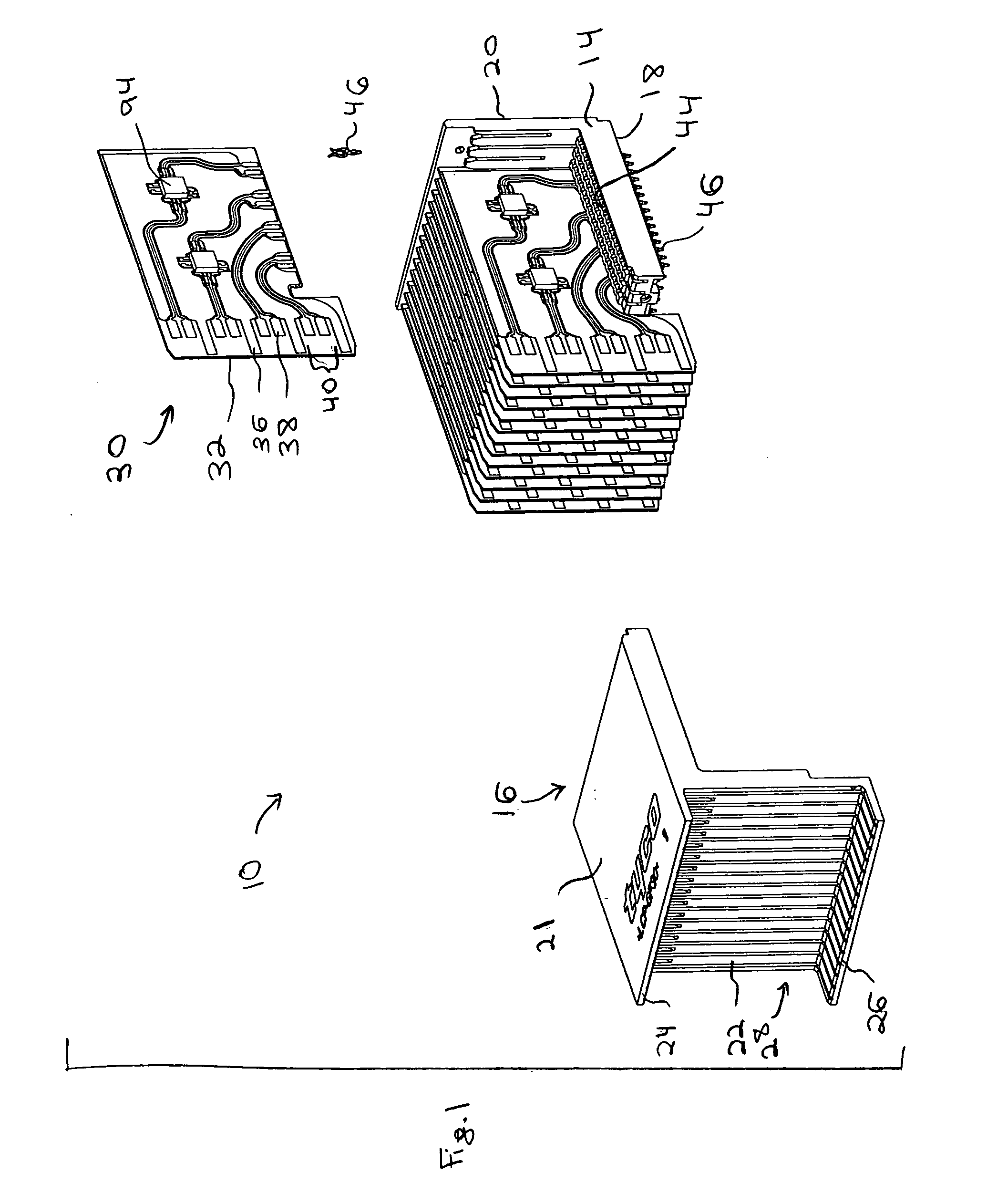

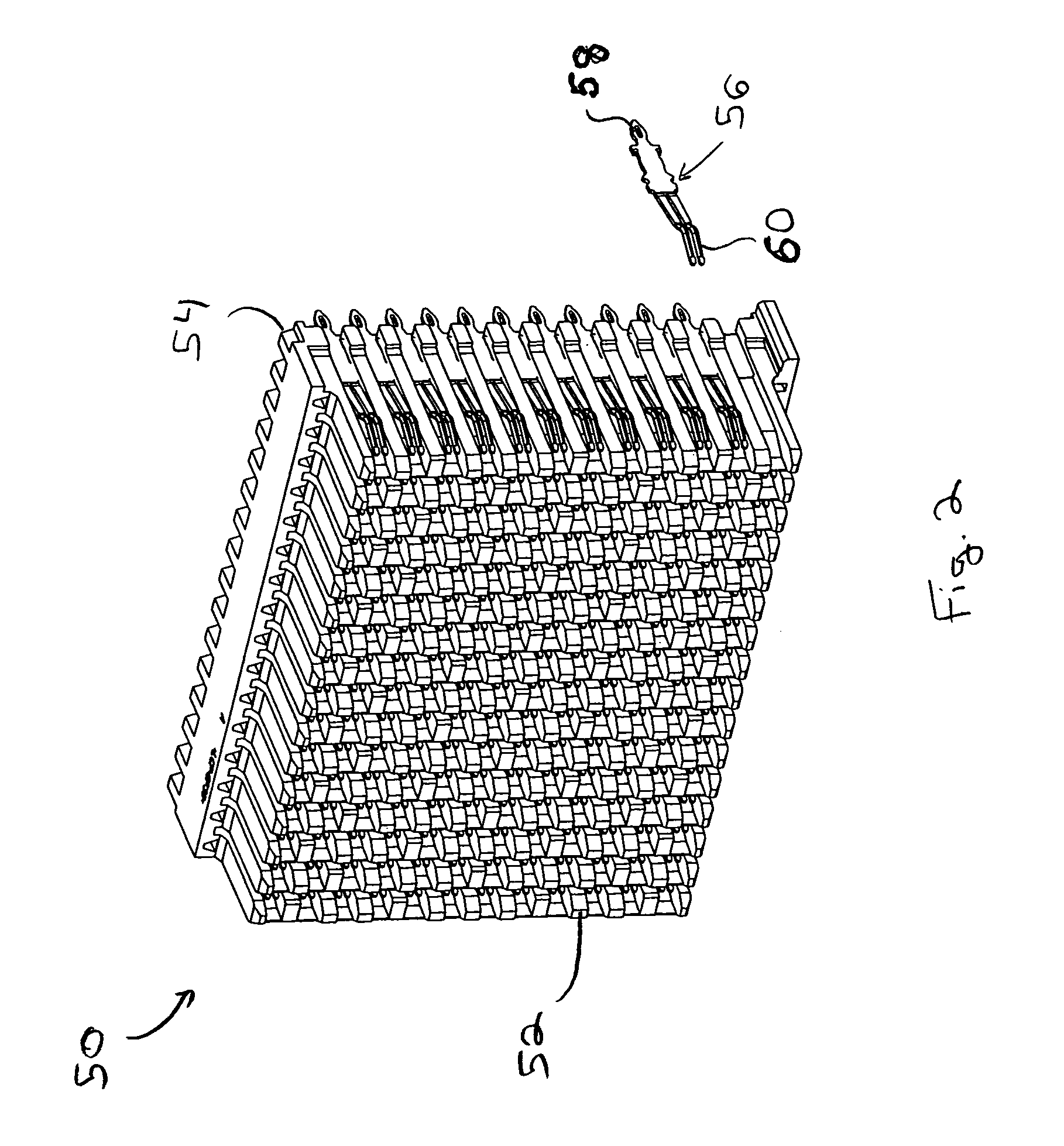

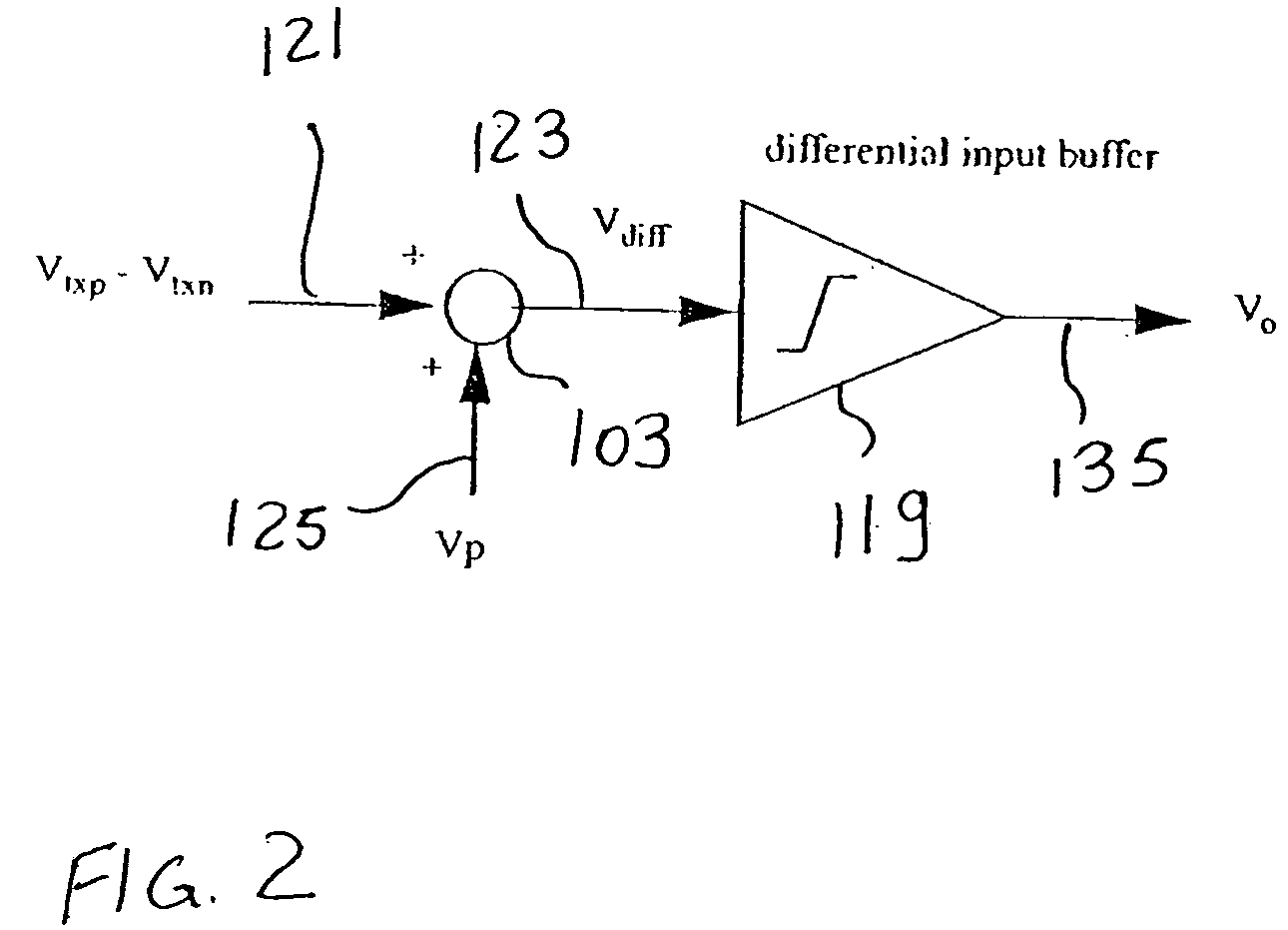

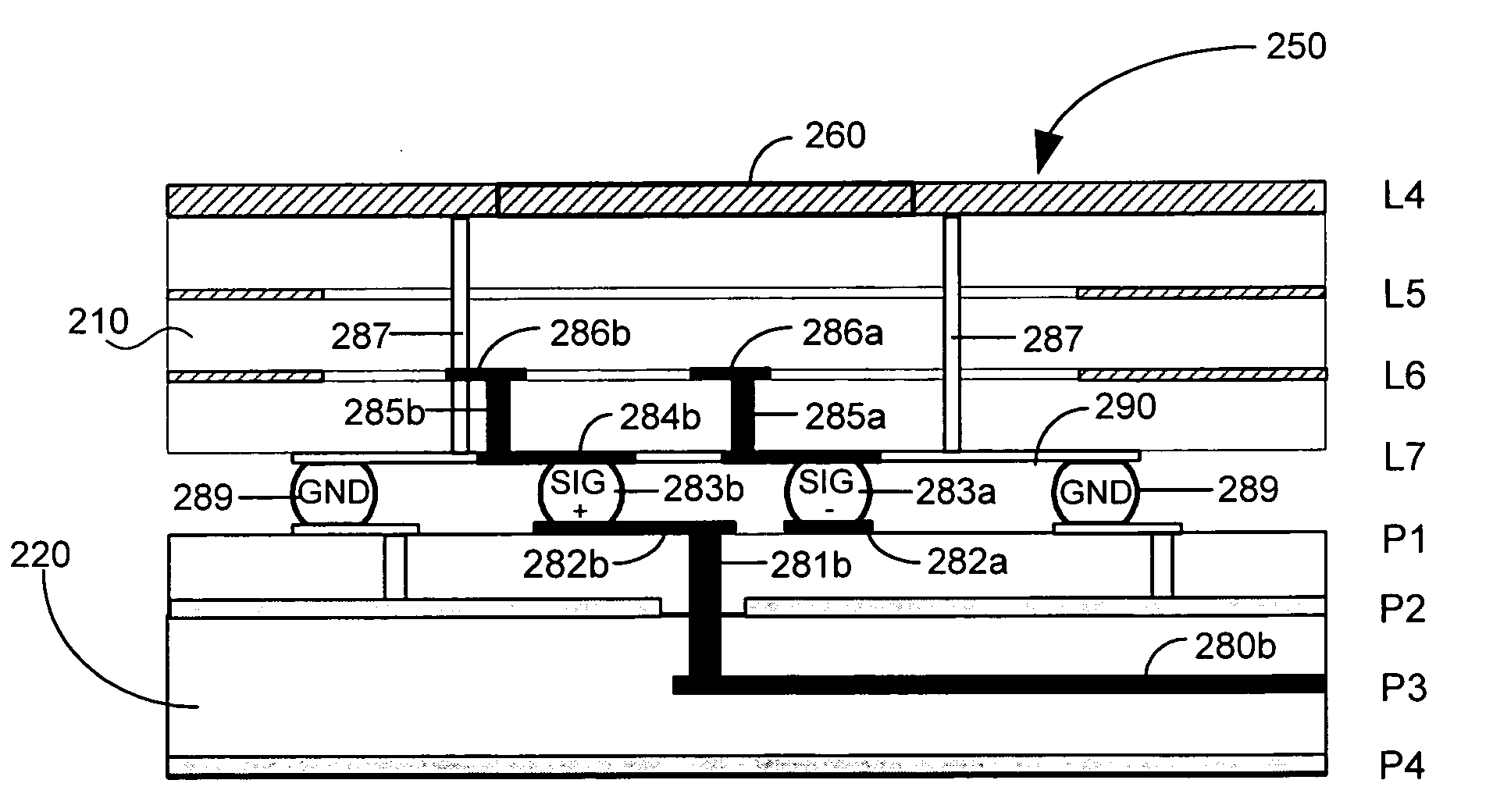

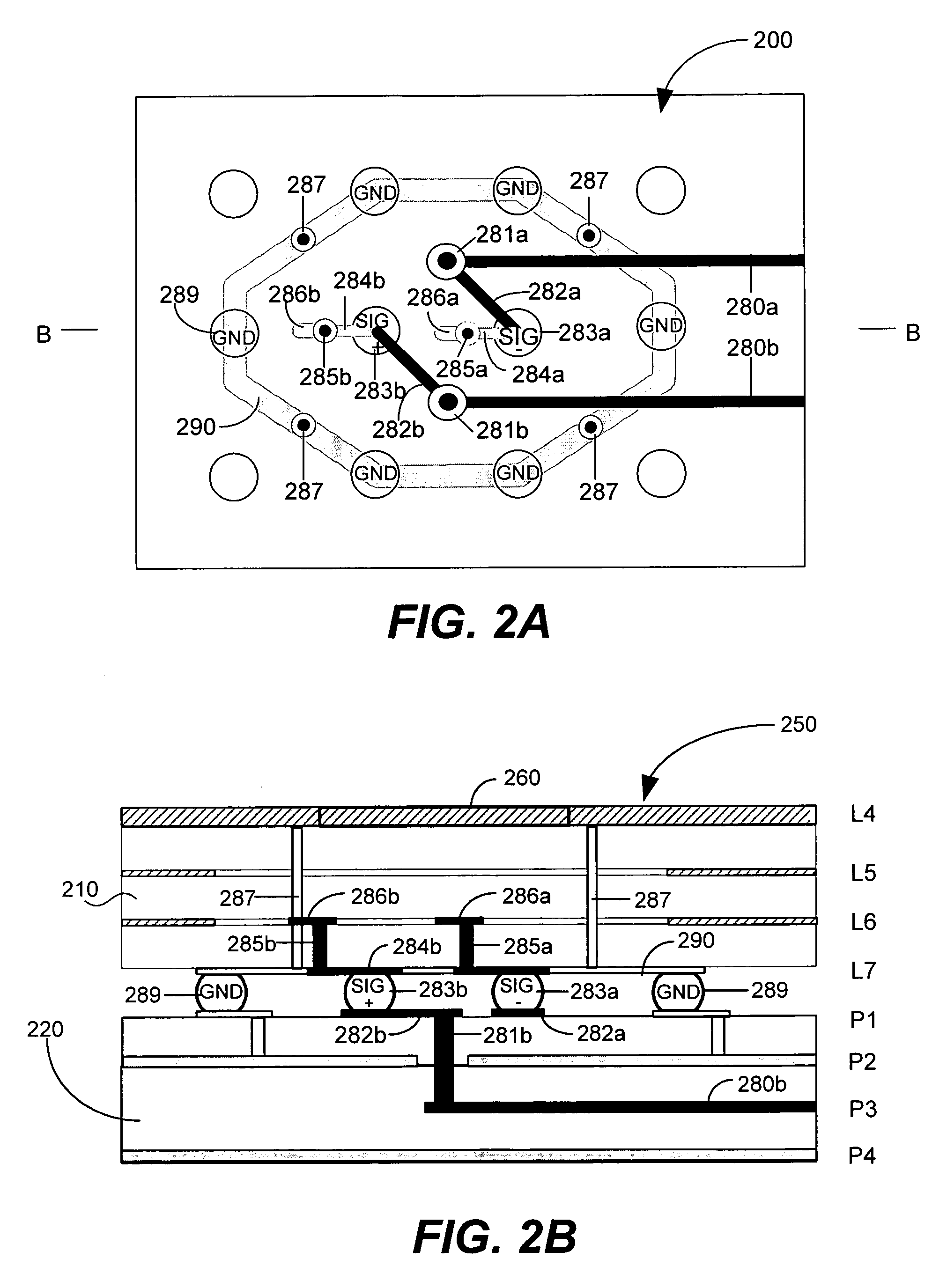

Active wafer for improved gigabit signal recovery, in a serial point-to-point architecture

ActiveUS6932649B1Increase magnitudeCoupling device detailsPrinted circuitsContact padDifferential signaling

An electrical connector is provided for operation in a point-to-point application. The connector includes an insulated housing having first and second card interfaces configured to mate with associated first and second circuit cards. An electrical wafer is held in the housing and configured to operate in a point-to-point architecture. The signal traces end at signal contact pads located proximate to first and second edges, respectively. The signal contact pads receive a unidirectional signal. Each of the signal traces include a break section at an intermediate point along a length thereof to form a disconnect in the signal traces. The connector further includes an active compensation component bridging the break section in the signal traces. The active compensation component compensates the differential signal incoming from the input contact pads for signal degradation and transmits a compensated signal outward to the output contact pads. The active compensation component transmits the signal only in a single direction within the point-to-point architecture.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

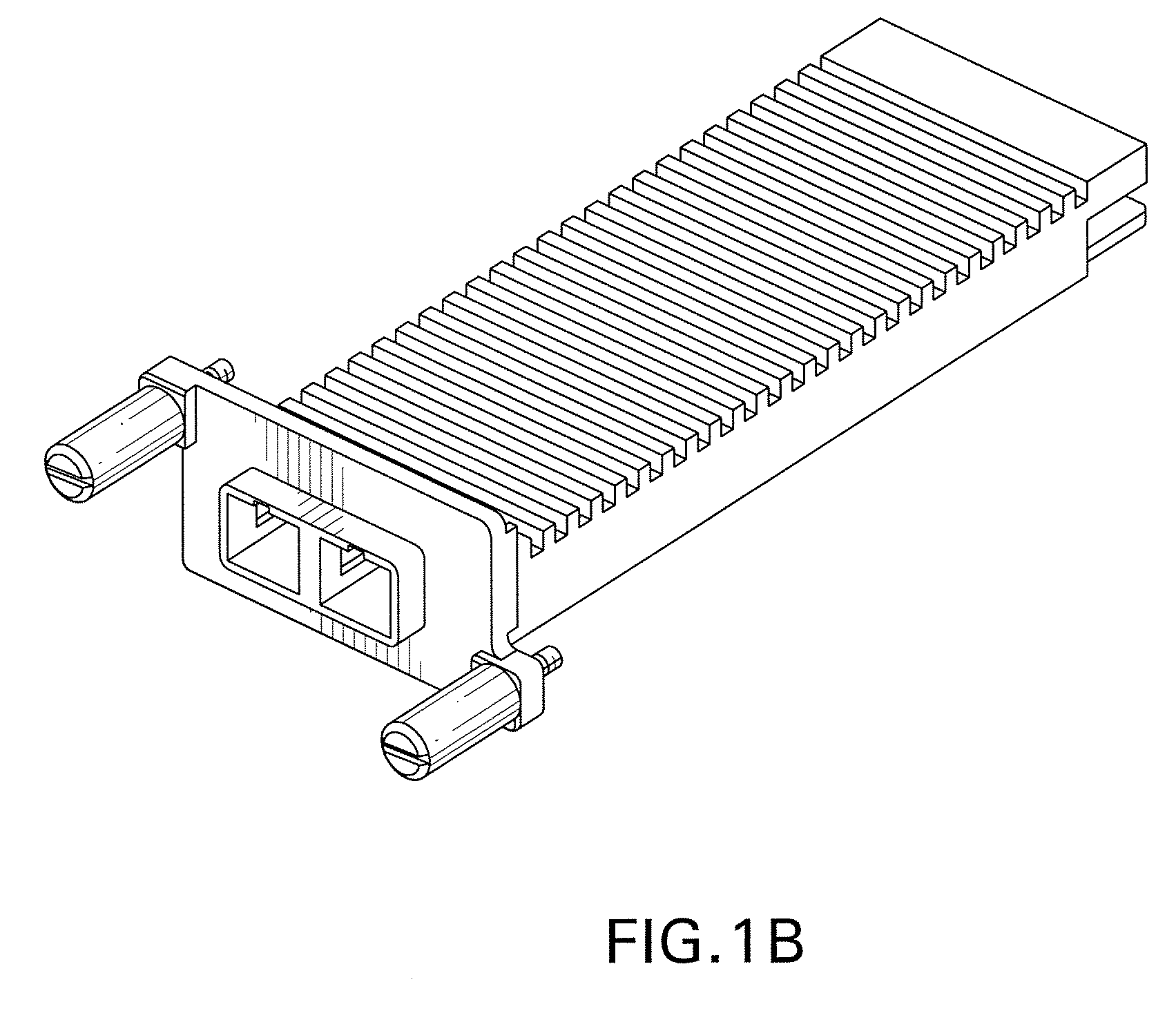

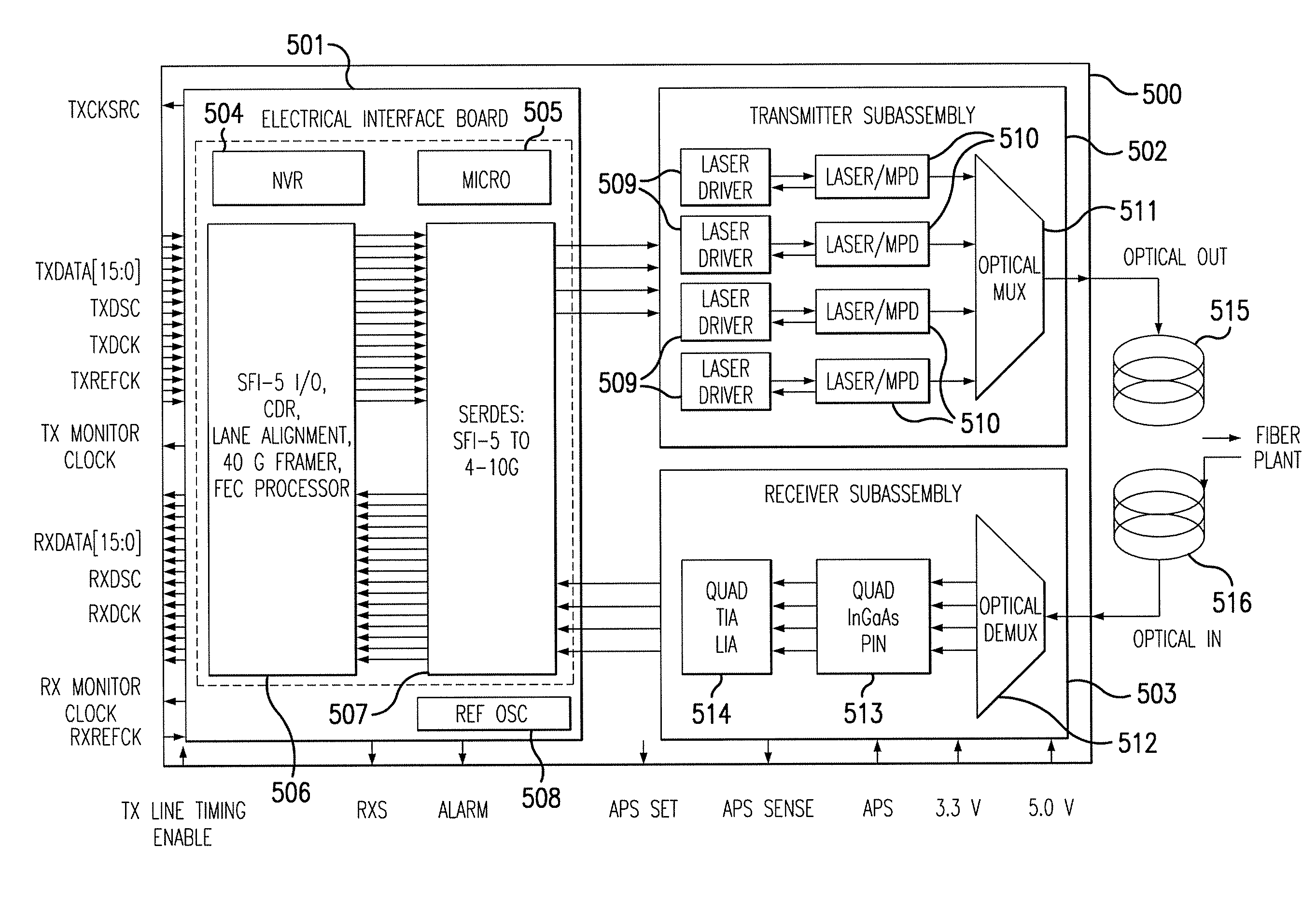

Optical transceiver for 40 gigabit/second transmission

An optical transceiver for converting and coupling an information-containing electrical signal with an optical including a housing having an electrical connector with a plurality of XFI electrical interfaces for coupling with an external electrical cable or information system device and for transmitting and / or receiving an information-containing electrical signal having a data rate ate least 10 Gigabits per second on each interface, and a fiber optic connector adapted for coupling with an external optical fiber for transmitting and / or receiving an optical communications signal having a data rate at least 40 Gigabits per second; and at least one electro-optical subassembly in the housing for converting between and information-containing electrical signal and a modulated optical signal corresponding to the electrical signals.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS U S A

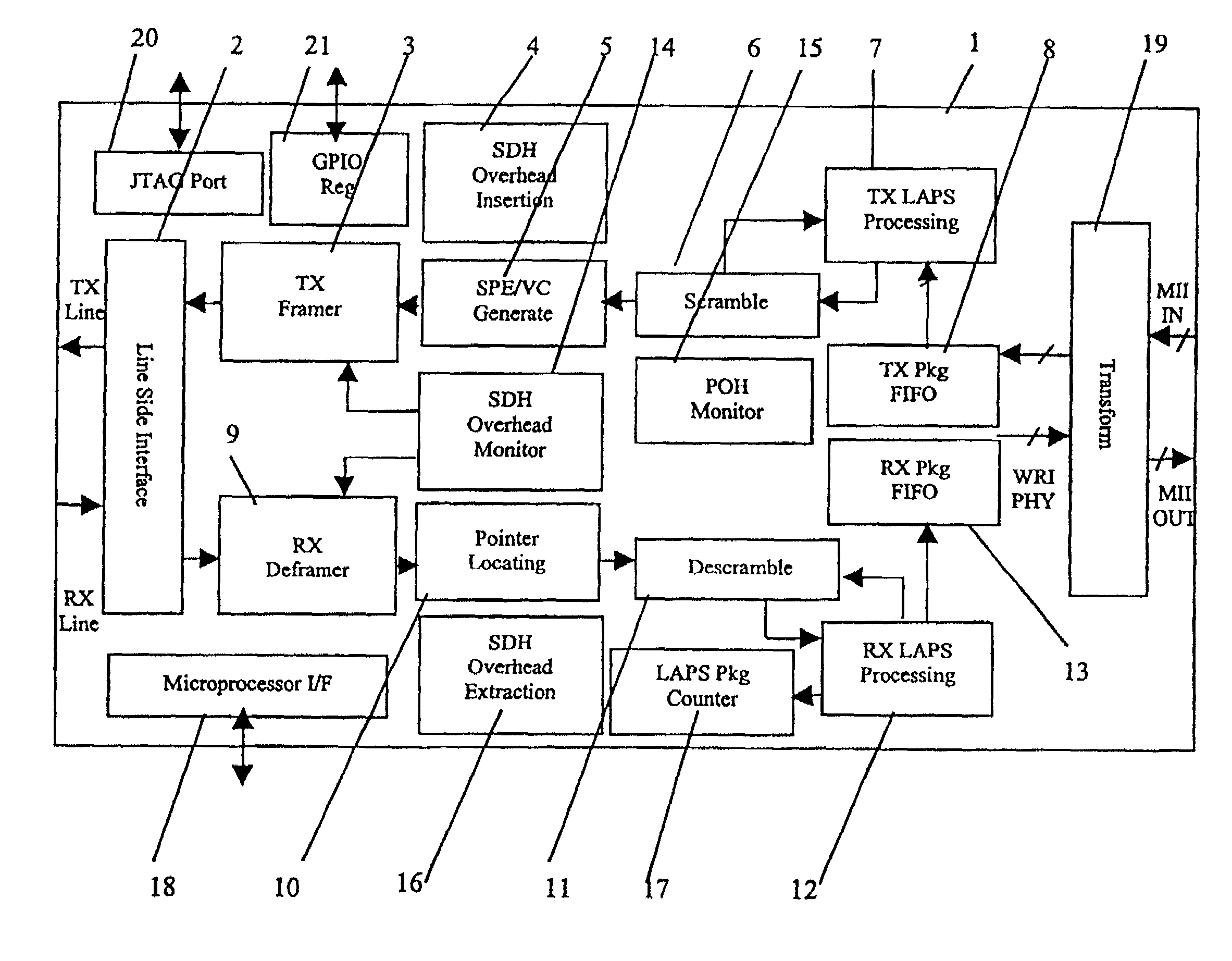

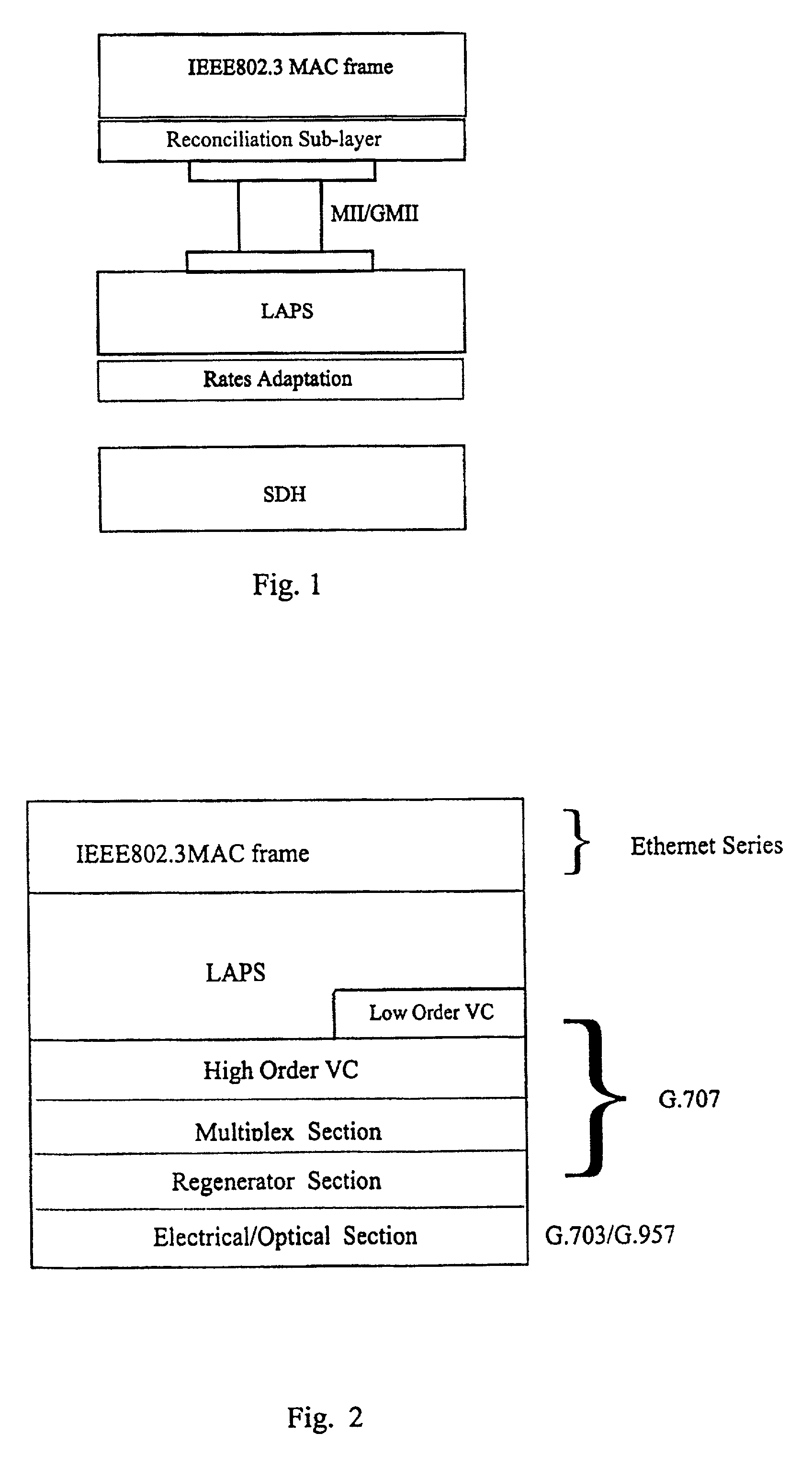

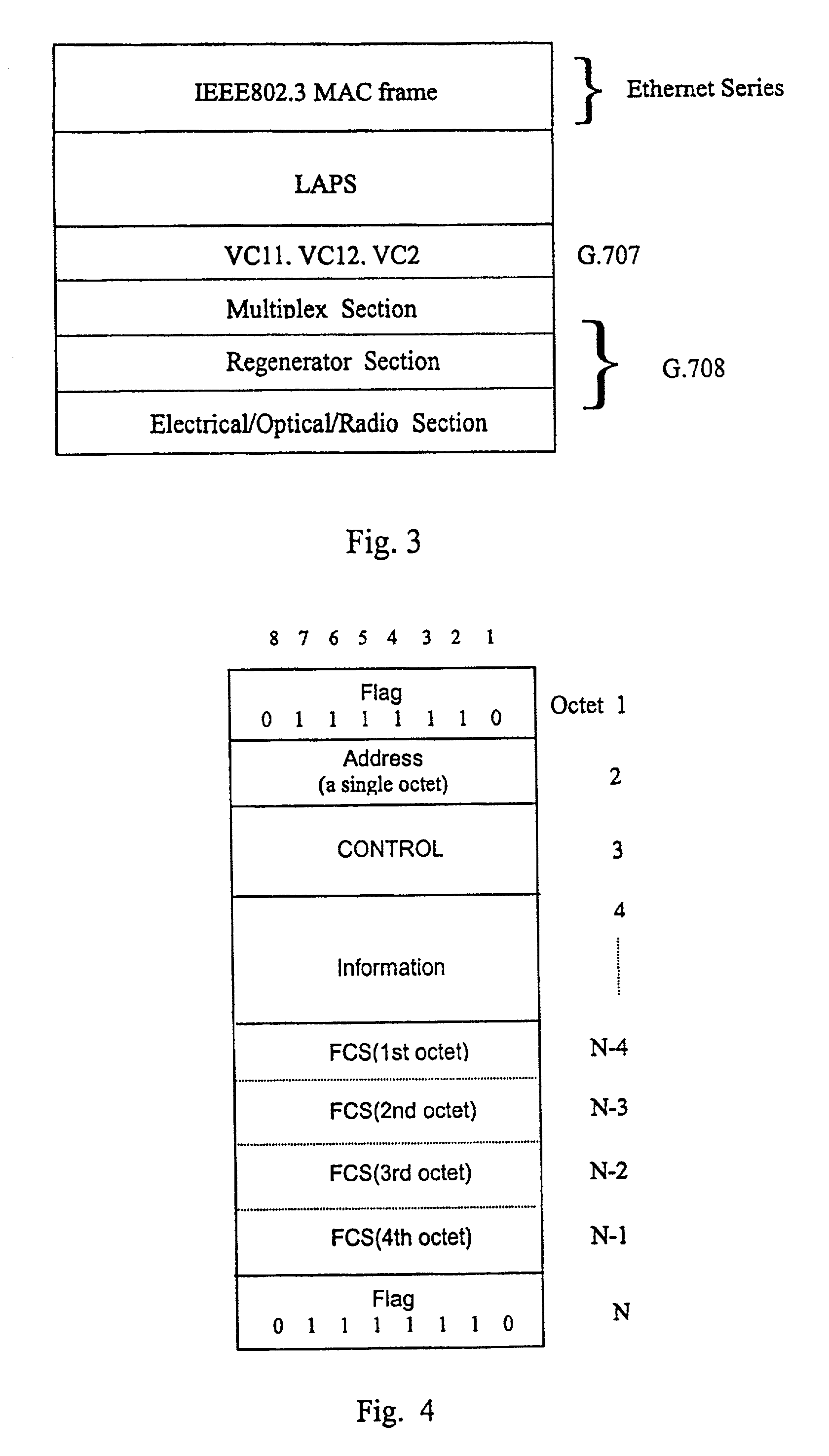

Interfacing apparatus and method for adapting Ethernet directly to physical channel

InactiveUS7031341B2Time-division multiplexTime-division multiplexing selectionLine cardFlag sequence

Owner:WUHAN RES INST OF POSTS & TELECOMM MII

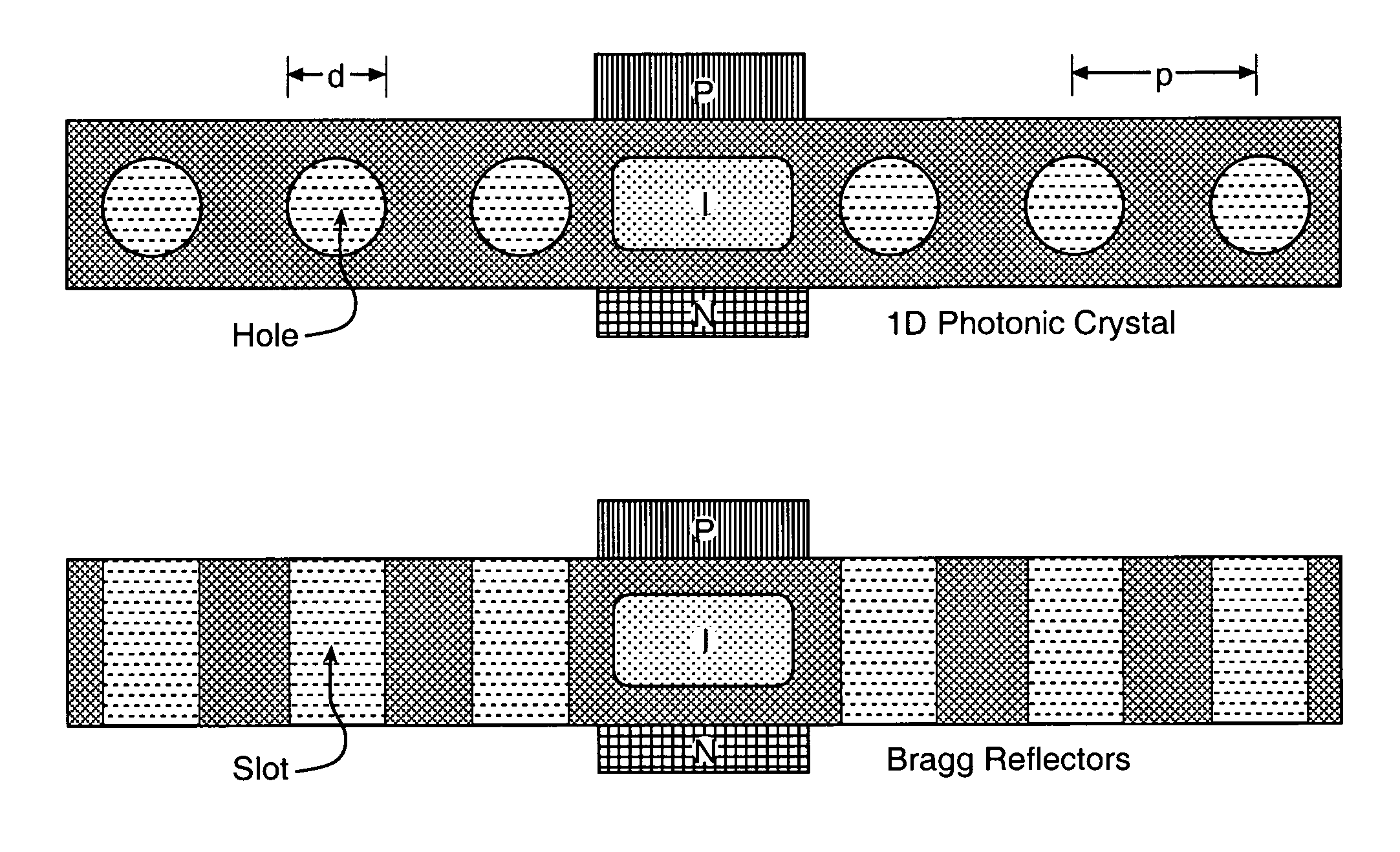

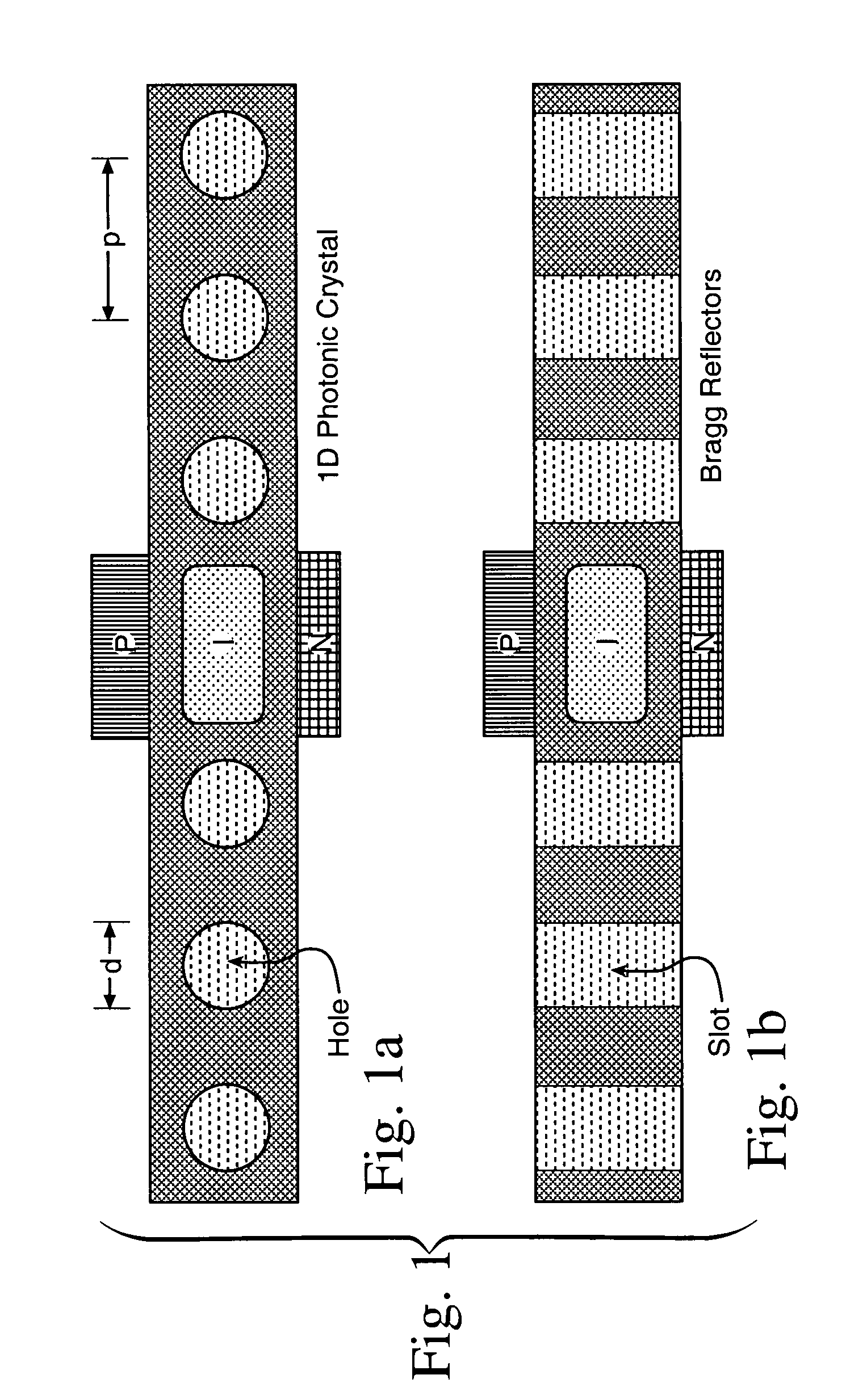

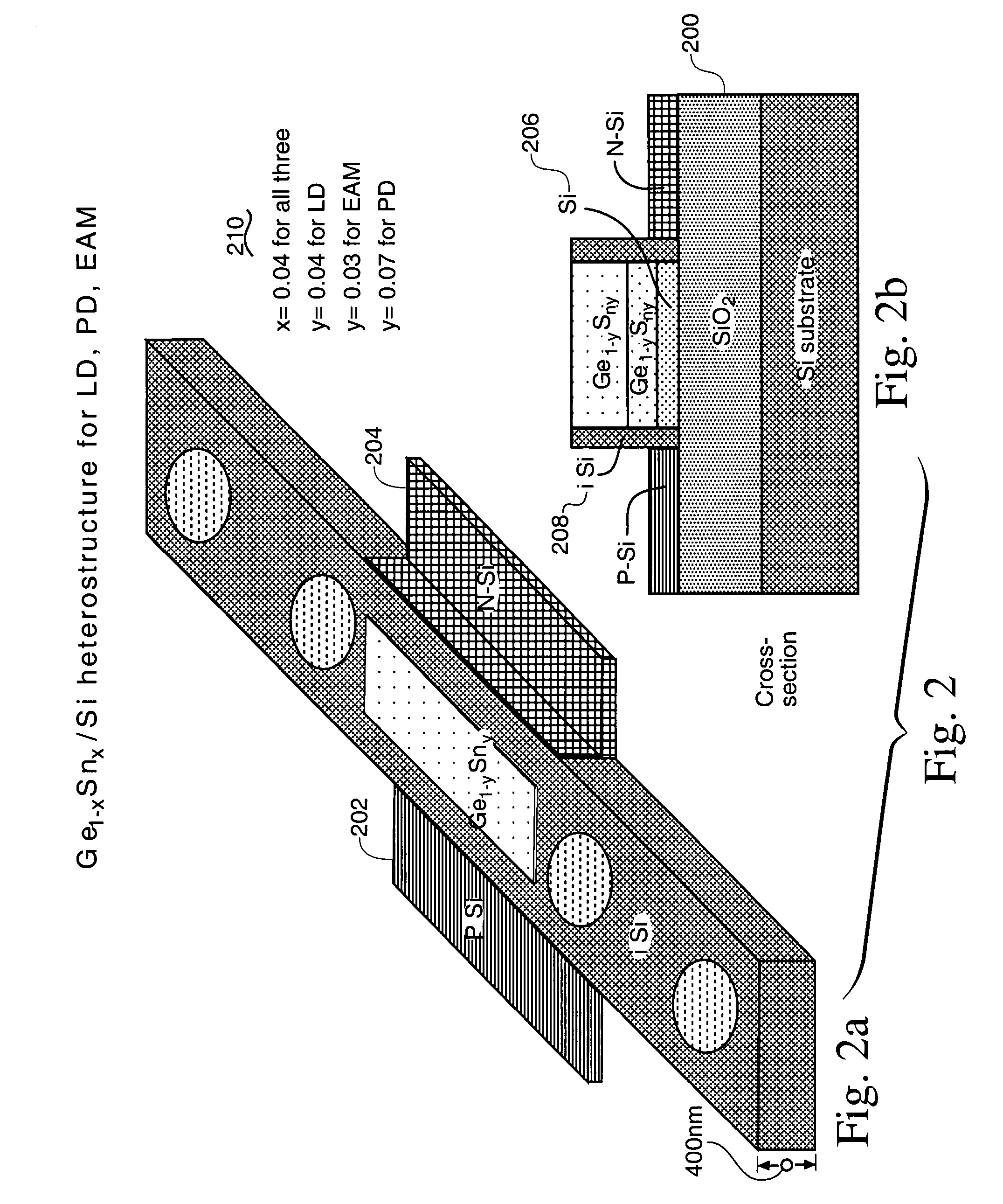

Semiconductor photonic nano communication link apparatus

InactiveUS7603016B1Eliminate needNanoopticsSemiconductor lasersElectro-absorption modulatorPhotonics

A CMOS compatible ten-gigabit-per-second region nano-waveguide included photonic communication link apparatus of low energy use per transmitted bit. An embodiment of the link includes an electrically pumped laser, an electro absorption modulator and a photodetector for the 1.5 to 2.0 micrometer infrared spectral region; omission of the separate electro absorption modulator is additionally disclosed. Each of these three nano-scale elements preferably includes active semiconductor crystal material situated in a preferably Silicon resonator within a nano-strip waveguide. The resonator is defined by dispersed resonator mirrors having tapered separation distance one dimensional photonic crystal lattice apertures of oxide holes or slots. Each of the three devices may be a semiconductor heterodiode pumped or controlled by laterally disposed wings enclosing the resonator to form a lateral PIN heterodiode for current injection or high E-field generation depending on bias and composition conditions selected.

Owner:US SEC THE AIR FORCE THE

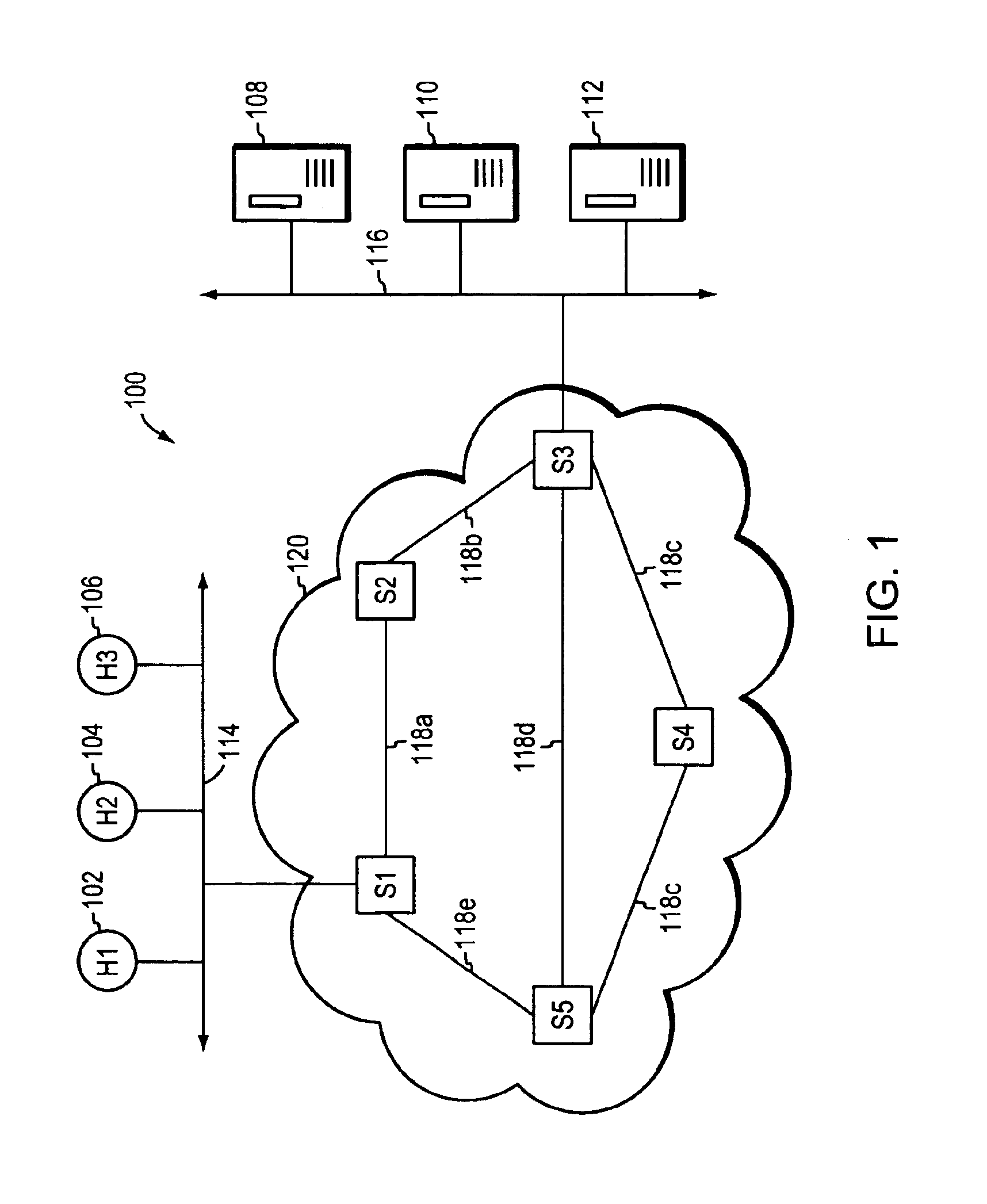

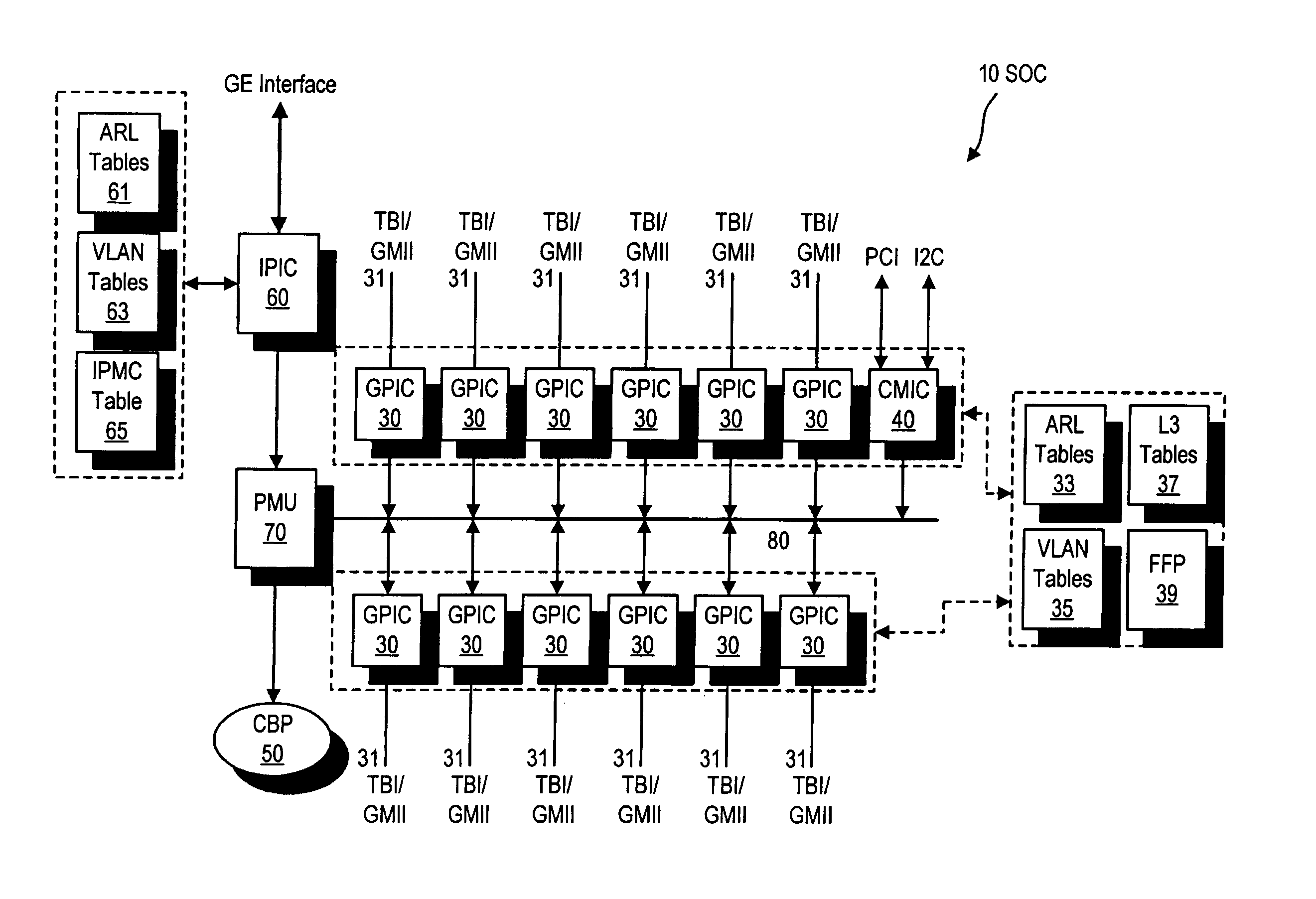

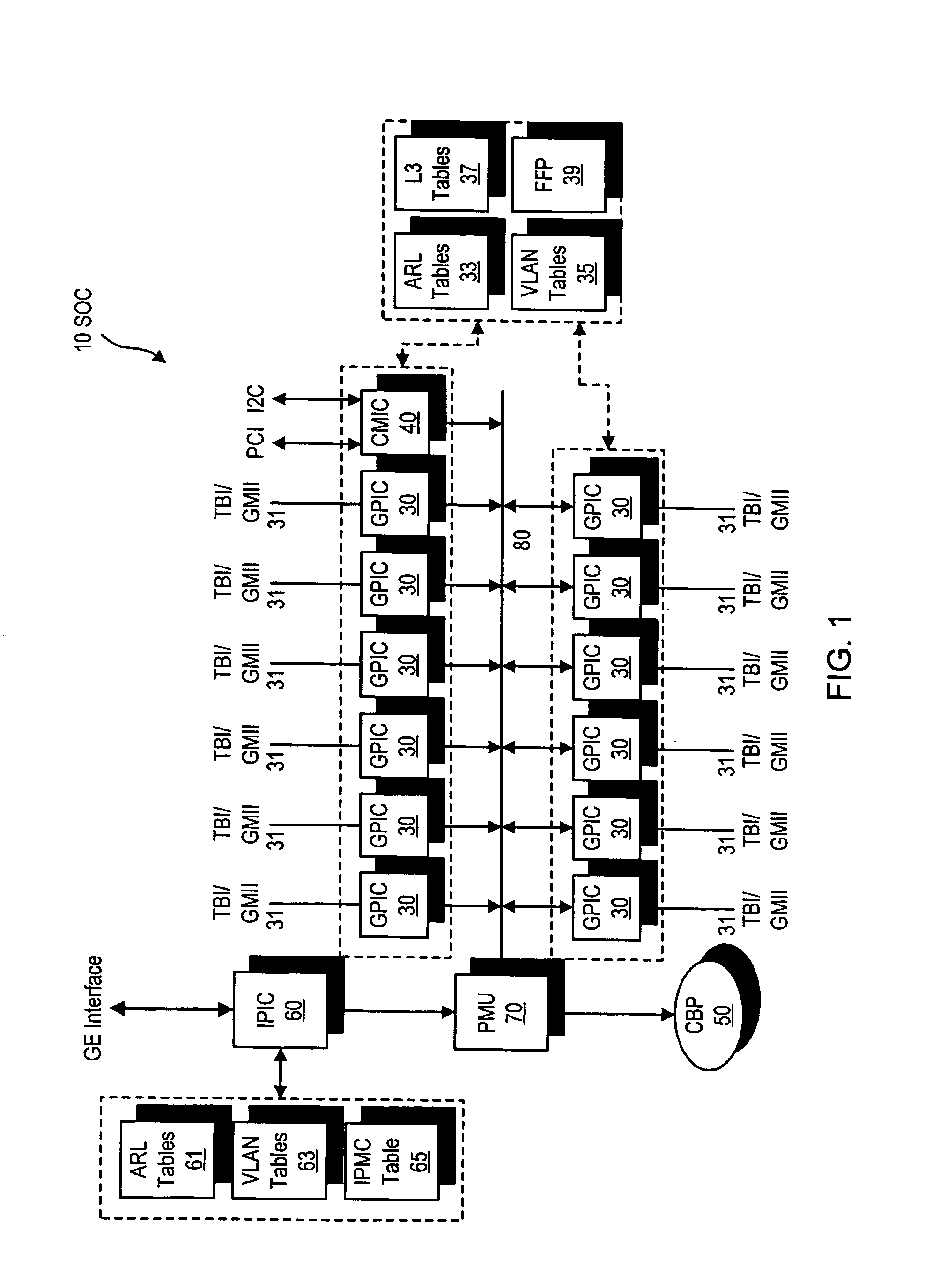

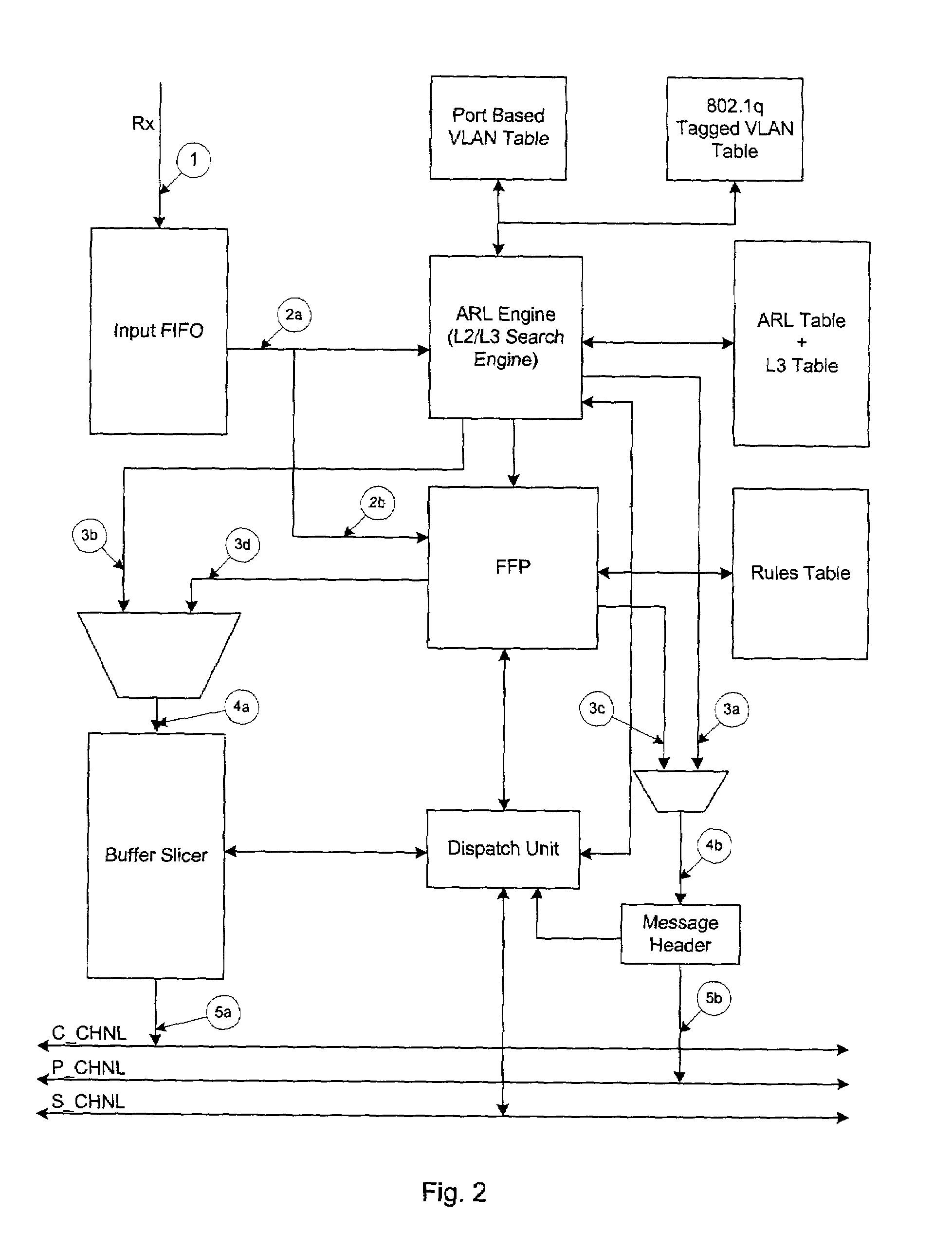

Gigabit switch supporting improved layer 3 switching

ActiveUS7009968B2Improved layer switchingEliminate needSpecial service provision for substationEnergy efficient ICTIP multicastNetwork communication

A network switch for network communications is disclosed. The switch includes a first data port interface, supporting at least one data port transmitting and receiving data at a first data rate and a second data port interface supporting a at least one data port transmitting and receiving data at a second data rate. The switch also has a CPU interface configured to communicate with a CPU and a memory management unit for communicating data from at least one of the first and second data port interfaces and a memory. It also has a communication channel for communicating data and messaging information between the first and second data port interfaces and the memory management unit and a plurality of semiconductor-implemented lookup tables including an address resolution lookup table, a layer three IP lookup table and VLAN tables. One of the first and second data port interfaces is configured to determine whether an incoming data packet is a unicast packet, a multicast packet or an IP multicast packet; and the address resolution lookup and layer three IP lookup tables are searched to find an egress port for the incoming data packet.

Owner:AVAGO TECH INT SALES PTE LTD

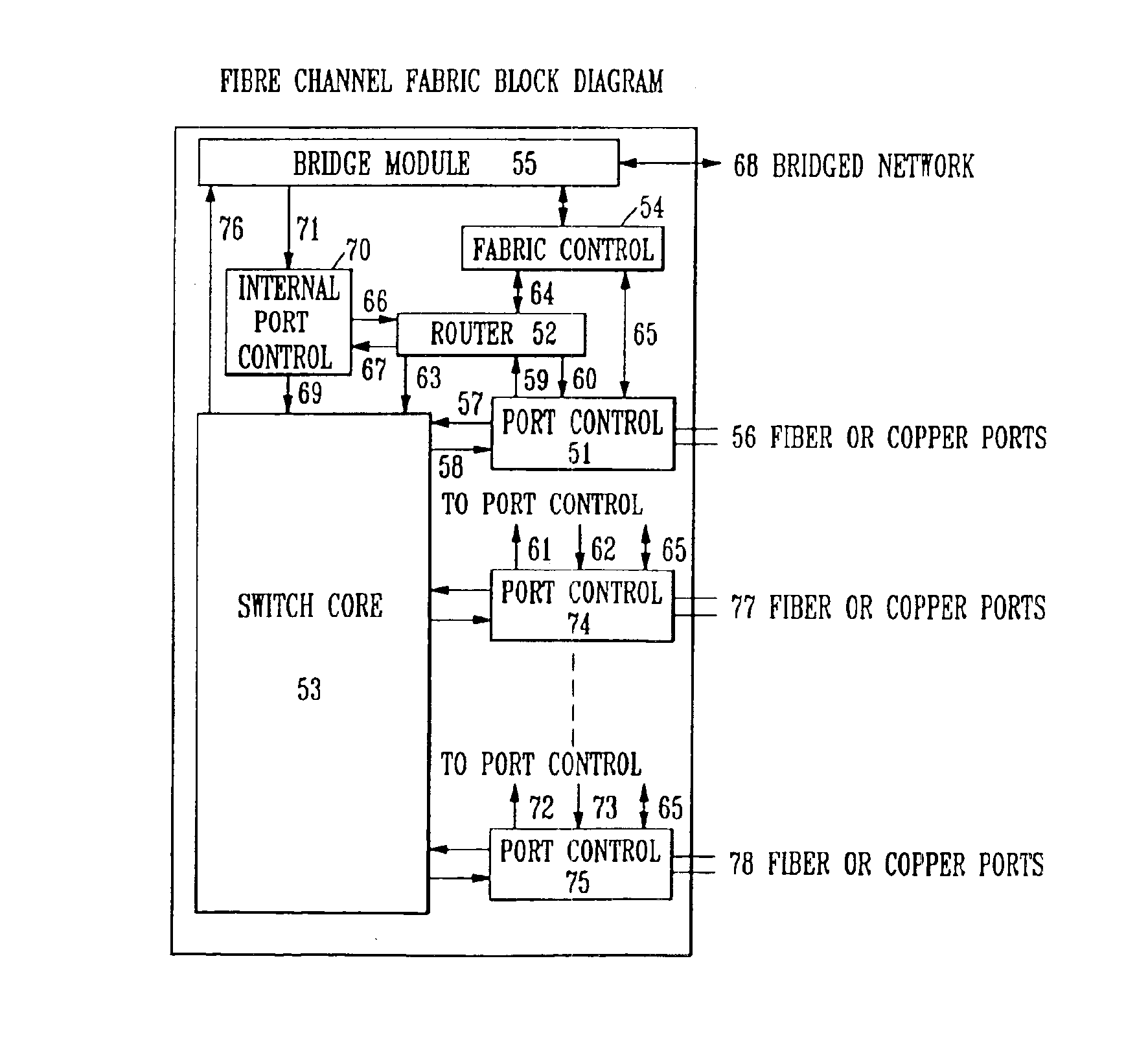

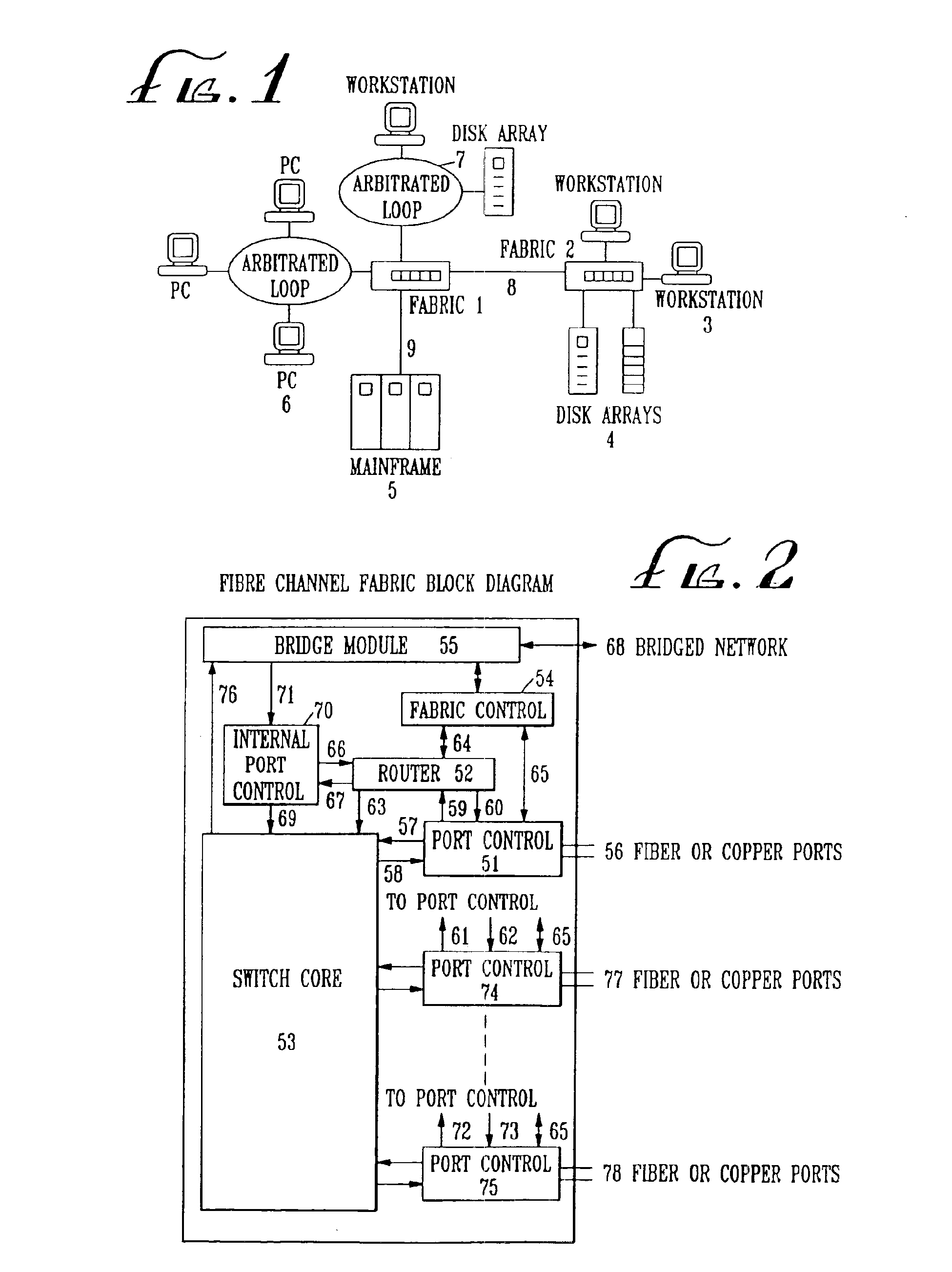

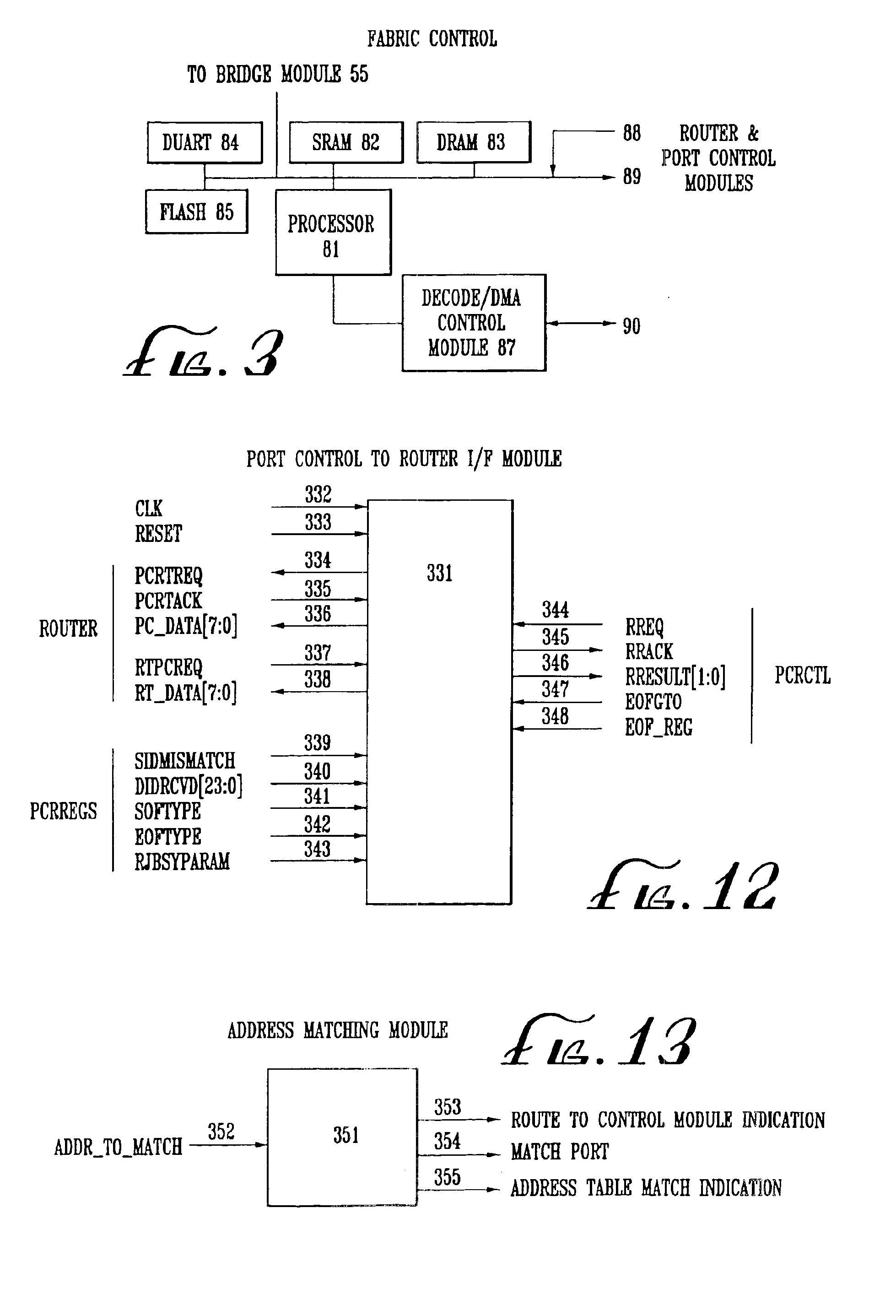

Fibre Channel switching fabric

The Fibre. Channel standard was created by the American National Standard for Information Systems (ANSI) X3T11 task group to define a serial I / O channel for interconnecting a number of heterogeneous peripheral devices to computer systems as well as interconnecting the computer systems themselves through optical fiber and copper media at gigabit speeds (i.e., one billion bits per second). Multiple protocols such as SCSI (Small Computer Serial Interface), IP (Internet Protocol), HIPPI, ATM (Asynchronous Transfer Mode) among others can concurrently utilize the same media when mapped over Fibre Channel. A Fibre Channel Fabric is an entity which transmits Fibre Channel frames between connected Node Ports. The Fibre Channel fabric routes the frames based on the destination address as well as other information embedded in the Fibre Channel frame header. Node Ports are attached to the Fibre Channel Fabric through links.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

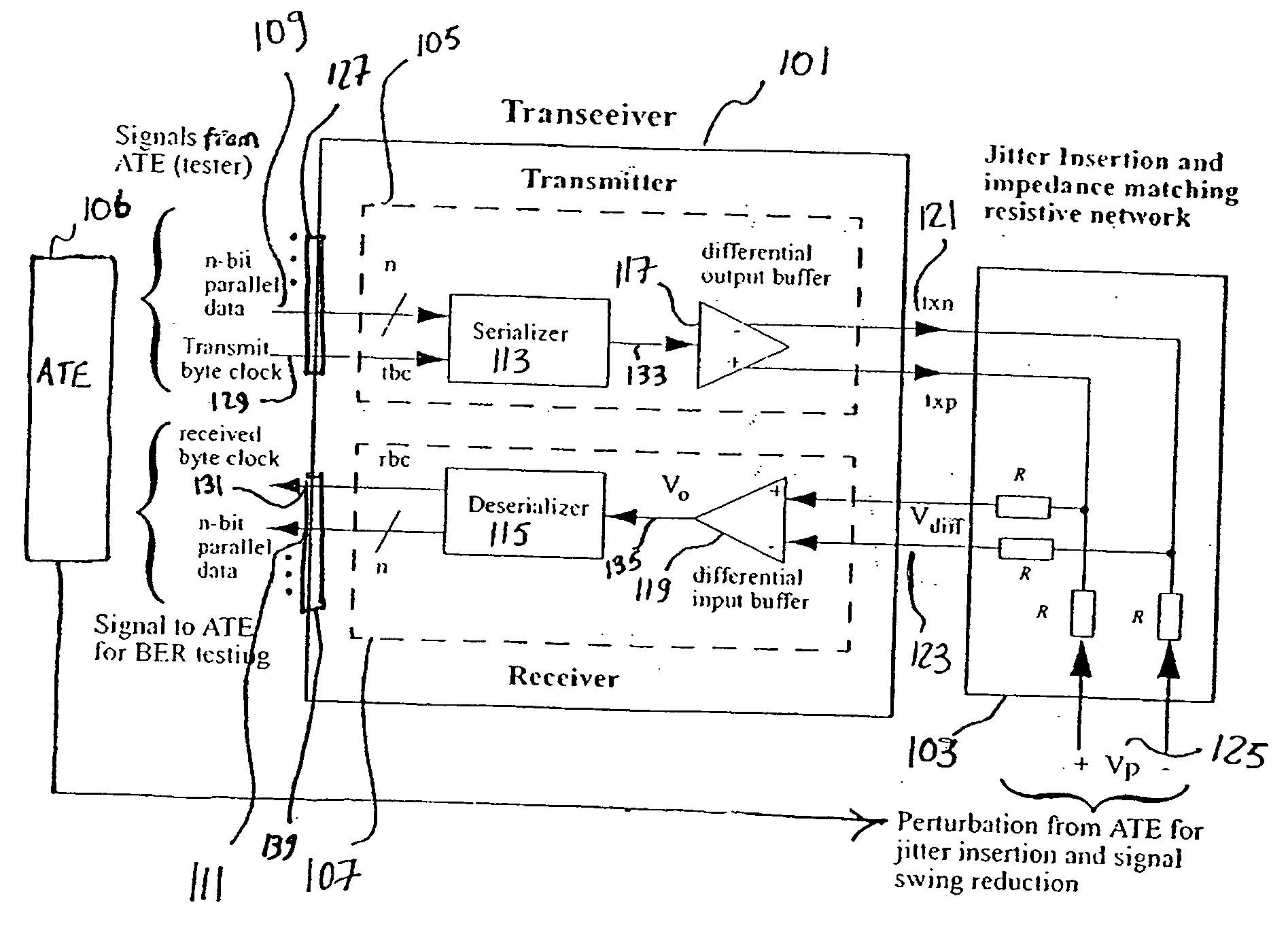

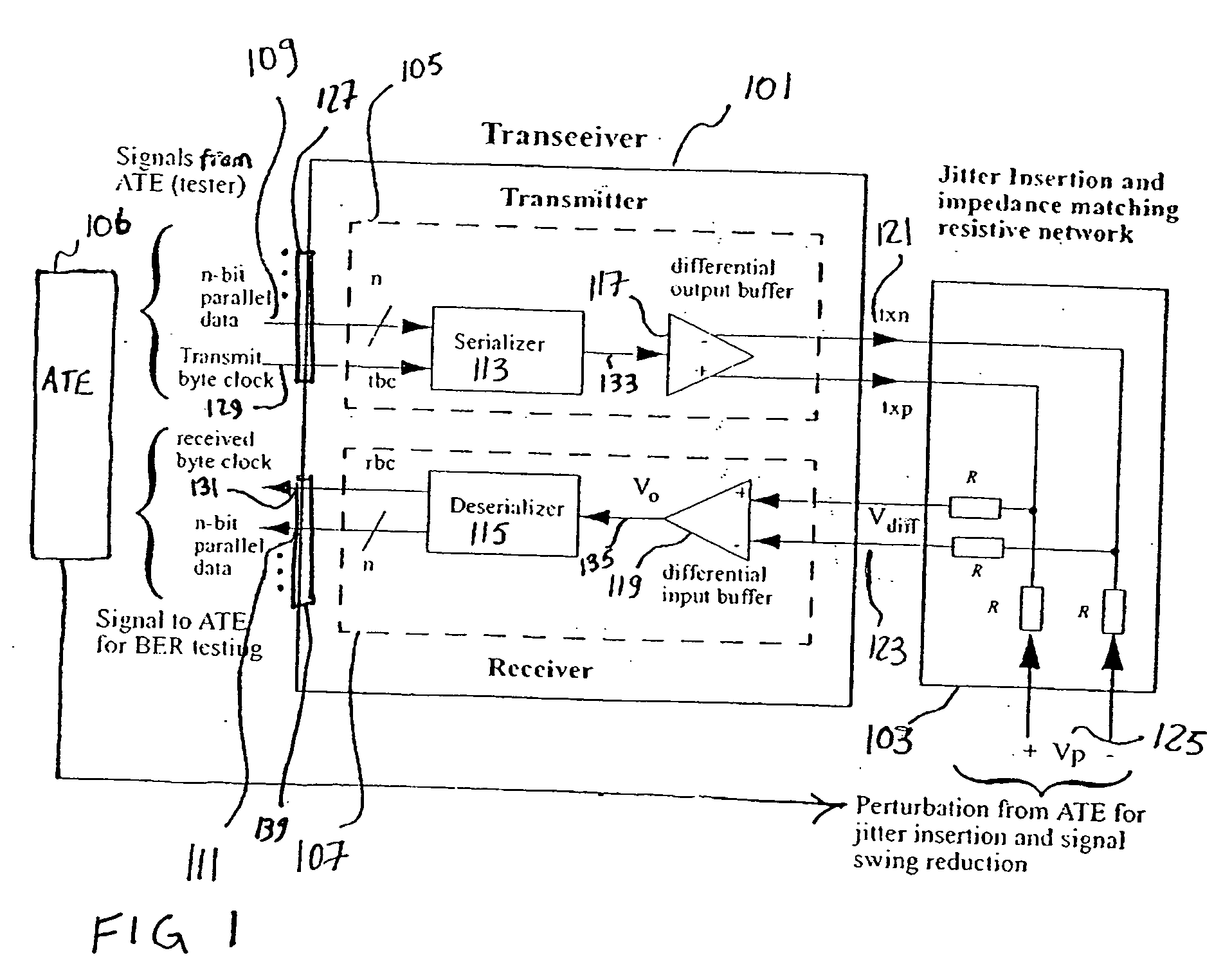

System and method for production testing of high speed communications receivers

InactiveUS20050172181A1Digital circuit testingElectrical measurement instrument detailsTransceiverLow voltage

A method for testing a semiconductor device with a multi-gigabit communications receiver includes combining a data output from a high-speed communications transmitter with a perturbation signal generated by automatic test equipment. The combined signal data signal including jitter and low voltage swings is input to the communications receiver port under test. The automatic test equipment determines the bit error rate of the parallel data output from the receiver port under test. This test method is appropriate for semiconductor devices with multiple transceiver ports.

Owner:MELLANOX TECHNOLOGIES LTD

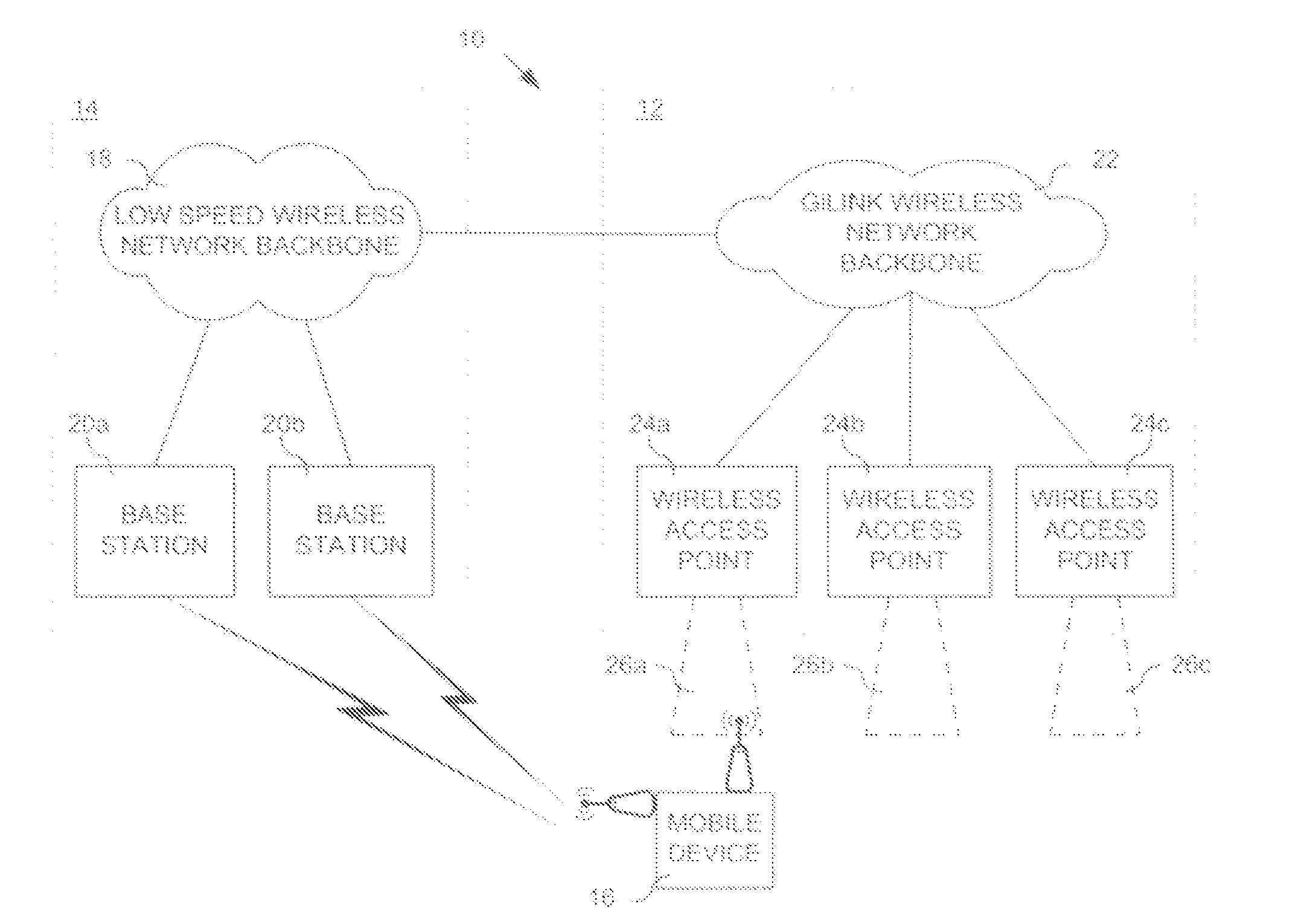

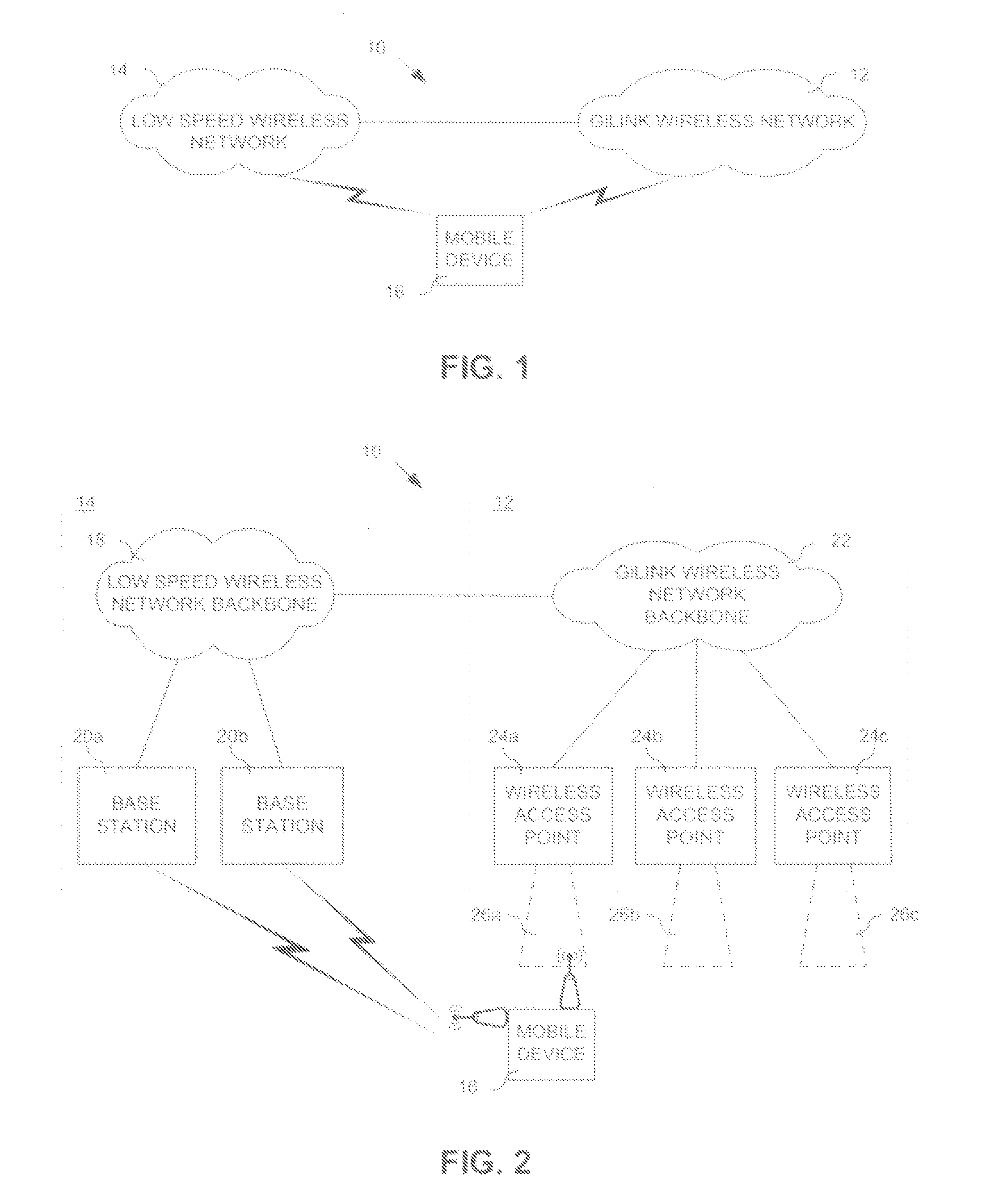

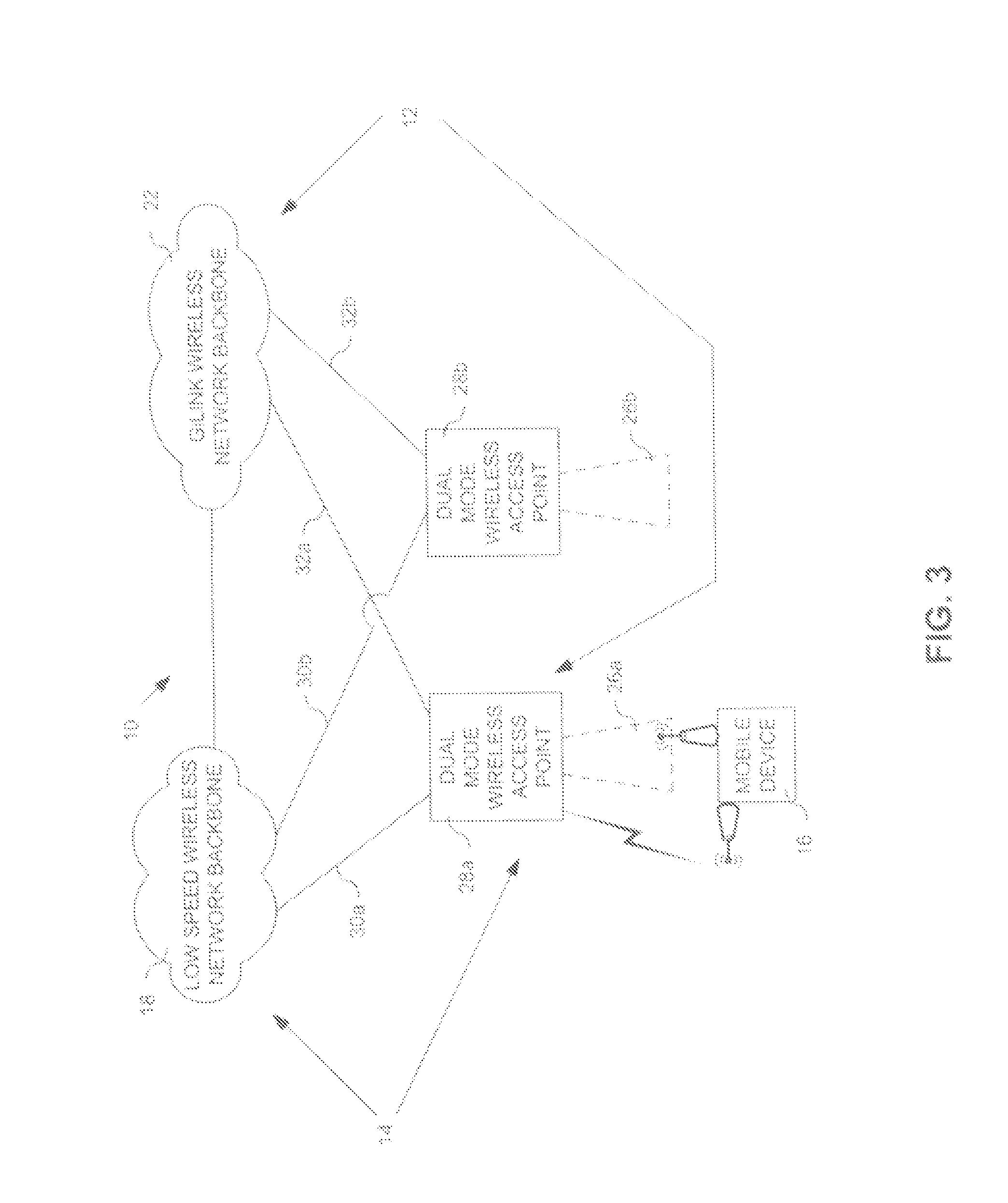

Method and system for gigabit wireless transmission

InactiveUS20100080197A1Cost-effectiveShorten speedAssess restrictionNetwork topologiesWireless transmissionPhotonics

A method and system for wireless communication with a mobile device. A first wireless communication network, such as a WiMax or cellular-based network, has a first maximum wireless speed. A second wireless communication network, such as a near-photonic speed gigabit link (“GiLink”) network, has a second maximum wireless speed. The second wireless maximum speed is less than the first maximum wireless speed. The second wireless communication network provides control plane services for wireless communication between the mobile device and the first wireless communication network.

Owner:APPLE INC

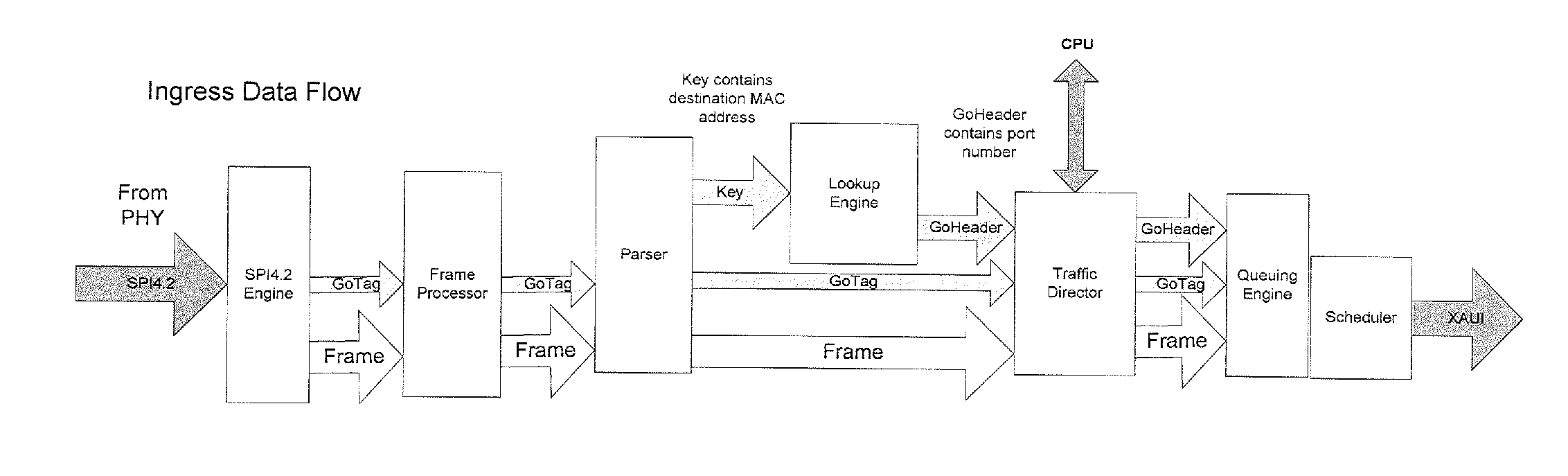

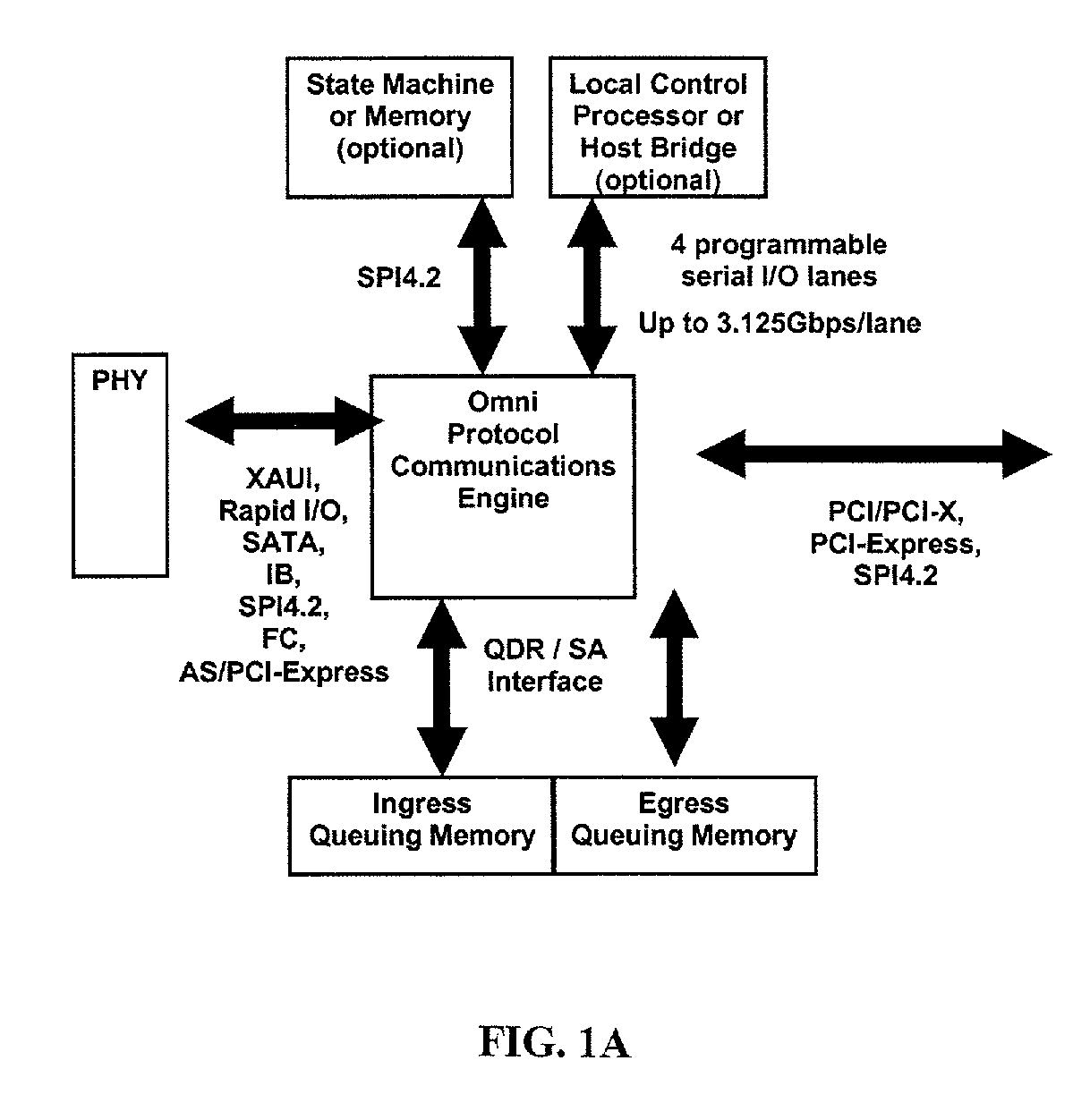

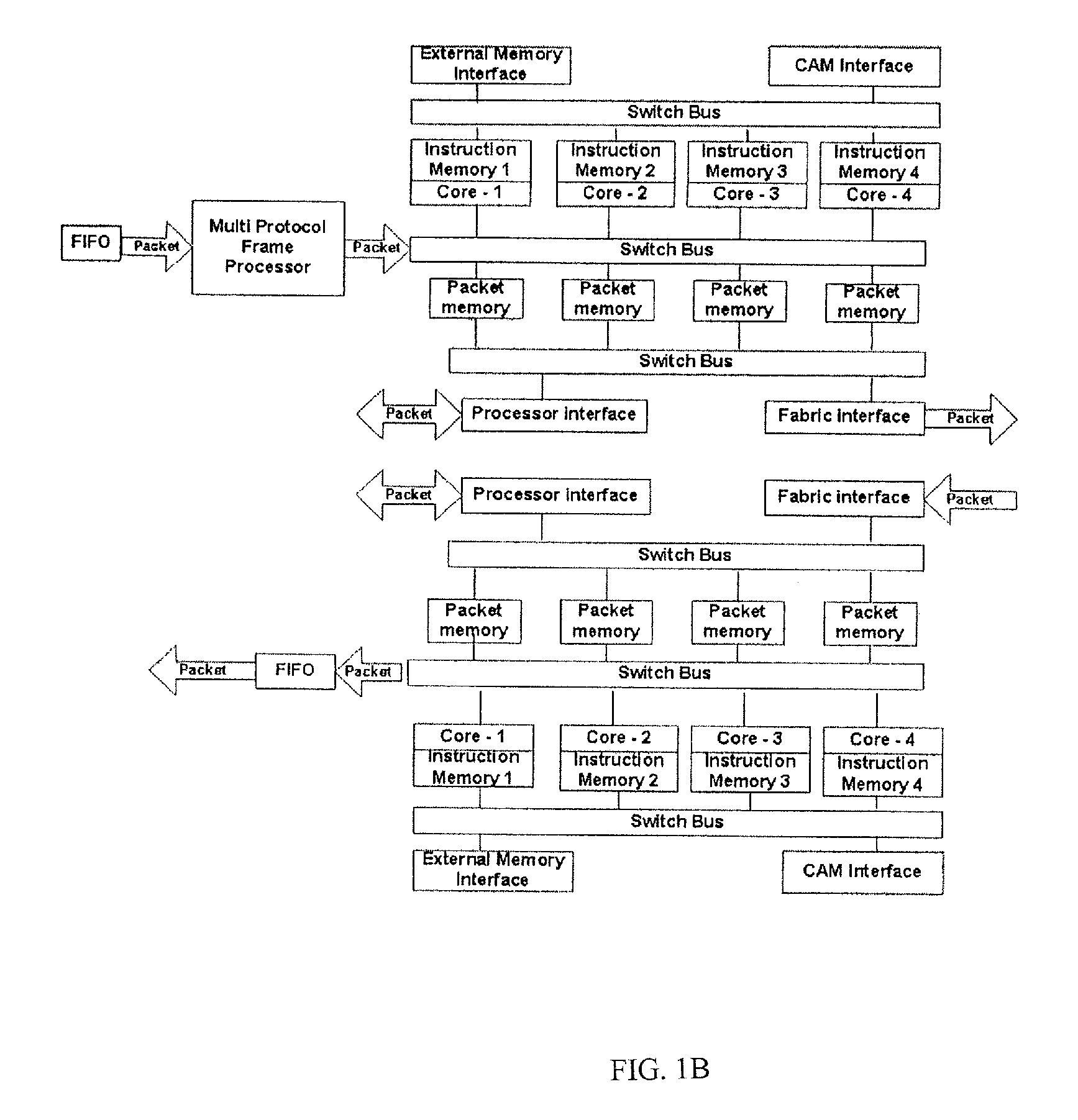

Omni-protocol engine for reconfigurable bit-stream processing in high-speed networks

InactiveUS20070067481A1Improve efficiencyImprove performanceError preventionFrequency-division multiplex detailsGigabitNetsniff-ng

A reconfigurable, protocol indifferent bit stream-processing engine, and related systems and data communication methodologies, are adapted to achieve the goal of providing inter-fabric interoperability among high-speed networks operating a speeds of at least 10 gigabits per second. The bit-stream processing engine operates as an omni-protocol, multi-stage processor that can be configured with appropriate switches and related network elements to create a seamless network fabric that permits interoperability not only among existing communication protocols, but also with the ability to accommodate future communication protocols. The method and systems of the present invention are applicable to networks that include storage networks, communication networks and processor networks.

Owner:RPX CORP

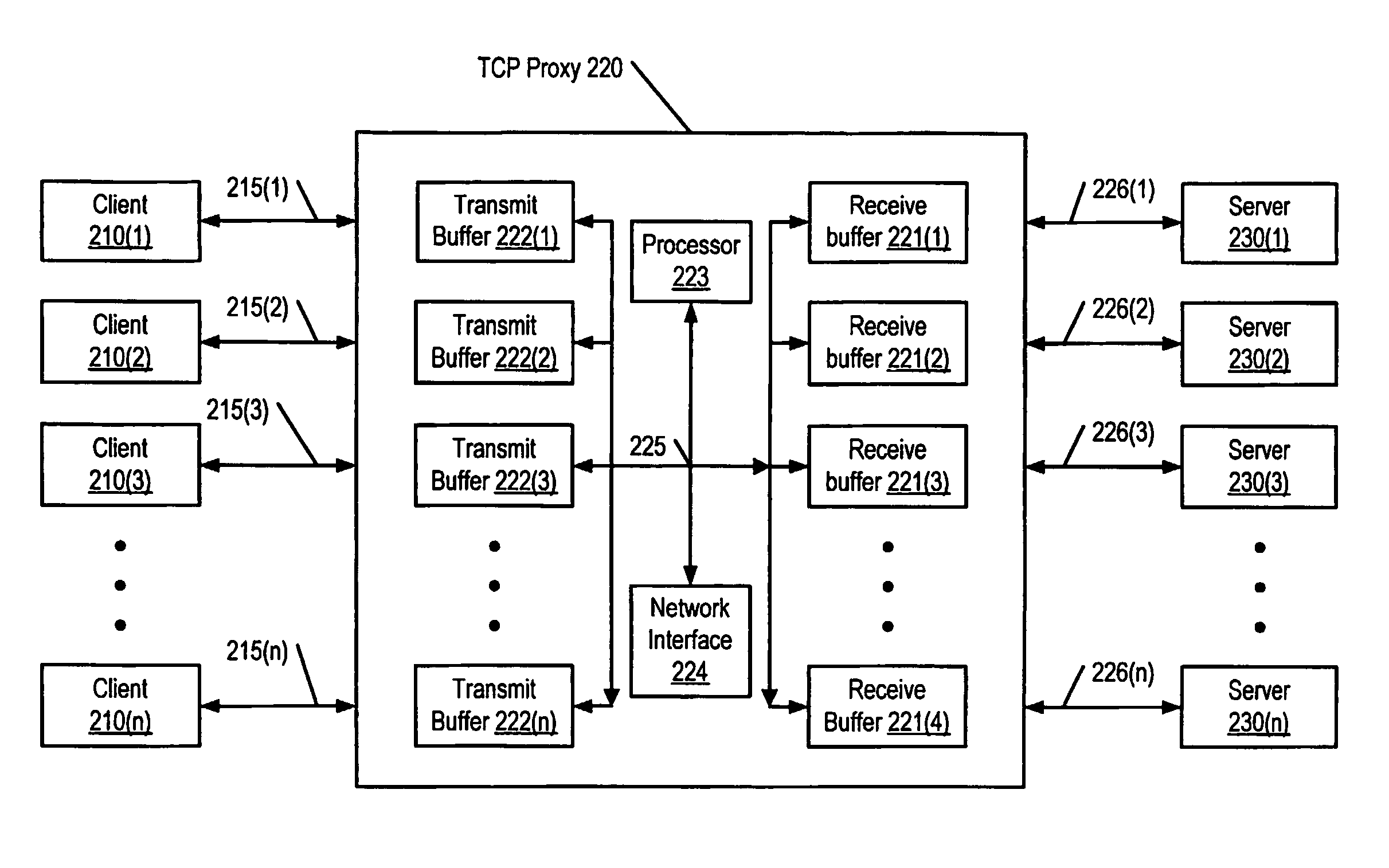

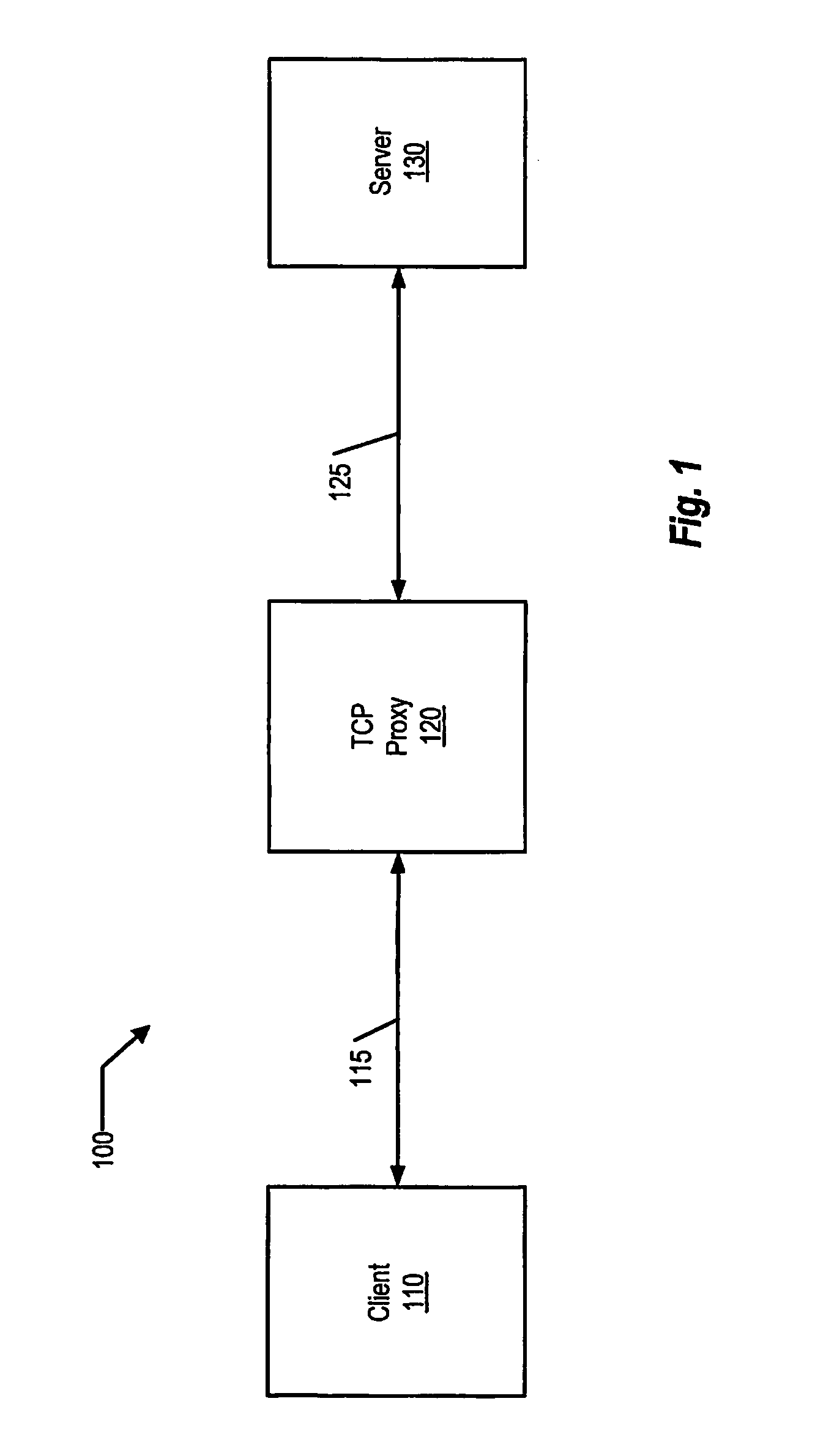

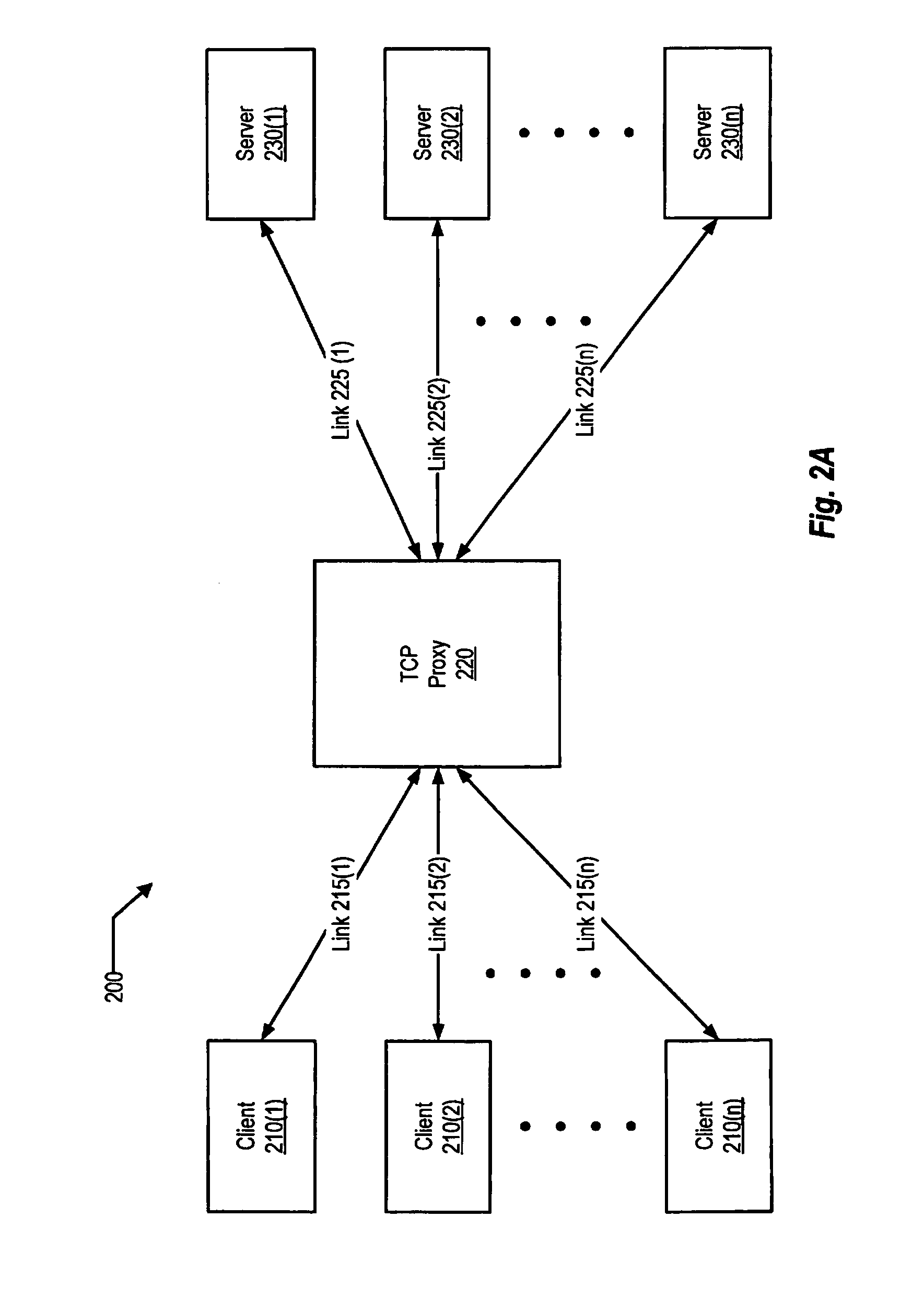

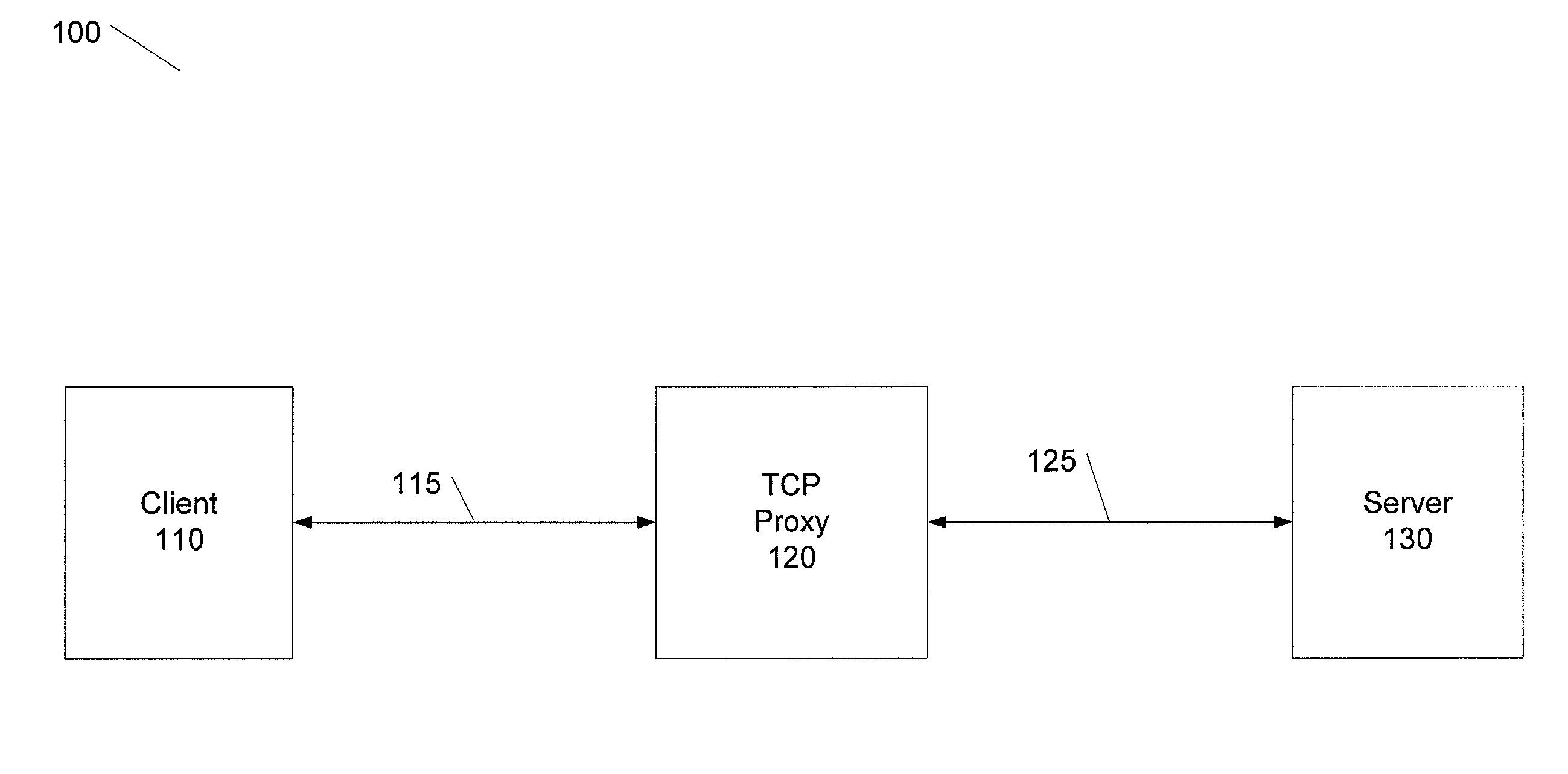

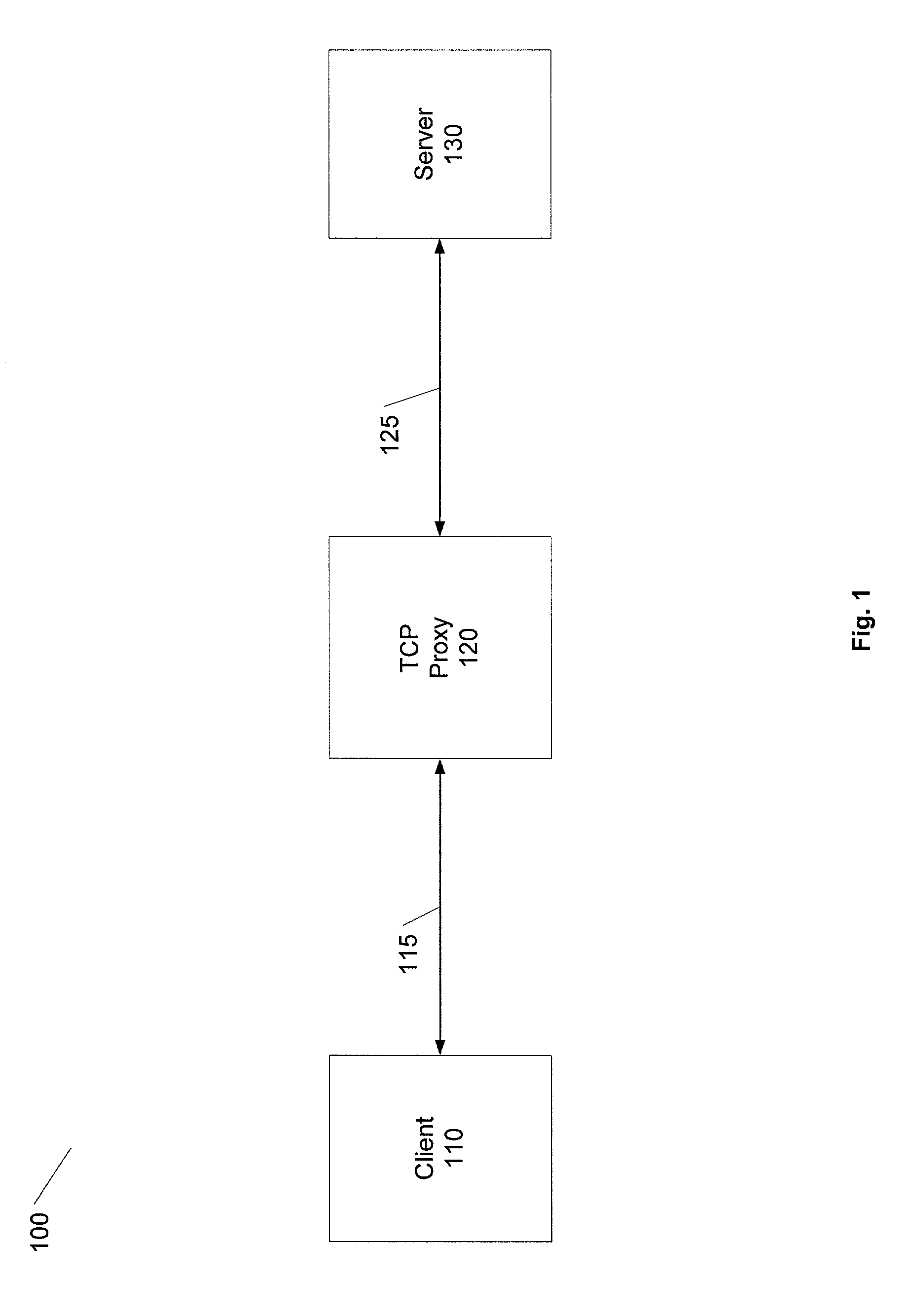

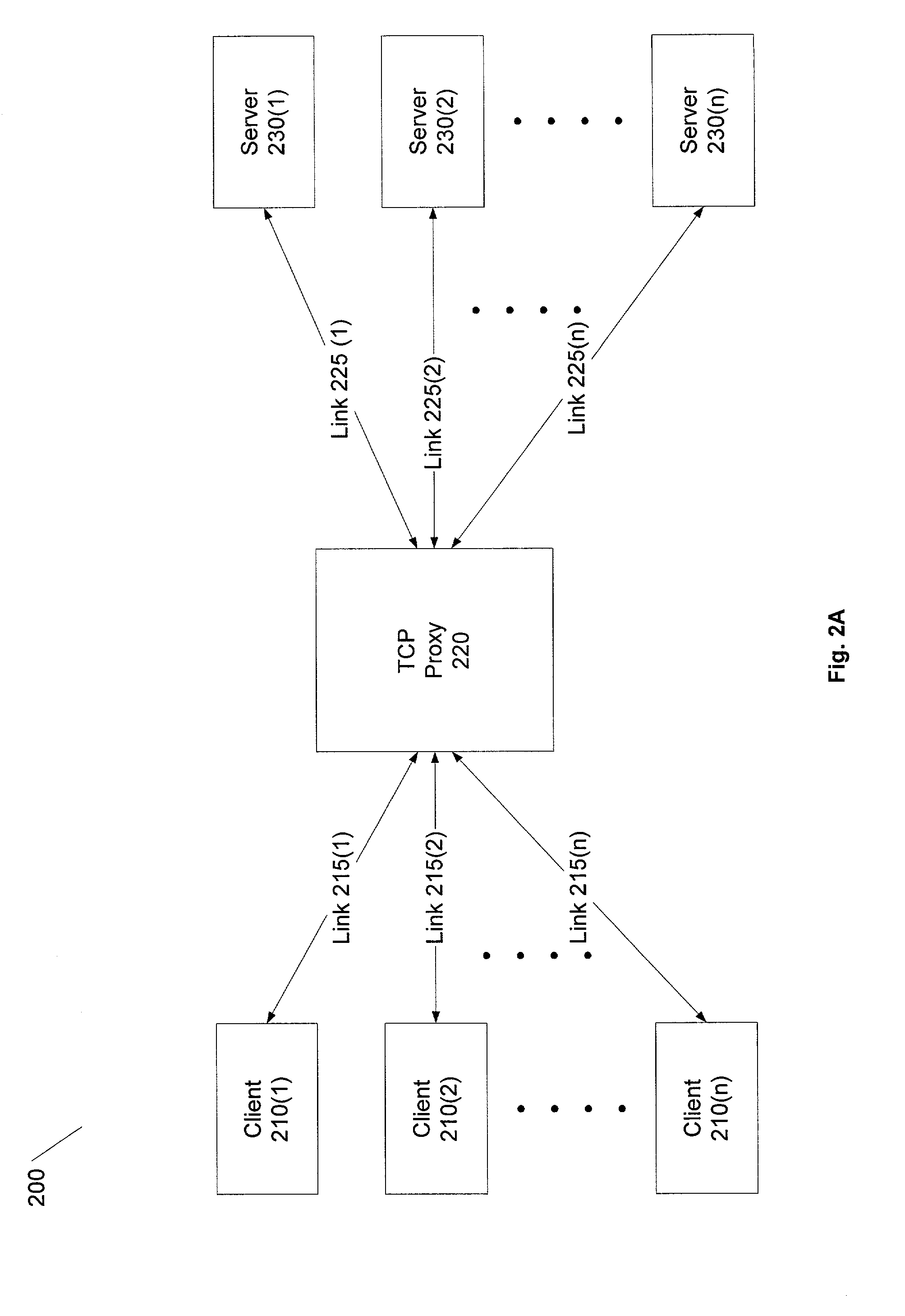

TCP proxy connection management in a gigabit environment

The present invention describes a method and apparatus to effectively manage data buffers for a client and a server connection in a multiple connection environment. The TCP processes of servers and clients are merged into an independent TCP process in a TCP ‘proxy’ server. The TCP proxy server includes a control unit and a data switching unit (the proxy application). The TCP proxy server terminates the client TCP connection and initiates a separate TCP connection with the server. The data switching unit binds the two individual connections. The TCP proxy server portrays the actual server TCP. The control unit in the TCP proxy server manages data buffers, control memory and supports multiple connections. The control unit ‘pushes’ the data into the buffers by monitoring the use of the buffers. The control unit does not wait for data requests from the data switching unit thus, eliminating the overhead of data request messages.

Owner:CISCO TECH INC

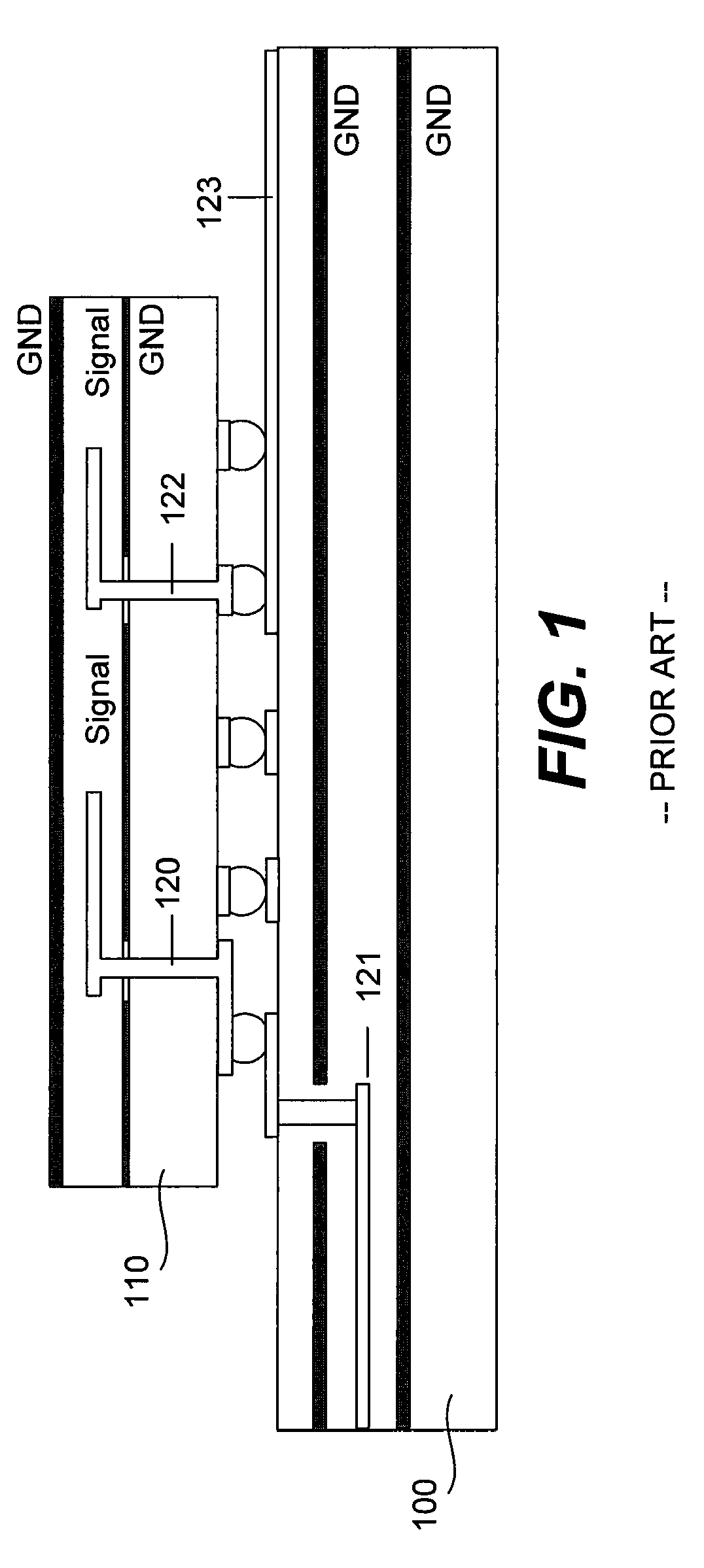

Ball grid array package-to-board interconnect co-design apparatus

InactiveUS7405477B1Signal transmission is convenientAvoid reflectionsSemiconductor/solid-state device detailsPrinted circuit aspectsCopper interconnectData stream

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

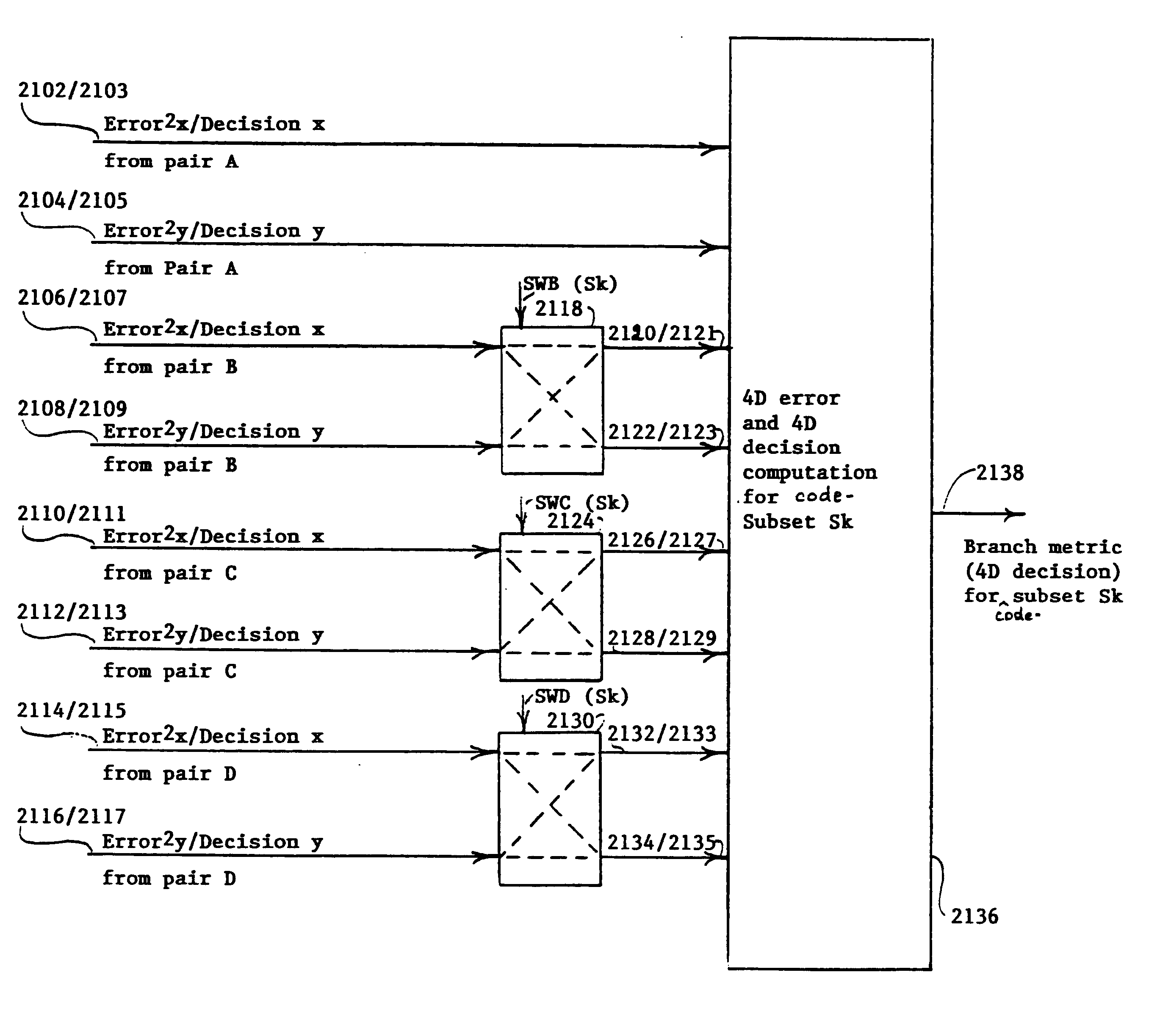

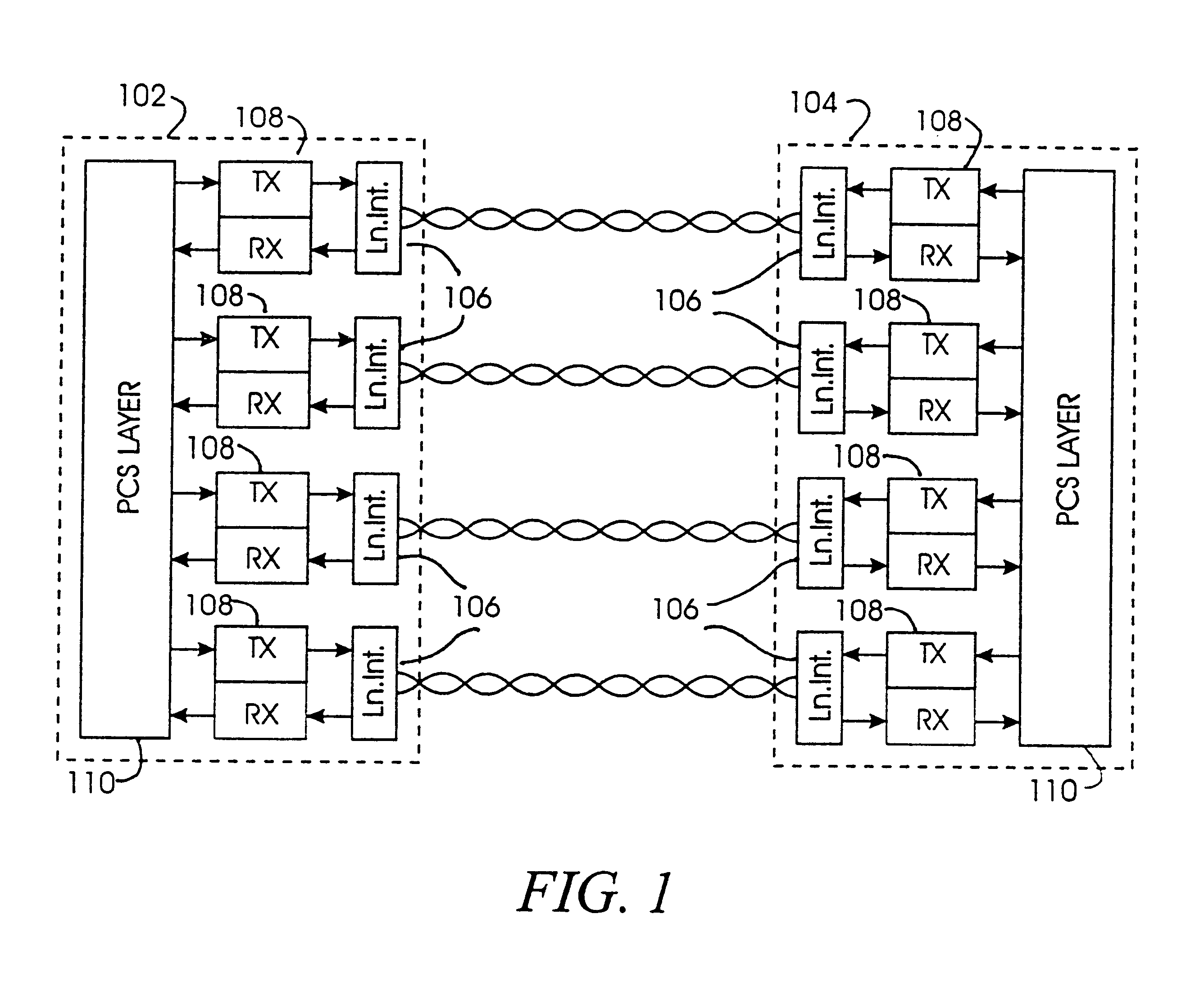

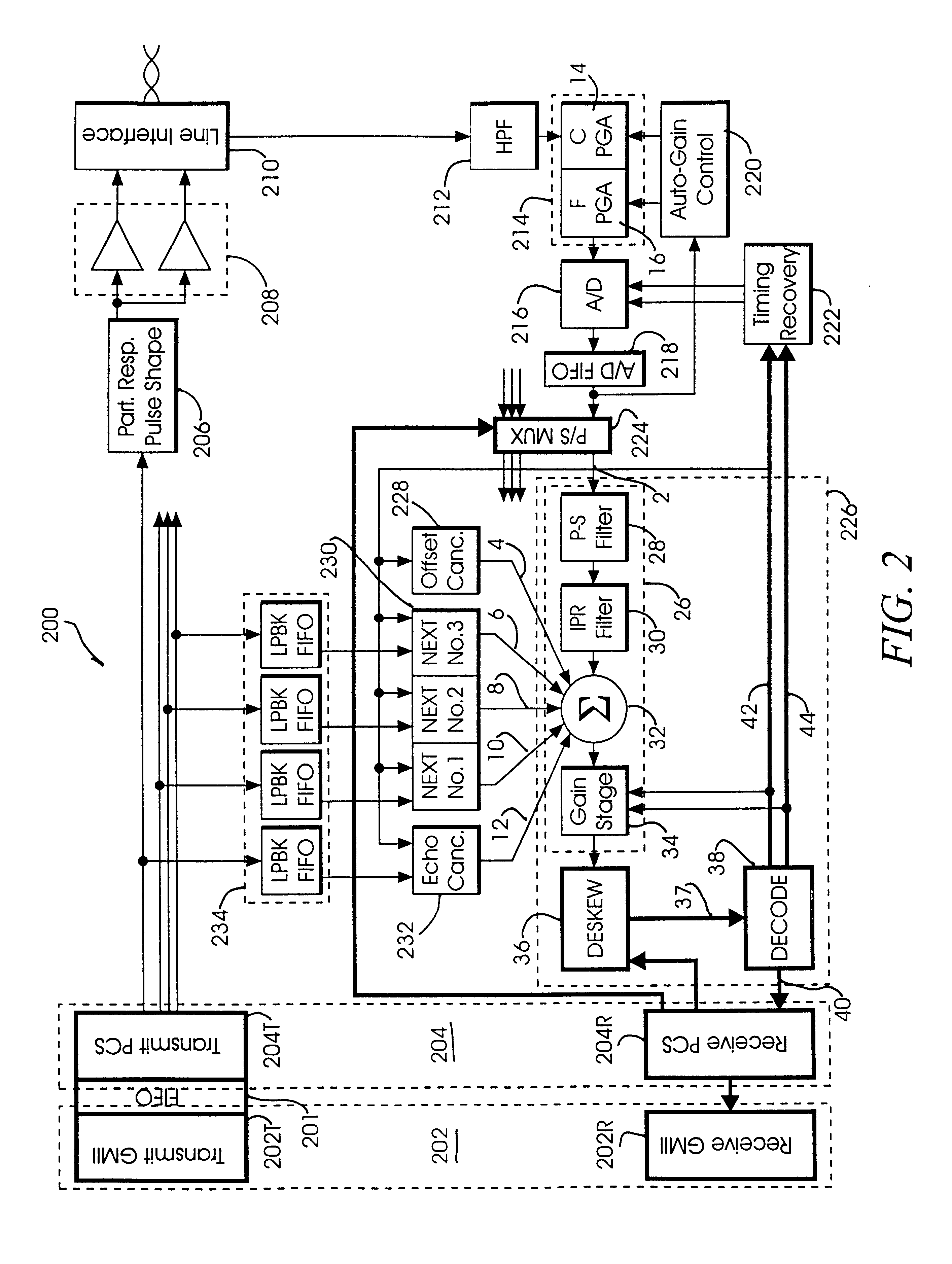

Pair-swap independent trellis decoder for a multi-pair gigabit transceiver

InactiveUS6865234B1Channel dividing arrangementsDigital circuit testingGigabitMulti-gigabit transceiver

A method and a system for compensating for a permutation of L pairs of cable such that the compensation is localized in a trellis decoder of a receiver. The L pairs of cable correspond to L dimensions of a trellis code associated with the trellis decoder. The trellis code includes a plurality of code-subsets. The permutation of the L pairs of cable is determined. A plurality of sets of swap indicators based on the permutation of the L pairs of cable is generated. Each of the sets of swap indicators corresponds to one of the code-subsets. The code-subsets are remapped based on the corresponding sets of swap indicators.

Owner:AVAGO TECH INT SALES PTE LTD

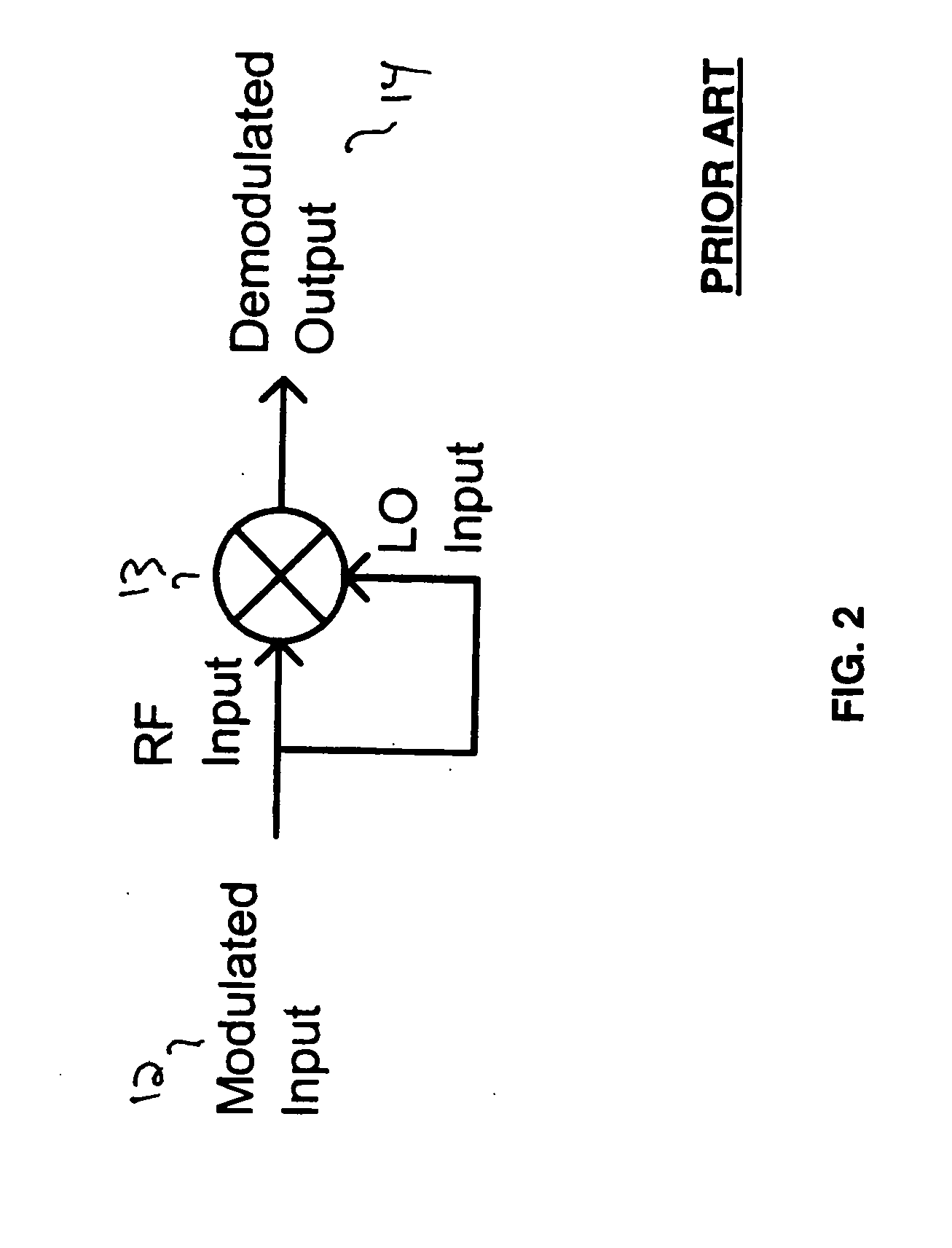

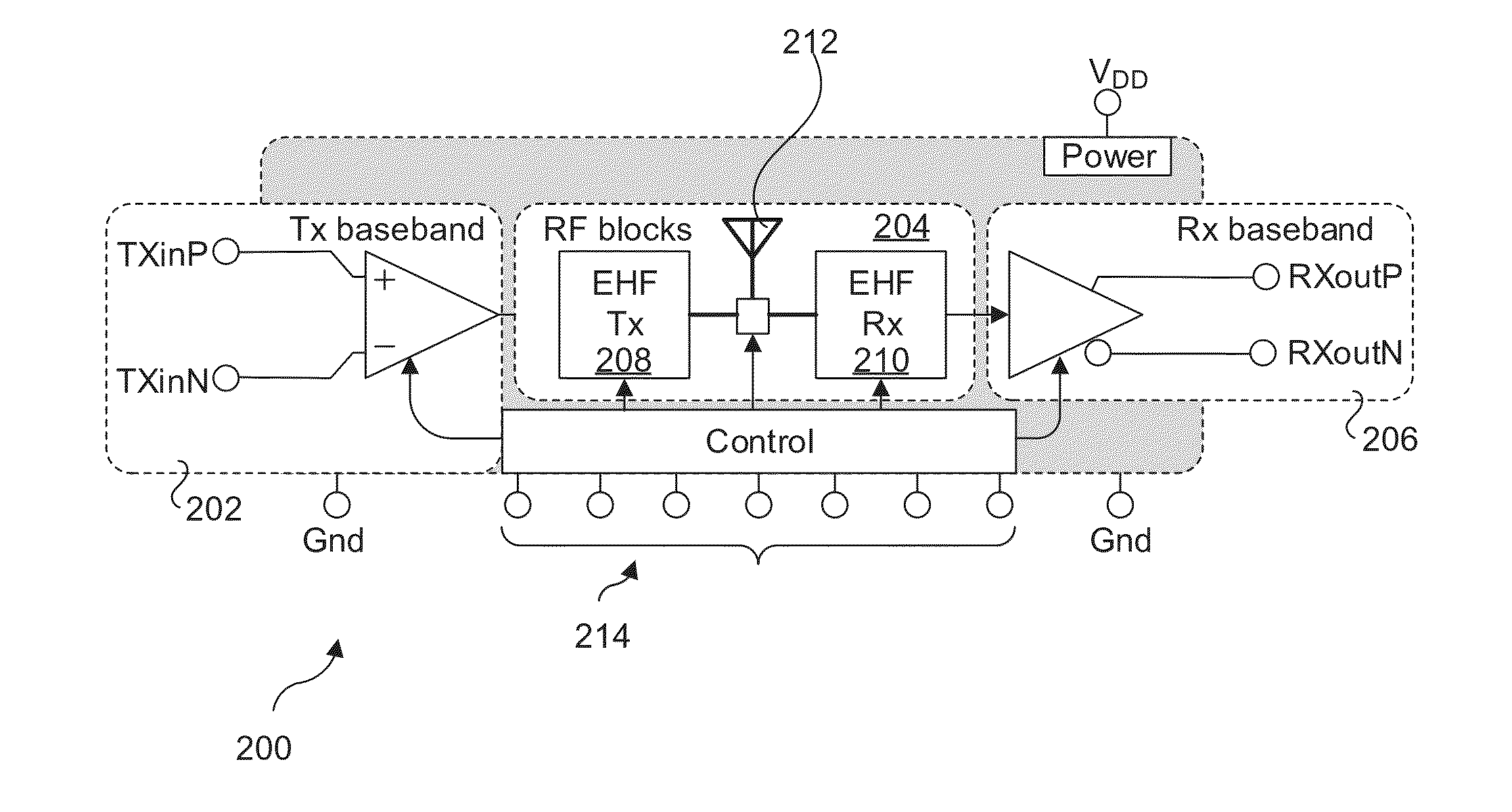

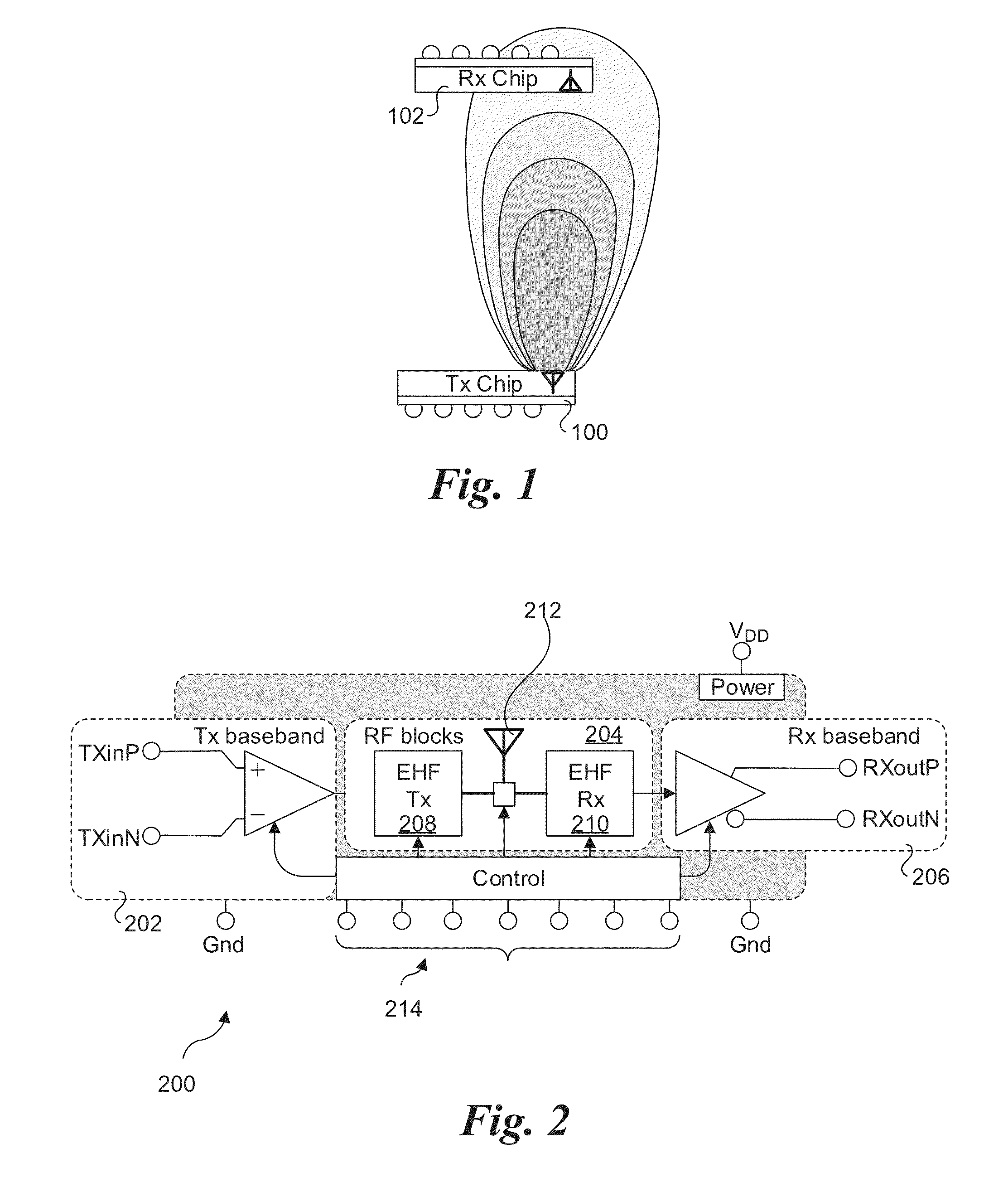

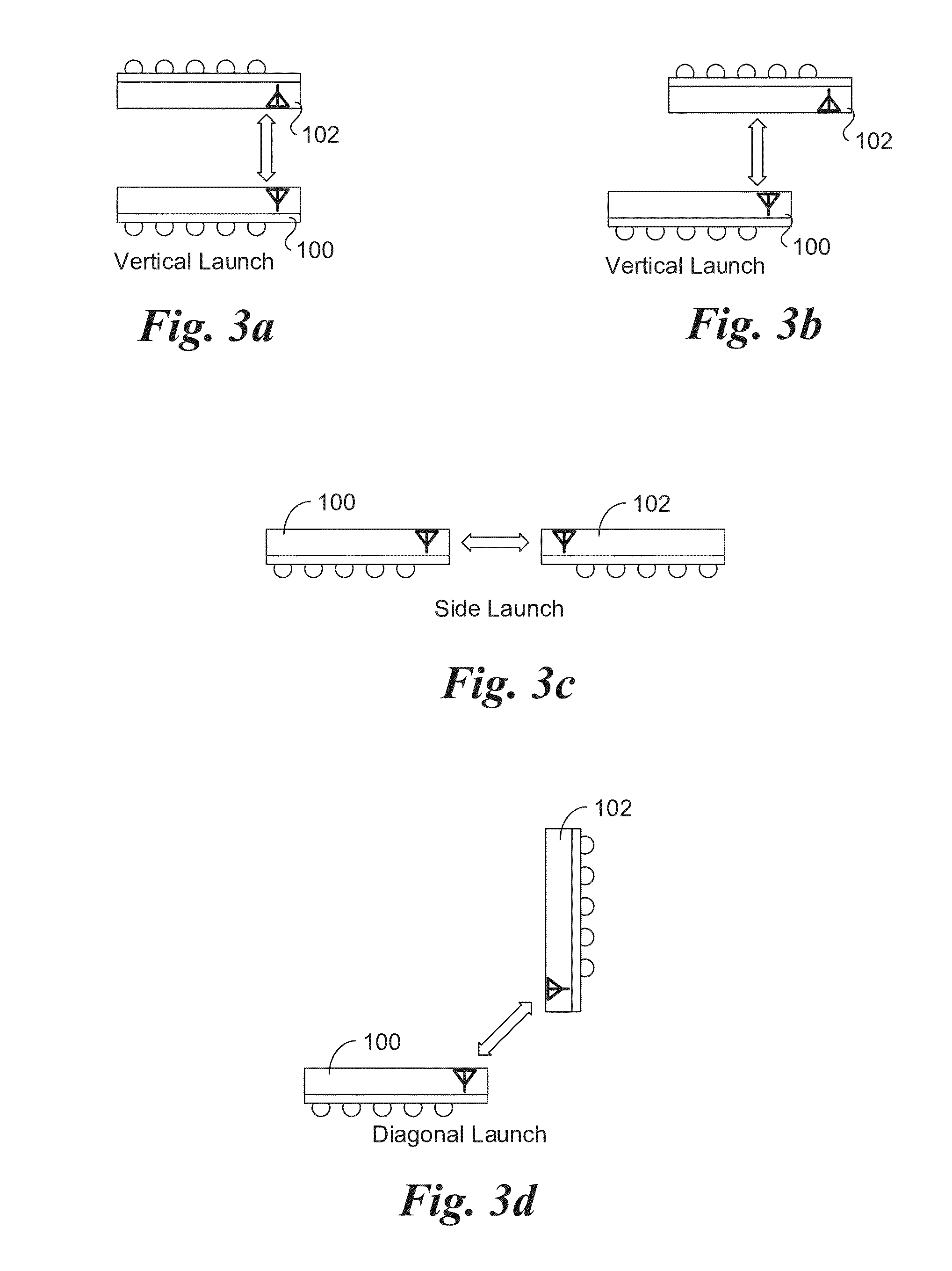

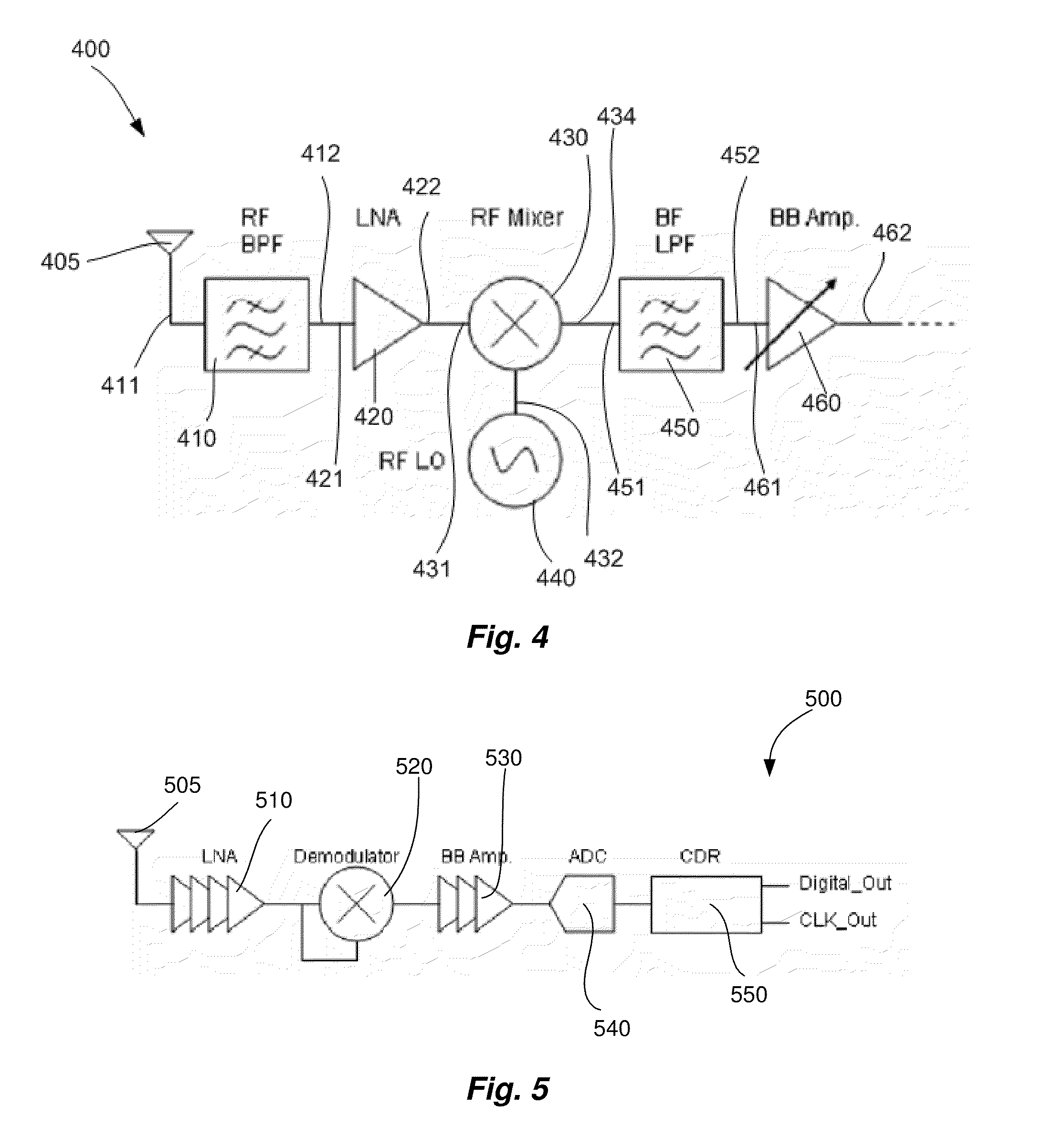

Receiver assembly and method for multi-gigabit wireless systems

The present invention describes a receiver assembly for receiving an analog signal and converting the analog signal to a digital signal. The receiver assembly is, preferably, capable of receiving a signal operating at approximately 60 GHz. The receiver assembly includes a filter, a down converter, a demodulator, a latch, a FIFO, and a logic circuit. A method of converting the 60 GHz analog signal to a digital signal is also described.

Owner:GEORGIA TECH RES CORP

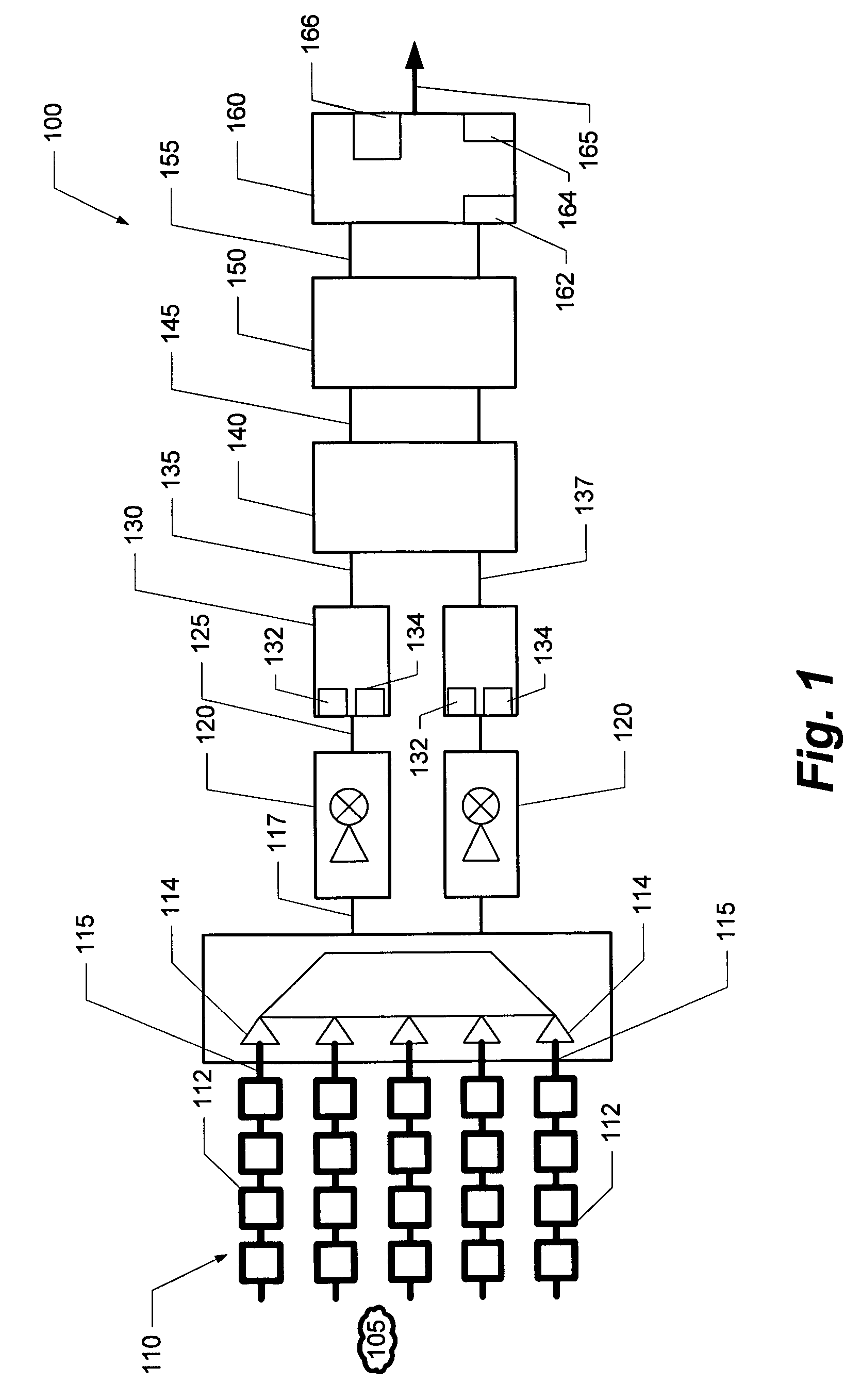

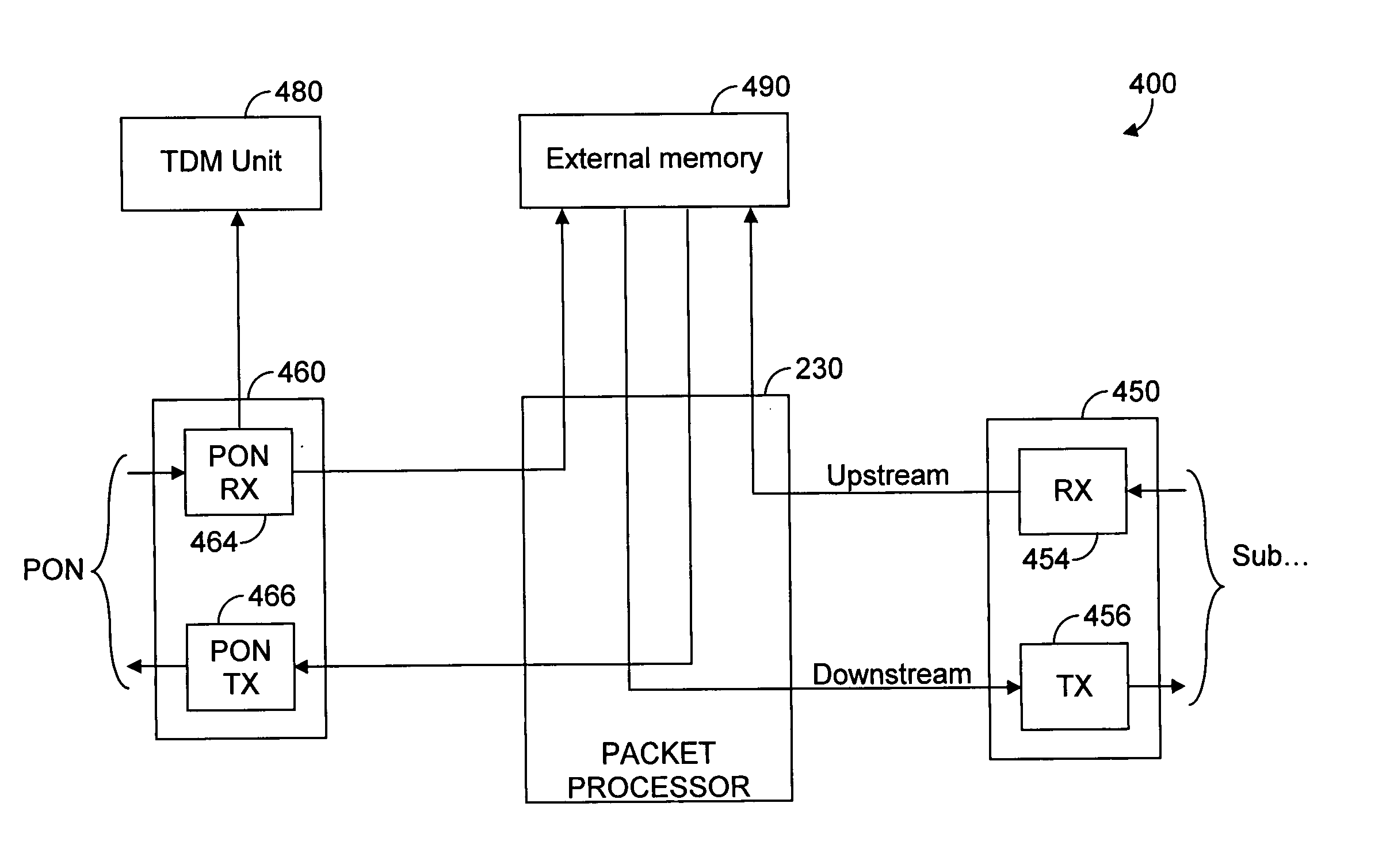

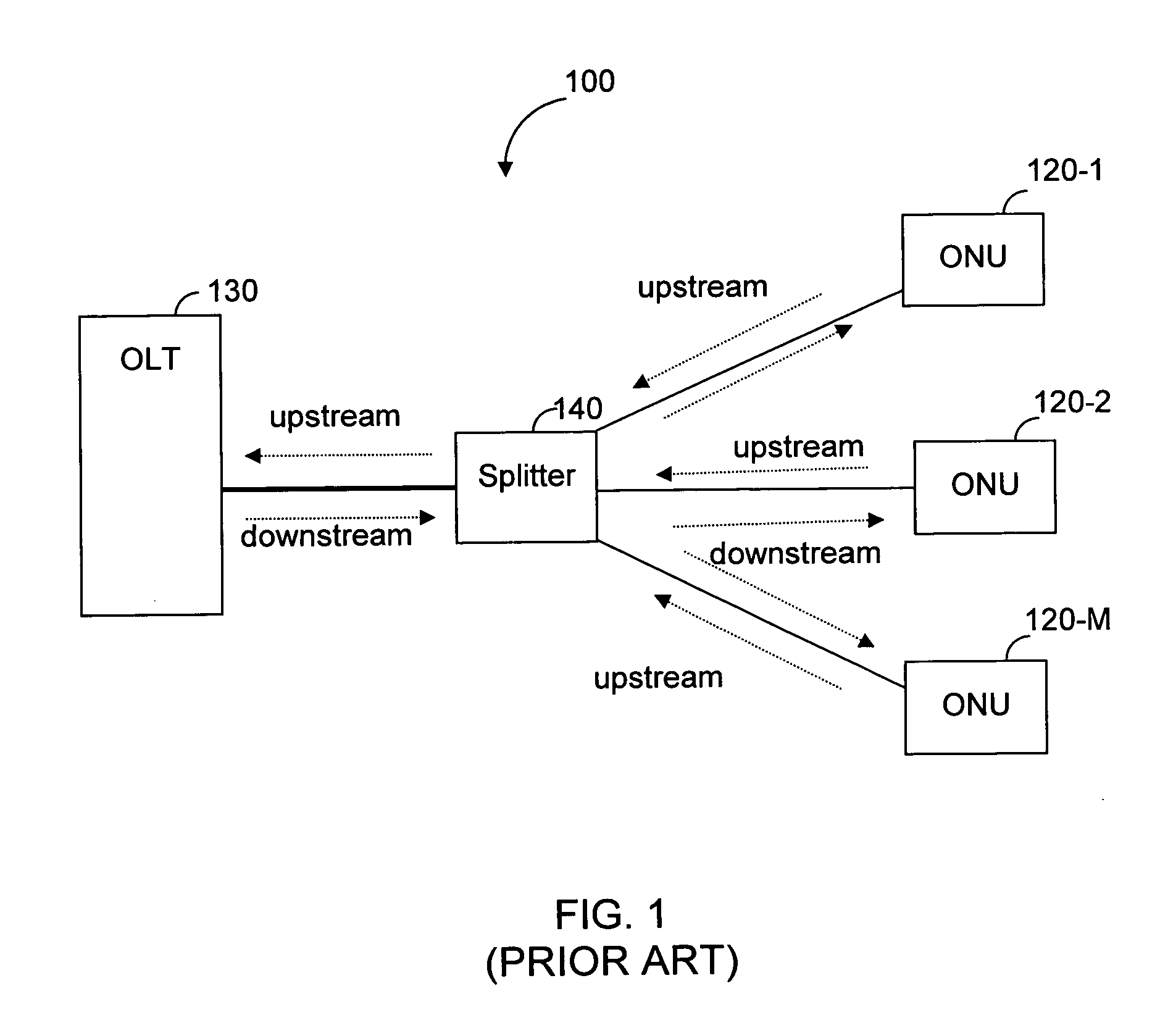

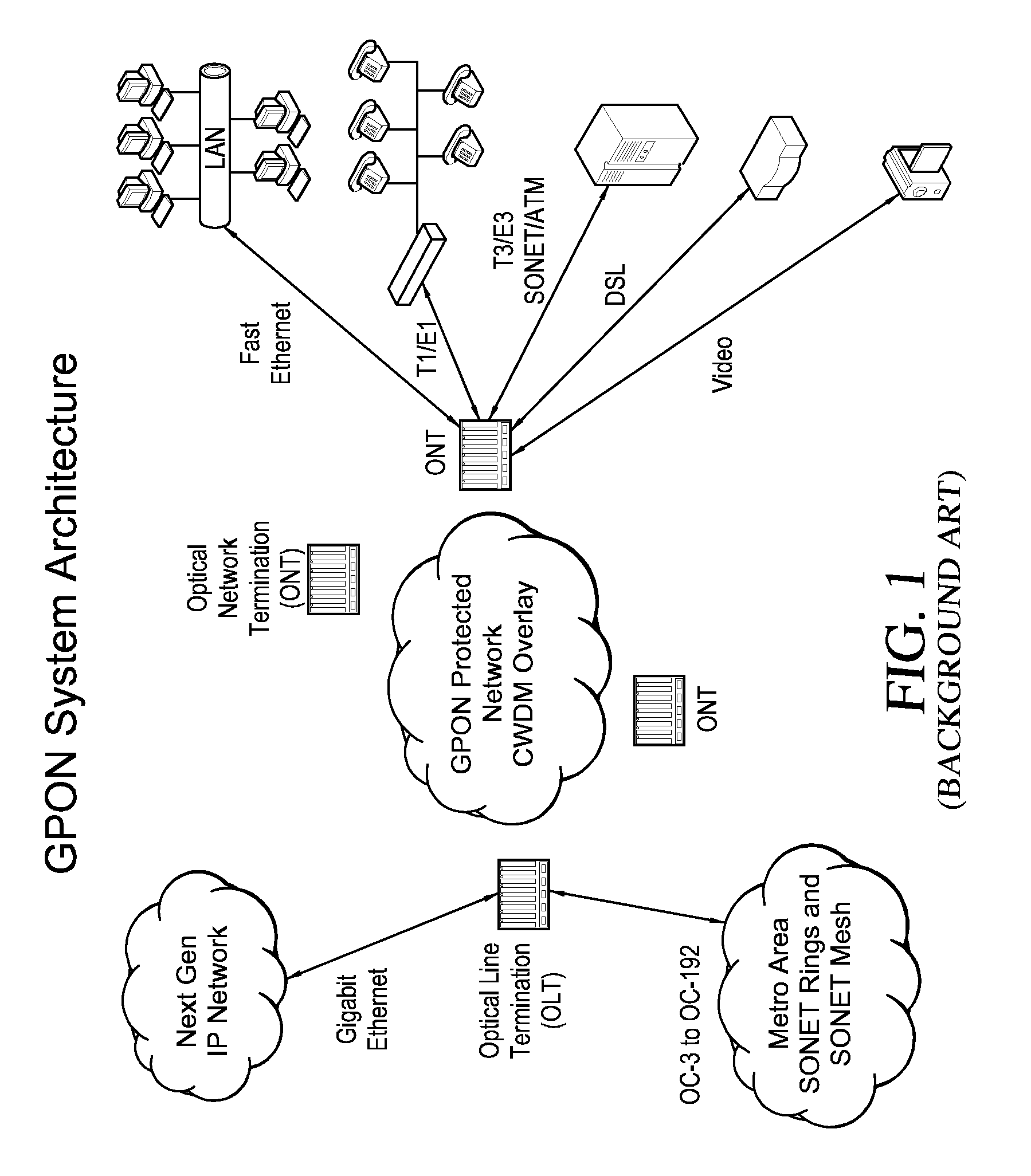

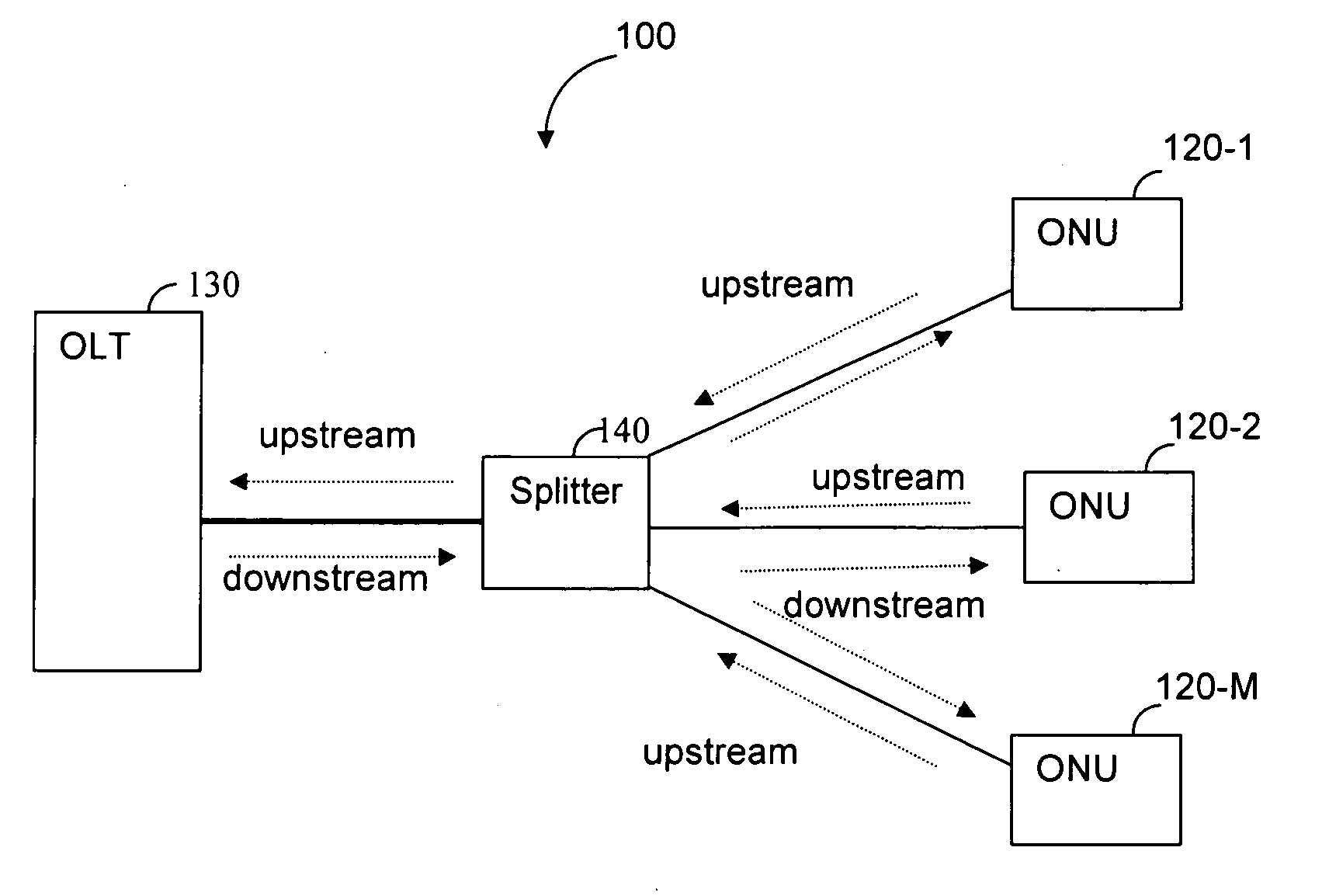

Enhanced passive optical network (PON) processor

InactiveUS20070070997A1Multiplex system selection arrangementsData switching by path configurationGigabitBroadband

An enhanced passive optical network (PON) processor adapted to serve a plurality of PON applications is disclosed. The PON processor is a highly integrated communications processor that can operate in different PON modes including, but not limited to, a gigabit PON (GPON), a broadband PON (BPON), an Ethernet PON (EPON), or any combination thereof. In an embodiment of the present invention the provided PON is fabricated on a single integrated circuit (IC).

Owner:AVAGO TECH INT SALES PTE LTD

TCP proxy connection management in a gigabit environment

The present invention describes a method and apparatus to effectively manage data buffers for a client and a server connection in a multiple connection environment. The TCP processes of servers and clients are merged into an independent TCP process in a TCP ‘proxy’ server. The TCP proxy server includes a control unit and a data switching unit (the proxy application). The TCP proxy server terminates the client TCP connection and initiates a separate TCP connection with the server. The data switching unit binds the two individual connections. The TCP proxy server portrays the actual server TCP. The control unit in the TCP proxy server manages data buffers, control memory and supports multiple connections. The control unit ‘pushes’ the data into the buffers by monitoring the use of the buffers. The control unit does not wait for data requests from the data switching unit thus, eliminating the overhead of data request messages.

Owner:CISCO TECH INC

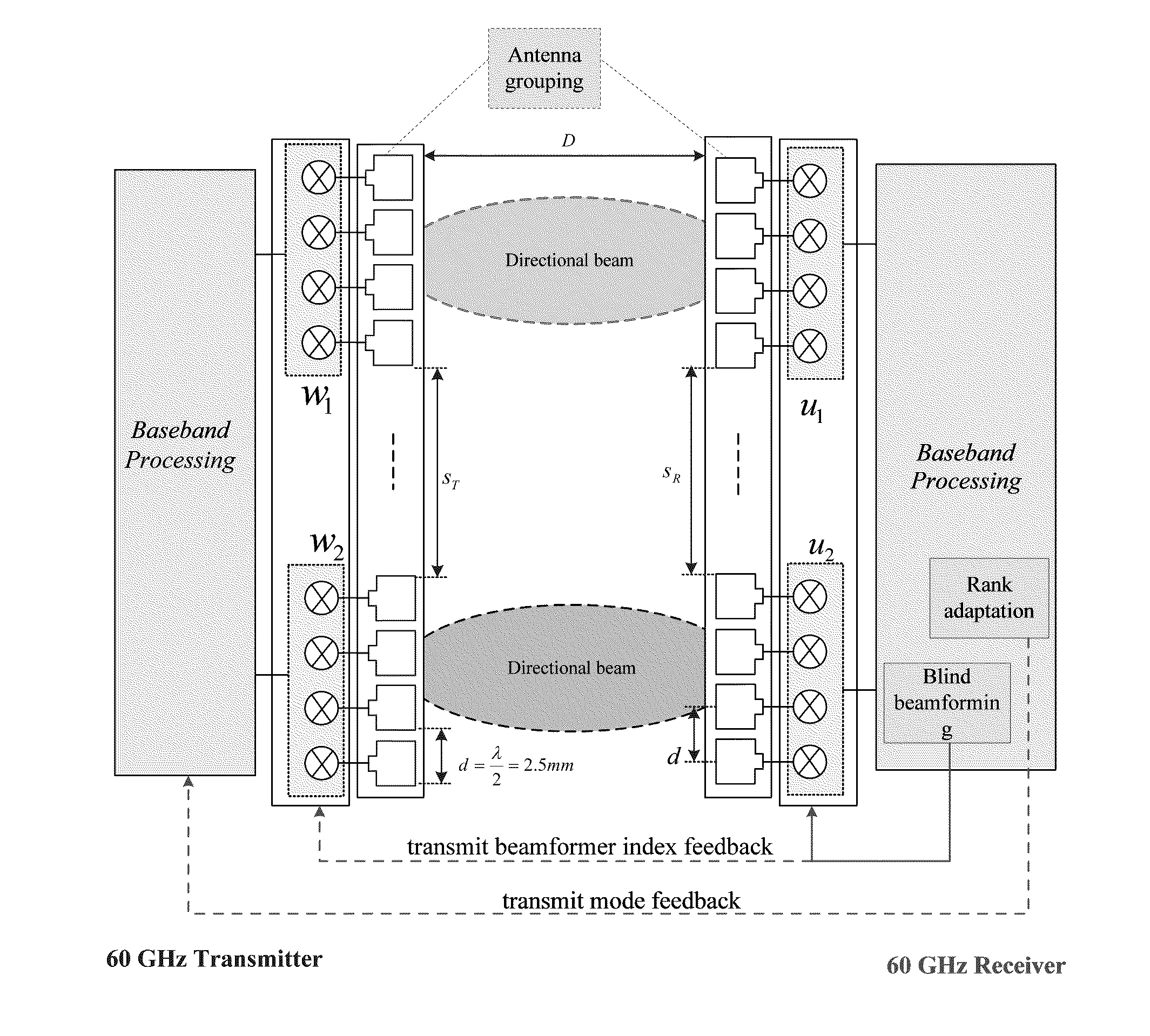

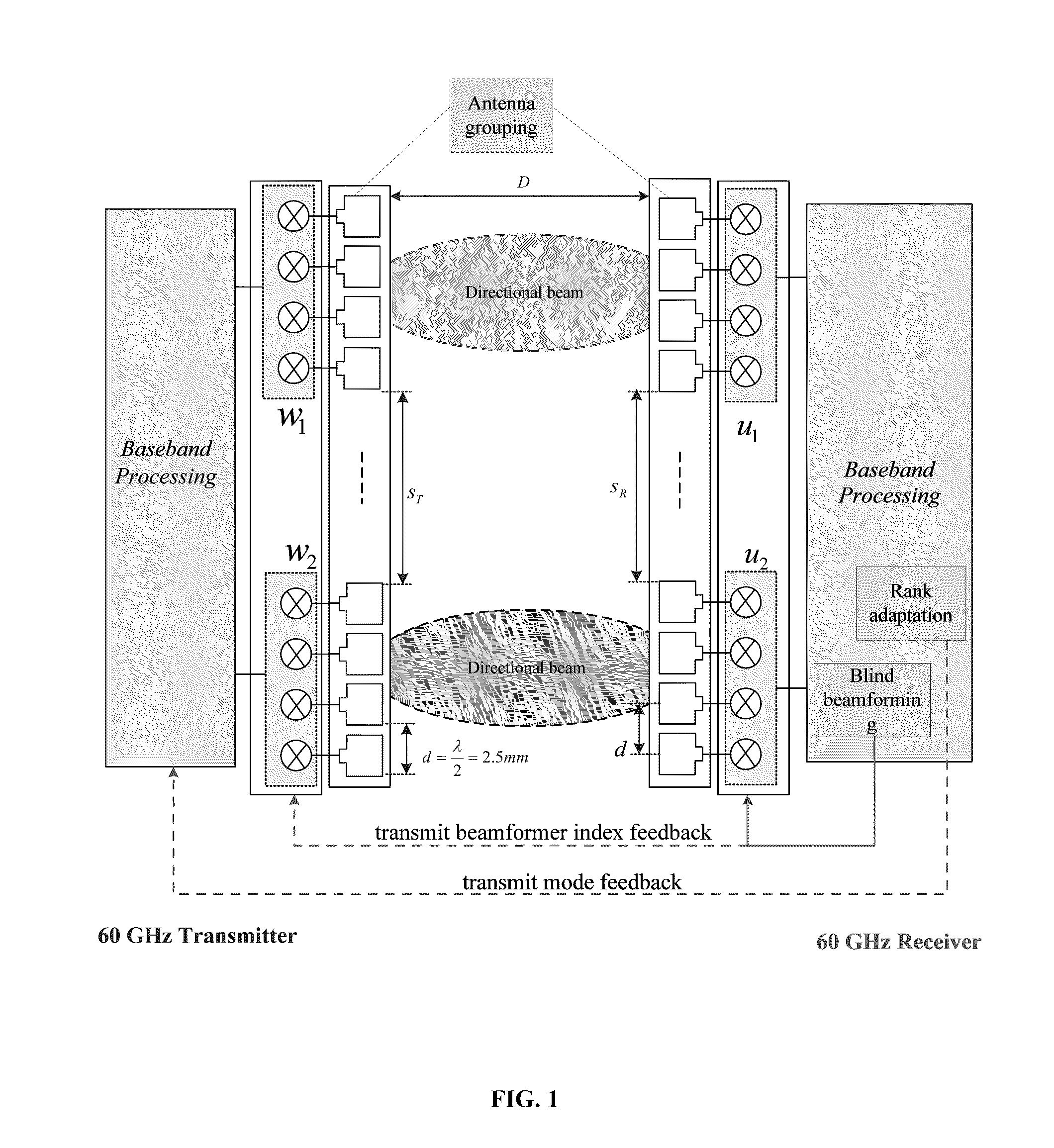

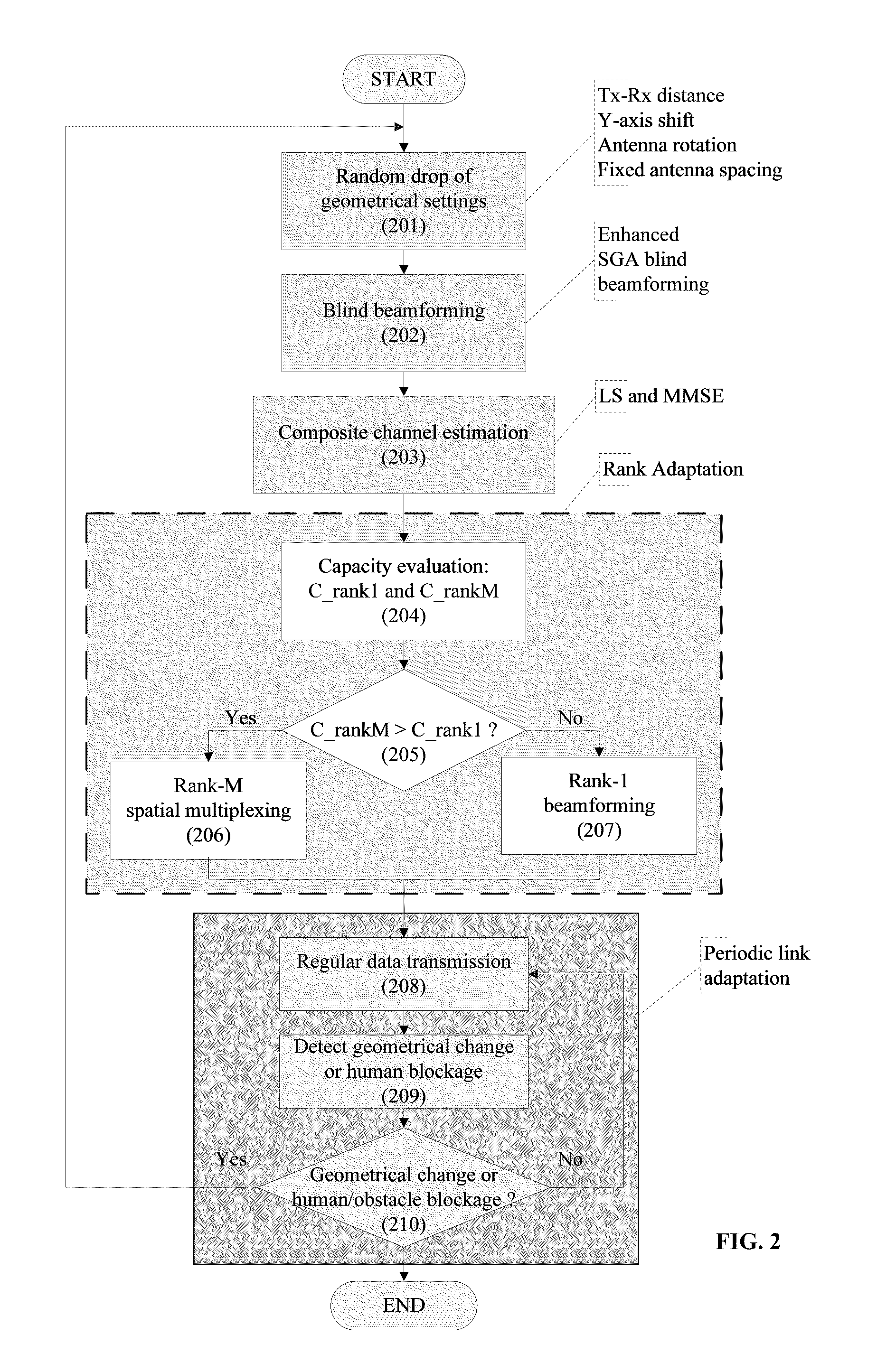

MIMO Transmission with Rank Adaptation for Multi-Gigabit 60 GHz Wireless

ActiveUS20110222616A1Reduce complexityImprove accuracySecret communicationRadio transmissionMimo transmissionGigabit

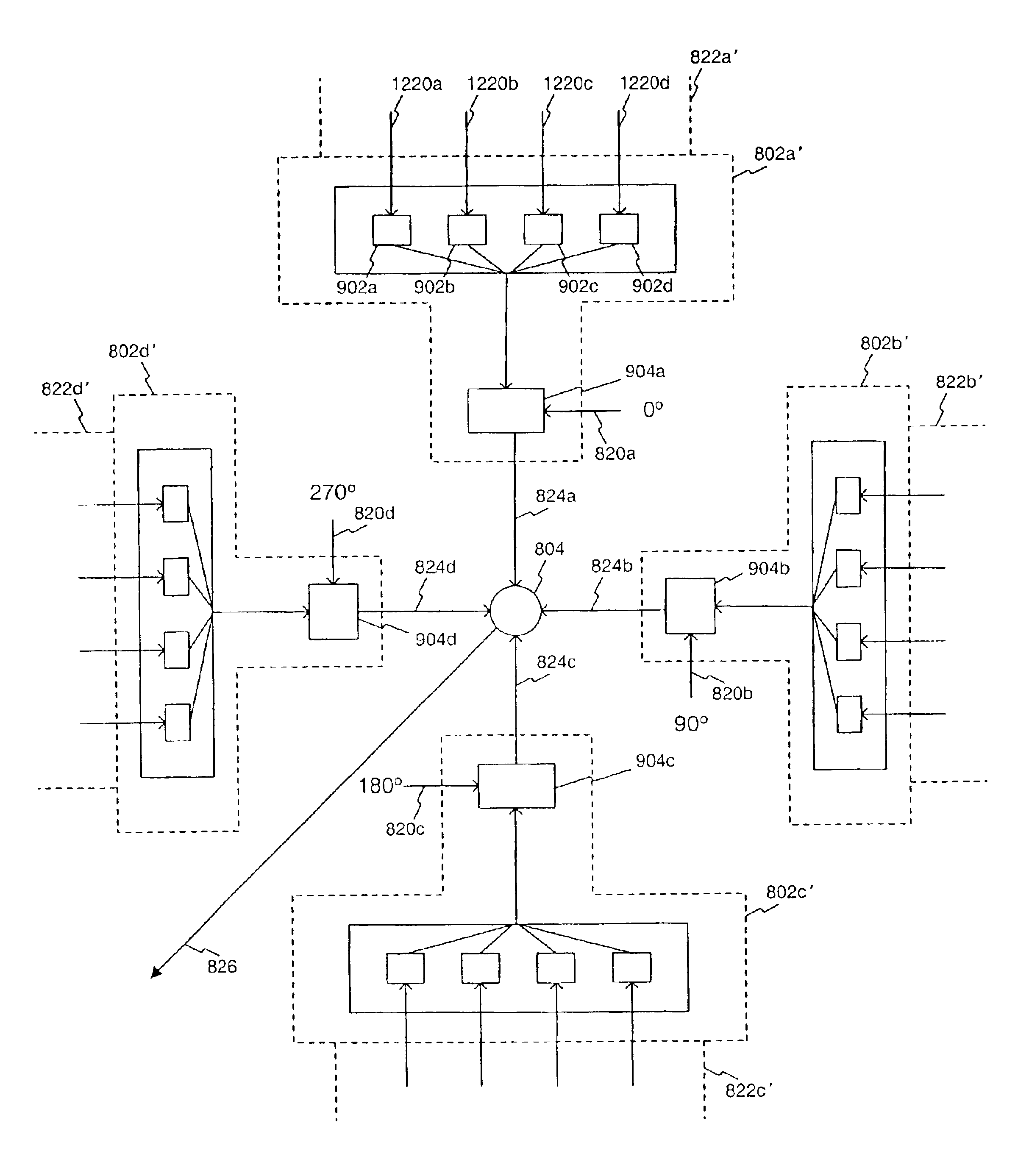

A wireless system includes a transmitter with a baseband processor responsive to groups of transmitter antenna arrays for communicating over directional beams; and a receiver with a baseband processor responsive to groups of receiver antenna rays for communicating with the transmitter over the directional beams, the receiver including both a rank adaptation providing a transmit mode feedback to the transmitter and a blind beamforming providing a transmit beamformer index feedback to the transmitter and receiver groups of antenna arrays.

Owner:NEC CORP

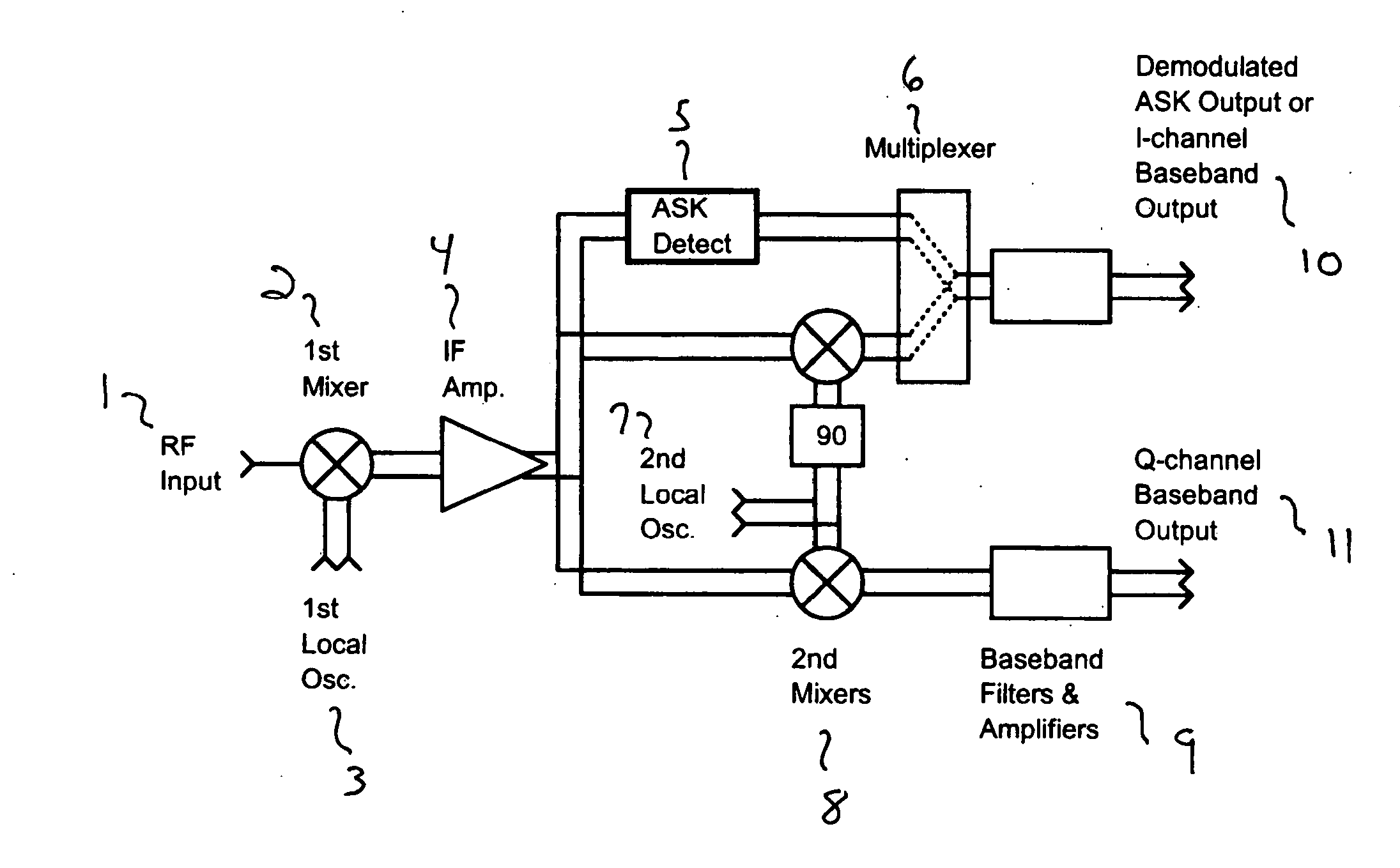

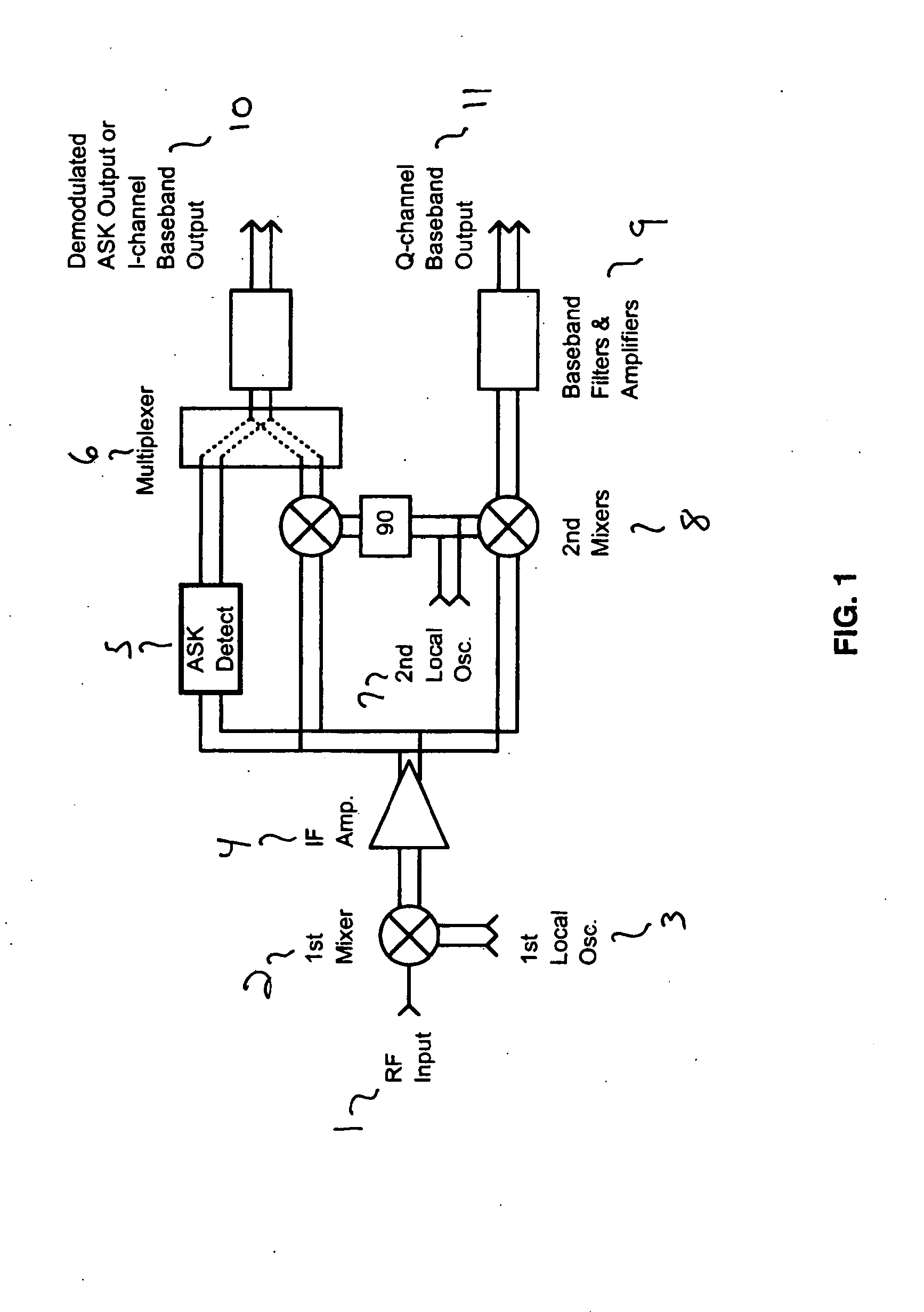

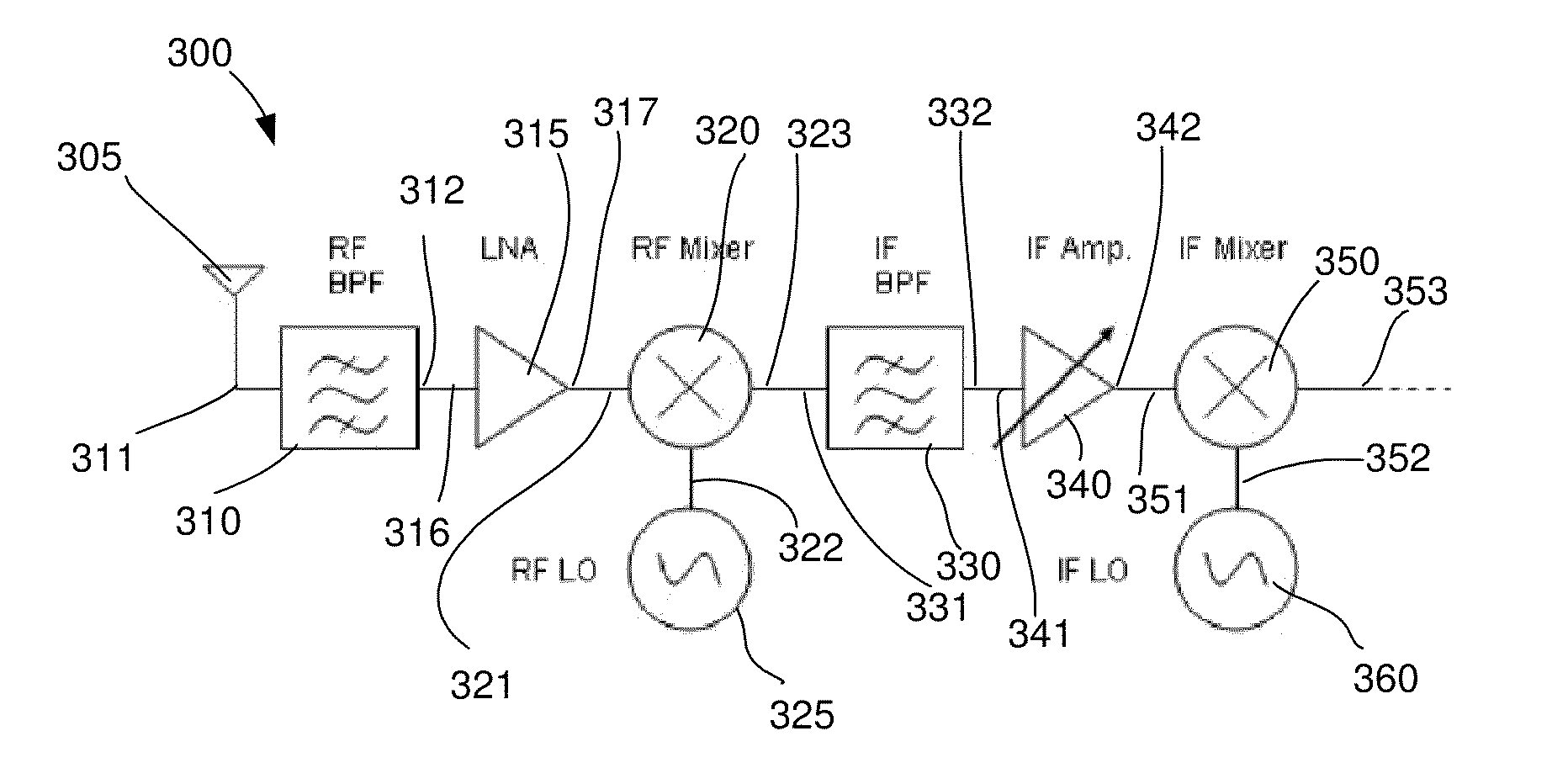

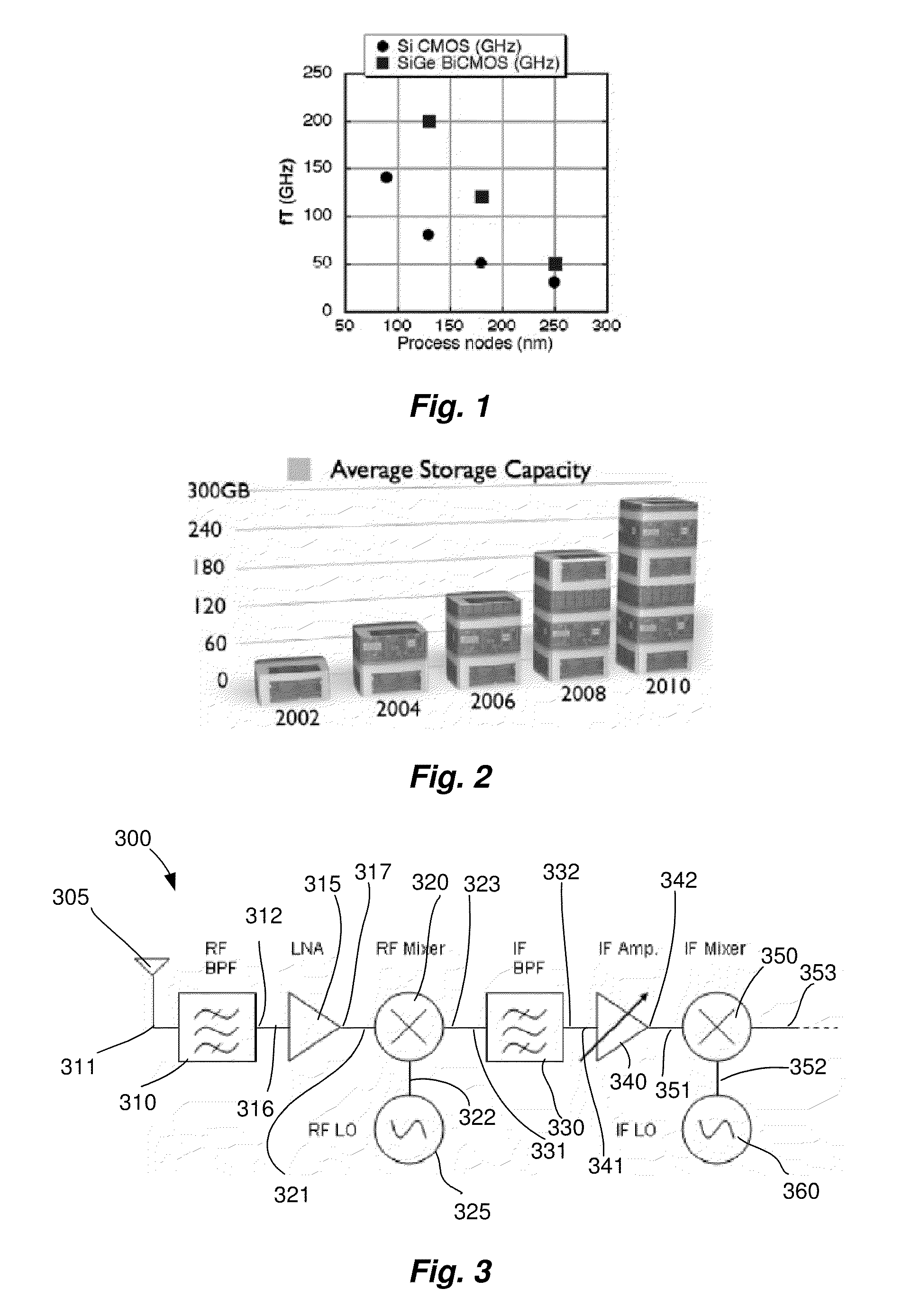

Receiver and integrated am-fm/iq demodulators for gigabit-rate data detection

ActiveUS20080280577A1Easily incorporated into integrated circuit receiver systemSimultaneous amplitude and angle demodulationAmplitude demodulationDiscriminatorDetector circuits

This disclosure addresses providing gigabit-rate data transmission over wireless radio links, using carrier frequencies in the millimeter-wave range (>30 GHz). More specifically, a circuit for detection of amplitude-shift keyed (ASK) or other amplitude modulations (AM) which can be easily incorporated into an integrated circuit receiver system is described, making the receiver capable of supporting both complex IQ modulation schemes and simpler, non-coherent on-off or multiple-level keying signals. Several novel radio architectures are also described which, with the addition of a frequency discriminator network, have the capability of handling frequency shift keyed (FSK) or other frequency modulations (FM), as well as AM and complex IQ modulation schemes. These radio architectures support this wide variety of modulations by efficiently sharing detector hardware components. The architecture for supporting both quadrature down-conversion and ASK / AM is described first, followed by the ASK / AM detector circuit details, then the AM-FM detector architecture, and finally the most general AM-FM / IQ demodulator system concept and the FSK / FM detector circuit details.

Owner:GLOBALFOUNDRIES US INC

System and method for high speed packet transmission implementing dual transmit and receive pipelines

ActiveUS20050175018A1Multiplex system selection arrangementsNetworks interconnectionGigabitMedia access control

The present invention provides systems and methods for providing data transmission speeds at or in excess of 10 gigabits per second between one or more source devices and one or more destination devices. According to one embodiment, the system of the present invention comprises a first and second media access control (MAC) interfaces to facilitate receipt and transmission of packets over an associated set of physical interfaces. The system also contemplates a first and second field programmable gate arrays (FPGA) coupled to the MAC interfaces and an associated first and second memory structures, the first and second FPGAs are configured to perform initial processing of packets received from the first and second MAC interfaces and to schedule the transmission of packets to the first and second MAC interface for transmission to one or more destination devices. The first and second FPGAs are further operative to dispatch and retrieve packets to and from the first and second memory structures. A third FPGA, coupled to the first and second memory structures and a backplane, is operative to retrieve and dispatch packets to and from the first and second memory structures, compute appropriate destinations for packets and organize packets for transmission. The third FPGA is further operative to receive and dispatch packets to and from the backplane.

Owner:AVAGO TECH INT SALES PTE LTD

Rack level pre-installed interconnect for enabling cableless server/storage/networking deployment

ActiveUS20150280827A1Multiplex system selection arrangementsNear-field transmissionNetwork deploymentTelecommunications link

Apparatus and methods for rack level pre-installed interconnect for enabling cableless server, storage, and networking deployment. Plastic cable waveguides are configured to couple millimeter-wave radio frequency (RF) signals between two or more Extremely High Frequency (EHF) transceiver chips, thus supporting millimeter-wave wireless communication links enabling components in the separate chassis to communicate without requiring wire or optical cables between the chassis. Various configurations are disclosed, including multiple configurations for server chassis, storage chassis and arrays, and network / switch chassis. A plurality of plastic cable waveguide may be coupled to applicable support / mounting members, which in turn are mounted to a rack and / or top-of-rack switches. This enables the plastic cable waveguides to be pre-installed at the rack level, and further enables racks to be installed and replaced without requiring further cabling for the supported communication links. The communication links support link bandwidths of up to 6 gigabits per second, and may be aggregated to facilitate multi-lane links.

Owner:INTEL CORP

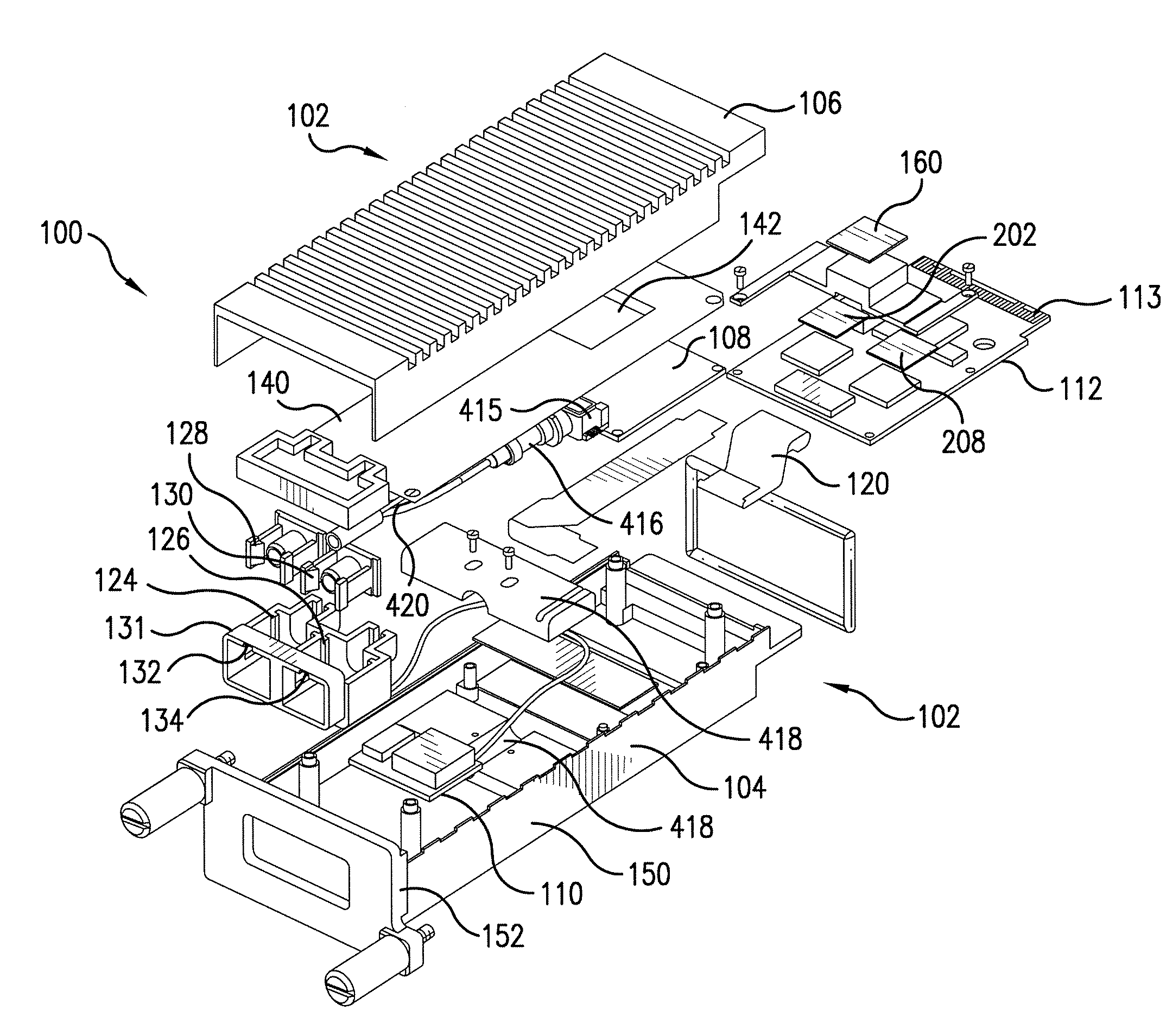

Optical transceiver for 40 gigabit/second transmission

An optical transceiver for converting and coupling an information-containing electrical signal with an optical fiber including a housing having an electrical connector with a plurality of XFI electrical interfaces for coupling with an external electrical cable or information system device and for transmitting and / or receiving an information-containing electrical signal having a data rate of at least 10 Gigabits per second on each interface, and a fiber optic connector adapted for coupling with an external optical fiber for transmitting and / or receiving an optical communications signal having a data rate at least 40 Gigabits per second; and at least one electro-optical subassembly in the housing for converting between an information-containing electrical signal and a modulated optical signal corresponding to the electrical signals.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS U S A

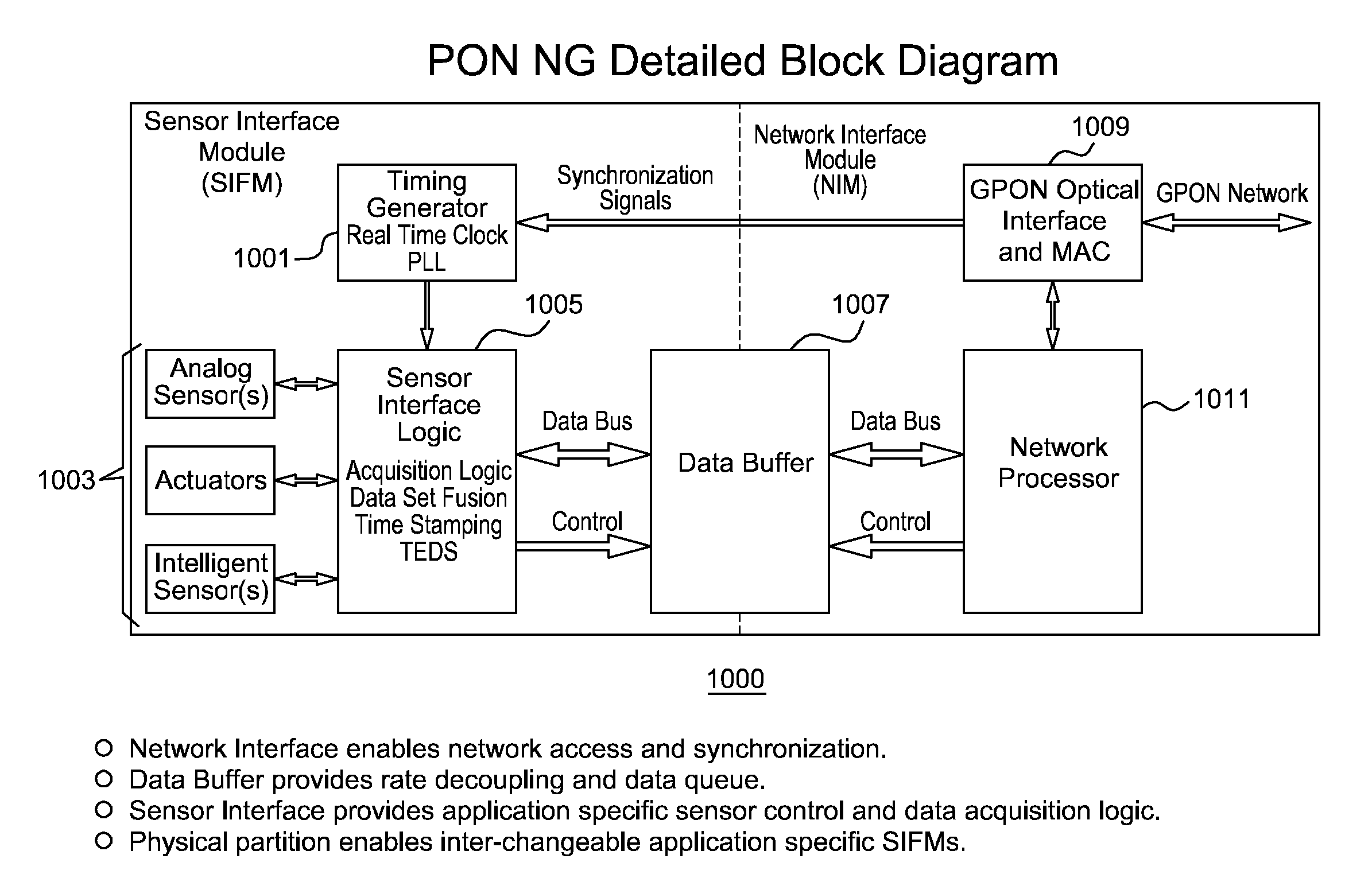

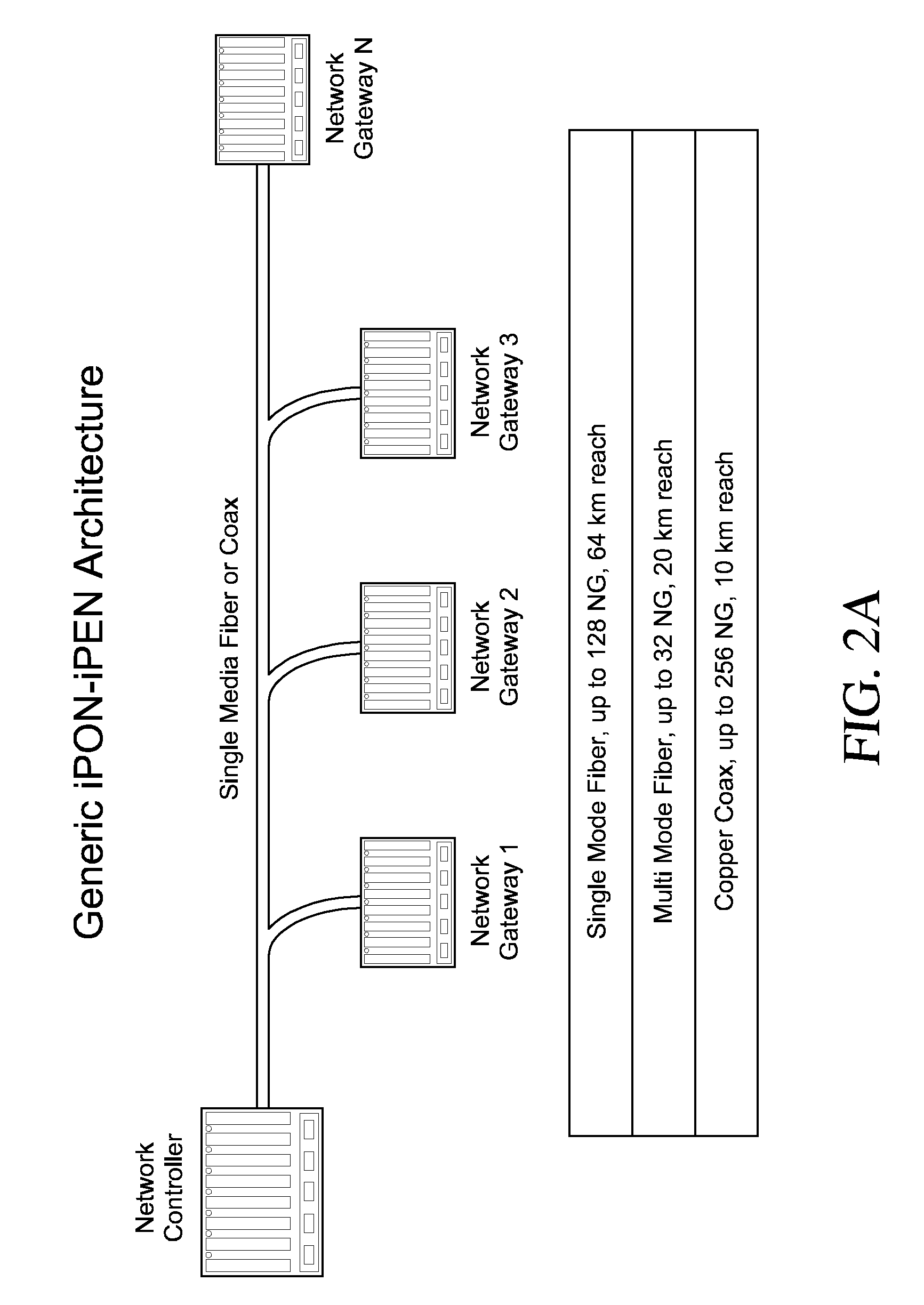

Inverted Passive Optical Network/inverted Passive Electrical Network (iPON/iPEN) Based Data Fusion and Synchronization System

InactiveUS20070291777A1Easy to integrateEasy to fuseTime-division multiplexData switching by path configurationTelecommunications linkLine rate

The present invention is an apparatus, method and system for time synchronizing data from various sensor types that enables data fusion and transport. To provide this capability, the present invention utilizes an inverted Passive Optical Network (PON) approach for synchronous communication. Further, the present invention introduces an inverted Passive Electrical Network (iPEN) that extends the iPON approach. Data that are in a common format with embedded time synchronization information can easily be integrated or fused and transported over such communication links. The present invention provides the ability to merge and aggregate data from a wide range of disparate sensors and systems while maintaining close synchronization. The present invention is appropriate for synchronization of data, voice, and video onto a single network and / or multi-tiered networks and can also handle signal processing and control technologies at line rates well into the Gigabits per second (Gbps) range.

Owner:3 PHOENIX

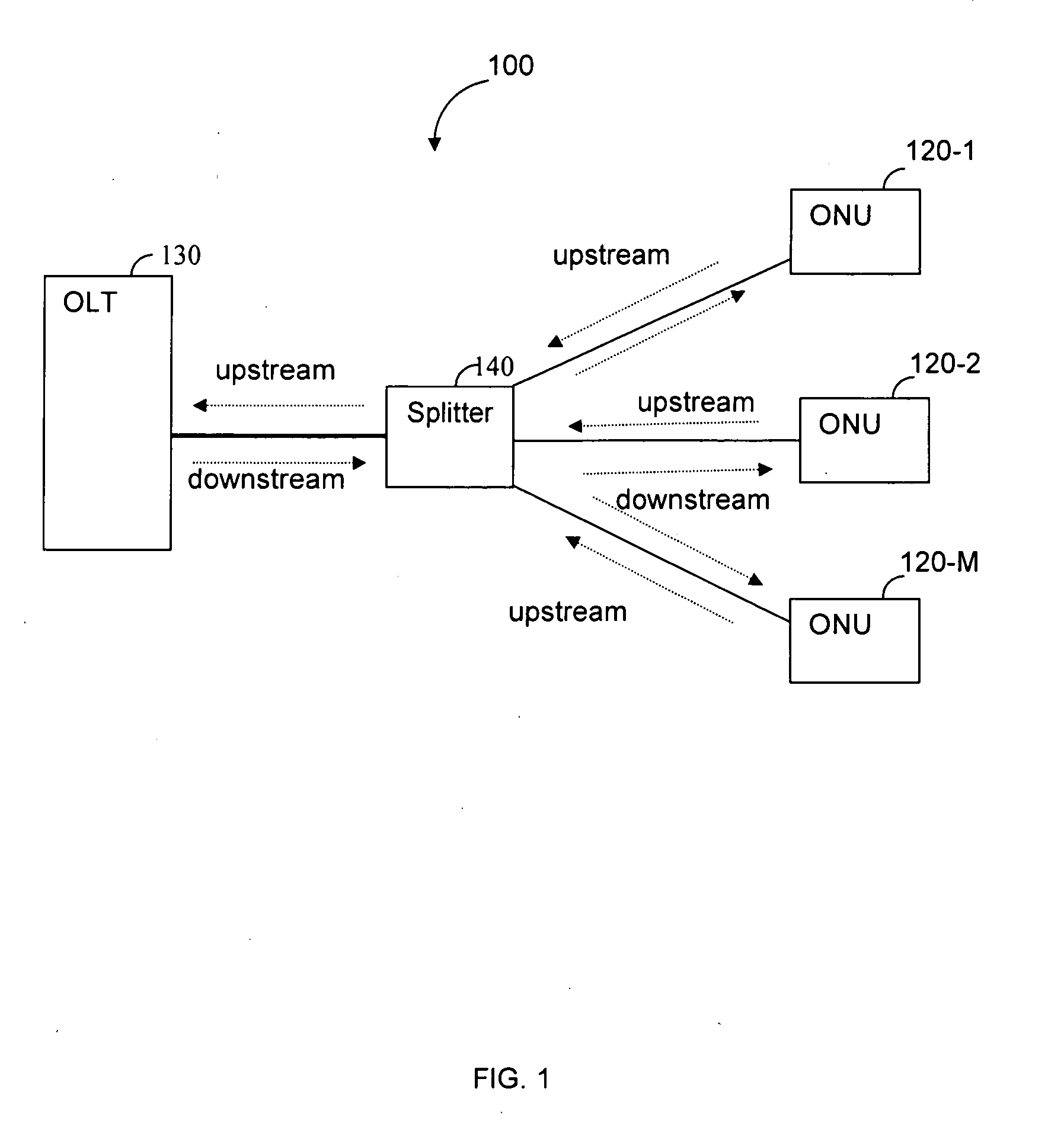

Gigabit passive optical network (GPON) residential gateway

InactiveUS20100098419A1Multiplex system selection arrangementsTime-division multiplexGigabitOptical line termination

A gigabit passive optical network (GPON) residential gateway comprising a microprocessor for at least processing packets including voice data and packets including video data; dual packet processors for performing GPON and residential gateway processing tasks; a plurality of Ethernet media access control (MAC) adapters for interfacing with a plurality of subscriber devices; a GPON MAC adapter for interfacing with an optical line terminal (OLT) of the GPON; and a digital signal processor (DSP) for processing voice signals.

Owner:AVAGO TECH INT SALES PTE LTD

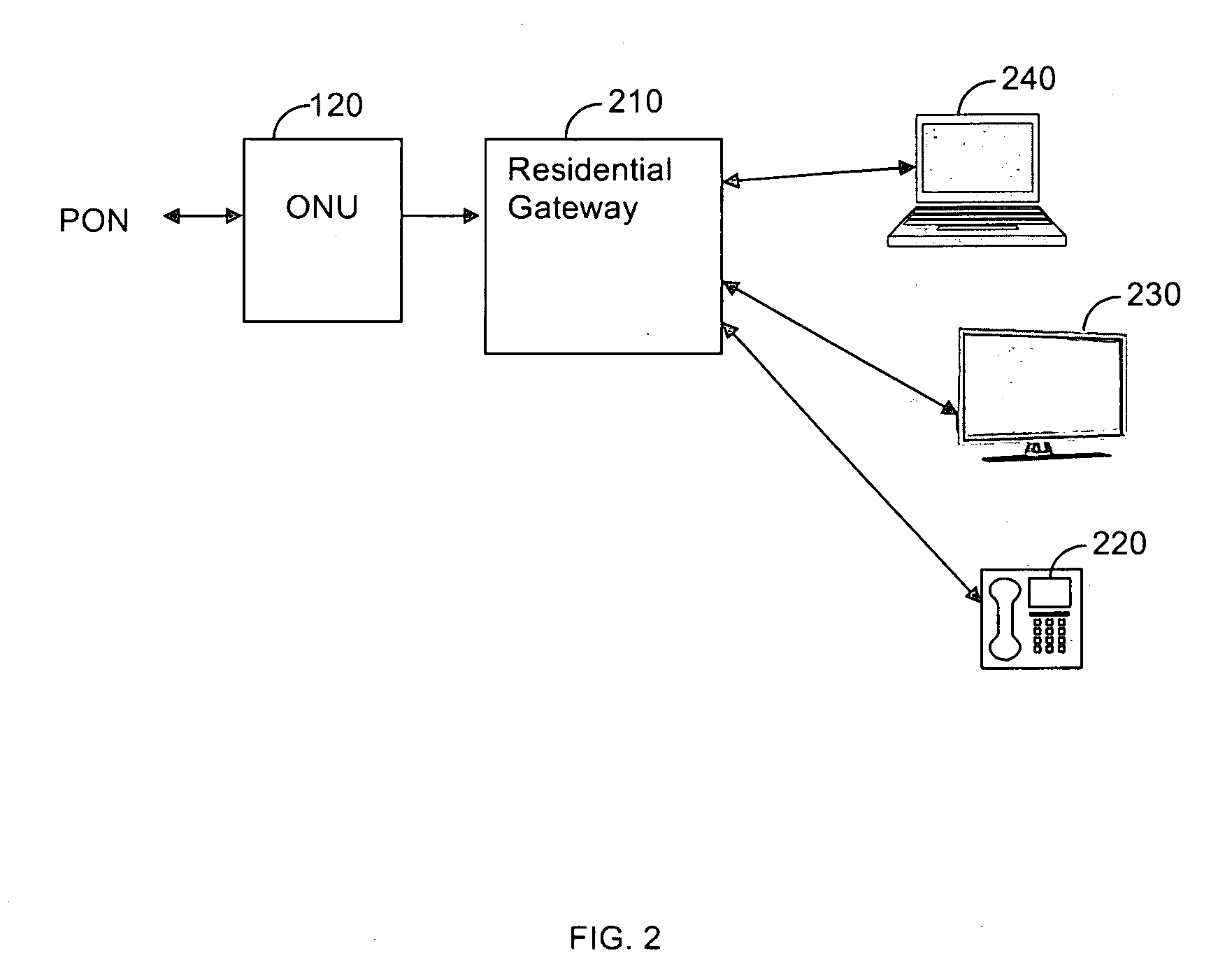

Multi-gigabit per second concurrent encryption in block cipher modes

InactiveUS7885405B1Improve performanceEfficient processingRandom number generatorsComputation using non-contact making devicesPlaintextComputer hardware

One embodiment is a system adapted to encrypt one or more packets of plaintext data in cipher-block chaining (CBC) mode. The system includes a plurality of digital logic components connected in series, where respective components are operative to process one or more rounds of a block cipher algorithm. A plurality of N bit registers are respectively coupled to the plurality of digital logic components. An XOR component receives blocks of plaintext data and blocks of ciphertext data, and XORs blocks of plaintext data for respective plaintext packets with previously encrypted blocks of ciphertext data for those plaintext packets. The XOR component iteratively feeds the XOR'd blocks of data into a first of the plurality of the digital logic components. In addition, a circuit component is operative to selectively pass blocks of ciphertext data fed back from an output of a final logic component to the XOR component.

Owner:GLOBALFOUNDRIES INC

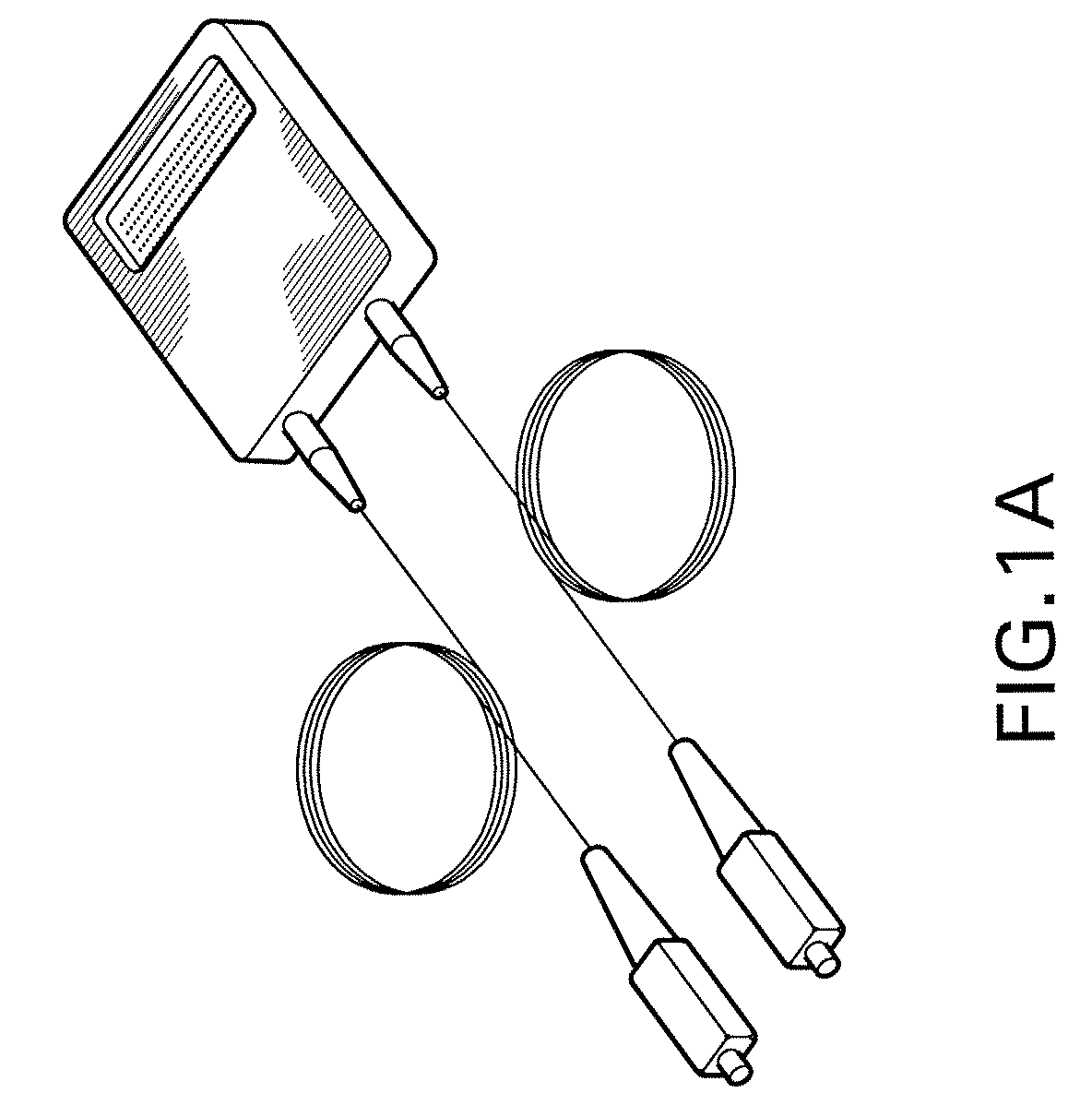

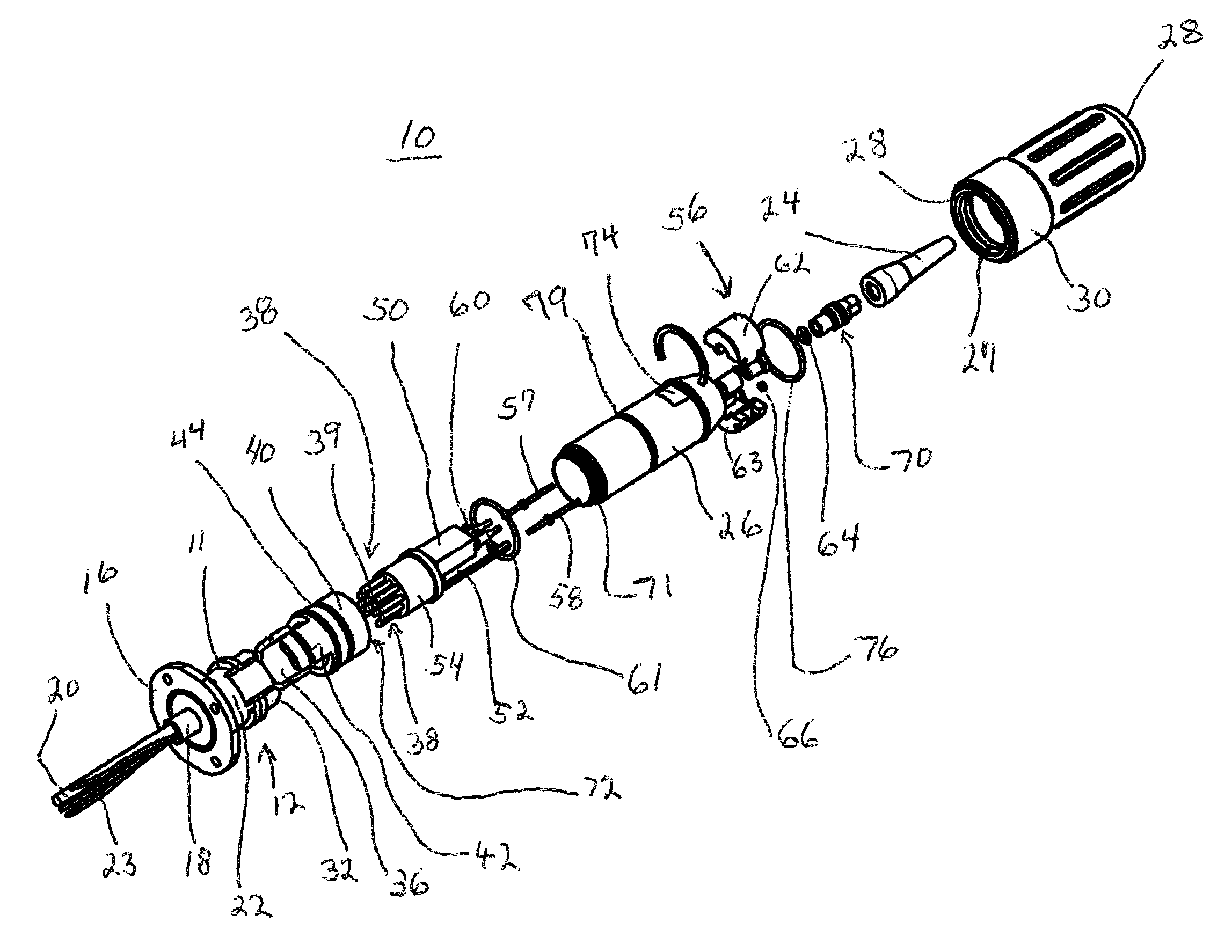

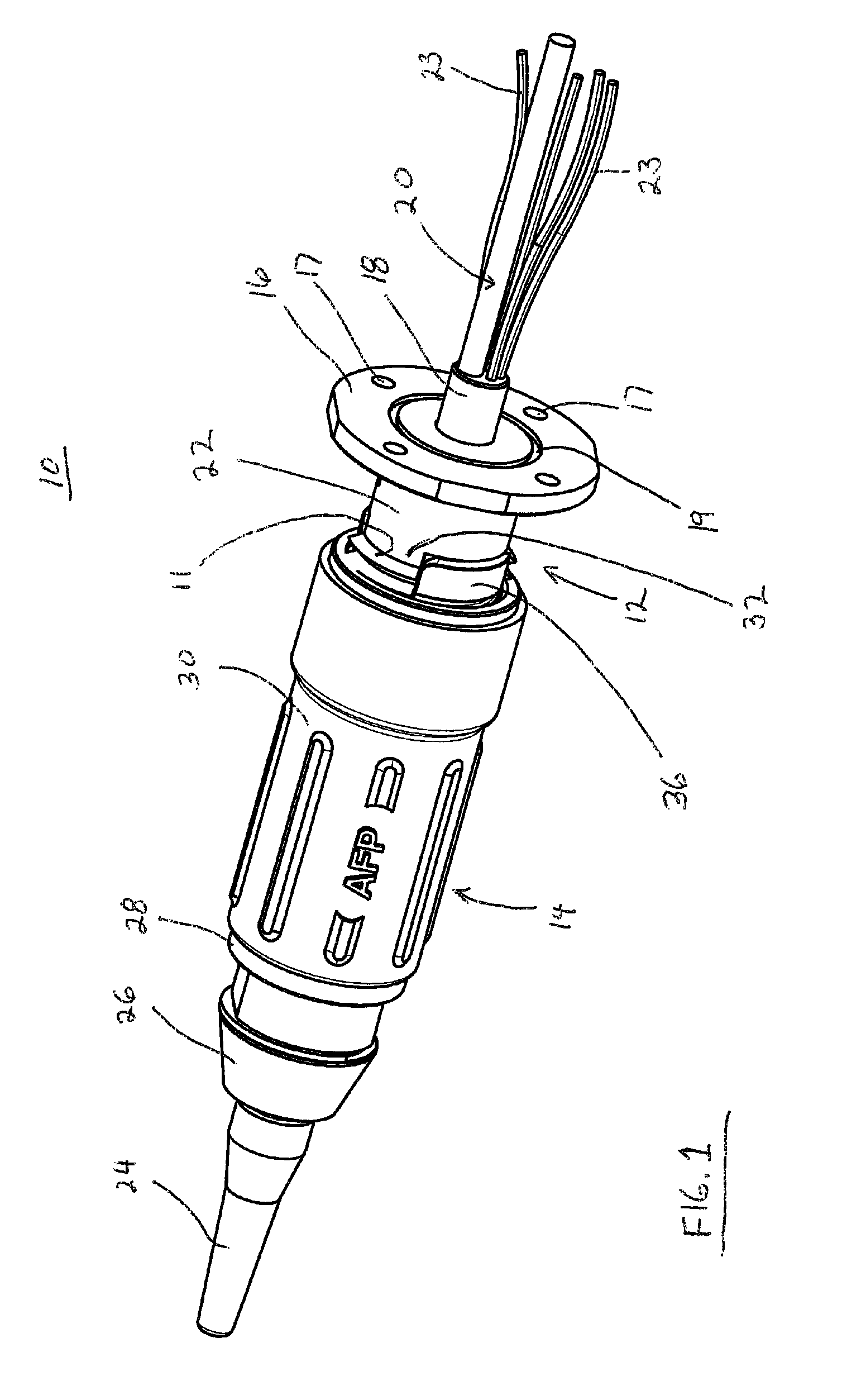

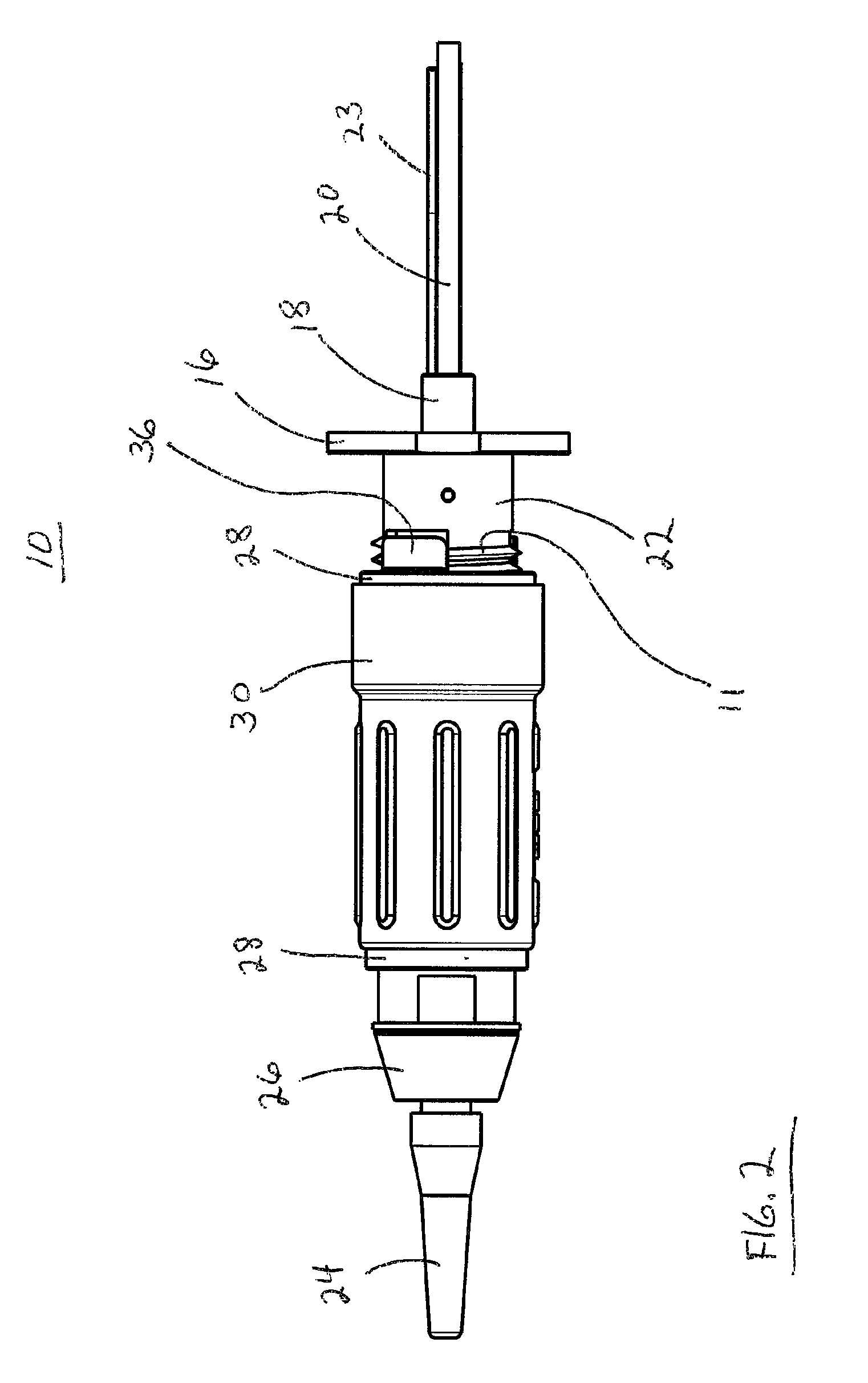

Gigabit wet mate active cable

InactiveUS8792759B2Convenient spacingMinimized in sizeCoupling light guidesFibre mechanical structuresElectricityTransceiver

A combination of a wet mate electrical connector and a gigabit miniature transceiver in a pressure resistant cable plug connector assembly. The cable plug connector assembly includes a wet mate connector, a miniature gigabit transceiver, and electrical and optical connections necessary to convert transmitted electrical data signals to optical data signals and vice versa.

Owner:ADVANCED FIBER PROD LLC

Phase interpolator device and method

InactiveUS6791388B2Reduce frequency offsetComputations using contact-making devicesPulse automatic controlTransceiverGigabit

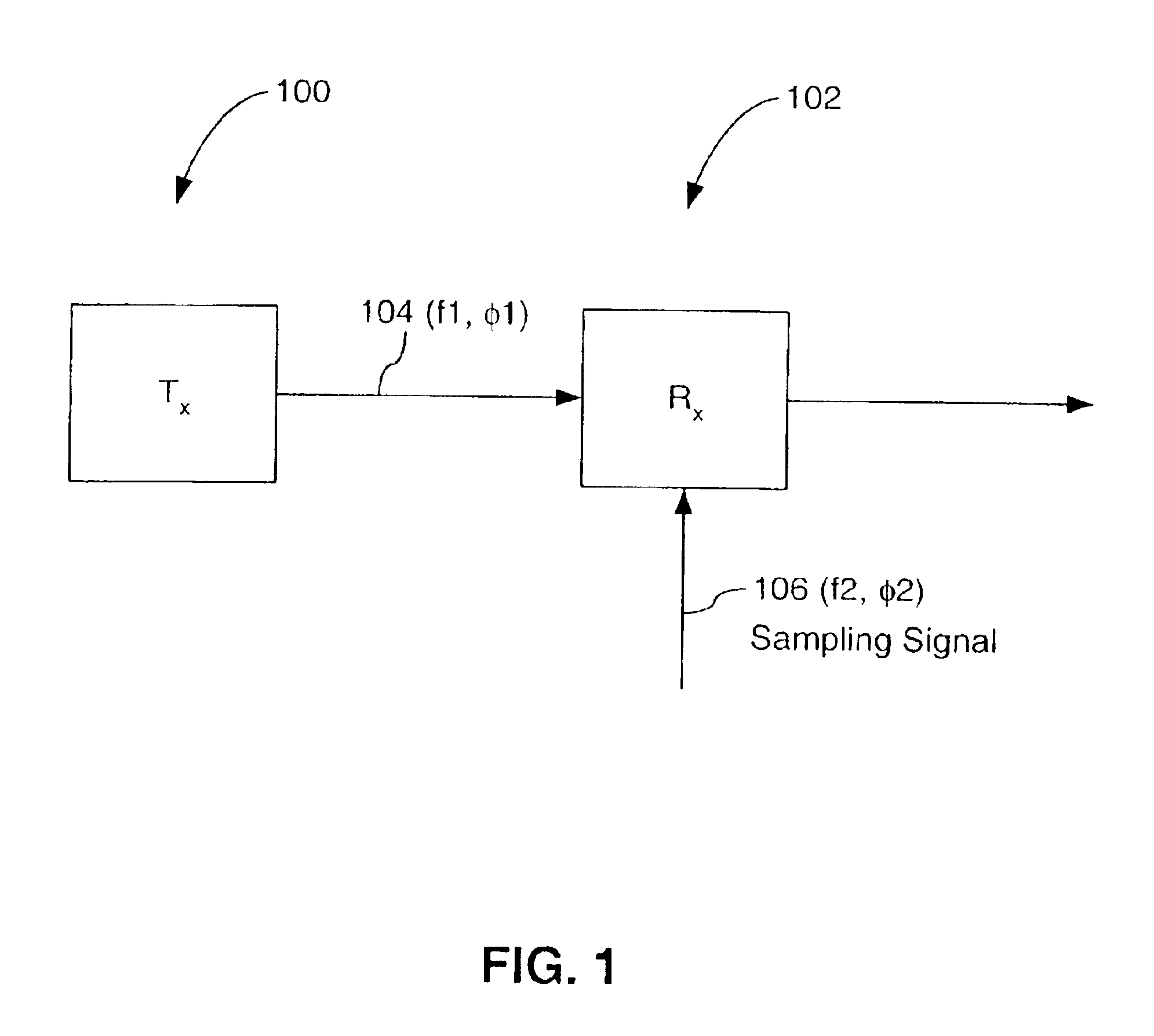

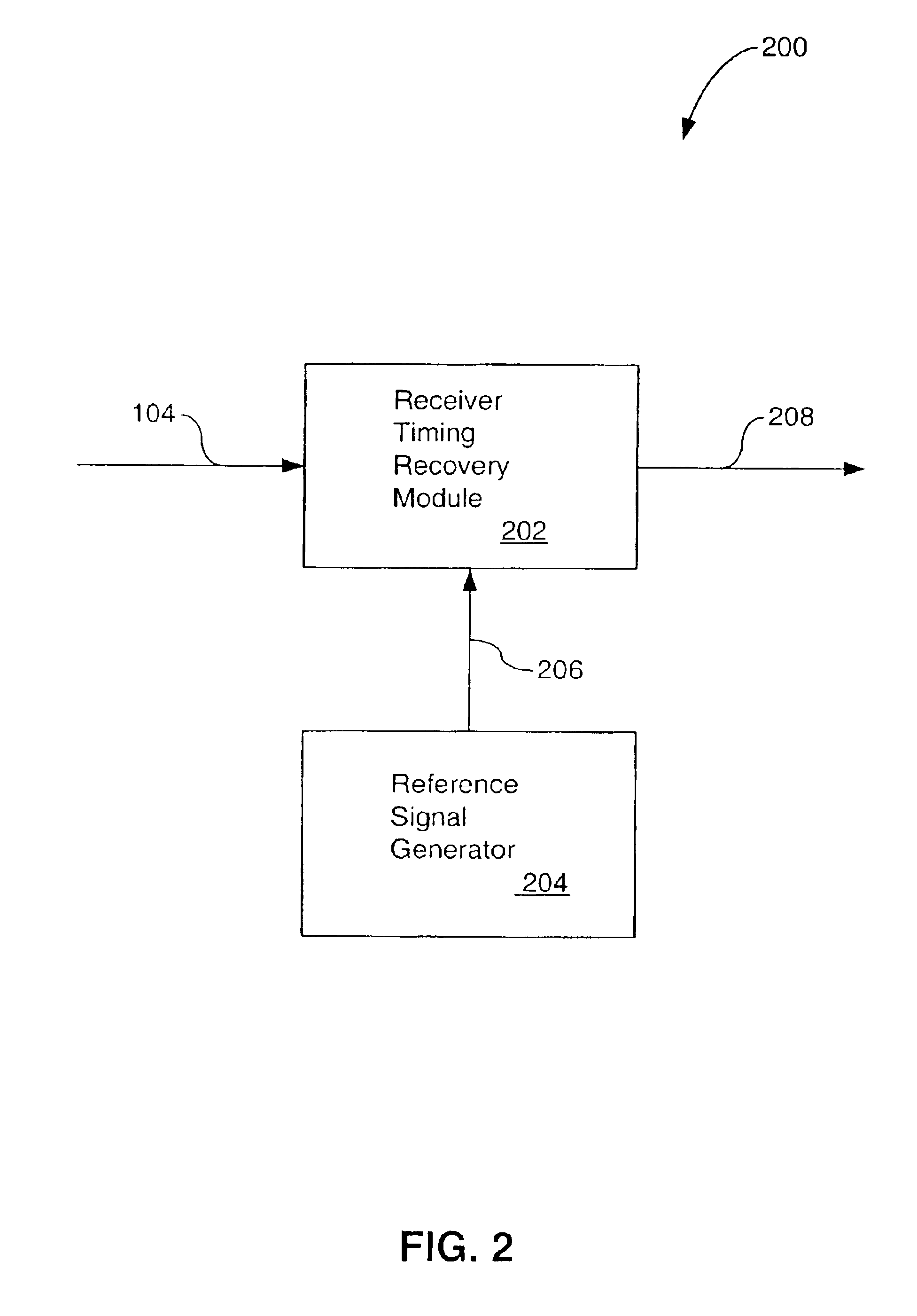

A high-speed serial data transceiver includes multiple receivers and transmitters for receiving and transmitting multiple analog, serial data signals at multi-gigabit-per-second data rates. Each receiver includes a timing recovery system for tracking a phase and a frequency of the serial data signal associated with the receiver. The timing recovery system includes a phase interpolator responsive to phase control signals and a set of reference signals having different predetermined phases. The phase interpolator derives a sampling signal, having an interpolated phase, to sample the serial data signal. The timing recovery system in each receiver independently phase-aligns and frequency synchronizes the sampling signal to the serial data signal associated with the receiver. A receiver can include multiple paths for sampling a received, serial data signal in accordance with multiple time-staggered sampling signals, each having an interpolated phase.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

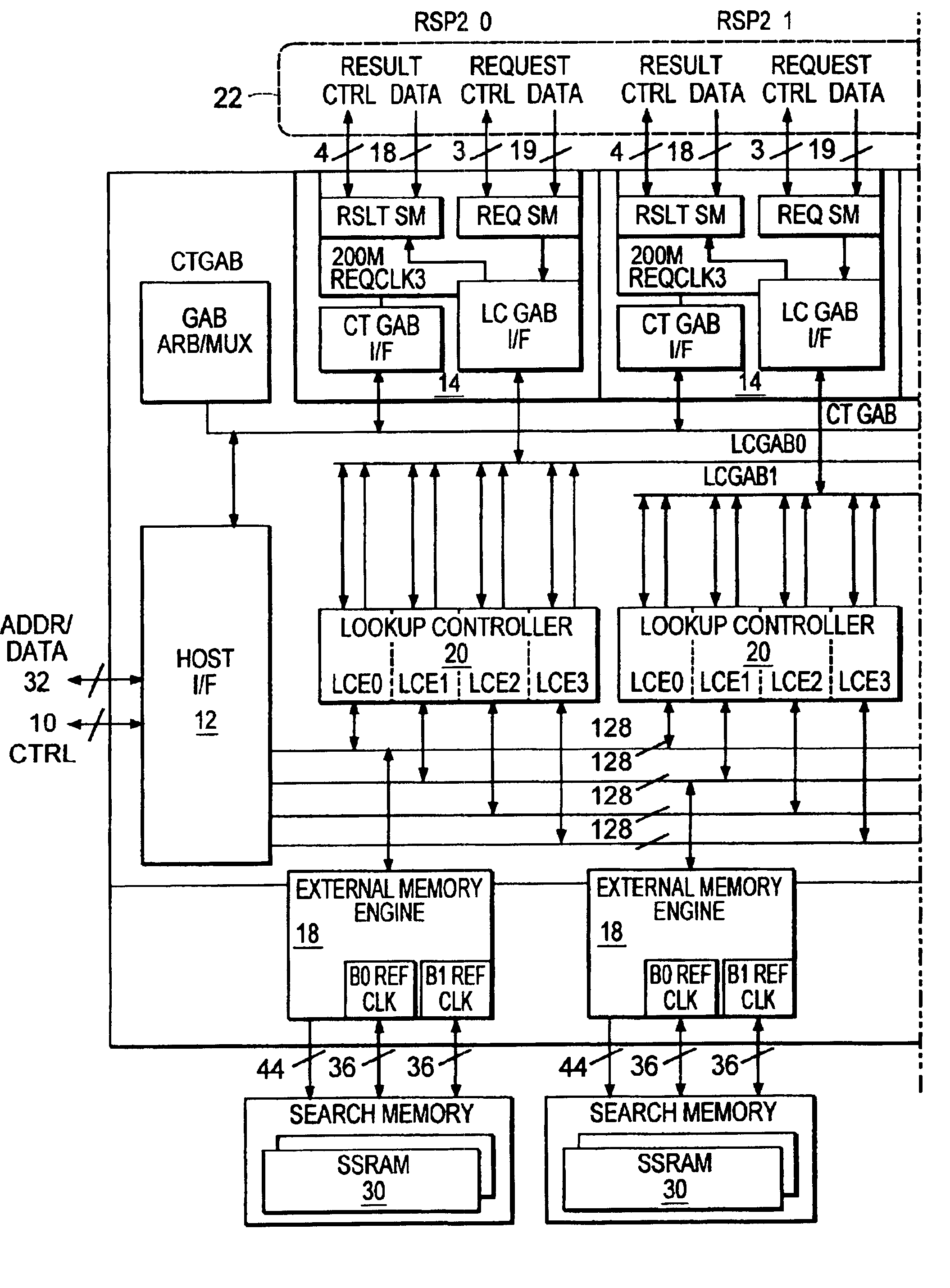

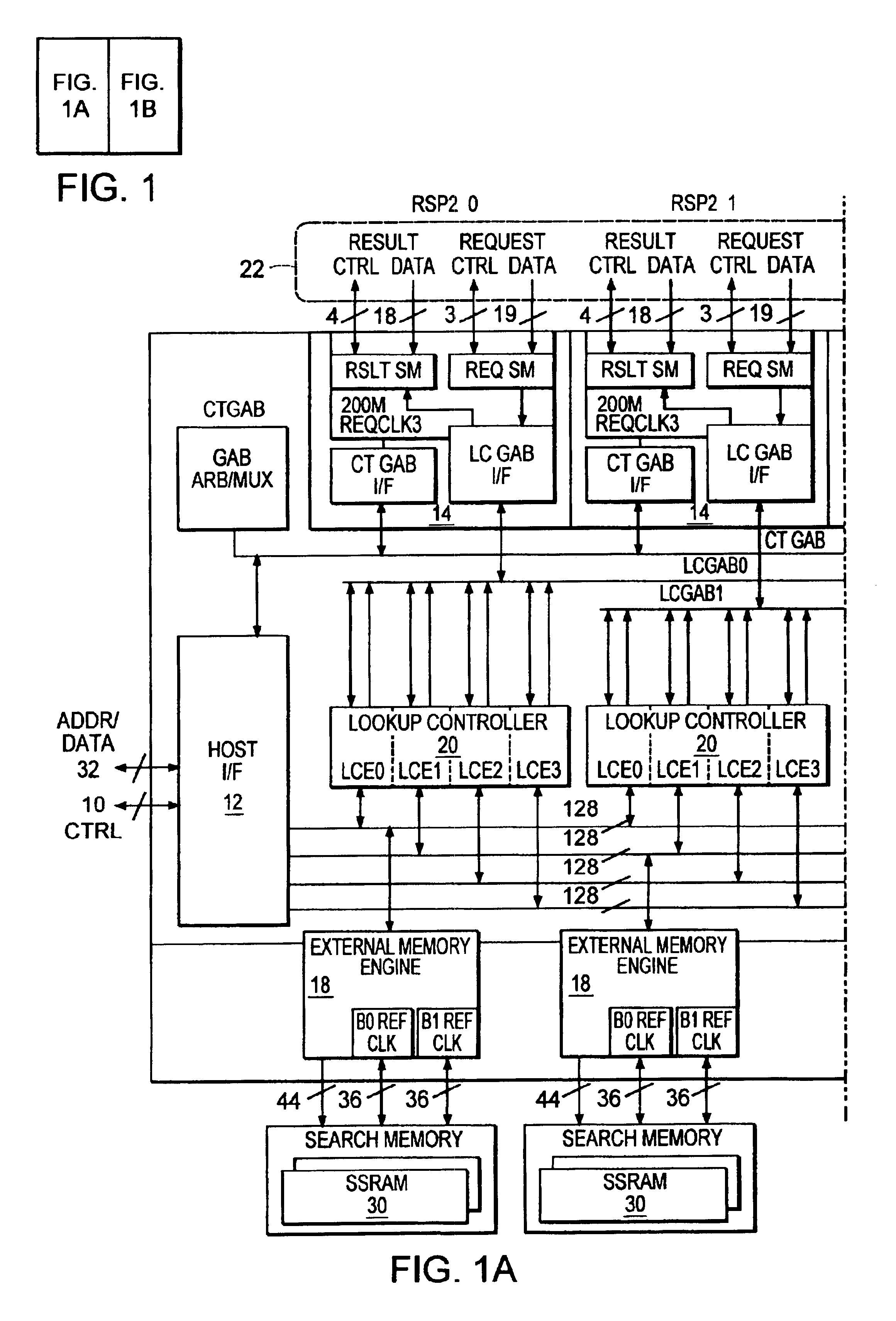

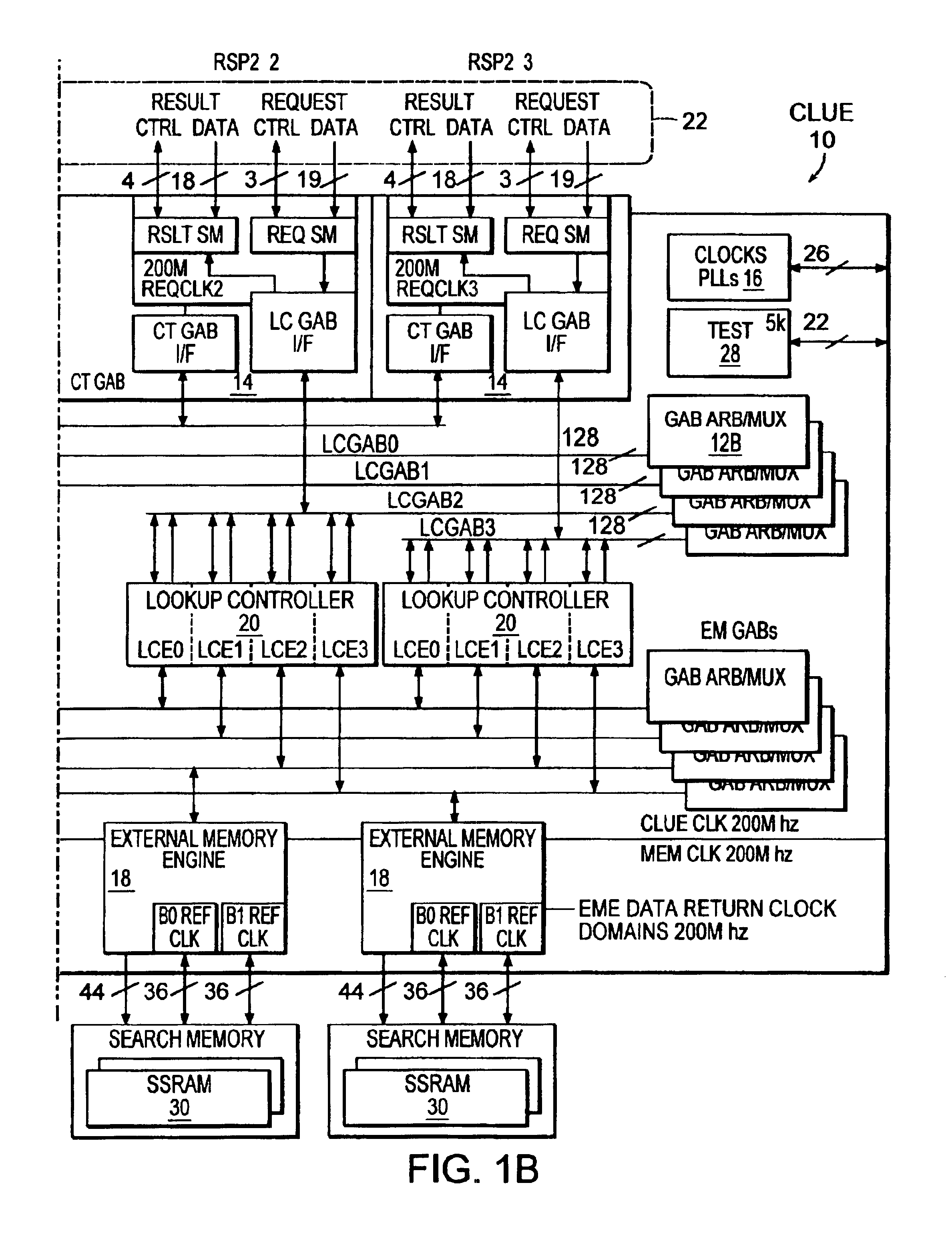

Centralized look up engine architecture and interface

A memory access processor and memory access interface for transferring data information to and from a plurality of SSRAM locations. The processor has a lookup controller for identifying a data request and locating the data requested from the SSRAM locations. The bus allows a data request and retrieval throughput from a routing processor to the memory access processor at a maximum rate, about 10 gigabits per second without substantial pipeline stalls or overflows.

Owner:AVAYA INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com