Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

171 results about "Logic simulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logic simulation is the use of simulation software to predict the behavior of digital circuits and hardware description languages. Simulation can be performed at varying degrees of physical abstraction, such as at the transistor level, gate level, register-transfer level (RTL), electronic system-level (ESL), or behavioral level.

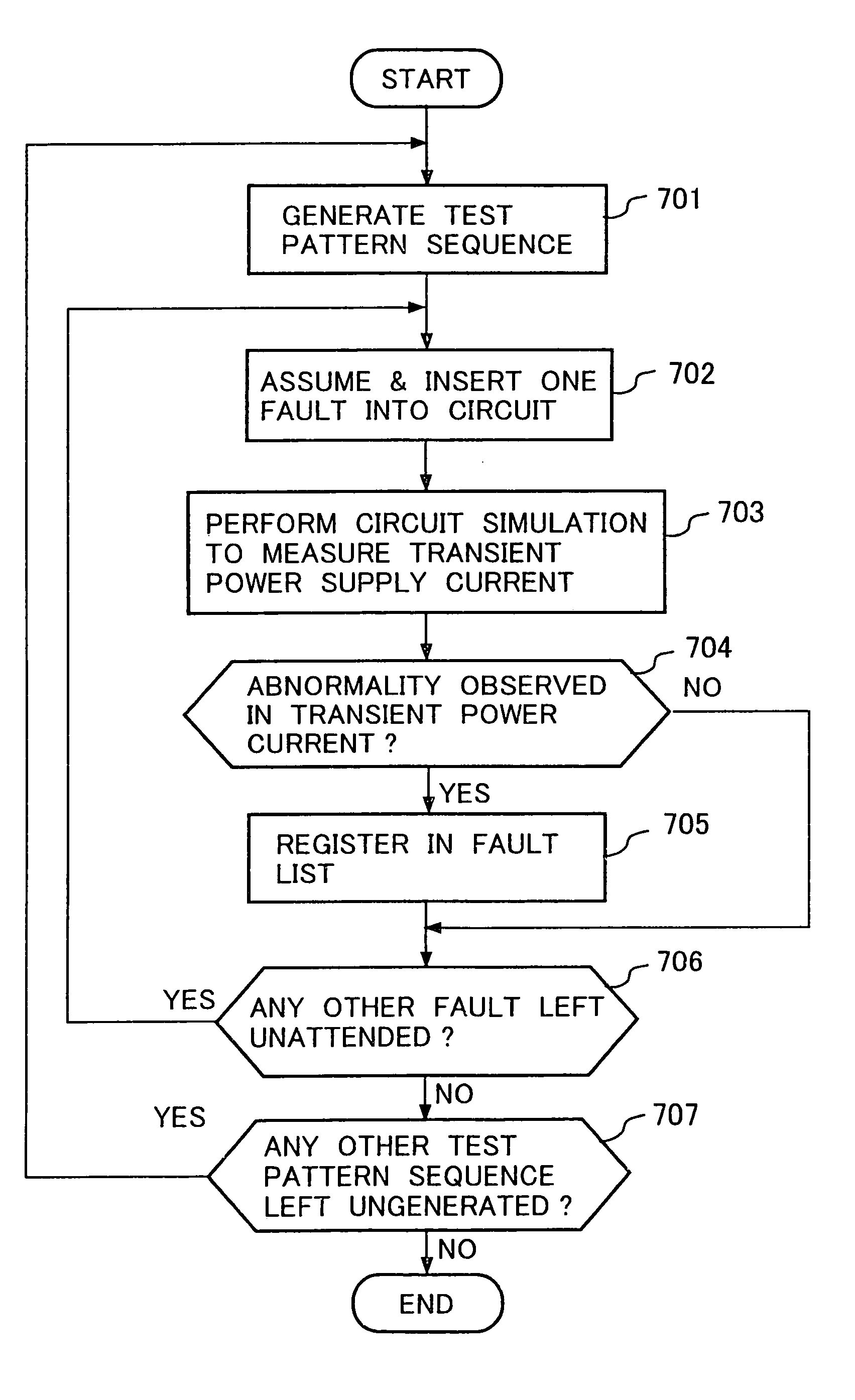

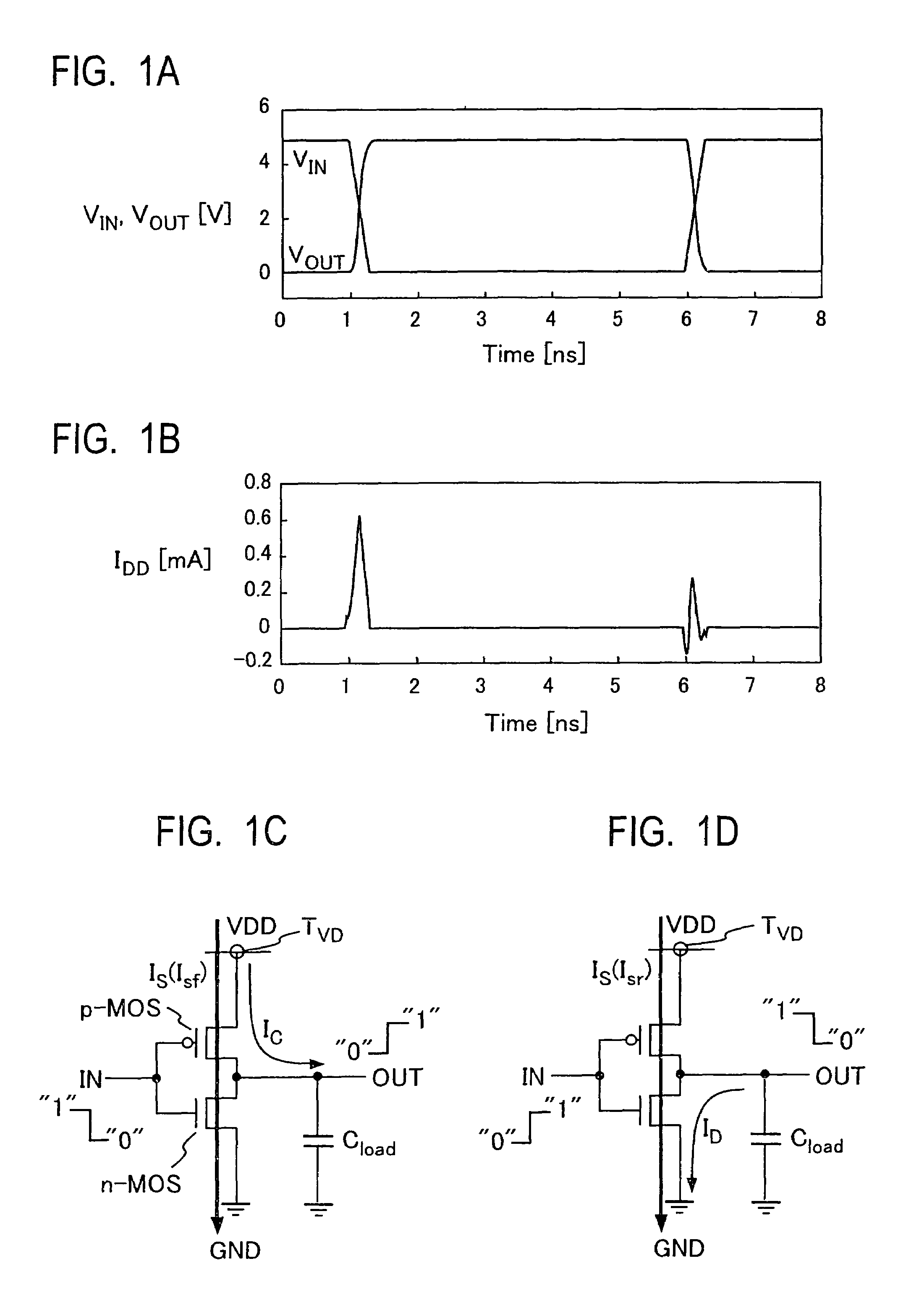

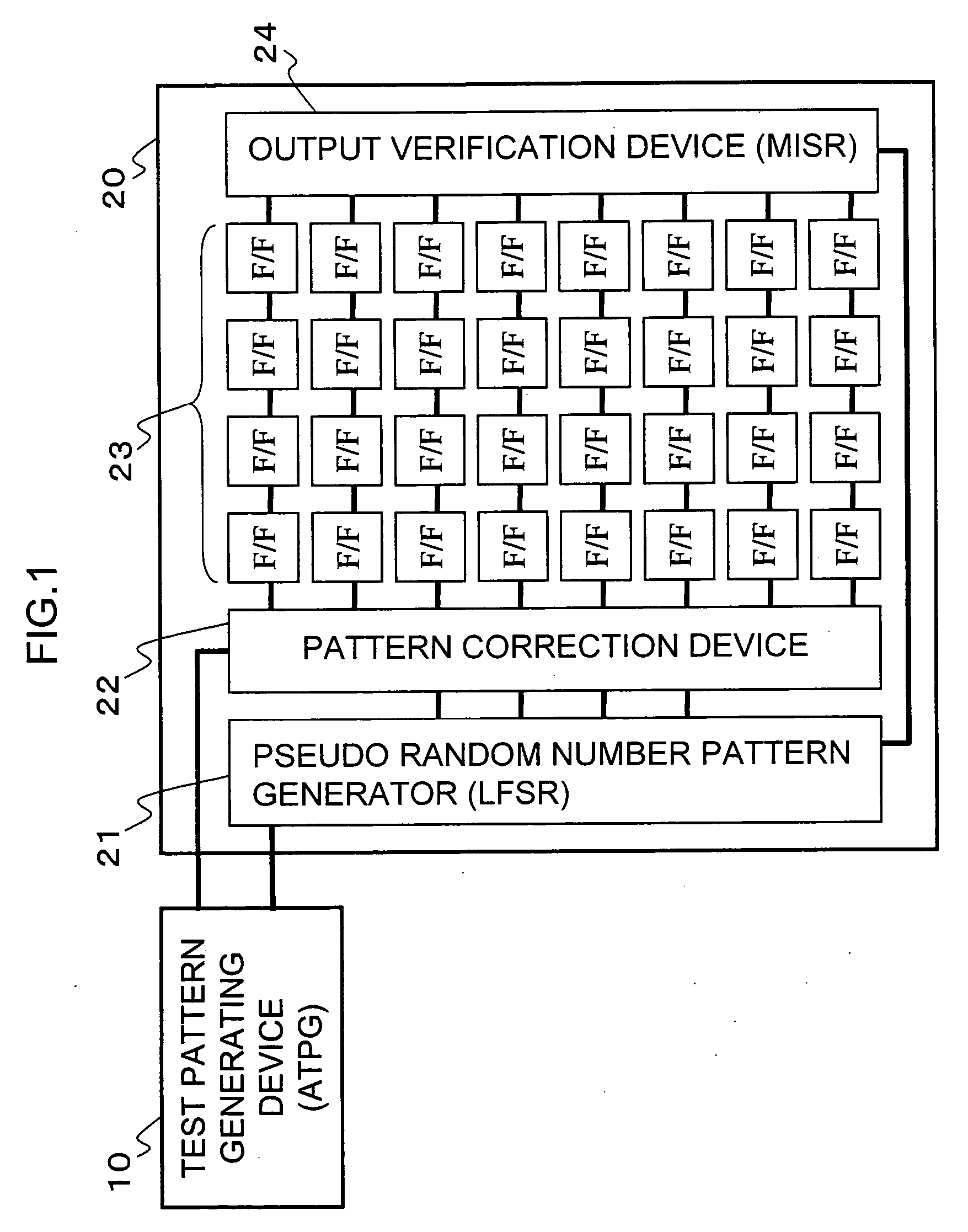

Method and apparatus for fault simulation of semiconductor integrated circuit

InactiveUS6975978B1Improve test efficiencyImpossible to detectSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwarePattern sequenceEngineering

A test pattern sequence is generated (101), then a logic simulation of the operation of an IC under test in the case of applying each test pattern of the test pattern sequence, and a logic signal value sequence occurring in each signal line of the IC under test (102). The logic signal value sequence in each signal line is used to register in a fault list parts (a logic gate, signal line or signal propagation path) in which a fault (a delay fault or an open fault) detectable by a transient power supply current testing using the test pattern sequence is likely to occur (103).

Owner:ADVANTEST CORP

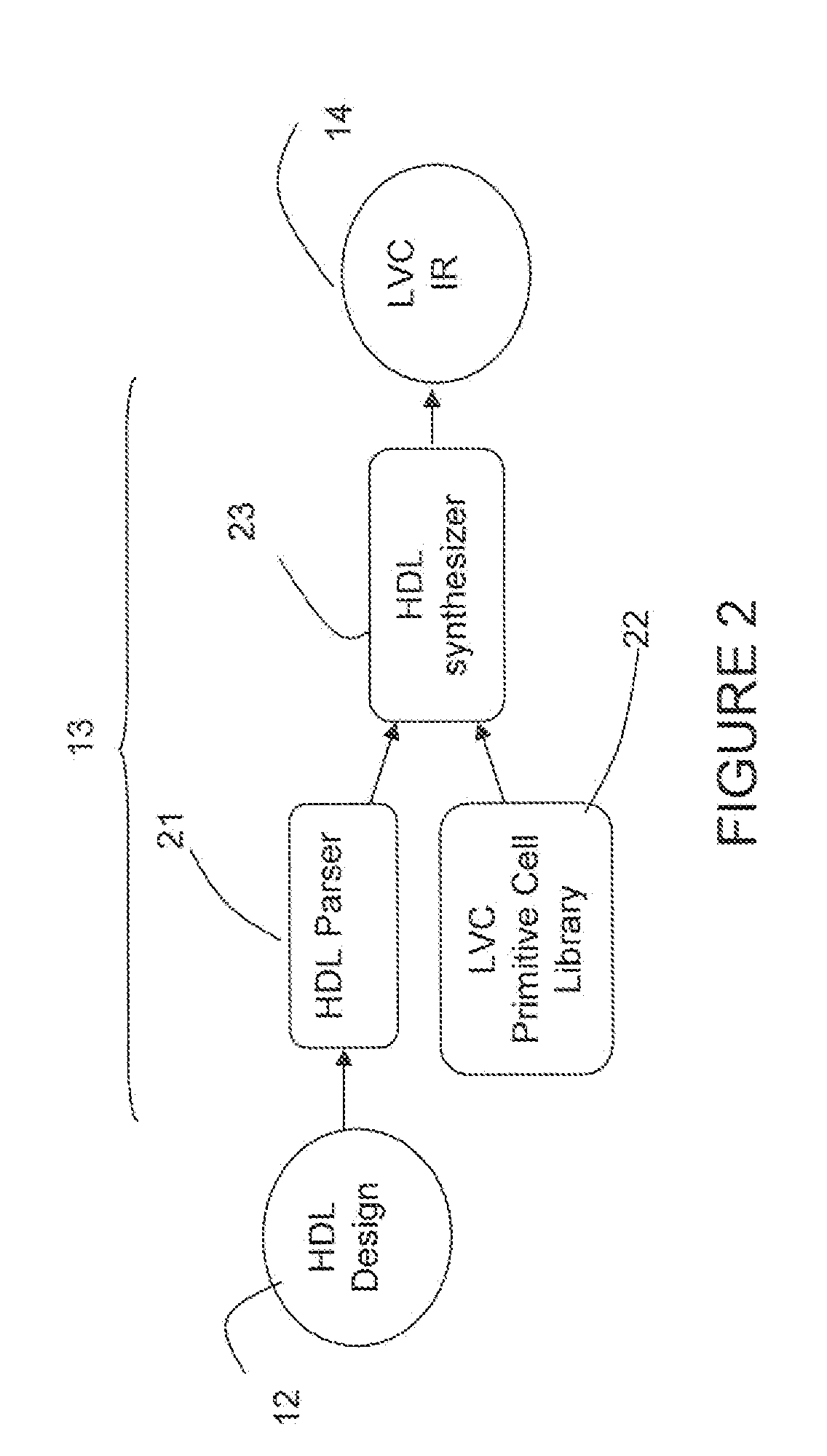

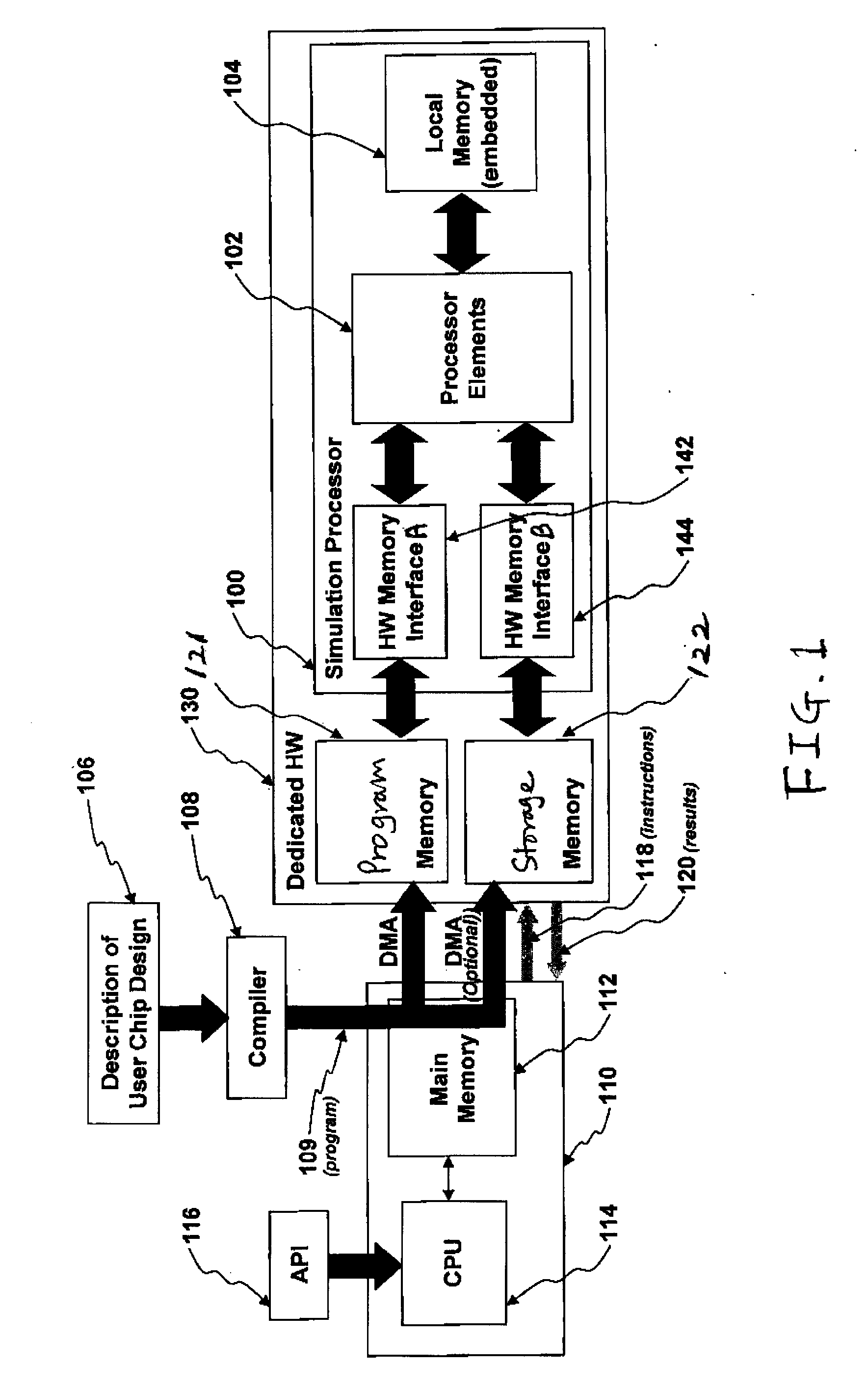

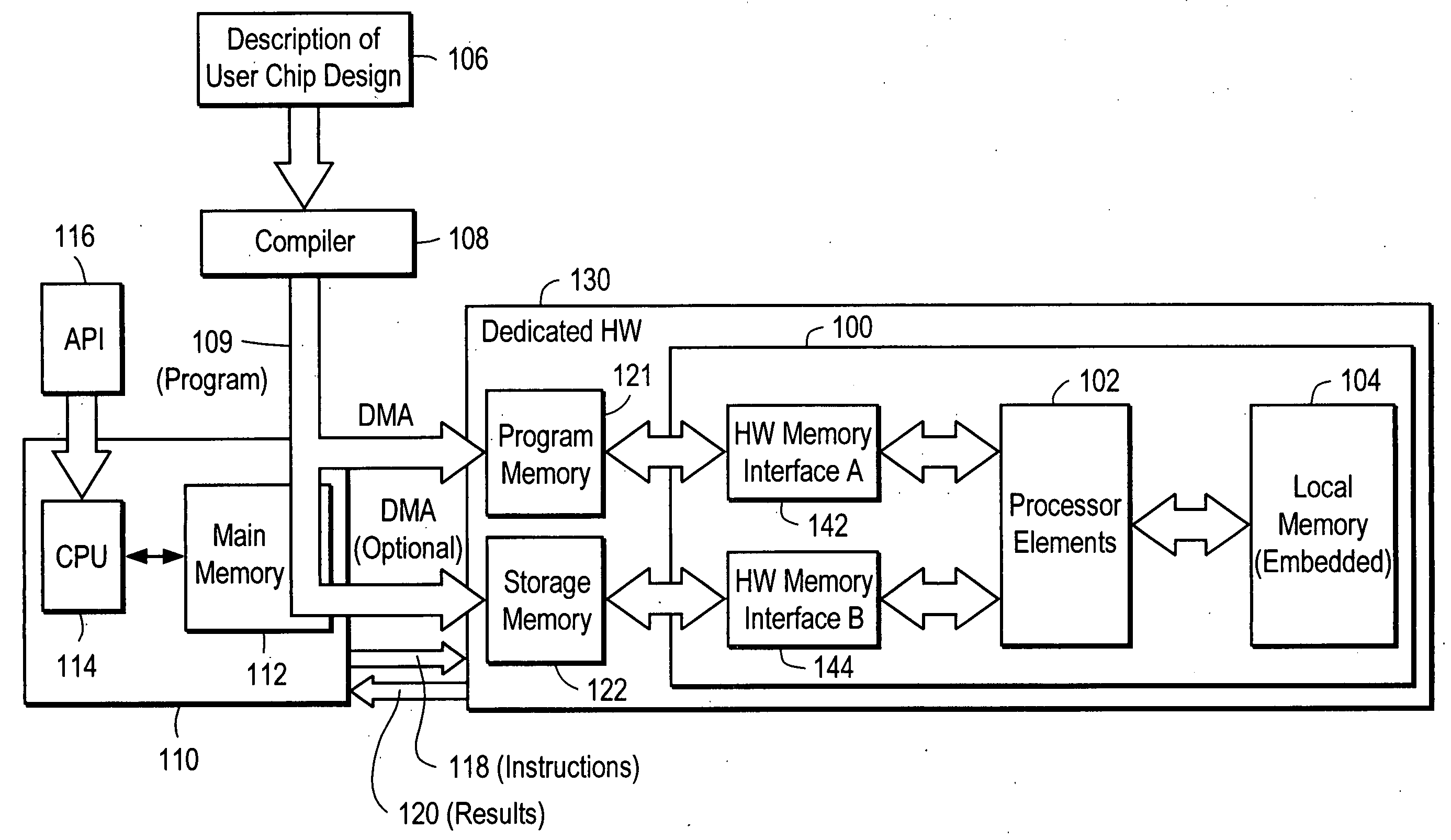

Systems and Methods for Logic Verification

ActiveUS20100286976A1CAD circuit designSoftware simulation/interpretation/emulationMulti processorParallel computing

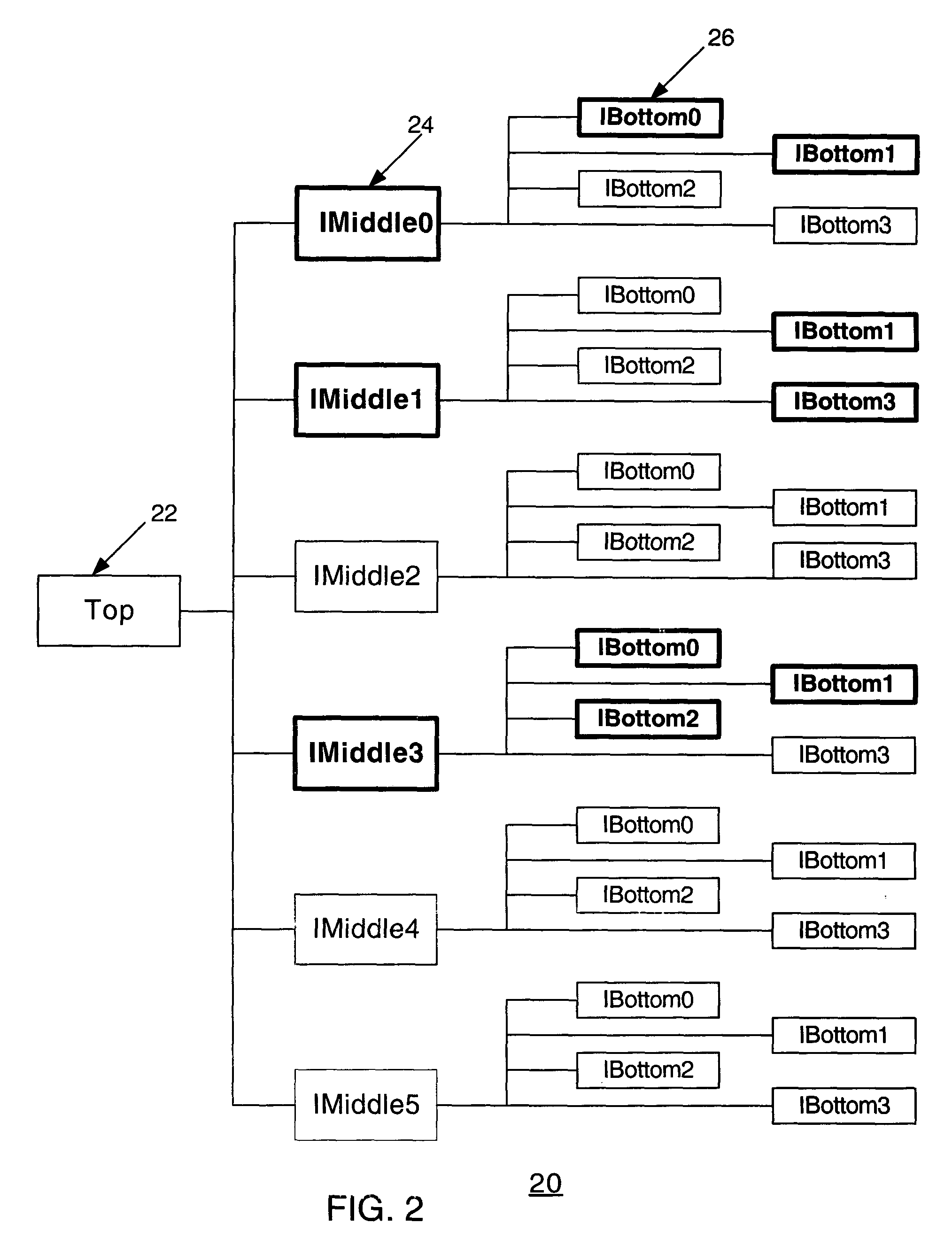

Methods and systems for simulating logic may translate logic design into executable code for a multi-processor based parallel logic simulation device. A system may implement one or more parallel execution methods, which may include IPMD, MPMD, and / or DDMT.

Owner:ET INT

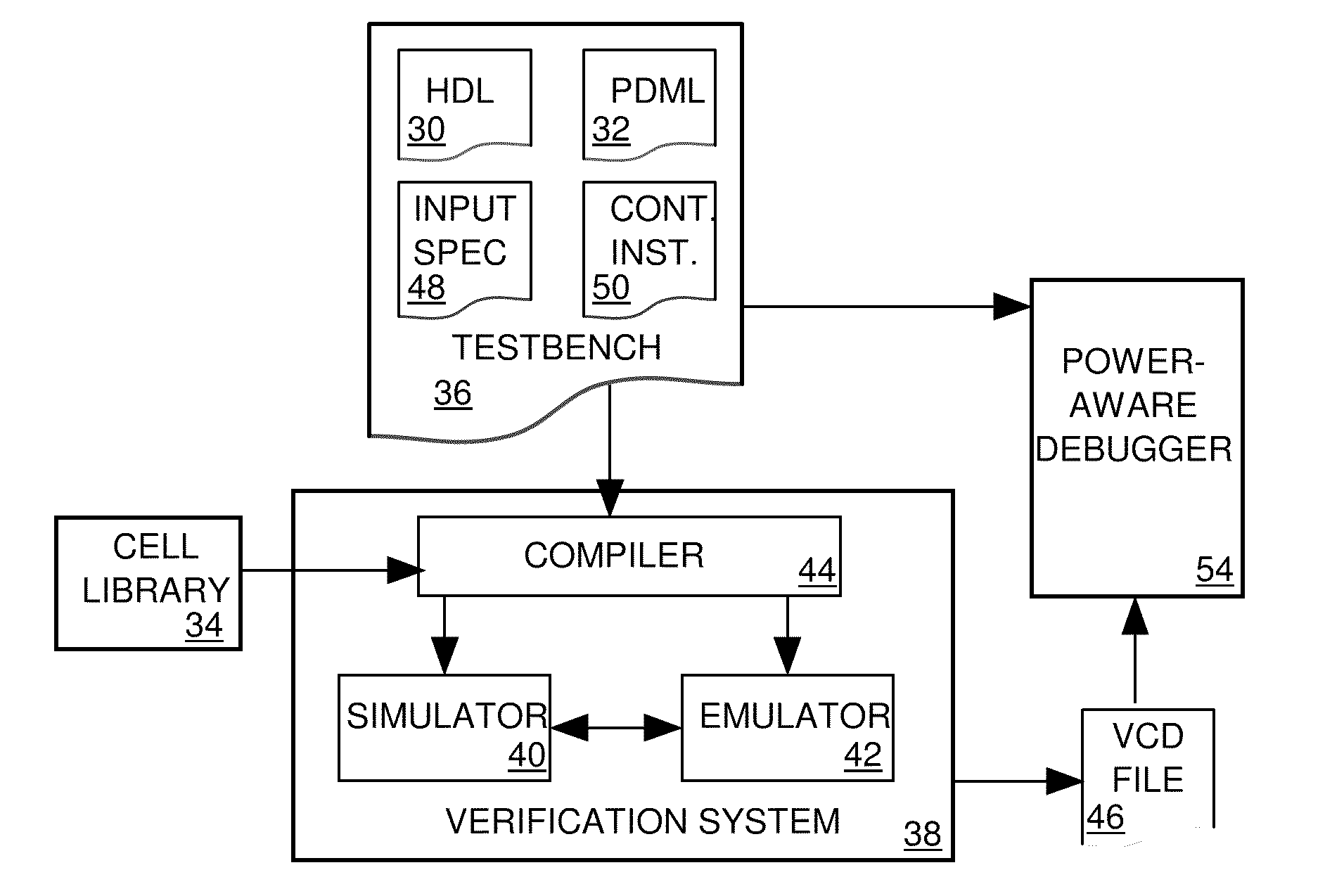

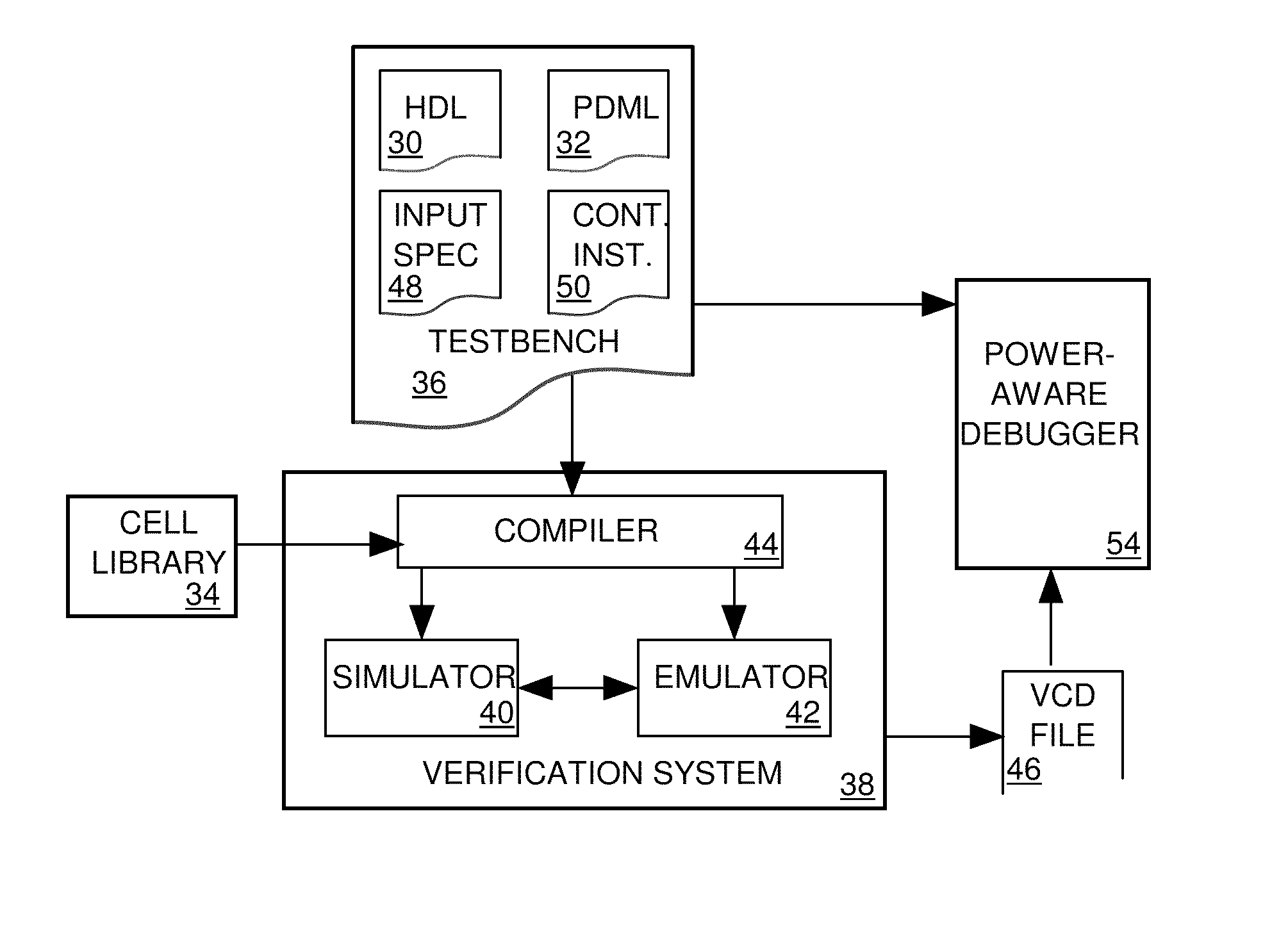

Power-aware debugging

ActiveUS20100192115A1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureDisplay device

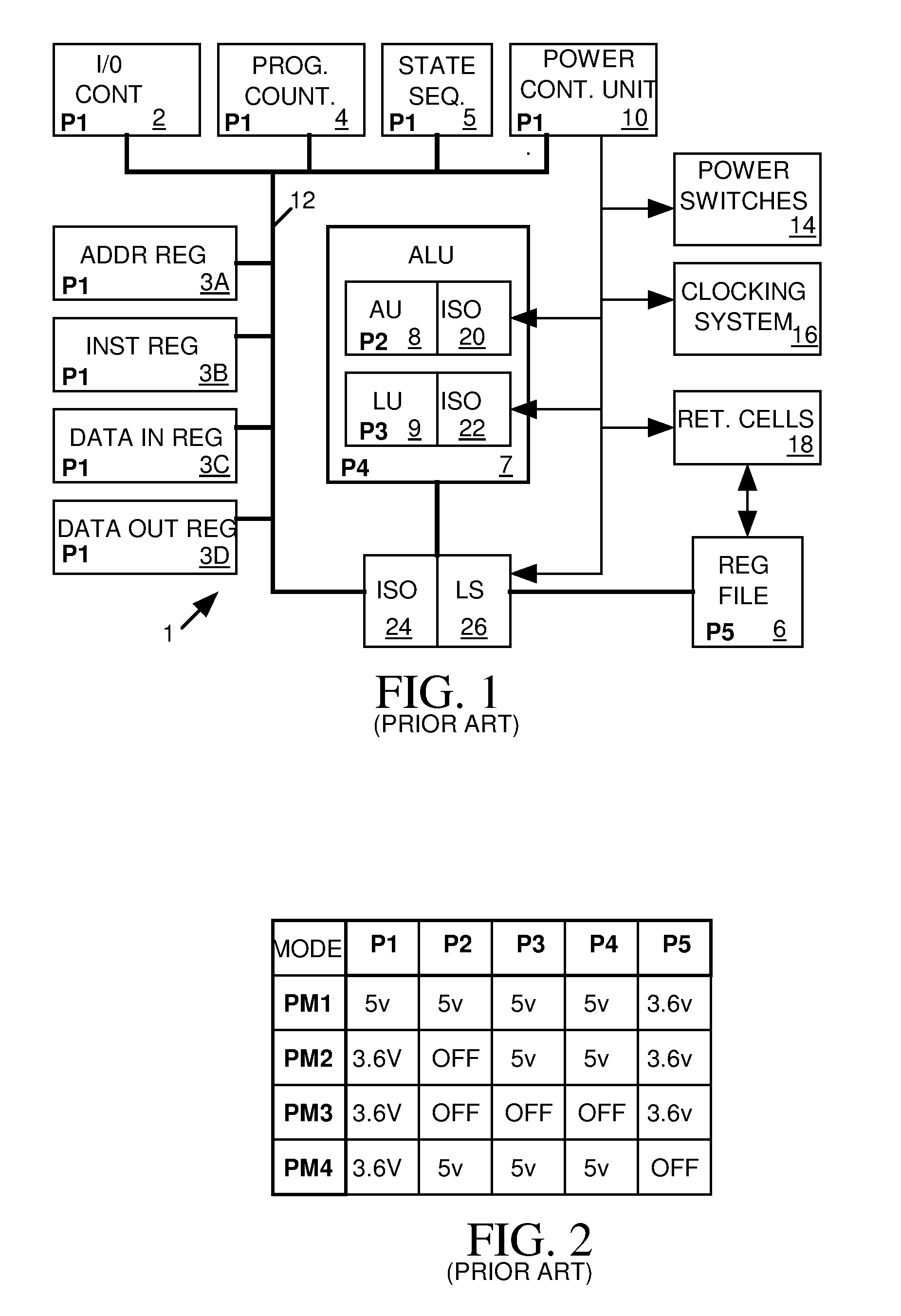

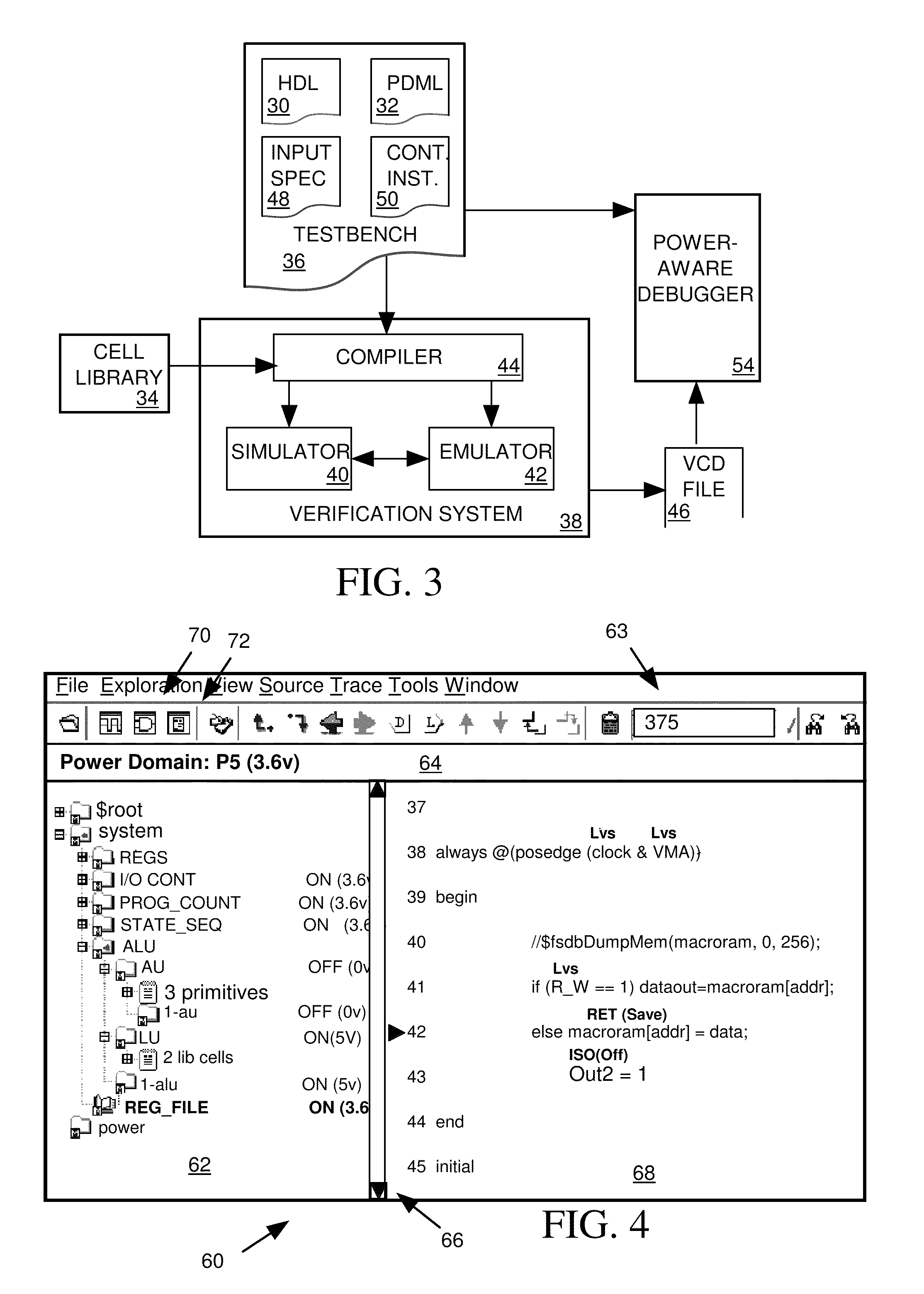

A debugging system produces displays in response to an IC design and results of a logic simulation of IC behavior based on the IC design. The IC design includes a hardware description language (HDL) model of the IC describing the IC as comprising cell instances communicating via data signals and power sources for supplying power to the cell instances. The IC design also includes power definition markup language (PDML) model describing a power intent of the IC design. The debugging system generates displays representing HDL code that are annotated to indicate how the power intent of the IC design described by the PDML model relates to the portion of the HDL model represented by the display. The debugging system also generates signals trace displays indicating how both the logic and power intent of the IC design affect the value of a user-selected signal at a user-selected time during the logic simulation.

Owner:SYNOPSYS INC

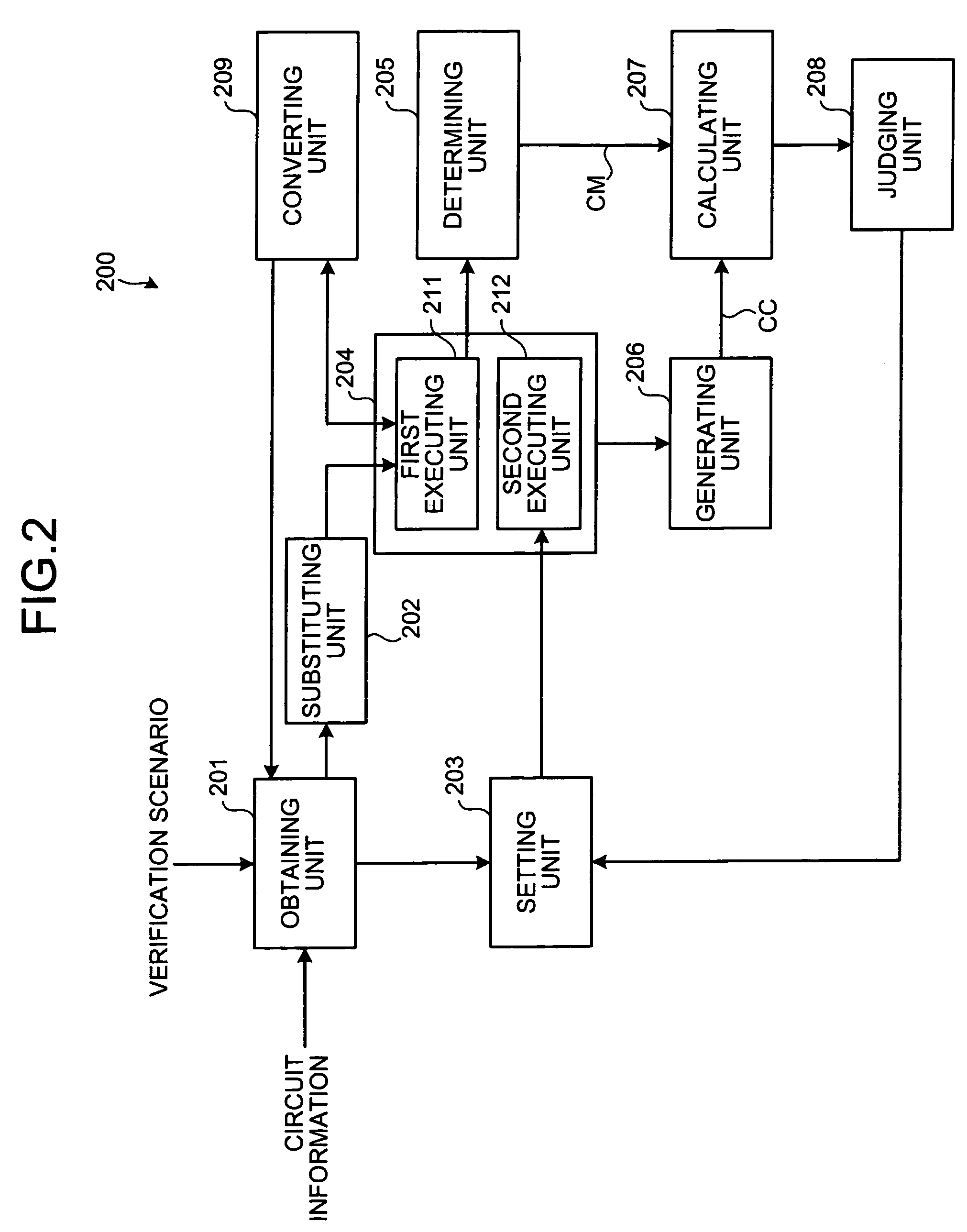

Method and apparatus for supporting verification, and computer product

InactiveUS20060155521A1Solve problemsComputation using non-denominational number representationCAD circuit designUndefined valueTheoretical computer science

In a verification supporting apparatus, when an obtaining unit obtains a verification scenario, a substituting unit substitutes an undefined value for a variable value in the verification scenario. A first executing unit executes a logic simulation using an input pattern. From a result of the logic simulation, a determining unit generates code-coverage upper-limit information. A setting unit sets input patterns by giving an arbitrary logic value to the variable value. A second executing unit executes a logic simulation using the input patterns set. A generating unit generates code coverage from the input patterns set. A calculating unit calculates a level of achievement of the code coverage with respect to the code-coverage upper-limit information.

Owner:FUJITSU LTD

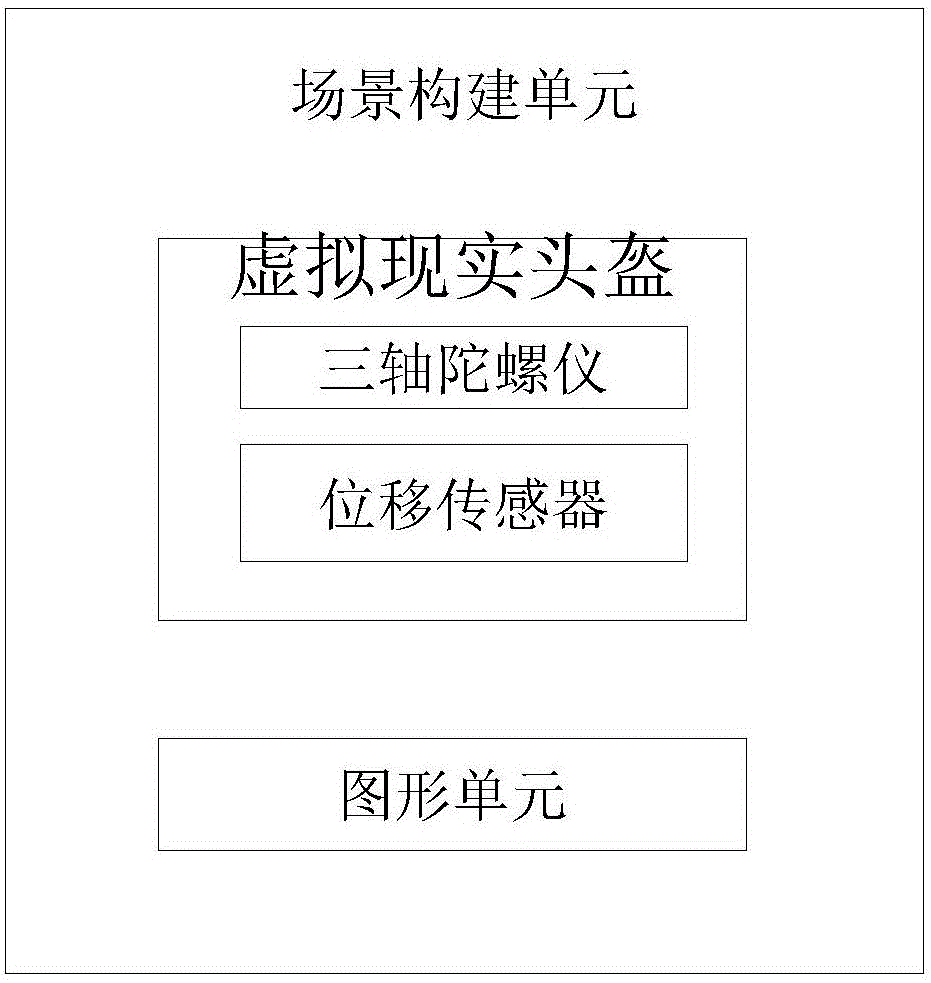

Driving training simulation system based on virtual reality technology

InactiveCN106652643ASave manpower and material resourcesCosmonautic condition simulationsSimulatorsGraphicsReal-time data

The invention discloses a driving training simulation system based on virtual reality technology, comprising: a data saving unit used to save the required data information of a driver in his driving training process and an action monitoring unit; a scenario constructing unit providing to the driver inside the vehicle a logic simulation model and functional module and a virtual reality scenario realizing unit in which based on virtual reality technology, the pattern units in the scenario constructing unit are accessed to generate an operation simulation space for the simulation model and training of the driver so that the driver puts on the virtual reality helmet for driving certificate evaluation and practice simulation. The scenario constructing unit is connected with the data saving unit and the virtual reality scenario realizing unit respectively for real time data communications. The system of the invention can be widely applied in people's daily life when they learn to obtain a driving license. With the system, the human labor and material devotion required by the actual evaluation are eliminated, and due to the use of the virtual reality technology, a user can get a more lifelike feel.

Owner:DALIAN VINCENT SOFTWARE TECH

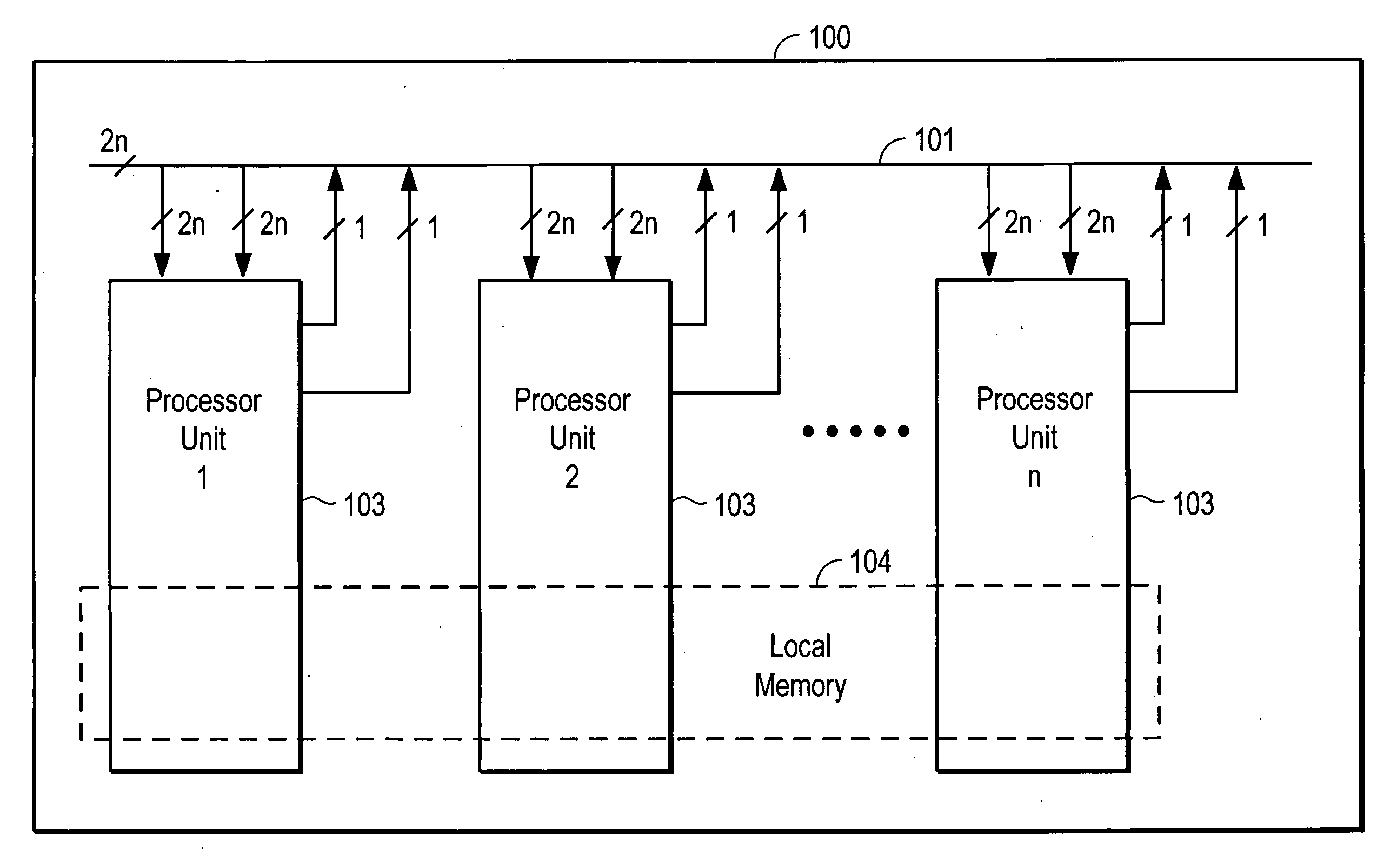

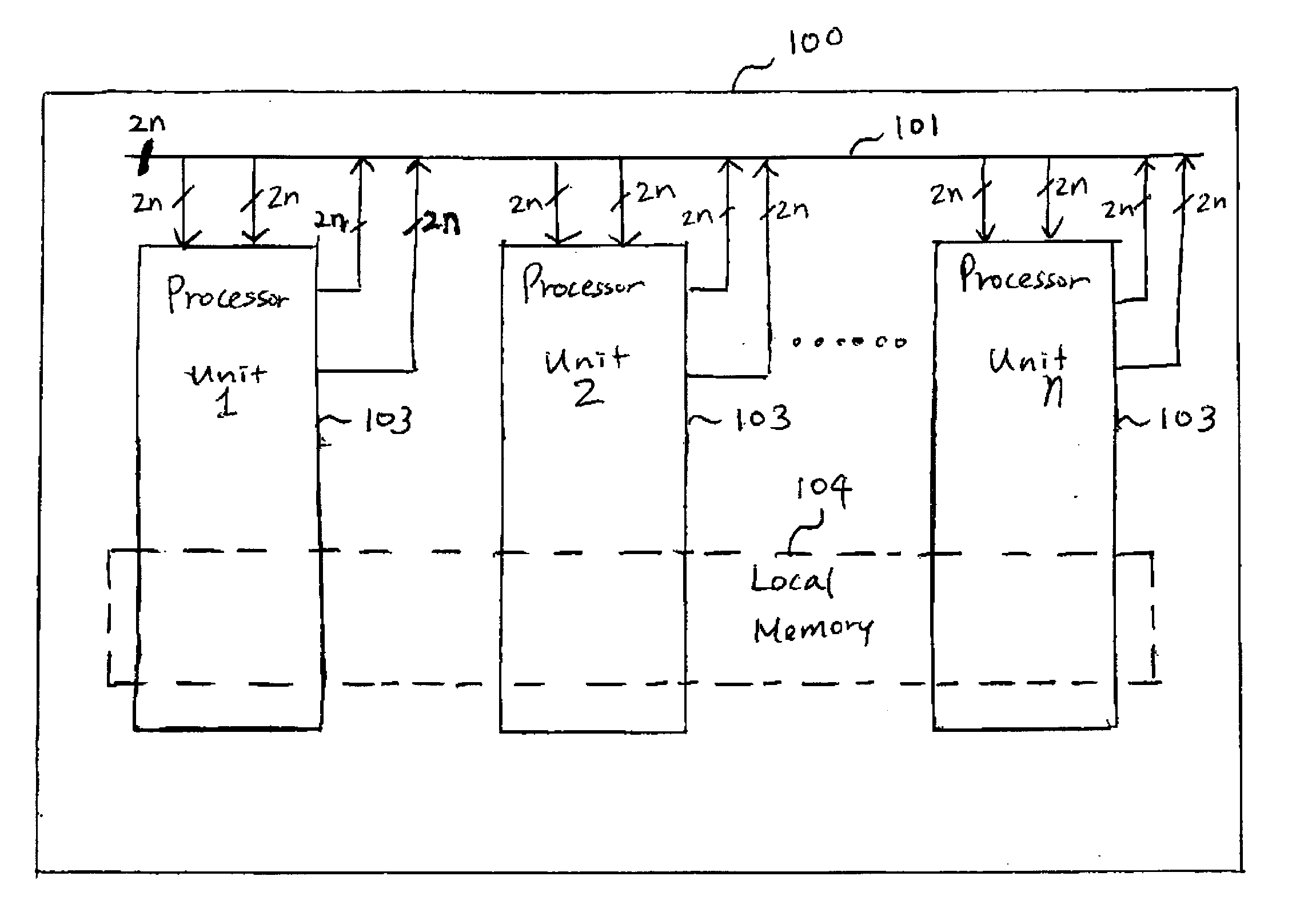

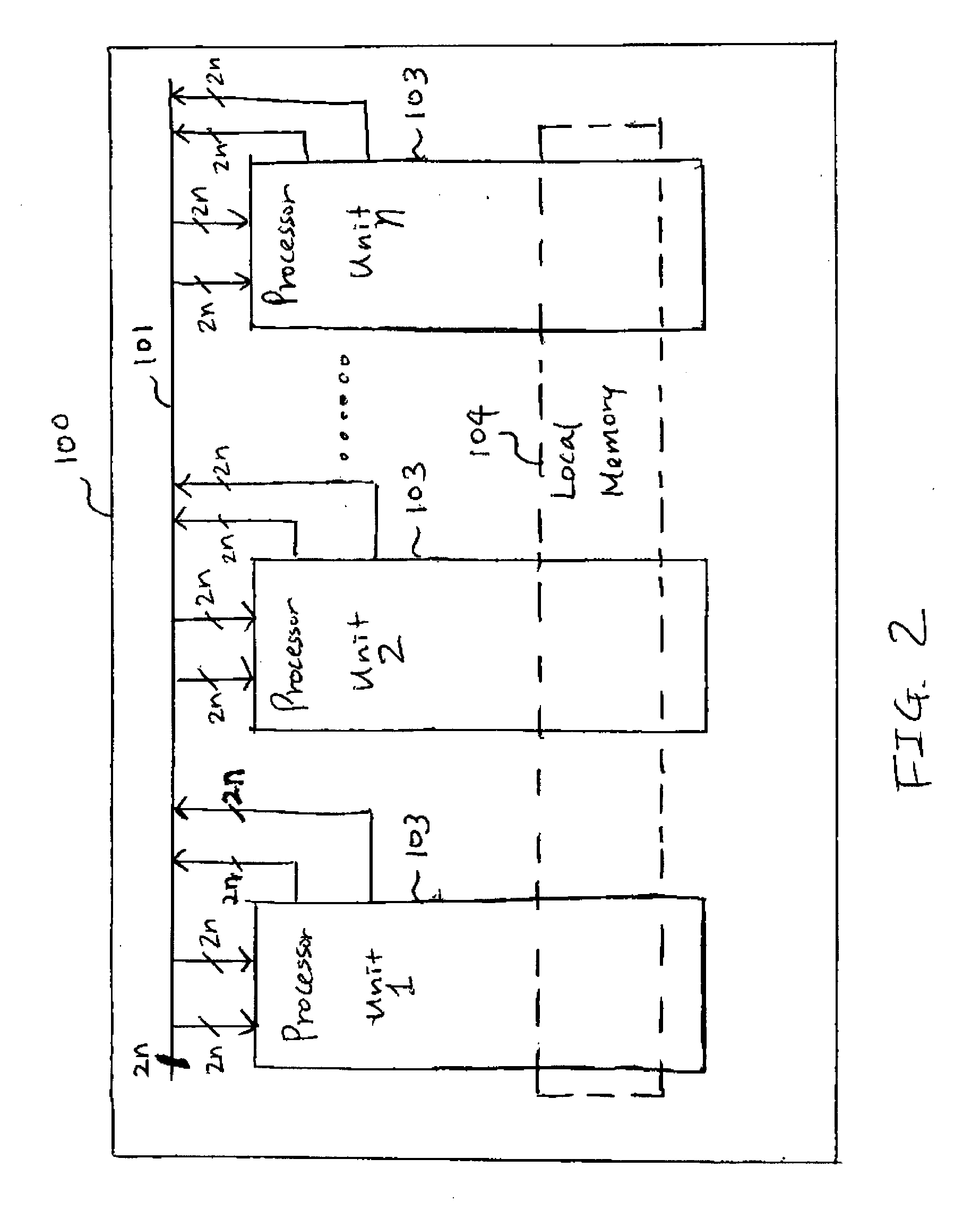

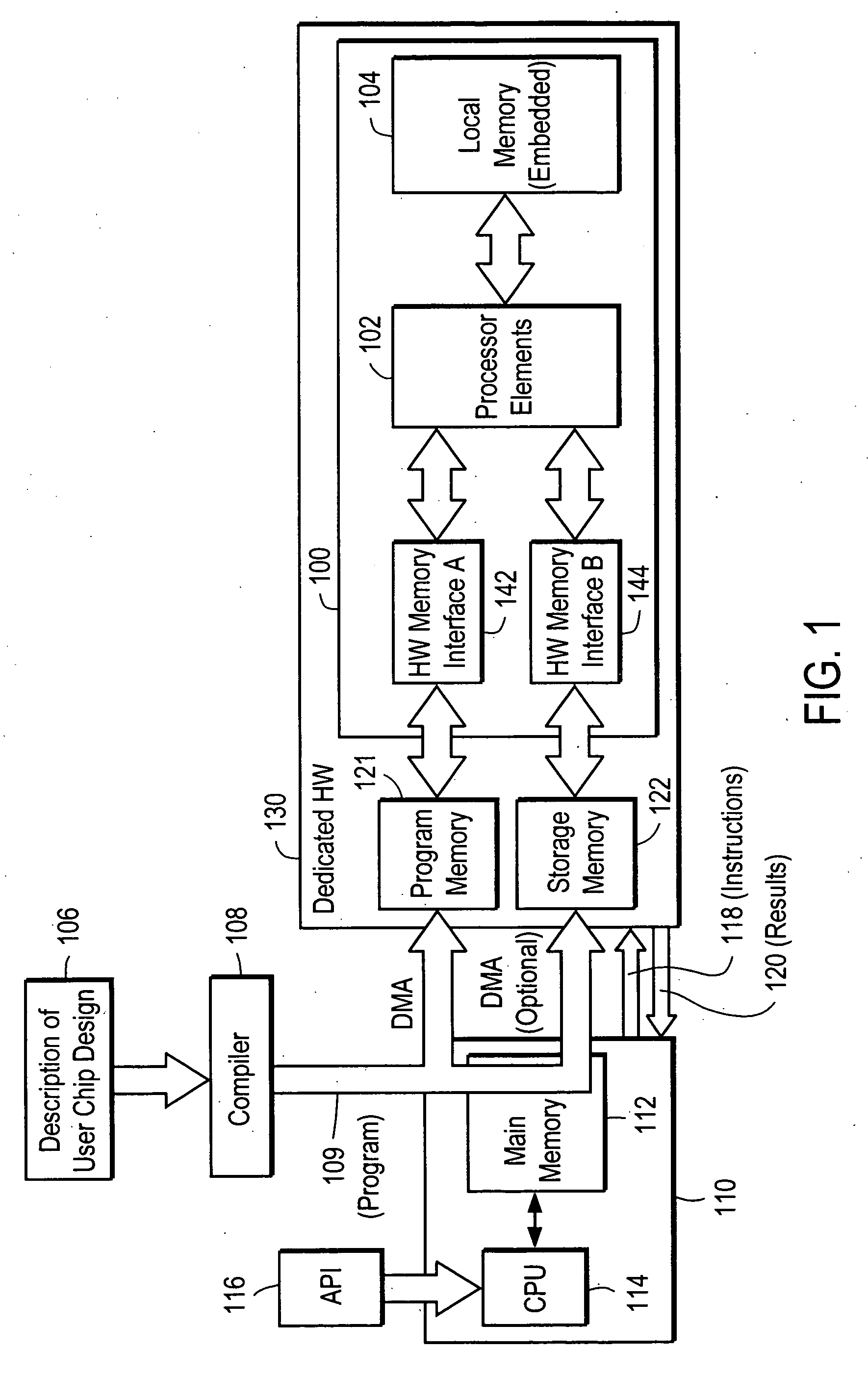

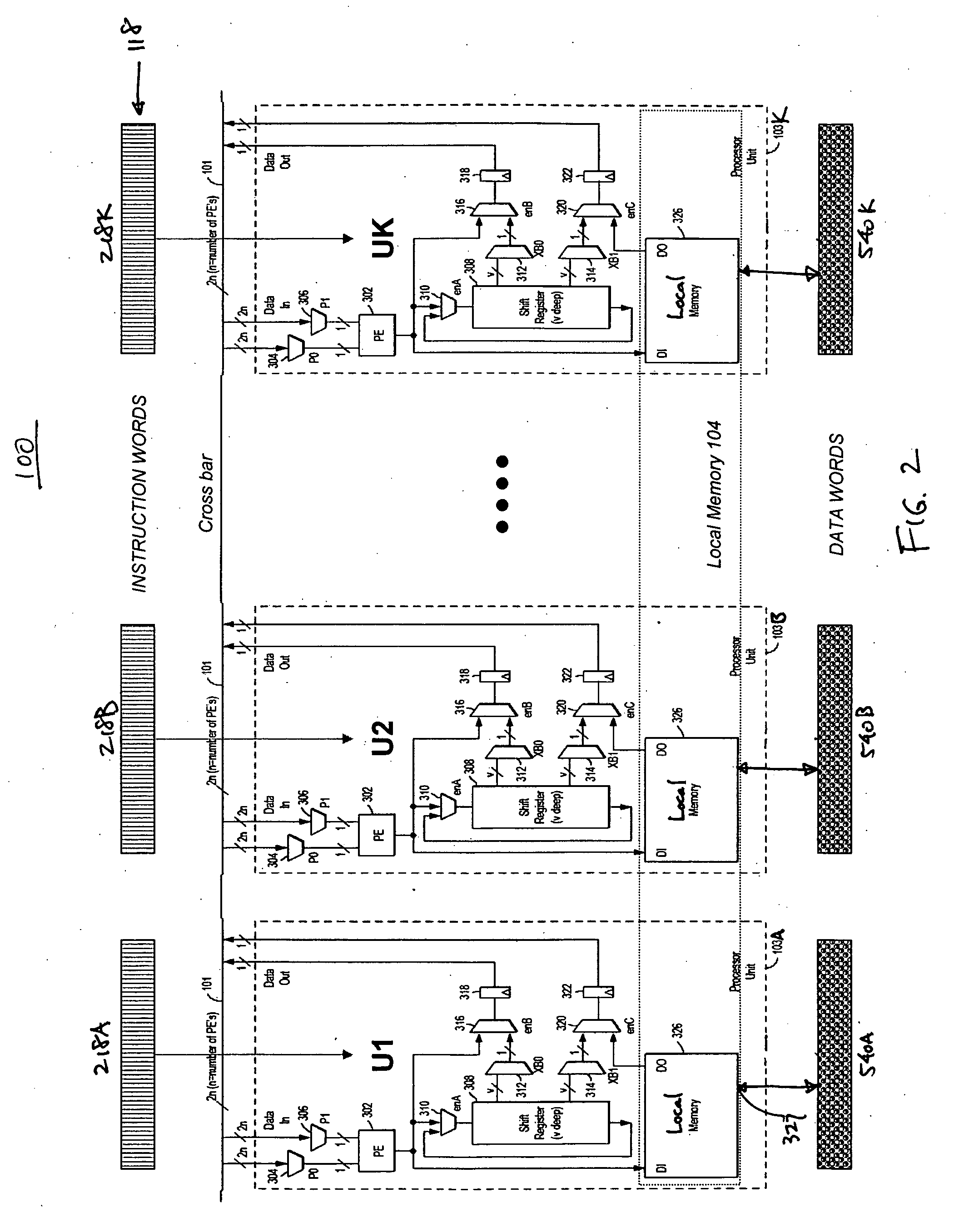

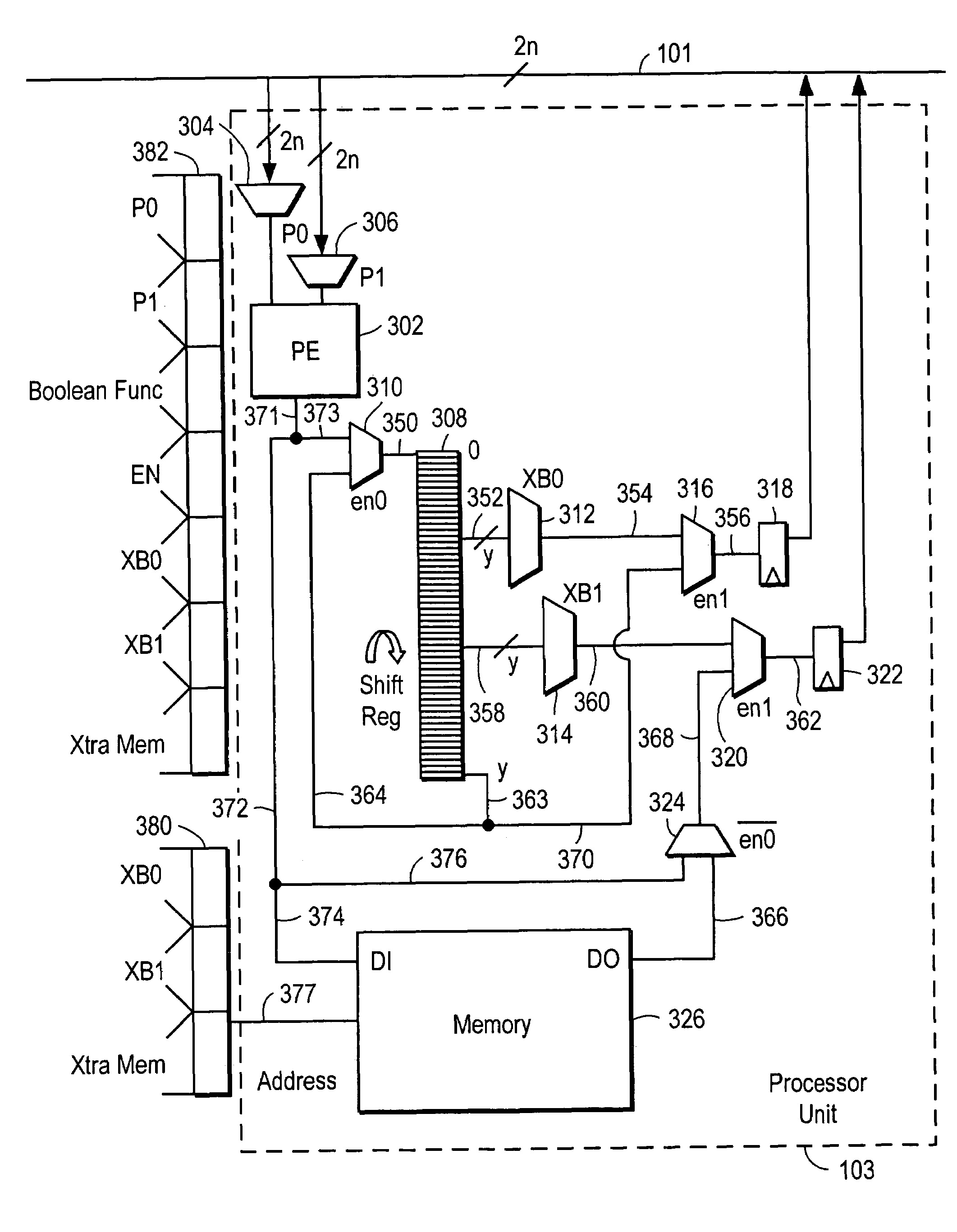

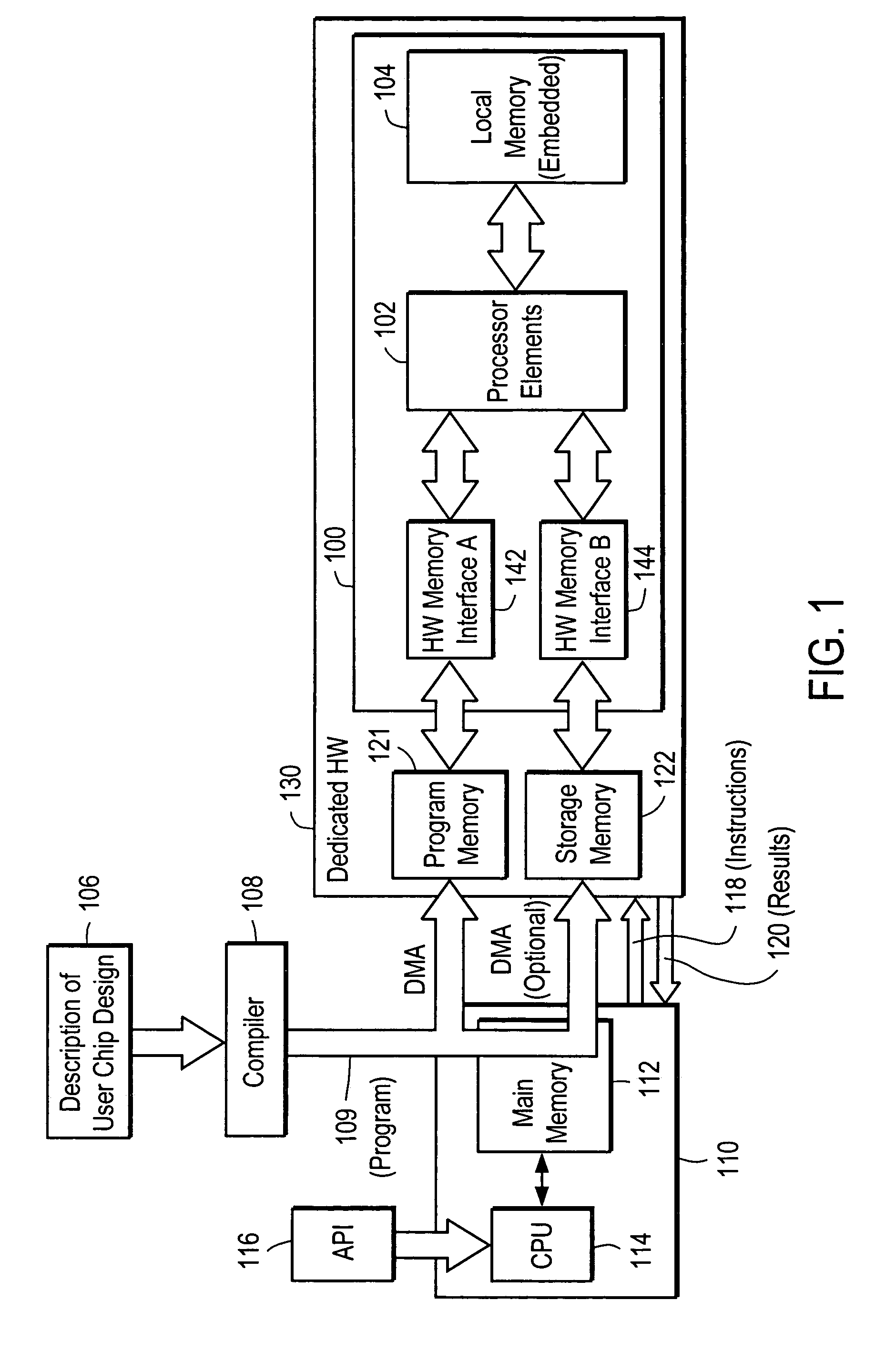

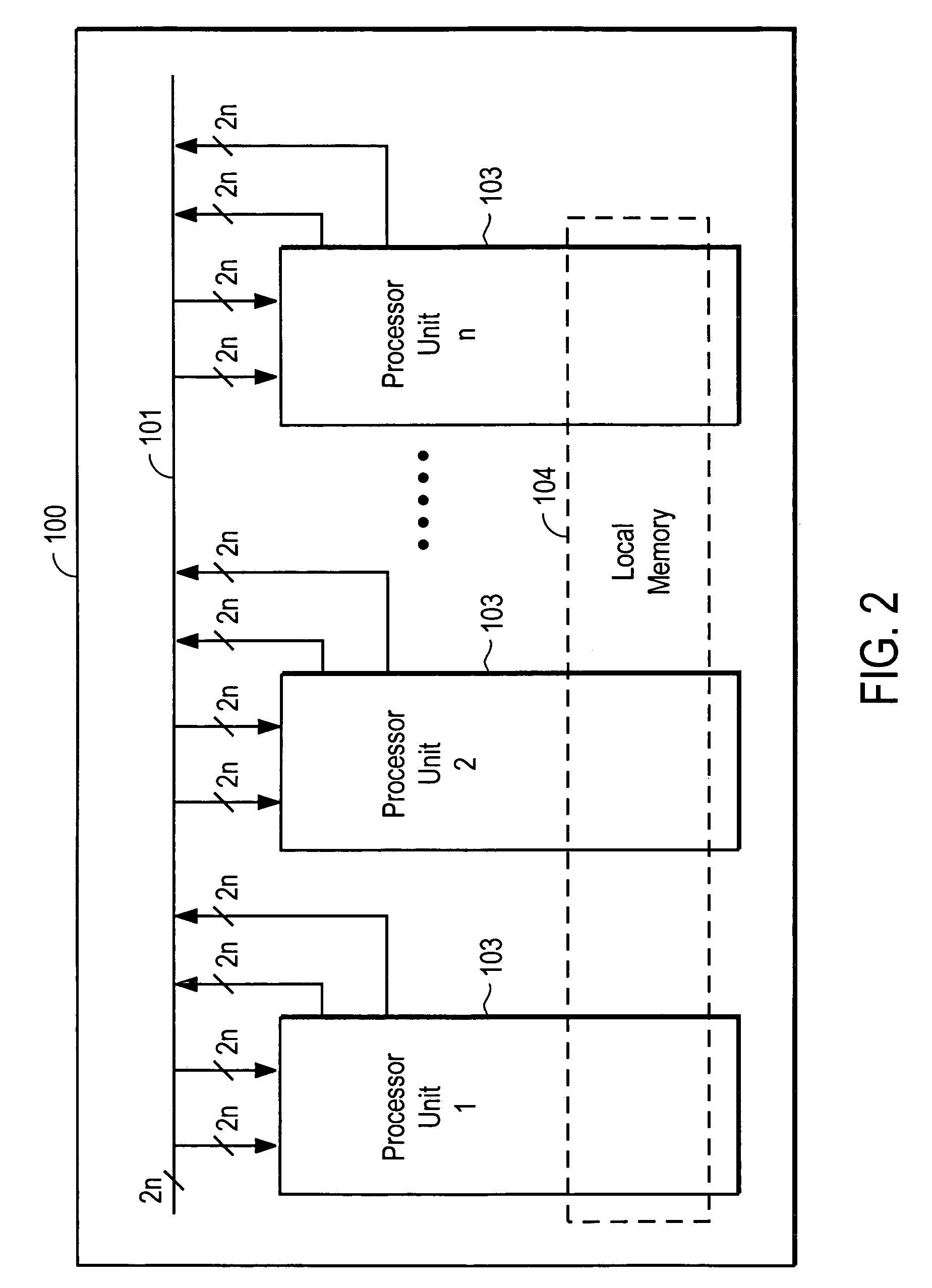

Hardware acceleration system for logic simulation using shift register as local cache with path for bypassing shift register

InactiveUS20070073999A1Reduces instruction lengthSimplify hardware designGeneral purpose stored program computerCAD circuit designShift registerProcessor element

A simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic operation, and a shift register for storing intermediate values generating during the logic simulation. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units can also include one or more bypass multiplexers coupled between the output of the processor element and the interconnect system, for providing a path for bypassing the shift register to provide the output of the processor element directly to the interconnect system.

Owner:LIGA SYST

VLIW Acceleration System Using Multi-state Logic

InactiveUS20070074000A1Instruction analysisGeneral purpose stored program computerSemiconductor chipLogic simulation

A logic simulation processor uses multi-state logic (e.g., in 4-state, signals may take the values 0, 1, X or Z in the simulation of a semiconductor chip design). Typically a reduced number of basic multi-state logic functions are selected for the instruction set of the processor. Logic functions that are not part of the basic set are simulated by constructing them from combinations of the basic logic functions. In this way, the instruction length remains a manageable size but all logic functions that may occur can be simulated. The basic VLIW architecture can be extended to other applications.

Owner:LIGA SYST

Partitioning of tasks for execution by a VLIW hardware acceleration system

InactiveUS20070129924A1Overcome limitationsReduce the amount requiredCAD circuit designSpecial data processing applicationsSemiconductor chipTheoretical computer science

In one aspect, logic simulation of a design of a semiconductor chip is performed on a domain-by-domain basis (e.g., by clock domain), but storing a history of the state space of the domain during simulation. In this way, additional information beyond just the end result can be reviewed in order to debug or otherwise analyze the design.

Owner:LIGA SYST

Hardware acceleration system for logic simulation using shift register as local cache

InactiveUS7444276B2Simplify hardware designShorten the lengthGeneral purpose stored program computerComputer aided designShift registerProcessor element

A logic simulation processor stores in a shift register intermediate values generated during the logic simulation. The simulation processor includes multiple processor units and an interconnect system that communicatively couples the processor units to each other. Each of the processor units includes a processor element configurable to simulate at least a logic gate, and a shift register associated with the processor element. The shift register includes multiple entries to store the intermediate values, and is coupled to receive the output of the processor element. Each of the processor units further includes one or more multiplexers for selecting one of the entries of the shift register as outputs to be coupled to the interconnect system. Each of the processor units may further include a local memory for storing data from, and loading the data to, the simulation processor.

Owner:LIGA SYST

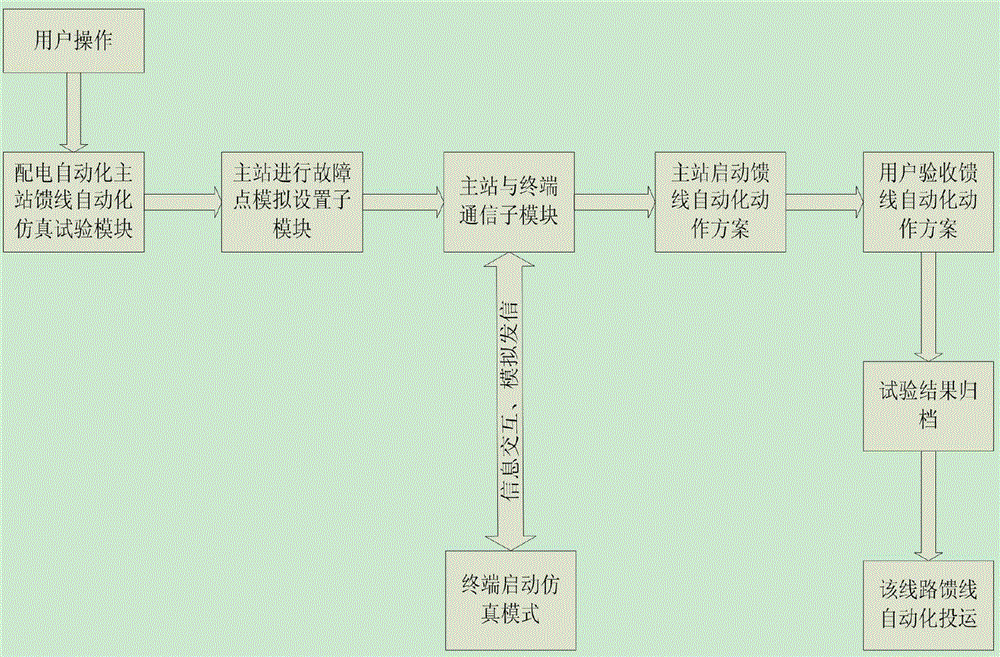

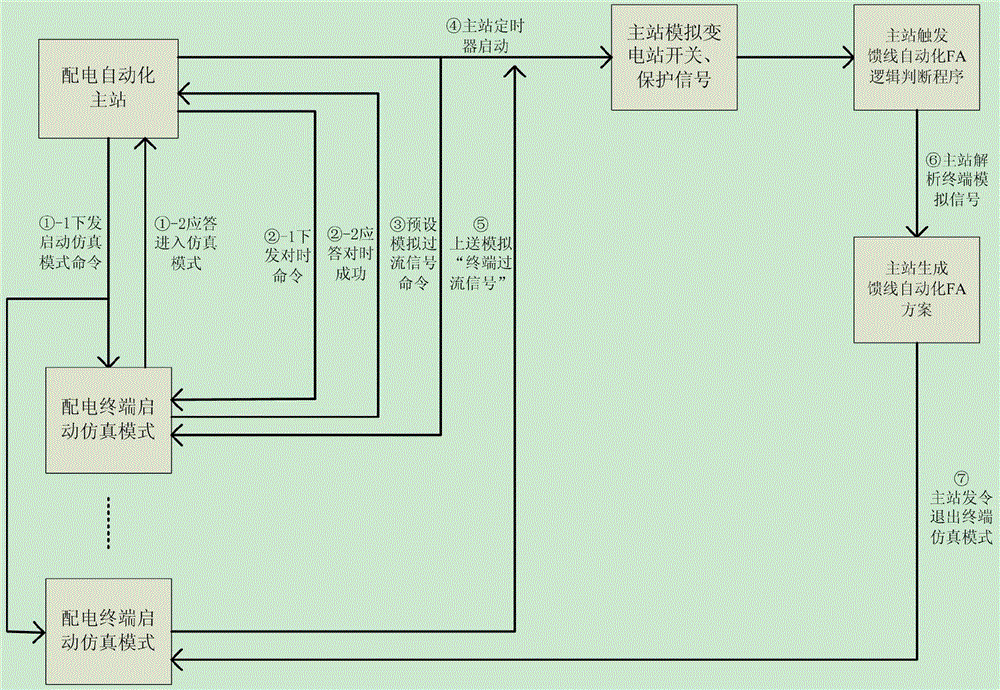

Feeder automation action logic test method based on power distribution terminal service verification

ActiveCN104460346ASolve action logic verificationSolve the problem that the test requires on-site synchronous incremental testSimulator controlFault locationSynchronous controlMaster station

The invention provides a feeder automation action logic test method based on power distribution terminal service verification. Feeder automation action logic simulation verification in the normal operating states of terminals can be achieved by the adoption of terminal service verification simulating a transmitting mode. The method includes the following steps that firstly, through synchronous control of a master power distribution station, the multiple terminals on multiple feeders can simultaneously enter simulation state modes, fault simulation transmitting of the power distribution terminal on one feeder is synchronized, centralized feeder automation action logic is verified, and the problem that tests need to be synchronously added in a field is solved; master station and terminal simulation transmitting technical protocols are formulated, and the transmitting procedure that the terminals enter the simulation modes is formulated; thirdly, it is guaranteed that normal operation of the terminals is not affected by the simulation states of the terminals, and if a true fault occurs to a power distribution line in the simulation states of the terminals, actual fault information of the terminals can be transmitted to the master station in time and is not lost; the terminals in the simulation states simultaneously record the operating information of the power distribution line, and the operating information is called by the master station at any time.

Owner:JIANGSU ELECTRIC POWER COMPANY YANGZHOU POWER +2

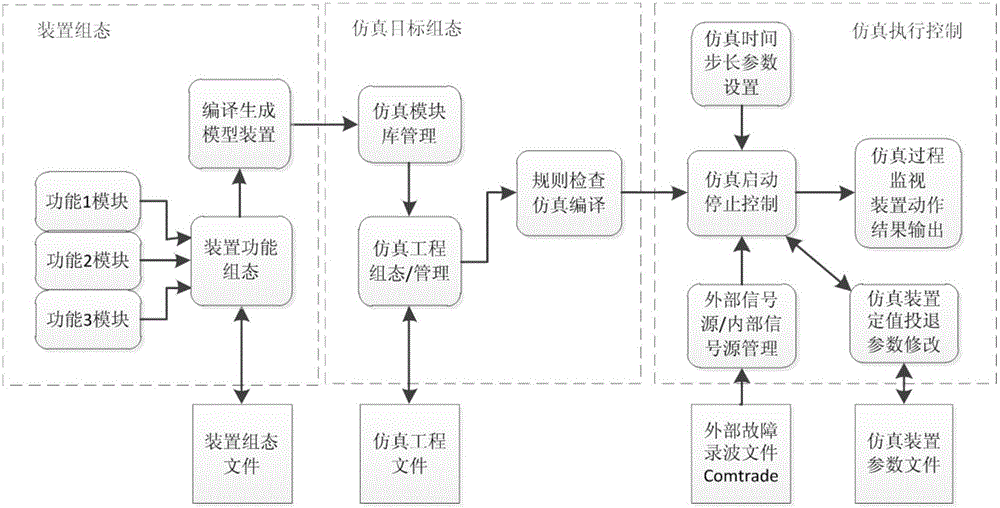

Logic simulation method of comprehensive automation system equipment of transformer substation

ActiveCN105005658ARealize the whole operation status monitoringMaster the working principleSpecial data processing applicationsControl layerTransformer

The invention discloses a logic simulation method of the comprehensive automation system equipment of a transformer substation. The logic simulation method comprises the following steps: equipment configuration module development, simulation module library management, simulation engineering configuration / management, simulation configuration rule examination, simulation compiling, simulation operation control, simulation energizing control and simulation monitoring. The comprehensive automation system in the transformer substation is subjected to the logic function decoupling of equipment according to a three-layer structure, forms a simulation module library capable of reconfiguring logics and implementation functions, constructs and generates a simulation target system, which is the same with a practical transformer substation, of a secondary system by construction modules, applies or imports an energizing quantity to carry out simulation operation and carries out whole-process simulation monitoring, wherein the three-layer structure comprises a station control layer, a spacing layer and a process layer. The method is favorable for quickly mastering working principles in the secondary system and equipment of the transformer substation and mastering relevant overhauling and maintaining skills, and provides a means for accident analysis and processing.

Owner:STATE GRID CORP OF CHINA +2

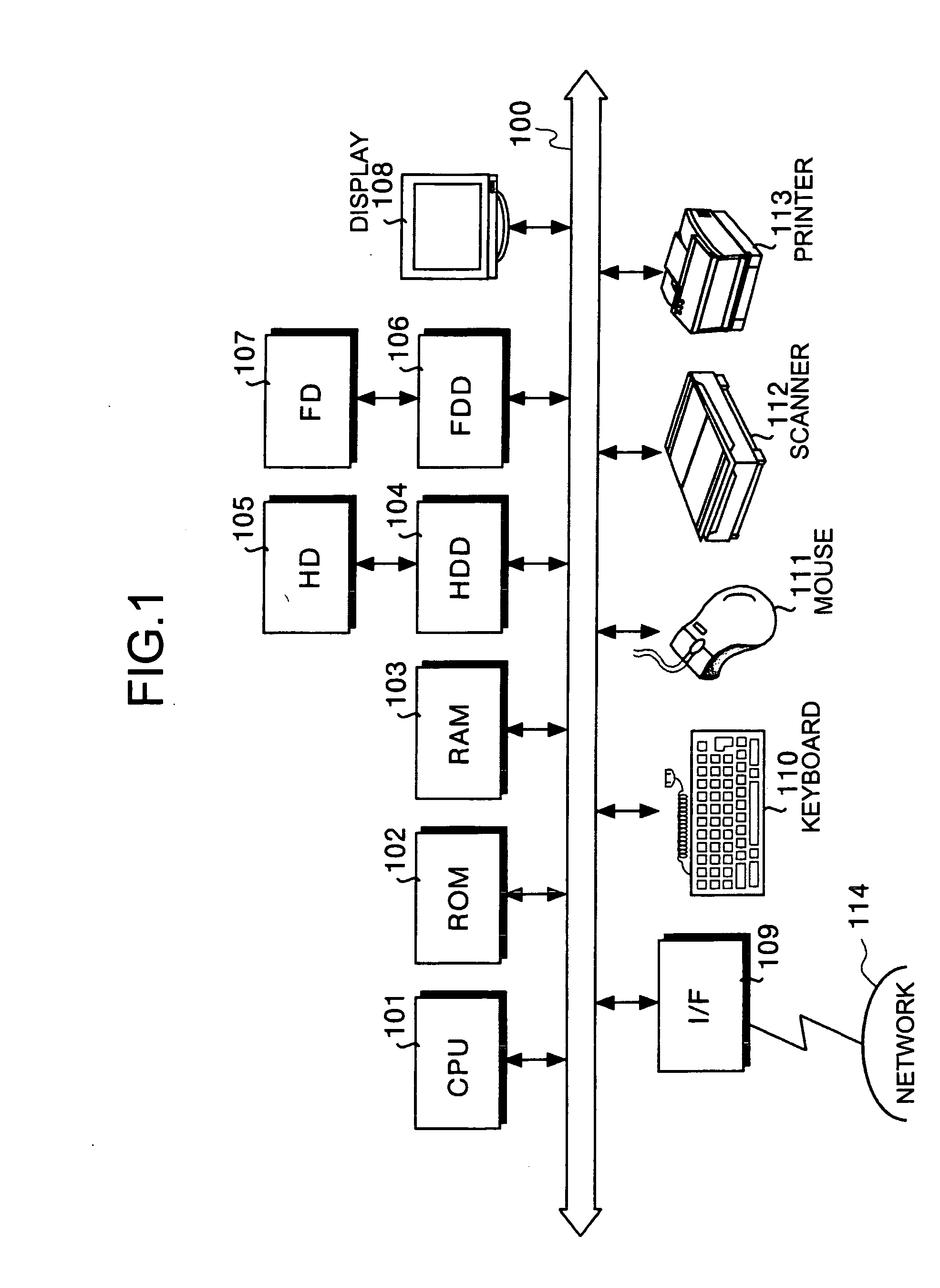

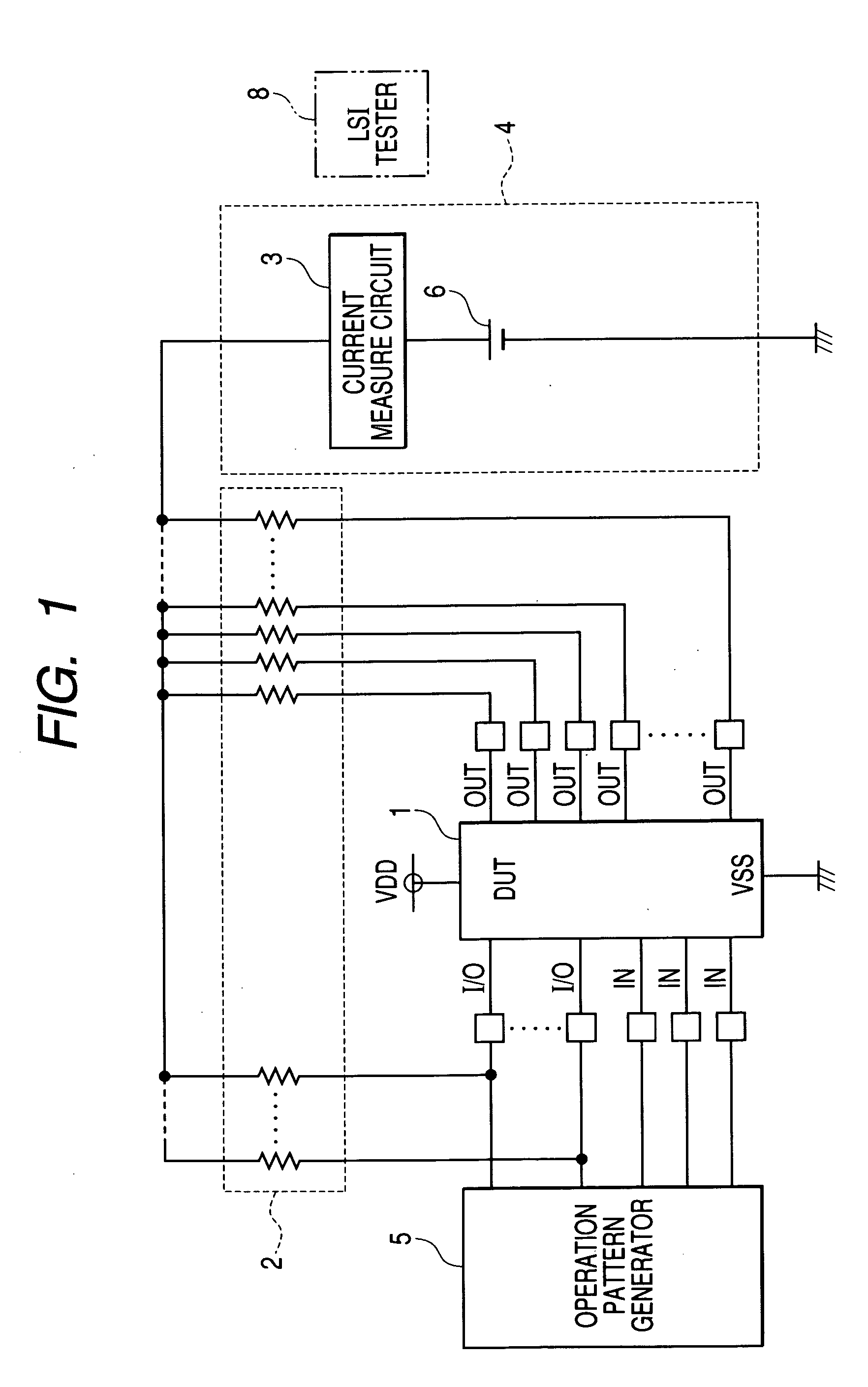

Semiconductor integrated circuit testing device and method

InactiveUS20050093561A1High speed machiningLow costDigital circuit testingMarginal circuit testingOperation modeLogic simulation

A plurality of resistors is connected to a plurality of output terminals of a semiconductor integrated circuit, respectively, and a predetermined voltage is applied to the plurality of resistors. Also, a predetermined operation pattern signal used to test functions of the semiconductor integrated circuit is input to a plurality of input terminals of the semiconductor integrated circuit. Thus, a total sum of amounts of currents caused to flow through the plurality of resistors, respectively, is measured. The total sum of amounts of currents thus measured is compared with a normal value of a total sum of amounts of currents which are measured in a non-defective sample which is used instead of the semiconductor integrated circuit and is verified in advance to normally operate. It is judged based on the comparison results whether or not the semiconductor integrated circuit is normal. As a result, whether or not the semiconductor integrated circuit is a non-defective or a defective can be simply judged without performing logic simulation and failure simulation.

Owner:CANON KK

Method and apparatus for supporting verification, and computer product

InactiveUS7464015B2Computation using non-denominational number representationCAD circuit designUndefined valueTheoretical computer science

In a verification supporting apparatus, when an obtaining unit obtains a verification scenario, a substituting unit substitutes an undefined value for a variable value in the verification scenario. A first executing unit executes a logic simulation using an input pattern. From a result of the logic simulation, a determining unit generates code-coverage upper-limit information. A setting unit sets input patterns by giving an arbitrary logic value to the variable value. A second executing unit executes a logic simulation using the input patterns set. A generating unit generates code coverage from the input patterns set. A calculating unit calculates a level of achievement of the code coverage with respect to the code-coverage upper-limit information.

Owner:FUJITSU LTD

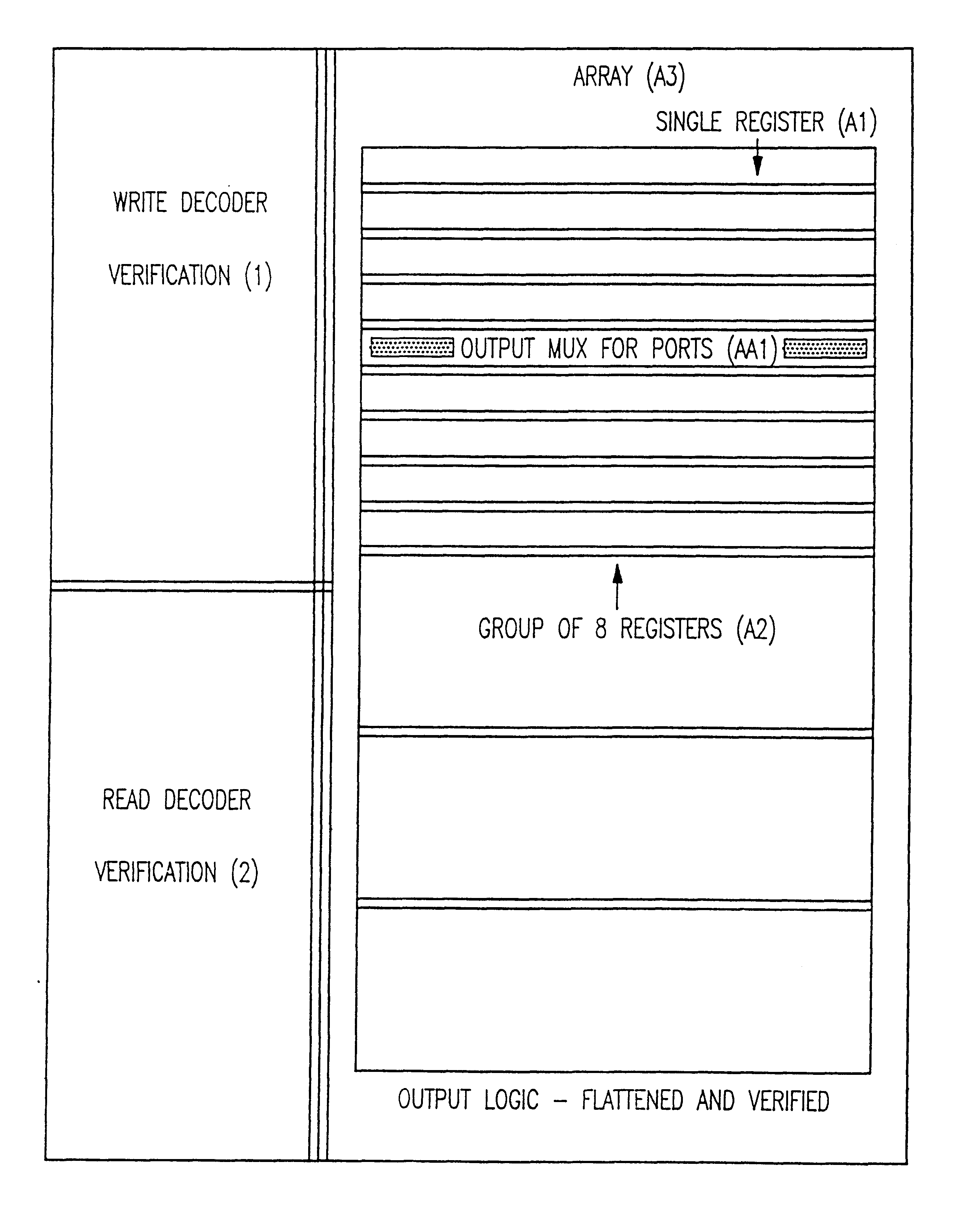

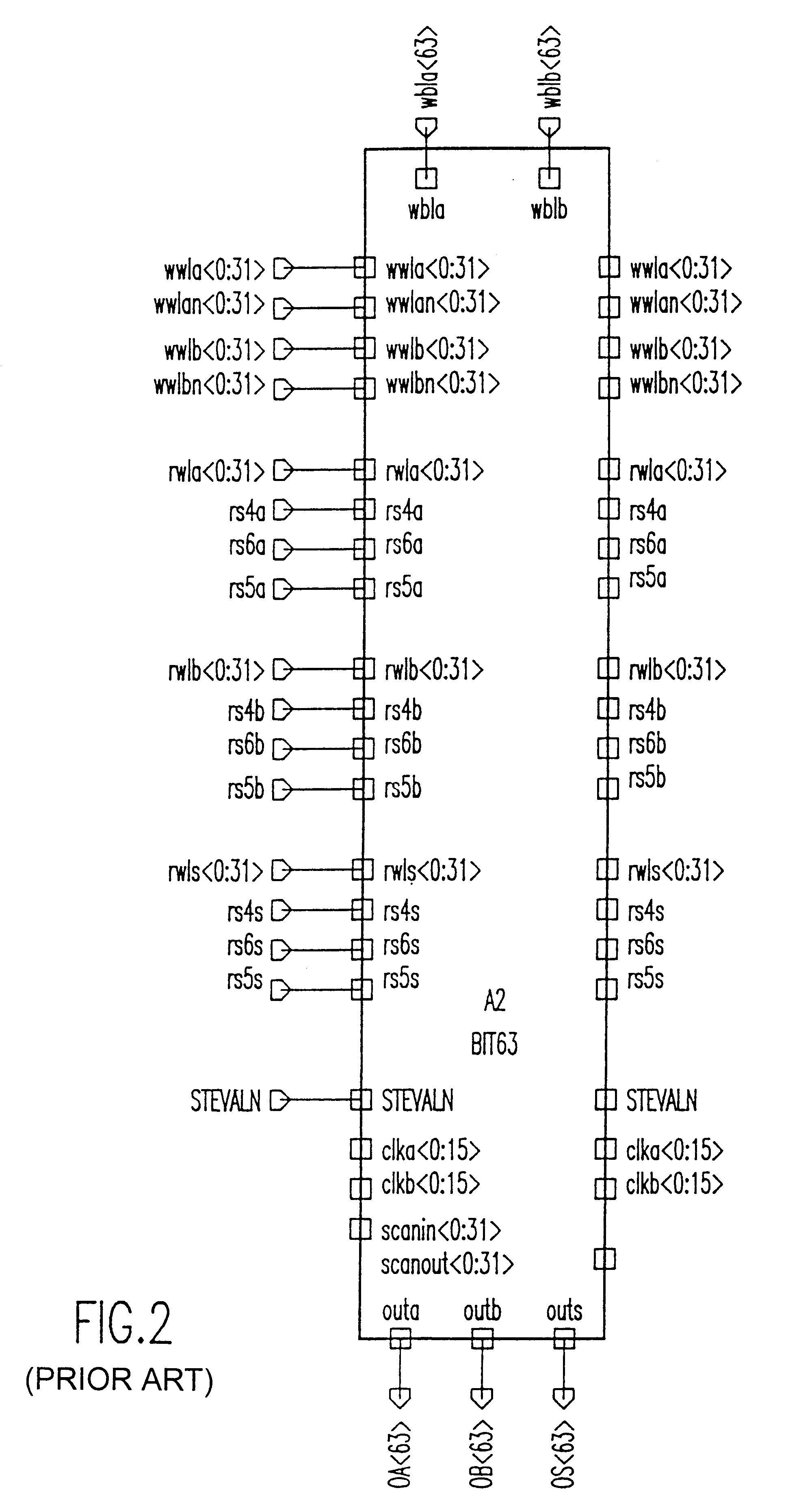

Provably correct storage arrays

A hardware design technique allows checking of design system language (DSL) specification of an element and schematics of large macros with embedded arrays and registers. The hardware organization reduces CPU time for logical verification by exponential order of magnitude without blowing up a verification process or logic simulation. The hardware organization consists of horizontal word level rather than bit level. A memory array cell comprises a pair of cross-coupled inverters forming a first latch for storing data. The first latch has an output connected to a read bit line. True and complement write word and bit line input to the first latch. A first set of pass gates connects between the true and complement write word and bit line inputs via gates and the input of said first latch. The first set of pass gates is responsive to a first clock via a second pass gate. A pair of cross-coupled inverters forms a second latch of a Level Sensitive Scan Design (LSSD). The second latch has output connected to an LSSD output for design verification. A second pass gate connects between the output of the first set of pass gates and the input of said first latch. The second pass gate is responsive to said first clock. A third pass gate connects between the output of said first latch and the input of said second latch. The third pass gate is responsive to a second clock. The first and second clocks are responsive to a black boxing process for incremental verification.

Owner:IBM CORP

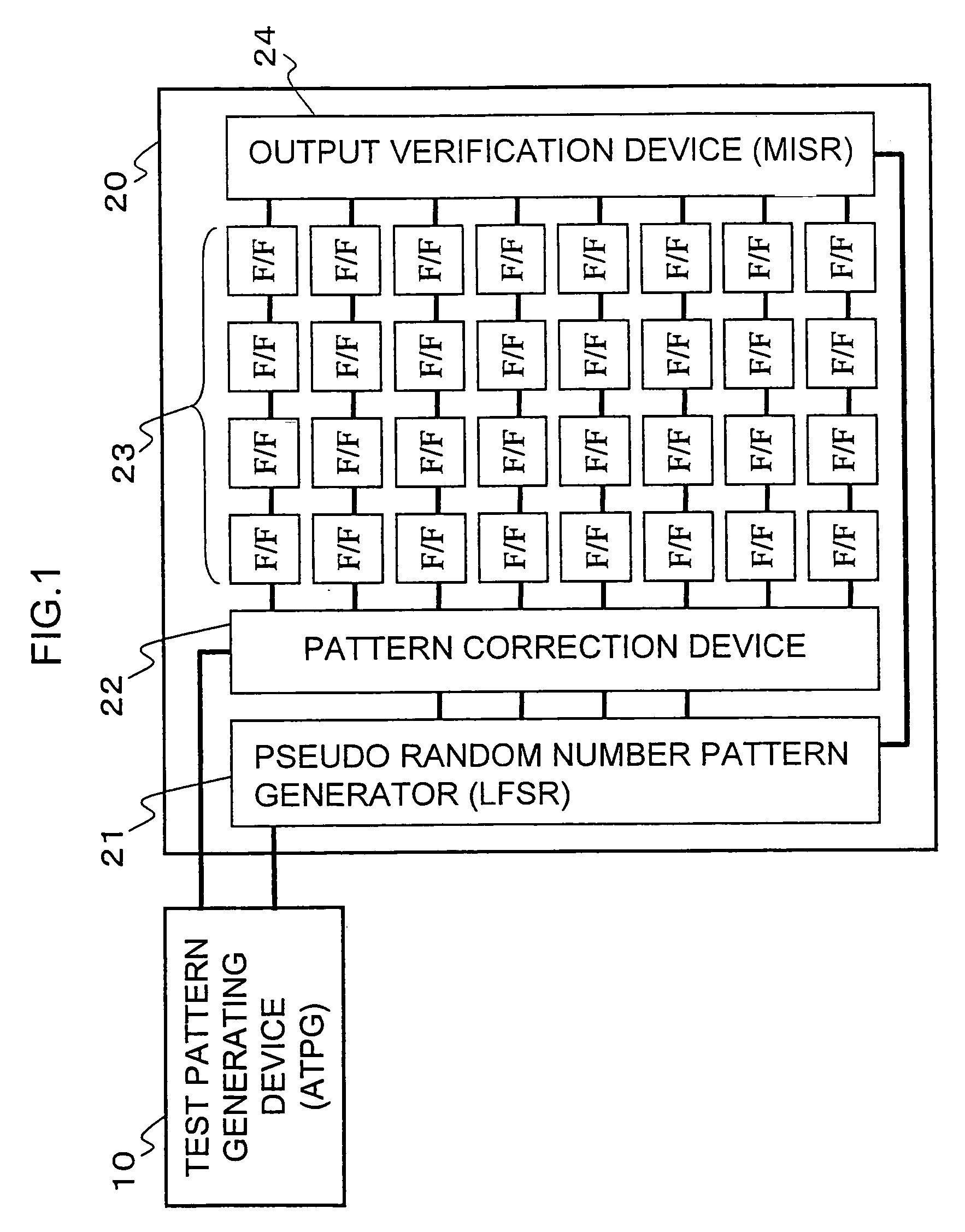

Device and method for testing integrated circuit

InactiveUS20050149804A1Electronic circuit testingError detection/correctionPath sensitizationPattern generation

The present invention provides an integrated circuit test device and method which creates a pattern for minimizing a difference from a pattern generated by a pattern generation device. In the invention, a list of all failures assumed to be in the circuit is created, and, for example, a random number pattern is inputted so that a signal value in the circuit is defined by a logic simulation using the inputted pattern, as a result of which the controllability, observability and testability are calculated. A target failure minimizing the testability is selected from the list, for which target failure path-sensitization is performed using the controllability and observability of the input pattern, which pattern is corrected so as to minimize the number of inversions of signal values of the input pattern. A failure simulation for the target failure is also performed using the corrected pattern, and when a failure to be detected further exists, the failure is removed from the failure list.

Owner:FUJITSU LTD

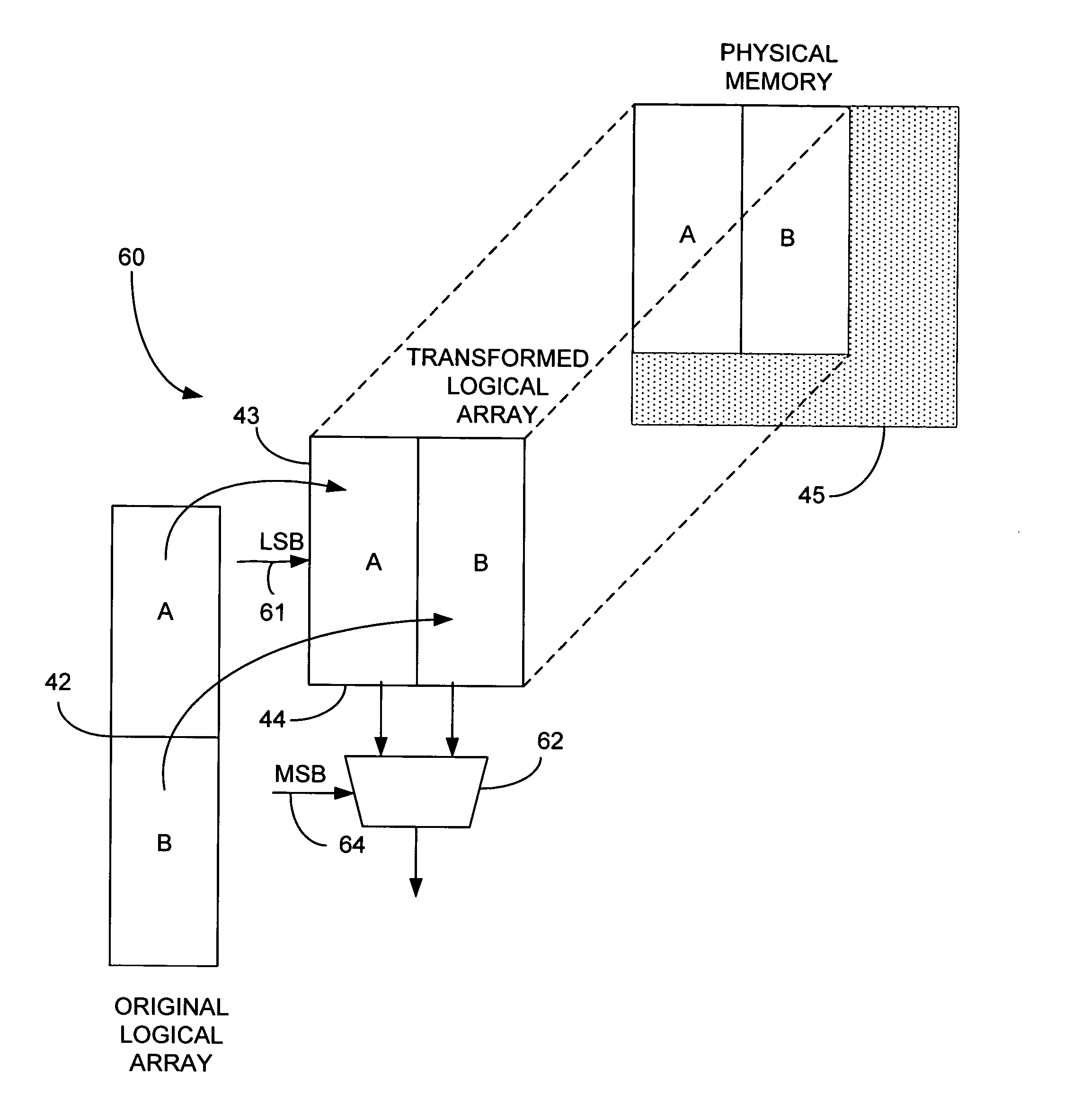

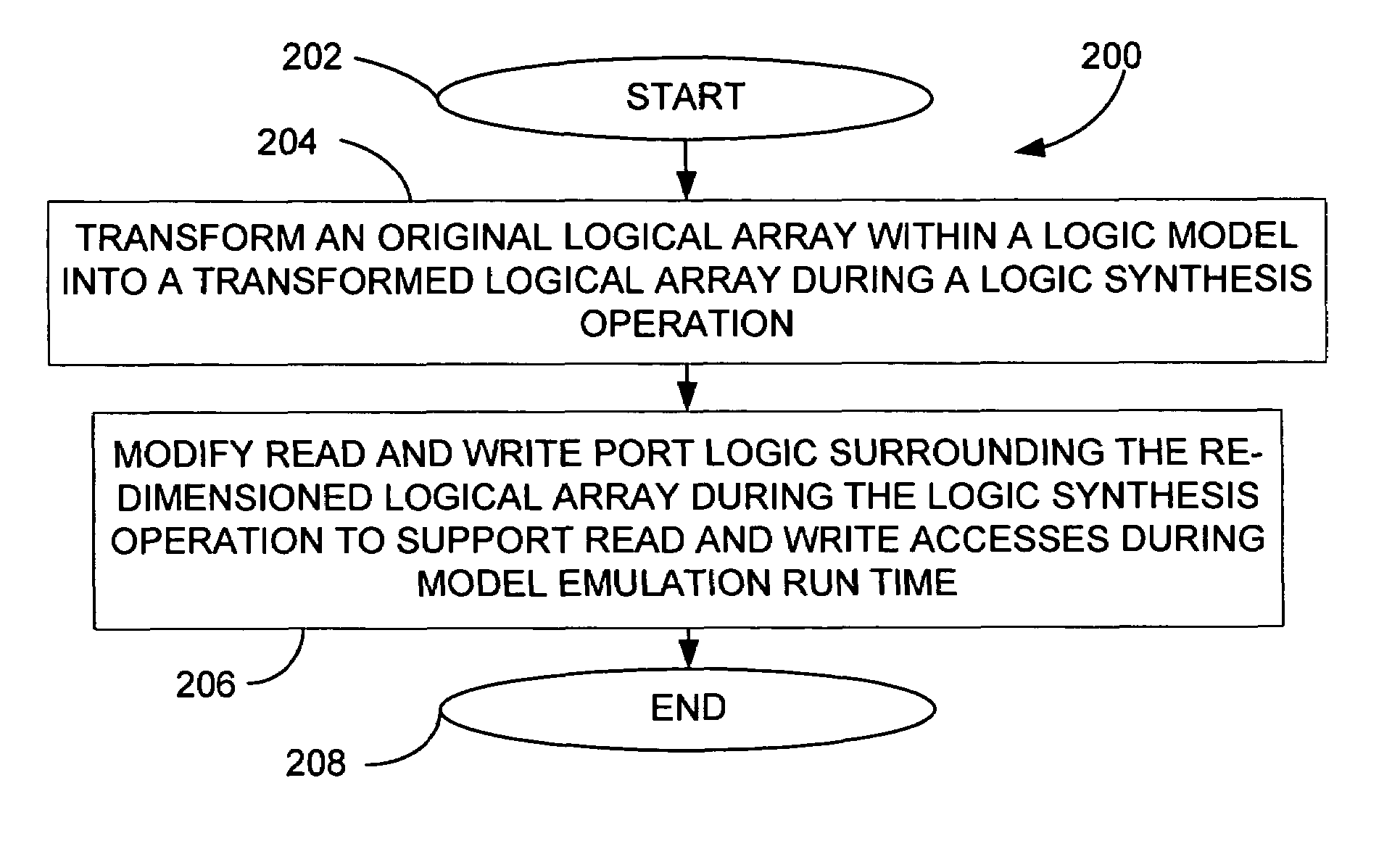

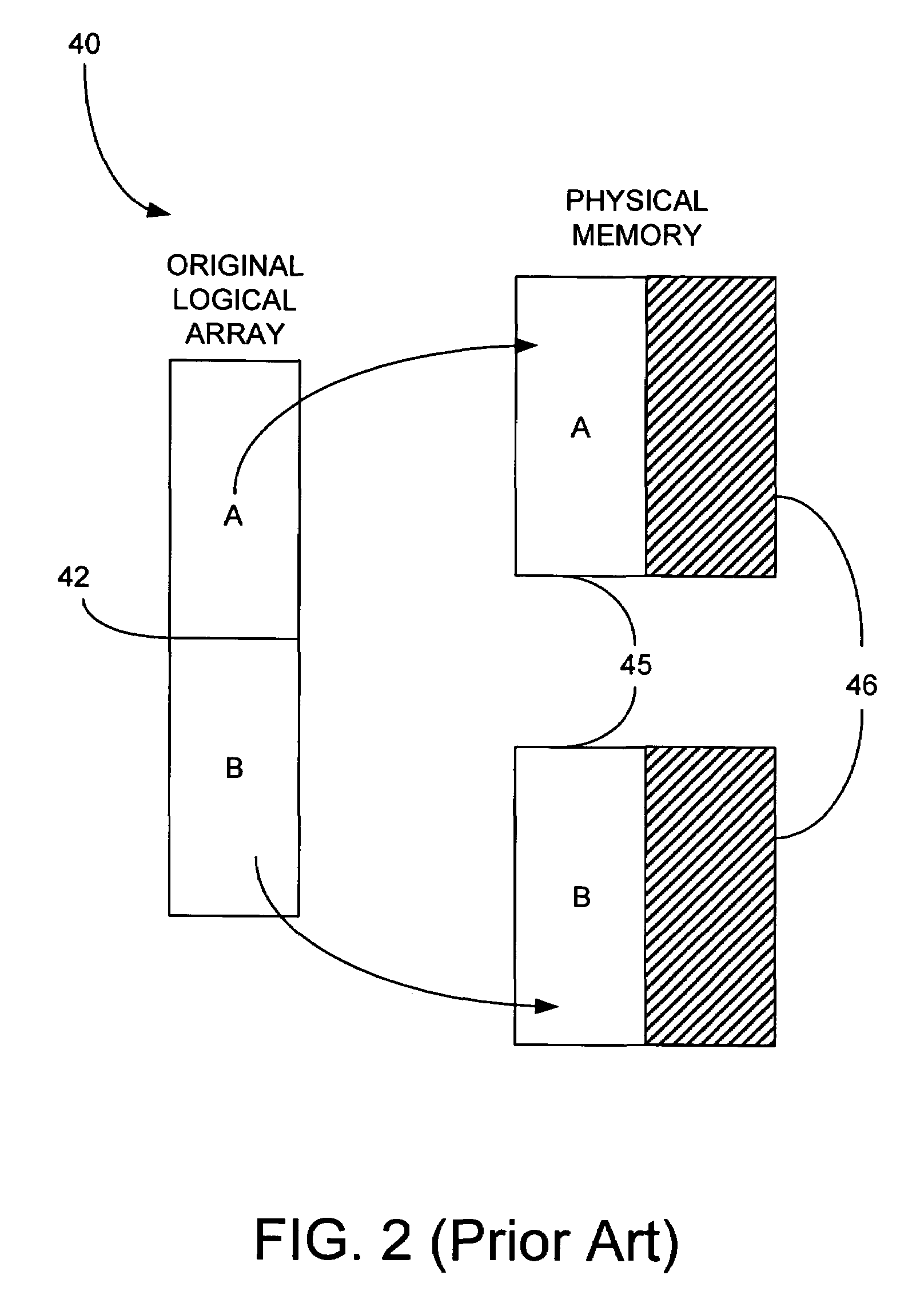

Method and apparatus to increase the usable memory capacity of a logic simulation hardware emulator/accelerator

InactiveUS20050256696A1Efficient use ofIncrease memory capacityComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceRunning time

A method, apparatus and program product are provided for increasing the usable memory capacity of a logic simulation hardware emulator. The present invention performs an additional logic synthesis operation during model build to transform an original logical array within a logic model into a transformed logical array, such that a row within the transformed logical array includes a plurality of merged logical array rows from the original logical array. The invention further modifies read and write port logic surrounding the transformed logical array during the logic synthesis operation to support read and write accesses during model emulation run time.

Owner:IBM CORP

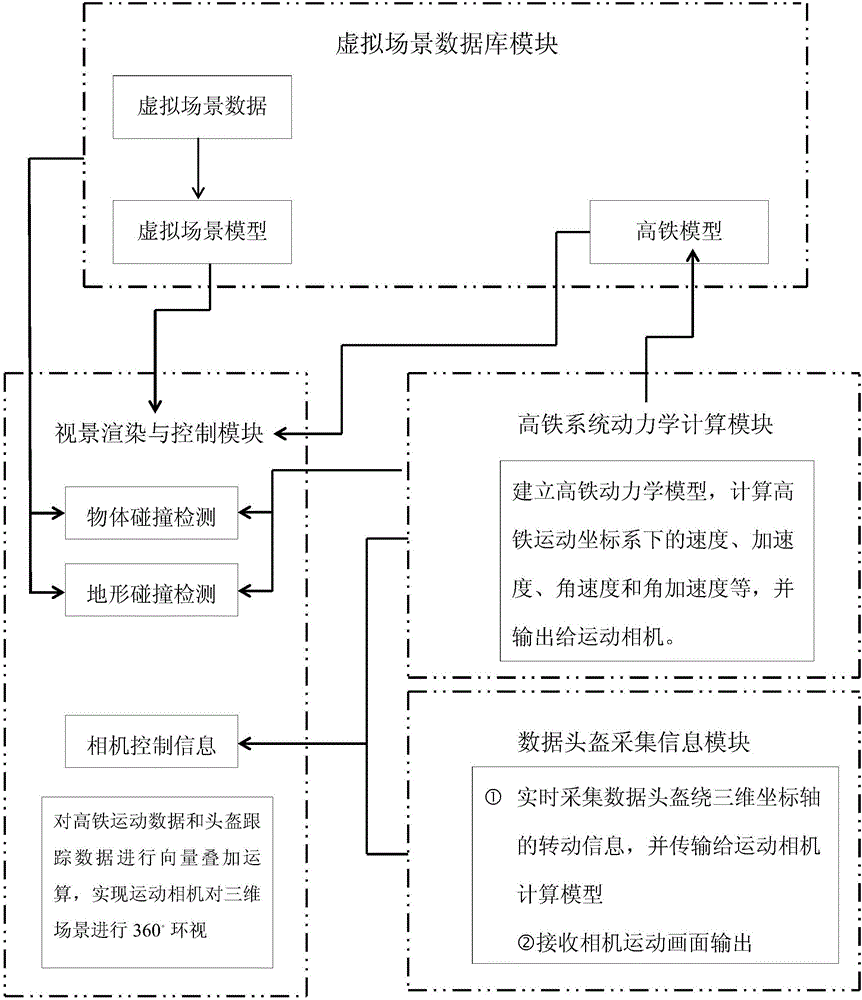

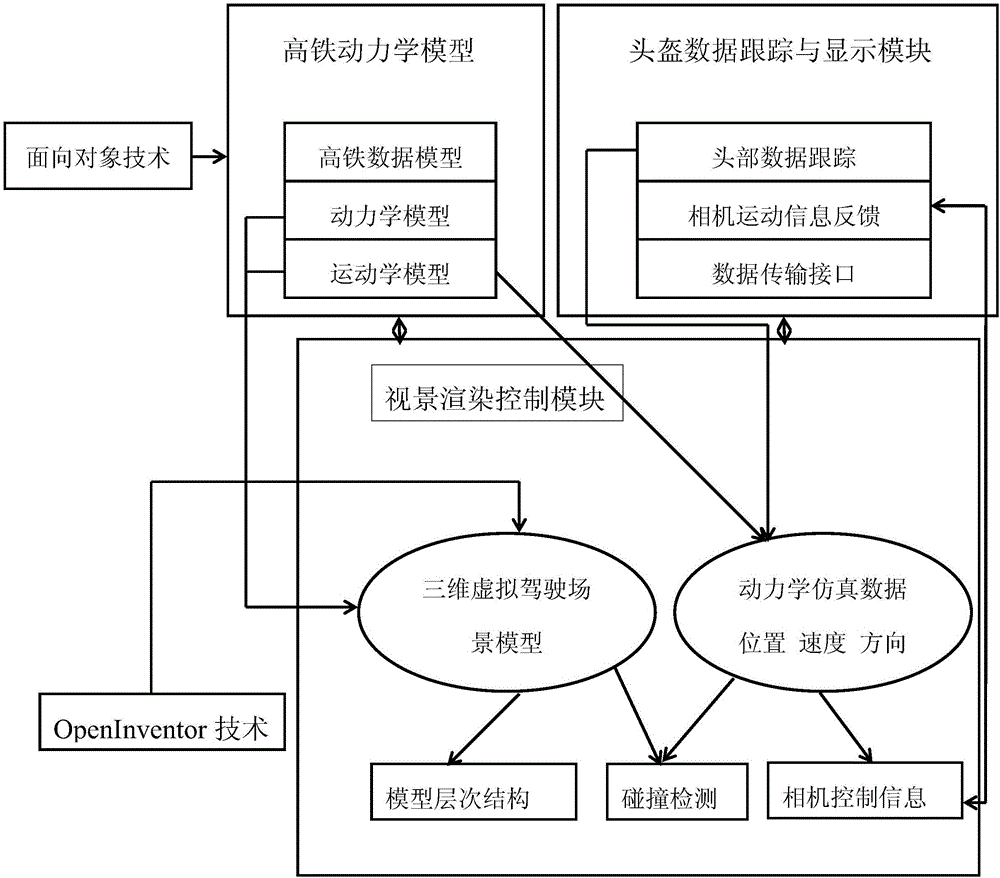

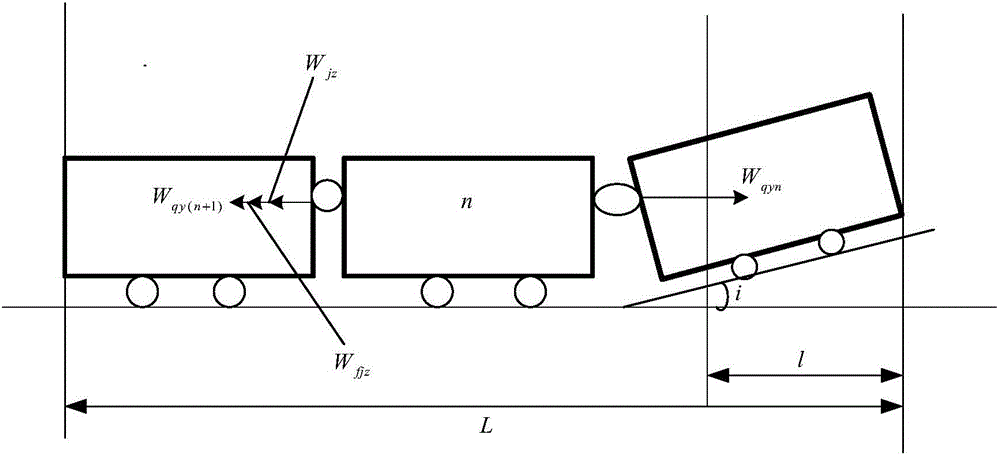

Intelligent immersive high-speed train virtual driving behavior evaluation method and simulation system

InactiveCN106373453ACosmonautic condition simulationsDesign optimisation/simulationDynamic learningDisplay device

The invention provides an intelligent immersive high-speed train virtual driving behavior evaluation method and a simulation system. According to the method, a virtual driving scene module is established, and various driving training scenes composed of multiple intelligent agents are constructed; a high-speed train dynamics module is established, including various subsystems of the high-speed train such as engine, power train system, steering mechanism and body modules; a virtual driving scene simulation module is established; a high-speed train logic simulation module is established; a data helmet display and man-machine interaction module is established, the head tracking technology of a helmet type display is researched on the basis of the virtual reality technology, and motion of the high-speed train in a virtual environment is controlled and manipulated through a high-speed operation mechanism; finally, intelligent driving behavior researching and evaluation are realized on the basis of a time varying dynamic bayesian networks (TVDBN) dynamic learning learning model according to the virtual driving operation data accumulated in a user and simulation system interaction process.

Owner:ZHENGZHOU J&T HI TECH

Device and method for testing integrated circuit

InactiveUS7266746B2Electronic circuit testingError detection/correctionPath sensitizationPattern generation

The present invention provides an integrated circuit test device and method which creates a pattern for minimizing a difference from a pattern generated by a pattern generation device. In the invention, a list of all failures assumed to be in the circuit is created, and, for example, a random number pattern is inputted so that a signal value in the circuit is defined by a logic simulation using the inputted pattern, as a result of which the controllability, observability and testability are calculated. A target failure minimizing the testability is selected from the list, for which target failure path-sensitization is performed using the controllability and observability of the input pattern, which pattern is corrected so as to minimize the number of inversions of signal values of the input pattern. A failure simulation for the target failure is also performed using the corrected pattern, and when a failure to be detected further exists, the failure is removed from the failure list.

Owner:FUJITSU LTD

Automatic testing technique applied before anti-fuse FPGA (field programmable gate array) programming

The invention relates to an automatic testing technique applied before anti-fuse FPGA (field programmable gate array) programming. The technique can automatically test any anti-fuse FPGA before programming. The technique includes: building a testing vector library, utilizing a software way to automatically extract testing vectors from the testing vector library by a testing vector sending module, and respectively inputting the testing vectors into a circuit logic simulation excitation applying module and a circuit response verifying module at the same time for anti-fuse FPGA circuit simulation; after circuit simulation analysis and verification, inputting a tested anti-fuse FPGA chip; collecting a result output by the FPGA chip by a testing response verifying module, and comparing the result with reference testing information input in advance to automatically generate a testing report so as to realize automatic testing of the anti-fuse FPGA before programming. The whole testing process can effectively avoid a lot of manual intervention; after testing is finished, a testing result of the chip can be known by checking the testing report. By the technique, automatic testing of the anti-fuse FPGA before programming can be completely quickly, and testing efficiency of the anti-fuse FPGA chip can be improved remarkably.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

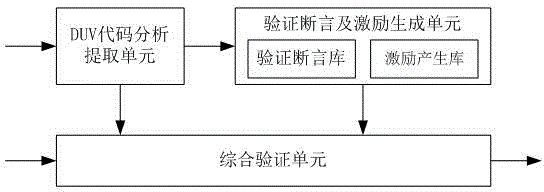

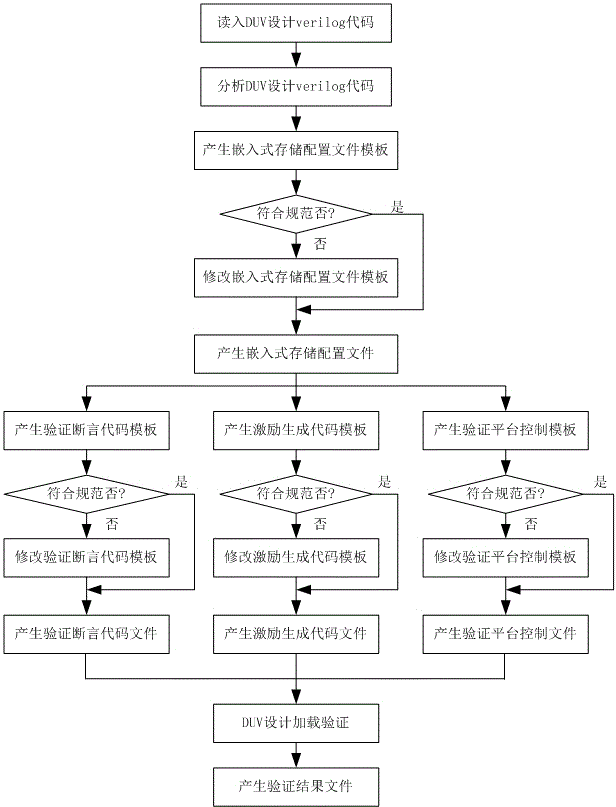

System and method for verifying embedded memory controller based on assertion

ActiveCN104408264AImplement autoload validationImprove functional coverageSpecial data processing applicationsComputer architectureControl store

The invention discloses a system and a method for verifying an embedded memory controller based on assertion, and relates to the field of logic verification of integrated circuits. The verification system mainly comprises a DUV code analysis and extraction unit (1), a verification assertion and excitation generation unit (2) and a comprehensive verification unit (3). A verification assertion code and an excitation generation code can be efficiently generated in combination with a verification assertion bank and an excitation generation bank of the memory controller by automatically analyzing and extracting a DUV design code, verification codes can be simultaneously applied to a simulation verification method and a formal verification method, and automatic loadable verification of the UDV design can be realized in the comprehensive verification unit, so the verification efficiency is improved. Compared with a conventional method adopting independent logic simulation verification, the method disclosed by the invention has many advantages in verification efficiency, coverage rate and the like.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

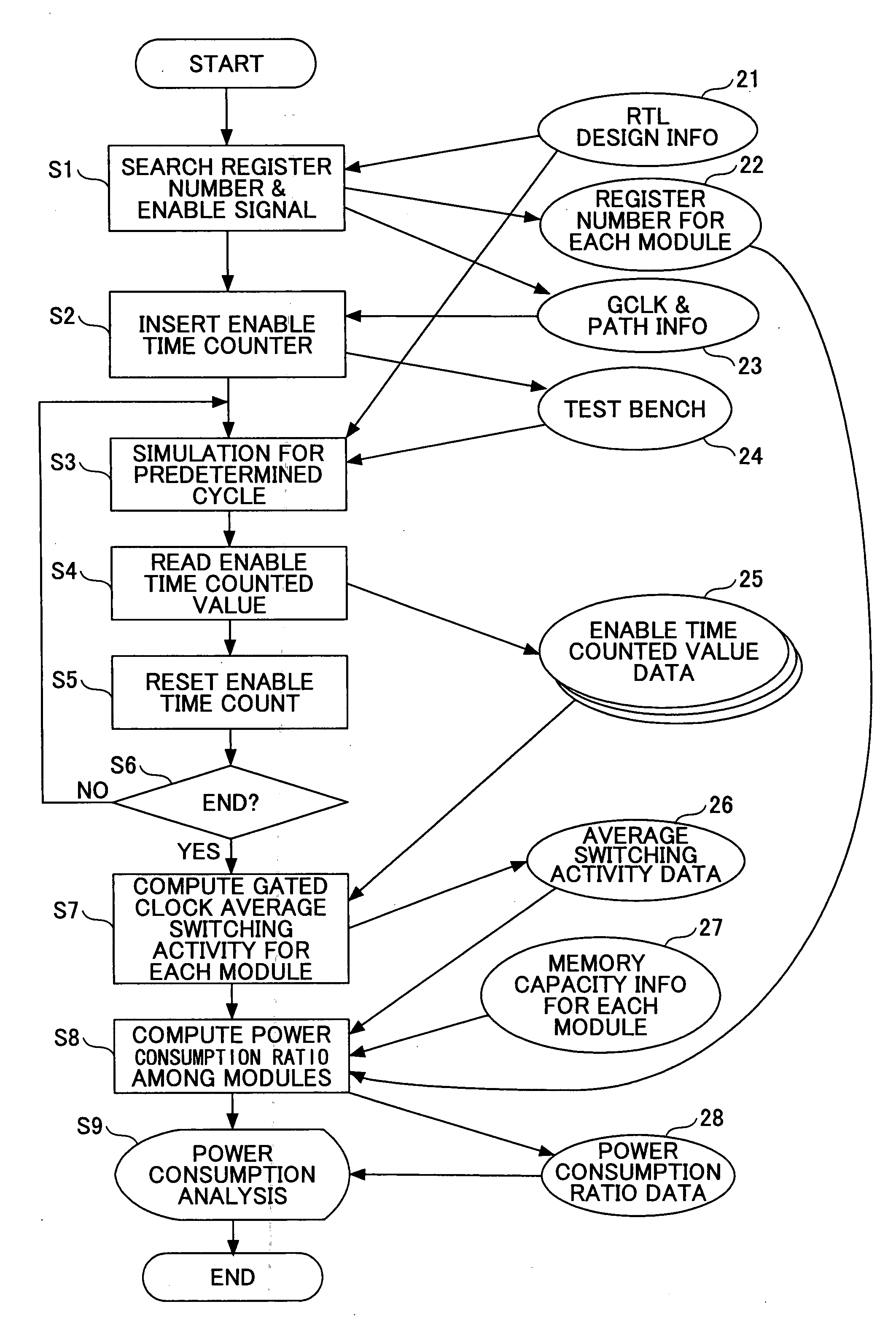

Power consumption analyzing method and computer- readable storage medium

InactiveUS20080127001A1Computer aided designSoftware simulation/interpretation/emulationProcessor registerEffective time

A power consumption analyzing method, to be implemented by a computer, is for a circuit developing procedure that makes a logic design of the circuit in an RTL design stage and inserts a gated clock with respect to the circuit in a subsequent logic synthesis stage. The method comprises an extraction step, implemented by the computer, extracting a signal which is judged that it will be transformed into a gated clock in the logic synthesis stage, and storing the signal in a memory part, a measuring step, implemented by the computer, measuring an valid time of the signal stored in the memory part by a logic simulation, and storing the valid time in the memory part, and a post-simulation step, implemented by the computer, computing a power consumption analysis result of the circuit from the valid time stored in the memory part, a number of registers for each of modules that are function units forming the circuit, and a memory capacity coefficient indicating an extent to which a memory capacity within the circuit affects the power consumption of the circuit, and outputting the power consumption analysis result.

Owner:FUJITSU LTD

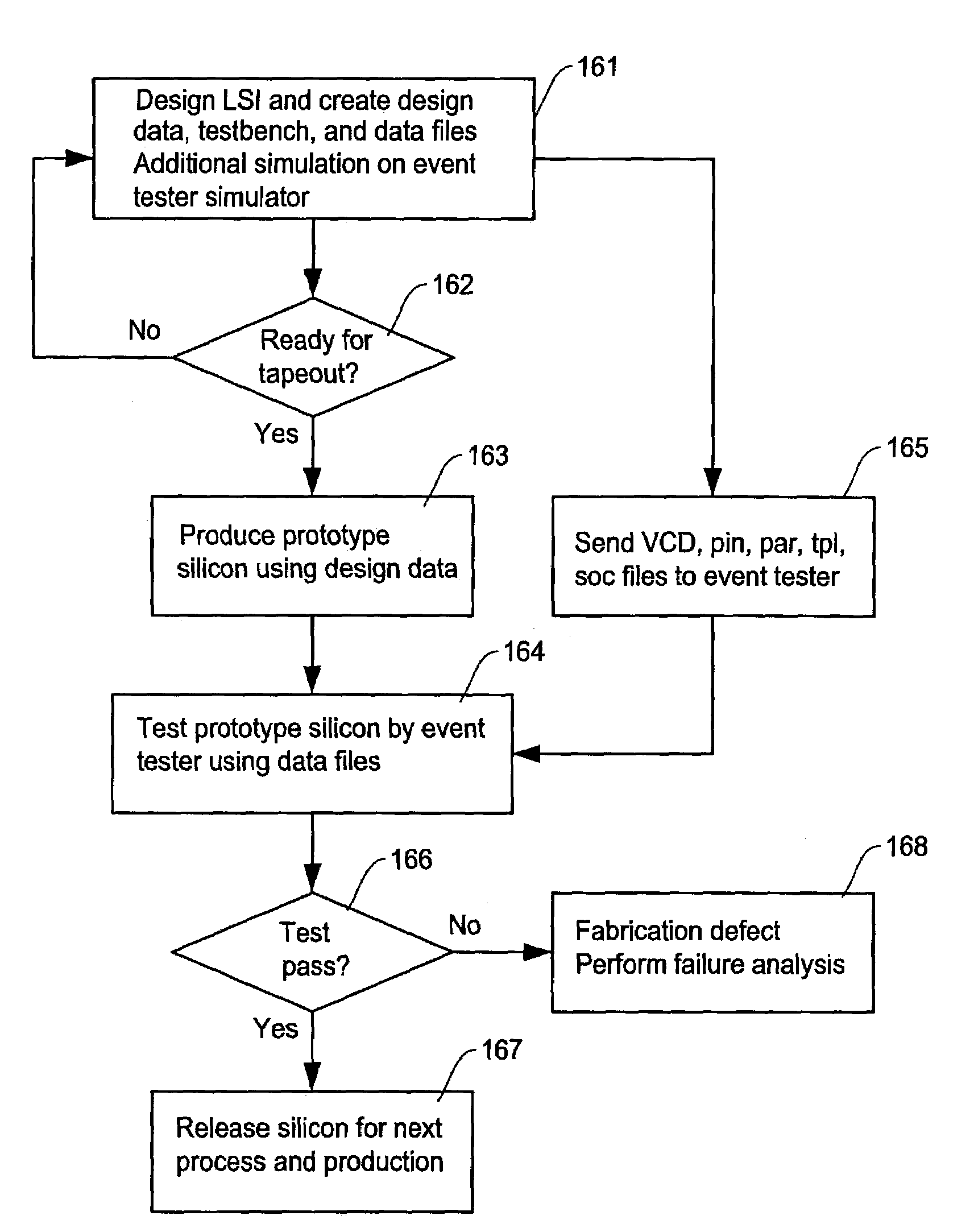

Manufacturing method and apparatus to avoid prototype-hold in ASIC/SOC manufacturing

InactiveUS7178115B2Eliminate needLow costDigital circuit testingSolid-state devicesData fileEngineering

A manufacturing process for LSIs uses an event tester simulator and an event tester to avoid prototype hold. In the LSI manufacturing method an LSI is designed under an EDA (electronic design automation) environment to produce design data of a designed LSI, and logic simulation is performed on a device model of the LSI design in the EDA environment with use of a testbench and producing a test vector file of an event format as a result of the logic simulation. Then, simulation data files are verified with use of the design data and the testbench by operating an event tester simulator, and a prototype LSI is produced through a fabrication provider by using the design data. The prototype LSI is tested by an event tester by using the test vector file and the simulation data files and test results is feedbacked to the EDA environment or the fabrication provider.

Owner:ADVANTEST CORP

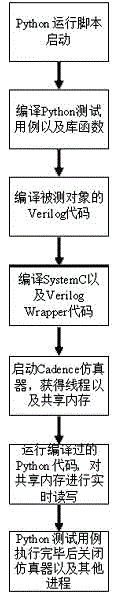

Python language based Rapidio switcher logic simulation verification platform and method

ActiveCN104965750AImprove writing efficiencyImprove reusabilitySoftware simulation/interpretation/emulationSystemCPython language

The present invention discloses a Python language based Rapidio switcher logic simulation verification platform and method. The verification platform comprises: a SystemC interface function for interpreting Python semantics, a DPI interface function used by SystemC to call SystemVerilog, and a test case and a running script realized by Python. According to the present invention, an interpreter between the Python language and the SystemC language is added, so that the Python language can directly control stimulus input of a logic simulator and compare responsive output and the test case programmed by using Python can be used directly in logic simulation and applied on a Rapidio switcher. By using the above environment, the programming efficiency and reusability of the test case can be greatly improved.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

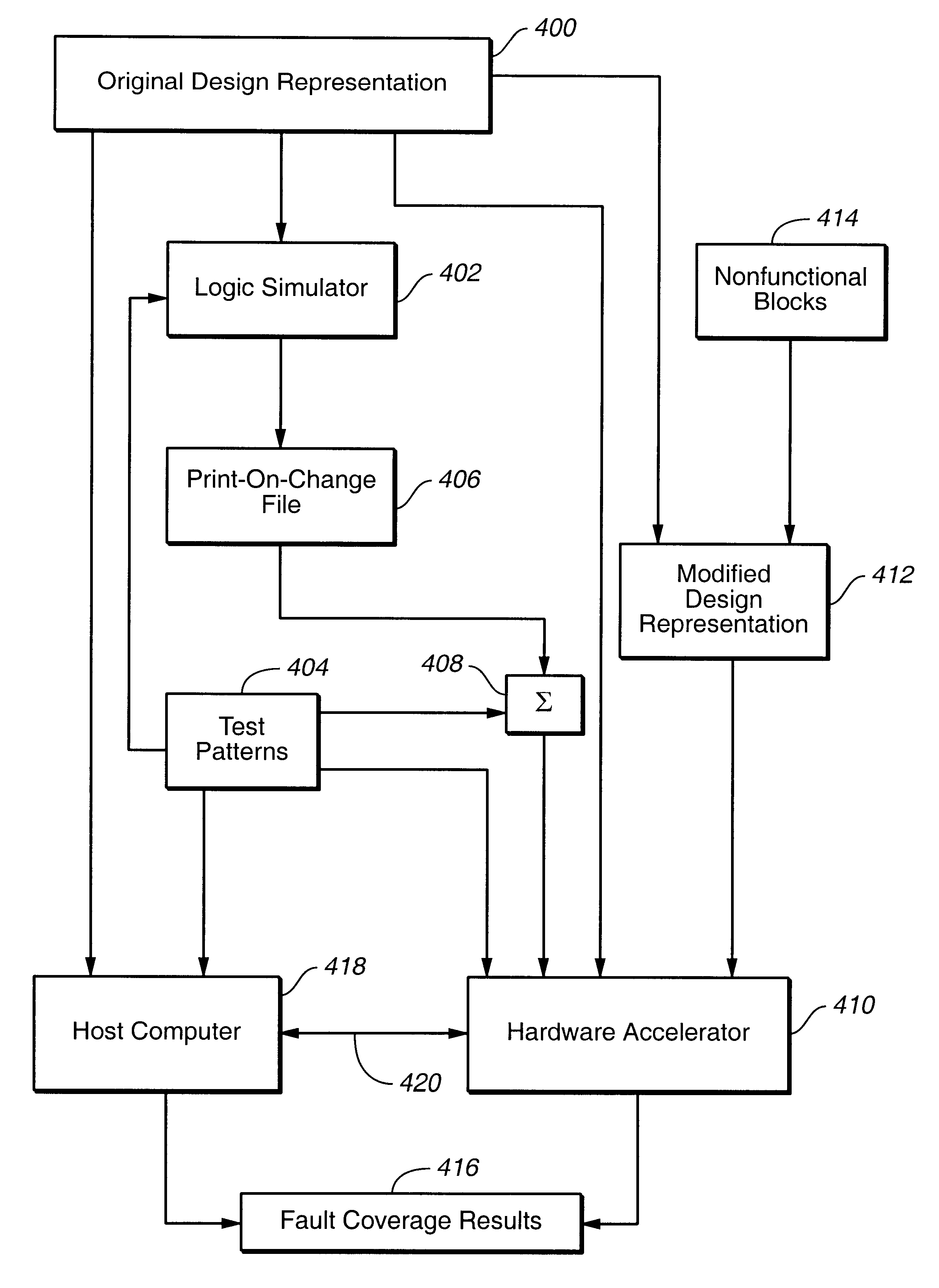

Modified design representation for fast fault simulation of an integrated circuit

InactiveUS6370492B1Improve simulation speedAnalogue computers for electric apparatusFunctional testingFault coverageEngineering

A system and method perform a two-pass fault simulation on an original design representation including a software-modeled design element and a hardware-modeled design element. Logic simulation generates input stimulus for a port on the boundary of the software-modeled design element and the hardware-modeled design element, where such ports are output ports of the software-modeled design element and input ports of the hardware-modeled design element. The input stimulus is merged with test patterns for the original design representation. A modified design representation is generated by replacing the software-modeled design element with a nonfunctional block. Most or all possible faults in the hardware-modeled design representation are seeded. The modified design representation is fault simulated in a first pass using the merged input stimulus and test patterns. Any unseeded faults from the first pass and other possible faults in the software-modeled design representation are then seeded and the original design representation is fault simulated in a second pass. The fault coverage results of the two passes are aggregated to generate an overall fault coverage for the original design representation.

Owner:BELL SEMICON LLC

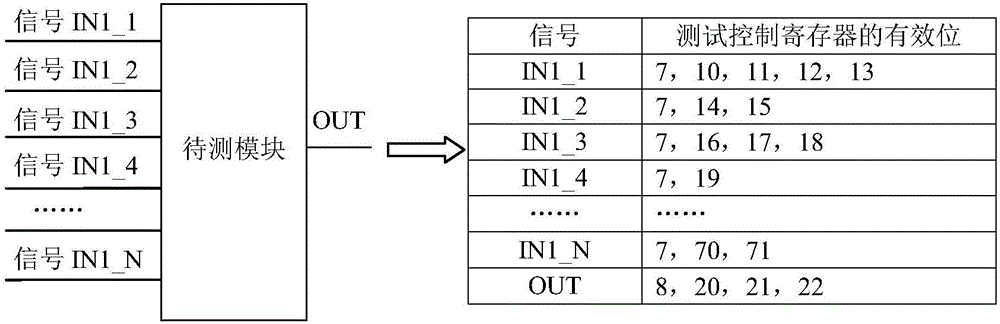

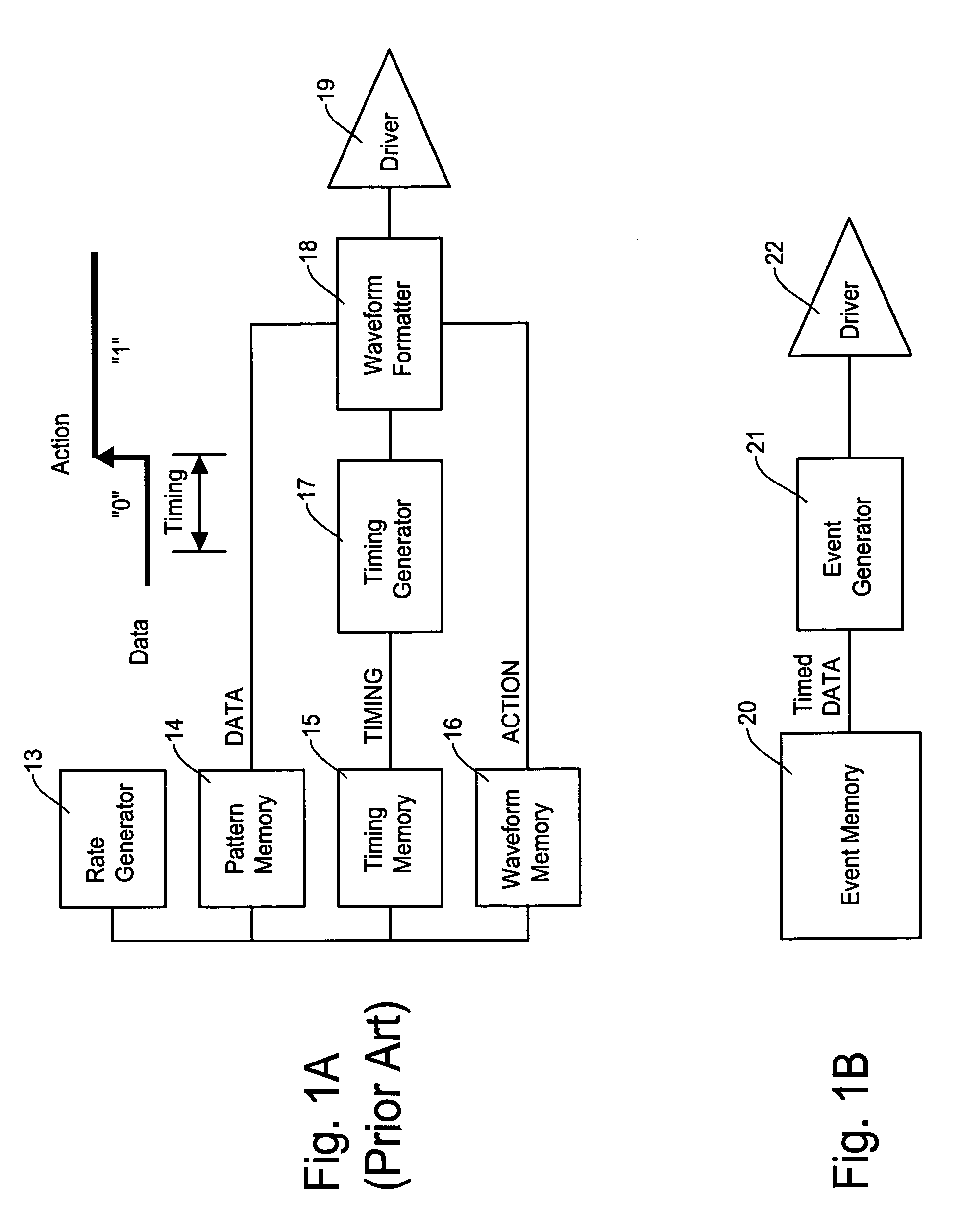

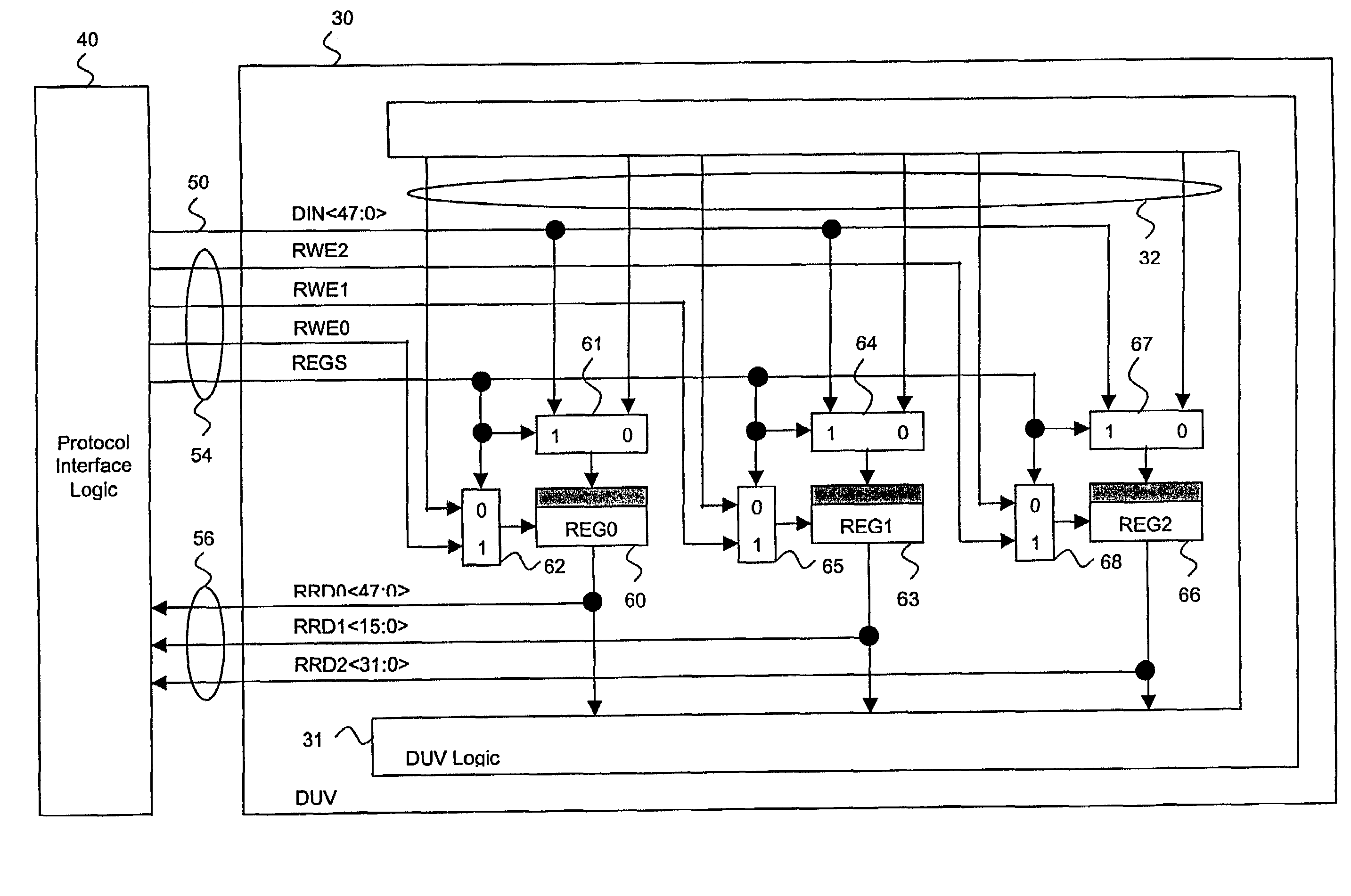

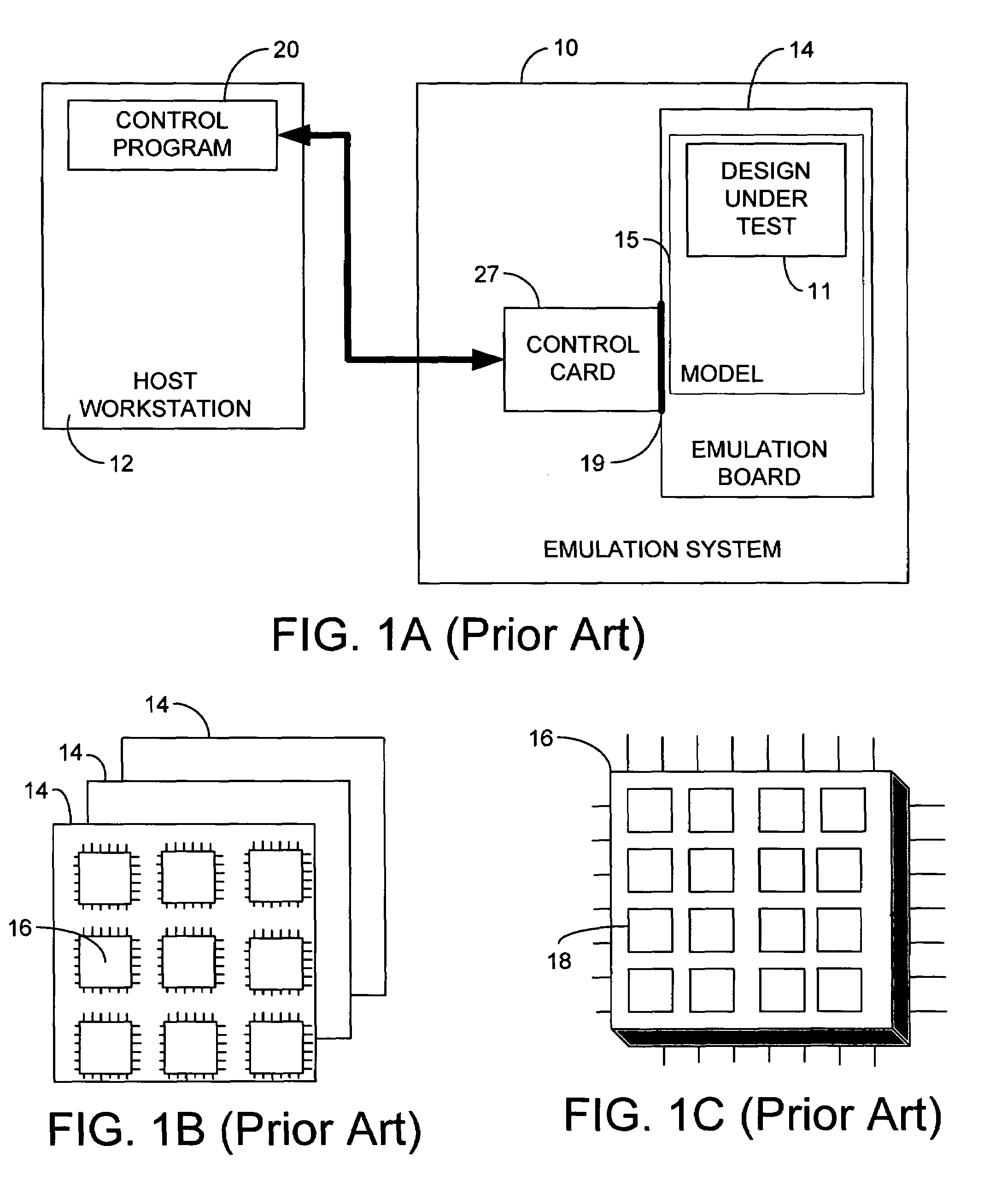

Hardware-assisted design verification system using a packet-based protocol logic synthesized for efficient data loading and unloading

A system is provided to increase the accessibility of registers and memories in a user's design undergoing functional verification in a hardware-assisted design verification system. A packet-based protocol is used to perform data transfer operations between a host workstation and a hardware accelerator for loading data to and unloading data from the registers and memories in a target design under verification (DUV) during logic simulation. The method and apparatus synthesizes interface logic into the DUV to provide for greater access to the registers and memories in the target DUV which is simulated with the assistance of the hardware accelerator.

Owner:CADENCE DESIGN SYST INC

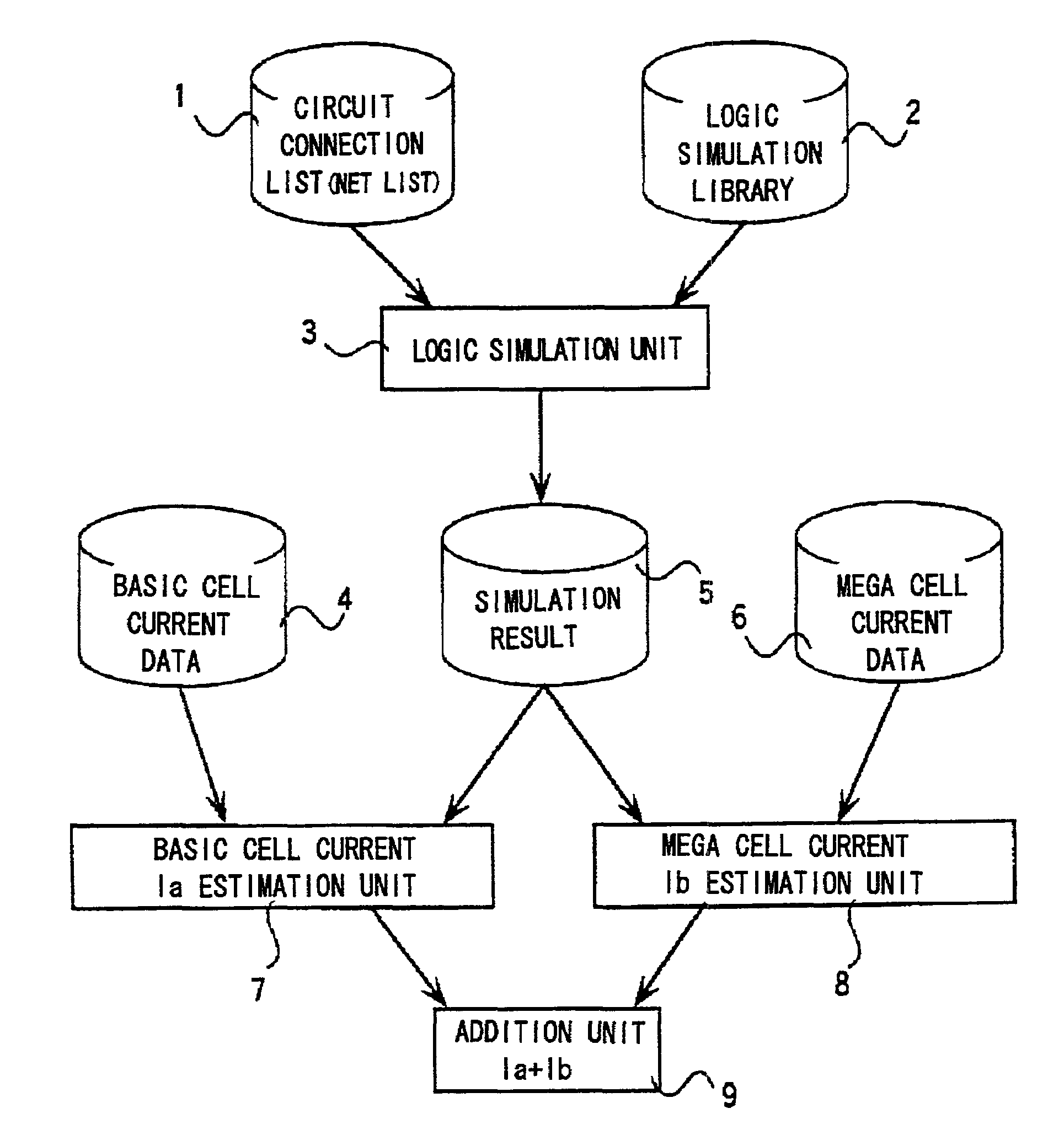

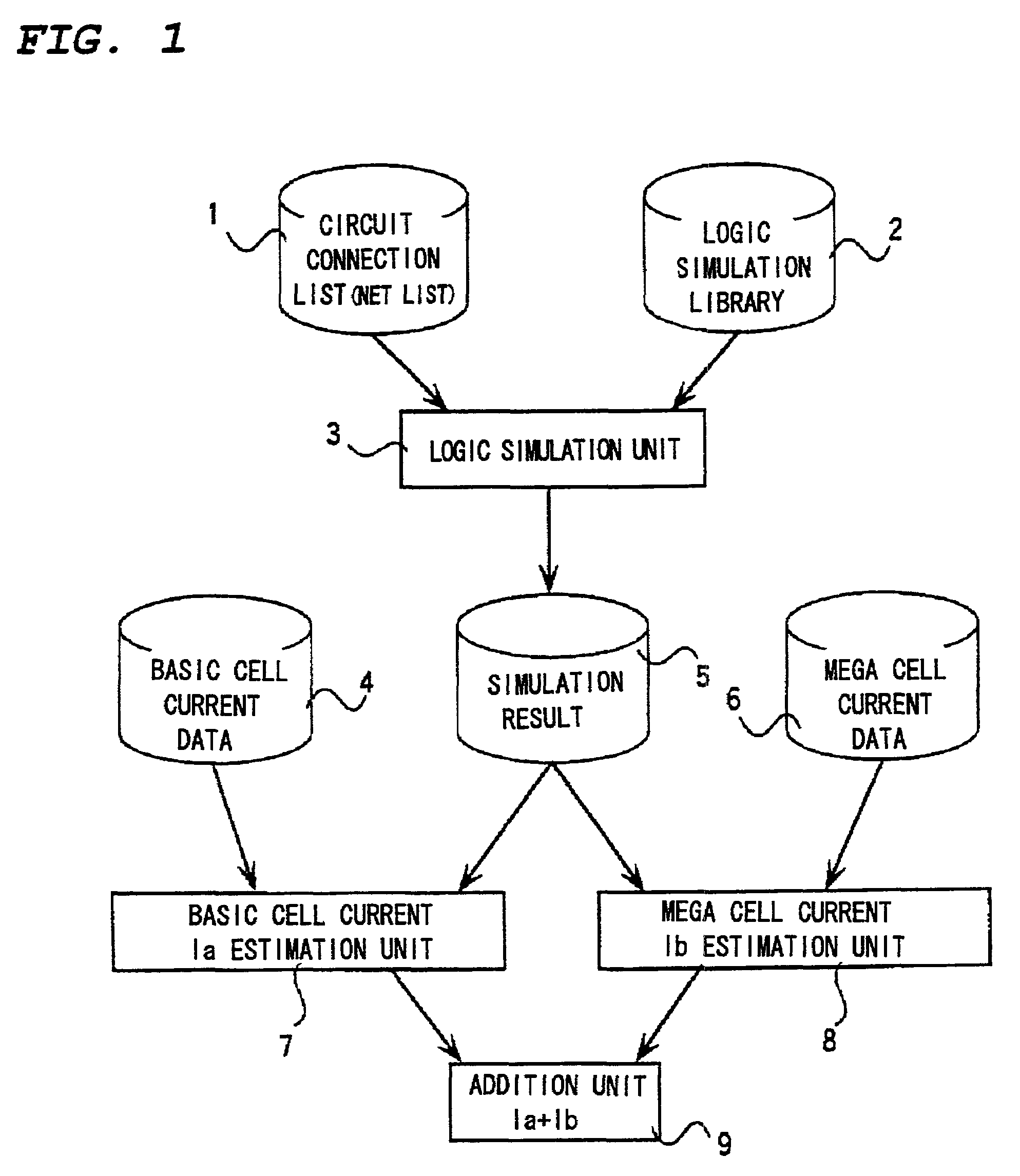

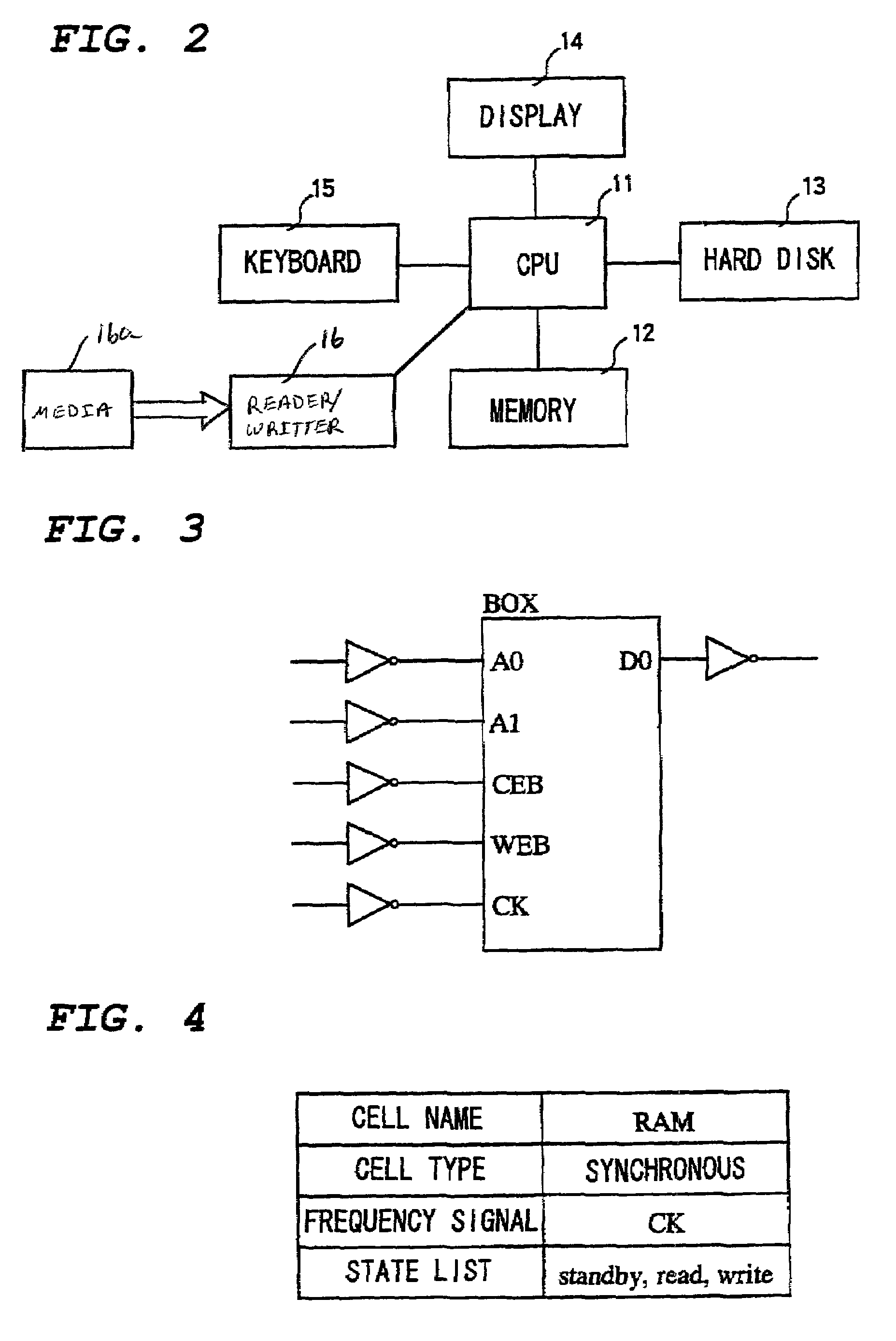

Recording media including code for estimating IC power consumption

InactiveUS7343276B1Electronic circuit testingLogical operation testingParallel computingAlternating current

A computer readable medium includes computer executable code stored thereon, the code for estimating power consumption of an integrated circuit, comprising code for simulating logic of basic and mega cells of the integrated circuit, code for estimating a current consumed by the mega cells by obtaining logic states for each mega cell, determining an average operation frequency for each logic state, and determining an alternating current component and a direct current component for each logic state to calculate said current consumed by the mega cells for estimating a first value of electric power consumed by said mega cells based on said logic simulations and pre-established power consumption data, code for estimating a current consumed by the basic cells for estimating a second value of electric power consumed by said basic cells based on said logic simulations and pre-established power consumption data and code for combining said first and second values to obtain the power consumption of the integrated circuit.

Owner:RICOH KK

Power-aware debugging

ActiveUS8176453B2CAD circuit designSoftware simulation/interpretation/emulationComputer architectureDisplay device

Owner:SYNOPSYS INC

Method and apparatus to increase the usable memory capacity of a logic simulation hardware emulator/accelerator

InactiveUS7480611B2Efficient use ofIncrease memory capacityComputer aided designSoftware simulation/interpretation/emulationComputer hardwareRunning time

A method, apparatus and program product are provided for increasing the usable memory capacity of a logic simulation hardware emulator. The present invention performs an additional logic synthesis operation during model build to transform an original logical array within a logic model into a transformed logical array, such that a row within the transformed logical array includes a plurality of merged logical array rows from the original logical array. The invention further modifies read and write port logic surrounding the transformed logical array during the logic synthesis operation to support read and write accesses during model emulation run time.

Owner:IBM CORP

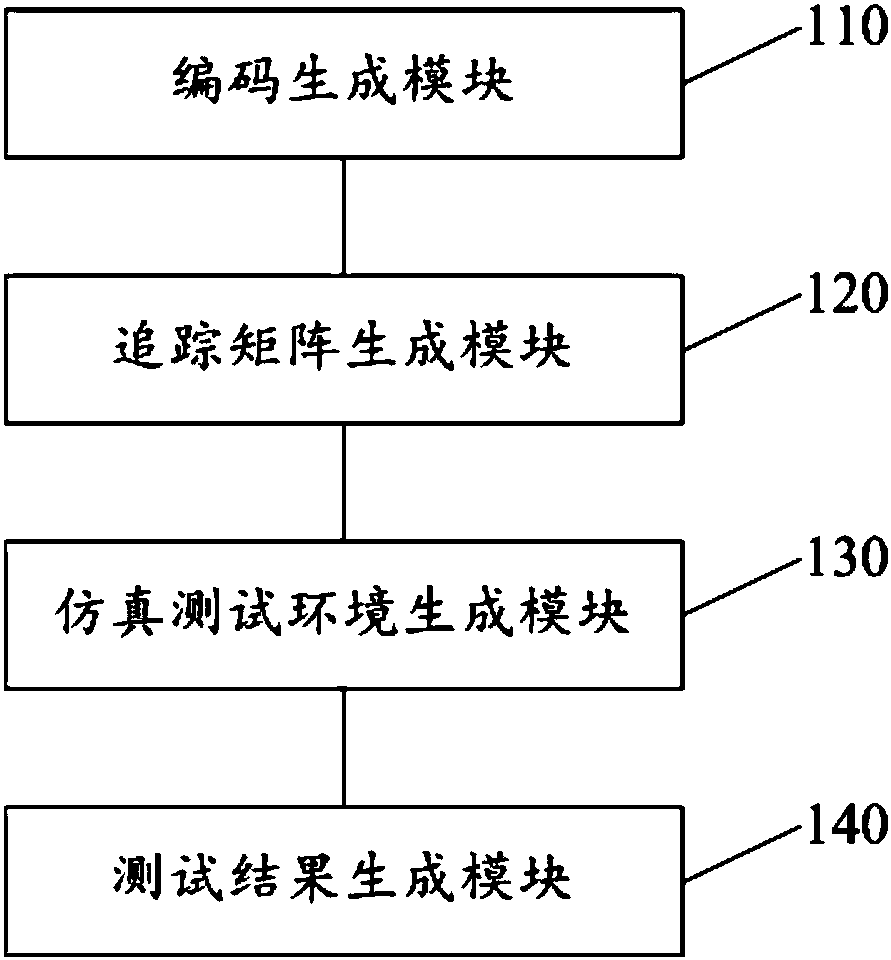

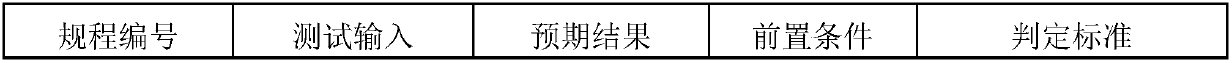

Statistical method and device of programmable-logic simulation test function coverage

ActiveCN107797929AImprove test activity completenessImprove completenessSoftware testing/debuggingComputer architectureDependability

The invention belongs to the technical field of safety level instrument control system simulation tests, aims to solve the technical problem that simulation test function coverage in the prior art cannot be accurately obtained, and provides a statistical method and device which can effectively increase programmable-logic simulation test function coverage. The statistical method includes: S1, carrying out formalized description on demand items in an HPD (HDL (hardware description language)-programmed device) demand specification book, and establishing a unique number for each demand item according to a predetermined coding rule; S2, establishing a tracking matrix of a to-be-tested system; S3, writing SVA (System Verilog Assertion) code corresponding to each test passing criterion in test regulations; and S4, automatically generating a test result through SVA after execution is completed according to test excitation corresponding to test cases. The function coverage can be visually represented through adding effective tracking and monitoring on a coding link in a simulation test process, and the simulation test process of programmable logic is enabled to be more rigorous and more accord with a requirement of high reliability.

Owner:CHINA TECHENERGY +1

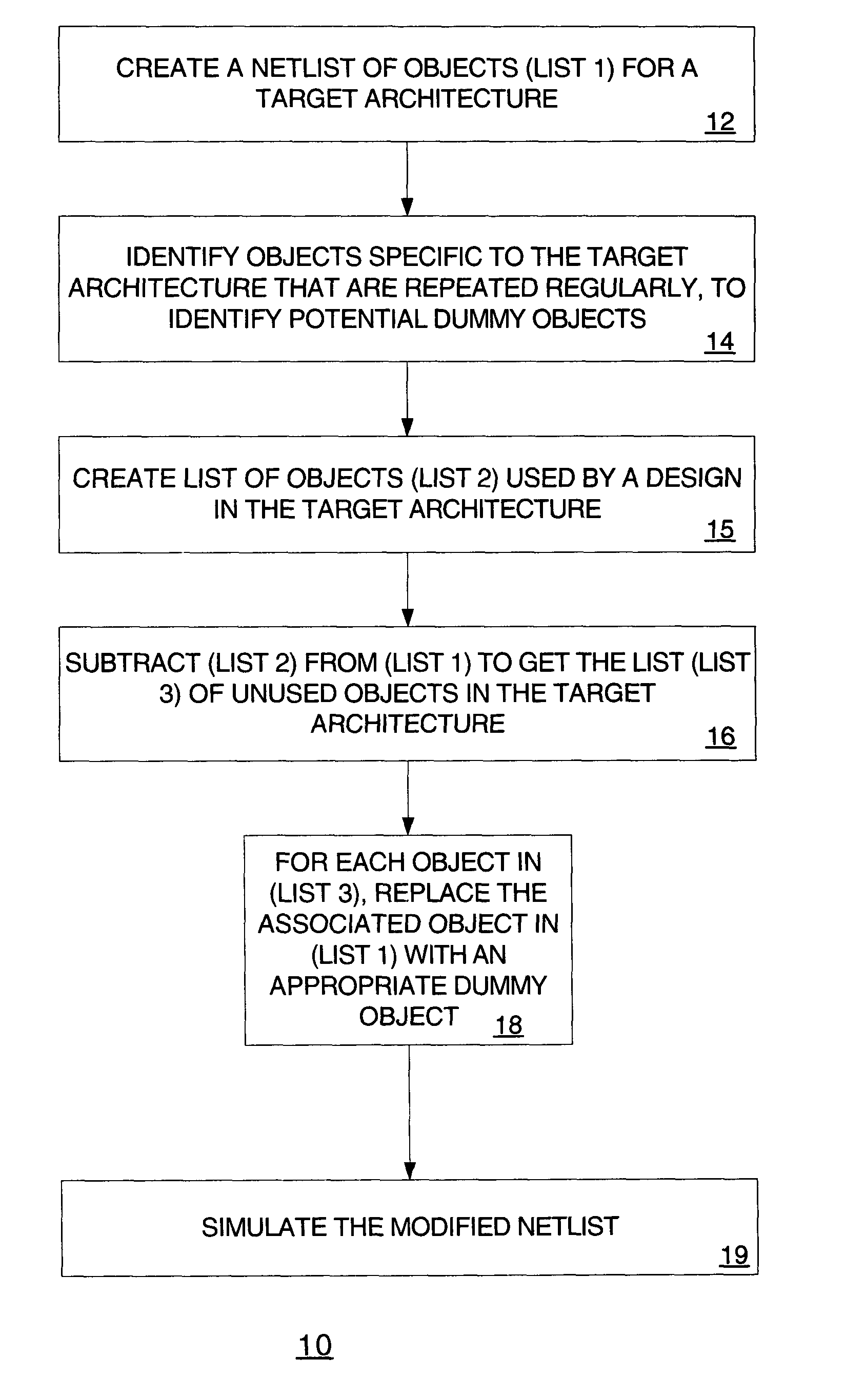

Dummy block replacement for logic simulation

InactiveUS7330808B1Significant comprehensive benefitsShorten the timeDetecting faulty computer hardwareCAD circuit designTheoretical computer scienceLogic simulation

A method (10) of reducing a size of a netlist for a target architecture can include the steps of creating (12) a netlist of objects for the target architecture, identifying (14) objects specific to the target architecture that are repeated regularly to identify potential dummy objects, creating (15) a list of objects used by a design in the target architecture, and forming (16) a list of unused objects in the target architecture from the netlist of objects and the list of objects used by the design. The method can further include the steps of replacing (18) at least one object in the list of unused objects with an appropriate dummy object to form a modified netlist and simulating (19) the modified netlist.

Owner:XILINX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com