Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

748 results about "Functional verification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronic design automation, functional verification is the task of verifying that the logic design conforms to specification. In everyday terms, functional verification attempts to answer the question "Does this proposed design do what is intended?" This is a complex task, and takes the majority of time and effort in most large electronic system design projects. Functional verification is a part of more encompassing design verification, which, besides functional verification, considers non-functional aspects like timing, layout and power.

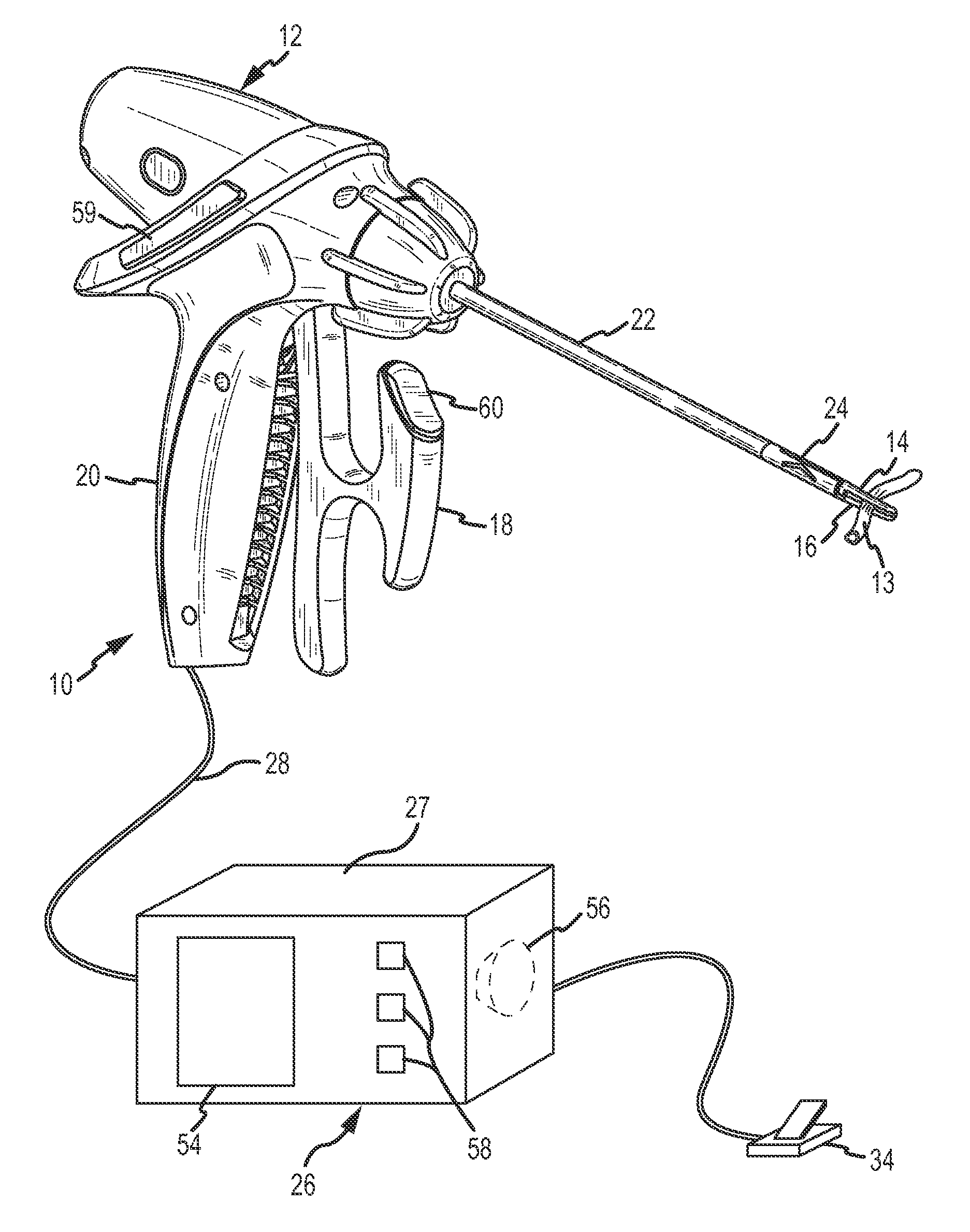

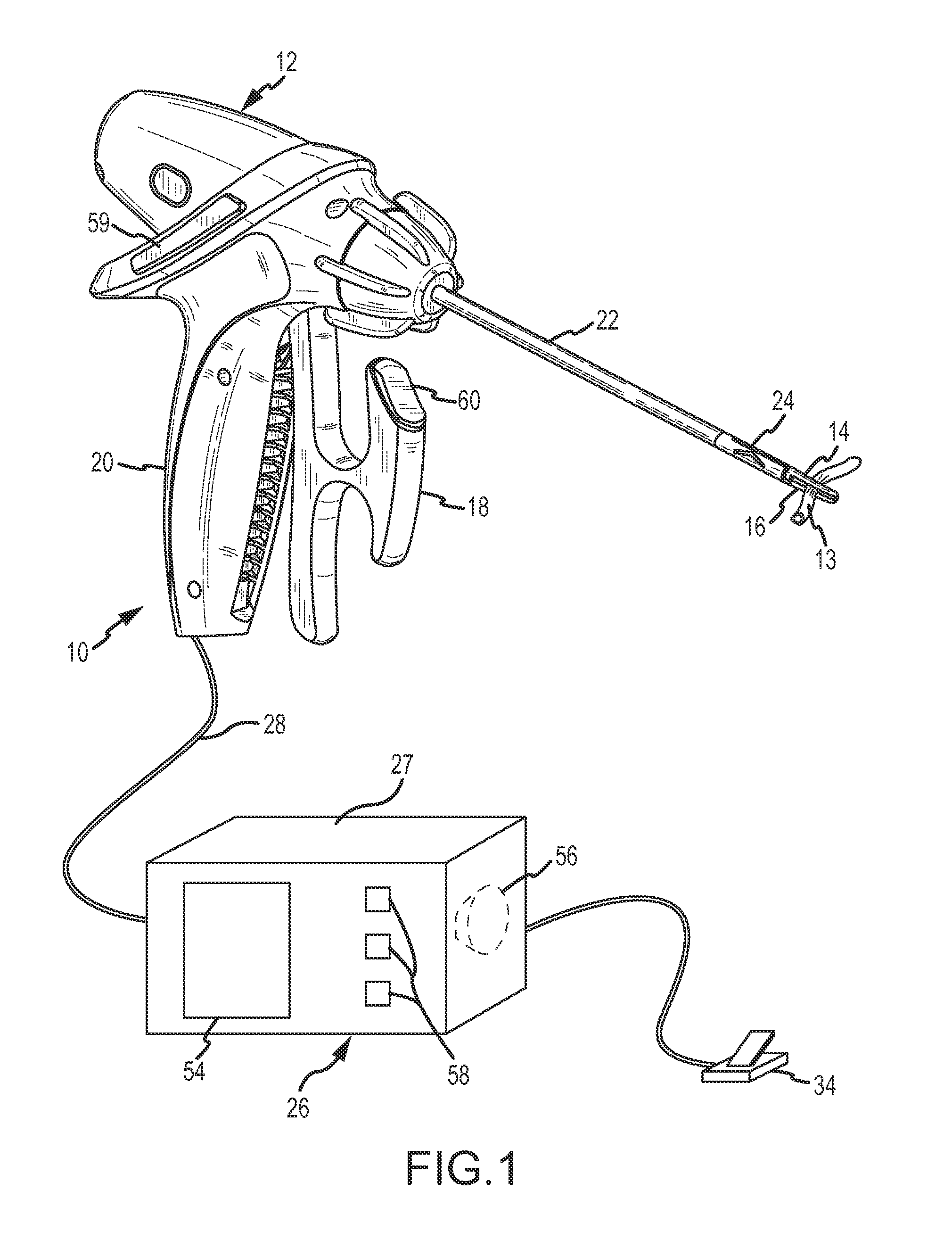

Tissue fusion system and method of performing a functional verification test

InactiveUS8840609B2Reduce traumaProlong surgery timeSurgical instruments for heatingSurgical forcepsElectrical resistance and conductanceOperational system

A jaw heating element of a handpiece of a thermal tissue operating system is tested on an ongoing basis by supplying a test heater power signal to the jaw heating element between individual thermal tissue operations. Voltage and current through the jaw heating element is sensed and the resistance of the jaw heating element is calculated. If the calculated resistance is outside a range of predetermined acceptable values, an error condition is indicated.

Owner:CONMED CORP

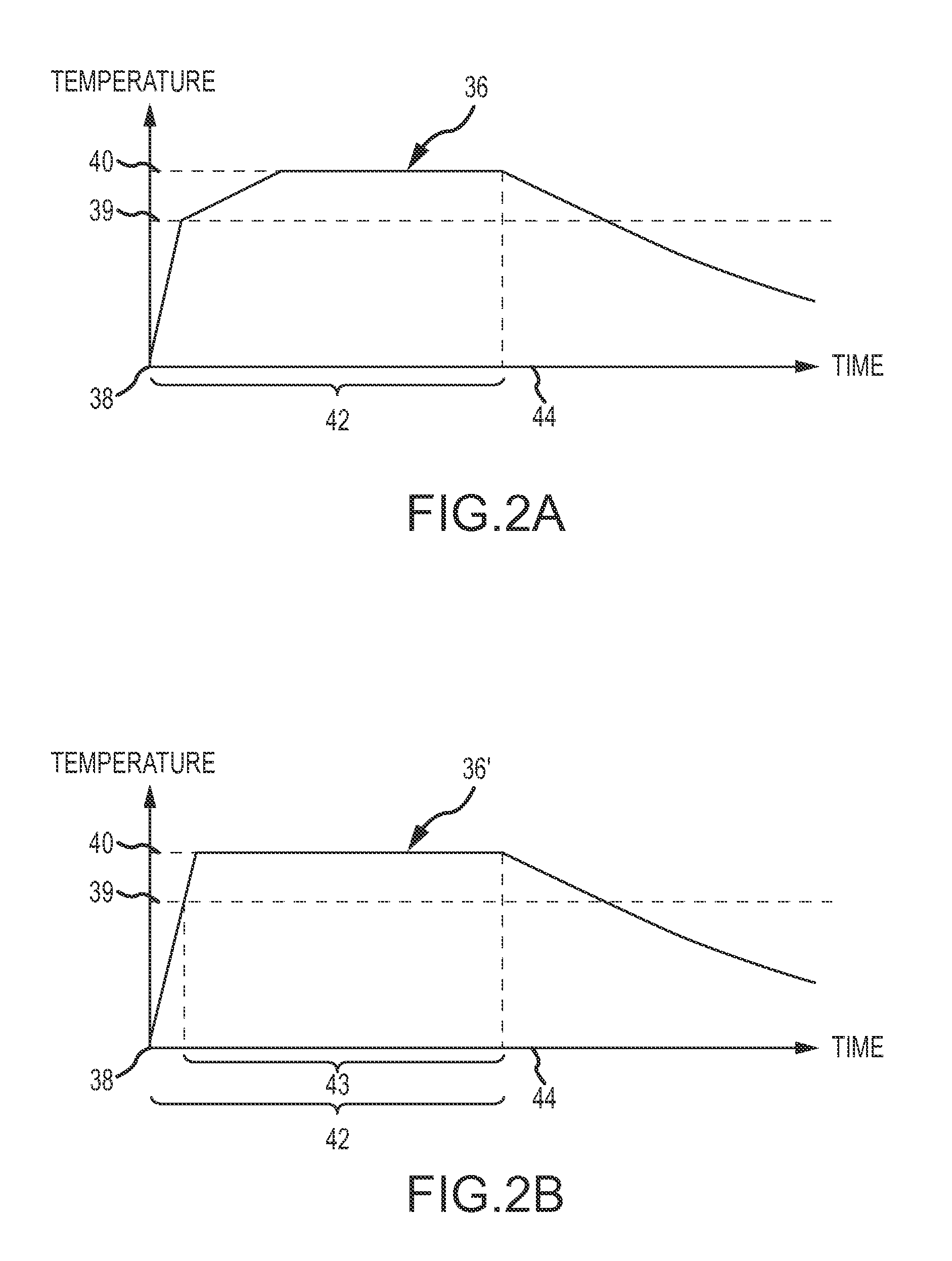

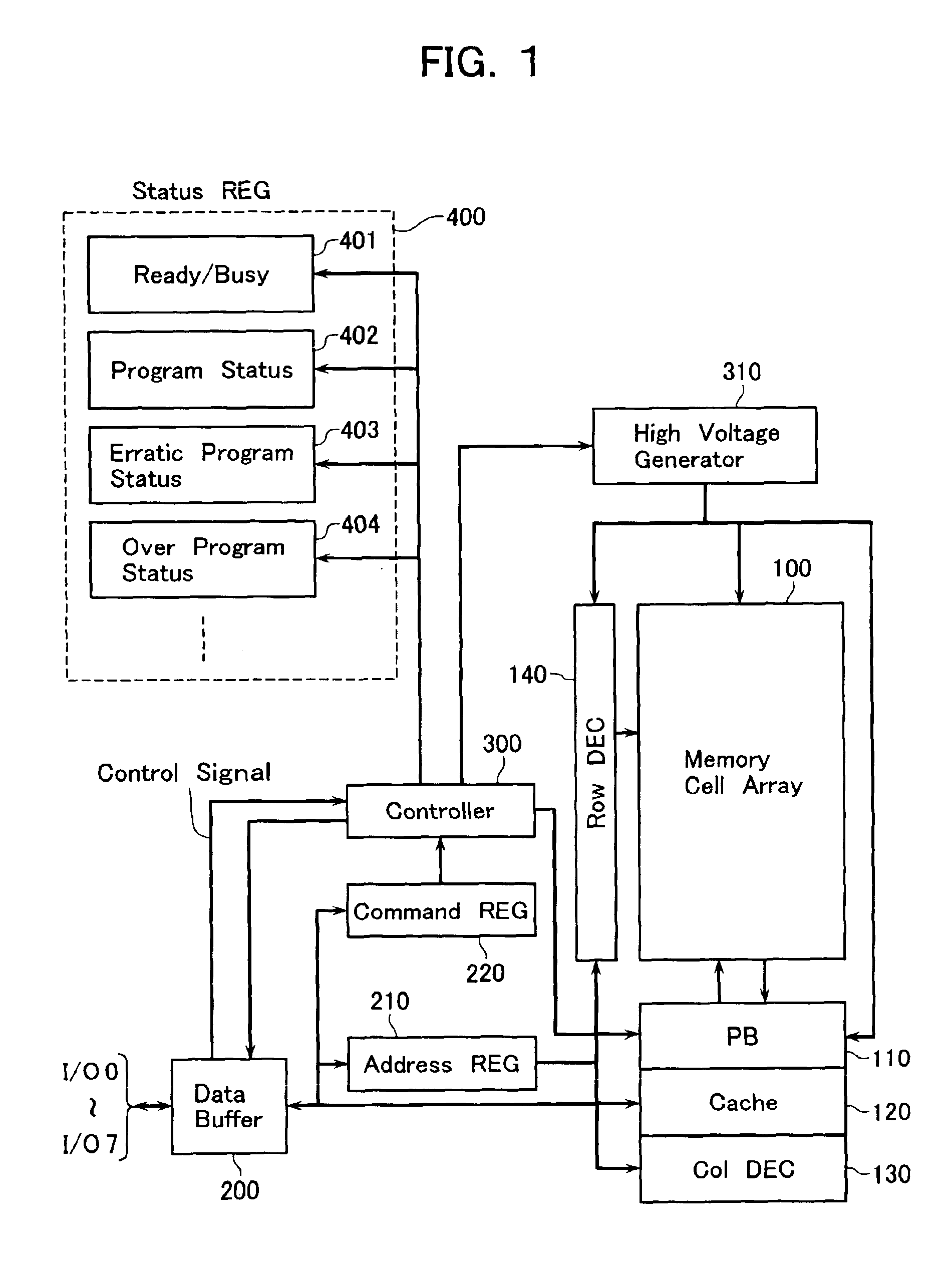

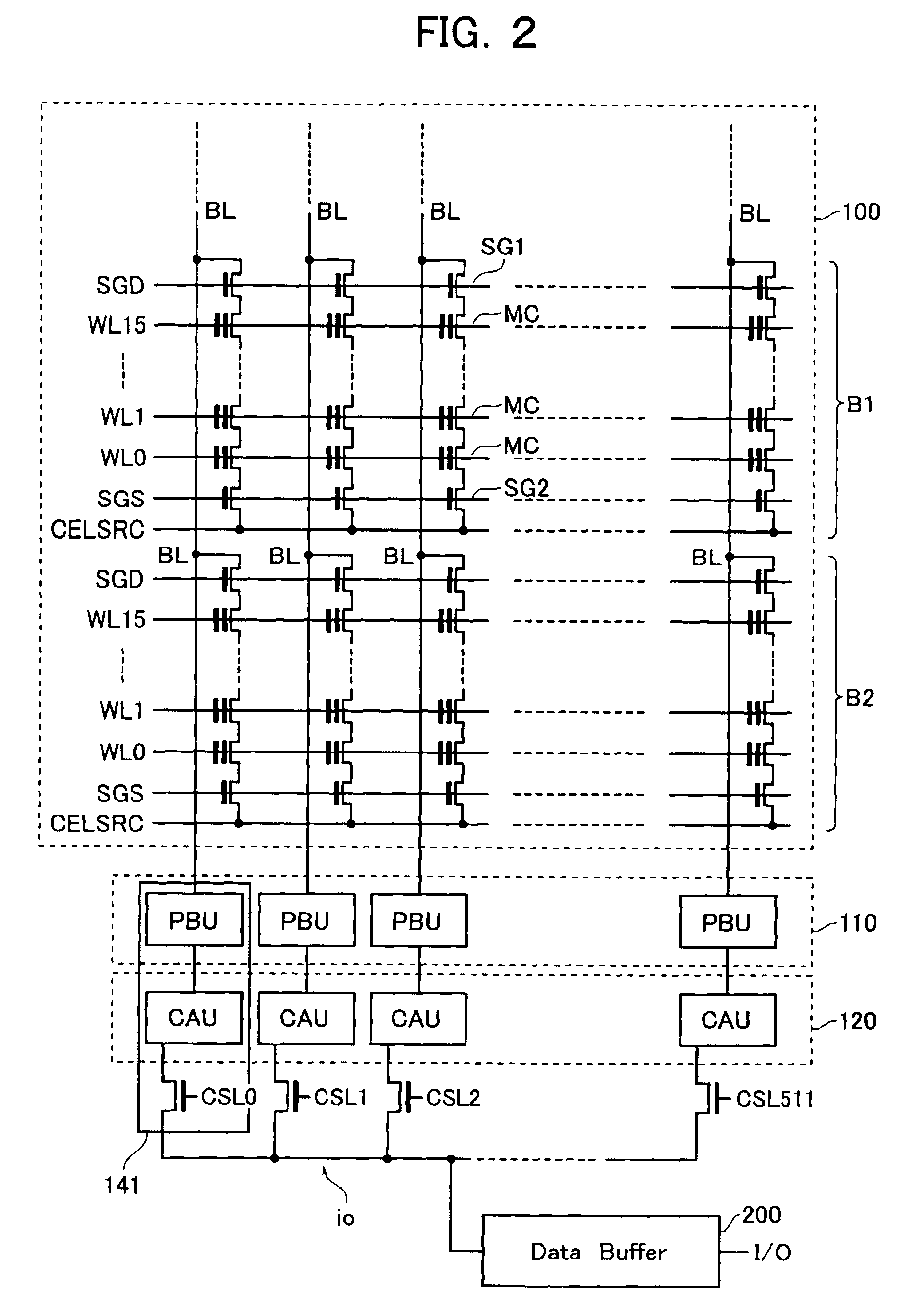

Non-volatile semiconductor memory device

A non-volatile semiconductor memory device includes a memory cell array, a data hold circuit, and a controller A program control function applies a program voltage to a selected memory cell to let data shift from a first logic state to a second logic state. A program verify control function verifies that a programmed data of the selected memory cell shifted to the second logic state. An erratic program verify control function checks that a threshold voltage of a memory cell to be held in the first logic state does not exceed a third value set as an upper limit value of a variation of the first logic state. An over-program verify control function checks that a threshold voltage of the selected memory cell shifted to the second logic state does not exceed a fourth value set as an upper limit thereof.

Owner:KK TOSHIBA

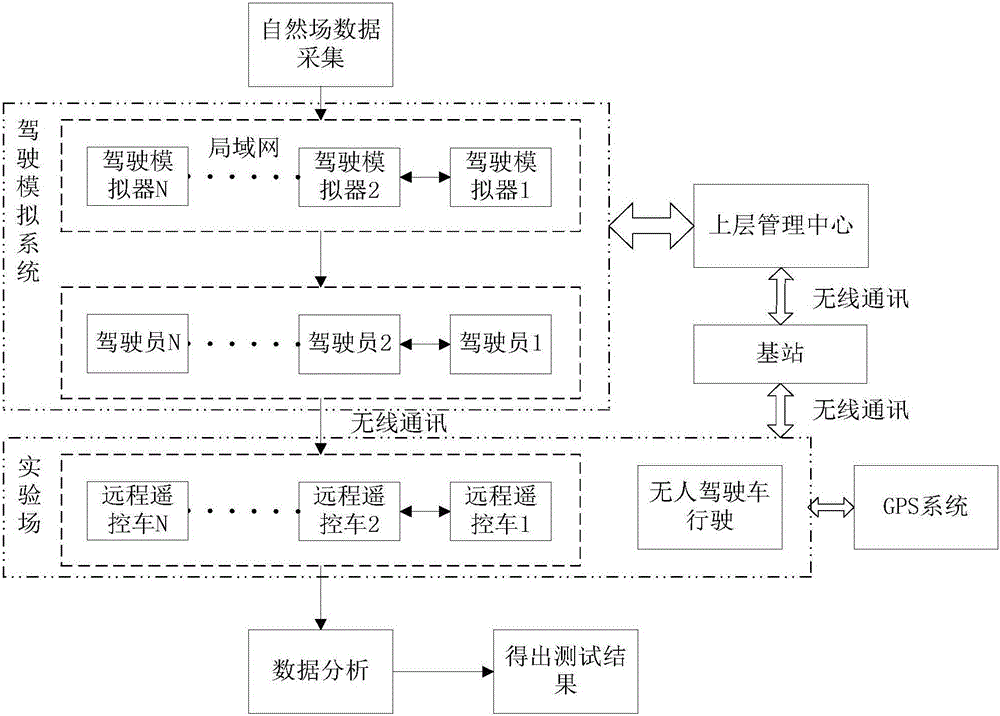

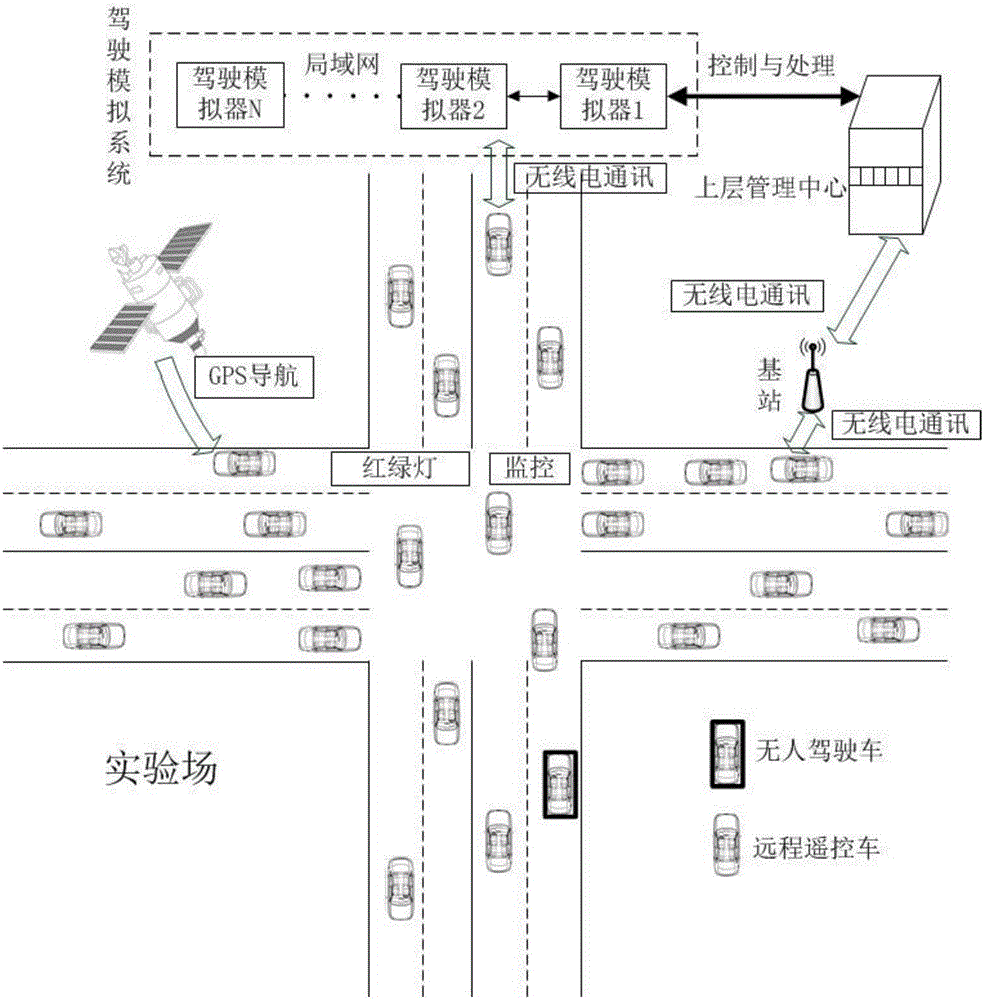

An unmanned vehicle test and verification platform and a test method thereof

ActiveCN106153352AGood for road testingNo experimental riskVehicle testingDetection of traffic movementVirtual vehicleEngineering

The invention belongs to an unmanned vehicle test and verification platform and a test method thereof in the field of unmanned vehicles. The platform comprises a driving simulation system, an experimental field, a network system, an upper level management center and an unmanned vehicle. The driving simulation system constructs a driving environment of a virtual vehicle according to the information collected in a natural scene; the traffic scene of the actual site of the experimental field coincides with the scene modeled by the driving simulation system; and the upper level management center is used for establishing a simulator driving environment, controlling the driving simulation system and processing data; the unmanned vehicle is a test vehicle and is automatically driven in the experimental field; and the driving information of the unmanned vehicle is transmitted to the upper level management center through a network system and then transmitted to the driving simulator of the driving simulation system. According to the invention, function verification and performance evaluation of the unmanned vehicle can be studied, and meanwhile, influences by the unmanned vehicle on an actual traffic flow can be studied and evaluated through the platform.

Owner:上海泽尔汽车科技有限公司

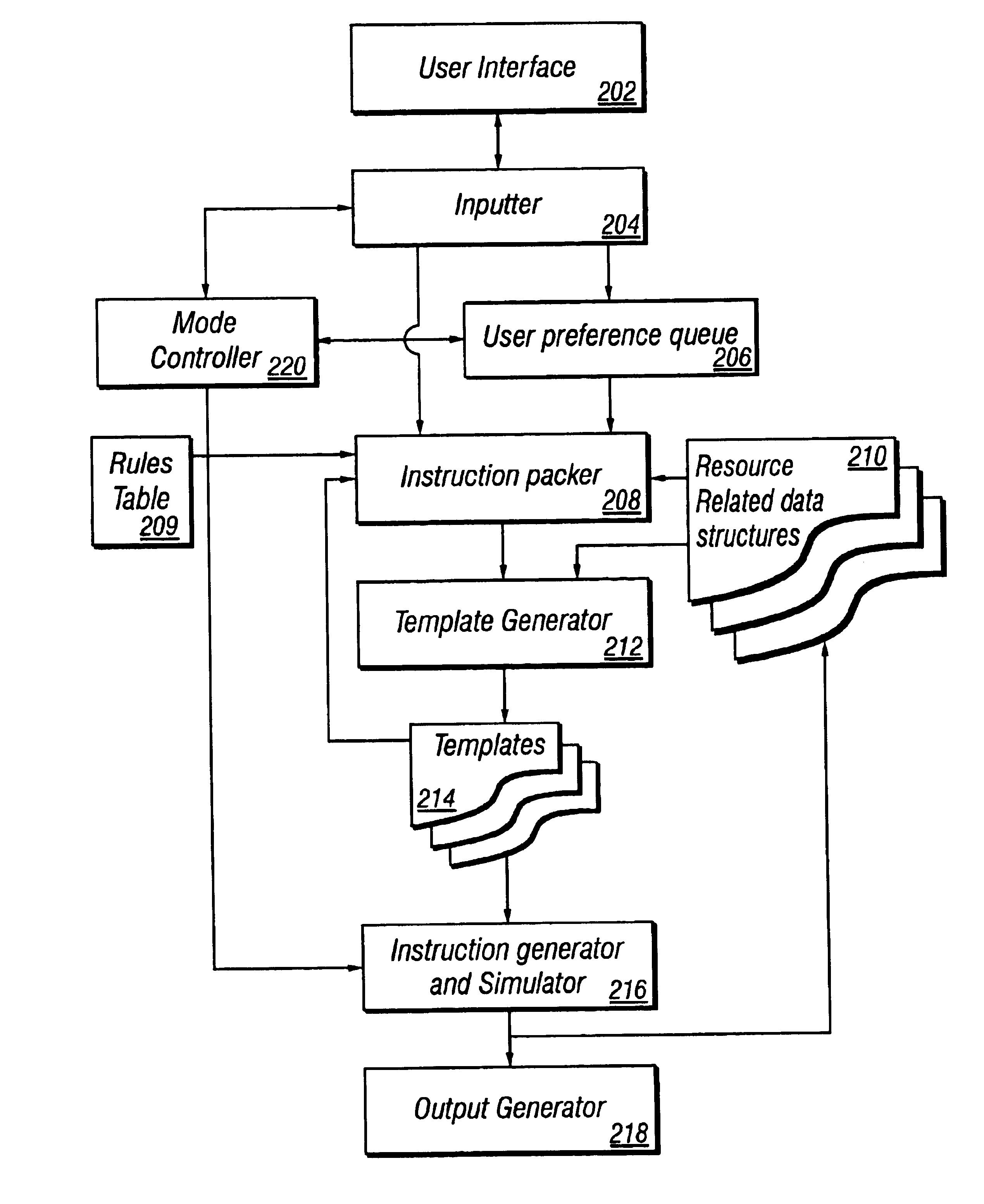

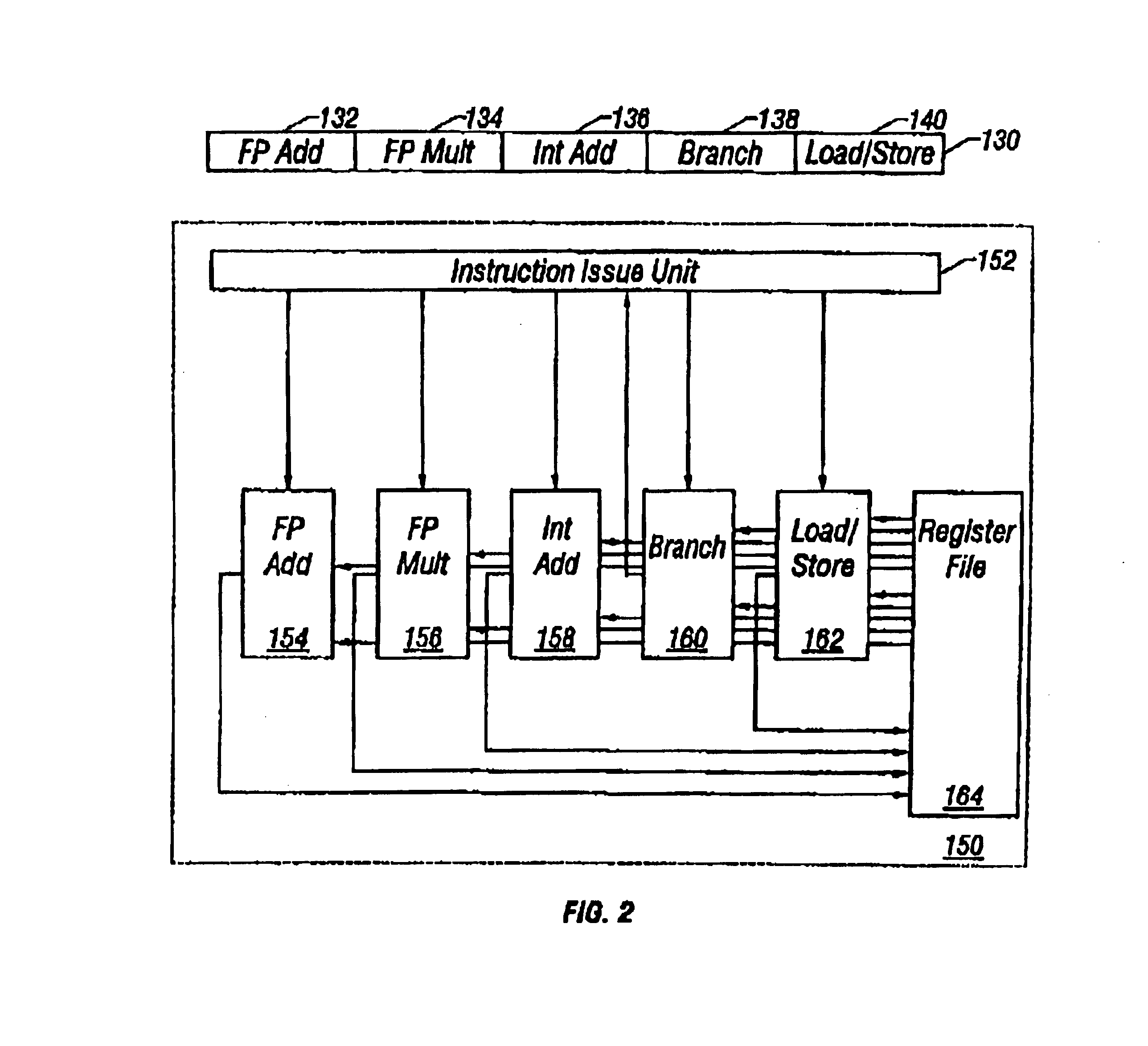

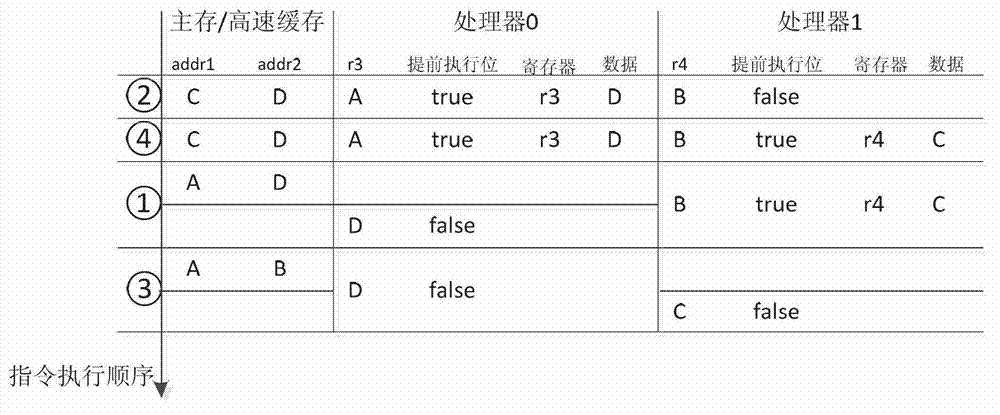

Method and apparatus that simulates the execution of paralled instructions in processor functional verification testing

InactiveUS6871298B1Properly be executeError detection/correctionDigital computer detailsAnalog processorParallel computing

A dynamic test generation method and apparatus enabling verification of the parallel instruction execution capabilities of VLIW processor systems is described. The test generator includes a user preference queue, a rules table, plurality of resource-related data structures, an instruction packer, and an instruction generator and simulator. The present invention generates a test by selecting instructions for parallel execution based upon resource availability as indicated by the resource-related data structures and the processor's instruction grouping rules, simulating the parallel execution of the instructions on a golden model, updating the resource-related data structures, and evaluating the updated architectural state of the golden model.

Owner:ARM INC

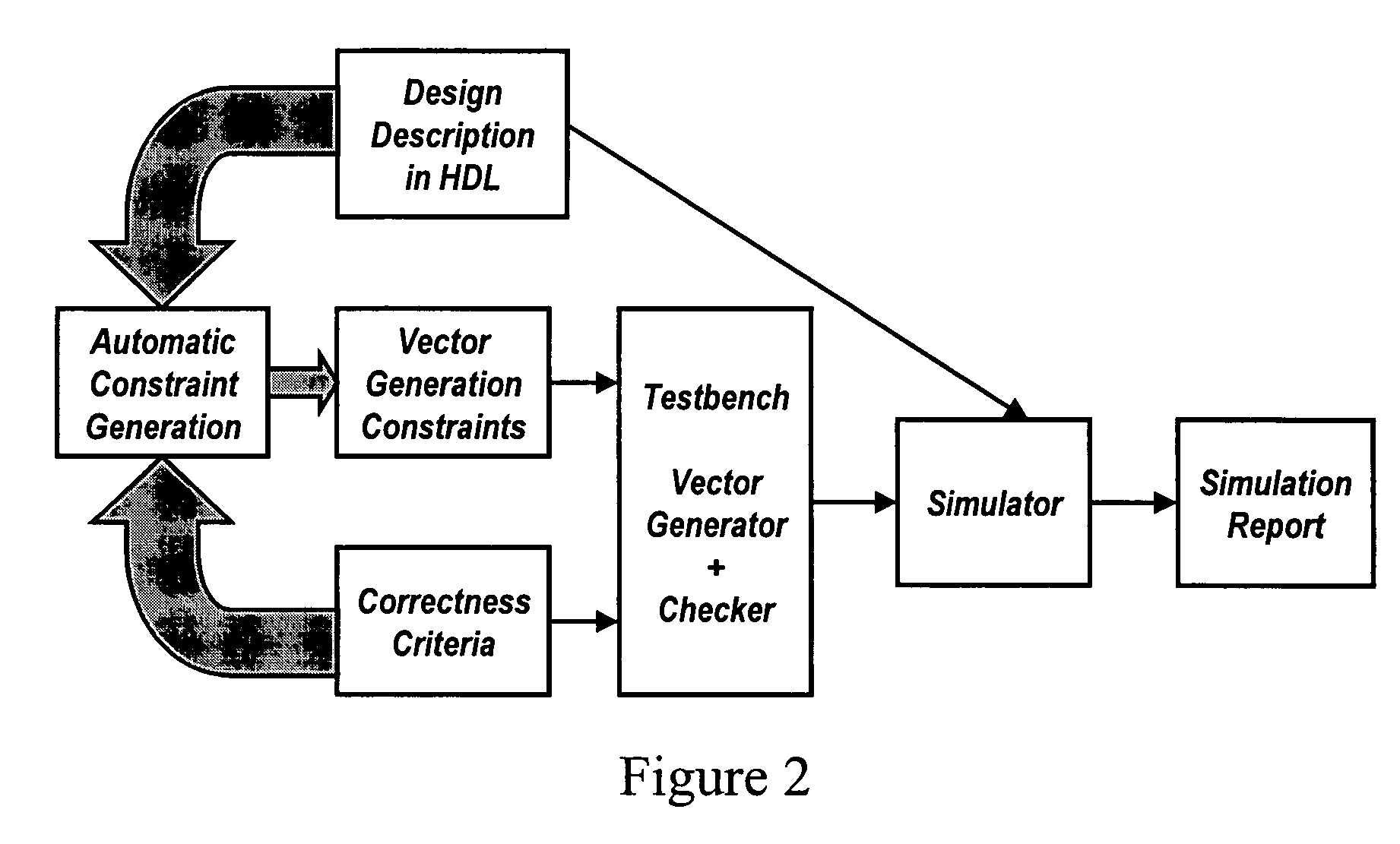

Property specific testbench generation framework for circuit design validation by guided simulation

InactiveUS6975976B1Electronic circuit testingDetecting faulty computer hardwareTheoretical computer scienceTest platform

Simulation continues to be the primary technique for functional validation of designs. It is important that simulation vectors be effective in targeting the types of bugs designers expect to find rather than some generic coverage metrics. The focus of this work is to generate property-specific testbenches that are targeted either at proving the correctness of a property or at finding a bug. It is based on performing property-specific analysis on iteratively less abstract models of the design in order to obtain interesting paths in the form of a Witness Graph, which is then targeted during simulation of the entire design. This testbench generation framework will form an integral part of a comprehensive verification system currently being developed.

Owner:NEC CORP

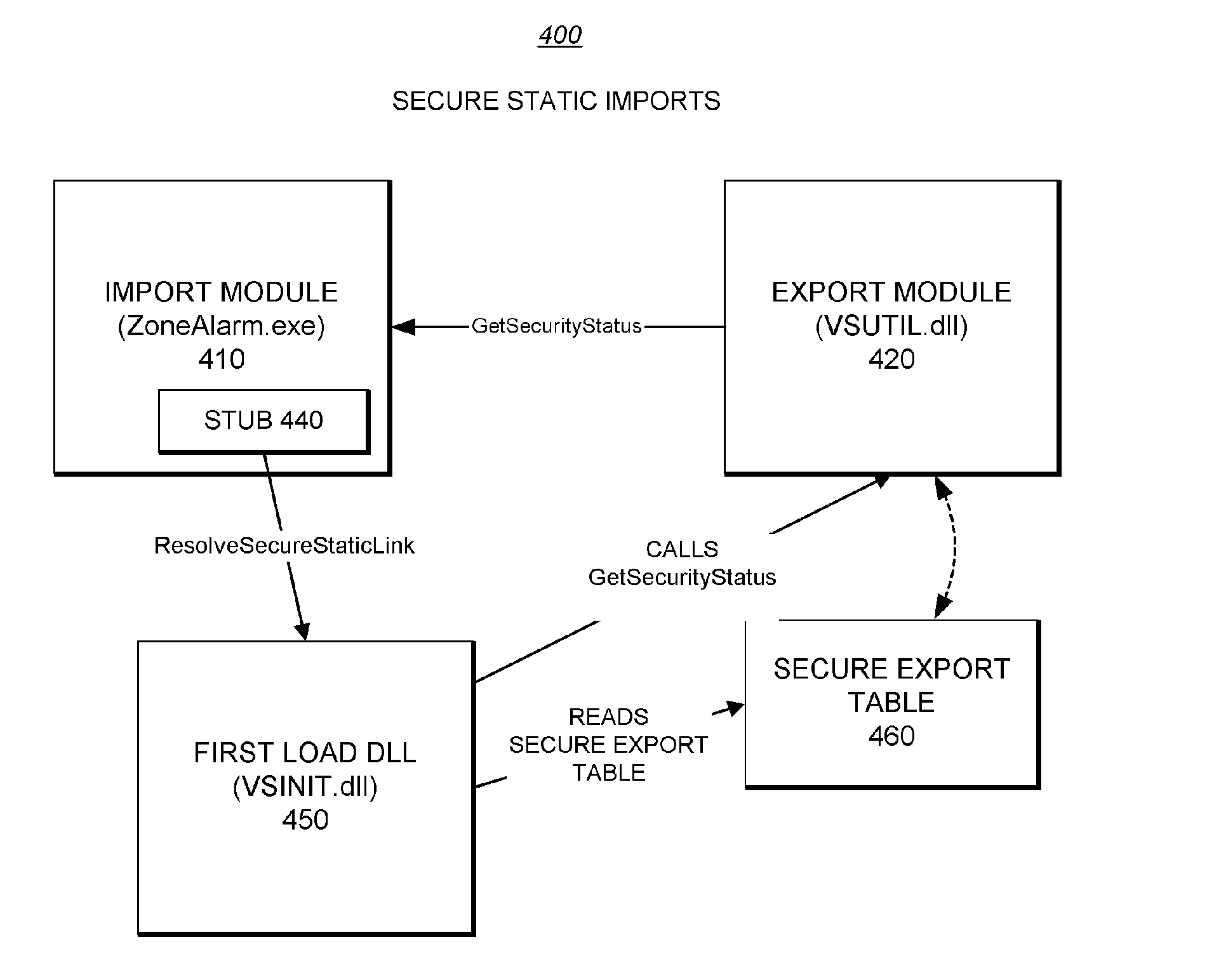

System Providing Methodology for Securing Interfaces of Executable Files

ActiveUS20050071633A1Unauthorized memory use protectionHardware monitoringInformation provisionComputer security

A system providing methodology for securing interfaces of executable files is described. In one embodiment, for example, a method is described for securing a program comprised of a plurality of interoperable components, the method comprises steps of: extracting information about a function of a first component of the program that is callable by at least one other component of the program; securing the extracted information; in response to an attempt by a second component of the program to invoke the function of the first component, validating authenticity of the second component; and if the second component is validated, providing access to the function of the first component using the secured extracted information.

Owner:CHECK POINT SOFTWARE TECH INC

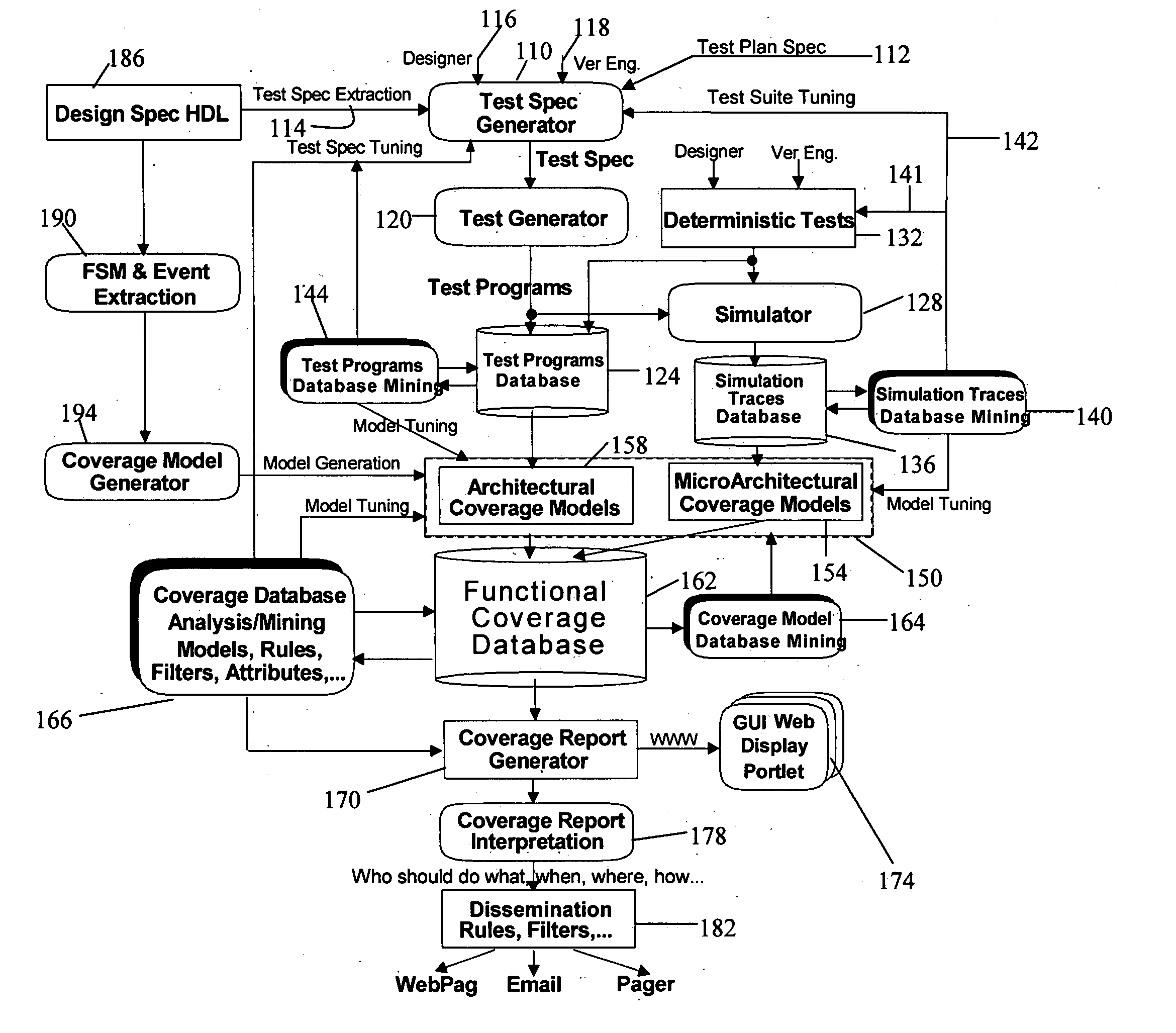

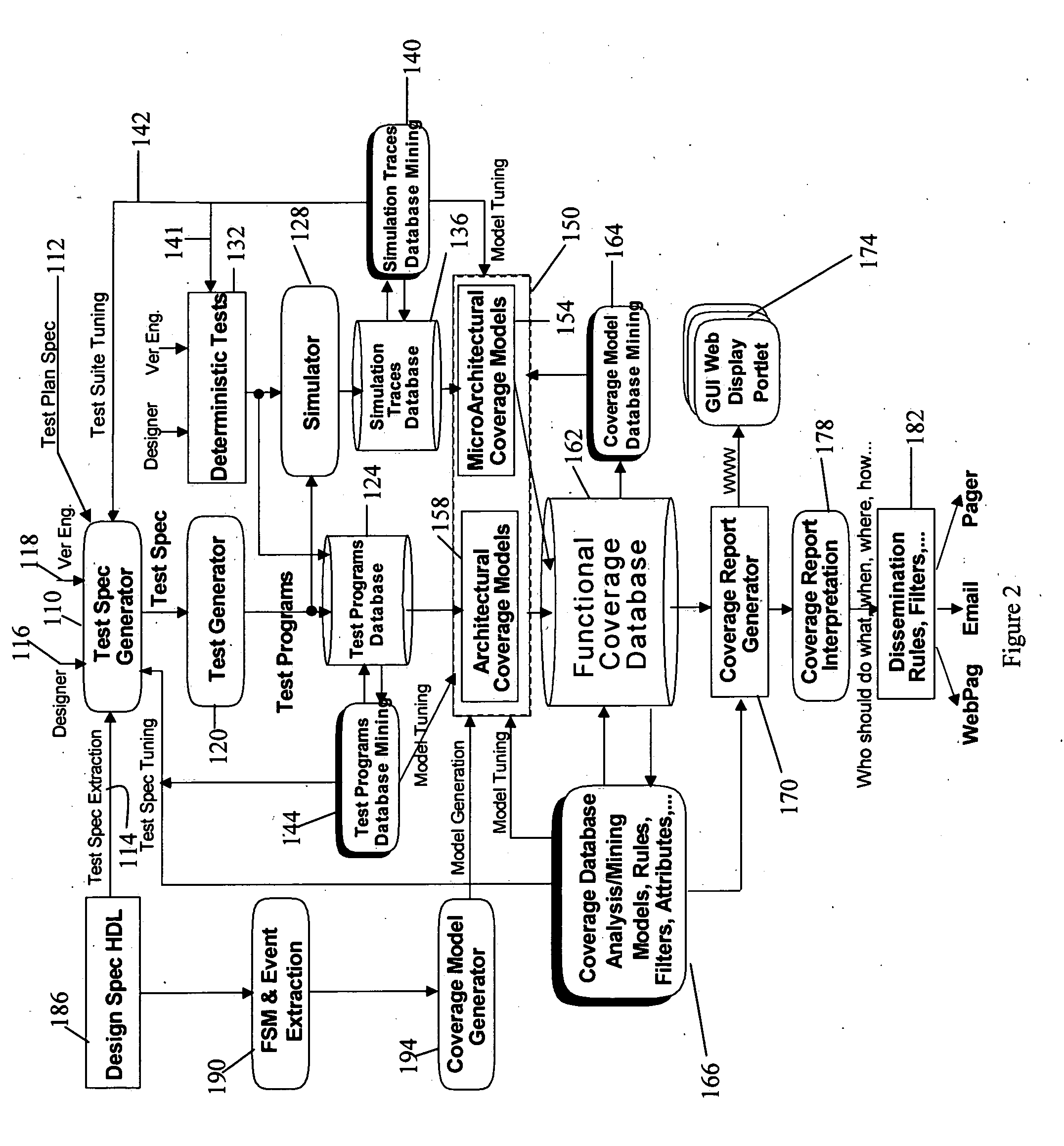

Database mining system and method for coverage analysis of functional verification of integrated circuit designs

InactiveUS20050102596A1Provide capabilityOrganic chemistryElectronic circuit testingPortletFinite-state machine

Database mining, analysis and optimization techniques in conjunction with the model-based functional coverage analysis are used to turn raw verification and coverage data into design intelligence (DI) and verification intelligence (VI). The required data and attributes are automatically extracted from verification, simulation and coverage analysis databases. Design finite state machine extraction, design functional event extraction, and automatic coverage model generation and optimization techniques are applied to the design HDL description. Coverage model tuning and optimization directives, as well as test spec tuning and optimization directives are generated based on the analysis and mining of various verification, simulation, and coverage databases. An integrated web-based interface portlet is used for access, analysis and management of the resulting databases, generated reports and verification directives. Dissemination rules are used to automatically generate and distribute analysis reports and verification directives to engineers at wired or wireless interface devices via Internet or Intranet.

Owner:GLOBALFOUNDRIES INC

Simulation-based functional verification of microcircuit designs

InactiveUS7130783B1Shorten the timeConfidenceDetecting faulty computer hardwareAnalogue computers for electric apparatusTest designFormal methods

System, methods, and apparatus for verifying microcircuit designs by interleaving between random and formal simulation techniques to identify input traces useful for driving designs under test into sequences of device states. In a method aspect the invention provides process for beginning random simulation of a sequence of states of a microcircuit design by inputting a sequence of random input vectors to a design under test model in order to obtain a sequence of random simulation states; monitoring a simulation coverage progress metric to determine a preference for switching from random simulation to formal methods of simulating states in the design under test; beginning formal simulation of states in the design under test and monitoring a formal coverage progress metric to determine a preference for resuming random simulation of states of said microcircuit design; and resuming random simulation. Preferably the process of interleaving simulation methods continues until an input vector suitable for driving the design under test model into each of a set of previously-identified goal states has been obtained.

Owner:SYNOPSYS INC

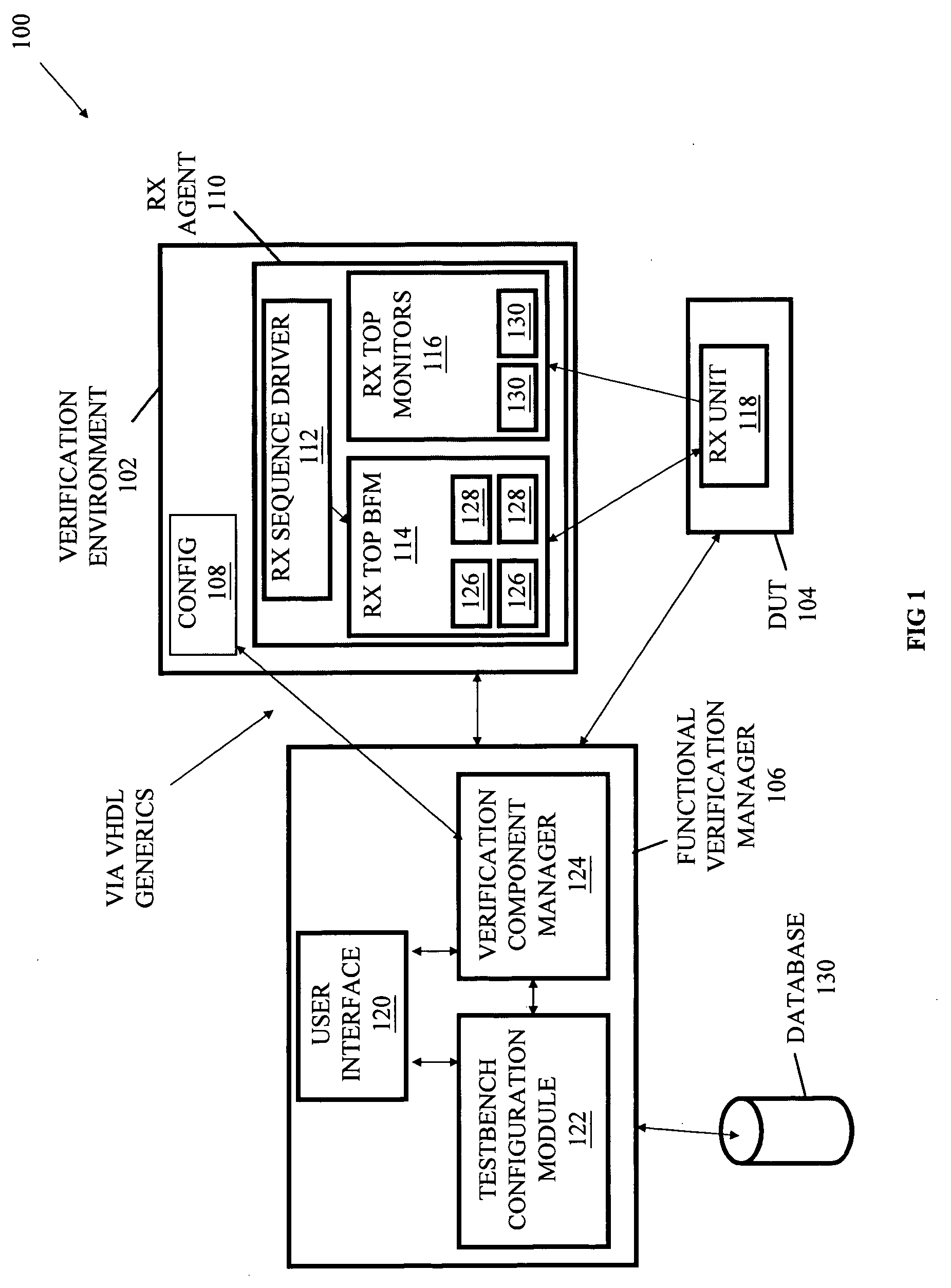

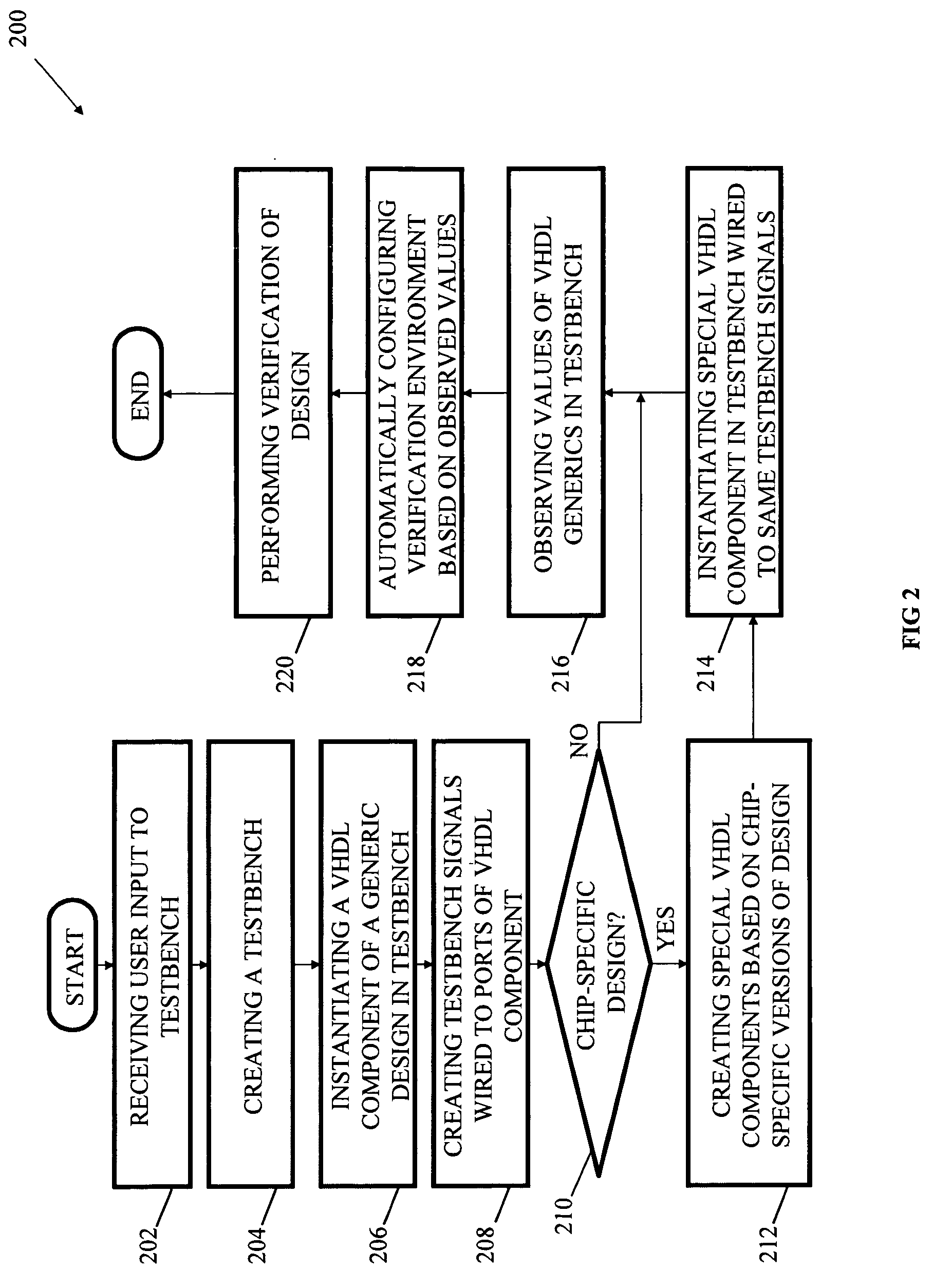

Methods, systems and media for managing functional verification of a parameterizable design

InactiveUS20060190871A1Electrical testingComputer programmed simultaneously with data introductionComputer architectureAuto-configuration

Methods, systems, and media for managing functional verification of a parameterizable design are disclosed. Embodiments include a system having a testbench configuration module adapted to configure a testbench, the testbench having testbench signals and one or more instantiated components having a plurality of ports of a generic design, where the testbench signals are wired to the plurality of ports. The testbench may also have one or more instantiated special components based on chip-specific versions of the design where the special components are wired to the same ports as the generic design. The system may also include a functional verification manager that, through a component module, observes values in the testbench and automatically configure a verification environment based on the observed values, including automatic insertion of checkers at different levels of hierarchy. The testbench may be a VHDL or Verilog testbench in some embodiments.

Owner:GLOBALFOUNDRIES INC

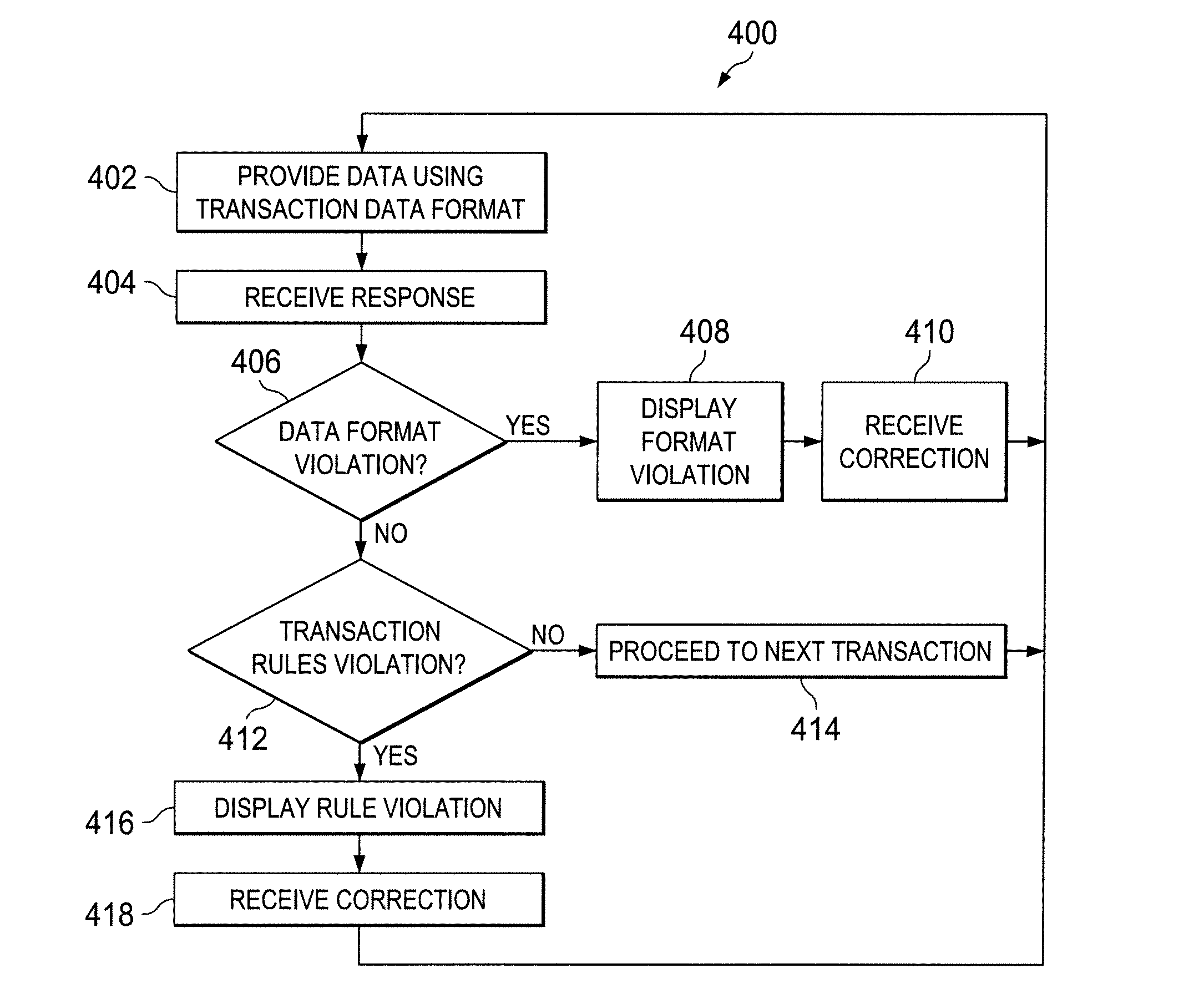

System and apparatus for transaction data format and function verification

A system for processing transaction data is provided. The system includes a transaction data format system receiving transaction data and generating transaction data format error data, such as when the transaction data is not in compliance with a transaction data format. The system also includes a transaction data rules system receiving the transaction data and generating transaction rule error data, such as when the transaction data is in the proper format but nevertheless violates a rule of one or more financial processing system.

Owner:CHASE PAYMENTECH SOLUTIONS

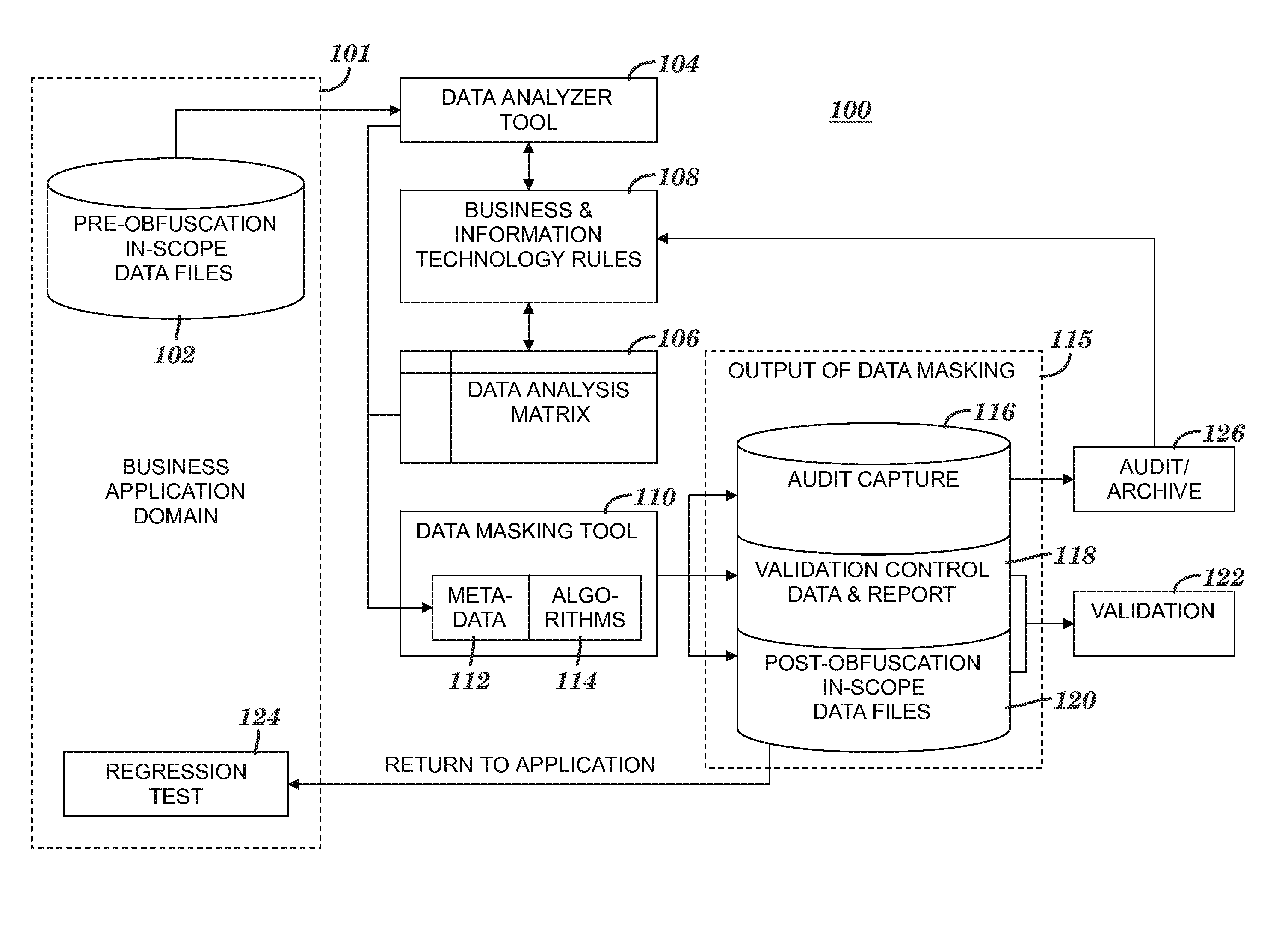

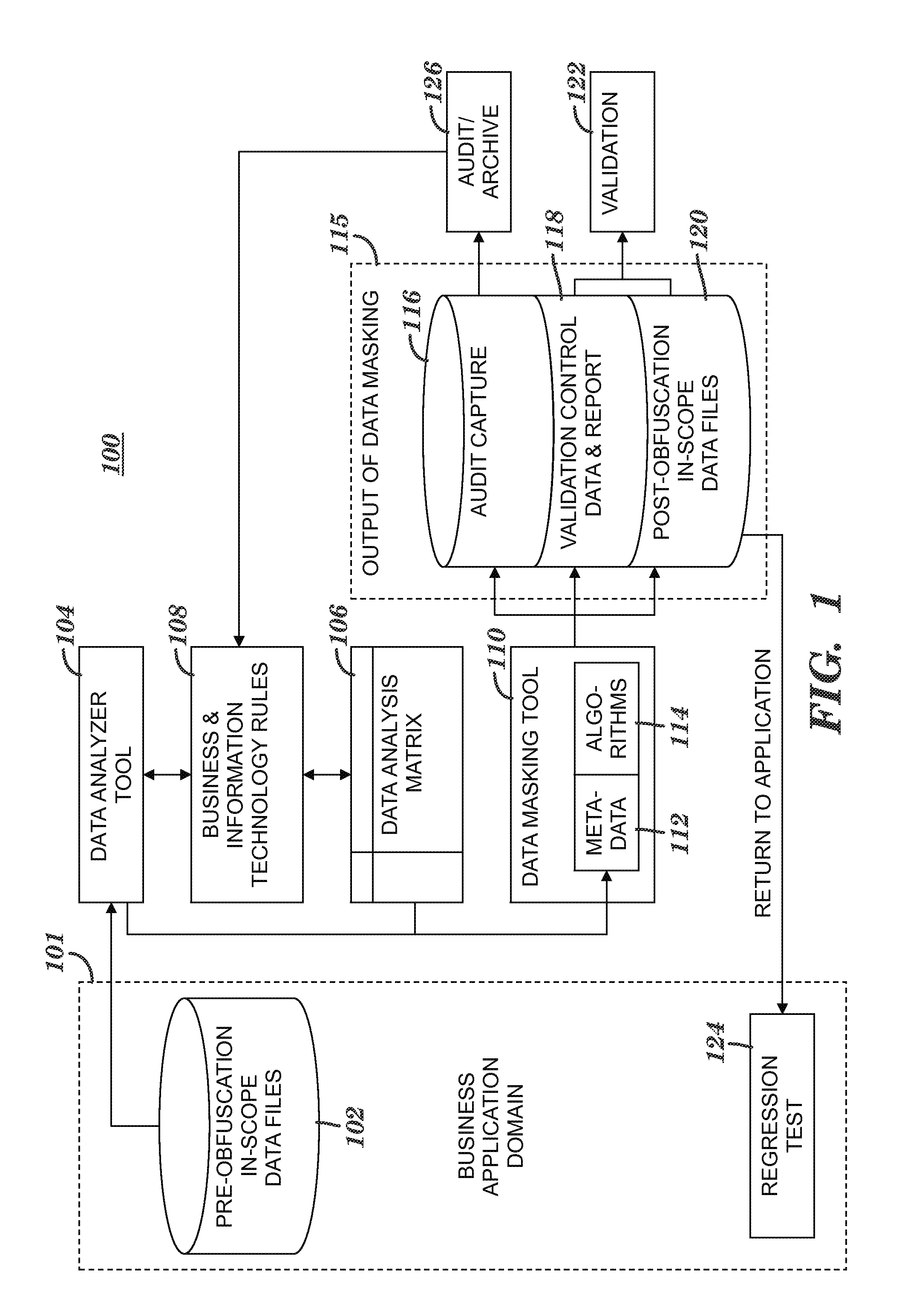

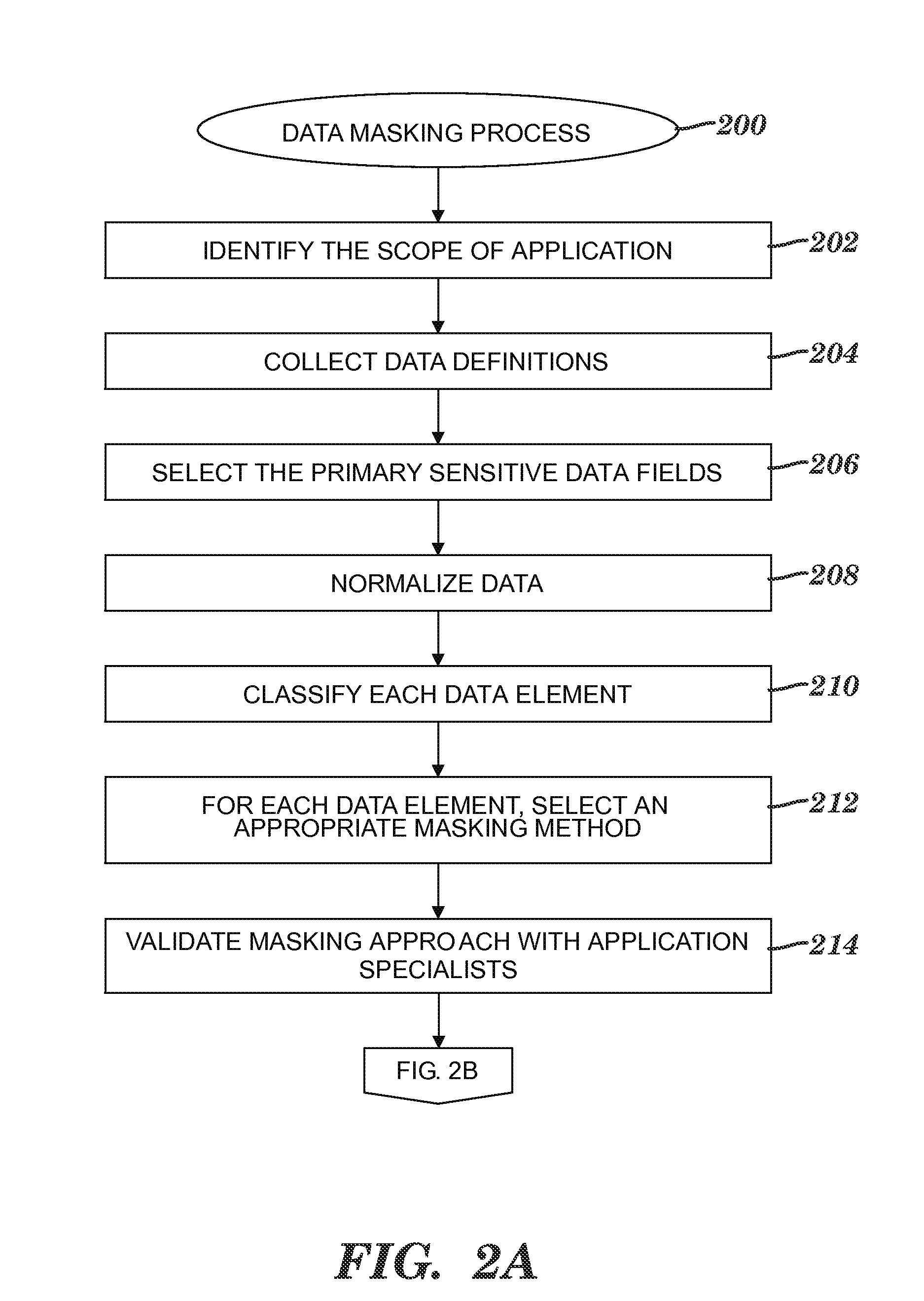

Obfuscating sensitive data while preserving data usability

InactiveUS20120272329A1Digital data processing detailsAnalogue secracy/subscription systemsConfidentialityData file

An approach for obfuscating sensitive data while preserving data usability is presented. The in-scope data files of an application are identified. The in-scope data files include sensitive data that must be masked to preserve its confidentiality. Data definitions are collected. Primary sensitive data fields are identified. Data names for the primary sensitive data fields are normalized. The primary sensitive data fields are classified according to sensitivity. Appropriate masking methods are selected from a pre-defined set to be applied to each data element based on rules exercised on the data. The data being masked is profiled to detect invalid data. Masking software is developed and input considerations are applied. The selected masking method is executed and operational and functional validation is performed.

Owner:INT BUSINESS MASCH CORP

Method for establishing network chip module level function checking testing platform

ActiveCN101183406ASimple and straightforward way to buildClear structureSpecial data processing applicationsReference modelProcessor register

The invention relates to a method for constructing a verification and test platform of network chip module level functions, comprising the construction of a simulation and reference model of the tested modules, which is characterized in that: the method comprises the construction of all modules and documents; the output of an excitation generating model is connected with the inputs of the tested module and the simulation and reference model, a clock and a reset generating module are connected with the tested module and the clock and reset signal of the simulation and reference model, a register initialization module is connected with the register of the tested module and the simulation and reference model, and a CPU simulation module is connected with the CPU of the tested module; the output of the tested module is connected with the simulation and reference model, thus, the network chip module level function verification and test platform can be constructed. The invention has the advantages that the platform can be constructed easily and directly, so the time required to construct the module level function verification and test platform can be shortened greatly in the high performance network chip verification process; meanwhile, the platform constructed by the method has clear structure which is easy to be understood and has improved reliability.

Owner:苏州盛科科技有限公司

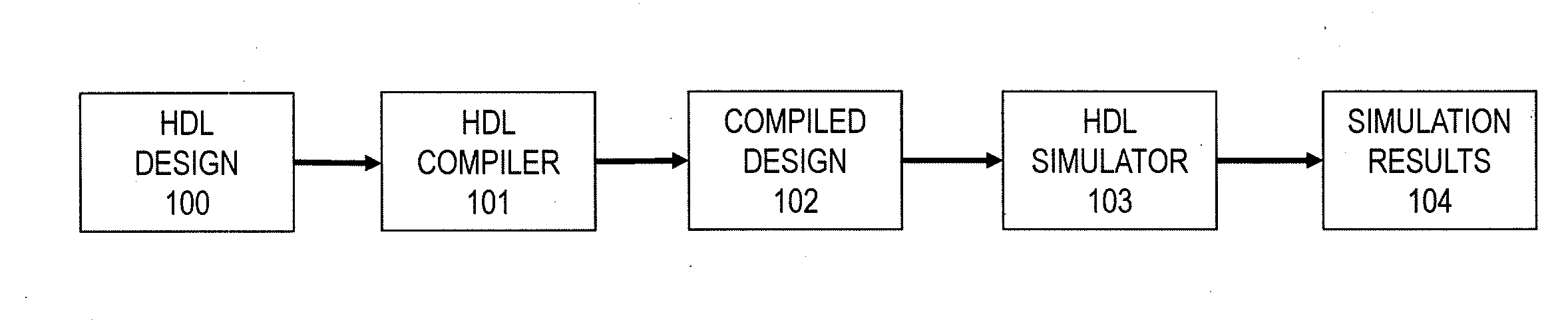

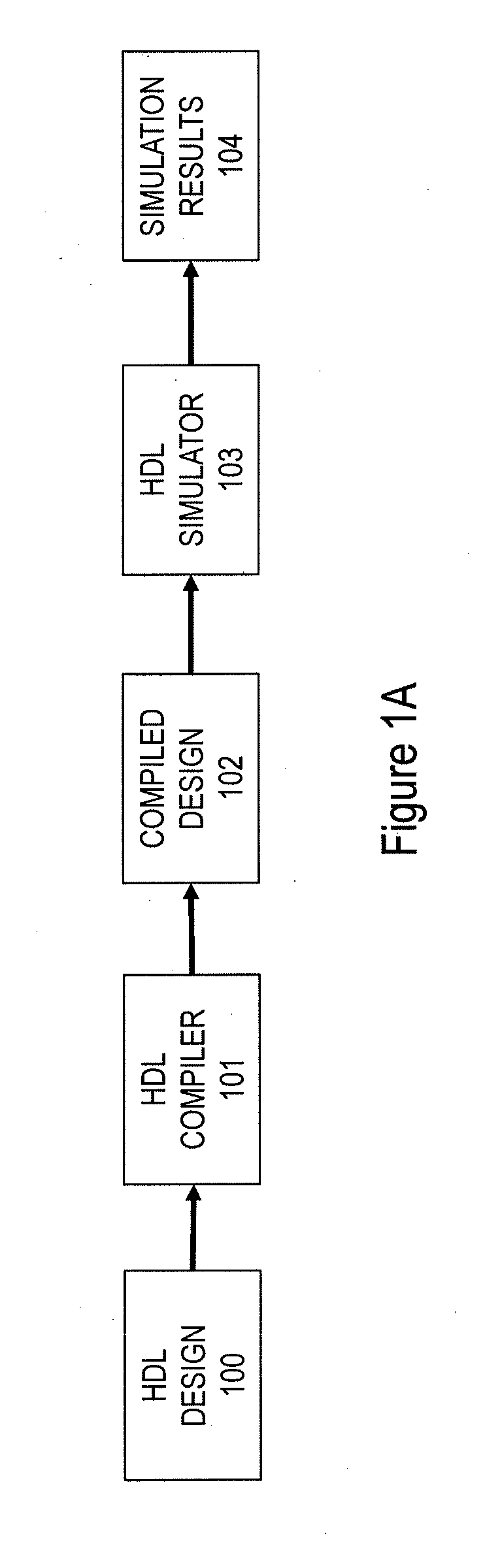

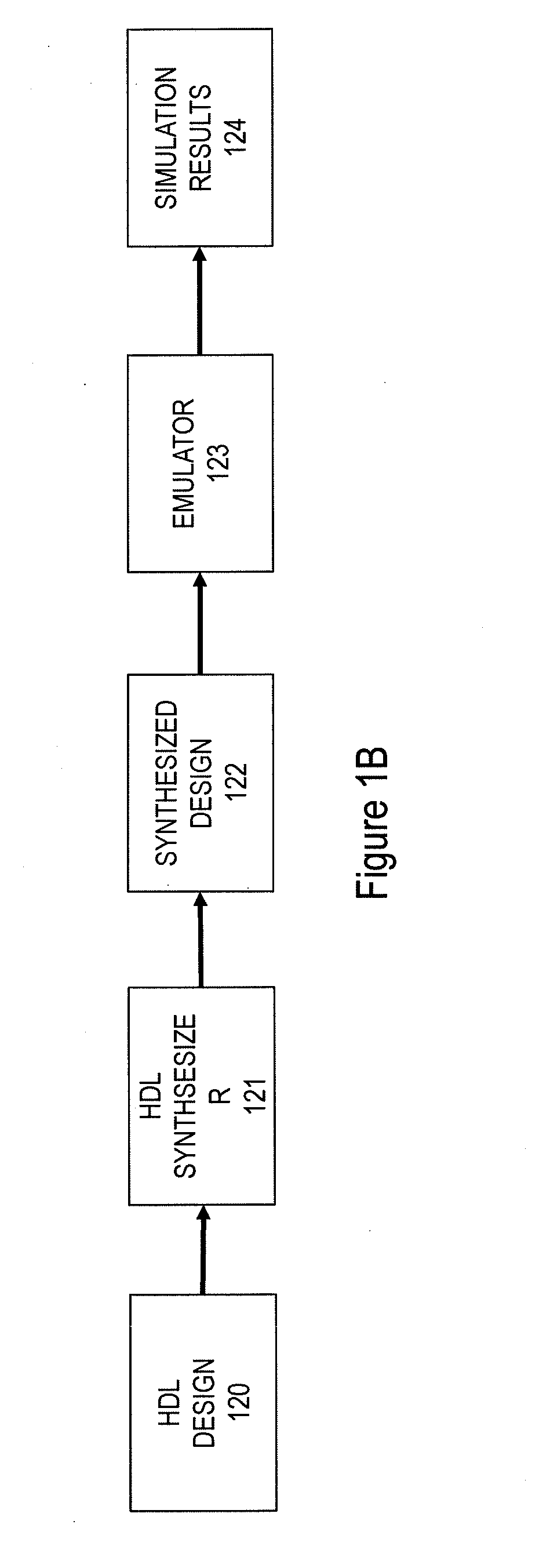

Hardware simulation controller, system and method for functional verification

ActiveUS20140282312A1CAD circuit designSoftware simulation/interpretation/emulationSimulation languageParallel computing

Systems and methods of using hardware to simulate software, specifically the semantic operations defined in HDL simulation languages. Traditional software HDL simulation kernel operations of advancing time, activating threads in response to notified events, and scheduling those threads of execution are handled via a simulation controller. The simulation controller is comprised of a timing wheel, an event-processor, a thread / process dispatch engine, a token processor, and a resource-allocator. These components work together with a control logic component to perform the semantic operations of an HDL software kernel.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

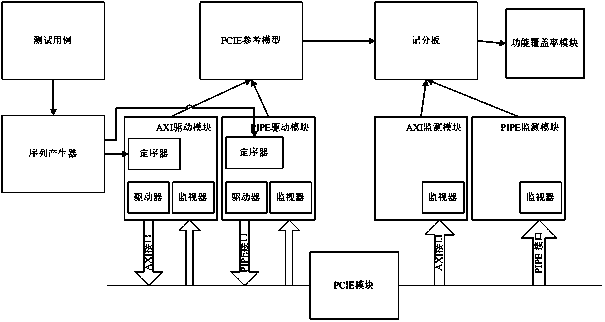

PCIE verification method based on UVM

ActiveCN103530216ASimple migration and verificationCoverage collection and monitoringError detection/correctionReference modelValidation methods

The invention relates to a PCIE verification method based on the UVM. The PCIE verification method is characterized in that the UVM and a system-level hardware descriptive language are adopted, a verification environment platform is set up through a high-level extensible interface bus behavior model, functional verification is implemented on a PCIE module, and the verification environment platform comprises a test case, a sequence generator, an AXI drive module, a PIPE drive module, an AXI monitoring module, a PIPE monitoring module, a PCIE reference model, a scoreboard and a functional coverage rate module. Due to the fact that the UVM is implemented, a stratified verification structure can be obtained, the PCIE with different types of configuration can be easily transplanted and verified, random data packet excitation can be generated through constraints, all instructions and addresses can be traversed, and the functional coverage rate module can also collect and monitor the coverage rate.

Owner:丁贤根

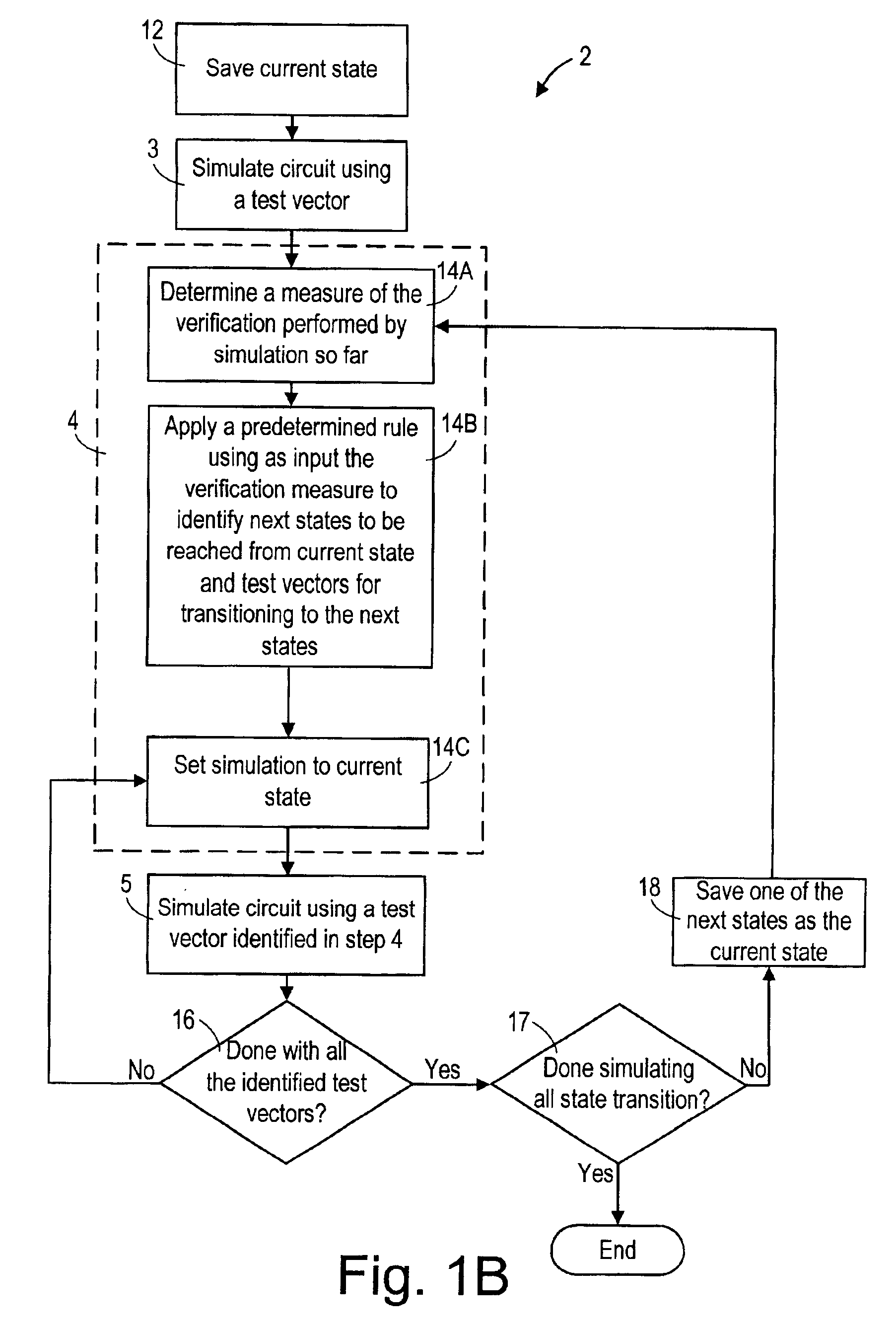

Method for automatically searching for functional defects in a description of a circuit

InactiveUS6885983B1Effective simulationEliminate needElectronic circuit testingDetecting faulty computer hardwareState switchingComputer science

A programmed computer searches for functional defects in a description of a circuit undergoing functional verification in the following manner. The programmed computer simulates the functional behavior of the circuit in response to a test vector, automatically restores the state of the simulation without causing the simulation to pass through a reset state, and then simulates the functional behavior of the circuit in response to another test vector. A predetermined rule can be used to identify test vectors to be simulated, and the predetermined rule can depend upon a measure of functional verification, including the number of times during simulation when a first state transition is performed by a first controller at the same time as a second state transition is performed by a second controller. During simulation of the test vectors, manually generated tests or automatically generated checkers can monitor portions of the circuit for defective behavior.

Owner:MENTOR GRAPHICS CORP

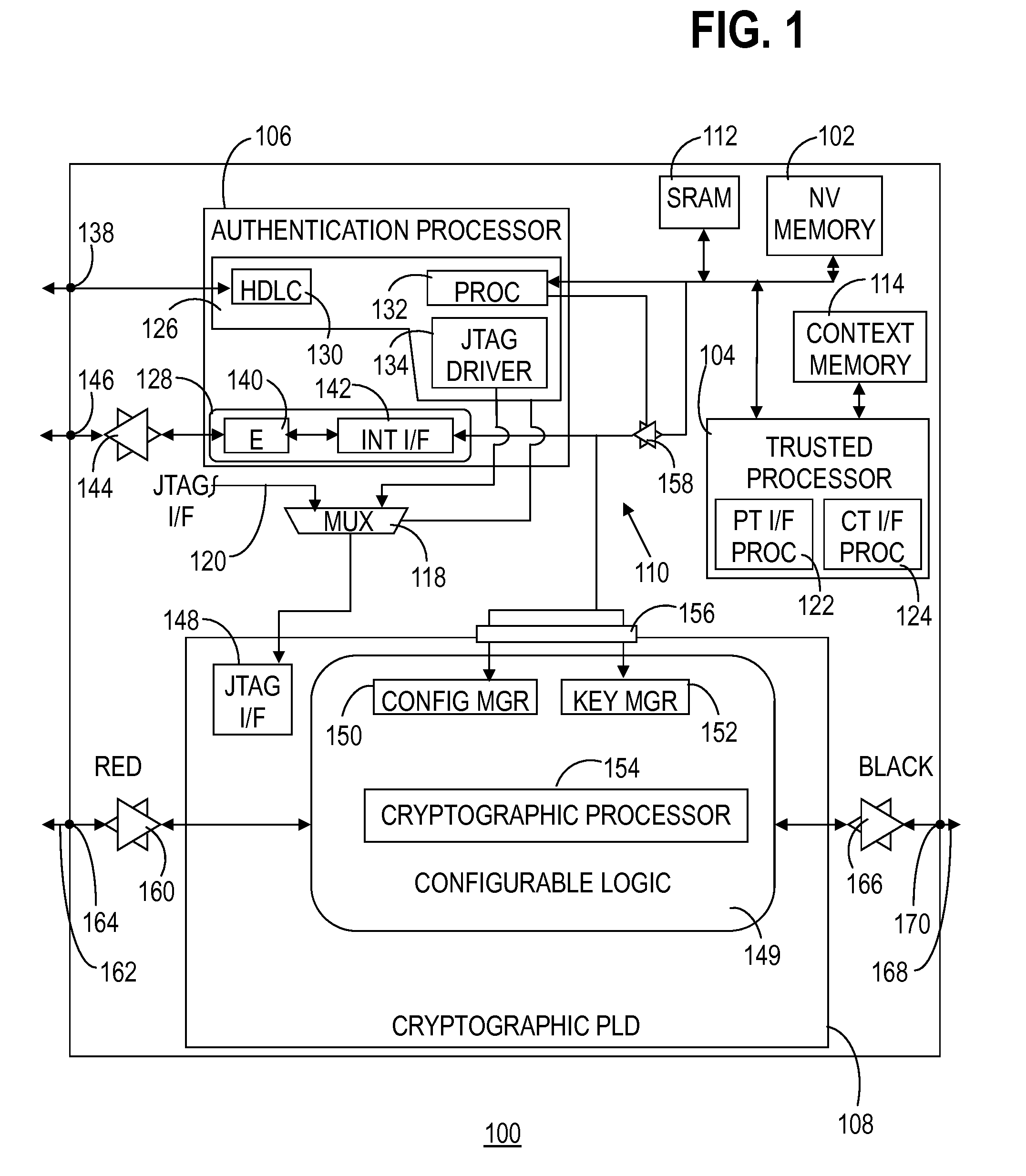

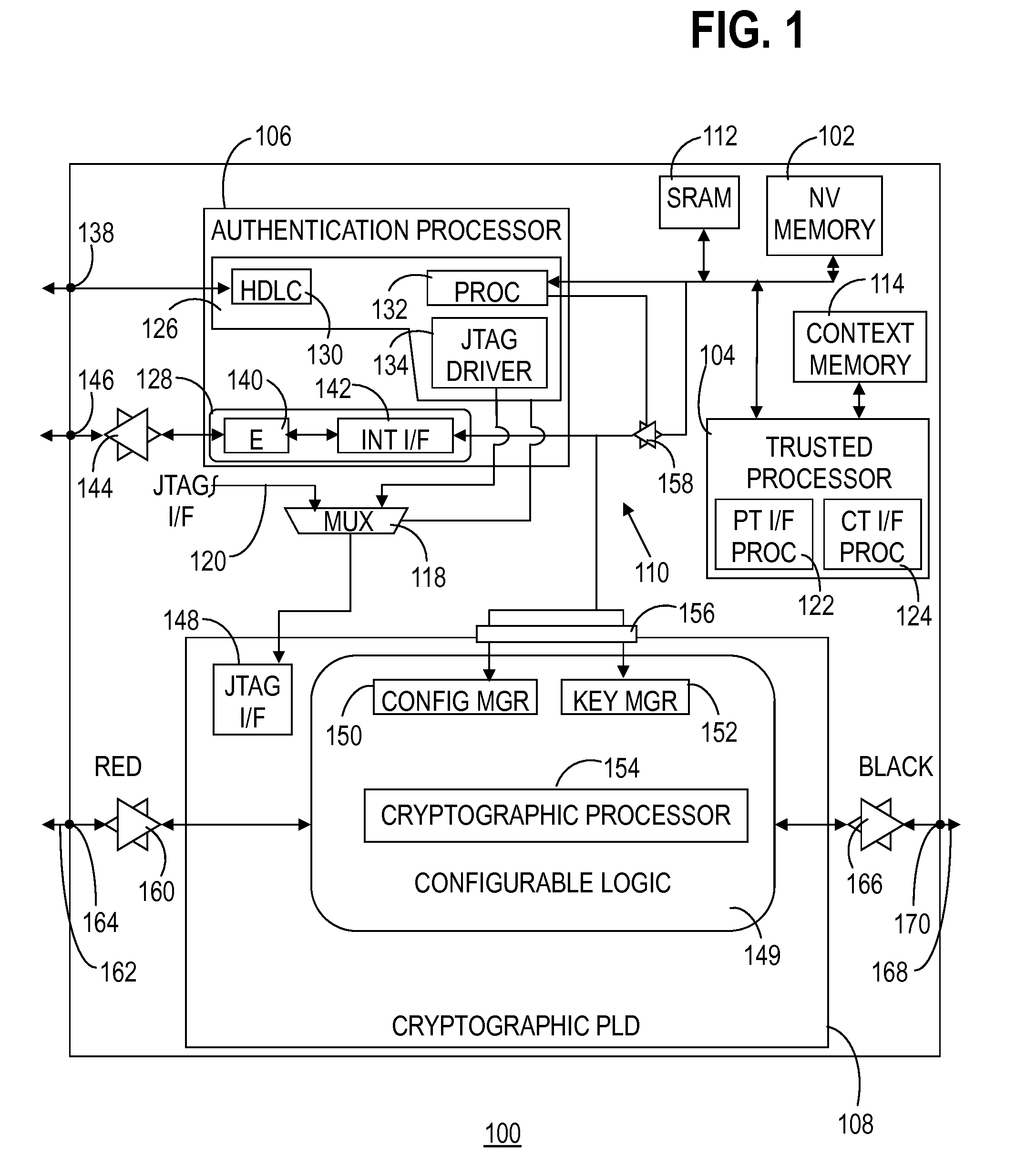

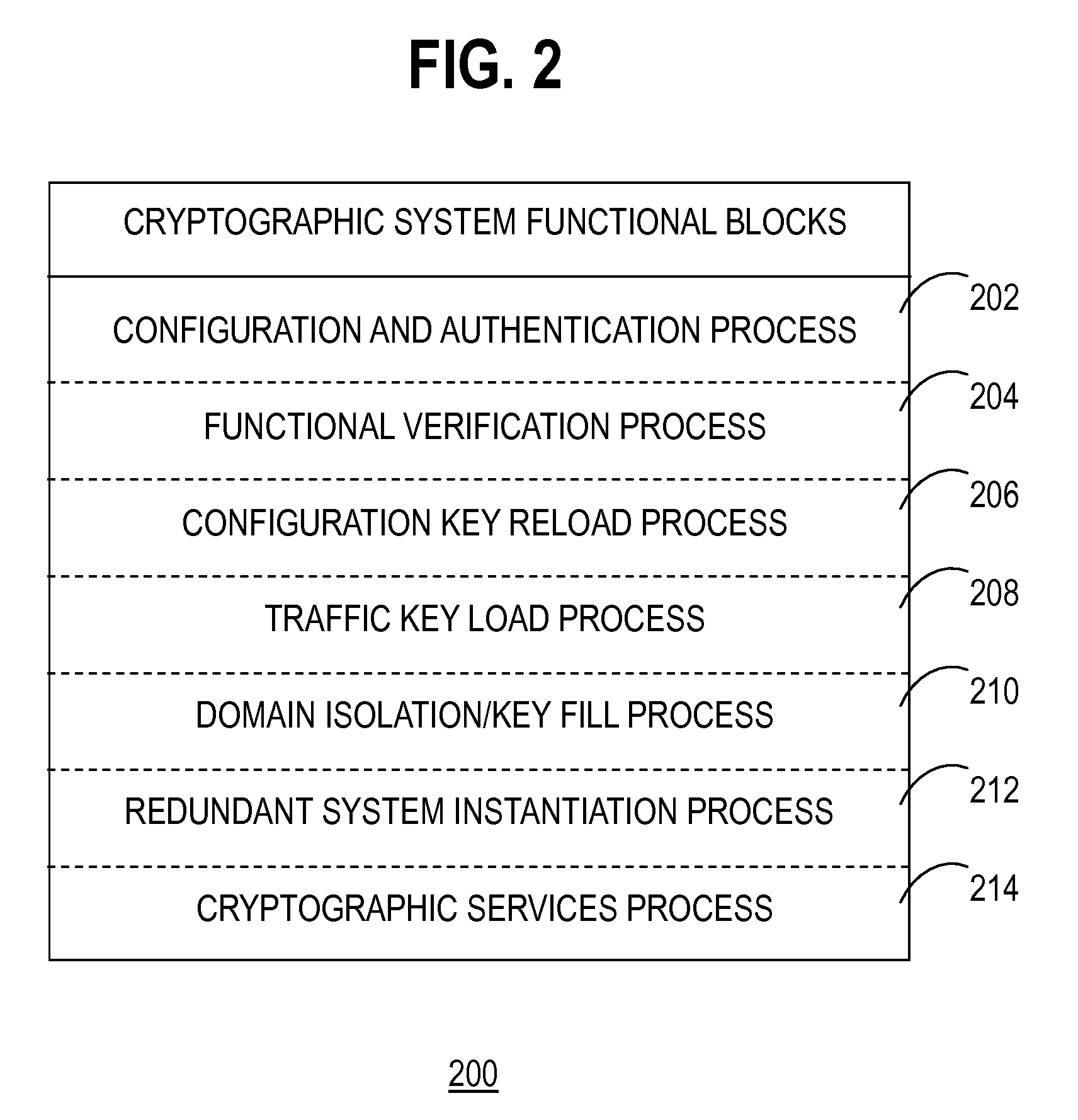

Secure configuration of programmable logic device

ActiveUS20100125739A1Encryption apparatus with shift registers/memoriesUnauthorized memory use protectionProgrammable logic deviceSingle chip

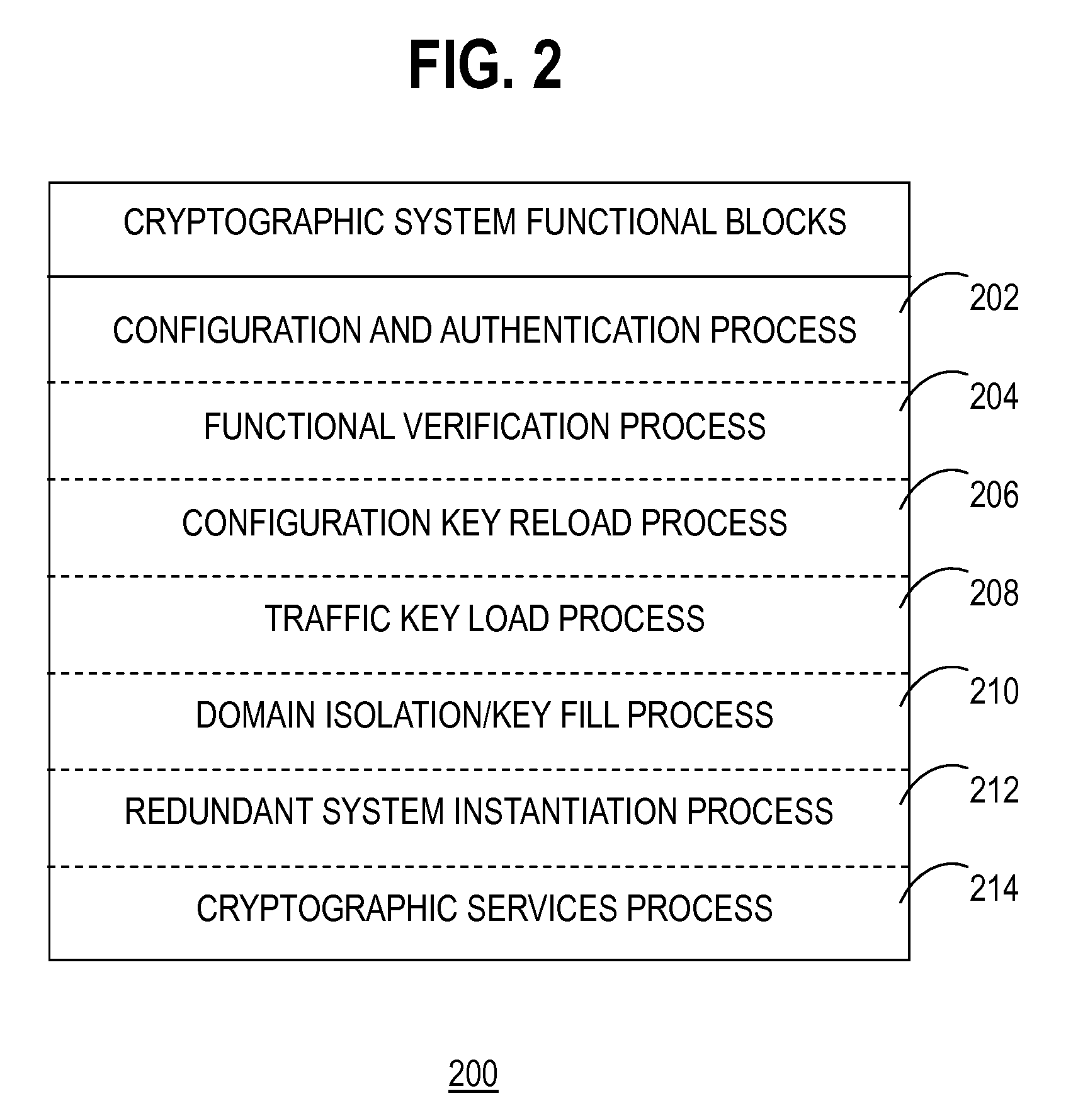

A cryptographic system (100) and methodology executable within the cryptographic system (100) enable the use of a programmable logic device PLD (108) in a single chip cryptographic design flow for secure cryptographic services. Methodology for secure configuration of the PLD (108) within a cryptographic system 100 entails secure configuration and authentication (202), functional verification (204), configuration key reload capability (206), traffic key load capability (208) using a split key technique, isolation between command and key fill domains for secure key fill (210) of key material, redundant system instantiation (212), and high speed comparison for secure operation.

Owner:GENERAL DYNAMICS MISSION SYST INC

Software and hardware collaborative simulation verification system and method based on FPGA

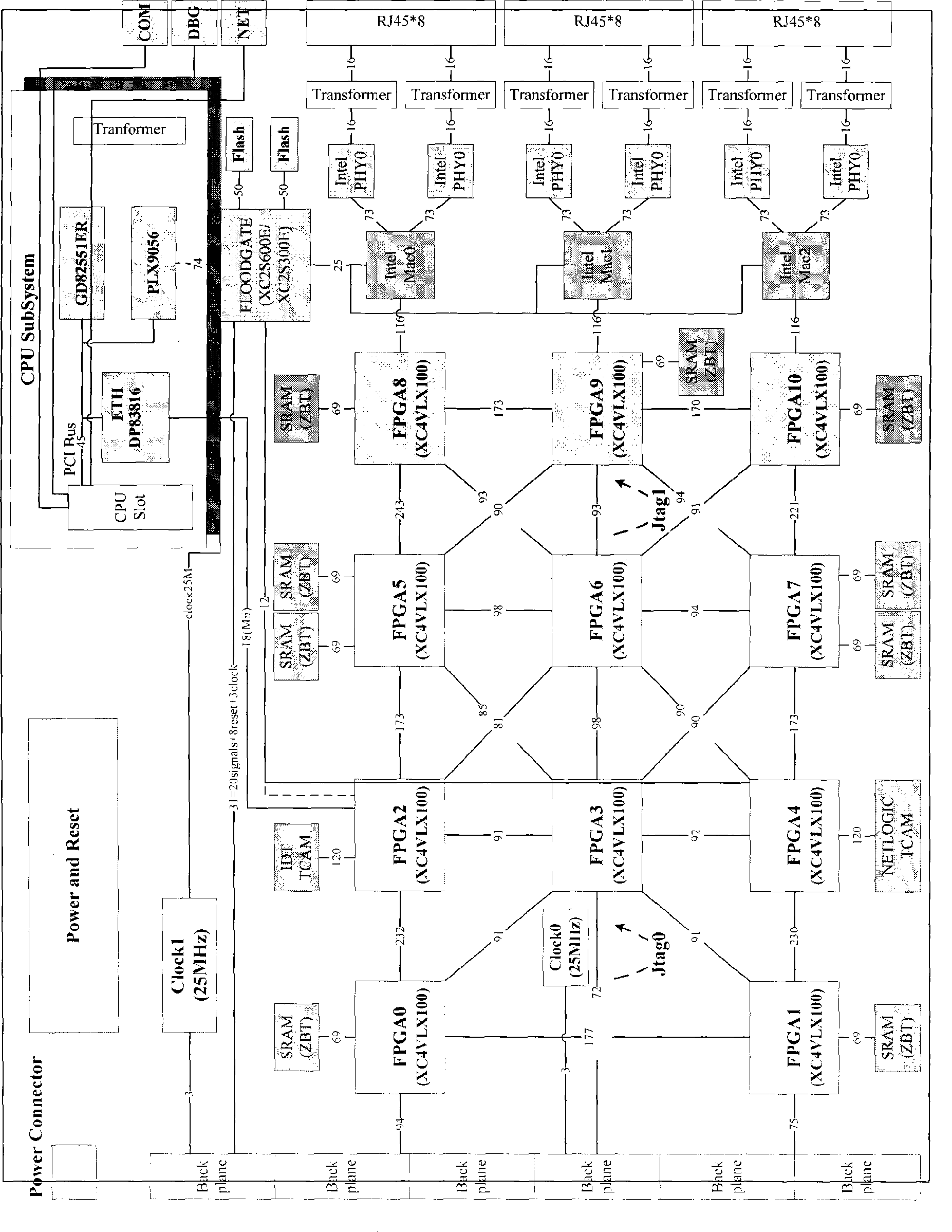

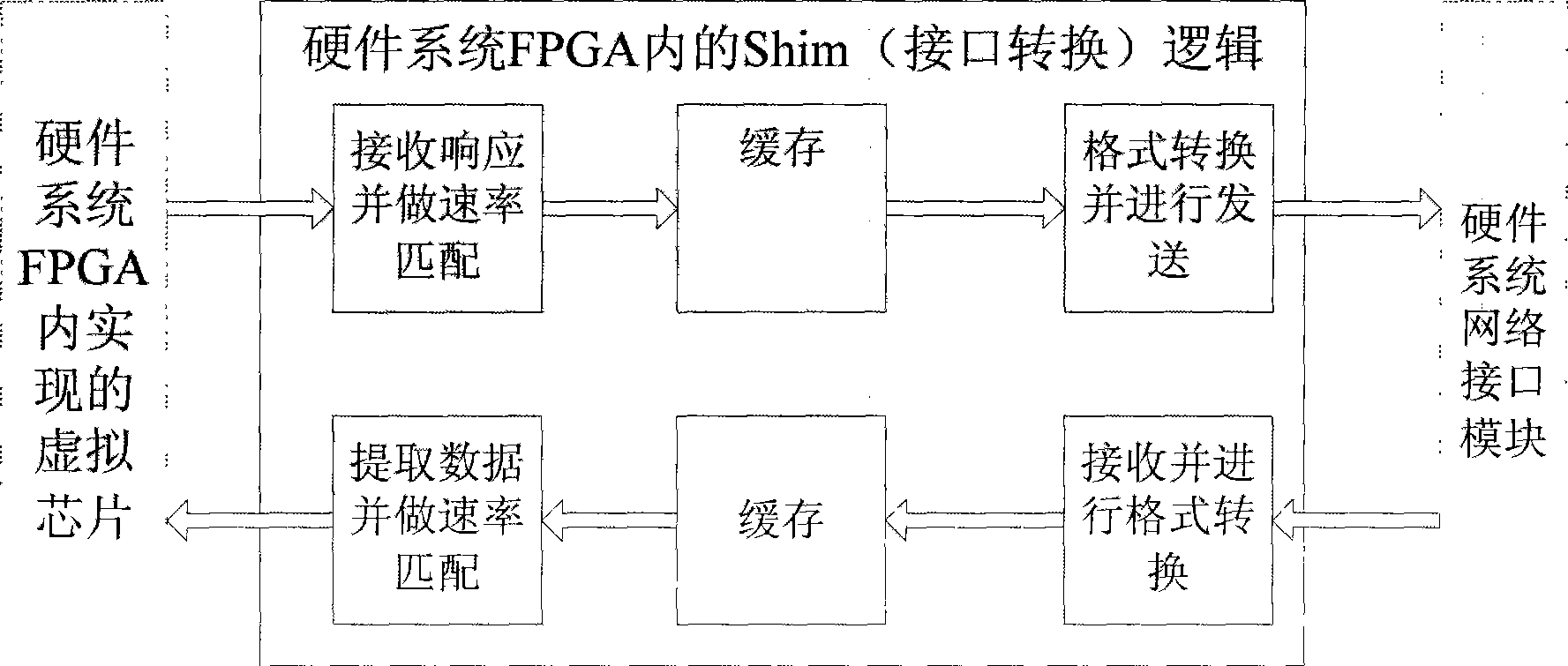

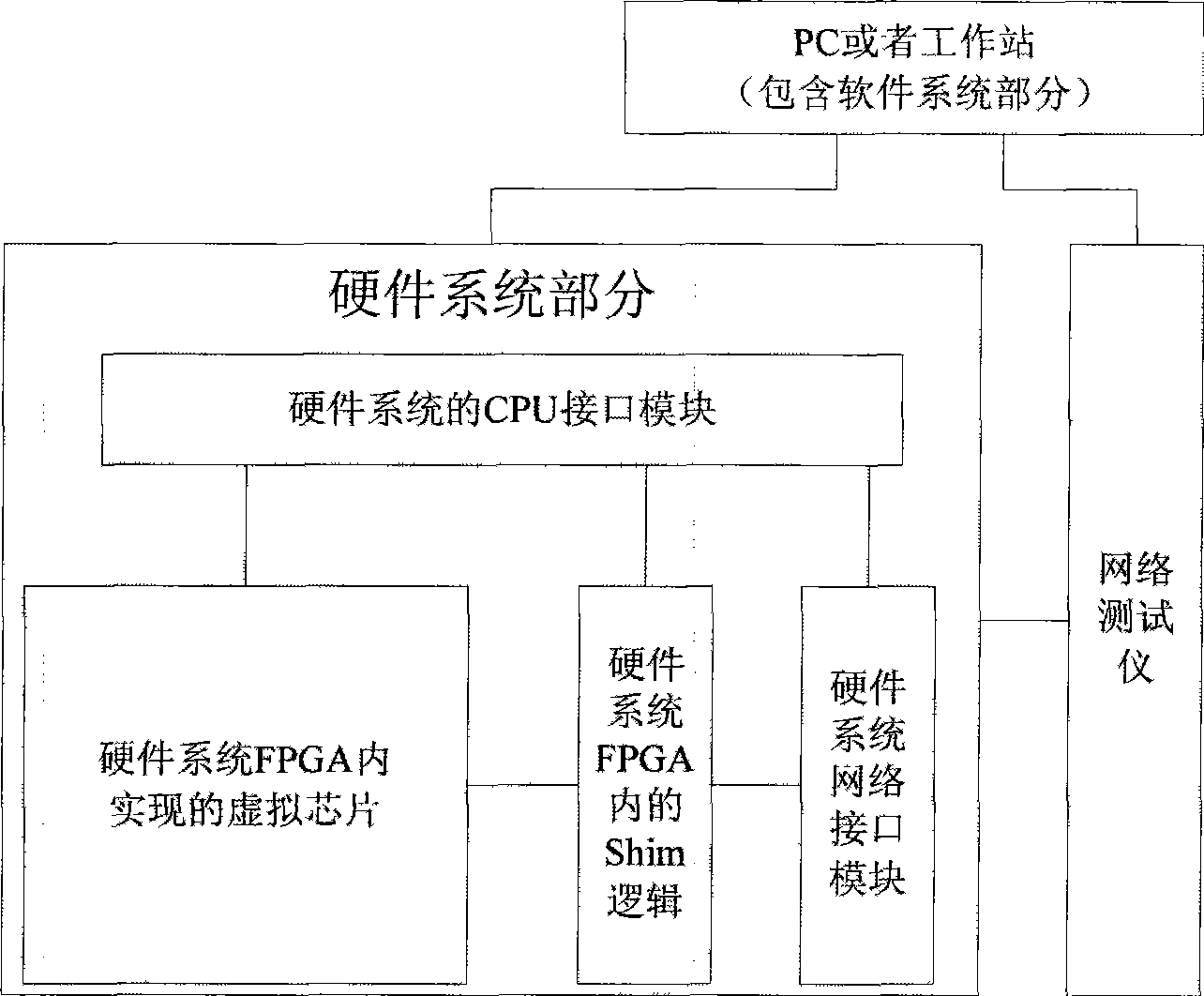

InactiveCN101499937AReduce verification timeShorten the timeData switching networksSpecial data processing applicationsSoftware systemTester device

The invention relates to a software and hardware co-emulation verification system based on FPGA and a method thereof. The system comprises a network tester, a software system part which is arranged on an user PC terminal and a hardware system part used for simulating an integrated circuit chip; wherein, the software system part comprises a controlling platform of the network tester and an embedded system interface module; the hardware system part comprises a CPU interface module, an interface converter logic module in FPGA, a virtual waiting-for-testing module and a network interface module which can be used for realizing data exchanging between the interface converter logic module and the controlling platform of the network tester. The method is formed on the basis of the systems. The software and hardware co-emulation verification system based on FPGA and the method thereof have the advantages of being capable of carrying out high-speed emulation, greatly saving the time consumption for testing, realizing the whole-chip and whole-function verification and supporting the testing of a plurality of varieties of chips; simultaneously, the invention also has good physical expandability, adopts good debugging tools and further increases the emulation verification efficiency.

Owner:SUZHOU CENTEC COMM CO LTD

Functional verification system

InactiveUS20030041308A1CAD circuit designSoftware simulation/interpretation/emulationStatic random-access memoryComputer architecture

A functional verification system suited for verifying the function of non-cycle based integrated circuits (IC) design. The IC design is divided into a plurality of combinatorial blocks connecting sequential elements. Truth tables corresponding the divided blocks are computed and stored in a memory. The output values of the IC design are determined by evaluating the blocks. The evaluation typically entails one memory access as the truth tables are pre-computed and stored in a memory storage. Accordingly the output values are computed quickly. The storage is implemented using random access memories and a XCON is designed to ensure the dependencies are preserved during the evaluations.

Owner:EVE

Semiconductor integrated circuit, circuit function veryfication device and method of veryfying circuit function

InactiveUS20100251043A1Detecting faulty computer hardwareStatic storageComputer scienceBuilt-in self-test

A semiconductor integrated circuit has a data generation circuit configured to generate first data used for function verification of a built-in self test circuit and a built-in redundancy allocation circuit of a memory, a failure data generation circuit configured to generate second data for conducting a built in self test by inverting at least one bit of the first data based on a failure injection indication signal, and a timing circuit configured to adjust timing of at least one of the first and the second data in order to use one of the first and the second data as writing data to the memory and to use the other as an output expected value compared with data read out from the memory.

Owner:KK TOSHIBA

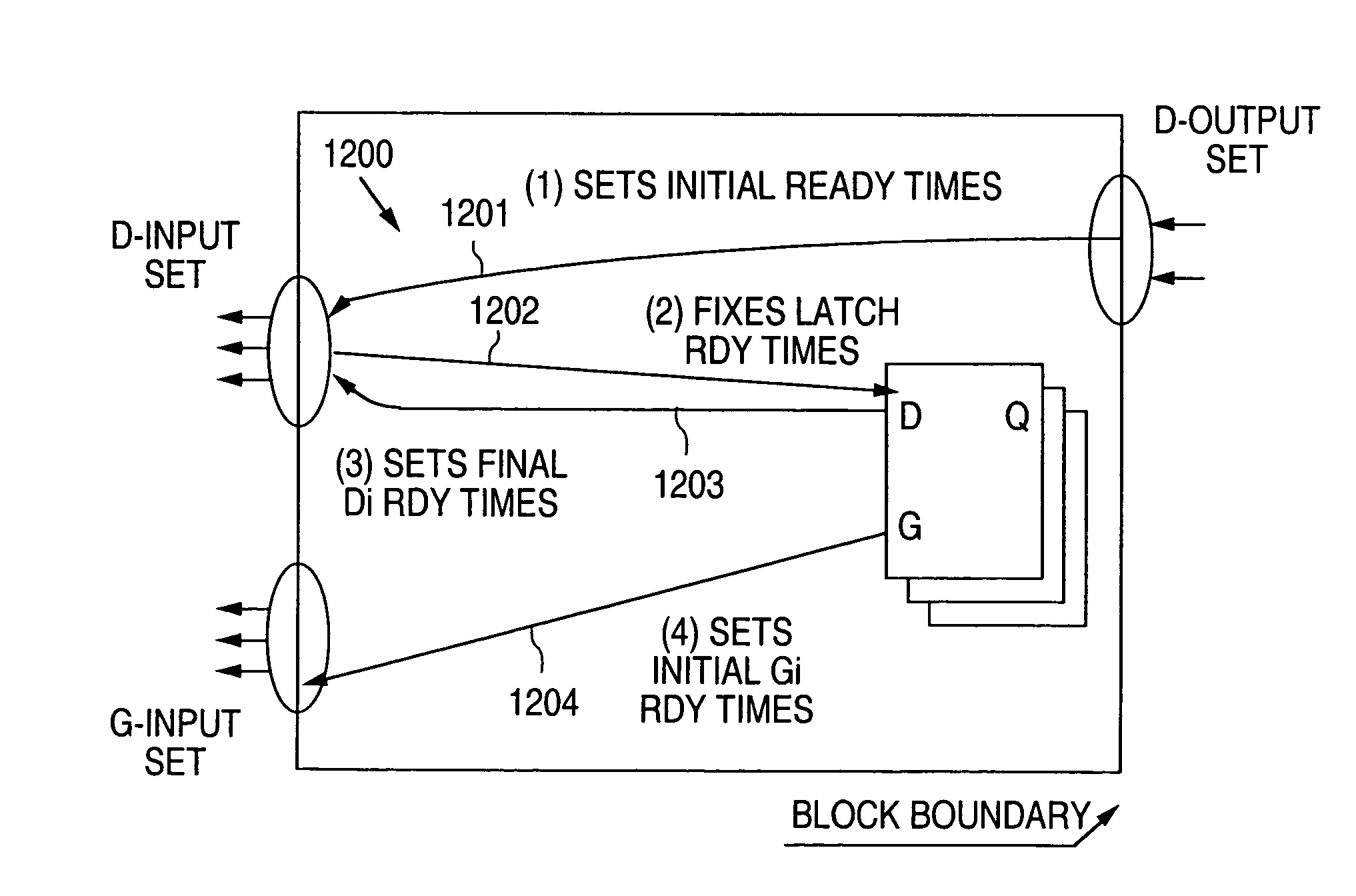

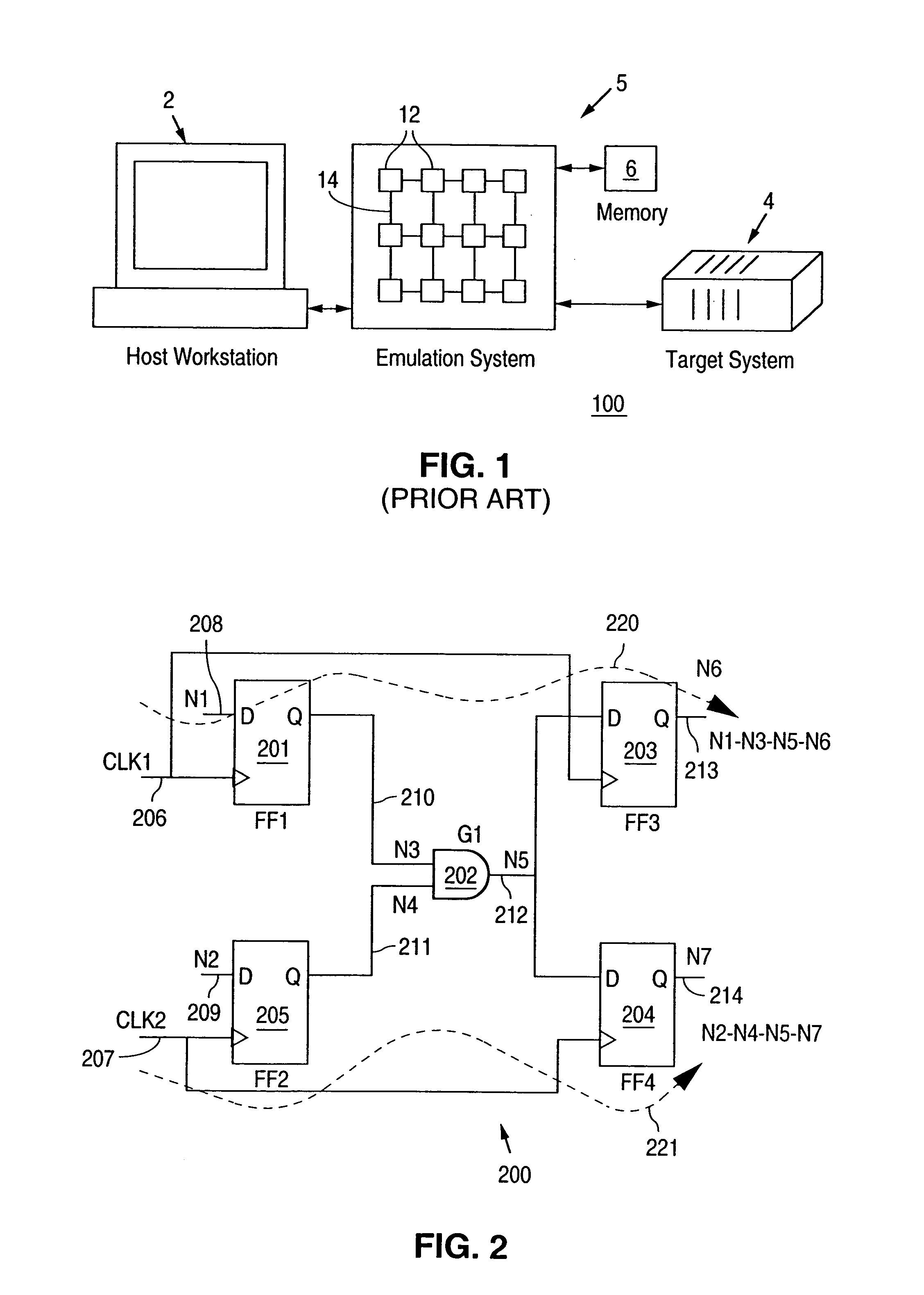

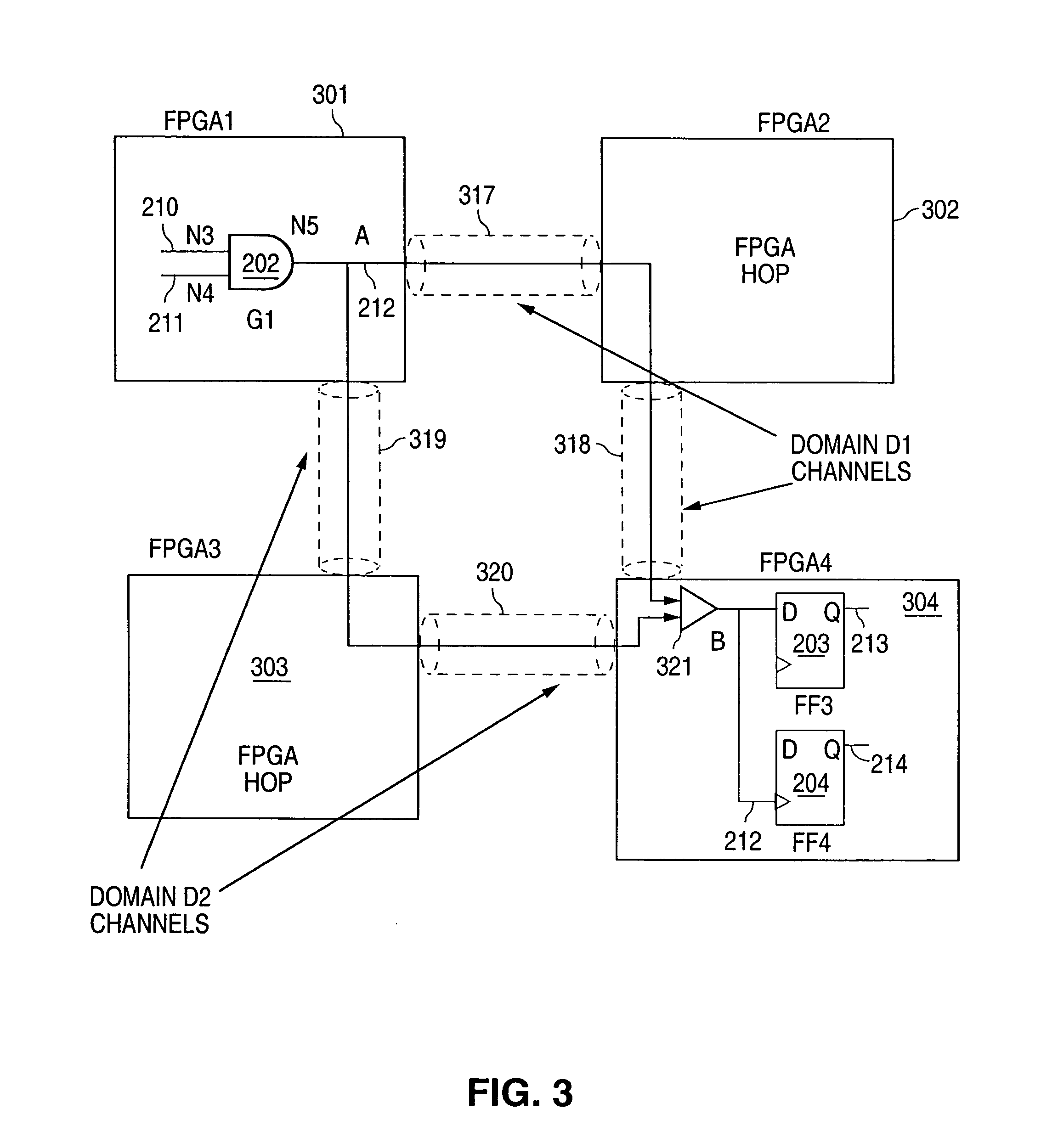

Functional verification of logic and memory circuits with multiple asynchronous domains

ActiveUS7143377B1Precise transportationConvenient ArrangementComputer aided designSoftware simulation/interpretation/emulationMemory circuitsCausality

In an emulation system, a method is provided to schedule evaluations of state elements and memory elements receiving signals from multiple asynchronous clock domains, such that causality and hold time requirements are satisfied. In addition, a method is provided such that logic signals responsive to multiple asynchronous clock domains are transported along separate single domain path of substantially equal transit times. In one implementation, the scheduling method computes departure times and ready times for output and input terminals of logic modules, such as FPGAS.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

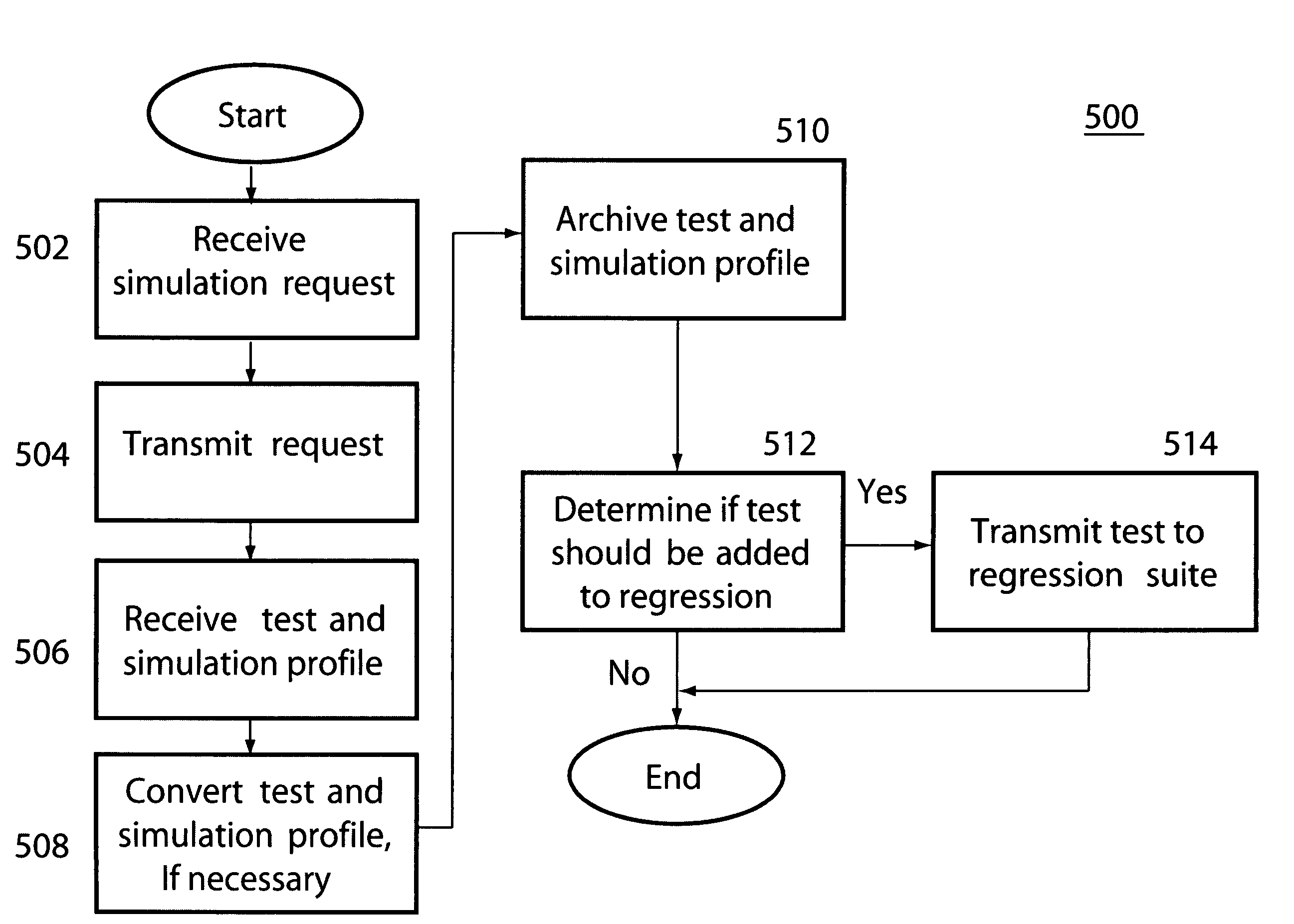

Methods, systems, and media for management of functional verification

InactiveUS7278056B2Detecting faulty computer hardwareElectrical testingRegression testingComputer architecture

Methods, systems and media for management of functional verification of a system are disclosed. One embodiment may be directed to methods, systems and media for management of functional verification of a computer system, such as a processor or IC chip. Embodiments may include a verification manager for user input and a functional verification database for centralized storage of functional verification information. Embodiment may also include a coverage analysis environment that receives test information from a simulation and test generation environment, converts it if necessary, and selectively stores information in the functional verification database. In a further embodiment, a harvest module determines whether a test should be saved for future regression testing, and tests that add to functional coverage are added to a regression suite.

Owner:GOOGLE LLC

Secure configuration of programmable logic device

ActiveUS8095800B2Unauthorized memory use protectionHardware monitoringProgrammable logic deviceSingle chip

A cryptographic system (100) and methodology executable within the cryptographic system (100) enable the use of a programmable logic device PLD (108) in a single chip cryptographic design flow for secure cryptographic services. Methodology for secure configuration of the PLD (108) within a cryptographic system 100 entails secure configuration and authentication (202), functional verification (204), configuration key reload capability (206), traffic key load capability (208) using a split key technique, isolation between command and key fill domains for secure key fill (210) of key material, redundant system instantiation (212), and high speed comparison for secure operation.

Owner:GENERAL DYNAMICS MISSION SYST INC

System and apparatus for transaction data format and function verification

A system for processing transaction data is provided. The system includes a transaction data format system receiving transaction data and generating transaction data format error data, such as when the transaction data is not in compliance with a transaction data format. The system also includes a transaction data rules system receiving the transaction data and generating transaction rule error data, such as when the transaction data is in the proper format but nevertheless violates a rule of one or more financial processing system.

Owner:CHASE PAYMENTECH SOLUTIONS

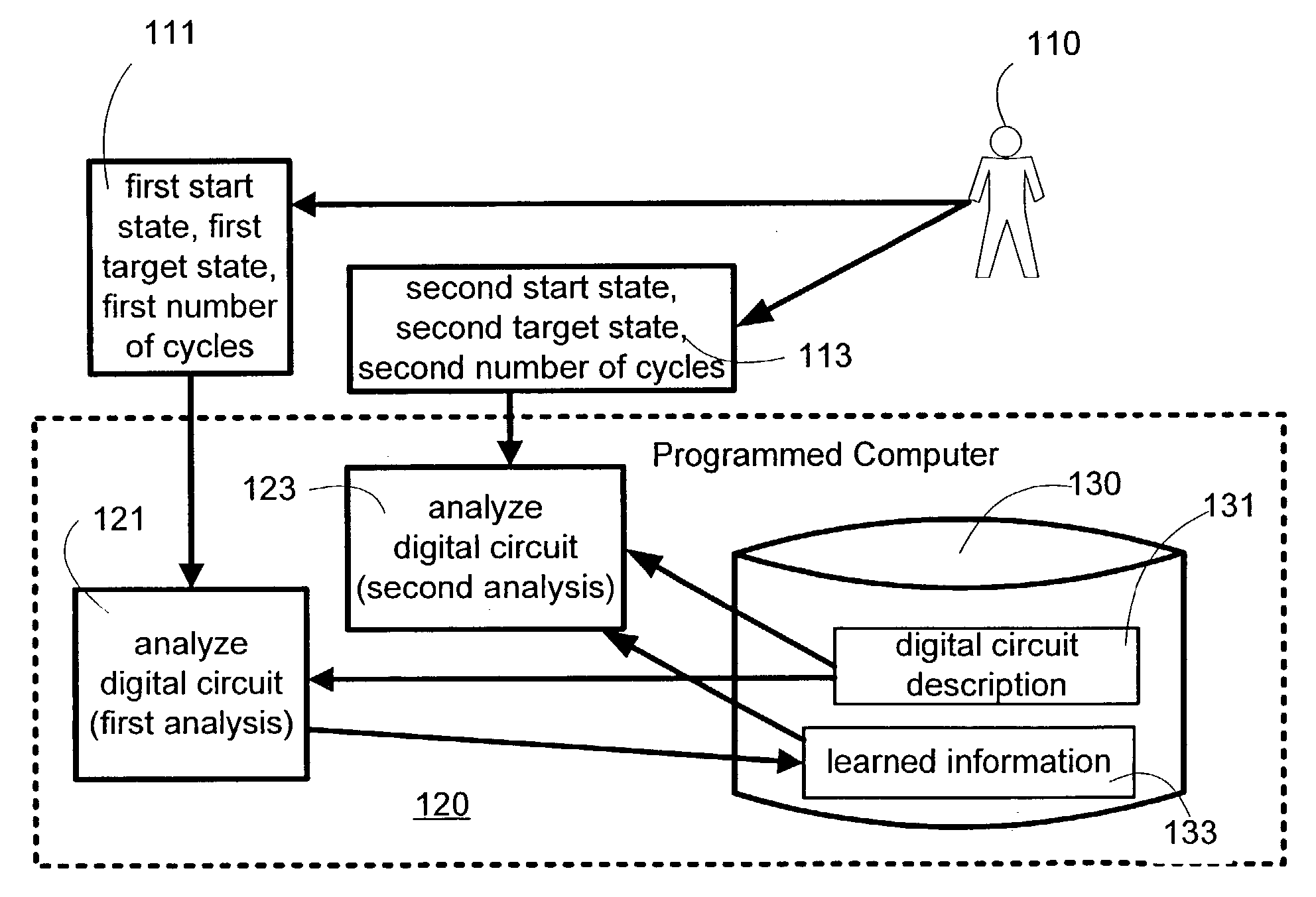

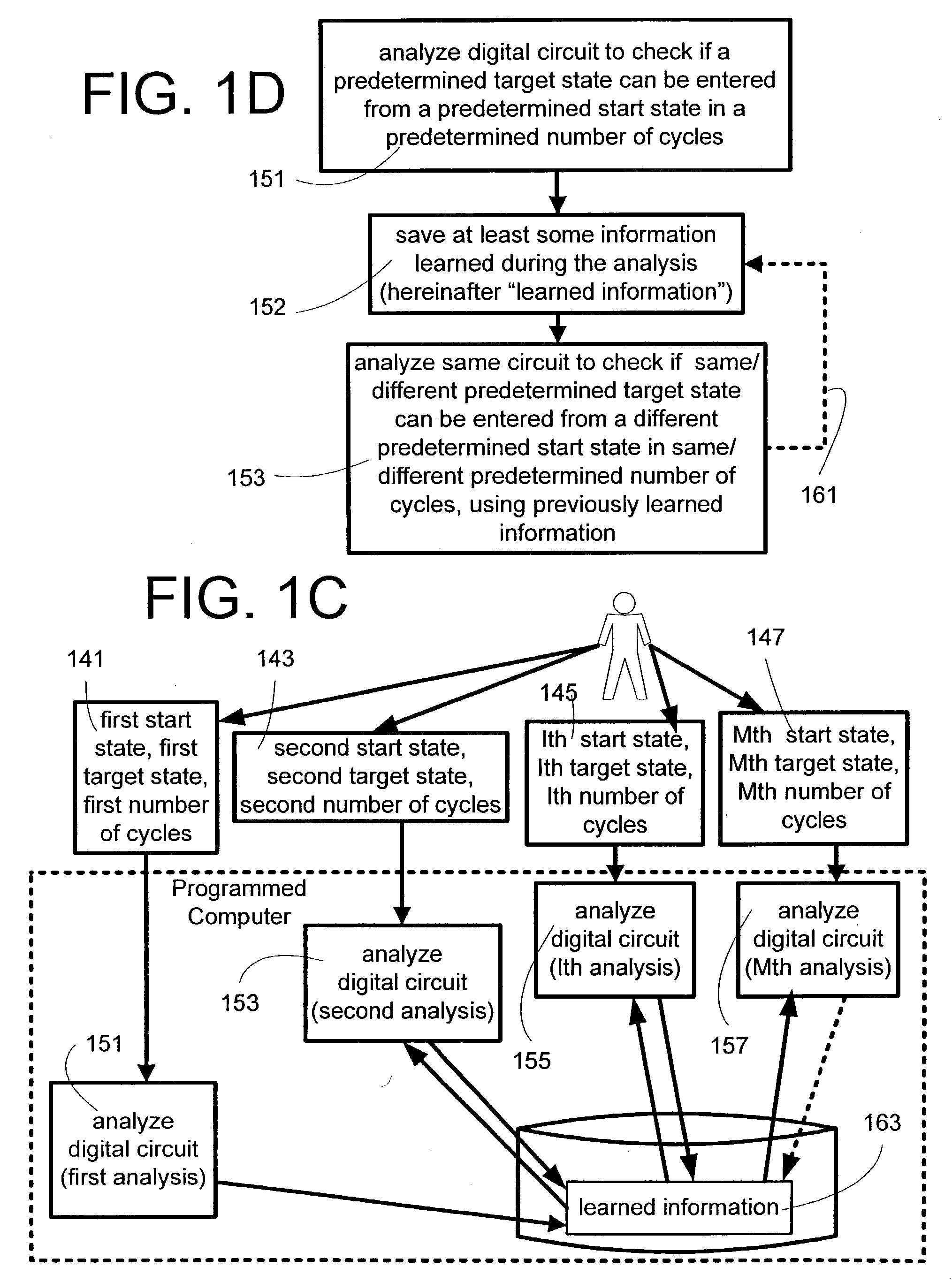

Reuse of learned information to simplify functional verification of a digital circuit

InactiveUS20070299648A1Easy to analyzeProgram controlComputer aided designComputer scienceFunctional verification

A computer is programmed in accordance with the invention to automatically analyze a digital circuit, to check if the digital circuit can enter a target state starting from a start state, by reusing information learned during a another analysis, checking if the same digital circuit can enter the same or different target state from a different start state. Use of learned information in accordance with the invention simplifies the analysis of the digital circuit (e.g. by allowing skipping one or more analysis acts). The learned information may be stored in a database. Depending on the embodiment, the two or more analyses may check on operation of the digital circuit for the same or different numbers of cycles.

Owner:MENTOR GRAPHICS CORP

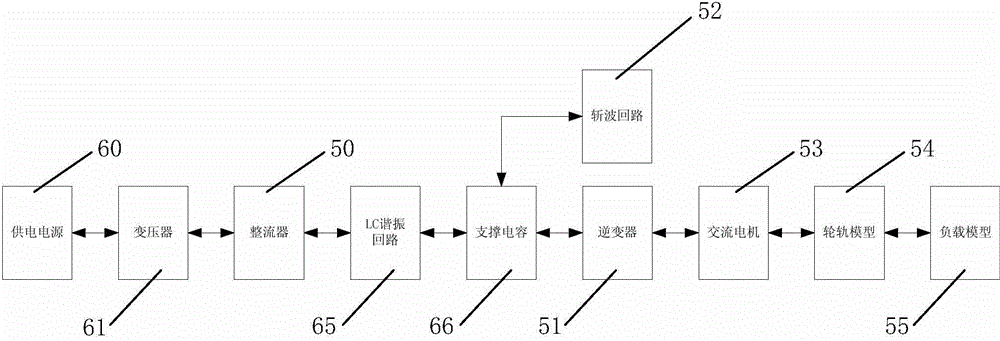

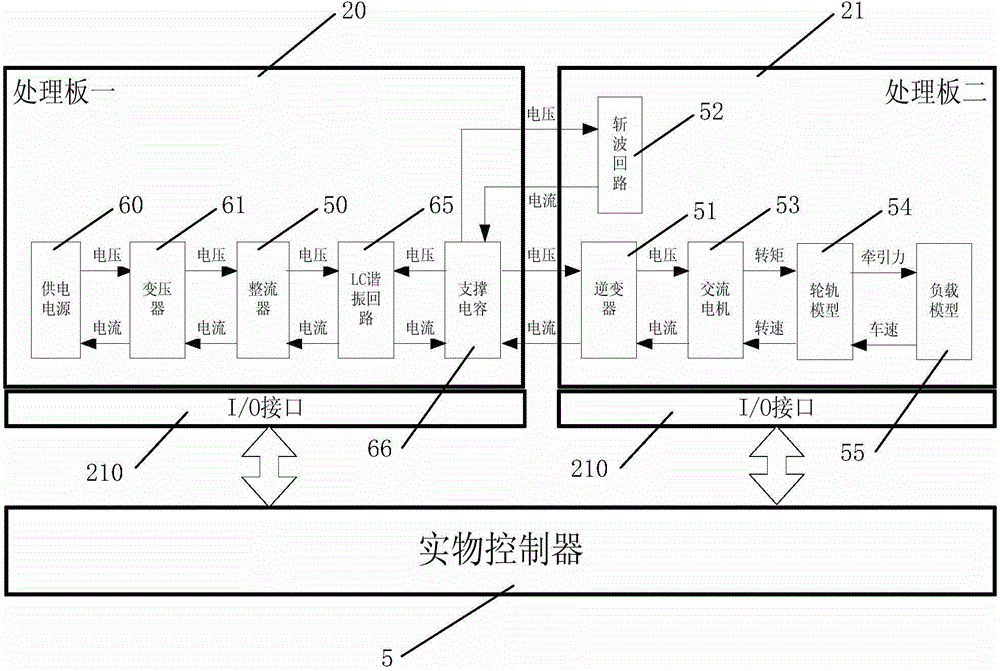

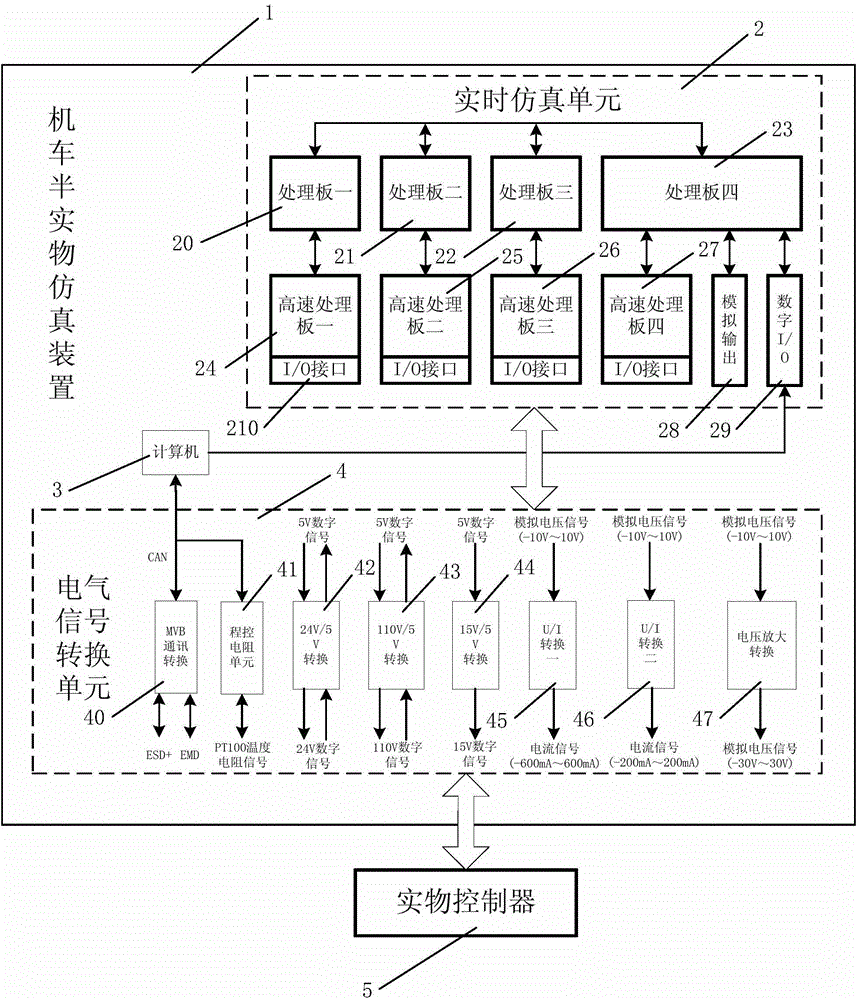

Locomotive semi-physical simulation device, system and method

ActiveCN105223832ADoes not affect the real-time performance of the simulationScale upSimulator controlElectric testing/monitoringComputer hardwareReal-time simulation

The invention discloses a locomotive semi-physical simulation device, system and method. The device comprises a real-time simulation unit, a computer and an electrical signal conversion unit. The computer converts a control instruction for simulating an upper-layer network control system into a bus communication protocol, and then sends the bus communication protocol to a communication conversion unit of the electrical signal conversion unit. The communication conversion unit sends the control instruction to an external physical controller, the physical controller outputs a control signal to a controlled object model according to the control instruction, the control signal is sent to a real-time simulation unit via the electrical signal conversion unit, the real-time simulation unit calculates a output result of a state signal of the controlled object model according to the control signal, the output result is sent to the physical controller via the electrical signal conversion unit, and the physical controller sends the state signal of the controlled object model back to the computer via the communication conversion unit. The technical problems that simulation integrity and precision of an existing system are not high, function verification cannot be accurately performed, the modification period is long, and efficiency and performability are low are solved.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

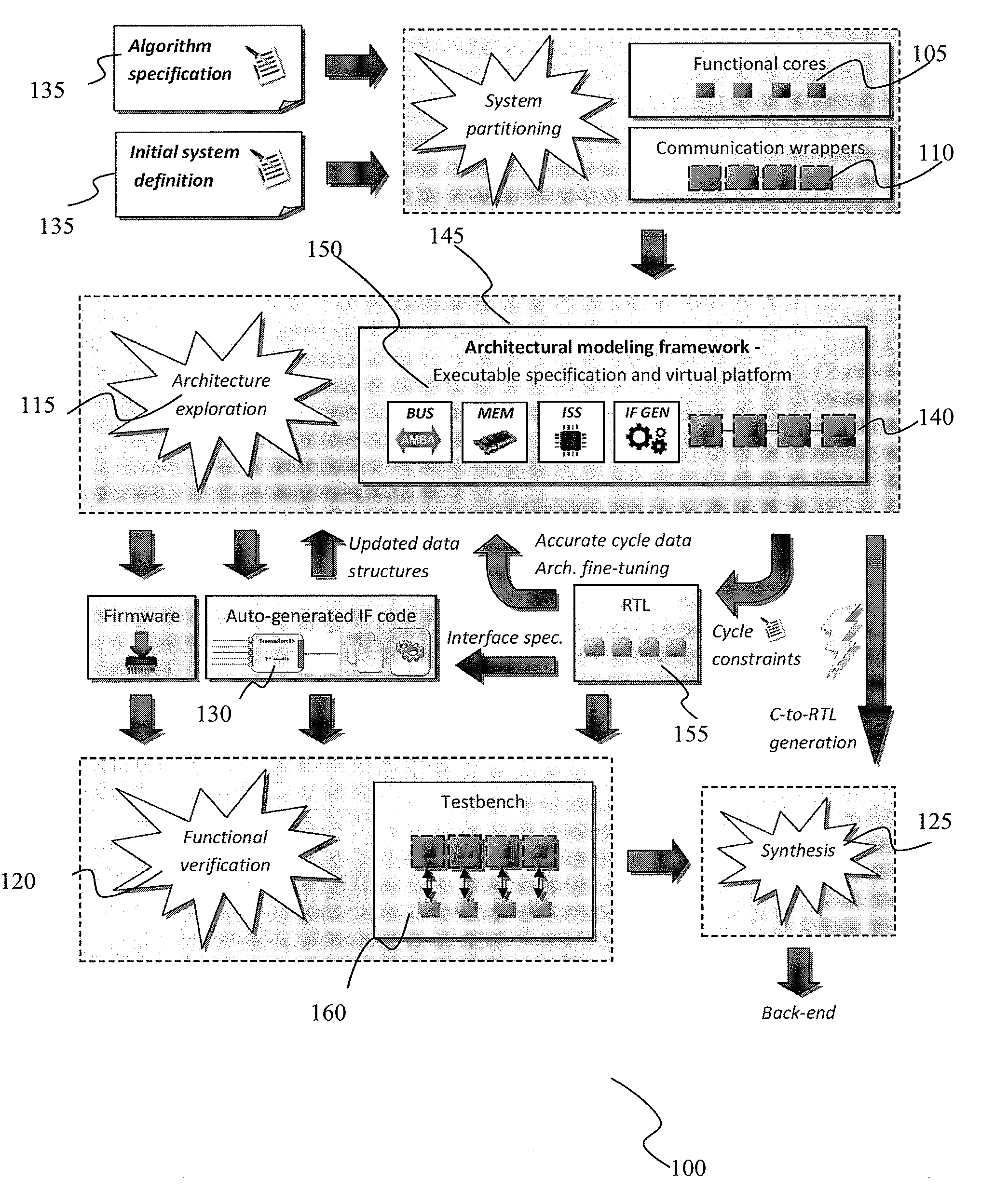

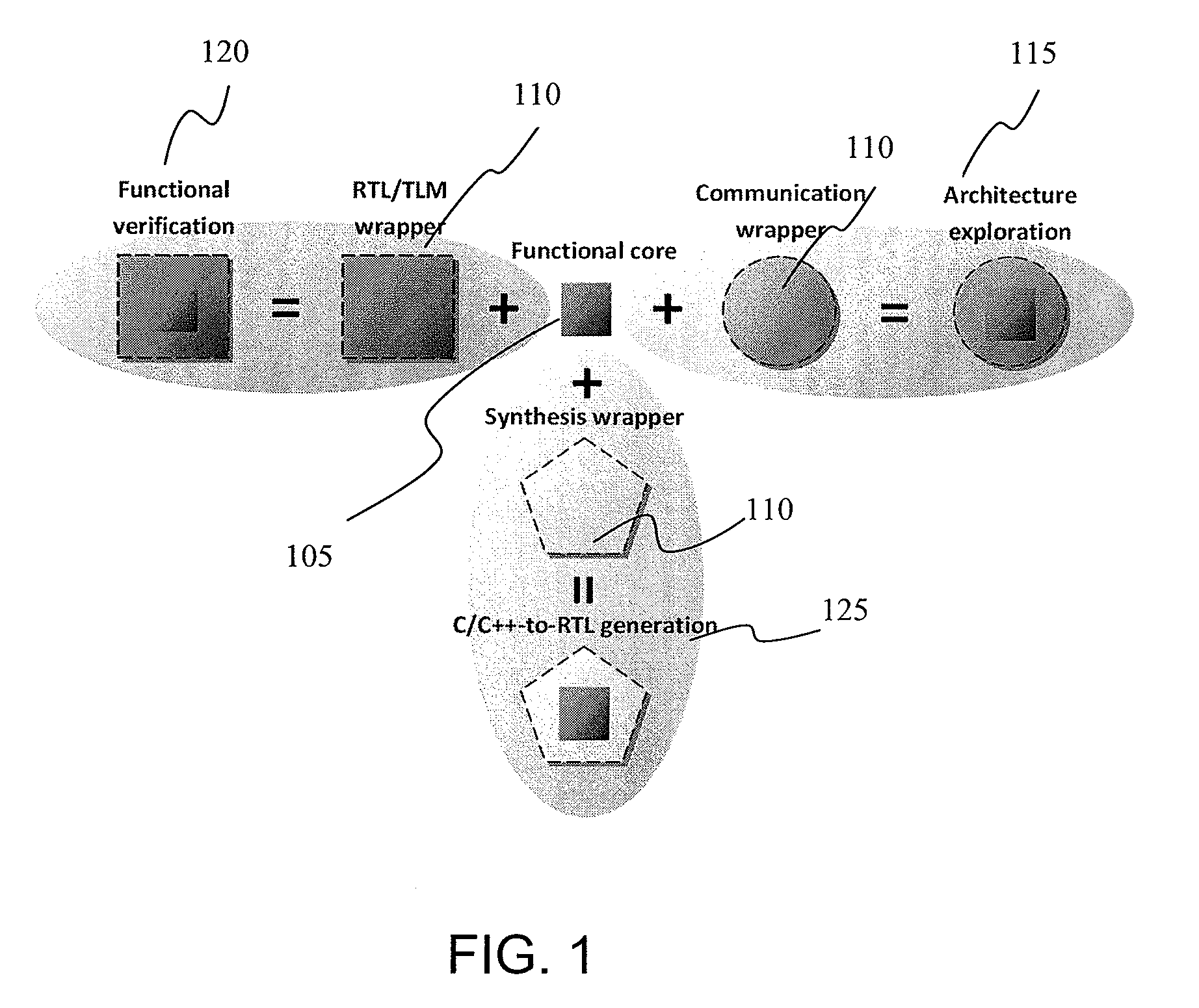

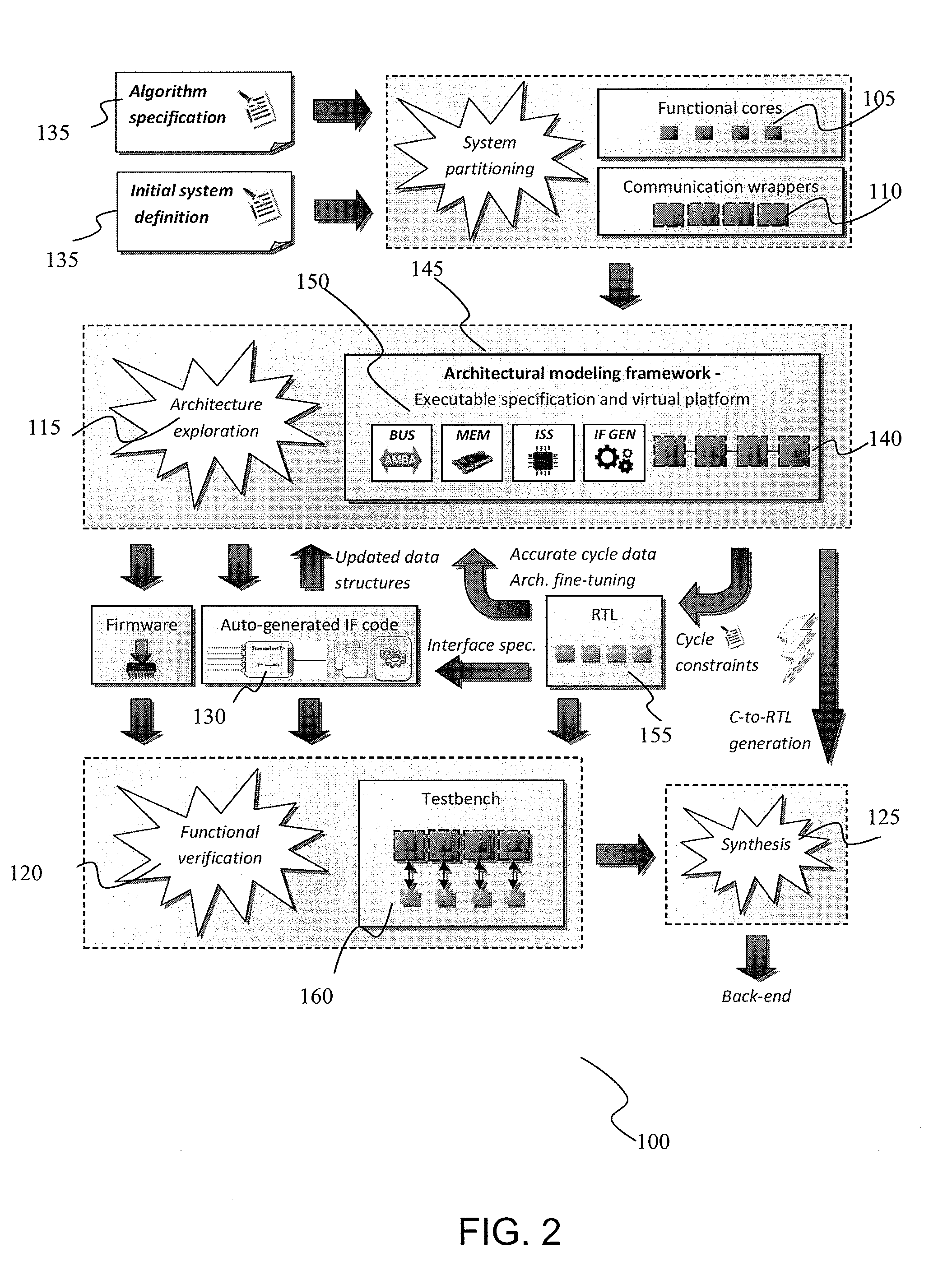

Integrated Circuit Modeling Method and Framework Tool

ActiveUS20110041106A1Easy to planImprove ease of useDetecting faulty computer hardwareCAD circuit designComputer architectureLanguage module

An integrated circuit modeling method 100 implementable on computer, which has an executable software model 145 having modules 140 of reusable functional cores 105 coded in a high level language and a virtual platform of the integrated circuit employable in an architecture exploration step 115. A modeling library of modules coded in high level languages and hardware level languages are provided and instantiated according to user input in a functional verification step 120 having a co-simulation environment, with interface code 170 between modules automatically generated by an interface generator 130 based on a two dimensional data array of hardware specification inputs 205, the interface code 170 further interfacing with wrappers engaged between high and hardware level language modules.

Owner:HONG KONG APPLIED SCI & TECH RES INST CO LTD A LIMITED LIABILITY

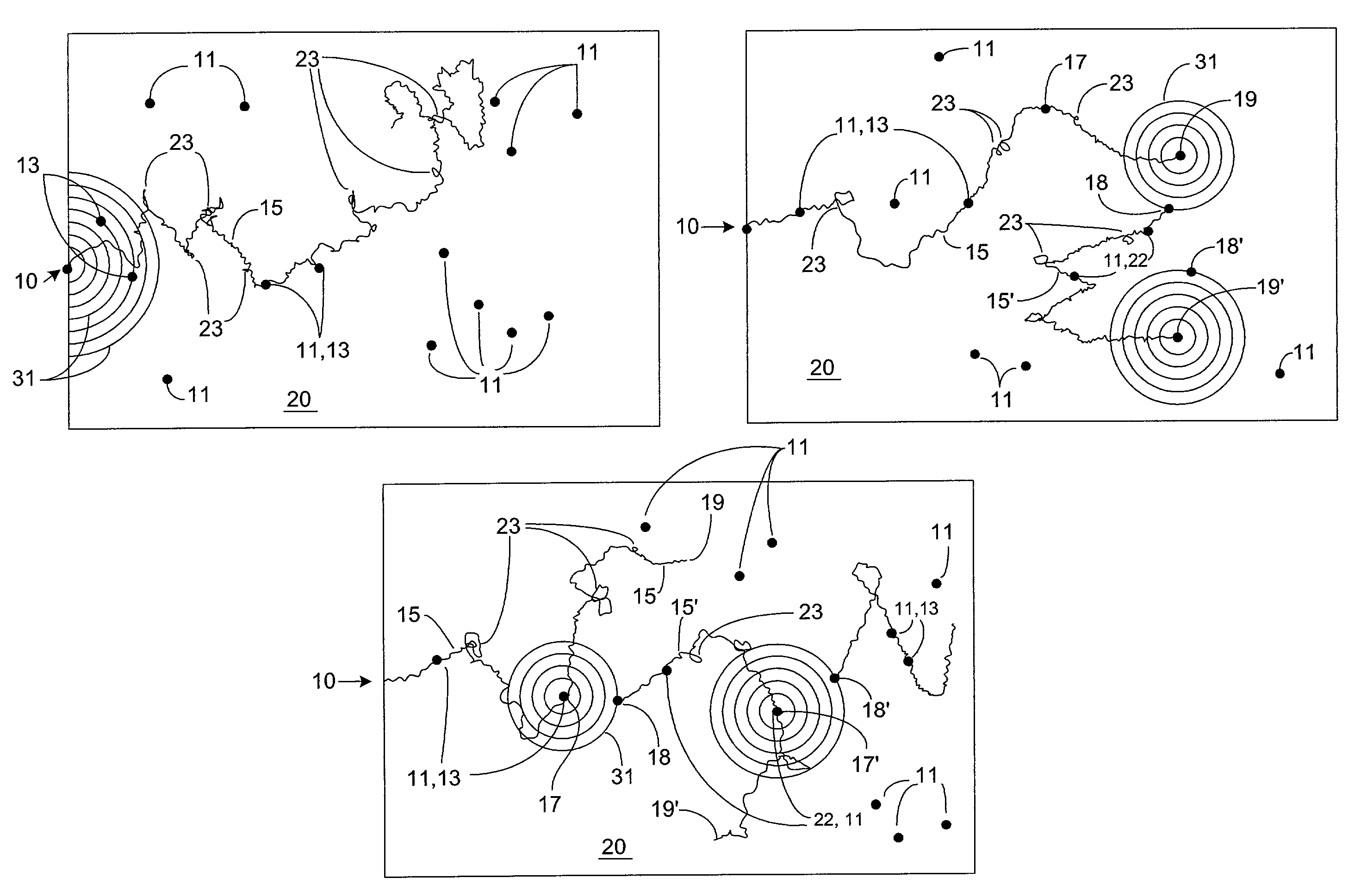

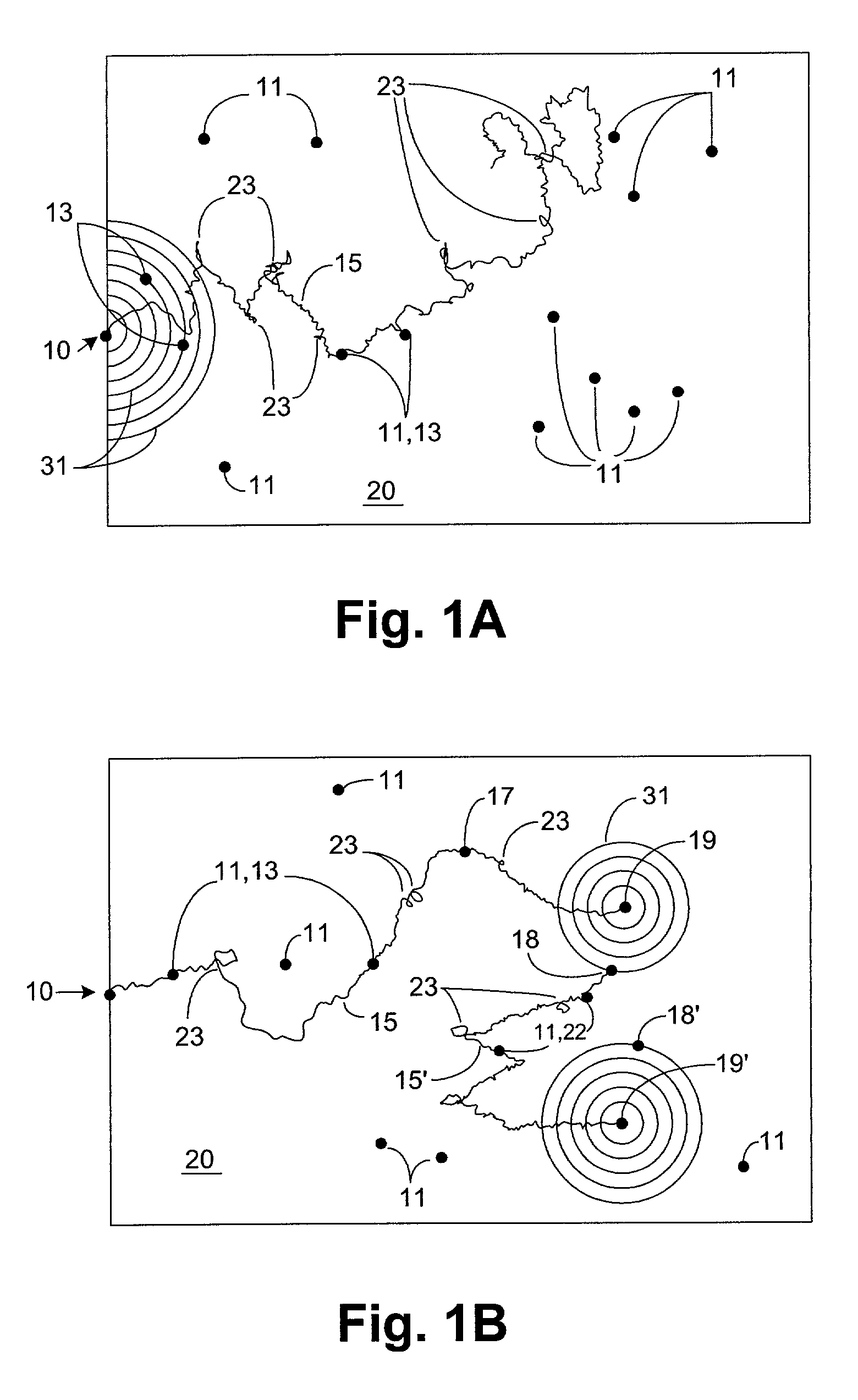

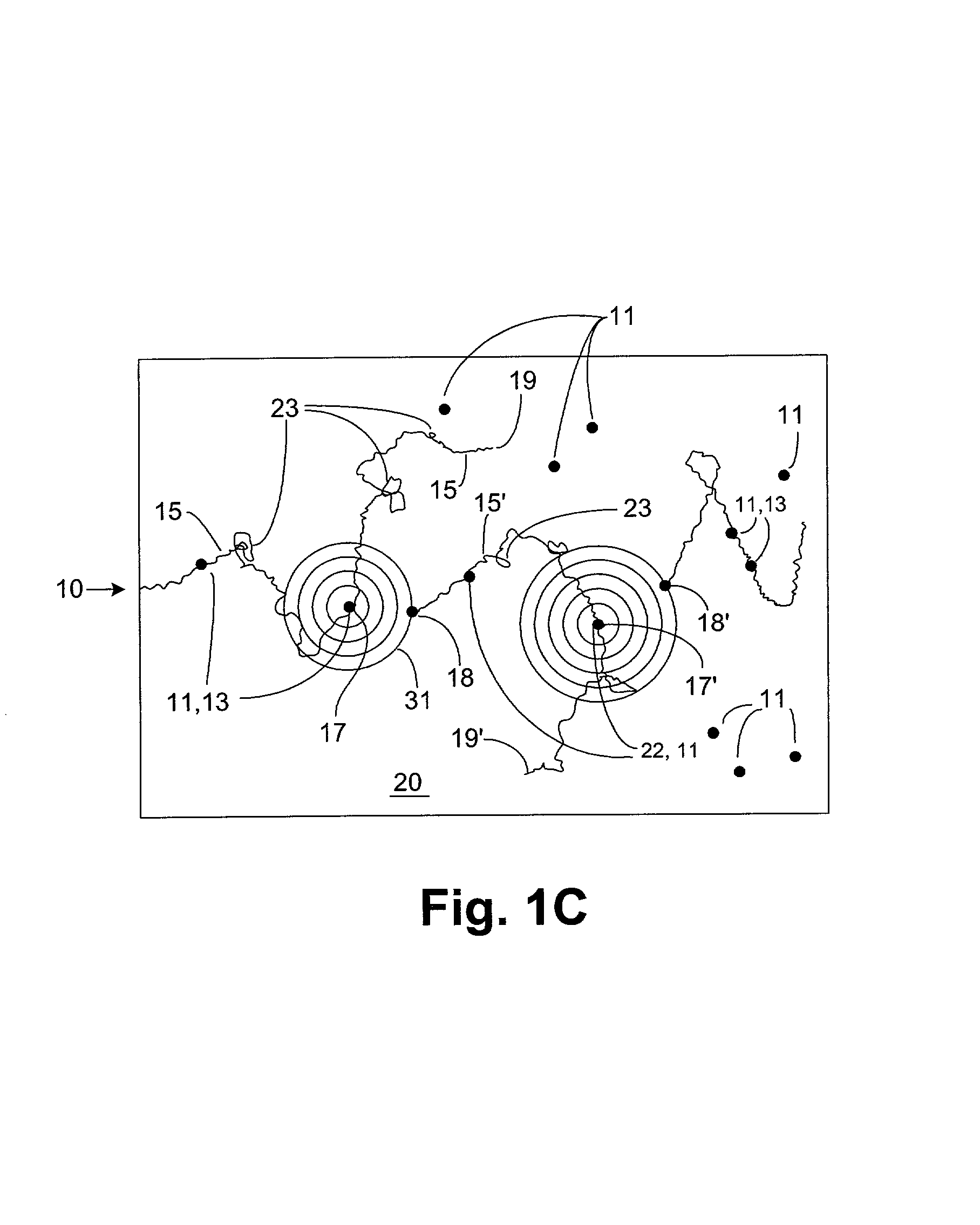

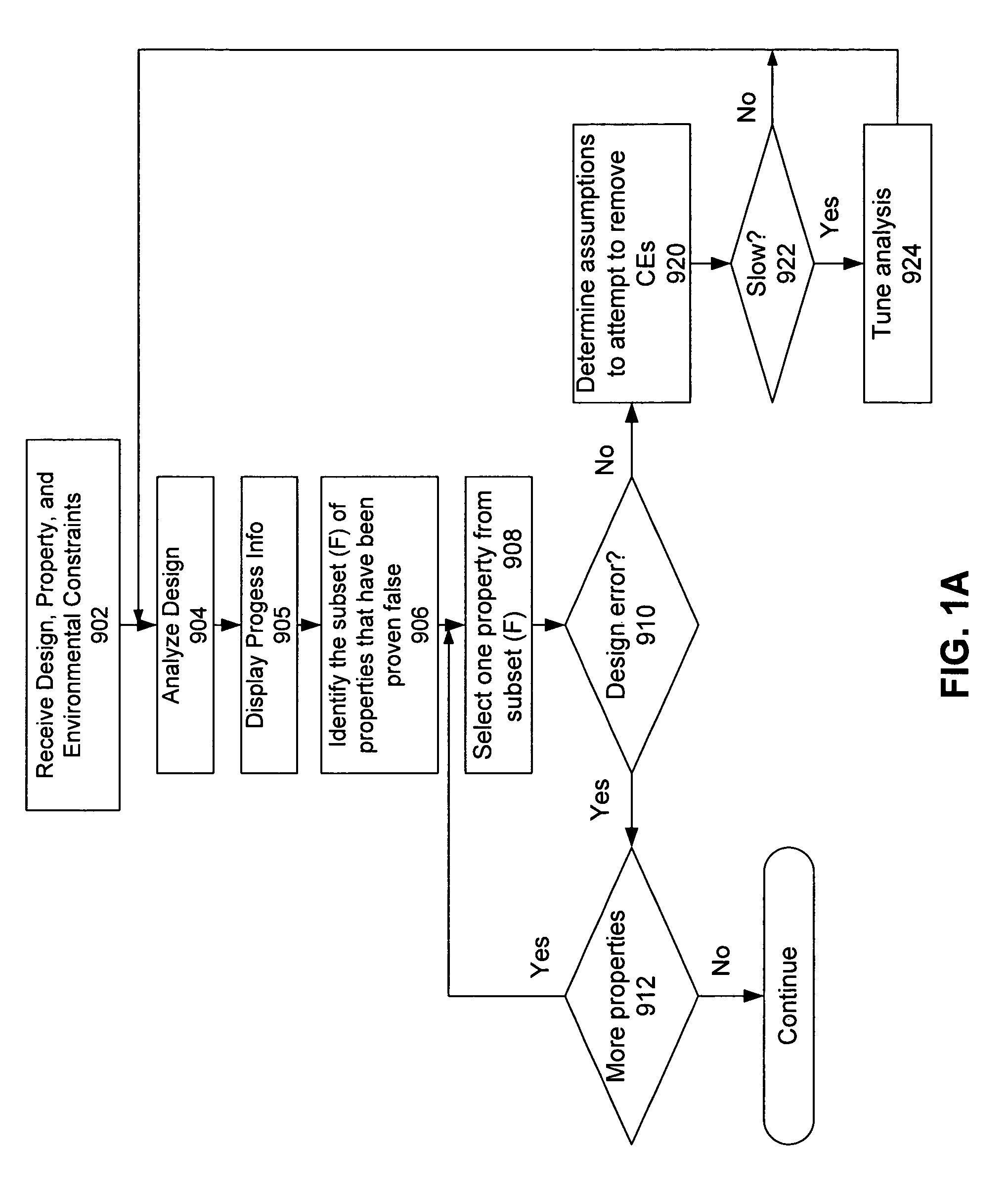

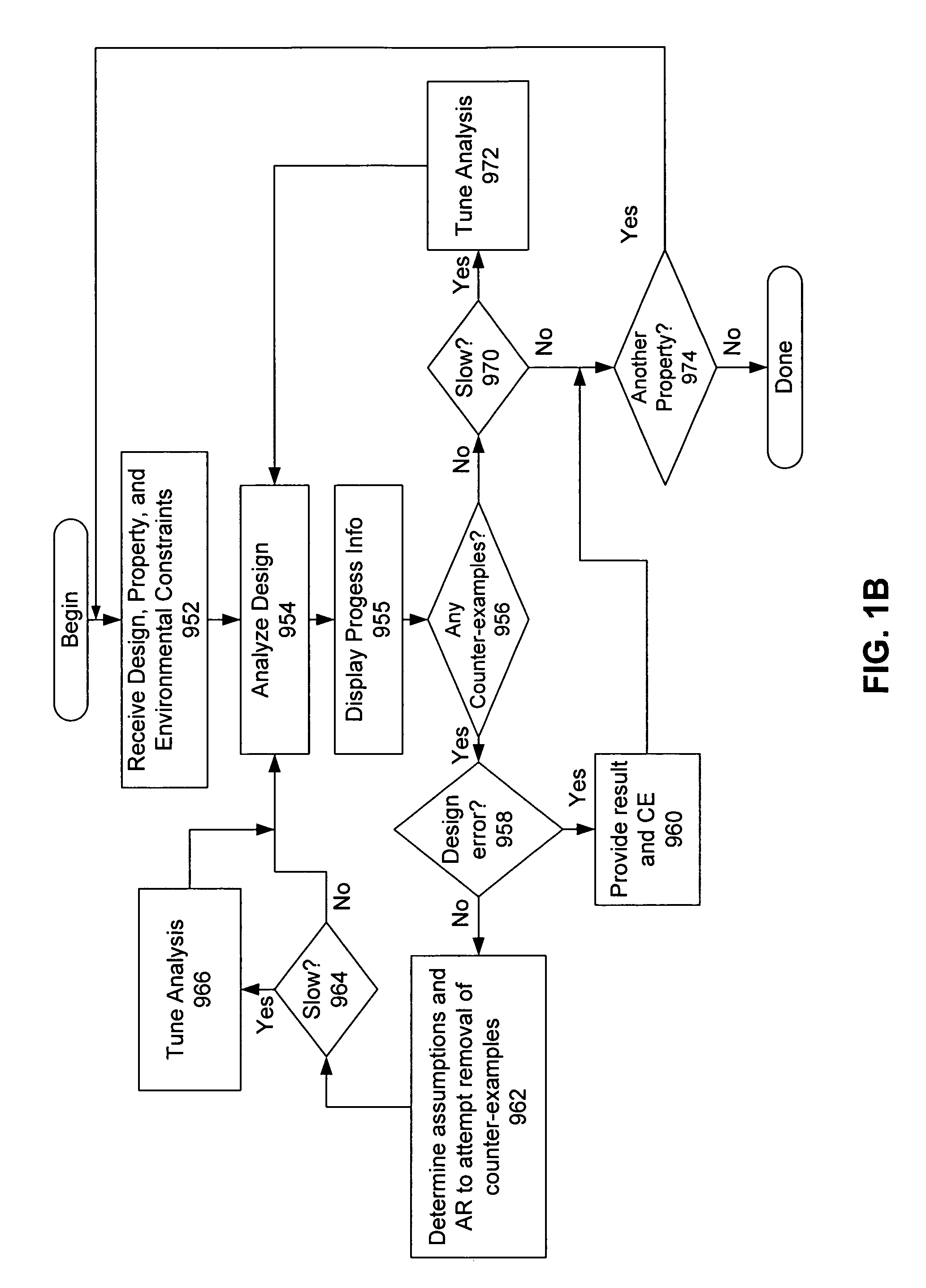

Extracting, visualizing, and acting on inconsistencies between a circuit design and its abstraction

ActiveUS7895552B1Improve practicalityUseful feedbackComputer aided designSoftware simulation/interpretation/emulationComputer architectureCircuit design

In the field of functional verification of digital designs in systems that use an abstraction for portions of a circuit design to perform the verification proof, a tool is described for resolving inconsistencies between the design and abstractions for the design. The tool provides information to a user about intermediate steps in the verification process. In response, the user may provide insight about the design to allow the tool to adjust the verification analysis of the design. The information provided to the user, including possible conflicts between the design and its abstractions, may include visualization techniques to facilitate the user's understating of any inconsistencies.

Owner:JASPER DESIGN AUTOMATION

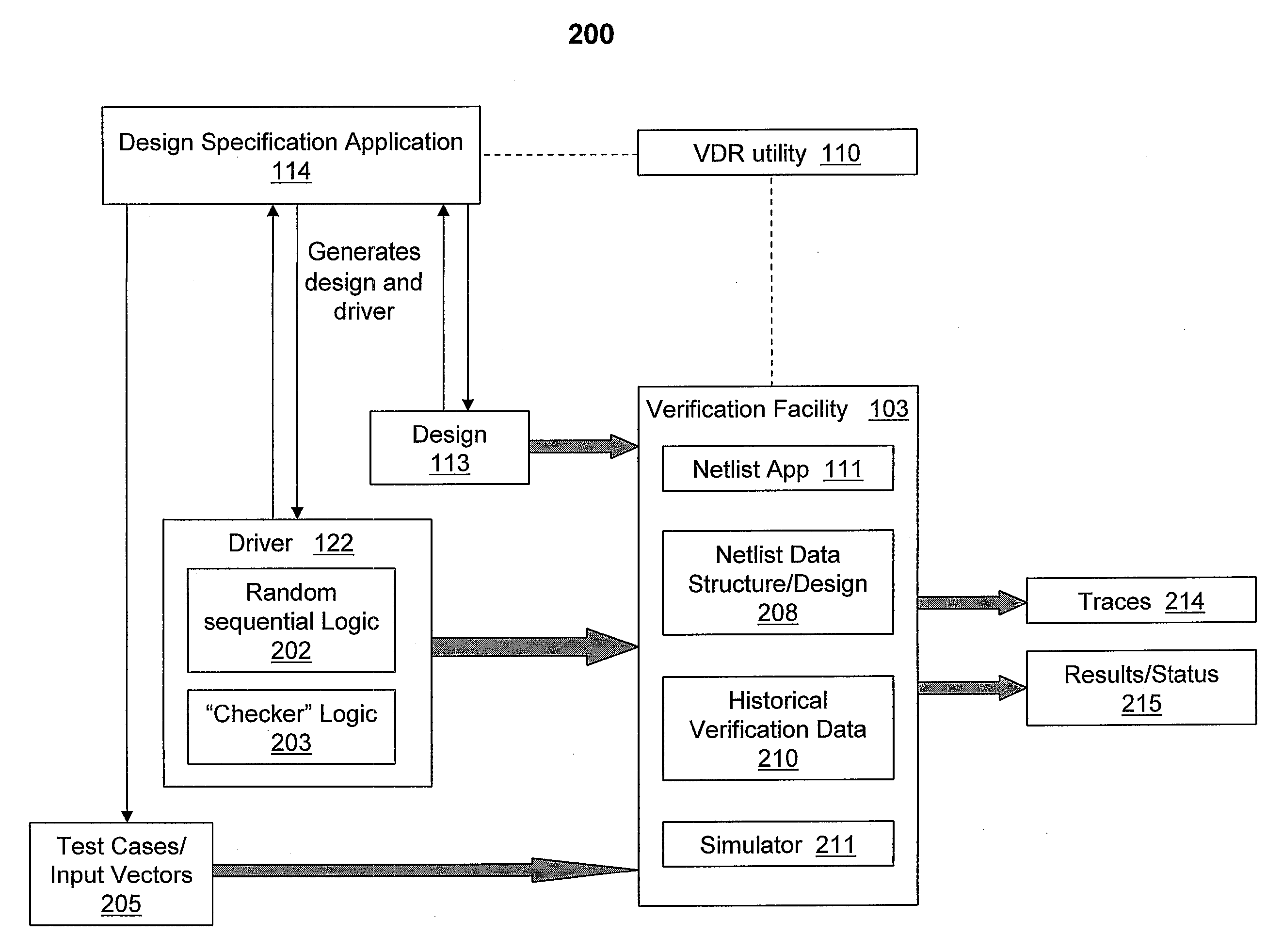

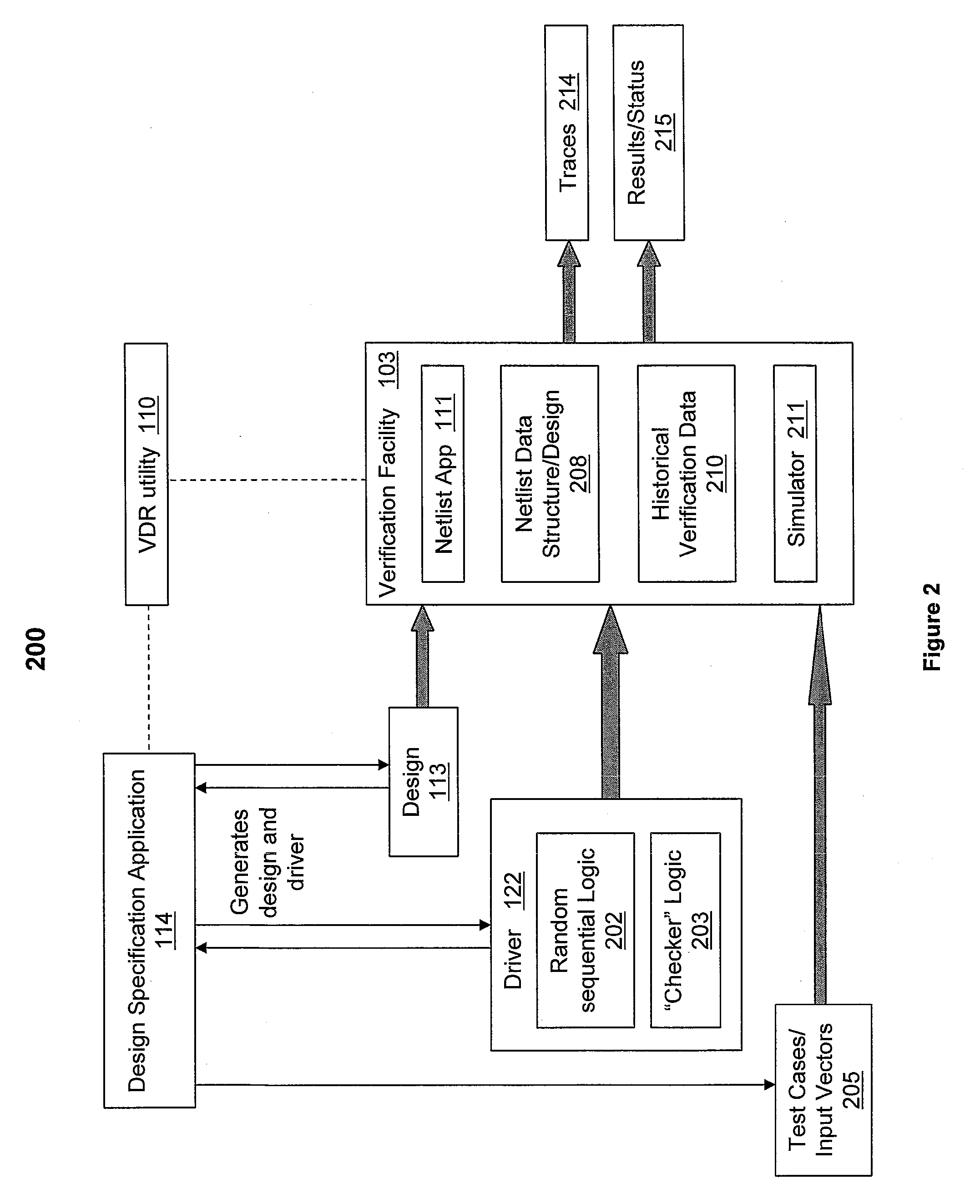

Enhancing Formal Design Verification By Reusing Previous Results

InactiveUS20100257494A1Computer aided designSoftware simulation/interpretation/emulationSoftware engineeringTarget signature

A method, a system and a computer program product for re-using verification results associated with a circuit design to eliminate a formal verification re-run associated with a subsequent verification of the circuit design. A Verification Data Re-use (VDR) utility initiates the creation of a first netlist data structure and a first set of target signatures for the circuit design. The VDR utility initiates an initial functional verification run of the circuit design and stores the results of the verification run. When a subsequent verification of the initial design is initiated, the VDR utility compares the first set of target signatures with a second set of target signatures for the subsequent verification run. A match of target signatures indicates that corresponding design targets have an identical functionality and the VDR utility re-uses verification results from the initial verification run to eliminate an extensive formal verification

Owner:MENTOR GRAPHICS CORP

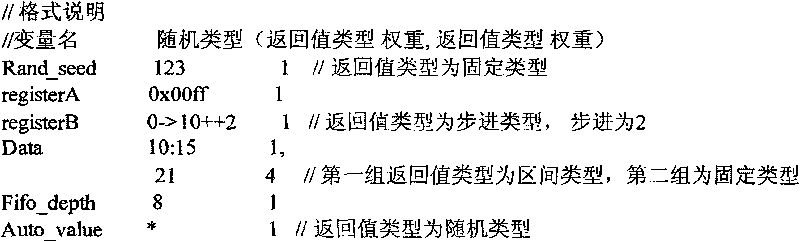

Method for establishing large-scale network chip verification platform

ActiveCN101763451ARealize multiplexingReduce build timeSpecial data processing applicationsRegister allocationReference model

The invention relates to a method for establishing a large-scale network chip verification platform. The method comprises the following steps of: firstly, establishing a control text document, and then writing an initial function of a random function library, and writing a calling function of the random function library; secondly, establishing a module-level function verification platform, comprising the following steps of: generating a top-level module of the module-level function verification platform, establishing a clock generating module and a reset generating module, establishing an interface signal module, establishing a test vector generating module, establishing a register configuring module and establishing a reference model module of a tested module; and thirdly, establishing a chip-level function verification platform, comprising the following steps of: generating a top-level module of the chip-level function verification platform, multiplexing the clock generating module, the rest module, the interface signal module, the test vector generating module, the register configuring module and the reference model module of the module-level function verification platform, and establishing a CPU simulation model. The method has a strong function, high efficiency, stability and simple structure. By means of the invention, the time for setting up the network chip verification platform can be greatly shortened and the stimulation efficiency can be improved.

Owner:丁贤根

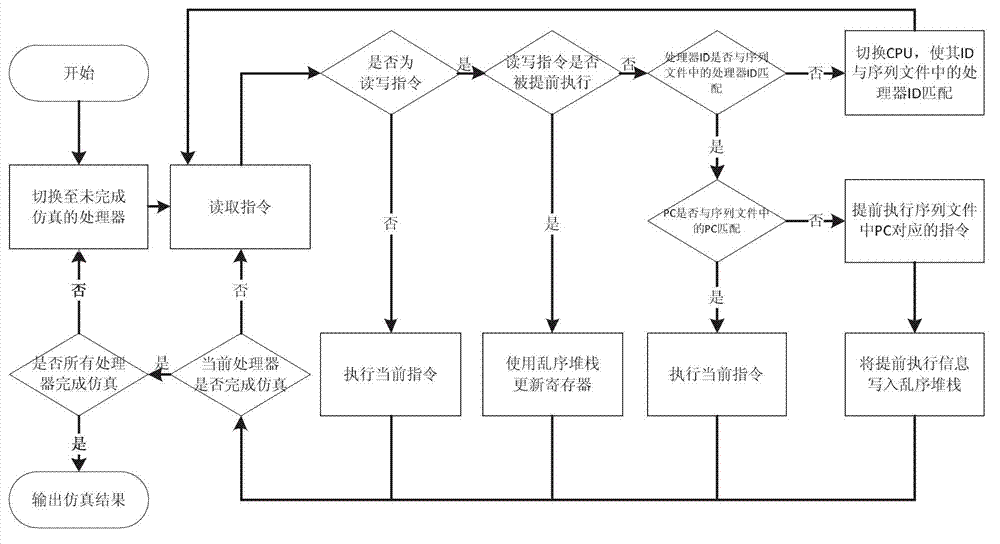

Functional verification method of on-chip multi-core processor

InactiveCN102929686AReduce verification timeReduce complexityResource allocationSoftware simulation/interpretation/emulationReference modelComputer architecture

The invention relates to a functional verification method of an on-chip multi-core processor. The functional verification method comprises the following steps that: a reference model and interfaces of the reference model and a multi-core processor to be verified are established, the reference model accepts the file input in a set format, carries out operations of instruction fetching, decoding, execution and the like, and outputs corresponding values in the processes; and the reference model compares an output value of the reference model with the output value of multi-core processor to be verified, thus finishing the functional verification. According to the functional verification method of the on-chip multi-core processor, the scheduling problem that the concurrent on-chip multi-core processors are stimulated by serial stimulators (reference models) can be effectively solved.

Owner:C SKY MICROSYST CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com