Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70 results about "Formal methods" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, specifically software engineering and hardware engineering, formal methods are a particular kind of mathematically based techniques for the specification, development and verification of software and hardware systems. The use of formal methods for software and hardware design is motivated by the expectation that, as in other engineering disciplines, performing appropriate mathematical analysis can contribute to the reliability and robustness of a design.

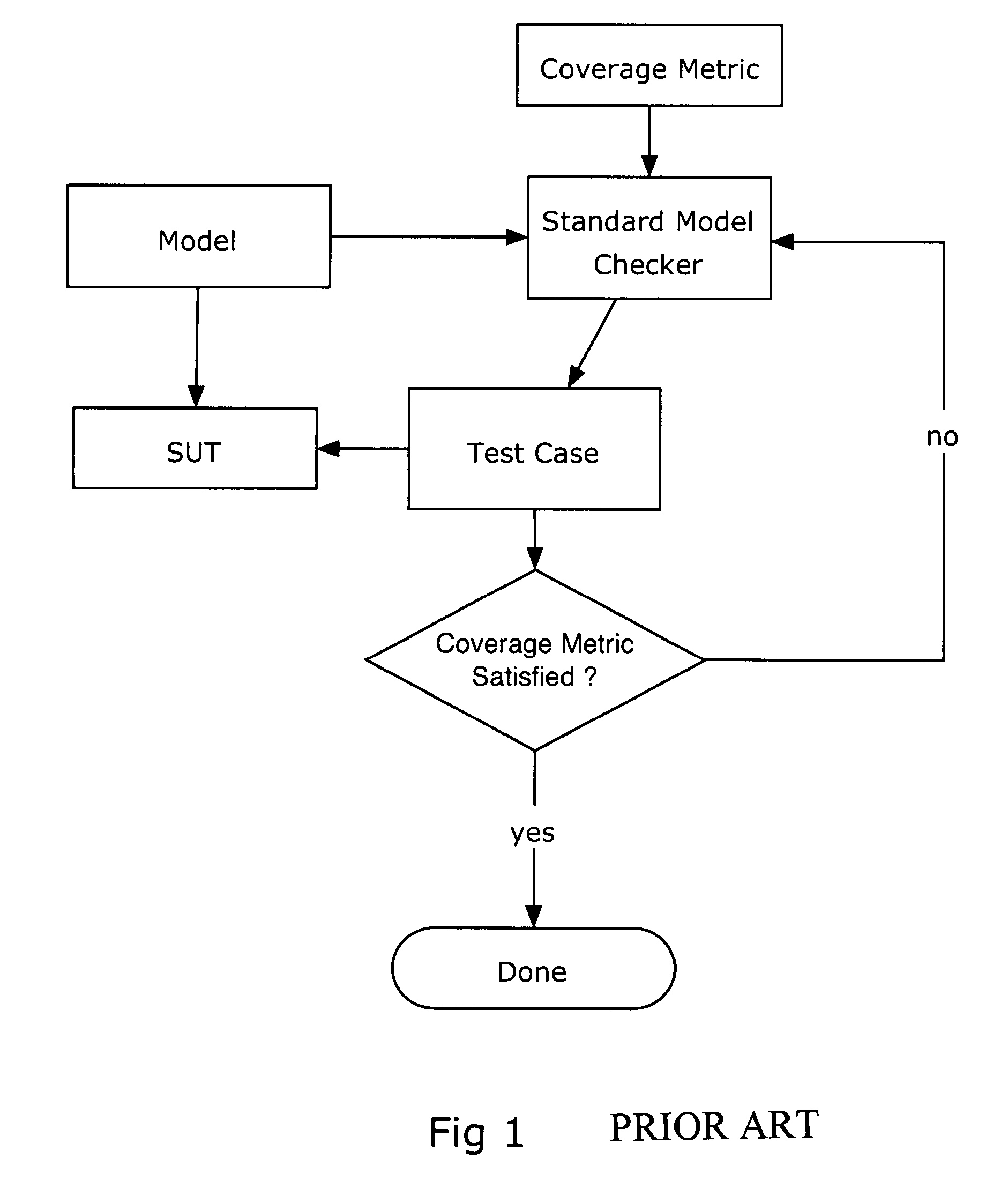

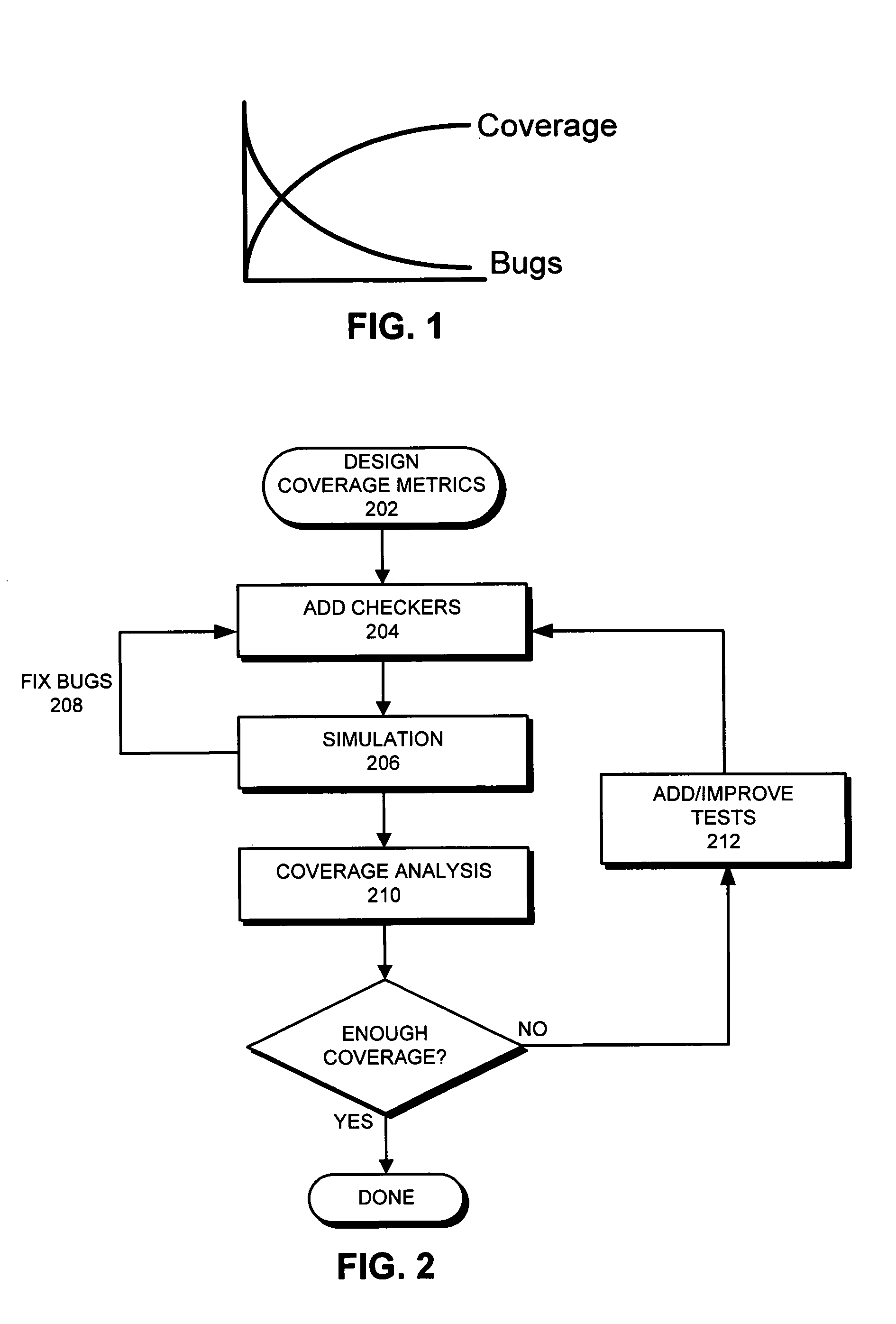

Formal methods for test case generation

ActiveUS20060010428A1Reduce development costsQuick testError detection/correctionComputation using non-denominational number representationSoftware systemFormal methods

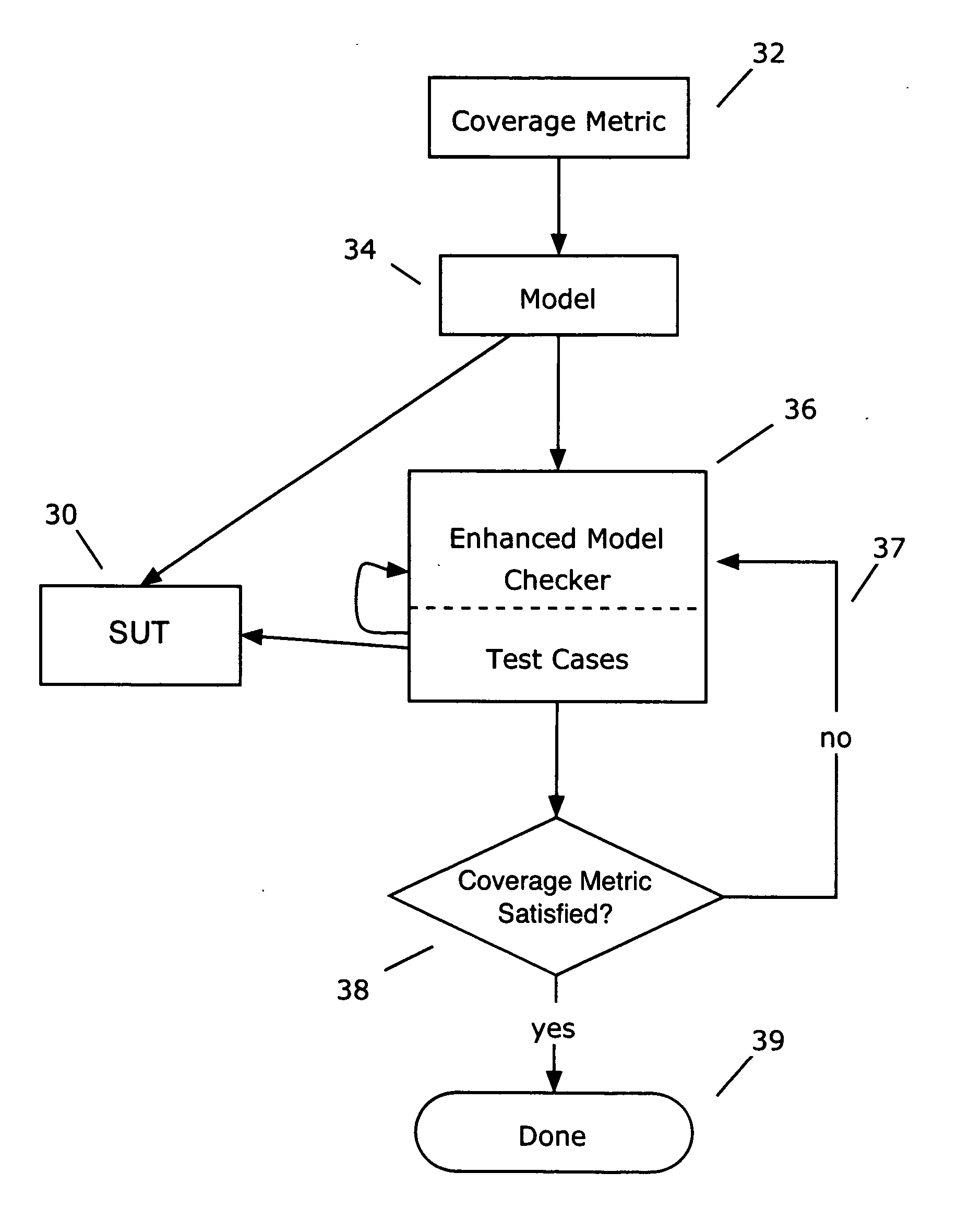

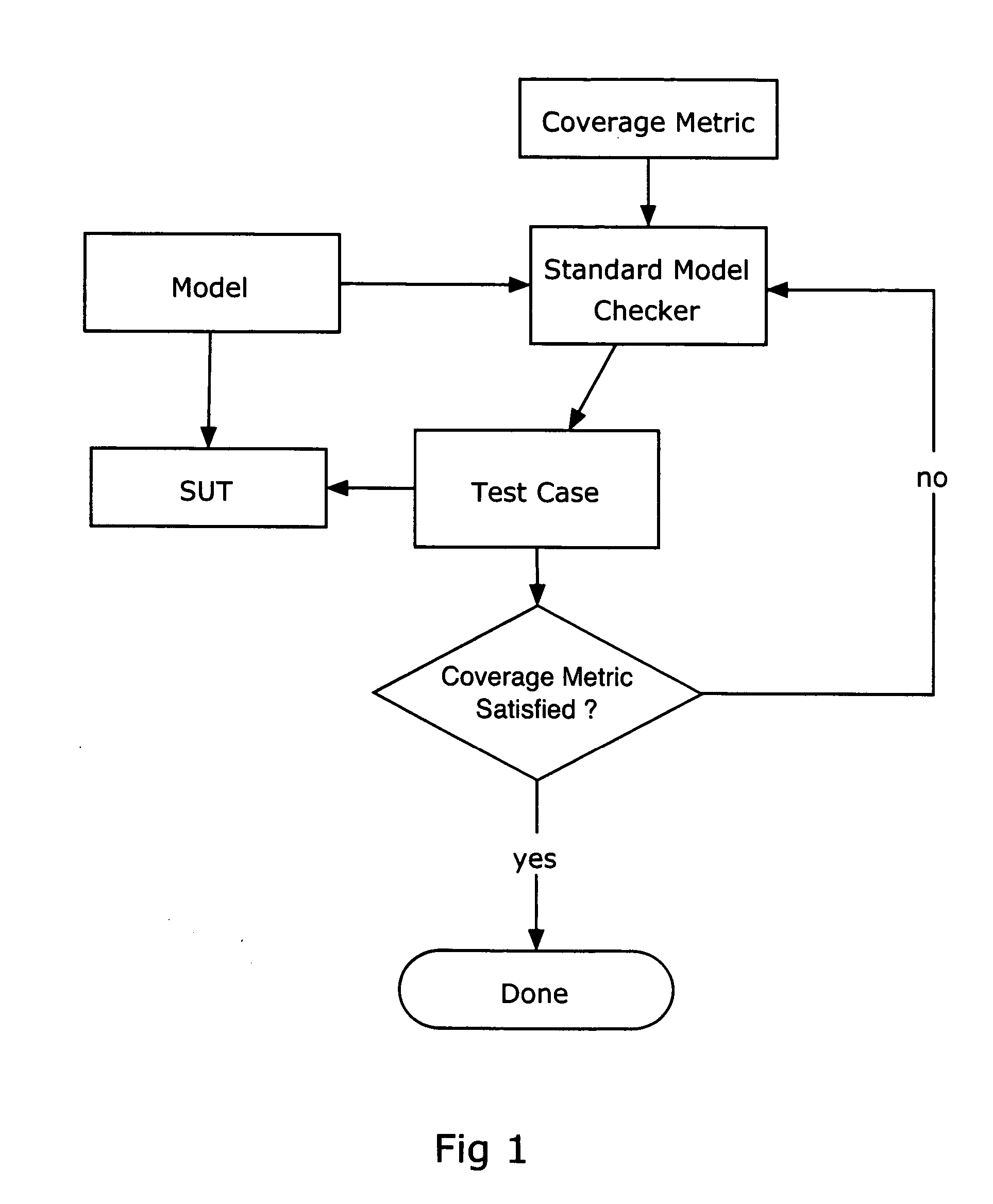

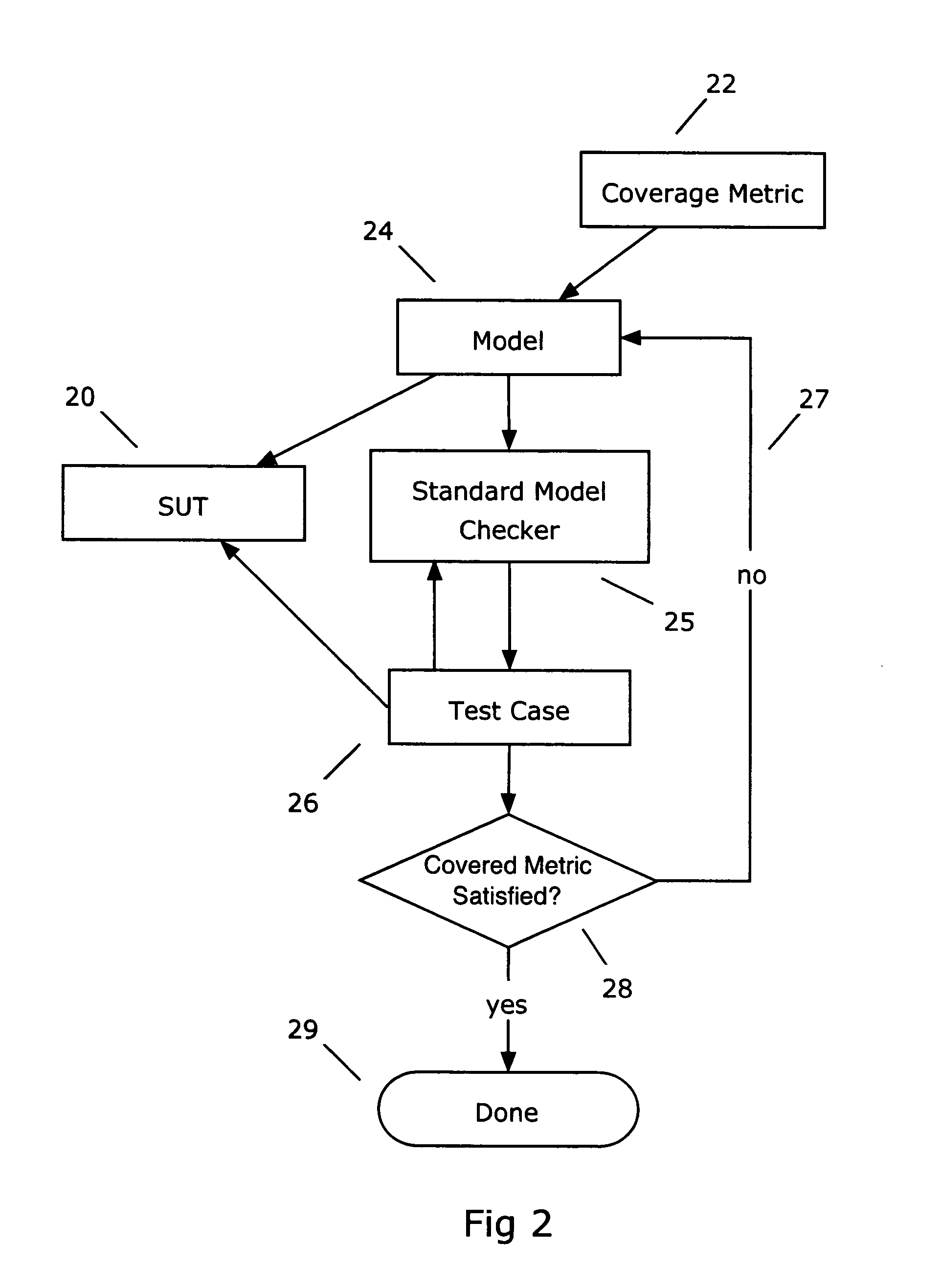

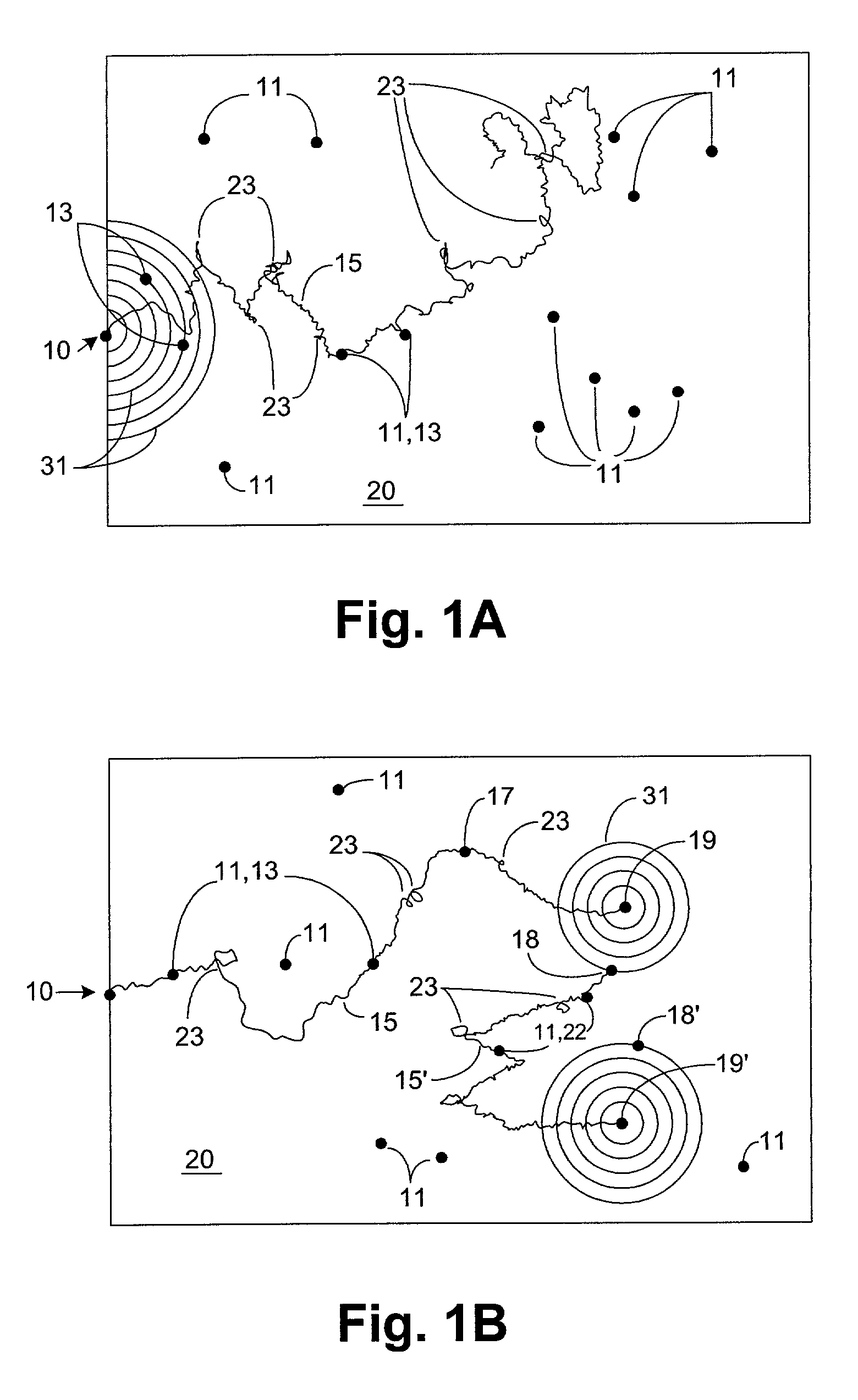

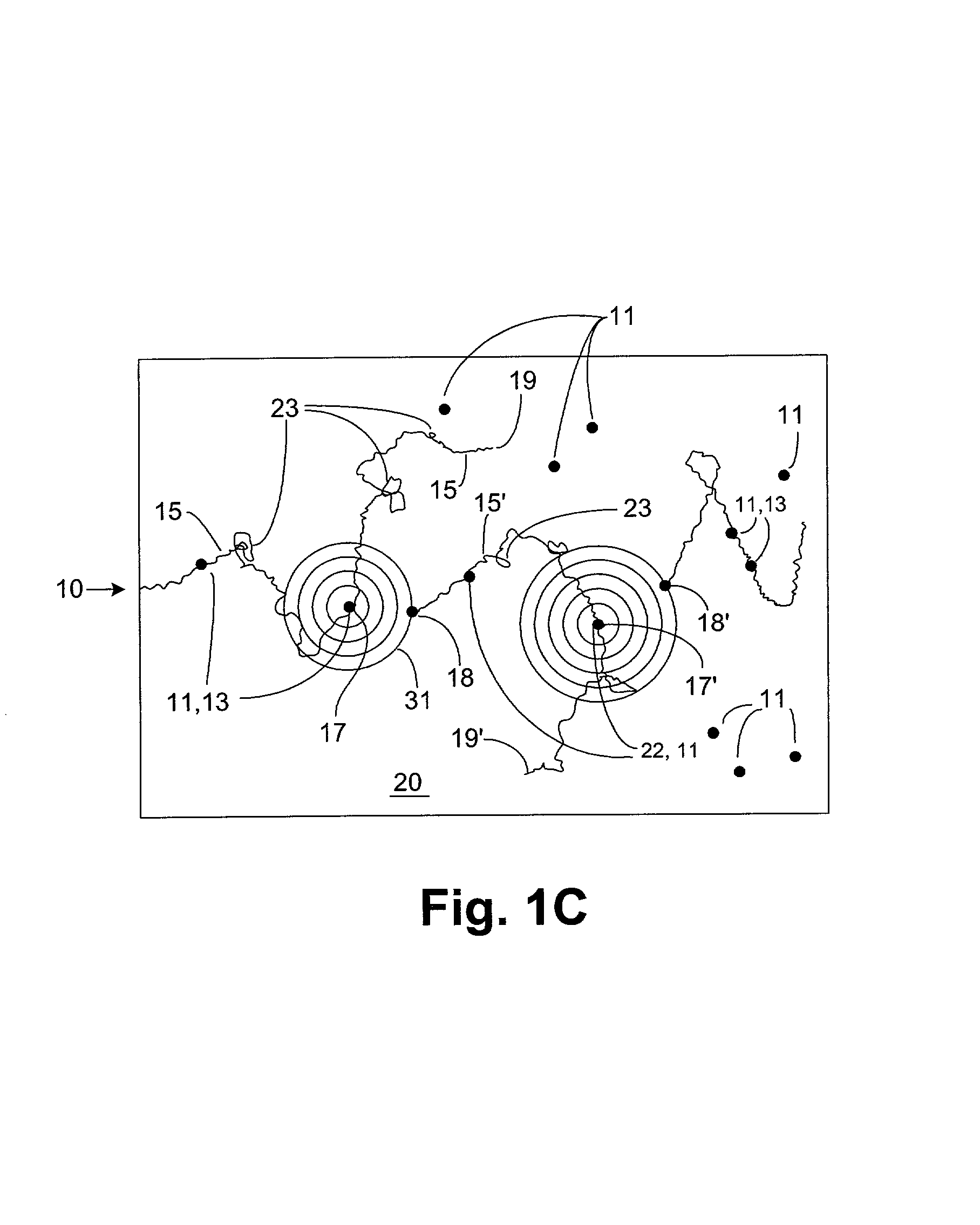

The invention relates to the use of model checkers to generate efficient test sets for hardware and software systems. The method provides for extending existing tests to reach new coverage targets; searching *to* some or all of the uncovered targets in parallel; searching in parallel *from* some or all of the states reached in previous tests; and slicing the model relative to the current set of coverage targets. The invention provides efficient test case generation and test set formation. Deep regions of the state space can be reached within allotted time and memory. The approach has been applied to use of the model checkers of SRI's SAL system and to model-based designs developed in Stateflow. Stateflow models achieving complete state and transition coverage in a single test case are reported.

Owner:SRI INTERNATIONAL

Simulation-based functional verification of microcircuit designs

InactiveUS7130783B1Shorten the timeConfidenceDetecting faulty computer hardwareAnalogue computers for electric apparatusTest designFormal methods

System, methods, and apparatus for verifying microcircuit designs by interleaving between random and formal simulation techniques to identify input traces useful for driving designs under test into sequences of device states. In a method aspect the invention provides process for beginning random simulation of a sequence of states of a microcircuit design by inputting a sequence of random input vectors to a design under test model in order to obtain a sequence of random simulation states; monitoring a simulation coverage progress metric to determine a preference for switching from random simulation to formal methods of simulating states in the design under test; beginning formal simulation of states in the design under test and monitoring a formal coverage progress metric to determine a preference for resuming random simulation of states of said microcircuit design; and resuming random simulation. Preferably the process of interleaving simulation methods continues until an input vector suitable for driving the design under test model into each of a set of previously-identified goal states has been obtained.

Owner:SYNOPSYS INC

Method of circuit verification in digital design

InactiveUS6728939B2Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureValidation methods

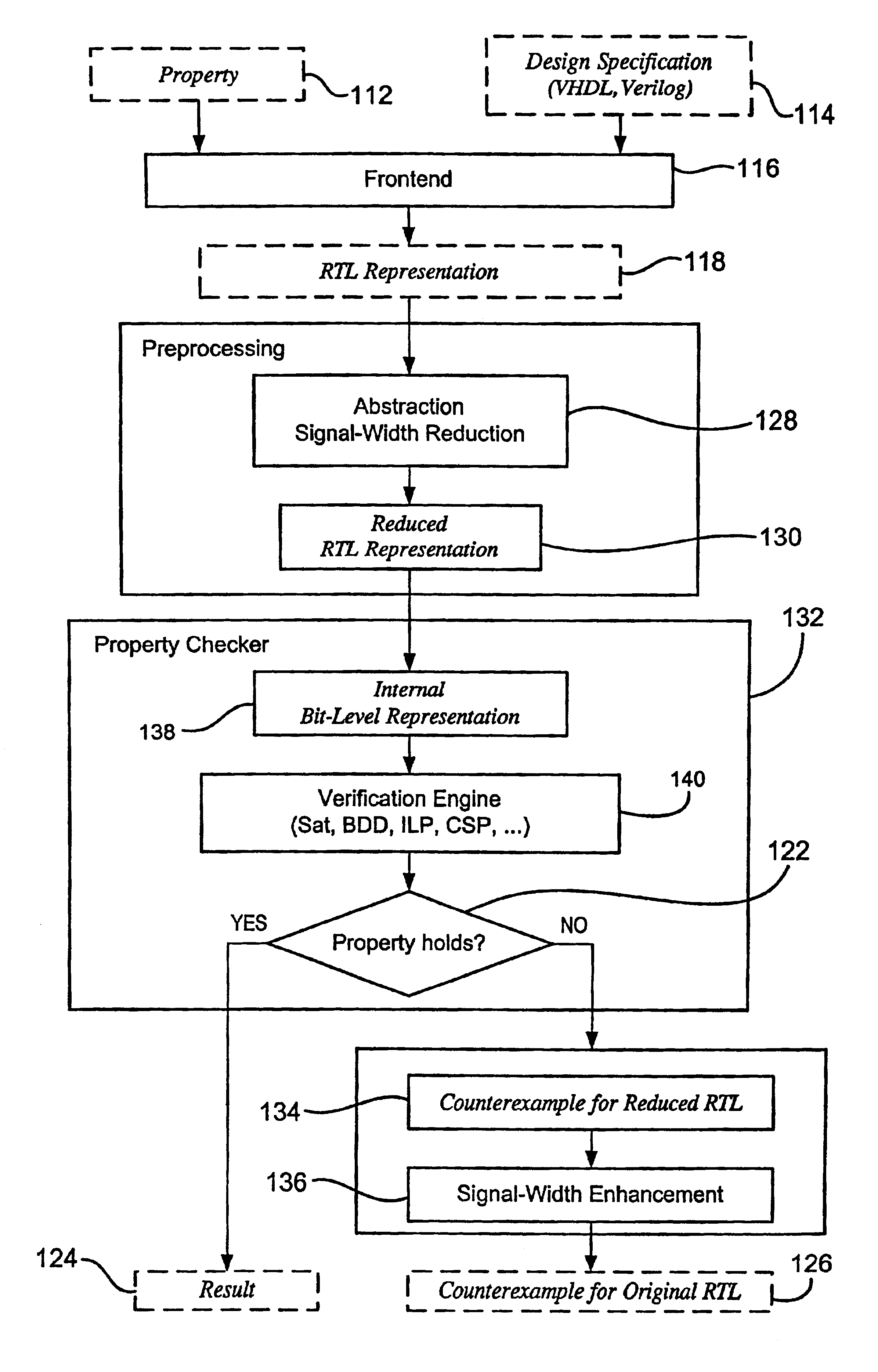

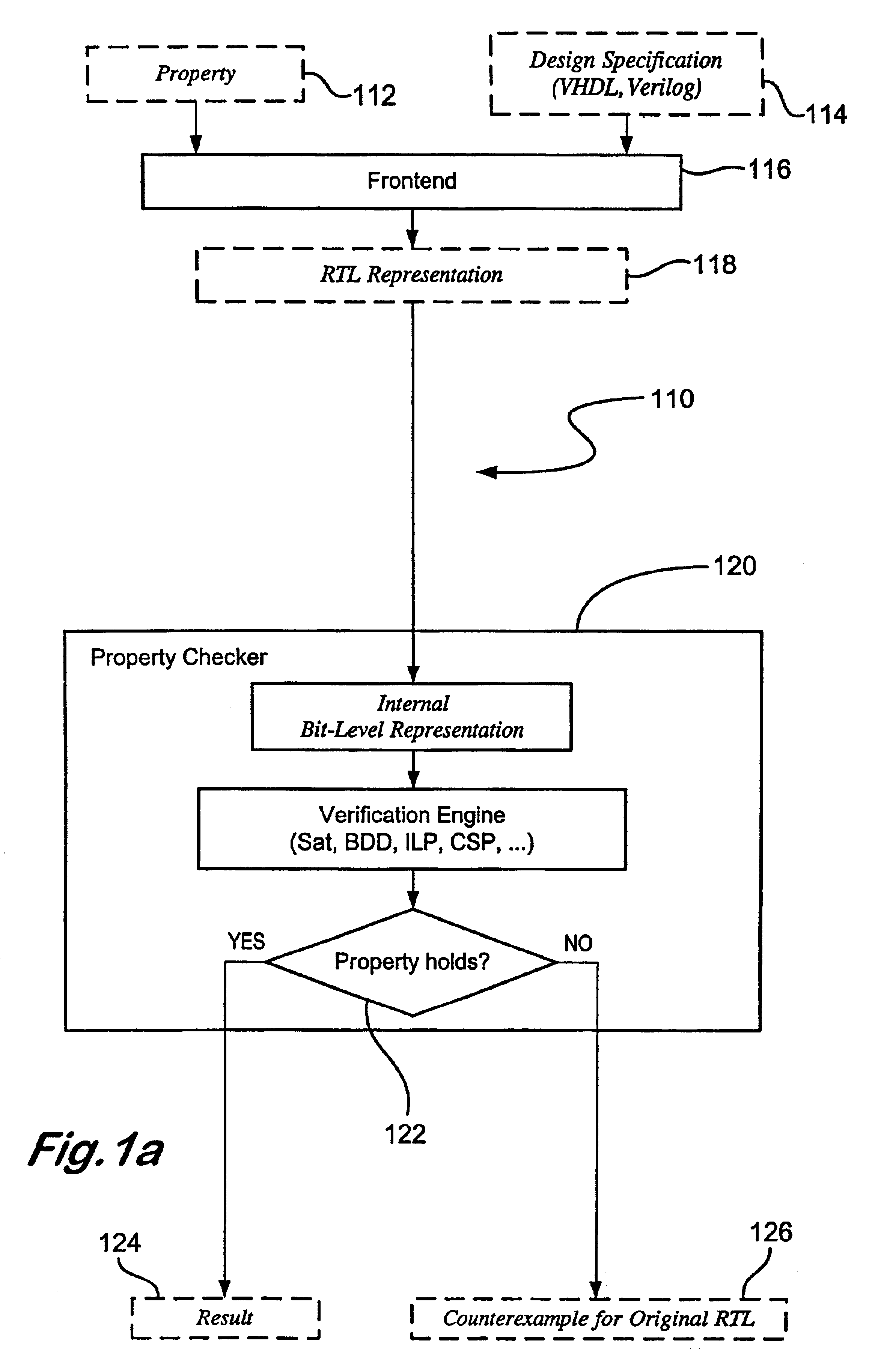

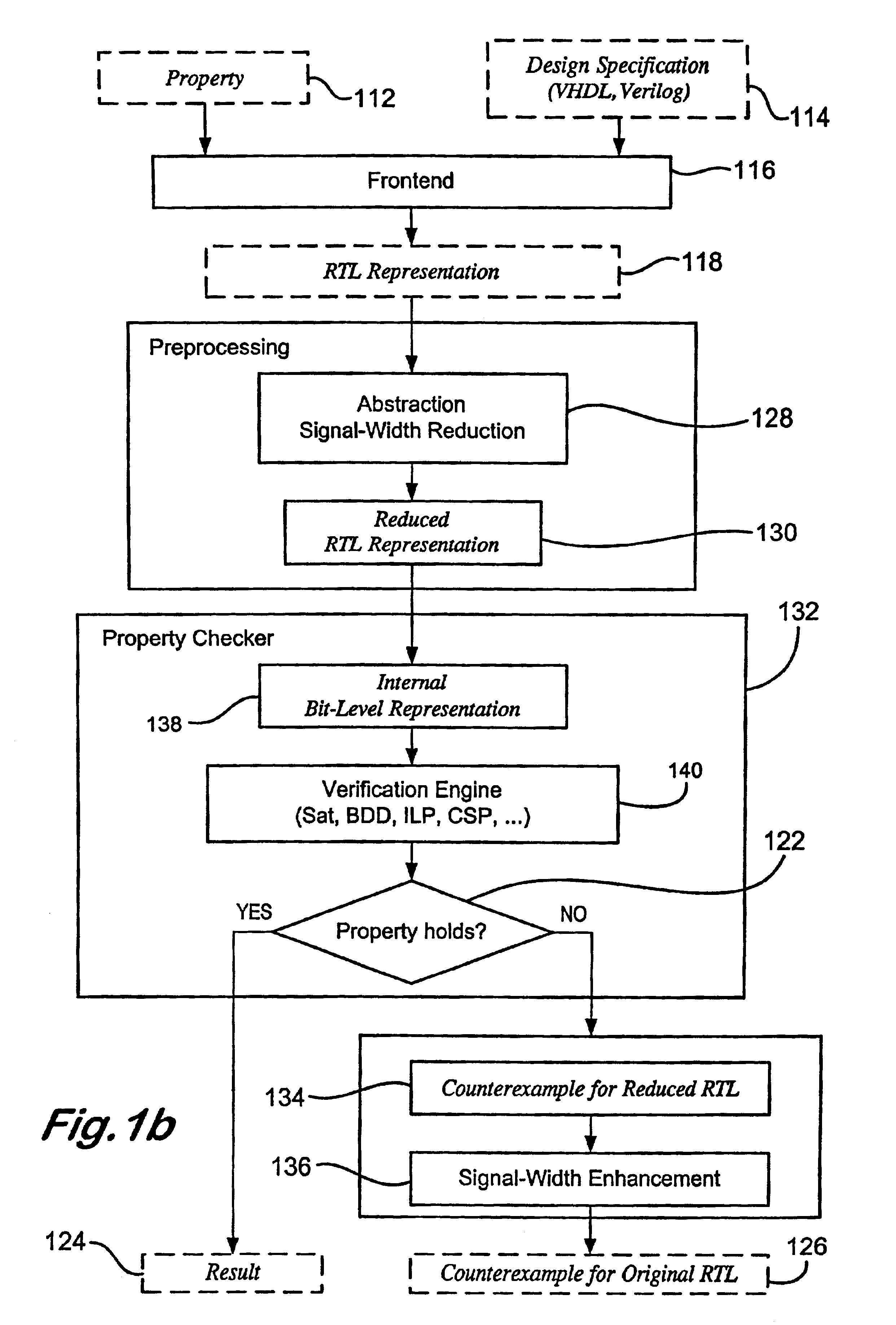

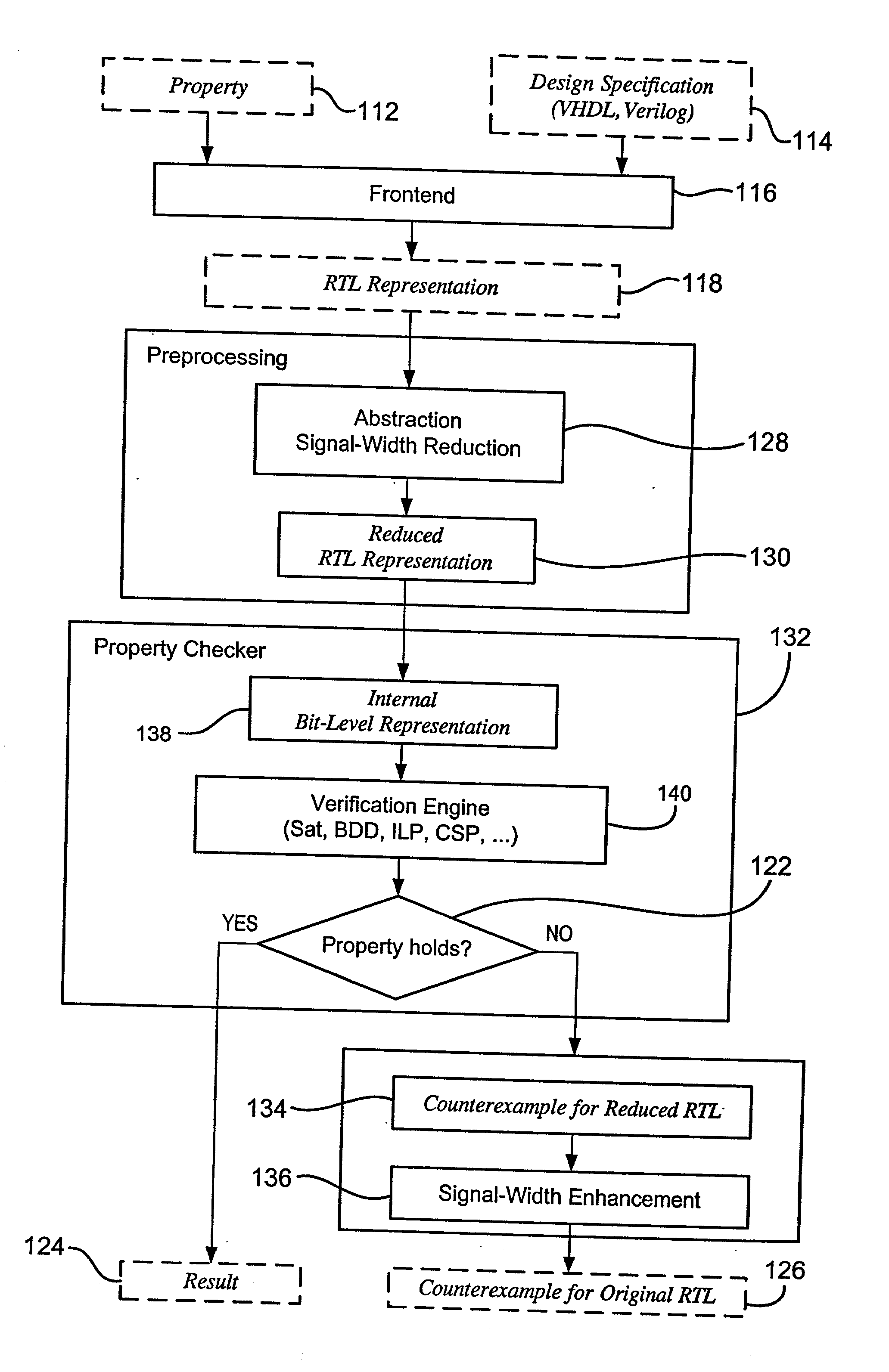

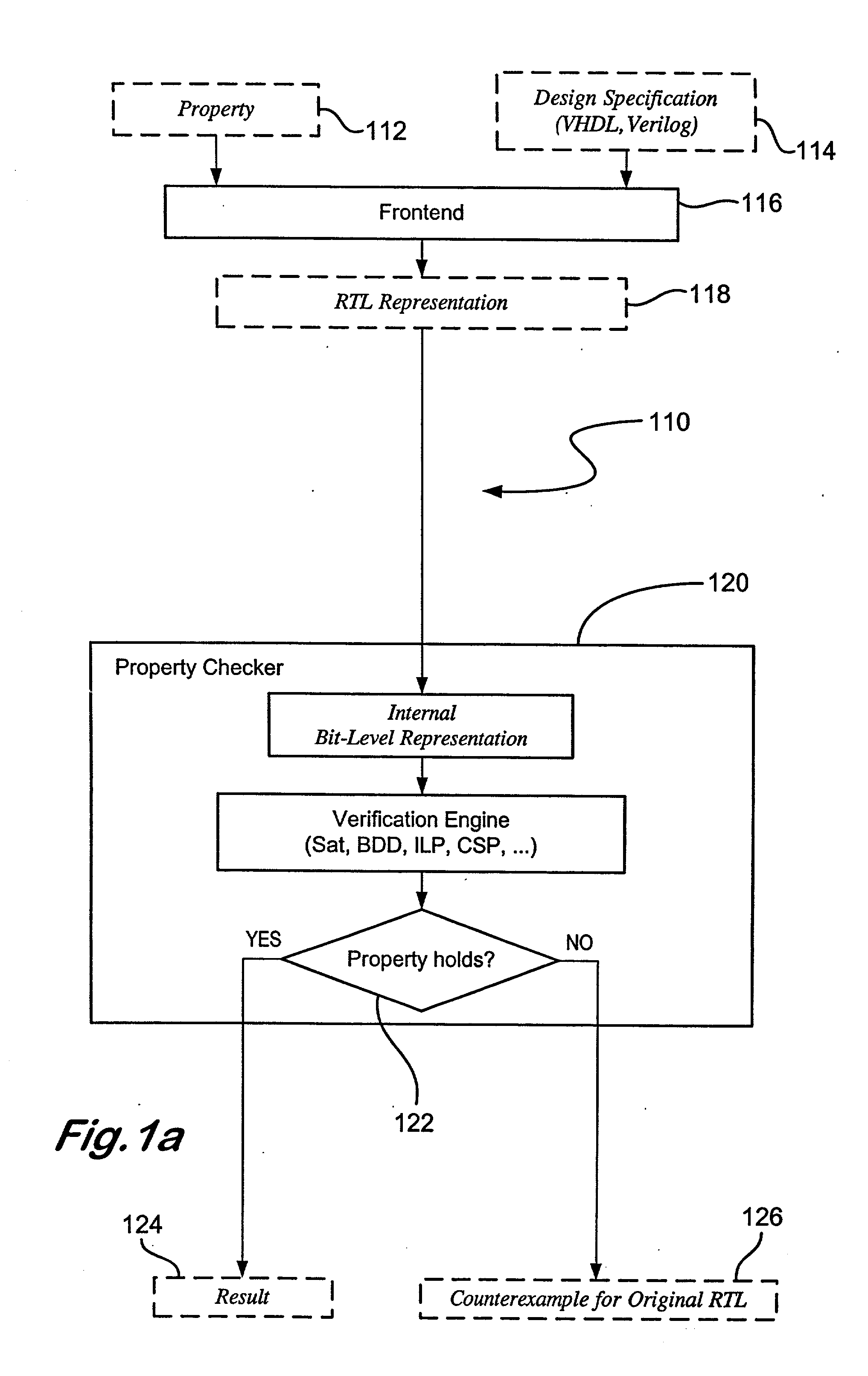

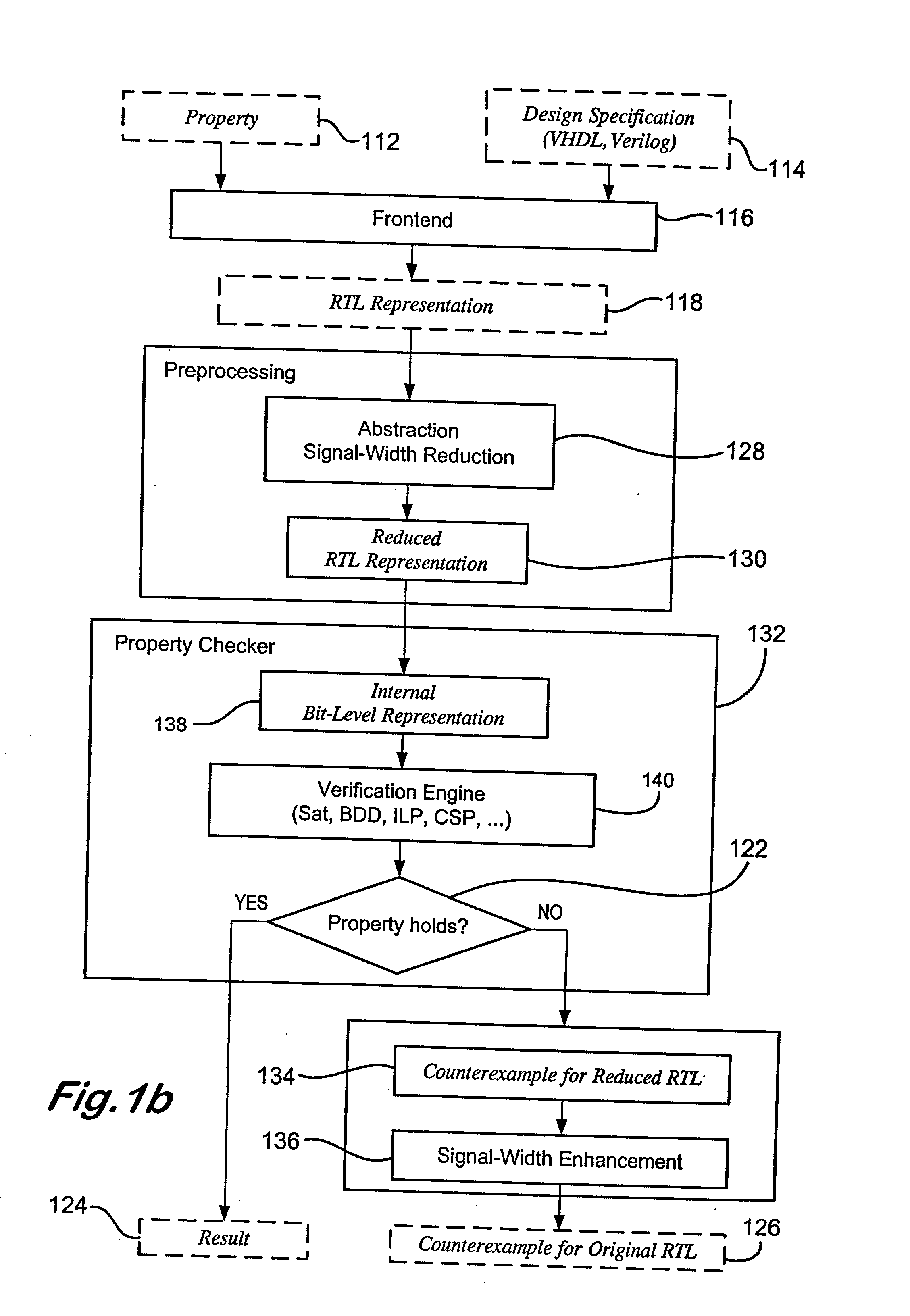

The present invention relates to a method of circuit verification in digital design and in particular, relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors, and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhausting simulating a design. A digital circuit design verification method, prior to a property checking process for each property of a non-reduced RTL model, determines a reduced RTL model which retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

Method of circuit verification in digital design

InactiveUS20020138812A1Reduce designEasy to understandComputer aided designSoftware simulation/interpretation/emulationComputer architectureCircuit design

The present invention relates to a method of circuit verification in digital design and in particular relates to a method of register transfer level property checking to enable the same. Today's electrical circuit designs frequently contain up to several million transistors and circuit designs need to be checked to ensure that circuits operate correctly. Formal methods for verification are becoming increasingly attractive since they confirm design behavior without exhaustively simulating a design. The present invention provides a digital circuit design verification method wherein, prior to a property checking process for each property of a non-reduced RTL model, a reduced RTL model is determined, which reduced RTL model retains specific signal properties of a non-reduced RTL model which are to be checked. A linear signal width reduction causes an exponential reduction of the induced state space. Reducing state space sizes in general goes hand in hand with reduced verification runtimes, and thus speeding up verification tasks.

Owner:ONESPIN SOLUTIONS

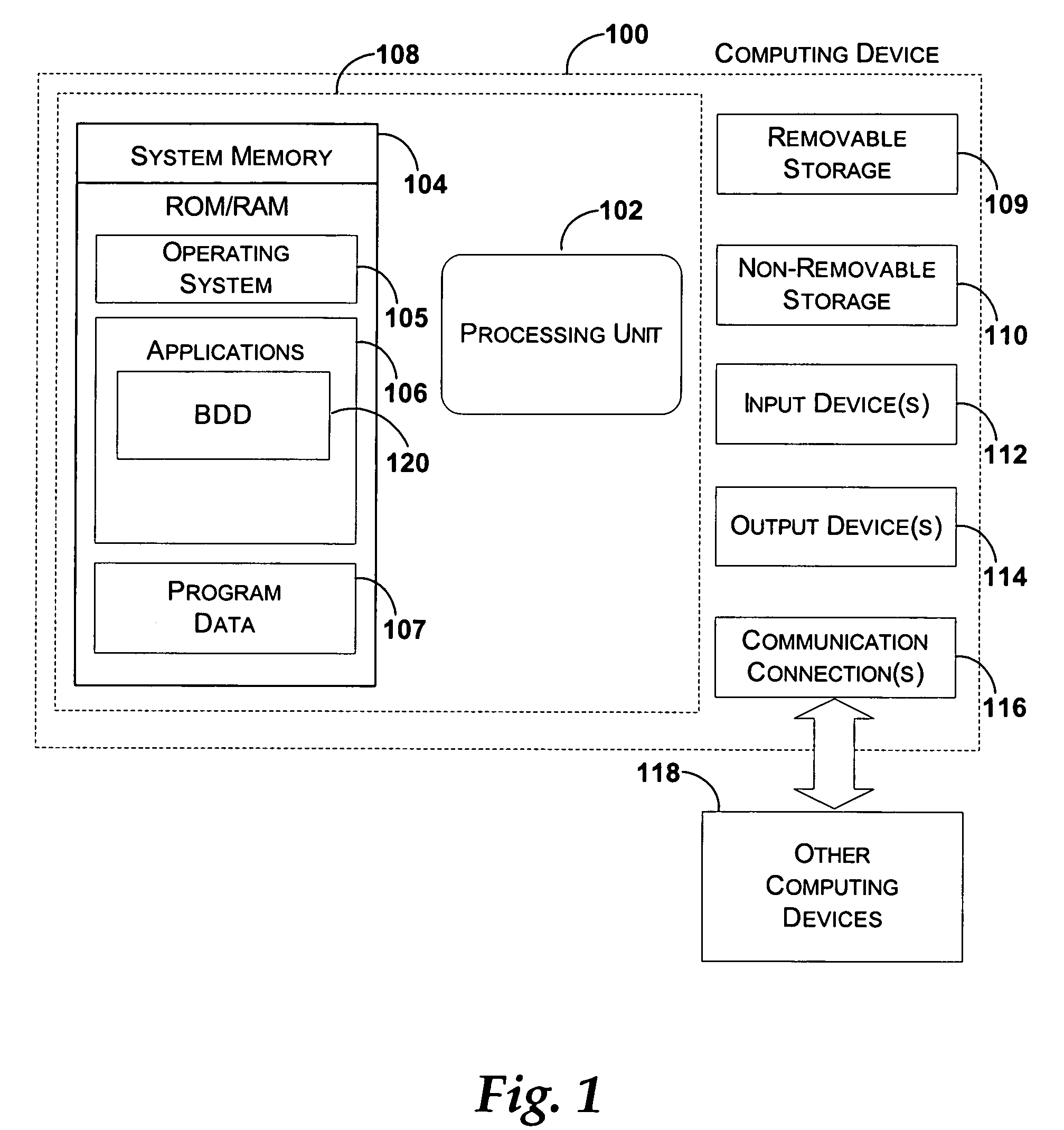

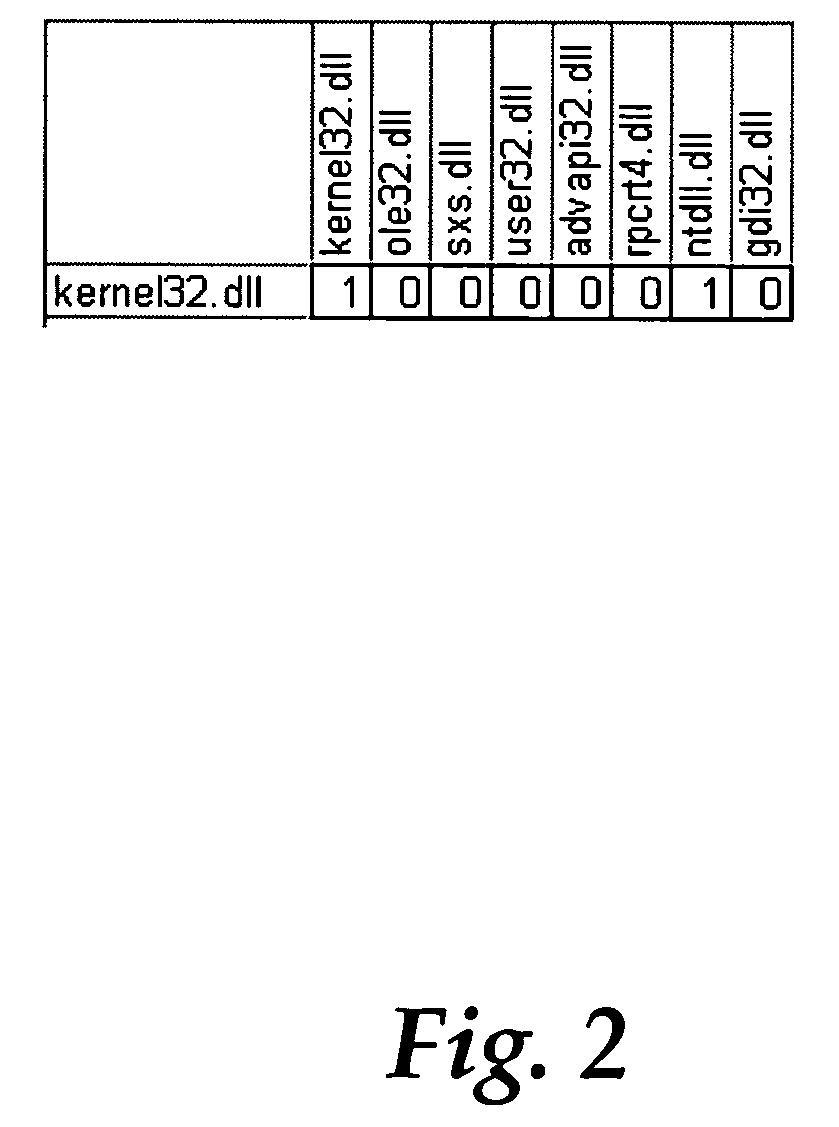

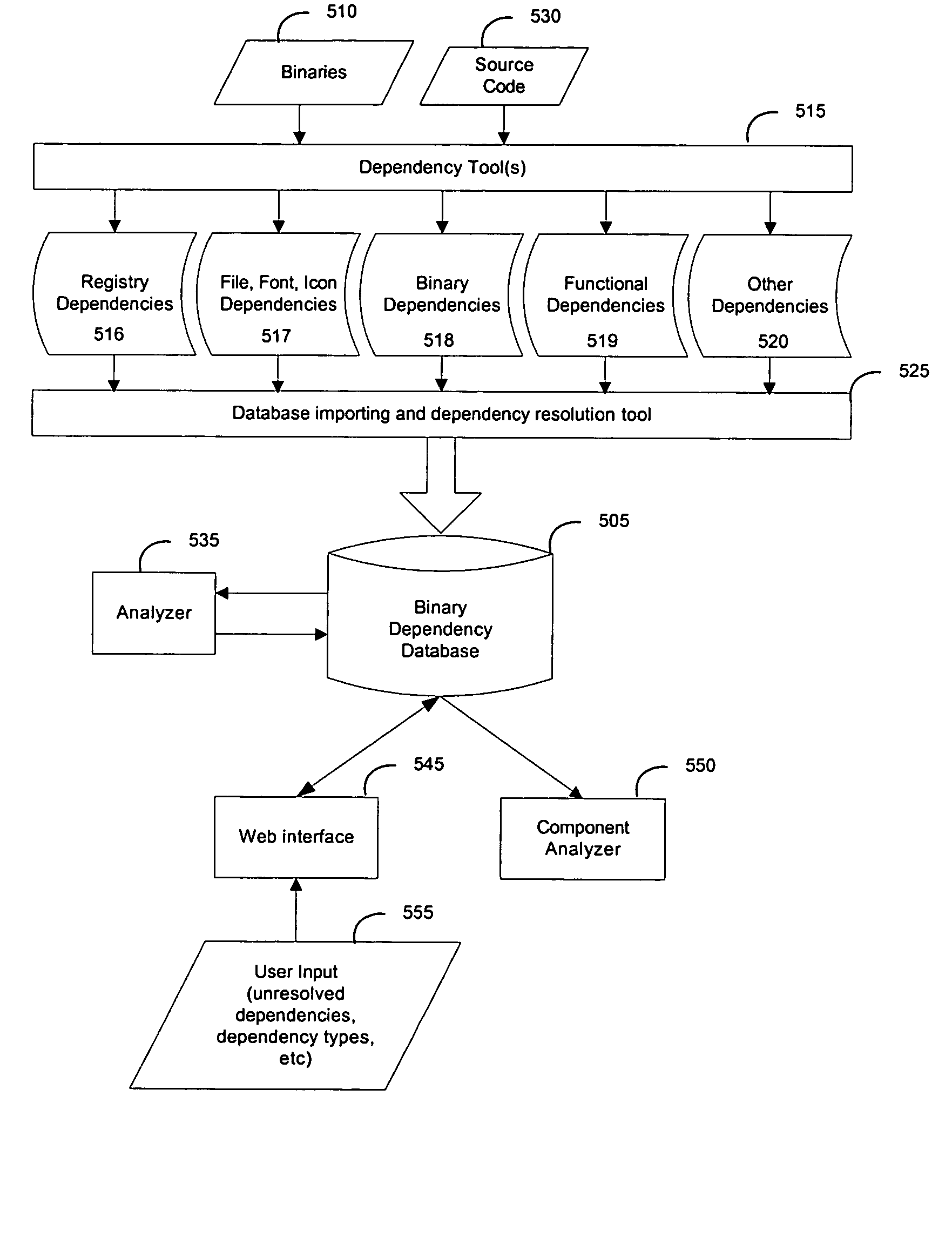

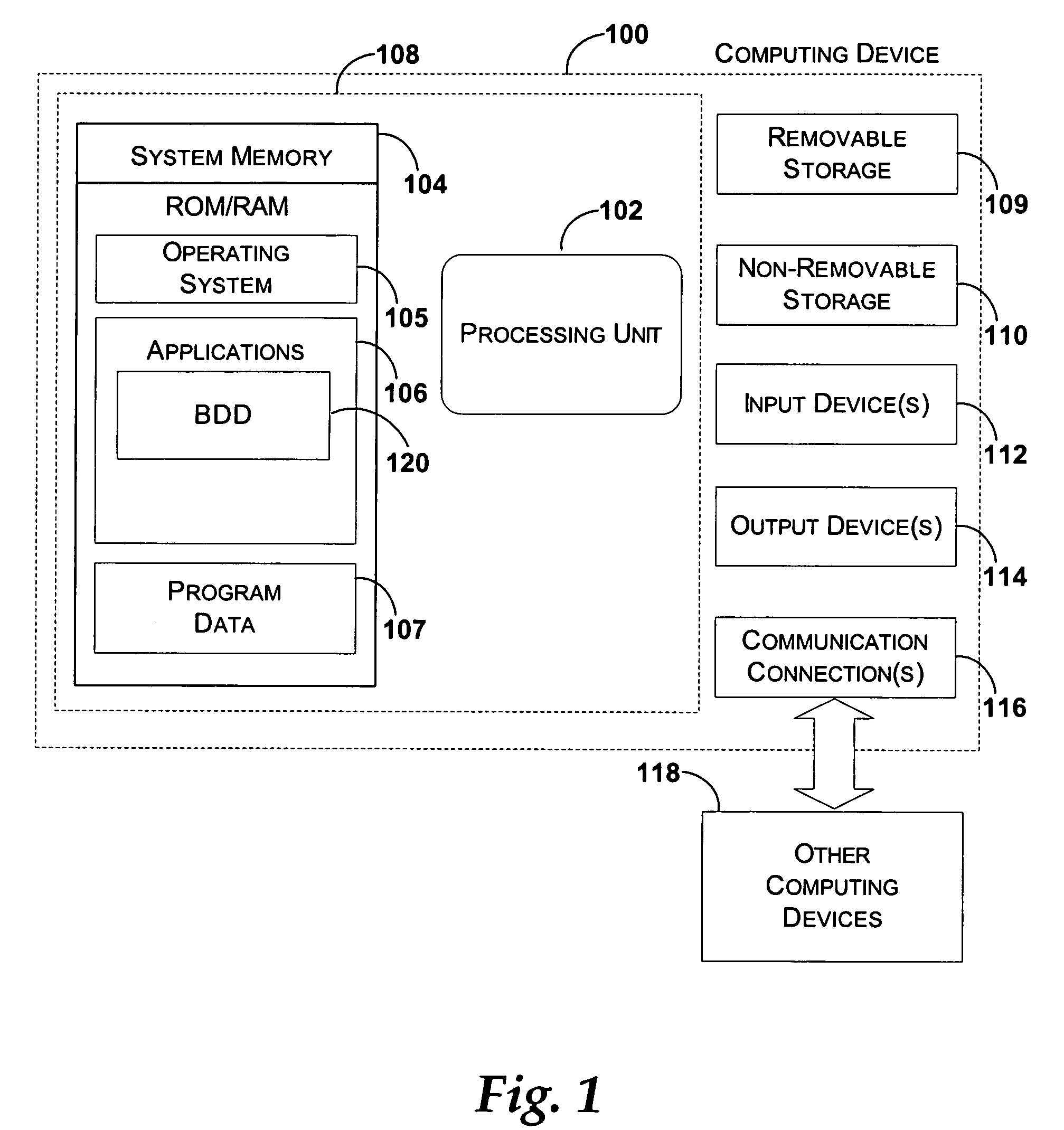

Binary dependency database

InactiveUS20050165823A1Easy to analyzeSimple designData processing applicationsVersion controlConfiguration optimizationFormal methods

The present invention facilitates the analysis of binaries, components, configurations, and their footprints for component design and optimization. Complete and meaningful binary, component, configuration, and footprint information allows formal methods for component analysis and configuration optimization. A binary dependency database persists and stores binary dependency information. The binary dependency database provides detailed dependency information among binaries.

Owner:MICROSOFT TECH LICENSING LLC

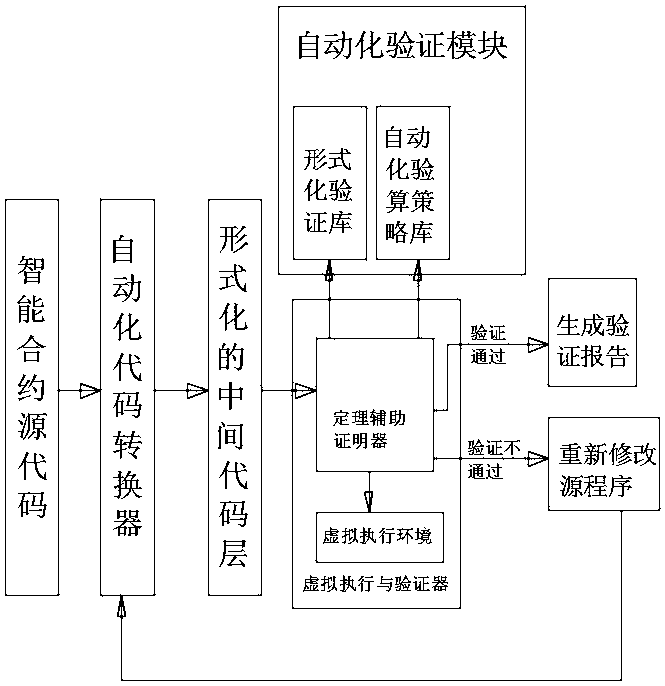

System and method oriented to supermatic formal verification of smart contract of blockchain

ActiveCN108536445AImprove verification efficiencyImprove efficiencyCode compilationFormal methodsSmart contract

The invention discloses a system and method oriented to supermatic formal verification of a smart contract of a blockchain. By using a code converter tool, the smart contract source code of the blockchain can be automatically converted into a language interlayer code for formal verification and identification so as to be used for formal verification input; by adopting a formal method, supermatic formal safety verification can be carried out on a converted source code so as to judge whether the security attribute requirement of the smart contract is safe or not. By relatively high-degree automation, formal safety verification can be carried out on the smart contract of the blockchain, wherein an automatic code converter can be used for automatically generating a formal to-be-verified program, the automatic checking calculation strategy improves verification efficiency, and the measures can be used for greatly improving the formal verification efficiency of the smart contract and reducing the artificial degree of participation.

Owner:成都链安科技有限公司

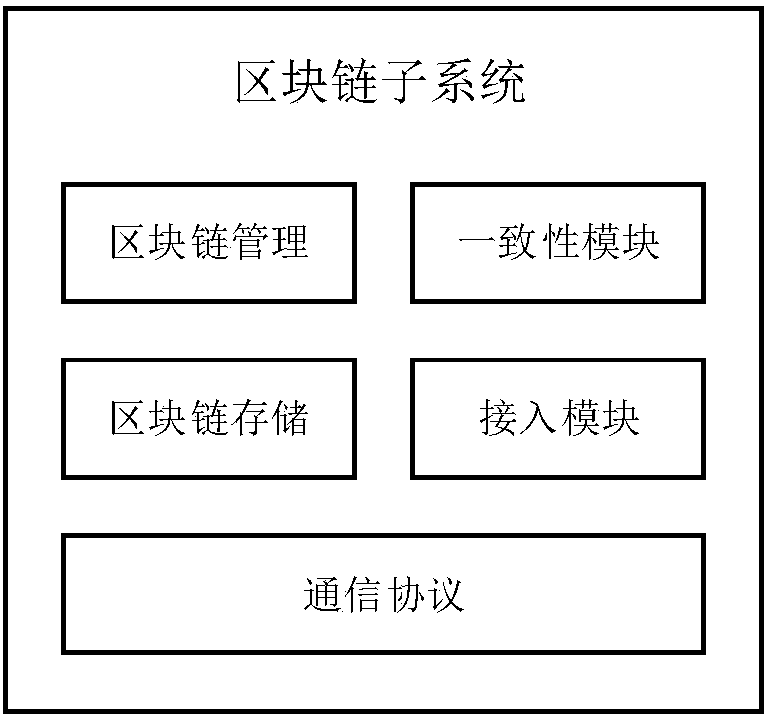

Medical management system based on block chain

The invention provides a medical management system based on a block chain. The system comprises a block chain subsystem, an identity authentication subsystem, an intelligent contract subsystem and anEMR subsystem. The block chain subsystem is used for storing partial electronic medical recording information, verification abstracts and electronic medical recording indexes and is compatible with anoriginal electronic medical recording (EMR) system; the identity authentication subsystem is used for user registration, safety certification and key management; the intelligent contract subsystem isused for achieving the functions of government (National Health and Family Planning Commission of the People's Republic of China) medical data monitoring management, prescription authentication, prescription medicine purchasing, medical insurance compensation and patient medical record authentication and sharing. The medical management system based on the block chain provides tools for writing, combination, formation verification and generation of an intelligent contract, and through a formation method, the full life circle of description, modelling, verification, generation and execution ofthe intelligent contract is managed; the EMR subsystem is used for storing a specific medical treatment record and providing service of management and querying for the electronic medical record.

Owner:BEIHANG UNIV

Model conversion and formalization verification method of semantic Web service combination

InactiveCN101808109ACorrectness and effective detectionSolve the correctness verification problemTransmissionService compositionOWL-S

The invention relates to a model conversion and formalization verification method of semantic Web service combination, which belongs to the field of semantic network and Web service. The invention is characterized in that a semantic Web service combination storage unit, a semantic Web service coloring Petri network storage sub module, a correctness verification sub module and a body tool Protege are established on the computer. The method uses a module conversion sub module for converting the OWL-S type semantic Web service combination module into the semantic Web service coloring Petri network module, the converted module can clearly represent the logic relationship between all sub processes in the service combination, and in addition, the correctness verification of the service combination can be carried out through a coloring Petri network formalization method. According to the invention, the correctness of the semantic Web service combination can be verified by a formalization method, so the correct execution of the service combination can be ensured.

Owner:TSINGHUA UNIV

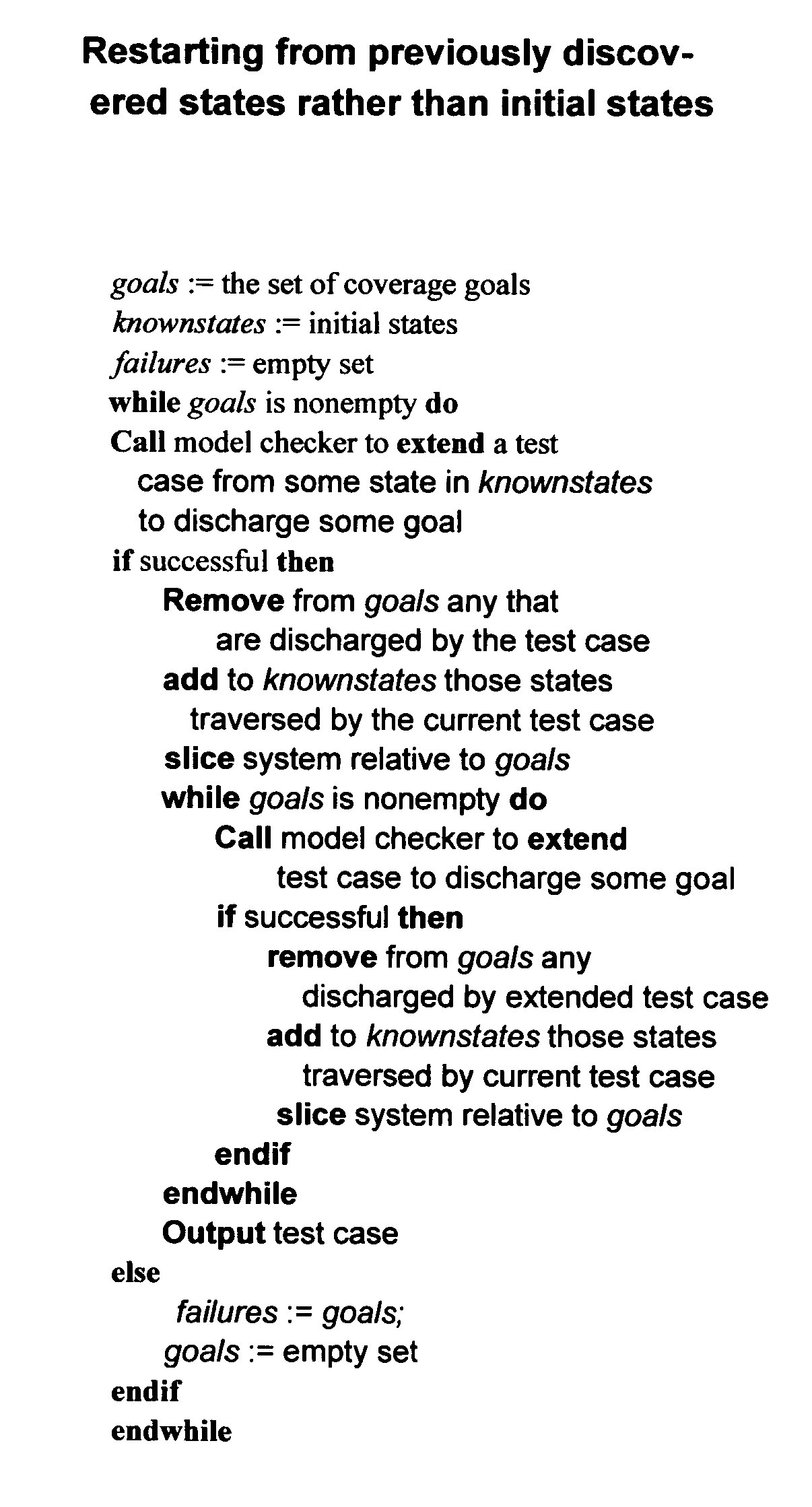

Formal methods for test case generation

ActiveUS7865339B2Reduce development costsQuick testError detection/correctionComputation using non-denominational number representationSoftware systemFormal methods

The invention relates to the use of model checkers to generate efficient test sets for hardware and software systems. The method provides for extending existing tests to reach new coverage targets; searching *to* some or all of the uncovered targets in parallel; searching in parallel *from* some or all of the states reached in previous tests; and slicing the model relative to the current set of coverage targets. The invention provides efficient test case generation and test set formation. Deep regions of the state space can be reached within allotted time and memory. The approach has been applied to use of the model checkers of SRI's SAL system and to model-based designs developed in Stateflow. Stateflow models achieving complete state and transition coverage in a single test case are reported.

Owner:SRI INTERNATIONAL

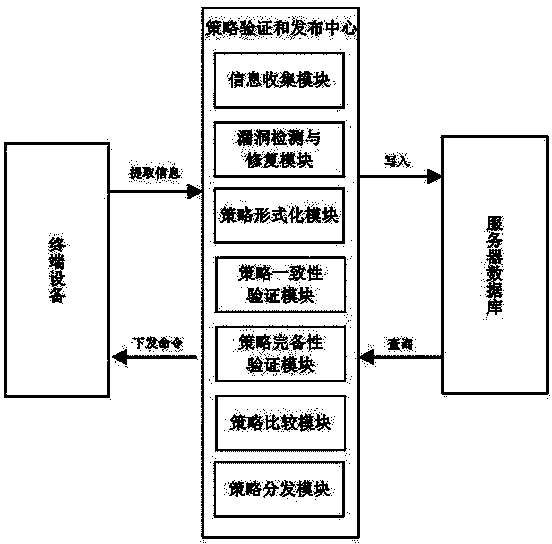

Network security strategy verification system and method on basis of formalizing method

ActiveCN103905464ATo overcome the lack of high professional requirementsEasy to operateTransmissionFormal methodsDatabase server

The invention provides a safety strategy verification system and method on the basis of a formalizing method. The system comprises a strategy verification and release center, a terminal device and a database server. The method includes the steps that information is extracted from the terminal device through an information collecting module of the strategy verification and release center, a leak detection and repair module carries out leak detection and repair, a safety strategy is generated through a strategy formalizing module, a strategy consistence verification module carries out conflict detection and elimination on the safety strategy, a strategy completeness verification module carries out completeness verification and repair on the safety strategy, a strategy comparison module compares the safety strategy operating on the current terminal device with configurations expected by an administrator, and the safety strategy is converted into a command capable of being identified by the terminal device through a strategy configuration module and is sent to the terminal device to be carried out. In terms of network safety strategy verification, the system and method have the advantages of universality, completeness, usability and automation.

Owner:XIDIAN UNIV

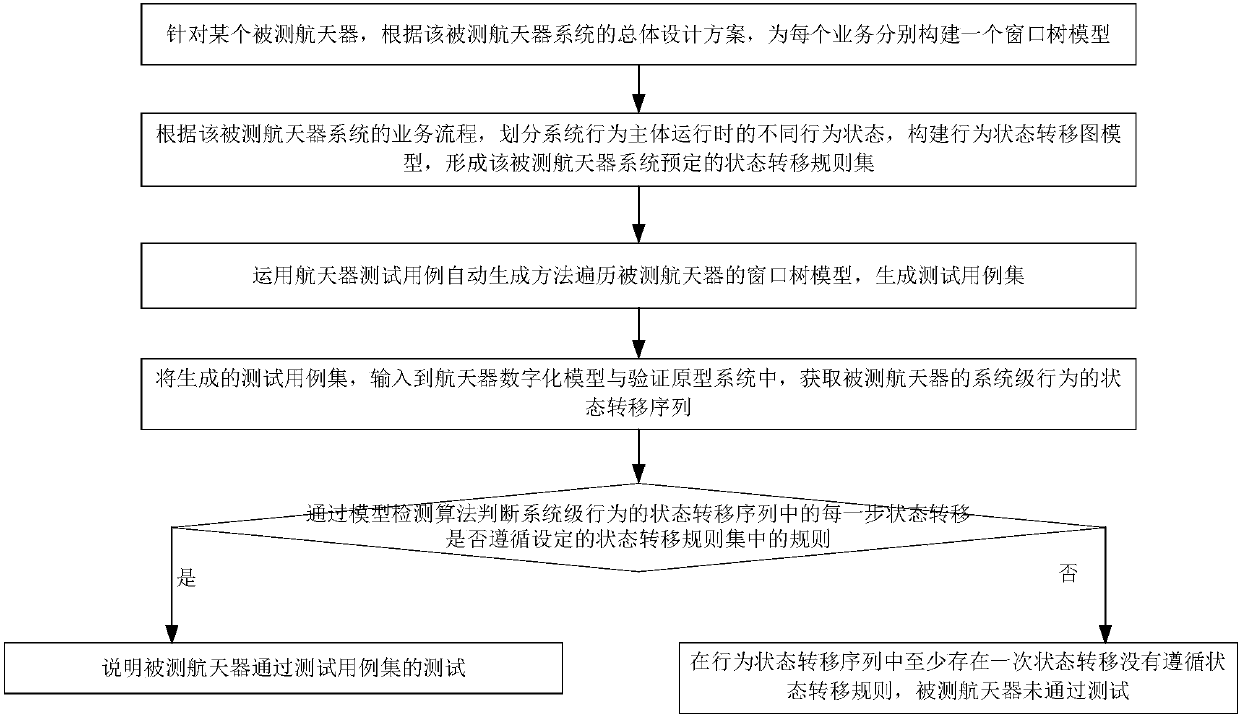

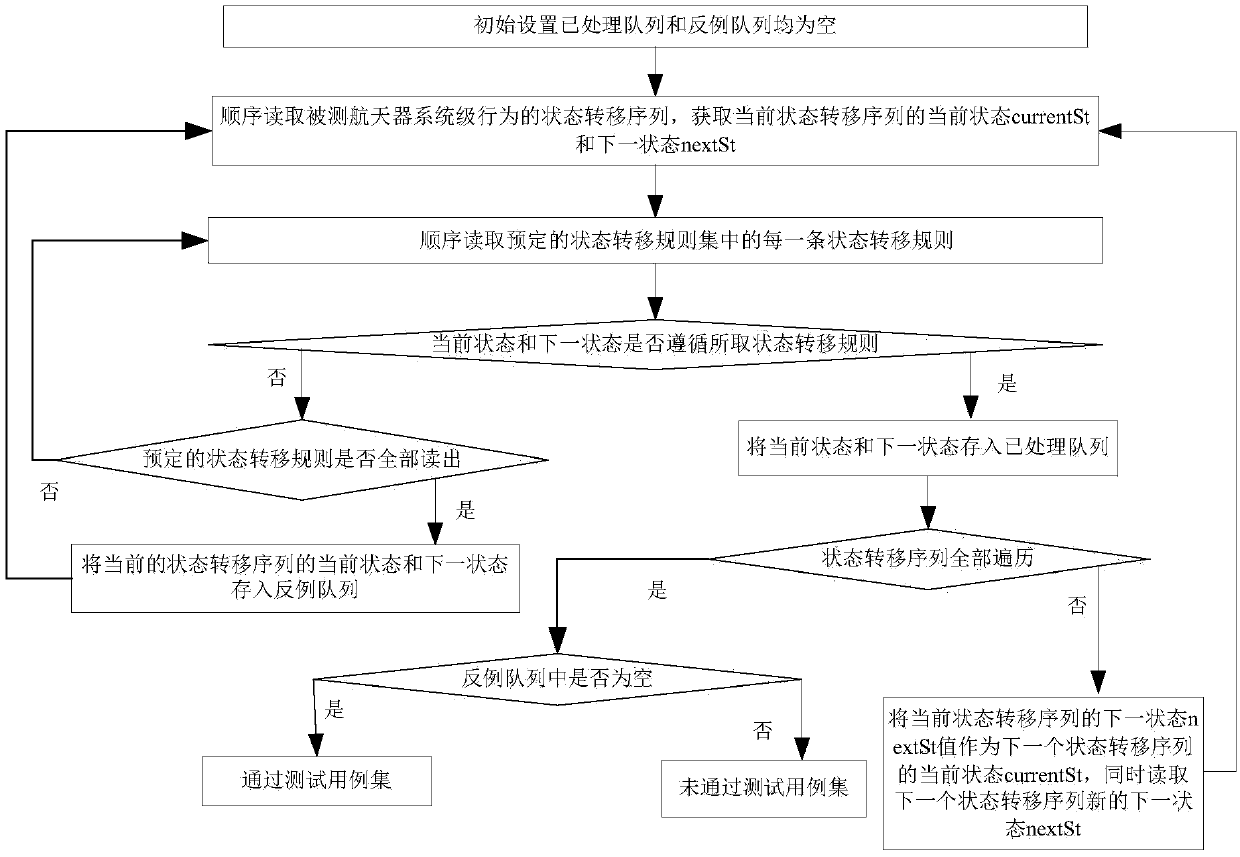

Model-based automated test method for spacecraft system

ActiveCN107066382AAutomatic verification of rigor and accuracyImprove test qualitySoftware testing/debuggingPresent methodInterface design

The invention discloses a model-based automated test method for a spacecraft system and belongs to the field of system testing. The method comprises the steps of firstly building a window tree model of a tested spacecraft system through a formalization method, classifying behavior states of the tested spacecraft system during operation according to business processes, and constructing a system behavior state transition diagram; secondly traversing a window tree to generate a test case set, running the test case set in a tested spacecraft digital model and validation prototype system, setting tracking points, obtaining system behavior states and recording a state transition sequence; and finally checking whether the obtained state transition sequence obeys a state transition rule or not through a model detection algorithm, thereby automatically validating overall design of the tested spacecraft system and interface design among modules. According to the method, the test cost of the spacecraft system and the whole research and development cycle of the spacecraft system are reduced and shortened by adopting a model-based test technology; and the quality and accuracy of spacecraft system testing are improved by adopting the formalization method and the model detection algorithm.

Owner:BEIHANG UNIV

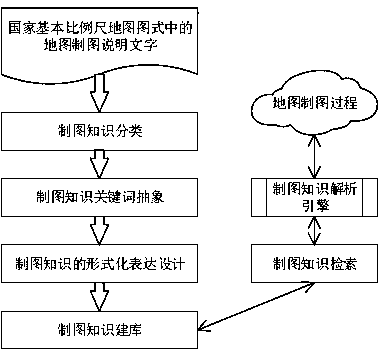

Method for mapping knowledge construction and formalized expression based on map symbols

InactiveCN103870608ASimplify the build processEasy to implementKnowledge representationGeographical information databasesFormal methodsData mining

The invention discloses a method for mapping knowledge construction and formalized expression based on map symbols. The method mainly comprises the following steps that map mapping knowledge (in text form) in basic scale map symbols is classified, keyword abstracting is conducted to the classified mapping knowledge, the formalized expression of different categories of mapping knowledge is designed, and a database of the mapping knowledge is built. The research of the mapping knowledge and the formalized expression aims to provide service for the automation of the map mapping. When the mapping knowledge is used in the map mapping process, the mapping knowledge is searched and queried firstly, the searched mapping knowledge is parsed secondly, and finally the results acquired in the above steps are used for guiding and regulating the map mapping process. The method for the mapping knowledge construction and the formalized expression based on the map symbols is easy to conduct, easy in the extending of a mapping knowledge base, and capable of making a map meeting the national basic scale topographic map.

Owner:WUHAN UNIV

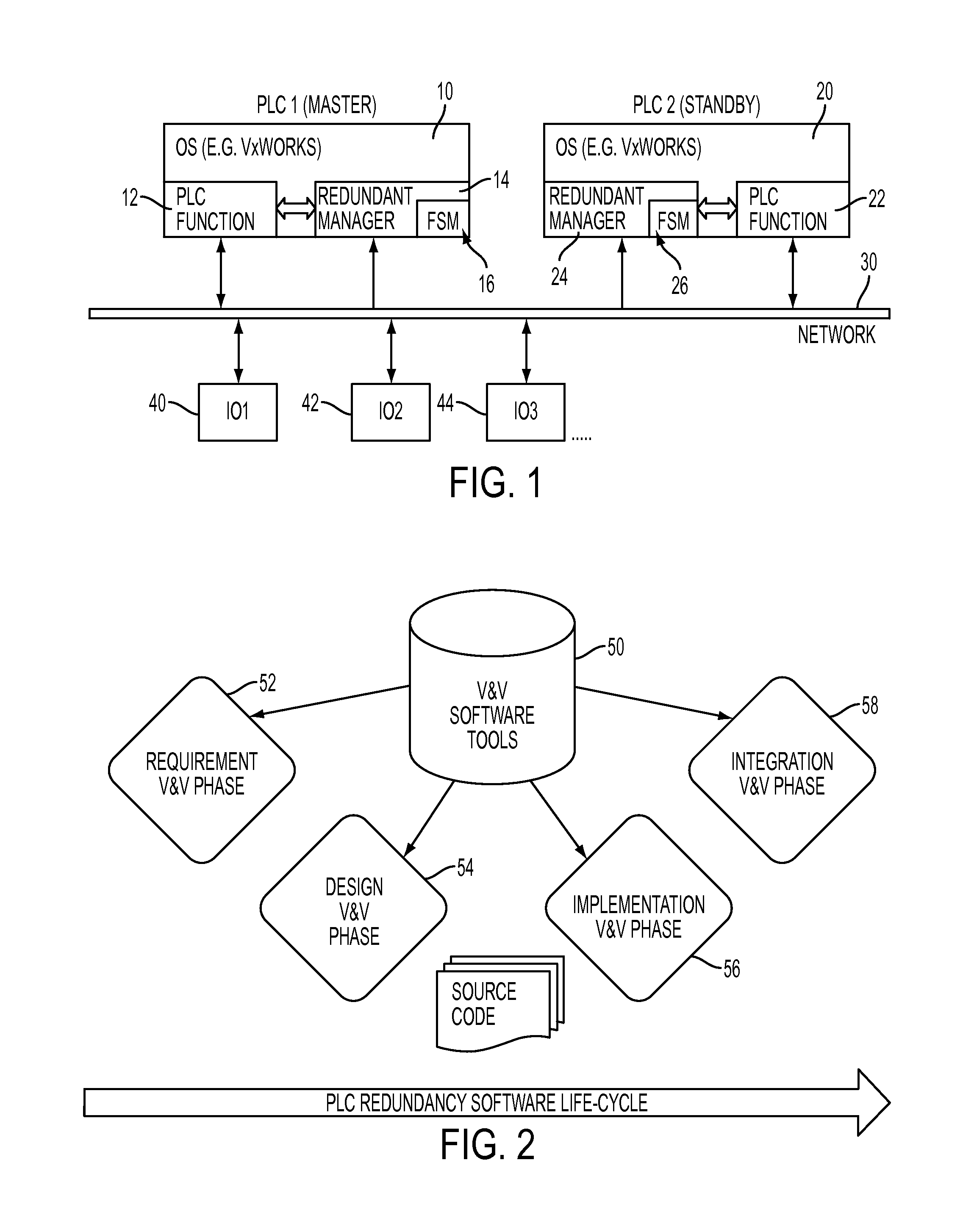

System and method for verification and validation of redundancy software in PLC systems

Formal methods are instituted to verify and validate the finite state machine (FSM) of PLC redundancy software. The method and system is implemented through each phase in the lifecycle of the redundancy software; that is, the requirement phase, design phase, implementation phase and, finally, integration phase (including system integration). At each step along the way, the verification and validation process uses tools such as a checklist-based review and inspection, a requirement traceability analysis, formal verification (model checking) and the like to ensure that the created redundancy software is error-free and will perform as intended when implemented in the redundant PLC system.

Owner:SIEMENS CORP

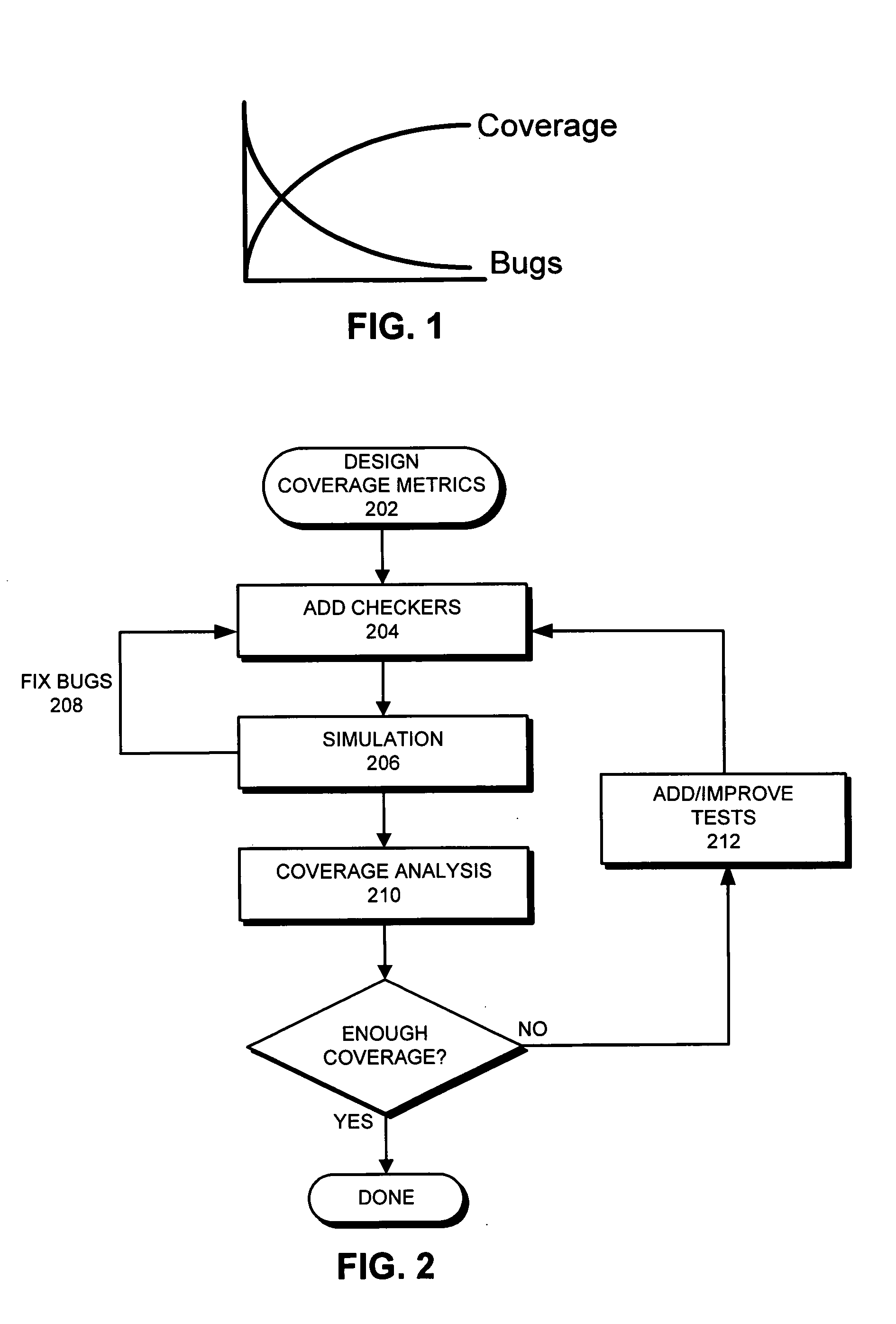

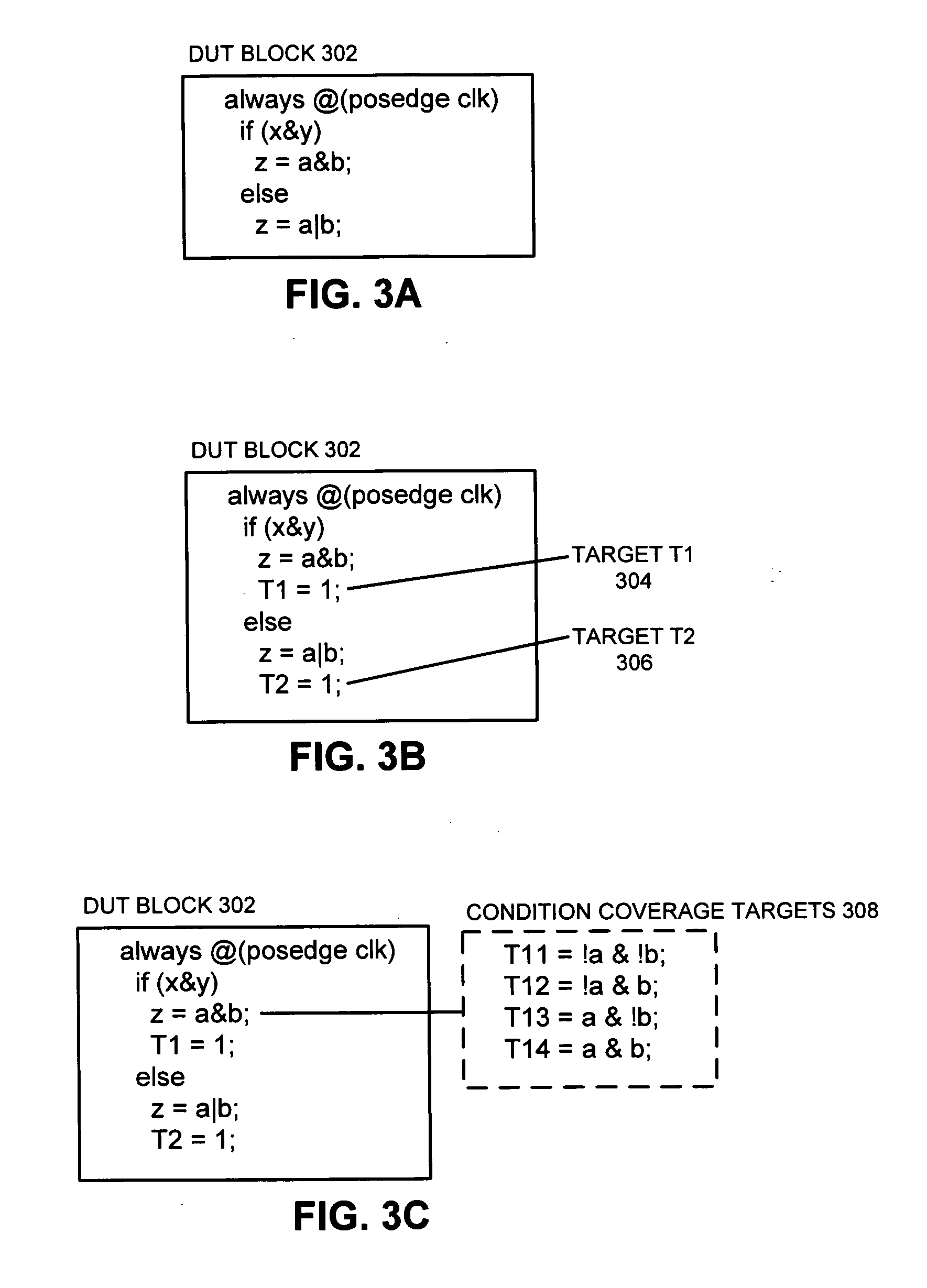

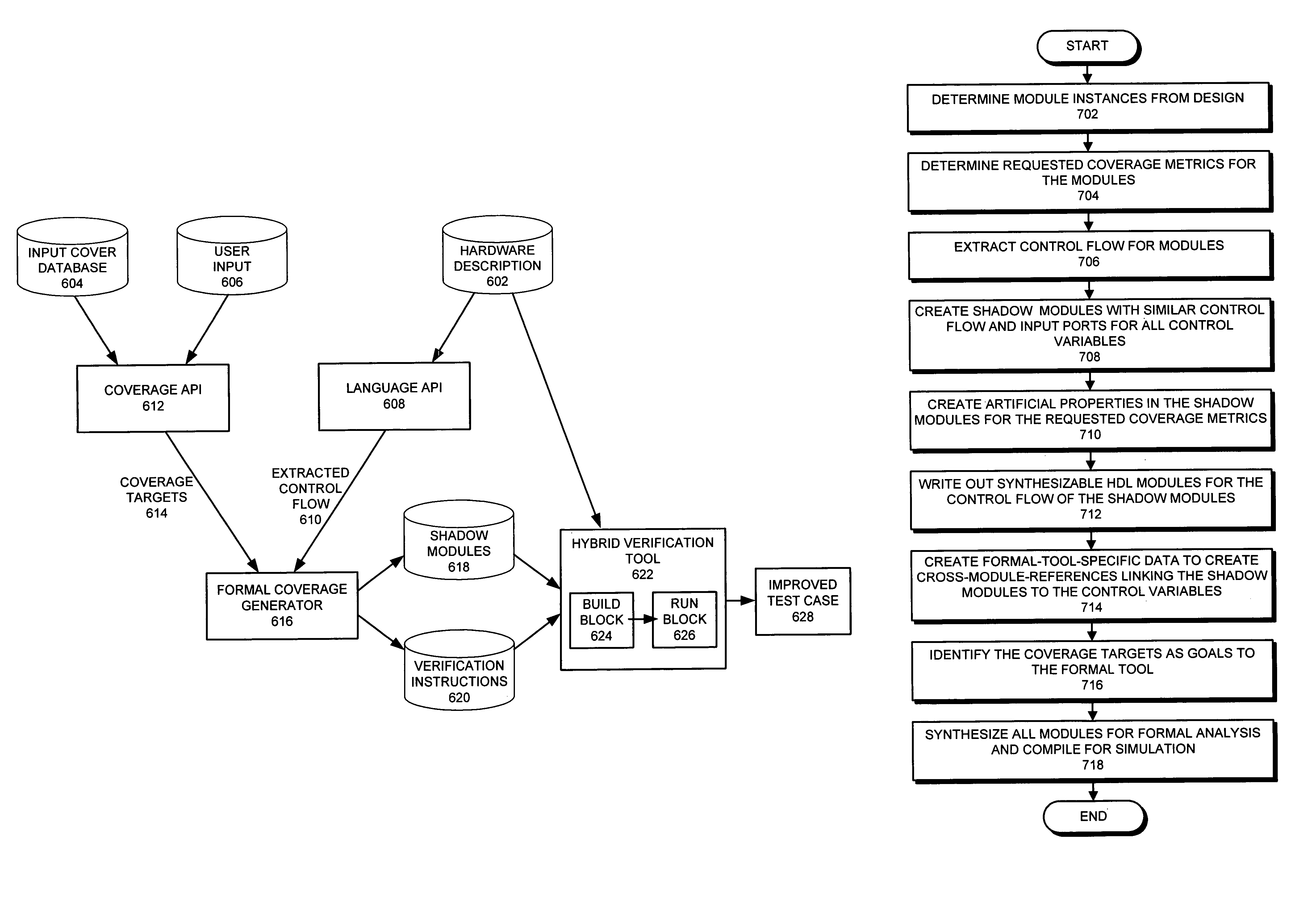

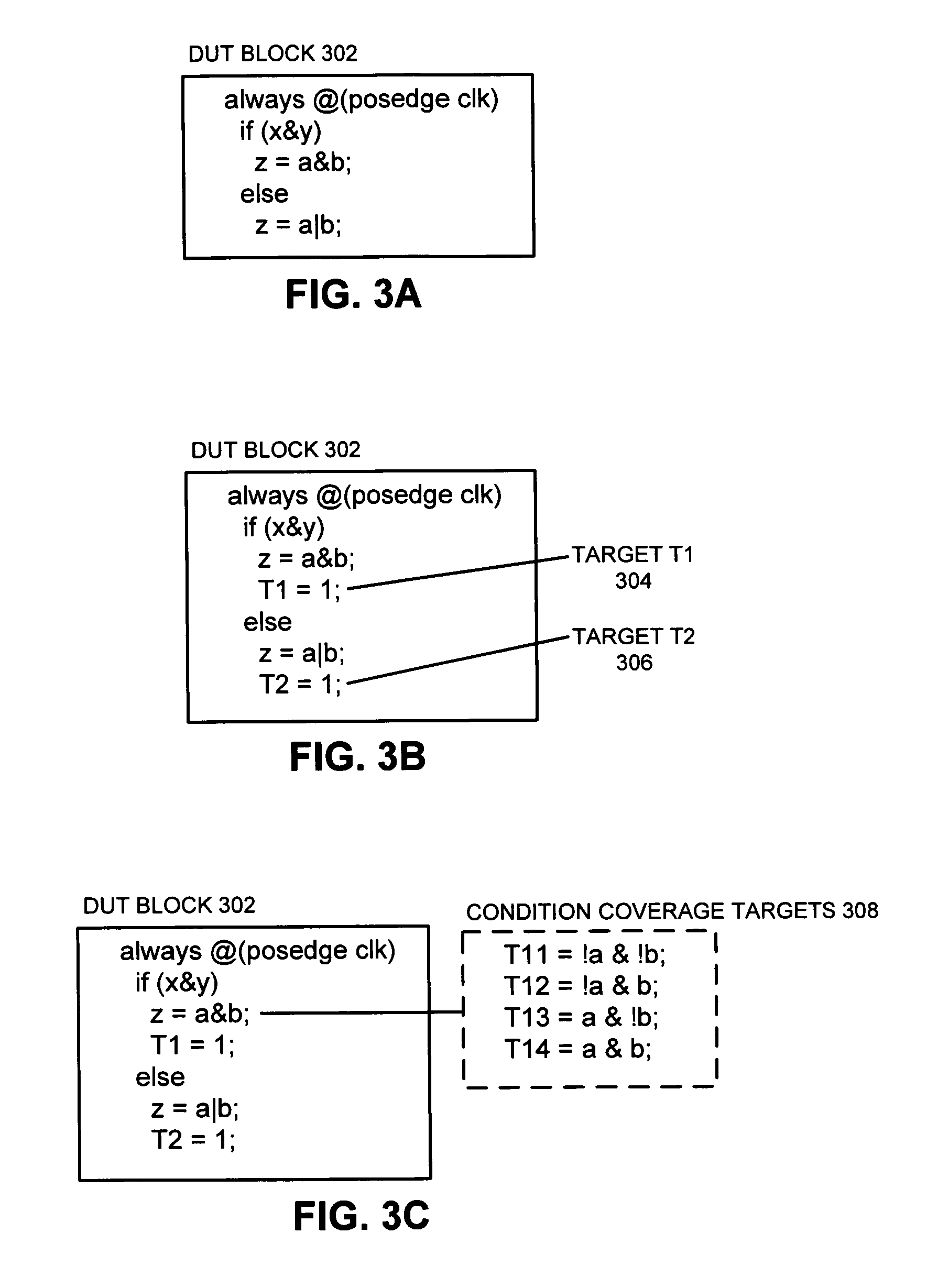

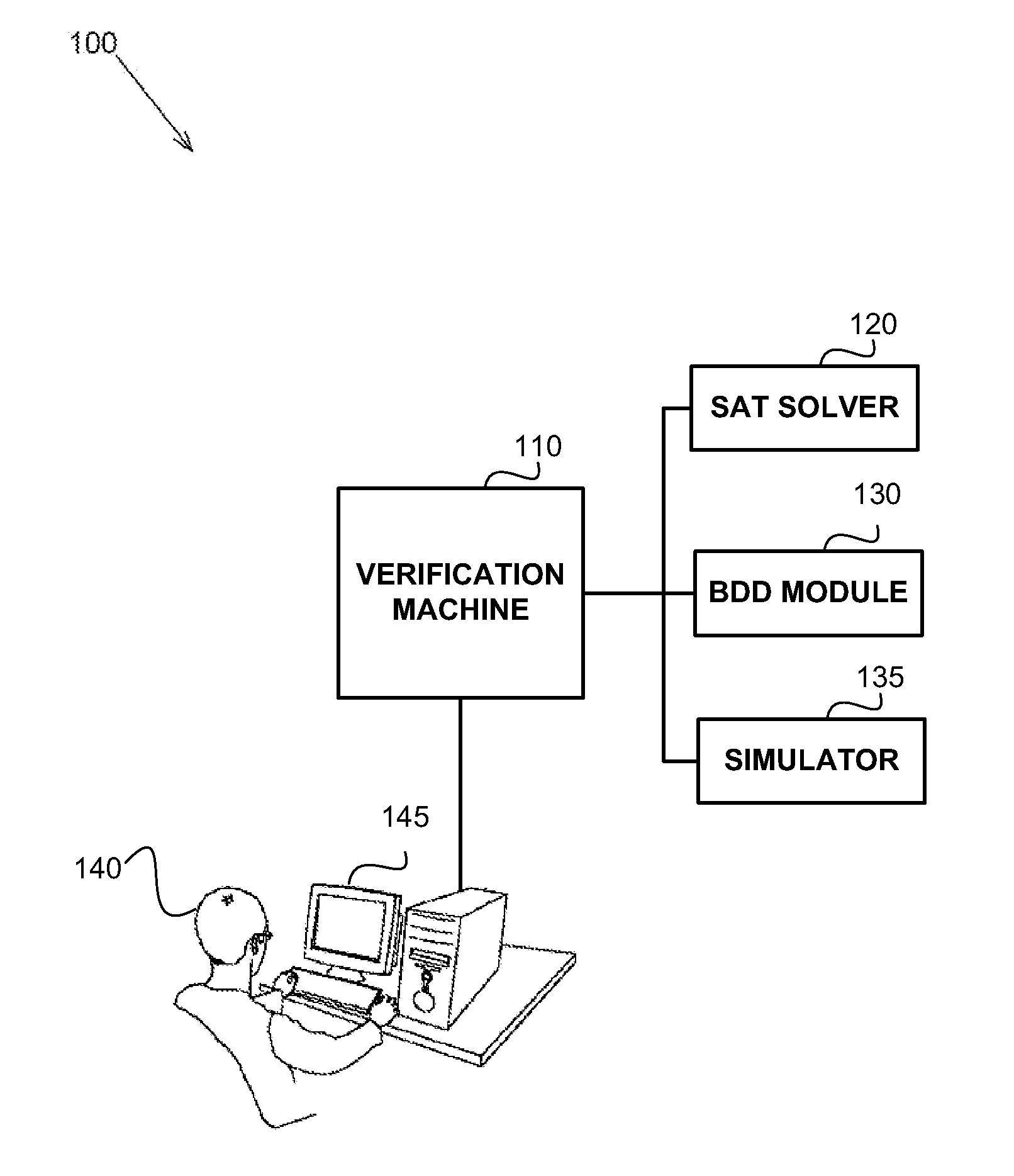

Facilitating structural coverage of a design during design verification

ActiveUS20070180414A1Convenient verificationCAD circuit designSoftware simulation/interpretation/emulationControl flowFormal methods

One embodiment of the present invention provides a method and a system that facilitates structural coverage of a design during a design verification process. During operation, the system receives a hardware description of the design, which contains one or more module instances and a set of structural coverage targets for a set of structures in the design. The system then extracts a control flow, the set of structural coverage targets, and a set of structural coverage metrics for the hardware description, and creates a shadow module with the same control flow as the hardware description. This shadow module contains a set of parallel structures that correspond to the set of structural coverage targets in the control flow of the hardware description and serve as targets for formal methods used to analyze the design. The system also generates a set of cross-module references to link the set of parallel structures in the shadow module with signals from the set of structures in the hardware description. The system then applies a formal verification tool to the design, including the shadow module and the cross-module references in an attempt to achieve the desired structural coverage.

Owner:SYNOPSYS INC

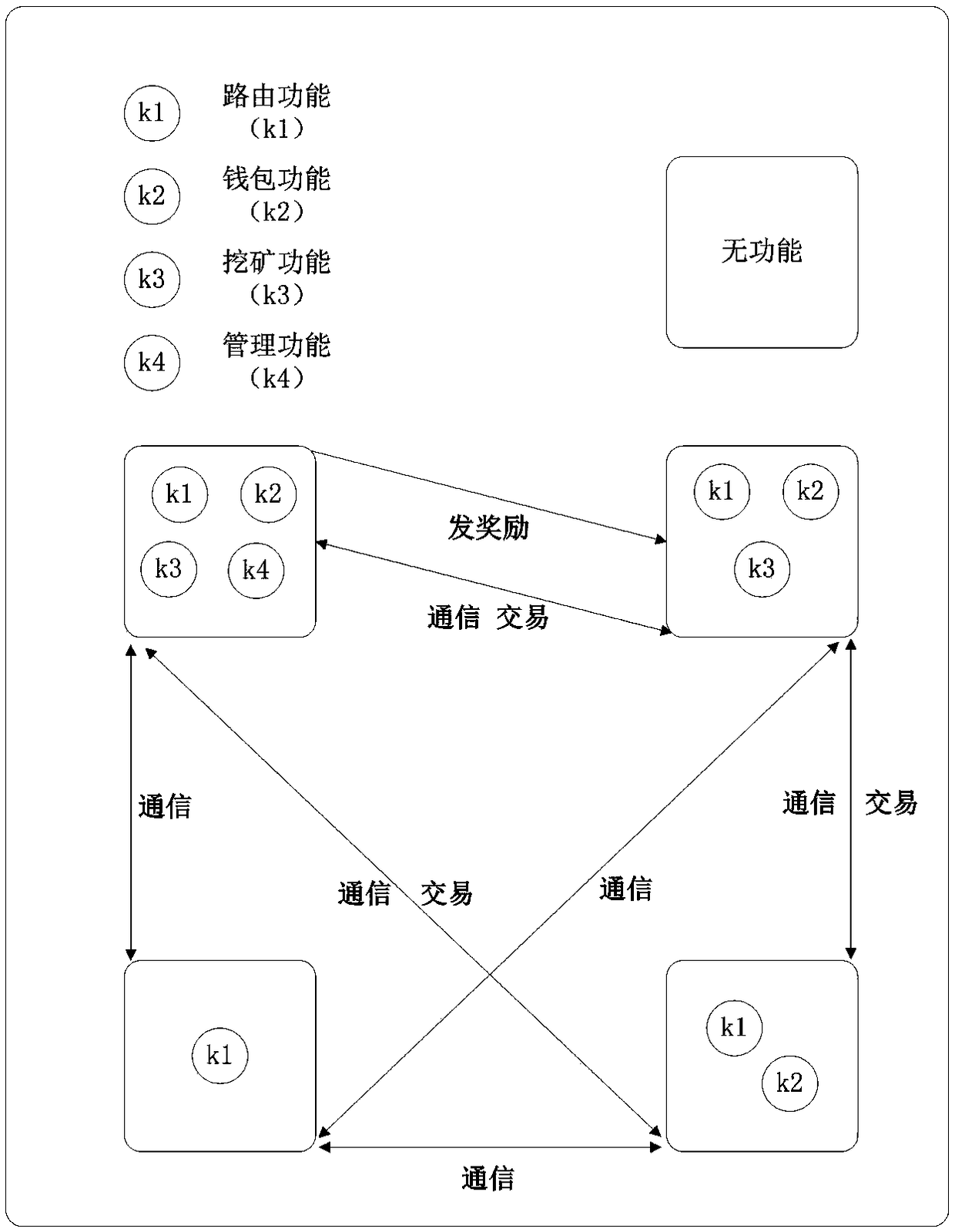

Blockchain system modeling and safety verification method and system based on MSVL

ActiveCN109347651AImprove accuracyImprove reliabilityProgramming languages/paradigmsSoftware designFormal methodsOperating system

The invention belongs to the field of formalization methods, and discloses a blockchain system modeling and safety verification method and system based on an MSVL. The method comprises the following steps: modeling a blockchain system by using the MSVL in MC, and representing the blockchain system by a program p; describing the property of the blockchain system by using a PPTL, and expressing theproperty by a formula phi; and in the MC, adding a modeling program p of the MSVL and the property phi described by using the PPTL, and verifying the safety of the blockchain system. According to theblockchain system modeling and safety verification method based on the MSVL provided by the invention, the blockchain is modeled by using an MSVL program, and the safety property of the blockchain isdescribed by using the PPTL; the PPTL is a proposition subset of PTL, and the MSVL is an executable subset of the PTL, so that the MSVL and the PPTL can be executed in the MC in a unified mode; compared with other methods, the method does not need to use another formal languages and also does not need to call other tools and a lot of manual certifications, and only needs to provide a PPTL formulaof the property to be verified, so that the proof process is automatically completed by the MC.

Owner:XIDIAN UNIV

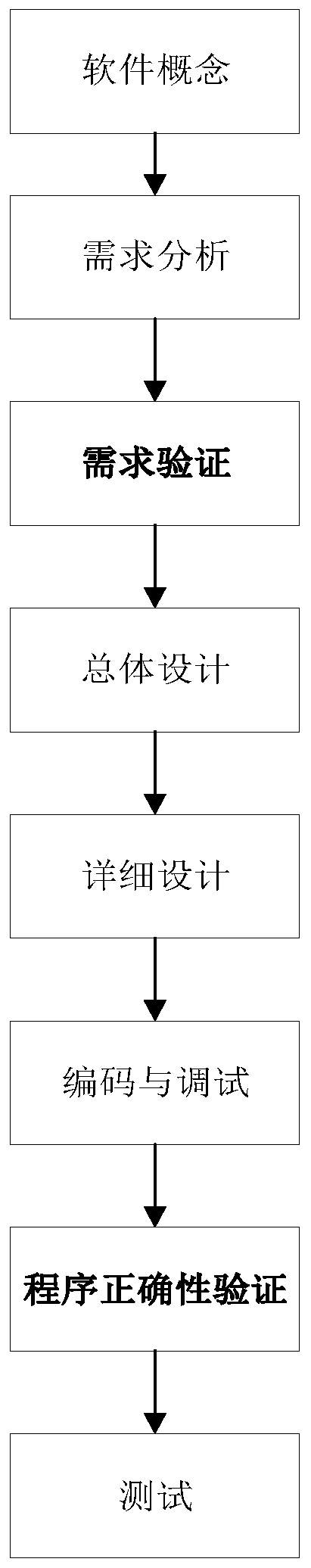

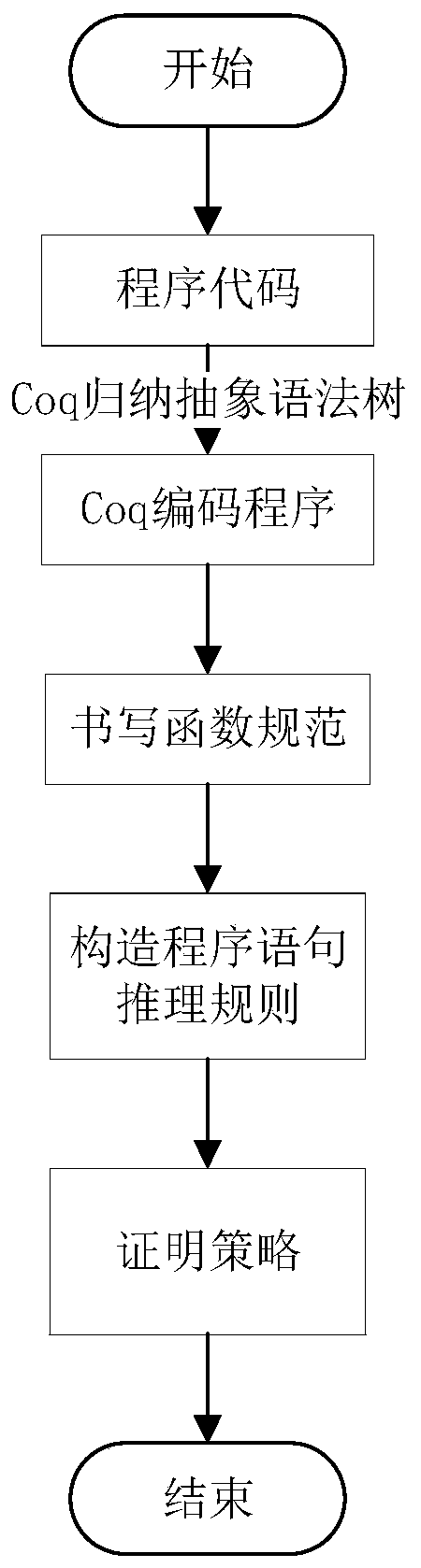

A formalized verification-based software development model verification method

InactiveCN109918049AHigh degree of credibilityGuaranteed reliabilitySoftware testing/debuggingSoftware designValidation methodsFormal methods

According to the formal verification-based software development model verification method provided by the invention, formal verification and a software development process are combined, so that the high credibility of software is improved, and the reliability of software development is logically guaranteed; the effect of formalized verification on the development logic in the software developmentprocess in the field of software error detection is exerted; and the possibility that the program operates in an abnormal state is reduced. According to the method, the high credibility of the software is improved, and the reliability of software development is logically guaranteed; verification is carried out in the demand stage, and the serious consequence of redevelopment caused by unreasonablesoftware demand analysis can be avoided; the function logic correctness in the software development process is verified in the field of formal verification in time; the formal method is introduced into the software development process, a specific model is given, and the limitation problem of the test technology in the field of software error detection is solved.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Binary dependency database

InactiveUS7321897B2Easy to analyzeData processing applicationsDigital data processing detailsConfiguration optimizationFormal methods

The present invention facilitates the analysis of binaries, components, configurations, and their footprints for component design and optimization. Complete and meaningful binary, component, configuration, and footprint information allows formal methods for component analysis and configuration optimization. A binary dependency database persists and stores binary dependency information. The binary dependency database provides detailed dependency information among binaries.

Owner:MICROSOFT TECH LICENSING LLC

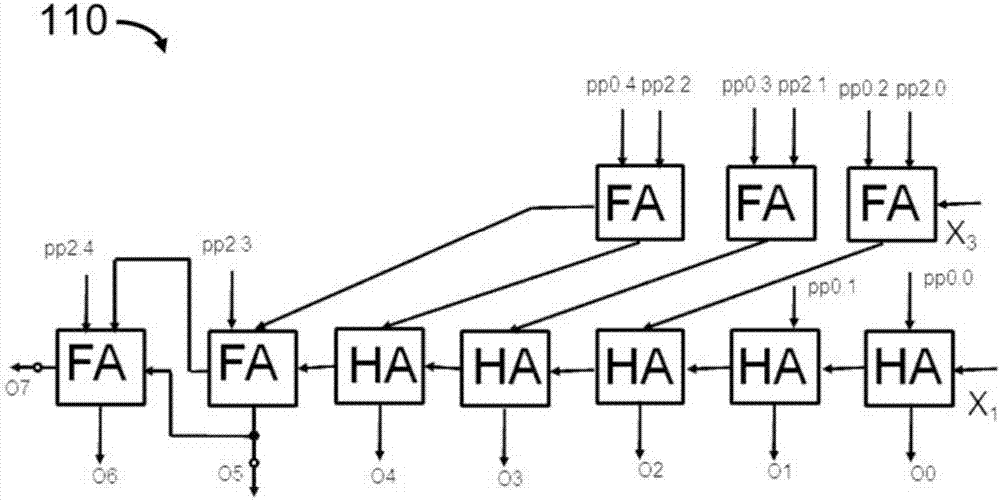

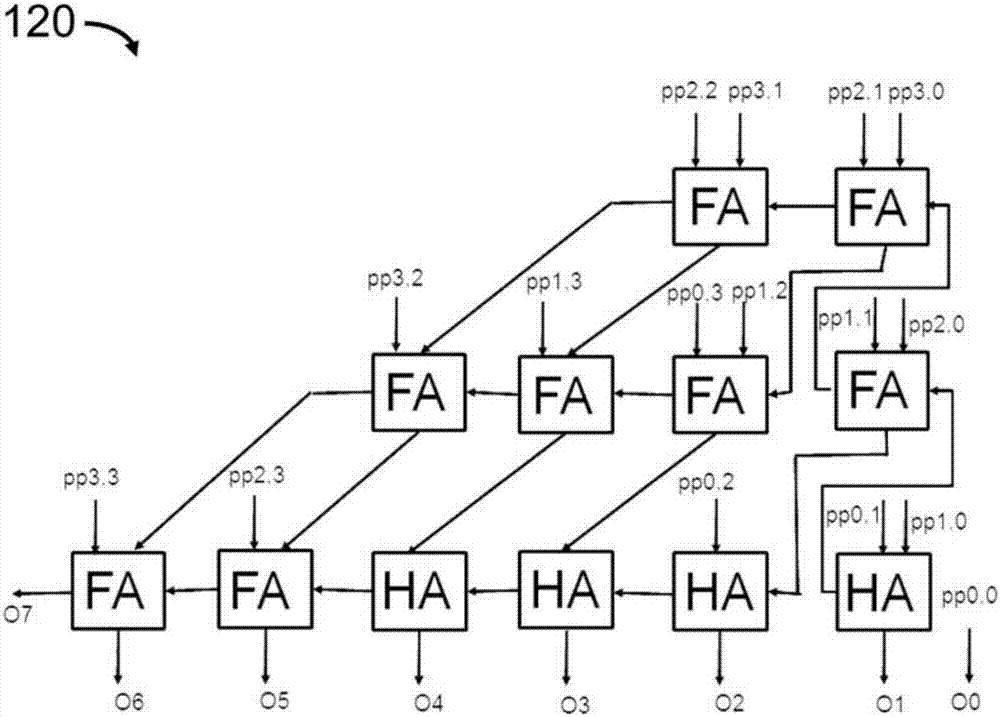

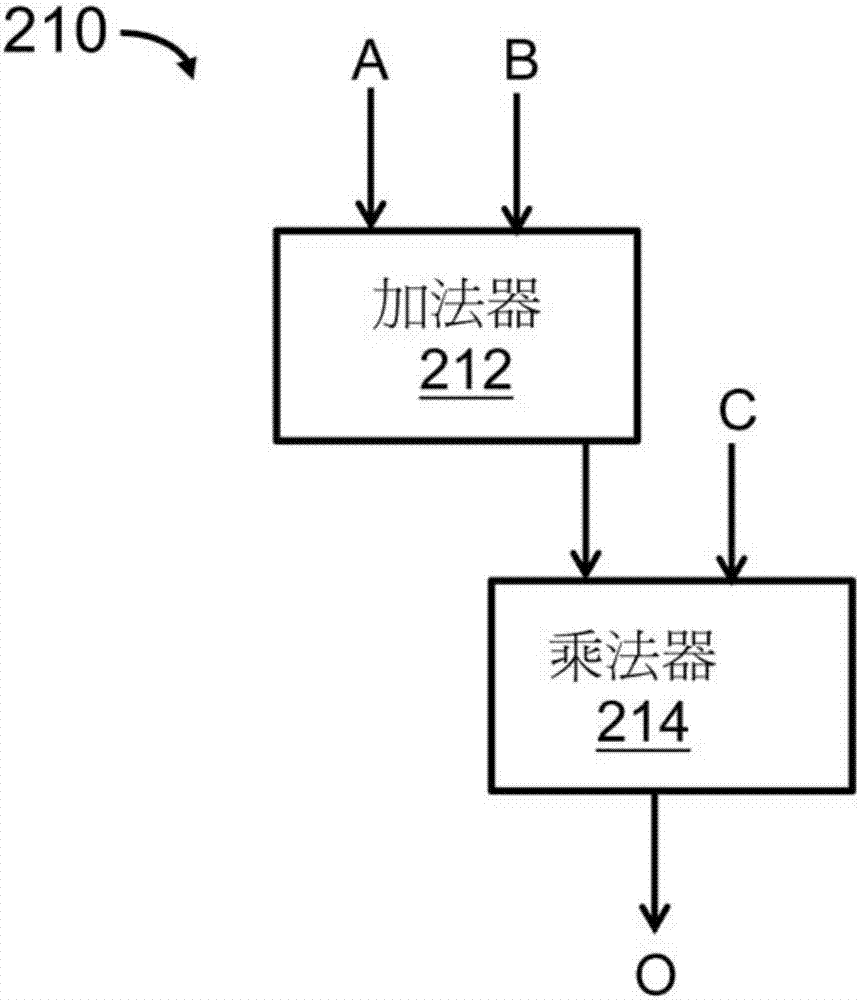

Circuit verification

InactiveCN106997408ACAD circuit designSpecial data processing applicationsStructure propertyFormal methods

Provided is a totally new formal verification algorithm aiming at an arithmetic circuit. One example embodiment provides a new formal method which couples (combines) a satisfiability (SAT) solver and a unique Reverse Engineering (RE) method which makes use the arithmetic logical circuit structure properties (e.g. 1-bit adder structure, Carry tree structure) to achieve the algorithm for arithmetic circuits regardless of its size. The example embodiment provides basic through of how to optimize the operational complexity of a conventional arithmetic circuit verification method. The basic through is shown as followed: assuming that there are two arithmetic circuits f and g; conducting equivalence checking of the two arithmetic circuits by firstly generating a conjunctive normal form (CNF) encoding; and determining whether the encoding of the two arithmetic circuits is equal through a satisfiability (SAT) tool. If the structural difference between f and g is minimized as far as possible before generating a conjunctive normal form (CNF) encoding, the arithmetic circuit verification is completed in polynomial time rather than in exponential time.

Owner:EASY LOGIC TECH LTD

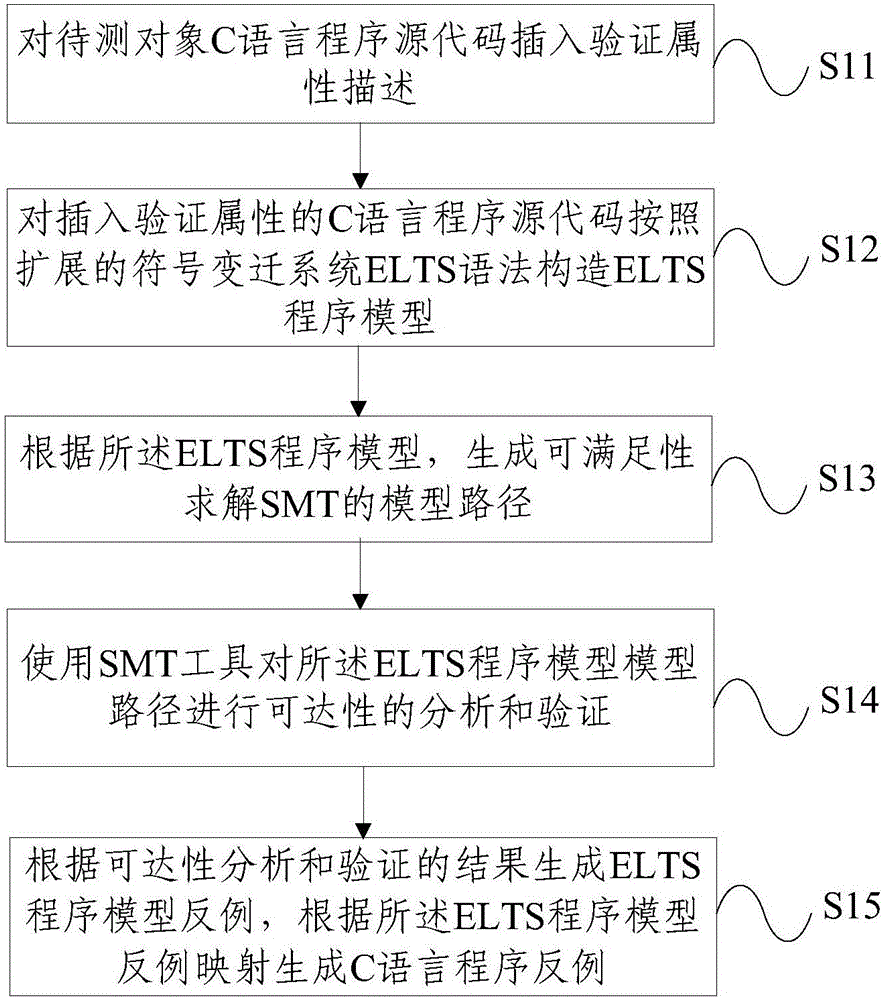

C language program software validation method and device based on expanded symbol transition system

InactiveCN106294148AImprove efficiencyImprove accuracySoftware testing/debuggingValidation methodsProgram counter

The invention provides a C language program software validation method and device based on an expanded symbol transition system. The method comprises the following steps: inserting verification attribute description into C language program source codes of an object to be tested; establishing an ELTS program model for the C language program source codes to which verification attribute is inserted according to an expanded symbol transition system ELTS syntax; generating a model path of a satisfiability solving SMT according to the ELTS program model; performing accessibility analysis and validation on the model path of the ELTS program model through an SMT tool; generating an ELTS program model counter-example according to an accessibility analysis and validation result, and generating a C language program counter-example according to ELTS program model counter-example mapping. The embodiment of the invention automatically establishes the ELTS program model, and obtains the validation result through model detection and strict mathematical reasoning, and compared with other formalization methods, the method has the characteristics of higher accuracy rate and better program coverage rate, and improves the efficiency and accuracy of software validation.

Owner:TSINGHUA UNIV

Ground autonomous mobile robot safety navigation method based on formal description

ActiveCN106681322AComplete security propertiesNavigational calculation instrumentsPosition/course control in two dimensionsAutonomous Navigation SystemFormal methods

The invention provides a ground autonomous mobile robot safety navigation method based on formal description. An abstract model of an autonomous robot navigation system is established, a formal method is used to describe a robot safety navigation algorithm, safety constraints of the navigation system are analyzed, and the algorithm is solved and verified under the constraints. The system model is established on the basis of a robot omnidirectional movement platform, the provided autonomous navigation algorithm follows restrictions of passive friendly safety, and the formal method is used to resolve control input to be verified in the navigation system. The effective robot autonomous navigation algorithm is provided, and differential dynamic logics are used to solve safety control input of next moment according to the present operation state of the system. The method can be applied to the autonomous navigation system of the robot, and the completeness of a safety mechanism of the navigation system is ensured.

Owner:EAST CHINA NORMAL UNIV

Formalization method for verification and performance analysis of high reliable communication system

ActiveCN103036739AEasy to exploitEasy logic errorData switching networksCommunications systemComputer architecture

Provided is a formalization method for verification and performance analysis of a high reliable communication system. The formalization method includes five steps. The formalization method is a method for communication system formal verification and analysis based on the combination of model testing and theorem proving. Based on the method of hypothesis guarantee, an environmental state machine is established to achieve layering modeling for design of a network communication system, the formal verification for determinant attributes is achieved, high order logical formalization with a random variable statistic character is achieved for protocol transmission processes and the method and design of attributive high order logical formal modeling, and based on the high-order logic model and the correlation theorem which are established on HOL4, automatic verification and dynamic performance analysis based on the formal model are achieved. The formalization method has good practical value and wide application prospects in the technical field of formal verification engineering.

Owner:CAPITAL NORMAL UNIVERSITY

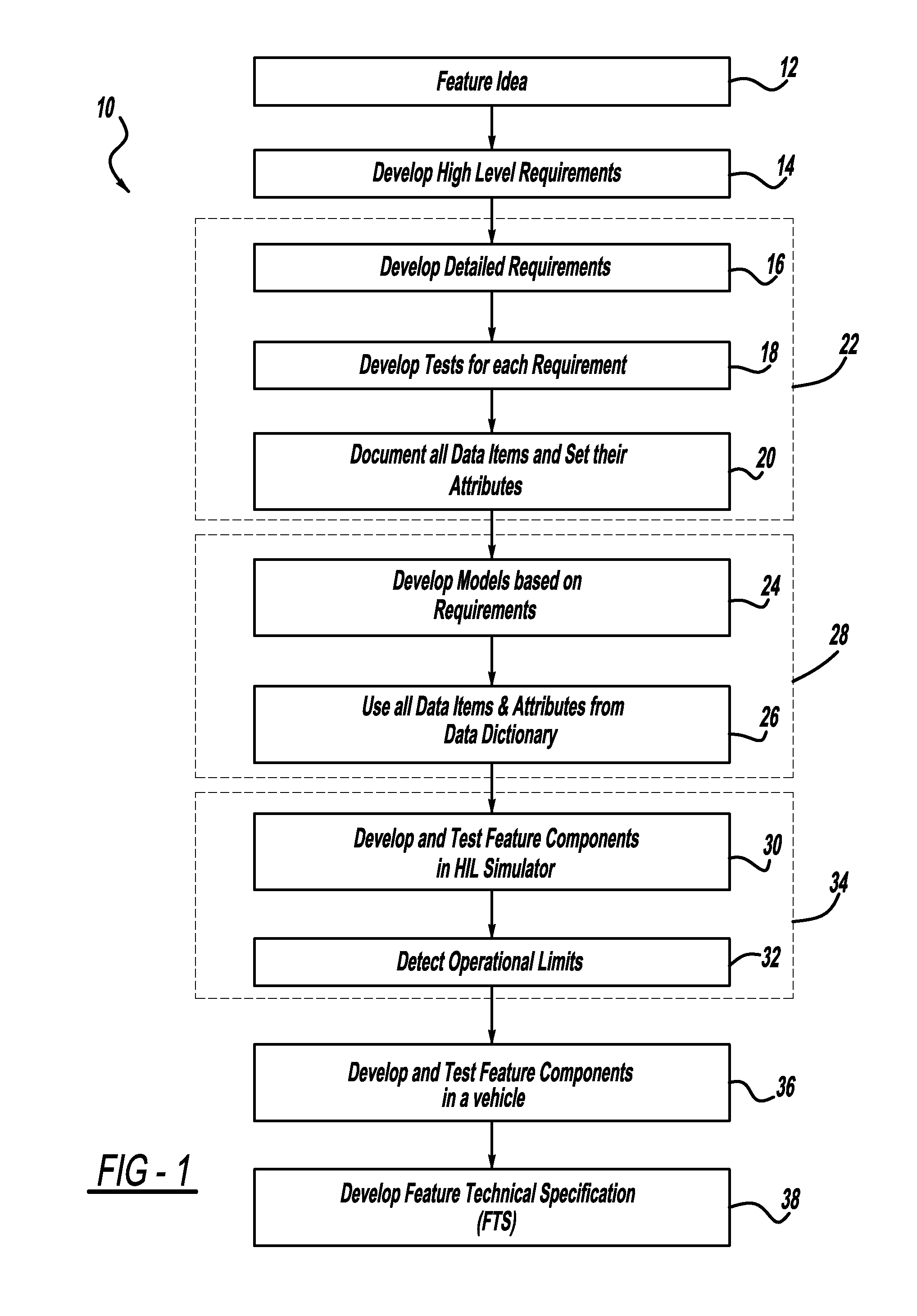

Requirements driven feature development process

InactiveUS8433550B2Geometric CADComputation using non-denominational number representationSoftware development processDocumentation procedure

Owner:GM GLOBAL TECH OPERATIONS LLC

Software test program generation

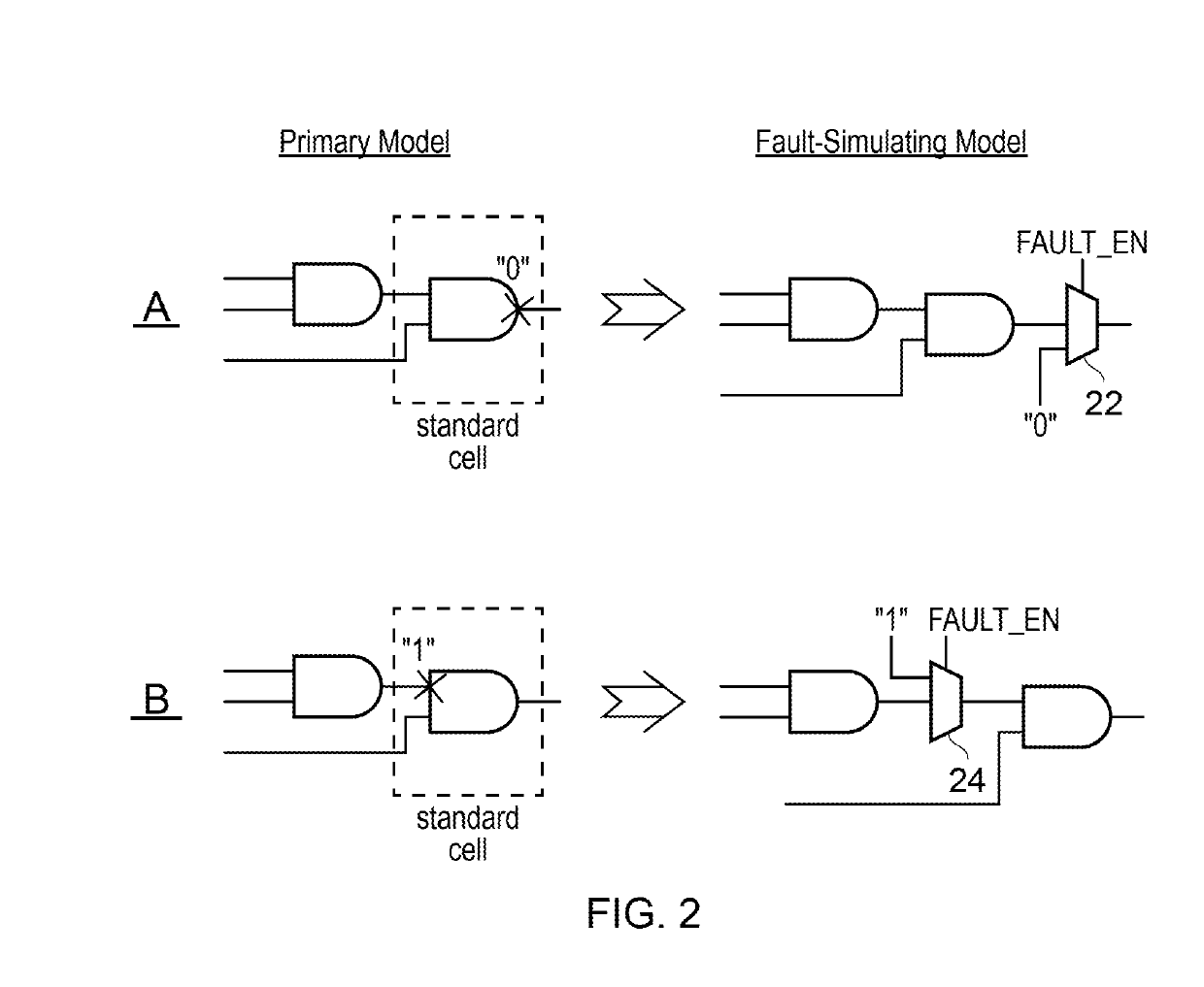

A simulation of software test program executing upon a primary model of a portion of a data processing apparatus is performed to identify uncovered (undetected) failures. A formal method analysis is then performed upon a combination of the primary model and a fault-simulating model simulating the uncovered failures in order to identify software stimuli that can render the uncovered failures detectable. The identified software stimuli are then added to the software test program to increase the failure coverage. The process is performed iteratively until a desired level of failure coverage is achieved.

Owner:ARM LTD

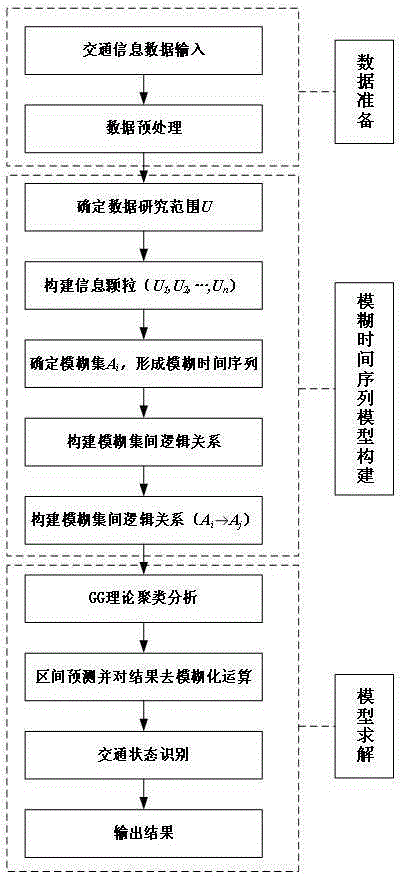

Road traffic flow parameter prediction method based on granular computing

ActiveCN105185106AGuaranteed forecast accuracyImprove practicalityDetection of traffic movementParticulatesTraffic flow

The present invention relates to the field of traffic information release and traffic management and control and discloses a road traffic flow parameter prediction method based on granular computing. The method comprises the steps of (1) replacing a data point by information particulate to be the basic unit of data mining analysis, (2) with granular computing ideology throughout the whole prediction framework, taking granular processing as a data processing method with a unified structure, allowing a policy maker to clearly understand the positions of various forms of systems in mutual interaction, grasping the communication mode of the systems, and establishing an enhanced harmonious environment among different ways, (3) with a fuzzy time series and the Gath-Geva cluster theory as the basis, by focusing on the commonalities of existing formal methods, recognizing the orthogonality of an existing good frame ( such as the probability theory and the probability density functions of various variables), with variable granularity concept as a basis, establishing the interval length analysis model of a granularity range according to a numerical entity, and thus realizing pattern recognition and speculation on the above basis.

Owner:丁宏飞 +7

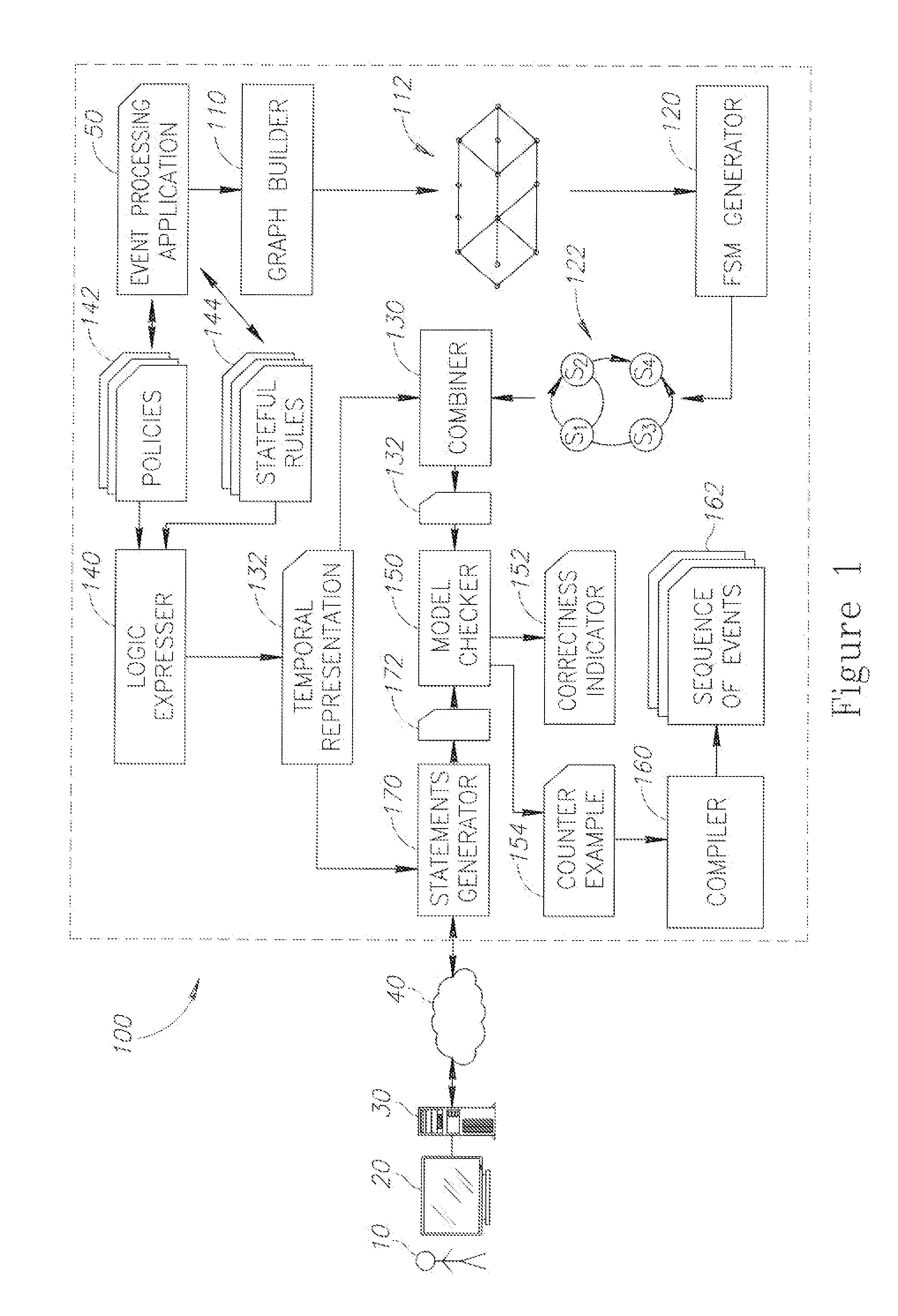

Conducting verification in event processing applications using formal methods

A method of applying formal verification methodologies to event processing applications is provided herein. The method includes the following stages: representing an event processing application as an event processing network, being a graph with event processing agents as nodes; generating a finite state machine based on the event processing network, wherein the finite state machine is an over-approximation of the event processing application; expressing stateful rules and policies that are associated with the event processing application using temporal logic, to yield a temporal representation of the event processing application; combining the temporal representation and the finite state machine into a model; generating a statement associated with a user-selected verification-related property of the event processing application, wherein the statement is generated using the temporal representation; and applying the statement to the model, to yield an indication for: (i) a correctness of the statement or (ii) a counter example, respectively.

Owner:IBM CORP

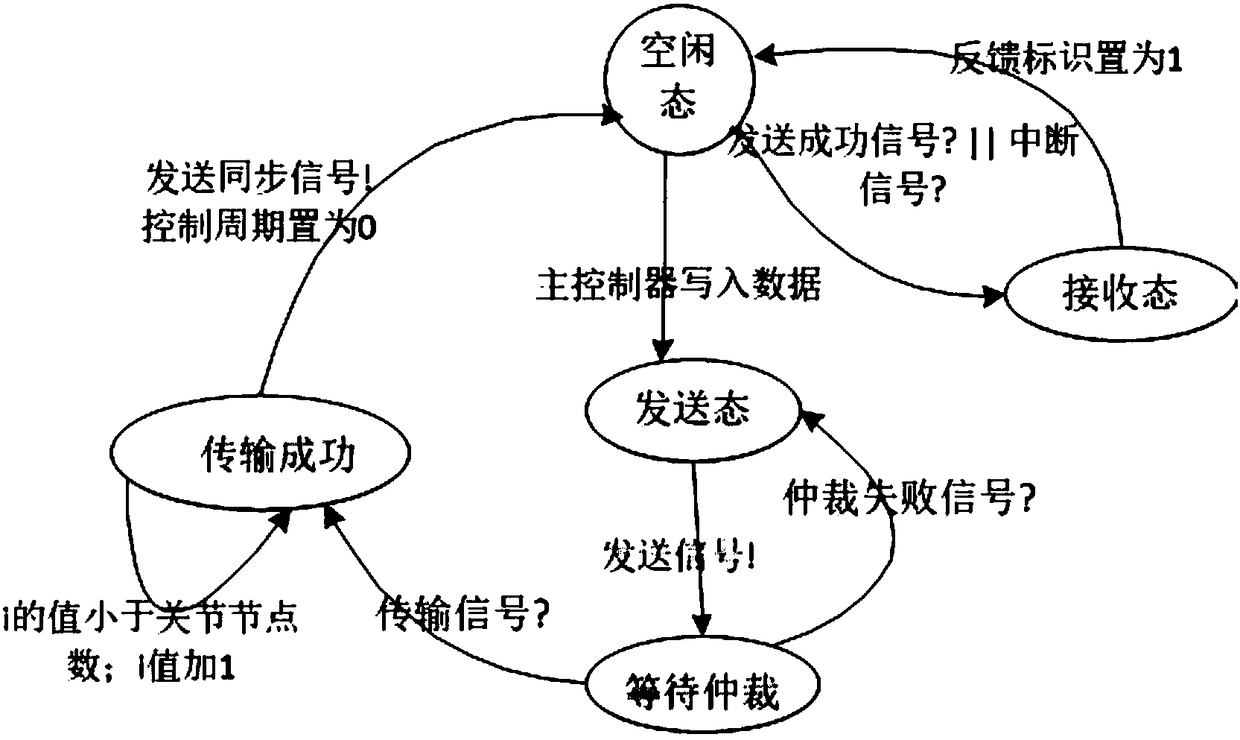

Verification method and system of robot joint communication system model

ActiveCN108199940AIncrease the node loadReduce Arbitration LatencyBus networksCommunications systemValidation methods

The invention relates to a verification method and system of a robot joint communication system model. The method comprises the steps of modeling for and analyzing a CAN-based field bus type control system in a formalization manner, wherein model abstracting is performed on the system, and then formal modeling and verification are performed; determining whether a timed automata meets constraints of correctness and timeliness; if the time automata does not meet the constraint of correctness, replanning a system solution; if the time automata does not meet the constraint of timeliness, improvingthe timeliness through deploying a dynamic priority policy. According to the method, a timed automata model is built in a formal description manner, and the correctness and timeliness of the timed automata are verified in a UPPAAL tool; if the constraint of timeliness is not met, the dynamic priority policy is deployed.

Owner:CAPITAL NORMAL UNIVERSITY

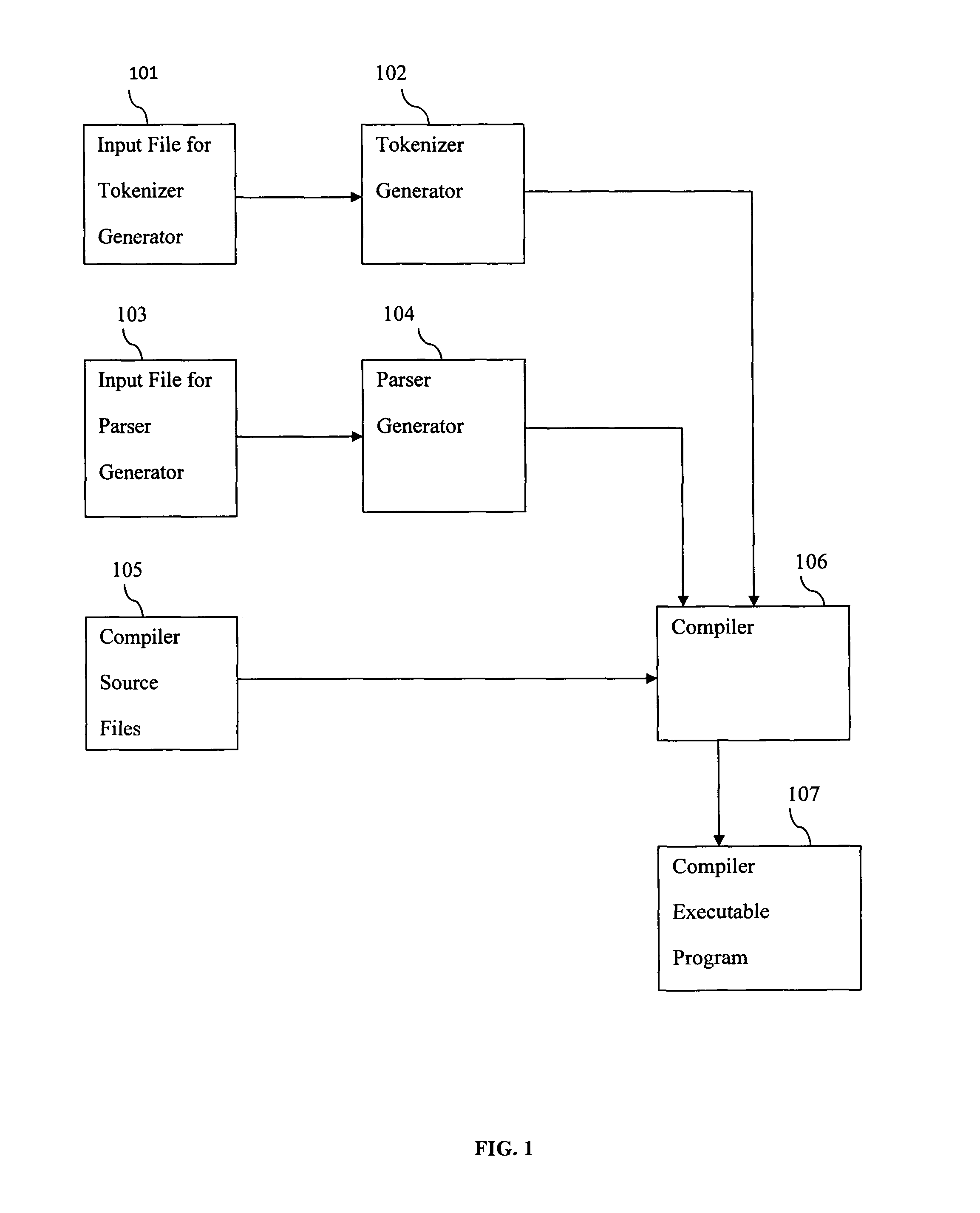

Compiler compiler system with syntax-controlled runtime and binary application programming interfaces

A compiler compiler system with a design paradigm different from traditional compiler compiler systems in many aspects. First, instead of parsing tree, compiler compiler runtime and binary are designed according to compiler compiler parsing model. Second, any semantics processing is totally separated from syntax processing. Third, the whole compilation process is defined as syntax processing and semantics processing followed by syntax processing performed under compiler compiler management supervision. Fourth, syntax processing has two phases: building compiler compiler runtime, and converting compiler compiler runtime into compiler compiler binary with available option to convert back compiler compiler binary to compiler compiler runtime. Fifth, compiler compiler runtime and binary syntax-controlled APIs are defined in terms of syntax. Sixth, there are formal methods de-compiling compiler compiler runtime and / or binary into original program text accordingly to syntax. Seventh, compiler compiler runtime and binary with their syntax-controlled APIs serve as a multiplatform for obfuscation, security, binary files processing, and program-to-program communication.

Owner:URAKHCHIN ALEKSANDR F

Facilitating structural coverage of a design during design verification

ActiveUS7415684B2Convenient verificationCAD circuit designSoftware simulation/interpretation/emulationControl flowFormal methods

One embodiment of the present invention provides a method and a system that facilitates structural coverage of a design during a design verification process. During operation, the system receives a hardware description of the design, which contains one or more module instances and a set of structural coverage targets for a set of structures in the design. The system then extracts a control flow, the set of structural coverage targets, and a set of structural coverage metrics for the hardware description, and creates a shadow module with the same control flow as the hardware description. This shadow module contains a set of parallel structures that correspond to the set of structural coverage targets in the control flow of the hardware description and serve as targets for formal methods used to analyze the design. The system also generates a set of cross-module references to link the set of parallel structures in the shadow module with signals from the set of structures in the hardware description. The system then applies a formal verification tool to the design, including the shadow module and the cross-module references in an attempt to achieve the desired structural coverage.

Owner:SYNOPSYS INC

Soft error verification in hardware designs

Soft error detection is performed by computation of states based on formal methods and by simulating a synthesized target identification logic together with the design. Soft errors may be simulated in response to detecting that a simulated state of the design is comprised by the states. A BDD representation of the design may be utilized to determine the states. A Boolean satisfiability problem may be defined and solved using an all-SAT solver in order to determine the states.

Owner:GLOBALFOUNDRIES INC

Z-specification-based test case generating method

InactiveCN102103539AAccurate descriptionImprove efficiencySoftware testing/debuggingSoftware systemObject code

The invention relates to data processing and testing. In order to test a measuring object efficiently and accurately, the technical scheme used by the invention is a Z-specification-based test method which comprises the following steps of: 1, describing the specification of a software system by using a Z language to make the description of a formalization method accurate and sufficiently exert an advantage without ambiguity; 2, generating a precondition in a predicate part of a basic module mode of the Z language and ensuring the integrity of a module and the non-verbosity of the precondition simultaneously; 3, generating a usable test case with high coverage ratio by a proper algorithm according to the acquired precondition; and 4, verifying whether the code of a user accords with the predicted code of a program or not by detecting the code, and providing a corresponding test report by comparing the output of a target code with the output of the acquired test case. The method is mainly applied to data processing and testing.

Owner:TIANJIN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com