Circuit verification

A circuit and sub-circuit technology, applied in the field of circuit verification, to achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

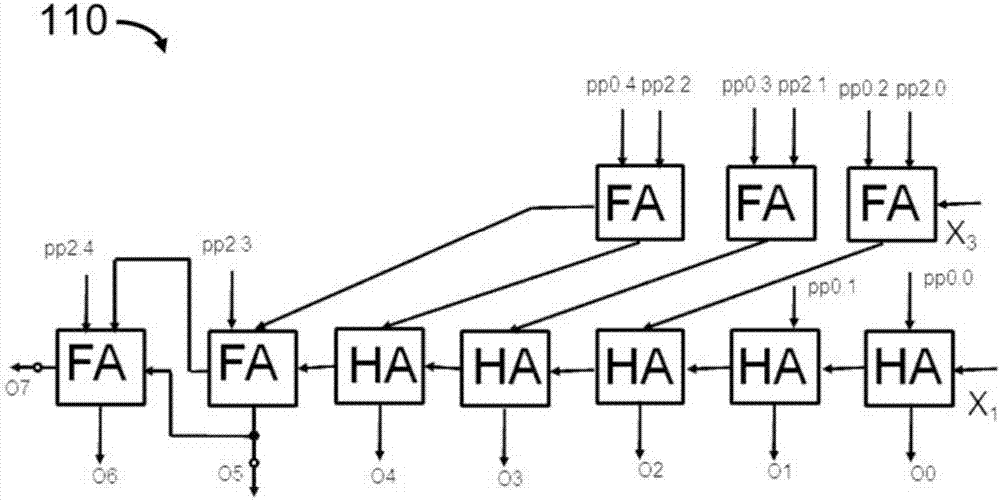

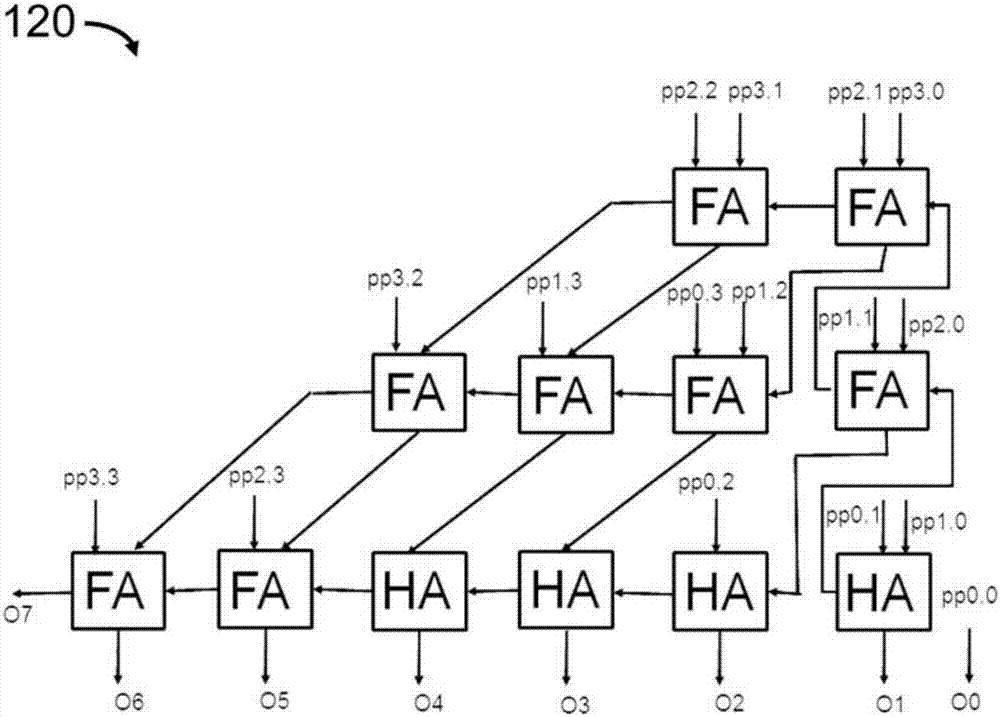

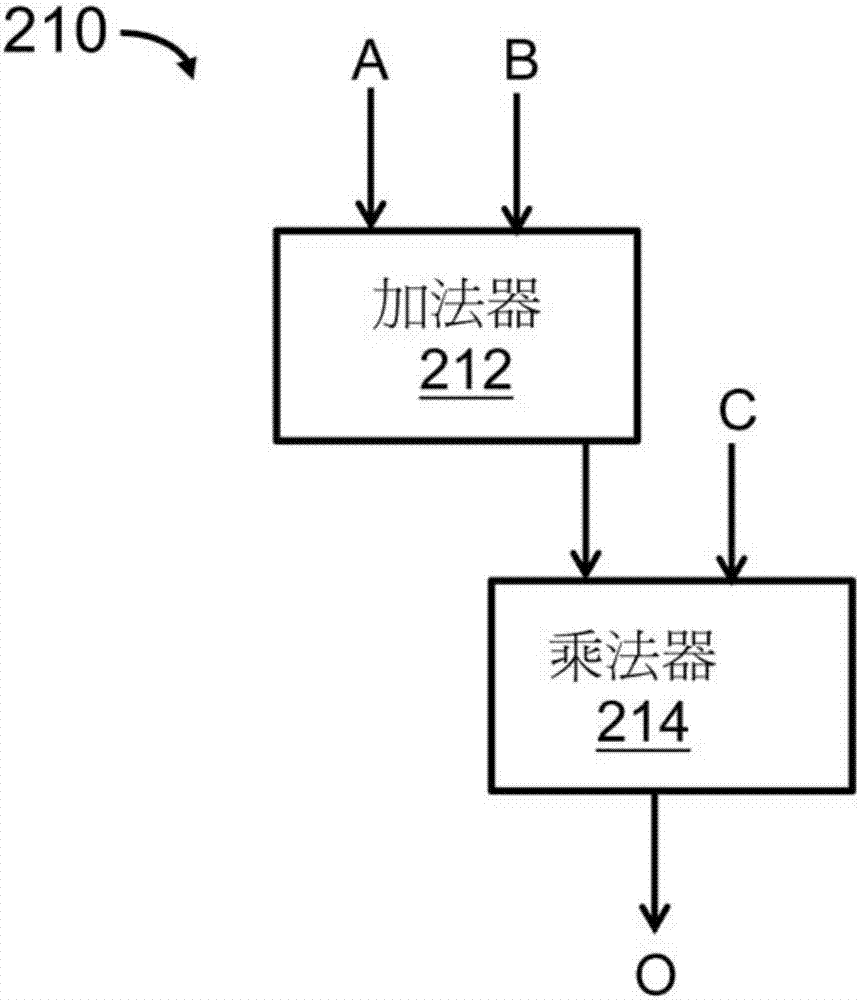

[0026] Exemplary embodiments relate to algorithms or devices that improve arithmetic circuit verification.

[0027] Circuit verification is a very necessary step in IC design and manufacturing. The verification process takes about 60% or more of the entire design cycle. Modern integrated circuits often contain millions of tiny circuit elements, such as circuit gates or transistors, so verification cannot be accomplished manually with paper and pen. Therefore, verification is usually accomplished with the aid of computer hardware and corresponding electronic design automation (EDA) software tools.

[0028] The effectiveness and efficiency of circuit verification has a great impact on the chip industry. Undetected errors make the entire chip worthless. Inefficient verification (such as too long run time or too high complexity) can lengthen the overall design cycle, thereby delaying the time to market to the detriment of benefits. In addition, too low efficiency or too high o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com