Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

107 results about "Design under test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

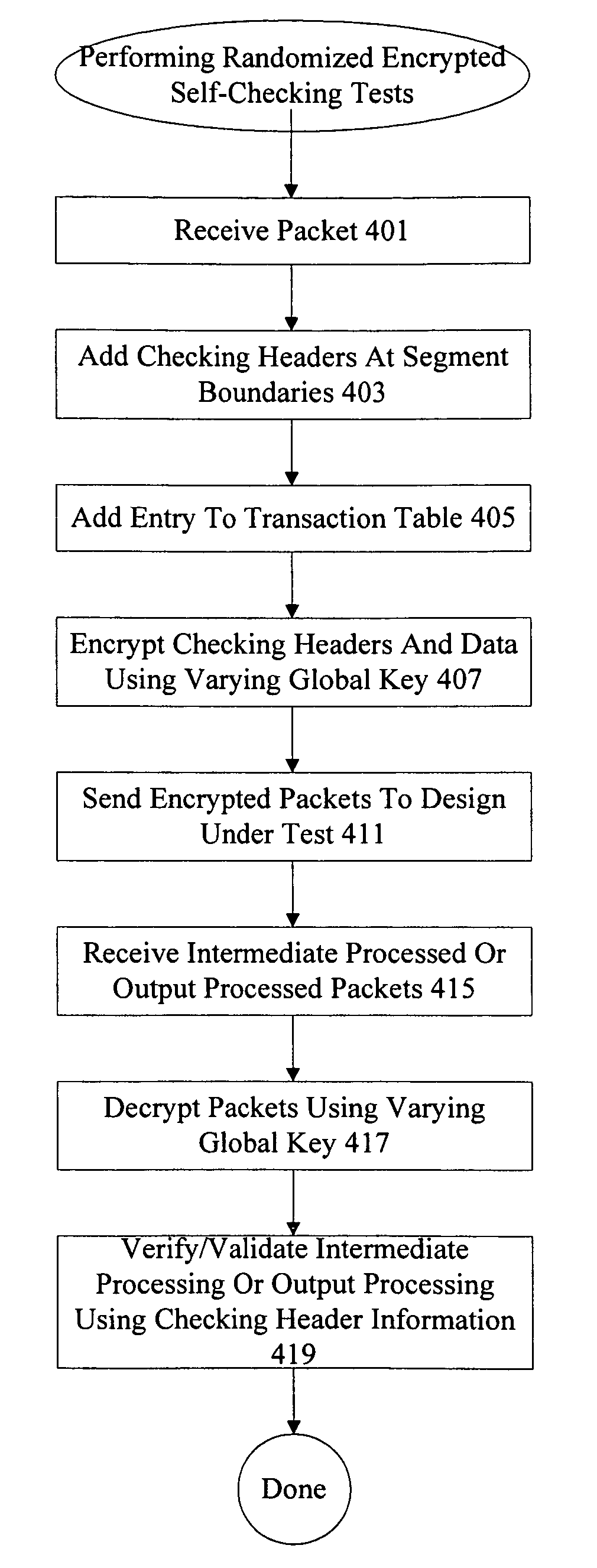

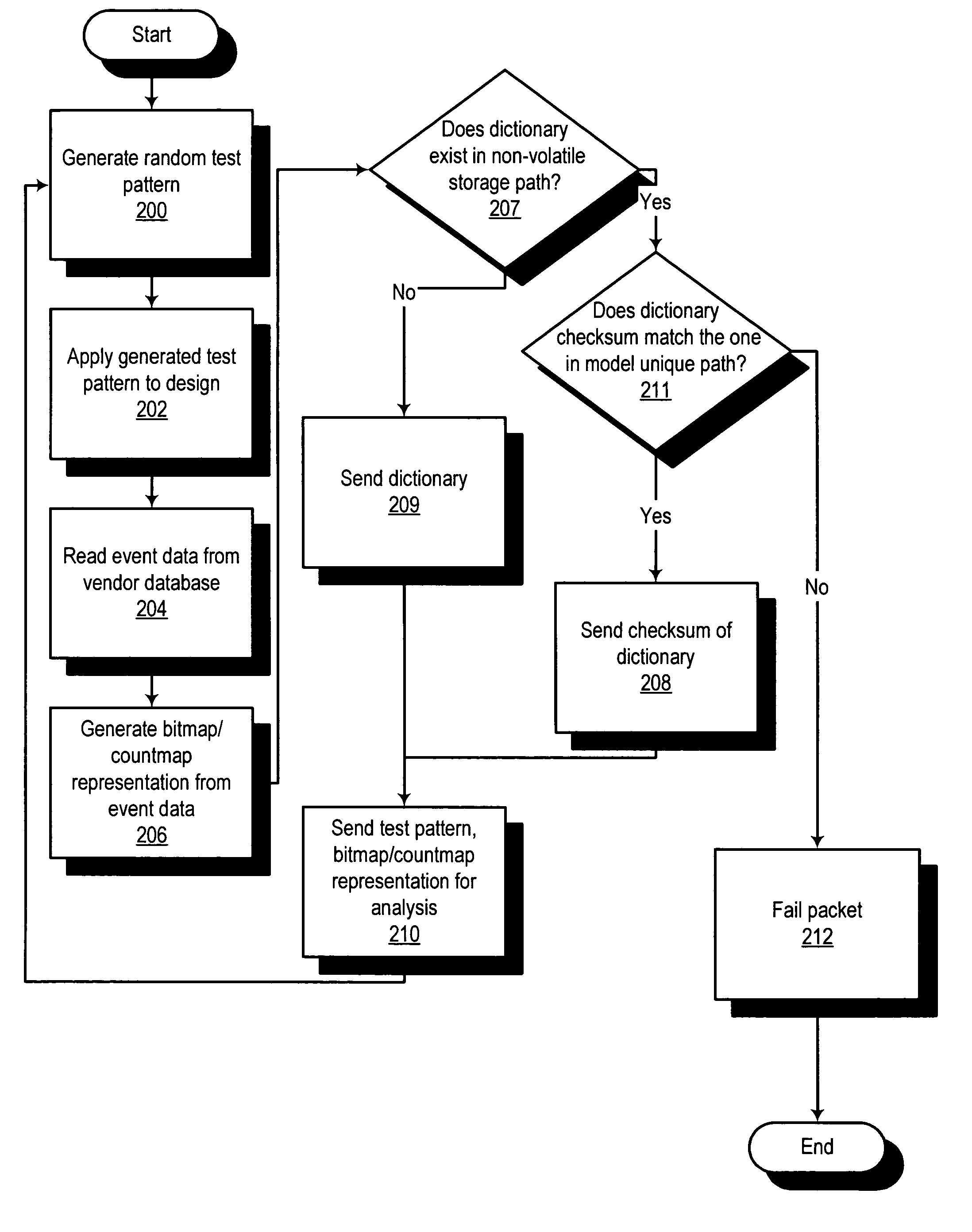

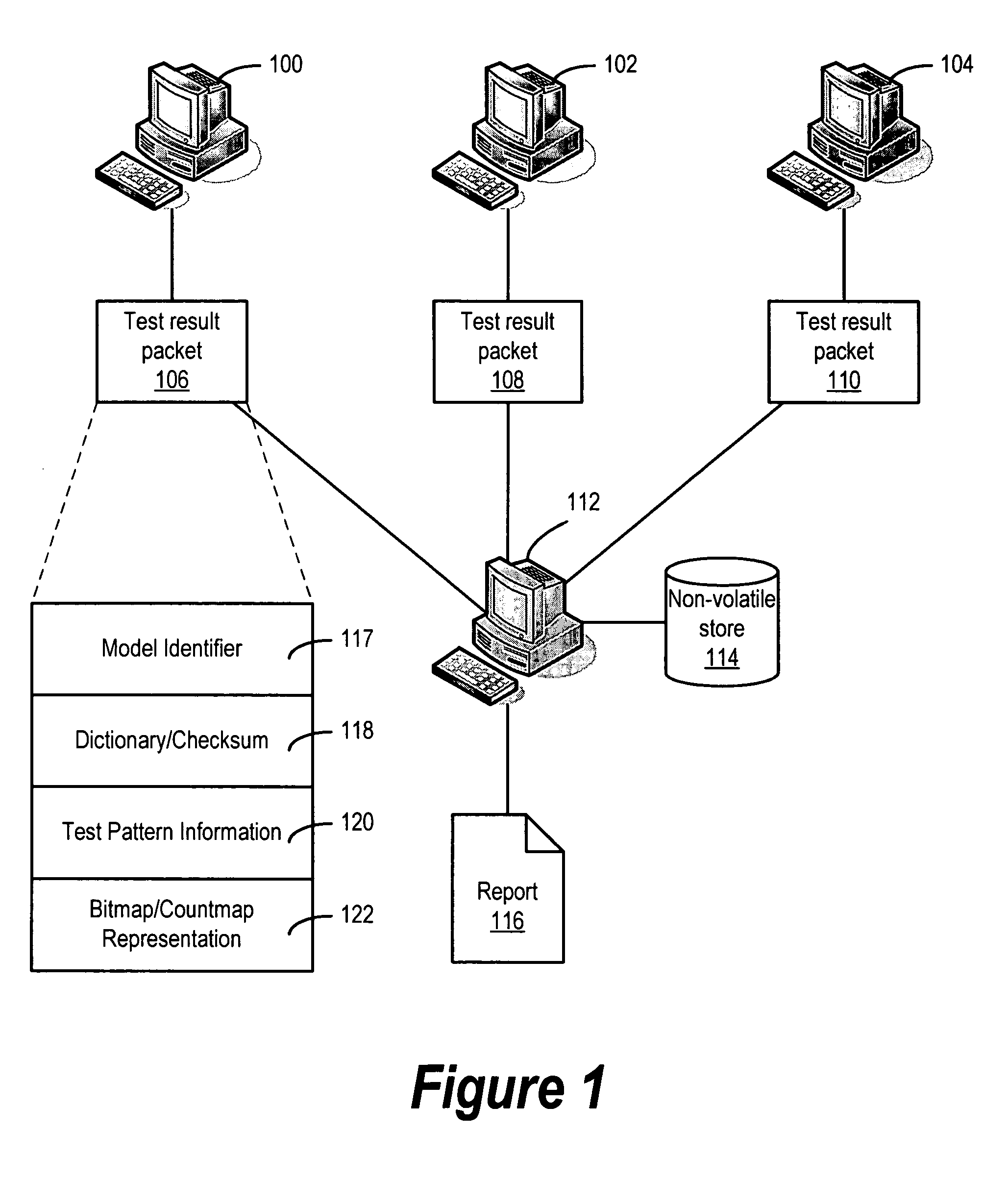

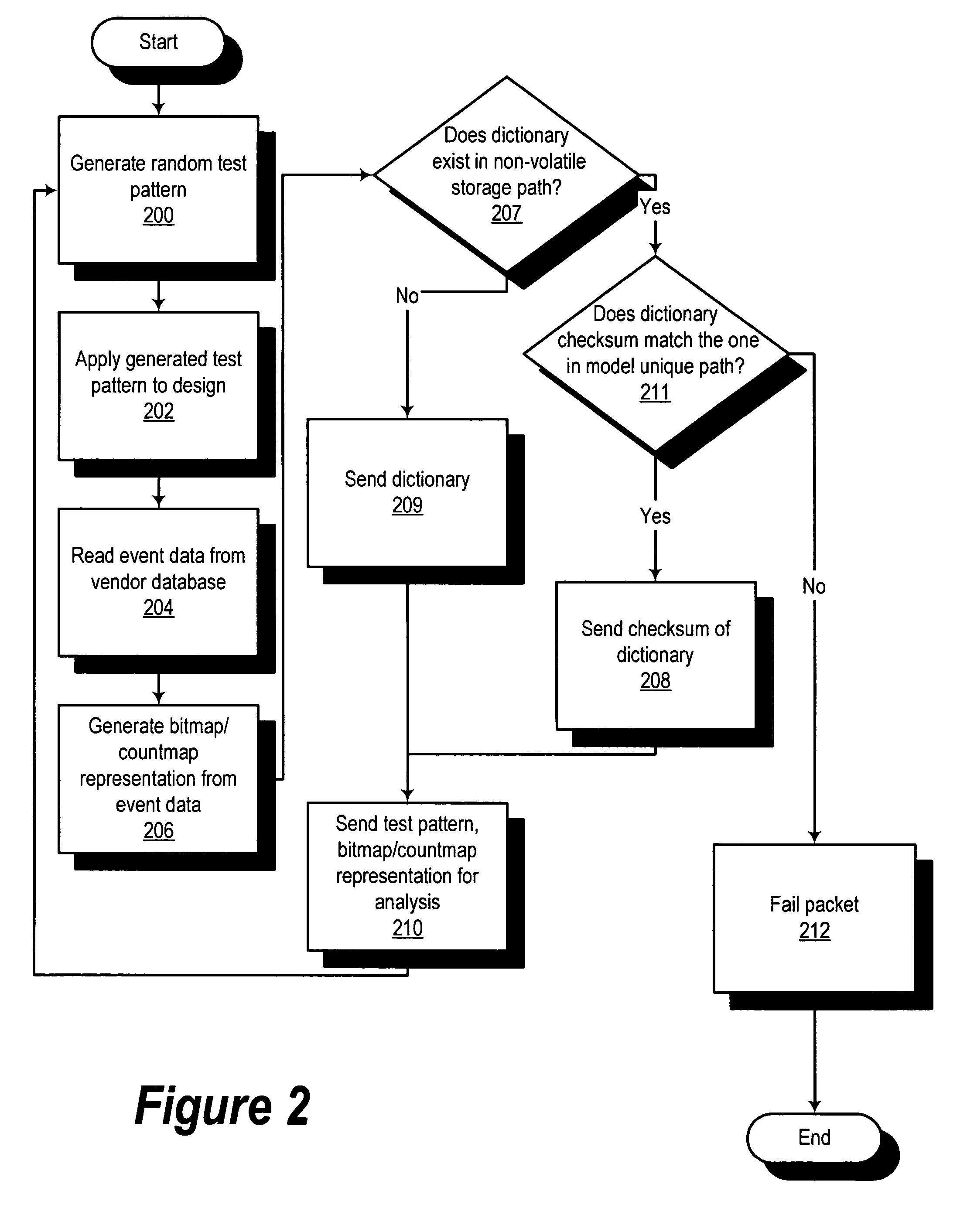

Randomized self-checking test system

ActiveUS7334178B1Data representation error detection/correctionElectrical testingRandomizationData sequences

Methods and apparatus are provided for verifying and validating operation of a design under test (DUT). Input data sequences having information used to check expected outputs are provided to a DUT. The input data sequences include checking headers and data. The checking headers and data are randomized using encryption to verify and validate operation of the DUT on a variety of bit sequences. Different keys are used to allow further scrambling.

Owner:ORACLE INT CORP

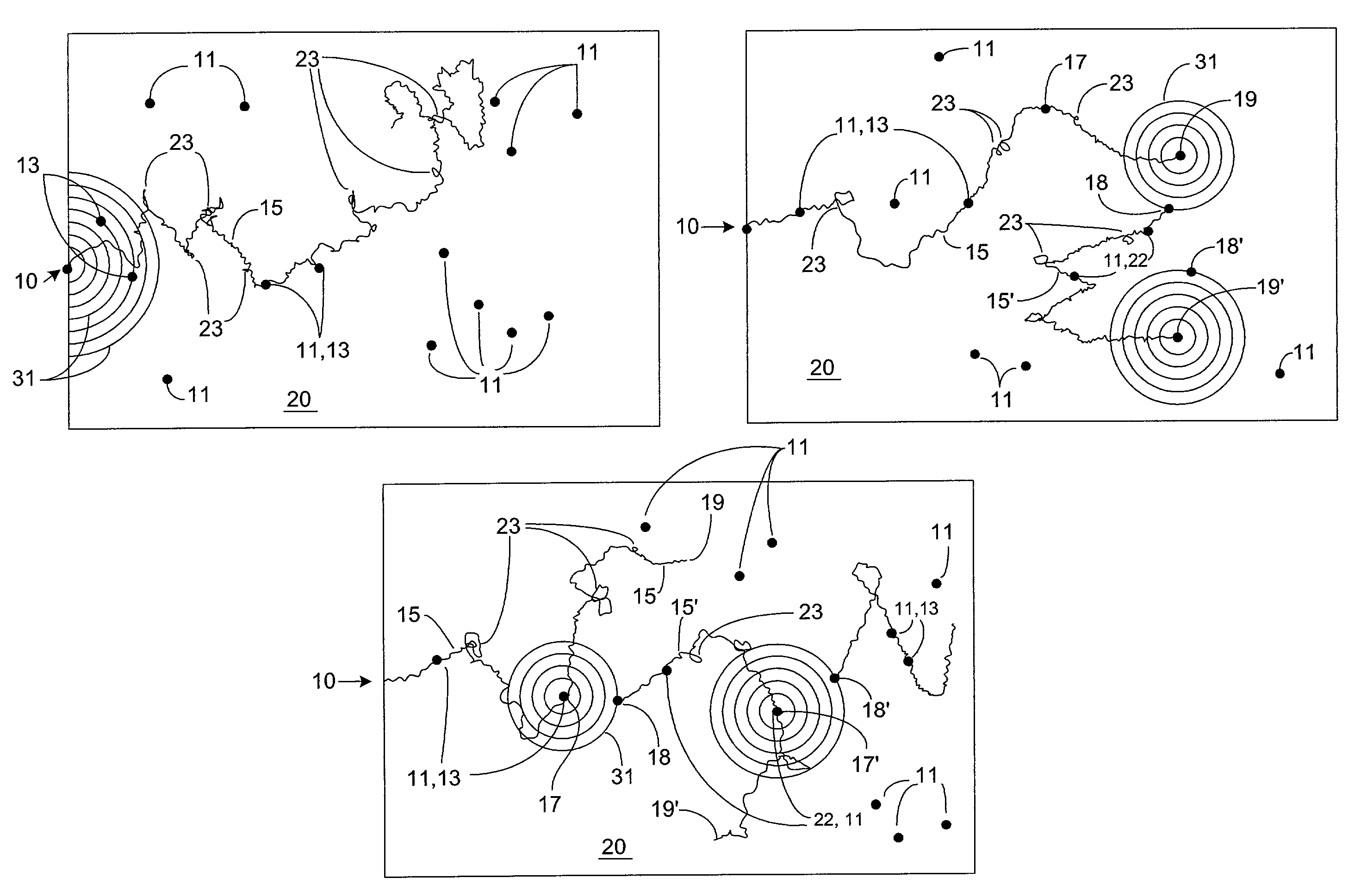

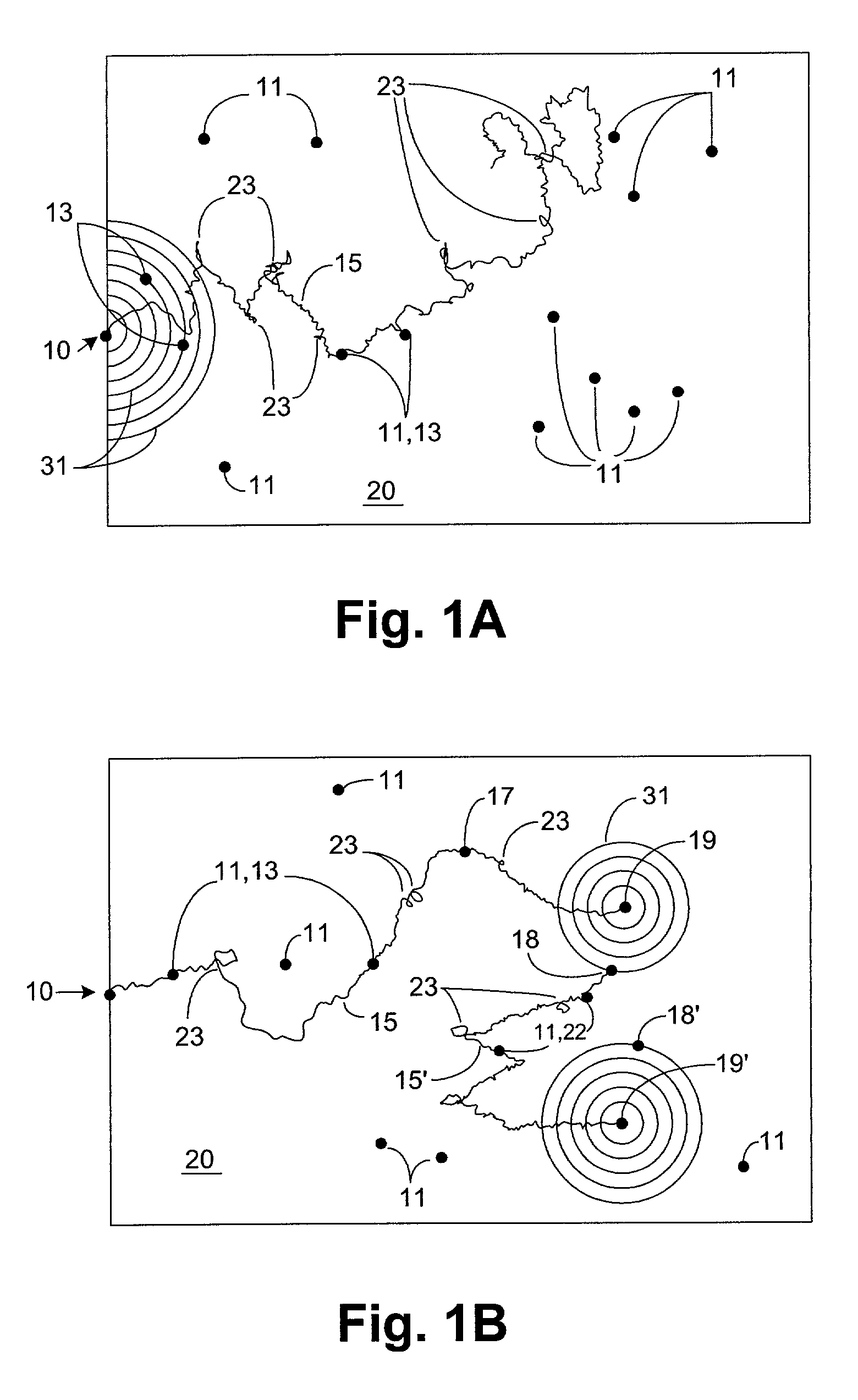

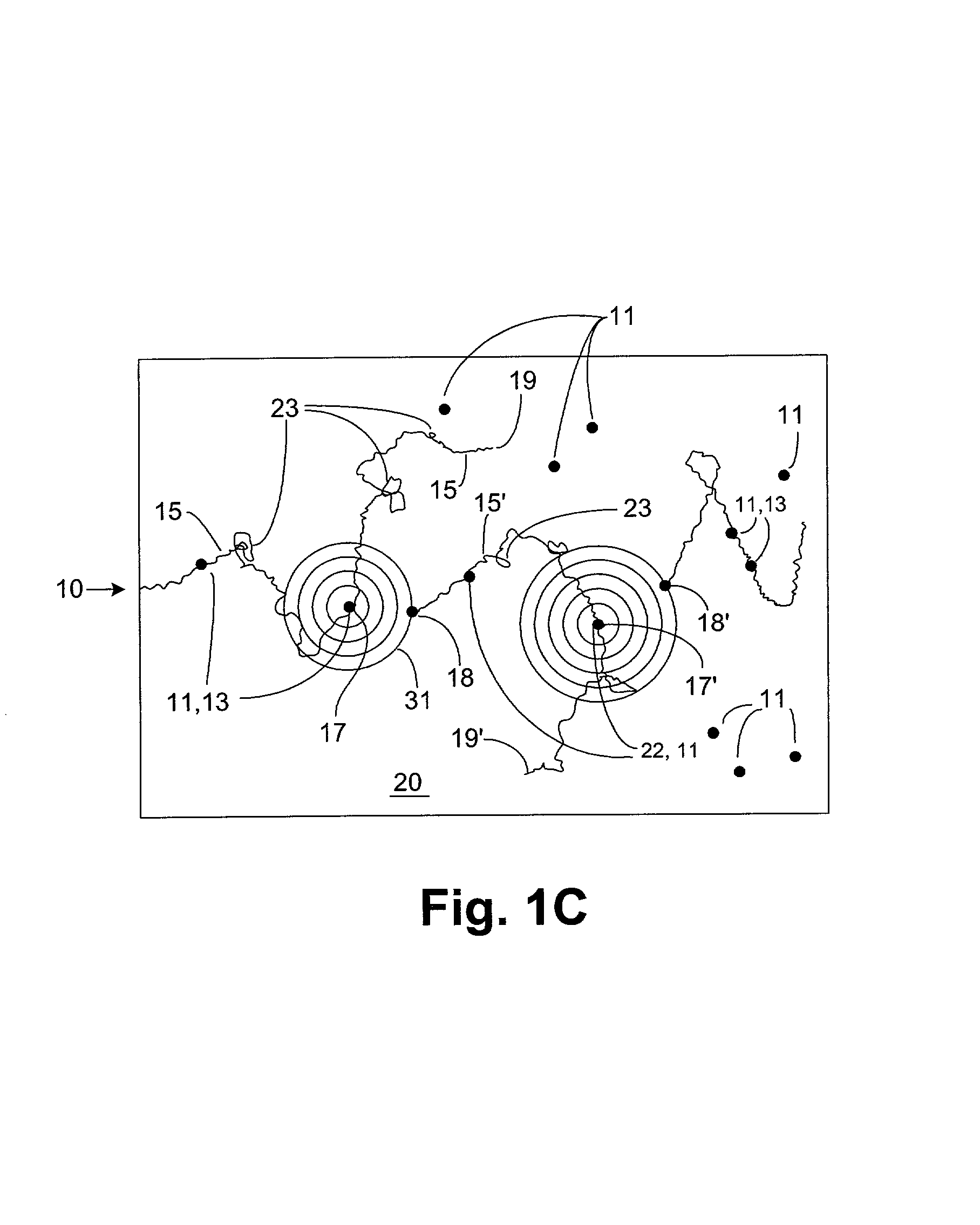

Simulation-based functional verification of microcircuit designs

InactiveUS7130783B1Shorten the timeConfidenceDetecting faulty computer hardwareAnalogue computers for electric apparatusTest designFormal methods

System, methods, and apparatus for verifying microcircuit designs by interleaving between random and formal simulation techniques to identify input traces useful for driving designs under test into sequences of device states. In a method aspect the invention provides process for beginning random simulation of a sequence of states of a microcircuit design by inputting a sequence of random input vectors to a design under test model in order to obtain a sequence of random simulation states; monitoring a simulation coverage progress metric to determine a preference for switching from random simulation to formal methods of simulating states in the design under test; beginning formal simulation of states in the design under test and monitoring a formal coverage progress metric to determine a preference for resuming random simulation of states of said microcircuit design; and resuming random simulation. Preferably the process of interleaving simulation methods continues until an input vector suitable for driving the design under test model into each of a set of previously-identified goal states has been obtained.

Owner:SYNOPSYS INC

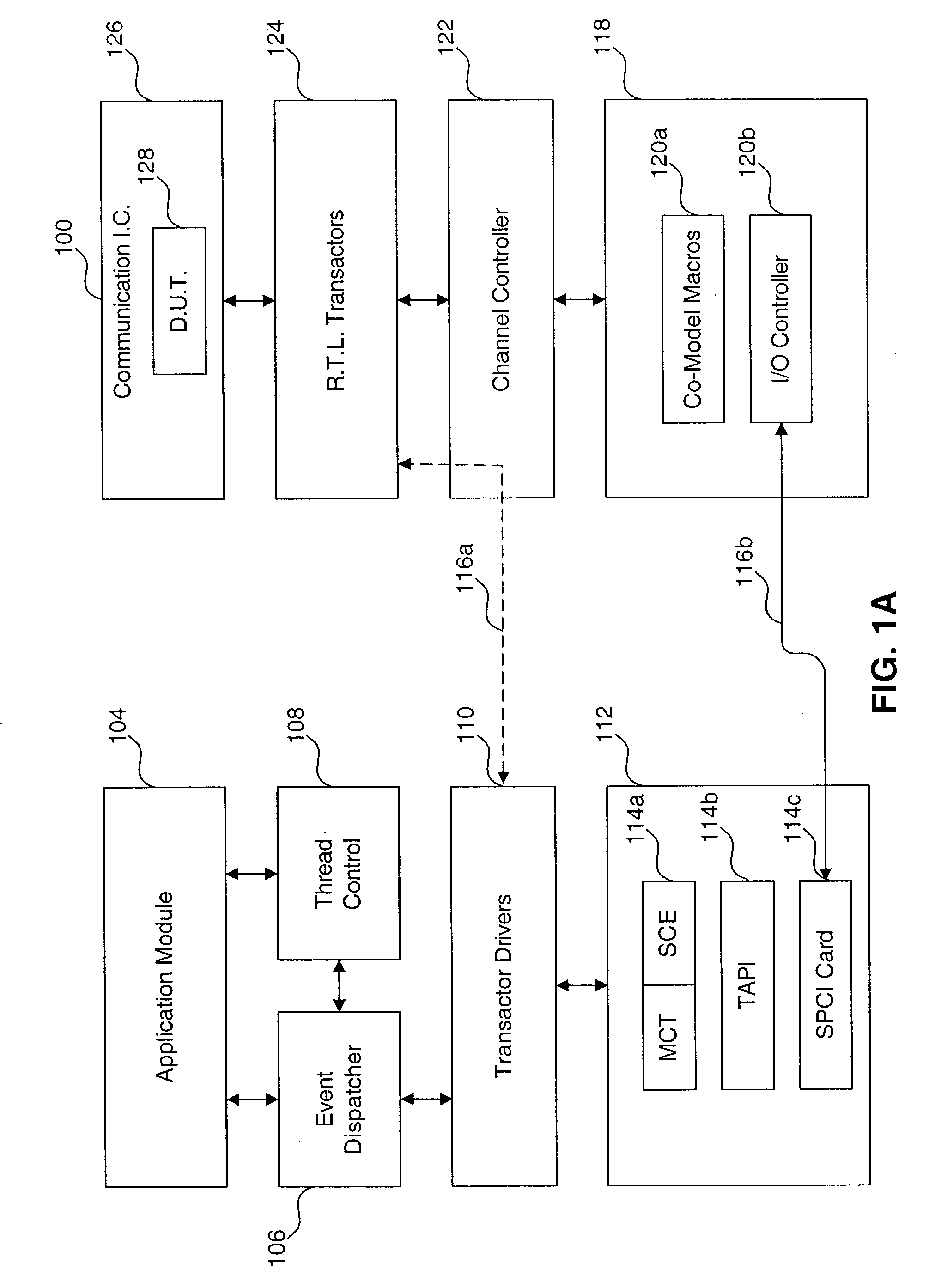

Method and system for deterministic control of an emulation

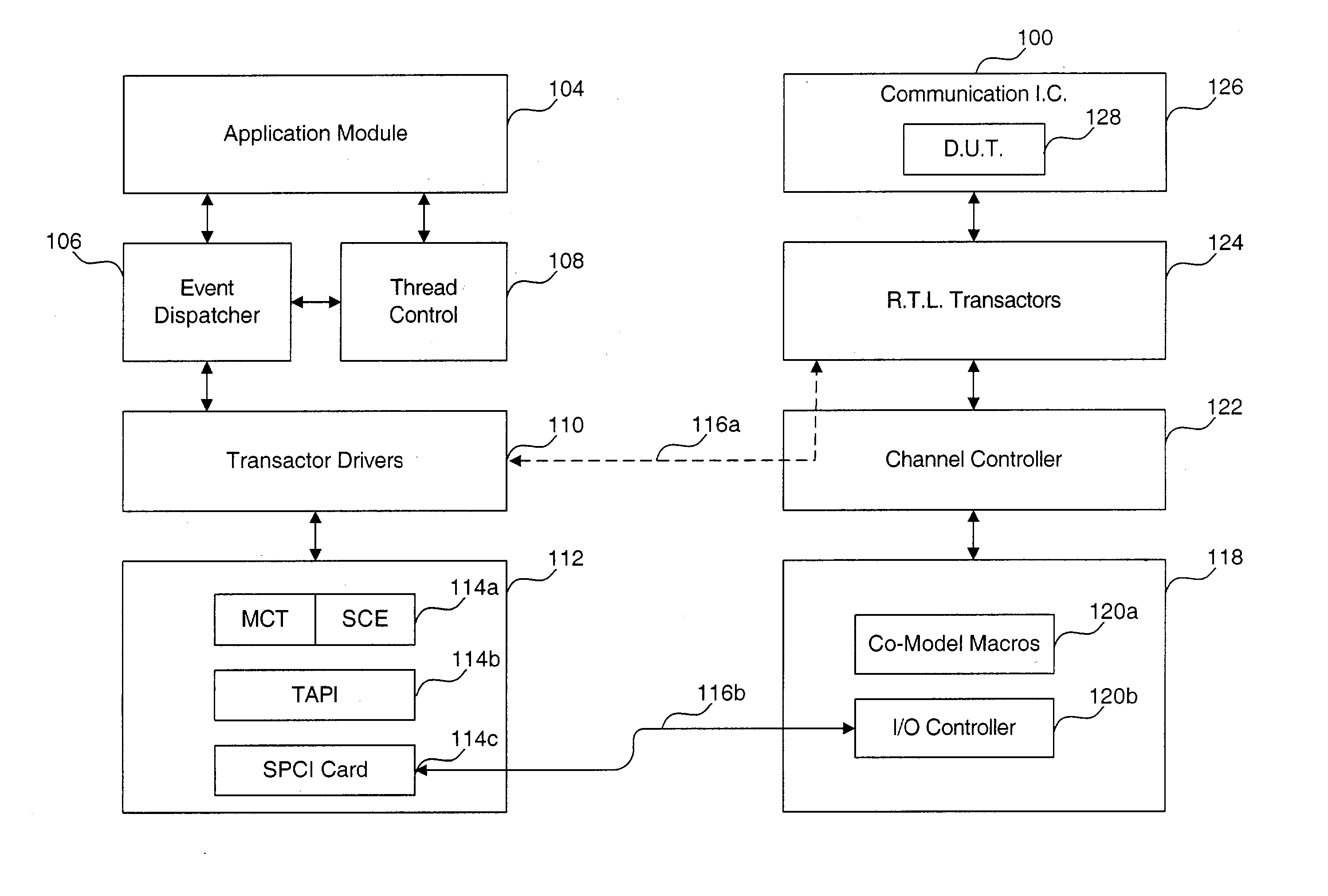

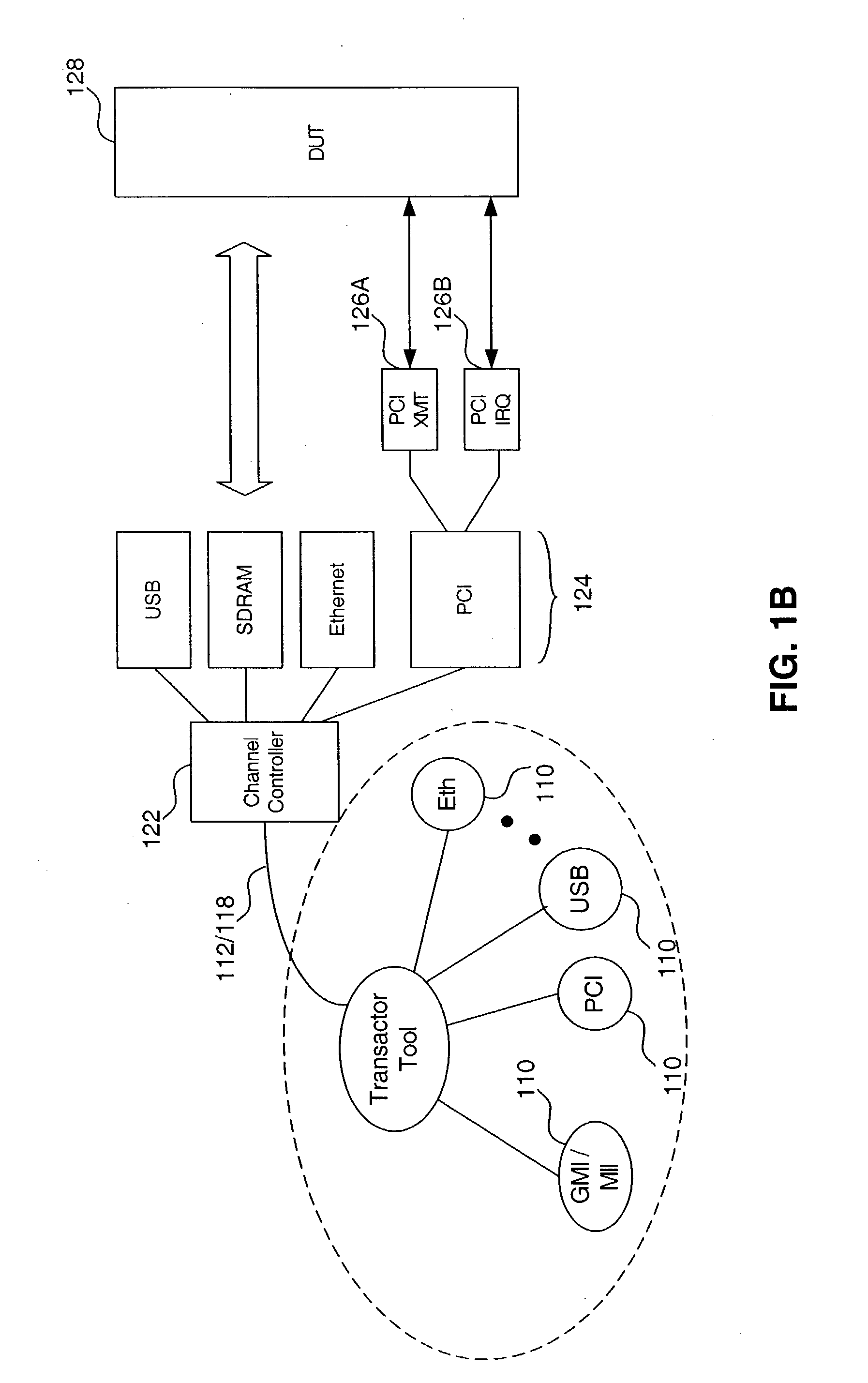

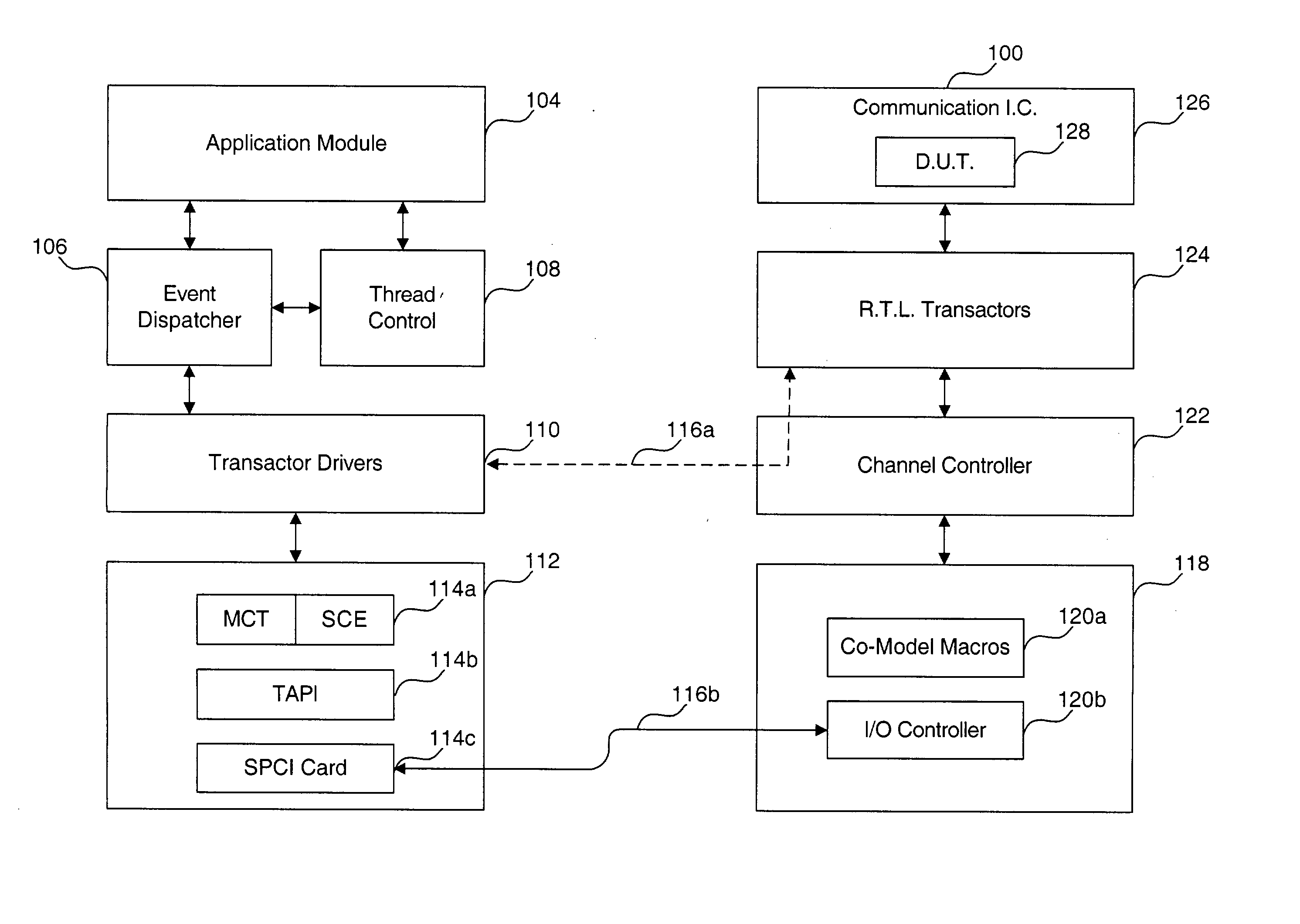

InactiveUS20030225565A1Digital computer detailsCAD circuit designApplication softwareDeterministic control

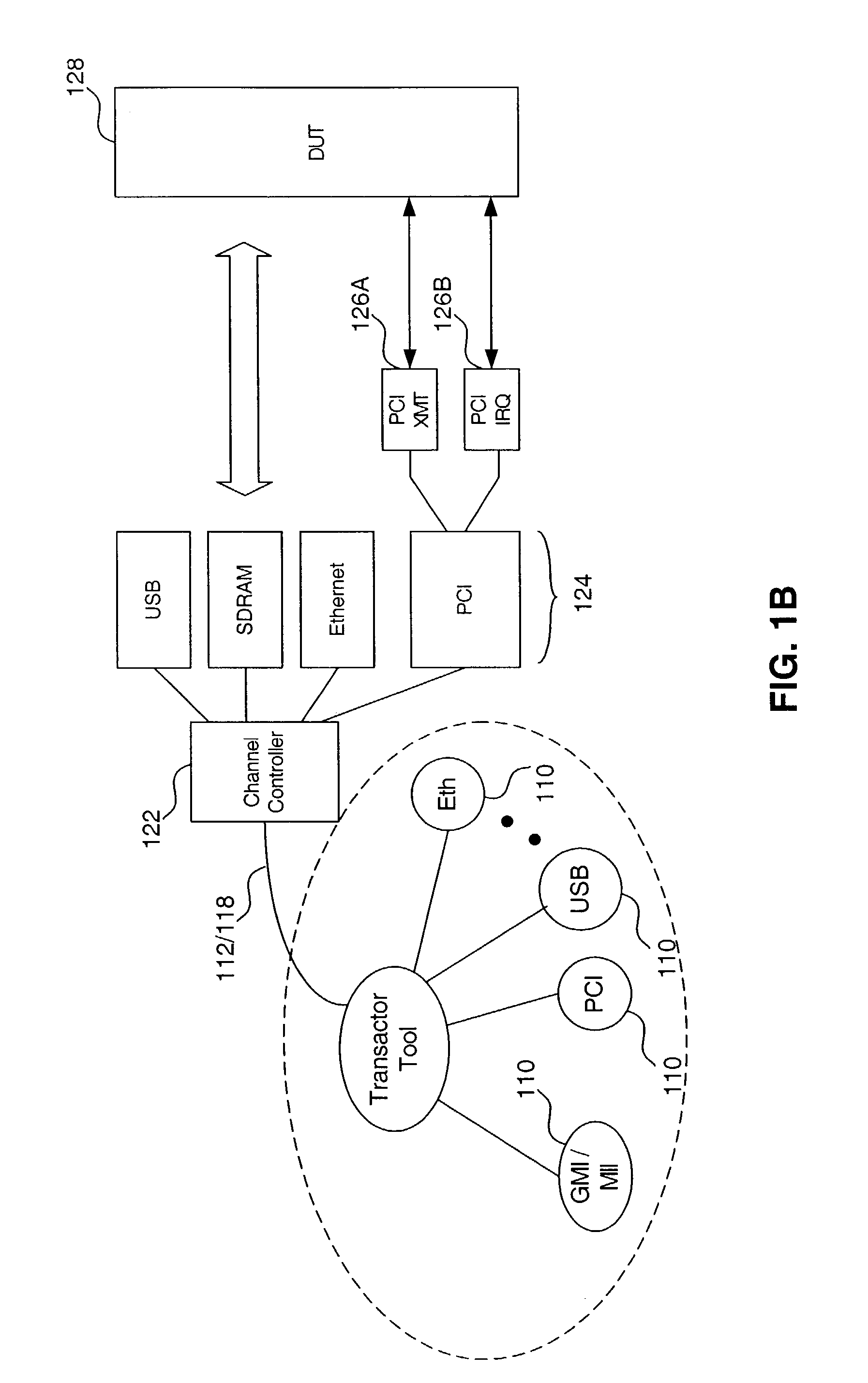

An emulation-based event-wait simulator including an application module to configure and command verification processes on a design under test (DUT). An event dispatcher is in communication with the application module to deliver commands to the DUT. A plurality of transactors are in communication with the event dispatcher to forward the commands to the DUT. A channel controller is in communication with the transactors to process and forward the commands to the DUT, wherein the channel controller also receives messages from the DUT, processes the messages, and forwards the messages to the transactors for delivery to the event dispatcher and the application module.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

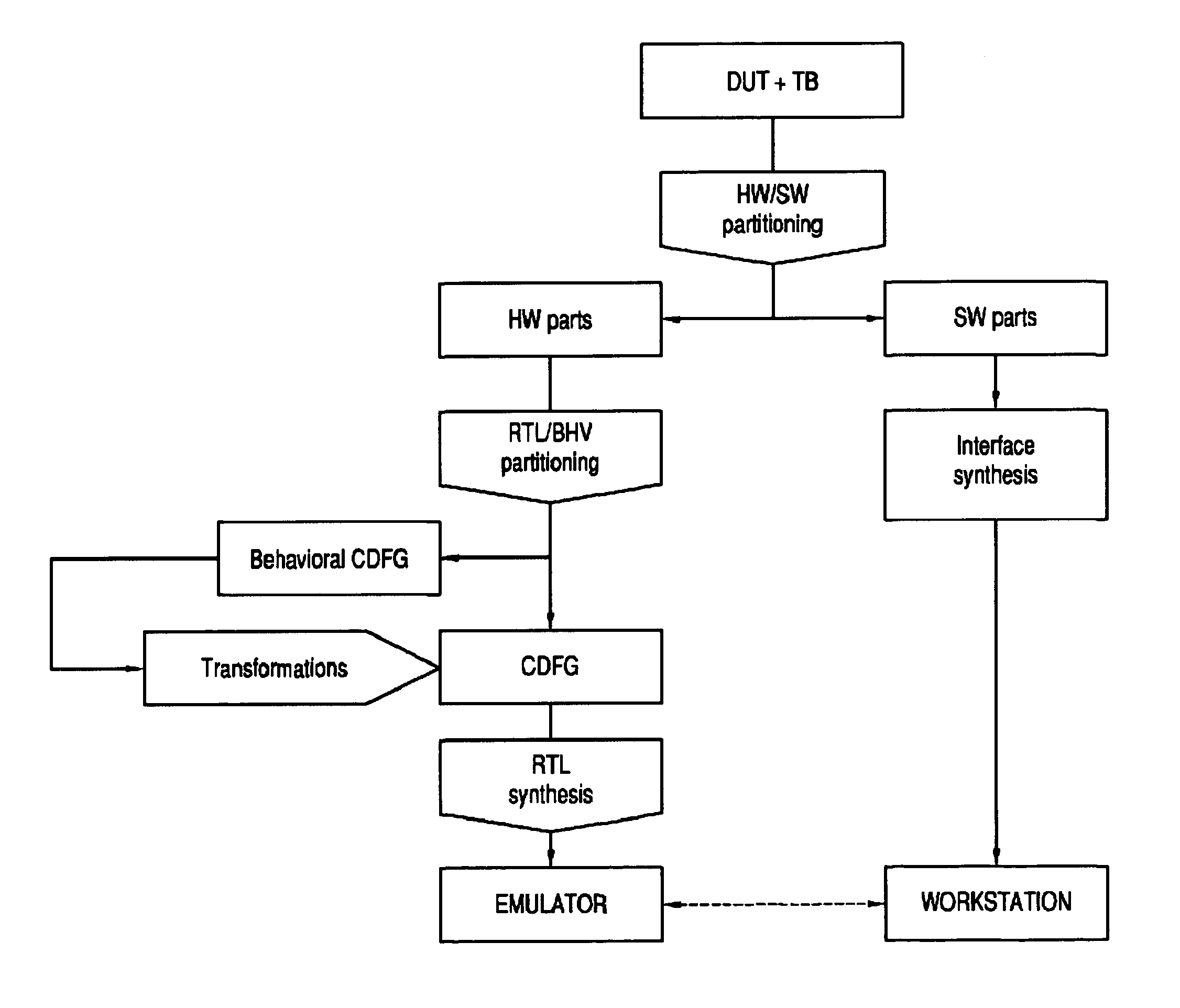

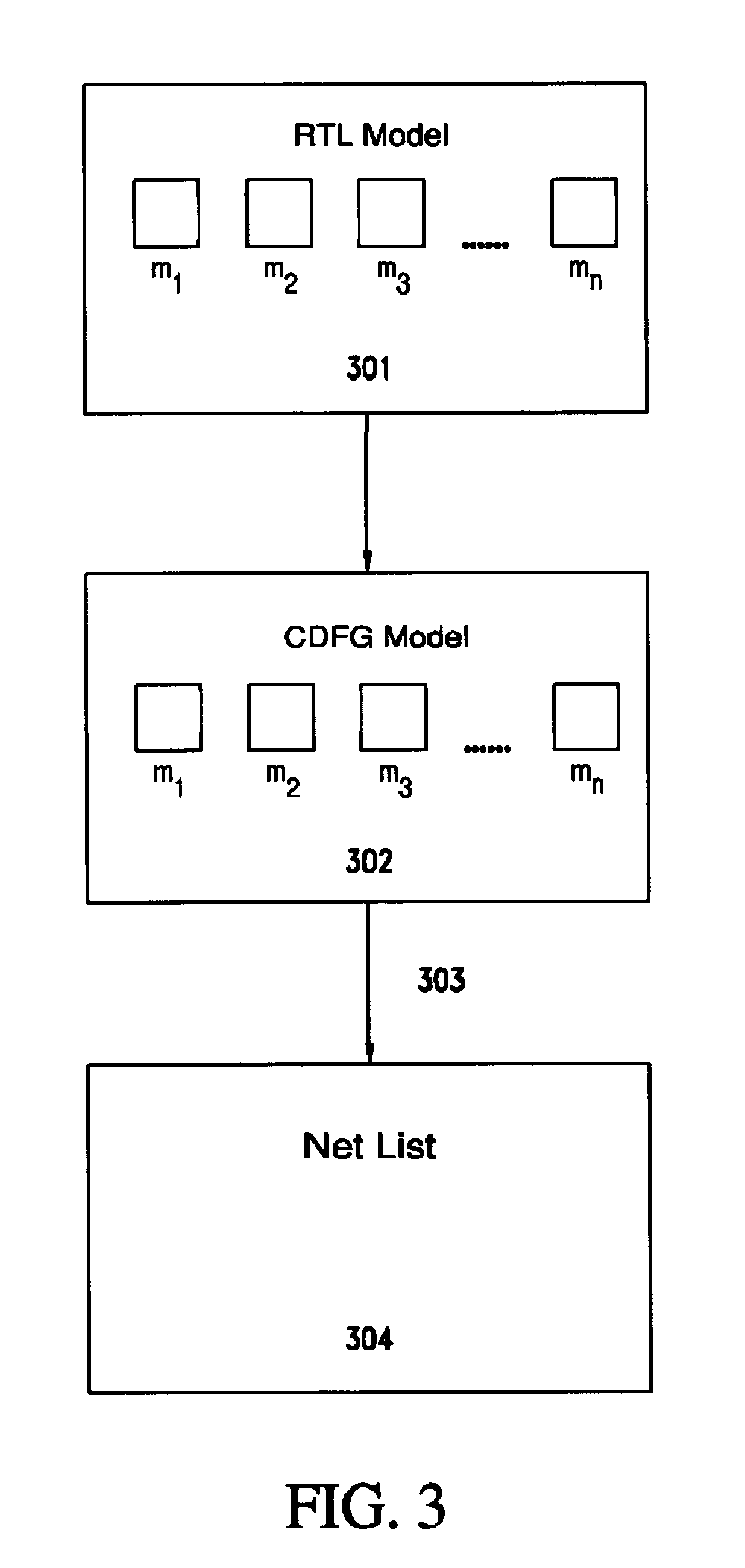

Method and system for hardware accelerated verification of digital circuit design and its testbench

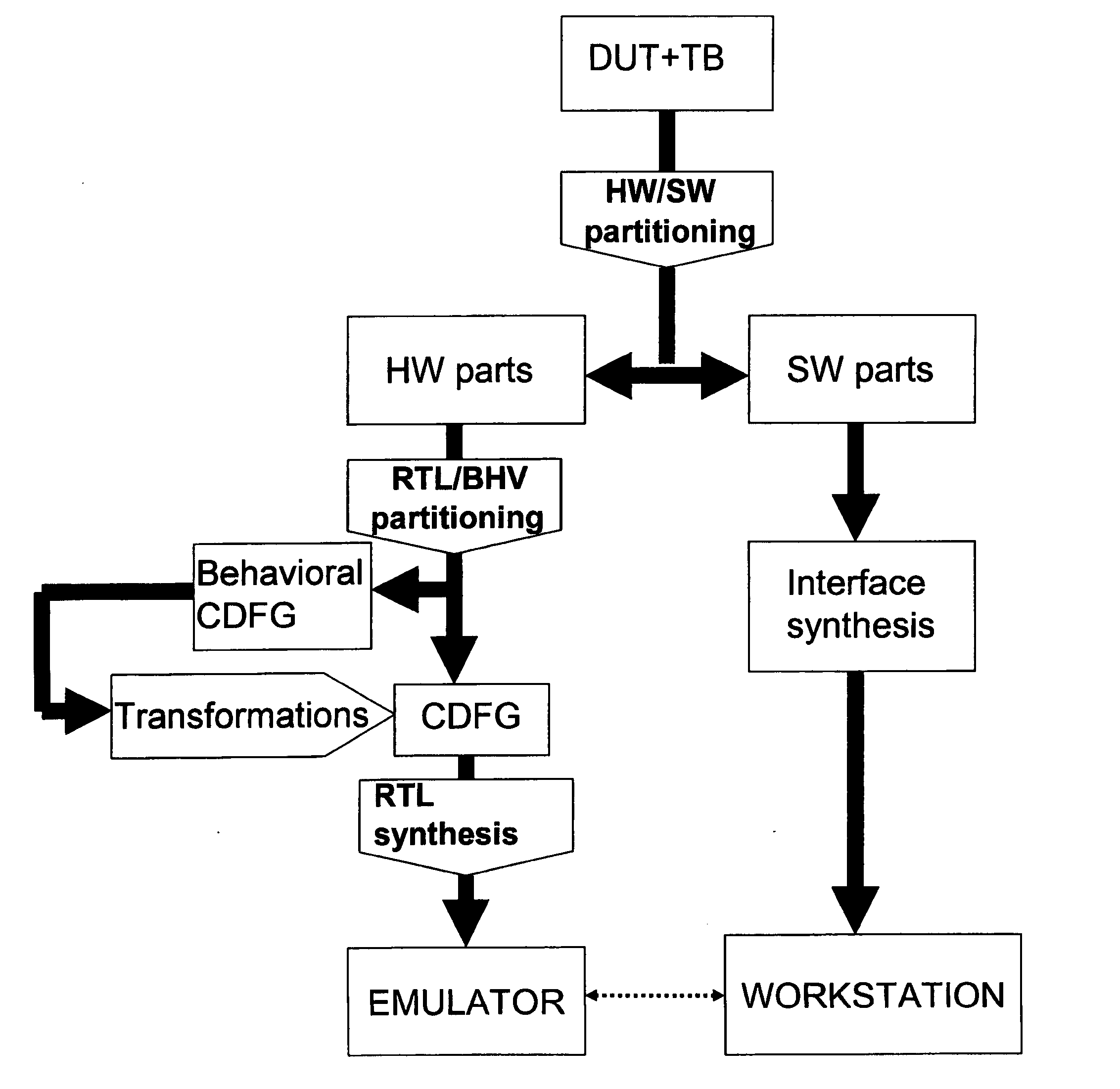

ActiveUS20050144585A1Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method and system for deterministic control of an emulation

InactiveUS20030225560A1Analogue computers for electric apparatusCAD circuit designApplication softwareDeterministic control

An emulation-based event-wait simulator including an application module to configure and command verification processes on a design under test (DUT). An event dispatcher is in communication with the application module to deliver commands to the DUT. A plurality of transactors are in communication with the event dispatcher to forward the commands to the DUT. A channel controller is in communication with the transactors to process and forward the commands to the DUT, wherein the channel controller also receives messages from the DUT, processes the messages, and forwards the messages to the transactors for delivery to the event dispatcher and the application module.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

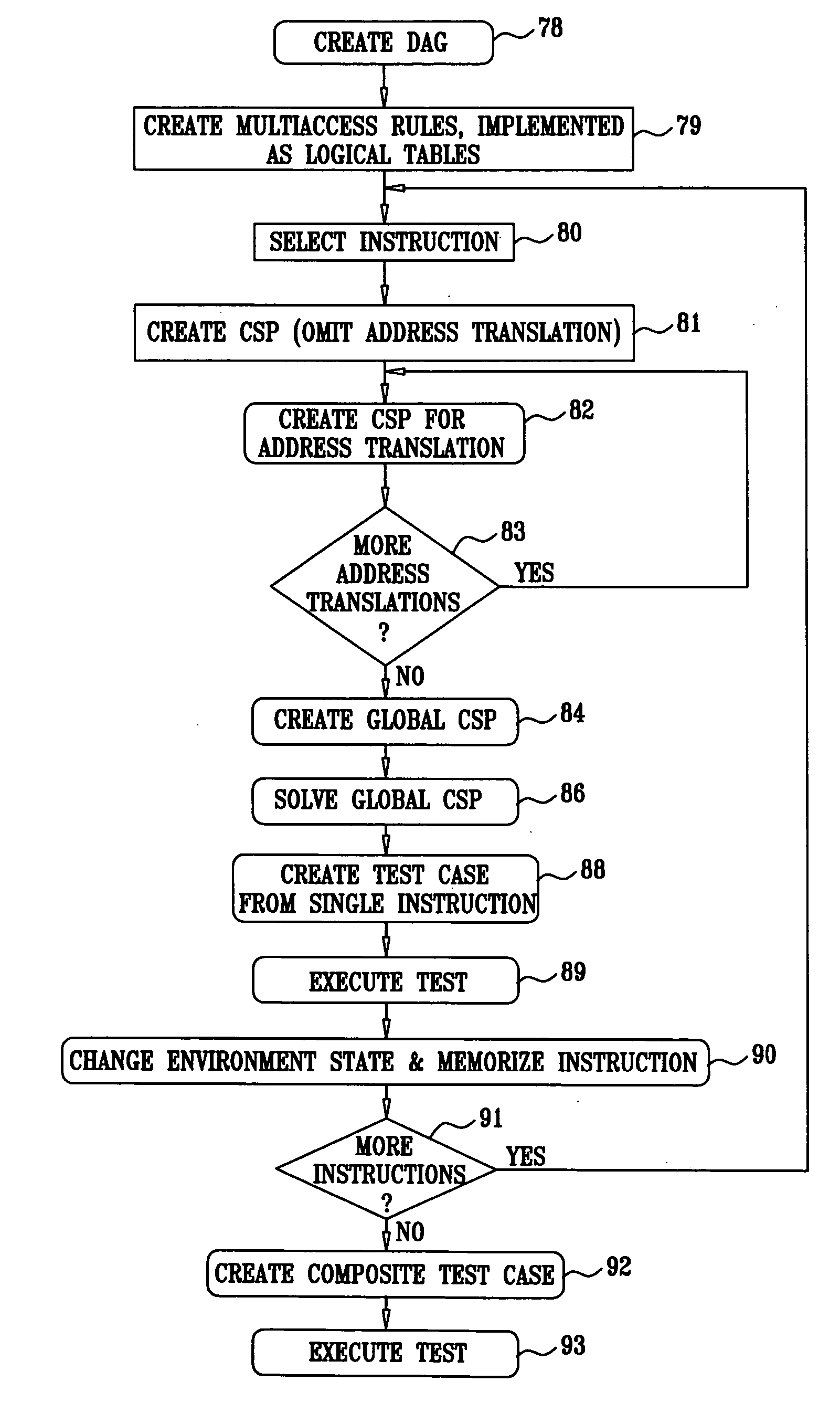

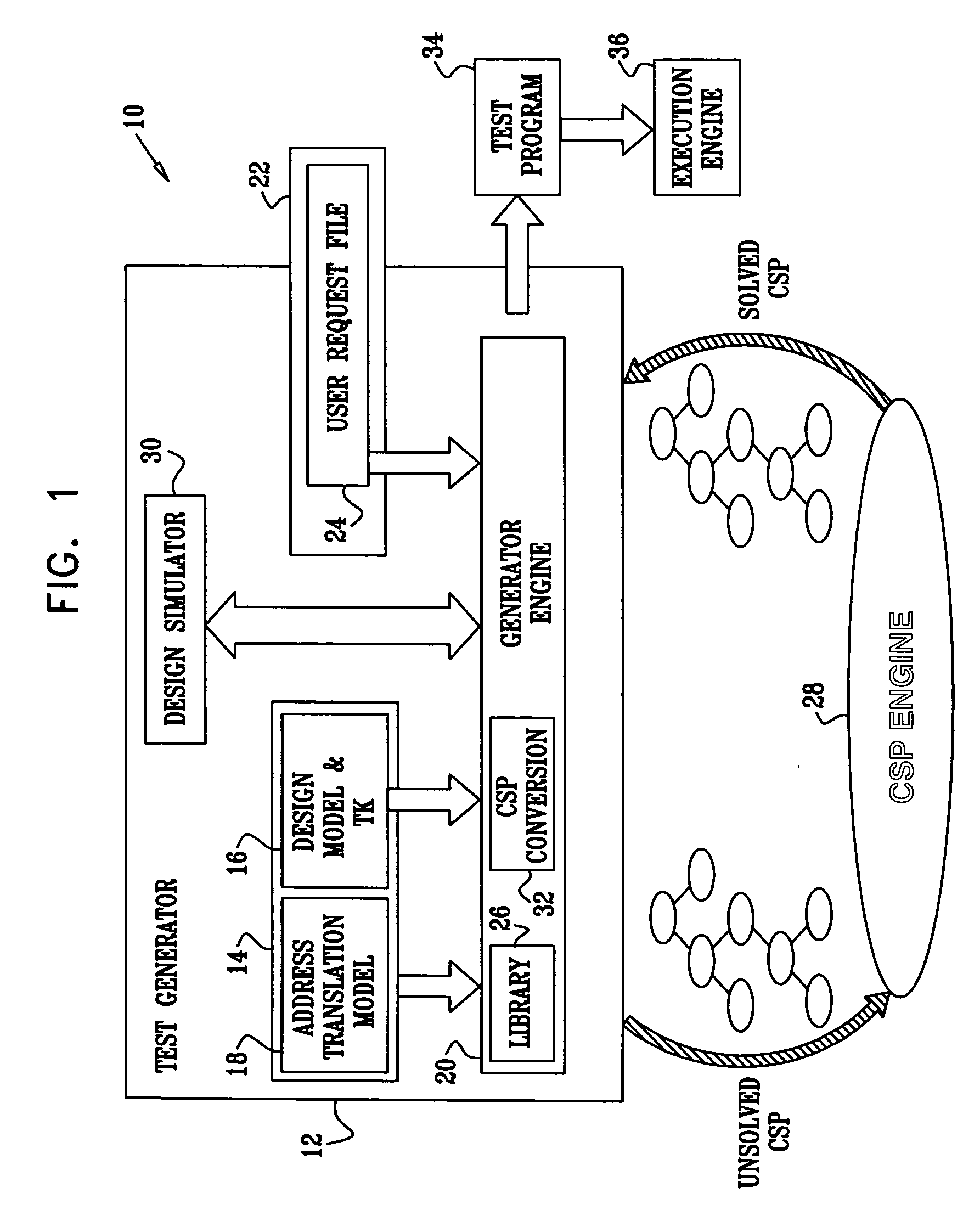

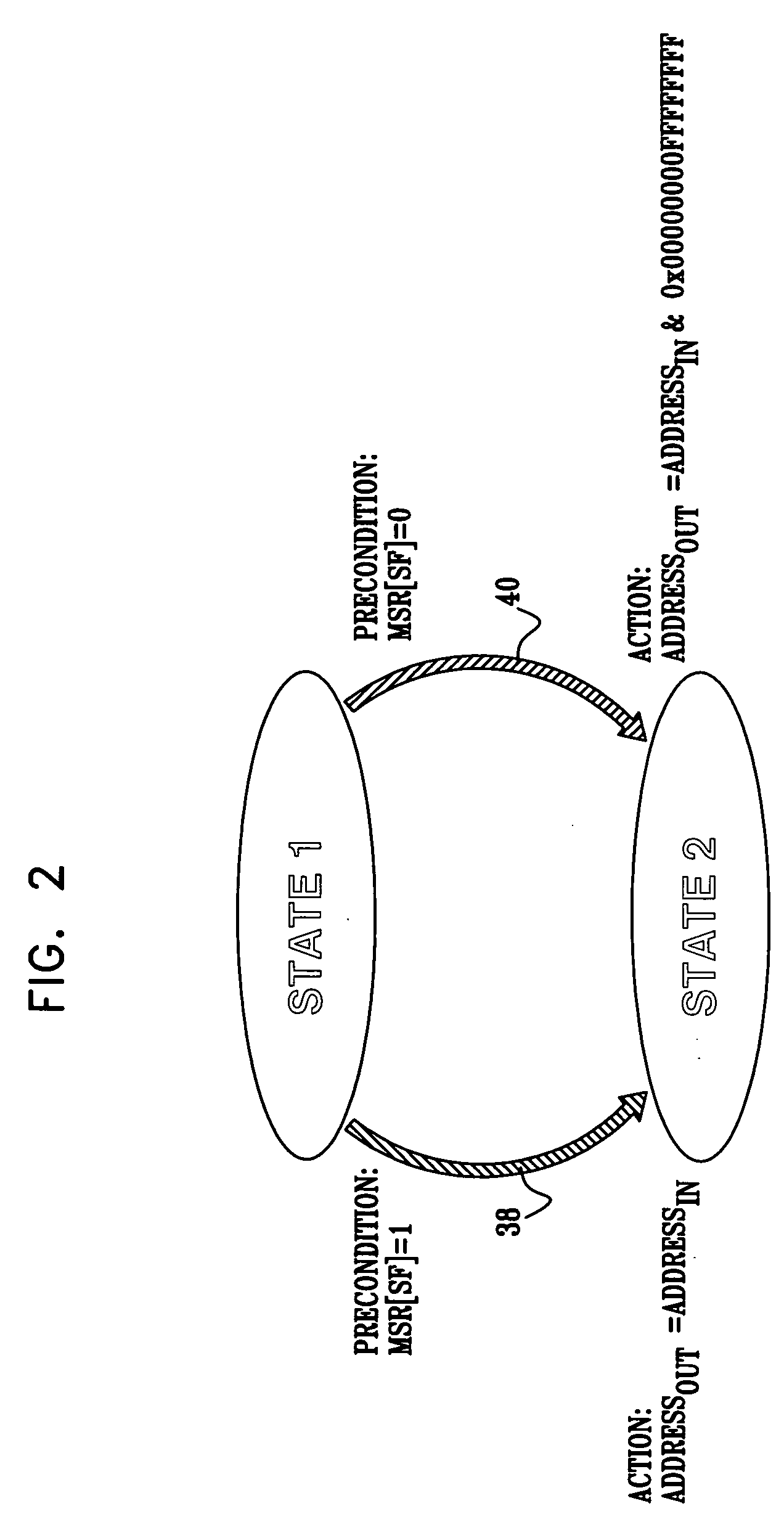

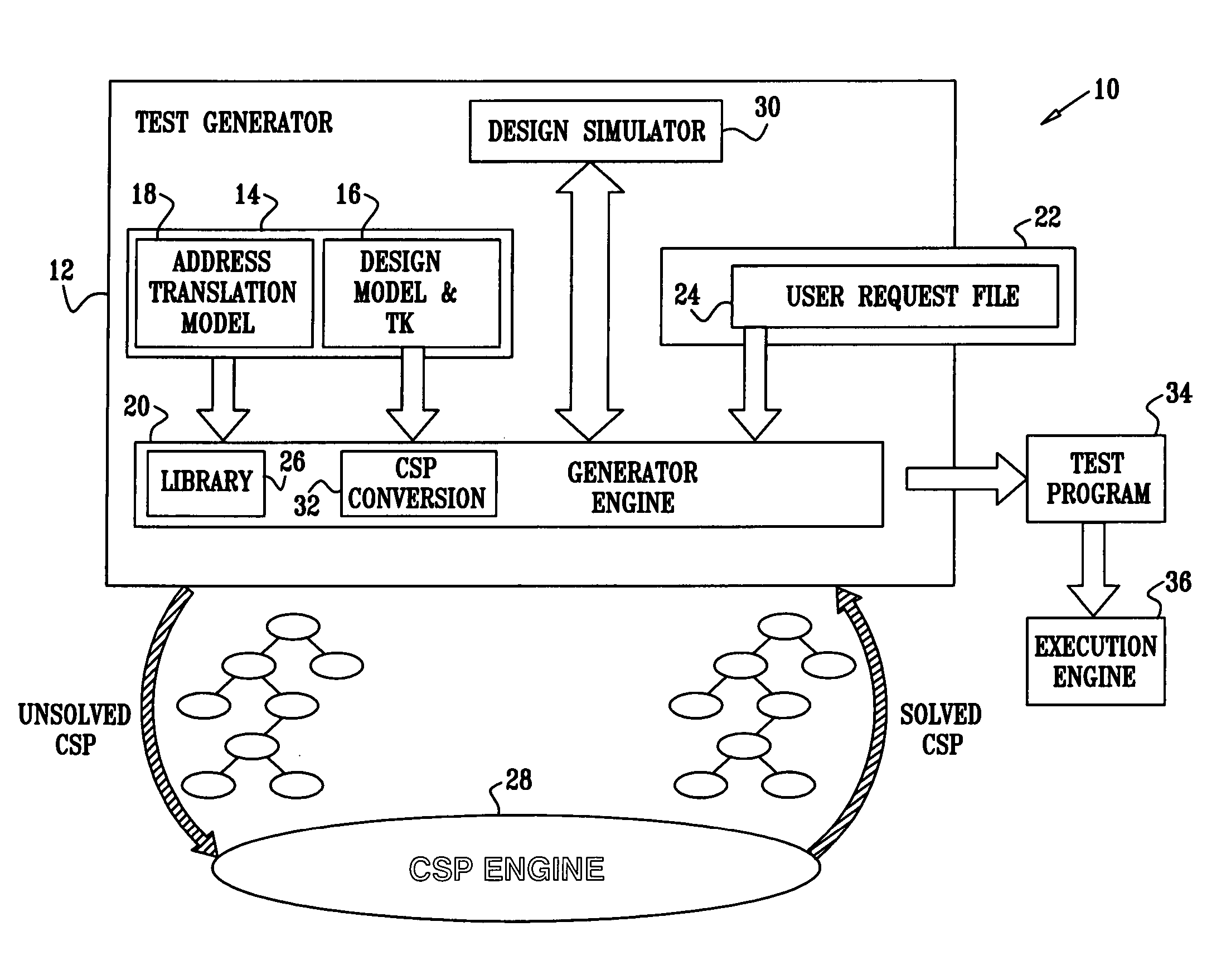

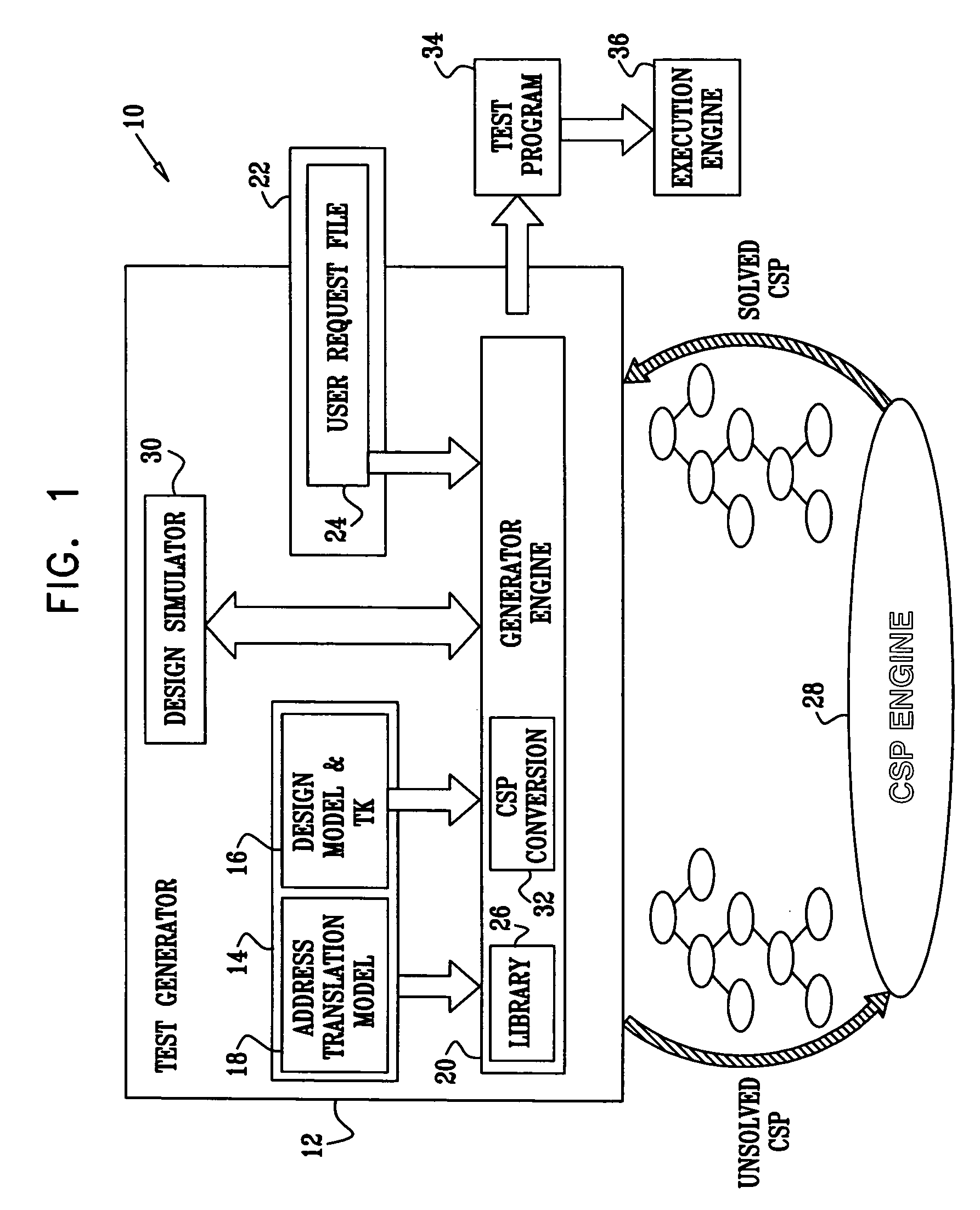

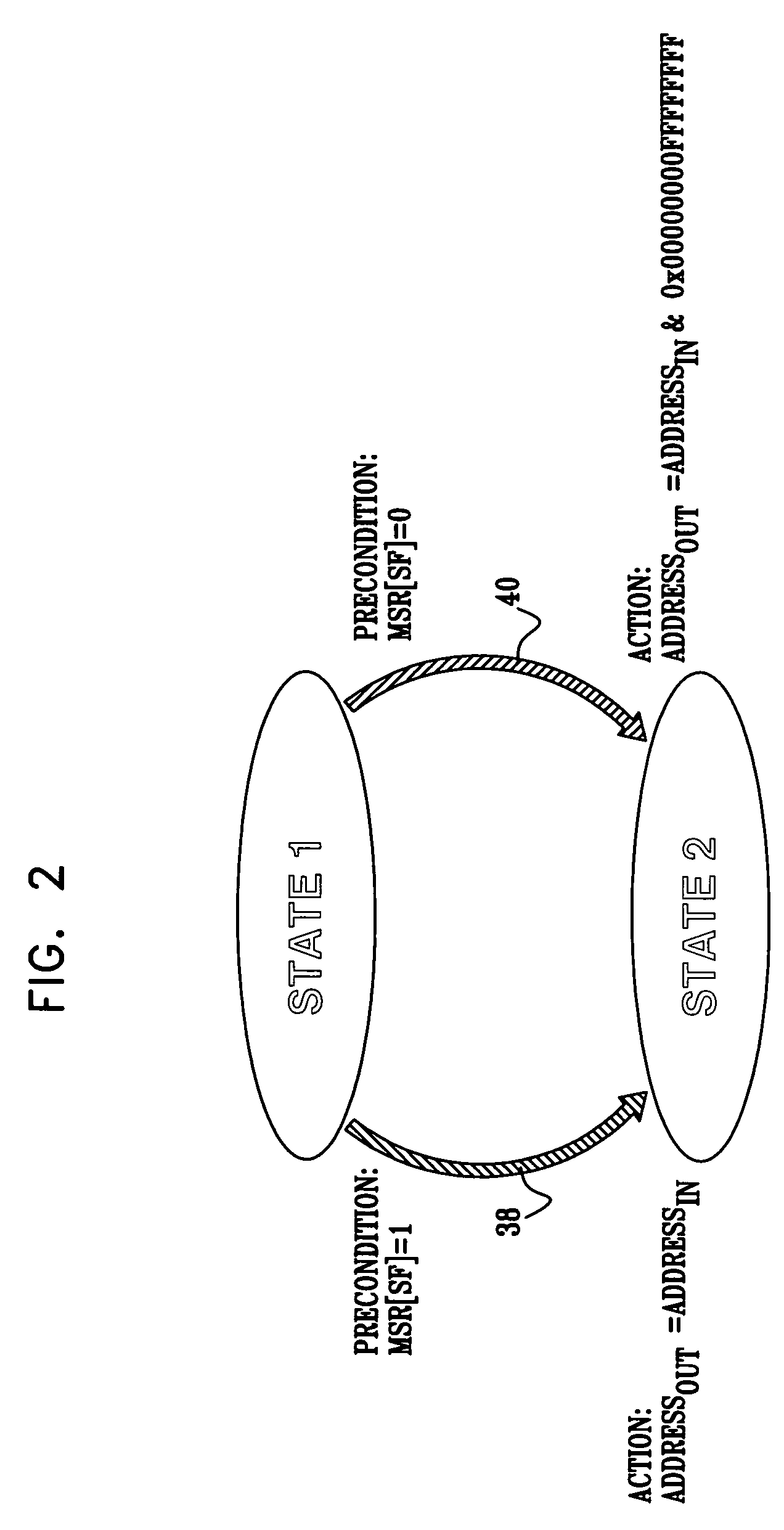

Modeling language and method for address translation design mechanisms in test generation

InactiveUS20050278702A1Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemModeling language

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

Modeling language and method for address translation design mechanisms in test generation

InactiveUS7370296B2Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemTheoretical computer science

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

Method and system for hardware accelerated verification of digital circuit design and its testbench

ActiveUS7257802B2Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

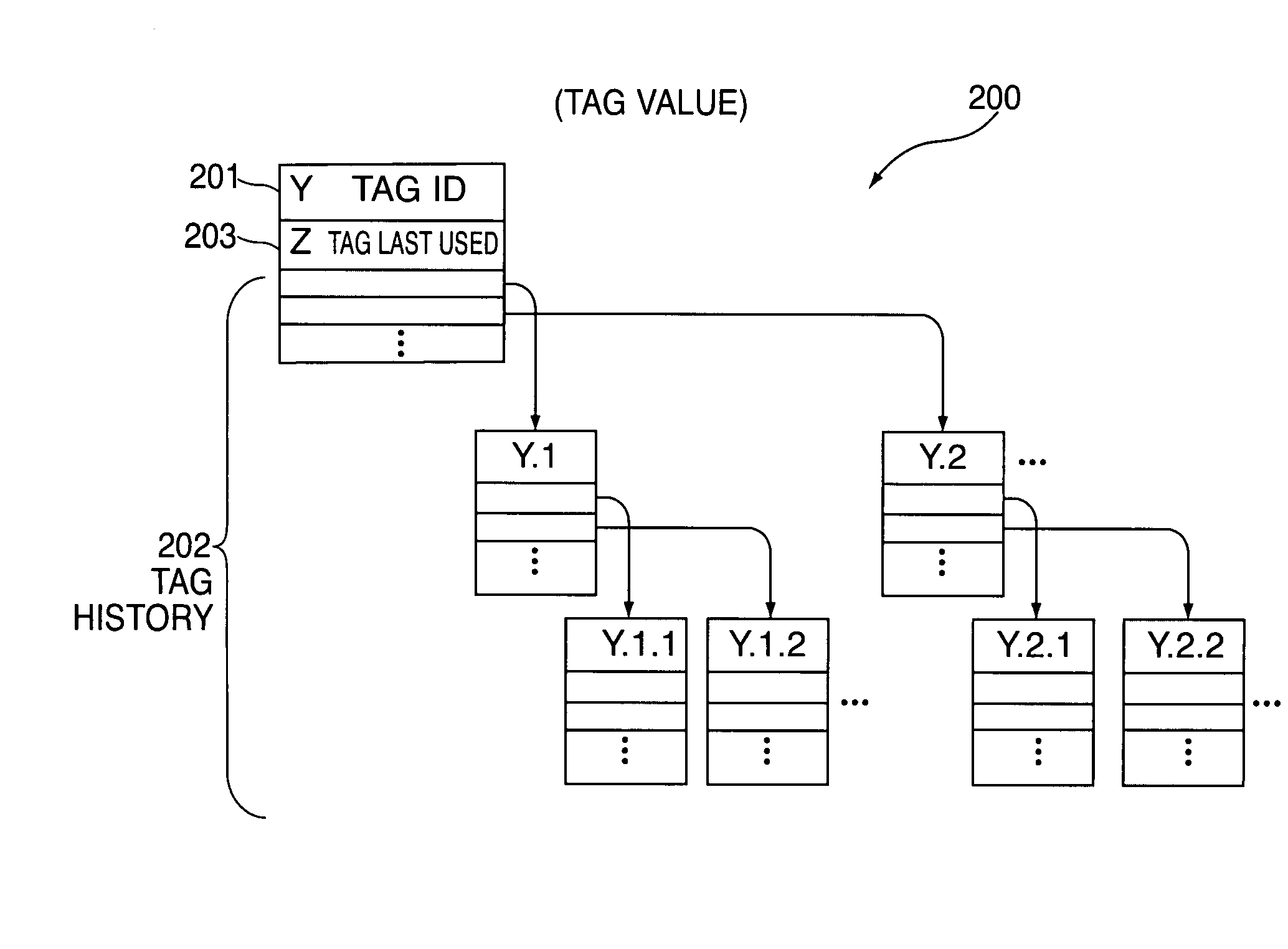

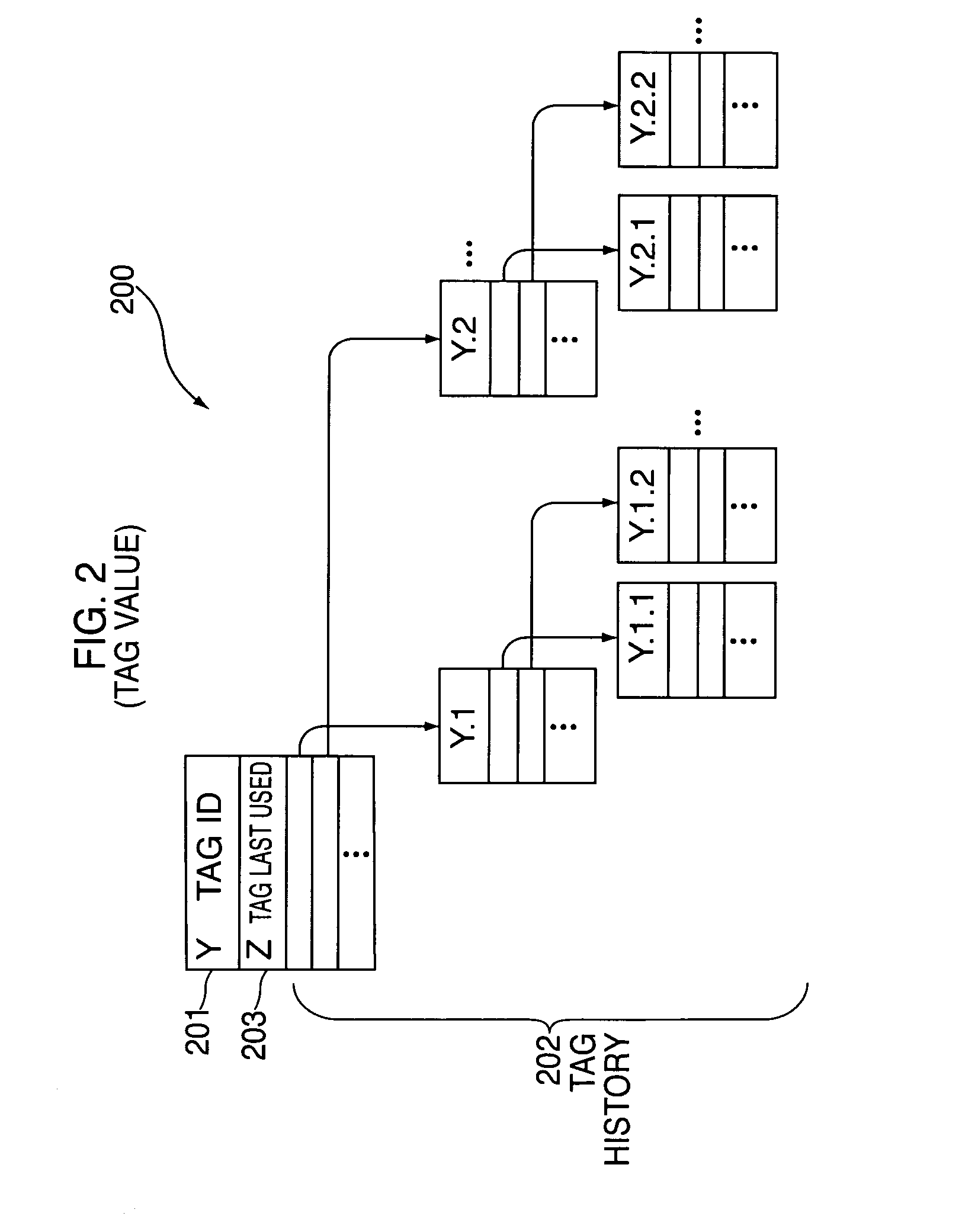

Method and apparatus for observability-based code coverage

A technique for observability based coverage of a design under test (DUT) is presented. A conventional simulation signal is augmented to include a “tag value.” In the course of a simulation, assignment statements (for which observability-based coverage is desired) “inject” tag values on their output signals. A tag value contains an identifier uniquely identifying the assignment statement that produced it. A tag value also contains a “tag history.” The tag history contains copies of the tag values for assignment statements earlier in the flow of control or in the flow of data. If a tag propagated through the DUT appears at an observable output, the circuit designer knows that the assignment statements it identifies have satisfied observability based coverage.

Owner:SYNOPSYS INC

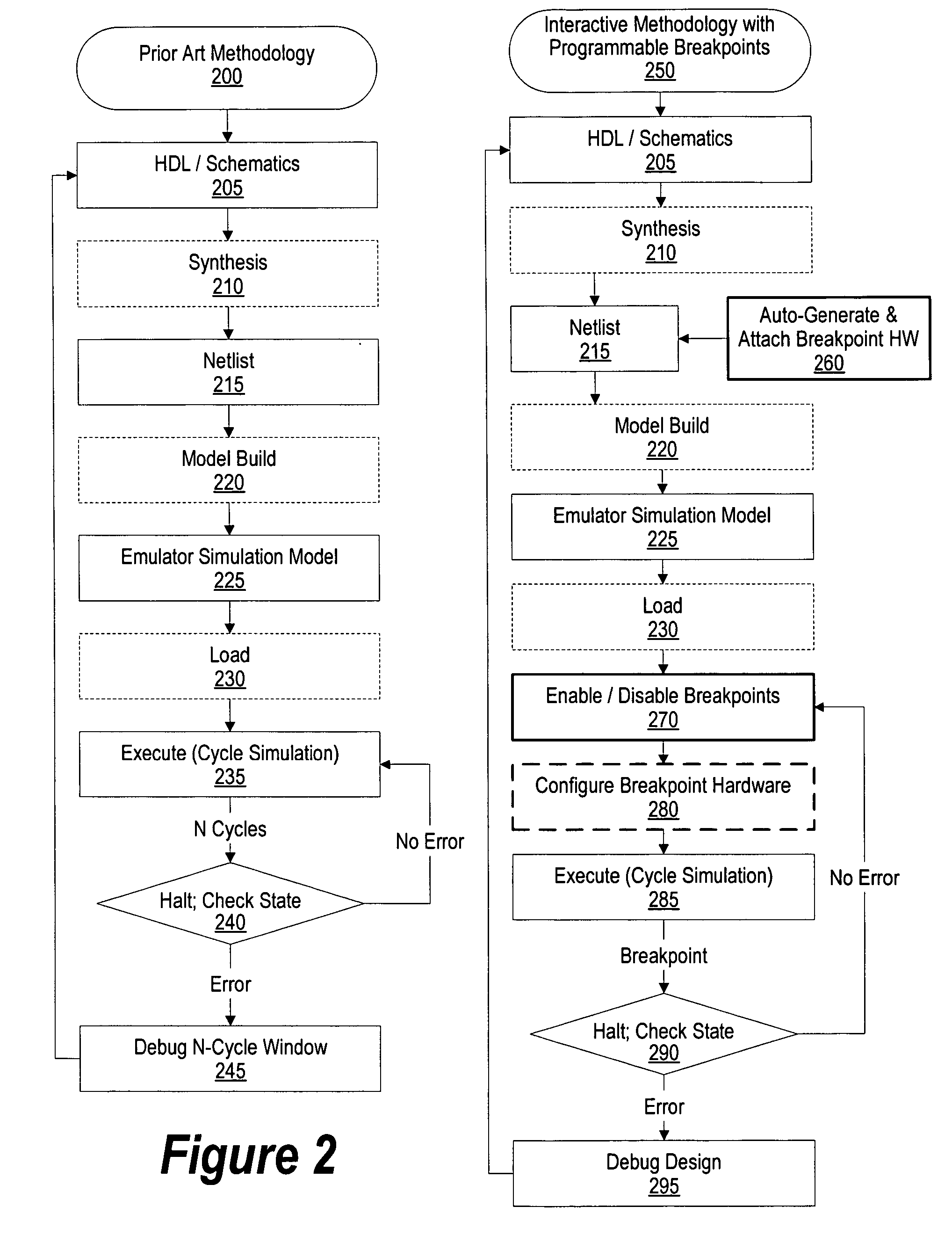

System and method of automating the addition of programmable breakpoint hardware to design models

InactiveUS20070005323A1Maximize simulator performanceFlexibilityDigital circuit testingCAD circuit designState variationHardware simulator

Hardware logic for generating breakpoint signals based on state changes in observed (“tagged”) hardware resource of a design under test is automatically generated and added to the simulation model of the design under test. These breakpoints halt simulation when a user programmable event, such as an assertion, test-case failure, or trigger occurs. Allowing the end-user to define the register values used in comparison to or timing of tagged resources, results in breakpoints that can be created, changed, enabled, or disabled without rebuilding the simulation model. Because the breakpoint logic is in-circuit, it takes full advantage of the acceleration made possible by hardware simulators, while providing an interactive environment for both functional hardware verification and software development on the simulated hardware mode.

Owner:IBM CORP

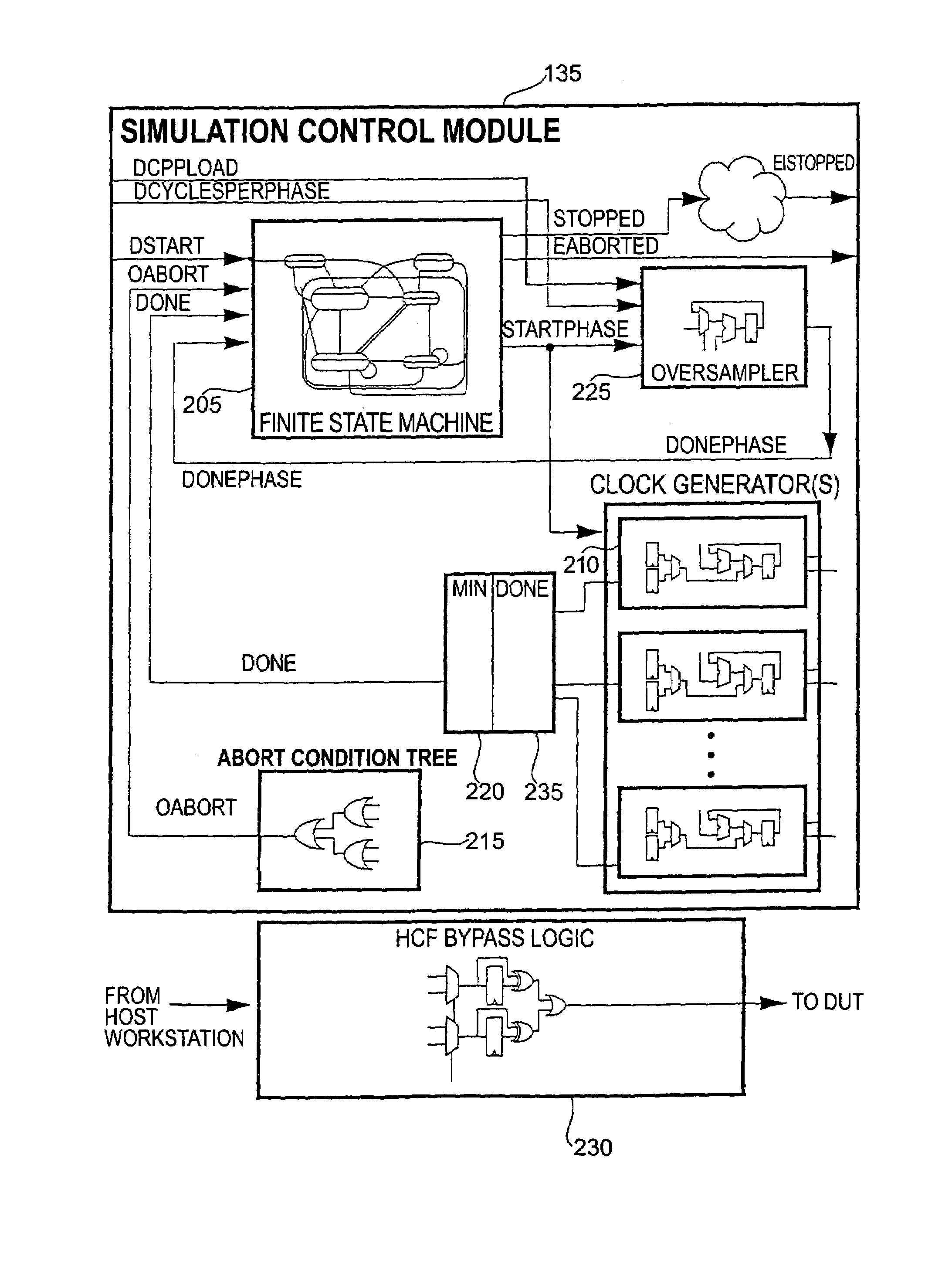

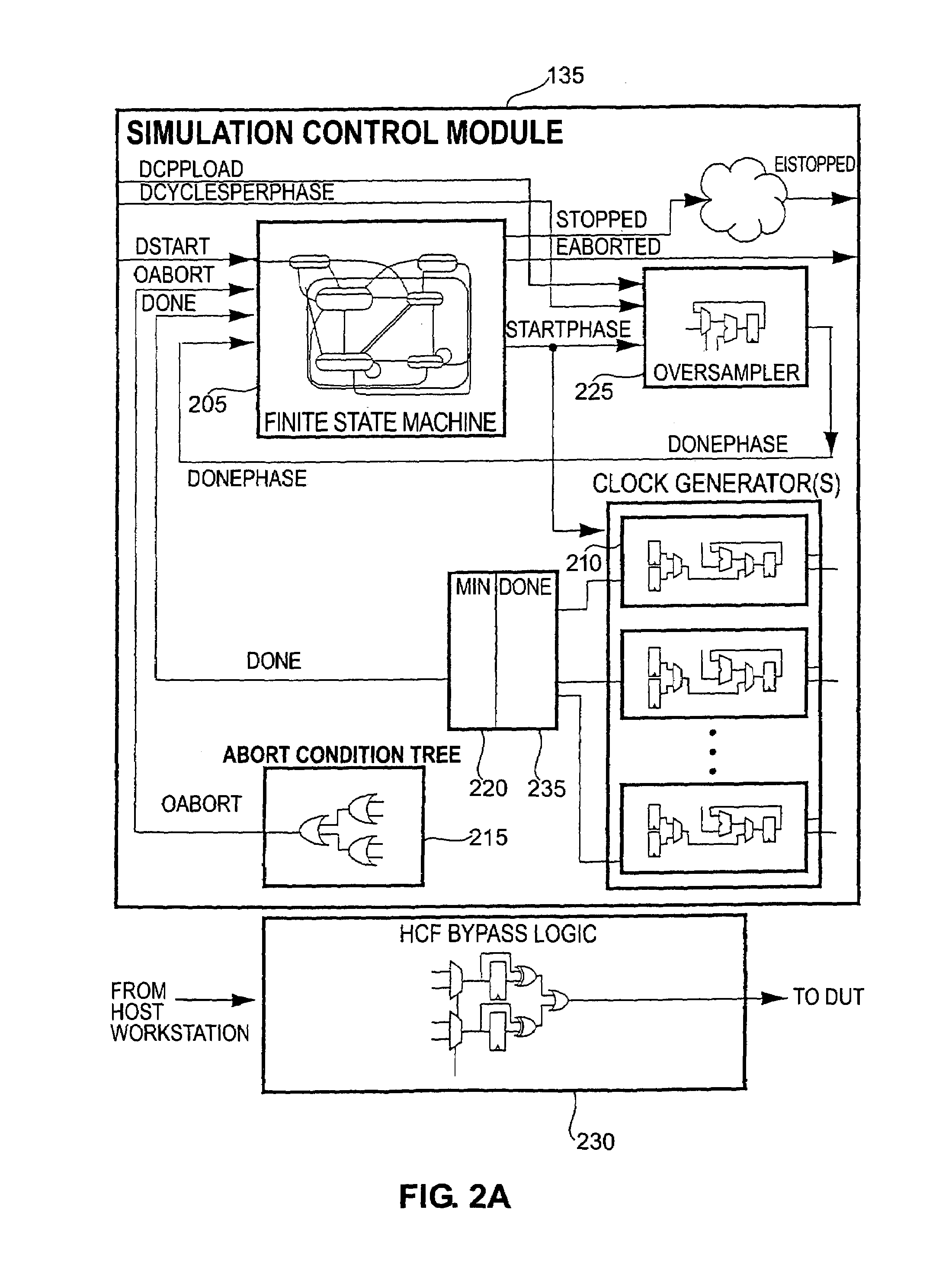

Simulation and timing control for hardware accelerated simulation

InactiveUS7257524B2Analogue computers for electric apparatusCAD circuit designCo-simulationWorkstation

A fully synthesizeable Simulation Control Module (SCM) controls and monitors the simulation of a design under test (DUT). A clock generator within the SCM and a Software clock facility residing on the host workstation are responsible for providing the clocks for the DUT. The SCM and the hardware clock facility are dynamically generated at build time to suit the needs of the DUT. They maximize performance by automatically generating clock waveforms for designs containing multiple asynchronous clocks, thereby decreasing the frequency of accelerator-workstation interaction. The software clock facility has the ability to directly drive the DUT and is responsible for managing the simulation time and clock parameters. The SCM is also responsible for monitoring an abort condition such as a trigger to execute an external software model. The SCM and the clock facilities allow the hardware accelerator to efficiently support multiple asynchronous clock domains, execution of external software models and co-simulation.

Owner:CADENCE DESIGN SYST INC

Isolated debugging in an FPGA based emulation environment

For a design under test (DUT) that is to be emulated, a host system partitions the DUT into multiple partitions and maps each partition to an FPGA of an emulator which will emulate the partition. The host system stores information describing to which FPGAs each component of the DUT has been mapped. Additionally, mapped to each FPGA is trace and injection logic that traces signals exchanged by the FPGA with other FPGAs during emulation of the DUT. After the emulation of the DUT is complete, if a user wishes to debug a component of the DUT, the FPGAs that are configured to emulate the component are identified. For each identified FPGA, the trace and injection logic injects previously traced signals into the logic of the FPGA in order to reemulate the component. The host system generates waveforms for the user that include signals traced during the reemulation of the component.

Owner:SYNOPSYS INC

System and method for complex programmable breakpoints using a switching network

InactiveUS20070005322A1Maximize simulator performanceFlexibilityDigital circuit testingCAD circuit designExchange networkTheoretical computer science

Hardware logic for generating breakpoint signals (basic events) based on state changes in observed (“tagged”) hardware resource of a design under test is automatically generated and added to the simulation model of the design under test. A switch / network is included in the model for mapping basic events to complex breakpoint logic. Complex breakpoints combine basic events to form more complex breakpoints that can be selectively enabled / disabled by the simulation user. In one embodiment, user settable values are compared with complex breakpoint values to further define a complex breakpoint.

Owner:IBM CORP

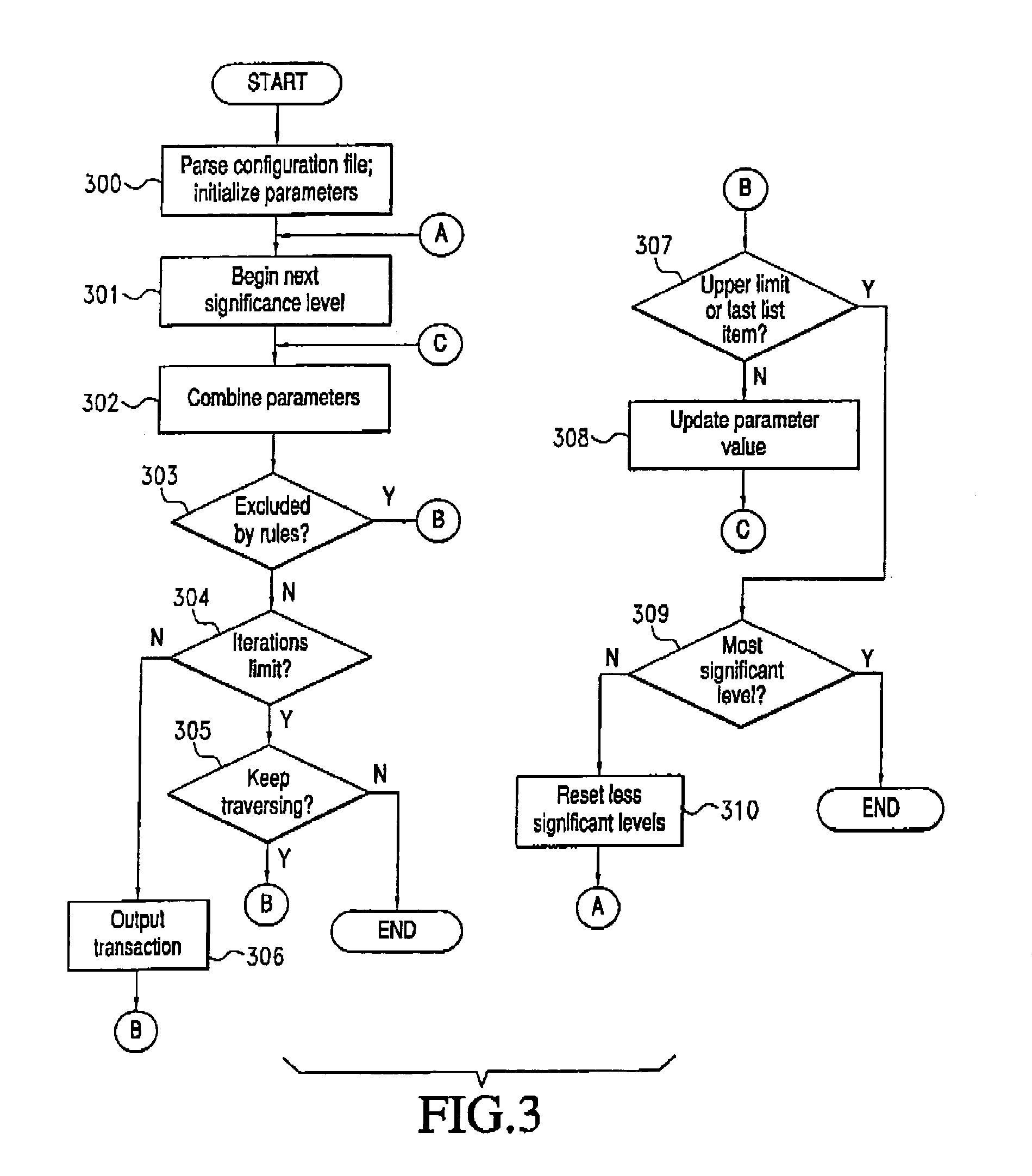

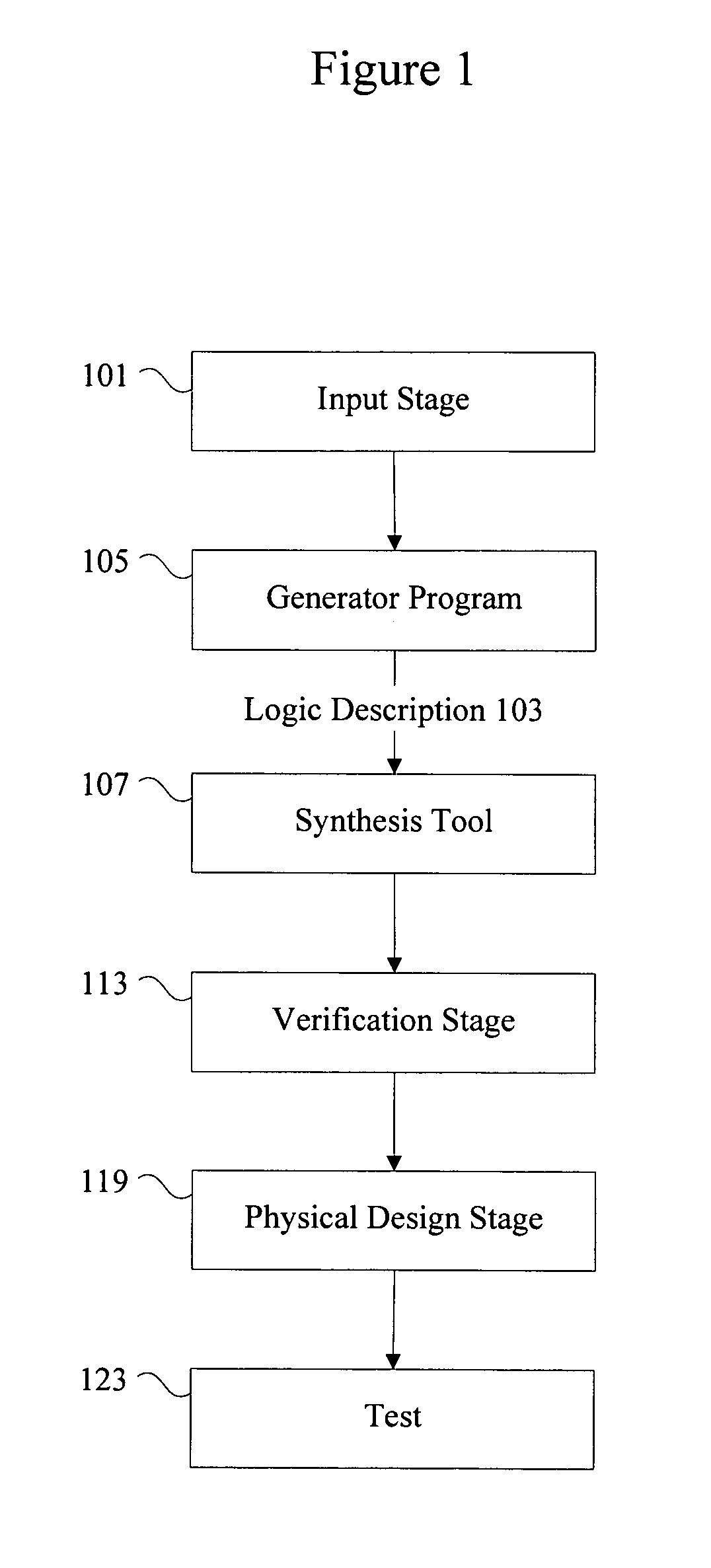

Method and system for efficiently generating parameterized bus transactions

InactiveUS6970816B1Easy to customizeEliminate timeAnalogue computers for electric apparatusCAD circuit designBus interfaceOperating system

A method and system for efficiently generating parameterized bus transactions for verification of a design-under-test (DUT) comprises providing a configuration file for the DUT to a generator program. The configuration file defines possible parameter combinations for bus transactions executable by the DUT, and the generator program systematically enumerates all the possible combinations to produce a test case for verifying the DUT. Rules specified within the configuration file can include or exclude selected parameter combinations to tailor the test case to a specific DUT-to-bus interface.

Owner:IBM CORP

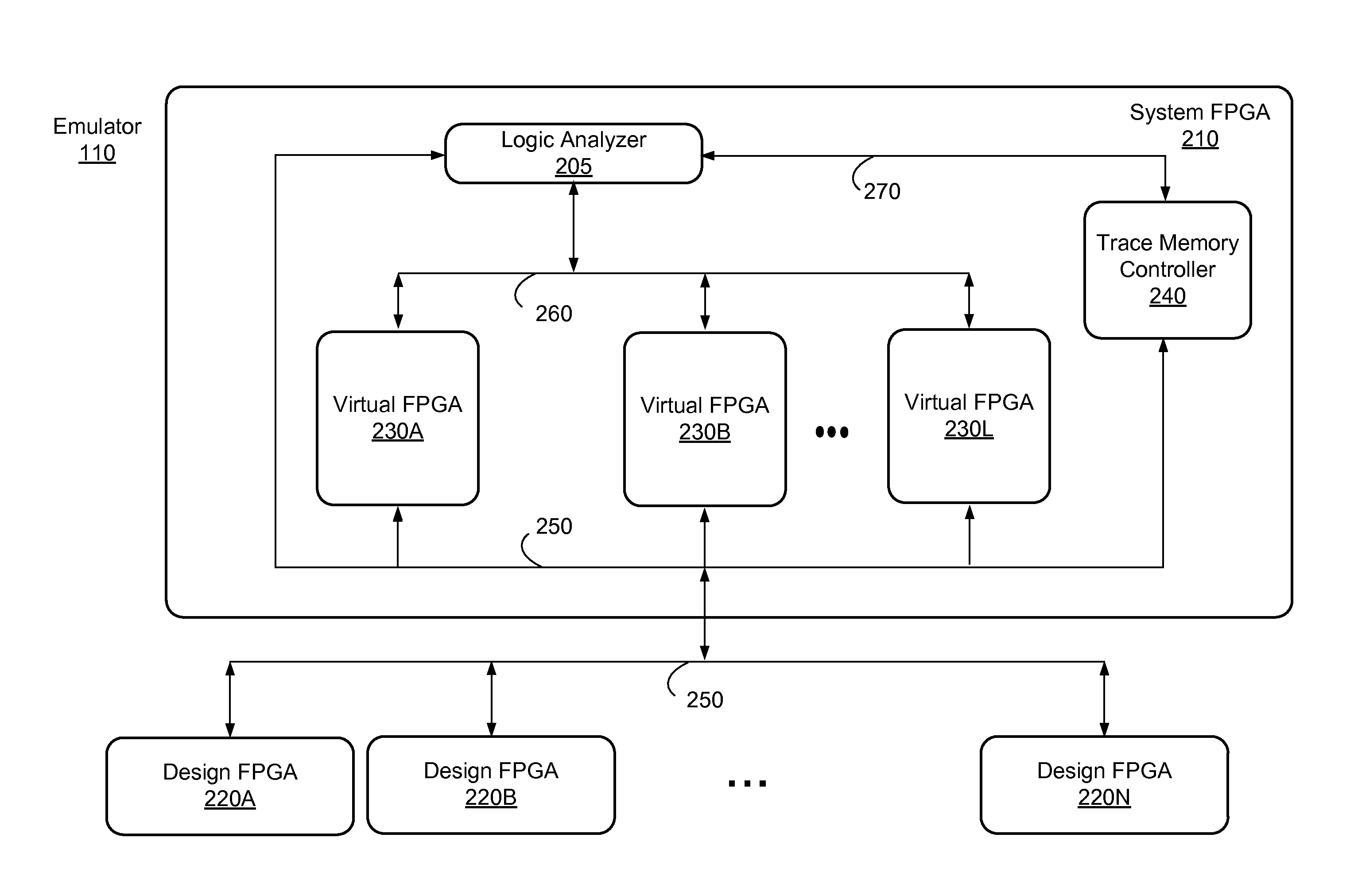

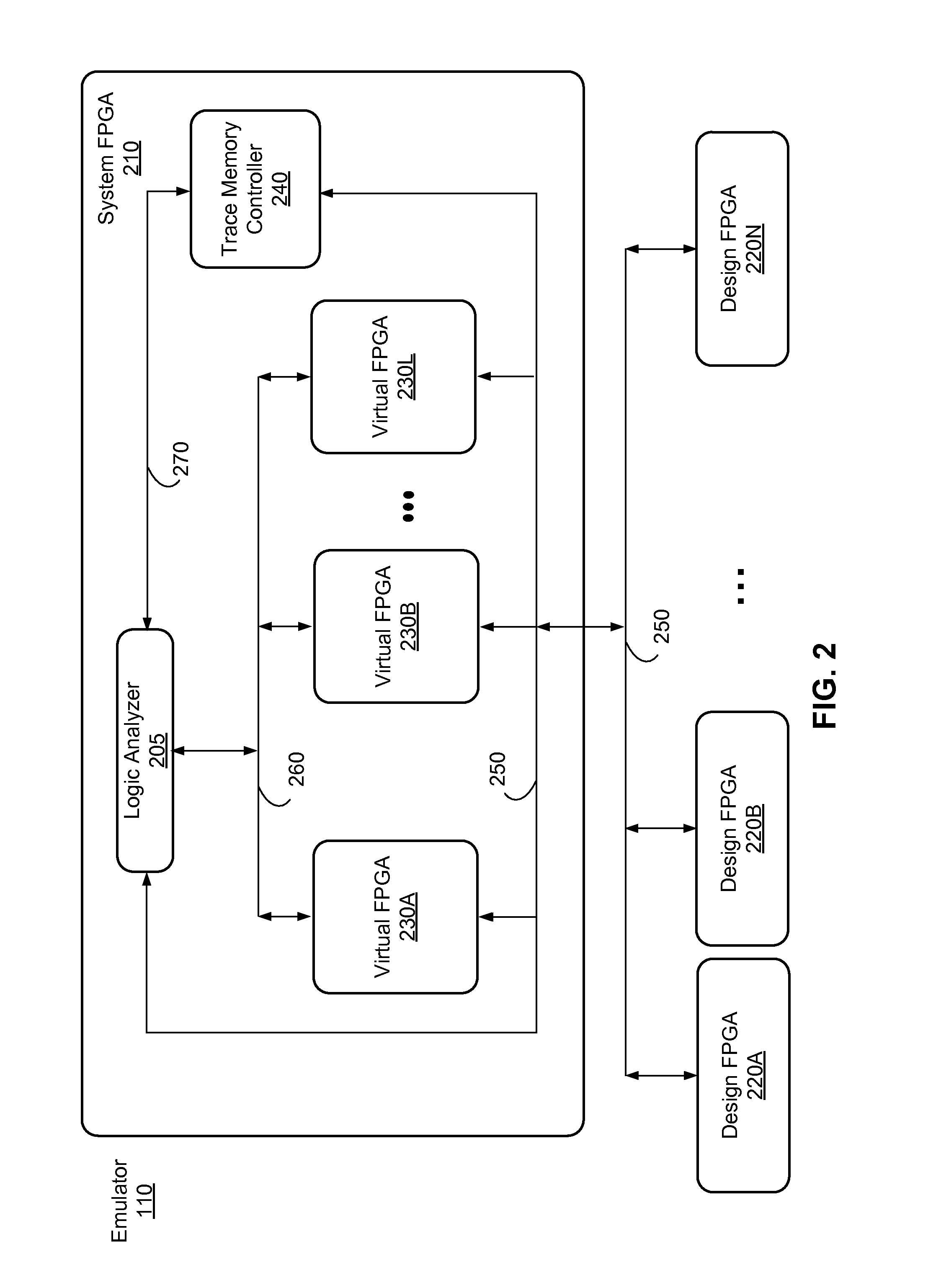

Efficient emulation and logic analysis

ActiveUS20160098505A1Computer aided designSpecial data processing applicationsParallel computingLogic analyzer

An emulation environment includes a host system and an emulator. The host system configures the emulator to load a design under test (DUT) and the emulator emulates the DUT. The emulator includes one or more design field-programmable gate arrays (FPGAs) that emulate the DUT. In addition, the emulator includes at least one system FPGA with a logic analyzer and multiple virtual FPGA. The virtual FPGAs emulate sections of the DUT. By the virtual FPGAs emulating sections of the DUT, the logic analyzer is able to obtain for performing logic analysis certain signals from the virtual FPGAs, rather than from the design FPGAs.

Owner:SYNOPSYS INC

Method and system for deterministic control of an emulation

InactiveUS7472055B2Computation using non-contact making devicesDigital computer detailsApplication softwareDeterministic control

An emulation-based event-wait simulator including an application module to configure and command verification processes on a design under test (DUT). An event dispatcher is in communication with the application module to deliver commands to the DUT. A plurality of transactors are in communication with the event dispatcher to forward the commands to the DUT. A channel controller is in communication with the transactors to process and forward the commands to the DUT, wherein the channel controller also receives messages from the DUT, processes the messages, and forwards the messages to the transactors for delivery to the event dispatcher and the application module.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

System for quickly specifying formal verification environments

ActiveUS8127261B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionGraphicsGraphical user interface

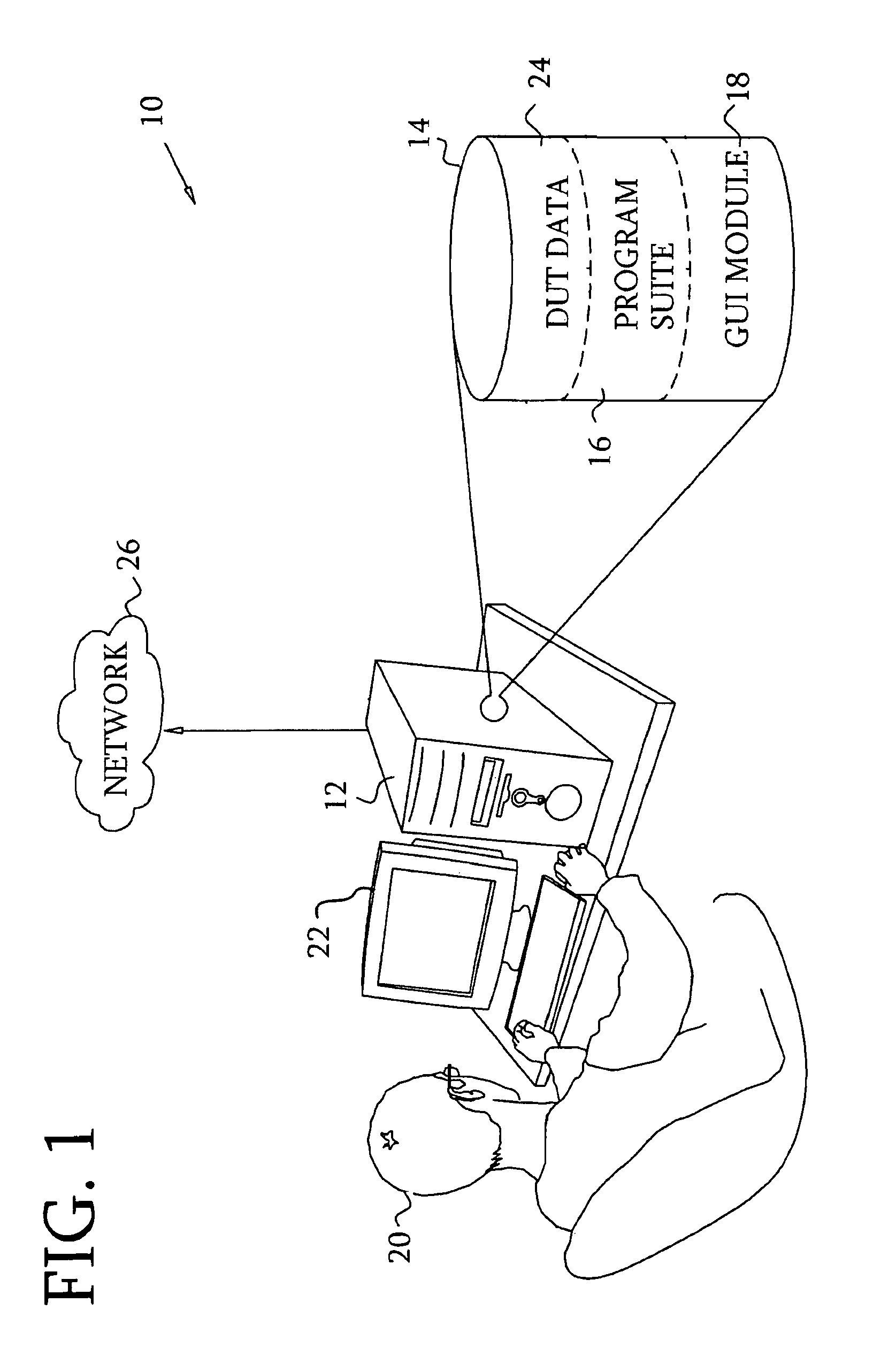

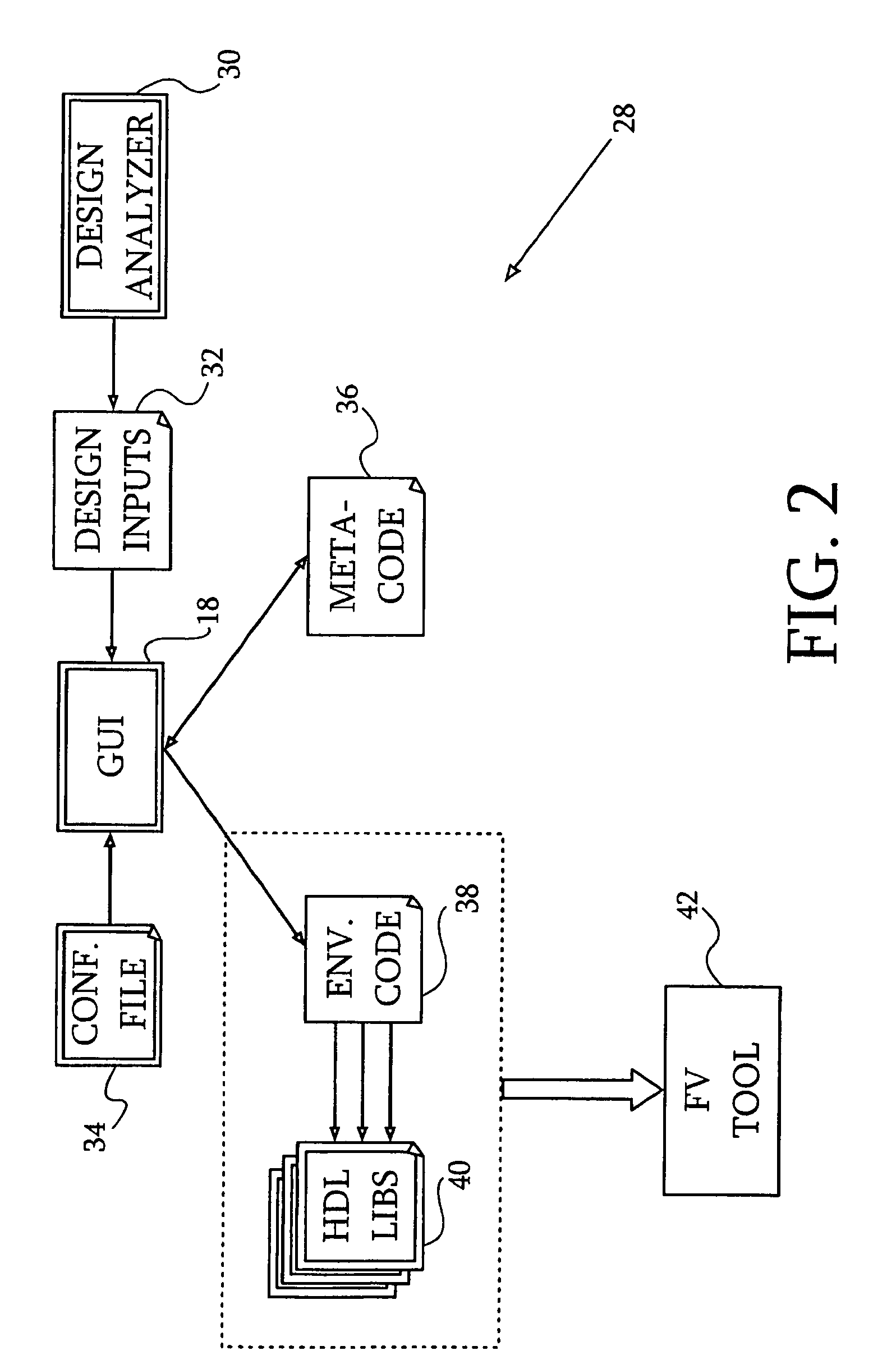

Computer-implemented techniques are disclosed for defining an environment for formal verification of a design-under-test. Initially there is extraction of design inputs by a design analysis module, and presentation of the inputs on a graphical user interface. Behavior options for the design inputs are offered on the graphical user interface for selection by an operator. Environment code that is descriptive of the design inputs and selected behavior options is emitted, typically in a hardware description language, for submission to a formal verification tool. A meta-code file containing the assigned behavior options is generated to aid subsequent sessions.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

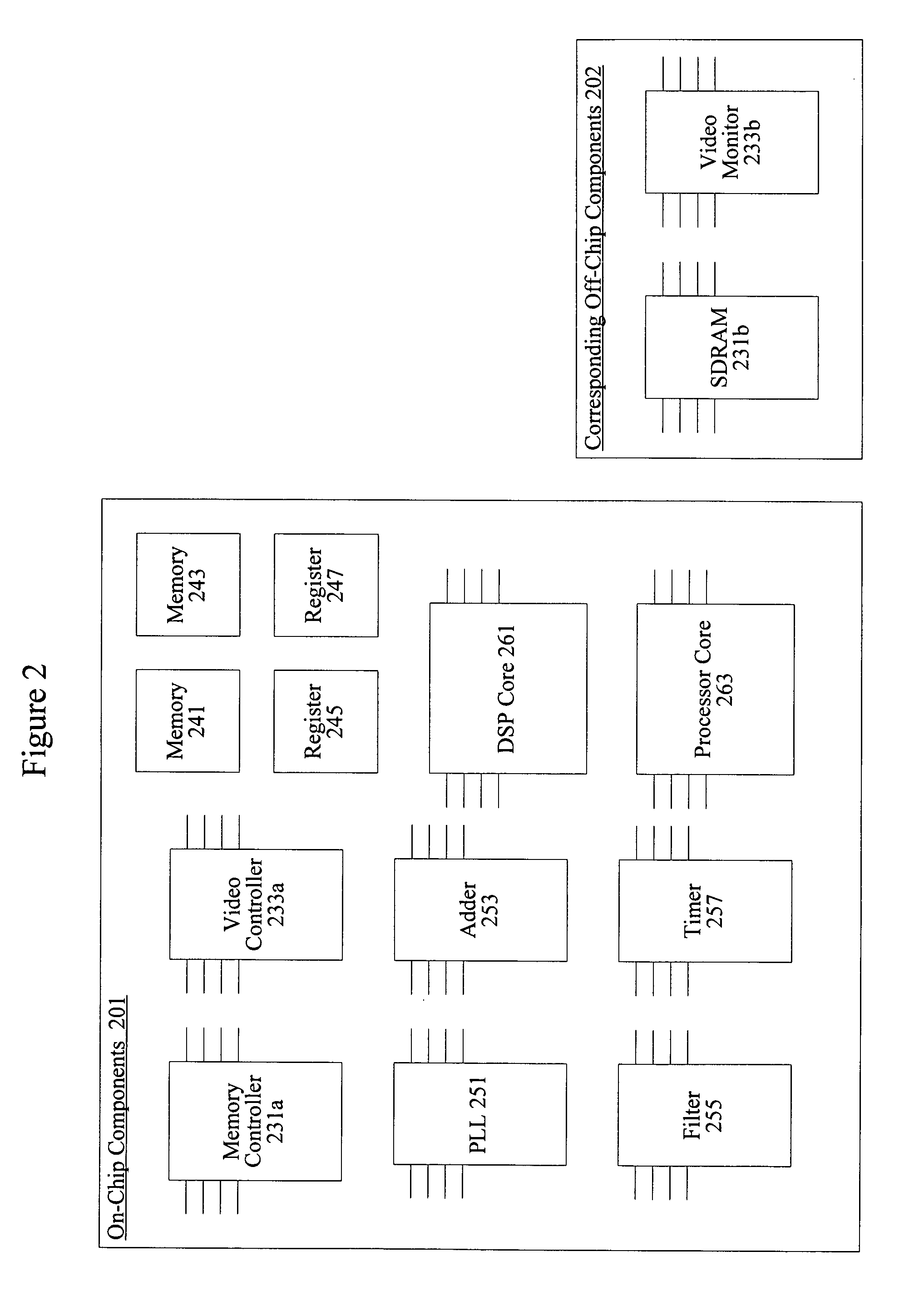

Methods and apparatus for automatic test component generation and inclusion into simulation testbench

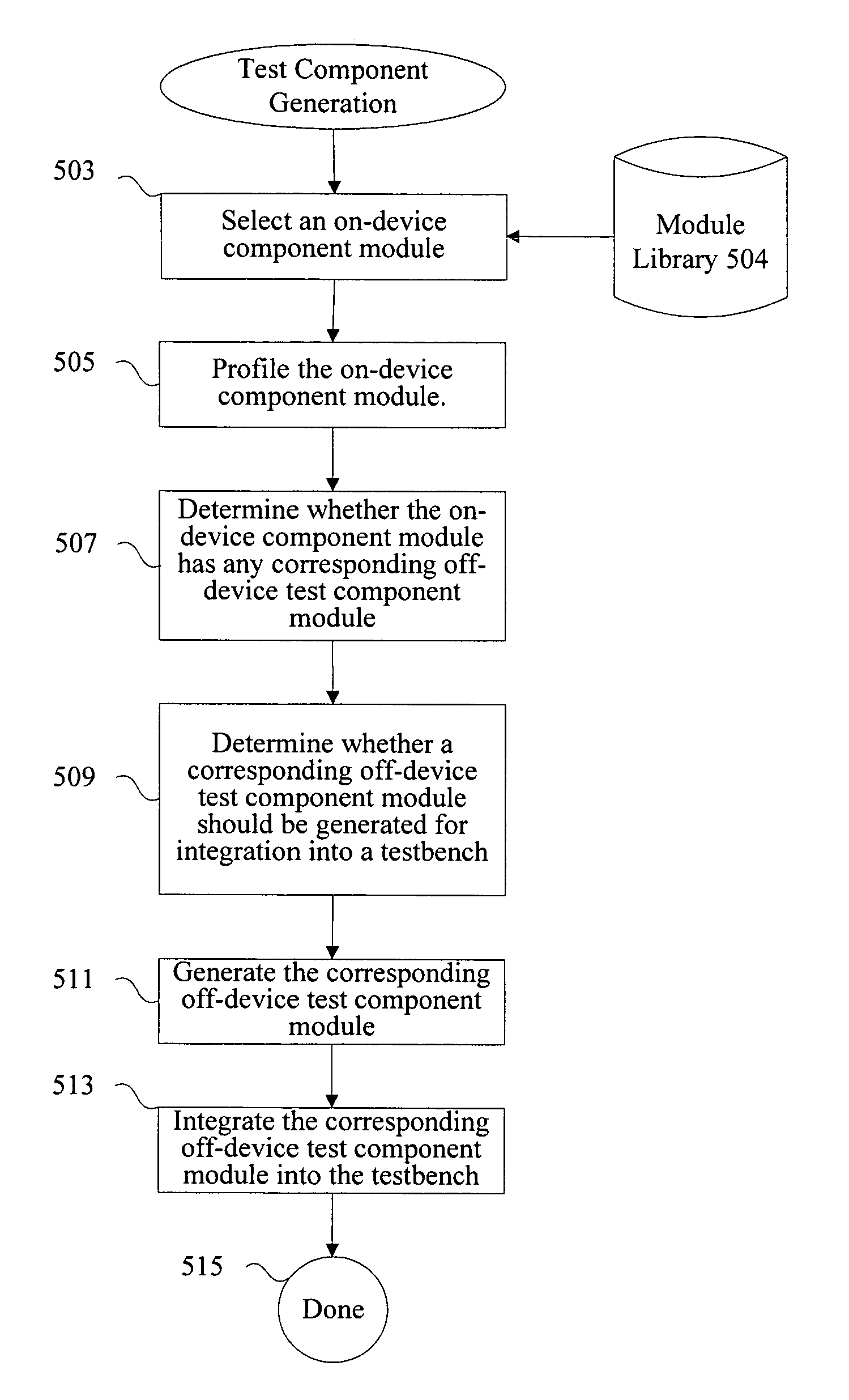

InactiveUS7225416B1Generate efficientlyDetecting faulty computer hardwareElectrical testingConfiguration designEngineering

Methods and apparatus are provided for efficiently generating test components for testing and evaluating a design under test. As a design is being configured, generated test components are made available. In one example, test components are automatically generated and included in a simulation testbench based on selected components in the design. Generally, the test components complement the selected components in the design. Moreover, the test components can be automatically seeded with initial contents.

Owner:ALTERA CORP

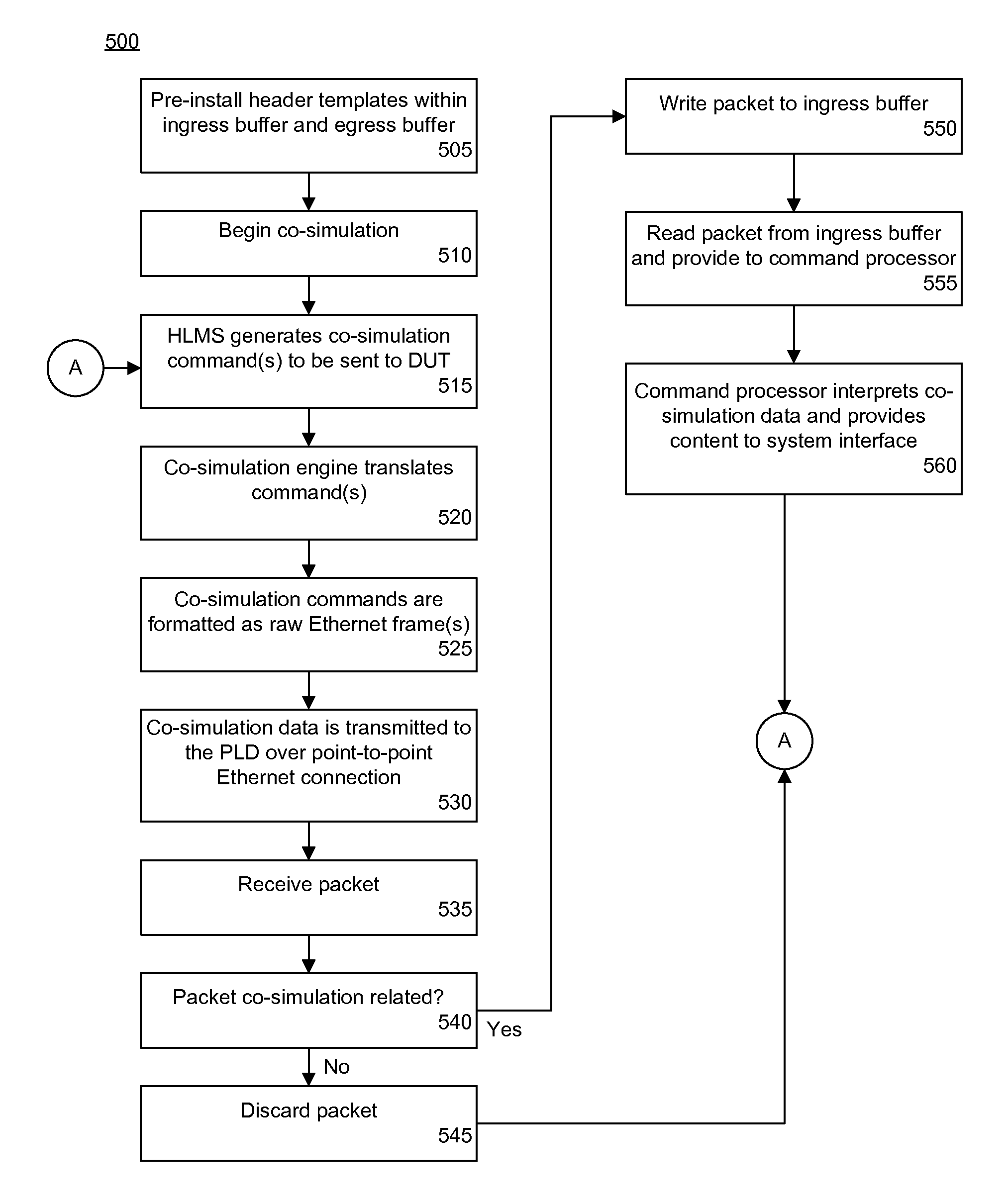

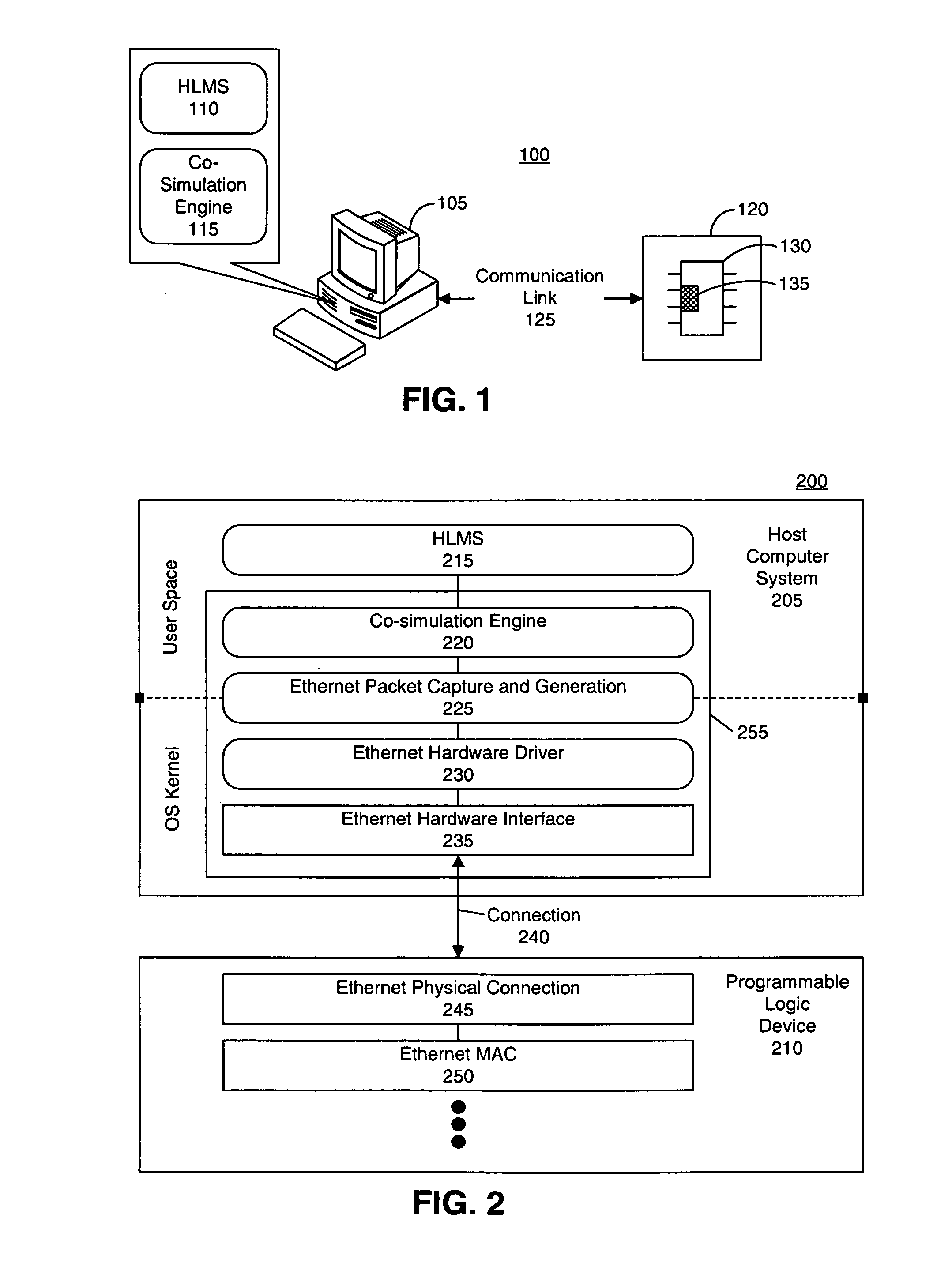

Point-to-point ethernet hardware co-simulation interface

ActiveUS7636653B1Facilitate communicationEasy data transferComputer aided designSoftware simulation/interpretation/emulationTelecommunications linkCommunication link

An Ethernet co-simulation interface for use with a software-based simulation tool and a design under test disposed on a programmable device can include a host interface and a network processor. The host interface can execute on a host computing system and facilitate data transfer between the software-based simulation tool and a communication link to the design under test. The network processor can be implemented within the programmable device and facilitate data transfer between the communication link and the design under test. The host interface and the network processor can exchange simulation data formatted as raw Ethernet frames over a point-to-point Ethernet connection.

Owner:XILINX INC

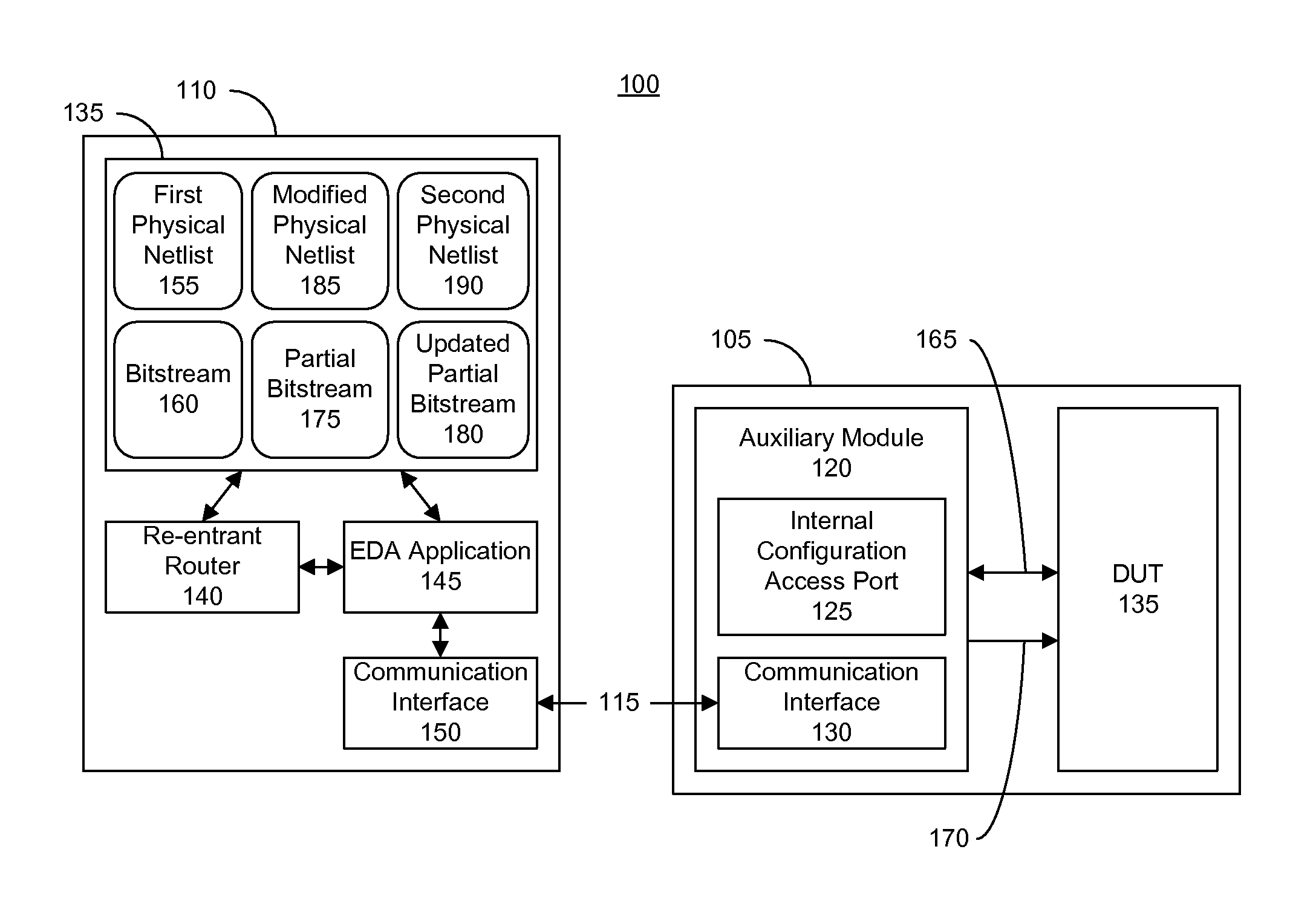

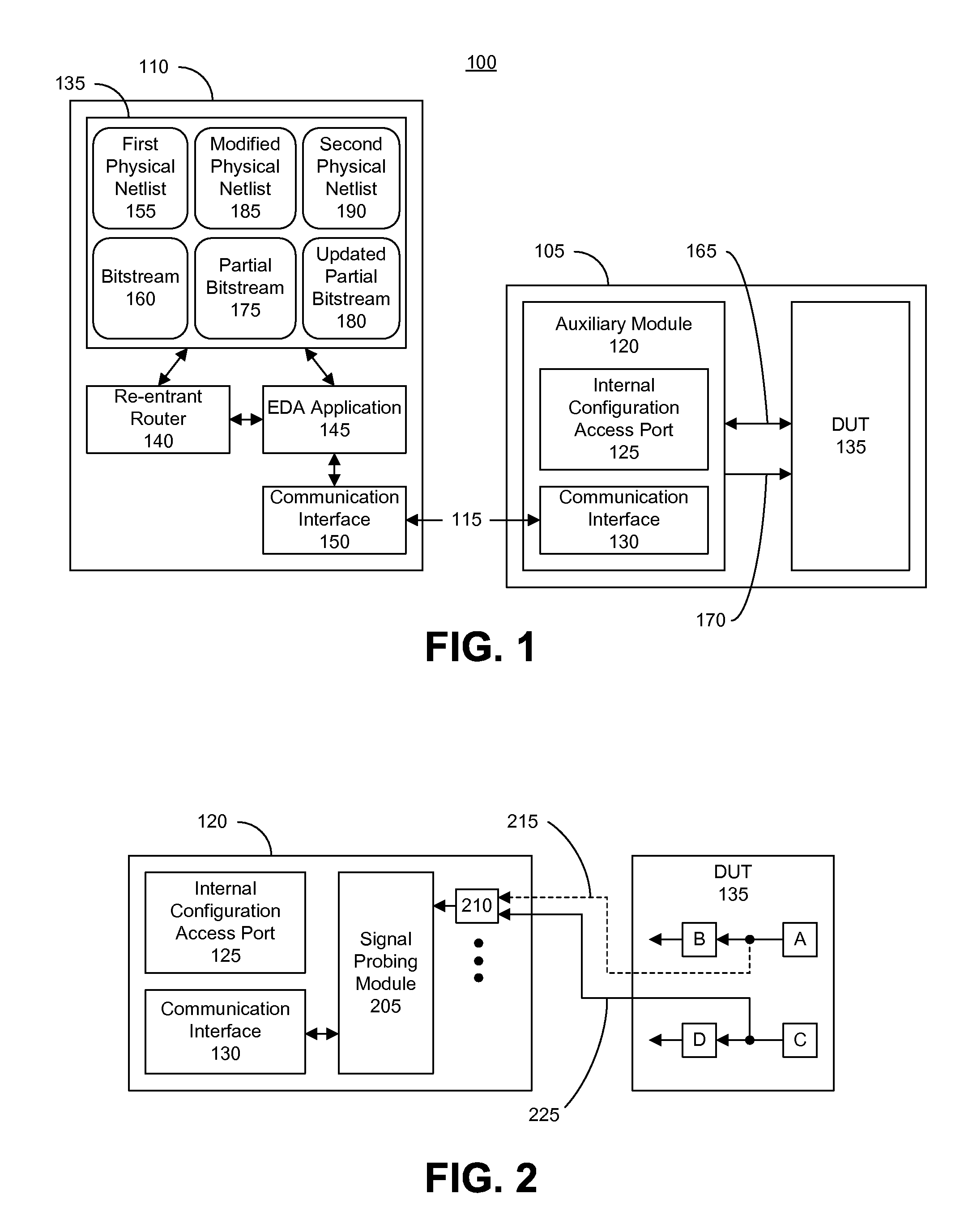

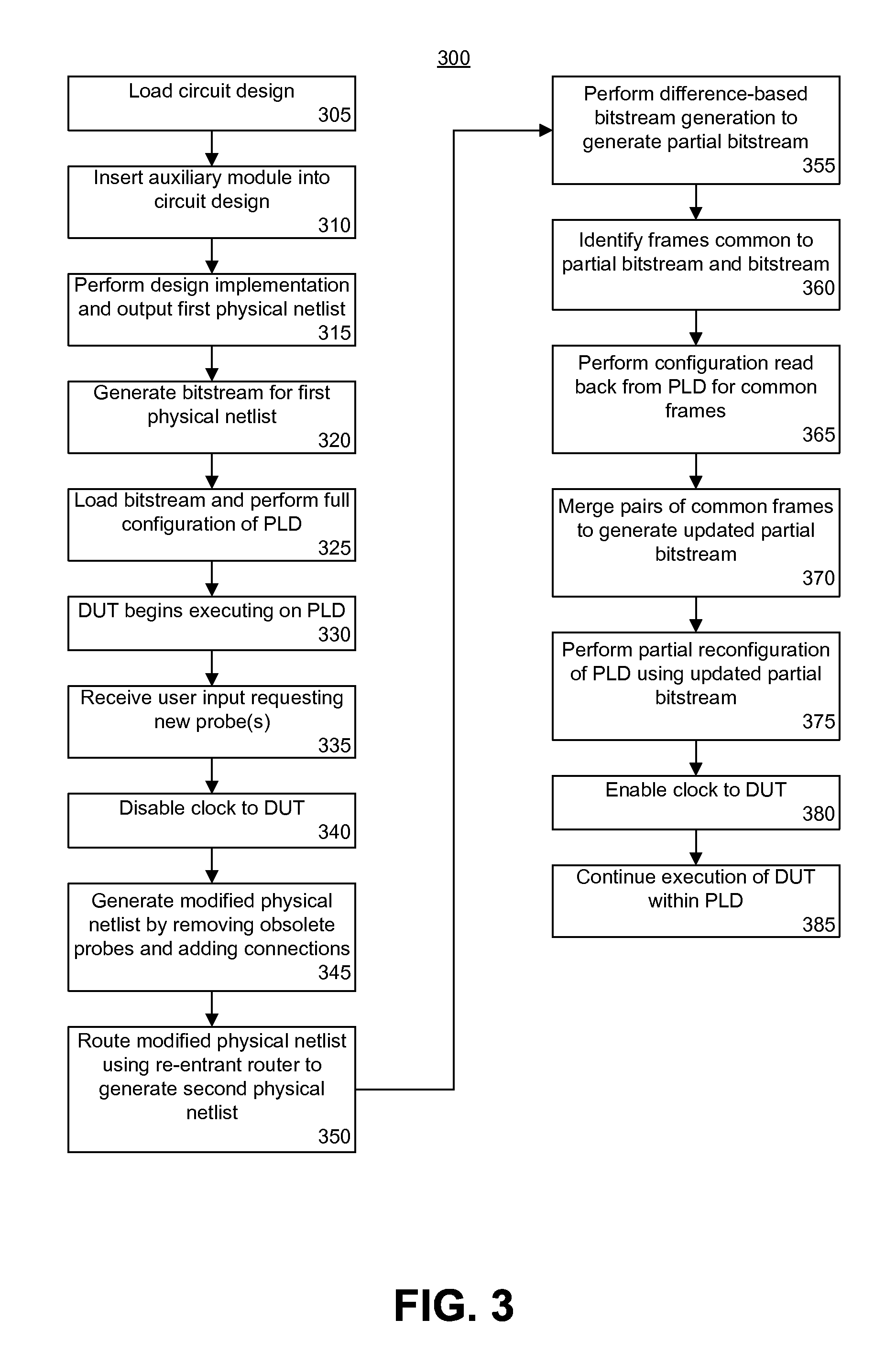

Rapid rerouting based runtime reconfigurable signal probing

InactiveUS8103992B1CAD circuit designSpecial data processing applicationsProgrammable logic deviceDesign under test

A computer-implemented method of probing a design under test (DUT) instantiated within a programmable logic device (PLD) can include disabling a clock signal provided to the DUT (340) and generating a partial bitstream specifying a new probe for the DUT (335). The partial bitstream can be merged with configuration data read-back from the PLD to create an updated partial bitstream (360, 365, 370). The updated partial bitstream can be loaded into the PLD (375). The clock signal provided to the PLD can be started and the DUT can continue to operate (380, 385).

Owner:XILINX INC

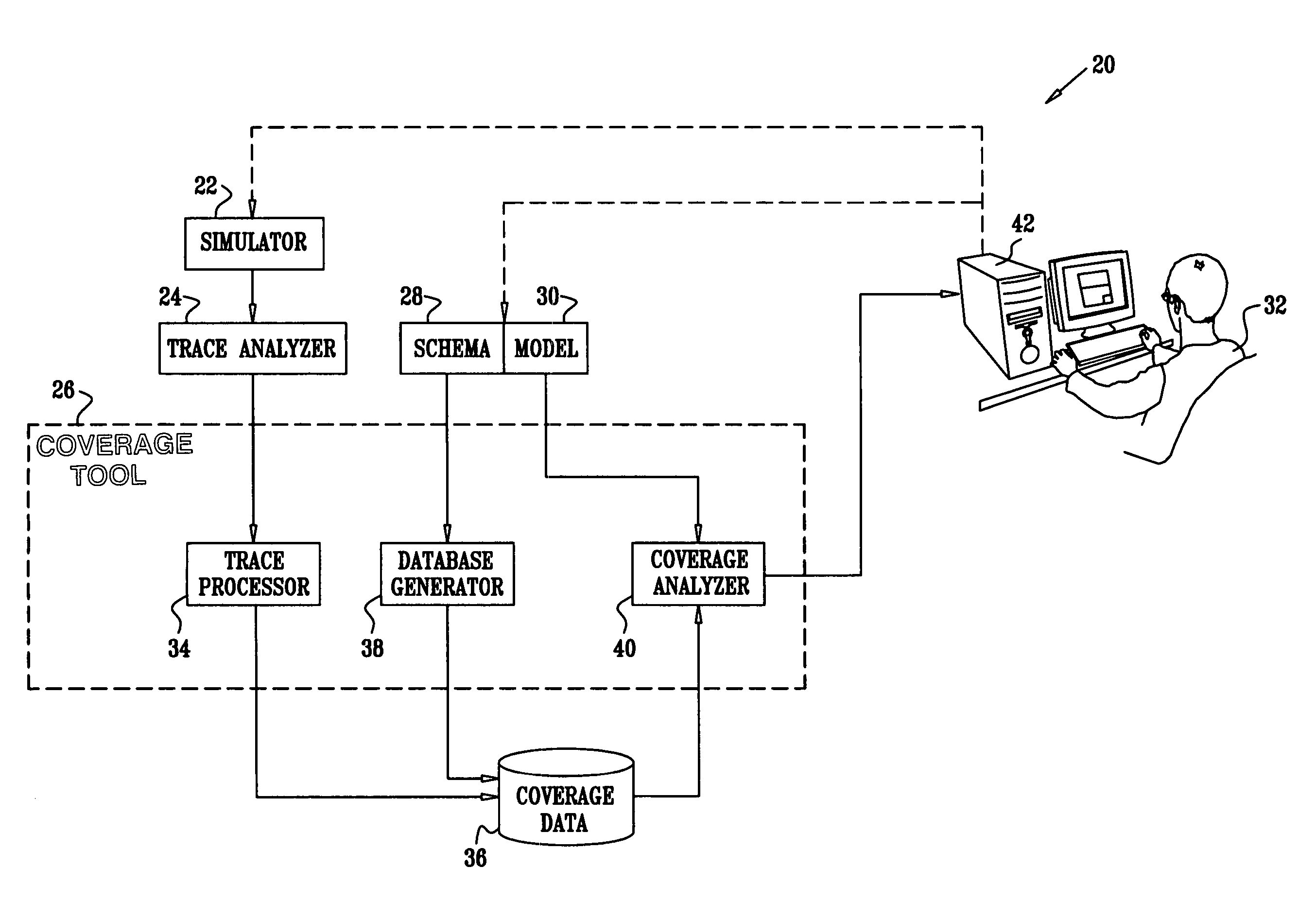

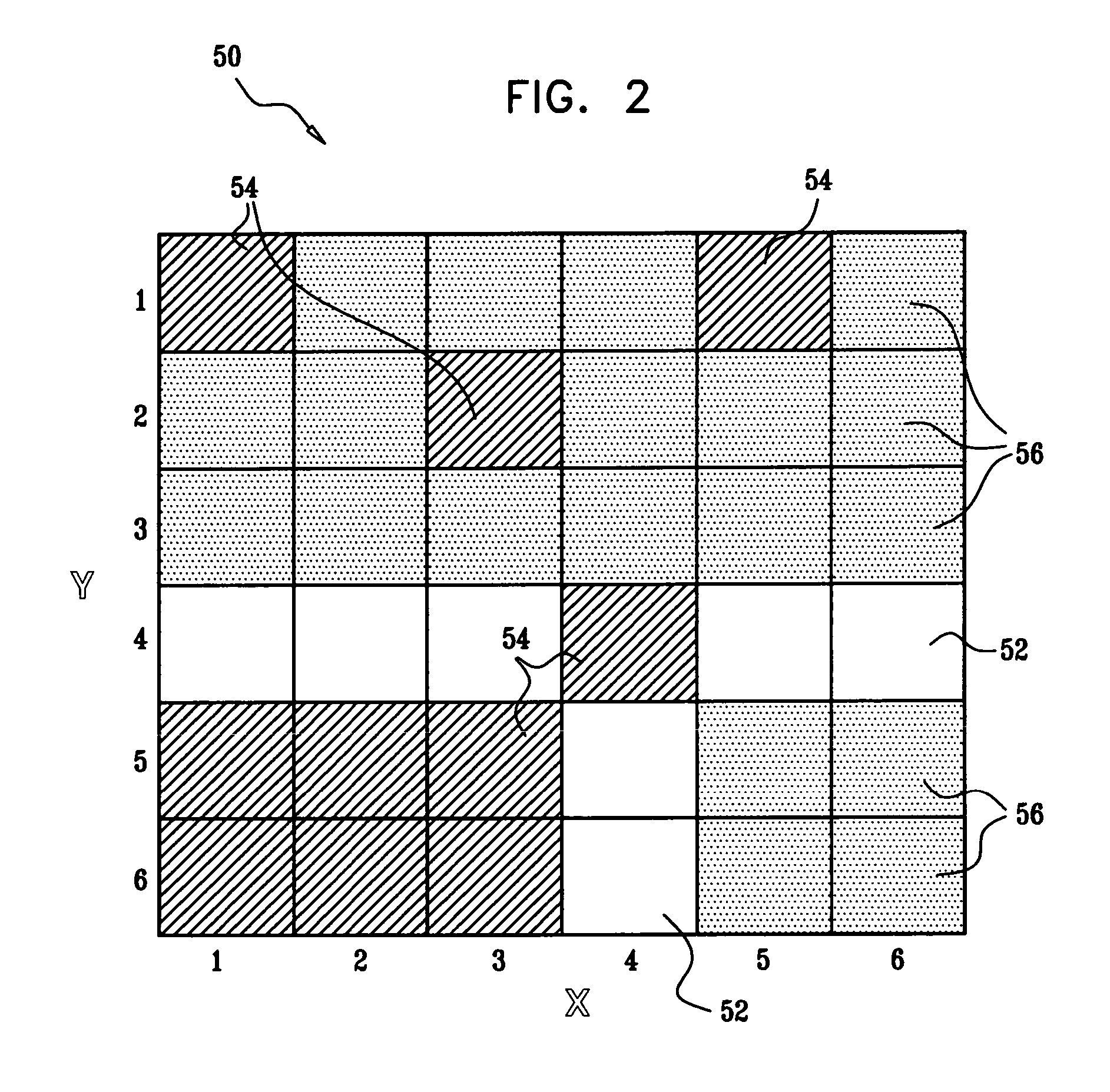

Efficient presentation of functional coverage results

InactiveUS7389215B2Simplify presentation and analysisImprove visualizationElectronic circuit testingAnalogue computers for electric apparatusData miningMulti dimensional

A method for presentation of functional coverage includes representing a set of attributes of a design under test as a multi-dimensional cross-product space, which includes events corresponding to combinations of values of the attributes to be tested, the events including legal and illegal events. At least one test is run on the design, and responsively to the at least one test, a first group of the legal events that were covered by the at least one test and a second group of the legal events that remain non-covered after the at least one test are identified. One or more of the illegal events are grouped with at least one of the first and second groups so as to present a simplified model of the coverage of the events in the cross-product space.

Owner:GLOBALFOUNDRIES INC

Method and system for deterministic control of an emulation

InactiveUS20030225561A1Analogue computers for electric apparatusDigital computer detailsApplication softwareDeterministic control

An emulation-based event-wait simulator including an application module to configure and command verification processes on a design under test (DUT). An event dispatcher is in communication with the application module to deliver commands to the DUT. A plurality of transactors are in communication with the event dispatcher to forward the commands to the DUT. A channel controller is in communication with the transactors to process and forward the commands to the DUT, wherein the channel controller also receives messages from the DUT, processes the messages, and forwards the messages to the transactors for delivery to the event dispatcher and the application module.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

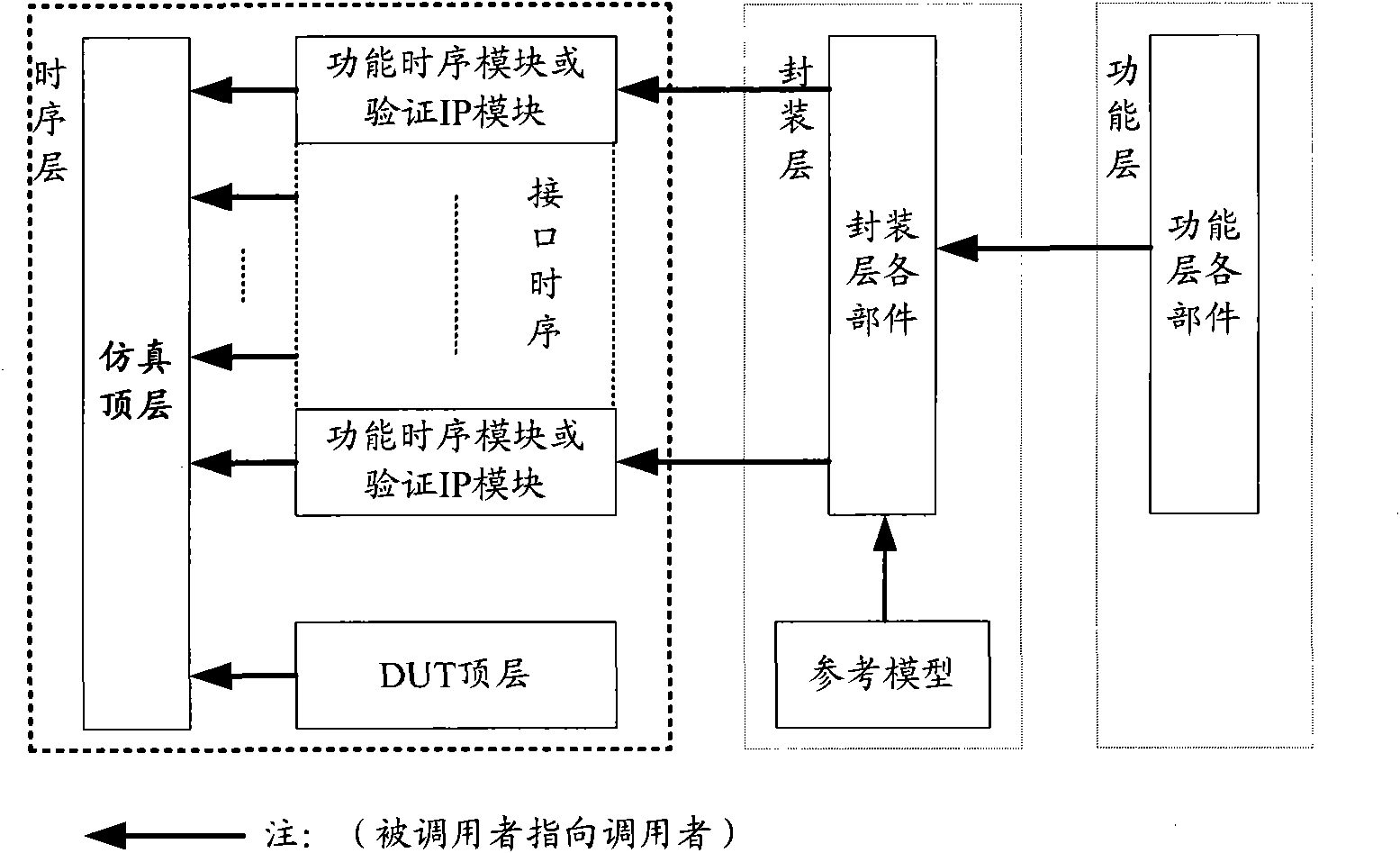

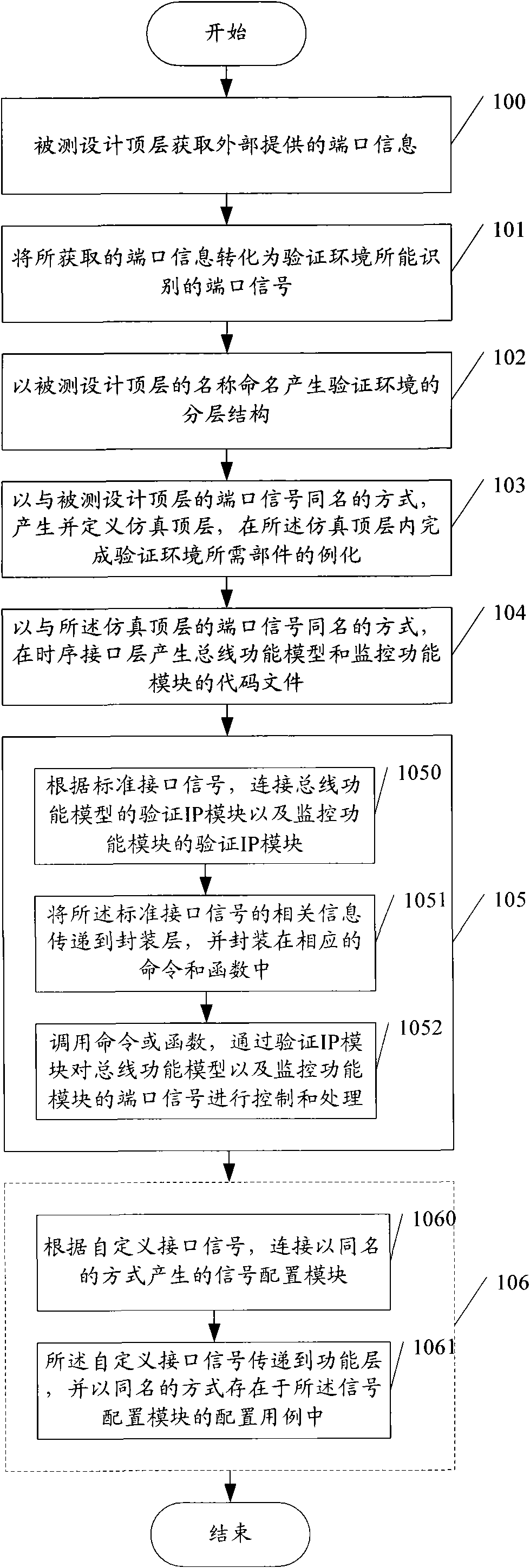

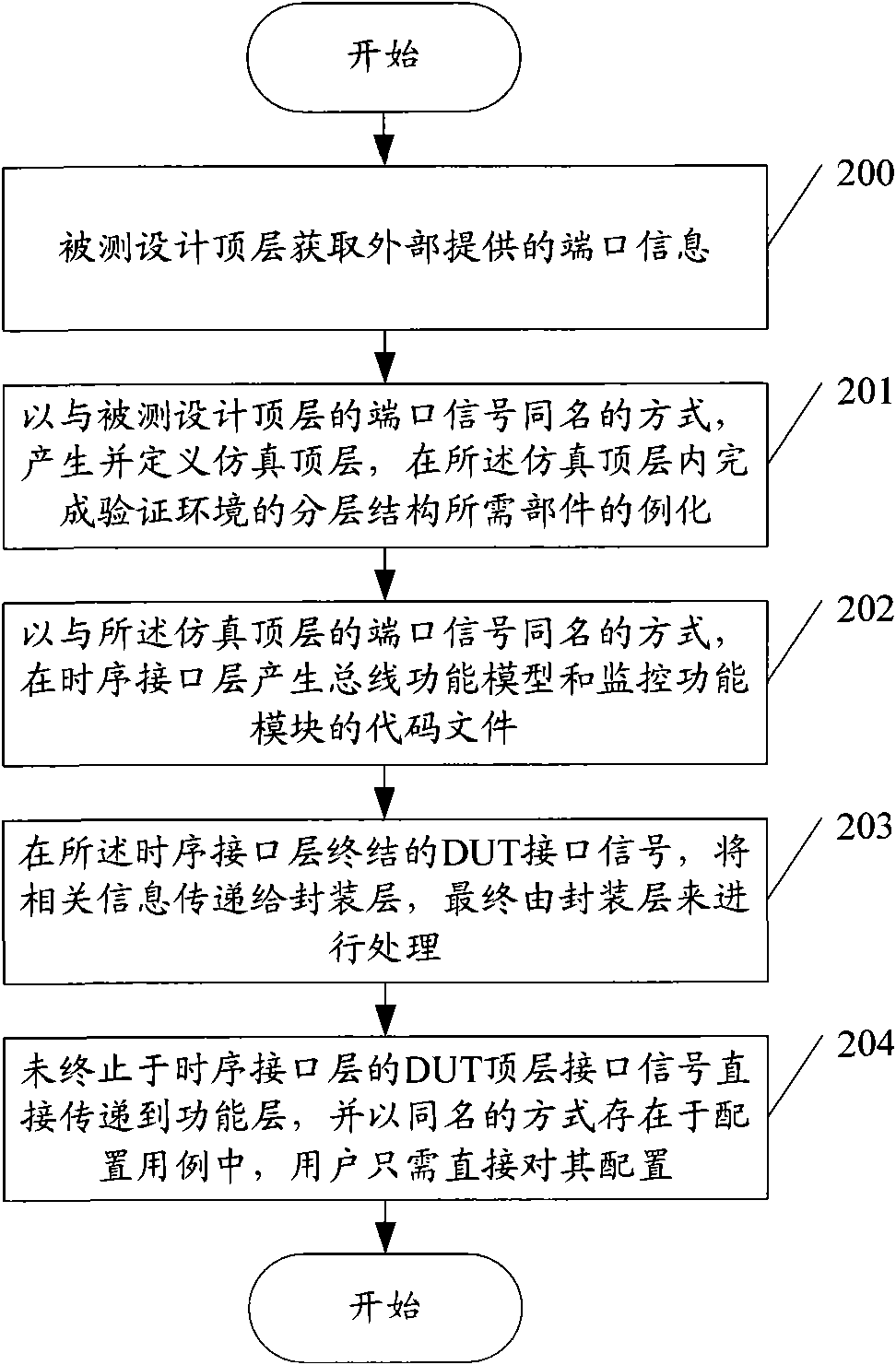

Verification environment system and construction method thereof

InactiveCN101625705AQuick buildEfficient reuseSpecial data processing applicationsEnvironmental systemsTest design

The embodiment of the invention discloses a verification environment system and a construction method thereof. The construction method of a verification environment comprises the following steps: acquiring port information required by the construction of the verification environment and generating a layered structure of the verification environment; and constructing, layer by layer, parts required by the layered structure of the verification environment in a direction opposite to configured data stream according to port signals from a tested designed top layer. The verification environment system and the construction method thereof can realize effective reuse and fast construction of the verification environment.

Owner:HUAWEI TECH CO LTD

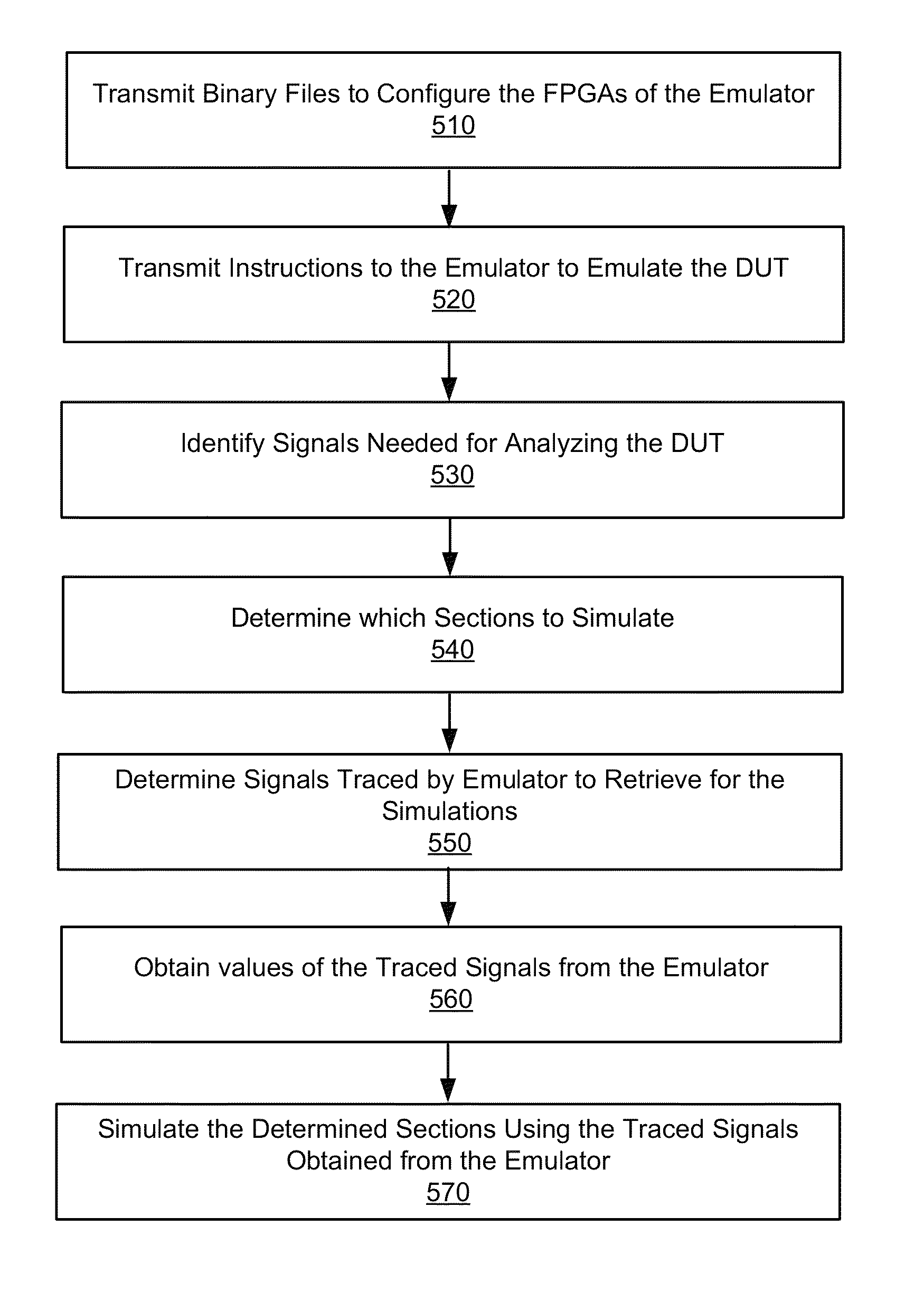

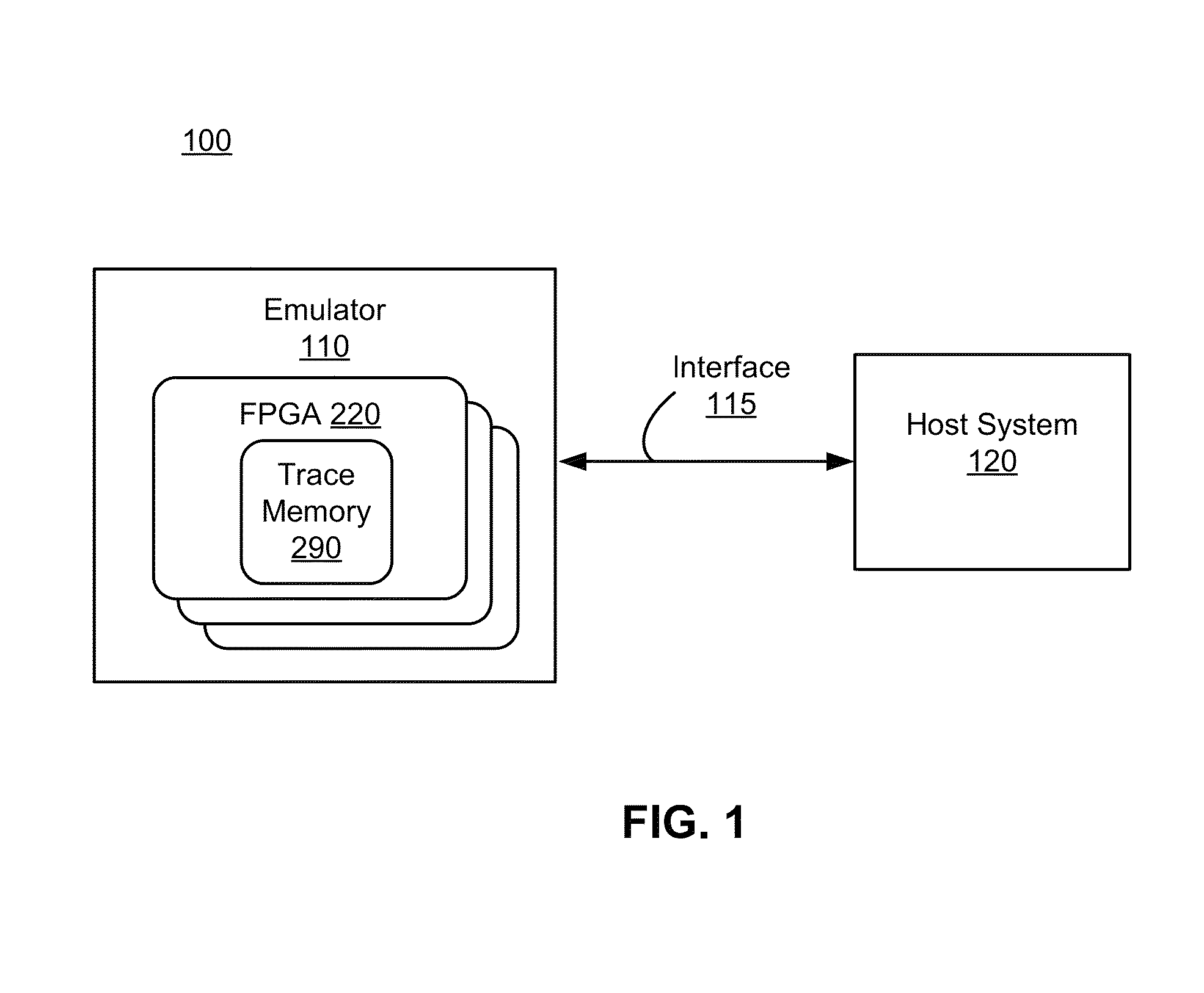

Efficient waveform generation for emulation

An emulation environment includes a host system and an emulator. The host system configures the emulator to emulate a design under test (DUT) and the emulator emulates the DUT accordingly. During emulation, the emulator traces limited signals of the DUT and stores values of the traced signals. When values of certain signals of the DUT are needed for analysis or verification of the DUT but the signals were not traced by the emulator, the host system simulates one or more sections of the DUT to obtain values of the signals. Signals traced by the emulator are used as inputs to simulate the one or more sections.

Owner:SYNOPSYS INC

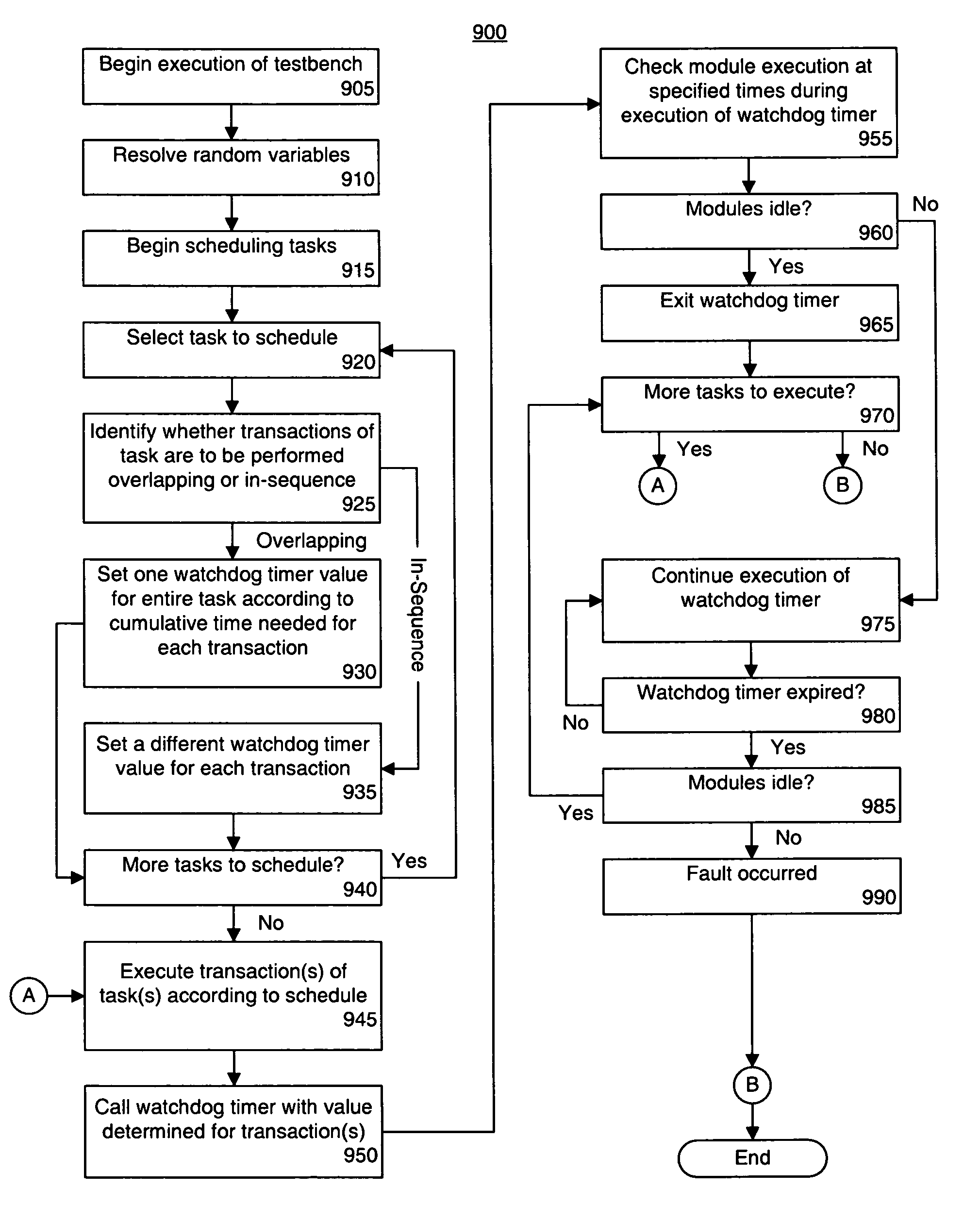

Dynamic timer for testbench interface synchronization

ActiveUS7797598B1Precise processElectronic circuit testingError detection/correctionTest platformTimer

A method of evaluating a design under test (DUT) can include executing a testbench involving the DUT and, during execution of the testbench, estimating an amount of time needed to perform a first transaction with the device under test according to resolved variables. The method also can include setting a timer with the estimated amount of time needed to perform the first transaction and invoking the first transaction with the device under test. Responsive to expiration of the timer, an indication as to whether the first transaction completed execution can be provided.

Owner:XILINX INC

System for Quickly Specifying Formal Verification Environments

ActiveUS20100185992A1Detecting faulty computer hardwareComputer programmed simultaneously with data introductionGraphicsGraphical user interface

Computer-implemented techniques are disclosed for defining an environment for formal verification of a design-under-test. Initially there is extraction of design inputs by a design analysis module, and presentation of the inputs on a graphical user interface. Behavior options for the design inputs are offered on the graphical user interface for selection by an operator. Environment code that is descriptive of the design inputs and selected behavior options is emitted, typically in a hardware description language, for submission to a formal verification tool. A meta-code file containing the assigned behavior options is generated to aid subsequent sessions.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

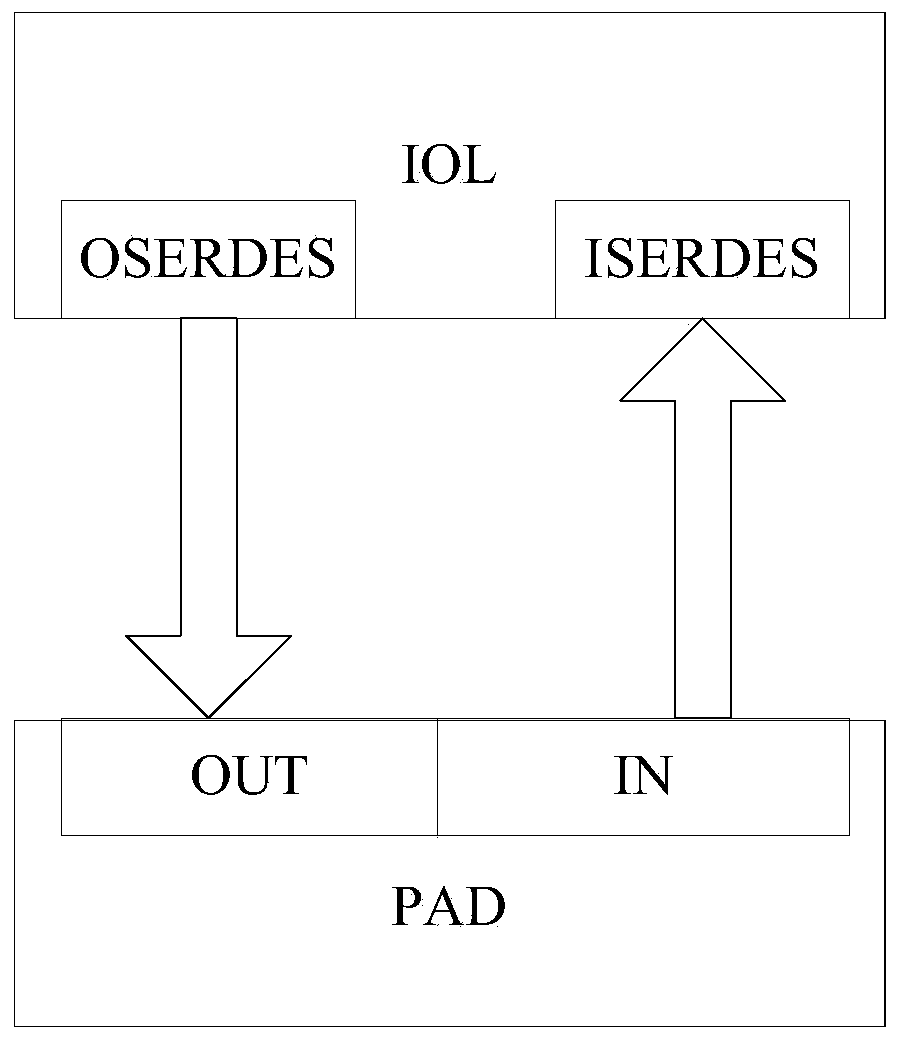

Built-in self-test method and system of FPGA input and output logic module

InactiveCN110308381ALower requirementReduce testing costsDigital circuit testingTest designData path

The invention provides a built-in self-test method and system of an FPGA input and output logic module. A PAD of an FPGA is configured, so that ISERDES and OSERDES belonging to the same IOL are communicated with the external of the FPGA, a serial data path is formed, the IOL can transfer data in a round trip way from a TX port to an RX port, and further the ISERDES and OSERDES are tested simultaneously by using a test vector generated by an excitation generator. At least one of first and second collection modules can be processed in a delayed way, and thus, the test scheme is highly repetitive; and a result analysis module can finally determine whether a tested design has a fault, so that requirements for external test equipment is low, and the test cost is reduced.

Owner:SHENZHEN PANGO MICROSYST CO LTD

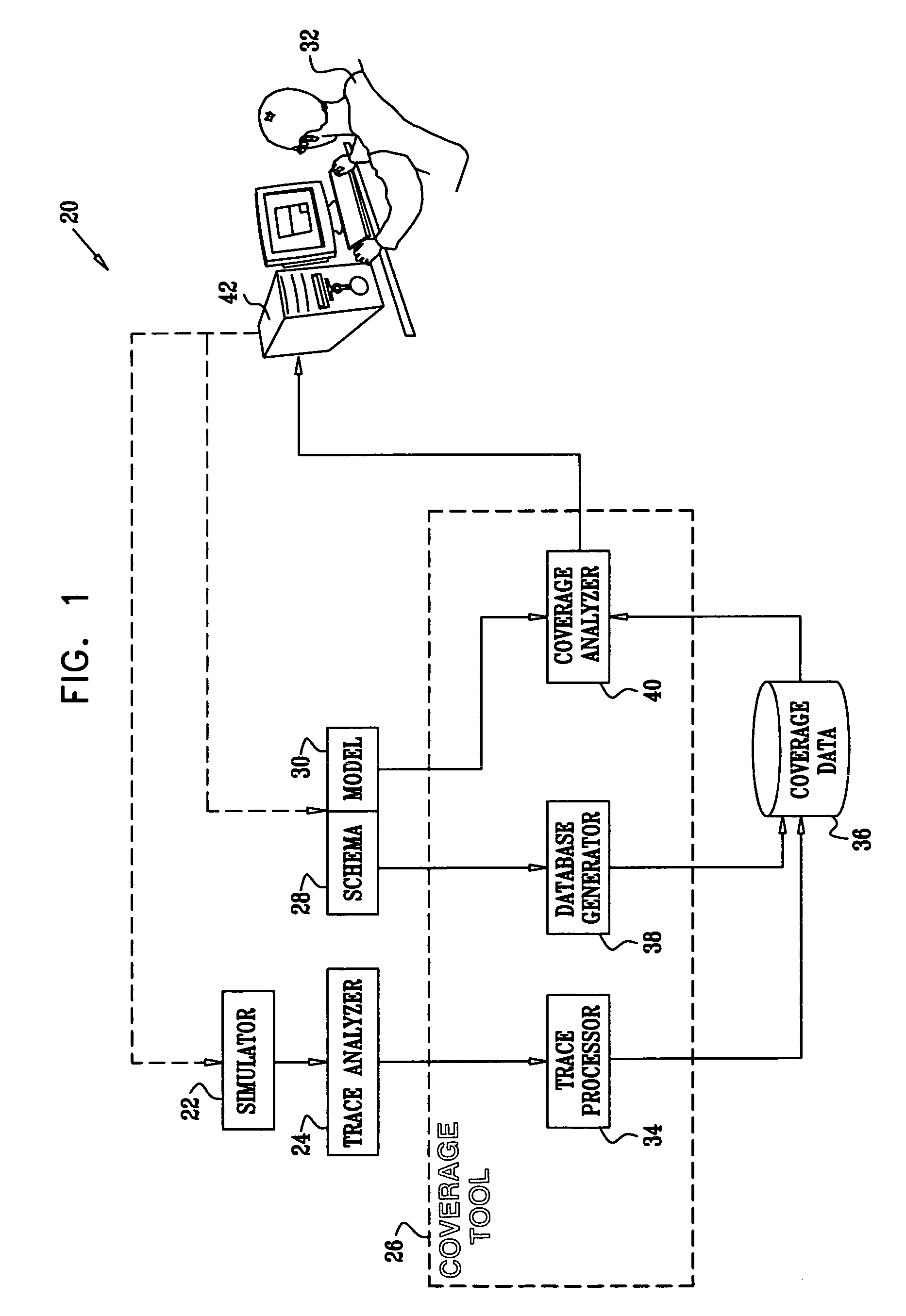

Method and apparatus for measuring test coverage

InactiveUS7308658B2Detecting faulty computer hardwareElectrical testingData processing systemMeasurement test

Owner:NORTH STAR INNOVATIONS

Development and debug environment in a constrained random verification

ActiveUS9202005B2Design optimisation/simulationSpecial data processing applicationsRestricted randomizationTest stimulus

Owner:SYNOPSYS INC

Efficient Waveform Generation for Emulation

ActiveUS20160328499A1Error detection/correctionDesign optimisation/simulationDesign under testSignal trace

An emulation environment includes a host system and an emulator. The host system configures the emulator to emulate a design under test (DUT) and the emulator emulates the DUT accordingly. During emulation, the emulator traces limited signals of the DUT and stores values of the traced signals. When values of certain signals of the DUT are needed for analysis or verification of the DUT but the signals were not traced by the emulator, the host system simulates one or more sections of the DUT to obtain values of the signals. Signals traced by the emulator are used as inputs to simulate the one or more sections.

Owner:SYNOPSYS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com