Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

71 results about "Hardware simulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for processing hidden process based on hardware simulator

InactiveCN101770551ATransparent analysisEnsure transparencyPlatform integrity maintainanceSoftware simulation/interpretation/emulationVirtual memoryData acquisition

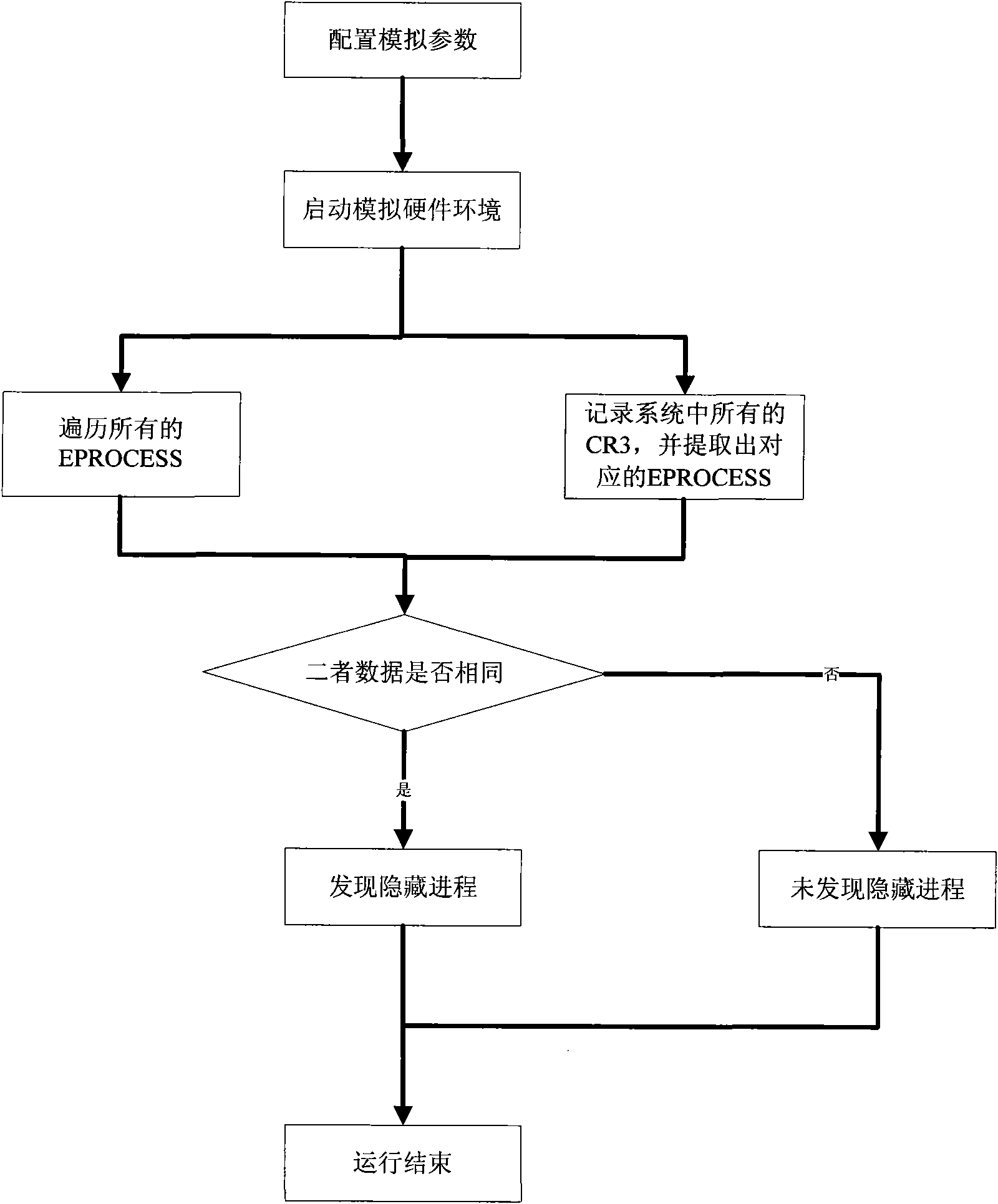

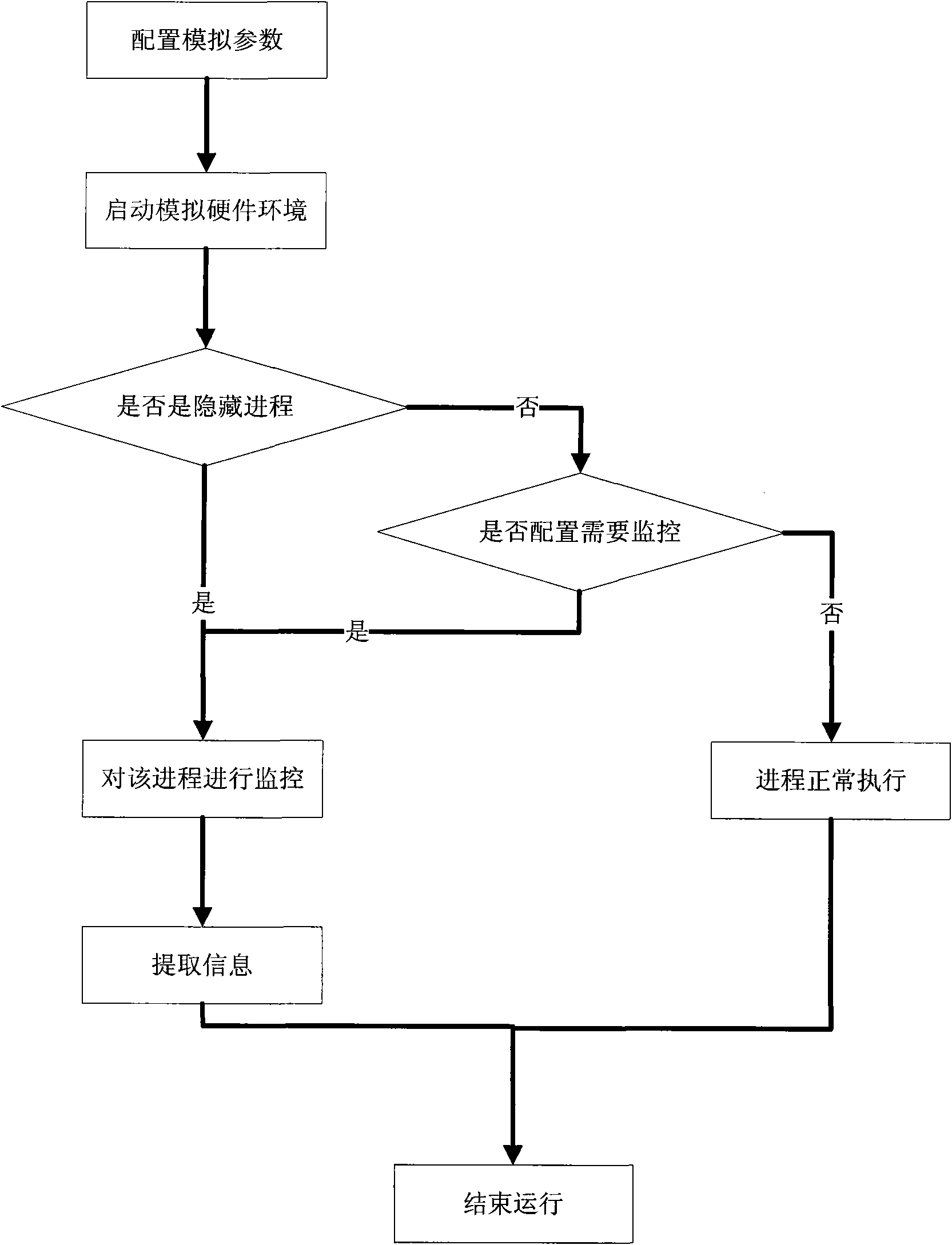

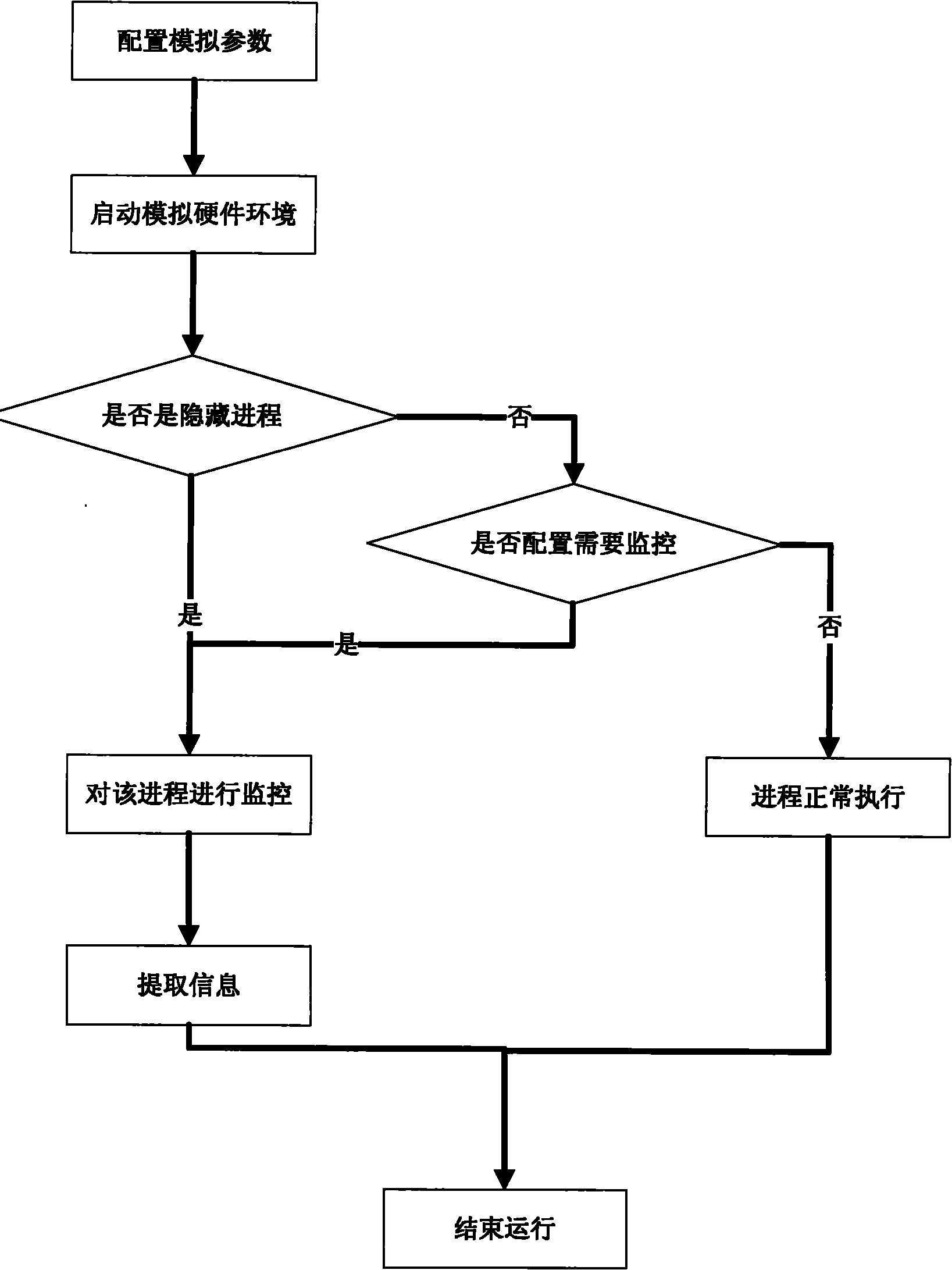

The invention belongs to the technical field of network security and particularly relates to a method for processing a hidden process based on a hardware simulator. By establishing a running environment of malicious codes in hidden codes in a hardware simulating environment and operating and controlling instructions simulating a CPU and various accessing operations simulating a memory, marked by a CR3 value in a CR3 register, the hidden process is detected, the running process of the hidden process is monitored, and the running information of the malicious codes in the hidden process is recorded by a data acquisition module; and the invention also provides a mirror image which extracts the malicious codes directly from a virtual memory. All instructions of a virtual CPU and various hardware operations of a hardware simulating device are executed in simulation after translation and are not executed in a real machine by using code segments directly, and the running time of the instruction in the instruction running process can be accurately calculated, thus realizing fully transparent analysis of the malicious codes in the hidden process.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

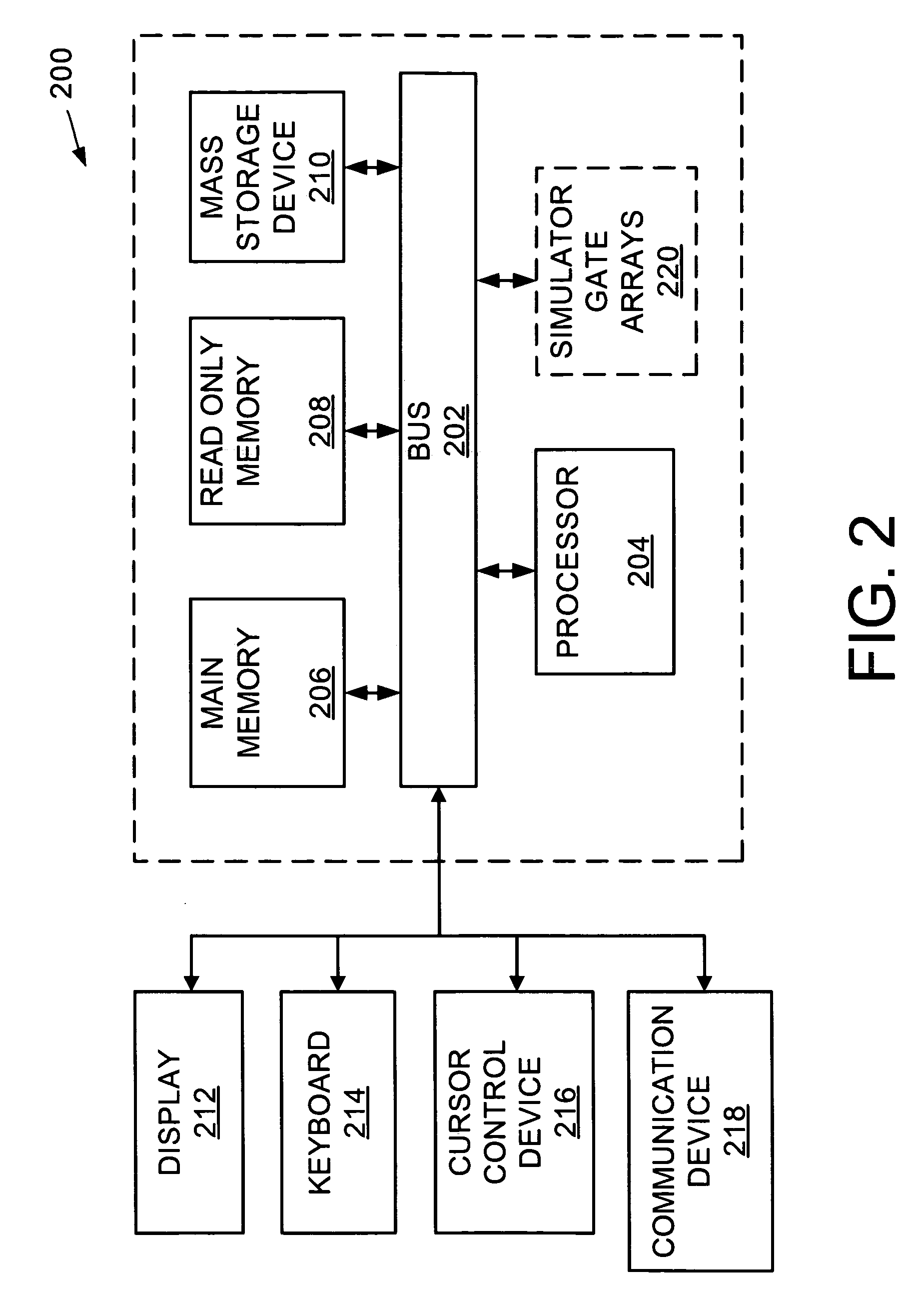

System and method for improved software simulation using a plurality of simulator checkpoints

InactiveUS20060155525A1CAD circuit designSoftware simulation/interpretation/emulationSoftware emulationParallel computing

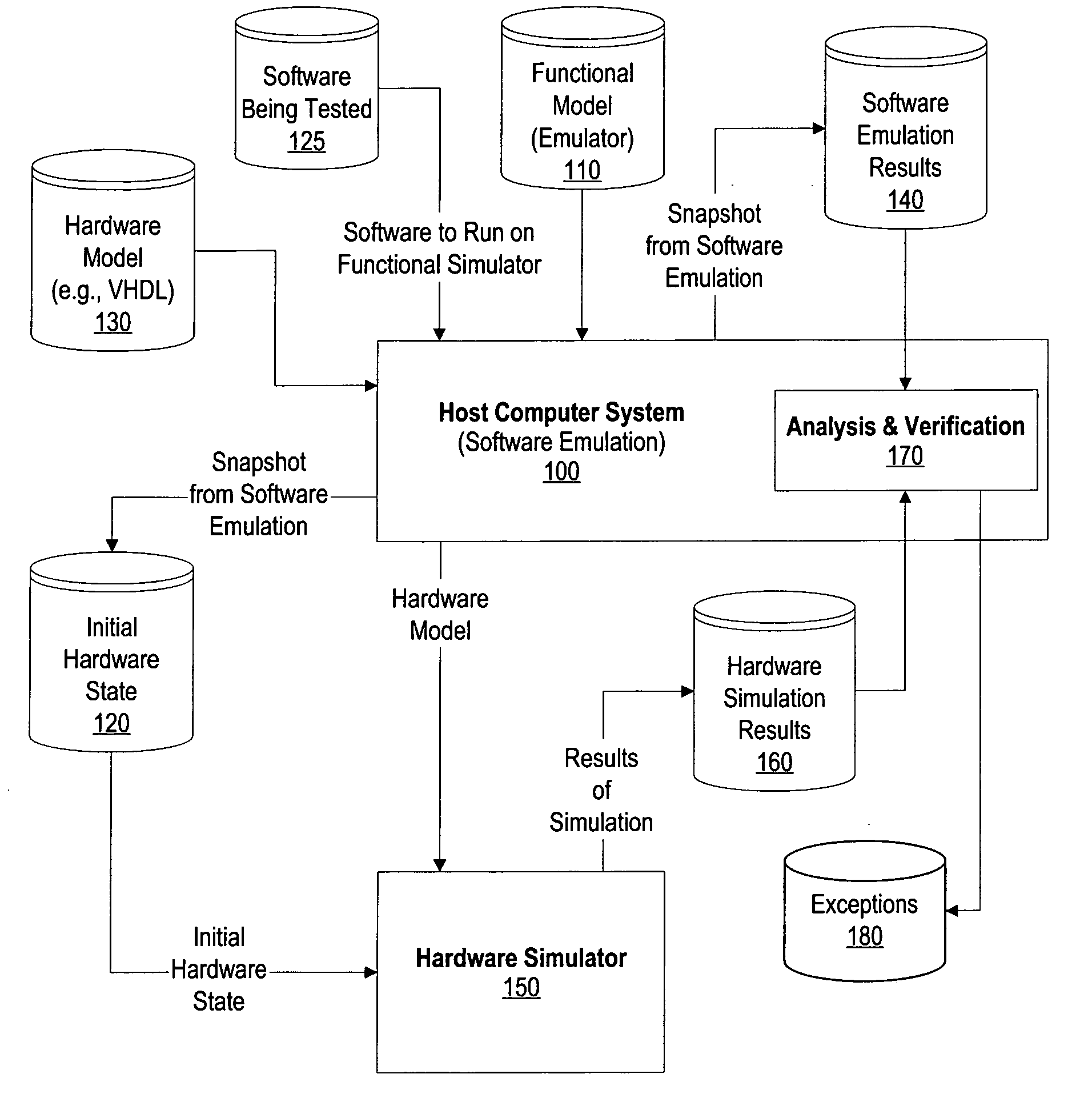

A system and method is provided to improve software simulation. A software emulator is used in conjunction with a hardware simulator. A special snapshot instruction is included in the software code that is emulated. When the snapshot instruction is encountered, values such as register, memory, and program stack values, are stored creating an initial snapshot. Code continues to be emulated and, when the next snapshot instruction is encountered, the values are written to create a second snapshot. The initial values are used to set an initial state in a hardware model that is simulated on a hardware simulator. The results of the hardware simulation are compared to the second snapshot to uncover software errors and / or hardware errors so that the software can be modified or the hardware design can be modified. Multiple sets of snapshots can be taken to analyze multiple sections of the software program.

Owner:IBM CORP

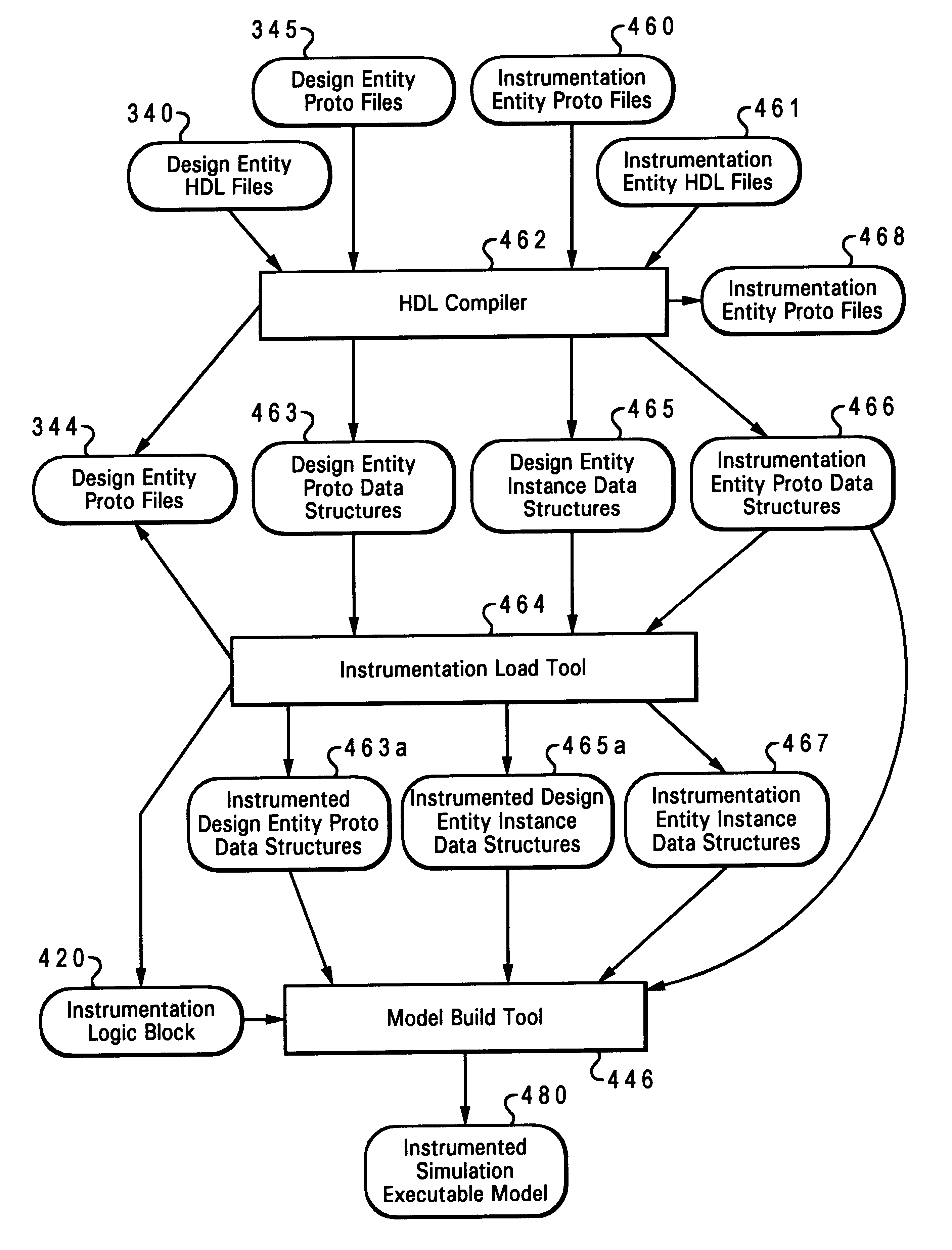

Hardware simulator instrumentation

InactiveUS6202042B1Complex designEasy to instrumentCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHardware simulator

A method and system are disclosed that utilize the expressiveness of hardware description languages for providing comprehensive runtime monitoring during hardware accelerated simulation of a digital circuit design. According to the present invention a design entity forming part of a digital circuit design that will be translated and assembled into a simulation executable model, is described utilizing a hardware description language. Next, an instrumentation entity designed to send a failure signal in response to detecting an occurrence of a failure event within the simulation executable model is described utilizing the same hardware description language. Thereafter, a simulation test is initiated on the simulation executable model utilizing a hardware simulator. Finally, during the simulation test, and in response to receiving a failure signal from the instrumentation entity, the simulation test is terminated such that the failure event may be efficiently identified and diagnosed.

Owner:IBM CORP

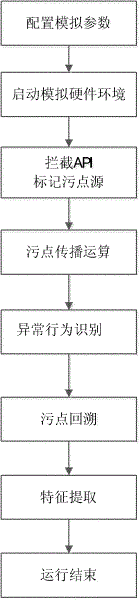

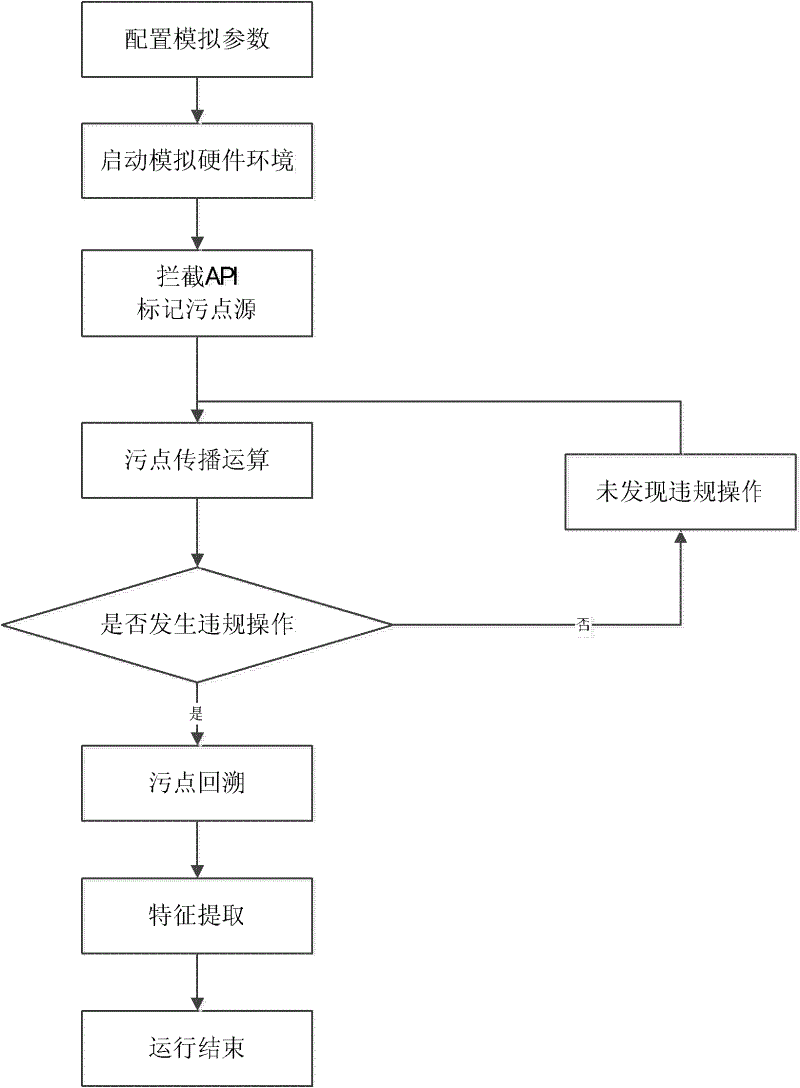

Method for catching malicious codes

ActiveCN102622536ATransparent analysisEnsure transparencyPlatform integrity maintainanceInternal memoryVirtual memory

The invention discloses a method for catching malicious codes, which belongs to the technical field of network safety. The method comprises the steps of (1) configuring a hardware simulator and loading and starting a target operating system; (2) enabling the hardware simulator to read virtual memory of the target operating system, identifying all courses and an export table in a dynamic library loaded by the courses and obtaining all application program interface (API) addresses in the export table and intercepting network received API functions; (3) marking network received data packages of the courses into stain data packages; (4) enabling the hardware simulator to disassemble commands executed by current courses and calculating stain spread; and (5) judging whether current curse states in the stain spread process produce abnormal behaviors, confirming the current curses as the malicious codes if the abnormal behaviors are produced and extracting mirror images of the malicious codes from an internal memory of the target operating system. The method for catching the malicious codes achieves fully transparent analysis of the malicious codes and has high efficiency and accuracy.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

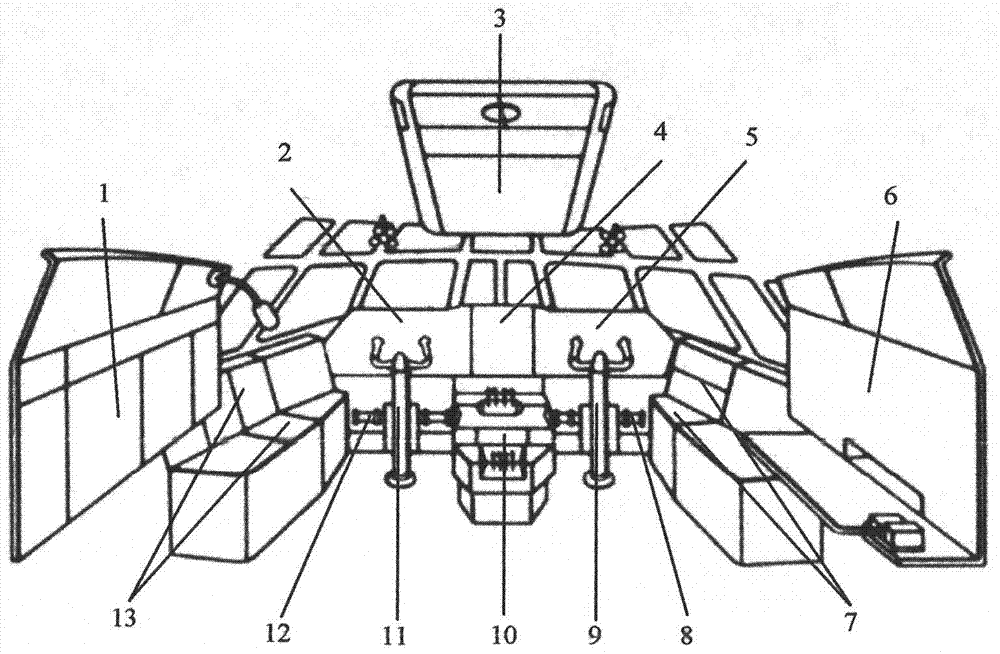

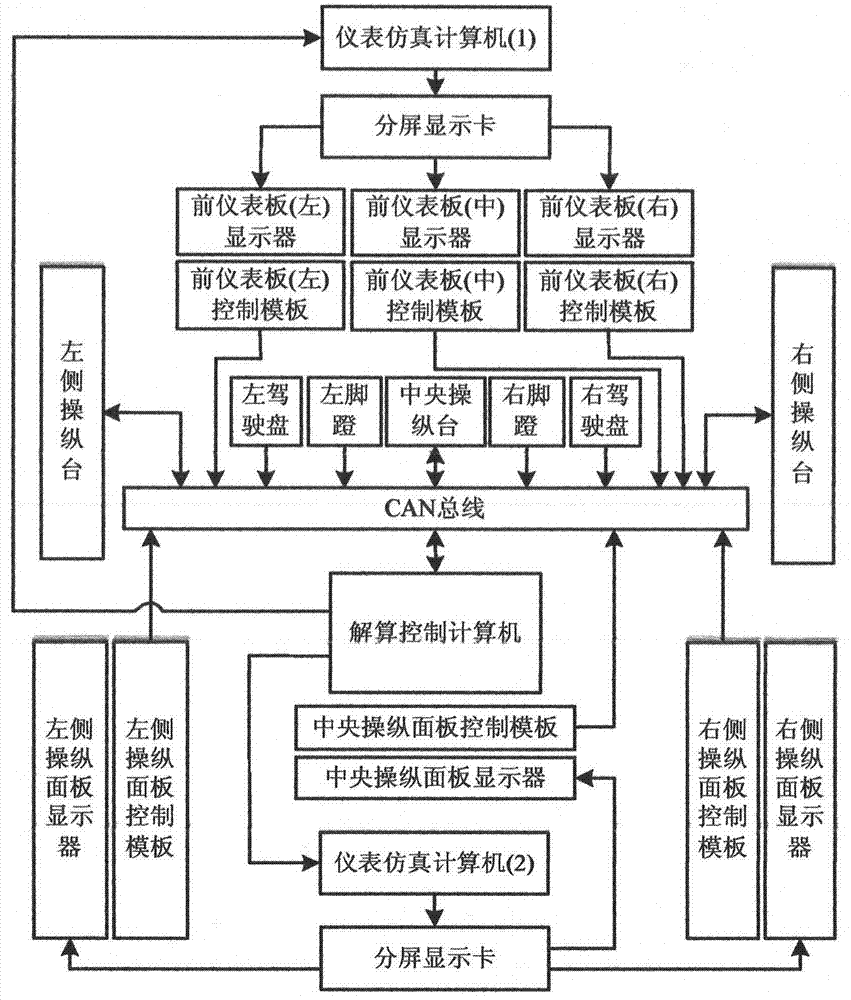

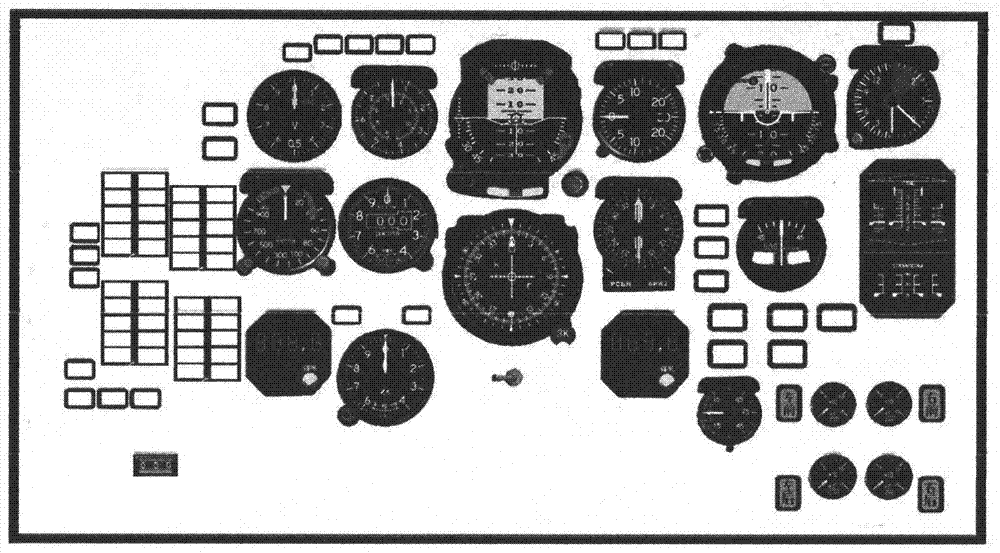

Low-cost flight simulator cabin display and control system

InactiveCN104269083ALow costEasy maintenanceCosmonautic condition simulationsSimulatorsControl systemControl signal

The invention discloses a low-cost flight simulator cabin display and control system which is a combined training simulator cabin display and control system used for large aircraft air-service and ground-service personal training. The low-cost flight simulator cabin display and control system is an interface for transmitting information between an operator and a flight simulator, is composed of a display part and a control part and is composed of a simulated cabin, control mechanisms, a resolving control computer, an instrument emulation computer, displayers and control templates. The displayers display instruments and various control signals, the control templates with integrated control knobs and switches are installed outside the displayers for achieving man-machine interaction, the control templates and the displayers are assembled according to the proportions of a true aircraft, and the simulated cabin is built. According to the low-cost flight simulator cabin display and control system, the method that the virtual instruments and the control templates are combined is used; compared with a full-hardware simulator based on solid instruments, the device structure of the simulator is simplified, the development cost is reduced, the development cycle is shortened, and the design change efficiency of the system is improved; meanwhile, the problem that the man-machine interaction fidelity of a virtual display and control system based on the touch technology is not high can be solved.

Owner:JINLIN MEDICAL COLLEGE

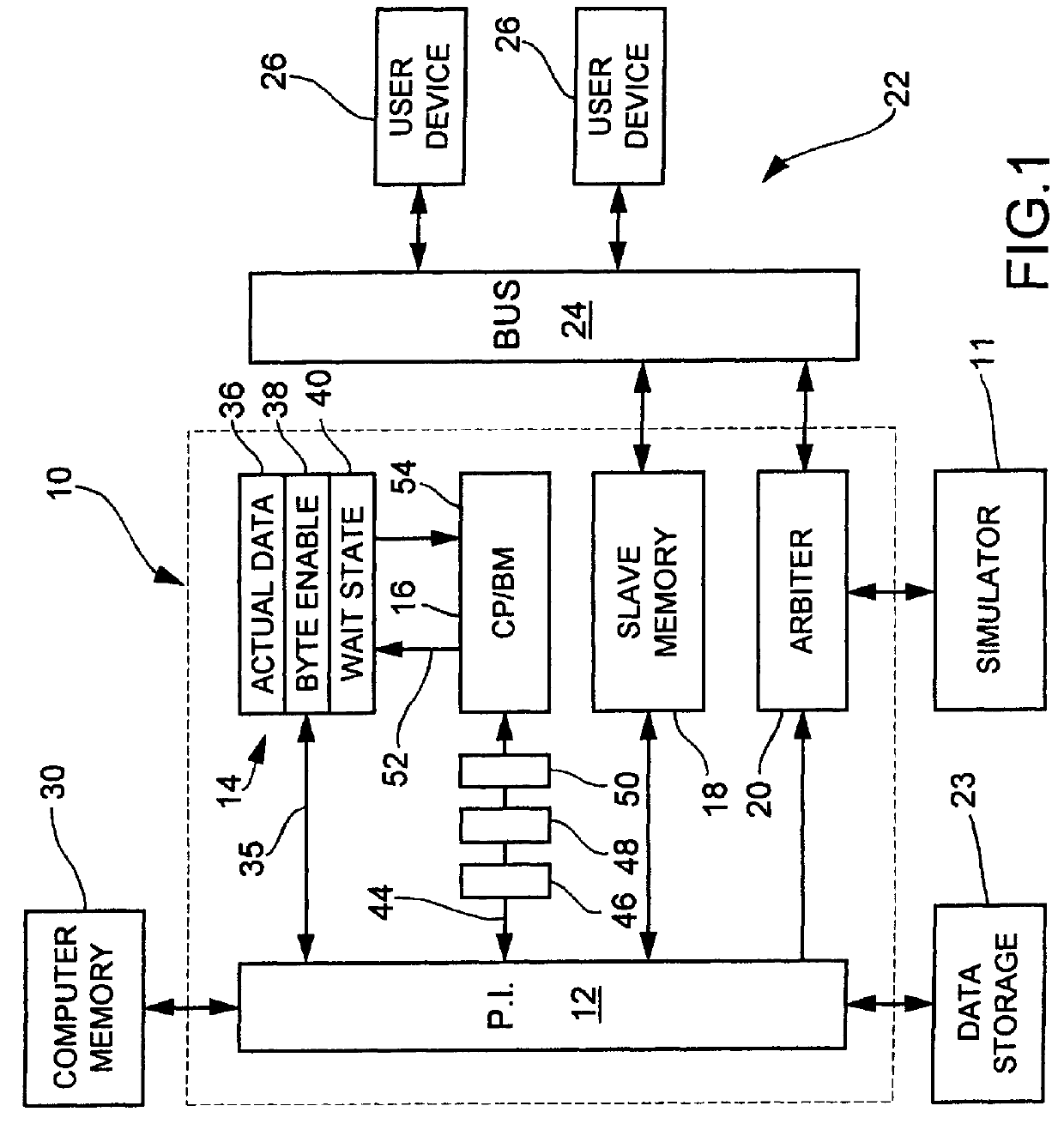

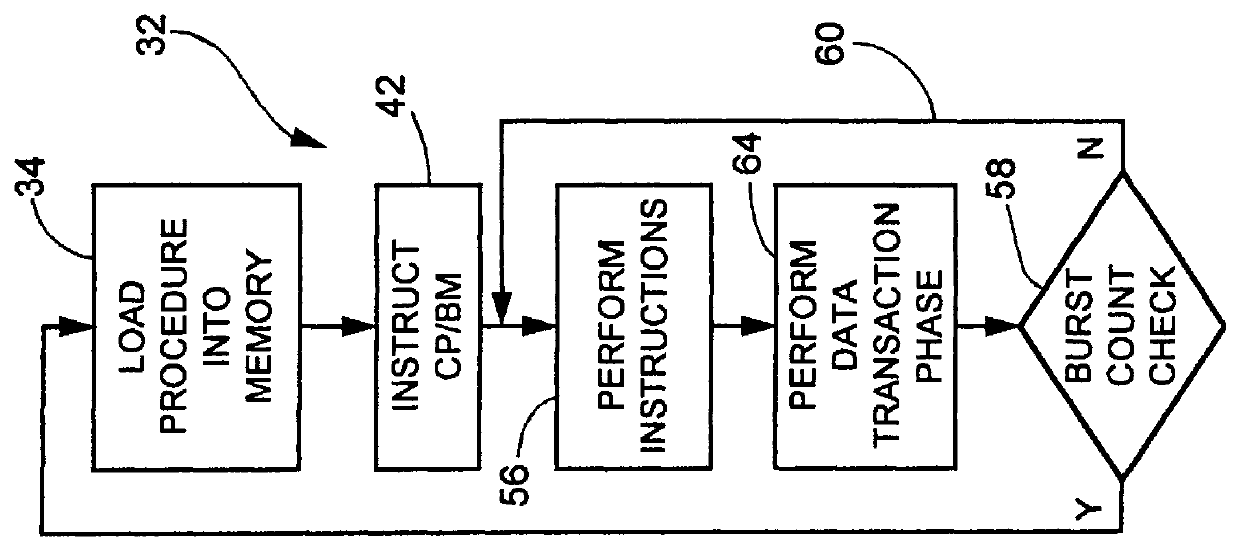

Method for simulating bus traffic

InactiveUS6123735ATest speed is optimizedMinimize development timeFunctional testingCAD circuit designUser deviceHardware simulator

A dynamic hardware emulation model (10) to be used with a hardware simulator for testing a user device (26) under test. A programming interface (12) controls a memory pool (14) and a command processor / bus manager (16) such that a command cycle is initiated to read and write data through a computer bus (24), to and from the user device (26). The programming interface (12) and the user device (26) can act in a master or slave mode. When the user device (26) is in slave mode, a slave memory (18) contains expected data for comparison purposes, and an arbiter (20) determines which device will have access to the computer bus (24).

Owner:SYNOPSYS INC

System and method of automating the addition of programmable breakpoint hardware to design models

InactiveUS20070005323A1Maximize simulator performanceFlexibilityDigital circuit testingCAD circuit designState variationHardware simulator

Hardware logic for generating breakpoint signals based on state changes in observed (“tagged”) hardware resource of a design under test is automatically generated and added to the simulation model of the design under test. These breakpoints halt simulation when a user programmable event, such as an assertion, test-case failure, or trigger occurs. Allowing the end-user to define the register values used in comparison to or timing of tagged resources, results in breakpoints that can be created, changed, enabled, or disabled without rebuilding the simulation model. Because the breakpoint logic is in-circuit, it takes full advantage of the acceleration made possible by hardware simulators, while providing an interactive environment for both functional hardware verification and software development on the simulated hardware mode.

Owner:IBM CORP

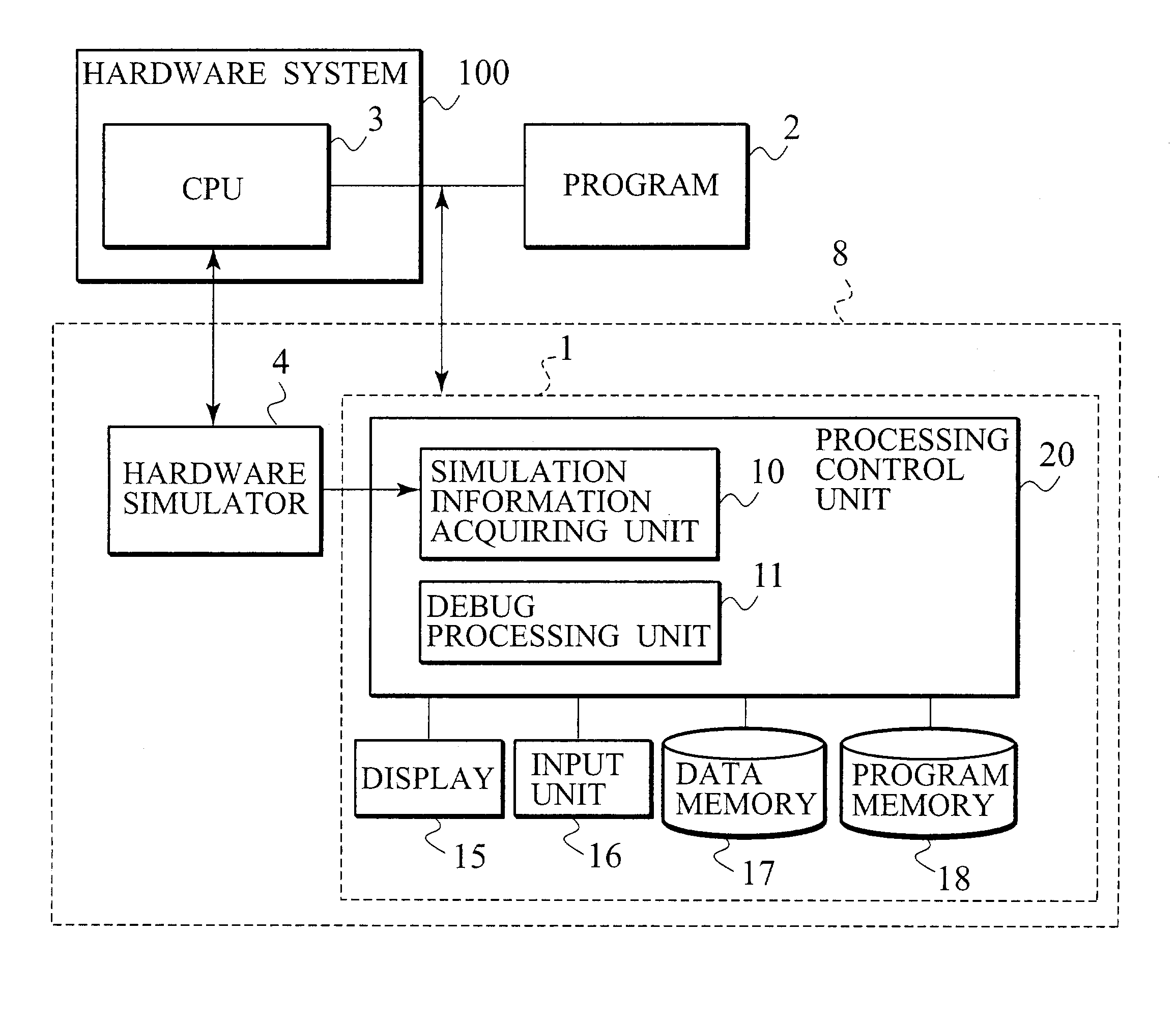

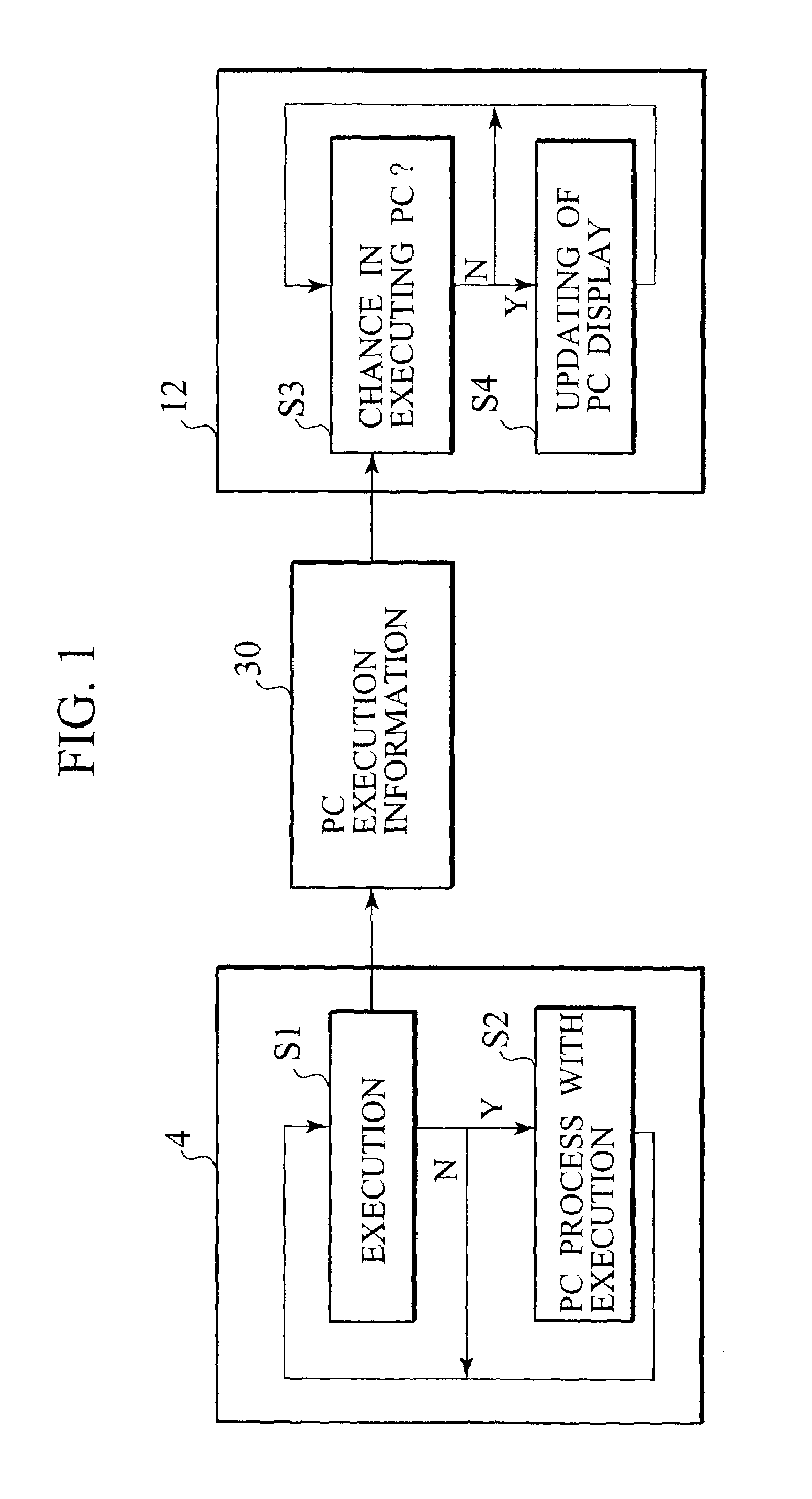

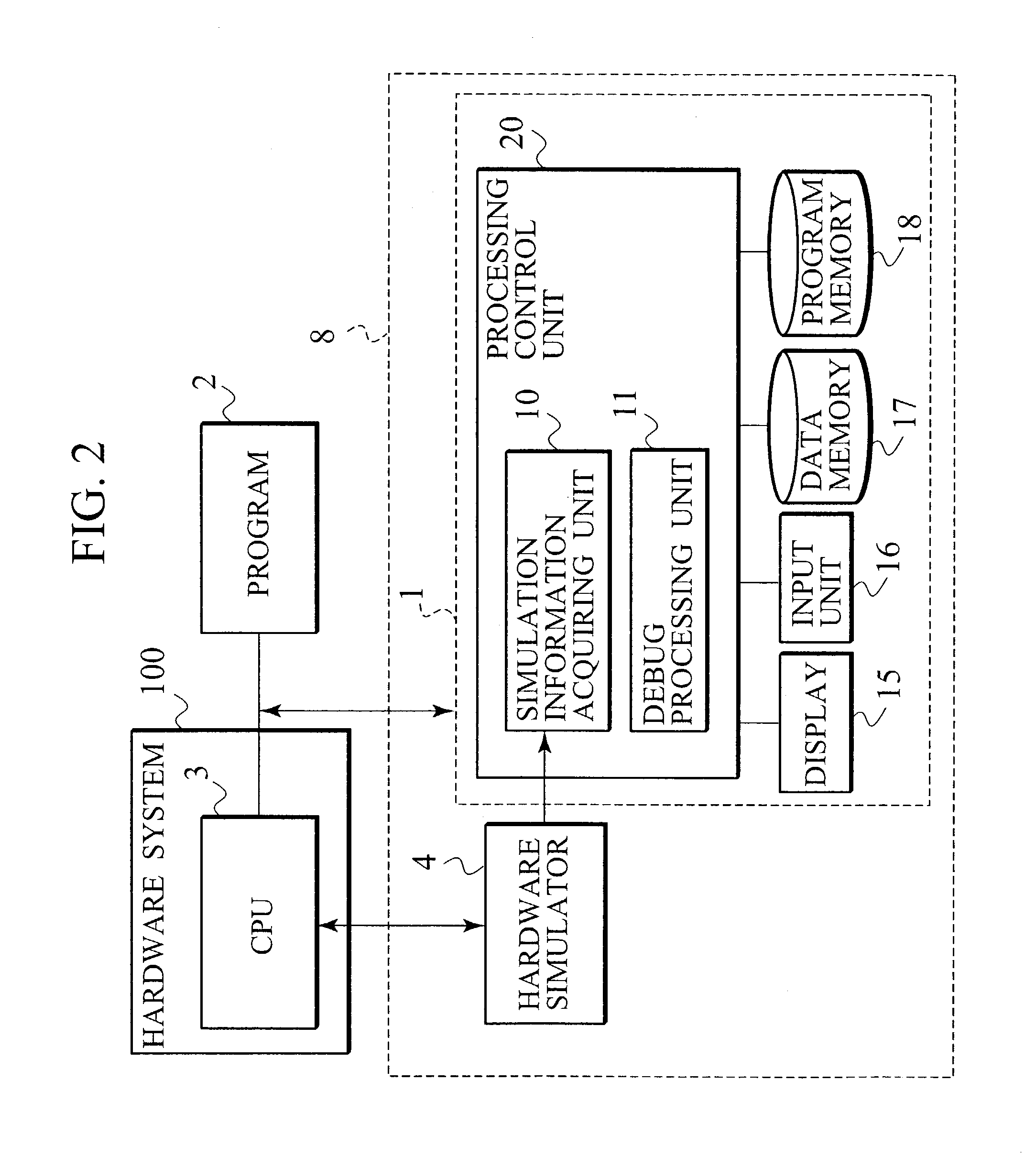

Debugging Method

InactiveUS7093165B2Concurrent instruction executionSoftware testing/debuggingParallel computingHardware simulator

A software debugger adapted for connection to a hardware simulator simulating a hardware system includes a simulation information acquiring unit for acquiring cycle level execution information from the hardware simulator, and a debug processing unit for executing debugging by setting a processing width for time of one step execution instruction during debugging of a program executed on the hardware system based on the cycle level execution information.

Owner:KK TOSHIBA

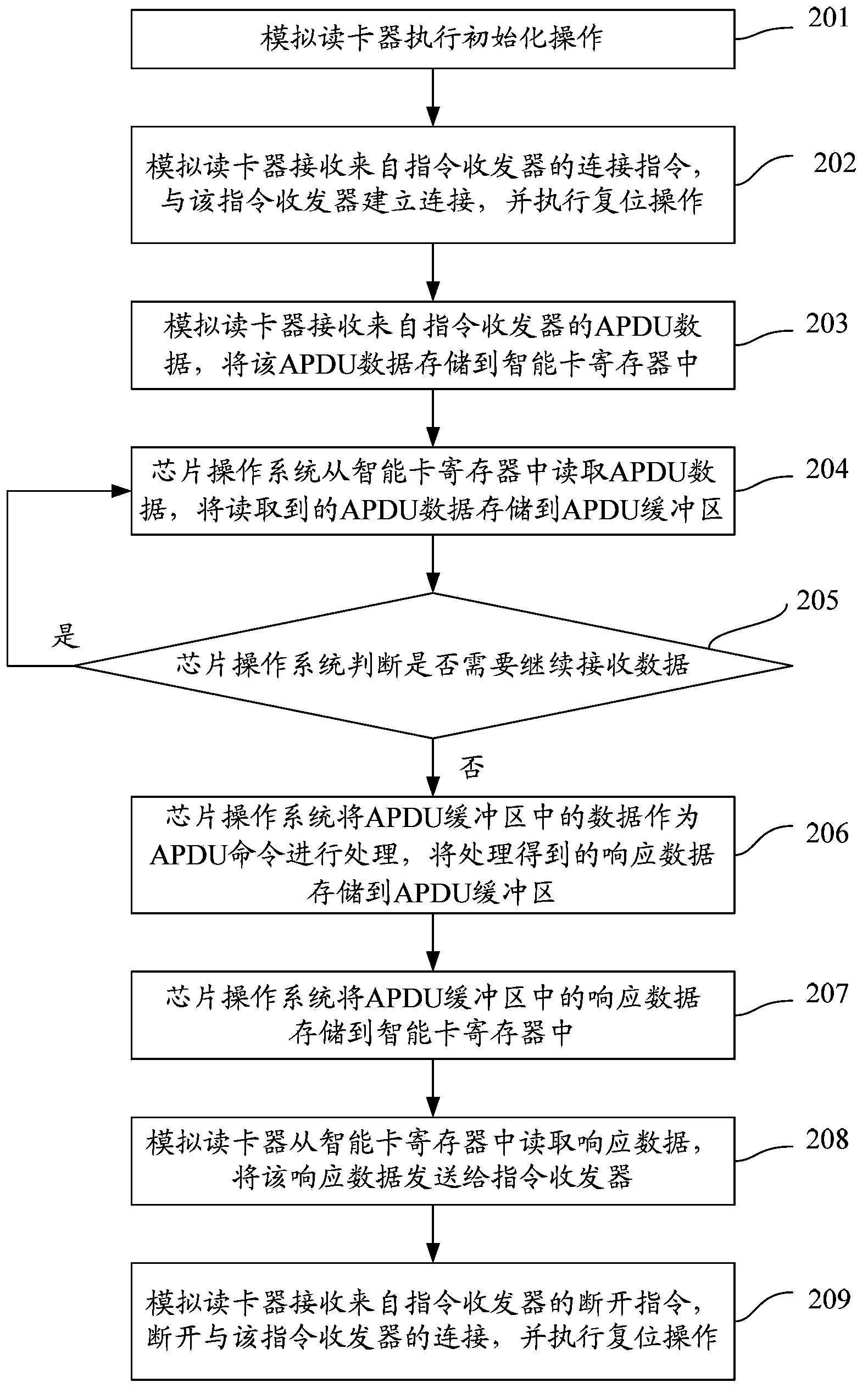

Work method of analog card reader and analog communication system

ActiveCN103365701ASave resourcesReduce Simulation Power ConsumptionSoftware testing/debuggingSoftware simulation/interpretation/emulationTransceiverChip operating system

The invention discloses a work method of an analog card reader and an analog communication system. The method is applied to a system comprising the analog card reader, a chip operating system, an instruction transceiver and a smart card register, wherein the analog card reader is used for detecting the communication state between the analog card reader and the instruction transceiver, and the state of the smart card register, conducting read-write operation on the smart card register according to the communication state and the state of the smart card register, and updating the state of the smart card register; the chip operating system is used for detecting the state of the smart card register, conducting read-write operation on the smart card register according to the detected result, and updating the state of the smart card register. As the analog communication between the chip operating system and the instruction transceiver is established through the analog card reader, the purpose of inputting terminal data to the chip operating system under the condition that no hardware simulator is used is realized, the emulation function range is broadened, hardware resource is saved, and emulation power consumption is reduced.

Owner:FEITIAN TECHNOLOGIES

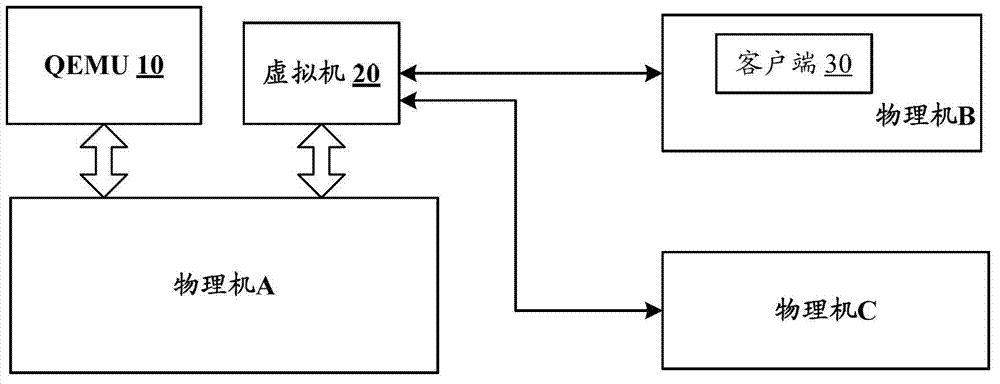

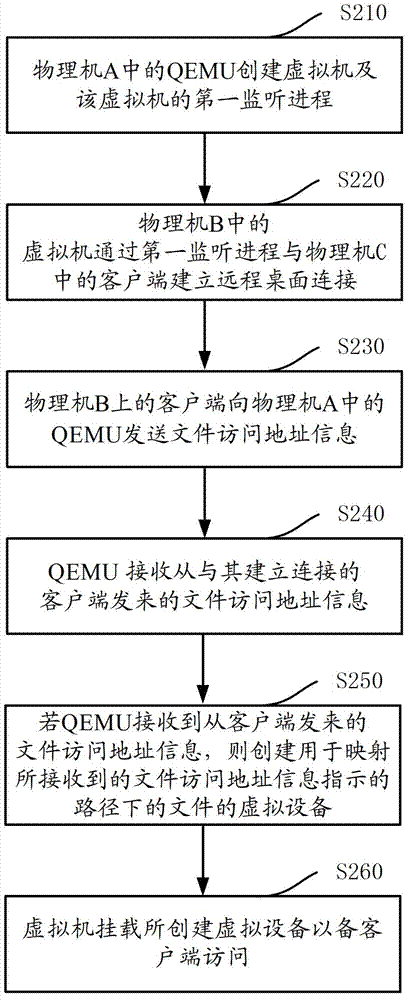

Virtual machine management system and file access method

ActiveCN102968331ASolve the technical problem that the remote virtual machine cannot access the files on the specified physical machine local to the remote virtual machineEasy accessTransmissionSoftware simulation/interpretation/emulationAccess methodRemote desktop

The invention discloses a virtual machine management system and a file access method. The method comprises the following steps: a creating step, a connection establishing step, a receiving step and an equipment creating step, wherein in the creating step, a virtual machine and a first monitoring progress of the virtual machine are created through a virtual machine hardware simulator; in the connection establishing step, remote desktop connection is established between the virtual machine hardware simulator and a client through the first monitoring progress; in the receiving step, the virtual machine hardware simulator receives file access address information transmitted from the client established connection with the virtual machine; the file access address information comprises a designated physical machine address and an access path; in the equipment establishing step, if the virtual machine hardware simulator receives the file access address information transmitted by the client established connection with the virtual machine, the virtual machine hardware simulator created virtual equipment for accessing a file under the path designated by the received file access address information; and the created virtual equipment is mounted on the virtual machine for the client to access. Through the adoption of the virtual machine management system and the file access method disclosed by the invention, users can access files in any designated physical machine through remote virtual machines.

Owner:CHINA STANDARD SOFTWARE

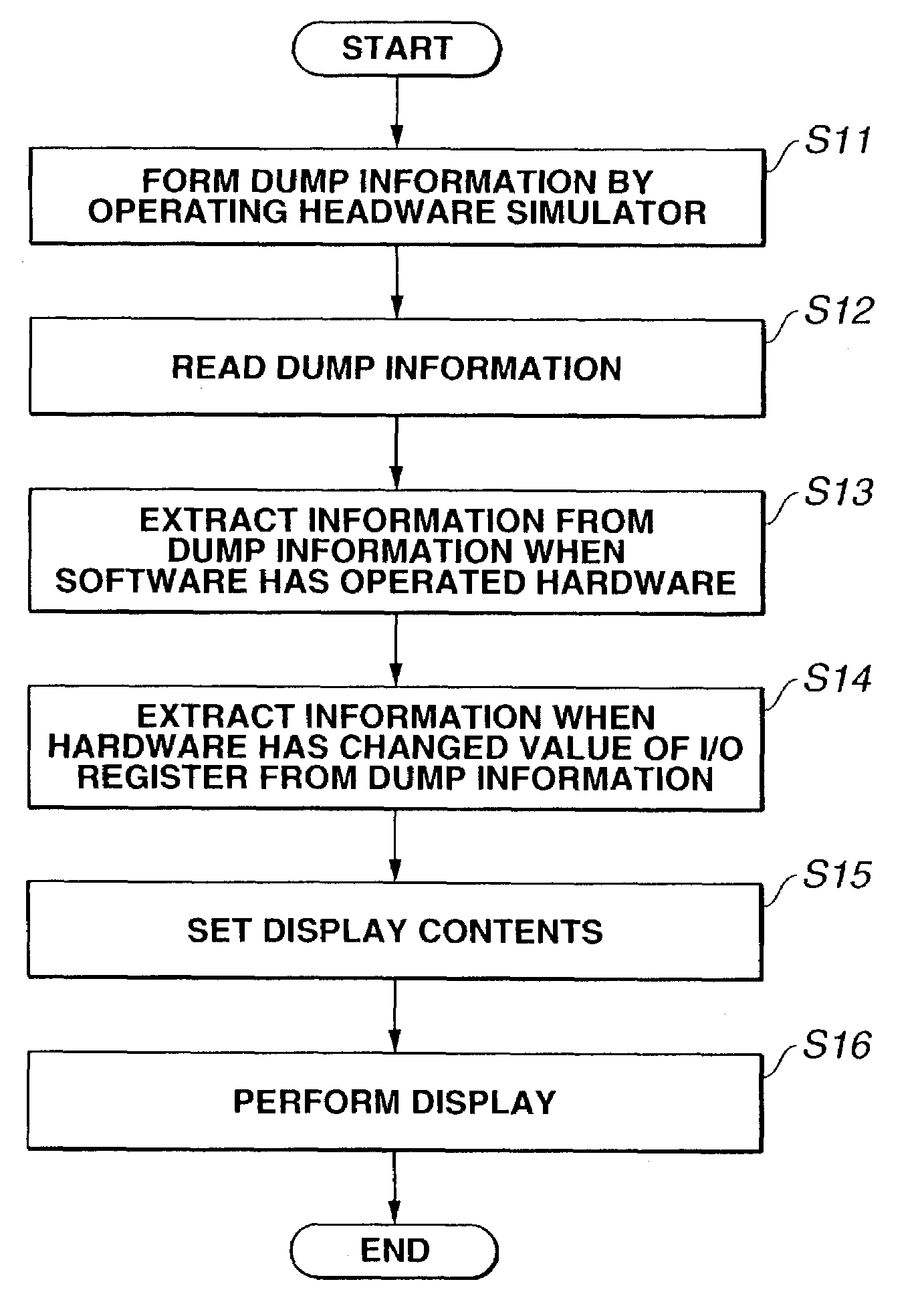

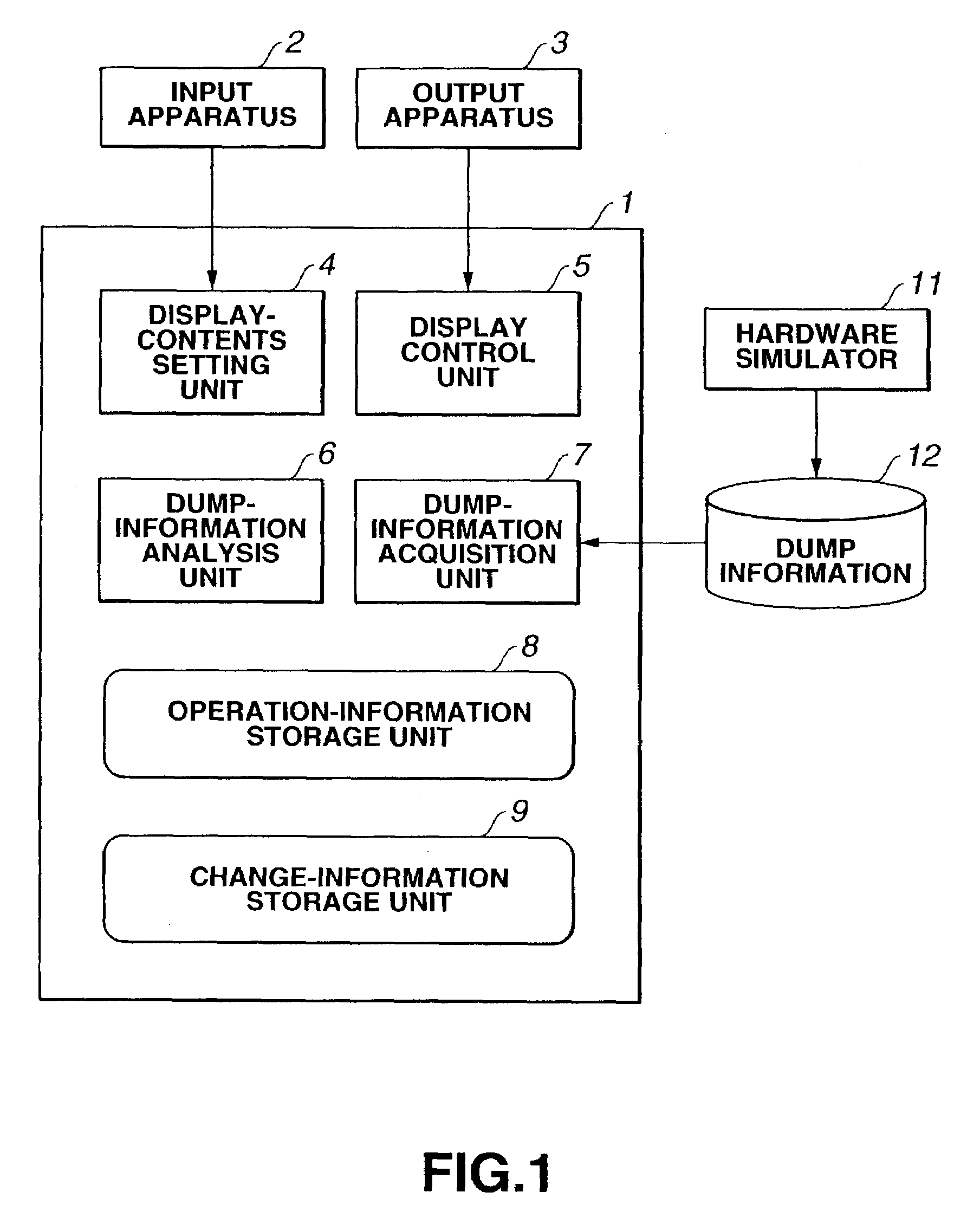

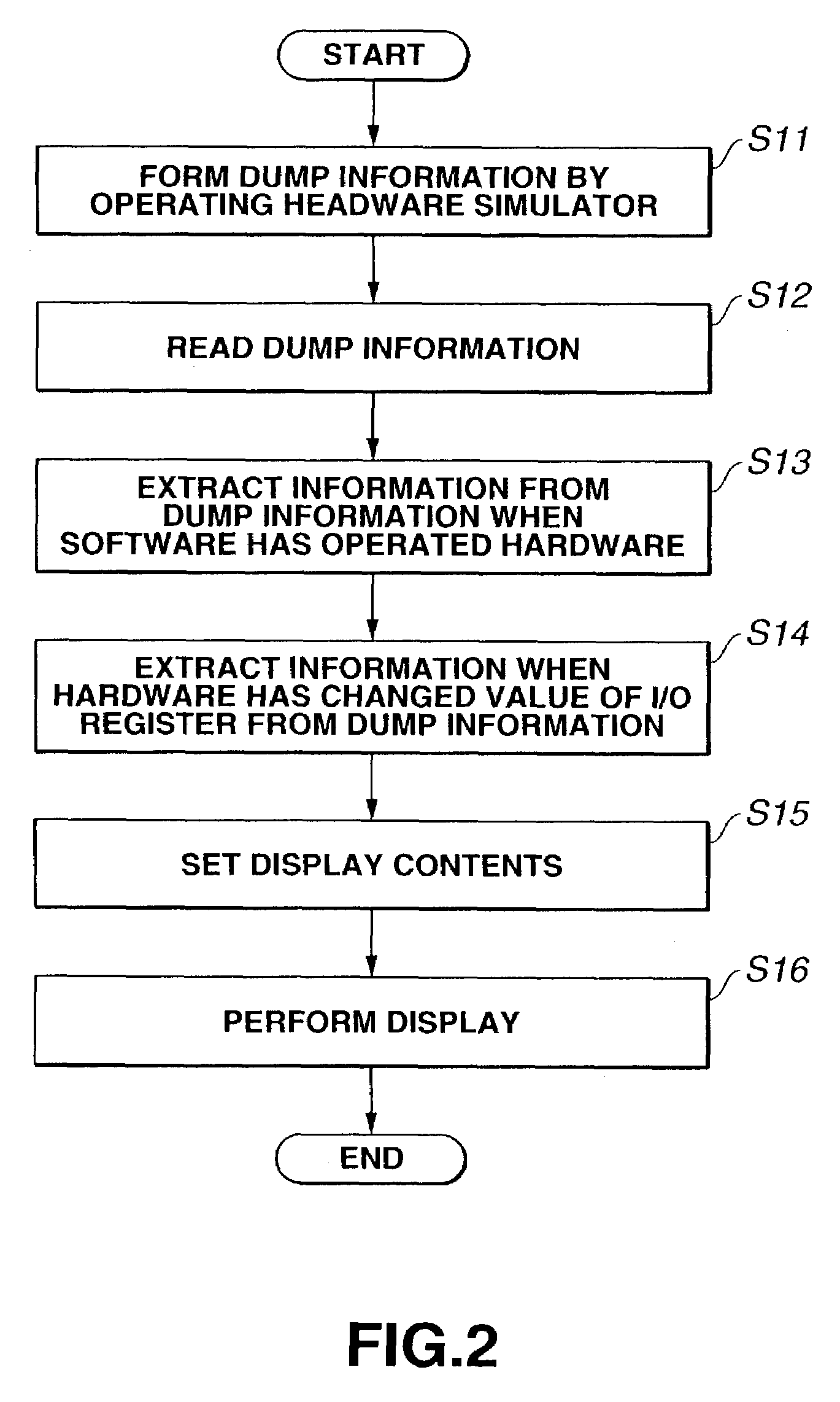

Apparatus and method for debugging software

InactiveUS7188338B2Easy to understandHardware monitoringSoftware testing/debuggingComputer hardwareHardware simulator

In a software debugging apparatus, dump information formed by a hardware simulator is acquired and analyzed. When displaying the result of the analysis, information when software has operated hardware and information when the hardware has changed the value of an I / O register are separately displayed.

Owner:CANON KK

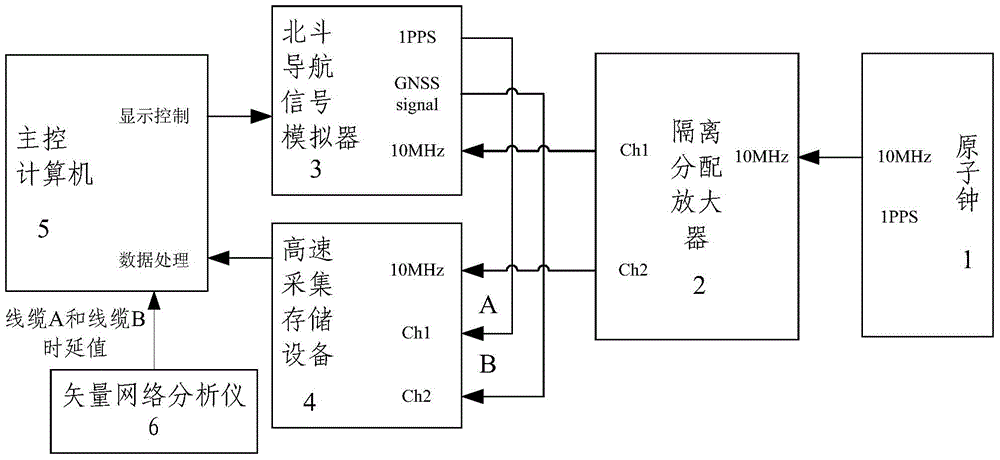

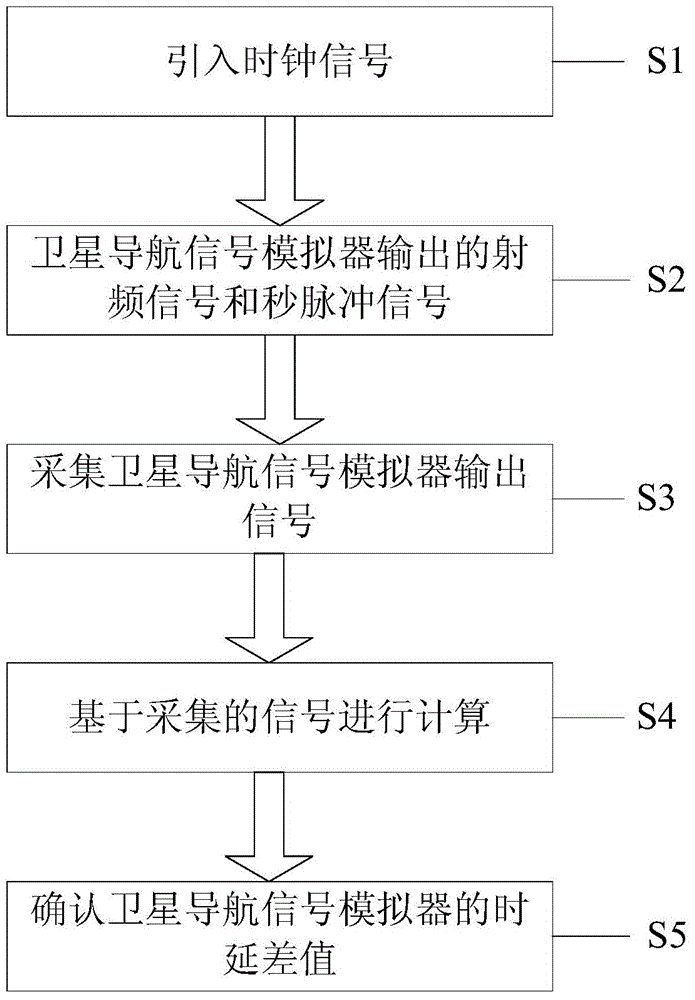

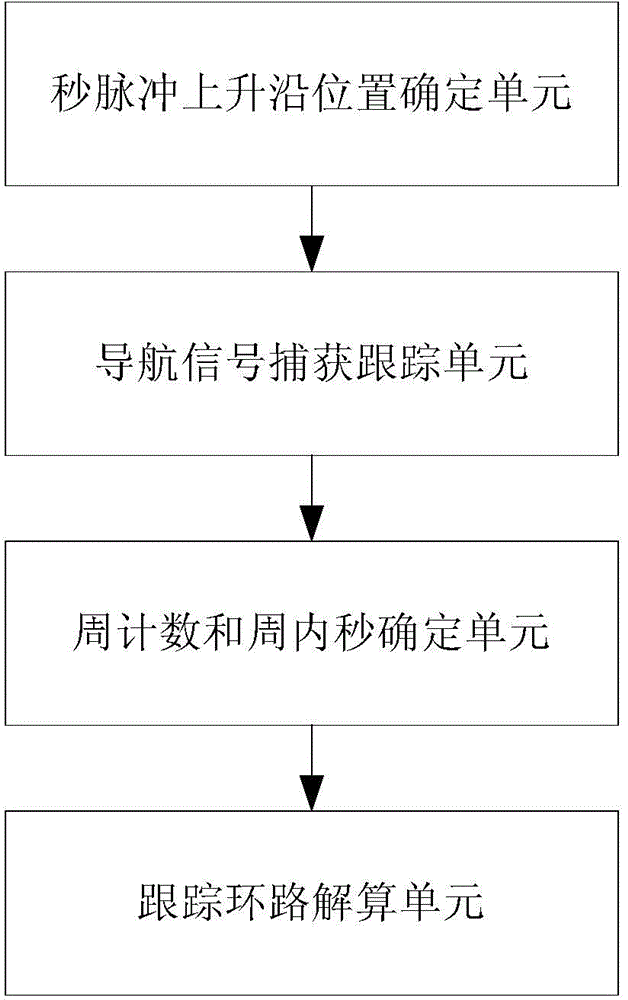

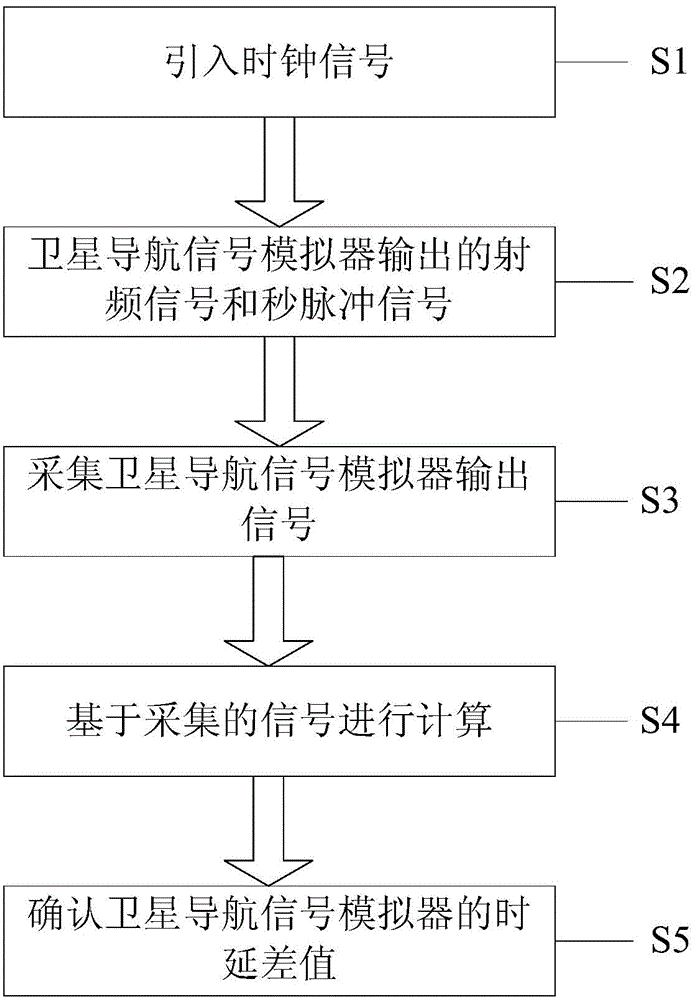

System and method for time delay calibration of Beidou navigation signal hardware simulator

The invention discloses a system and a method for time delay calibration of a Beidou navigation signal hardware simulator. The system comprises a satellite navigation signal simulator, a signal acquisition module, an isolation amplifier and a signal processing module, wherein the isolation amplifier outputs a first clock signal and a second clock signal; the satellite navigation signal simulator takes the first clock signal as a work clock and outputs a radio frequency analog signal and a pulse per second signal; the signal acquisition module takes the second clock signal as a sampling clock and is used for acquiring the radio frequency GEO (geosynchronous) satellite analog signal and the pulse per second signal; and the signal processing module calculates delay inequality between an initial code phase of the radio frequency GEO satellite analog signal and a pulse per second rising edge of the pulse per second signal based on the acquired radio frequency analog signal and the pulse per second signal to obtain the time delay of the simulator. With the adoption of the technical scheme, a special zero-pseudorange or fixed-pseudorange testing scene is not required to be set in the simulator, and the time delay of the simulator can be calibrated when the simulator simulates output normally.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

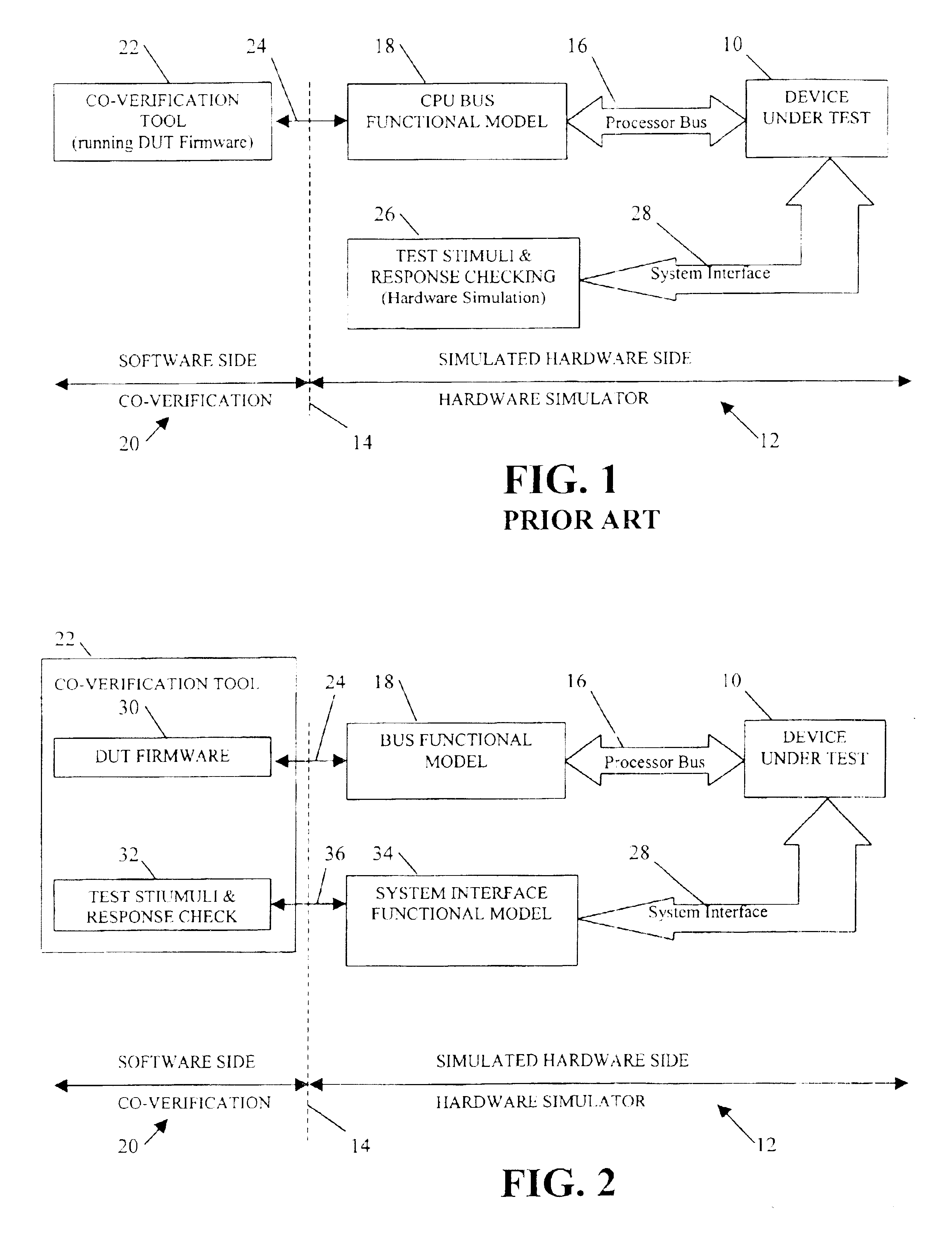

Application of co-verification tools to the testing of IC designs

An IC design is tested on a workstation through a hardware simulator. The workstation includes a co-verification software tool that executes IC firmware to operate the IC design and test the IC design and IC firmware. The co-verification software tool further operates to supply test stimuli to the IC design and to receive responses for analysis. The test stimuli are written in a programming language, which permits ease of testing and analysis of the IC design.

Owner:BELL SEMICON LLC

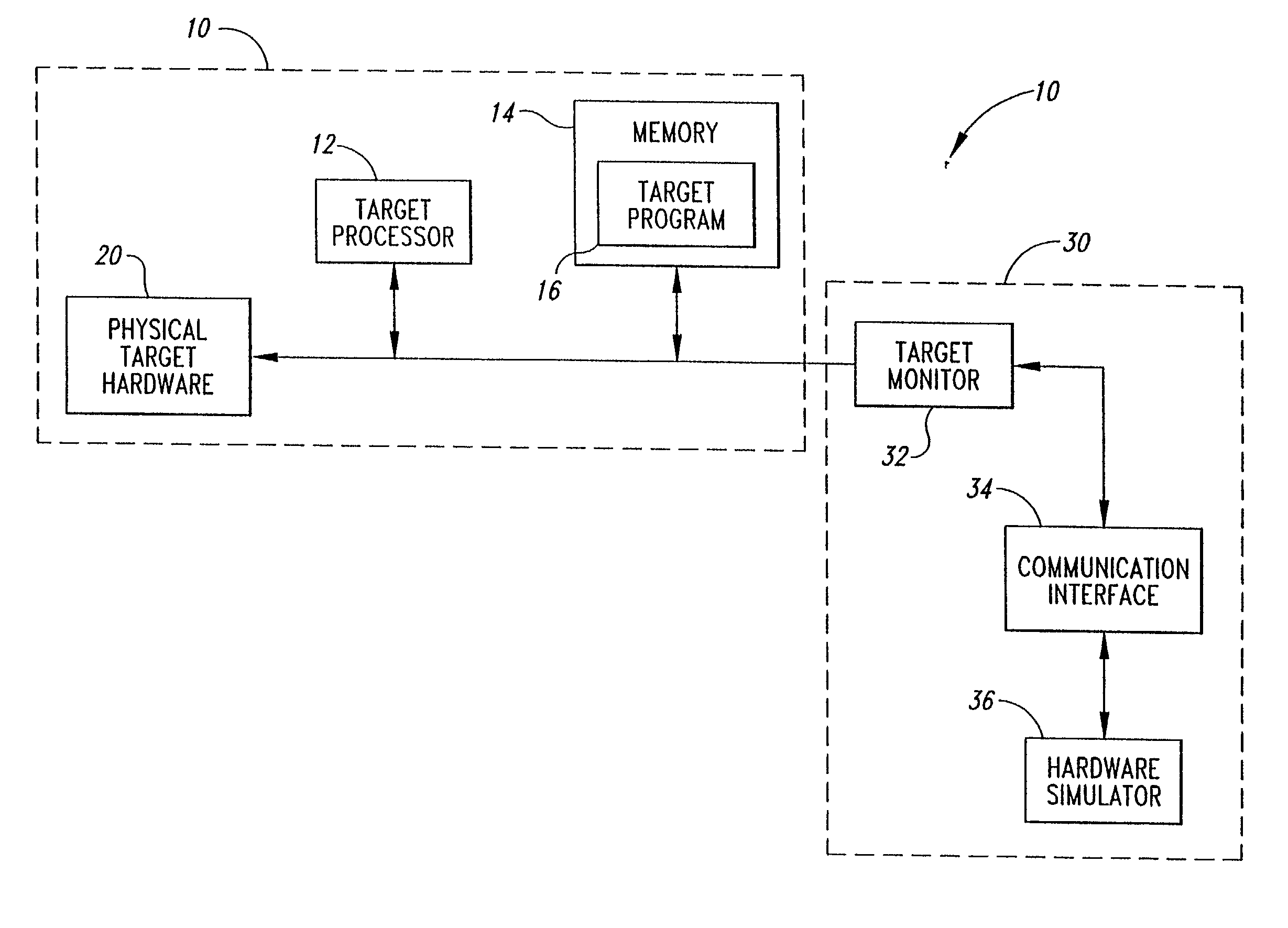

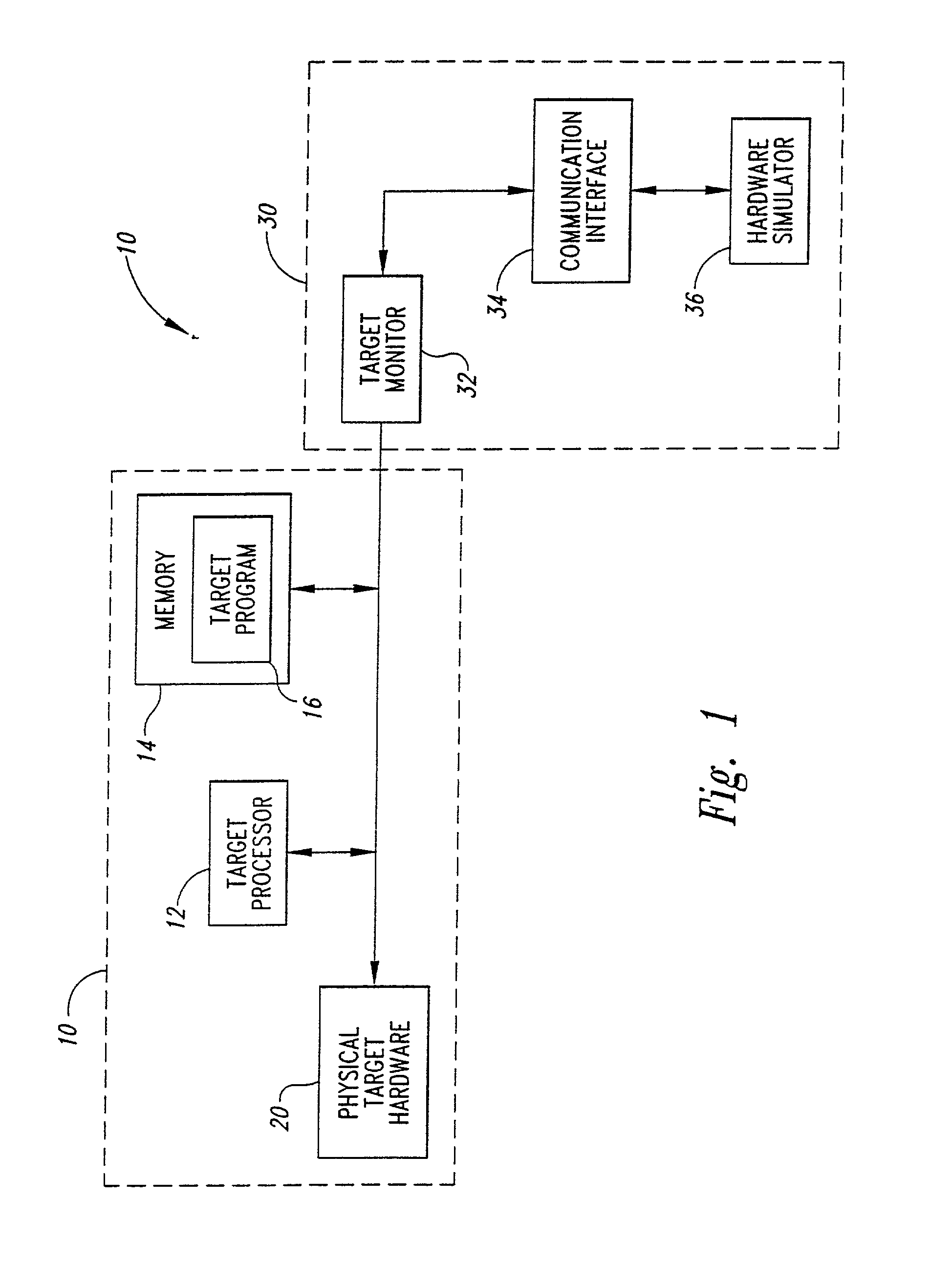

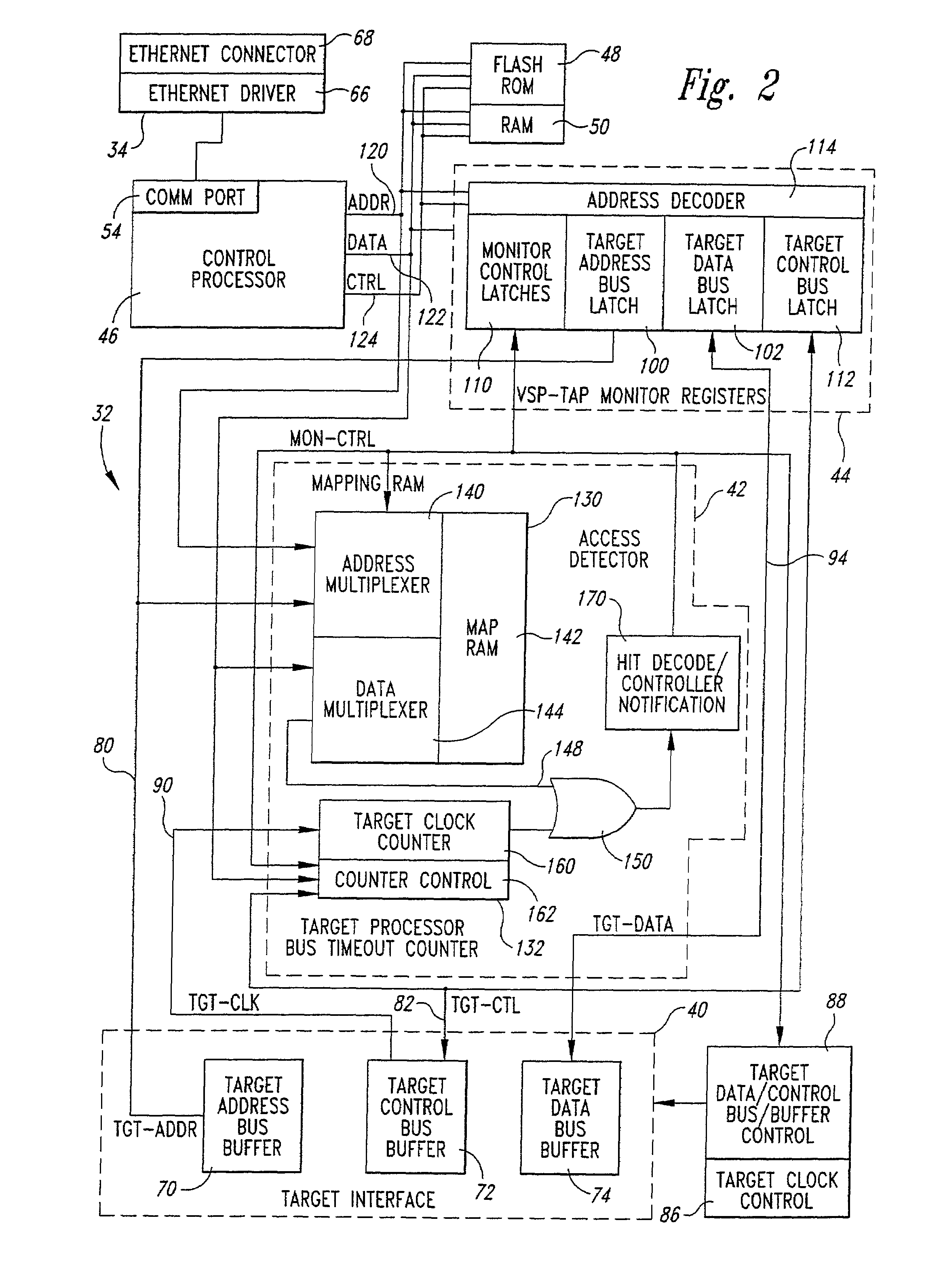

System and method for testing an embedded microprocessor system containing physical and/or simulated hardware

InactiveUS7089170B2General purpose stored program computerFunctional testingCommunication interfaceSignal on

A system for testing an embedded system containing a target processor executing a target program and target hardware that has a physical portion and a simulated portion. A target monitor determines when the target processor is attempting to access simulated hardware. The address bus of the microprocessor is monitored to detect an address in the address space of the simulated hardware. Lack of an acknowledge signal from the physical hardware within a predetermined period after the target processor attempts to access the target hardware may also indicate simulation. A bus capture circuit captures output signals on the bus connections of the target processor and converts the output signals to output data. The output data is then coupled through a communications interface to a hardware simulator. The hardware simulator processes the data in the same manner that the physical hardware would respond to signals corresponding to the output data.

Owner:NXP USA INC

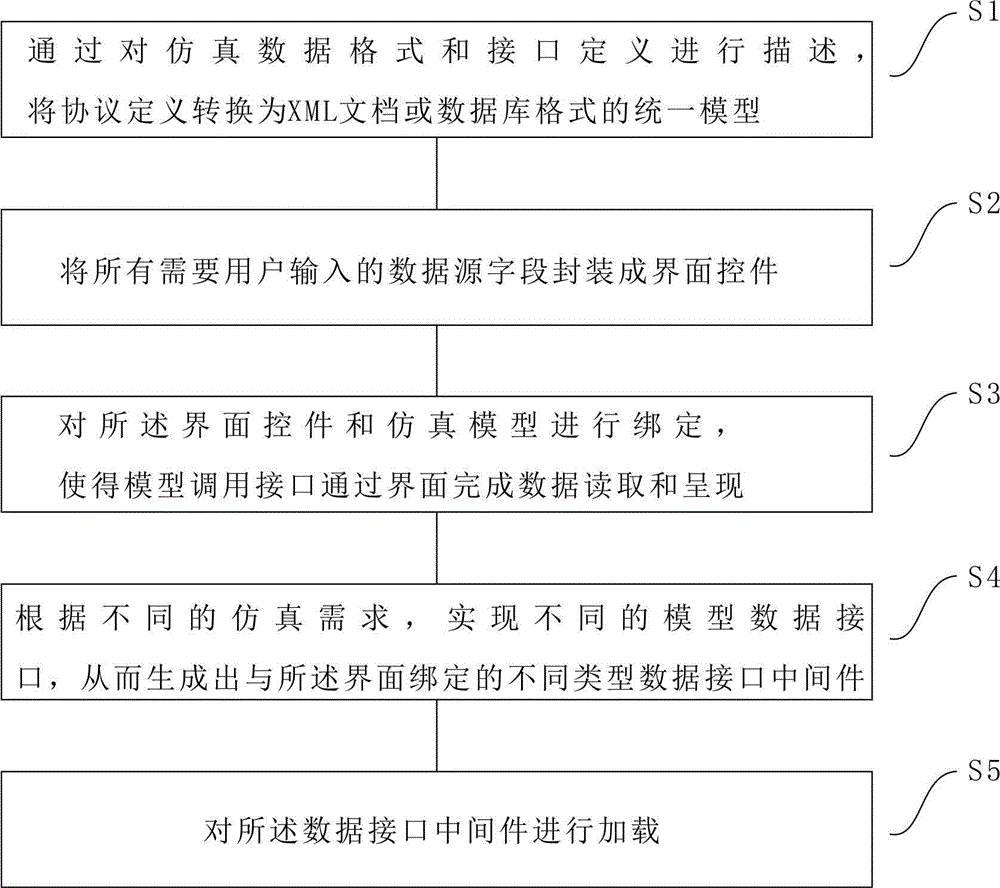

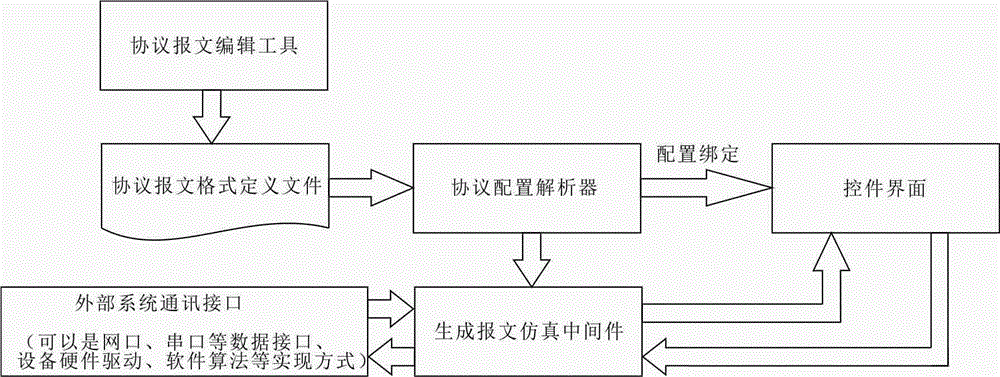

Digital simulation framework design method based on interface binding unified model

The invention provides a digital simulation framework design method based on an interface binding unified model. The method comprises the following steps: by describing a simulation data format and an interface definition, converting a protocol definition into an unified model in an XML document or database format; packaging all data source fields needing to be input by users into interface controls; binding the interface controls and a simulation data model, so that a data model call interface completes the reading and presentation of data through the interface controls; according to different simulation requirements, realizing different model data interfaces, thus generating different types of interface binding data interface middleware; and loading the data interface middleware. The digital simulation framework design method based on the interface binding unified model can be used for solving the problems that equipment protocol formats are numerous, the integration of hardware simulator equipment is complex, and the interface input difference is relatively large, codes cannot be reused although the work principle of software is similar, more complex work needs to be done, and the investment workload is heavy.

Owner:成都能通科技股份有限公司

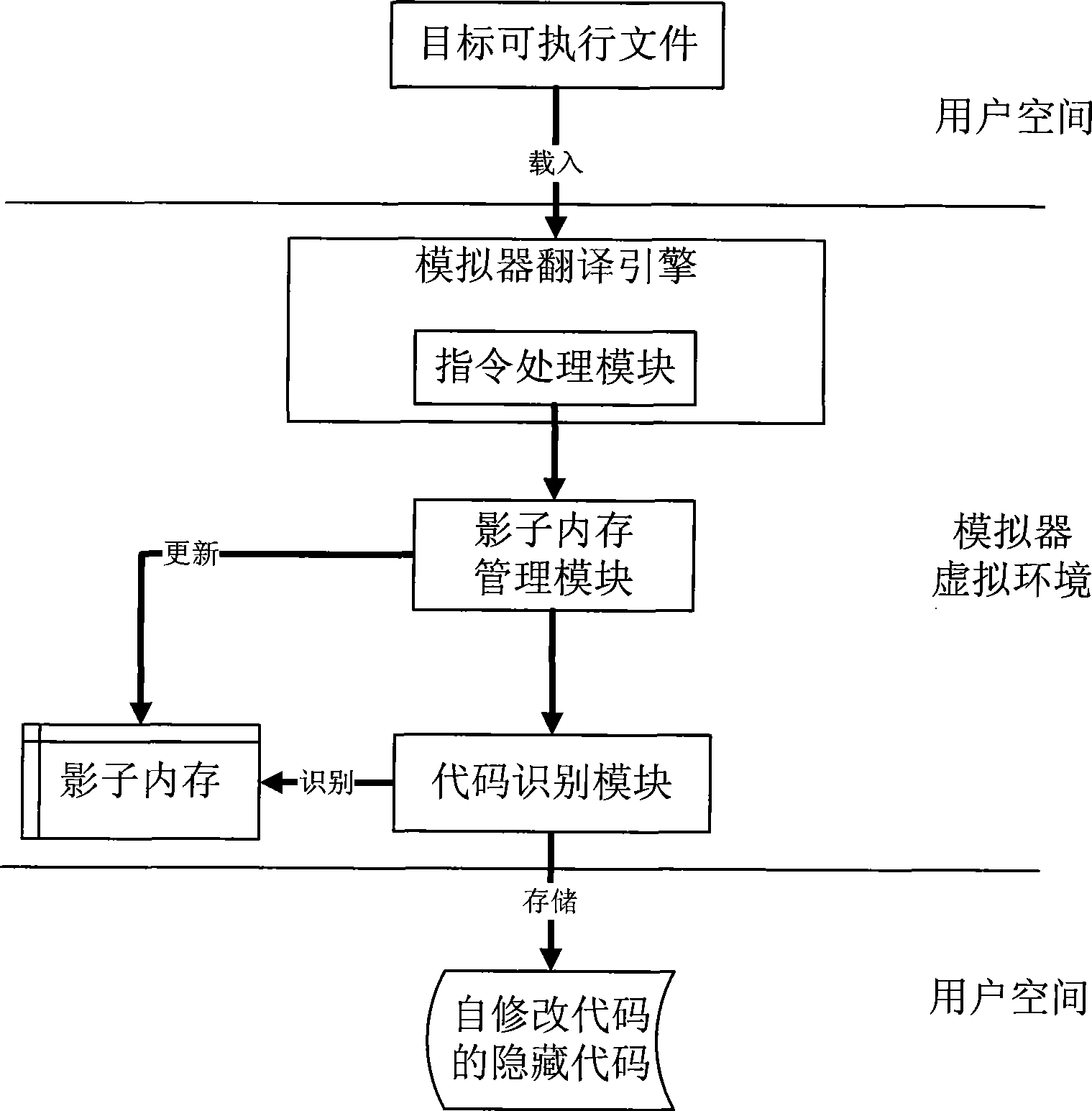

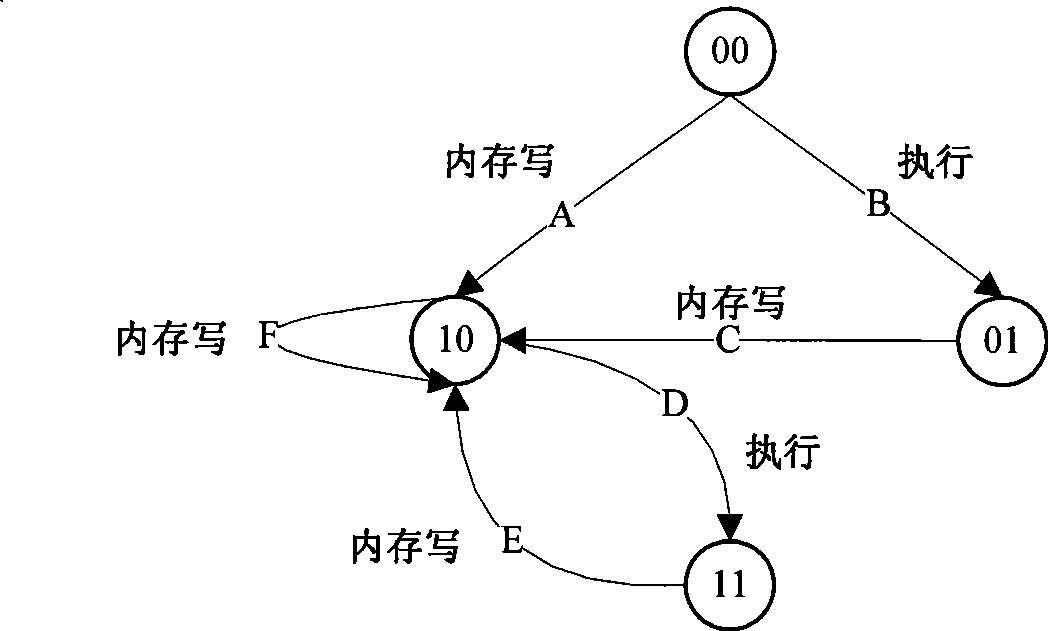

Self-modifying code identification method based on hardware emulator

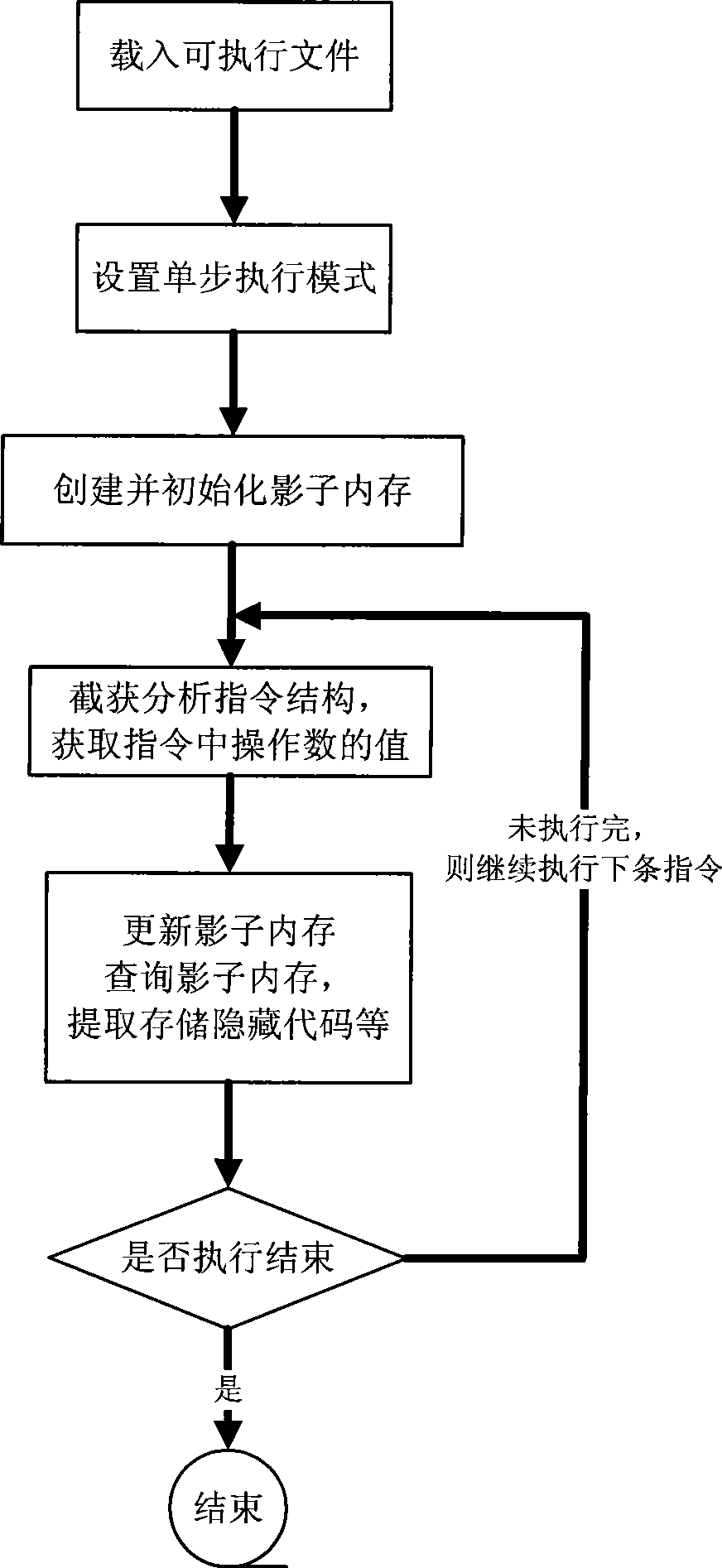

ActiveCN101458630AImprove analysis efficiencyHigh transparencyProgram controlProgram/content distribution protectionSelf-modifying codeSecurity measurement

The invention belongs to the technical field of software security measurement and evaluation, especially relates to a self-modifying code recognition method based on a hardware simulator. The invention is provided with a marker in the hardware simulator in order to only execute a target executable file by one step and capture a virtual system execute instruction, the information in the process can be executed by using a shadow memory monitoring program, the code which is dynamically released into the memory and is executed can be recognized and executed in the course of program execution, so that data information of the analysis target can be acquired. The data acquisition of the invention is implemented by the simulation hardware, is not executed by placing the malevolence code on a true CPU, so the actual system can not be affected. The invention adopts the hardware simulator as a dynamic analysis platform, which can improve the transparency between the analysis platform and the code and can effectively defend against the detection of the code.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

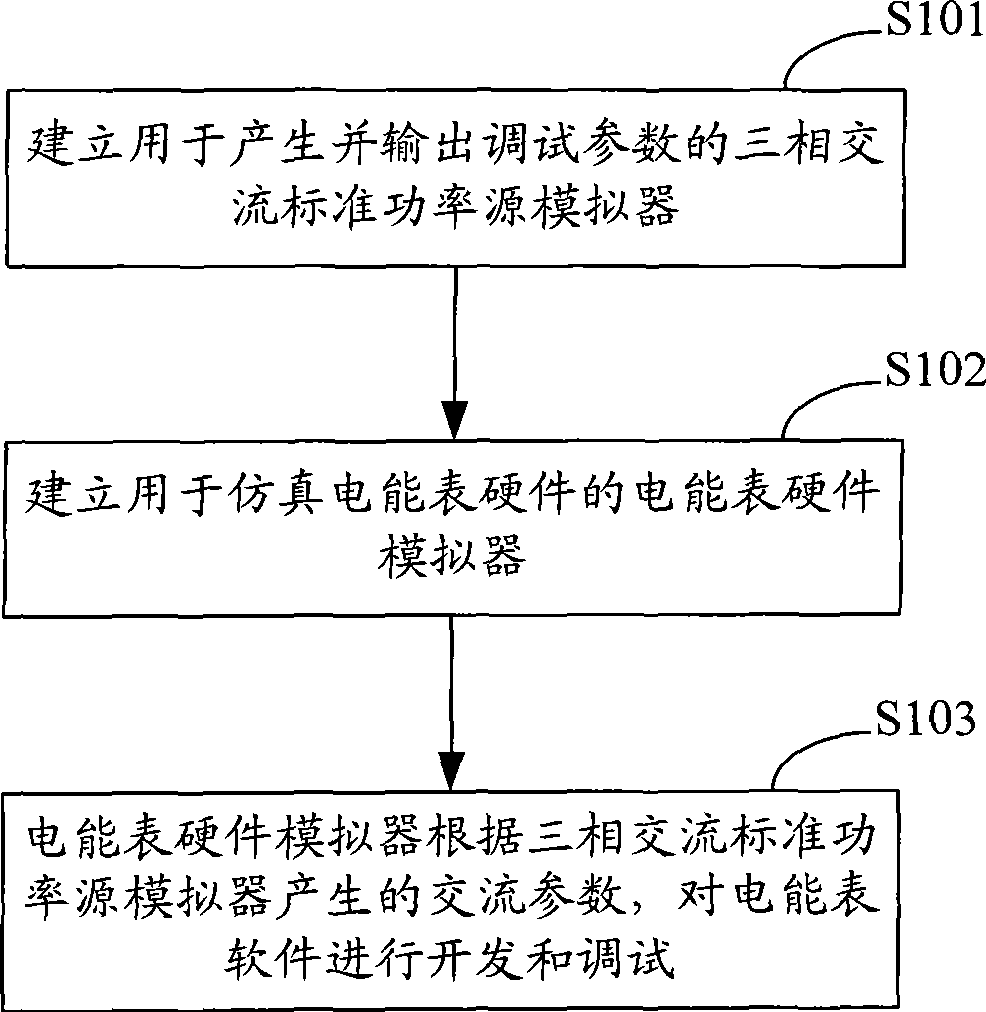

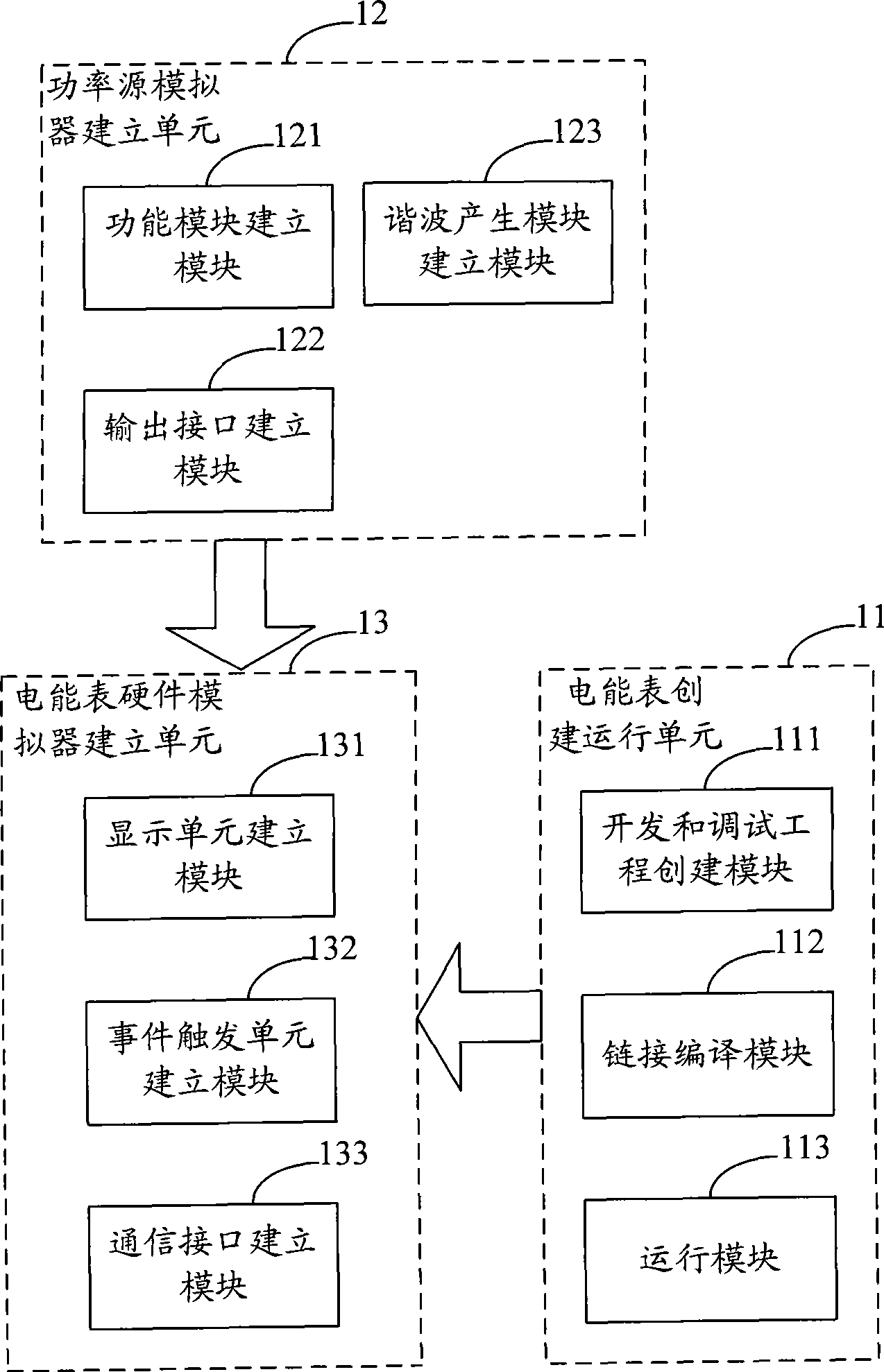

Method and system for developing and debugging electric energy meter software

ActiveCN101504611AAvoid situations where debugging must be done on the energy meter hardwareRealize developmentElectrical measurementsSpecific program execution arrangementsHardware simulatorParallel computing

The invention applies to the technical field of computer simulation and electric energy meters, and provides a method and a system for developing and debugging electric-energy-meter software, wherein the method comprises the following steps that: a three-phase AC standard power-source simulator used for generating and outputting debugging parameters is established; an electric-energy-meter hardware simulator used for simulating electric-energy-meter hardware is established; and the electric-energy-meter hardware simulator debugs the electric-energy-meter software according to the debugging parameters generated by the three-phase AC standard power-source simulator. In the invention, as the electric-energy-meter software is developed and debugged by establishing the three-phase AC standard power-source simulator for generating and outputting the debugging parameters and the electric-energy-meter hardware simulator for simulating the electric-energy-meter hardware, the situation that the electric-energy-meter software needs to be debugged on the electric-energy-meter hardware during development is avoided so as to improve debugging efficiency, reduce difficulty, have better suitability for team development and shorten development cycle.

Owner:JIANGSU HUAYUAN APP & INSTR

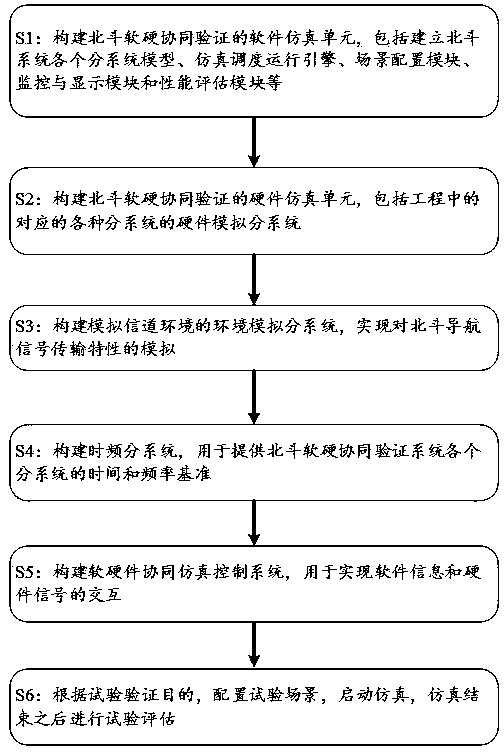

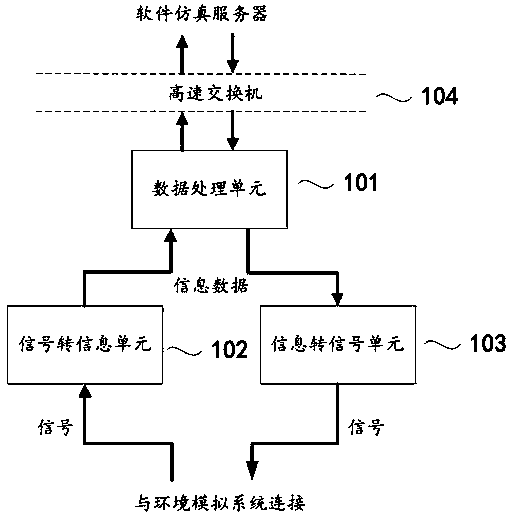

Beidou global system soft and hard collaborative simulation test verification system and establishment method

ActiveCN111208746AExpandable and flexibleThe sequence is logically correctSimulator controlSoftware emulationSoftware engineering

The invention provides a Beidou global system soft and hard collaborative simulation test verification system. The Beidou global system soft and hard collaborative simulation test verification systemcomprises a software simulation unit, a hardware simulation unit, a software and hardware collaborative simulation control system, an environment simulation system and a time-frequency subsystem. Thesoftware simulation unit comprises a simulation model library, a simulation scheduling operation module, a scene configuration module, a monitoring and display module and a performance evaluation module. The hardware simulation unit comprises a hardware simulation system and an external interface system. The invention further provides an establishment method of the Beidou global system soft and hard collaborative simulation test verification system. The establishment method comprises the following steps of establishing the software simulation part, establishing the hardware simulation part, establishing the environment simulation subsystem, establishing the time frequency subsystem and establishing the software and hardware collaborative simulation control system; and performing test verification. Through the hardware simulator and the software model, the state of the Beidou engineering system can be approximated to the maximum extent, the number and the state of the test models can beflexibly configured, and butt joint verification with the real Beidou engineering system can be carried out.

Owner:NAT UNIV OF DEFENSE TECH

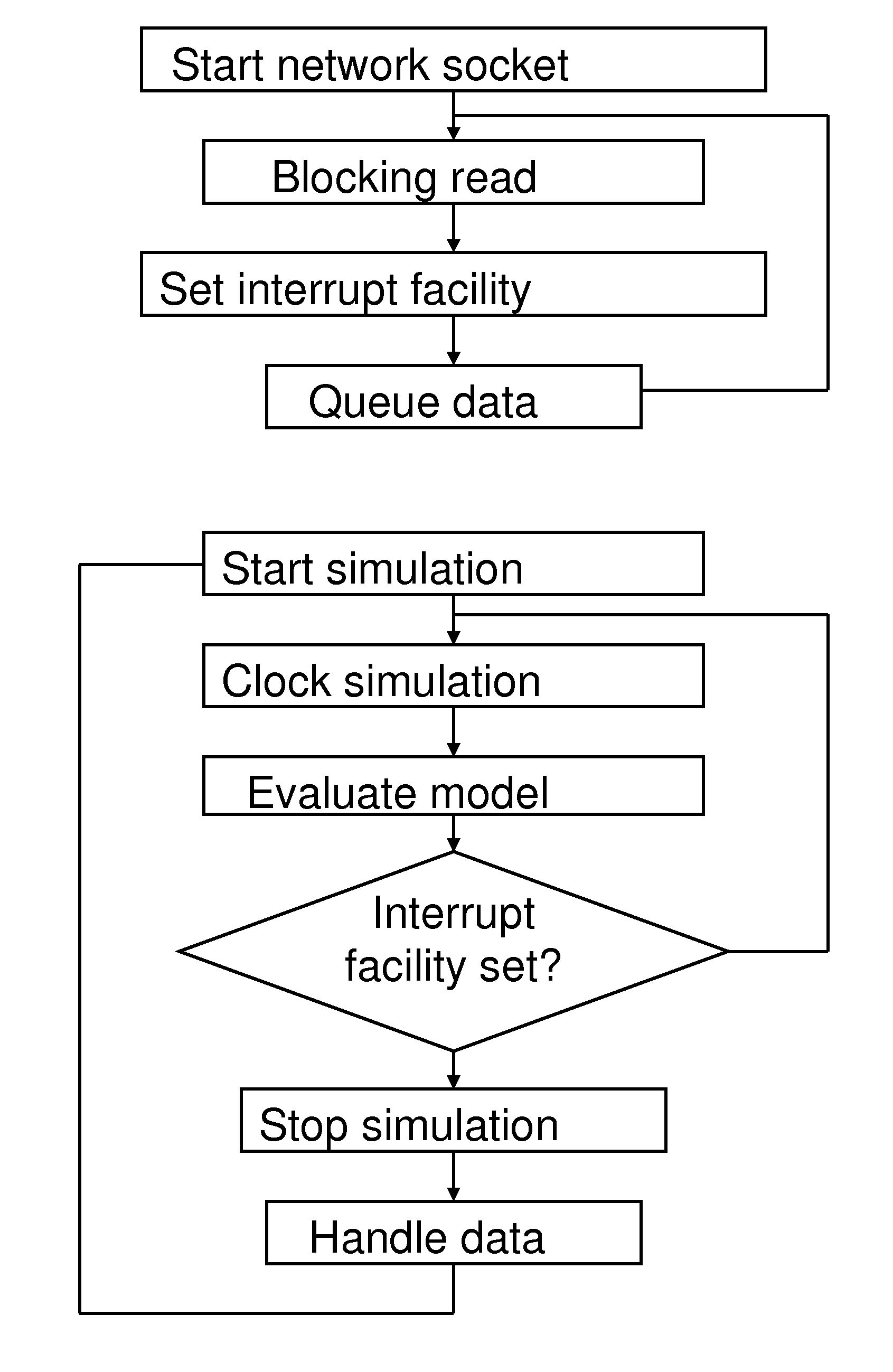

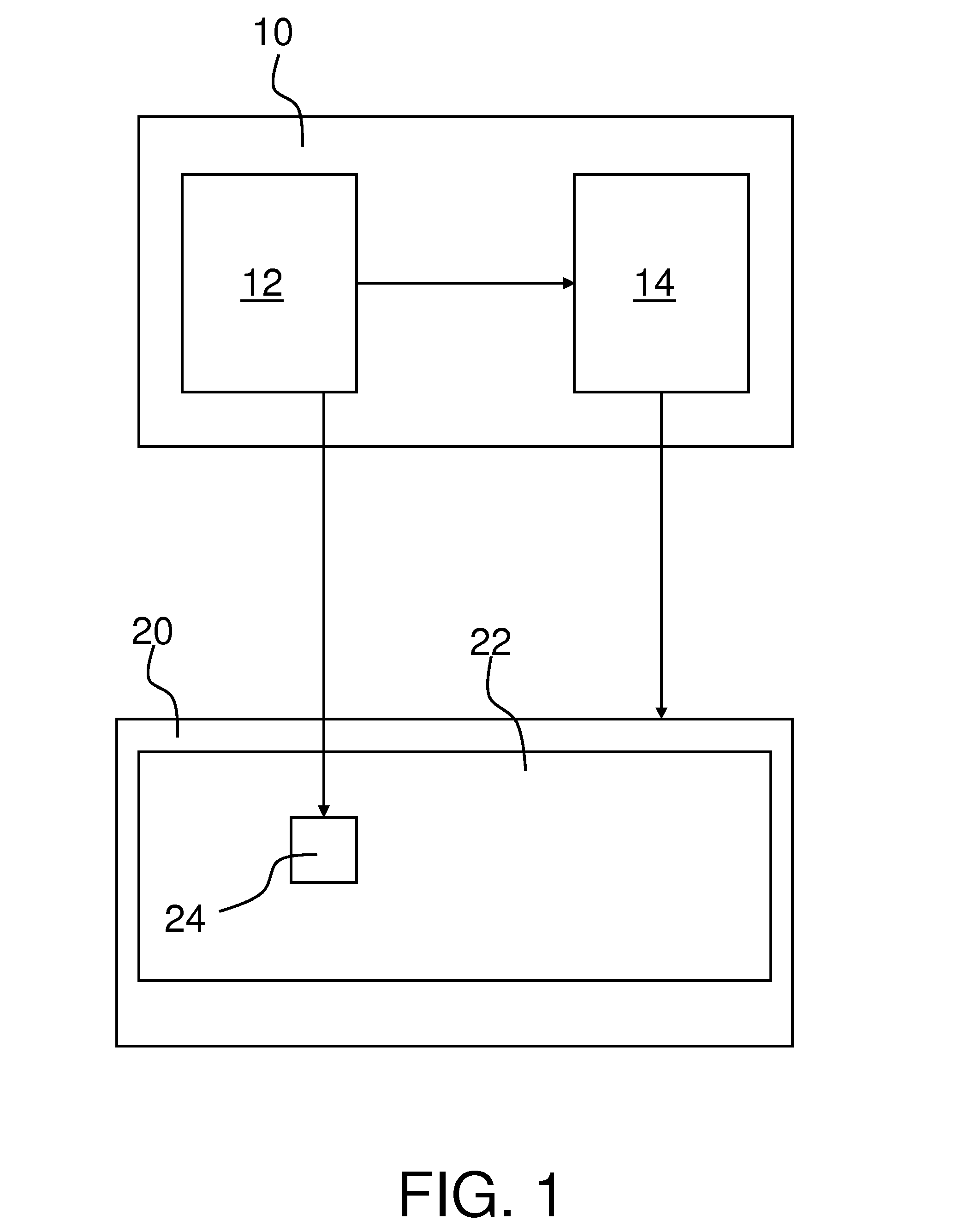

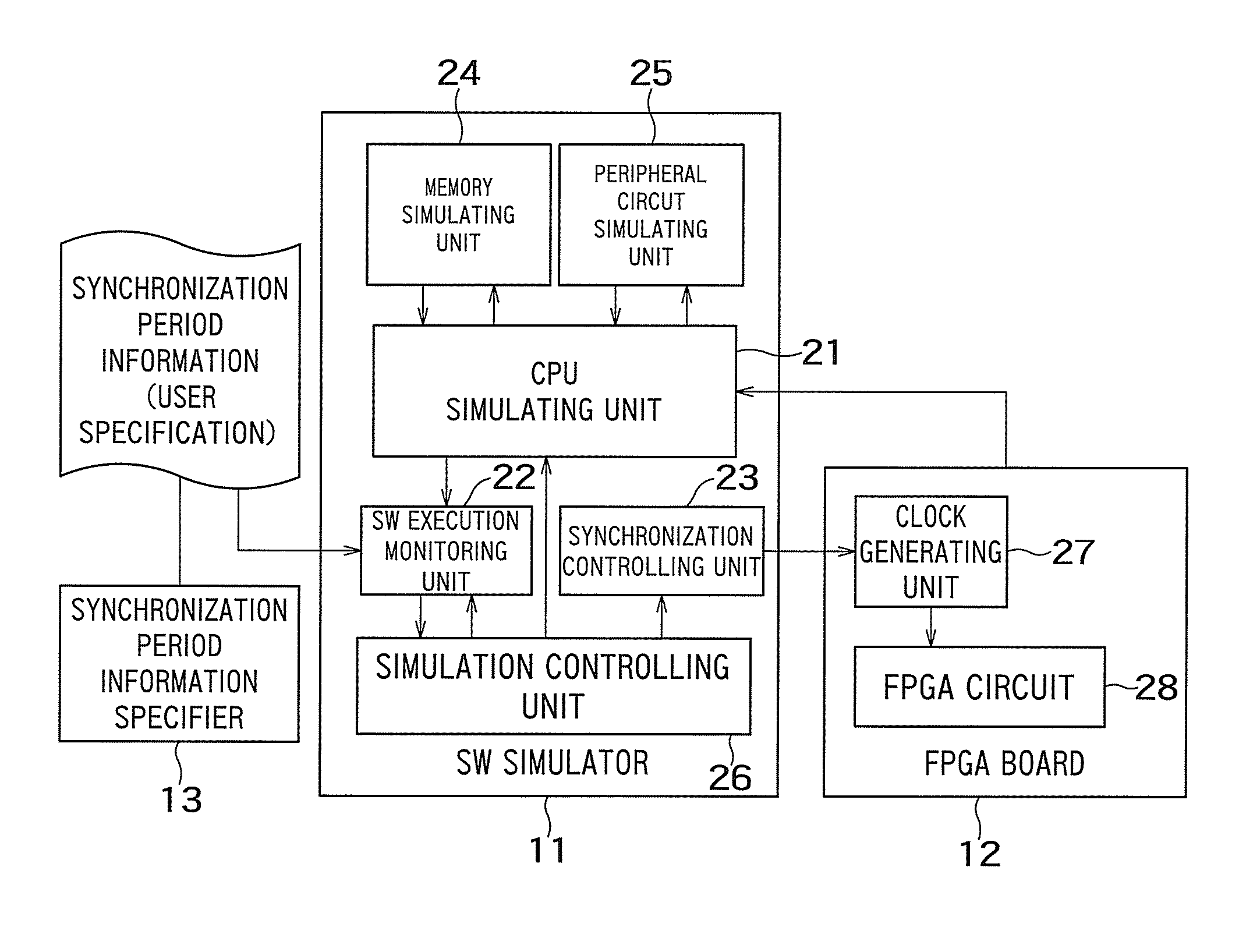

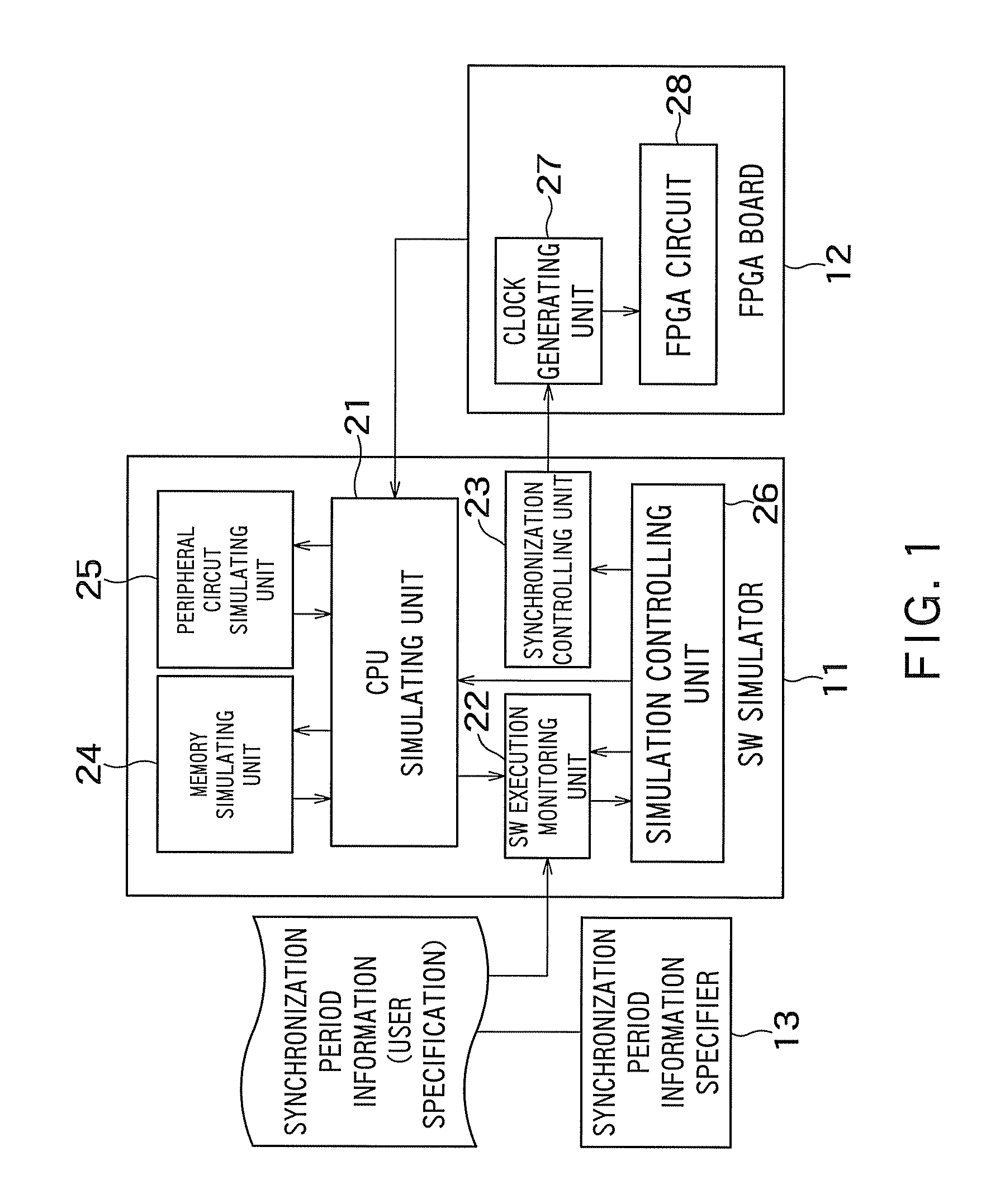

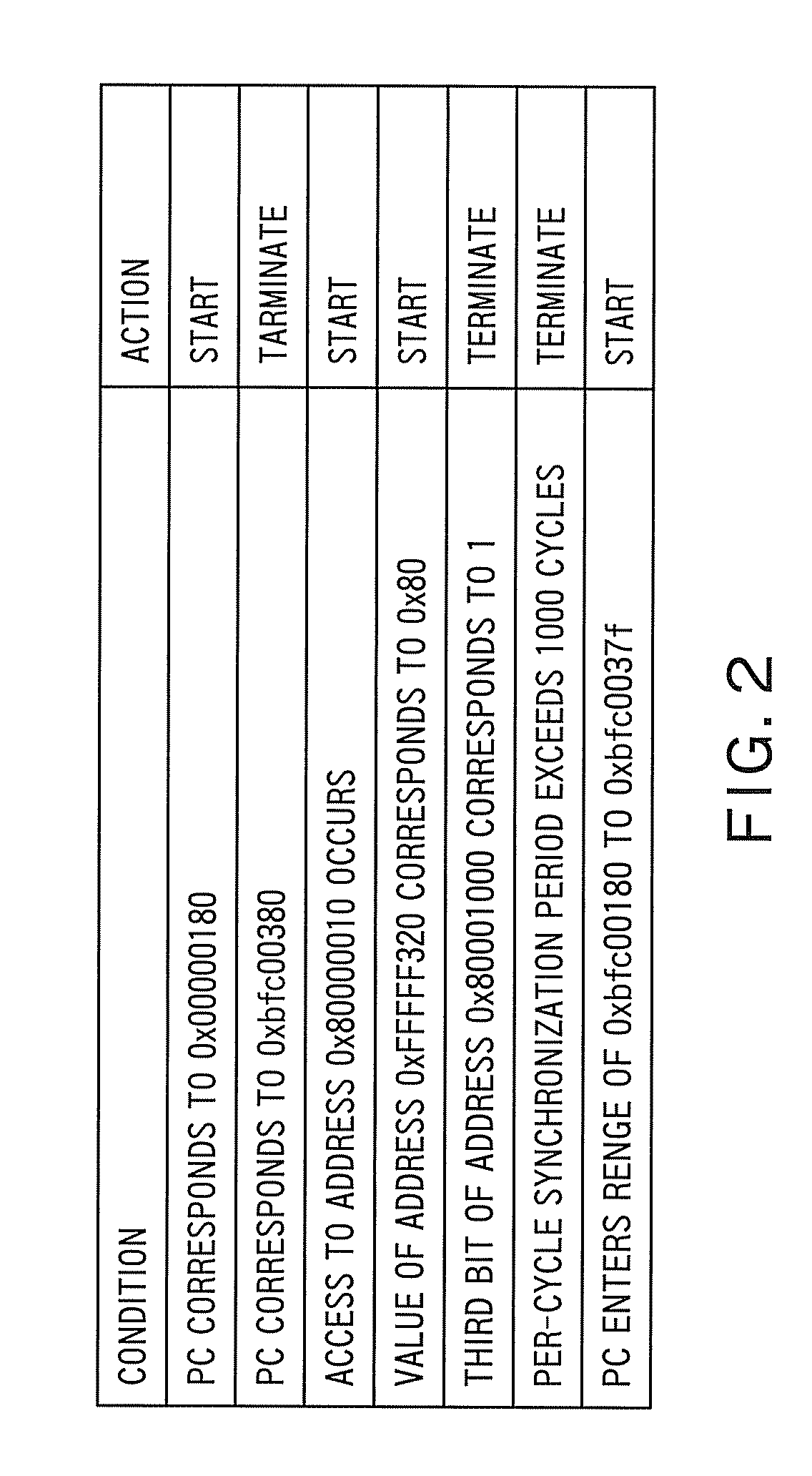

System for Performing a Co-Simulation and/or Emulation of Hardware and Software

ActiveUS20090063120A1Error detection/correctionAnalogue computers for electric apparatusComputer hardwareHardware simulator

The present invention relates to a system for performing a co-simulation and / or emulation of hardware and software. The system includes a hardware simulator with an integrated hardware model, a hardware and / or software environment for controlling the hardware simulator and performing a software simulation and / or a direct software application, at least one synchronization facility within the hardware model for indicating a request from the hardware and / or software environment, a receiver for setting the synchronization facility into a predetermined state, and a controller for switching the hardware simulator between a free-running state and a request-handling state.

Owner:GLOBALFOUNDRIES US INC

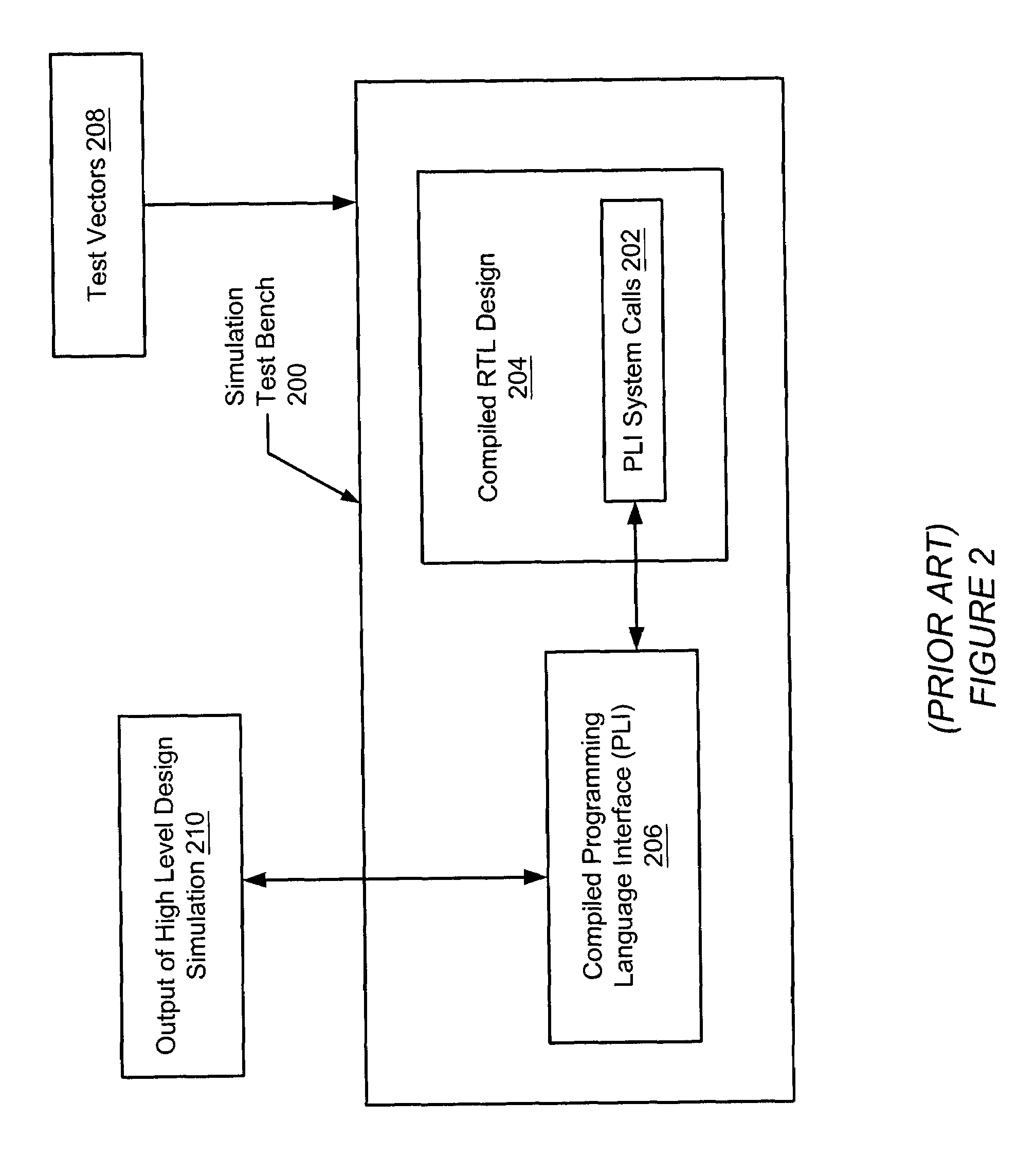

PLI-less co-simulation of ISS-based verification systems in hardware simulators

A method for providing verification for a simulation design, including obtaining the simulation design comprising a programming language interface system call, encoding a target of the programming language interface system call into the simulation design to obtain a first modified simulation design, modifying the programming language interface system call to reference the target in the first modified simulation design to obtain a second modified simulation design, and verifying the second modified simulation design using a simulation testbench.

Owner:ORACLE INT CORP

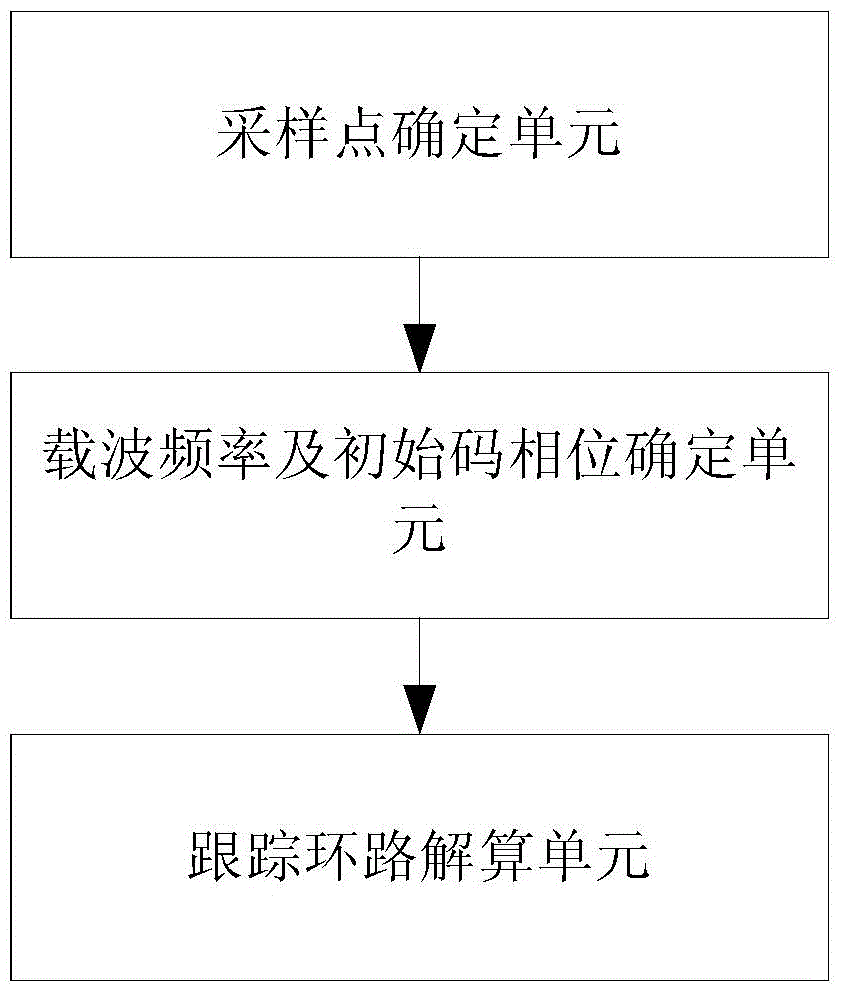

GNSS signal simulator time delay calibration system and GNSS signal simulator time delay calibration method

The invention discloses a GNSS signal simulator time delay calibration system and a GNSS signal simulator time delay calibration method. The GNSS signal simulator time delay calibration system comprises an isolation amplifier, a satellite navigation signal simulator, a data acquisition module, and a signal processing module. The isolation amplifier is used to divide an external clock signal into a first clock signal and a second clock signal. The satellite navigation signal simulator adopts the first clock signal as the working clock, and is used to output a radio frequency navigation signal and a second pulse signal in a normal simulation scene that the receiving device is in the static state, and the simulator pseudo-range is time-varying. The data acquisition module adopts the second clock signal as the sampling clock, and is used to acquire the radio frequency navigation signal and the second pulse signal. The signal processing module is used to calculate the pseudo-range corresponding to the radio frequency navigation signal and the pseudo-range recorded by the simulation epoch moment simulator disposed on the rising edge of the second pulse signal based on the acquired radio frequency navigation signal and the acquired second pulse signal, and then the own time delay of the satellite navigation signal simulator can be acquired. By adopting the technical scheme, the special scene of the zero pseudo-range or the fixed pseudo-range is not required, and the calibration of the simulator time delay can be realized under the condition of the simulator normal simulation scene signal output.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

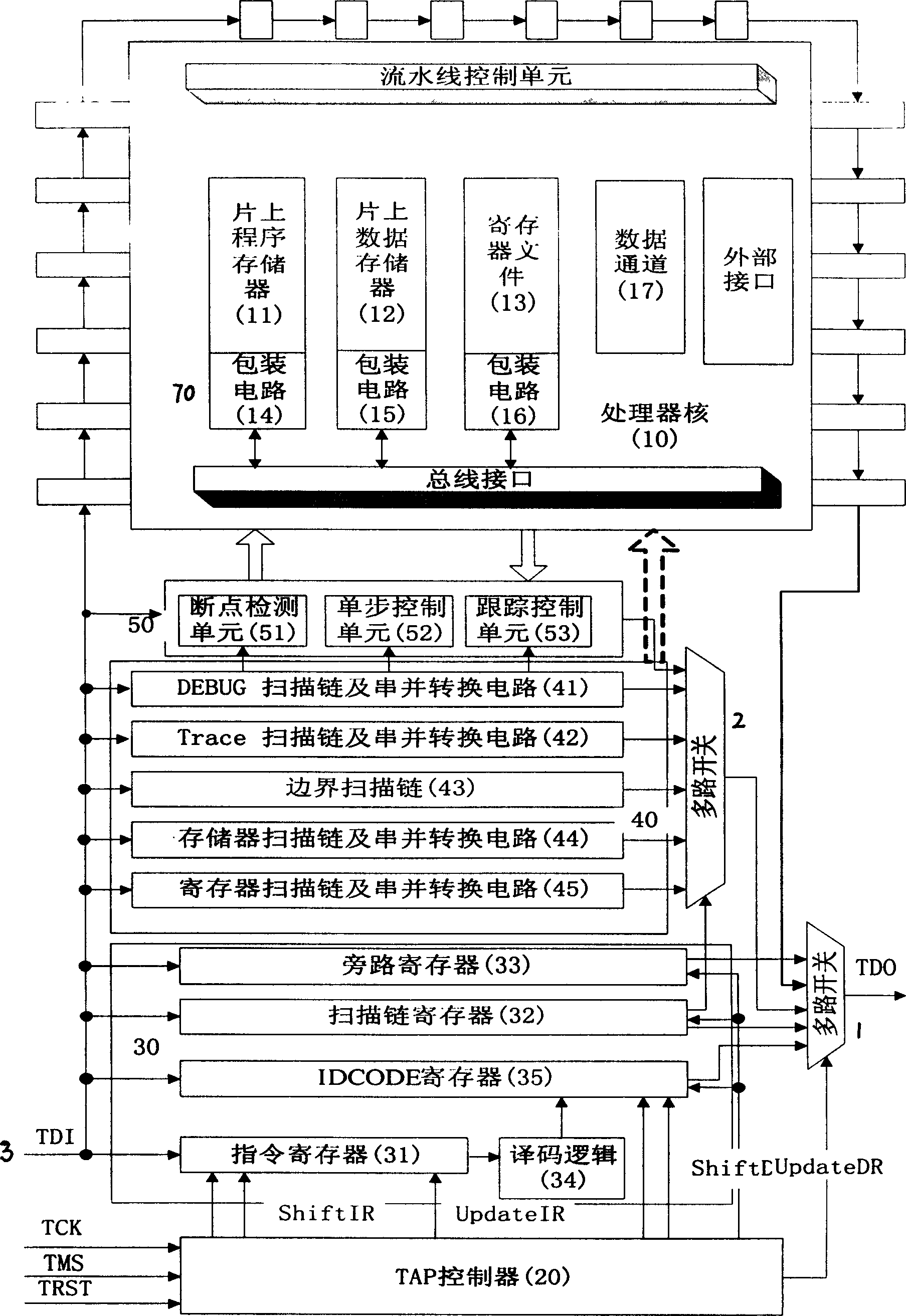

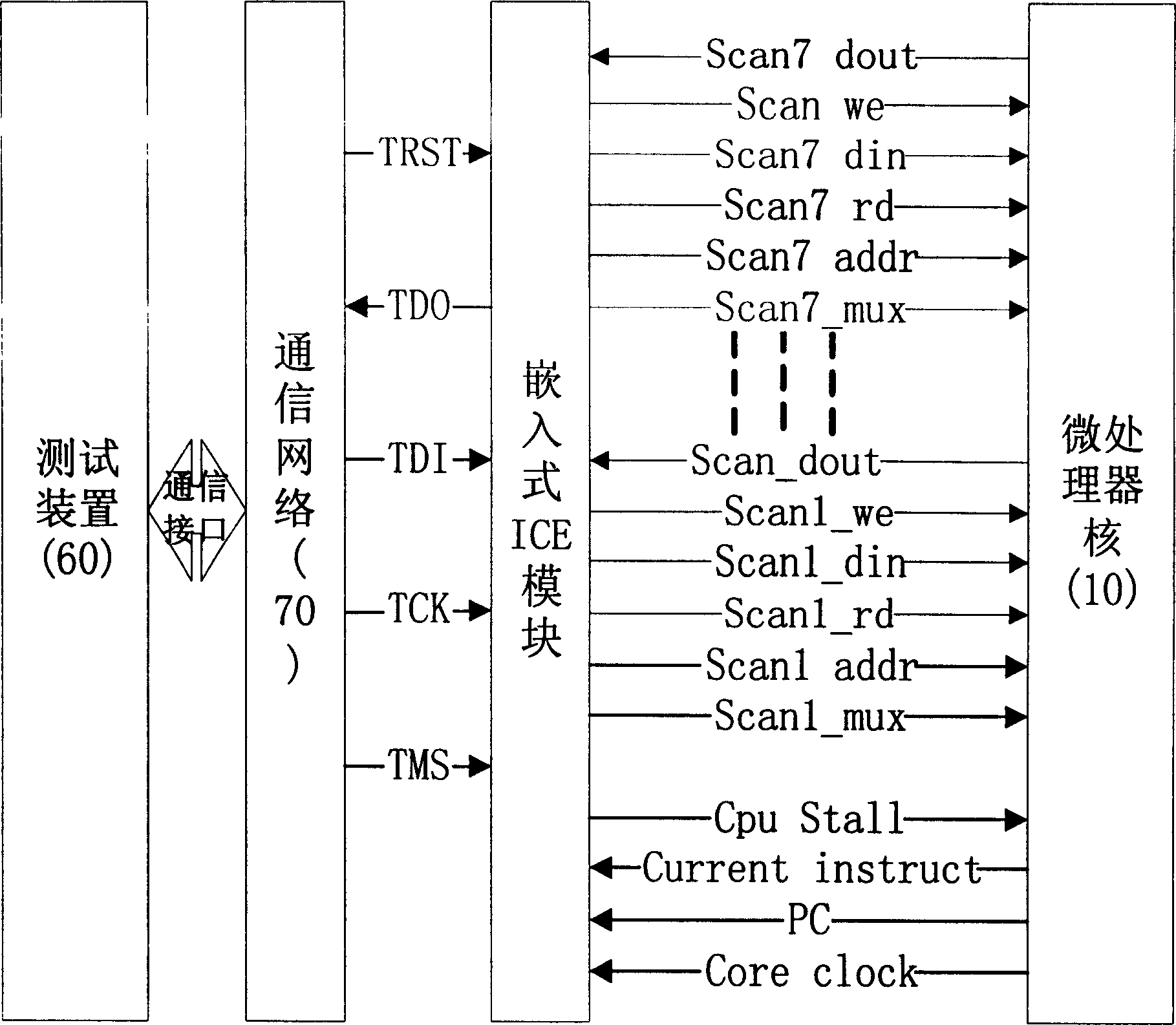

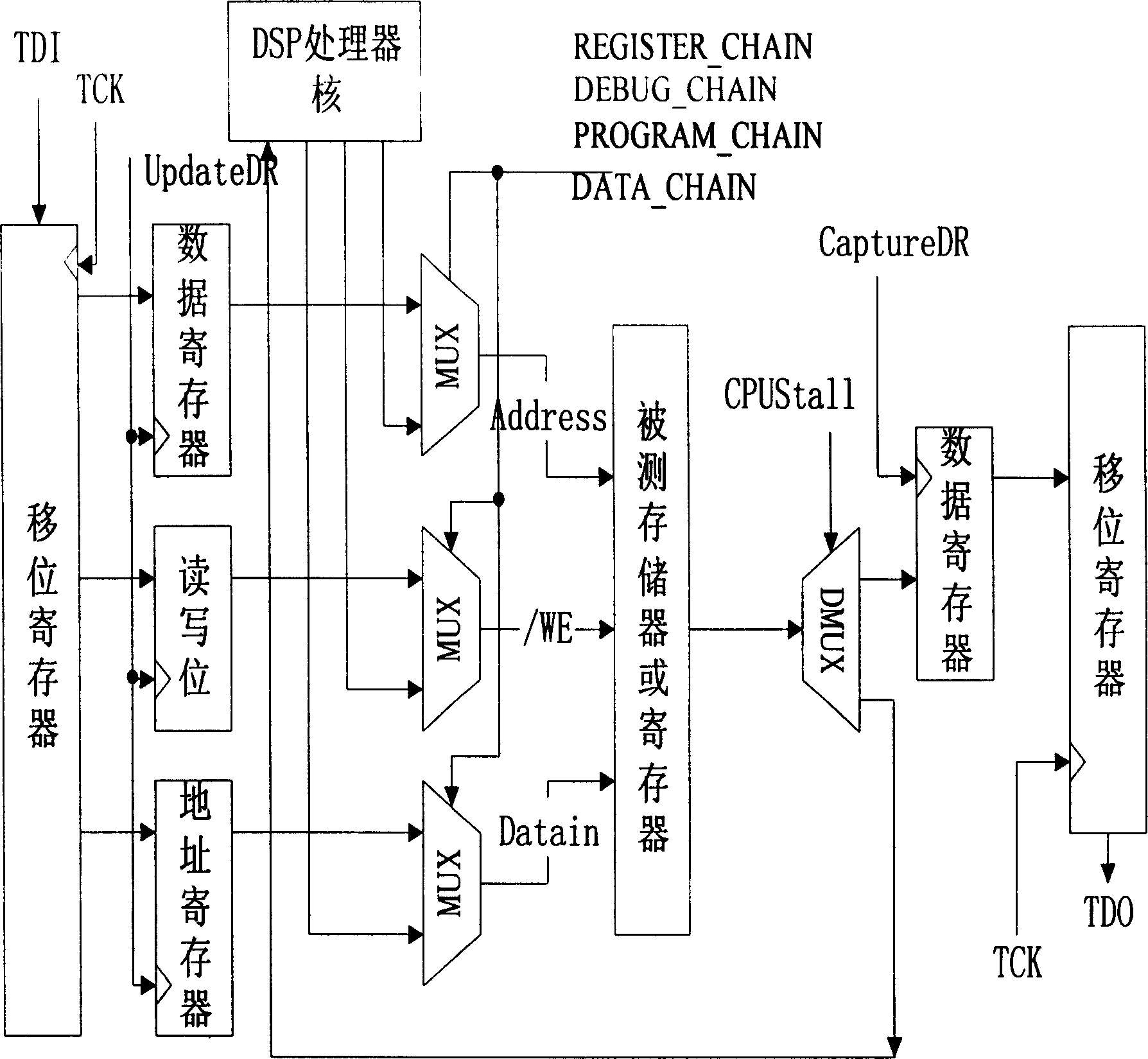

Embedded signal processor simulator

InactiveCN1622052ASolve the shortcomings of slow speedSolve the shortcomings of lack of debugging meansSoftware testing/debuggingInstruction registerMicroprocessor

The present invention discloses one kind of microprocessor and computer system, and aims at providing one kind of embedded signal processor simulator capable of completing the function verification of DSP kernel and making the DSP processor possess real-time simulating and verifying functions. The embedded signal processor simulator includes standard TAP module controller, serial / parallel converter circuit module, wrapper circuit module Wrapper and debugger module Debugger. The standard TAP module controller, the instruction register and decoding logic module are connected successively; the scanning chain register, Debugger, by-pass register and IDCODE register are connected in parallel; and it has one end connected to the datan input TDI pin and the other end connected to multiplexer. The present invention is superior to hardware simulator and has high speed and debugging measures.

Owner:ZHEJIANG UNIV

Single chip microcomputer hardware simulator and simulation method for same

ActiveCN102508752AAchieve interactionAchieve synchronizationFunctional testingMicrocontrollerMicrocomputer

The invention discloses a single chip microcomputer hardware simulator and a simulation method for the same. The simulation method includes the steps: operating a Proteus software on a PC (personal computer) to perform software simulation for a virtual circuit, and selecting a corresponding simulation model during software simulation; utilizing the simulation model to logically process digital level signals of pins of a master controller in the virtual circuit and signals acquired by the single chip microcomputer hardware simulator, and packing the processed signals into a data packet; transmitting the data packet into the single chip microcomputer hardware simulator through a USB (universal serial bus) interface; enabling the single chip microcomputer hardware simulator to receive the data packet from the simulation model and drive an output simulation head to output signals; and enabling a hardware circuit to respond the signals from the simulation head so that hardware simulation is completed. The simulation method realizes interaction and synchronization of the virtual circuit and the practical hardware circuit, so that experimental effect of experimental training equipment is enhanced, and study of students and embedded development and design of developers are facilitated.

Owner:广州市风标电子技术有限公司

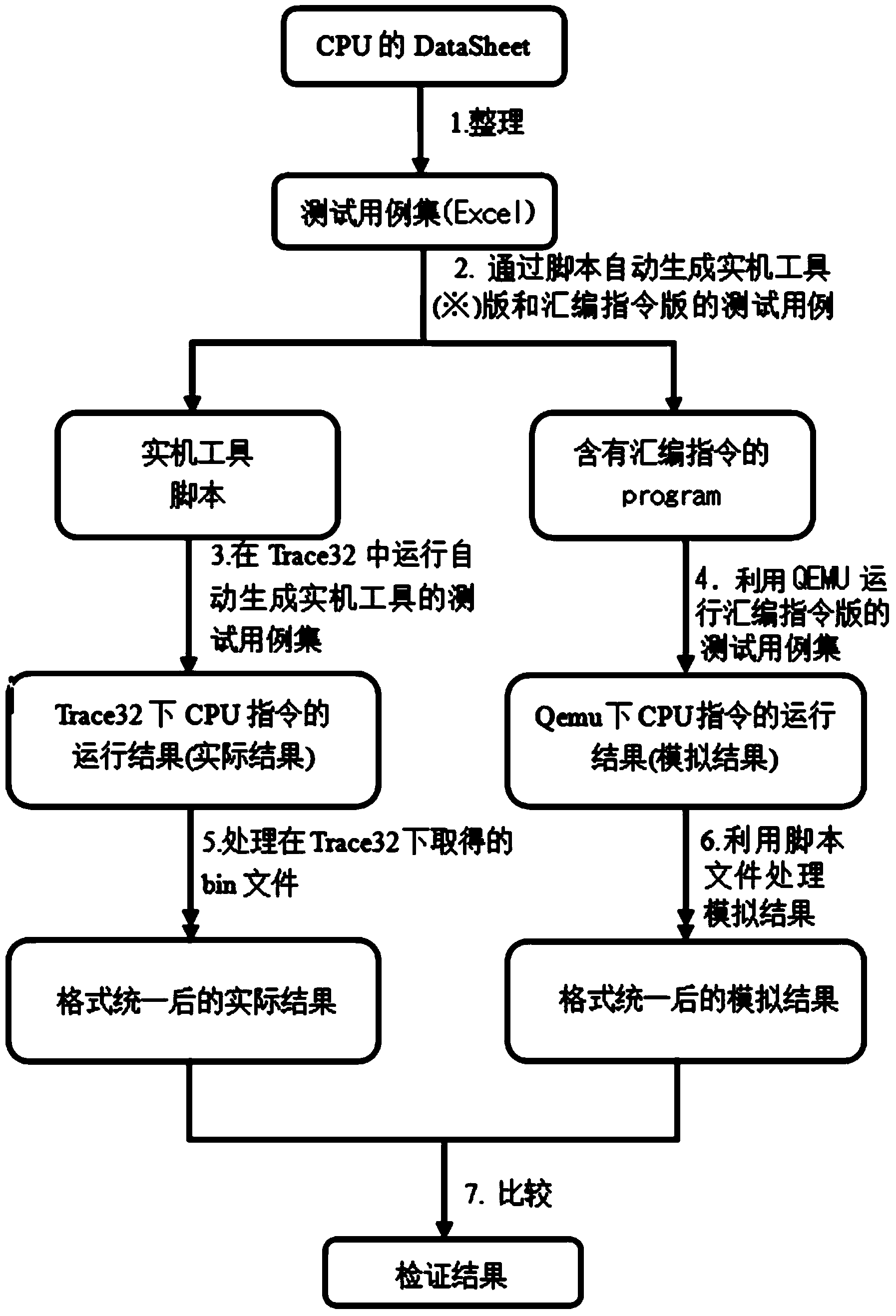

Simulator based automatic functional test implementation method for central processing unit instruction sets

InactiveCN104317715AEasy to create/modify/append/deleteEasy to readSoftware testing/debuggingDatasheetFunctional testing

The invention discloses a simulator based automatic functional test implementation method for central processing unit instruction sets and belongs to the technical field of processors. The method includes the steps of 1), managing DataSheet in a central processing unit and writing out test items in an Excel table; 2), analyzing the Excel table and generating script files for real machine tool and assembling files capable of being recognized by the to-be-tested central processing units; 3), operating the script files by the aid of the real machine tool to obtain actual results; 4), utilizing a hardware simulator to operate the assembling files to obtain simulated results; 5), converting the actual results and the simulated results to a uniform format by the aid of a resolver; 6), comparing the actual results with the simulated results unified in format in the step to generate final test results. The central processing units of optional types can be tested supportively and theoretically, the simulated results can be tested without the actual results obtained by the real machine tool of to-be-simulated hardware products, the central processing units can be matched with optional simulators for test, and the method is rich in test means.

Owner:NANJING FUJITSU NANDA SOFTWARE TECH

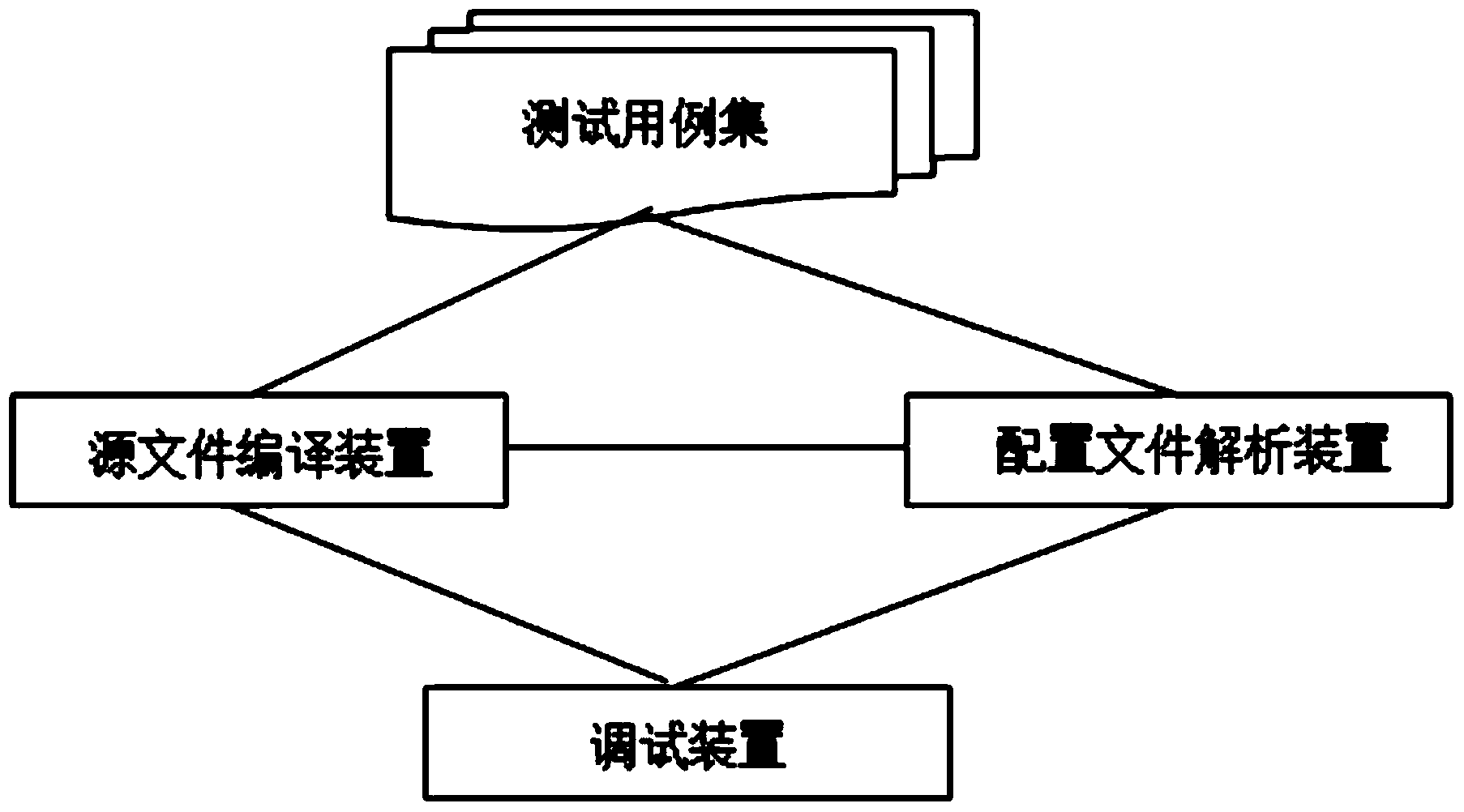

Method for automatically testing C compiler

ActiveCN107329889AFast automated testingReduce work intensitySoftware testing/debuggingIndirect testHardware simulator

The invention discloses a method for automatically testing a C compiler. According to the method, an assembly is embedded into a C source file, and an HEX file obtained through the C compiler, an assembler and a linker in a compiling mode is combined with a lower computer hardware simulator to verify an expected result, so that the aim of verifying a CSCC compiler is achieved. Automatic testing is quickly achieved through the method, the correctness of a tool chain of the whole C compiler is indirectly tested by utilizing the whole IDE development environment, and the problems that the C compiler is used for compiling manually, simulation setting is tedious and the operation speed is low are solved.

Owner:CHIPSEA TECH SHENZHEN CO LTD

Method and apparatus for creating integrated circuit simulator test source files

InactiveUS7386434B1Improve integrityElectrical testingSpecial data processing applicationsComputer hardwareData integrity

An apparatus and method for generating test files for design verification of a simulated integrated circuit design such as a cache memory circuit, that involve steps of creating a series of functions, updating a data integrity buffer after each function is created, creating a series of integrity check functions from the data in the data integrity buffer, and writing the series of functions and the series of integrity check functions to a test file. This file can be compiled if necessary and executed by a software or hardware simulator.

Owner:UNISYS CORP

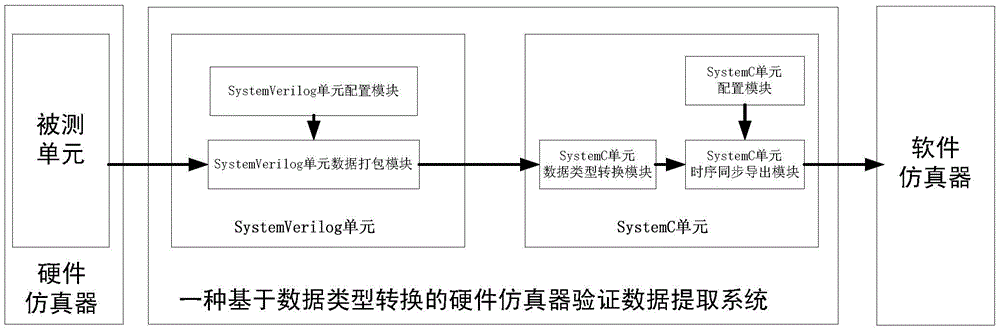

Data type conversion-based hardware simulator validation data extraction system

ActiveCN105653409ASimple structureEasy to implementFaulty hardware testing methodsSystemCData ingestion

The invention provides a data type conversion-based hardware simulator validation data extraction system. The system comprises a SystemVerilog unit and a SystemC unit, wherein the SystemVerilog is used for receiving input data sent from an external hardware simulator, checking the input data, packing the data into a data package and then sending the data package to the SystemC unit; and the SystemC unit is used for 6 data types defined in SystemVerilog into 6 data types defined in SystemVerilog according to a one-to-one corresponding manner, sending the data package to a software simulator according to the simulation precision of the software simulator, extracting the running result of a tested unit running on the hardware simulator with relatively high efficiency, and comparing the running result with a structure preset in the software simulator on a workstation so as to realize the determination of the running result of the tested unit. The method has the advantages of being flexible in data package, high in simulation speed and flexible in software simulator interface.

Owner:BEIJING MXTRONICS CORP +1

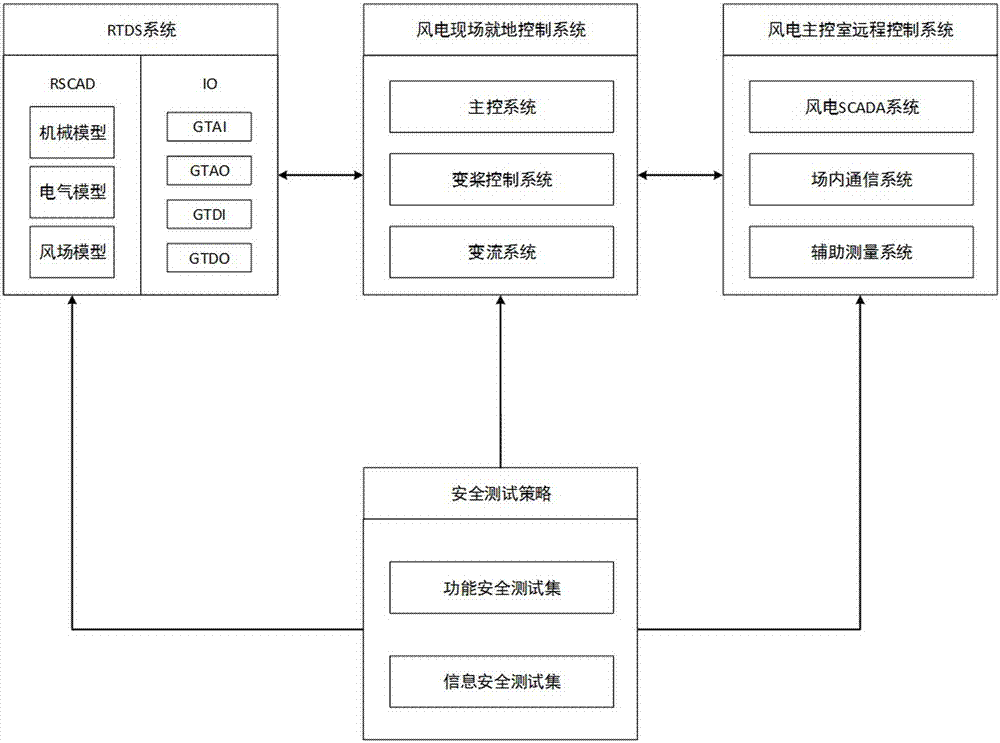

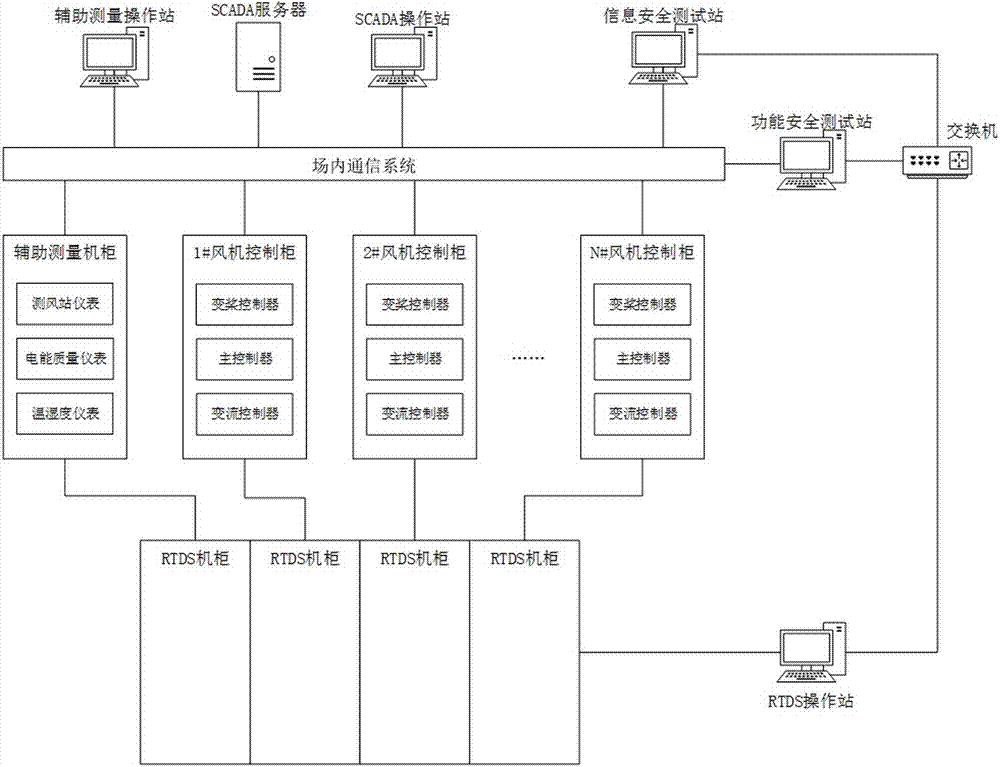

Wind power control system function and information safety test system and device based on RTDS

InactiveCN107544456AAddress effectivenessSolve the problem of verifying the platformElectric testing/monitoringData connectionTest platform

The invention discloses a wind power control system function and information safety test platform and a test method based on an RTDS, which relate to the technical field of simulation test. An RTDS hardware-in-the-loop simulation system and a wind power main control room remote control system which are in data connection through a wind power field local control system are included. The RTDS systemcomprises RSCAD simulation software and a hardware simulator; the hardware simulator comprises an I / O interface; the RSCAD simulation software is used for compiling and designing a wind turbine generator simulation model; the RTDS hardware-in-the-loop simulation system carries out simulation on the wind turbine generator and the field environment thereof, the hardware-in-the-loop simulation function of an actually-controlled object and the physical process is realized, the RTDS hardware-in-the-loop simulation technology is used, the real wind power control system used in the field is combined, a function safety test set and an information safety test set are designed, influences possibly caused to the running wind power control system by hidden safety dangers are evaluated, and whether the control system and the information system of the wind power control system meet the national standard can be verified in a key mode.

Owner:中国东方电气集团有限公司

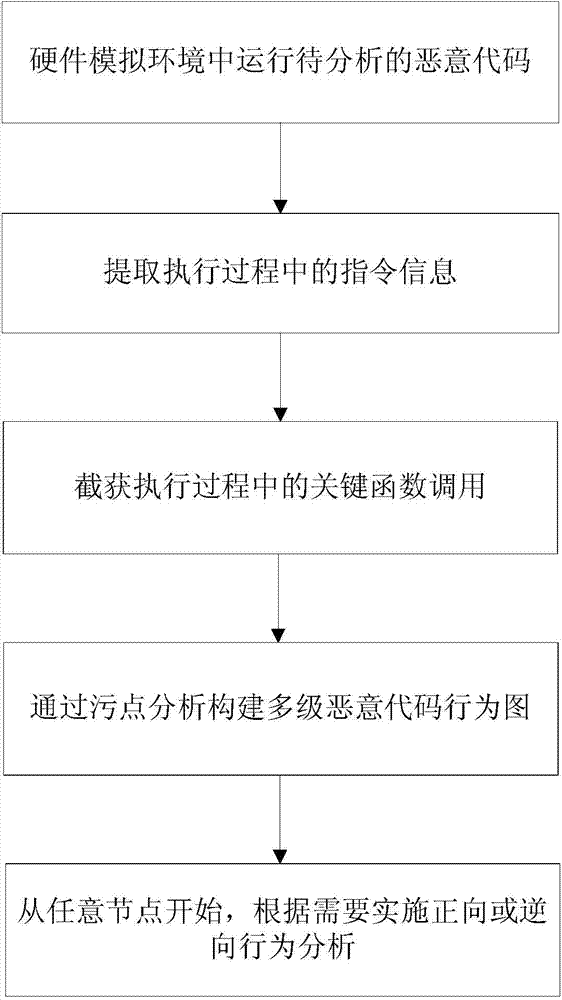

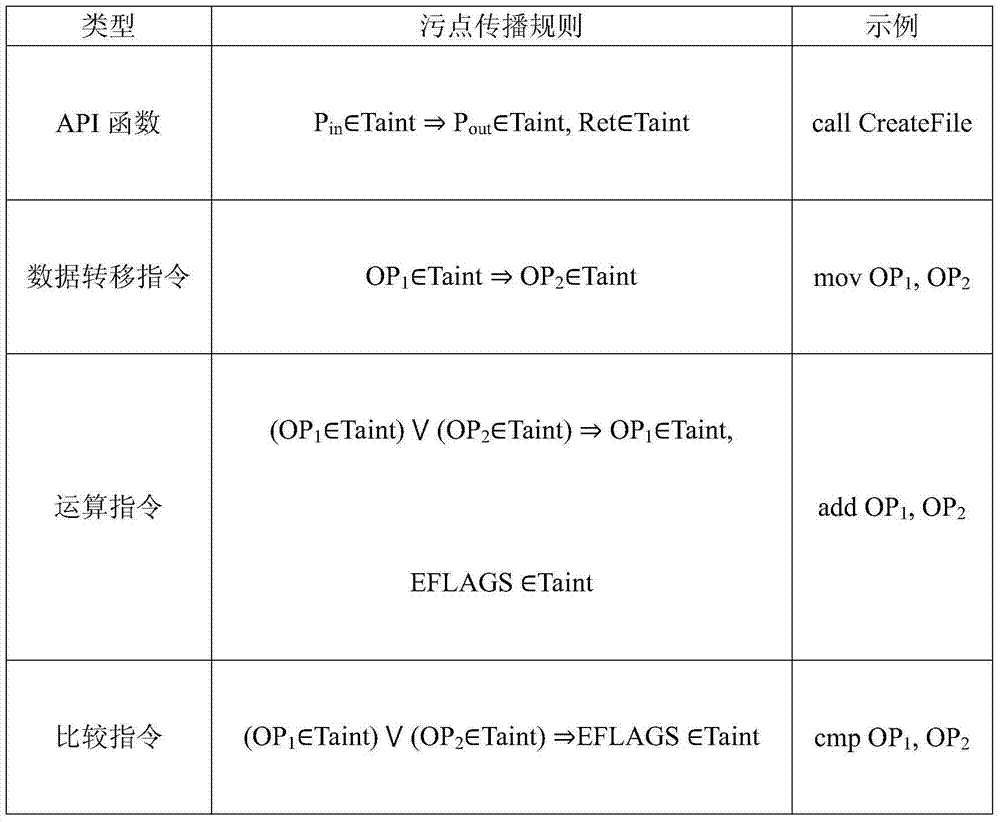

Method and system for dynamic multilevel behavioral analysis of malicious code

InactiveCN104850781AImprove behavioral analysis skillsAnalysis helpsPlatform integrity maintainanceBehavioral analyticsHardware simulator

The invention relates to a method and a system for dynamic multilevel behavioral analysis of malicious code. The method comprises the following steps of running the malicious code in a hardware simulator, and extracting command information executed by the malicious code in a running process; intercepting a key function executed by the malicious code in a simulation memory of the hardware simulator in the running process of the malicious code; constructing a multilevel malicious code behavior diagram according to the obtained command information and the key function information of the malicious code; and utilizing the multilevel malicious code behavior diagram to carry out forward or adverse behavioral analysis from any node according to the analysis requirement. The system comprises the hardware simulator, a command information extraction module, a function information extraction module, a behavior diagram construction module and a behavioral analysis module. According to the method and the system, the analytical ability of a behavior mechanism of the malicious code is improved to provide a sufficient support for detection and prevention of the malicious code.

Owner:INST OF INFORMATION ENG CAS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com