Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

173 results about "Hardware emulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In integrated circuit design, hardware emulation is the process of imitating the behavior of one or more pieces of hardware (typically a system under design) with another piece of hardware, typically a special purpose emulation system. The emulation model is usually based on a hardware description language (e.g. Verilog) source code, which is compiled into the format used by emulation system. The goal is normally debugging and functional verification of the system being designed. Often an emulator is fast enough to be plugged into a working target system in place of a yet-to-be-built chip, so the whole system can be debugged with live data. This is a specific case of in-circuit emulation.

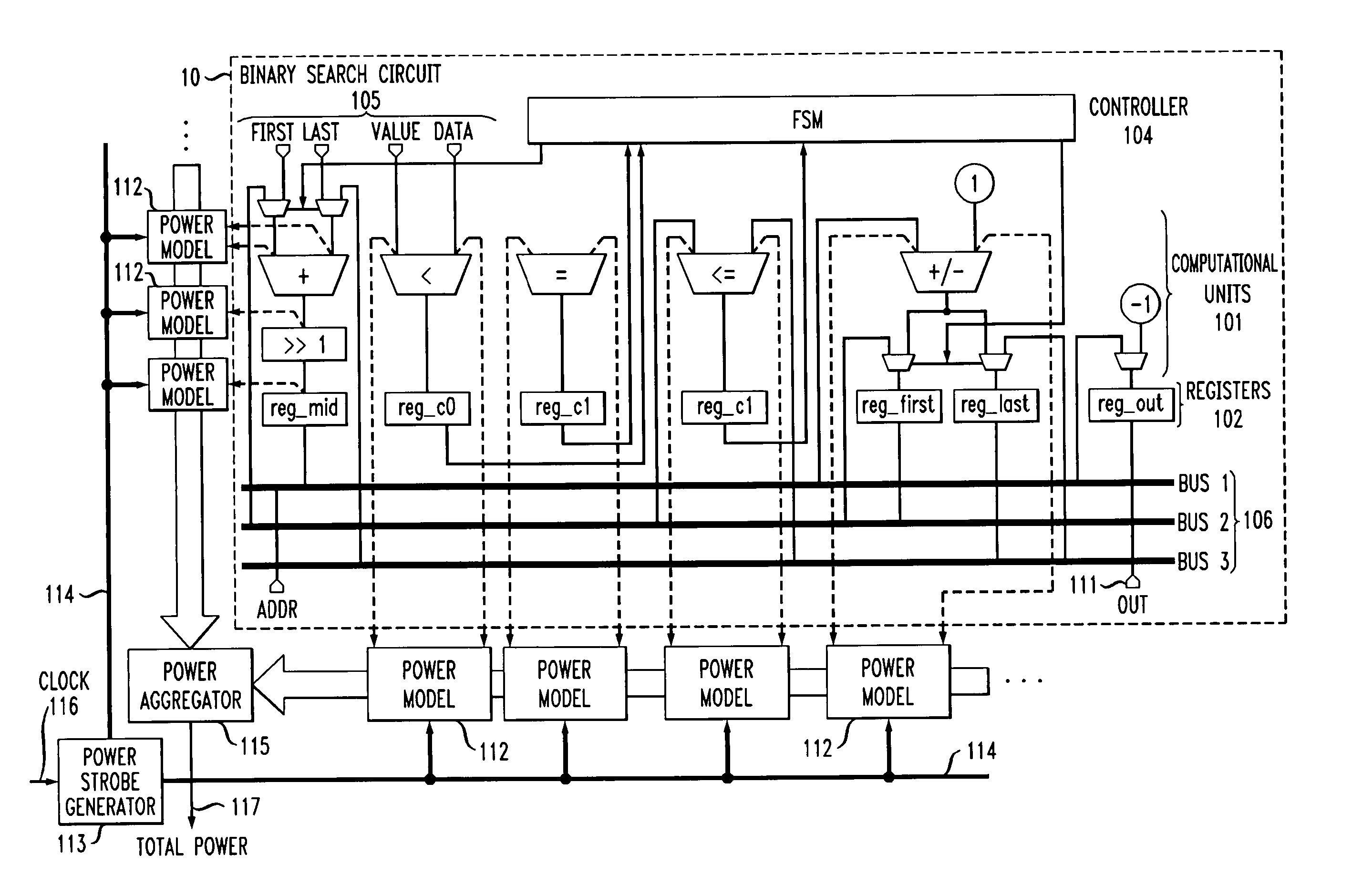

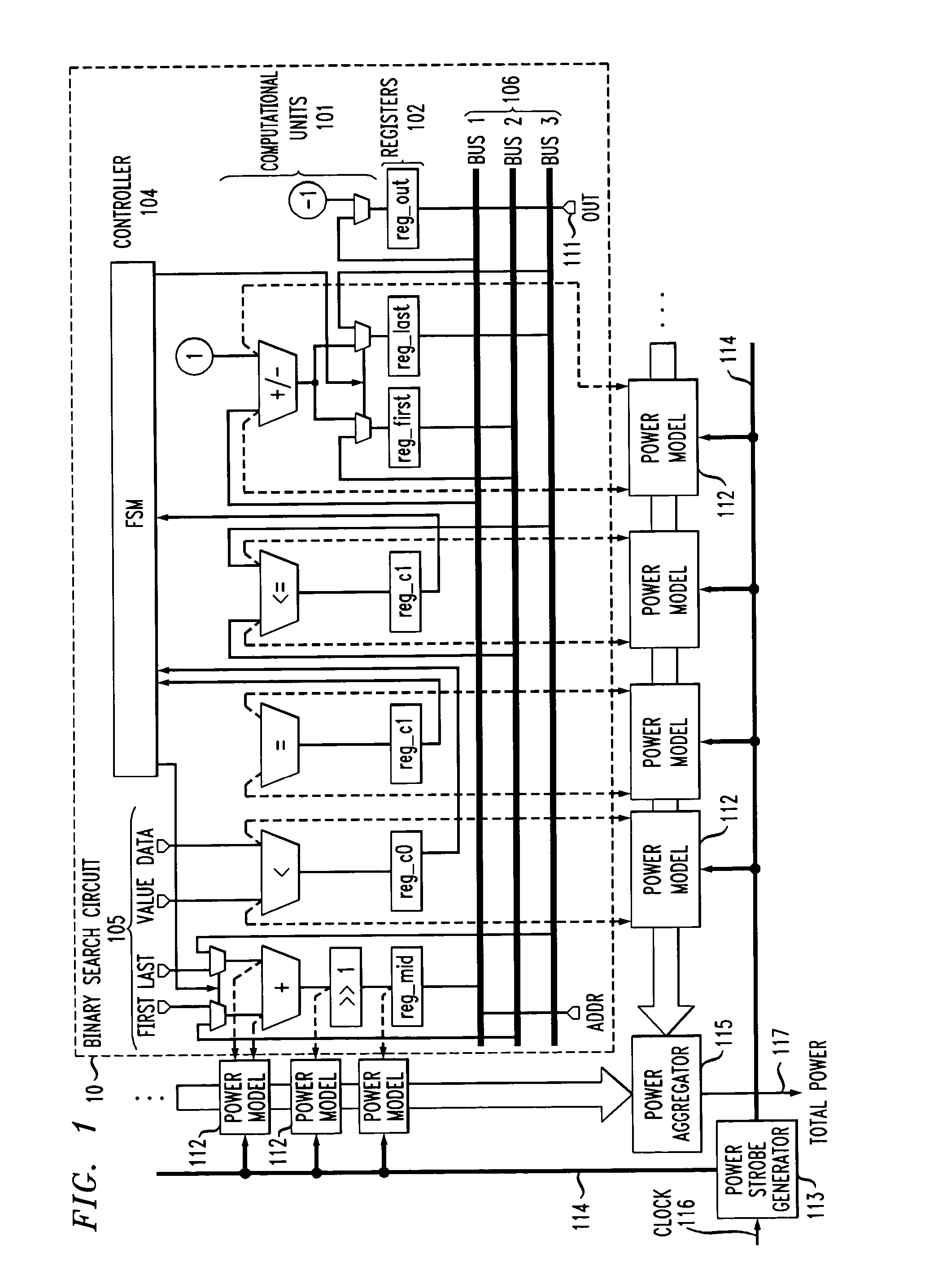

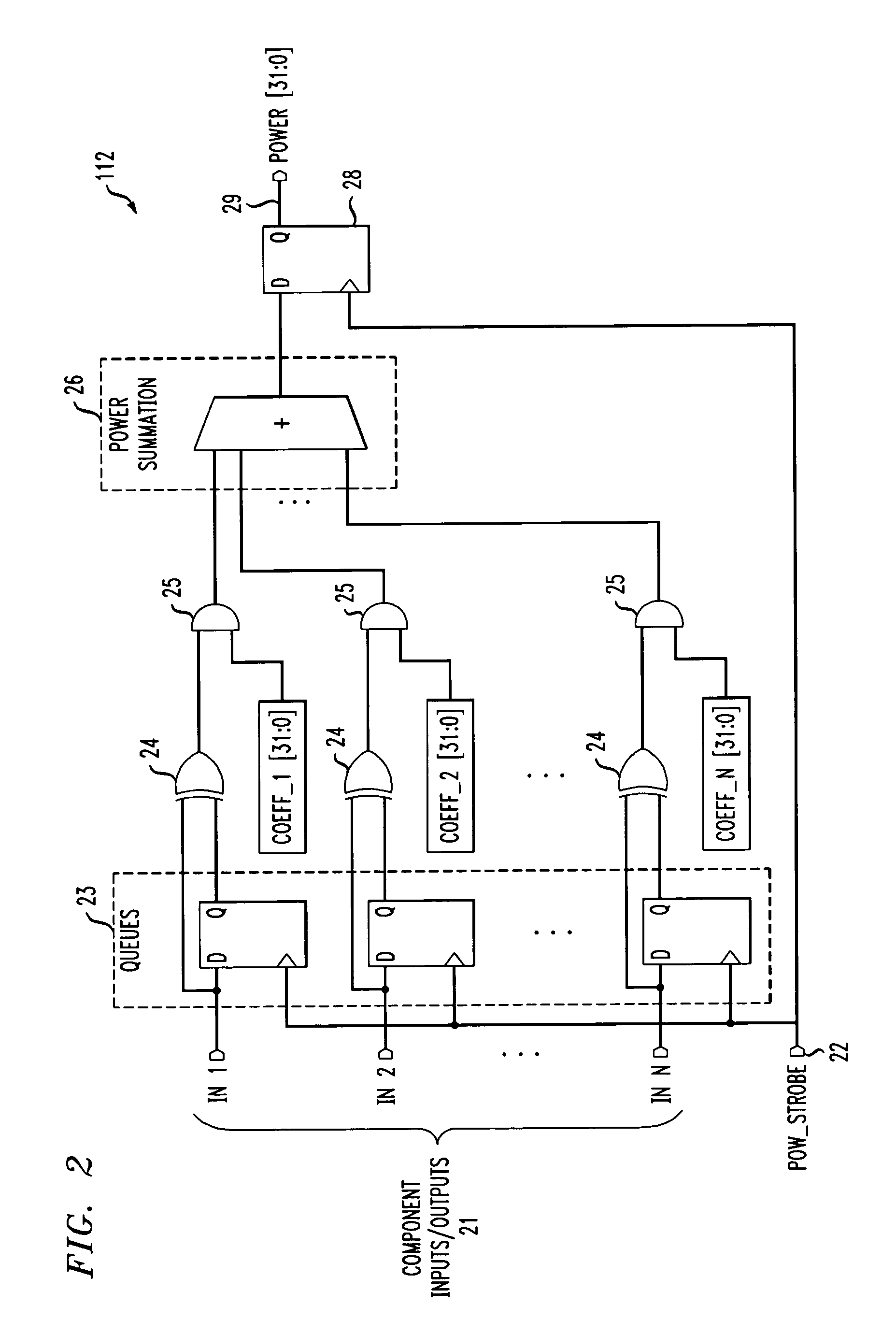

Power estimation through power emulation

InactiveUS20060058994A1Shorten the timeIncrease the areaCAD circuit designSoftware simulation/interpretation/emulationHardware emulationCircuit design

The time required to estimate the amount of power that will be consumed by a circuit under design is significantly speeded up. Specifically, the steps involved in power estimation (power model evaluation, aggregation) are implemented as power estimation circuitry that is added to the design of the functional circuit during circuit design. The resulting power-model-enhanced circuit is mapped onto a hardware emulation platform, one of whose outputs is a computation of the estimated power computed by the power estimation circuitry during the emulation. As compared to state-of-the-art commercial power estimation tools, speed-ups from around 10-fold to over 500-fold can be realized.

Owner:NEC LAB AMERICA

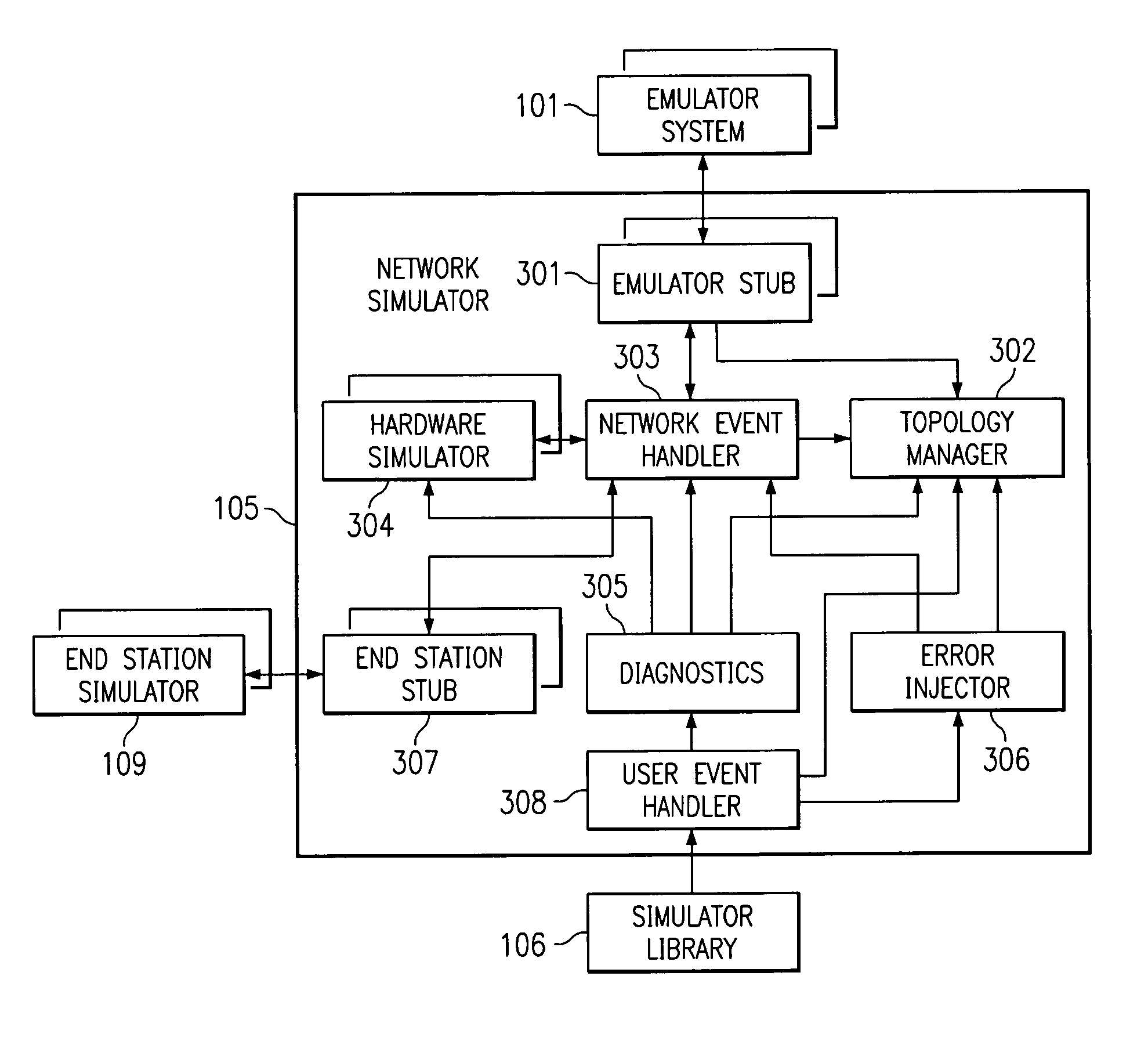

Method and system for hardware simulation

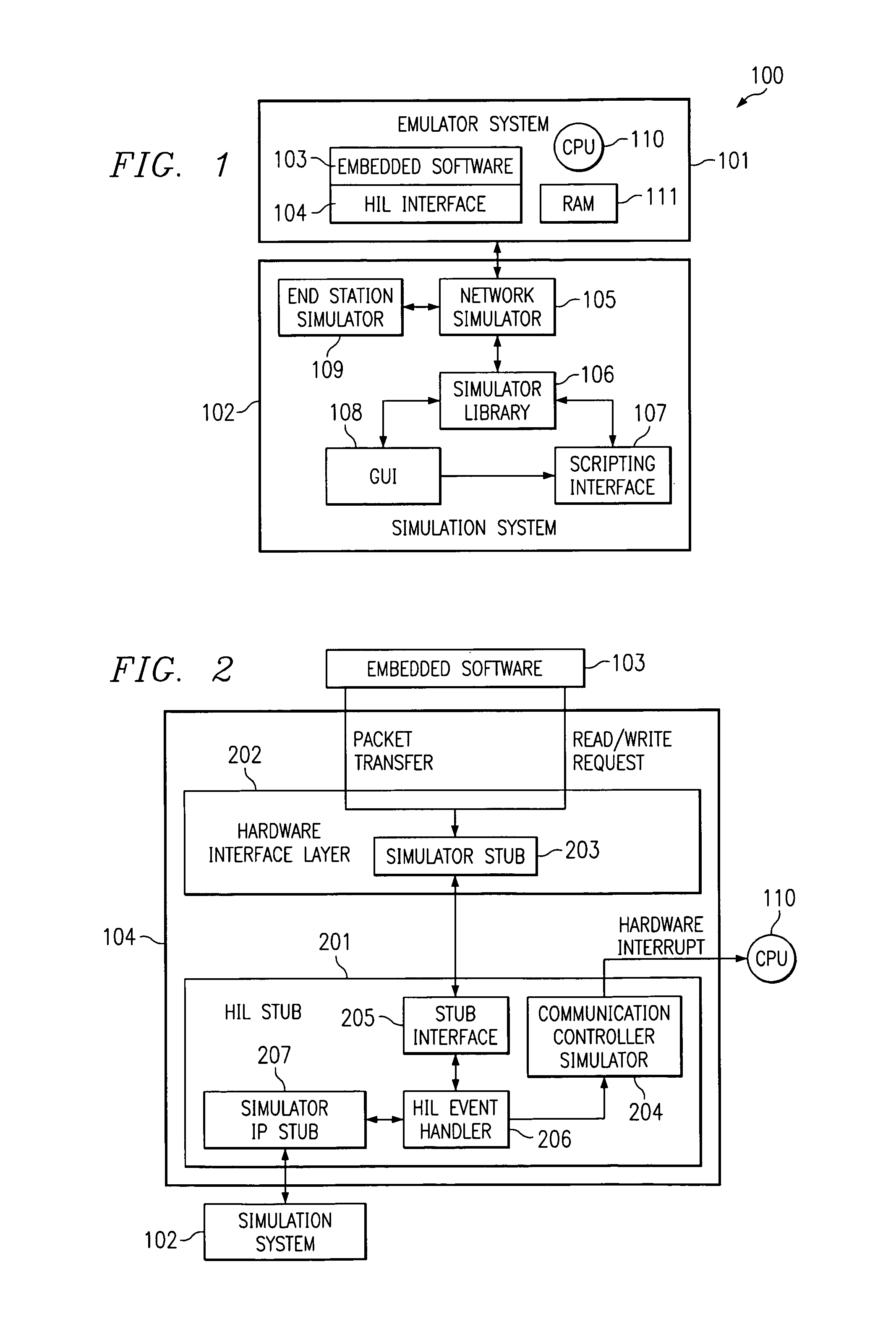

InactiveUS7047176B2Easy to readAnalogue computers for electric apparatusDigital computer detailsNetworked systemEmbedded software

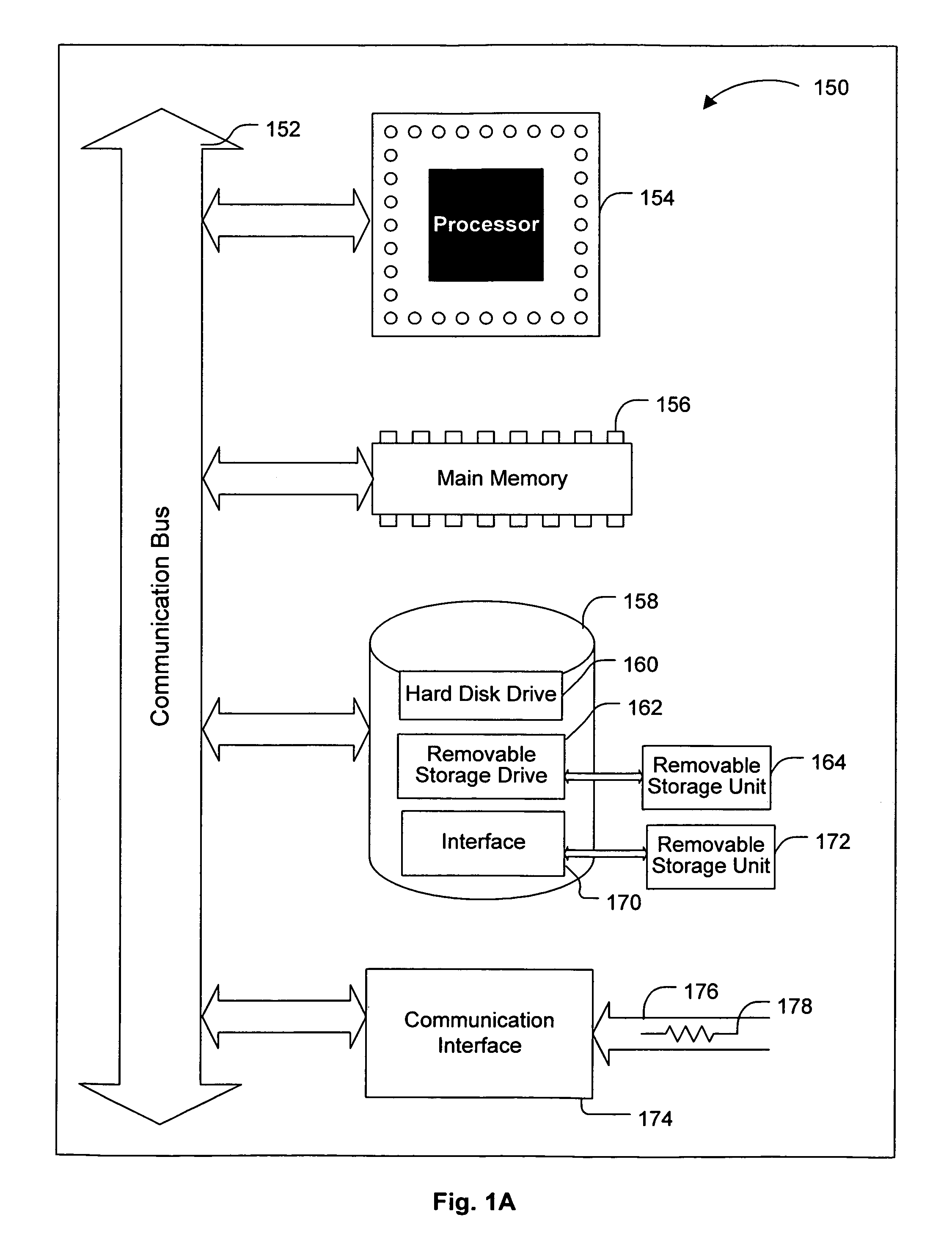

A system and method for simulating a networked system for testing of embedded software on an emulated hardware device. The system provides for automated generation of a simulated hardware and facilitates testing of embedded software response to simulated error conditions created by the simulated hardware. Communications from the embedded software are intercepted at a low software level and redirected from the emulated hardware device to the simulated hardware.

Owner:FUJITSU LTD

Dynamic-Verification-Based Verification Apparatus Achieving High Verification Performance and Verification Efficiency and the Verification Methodology Using the Same

InactiveUS20080306721A1Improve efficiencyImprove performanceFunctional testingSpecial data processing applicationsSimulation basedHardware emulation

The present invention relates to a simulation-based verification apparatus and a verification method, which enhance the simulation performance and efficiency greatly, for verifying a digital system containing at least million gates. Also, the present invention relates to a simulation-based verification apparatus and a verification method used together with formal verification, simulation acceleration, hardware emulation, and prototyping to achieve the high verification performance and efficiency for verifying a digital system containing at least million gates.

Owner:YANG SEI YANG

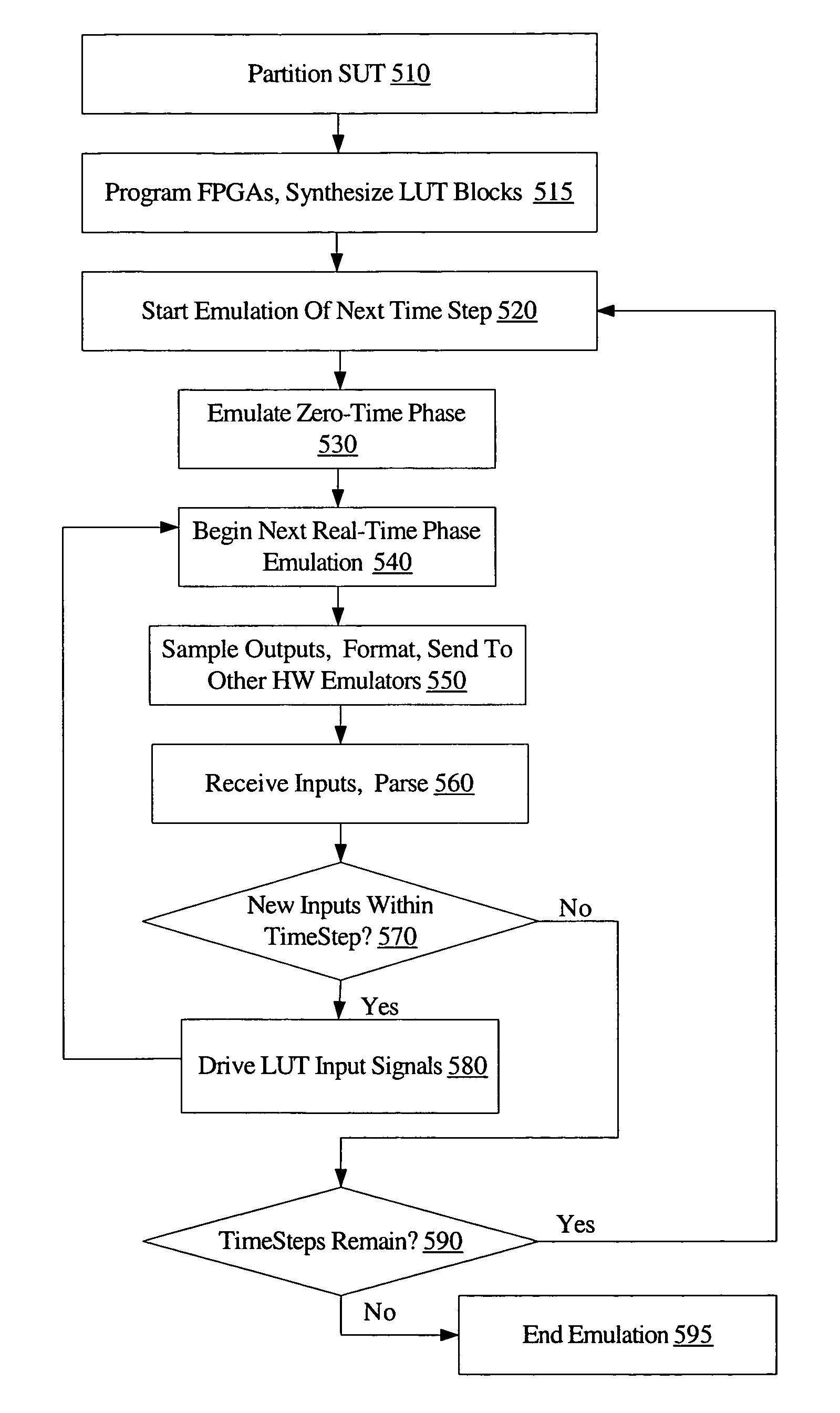

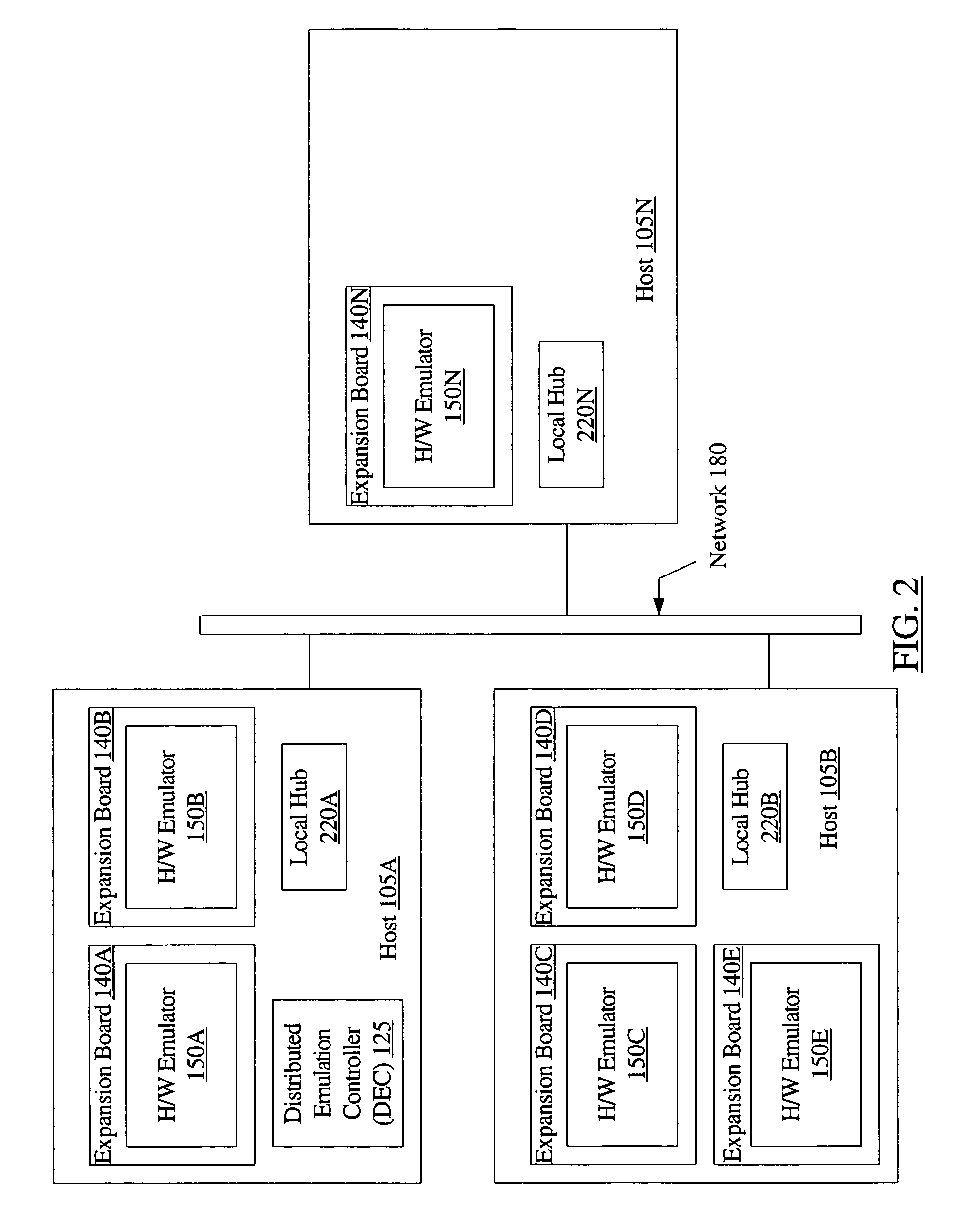

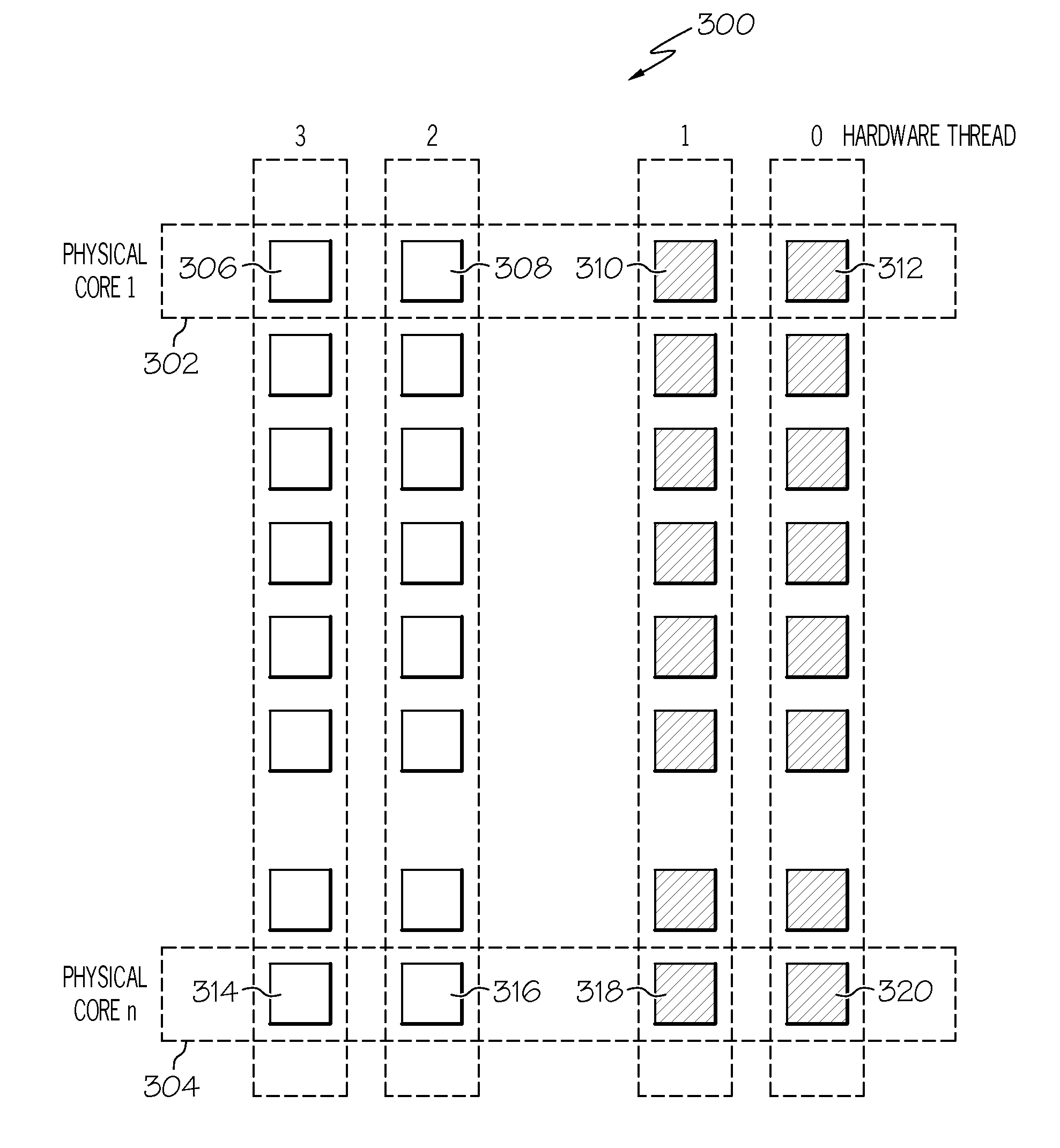

Applying distributed simulation techniques to hardware emulation

ActiveUS7480609B1Analogue computers for electric apparatusComputer aided designSoftware emulationSystem under test

A system for applying distributed software simulation techniques to hardware emulation may include a first hardware emulator mounted on a first expansion board at a first host, and a second hardware emulator mounted on a second expansion board at a second host. The first hardware emulator may be configured to emulate a first portion of a system under test, and the second hardware emulator may be configured to emulate a second portion of the system under test, and the first and second hardware emulators may coordinate an emulation of the system under test using one or more messages, i.e., a coordination of an emulation of the system under test may be accomplished using communications between the first and second hardware emulators.

Owner:ORACLE INT CORP

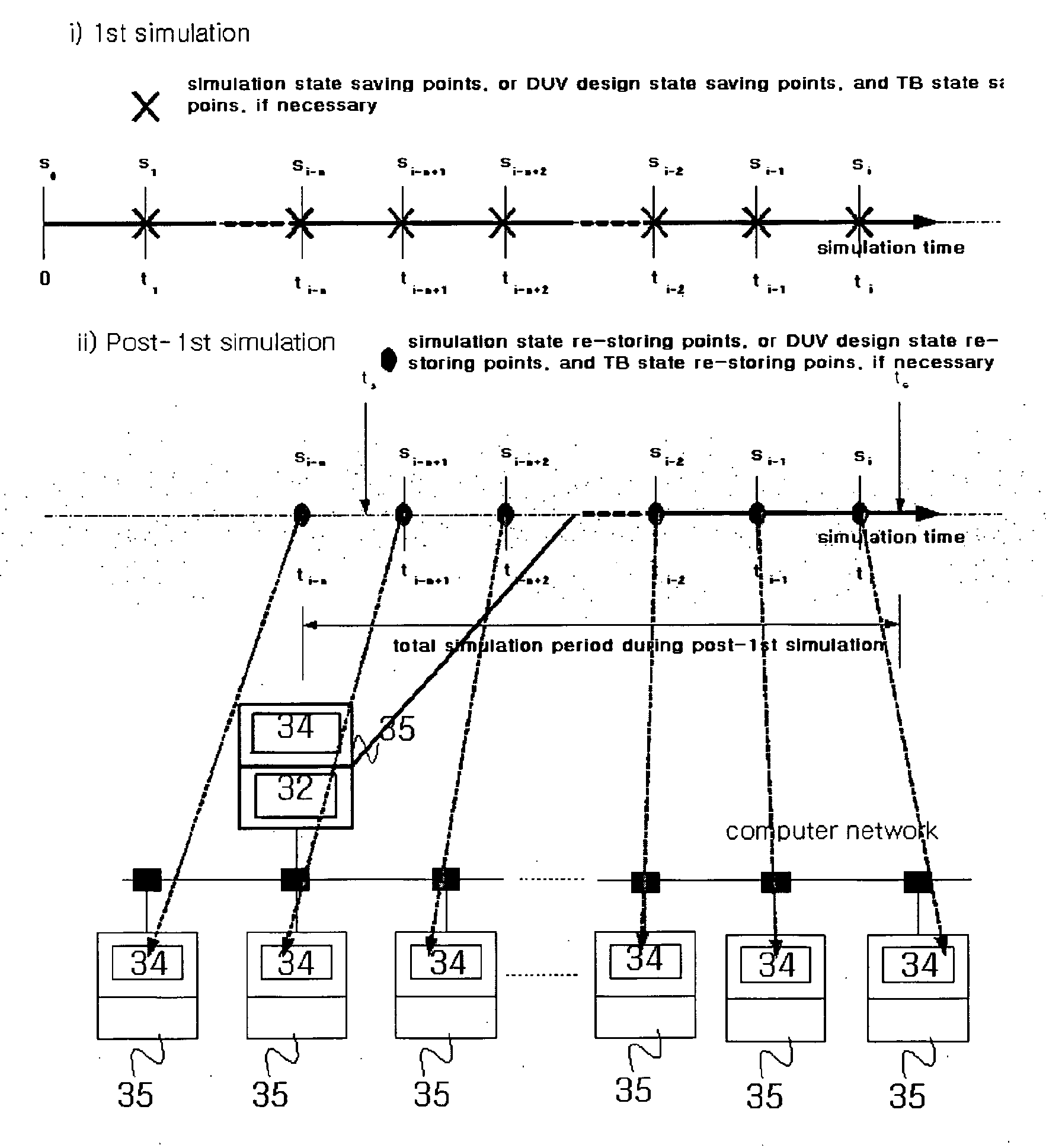

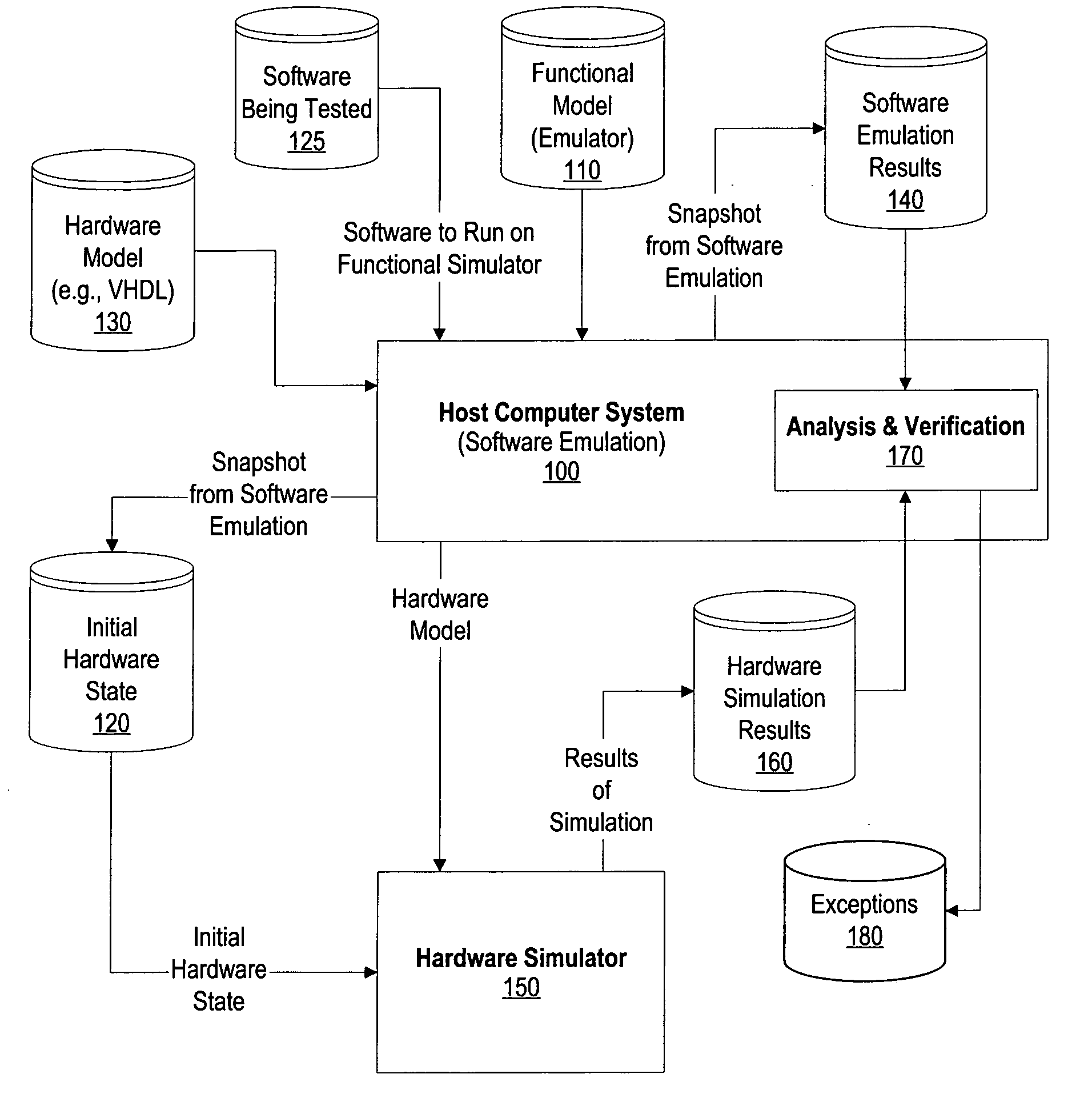

System and method for improved software simulation using a plurality of simulator checkpoints

InactiveUS20060155525A1CAD circuit designSoftware simulation/interpretation/emulationSoftware emulationParallel computing

A system and method is provided to improve software simulation. A software emulator is used in conjunction with a hardware simulator. A special snapshot instruction is included in the software code that is emulated. When the snapshot instruction is encountered, values such as register, memory, and program stack values, are stored creating an initial snapshot. Code continues to be emulated and, when the next snapshot instruction is encountered, the values are written to create a second snapshot. The initial values are used to set an initial state in a hardware model that is simulated on a hardware simulator. The results of the hardware simulation are compared to the second snapshot to uncover software errors and / or hardware errors so that the software can be modified or the hardware design can be modified. Multiple sets of snapshots can be taken to analyze multiple sections of the software program.

Owner:IBM CORP

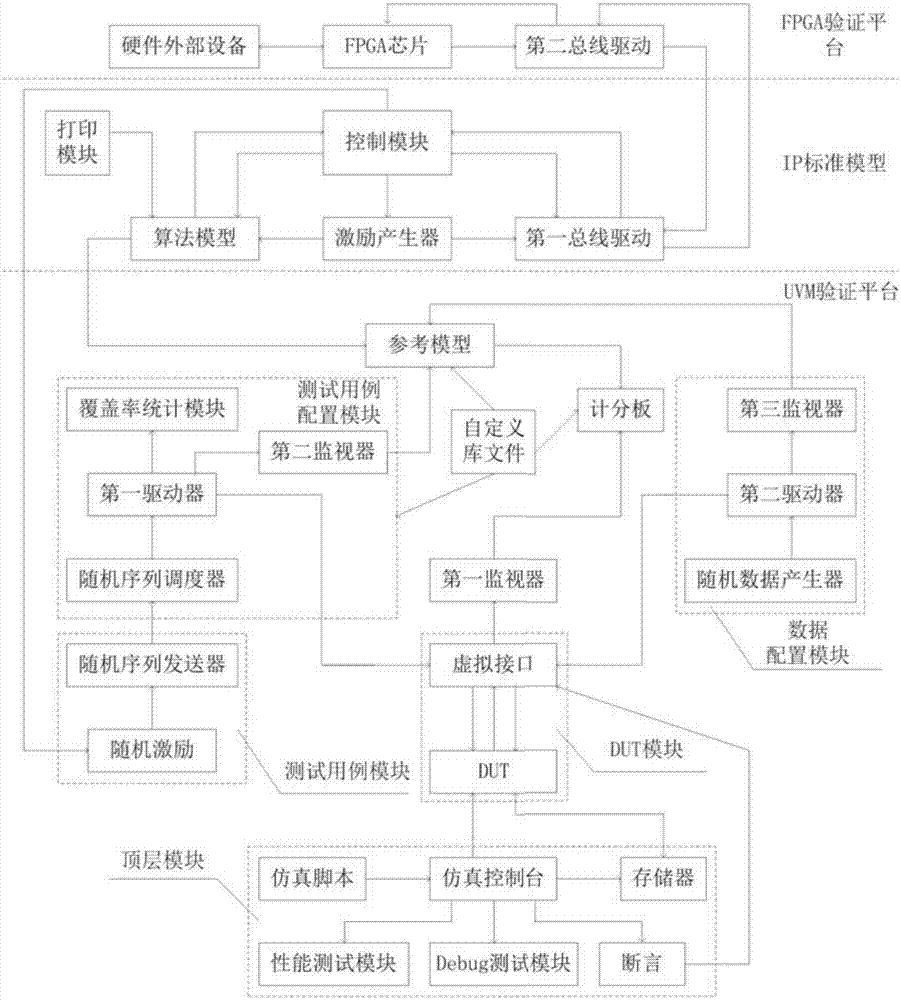

Chip software and hardware simulation environment based on UVM and FPGA

ActiveCN107463473AExtended cycleQuality improvementFunctional testingFaulty hardware testing methodsComputer hardwareHardware emulation

The invention discloses a chip software and hardware simulation environment based on the UVM and the FPGA. The simulation environment comprises an FPGA verification platform, a UVM verification platform and an IP standard model. The IP standard model is connected with the FPGA verification platform, and the FPGA is driven to perform simulation verification and sends the FPGA verification result as scene environment configuration to the UVM verification platform. The UVM verification platform is connected with the IP standard model and calls an algorithm in the IP standard model to perform UVM simulation verification to the FPGA verification result. According to the chip software and hardware simulation environment based on the UVM and the FPGA, the IP standard model is connected with the FPGA verification platform and the UVM verification platform, and the software and hardware simulation environment which performs FPGA verification and UVM verification simultaneously is prepared. The FPGA verification focuses on the chip application layer and completes verification of a chip code to a lot of random excitation scenes; the UVM verification focuses on the chip bottom layer and performs further verification to the FPGA verification result by directly calling the algorithm in the IP standard model; the two kinds of verification are mutually matched, the verification period of the chip is accelerated, and the chip verification quality is improved.

Owner:ZHUHAI HUGE IC CO LTD

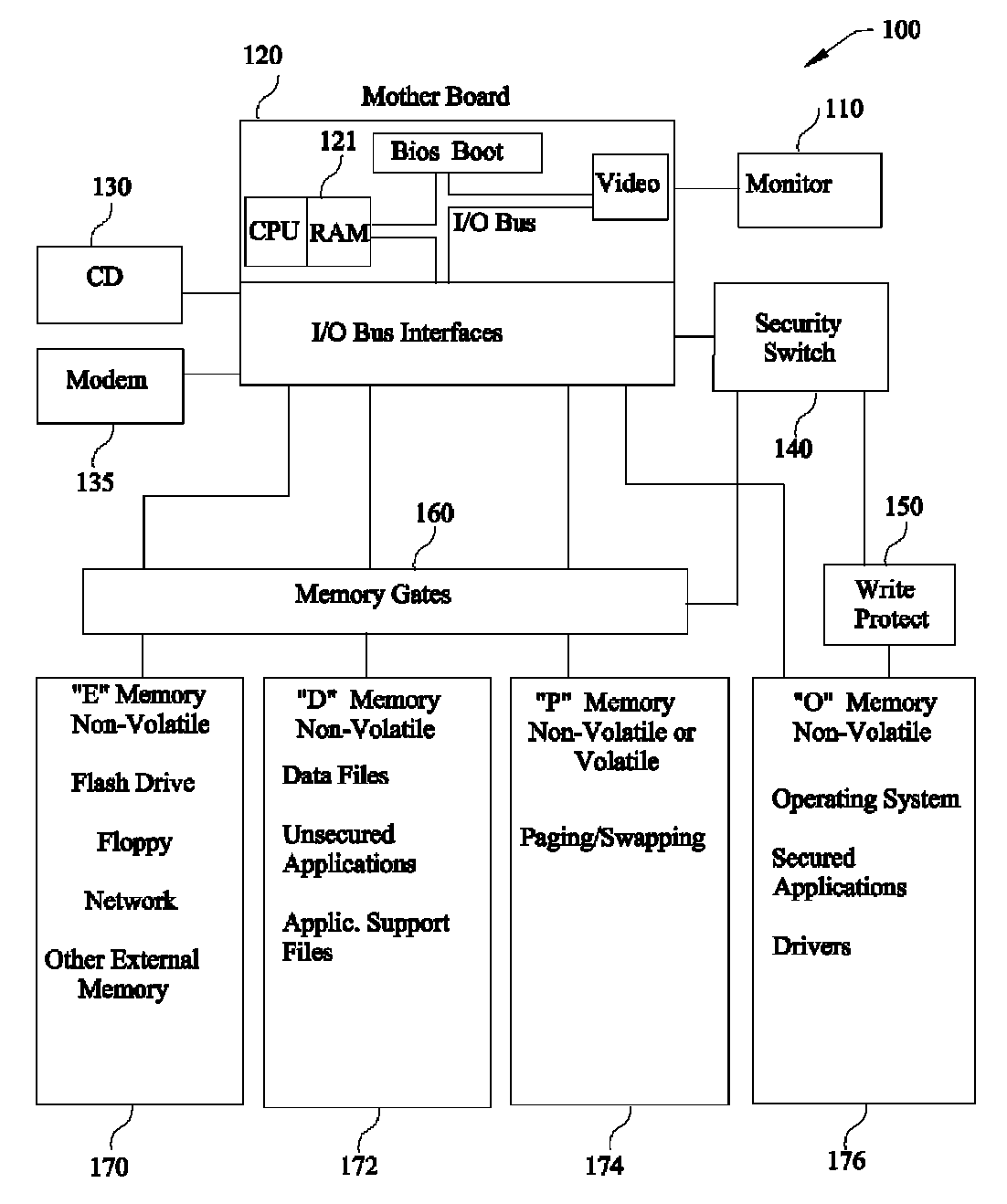

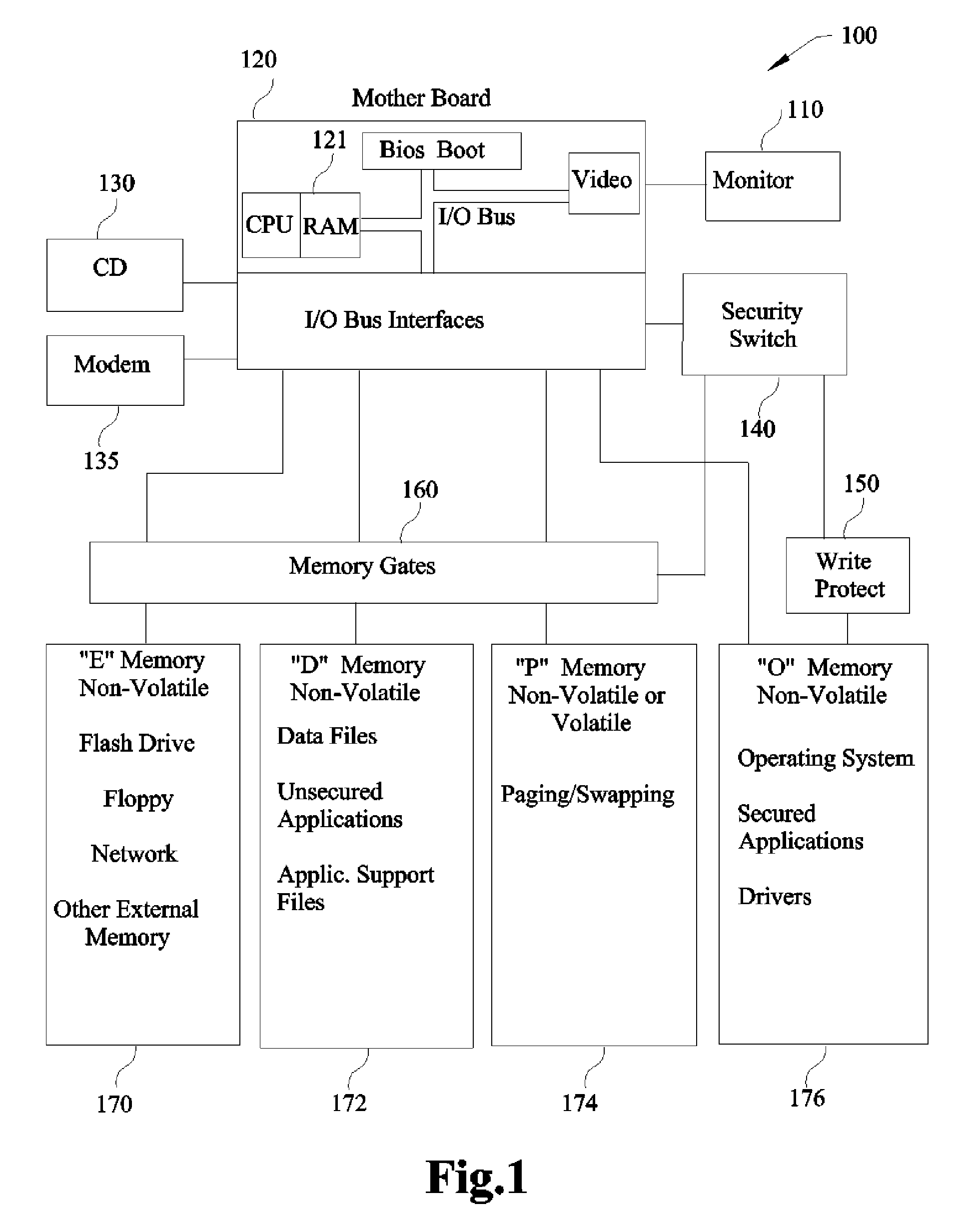

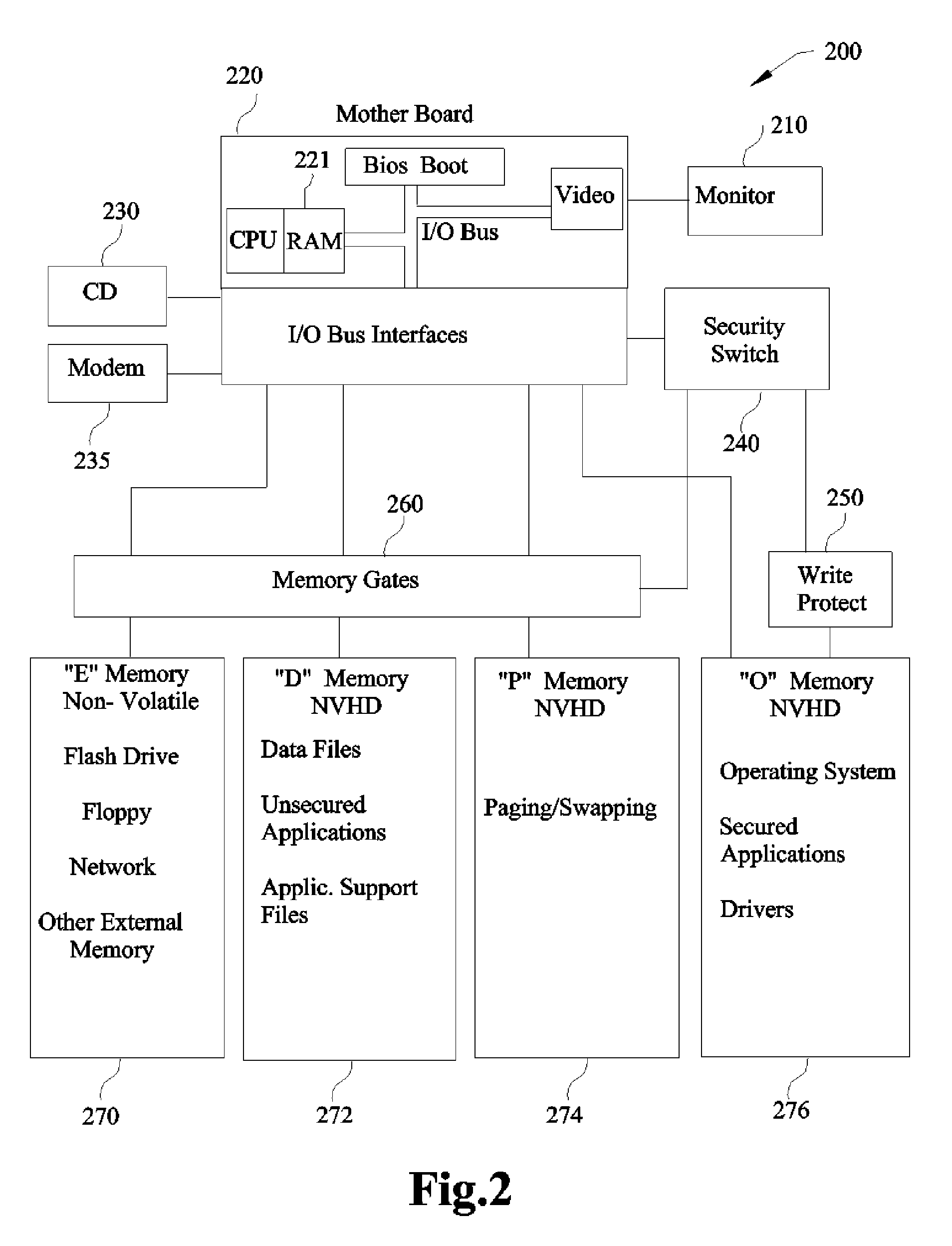

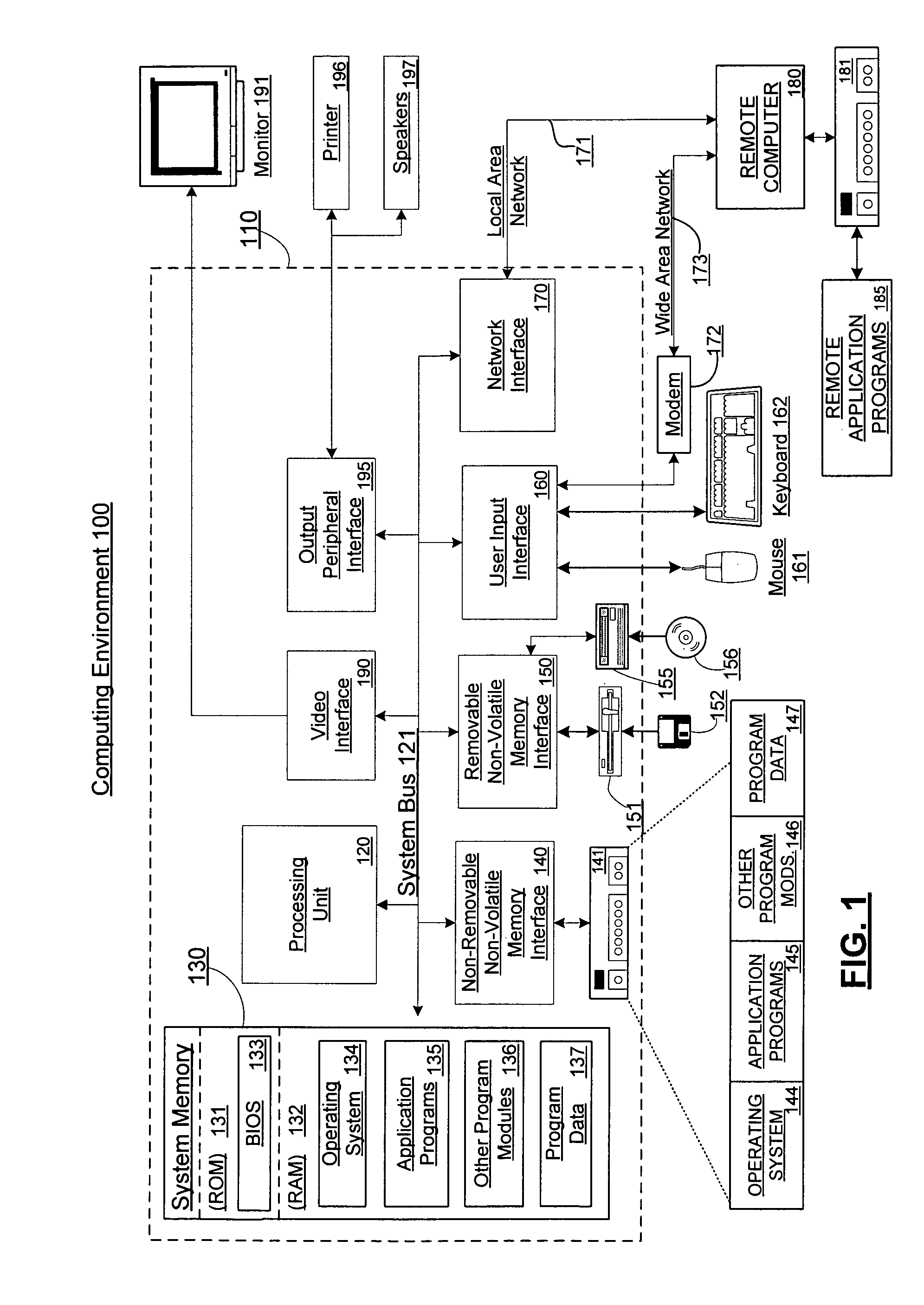

Protecting computers from malware using a hardware solution that is not alterable by any software

InactiveUS8082585B1Memory loss protectionDigital data processing detailsComputer hardwareOperational system

A Computer System that protects itself from Malware by assuring the security of critical software elements including but not limited to Operating Systems, Applications and I / O Drivers. These critical software elements cannot be altered by Malware during normal operation of the Computer especially when connected to the Internet, the primary vehicle for malware. When deviating from normal computer operation such as downloading updated Operating Systems or secured Applications, this invention erases or blocks all memory that could possibly be contaminated with Malware from affecting the critical software elements. This invention is unique because the Malware protection is invoked and implemented by hardware not alterable by any software, or dependent on understanding existing or new Malware.

Owner:GIVONETTI RAYMOND R

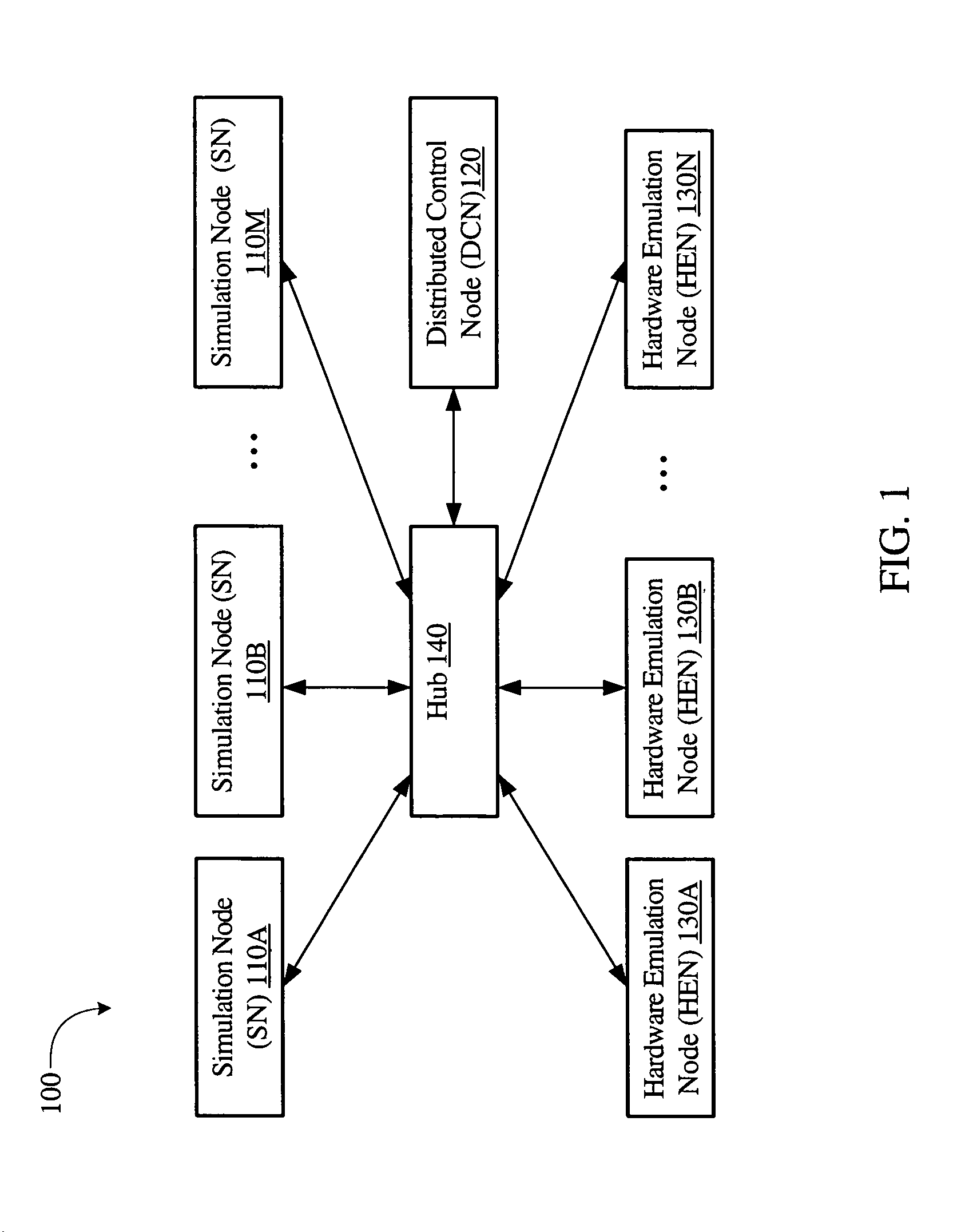

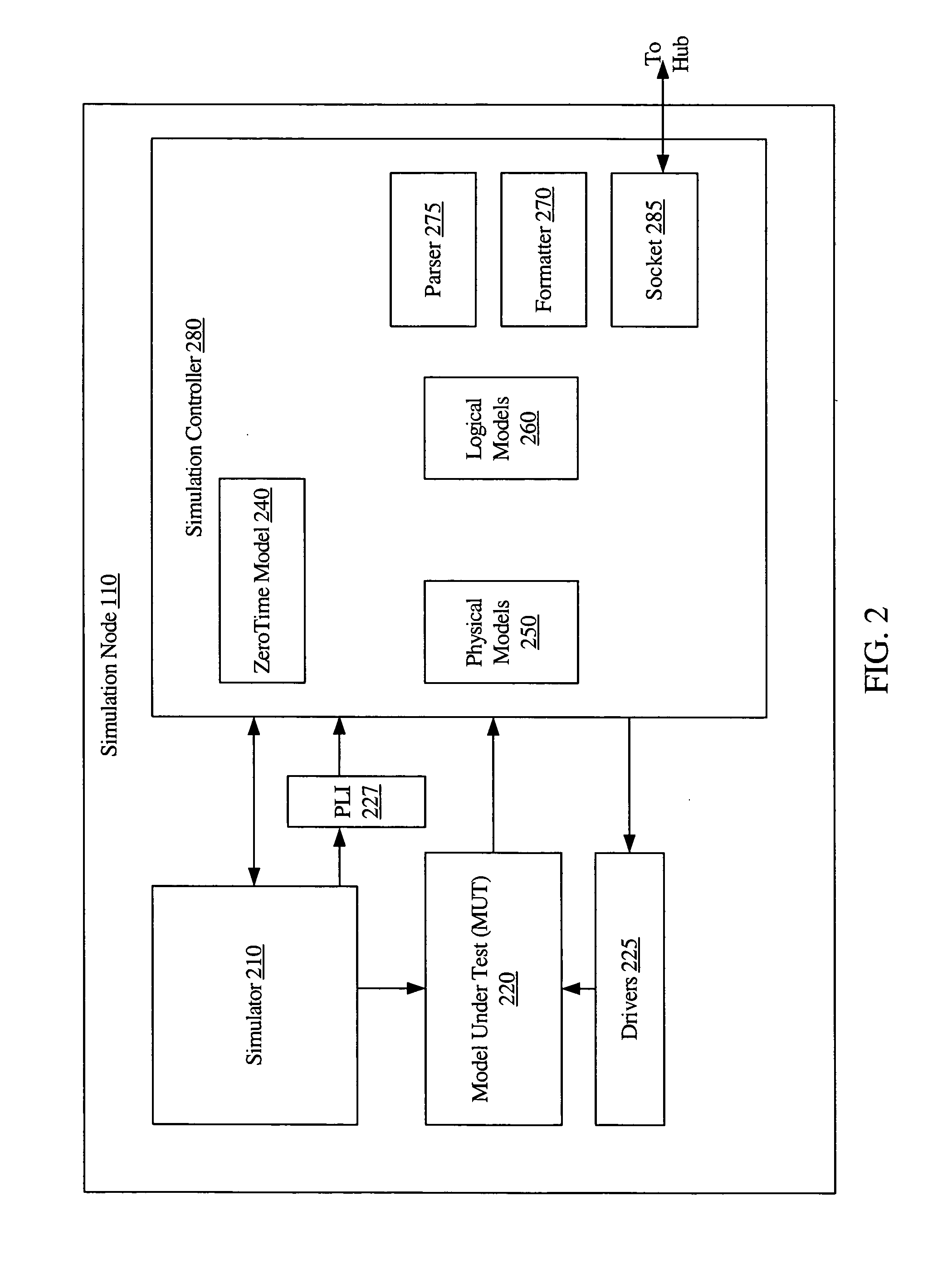

Interfacing hardware emulation to distributed simulation environments

ActiveUS7424416B1Analogue computers for electric apparatusCAD circuit designSoftware emulationSystem under test

A system for interfacing hardware emulation to software simulation environments may include a simulation node configured to simulate a first portion of a system under test and a hardware emulation node configured to emulate a second portion of the system under test. The hardware emulation node may also be configured to exchange simulation information (such as representations of signal values obtained as output from the emulated portion of the system under test) with the simulation node. The hardware emulation node may contain a field programmable gate array devices (FPGA) configured to perform the hardware emulation. The FPGA may be mounted on an expansion board, such as a PCI (Peripheral Component Interconnect) board.

Owner:ORACLE INT CORP

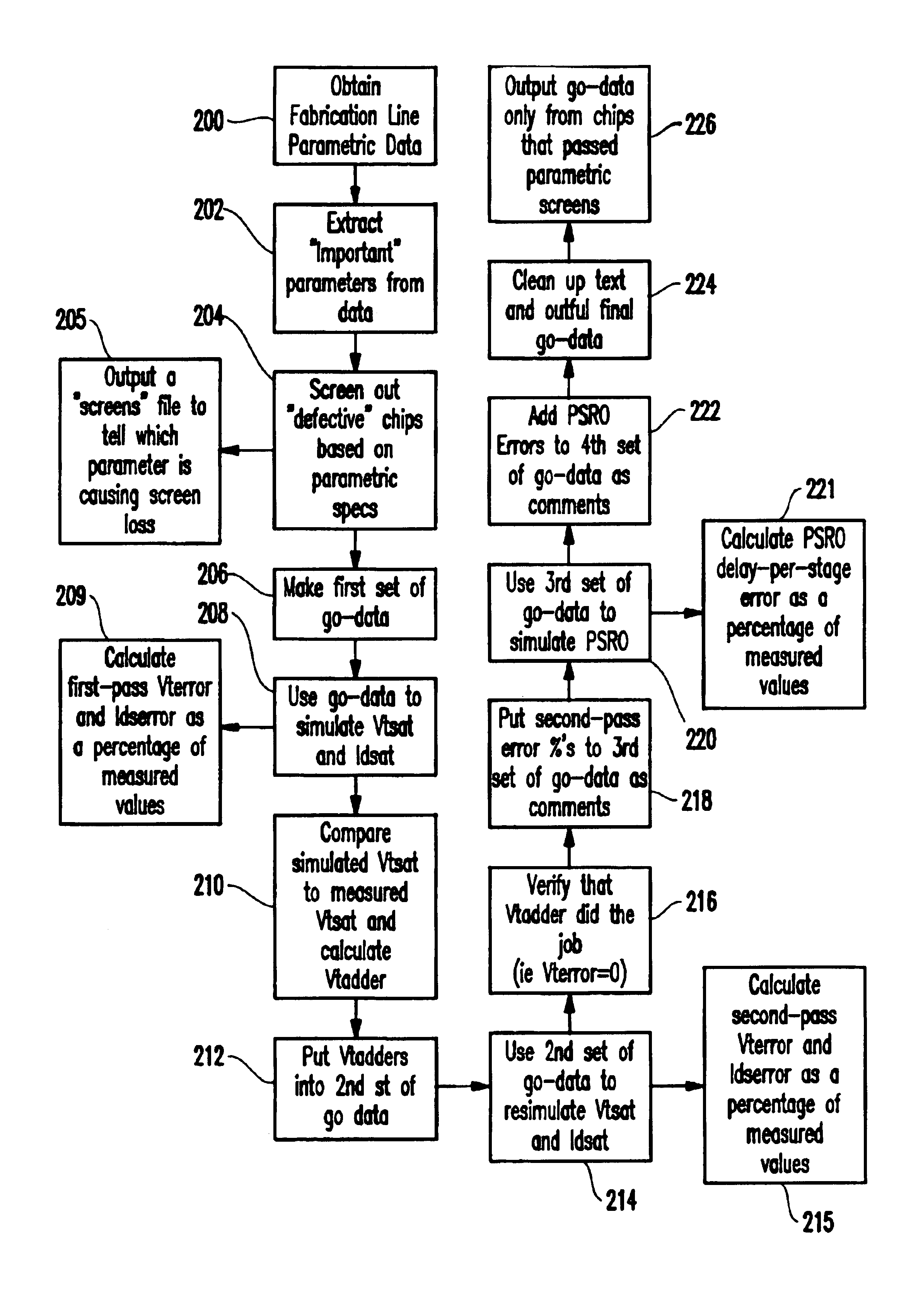

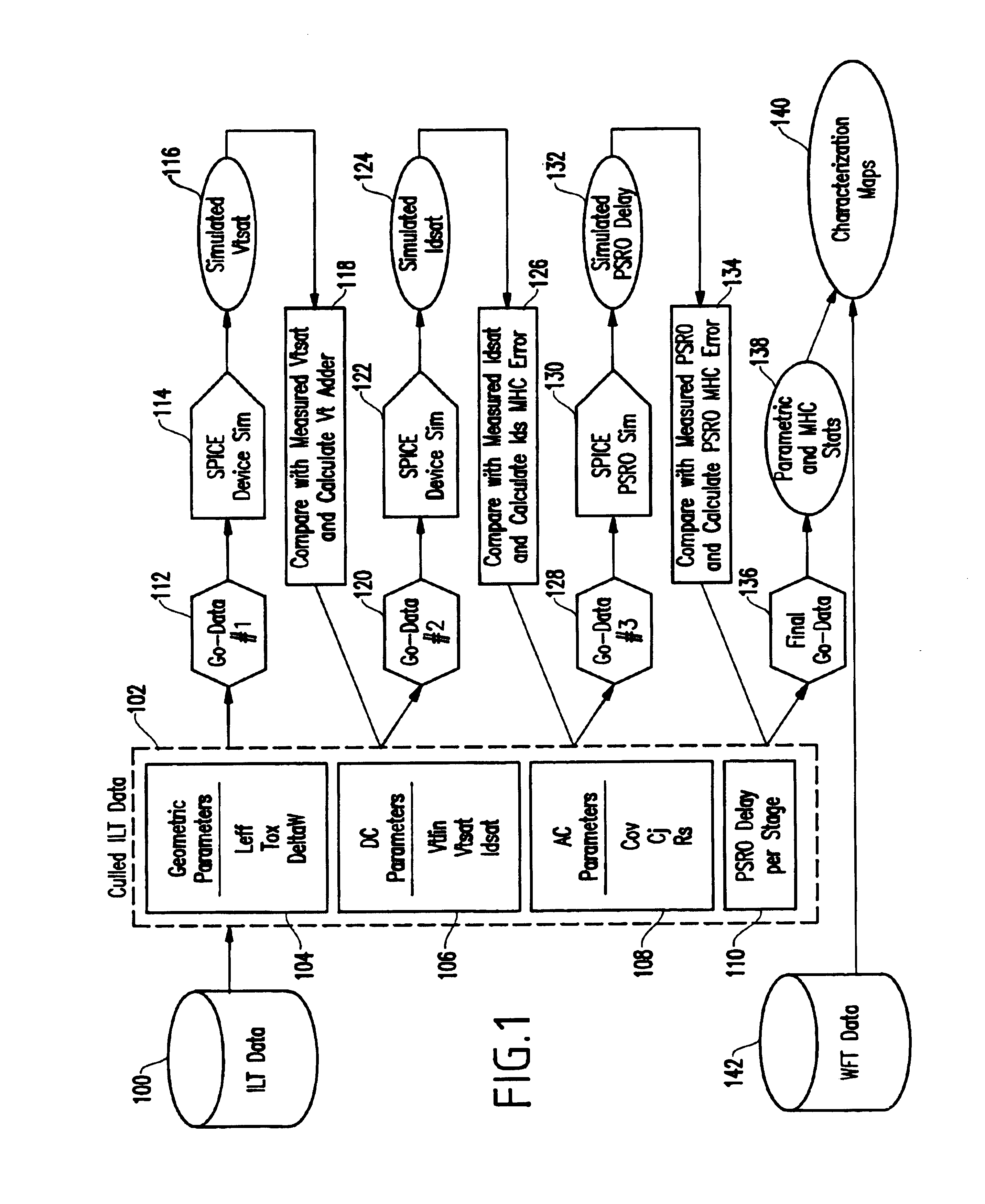

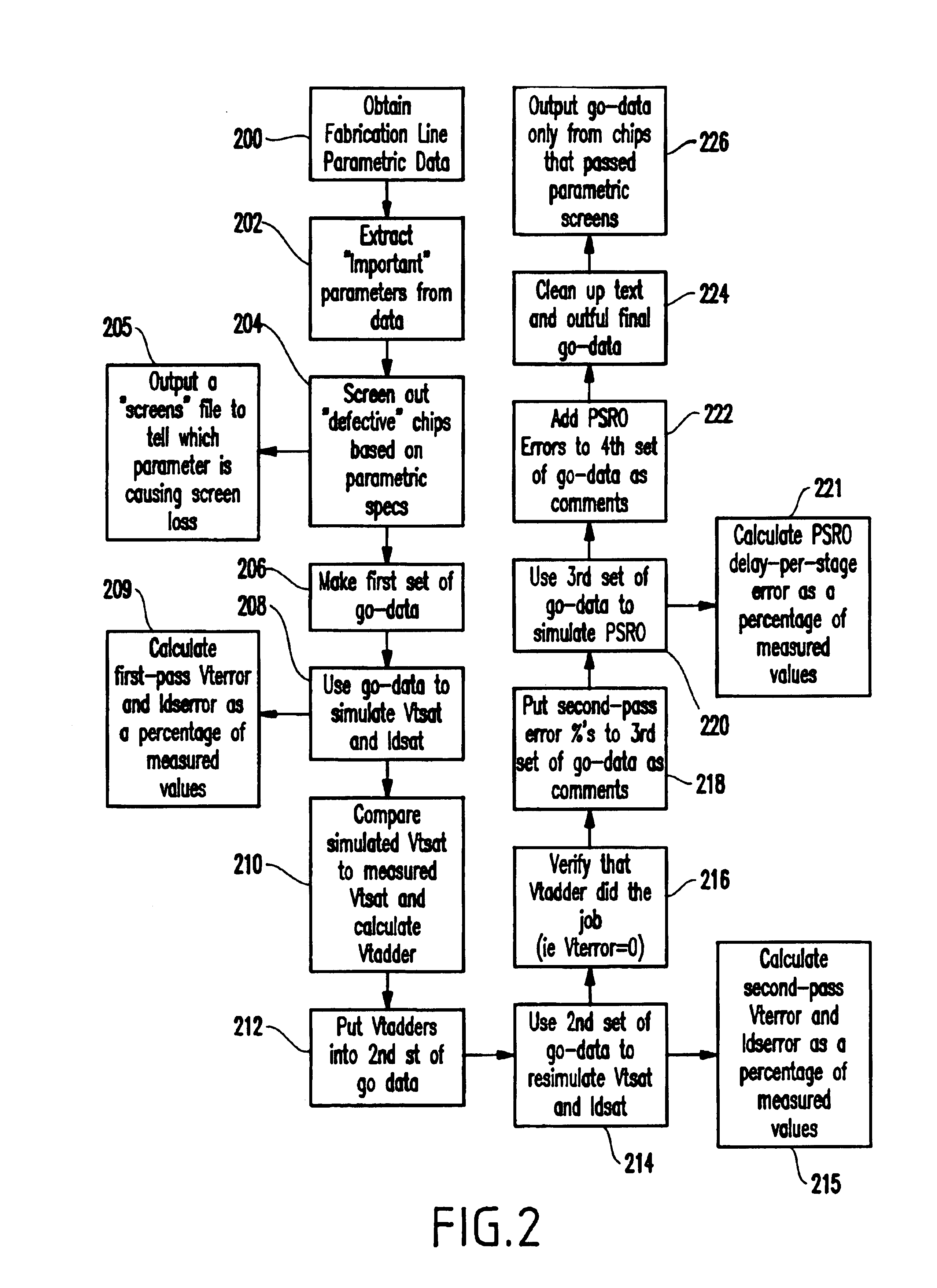

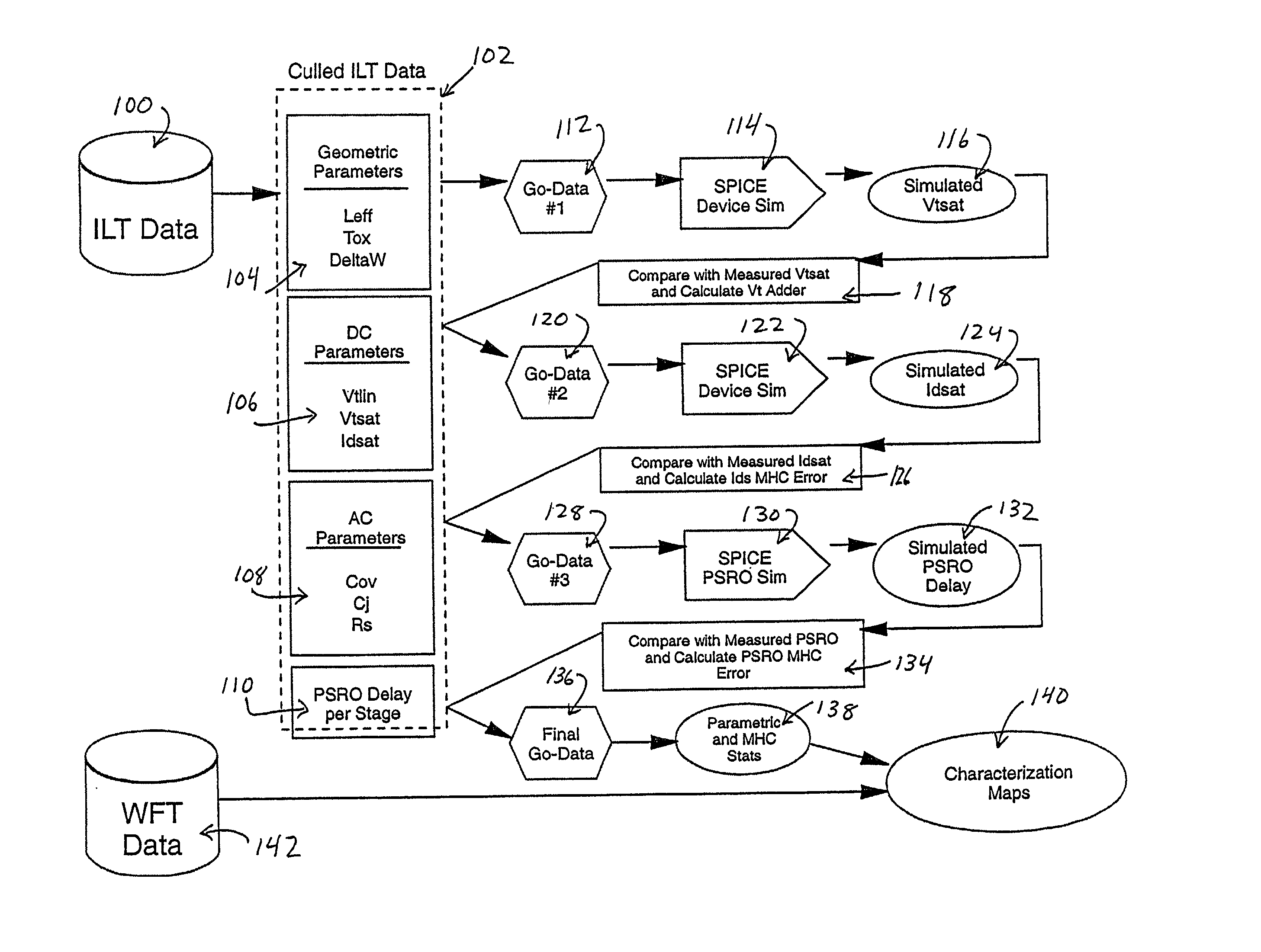

Method and system for including parametric in-line test data in simulations for improved model to hardware correlation

InactiveUS6934671B2Resistance/reactance/impedenceAnalogue computers for electric apparatusDesign standardHardware emulation

Owner:INTELLECTUAL DISCOVERY INC

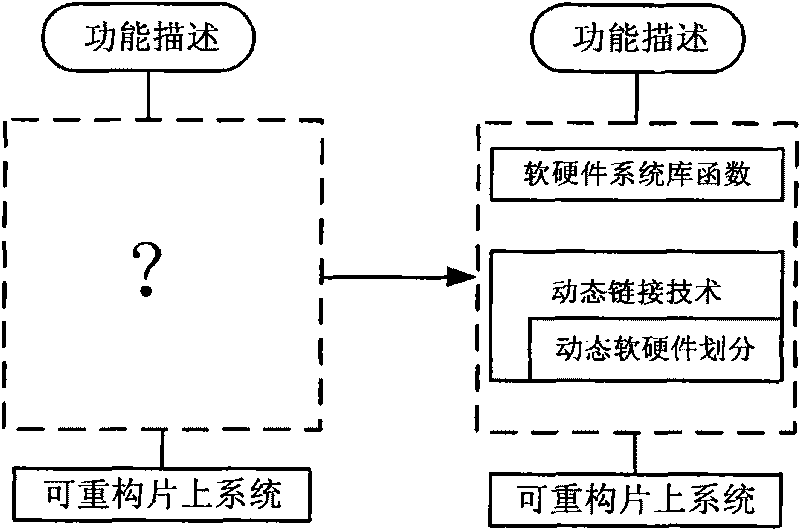

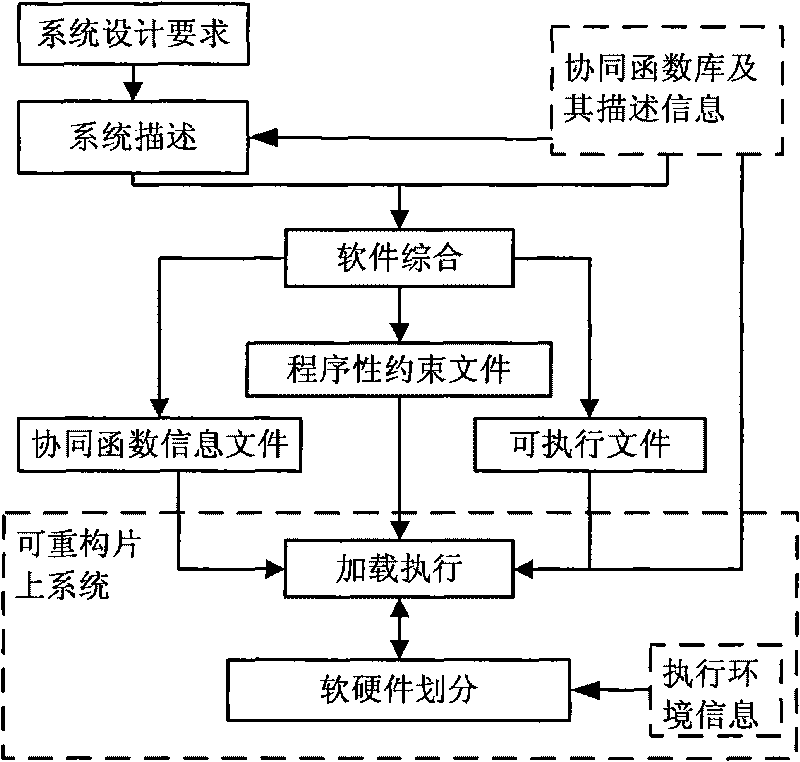

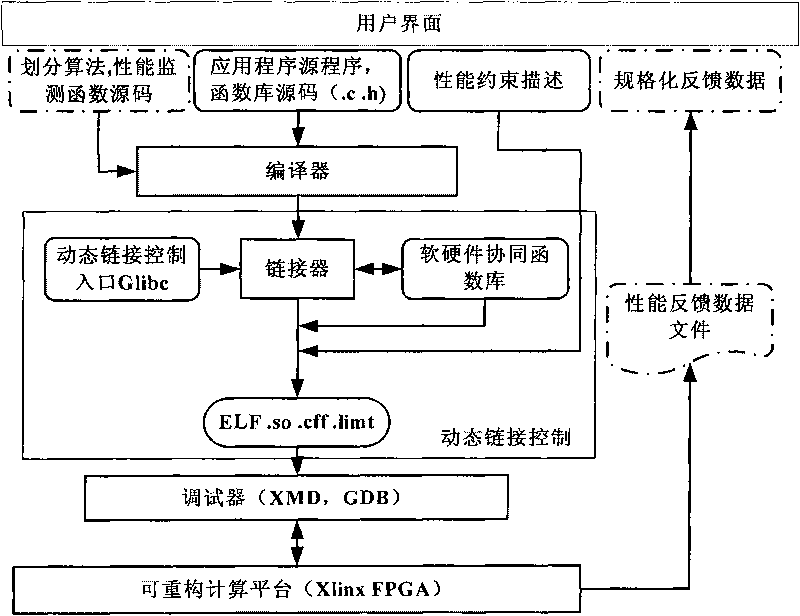

Procedure level software and hardware collaborative design automatized development method

InactiveCN101763265AIncrease profitEasy to divideSpecific program execution arrangementsHigh-level programming languageHardware implementations

The invention provides a procedure level software and hardware collaborative design automatized development method, which is characterized in that the method comprises the following steps: step 1, using high level languages to complete the system function description which comprises the transfer of the software and hardware collaborative functions; step 2, dynamically dividing the software and hardware functions; step 3, linking and executing the step; and step 4, judging and ending the step (judging whether the execution of all functions is completed, ending the step if the execution of all functions is completed, and otherwise, returning parameters used for dividing to the second step to enter a next circulation). The invention uses the procedure level software and hardware uniform programming model for shielding the difference realized by bottom layer hardware to realize the goal of transparent effect of reconstruction devices on program users. The programming model encapsulates the hardware accelerator into C Language functions for bringing convenience for the programming by users, and in addition, the dynamic software and hardware division during the operation is supported, so the division is transparent to programmers, and the utilization rate of reconstruction resources is improved.

Owner:HUNAN UNIV

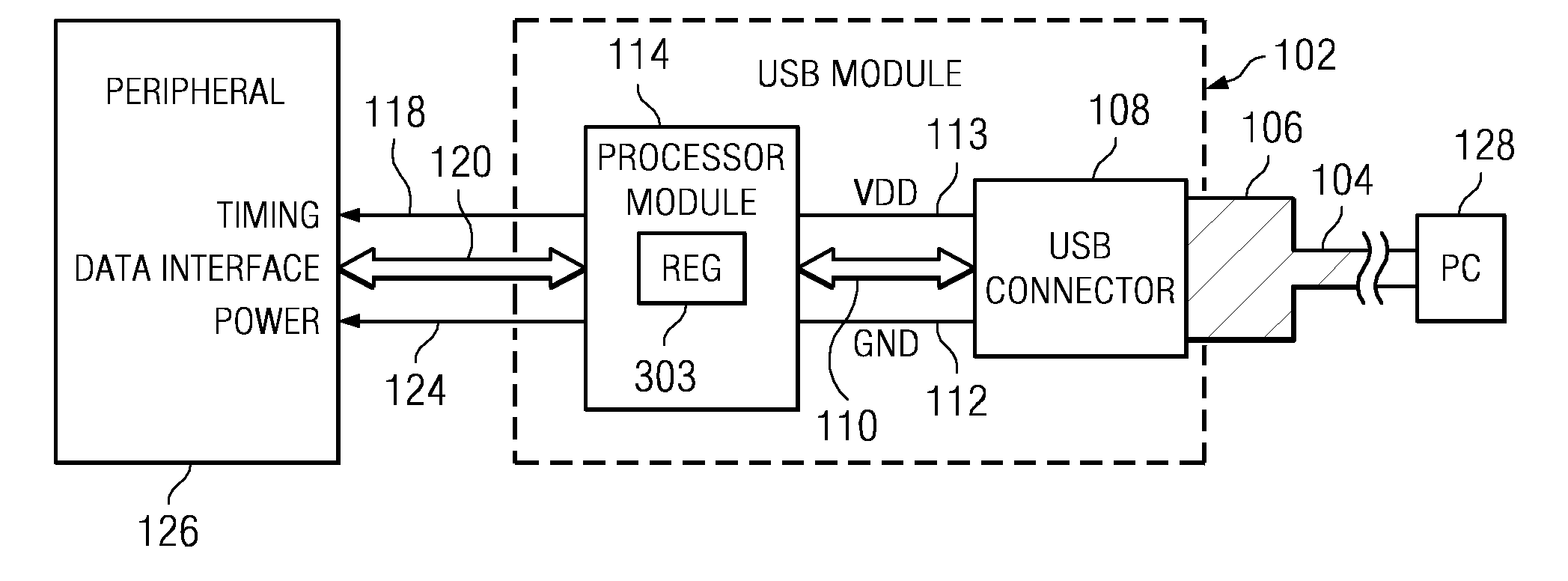

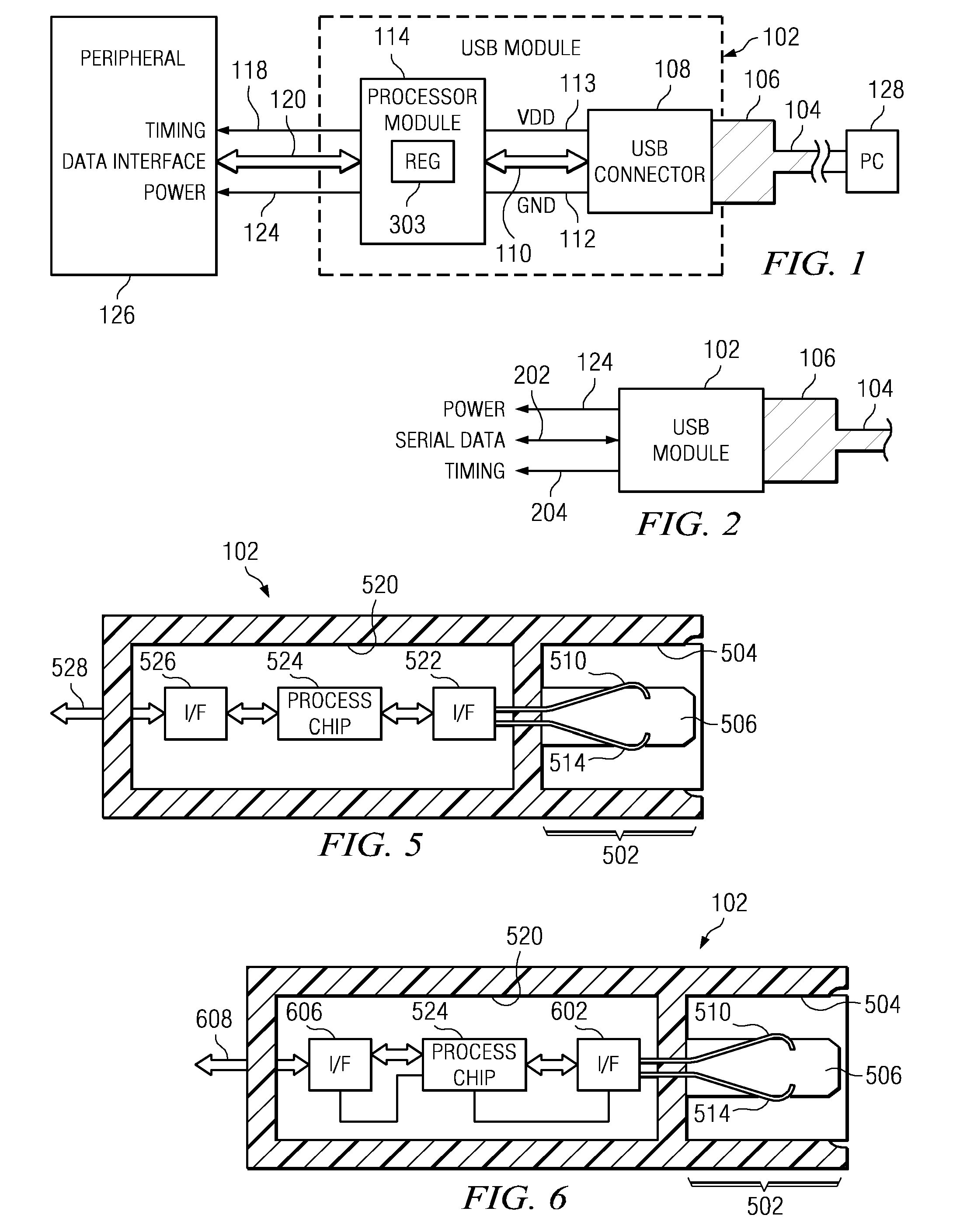

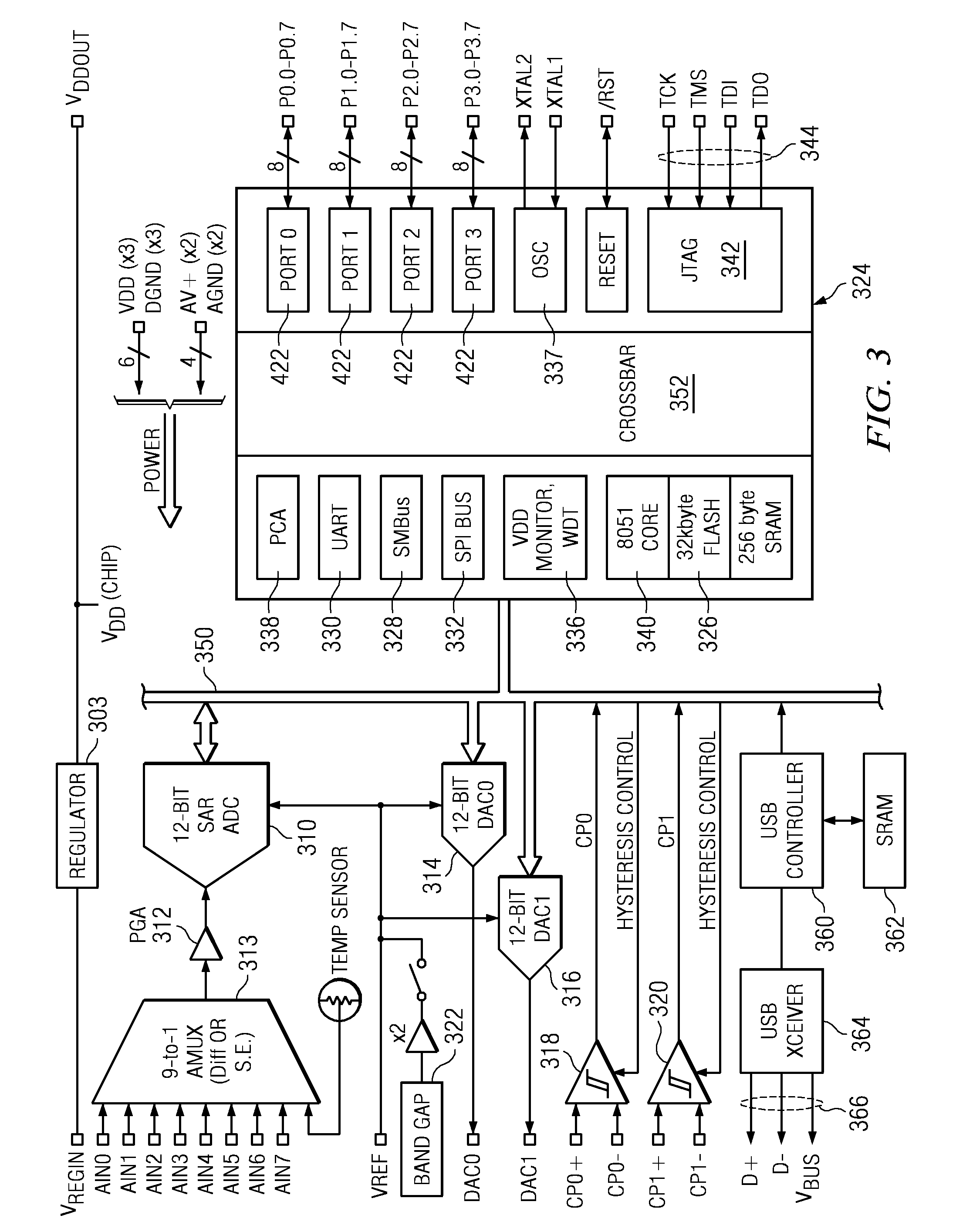

USB tool stick with multiple processors

The present invention disclosed and claimed herein, in one aspect thereof, comprises a development system operating on a computer for evaluating compiled program code that was developed to run on a specific processor based functional IC having associated therewith memory and configurable data I / O modules, and which code defines the manner by which the functional IC will operate in a predetermined end application. An evaluation program is provided that is operable to run on the computer. A tool stick interfaces with the computer and includes a functional IC that is substantially operationally identical to the functional IC for which the compiled program code was developed to run on. The evaluation program is operable to interface with the tool stick to load the code in the functional IC associated with the tool stick and operable therewith such that the functional IC in the tool stick functions as a hardware emulator for the end application, such that the compiled code can be operated in hardware.

Owner:SILICON LAB INC

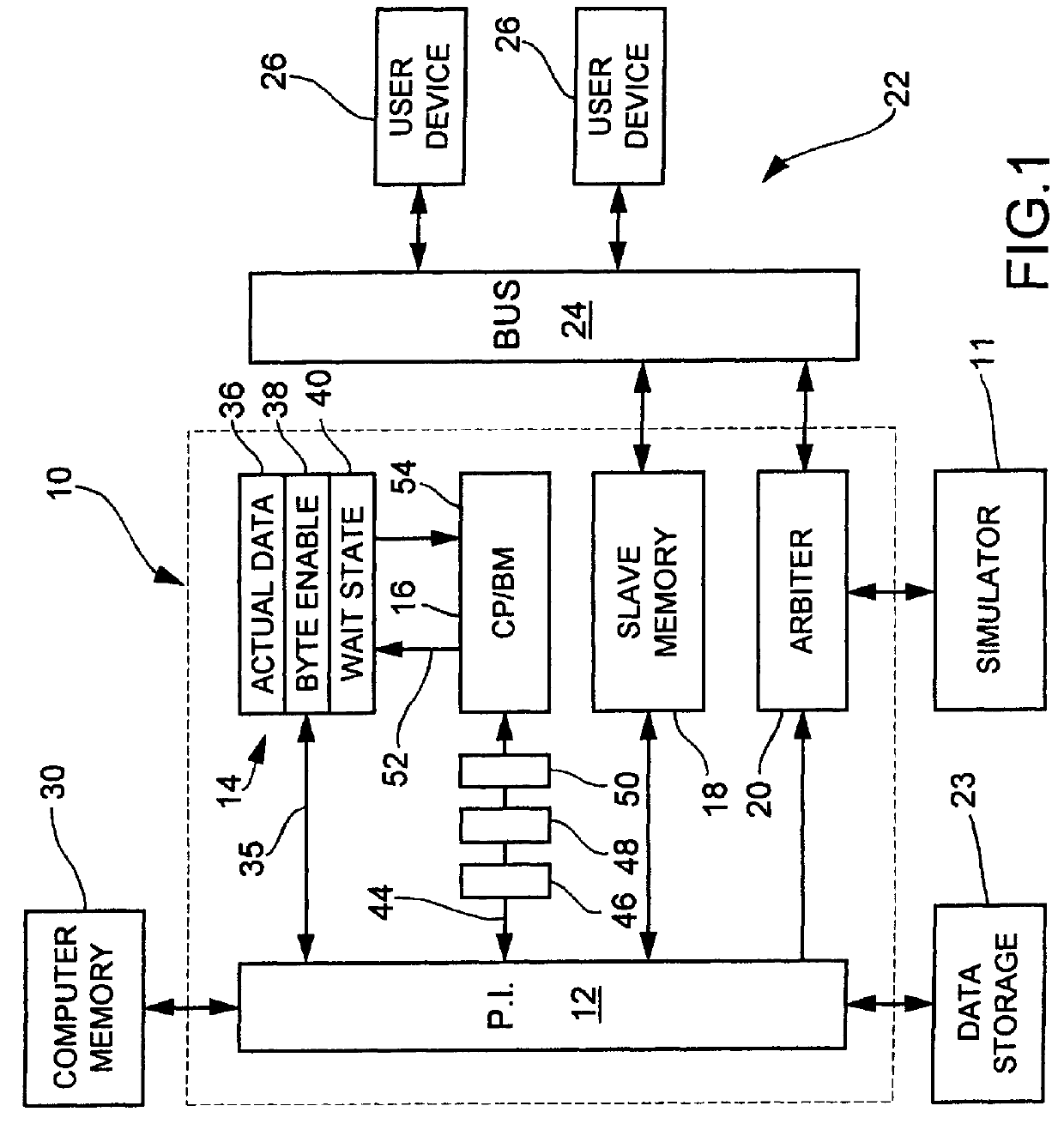

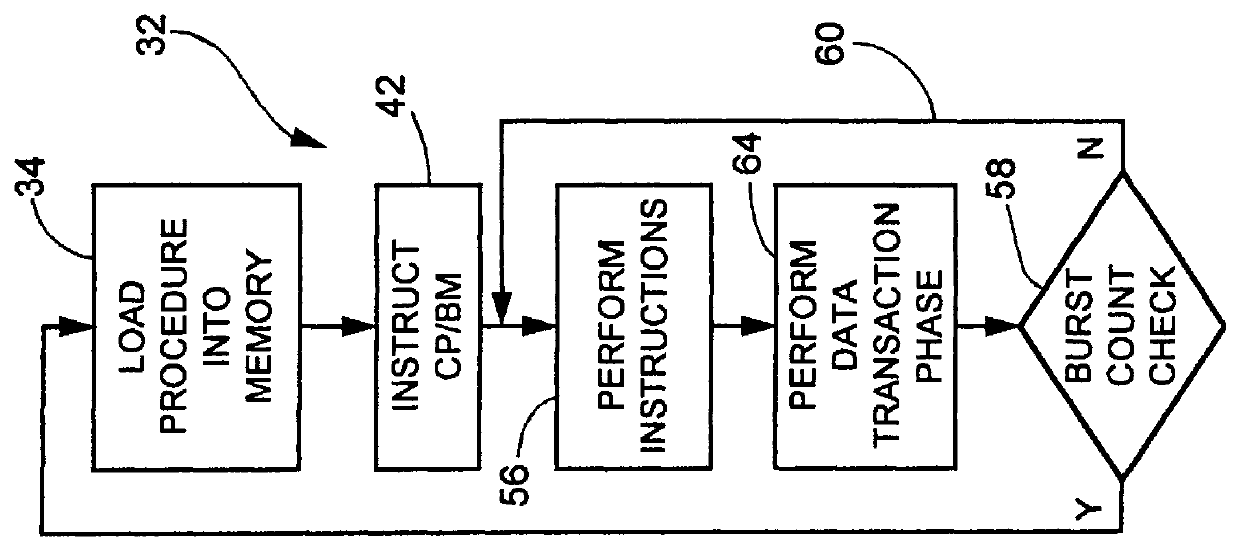

Method for simulating bus traffic

InactiveUS6123735ATest speed is optimizedMinimize development timeFunctional testingCAD circuit designUser deviceHardware simulator

A dynamic hardware emulation model (10) to be used with a hardware simulator for testing a user device (26) under test. A programming interface (12) controls a memory pool (14) and a command processor / bus manager (16) such that a command cycle is initiated to read and write data through a computer bus (24), to and from the user device (26). The programming interface (12) and the user device (26) can act in a master or slave mode. When the user device (26) is in slave mode, a slave memory (18) contains expected data for comparison purposes, and an arbiter (20) determines which device will have access to the computer bus (24).

Owner:SYNOPSYS INC

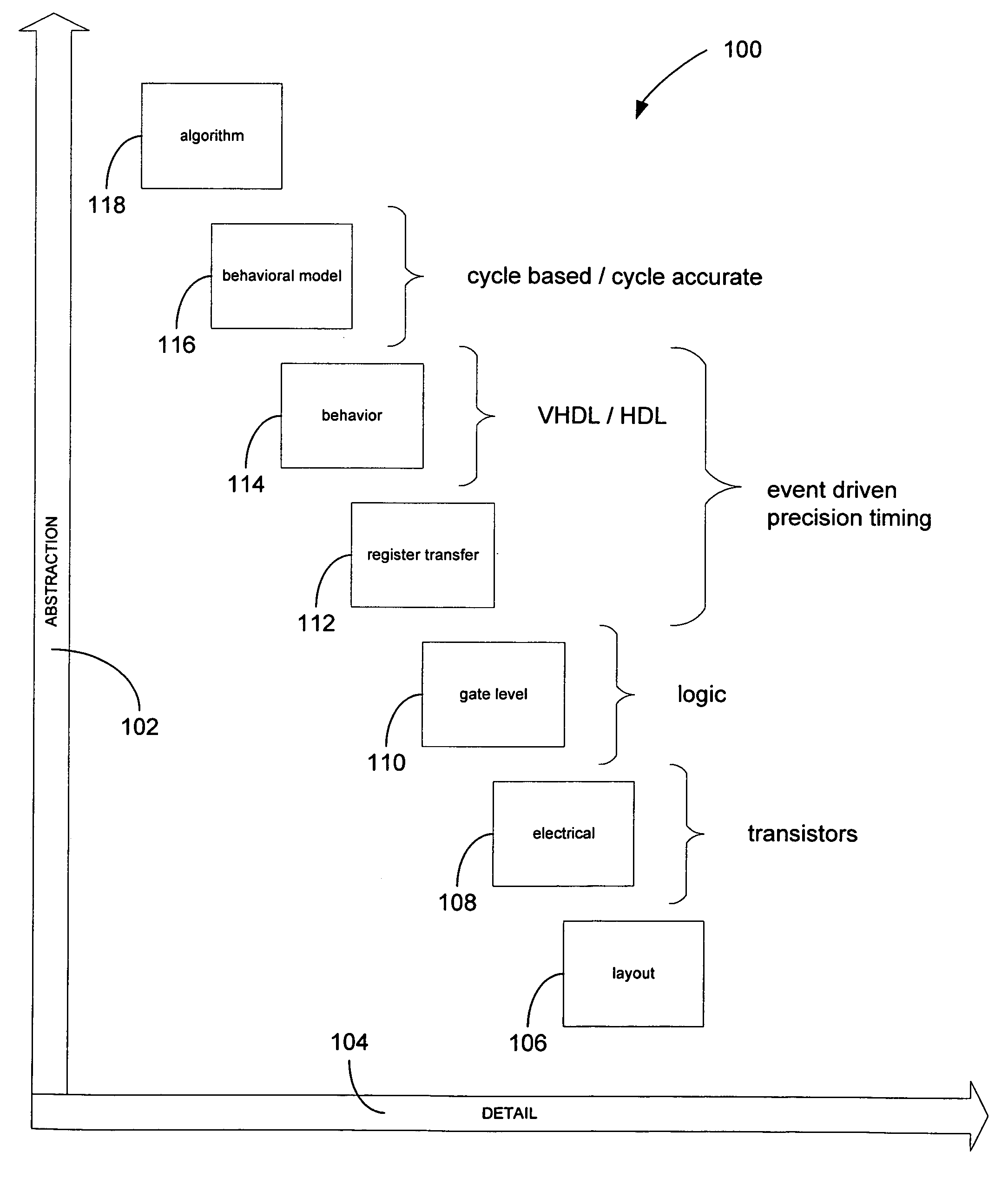

Method and apparatus for accelerating hardware simulation

InactiveUS7050958B1Reduce in quantityFunction increaseAnalogue computers for electric apparatusCAD circuit designCommunication interfaceSystems design

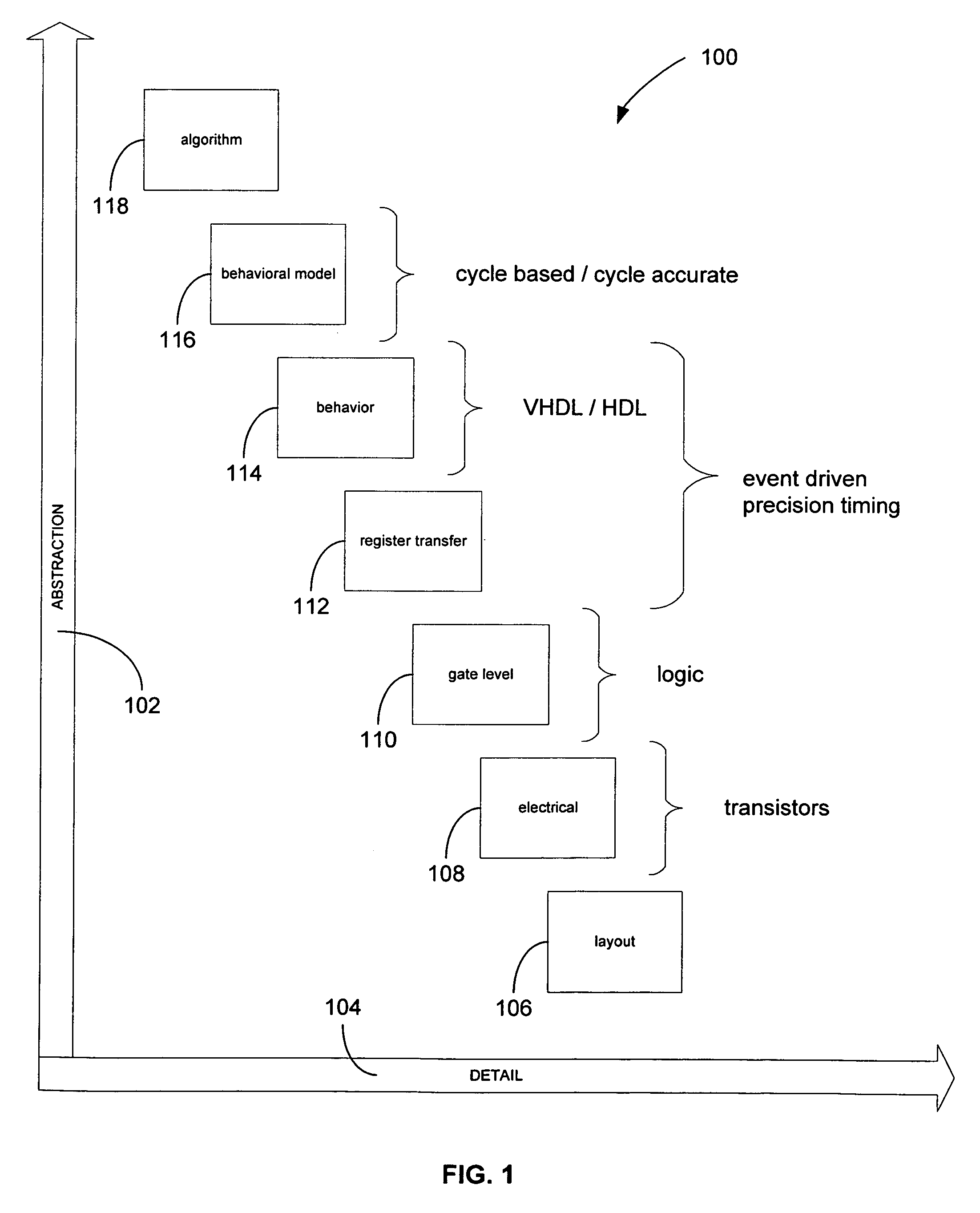

A method for accelerating hardware simulation is presented wherein cycle based simulations of digital system designs are generated by raising the level of abstraction in a hardware simulation environment. Behavioral models of the digital system components are created in a high level general purpose programming language. Function calls created in a high level general purpose programming language provide a transaction based communication interface. During a simulation of the system design, the behavioral models communicate with each other through the transaction based communication interface. Additionally, the behavioral models employ an execute and update method of instruction processing that generates cycle accurate information for the simulation.

Owner:ARM LTD

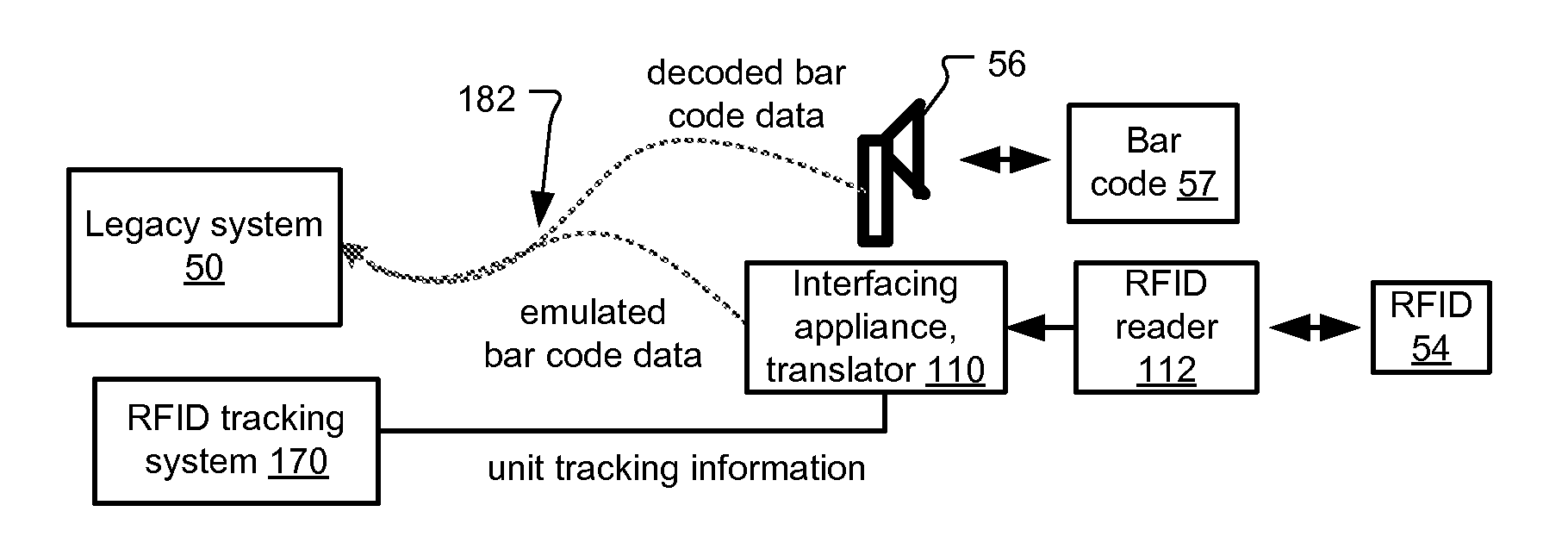

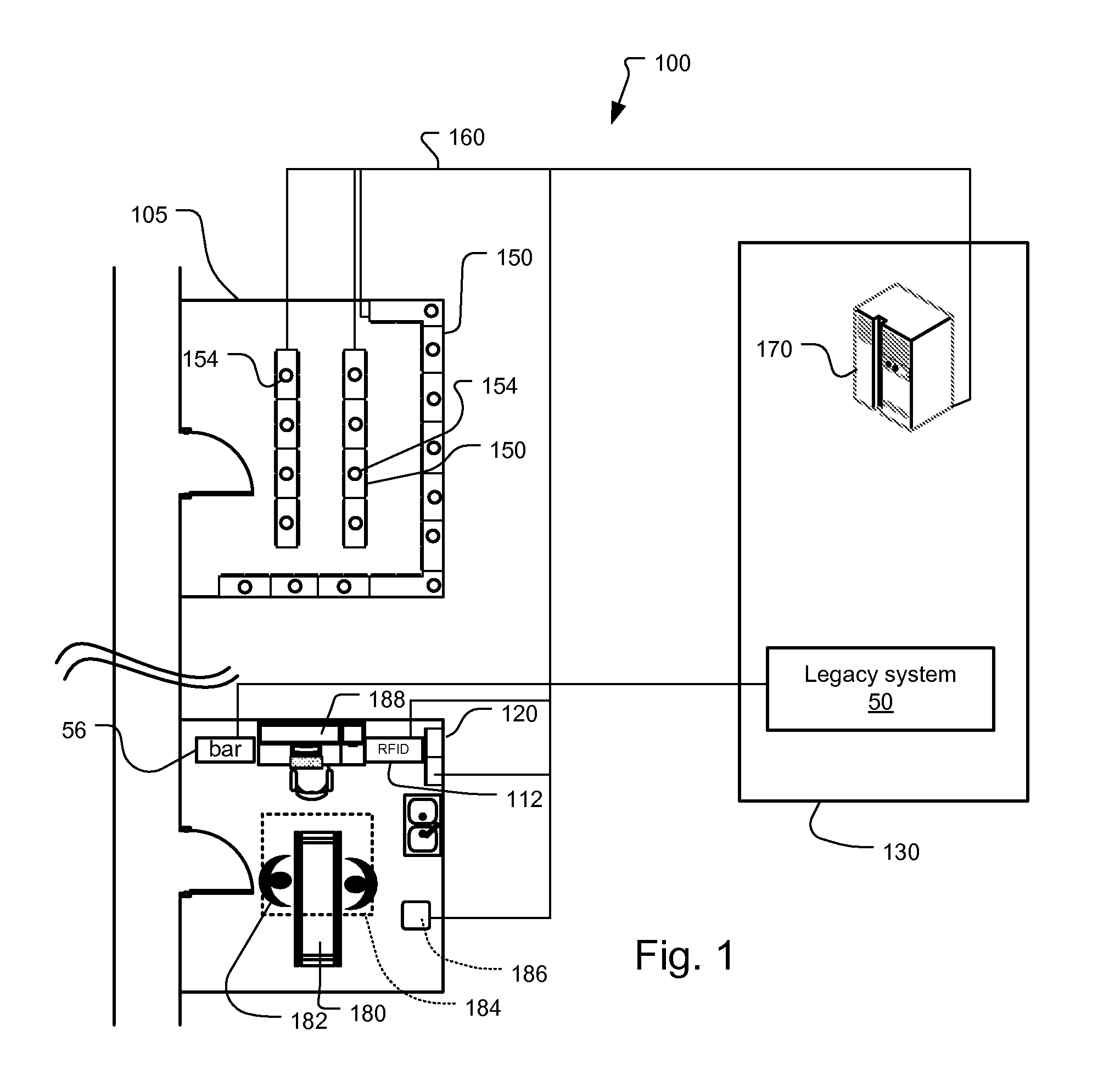

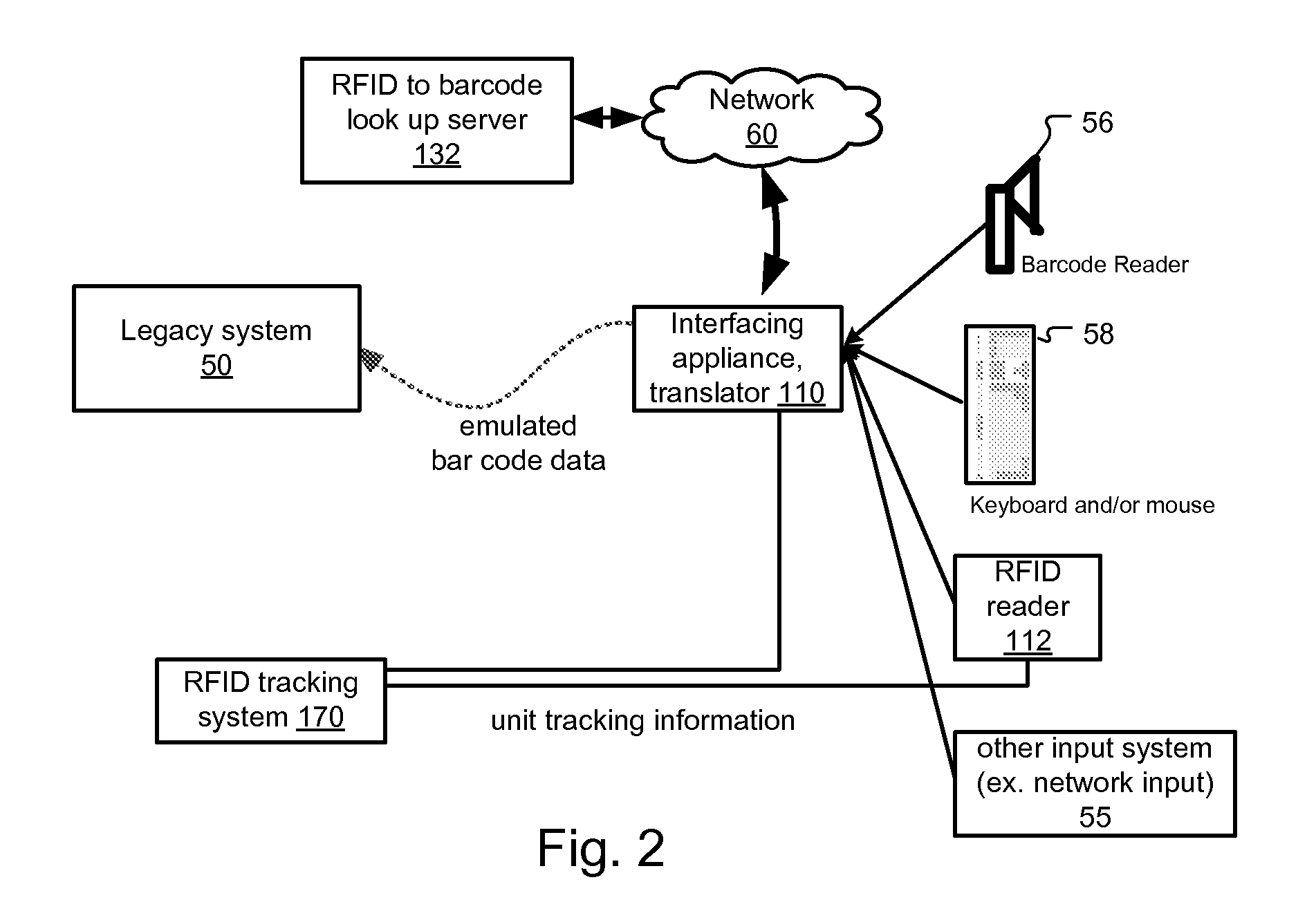

Barcode emulation in medical device consumption tracking system

ActiveUS8281994B1Minimize the numberIncrease speedHealthcare resources and facilitiesCommerceBarcodeLegacy system

An interface system for providing product identifier data to a legacy system for a unit tracking system comprises a reader for reading unit tracking information for items. The unit tracking information uniquely identifies each of the items. In one example, this unit tracking information is an RFID serial number. Then, a translator looks up universal product numbers associated with the items with which the unit tracking number is associated. The translator passes the universal product number to the legacy system.

Owner:WAVEMARK

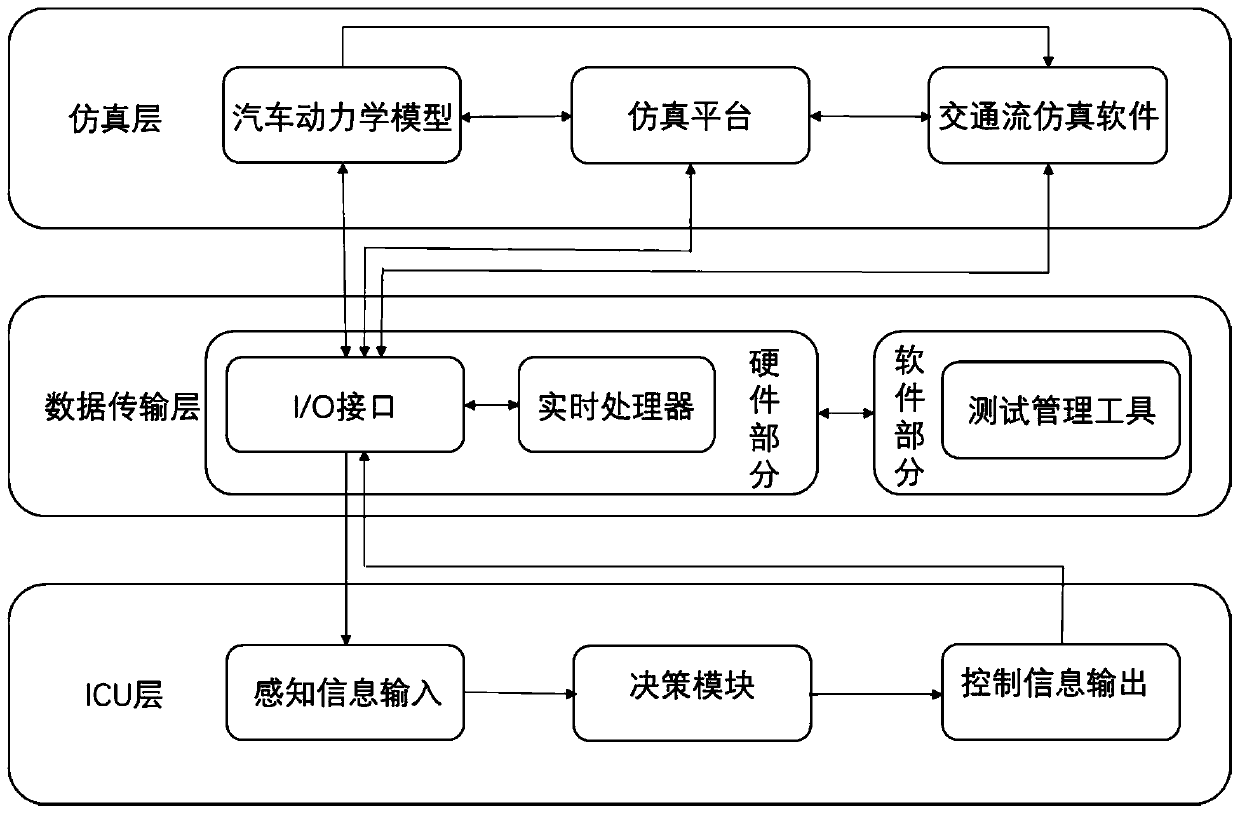

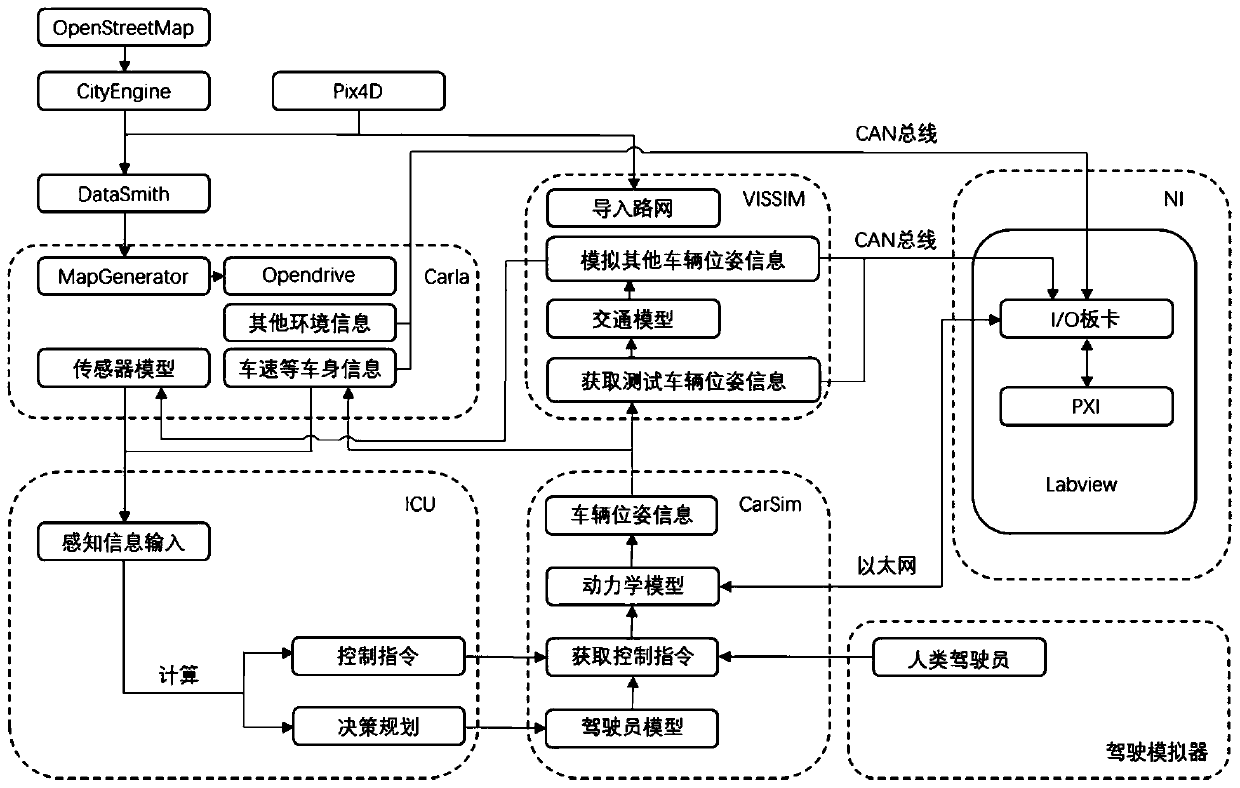

Multi-ICU co-spatiotemporal hardware simulation testing system and method for automatic driving vehicle

InactiveCN109765803AImprove traffic efficiencyEase traffic congestionSimulator controlVehicle dynamicsSystem requirements

The invention discloses a multi-ICU co-spatiotemporal hardware simulation testing system and method for an automatic driving vehicle. The testing system is integrally divided into a simulation layer,an ICU (Intelligent Control Unit) layer and a data transmission layer. The simulation layer provides a virtual environment model, a sensor model, a traffic participant model, a traffic flow model anda vehicle dynamics model of simulation testing; the ICU layer is a simulation testing object; and the data transmission layer provides a communication interface of the simulation layer and the ICU layer, software for testing monitoring and automatic testing, and a high-performance processor for ensuring the real-time performance of the whole simulation process. The testing method provides a construction method for quickly generating a virtual environment required by testing and a multi-ICU co-spatiotemporal testing method. Compared with the prior art, the testing system and method has the advantages that multiple ICUs are co-spatiotemporal, multi-stage simulation data oriented to decision planning system requirements is generated, a rapid construction method for a virtual testing scene isprovided, and the like.

Owner:TONGJI UNIV

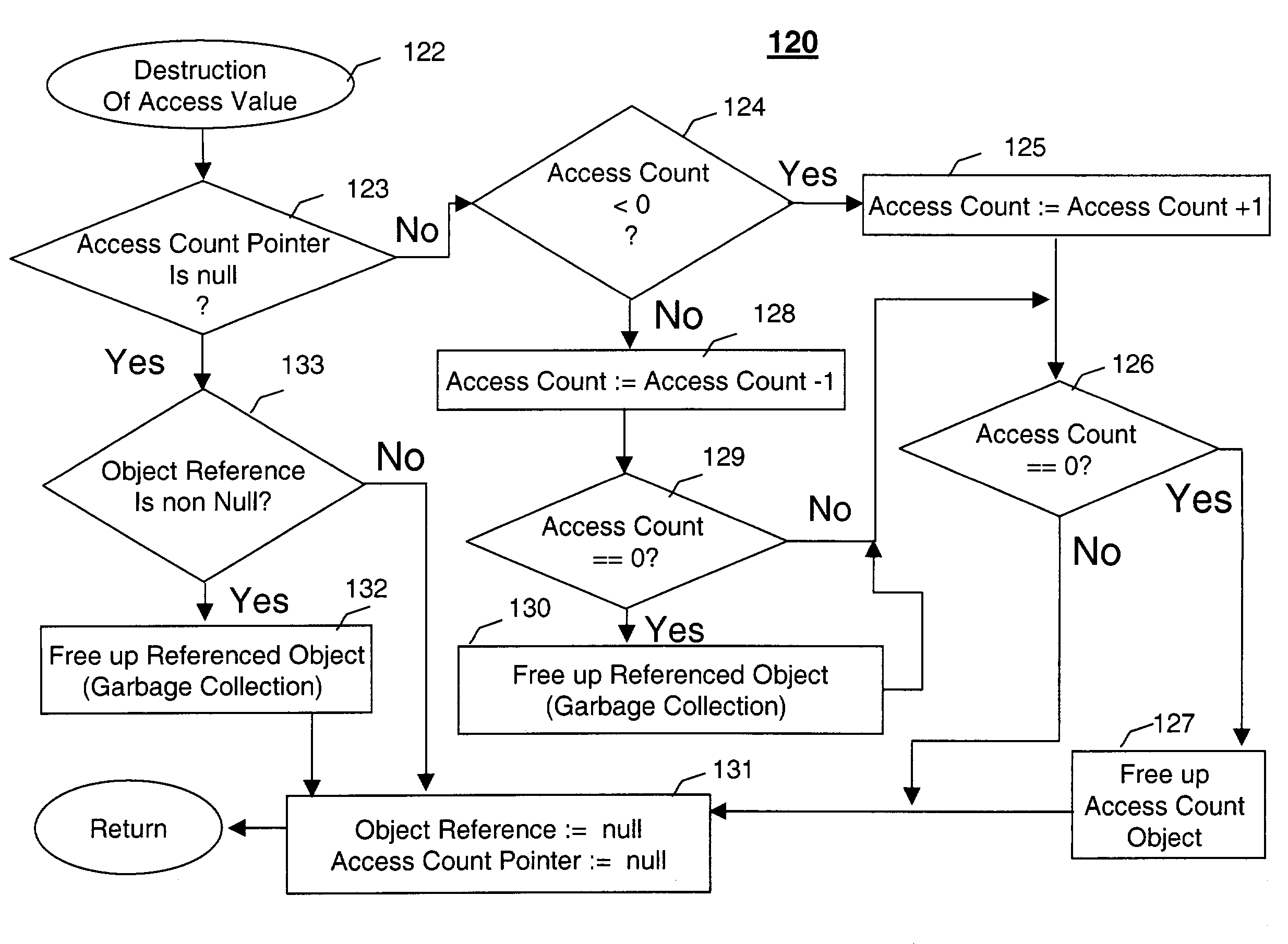

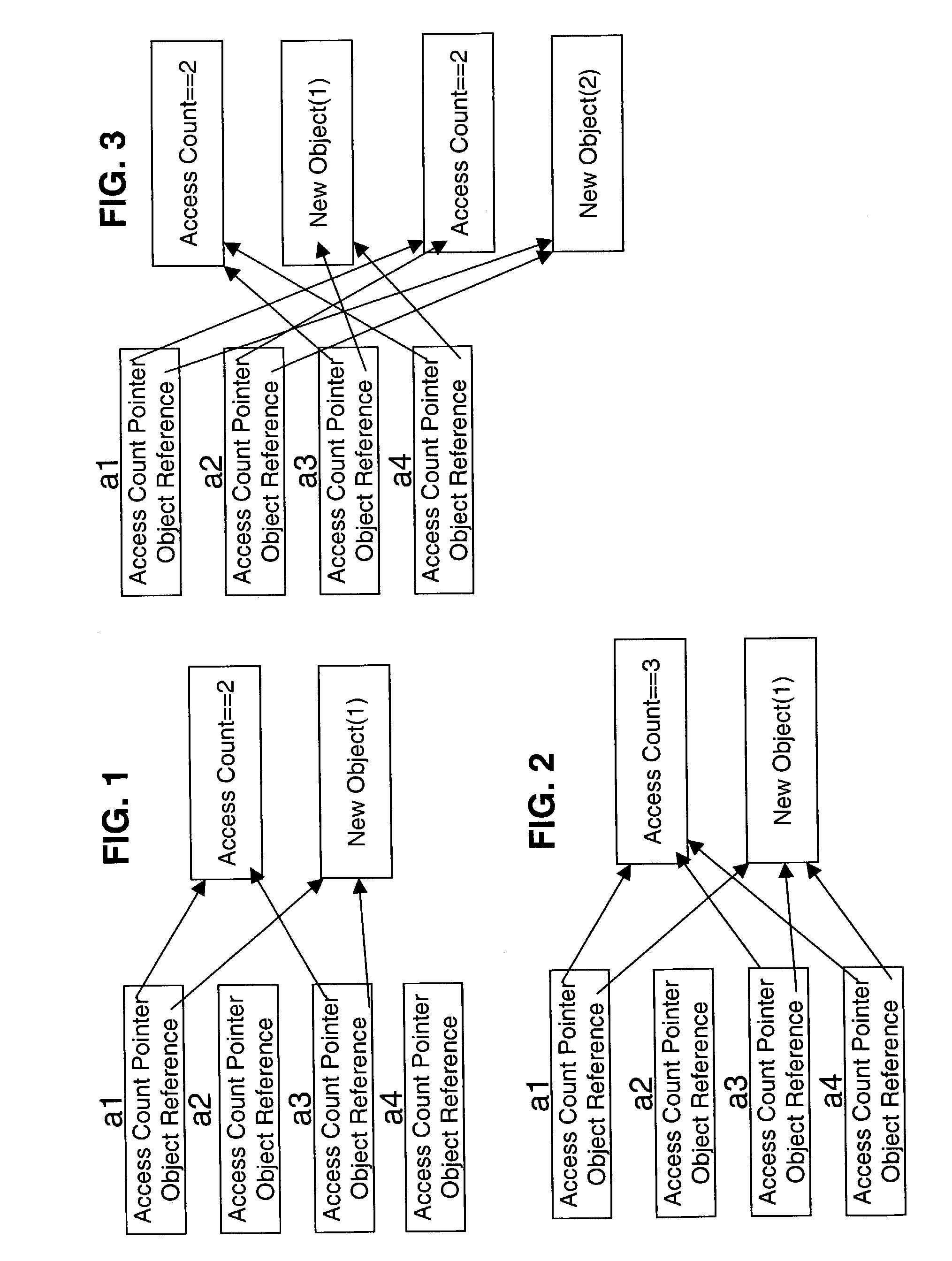

Dangling reference detection and garbage collection during hardware simulation

ActiveUS7403961B1Significant performance benefitSignificant comprehensive benefitsError detection/correctionAnalogue computers for electric apparatusWaste collectionHardware emulation

A method of dangling reference detection and garbage collection of VHDL objects within a program includes the steps of providing an Access Value having an Object Reference pointing to an Allocated Object and having and an Access Count pointer pointing to an integer object named Access Count which models a shared access count for the access values. The method sets the Object Reference and the Access Count pointer to null when constructing a new access value and enables an assignment of a negative Access Count to the shared access count when de-allocating a pointer to the Allocated Object. The method also maintains an exact count of a number of pointers pointing to the Allocated Object.

Owner:XILINX INC

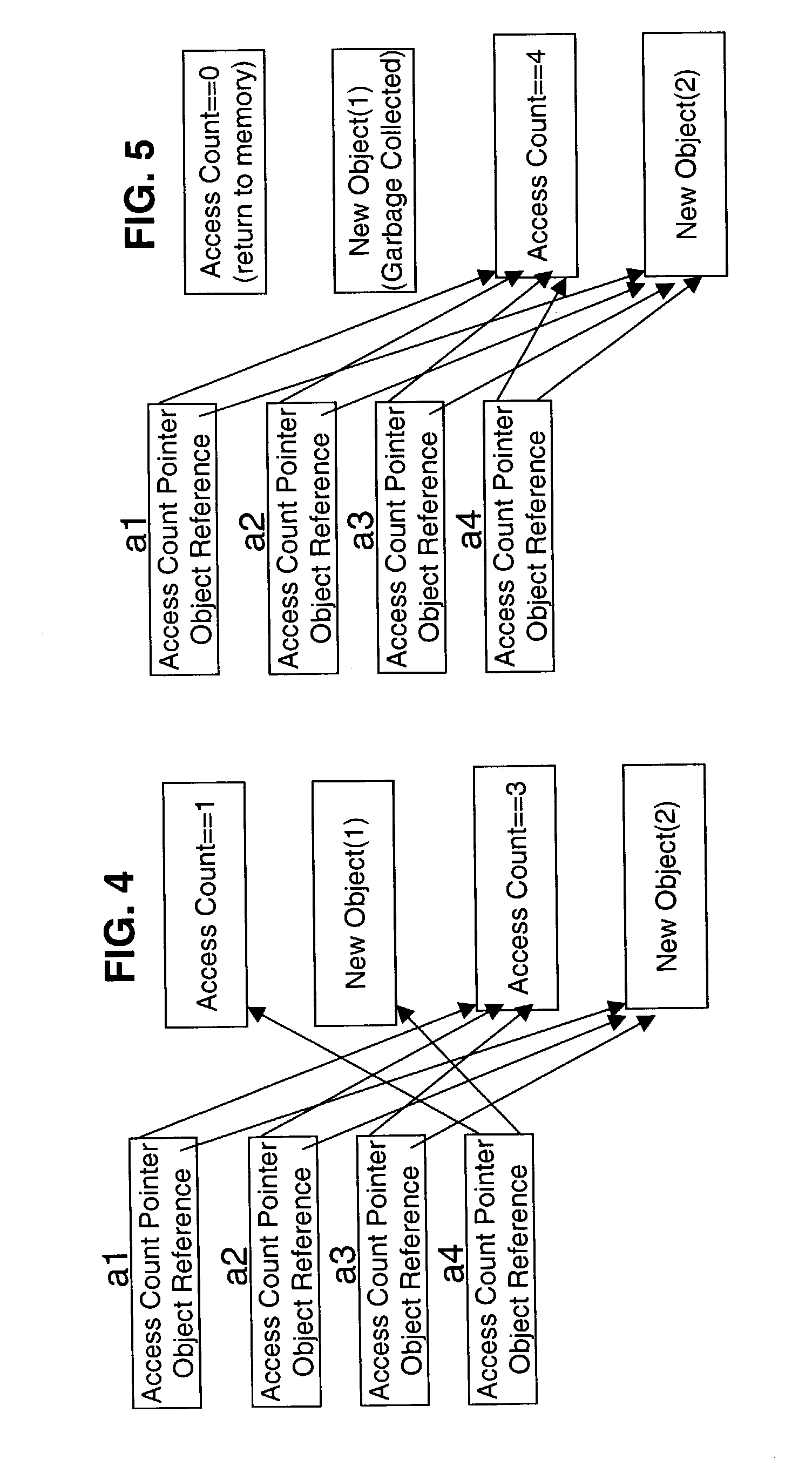

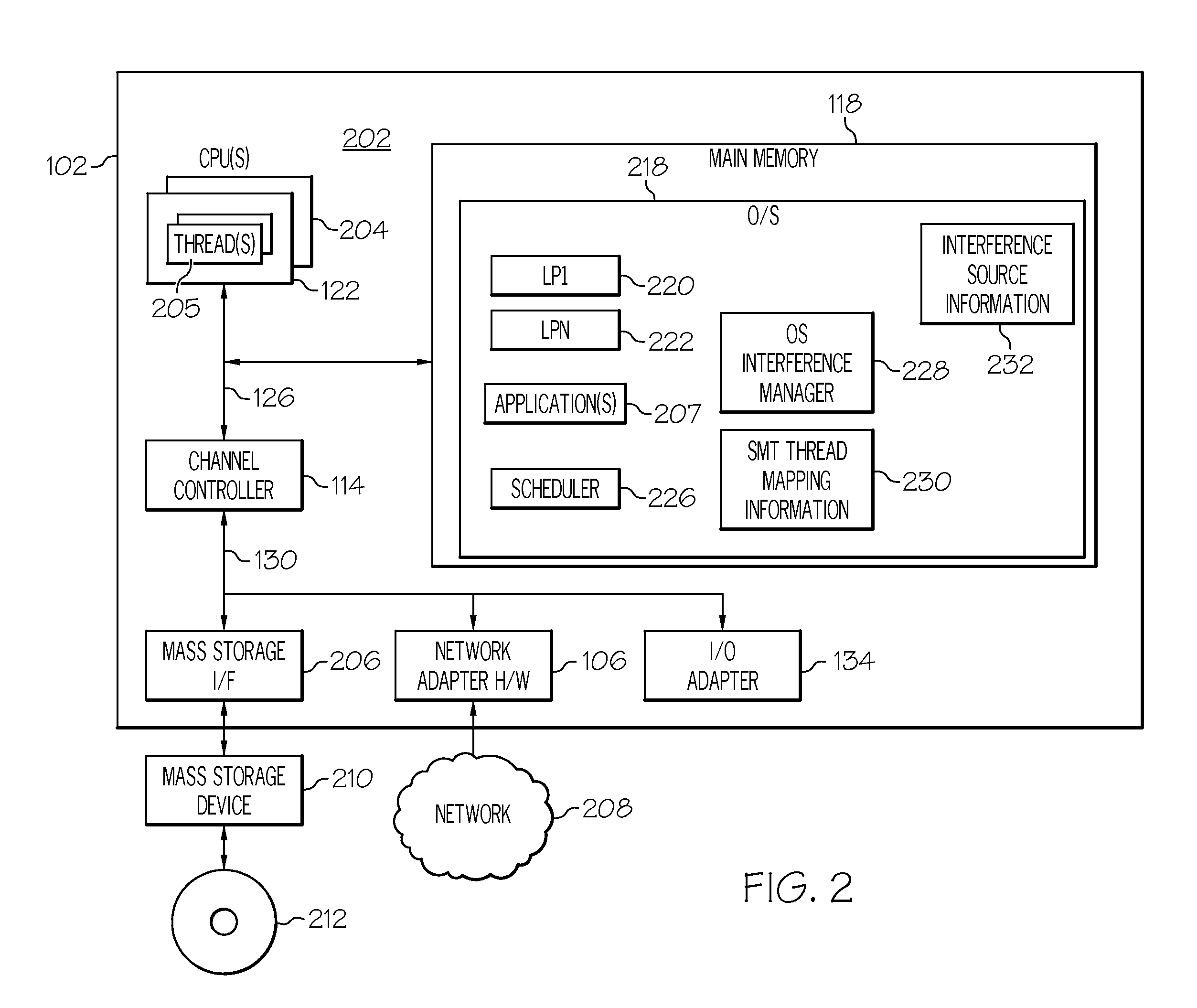

Hardware multi-threading co-scheduling for parallel processing systems

InactiveUS20110093638A1Program control using stored programsGeneral purpose stored program computerInformation processingData processing system

A method, information processing system, and computer program product are provided for managing operating system interference on applications in a parallel processing system. A mapping of hardware multi-threading threads to at least one processing core is determined, and first and second sets of logical processors of the at least one processing core are determined. The first set includes at least one of the logical processors of the at least one processing core, and the second set includes at least one of a remainder of the logical processors of the at least one processing core. A processor schedules application tasks only on the logical processors of the first set of logical processors of the at least one processing core. Operating system interference events are scheduled only on the logical processors of the second set of logical processors of the at least one processing core.

Owner:IBM CORP

Method and system for including parametric in-line test data in simulations for improved model to hardware correlation

InactiveUS20020193892A1Resistance/reactance/impedenceDetecting faulty computer hardwareDesign standardHardware emulation

Owner:INTELLECTUAL DISCOVERY INC

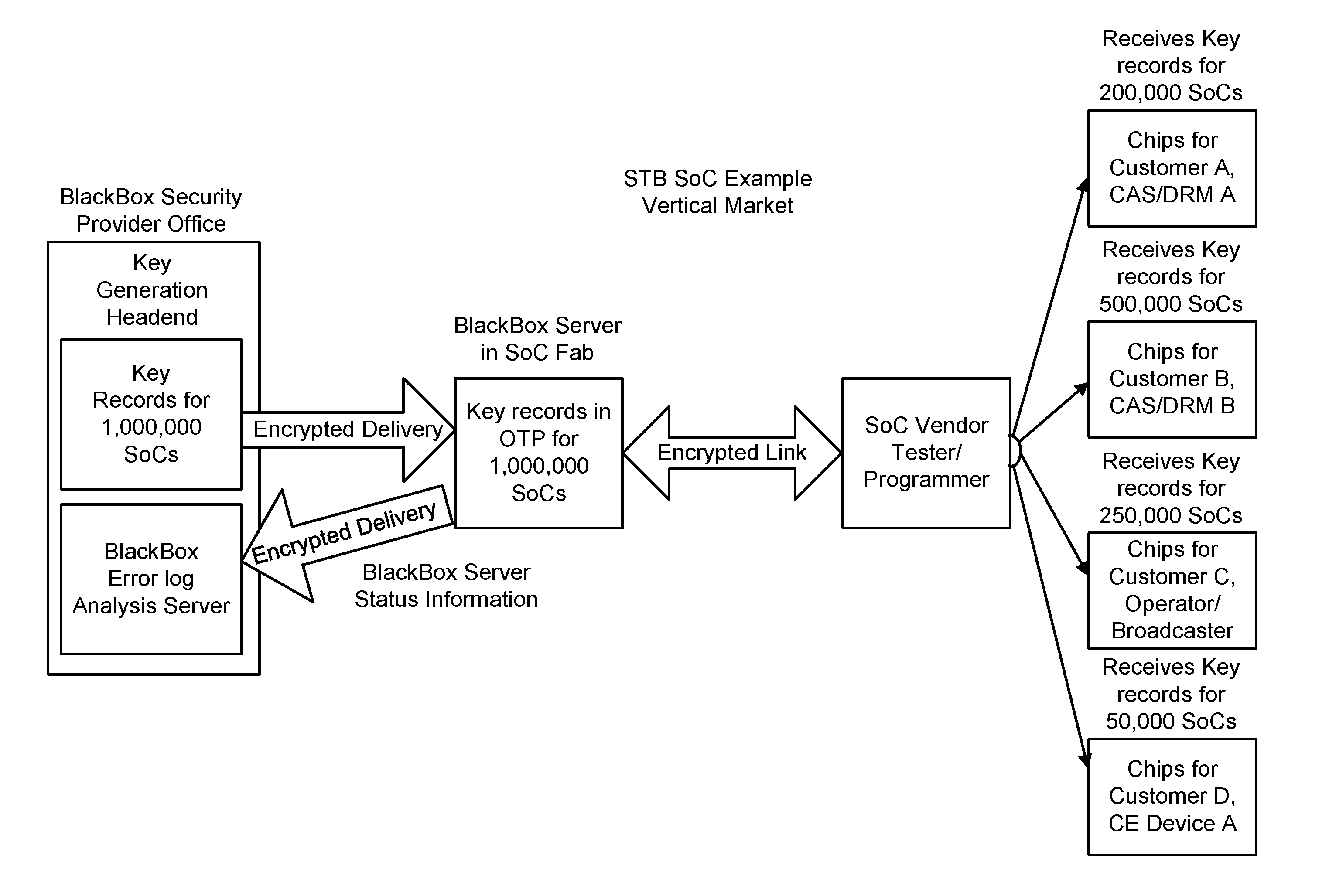

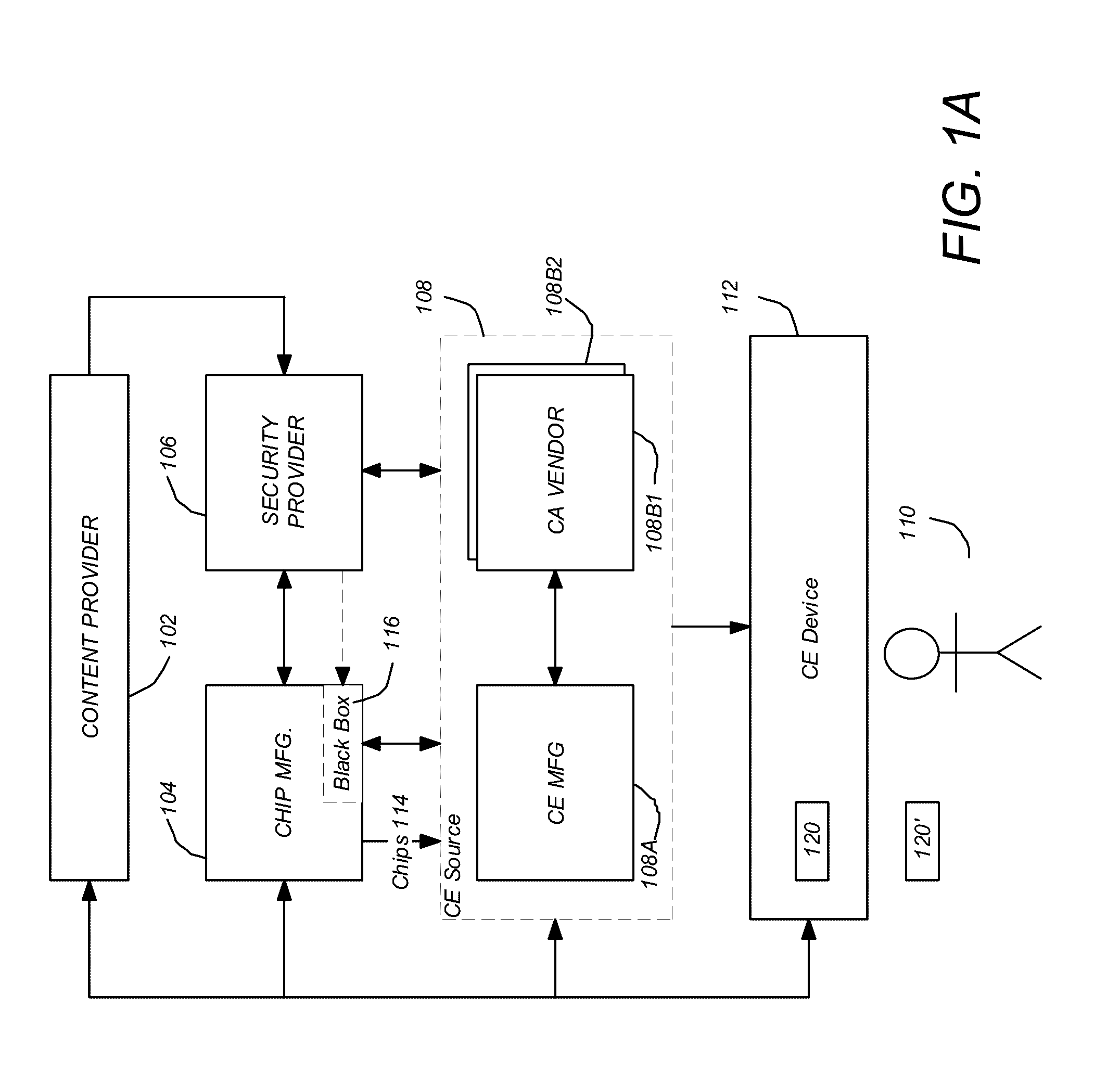

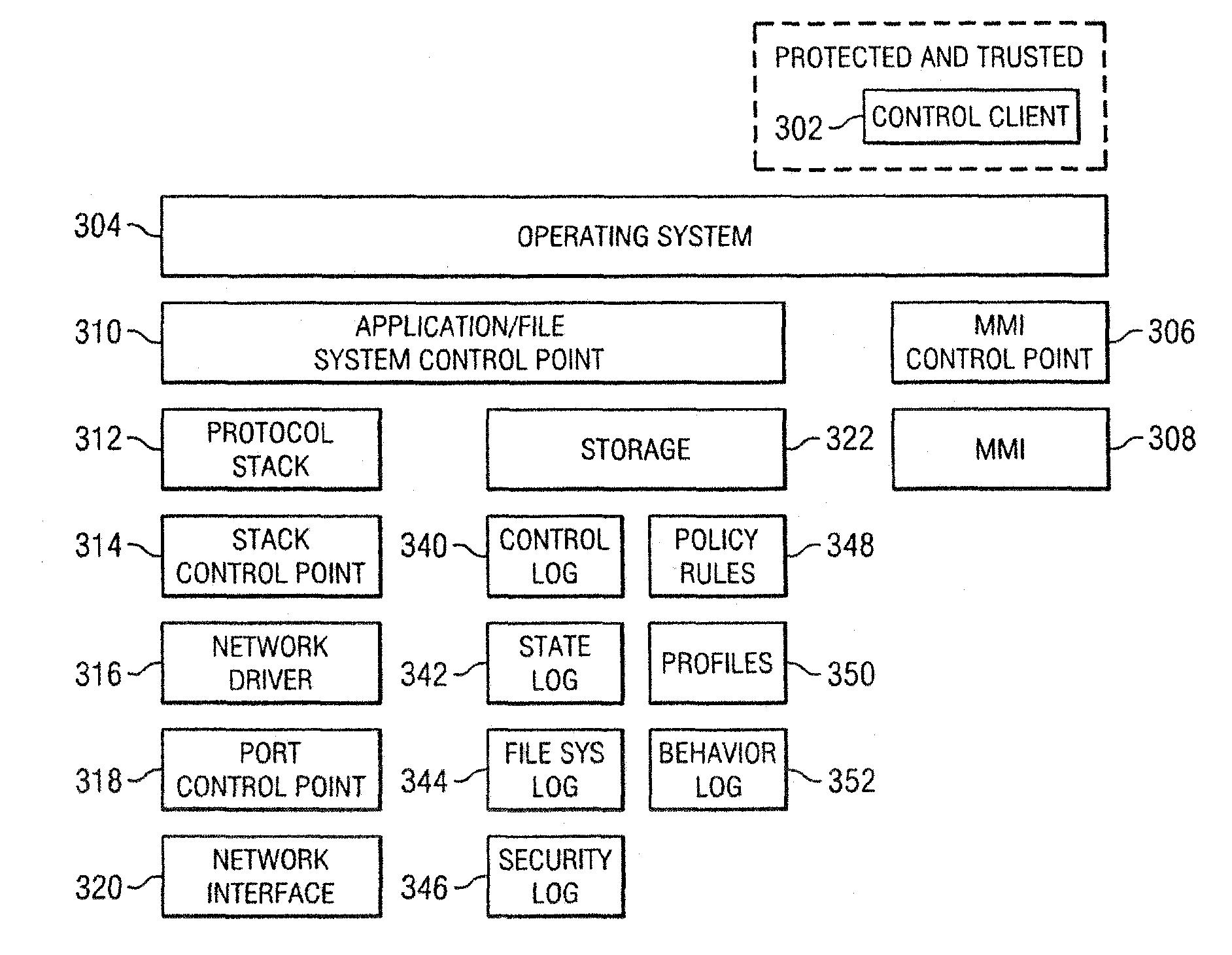

Method and apparatus for a blackbox programming system permitting downloadable applications and multiple security profiles providing hardware separation of services in hardware constrained devices

InactiveUS20170012952A1Key distribution for secure communicationMultiple keys/algorithms usageStructure of Management InformationApplication software

A method, apparatus, article of manufacture, and a memory structure for providing a security infrastructure that permits the programming of limited hardware resources that can accept newly downloaded applications and securely support a very large number of services offered by content providers each have the potential to utilize their own independent CAS / DRM system. The CE device owner can consume content from a variety of sources and enable switching among different and existing CAS / DRM security profiles as required by the content provider applications loaded in CE devices.

Owner:RAMBUS INC

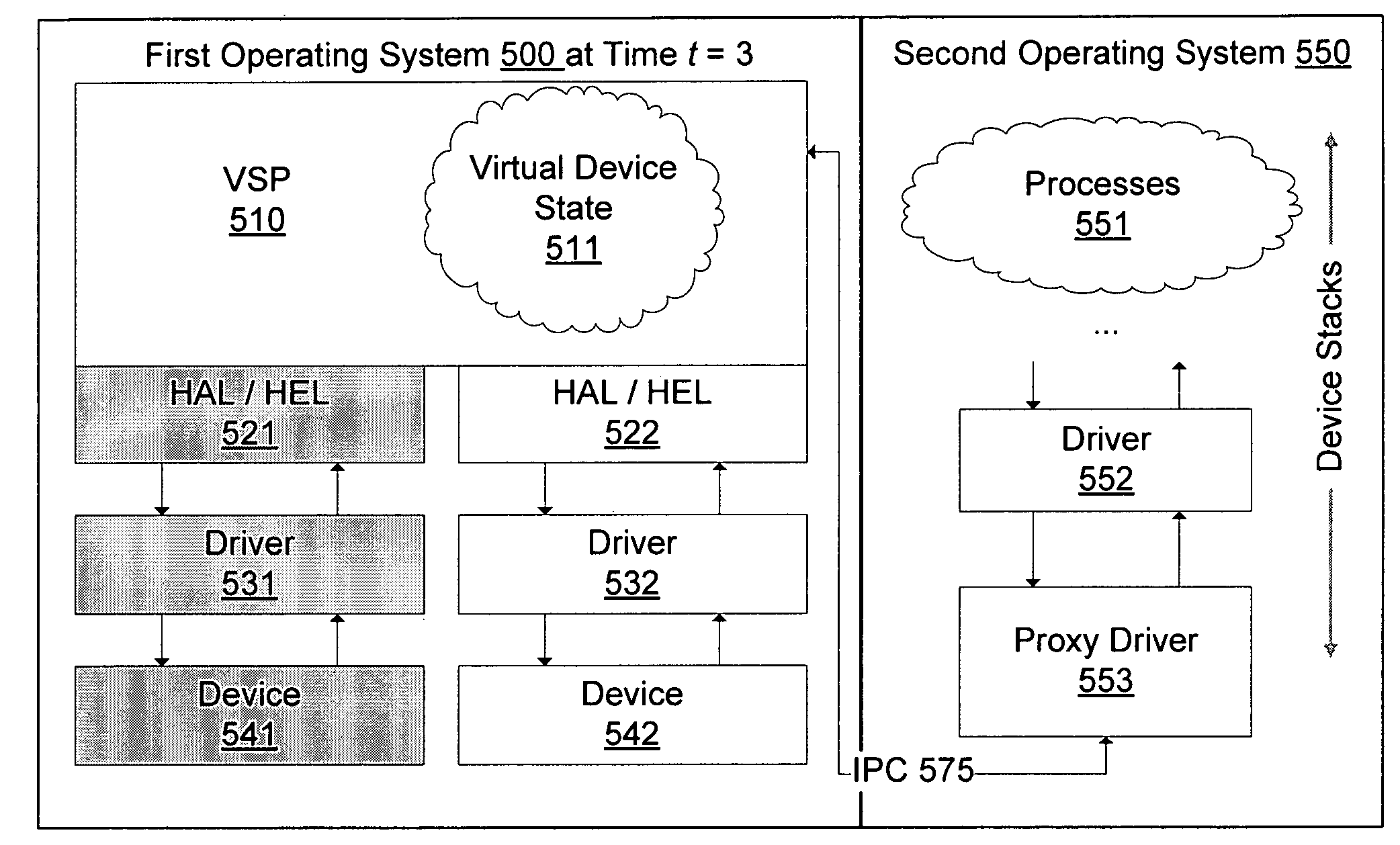

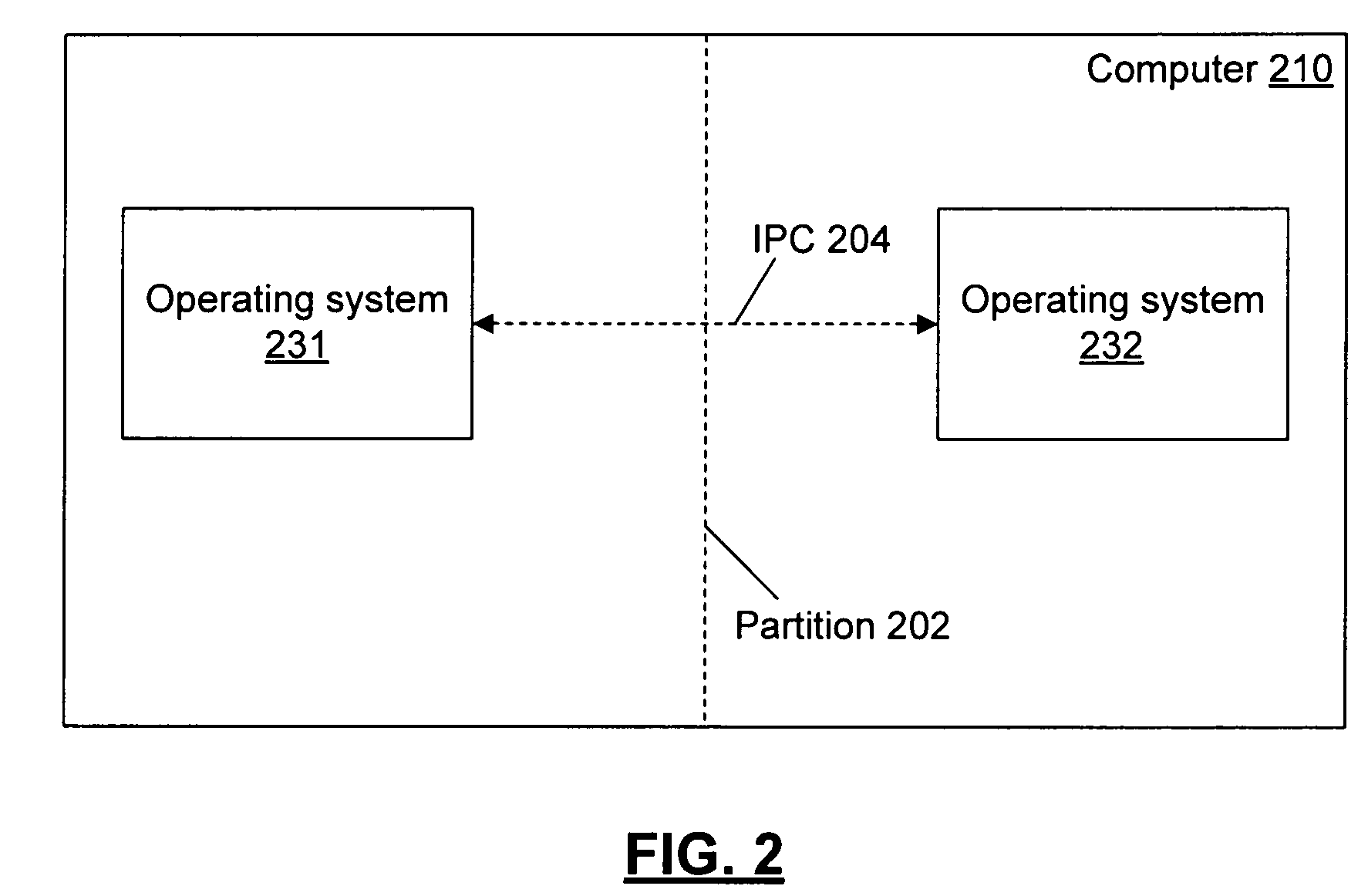

Systems and methods for supporting device access from multiple operating systems

ActiveUS7581229B2Software simulation/interpretation/emulationMemory systemsComputer hardwareOperational system

Owner:MICROSOFT TECH LICENSING LLC

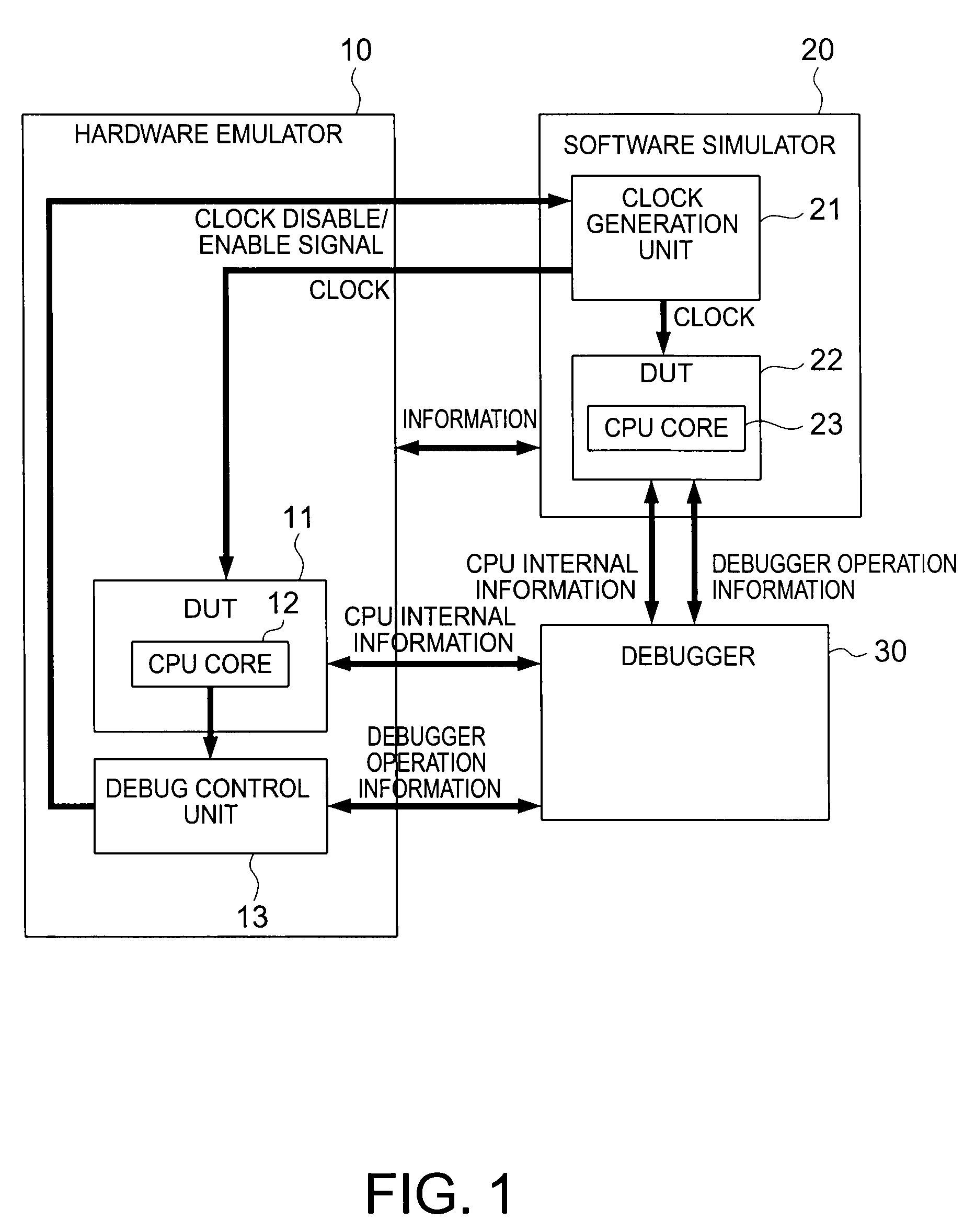

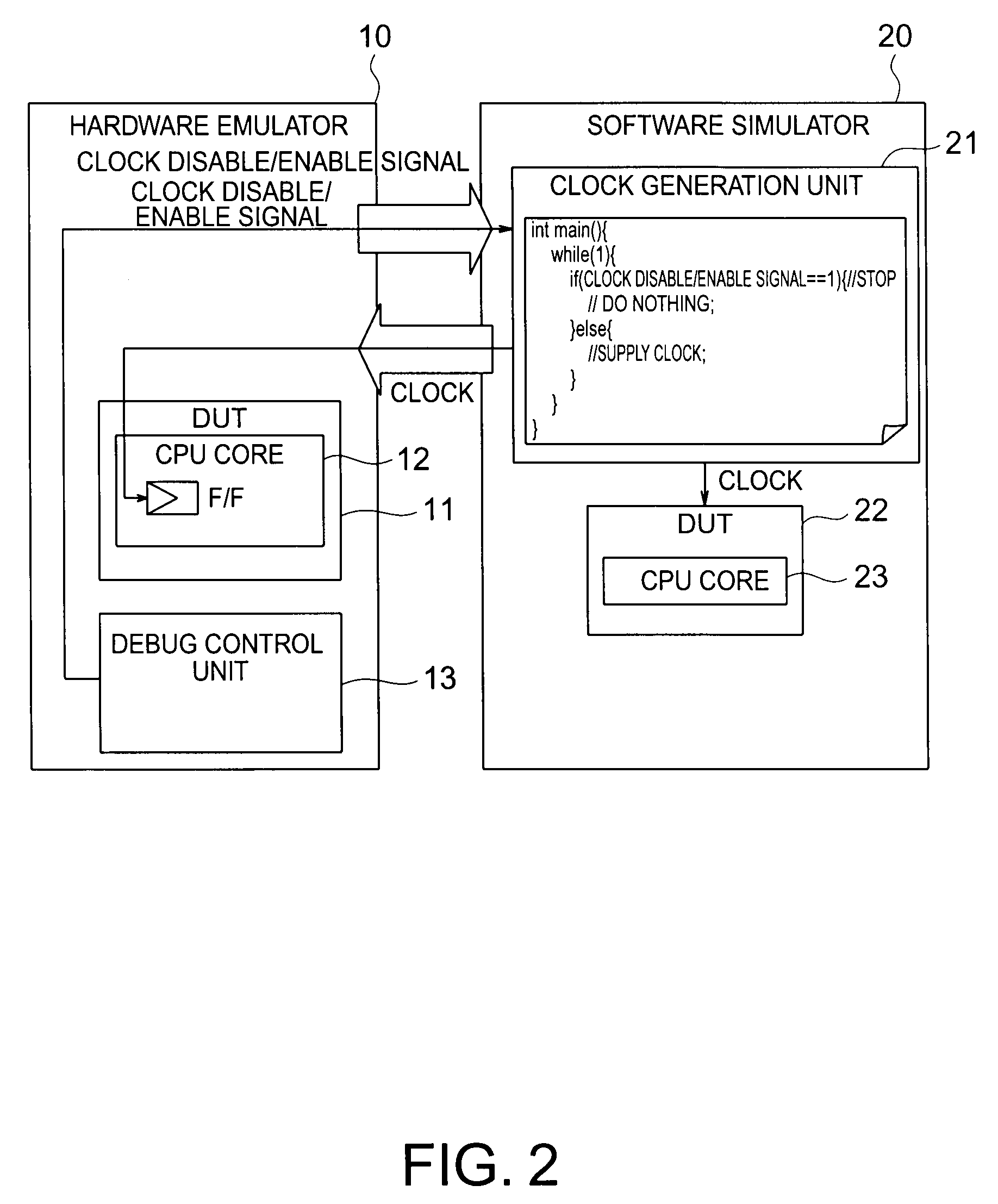

Simulation apparatus and simulation method

InactiveUS20080312900A1Error detection/correctionSoftware simulation/interpretation/emulationComputer hardwareComputer architecture

According to the present invention, there is provided a simulation apparatus having, a hardware emulator which includes a first CPU core as a simulation target, and a debug control unit; a software simulator which includes a second CPU core as a simulation target, and a clock generation unit which generates a clock and supplies the clock to the first CPU core and the second CPU core; and a debugger which debugs the first CPU core and the second CPU core and in which a clock disable condition is set, wherein upon determining that the clock disable condition set in the debugger is satisfied, the debug control unit outputs a clock disable signal, and upon receiving the clock disable signal, the clock generation unit stops generating the clock.

Owner:KK TOSHIBA

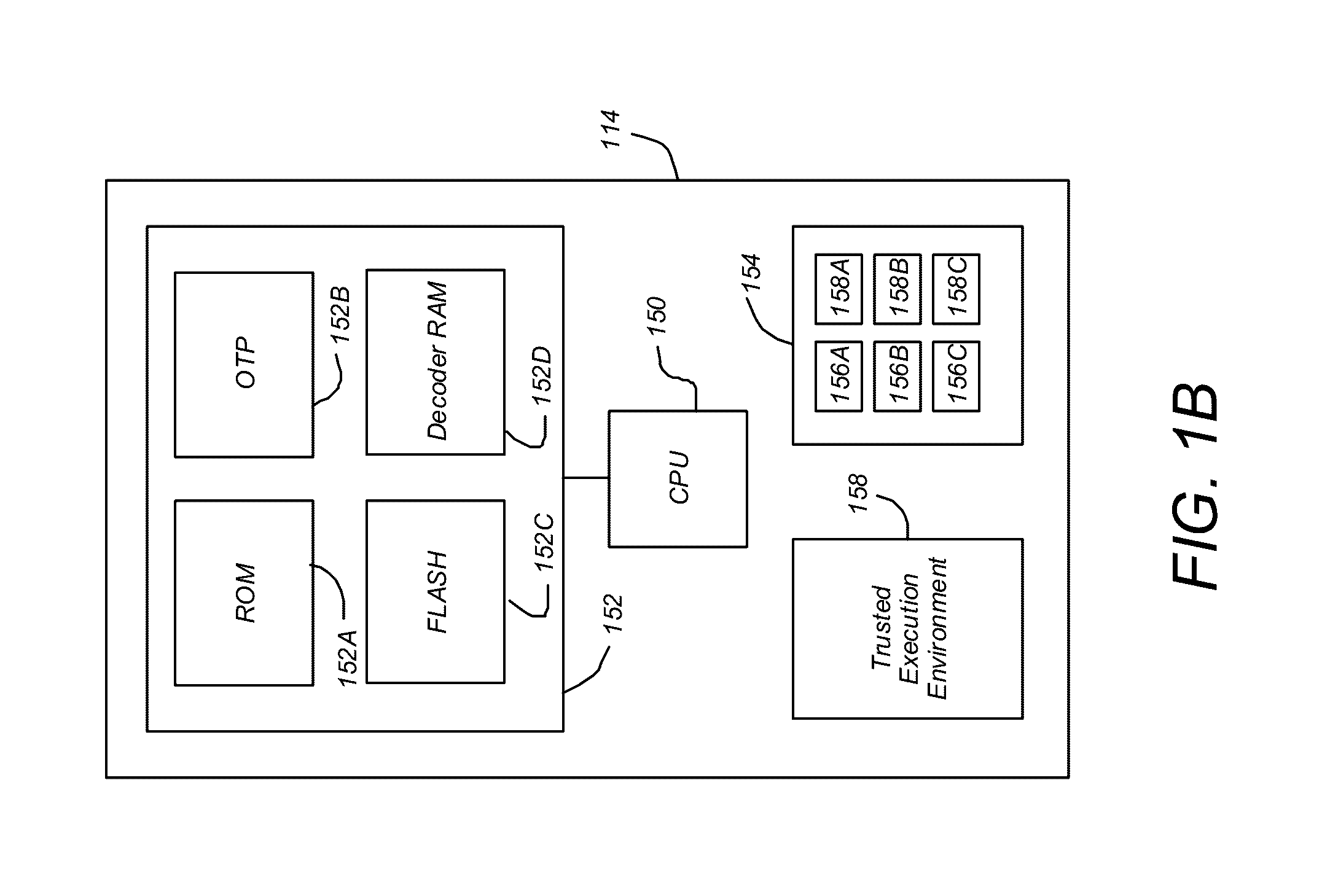

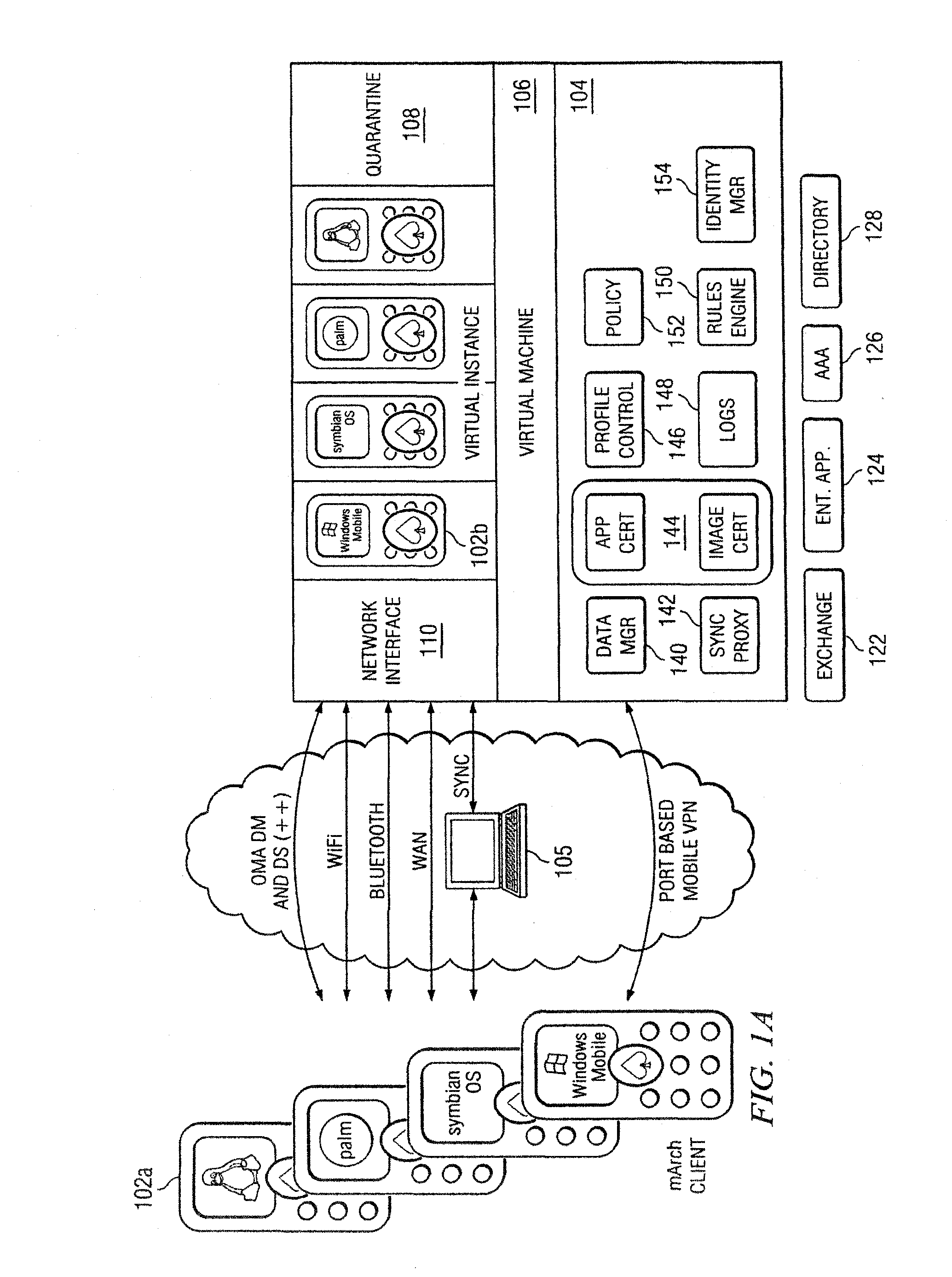

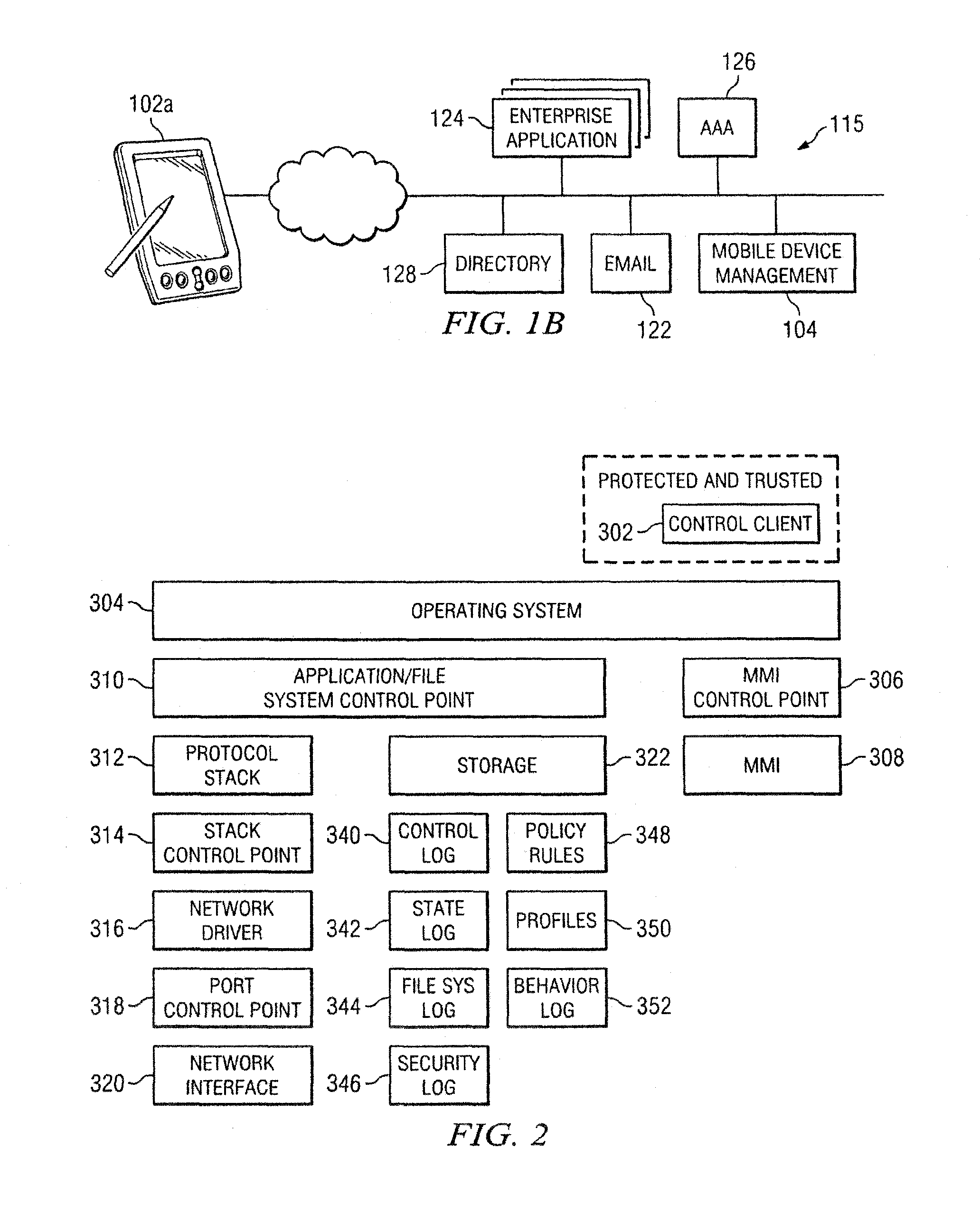

Virtual instance architecture for mobile device management systems

System and method for remotely managing mobile devices. A virtual instance mobile device is maintained for each physical mobile device to be managed. Each virtual instance mobile device is executable in a computer runtime environment and includes a hardware emulation component configured to emulate the hardware components of the corresponding physical mobile device and a software emulation component corresponding to the software components of the physical mobile device, which is executable within the context of the hardware emulation component. Synchronization between the virtual instance mobile devices and their corresponding physical mobile devices is maintained, and data obtained from the physical mobile devices is stored. The physical mobile devices are remotely managed by utilizing their corresponding virtual instance mobile devices respectively.

Owner:IVANTI INC

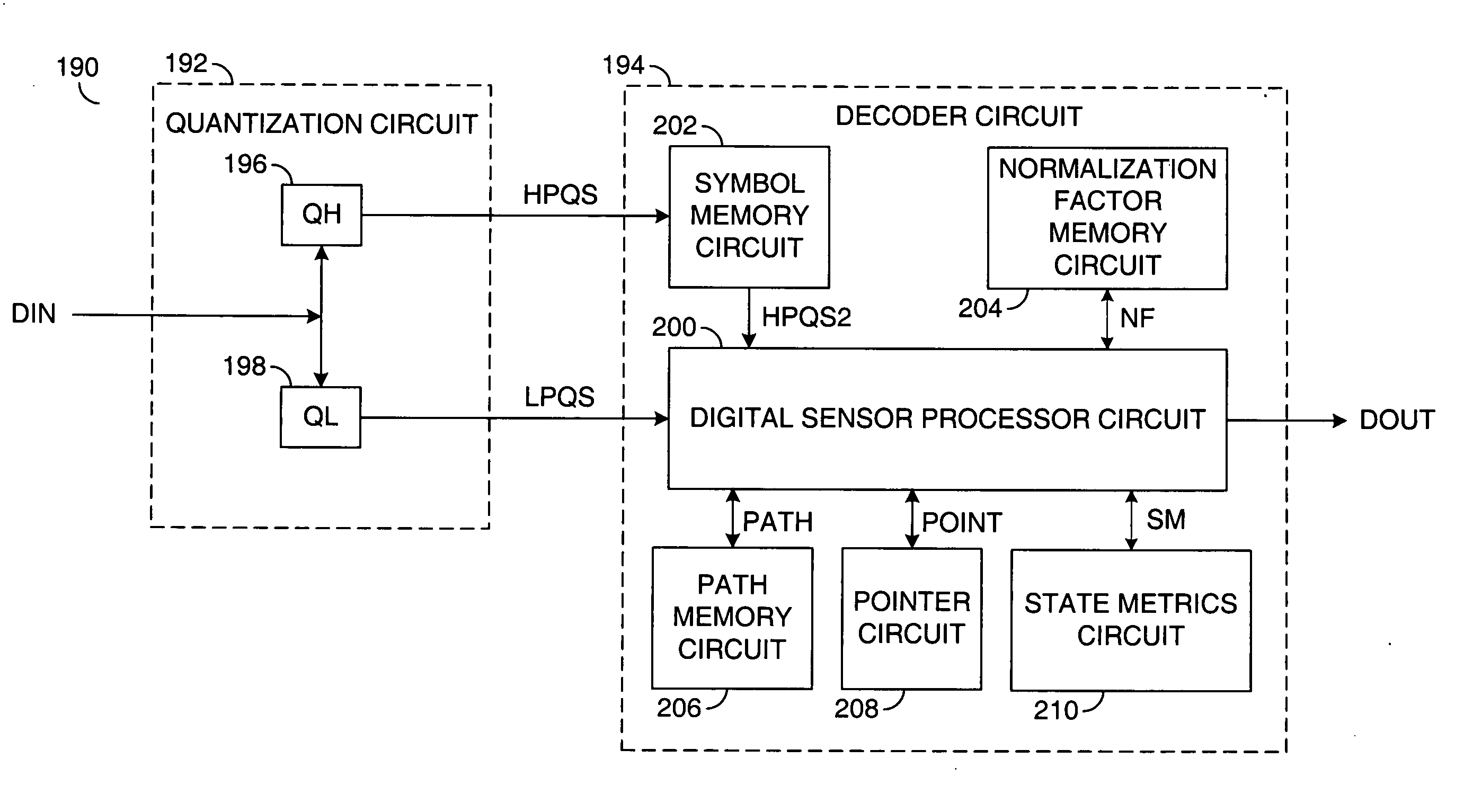

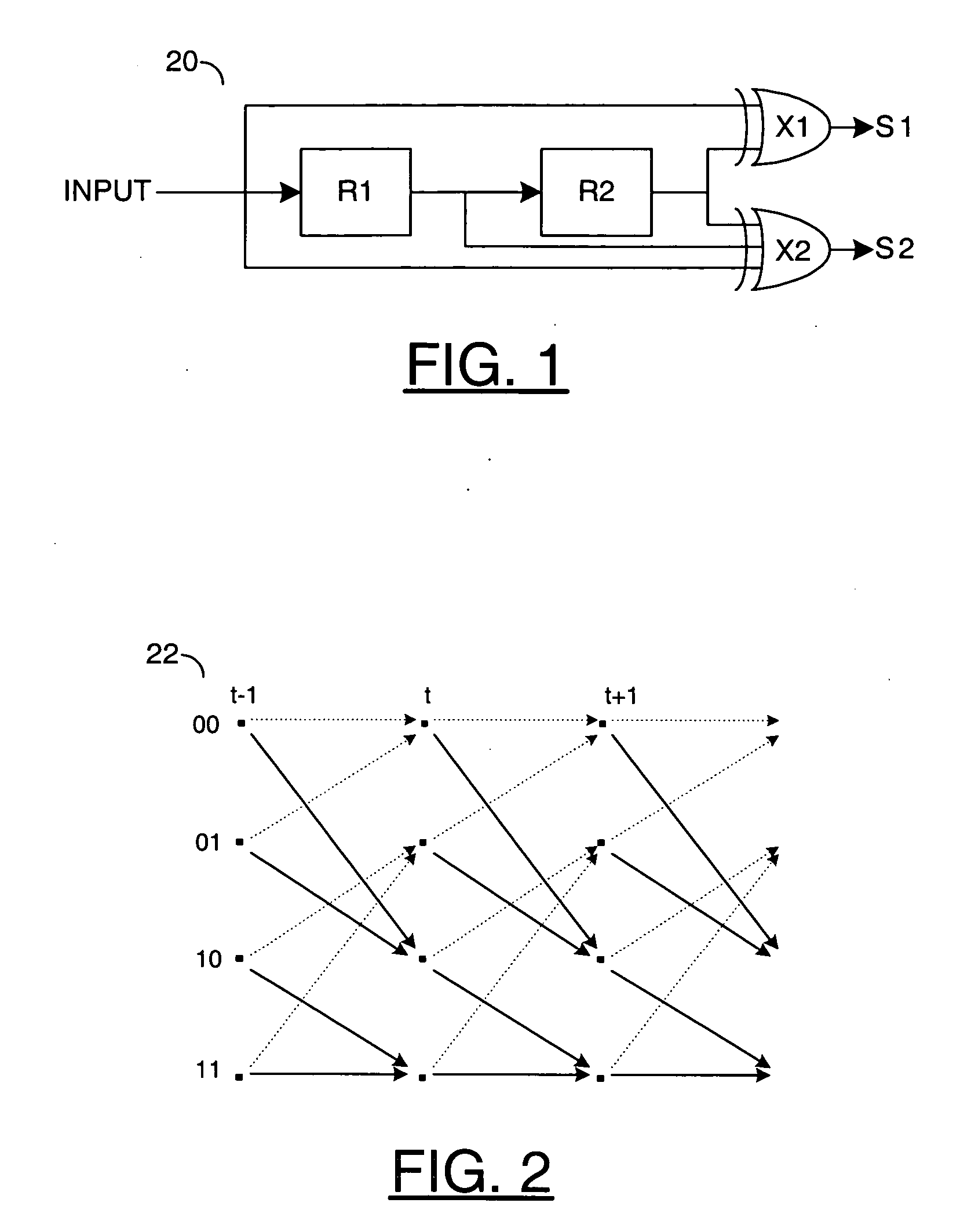

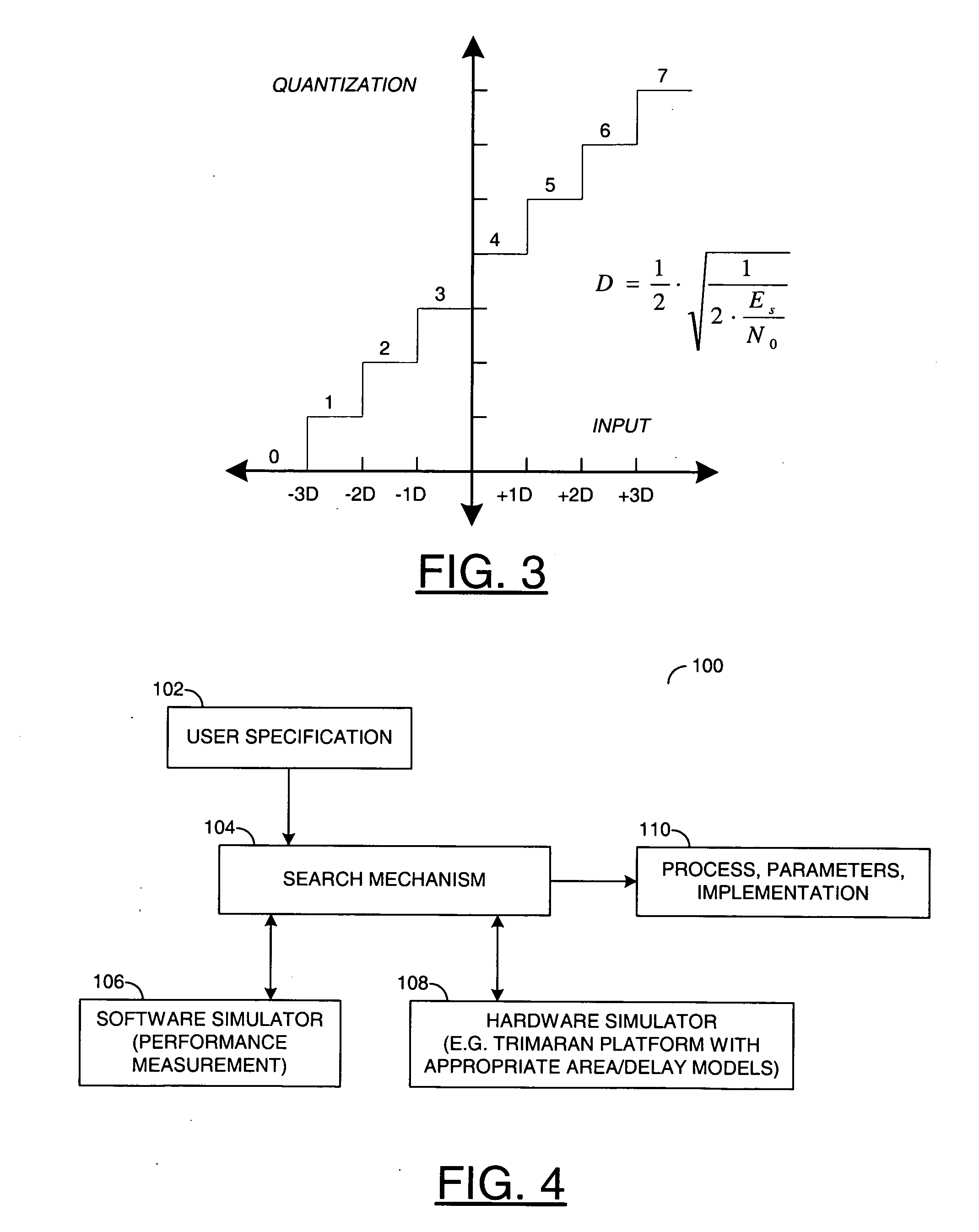

Metacores: design and optimization techniques

InactiveUS20060067436A1Improve performanceLow costData representation error detection/correctionError preventionAlgorithmSoftware simulation

A method for developing a circuit is disclosed. The method generally comprises the steps of (A) generating a solution space having a dimension for each of a plurality of parameters for the circuit, (B) evaluating a plurality of instances of the circuit in the solution space through a software simulation, (C) evaluating the instances through a hardware simulation, and (D) updating the instances in response to the software simulation and the hardware simulation to approach an optimum instance of the instances for the circuit.

Owner:BELL SEMICON LLC

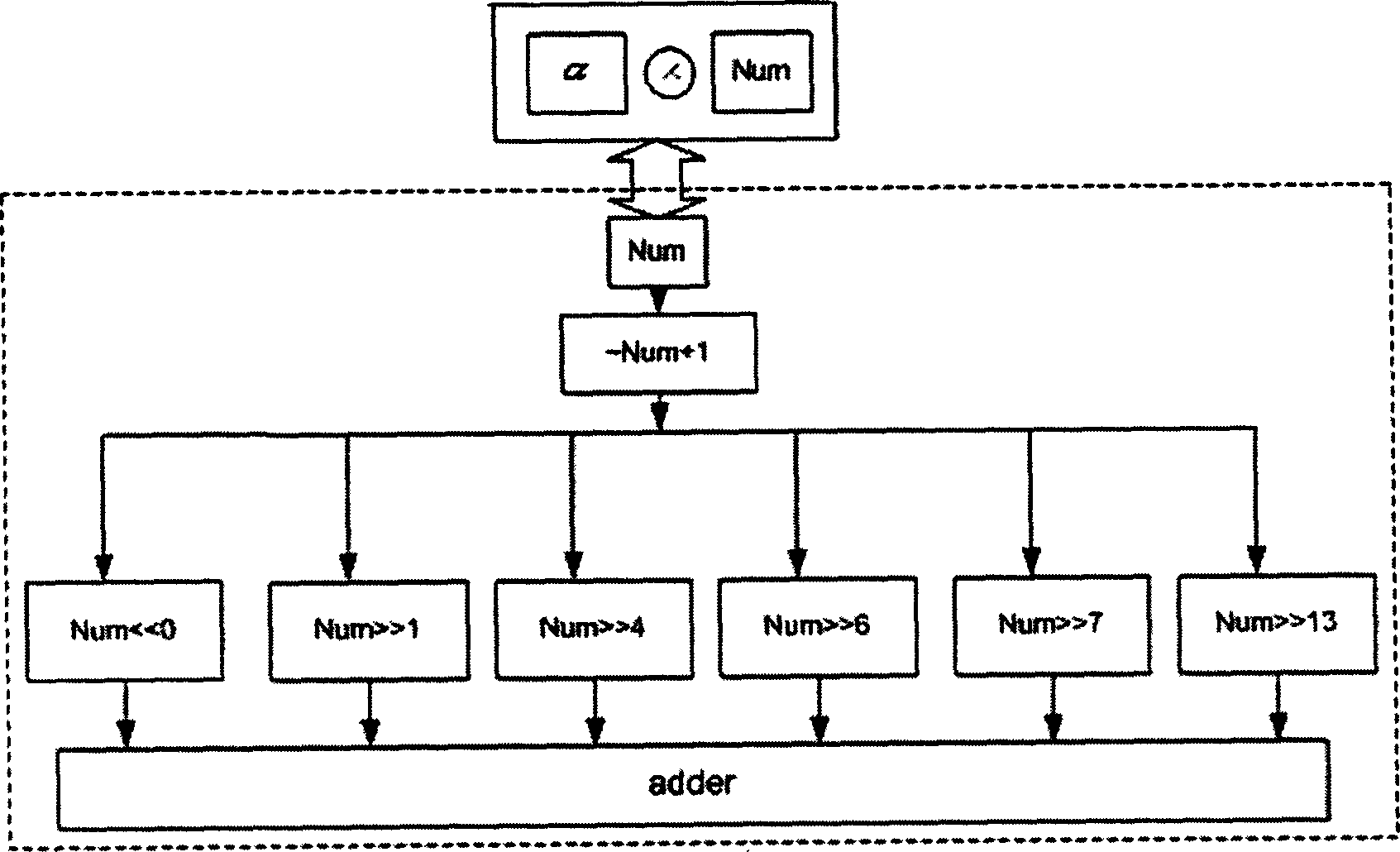

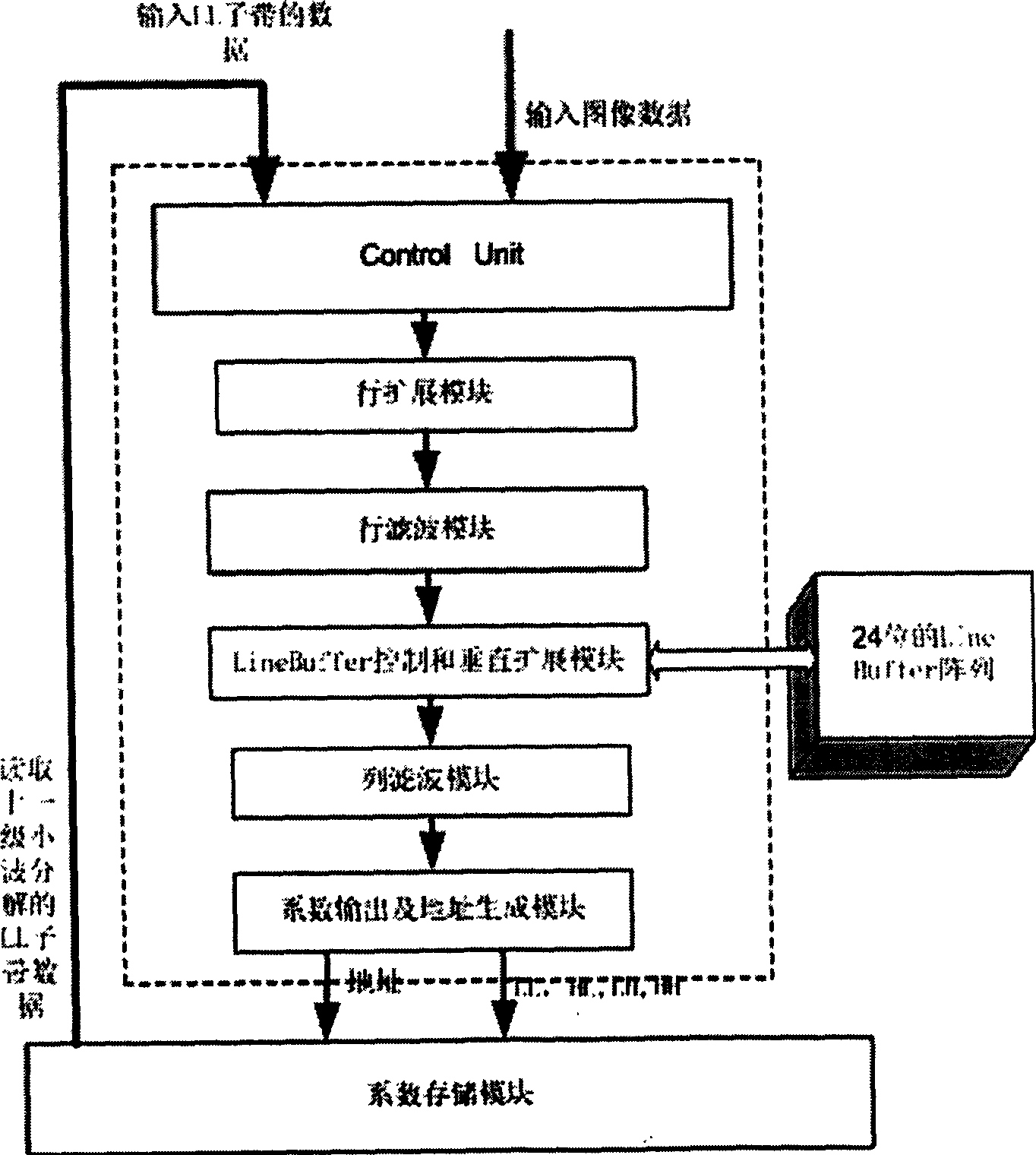

Design method of built-in parallel two-dimensional discrete wavelet conversion VLSI structure

InactiveCN1448871AIncrease profitImprove processing speedSpecial data processing applicationsHardware structureShift register

The VLSI structure design method includes shift adding technology to converting the multiplication operation in the filter into shift register and adder operation to reduce the operation amount save hardware spending greatly; buffering technology to connect row and line filters for concurrent performing to save memory space; delay register technology for streamline processing to speed hardware processing and raise hardware utilization; and united symmetrical expanding technology to raise the versatility of the present invention. The present invention is one efficient 2D DWT hardware scheme with several advantages. Through the optimized design of row filter and line filter for 2D discrete wavelet conversion, the hardware utilization is made to reach 100 %, there are two outputs within one work clock, parallel processing is realized without increasing hardware spending, and the obtained hardware structure is simple and easy to realize with VLSI.

Owner:XI AN JIAOTONG UNIV

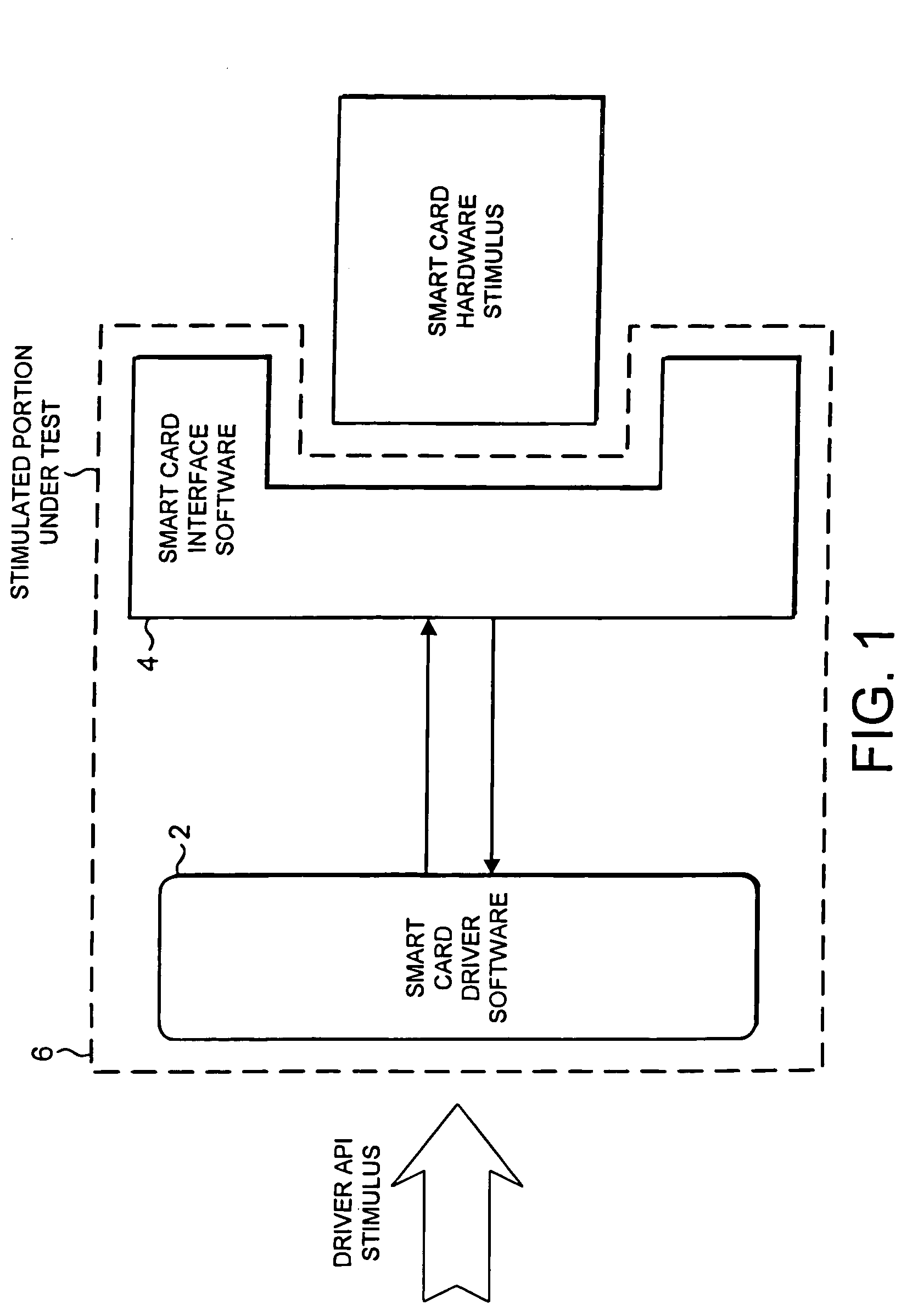

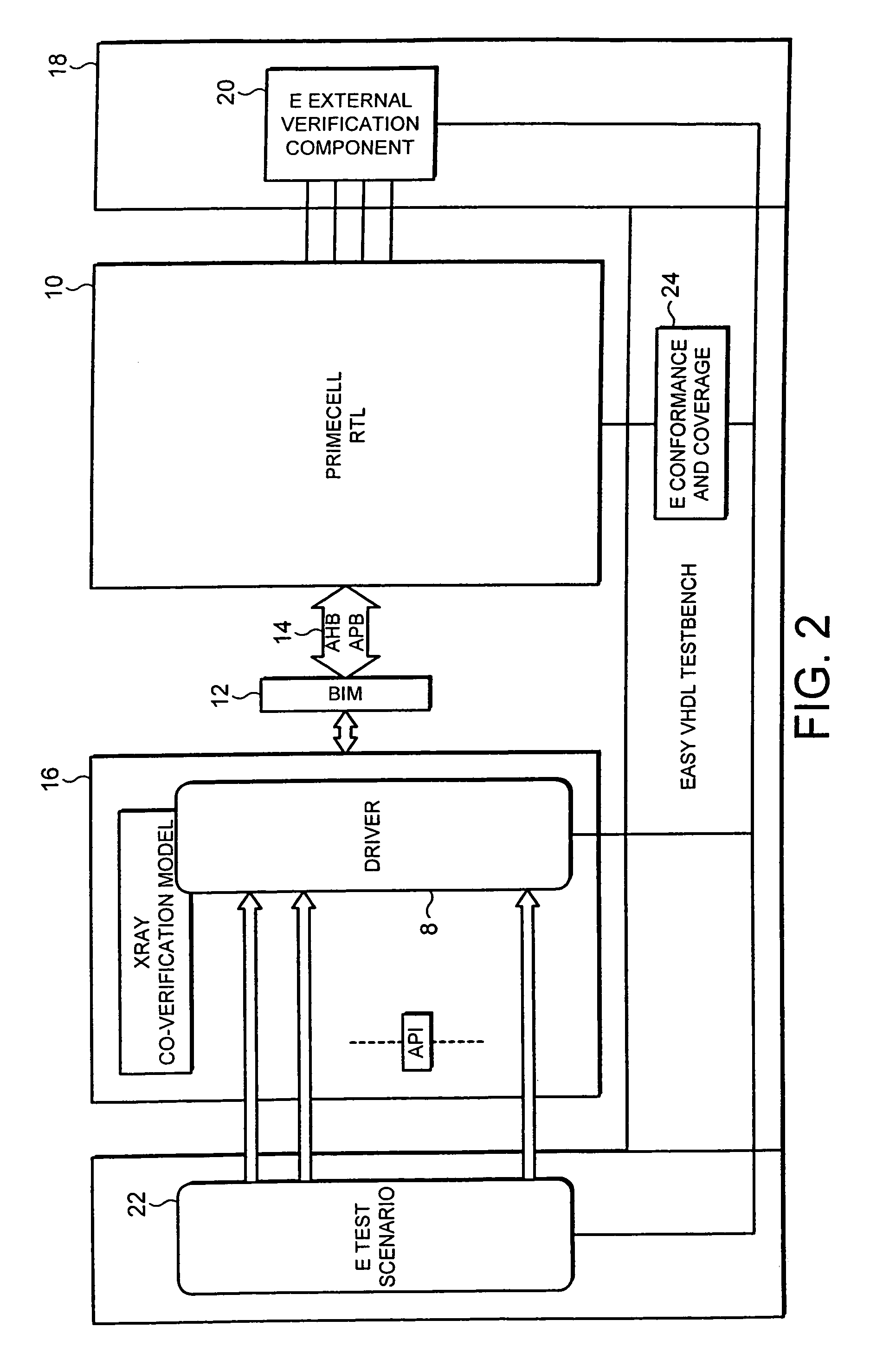

Software and hardware simulation

InactiveUS7366650B2ConfidenceShorten the timeElectronic circuit testingAnalogue computers for electric apparatusComputer hardwareHardware emulation

A verification environment is provided that co-verifies a software component 8 and a hardware component 10. Within the same environment using a common test controller 18 both hardware stimuli and software stimuli may be applied to their respective simulators. The response of both the software and the hardware to the simulation conducted can be monitored to check for proper operation.

Owner:ARM LTD

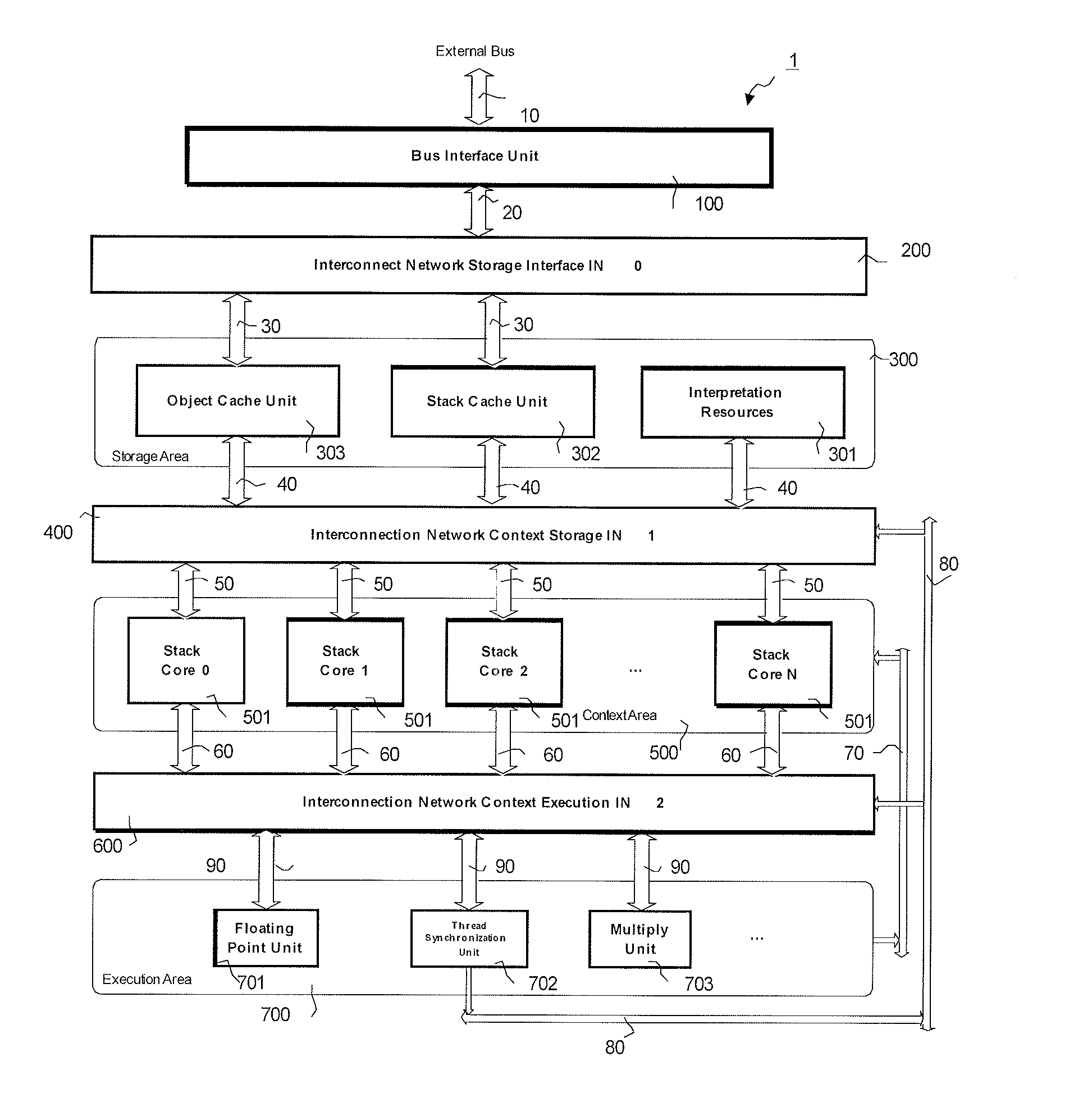

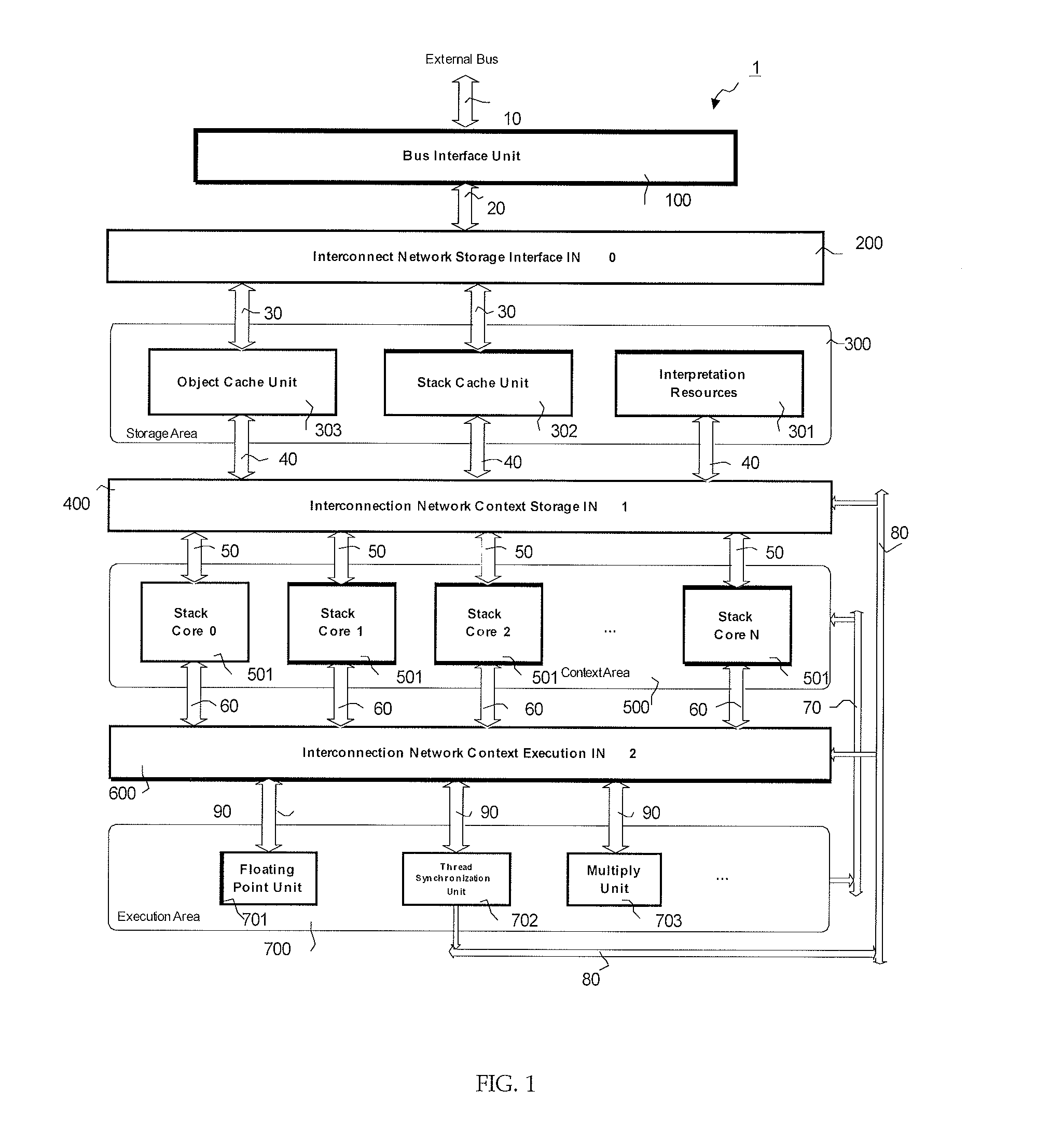

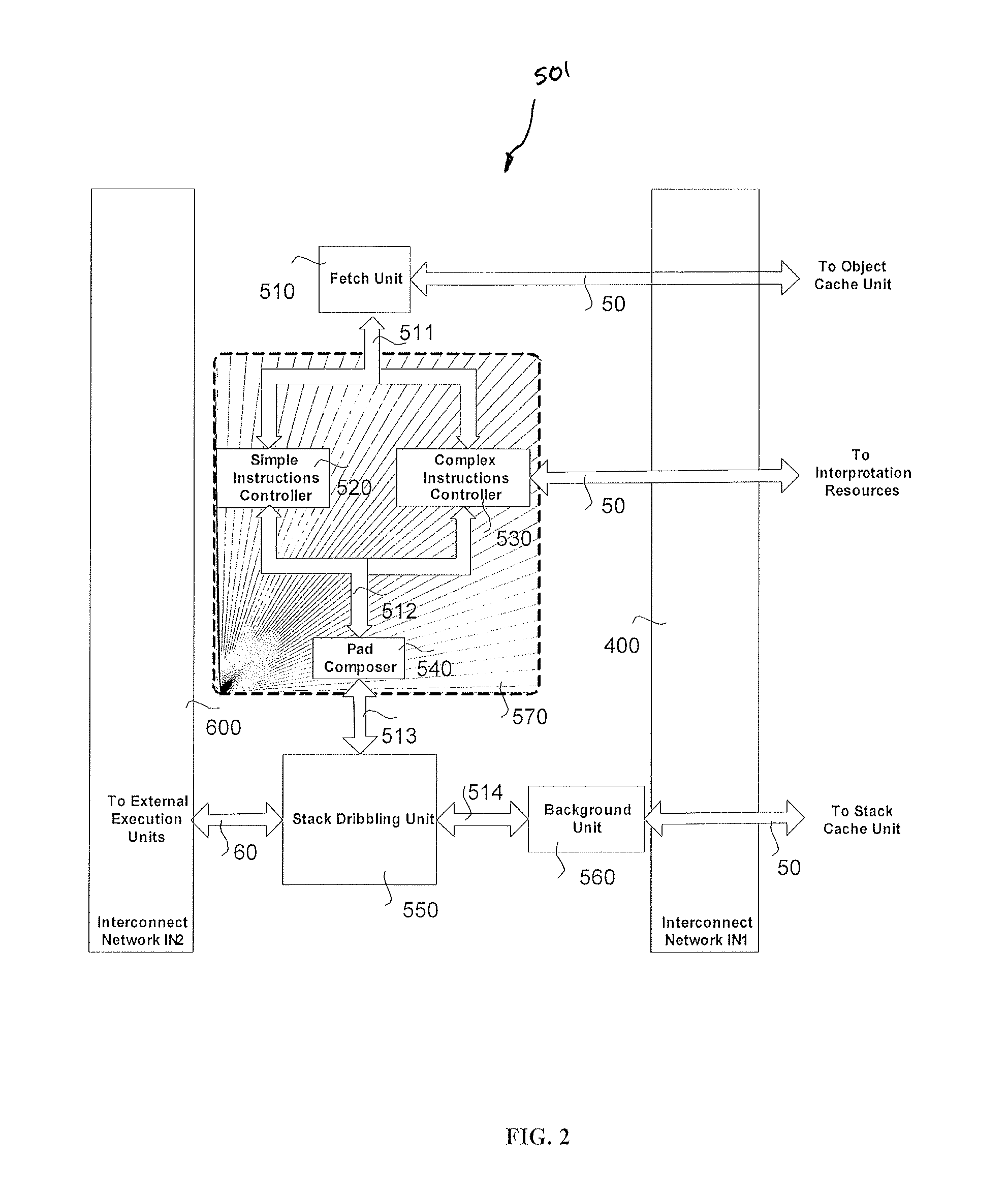

Hardware multi-core processor optimized for object oriented computing

InactiveUS20080177979A1Improve performanceEasy to associateInstruction analysisProgram control using wired connectionsContext managementProcessing element

A multi-core processor system includes a context area, which contains an array of stack core processing elements, a storage area that contains expensive shared resources (e.g., object cache, stack cache, and interpretation resources), and an execution area, which contains complex execution units such as an FPU and a multiply unit. The execution resources of the execution area, and the storage resources of the storage area, are shared among all the stack cores through one or more interconnection networks. Each stack core contains only frequently used resources, such as fetch, decode, context management, an internal execution unit for integer operations (except multiply and divide), and a branch unit. By separating the complex and infrequently used units (e.g., FPU or multiply / divide unit) from the simple and frequently used units in a stack core, all the complex execution resources are shared among all the stack cores, improving efficiency and processor performance.

Owner:STEFAN GHEORGHE +1

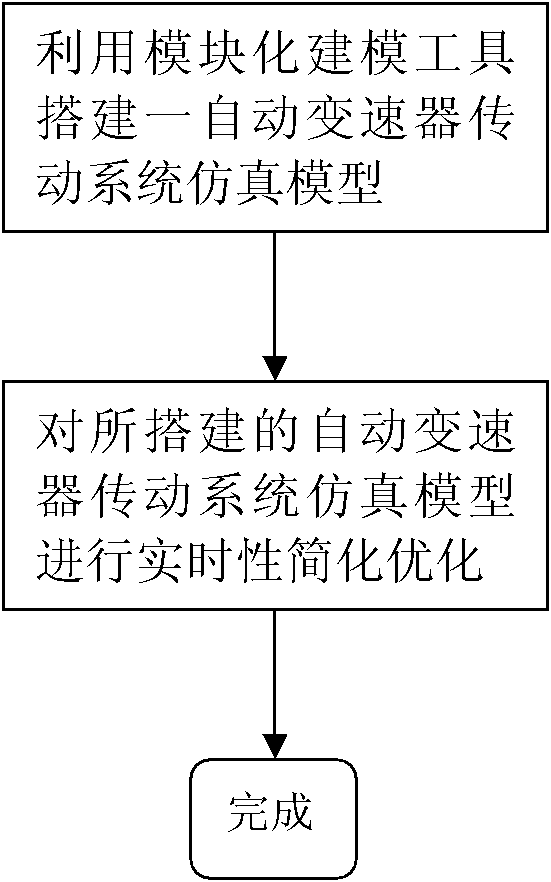

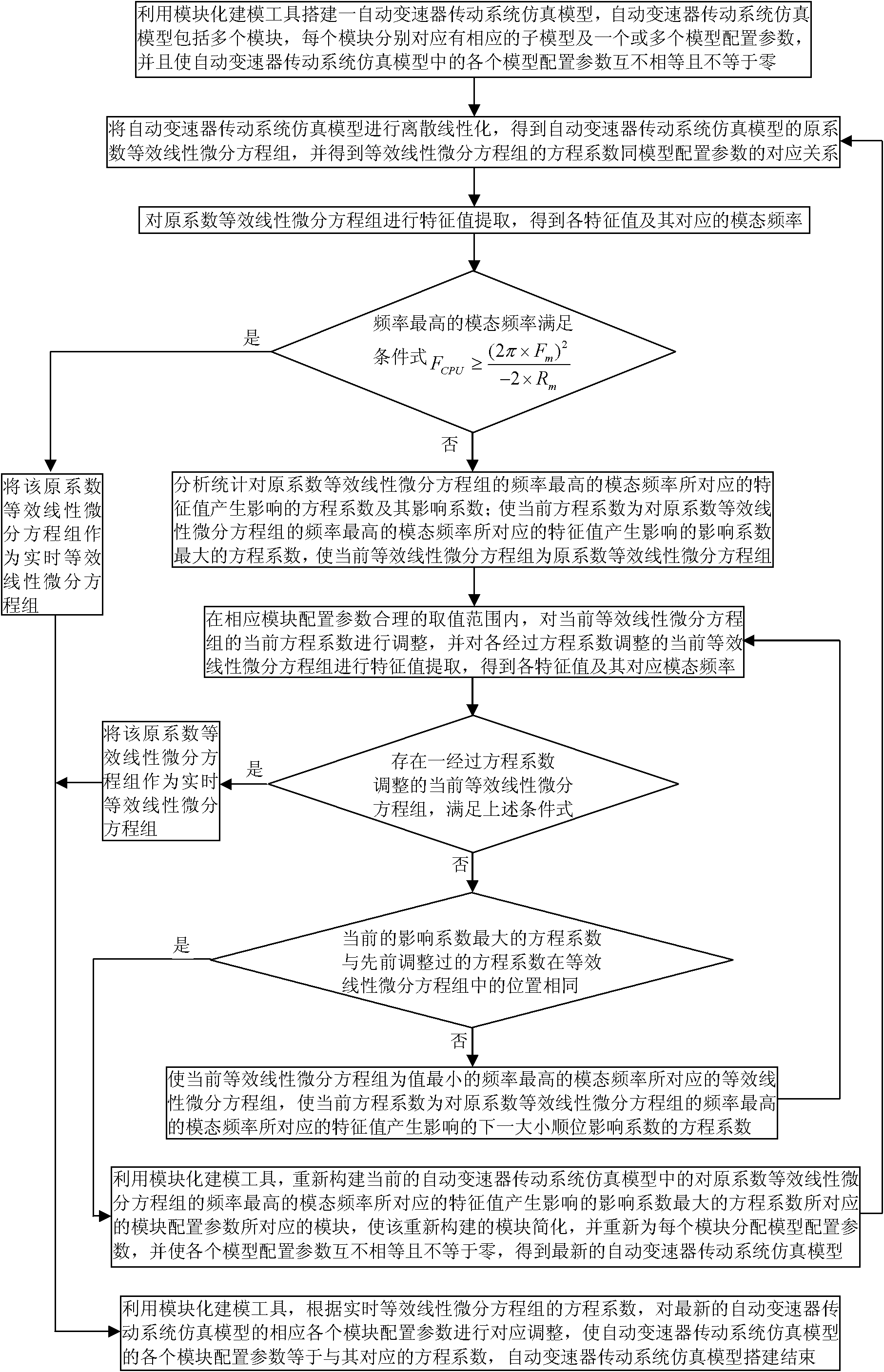

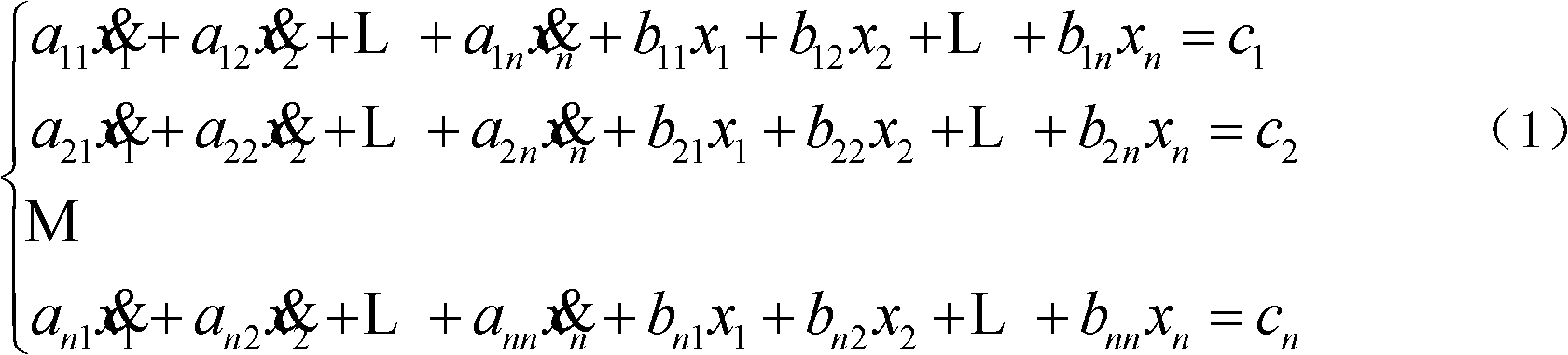

Construction method of simulation model of automatic transmission transmission system

InactiveCN102269975AAccurate descriptionEasy to adjustSimulator controlBuilding simulationAutomatic transmission

The invention discloses a method for building a simulation model of an automatic transmission transmission system. First, a modular modeling tool is used to construct a simulation model of an automatic transmission transmission system, and then the built automatic transmission transmission system simulation model is simplified and optimized in real time. The automatic transmission transmission system simulation model built by the automatic transmission transmission system simulation model building method of the present invention can accurately simulate the working state of the automatic transmission, avoid system oscillation, and perform hardware-in-the-loop real-time simulation.

Owner:UNITED AUTOMOTIVE ELECTRONICS SYST

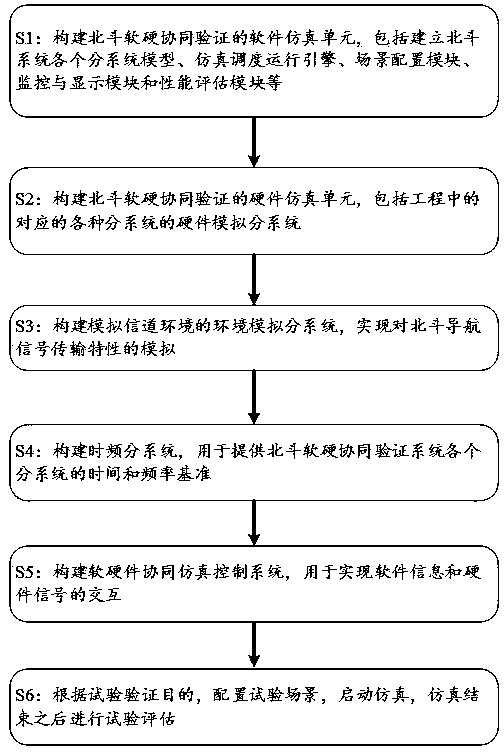

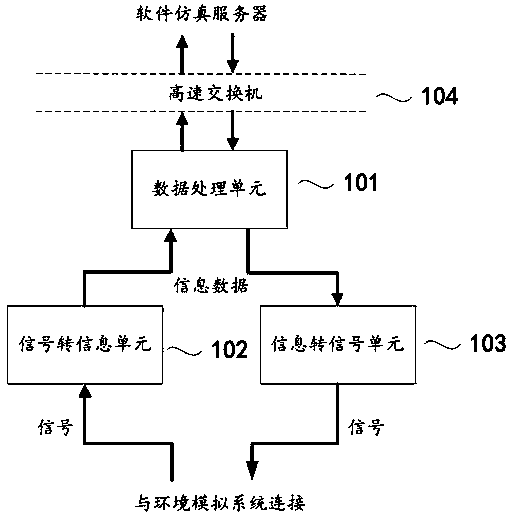

Beidou global system soft and hard collaborative simulation test verification system and establishment method

ActiveCN111208746AExpandable and flexibleThe sequence is logically correctSimulator controlSoftware emulationSoftware engineering

The invention provides a Beidou global system soft and hard collaborative simulation test verification system. The Beidou global system soft and hard collaborative simulation test verification systemcomprises a software simulation unit, a hardware simulation unit, a software and hardware collaborative simulation control system, an environment simulation system and a time-frequency subsystem. Thesoftware simulation unit comprises a simulation model library, a simulation scheduling operation module, a scene configuration module, a monitoring and display module and a performance evaluation module. The hardware simulation unit comprises a hardware simulation system and an external interface system. The invention further provides an establishment method of the Beidou global system soft and hard collaborative simulation test verification system. The establishment method comprises the following steps of establishing the software simulation part, establishing the hardware simulation part, establishing the environment simulation subsystem, establishing the time frequency subsystem and establishing the software and hardware collaborative simulation control system; and performing test verification. Through the hardware simulator and the software model, the state of the Beidou engineering system can be approximated to the maximum extent, the number and the state of the test models can beflexibly configured, and butt joint verification with the real Beidou engineering system can be carried out.

Owner:NAT UNIV OF DEFENSE TECH

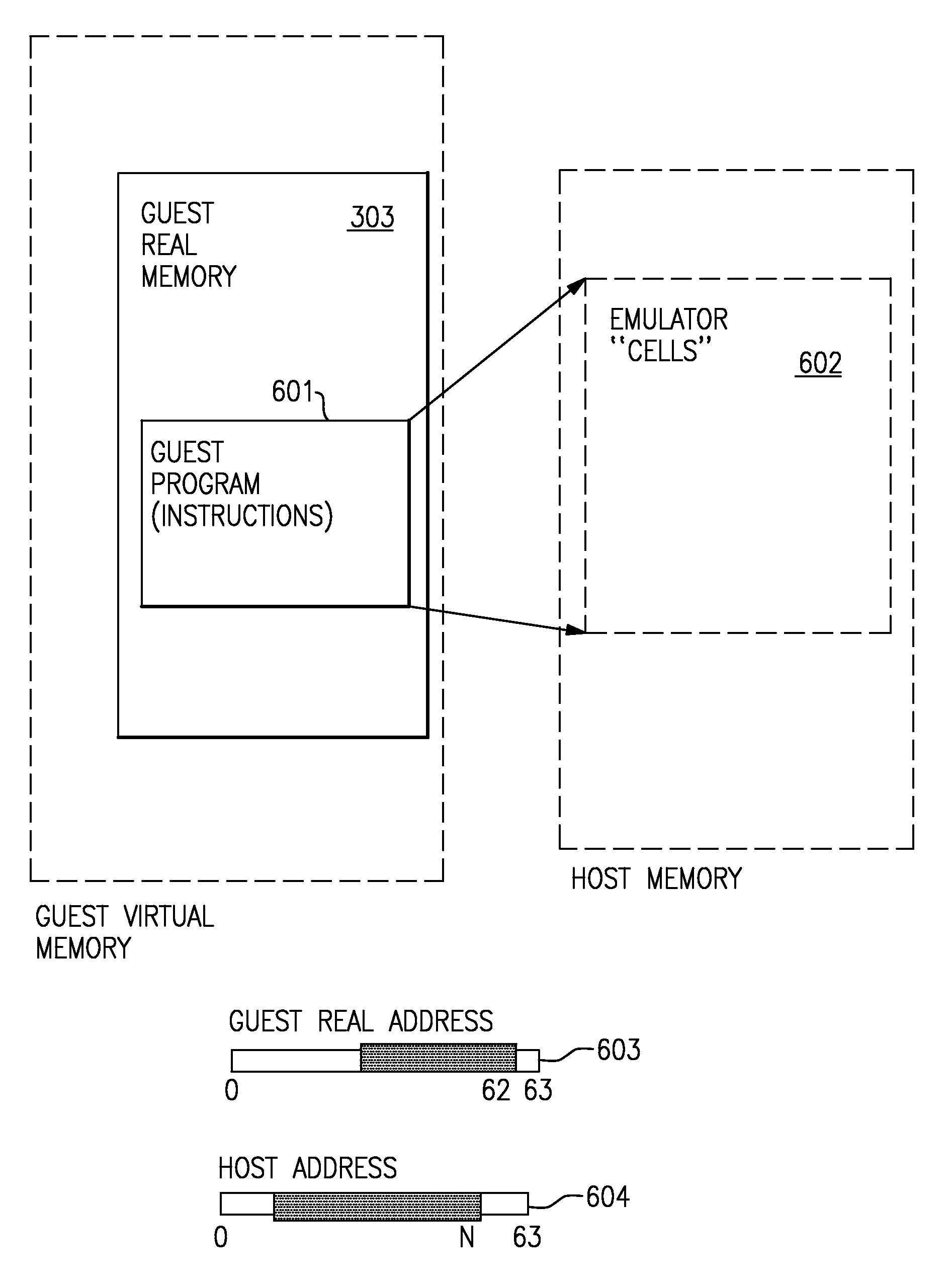

Page mapped spatially aware emulation of computer instruction set

Dynamic creation of a spatially aware emulation environment comprising Host cells of Host pages corresponding to Guest cells of Guest pages of Guest instructions. Each Host cell comprises a semantic routine for emulating a corresponding Guest instruction located at the corresponding Guest cell of the guest page.

Owner:INT BUSINESS MASCH CORP

Fpga-based hardware emulator system with an inter-fpga connection switch

ActiveUS20190179989A1Avoid lossEnhance run-time performanceComputer aided designSpecial data processing applicationsIntegrated circuitHardware emulation

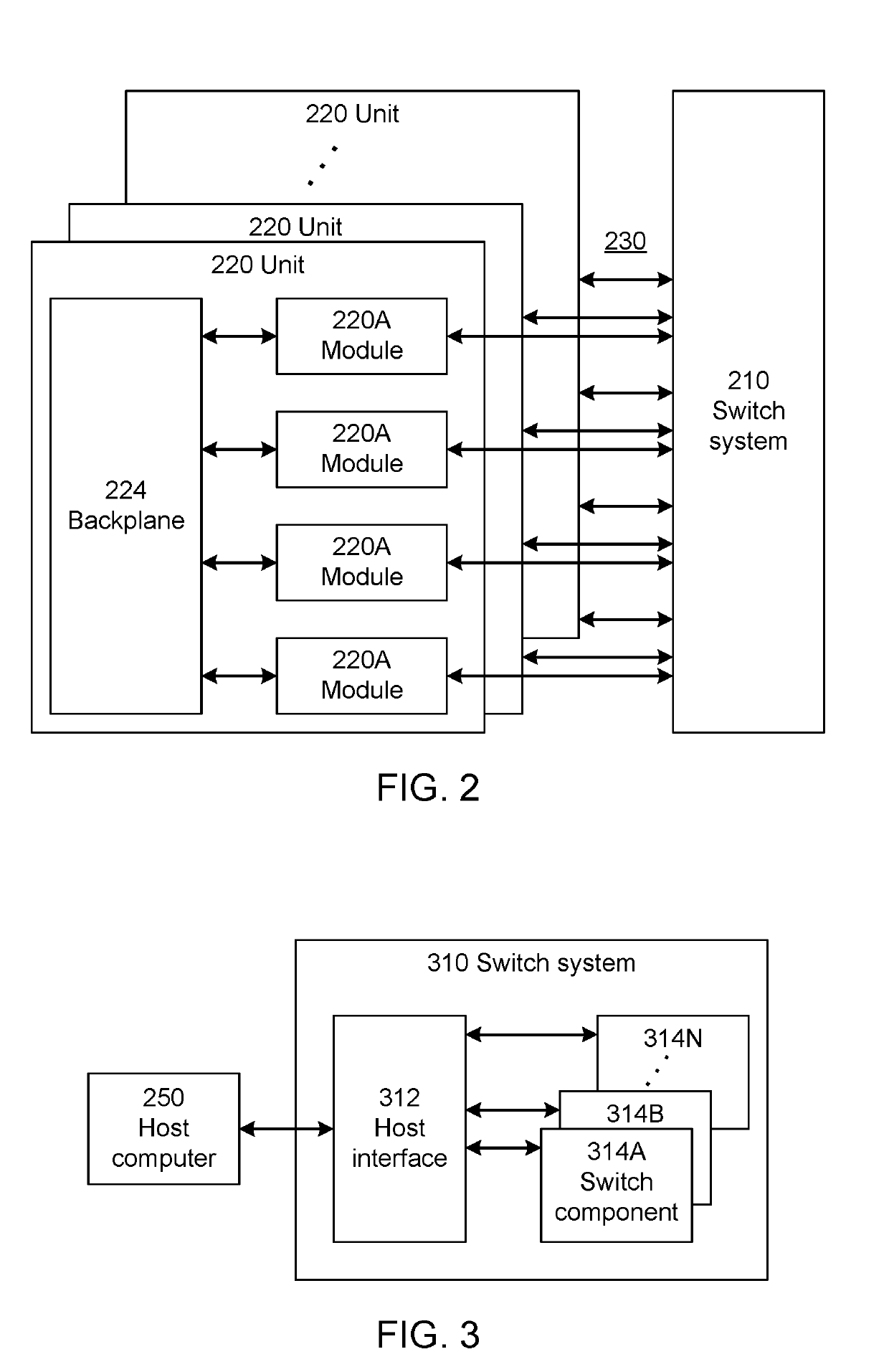

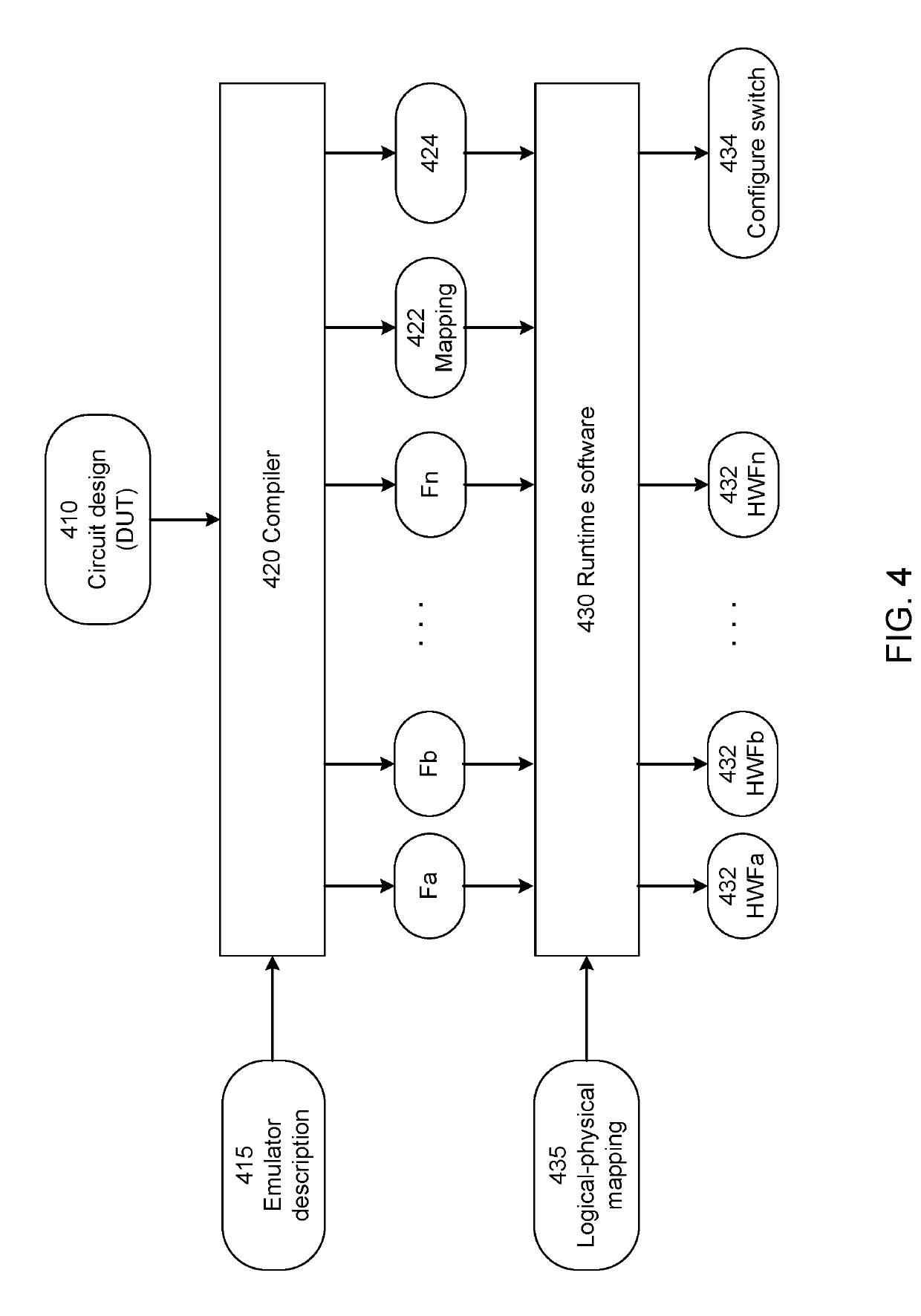

A hardware emulation system for emulating an integrated circuit design under test (DUT) includes a switch system, FPGAs and serial transmitter and receiver circuitry. The switch system has input and output ports and is configurable to change which ports are connected to each other. The FPGAs are configurable to emulate a functionality of the DUT. The functionality of the DUT is partitioned across multiple FPGAs. The serial transmitter circuitry transmits data from the FPGAs on serial lines to the ports of the switch system. The serial receiver circuitry receives data for the FPGAs on serial lines from the ports of the switch system.

Owner:SYNOPSYS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com