Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

52 results about "Software simulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Simulator is a piece of software that performs operations of the other software. Here both softwares will have the same internal states. Simulator actually recreates the behavior of the target software. Flight simulator is a software that simulates the real look and feel of an aircraft flying.

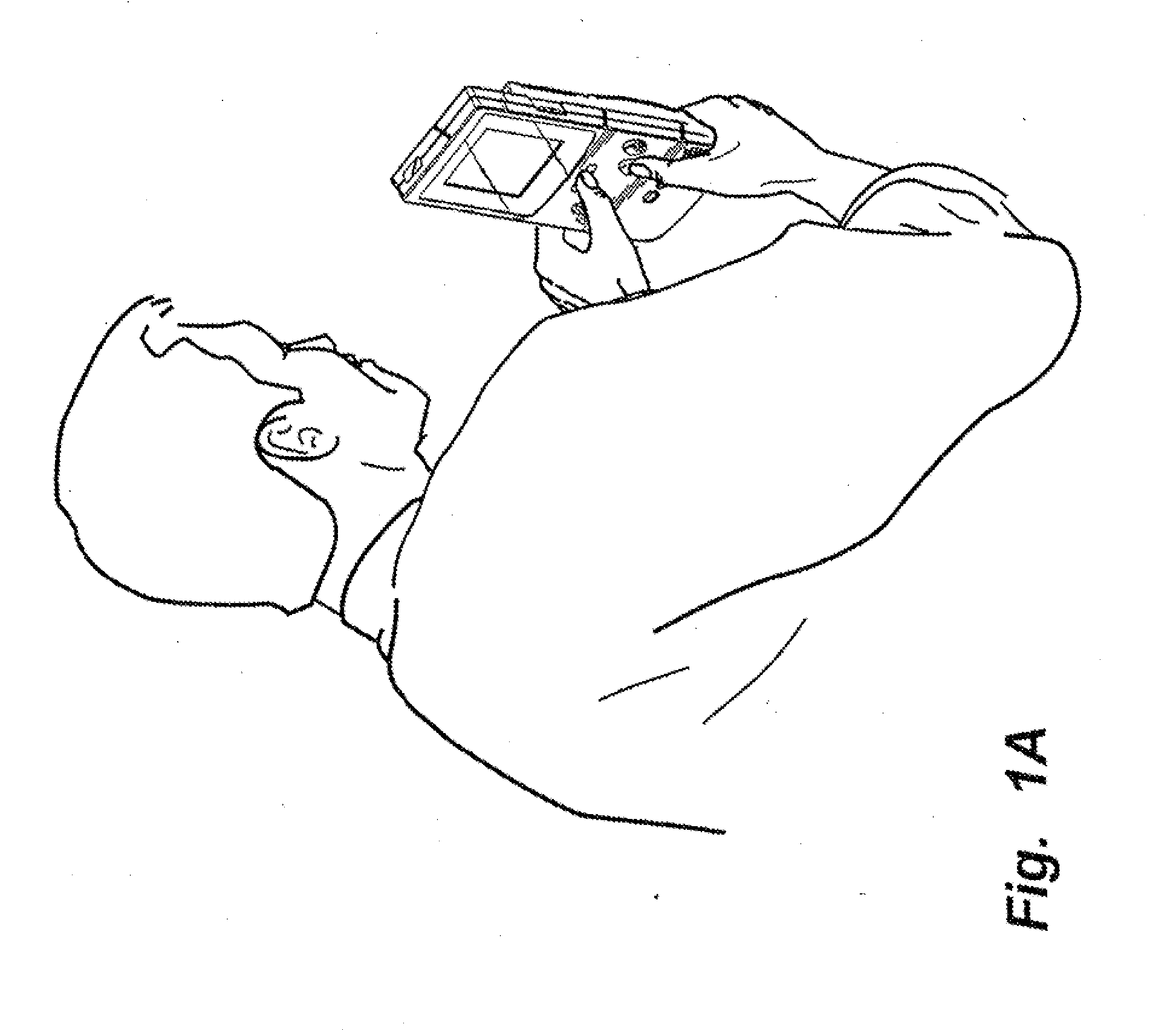

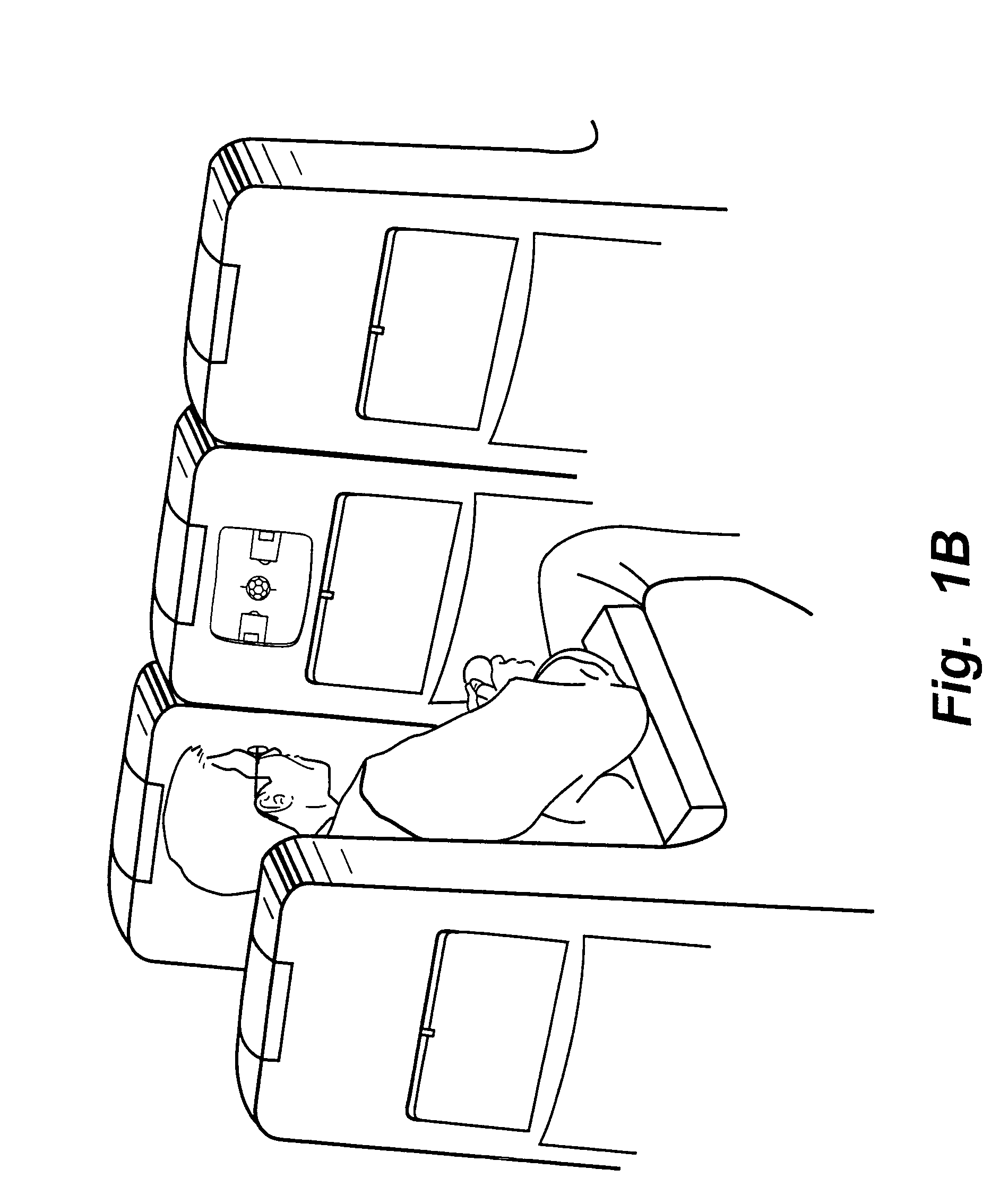

Video game distribution network

InactiveUS6884171B2Keep them occupied and happyVideo gamesSpecial data processing applicationsSoftware emulationInteractive video

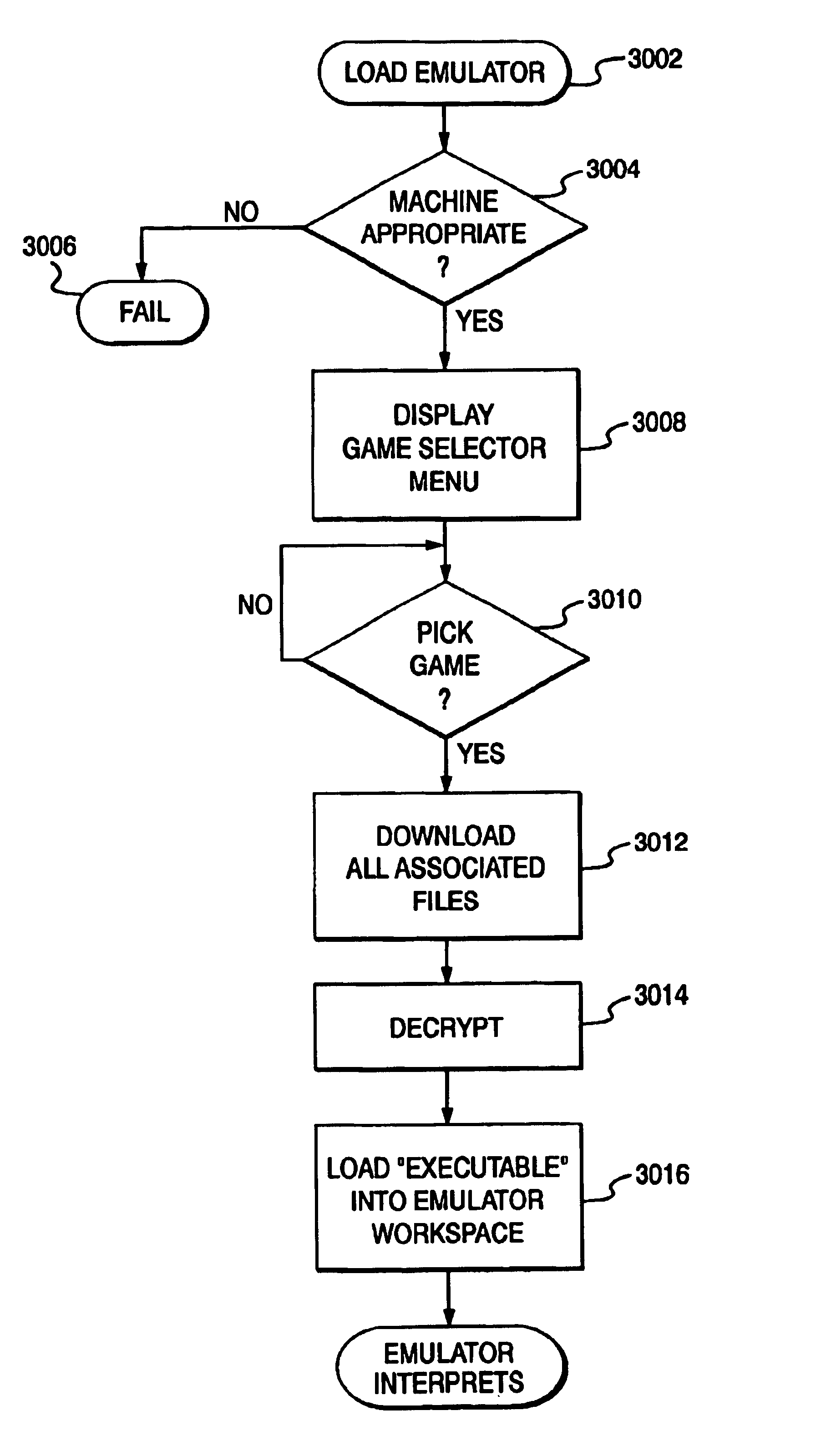

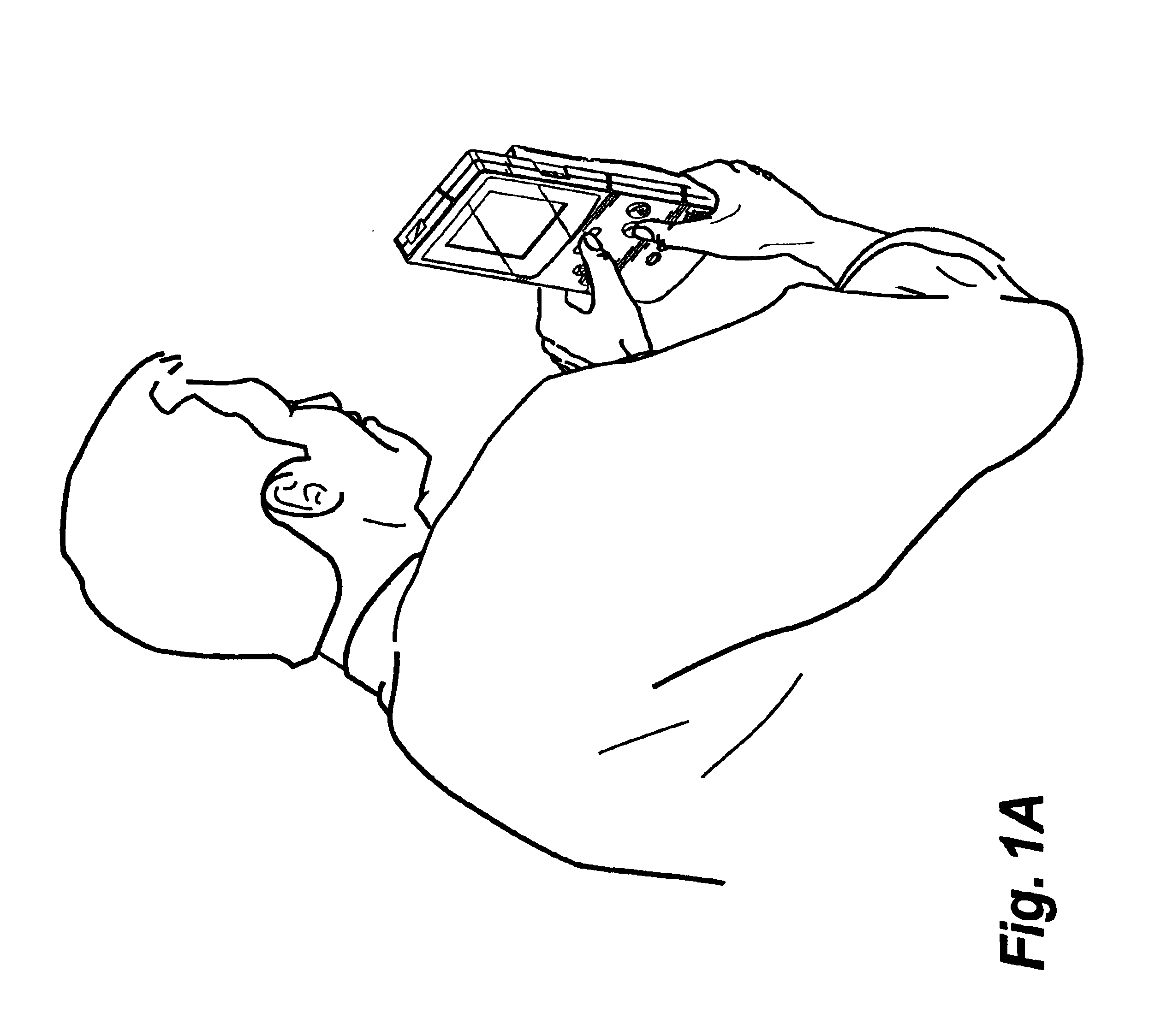

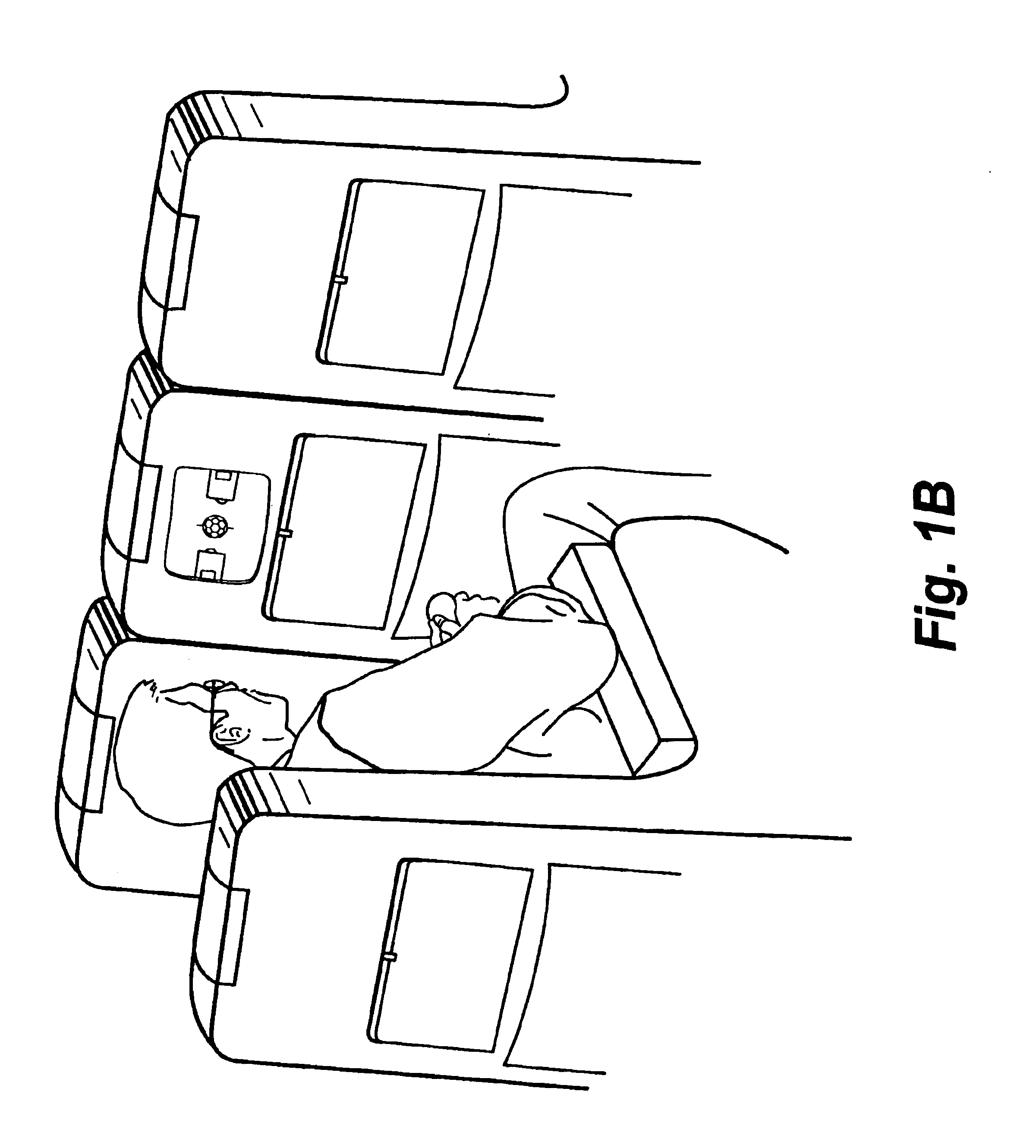

A video game distribution network for use in airlines, trains, hotels, cruise ships, set top boxes, cable television systems, satellite and other wireless systems or other communications systems, distributes special purpose game binary image files to general purpose computing / display devices. Software emulators running on the general purpose computing / display devices model the game source platform and interpret and / or compile the game files to provide interactive video game play. Software emulators for emulating a handheld video game platform such as GAME BOY®, GAME BOY COLOR® and / or GAME BOY ADVANCE® on a low-capability target platform (e.g., a seat-back display for airline or train use, a personal digital assistant, a cell phone) may provide any number of features and optimizations to provide high quality graphics and sound that nearly duplicates the game playing experience on the native platform.

Owner:NINTENDO CO LTD

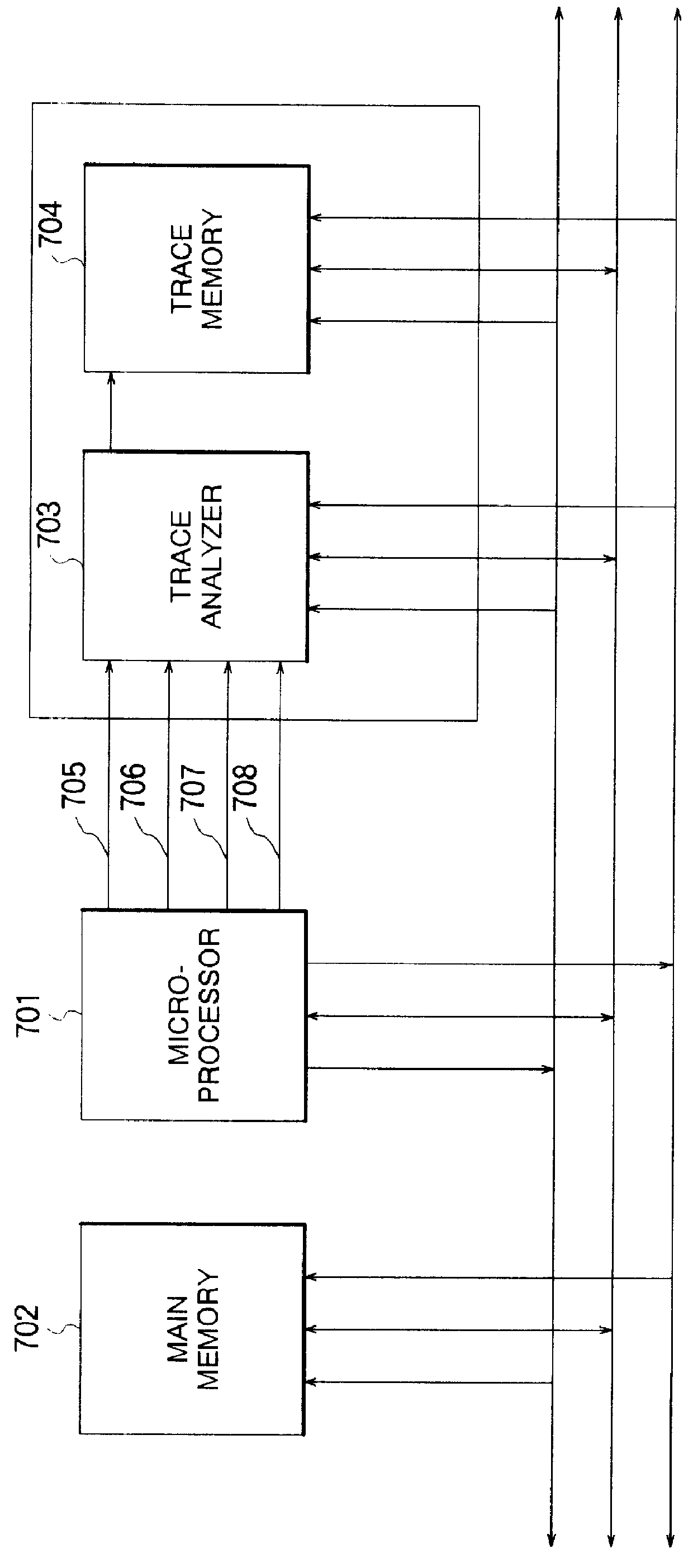

Debugging system

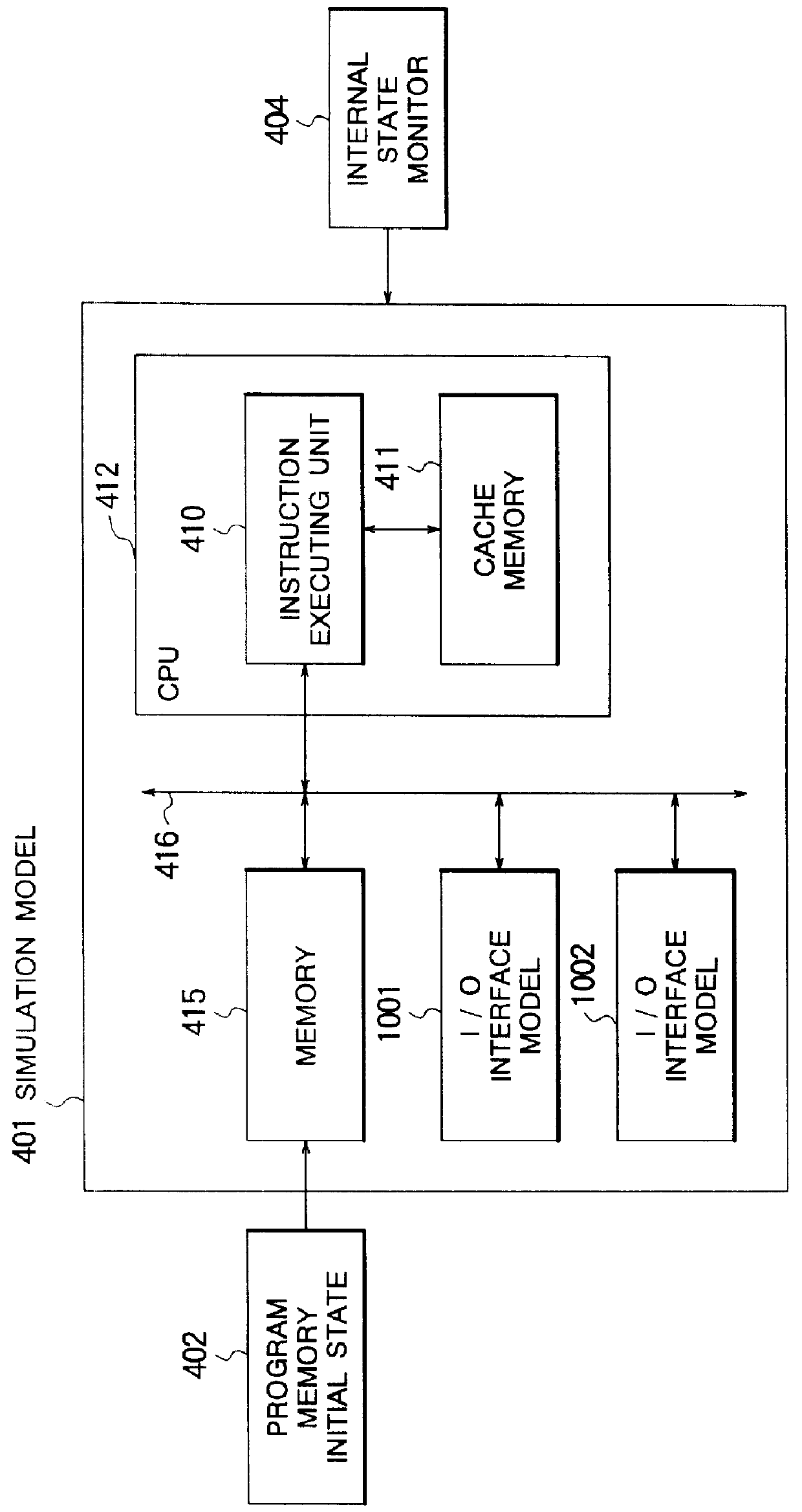

In a debugging system for use in realizing simultaneously complete observation of internal operation and reproduction of malfunction actually caused in a target system which includes an integrated circuit, such as a microprocessor, contents of a memory and an internal initial state of the target system are snooped and stored in a snoop unit and a trace memory, respectively, both of which are included in a probe unit attached to the target system. The internal operation and the reproduction are simulated by a software simulator model by the use of the contents and the internal initial state which are stored in the trace memory and which are sent from the probe unit.

Owner:NEC CORP

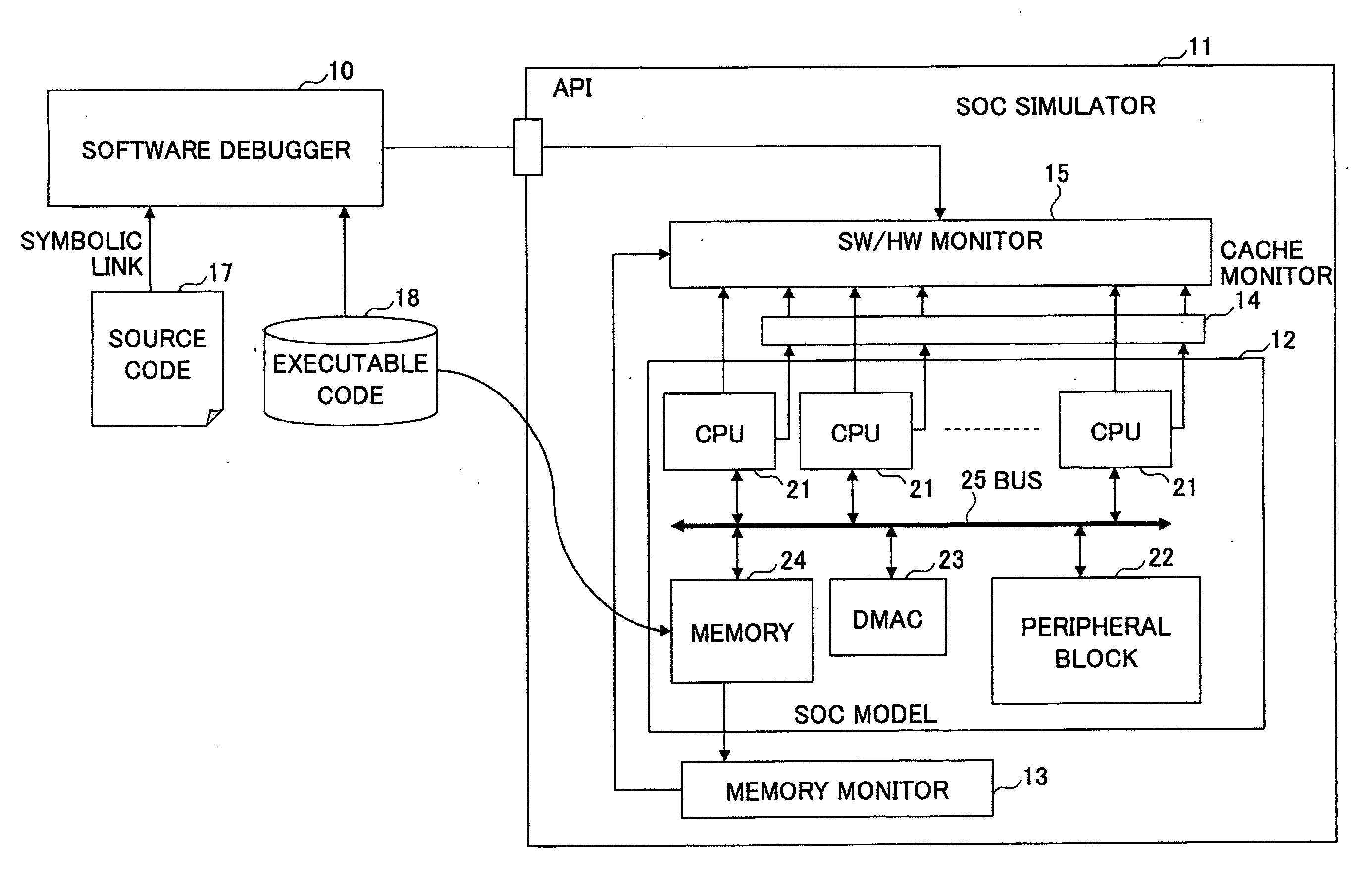

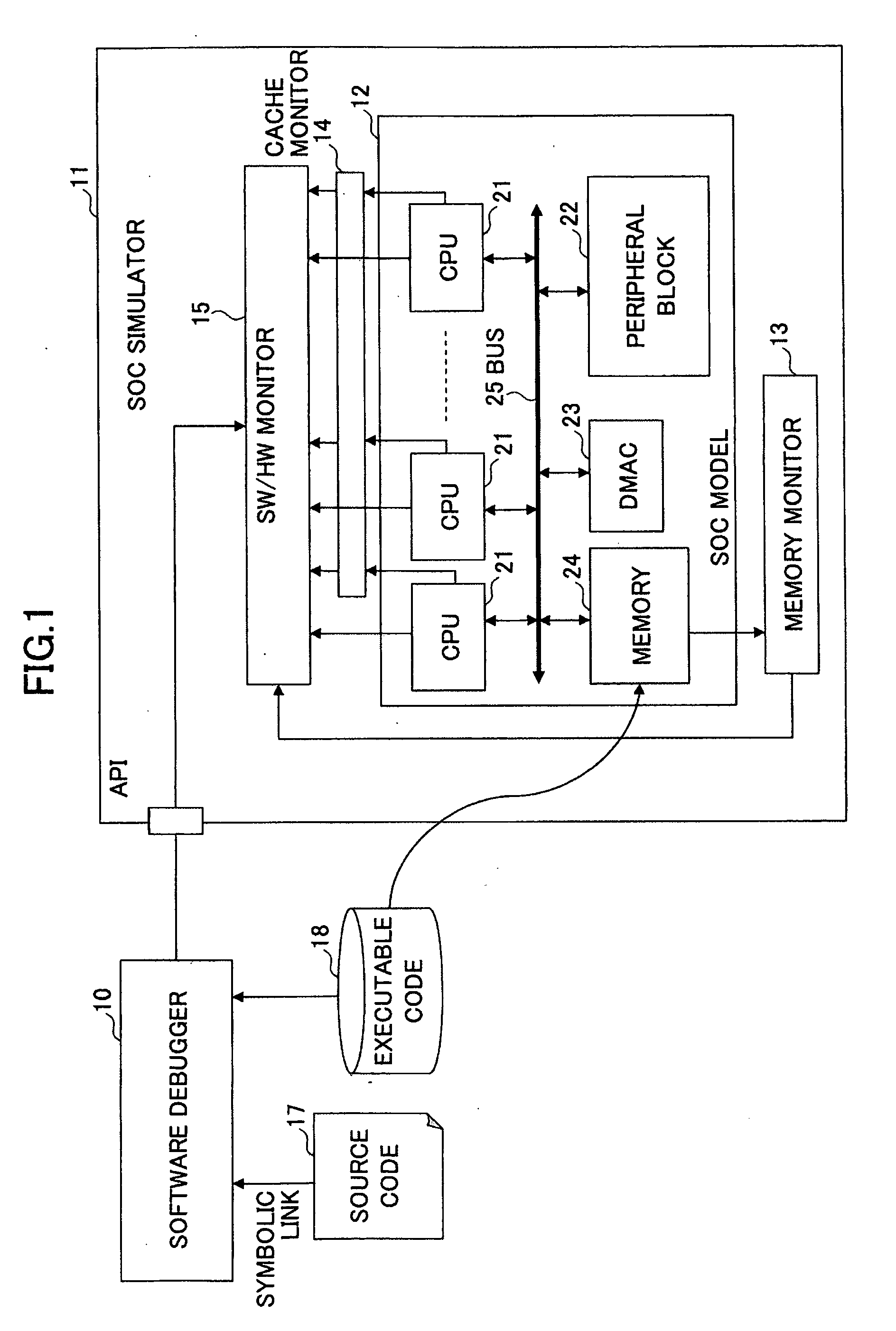

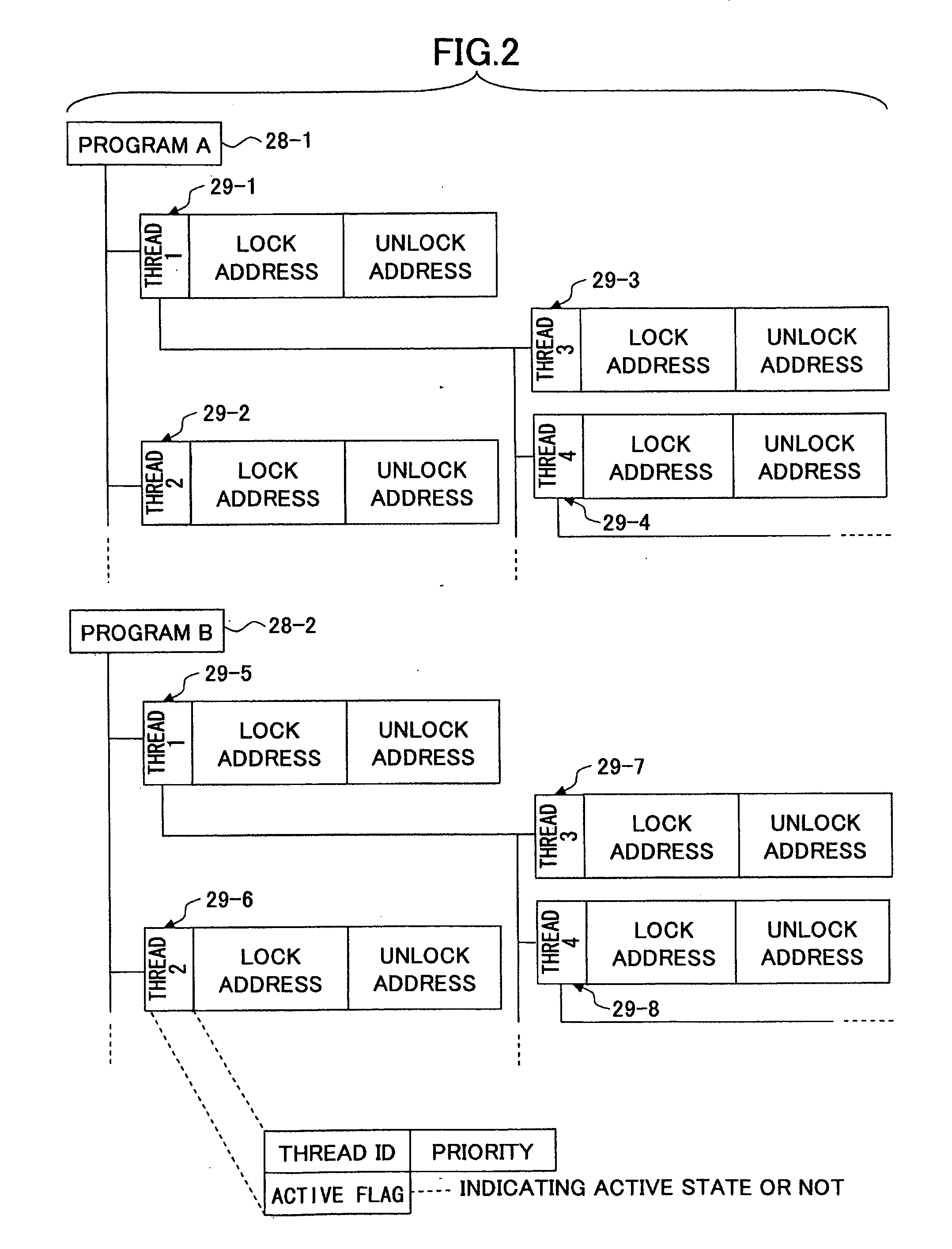

Simulation of program execution to detect problem such as deadlock

InactiveUS20090037888A1Error detection/correctionSpecific program execution arrangementsDeadlockMonitor function

A method of simulating software by use of a computer includes executing a program inclusive of a plurality of threads by a hardware model implemented as software on a software simulator, utilizing a monitor function of the simulator to collect information about accesses by monitoring accesses made by the plurality of threads with respect to resources provided in the hardware model, utilizing the monitor function to detect, from the collected information, overlapping accesses made to an identical resource area by two or more of the threads, and utilizing the monitor function to generate a message for warning of the overlapping accesses.

Owner:CYPRESS SEMICON CORP

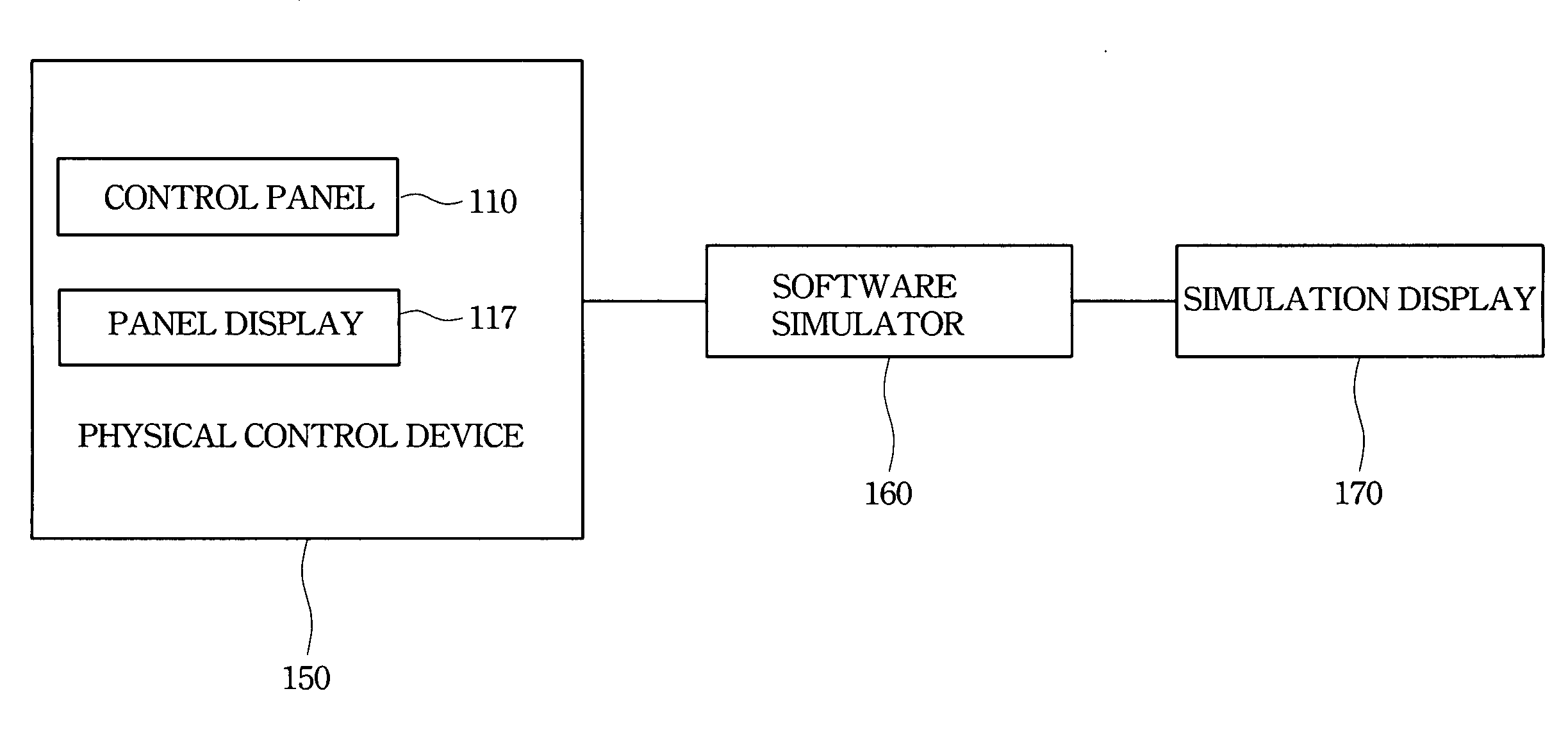

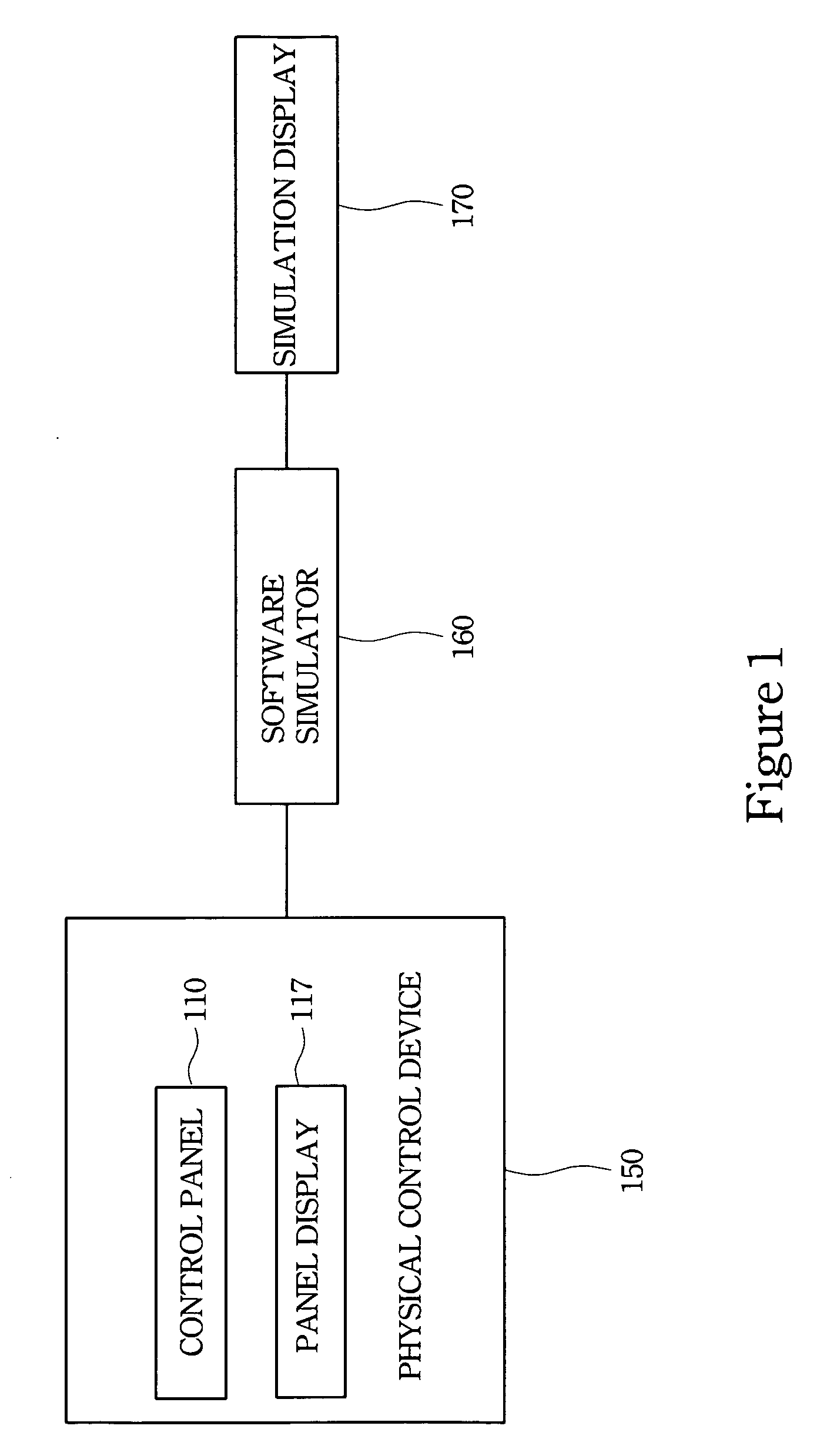

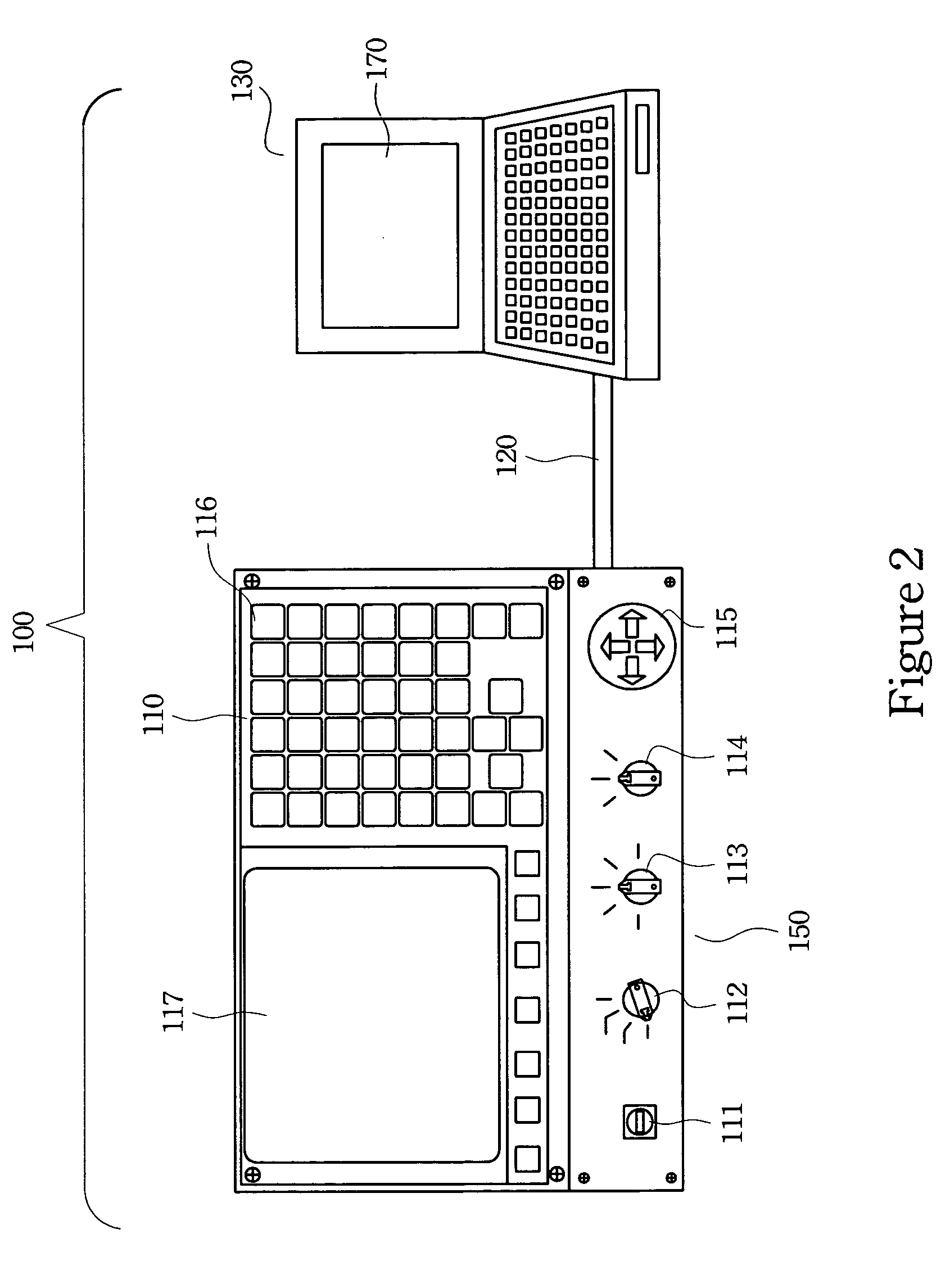

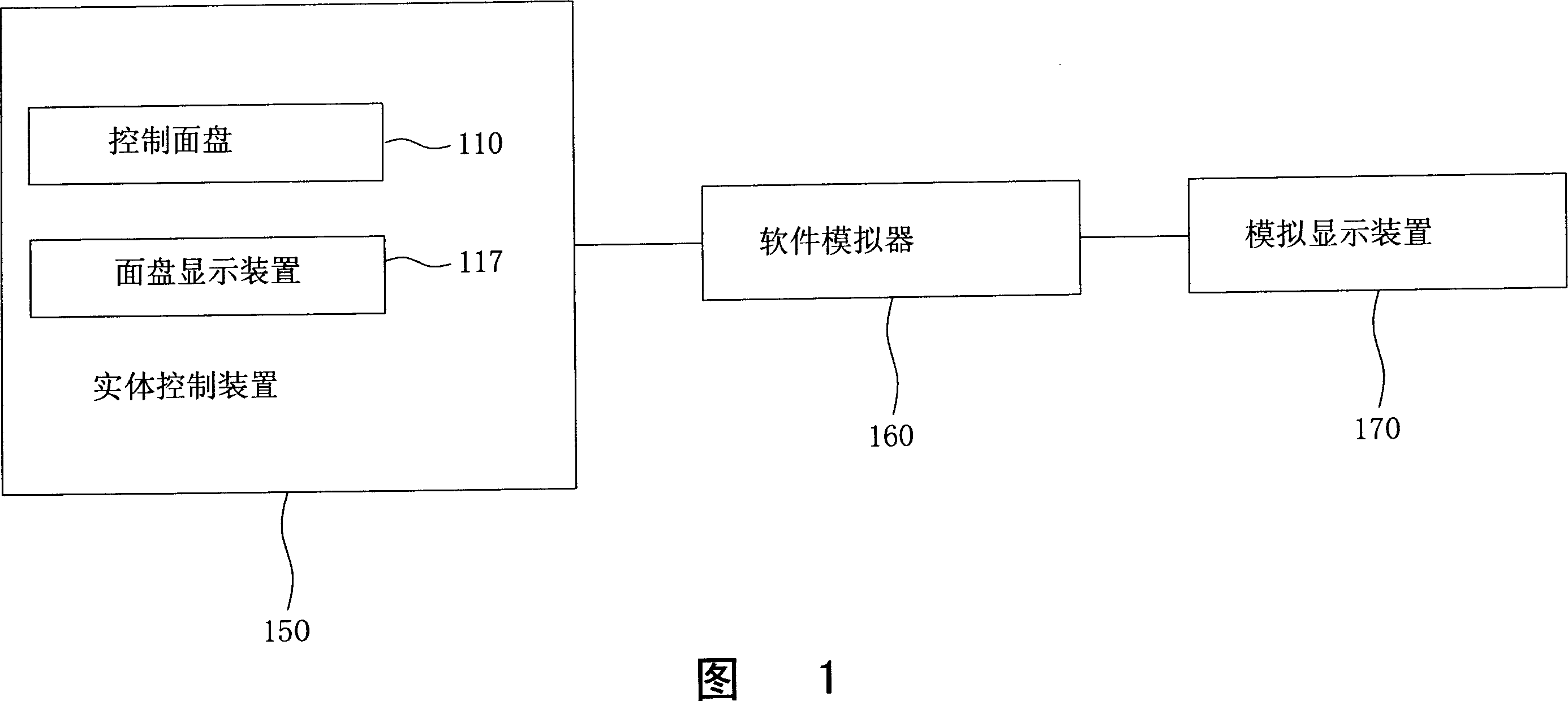

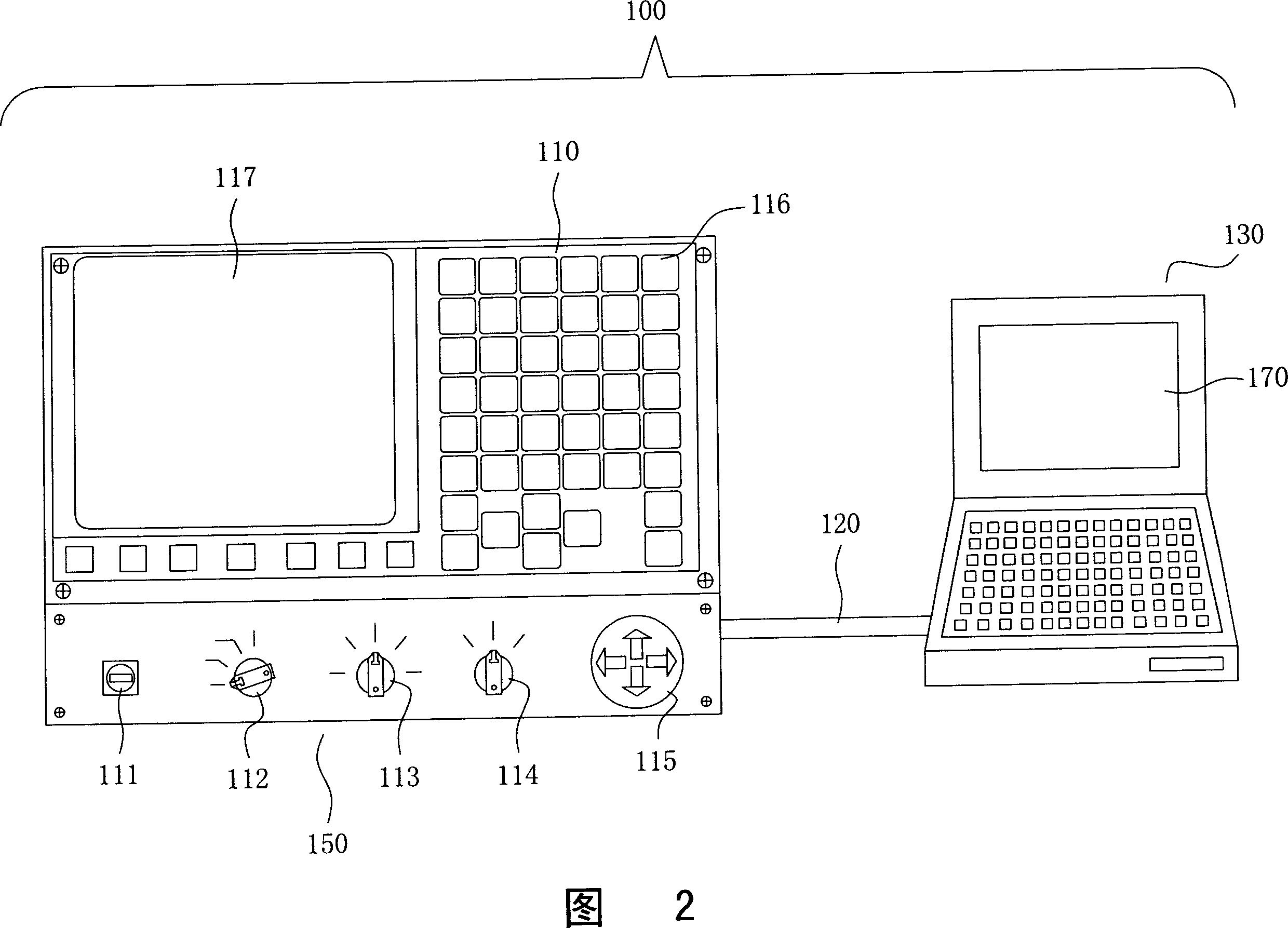

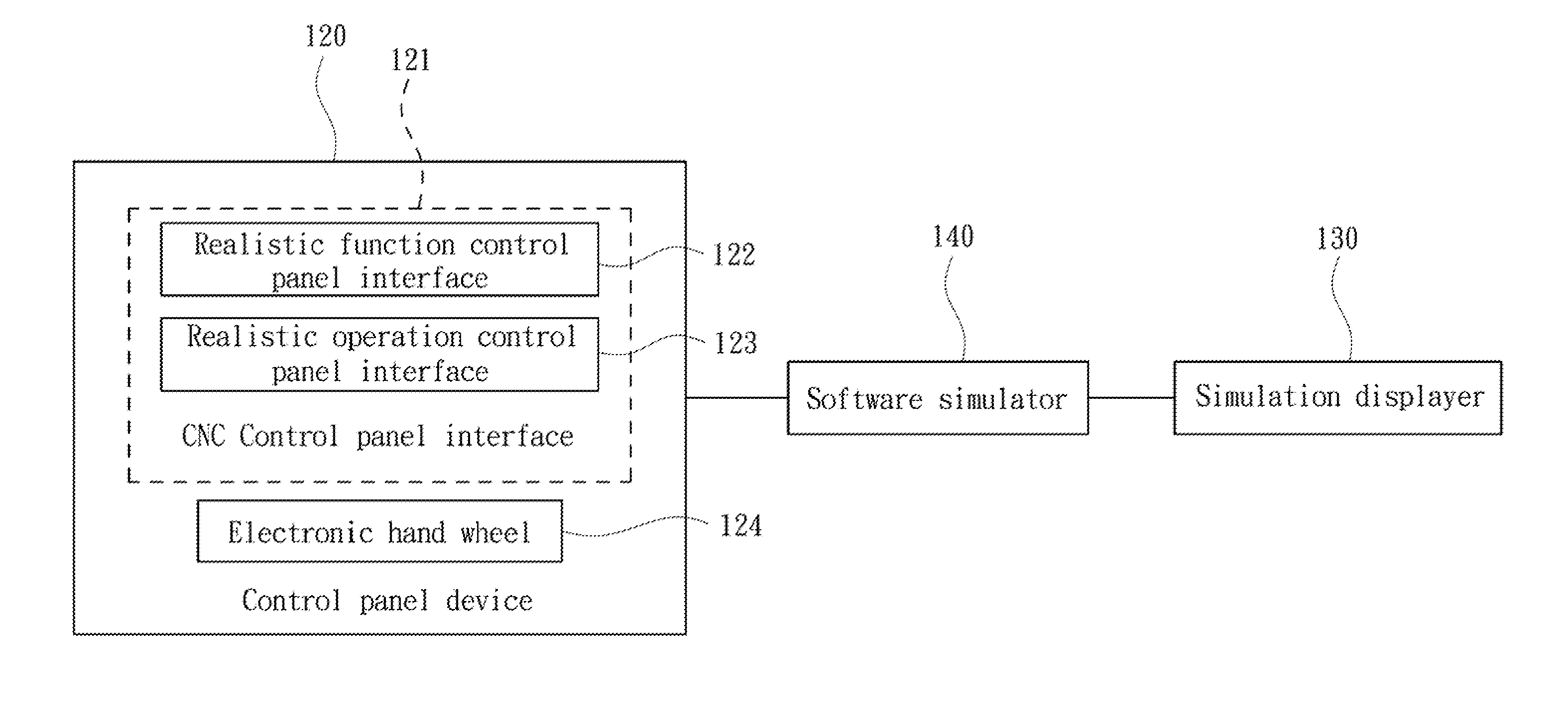

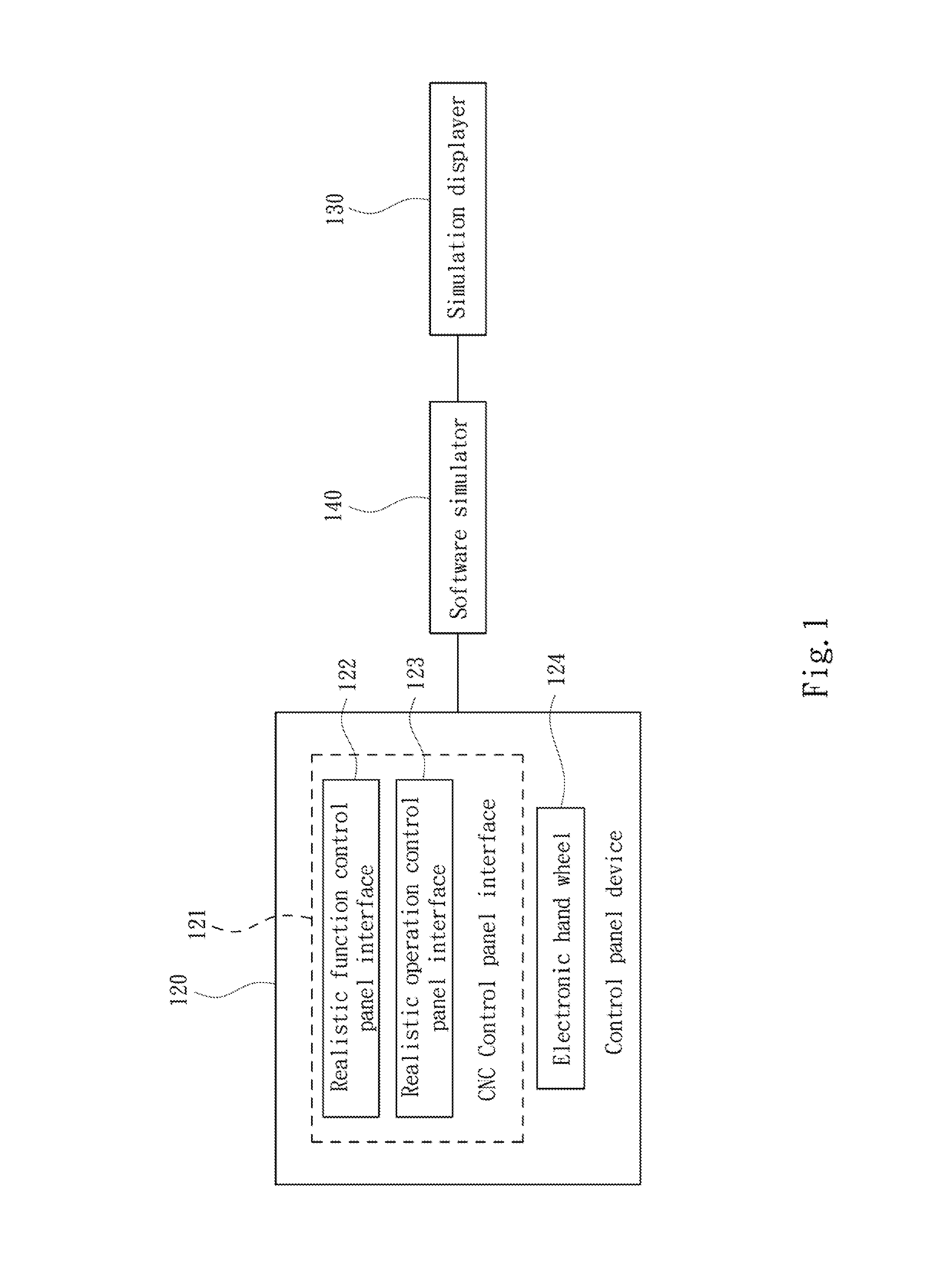

Operation training simulation system for computer numerical control (CNC) machine

InactiveUS20070248937A1Enhance the trainee's familiarizationEasily realizedCosmonautic condition simulationsSimulatorsDisplay deviceSimulation based

An operation training simulation system for a computer numerical control (CNC) machine includes a physical control device for inputting control and operation commands, a software simulator connected with the physical control device, a transmission apparatus connecting the physical control device with the software simulator and a simulation display electrically connected to the software simulator. The software simulator generates machining and operation simulations based on the inputted control and operation conditions through the physical control device, and the simulation display visualizes the machining and operation simulations generated by the software simulator. Therefore, using the operation training simulation system for CNC machine not only eliminates the consumptive materials cost but also solve the personal injury problem. Consequently, the learning efficiency of the trainees and the familiarization to machine are raised in this way.

Owner:REN AN INFORMATION TECH CO LTD

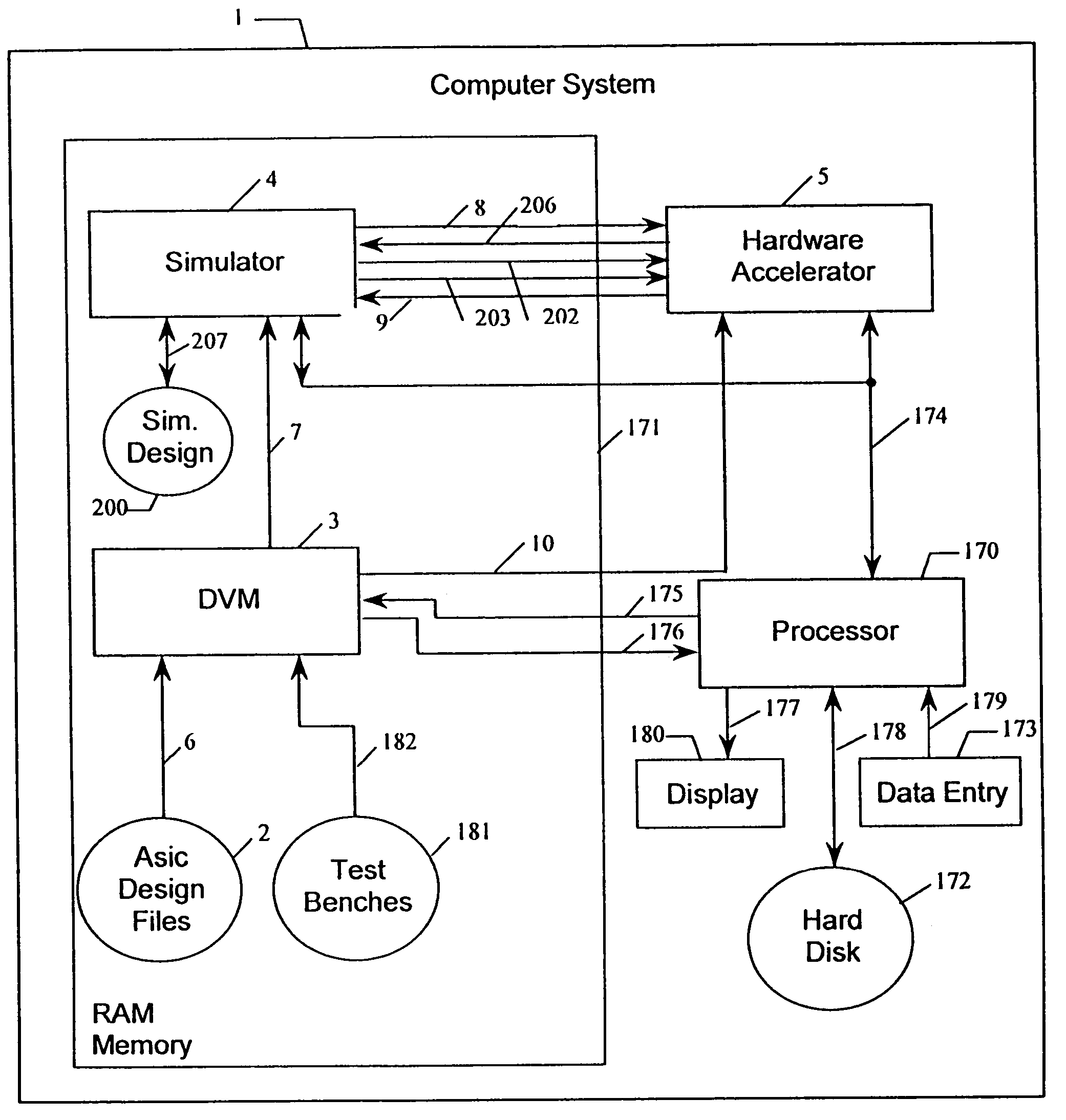

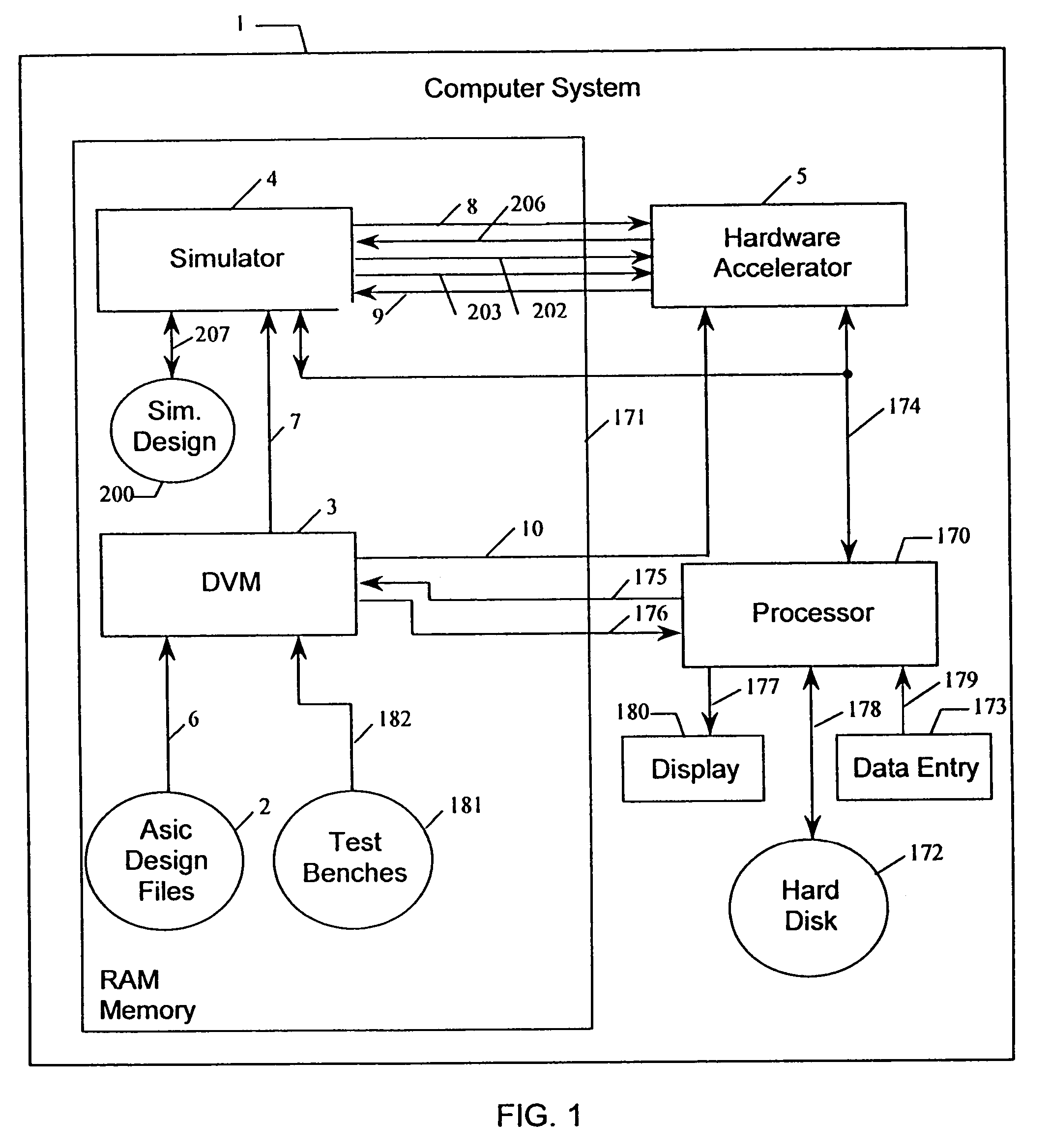

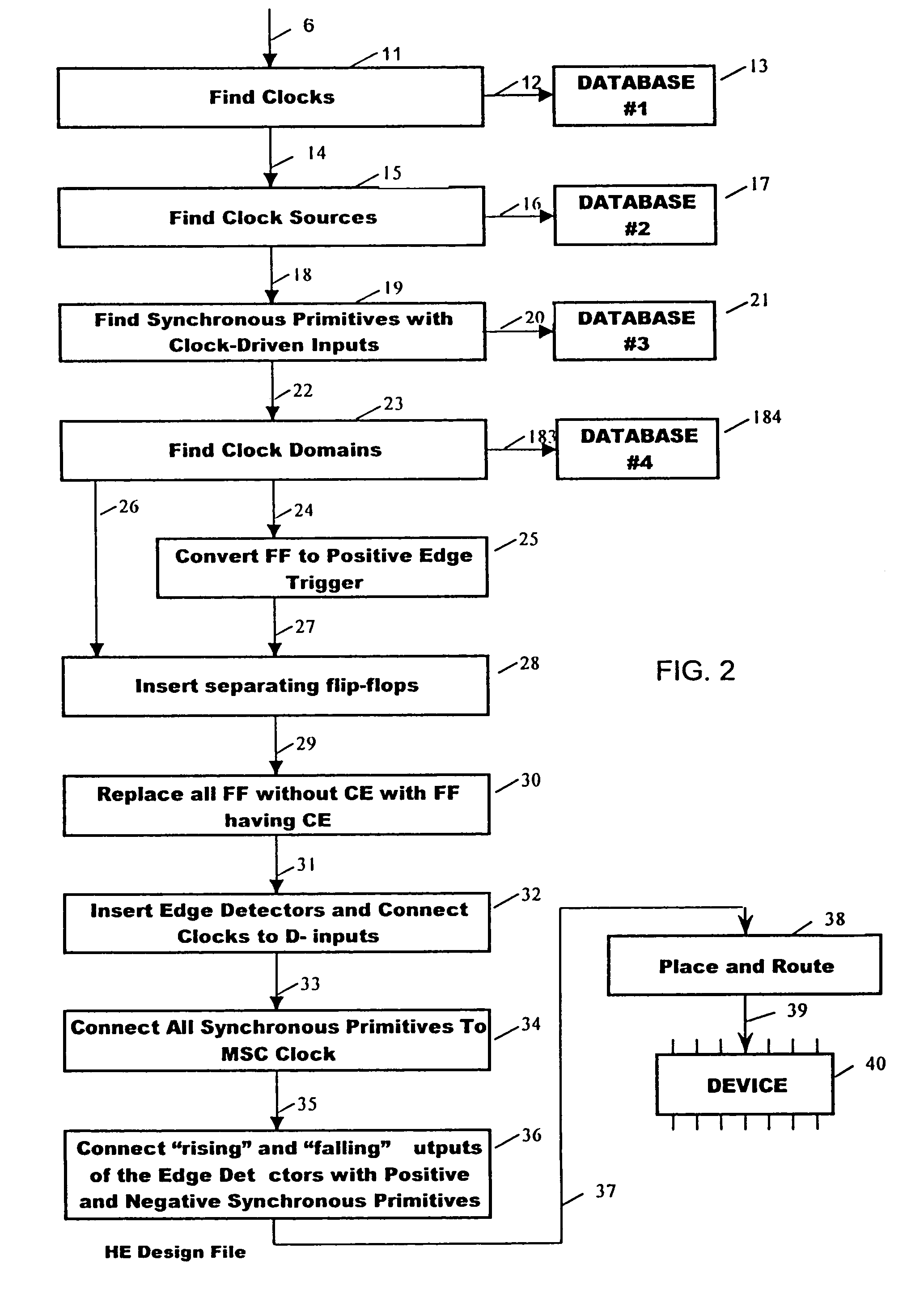

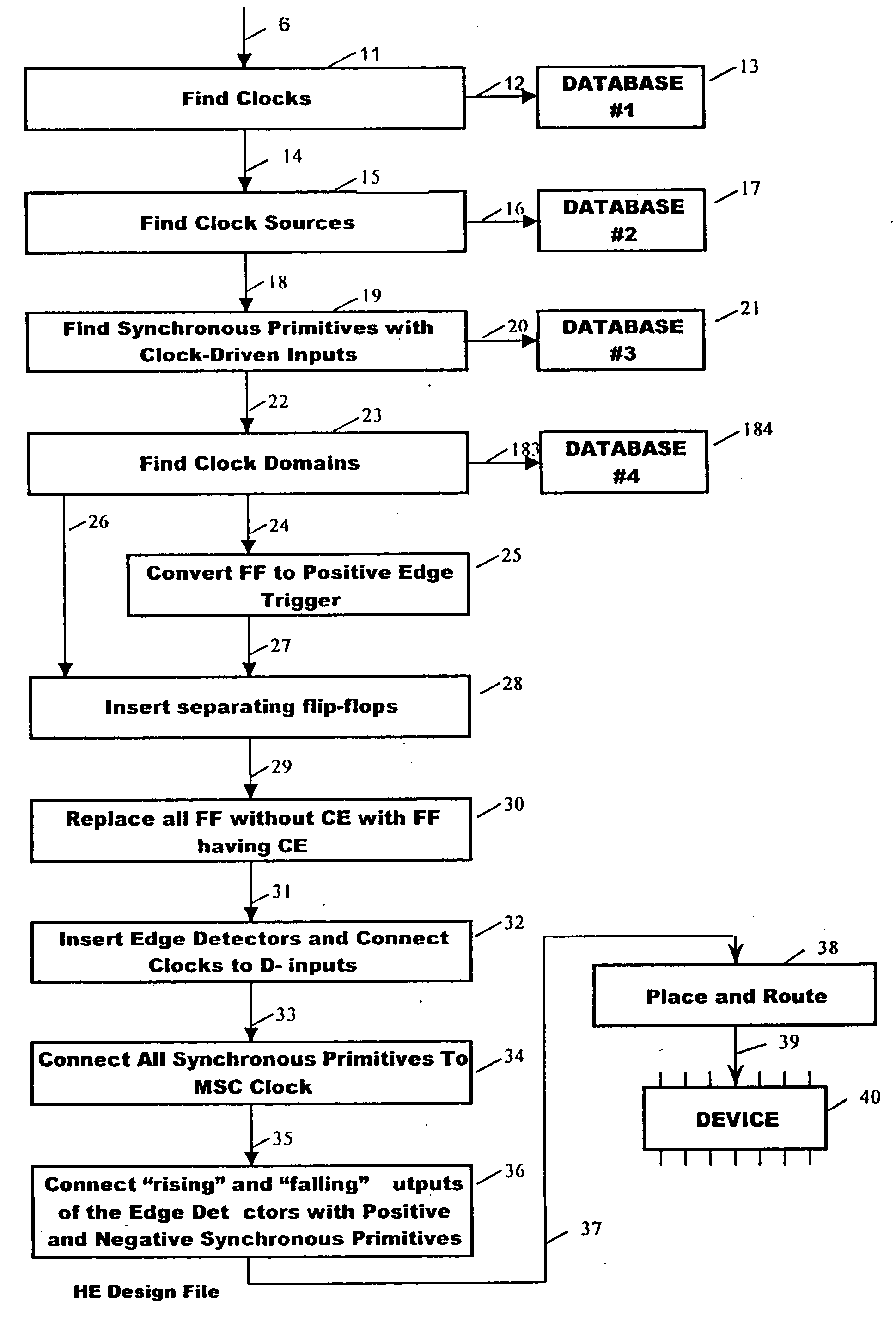

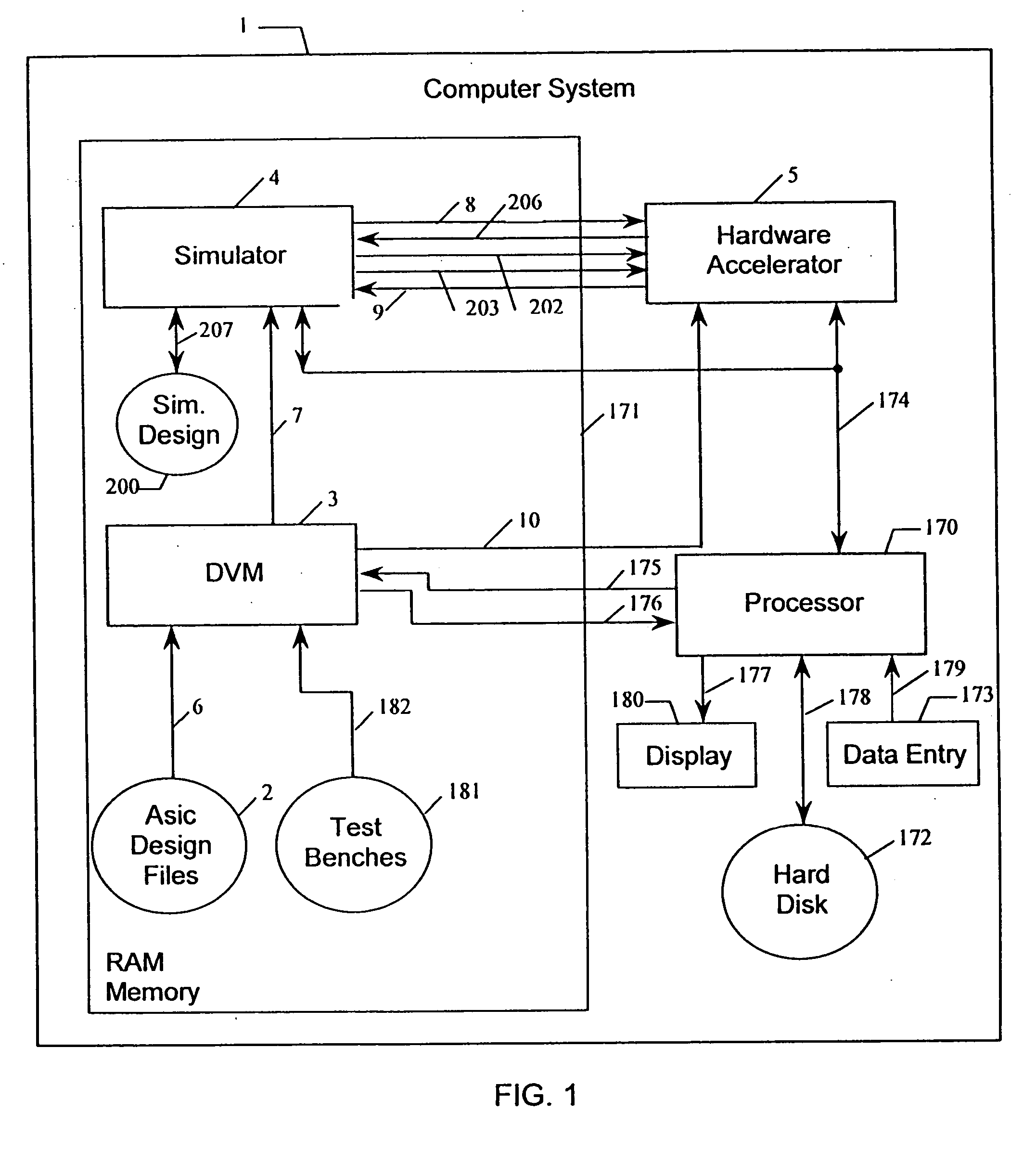

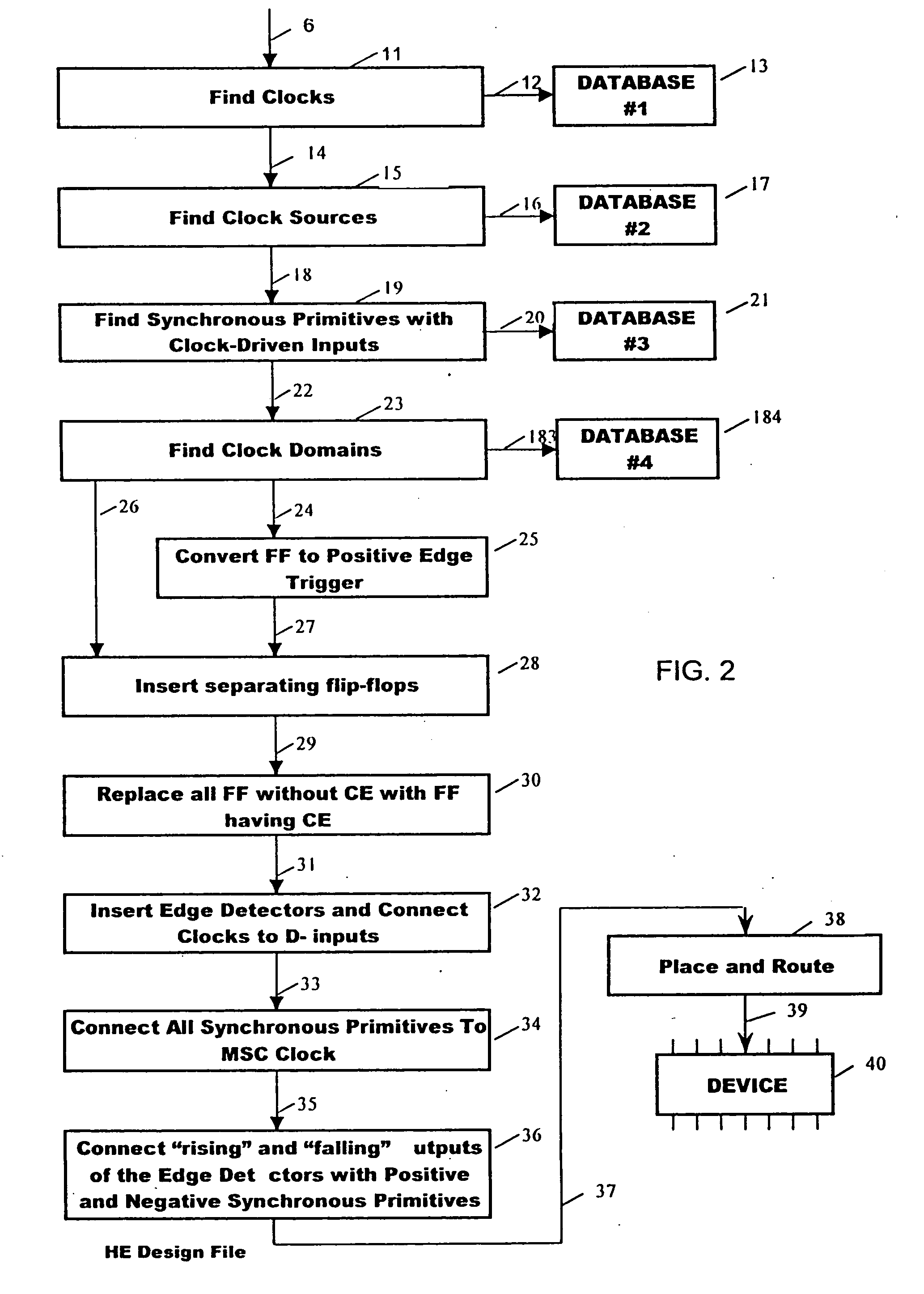

Method and apparatus for accelerating the verification of application specific integrated circuit designs

ActiveUS7003746B2Digital data processing detailsAnalogue computers for electric apparatusDetector circuitsField-programmable gate array

A method and system for accelerating software simulator operation with the aid of reprogrammable hardware such as Field Programmable Gate Array devices (FPGA). The method and system aid in emulation and prototyping of Application Specific Integrated Circuits (ASIC) digital circuit designs by means of reprogrammable devices. The system includes a design verification manager and software program that includes subroutines of finding clock sources, finding synchronous primitives that are receiving clock signals from the clock sources, and a subroutine for inserting edge detector circuits between such clock sources and synchronous primitives. This new method allows eliminating of clock timing issues by applying basic design clocks to the clock enable instead of clock trigger inputs and generating and applying to clock trigger inputs a new clock that is automatically delayed in respect to all other clocks in the design. This system solves the major obstacle for automatic retargeting of ASIC designs into reprogrammable devices that have different timings of the clocking chains in ASICs and FPGAs that result in triggering of associated flip-flops and latches at different times.

Owner:HYDUKE STANLEY M +1

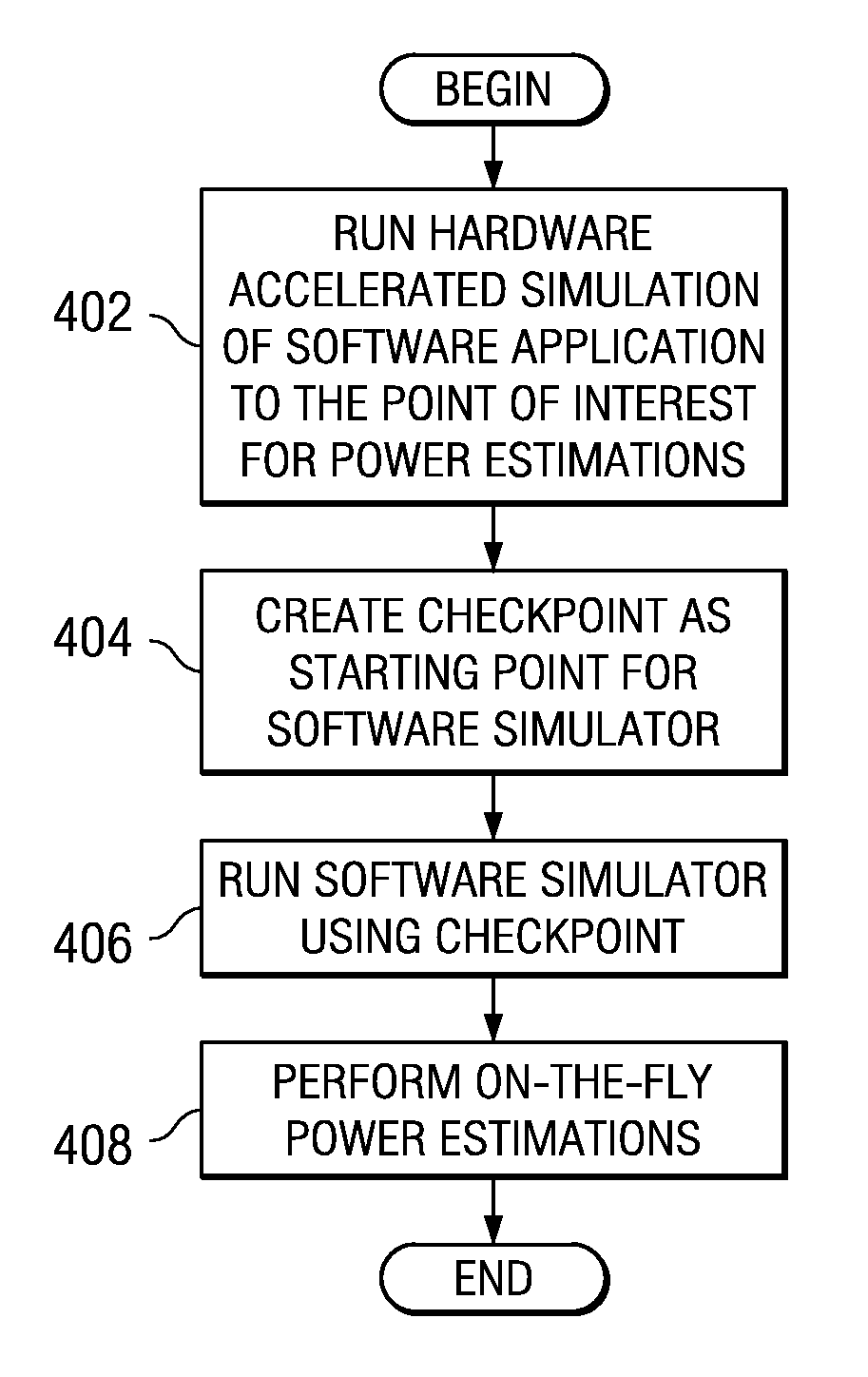

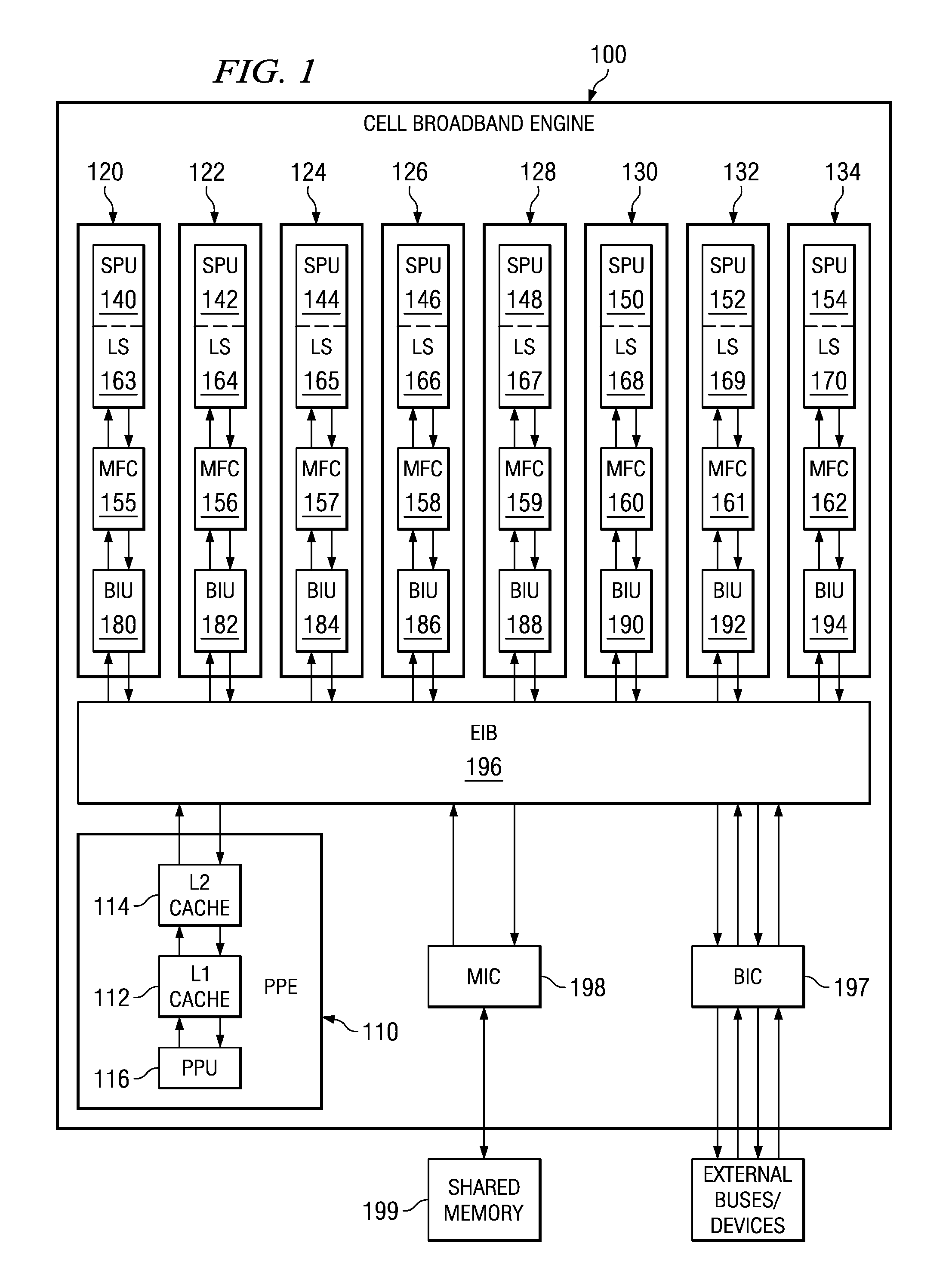

Method for performing power simulations on complex designs running complex software applications

InactiveUS20080021692A1Accurate power estimateAccurate powerEnergy efficient ICTDigital data processing detailsApplication softwareSystem usage

A power estimation system uses a hardware accelerated simulator to advance simulation to a point of interest for power estimation. The hardware accelerated simulator generates a checkpoint file, which is then used by a software simulator to initiate simulation of the processor design model for power estimation. An on-the-fly power estimator provides power calculations in memory. Thus, the power estimation system described herein isolates instruction sequences to determine portions of software code that may consume excess power or generate noise and to provide a more accurate power estimate on the fly.

Owner:IBM CORP

Method and apparatus for co-verification of digital designs

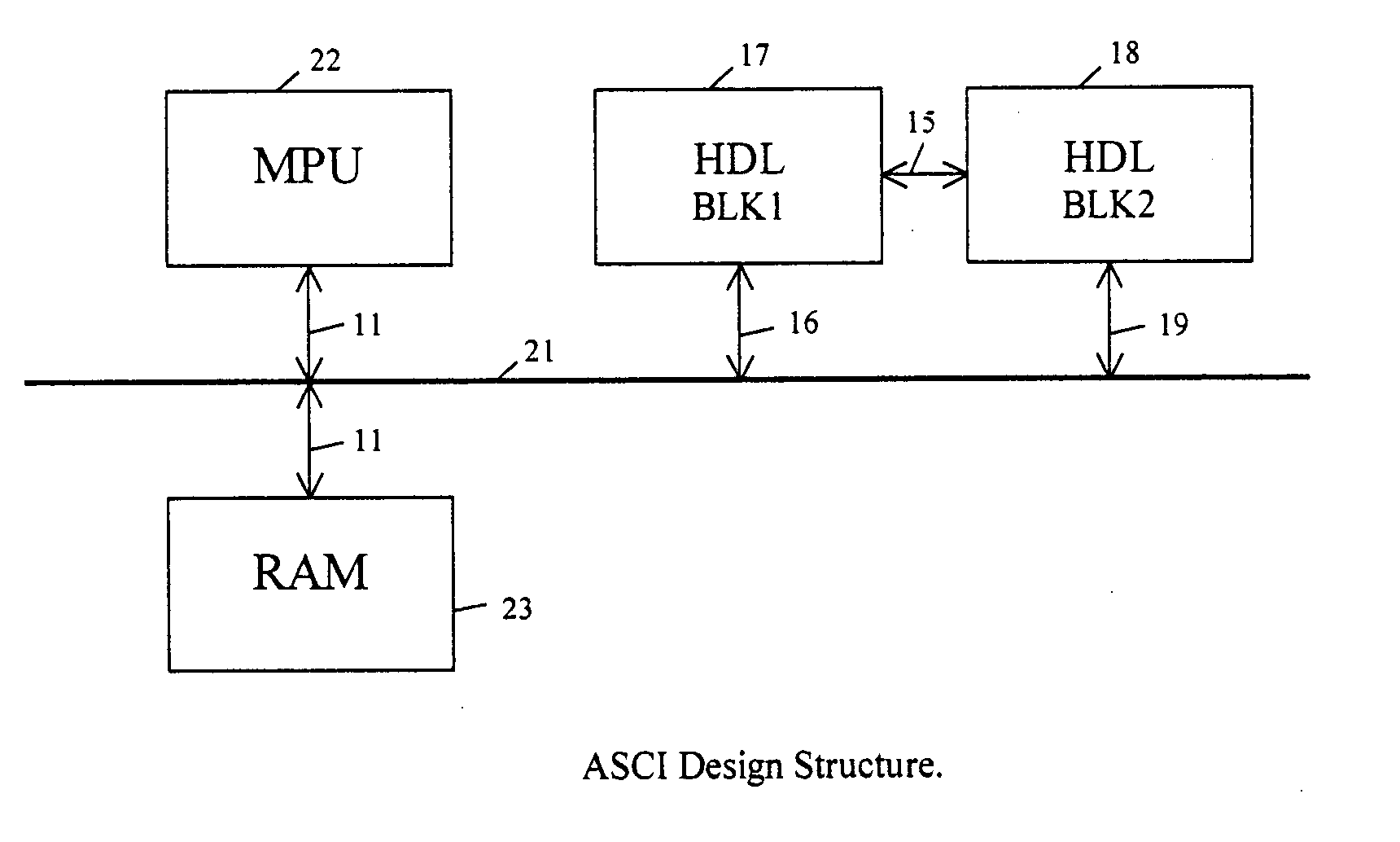

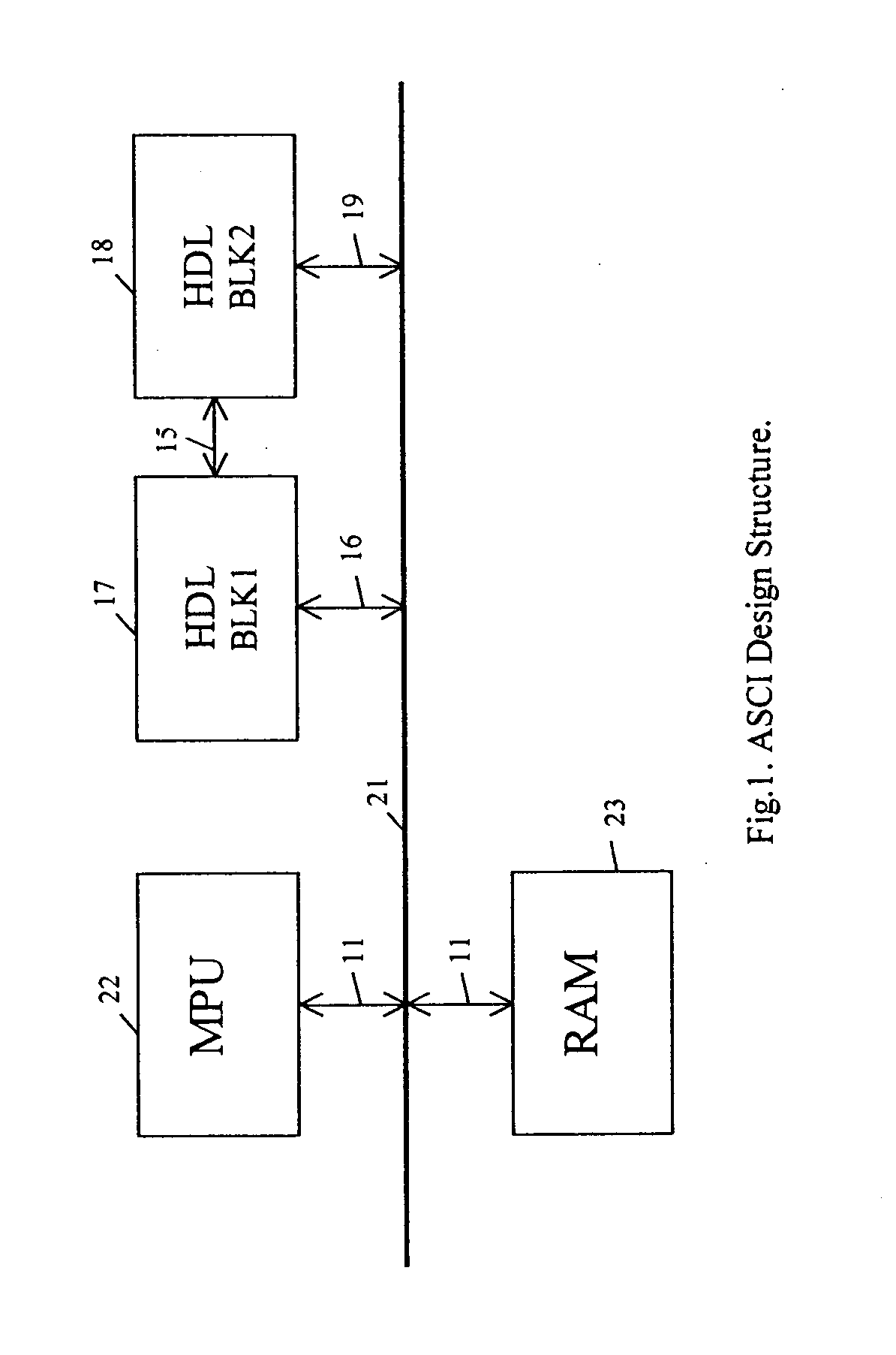

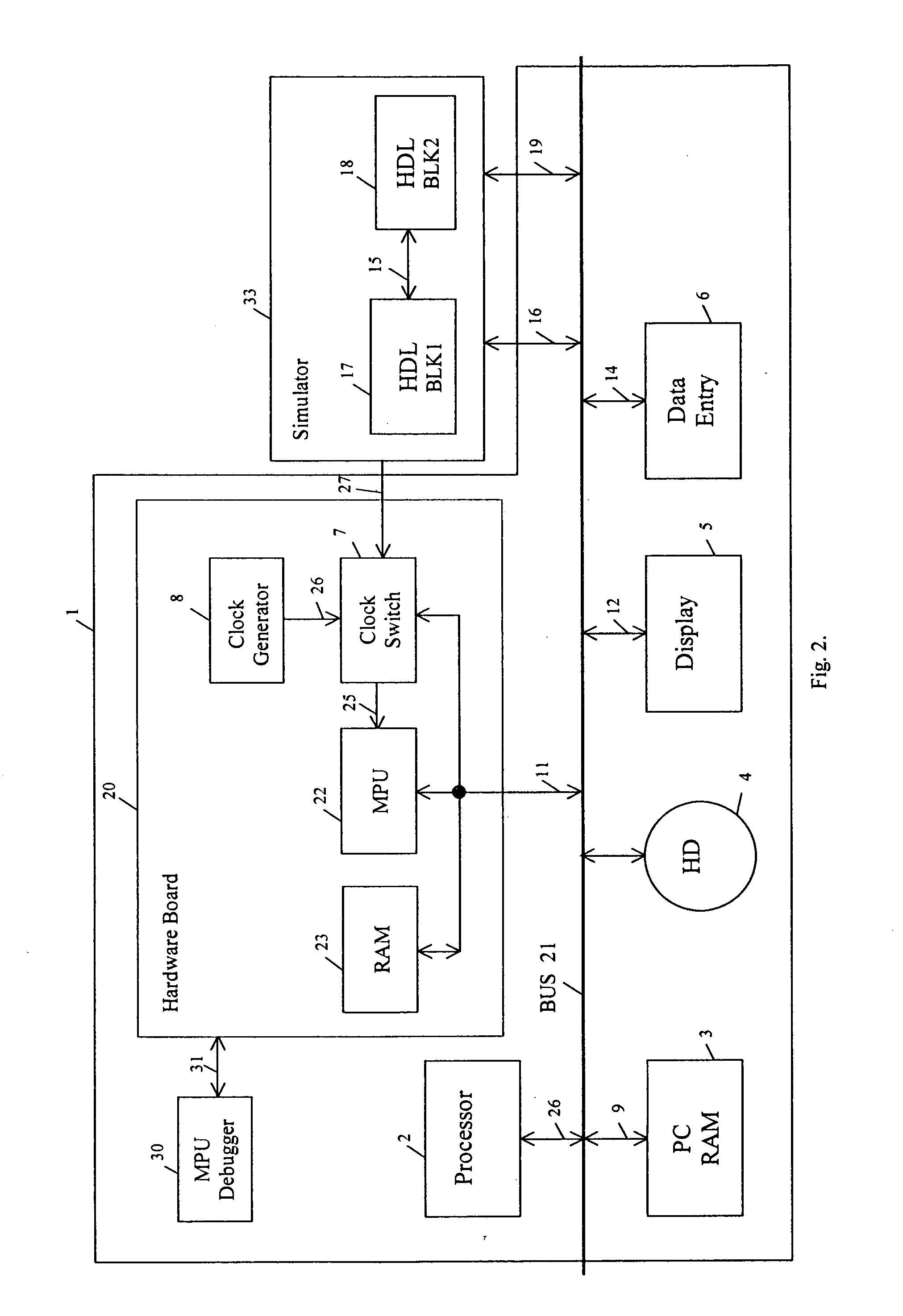

InactiveUS20050138515A1Quickly and accurately verifiedElectronic circuit testingFunctional testingHardware software designClock generator

A method and apparatus for development and concurrent verification of digital designs including a combination of a microprocessor and discrete logic design blocks. The hardware / software design development and co-verification processing of digital designs is accelerated by placing the microprocessor in an FPGA device and logic circuits in an HDL simulator. The microprocessor and logic circuits are connected via a common bus and synchronization of both environments is achieved by using a simulator clock exclusively when both microprocessor and logic simulator need to communicate with each other. The system and method of the present invention provides a unique arrangement of a processor clocking scheme. An essential part of the invention is a clock switch responsive to the areas of RAM a processor is addressing and accordingly switching a clock signal to the processor from either a hardware clock generator or a software simulator.

Owner:HYDUKE STANLEY M +1

Method and apparatus for accelerating the verification of application specific integrated circuit designs

ActiveUS20050081170A1Analogue computers for electric apparatusComputer aided designDetector circuitsField-programmable gate array

A method and system for accelerating software simulator operation with the aid of reprogrammable hardware such as Field Programmable Gate Array devices (FPGA). The method and system aid in emulation and prototyping of Application Specific Integrated Circuits (ASIC) digital circuit designs by means of reprogrammable devices. The system includes a design verification manager and software program that includes subroutines of finding clock sources, finding synchronous primitives that are receiving clock signals from the clock sources, and a subroutine for inserting edge detector circuits between such clock sources and synchronous primitives. This new method allows eliminating of clock timing issues by applying basic design clocks to the clock enable instead of clock trigger inputs and generating and applying to clock trigger inputs a new clock that is automatically delayed in respect to all other clocks in the design. This system solves the major obstacle for automatic retargeting of ASIC designs into reprogrammable devices that have different timings of the clocking chains in ASICs and FPGAs that result in triggering of associated flip-flops and latches at different times.

Owner:HYDUKE STANLEY M +1

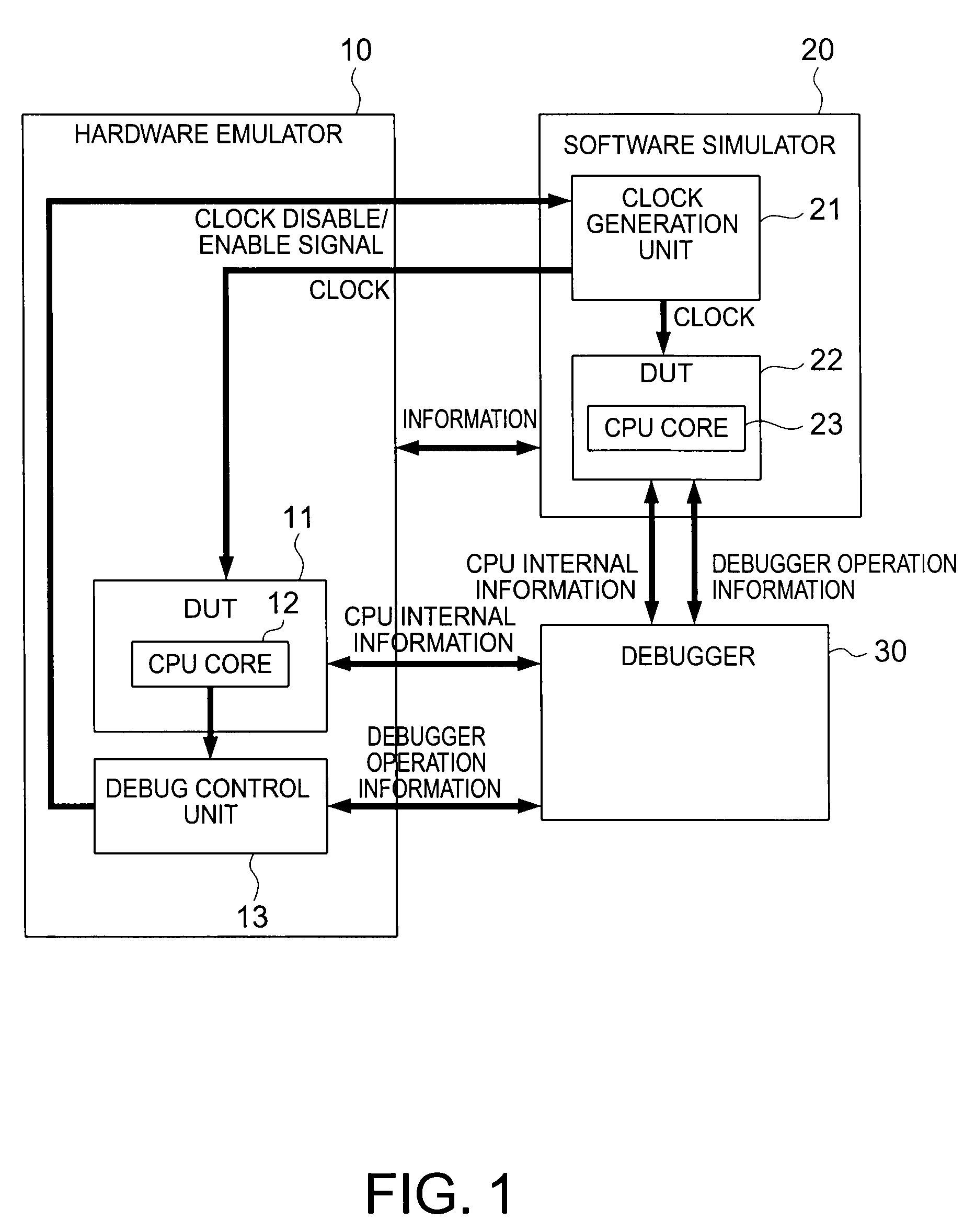

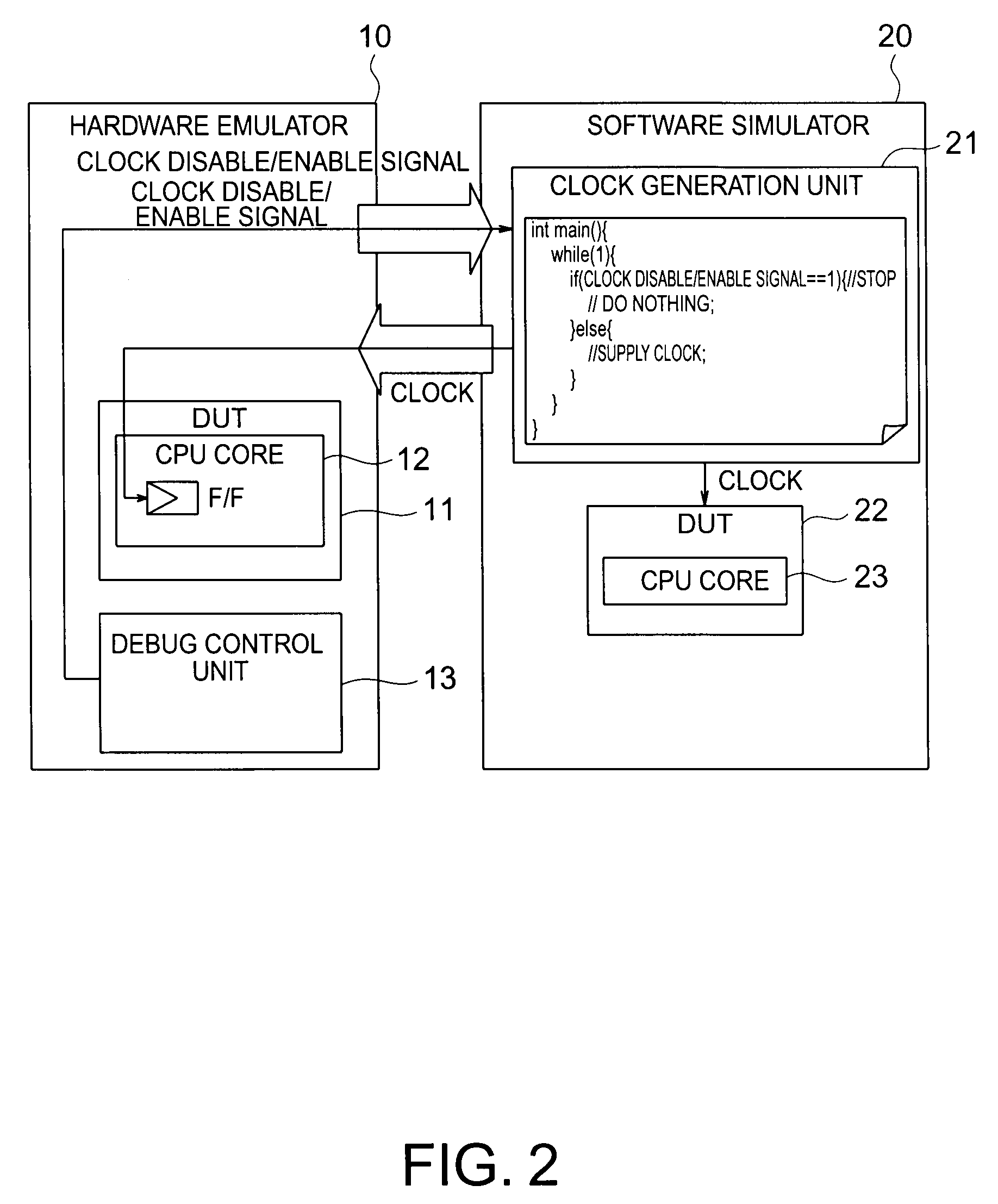

Simulation apparatus and simulation method

InactiveUS20080312900A1Error detection/correctionSoftware simulation/interpretation/emulationComputer hardwareComputer architecture

According to the present invention, there is provided a simulation apparatus having, a hardware emulator which includes a first CPU core as a simulation target, and a debug control unit; a software simulator which includes a second CPU core as a simulation target, and a clock generation unit which generates a clock and supplies the clock to the first CPU core and the second CPU core; and a debugger which debugs the first CPU core and the second CPU core and in which a clock disable condition is set, wherein upon determining that the clock disable condition set in the debugger is satisfied, the debug control unit outputs a clock disable signal, and upon receiving the clock disable signal, the clock generation unit stops generating the clock.

Owner:KK TOSHIBA

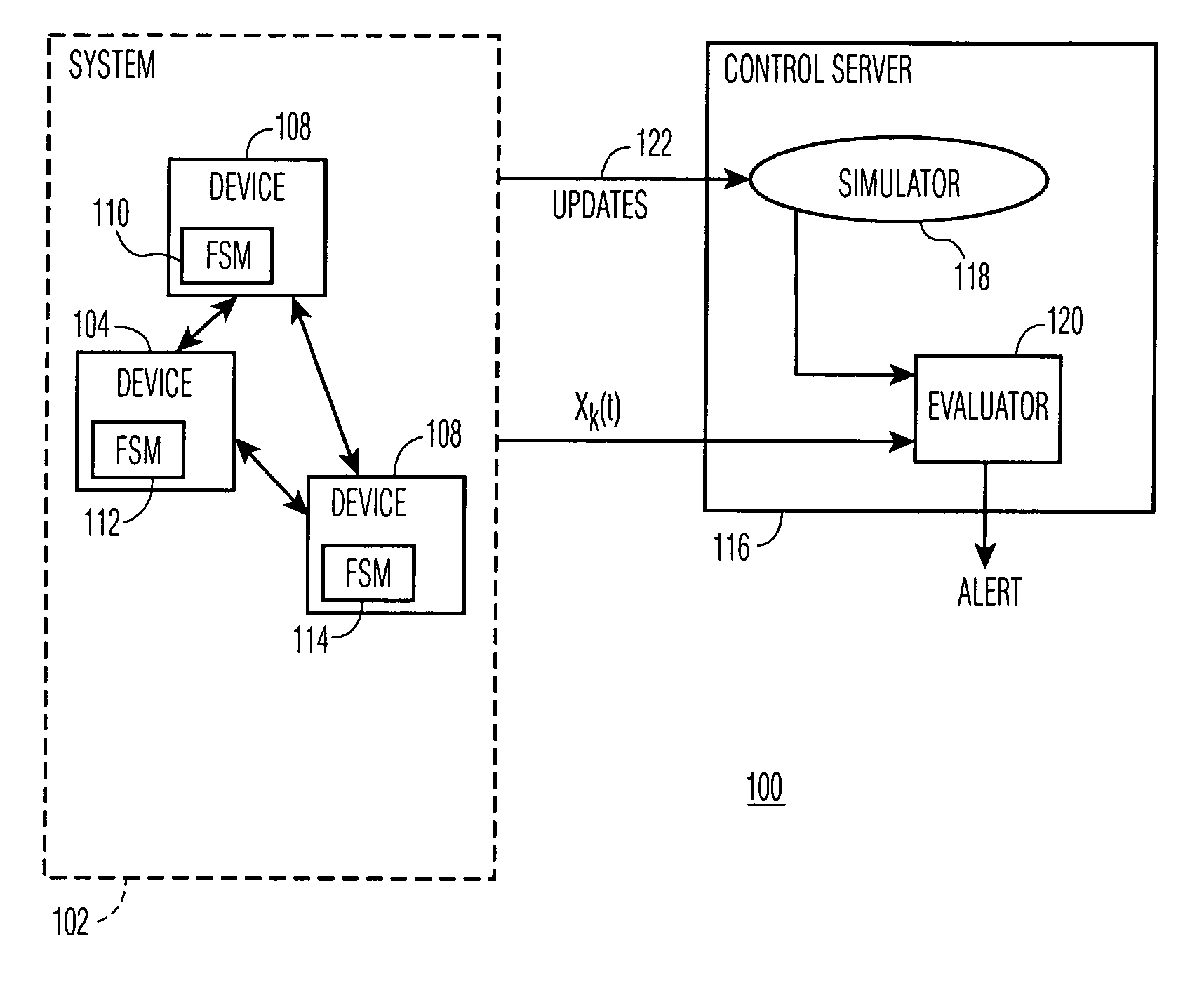

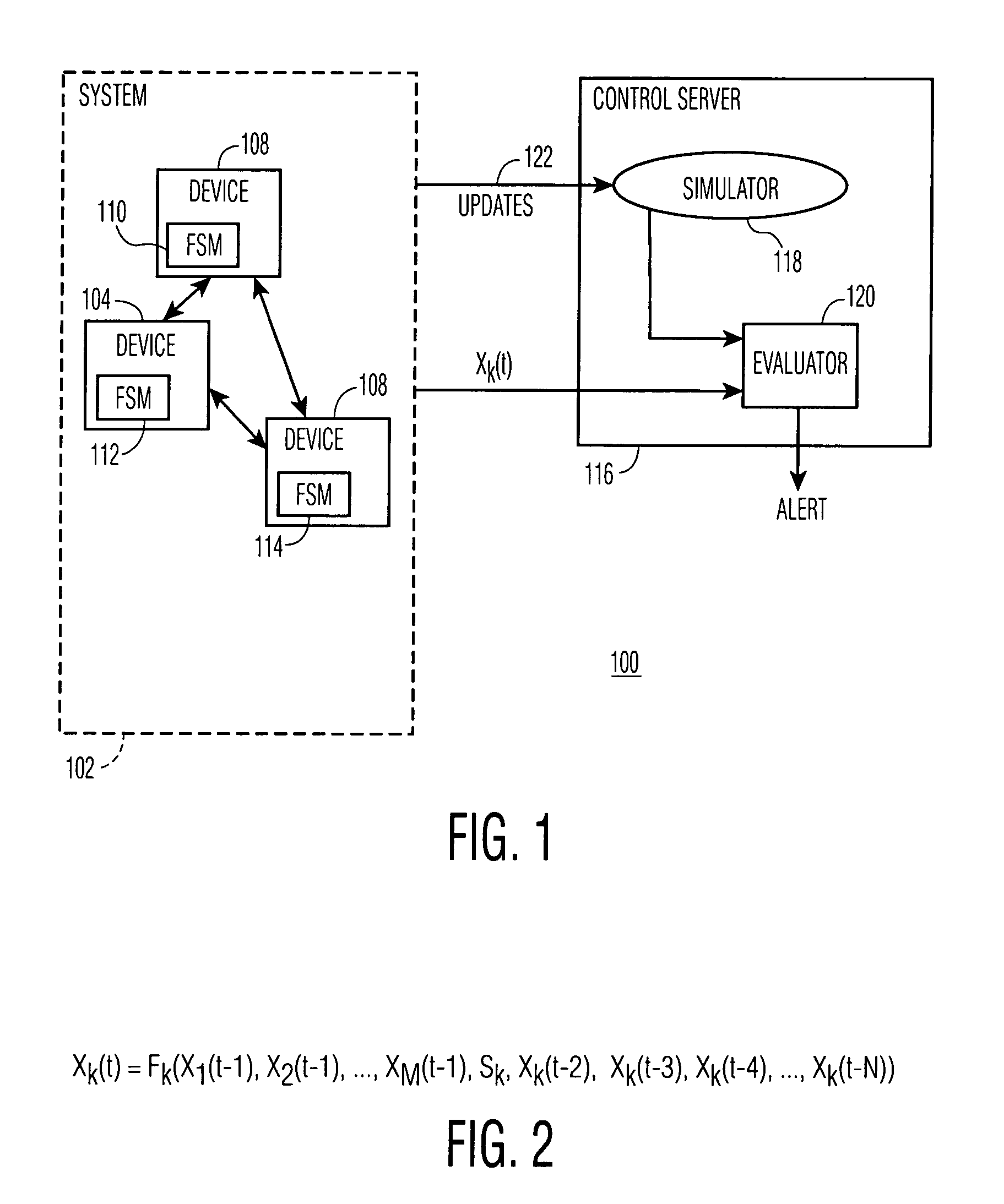

Security monitor of system runs software simulator in parallel

InactiveUS6985845B1Reduce in quantityUnauthorized memory use protectionHardware monitoringIdle timeTheoretical computer science

A monitoring system monitors a system that has multiple devices that perform respective primary tasks. For the purpose of the monitoring, each device has a finite state machine (FSM) with stochastic non-periodic behavior. The monitoring system simulates in software the behavior of the FSM's. A discrepancy between the states assumed by the FSM's after each time step and the states assumed in the simulation in each time step indicates a failure or a breach of the network's integrity. Hacking such as primary system is practically impossible without being detected. Each device comprises computational resources. In order to reduce the computational environment available to a virus, the idle time of the resources is absorbed by dynamically increasing the complexity of the FSM's.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

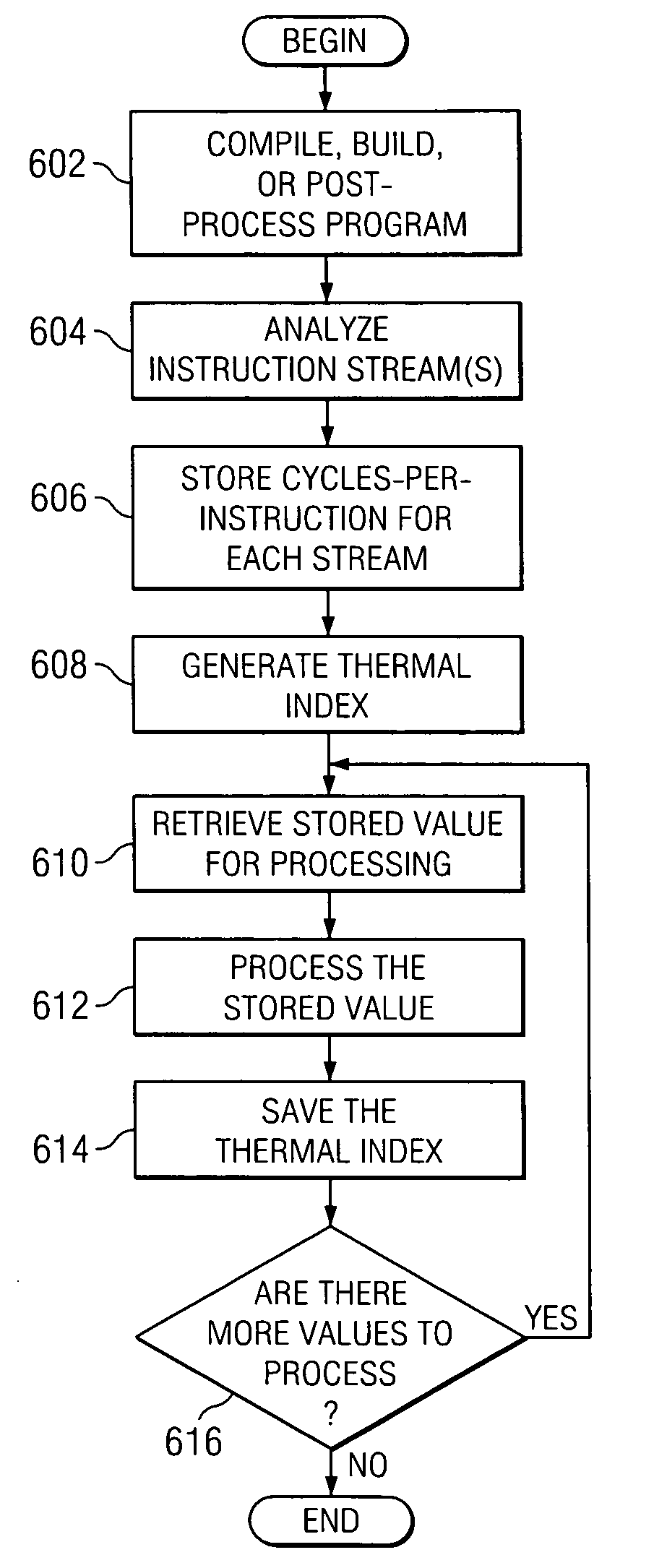

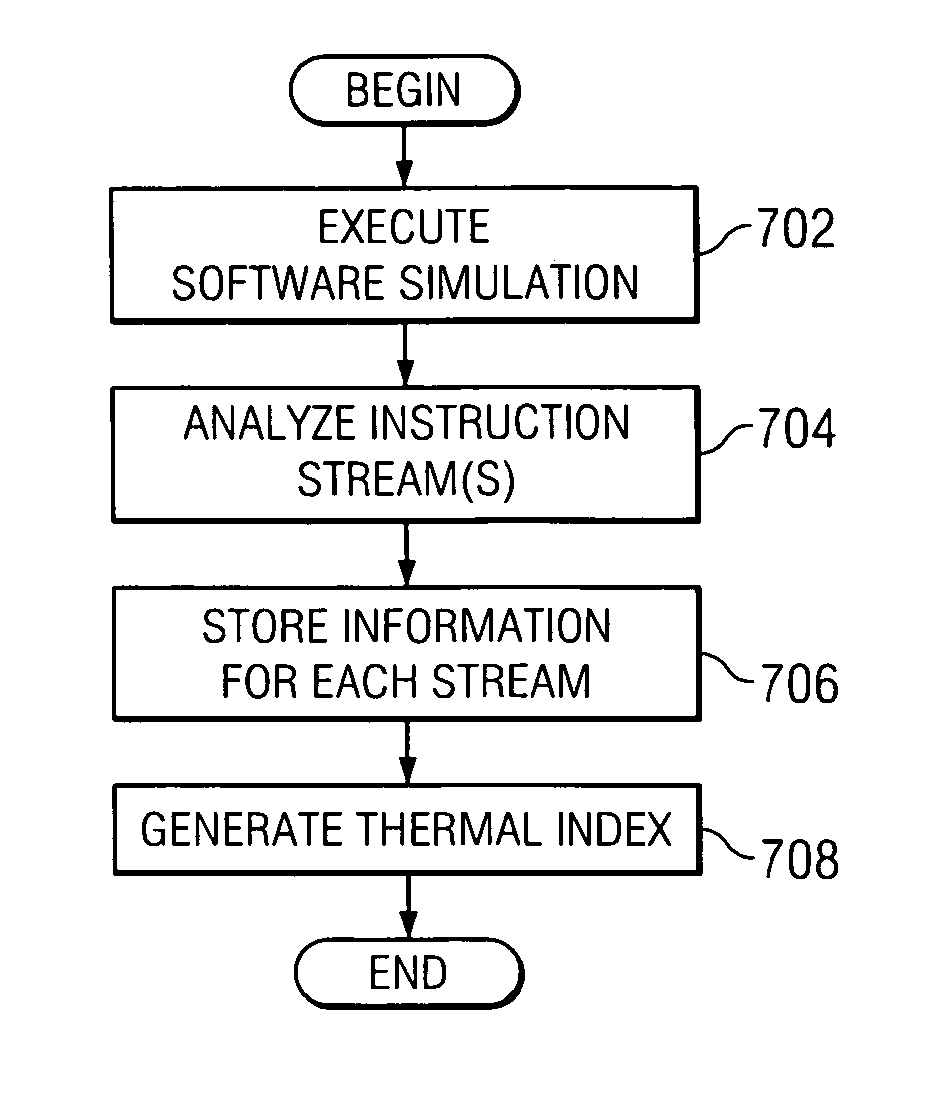

Generation of software thermal profiles for applications in a simulated environment

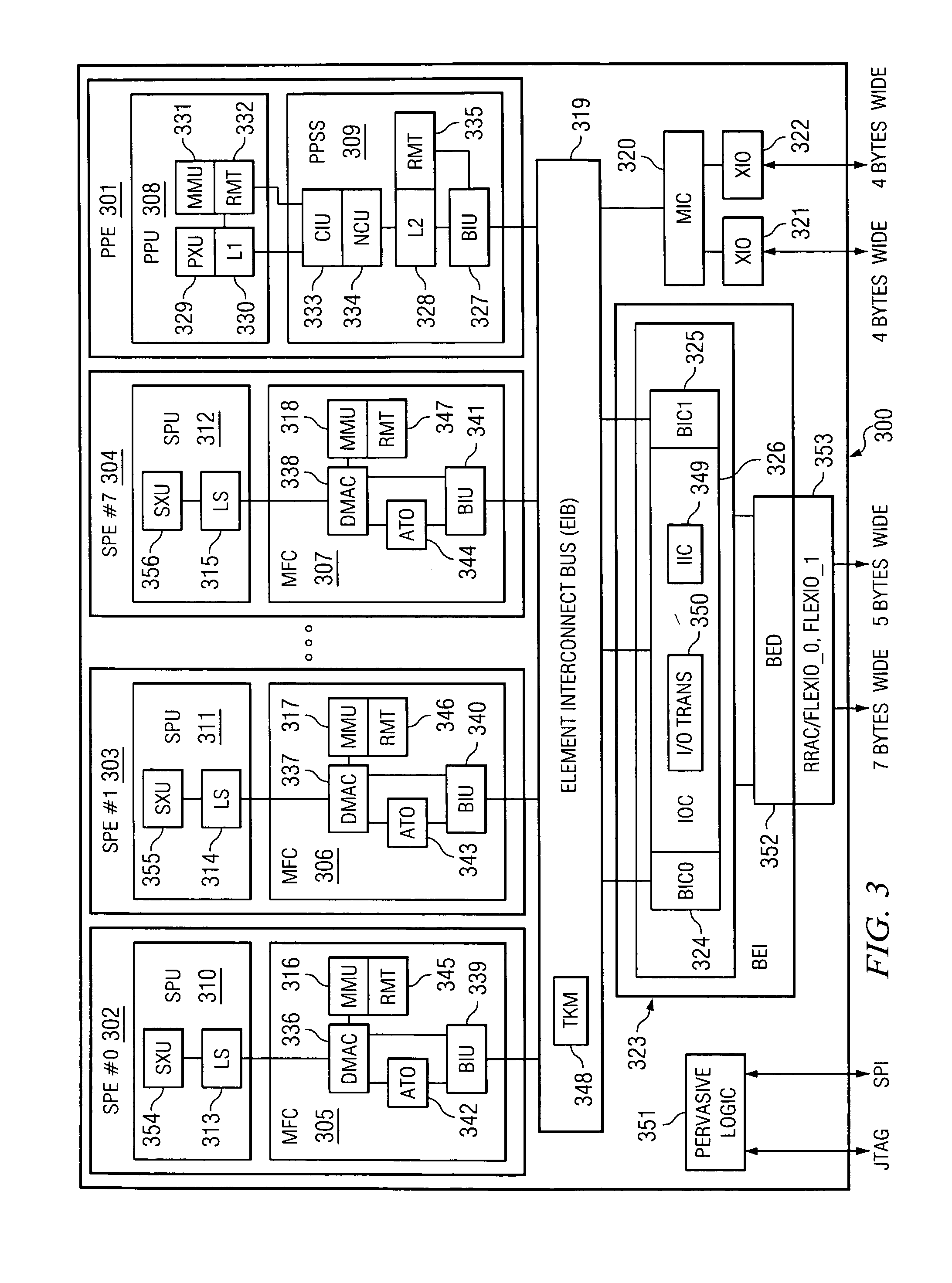

InactiveUS7512530B2Energy efficient ICTAnalogue computers for electric apparatusParallel computingApplication software

A computer implemented method and system for the generation of software thermal profiles for applications executed on a set of processors in a simulated environment. Execution of a software program being run on a software simulator is detected and hardware operations for the software program being executed by the set of processors are analyzed to create analyzed information. Then, a thermal index is generated based on the analyzed information.

Owner:IBM CORP

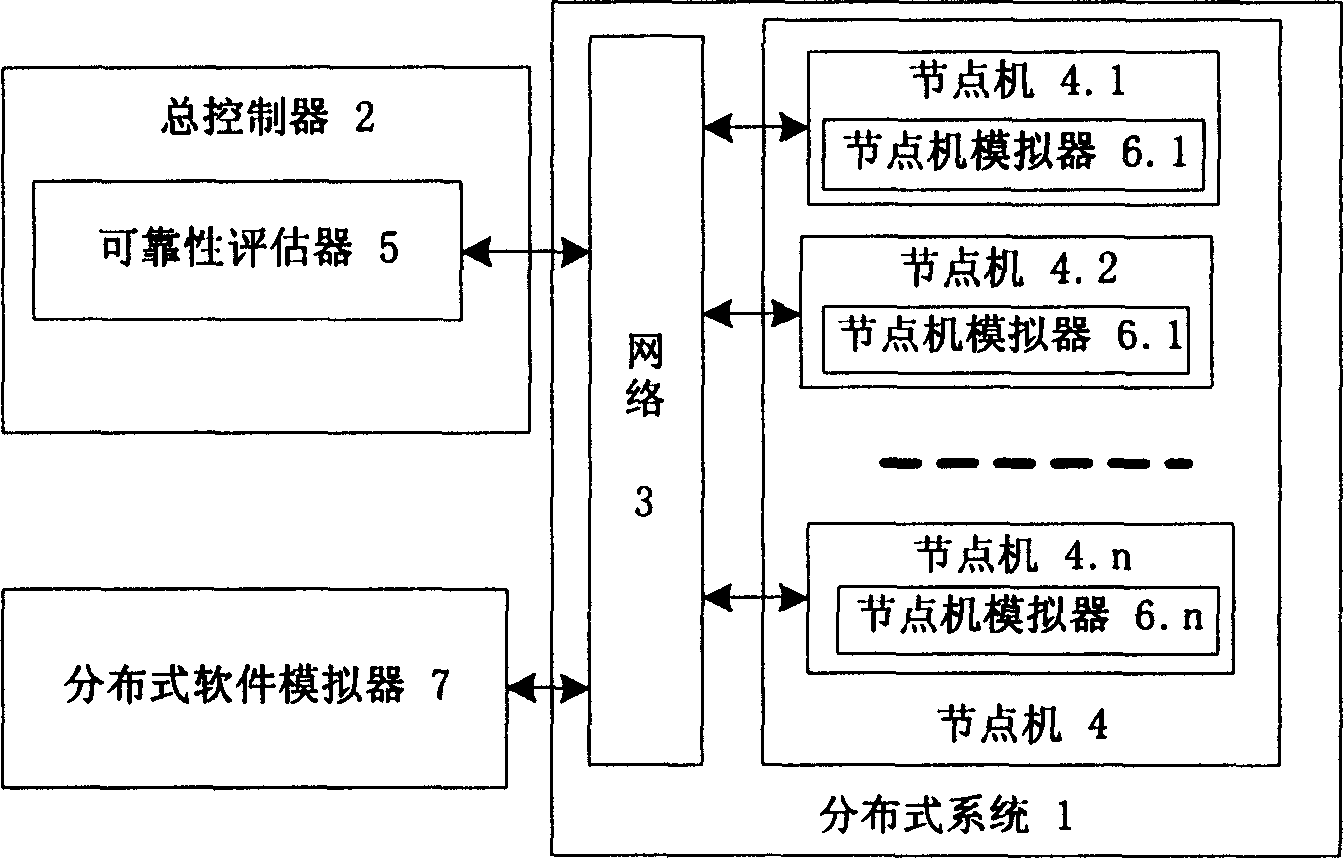

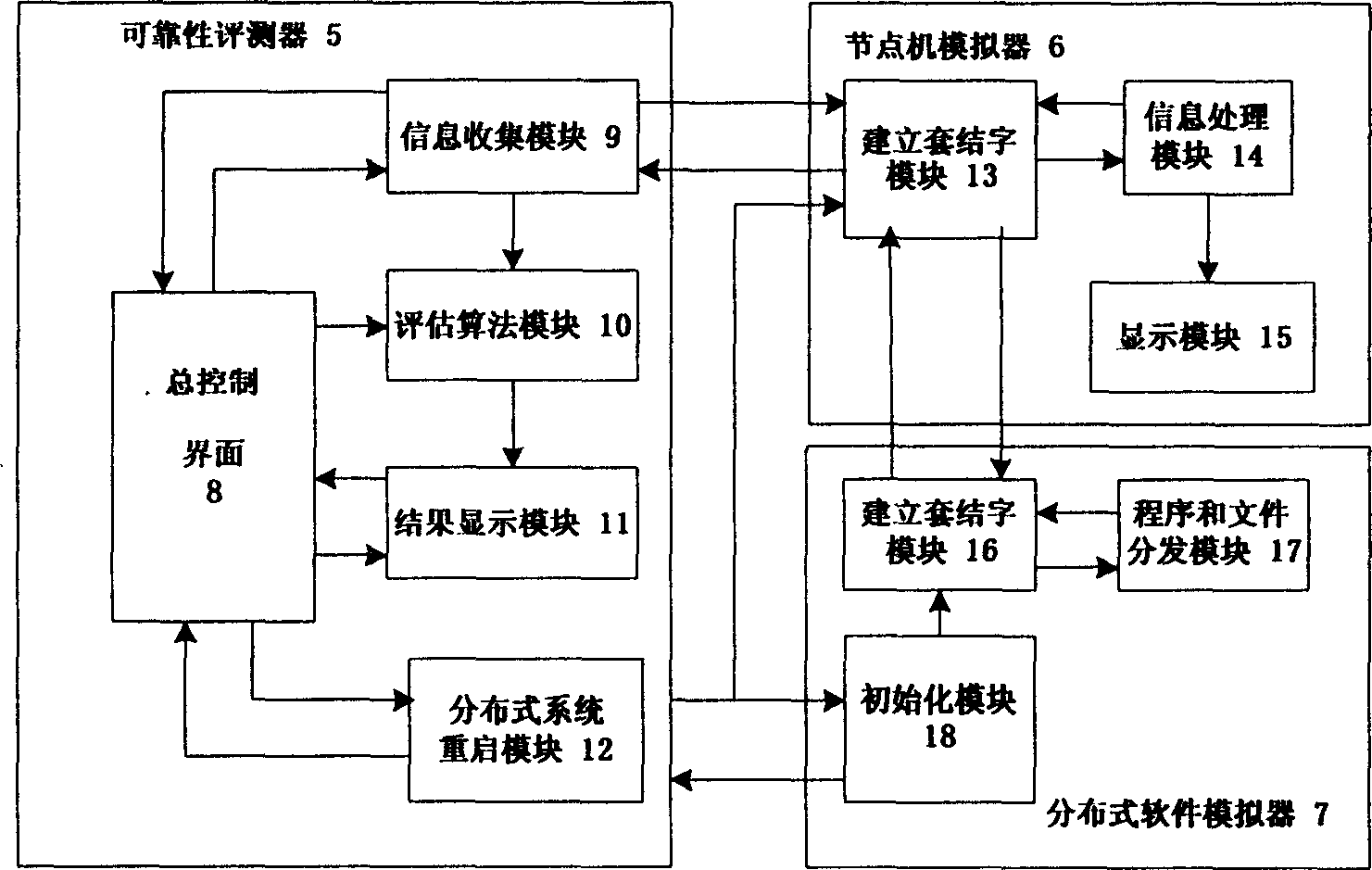

Distribution type software reliability evaluation system having time restraint

The invention relates to a distributed software reliability evaluating system with time constraint, comprising of reliability evaluator on the main control terminal, simulator on each node machine in the distributed system and distribution software simulator. The reliability evaluator is used for receiving configuration file and doing original configuration, controlling simulation of simulator to the node machine; the simulator is used to received test information sent from the reliability evaluator, and executable program and data file from the simulator of the distributed software; the simulator of the distributed software is generating program in program listing and data file in file program listing and distributing them with random to simulator of node machine.

Owner:HUAZHONG UNIV OF SCI & TECH

Generation of software thermal profiles for applications in a simulated environment

InactiveUS20070124124A1Energy efficient ICTAnalogue computers for electric apparatusData processing systemConfigfs

A computer implemented method, data processing system, and computer usable code are provided the generation of software thermal profiles for applications executed on a set of processors in a simulated environment. Execution of a software program being run on a software simulator is detected and hardware operations for the software program being executed by the set of processors are analyzed to create analyzed information. Then, a thermal index is generated based on the analyzed information.

Owner:IBM CORP

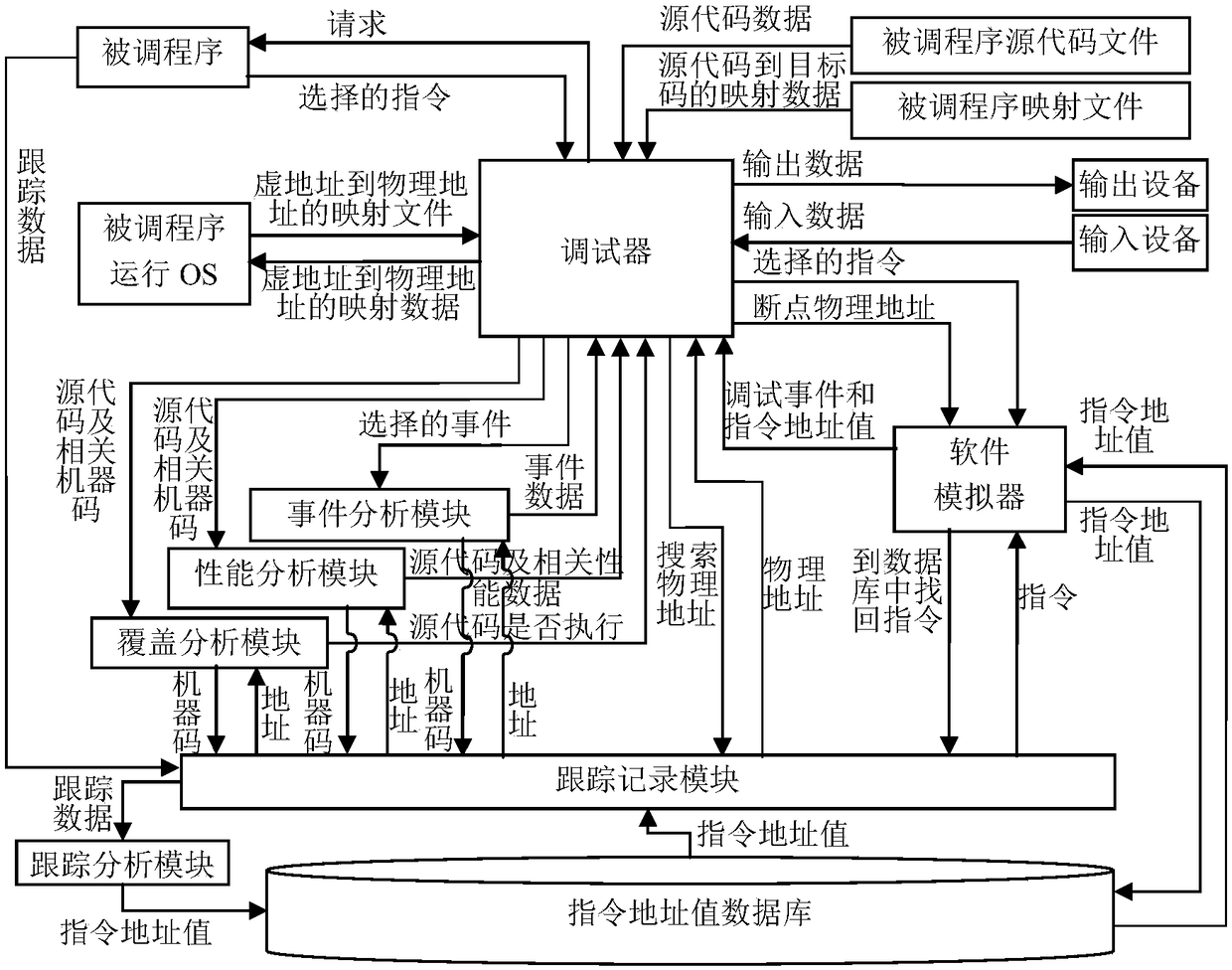

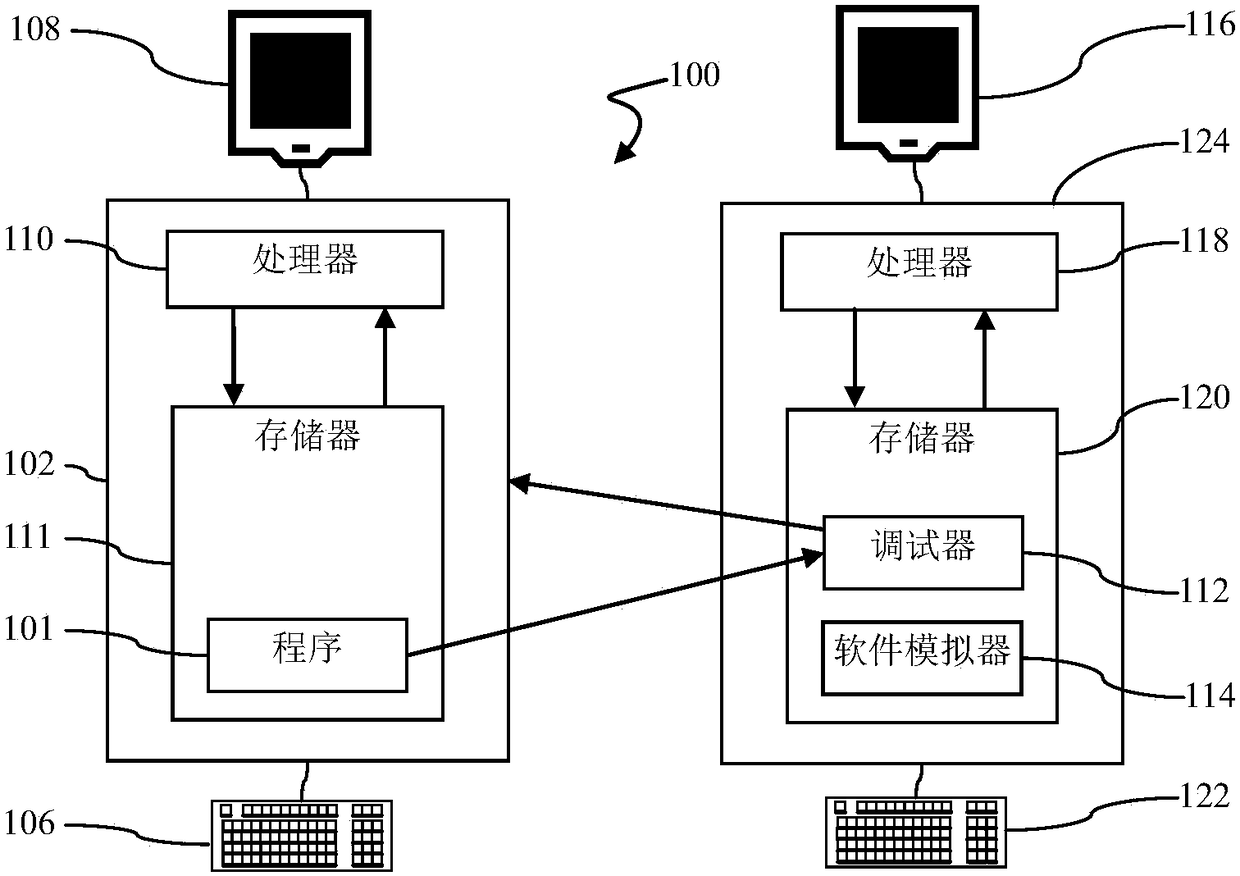

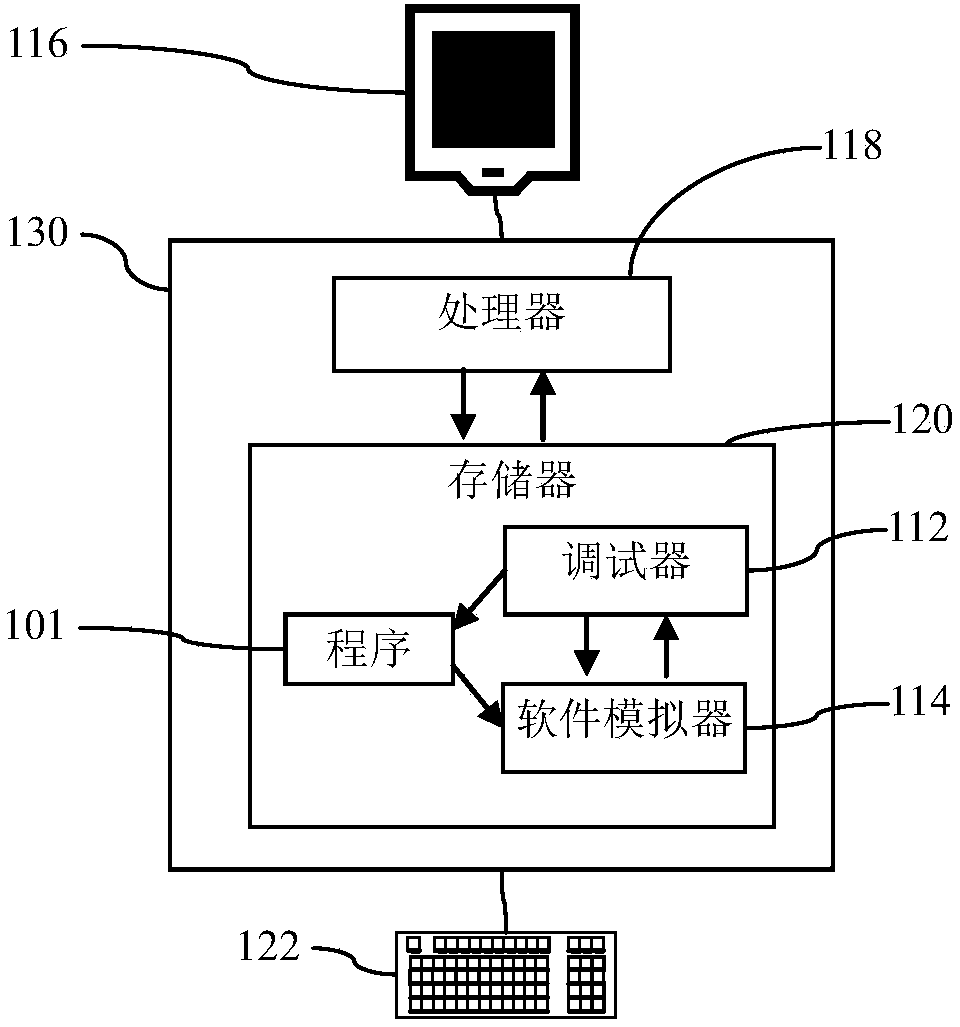

Post-execution software debugging system having performance display and debugging method

The content disclosed by the invention relates to a computer program executed on computer equipment, belongs to the special technical field of computer system software, and especially focuses on software debugging systems and debugging methods for detecting computer program errors. The provided post-execution software debugging system framework having performance display contains a called program,an operation system running the called program, a called program source code file, a called program mapping file, display equipment, a tracking record module, a tracking analysis module, an instruction address value database, a software simulator, an event analysis module, a performance analysis module, a coverage analysis module and a debugger. A debugging method is provided based on the software debugging system, and therefore, post-execution debugging for software can be achieved; and the method is helpful for finding reproducible bugs and non-reproducible bugs in computer programs.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

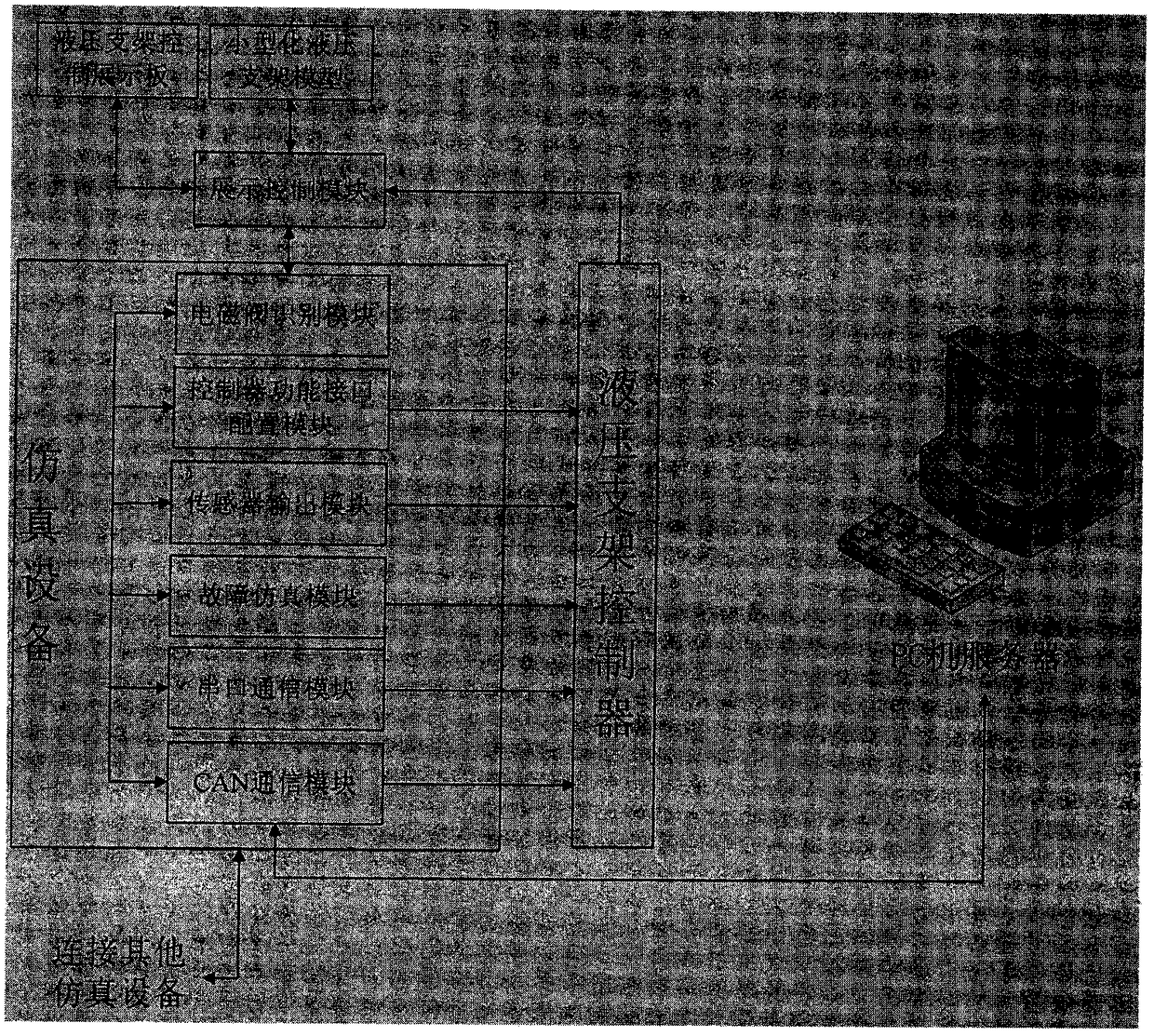

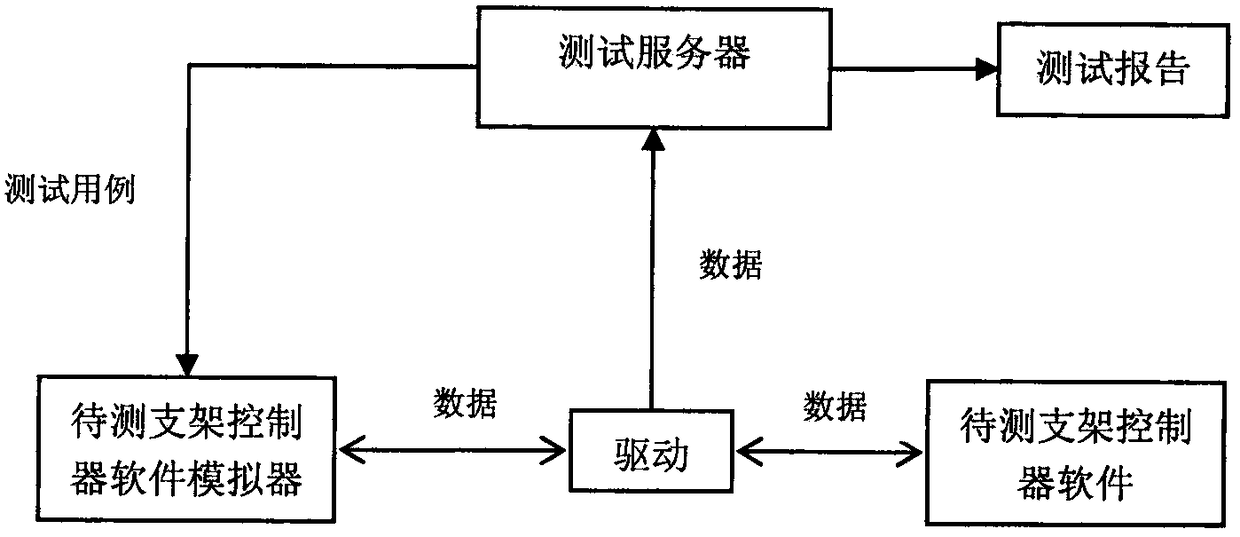

Simulation testing method and system for hydraulic support controller software

InactiveCN108170889AImprove test coverageImplement scheduling operationsGeometric CADSoftware testing/debuggingTrue Case StatusData interface

The invention provides an automatic simulation testing method and system for hydraulic support controller software. According to the method, a test server is used to generate test cases based on realconditions or virtual conditions, and the test cases are output to a simulator of to-be-tested support controller software; the software simulator simulates external information, such as environment information, peripheral information and communication information, of a hydraulic support through a software mode, all kinds of sensor data connected to a hydraulic support controller in a real environment is transmitted to the hydraulic support controller software through an API or other data interface forms, the hydraulic support controller software generates a control action of test conditions represented by the test cases according to the external information simulated by the simulator and outputs the control action to the test server, and the test server checks whether the output of the controller software is consistent with an expected result; and the test server is also responsible for managing various test cases, scheduling test tasks, collecting test process data and forming a testreport.

Owner:BEIJING TIANMA INTELLIGENT CONTROL TECH CO LTD +1

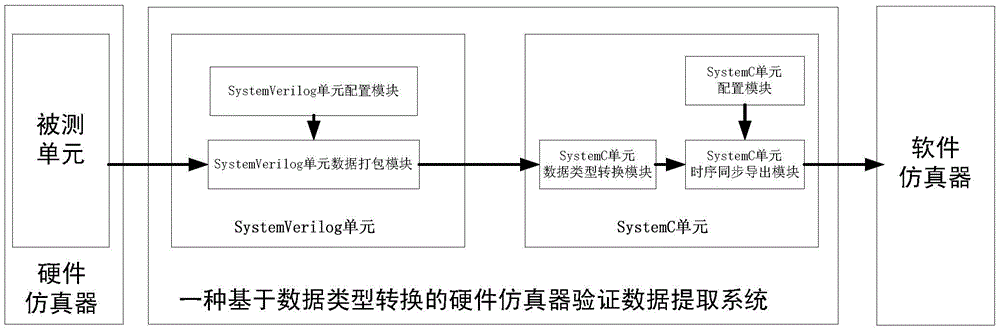

Data type conversion-based hardware simulator validation data extraction system

ActiveCN105653409ASimple structureEasy to implementFaulty hardware testing methodsSystemCData ingestion

The invention provides a data type conversion-based hardware simulator validation data extraction system. The system comprises a SystemVerilog unit and a SystemC unit, wherein the SystemVerilog is used for receiving input data sent from an external hardware simulator, checking the input data, packing the data into a data package and then sending the data package to the SystemC unit; and the SystemC unit is used for 6 data types defined in SystemVerilog into 6 data types defined in SystemVerilog according to a one-to-one corresponding manner, sending the data package to a software simulator according to the simulation precision of the software simulator, extracting the running result of a tested unit running on the hardware simulator with relatively high efficiency, and comparing the running result with a structure preset in the software simulator on a workstation so as to realize the determination of the running result of the tested unit. The method has the advantages of being flexible in data package, high in simulation speed and flexible in software simulator interface.

Owner:BEIJING MXTRONICS CORP +1

Operations exercitation simulator suitable for CNC toolroom machine

InactiveCN101097661AEasy to useReduce malfunctionEducational modelsDisplay deviceSoftware engineering

A kind of stimulation device of operation training for CNC machine tool includes control device for entity, software simulator, transmitting device and stimulating display device; the control device for entity provides operation command; the software simulator is connected with the control device, and generates the stimulation of operation action according to operating action command input by the control device for entity; the transmitting device connects with the control device for entity and the software simulator; the stimulating display device is connected with the software simulator and display the operating action stimulation generated by the software simulator.

Owner:REN AN INFORMATION TECH CO LTD

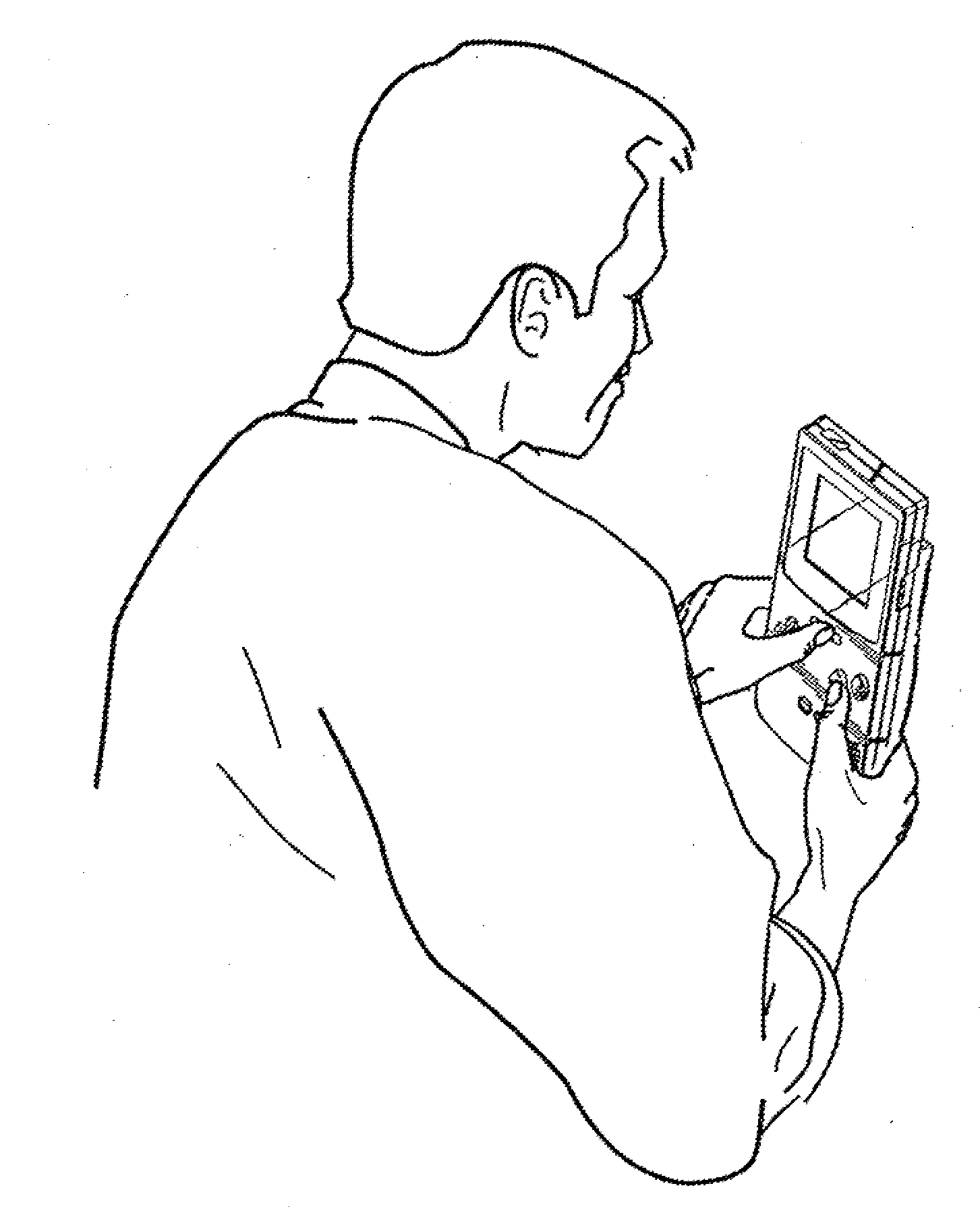

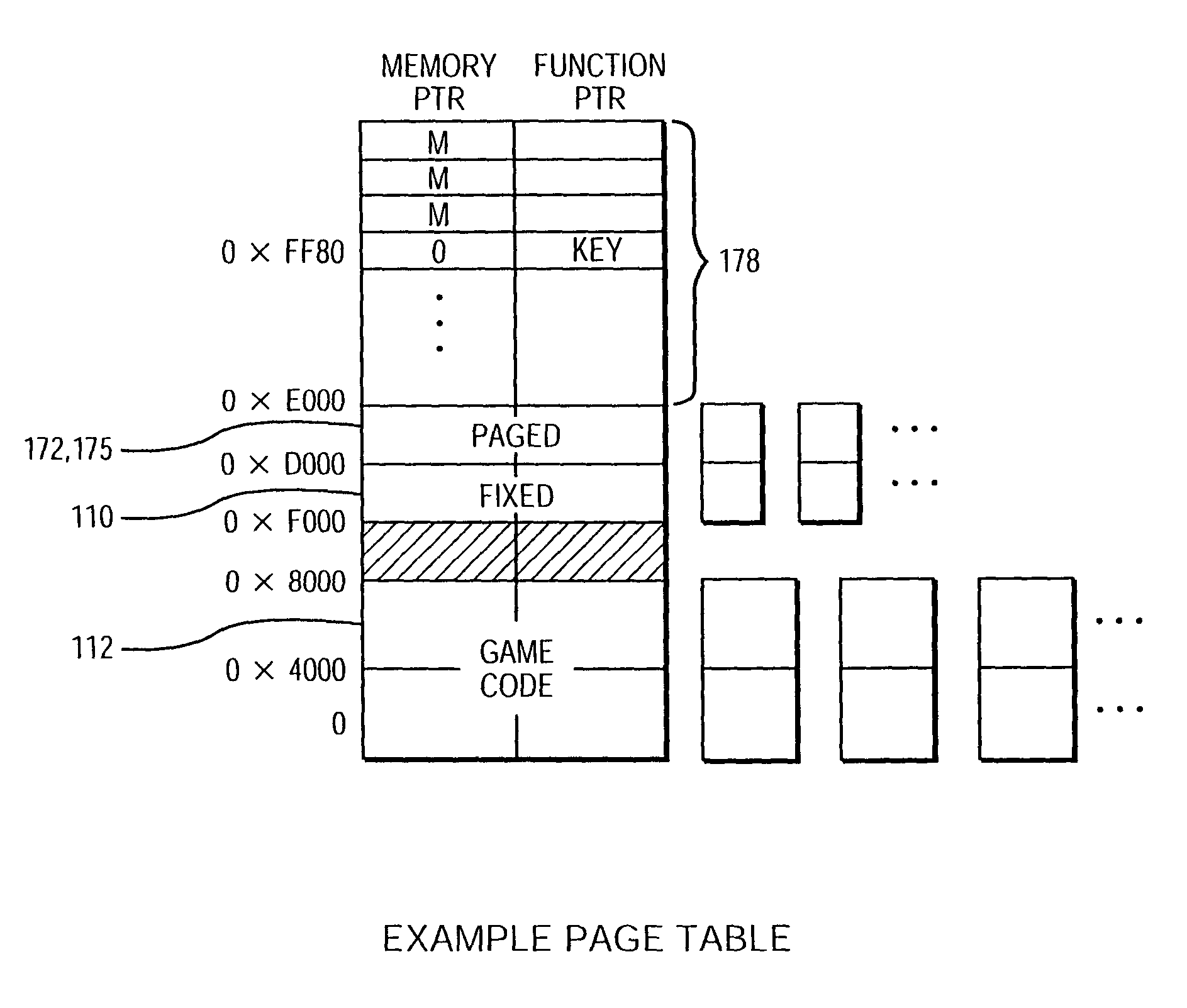

Hand-held video game platform emulation

InactiveUS20130095922A1Good emulationEnabling and disabling visibilityVideo gamesSelective content distributionGraphicsLiquid-crystal display

A software emulator for emulating a handheld video game platform such as GAME BOY®, GAME BOY COLOR® and / or GAME BOY ADVANCE® on a low-capability target platform (e.g., a seat-back display for airline or train use, a personal digital assistant, a cell phone) uses a number of features and optimizations to provide high quality graphics and sound that nearly duplicates the game playing experience on the native platform. Some exemplary features include use of bit BLITing, graphics character reformatting, modeling of a native platform liquid crystal display controller using a sequential state machine, and selective skipping of frame display updates if the game play falls behind what would occur on the native platform.

Owner:NINTENDO CO LTD

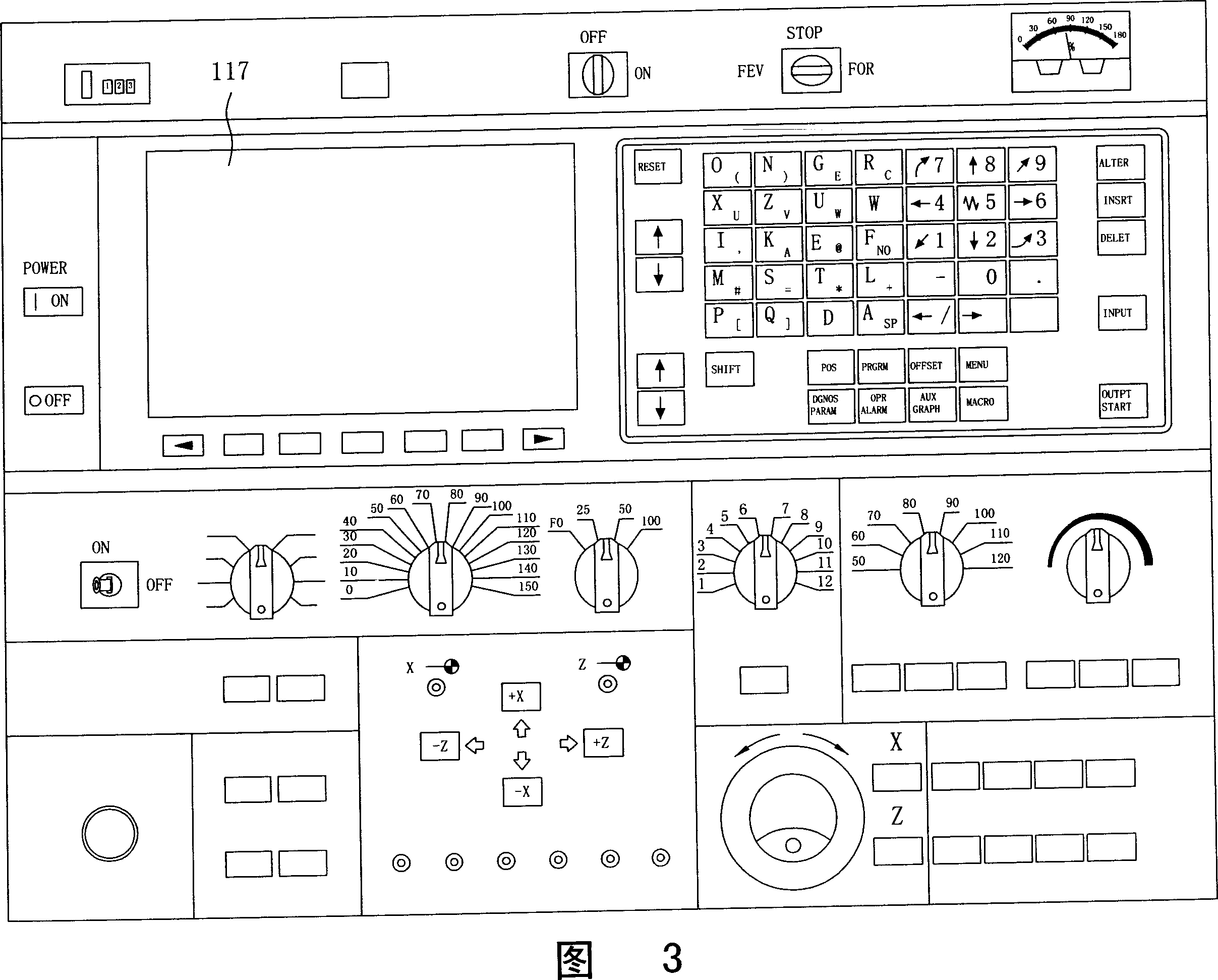

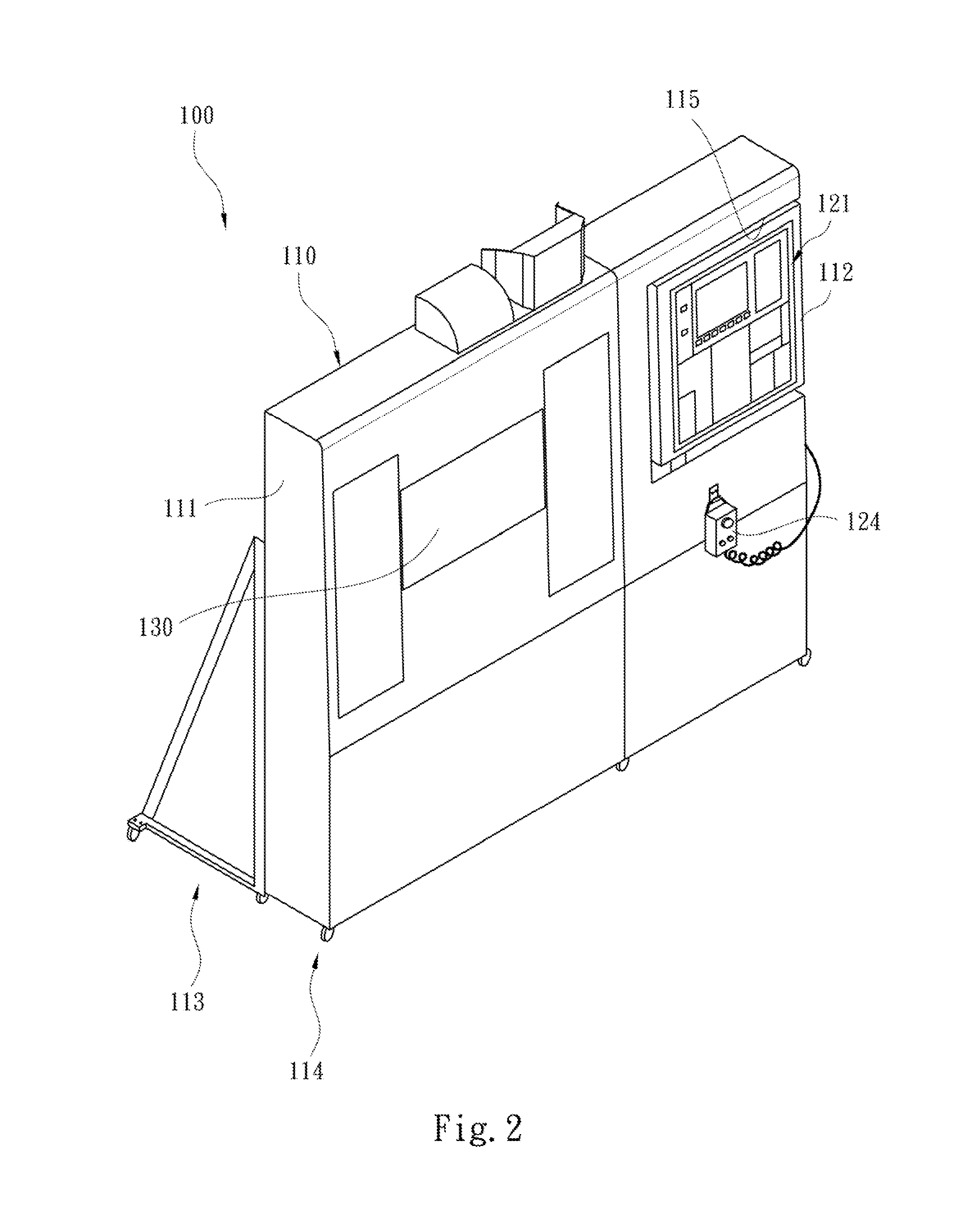

Operation Training Simulation Apparatus for Computer Numerical Control Machine

InactiveUS20120004897A1Educational modelsSpecific program execution arrangementsElectricityNumerical control

An operation training simulation apparatus for a computer numerical control (CNC) machine includes a CNC casing assembly, a control panel device for inputting control and operation commands, a software simulator connected with the simulated control panel displayer, and a simulation displayer electrically connected to the software simulator. The casing assembly includes a CNC frame body. The control panel device is mounted on the casing assembly and has a realistic function control panel interface and a realistic operation control panel interface. The software simulator generates machining and operation simulations based on the inputted control and operation commands through the control panel device, and the simulation displayer visualizes the machining and operation simulations generated by the software simulator.

Owner:REN AN INFORMATION TECH CO LTD

Hand-held video game platform emulation

ActiveUS8157654B2Low costImprove performanceVideo gamesSelective content distributionGraphicsLiquid-crystal display

A software emulator for emulating a handheld video game platform such as GAME BOY®, GAME BOY COLOR® and / or GAME BOY ADVANCE® on a low-capability target platform (e.g., a seat-back display for airline or train use, a personal digital assistant, a cell phone) uses a number of features and optimizations to provide high quality graphics and sound that nearly duplicates the game playing experience on the native platform. Some exemplary features include use of bit BLITing, graphics character reformatting, modeling of a native platform liquid crystal display controller using a sequential state machine, and selective skipping of frame display updates if the game play falls behind what would occur on the native platform.

Owner:NINTENDO CO LTD

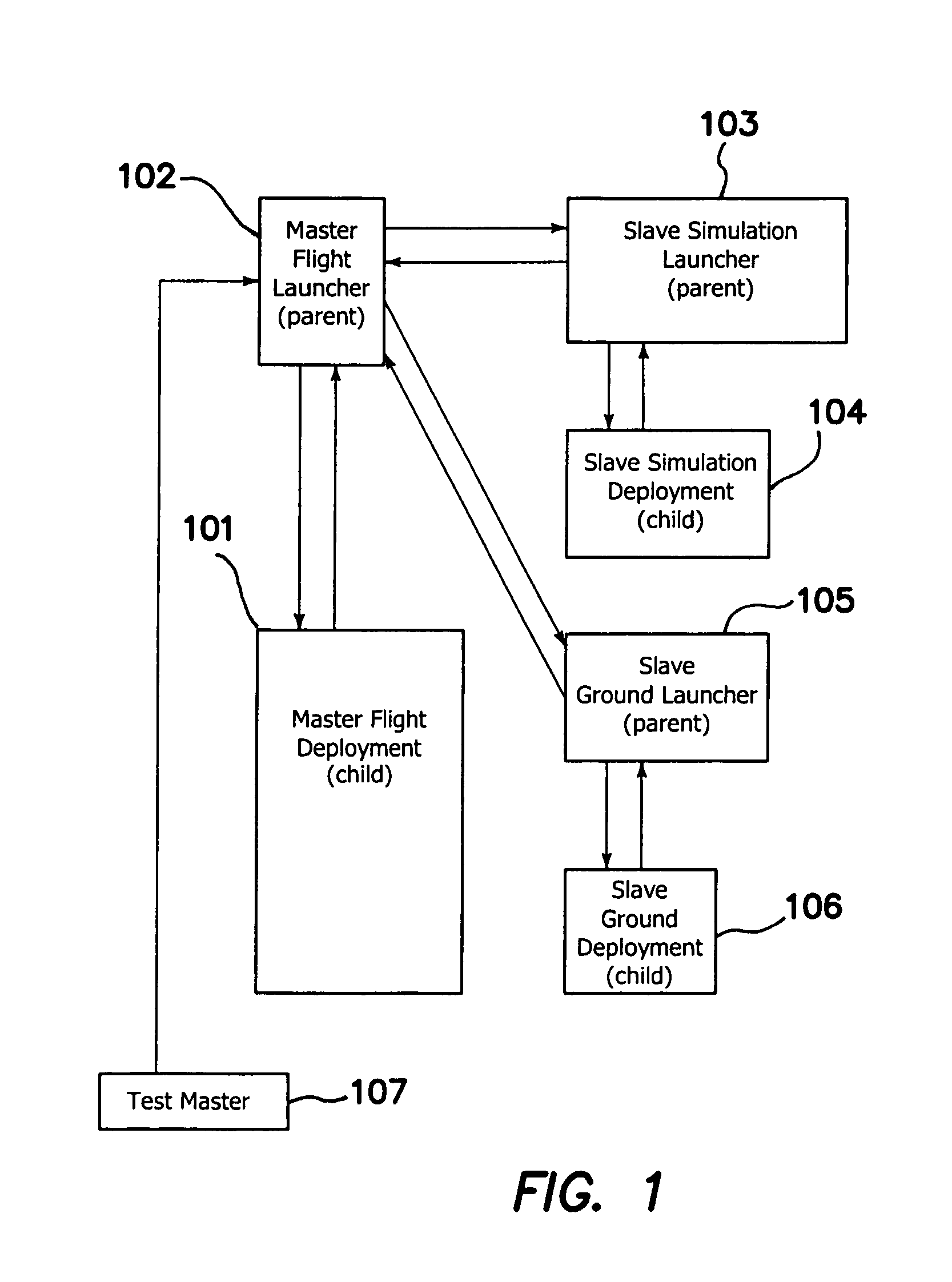

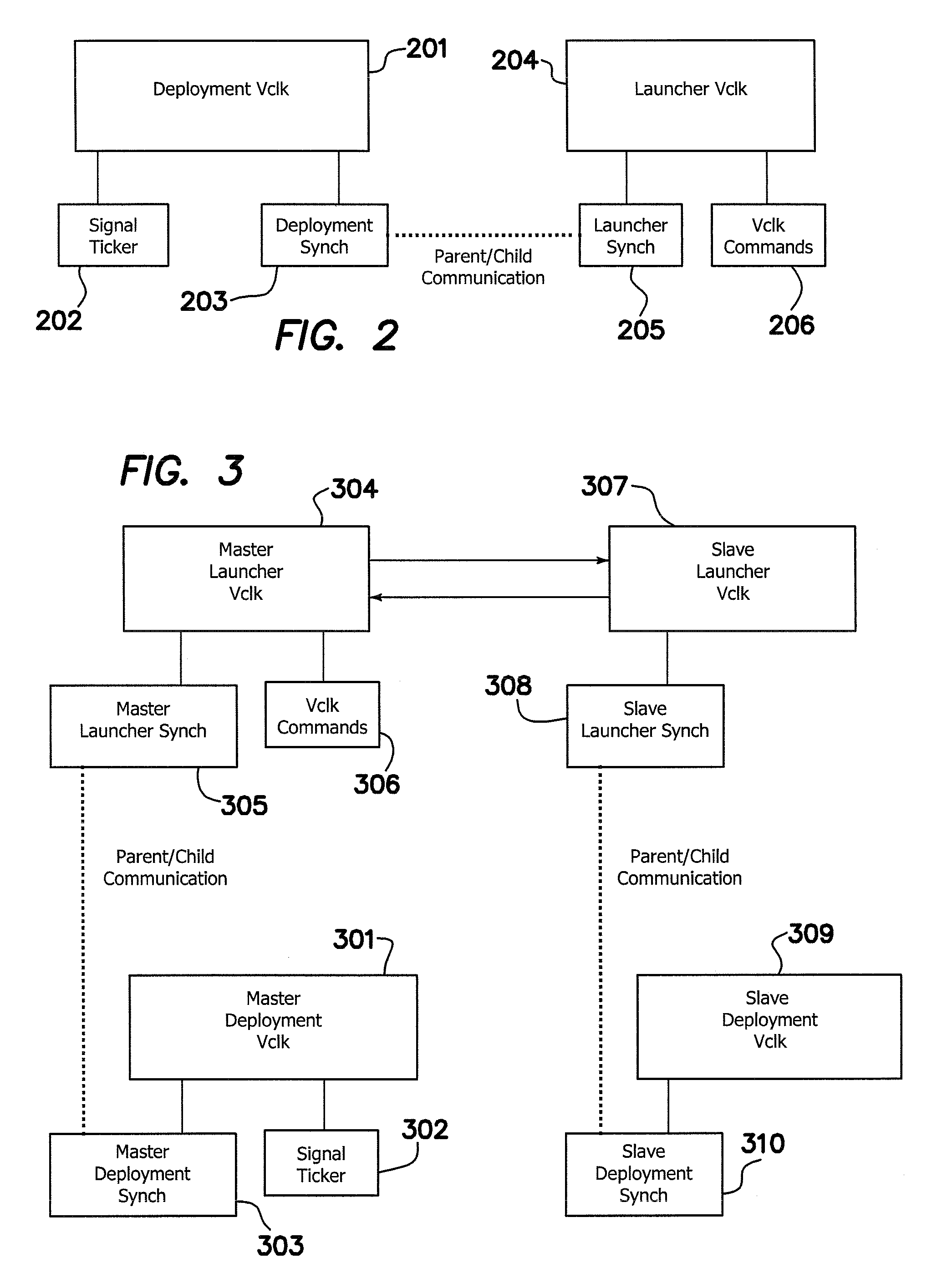

Method and apparatus for computer simulation of flight test beds

InactiveUS7313511B2High timing fidelityImprove performanceGeometric CADAnalogue computers for electric apparatusWorkstationTime scaling

Virtual Real Time (VRT) provides high fidelity timing for software simulator environment running in a workstation. VRT is scalable and controllable. VRT provides flight and simulation software synchronization mechanism. This feature guarantees that the causality effect between flight software when interacting with simulated devices is the same as running flight software in a real test-bed environment. VRT provides high-resolution timing, which facilitates monitoring and detection of timing related faults while running the simulation software system on a workstation. VRT is modularized, such that the switchover from virtual clock to real clock is a trivial task. Running the system on a workstation using VRT behaves exactly like a real system, with the added benefits of user controllable features such as start, stop, monitor and time-scale. Performance of systems running with VRT is generally very good, equal to or better than the hardware, as the software runs natively on a faster workstation.

Owner:CALIFORNIA INST OF TECH

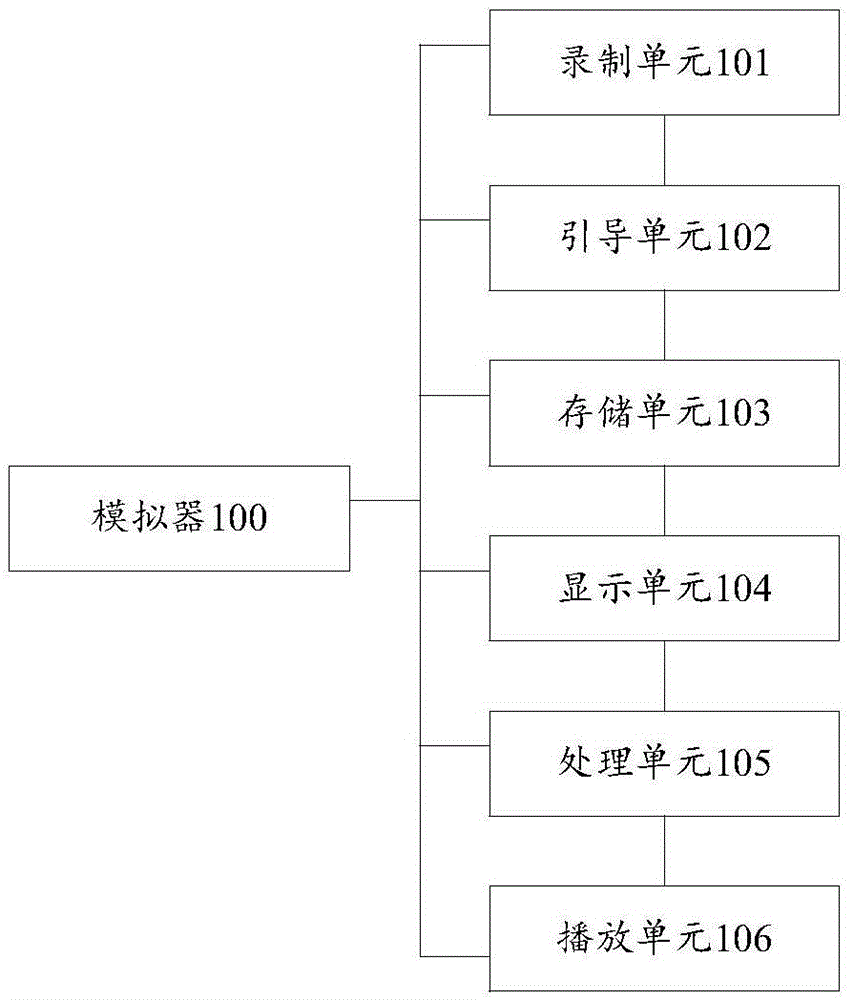

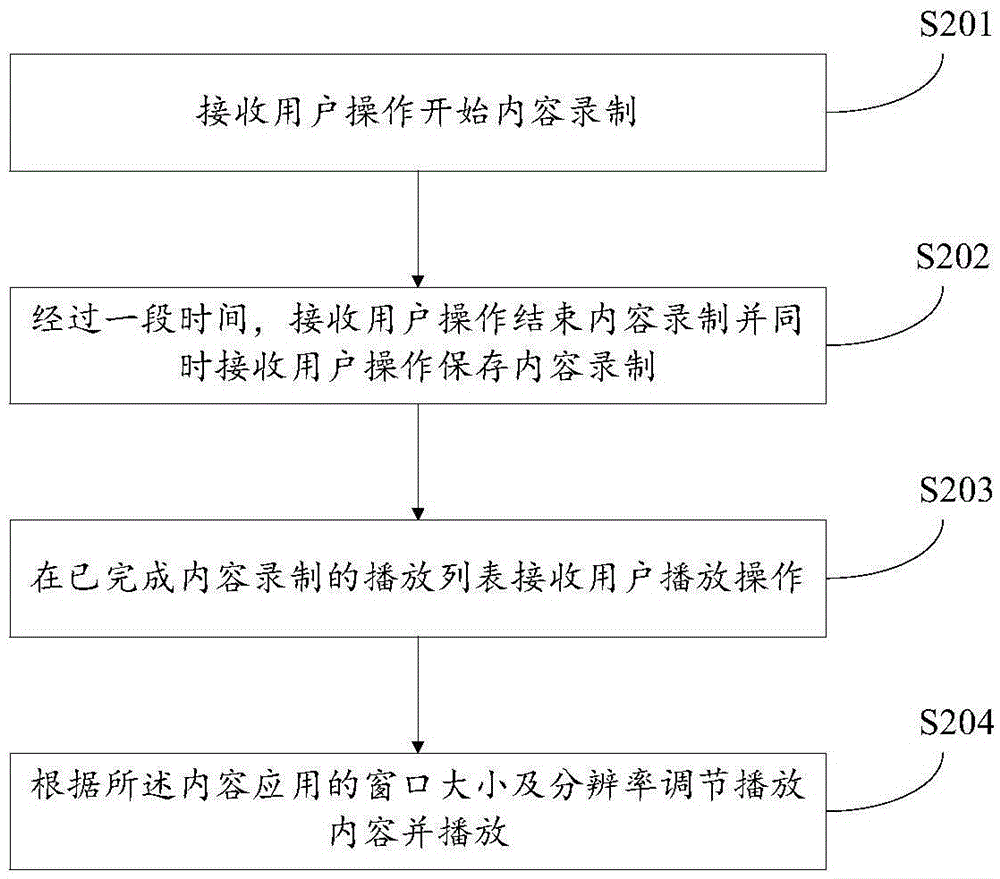

Simulator and content recording and playing method

InactiveCN105528236AEasy to recordSoftware simulation/interpretation/emulationInput/output processes for data processingRelative displacementTimestamp

The present invention relates to the field of computer software simulators, and discloses a simulator and a content recording and playing method. The simulator comprises a recording unit, a guiding unit, a storage unit, a display unit, a processing unit and a playing unit, wherein the storage unit is used for recording times of click operation of a mouse or a keyboard and relative displacement coordinates of movement of the mouse during a recording process, sending the record to the display unit, and simultaneously recording timestamps corresponding to the times of click operation of the mouse and the keyboard and timestamps corresponding to the relative displacement coordinates of movement of the mouse. According to the simulator and the content recording and playing method based on the simulator, the recorded contents can be automatically readjusted according to window sizes, resolution or position variation without debugging each recording action again by users, and the recorded contents can help the users to complete a portion of repeated cycle operation.

Owner:SHENZHEN THINKSKY TECH

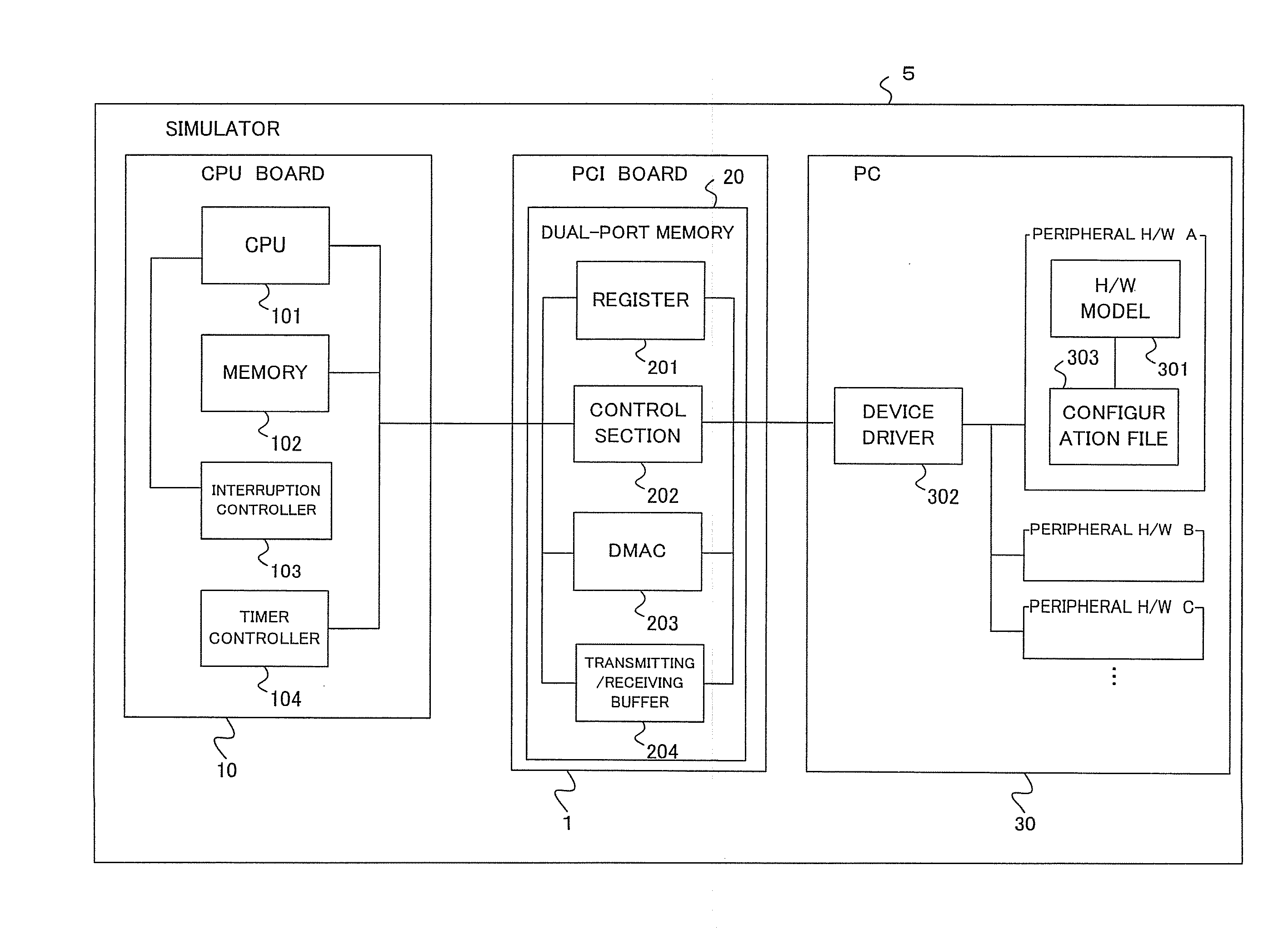

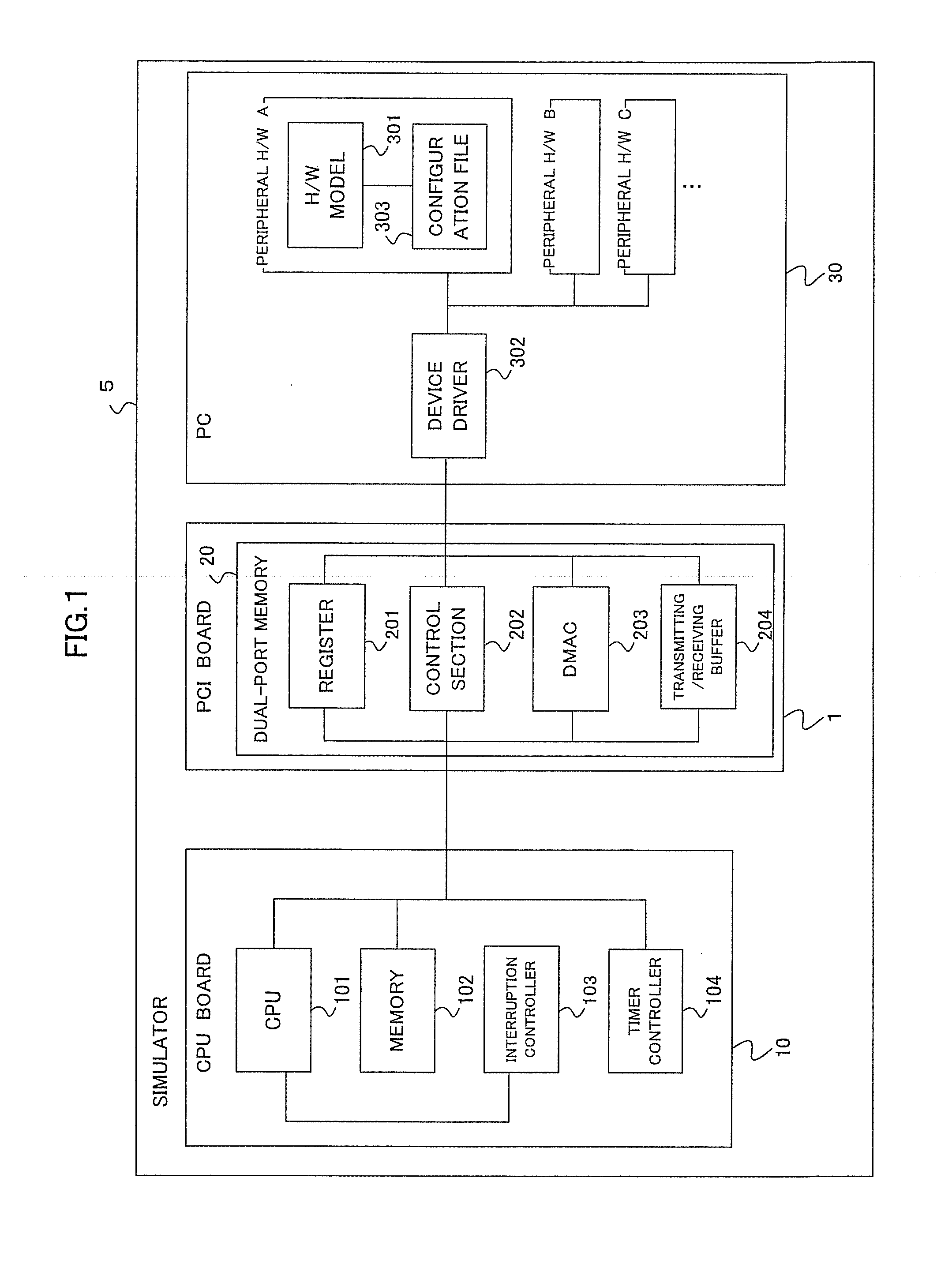

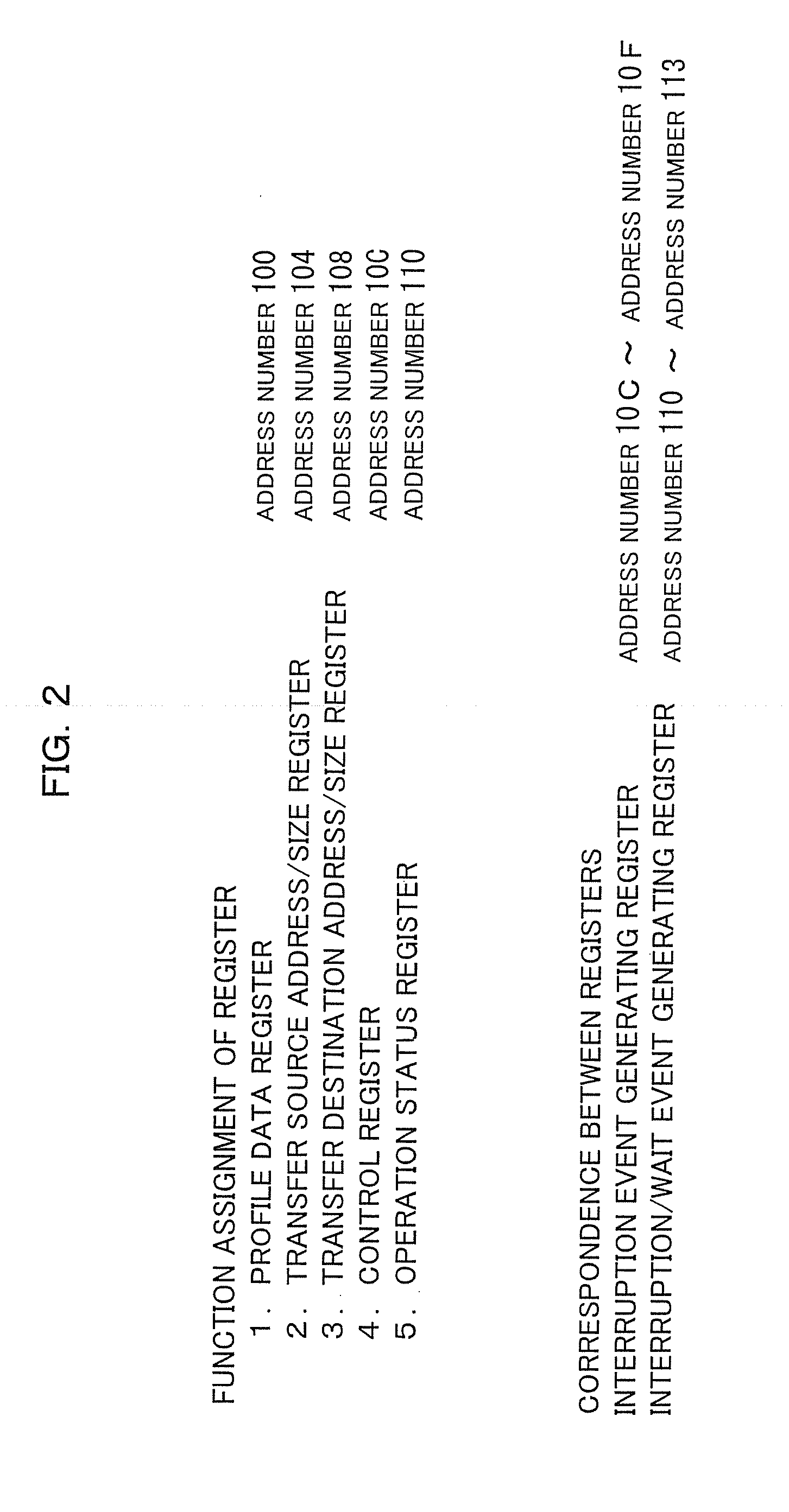

Simulator and simulation method

ActiveUS20080288233A1Low costAnalogue computers for electric apparatusComputation using non-denominational number representationComputer hardwareSoftware simulator

An object of the present invention is to provide a simulator for verifying plural products with common hardware configuration, in which peripheral hardware that can be reused are constituted by hardware and other peripheral hardware is constituted by software simulator, and simulation method.A simulator comprises: a hardware section that includes a peripheral hardware configuration with a structure required for a CPU and OS to operate alone; a software section that simulates the operation of peripheral hardware other than hardware constituting the hardware section as a peripheral hardware model; and an interface board that connects the hardware section and software section.

Owner:TOSHIBA DIGITAL SOLUTIONS CORP +1

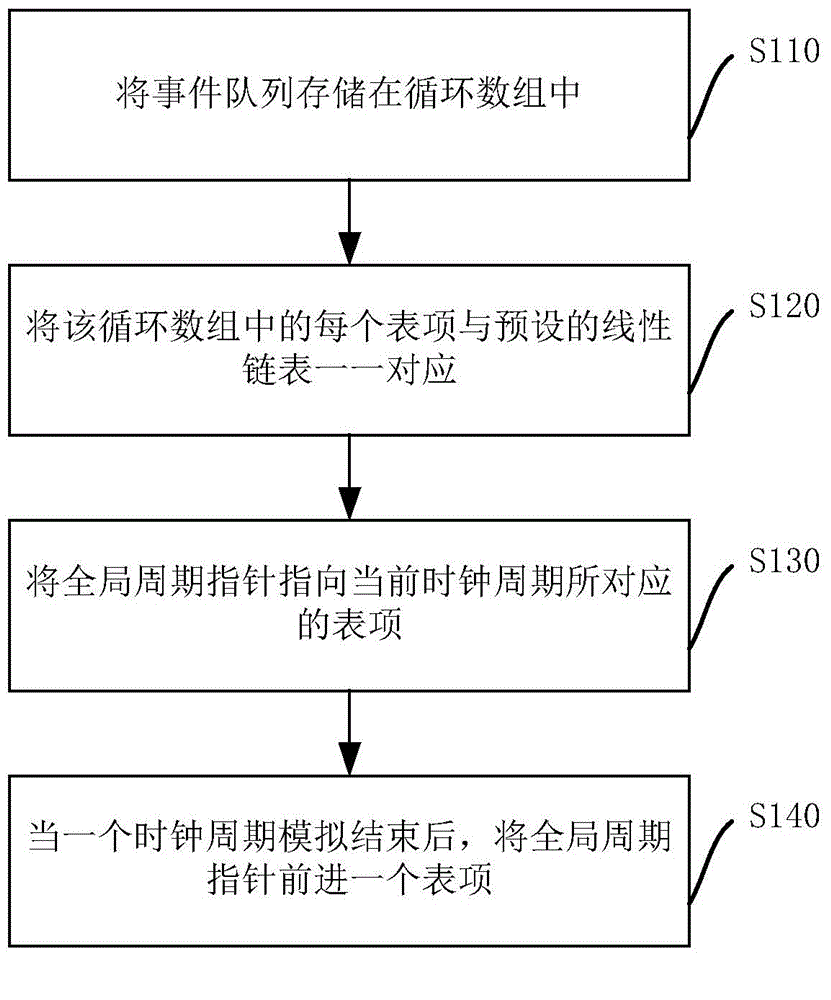

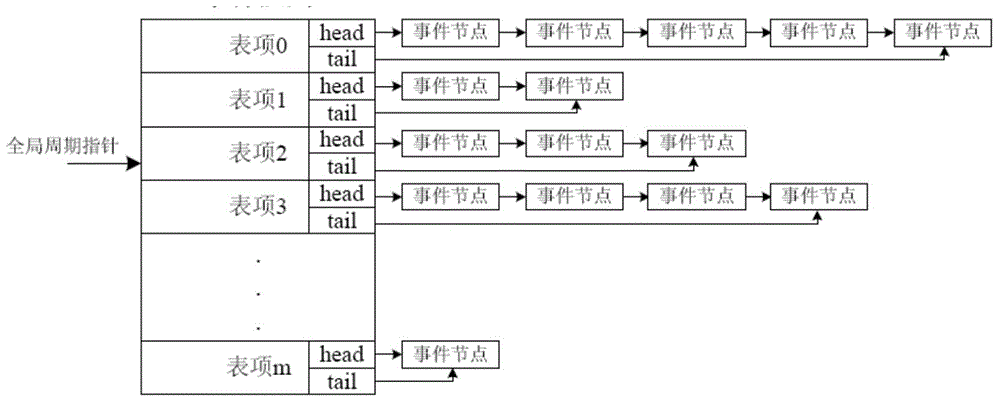

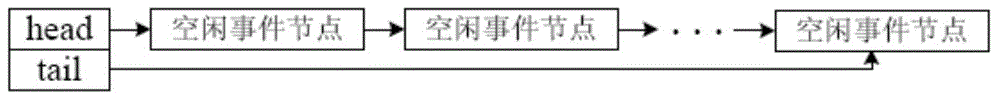

Method and system for managing event queue of software simulator of microprocessor

ActiveCN104657108AHigh and low sizeHigh and low requirementsOperational speed enhancementSoftware simulation/interpretation/emulationArray data structureParallel computing

The invention discloses a method and system for managing an event queue of a software simulator of a microprocessor. The method and the system are used for overcoming the defect in the prior art that the efficiency of the event queue of the software simulator of the microprocessor is low. The method comprises the steps: the event queue is stored in a circular array; the circular array contains a plurality of table entries, and each table entry corresponds to one clock cycle of the software simulator; all the table entries in the circular array are enabled to be in one-to-one correspondence to preset linear chain tables, and a head pointer and a tail pointer of each table entry respectively point to a head element and a tail element of a corresponding linear chain table; each linear chain table stores events, which should be triggered in the clock cycle represented by corresponding table entry; a global cycle pointer is enabled to point to the table entry corresponding to the current clock cycle; after the simulation of one clock cycle ends, the global cycle pointer goes forwards by one table entry. The method and the system disclosed by the invention have very high efficiency in the aspects of event insertion, event query and event removal.

Owner:BEIJING UNIV OF POSTS & TELECOMM +1

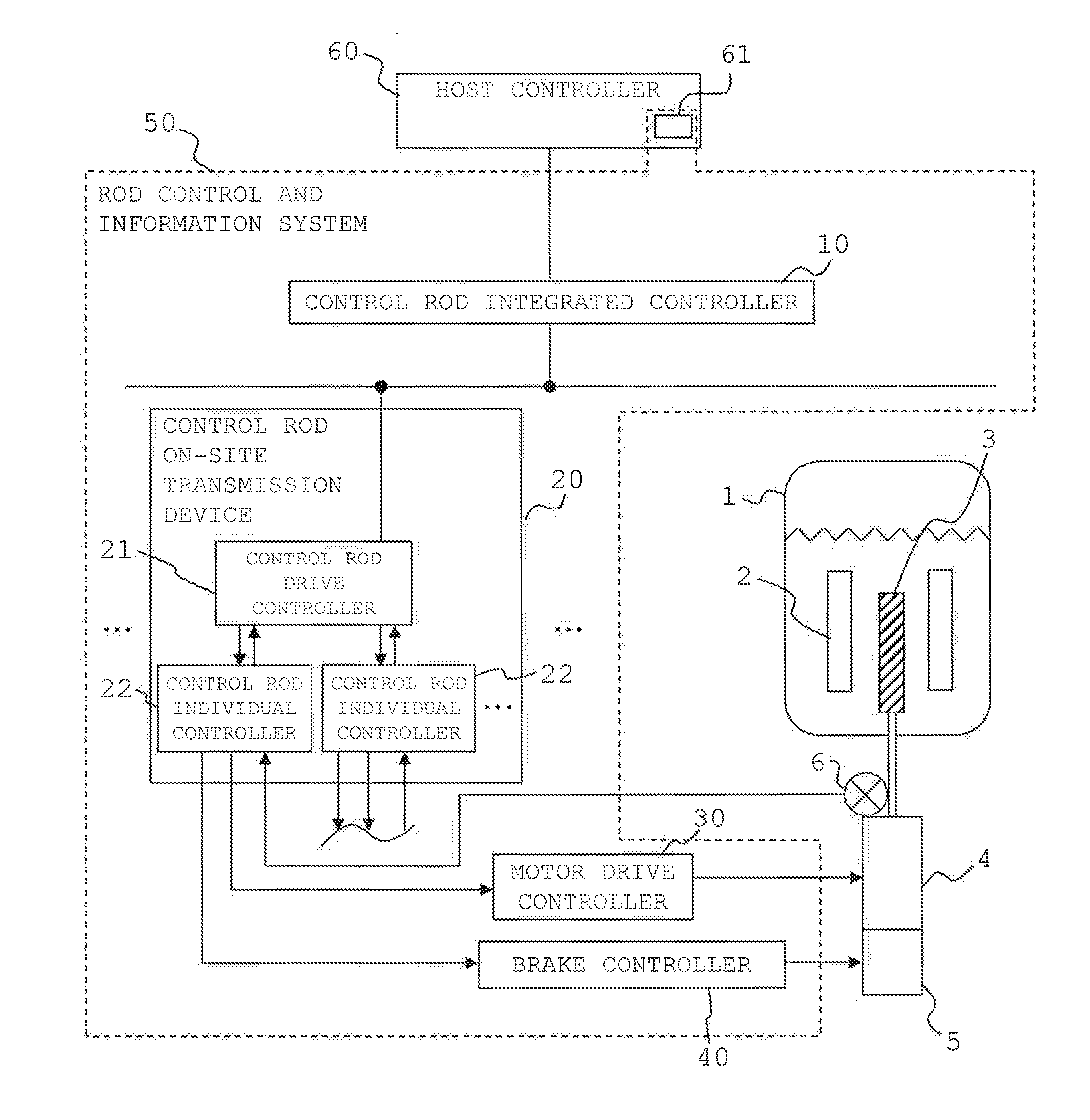

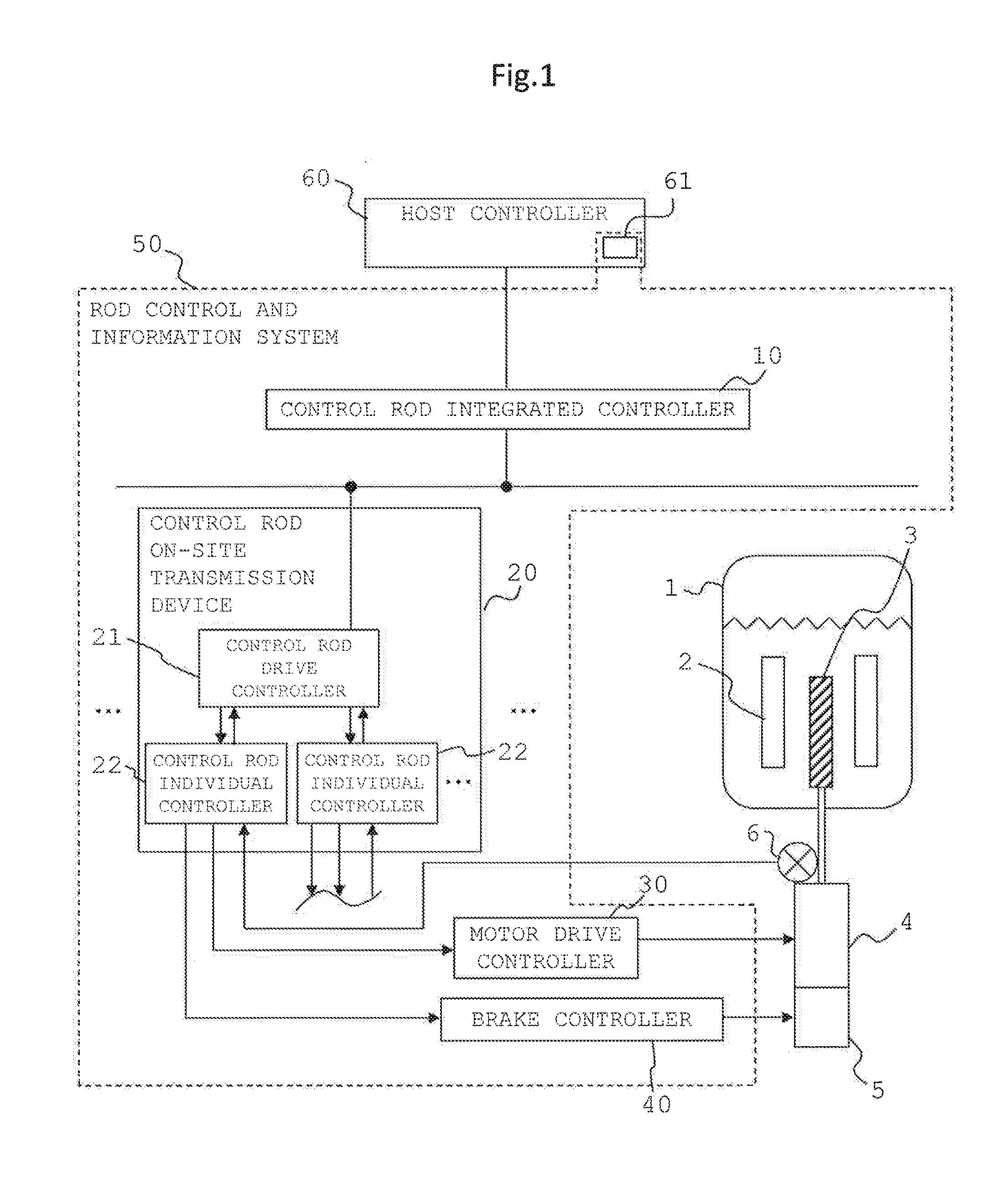

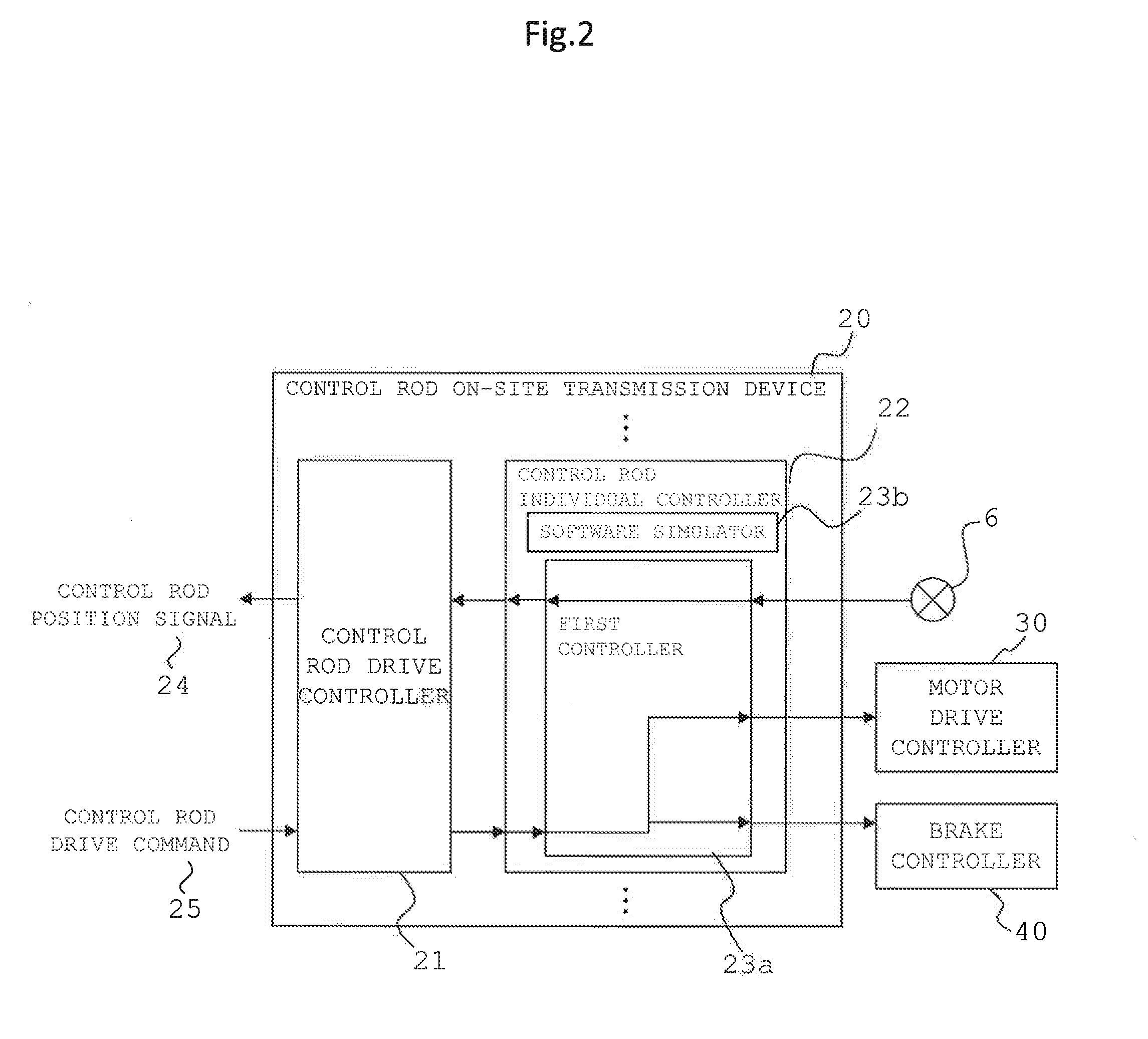

Rod Control and Information System, Control Rod Individual Controller, and Test Method for Rod Control and Information System

InactiveUS20150332795A1Efficient conductionImprove test efficiencyNuclear energy generationNuclear monitoringNuclear reactorBiological activation

The invention includes conducting efficiently a functional verification test of a rod control and information system as a whole and of control rod on-site transmission devices only, the system performing and monitoring insertion and extraction of control rods to and from a nuclear reactor. Each on-site transmission device in the system includes a control rod drive controller and multiple control rod individual controllers each incorporating beforehand a software simulator that calculates position change of the control rods corresponding to a control rod drive command input to the individual controller via the control rod drive controller. During the test, a software simulator activation signal is issued to activate the software simulator calculating a simulated control rod position and outputting the position as a control rod position signal for use in determining the integrity of the on-site transmission devices and that of the system.

Owner:HITACHI LTD

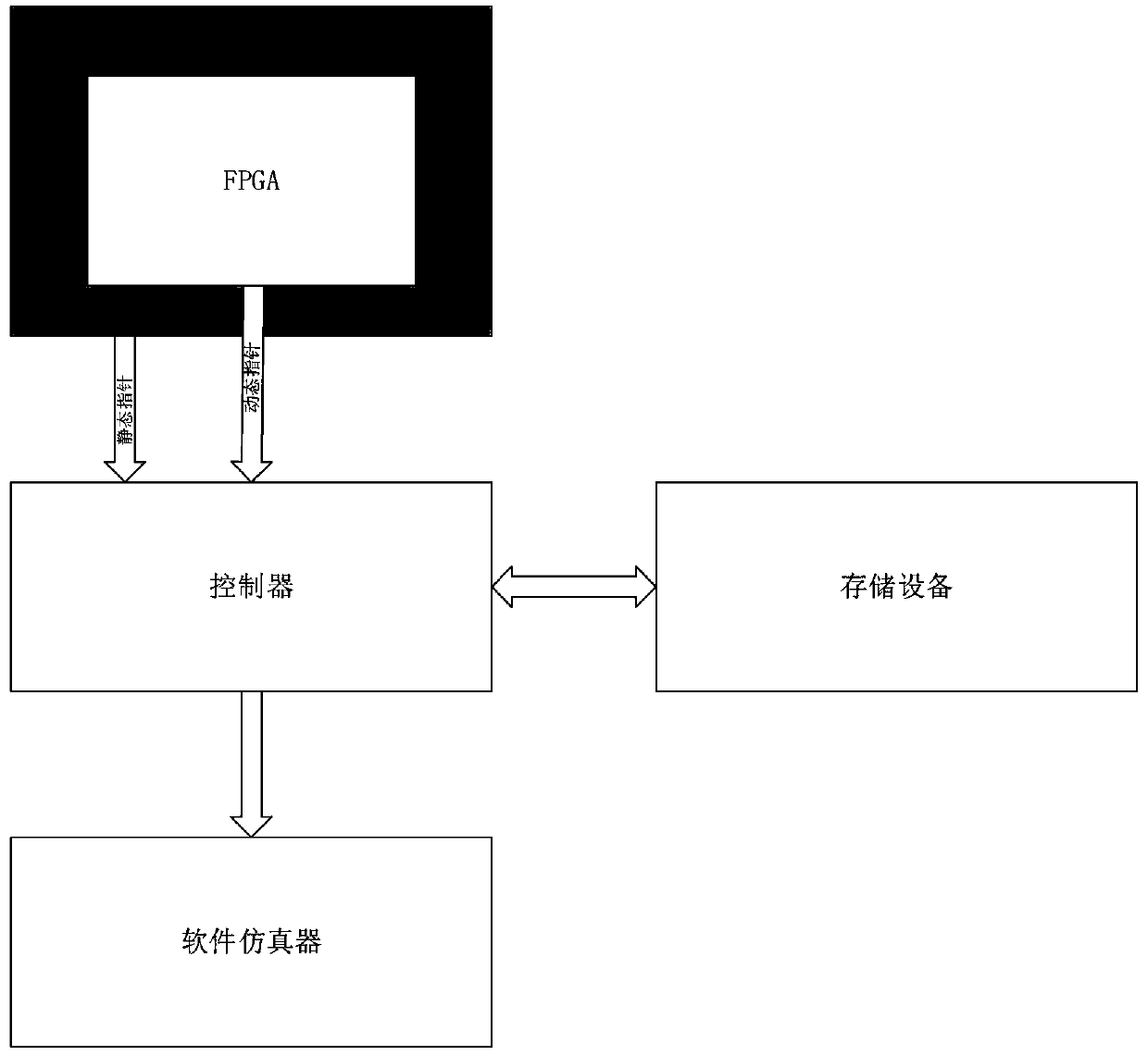

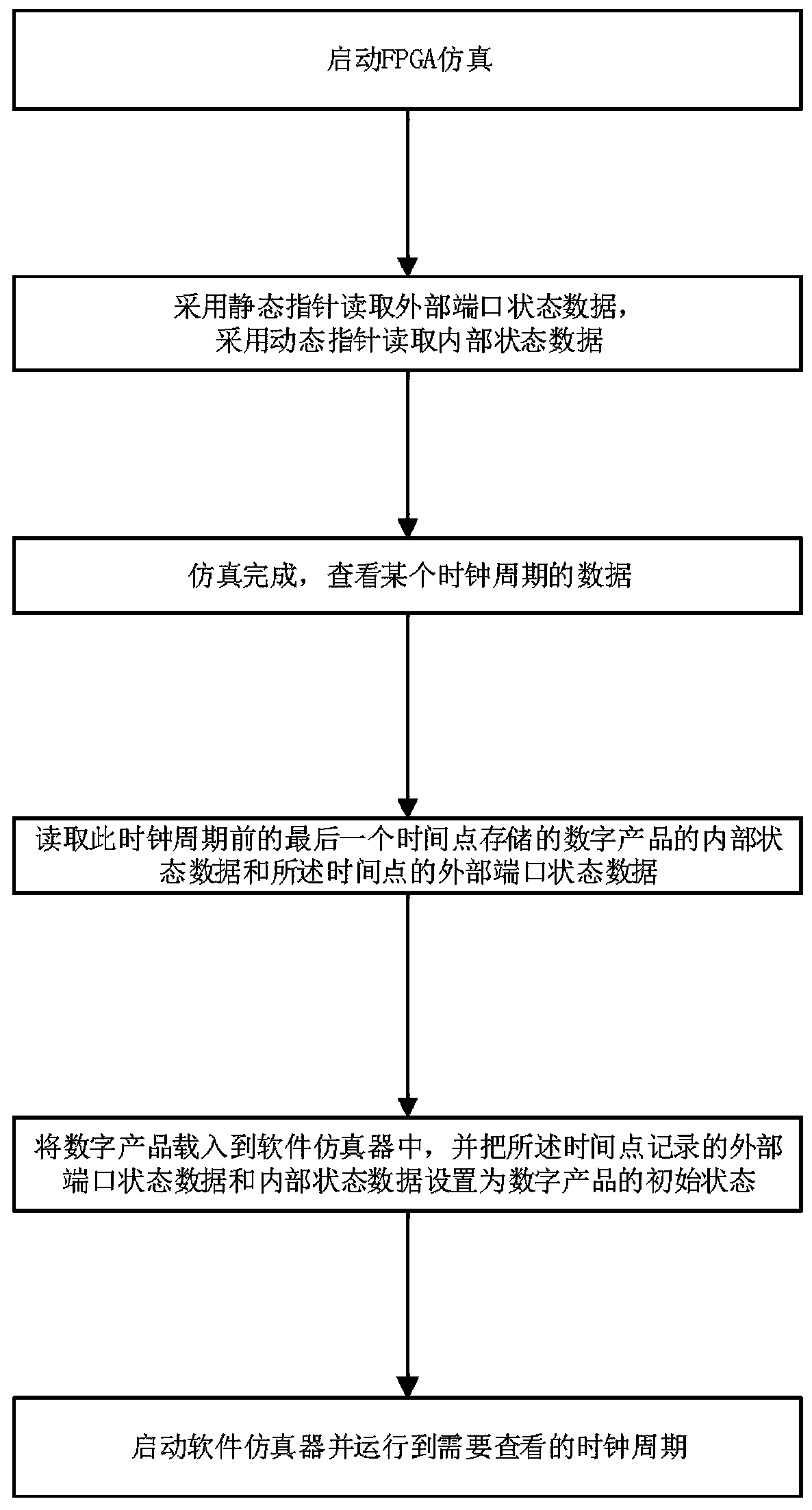

Simulation signal viewing method and system for digital product

PendingCN110765716AReduce running timeShorten the timeComputer aided designSpecial data processing applicationsSoftware simulatorReal-time computing

The invention discloses a simulation signal checking method and a simulation system for a digital product, and the method comprises the steps: reading and recording the state data of all external ports of the digital product in real time when FPGA simulation is carried out on the digital product, and reading and recording all internal state data of the digital product at set intervals; after simulation, when the data of a certain clock period of the digital product needs to be traced back and checked, in the recorded simulation data, reading the internal state data of the digital product and the external port state data of the time point stored at the last time point before the clock period at the moment; and loading the digital product into a software simulator, setting the external portstate data and the internal state data recorded at the time point as the initial state of the digital product, starting the software simulator, and running the software simulator to a clock period required to be checked. By adopting the technical scheme of the invention, all simulation data of any clock period can be quickly backtracked and checked.

Owner:深圳国微芯科技有限公司

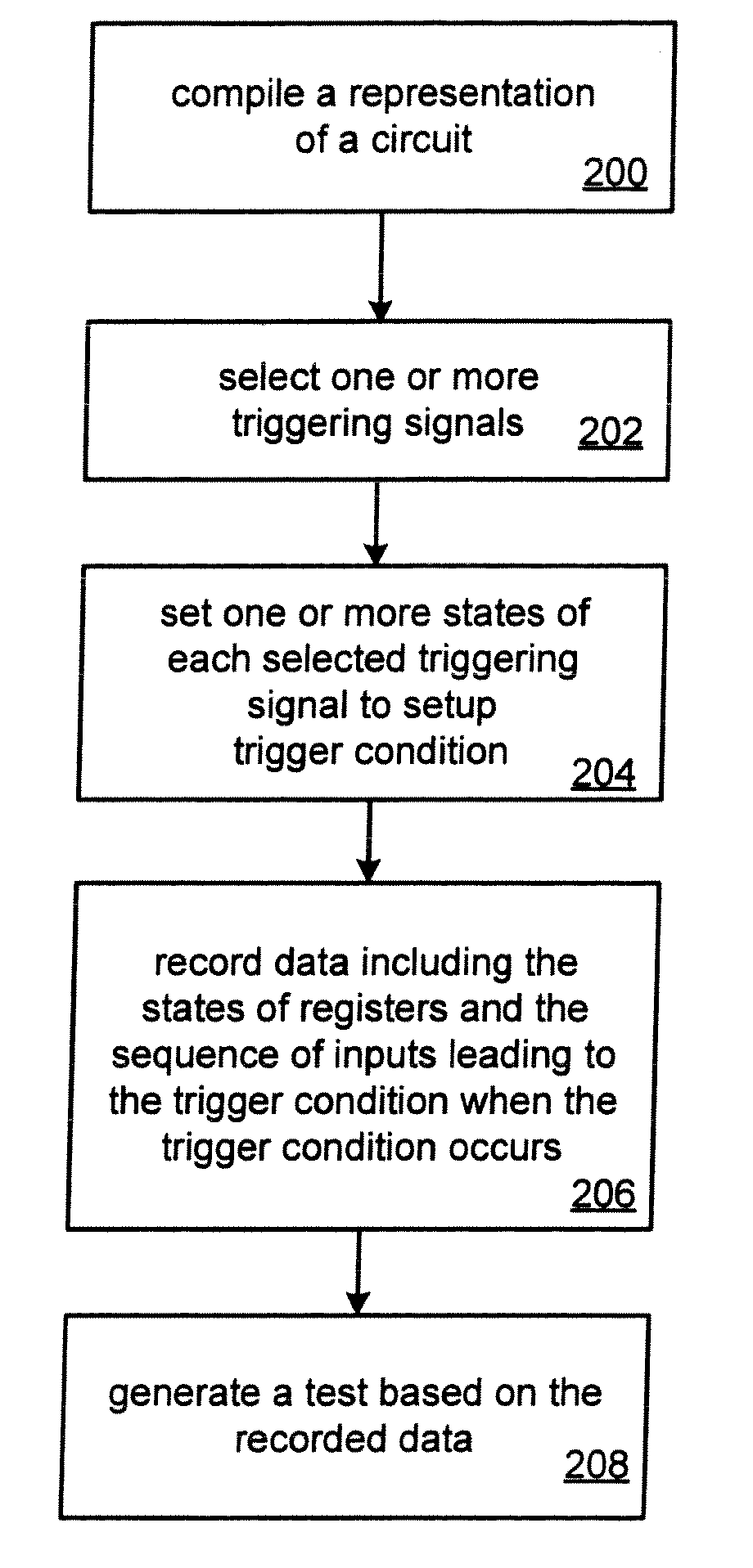

Method and system for debug and test using replicated logic

InactiveUS20080270958A1Digital circuit testingSemiconductor/solid-state device manufacturingProcessor registerComputer science

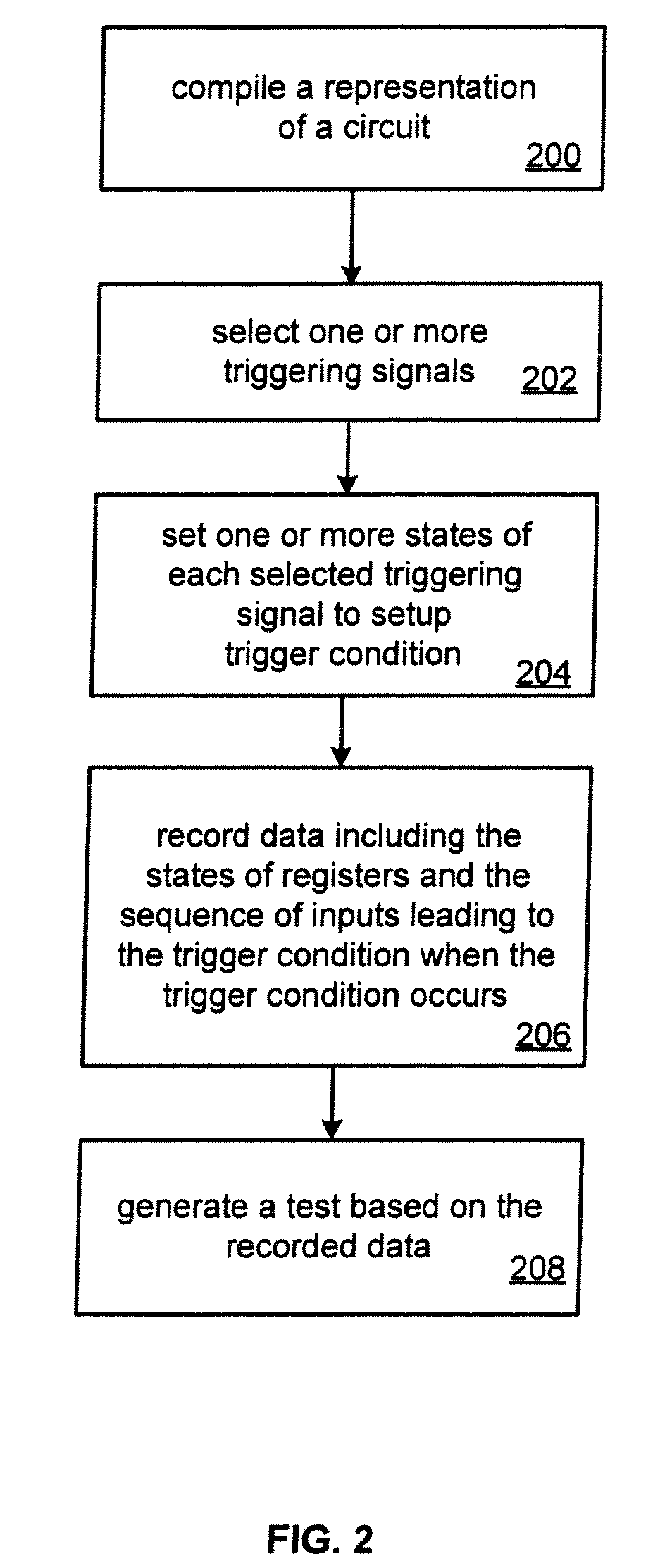

A method and system for debug and test using replicated logic is described. A representation of a circuit is compiled. The circuit includes a replicated portion and delay logic to delay inputs into the replicated portion. The circuit may also include trigger logic and clock control logic to enable execution of the replicated portion of the circuit to be paused when a trigger condition occurs. The compiled representation of the circuit may be programmed into a hardware device. A debugger may then be invoked. One or more triggering signals are selected. For each selected triggering signal, one or more states are selected to setup a trigger condition. The hardware device may then be run. The replicated portion of the circuit will be paused when the trigger condition occurs. The states of registers in the replicated portion of the circuit and the sequence of inputs that led to the trigger condition are recorded. This recorded data may then used to generate a test to be run on a software simulator when the circuit is modified.

Owner:SYNOPSYS INC

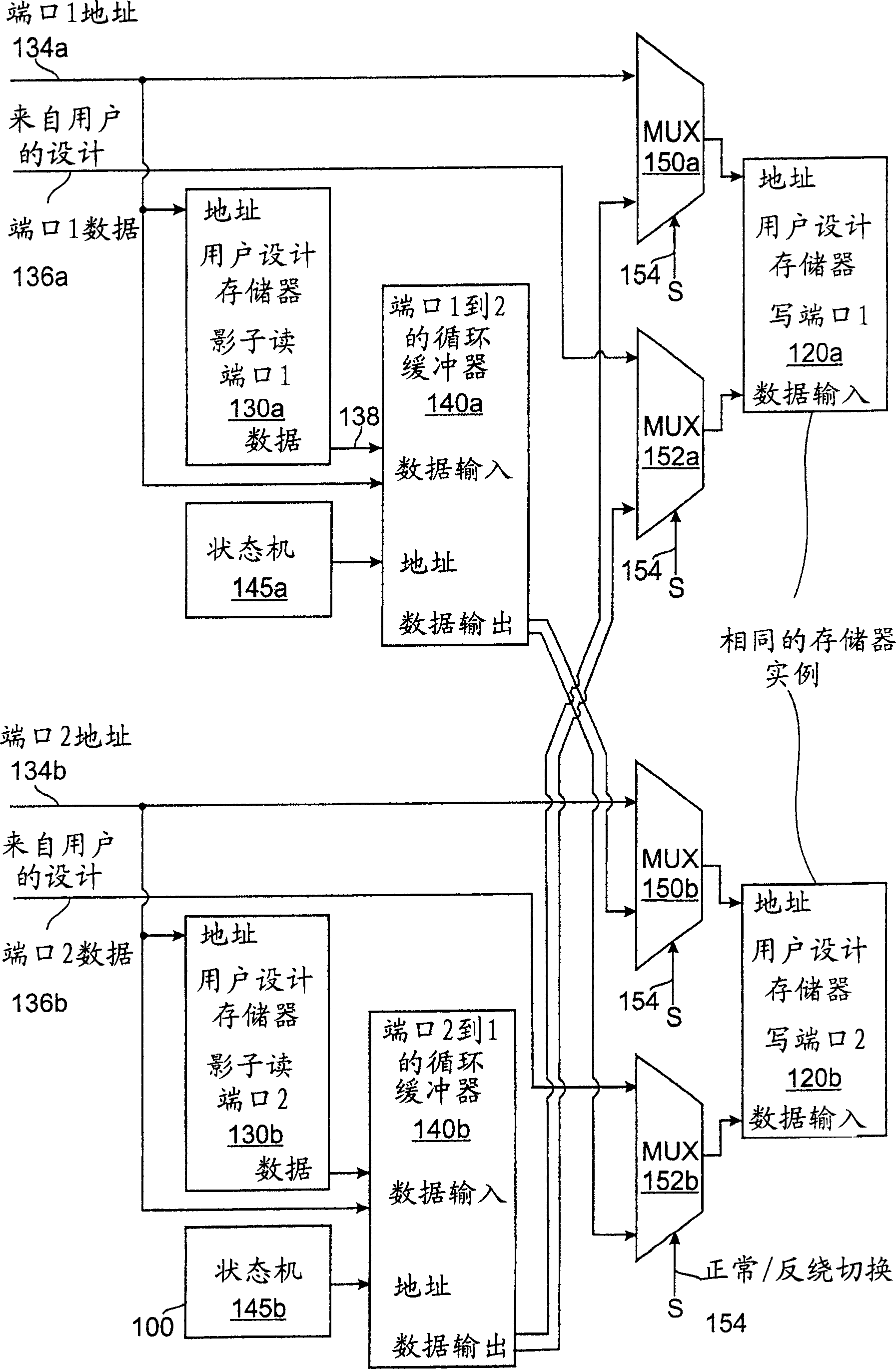

Memory rewind and reconstruction for hardware emulator

InactiveCN1573695AElectronic circuit testingDetecting faulty computer hardwareLogic emulationRandom access memory

A method and apparatus are disclosed for debugging circuit designs having random access memory (RAM) therein. The circuit design is emulated on a hardware logic emulator or software simulator. The RAM can be rewound or reconstructed to a previous state, and then replayed. The RAM can also be reconstructed to a state in which the RAM was maintained at some point during a trace window.

Owner:快速转动设计系统公司

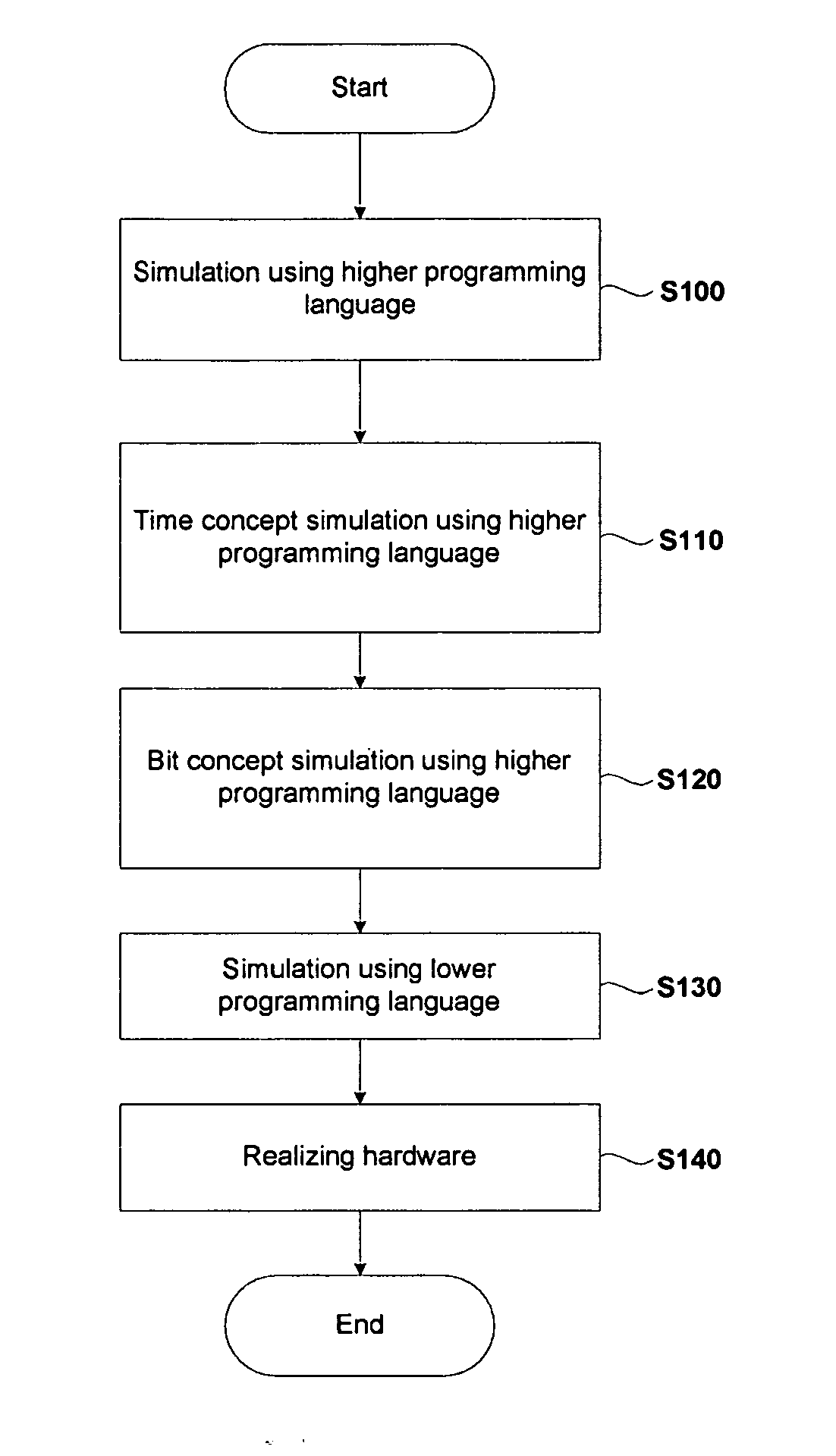

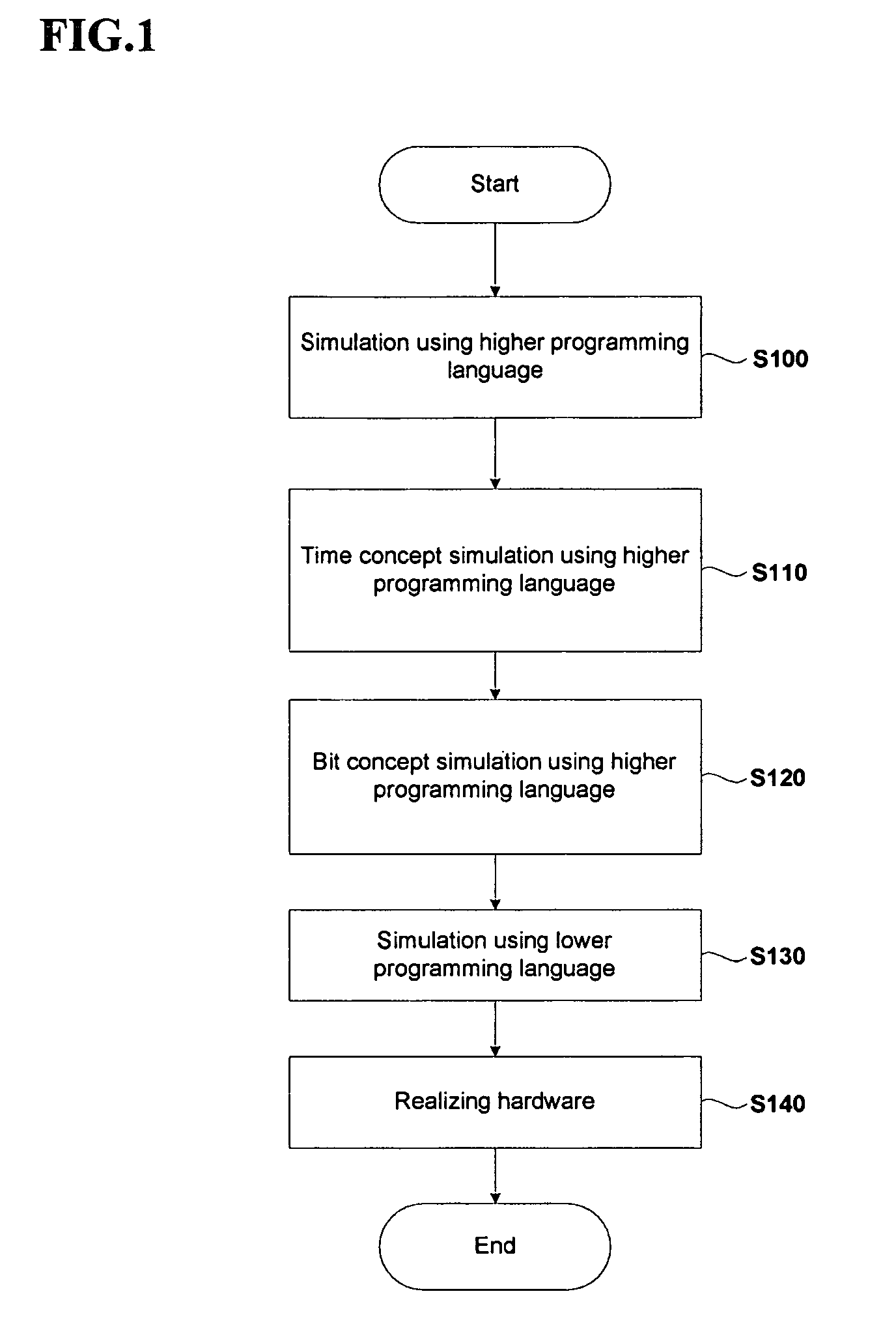

Method for digital system modeling by using higher software simulator

InactiveUS7783467B2Reduced simulation timeReduce configuration timeAnalogue computers for electric apparatusCAD circuit designProgram validationSystems design

Owner:ELECTRONICS & TELECOMM RES INST

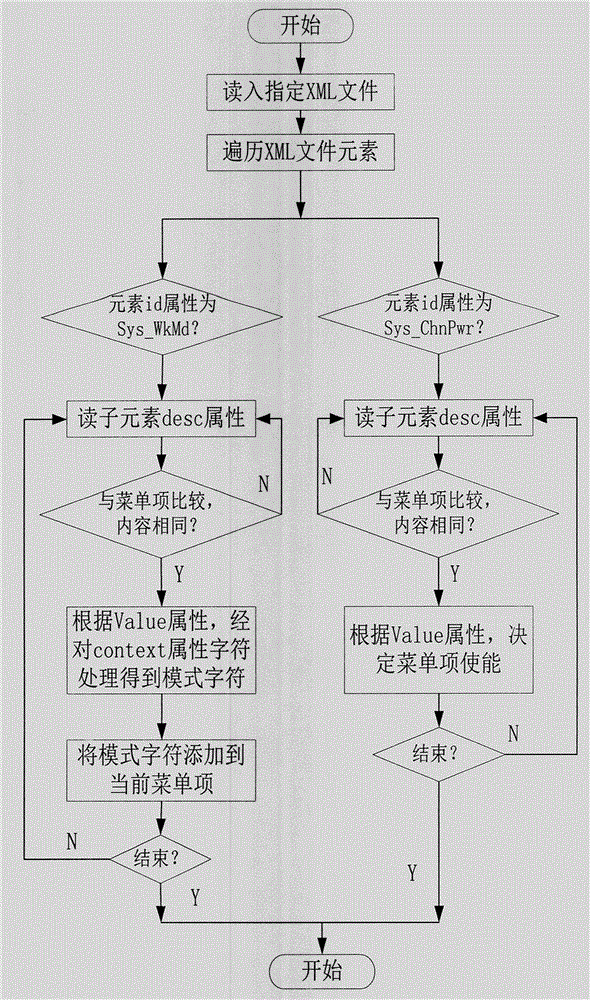

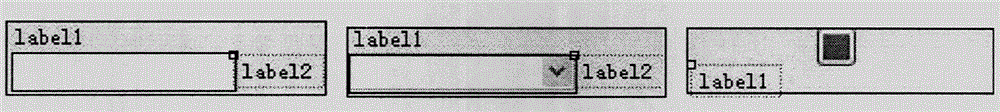

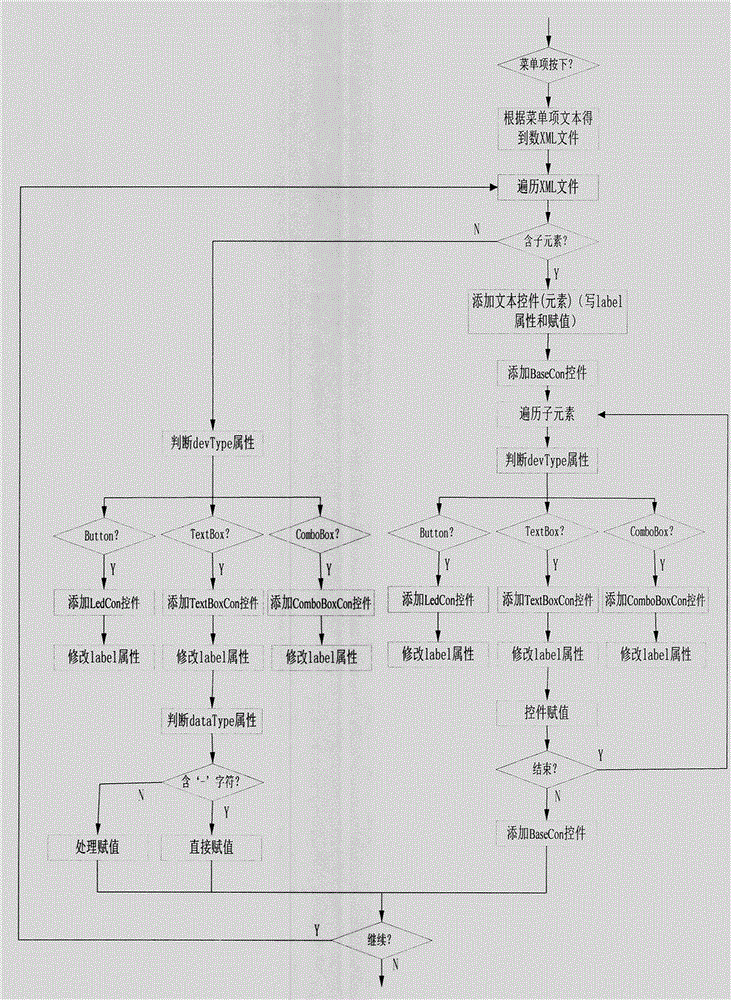

Method for realizing multi-mode big data software simulator

InactiveCN105824684AReduced development effortReduce workloadSoftware testing/debuggingSoftware simulation/interpretation/emulationLogical relationsXML

The invention relates to a method for realizing a multi-mode big data software simulator. The method comprises the following steps: 1, generating an XML file dictionary needing to call and characterize equipment parameter information according to a keyword search mode by designing an XML file for characterizing the mode information by utilizing menu content; 2, realizing automatic structured generation of interface elements by taking flow layout panel (Flow Layout Panel) control as a container by virtue of design of multiple user-defined controls; 3, realizing automatic framing when interface parameter data changes by virtue of a mode of interpreting the interface control and XML file in parallel. According to the method disclosed by the invention, multi-mode logical relation is simply realized through associated design, big data can be called by respectively compiling XML files and depending on multi-mode logical relation, interface generation is conveniently realized by virtue of an automatic software interface generation technology, the working efficiency is greatly improved, and the labor intensity is reduced.

Owner:PLA NO 63686 CORPS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com