Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

993 results about "Test vector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

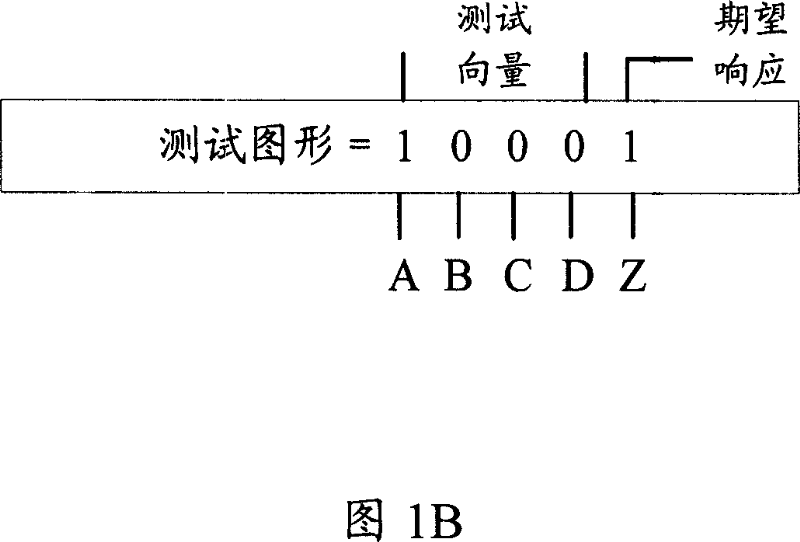

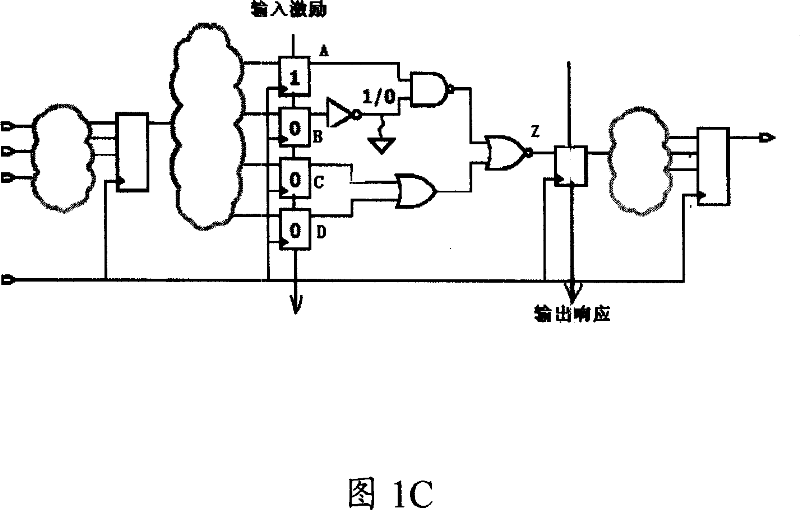

In computer science and engineering, a test vector is a set of inputs provided to a system in order to test that system. In software development, test vectors are a methodology of software testing and software verification and validation.

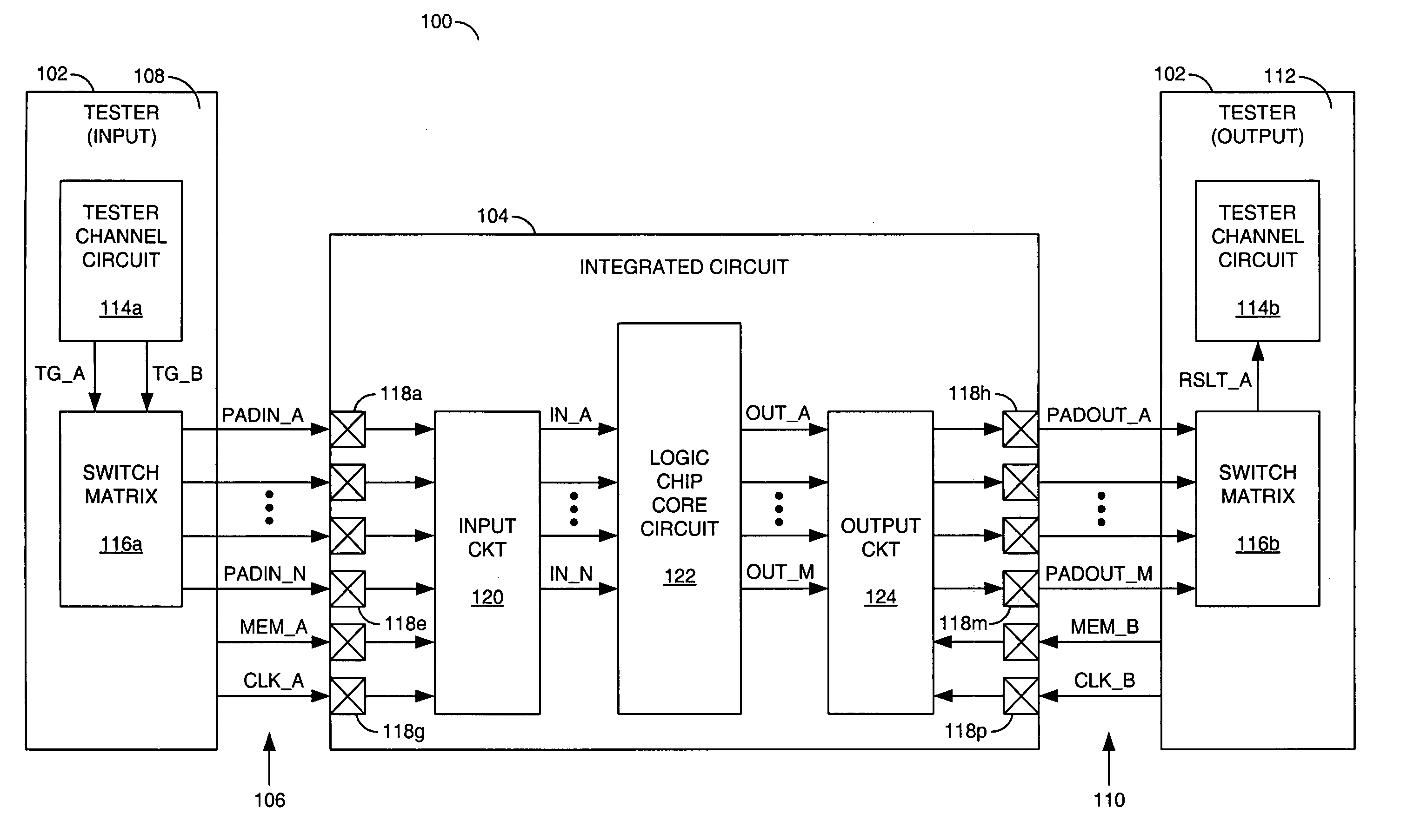

System and method for testing high speed VLSI devices using slower testers

InactiveUS6345373B1Shorten application timeLow fault coverageDigital circuit testingError detection/correctionGeneration processFault coverage

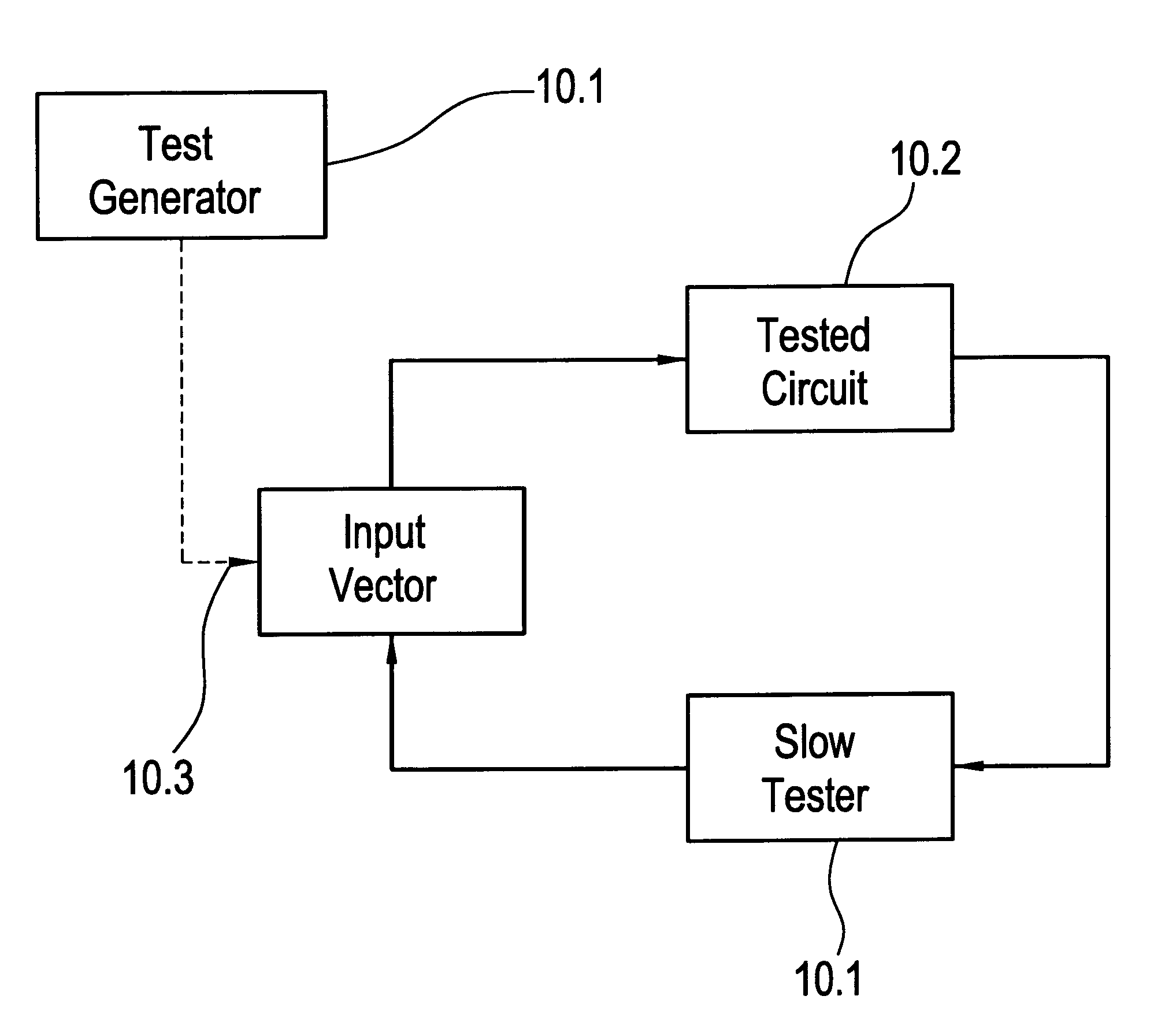

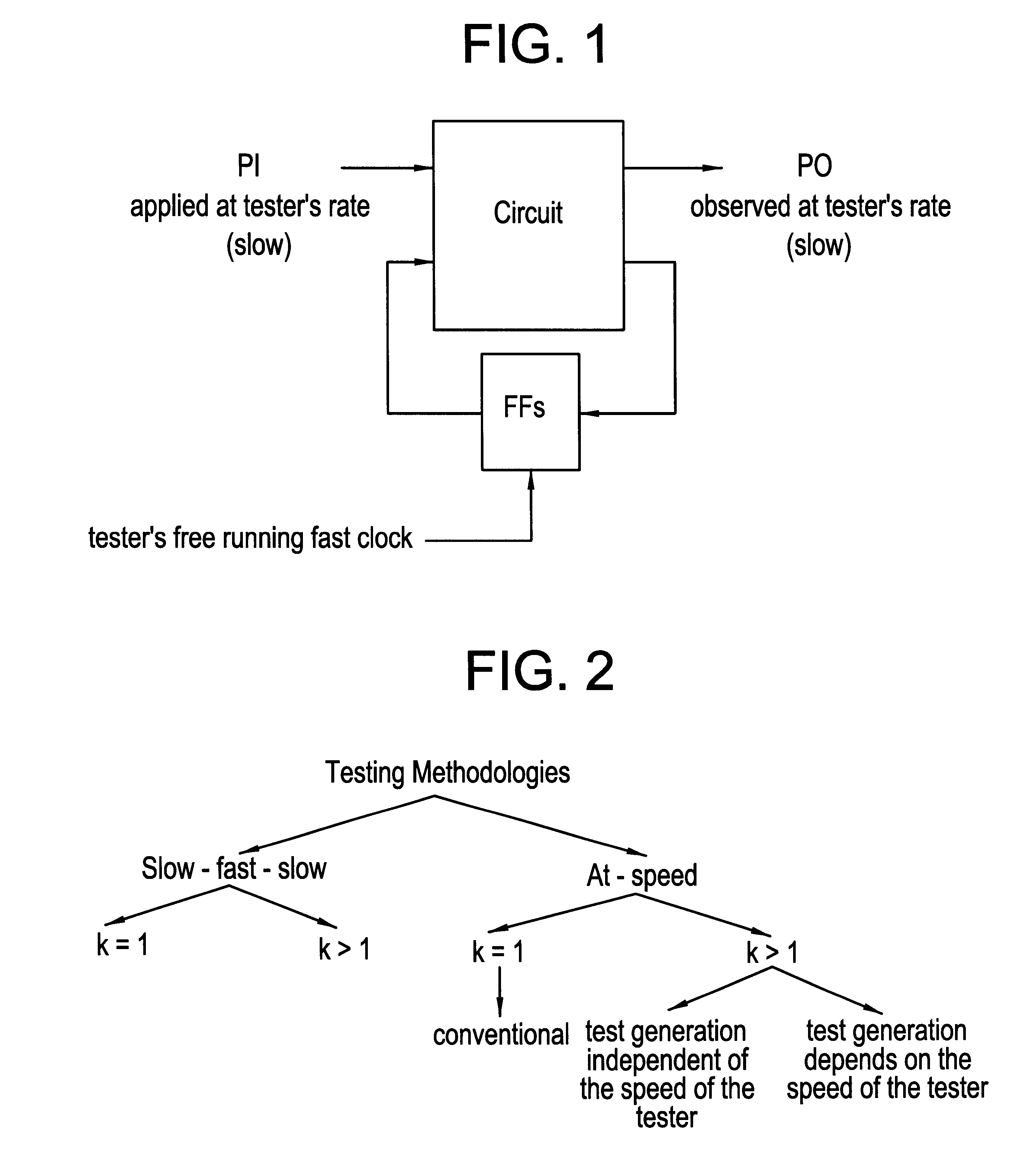

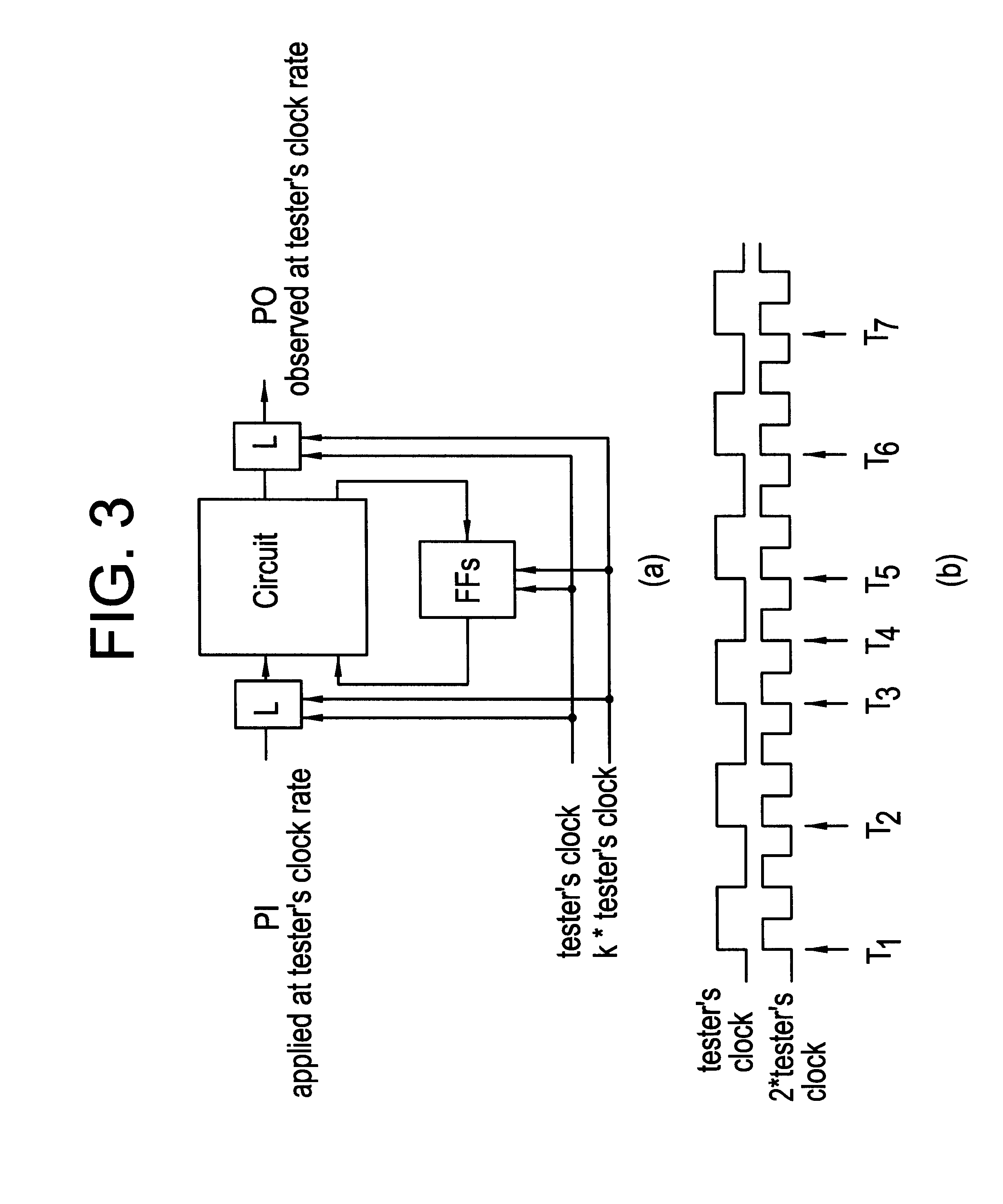

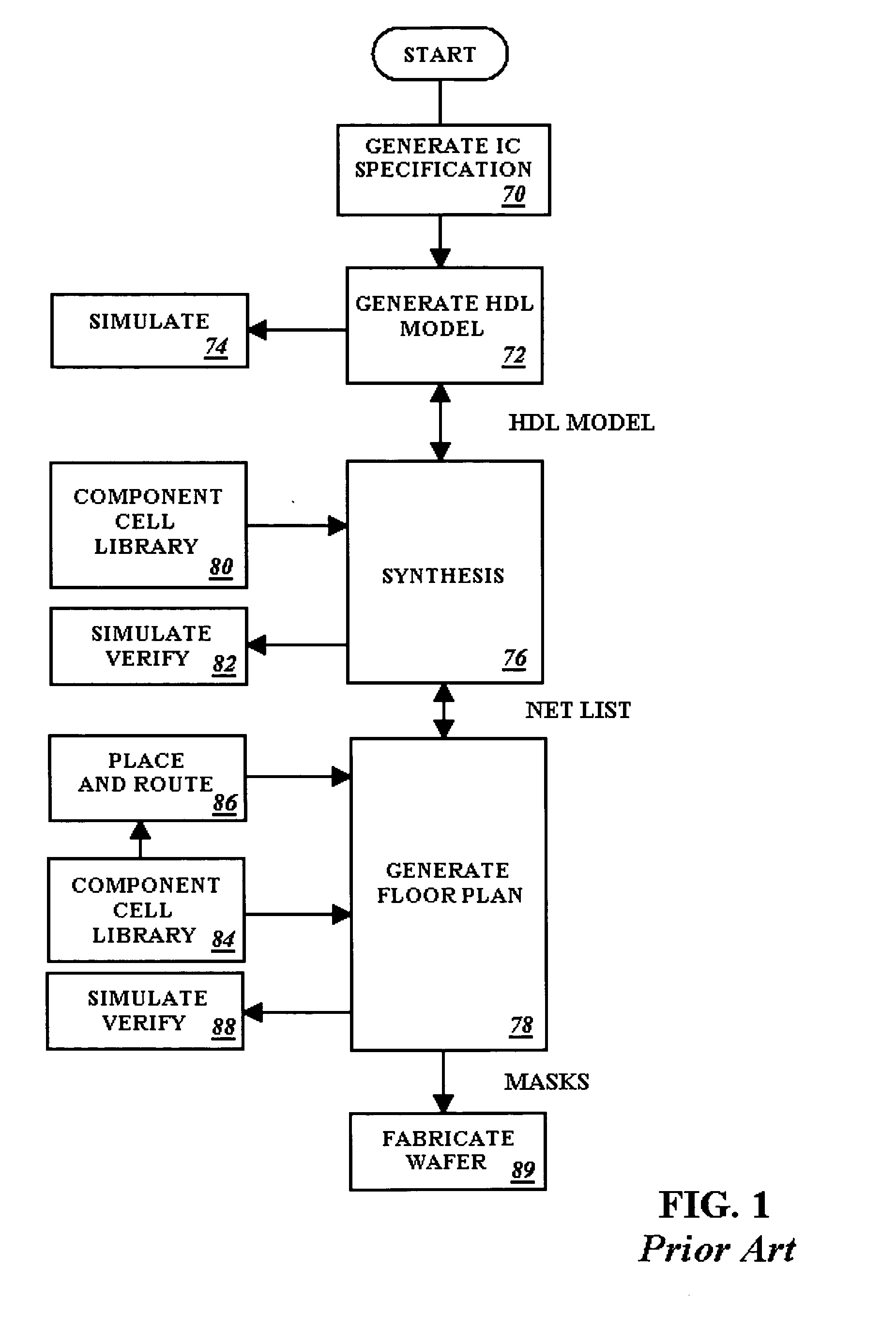

At-speed strategies for testing high speed designs on slower testers. At-speed testing schemes is provided that integrates the tester's speed limitations with the test generation process. Due to constraints placed at the test generation process, these schemes might result in a reduced fault coverage. To increase the fault coverage and reduce the test application time, the slow-fast-slow and at-speed strategies can be combined for testing high speed designs on slower testers. A slow tester that uses test vectors that are generated while taking into account the speed of the tester.

Owner:NEC CORP +1

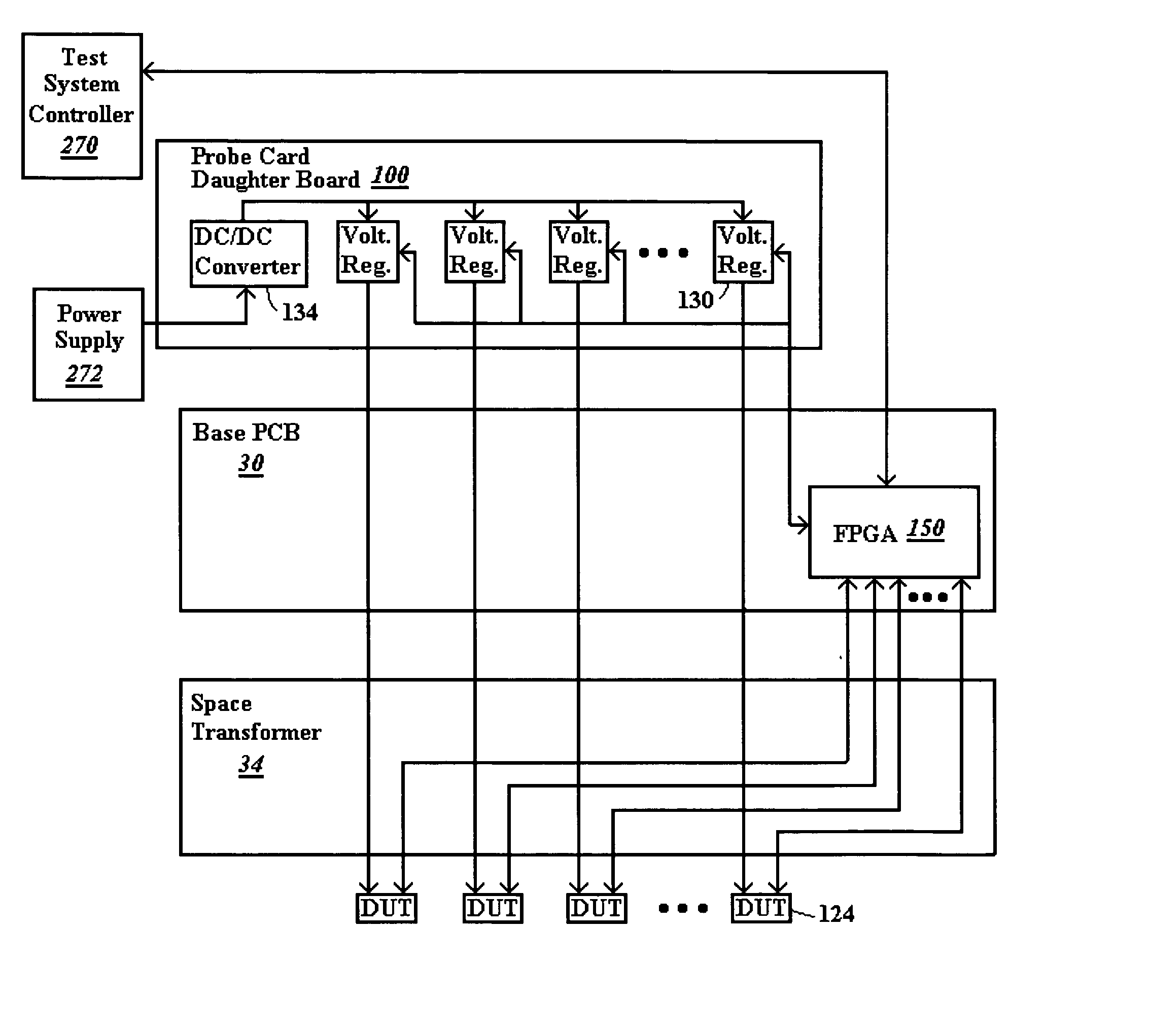

Method of designing an application specific probe card test system

InactiveUS20060273809A1Eliminate needDigital circuit testingOverload protection arrangementsProbe cardOn board

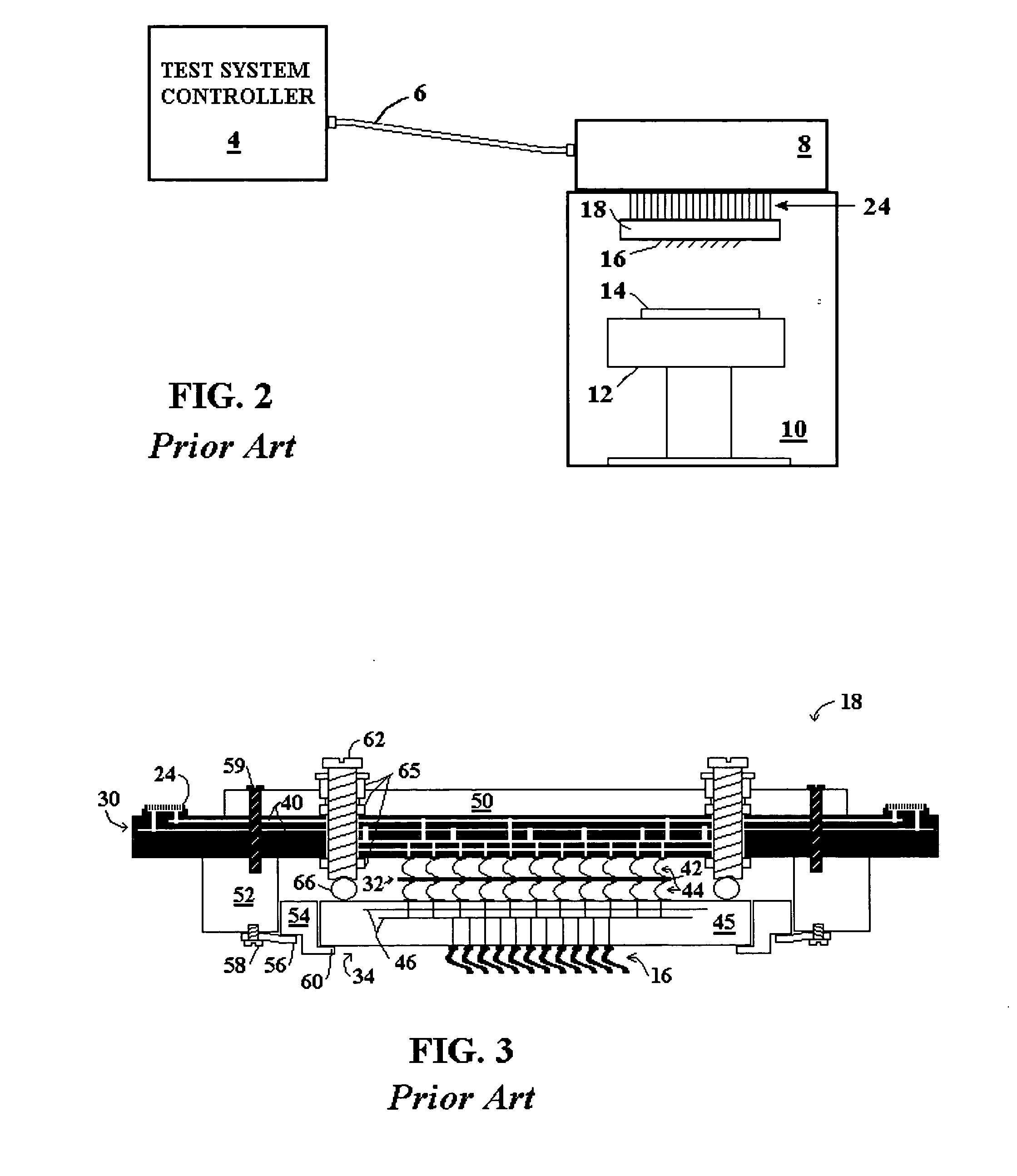

A method is provided for design and programming of a probe card with an on-board programmable controller in a wafer test system. Consideration of introduction of the programmable controller is included in a CAD wafer layout and probe card design process. The CAD design is further loaded into the programmable controller, such as an FPGA to program it: (1) to control direction of signals to particular ICs, even during the test process (2) to generate test vector signals to provide to the ICs, and (3) to receive test signals and process test results from the received signals. In some embodiments, burn-in only testing is provided to limit test system circuitry needed so that with a programmable controller on the probe card, text equipment external to the probe card can be eliminated or significantly reduced from conventional test equipment.

Owner:FORMFACTOR INC

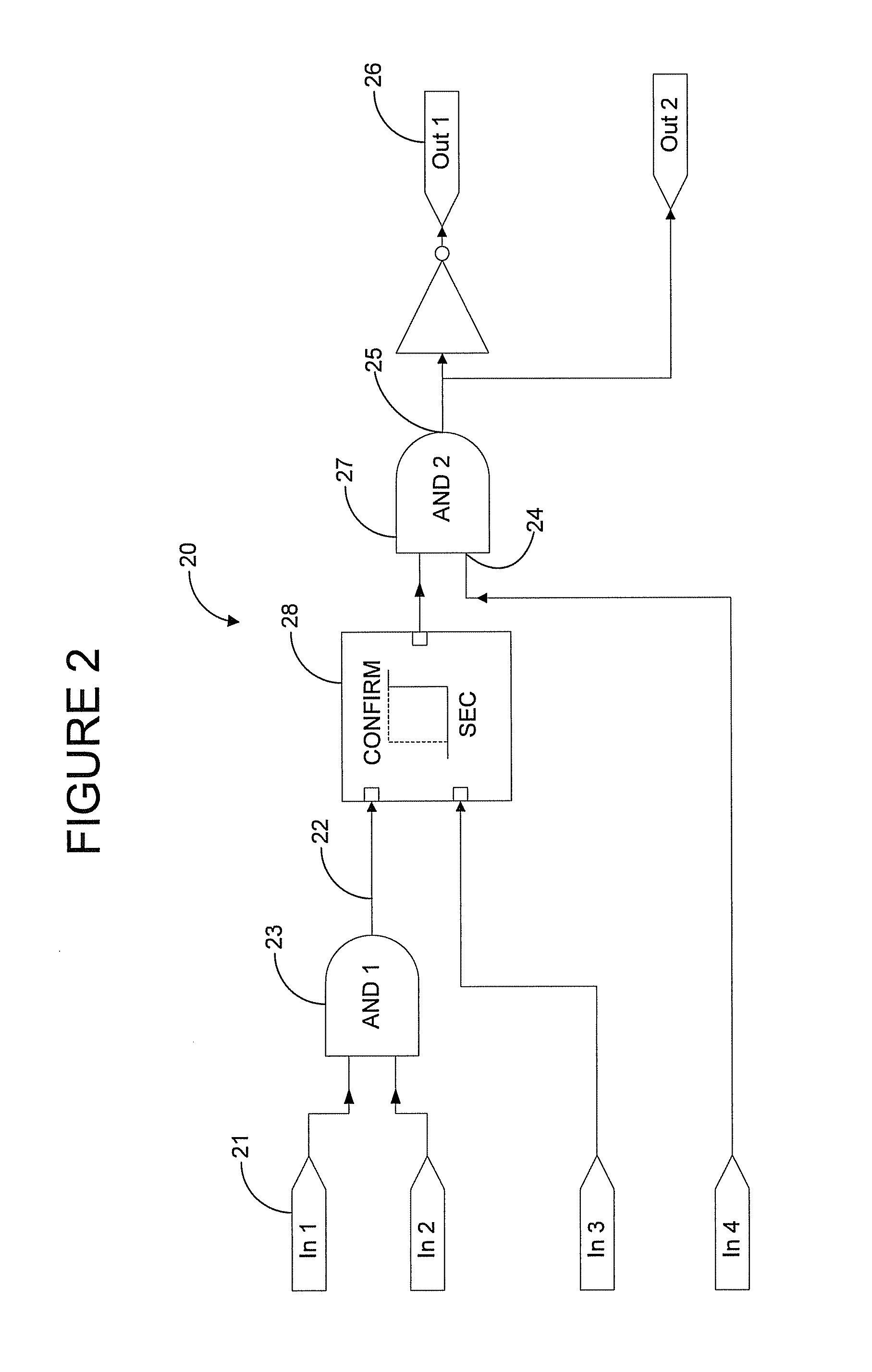

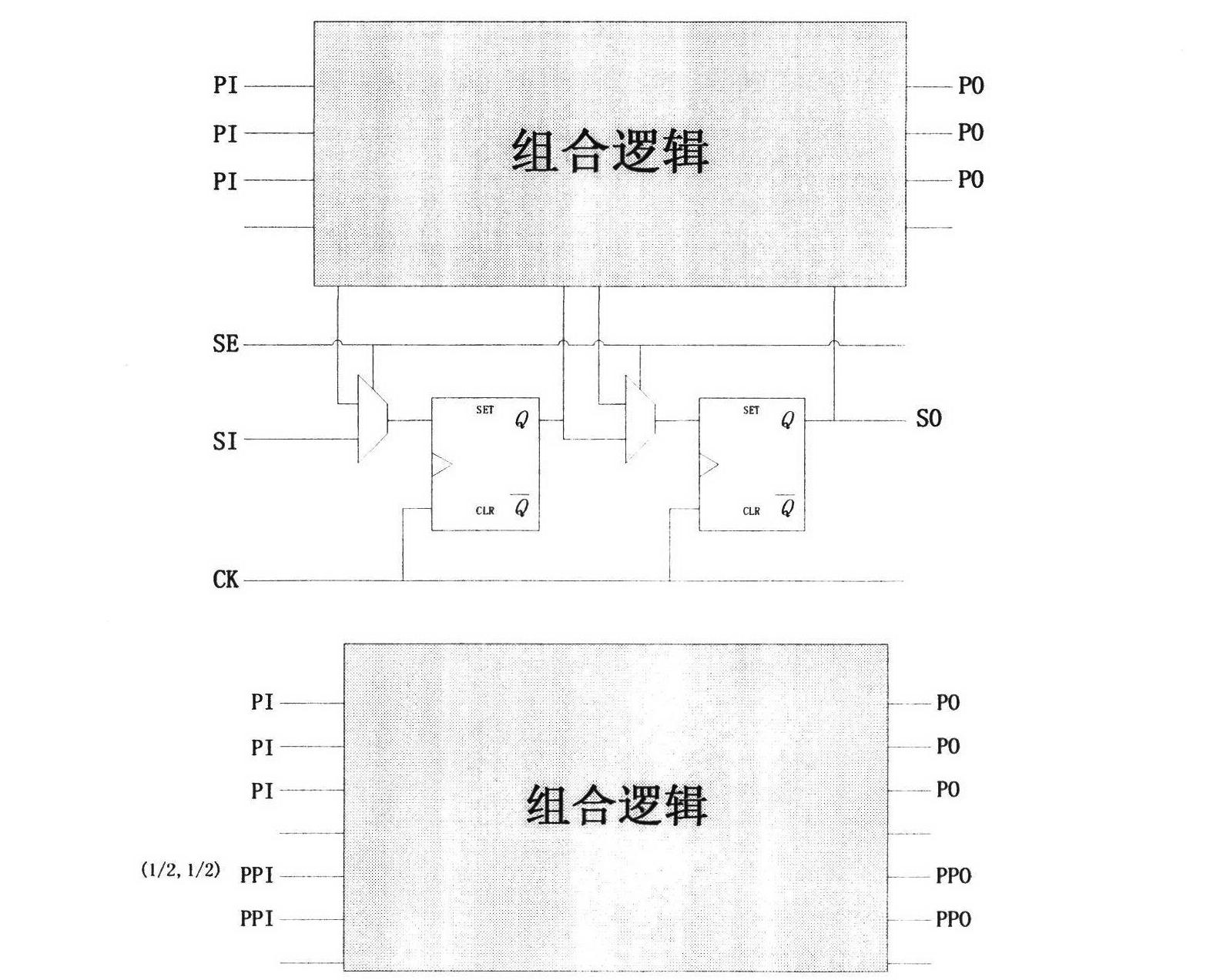

Bist architecture for detecting path-delay faults in a sequential circuit

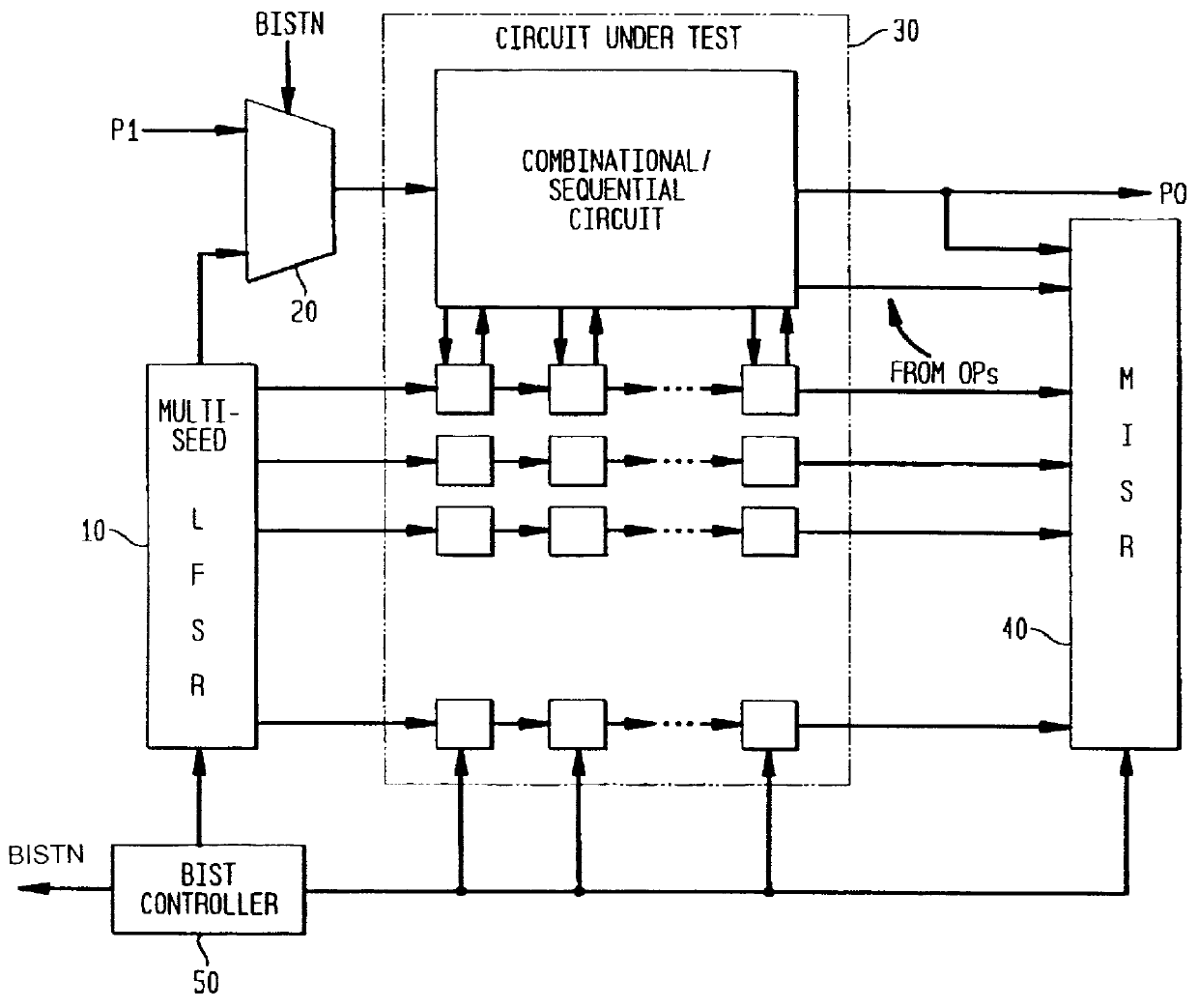

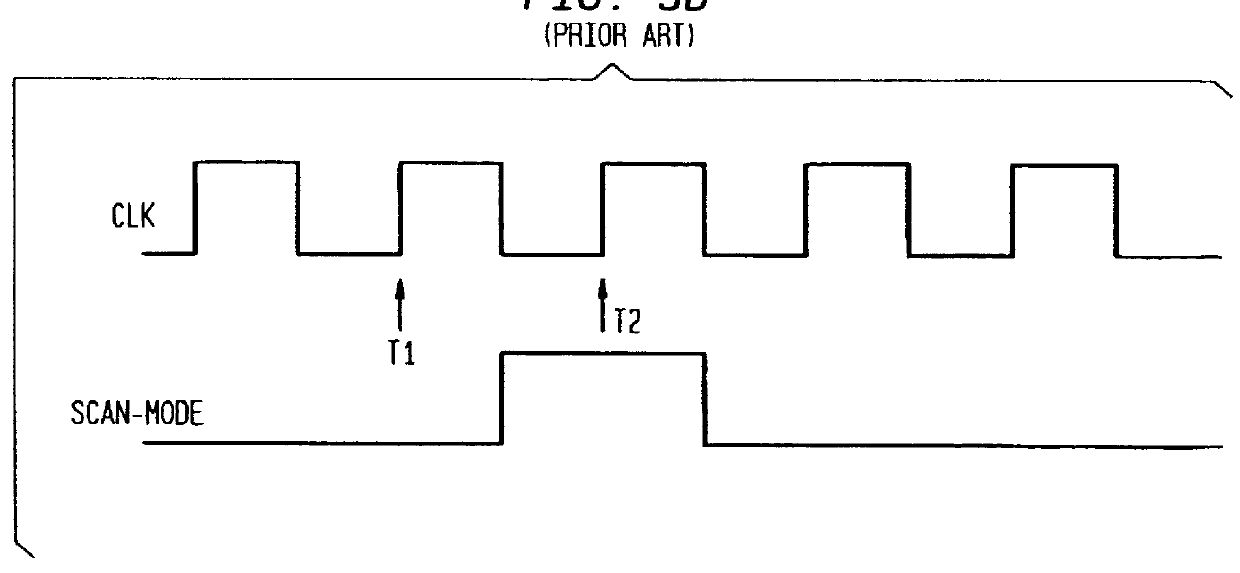

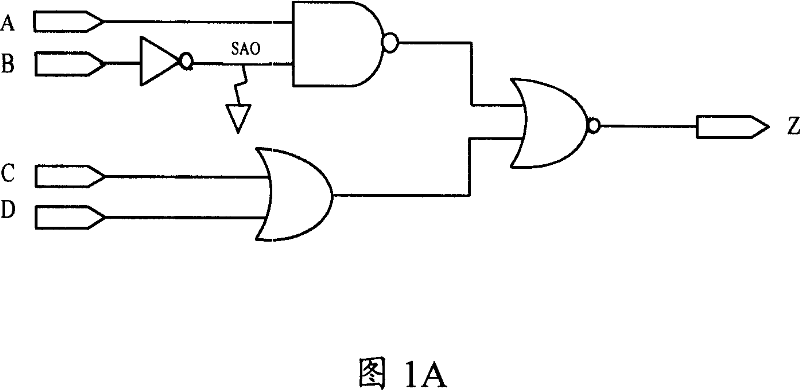

A scan-based BIST architecture for detecting path-delay faults in a sequential circuit converted to a combinational circuit or a less complex sequential circuit including a combinational portion and a plurality of scan flip-flops. The BIST structure includes a test pattern generator for generating two test patterns and a controller for generating a clock signal and an extended scan mode signal which is held high for two clock cycles while the output response of the combinational portion to the first and second test vectors is latched into the scan flip-flops in order to detect a signal transition. The invention is further directed to a method for detection of path-delay faults using this scan-based BIST architecture. To improve the fault coverage for path-delay faults, observation points may be inserted at the inputs of selected scan flip-flops. A predetermined number of scan flip-flops having the highest activation frequency are selected as the observation points.

Owner:LUCENT TECH INC +1

Method and device for verifying SoC (system on a chip) chips

ActiveCN101515301AReduce complexityReduce maintenance difficultySpecial data processing applicationsReusabilityVerification system

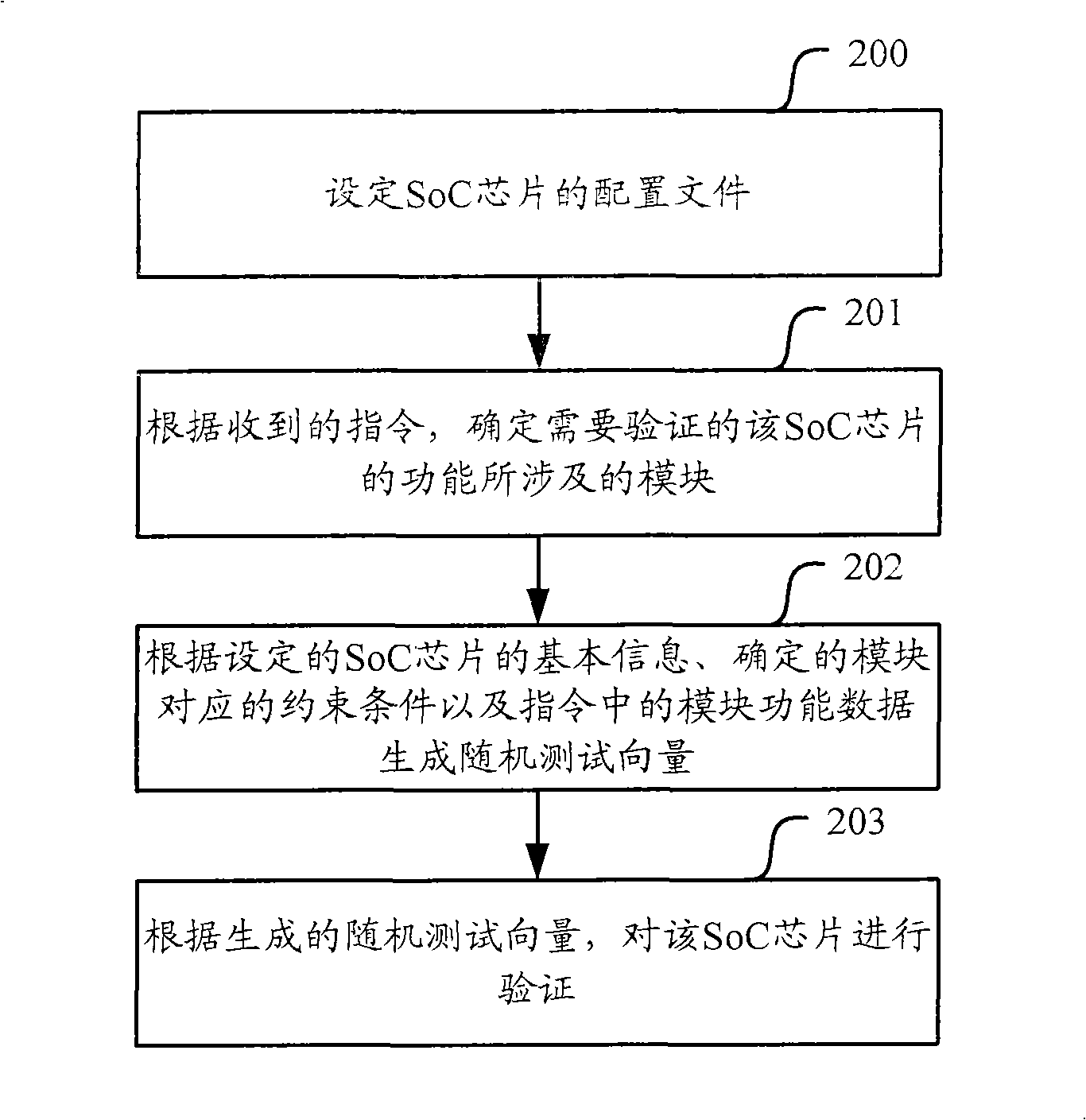

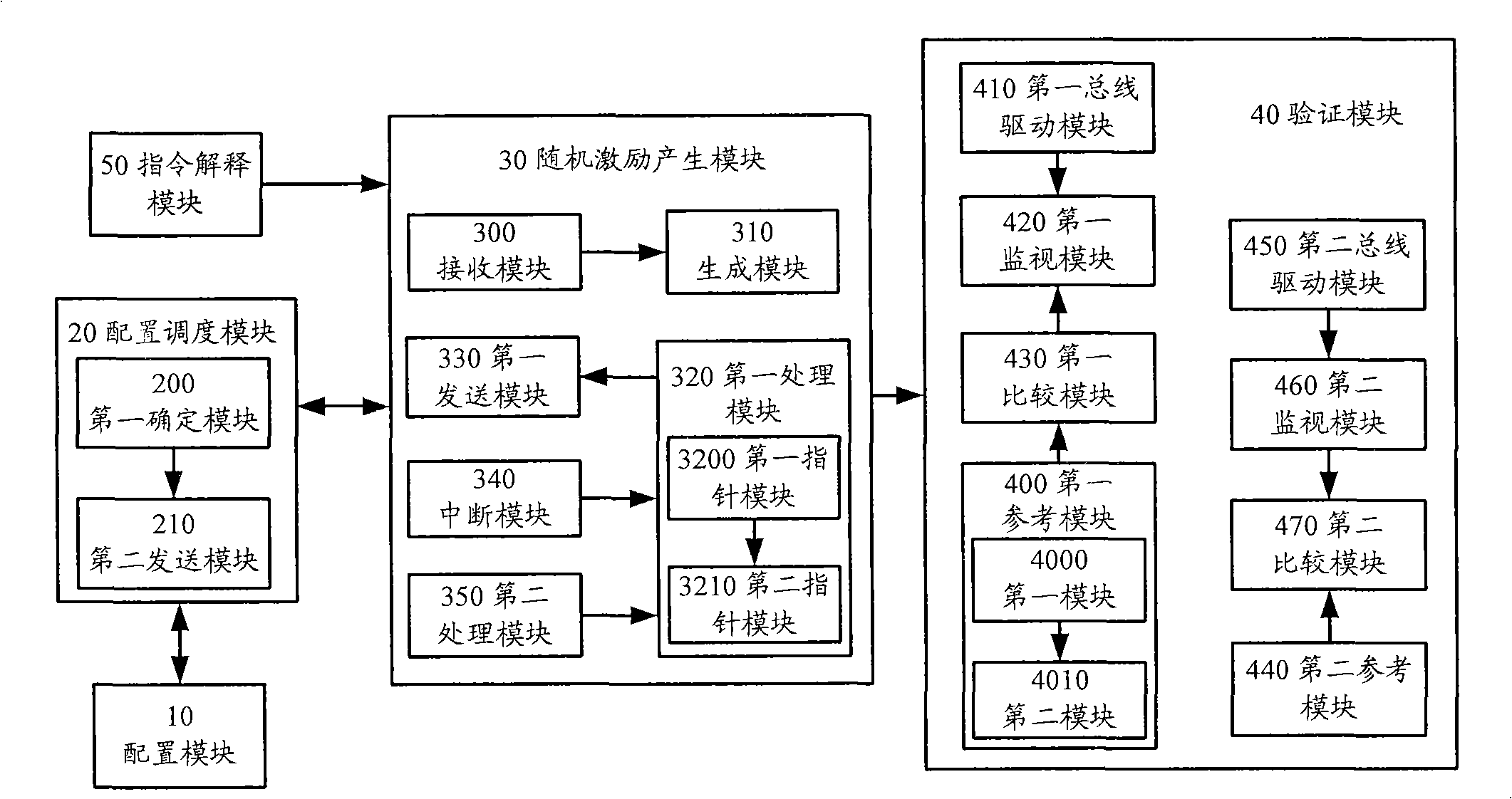

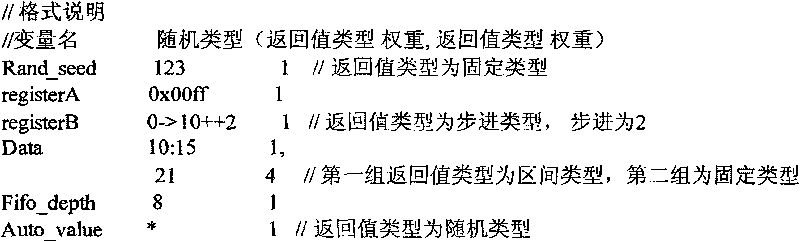

The invention relates to the field of SoC chips, in particular to a method and a device for SoC chips, which is used for solving the problem that the occurrence of random vectors and control difficulty are increased because each verification needs to be compiled again when different functions of the same SoC chip are verified in the prior art. The method of the embodiment of the invention comprises the following steps: setting a configuration file of an SoC chip, wherein the configuration file comprises the basic information of the SoC chip and constraint conditions of modules in the SoC chip; according to received instructions, determining the modules referring to the functions of the SoC chip which need to be verified; according to the basic information, the constraint conditions of the determined modules and module function data in the instructions, generating a random test vector; and according to the random test vector, verifying the SoC chip. The embodiment of the invention has the advantages of reducing the complexity of constructing verification systems and maintenance difficulty, increasing the reusability of verification components, lowering verification difficulty and saving time.

Owner:ACTIONS ZHUHAI TECH CO

Method and device for testing chip

InactiveCN101038325AEasy to debugReduce testing costsDigital circuit testingTester deviceTest response

The invention discloses a device for testing the chip, including the mutually stand-alone server, simulator, control circuit board and running circuit board, in which: the server is used for creating the test program according to the test tasks, and output to the simulator; the simulator is connected with the server for simulation processing of the test program, and creating the simulation document with test data and sending to the control circuit board; the control circuit board is connected with the simulator for reading the relevant test vectors from the simulation document, and sending this test vector to the running circuit board, and decide whether the relevant chip is in good conditions or not according to the test response feedback from the running circuit board; the running circuit board is connected with the control circuit board for testing the relevant chip according to the test vector from the control circuit board, and sending the test response to the control circuit board. Thus, during the batch production testing of chip, the automatic tester with expensive rent may be not rented, thereby greatly reduce the test cost. The invention still discloses a test method for chip.

Owner:VIMICRO CORP

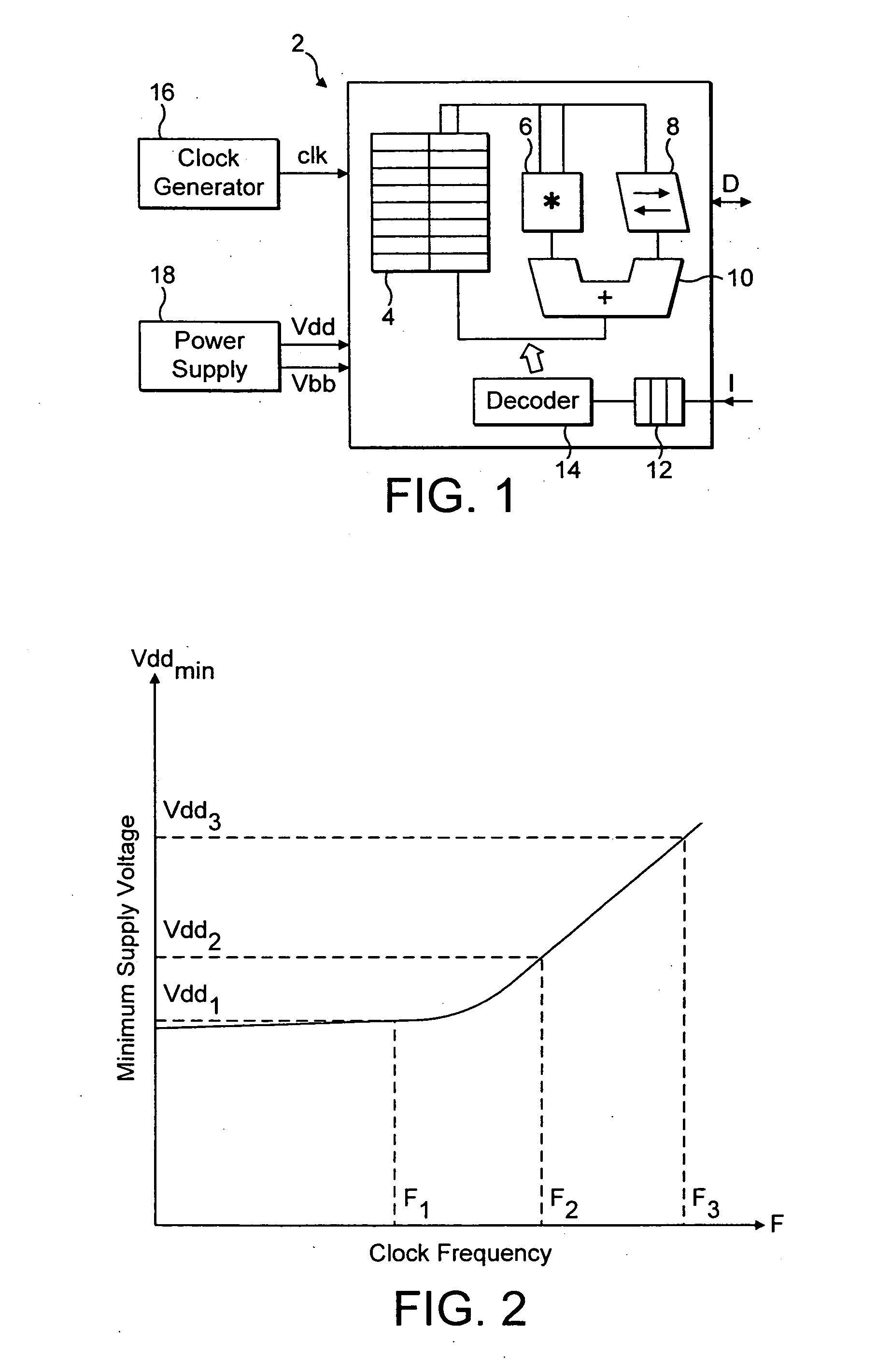

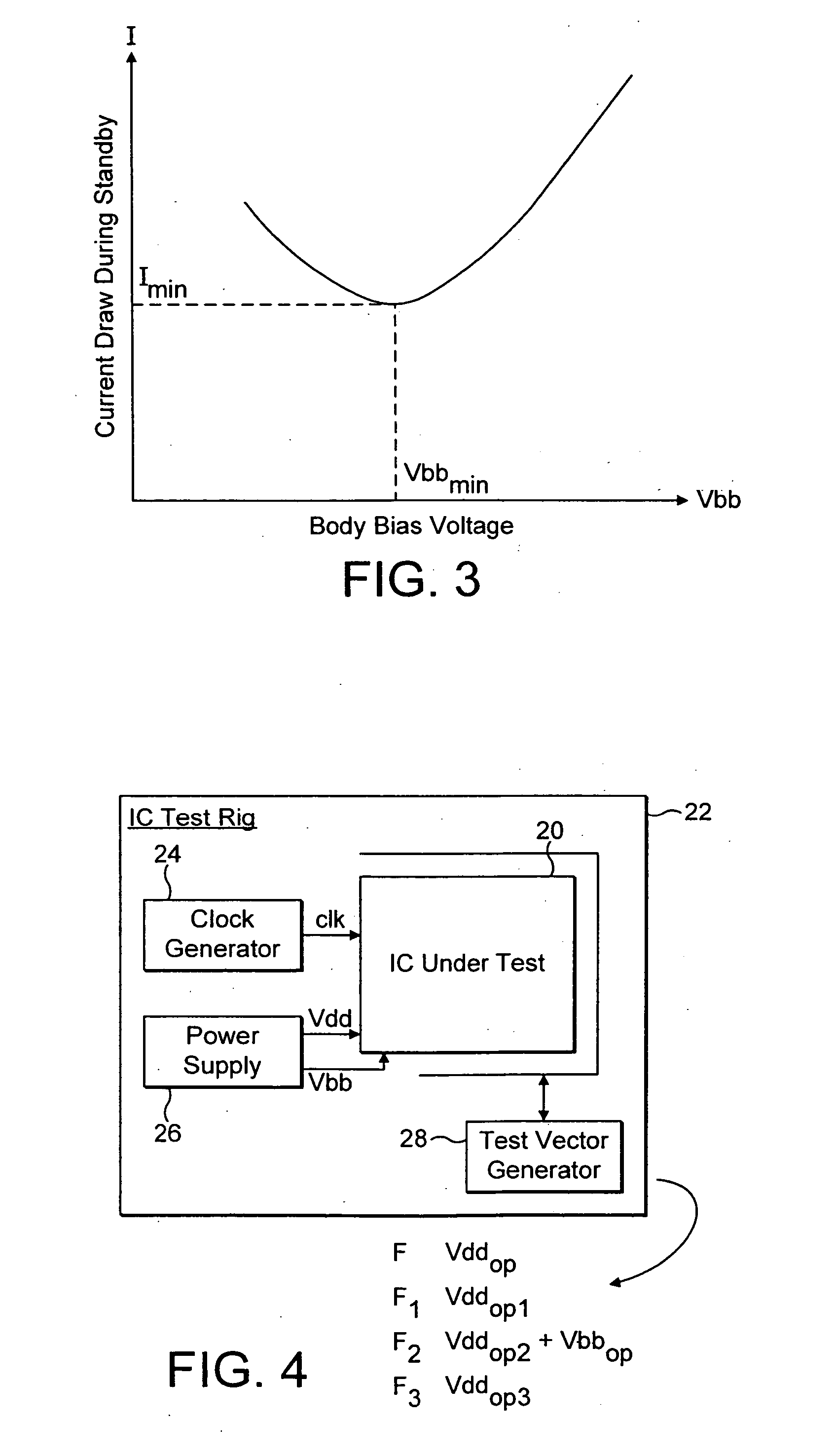

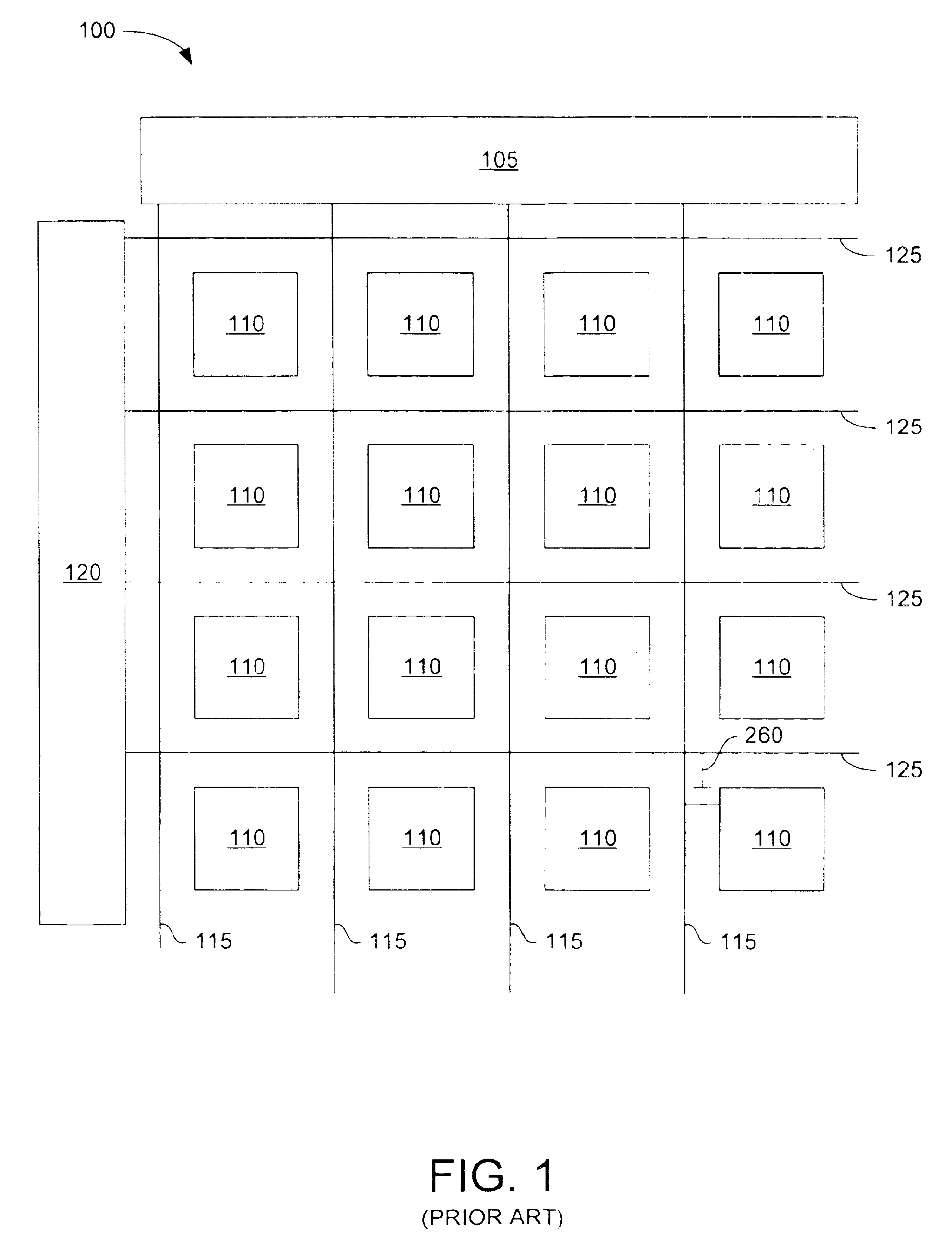

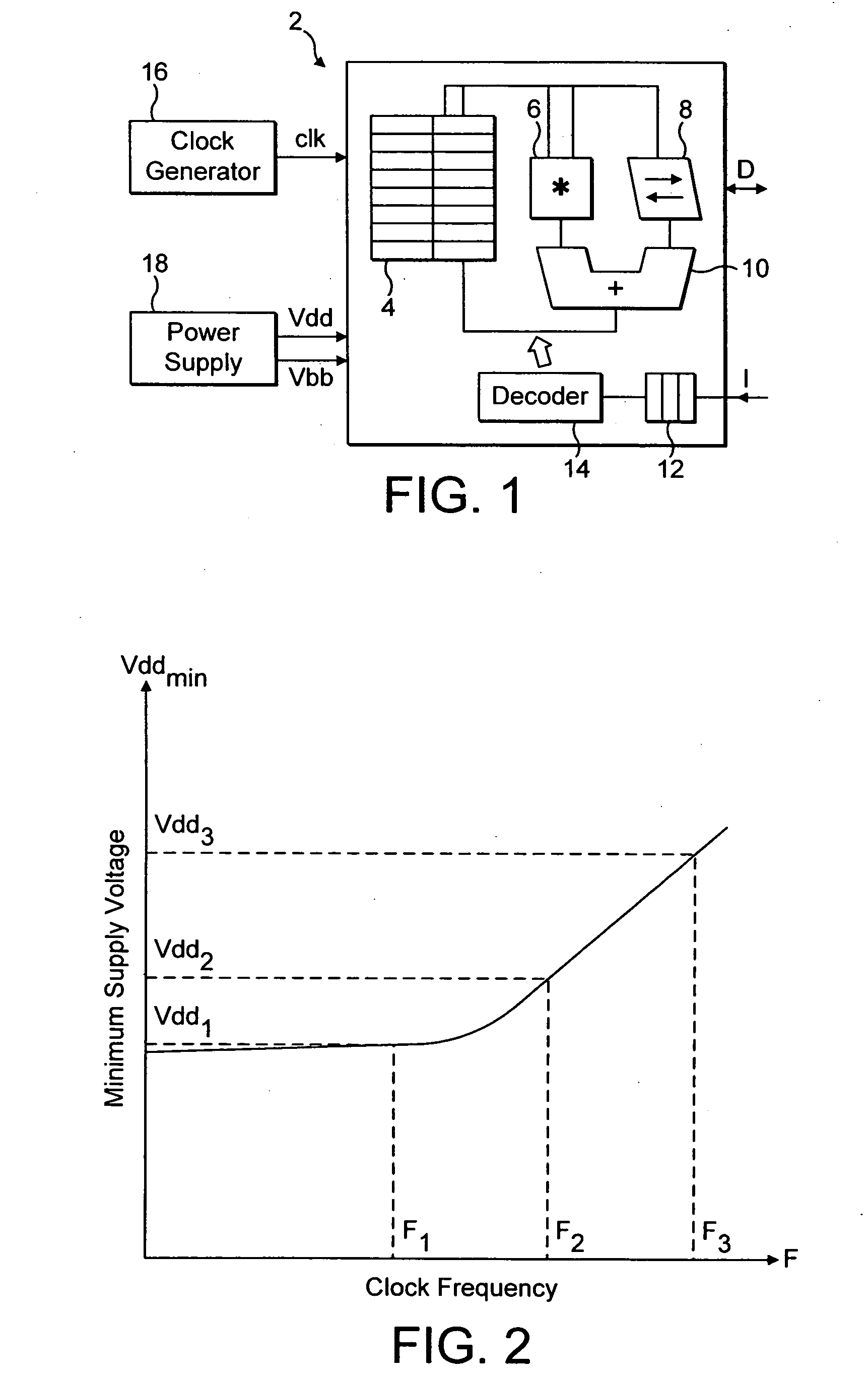

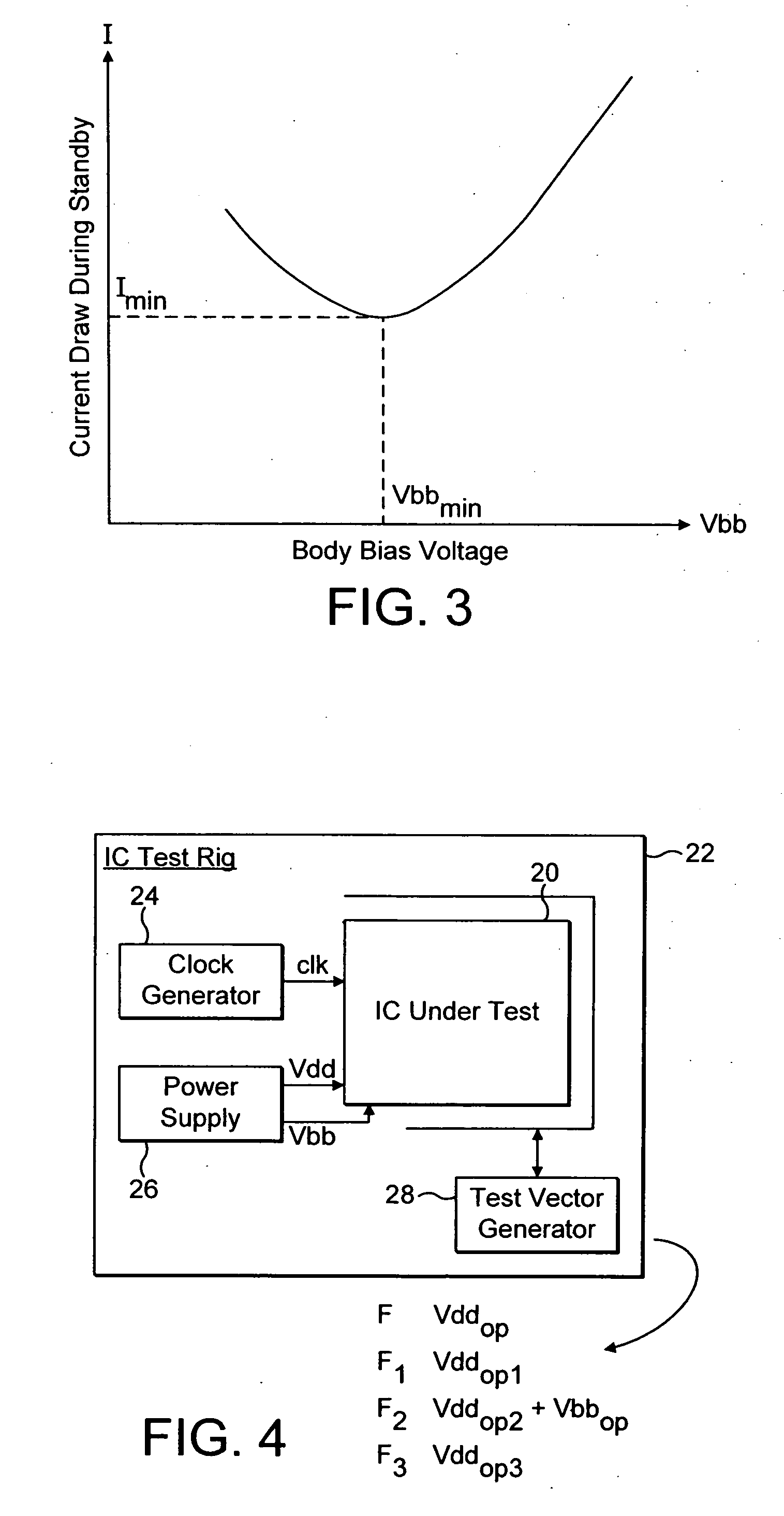

Operating voltage determination for an integrated circuit

ActiveUS20060074576A1Easy to useHigh voltageEnergy efficient ICTCurrent/voltage measurementClock rateTest vector

Owner:ARM LTD

Methods and systems employing infrared thermography for defect detection and analysis

InactiveUS6840666B2Radiation pyrometryMaterial analysis by optical meansThermodynamicsImaging equipment

Described are methods and systems for providing improved defect detection and analysis using infrared thermography. Test vectors heat features of a device under test to produce thermal characteristics useful in identifying defects. The test vectors are timed to enhance the thermal contrast between defects and the surrounding features, enabling IR imaging equipment to acquire improved thermographic images. In some embodiments, a combination of AC and DC test vectors maximize power transfer to expedite heating, and therefore testing. Mathematical transformations applied to the improved images further enhance defect detection and analysis. Some defects produce image artifacts, or “defect artifacts,” that obscure the defects, rendering difficult the task of defect location. Some embodiments employ defect-location algorithms that analyze defect artifacts to precisely locate corresponding defects.

Owner:MARENA SYST CORP

Automatic test system and method of programmable logic device on basis of boundary scan

The invention belongs to the field of electronic technology, in particular to an automatic test system and method of a programmable logic device on the basis of boundary scan. The test method comprises the following steps: generating a chip configuration file; downloading and configuring an FPGA (field programmable gate array) chip; generating and loading a test vector; comparing test results; building a corresponding test system; and completely realizing automation. In the invention, the test vector of an item to be tested is automatically generated by a user through software, and the on-line test of the hardware function of a user circuit is realized by combining JTAG (joint test action group) automatic downloading test software. Scripted test environment converts a series of complex manual test operation into full automatic software flow so as to greatly improve test speed and accuracy.

Owner:FUDAN UNIV

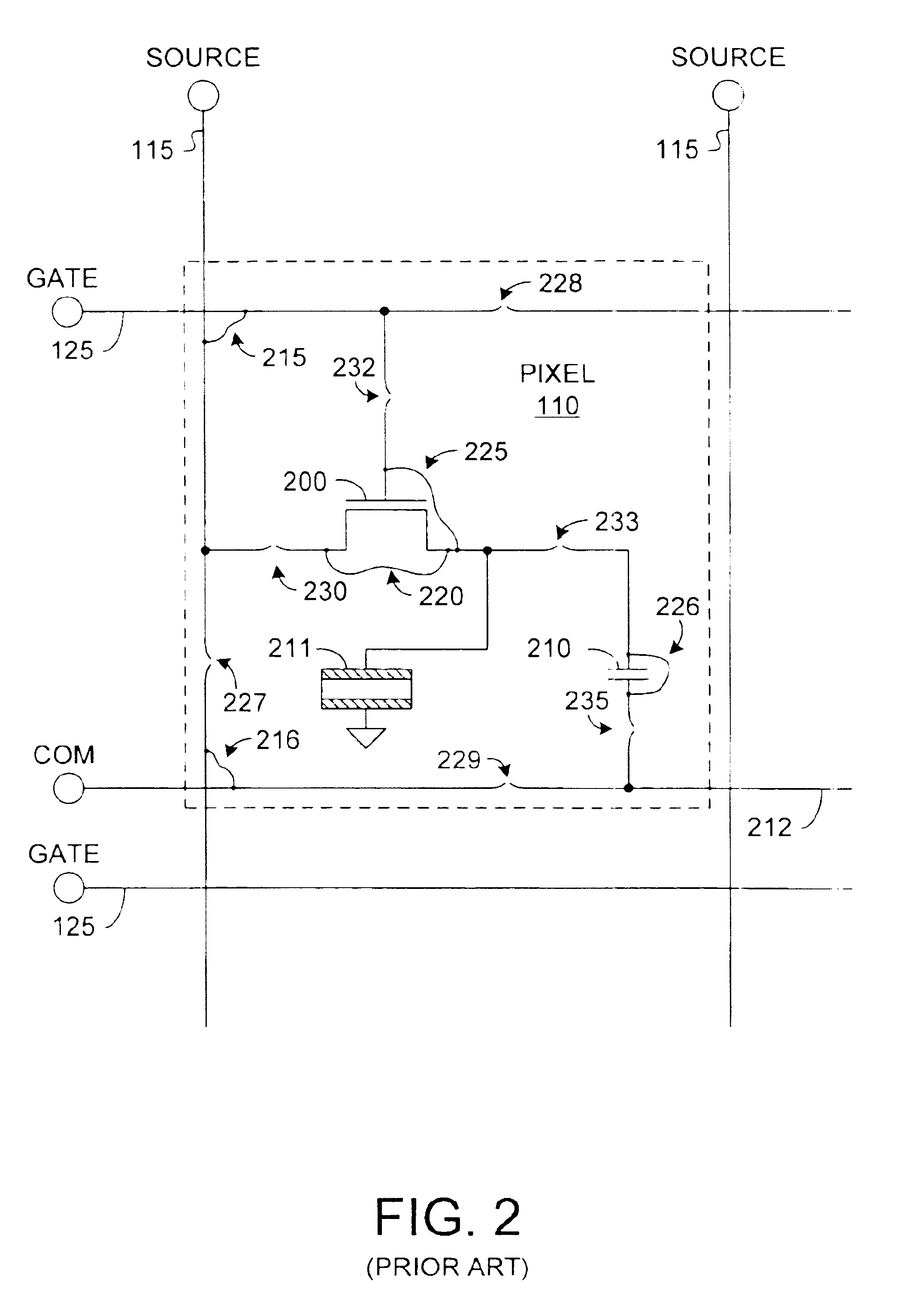

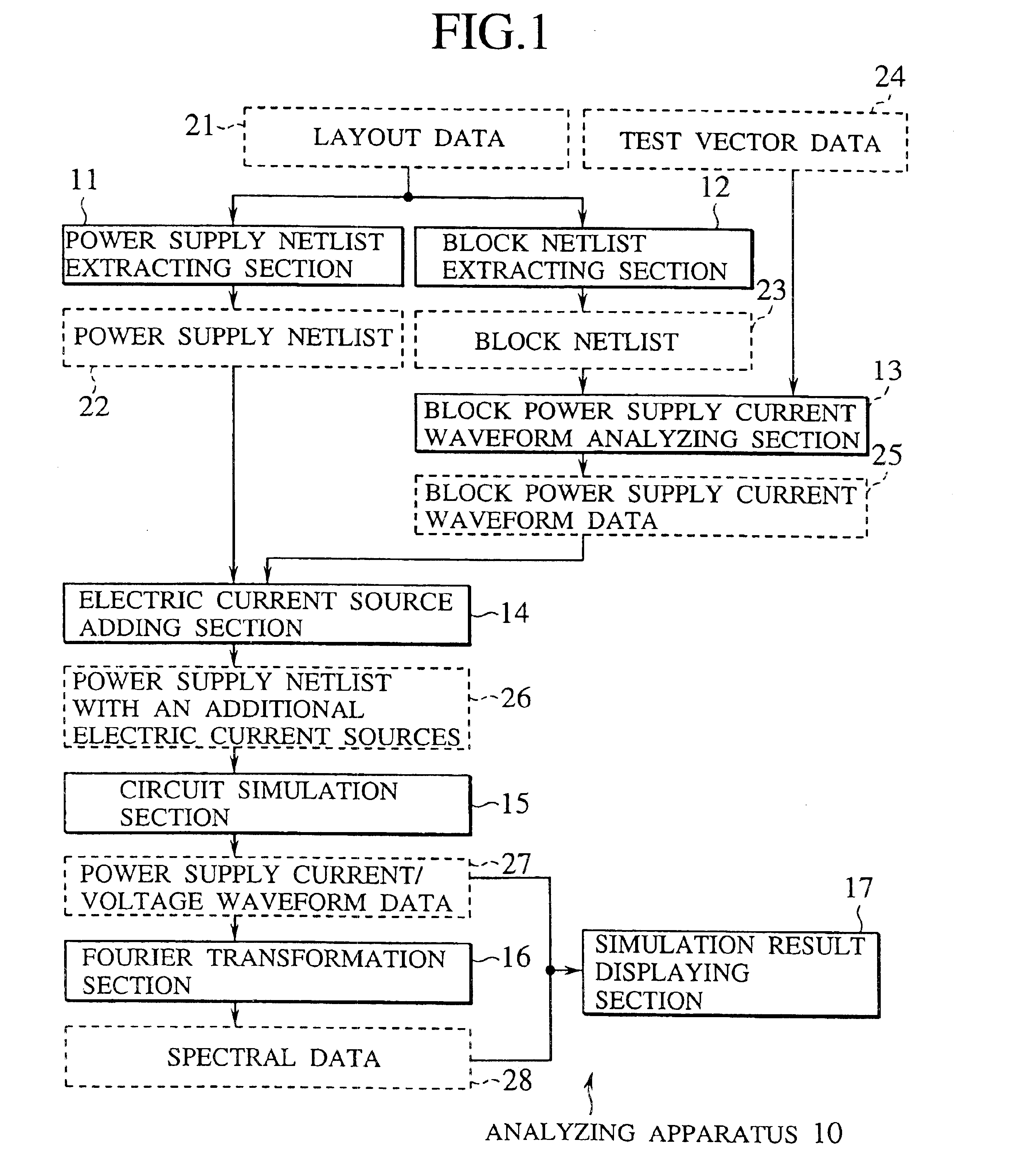

Device and method for analyzing EMI noise and semiconductor device

InactiveUS6842727B1Reduce EMI noiseEfficient reductionDrawing from basic elementsSemiconductor/solid-state device testing/measurementFrequency spectrumElectric power system

A technique for effectively attenuating EMI noise, which is generated from the electric power system of semiconductor devices, is described. In accordance with the technique, a power supply netlist with an additional electric current source(s) is generated by adding block power supply current waveform data, as extracted from test vector data and a block netlist, to the power supply netlist as extracted from the layout data of the circuit under analysis. A circuit simulation of the power supply netlist with an additional electric current source(s) is then performed in order to calculate power supply current / voltage waveform data. Furthermore, current / voltage spectral data is calculated by the Fourier transformation of the power supply current / voltage waveform data followed by displaying the current / voltage spectral data as the result of the Fourier transformation.

Owner:KK TOSHIBA

Digital integrated circuit chip testing system

InactiveCN102540060AImprove stabilityImprove mean time between failuresElectrical testingFpga implementationsTest object

The invention provides a test pattern-based testing system for realizing a functional test on a digital integrated circuit. The functional test is mainly used for testing logical functions of a chip under a certain timing sequence, and a basic principle is that the chip is excited by means of test patterns and whether the response of the chip is consistent with expected response is observed. The functional test can cover failure models of extremely high proportion logic circuits. A debugging technology supported one-step testing system comprises two parts, namely test pattern file conversion software applied to a personal computer (PC) and a digital integrated circuit chip testing machine, wherein the digital integrated circuit chip testing machine consists of architectures of a central processing unit (CPU) and a field programmable gate array (FPGA); the CPU is used for storing and converting pattern files, controlling the testing process, communicating with a host, and the like. A pattern controlling logic circuit is realized by an FPGA, the waveform generation, the control of Pattern random access memory (RAM) and sampling control are finished through the FPGA, and a drive and a comparator are controlled so as to test and control a tested object.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

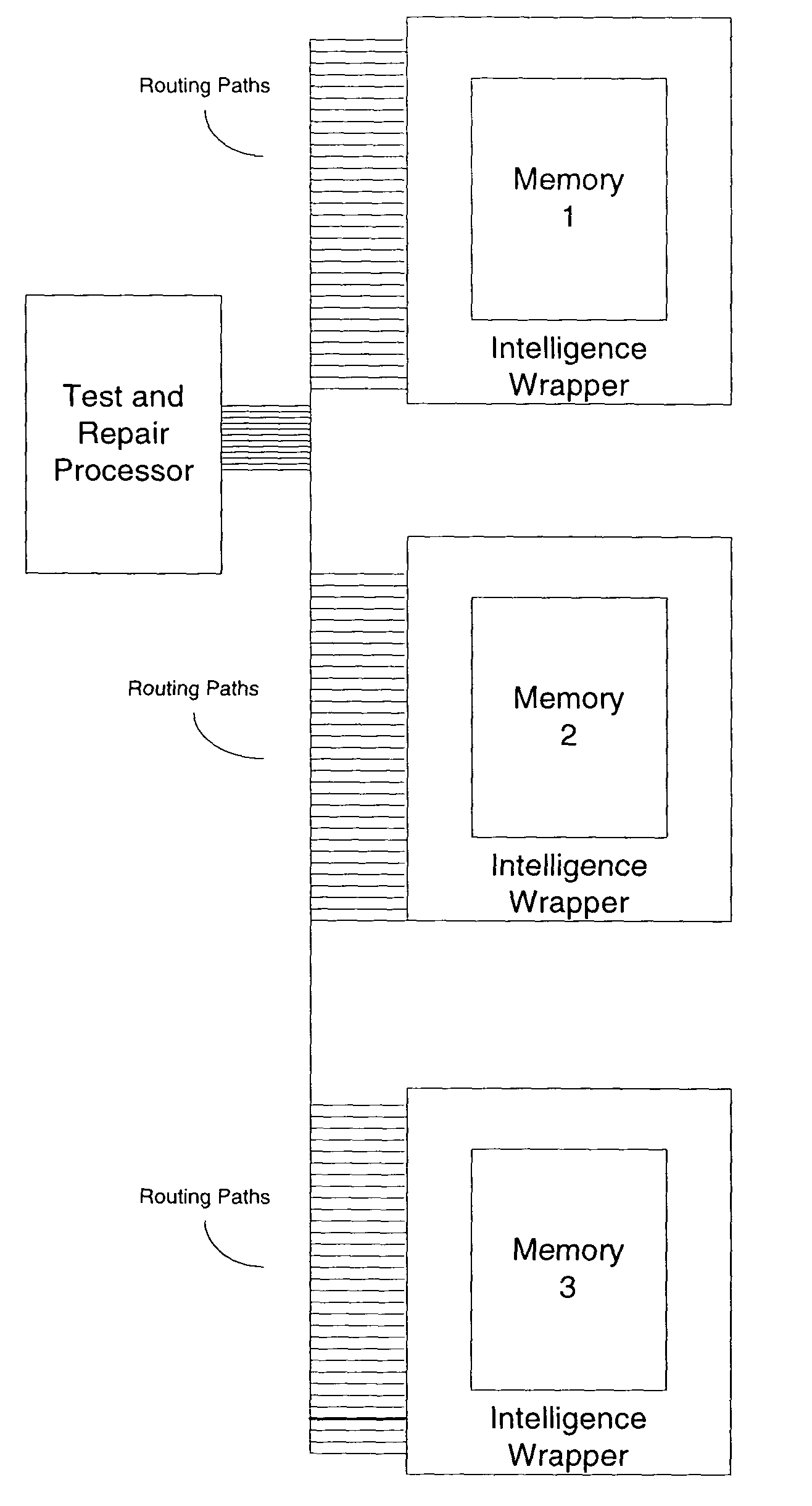

Method and apparatus for a command based bist for testing memories

Methods and apparatuses in which two or more memories share a processor for Built In Self Test algorithms and features are described. The processor initiates a Built In Self Test for the memories. Each memory has an intelligence wrapper bounding that memory. Each intelligence wrapper contains control logic to decode a command from the processor. Each intelligence wrapper contains logic to execute a set of test vectors on a bounded memory. The processor sends a command based self-test to each intelligence wrapper at a first clock speed and the control logic executes the operations associated with that command at a second clock speed asynchronous with the first speed. The processor loads the command containing representations of a march element and data to one or more of the intelligence wrappers via a serial bus.

Owner:SYNOPSYS INC

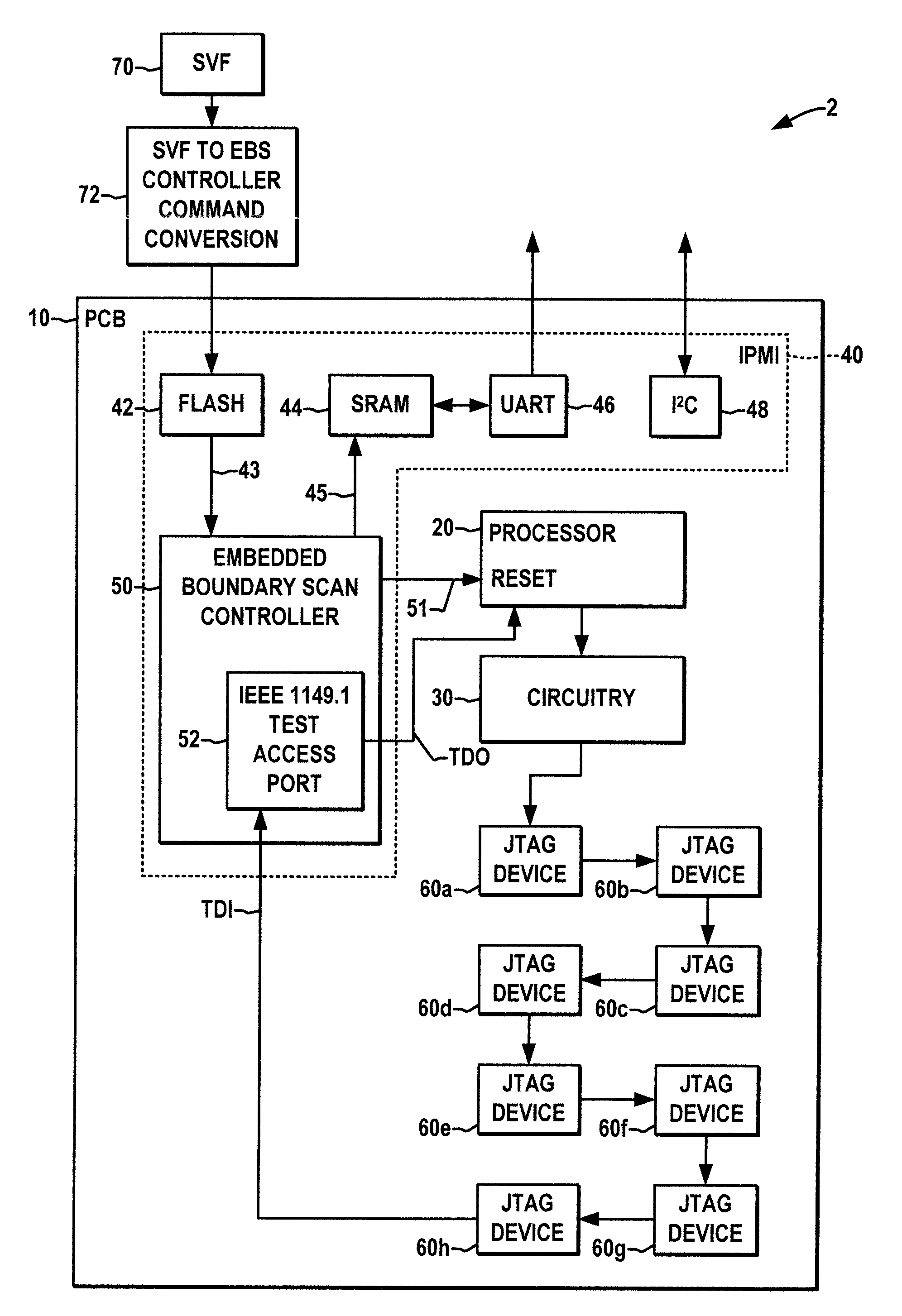

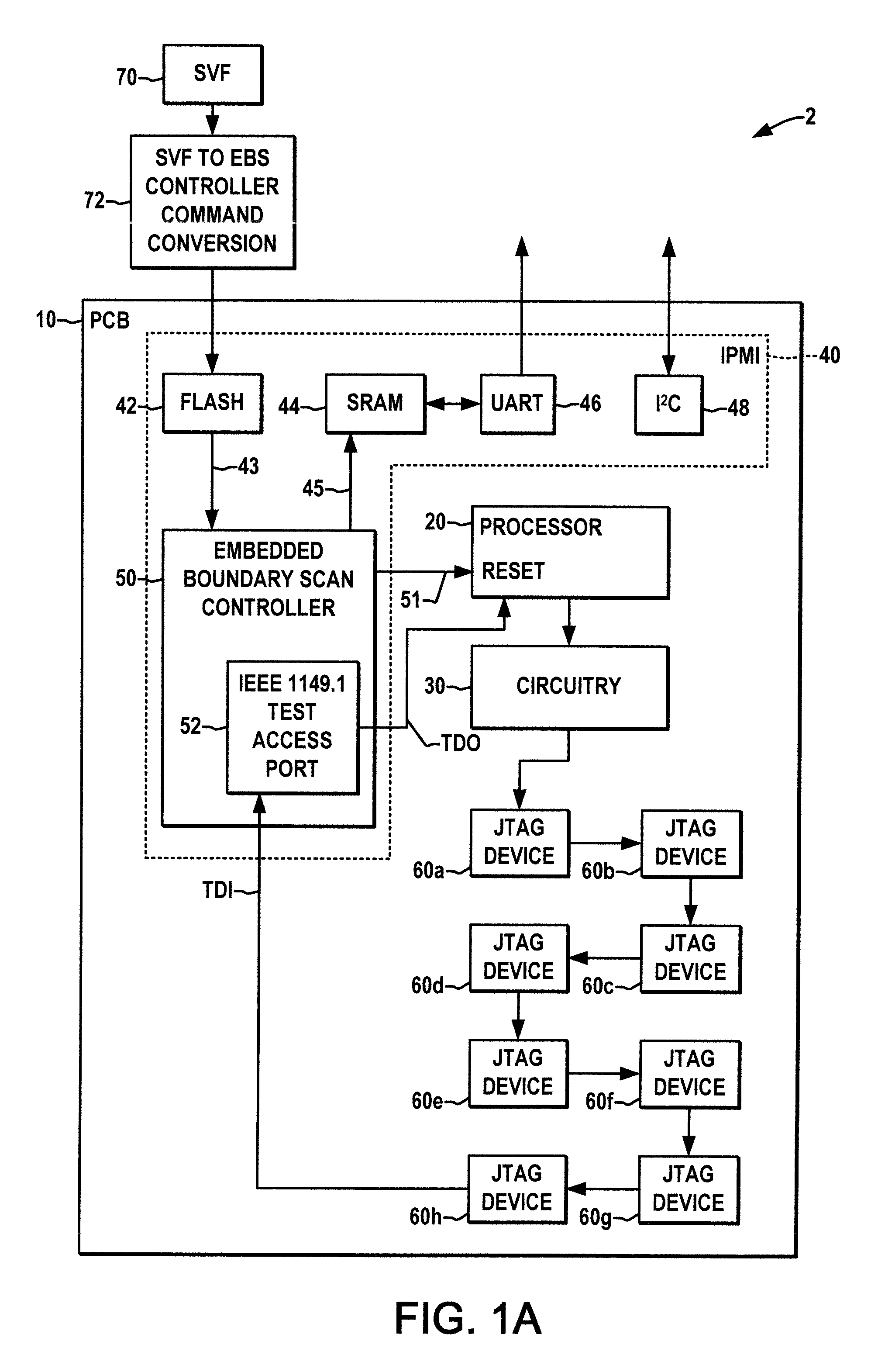

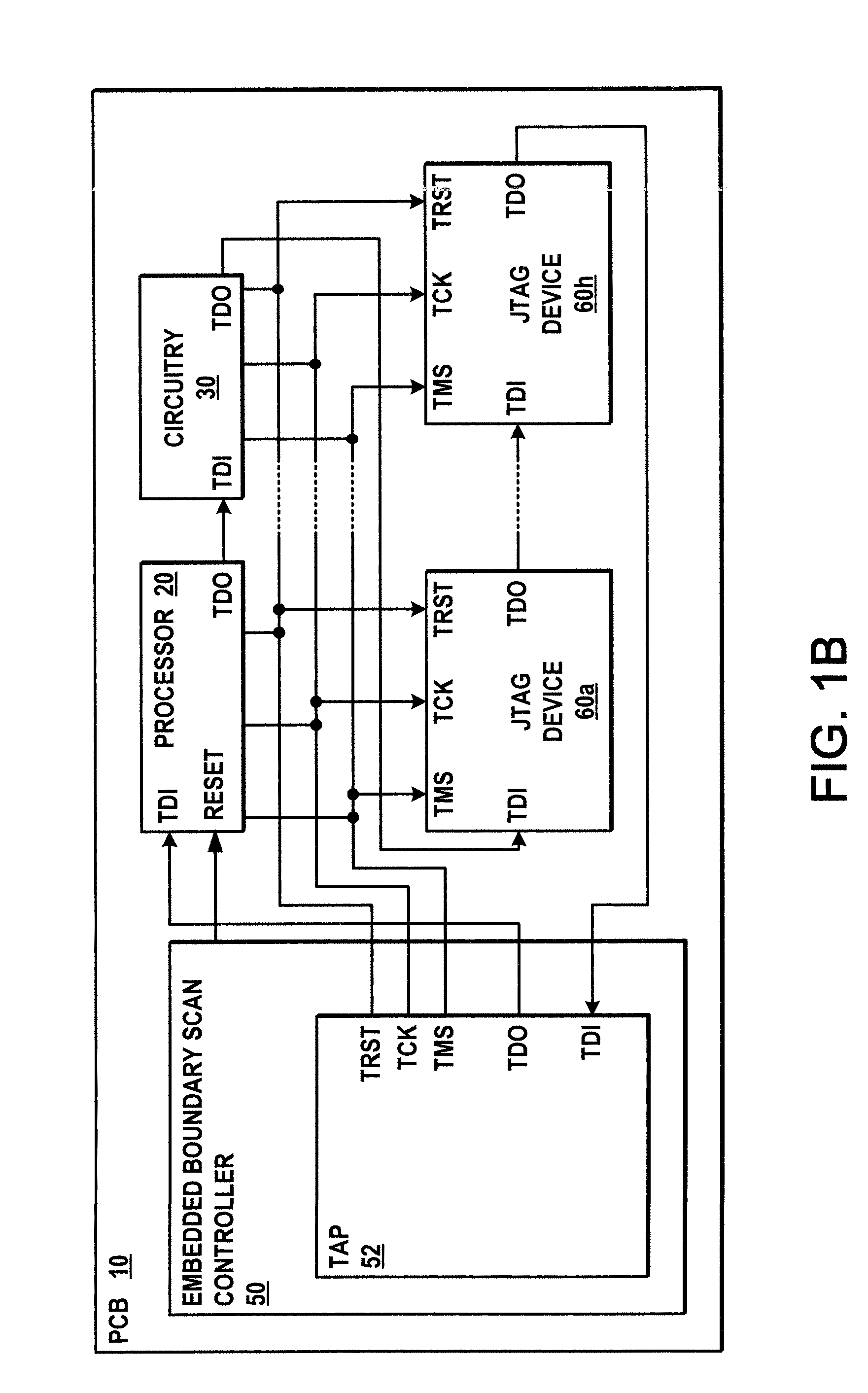

Apparatus and method for embedded boundary scan testing

ActiveUS20090006915A1Small sizeElectronic circuit testingLogical operation testingOn boardJoint Test Action Group

Embedded boundary scan testing apparatus and methodologies are disclosed for testing processor-based circuit boards without processor intervention. A boundary scan controller is embedded in a circuit board along with a boundary scan chain having JTAG devices connected with an electrical circuit of the board. Upon power up, the boundary scan controller holds an on-board processor system in reset, loads boundary scan test vectors and commands from an on-board non-volatile memory, and runs boundary scan testing while holding the processor system in the reset state. The boundary scan controller preferably includes a test access port controller that implements only a subset of the JTAG standard 16 machine states to optimize performance and minimize controller hardware. The test results may be stored in an externally accessible on-board memory for subsequent retrieval in order to facilitate board troubleshooting and / or repair, where the provision of on-board boundary scan testing allows testing of boards while installed in the field, and the embedded scan controller allows field testing of on-board processor systems and related circuitry to enhance the test coverage over processor-driven boundary scan testing.

Owner:ALCATEL-LUCENT USA INC

Method for automatically searching for functional defects in a description of a circuit

InactiveUS6885983B1Effective simulationEliminate needElectronic circuit testingDetecting faulty computer hardwareState switchingComputer science

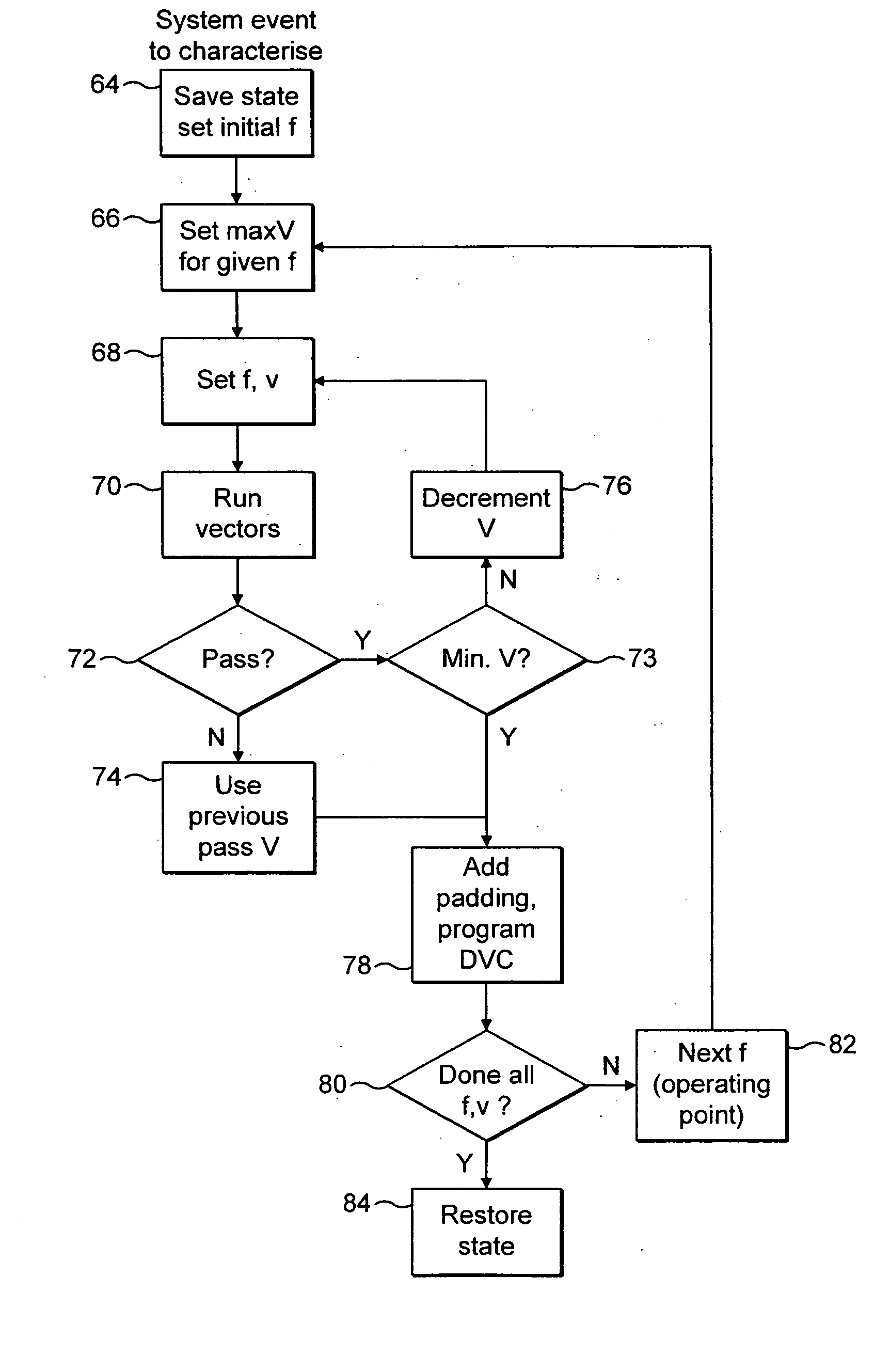

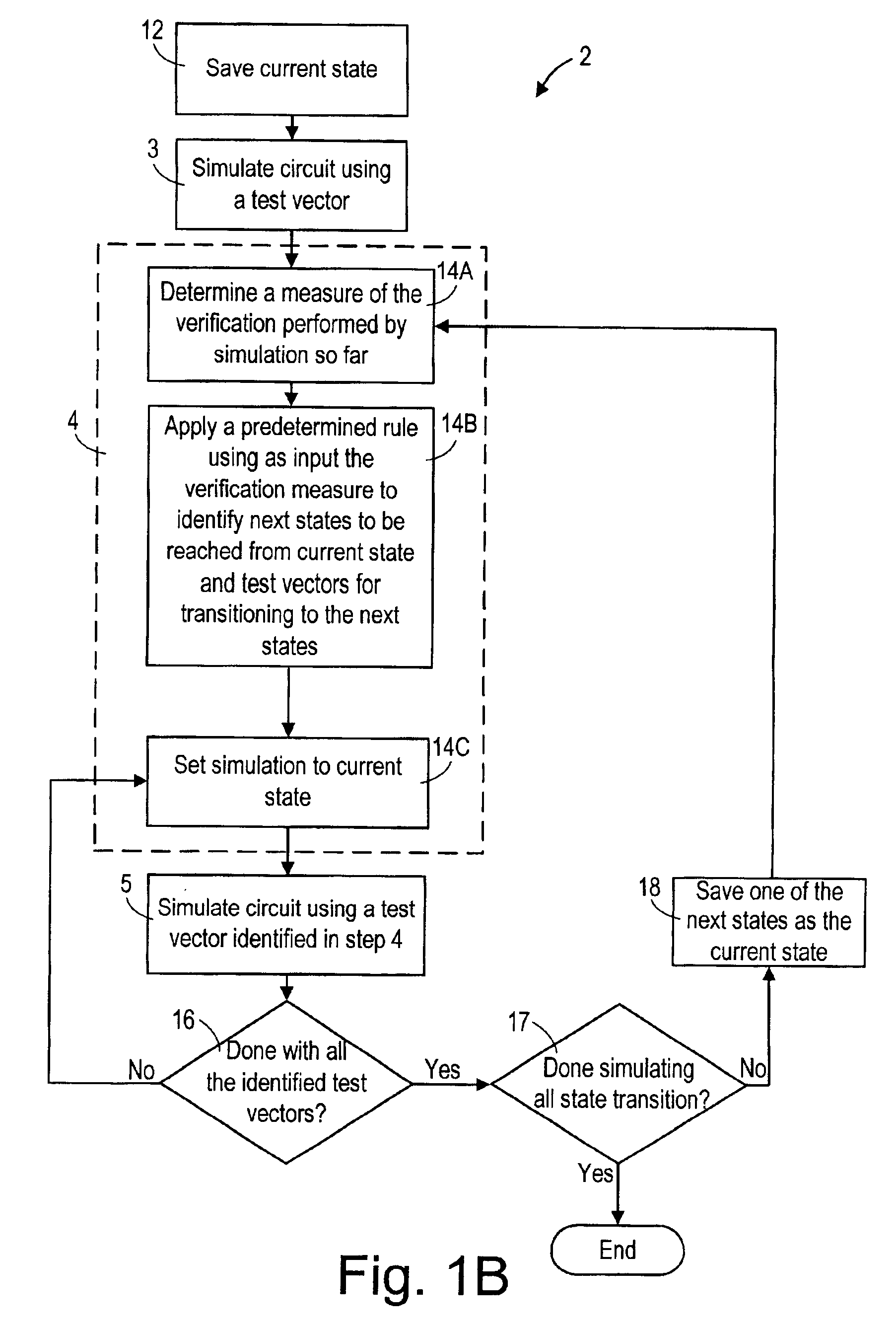

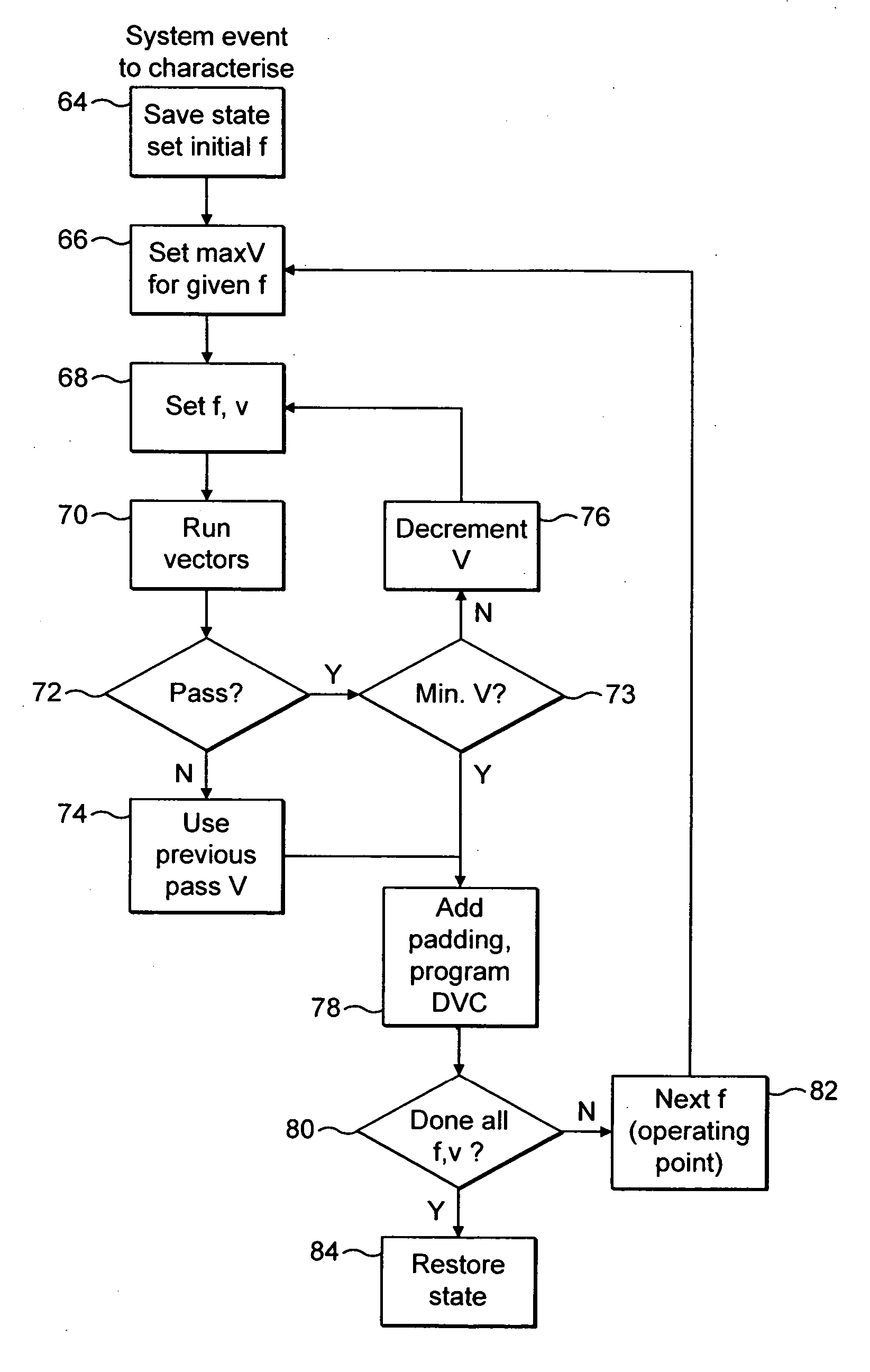

A programmed computer searches for functional defects in a description of a circuit undergoing functional verification in the following manner. The programmed computer simulates the functional behavior of the circuit in response to a test vector, automatically restores the state of the simulation without causing the simulation to pass through a reset state, and then simulates the functional behavior of the circuit in response to another test vector. A predetermined rule can be used to identify test vectors to be simulated, and the predetermined rule can depend upon a measure of functional verification, including the number of times during simulation when a first state transition is performed by a first controller at the same time as a second state transition is performed by a second controller. During simulation of the test vectors, manually generated tests or automatically generated checkers can monitor portions of the circuit for defective behavior.

Owner:MENTOR GRAPHICS CORP

Deterministic testing of edge-triggered logic

InactiveUS6904553B1Skew problemEliminates the timing uncertainties in the test environmentElectronic circuit testingDatapathData path

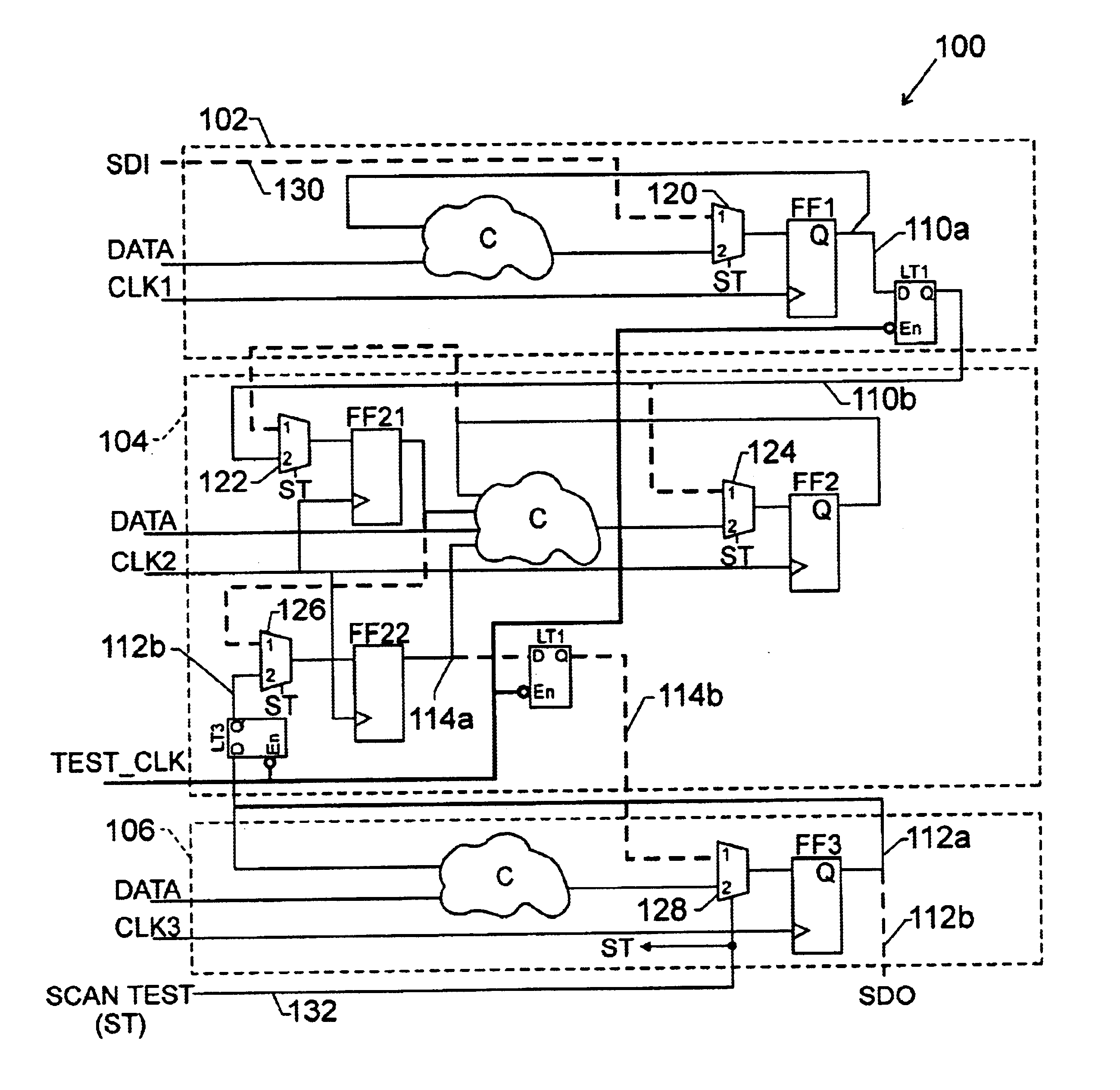

A digital system having multiple clock domain, each including at least one edge-triggered device, such as a flip-flop, is structured to be submitted to scan testing. Each data path from one clock domain to another includes a latch that is operated by a test clock. During scan testing, when the digital system is logically reconfigured to form one or more scan chains for receiving a test vector, the latches are operated to ensure that the test vector is passed from one domain to another.

Owner:SAMSUNG ELECTRONICS CO LTD

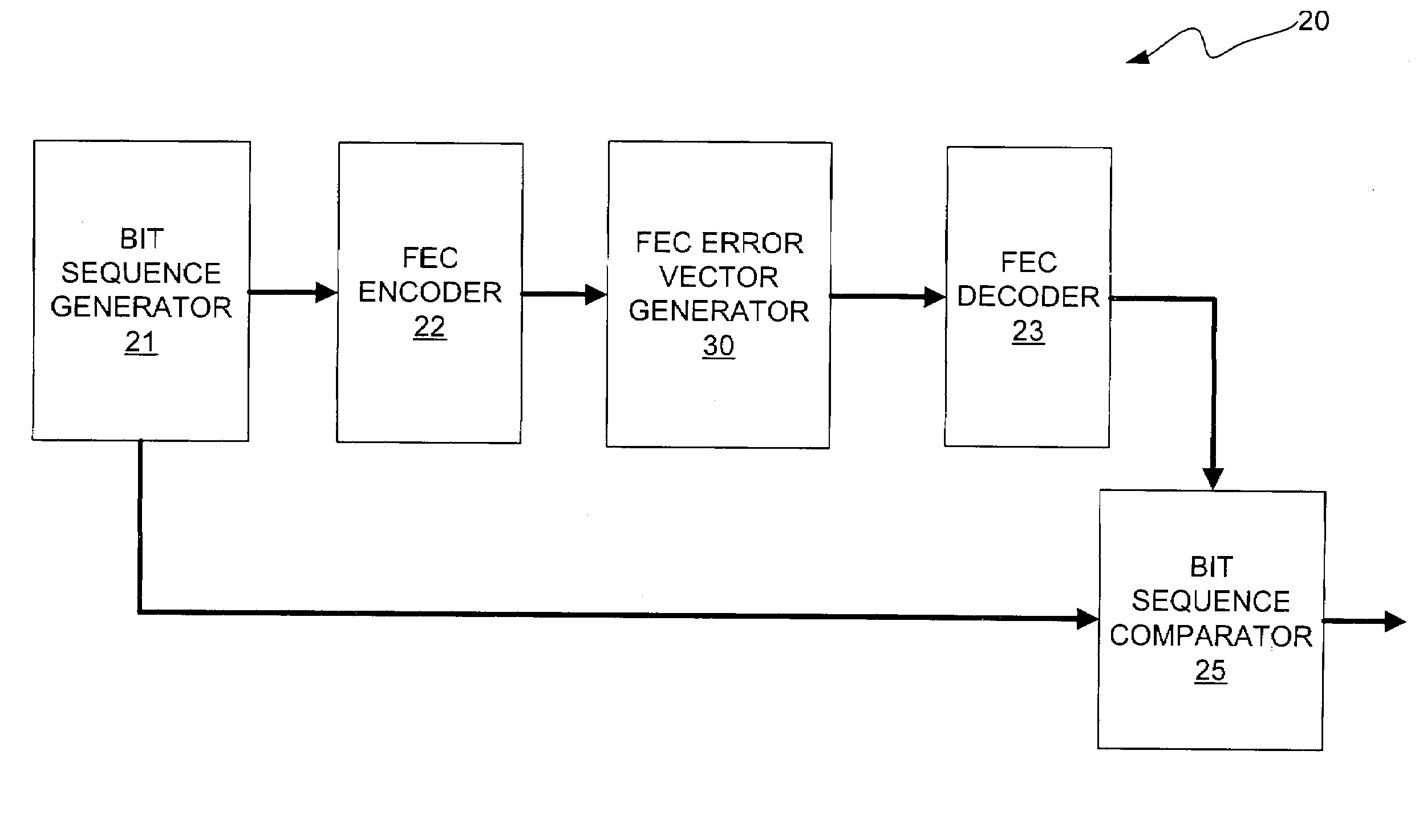

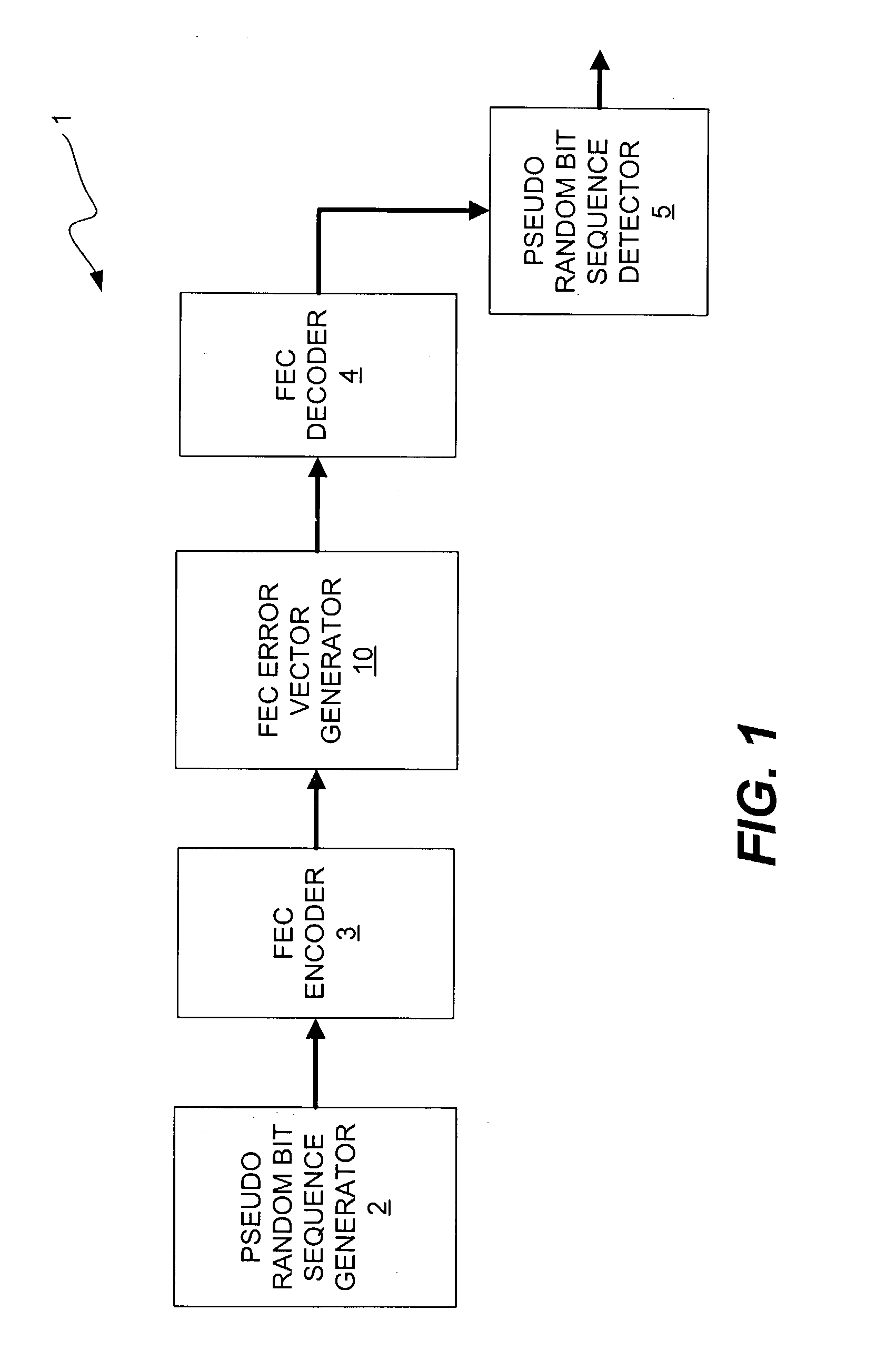

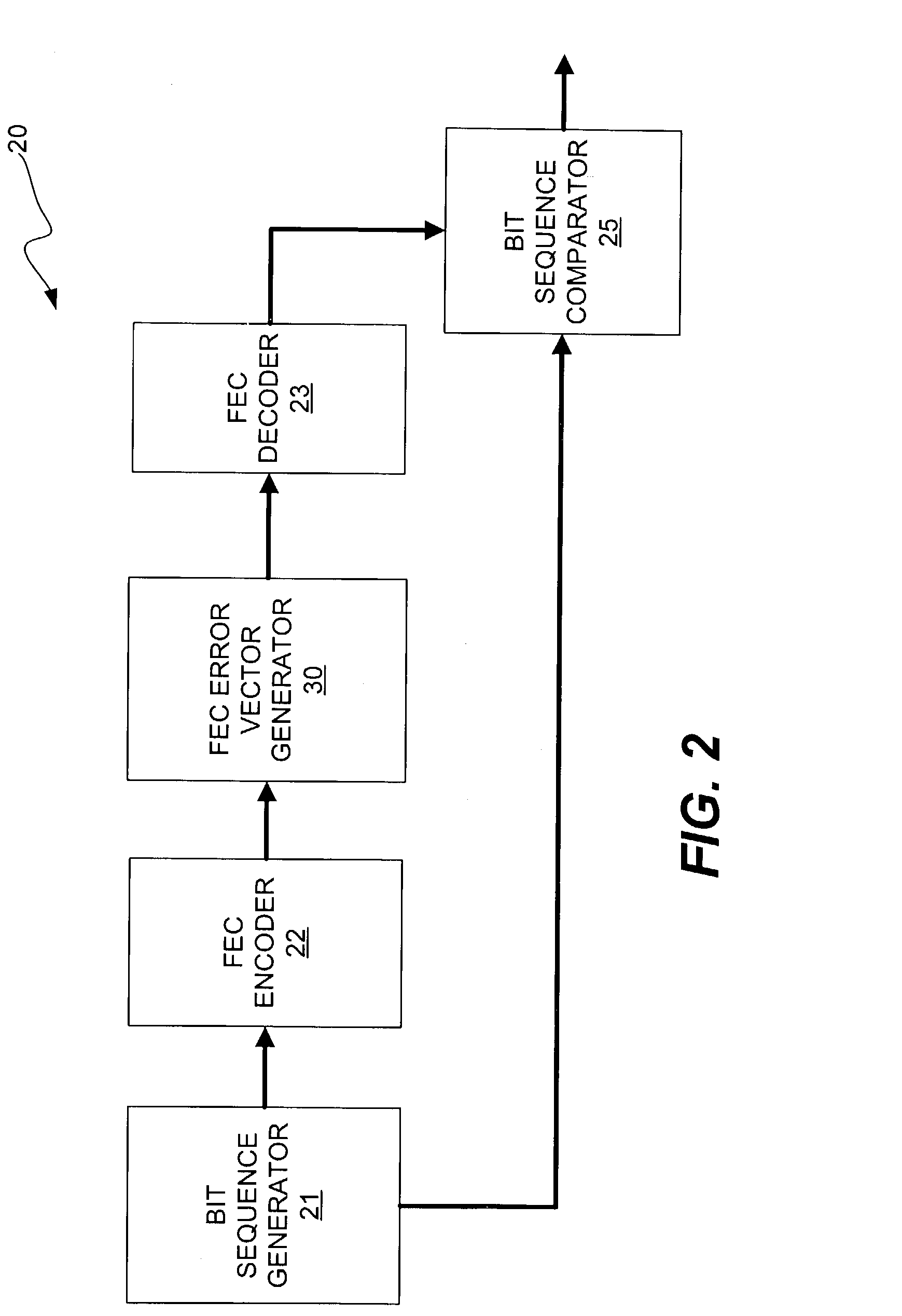

Method and apparatus for generating bit errors in a forward error correction (FEC) system to estimate power dissipation characteristics of the system

ActiveUS7073117B1Precision productionPower dissipationData representation error detection/correctionCode conversionFir systemForward error correction

A method and apparatus for generating and inserting bit errors in data words that have been encoded in a forward error correction (FEC) system in order to estimate power dissipation. In accordance with the present invention, it has been determined that a burst error generator that is capable of erroring the maximum number of correctable data bits in every FEC encoded frame, which allows the designer to accurately produce test vectors that are suitable for use in commercially available power estimation tools. In addition, after the IC is produced, the burst error generator of the present invention can be enabled to provide real-time FEC power dissipation data for use in system thermal modeling, thus obviating the need to use costly external devices that emulate a given error rate. Furthermore, the power dissipation data obtained in real-time may be used to refine the initial design power estimate, which will then allow the designer to develop a more accurate prediction of power consumption for future IC designs. Thus, the burst error generator of the present invention is capable of reducing iterations of IC designs by accurately estimating the worst-case power dissipation of FEC decoders.

Owner:CIENA

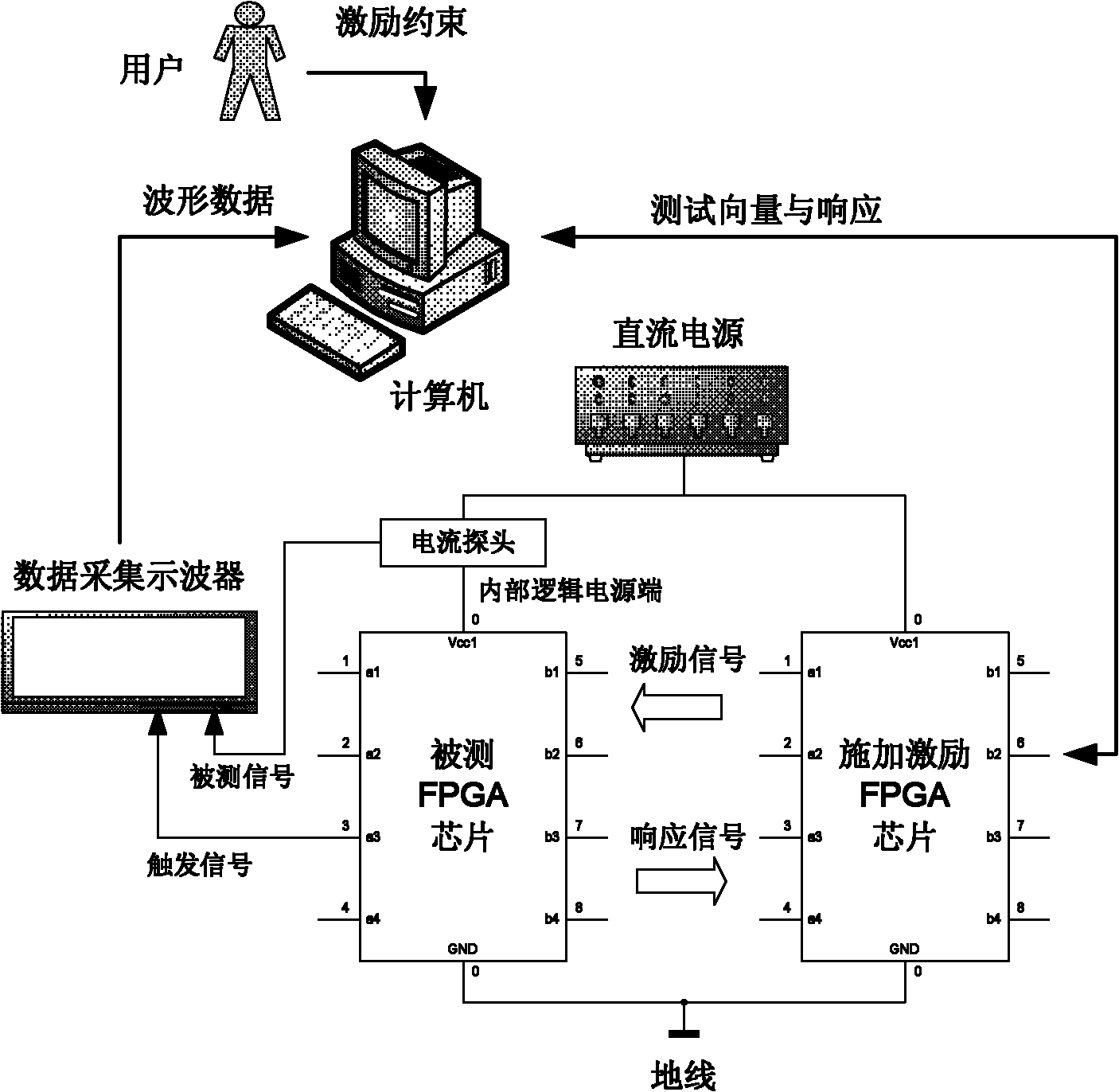

Method for detecting malicious circuit in FPGA (field programmable gate array) chip by power consumption analysis and system thereof

ActiveCN102592068AHigh measurement accuracyAchieve installationInternal/peripheral component protectionVoltage sourceFpga chip

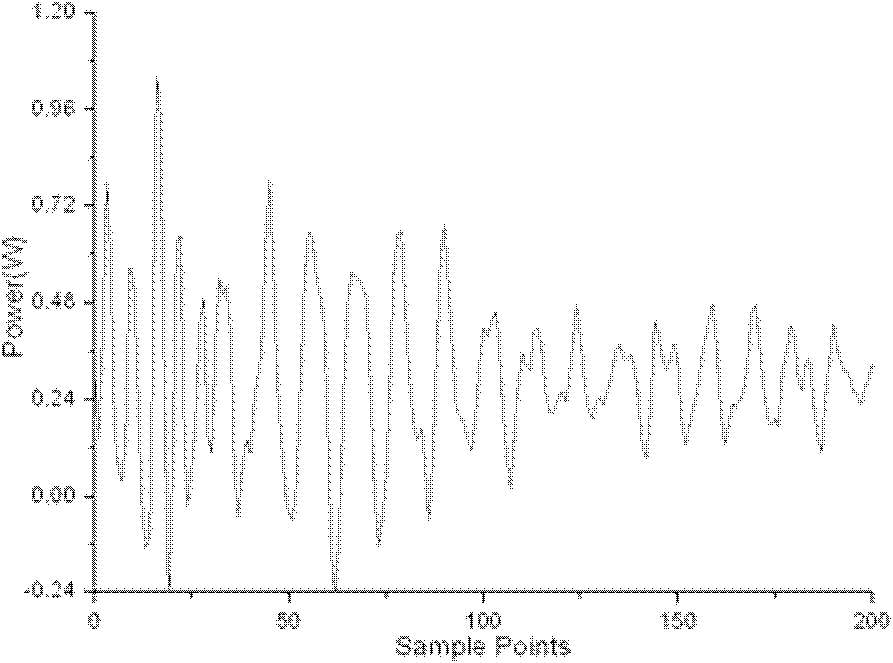

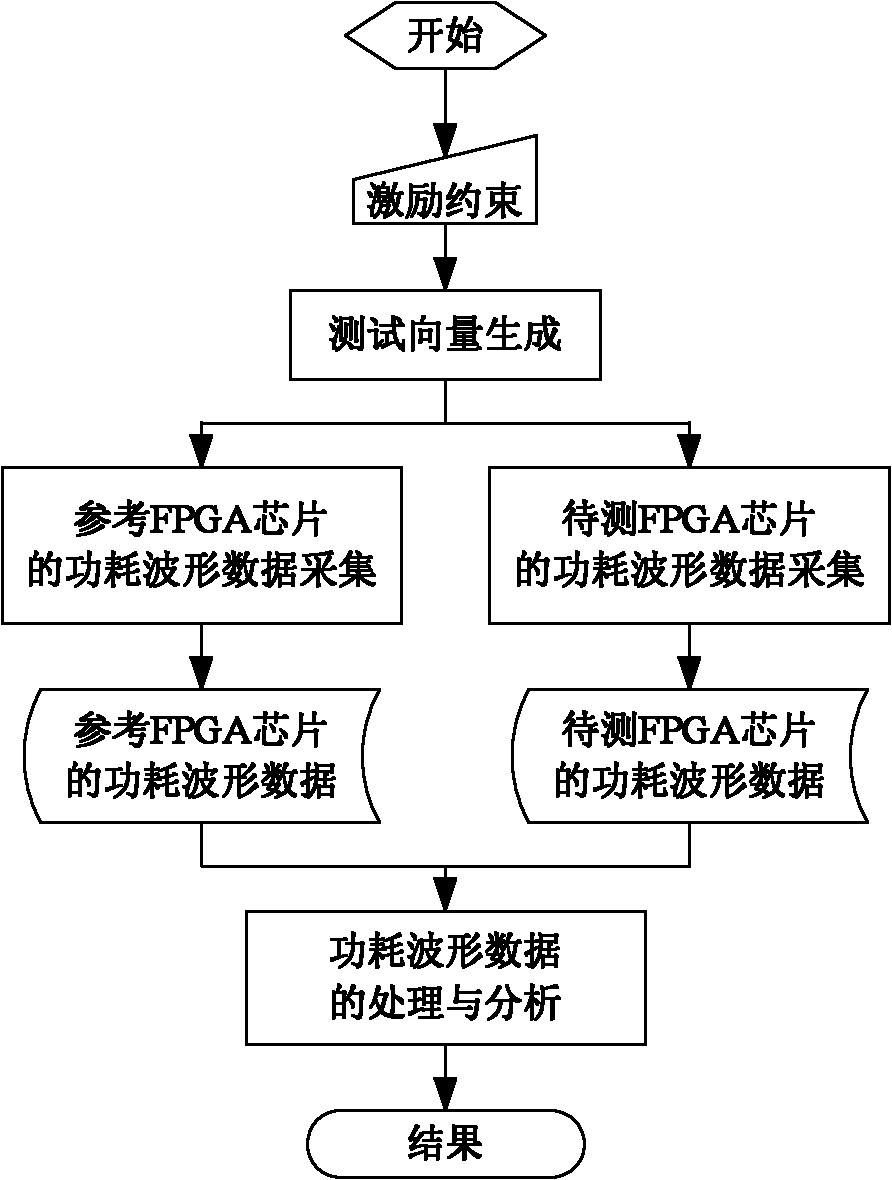

The invention discloses a system for detecting malicious circuits in an FPGA (field programmable gate array) chip by power consumption analysis. The system comprises a DC (direct current) stabilized voltage source for supplying DC power to a to-be-detected FPGA chip and an excitation applying FPGA chip; a current probe for measuring a transient current at the power end of the to-be-detected FPGA chip; an oscilloscope triggered by a trigger signal generated by the to-be-detected FPGA chip to collect the current signal measured by the current probe; the excitation applying FPGA chip for applying an excitation signal to the to-be-detected FPGA chip, and transmitting the response signal of the to-be-detected FPGA chip to a computer for further verification and comparison with an expected response value; and the computer for receiving excitation restraint compiled by a user, generating a test vector, and completing response verification, oscilloscope setting, waveform data collection, data analysis and treatment. The invention also discloses a method for detecting malicious circuits in the FPGA chip by using the above system.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST

Built-in self-testing method of FPGA input/output module

The present invention provides a built-in self-testing method of FPGA input / output module. Firstly all input / output modules in FPGA are configured to that a bidirectional IO buffer is used as a circuit to be tested. The logical resource of middle part of FPGA device is configured to a test vector generating circuit. The logical resource surrounding the IO buffer is configured to an output response analysis circuit of scanning chain structure. In testing, the test vector generating circuit generates a pseudo-random exhaustive vector for exerting a test pattern for each circuit to be tested; after executing the test vector, actuating the operation of scanning chain of output response analysis circuit, outputting the built-in self-testing result which is configured this time by the input / output module in the control of test clock by the output response analysis circuit until when the test covers all resources in the input / output module. The method of the invention has the following advantages: simplified built-in self-testing result retrieval mode, reduced test configuration number of times, reduced test cost and increased test efficiency under the precondition of guaranteeing 100% test coverage rate.

Owner:BEIJING MXTRONICS CORP +1

Geocoding method using multidimensional vector spaces

InactiveUS20060245572A1Interconnection arrangementsFuzzy logic based systemsFeature vectorData element

A process for evaluating and geocoding of GIS data elements utilizes a plurality of “locate” tests and a weighting scheme to express the match results as a multidimensional vector. Multiple inputs and data sources, as well as ambiguous and partial input data, are used to generate an output with improved precision by applying a weighting function to each input element and generating a set of test vectors (i.e., the input data element weighted by the known accuracy of the element / source). A sum of a plurality of tests is then generated as the “characteristic vector” of the test set. By using two (or more) different sets of test, two (or more) characteristic vectors are formed. Various well-known algebraic techniques can then be used to evaluate the results of each set of tests and select the “best match” result.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

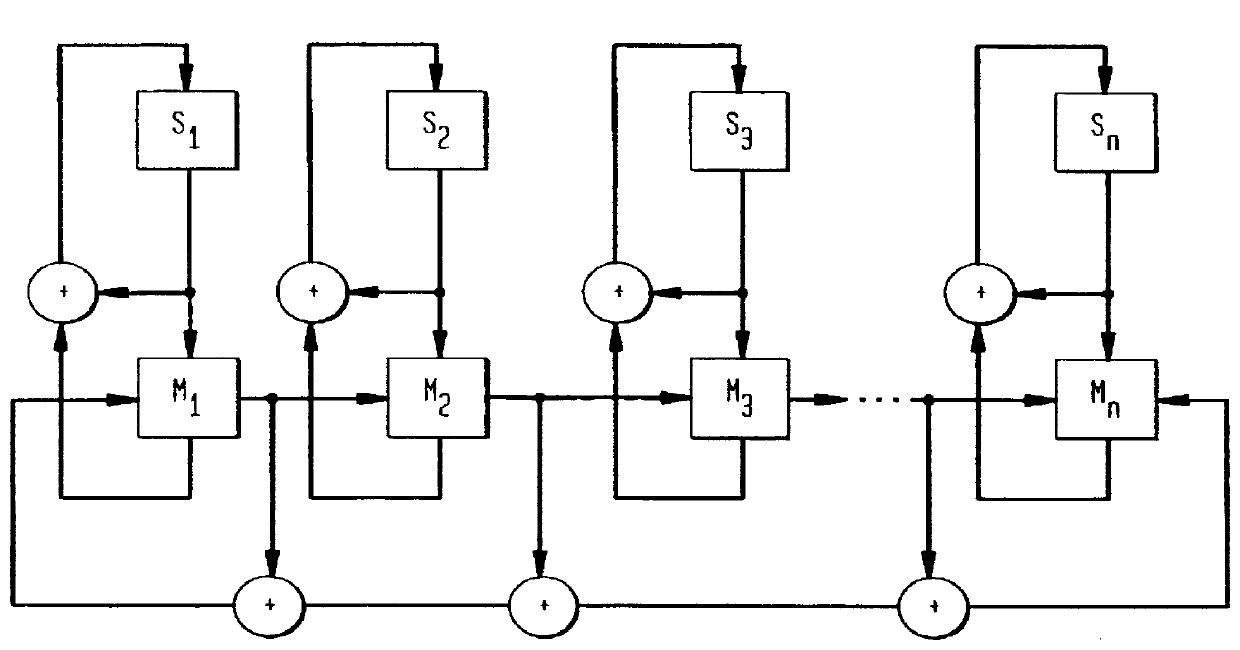

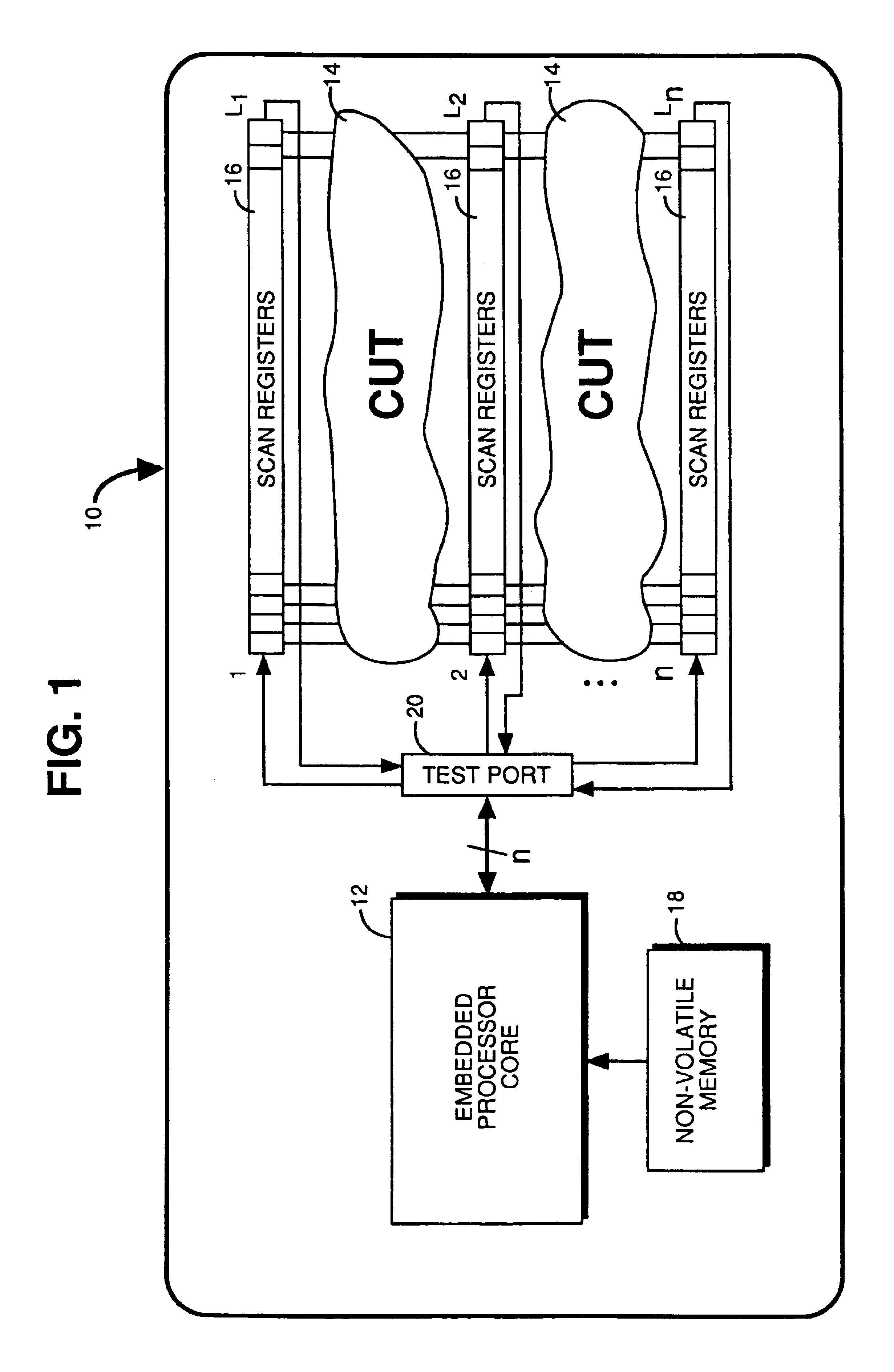

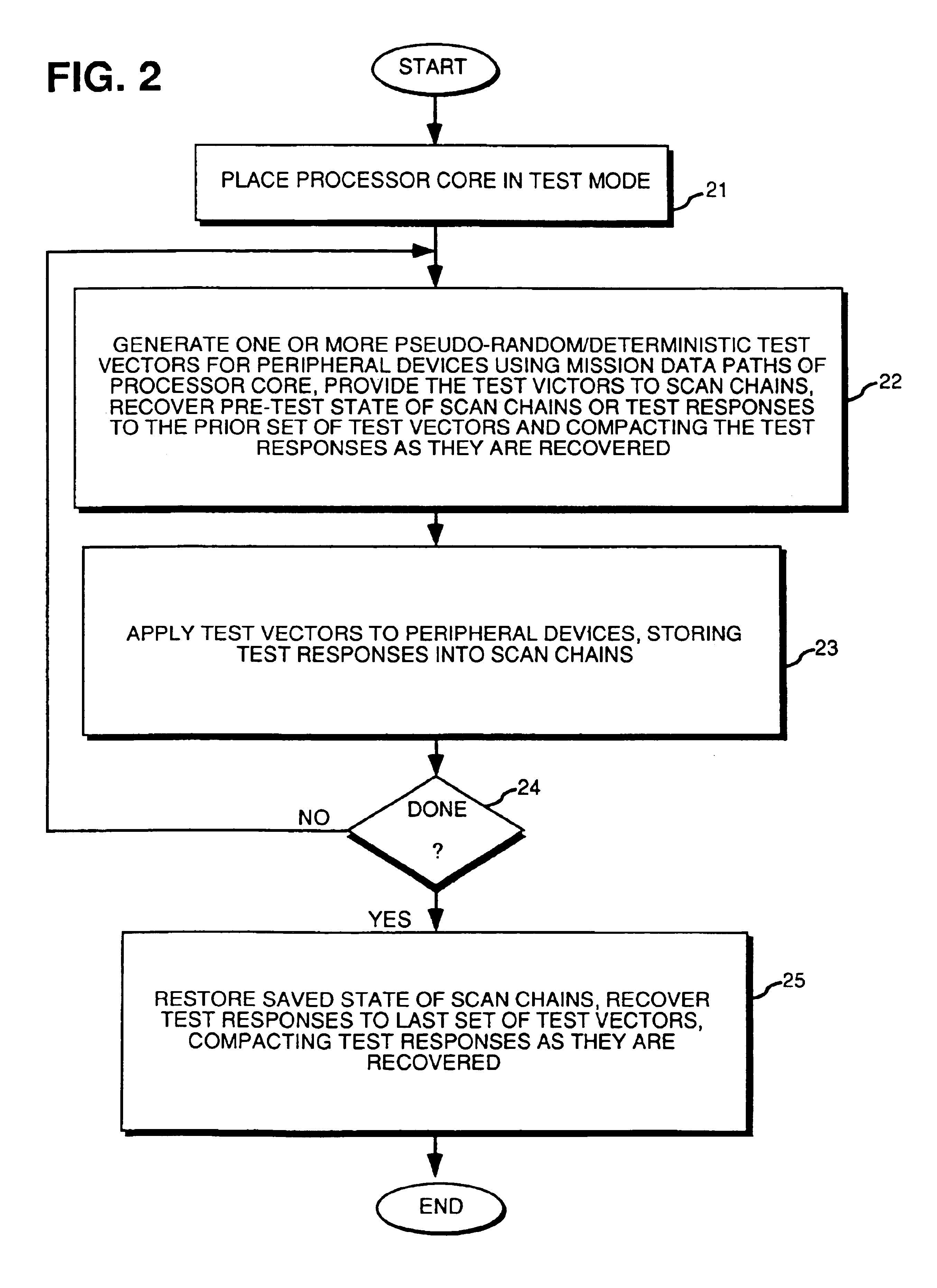

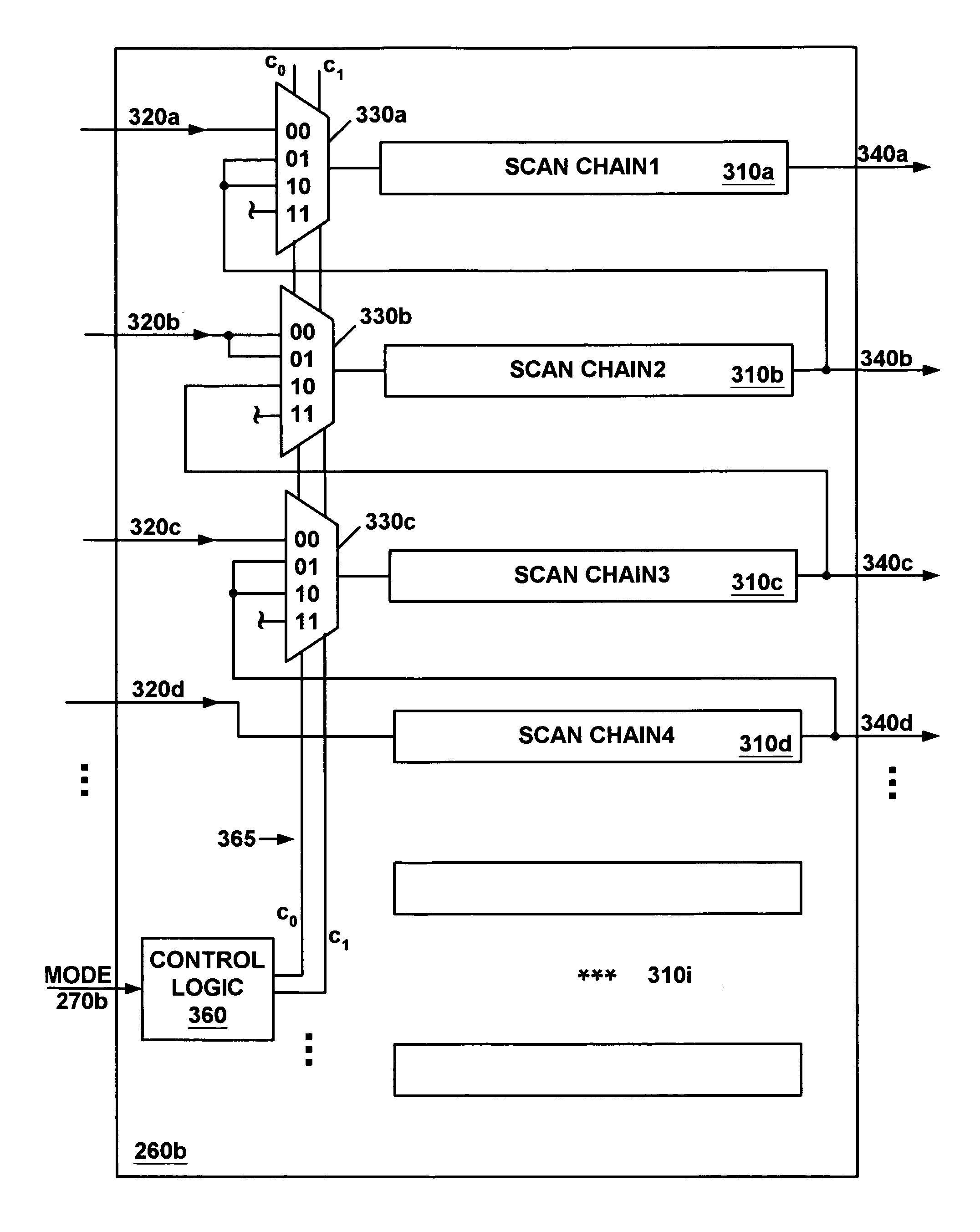

Arithmetic built-in self-test of multiple scan-based integrated circuits

InactiveUS6954888B2Reduce error impactElectronic circuit testingHardware monitoringProcessor registerLeast significant bit

Owner:MENTOR GRAPHICS CORP

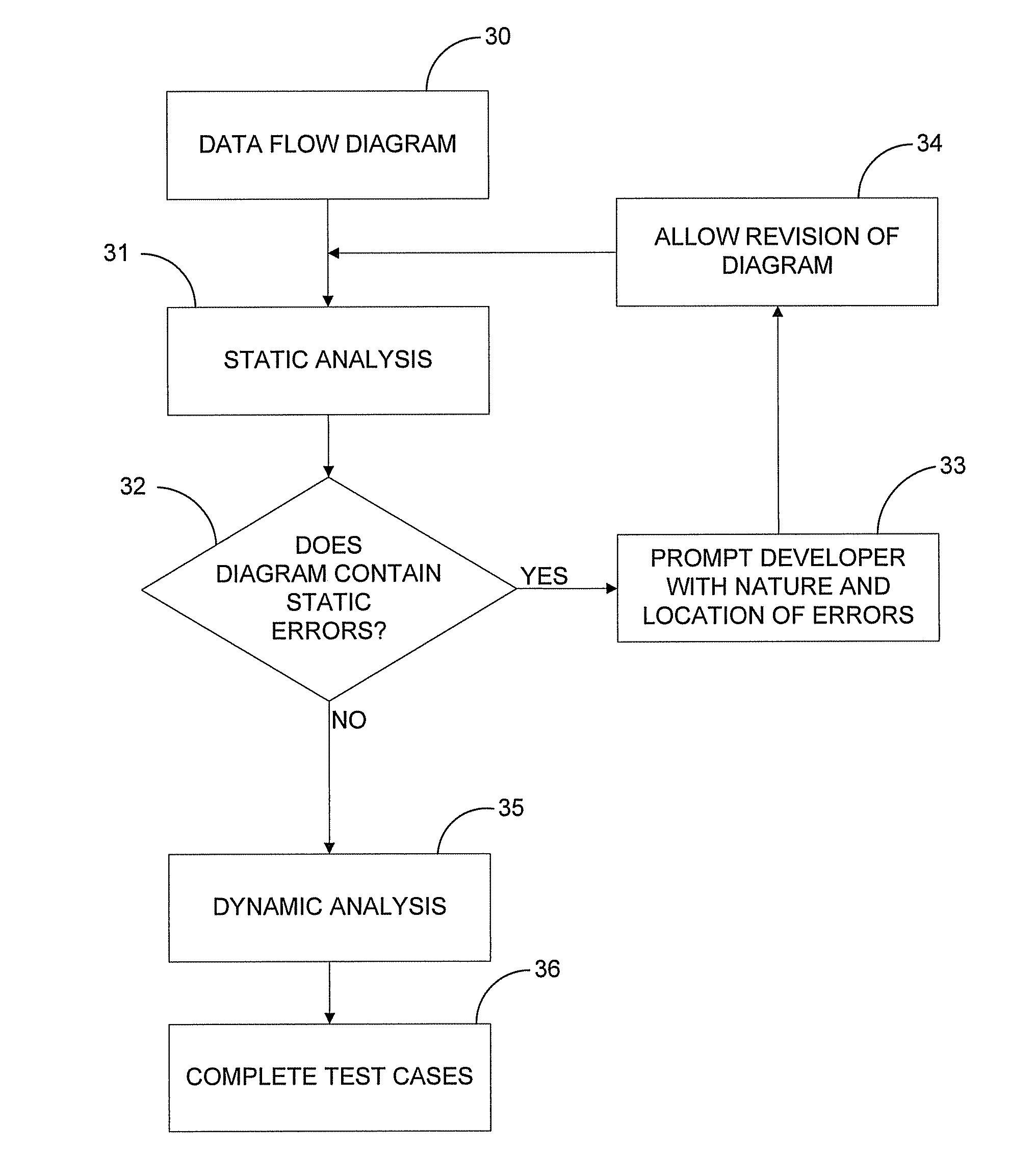

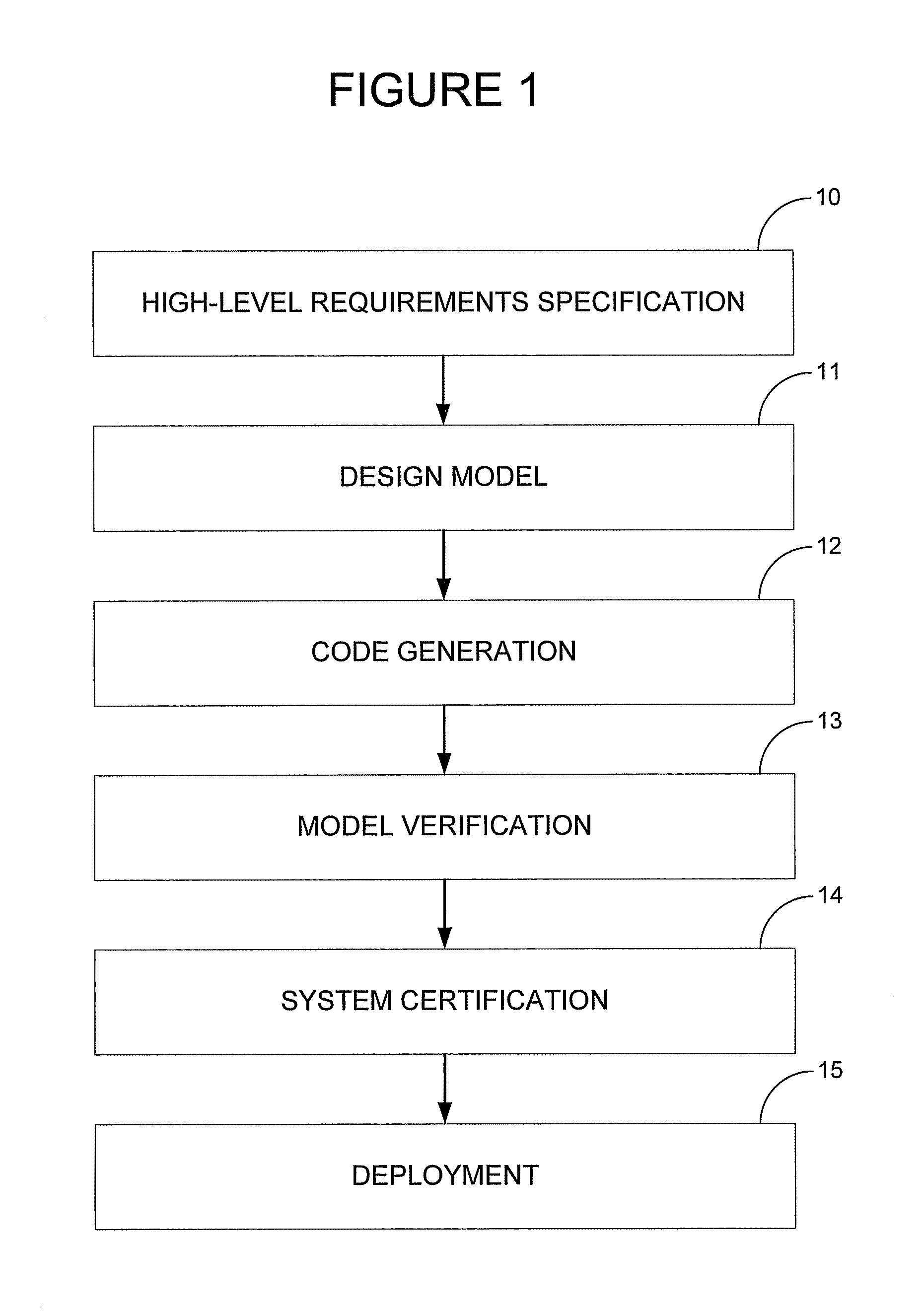

Requirements-based test generation

ActiveUS7644334B2Facilitates meeting DO-178B objectivesReducing resourceElectronic circuit testingError detection/correctionBlock typeTest vector

This test generator takes data flow block diagrams and uses requirements-based templates, selective signal propagation, and range comparison and intersection to generate test cases containing test vectors for those diagrams. The templates are based on the functionality and characteristics of a block type, and each block type has associated templates. These templates provide maps for the creation of test values that verify the functionality of particular instances of that block type. Signal propagation allows the generation of diagram-level test cases that verify particular characteristics of a single embedded block. The methods disclosed for signal propagation utilize range intersection, equivalence classes, and block type formulae to create efficient and complete test cases. This test generation method would preferably be repeated until all blocks in a data flow block diagram were verified in their respective contexts, and it creates test cases that cover multiple time steps.

Owner:HONEYWELL INT INC

System and method for automatically retargeting test vectors between different tester types

Owner:SYNOPSYS INC

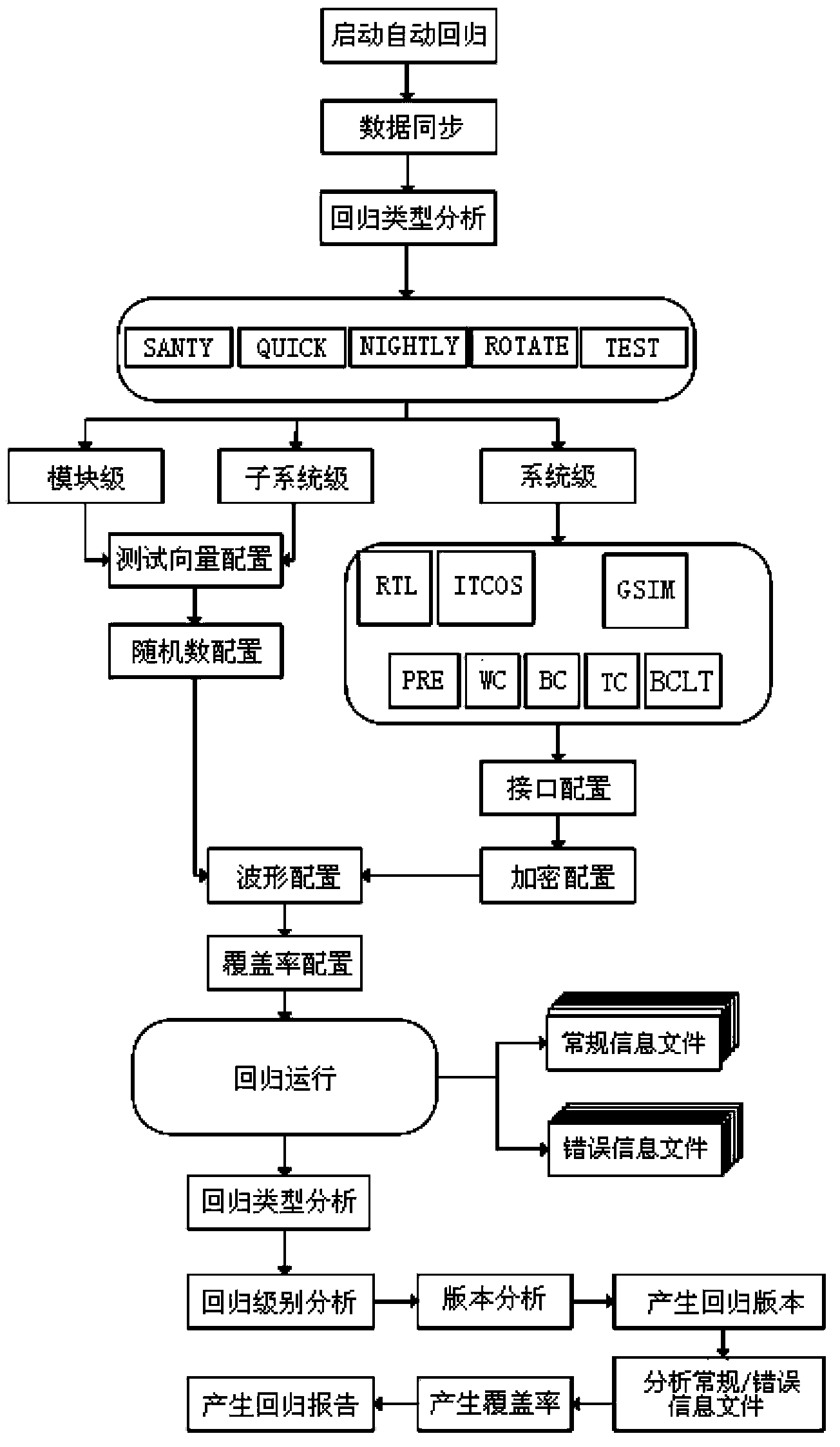

Automatic regression testing method

InactiveCN103823747AImprove the efficiency of the verification processImprove efficiencySoftware testing/debuggingRegression testingHome page

The invention discloses an automatic regression testing method. The automatic regression testing method includes a first step, performing regression starting and running, in other words, respectively managing regression tests on different kinds of test vectors in a classified and graded manner according to specific conditions of projects, respectively selectively performing the module-level, subsystem-level or system-level regression tests for different stages of hierarchical verification and generating conventional information files and error information files; a second step, performing regression information post-processing, in other words, statistically analyzing each grade of regression test results, generating project regression home pages, generating module or regression classification branch pages and generating detailed regression result branch pages of each module. The project regression home pages contain project information, regression versions and coverage rates. The module or regression classification branch pages contain module classification type lists and pass or fail test case summaries. The detailed regression result branch pages of each module contain each test case name, simulation running time, random frequencies, case passing information, fail type statistics and simulation result conventional information file indexes. The automatic regression testing method has the advantage that the design verification process efficiency and the verification completeness can be improved by the aid of the automatic regression testing method.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Remote integrated circuit testing method and apparatus

ActiveUS20060242499A1Low costElectronic circuit testingDetecting faulty hardware by remote testEngineeringRemote computer

A method and system for remotely testing an integrated circuit installed in an integrated circuit system is presented. The integrated circuit is equipped with test structures for testing functional blocks within the integrated circuit, and a test access mechanism configured to receive test vectors for controlling the test structures. Test vectors are applied, via the parallel port of a remote computer and parallel cable, to pins of the parallel port of the integrated circuit system, which are connected to the signal ports of the test access mechanism implemented in the integrated circuit of interest, thereby allowing remote testing of the integrated circuit while the integrated circuit is installed in its native system.

Owner:AVAGO TECH INT SALES PTE LTD

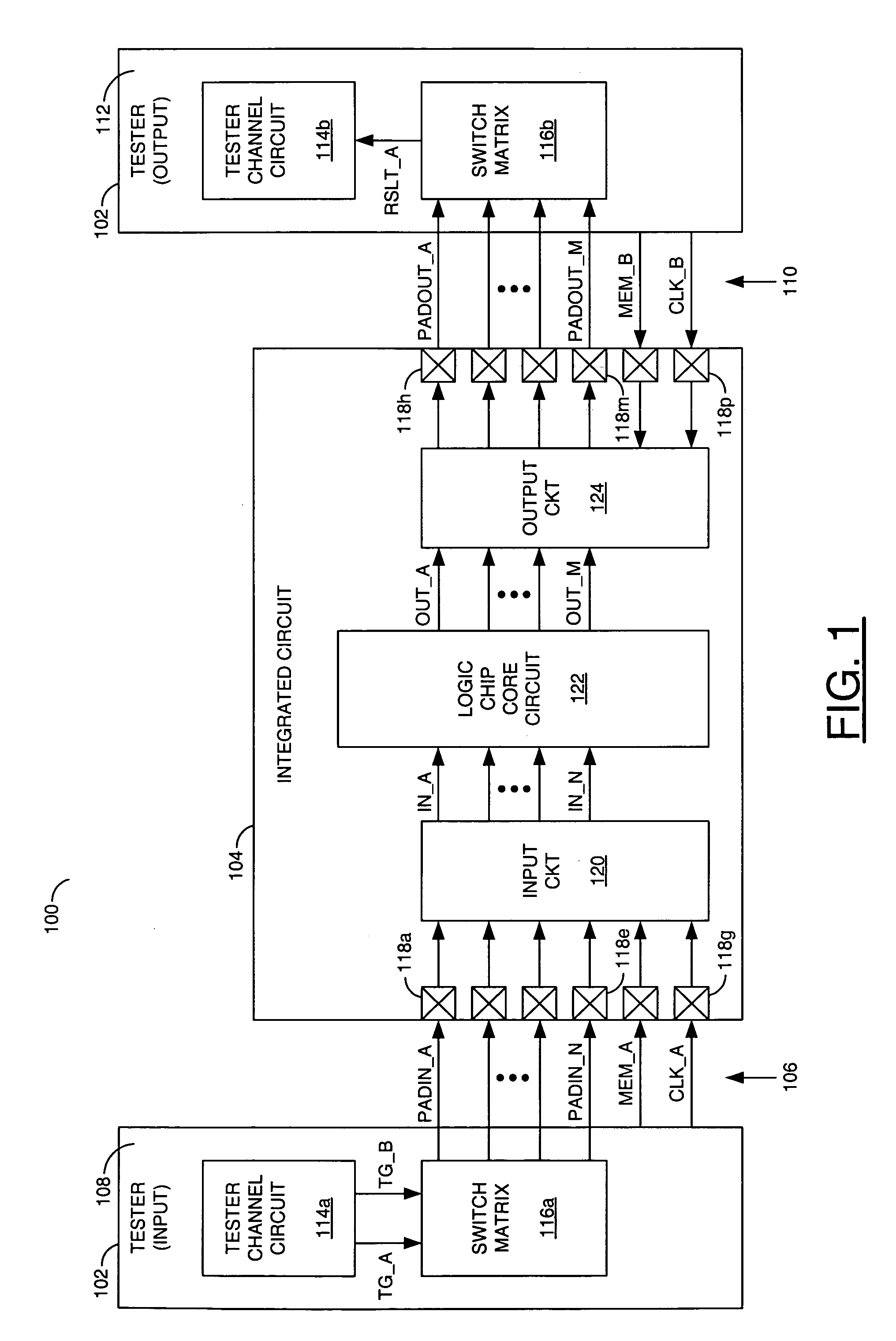

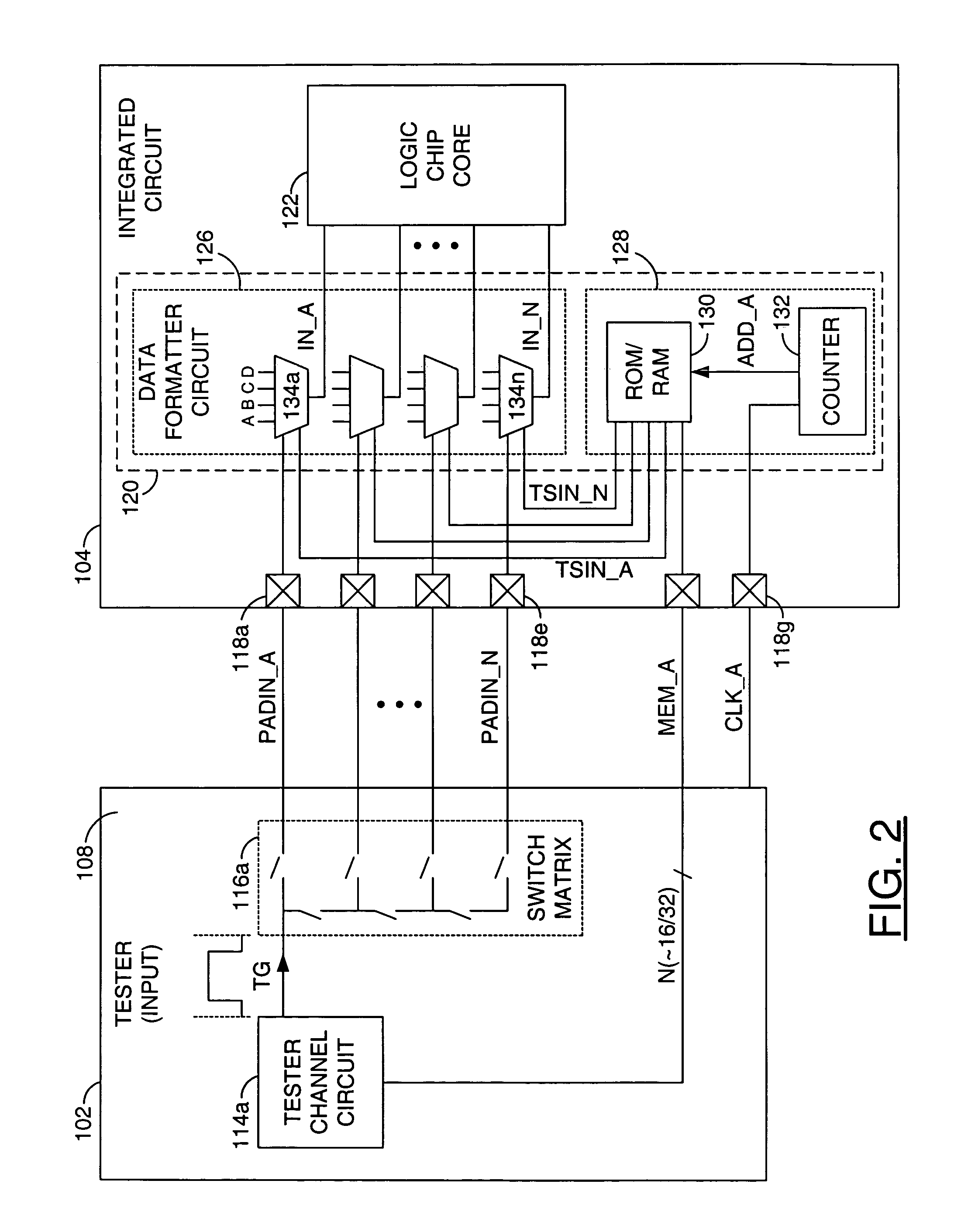

Reducing tester channels for high pinout integrated circuits

InactiveUS6971045B1Short test timeReduce testing costsDigital circuit testingError detection/correctionEngineeringOperation mode

An integrated circuit generally comprising a plurality of input pads, an input circuit, and a core circuit. The input pads may be configured to receive a plurality of first input signals. The input circuit may be configured to generate a plurality of second input signals (i) equal to the first input signals while in an operational mode and (ii) responsive to a plurality of test vectors with timing generation determined by the first signals while in a test mode. The core circuit may be responsive to the second input signals.

Owner:MONTEREY RES LLC

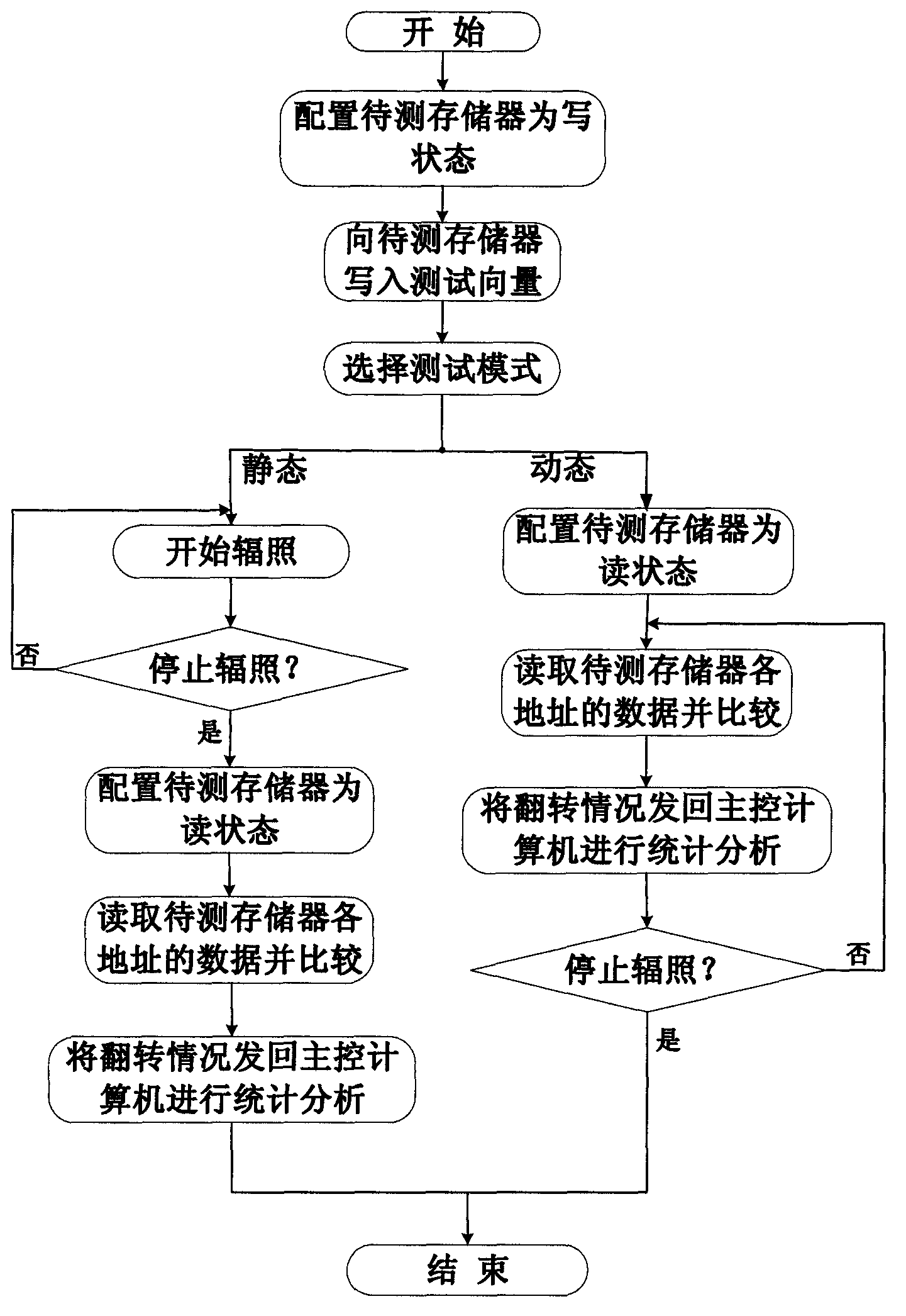

Universal single event effect detecting method of memory circuit

InactiveCN103021469ASuitable for single event effect testingMeet different testing needsStatic storageMemory circuitsFile comparison

Owner:BEIJING MXTRONICS CORP +1

Activity measurement-based hardware trojan detection method

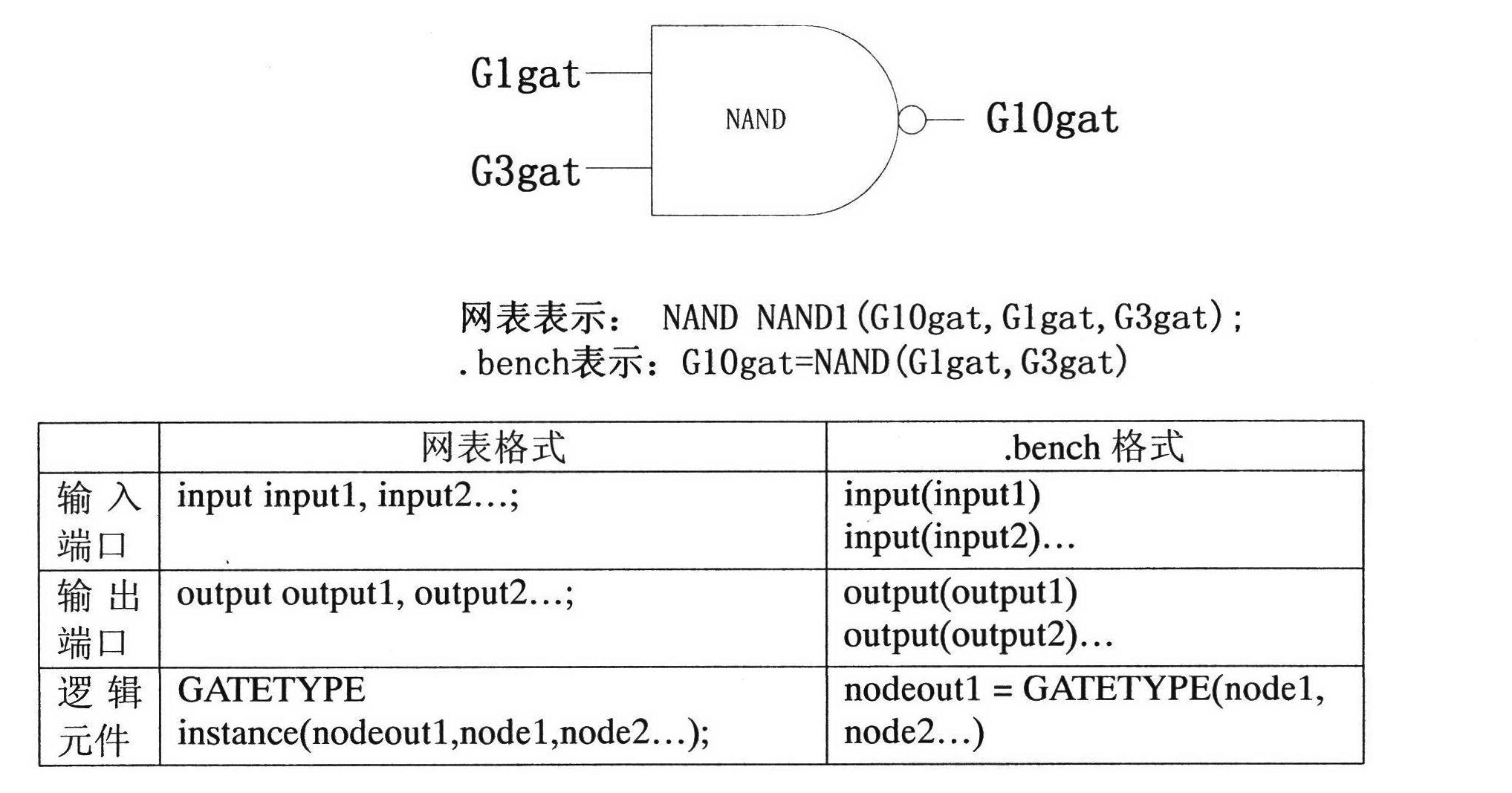

Disclosed in the invention is an activity measurement-based hardware trojan detection method, comprising three parts: bench file generation, circuit activity measurement and hardware tojan detection test vector set generation. More specifically, a circuit netlist is analyzed; activity values of internal nodes of the circuit are calculated; lists of circuit nodes with low 0 activity and low 1 activity are generated; and determination and grouping are carried out on the nodes to generate a hardware trojan detection test vector set. According to the invention, different activity threshold values can be arranged; there is no extra hardware cost for hardware trojan detection; and combined logical type hardware trojan can be effectively detected. Besides, the provided method can be applied for target node extraction in a hardware trojan detectable design method.

Owner:PEKING UNIV

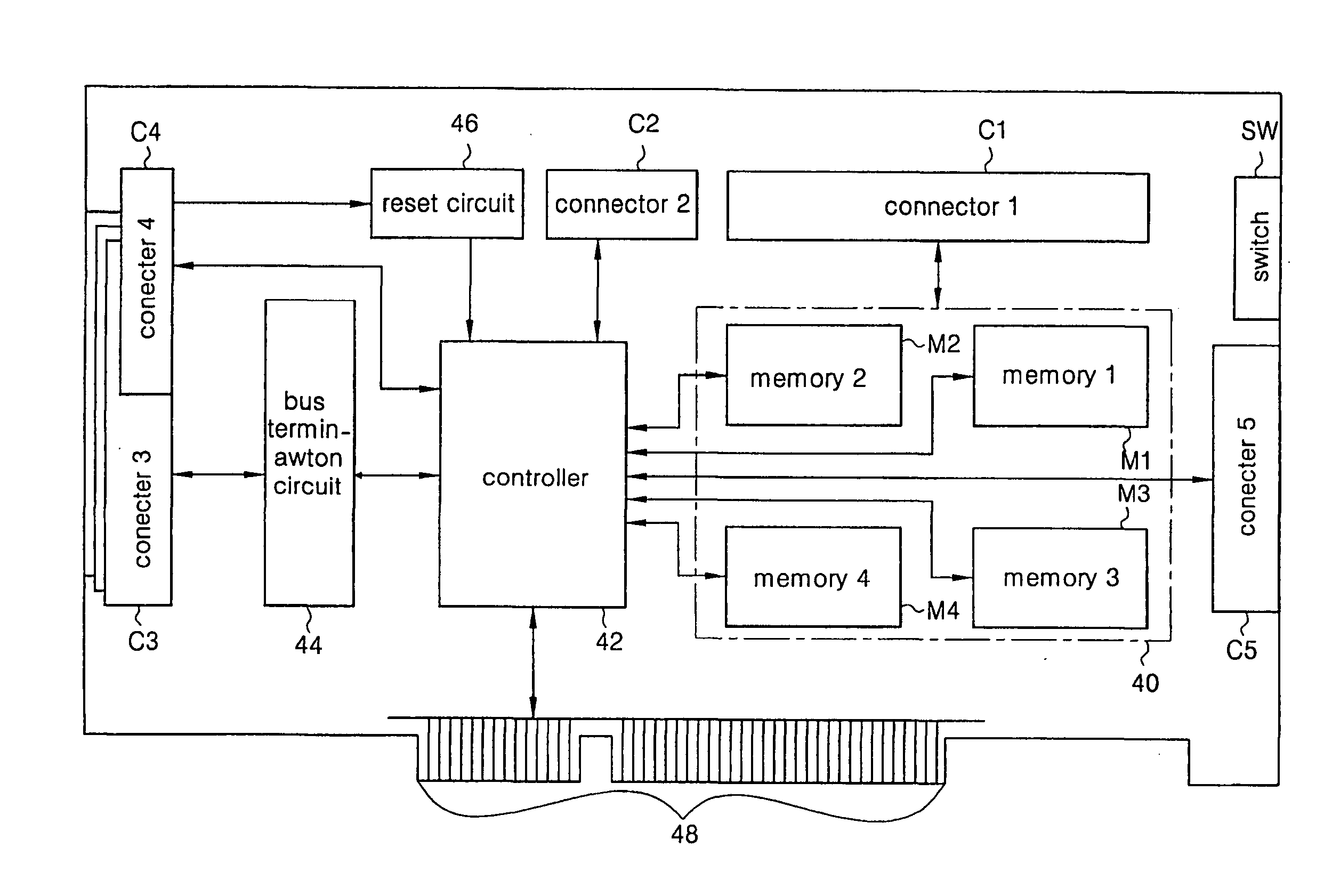

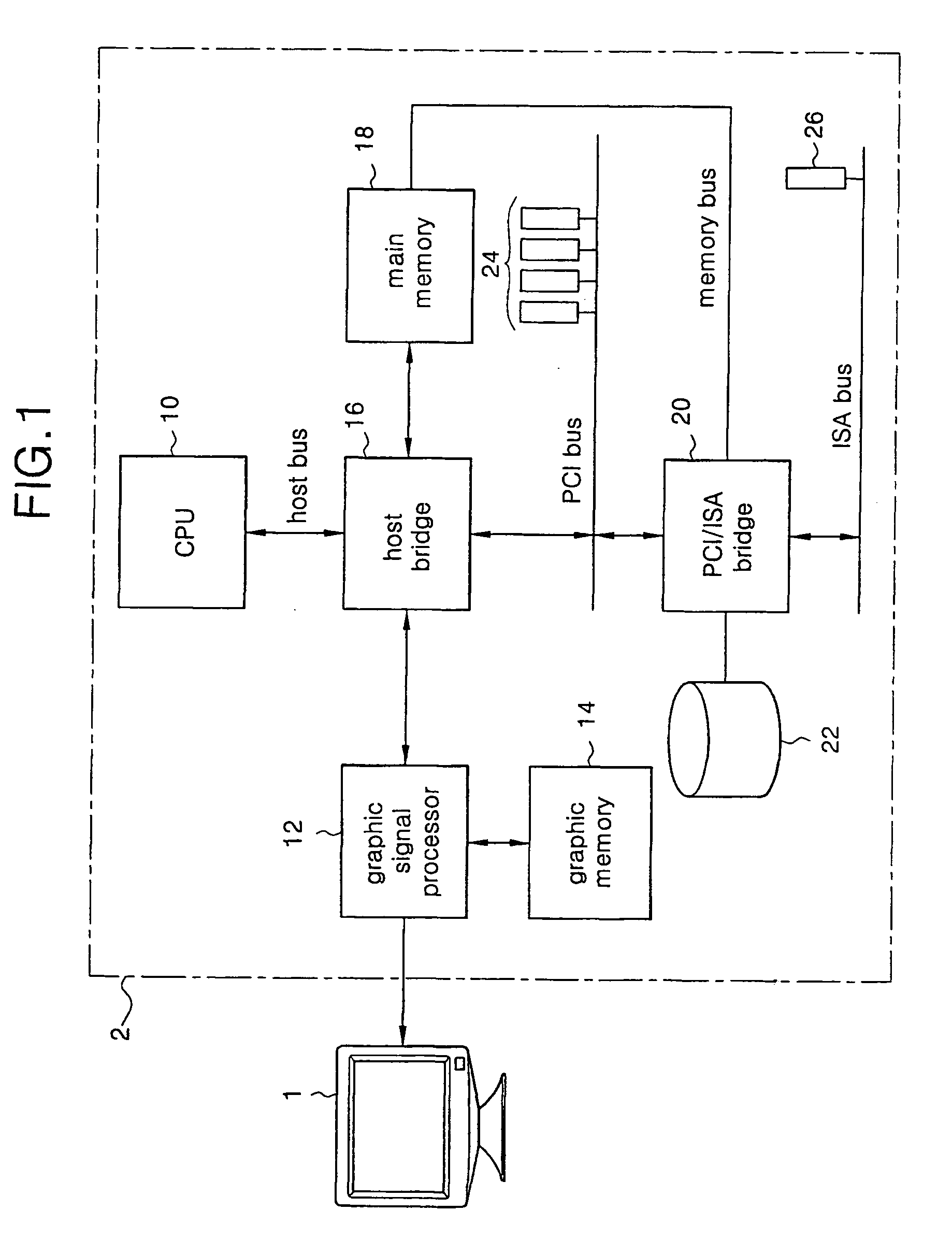

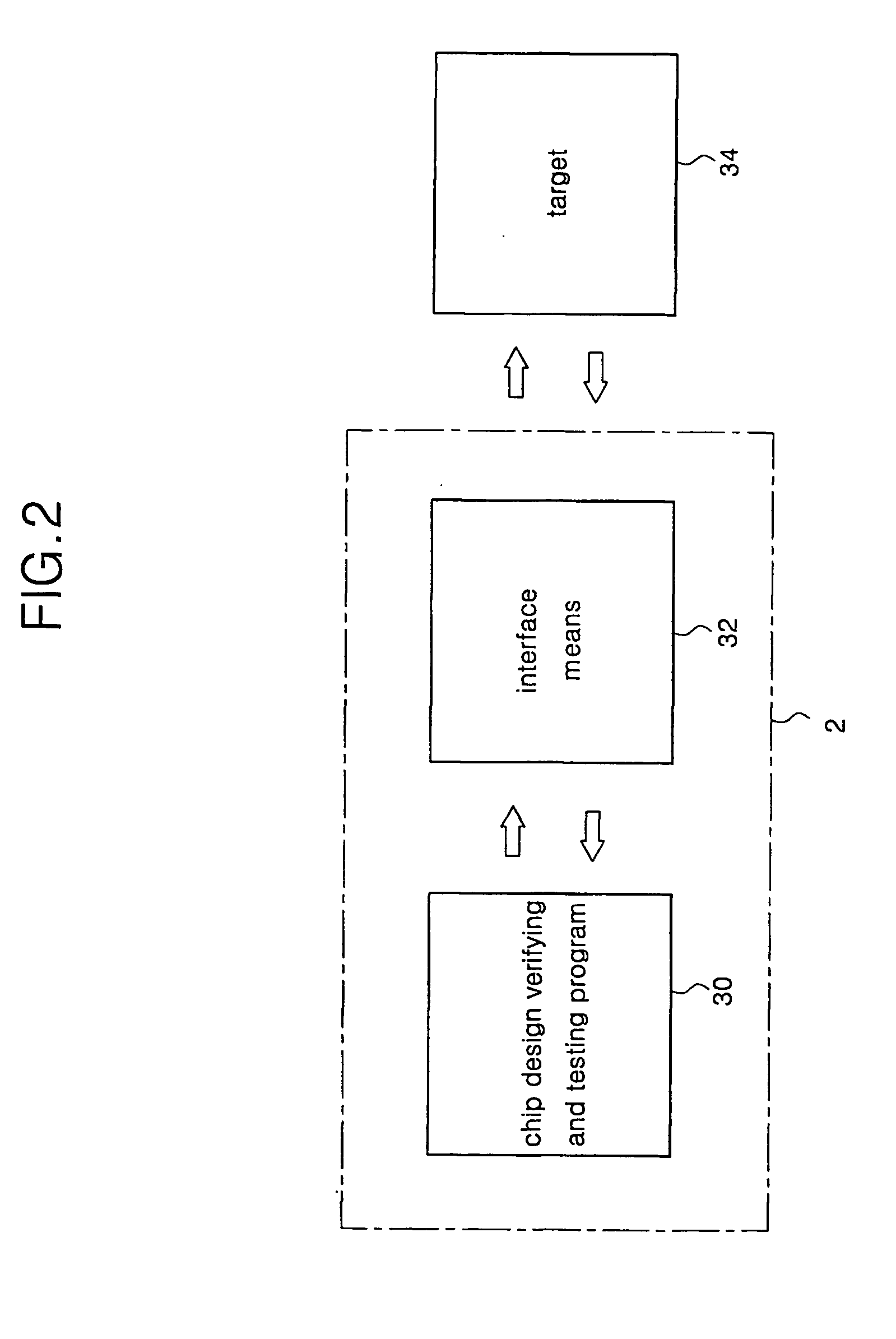

Chip design verifying and chip testing apparatus and method

InactiveUS20040138845A1Easy to detectDigital circuit testingFunctional testingData transmissionData storing

A chip design verifying and chip testing apparatus includes a storing means for storing an application program verifying an operation of a designed chip and testing a manufactured chip having a plurality of blocks, an I / O file, and a test vector; an interface means controlling a data transmission between the storing means and the chip, and having a data applying means for applying the I / O file and / or the test vector outputted from the storing means and a data storing means for storing data outputted from the chip; and a computer including a CPU for performing and controlling the application program.

Owner:PARK HYUNJU +1

Operating voltage determination for an integrated circuit

ActiveUS20050107967A1Easy to useReduce the likelihood of failureEnergy efficient ICTCurrent/voltage measurementClock rateEngineering

Owner:ARM LTD

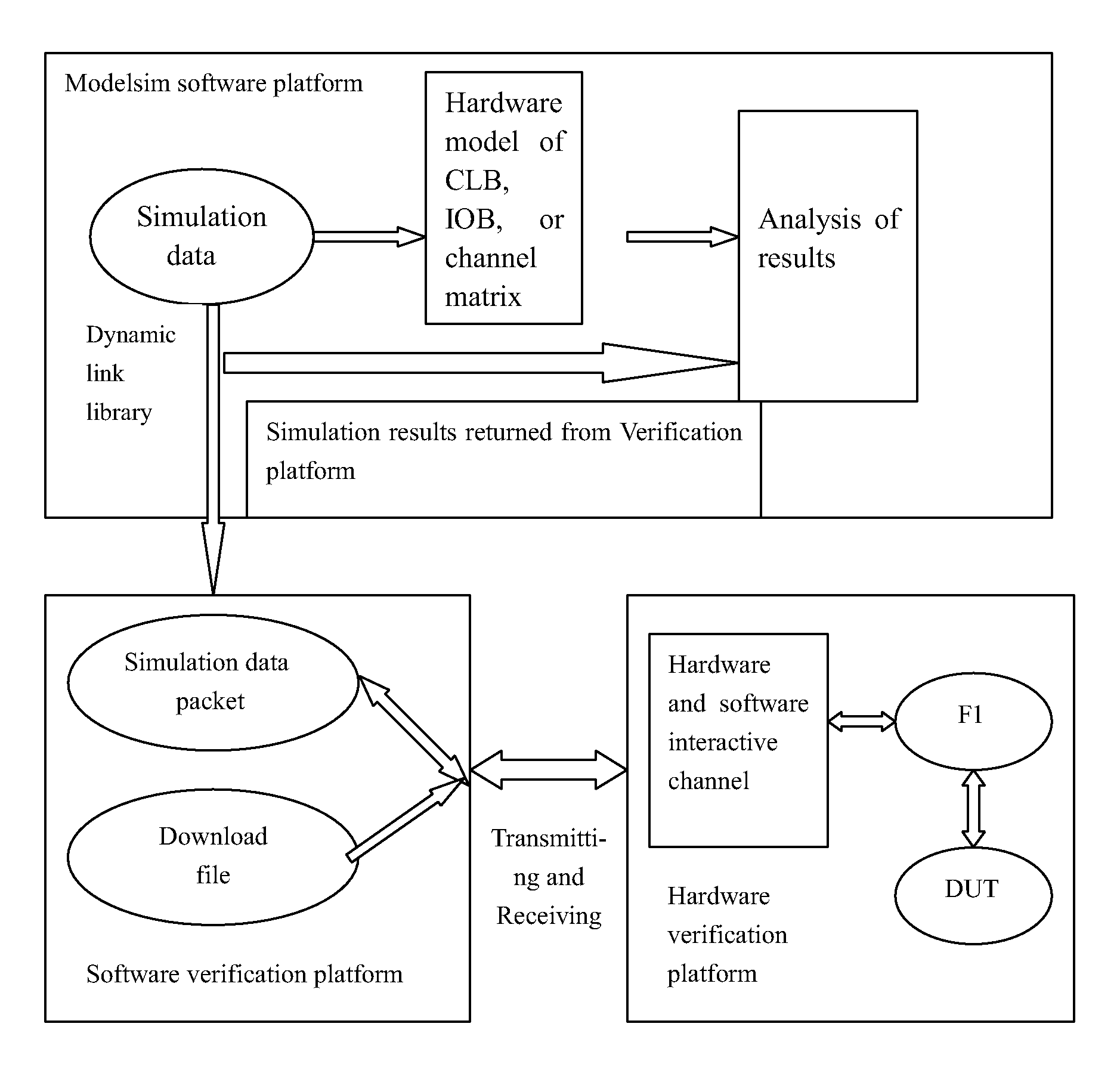

Hardware and Software Co-test Method for FPGA

InactiveUS20090100304A1Improve test efficiencyElectronic circuit testingLogical operation testingHardware accelerationTest vector

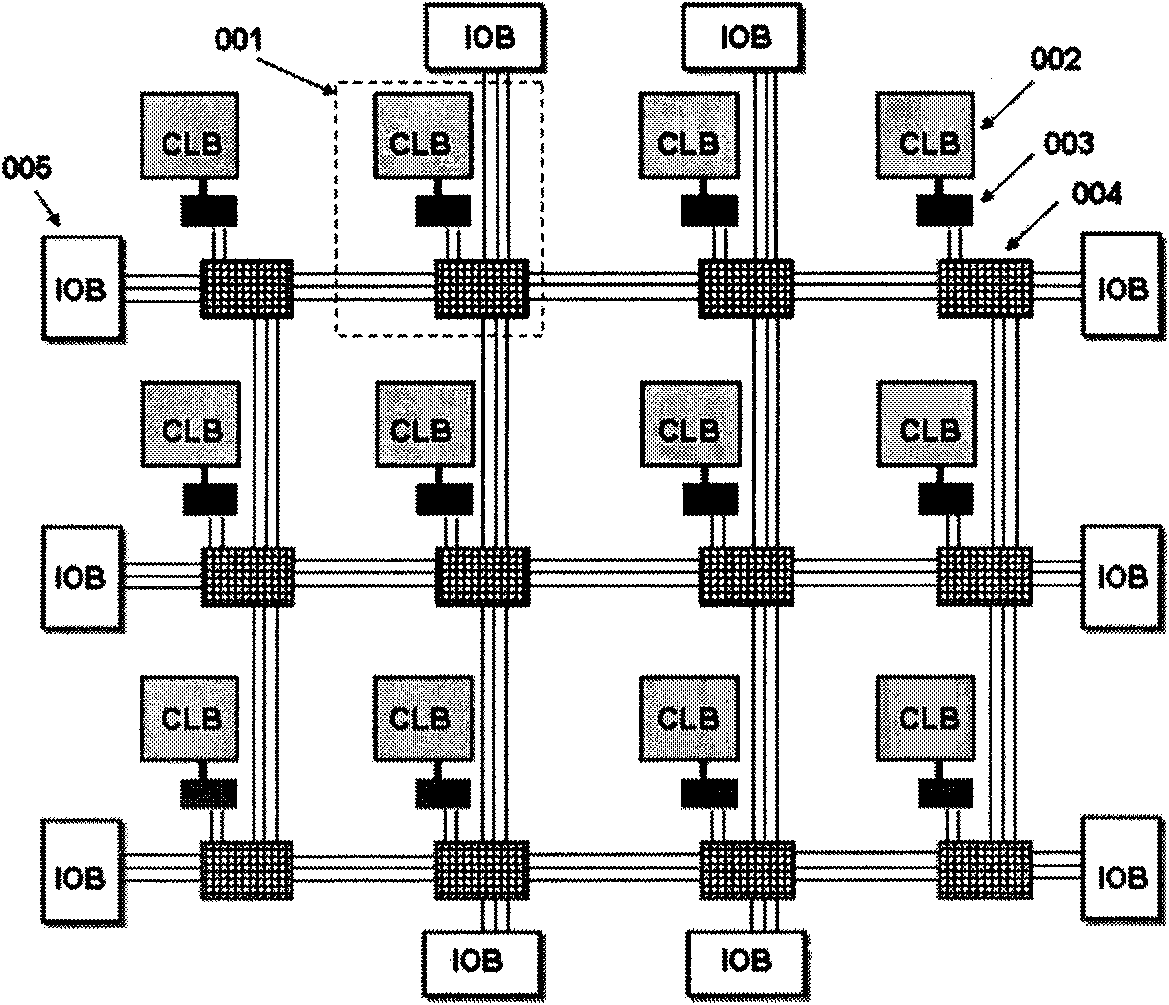

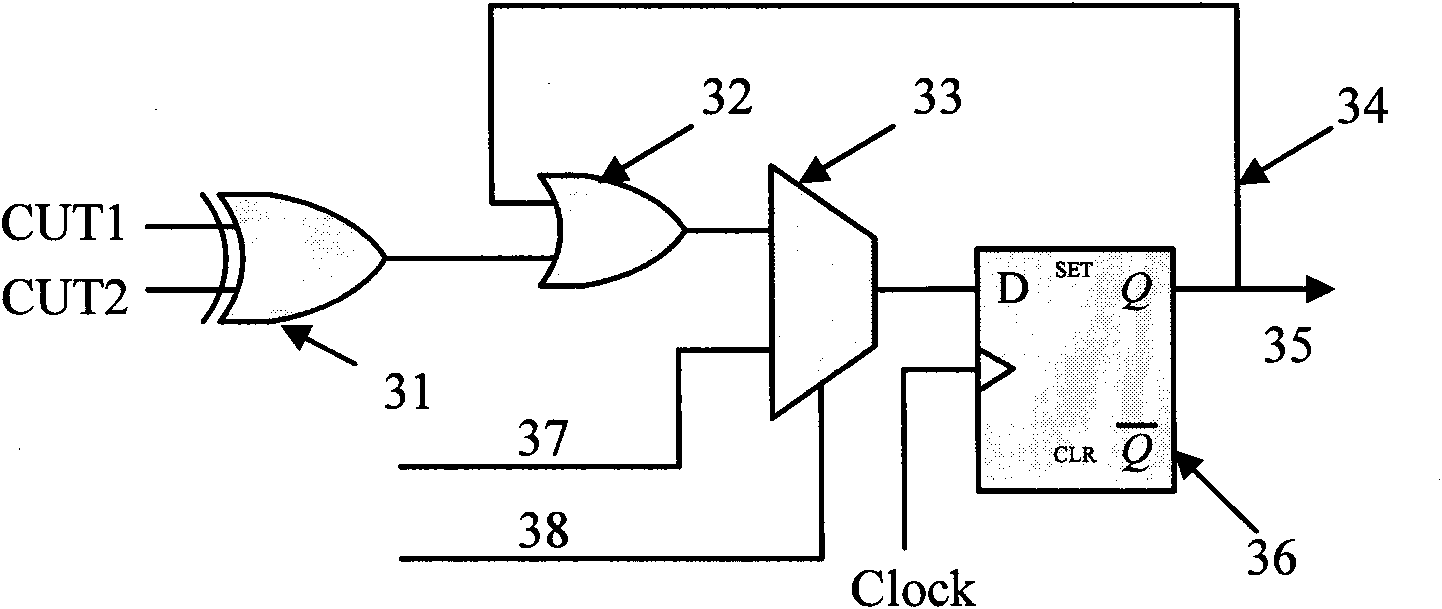

A hardware and software co-test method for FPGA comprises the following steps of: setting up a HW / SW co-test system comprising a PC, a software part, HW / SW communication modules, a hardware accelerator for testing a DUT FPGA which is mapped with a configuration file of DUT; predefining a table of test vectors for FPGA by software part in PC; generating configuration files based on the tables of test vector for I / O module, CLB and routing matrix, and then sending the configuration file into DUT FPGA to configure the FPGA; testing DUT FPGA in terms of the tables of test vector for lo I / O module, CLB and routing matrix, and returning results to the software part; and comparing the test results with expected data in the software part, generating a test report, and during the above steps, the error cells in the FPGA are capable of being automatically positioned.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Method for establishing large-scale network chip verification platform

ActiveCN101763451ARealize multiplexingReduce build timeSpecial data processing applicationsRegister allocationReference model

The invention relates to a method for establishing a large-scale network chip verification platform. The method comprises the following steps of: firstly, establishing a control text document, and then writing an initial function of a random function library, and writing a calling function of the random function library; secondly, establishing a module-level function verification platform, comprising the following steps of: generating a top-level module of the module-level function verification platform, establishing a clock generating module and a reset generating module, establishing an interface signal module, establishing a test vector generating module, establishing a register configuring module and establishing a reference model module of a tested module; and thirdly, establishing a chip-level function verification platform, comprising the following steps of: generating a top-level module of the chip-level function verification platform, multiplexing the clock generating module, the rest module, the interface signal module, the test vector generating module, the register configuring module and the reference model module of the module-level function verification platform, and establishing a CPU simulation model. The method has a strong function, high efficiency, stability and simple structure. By means of the invention, the time for setting up the network chip verification platform can be greatly shortened and the stimulation efficiency can be improved.

Owner:丁贤根

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com