Method and device for verifying SoC (system on a chip) chips

A system-on-chip, chip technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of complex test system construction, long construction time, poor reusability, etc., to reduce complexity and maintenance difficulty, reduce Verifying difficulty and enhancing the effect of reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

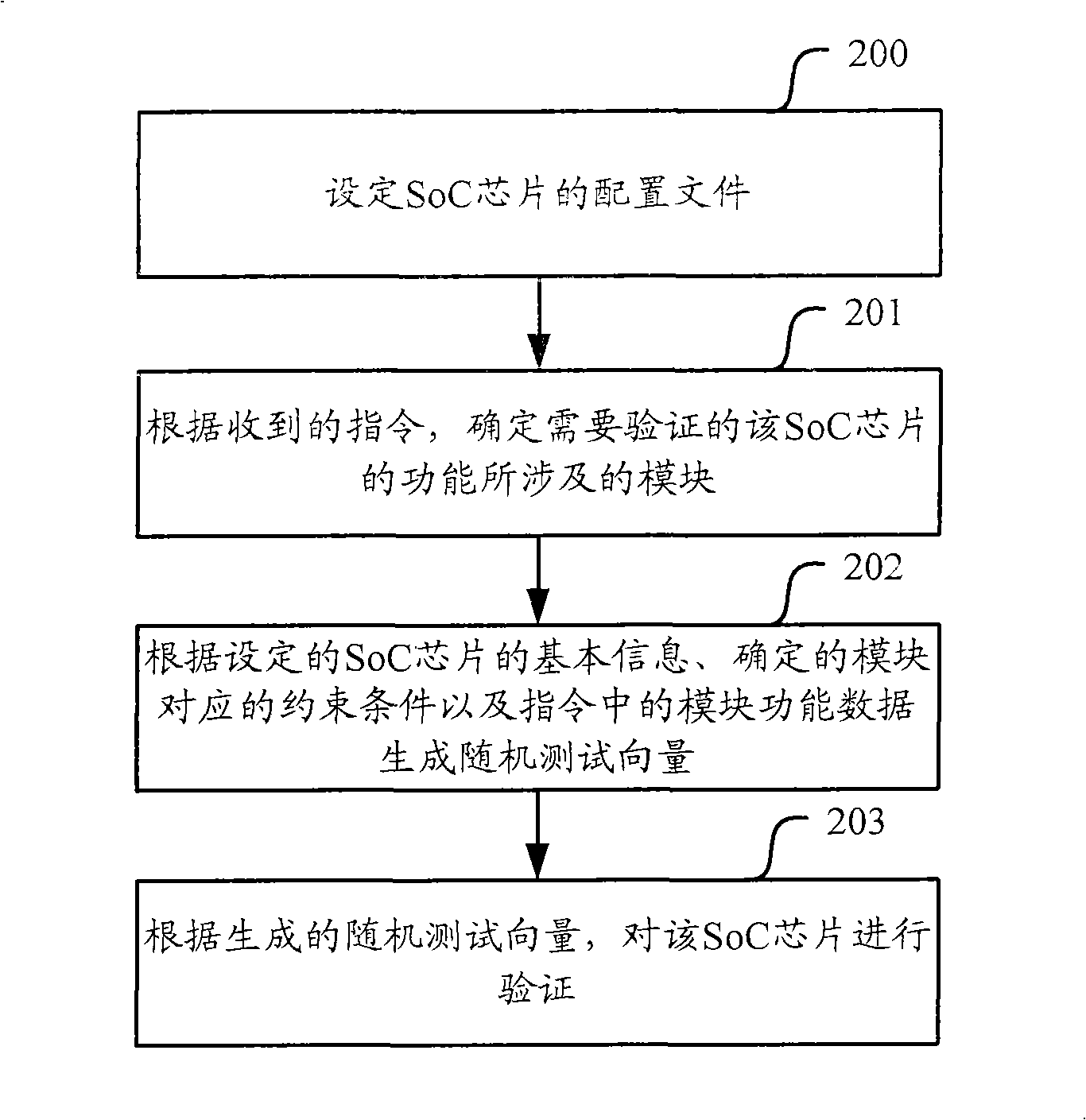

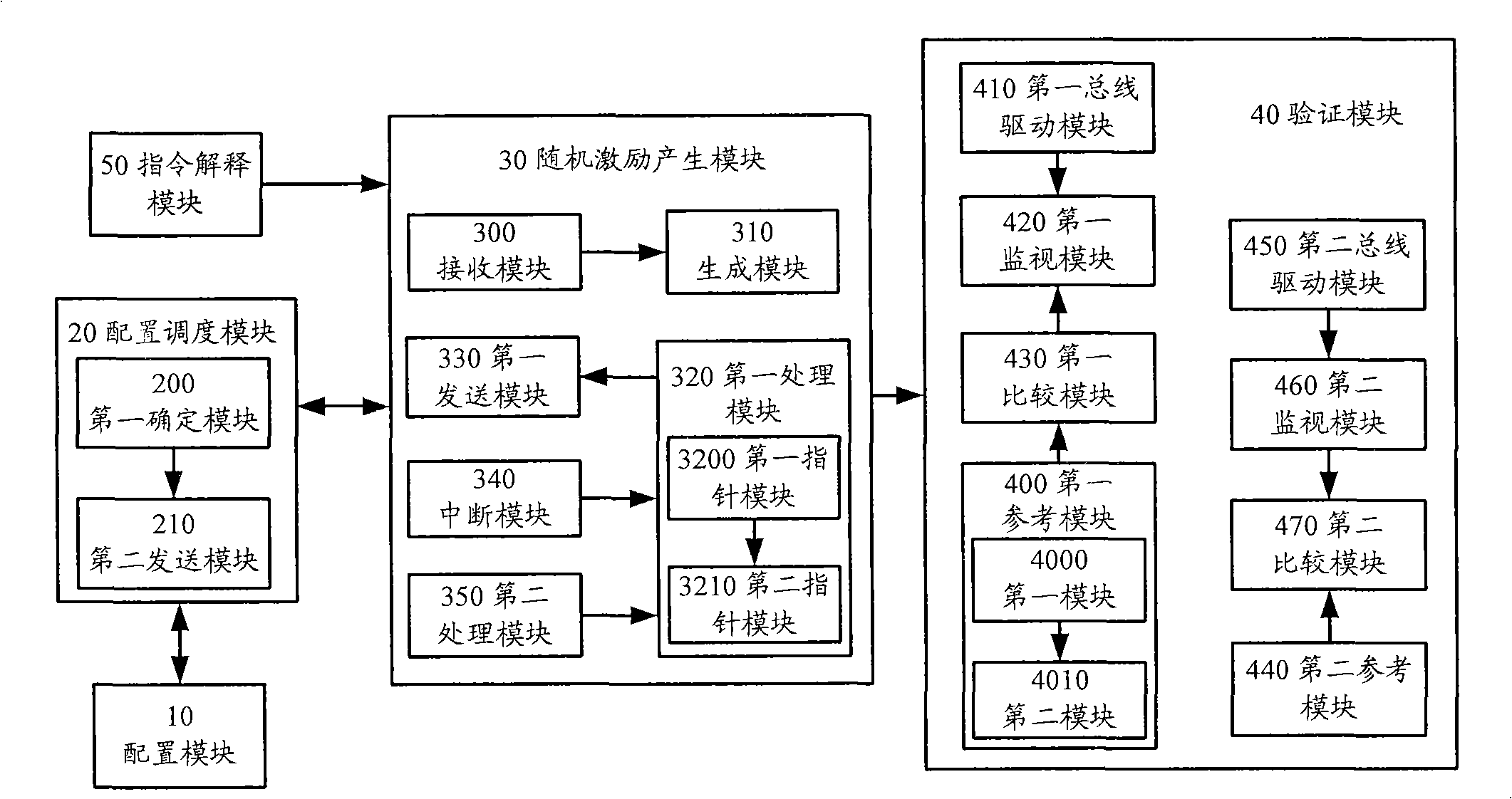

[0040] In the embodiment of the present invention, the SoC chip to be verified is divided into modules, and the configuration file of the SoC chip is set. The configuration file includes the basic information of the SoC chip and the constraints of the modules in the SoC chip, and the SoC to be verified is added to the instruction. The module function data of the modules involved in the function of the chip, according to the basic information, constraints and module function data, generate random test vectors to verify the SoC chip. When testing other functions of the chip next time, only need to add in the instruction The module function data of the modules involved in the function of the SoC chip that needs to be verified is sufficient, and the entire test system does not need to be recompiled, thereby reducing the complexity and difficulty of verifying the SoC chip, and saving the time for verifying the SoC chip.

[0041] Among them, the basic information of the SoC chip incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com