Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

256 results about "Random testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Random testing is a black-box software testing technique where programs are tested by generating random, independent inputs. Results of the output are compared against software specifications to verify that the test output is pass or fail. In case of absence of specifications the exceptions of the language are used which means if an exception arises during test execution then it means there is a fault in the program, it is also used as way to avoid biased testing.

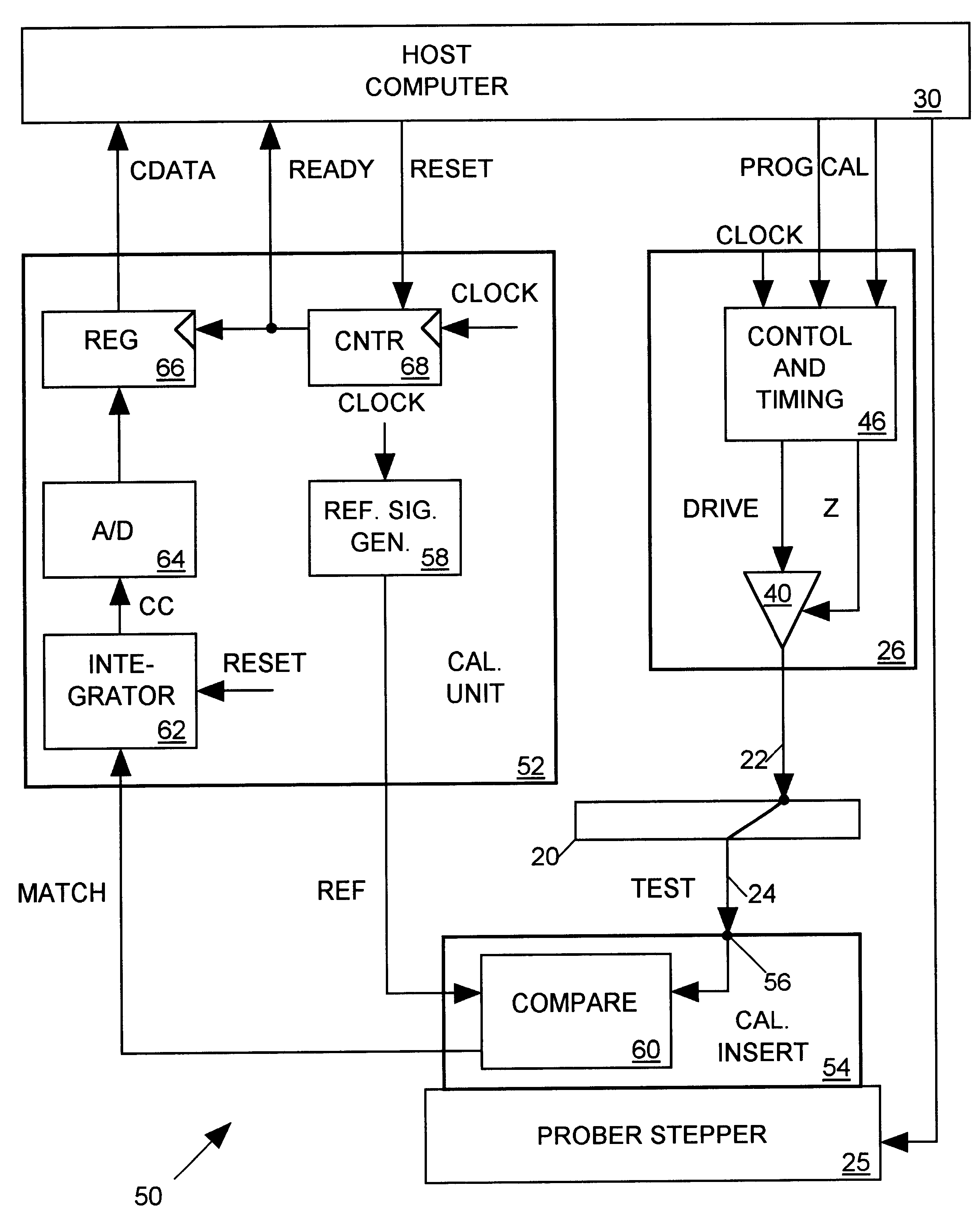

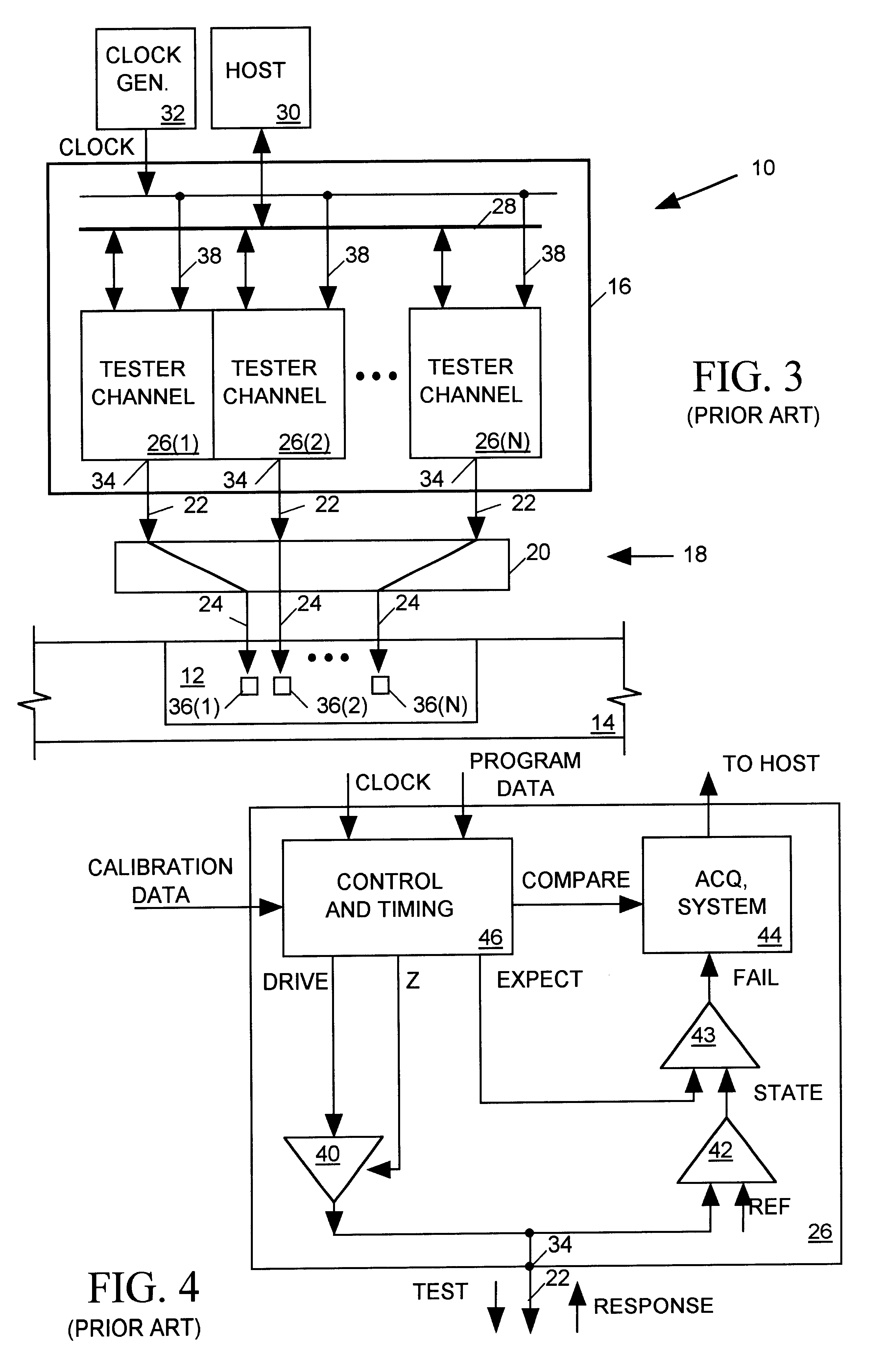

Cross-correlation timing calibration for wafer-level IC tester interconnect systems

InactiveUS6606575B2Easy accessDigital circuit testingTesting/calibration apparatusEngineeringSignal edge

To calibrate timing of test signals generated by all channels of an integrated circuit, each channel is programmed to generate a test signal having a repetitive pseudo-random test signal edge pattern. The test signal pattern of each channel is compared to a reference signal having the same edge pattern and the delay of each channel is adjusted to maximize cross-correlation between the test signal and the reference signal.

Owner:FORMFACTOR INC

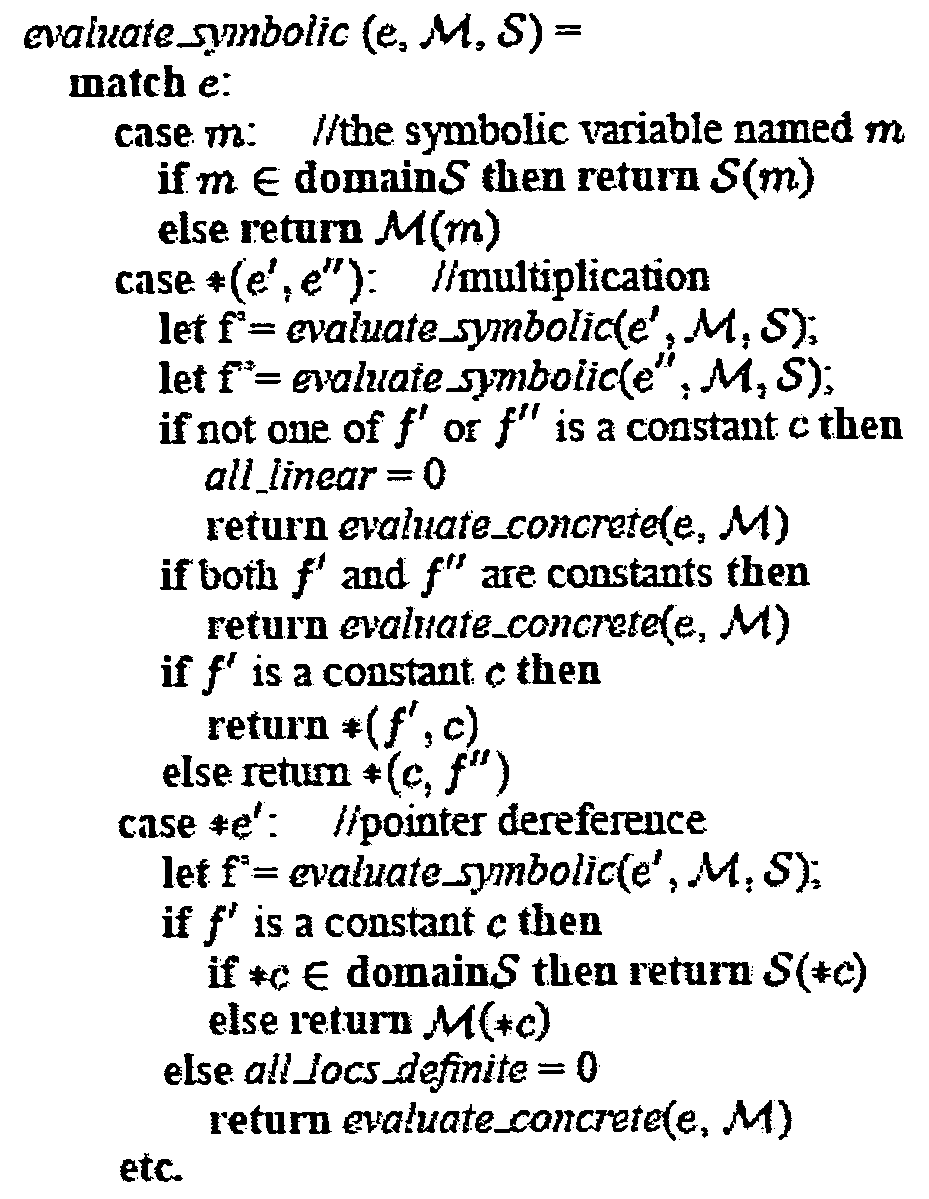

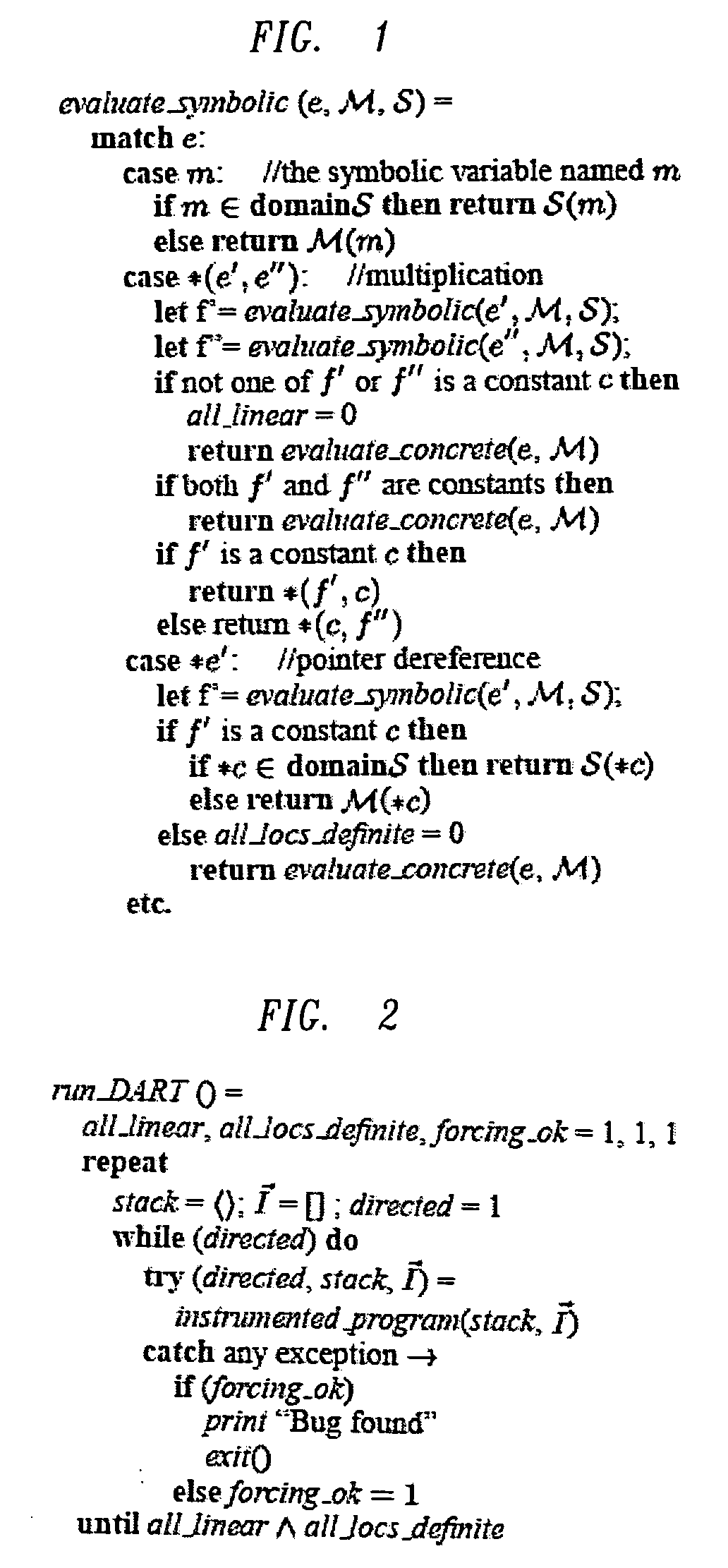

Method and apparatus for performing unit testing of software modules with use of directed automated random testing

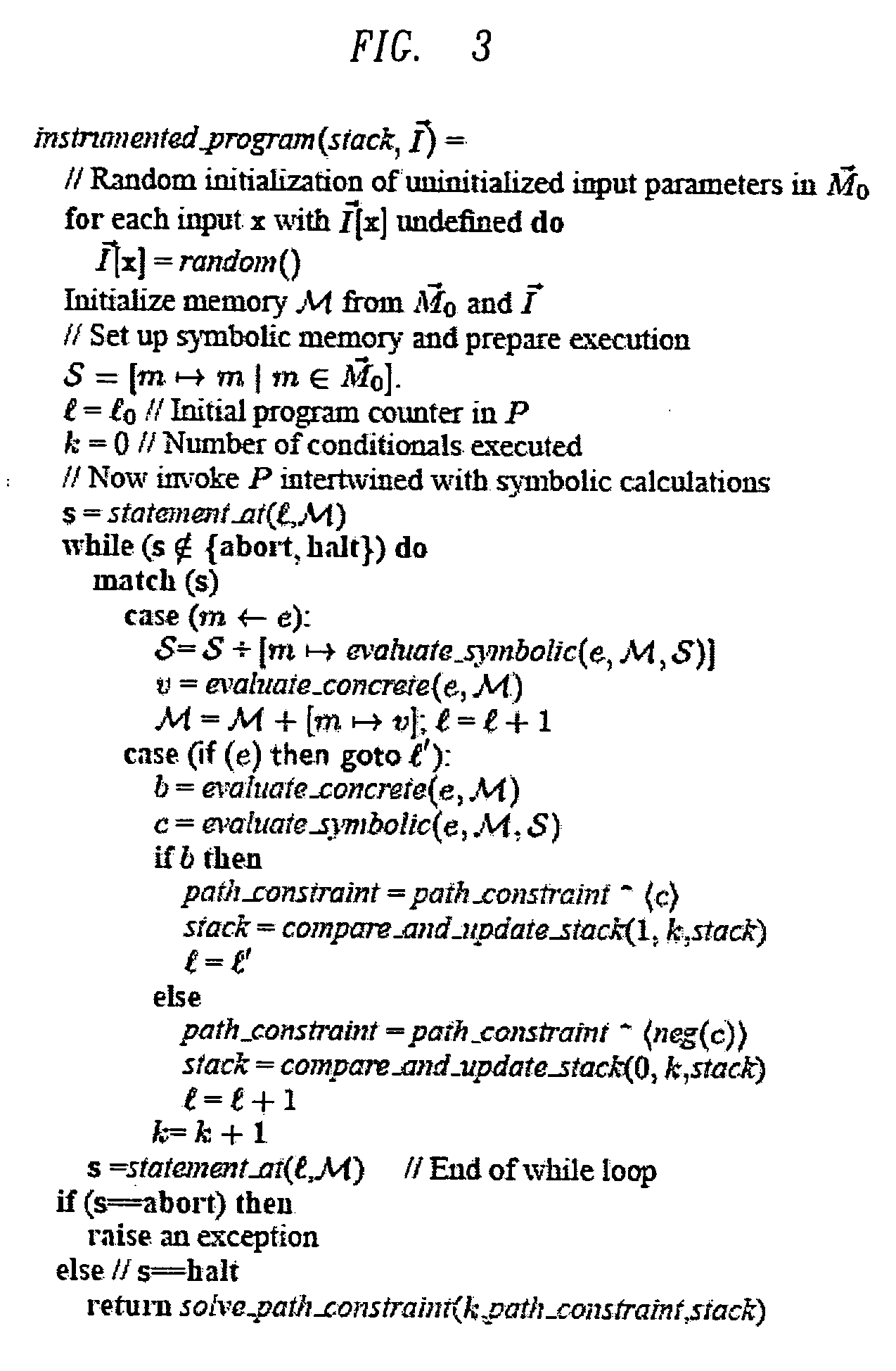

A method and apparatus for performing unit testing of software modules uses a novel directed automated random testing approach that advantageously combines automated extraction of the interface of a program with its external environment using static source code parsing; automatic generation of a test driver for this interface that advantageously performs random testing to simulate the most general environment the program can operate in; and dynamic analysis of how the program behaves under random testing and automatic generation of new test inputs to direct systematically the execution along alternative program paths. Together, these techniques constitute a directed automated random testing approach (DART). With DART, testing can be performed completely automatically on any program that compiles without the need to write any test driver or harness code. During testing, DART detects standard errors such as program crashes, assertion violations, and non-termination conditions.

Owner:LUCENT TECH INC

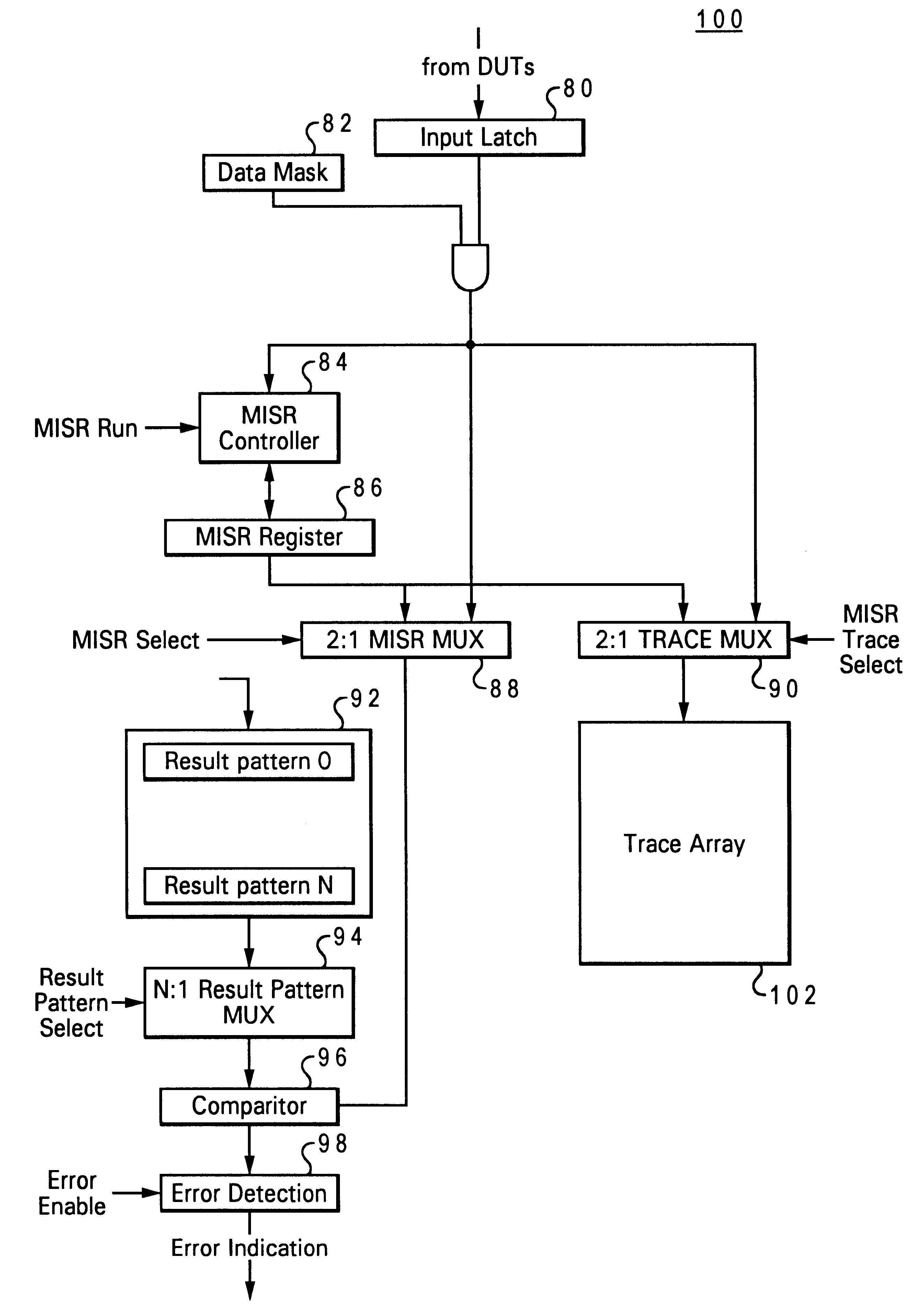

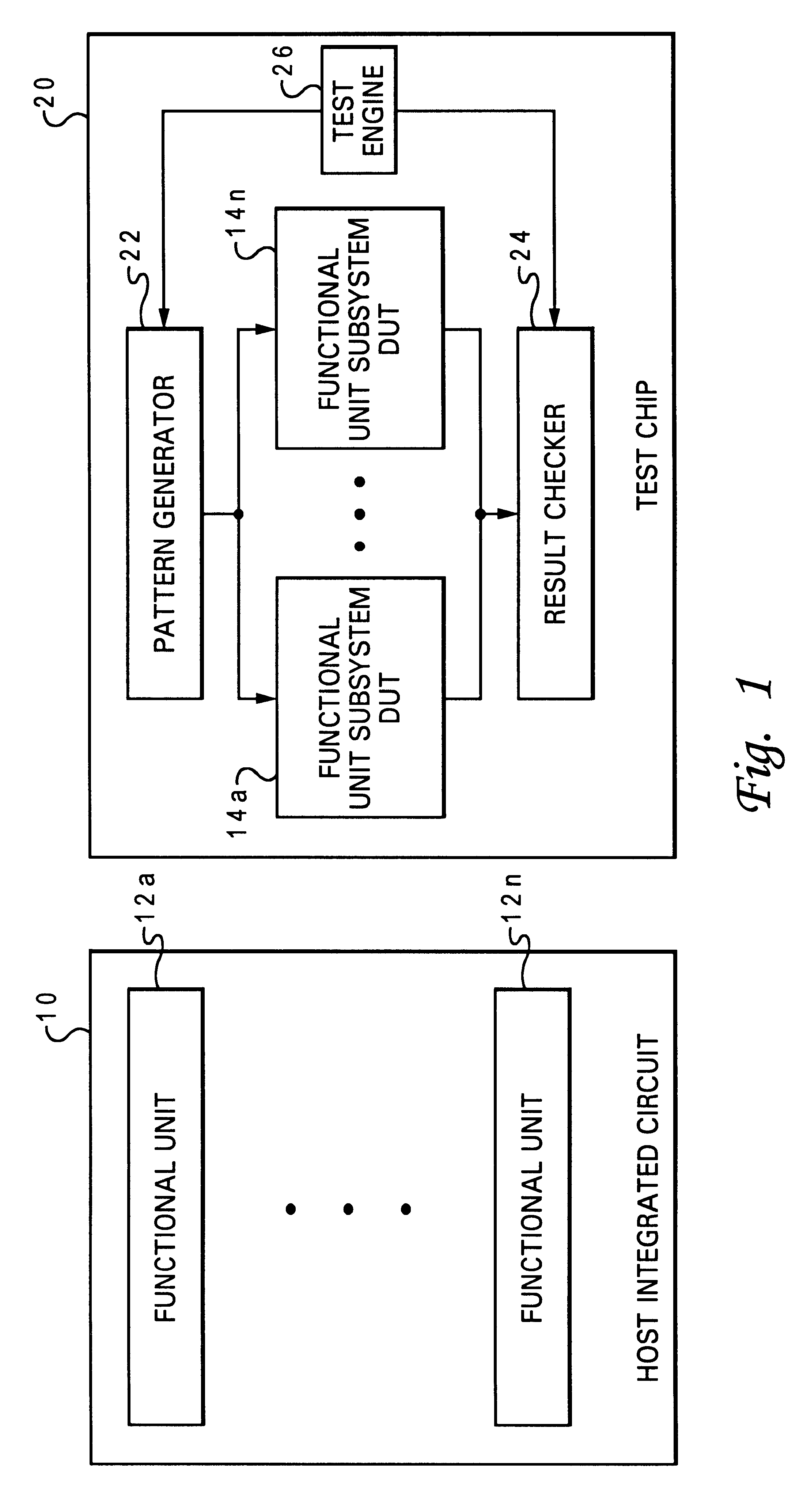

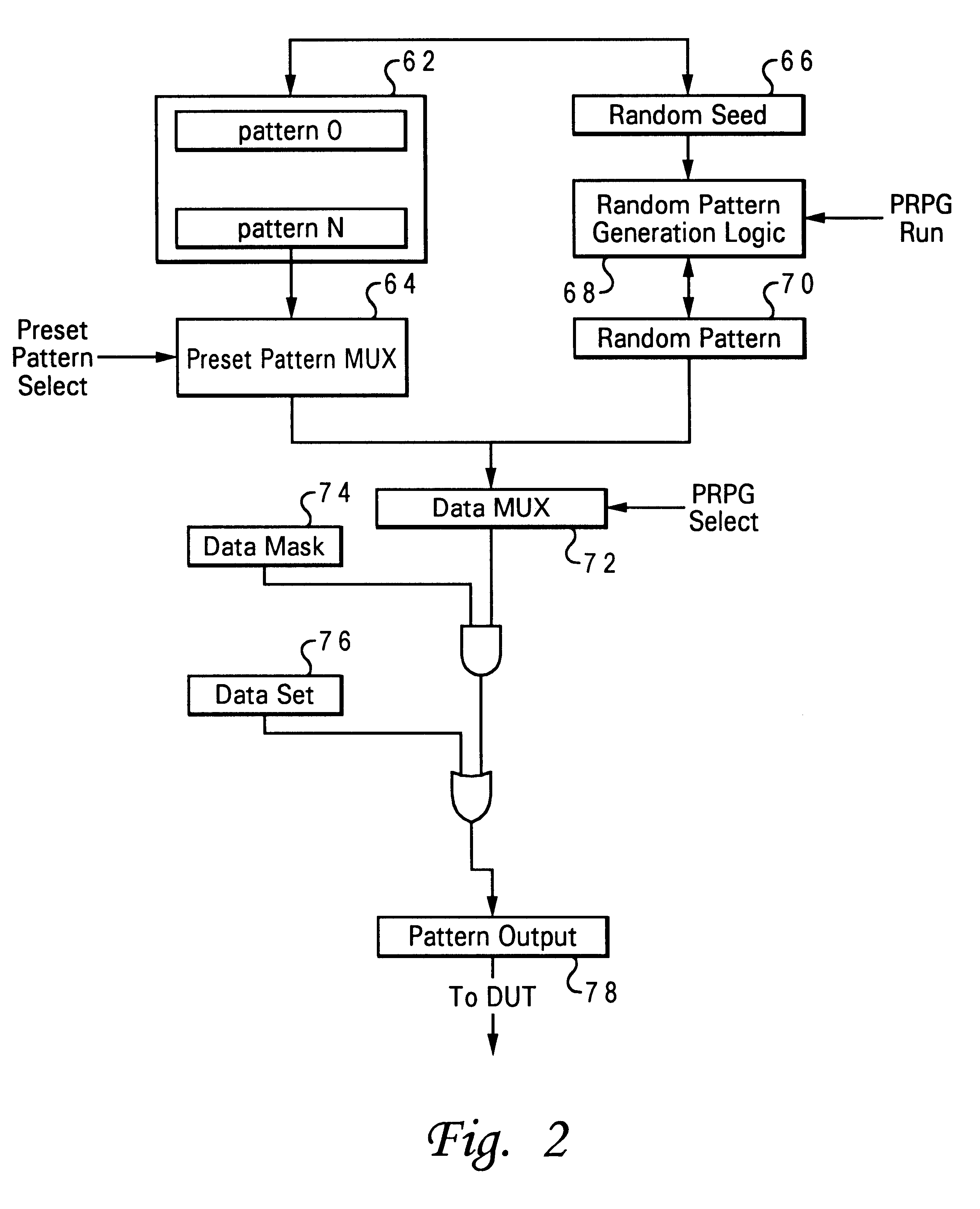

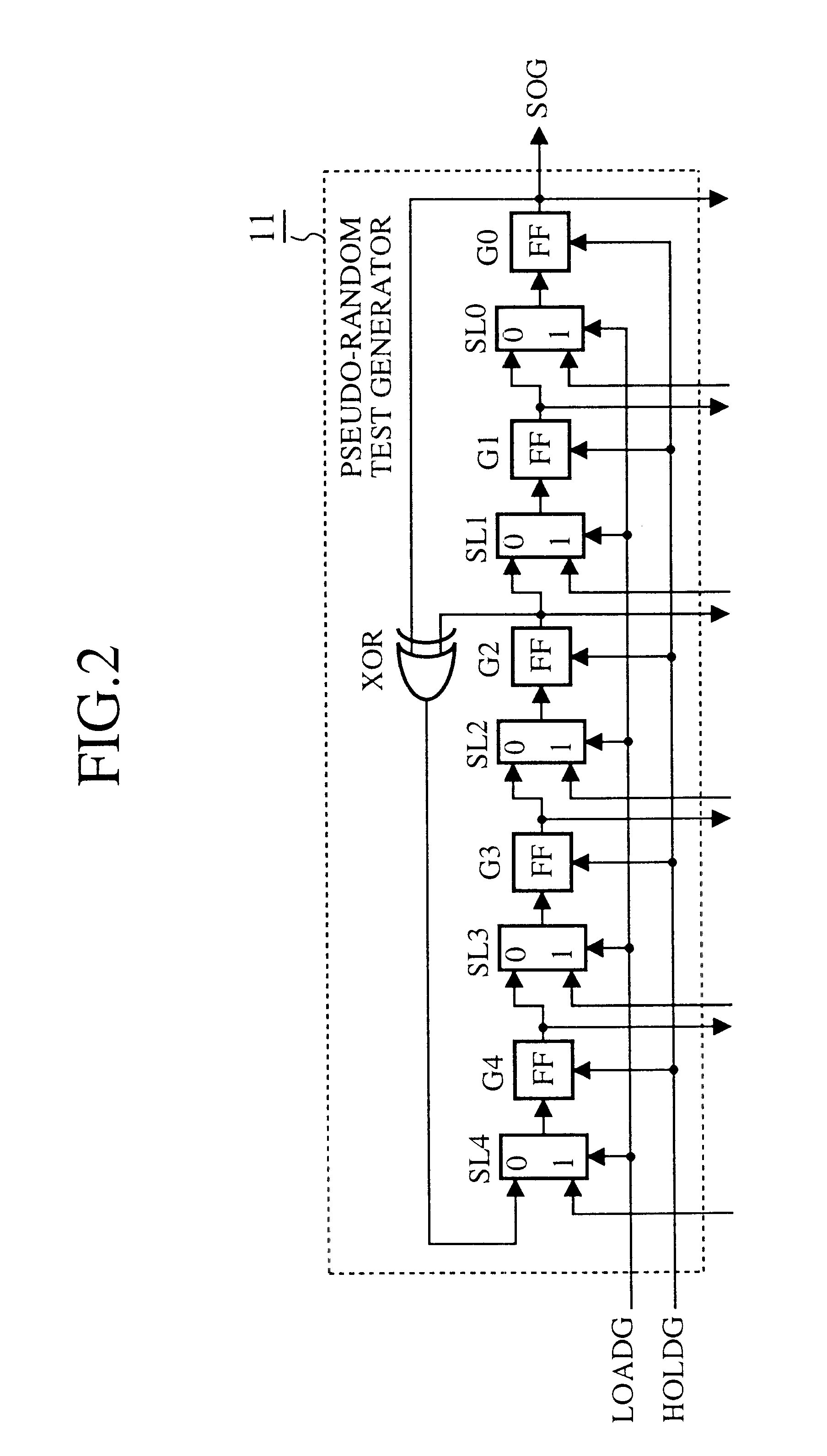

Method and system for performing pseudo-random testing of an integrated circuit

InactiveUS6393594B1Electronic circuit testingError detection/correctionEngineeringIntegrated circuit

A method and system for testing an integrated circuit. A test substrate is provided which is manufactured by the same particular production technology for which the integrated circuit is designed. A pattern generator for generating test data and a result checker for comparing output data are embedded on the test substrate. Isolated portions of circuitry of the integrated circuit are selectively embedded onto the test substrate. Test data from the pattern generator is applied to the isolated portions of circuitry under a first operating condition. The data output from the isolated portions of circuitry is selectively recorded into the result checker. The isolated portions of circuitry are then subjected to testing by applying test data from the pattern generator to the isolated portions of circuitry under a second operating condition. Errors in the isolated portions of circuitry are detected with the result checker by comparing data output from the isolated portions of circuitry with the selectively recorded data output, such that the integrated circuit is tested by subsets, independently of testing the integrated circuit in its entirety.

Owner:IBM CORP

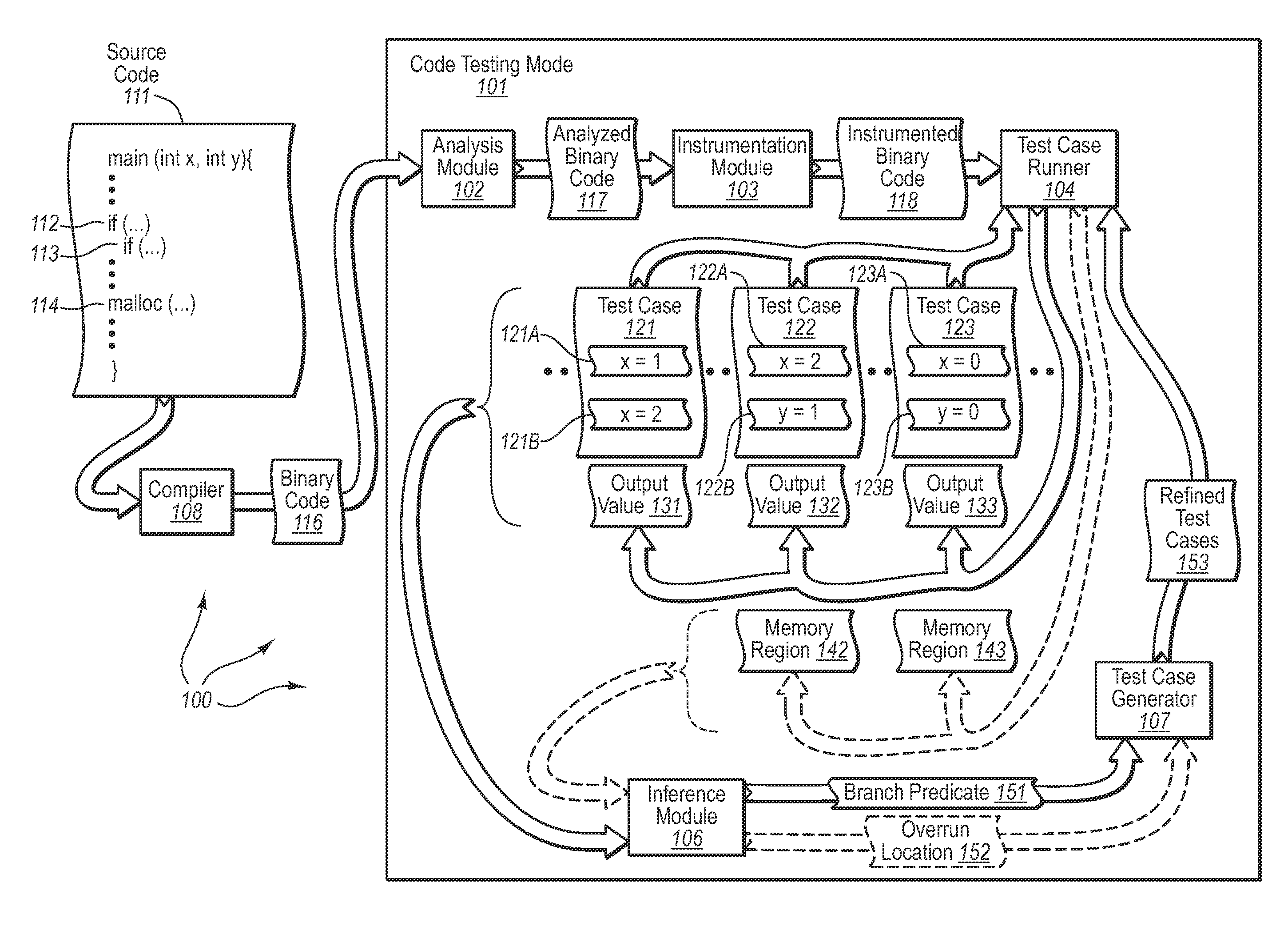

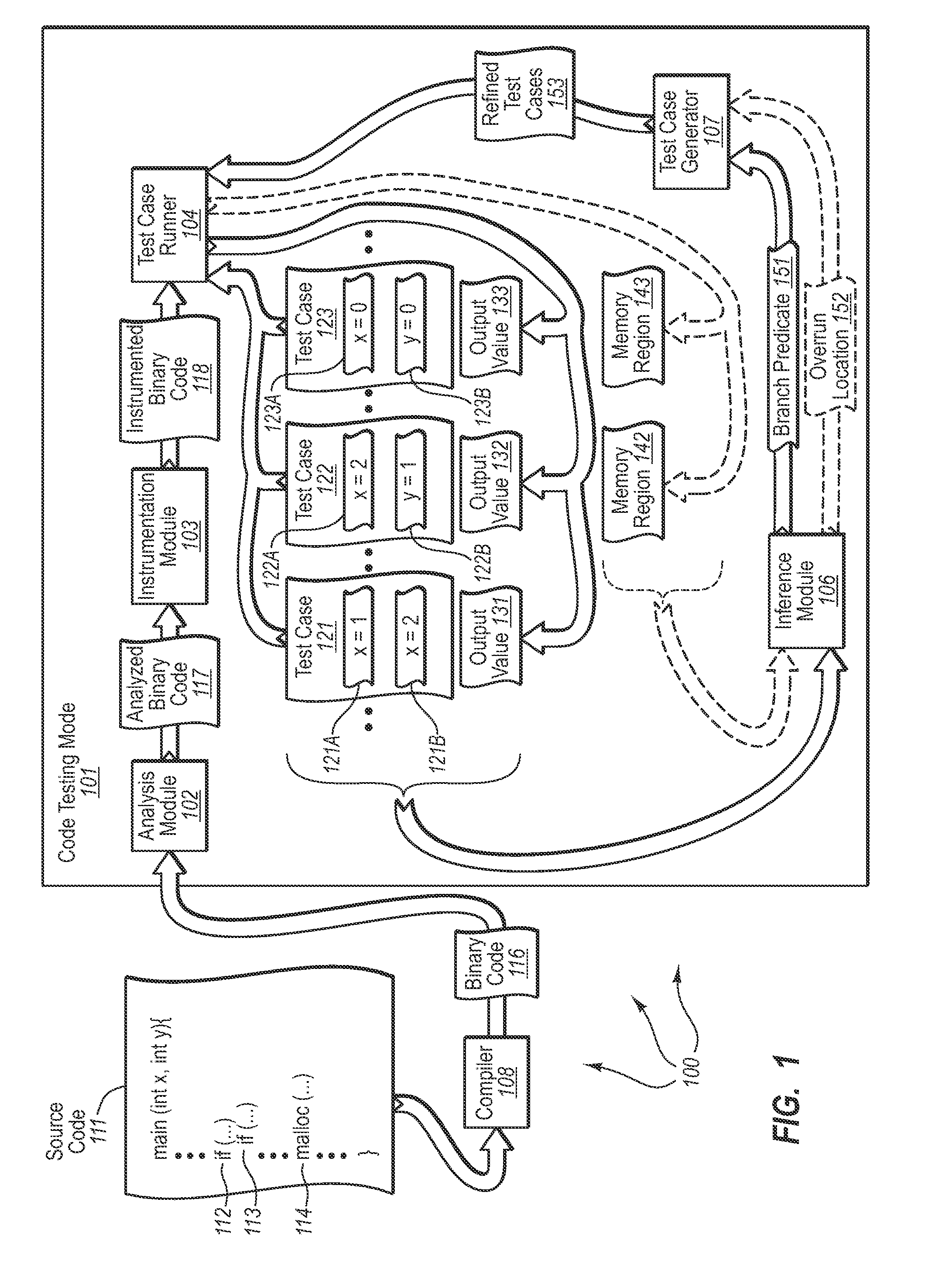

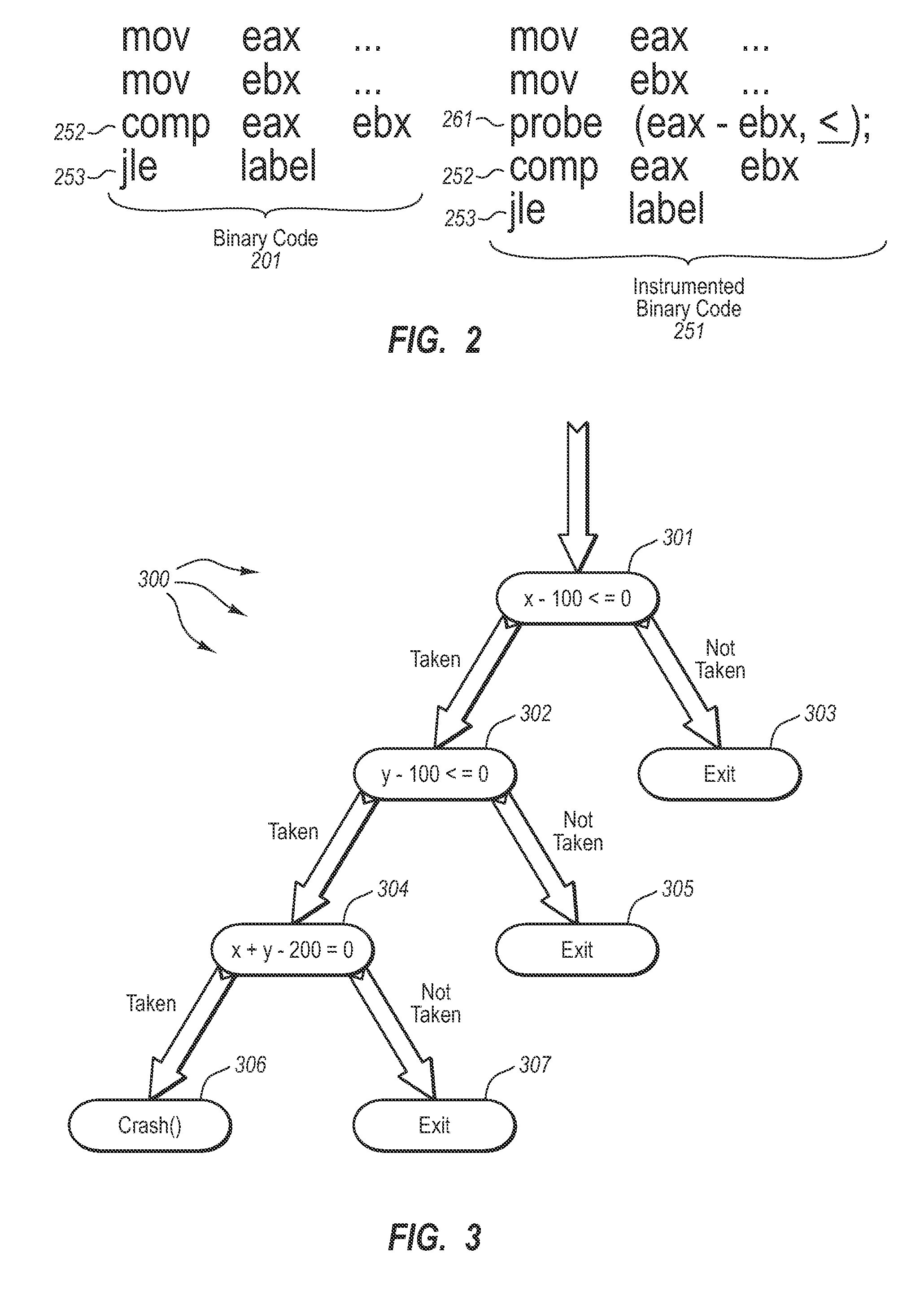

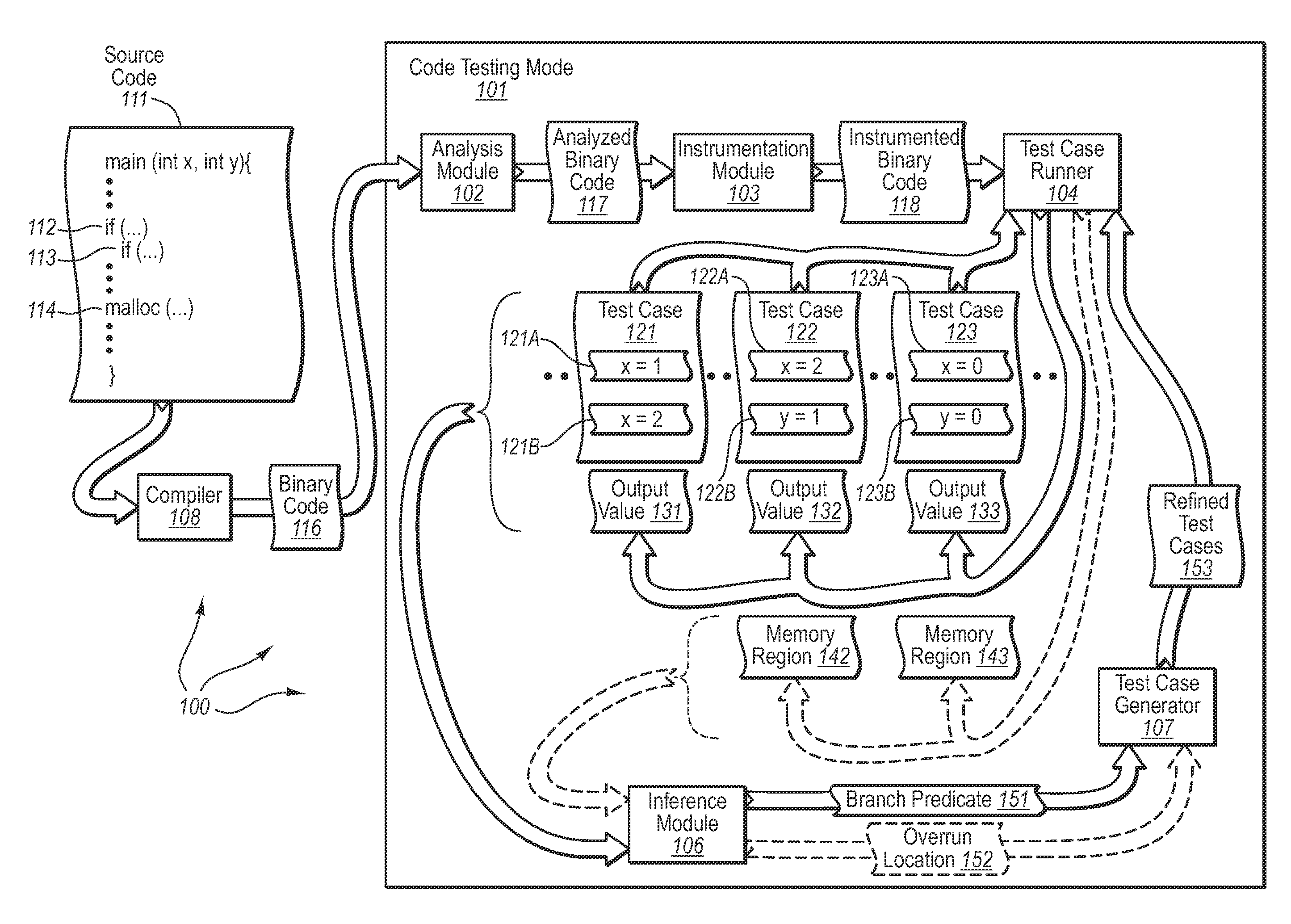

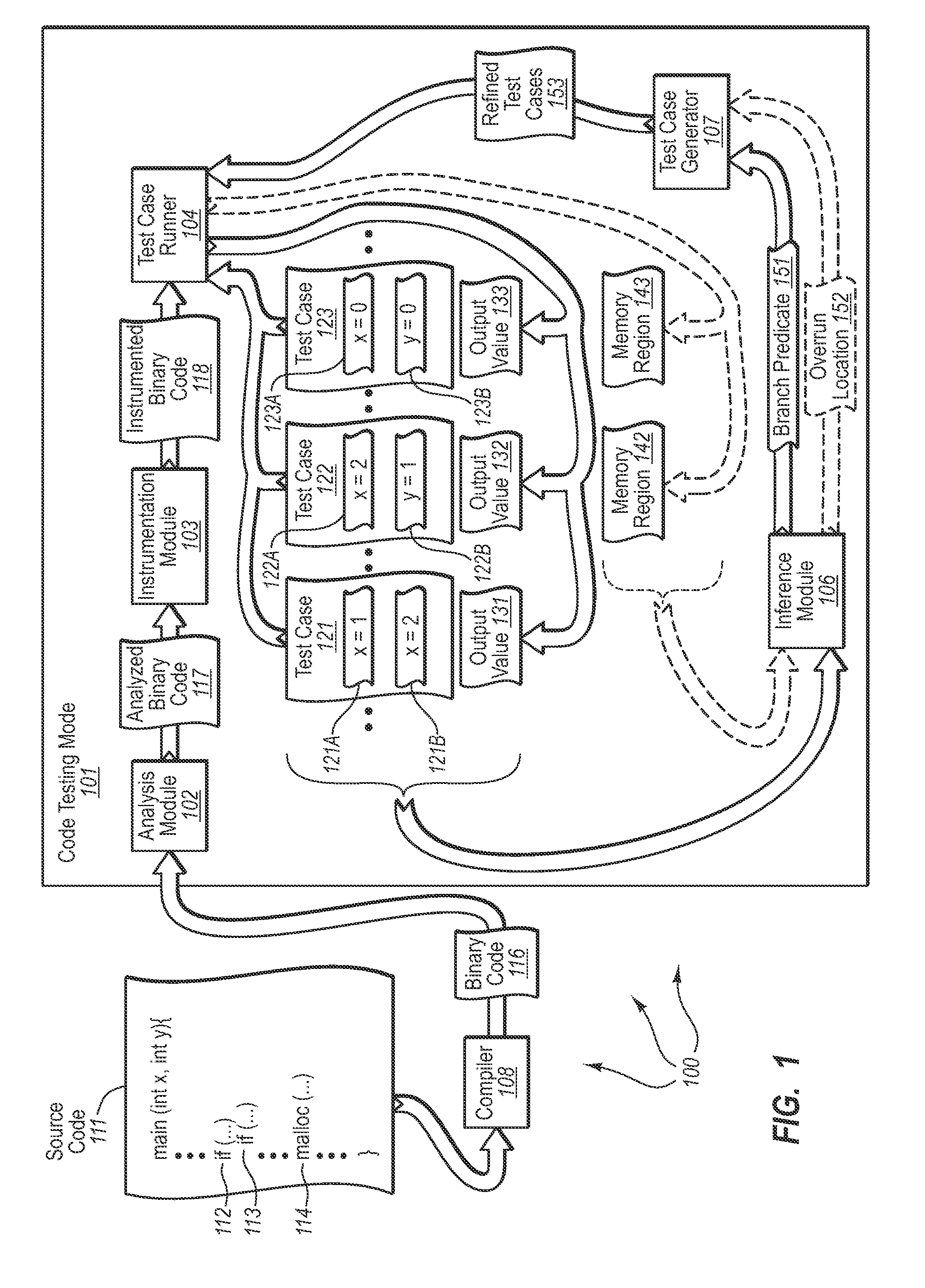

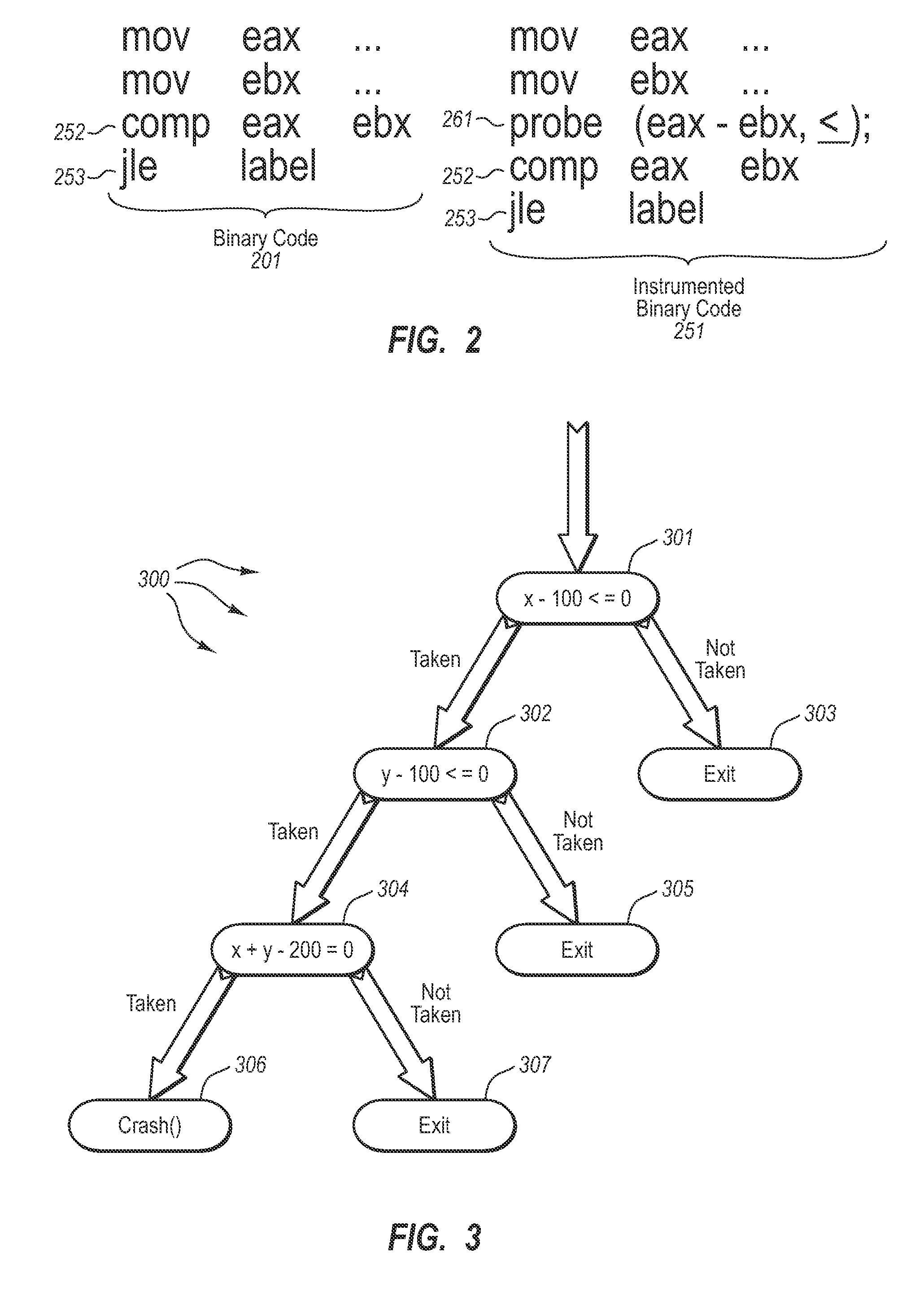

Automatically generating test cases for binary code

InactiveUS20090007077A1Efficient testingError detection/correctionSpecific program execution arrangementsTest inputParallel computing

The present invention extends to methods, systems, and computer program products for automatically generating test cases for binary code. Embodiments of the present invention can automatically generate test inputs for systematically covering program execution paths within binary code. By monitoring program execution of the binary code on existing or random test cases, branch predicates on execution paths can be dynamically inferred. These inferred branch predicates can then be used to drive the program along previously unexplored execution paths, enabling the learning of further execution paths. Embodiments of the invention can be used in combination with other analysis and testing techniques to provide better test coverage and expose program errors.

Owner:MICROSOFT TECH LICENSING LLC

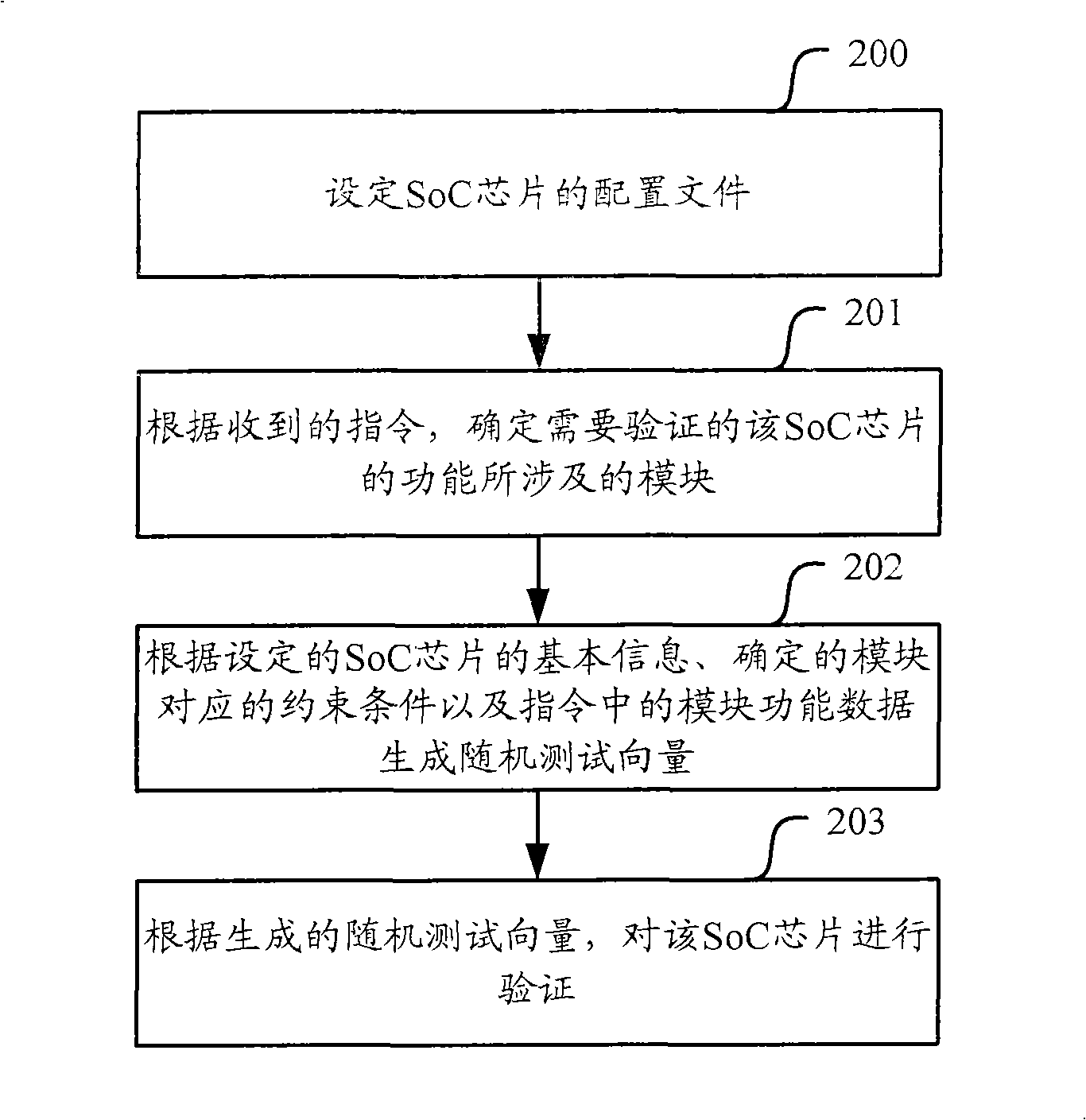

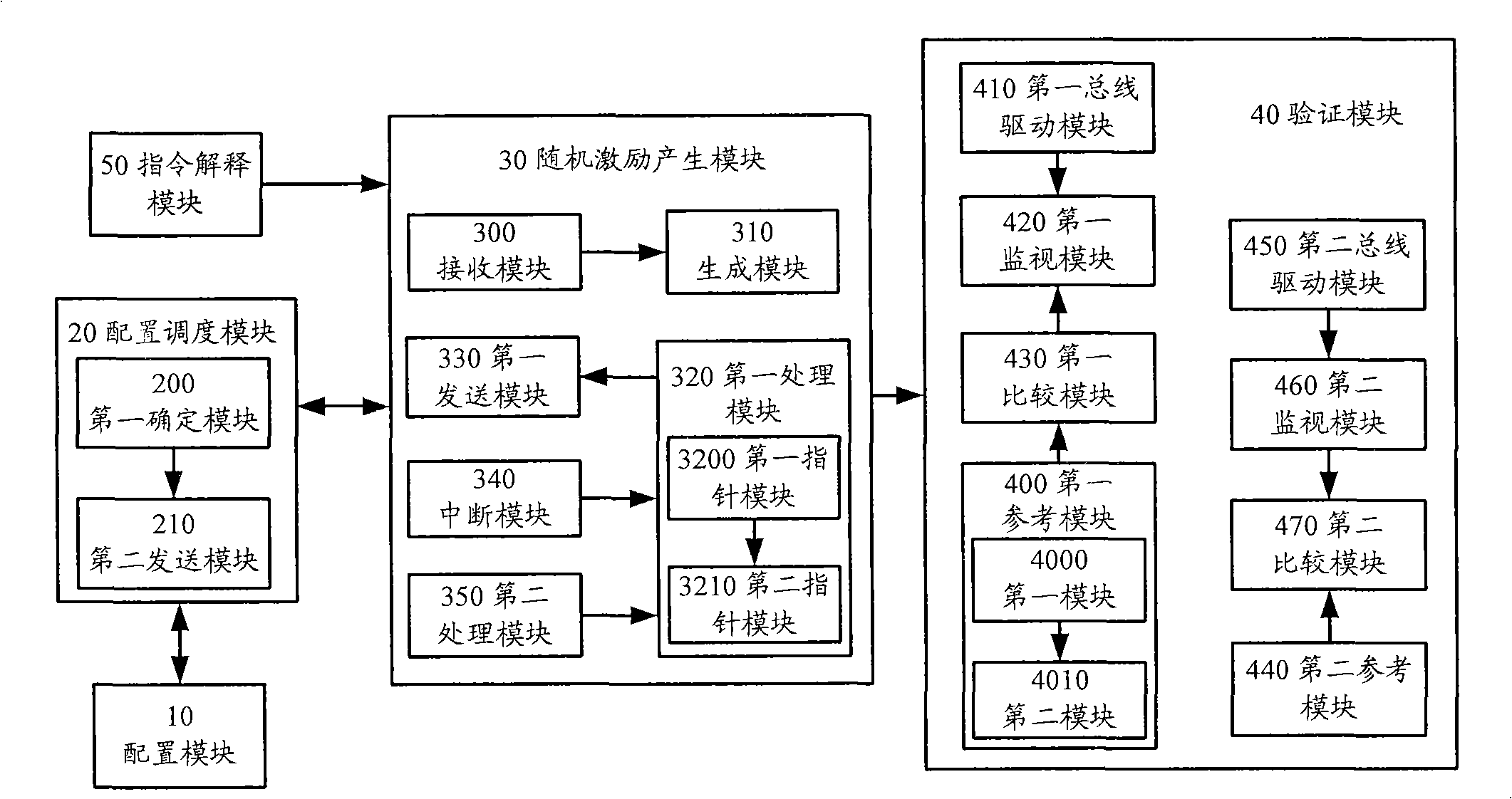

Method and device for verifying SoC (system on a chip) chips

ActiveCN101515301AReduce complexityReduce maintenance difficultySpecial data processing applicationsReusabilityVerification system

The invention relates to the field of SoC chips, in particular to a method and a device for SoC chips, which is used for solving the problem that the occurrence of random vectors and control difficulty are increased because each verification needs to be compiled again when different functions of the same SoC chip are verified in the prior art. The method of the embodiment of the invention comprises the following steps: setting a configuration file of an SoC chip, wherein the configuration file comprises the basic information of the SoC chip and constraint conditions of modules in the SoC chip; according to received instructions, determining the modules referring to the functions of the SoC chip which need to be verified; according to the basic information, the constraint conditions of the determined modules and module function data in the instructions, generating a random test vector; and according to the random test vector, verifying the SoC chip. The embodiment of the invention has the advantages of reducing the complexity of constructing verification systems and maintenance difficulty, increasing the reusability of verification components, lowering verification difficulty and saving time.

Owner:ACTIONS ZHUHAI TECH CO

Automated testing of applications with scripting code

InactiveUS20130290786A1Expand coverageIncrease coverageSoftware testing/debuggingComputer programJavaScript

A novel system, computer program product, and method are disclosed for feedback-directed automated test generation for programs, such as JavaScript, in which execution is monitored to collect information that directs the test generator towards inputs that yield increased coverage. Several instantiations of the framework are implemented, corresponding to variations on feedback-directed random testing, in a tool called Artemis.

Owner:IBM CORP

Fuzz testing method based on static detection

InactiveCN104573524AImprove efficiencyExclude false positivesPlatform integrity maintainanceSource codeFalse alarm

The invention belongs to the technical field of network security, and relates to a fuzz testing method based on static detection. The method comprises source code static analysis and executable code fuzz testing. According to the method, firstly, target software is subjected to static analysis through source code static analysis related software, and fuzz testing is carried out to obtain a static analysis result, then, code segments considered to have problems through the static analysis are subjected to pile inserting marking, and finally, testing cases are subjected to variation on the basis of the pile inserting marking, so that the testing cases can cover all code segments with problems. The fuzz testing method has the advantages that the advantages of the static detection and the fuzz testing are combined, the static detection is verified through the fuzz testing, and the false alarm condition of the static detection is excluded; on the other hand, the fuzz testing is guided by the static detection result, so that random testing cases used by the fuzz testing have a higher pertinence, and the fuzz testing efficiency is improved. The defects of high false alarm rate, low detection efficiency and the like of the traditional method adopting the random testing cases for testing are overcome.

Owner:706 INST SECOND RES INST OF CHINAAEROSPACE SCI & IND

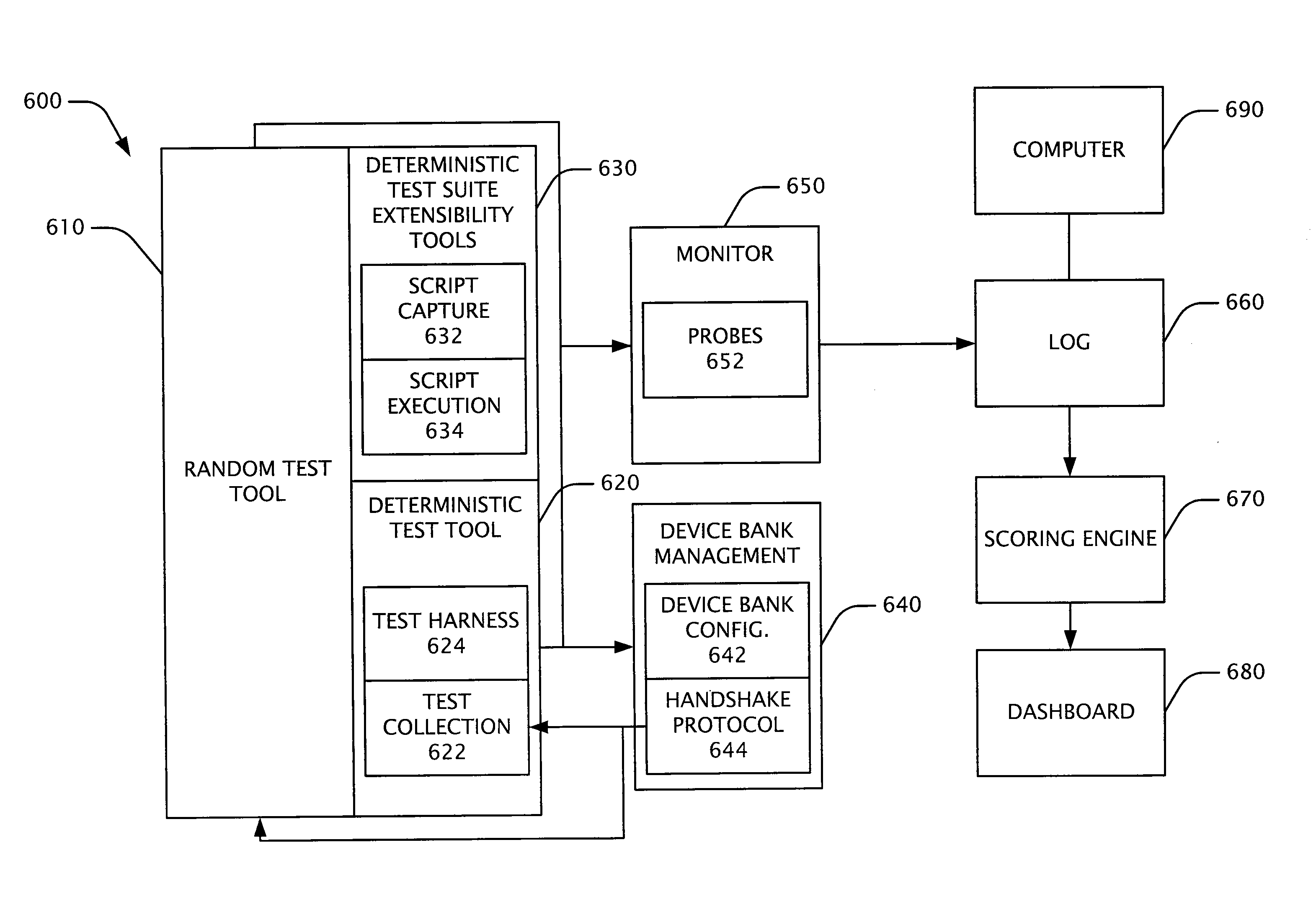

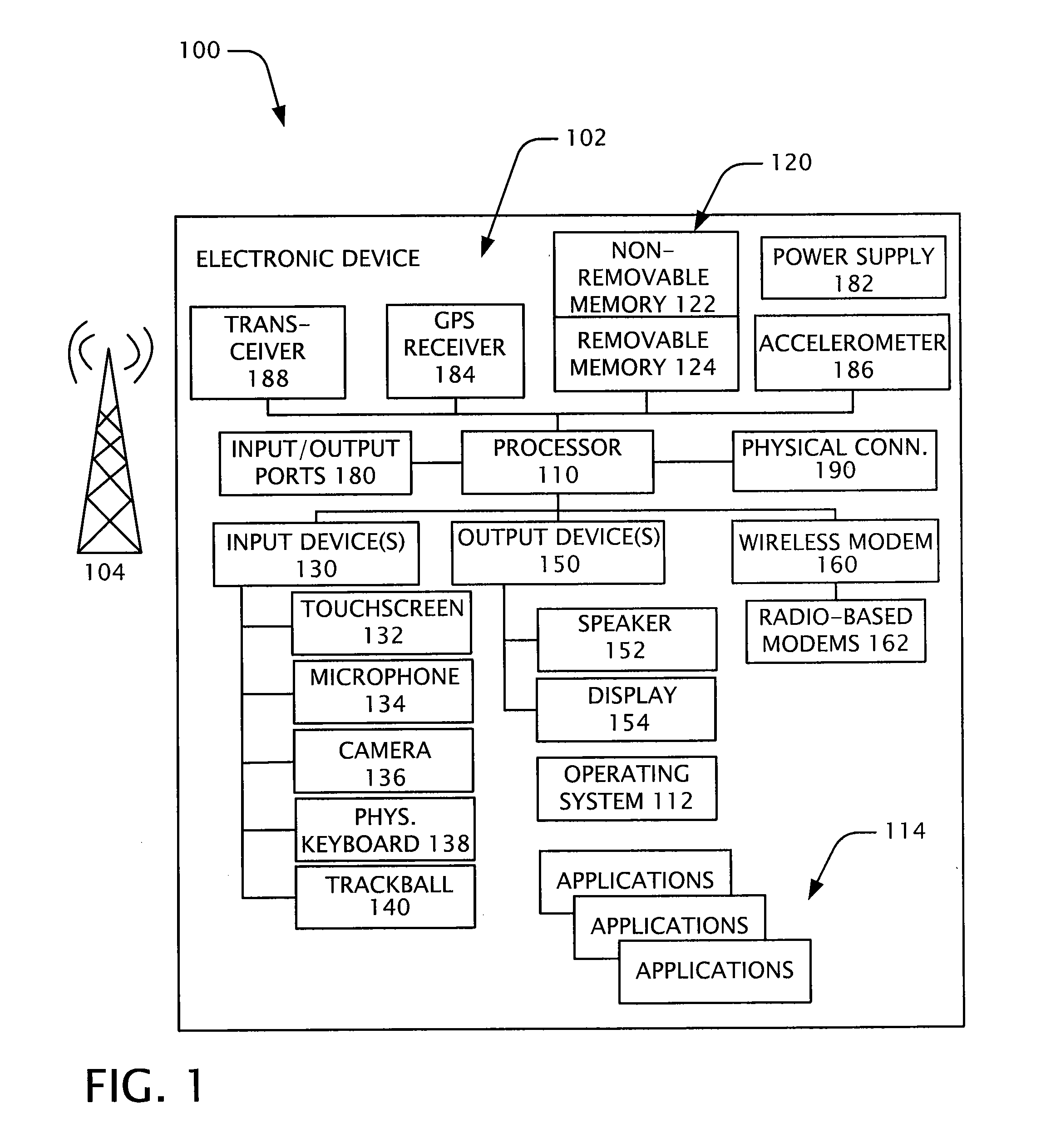

Testing software in electronic devices

Software in an electronic device can be tested using a combination of random testing and deterministic testing. In various embodiments, deterministic tests can run for a prescribed duration and / or a prescribed number of iterations before and / or after random testing. Test results can be weighted using a metric representing an amount of code that was stressed during testing. This metric can be determined by tracking software code that is loaded into memory during testing.

Owner:MICROSOFT TECH LICENSING LLC

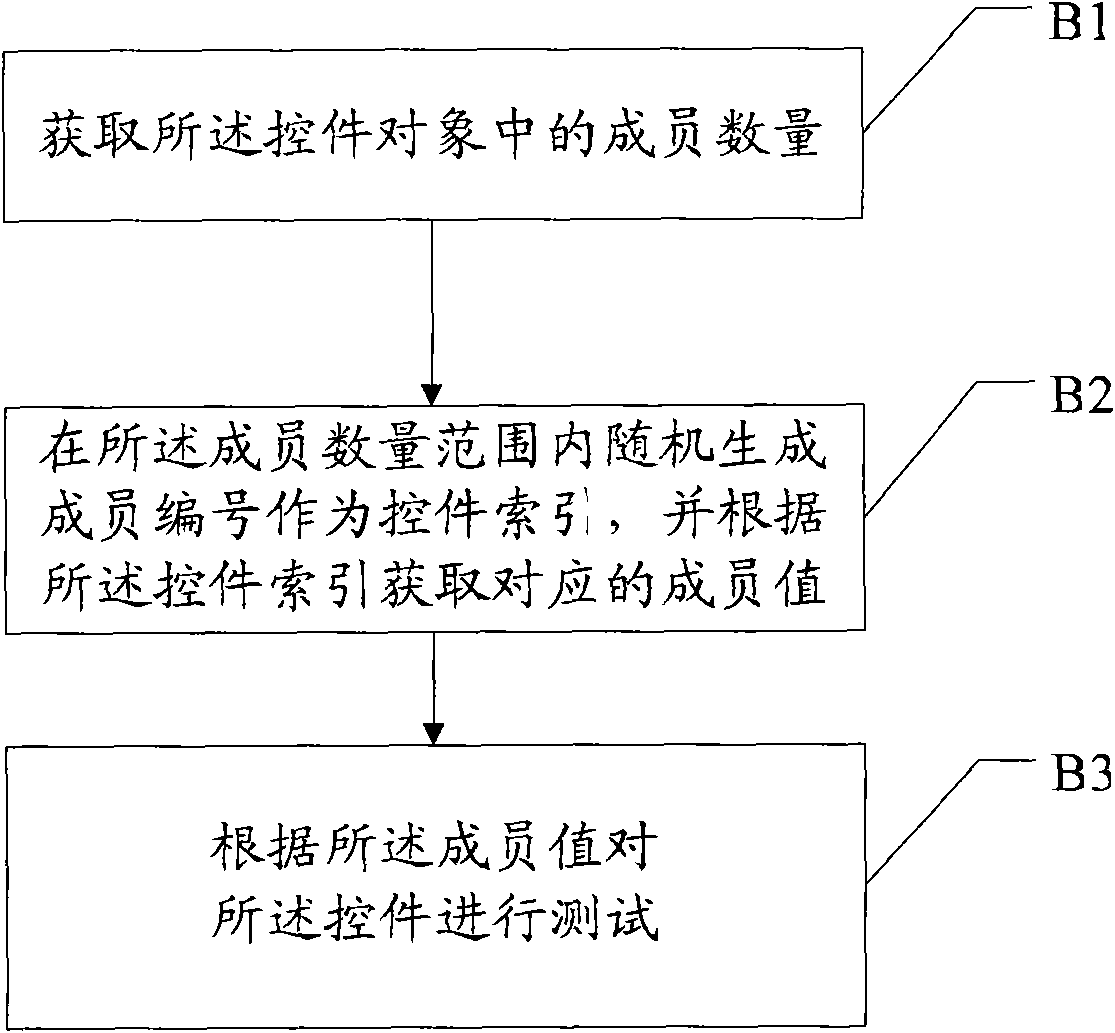

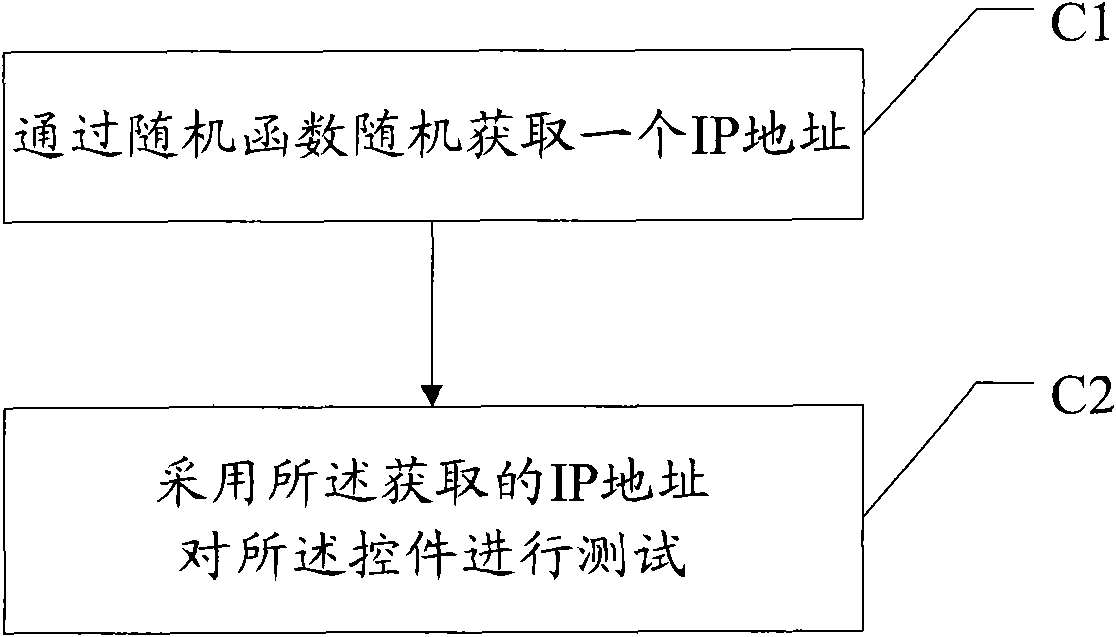

Method and apparatus for testing graphical user interface

InactiveCN101655817AReduce maintenanceImprove acceleration performanceSoftware testing/debuggingTest fixtureGraphical user interface testing

The present invention discloses a method and apparatus for testing graphical user interface. According to the embodiment of the invention, GUI controls are assorted, and a control object to be testedis searched according to a control name; a corresponding control type of the control object is recognized; and random testing data are obtained according to the control type obtained by the recognition and the control is tested by using the accidental testing data. Automatic tests are applied to the GUI controls by using random numbers, such that the maintenance of a data pool is reduced comparedwith a tranditional data drive mode, and the expandability and maintenability of GUI automatization embodiments are improved. The testing data are generated randomly, and a testing coverage rate is linearly increased along with times of performing the test embodiments, thereby, compared with tranditional static testing embodiment, the more the testing times are, the higher the testing coverage rate is, the easier a complete test is performed, which improve testing accuracy.

Owner:HUAWEI DIGITAL TECH (CHENGDU) CO LTD

Electronic system with self-test function and simulation circuit for electronic system

InactiveUS6401226B1Electronic circuit testingError detection/correctionElectronic systemsEngineering

An electronic system with a self-test function has a pseudo-random test pattern generator that serially generates data constituting a pseudo-random test pattern, and stores a 1-bit shifted pseudo-random test pattern obtained by shifting the pseudo-random test pattern by one bit. When a scan-path circuit supplies the pseudo-random test pattern to a tested circuit which carries out an operation based on the pseudo-random test pattern, and then loads an operation result of the tested circuit, the 1-bit shifted pseudo-random test pattern is supplied to the tested circuit as the next pseudo-random test pattern. This makes it possible to solve a problem of a conventional electronic system in that it takes a long time to evaluate the operation results of the tested circuit because it takes at least (1+n)xm clock cycles, where m is the number of pseudo-random test patterns supplied to the tested circuit and n is the number of stages of the scan-path circuit.

Owner:MITSUBISHI ELECTRIC CORP

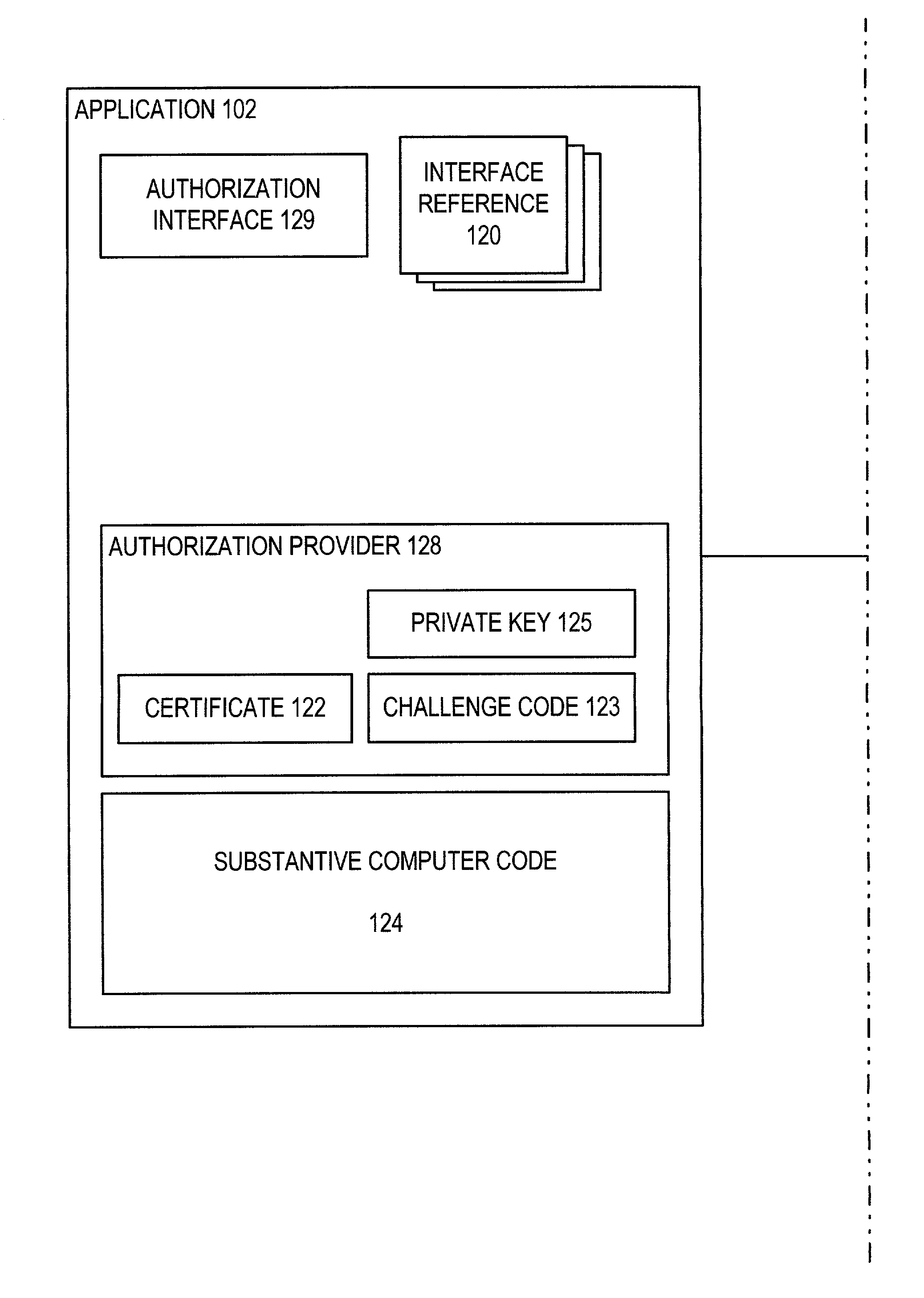

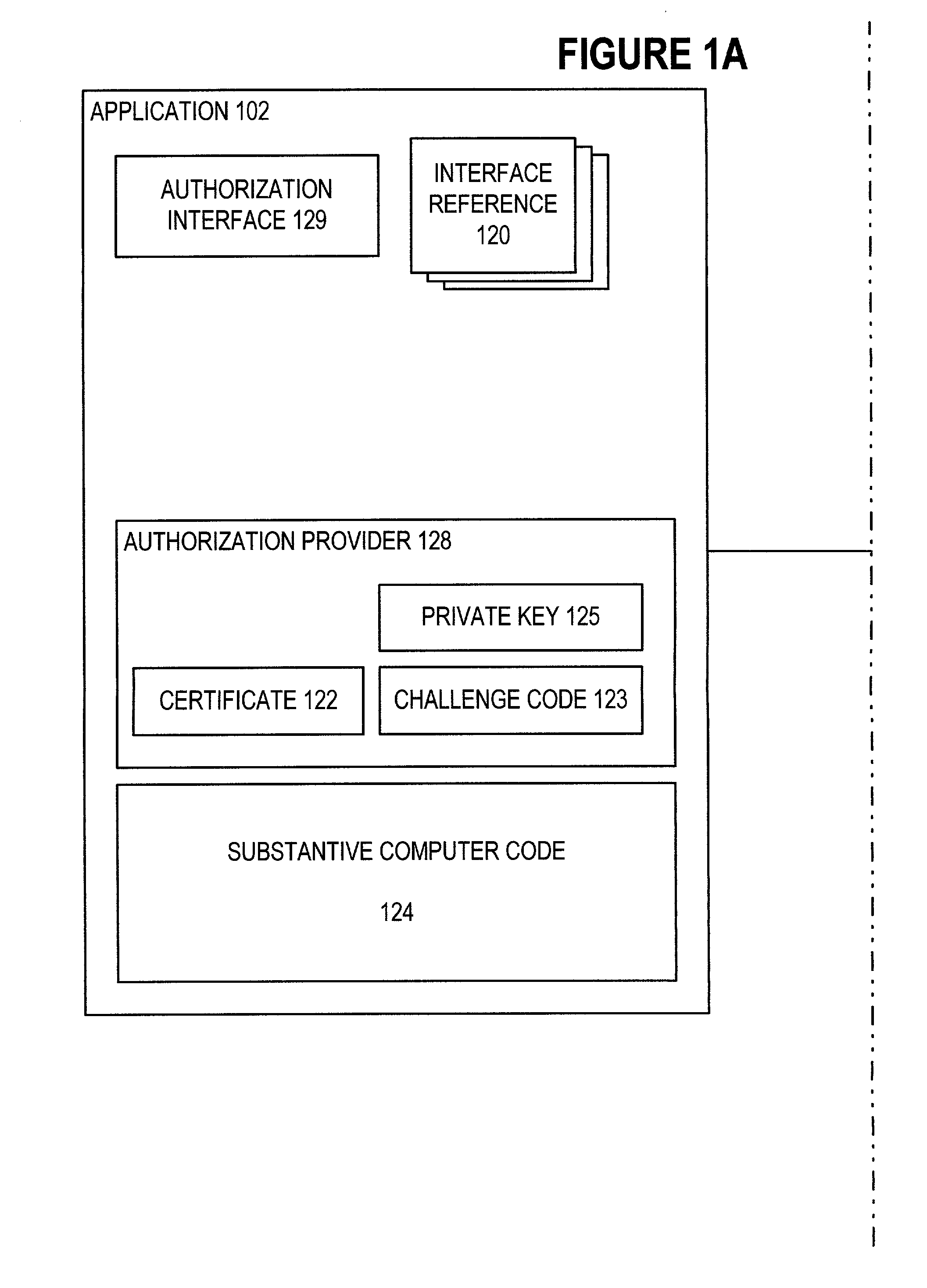

Security mechanism for computer processing modules

InactiveUS6965994B1Improve securityIncrease flexibilityDigital data processing detailsUser identity/authority verificationProcessingAuthorization

To provide improved security in adjunct program modules such as plug-ins and dynamic link libraries, a requesting module provides an authorization interface to the invoked module such that the invoked module can require a certificate of the requesting module and can also challenge the authority of the requesting module. The certificate can include one or more permissions which are prerequisites for processing by the invoked module. The invoked module can challenge the authority of the requesting module by sending random test data to the requesting module and receiving in response a cryptographic signature of the test data. By verifying the signature of the requesting module using the received certificate, the invoked module confirms that the requesting module is, in fact, the owner of the receive certificate.

Owner:MICROSOFT TECH LICENSING LLC

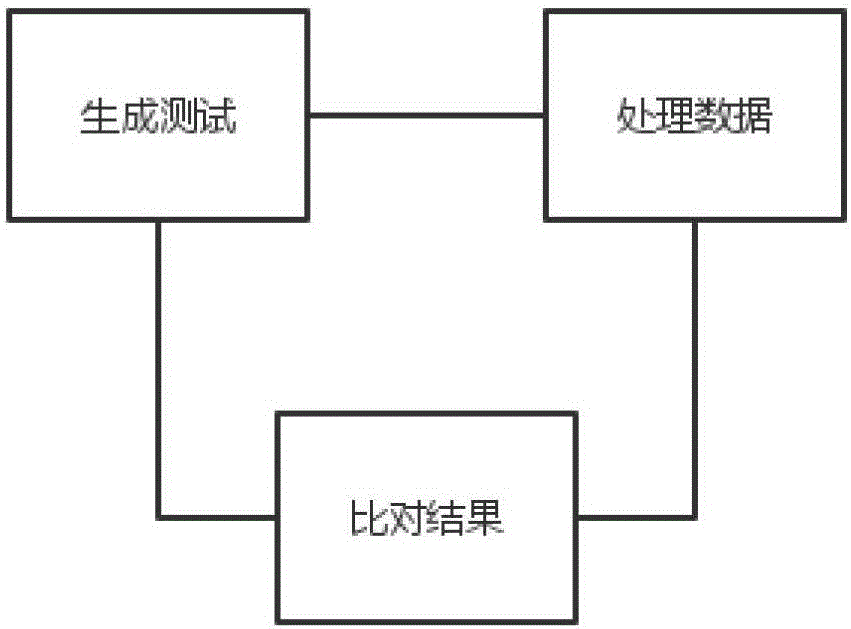

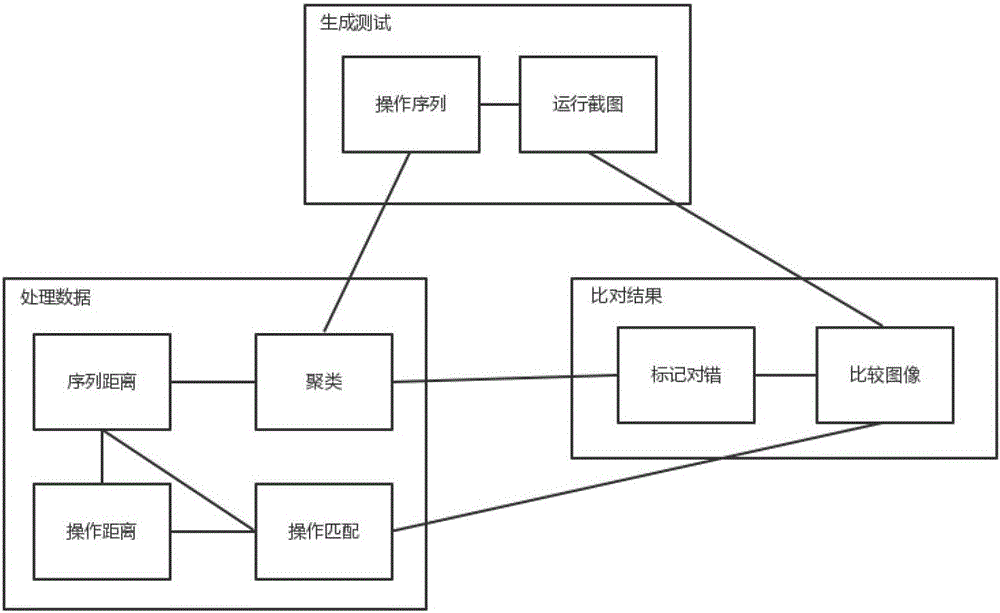

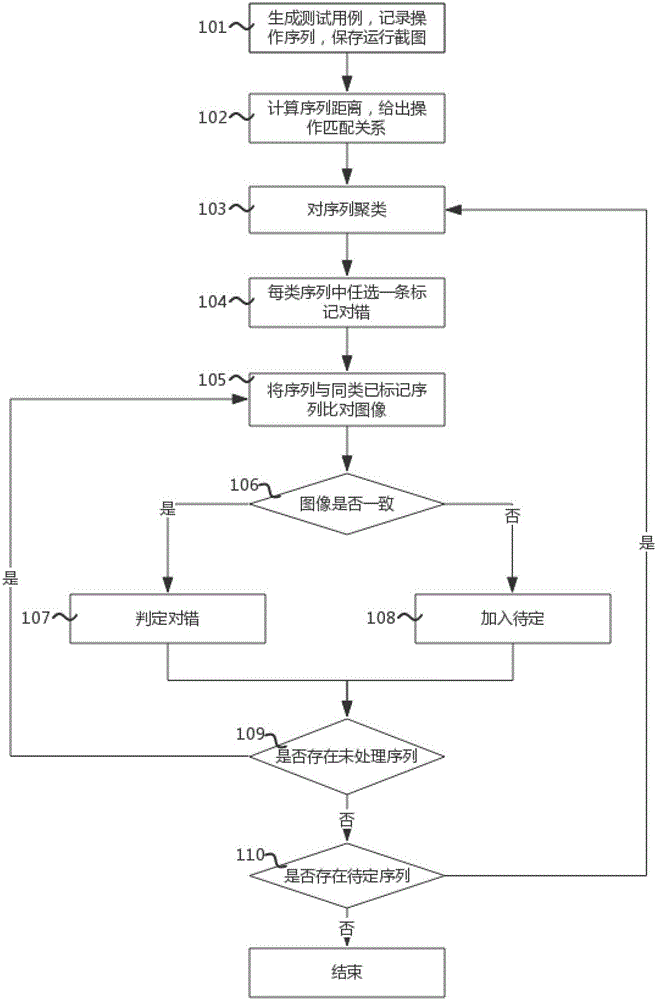

Graphic interface automated test method

ActiveCN105955889AImprove accuracyImprove test efficiencySoftware testing/debuggingGraphicsTest efficiency

The invention relates to a graphic interface automated test method. The method comprises the following steps of automatically generating random test cases for to-be-tested software, generating records of operation sequences for function modules of test software, and storing a running screenshot; calculating the similarity between the operation sequences according to the records of the operation sequences, and giving out a matching relationship of operations in the operation sequences; clustering the operation sequences according to the similarity between the operation sequences; in each class, arbitrarily selecting one sequence and artificially marking right and wrong; in each class, performing image comparison on other similar sequences and the marked sequence; if comparison results are consistent, directly judging right and wrong, otherwise, regarding the sequence as an undetermined sequence; and if the undetermined sequence exists, returning to perform clustering. According to the method, similar operation sequences are subjected to image comparison in combination with OCR by applying an image comparison algorithm, and it is judged that function defects exist according to results or an iterative process is repeated; and the manual interventions are reduced by using machine learning and image comparison technologies, so that the test automation is realized and the software test efficiency is improved.

Owner:NANJING UNIV

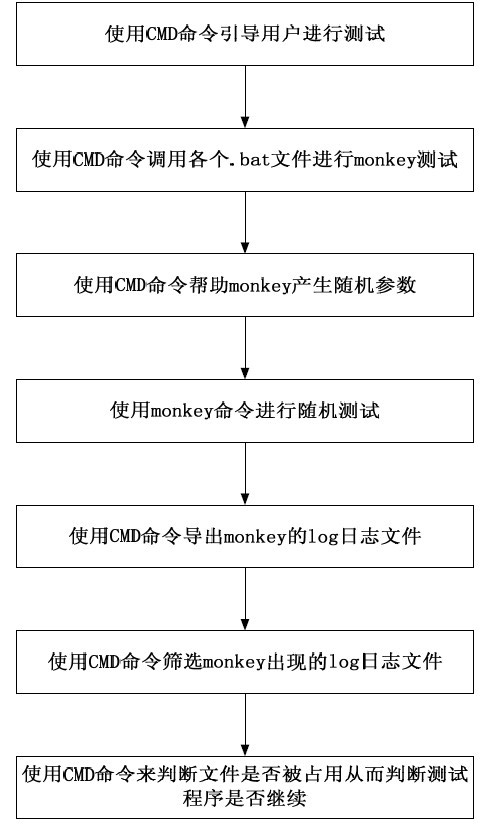

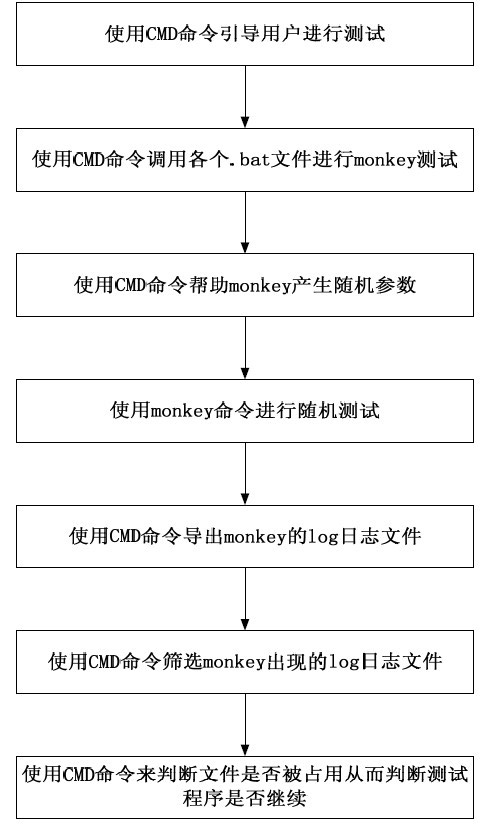

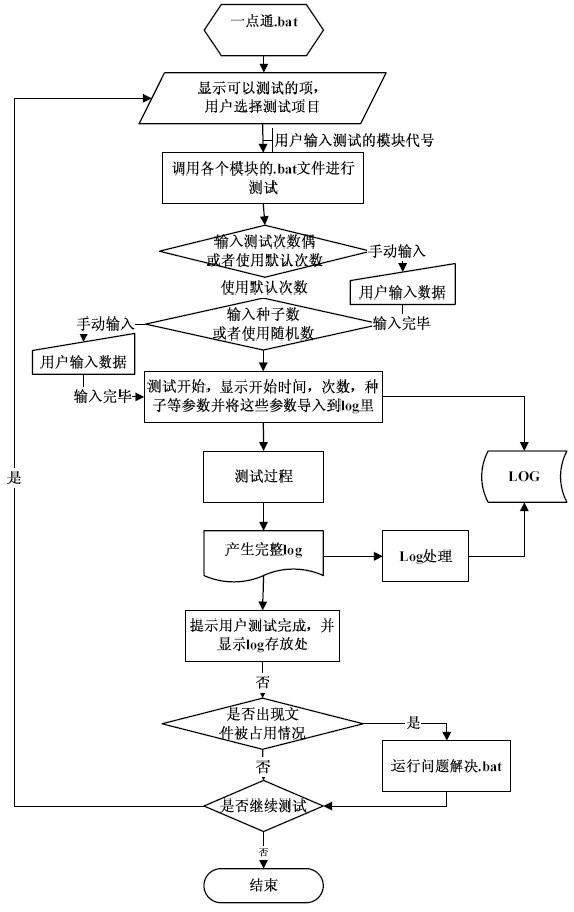

Random testing method based on Android

ActiveCN102110053AEasy to testImprove test efficiencySoftware testing/debuggingTest efficiencyMicrochiroptera

A random testing method based on Android comprises the following steps: (1) using a Windows CMD (command) to guide a user to conduct testing; (2) calling each.bat file by use of the CMD to carry out monkey testing; (3) using the CMD to help monkey generate a random parameter; (4) using the monkey command to conduct random testing; (5) using the CMD to export a log file of monkey; (6) using the CMD to screen the existing log file of monkey; and (7) using the CMD to determine whether the file is occupied so as to determine whether to continue the testing program or not. By integrating the CMD of the Windows with the Monkey command of Android, the method can simplify the software testing of mobile phones, improve the testing efficiency and lower the use threshold.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

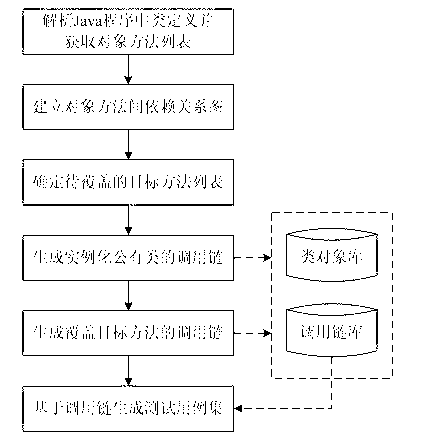

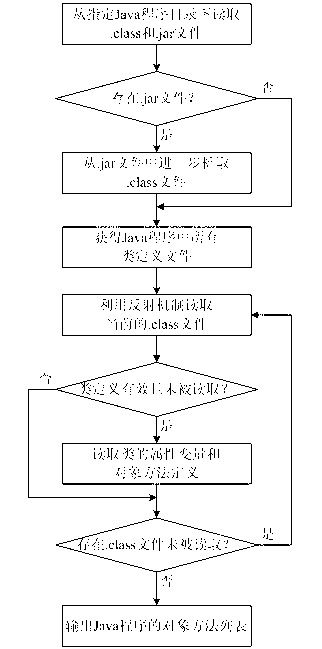

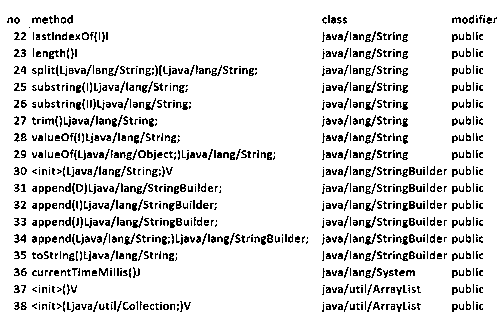

Random test case generation method facing Java program

The invention discloses a random test case generation method facing a Java program. The random test case generation method comprises the following steps of: (1) resolving a class definition of the Java program, and acquiring an object method list; (2) establishing a dependency relation graph comprising a method calling graph and a property dependency graph among object methods; (3) determining a target method list to be covered; (4) generating a calling chain by aiming at instantiation for public classes, and maintaining a class object base; (5) generating a calling chain by aiming at covering target methods, and maintaining a calling chain base; and (6) generating a test case set for the Java program based on the calling chain base. The method can be widely applied to automatic test work of medium-and large-size Java software systems and can automatically generate test cases completely; the highest code coverage rate is achieved by the least number of test cases; complicated data structures can be processed; test assertion can be automatically generated; and the test case generation method is simple and effective, and has high applicability and expandability.

Owner:NANJING UNIV

Automatically generating test cases for binary code

InactiveUS7873945B2Efficient testingError detection/correctionSpecific program execution arrangementsBranch predicationTest input

Owner:MICROSOFT TECH LICENSING LLC

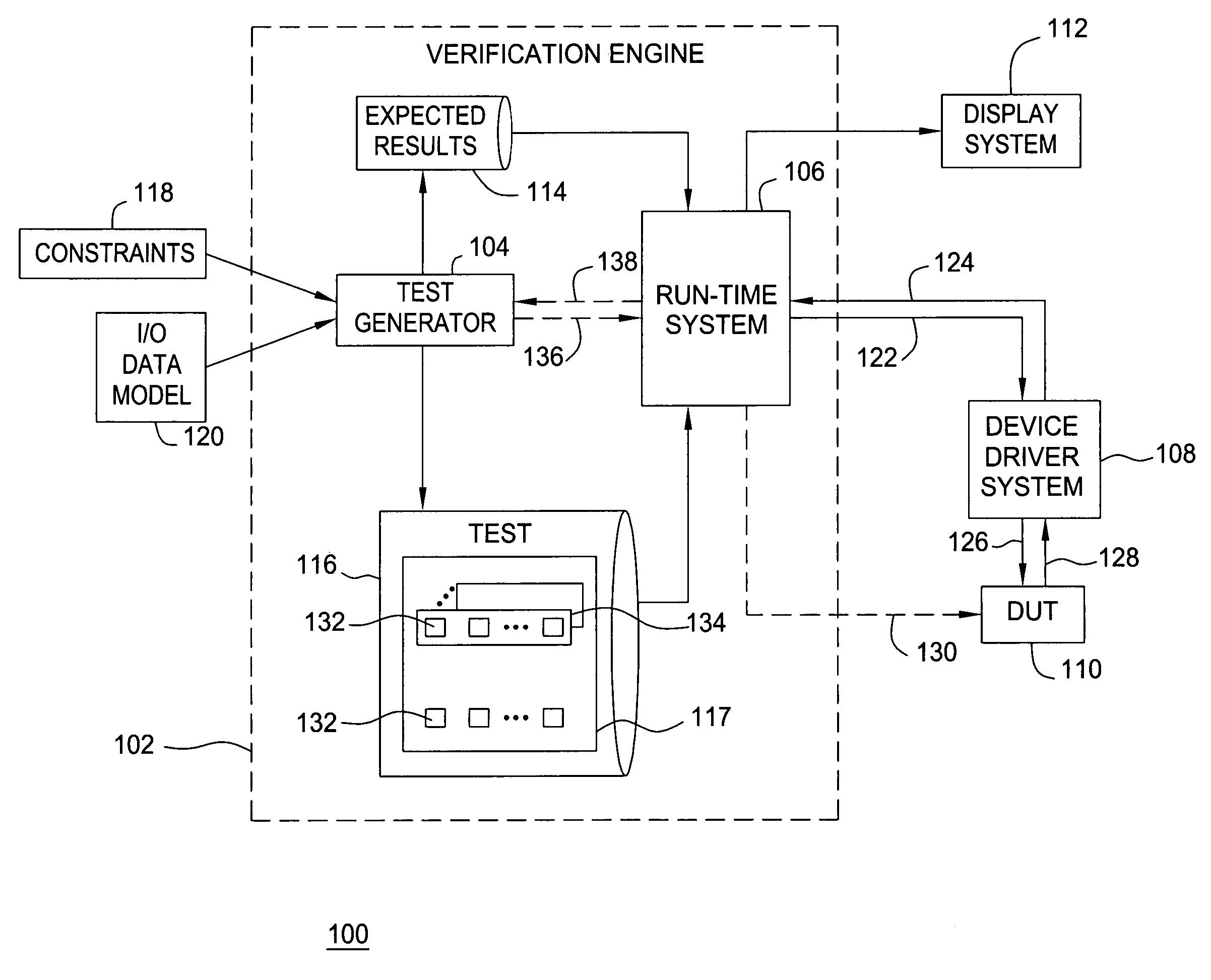

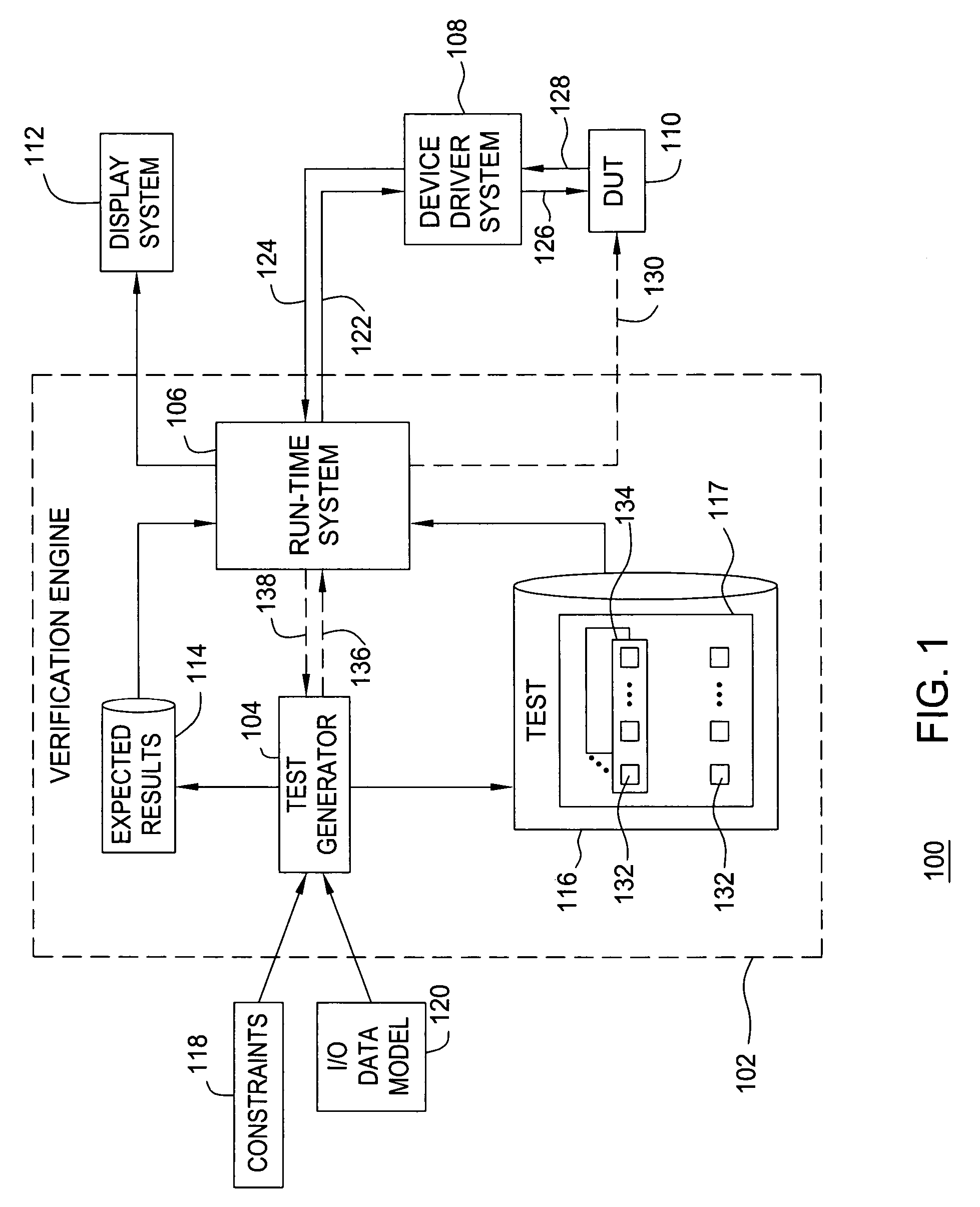

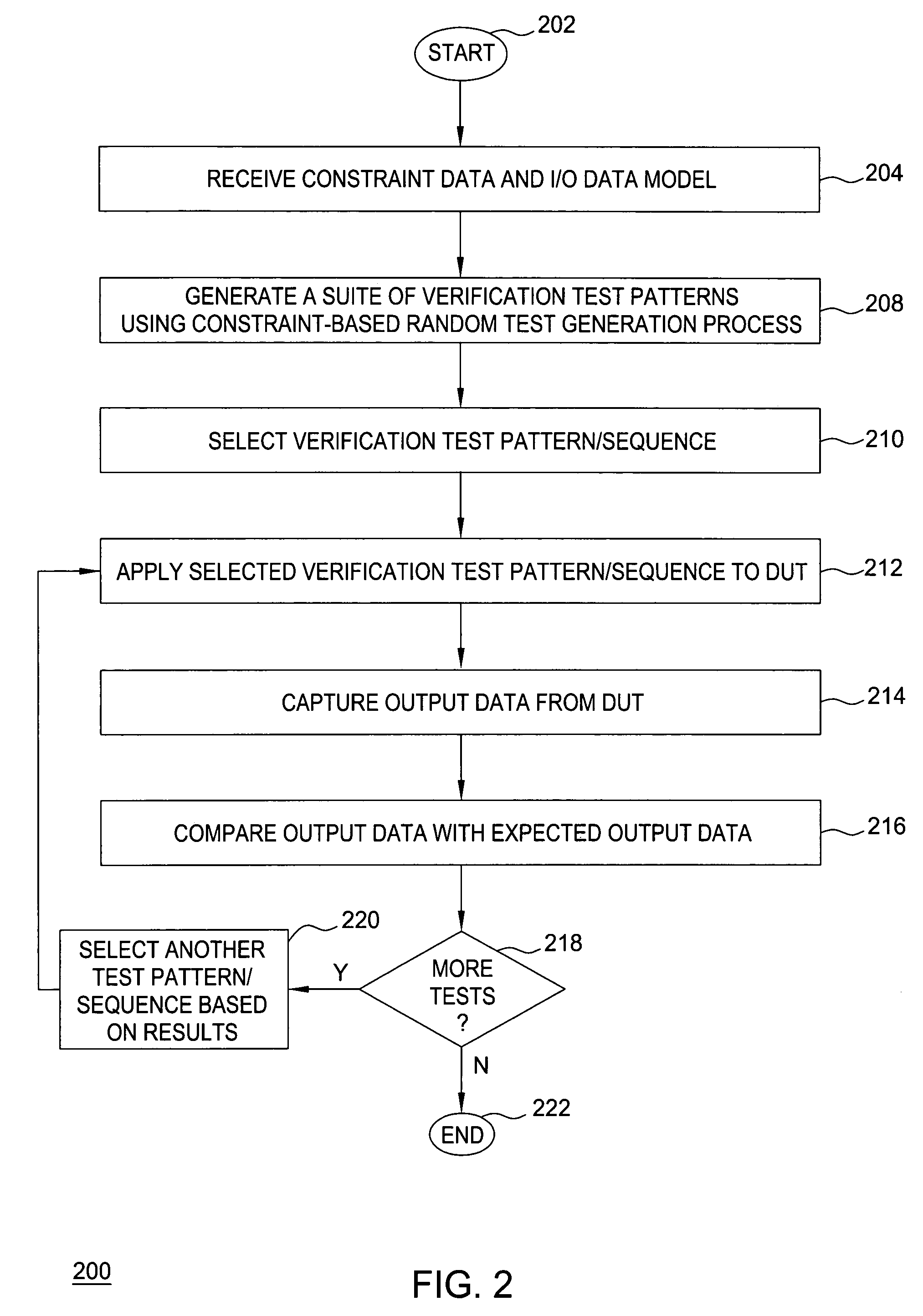

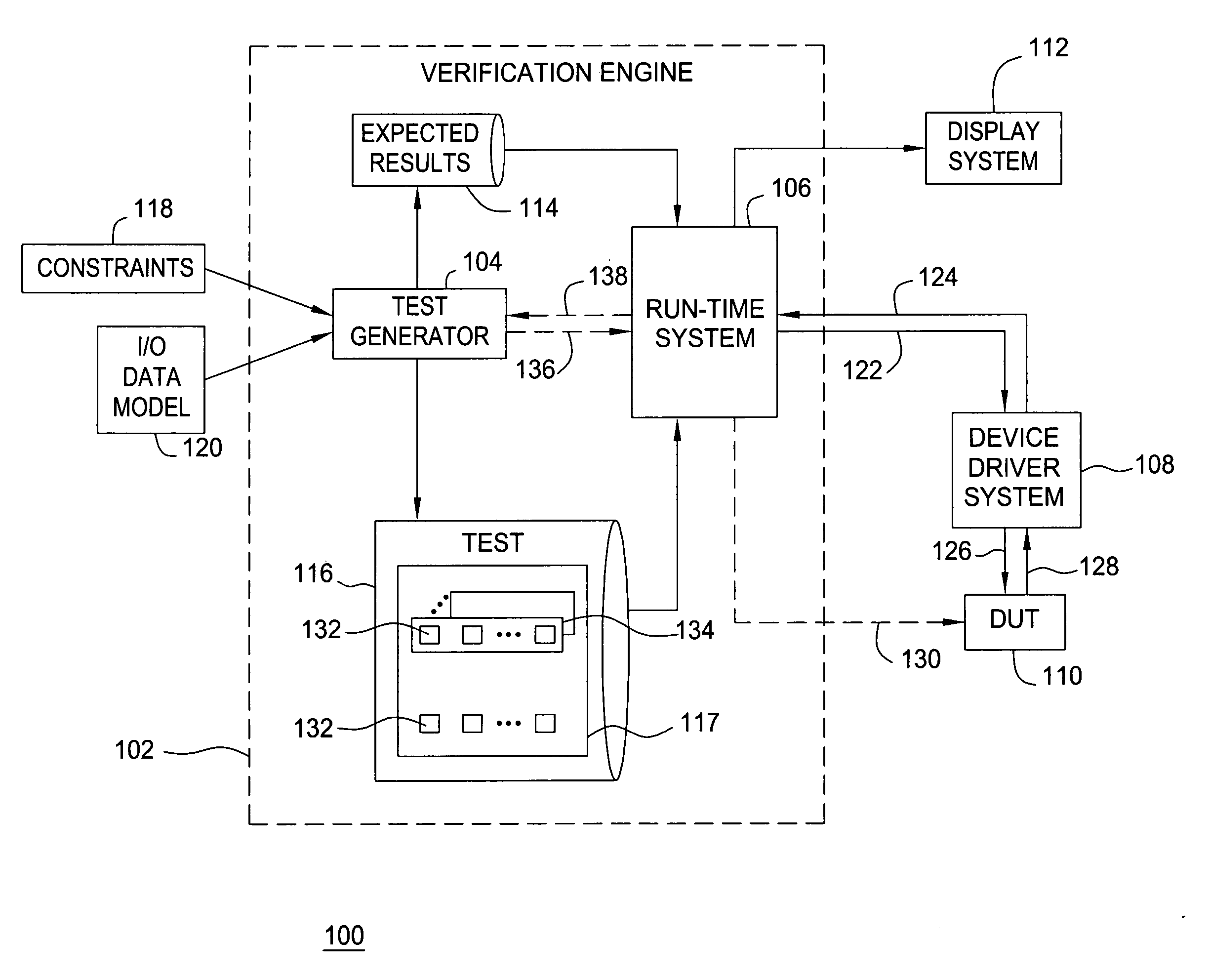

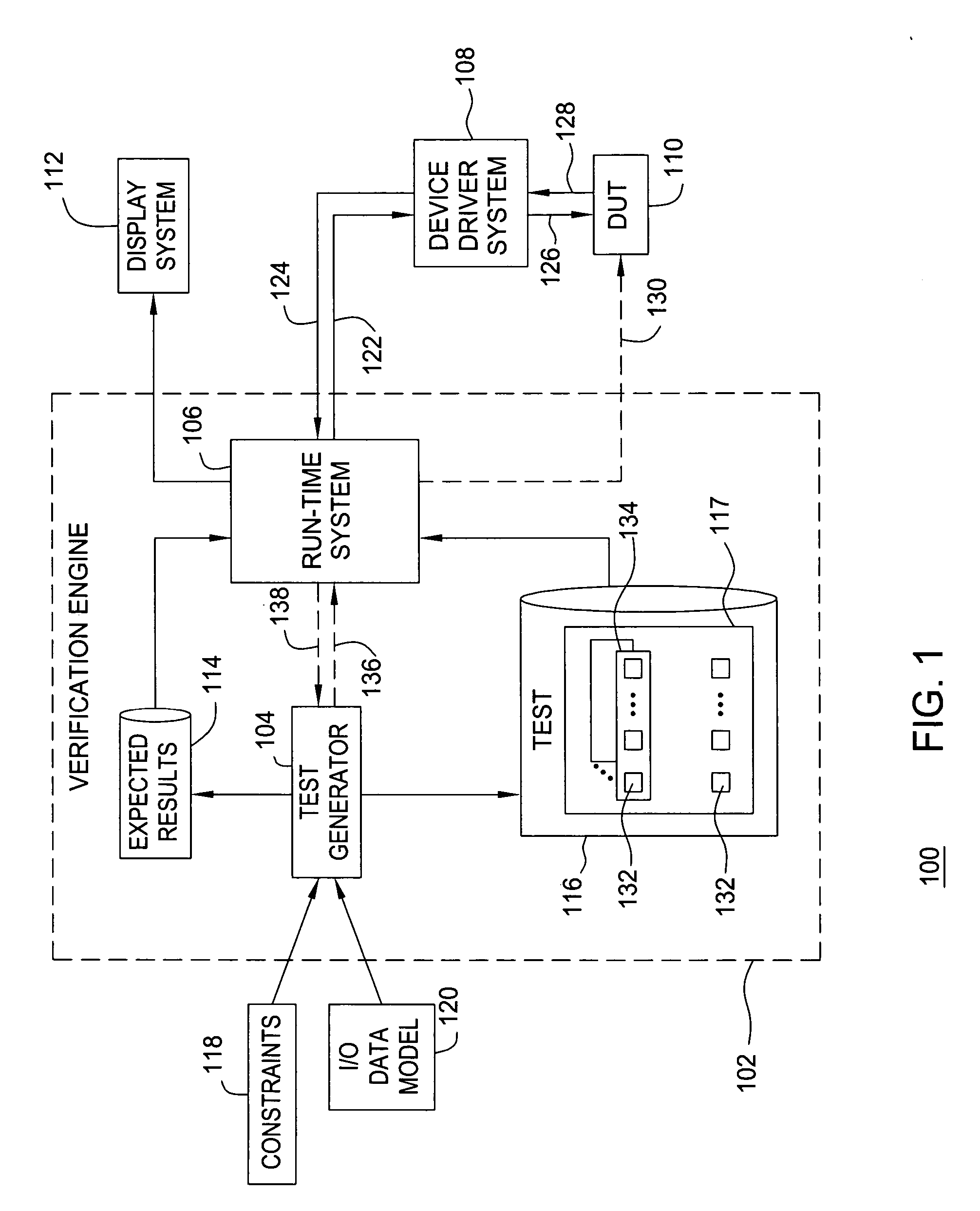

Method and apparatus for functionally verifying a physical device under test

ActiveUS7284177B2Electronic circuit testingError detection/correctionComputer hardwareGeneration process

Method, apparatus, and computer readable medium for functionally verifying a physical device under test (DUT) is described. In one example, verification test data is generated for the physical DUT using a constraint-based random test generation process. For example, the architecture, structure, and / or content of the verification test data may be defined in response to constraint data and an input / output data model. A first portion of the verification test data is applied to the physical DUT. Output data is captured from the physical DUT in response to application of the first portion of the verification test data. A second portion of the verification test data is selected in response to the output data. Expected output data for the physical DUT associated with the verification test data may be generated and compared with the output data captured from the DUT to functionally verify the design of the DUT.

Owner:VERISITY

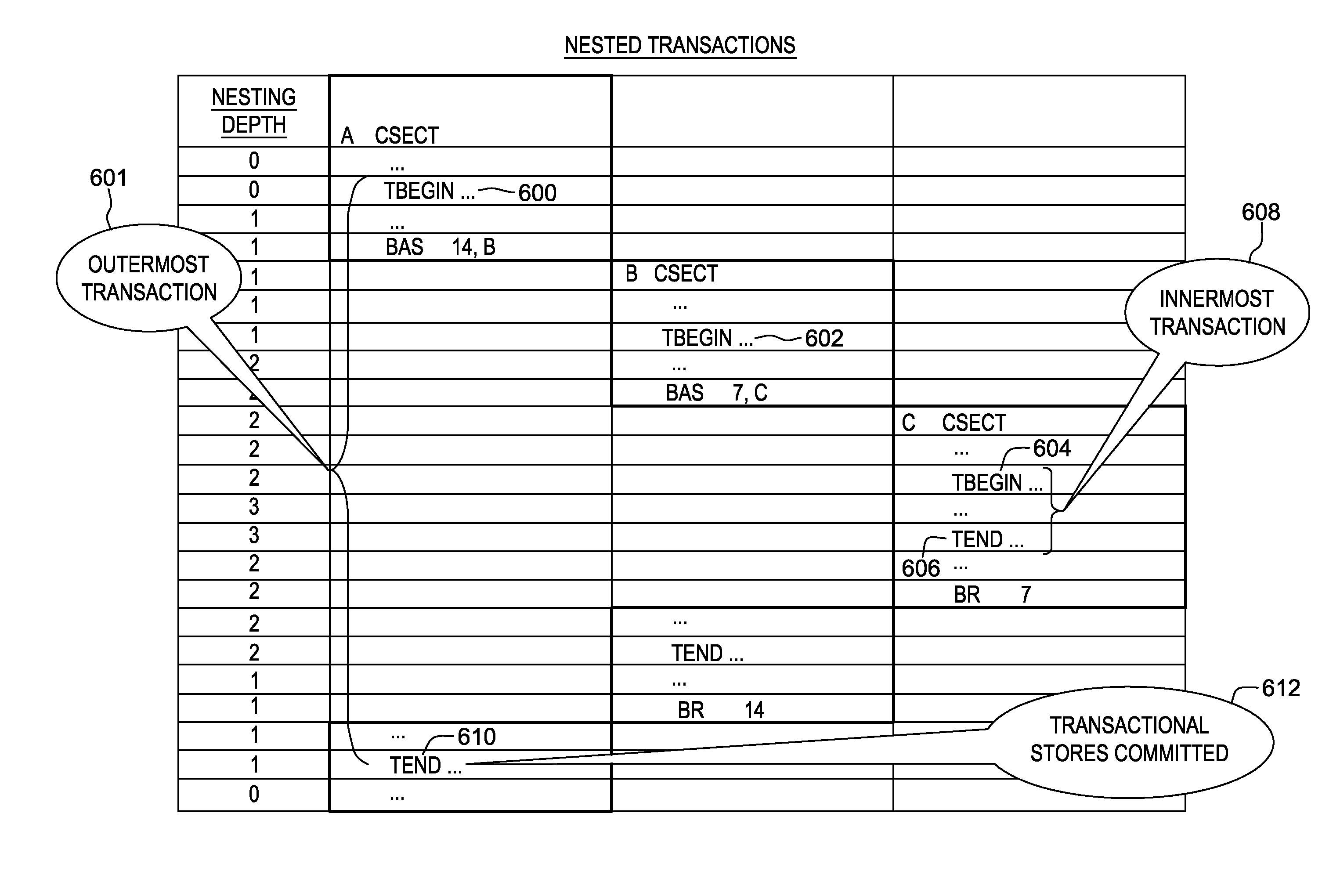

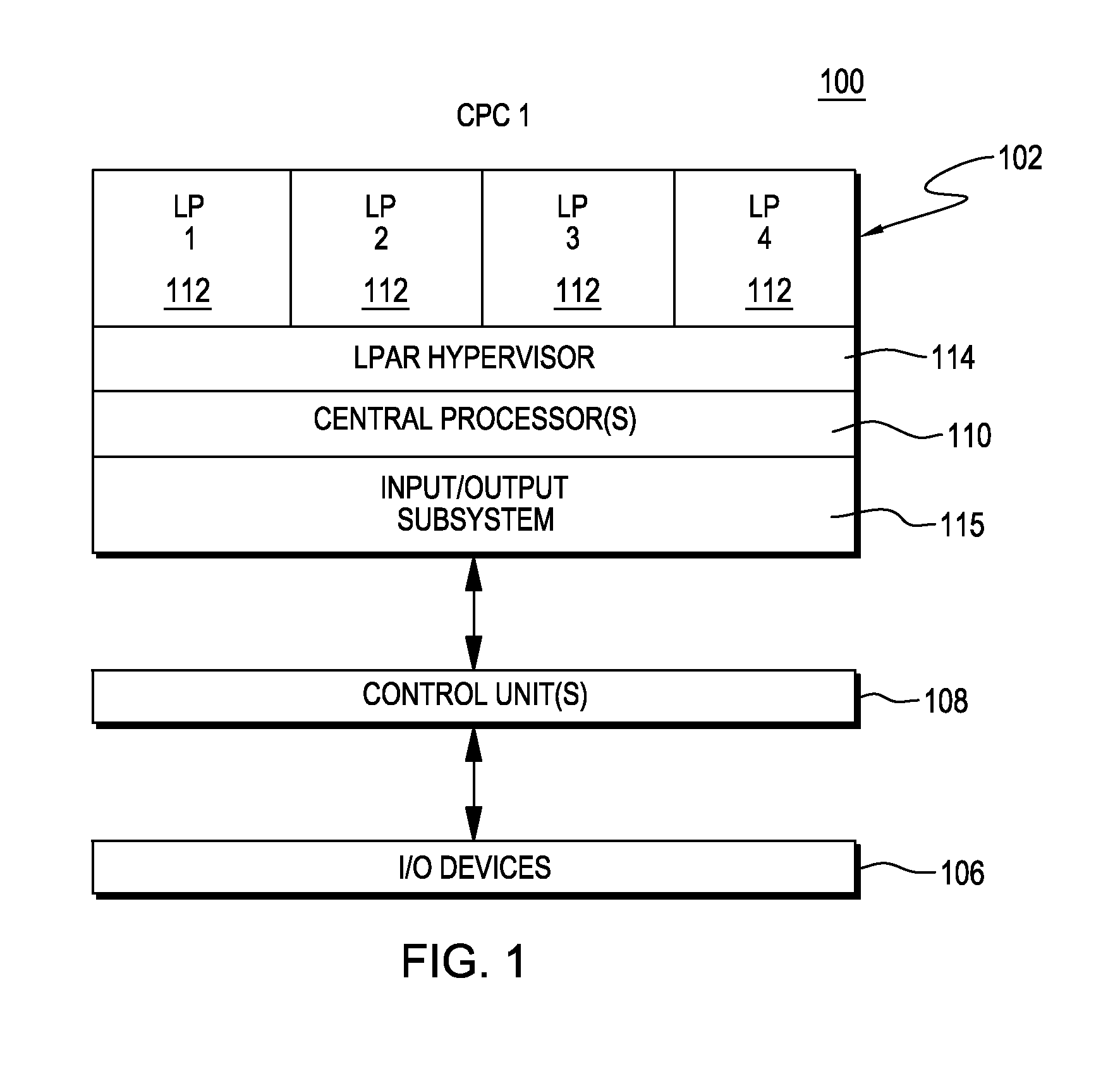

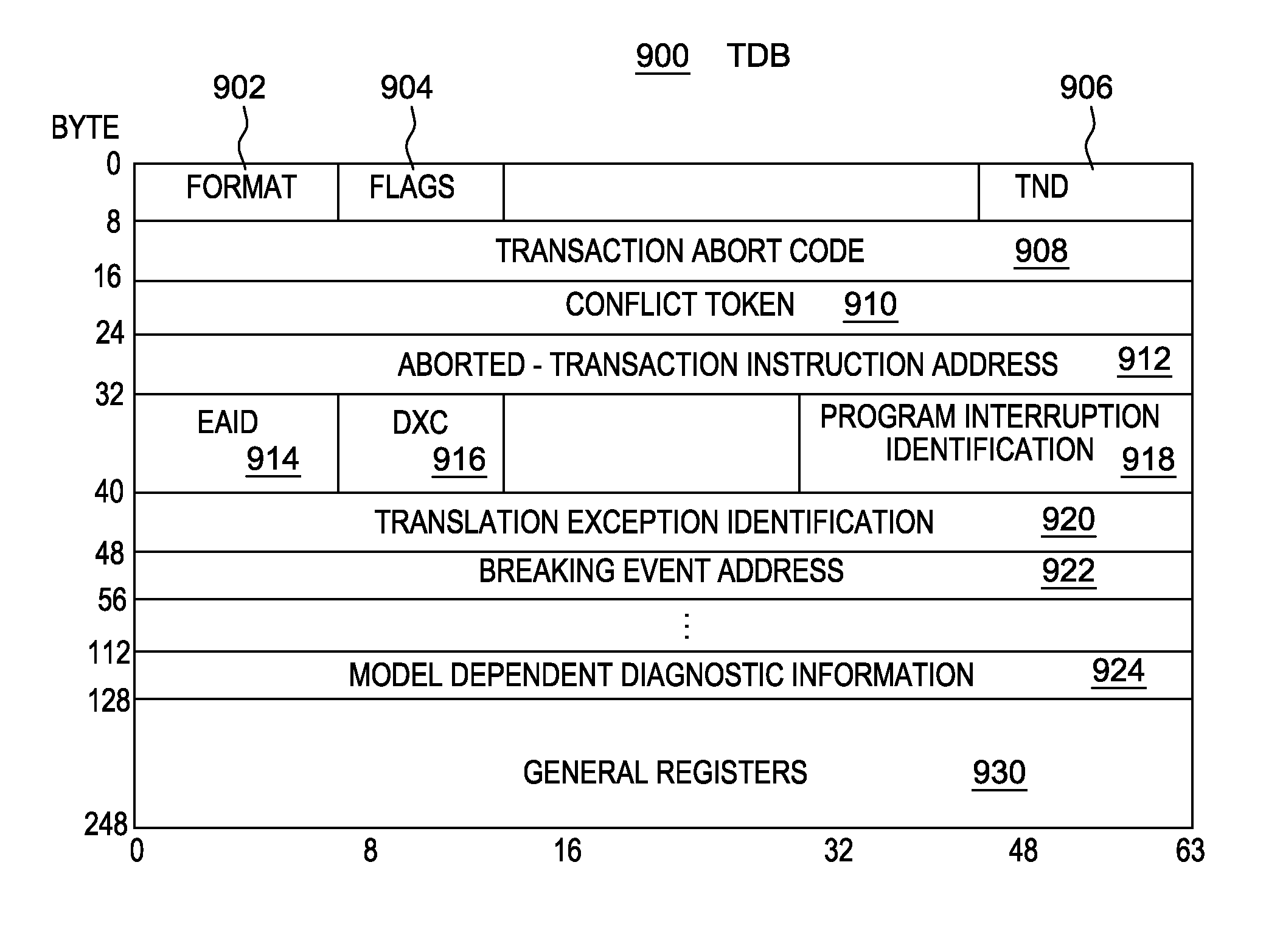

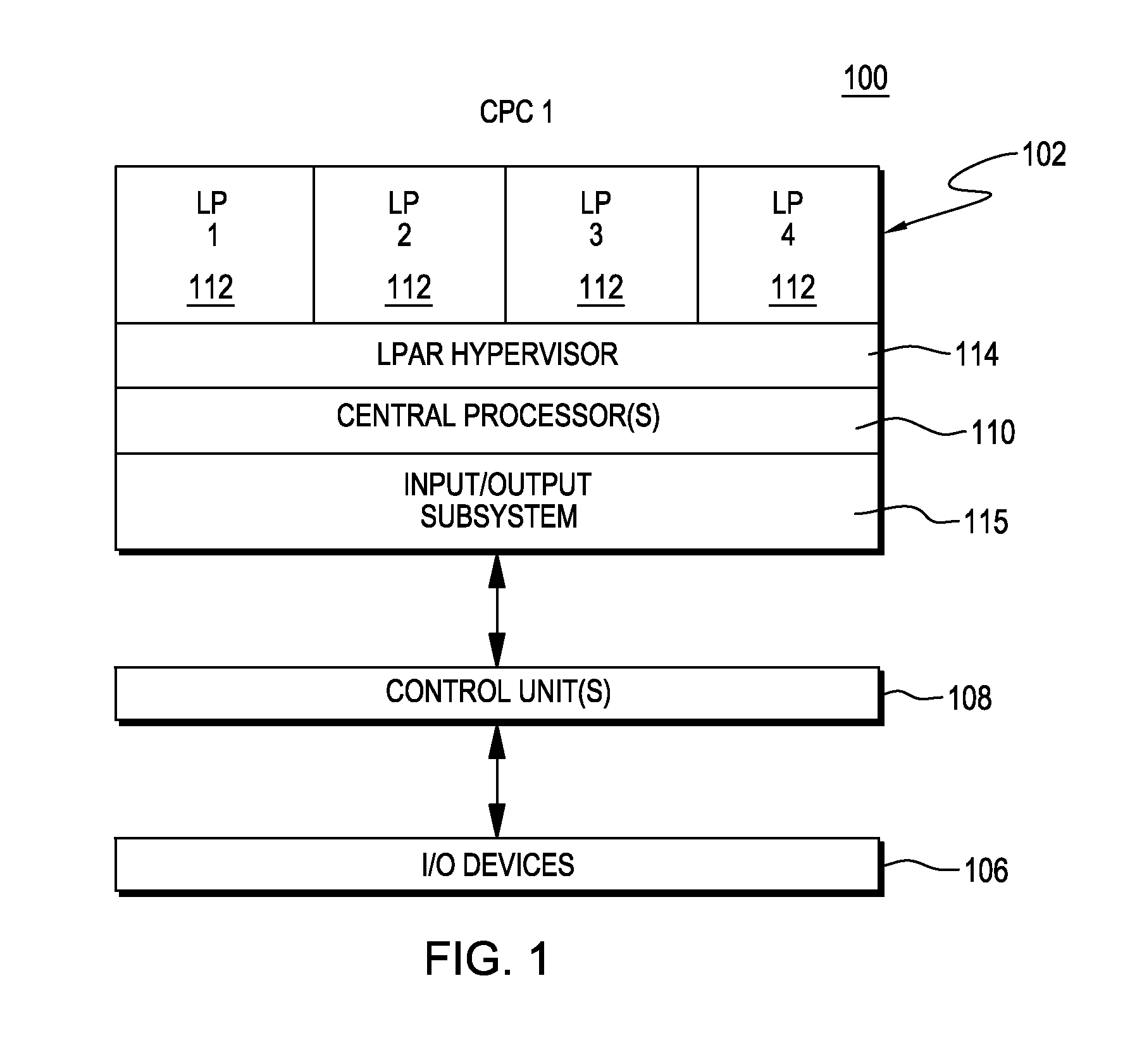

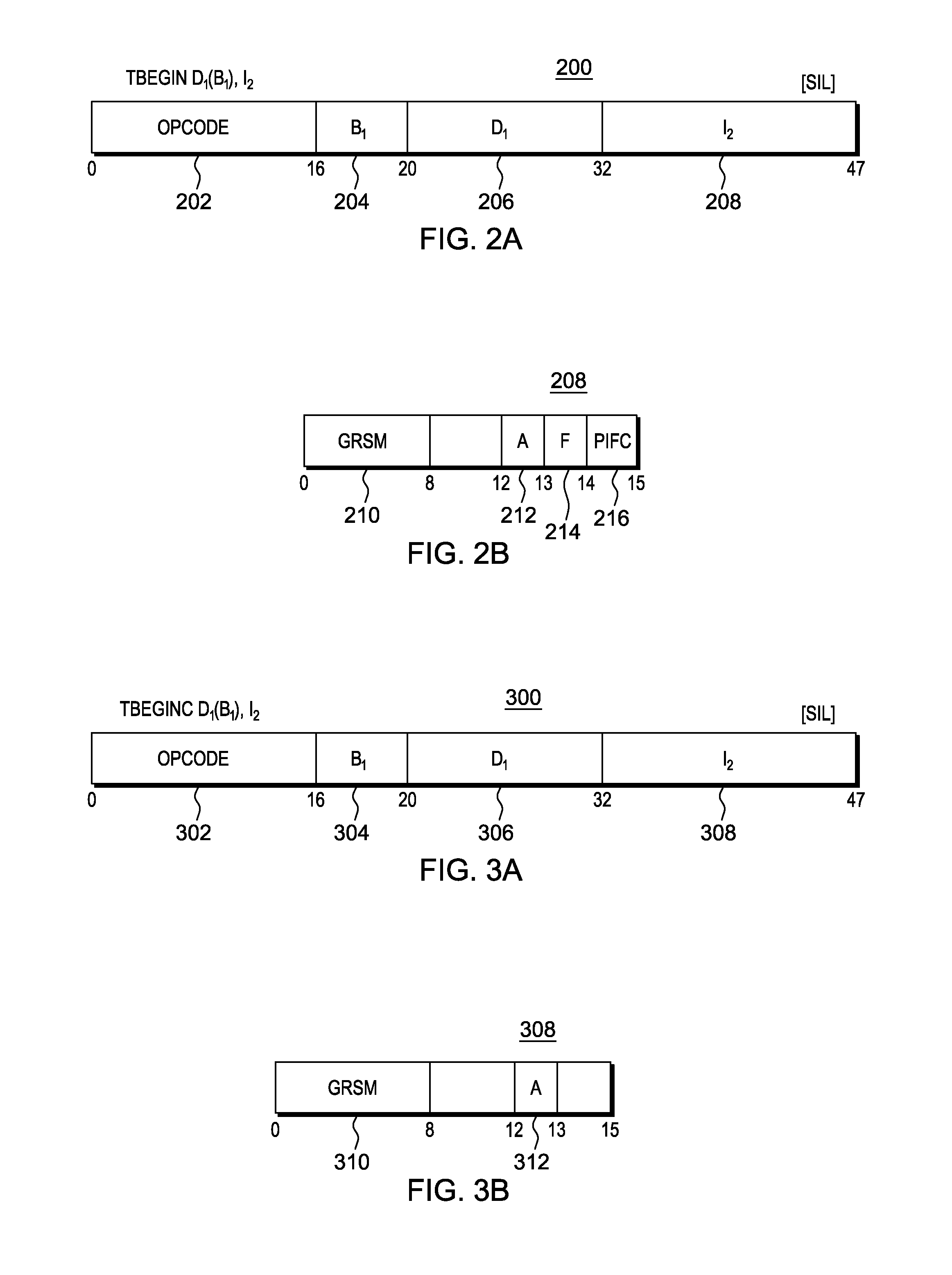

Randomized testing within transactional execution

ActiveUS20130339705A1Error detection/correctionDigital computer detailsSoftware engineeringRandom testing

Owner:IBM CORP

Crossed dynamic software testing method and device

InactiveCN102508780AAvoid falling intoReduce overheadSoftware testing/debuggingCoding blockCode coverage

The invention discloses a crossed dynamic software testing method and a crossed dynamic software testing device. The crossed dynamic software testing method comprises the following steps: 1, executing a random detection on a tested application by a dynamic random testing method and detecting application bugs; if an abnormal application is detected, recording abnormal information and exiting the test; otherwise, after completion of the current test, computing a code coverage and detecting whether the code coverage is saturated; if the code coverage is saturated, invoking a symbol switching function and switching into dynamic symbolic execution to hold on a parent process; otherwise, continuing to execute the next test till the code coverage is detected to be saturated; and 2, searching a new uncovered code block by a dynamic symbolic execution method; if a new code block is detected, restoring the state to a random executing state in the step 1; and if all basic blocks are covered, exiting the test. By the crossed dynamic software testing method, relatively large applications can be tested in an all-around way, so that a relatively high code coverage can be obtained and the explosion problem of a dynamic symbolic execution route can be relieved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

Method for effectively improving hardware Trojan activation probability

InactiveCN106778263AHigh activation rateIncrease activationPlatform integrity maintainanceLow activityHardware Trojan

The invention relates to the technical field of integrated circuit trustworthiness detection, in order to effectively remove the low activity node in the circuit, to improve the activation of the circuit, to greatly shorten the activation time of the low active node and to reduce the random and the uncertainty of the activation time of the hardware Trojan horse in the process of the hardware Trojan horse detection to a great extent. In addition, in the combination of the bypass signal analysis method or the logic test method, the activation time of the hardware Trojan horse is greatly shortened and the detection rate of the hardware Trojan horse is effectively increased. The technical proposal of the method for effectively improving the hardware Trojan horse activation probability is an effective method for improving the activation probability of the hardware Trojan horse. The method comprises the following steps that1, generating a random test vector and an excitation circuit; 2, counting the transition information of each node of the circuit; 3, setting the critical probability threshold; 4, determining the location of the implanted node; 5, integrating the circuit and detecting. The integrated circuit trustworthiness detection is mainly applied to the case of the integrated circuit trustworthiness detection.

Owner:TIANJIN UNIV

Method and apparatus for functionally verifying a physical device under test

ActiveUS20060242525A1Electronic circuit testingError detection/correctionComputer hardwareGeneration process

Method, apparatus, and computer readable medium for functionally verifying a physical device under test (DUT) is described. In one example, verification test data is generated for the physical DUT using a constraint-based random test generation process. For example, the architecture, structure, and / or content of the verification test data may be defined in response to constraint data and an input / output data model. A first portion of the verification test data is applied to the physical DUT. Output data is captured from the physical DUT in response to application of the first portion of the verification test data. A second portion of the verification test data is selected in response to the output data. Expected output data for the physical DUT associated with the verification test data may be generated and compared with the output data captured from the DUT to functionally verify the design of the DUT.

Owner:VERISITY

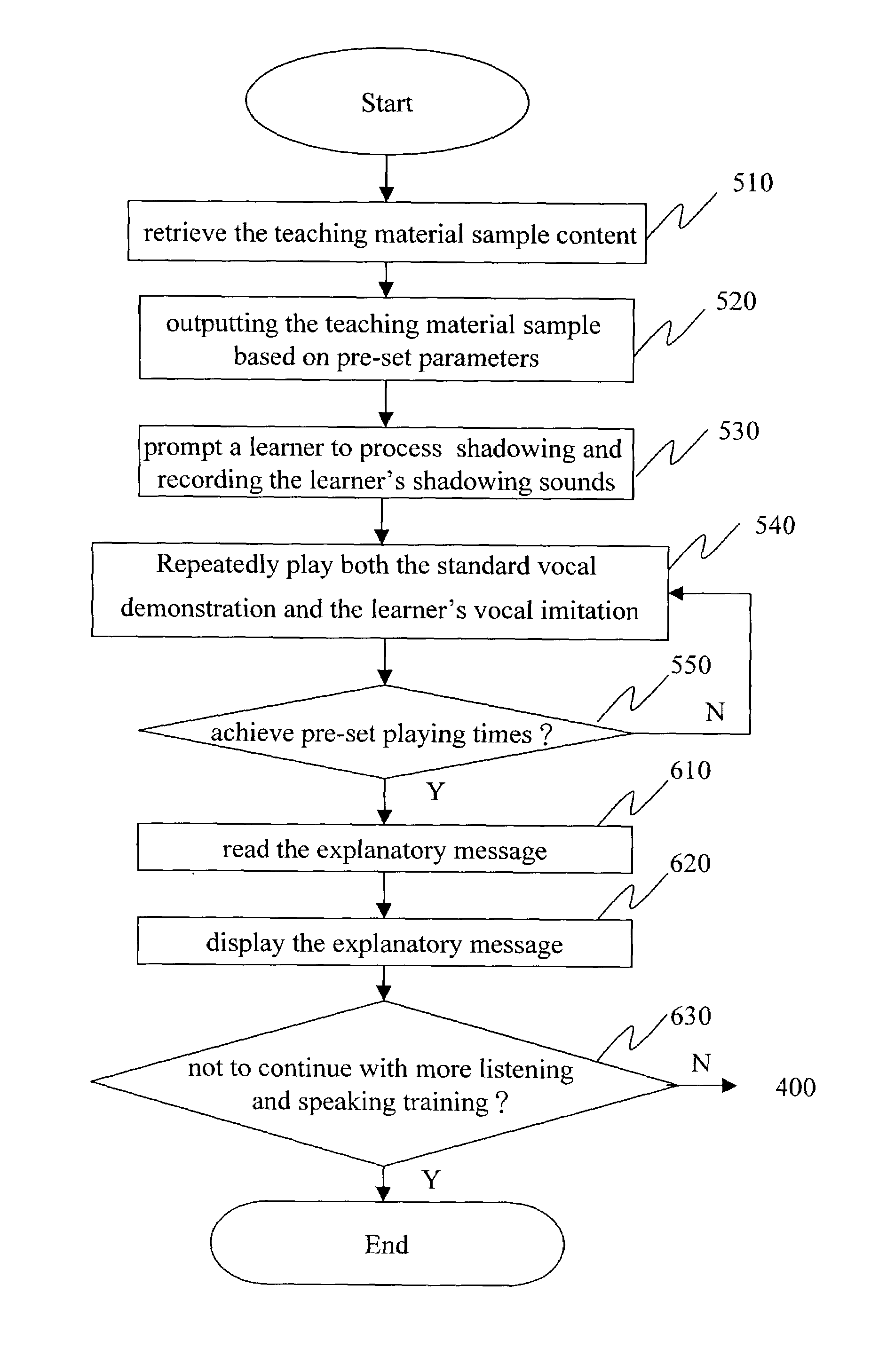

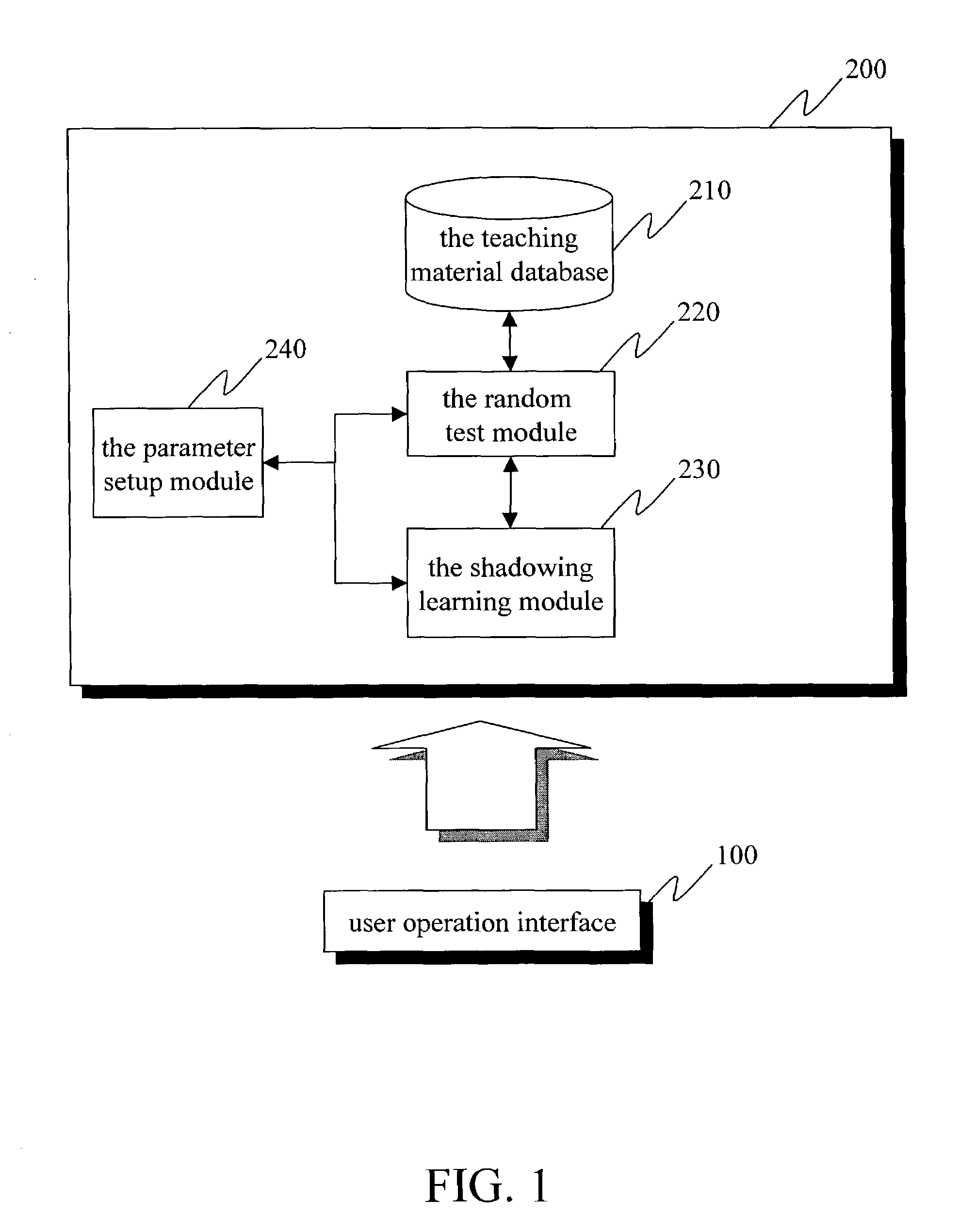

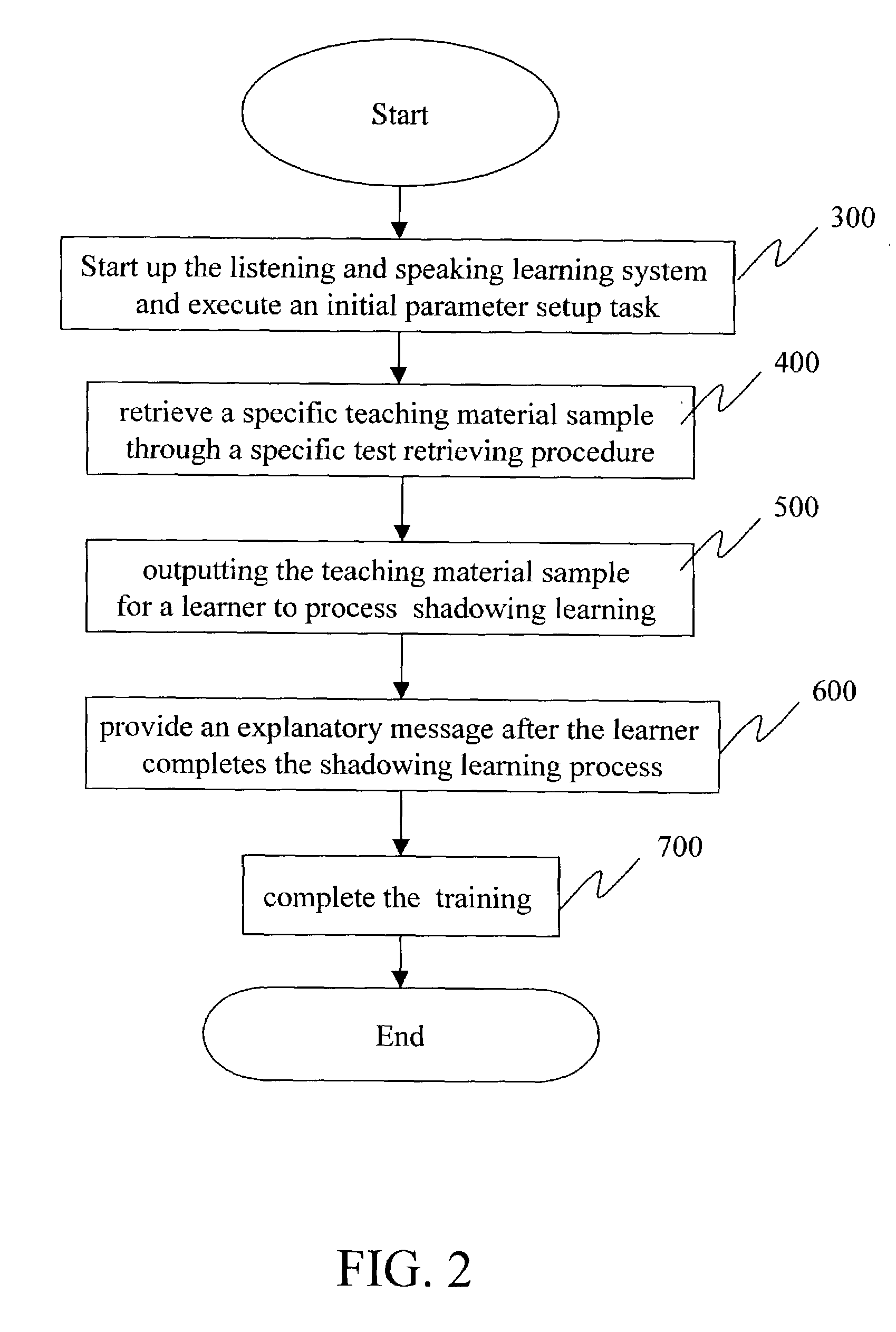

Language listening and speaking training system and method with random test, appropriate shadowing and instant paraphrase functions

InactiveUS7409348B2Ability of to developShort timeNatural language translationSound input/outputShadowingsParaphrase

A language listening and speaking teaching system and method that utilize a random tests function to provide full-scale and various language training subjects and enable a learner to set up the listening and speaking training process according to his / her preference and create a more well-chosen shadowing learning process. Moreover, it assists a learner by enhancing and deepening the listening and speaking training content through an instant paraphrase and definition function, following completion of the shadowing learning process.

Owner:INVENTEC CORP

Randomized testing within transactional execution

ActiveUS20130339675A1None provides advantagesError detection/correctionDigital computer detailsSoftware engineeringRandom testing

Owner:IBM CORP

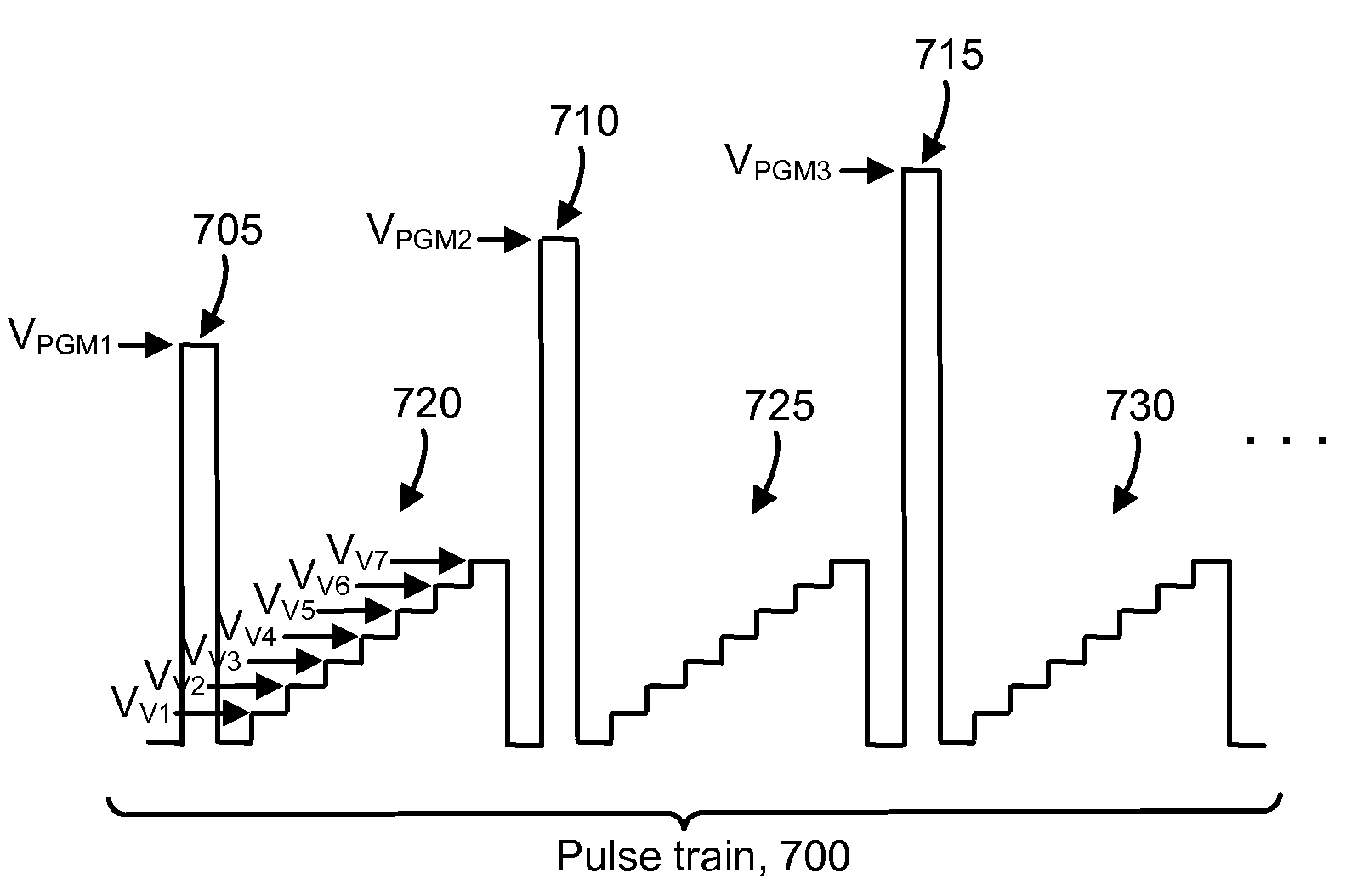

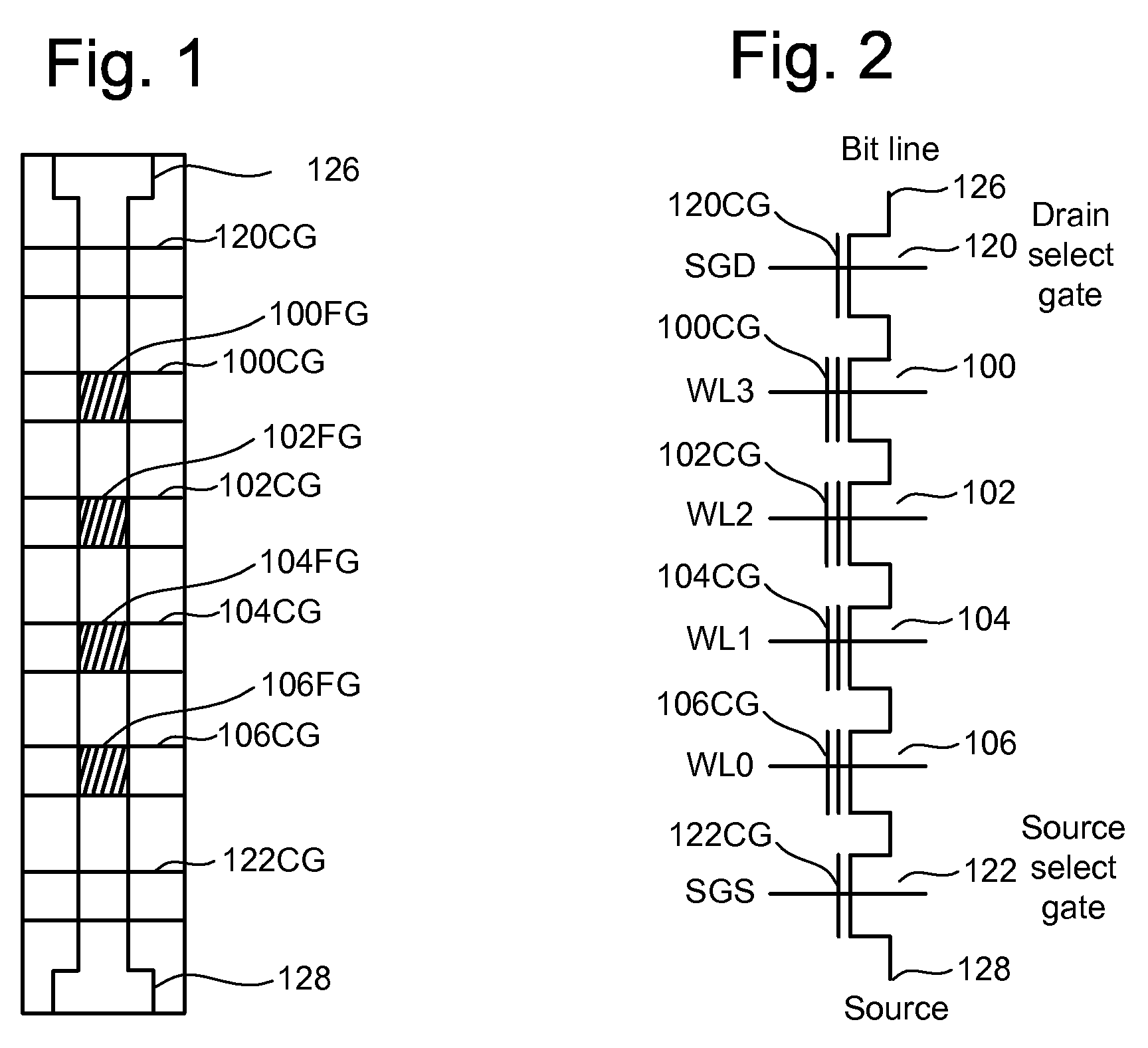

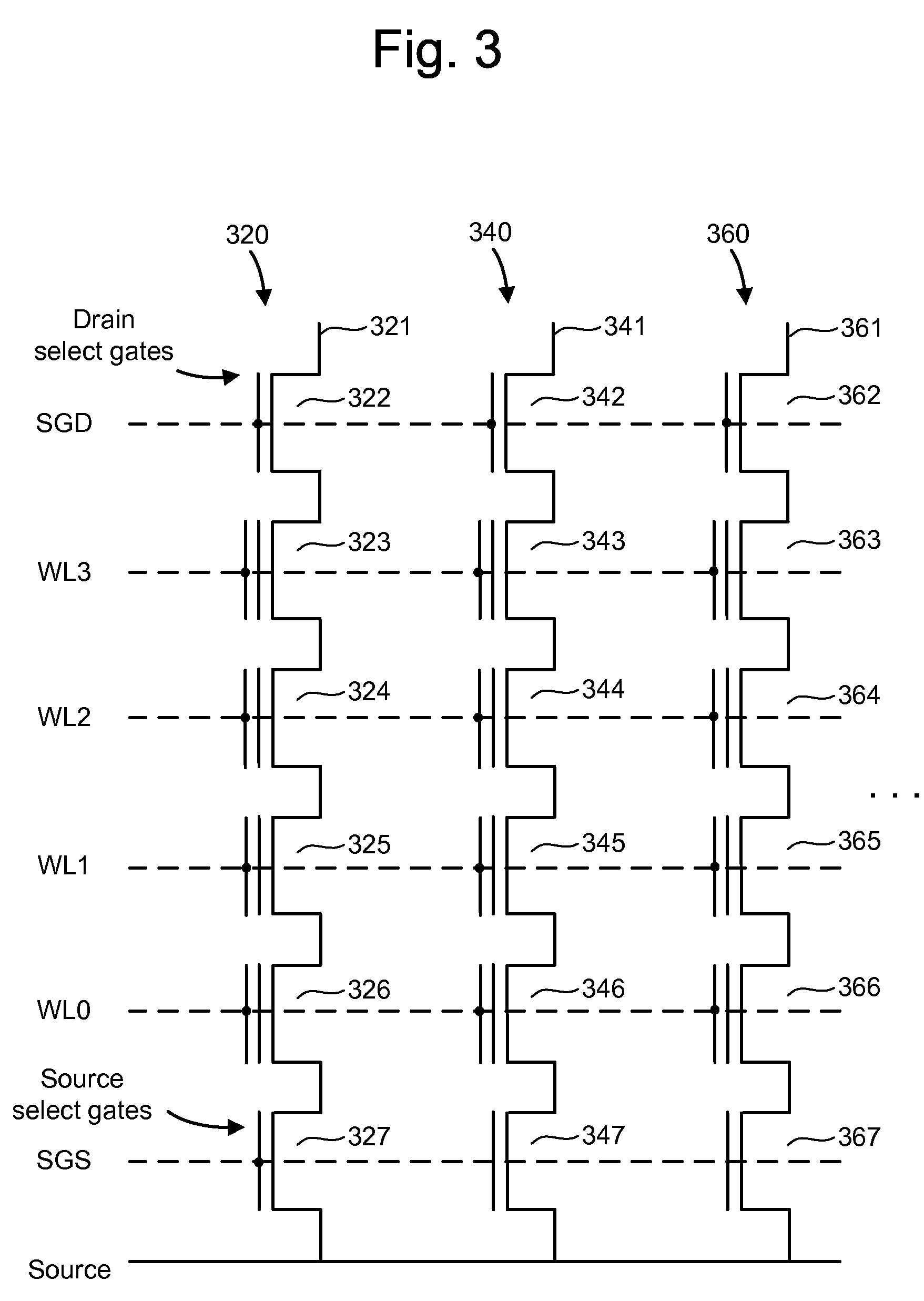

Non-volatile memory with adaptive setting of state voltage levels

A non-volatile memory device is accessed using voltages which are customized to the device, and / or to portions of the device, such as blocks or word lines of non-volatile storage elements. The accessing can include programming, verifying or reading. By customizing the voltages, performance can be optimized, including addressing changes in threshold voltage which are caused by program disturb. In one approach, different sets of storage elements in a memory device are programmed with random test data. A threshold voltage distribution is determined for the different sets of storage elements. A set of voltages is determined based on the threshold voltage distribution, and stored in a non-volatile storage location for subsequent use in accessing the different sets of storage elements. The set of voltages may be determined at the time of manufacture for subsequent use in accessing data by the end user.

Owner:WESTERN DIGITAL ISRAEL LTD

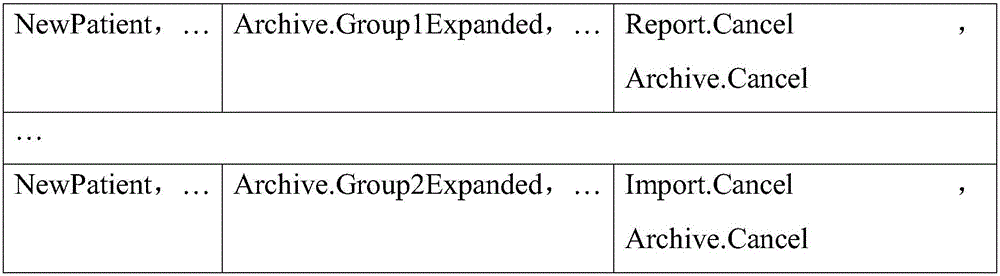

Highly specialized scenarios in random test generation

Improvements in functional verification of a design are achieved by providing a test template that specifies test parameters directed to a function of the design. An exemption mode of operation is associated with a portion of the template, in which constraints and variables associated with the template are revised. The template is an input to a CSP engine, which, in cooperation with a test generator engine, produces test scenarios that lie in an expanded region of the generator's usual operational space. Provision is made for independently enabling and disabling a plurality of exemption modes of operation that are associated with the same or different areas of the template.

Owner:GLOBALFOUNDRIES INC

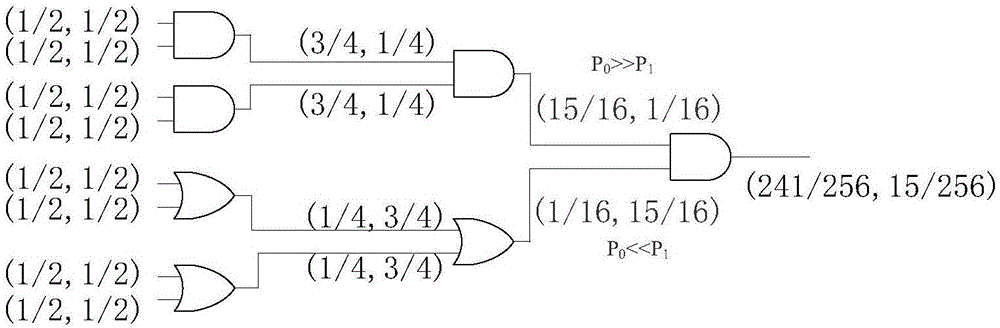

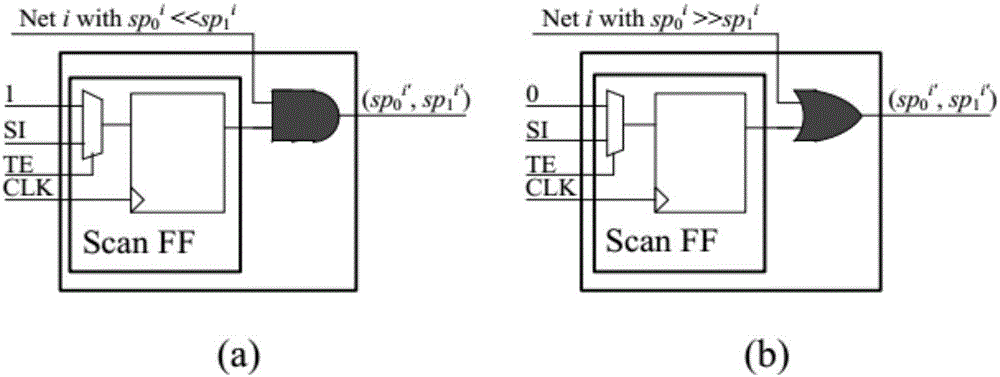

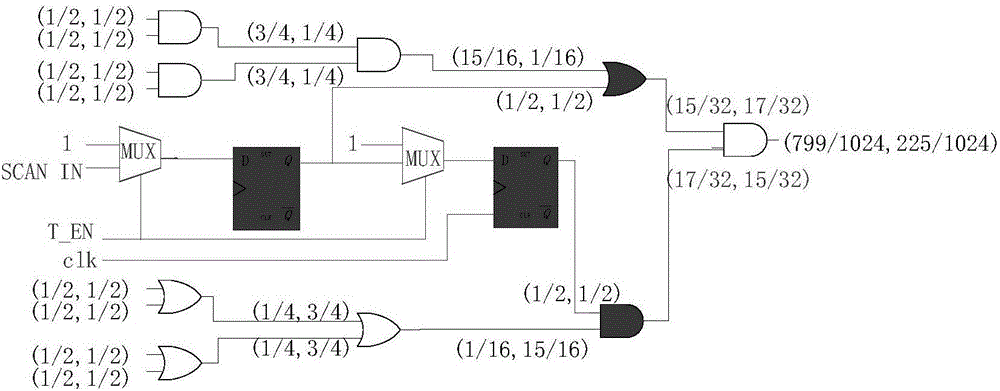

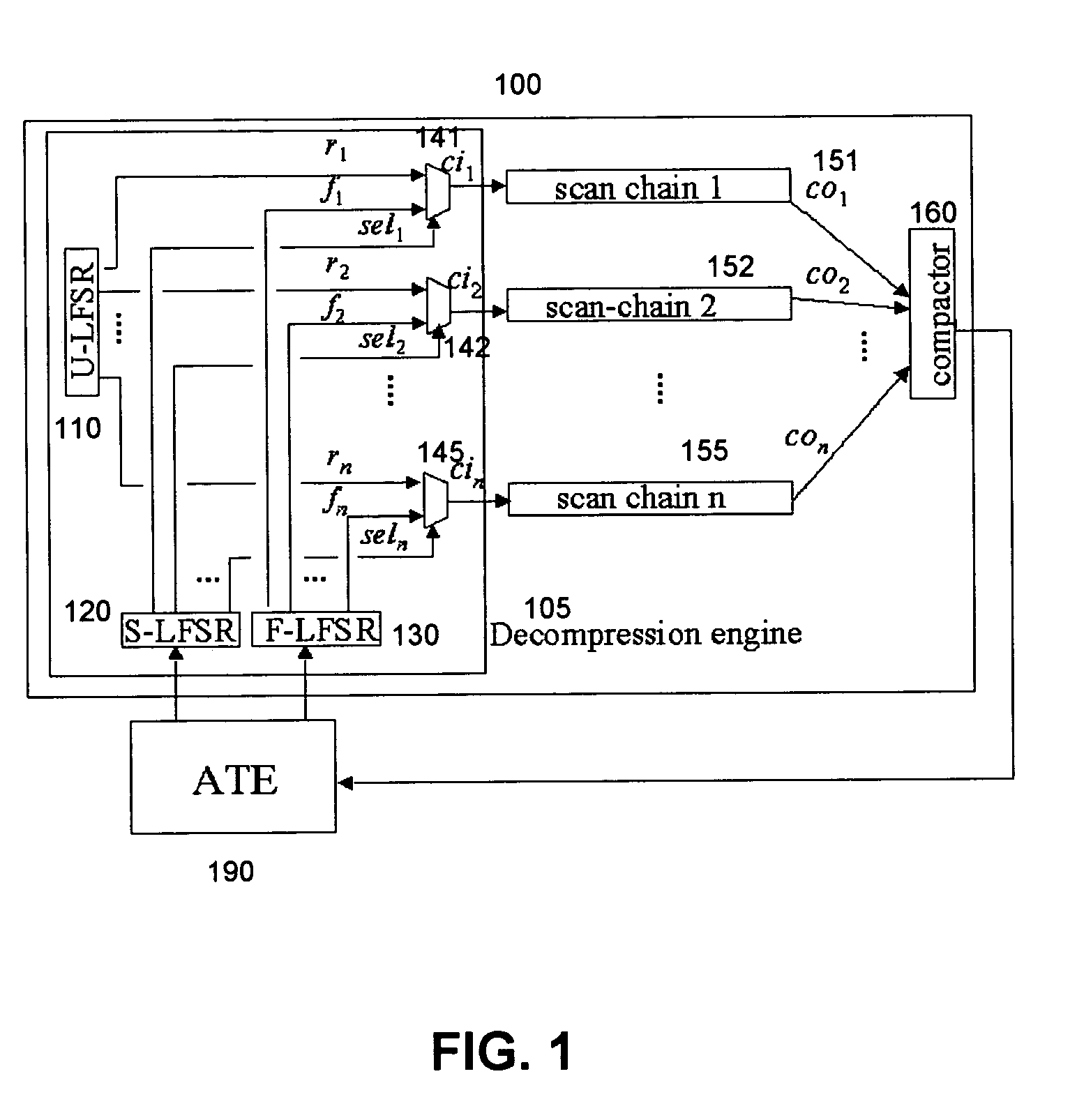

Externally-loaded weighted random test pattern compression

InactiveUS20060015787A1Easy to implementElectronic circuit testingError detection/correctionComputer hardwareLogic testing

The present invention is directed to a logic testing architecture with an improved decompression engine and a method of decompressing scan chains for testing logic circuits.

Owner:NEC CORP

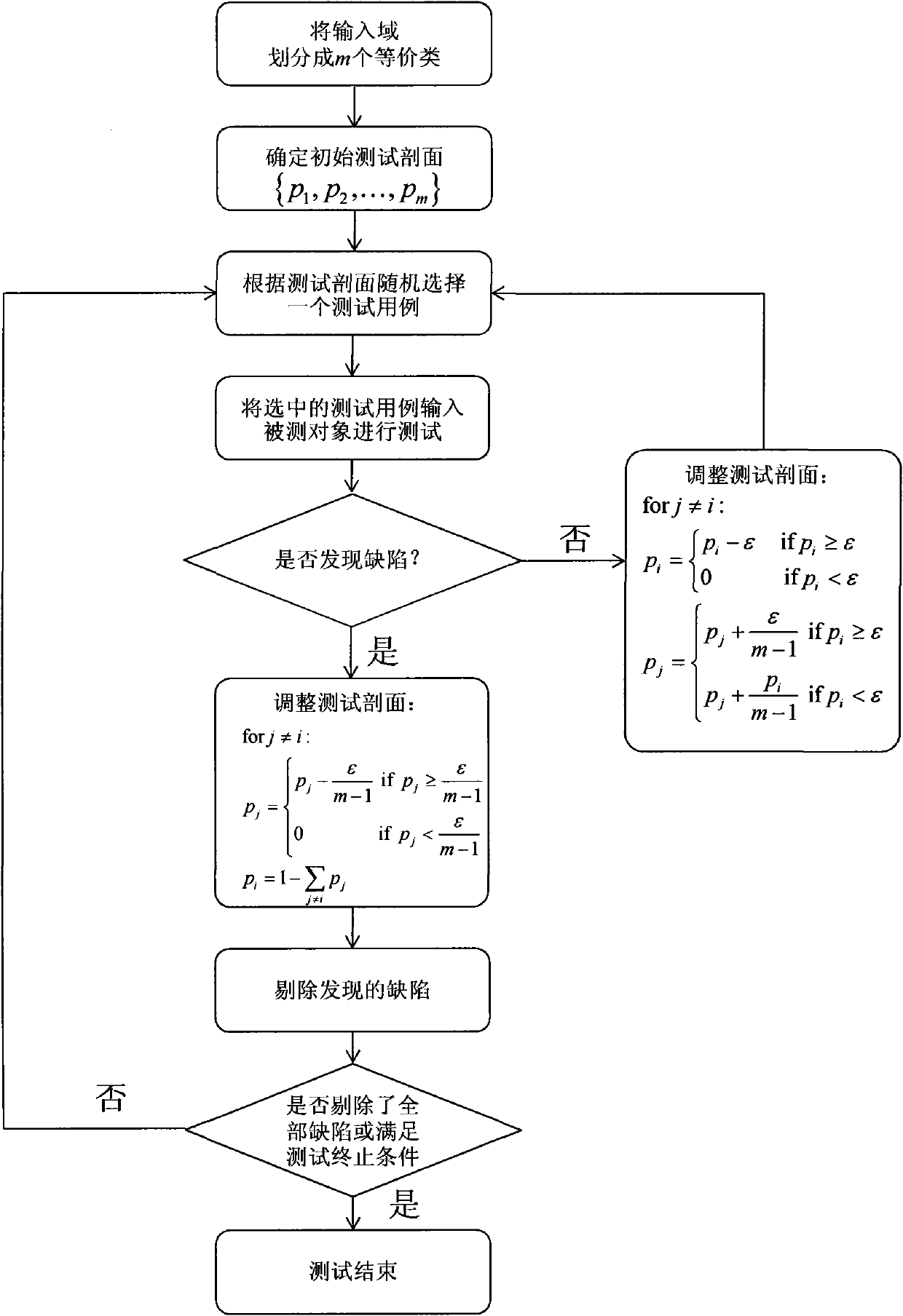

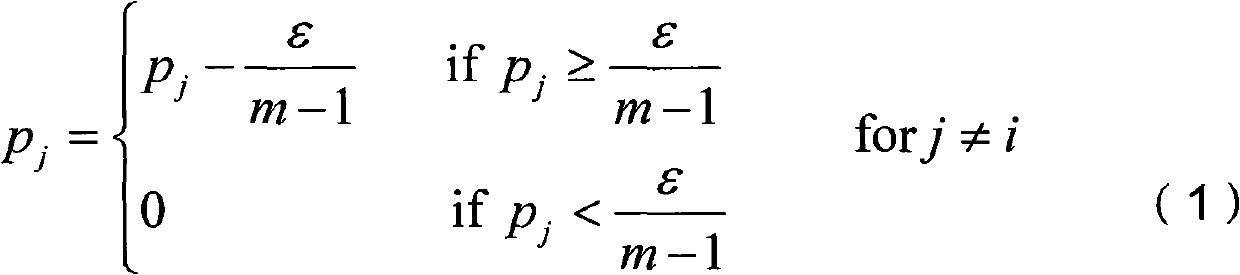

Dynamic random testing method

InactiveCN101620566AThe principle is simpleImprove defect detection efficiencySoftware testing/debuggingProgramming languageGreek letter epsilon

The invention relates to a dynamic random testing method. The method comprises the following steps: (1), a test case or test object input domain is divided into a plurality of equivalence classes {C1, C2, etc., Cm-1, Cm}; (2), an initial test profile {p1, p2, etc., pm-1, pm} is determined, a test case set Ci is selected at random according to the profile and a test case is selected from the Ci at random for testing; (3), the test profile is adjusted according to the test result, if a defect exists, pi is equal to pi + Epsilon, and the found defect is eliminated at the same time; and if no defect exists, pi is equal to pi-Epsilon, Epsilon is a given parameter before test, and meanwhile, other elements of the test profile are correspondingly corrected so that pi is equal to or more than 0, I is equal to 1, 2, etc., m and *pi is equal to 1; (4), a test case set is selected according to the adjusted test profile, and a test case is selected from the test case set at random for testing; (5), the test profile is adjusted according to the test result and the adjustment rule is same as the step (3); and (6), and so forth, the operation is continued until all defects are found and eliminated or the other test completion conditions are met. The method is simple in principle and convenient in application.

Owner:BEIHANG UNIV

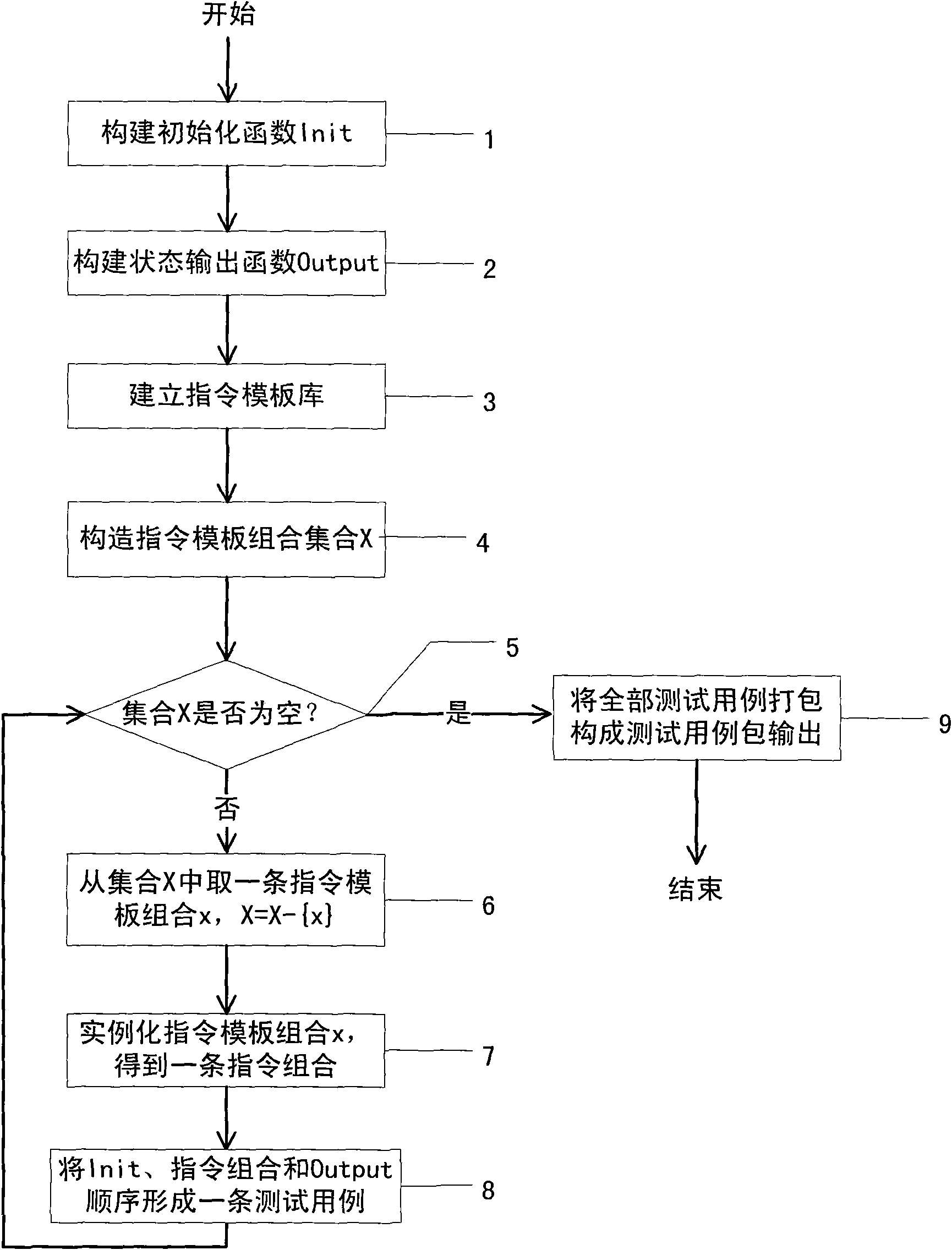

Full-covered automatic generating method of test case package of microprocessor

InactiveCN101673236AMeet the needs of complete functional verificationFunctional testingSoftware testing/debuggingProgramming languageInit

The invention discloses a full-covered automatic generating method of a test case package of a microprocessor, aiming to solve the problem that the formalizing method and the random testing method ofthe microprocessor can not cover all instruction combinations. The invention adopts the technical scheme that the identification, the assembling name, the source operand type and the destination operand type of each instruction are constituted into an instruction template, M instruction templates are constituted into an instruction template base with the size of M; N instruction templates are selected from the instruction template base according to instruction number N needing to be tested by users and are arranged into instruction template combinations to form MN instruction template combinations; each instruction template combination is instantiated into an instruction combination in an instantiating method; an initialization function Init, the instruction combinations and a state outputfunction Output are orderly connected into a test case, and all test cases are constituted into a test case package. The invention ensures that all test cases are covered so as to satisfy the requirements that special chip for some specific fields can not avoid omitting any function verification.

Owner:NAT UNIV OF DEFENSE TECH

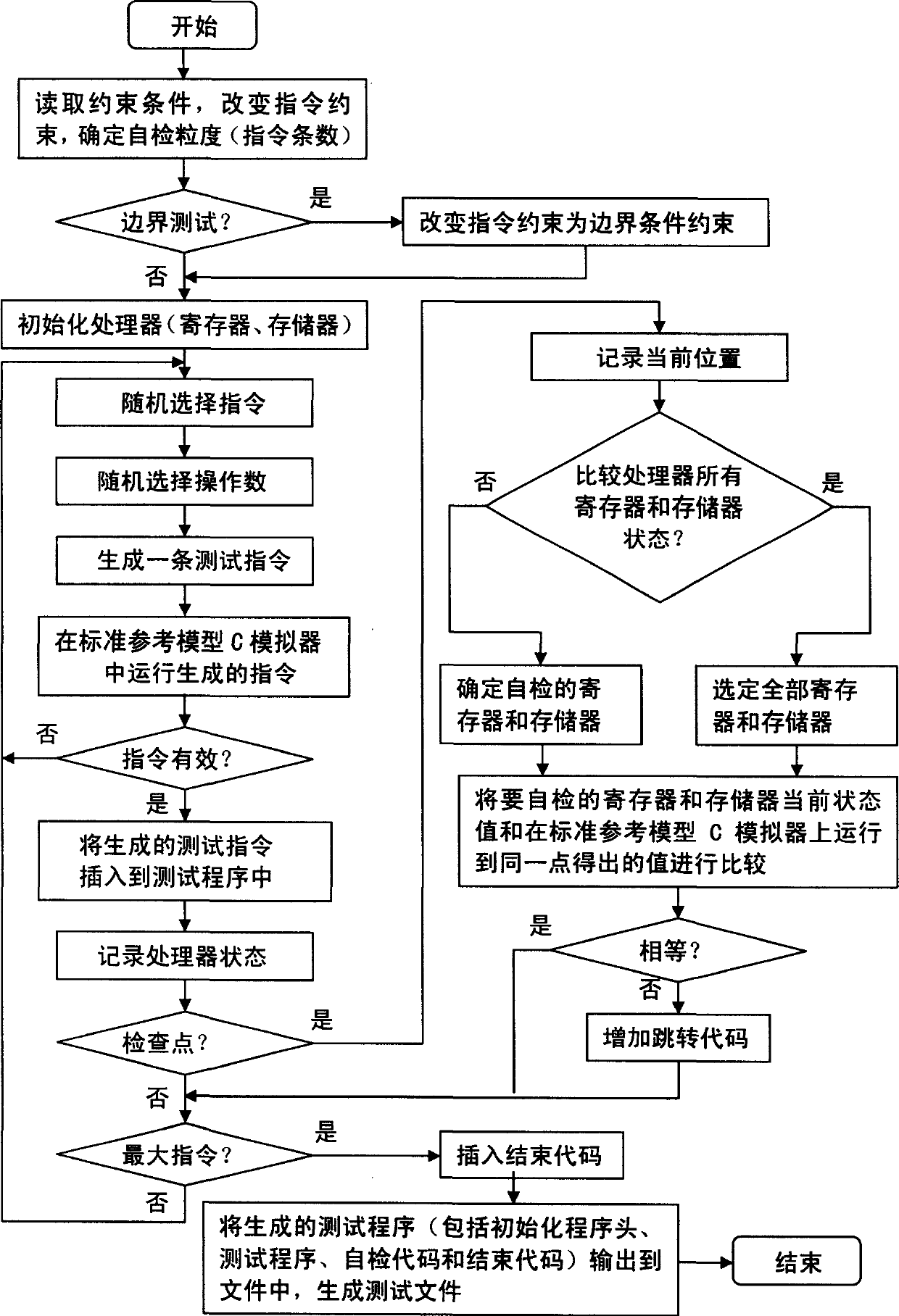

CPU restraint forming and verifying method based on boundary condition and self detection random test

InactiveCN1684047AQuality improvementSpeed up the verification processSoftware testing/debuggingReference modelProcessor model

The present invention belongs to the field of automatic computer verifying technology, and is the CPU restraint creating and verifying method based on boundary condition and random self test. The specific mode is one random test environment including system structure model and RTL model. The system structure model is expected processor model realized with C simulator and used as the standard reference model. The RTL model is one to be tested and verified, and the random test and verification aims at testing the consistency of the RTL model to the system structure model. Both the RTL model and the system structure model can output separate processor state in each clock period, and comparing the processor state of these two model can judge the consistency. The present invention has independent system structure, and can constitute new verifying platform easily to raise the verification speed and quality greatly.

Owner:TSINGHUA UNIV

An ultrasonic apparatus reliability testing method and testing system

The invention provides an ultrasonic apparatus reliability testing method and testing system. The method comprises the steps of extracting behavior action in a code of a to-be-tested product; retrieving an instruction invoking mapping table according to the behavior action and generating an execution function; encapsulating the execution results of the execution function into a testing program and converting the same into a plurality of testing vectors; extracting testing vectors associated with user interaction from the testing vectors to establish a formal rule database associated with user interaction behavior; randomly selecting testing vectors to generate random testing vector sequences and performing function classification on the testing vectors and the random testing vector sequences, matching the testing vectors and / or random testing vector sequences subjected to the function classification and associated with user interaction with the formal rule database; after the matching is successful, determining that the current testing vectors and / or random testing sequences cover user requirements and continuing tests. The method and the system optimize testing sequence generate, remove redundant testing sequences and greatly shorten testing time.

Owner:VINNO TECH (SUZHOU) CO LTD

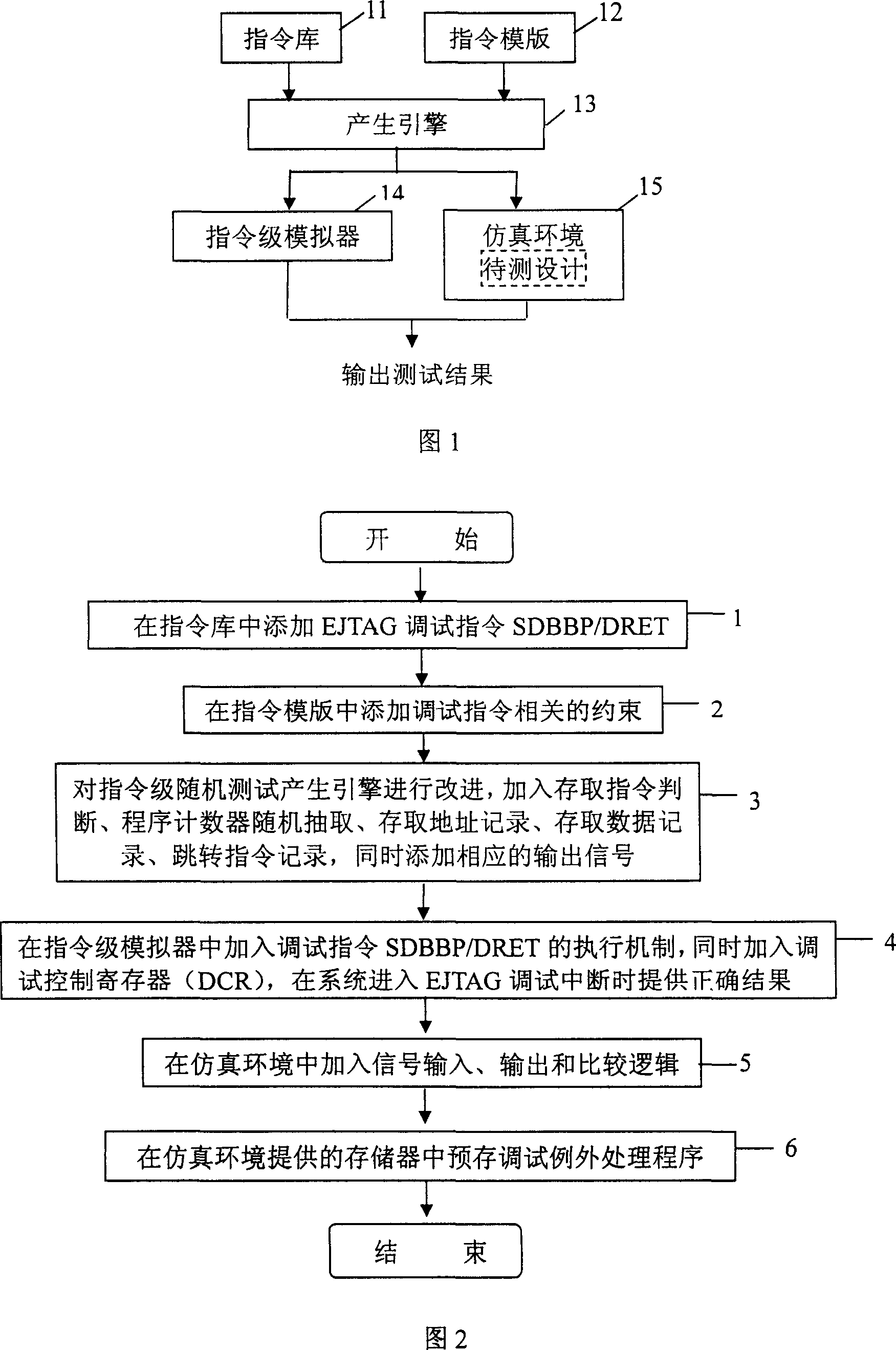

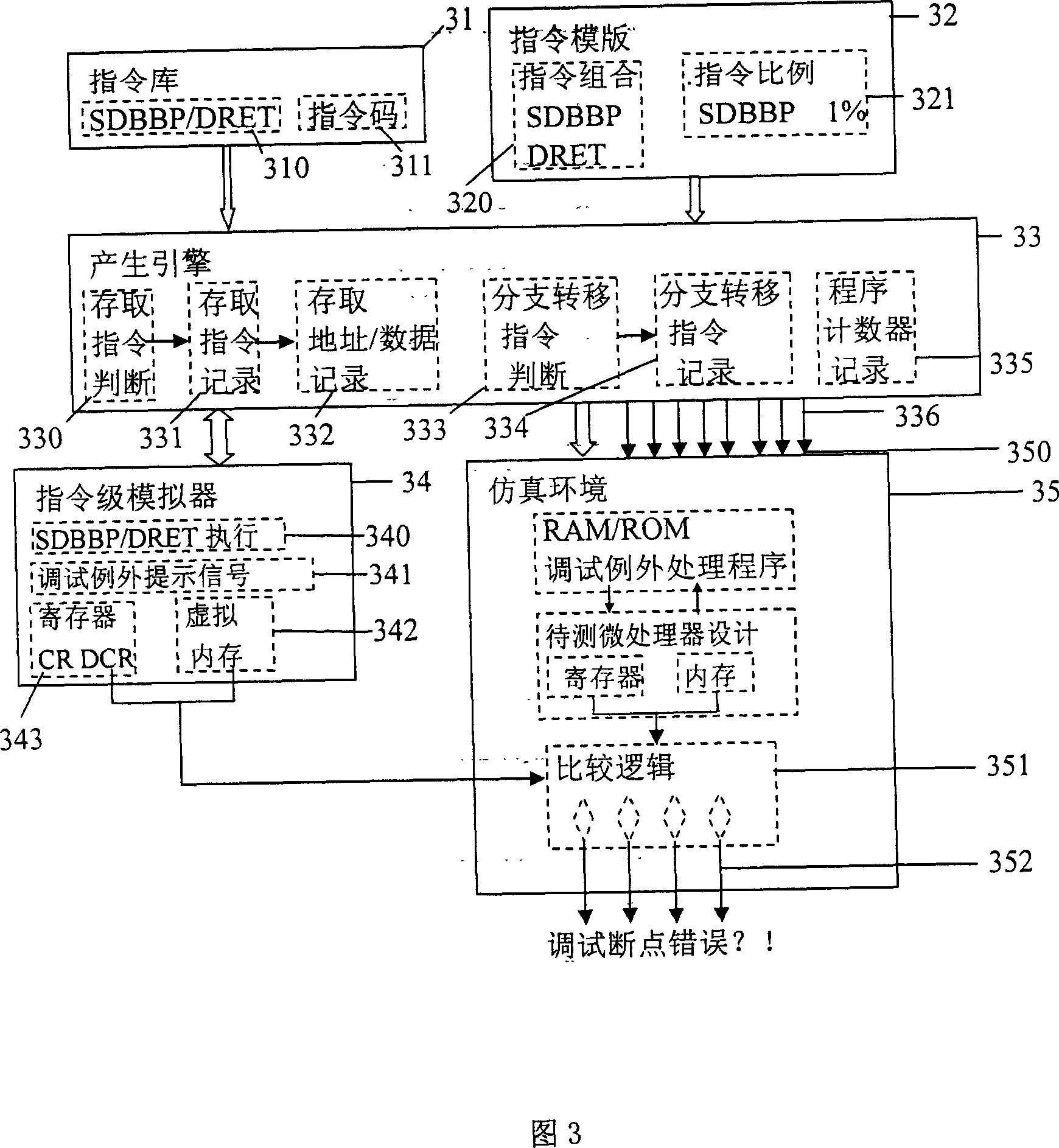

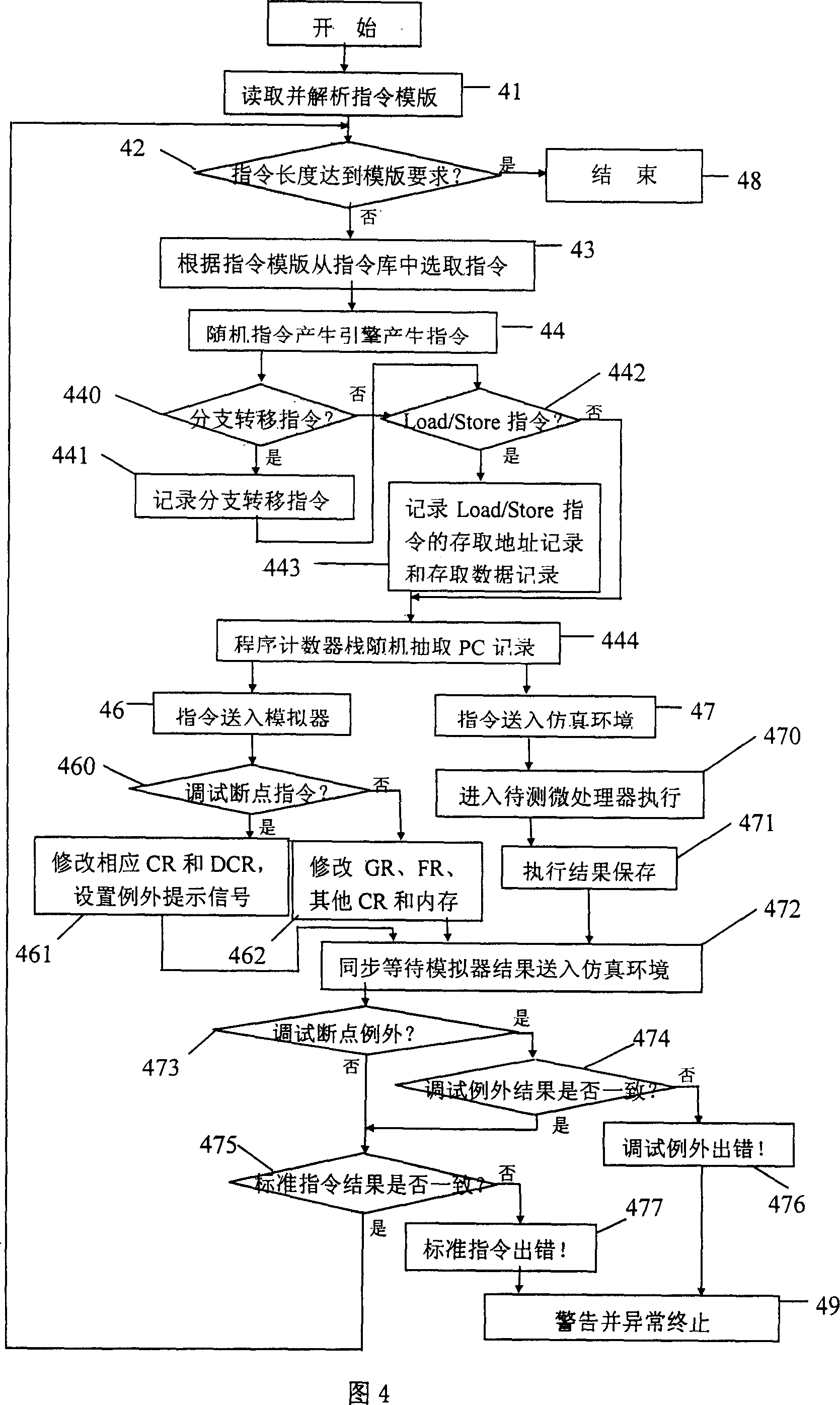

Method for realizing supporting of EJTAG detection in instruction grade random detection

ActiveCN1936860AIncrease coverageUniform coverageSoftware testing/debuggingProcessor registerControl register

This invention discloses a method supporting EJTAG test in dictation random testing. It includes the following steps: add SDBBP / DRET dictation to the library; add corresponding restriction to the dictation stencil; generate engine to improve the random testing; add executive mechanism of SDBBP / DRET to the simulator and add debugging control register; add input / output signals and comparison logic in simulating circumstance; pre-store EJTAG debugging exceptional processing program in memorizer. This invention not only preserves advantages of traditional dictation random testing, but also supports testing and validating the debugger on the EJTAG.

Owner:LOONGSON TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com