Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Deterministic testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and software behaviors (specifically, the test outputs and postconditions) are deterministic. They think that they are able to control (and observe) the test preconditions and inputs. The test oracle provides only a single outcome (outputs and postconditions) for any given set of test preconditions and inputs.

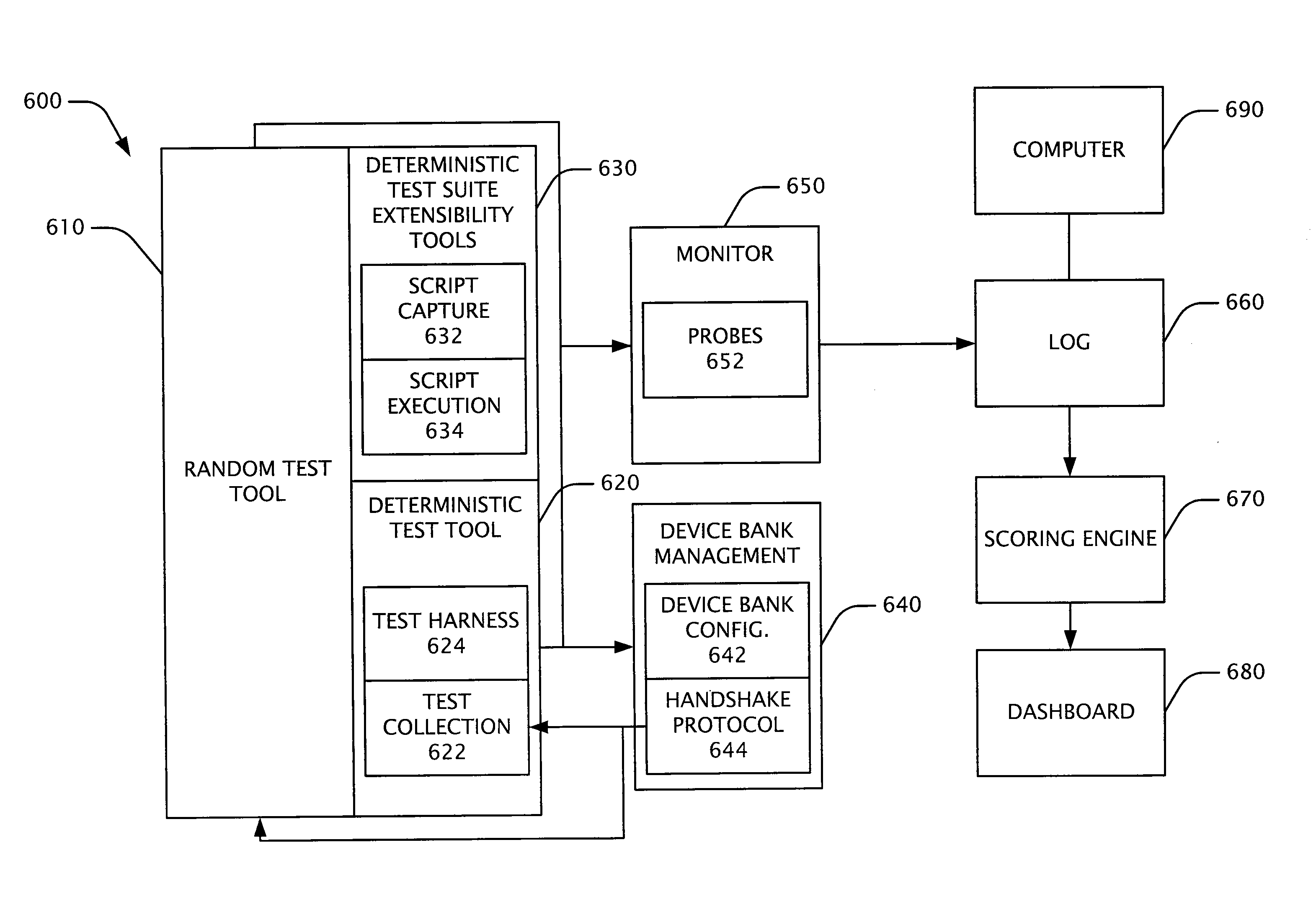

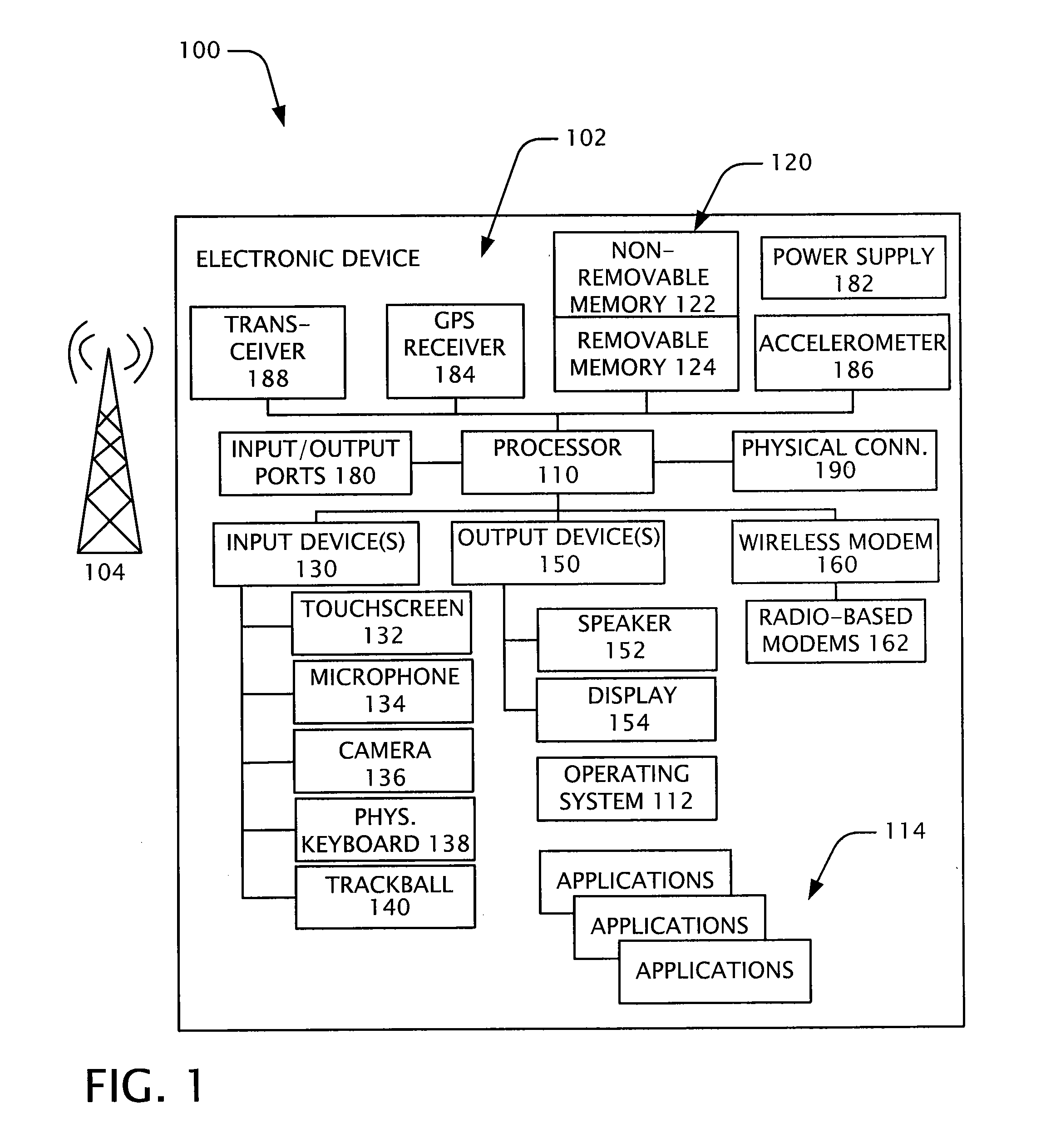

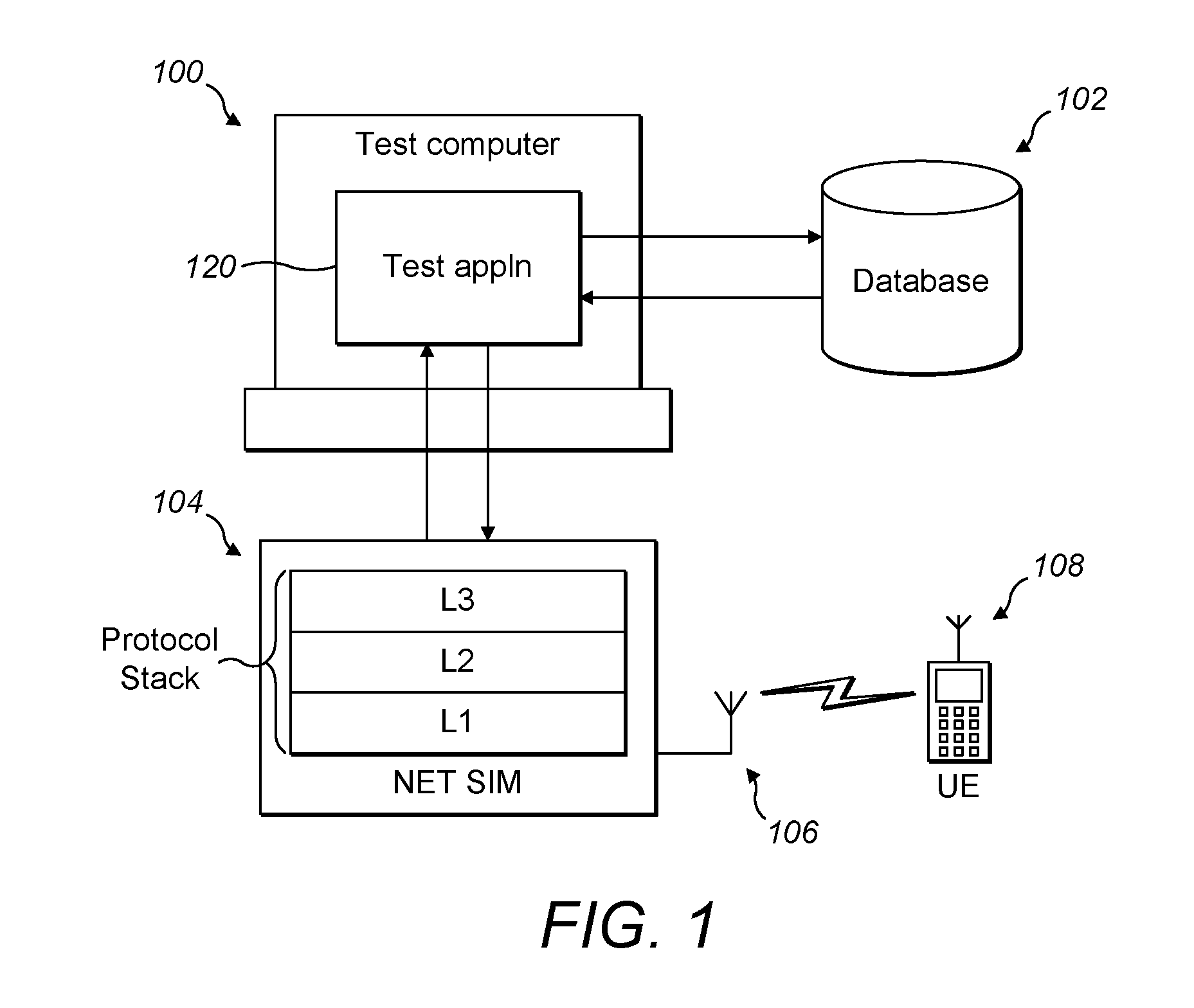

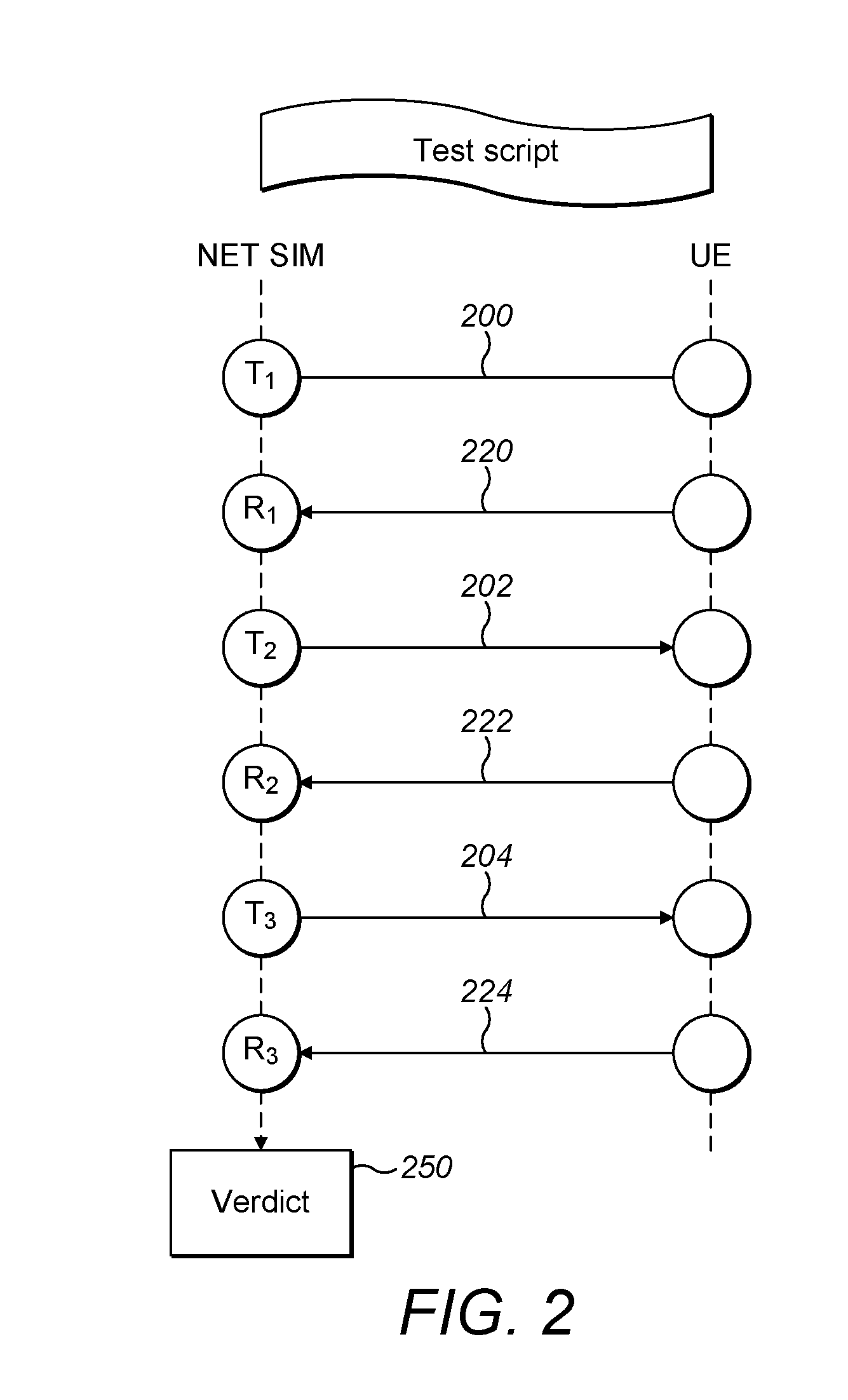

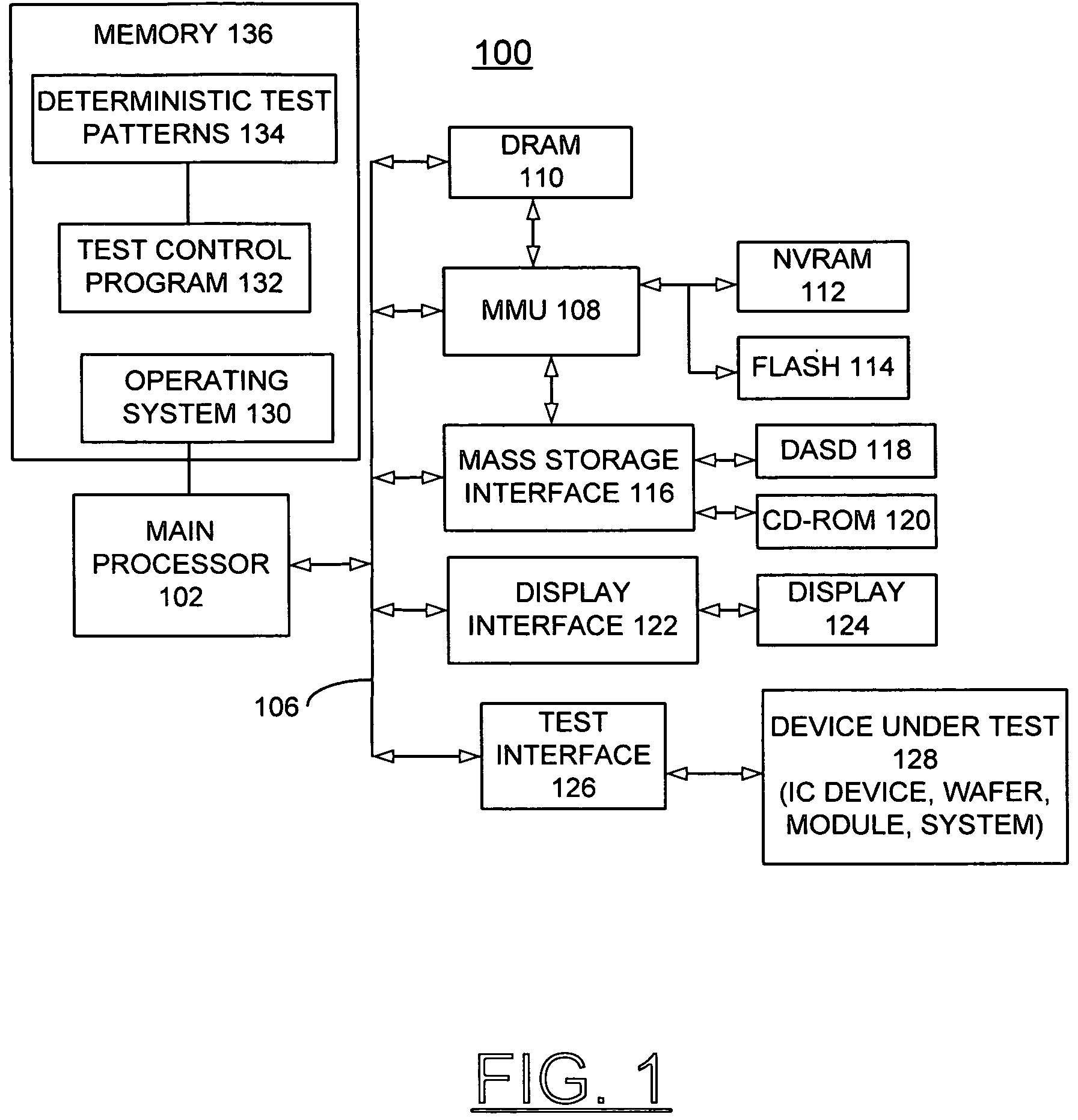

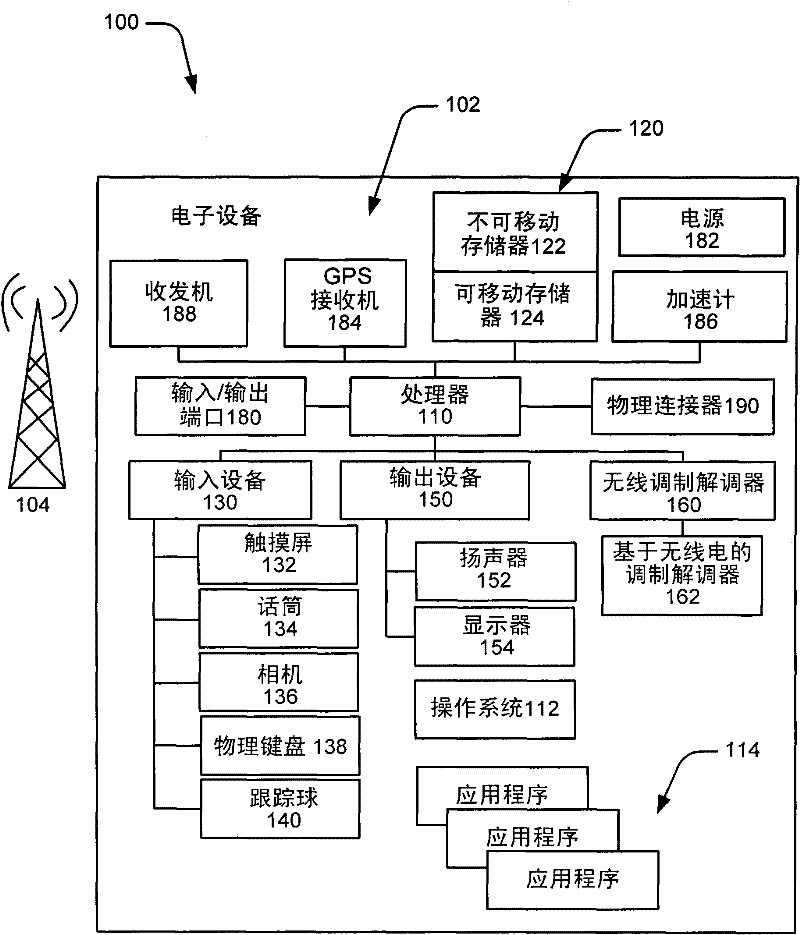

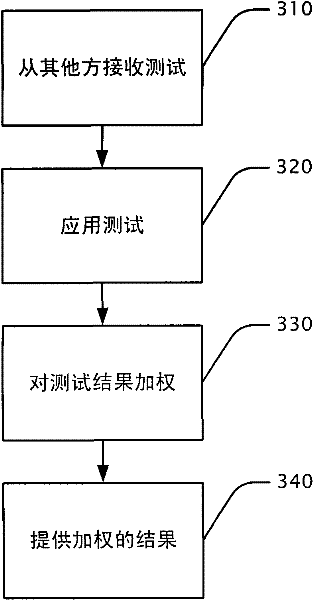

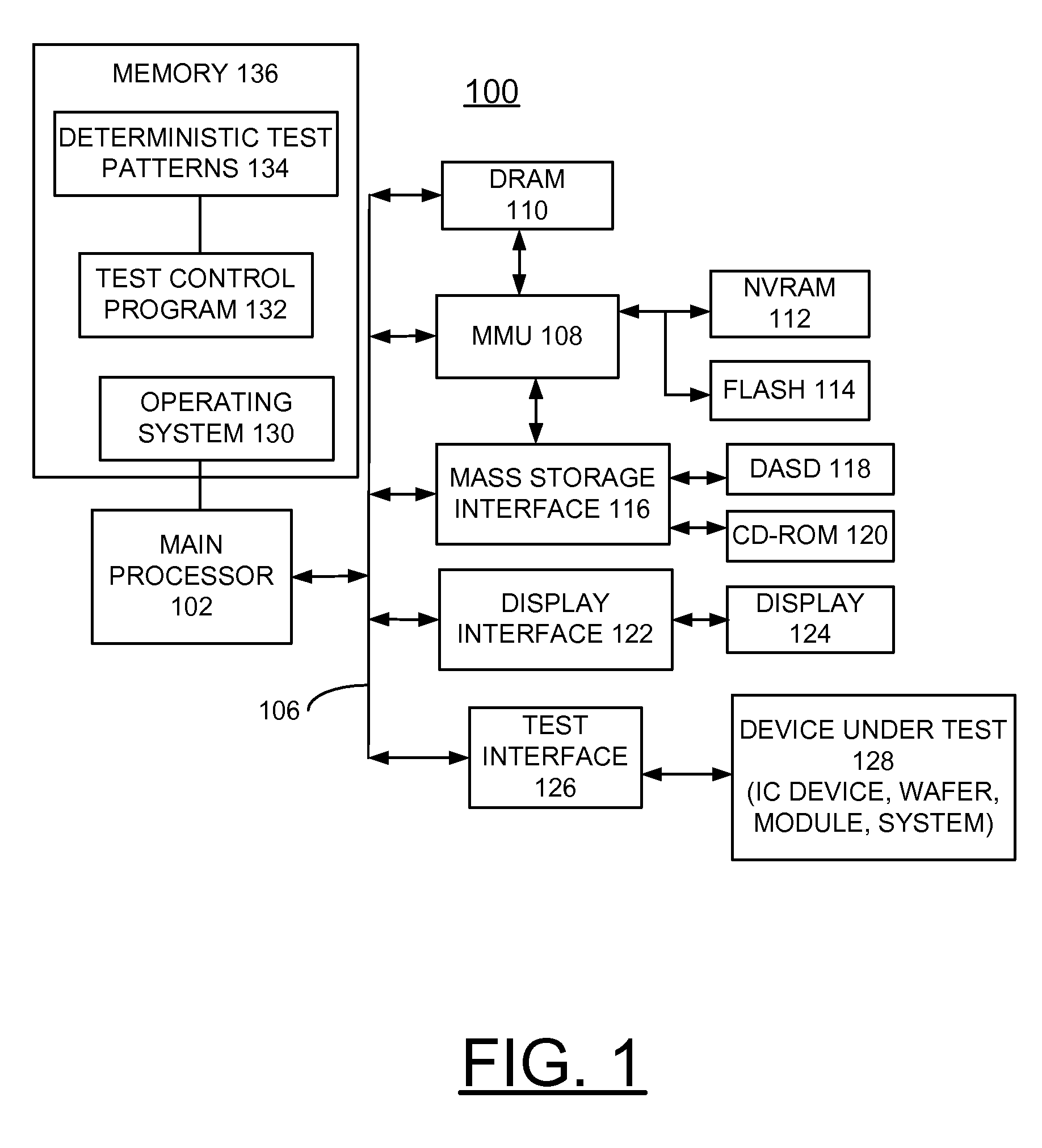

Testing software in electronic devices

Software in an electronic device can be tested using a combination of random testing and deterministic testing. In various embodiments, deterministic tests can run for a prescribed duration and / or a prescribed number of iterations before and / or after random testing. Test results can be weighted using a metric representing an amount of code that was stressed during testing. This metric can be determined by tracking software code that is loaded into memory during testing.

Owner:MICROSOFT TECH LICENSING LLC

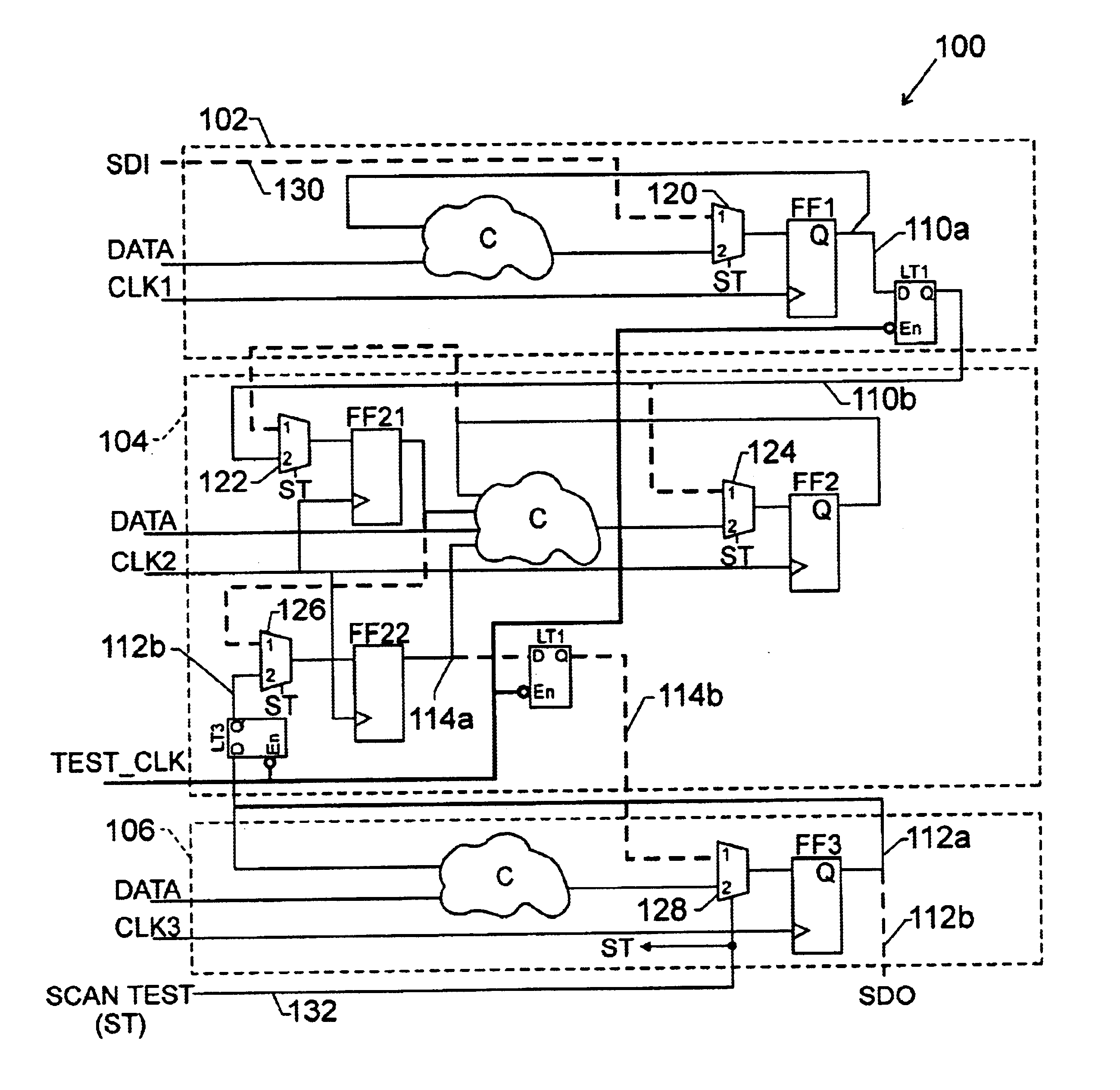

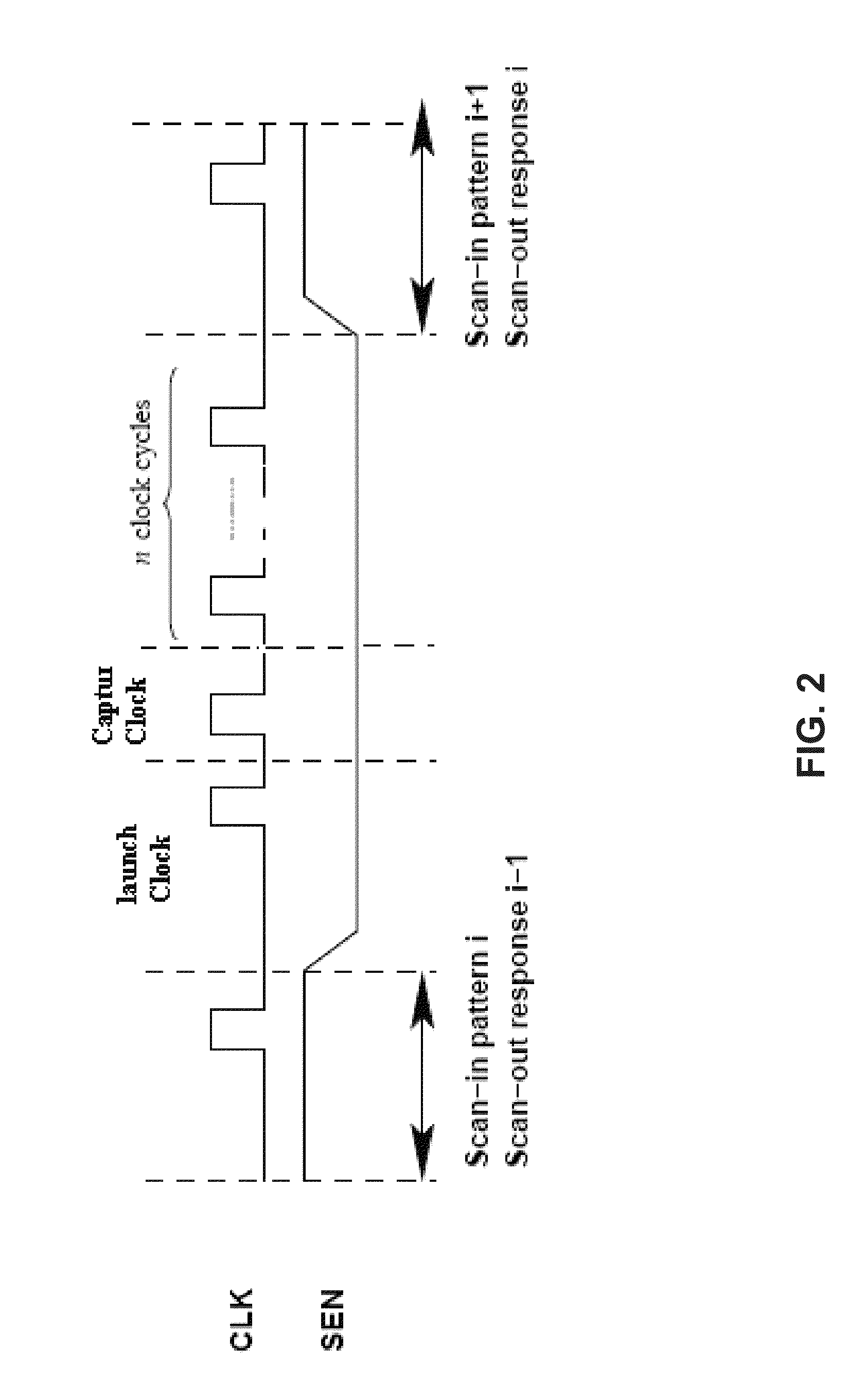

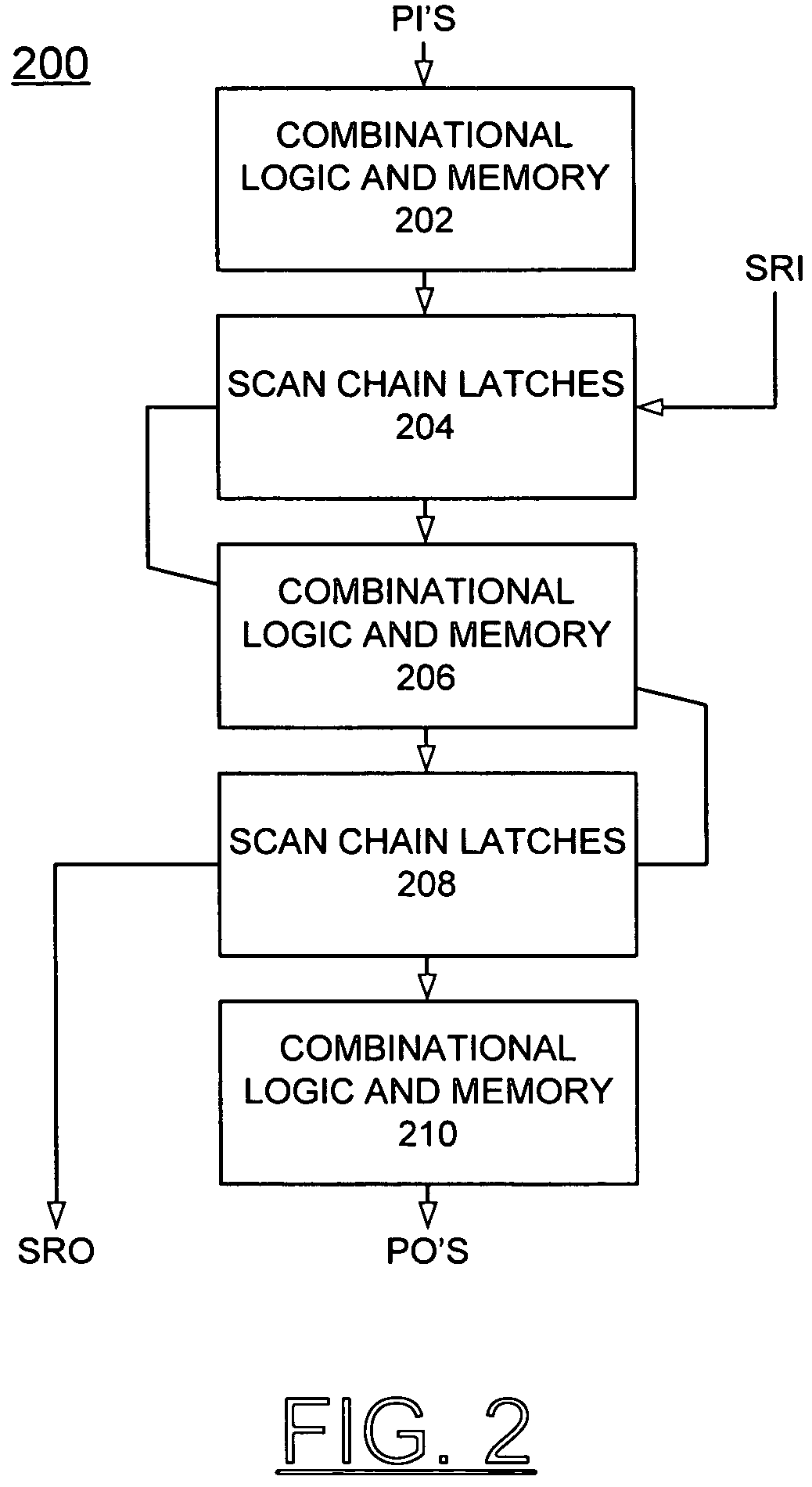

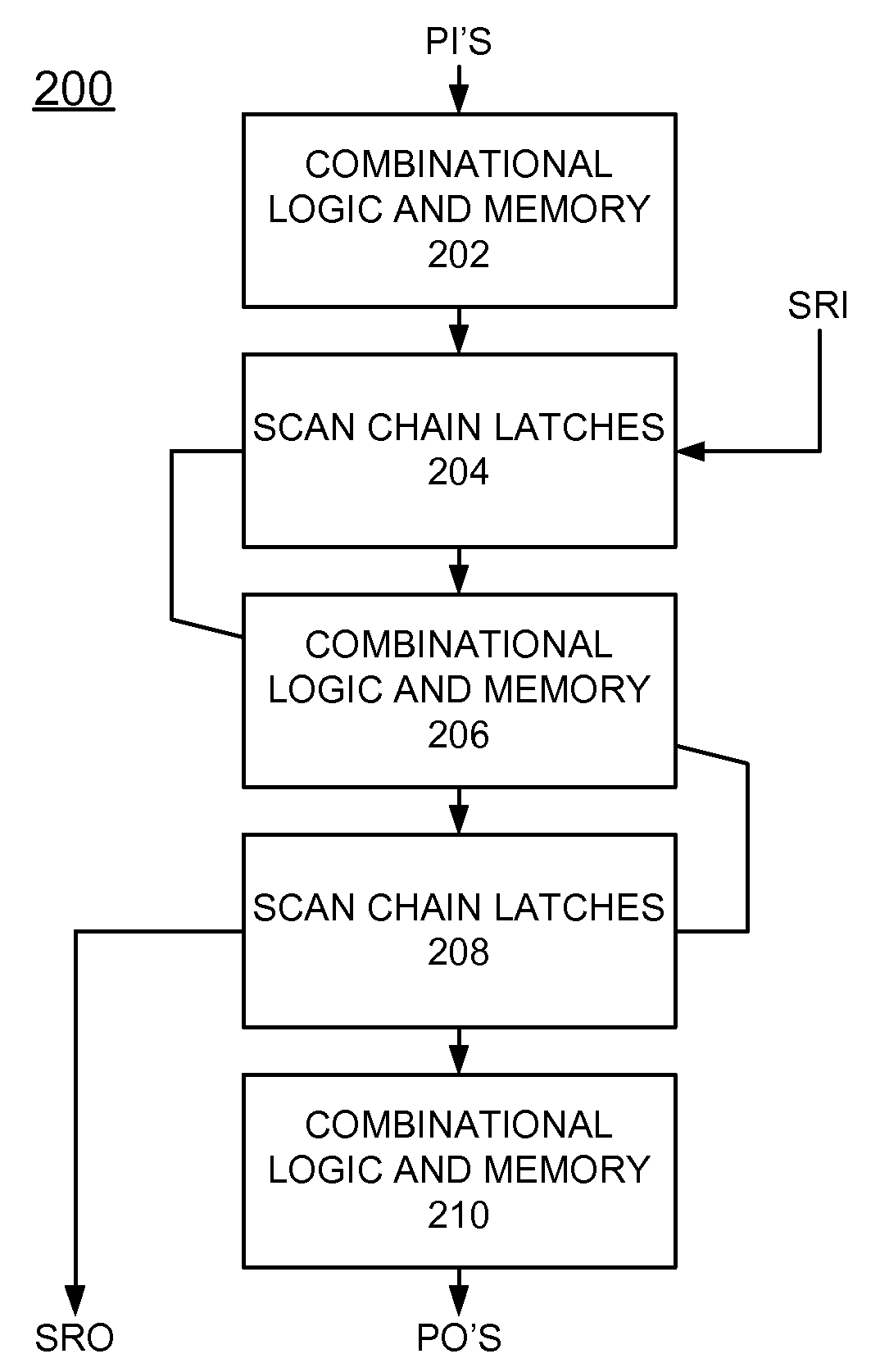

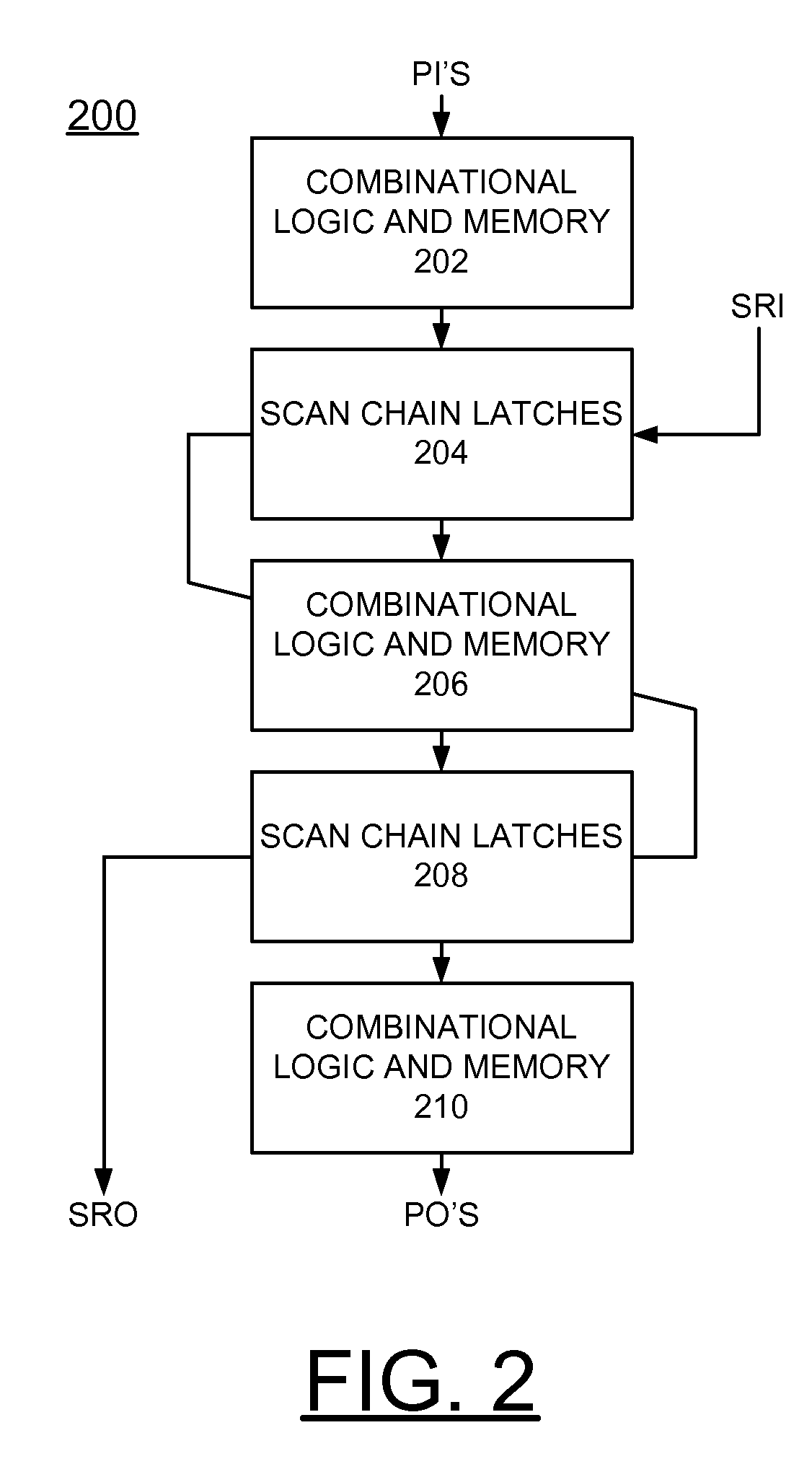

Deterministic testing of edge-triggered logic

InactiveUS6904553B1Skew problemEliminates the timing uncertainties in the test environmentElectronic circuit testingDatapathData path

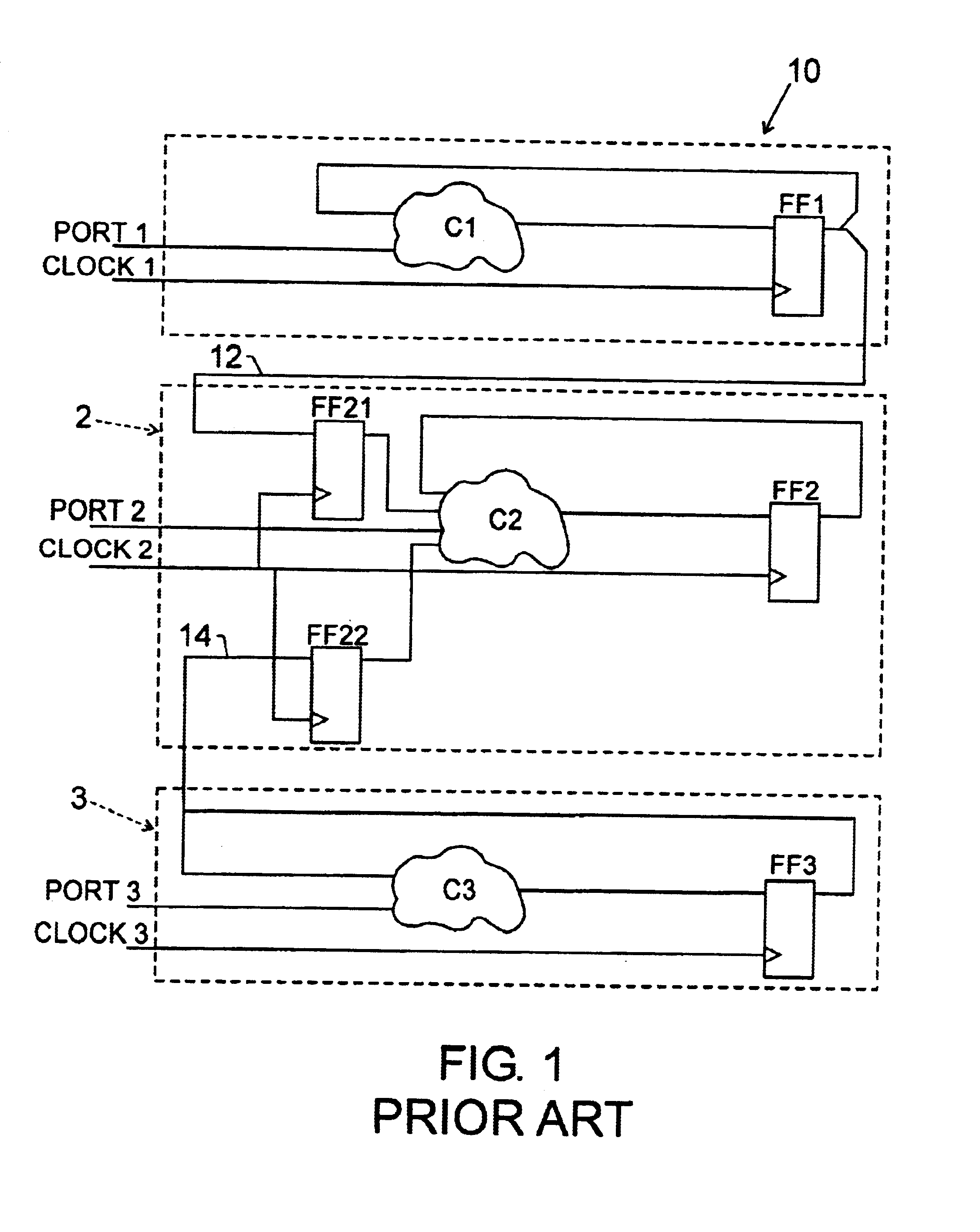

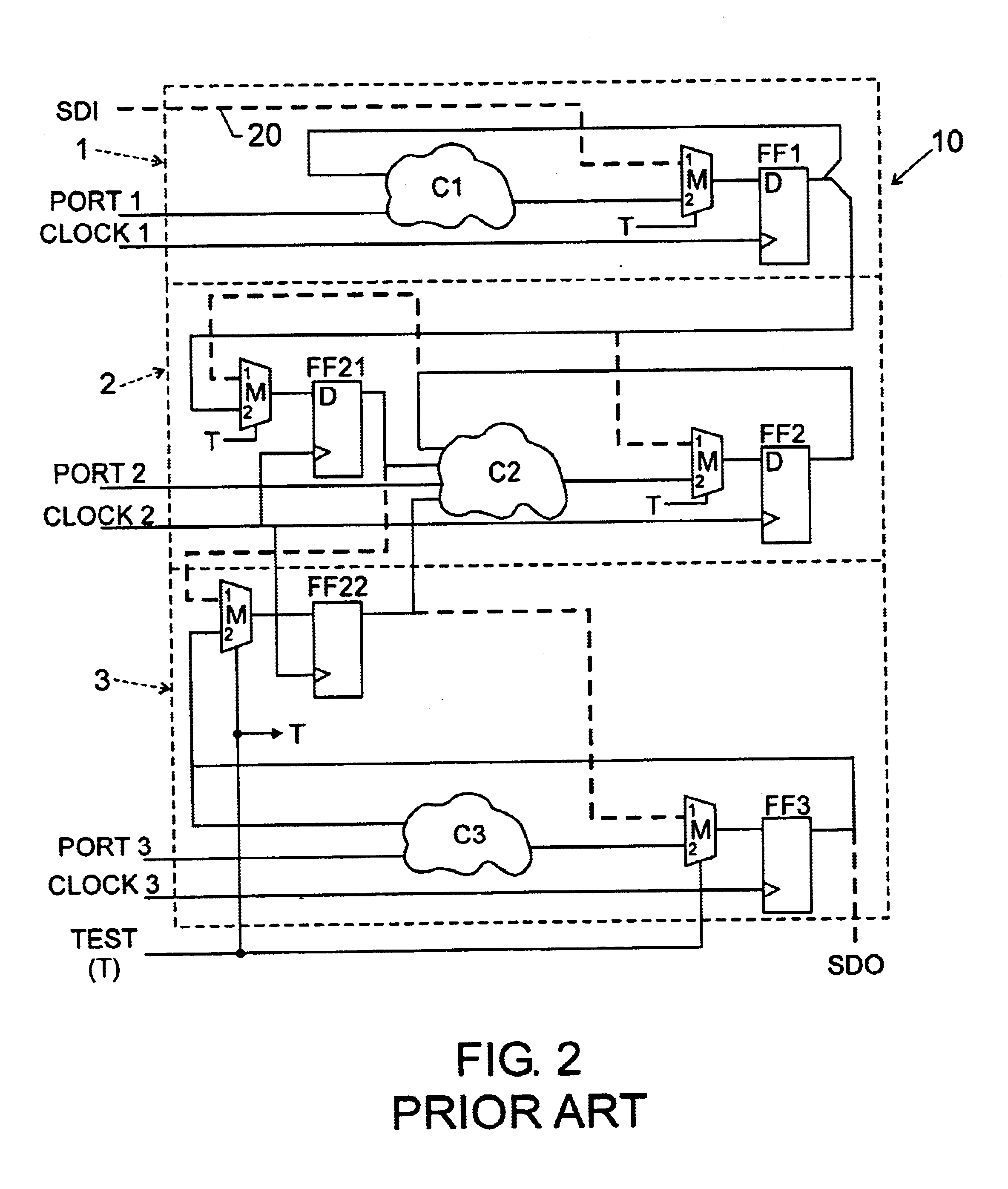

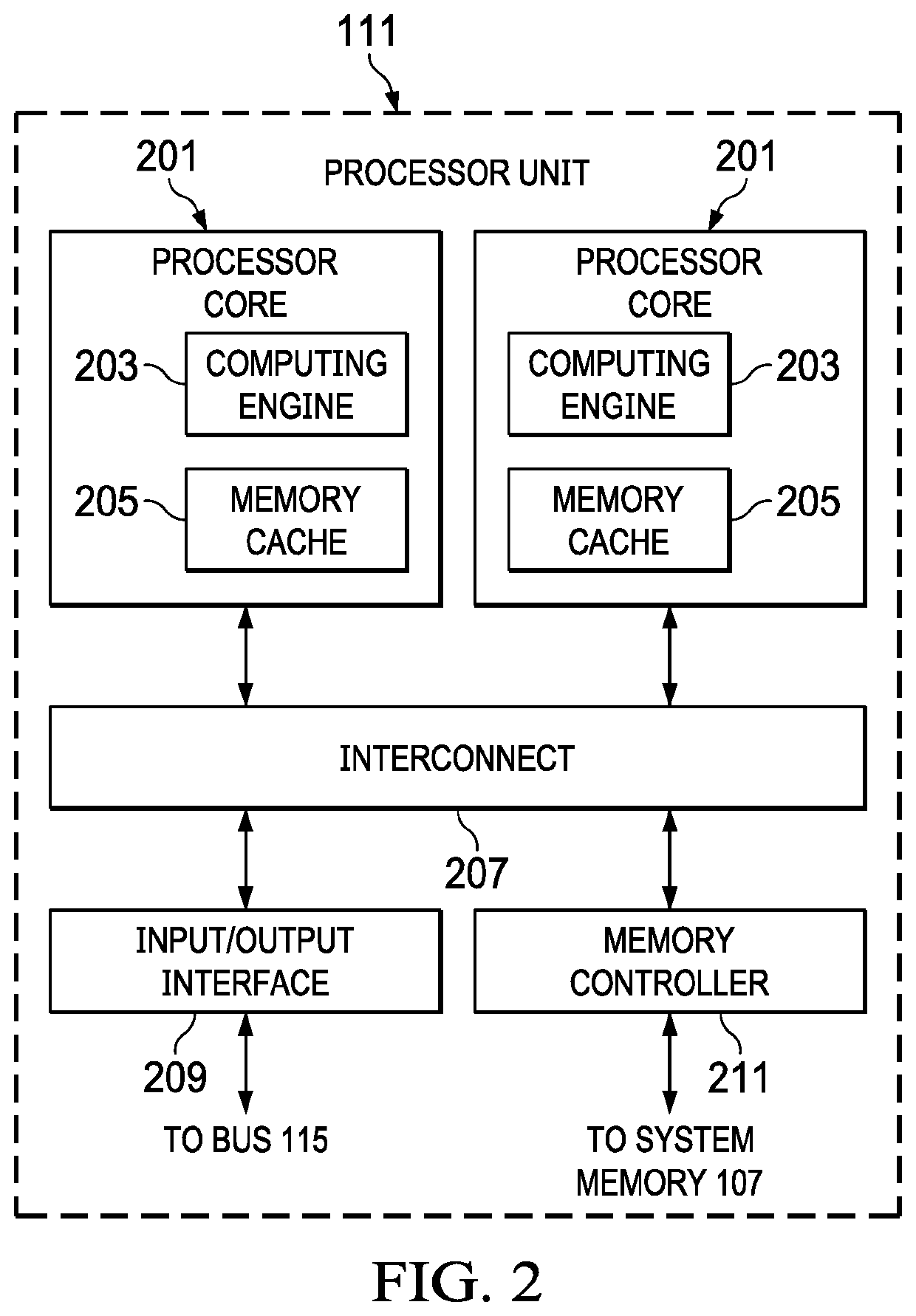

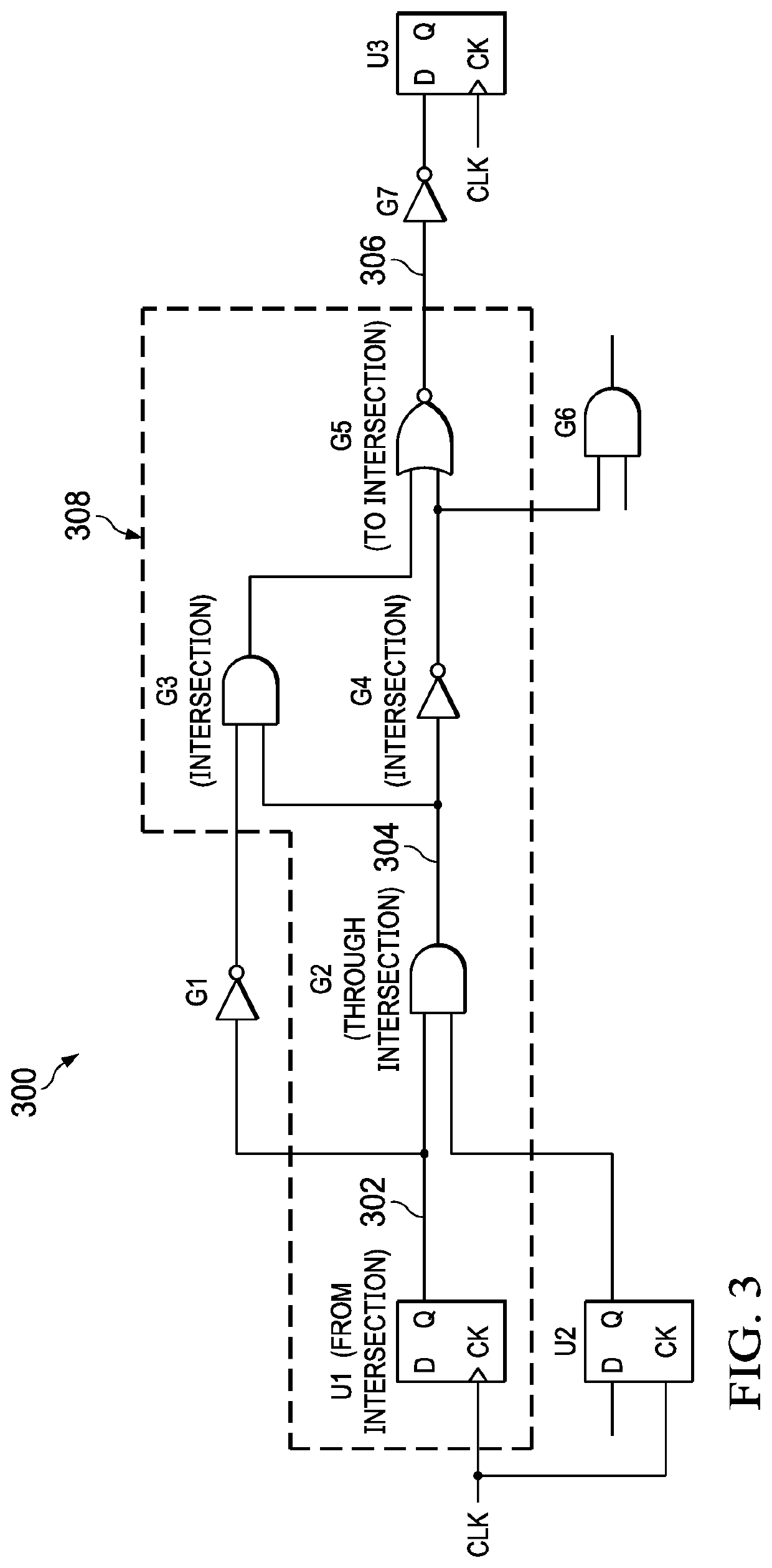

A digital system having multiple clock domain, each including at least one edge-triggered device, such as a flip-flop, is structured to be submitted to scan testing. Each data path from one clock domain to another includes a latch that is operated by a test clock. During scan testing, when the digital system is logically reconfigured to form one or more scan chains for receiving a test vector, the latches are operated to ensure that the test vector is passed from one domain to another.

Owner:SAMSUNG ELECTRONICS CO LTD

Asynchronous-mode sync FIFO having automatic lookahead and deterministic tester operation

ActiveUS7287105B1Safe latencyEfficient implementationDigital storageGenerating/distributing signalsControl logicWaiting time

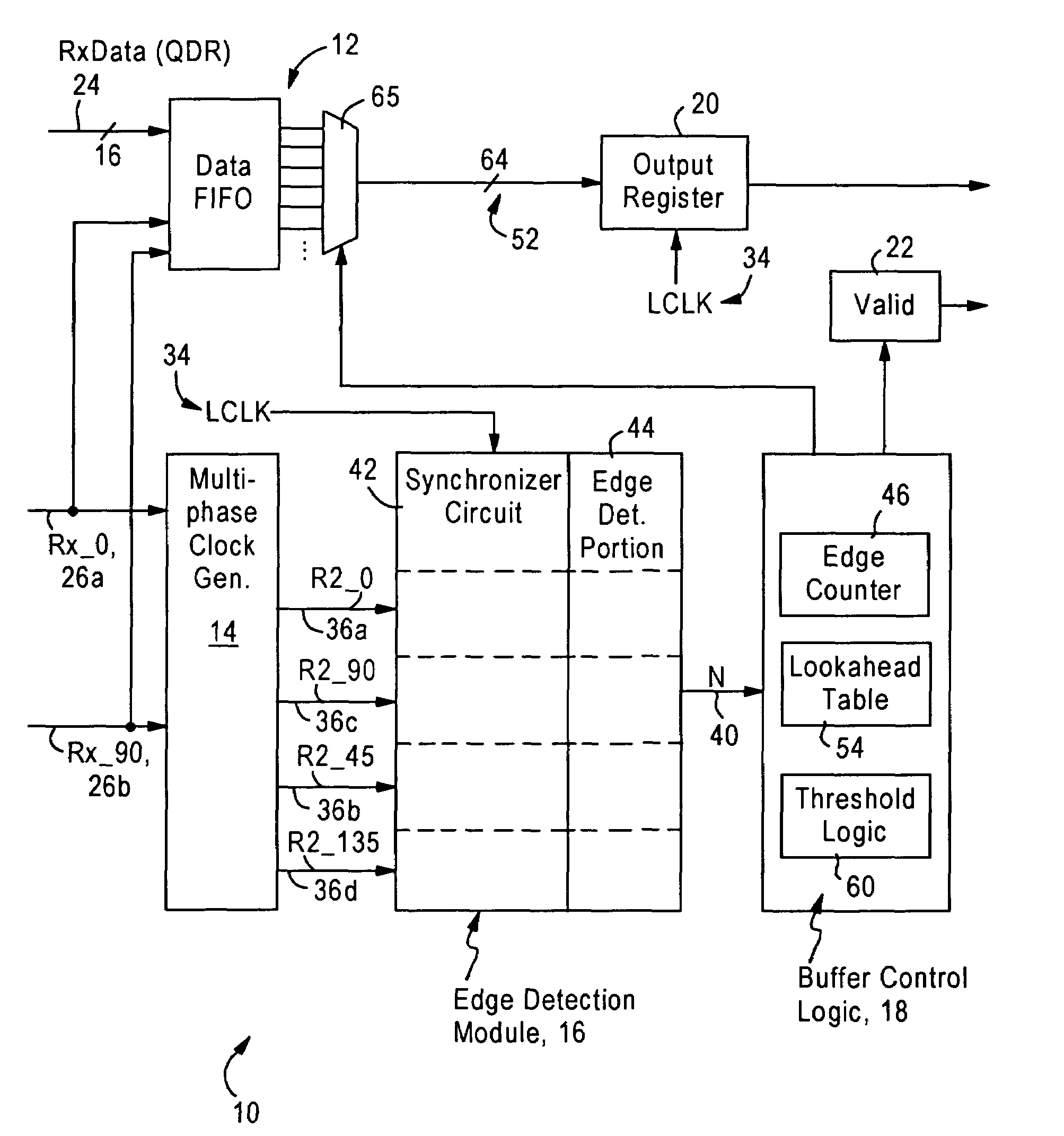

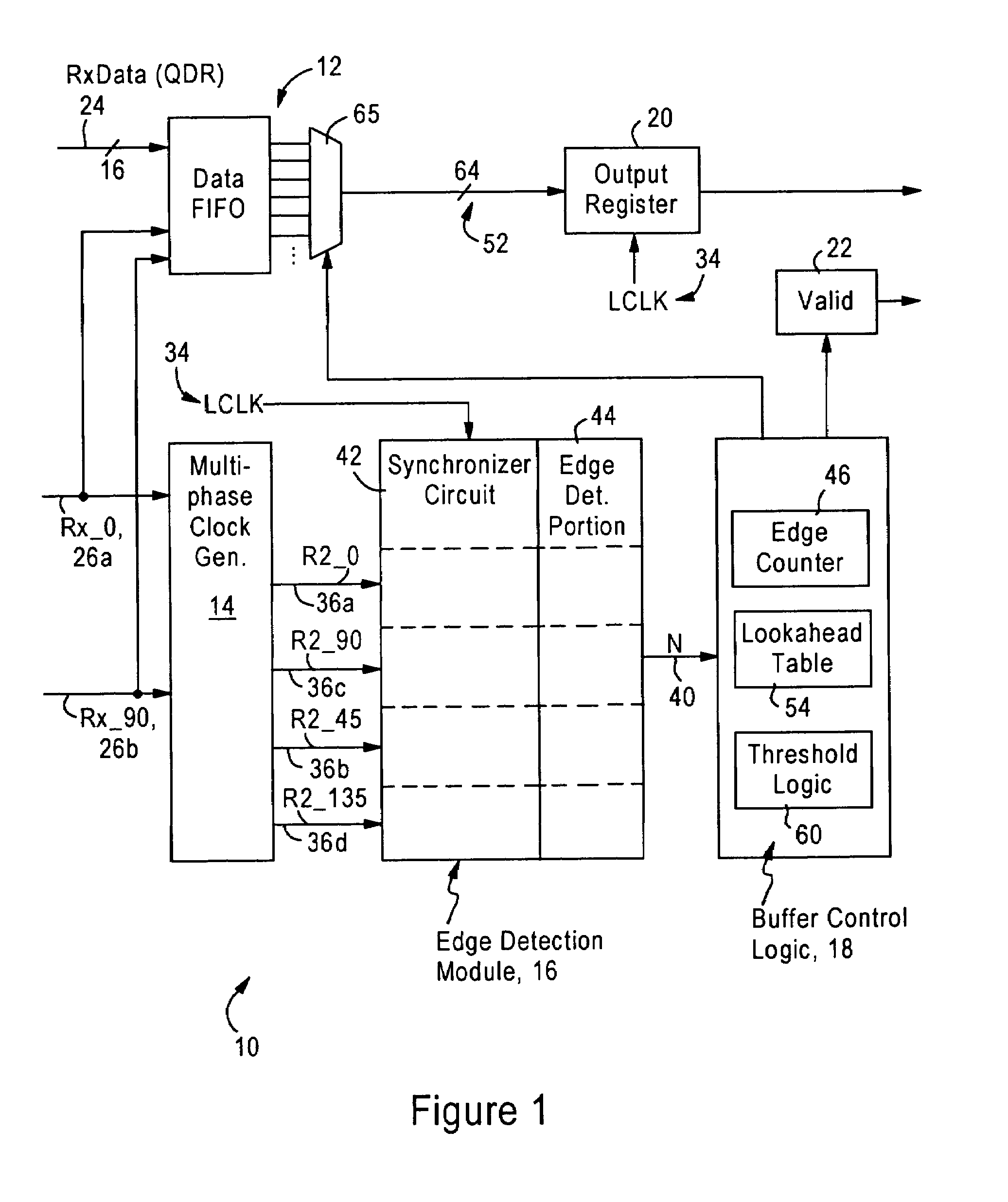

Precise estimation of latency is attained based on identifying that a receive clock is configured to operate only at prescribed available frequencies. A receive buffer circuit includes buffer control logic configured for reading a selected number of the buffer entries based on a detected number of receive clock edges within one local clock cycle. Valid data is identified based on the number of clock edges exceeding a selected threshold. A selected pointer offset is obtained from a lookahead table, specifying multiple pointer offsets for accommodating latency encountered at respective prescribed available frequencies, based on matching the determined frequency to one of the prescribed available frequencies. The selected pointer offset is added to a read pointer to offset the latency encountered from edge detection.

Owner:ADVANCED MICRO DEVICES INC

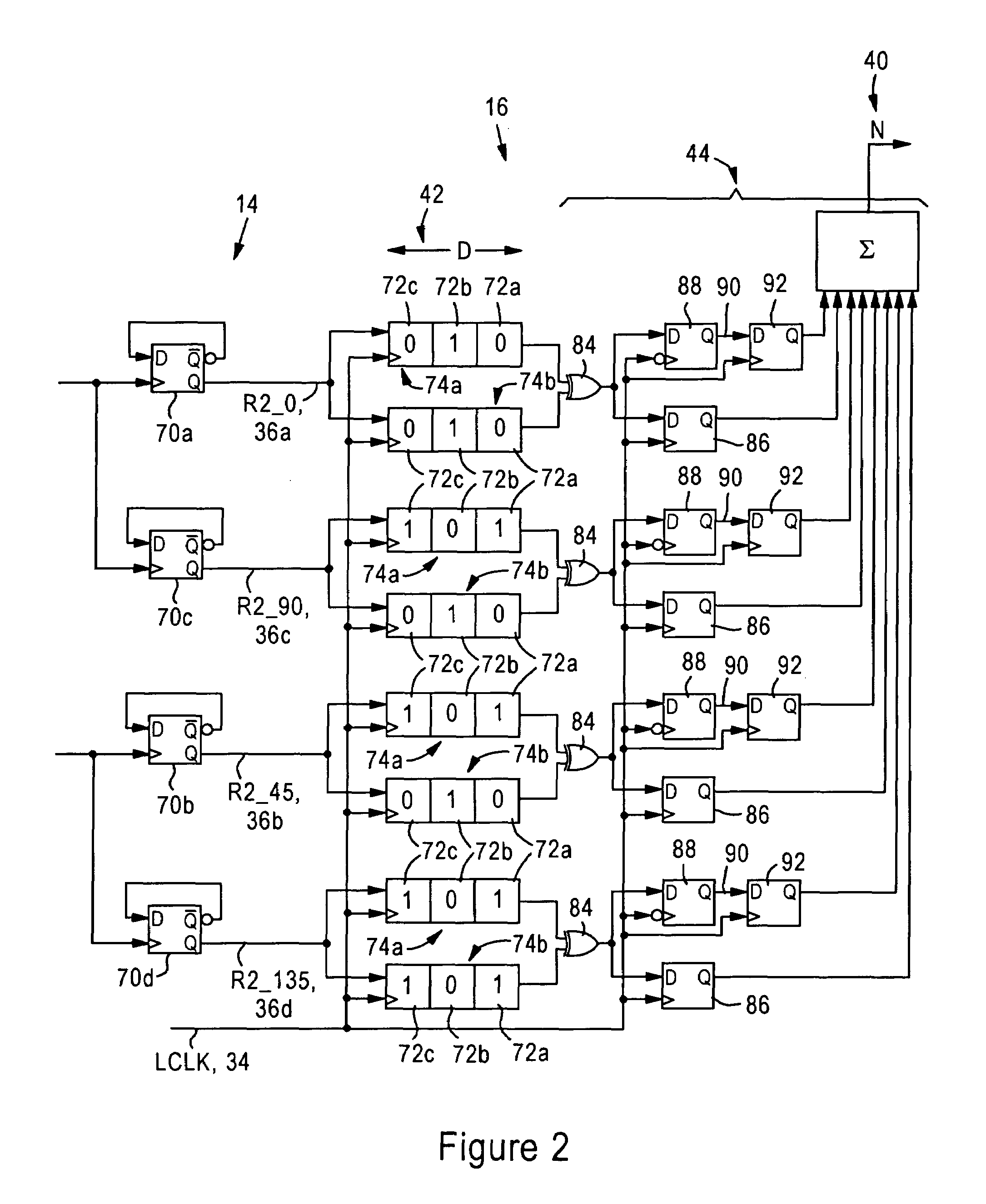

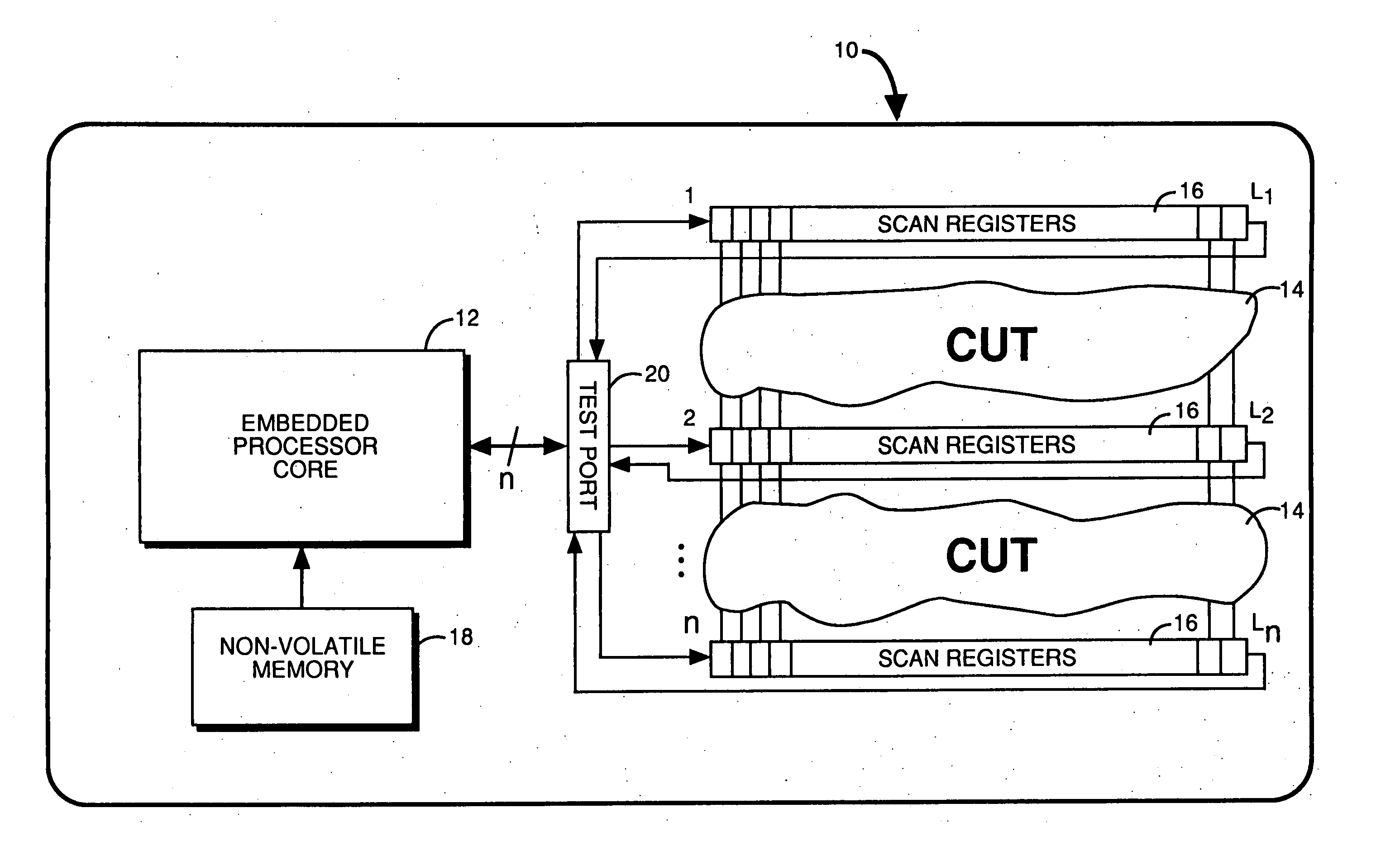

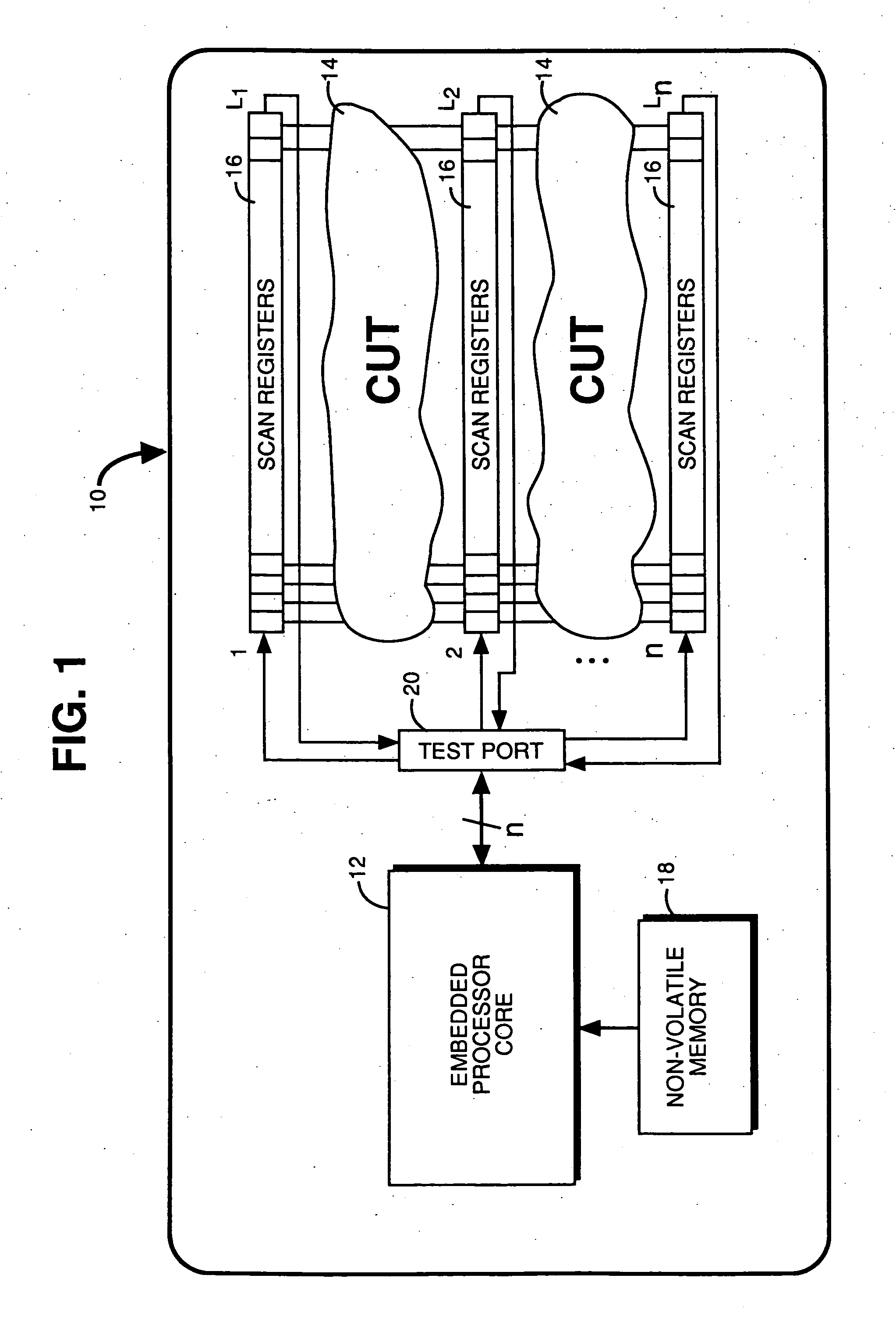

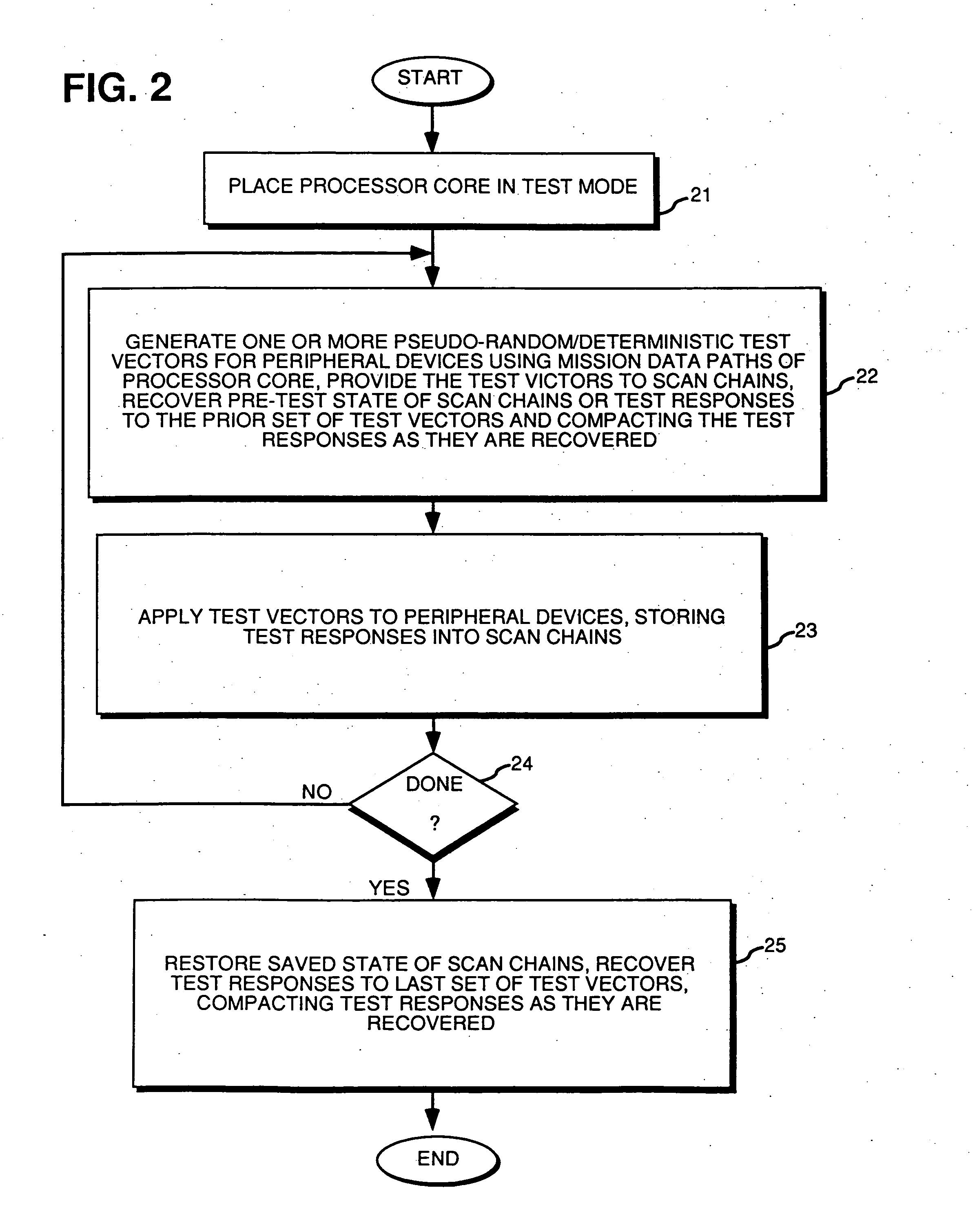

Arithmetic built-in self-test of multiple scan-based integrated circuits

InactiveUS20050060626A1Reduce error impactElectronic circuit testingError detection/correctionTest vector generatorNumber generator

In one embodiment, an IC with an embedded processor core, peripheral devices, and associated multiple scan chains, is provided with microcode that implements an arithmetic pseudo-random number generator and an arithmetic deterministic test vector generator, when executed by the embedded processor core, generates 2-D pseudo-random and deterministic test vectors for testing the peripheral devices respectively. The IC is further provided with microcode that implements an arithmetic test response compactor, which when executed by the embedded processor core, compacts test responses of the peripheral devices into a signature. The IC further includes a test port register and microcode that implements a number of ABIST instructions.

Owner:MENTOR GRAPHICS CORP

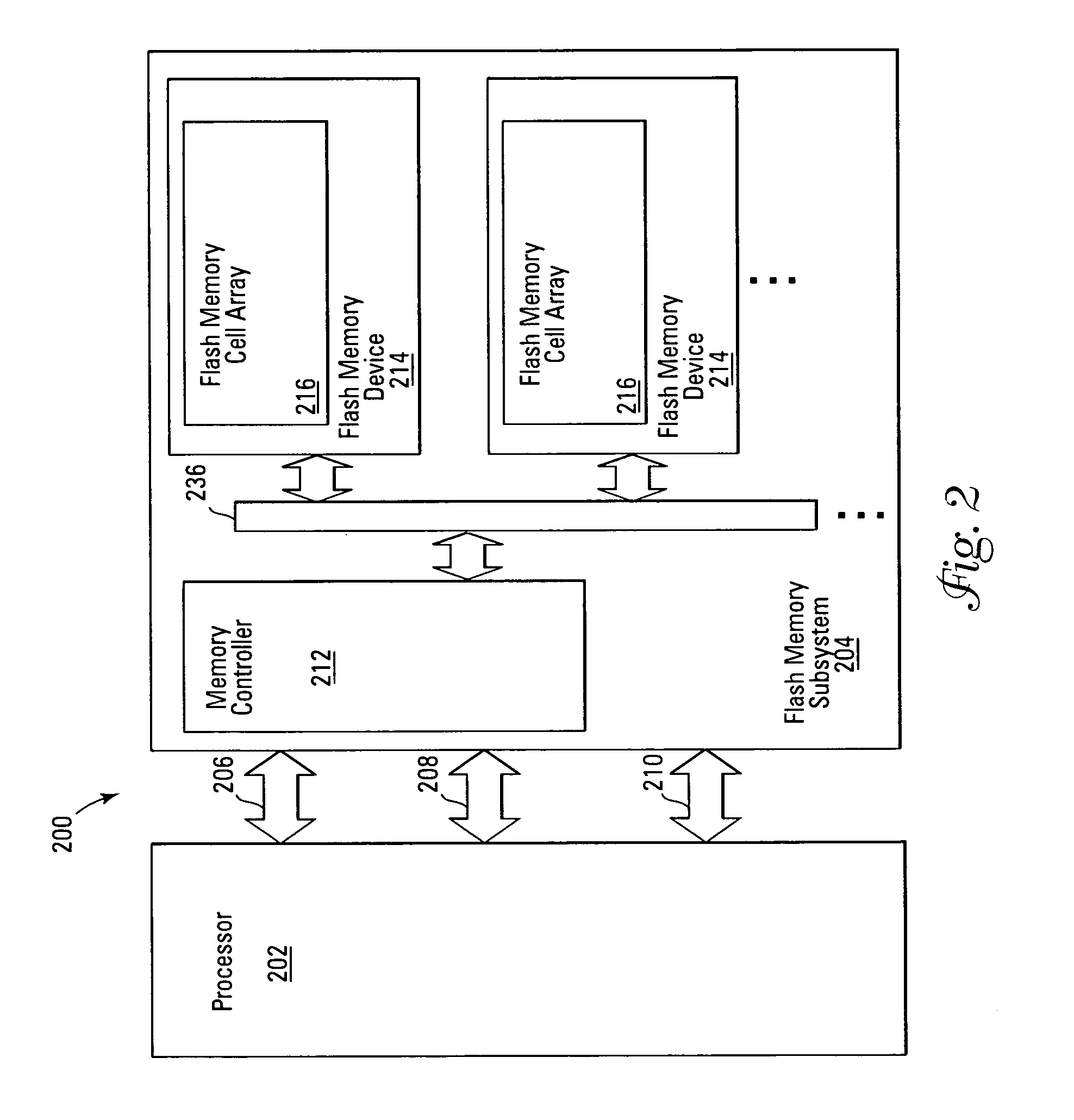

Method for testing flash memory power loss recovery

ActiveUS7321951B2Improved and deterministic testingQuick testRead-only memoriesMemory systemsNon-volatile memoryRecovery cycle

Owner:MICRON TECH INC

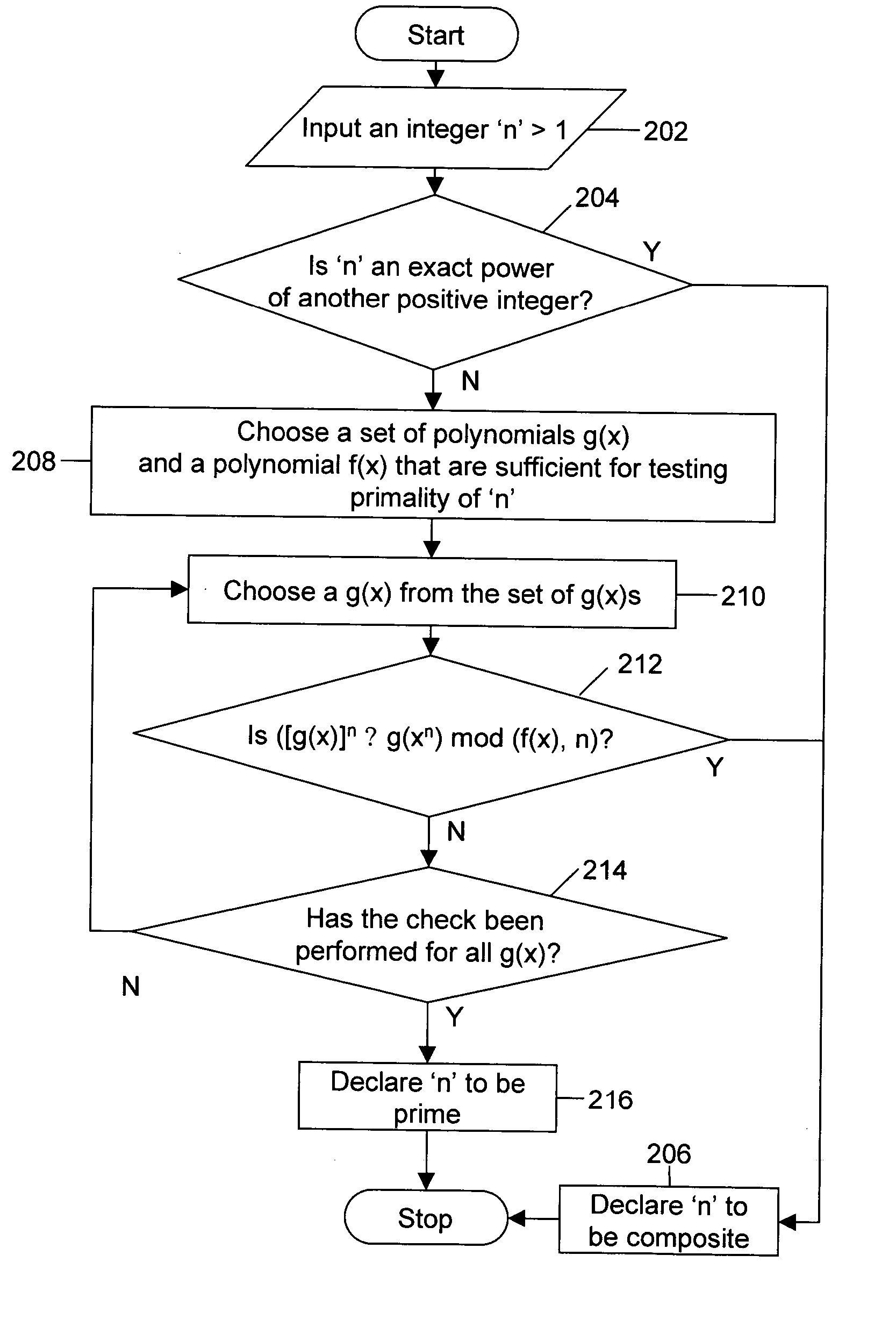

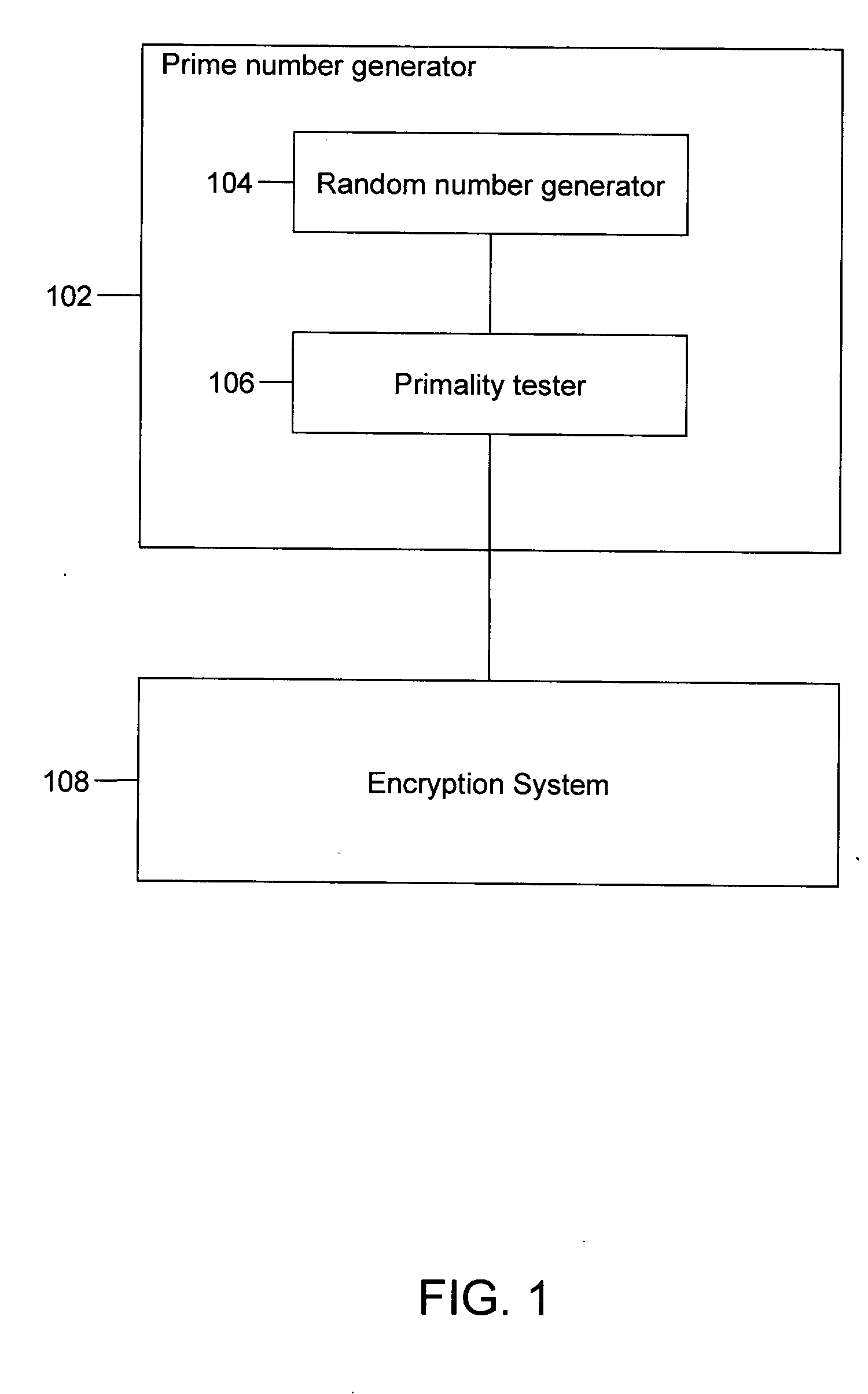

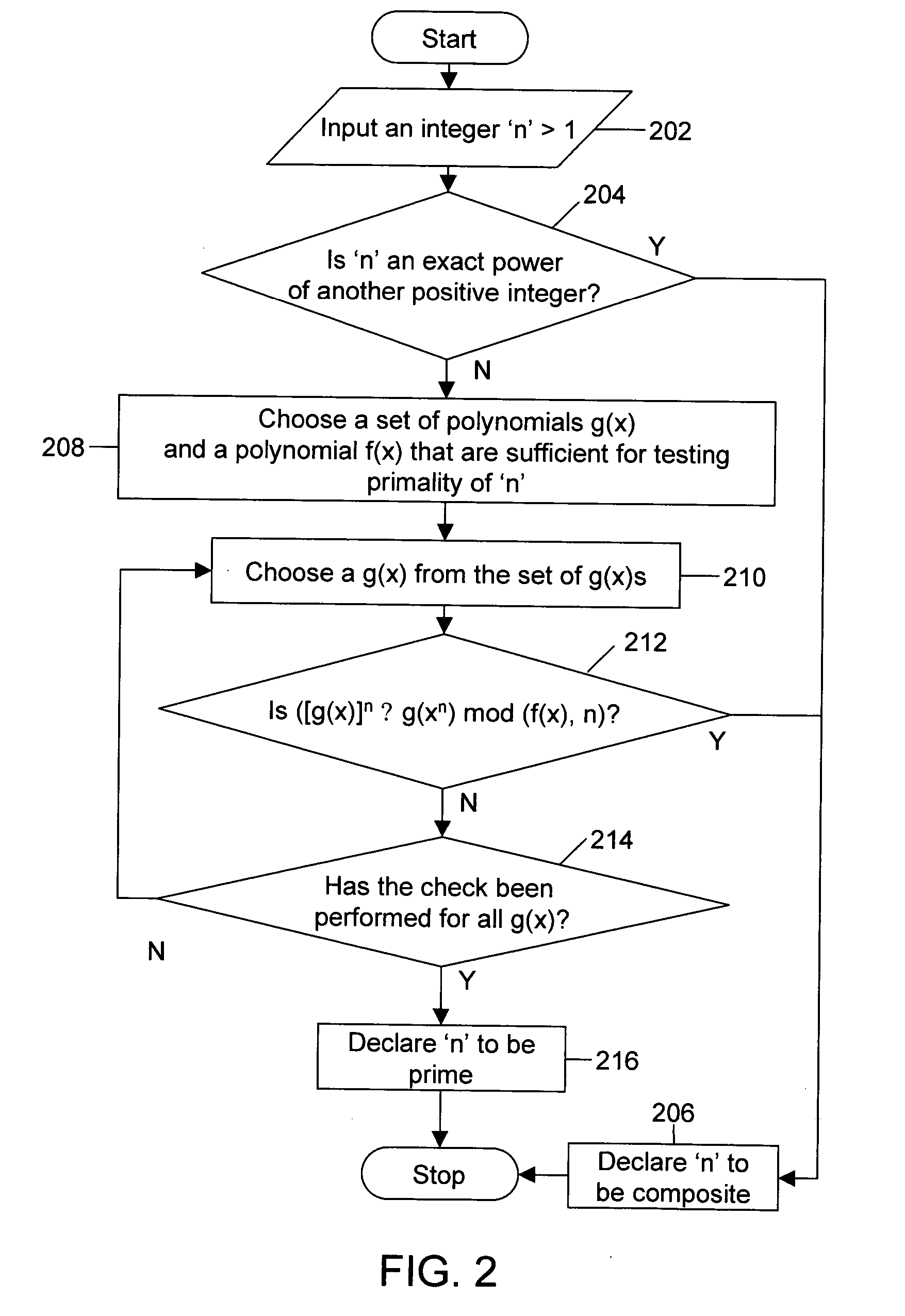

Polynomial time deterministic method for testing primality of numbers

InactiveUS20050027764A1Random number generatorsPublic key for secure communicationDeterministic methodNumber generator

A method and a system for generating prime numbers and testing for primality of an integer. This invention has applicability to “public key” and other encryption techniques that play an important role in the security of information technology and electronic commerce. Generation of prime numbers requires the step of testing the primality. The method includes a deterministic test for testing the primality of a number in polynomial time. The system comprises a random number generator and a primality tester. The random number generator generates a random number and the primality tester tests the primality of this random number. The primality tester can also be used independent of the random number generator. In such a case, the number whose primality is to be tested can be input via a user interface.

Owner:INDIAN INSTITUTE OF TECHNOLOGY KANPUR

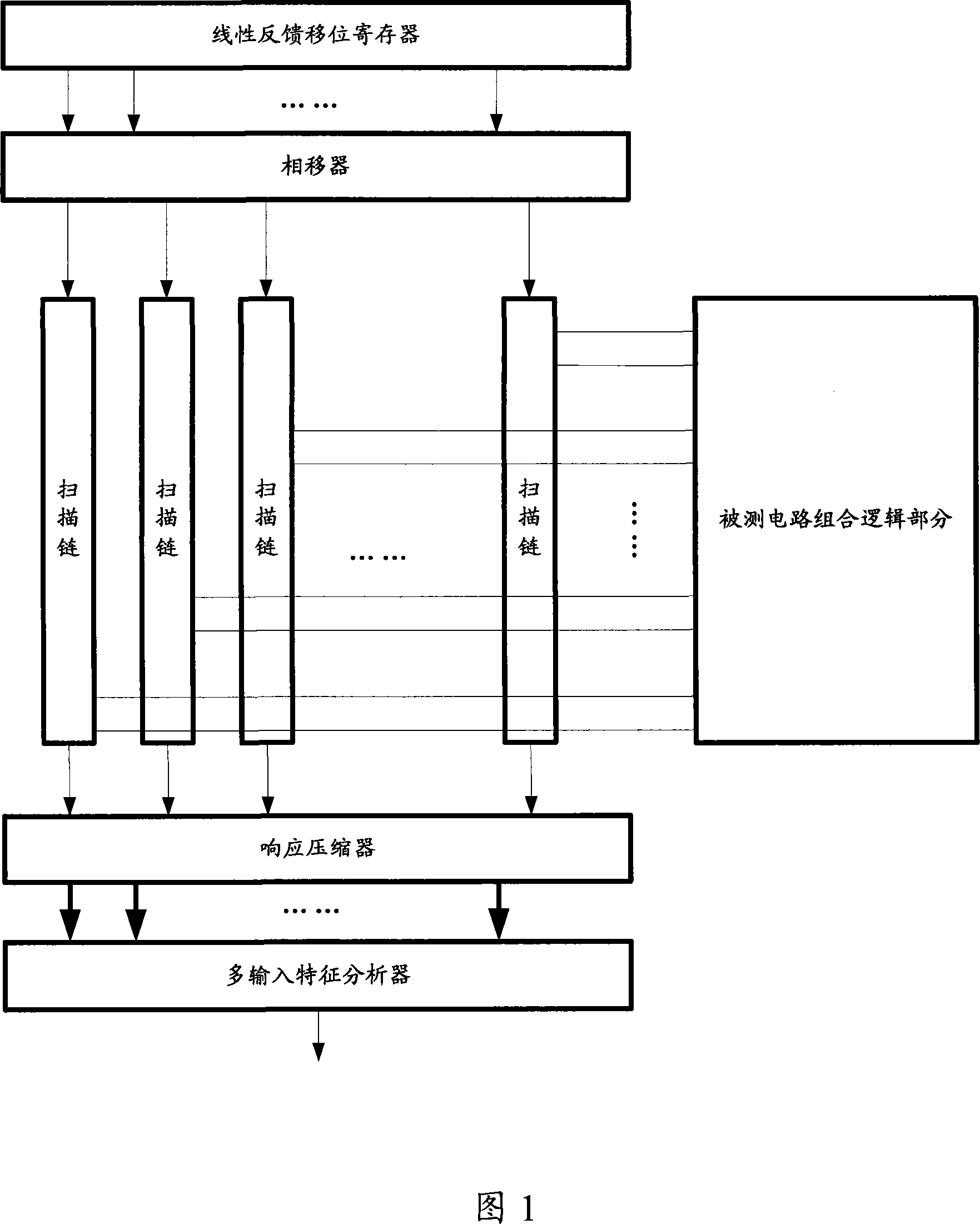

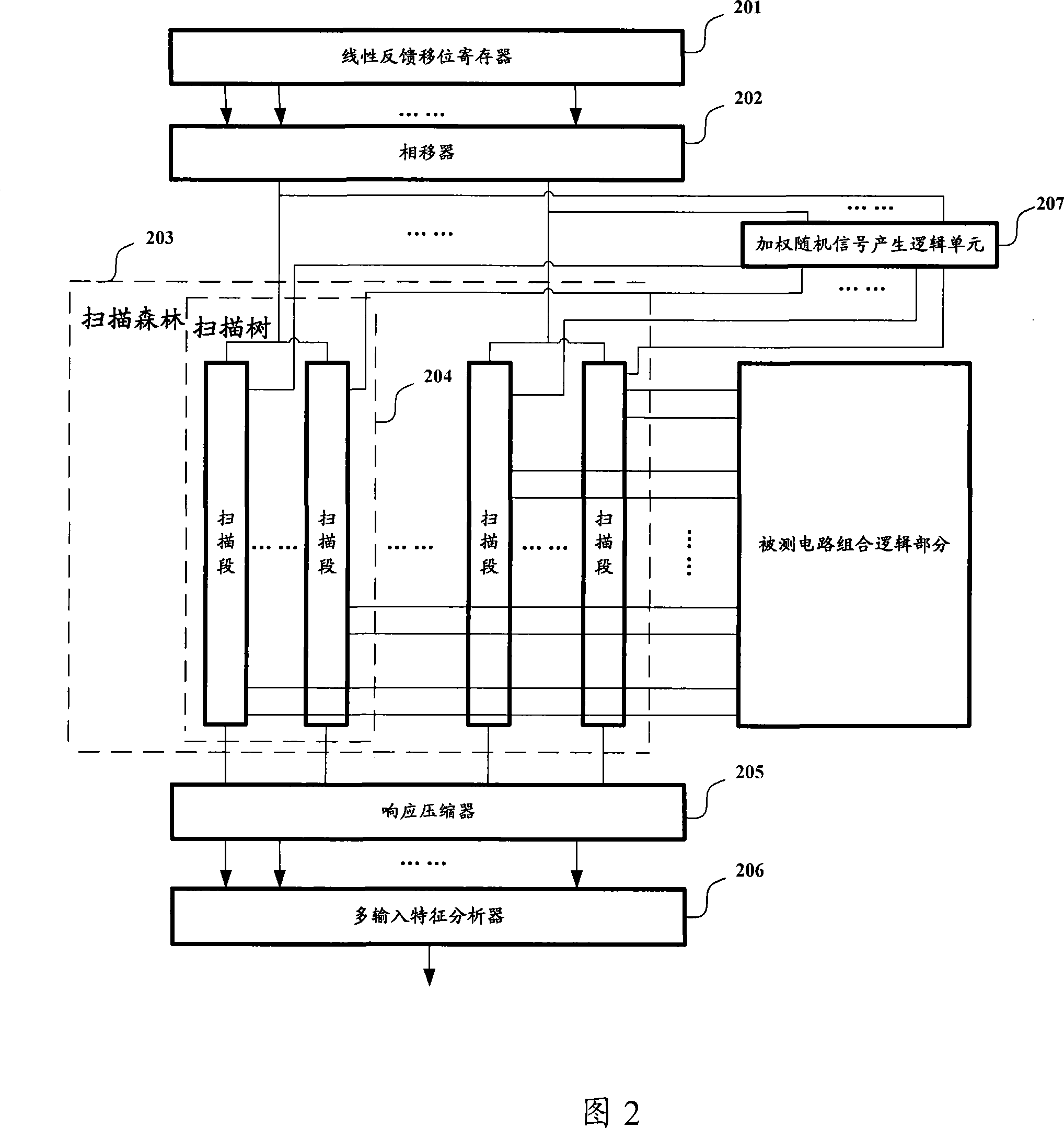

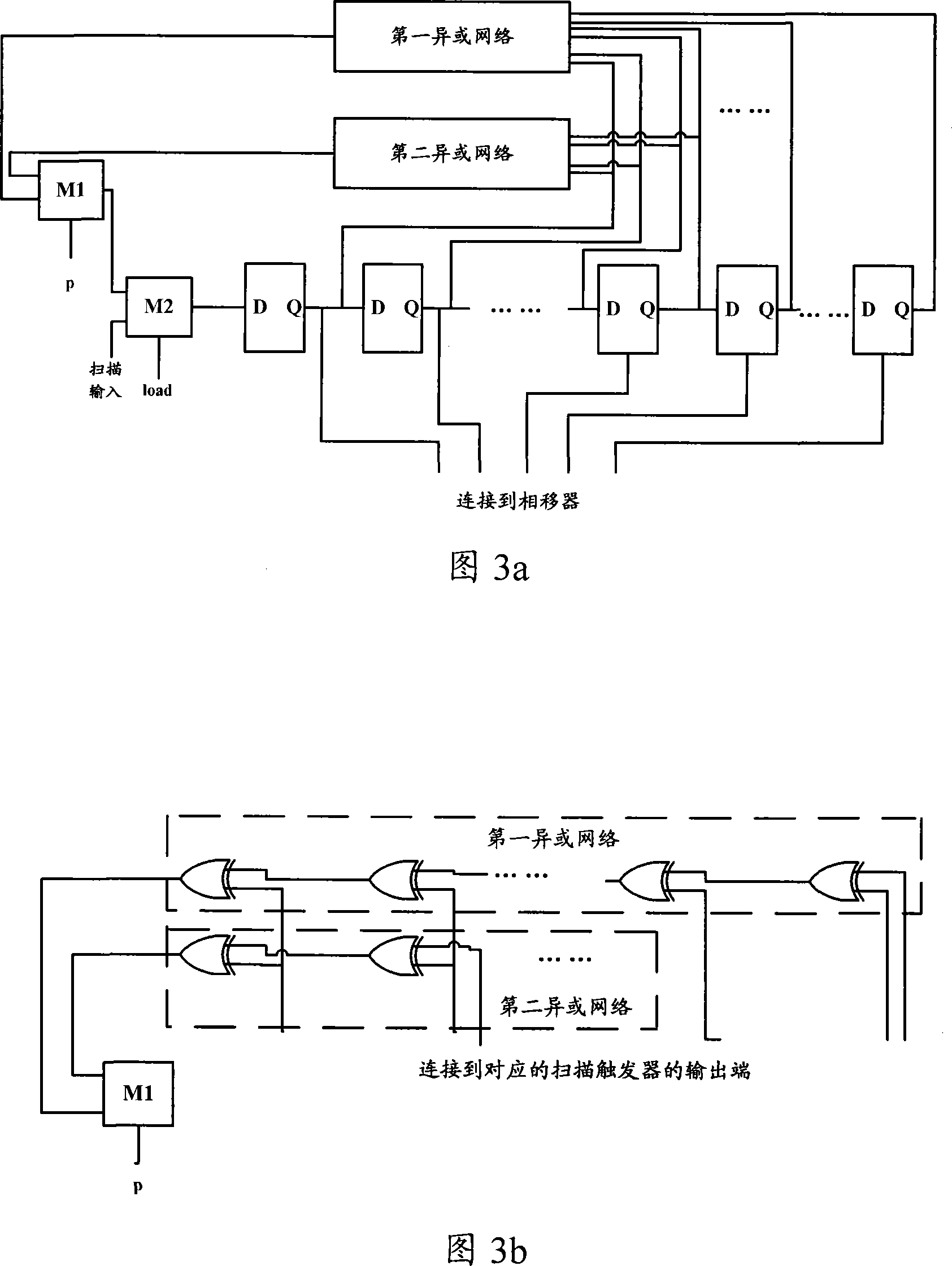

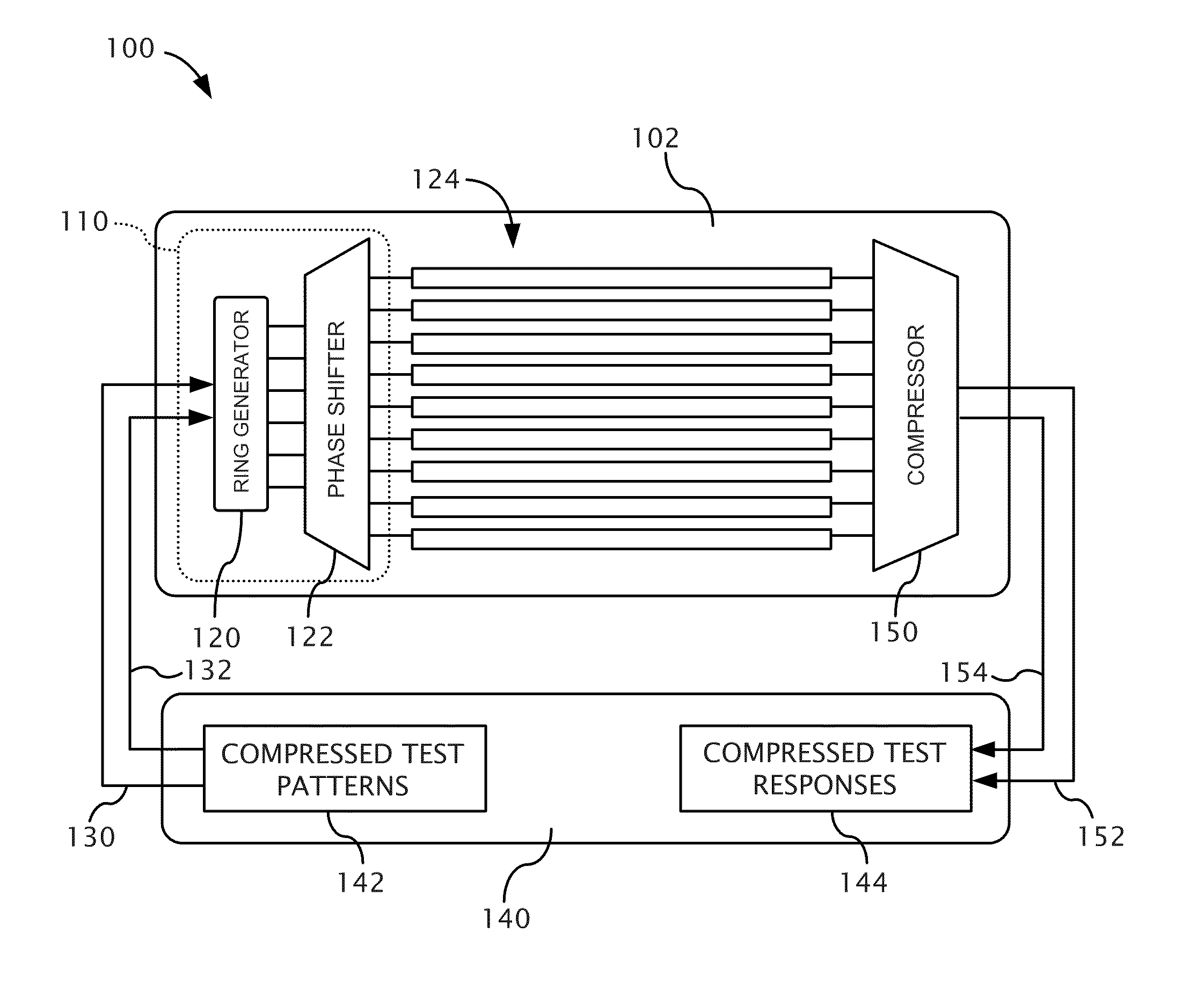

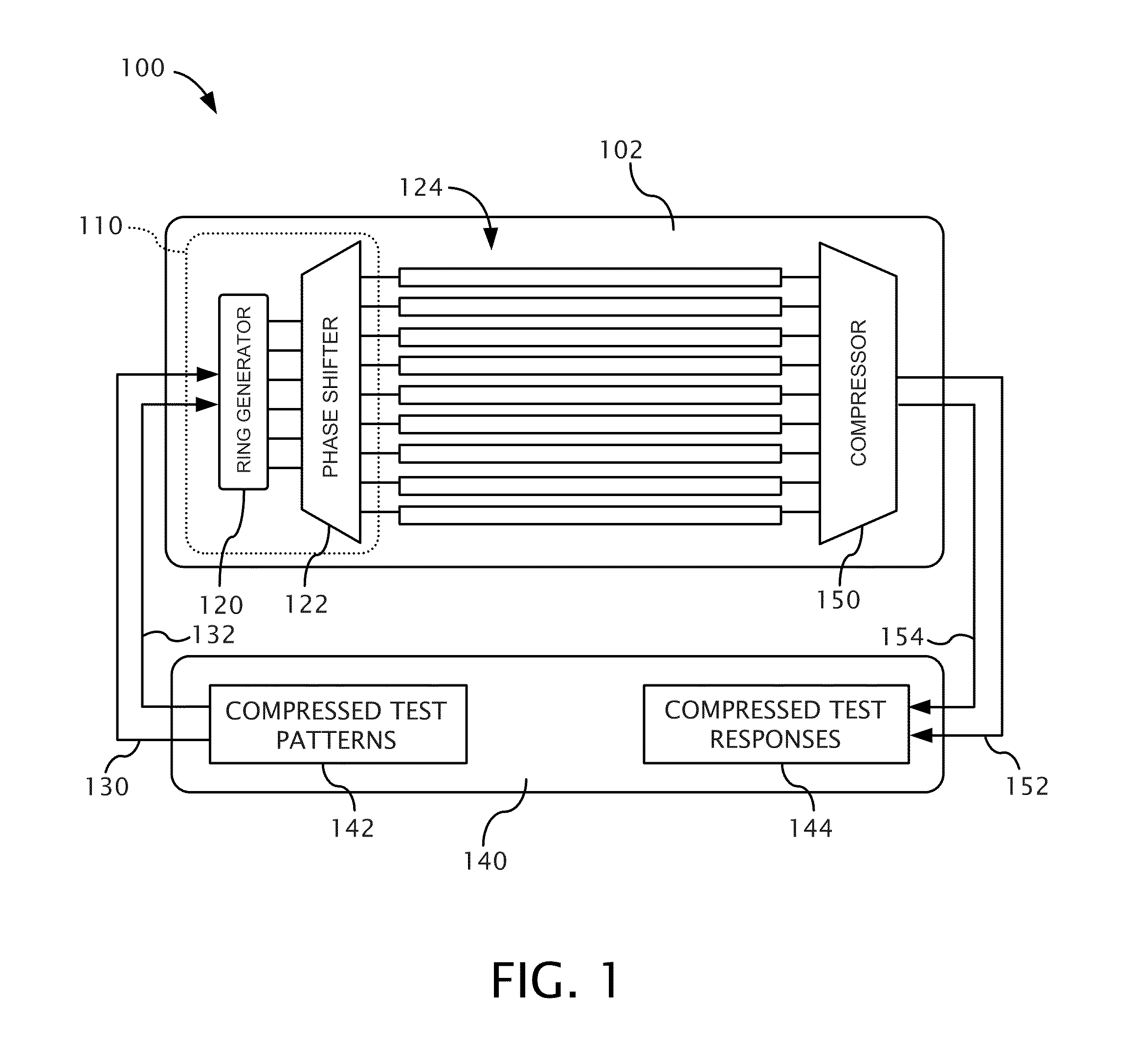

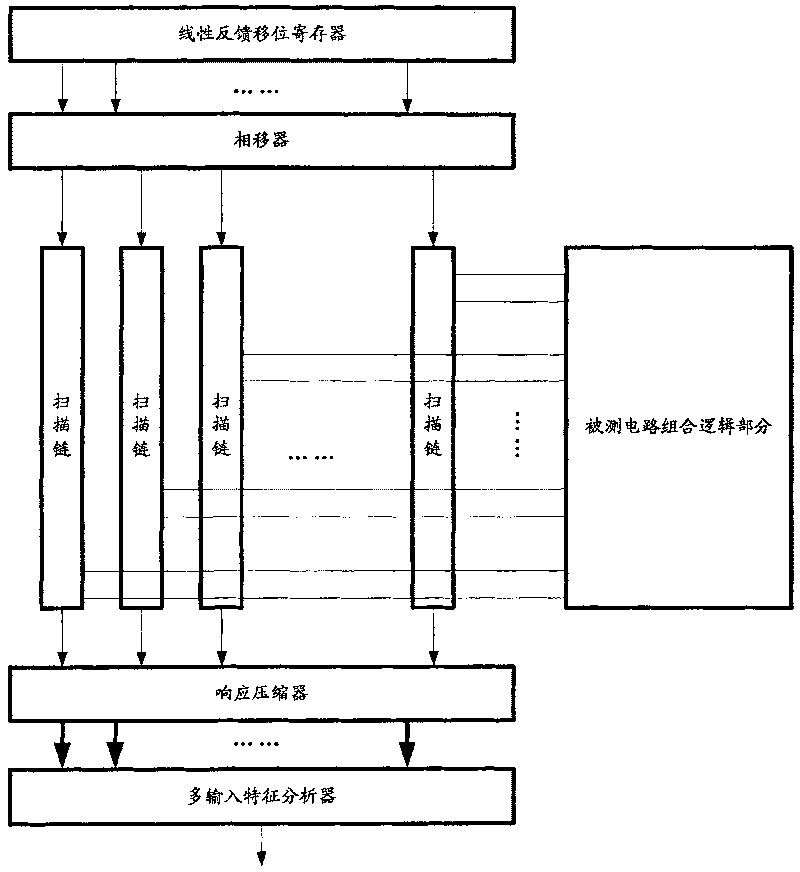

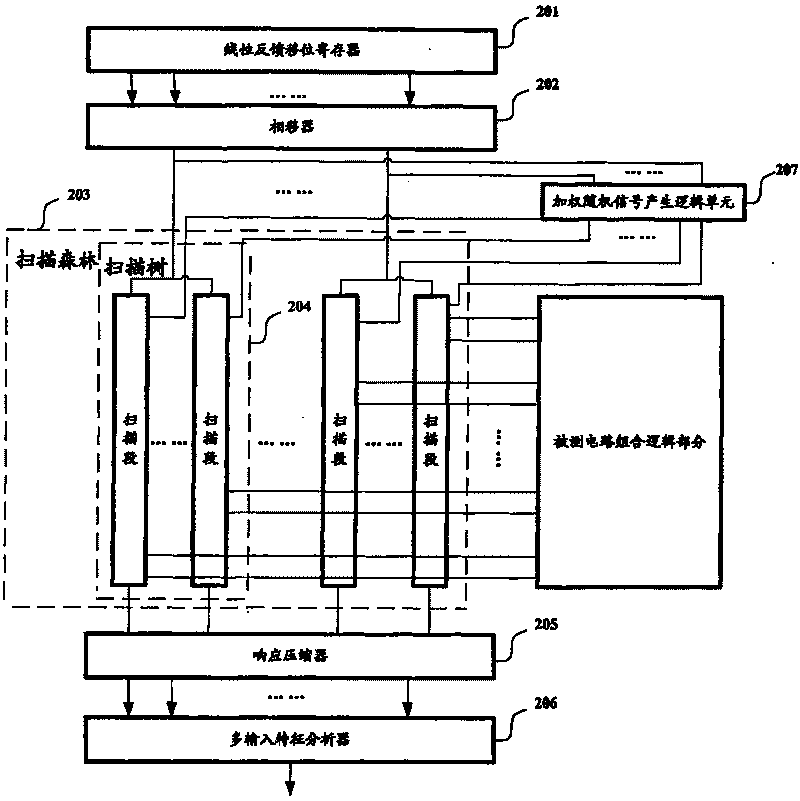

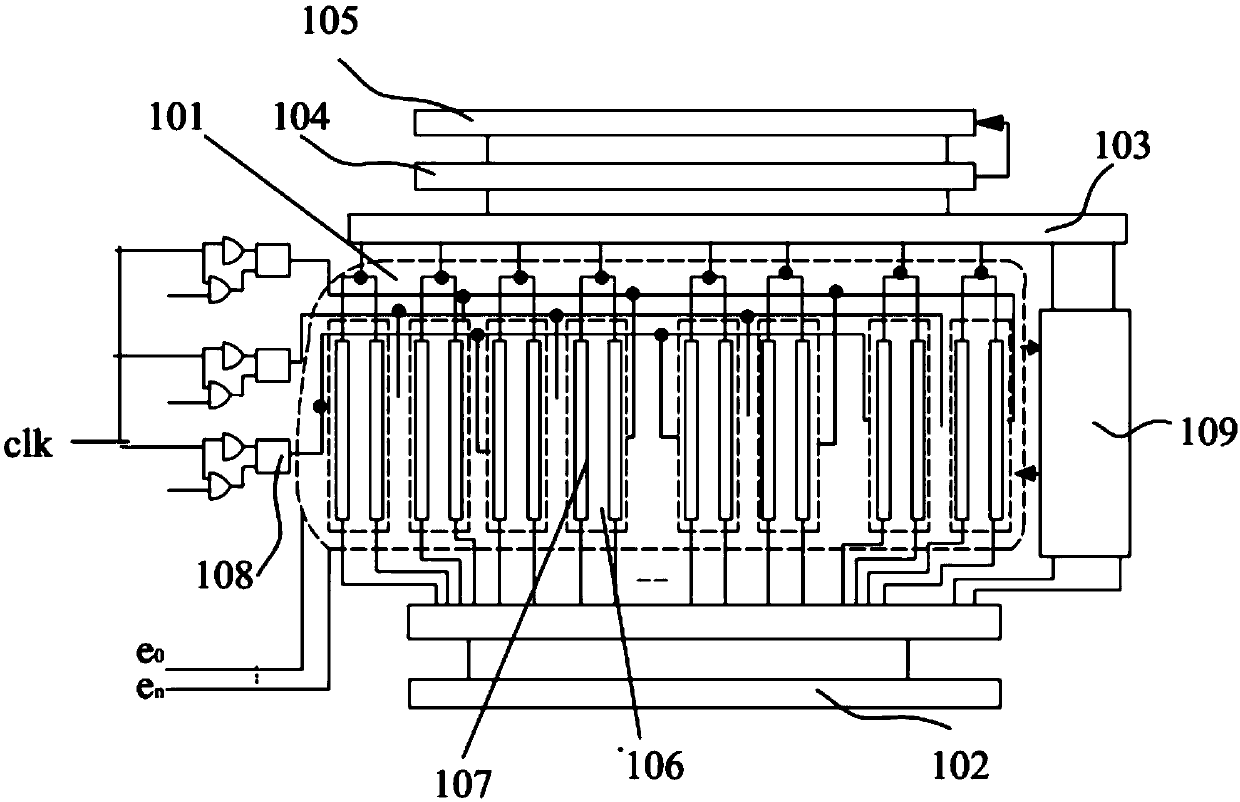

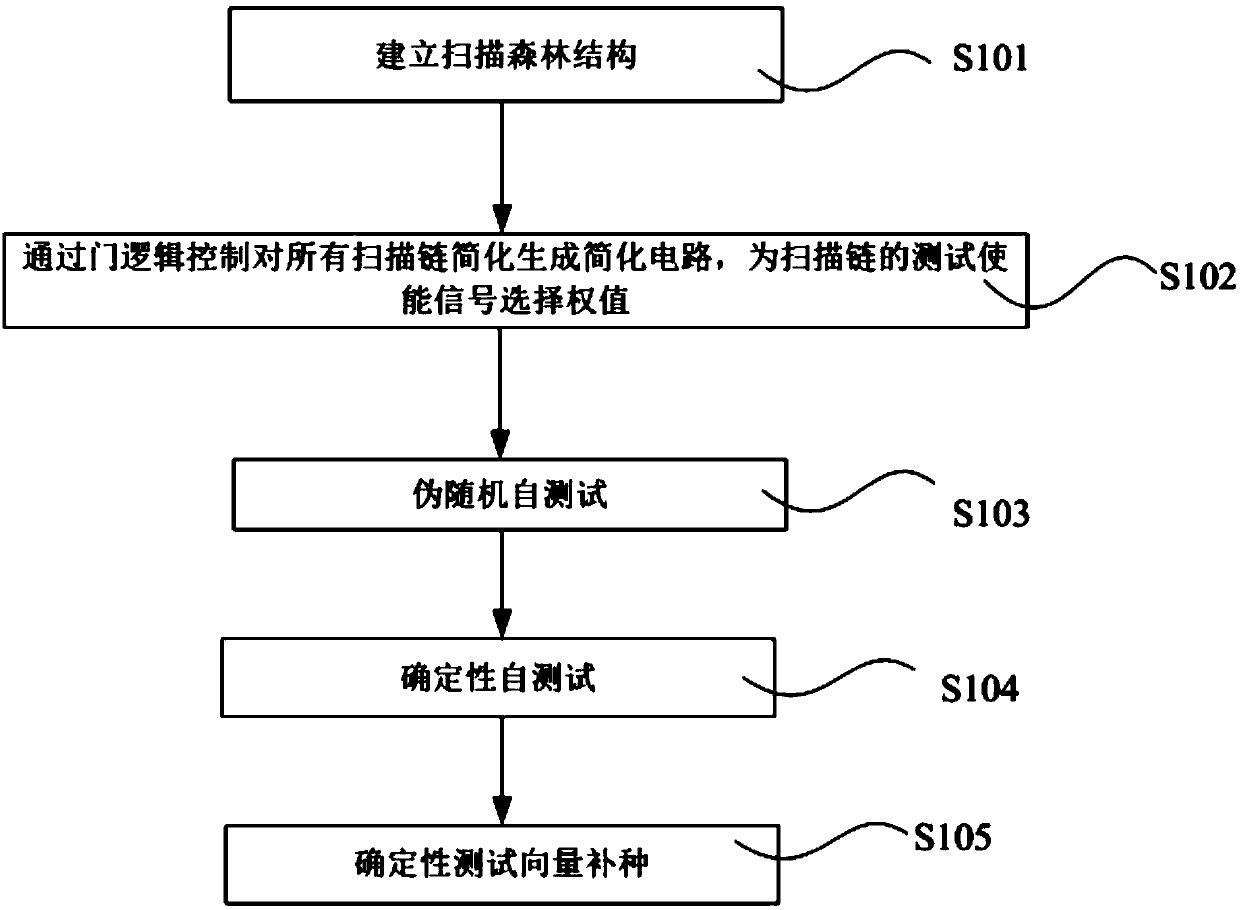

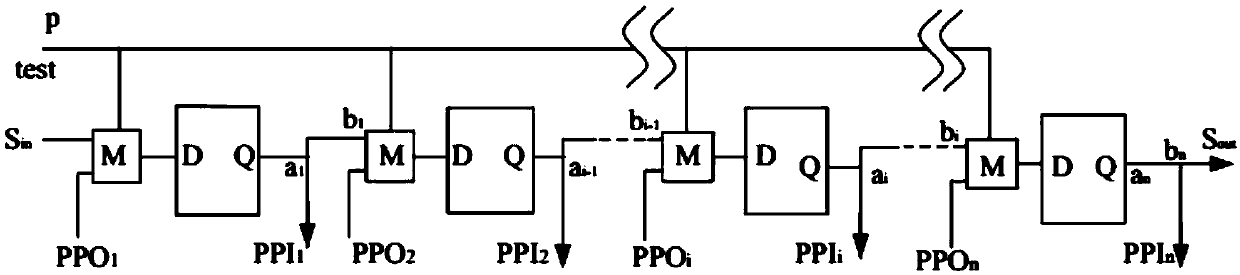

Device and method for determinacy self-testing test data compression

ActiveCN101226228ASave storage spaceCoverage with a high probability of failureElectrical testingLogic circuits using elementary logic circuit componentsFault coverageData memory

The invention relates to a method for compressing the test data of integrated circuit, belonging to integrated circuit technical field, in particular to a deterministic self-test test data compressor. The invention comprises a phase shifter, a response compressor, a linear feedback shift register with a first and a second xor network while the shift register is connected with the phase shift, a scanning tree and a weigh random signal generating logic unit while the scan forest is connected with the phase shift, the gating signal end of the scan forest is connected with the weight random signal generating logic unit, and the output of the scan forest is connected with the response compressor. The invention further provides a deterministic self-test test data compression method. The invention uses the weight random signal generating logic unit to control the frequency of special signal of the input signal of the scan forest, to improve the fault coverage rate into the false random self-test process, to reduce the test data memory space generated by deterministic test vector.

Owner:TSINGHUA UNIV

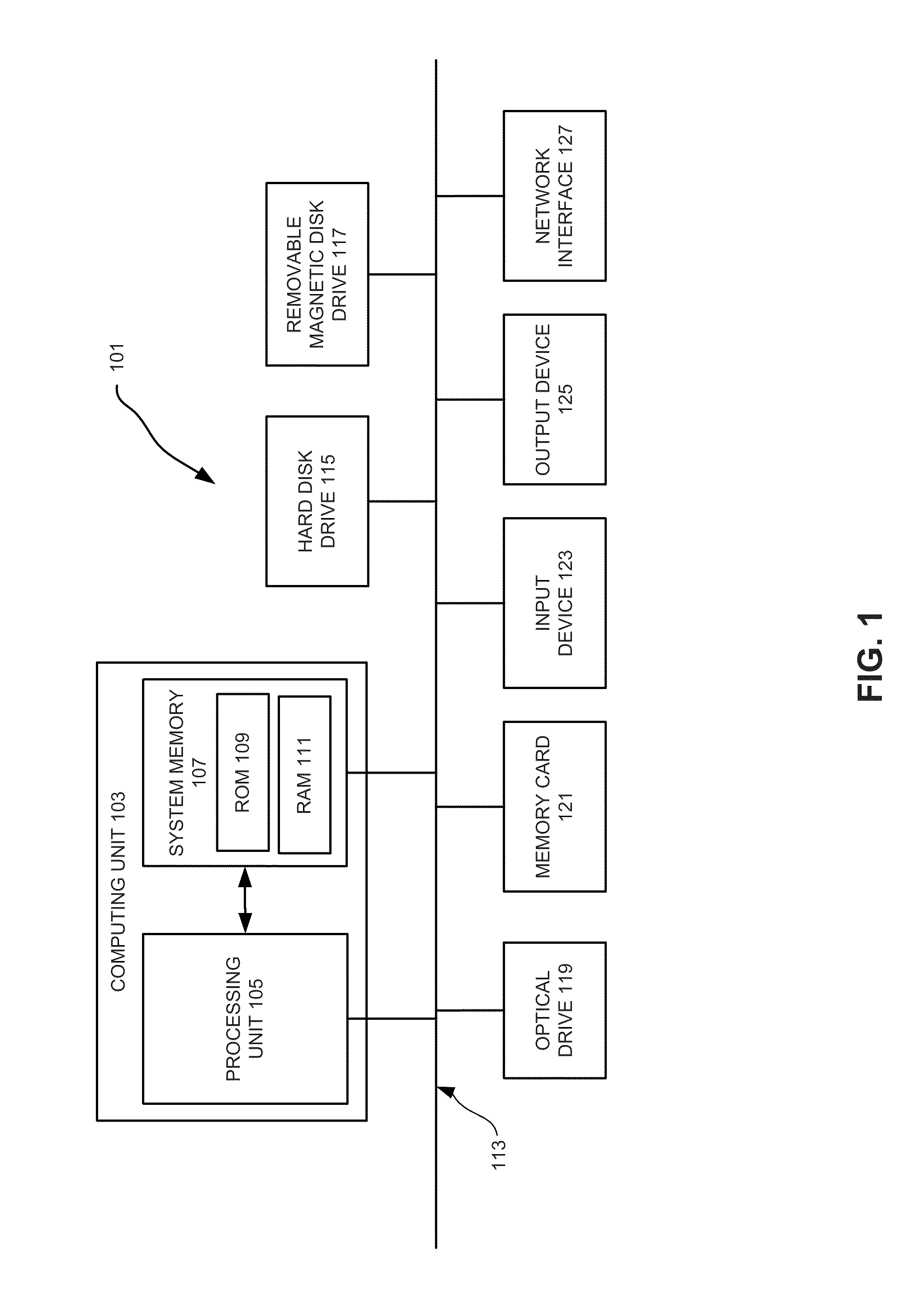

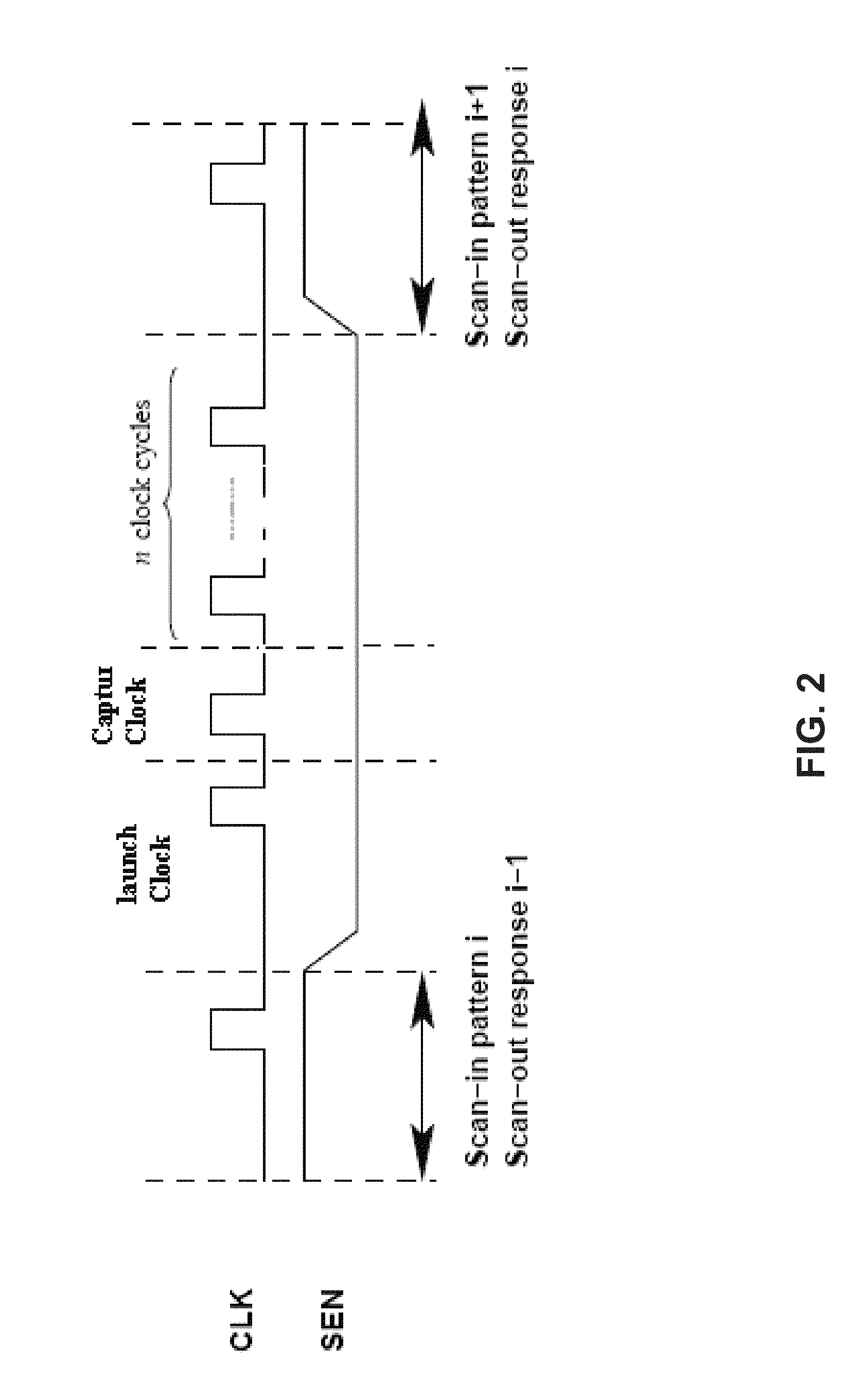

At-Speed Scan Testing With Controlled Switching Activity

ActiveUS20100275077A1Electronic circuit testingLogical operation testingStable stateComputer hardware

Test patterns for at-speed scan tests are generated by filling unspecified bits of test cubes with functional background data. Functional background data are scan cell values observed when switching activity of the circuit under test is near a steady state. Hardware implementations in EDT (embedded deterministic test) environment are also disclosed.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

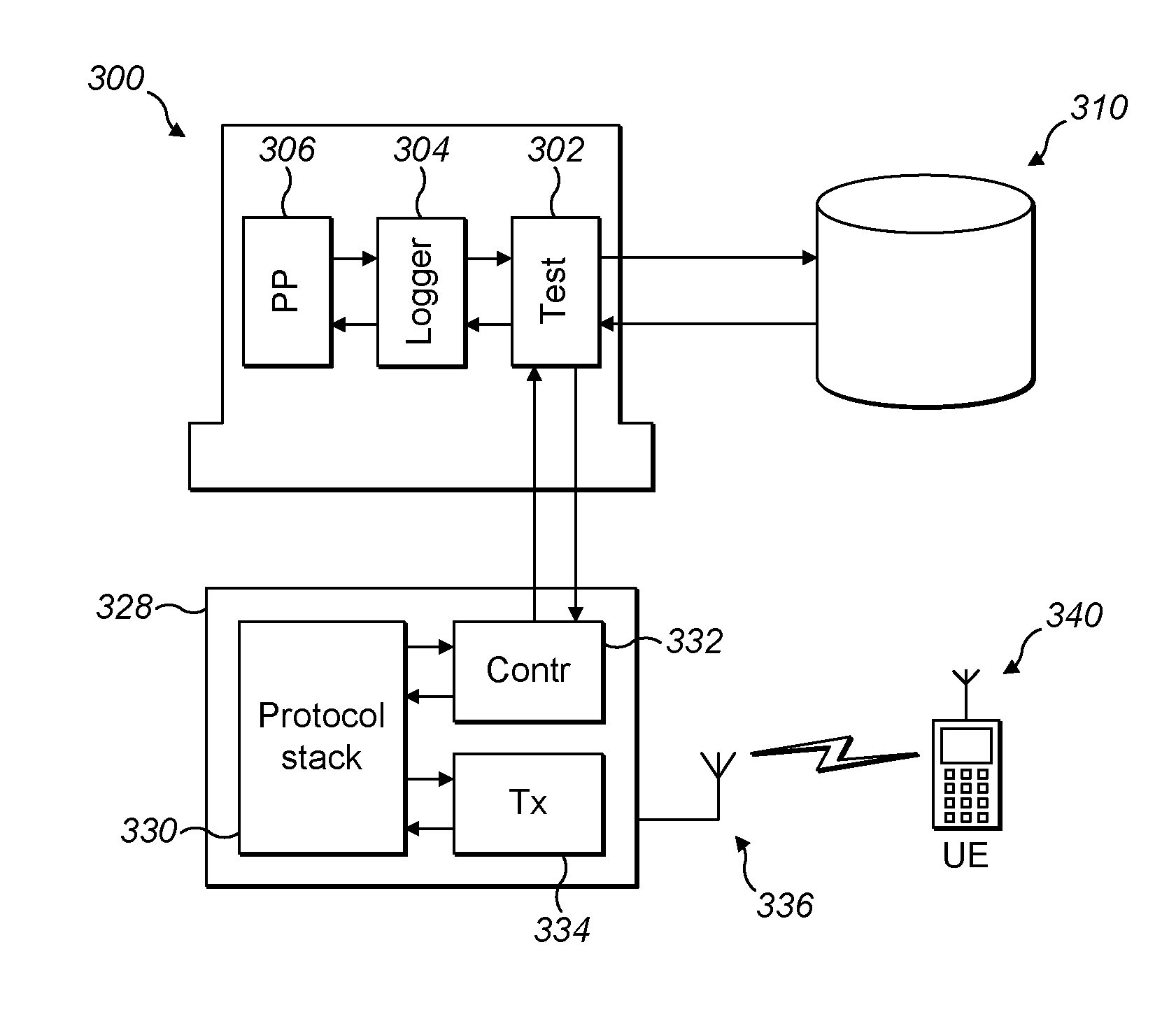

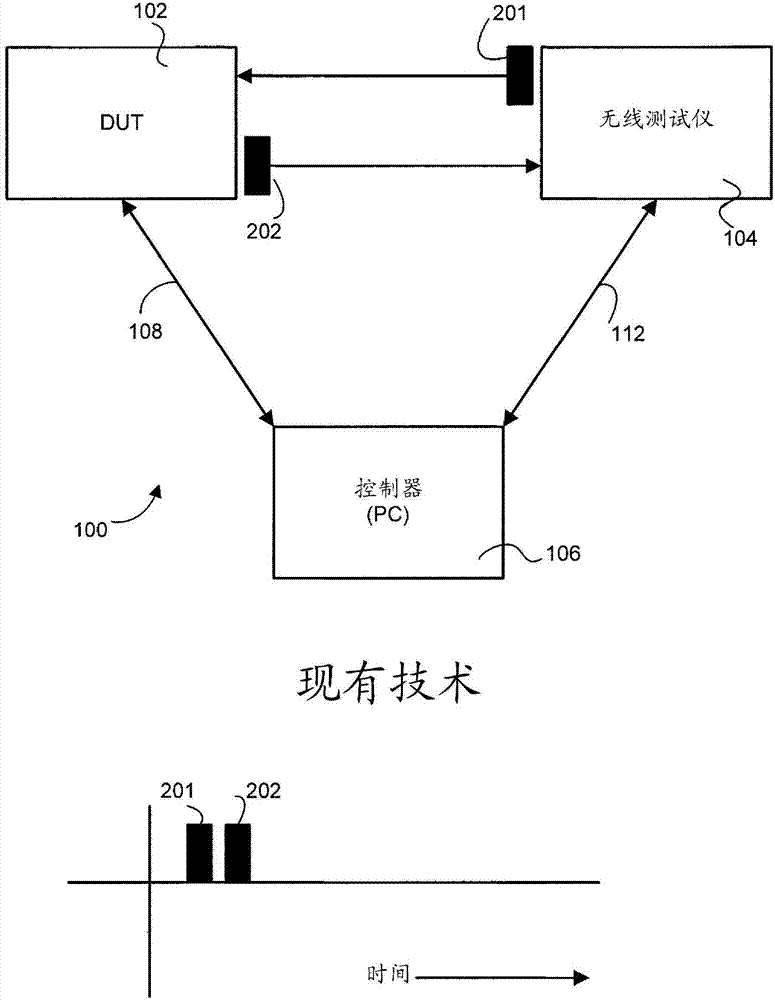

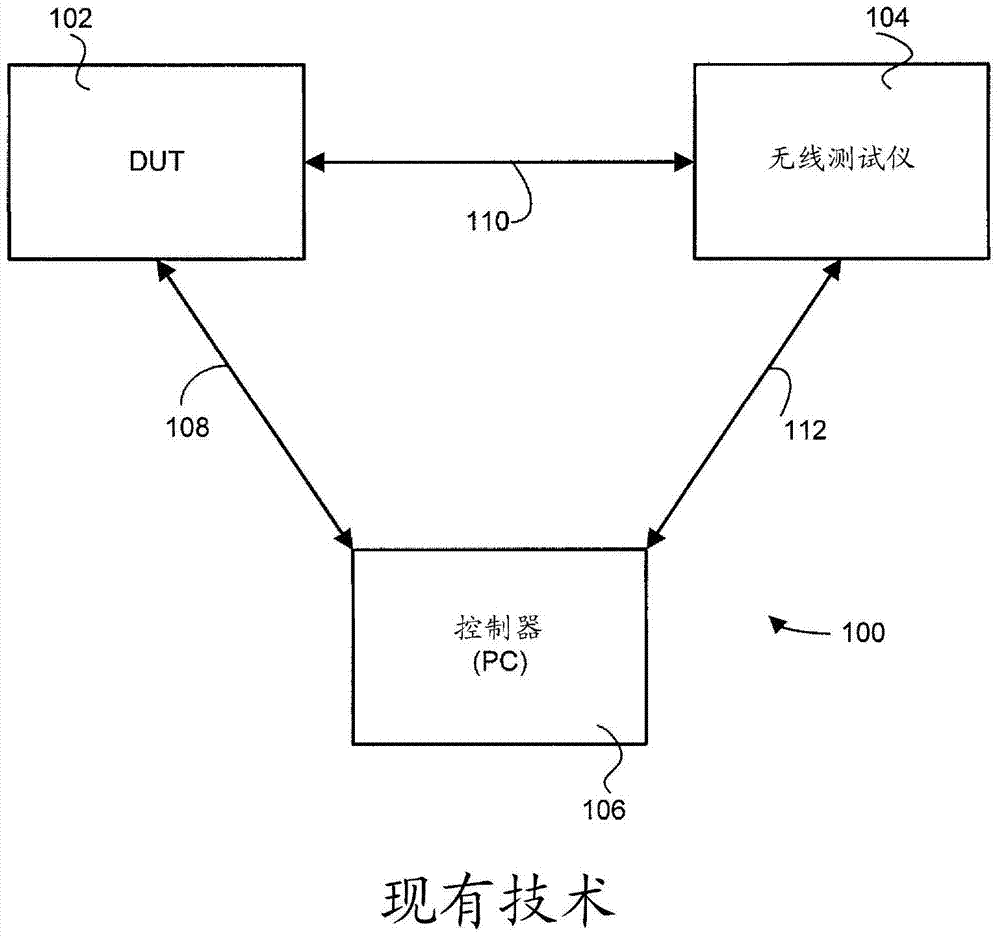

Apparatus and method for testing

ActiveUS20150318935A1Well formedTransmitters monitoringCorrect operation testingEquipment under testTest fixture

A test apparatus is configured to perform non-determinative testing of equipment. The test apparatus comprises a test computer arranged to automatically execute a non determinative test regime under the control of a test application. A network simulator connected to the test computer is provided with communication circuitry operable to communicate with the equipment under test. The network simulator is configurable into different network states according to the non-determinative test regime, and the test application is operable to control the network simulator to transition between a plurality of different network states. Data about unscripted communications between the network simulator and the equipment under test is monitored and can be analyzed to reach a test verdict.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

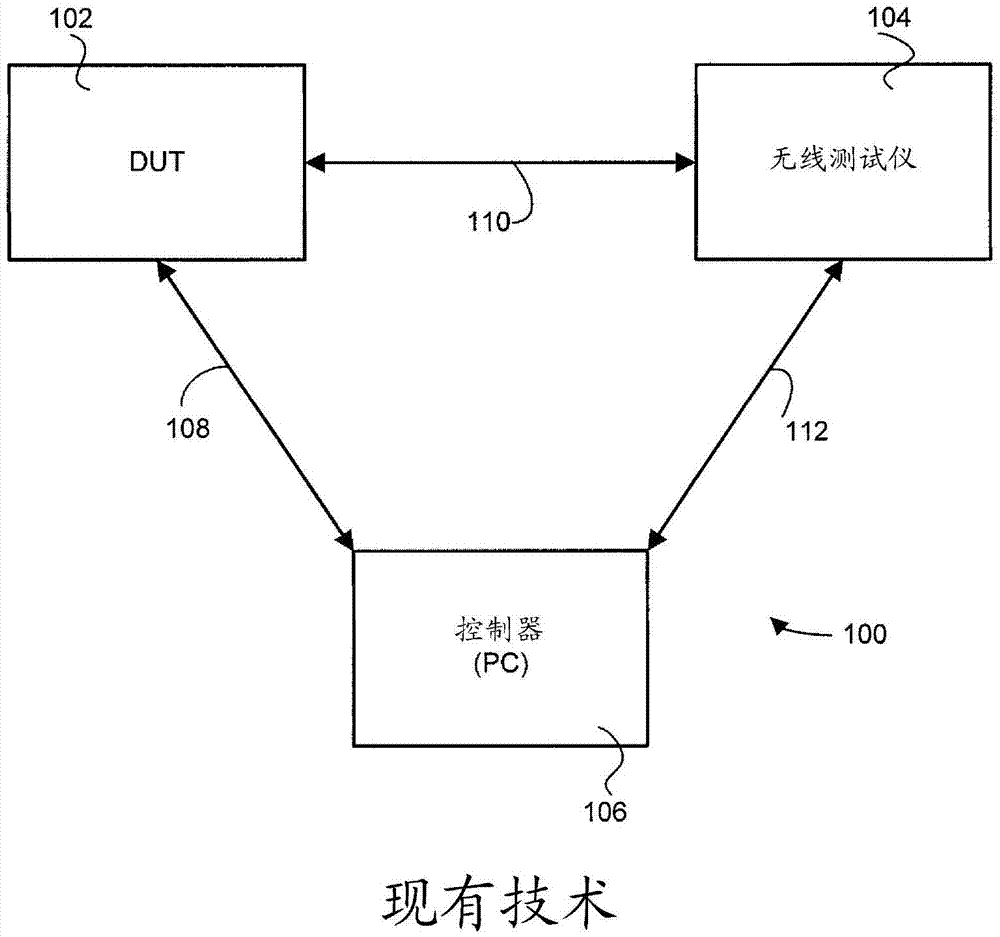

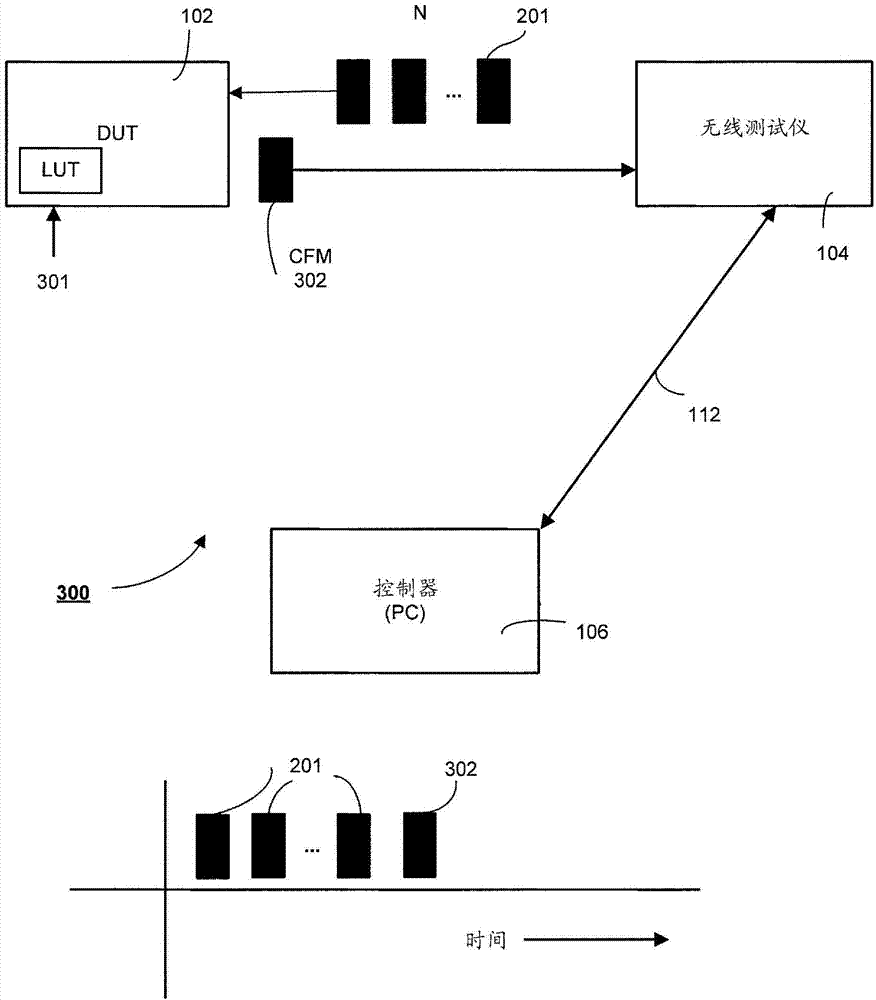

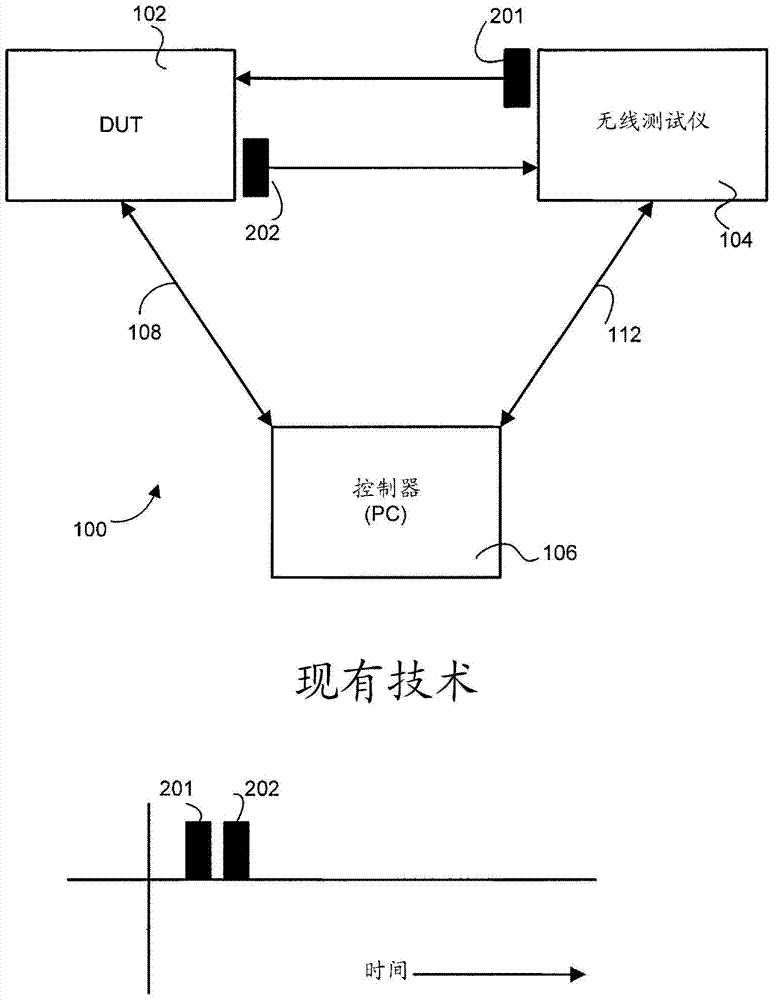

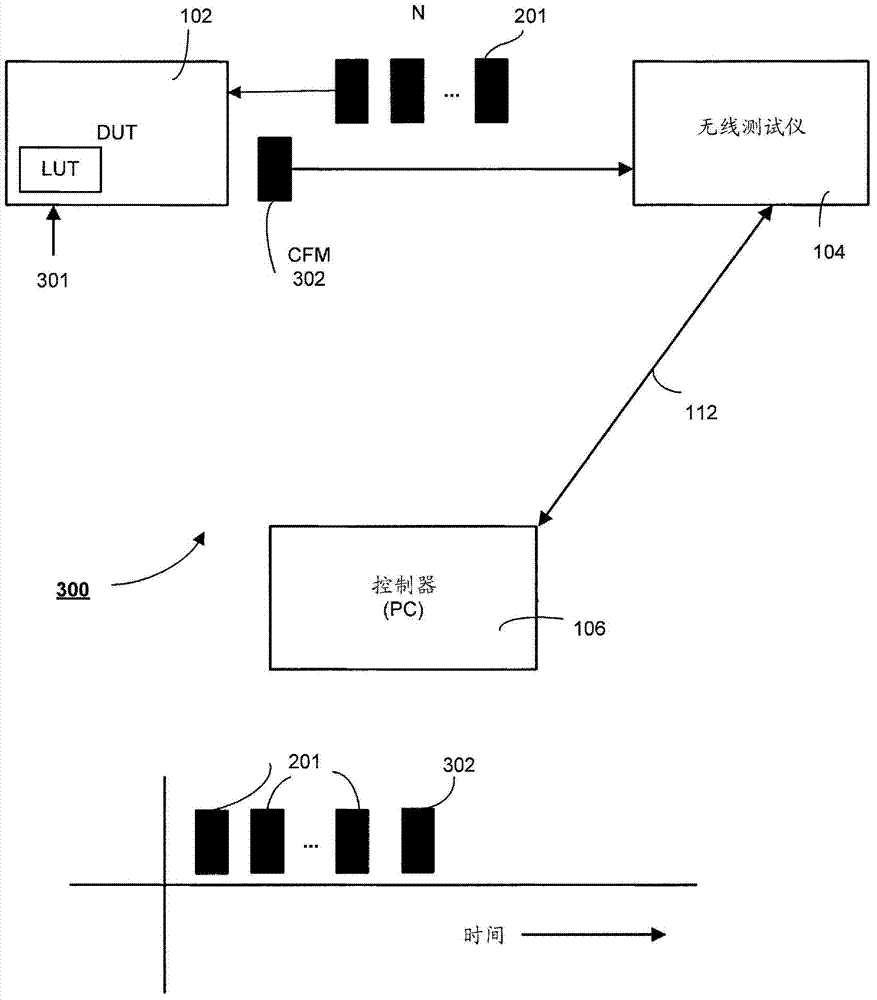

System and method for deterministic testing of packet error rate in electronic devices

ActiveCN102904701AError detection/prevention using signal quality detectorCorrect operation testingNetwork packetSeries data

A method and system for testing packet error rate in electronic devices by transmitting a series of data packets from a testing device to a device under test (DUT) and setting a predefined number of received error-free data packets; evaluating whether a number of data packets from the series of data packets received error-free by the DUT equals the predefined number of received error-free data packets and transmitting additional data packets from the testing device to the DUT, at a power level known to produce zero received-packet errors in a correctly operating DUT, if the number of data packets from the series of data packets received error-free by the DUT does not equal the predefined number of received error-free data packets. Additional possible embodiments include evaluating whether a total number of data packets from the series of data packets and the additional error-free-power-level data packets received error-free by the DUT equals the predefined number of received error-free data packets and transmitting a confirmation data packet to the testing device in response to reception by the DUT of the predefined number of received error-free data packets.

Owner:LITEPOINT

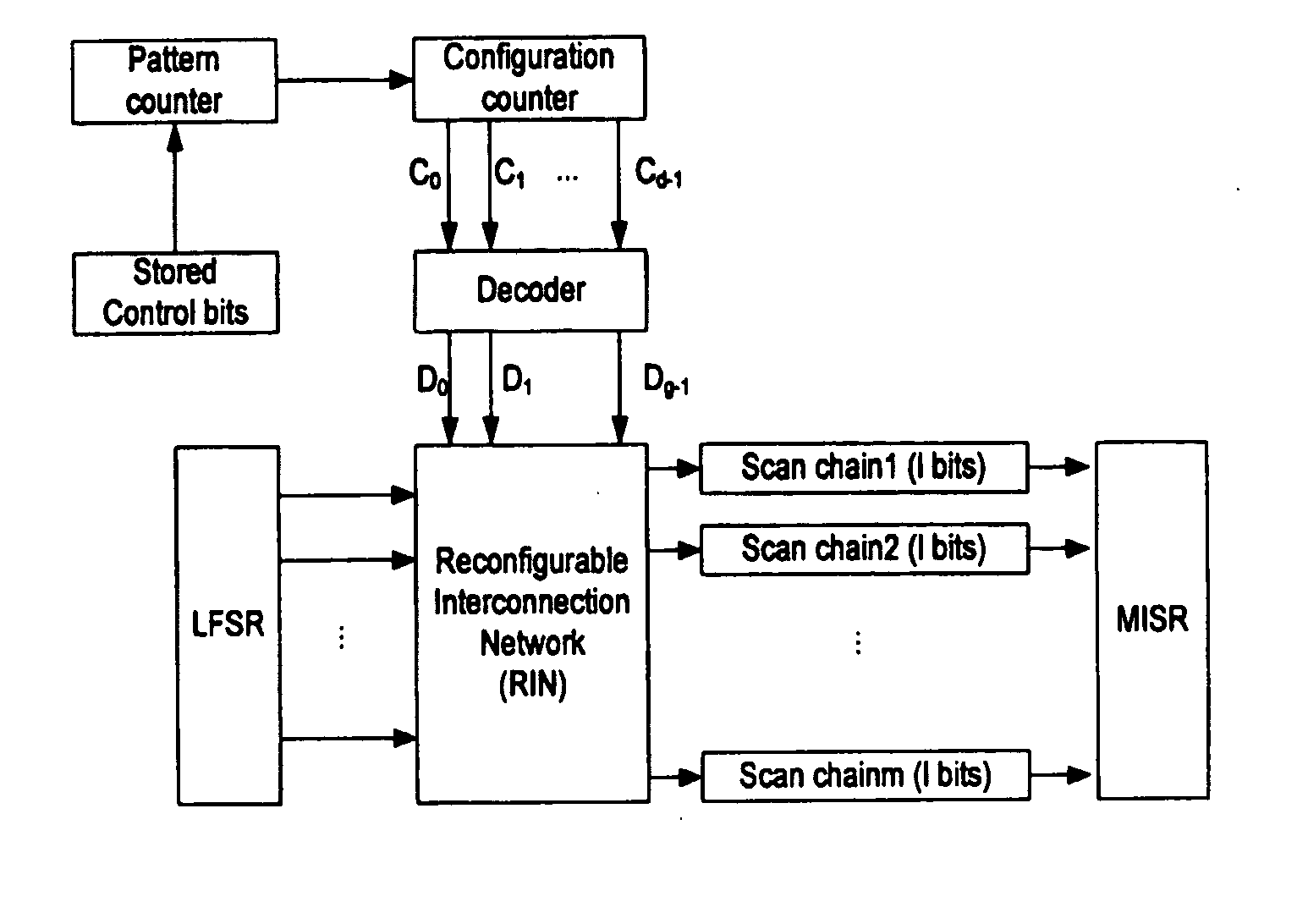

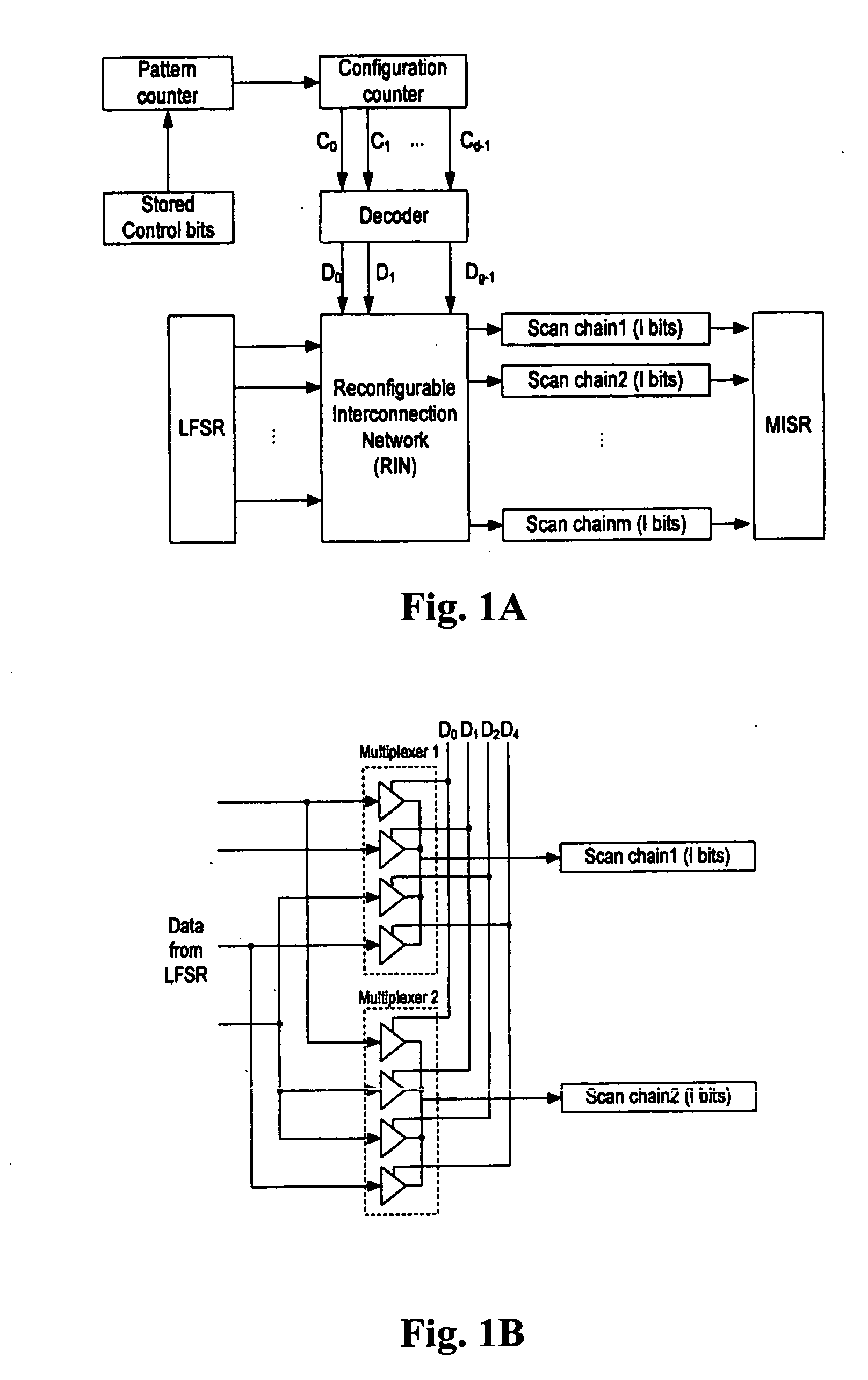

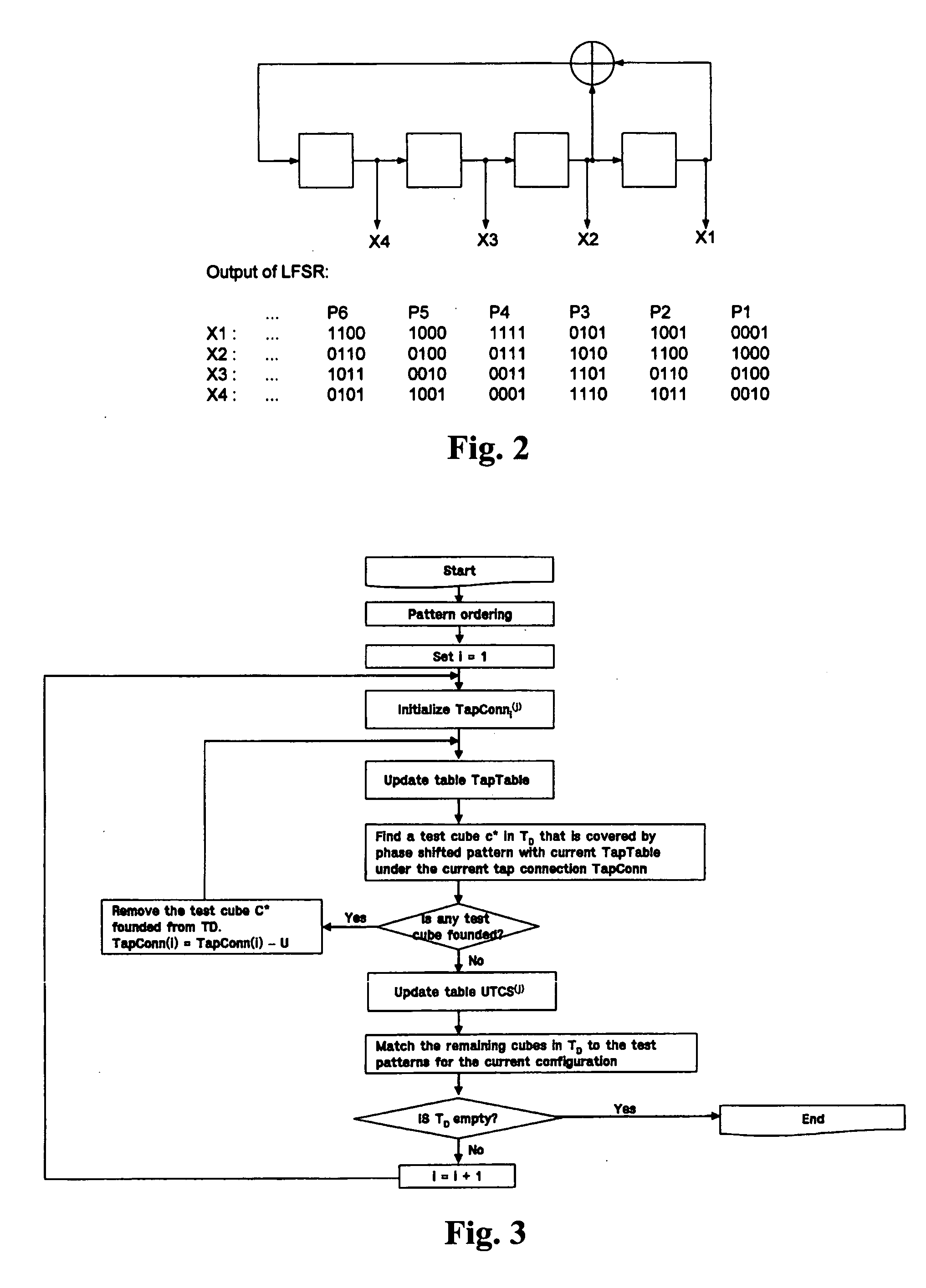

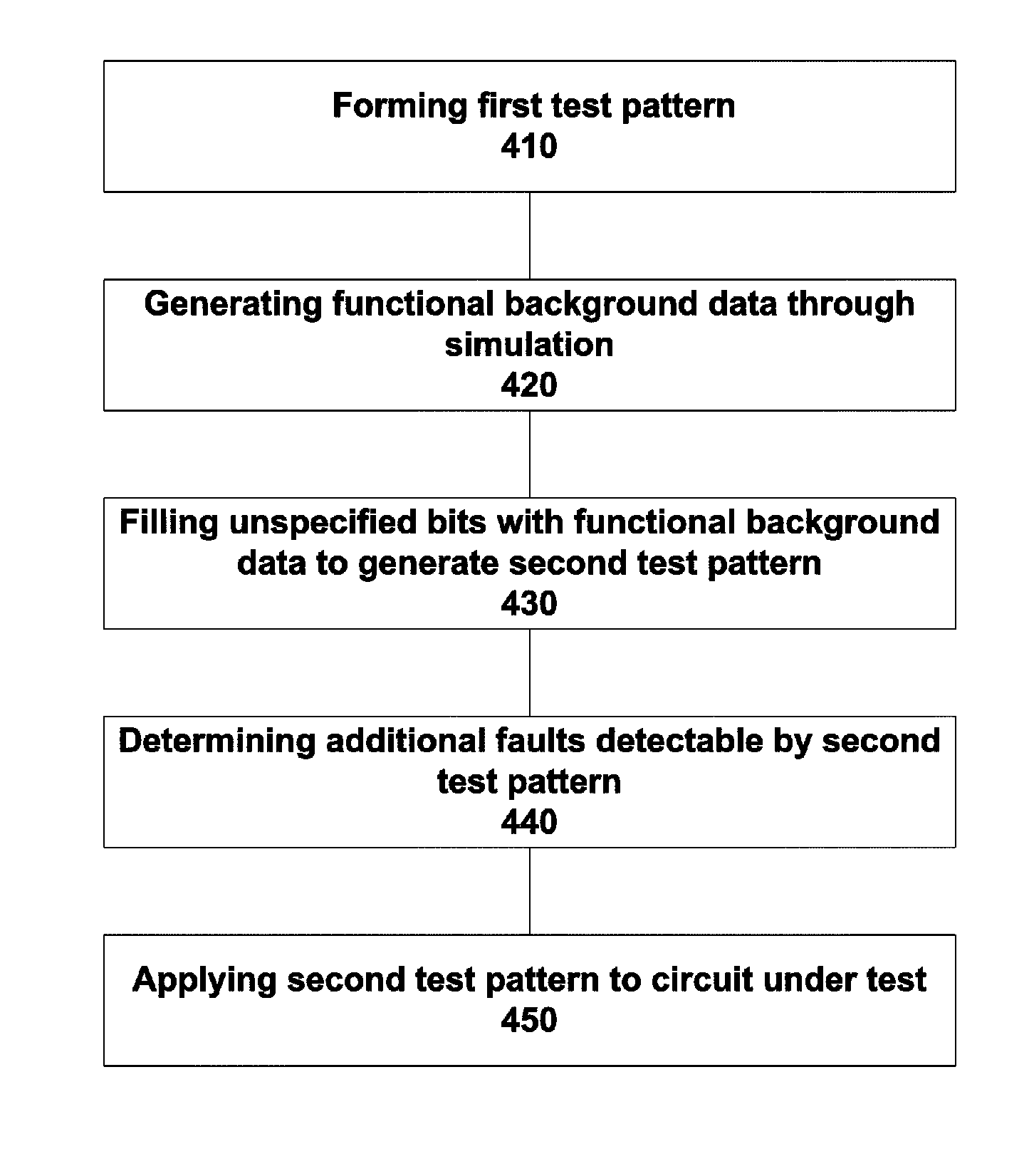

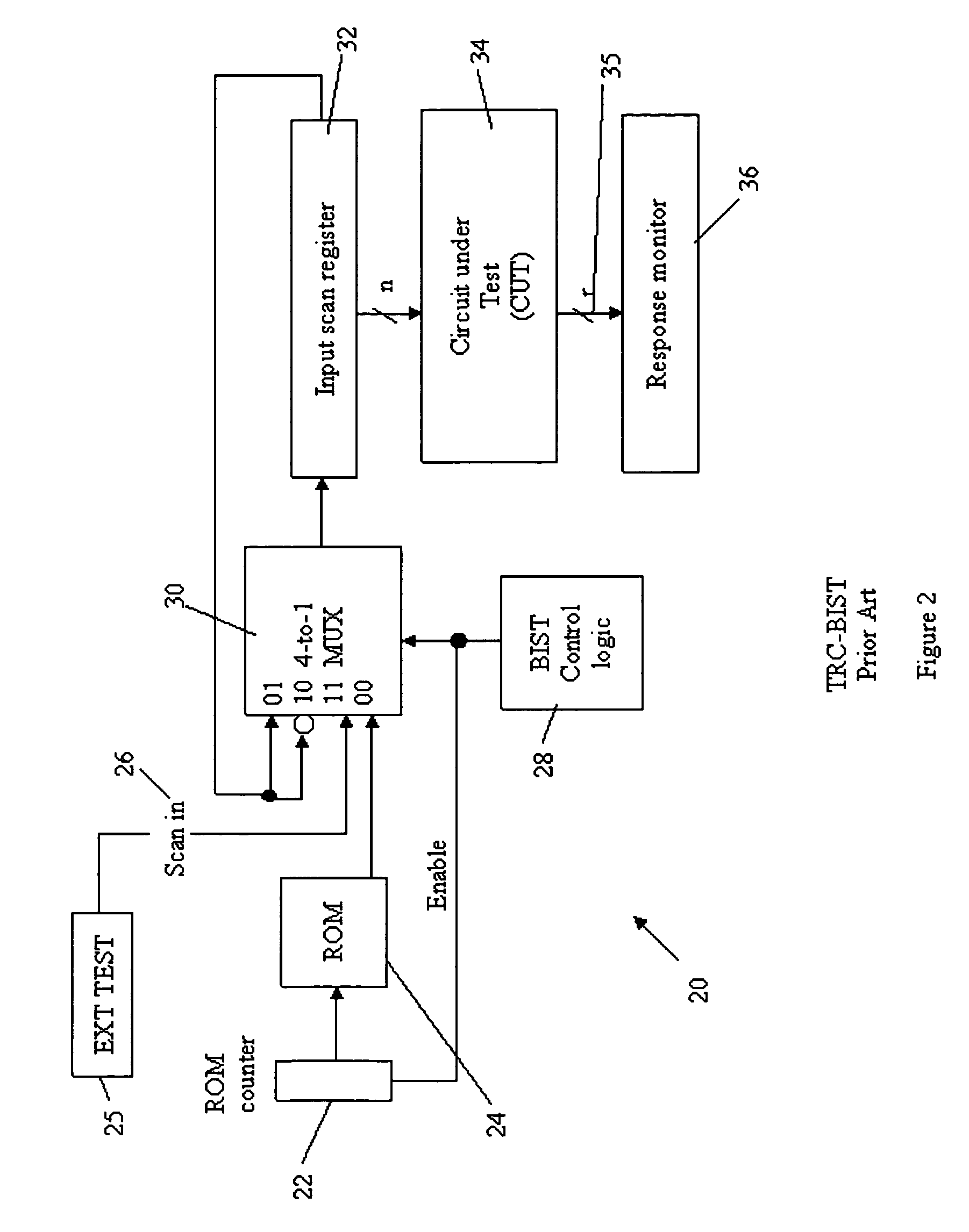

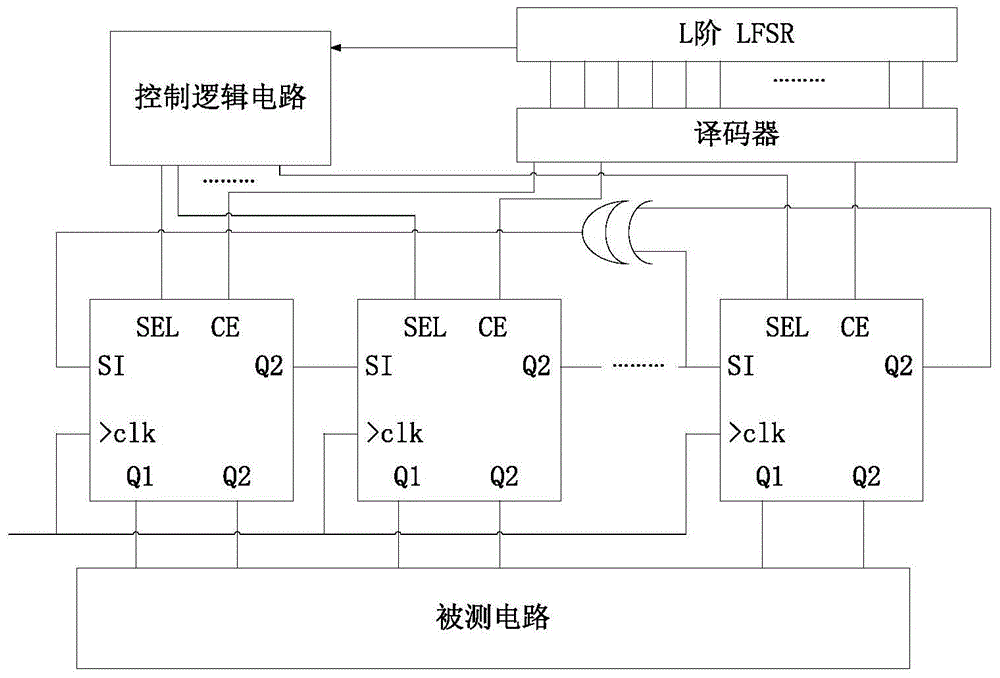

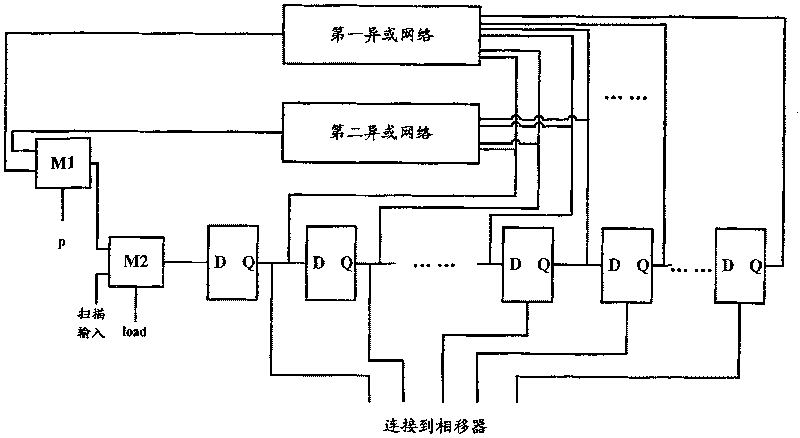

Apparatus for generating deterministic test pattern using phase shifter

InactiveUS20060020862A1Improve fault coverageShort test timeElectronic circuit testingFunctional testingComputer scienceDeterministic testing

An apparatus for generating a deterministic test pattern is provided for a BIST having a scan chain, comprising the control bits storing devise for storing the number of a deterministic test pattern that is covered by a tap configuration; pattern counter devise for receiving the values stored in the control bits storing devise one by one and then counting the values backward; configuration counter devise for tracing the order of a current tap configuration and incrementing the order by 1 whenever the value of the pattern counter passes through 1; a decoder for constituting a phase shifting network depending on the value of the configuration counter devise and determining an input signal of an XOR gate depending on TapConni(j); and a reconfigurable phase shifter for receiving the input signal from the decoder to constitute an actual phase shifter.

Owner:KANG SUNG HO +1

At-speed scan testing with controlled switching activity

ActiveUS8499209B2Electronic circuit testingDetecting faulty computer hardwareComputer hardwareStable state

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

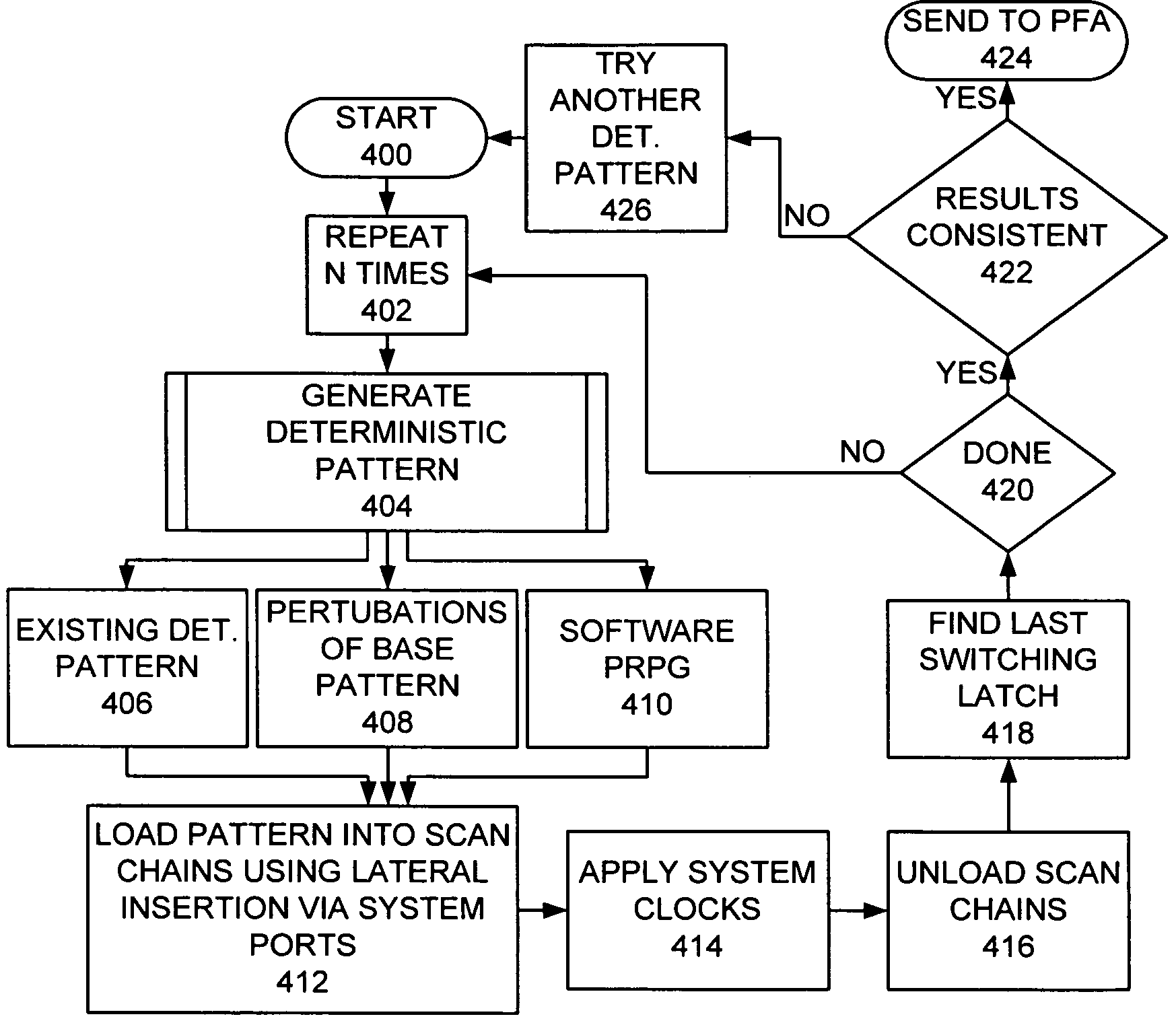

Method for implementing deterministic based broken scan chain diagnostics

A method, apparatus and computer program product are provided for implementing deterministic based broken scan chain diagnostics. A deterministic test pattern is generated and is loaded into each scan chain in the device under test using lateral insertion via system data ports applying system clocks. Then each scan chain is unloaded and a last switching latch is identified. The testing steps are repeated a selected number of times. Then checking for consistent results is performed. When consistent results are identified, then the identified last switching latch is sent to a Physical Failure Analysis system.

Owner:META PLATFORMS INC

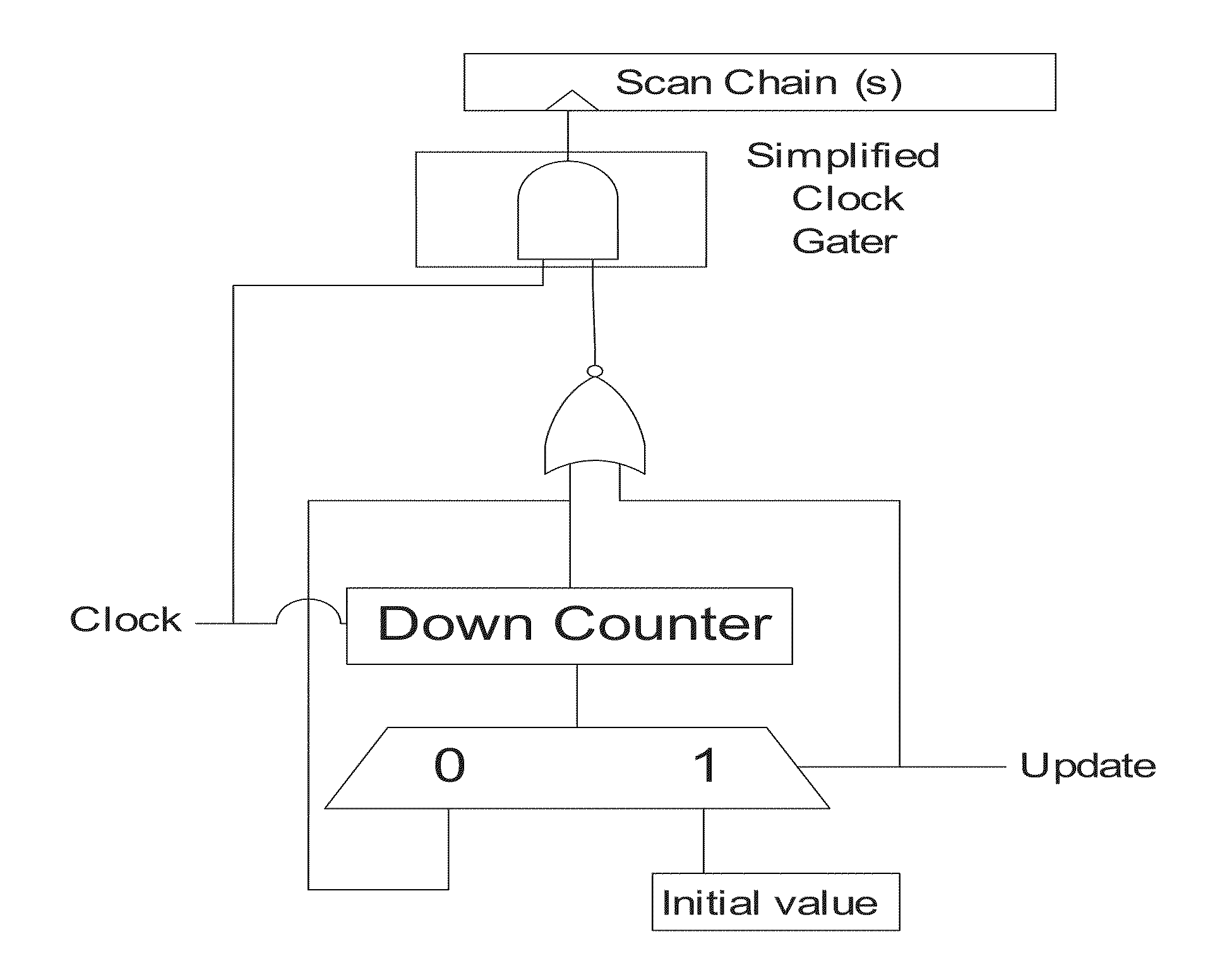

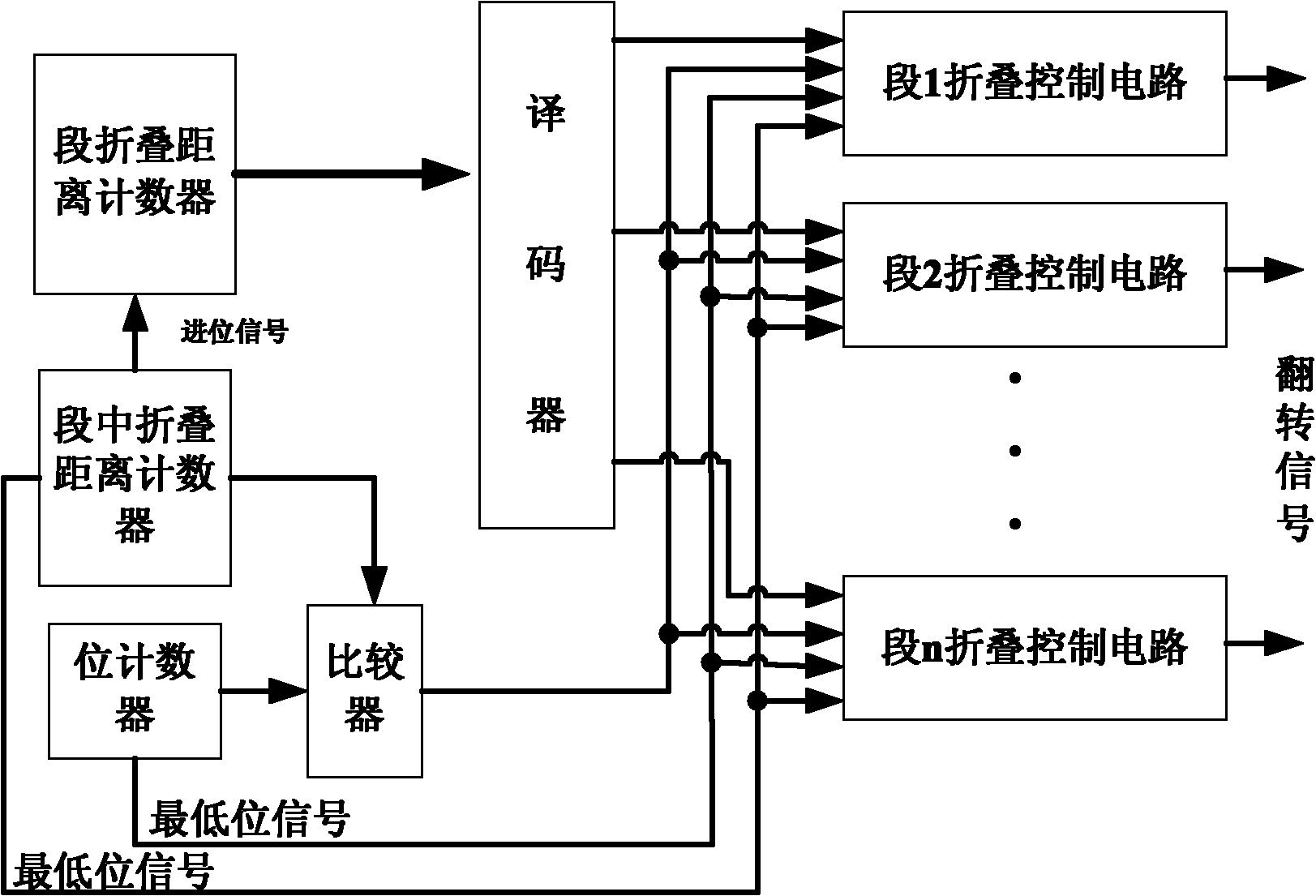

Re-sowing test plan based on parallel folding counter

InactiveCN102081142AReduce storage capacityShorten test timeDigital circuit testingTested timeControl circuit

The invention discloses a re-sowing test plan based on a parallel folding counter; the re-sowing test plan is characterized in that a test set is doubly compressed by a linear feedback shifting register (LFSR) and a folding counter code; a tested circuit moved into a multi-scan link structure in parallel by a phase shifter and a parallel folding control circuit in the test process completes the test function. In the plan of the invention, the circuit scanning structure is not changed, and the original mono-scan serial input is transformed to be multi-scan parallel input which is suitable for a plurality of test modes like random test mode, deterministic test and mixed test mode and the like; the test data storage volumes needed by tests are reduced, and the test time is greatly saved.

Owner:HEFEI UNIV OF TECH

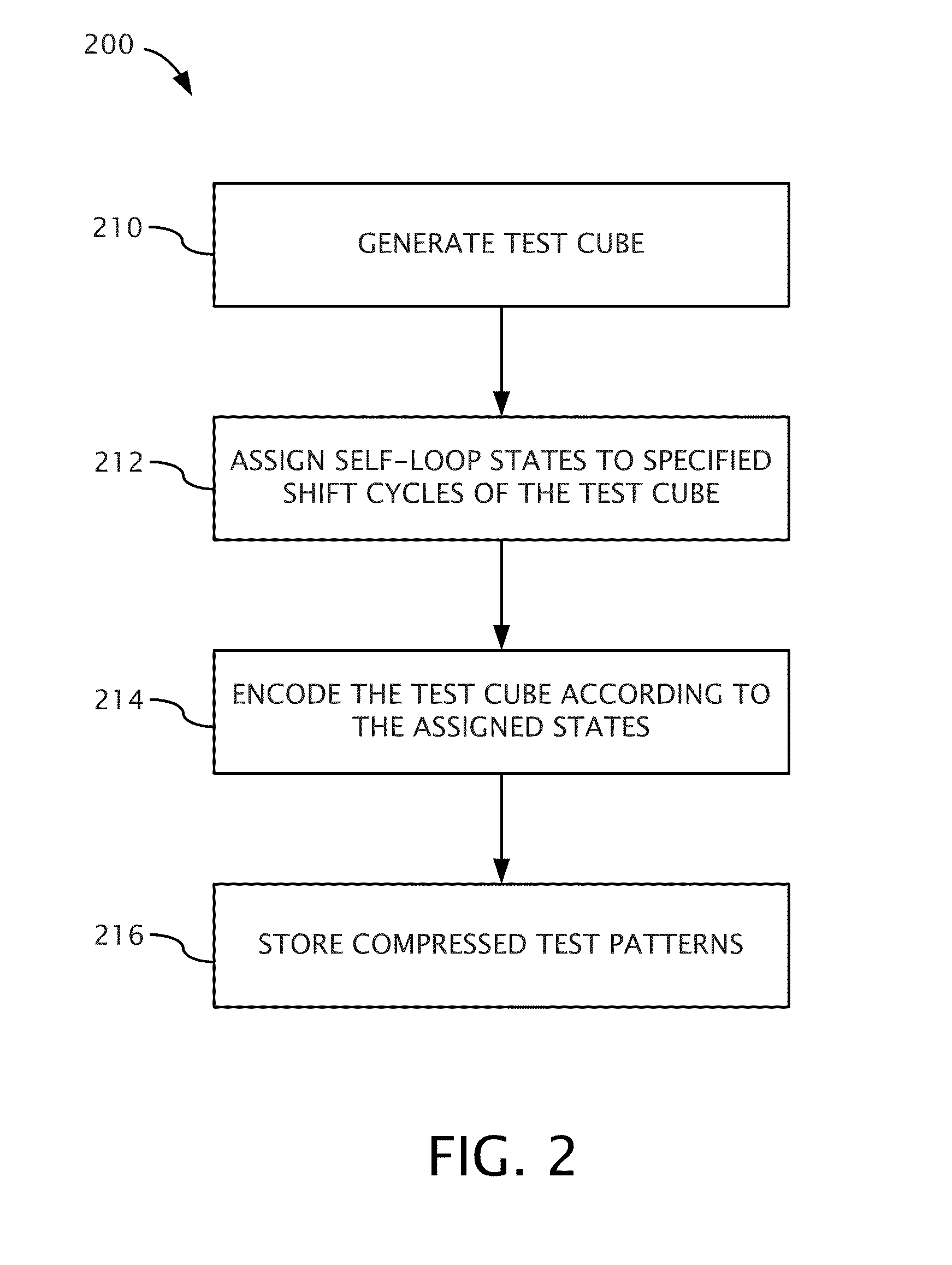

Low power decompression of test cubes

ActiveUS8046653B2Reduce ratePower dissipationElectronic circuit testingError detection/correctionHardware architecturePower test

Disclosed below are representative embodiments of methods, apparatus, and systems used to generate test patterns for testing integrated circuits. Embodiments of the disclosed technology can be used to provide a low power test scheme and can be integrated with a variety of compression hardware architectures (e.g., an embedded deterministic test (“EDT”) environment). Certain embodiments of the disclosed technology can reduce the switching rates, and thus the power dissipation, in scan chains with no hardware modification. Other embodiments use specialized decompression hardware and compression techniques to achieve low power testing.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

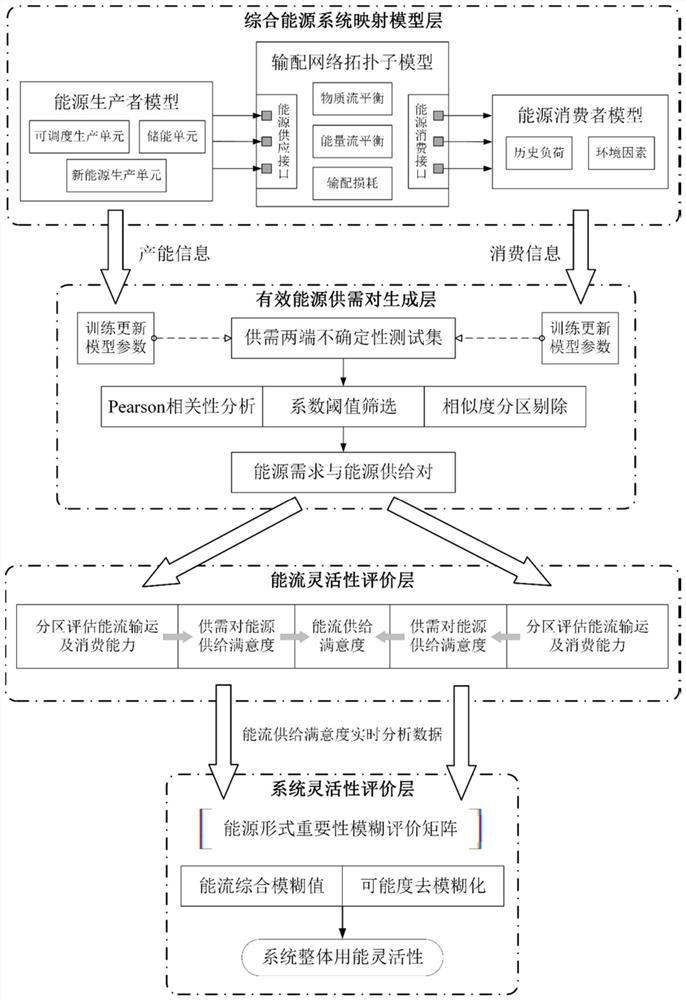

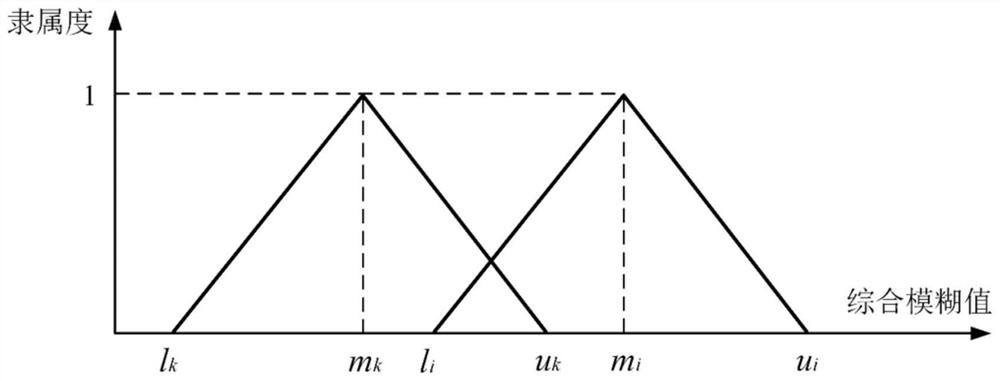

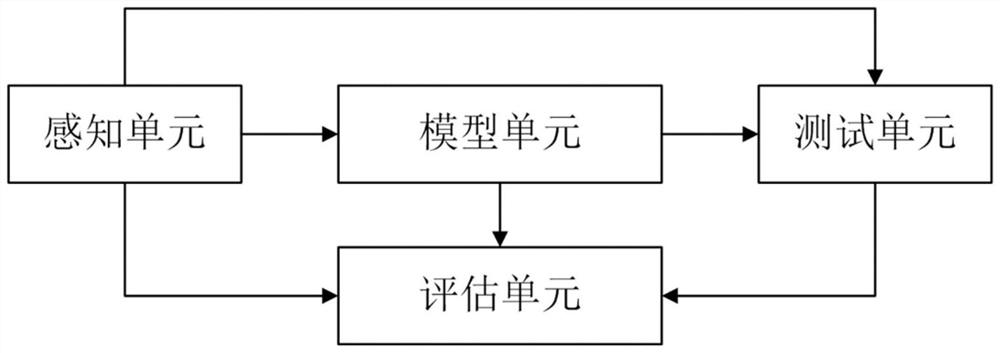

Comprehensive energy system energy use flexibility evaluation method and system

ActiveCN111695793AReduce wasteImprove utilization efficiencyTechnology managementResourcesEnergy gradientIntegrated energy system

The invention relates to a comprehensive energy system energy use flexibility evaluation method and system. The method comprises the following steps: S1, establishing a comprehensive energy system mapping model based on physical characteristics of energy equipment and an energy network topology structure; s2, according to the historical operation data of the comprehensive energy system and the historical load data in the supply area, establishing an uncertainty test set of the supply end and the demand end, and generating energy demand and energy supply pairs of the demand end under all the test sets; s3, calculating the flexibility of different energy flows according to the generated energy demand and energy supply pair; and S4, determining the overall energy use flexibility of the comprehensive energy system based on a fuzzy analytic hierarchy process. According to the method, guidance can be provided for energy gradient utilization and operation scheduling optimization of the comprehensive energy system, interaction between the supply end and the demand end is enhanced, and adverse effects caused by system uncertainty are reduced.

Owner:ZHEJIANG UNIV

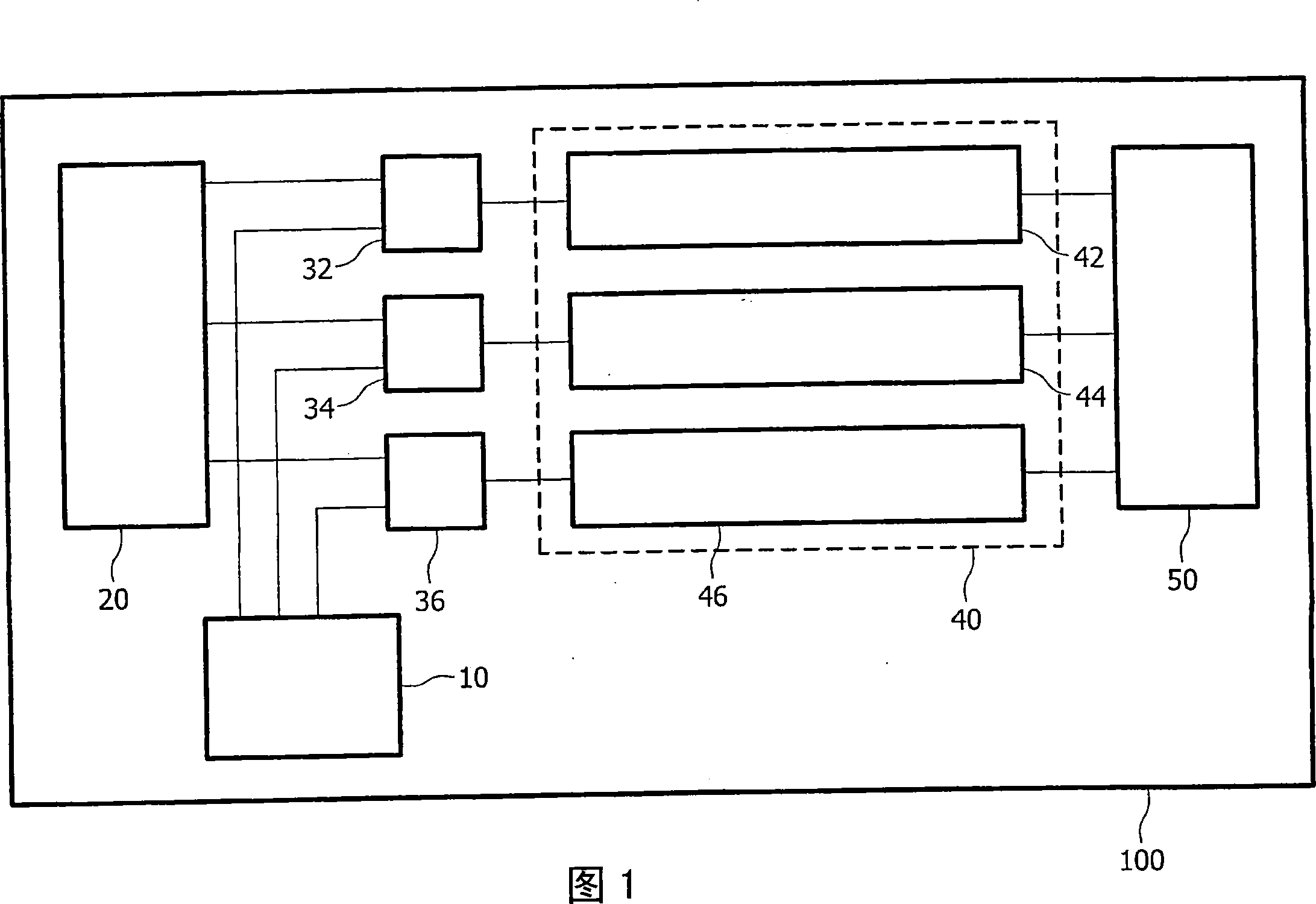

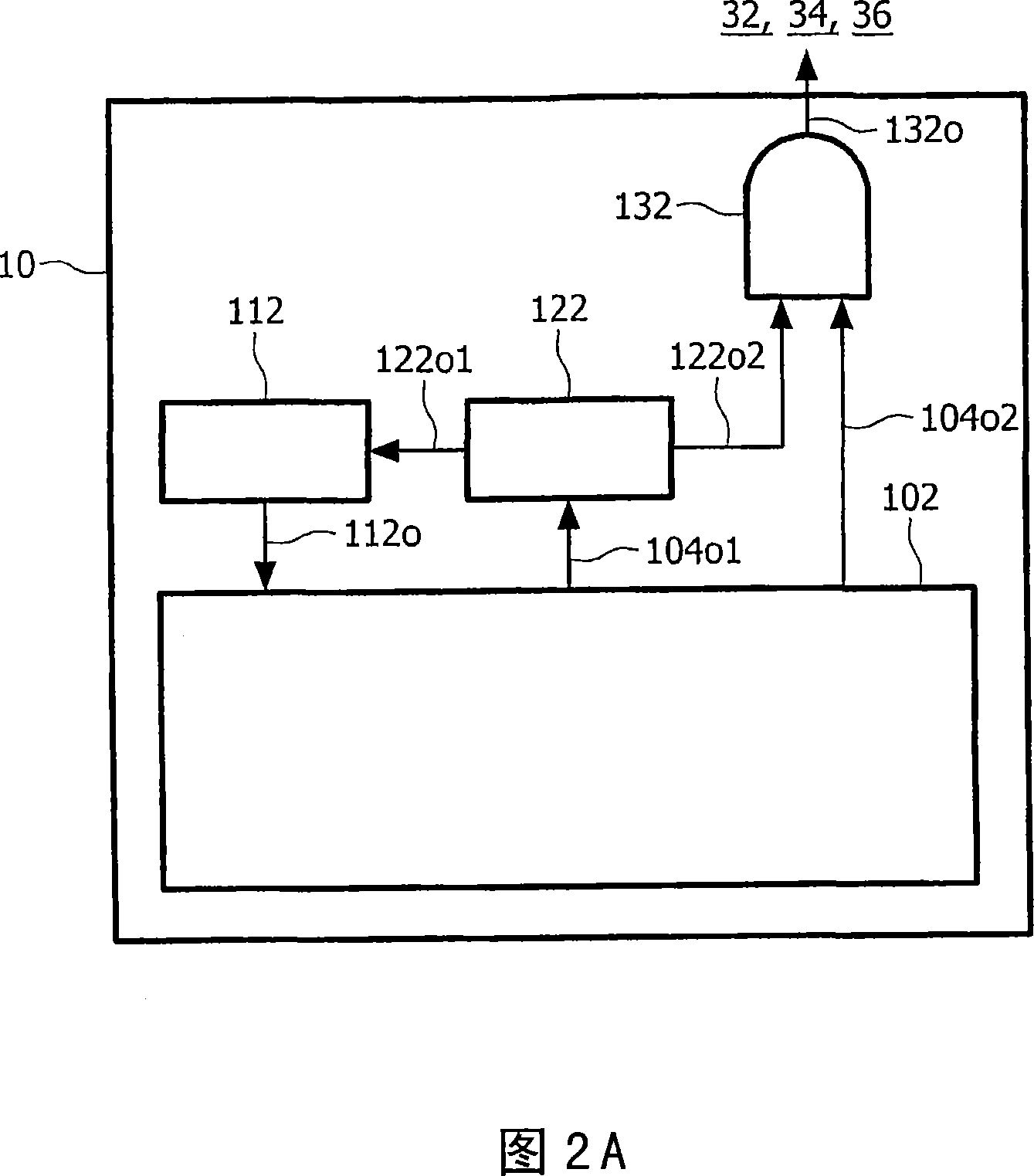

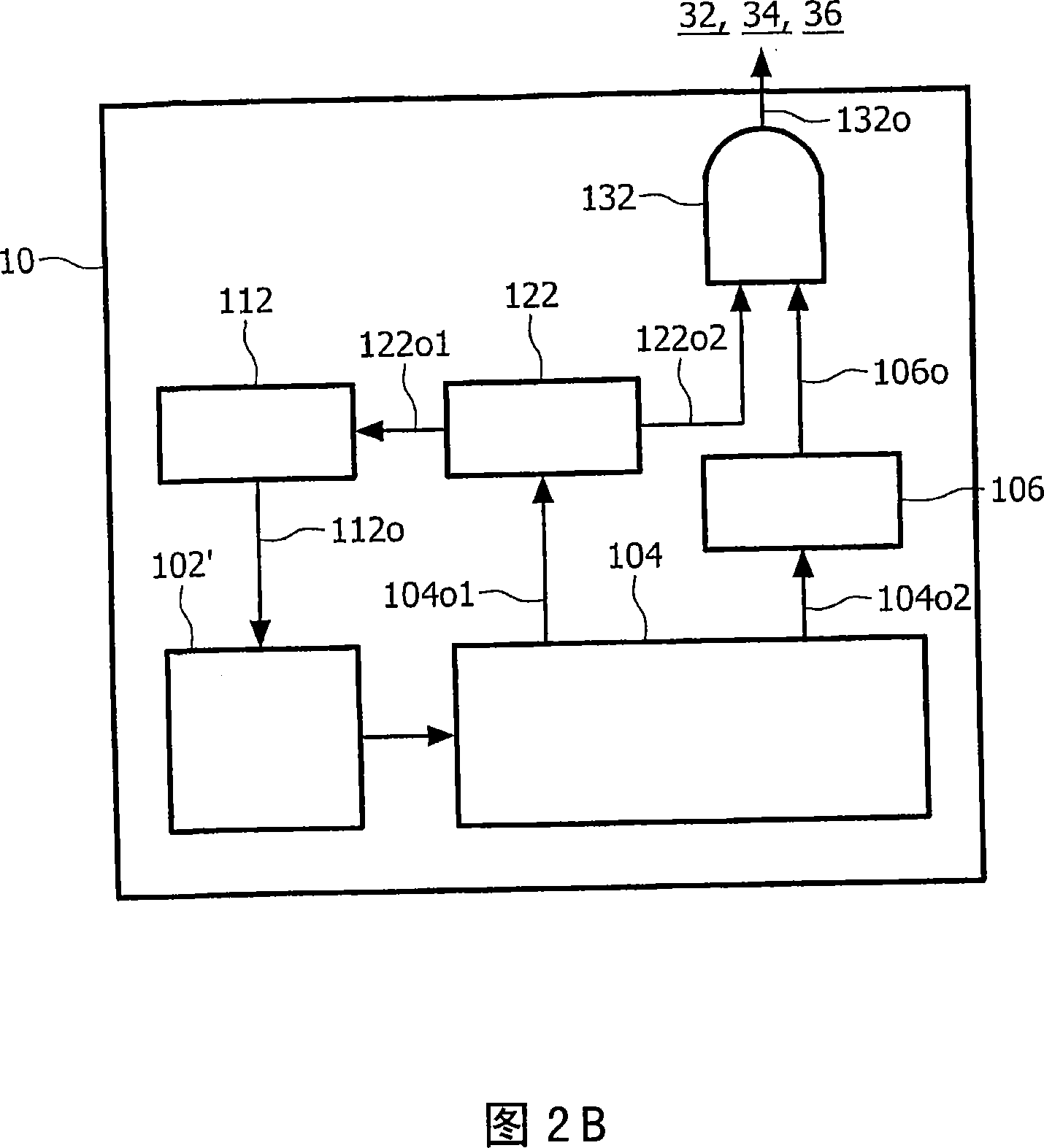

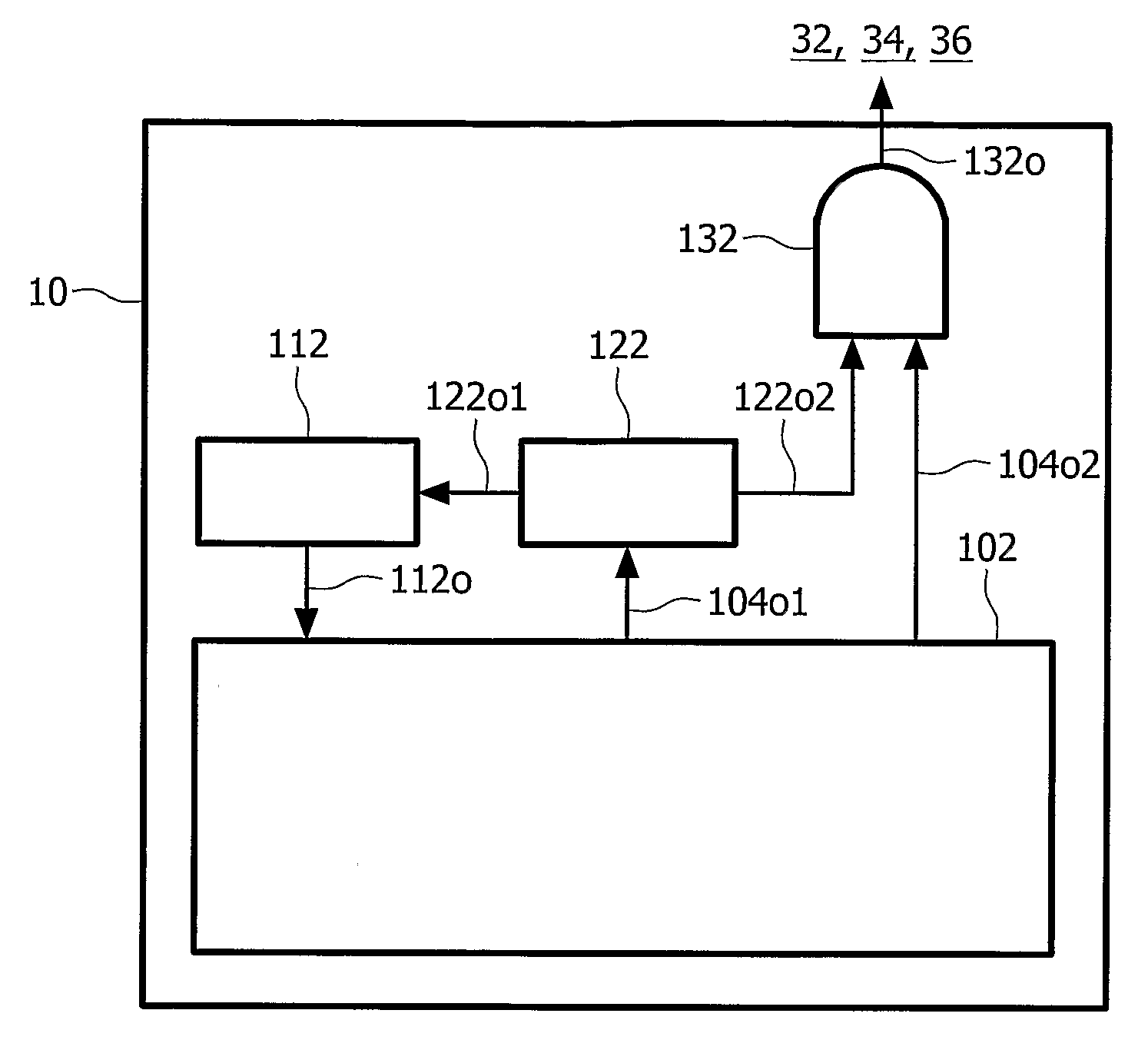

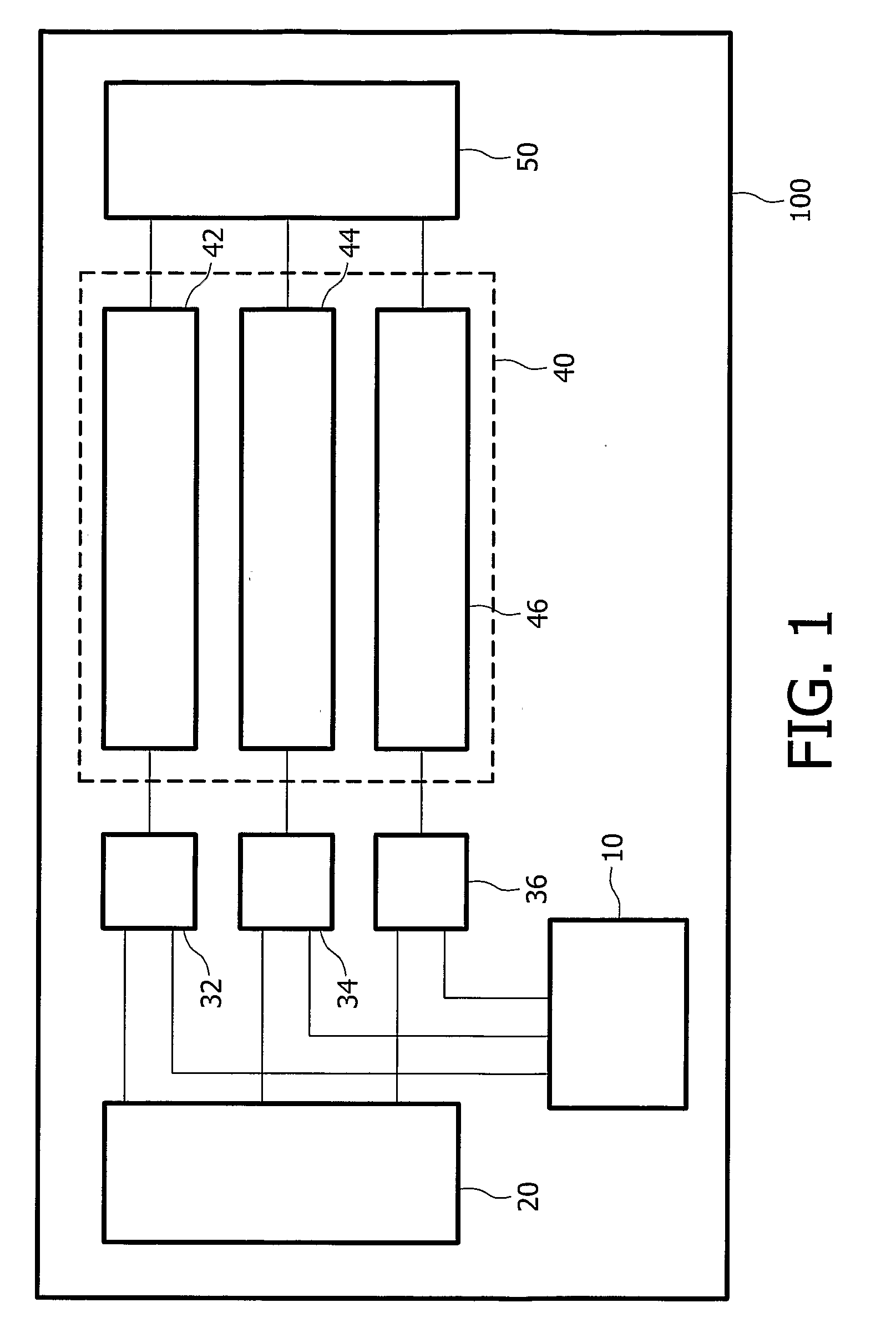

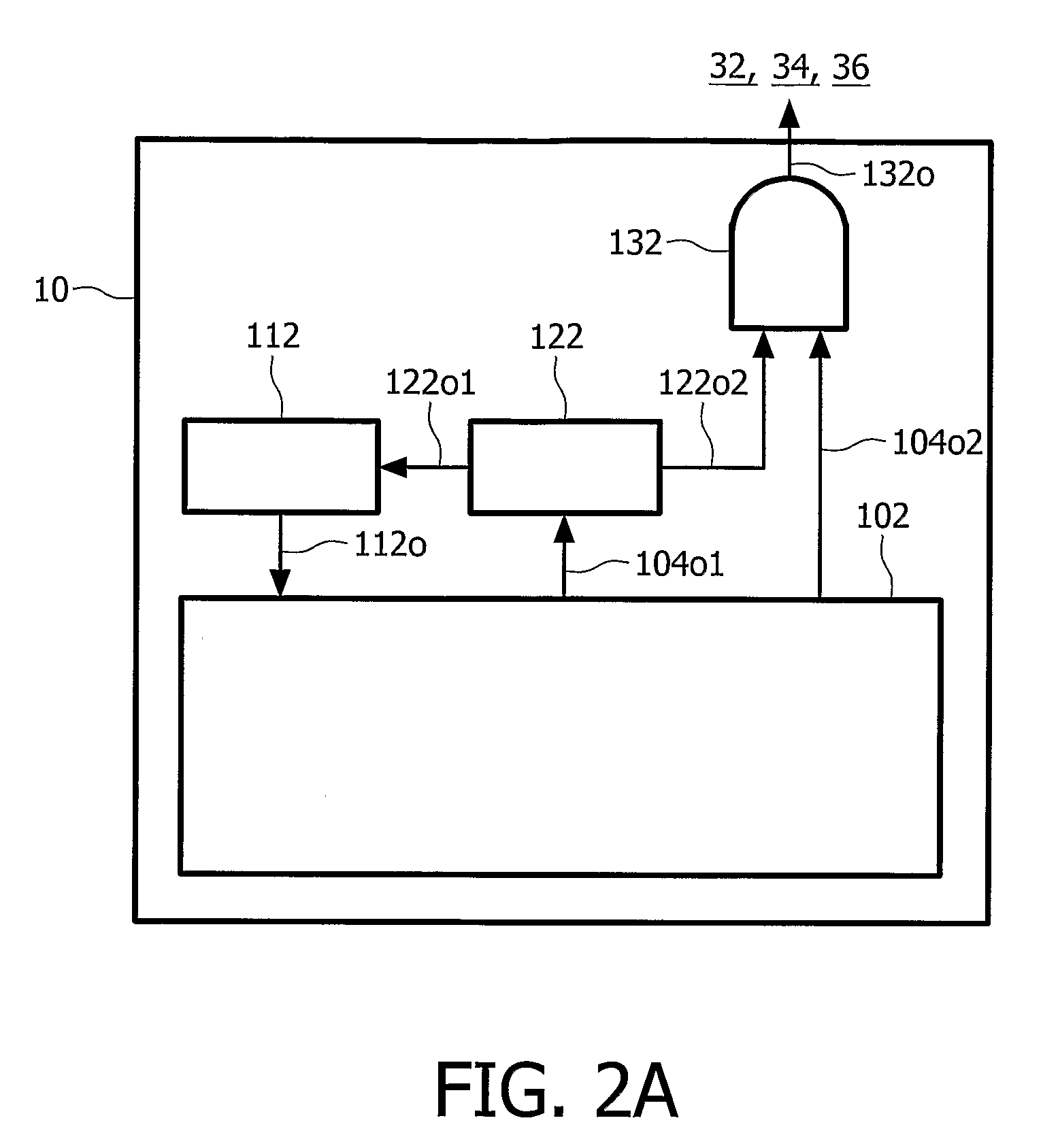

Circuit arrangement and method of testing an application circuit provided in said circuit arrangement

InactiveCN101014869AImproved error coverageLow costElectrical testingSoftware engineeringHemt circuits

The object is to develop an integrated circuit arrangement (100) with at least one application circuit (40) to be tested. In addition, with at least one self-test circuit (10, 20, 32, 34, 36, 50) provided for testing the application circuit (40) and generating at least one pseudo-random test sample, wherein the said pseudo-random test sample can be converted into at least one test vector that is programmable and / or deterministic. Moreover, that can be supplied to the application circuit (40) for testing purposes via at least one logic gate (32, 34, 36). And by means of at least one signal that can be applied to said logic gate (32, 34, 36), and wherein the output signal arising in dependence on the deterministic test vector can be evaluated by the application circuit (40) by means of at least one signature register (50). As well as a method of testing the application circuit (40) present in the integrated circuit arrangement (100) by means of the self-test circuit (10, 20, 32, 34, 36, 50) further such that the BIST [build in self test] hardware connected to the additional deterministic logic can be reduced. It is suggested that the signal to be supplied to the logic gate (32, 34, 36) can be made available by a BFF [bit flipping function] logic circuit (10) based on at least one.

Owner:NXP BV

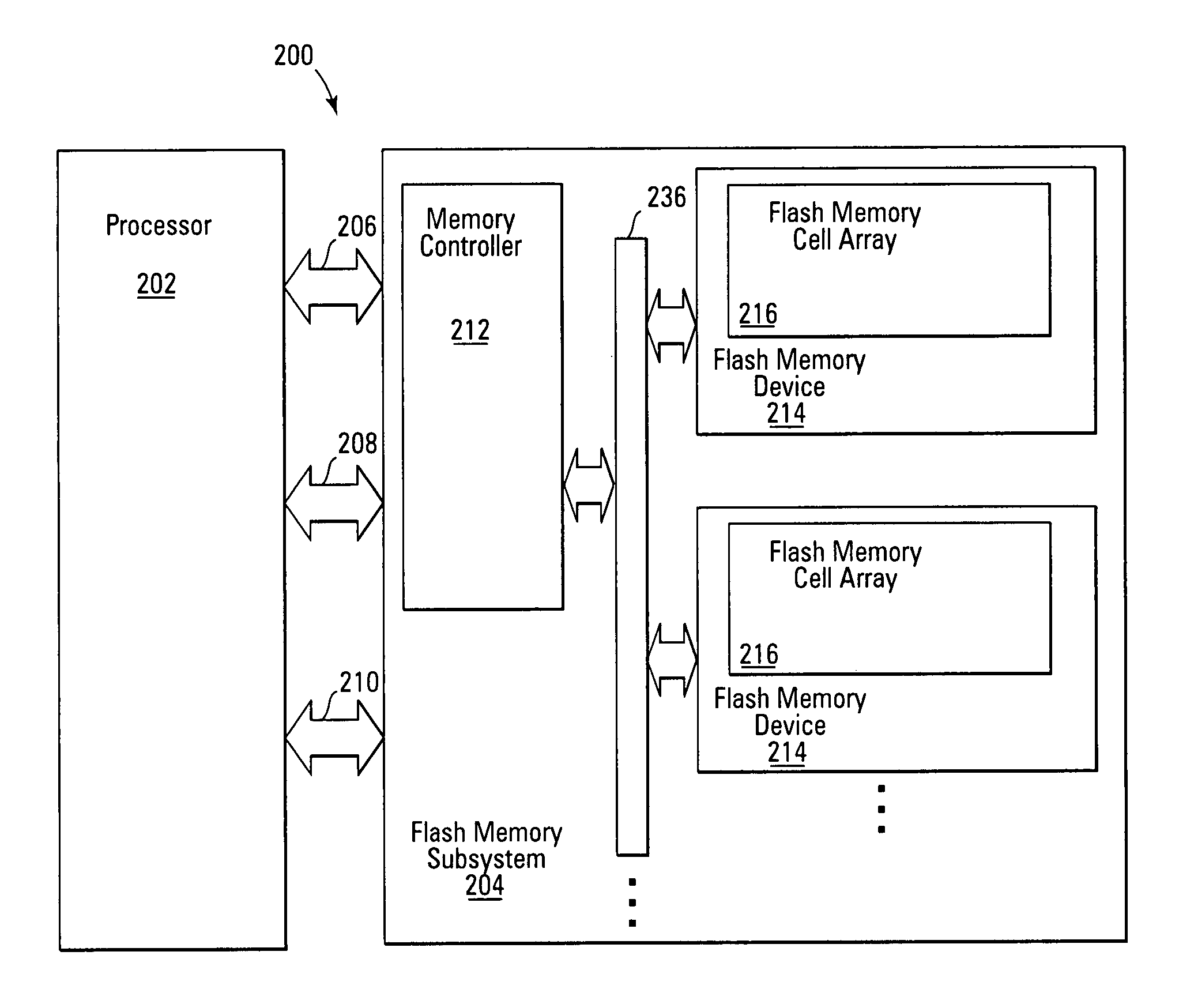

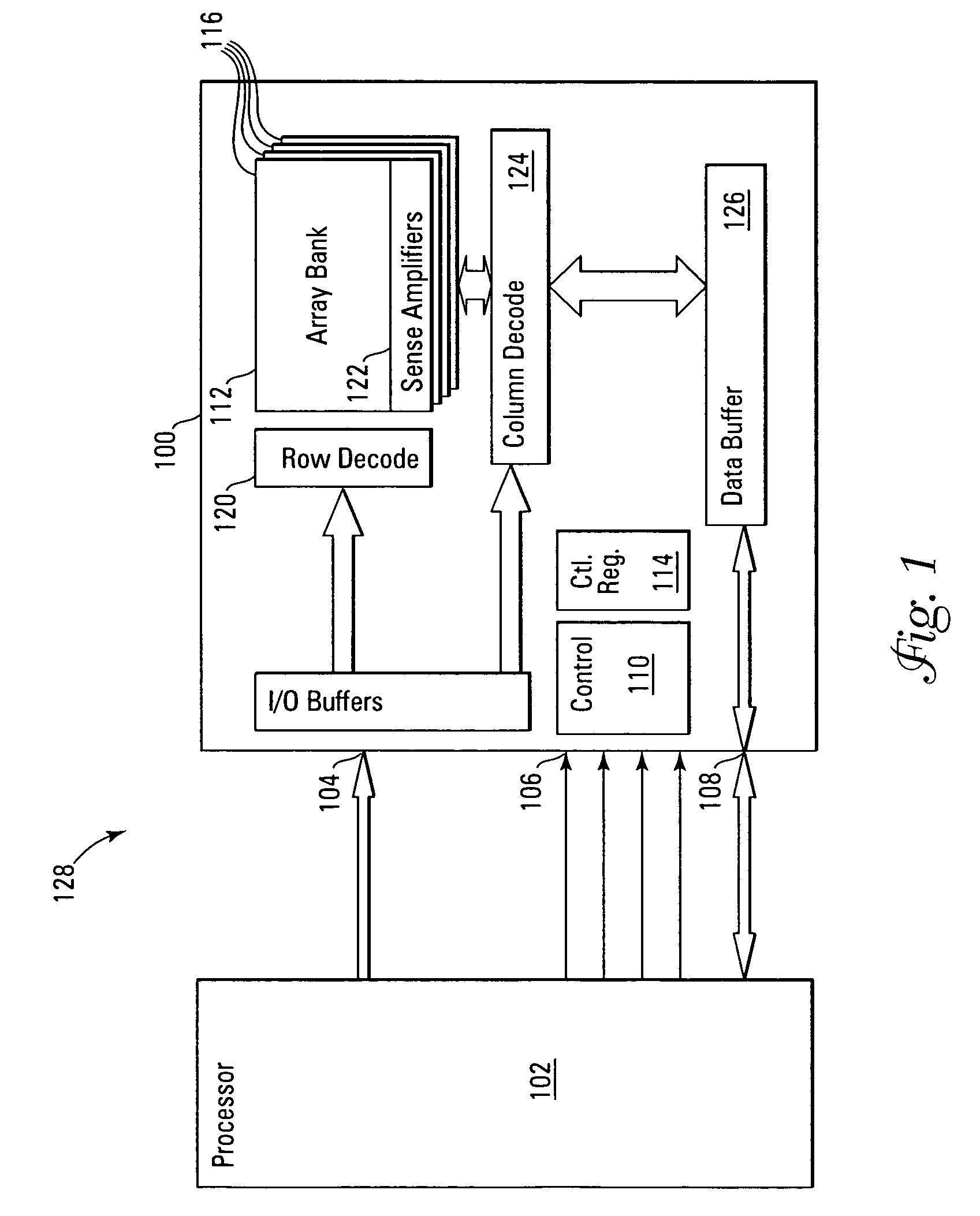

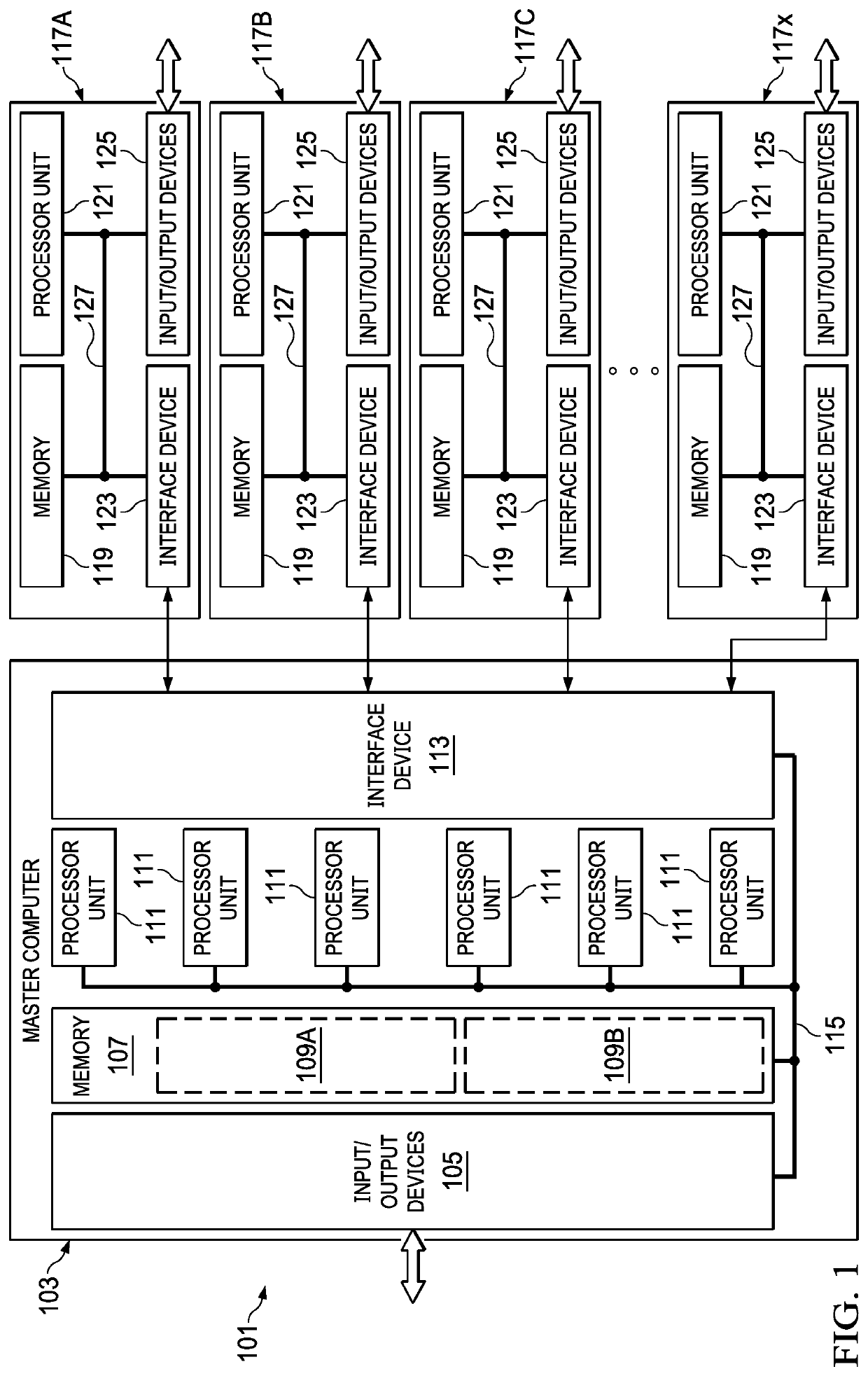

Testing software in electronic device

Software in an electronic device can be tested using a combination of random testing and deterministic testing. In various embodiments, deterministic tests can run for a prescribed duration and / or a prescribed number of iterations before and / or after random testing. Test results can be weighted using a metric representing an amount of code that was stressed during testing. This metric can be determined by tracking software code that is loaded into memory during testing.

Owner:MICROSOFT TECH LICENSING LLC

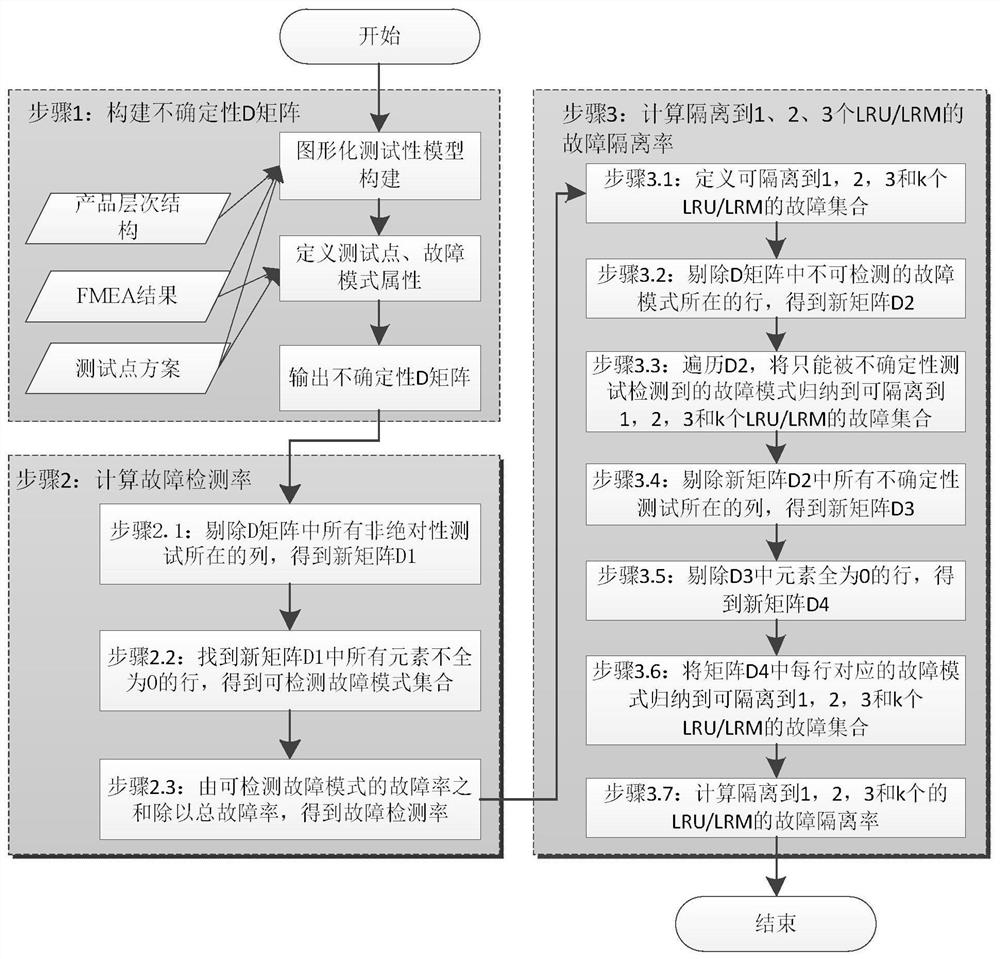

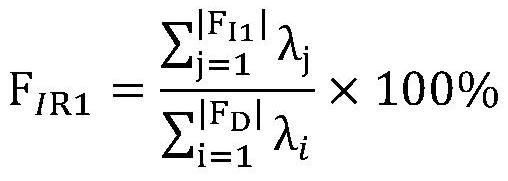

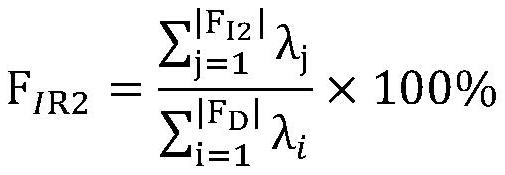

Uncertainty fault diagnosis efficiency evaluation method for the complex electronic system

PendingCN113626267AHigh degree of automationImprove accuracySoftware testing/debuggingFaulty hardware testing methodsElectronic systemsEngineering

The uncertainty fault diagnosis efficiency evaluation method for the complex electronic system is high in automation degree and accurate in conclusion, and the average diagnosis step number and the diagnosis cost can be reduced. According to the technical scheme, the method comprises the steps that an electronic system hierarchical framework, an FMEA result and a test point scheme serve as input, and an uncertainty fault-test dependency matrix (D matrix) of a system is constructed for three test types of absolute test, non-absolute test and uncertainty test; then, the influence of non-absolute testing on the detectable fault mode set is eliminated, and a fault detection rate index is calculated; then, the influence of non-absolute testing on the detectable fault mode set is eliminated, and a fault detection rate index is calculated; next, the influence of uncertainty on the isolatable fault mode set is eliminated, and the fault mode set isolated to 1, 2 and 3 external field replaceable units or modules (LRU / LRM) and a fault isolation rate index are obtained;.

Owner:10TH RES INST OF CETC

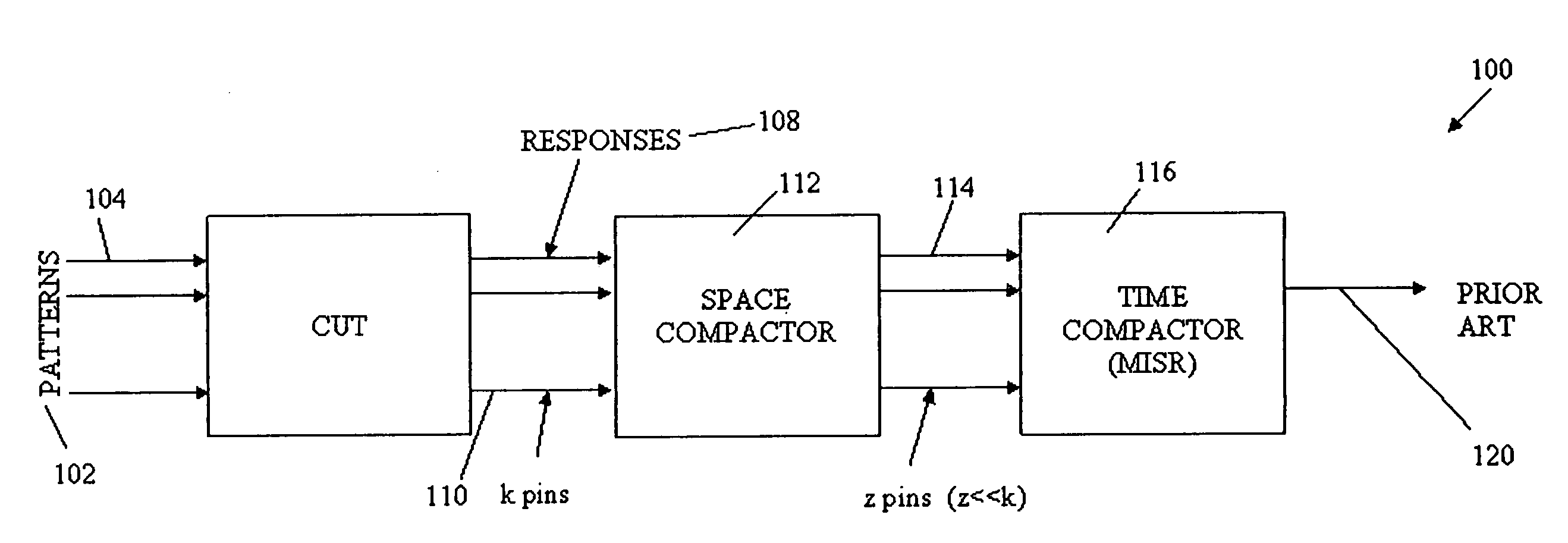

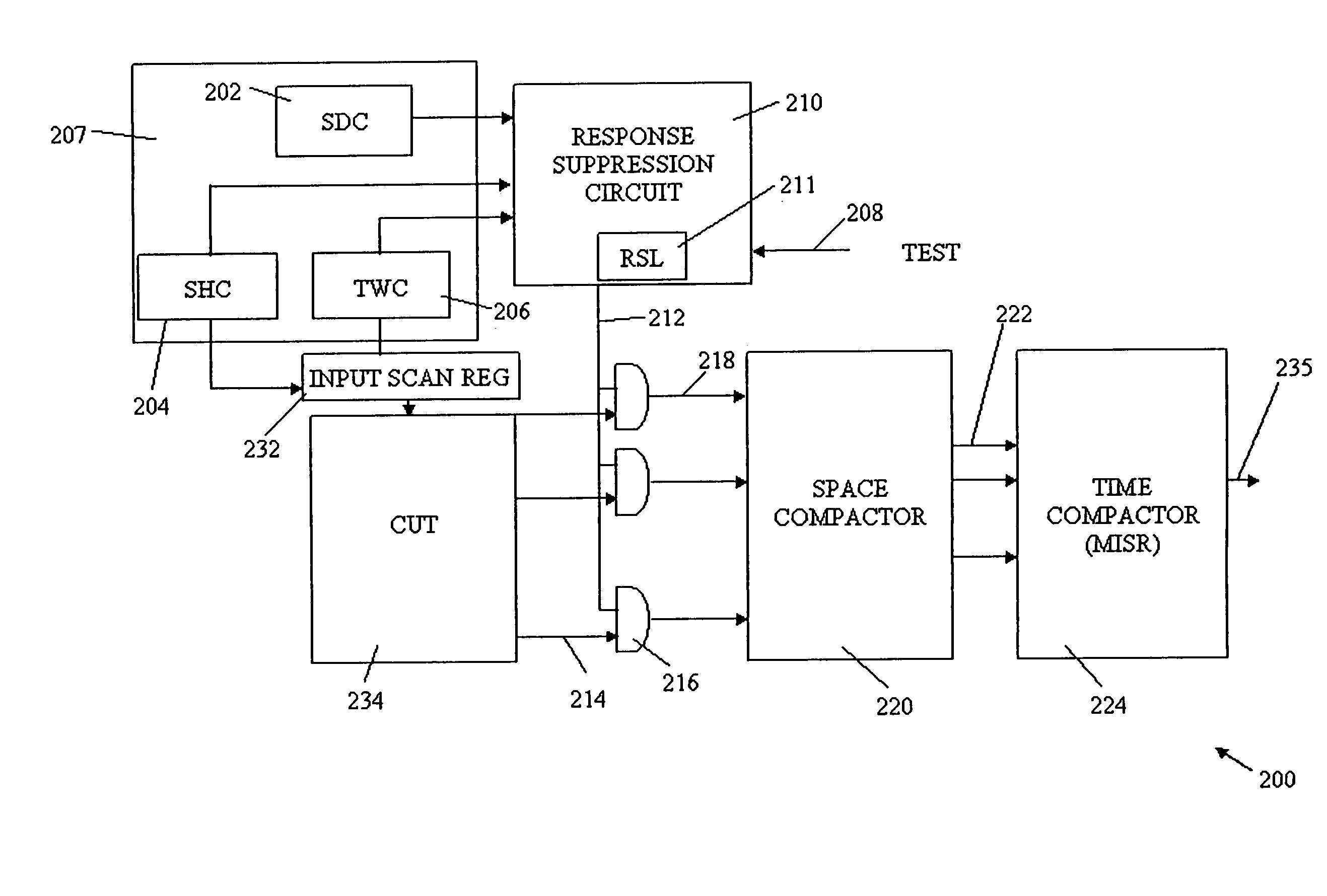

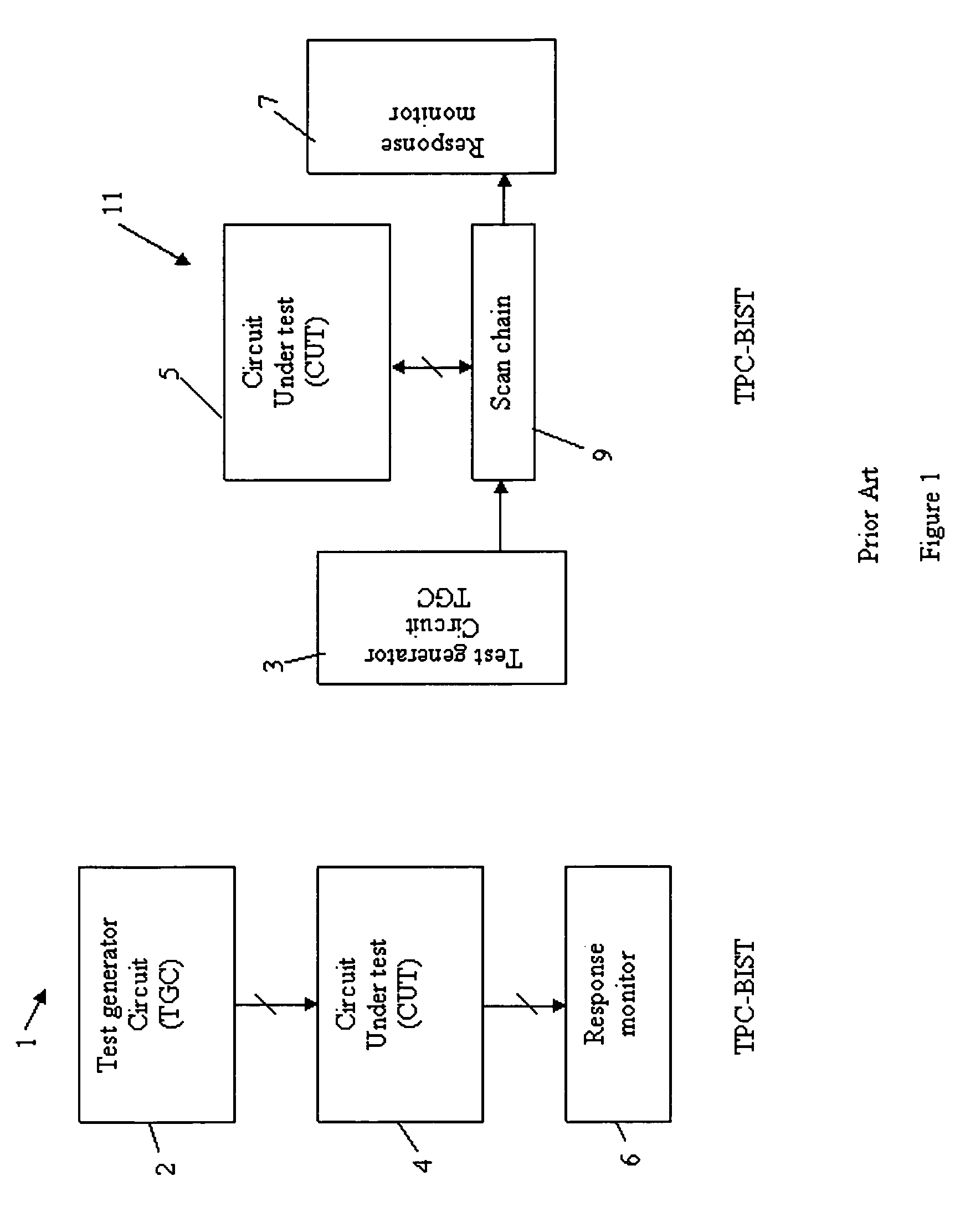

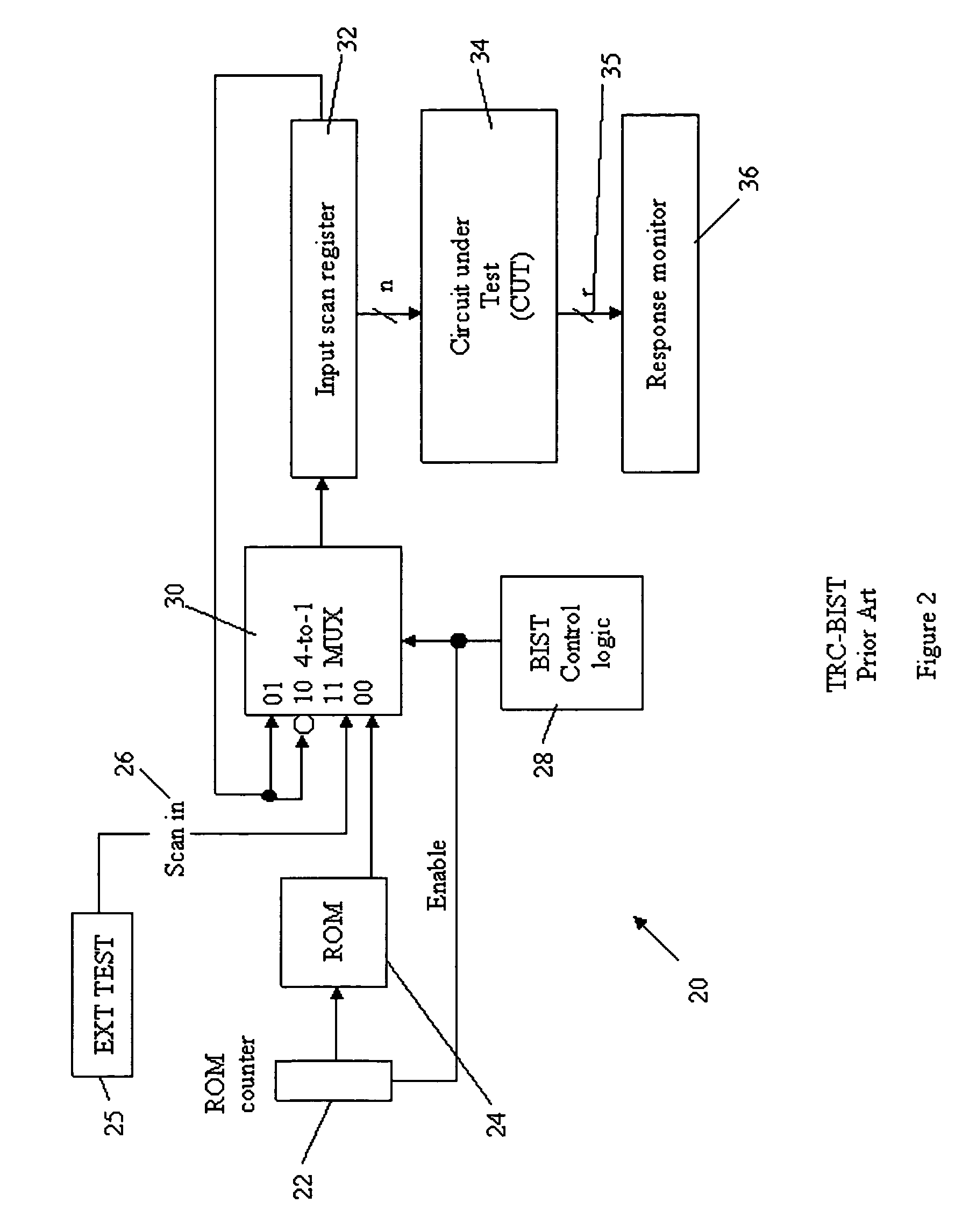

Method and apparatus to disable compaction of test responses in deterministic test-set embedding-based BIST

InactiveUS20060248423A1Electronic circuit testingError detection/correctionComputer hardwareCircuit under test

A method and system for built-in self-testing for high-performance circuits, configured to generate and apply a test pattern to a circuit under test (CUT). A logic structure in communication with the CUT and a memory device generates a plurality of test seeds from a plurality of original test seeds, the generated test seeds and original test seeds defining a total test seed plurality and a subset deterministic test pattern plurality. A response suppression circuit suppresses test responses from the CUT if not generated responsive to a deterministic test seed of the deterministic test pattern plurality.

Owner:GLOBALFOUNDRIES INC

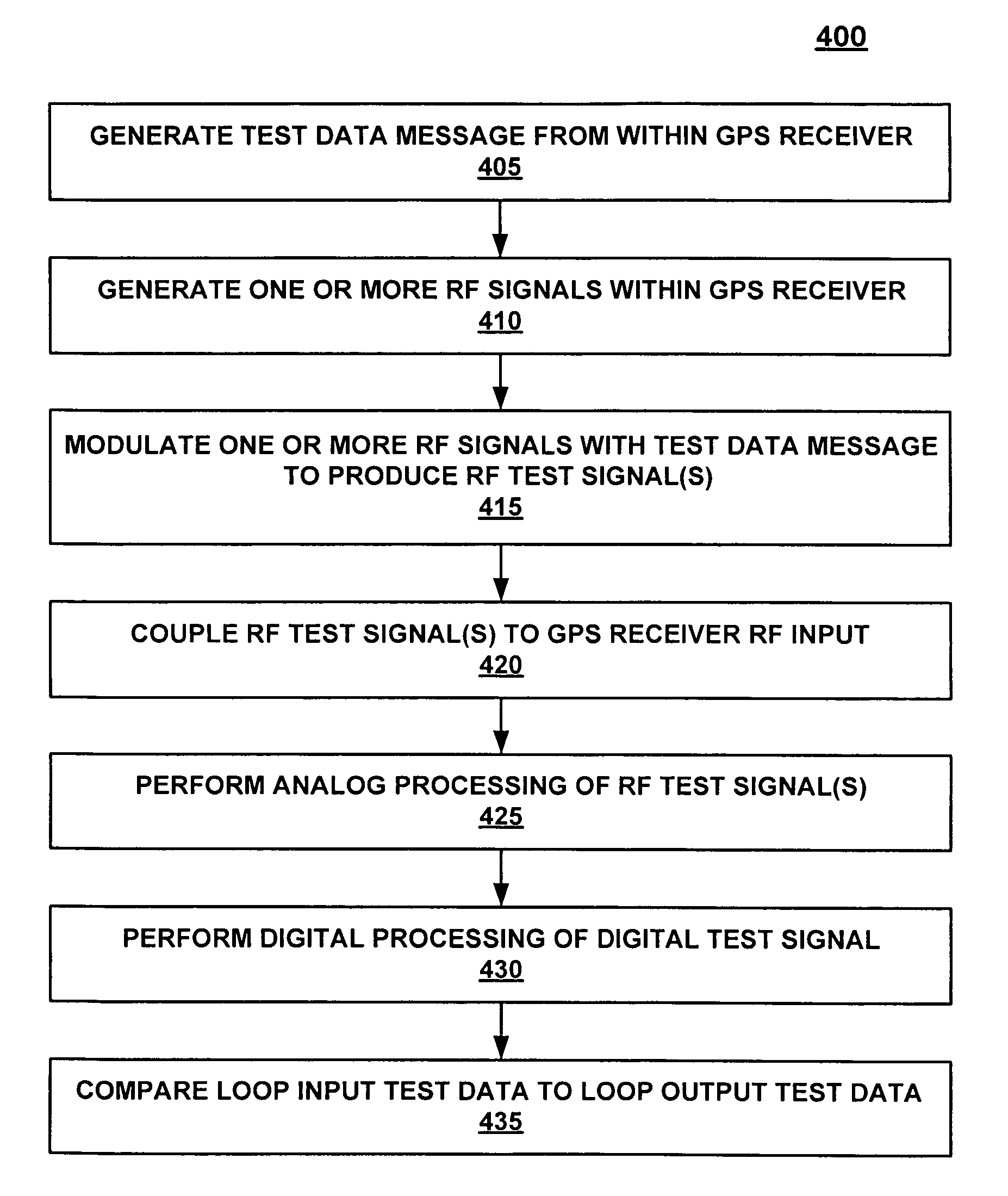

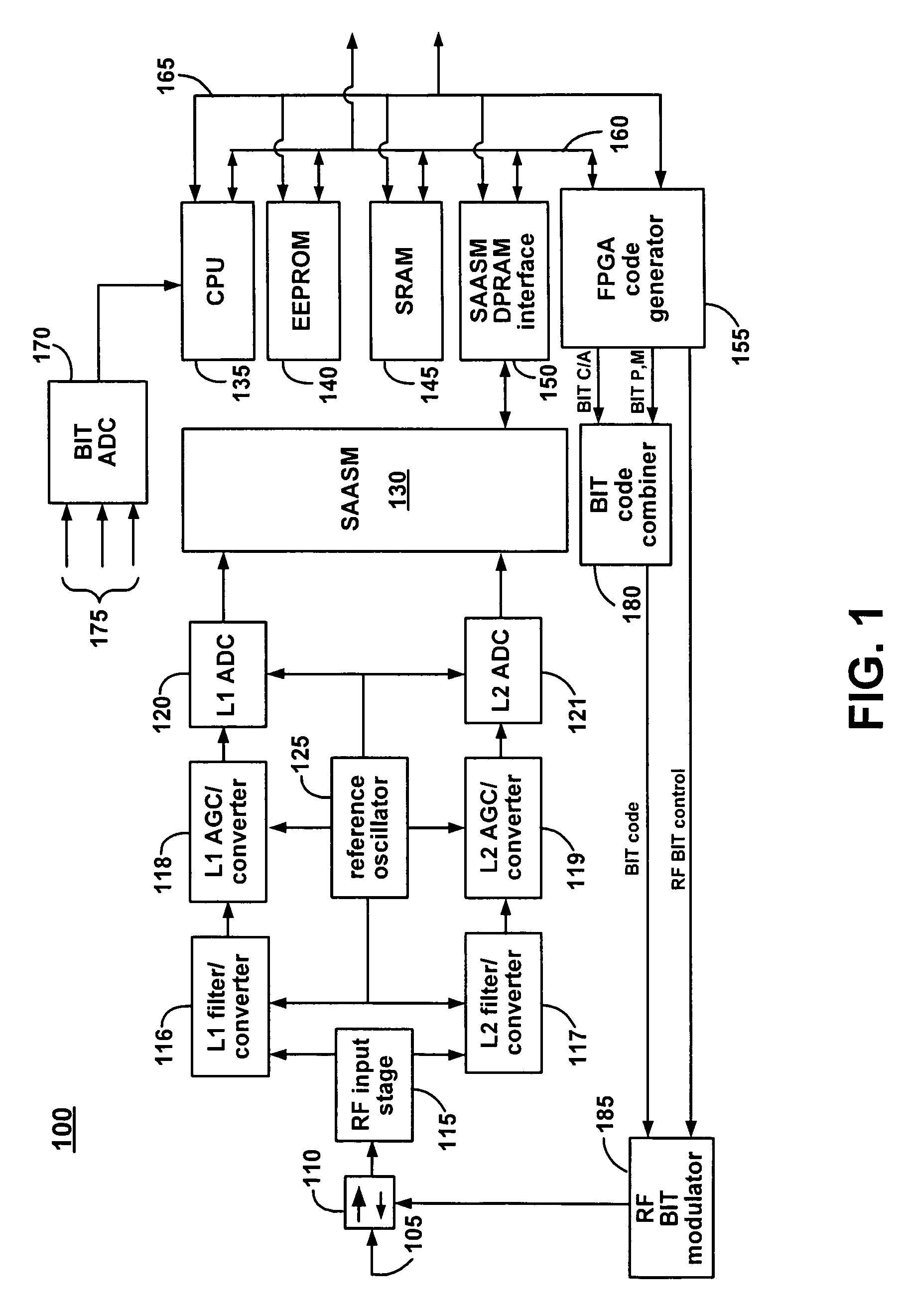

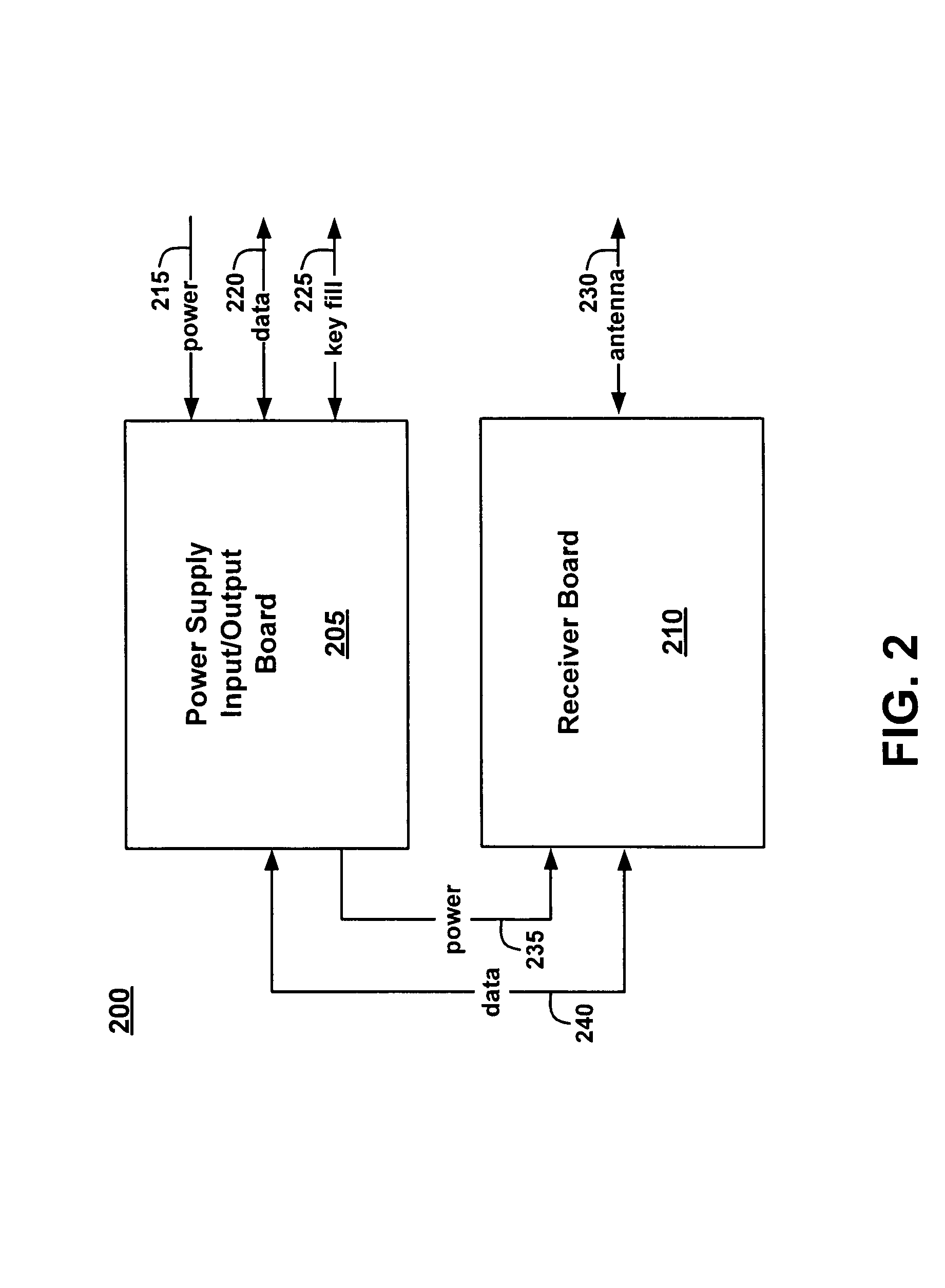

System and method for built-in testing of a GPS receiver

ActiveUS7596465B2Comprehensive testElectronic circuit testingPosition fixationGps receiverEngineering

Built-in test equipment (BITE) incorporated in a GPS receiver for providing a loop forward test. The loop forward test capability may be combined with a loop backward capability to provide a comprehensive built-in test (BIT) capability for the signal path in a GPS receiver. A code generator generates deterministic test code signals such as C / A code, P code and pseudo M code that are used to modulate one or more radio frequency (RF) carriers to produce RF test signals. The RF test signals are injected into the GPS receiver's RF input. The RF test signal signals are then down-converted and demodulated through an operational signal path of the GPS receiver. The processed test signals may then be compared to the initial test data. A loop backward BITE may also be used to sample the positioning data output by the receiver.

Owner:TRIMBLE NAVIGATION LTD

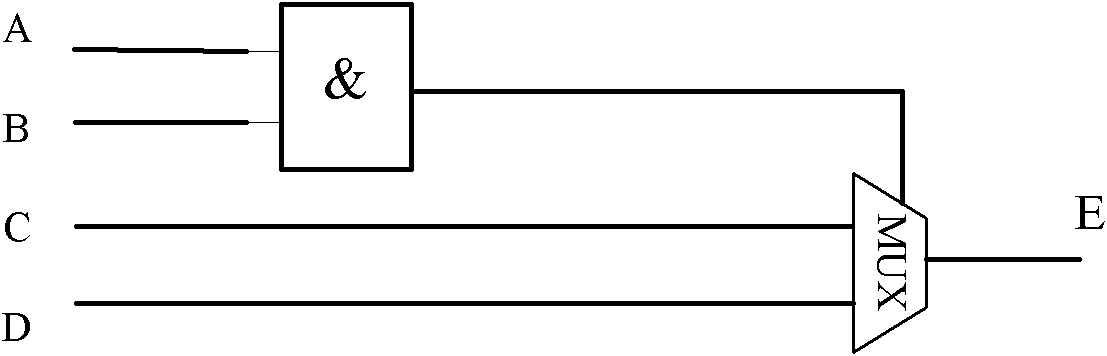

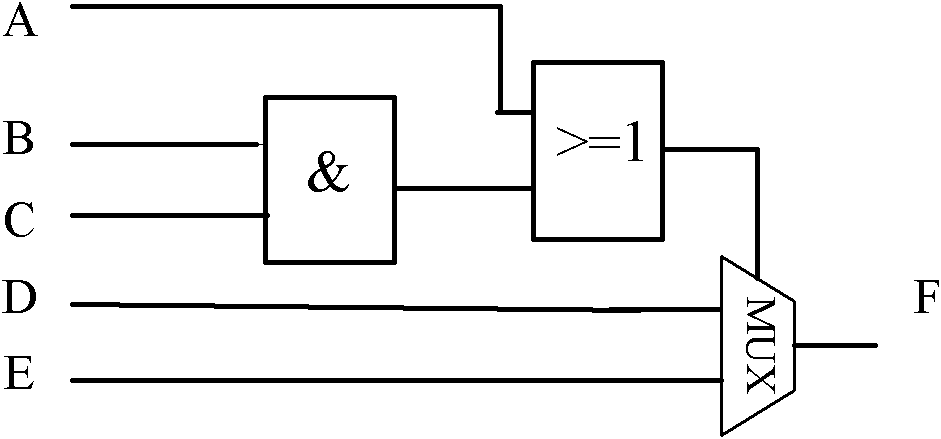

Circuit Arrangement and Method of Testing an Application Circuit Provided in Said Circuit Arrangement

InactiveUS20080195907A1Clear surfaceLow costElectronic circuit testingLogical operation testingTest sampleProcessor register

The object being to develop an integrated circuit arrangement (100) with at least one application circuit (40) to be tested, and with at least one self-test circuit (10, 20, 32, 34, 36, 50) provided for testing the application circuit (40) and generating at least one pseudo-random test sample, wherein said pseudo-random test sample can be converted into at least one test vector that is programmable and / or deterministic and that can be supplied to the application circuit (40) for testing purposes via at least one logic gate (32, 34, 36) and by means of at least one signal that can be applied to said logic gate (32, 34, 36), and wherein the output signal arising in dependence on the deterministic test vector can be evaluated by the application circuit (40) by means of at least one signature register (50), as well as a method of testing the application circuit (40) present in the integrated circuit arrangement (100) by means of the self-test circuit (10, 20, 32, 34, 36, 50) further such that the B[uild-]I[n]S[elf-]T[est] hardware connected to the additional deterministic logic can be reduced, it is suggested that the signal to be supplied to the logic gate (32, 34, 36) can be made available by a B[it]F[lipping]F[unction] logic circuit (10) based on at least one

Owner:NXP BV

Apparatus, and computer program product for implementing deterministic based broken scan chain diagnostics

InactiveUS20080189583A1Electronic circuit testingError detection/correctionData portFailure analysis

A method, apparatus and computer program product are provided for implementing deterministic based broken scan chain diagnostics. A deterministic test pattern is generated and is loaded into each scan chain in the device under test using lateral insertion via system data ports applying system clocks. Then each scan chain is unloaded and a last switching latch is identified. The testing steps are repeated a selected number of times. Then checking for consistent results is performed. When consistent results are identified, then the identified last switching latch is sent to a Physical Failure Analysis system.

Owner:META PLATFORMS INC

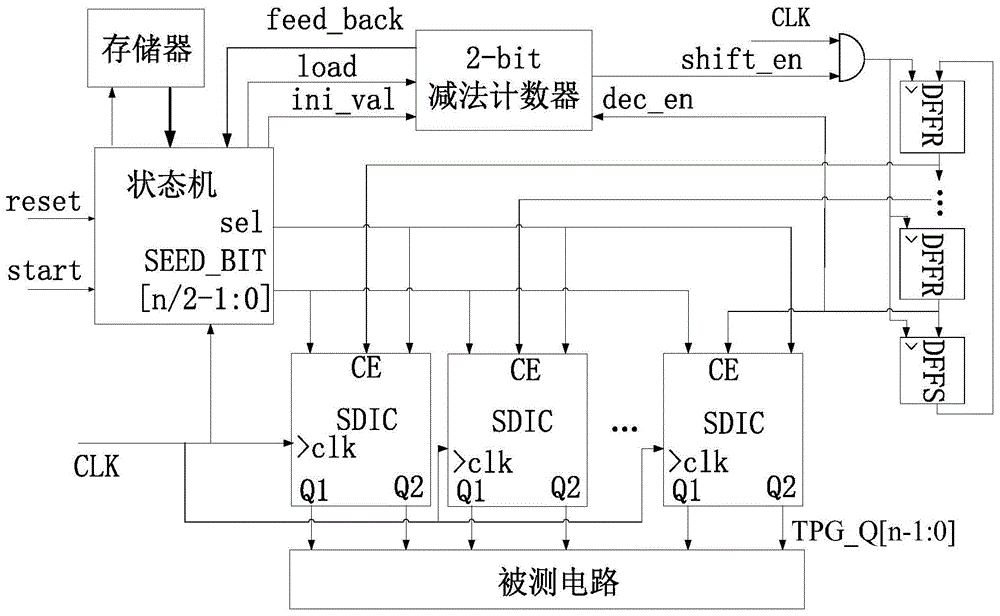

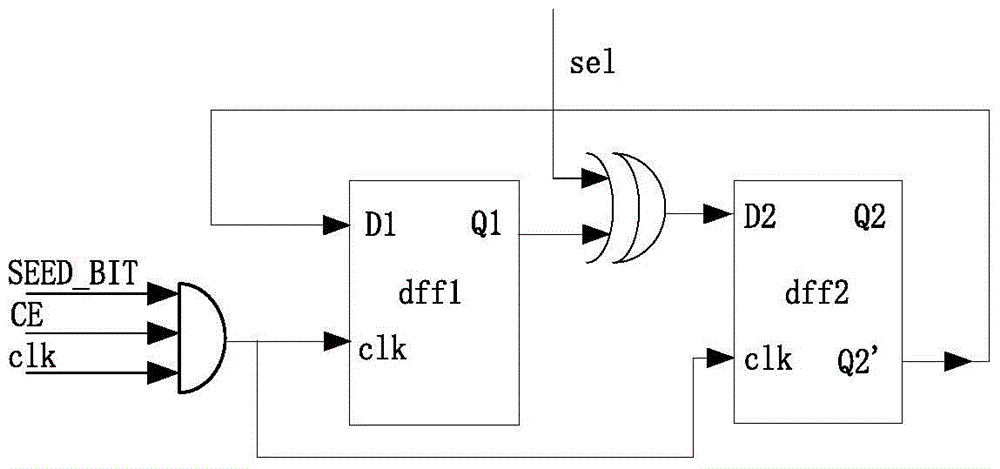

Low-power-consumption certainty BIST based on single and double jump and seed compression method thereof

ActiveCN105738800AReduce test power consumptionShorten test timeElectrical testingTest powerTest performance

The invention relates to the technical field of large-scale digital integrated circuits, and provides a low-power-consumption certainty BIST based on single and double jump and a seed compression method thereof. In order to reduce test power consumption, a novel single and double jump unit and an ROM control signal are applied to generate a certainty seed through single and double hybrid jump, and then certainty test vectors are generated by utilizing a single jump reseeding technology. Meanwhile, the generation number of the certainty test vectors in the reseeding process is constrained by additional arrangement of a 2-bit subtracting counter so as to reduce the number of redundant vectors and reduce test time. Besides, the corresponding seed compression method is also put forward so as to compress area overhead and generate the control signal. The experiment result proves that the test performance, such as test time, the area overhead and test power consumption, of the BIST and the seed compression method can be reduced to a large extent.

Owner:厦门润积集成电路技术有限公司

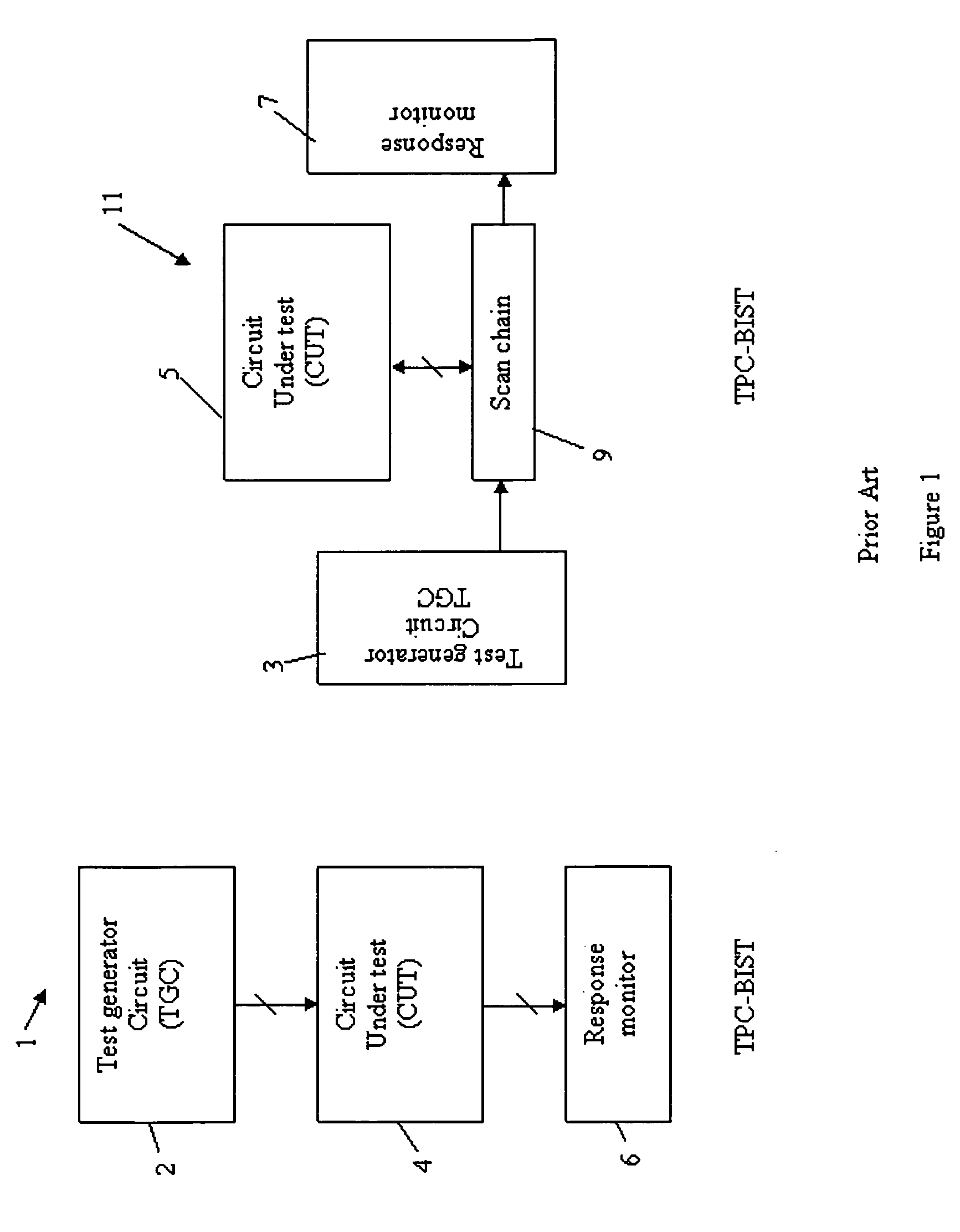

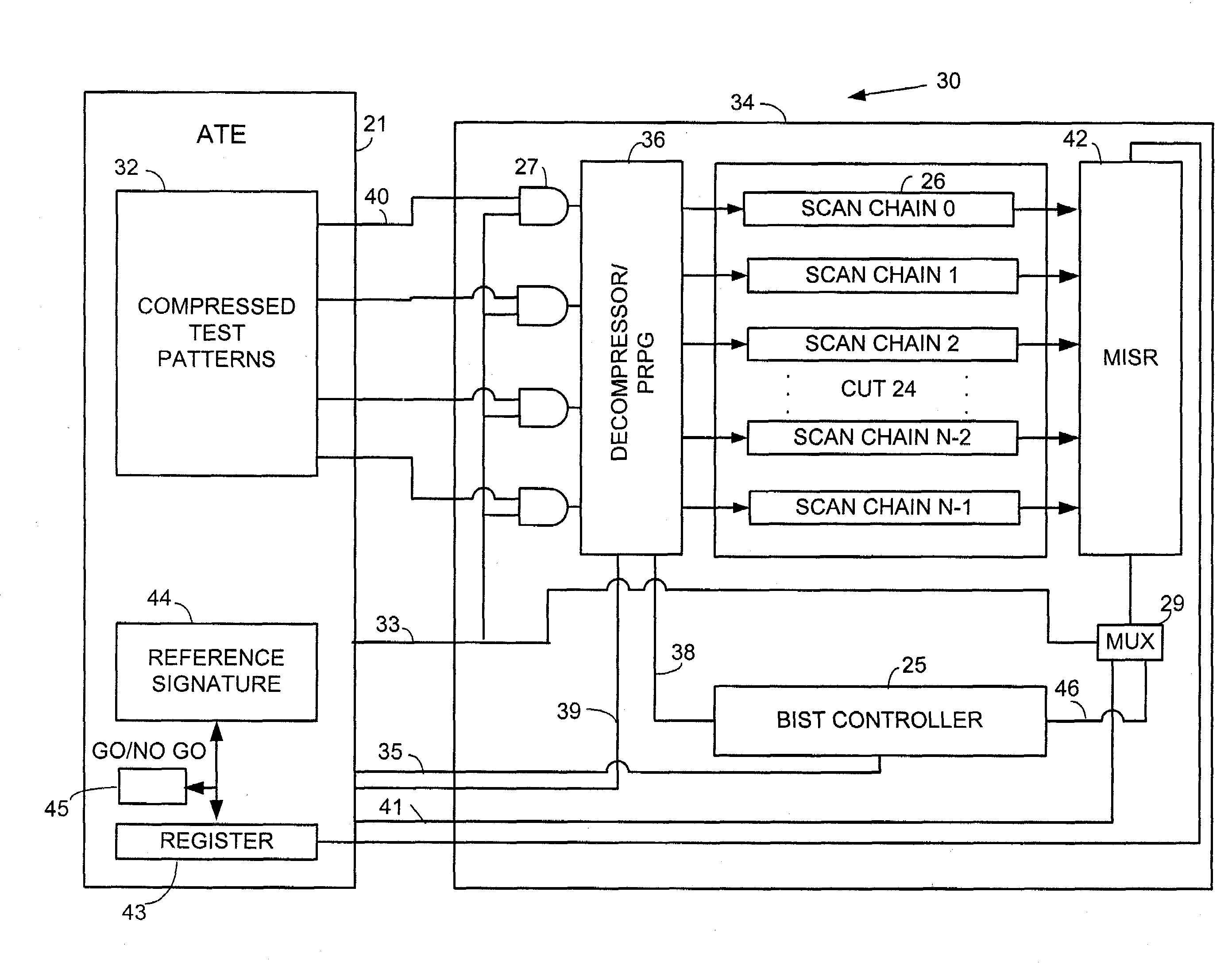

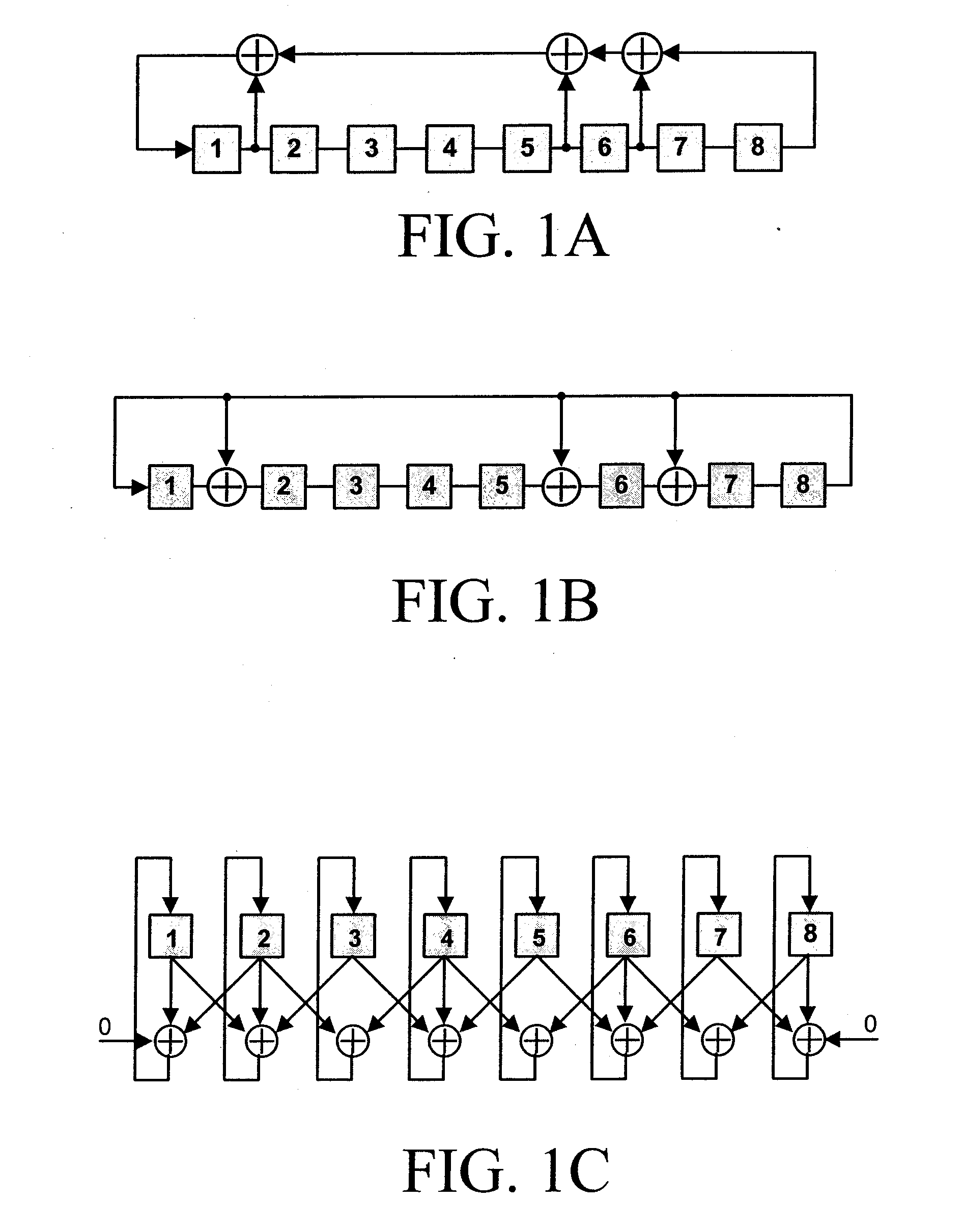

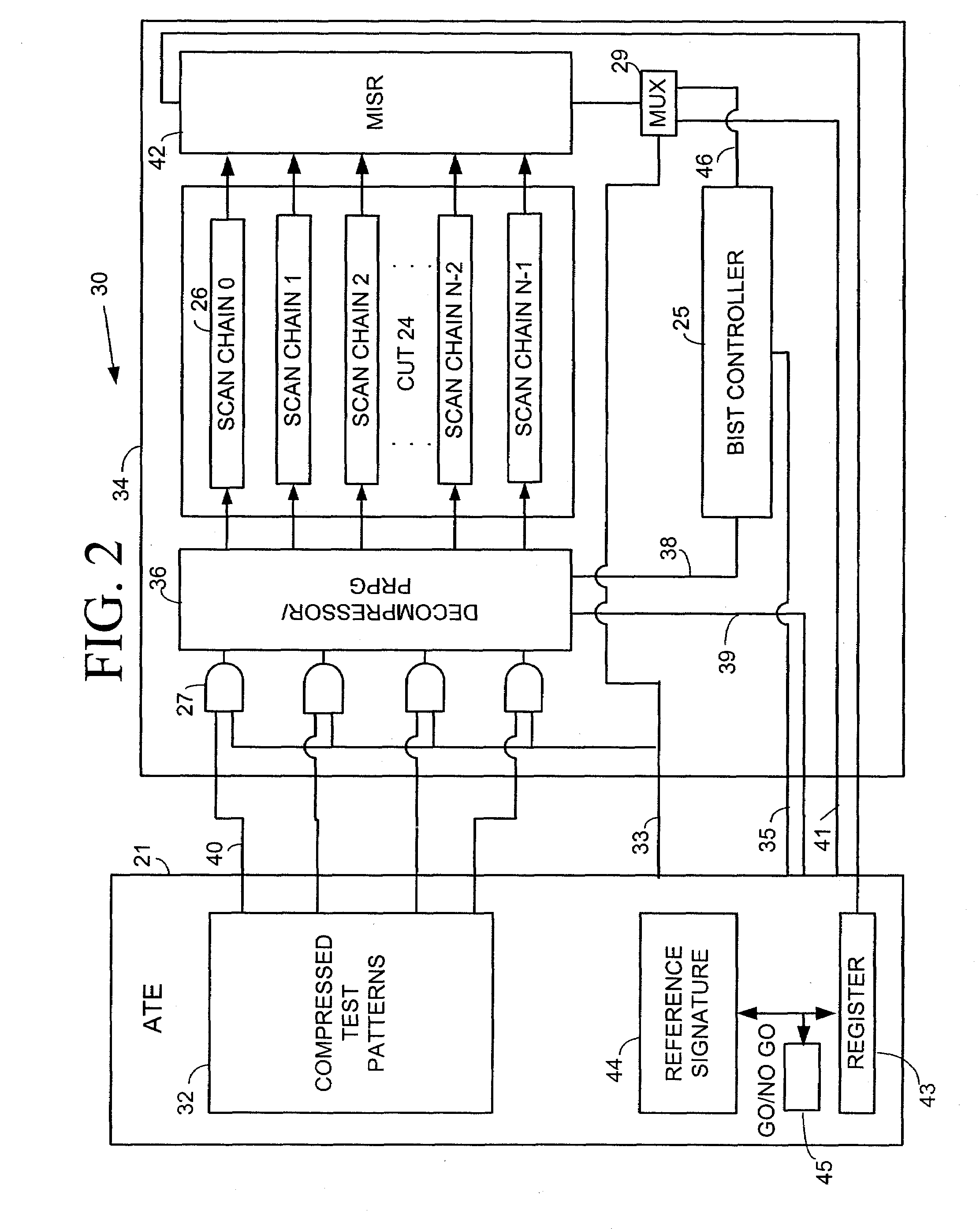

Decompressor/prpg for applying pseudo-random and deterministic test patterns

InactiveUS20090177933A1Semiconductor/solid-state device testing/measurementElectronic circuit testingFault coverageCircuit under test

A novel decompressor / PRPG on a microchip performs both pseudo-random test pattern generation and decompression of deterministic test patterns for a circuit-under-test on the chip. The decompressor / PRPG has two phases of operation. In a pseudo-random phase, the decompressor / PRPG generates pseudo-random test patterns that are applied to scan chains within the circuit-under test. In a deterministic phase, compressed deterministic test patterns from an external tester are applied to the decompressor / PRPG. The patterns are decompressed as they are clocked through the decompressor / PRPG into the scan chains. The decompressor / PRPG thus provides much better fault coverage than a simple PRPG, but without the cost of a complete set of fully-specified deterministic test patterns.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Deterministic test pattern generation for designs with timing exceptions

ActiveUS20200410065A1Improve test qualityReduce testing costsCAD circuit designSpecial data processing applicationsPattern generationAutomatic test generation

Systems and methods for a deterministic automatic test generation (ATPG) process including Timing Exception ATPG (TEA). A method includes performing an automated test pattern generation (ATPG) process that uses timing exception information to generate a test pattern for a targeted fault of a circuit design with at least one timing exception path. The method includes testing the targeted fault of the circuit design using the test pattern to produce a test result for the targeted fault.

Owner:MENTOR GRAPHICS CORP

Method and apparatus to disable compaction of test responses in deterministic test-set embedding-based BIST

InactiveUS7260760B2Electronic circuit testingError detection/correctionComputer hardwareCircuit under test

A method and system for built-in self-testing for high-performance circuits, configured to generate and apply a test pattern to a circuit under test (CUT). A logic structure in communication with the CUT and a memory device generates a plurality of test seeds from a plurality of original test seeds, the generated test seeds and original test seeds defining a total test seed plurality and a subset deterministic test pattern plurality. A response suppression circuit suppresses test responses from the CUT if not generated responsive to a deterministic test seed of the deterministic test pattern plurality.

Owner:GLOBALFOUNDRIES INC

Compression device and method for determined self-testing data

ActiveCN101226228BSave storage spaceCoverage with a high probability of failureElectrical testingLogic circuits using elementary logic circuit componentsFault coverageCompression device

The invention relates to a method for compressing the test data of integrated circuit, belonging to integrated circuit technical field, in particular to a deterministic self-test test data compressor.The invention comprises a phase shifter, a response compressor, a linear feedback shift register with a first and a second xor network while the shift register is connected with the phase shift, a scanning tree and a weigh random signal generating logic unit while the scan forest is connected with the phase shift, the gating signal end of the scan forest is connected with the weight random signalgenerating logic unit, and the output of the scan forest is connected with the response compressor. The invention further provides a deterministic self-test test data compression method. The invention uses the weight random signal generating logic unit to control the frequency of special signal of the input signal of the scan forest, to improve the fault coverage rate into the false random self-test process, to reduce the test data memory space generated by deterministic test vector.

Owner:TSINGHUA UNIV

Systems and methods for deterministically testing packet error rates in electronic devices

ActiveCN102904701BError detection/prevention using signal quality detectorCorrect operation testingNetwork packetSeries data

The present invention discloses a system and method for deterministically testing the packet error rate in electronic equipment, including: transmitting a series of data packets from the test equipment to the device under test (DUT) and setting the error-free data packets received a predetermined number; assessing whether the number of data packets received by the DUT without error in a series of data packets is equal to the predetermined number of error-free data packets received; and if not equal to the predetermined number of error-free data packets received, it will have Additional packets are transmitted from the test equipment to the DUT at a power level that produces zero received packet errors in a correctly functioning DUT. Other possible embodiments include evaluating whether the total number of data packets received without error by the DUT in a series of data packets and additional error-free power level data packets is equal to a predetermined number of received error-free data packets; and in response to the DUT receiving Upon said predetermined number of error-free data packets received, an acknowledgment packet is sent to the test device.

Owner:LITEPOINT CORP

A low-power scanning self-test circuit and self-test method

ActiveCN106546907BRealize low energy consumption replantingElectronic circuit testingMulti inputProcessor register

Owner:TSINGHUA UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com