Circuit arrangement and method of testing an application circuit provided in said circuit arrangement

A circuit device, circuit technology, applied in the direction of measuring device, measuring electricity, measuring electrical variables, etc., to achieve the effect of saving surface area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

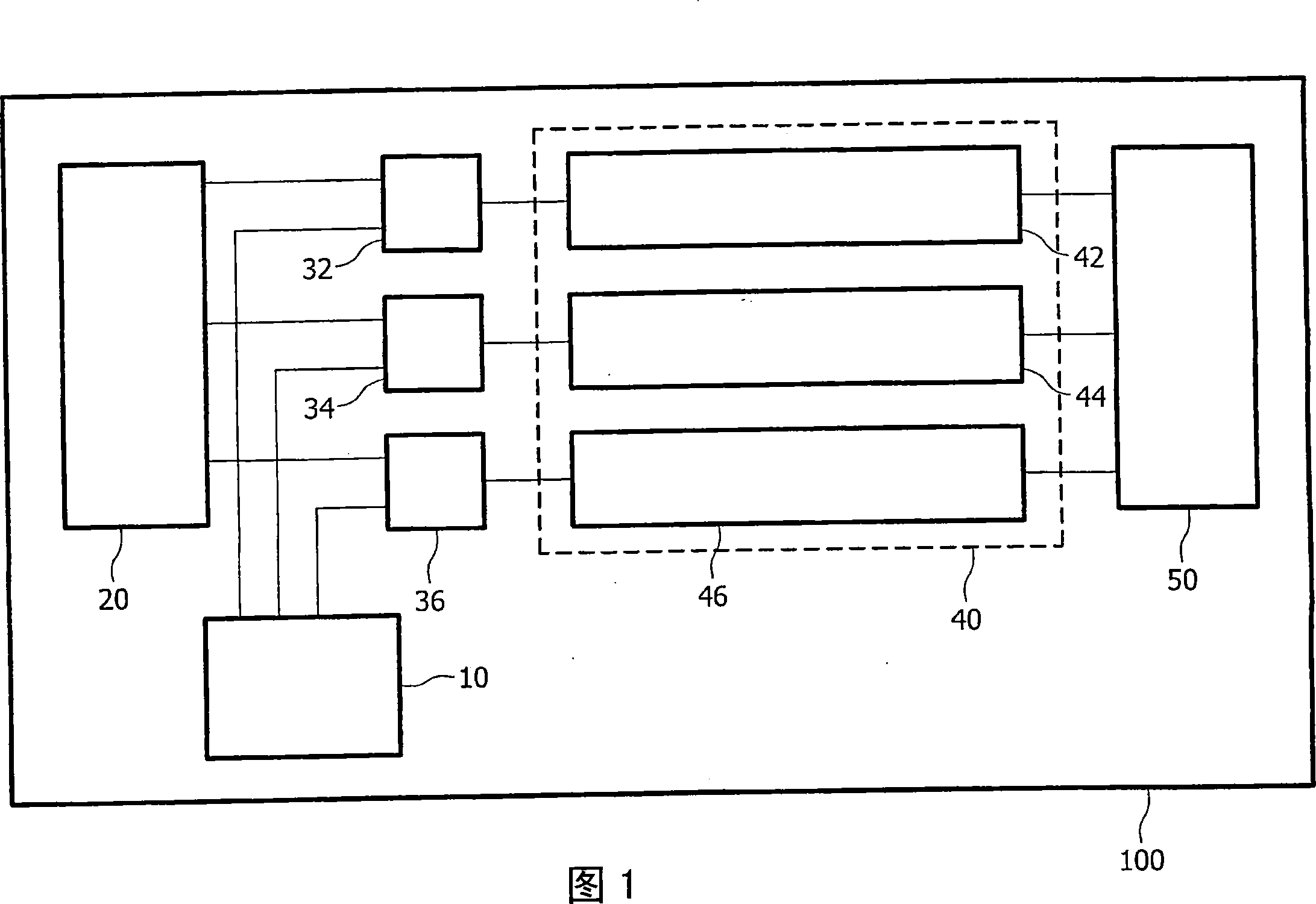

[0018] FIG. 1 is a block diagram of an integrated circuit device (IC) 100 including application circuitry 40 . The application circuit 40 is a circuit designed for the actual use purpose of the integrated circuit 100 .

[0019] It is desirable to test application circuit 40 after fabrication of IC 100 in order to perfect operation. For this purpose, a self-test circuit is provided on the integrated circuit 100 , which self-test circuit comprises circuit elements 10 , 20 , 32 , 34 , 36 , 50 as shown in FIG. 1 .

[0020] The self-test circuit is designed in the integrated circuit 100 according to the invention in such a way that the relevant circuit elements 10, 20, 32, 34, 36, 50 are arranged completely outside the application circuit 40, so that the behavior of the application circuit 40 is normal. Unaffected by self-test circuitry during operation.

[0021] It is assumed that in the embodiment of FIG. 1 the application circuit 40 comprises two circuit chains (said scan chai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com