Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Clear surface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

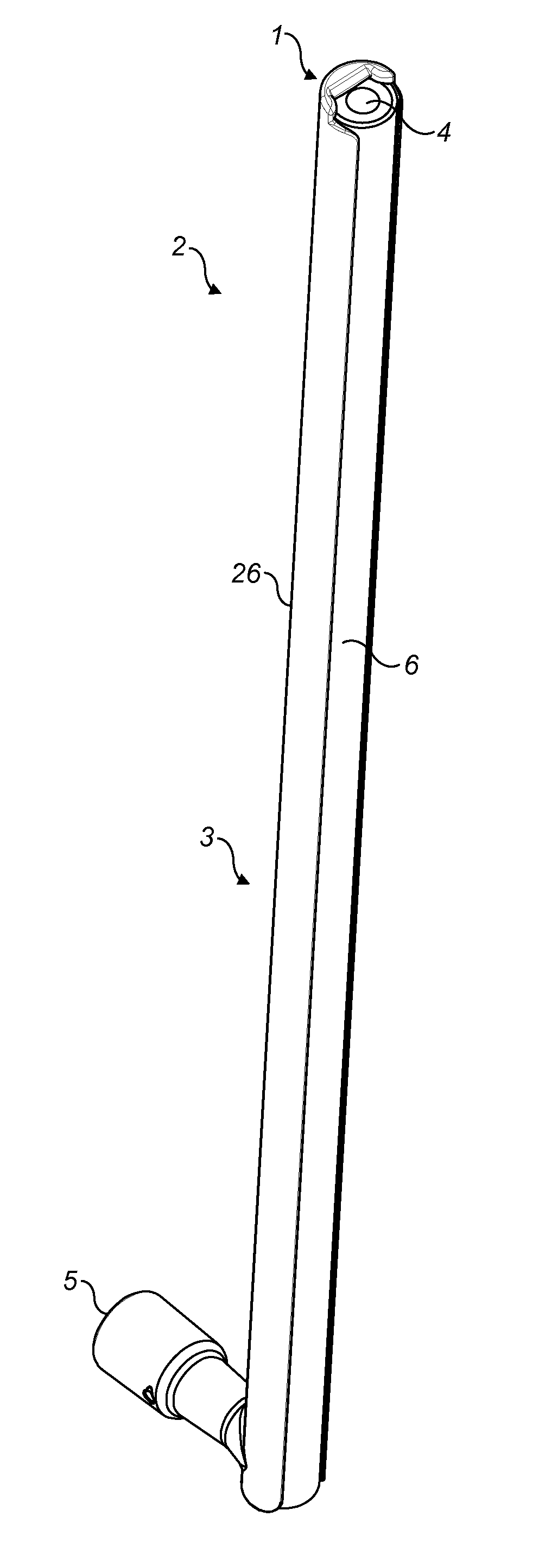

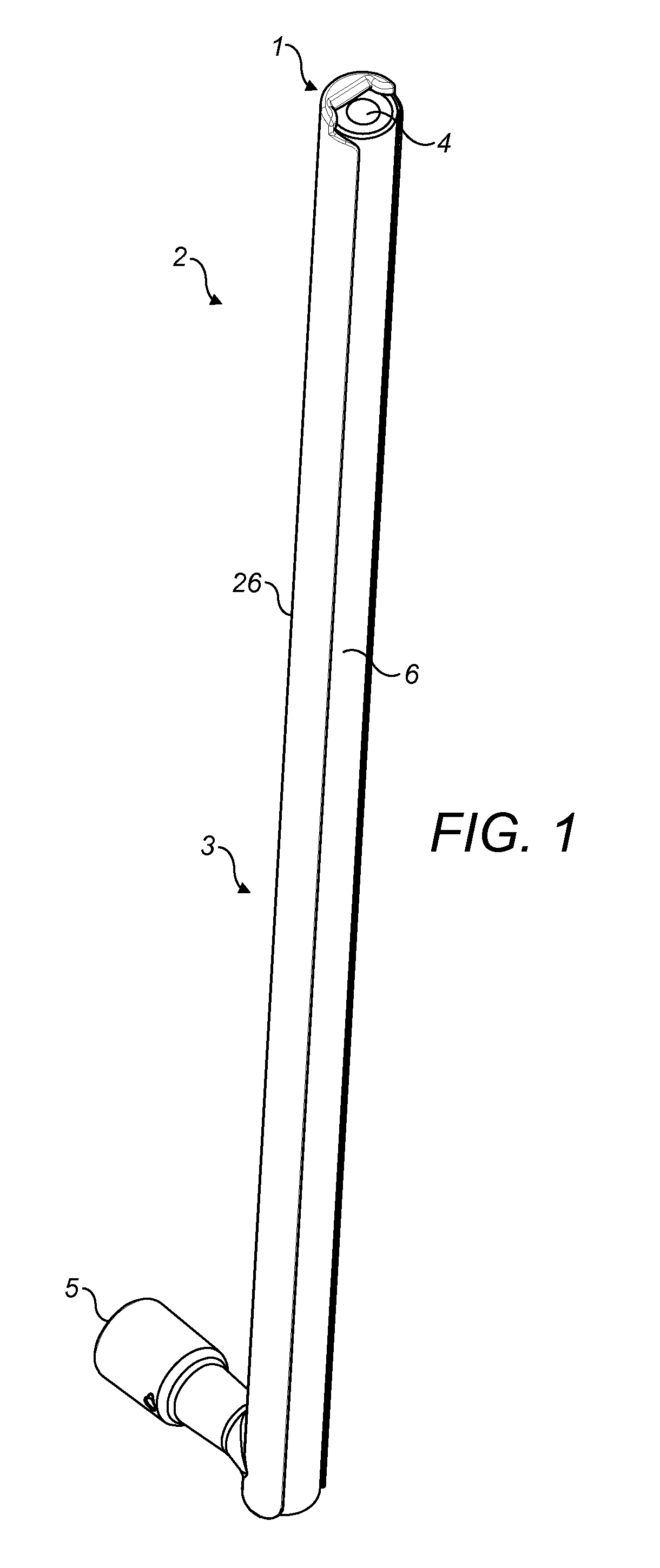

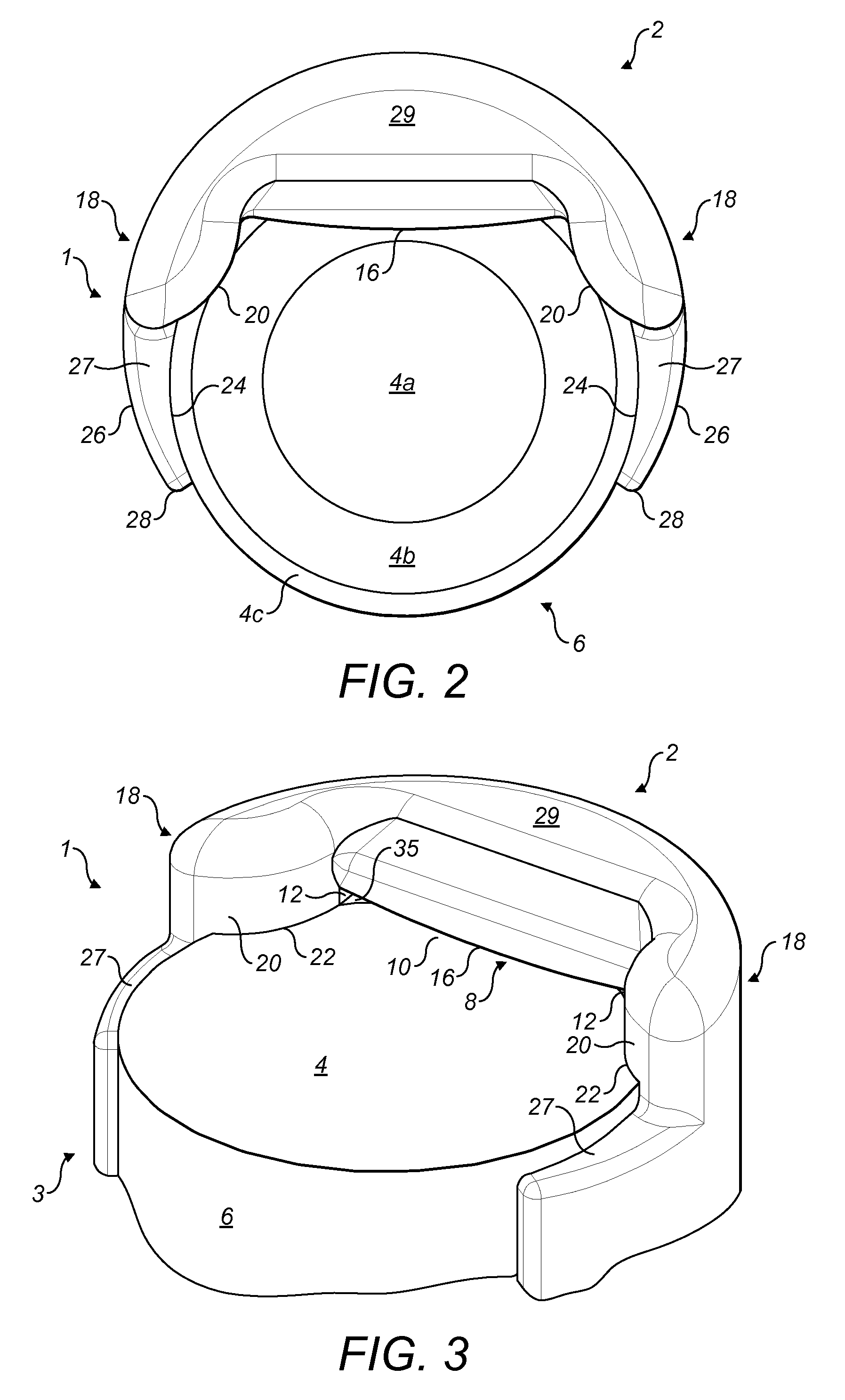

Flow guide

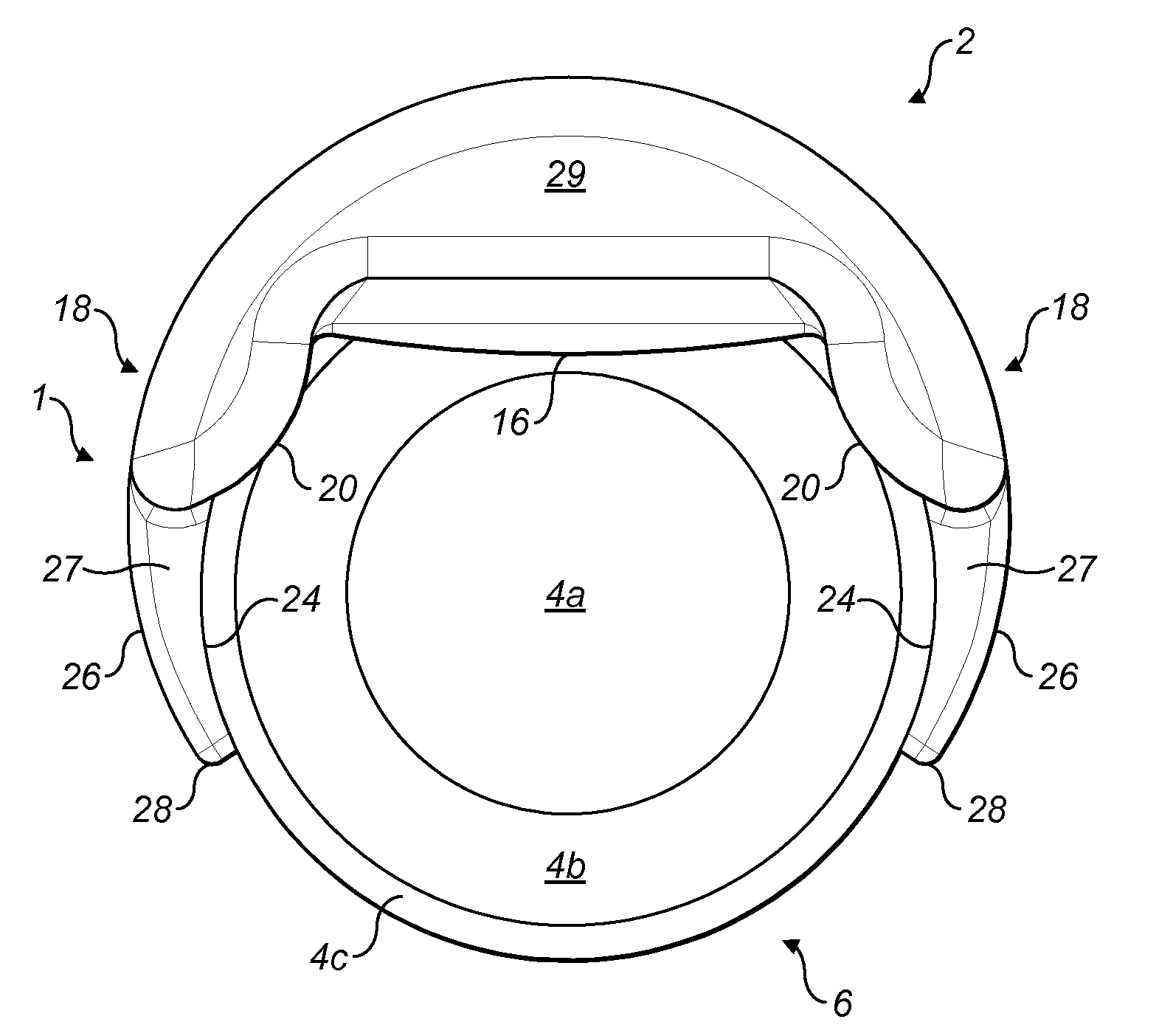

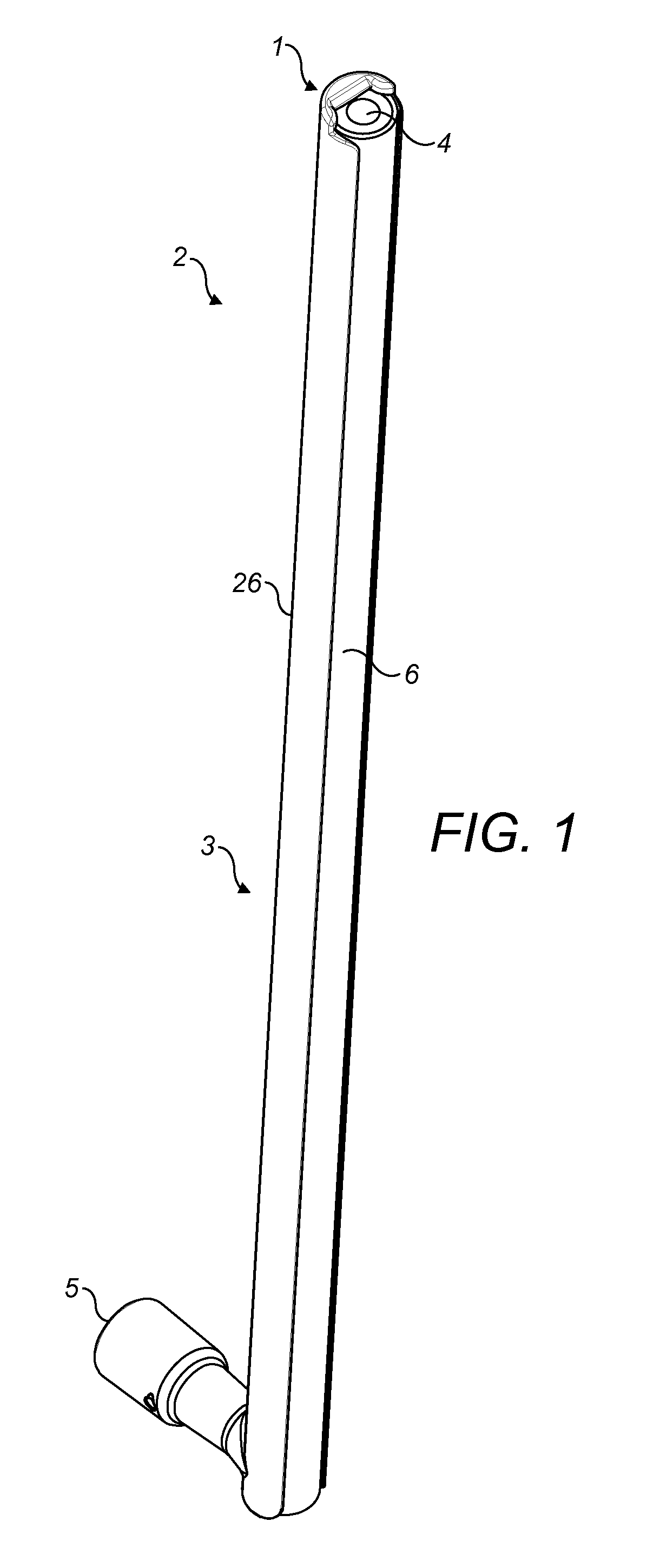

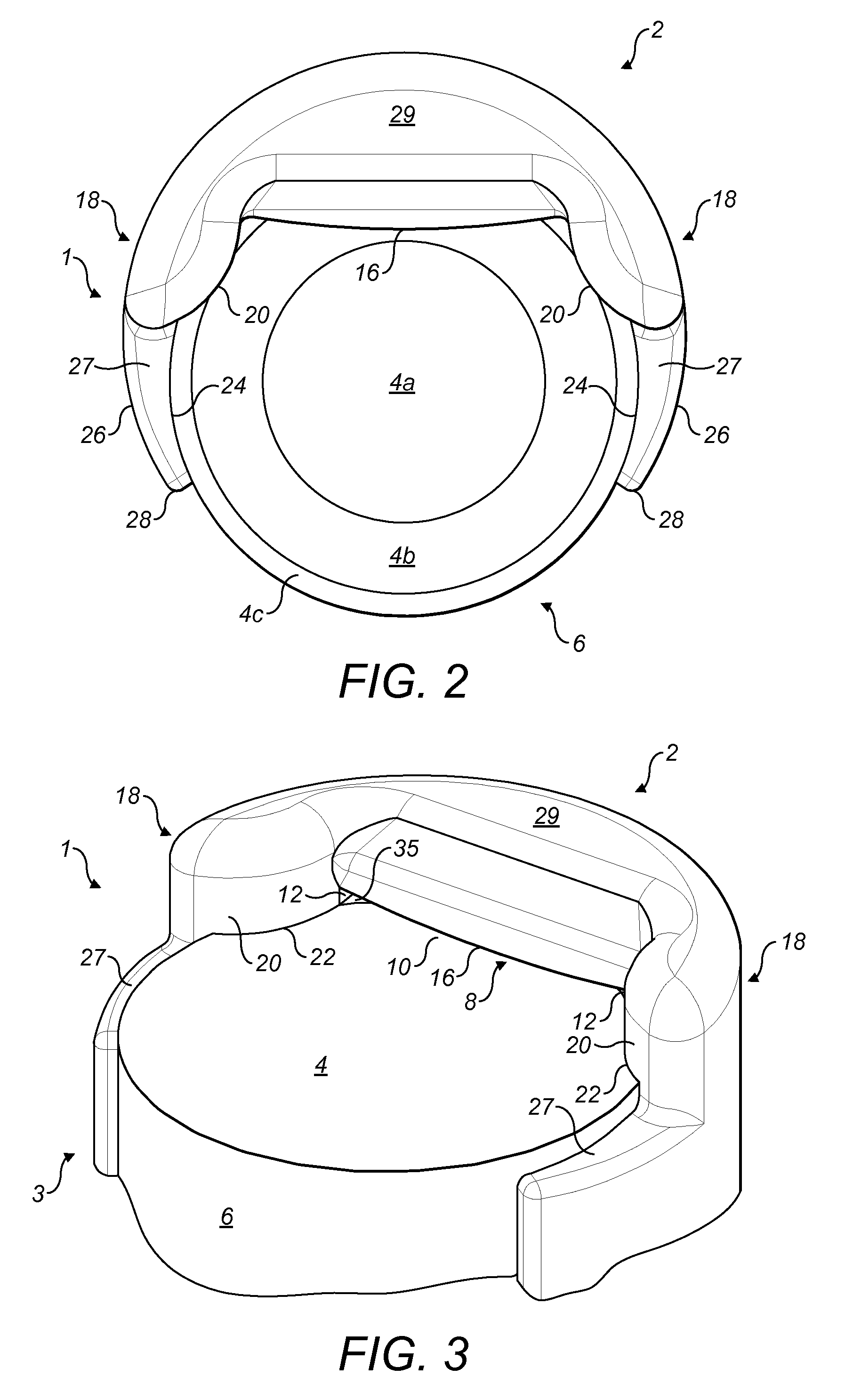

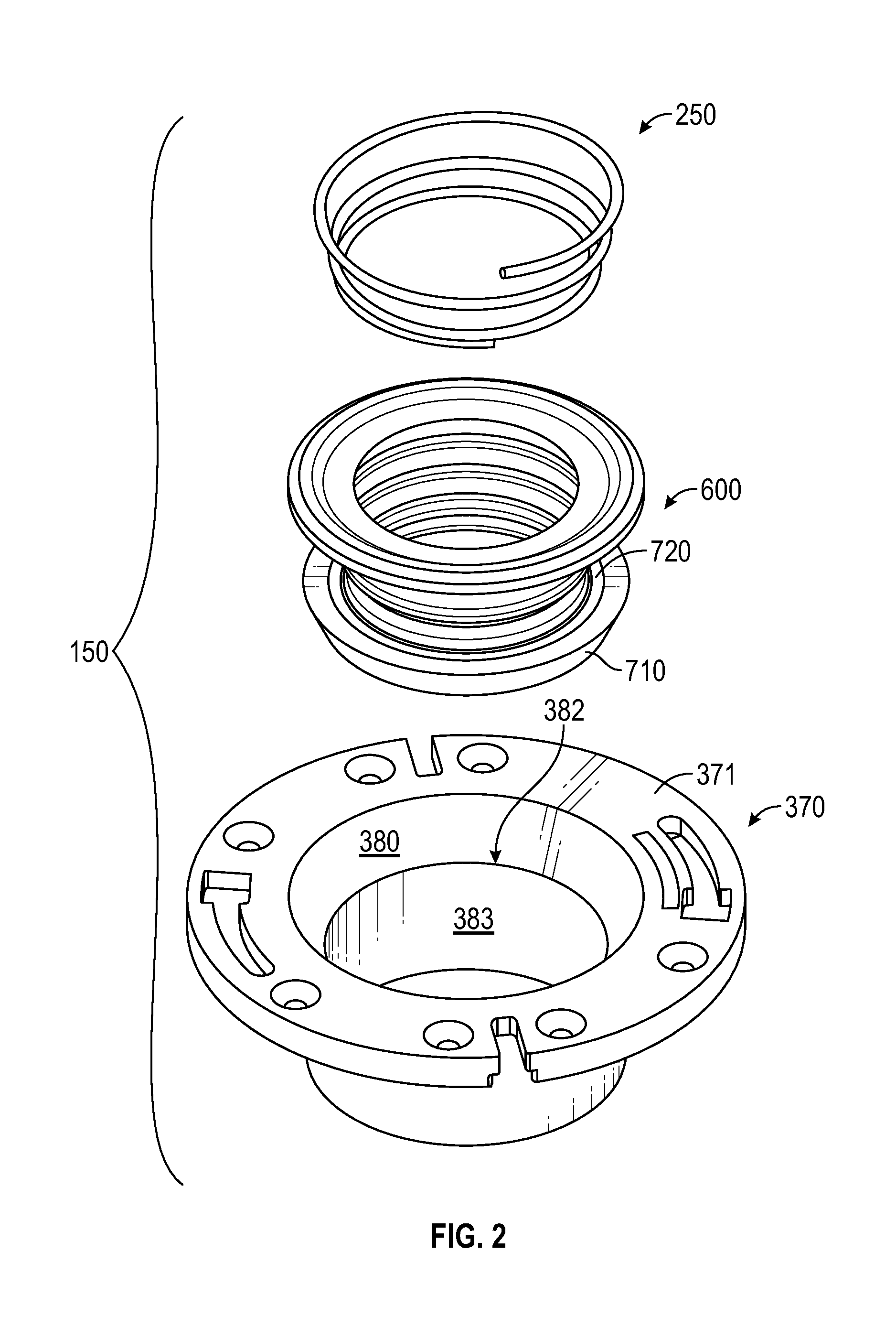

A flow guide directs a fluid flow across a surface of a device, for example a lens surface of an endoscope, in a controlled manner to facilitate flow attachment to the surface. Embodiments include features that impart a non-uniform velocity profile and / or include guide surfaces for facilitating flow attachment and / or coverage.

Owner:ENDOGUARD

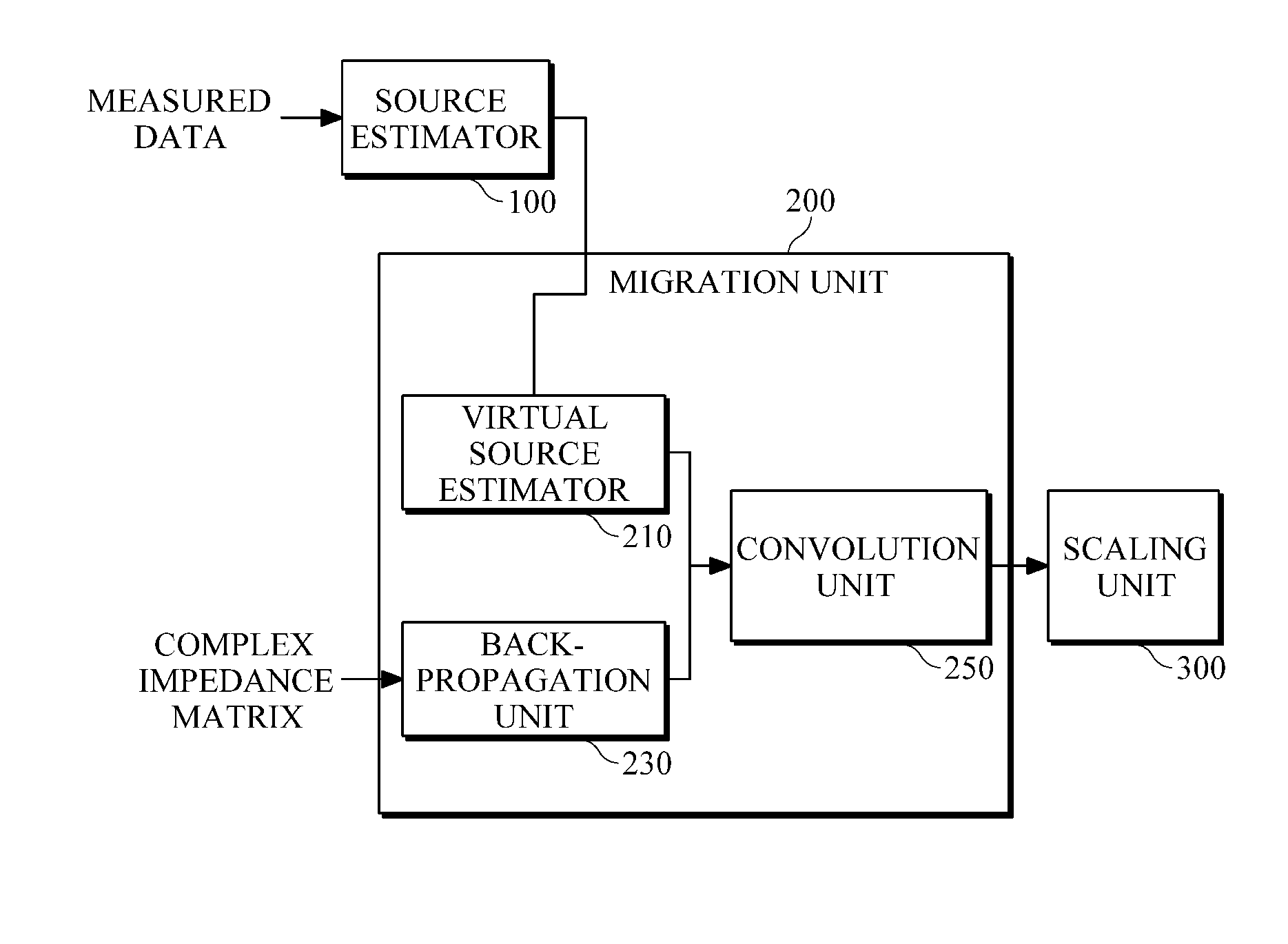

Method and apparatus for time-domain reverse-time migration with source estimation

Provided is seismic imaging, particularly, a time-domain reverse-time migration technique for generating a real subsurface image from modeling parameters calculated through waveform inversion, etc. A reverse-time migration apparatus according to an example includes a source estimator configured to estimate sources by obtaining transmission waveforms from data measured by a plurality of receivers, through waveform inversion, and a migration unit configured to receive information about the estimated sources, and to perform reverse-time migration in the time domain. The source estimator estimates sources, by solving first-order matrix equation including a Toeplitz matrix composed of autocorrelation values of the Green's function, and a cross-correlation matrix of measured data and the Green's function, through Levinson Recursion. In more detail, the migration unit includes a back-propagation unit configured to back-propagate the measured data; a virtual source estimator configured to estimate virtual sources from the sources estimated by the source estimator; and a convolution unit that configured to convolve the back-propagated data with the virtual sources and output the results of the convolution.

Owner:SEOUL NAT UNIV R&DB FOUND

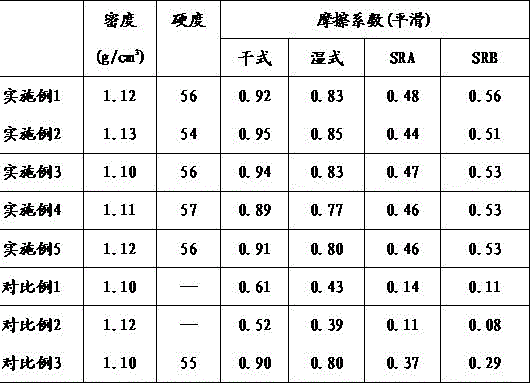

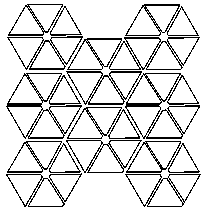

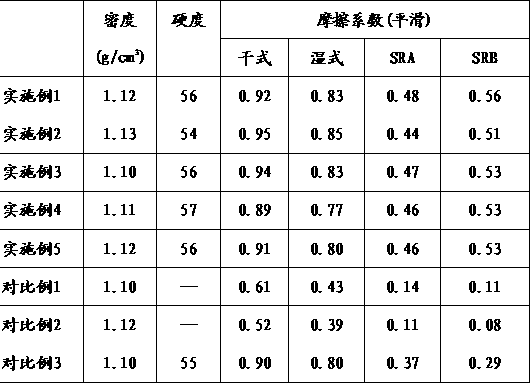

Anti-skid rubber sole and preparation method thereof

ActiveCN106832470AImprove skid resistanceIncrease polaritySolesDomestic articlesPolymer scienceVulcanization

The invention relates to a rubber sole, and provides an anti-skid rubber sole. The anti-skid rubber sole is prepared from the following raw materials: NBR / PVC emulsion co-precipitation alloy, low-melting point polyamide, natural rubber, soluble polymerized styrene-butadiene rubber, brominated butyl rubber, white carbon black, an anti-aging agent, polyethylene glycol, a silane coupling agent, polyethylene wax, diethylene glycol, zinc oxide, stearic acid, insoluble sulfur, a vulcanization accelerator D and a vulcanization accelerator DM. The anti-skid rubber sole is vulcanized and molded in a mold of a space aluminum material, the vulcanizing temperature is 170 DEG C, the pressure is 16.5MPa-17.5MPa, and the vulcanizing time is 210-250s.

Owner:MAOTAI FUJIAN SOLES CO LTD

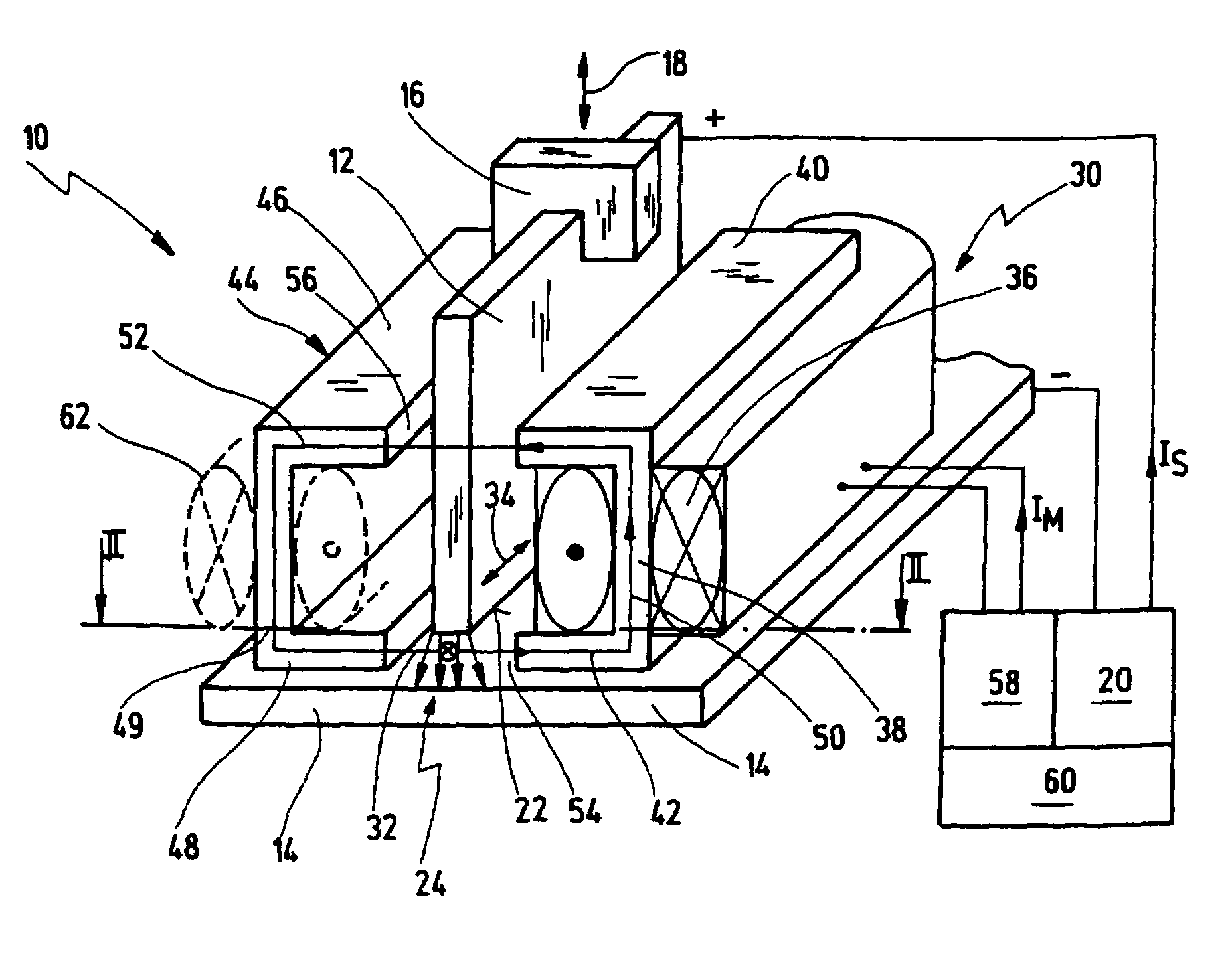

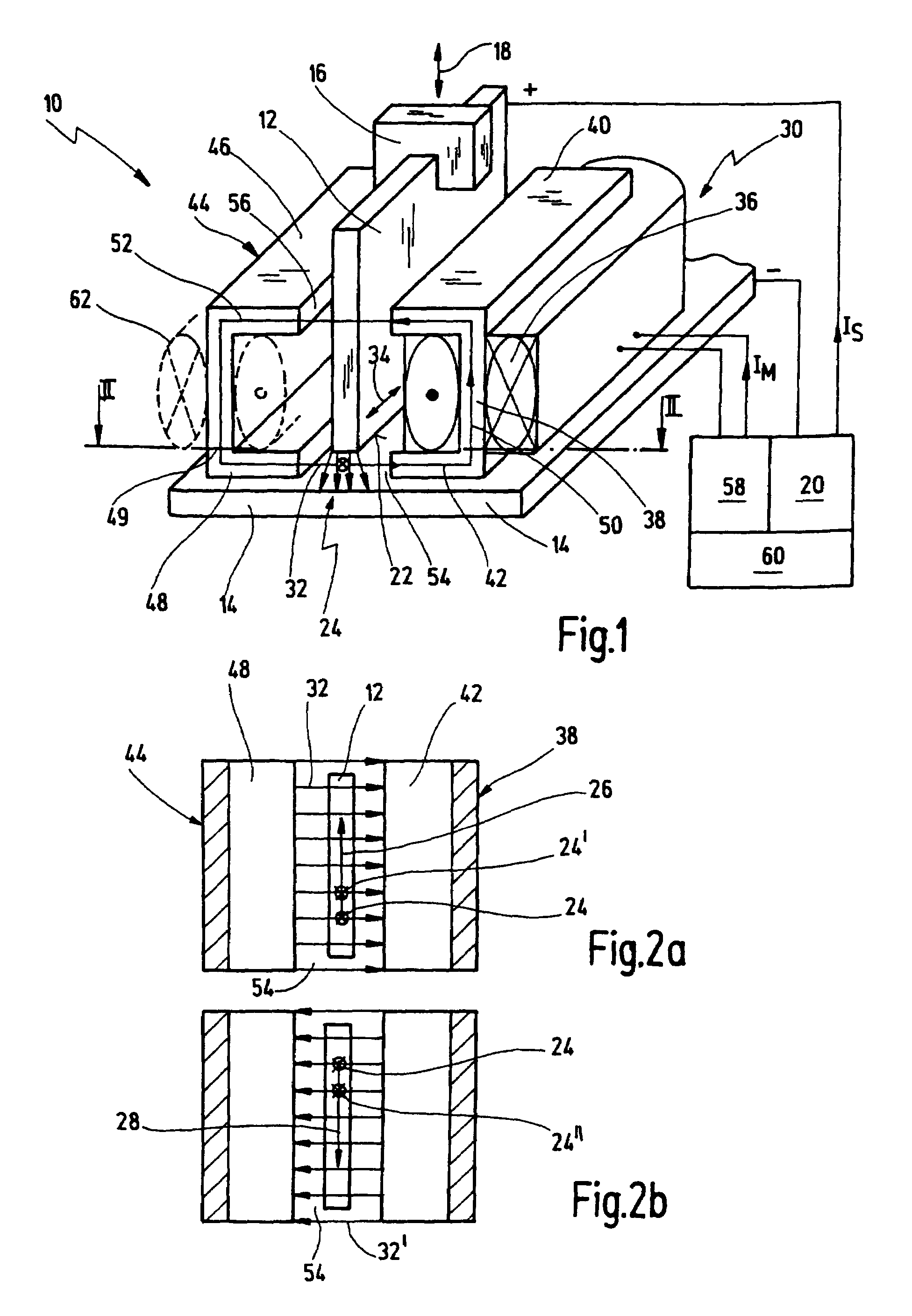

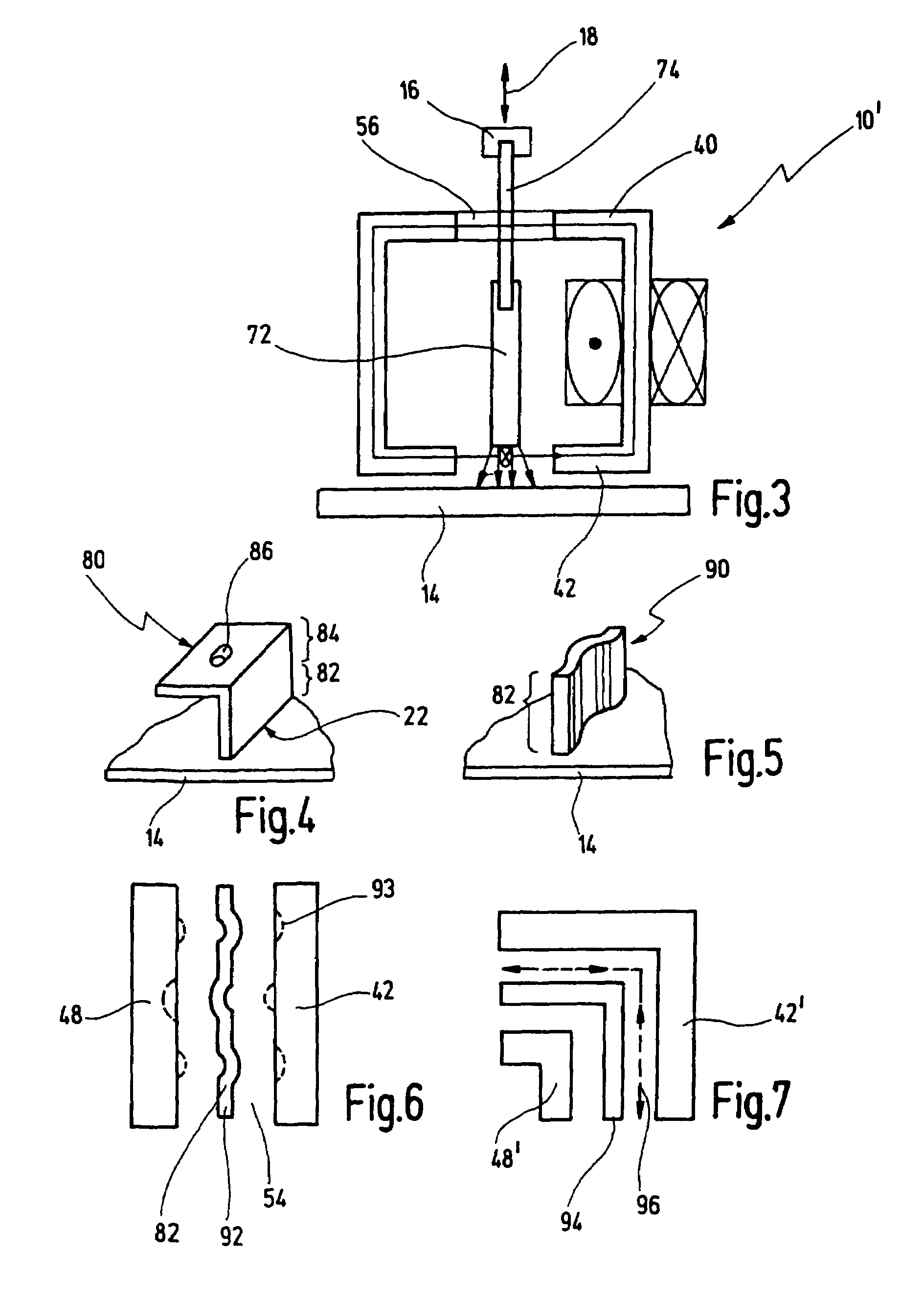

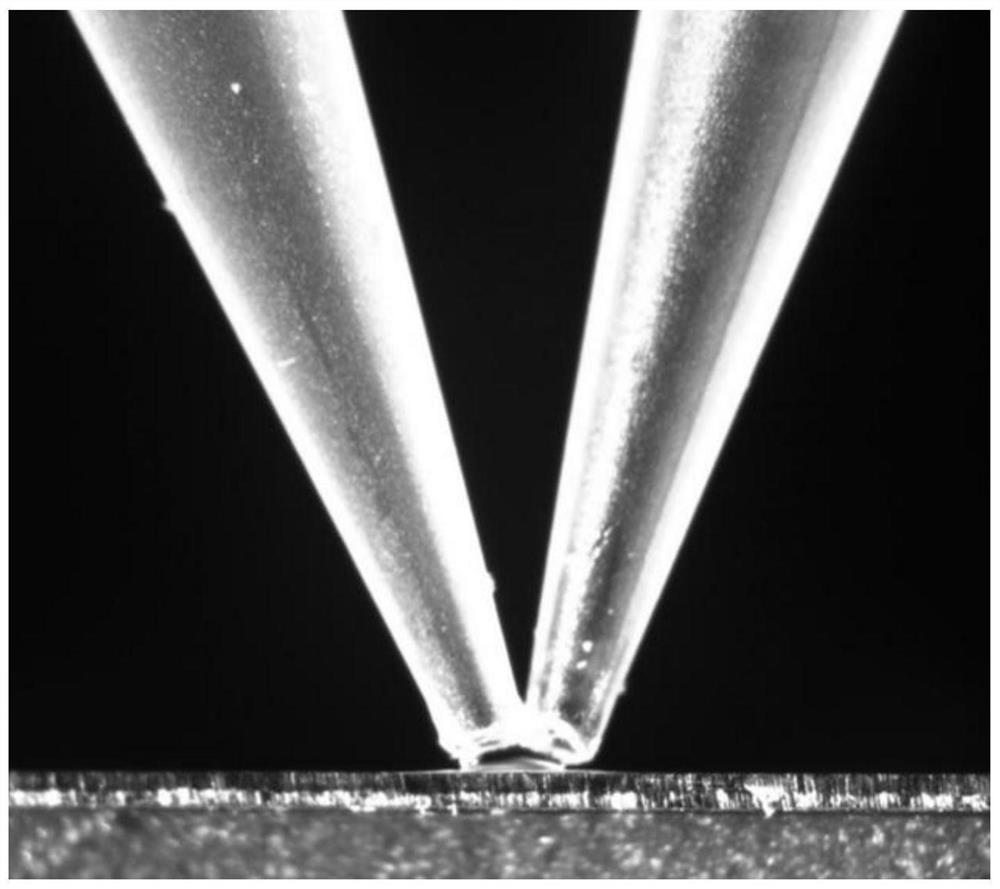

Electric arc welding device, method of welding metal sheets to metallic counterpieces, and welding element

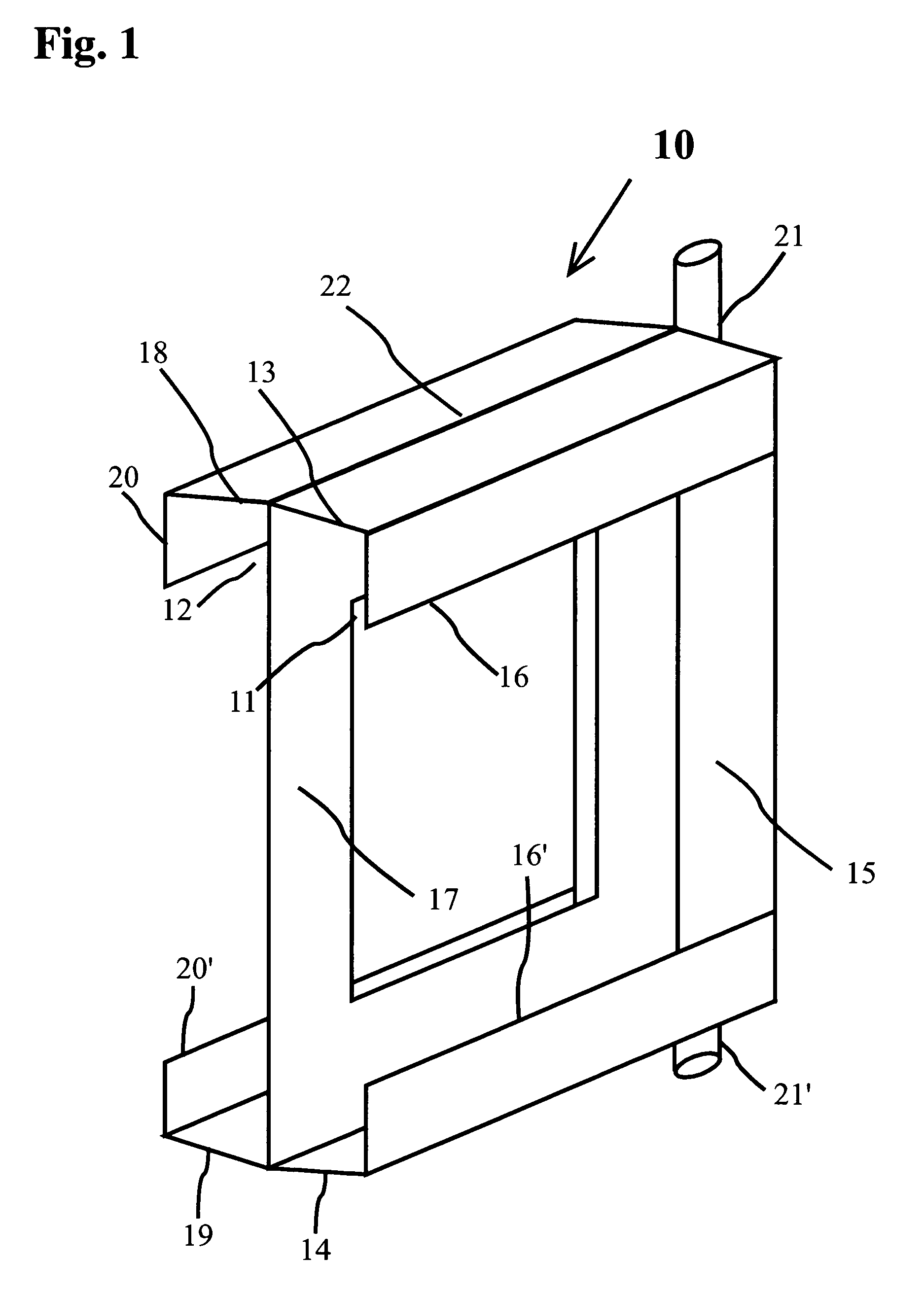

An electric arc welding device (10) for butt welding metallic sheets (12; 72; 80; 90; 92; 94; 100) is provided having an elongated face (22) onto metallic counterpieces (14), having a holding device (16; 16, 74) for holding a sheet (12, 72; 80; 90; 92; 94; 100), a reciprocating device (18) for moving the holding device (16; 16, 74) to and fro towards the counterpiece (14) and away from it, and a voltage supply device (20) for applying a voltage between sheet (12; 72; 80; 90; 92; 94; 100) and counterpiece (14) in order to generate an electric arc (24) between them. A magnetic field generating device (30) is provided, designed to generate a magnetic field (50, 32) having a component (32) transverse to the extent of the elongated face (22) and transverse to the extent of the electric arc (24) generated in the welding operation, in order to move the electric arc (24) in the direction of the extent of the elongated face (22).

Owner:NEWFREY

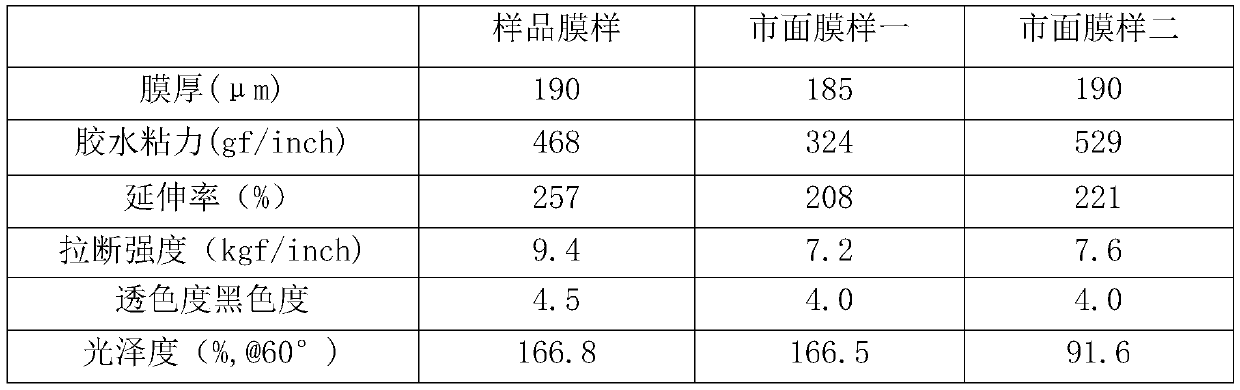

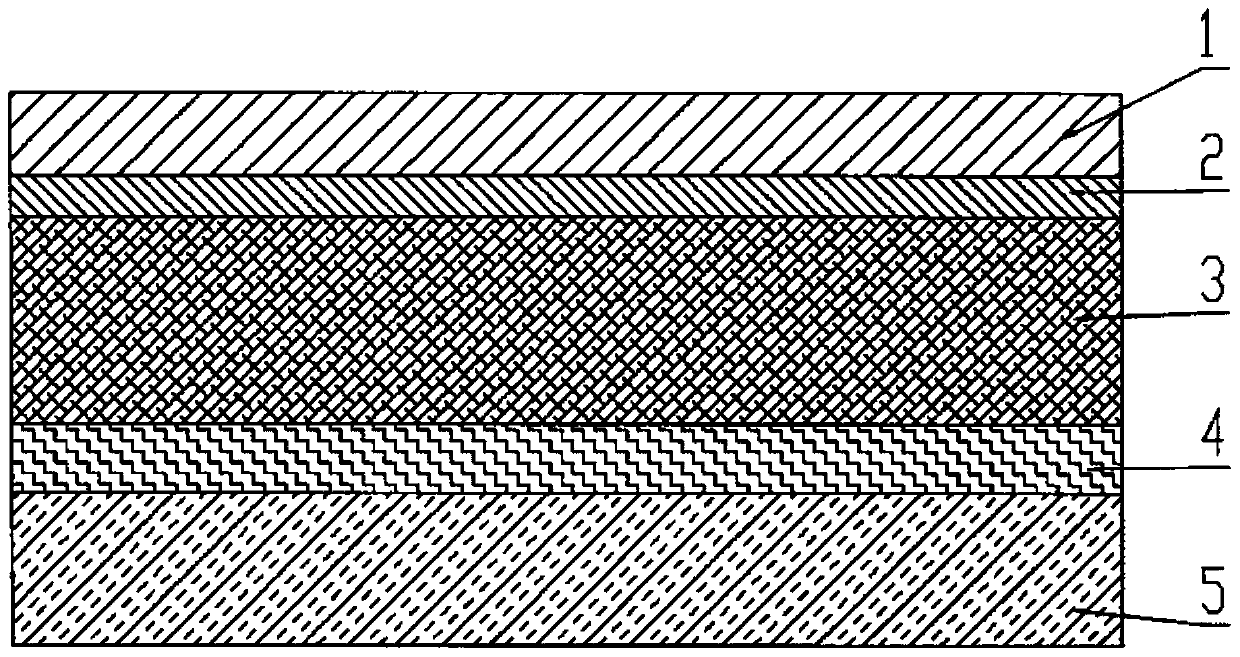

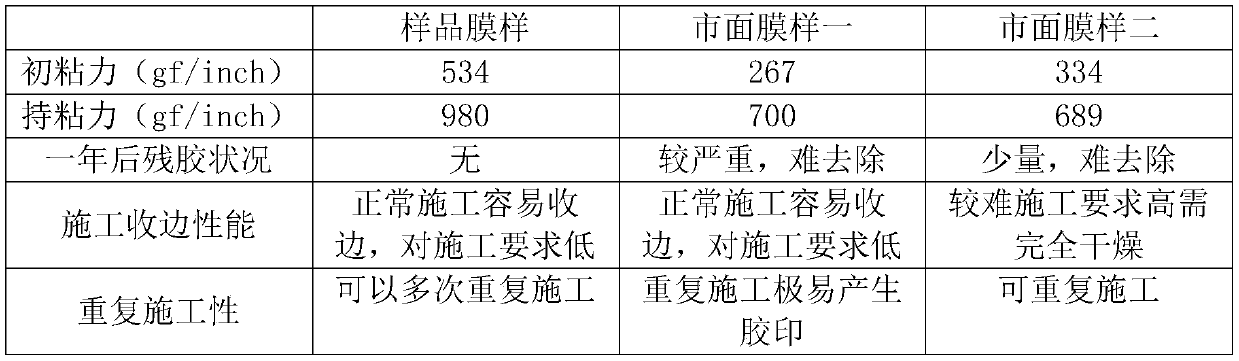

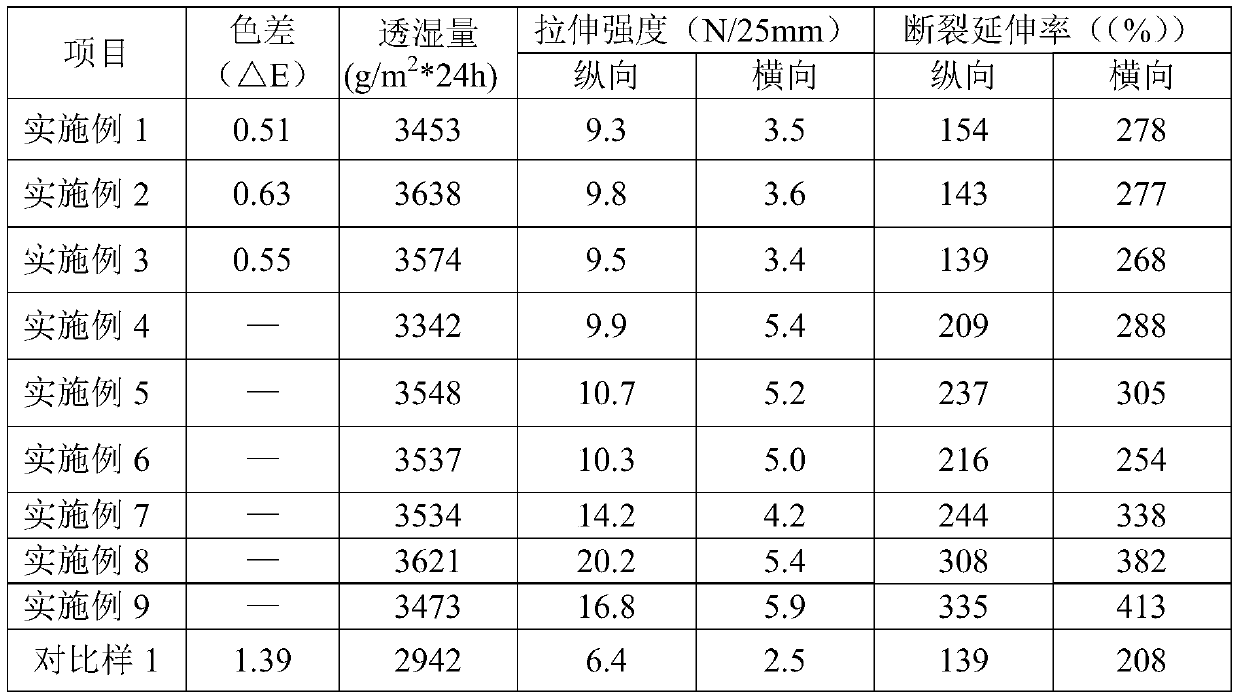

Invisible car cover protective film with TPU substrate and preparation process

InactiveCN110218525AImprove bindingIncrease profitPolyureas/polyurethane adhesivesOrganic non-macromolecular adhesivePolyesterTectorial membrane

The invention discloses an invisible car cover protective film with a TPU substrate. The invisible car cover protective film comprises a protective layer, a substrate layer and a release layer, wherein the protective layer is prepared from PET, the substrate layer is prepared from a polyester / polyether copolymer system, and the release layer is prepared from PET; a lower adhesive layer and an upper adhesive layer are separately adhered to main surfaces on both sides of the substrate layer, an aliphatic pressure-sensitive adhesive is coated on the surface of the release layer, and then the lower adhesive layer is adhered to one main surface of the substrate layer in a film transfer mode; and the upper adhesive layer is directly coated on the other main surface of the substrate layer. The invention also provides a preparation process of the invisible car cover protective film with the TPU substrate, and the preparation process comprises the steps: (1) preparing the TPU substrate layer, (2) pretreating the substrate layer, (3) preparing the lower adhesive layer, (4) performing film transfer, (5) preparing the upper adhesive layer, and (6) preparing the protective layer. The bonding force between the adhesive layers and the substrate layer is good, a high product strength and a high utilization rate of raw materials are achieved, and automatic repair of scratches can be achieved through polyurethane microcapsule particles in the adhesive layers.

Owner:NINGBO JIAHUA NEW MATERIAL TECH CO LTD

Production technology of TPU-substrate invisible car cover protection film

InactiveCN110183985AImprove bindingIncrease profitFilm/foil adhesive primer layersPressure sensitive film/foil adhesivesPolyesterTectorial membrane

The invention discloses a production technology of a TPU-substrate invisible car cover protection film. The TPU-substrate invisible car cover protection film is produced according to the following steps: (1), forming a TPU substrate layer; (2), pretreating the substrate layer; (3), forming a lower adhesive layer; (4), performing film transfer; (5), forming an upper adhesive layer; (6), forming a protective layer. In the TPU-substrate invisible car cover protection film, the protective layer is made of PET, the substrate layer is made of a polyester-polyether copolymer system, and a release layer is made of PET; the lower adhesive layer is an aliphatic pressure-sensitive adhesive, and the upper adhesive layer is aliphatic polyurethane or carbamate-acrylic based surface coating. A TPU substrate of the of TPU-substrate invisible car cover protection film has relatively high modulus and strength, so that good weather resistance, gloss, transparency, crystal flow pattern and other requirements are guaranteed; the adhesive layers have strong adhesion to the substrate layer and have high raw material utilization rate, and during using, the adhesive layers provide suitable initial adhesionand permanent adhesion for the surface of car paint, so that the advantage that glue does not remain on the paint surface is achieved.

Owner:NINGBO JIAHUA NEW MATERIAL TECH CO LTD

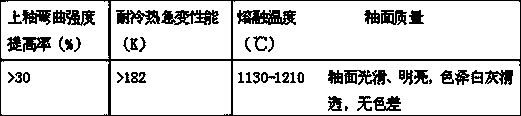

High-strength electric-porcelain ash glaze formula and its preparation method

The invention relates to a high-strength electrotechnical porcelain ash glaze formulation which comprises white glaze base materials and coloring materials with mass of 15 to 35% of that of the white glaze base materials, wherein the white glaze base material comprises the following components in parts by weight: 23 to 27 parts of potassium feldspar, 25 to 29 parts of quartz, 8 to 15 parts of Xinhui powder, 4 to 9 parts of washed kaolin, 5 to 8 parts of Xingzi kaolin, 8 to 15 parts of talc, 4 to 7 parts of limestone, 3 to 8 parts of Zuoyun earth, 2 to 6 parts of zirconium silicate, and 5 to 15 parts of alumina. The preparation method comprises the following steps of: roasting three colorant raw materials at a high temperature firstly; grinding finely; and then milling in a wet way along with white glaze based on the ratio until the size fineness reaches to 325 meshes; and finally sieving to residue of 4 to 6%. The electrotechnical porcelain ash glaze prepared based on the formulation is suitable for various porcelain blank bodies, and can be coated to form a good intermediate layer which can be combined with the porcelain body well, thus, the mechanical performance of the porcelain can be greatly improved, and the bending strength of the porcelain can be increased by more than 30%; and meanwhile, the glazed surface of a porcelain component is smooth, the color is white gray and clear, and the surface has no defect, and the market demand can be met.

Owner:JIANGSU SOUTH PORCELAIN INSULATOR CO LTD

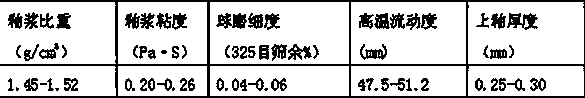

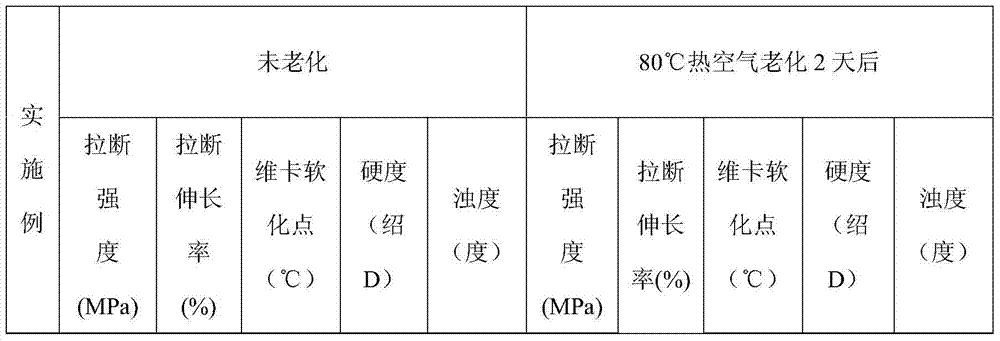

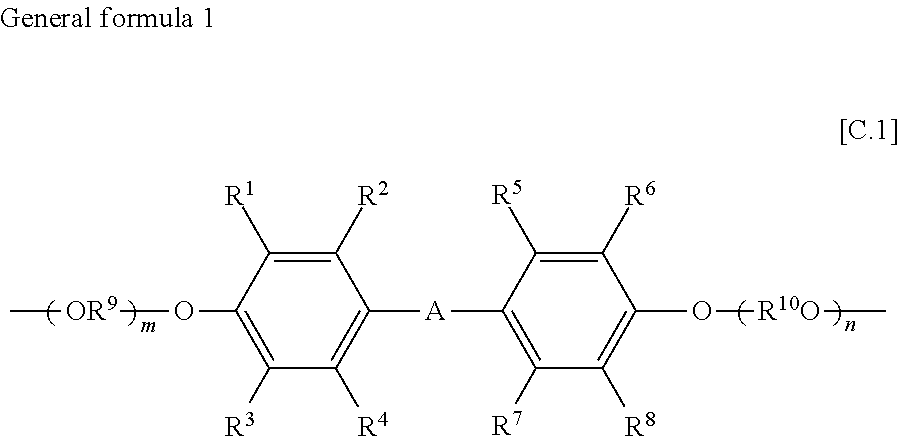

Transparent hydrogenated polystyrene-b-random copolymerized conjugated diene/styrene resin and preparation method therefor

The invention discloses transparent hydrogenated polystyrene-b-random copolymerized conjugated diene / styrene resin and a preparation method therefor. The transparent resin is composed of a styrene block and a random copolymerized block of styrene, conjugated diene and divinyl benzene, and the double bond degree of hydrogenation in the conjugated diene unit in the block copolymer reaches over 98%. The preparation method comprises: firstly homopolymerizing a styrene monomer under initiation of lithium alkyl; then carrying out random copolymerization with mixed monomers of styrene, conjugated diene and divinyl benzene; and carrying out hydrogenation reaction on the copolymerized product to obtain the resin. The preparation method is simple, and the prepared hydrogenated polystyrene-b-random copolymerized conjugated diene / styrene resin is high in strength, has the characteristics of being relatively good in processing property and aging resistance, low in turbidity, high in transparency and the like, can be molded by injection and film-drawing, and is wide in application field.

Owner:SINOPEC BALING PETROCHEMICAL CO LTD

Flow guide

ActiveUS20110087072A1Significant proportionFacilitates flow divergenceSurgeryEndoscopesControl mannerEngineering

A flow guide directs a fluid flow across a surface of a device, for example a lens surface of an endoscope, in a controlled manner to facilitate flow attachment to the surface. Embodiments include features that impart a non-uniform velocity profile and / or include guide surfaces for facilitating flow attachment and / or coverage.

Owner:ENDOGUARD

Process for manufacturing veneer by using calcium silicate as substrate

The invention discloses a process for manufacturing a veneer by using calcium silicate as a substrate, belonging to the method for processing the veneer. The process uses the wood-based panel as the substrate and comprises the following steps: A, producing facing paper: immersing the printed facing paper into a prepared liquid adhesive for adhesive coating, and drying the facing paper for later use, wherein the proportion of the amount of adhesive on the surface of the facing paper coated with the adhesive to that of the adhesive on the surface of the facing paper uncoated with the adhesive is (1.5-1.9):1; and B pre-treating the calcium silicate substrate: grinding and polishing the surface of the calcium silicate substrate, removing the impurities on the surface of the calcium silicate substrate, making liquid adhesive permeate from the surface of the calcium silicate substrate, and drying the calcium silicate substrate for later use. The process for manufacturing the veneer by using calcium silicate as the substrate is simple, is less restricted by the manufacturing environment and has a wide range of application.

Owner:成都帝龙新材料有限公司

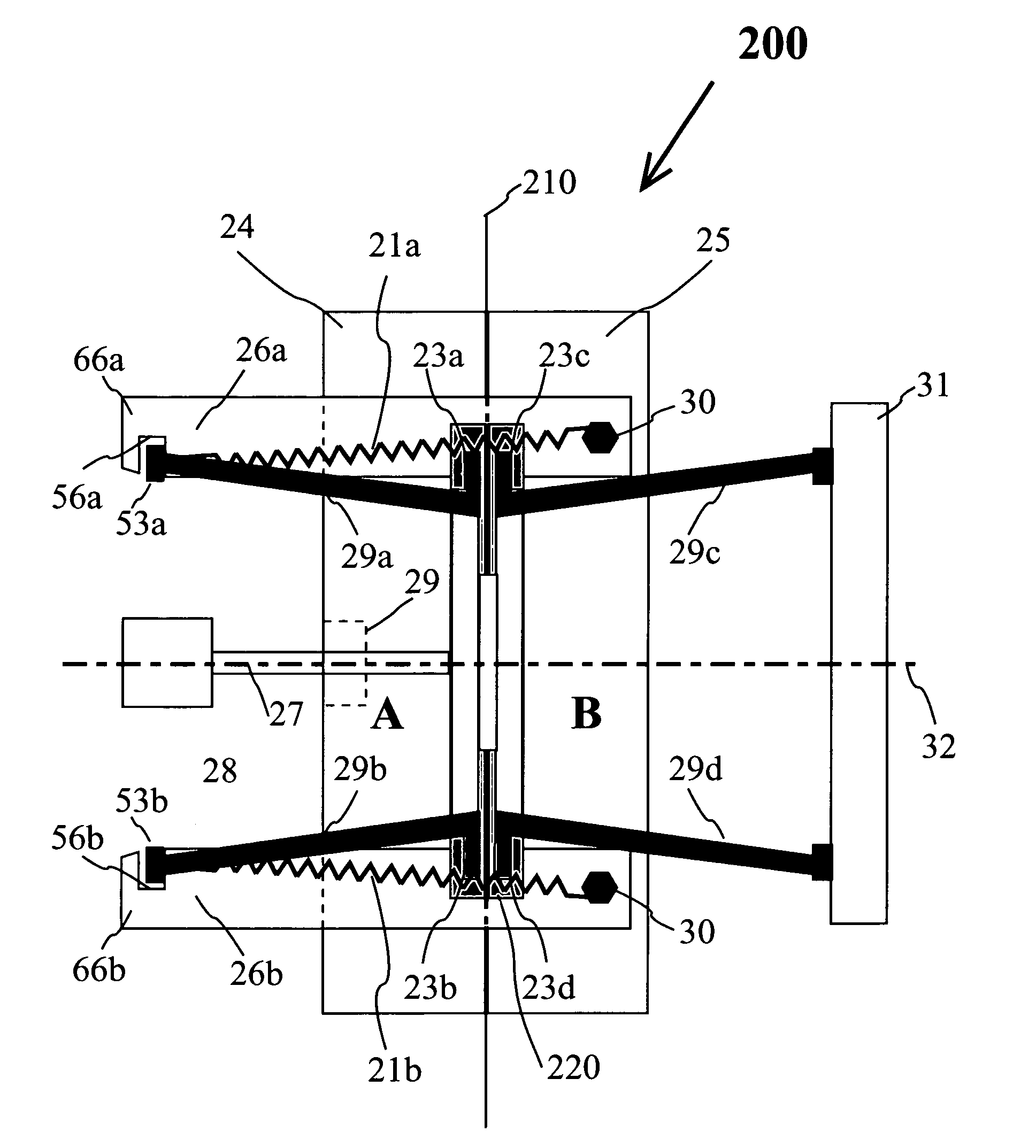

Polymeric injection mold with retractable bars for producing re-entrant molded surfaces

Owner:PIERSON INDS

Polymeric injection mold with retractable bars for producing re-entrant molded surfaces

InactiveUS20070054006A1Facilitated releasePrevent leakageMouldsConfectioneryEngineeringMechanical engineering

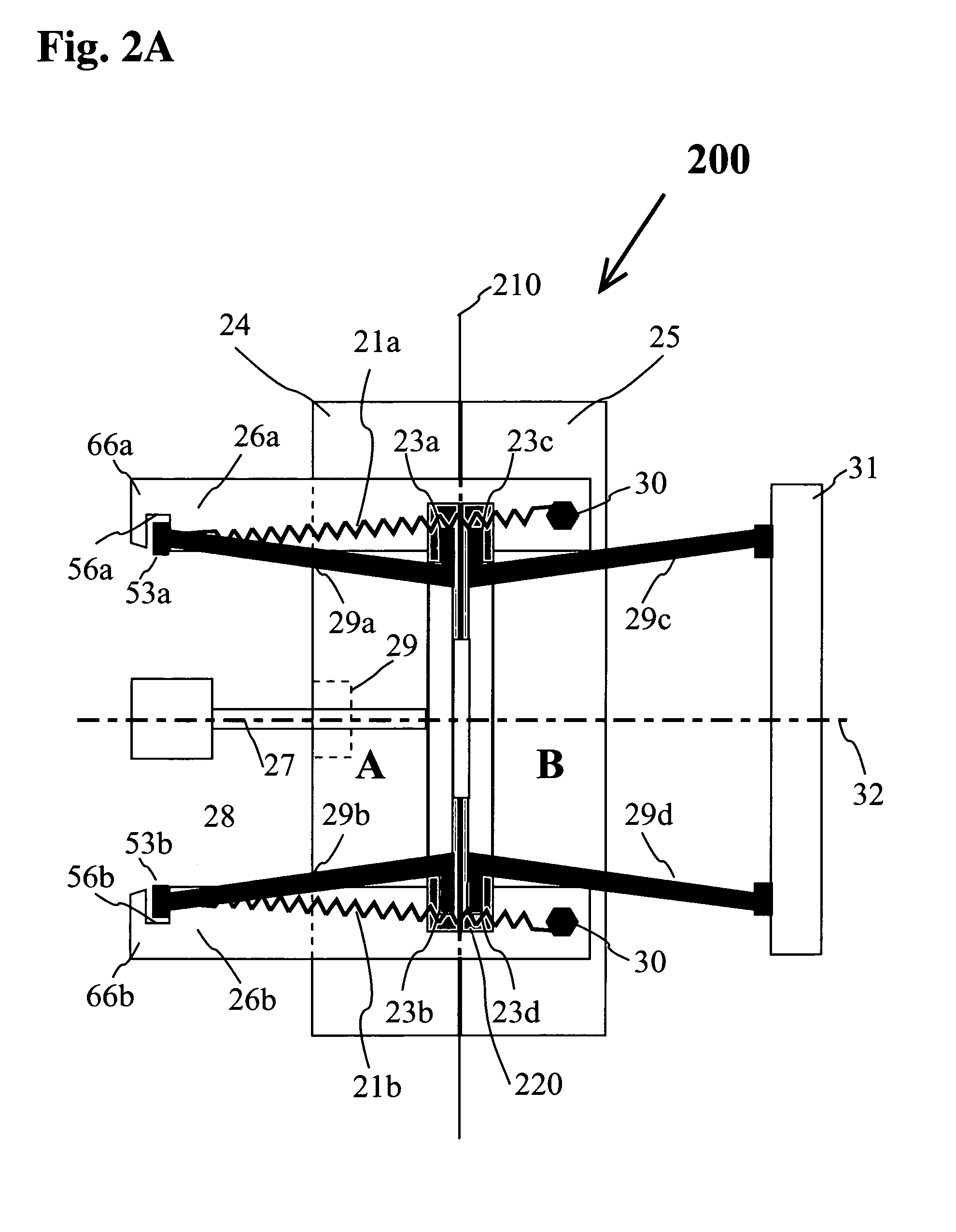

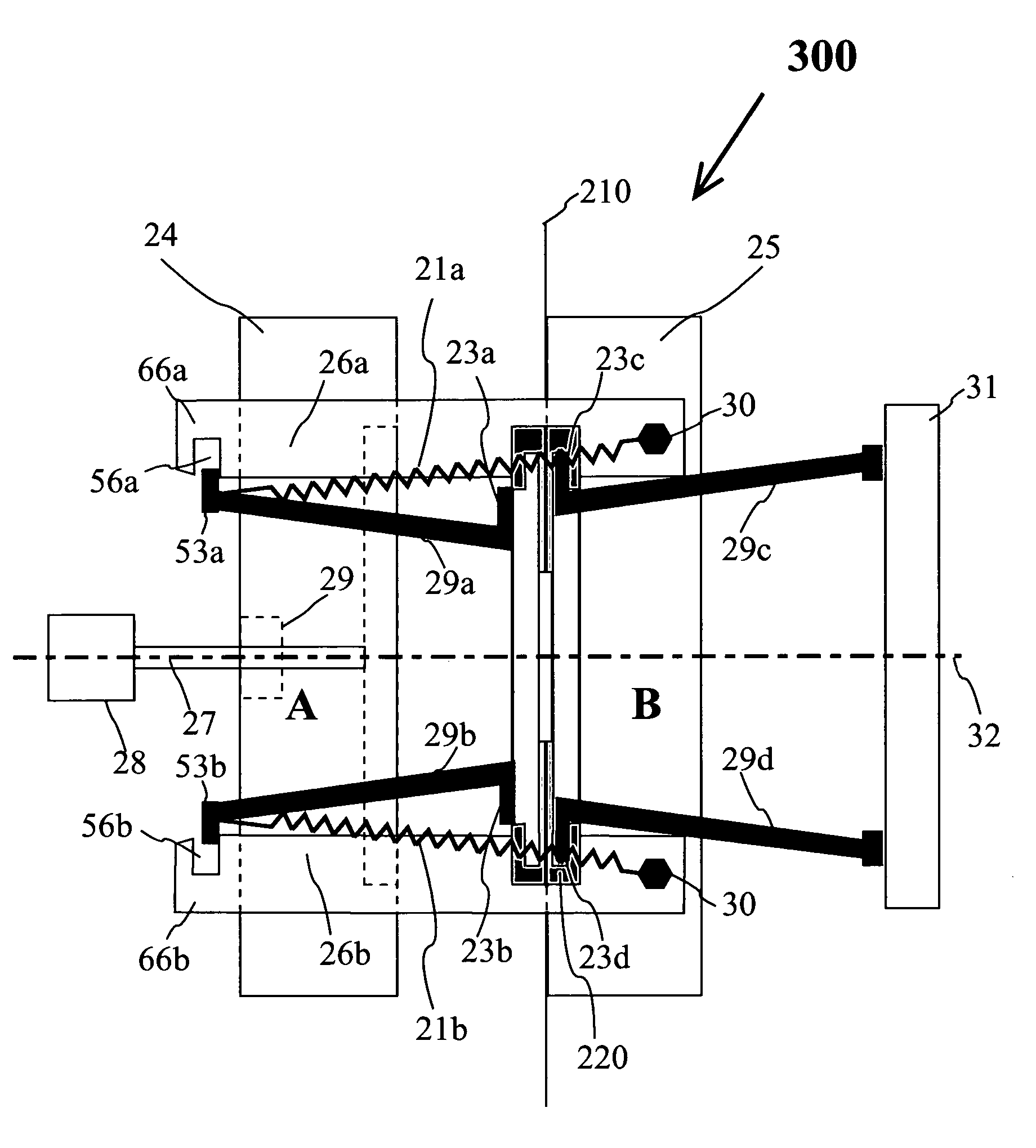

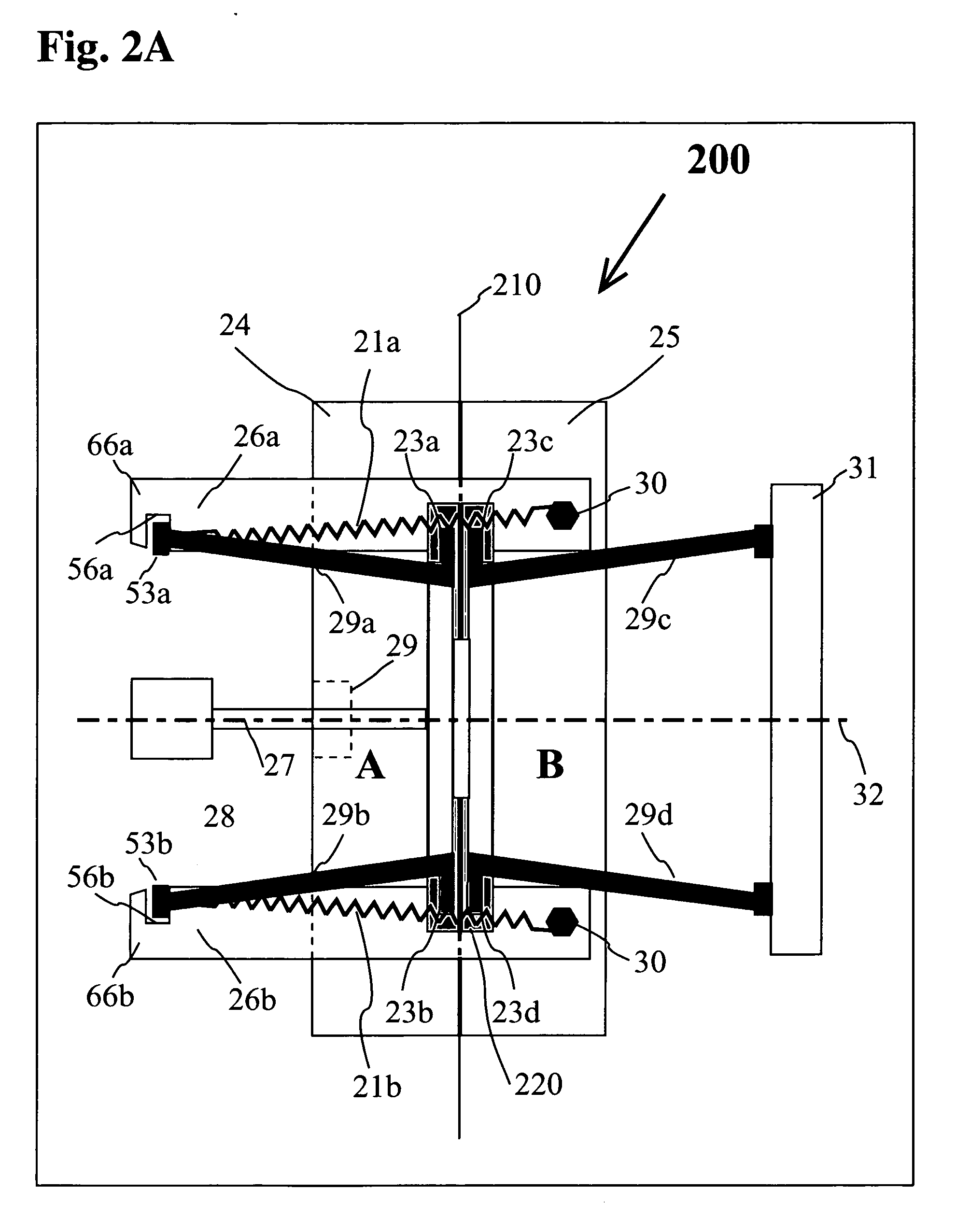

A polymeric injection mold has stationary and movable parts of a mold mating at a parting line. The polymeric part has one or more re-entrant surfaces on both sides of the parting line, wherein the re-entrant surfaces are defined by slide bar projections inserted into the mold. During mold separation the slide bar projections are displaced towards a centerline of the mold to clear the re-entrant surfaces. The slide bar projections are attached to slide bars that pass through tapered slots in the side walls of the stationary and movable sides of the mold and are inclined at an angle to the centerline of the mold. The slide bars of the stationary side of the mold are removably connected to pull bars, wherein the pull bars are rigidly attached at their opposite ends to the movable side of the mold. When the movable side of the mold is withdrawn, the injection molded part is pulled out of the stationary side of the mold and the slide bar projections in the stationary side clear the re-entrant surfaces. The slide bars in the movable side are cleared from the re-entrant surfaces by moving the slide bars located on the movable side of the mold through the use of an ejector plate.

Owner:PIERSON INDS

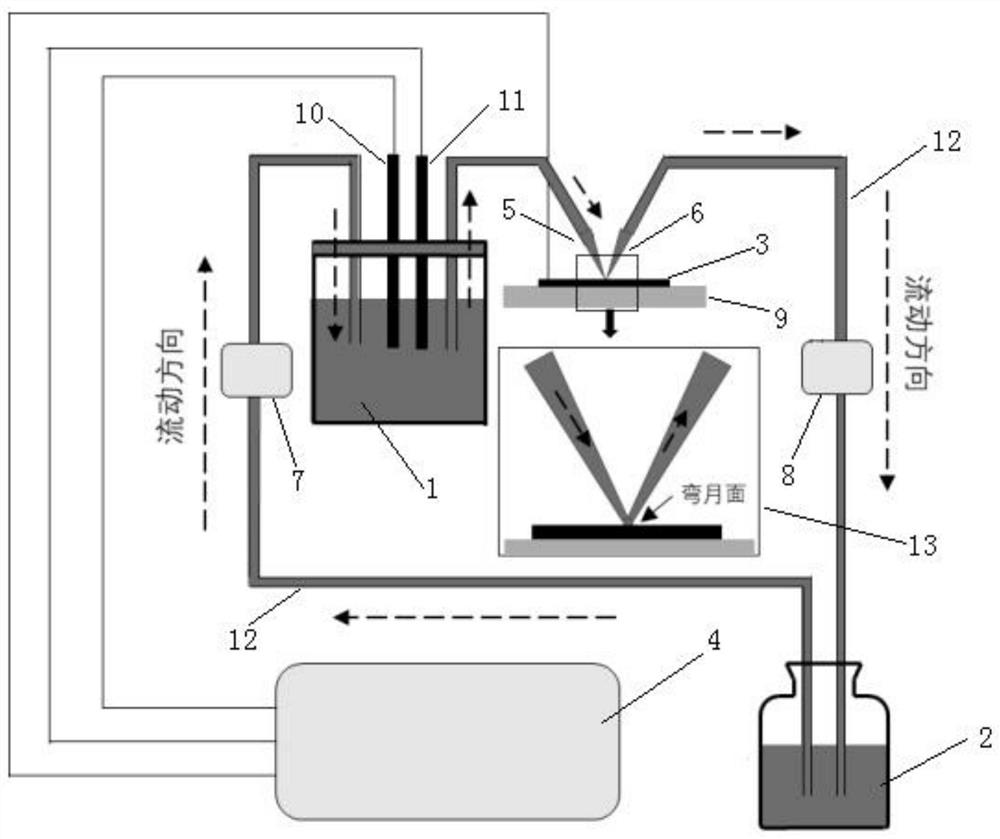

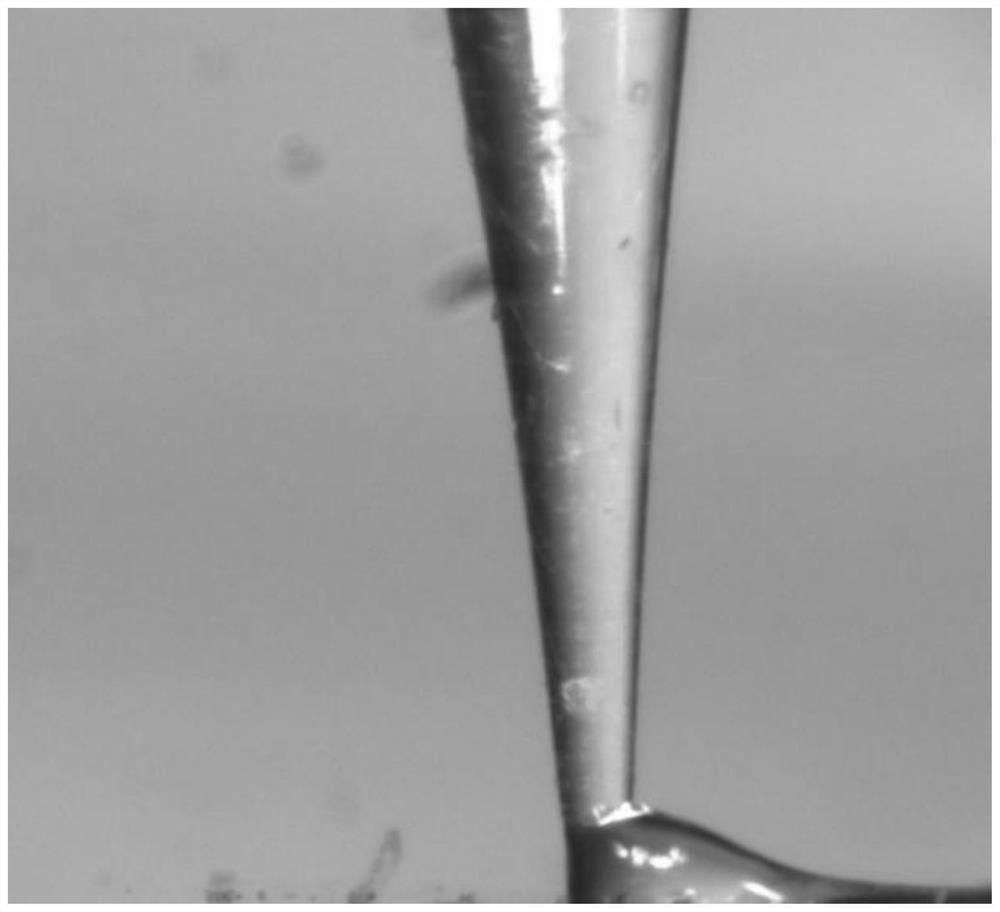

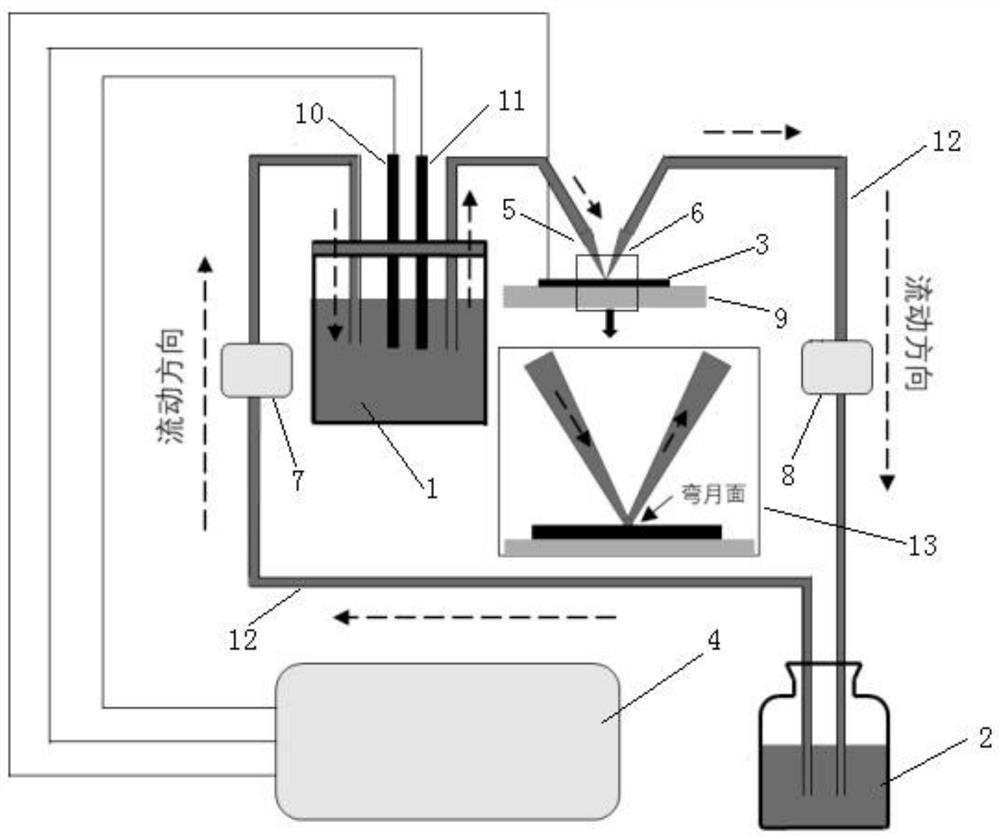

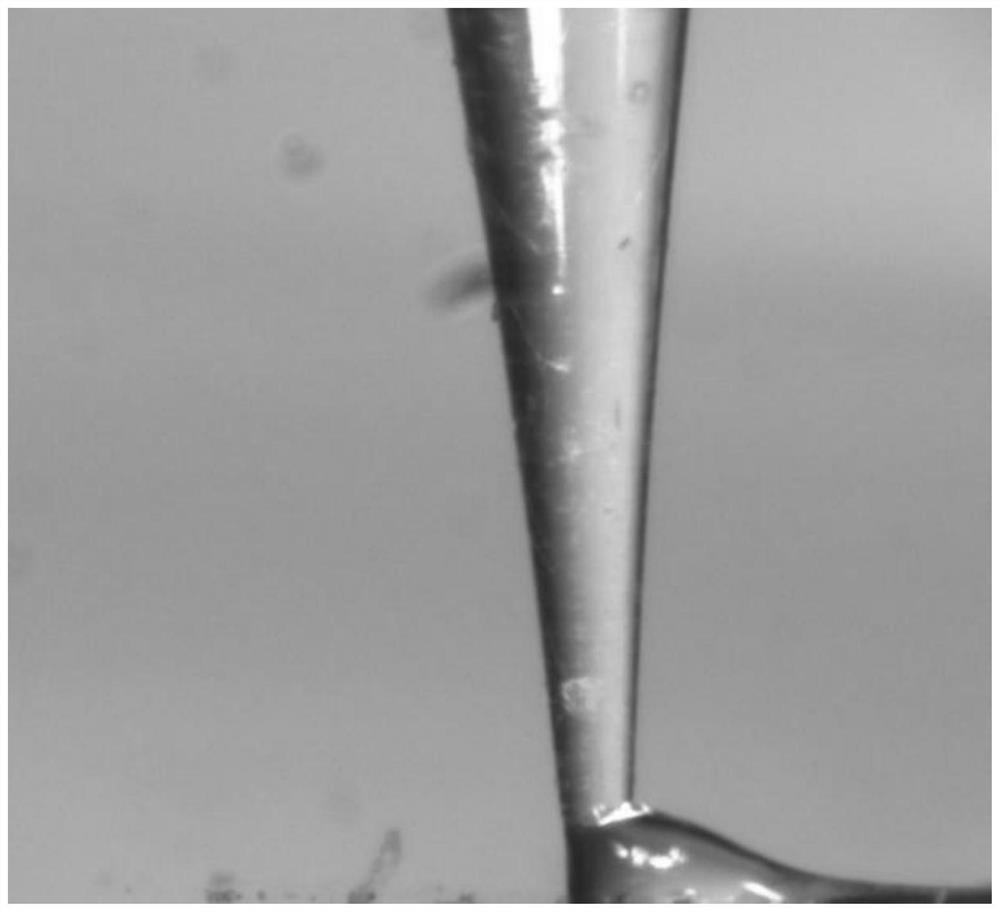

Suction combined type electrochemical micro-additive preparation method and device

ActiveCN112522766AImprove stabilityIncrease flow rateCellsAdditive manufacturing apparatusManufacturing technologyLiquid storage tank

The invention belongs to the technical field of additive manufacturing, particularly relates to a suction combined type electrochemical micro-additive preparation method and device, and provides a suction combined type electrochemical micro-additive device. The suction combined type electrochemical micro-additive device comprises a sealed electrolytic tank, a liquid storage tank, a base plate, anelectrochemical workstation, a spray head, an electrode, an infusion pump and a three-dimensional displacement table. The electrochemical micro-additive preparation method is provided on the basis ofthe micro-additive device, and the problems that in the meniscus electrochemical micro-additive manufacturing technology, when a syringe needle moves, the meniscus stability is poor, and liquid overflowing and liquid leakage are likely to happen are solved by introducing the mode of the suction combined type spray head, and therefore, the stability of the meniscus and the printing fluency are improved; and meanwhile, the technology increases the ion flow rate in the meniscus, supplements ions consumed in the printing process, and enables a printed finished product to have a uniform surface, aclear edge and relatively low roughness, thereby improving the printing morphology.

Owner:SUN YAT SEN UNIV

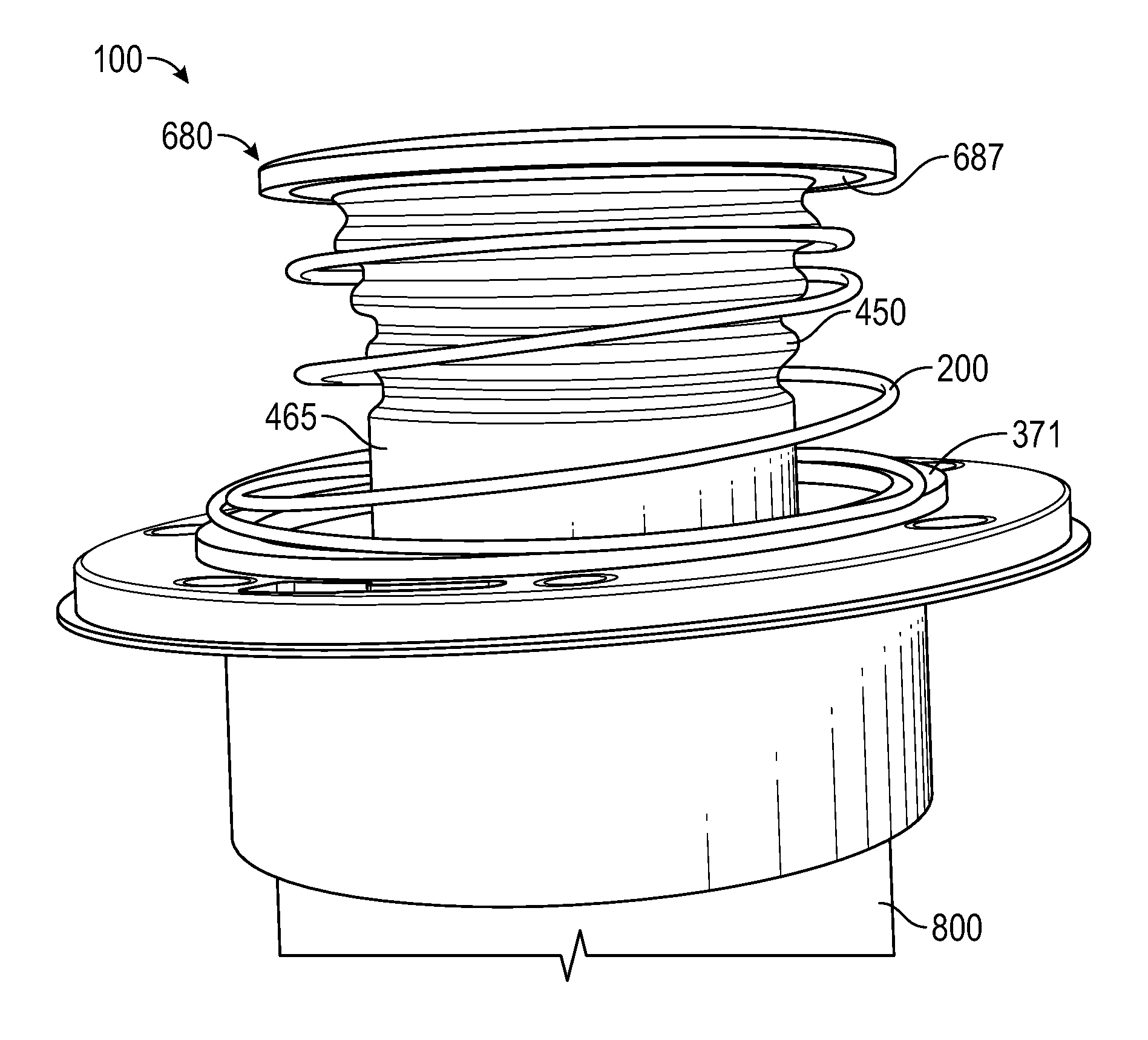

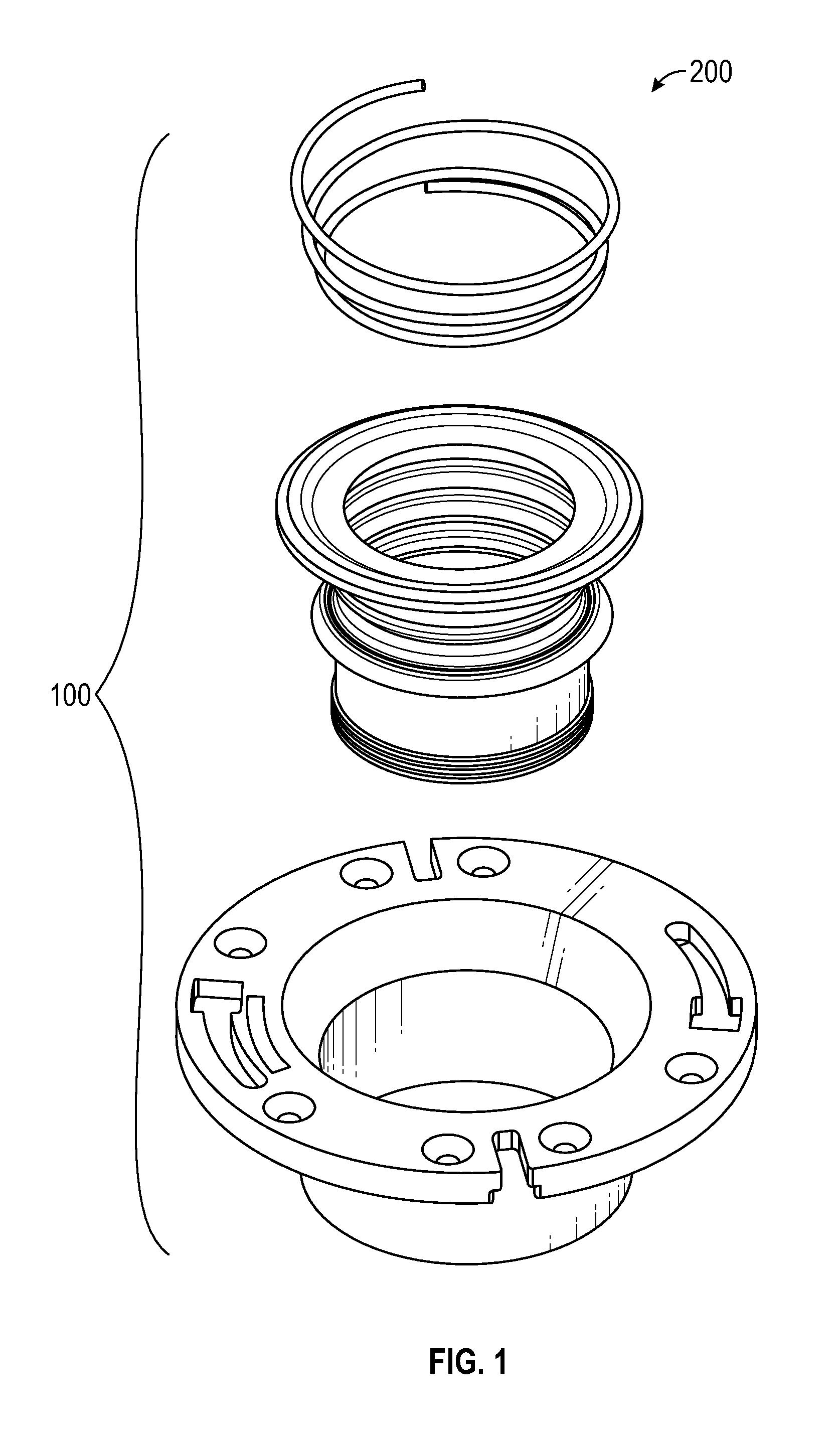

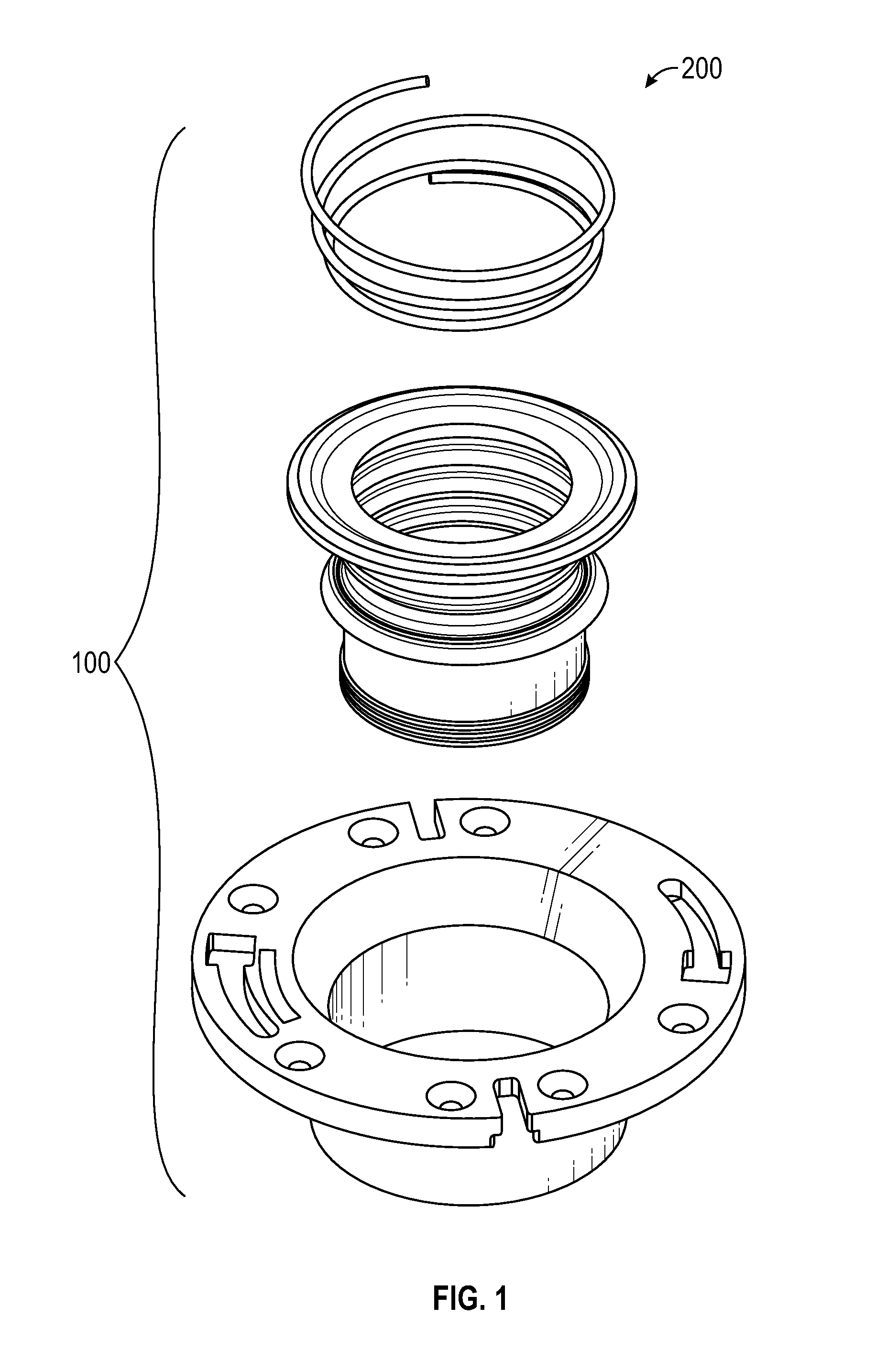

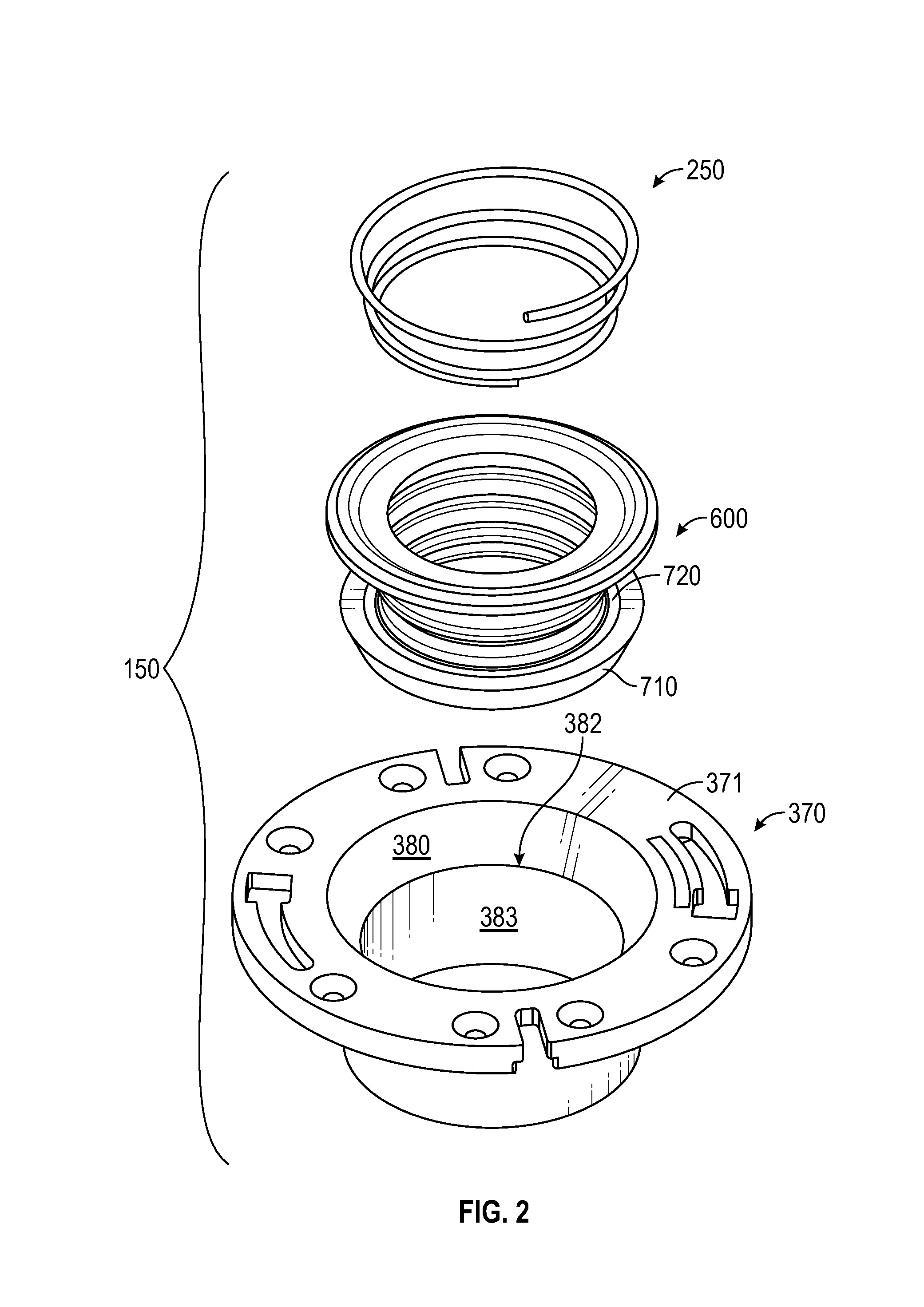

Wax free systems with springs for new and existing toilets

Owner:DUNCAN SCOTT E MR

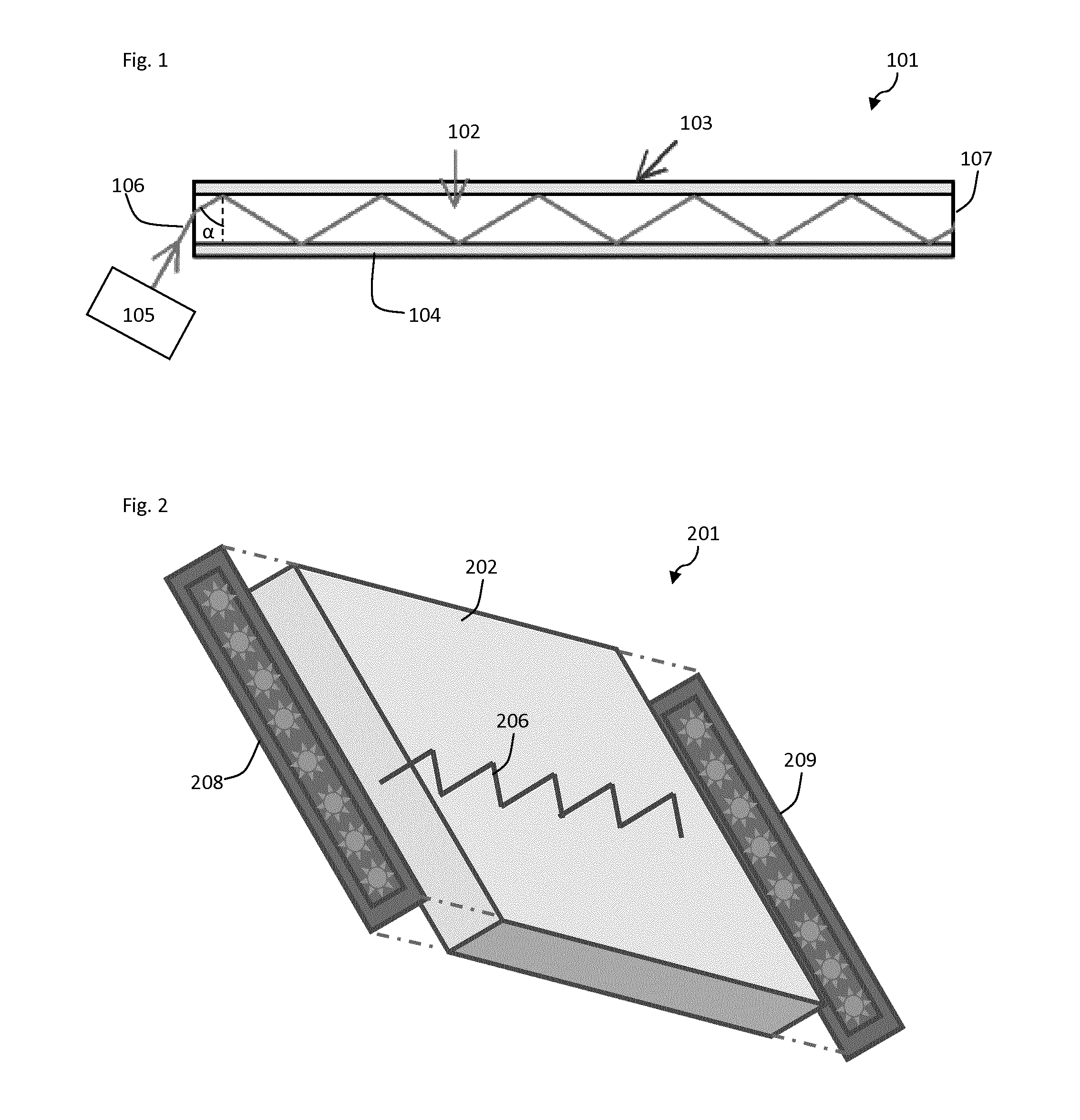

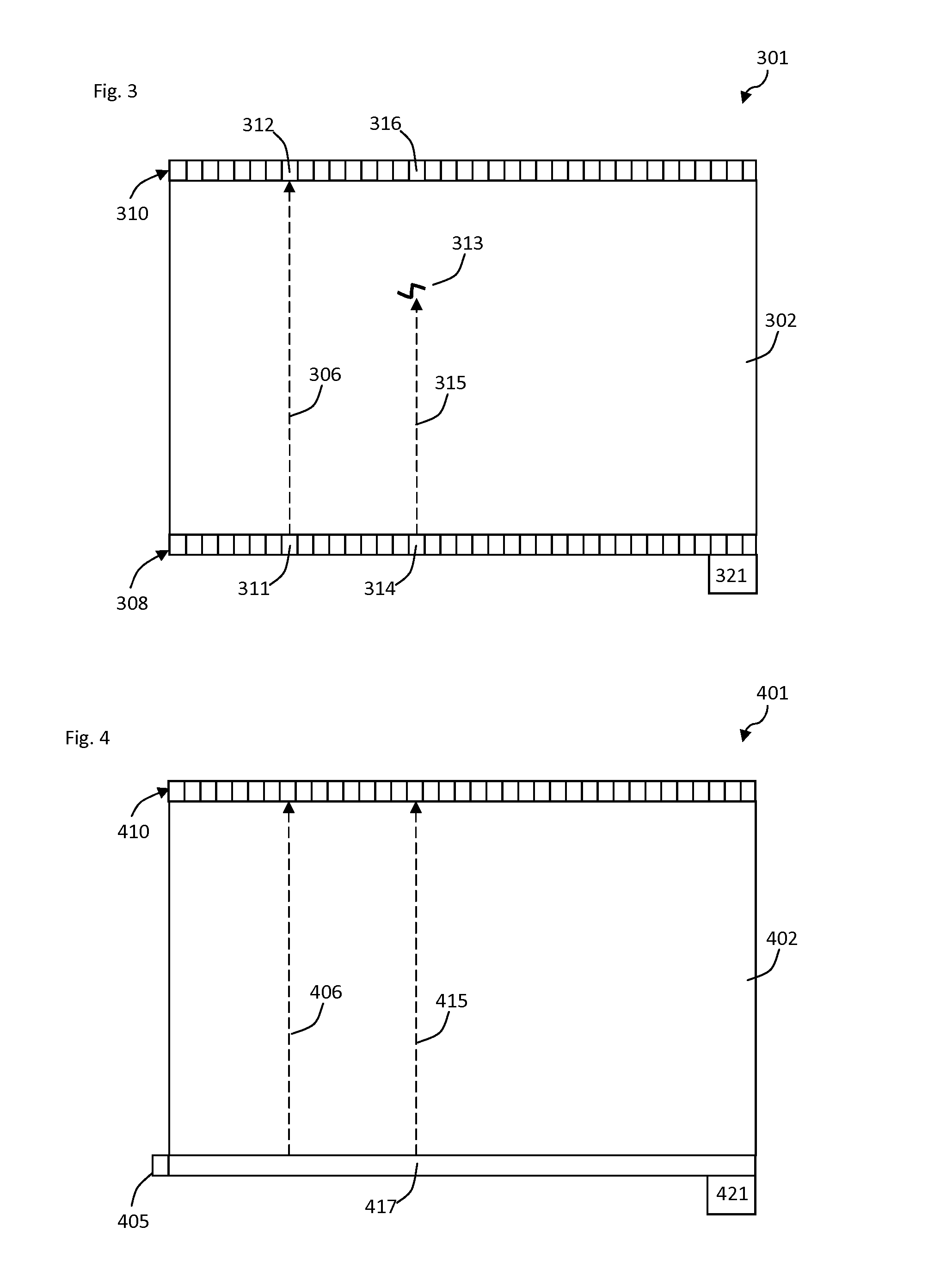

Windowpane System and Vehicle Incorporating Same

InactiveUS20170013679A1Prevent foggingEffectively heatWindowsWindscreensLight sourceTotal internal reflection

A windowpane system (101) comprising: a windowpane (102); and at least one primary light source (105); each primary light source (105) being arranged so that light (106) from the primary light source (105) passes into the windowpane (102) through a first surface of the windowpane (102), the light (106) then travelling within the windowpane until it has undergone total internal reflection from one or more second surfaces of the windowpane a plurality of times, wherein at least some of the light from the primary light source is absorbed by the windowpane as the light from the primary light source passes through the windowpane.

Owner:JAGUAR LAND ROVER LTD

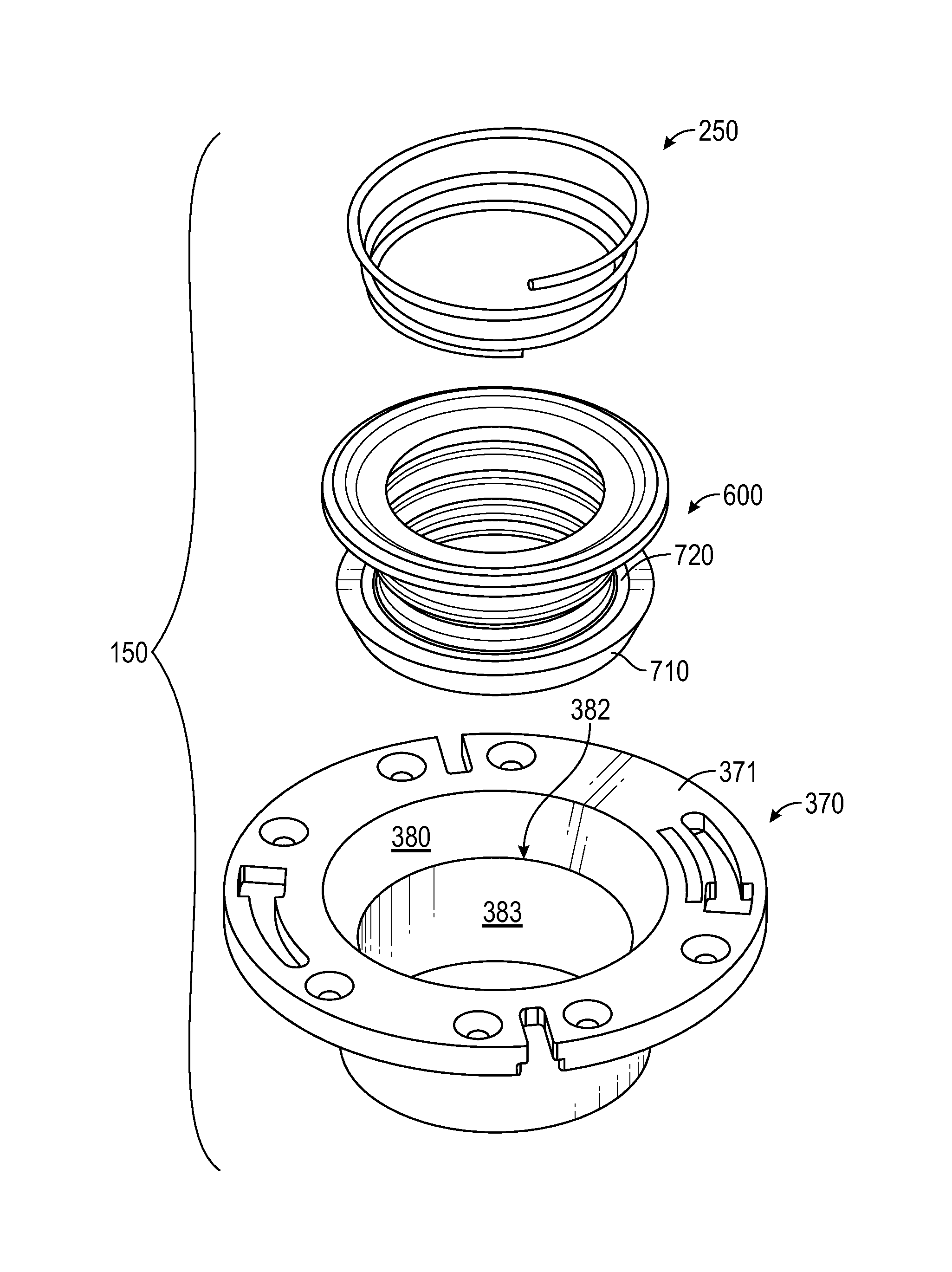

Wax Free Systems with Springs for New and Existing Toilets

ActiveUS20150000020A1Overcome deficienciesEasy to disassembleEngine sealsWater closetsWaxEngineering

A wax free pop-up seal 450 may be integrated with a spring 200 or other resilient component to connect a toilet to an existing soil pipe flange 325. A pop-up seal system 100 provides toolless, nondestructive and seamless height adjustment and comports with both smaller and larger diameter soil pipe flanges. For retro fit installations, a pop-up seal may comprise extended fins 471 for use with larger diameter soil pipe flanges and for use with smaller diameter soil pipe flanges, the extended fins may be removed. For new construction a new soil pipe flange is provided and a customized pop-up seal 600 comprises a seal system well suited for the new soil pipe flange. The pop-up seals may operate with or without springs or other external flexible components.

Owner:DUNCAN SCOTT E MR

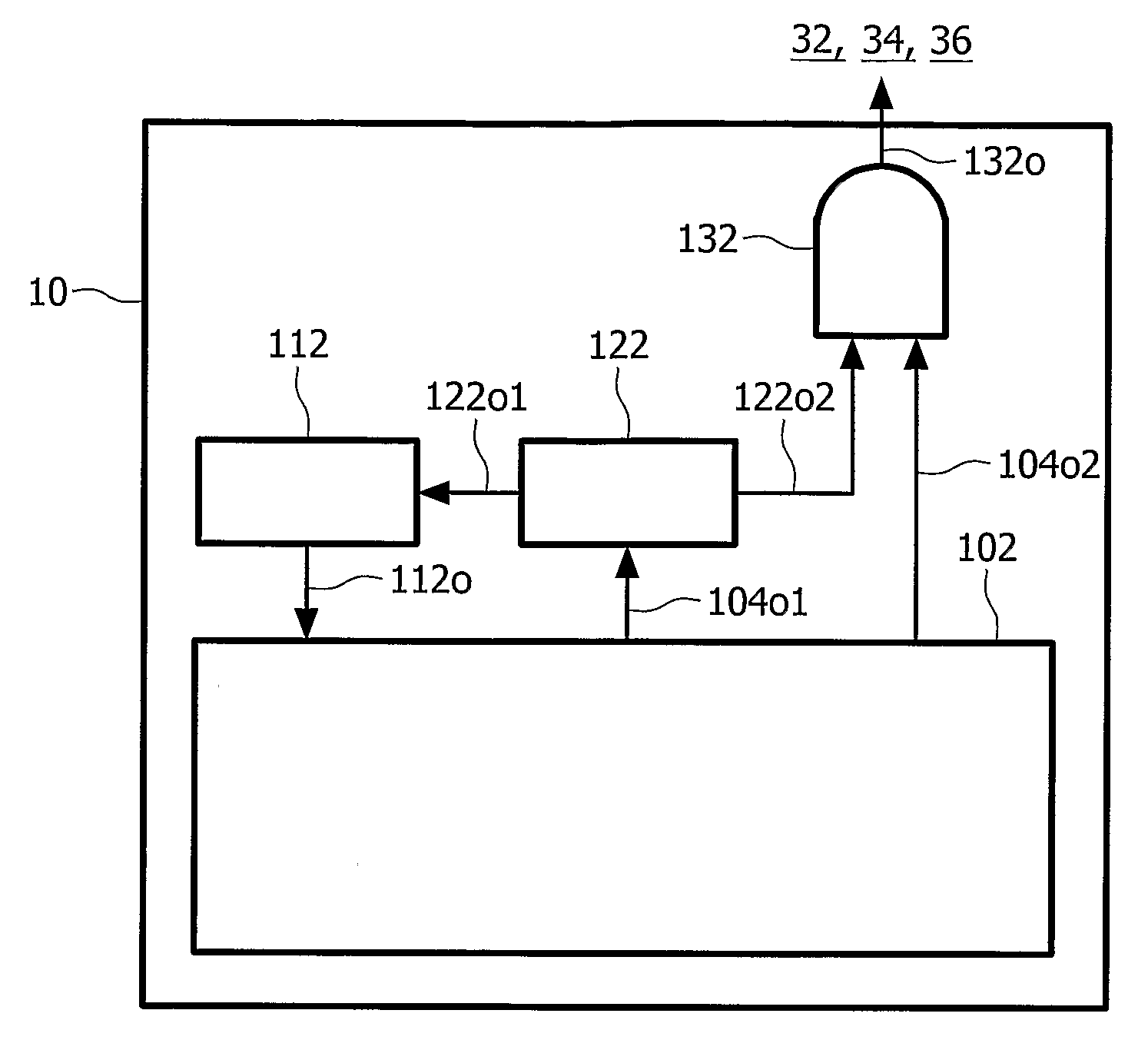

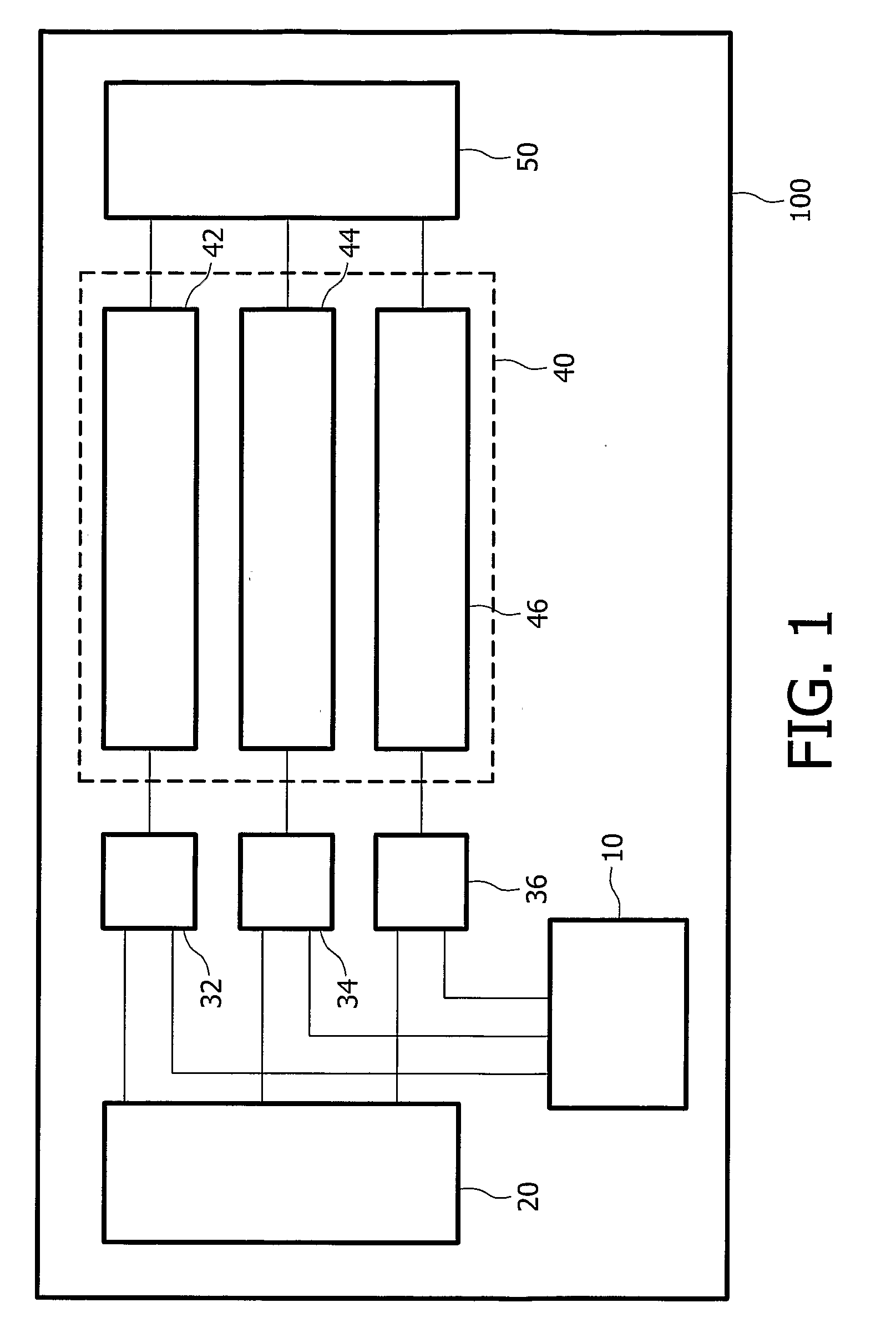

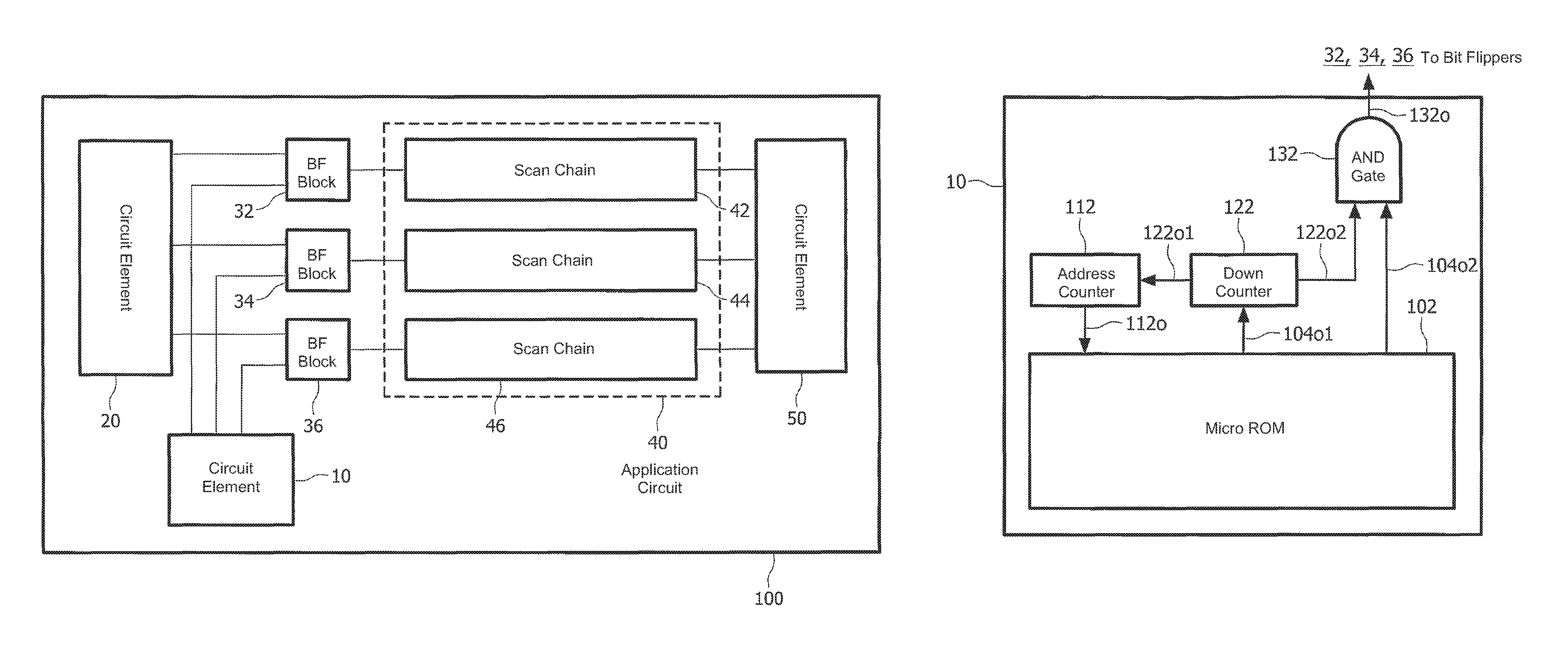

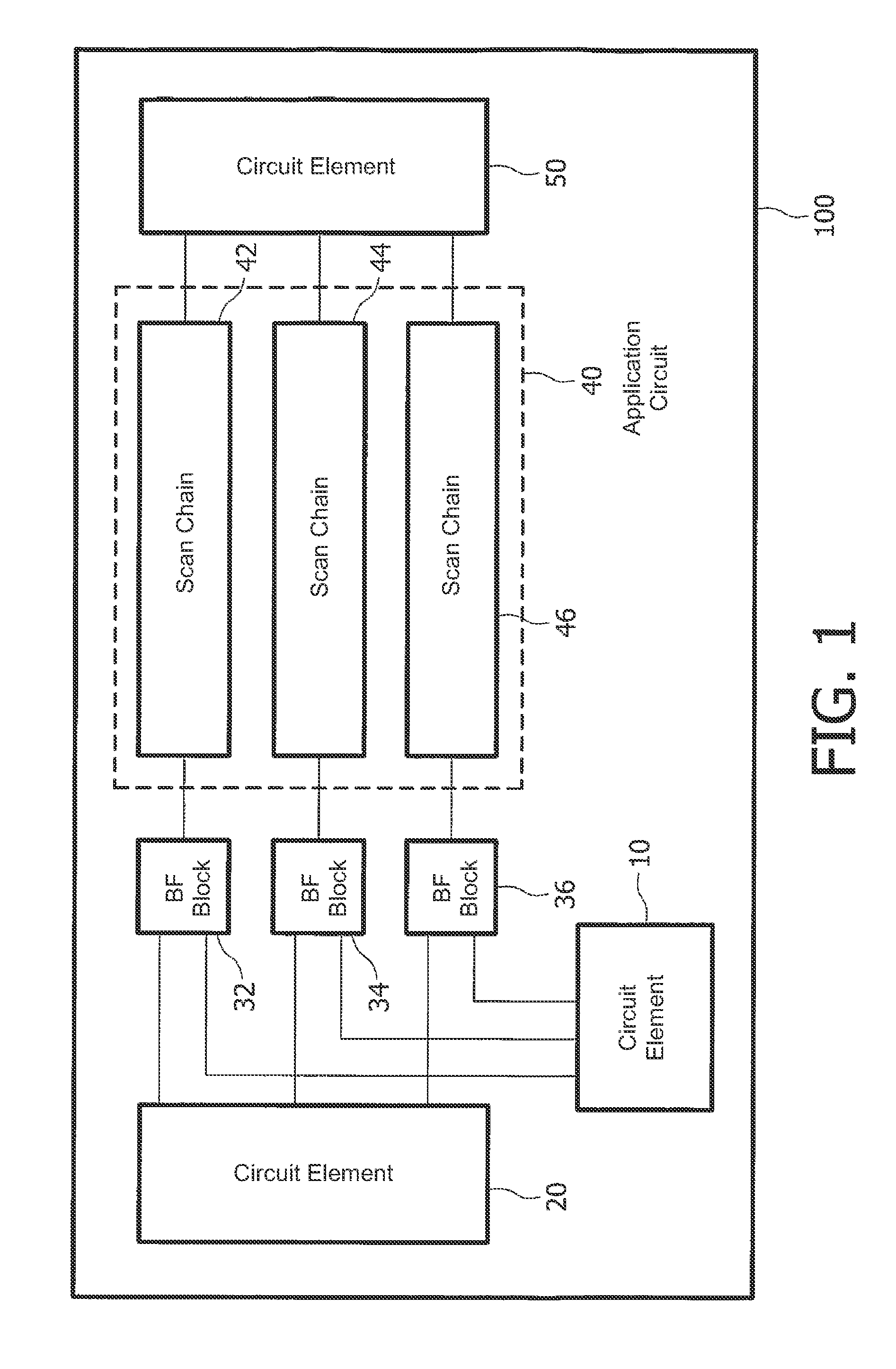

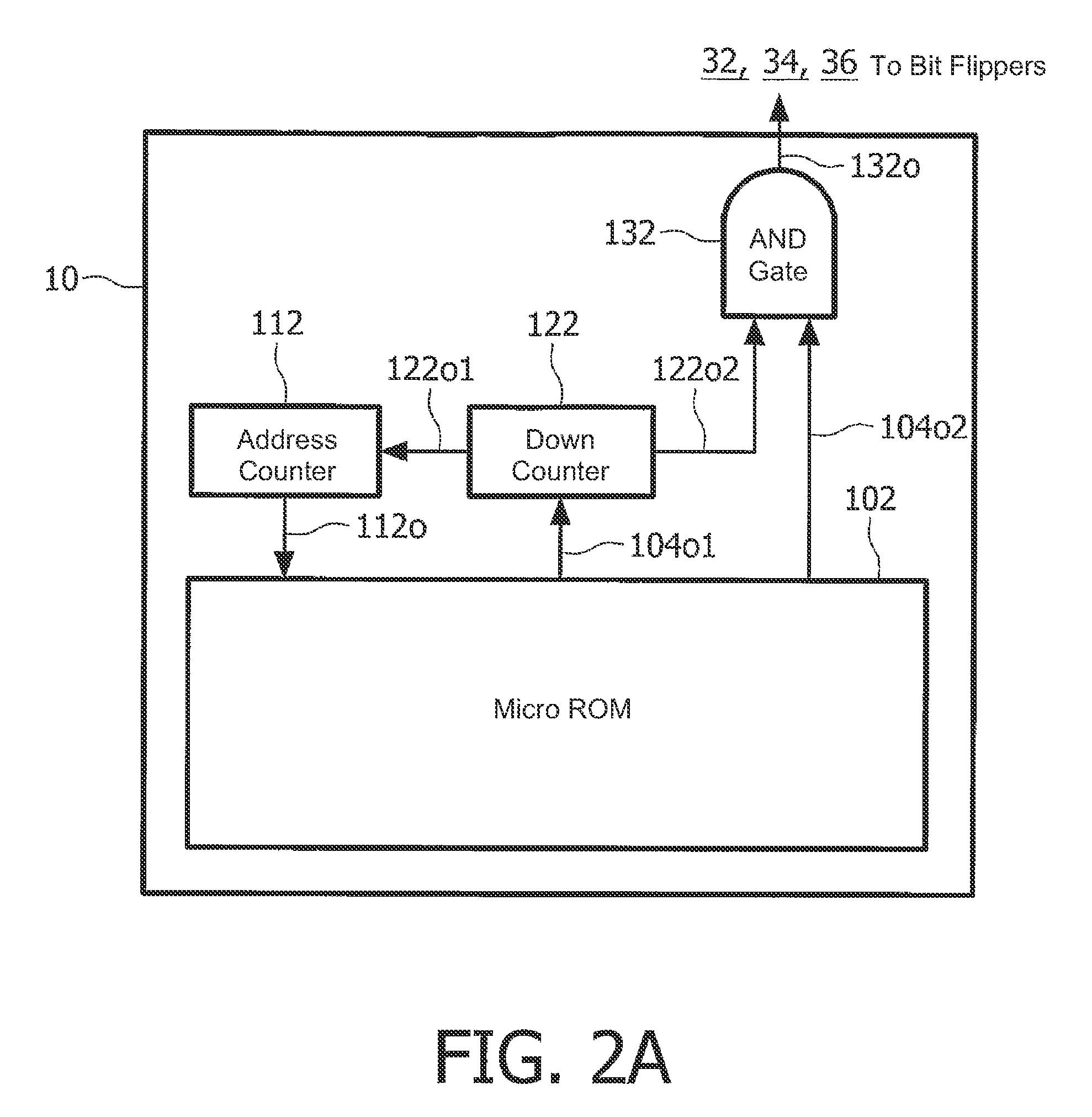

Circuit Arrangement and Method of Testing an Application Circuit Provided in Said Circuit Arrangement

InactiveUS20080195907A1Clear surfaceLow costElectronic circuit testingLogical operation testingTest sampleProcessor register

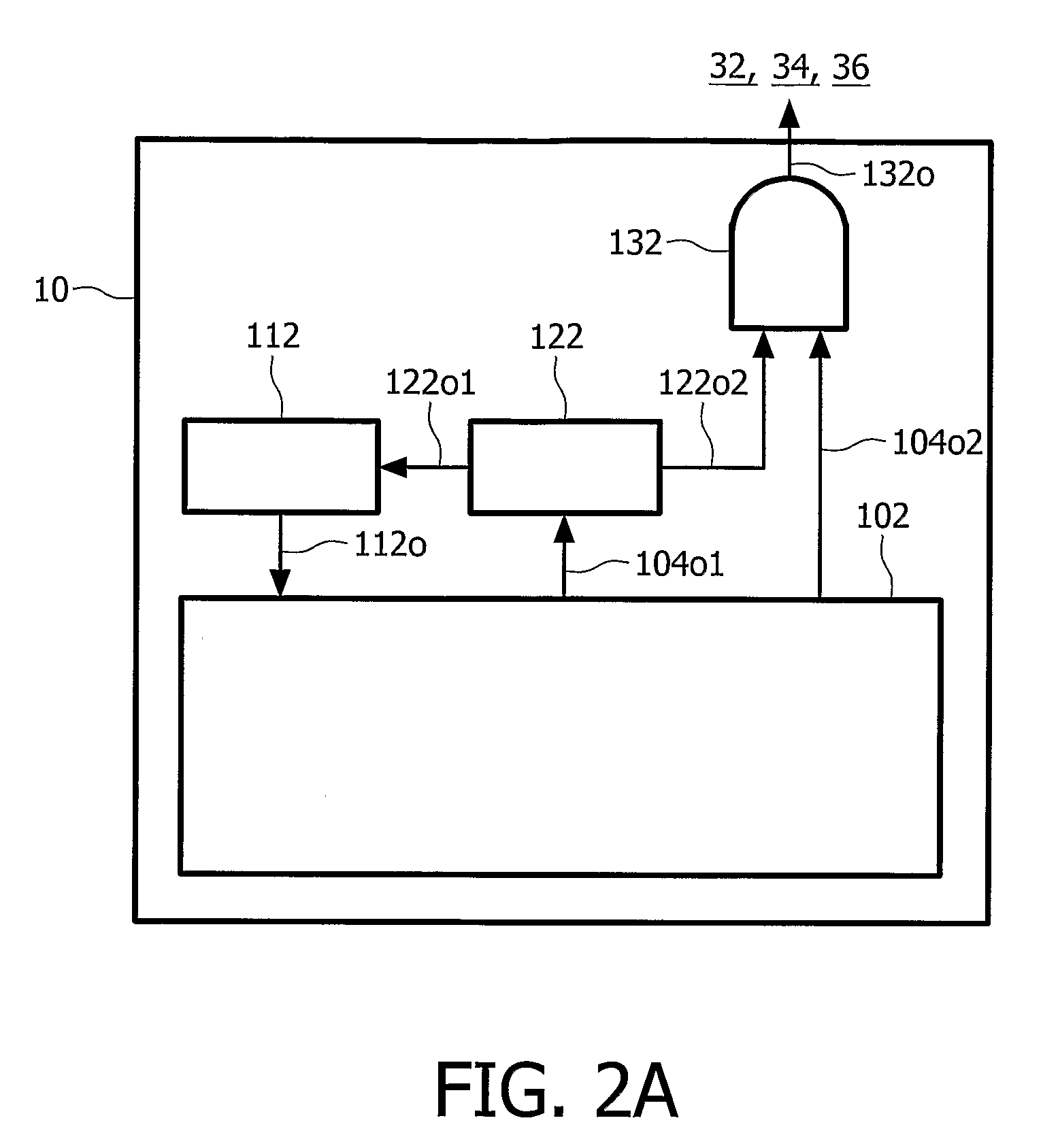

The object being to develop an integrated circuit arrangement (100) with at least one application circuit (40) to be tested, and with at least one self-test circuit (10, 20, 32, 34, 36, 50) provided for testing the application circuit (40) and generating at least one pseudo-random test sample, wherein said pseudo-random test sample can be converted into at least one test vector that is programmable and / or deterministic and that can be supplied to the application circuit (40) for testing purposes via at least one logic gate (32, 34, 36) and by means of at least one signal that can be applied to said logic gate (32, 34, 36), and wherein the output signal arising in dependence on the deterministic test vector can be evaluated by the application circuit (40) by means of at least one signature register (50), as well as a method of testing the application circuit (40) present in the integrated circuit arrangement (100) by means of the self-test circuit (10, 20, 32, 34, 36, 50) further such that the B[uild-]I[n]S[elf-]T[est] hardware connected to the additional deterministic logic can be reduced, it is suggested that the signal to be supplied to the logic gate (32, 34, 36) can be made available by a B[it]F[lipping]F[unction] logic circuit (10) based on at least one

Owner:NXP BV

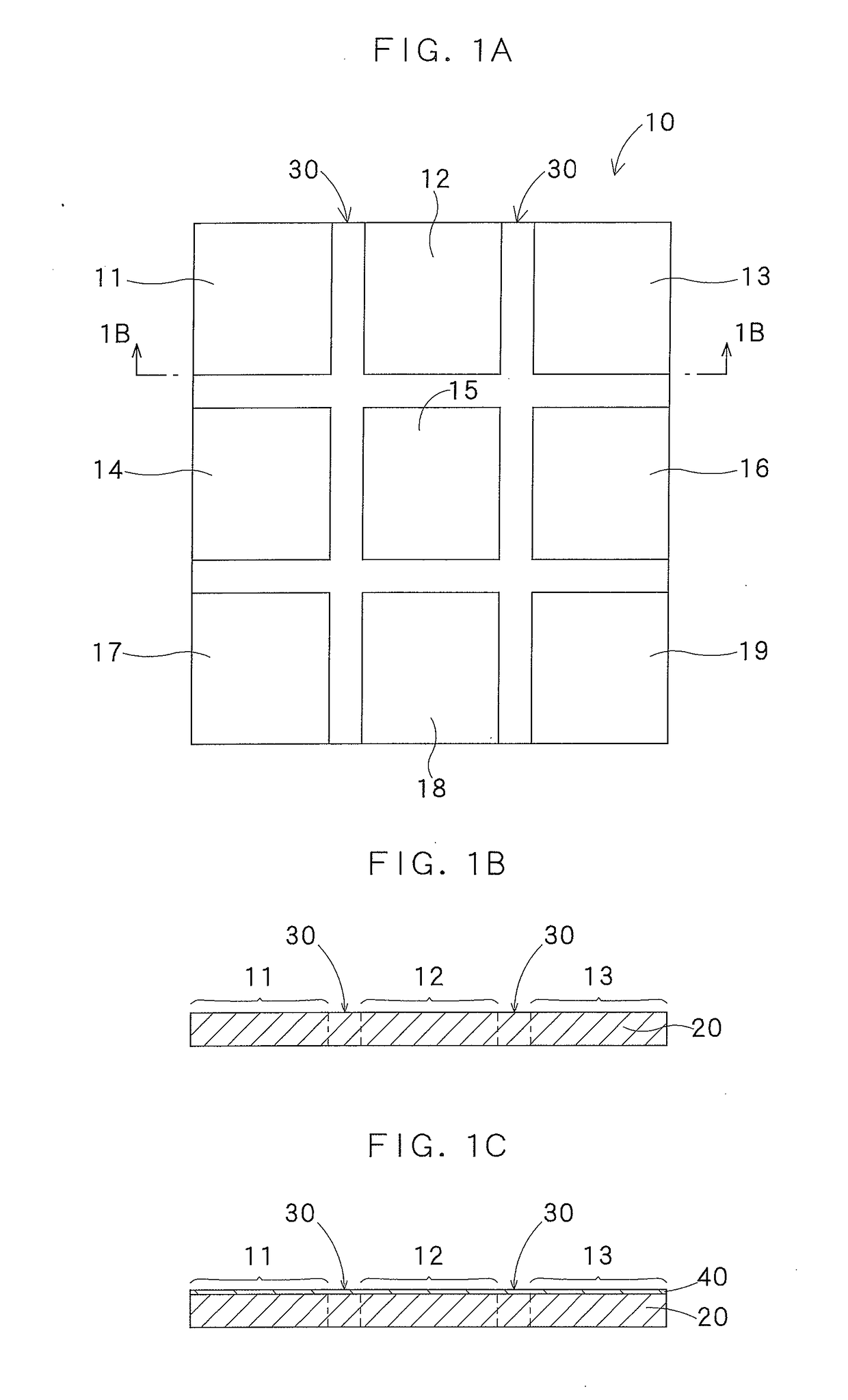

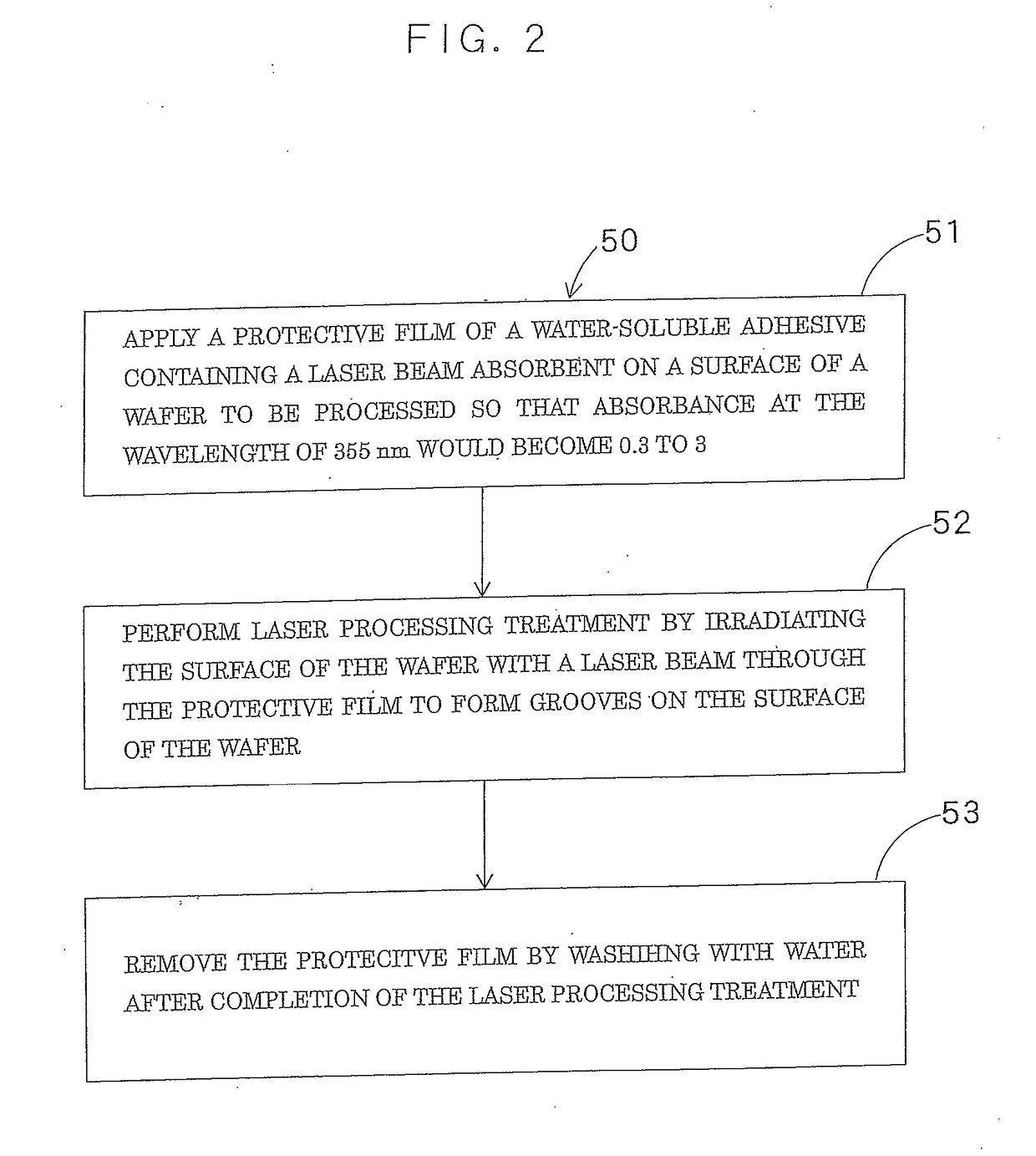

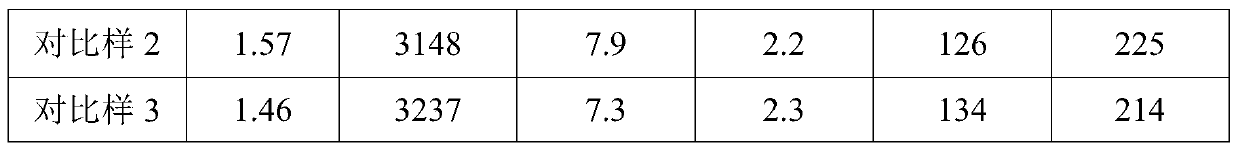

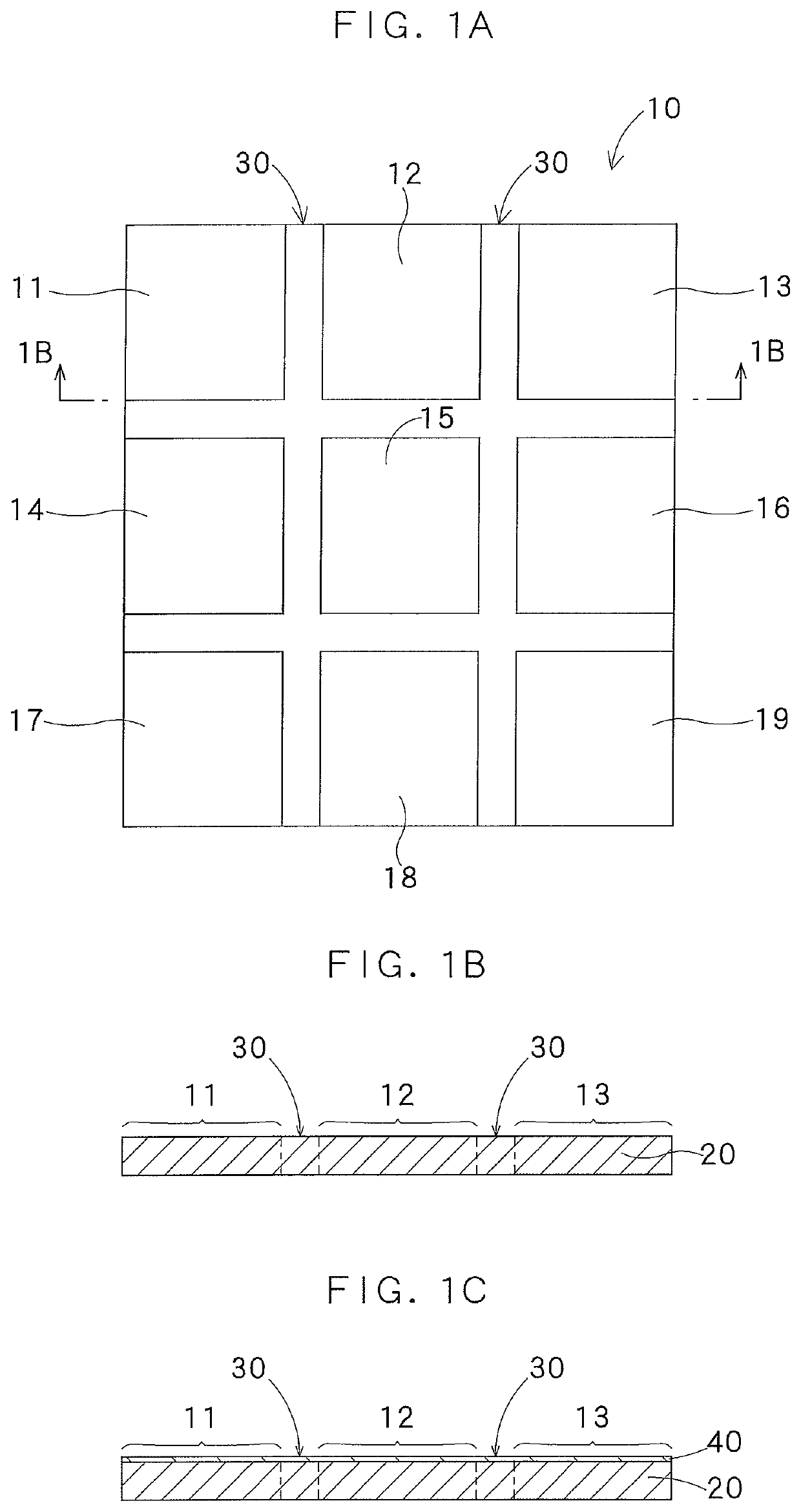

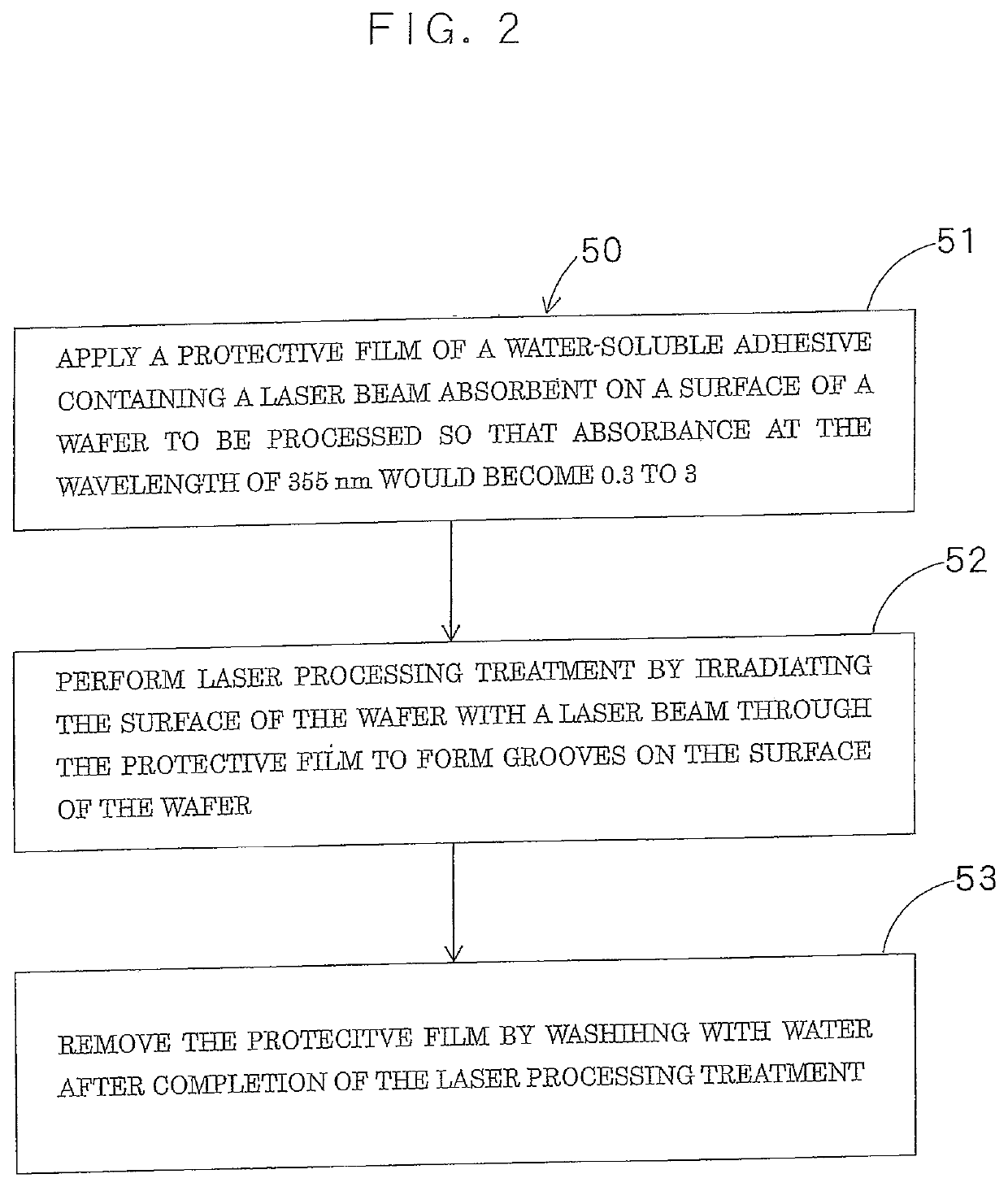

Protective film material for laser processing and wafer processing method using the protective film material

ActiveUS20190006295A1Reduce dispersionEasy to disassembleSemiconductor/solid-state device detailsSolid-state devicesTectorial membranePolyvinyl alcohol

A protective film material for laser processing comprises a solution of a water-soluble adhesive and a water-soluble laser beam absorbent added to adjust absorbance at a wavelength of 355 nm (absorbance as calculated as a 200-times diluted solution) to 0.3 to 3. The protective film effectively absorbs an irradiated laser beam, reduces generation of debris during laser beam irradiation, and can be removed by washing with water after completion of the laser processing treatment, thereby providing reliable processing. The water-soluble adhesive is preferably a blend of polyvinyl alcohol and poly-N-vinyl acetamide, which are preferably blended at a ratio of 100 to 200:1 in terms of amounts of respective components.

Owner:NIKKA SEIKO

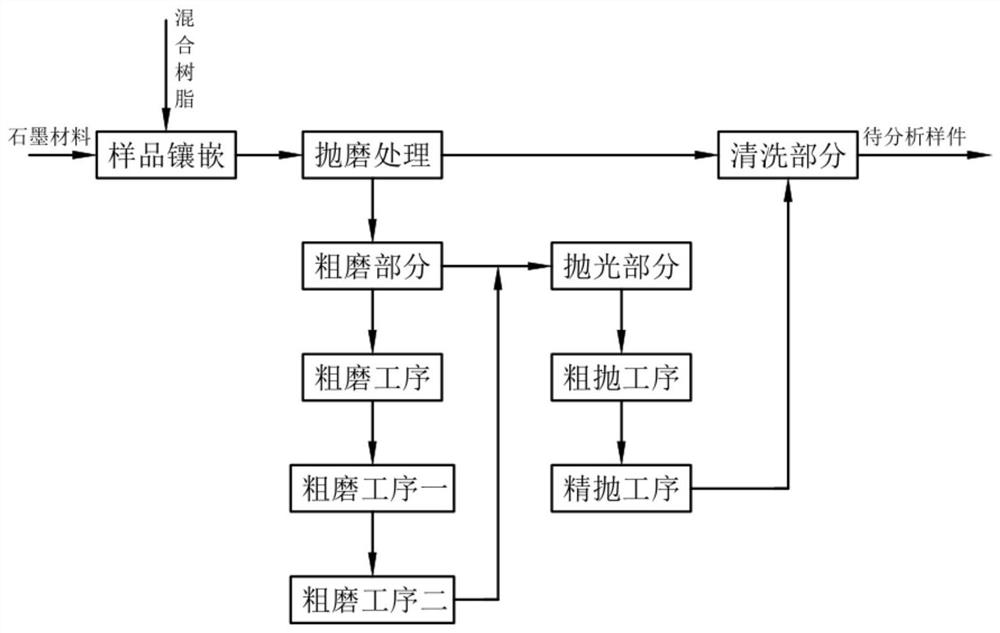

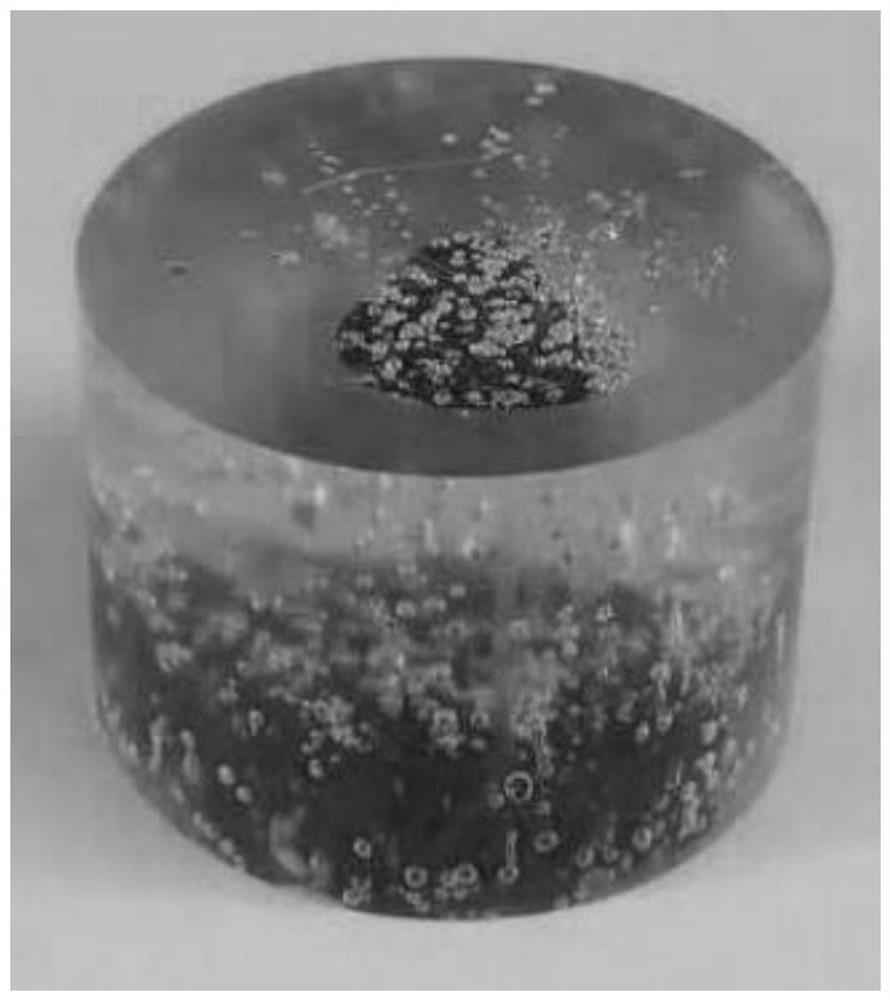

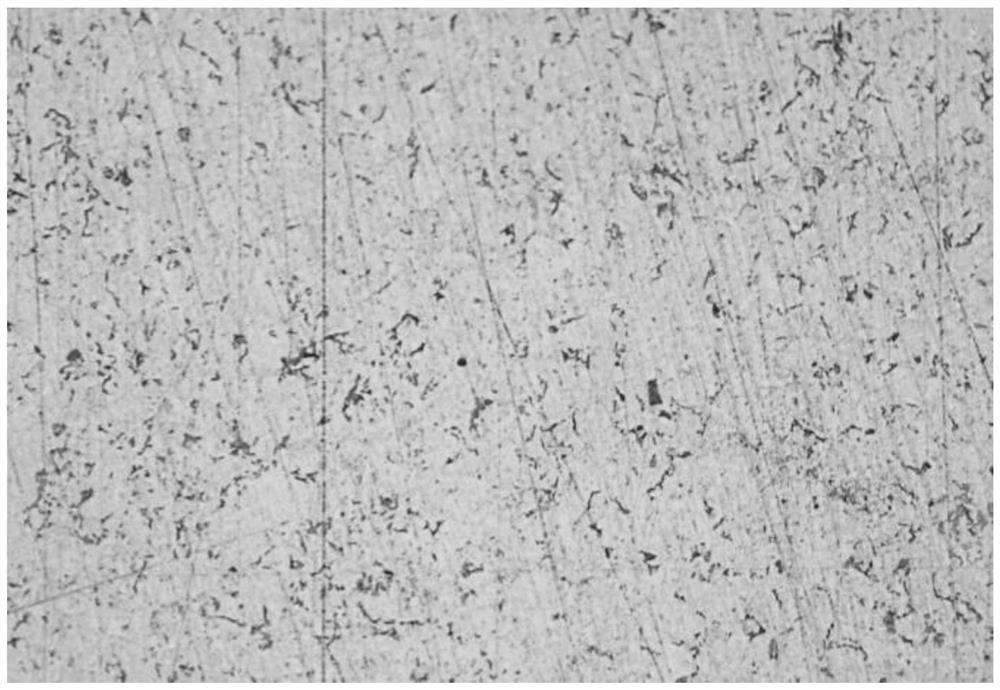

Preparation method of sample for representing graphite optical microscopic structure

ActiveCN108871892ASelf-removalHigh surface flatnessPreparing sample for investigationTest sampleGraphite

The invention relates to the technical field of the production of artificial graphite, in particular to a preparation method of a sample for representing a graphite optical microscopic structure. Thepreparation method comprises the following steps: inlaying a sample, grinding and polishing, cleaning, performing the gas emission for a graphite material and mixed resin in a vacuumizing way, mixingthe graphite material and the mixed resin in a pouring way, clamping a sample to-be-ground part on a grinding and polishing device by virtue of a horizontal positioning manner, pressing the sample to-be-ground part in an elastic pressurizing way, performing the multisection grinding treatment for the sample, cleaning, washing and blowing the sample, and forming a test sample; and discharging the gas in the graphite material and mixed resin by virtue of a negative-pressure exhaust way, mixing and solidifying the graphite material and mixed resin, horizontally fixing the test sample by virtue ofa horizontal positioning and clamping way, and performing the multi-step surface grinding for the sample by virtue of a variable pressing and loading force, so that the technical problem in the priorart the grinding effect of the test sample is poor can be solved.

Owner:SINOSTEEL NEW MATERIAL ZHEJIANG

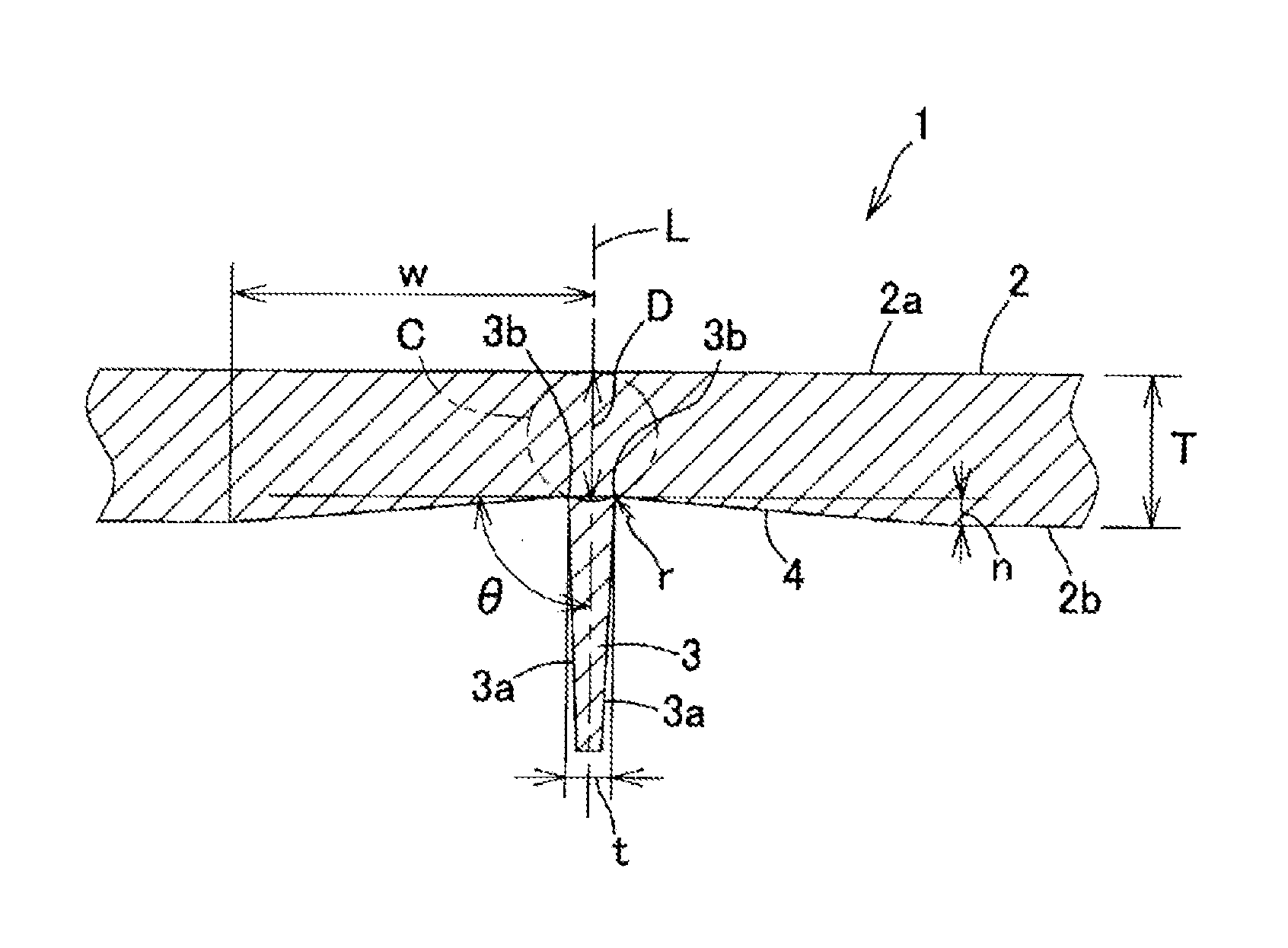

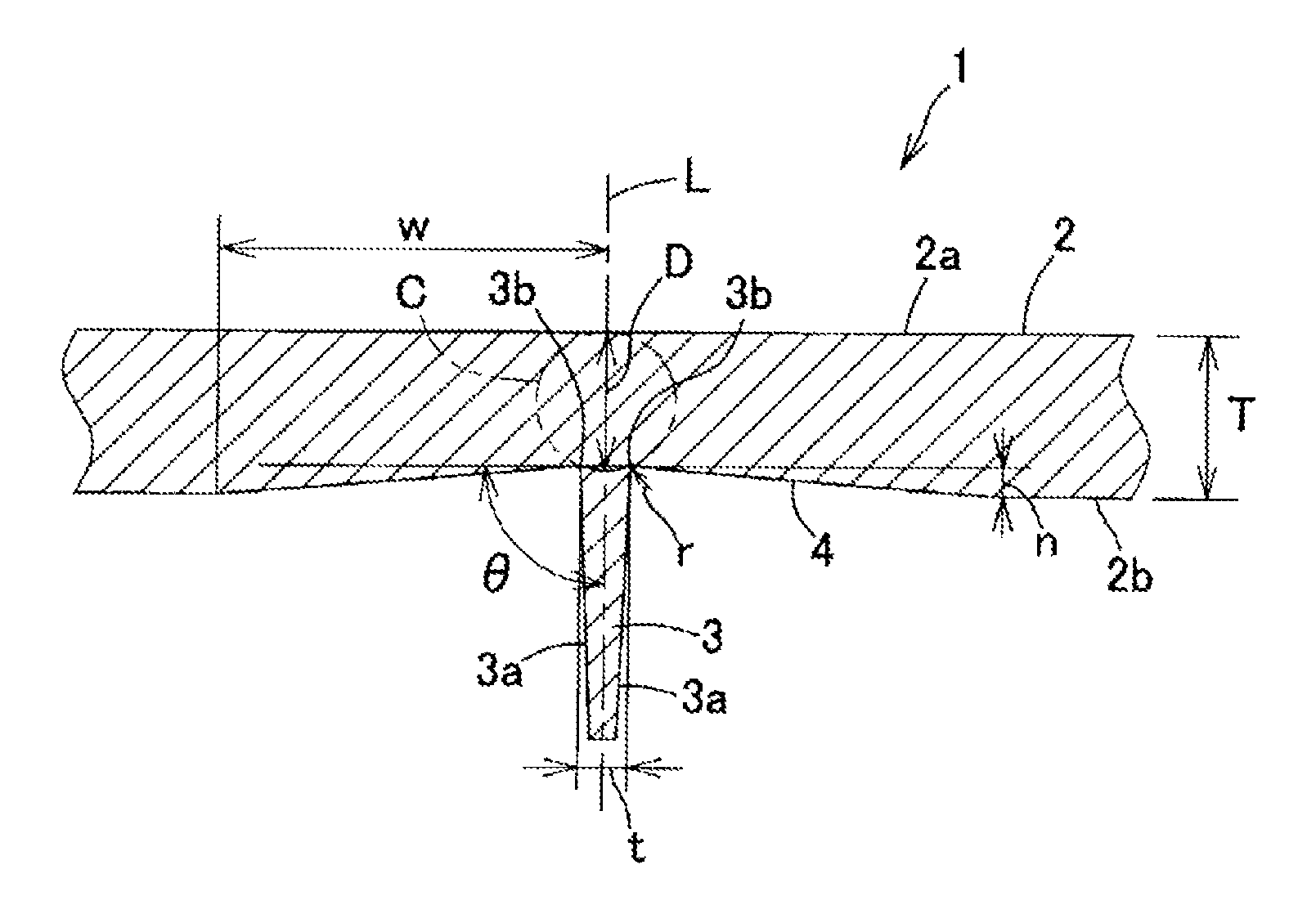

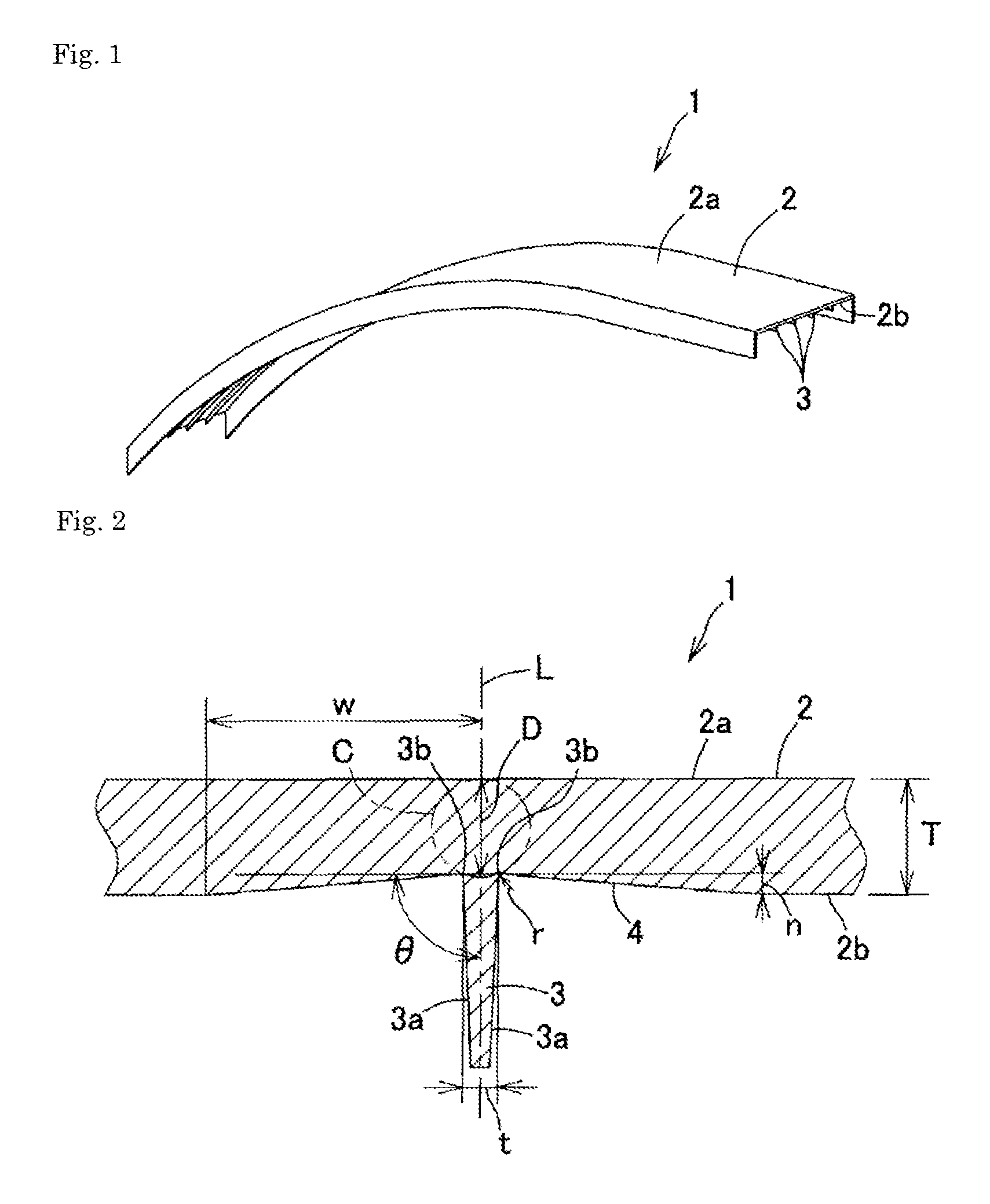

Moulded body having specific cross-sectional structure

ActiveUS20150165659A1Reduce the differenceSuppresses and prevents generationLayered productsDomestic articlesEngineering

A moulded body 1 includes a rib part 3 standing on a back surface 2b opposite to a design surface 2a of a main body 2 of the moulded body 1. A reduced thickness part 4 is formed on the back surface 2b of the main body 2, the ratio D / T is 0.975 to 1.07 where D is the diameter of a circle that passes through base ends 3b of both side faces 3a of the rib part 3 and is in contact with the design surface 2a of the main body 2 positioned between the base ends 3b, and T is the thickness of the main body 2 at an outer side of the reduced thickness part 4, and t<1.3(T−n) is satisfied where t is the thickness of the rib part 3, and n is the thickness of the reduced thickness part 4.

Owner:KANEKA CORP

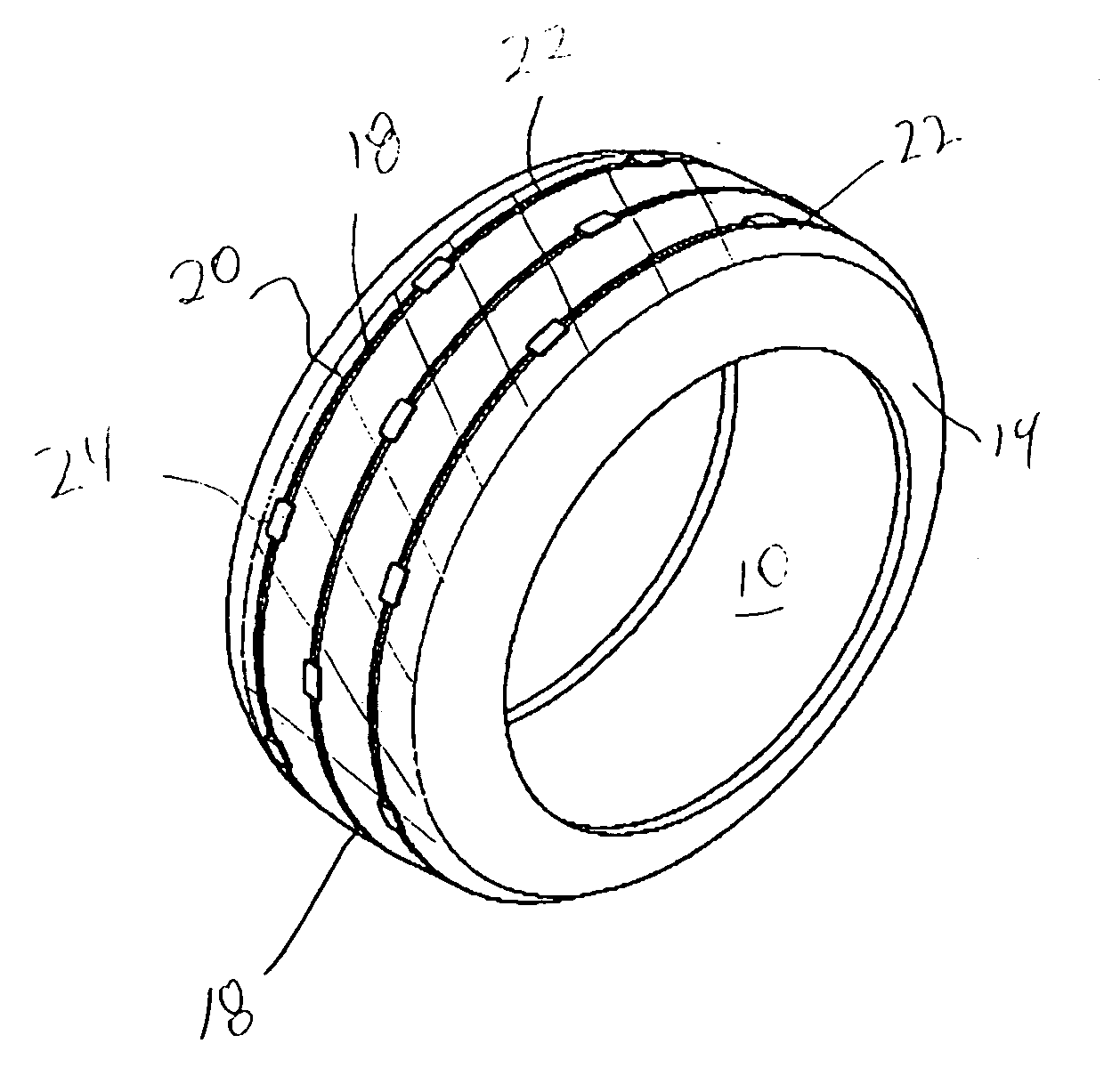

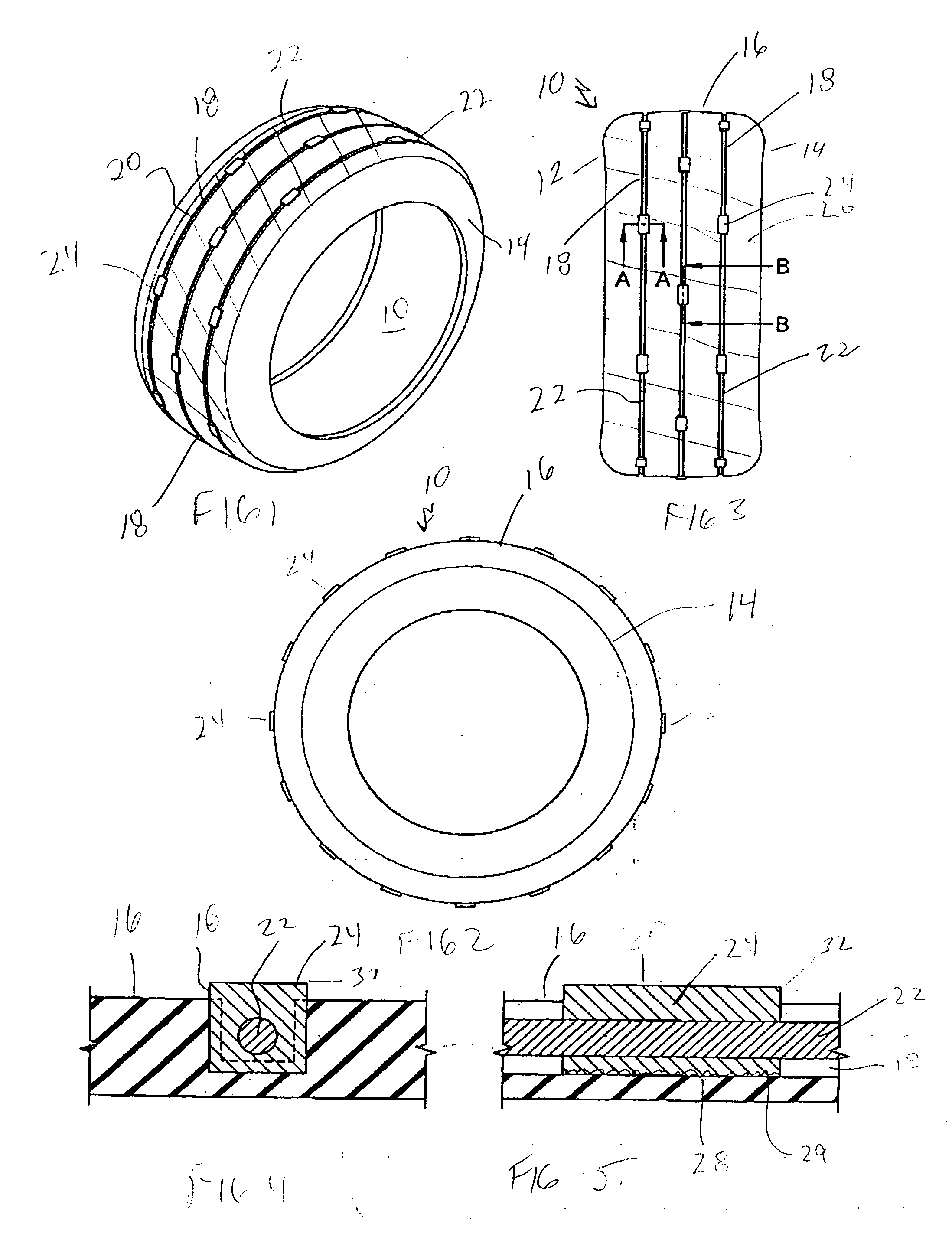

Traction aid for wheeled vehicles

InactiveUS20070017616A1Great tractionEasy to fixNon-inflatable tyresPneumatic tyre reinforcementsTreadAutomotive engineering

A traction aid for wheeled vehicles cooperable with the circumferential peripheral grooves of a tire of the wheeled vehicle, the traction aid comprising a cable securable at both ends, forming a loop, fixedly secured to the cable, there being a plurality of beads such that when installed, the cable lies completely recessed within a respective circumferential peripheral groove of the tire and the respective beads extend outwardly and above the upper surface of the tread of the tire thereby providing additional traction and grip in cooperation with the cross grooves of the tire in snowy and icy climatic conditions.

Owner:ABANTO POWER

A kind of transparent hydrogenated polystyrene-b-randomly copolymerized conjugated diene/styrene resin and preparation method thereof

The invention discloses transparent hydrogenated polystyrene-b-random copolymerized conjugated diene / styrene resin and a preparation method therefor. The transparent resin is composed of a styrene block and a random copolymerized block of styrene, conjugated diene and divinyl benzene, and the double bond degree of hydrogenation in the conjugated diene unit in the block copolymer reaches over 98%. The preparation method comprises: firstly homopolymerizing a styrene monomer under initiation of lithium alkyl; then carrying out random copolymerization with mixed monomers of styrene, conjugated diene and divinyl benzene; and carrying out hydrogenation reaction on the copolymerized product to obtain the resin. The preparation method is simple, and the prepared hydrogenated polystyrene-b-random copolymerized conjugated diene / styrene resin is high in strength, has the characteristics of being relatively good in processing property and aging resistance, low in turbidity, high in transparency and the like, can be molded by injection and film-drawing, and is wide in application field.

Owner:SINOPEC BALING PETROCHEMICAL CO LTD

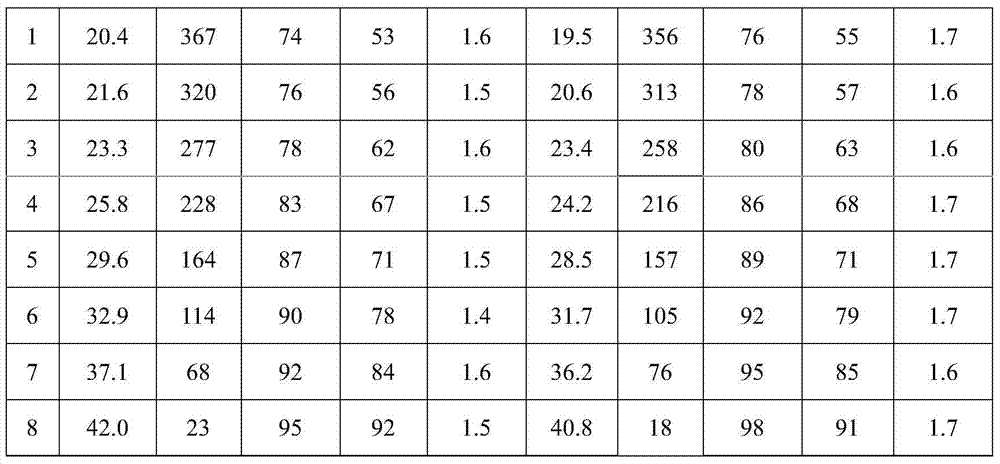

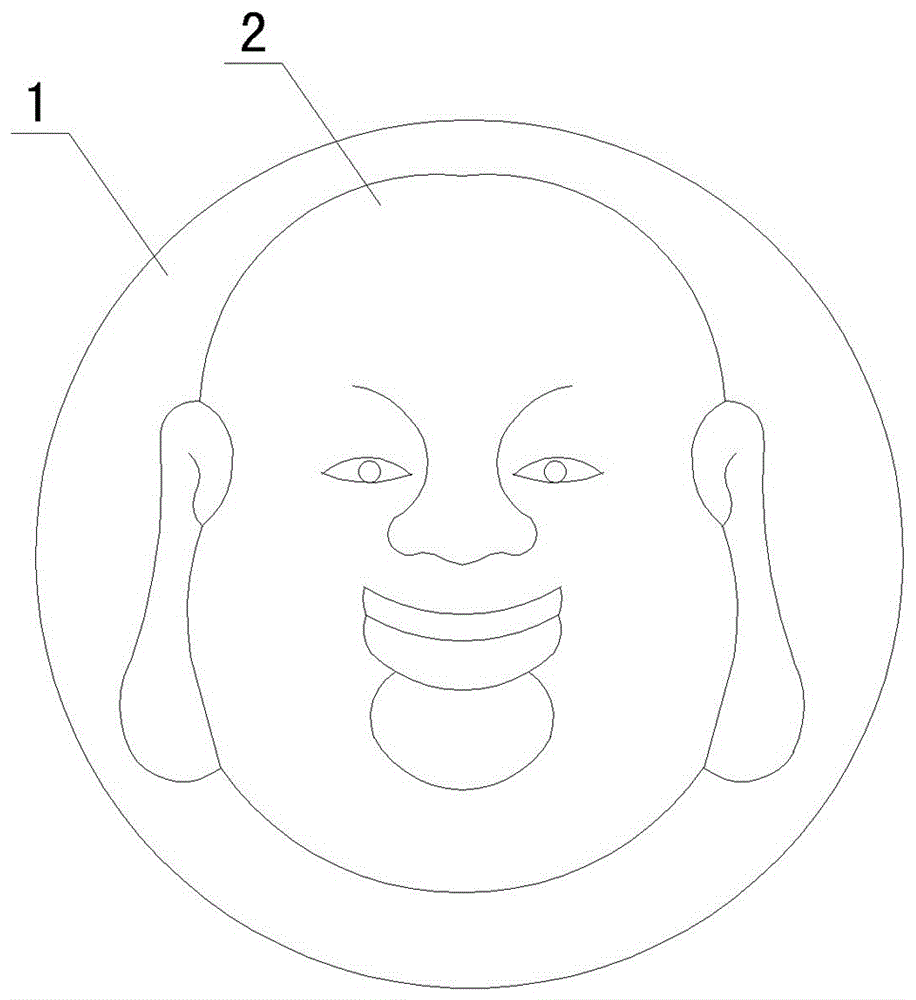

A method for cultivating shaped pearls in viscera of river mussels

InactiveCN104012436BNot easy to fall offHigh Quality Pearl RateClimate change adaptationPisciculture and aquariaEngineeringCultured pearl

The invention relates to a method for cultivating shaped pearls in mussel viscera. The method for cultivating mussel viscera-shaped pearls comprises the following steps: firstly making a molding core, and setting patch grooves on the imaging secondary end or secondary surface of the modeling core, and then pasting small cell pieces on the patch In the concave groove, make it depend on the patch concave groove, and then implant the mold core into the nucleus of the viscera mass of the mother clam, and put the core-planted mother clam back into the culture waters to cultivate and raise pearls. After maturity, high-value shaped pearls can be harvested from the viscera of the mother mussel. The shaped pearls produced by the invention not only have a uniform and smooth pearl surface and a high rate of high-quality pearls, but also have clear pictures and texts, vivid images, strong three-dimensional sense, and the economic value can reach the highest point of jewelry level.

Owner:谢绍河

Moulded body having specific cross-sectional structure

ActiveUS9522493B2Reduce the differenceSuppresses and prevents generationLayered productsDomestic articlesEngineeringMechanical engineering

A molded body 1 includes a rib part 3 standing on a back surface 2b opposite to a design surface 2a of a main body 2 of the molded body 1. A reduced thickness part 4 is formed on the back surface 2b of the main body 2, the ratio D / T is 0.975 to 1.07 where D is the diameter of a circle that passes through base ends 3b of both side faces 3a of the rib part 3 and is in contact with the design surface 2a of the main body 2 positioned between the base ends 3b, and T is the thickness of the main body 2 at an outer side of the reduced thickness part 4, and t<1.3(T−n) is satisfied where t is the thickness of the rib part 3, and n is the thickness of the reduced thickness part 4.

Owner:KANEKA CORP

Circuit arrangement and method of testing an application circuit provided in said circuit arrangement

According to an example embodiment, there is an integrated circuit arrangement with at least one application circuit to be tested, and with at least one self-test circuit for testing the application circuit and generating at least one pseudo-random test sample. wherein said The pseudo-random test sample is converted into at least one test vector that is programmable and / or deterministic and is supplied to the application circuit for testing purposes via at least one logic gate and at least one signal that is applied to said logic gate. The output signal arising in dependence on the deterministic test vector is evaluated by the application circuit by at least one signature register. Furthermore, there is a method of testing the application circuit such that Built In Self Test (BIST) hardware connected to the additional deterministic logic is reduced; it is suggested that the signal supplied to the logic gate is made available by a Bit Flipping Function (BFF) logic circuit based on at least one self-test circuit.

Owner:NXP BV

A suction-combined electrochemical micro-additive preparation method and device thereof

ActiveCN112522766BImprove stabilityIncrease flow rateCellsAdditive manufacturing apparatusManufacturing technologyEngineering

The invention belongs to the technical field of additive manufacturing, and specifically relates to a method for preparing a suction-combined electrochemical micro-additive material and a device thereof. The invention provides a suction-combined electrochemical micro-additive device, which includes a sealed electrolytic cell, a storage Liquid tanks, substrates, electrochemical workstations, nozzles, electrodes, liquid pumps, and three-dimensional translation stages. On the basis of the above-mentioned micro-additive device, an electrochemical micro-additive preparation method is proposed. By introducing a suction combined nozzle, it solves the problem that when the syringe needle moves in the meniscus electrochemical micro-additive manufacturing technology, The stability of the meniscus is poor, and the problem of liquid leakage is prone to occur, thereby improving the stability of the meniscus and the smoothness of printing; at the same time, this technology increases the flow rate of ions in the meniscus, supplementing the printing The ions consumed in the process make the printed product have a uniform surface, clear edges and less roughness, thereby improving the printing shape.

Owner:SUN YAT SEN UNIV

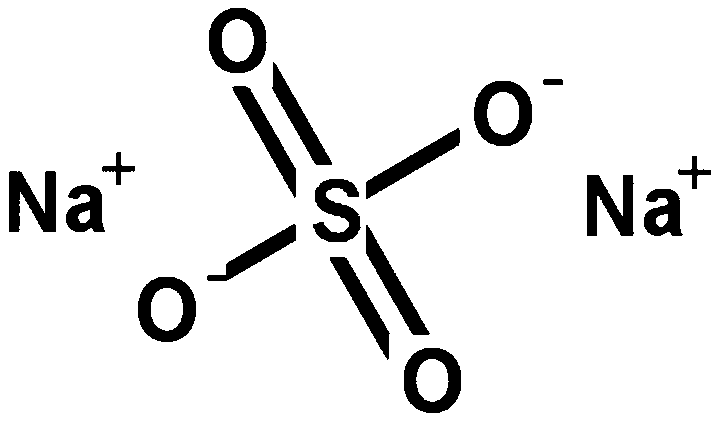

A soft color breathable film

ActiveCN108382034BThe effect of colorHigh lusterSynthetic resin layered productsCoatingsMasterbatchPolyolefin

The invention relates to a soft color gas permeable film, which is formed by carrying out co-extrusion compounding on three layer of a first gas permeable film layer, a second gas permeable film layerand a third gas permeable film layer, wherein the first gas permeable film layer and the third gas permeable film layer are respectively prepared from the following raw materials by weight: 5-20 parts of color masterbatch, 40-75 parts of a polyolefin resin, and 20-40 parts of anhydrous sodium sulfate filling masterbatch, the second gas permeable film layer comprises 40-60 parts of a polyolefin resin, 40-60 parts of anhydrous sodium sulfate filling masterbatch, and 1-10 parts of a block polymer, and the conjugated olefin is one selected from butadiene, isoprene and butadiene derived conjugateddiolefin. According to the present invention, the color of the color gas permeable film product cannot be affected in the production stretching pore-forming process, the chroma is high, and the toughness, the tensile strength, the elongation at break and the softness of the gas permeable film product are further increased.

Owner:FUJIAN HENGAN HYGIENE MATERIAL

Protective film material for laser processing and wafer processing method using the protective film material

ActiveUS10700016B2Reduce dispersionEasy to disassembleSemiconductor/solid-state device detailsSolid-state devicesLaser processingWafering

A protective film material for laser processing comprises a solution of a water-soluble adhesive and a water-soluble laser beam absorbent added to adjust absorbance at a wavelength of 355 nm (absorbance as calculated as a 200-times diluted solution) to 0.3 to 3. The protective film effectively absorbs an irradiated laser beam, reduces generation of debris during laser beam irradiation, and can be removed by washing with water after completion of the laser processing treatment, thereby providing reliable processing. The water-soluble adhesive is preferably a blend of polyvinyl alcohol and poly-N-vinyl acetamide, which are preferably blended at a ratio of 100 to 200:1 in terms of amounts of respective components.

Owner:NIKKA SEIKO

A sample preparation method for graphite optical microstructure characterization

ActiveCN108871892BSelf-removalHigh surface flatnessPreparing sample for investigationTest samplePhysical chemistry

Owner:SINOSTEEL NEW MATERIAL ZHEJIANG

A kind of antiskid rubber sole and preparation method thereof

ActiveCN106832470BImprove skid resistanceIncrease polaritySolesDomestic articlesPolymer scienceVulcanization

The invention relates to a rubber sole, and provides an anti-skid rubber sole. The anti-skid rubber sole is prepared from the following raw materials: NBR / PVC emulsion co-precipitation alloy, low-melting point polyamide, natural rubber, soluble polymerized styrene-butadiene rubber, brominated butyl rubber, white carbon black, an anti-aging agent, polyethylene glycol, a silane coupling agent, polyethylene wax, diethylene glycol, zinc oxide, stearic acid, insoluble sulfur, a vulcanization accelerator D and a vulcanization accelerator DM. The anti-skid rubber sole is vulcanized and molded in a mold of a space aluminum material, the vulcanizing temperature is 170 DEG C, the pressure is 16.5MPa-17.5MPa, and the vulcanizing time is 210-250s.

Owner:MAOTAI FUJIAN SOLES CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com