Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

798results about How to "High surface flatness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

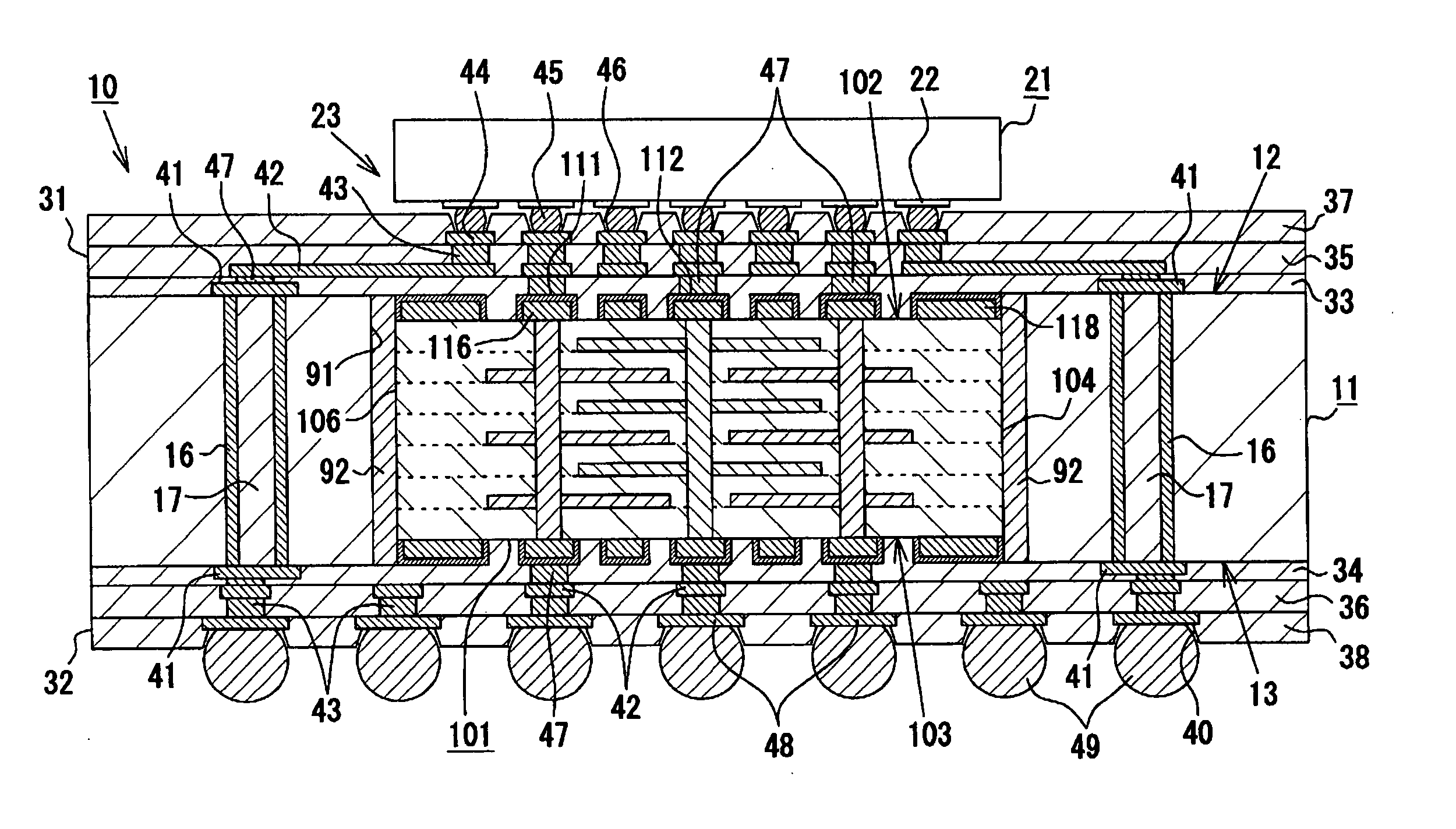

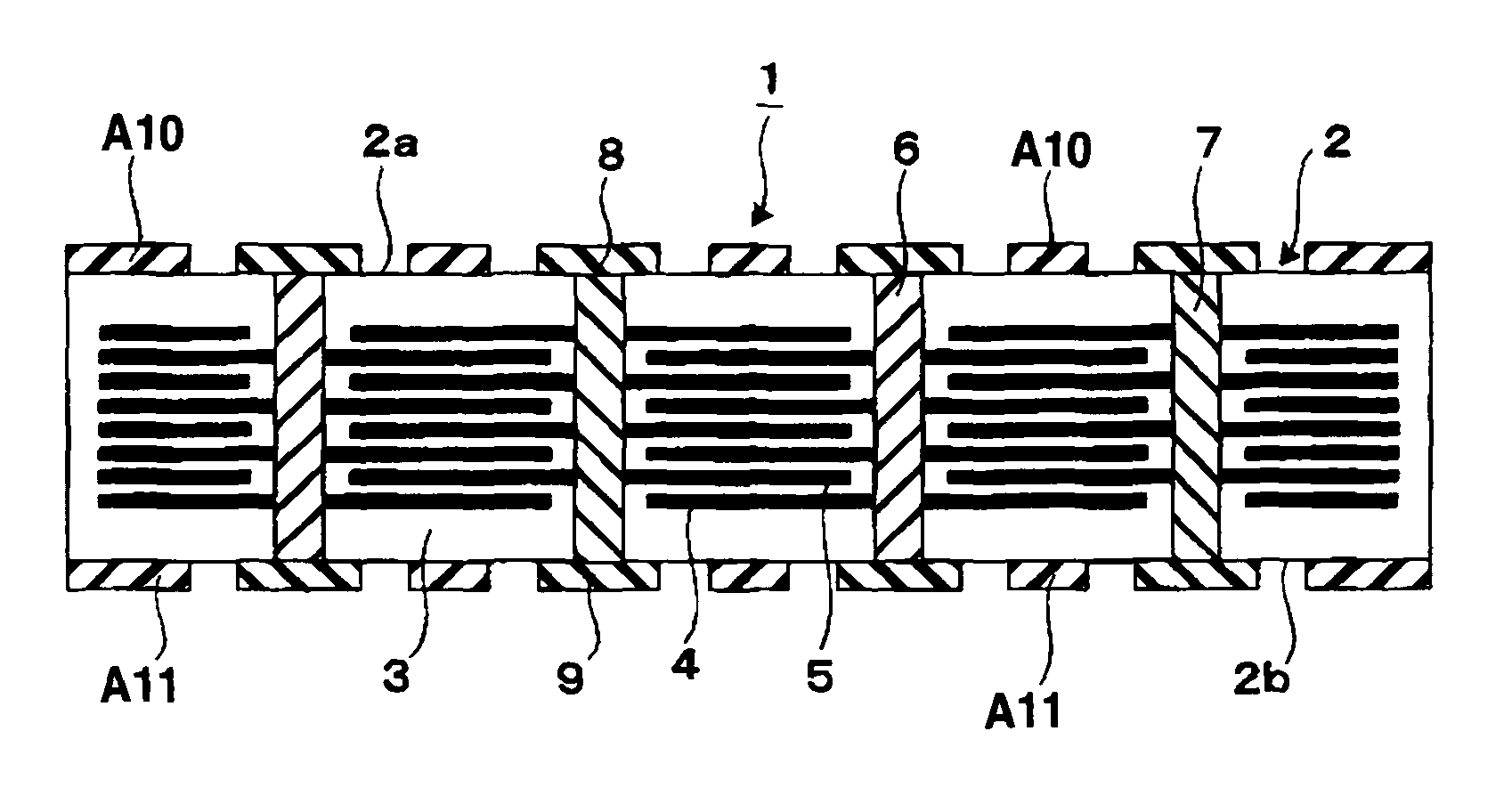

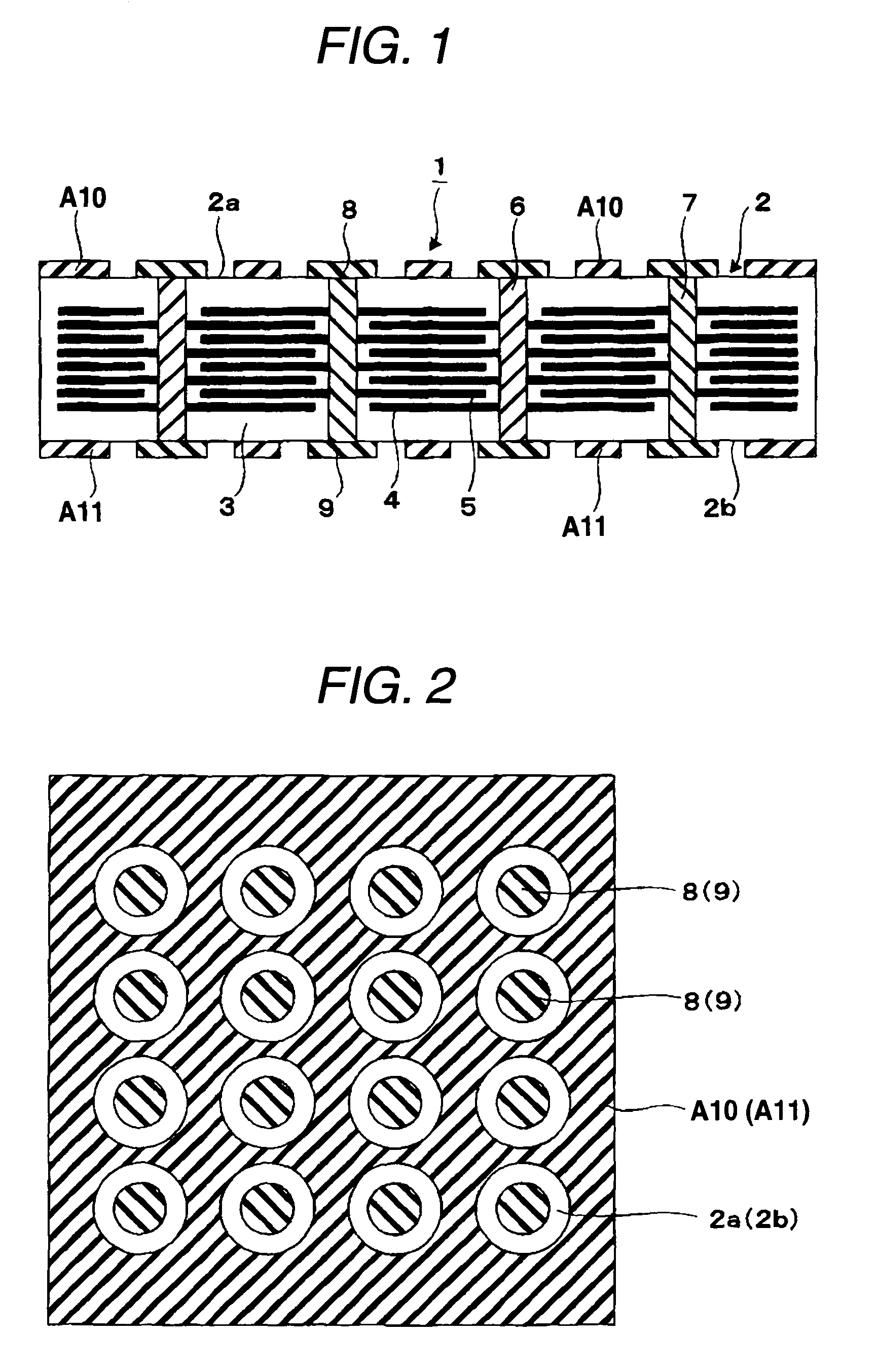

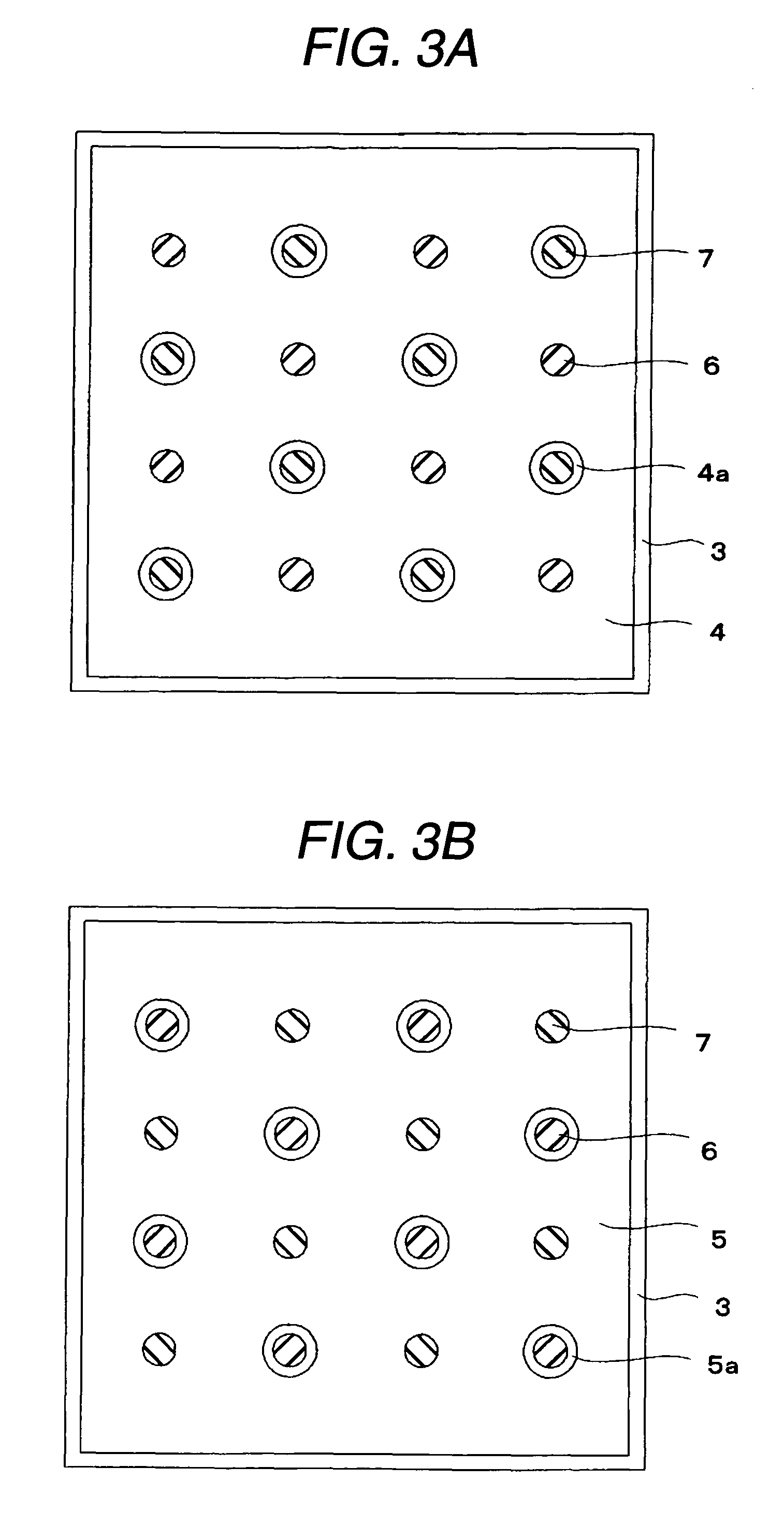

Capacitor for incorporation in wiring board, wiring board, method of manufacturing wiring board, and ceramic chip for embedment

InactiveUS20070030628A1High bonding strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectric layerCapacitor

A capacitor comprising: a capacitor body including a plurality of laminated dielectric layers, a plurality of inner electrode layers which are respectively disposed between mutually adjacent ones of the dielectric layers, a first main surface located in a laminated direction of the dielectric layers, and a second main surface opposite to the first main surface; a first outer electrode formed on the first main surface of the capacitor body and electrically connected to the inner electrode layers; a second outer electrode formed on the second main surface of the capacitor body and electrically connected to the inner electrode layers; a first dummy electrode formed on the first main surface of the capacitor body; and a second dummy electrode formed on the second main surface of the capacitor body.

Owner:NGK SPARK PLUG CO LTD

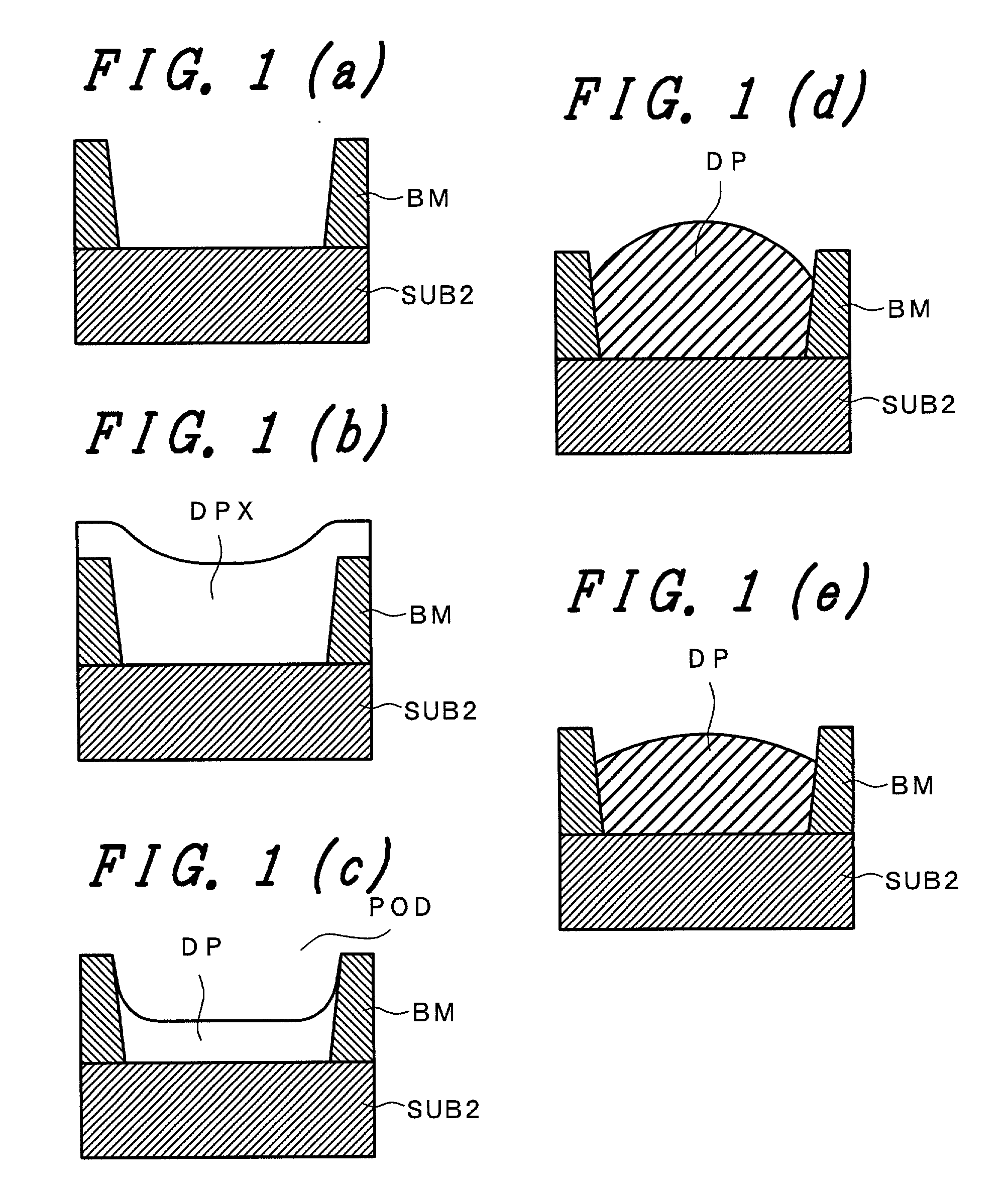

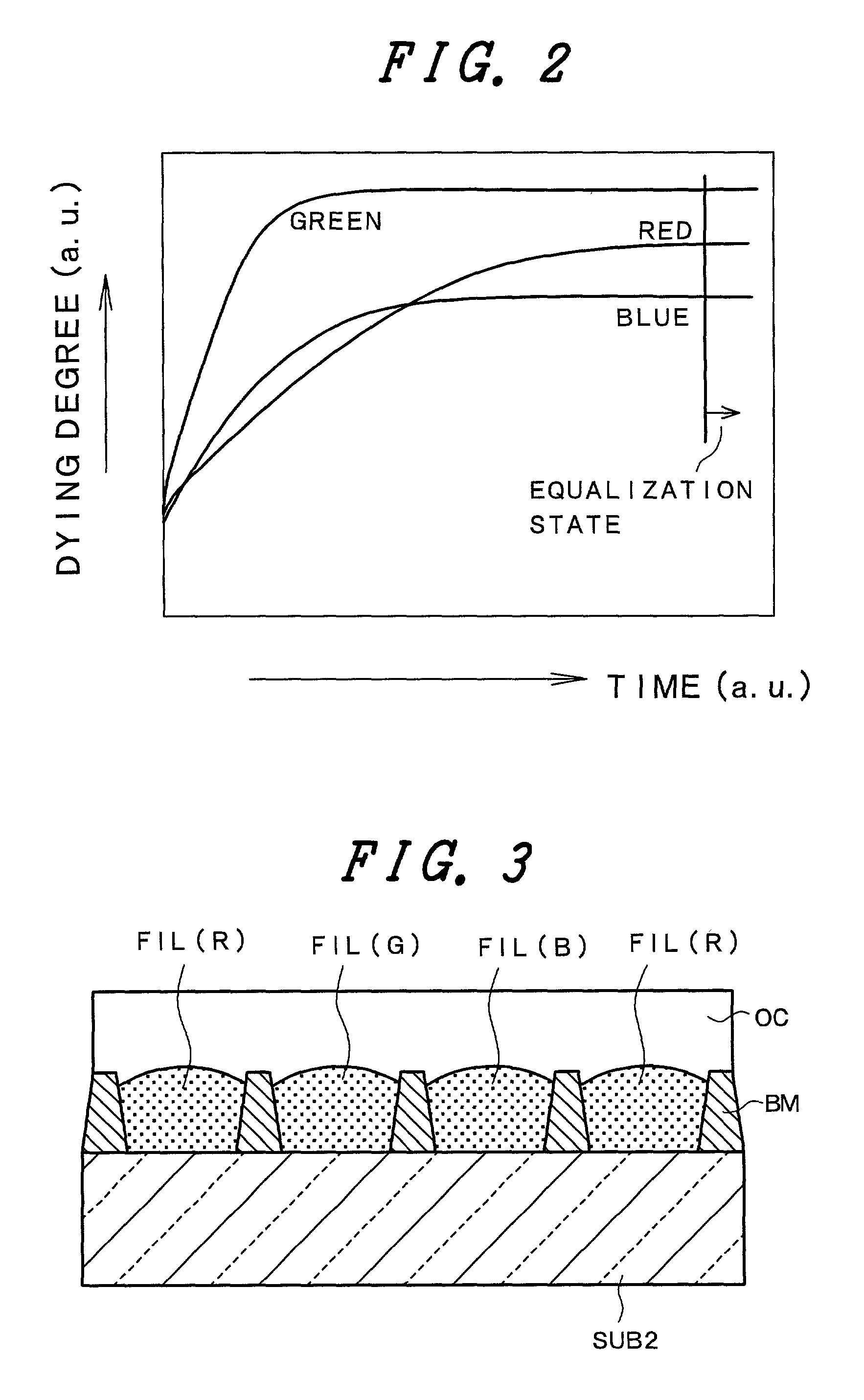

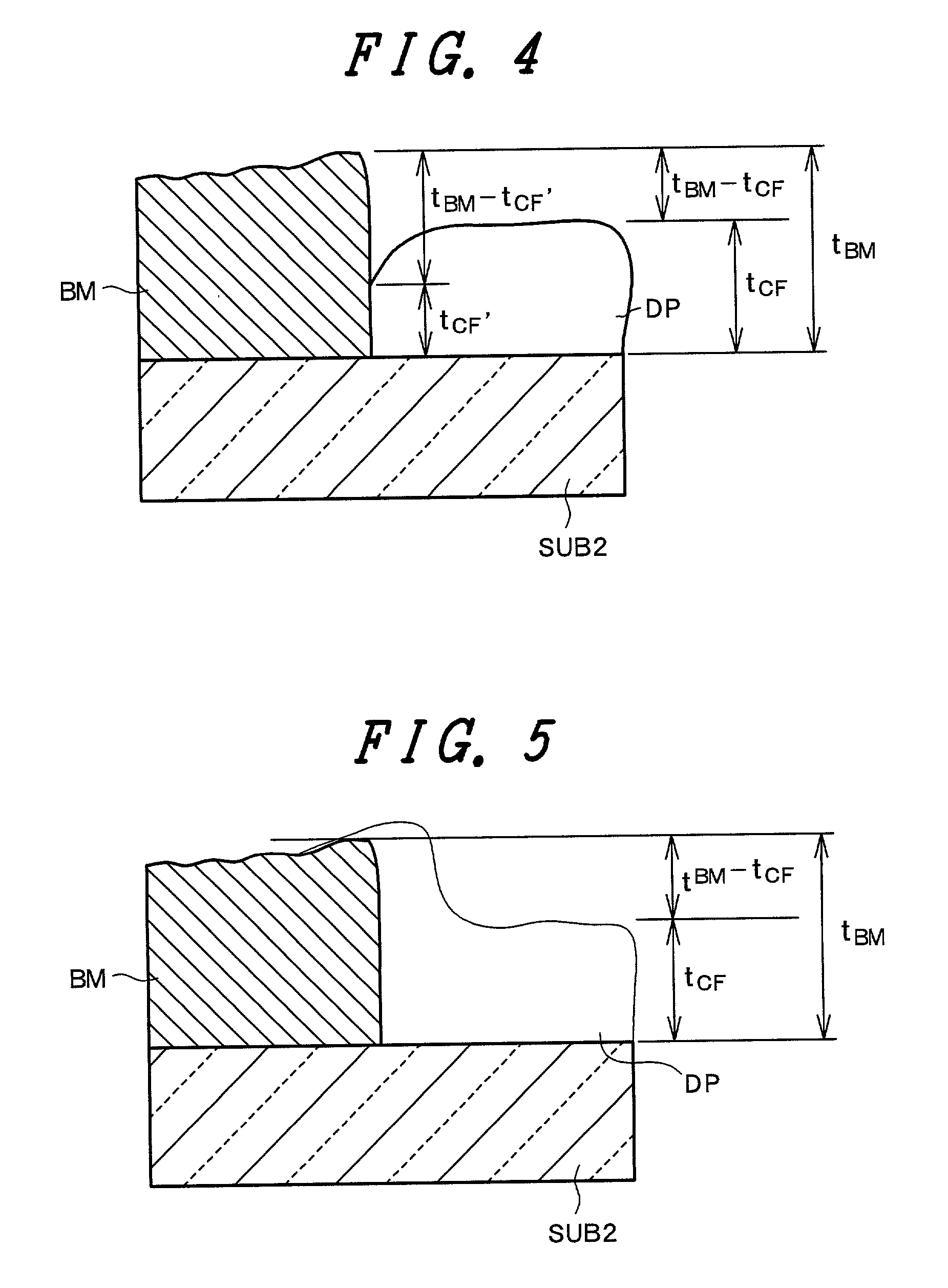

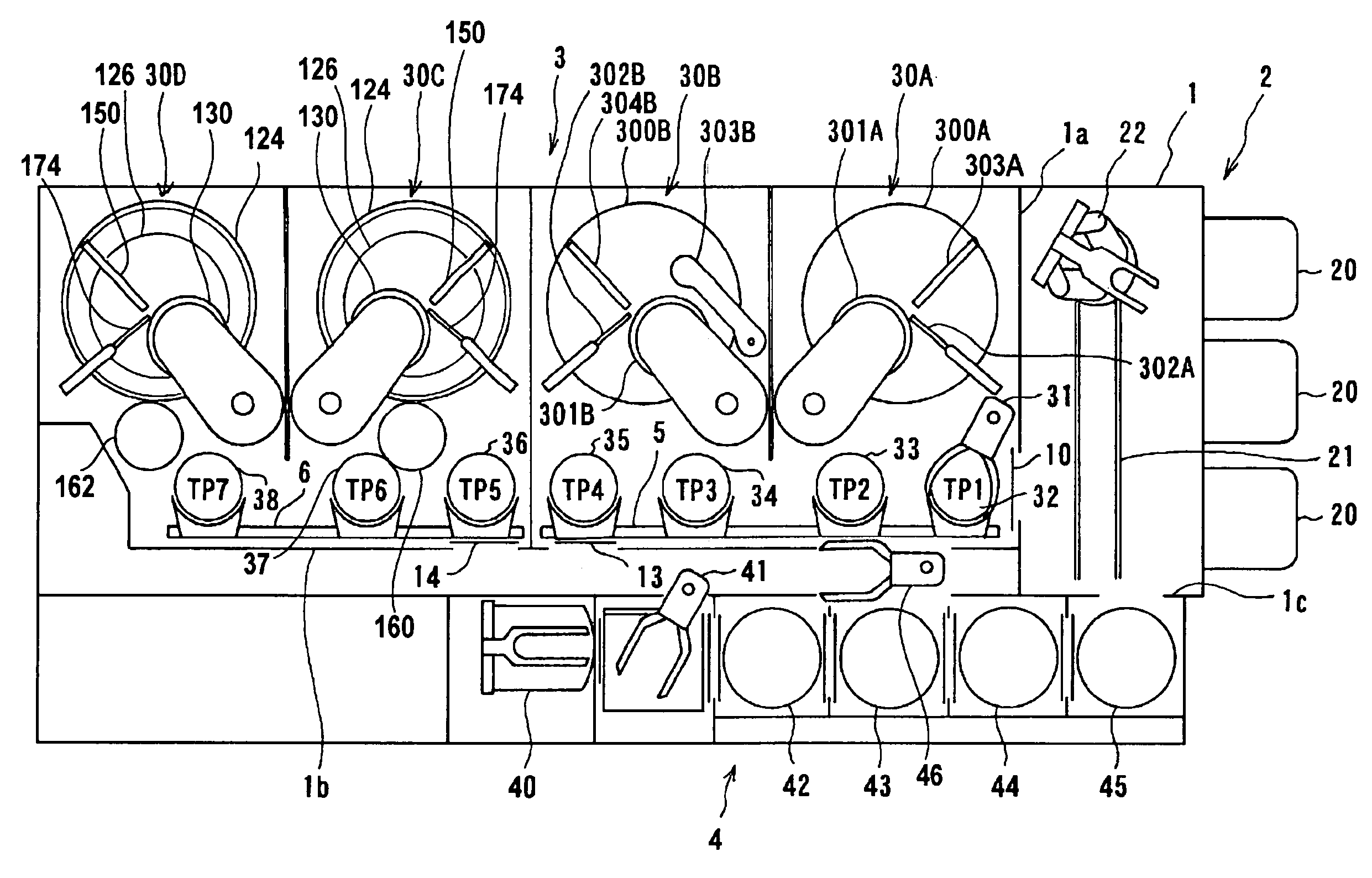

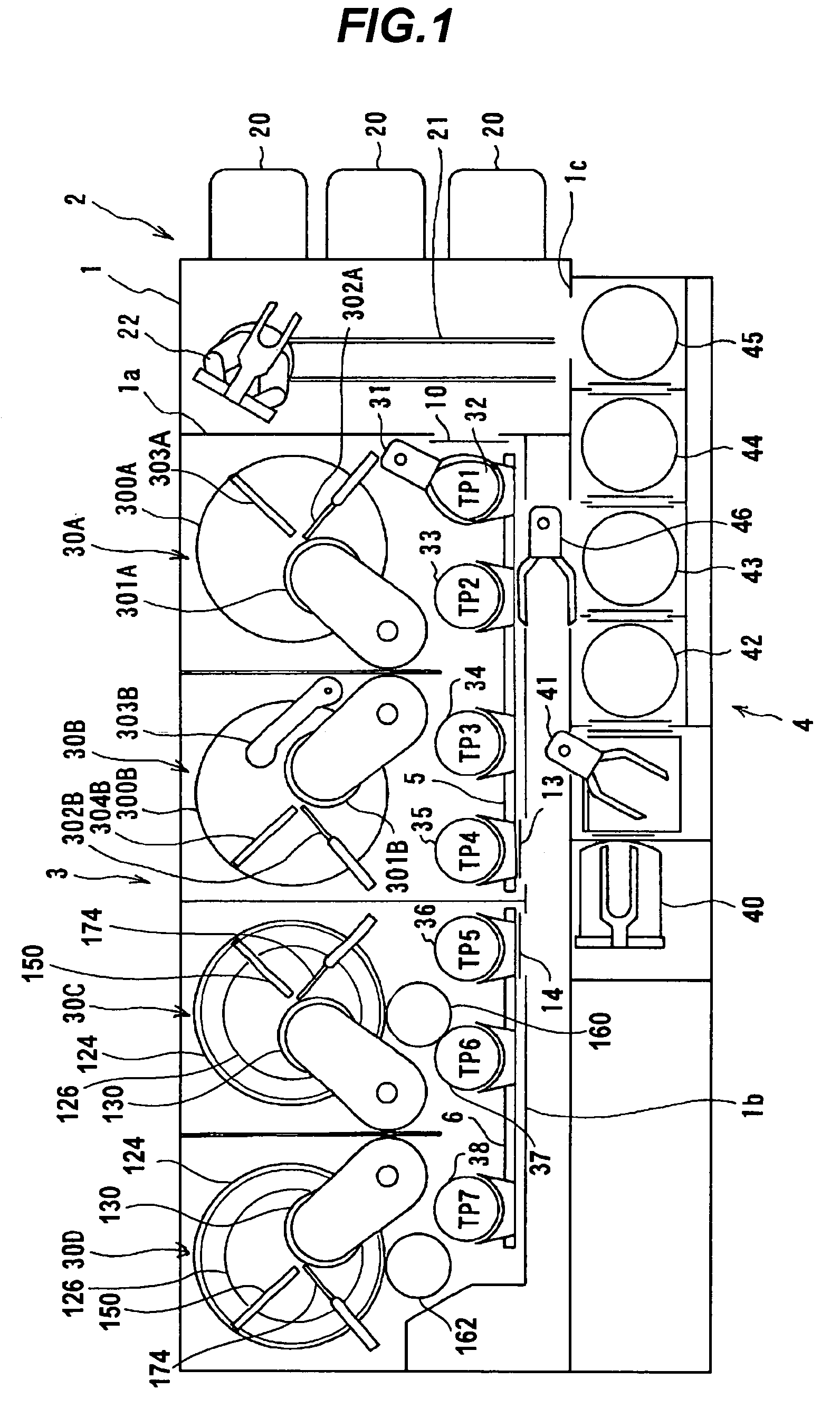

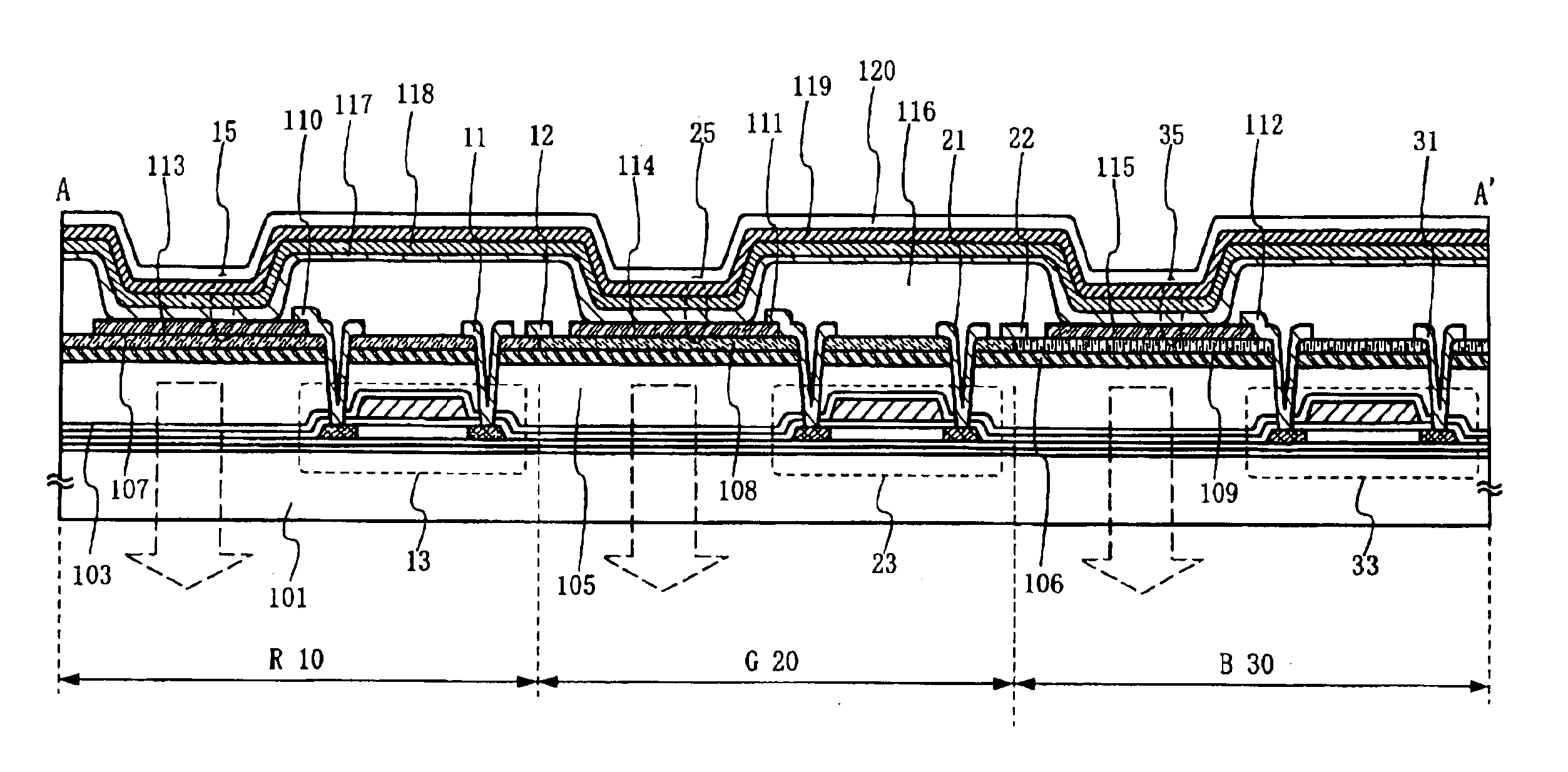

Method of manufacturing color filters and liquid crystal display device using these color filters

InactiveUS20010007733A1Improve flatnessImprove display qualityOptical filtersTypewritersUltravioletEngineering

After forming a black matrix which defines pixel regions on a substrate, dyed substrate layers of photo hardening property are formed. By irradiating ultraviolet rays to the dyed substrate layers from the back of the substrate and by developing, ink reservoirs which use the black matrix as partition walls are formed. The dyeing material such as the dye is supplied to these ink reservoirs by an ink jet system. Due to these partition walls, there is no possibility that the dyeing material scatters to the neighboring or adjacent pixel regions to cause the mixed color. Further, since the filters having a sufficient thickness can be formed in the ink reservoirs, the surface flatness of the color filters can be sufficiently ensured without coating the thick overcoat layer.

Owner:HITACHI LTD +1

Flattening method and flattening apparatus

ActiveUS20090095712A1Improve flatnessSufficient processing rateDecorative surface effectsSemiconductor/solid-state device manufacturingPlatinumMetal

A flattening method, by utilizing the advantages of the CARE method and making up for the disadvantages, can perform removal processing of a surface of a workpiece at a sufficient processing rate and can provide a processed surface having enhanced flatness without leaving damage in the processed surface. A flattening method comprises at least two surface removal steps and at least two cleaning steps, the final surface removal step being a catalyst-referred etching step comprising immersing a workpiece in a processing solution containing at least one of hydrohalic acid, hydrogen peroxide water and ozone water, and bringing a surface of a catalyst platen into contact with or close proximity to a surface to be processed of the workpiece to process the surface, said catalyst platen having in a surface a catalyst selected from the group consisting of platinum, gold, a ceramic solid catalyst, a transition metal, glass, and an acidic or basic solid catalyst.

Owner:EBARA CORP

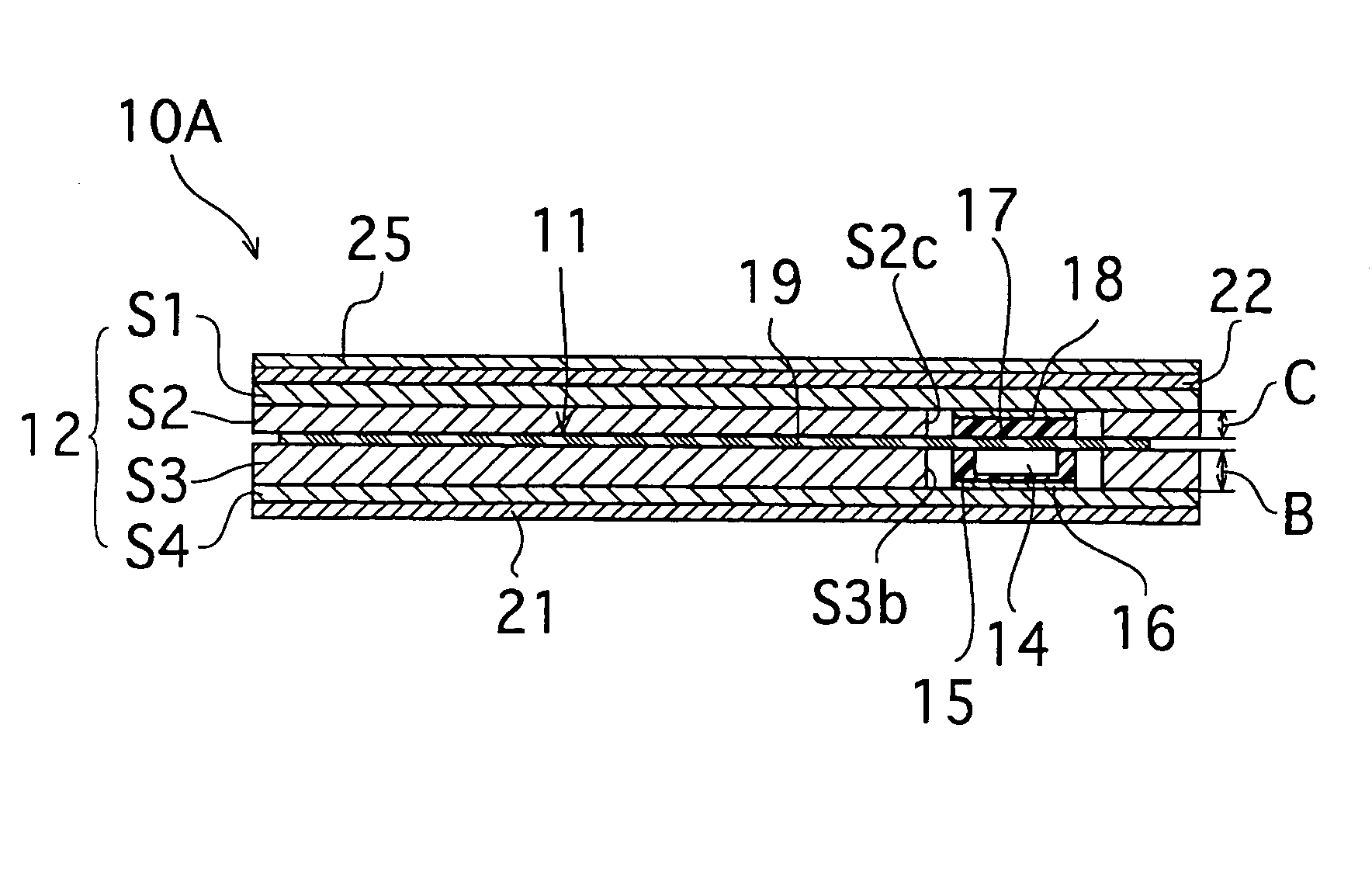

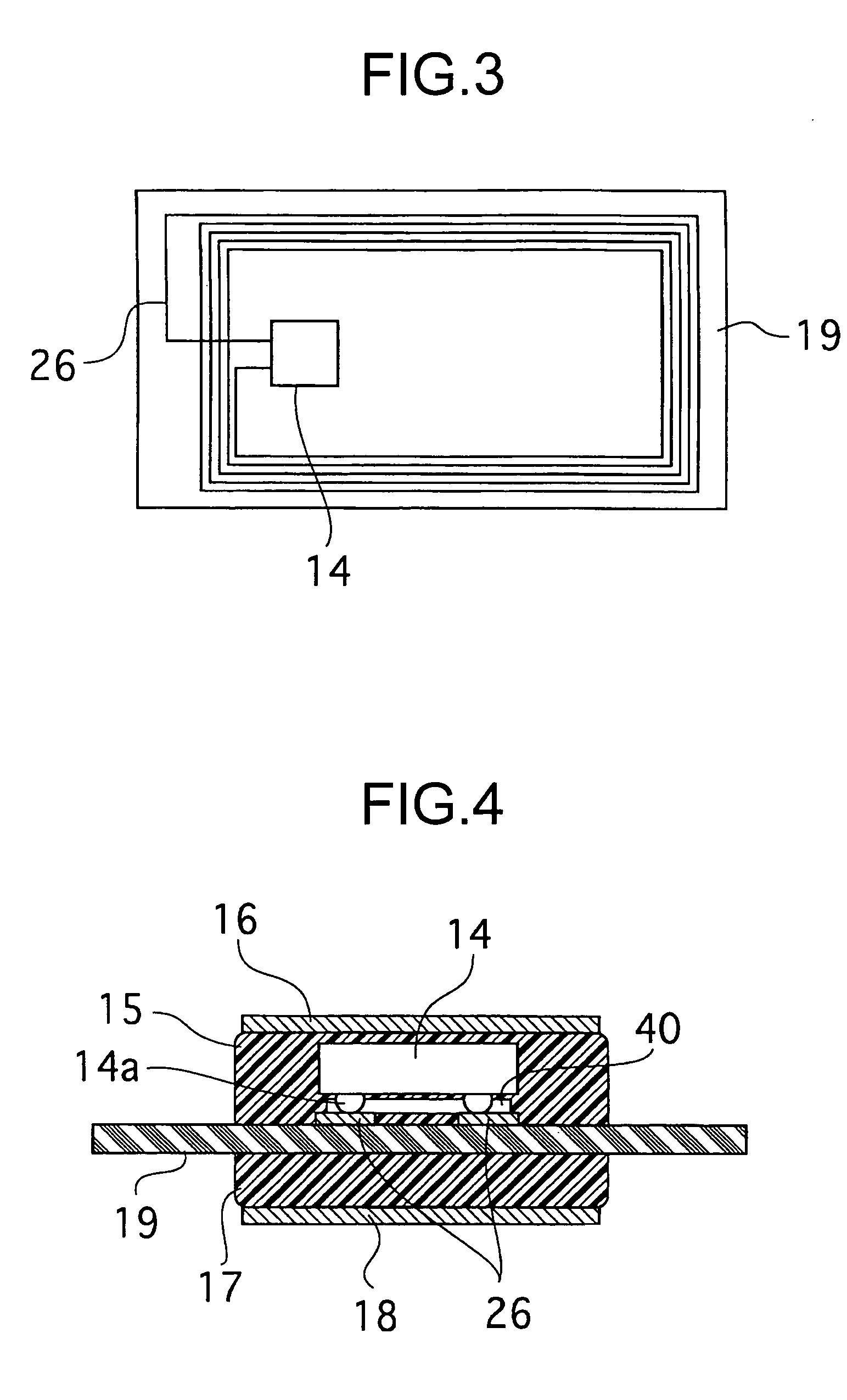

IC card

InactiveUS7377446B2Improve flatnessImprove printing effectComplete banking machinesOther printing matterComputer moduleEngineering

Owner:SONY CORP

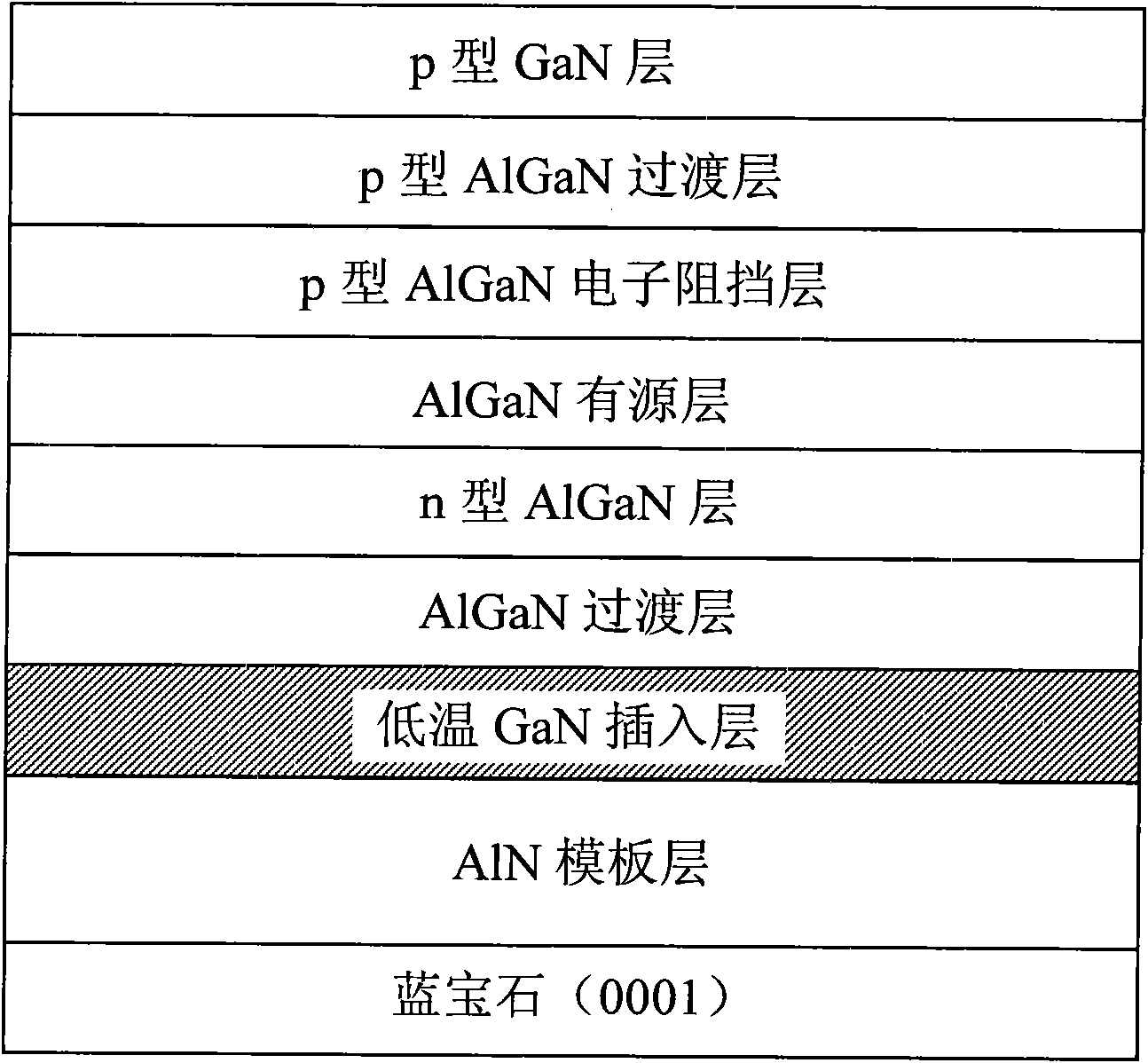

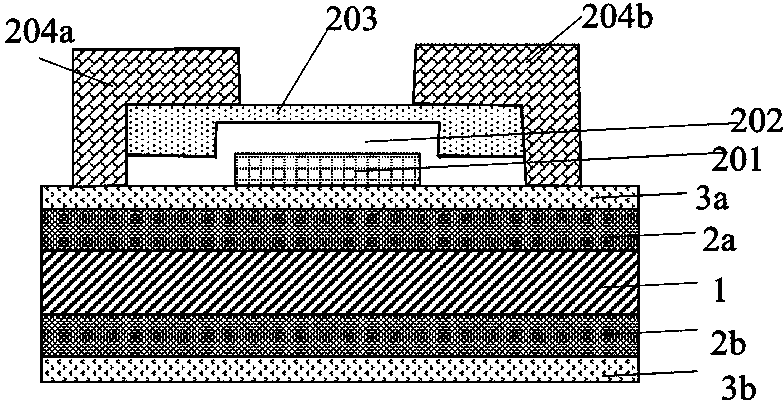

Deep-UV light-emitting diode and preparation method thereof

InactiveCN101604716AReduce dislocation densityImprove crystal qualitySemiconductor devicesDislocationSmooth surface

The invention provides a deep-UV light-emitting diode and a preparation method thereof. A low-temperature GaN insertion layer is used to replace an AlN / AlGaN superlattice or a high-temperature GaN insertion layer to grow the deep-UV light-emitting diode. The low-temperature GaN insertion layer is a GaN with thickness of 20-50nm under the conditions of temperature being 400-900 DEG C, pressure being 30-200torr, and V / III being 1500-2500. The method can effectively lower the dislocation density in an epitaxial AlGaN layer and a quantum well, and improves the surface planeness. The prepared LED component has smooth surface, better crystal quality, starting voltage reduction, and smaller serial resistances of the component; and the electroluminescene peak value is ranged from 300nm to 370nm.

Owner:PEKING UNIV

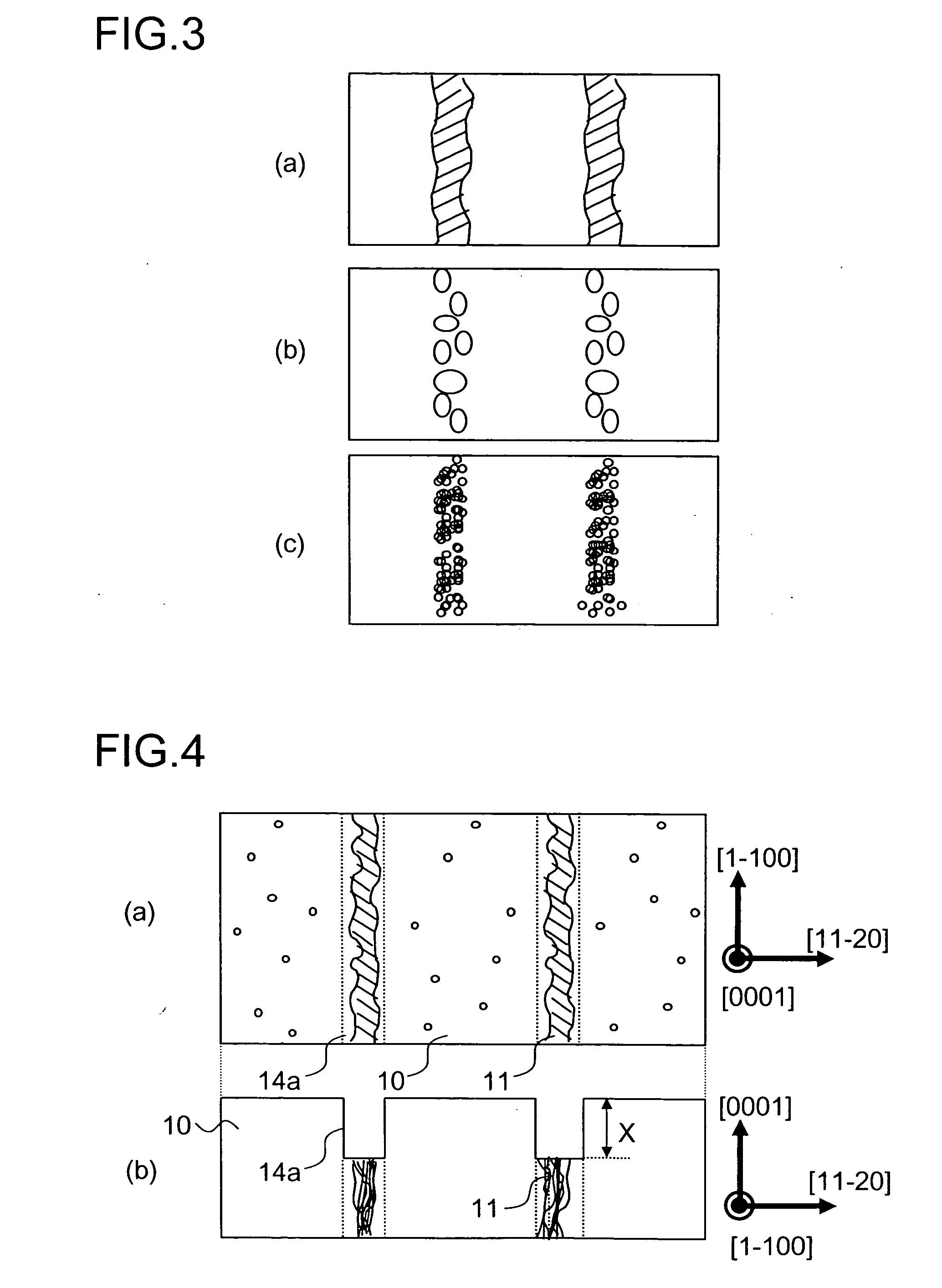

Nitride semiconductor light-emitting device

InactiveUS20070051961A1Improve yieldUniform characteristicsLaser detailsDischarge tube luminescnet screensLight emitting deviceNitride semiconductors

A nitride semiconductor light-emitting device wherein a substrate or nitride semiconductor layer has a defect concentration region and a low defect density region other than the defect concentration region. A portion including the defect concentration region of the nitride semiconductor layer or substrate has a trench region deeper than the low defect density region. Thus by digging the trench in the defect concentration region, the growth detection is uniformized, and the surface planarity is improved. The uniformity of the characteristic in the wafer surface leads to improvement of the yield.

Owner:SHARP KK +1

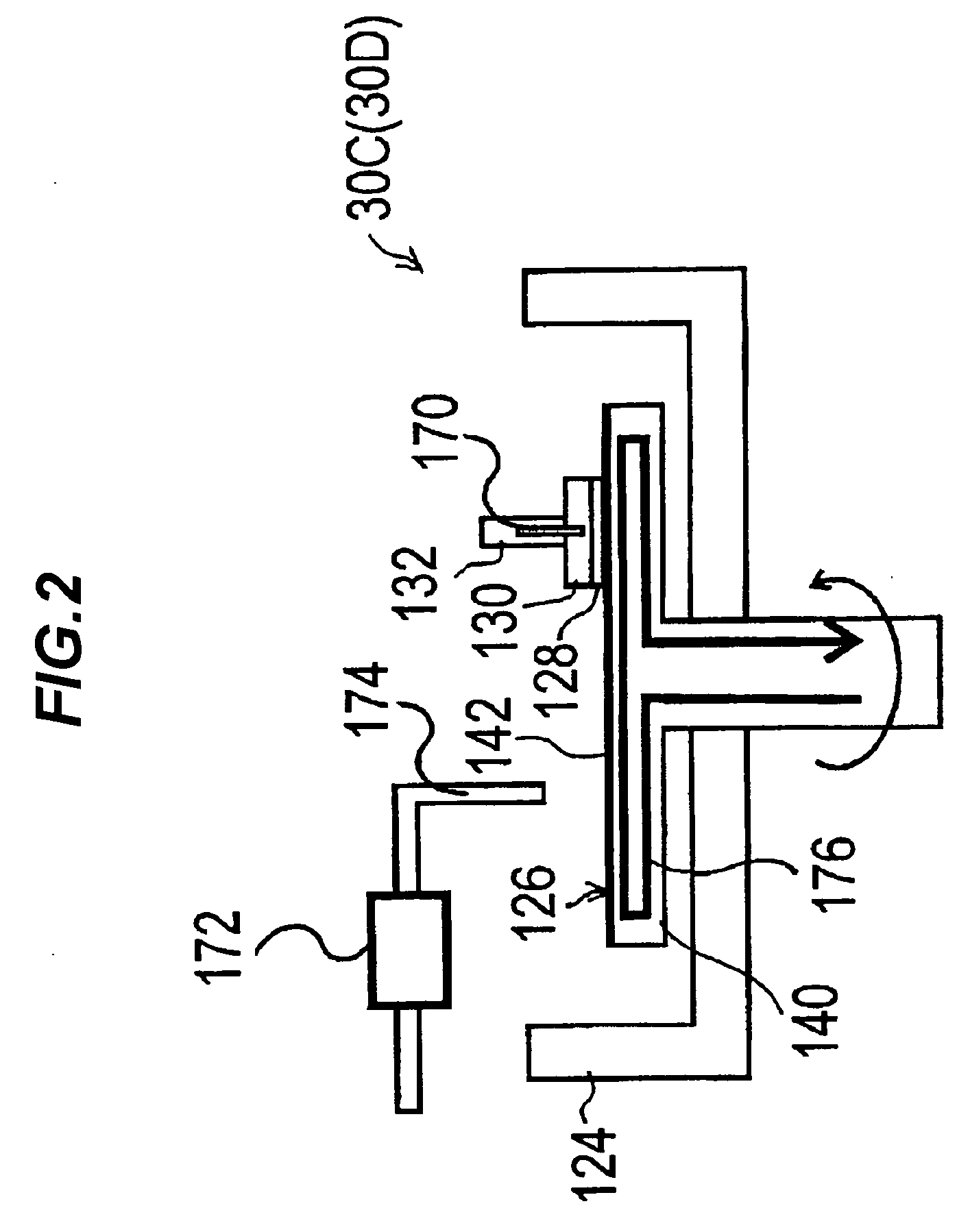

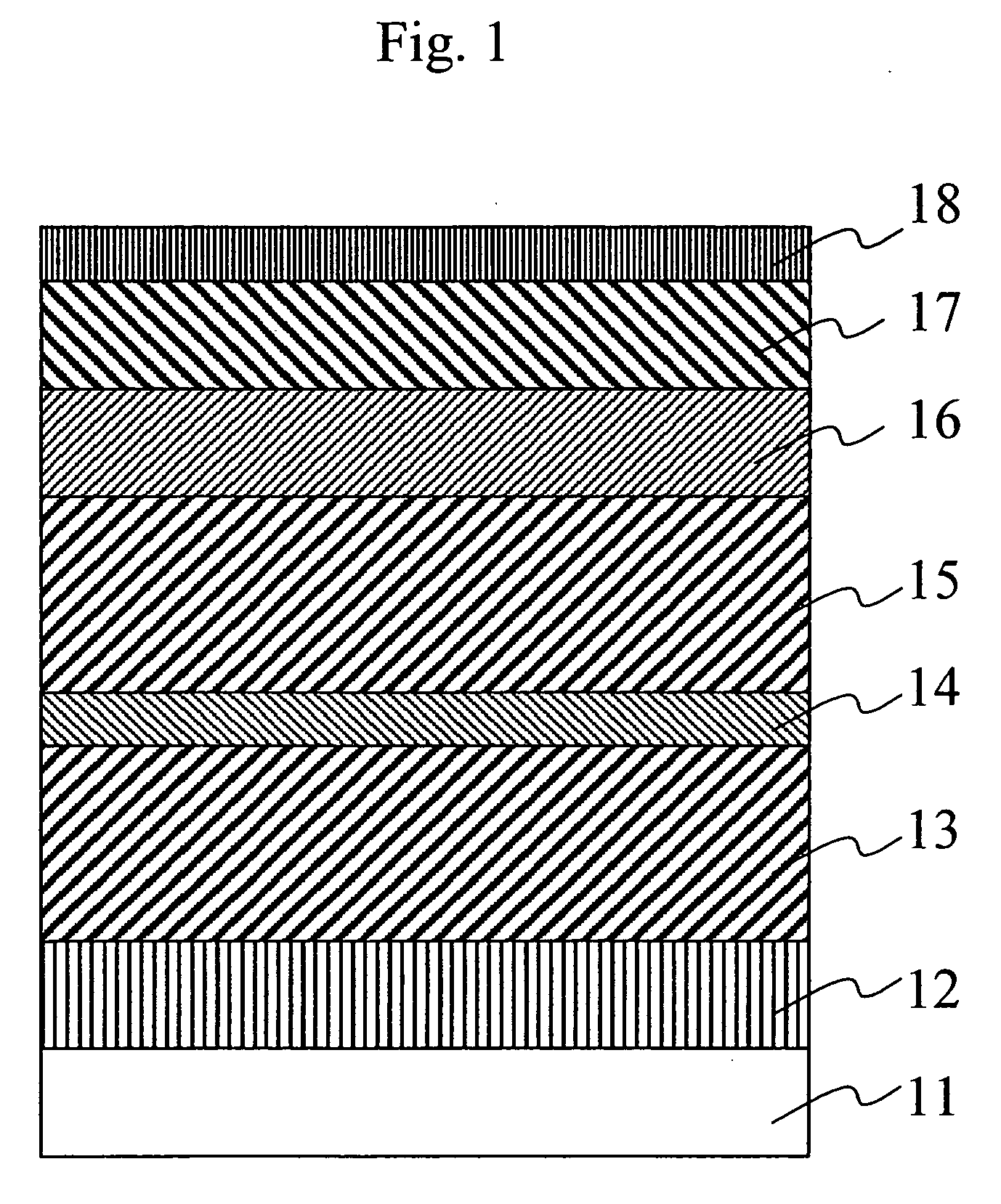

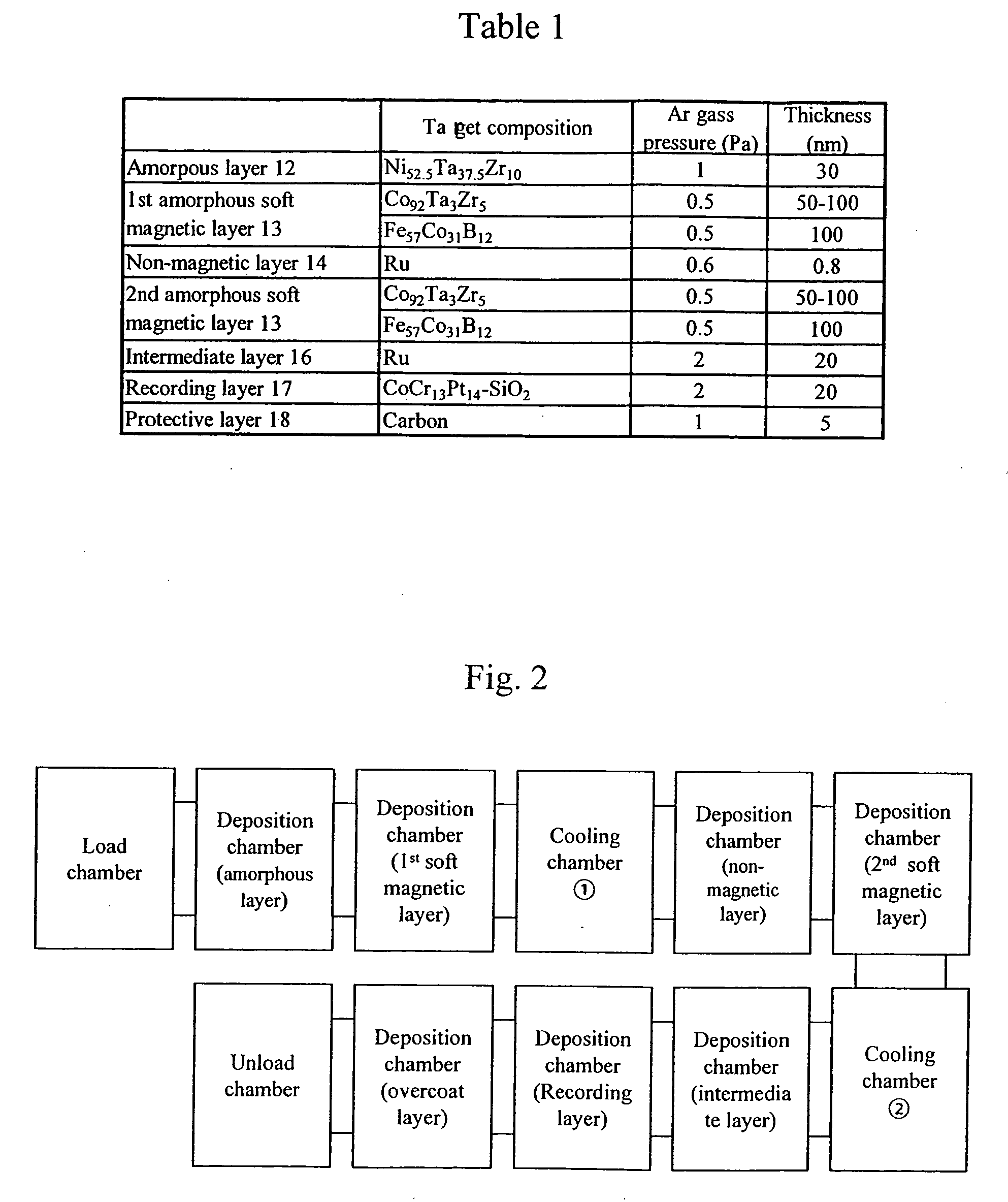

Perpendicular magnetic recording medium, manufacturing process of the same, and magnetic recording/reproducing apparatus using the same

ActiveUS20050244679A1Suppressing amplitude modulationSuppressing spike noiseMagnetic field orientationBase layers for recording layersSignal qualityAntiferromagnetic coupling

Embodiments of the invention provide a perpendicular magnetic recording medium improved for fly ability, high in read signal quality, and capable of suppressing magnetic decay of recorded magnetization to be caused by stray fields. In one embodiment, a perpendicular recording layer is formed over a substrate with a soft magnetic underlayer therebetween, then an amorphous or nano-crystalline layer is formed between the substrate and the soft magnetic underlayer. The soft magnetic underlayer includes first and second amorphous soft magnetic layers, as well as a nomnagnetic layer formed between those first and second amorphous soft magnetic layers. The first and second amorphous soft magnetic layers are given uniaxial anisotropy in the radial direction of the substrate respectively and coupled with each other antiferromagnetically.

Owner:WESTERN DIGITAL TECH INC

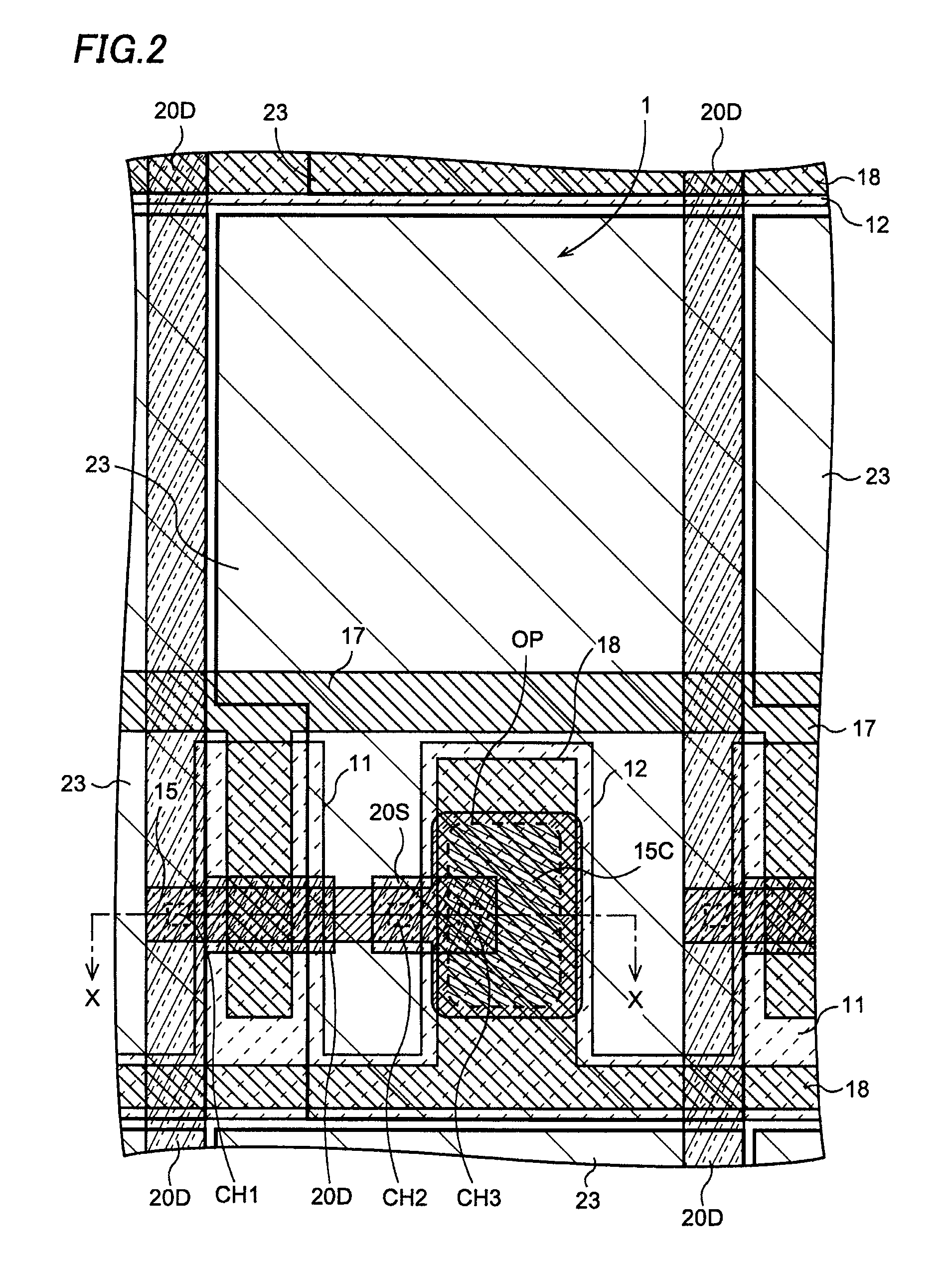

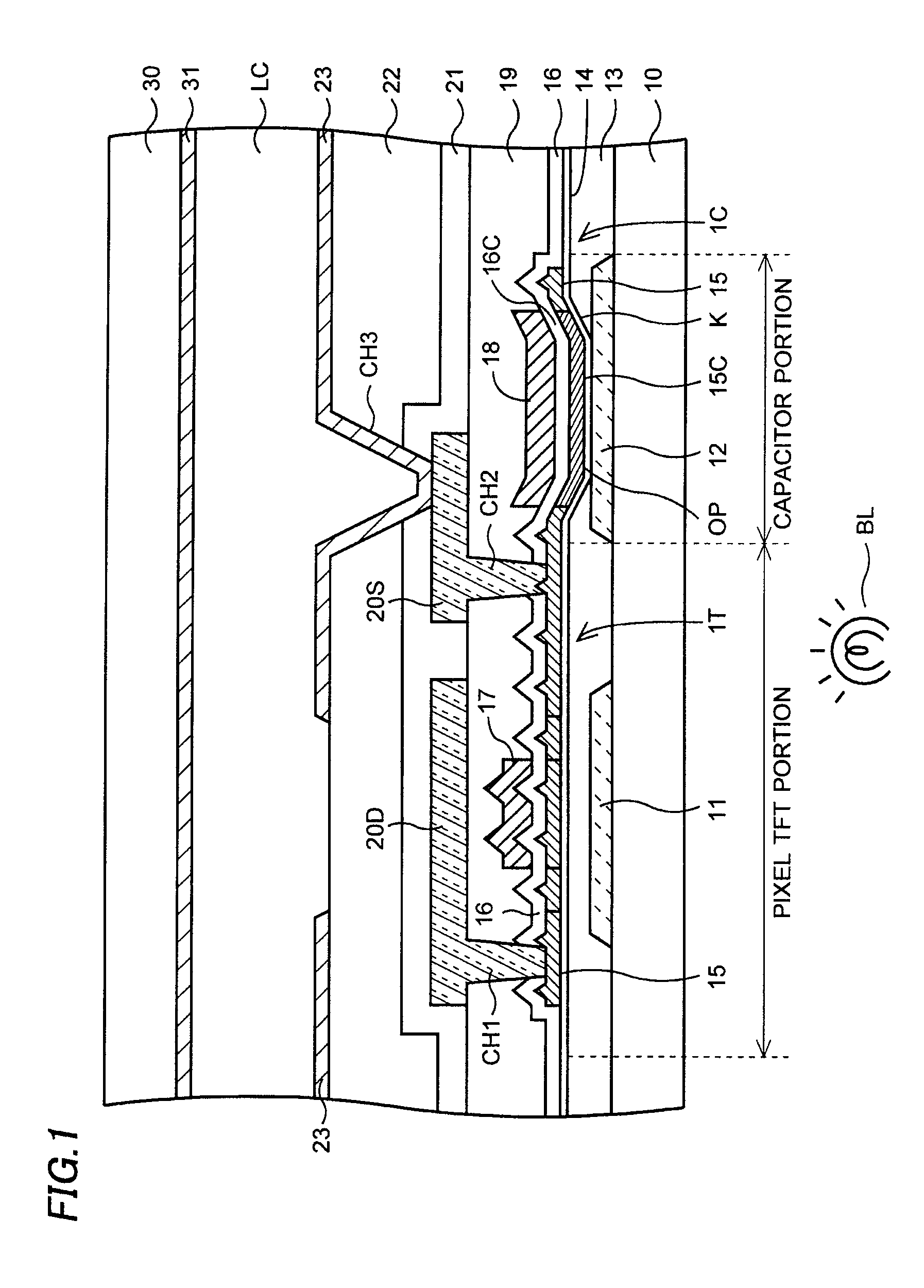

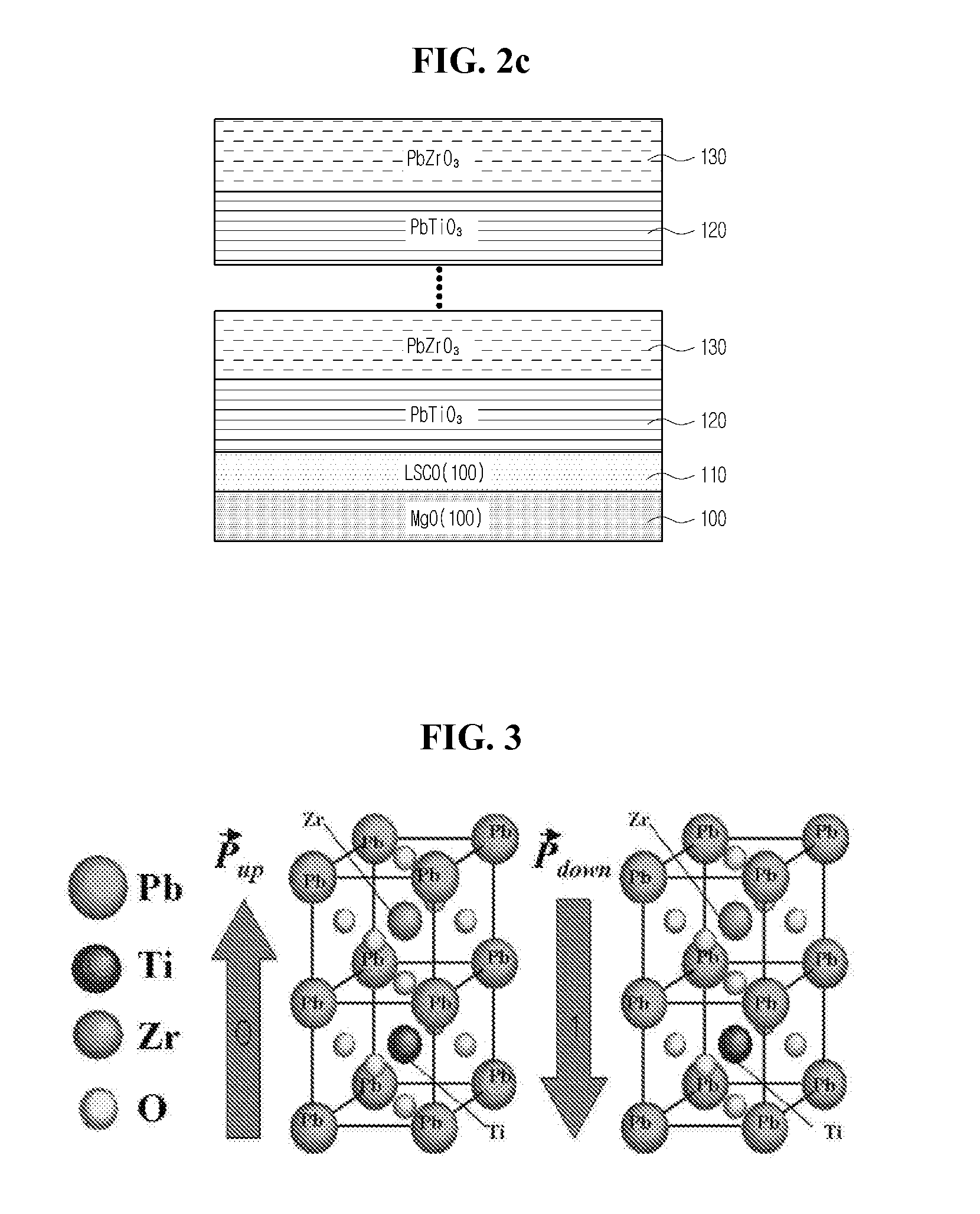

Display device and method of manufacturing the same

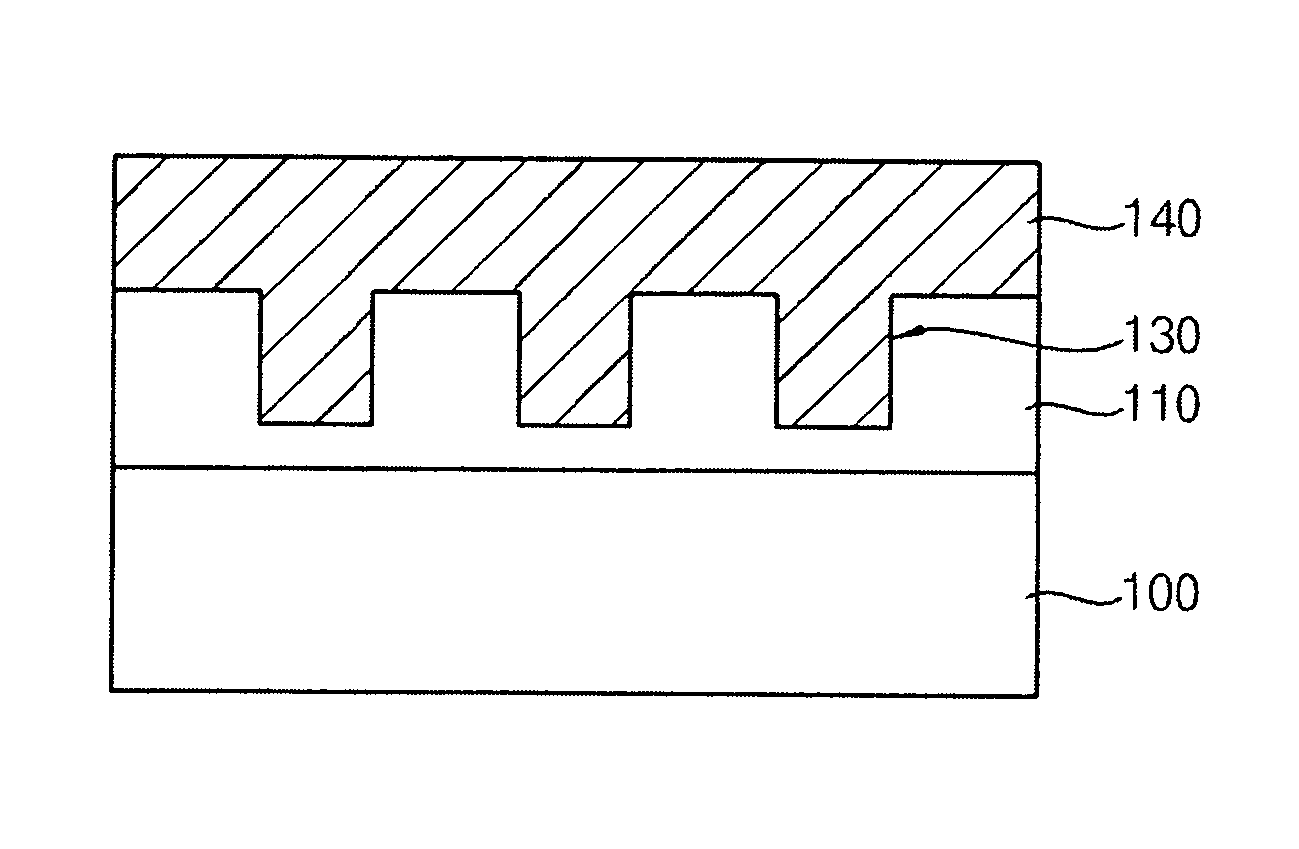

ActiveUS20080067519A1Reduce contact resistanceReduce peripheral resistanceTransistorSolid-state devicesDisplay deviceCapacitor

The invention provides a display device having a thin film transistor and a storage capacitor storing a display signal applied to a pixel electrode through this thin film transistor on a substrate, where dielectric strength between electrodes forming the storage capacitor is enhanced for increasing the yield. In the storage capacitor, a lower storage capacitor electrode, a thin lower storage capacitor film, a polysilicon layer, an upper storage capacitor film and an upper storage capacitor electrode are layered. The polysilicon layer is formed by crystallization by laser annealing. The polysilicon layer of the storage capacitor is microcrystalline and thus the flatness of its surface is enhanced. The pattern of the polysilicon layer (storage capacitor electrode) is formed larger than the bottom portion of an opening, and the edge of its peripheral portion is located on a buffer film on the slant portion of the opening or on the buffer film on the outside of the opening.

Owner:JAPAN DISPLAY WEST

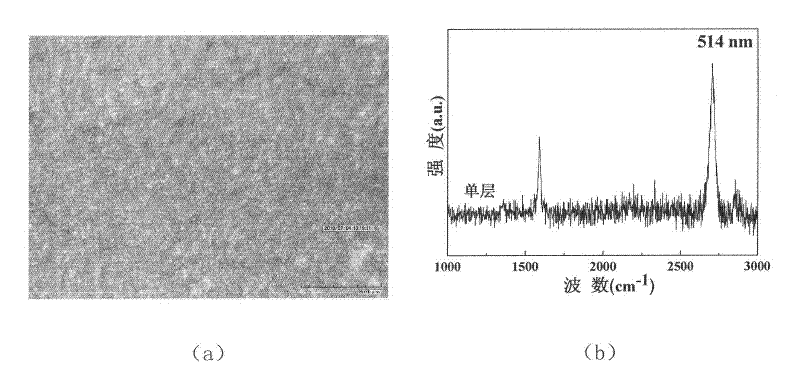

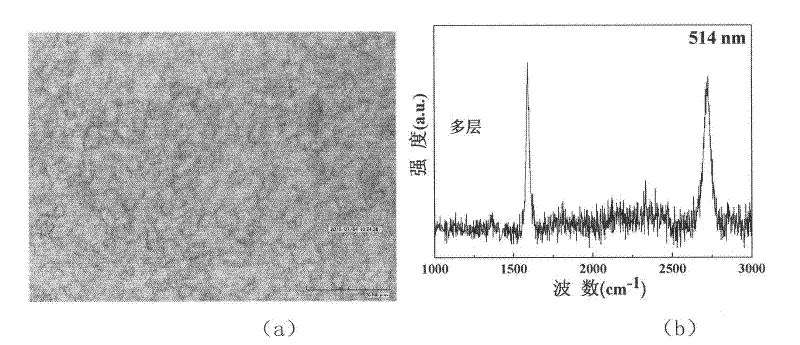

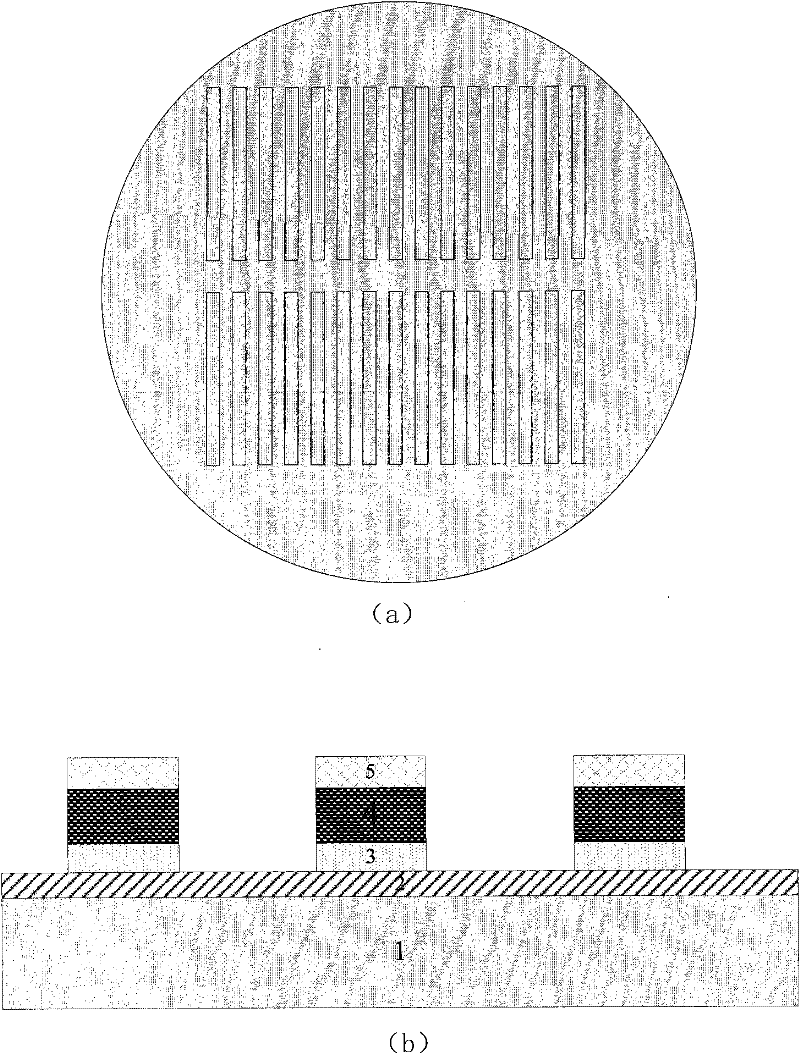

Copper plating substrate-based method for preparing large-area graphene film

ActiveCN102212794AThe method is simpleEasily damagedVacuum evaporation coatingSputtering coatingCopper platingHydrogen

The invention relates to a method for preparing graphene on a copper plating substrate. The method is characterized by comprising the following steps of: preparing the graphical copper plating substrate on a silicon chip; and growing the graphene on the copper plating substrate for 2 to 5 minutes at the temperature of between 800 and 1,000 DEG C by using a normal pressure chemical vapor deposition method, using methane as a carbon source and using argon and hydrogen as carrier gases. A graphical graphene film can be directly prepared by the method, and the substrate can be compatible with an integrated circuit (IC) process; and the manufacturing method is simple and low in cost, and can be used for large-scale manufacture.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Composition for copper plating and associated methods

InactiveUS20100084277A1High aspect ratioReducing generation voidSemiconductor/solid-state device manufacturingSemiconductor devicesBetaine compoundCopper plating

A composition for copper plating and associated methods, a method of forming a copper wiring including forming an insulation layer having a recessed portion on a substrate, and forming a copper layer on the insulation layer to fill the recessed portion by performing an electroplating process using a composition that includes an aqueous electrolyte solution containing a copper ion and at least one of a disulfide compound represented by Formula 1, a betaine compound represented by at least one of Formulae 3 and 4, and a triblock copolymer of polyethylene oxide-polypropylene oxide-polyethylene oxide (PEO-PPO-PEO) having a weight average molecular weight of about 2,500 to about 5,000 g / mol and an ethylene oxide content (EO %, w / w) of about 30% to about 60%.

Owner:SAMSUNG ELECTRONICS CO LTD

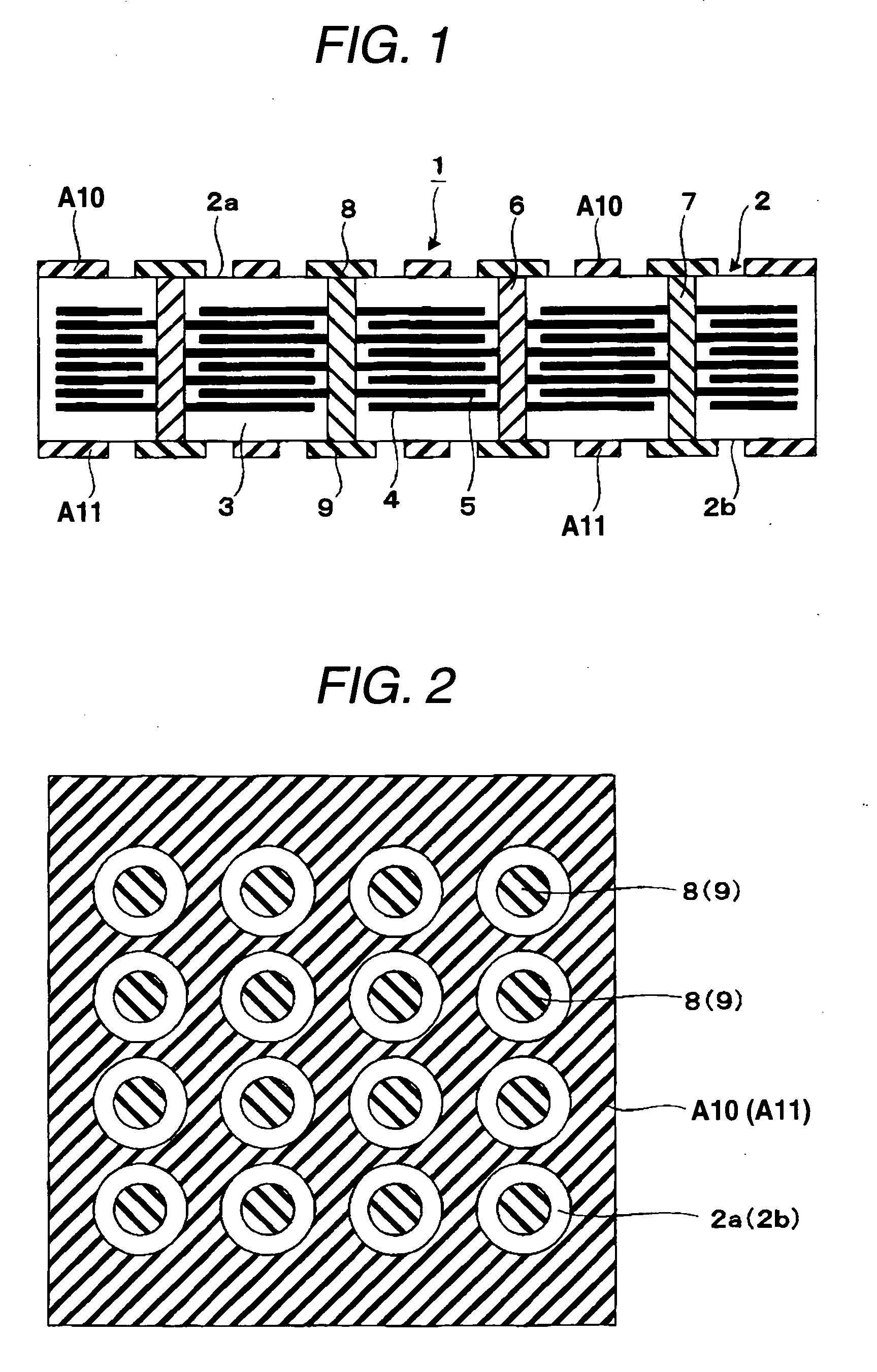

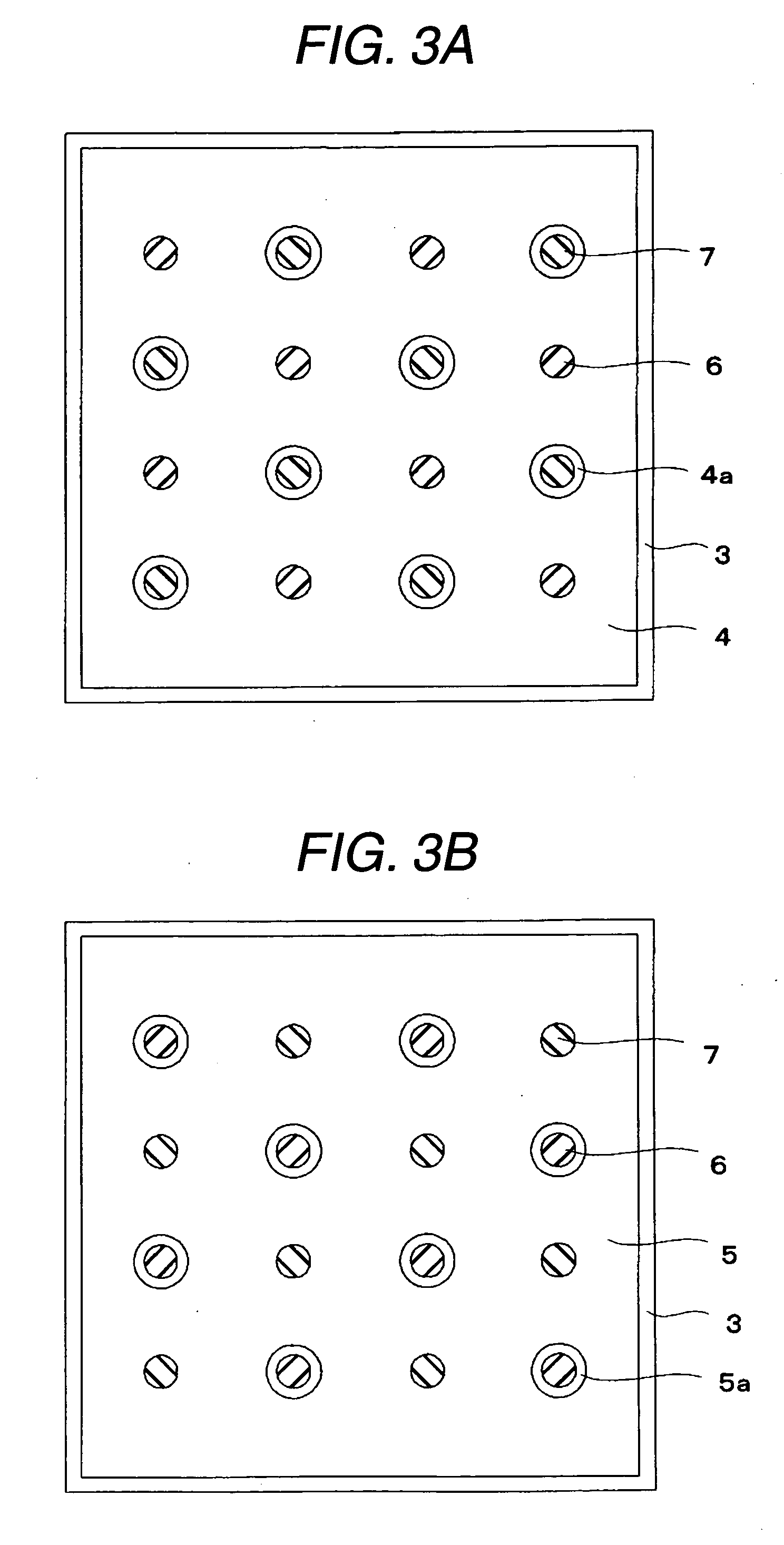

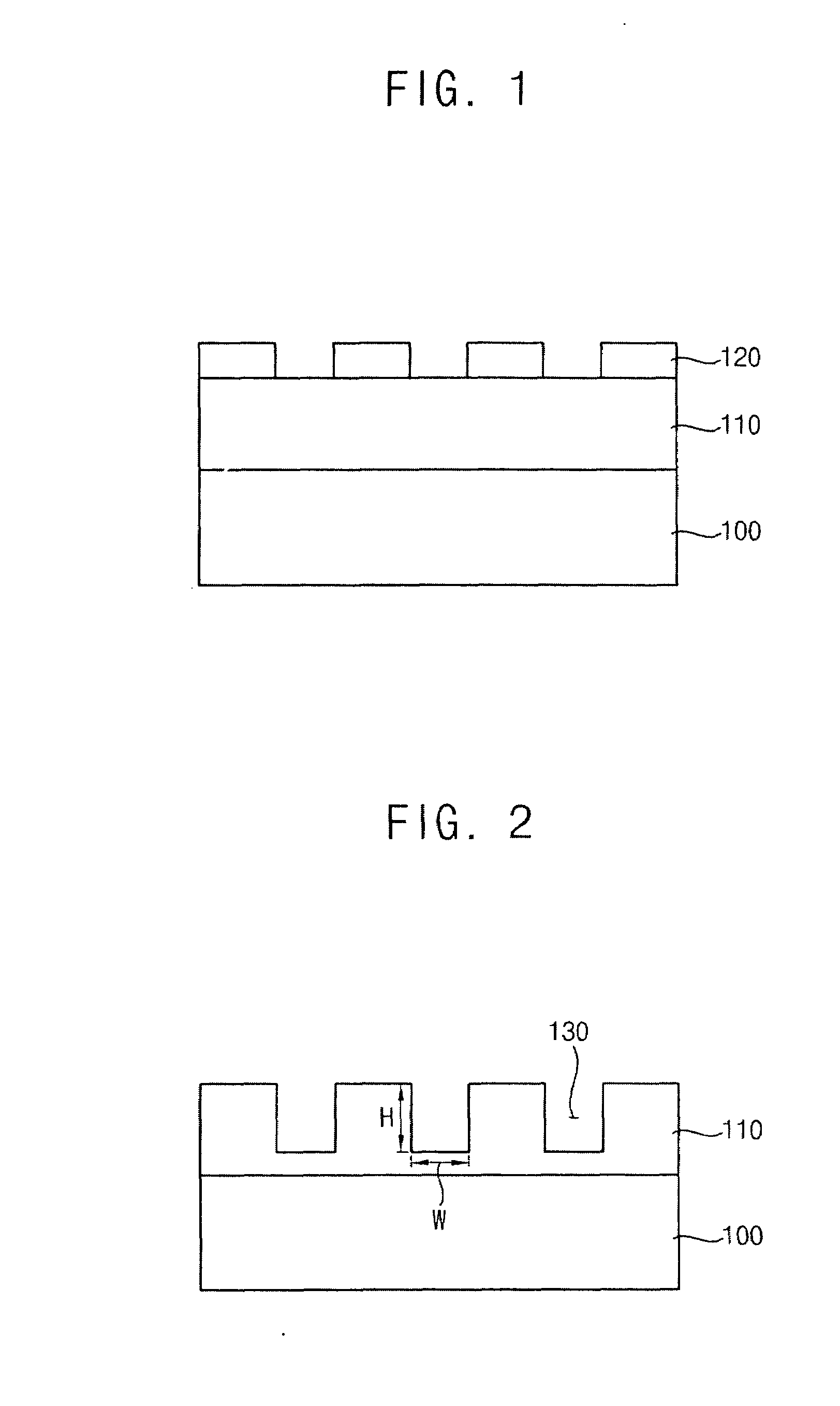

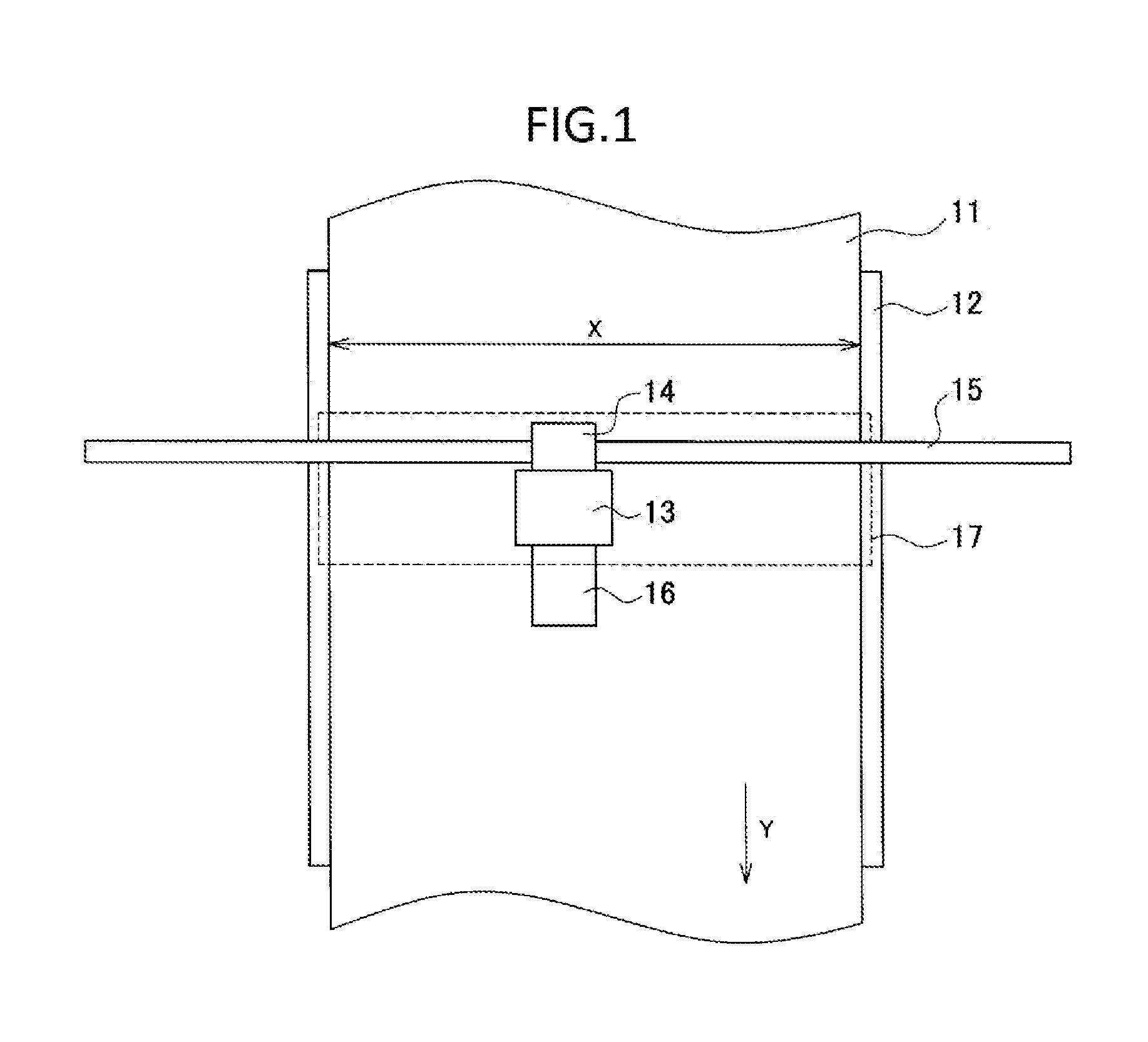

Multi-layer wiring structure with dummy patterns for improving surface flatness

ActiveUS7161248B2High surface flatnessExclude influenceSemiconductor/solid-state device detailsSolid-state devicesSurface flatnessElectrical and Electronics engineering

Owner:FUJITSU SEMICON LTD

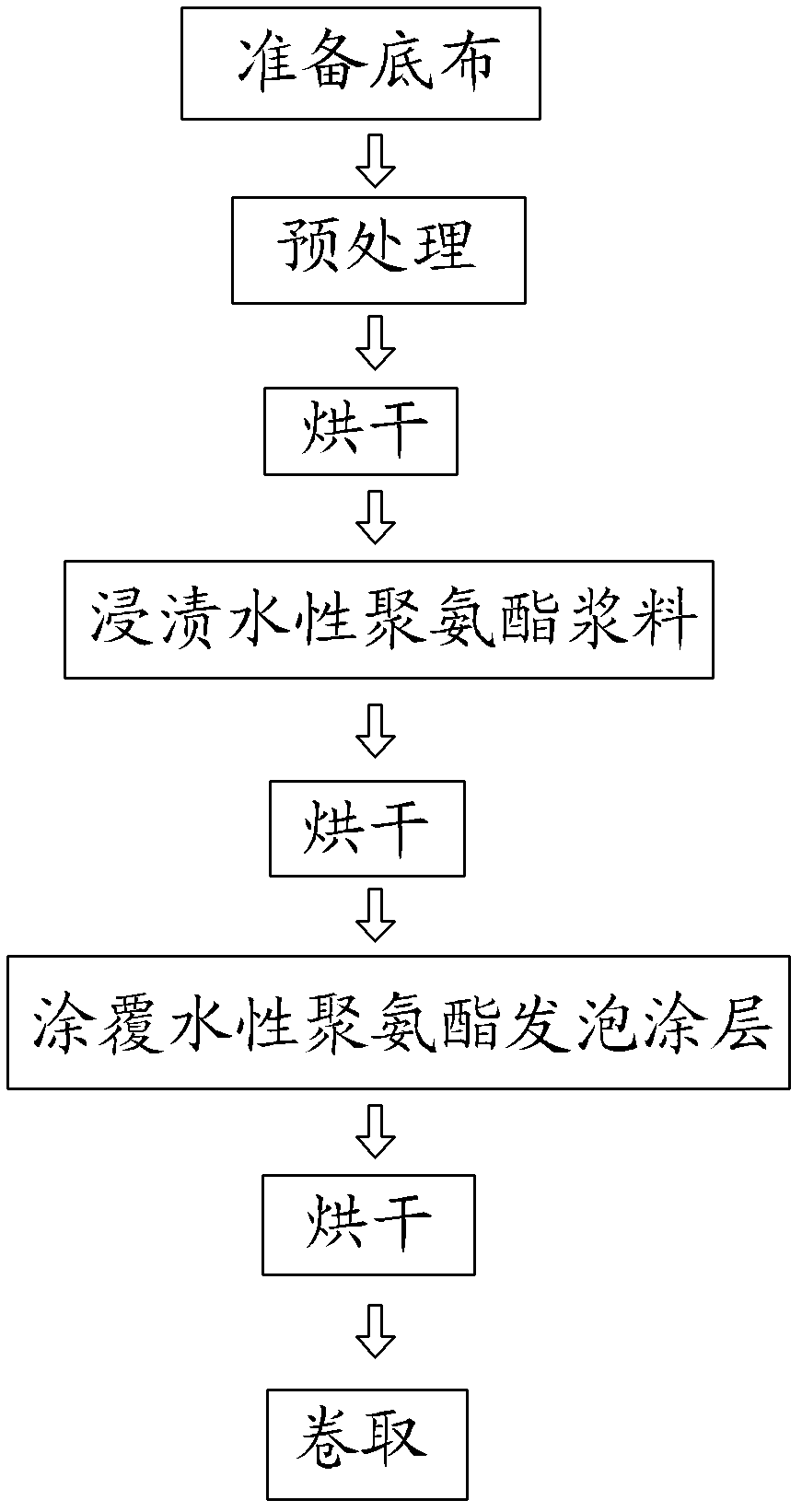

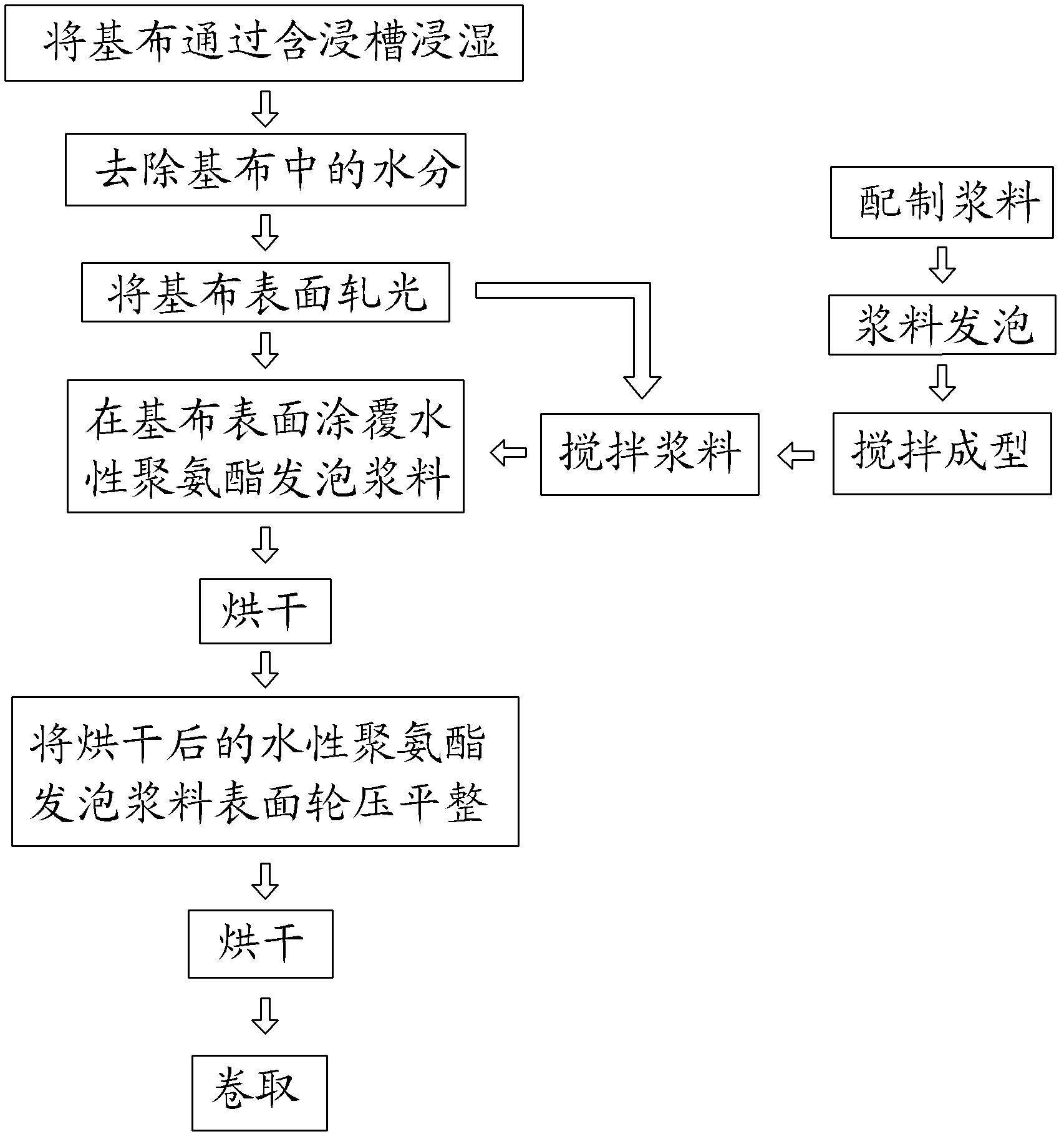

Preparation method of water-soluble polyurethane leather beth

ActiveCN102418284AReduce dosageHigh surface flatnessLiquid/gas/vapor textile treatmentPolymer scienceSolvent based

The invention relates to a preparation method of water-soluble polyurethane leather beth. The preparation method sequentially comprises the following steps of: a step A, soaking a base fabric; a step B, removing moisture in the base fabric; a step C, calendaring the surface of the base fabric; a step D, coating a water-soluble polyurethane foaming paste on the surface of the base fabric and then drying; and a step E, carrying out wheel loading and flattening on the surface of the dried water-soluble polyurethane foaming paste. By adopting the preparation method of the water-soluble polyurethane leather beth provided by the invention, the surface evenness of the product can be improved, the production cost can be reduced, the handfeel of the product is softer, and simultaneously the product is closer to a solvent-based synthetic leather beth product in appearance performance and physical properties.

Owner:FUJIAN POLYTECH TECH CO LTD

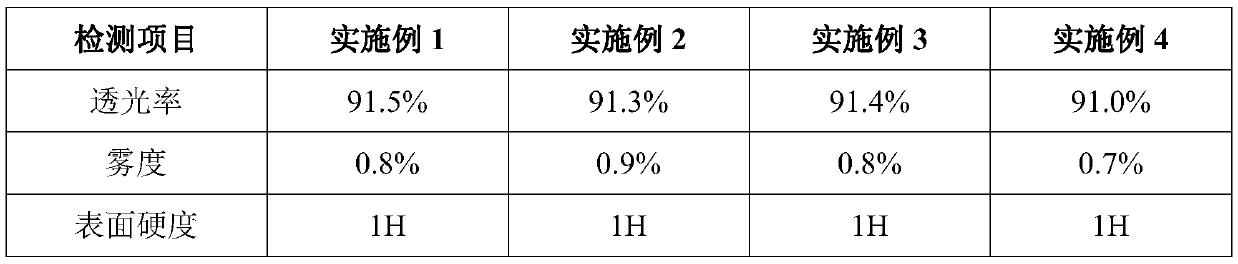

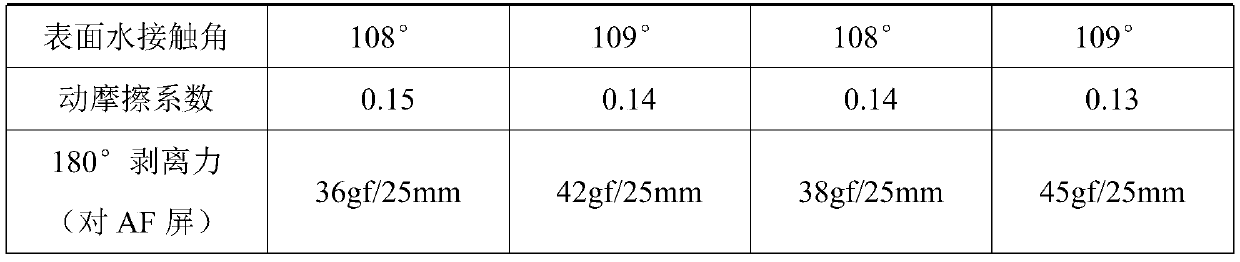

Anti-fingerprint TPU protective film for 3D curved screen and preparation method of anti-fingerprint TPU protective film

PendingCN111484810AGood optical performanceImprove smoothnessNon-macromolecular adhesive additivesMacromolecular adhesive additivesPolyesterColloidal silica

The invention discloses an anti-fingerprint TPU protective film for a 3D curved screen. The protective film comprises a low-viscosity protective film, an anti-fingerprint UV hardening coating, an optical hard TPU resin film layer, an optical-grade high-viscosity silica gel pressure-sensitive adhesive layer and a fluorine element release film which are attached from top to bottom; the anti-fingerprint UV hardening coating is formed by coating an anti-fingerprint UV hardening coating; the optical hard TPU resin film layer is formed by coating optical hard TPU glue, the optical-grade high-viscosity silica gel pressure-sensitive adhesive layer is formed by coating an optical-grade high-viscosity silica gel pressure-sensitive adhesive; the anti-fingerprint UV hardening coating is prepared fromthe following components: UV prepolymer resin, an acrylate reactive diluent, a photoinitiator, a slipping aid and a first solvent, the optical-grade hard TPU glue is formed by polymerizing polyisocyanate, polyester polyol and a chain extender in a second solvent under the action of a first catalyst; the optical-grade high-viscosity silica gel pressure-sensitive adhesive is composed of silica gel resin, a cross-linking agent, an anchoring agent and a second catalyst. The anti-fingerprint TPU protective film for a 3D curved screen has the properties of fingerprint resistance, scratch resistance,difficulty in bursting and good fitting property of the curved screen.

Owner:GUANGDONG BANGGU FILM COATING INNOVATION ACAD CO LTD

Light emitting device

InactiveUS6933520B2Inhibited DiffusionHigh color yieldElectroluminescent light sourcesSolid-state devicesHeat resistanceBoundary region

It is considered that in the fabricating steps of a TFT substrate, a color filter layer is prepared at the same alignment accuracy. However, since the heat resistance temperature is about 200° C., it could not withstand the process temperature of about 450° C. in the TFT. The pixel section is formed by arraying in a matrix shape a light emitting element in which an organic compound layer having the luminous property is formed between a pair of electrodes consisting of a translucent electrode and a non-translucent electrode and a TFT, the coloring layer of color filter provided corresponding to each pixel is provided in contact with the flat surface of the flattened insulating film composed of an inorganic or organic material between the light emitting element and the TFT, the boundary region of coloring layers adjacent each other is provided while overlapping with a gate signal line or data line for transmitting a signal to the TFT, and the translucent electrode is provided while overlapping with the layer inside of the coloring layer.

Owner:SEMICON ENERGY LAB CO LTD

Display device and method of manufacturing the same

ActiveUS8071985B2High surface flatnessDielectric strengthTransistorSolid-state devicesCapacitanceDisplay device

The invention provides a display device having a thin film transistor and a storage capacitor storing a display signal applied to a pixel electrode through this thin film transistor on a substrate, where dielectric strength between electrodes forming the storage capacitor is enhanced for increasing the yield. In the storage capacitor, a lower storage capacitor electrode, a thin lower storage capacitor film, a polysilicon layer, an upper storage capacitor film and an upper storage capacitor electrode are layered. The polysilicon layer is formed by crystallization by laser annealing. The polysilicon layer of the storage capacitor is microcrystalline and thus the flatness of its surface is enhanced. The pattern of the polysilicon layer (storage capacitor electrode) is formed larger than the bottom portion of an opening, and the edge of its peripheral portion is located on a buffer film on the slant portion of the opening or on the buffer film on the outside of the opening.

Owner:JAPAN DISPLAY WEST

Ink, inkjet printer, and method for printing

ActiveUS20120075394A1Easy to removeHigh glossDuplicating/marking methodsInksUV curingOrganic solvent

An ink includes a volatile organic solvent and a UV curable ink. The ink has a viscosity greater than or equal to 3 mPa·sec and less than or equal to 18 mPa·sec (at 25° C.). The UV curable ink has a viscosity of greater than or equal to 20 mPa·sec (at 25° C.). The UV curable ink comprises a pigment, an ultraviolet curable resin curable by an ultraviolet light, and a photopolymerization initiator.

Owner:MIMAKI ENG

Method for making flexible, transparent and conductive film made of metal nanowires

InactiveCN103594195AImprove conductivityGood visible light transmittanceSolid-state devicesSemiconductor/solid-state device manufacturingAdhesion forcePlanar substrate

The invention provides a method for making a flexible, transparent and conductive film made of metal nanowires, and belongs to the technical field of conductive film materials. A layer of metal nanowire film is made on a rigid plane substrate according to a solution processing method, then a layer of transparent and flexible substrate is made on the metal nanowire film according to the solution processing method, and finally the flexible substrate with the metal nanowires on the surface is removed from the plane substrate to form the flexible, transparent and conductive film made of the metal nanowires. Compared with a traditional flexible, transparent and conductive film made of metal nanowires directly on a flexible substrate, the flexible, transparent and conductive film made of the metal nanowires through the method has the advantages of being high in surface flatness, large in adhesion force and the like and effectively solving the problems that a flexible, transparent and conductive film made of metal nanowires is large in roughness and small in adhesion force. The flexible, transparent and conductive film made of the metal nanowires has the potential of being applied in the fields of photoelectric devices like film solar cells and organic light-emitting diodes.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Polishing solution for reducing copper chemical mechanical polishing roughness

InactiveCN101665665AAvoid damageReduce roughnessPolishing compositions with abrasivesSurface roughnessNitrogen

The invention discloses a polishing solution for reducing the copper chemical mechanical polishing roughness. The polishing solution is formed by the following components by mass weight: 0.1%-30% of abrasive particles, 0.1%-10% of nitrogen-contained polymers, 0.1%-3% of chelating agents, 0.1%-10% of surfactants, 0.001%-2% of corrosion inhibitors, 0.1%-20% of oxidant and less than or equal to 90% of de-ionized water. The components are firstly mixed, and then pH of the mixture is adjusted to 1.0-7.0 by KOH or HNO3. The polishing solution shows small damage on the copper chemical mechanical polishing, reduces the surface roughness (8-18nm) of the polished copper, and increases the surface smoothness; and cleaning is easier after polishing.

Owner:DALIAN SANDAAOKE CHEM

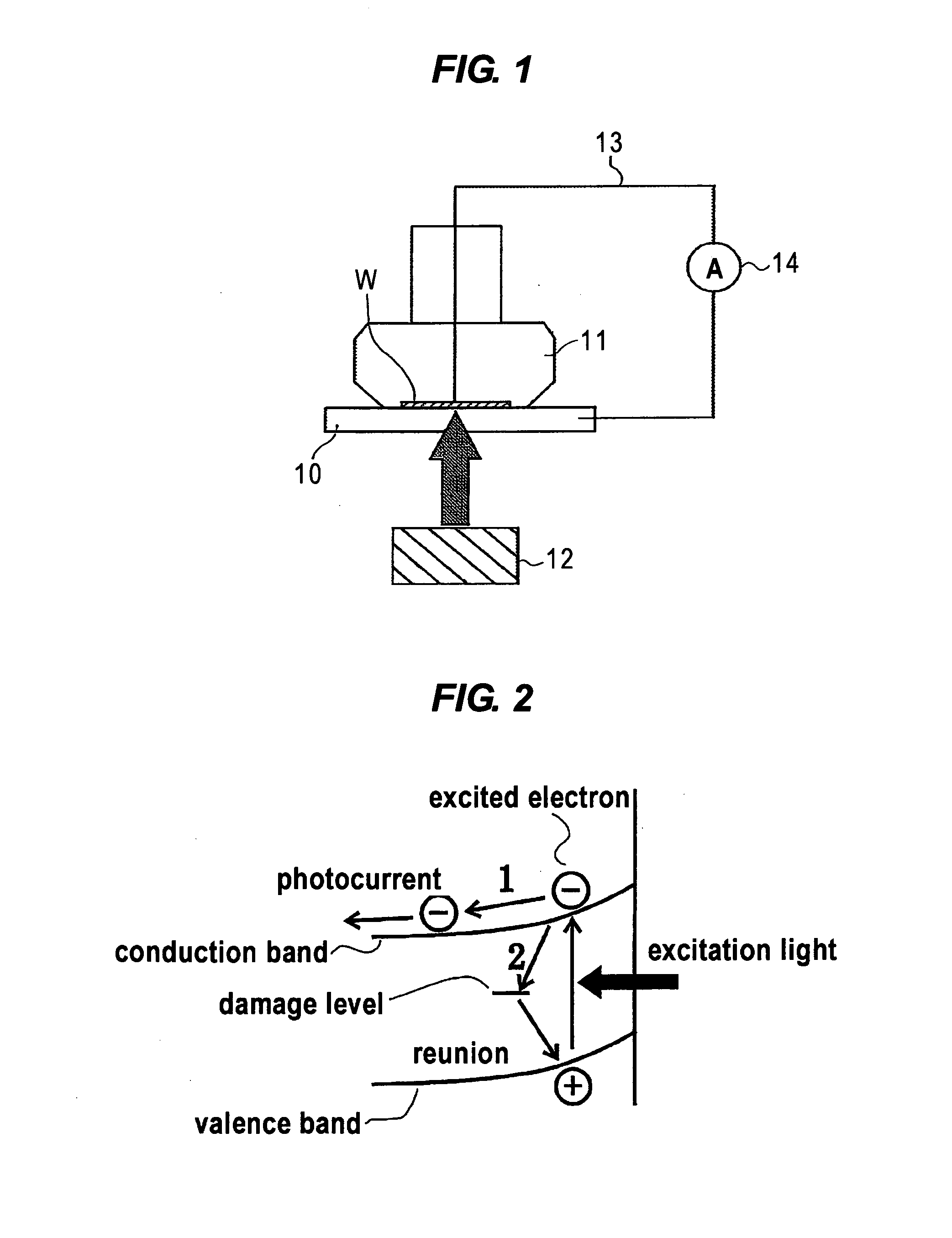

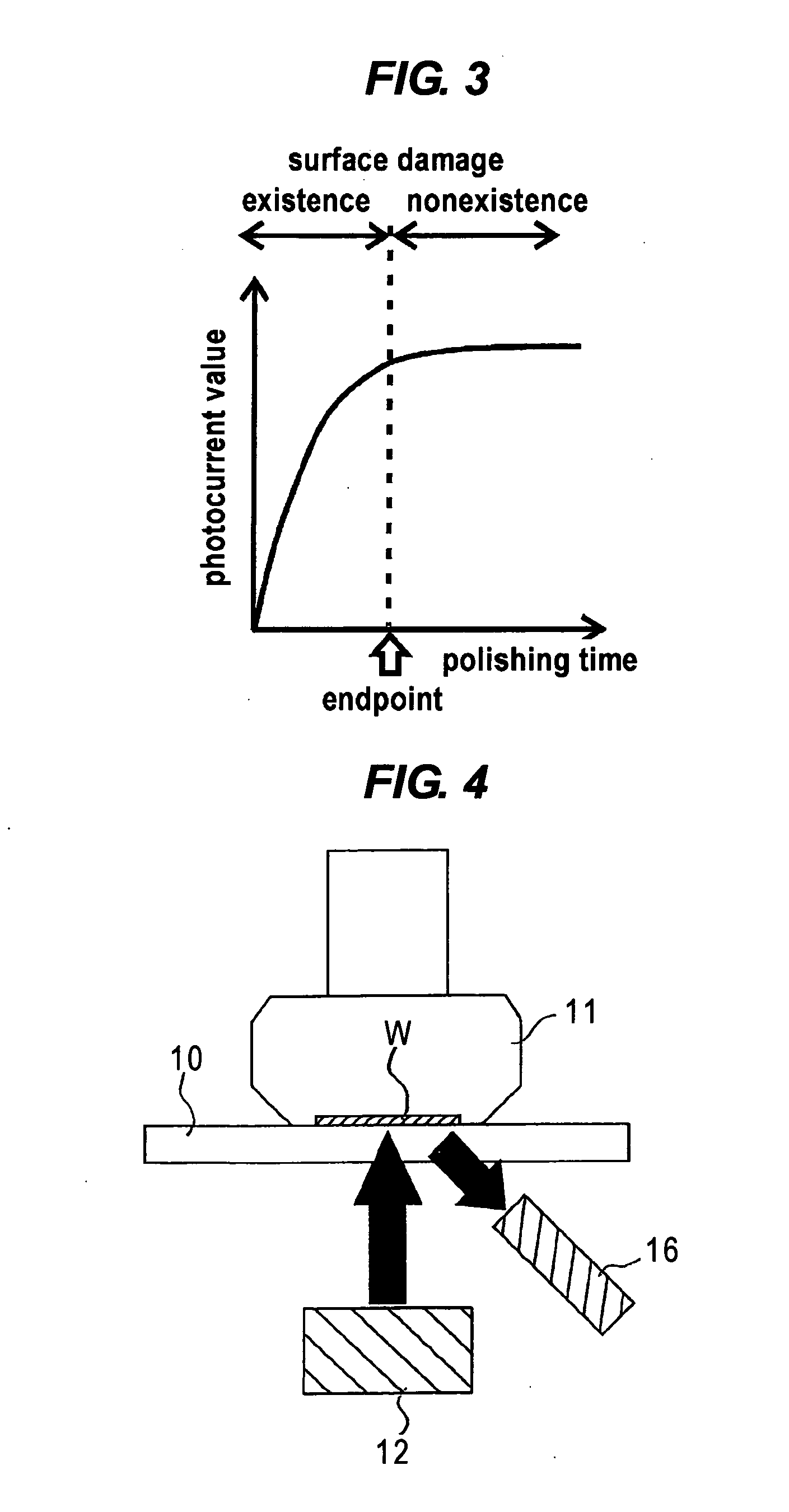

Polishing method, polishing apparatus and polishing tool

ActiveUS20120244649A1Improve flatnessHigh polishing rateSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingAcid waterElectrolysis

A polishing method and a polishing apparatus particularly suitable for finishing a surface of a substrate of a compound semiconductor containing an element such as Ga or the like to a desired level of flatness, so that a surface of a substrate of a compound semiconductor containing an element of Ga can be flattened with high surface accuracy within a practical processing time. In the presence of water (232) such as weak acid water, water with air dissolved therein, or electrolytic ion water, a surface of a substrate (142) made of a compound semiconductor containing either one of Ga, Al, and In and the surface of a polishing pad (242) having an electrically conductive member (264) in an area of the surface which is held in contact with the substrate (142) are relatively moved while being held in contact with each other, thereby polishing the surface of the substrate (142).

Owner:OSAKA UNIV +1

Glass substrate and leveling thereof

InactiveUS6855908B2High surface flatnessEliminate variationSemiconductor/solid-state device manufacturingArc welding apparatusOptoelectronicsSubstrate surface

A glass substrate having a surface which has been leveled, preferably to a flatness of 0.04-1.3 nm / cm2 of the surface, by local plasma etching is provided. A glass substrate whose surface carries microscopic peaks and valleys is leveled by measuring the height of peaks and valleys on the substrate surface, and plasma etching the substrate surface while controlling the amount of plasma etching in accordance with the height of peaks.

Owner:SHIN ETSU CHEM IND CO LTD

Control technological method for planeness of surface of LTCC substrate

ActiveCN102724822AImprove surface flatnessLow costMultilayer circuit manufactureCo-fired ceramicFiller metal

The invention discloses a control technological method for the planeness of the surface of an LTCC (low temperature co-fired ceramic) substrate. Specific steps are as follows: preparing raw ceramic sheets for the preparation of an LTCC substrate, and punching circuit through holes with a punch press; tearing off a Mylar film; filling LTCC technological hole metal slurry on the raw ceramic sheets, using a roller to roll the holes so as to evenly press flat the protrusions of the holes filled with the metal slurry, and printing LTCC technological metal conductor slurry on the raw ceramic sheets so as to form a circuit figure; aligning and stacking all the raw ceramic sheets layer by layer, and laminating so as to obtain a large bulk of LTCC raw ceramic blank; and after cutting the large bulk of LTCC raw ceramic blank into circuits in the shape of small blocks, sintering so as to obtain the compact and flat LTCC circuit substrate. Therefore, the technological process of planeness control for the surface of the LTCC substrate is achieved. The method, which is low in cost, simple and effective, is suitable for the development and production of substrates with a complex cavity structure of an embedded chip requiring a lot for surface planeness, and substrates automatically micropackaged in a batch manner.

Owner:中国航天科工集团第二研究院二十三所

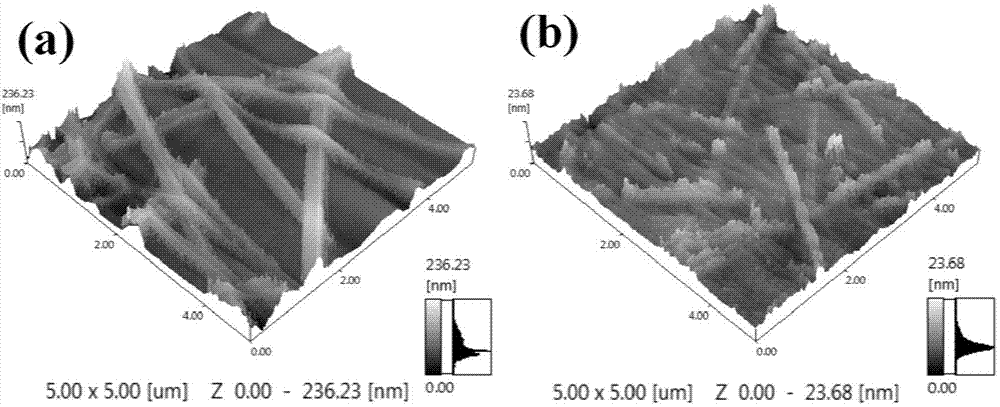

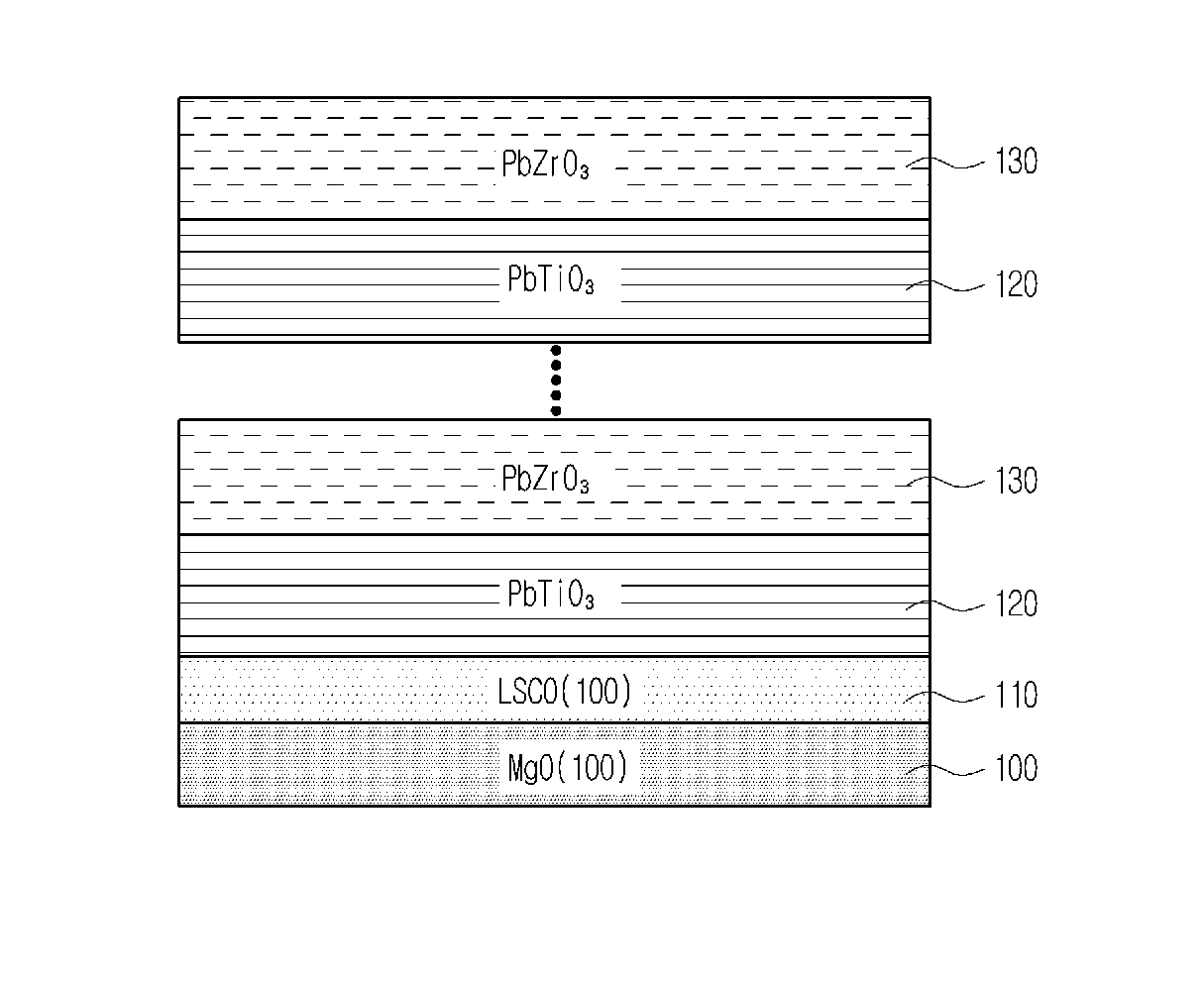

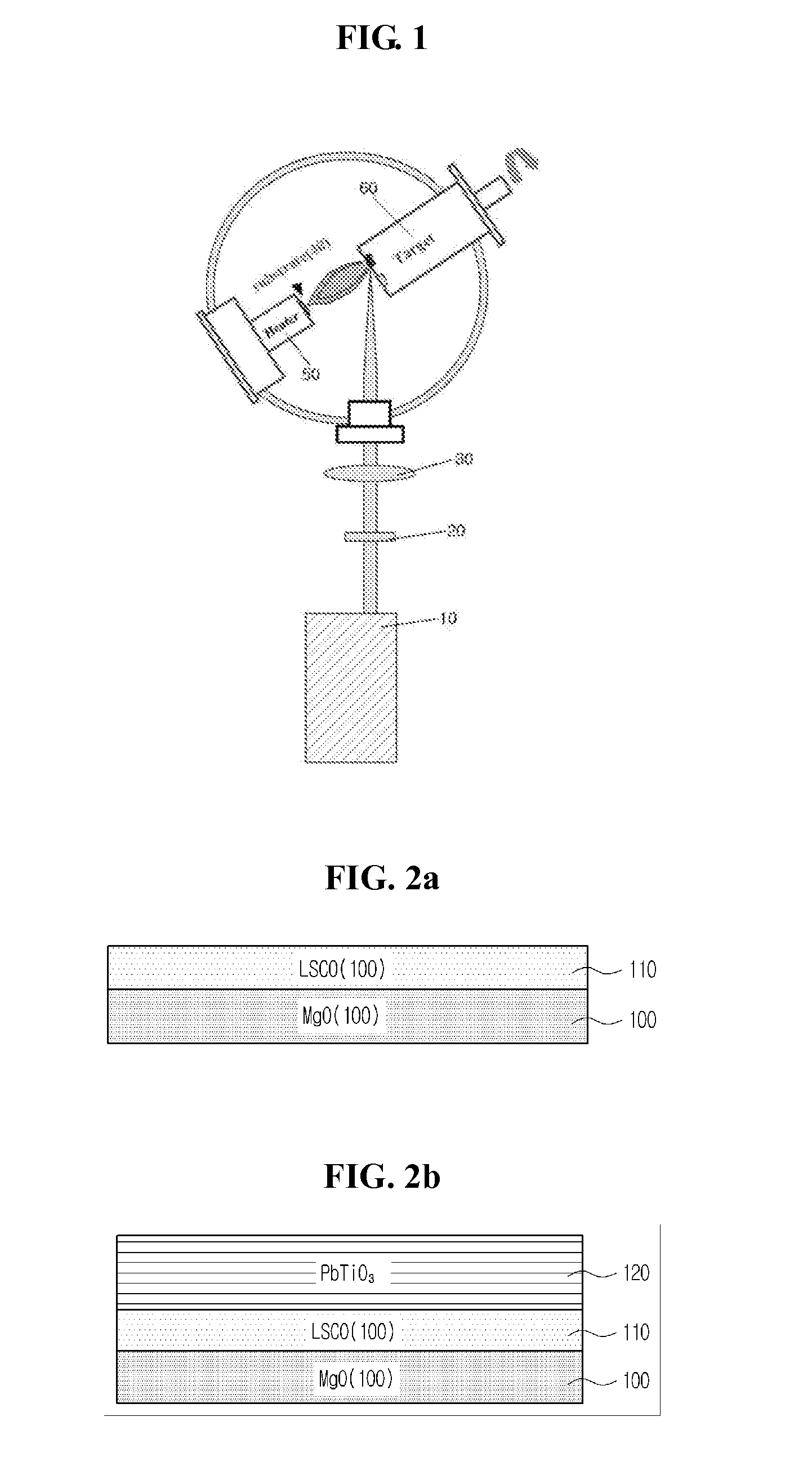

Ferroelectric Oxide Artificial Lattice, Method For Fabricating The Same And Ferroelectric Storage Medium For Ultrahigh Density Data Storage Device

ActiveUS20070152253A1Increased anisotropyOvercome problemsSemiconductor/solid-state device detailsSolid-state devicesLong term dataCrystal structure

The present invention is related to a ferroelectric storage medium for ultrahigh density data storage device and a method for fabricating the same. A supercell having high anisotropy is formed by controlling crystal structure and symmetry of unit structure (supercell) of artificial lattice by using an ordered alignment of predetermined ions having orientation of (perpendicular) deposition direction. Unit atomic layers of oxides having different polarization characteristic are deposited so that the supercell itself shows electric polarization having only two, upward and downward directions as one block of supercell having single-directional polarization. Oxide artificial lattices can be formed so as to have solely 180 degree domain structure, thus a single electric domain having improved anisotropic characteristic can be formed, thereby allowing capability of ultrahigh density data storage and long term data retention.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

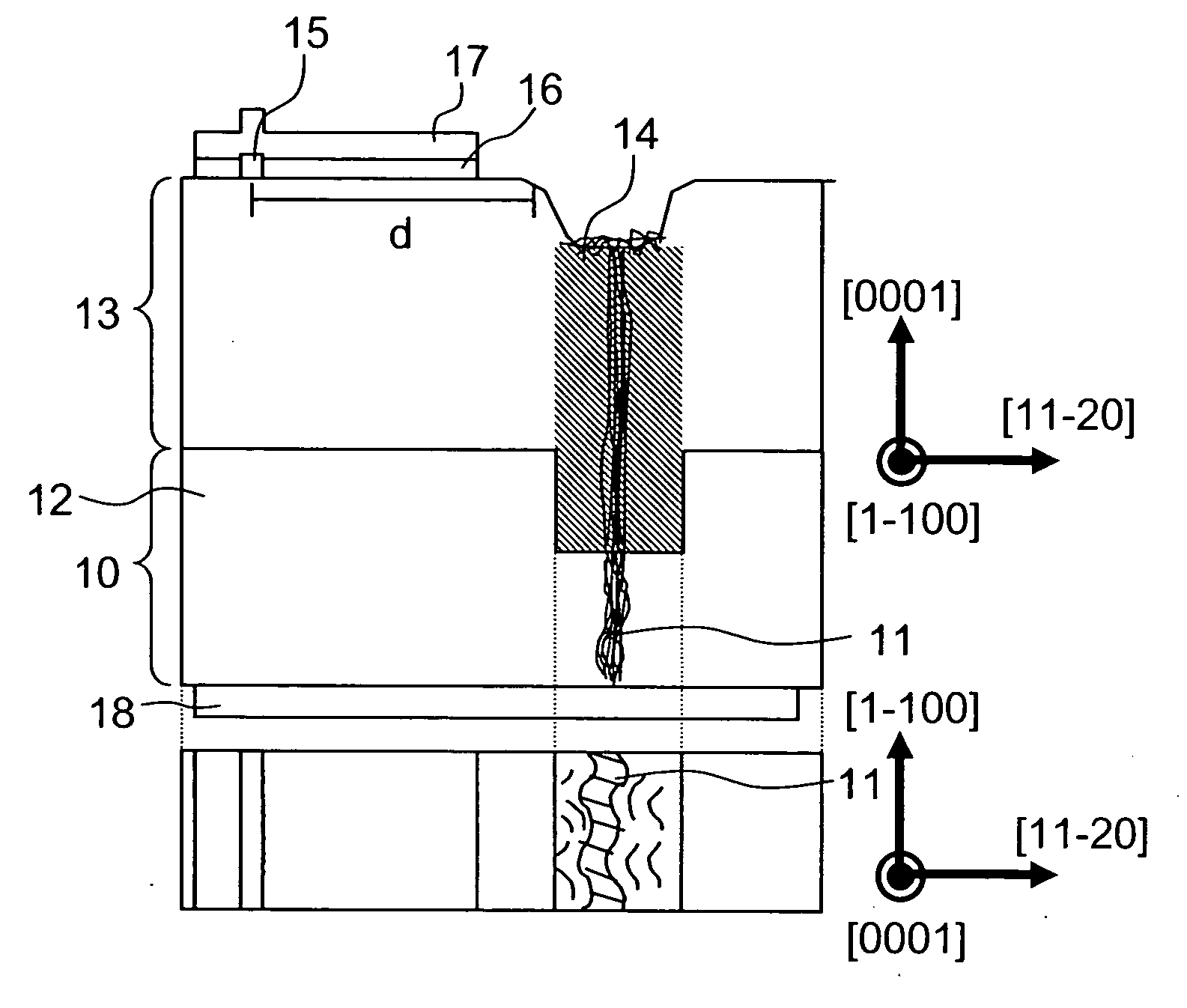

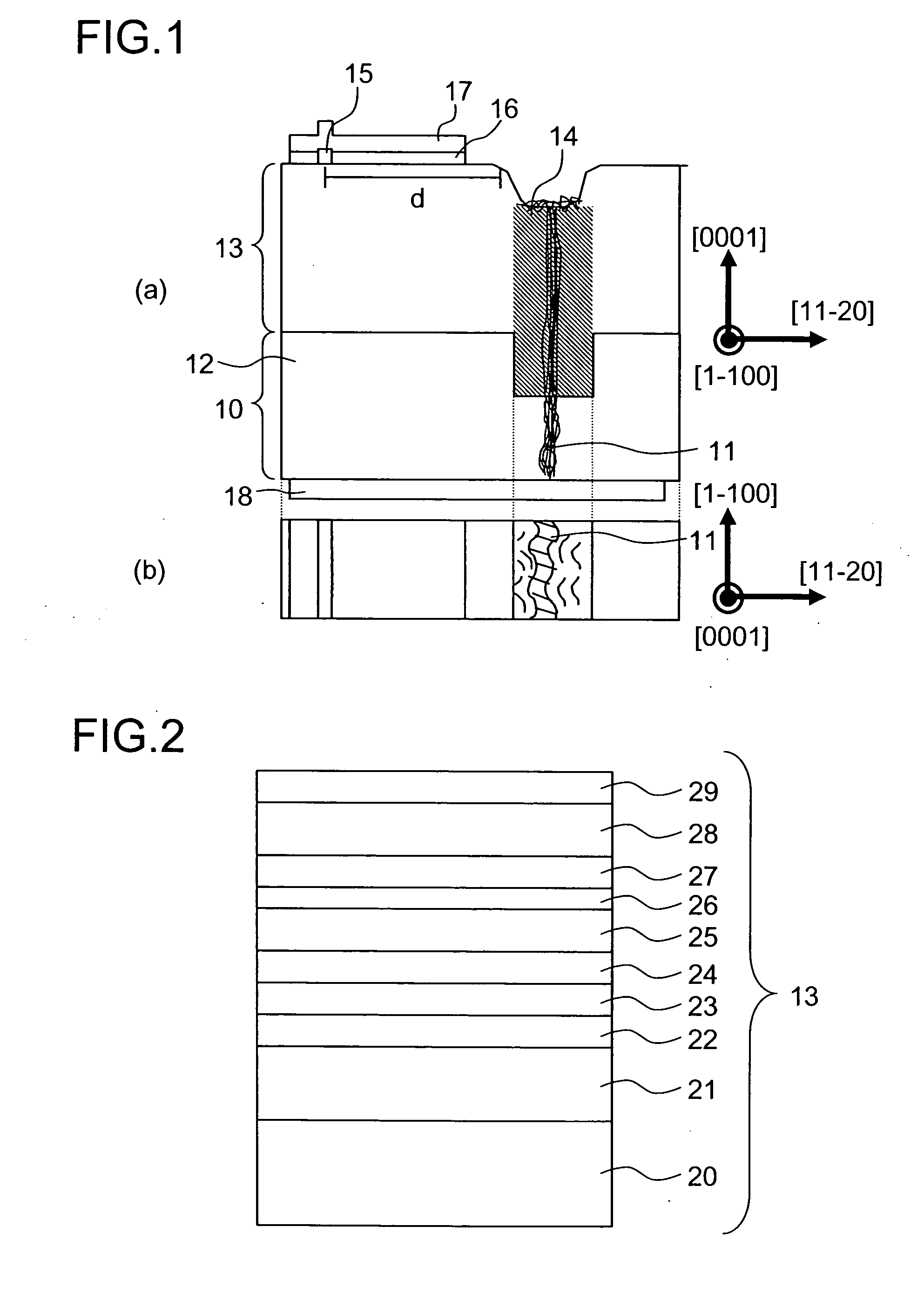

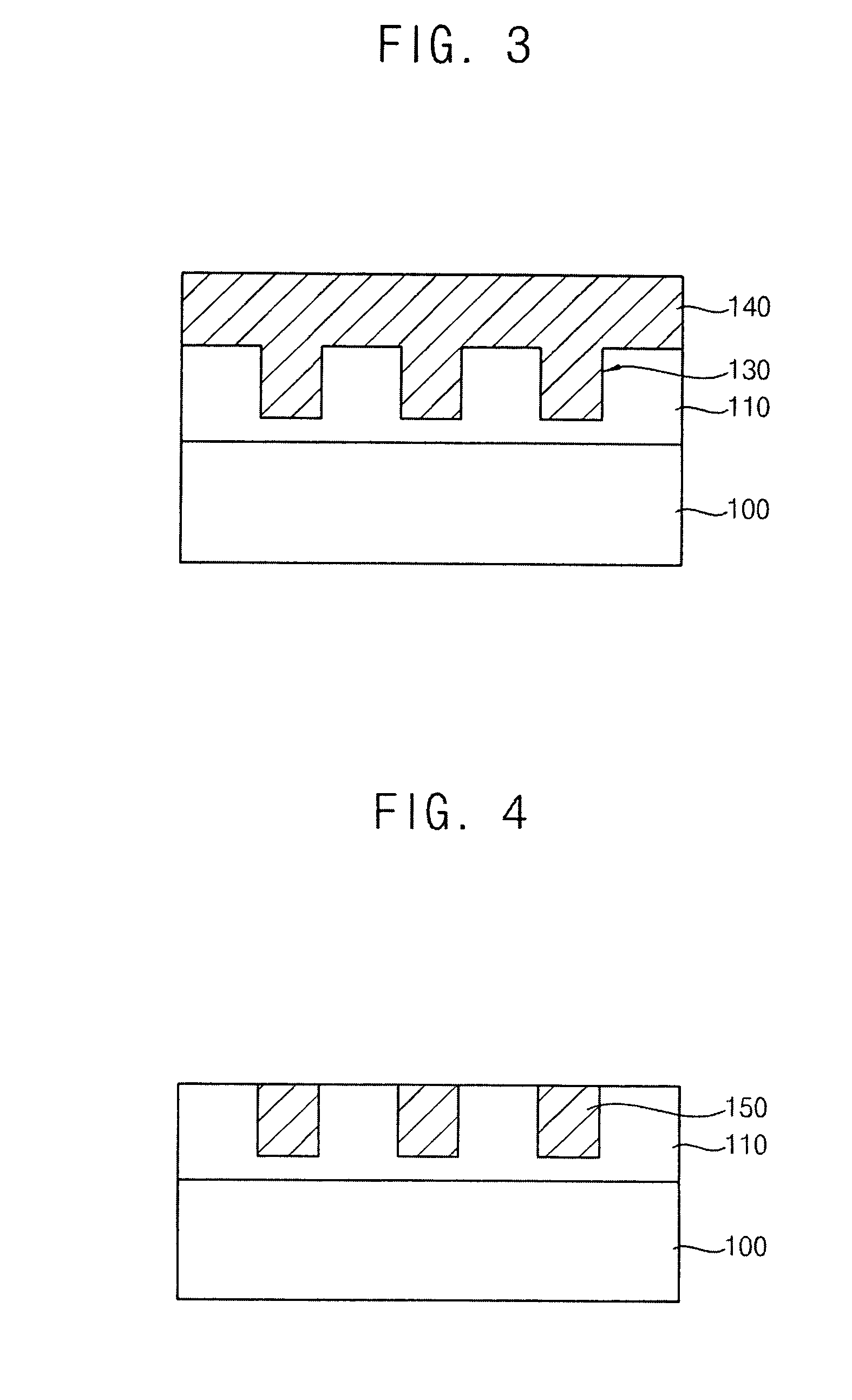

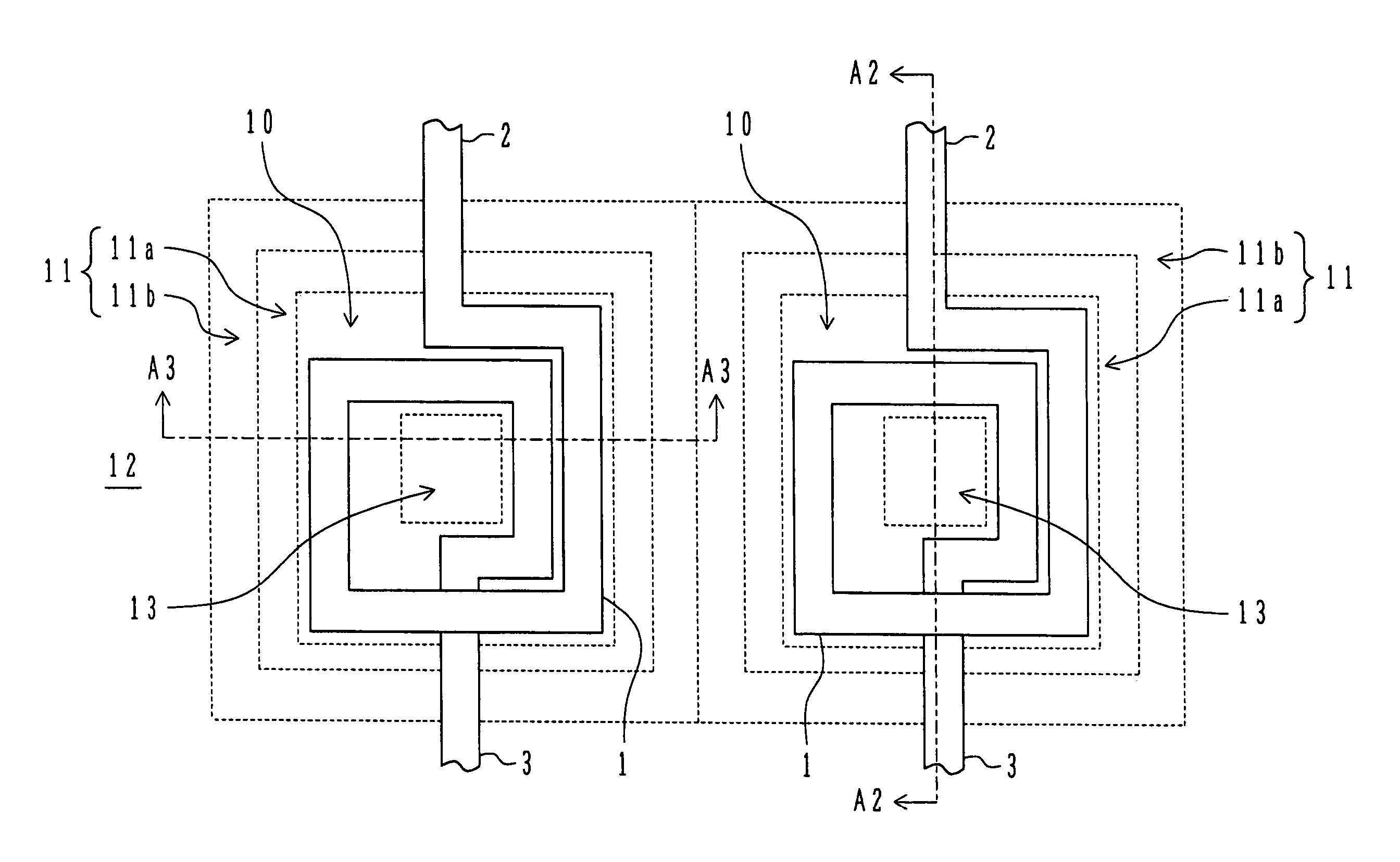

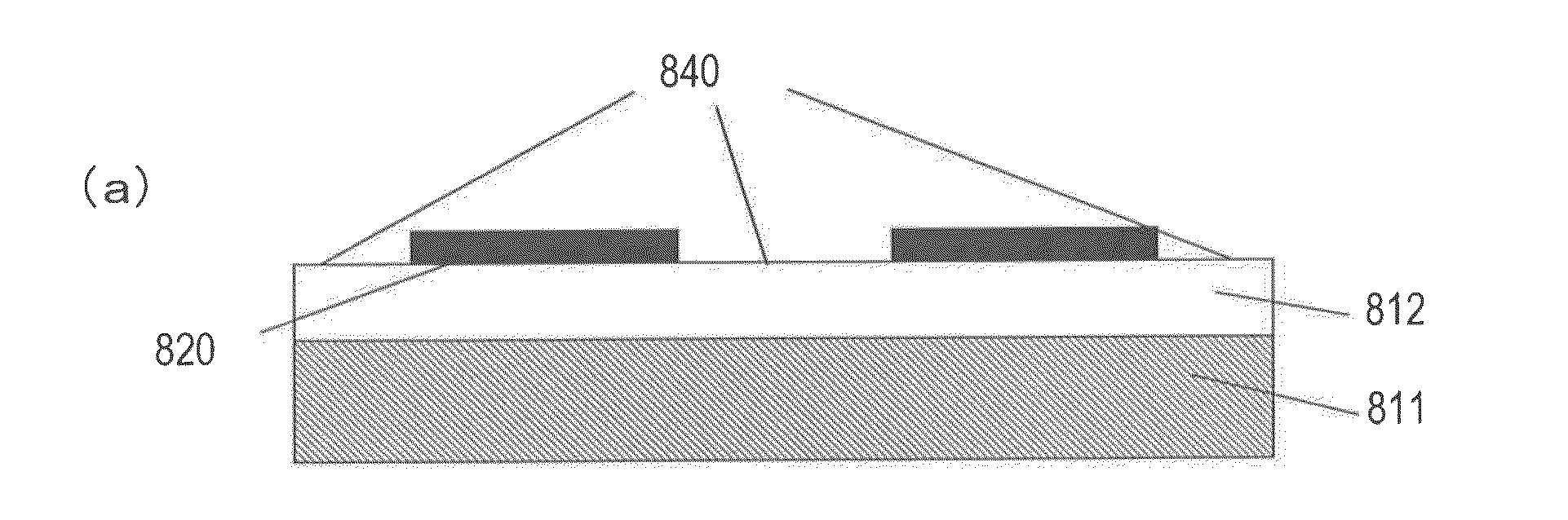

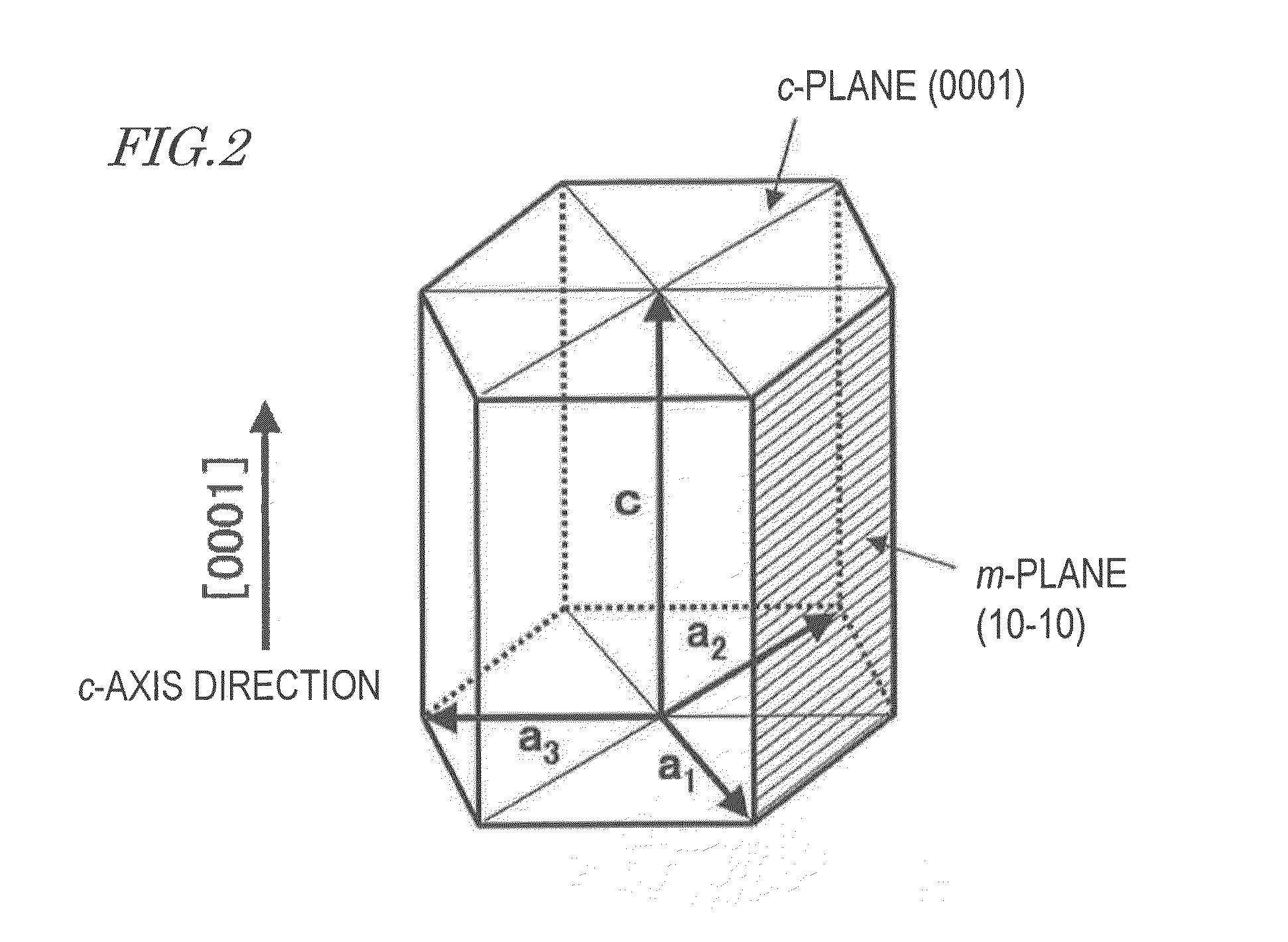

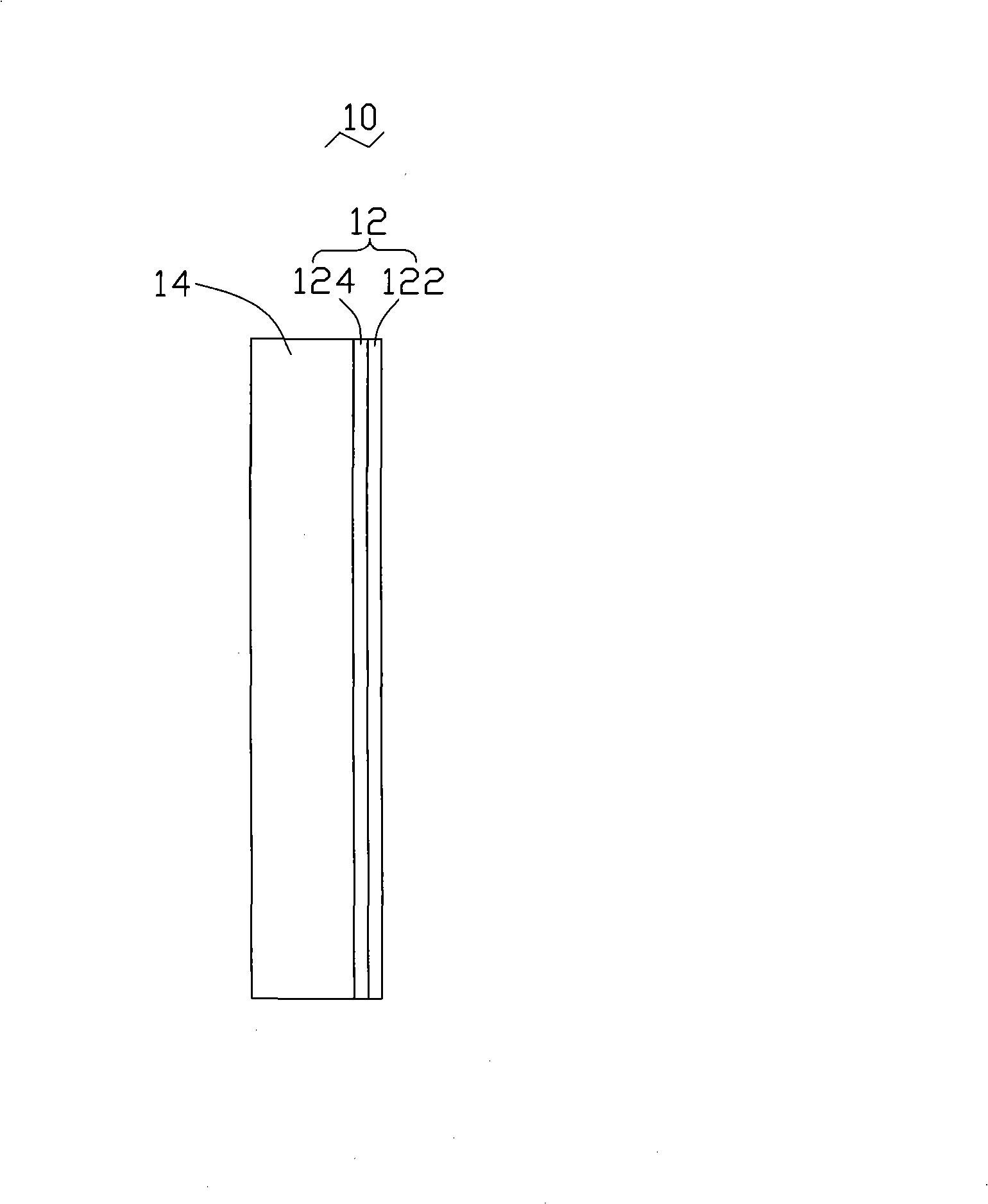

Structure for growth of nitride semiconductor layer, stacked structure, nitride-based semiconductor element, light source, and manufacturing method for same

InactiveUS20140077223A1Improved quality for formationLow costPolycrystalline material growthSolid-state devicesNitride semiconductorsLight source

A structure for growth of a nitride semiconductor layer which is disclosed in this application includes: a sapphire substrate of which growing plane is an m-plane; and a plurality of ridge-shaped nitride semiconductor layers provided on the growing plane of the sapphire substrate, wherein a bottom surface of a recessed portion provided between respective ones of the plurality of ridge-shaped nitride semiconductor layers is the m-plane of the sapphire substrate, the growing plane of the plurality of ridge-shaped nitride semiconductor layers is an m-plane, and an absolute value of an angle between an extending direction of the plurality of ridge-shaped nitride semiconductor layers and a c-axis of the sapphire substrate is not less than 0° and not more than 35°.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

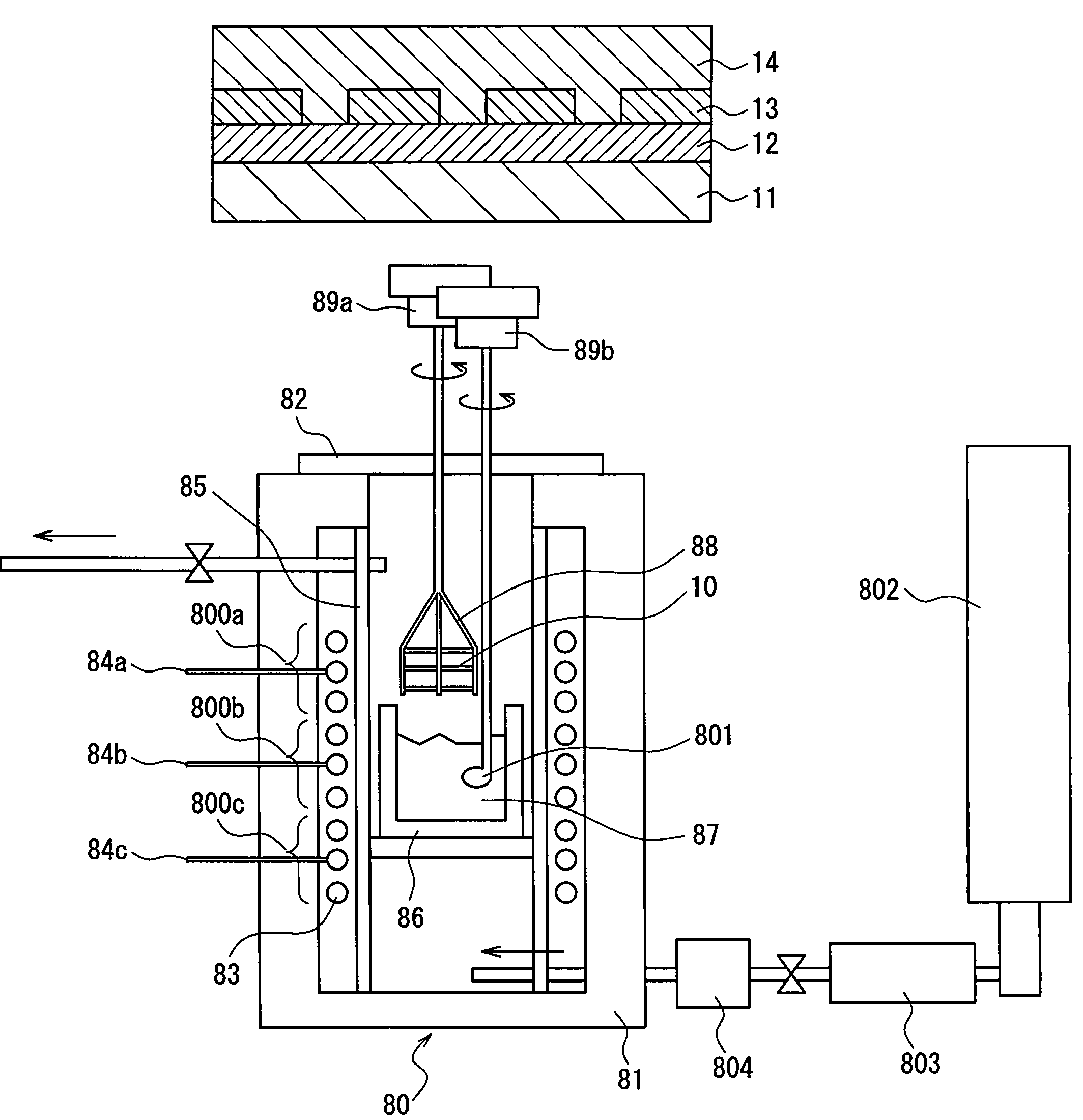

Method of manufacturing Group III nitride substrate and semiconductor device

InactiveUS7176115B2Few dislocationLarge areaPolycrystalline material growthLaser detailsDislocationSeed crystal

The present invention provides a manufacturing method that allows a Group III nitride substrate with a low dislocation density to be manufactured, and a semiconductor device that is manufactured using the manufacturing method. The manufacturing method includes, in an atmosphere including nitrogen, allowing a Group III element and the nitrogen to react with each other in an alkali metal melt to cause generation and growth of Group III nitride crystals. In the manufacturing method, a plurality of portions of a Group III nitride semiconductor layer are prepared, selected as seed crystals, and used for at least one of the generation and the growth of the Group III nitride crystals, and then surfaces of the seed crystals are brought into contact with the alkali metal melt.

Owner:PANASONIC CORP +1

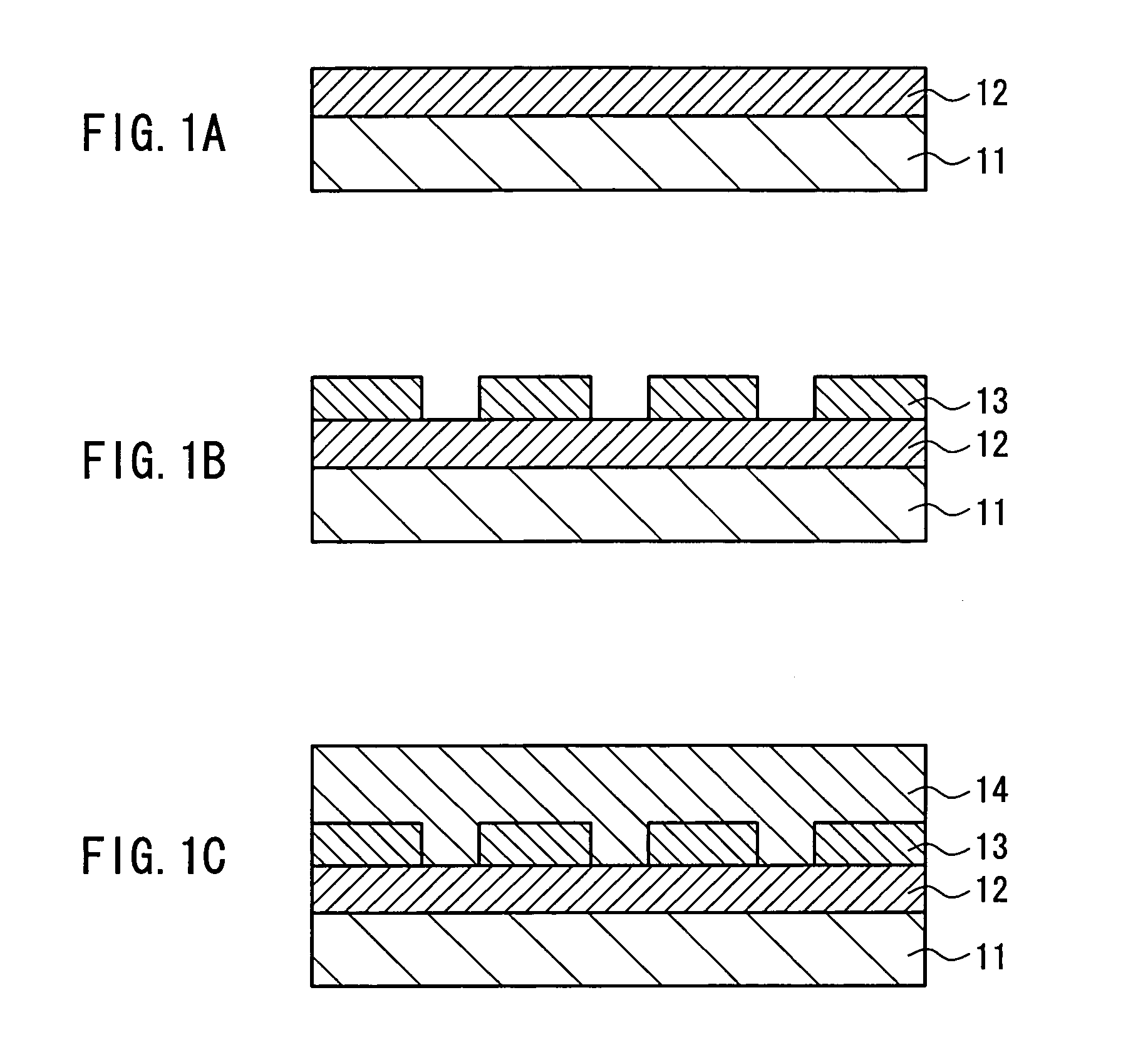

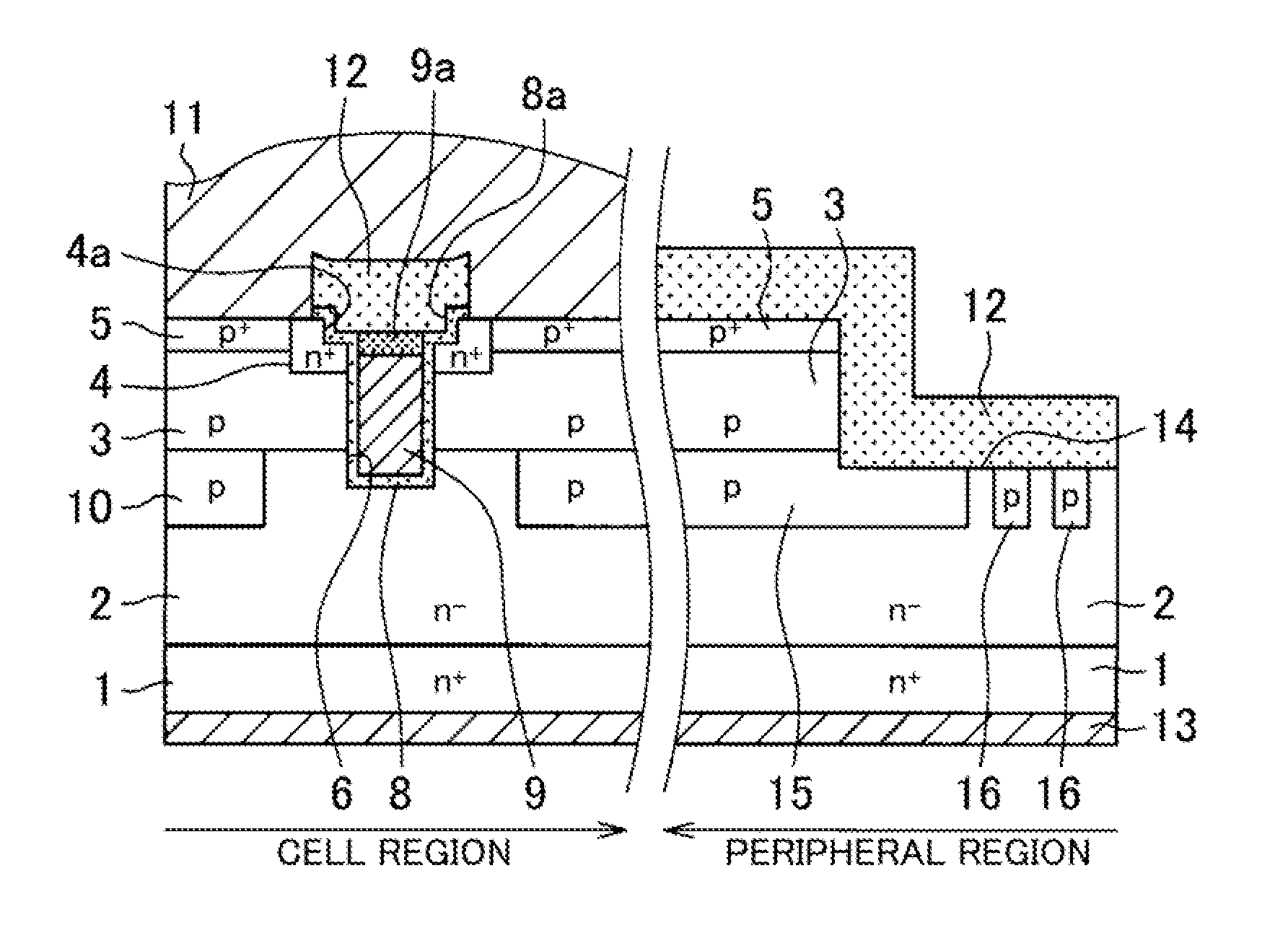

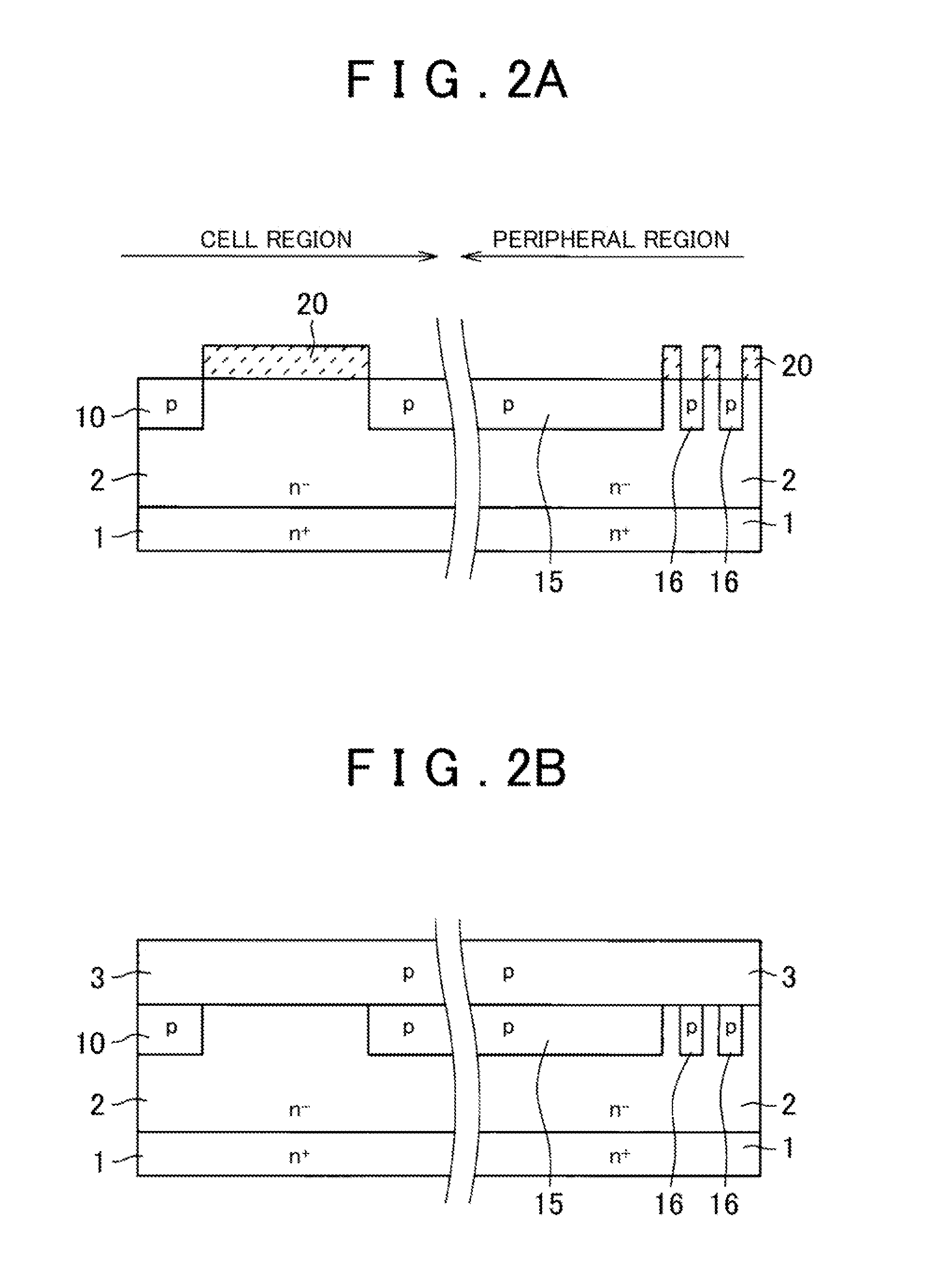

Silicon carbide semiconductor device and method for manufacturing the silicon carbide semiconductor device

InactiveUS20160133741A1Simple manufacturing processLarge process marginTransistorSemiconductor/solid-state device manufacturingMOSFETSemiconductor

A silicon carbide semiconductor device includes a MOSFET and a peripheral high-breakdown-voltage structure. A source region has a first recess. Trenches extend from the bottom of the first recess. A gate insulating film has an extension the shape of which follows the shape of the first recess. The surface of a gate electrode is positioned to be flush with or below the upper surface of the extension.

Owner:TOYOTA JIDOSHA KK

Case of electronic device and manufacturing method therefor

InactiveCN101274498AHigh surface flatnessImprove appearance qualitySynthetic resin layered productsInstrument housingAdhesiveEngineering

The invention provides an electronic device housing body and a production method thereof. The electronic device housing body comprises a decorative layer and a plastic layer, wherein, the decorative layer comprises a film layer and an electronic ink layer which is coated on the film layer. The electronic device housing body is integrated by the decorative layer and the plastic layer as a whole, and the production process thereof is that: the decorative layer is firstly provided and arranged in a mould into which plastic is then poured, and then the plastic and the decorative layer are integrated as a whole to form the electronic device housing body. The electronic device housing body provided by the invention adopts the method that the plastic housing body is integrated as a whole by in-mold lamination to improve the production efficiency; meanwhile, a method that an adhesive is used for bonding can be avoided to ensure that the layers are bonded more fixedly and higher flatness of the surface of the electronic device housing body can be obtained, thus improving the appearance quality and the yield rate of the product.

Owner:SHENZHEN FUTAIHONG PRECISION IND CO LTD

Capacitive touch control panel

ActiveCN105183246AImprove touch sensitivityReduce light transmissionInput/output processes for data processingElectrical and Electronics engineeringElectrode

Owner:TPK TOUCH SOLUTIONS (XIAMEN) INC

Flexible ZnO based thin film transistor and preparation method thereof

InactiveCN103413833AIncrease roughnessEasy to operateTransistorSemiconductor/solid-state device manufacturingLithographic artistEngineering

The invention belongs to the technical field of microelectronic and flat panel display, and particularly relates to a flexible ZnO based thin film transistor and a preparation method thereof. The flexible thin film transistor comprises a flexible substrate, a flat layer, an isolation buffer layer, a gate, a gate insulating layer, a source electrode, a drain electrode and semiconductor channel layers. N type and P type zinc oxide semiconductor channel layers are prepared by using a simple inorganic solution method, and the temperature of the whole process is controlled within 200 DEG C. When in manufacturing, the flat layer and the isolation buffer layer with the same thickness are grown at two sides of the substrate, the flexible substrate bending in the process is alleviated through a thermal annealing mode, and the subsequent lithography alignment accuracy is improved. According to the transistor and the preparation method, the maneuverability and stability of the flexible TFT and subsequent devices can be improved, the preparation process is simple, and the production cost is low.

Owner:FUDAN UNIV

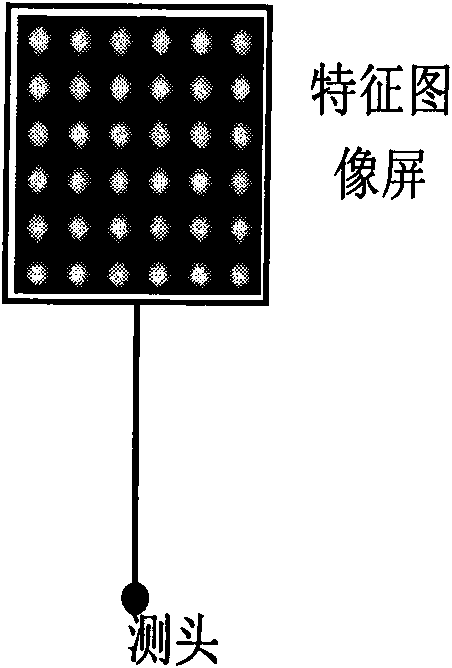

Phase target-based optical three-coordinate measuring method

InactiveCN101561251AHigh surface flatnessEasy to adjustUsing optical meansThree-dimensional spaceVisual perception

The invention discloses a phase target-based optical three-coordinate measuring method, and relates to the field of visual measurement. A measuring system consists of a camera, a computer, and a phase target consisting of a characteristic image screen, a measuring rod and a measuring head. The camera acquires a characteristic image on the characteristic image screen of the phase target; a fringe analysis method is adopted to calculate the phase distribution, the corresponding relation between points on the target screen and pixels of the camera is established, and three-dimensional coordinates of a contact of the measuring head of the target is further determined. When the phase target is used for the optical three-coordinate measurement, compared with an auxiliary target (a conventional target) with more than 3 marking points, the phase target has a more accurate and reliable measuring result due to the greatly increased number of characteristic points and accurate extraction of the characteristic points based on phase calculation. The phase target has the advantages of high measuring accuracy, small size, easy carrying and motion, easy adjustment of the size of the target image screen, and the like.

Owner:SICHUAN UNIV

Capacitor for incorporation in wiring board, wiring board, method of manufacturing wiring board, and ceramic chip for embedment

InactiveUS7932471B2Improve reliabilityReduce conductionSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

A capacitor comprising: a capacitor body including a plurality of laminated dielectric layers, a plurality of inner electrode layers which are respectively disposed between mutually adjacent ones of the dielectric layers, a first main surface located in a laminated direction of the dielectric layers, and a second main surface opposite to the first main surface; a first outer electrode formed on the first main surface of the capacitor body and electrically connected to the inner electrode layers; a second outer electrode formed on the second main surface of the capacitor body and electrically connected to the inner electrode layers; a first dummy electrode formed on the first main surface of the capacitor body; and a second dummy electrode formed on the second main surface of the capacitor body.

Owner:NGK SPARK PLUG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com