Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1275 results about "Scan chain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

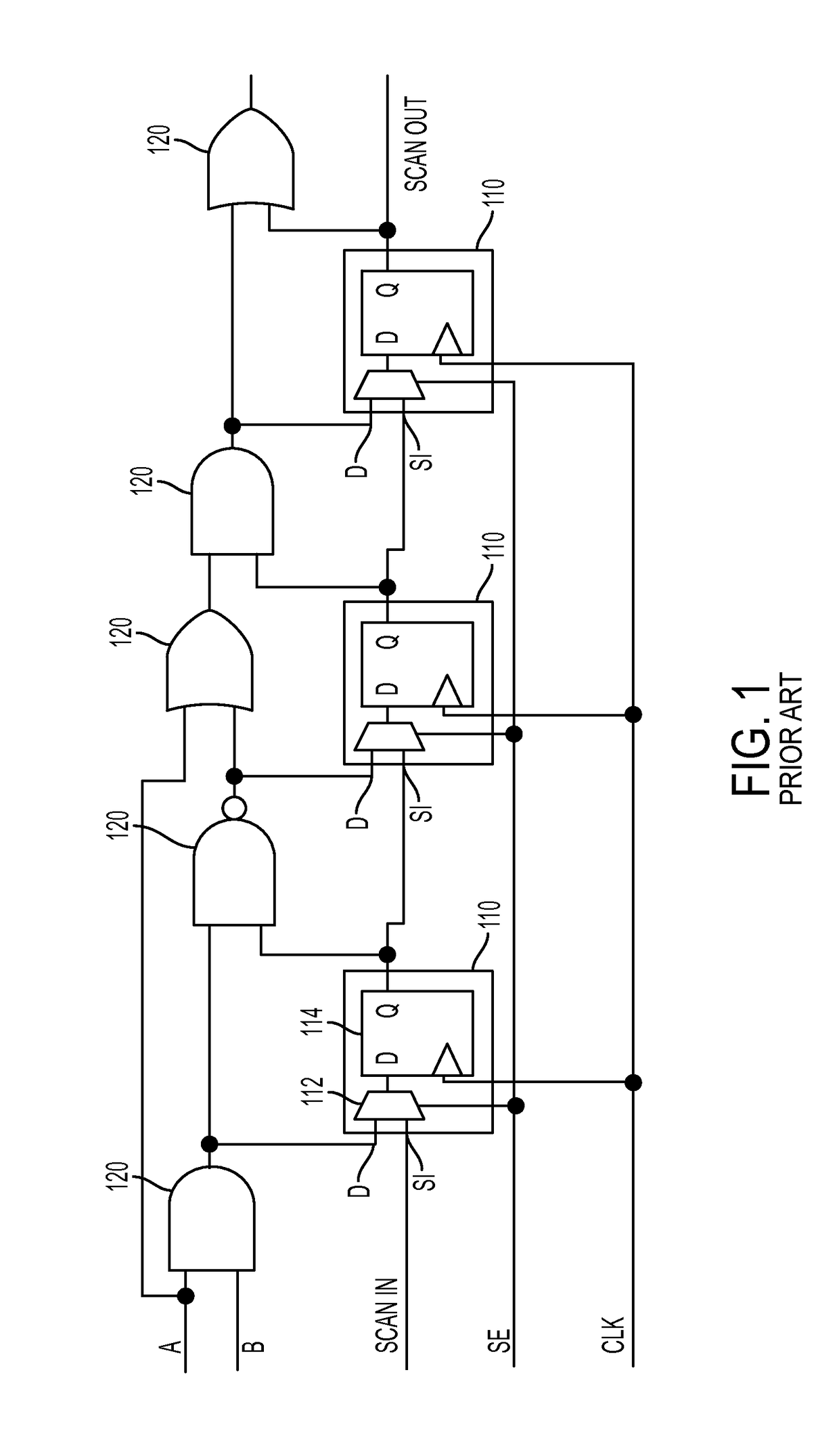

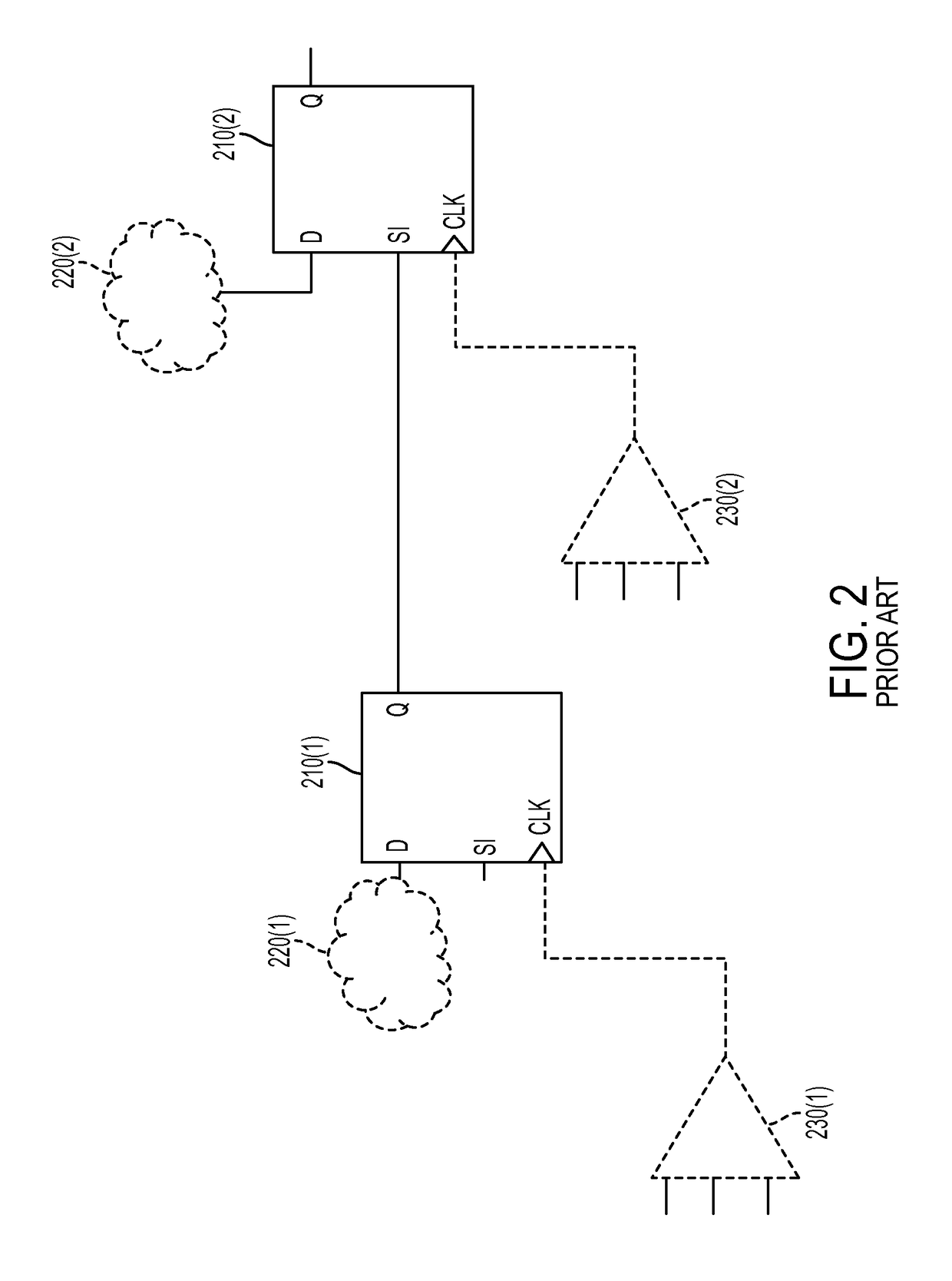

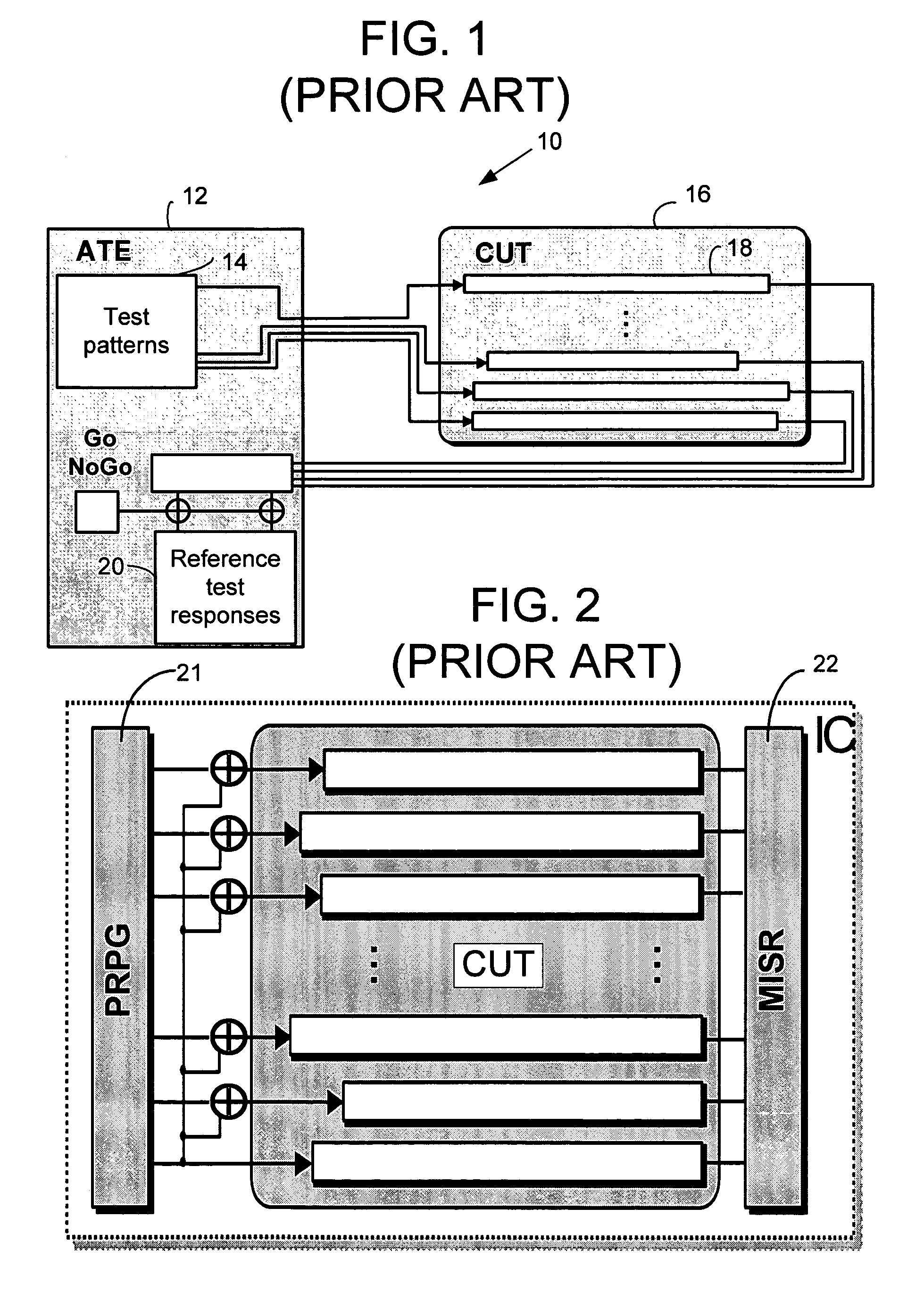

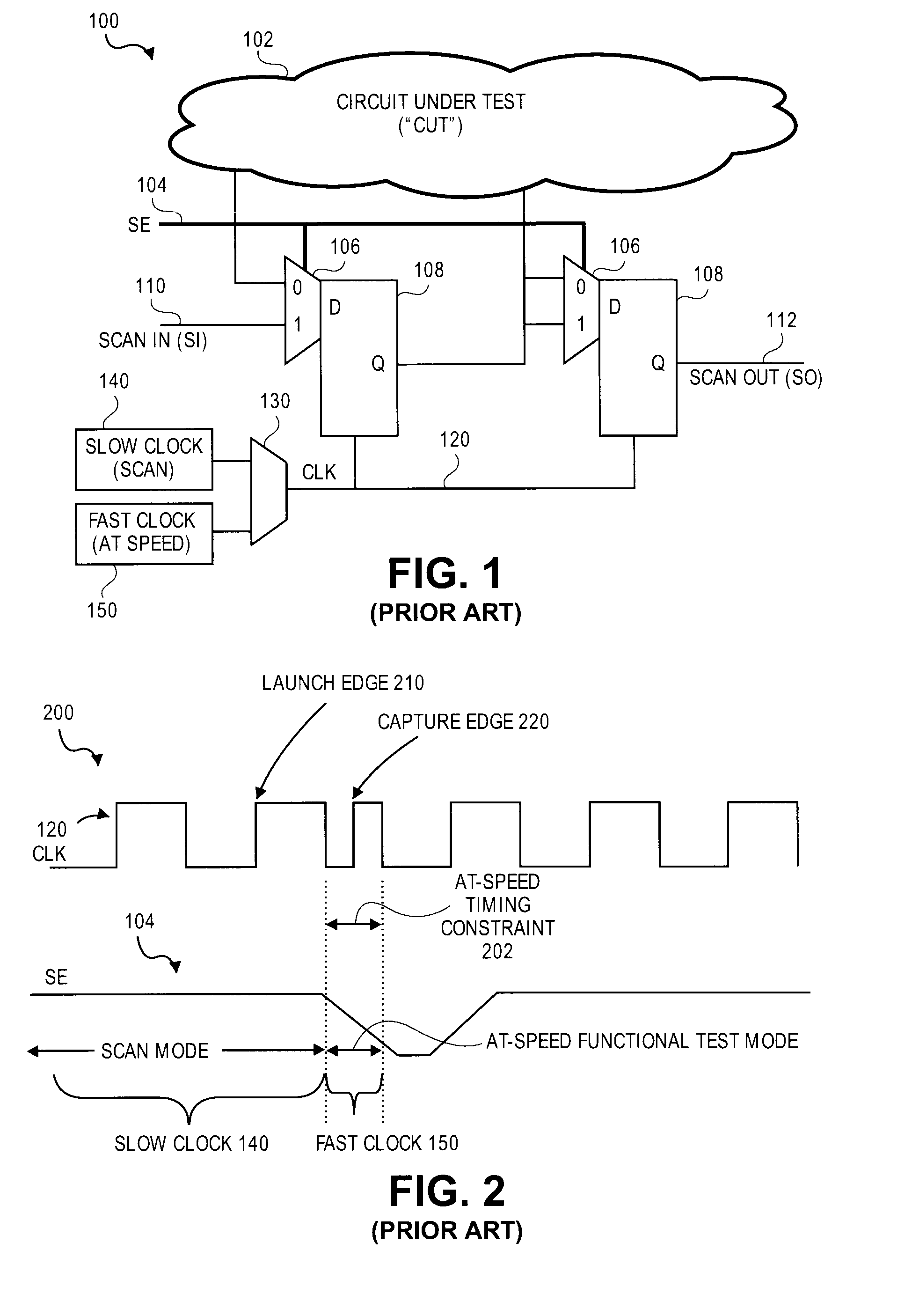

Scan chain is a technique used in design for testing. The objective is to make testing easier by providing a simple way to set and observe every flip-flop in an IC.The basic structure of scan include the following set of signals in order to control and observe the scan mechanism.

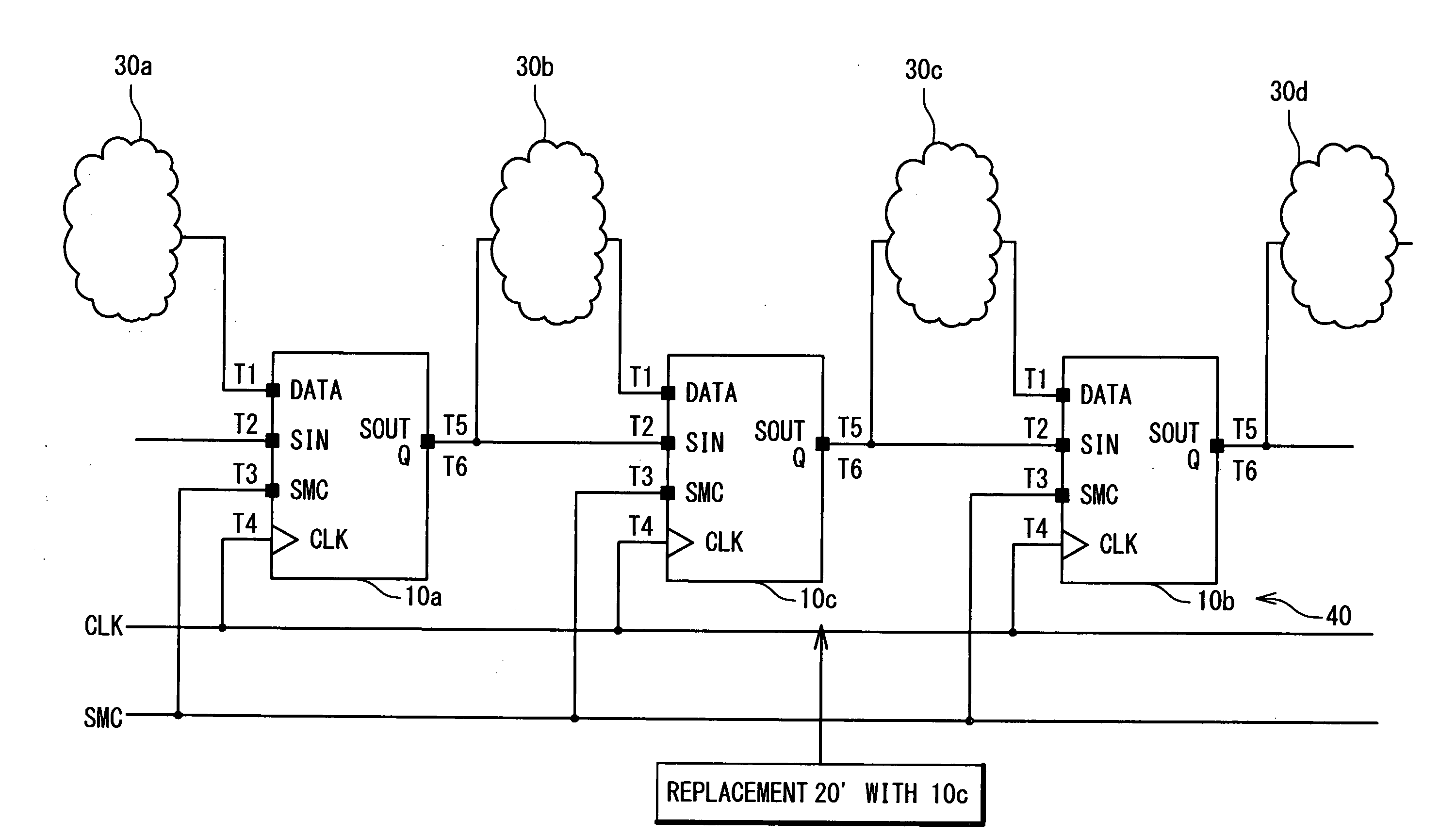

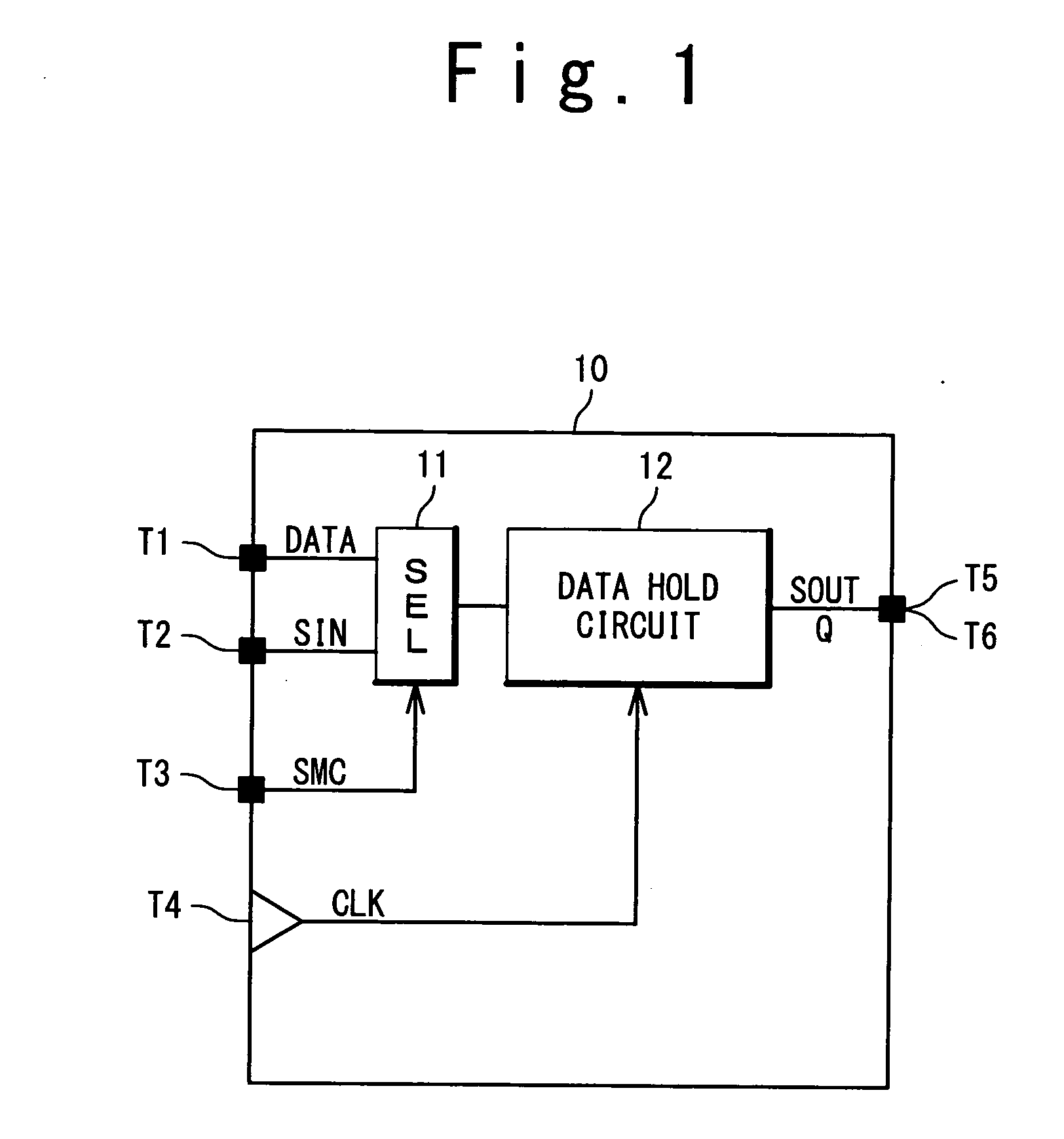

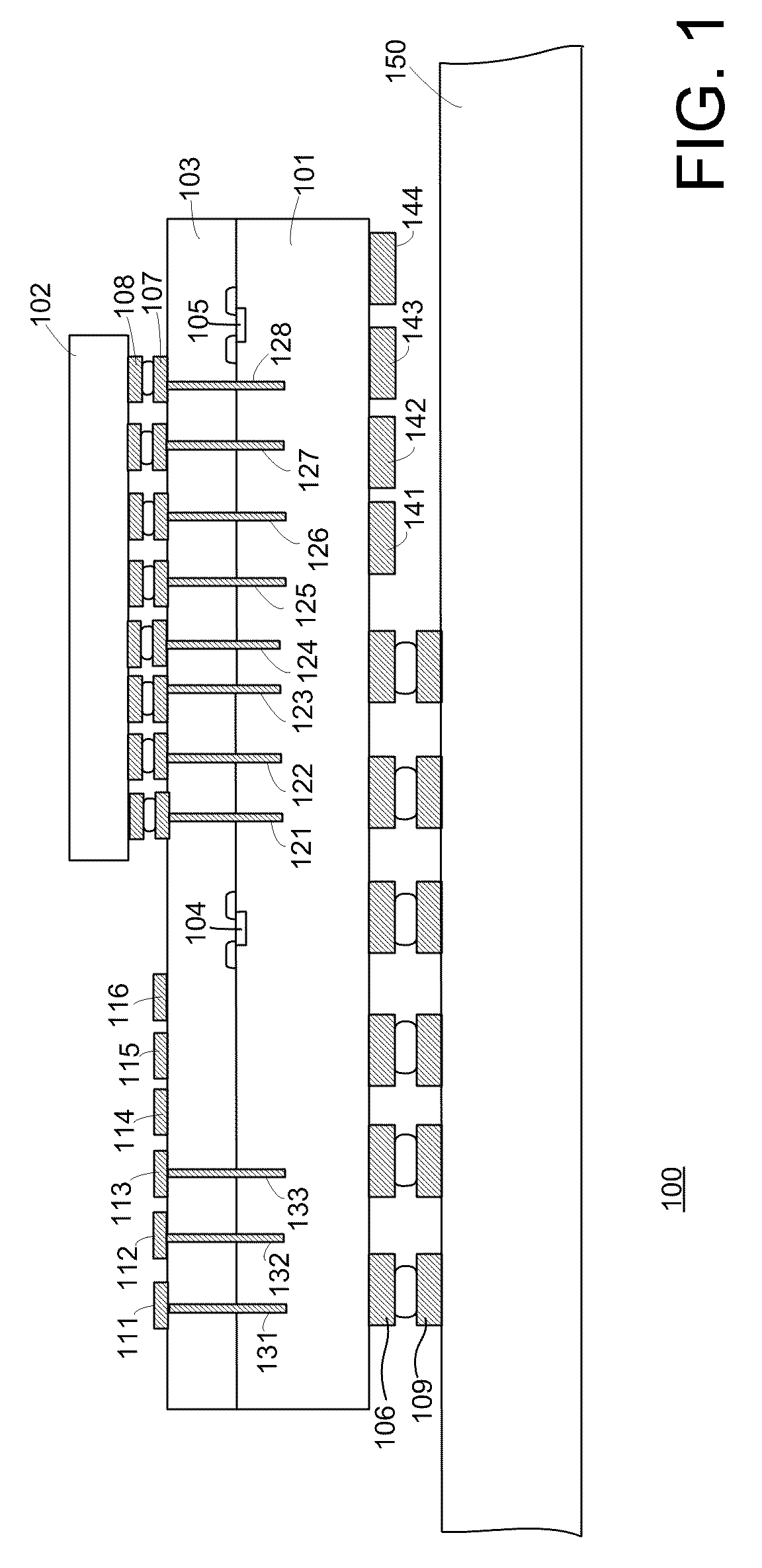

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

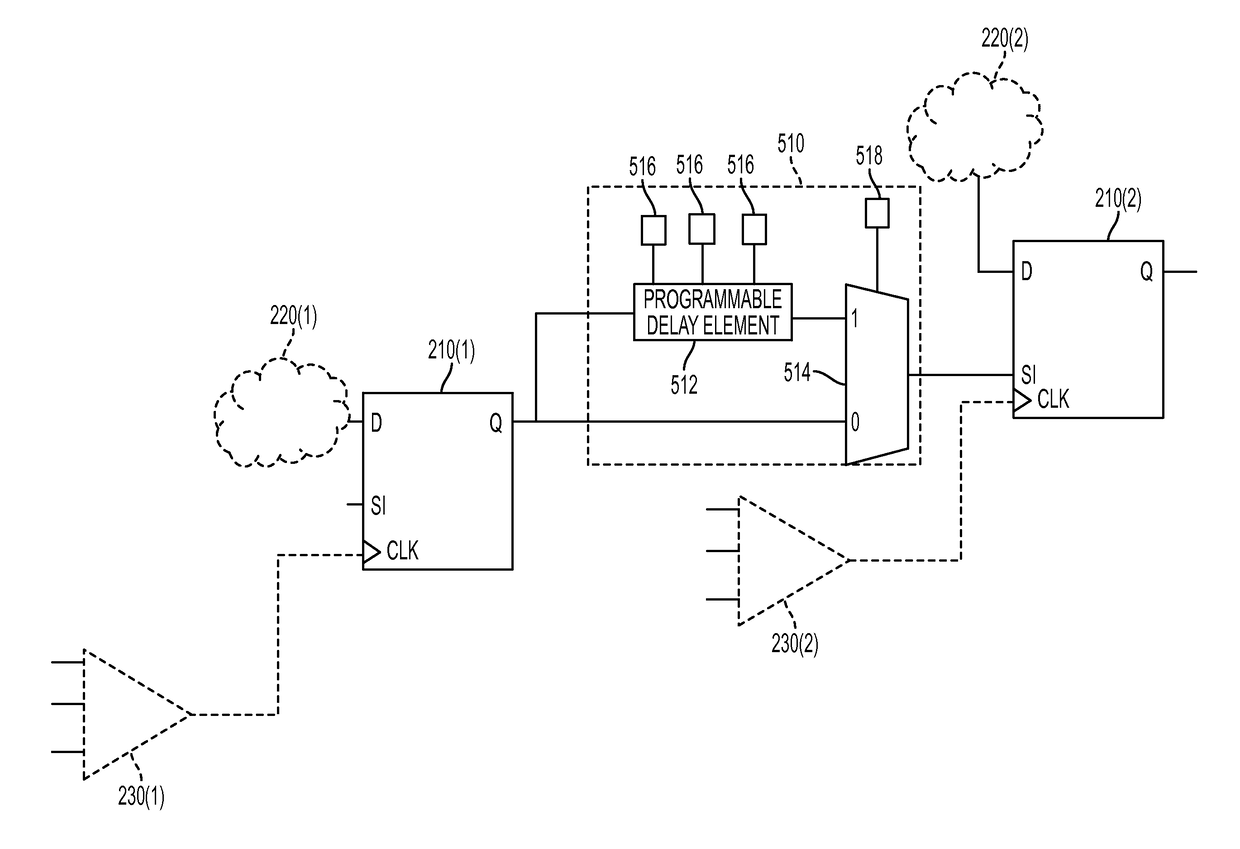

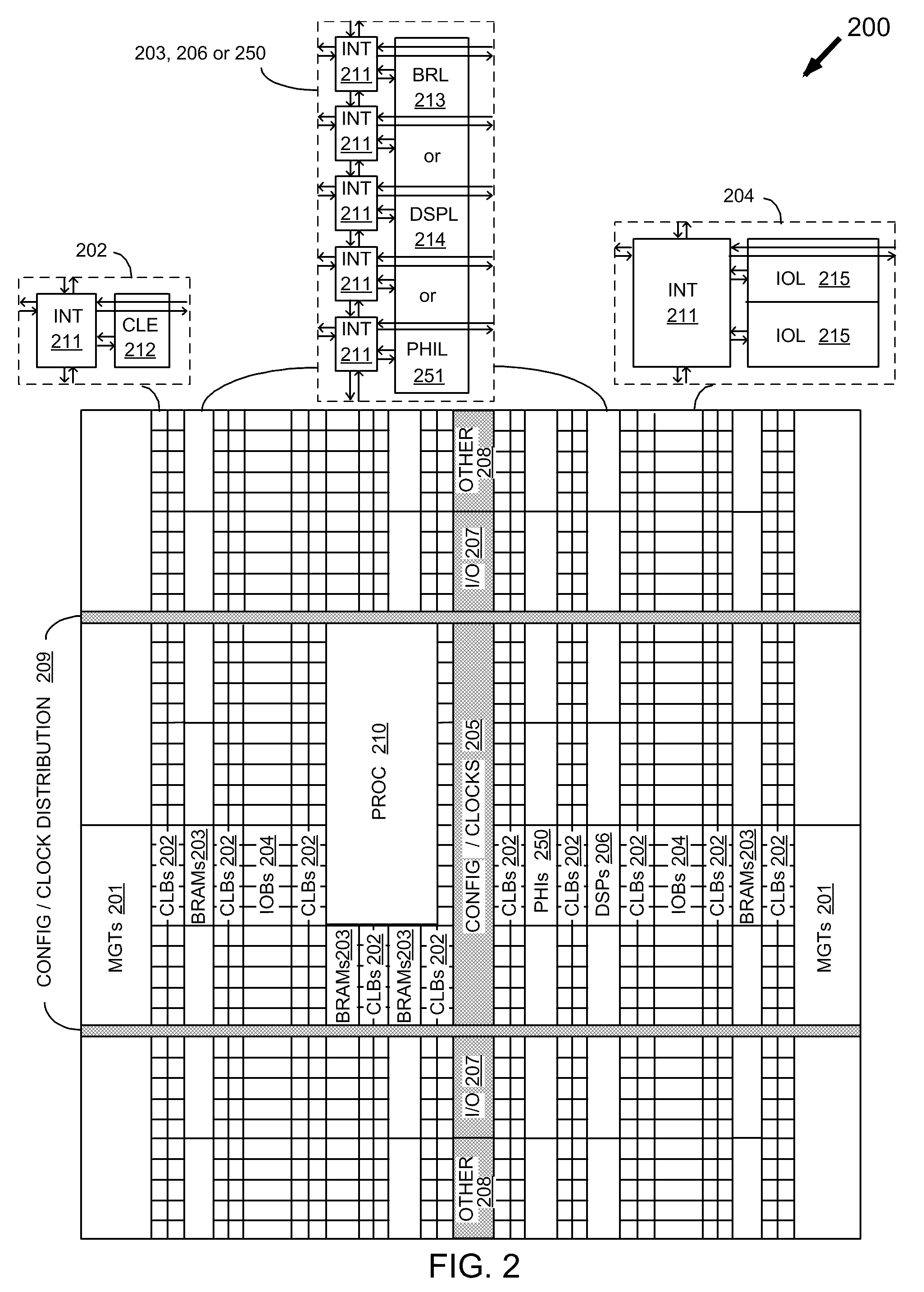

Programmable circuits for correcting scan-test circuitry defects in integrated circuit designs

ActiveUS9618579B2Digital circuit testingDetecting faulty computer hardwareComputer hardwareComputer architecture

In certain embodiments, an integrated circuit has scan-test circuitry that performs scan testing on circuitry under scan test (CUST) within the IC, where the scan-test circuitry is susceptible to a defect. In order to enable the defect to be corrected after it occurs, the scan-test circuitry includes a set of programmable circuitry connected to provide a signal to other circuitry (e.g., a scan chain) within the scan-test circuitry, where the set of programmable circuitry includes one or more configurable memory cells connected to control the programming of the set of programmable circuitry. The memory cell(s) can be configured to program the set of programmable circuitry to enable the scan testing to be performed without modification. The memory cell(s) can also be configured to program the set of programmable circuitry to modify the scan testing to correct the defect in the scan-test circuitry.

Owner:LATTICE SEMICON CORP

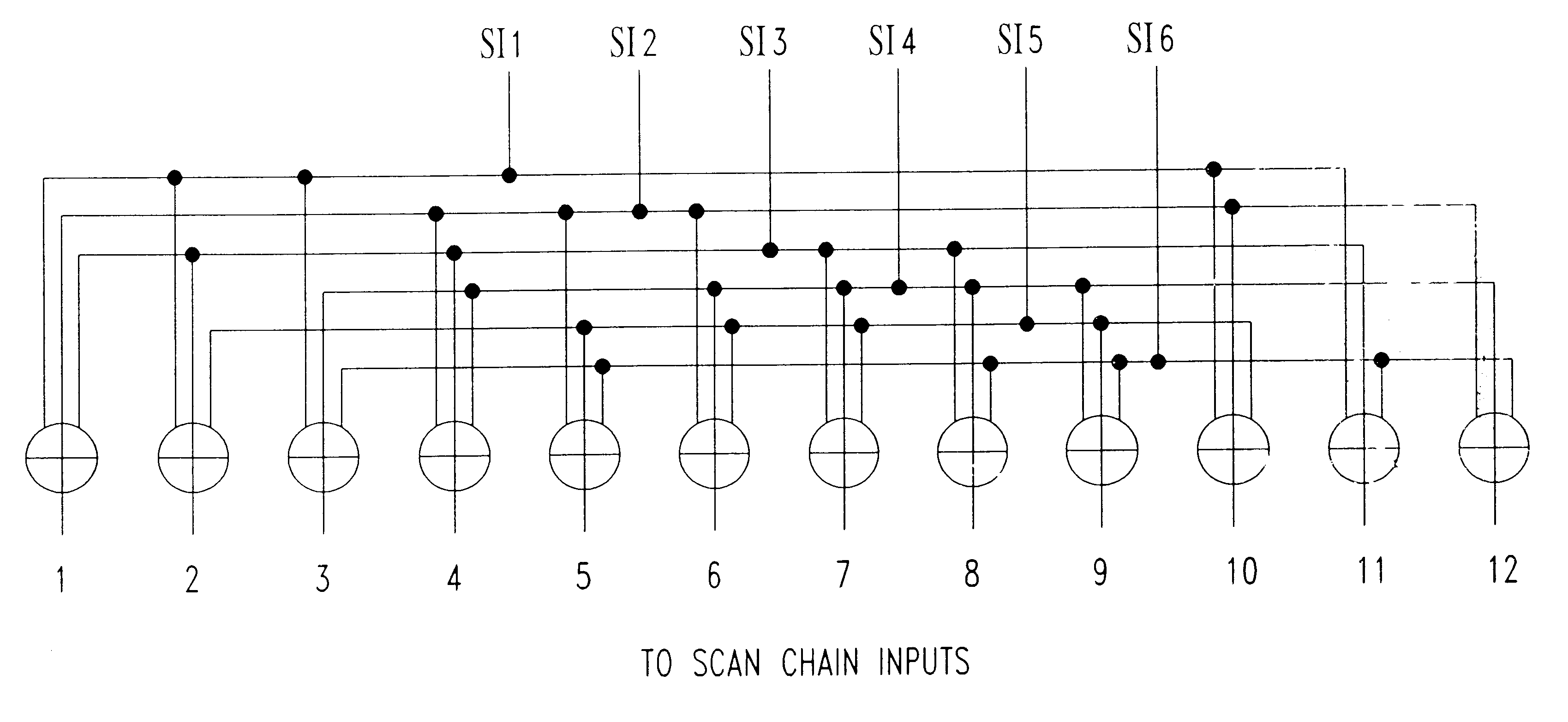

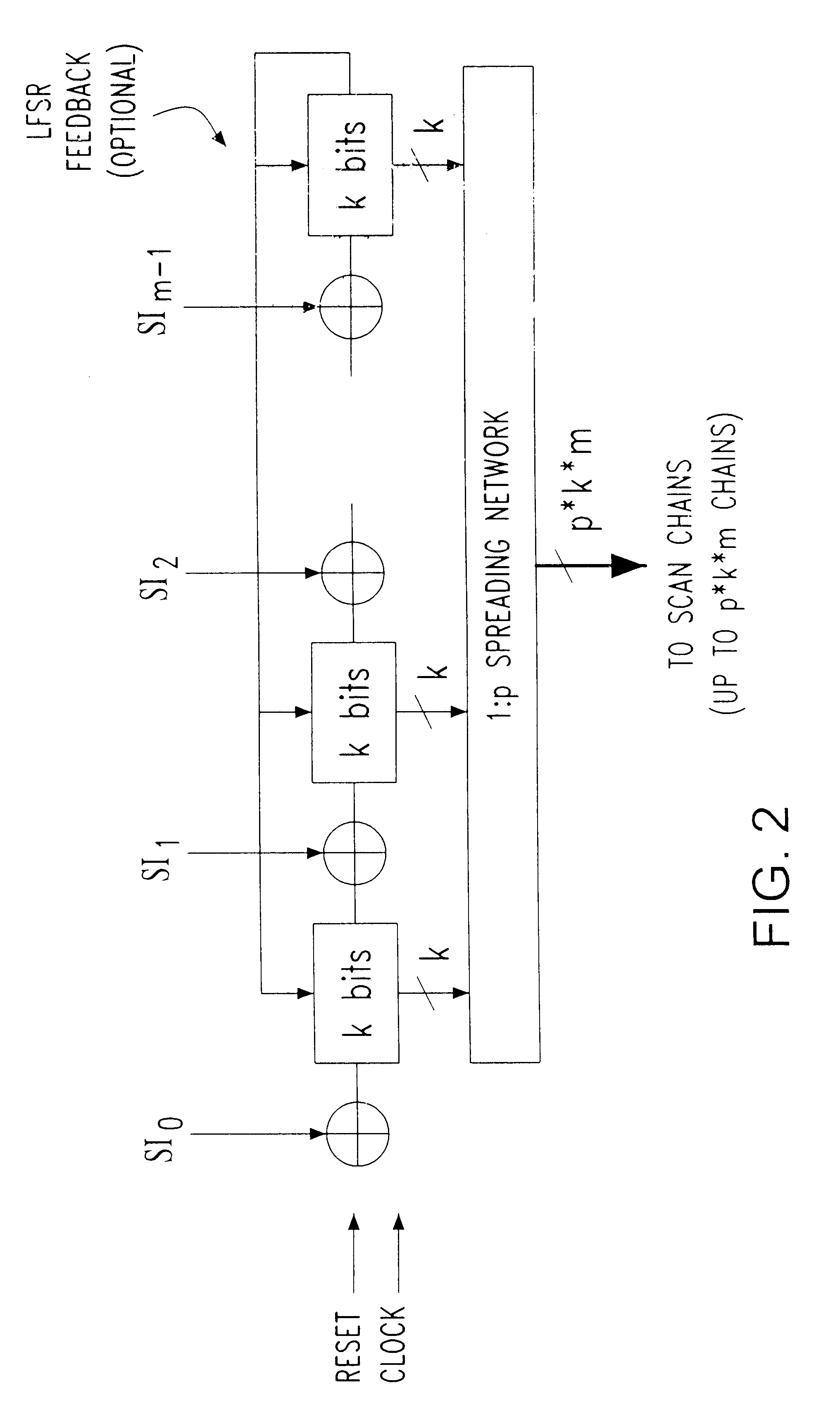

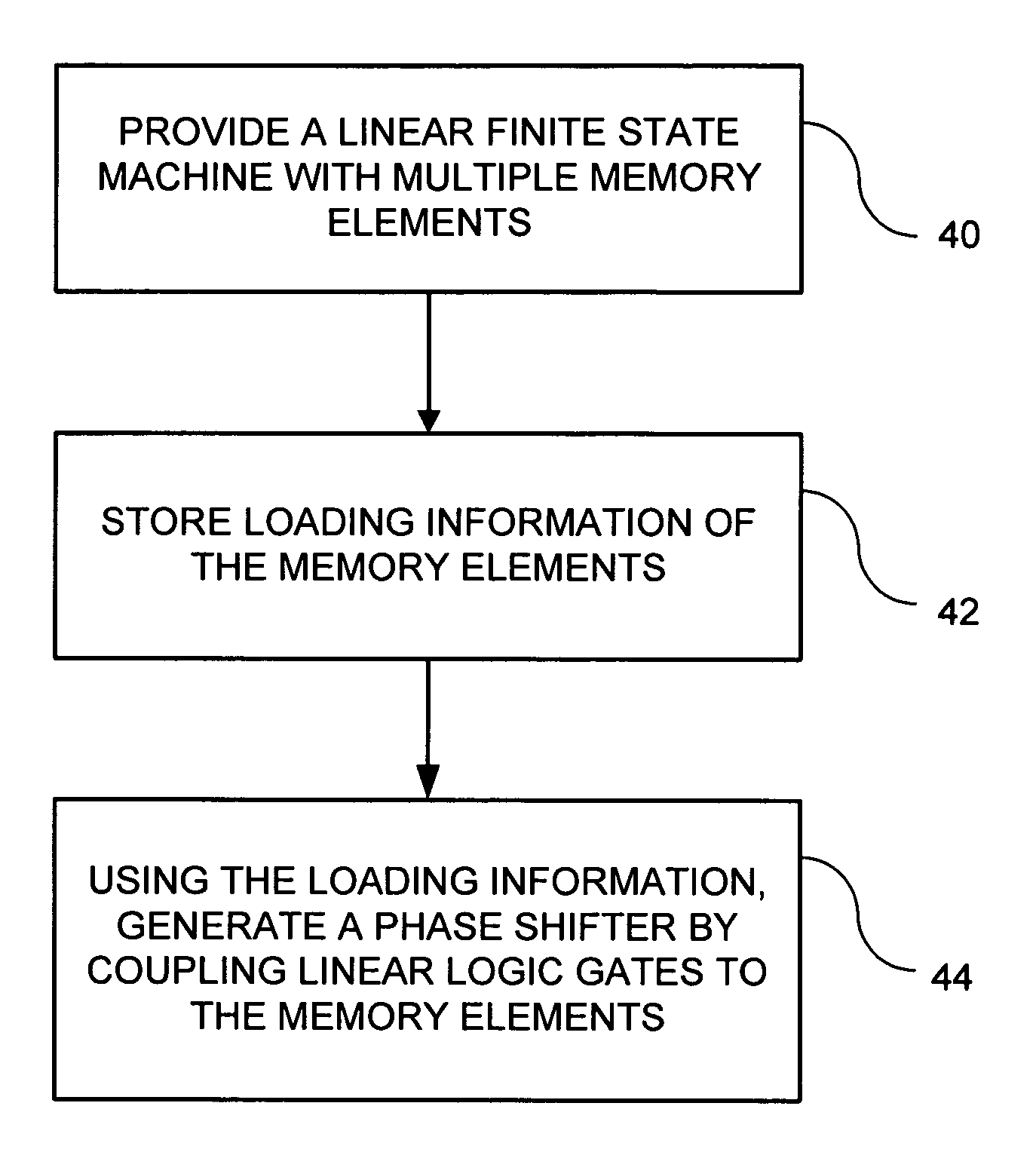

Phase shifter with reduced linear dependency

InactiveUS6874109B1Electronic circuit testingError detection/correctionCircuit complexityLinear dependency

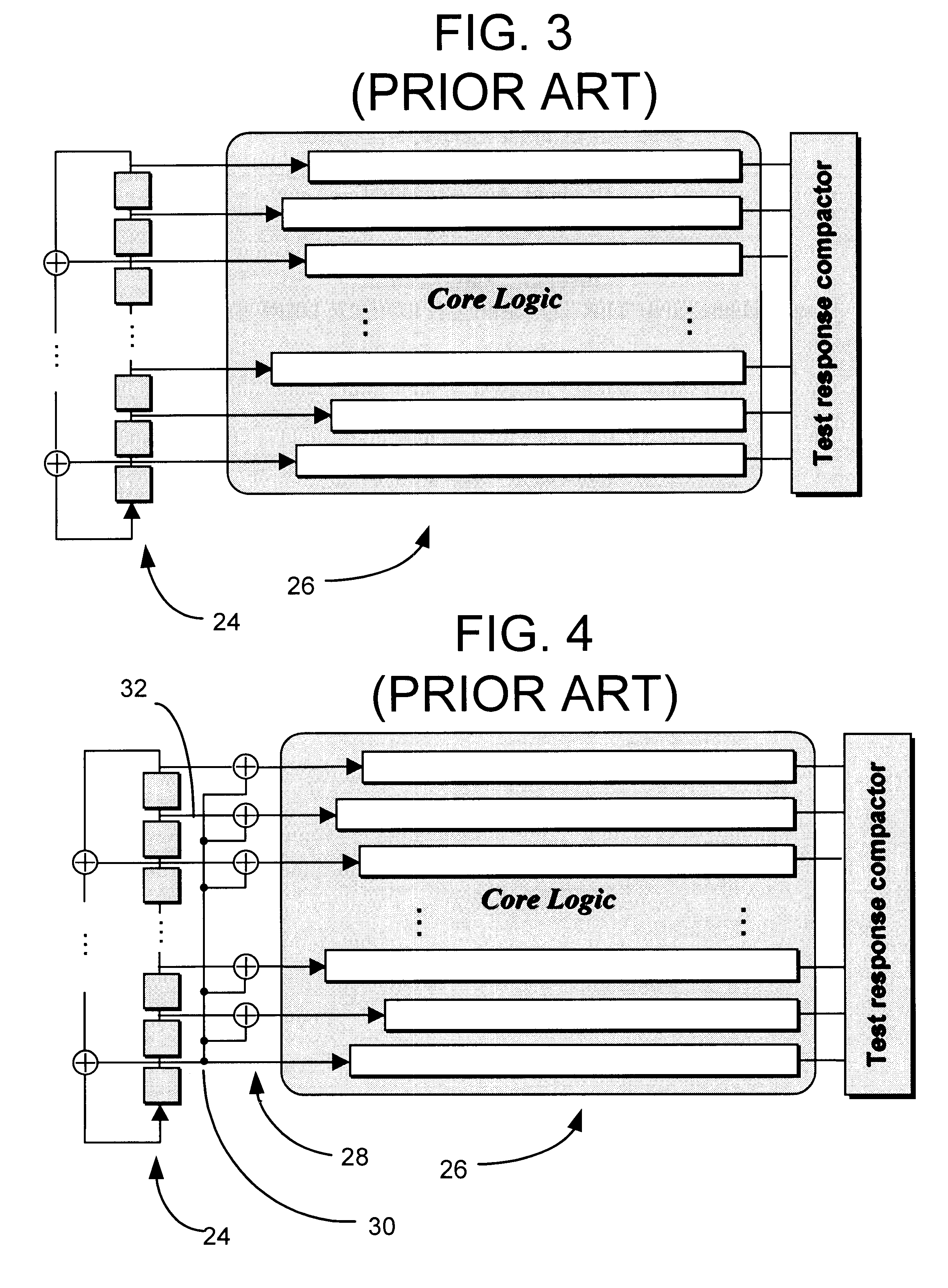

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Combinational test pattern generation method and apparatus

InactiveUS6480980B2Electronic circuit testingError detection/correctionPattern generationEngineering

Owner:RENESAS ELECTRONICS AMERICA

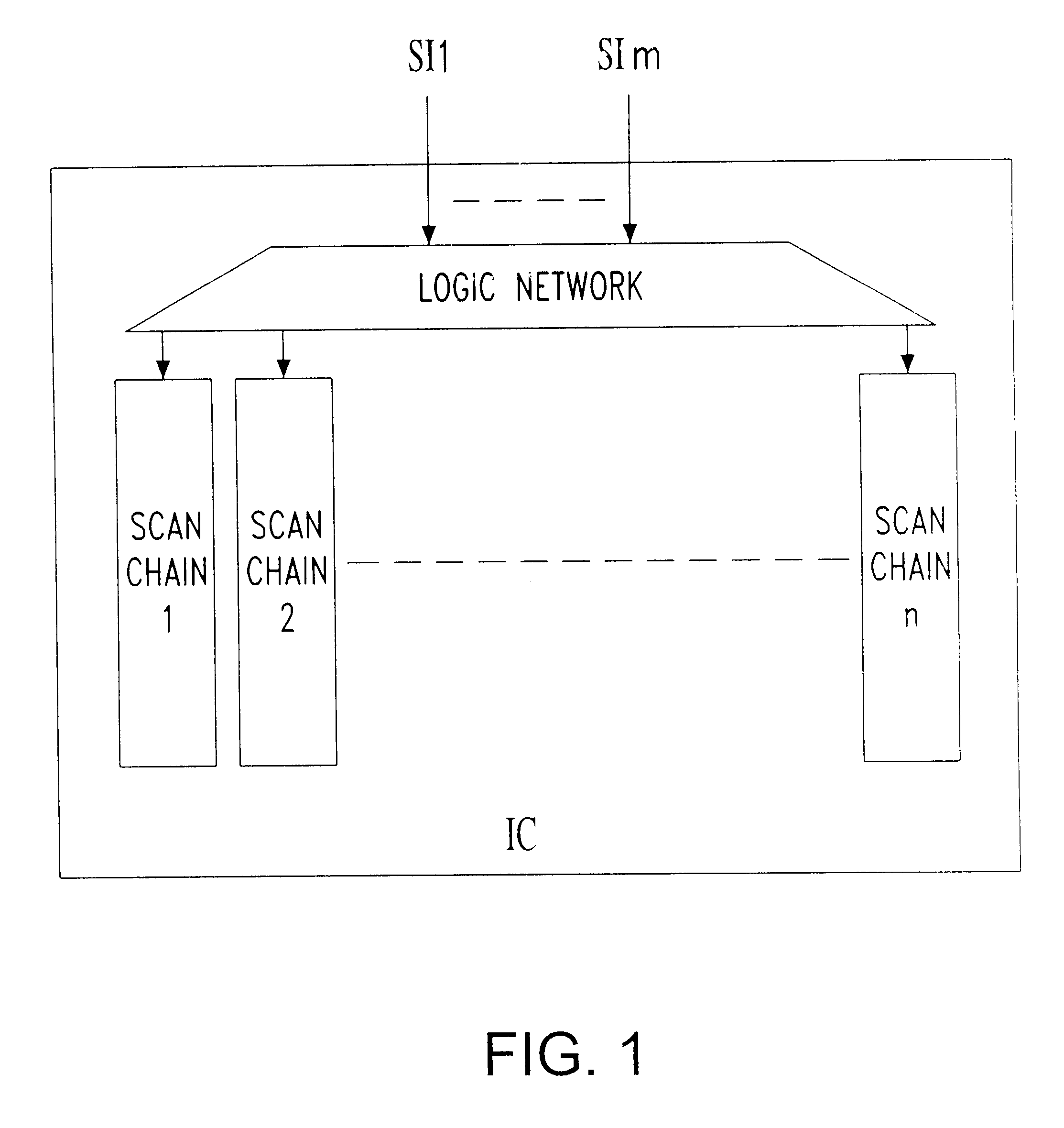

Real-time decoder for scan test patterns

InactiveUS6611933B1Cost-efficiently integratedForming accuratelyElectronic circuit testingError detection/correctionComputer hardwareTest efficiency

A method and apparatus for improving the efficiency of scan testing of integrated circuits is described. This efficiency is achieved by reducing the amount of required test stimulus source data and by increasing the effective bandwidth of the scan-load operation. The reduced test data volume and corresponding test time are achieved by integrating a real-time test data decoder or logic network into each integrated circuit chip. The apparatus, servicing a plurality of internal scan chains wherein the number of said internal scan chains exceeds the number of primary inputs available for loading data into the scan chains, includes: a) logic network positioned between the primary inputs and the inputs of the scan chains, the logic network expanding input data words having a width corresponding to the number of the primary inputs, and converting the input data words into expanded output data words having a width that corresponds to the number of the internal scan chains; and b) coupled to the internal scan chains, registers loaded with bit values provided by the expanded output data words while data previously loaded into the scan chains shifts forward within the scan chains by one bit position at a time; wherein a first plurality of the input data words supplied to the primary inputs produce a second plurality of expanded data words that are loaded into the internal scan chains to achieve an improved test coverage.

Owner:GOOGLE LLC

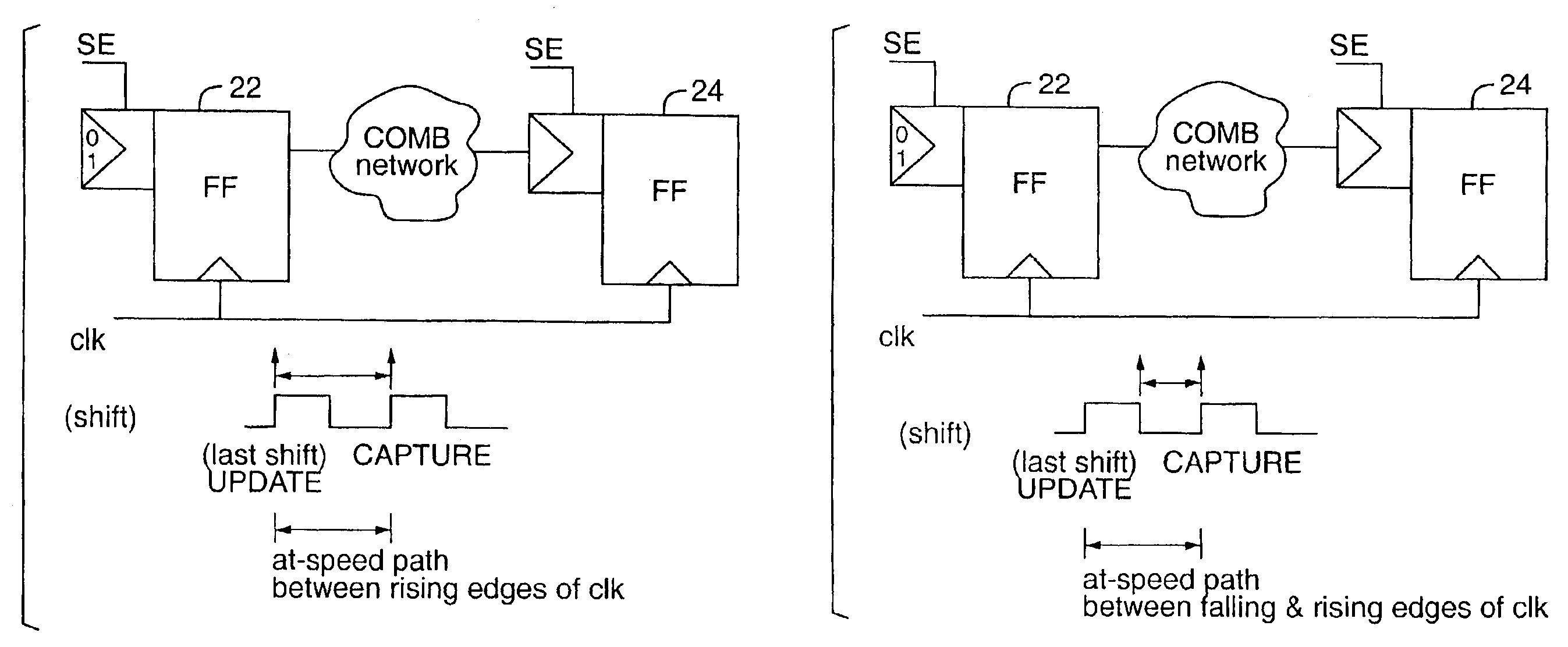

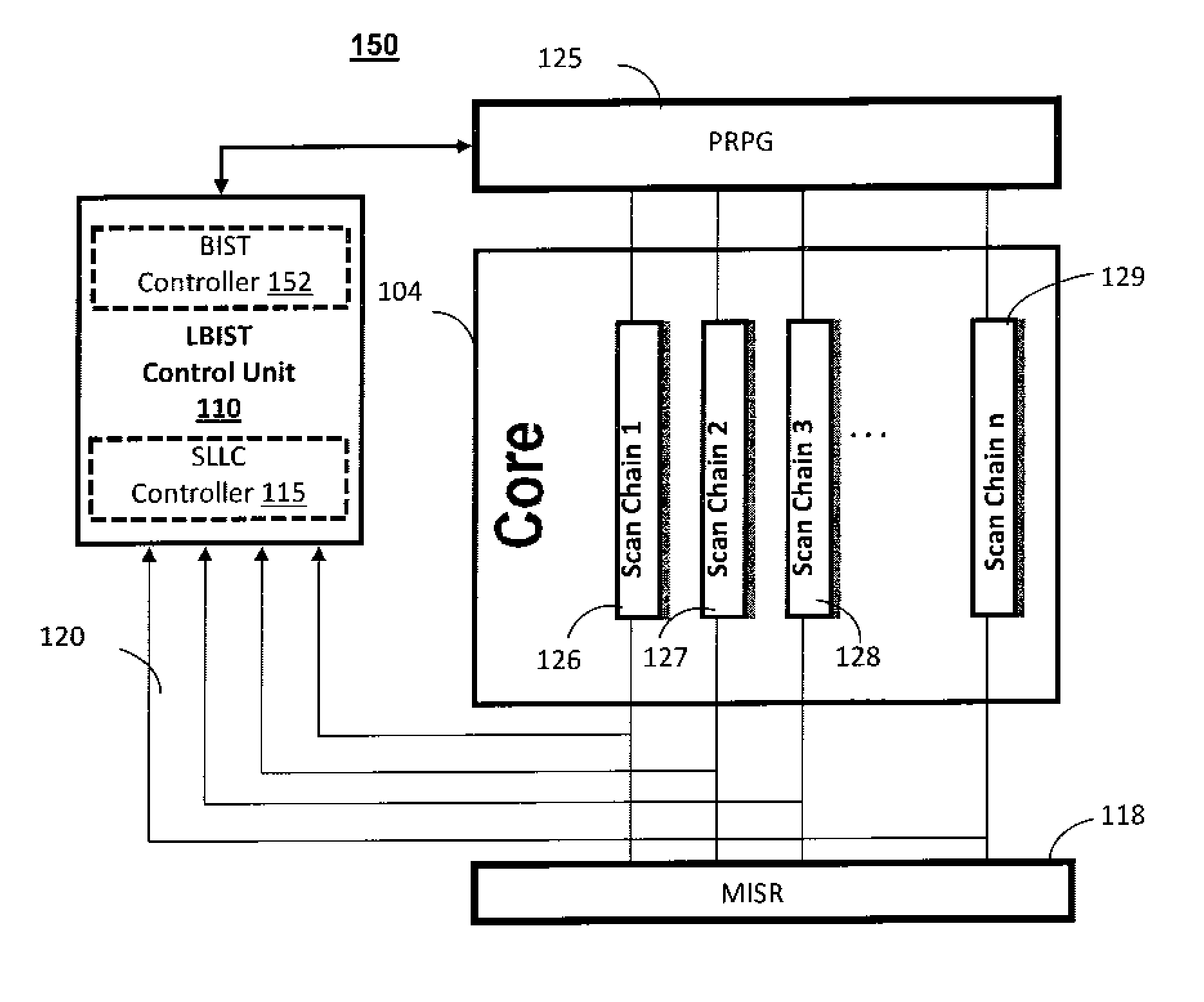

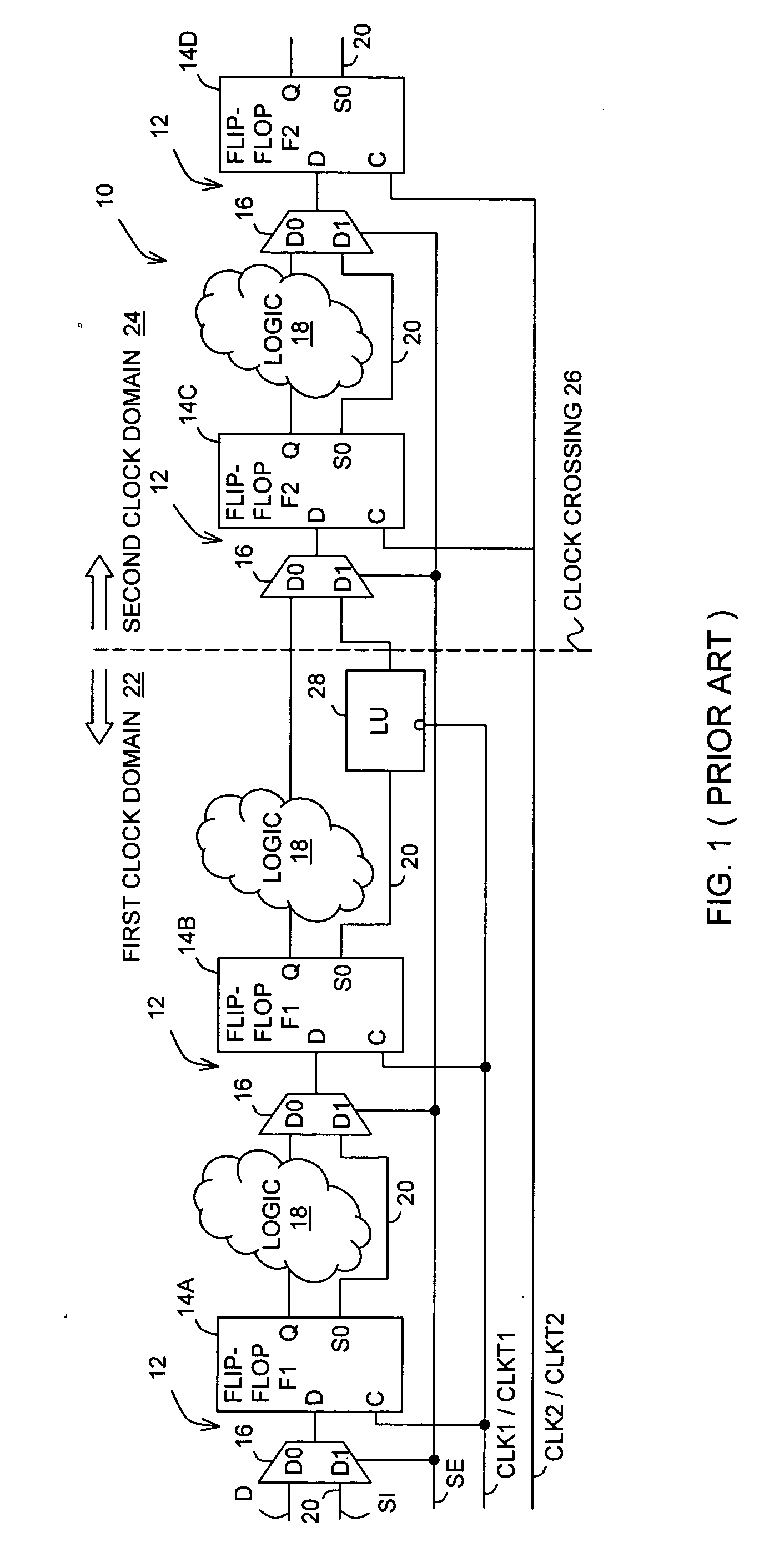

Method and apparatus for at-speed testing of digital circuits

InactiveUS6966021B2Electronic circuit testingError detection/correctionMulti inputProcessor register

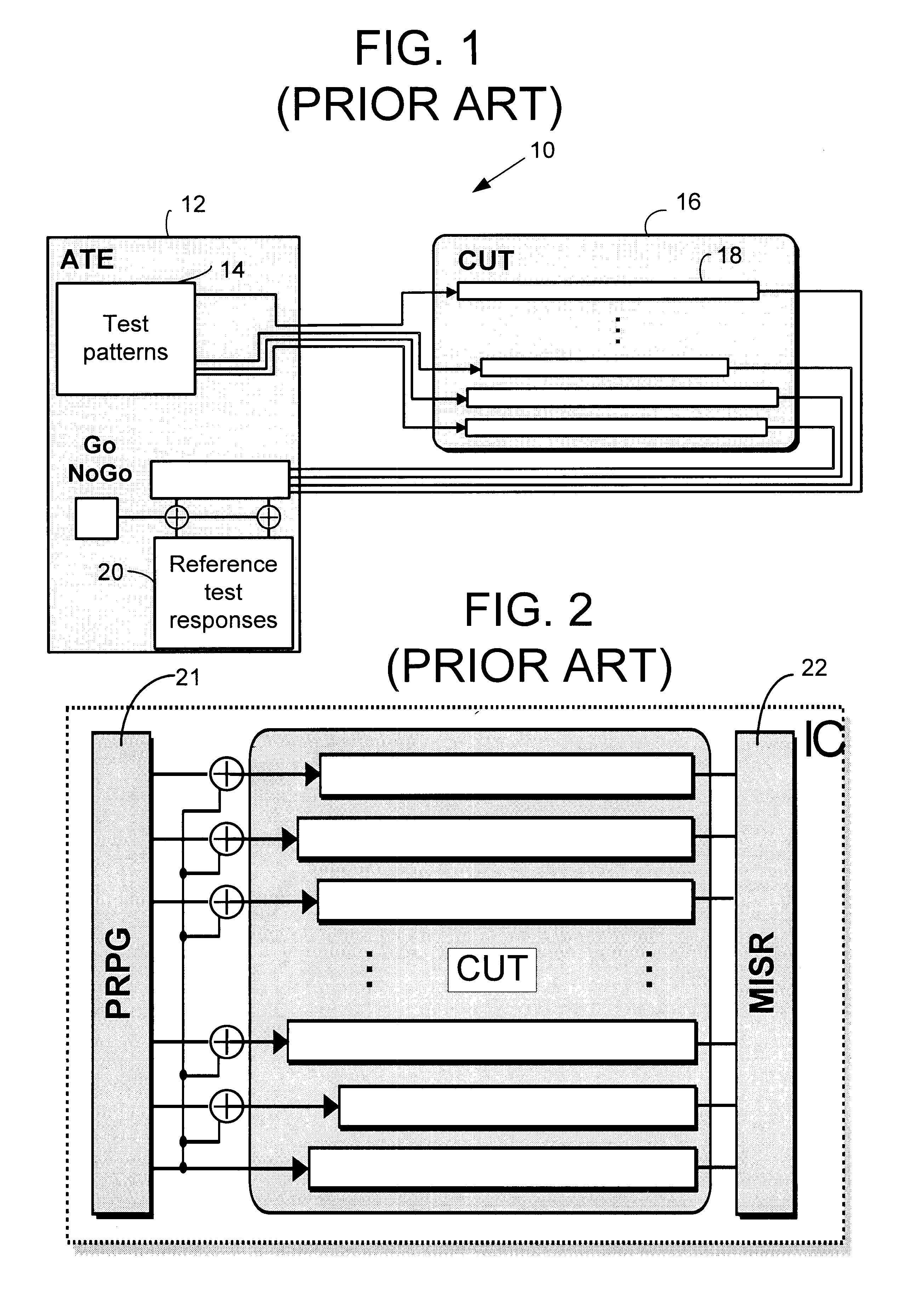

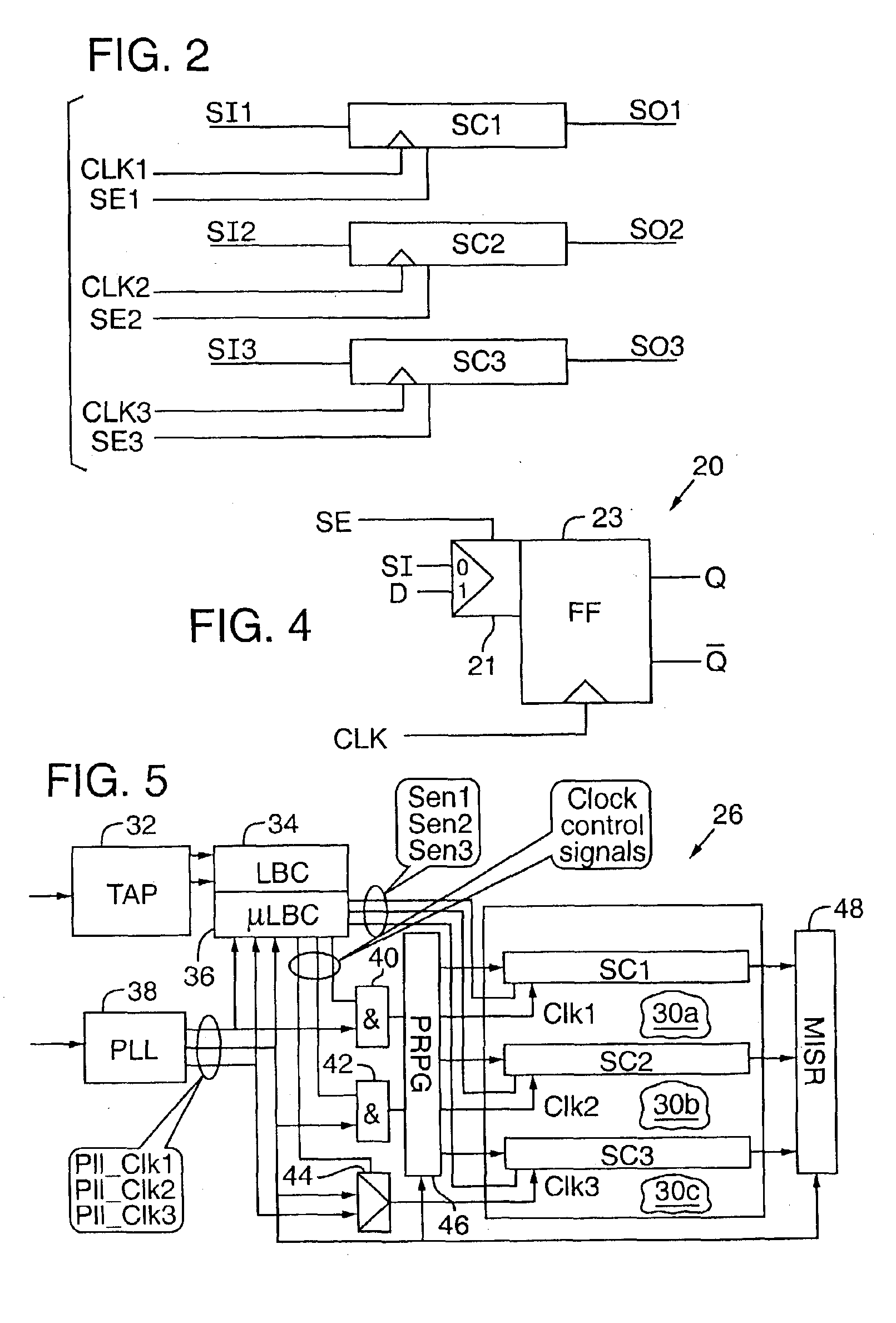

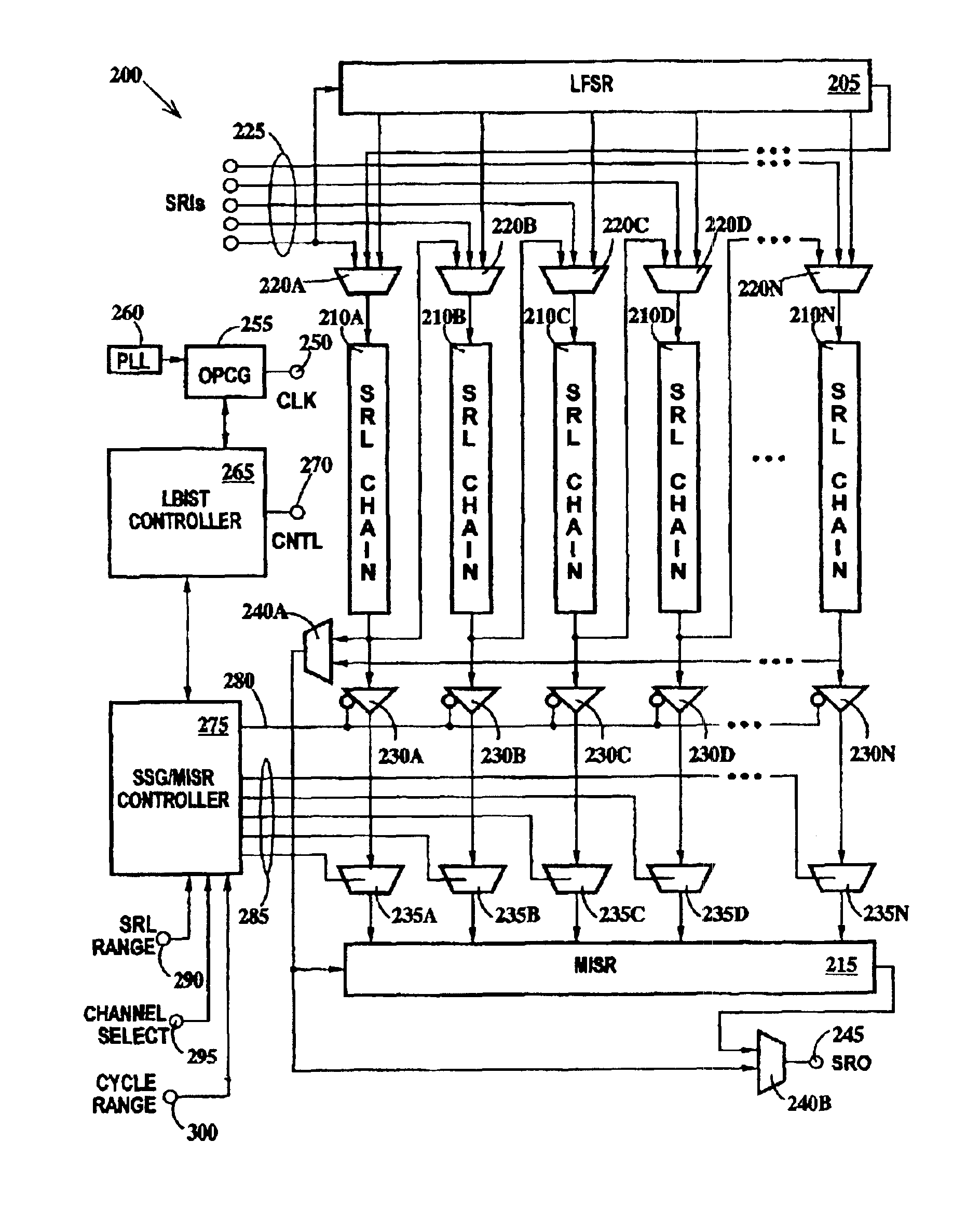

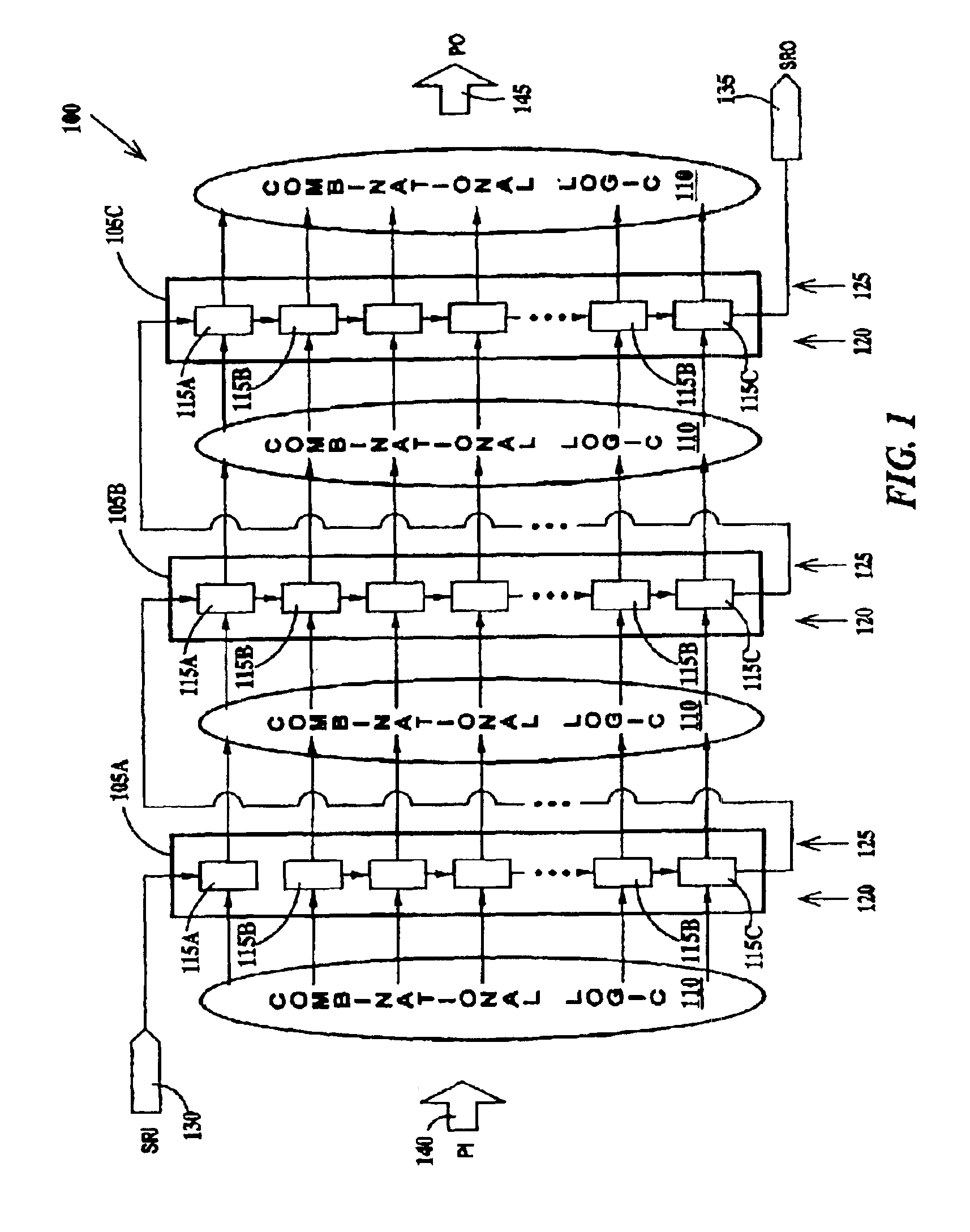

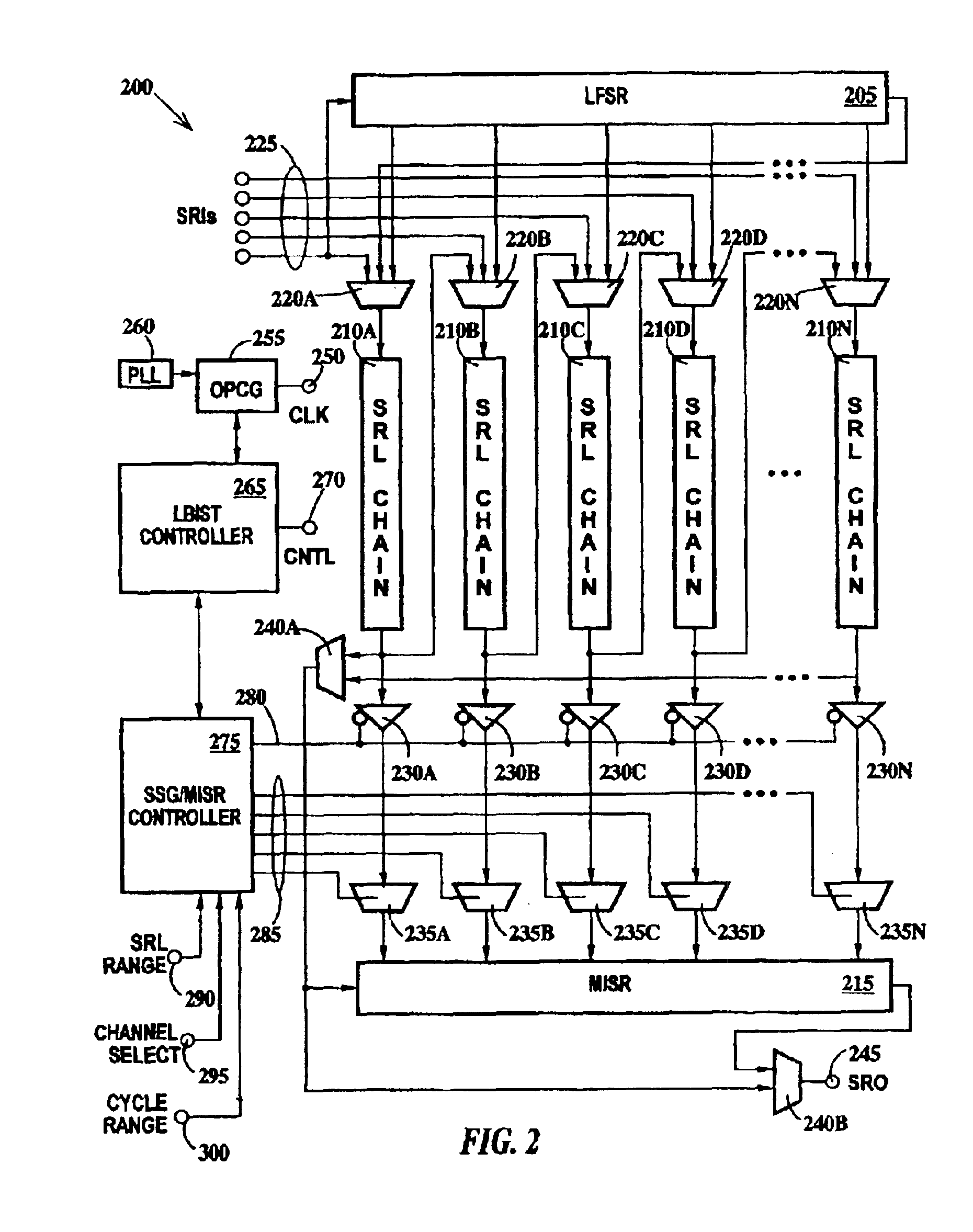

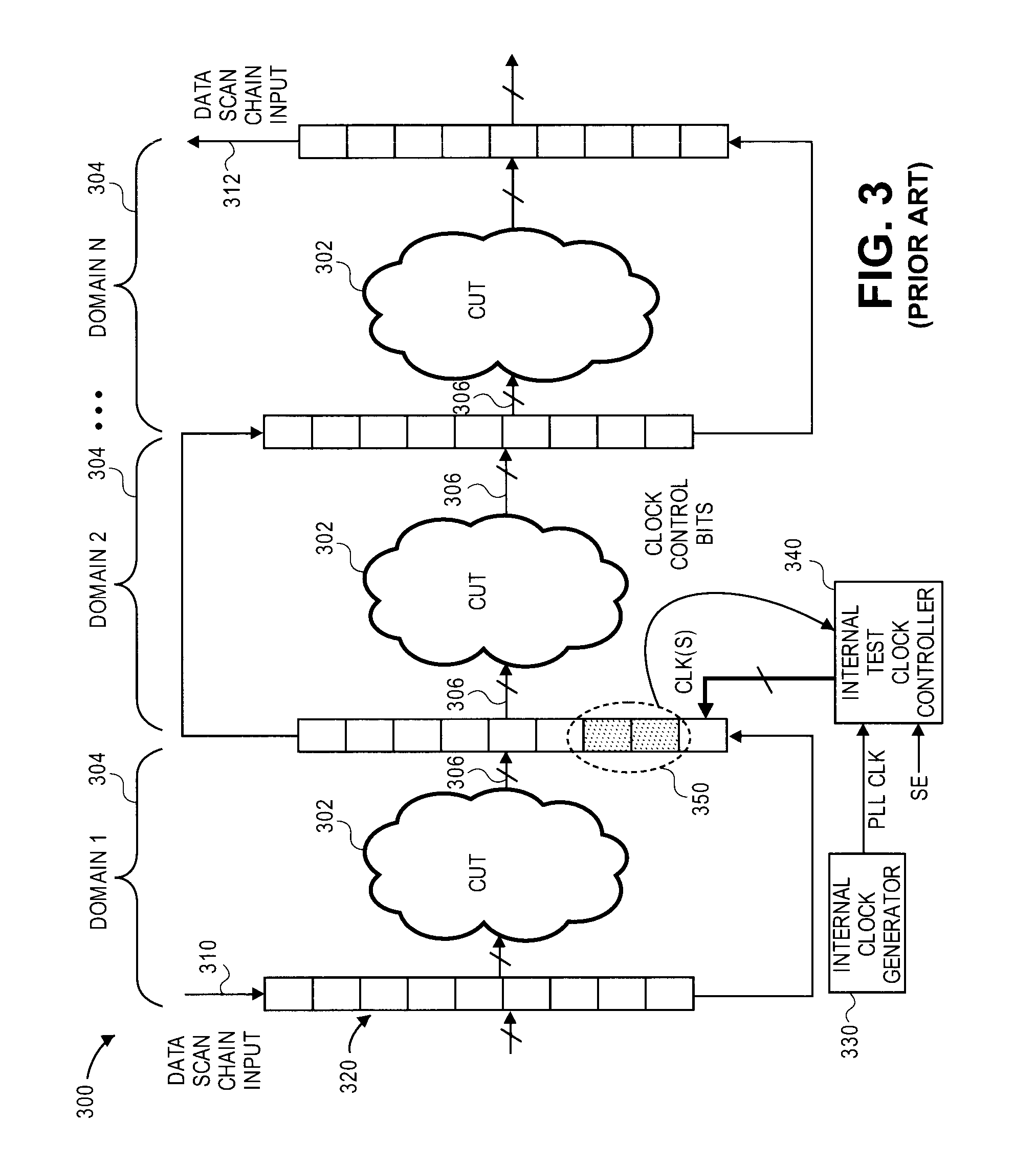

A scheme for multi-frequency at-speed logic Built-In Self Test (BIST) is provided. This scheme allows at-speed testing of very high frequency integrated circuits controlled by a clock signal generated externally or on-chip. The scheme is also applicable to testing of circuits with multiple clock domains which can be either the same frequency or different frequency. Scanable memory elements of the digital circuit are connected to define plurality of scan chains. The loading and unloading of scan chains is separated from the at-speed testing of the logic between the respective domains and may be done at a faster or slower frequency than the at-speed testing. The BIST controller, Pseudo-Random Pattern Generator (PRPG) and Multi-input Signature Register (MISR) work at slower frequency than the fastest clock domain. After loading of a new test pattern, a clock suppression circuit allows a scan enable signal to propagate for more that one clock cycle before multiple capture clock is applied. This feature relaxes the speed and skew constraints on scan enable signal design. Only the capture cycle is performed at the corresponding system timing. A programmable capture window makes it possible to test every intra- and inter-domain at-speed without the negative impact of clock skew between clock domains.

Owner:MENTOR GRAPHICS CORP

Test access control apparatus and method thereof

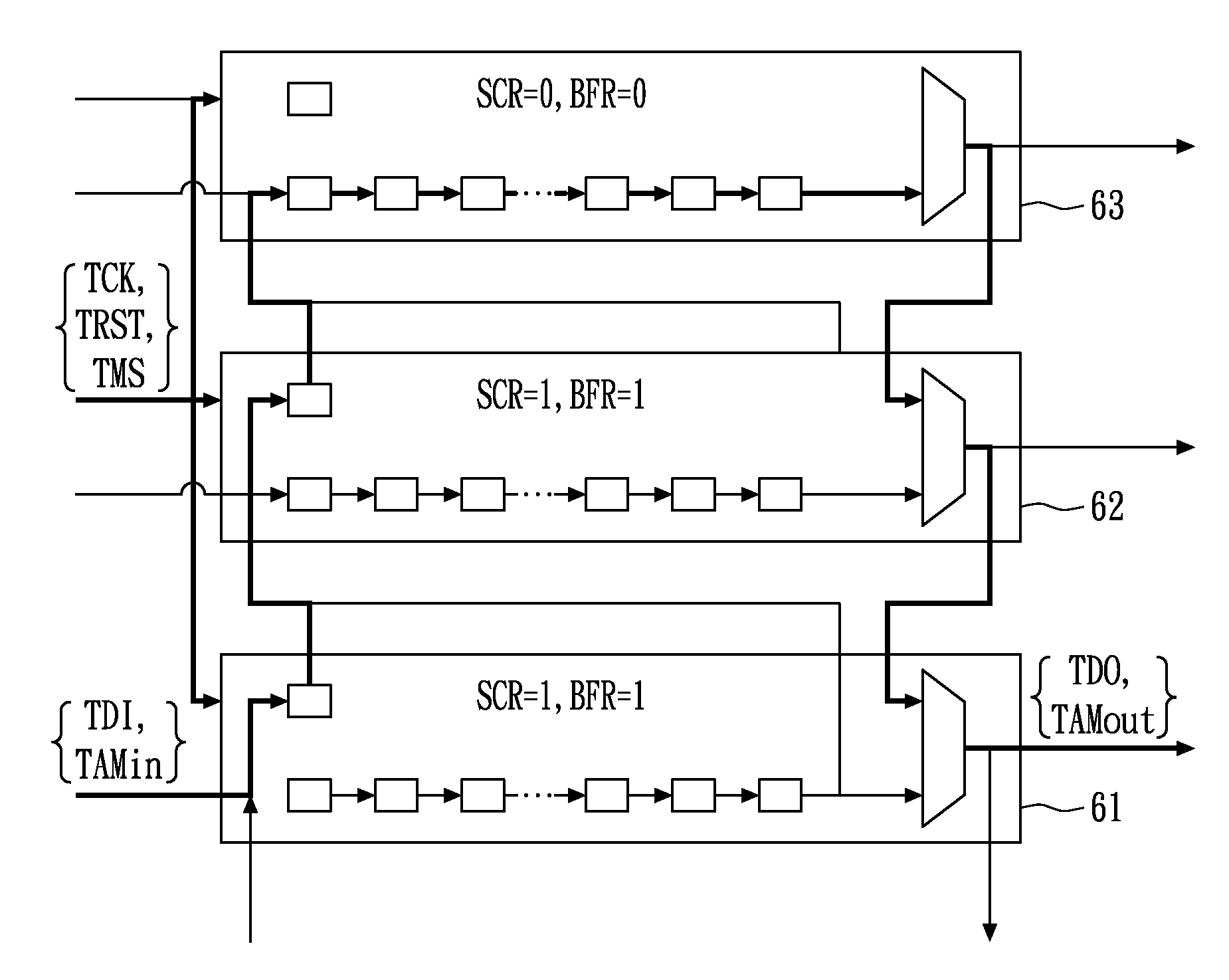

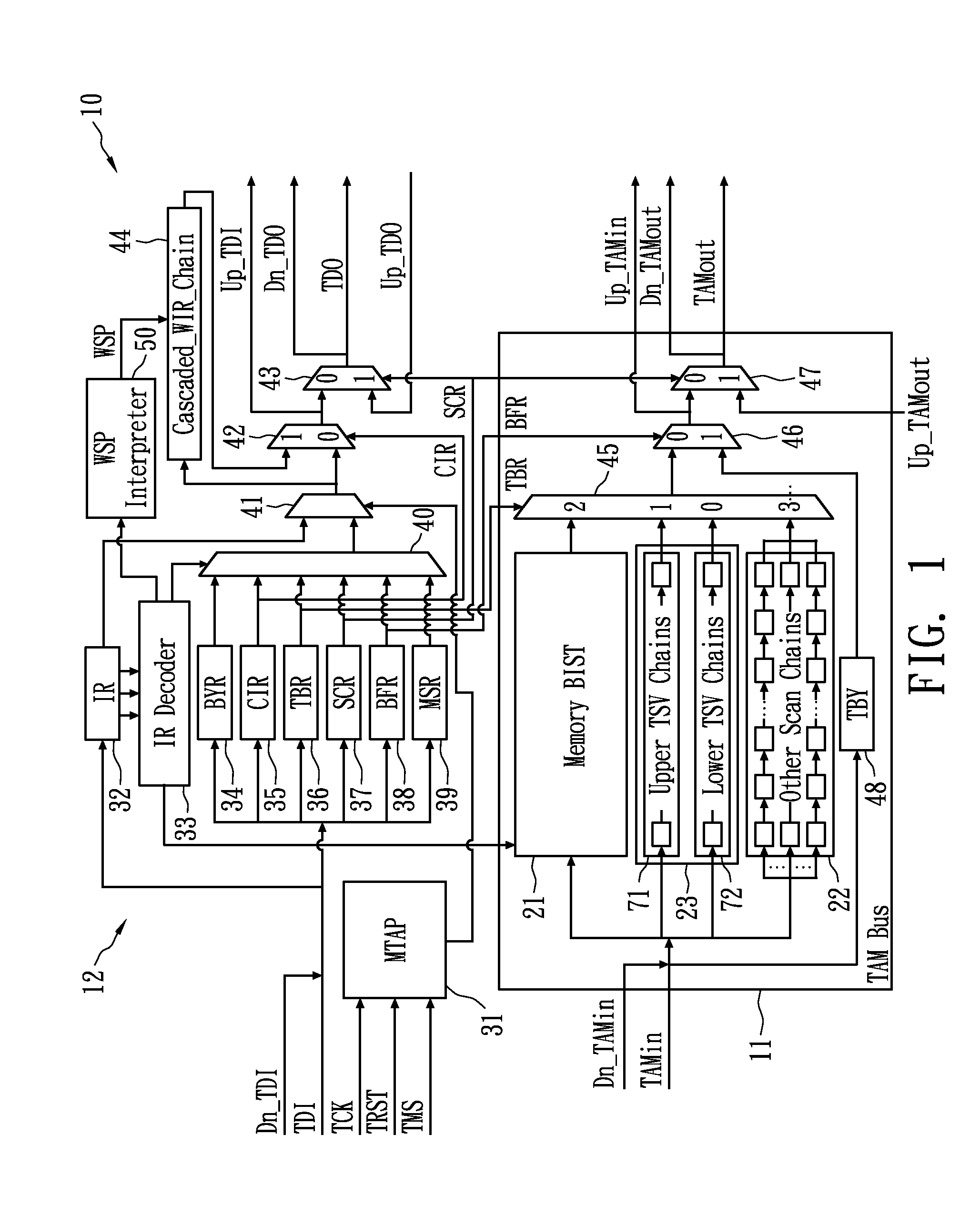

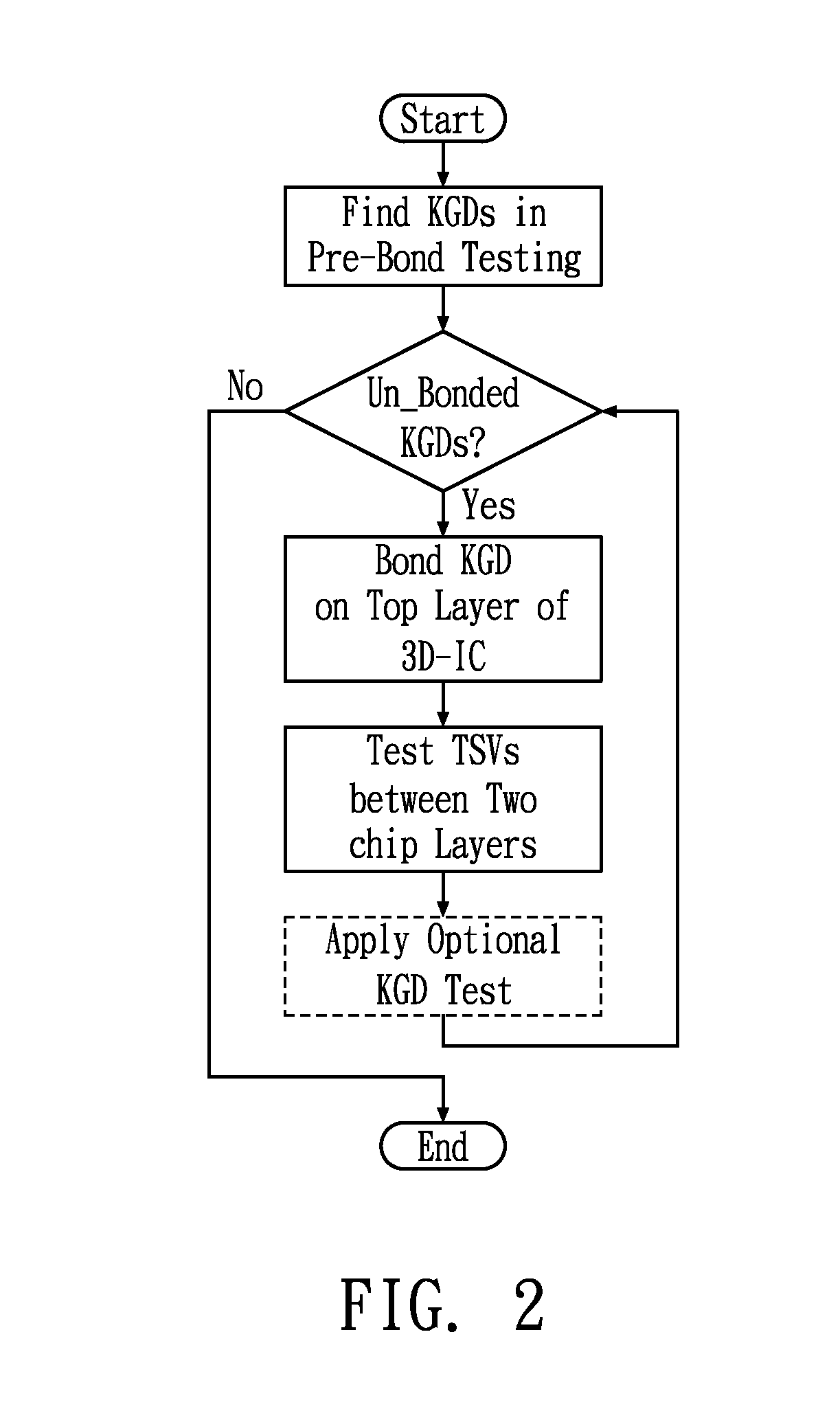

InactiveUS20100332177A1High yieldResistance/reactance/impedenceStatic storageEngineeringBuilt-in self-test

A test access control apparatus includes test access mechanism (TAM) buses and an extended IEEE 1149.1 Test Access Port (TAP) Controller. The TAM buses support memory built-in-self-test (BIST) circuit for the memory known-good-die (KGD) test, scan chains for the logic KGD test; and through-silicon-via (TSV) chains that are configured to conduct the TSV test that verifies any defect in vertical interconnects between any two chip layers of the stacked chip device. The TAP Controller is coupled to the TAM buses and is configured to control the memory KGD test, the logic KGD test and the TSV test between two chip layers. A cost-effective connection or configuration of test access control apparatus in 3D-IC is also present. In accordance with an embodiment of the present invention, a test access control method includes a yield-concerned test methodology for 3D-IC, and an integrated flow of test access control apparatus supporting heterogeneous test protocols of SOC

Owner:NATIONAL TSING HUA UNIVERSITY

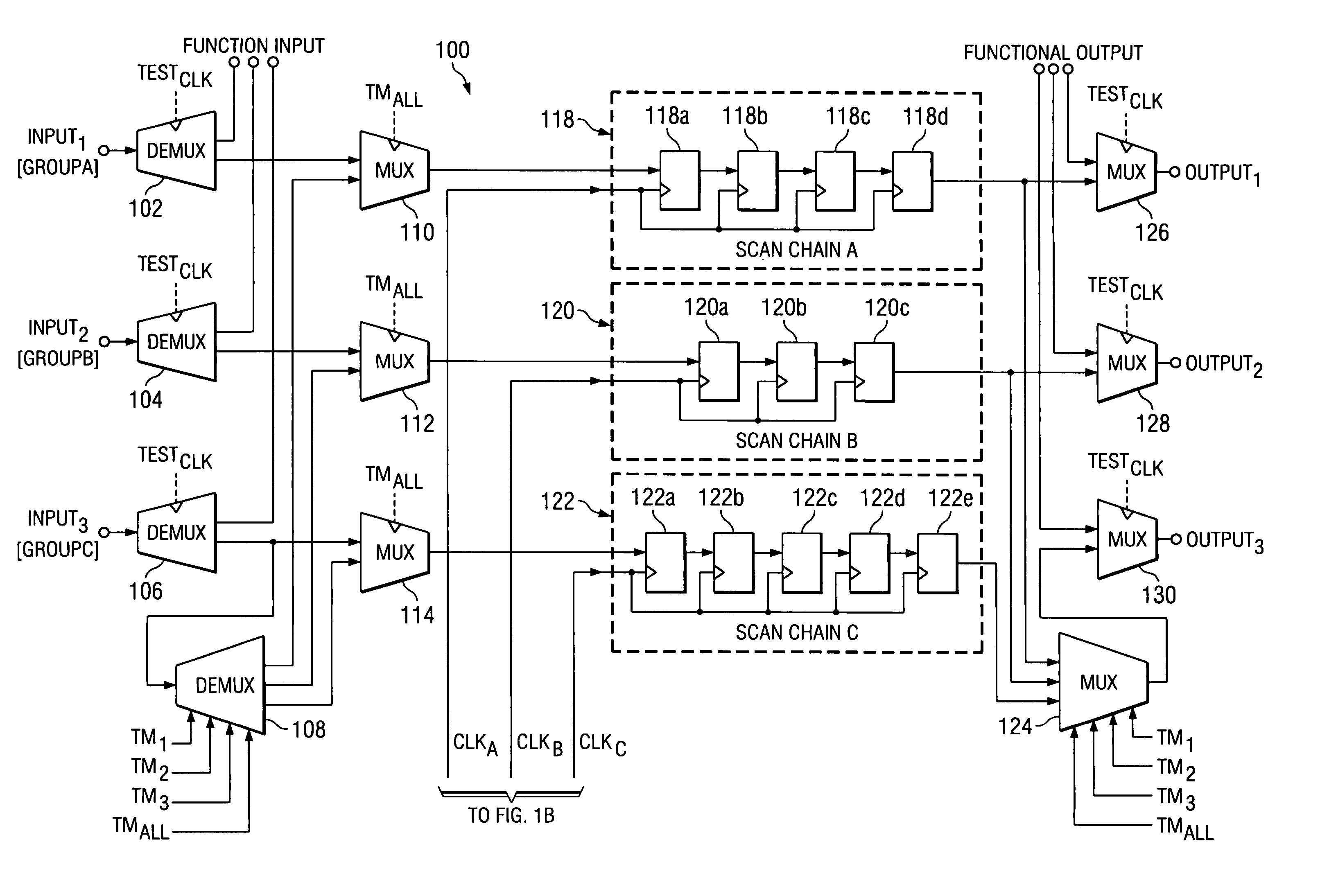

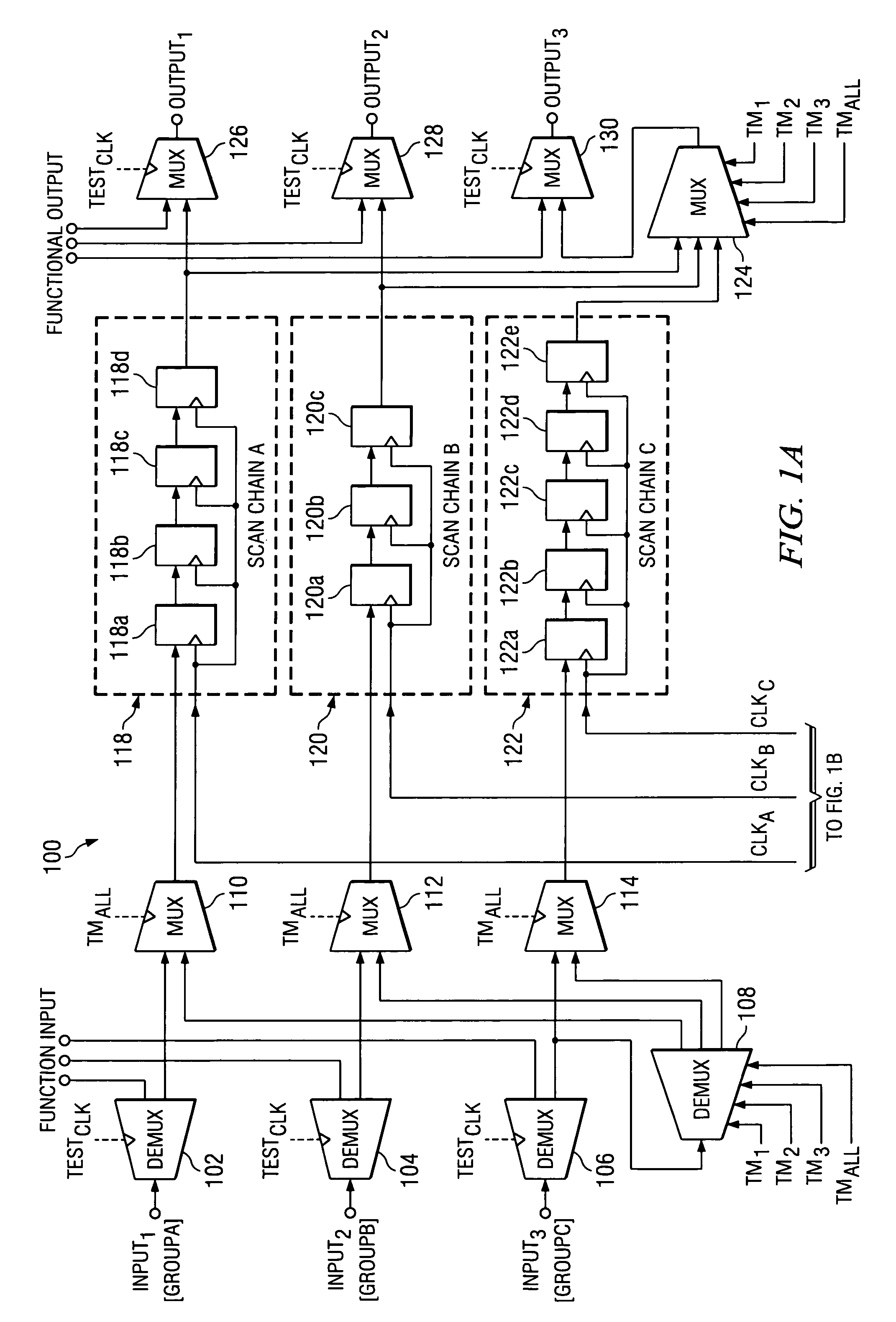

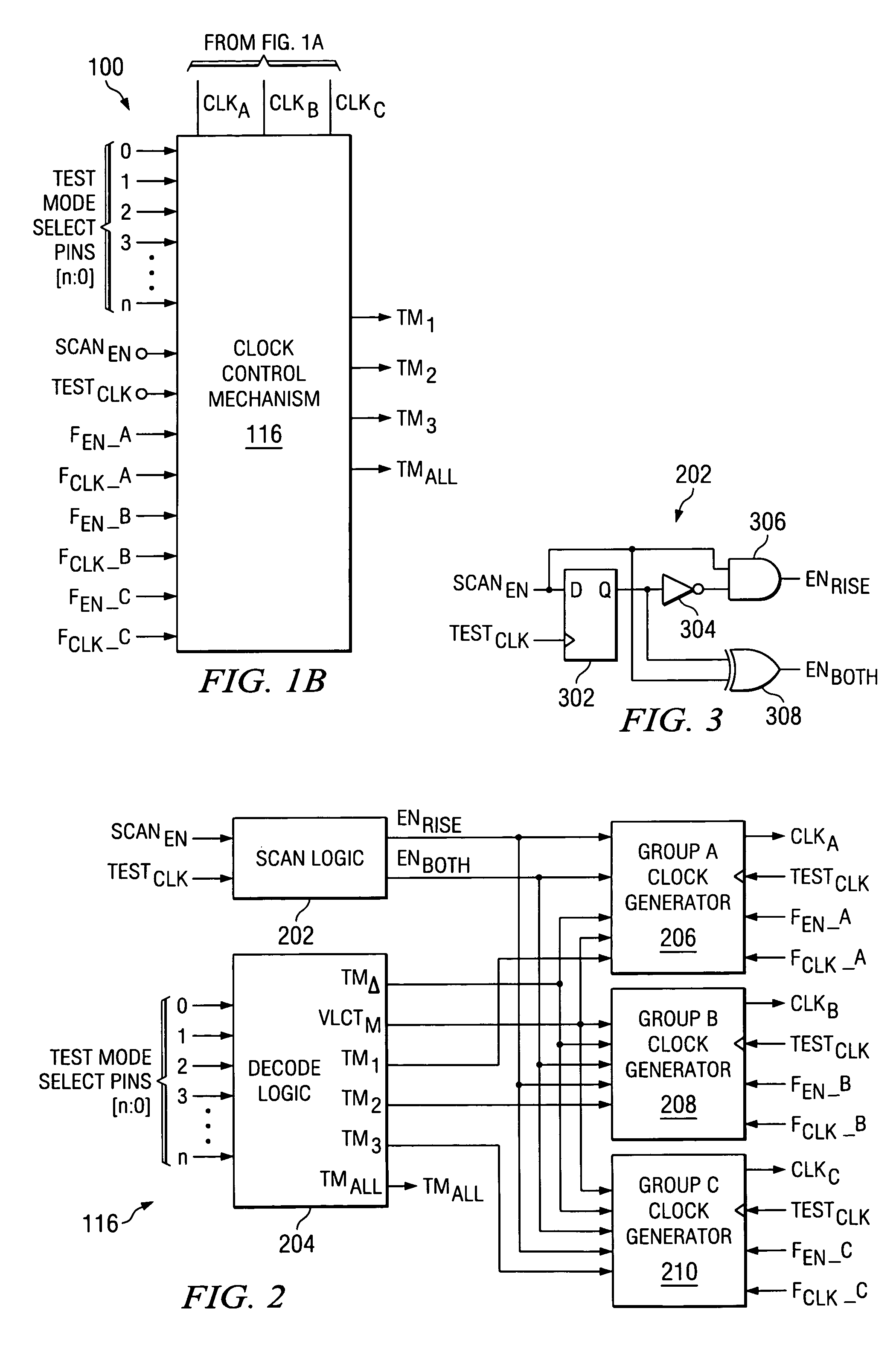

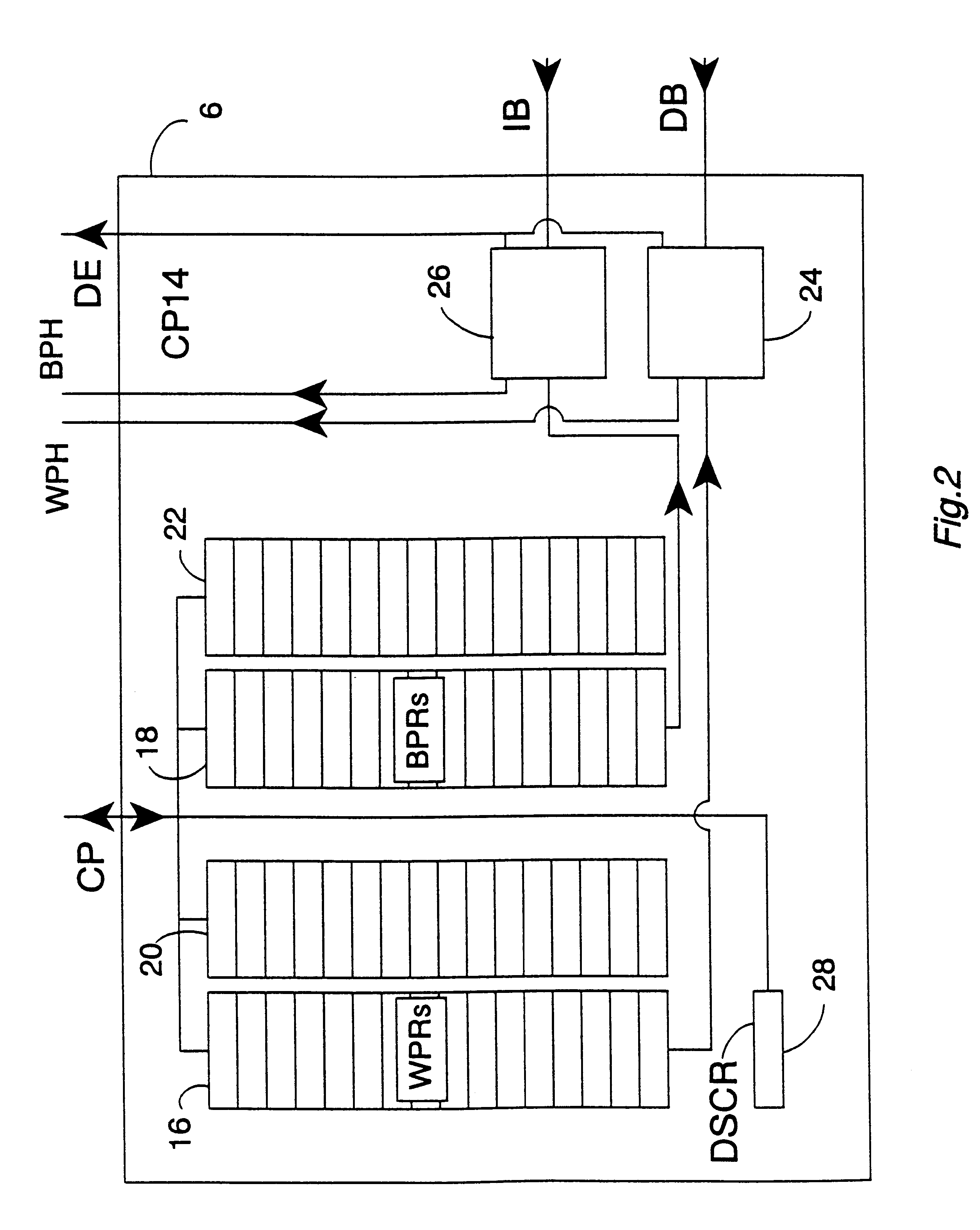

At-speed ATPG testing and apparatus for SoC designs having multiple clock domain using a VLCT test platform

ActiveUS20050055615A1Increase savingsThe testing process is simpleElectronic circuit testingControl signalClock rate

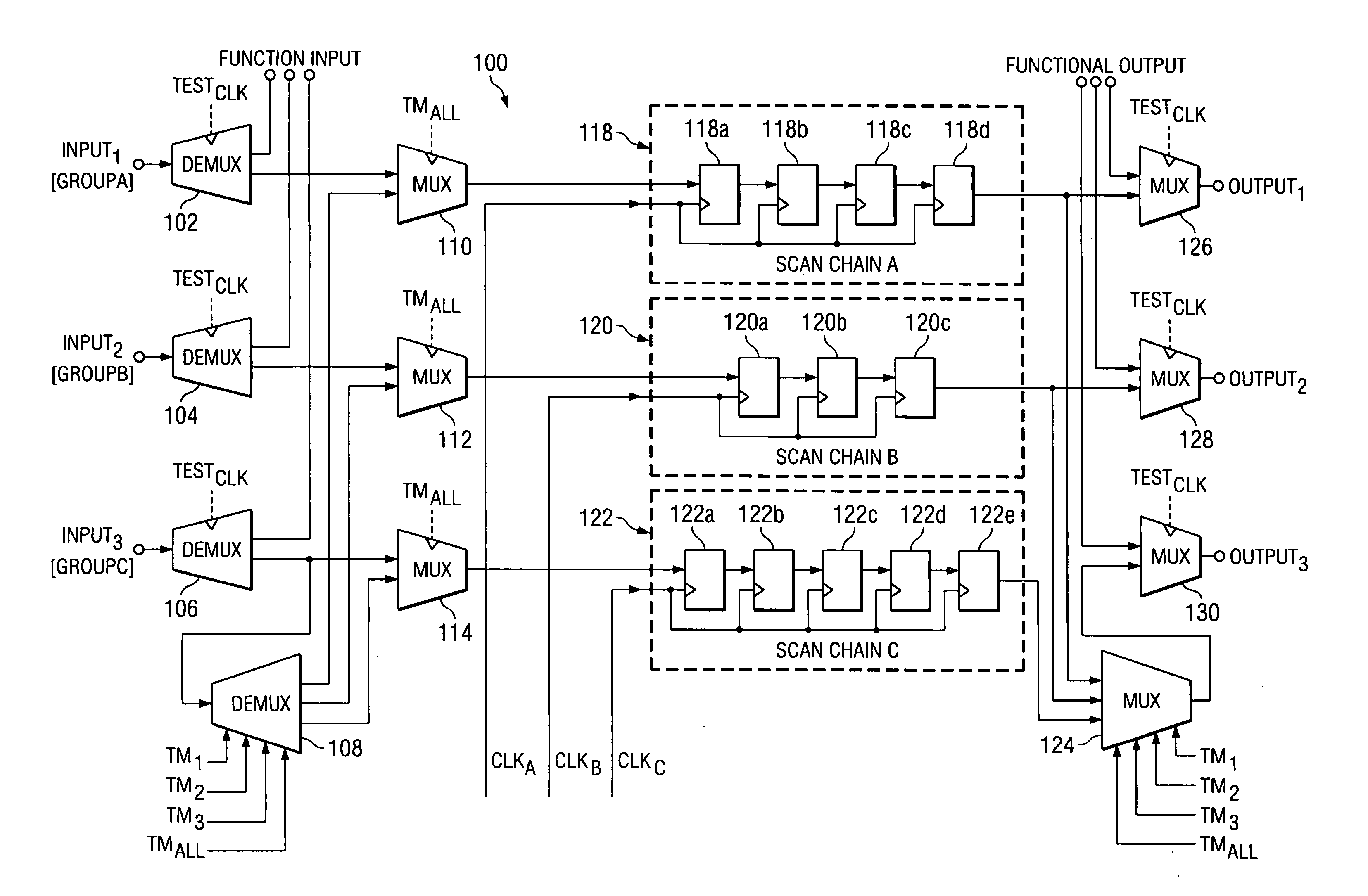

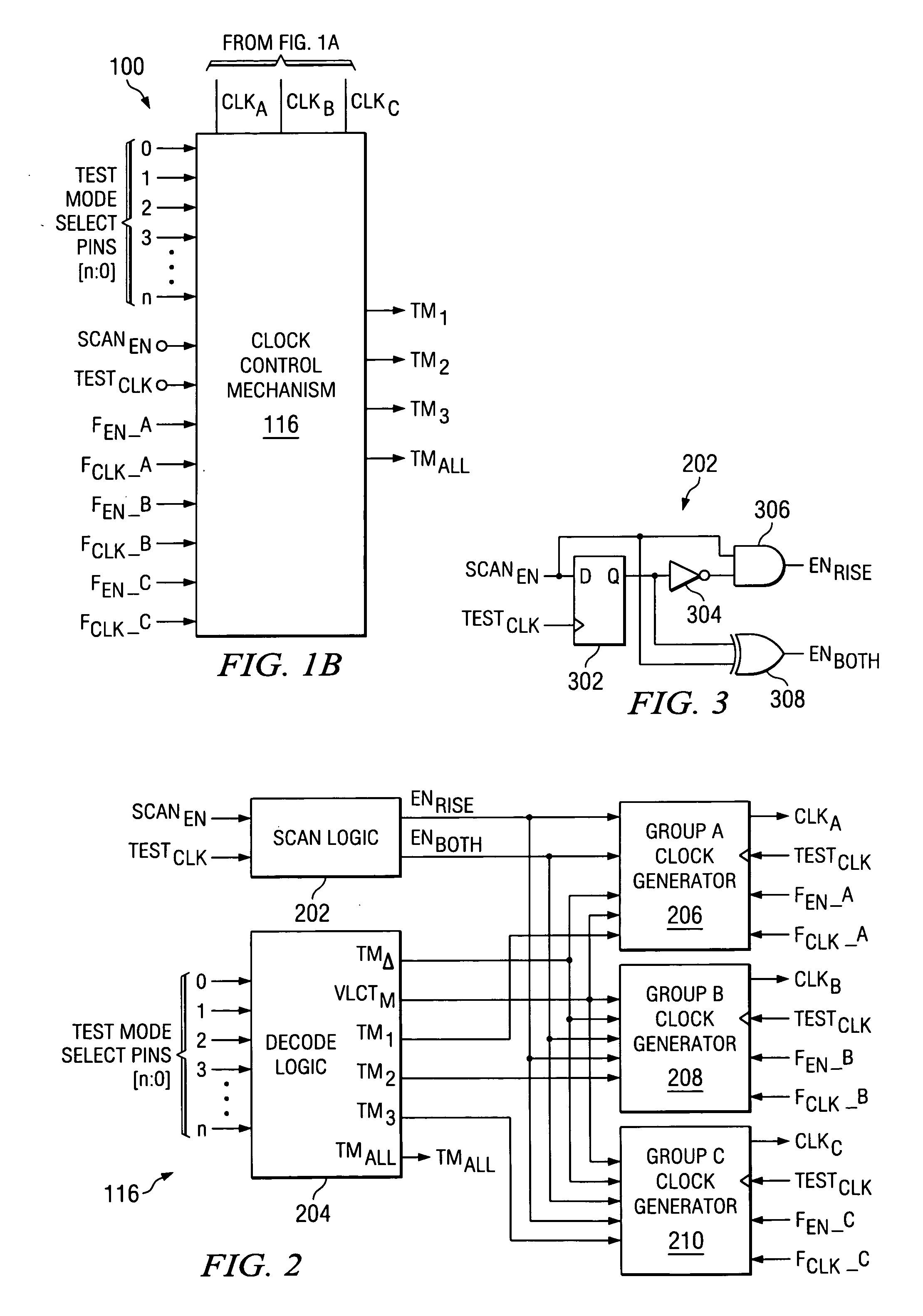

A scan test circuitry design imbedded on an SoC having the scan architecture of a VLCT platform is disclosed herein. This BIST circuitry design that is not limited in the number of scan test ports supported includes at least one scan chain group having a corresponding clock domain that couples to receive test stimulus data. Each scan chain group has a corresponding test mode signal to shift the test stimulus data at a shift clock rate derived from its corresponding clock domain. A controlling demultiplexer connects to each multiplexer unit within each scan chain group to provide control signals for shifting in the test stimulus. A clock control mechanism provides a control signal for each scan chain to shift test stimulus and capture resultant data. Furthermore, when a simultaneous test mode signal is enabled, the clock control mechanism couples to each scan chain to enable simultaneous capture of each scan chain group.

Owner:TEXAS INSTR INC

Semiconductor integrated circuit with a test circuit

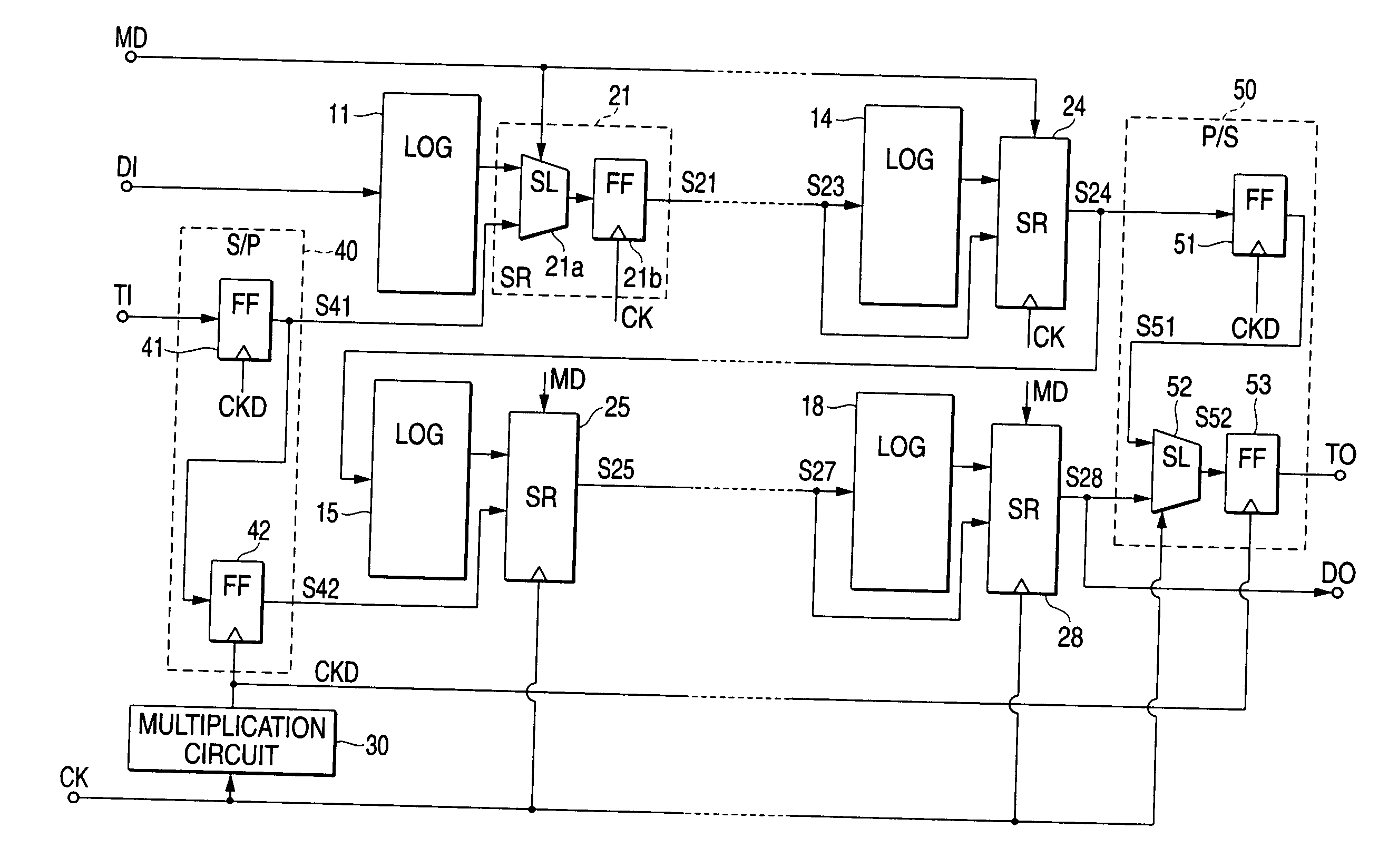

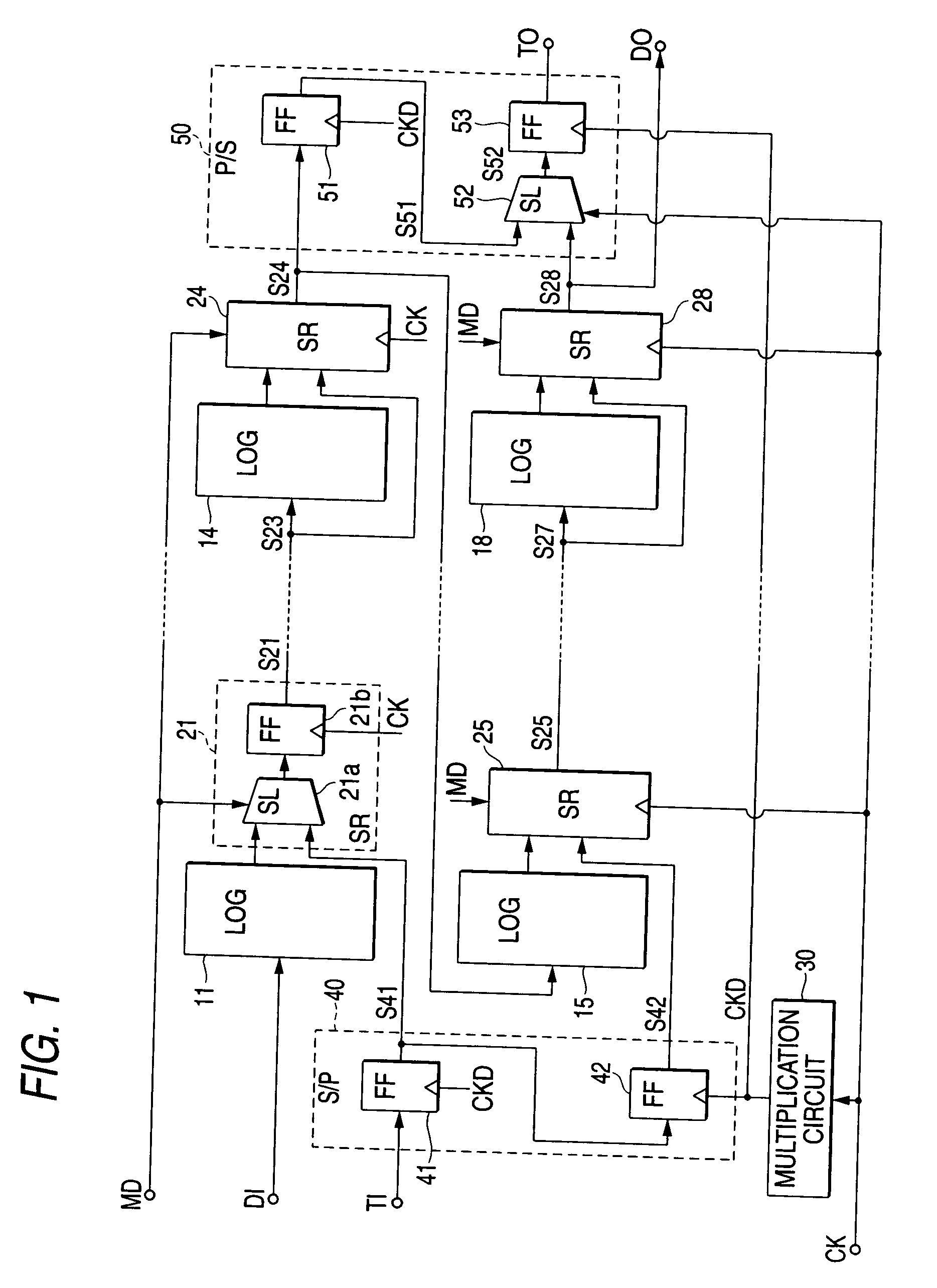

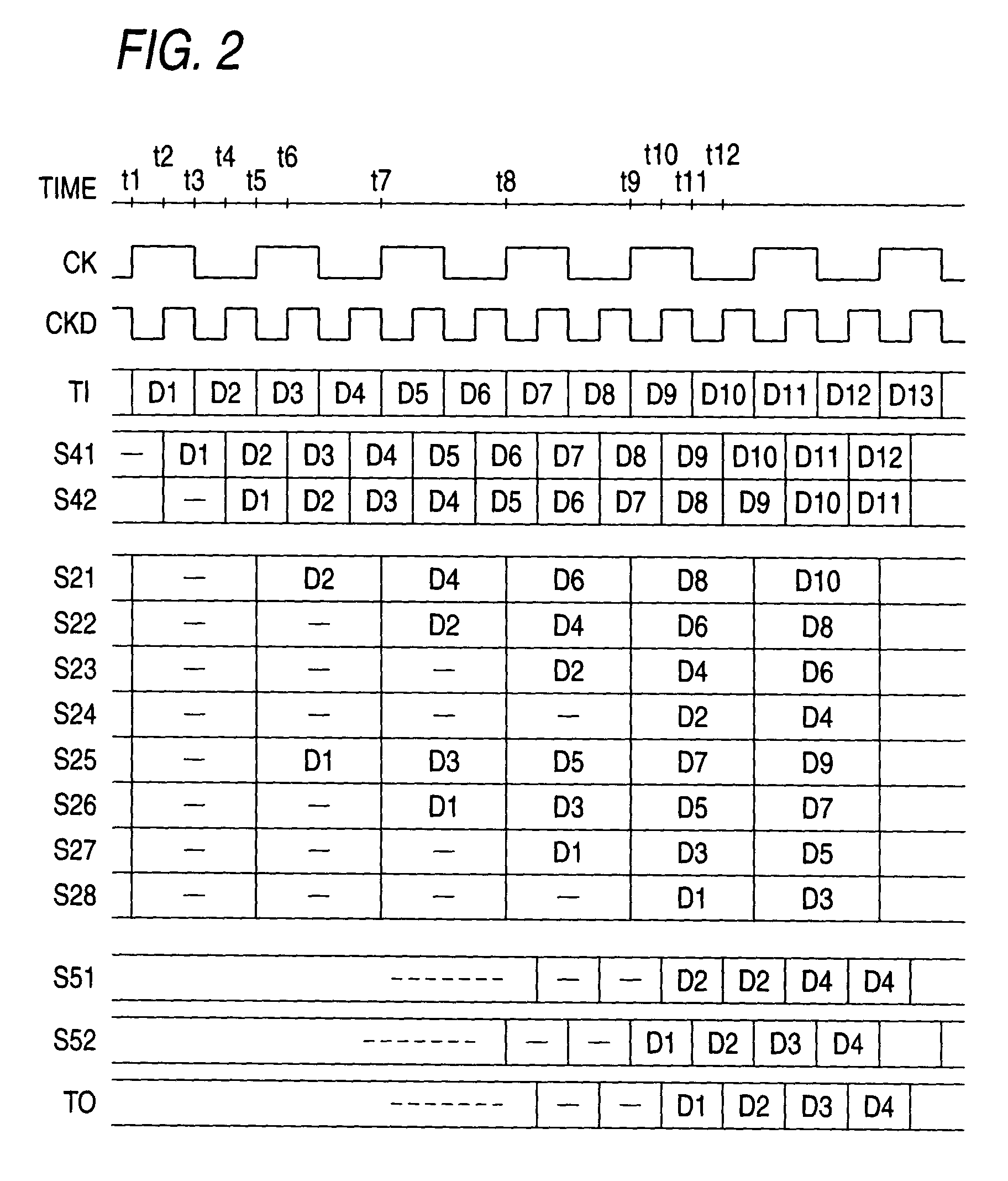

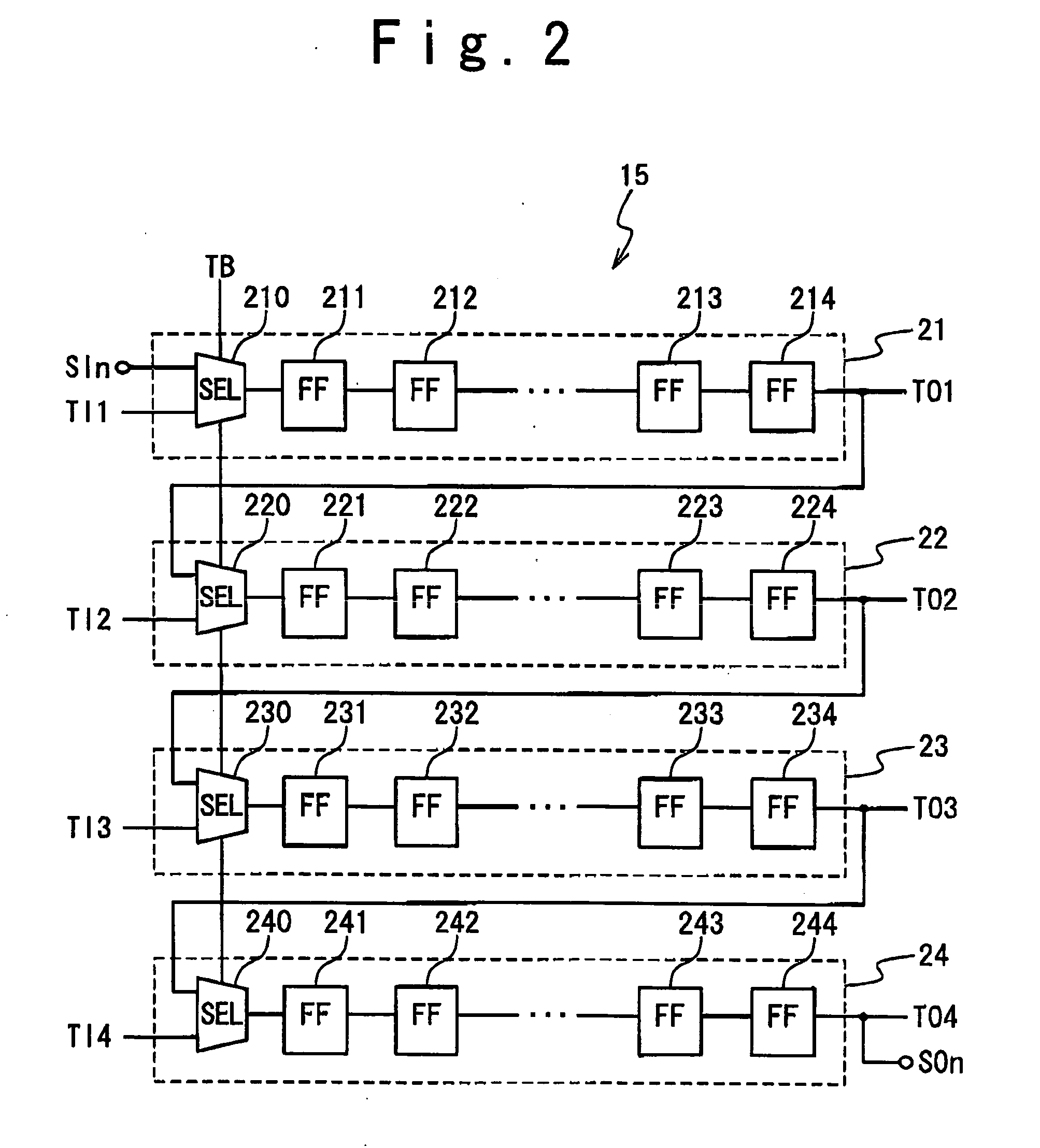

A shift scan chain includes logic circuit blocks 11-18 and scan registers 21-28 connected at stages succeeding them. The shift chain is divided into divisional chains including the scan registers 21-24 and the scan registers 25-28. In the test operation mode of a semiconductor integrated circuit, test input data TI are supplied in synchronism with a multiplied clock signal CKD at a frequency twice of that of a clock signal CK. The test input data TI are converted by a serial / parallel conversion circuit 40 into parallel data S41 and S42, which are respectively supplied to the head scan registers 21 and 25 of the corresponding divisional chains. The length of each divisional chains becomes ½, and a test time period can be shortened.

Owner:LAPIS SEMICON CO LTD

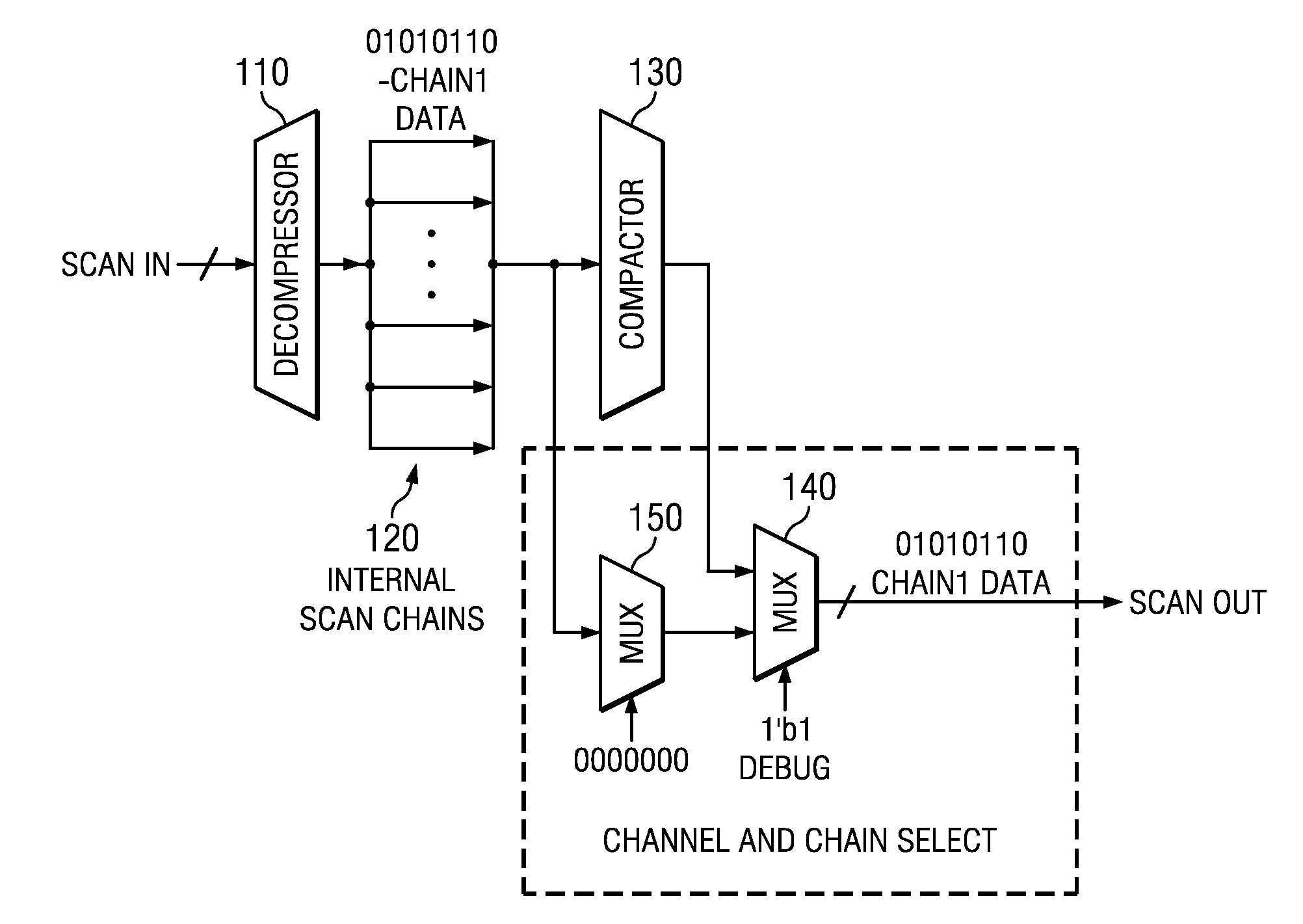

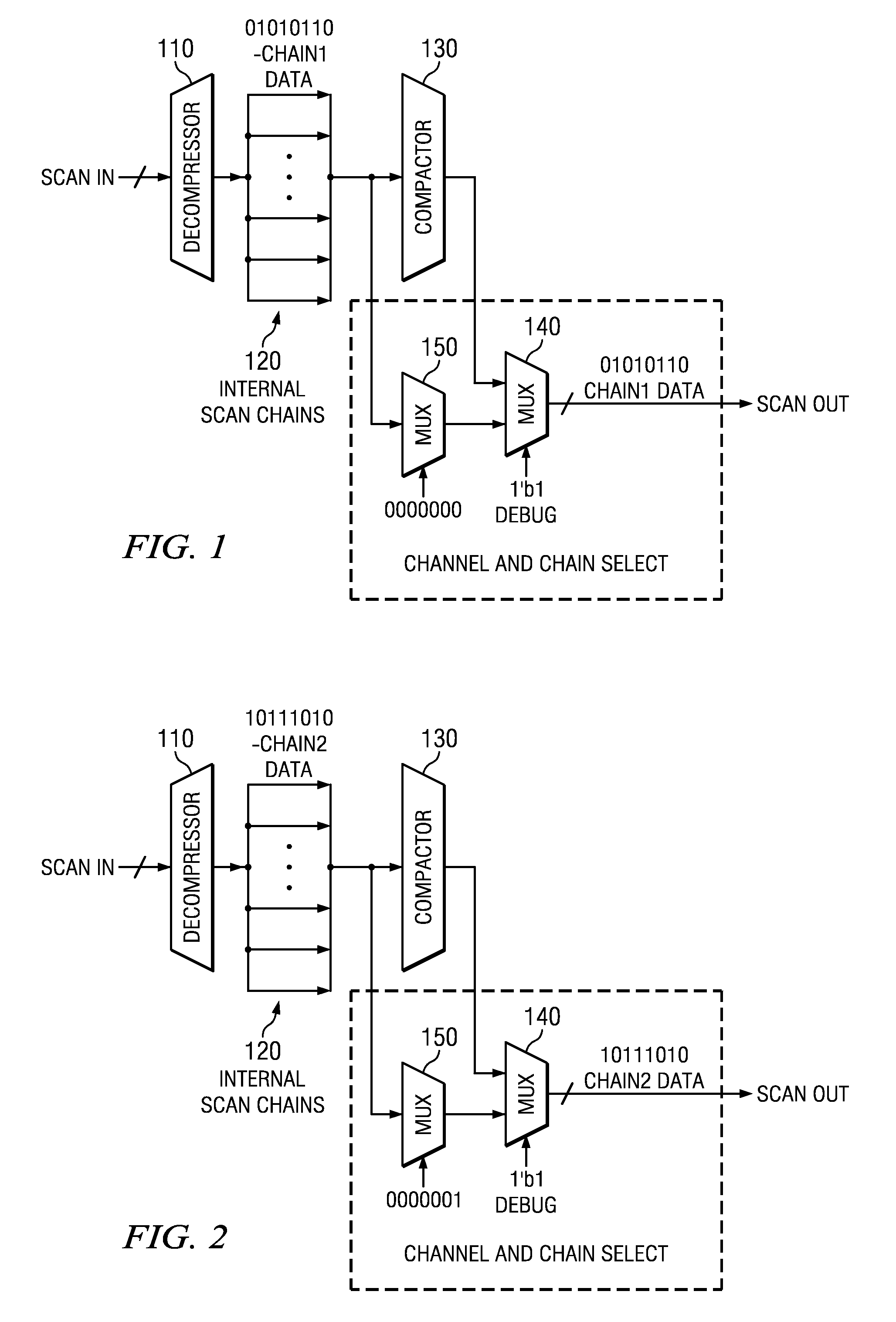

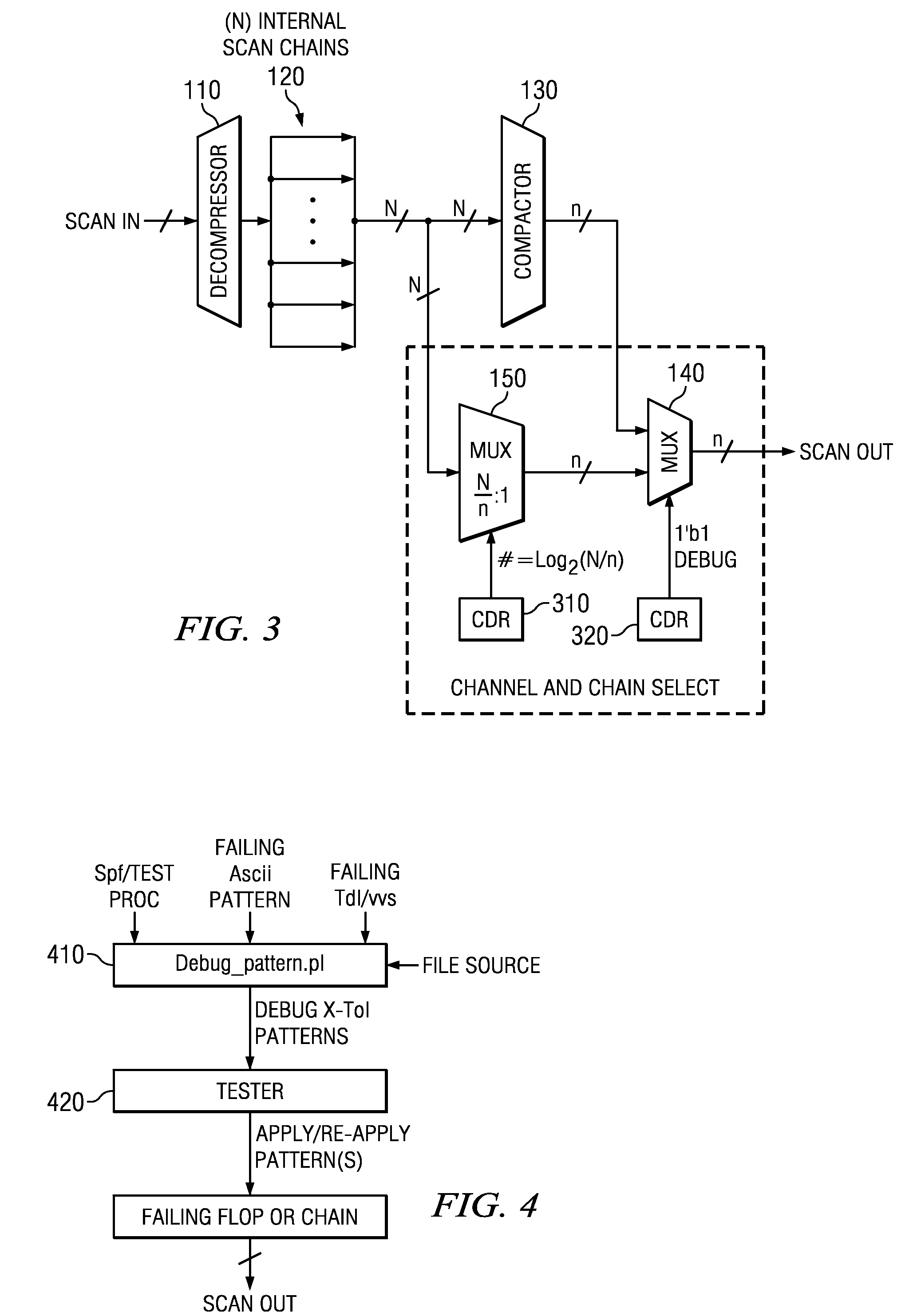

Compressed scan chain diagnosis by internal chain observation, processes, circuits, devices and systems

ActiveUS20110307750A1Electronic circuit testingRedundant hardware error correctionScan circuitsEngineering

Owner:TEXAS INSTR INC

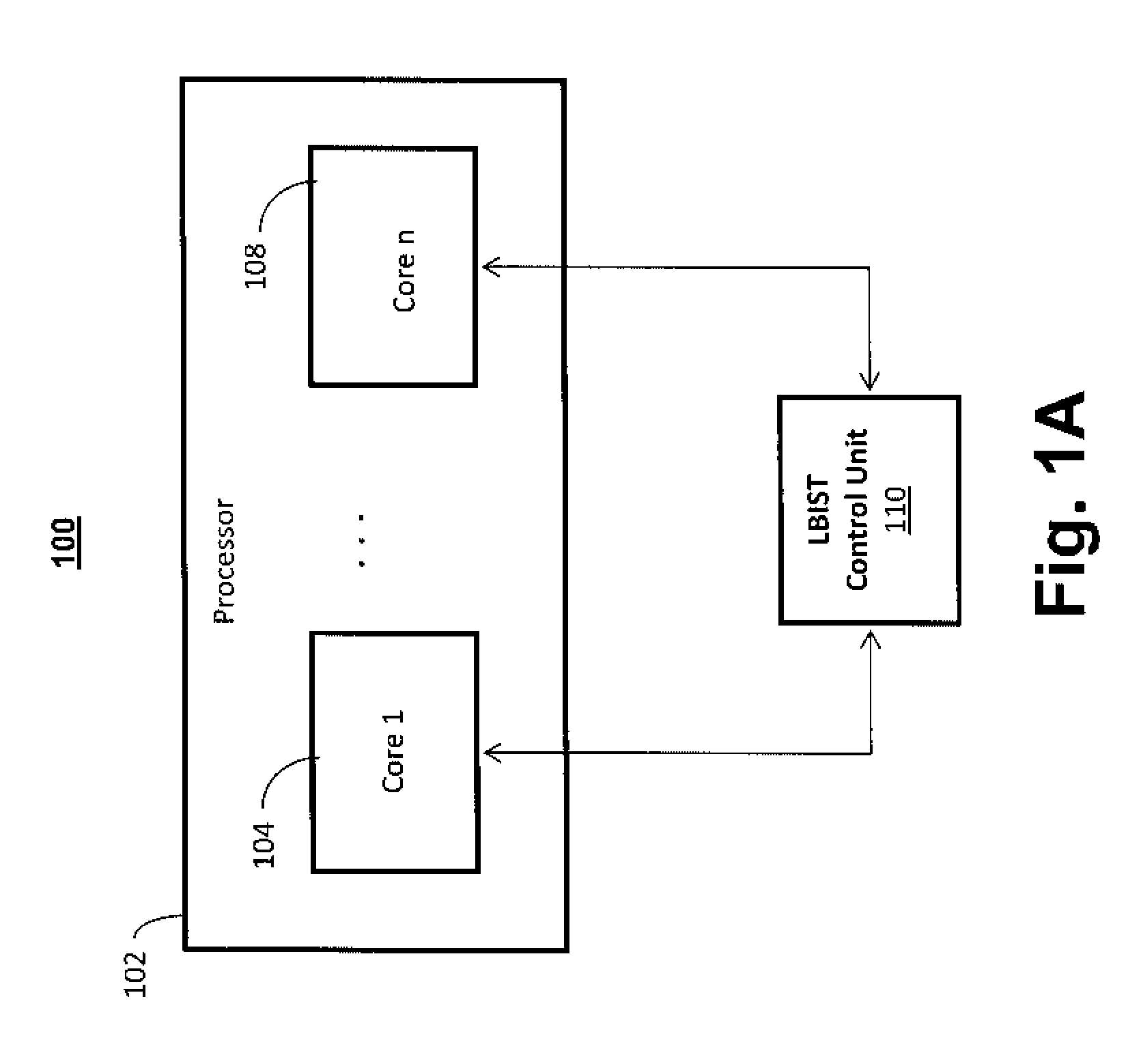

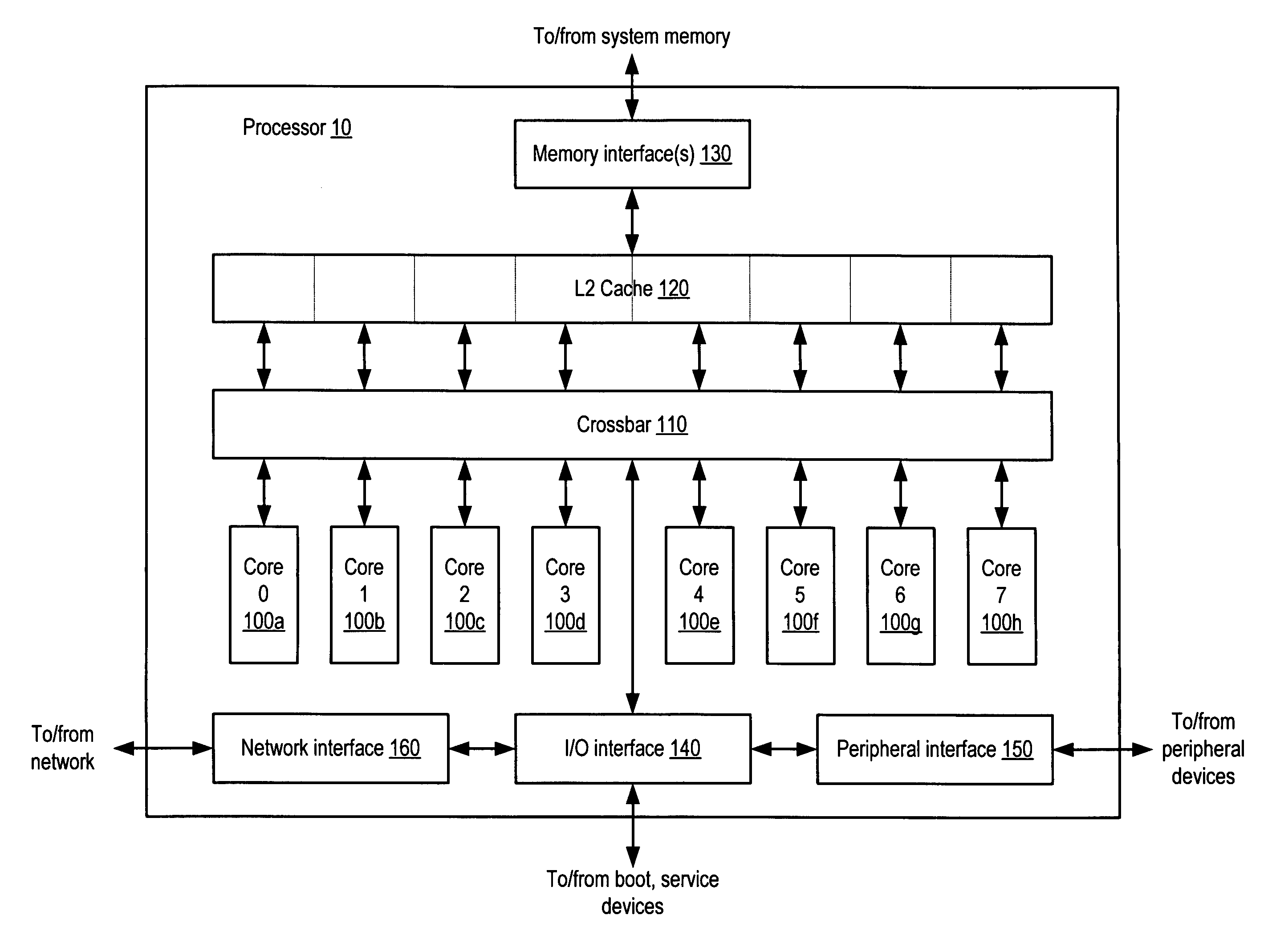

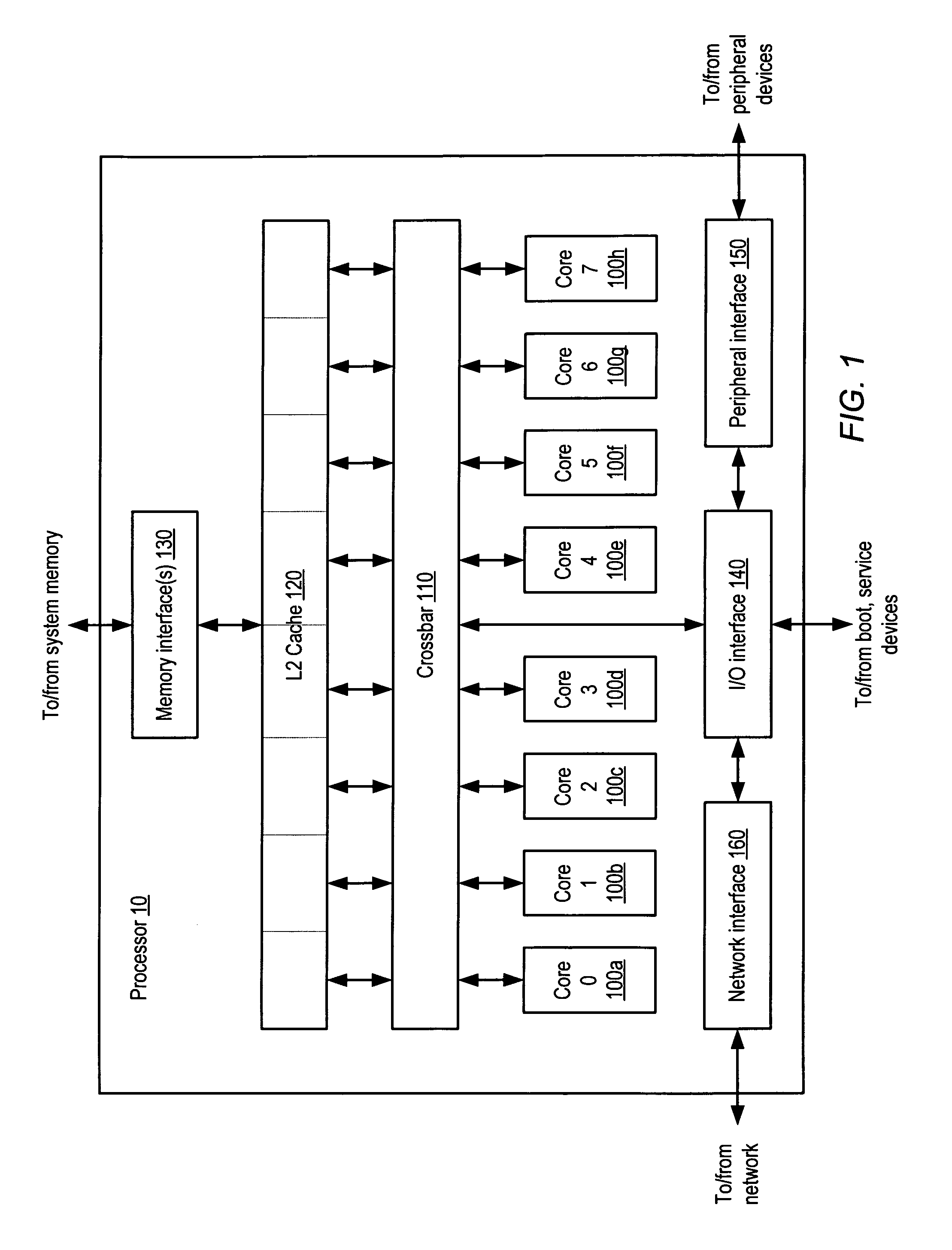

Multicore processor test method

ActiveUS20050240850A1Efficient testingEfficient executionMemory loss protectionElectronic circuit testingComputer hardwareMulti-core processor

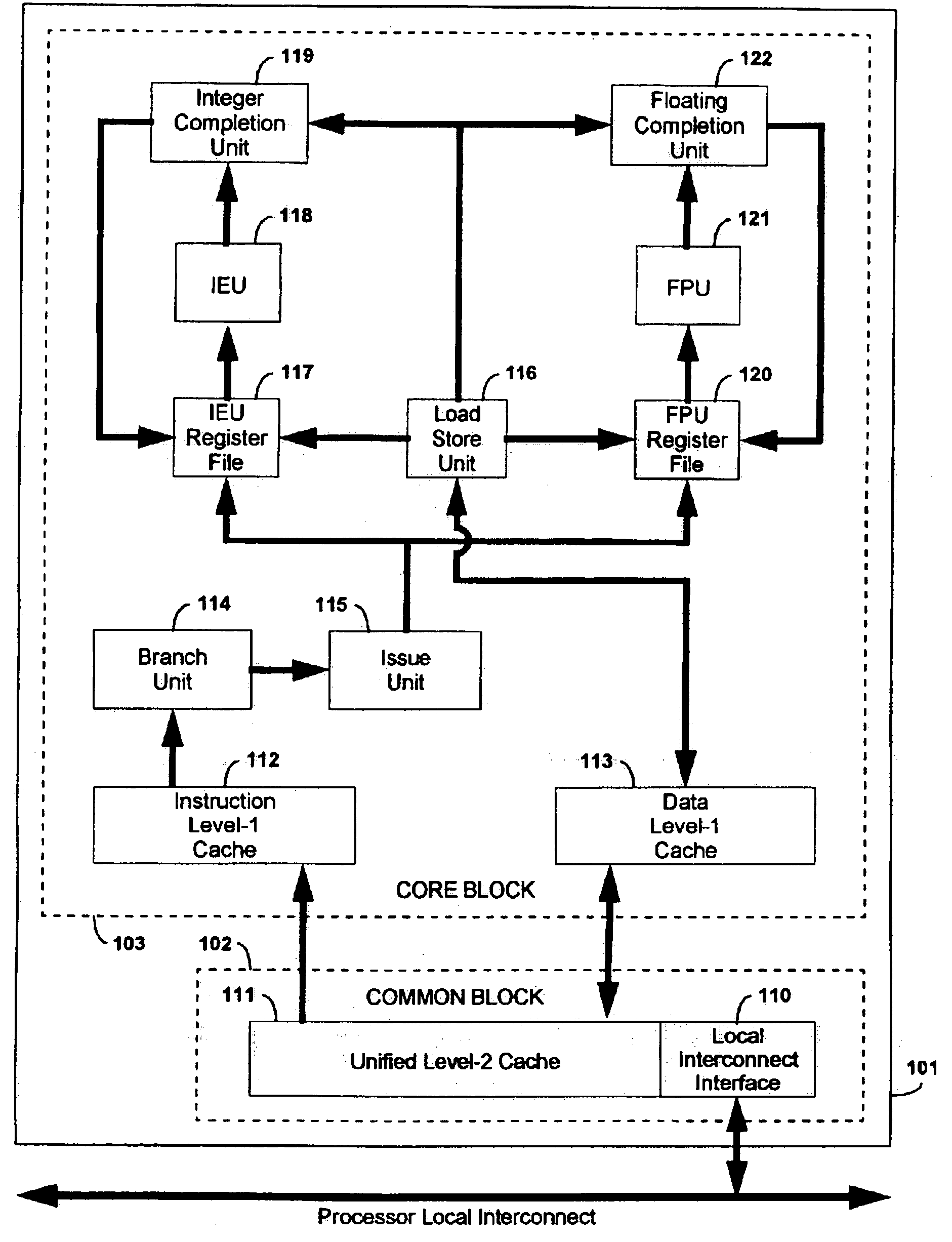

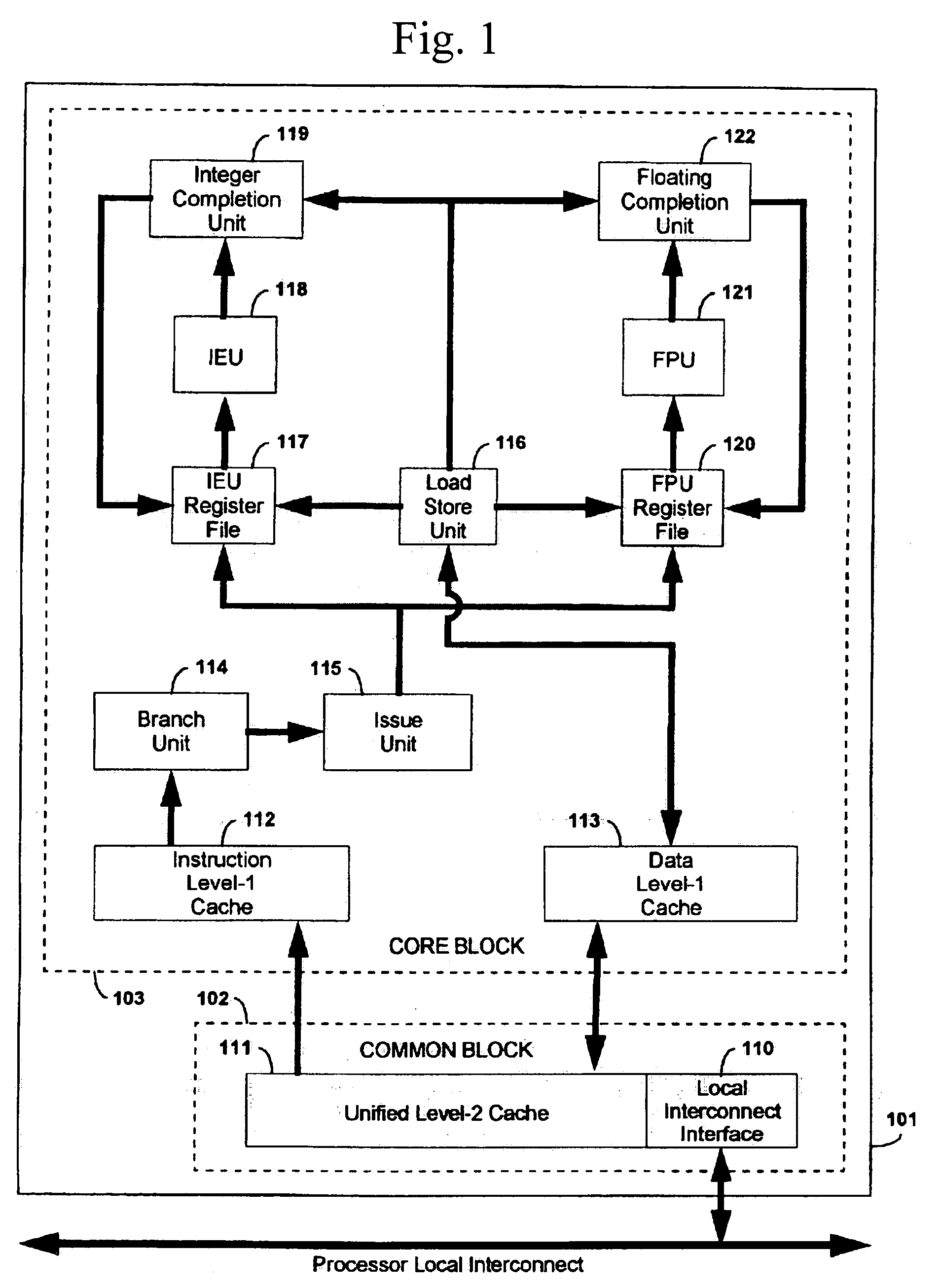

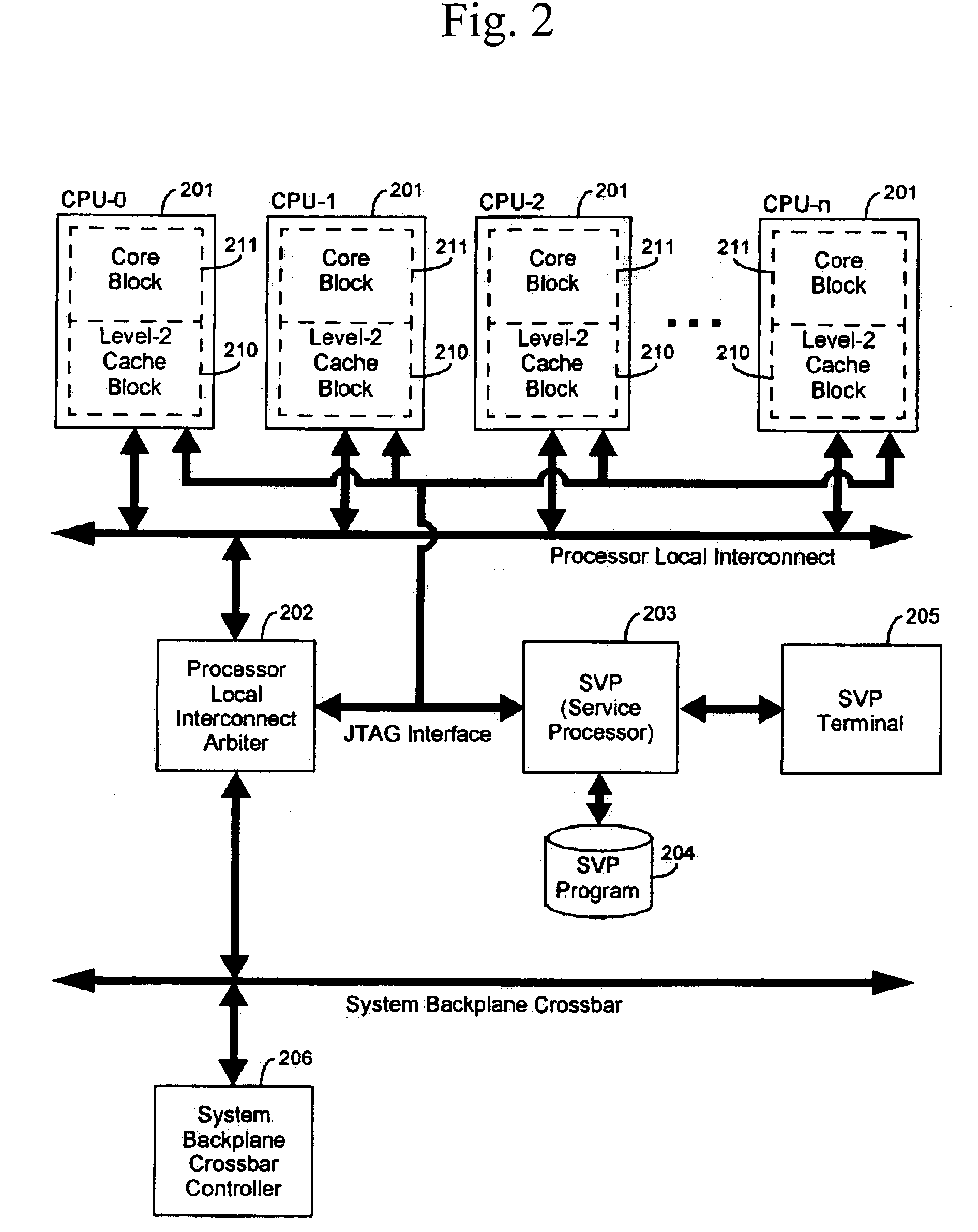

In processors having a multicore, such as CMPs, an independent MISR test pattern compression circuit is provided for each logic block in a multicore processor such as a CMP comprising a plurality of processor cores makes it possible to perform LSI tests more efficiently. A processor comprises a plurality of logic block circuits, plurality of logic block circuits comprising at least a first processor core circuit and a second processor core circuit, each processor core circuit having a scan chain circuit and being operable independently, and a common block circuit having a scan chain circuit and a cache circuit that is shared by the first processor core circuits and the second processor core circuits, the processor further comprising, for each logic block, a test pattern generating circuit operable to generate a test pattern and input the test pattern to the scan chain of each logic block circuit, and a test pattern compression circuit operable to accept as input and compress the test pattern output by the scan chain of each logic block circuit.

Owner:FUJITSU LTD

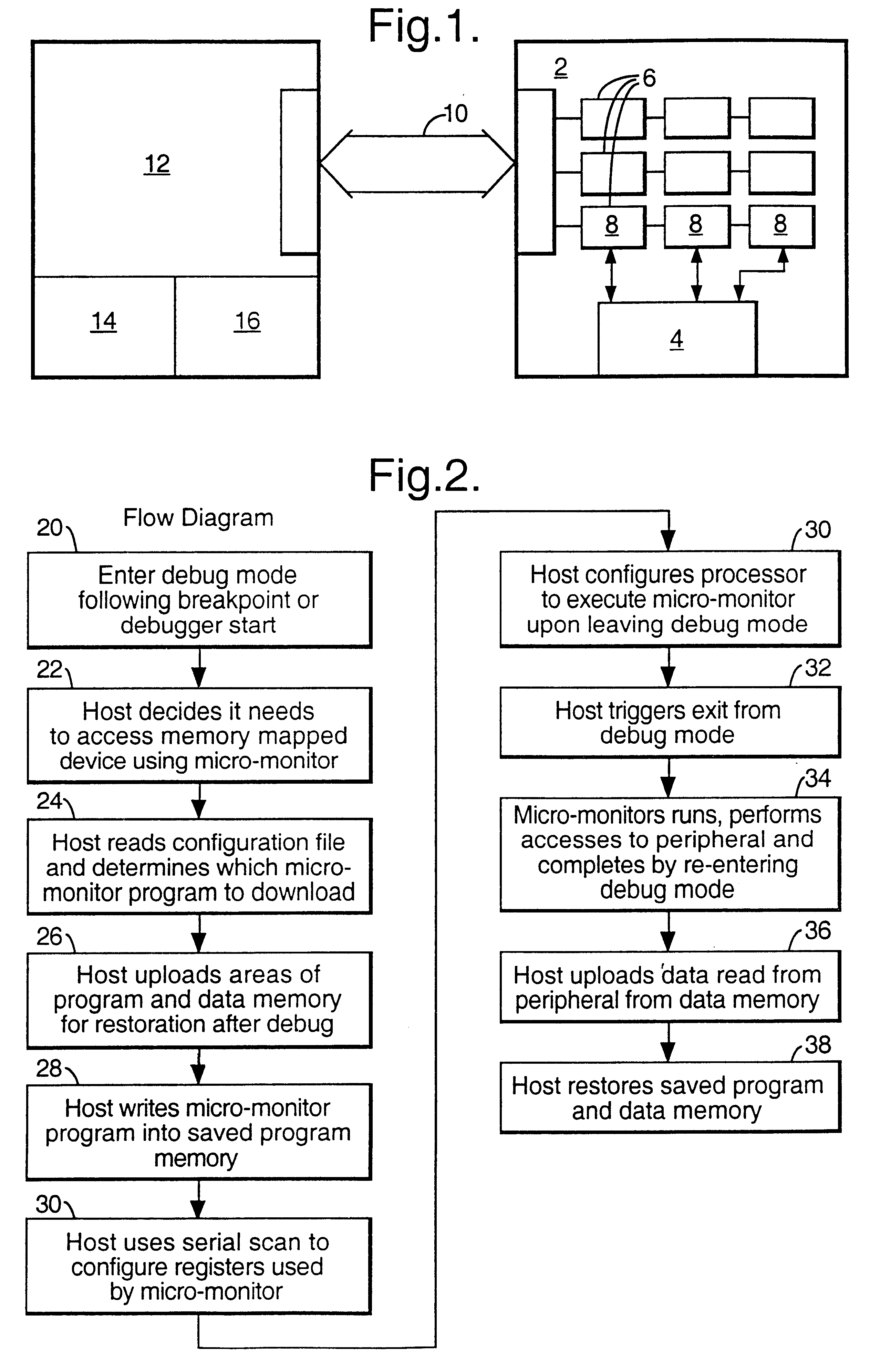

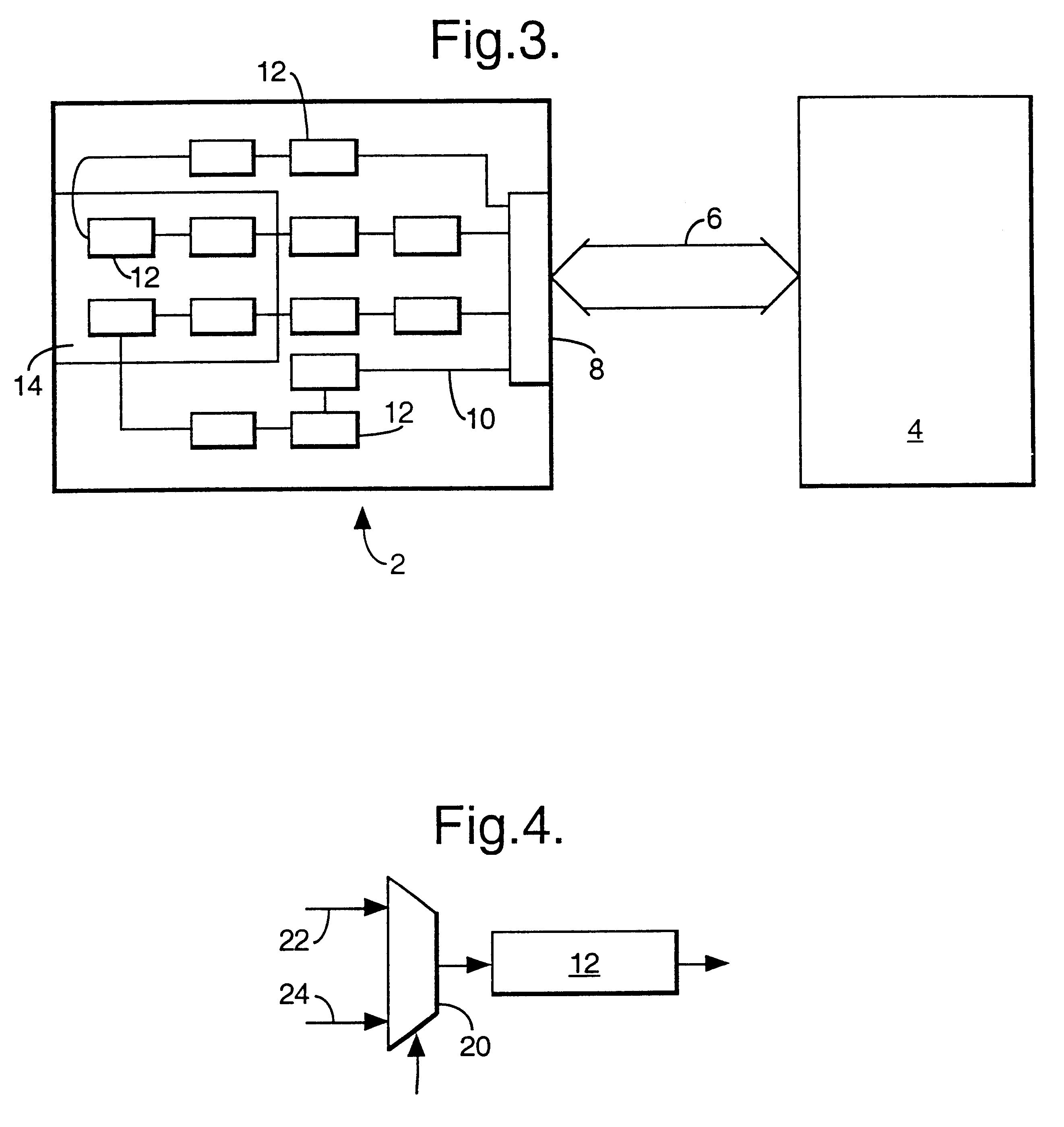

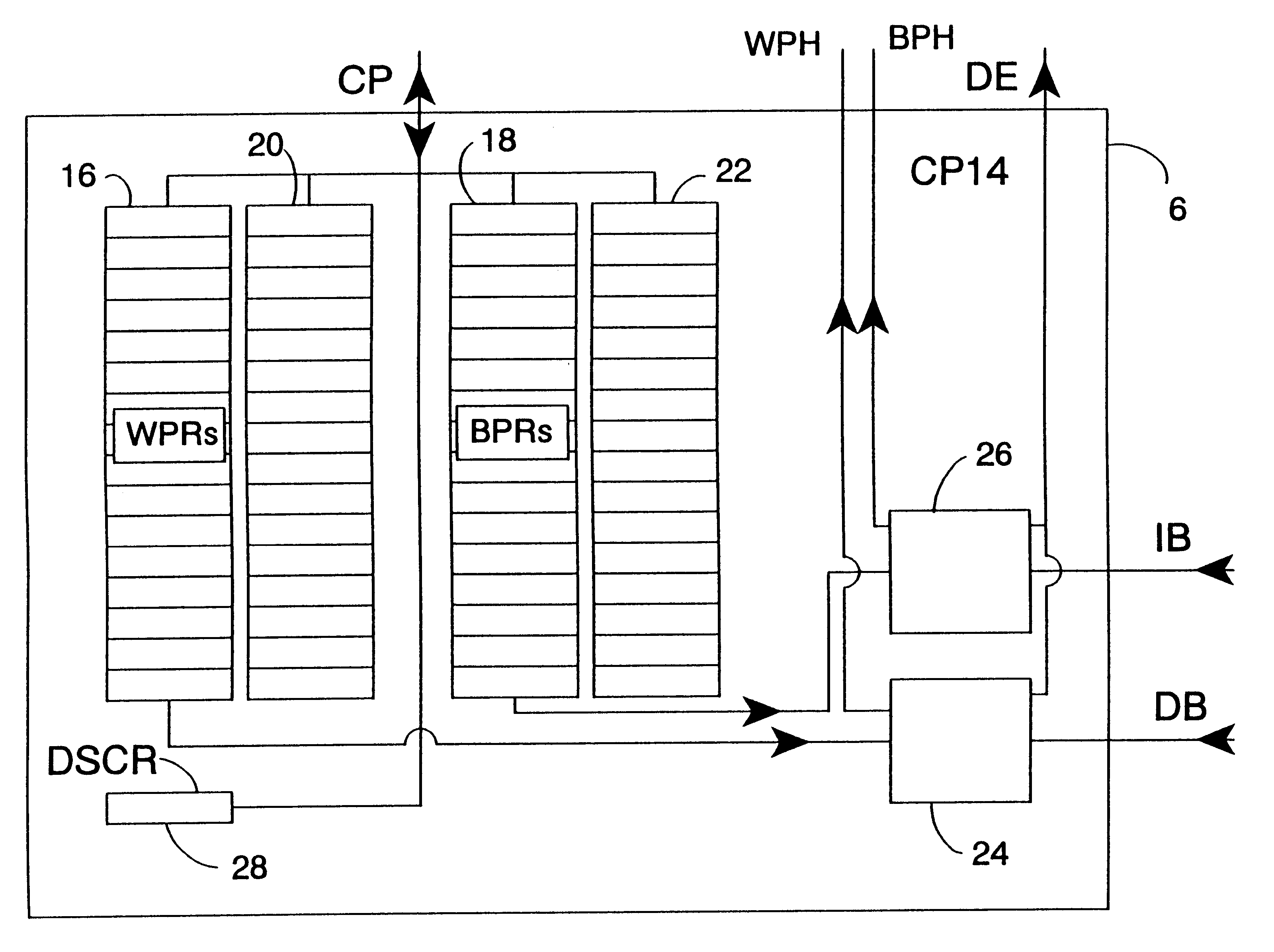

Microprocessor development systems

InactiveUS6574590B1Difficult to useSimple memory accessElectronic circuit testingDigital computer detailsEmbedded applicationsTime delays

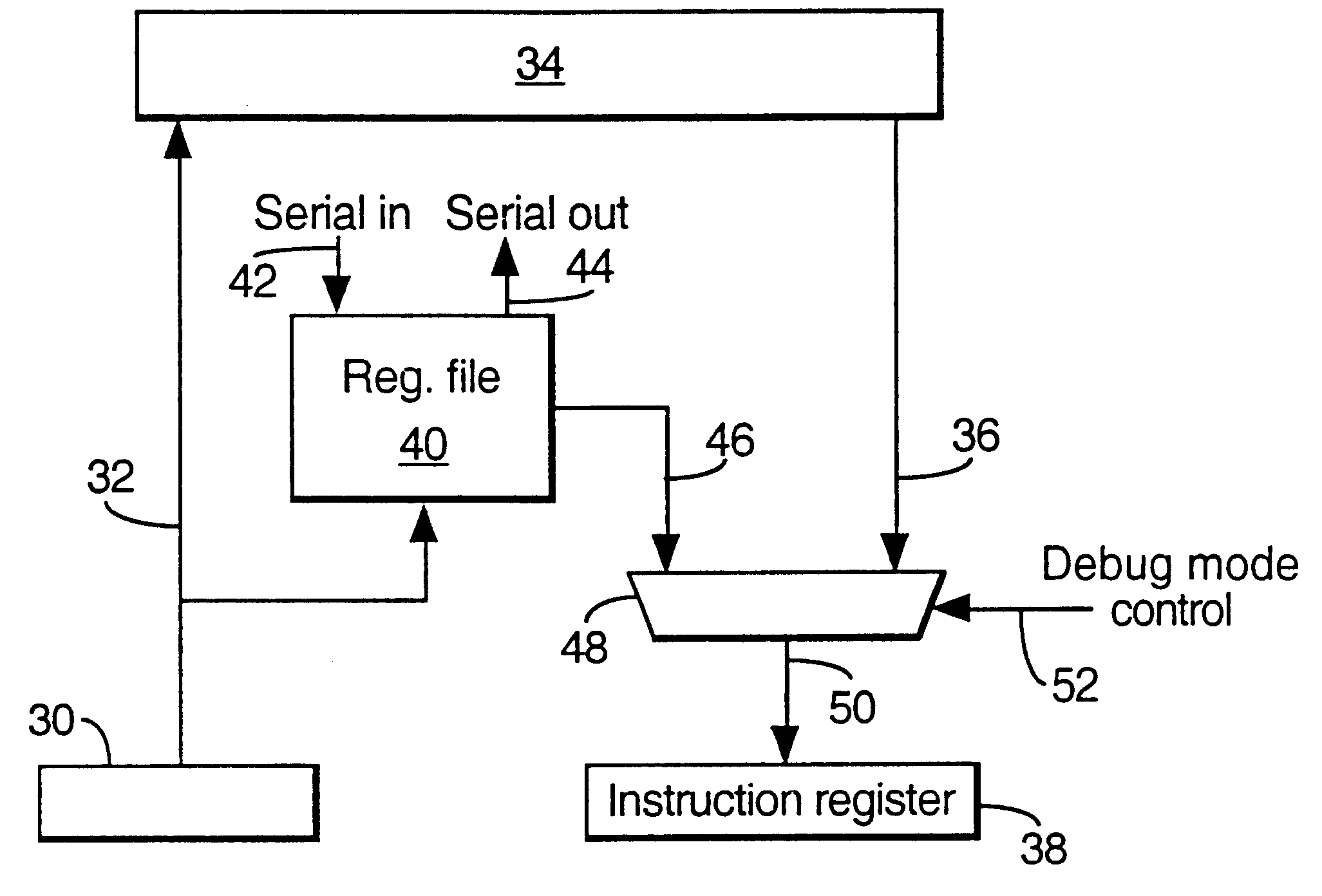

A procedure and processor are disclosed for avoiding lengthy delays in debug procedures during access by a memory mapped peripheral device. The processor includes in-circuit emulation means comprising one or more scan chains or serially connected registers for access by an external host computer system. The procedure comprises:a) the host computer system carrying out a debug procedure via said scan chains, and selectively interrupting such debug procedure for access to a peripheral memory mapped device;b) the host computer system writing into an area or memory of the processor a program for reading and / or writing data at a specified memory location; andc) the host computer system causing said processor to run said program, and then to return to said debug procedure.In another aspect, in order to permit small debugging programs to run, in serial scan in circuit emulation processes, on a processor in a deeply embedded application where no program RAM is provided, the processor includes one or more chains of serially connected registers coupled to interface means for access by an external host to enable a serial scan procedure to be carried out, one such chain including a set of serially coupled registers for storing one or more processor instructions read into a set of registers through the interface means, and the processor including address means, for addressing program memory, coupled to said set of registers for addressing the set of registers, and means for reading the processor instructions in the set of registers to an instruction resister of the processor.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

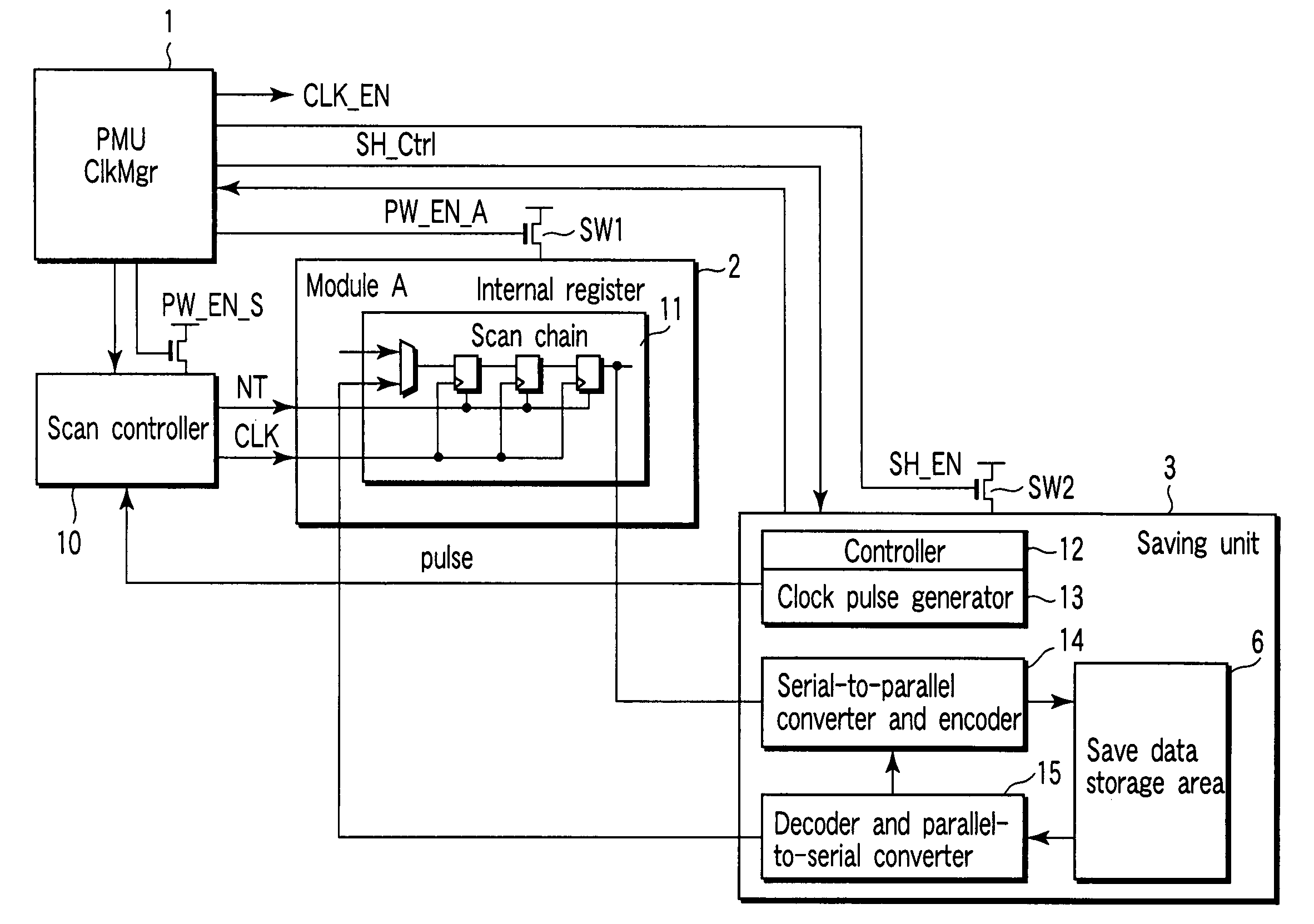

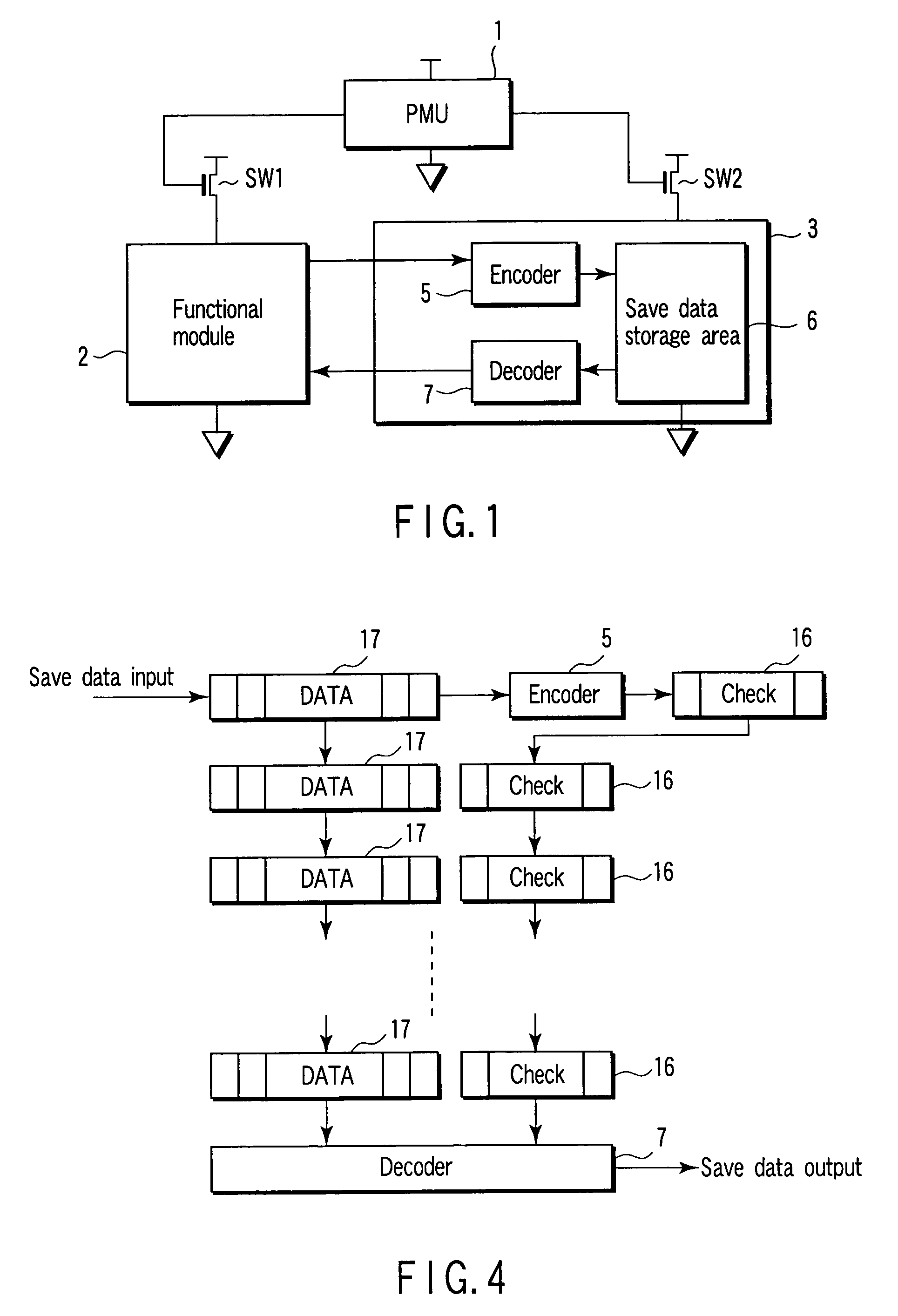

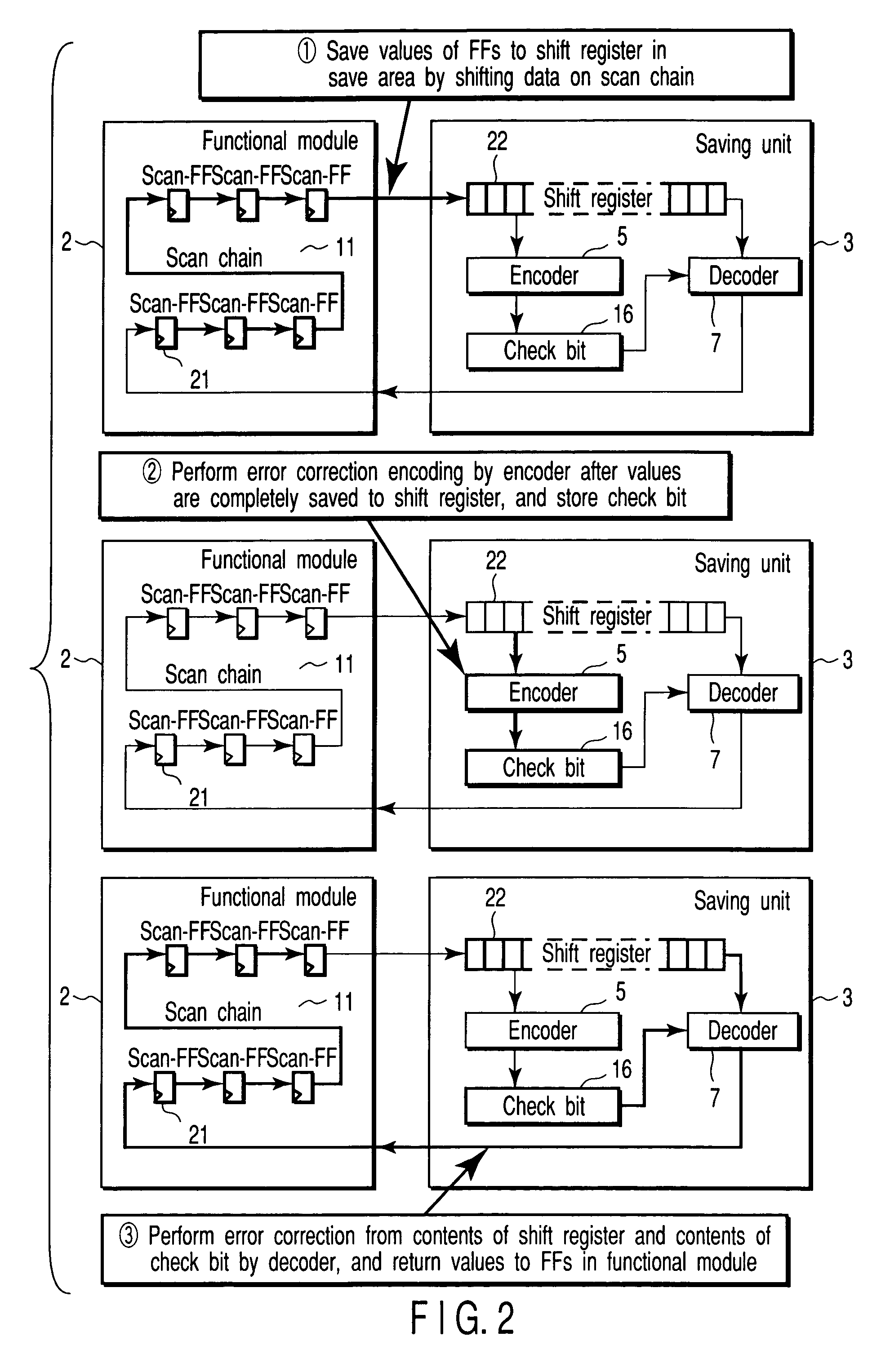

Power management for circuits with inactive state data save and restore scan chain

An integrated circuit device includes at least one functional module which outputs save data in synchronism with a saving clock signal, a power supply control unit which selects one of the functional modules, and controls stop and resumption of power supply to the selected functional module, a save data storage unit which stores save data output from a functional module selected by the power supply control unit, and an error checking and correction unit which performs error checking and correction for the save data stored in the save data storage unit when the save data is to be restored to the functional module in synchronism with a restoration clock signal.

Owner:SOCIONEXT INC

At-speed ATPG testing and apparatus for SoC designs having multiple clock domain using a VLCT test platform

ActiveUS7134061B2Increase savingsThe testing process is simpleElectronic circuit testingControl signalClock rate

A scan test circuitry design imbedded on an SoC having the scan architecture of a VLCT platform is disclosed herein. This BIST circuitry design that is not limited in the number of scan test ports supported includes at least one scan chain group having a corresponding clock domain that couples to receive test stimulus data. Each scan chain group has a corresponding test mode signal to shift the test stimulus data at a shift clock rate derived from its corresponding clock domain. A controlling demultiplexer connects to each multiplexer unit within each scan chain group to provide control signals for shifting in the test stimulus. A clock control mechanism provides a control signal for each scan chain to shift test stimulus and capture resultant data. Furthermore, when a simultaneous test mode signal is enabled, the clock control mechanism couples to each scan chain to enable simultaneous capture of each scan chain group.

Owner:TEXAS INSTR INC

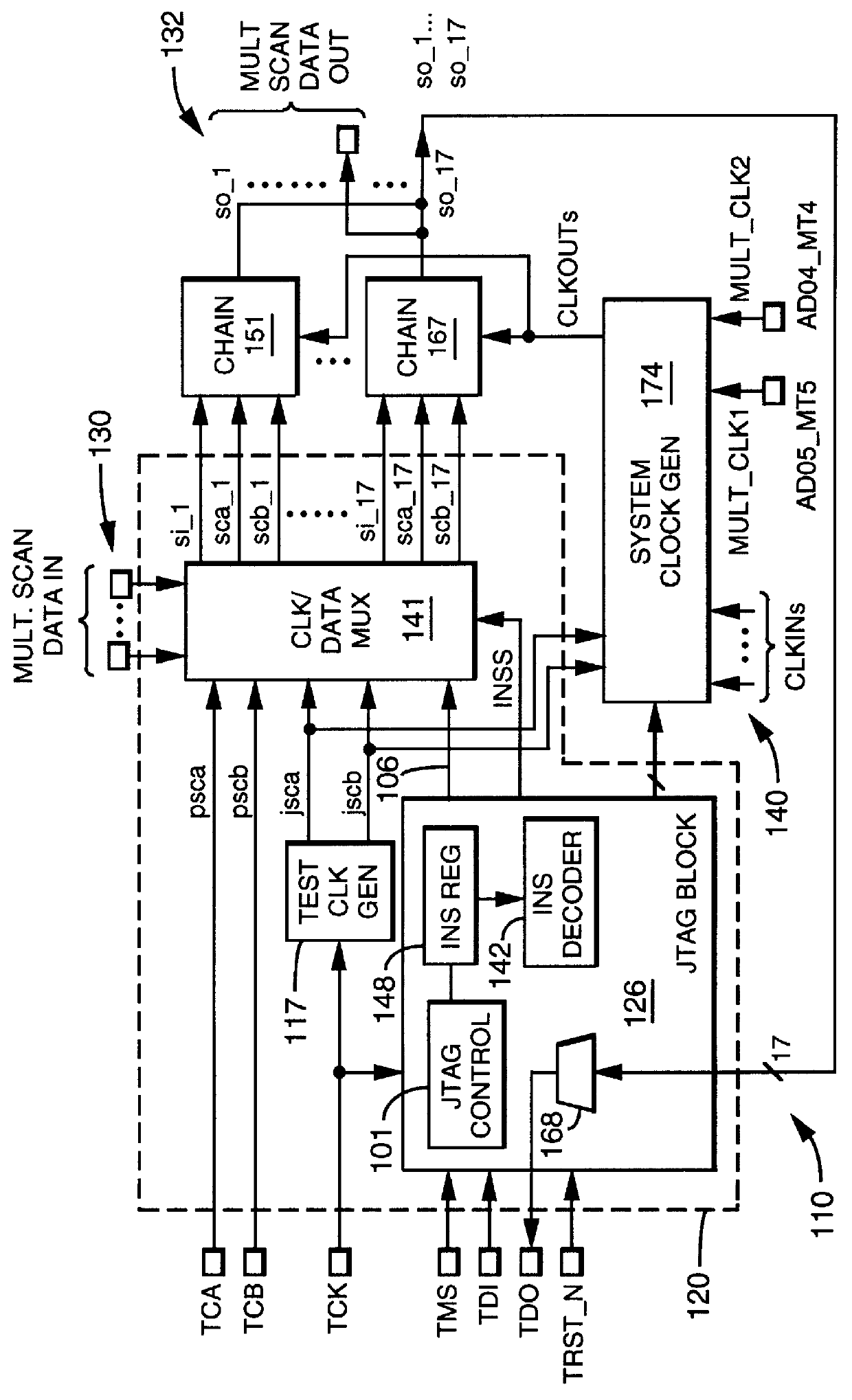

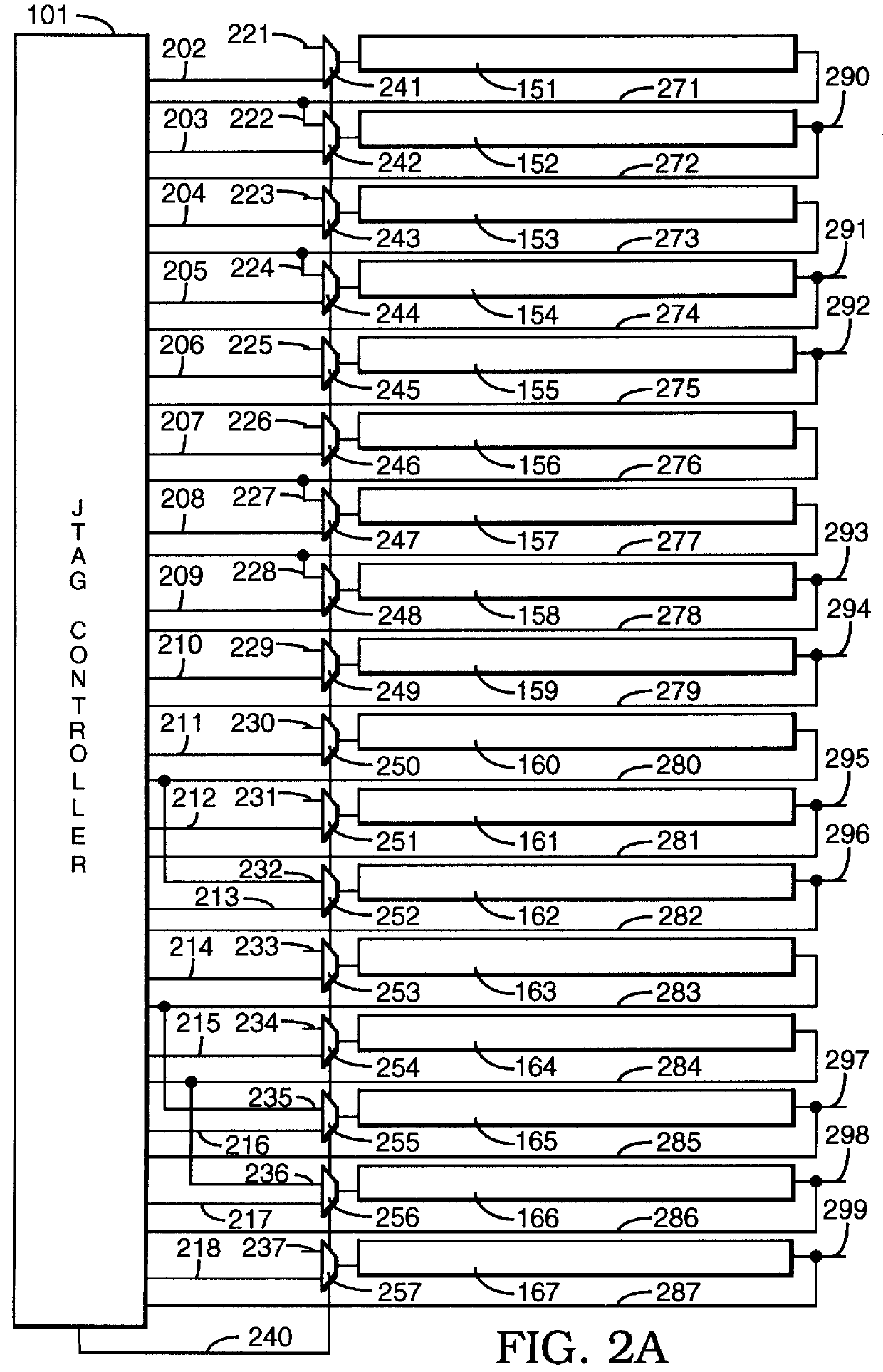

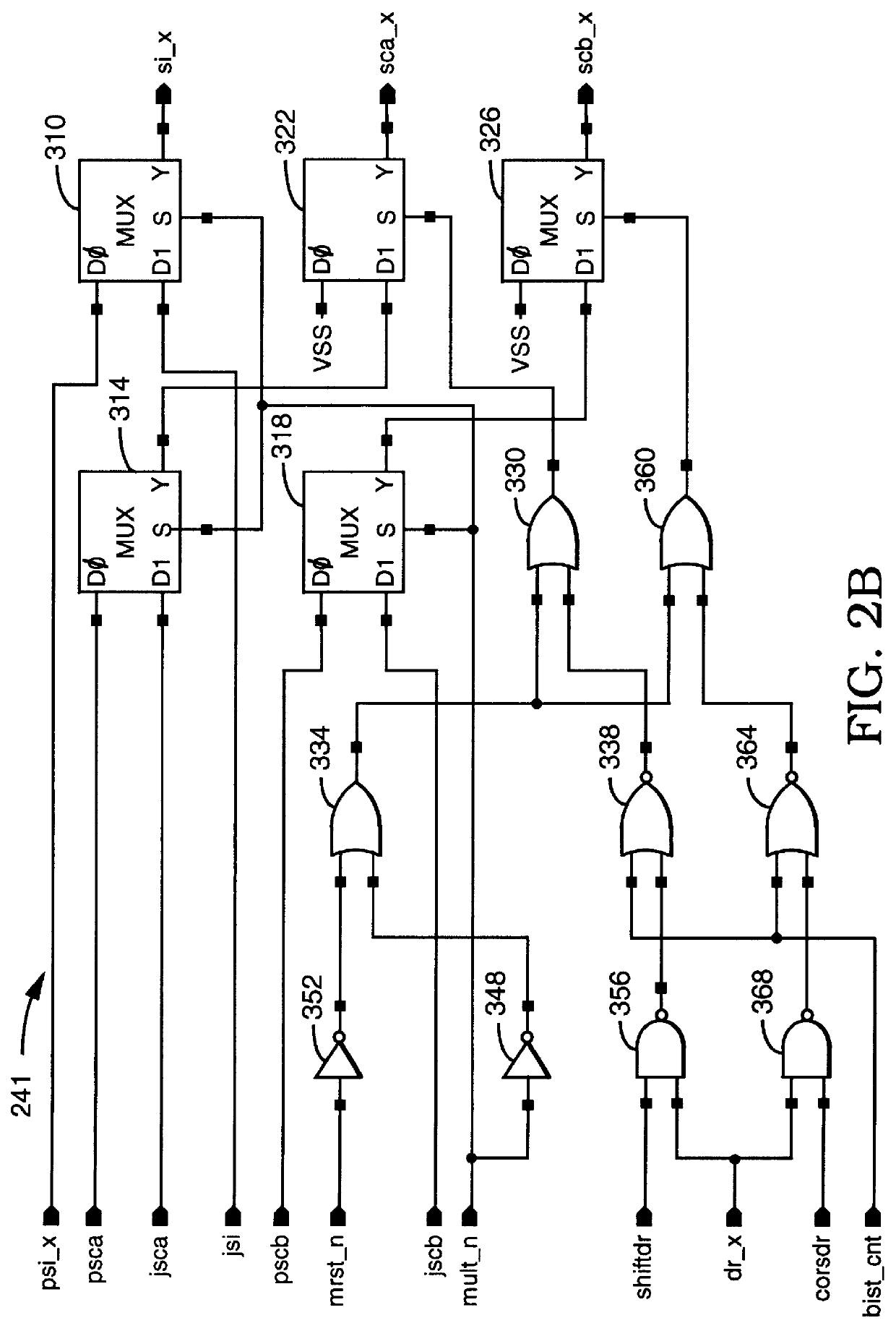

Adaptable scan chains for debugging and manufacturing test purposes

InactiveUS6018815AReducing scan time operationAvoid Design MistakesDigital circuit testingSolid-state devicesEngineeringJoint Test Action Group

Scan chains to support debugging and manufacturing test modes for integrated circuit chips are made adaptable. Scan chains may be configured either in a multiple scan chain JTAG mode or in a multiple independent and parallel scan chain mode. The configuration transition between the scan modes is made by private instructions implemented in a JTAG controller, which supports the IEEE 1149.1 standard.

Owner:SAMSUNG ELECTRONICS CO LTD

System and method for debugging system-on-chips

InactiveUS7219265B2Electronic circuit testingError detection/correctionComputer hardwareProcessor register

Large, complex SoCs comprise interconnections of various functional blocks. Such functional blocks contain scan chains that are used for their individual production testing. The present invention utilizes these scan chains as a tool in the debugging of these SoCs by providing the internal contents of registers and memories contained on the SoC device. Accordingly, both hardware and software designers are provided a means to observe the effect of their designs on the internal operation of the SoC device. The invention is compatible with current integrated circuit design methodology and requires minimal area on the SoC for support circuitry.

Owner:AVAGO TECH INT SALES PTE LTD

Diagnostic method for structural scan chain designs

A method for testing and diagnosing shift register latch chains coupled to logic circuits in an integrated circuit, the method including: (a) determining which of the shift register latch chains are failing by propagating a test pattern of zeros and ones through the shift register latch chains while gating which of the shift register latch chains contents are propagated into the means for generating a test signature; and (b) for each failing shift register latch chain: (b1) propagating a test pattern through the shift register latch chains while gating a selected sequential group of latches in a failing shift register latch to propagate into the means for generating a test signature; (b2) reducing the number of latches in the sequential group of latches; and (b3) repeating steps (b1) and (b2) until all failing latches of the failing shift register latch chain have been determined.

Owner:IBM CORP

Phase shifter with reduced linear dependency

InactiveUS20050015688A1Electronic circuit testingRecord information storageCircuit complexityLinear correlation

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

System and method for automatic masking of compressed scan chains with unbalanced lengths

ActiveUS20060095818A1Restrict propagationElectronic circuit testingError detection/correctionComputer hardwareControl signal

A scan test architecture is implemented. The scan test architecture provides a method of performing scan test of unbalanced scan chains. The scan test architecture generates a control signal (i.e., masking signal) to mask bits in an unbalanced scan chain. In one embodiment, the control signal is generated with a logic gate, a comparator, and a counter.

Owner:AVAGO TECH INT SALES PTE LTD

Method and Apparatus for Logic Built In Self Test (LBIST) Fault Detection in Multi-Core Processors

InactiveUS20090089636A1Advanced technologyElectronic circuit testingLogical operation testingLogic built-in self-testMulti-core processor

Owner:IBM CORP

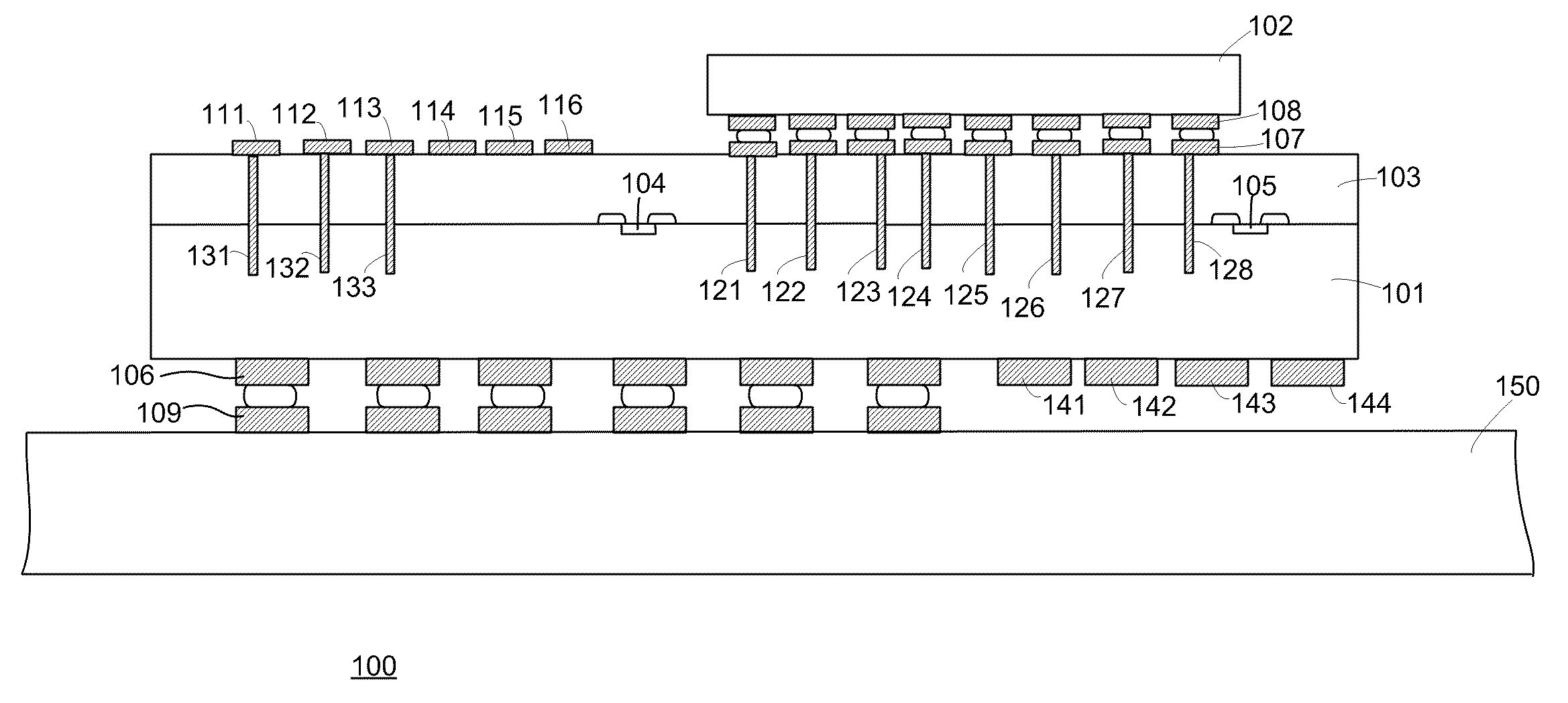

Apparatus and method for testing of stacked die structure

ActiveUS8063654B2Less timeShorten the timeSolid-state devicesSemiconductor devicesTest inputControl signal

An integrated circuit device includes a stacked die and a base die having probe pads that directly couple to test logic of the base die to implement a scan chain for testing of the integrated circuit device. The base die further includes contacts disposed on a back side of the base die and through-die vias coupled to the contacts and coupled to programmable logic of the base die. The base die also includes a first probe pad configured to couple test input, a second probe pad configured to couple test output, and a third probe pad configured to couple control signals. Test logic of the base die is configured to couple to additional test logic of the stacked die to implement the scan chain. The probe pads are coupled directly to the test logic such that configuration of the programmable logic is not required to implement the scan chain.

Owner:XILINX INC

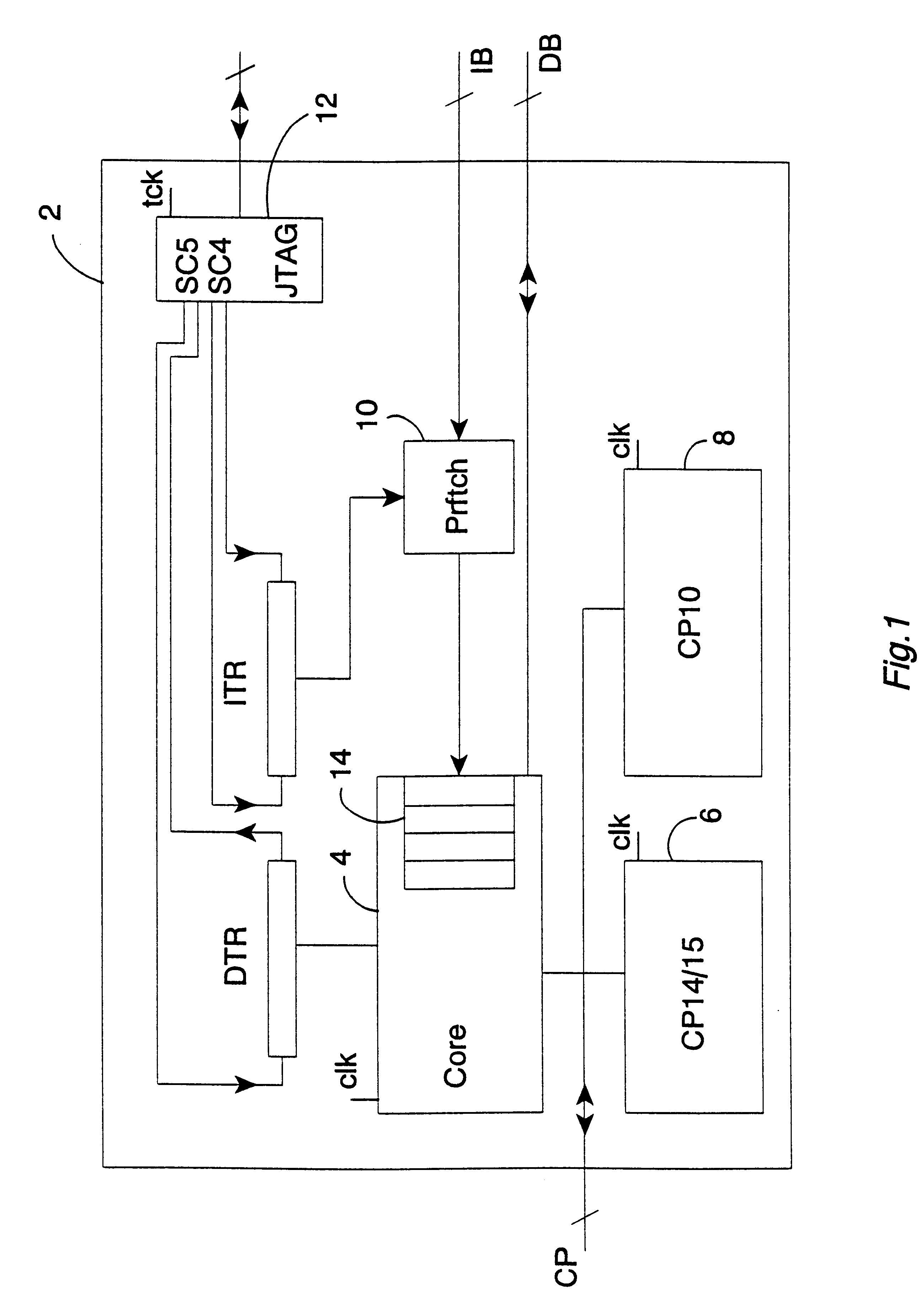

Executing multiple debug instructions

InactiveUS6343358B1Reduce the degree of variationEasy to implementElectronic circuit testingDetecting faulty computer hardwareComputer hardwareProcessor register

Apparatus for processing data is provided, said apparatus comprising: a main processor 4; an instruction transfer register ITR for holding a data processing instruction and accessible via a first serial scan chain SC4; a data transfer register DTR for holding a data value and accessible via a second serial scan chain SC5; debug logic 6, 12 for controlling said main processor 4, said instruction transfer register ITR and said data transfer register DTR such that a data processing instruction held within said instruction transfer register ITR is passed a plurality of times to said main processor 4 for execution upon a sequence of data values scanned into or from said data transfer register via said second serial scan chain. In this way operational speed of the debug mode is increased since the data processing instruction only needs to be transferred once.

Owner:ARM LTD

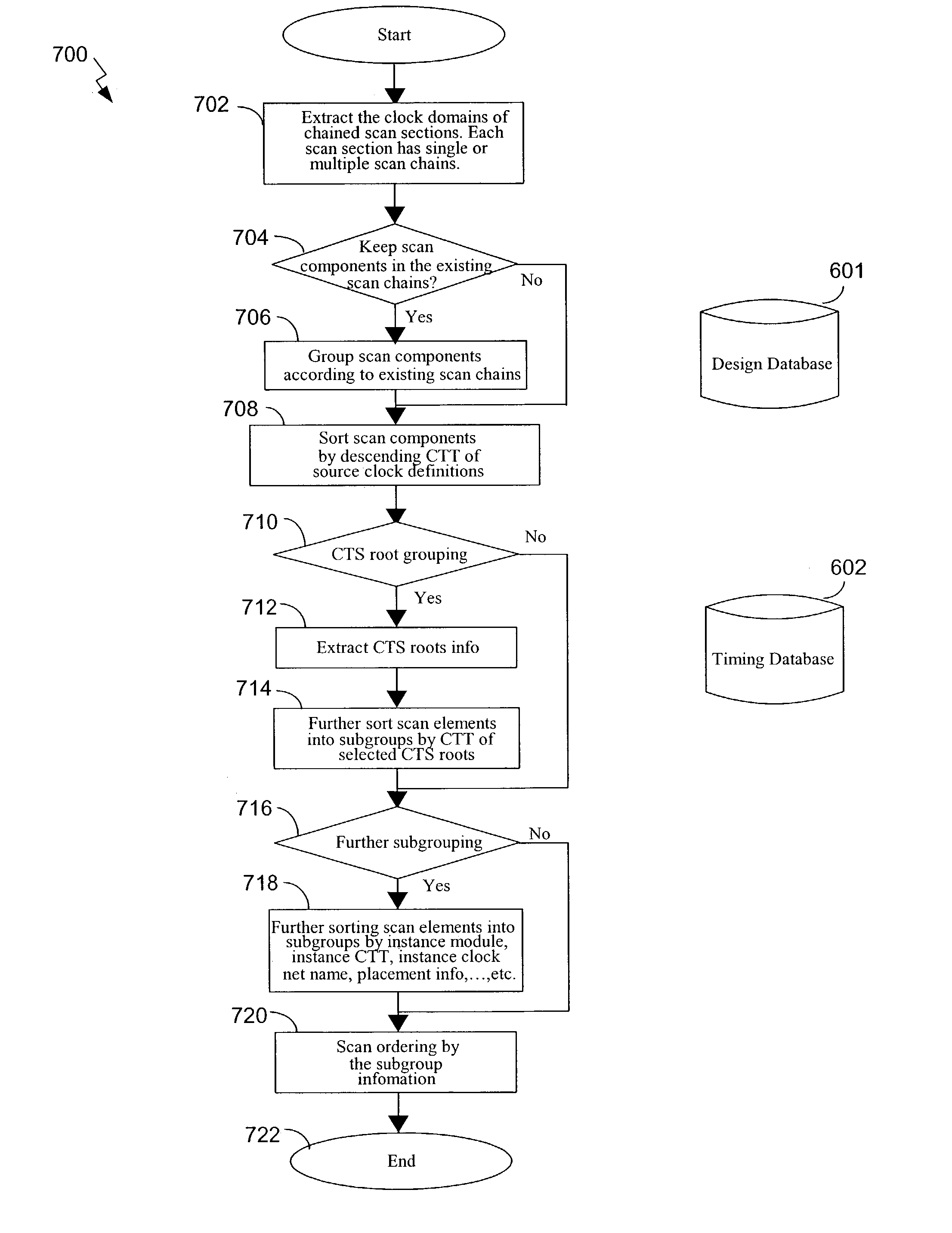

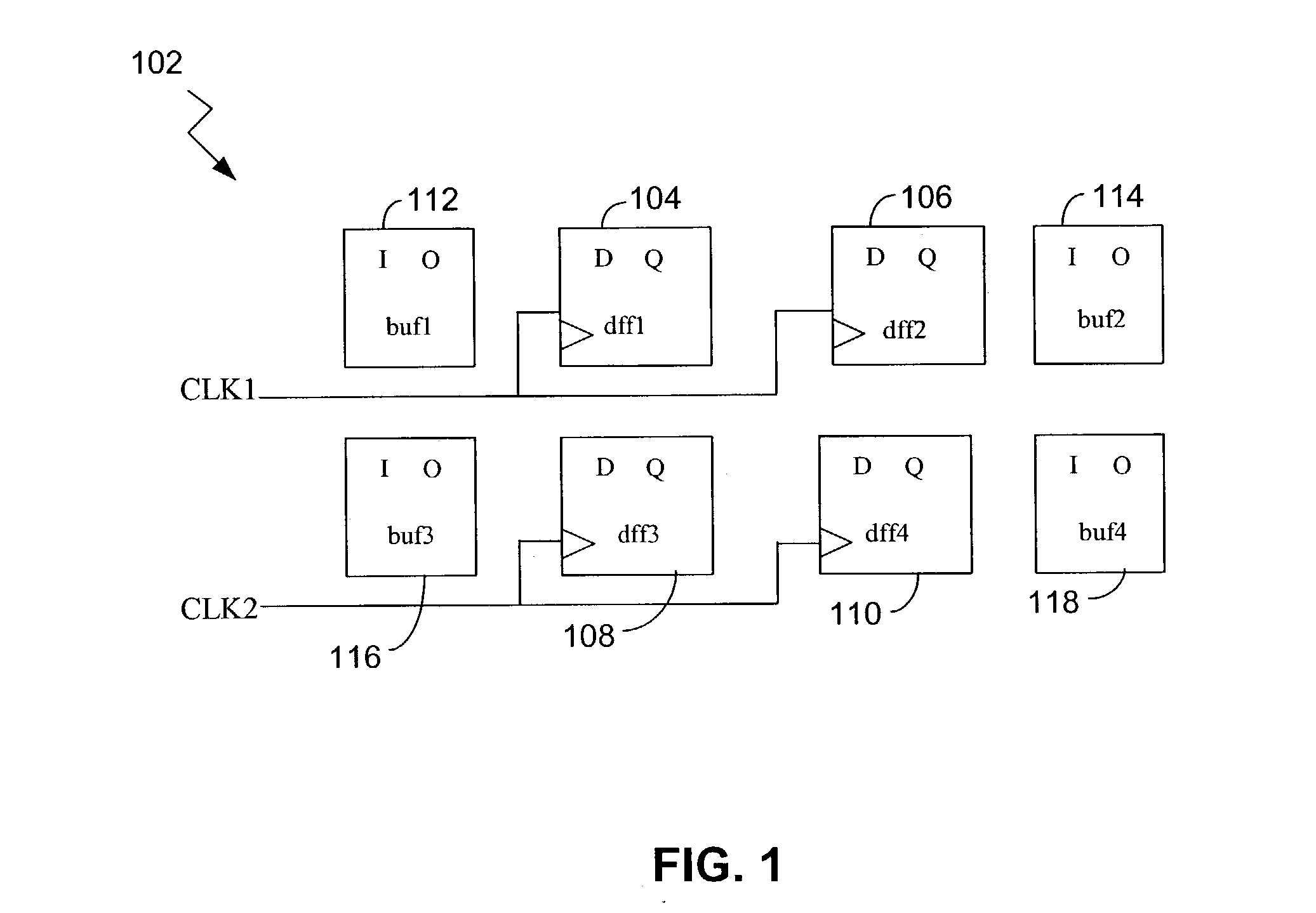

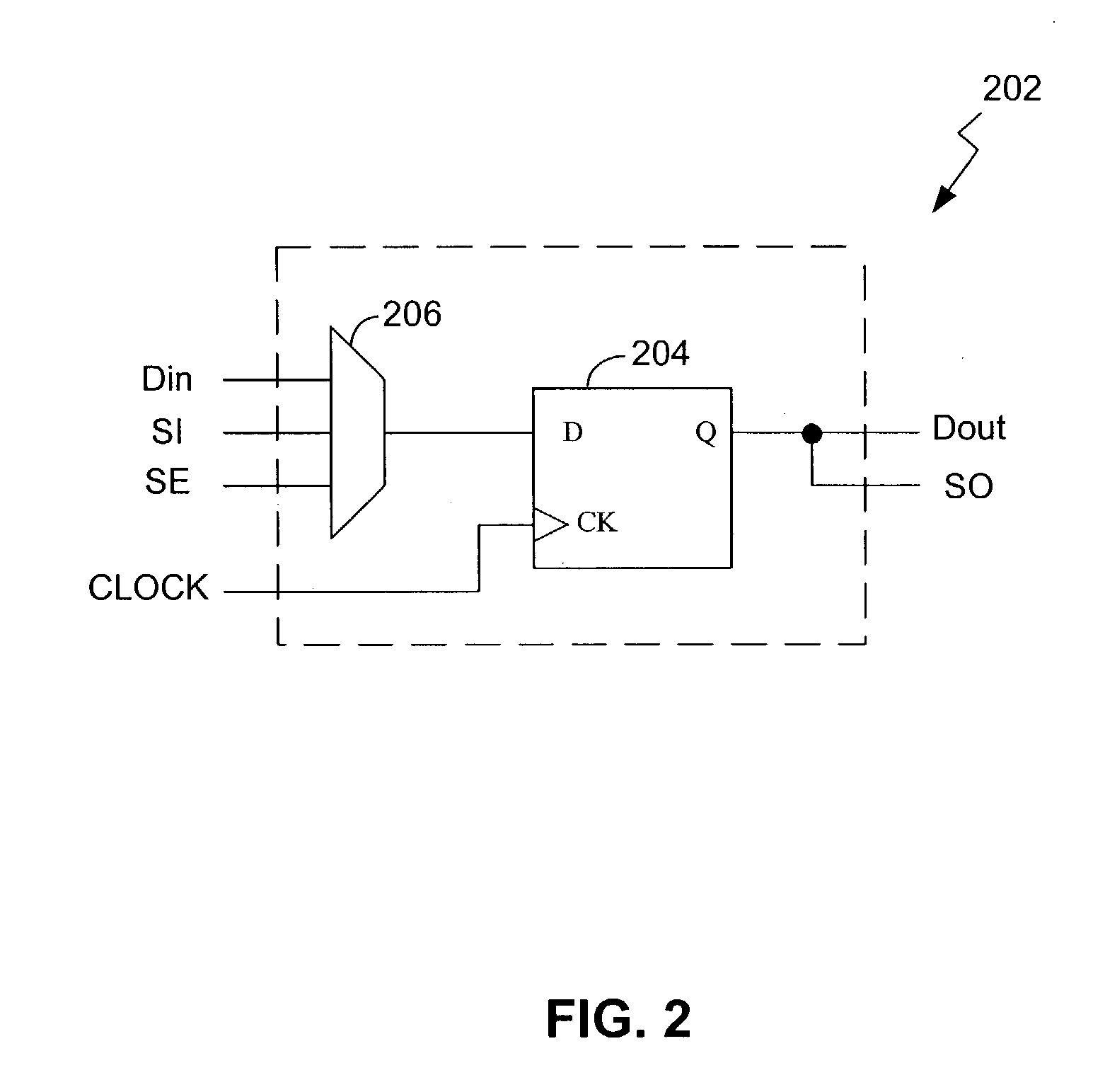

Timing based scan chain implementation in an IC design

InactiveUS7127695B2Reduce time impactEasy to placeElectrical testingCAD circuit designComputer architectureNetlist

For use with a design database and a timing database, a computer implemented process for electronic design automation comprising: receiving a netlist that includes cells interconnected by circuit paths, wherein a plurality of the cells are scan cells connected in at least one scan chain; ordering the scan cells according to a prescribed scan cell ordering rule so as to produce a plurality of ordering relationships among scan cells; assigning respective weights from a first category of one or more weights to respective prescribed scan cell order relationships among scan cells of the netlist; assigning respective weights from a second category of one or more weights to prescribed circuit path relationships among cells of the netlist; and determining a physical placement of the cells of the netlist, including the scan cells, using a cost function that places the cells according to the assigned weights.

Owner:INCENTIA DESIGN SYST

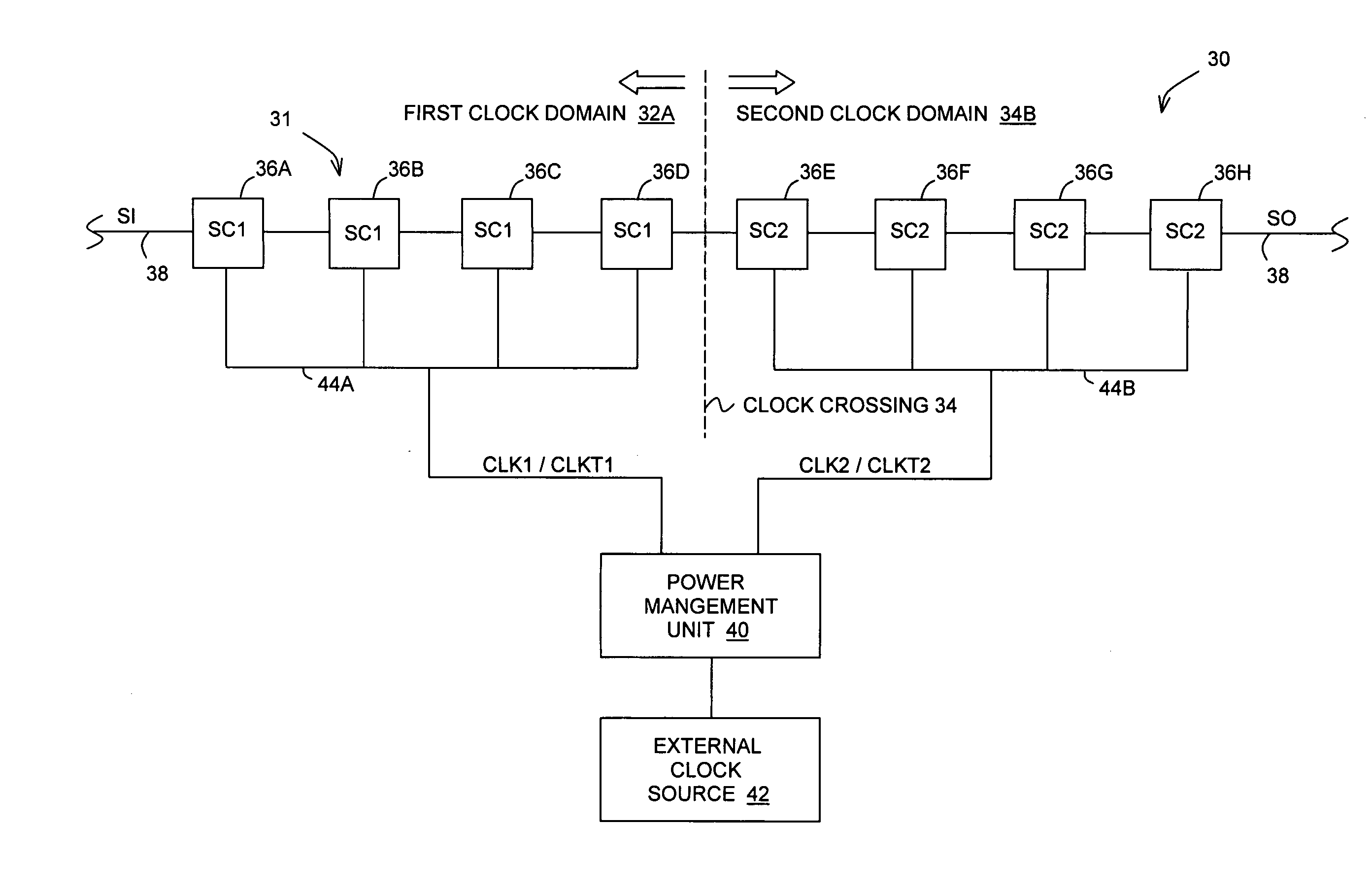

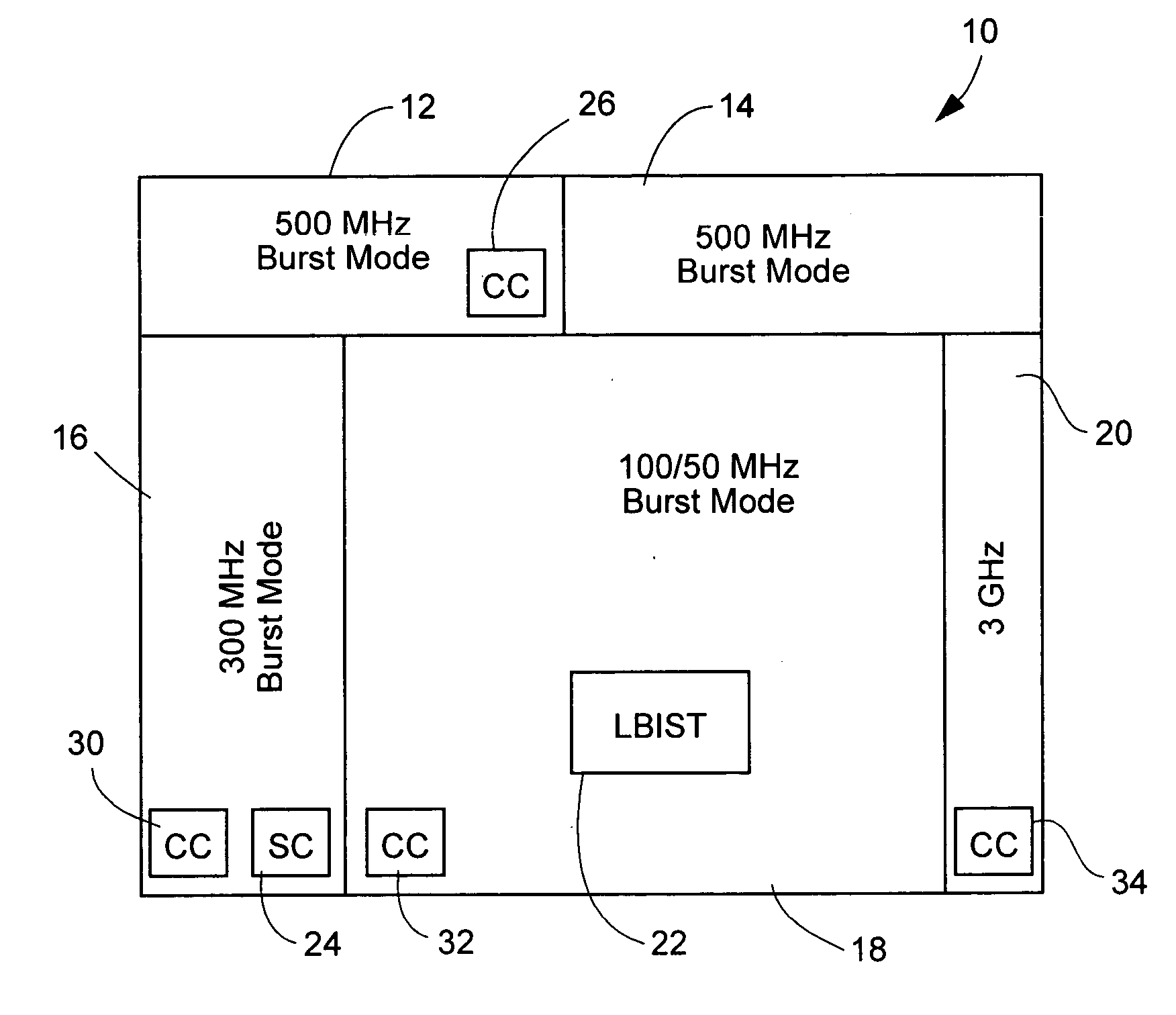

Test clock control structures to generate configurable test clocks for scan-based testing of electronic circuits using programmable test clock controllers

ActiveUS20080010573A1Reduce the number of timesLow costElectronic circuit testingFunctional testingControl layerProgrammable logic controller

Systems, structures and methods for generating a test clock for scan chains to implement scan-based testing of electronic circuits are disclosed. In one embodiment, a test clock control structure includes a programmable test clock controller. The programmable test clock controller includes a test clock generator for generating a configurable test clock. It also includes a scan layer interface to drive a scan chain portion with the configurable test clock, and a control layer interface configured to access control information for controlling the scan chain portion. In another embodiment, a method effectuates scan-based testing of circuits. The method includes performing at least one intra-domain test and performing at least one inter-domain test using implementing dynamic fault detection test patterns, which can include last-shift-launch test patterns and broadside test patterns.

Owner:LATTICE SEMICON CORP

Inversion of scan clock for scan cells

In one embodiment, an apparatus comprises a scan circuit including at least a first and a second clock domain and a scan chain having a first plurality of scan cells positioned in the first clock domain and a second plurality of scan cells positioned in the second clock domain. A scan clock source, coupled to the scan chain, generates a first scan clock signal to the first plurality of scan cells and a second scan clock signal to the second plurality of scan cells. The first and the second clock signals have an inverted relationship.

Owner:MARVELL ASIA PTE LTD

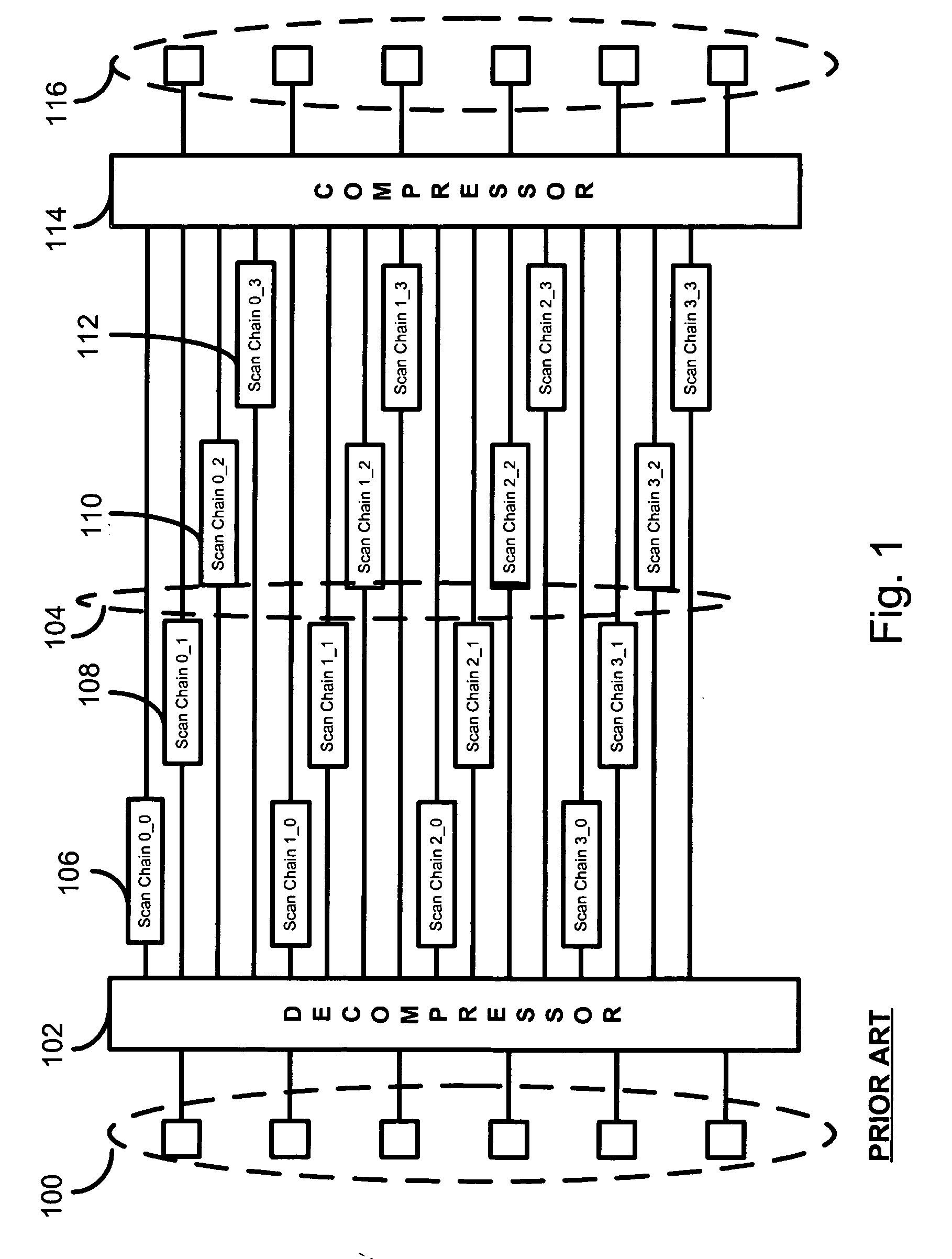

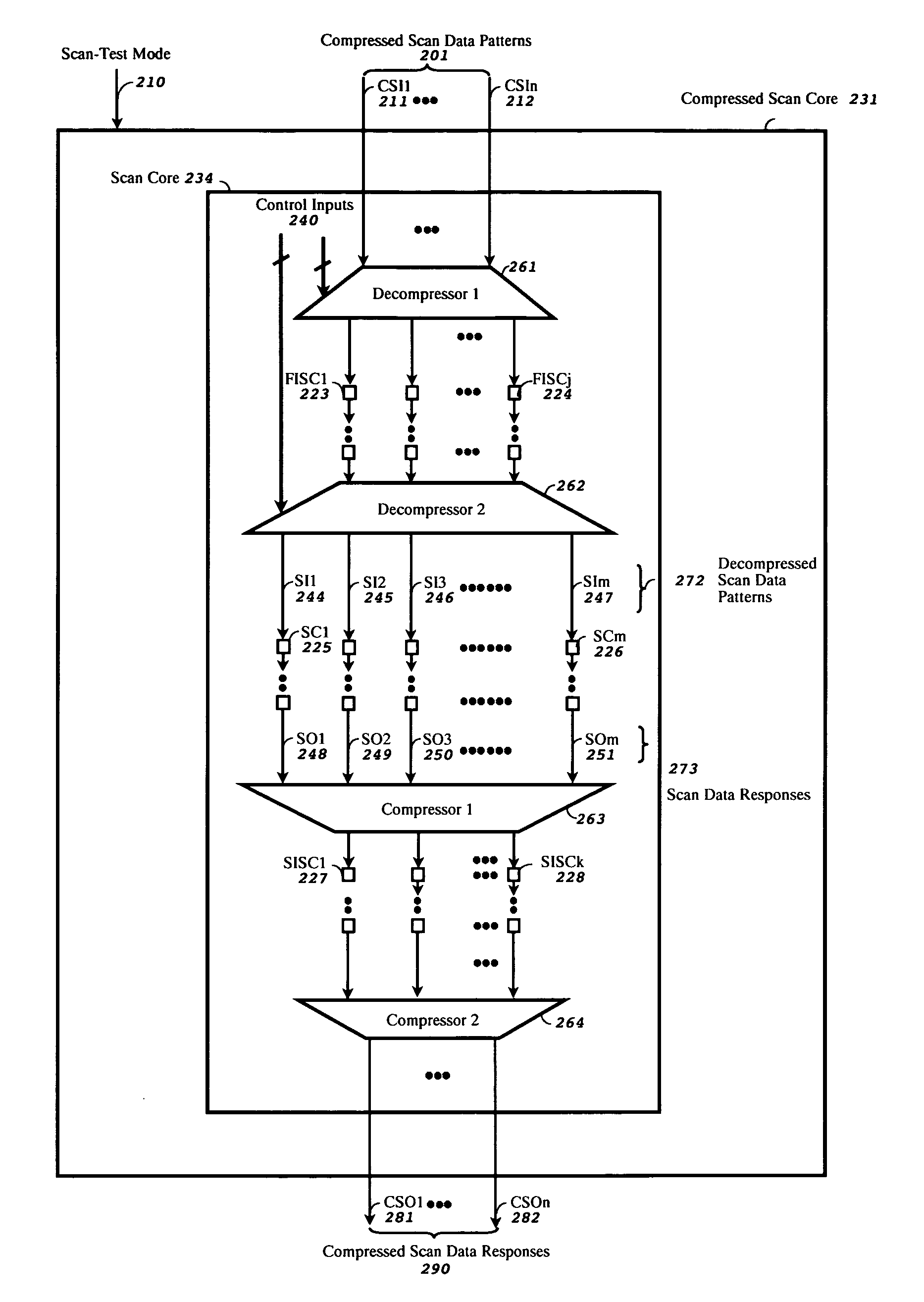

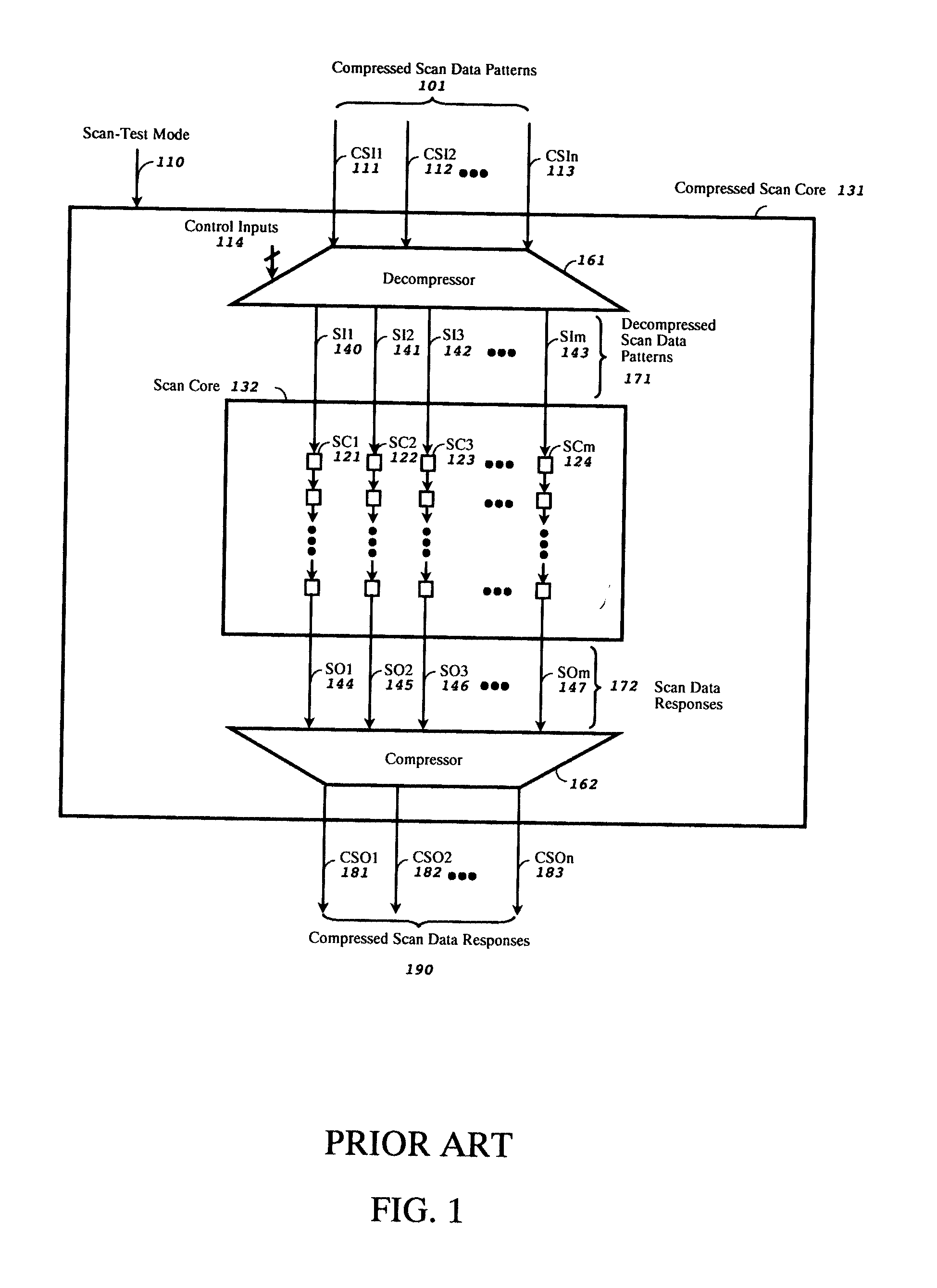

Method and apparatus for multi-level scan compression

InactiveUS20050268194A1Improve balanceElectronic circuit testingError detection/correctionEngineeringApplication time

A multi-level scan compression method and apparatus for reducing test data volume and test application time in a scan-based integrated circuit without reducing the speed of the scan chain operation in scan-test mode or self-test mode. The scan-based integrated circuit contains one or more scan chains, each scan chain comprising one or more scan cells coupled in series. The method and apparatus comprises two or more decompressors embedded between N compressed scan inputs and M scan chains, where N<M, to broadcast compressed scan data patterns driven through the N compressed scan inputs into decompressed scan data patterns stored in the M scan chains. The multi-level scan compression approach allows us to speed up the shift-in / shift-out operation during decompression using two or more decompressors separated by intermediate scan chains. The method and apparatus further comprises two or more compressors separated by intermediate scan chains to speed up the shift-in / shift-out operation during compression.

Owner:SYNTEST TECH

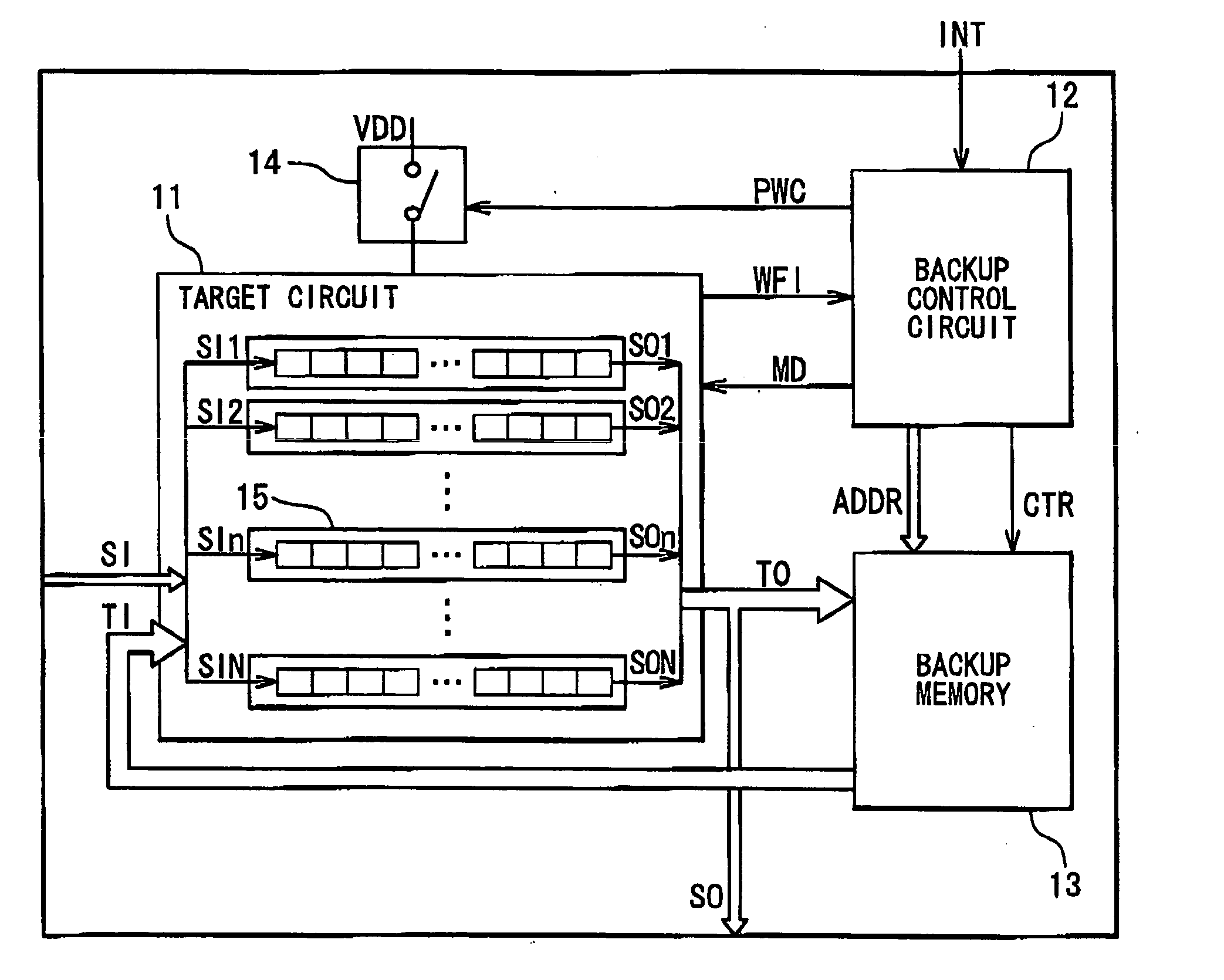

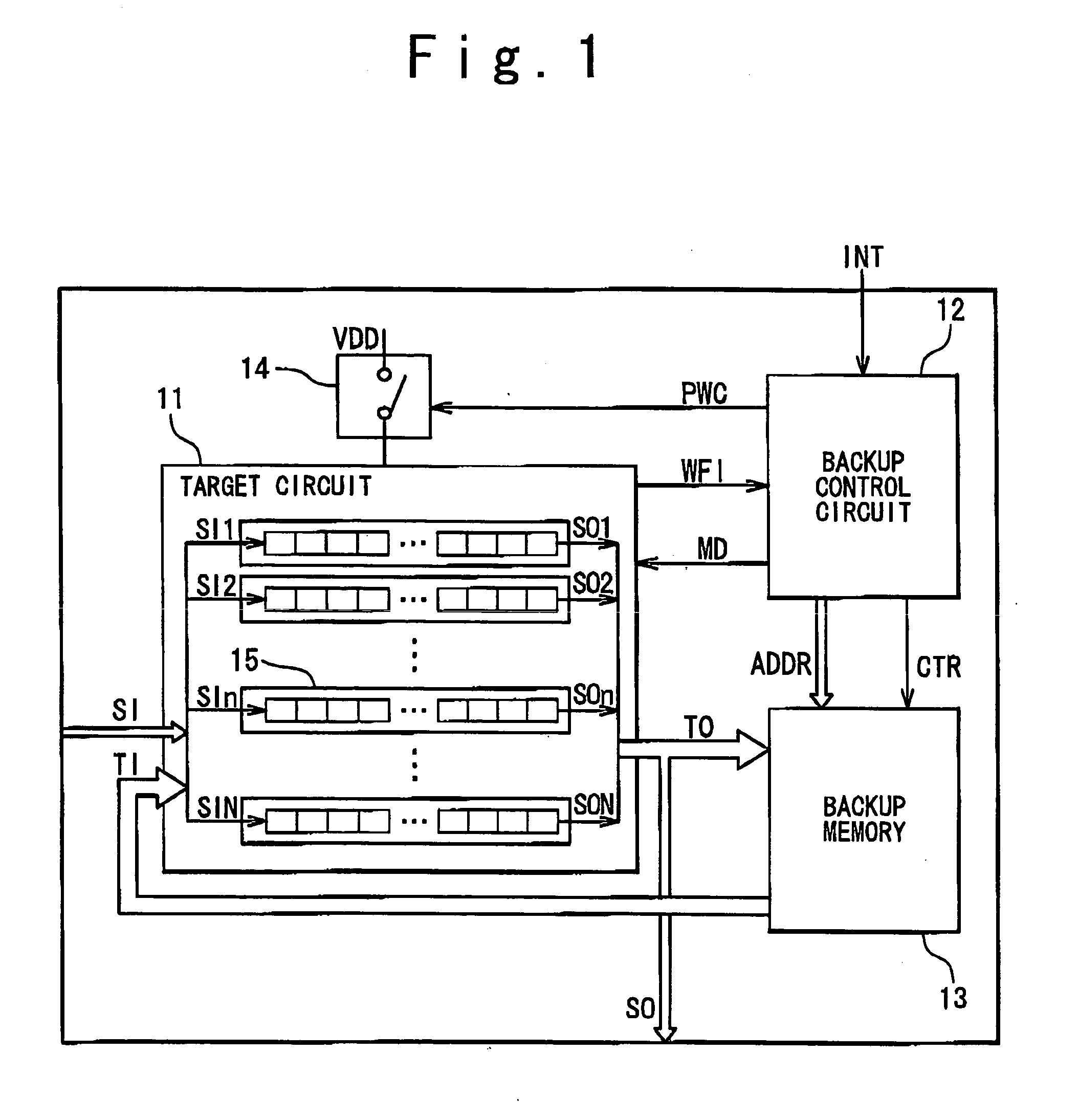

Semiconductor integrated circuit and method for controlling the same

ActiveUS20070150780A1Electronic circuit testingDigital data processing detailsEngineeringControl circuit

A semiconductor integrated circuit includes a target circuit with at least a scan chain having sub scan chains of stages to sequentially shift a test data in response to a clock signal in a scan path test mode, and each of the sub scan chains includes first flip-flops connected in series. A backup control circuit controls the target circuit and a memory such that a plurality of sub internal state data of a data indicating an internal state of the target circuit are stored as a plurality of write data in the memory in a save mode through the sub scan chains and the plurality of sub internal state data are read out from the memory as a plurality of read data and set in the sub scan chains in a restore mode.

Owner:RENESAS ELECTRONICS CORP

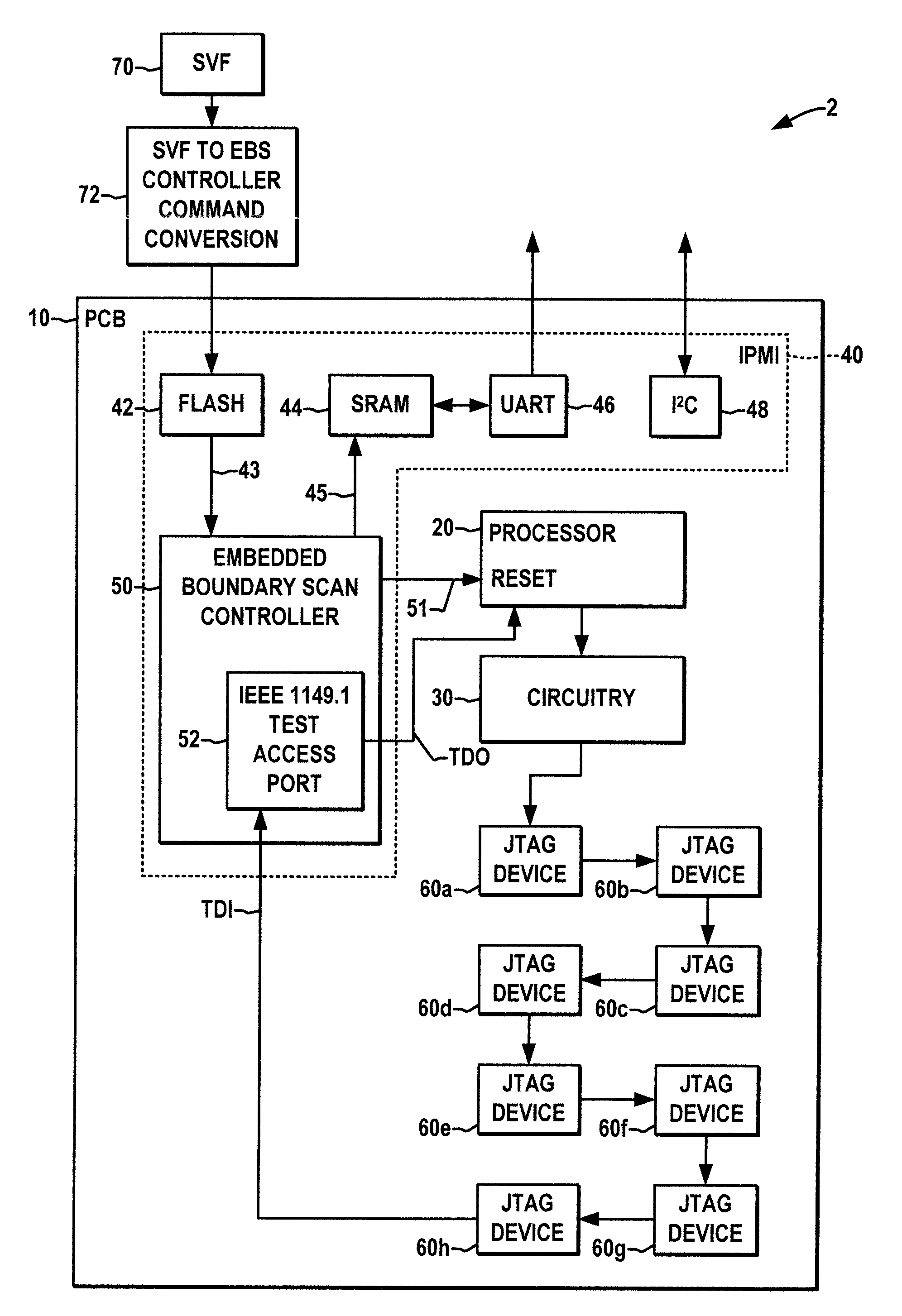

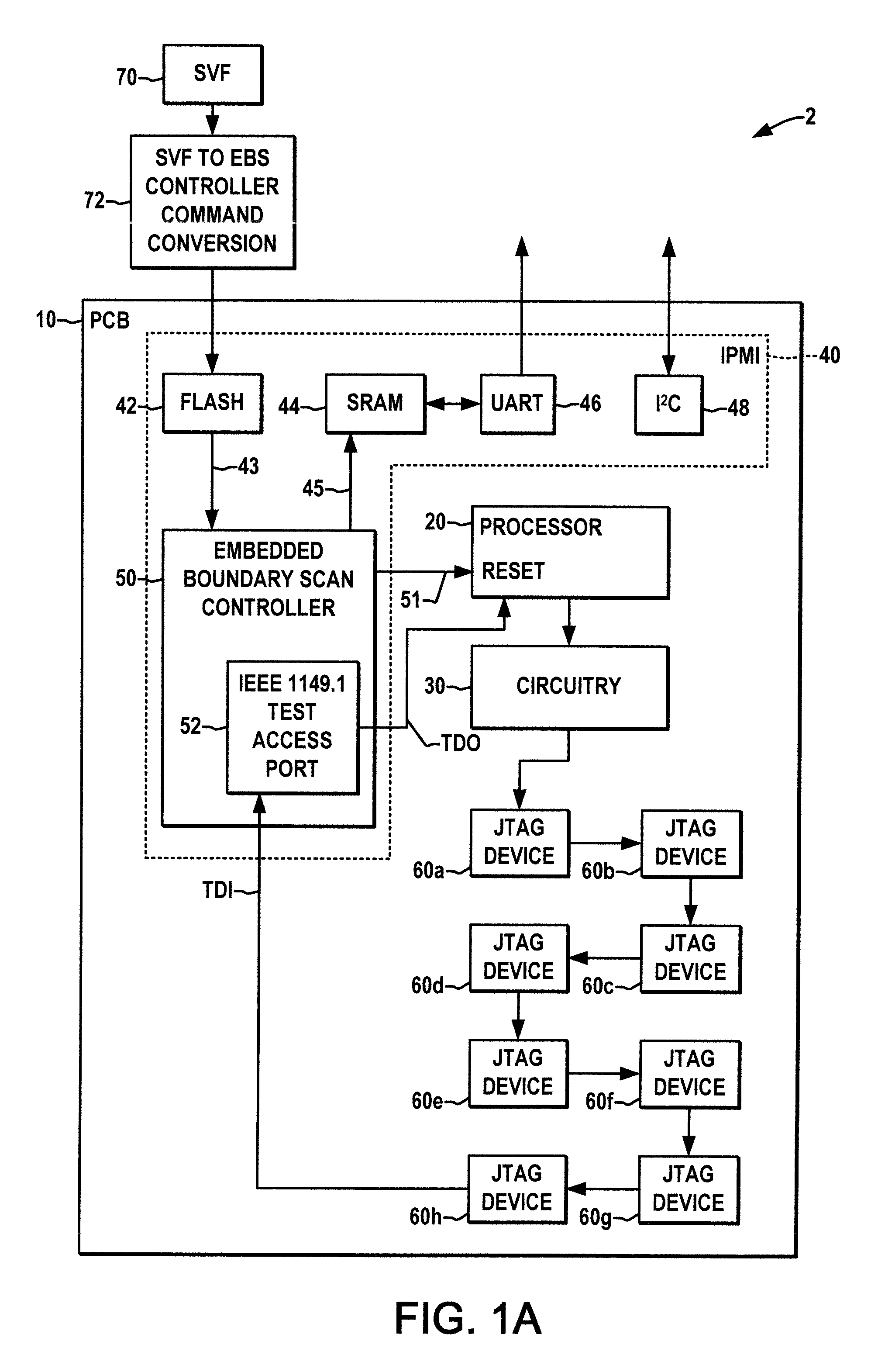

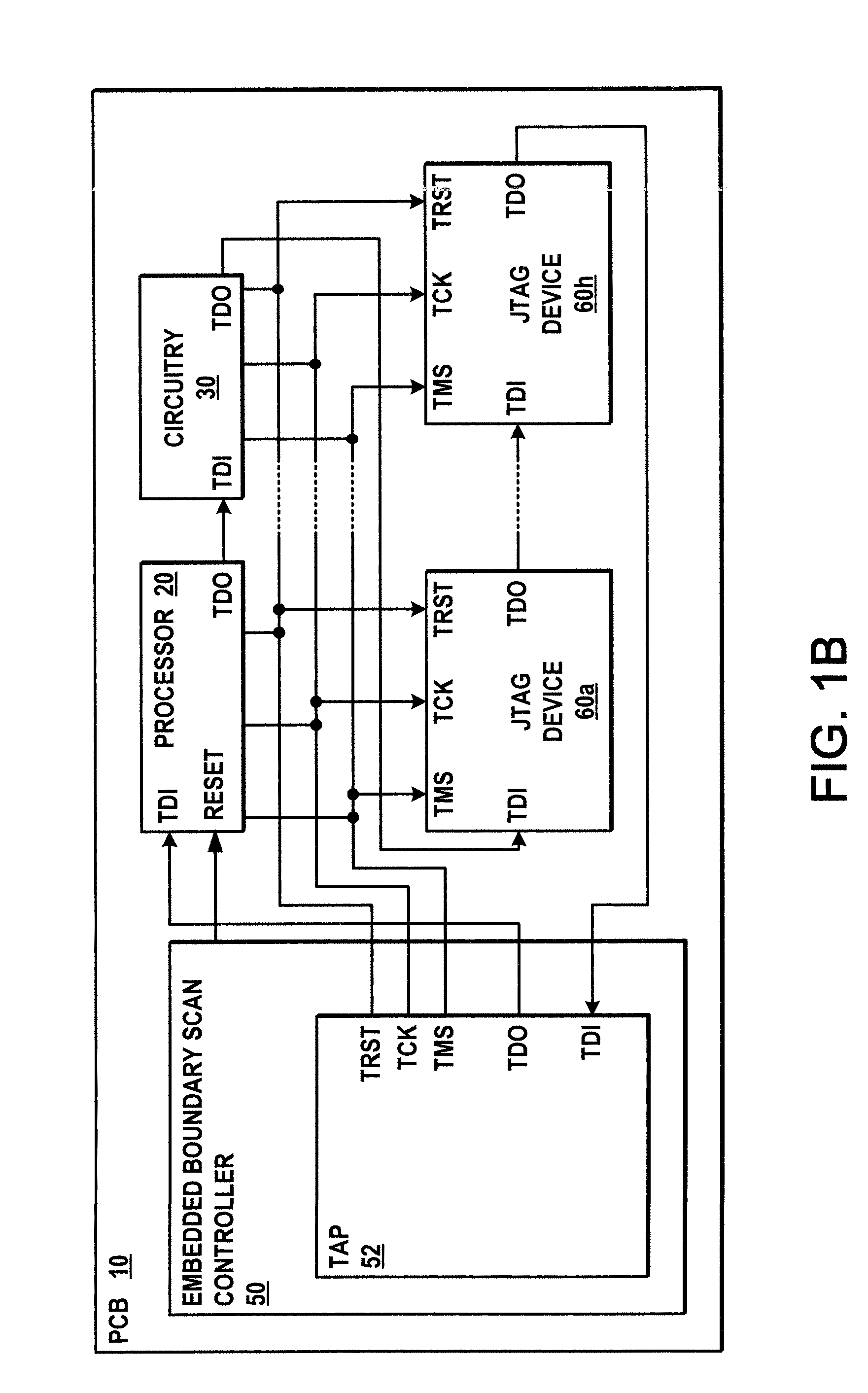

Apparatus and method for embedded boundary scan testing

ActiveUS20090006915A1Small sizeElectronic circuit testingLogical operation testingOn boardJoint Test Action Group

Embedded boundary scan testing apparatus and methodologies are disclosed for testing processor-based circuit boards without processor intervention. A boundary scan controller is embedded in a circuit board along with a boundary scan chain having JTAG devices connected with an electrical circuit of the board. Upon power up, the boundary scan controller holds an on-board processor system in reset, loads boundary scan test vectors and commands from an on-board non-volatile memory, and runs boundary scan testing while holding the processor system in the reset state. The boundary scan controller preferably includes a test access port controller that implements only a subset of the JTAG standard 16 machine states to optimize performance and minimize controller hardware. The test results may be stored in an externally accessible on-board memory for subsequent retrieval in order to facilitate board troubleshooting and / or repair, where the provision of on-board boundary scan testing allows testing of boards while installed in the field, and the embedded scan controller allows field testing of on-board processor systems and related circuitry to enhance the test coverage over processor-driven boundary scan testing.

Owner:ALCATEL-LUCENT USA INC

Integrated circuit with embedded test functionality

An integrated circuit including embedded test functionality. An integrated circuit may include a plurality of processor cores each configured to execute instructions, and a test access port configured to interface circuits included within the integrated circuit with a test environment external to the integrated circuit for testing of the circuits. The test access port may include virtualization logic configured to allow a first set of instructions executing on the given processor core to control activity of the test access port for testing of the circuits. In one embodiment, the circuits may be accessible for testing via a plurality of scan chains, wherein the scan chains and the test access port are compliant with a version of Joint Test Access Group (JTAG) standard IEEE 1149, and wherein the test access port includes a Test Data In (TDI) pin, a Test Data Out (TDO) pin, and a Test Clock (TCK) pin.

Owner:ORACLE INT CORP

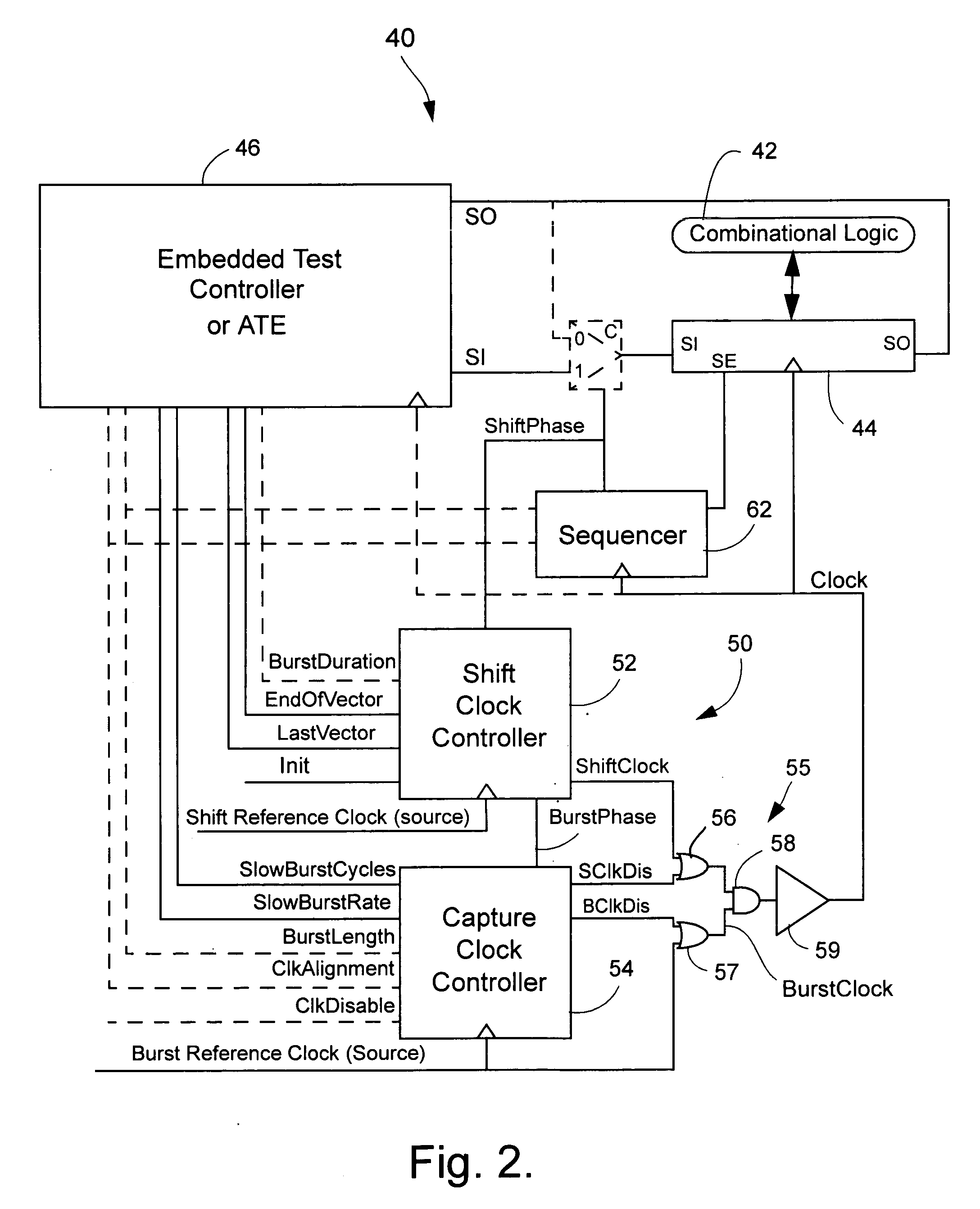

Clock controller for at-speed testing of scan circuits

A test clock controller for generating a test clock signal for scan chains in integrated circuits having one or more clock domains, comprises a shift clock controller for generating a shift clock signal for use in loading test patterns into scan chains in the clock domains and for unloading a test response patterns from the scan chains and for generating a burst phase signal after loading a test pattern; and a burst clock controller associated with each of one or more clock domains and responsive to a burst phase signal for generating a burst of clock pulses derived from a respective reference clocks and including a first group of burst clock pulses having a selected reduced frequency relative to the reference clock and a second group of burst clock pulses having a frequency corresponding to that of the reference clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com