Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

317 results about "Scan circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

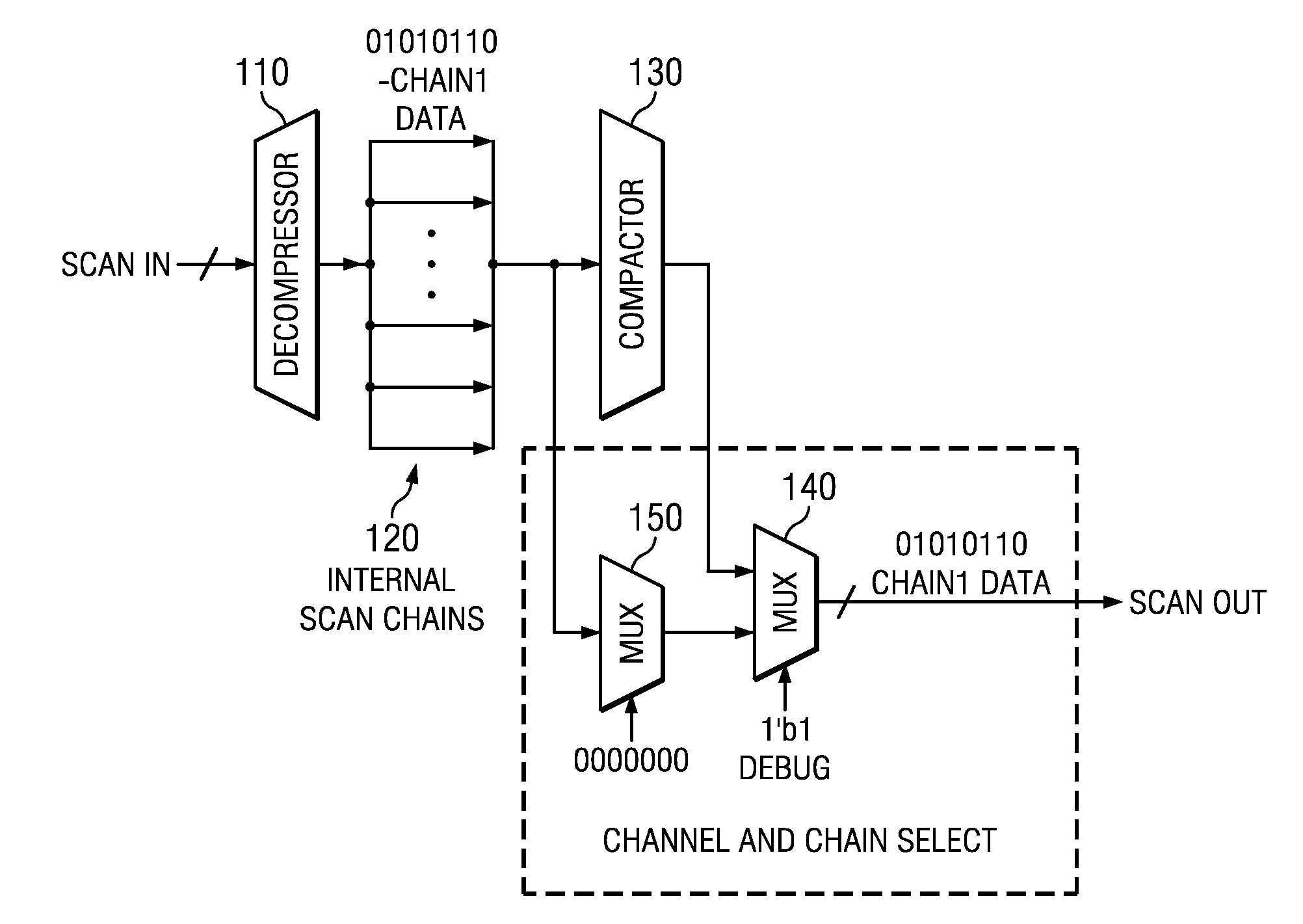

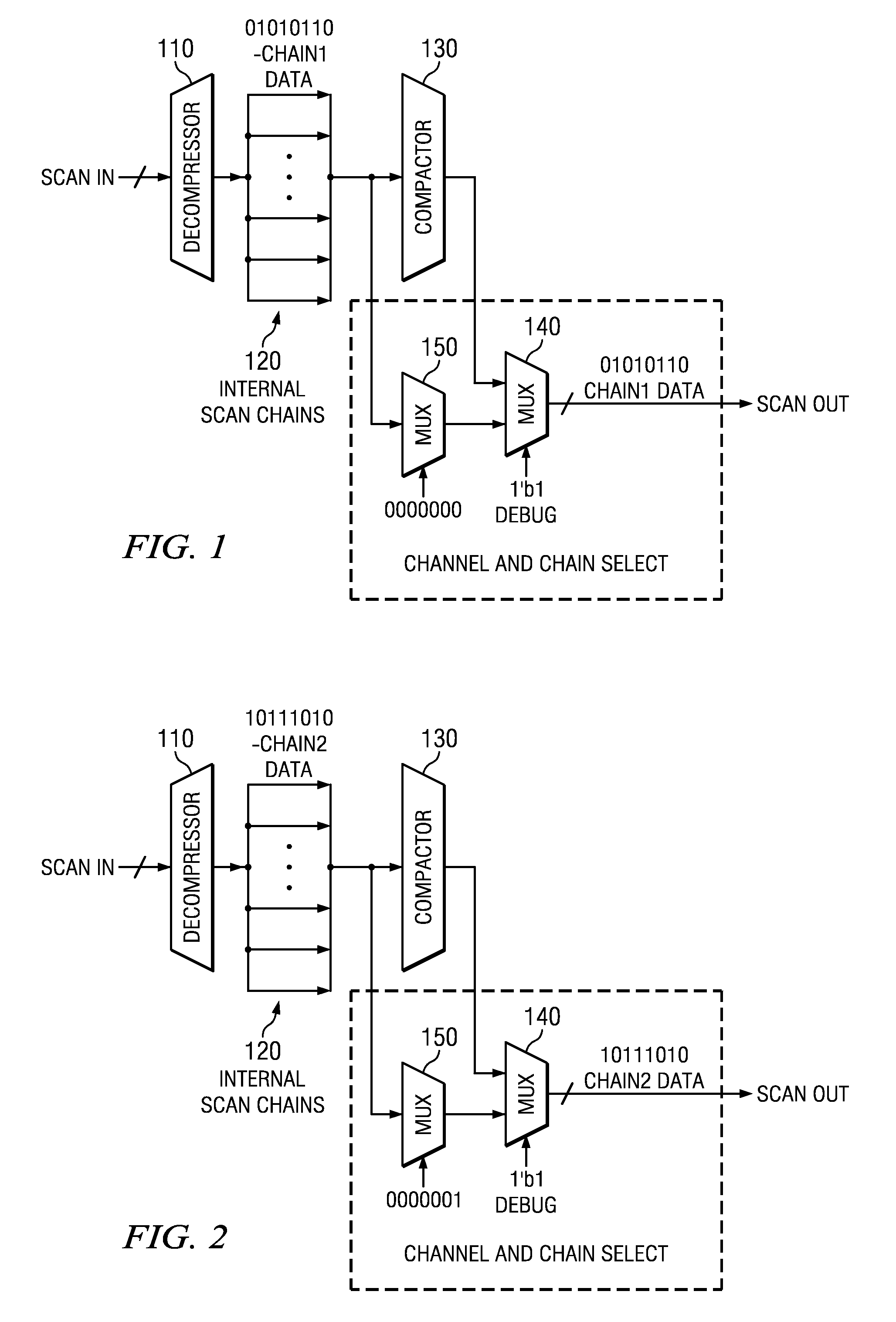

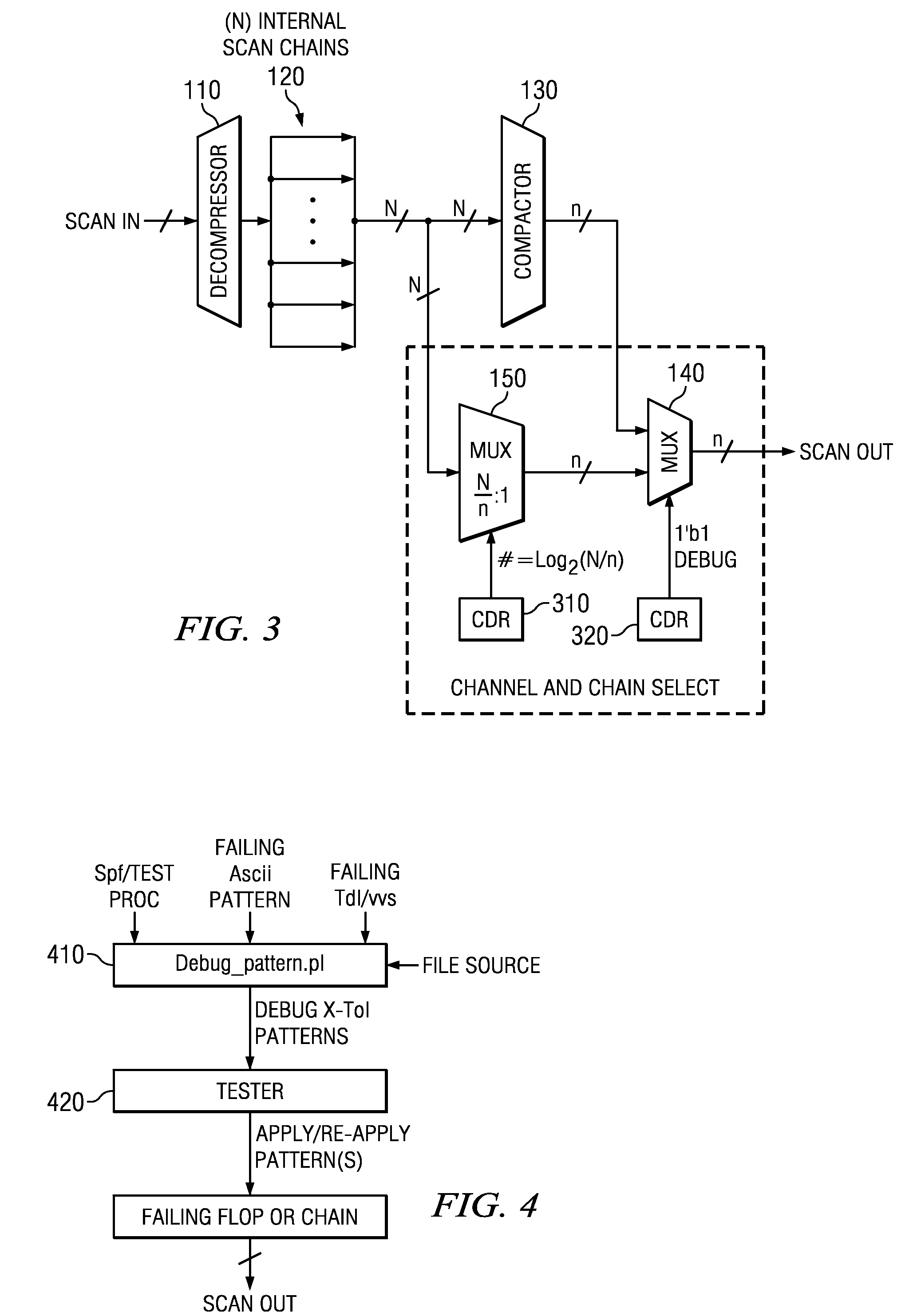

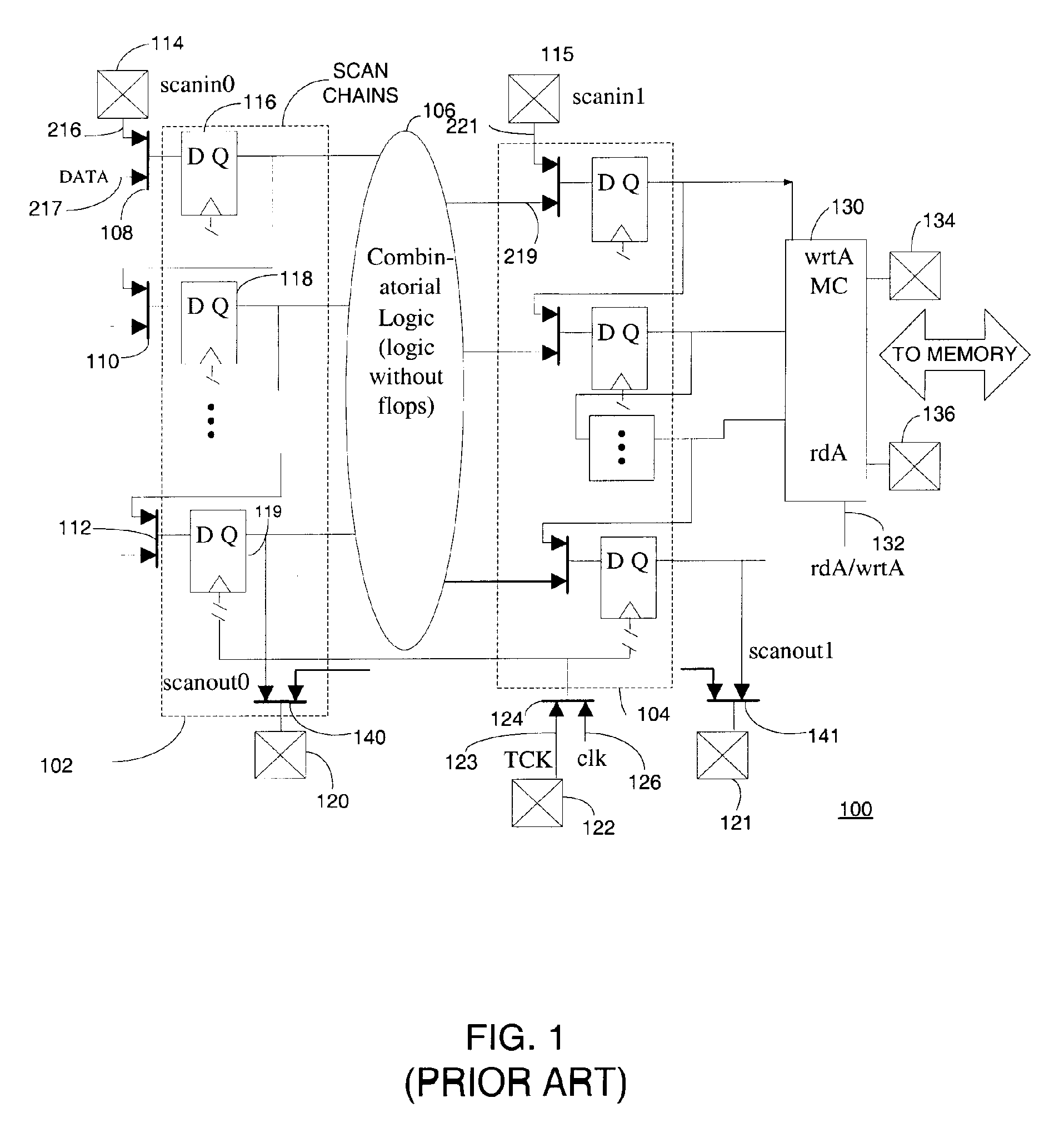

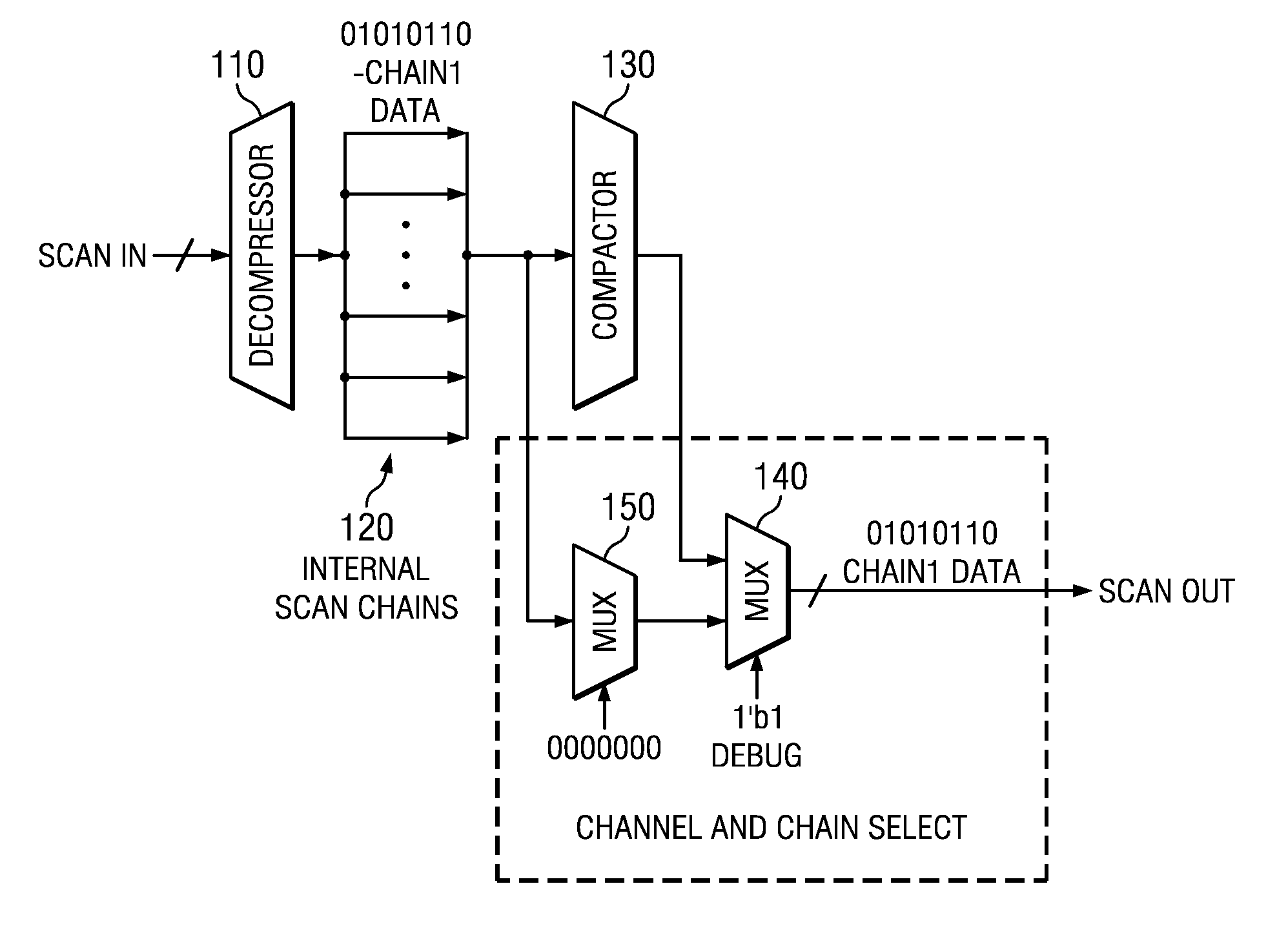

Compressed scan chain diagnosis by internal chain observation, processes, circuits, devices and systems

ActiveUS20110307750A1Electronic circuit testingRedundant hardware error correctionScan circuitsEngineering

Owner:TEXAS INSTR INC

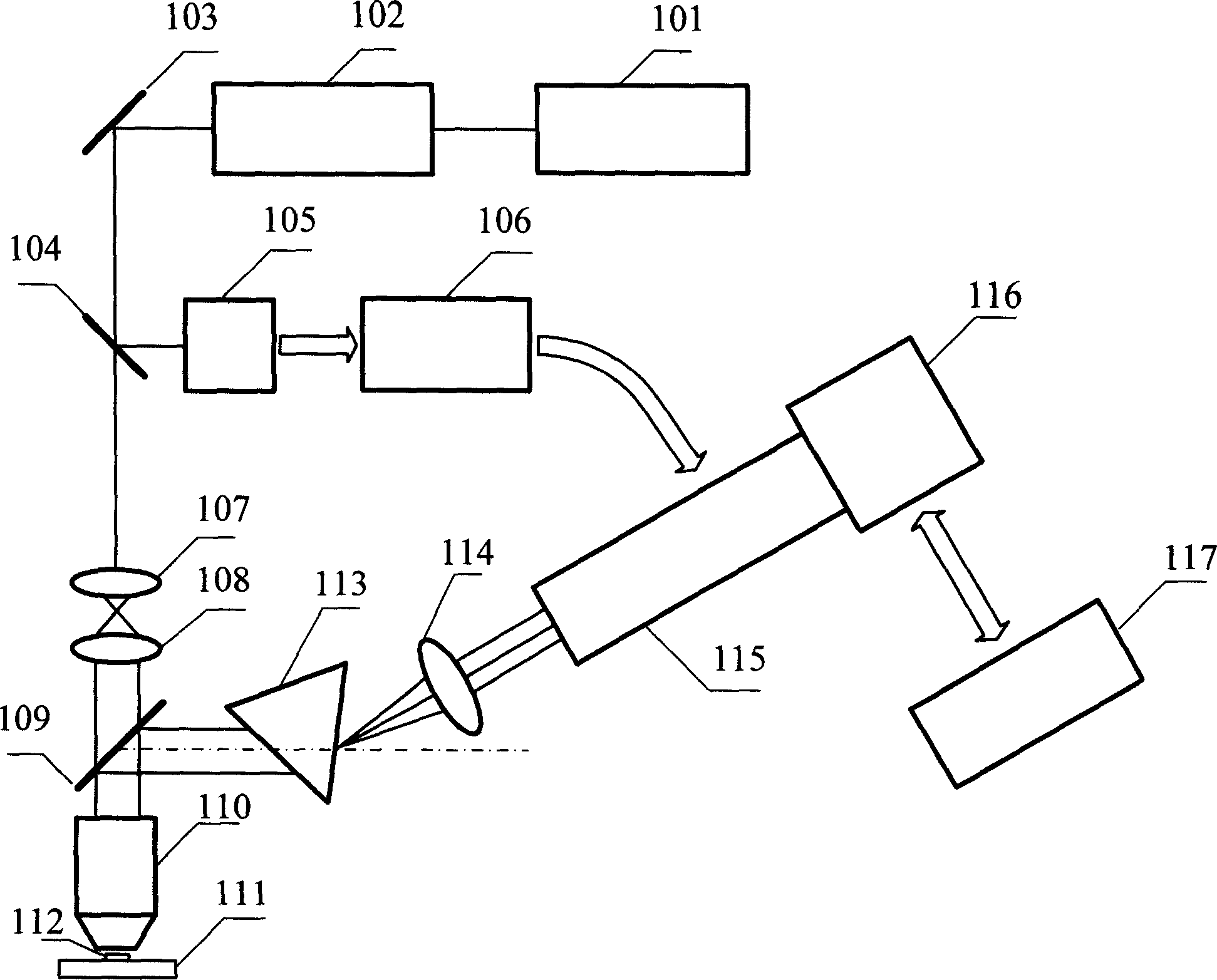

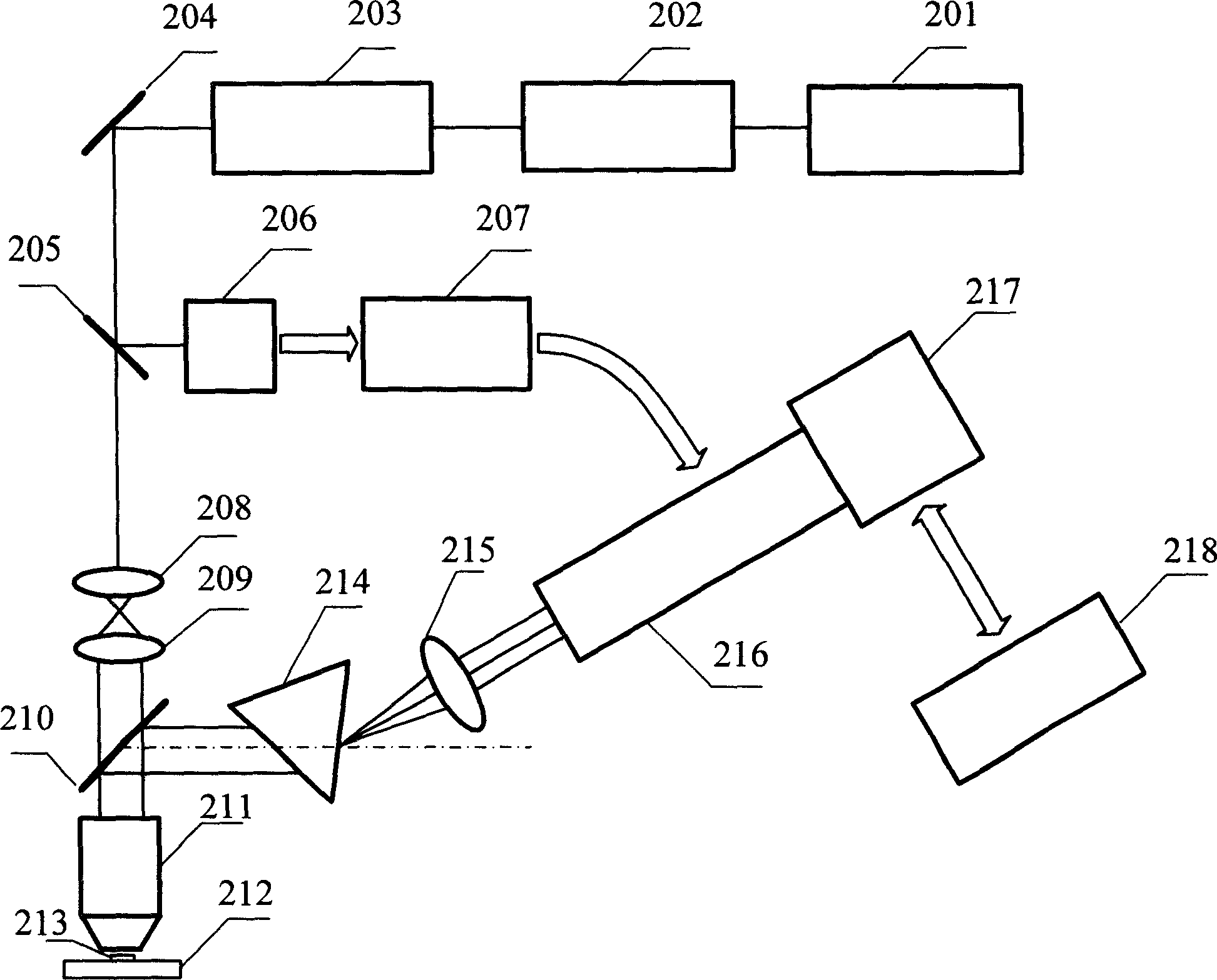

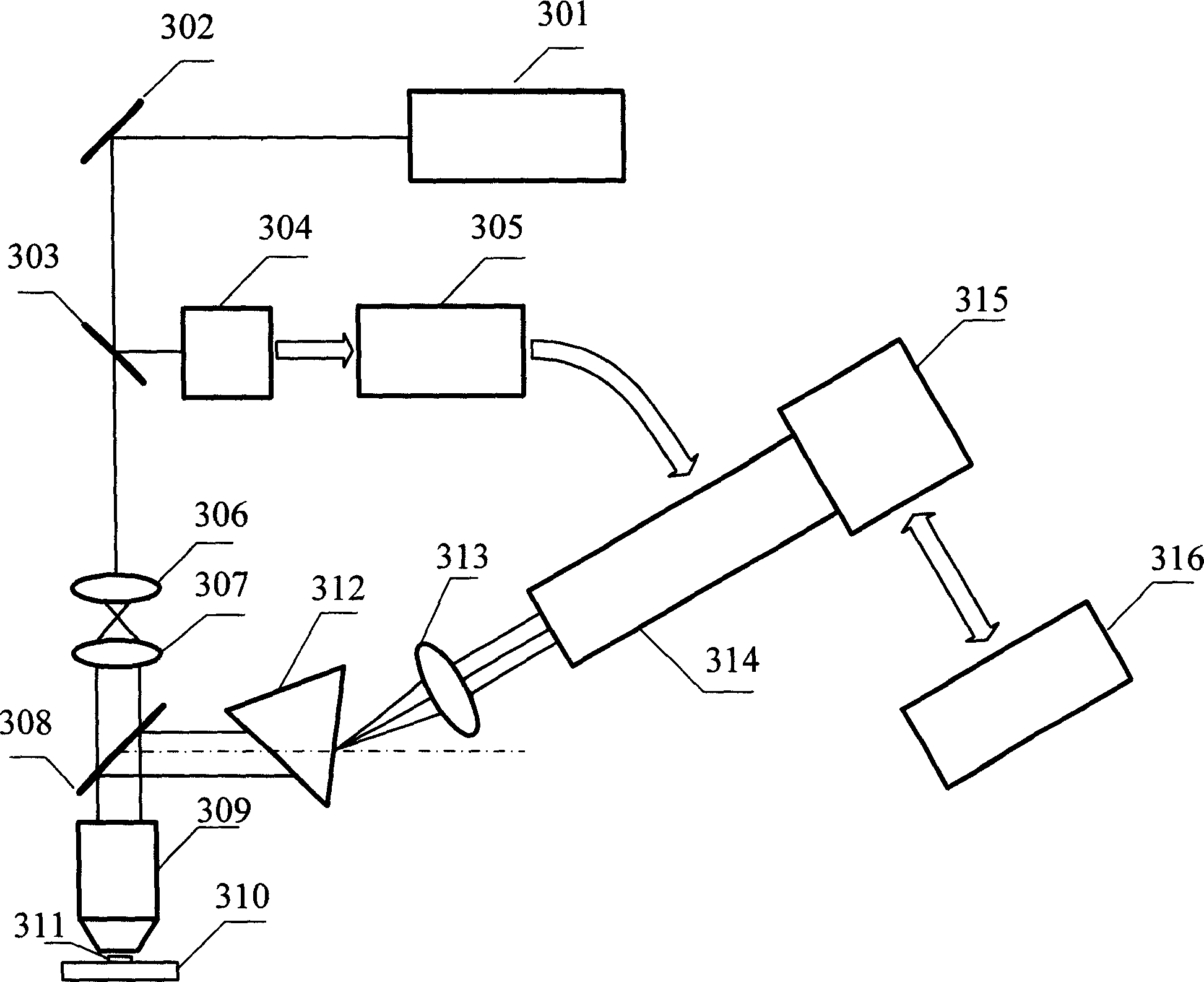

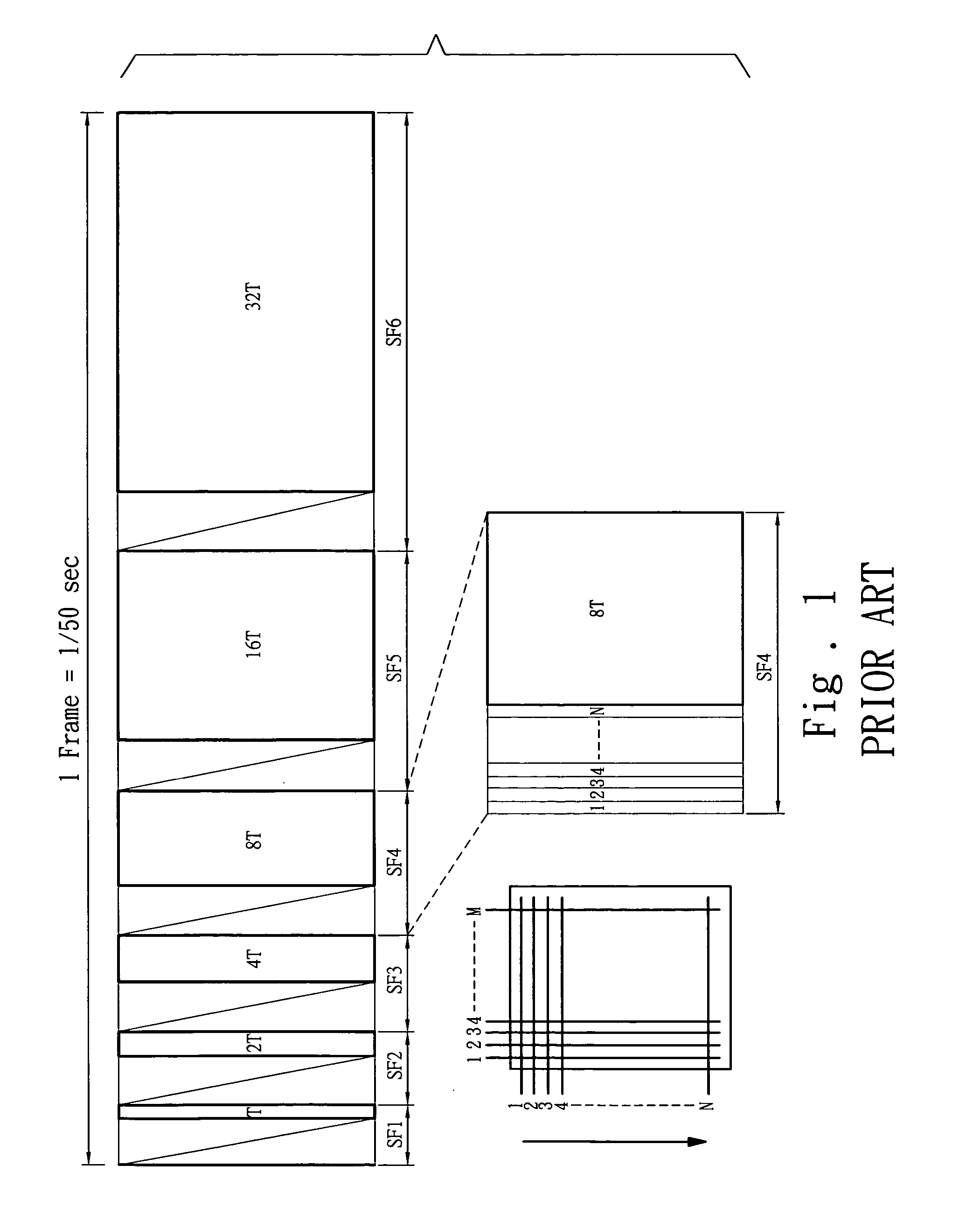

Time resolution fluorescence spectral measuring and image forming method and its device

InactiveCN1912587ADifferent temporal resolutionsAchieving high-sensitivity detectionFluorescence/phosphorescencePhotocathodePicosecond

A method of using picosecond scan camera to simultaneously obtain fluorescent light spectrum and fluorescent lifetime of sample includes focusing blue violet light emitted by laser on sample by objective to excite sample single photon, collecting fluorescent from sample then splitting it and focusing it to be image on photoelectric cathode of picosecond scan camera, setting dispersion direction of fluorescent to be the same as slit direction of said camera but to be vertical to scan direction in order to measure out fluorescent lifetime of different light spectrum simultaneously under coaction of scan circuit and image intensifier deflection system.

Owner:SHENZHEN UNIV

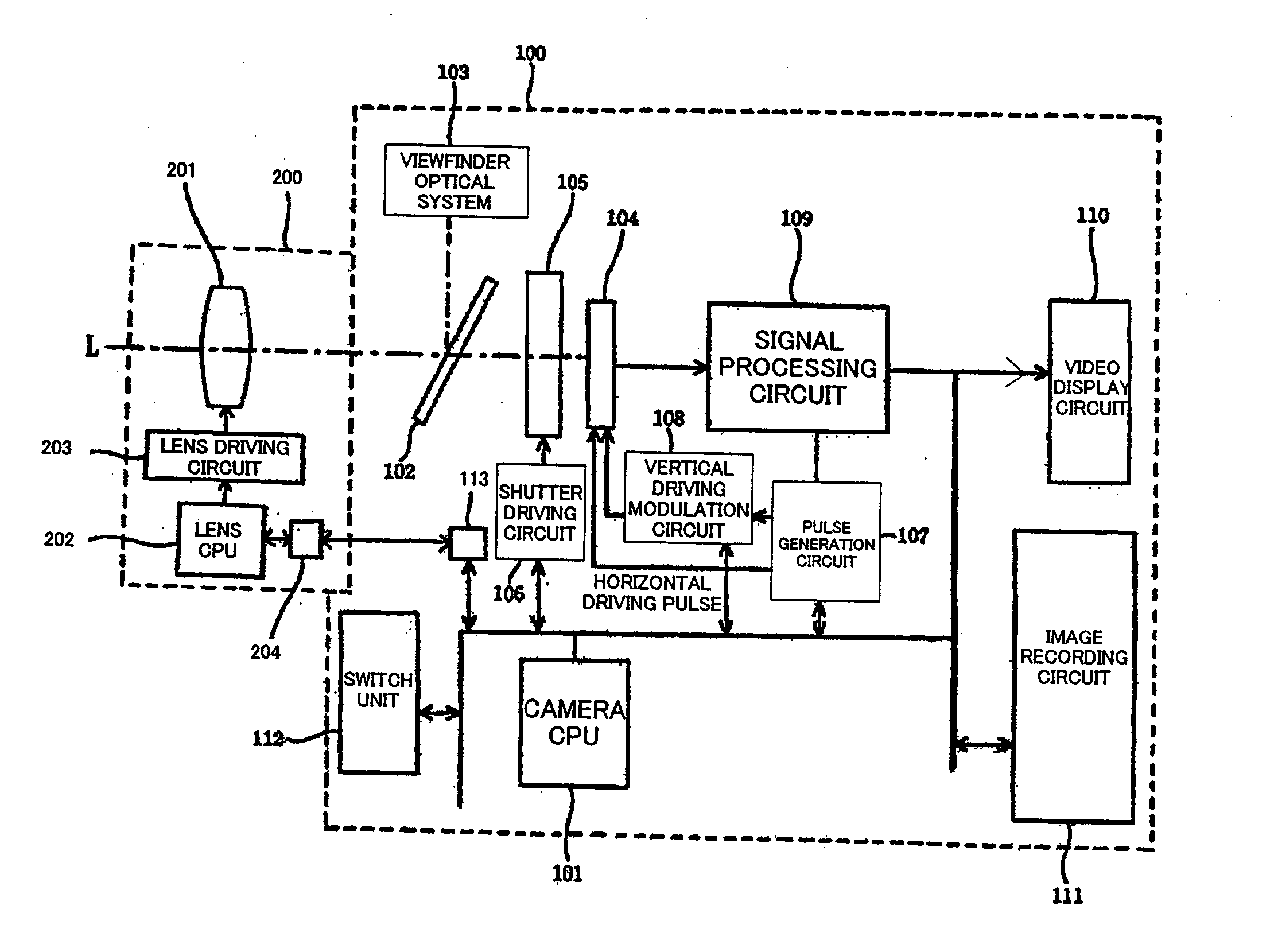

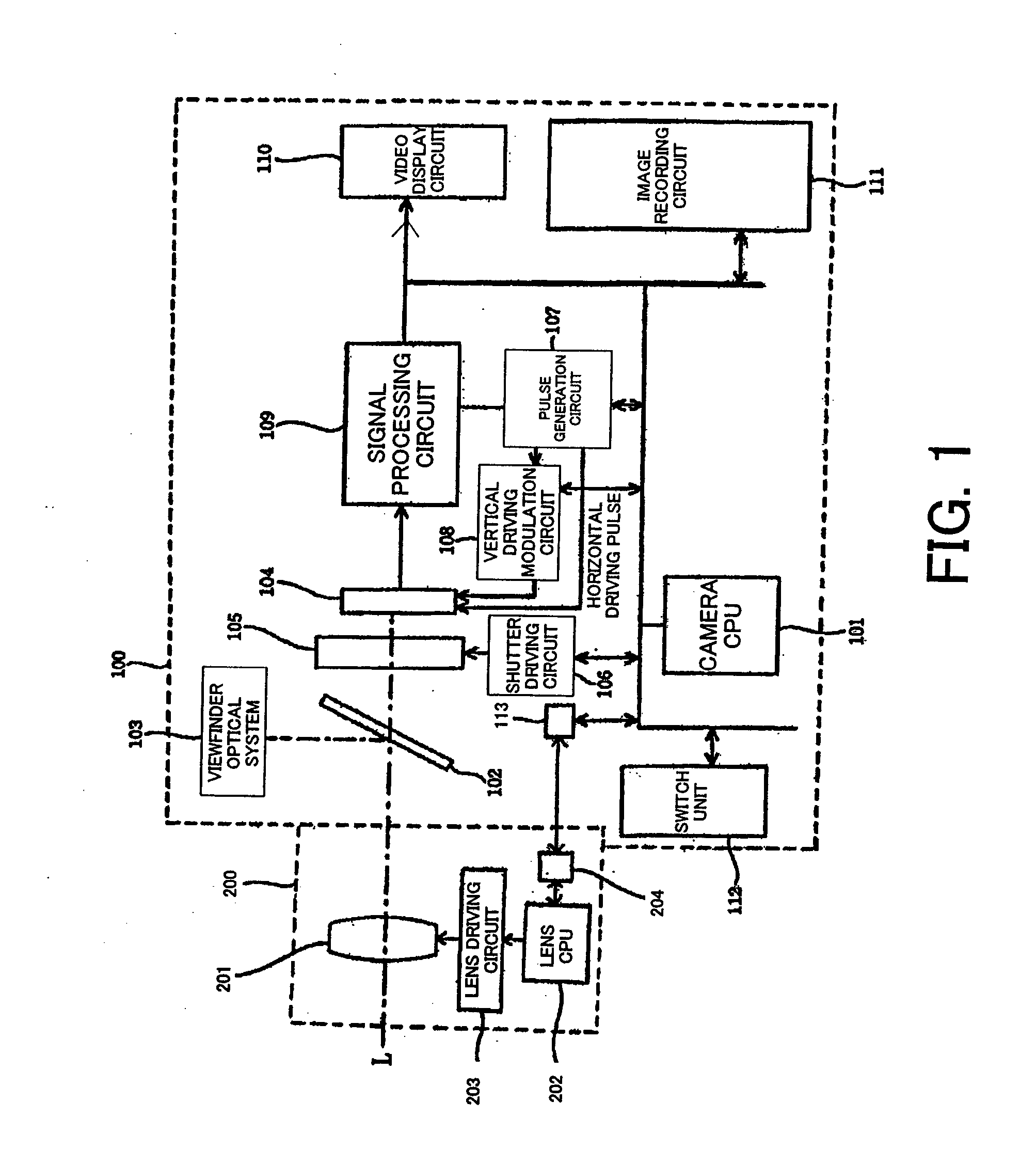

Image-taking apparatus and control method of image-taking apparatus

ActiveUS20060087573A1Easy to chargeTelevision system detailsTelevision system scanning detailsScan circuitsMethod of images

The present invention provides an image-taking apparatus having an image-pickup device which accumulates charge in accordance with an amount of light received thereon, a light-shielding device which changes a light-shielded area in the image-pickup device by causing a light-shielding blade to travel, the light-shielding blade shielding a light-receiving surface of the image-pickup device, a scan circuit which performs first scan for staring accumulation of charge for each area of the image-pickup device and performs second scan for reading the accumulated charge for each area of the image-pickup device, and a control circuit which calculates a travel characteristic of the light-shielding device based on an amount of first charge accumulated in a time period between one of the first and second scans and the travel of the light-shielding device.

Owner:CANON KK

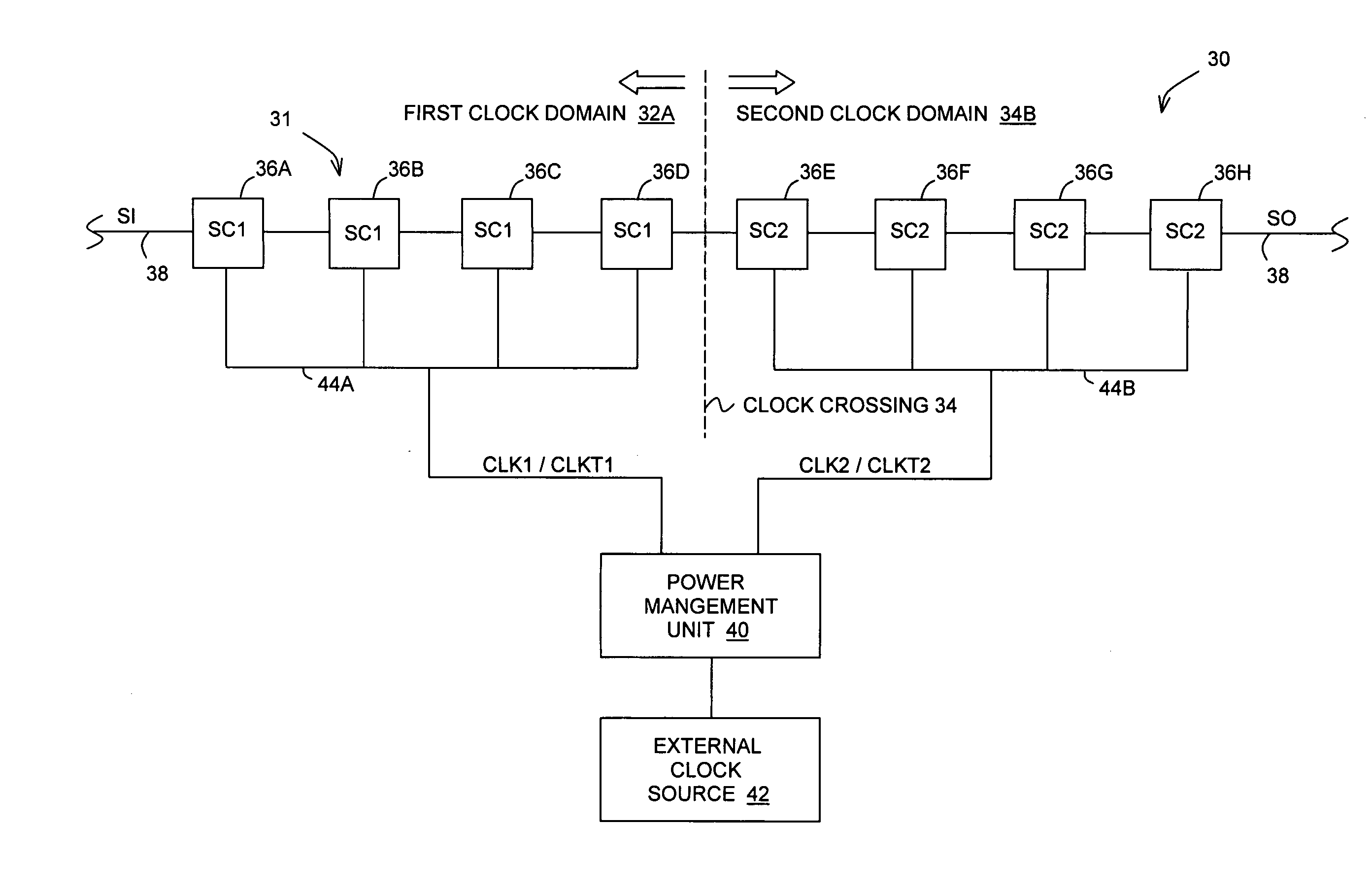

Scan-based state save and restore method and system for inactive state power reduction

A scan-based state save and restore method and system for inactive state power reduction. An integrated circuit that has an inactive state has normal circuitry and scan circuitry. Upon receipt of a sleep signal, the state of the normal circuitry is accessed by employing scan circuitry. The state is then stored in a memory. The power is disconnected from the normal circuitry. Upon wake-up, the normal circuitry is re-connected to the power. The state of the circuit is accessed from the memory and restored to the normal circuitry by employing scan circuitry.

Owner:AVENPORE PROPERTIES LLC

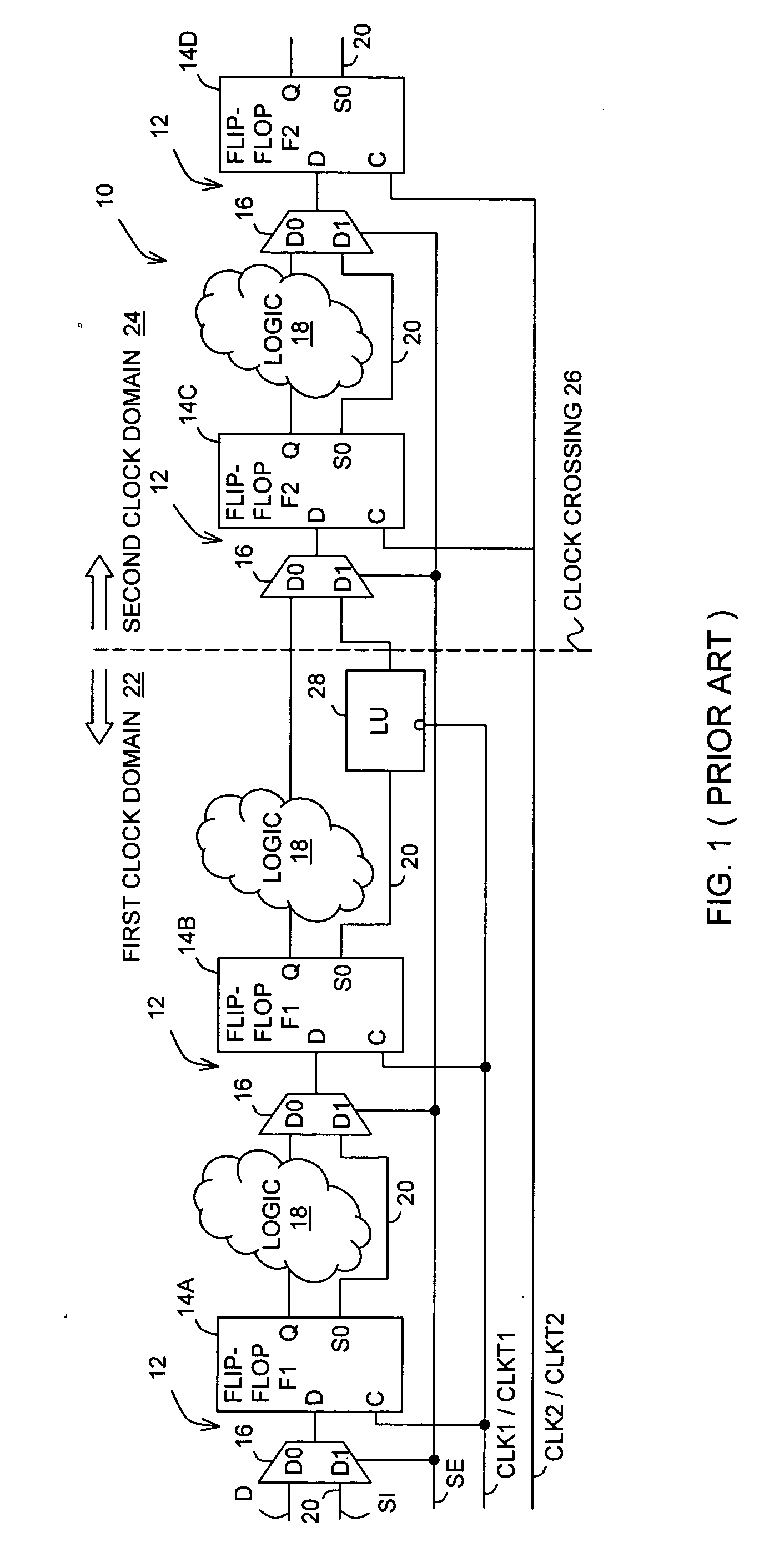

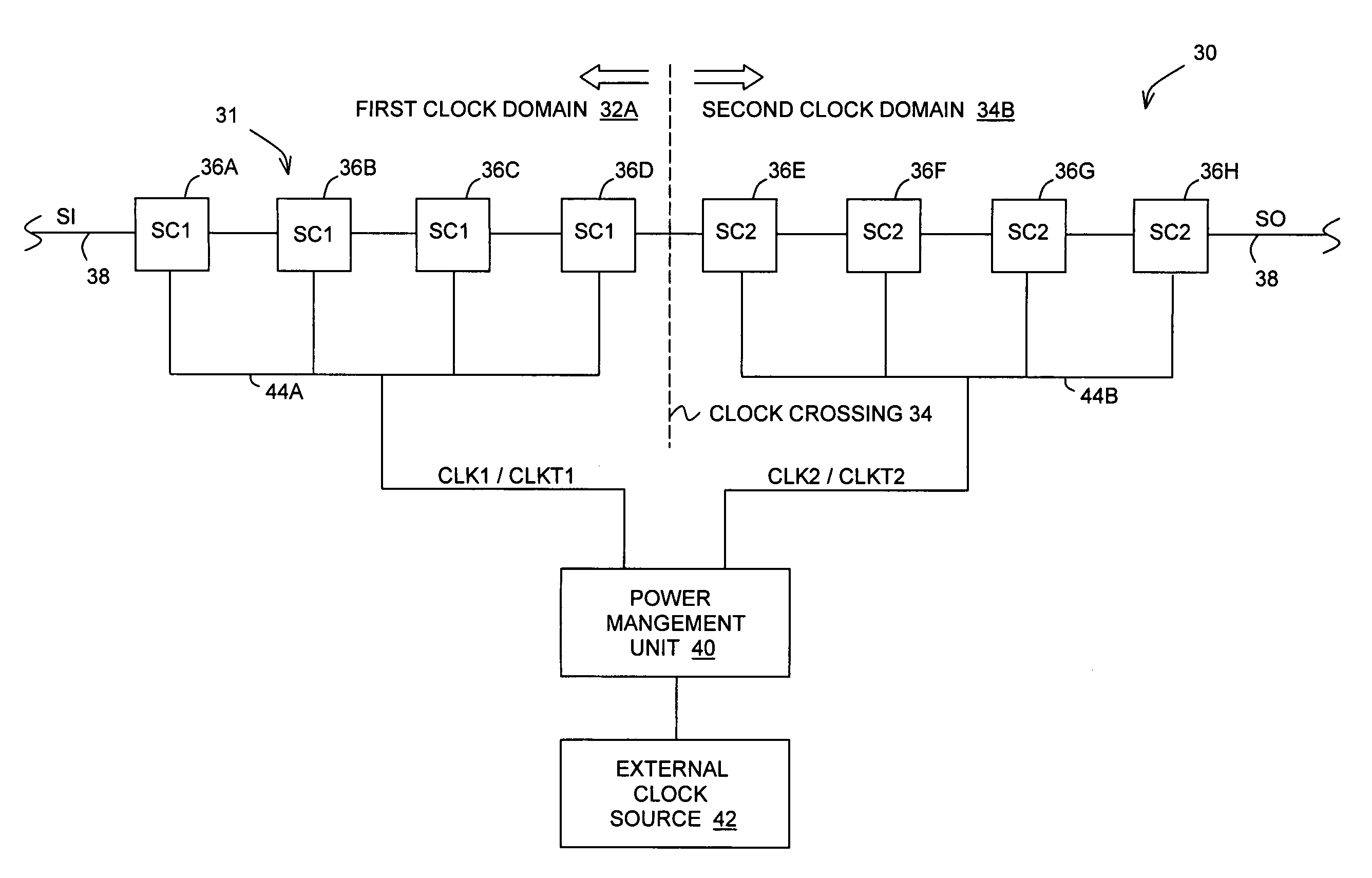

Inversion of scan clock for scan cells

In one embodiment, an apparatus comprises a scan circuit including at least a first and a second clock domain and a scan chain having a first plurality of scan cells positioned in the first clock domain and a second plurality of scan cells positioned in the second clock domain. A scan clock source, coupled to the scan chain, generates a first scan clock signal to the first plurality of scan cells and a second scan clock signal to the second plurality of scan cells. The first and the second clock signals have an inverted relationship.

Owner:MARVELL ASIA PTE LTD

Method and apparatus for providing context switching of logic in an integrated circuit

InactiveUS20070101108A1Digital computer detailsSpecific program execution arrangementsScan circuitsControl logic

A method and apparatus provides context switching of logic in an integrated circuit using one or more test scan circuits that use test data during a test mode of operation of the integrated circuit to store and / or restore non-test data during normal operation of the integrated circuit. The integrated circuit includes context control logic operative to control the test scan circuit to at least one of: store and restore context state information contained in functional storage elements in response to detection of a request for a change in context during normal operation of the integrated circuit.

Owner:ATI TECH INC

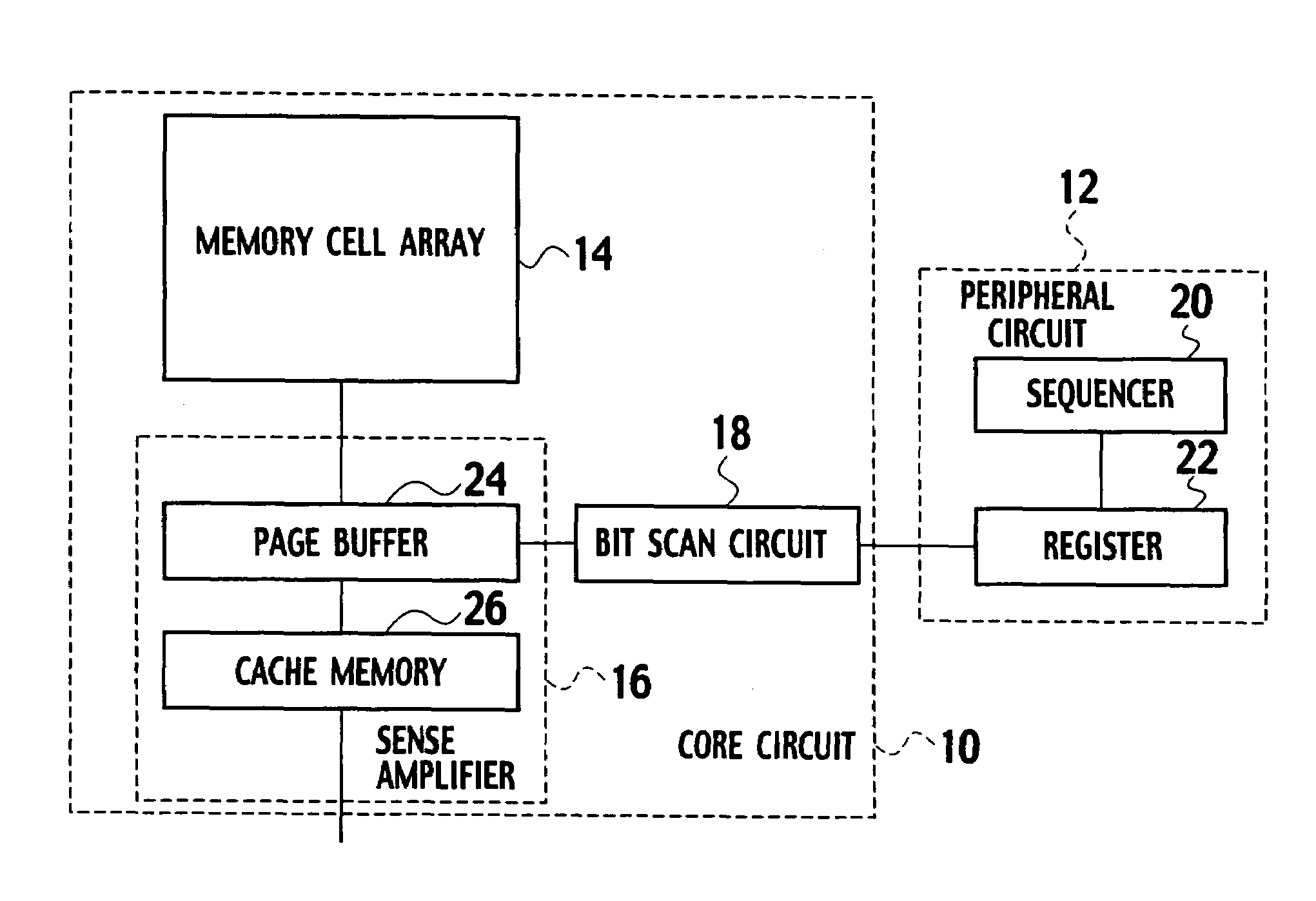

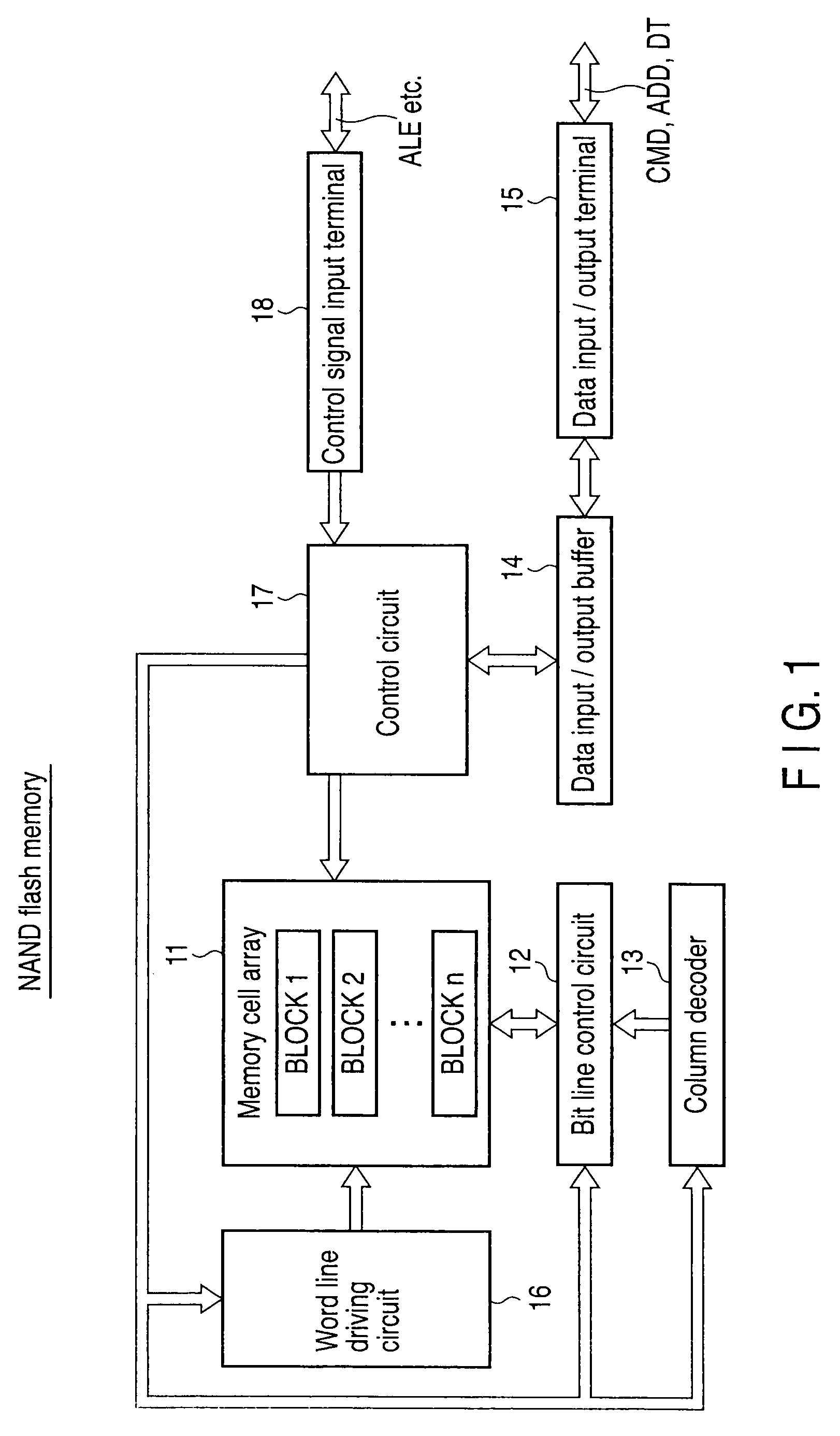

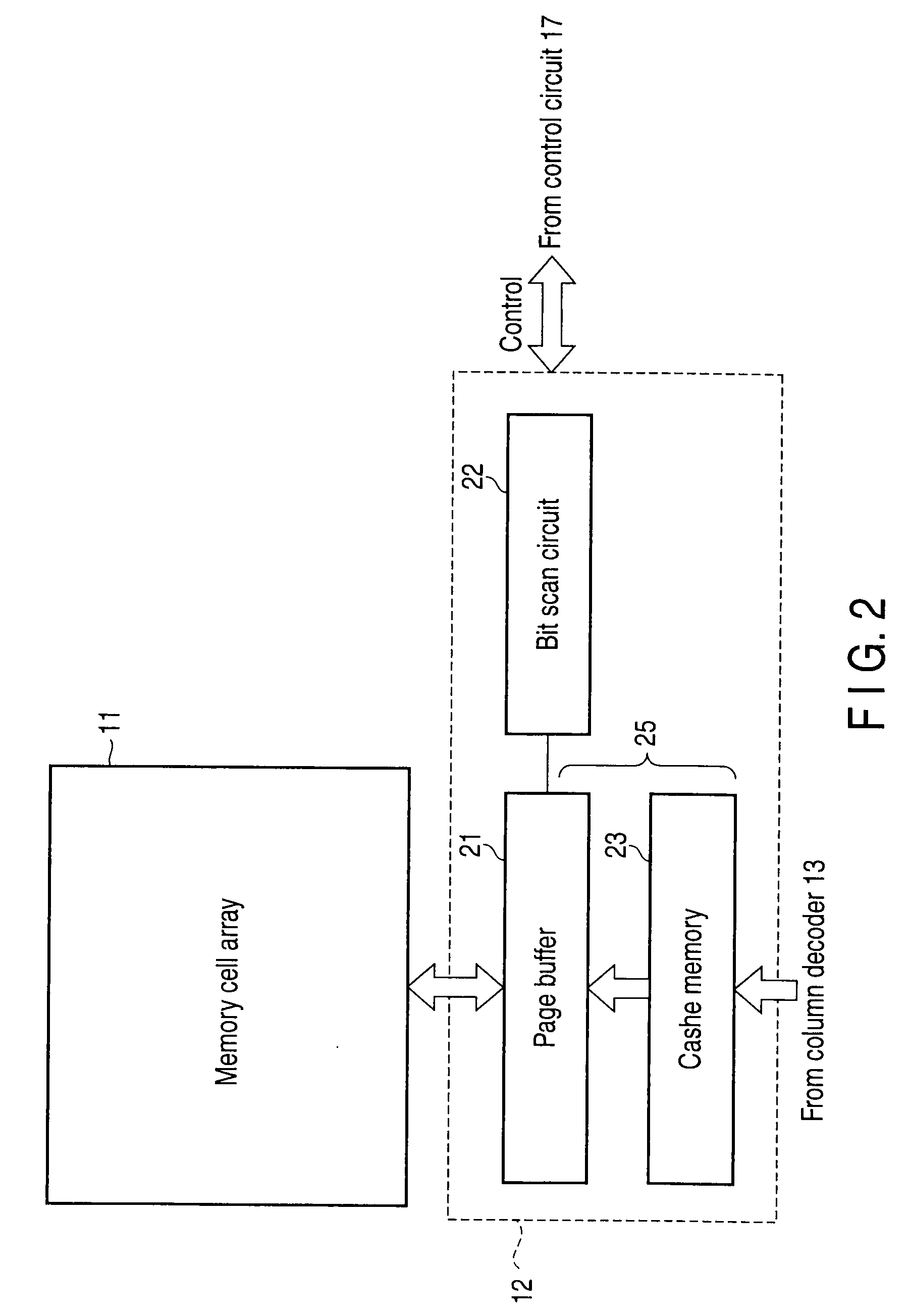

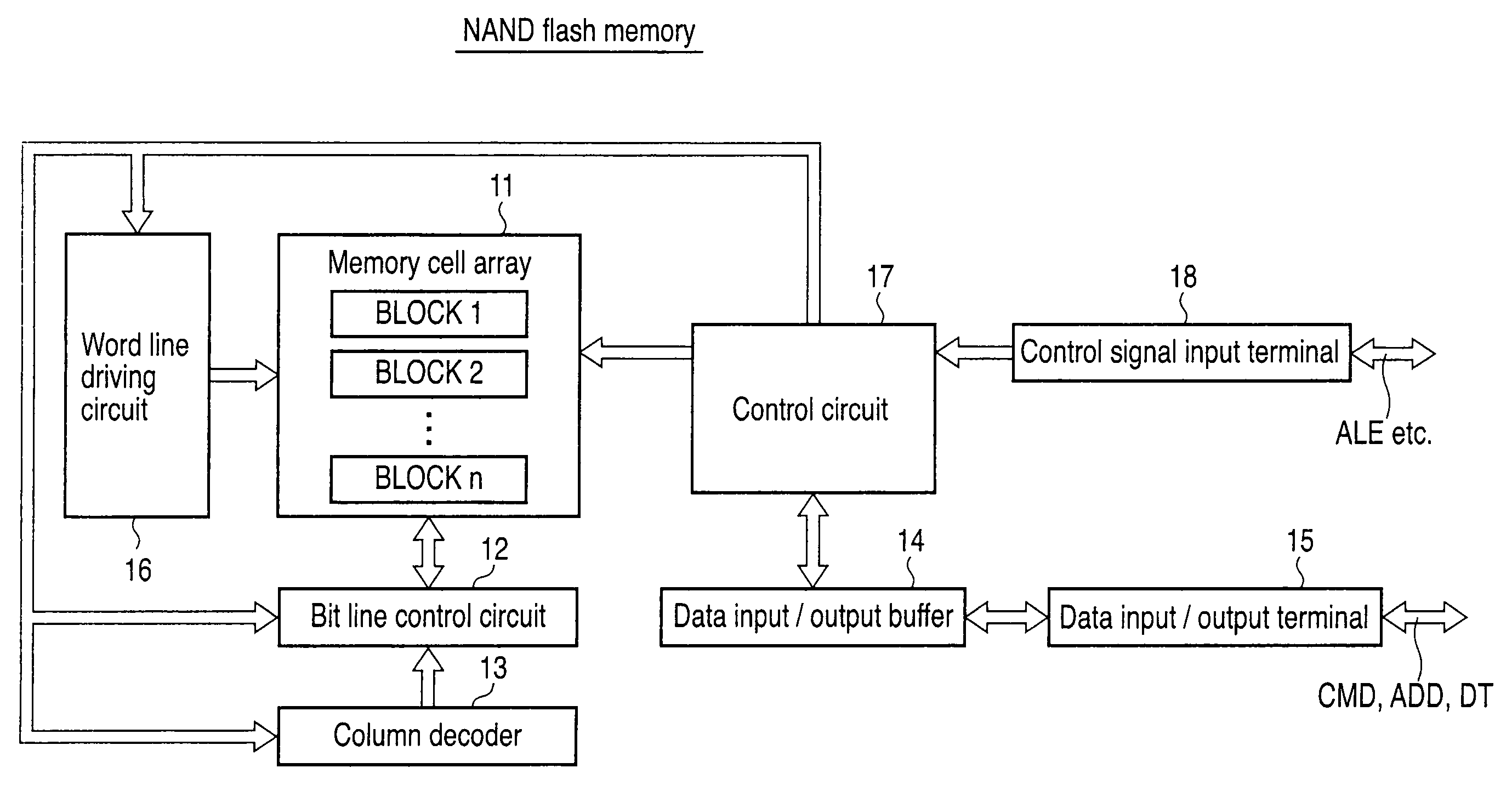

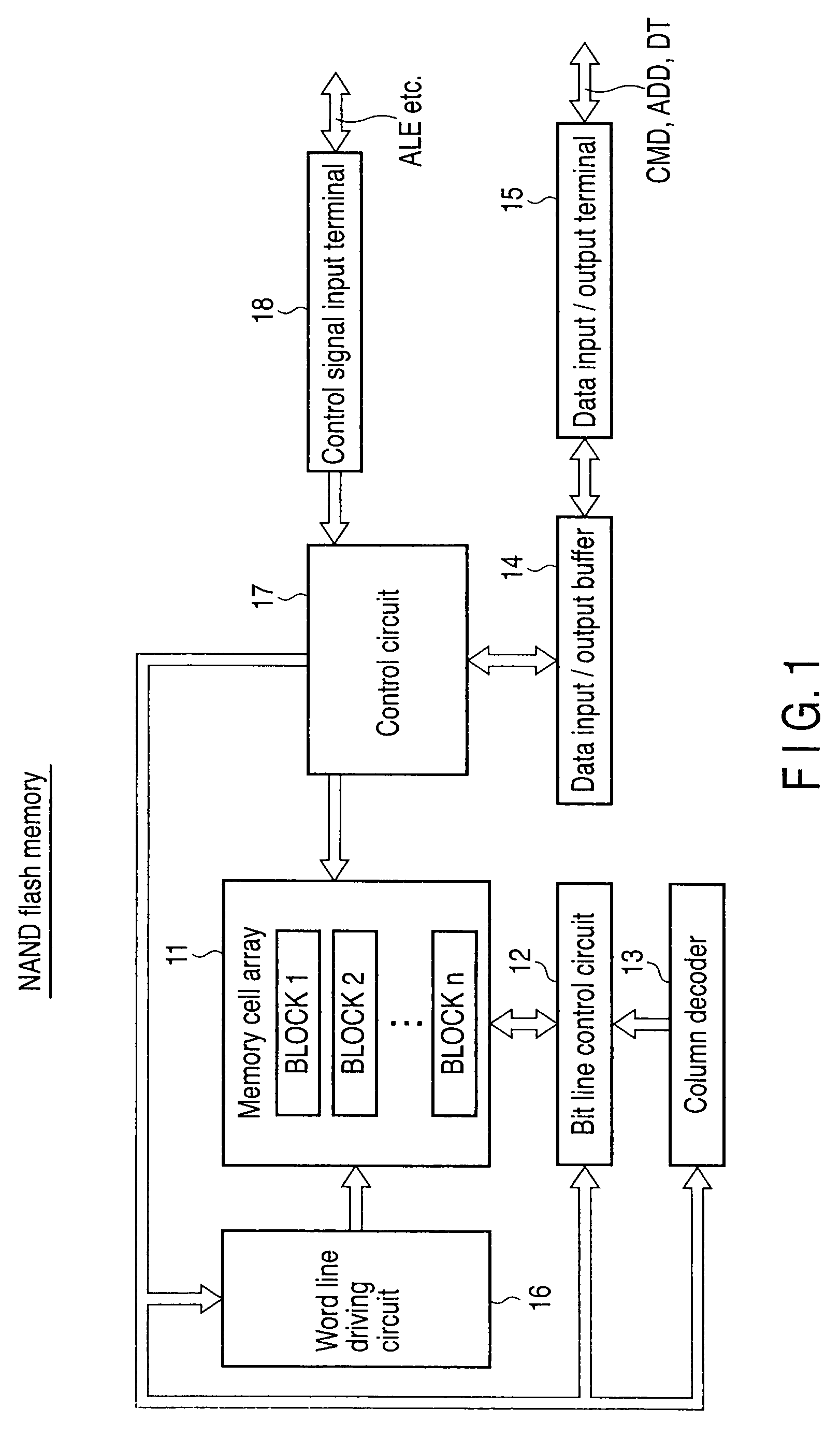

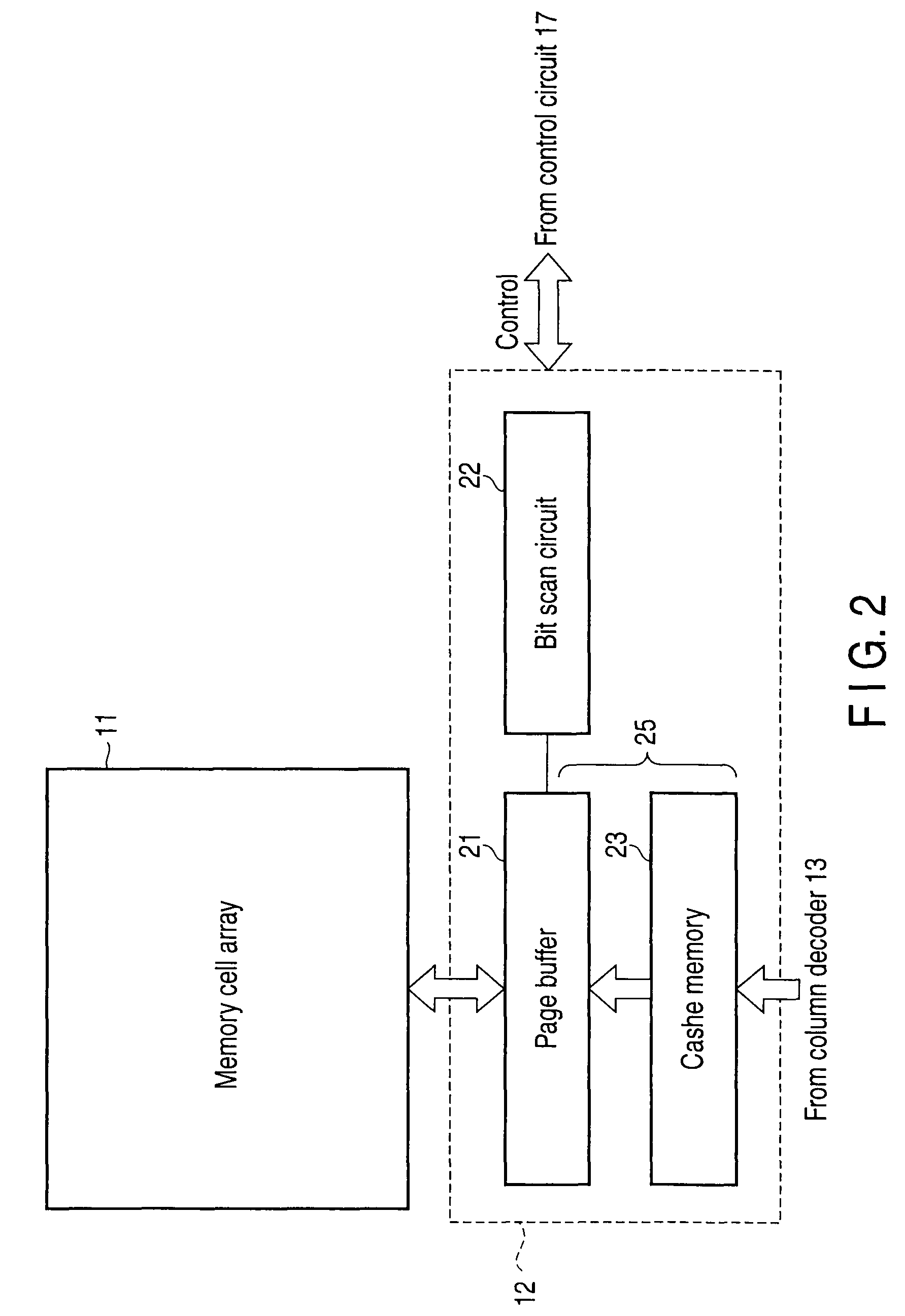

Nonvolatile semiconductor memory, a data write-in method for the nonvolatile semiconductor memory and a memory card

A nonvolatile semiconductor memory includes a memory cell array, a page buffer that is connected to the memory cell array and retains program verification results of a write-in operation of repeating data write-in and program verification, a bit scan circuit that is connected to the page buffer and determines whether or not the number of fail bits is equal to or less than number of reference bits based on the program verification results retained in the page buffer, a register that is connected to the bit scan circuit and retains determination results of the bit scan circuit, and a sequencer that controls the write-in operation and an operating sequence of the bit scan circuit and terminates the write-in operation while leaving the number of fail bits in response to the results temporarily stored in the register.

Owner:KIOXIA CORP

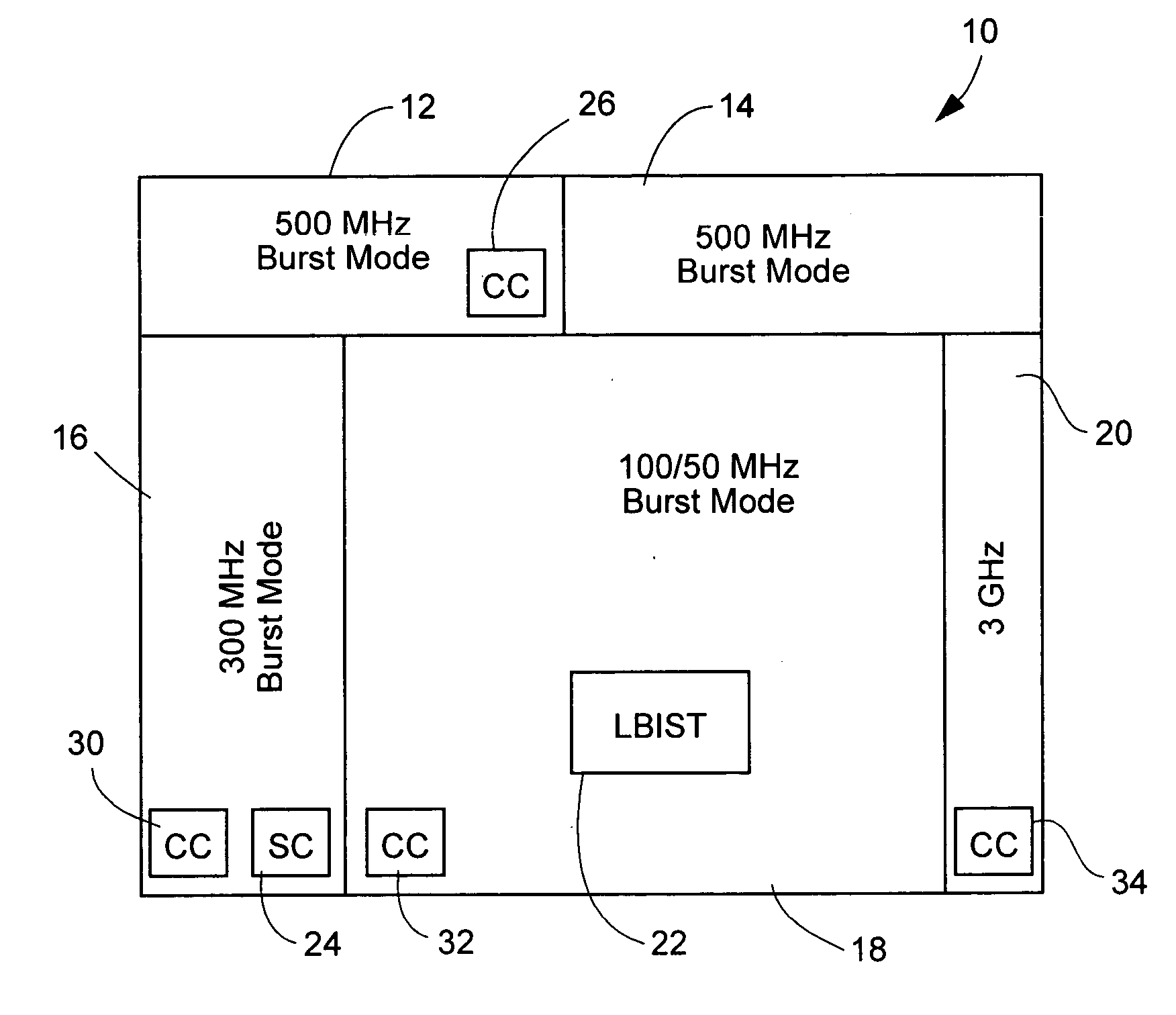

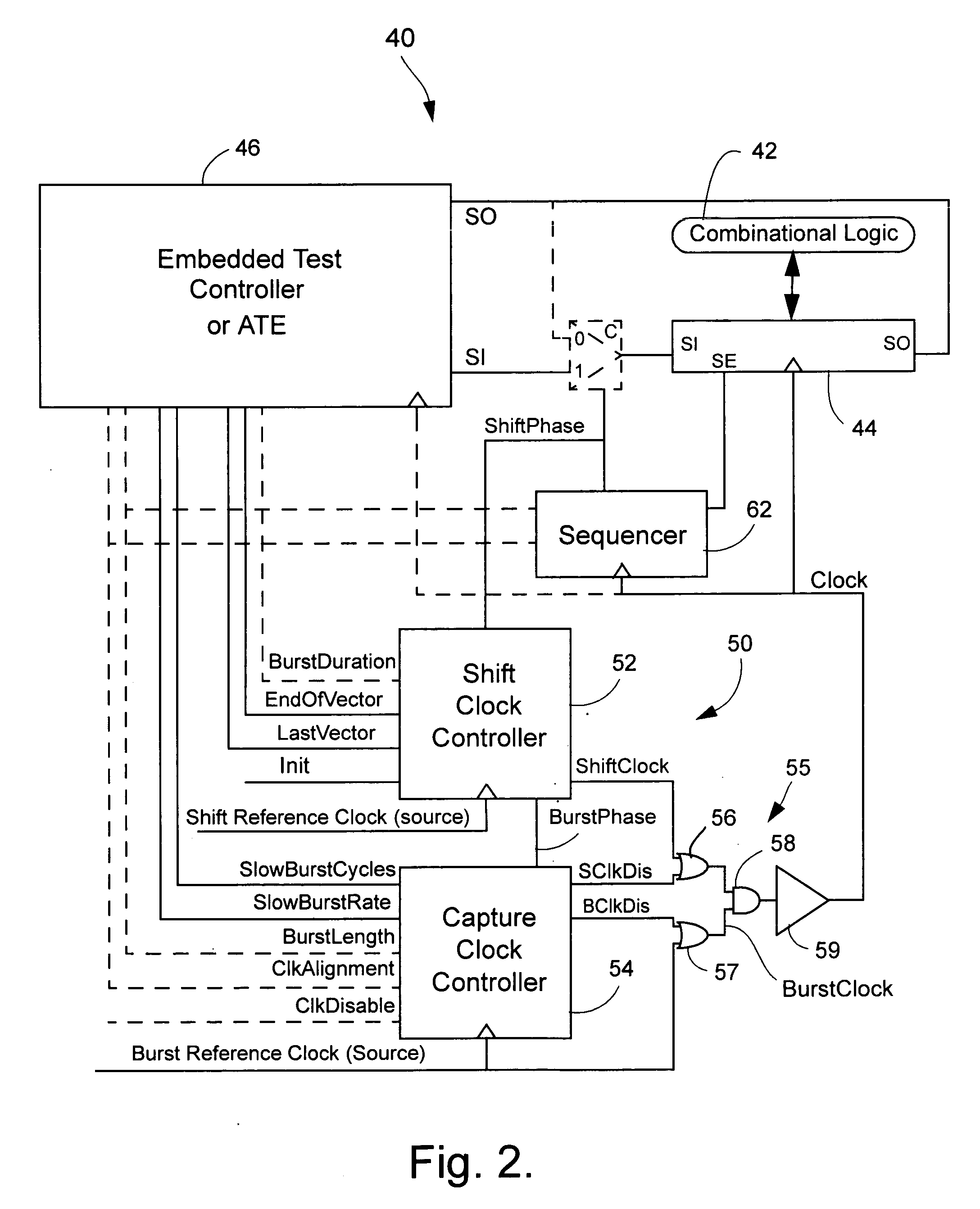

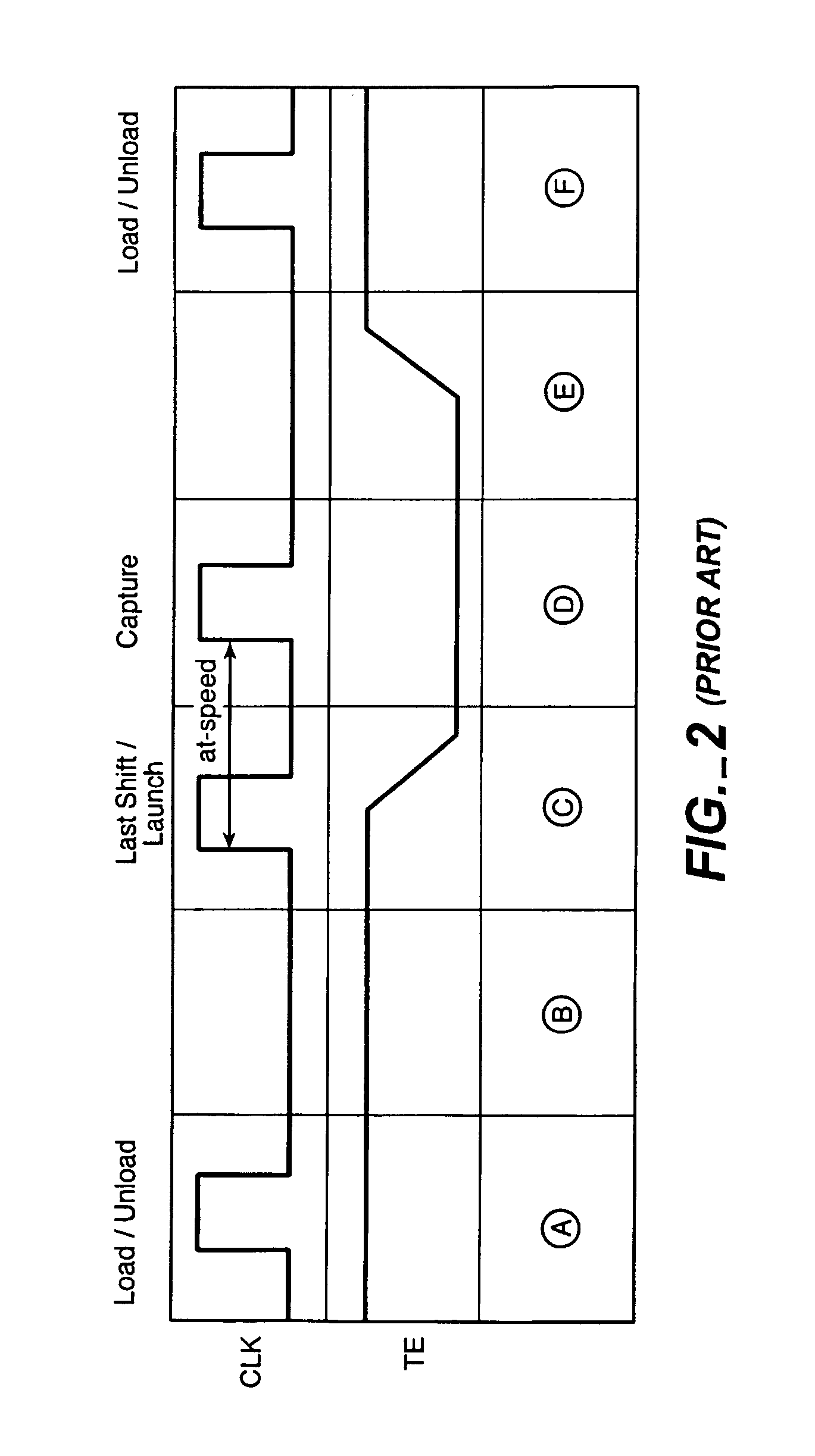

Clock controller for at-speed testing of scan circuits

A test clock controller for generating a test clock signal for scan chains in integrated circuits having one or more clock domains, comprises a shift clock controller for generating a shift clock signal for use in loading test patterns into scan chains in the clock domains and for unloading a test response patterns from the scan chains and for generating a burst phase signal after loading a test pattern; and a burst clock controller associated with each of one or more clock domains and responsive to a burst phase signal for generating a burst of clock pulses derived from a respective reference clocks and including a first group of burst clock pulses having a selected reduced frequency relative to the reference clock and a second group of burst clock pulses having a frequency corresponding to that of the reference clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Semiconductor memory device and data write method thereof

A semiconductor memory device includes a control circuit. The control circuit executes control to perform a verify operation with respect to only a lowest threshold voltage level of a memory cell at a time of a data write operation, and to skip the verify operation with respect to the other threshold voltage levels. The control circuit determines whether a verify pass bit number of the lowest threshold voltage level, which is counted by a bit scan circuit, is a prescribed bit number or more, and the control circuit further executes control, if the verify pass bit number is the prescribed bit number or more, to perform the verify operation with respect to only the lowest threshold voltage level and a threshold voltage level that is higher than the lowest threshold voltage level, and to skip the verify operation with respect to the other threshold voltage levels.

Owner:KIOXIA CORP

Clock controller for at-speed testing of scan circuits

A test clock controller for generating a test clock signal for scan chains in integrated circuits having one or more clock domains, comprises a shift clock controller for generating a shift clock signal for use in loading test patterns into scan chains in the clock domains and for unloading a test response patterns from the scan chains and for generating a burst phase signal after loading a test pattern; and a burst clock controller associated with each of one or more clock domains and responsive to a burst phase signal for generating a burst of clock pulses derived from a respective reference clocks and including a first group of burst clock pulses having a selected reduced frequency relative to the reference clock and a second group of burst clock pulses having a frequency corresponding to that of the reference clock.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Inversion of scan clock for scan cells

In one embodiment, an apparatus comprises a scan circuit including at least a first and a second clock domain and a scan chain having a first plurality of scan cells positioned in the first clock domain and a second plurality of scan cells positioned in the second clock domain. A scan clock source, coupled to the scan chain, generates a first scan clock signal to the first plurality of scan cells and a second scan clock signal to the second plurality of scan cells. The first and the second clock signals have an inverted relationship.

Owner:MARVELL ASIA PTE LTD

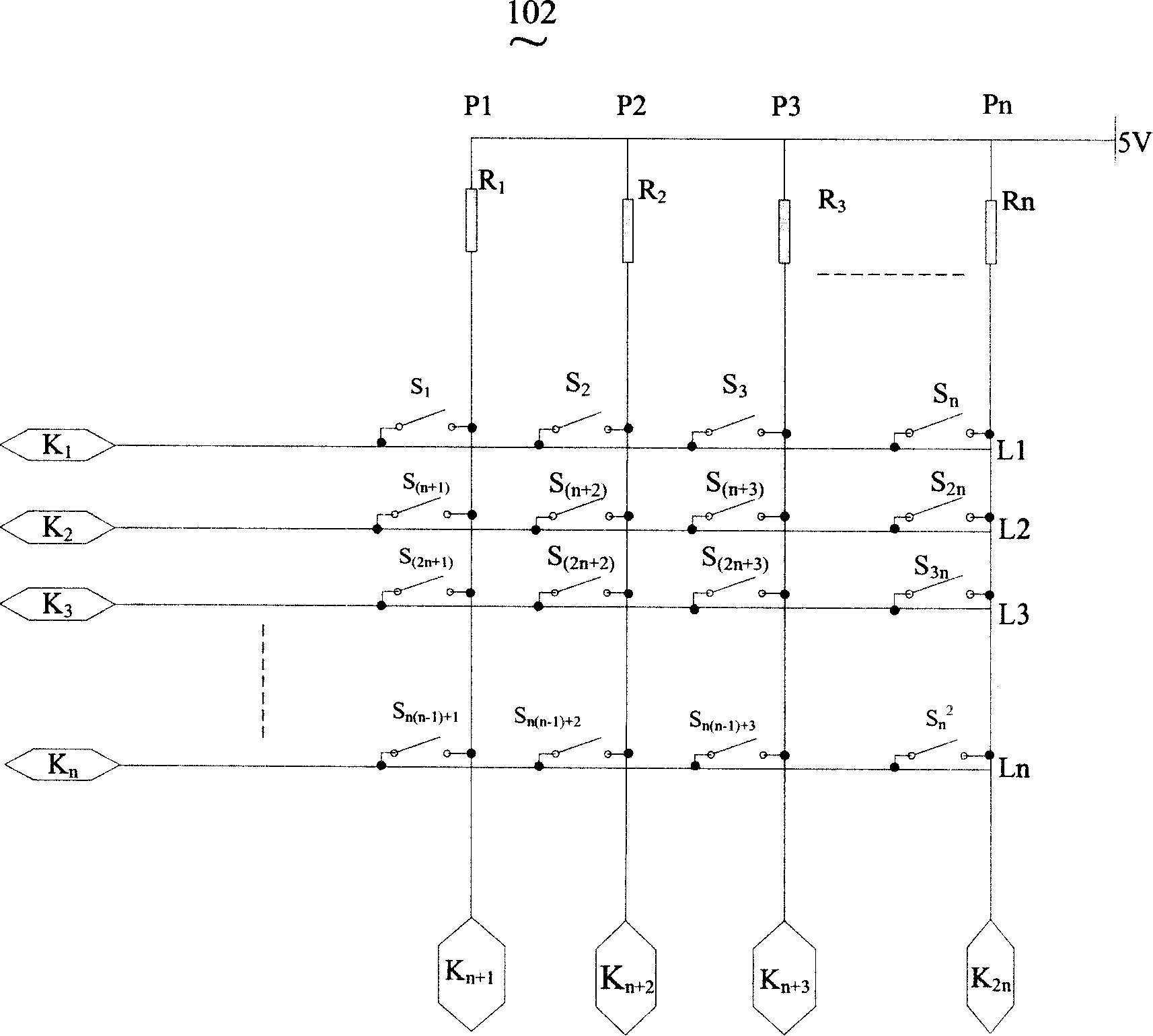

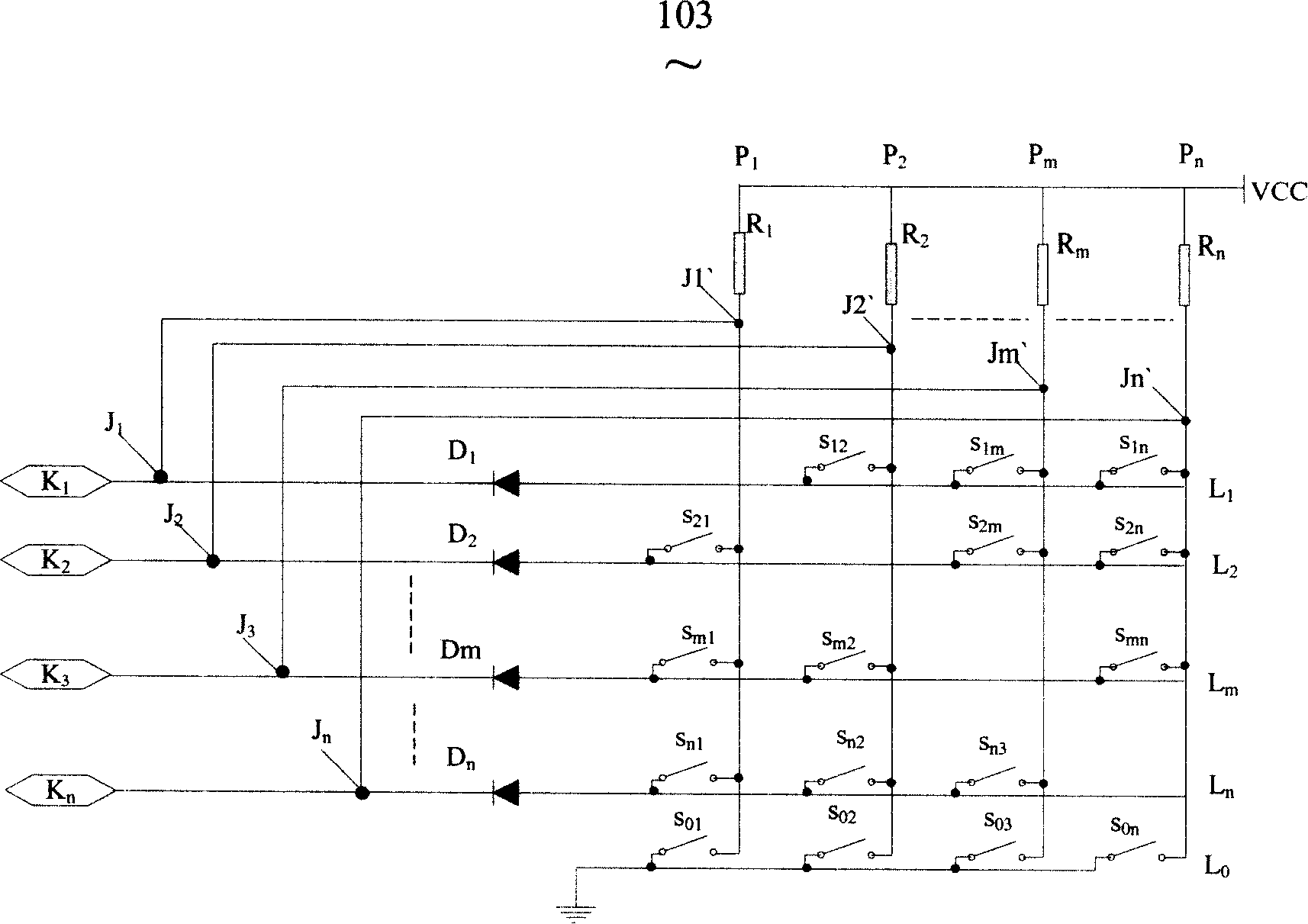

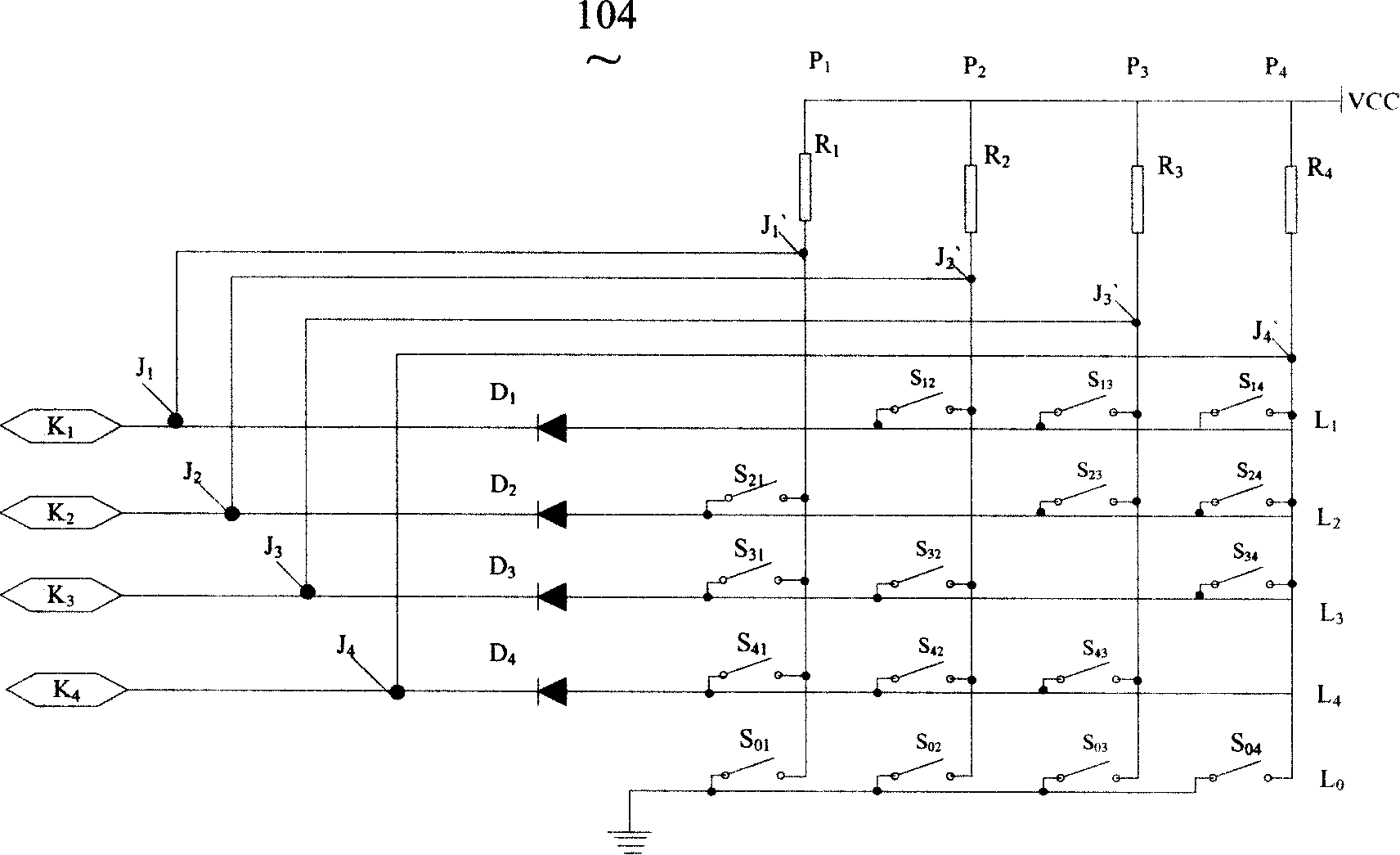

Keyboard scanning circuit and method

InactiveCN101162905ASimple structureGuaranteed single flowDynamic codingInput/output processes for data processingElectrical resistance and conductanceResistor

The invention relates to a keyboard scanning circuit, comprising N vertical lines, N*N keys formed by N first horizontal lines and second horizontal lines, N I / O ports (in-out ports), N diodes, N resistors and a power supply VCC. The N vertical lines, N first horizontal lines and second lines are arranged in a matrix manner to form a plurality of cross points. The N*N cross points are arranged in a manner corresponding to the N*N keys. Each horizontal line is connected to an I / O port through a diode; and each second horizontal line is grounded. Each vertical line is connected to the power supply VCC through a resistor in an electric manner. The N first horizontal lines correspond to the N vertical lines respectively; each pair of horizontal line and vertical line corresponding to each other communicate with each other and no key is arranged on the N cross points between the horizontal line and the vertical line. The keyboard scanning circuit is capable to use N I / O ports to scan N*N keys, the structure is simple, I / O port resource is saved and the cost is reduced. Besides, a keyboard scanning method is provided.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

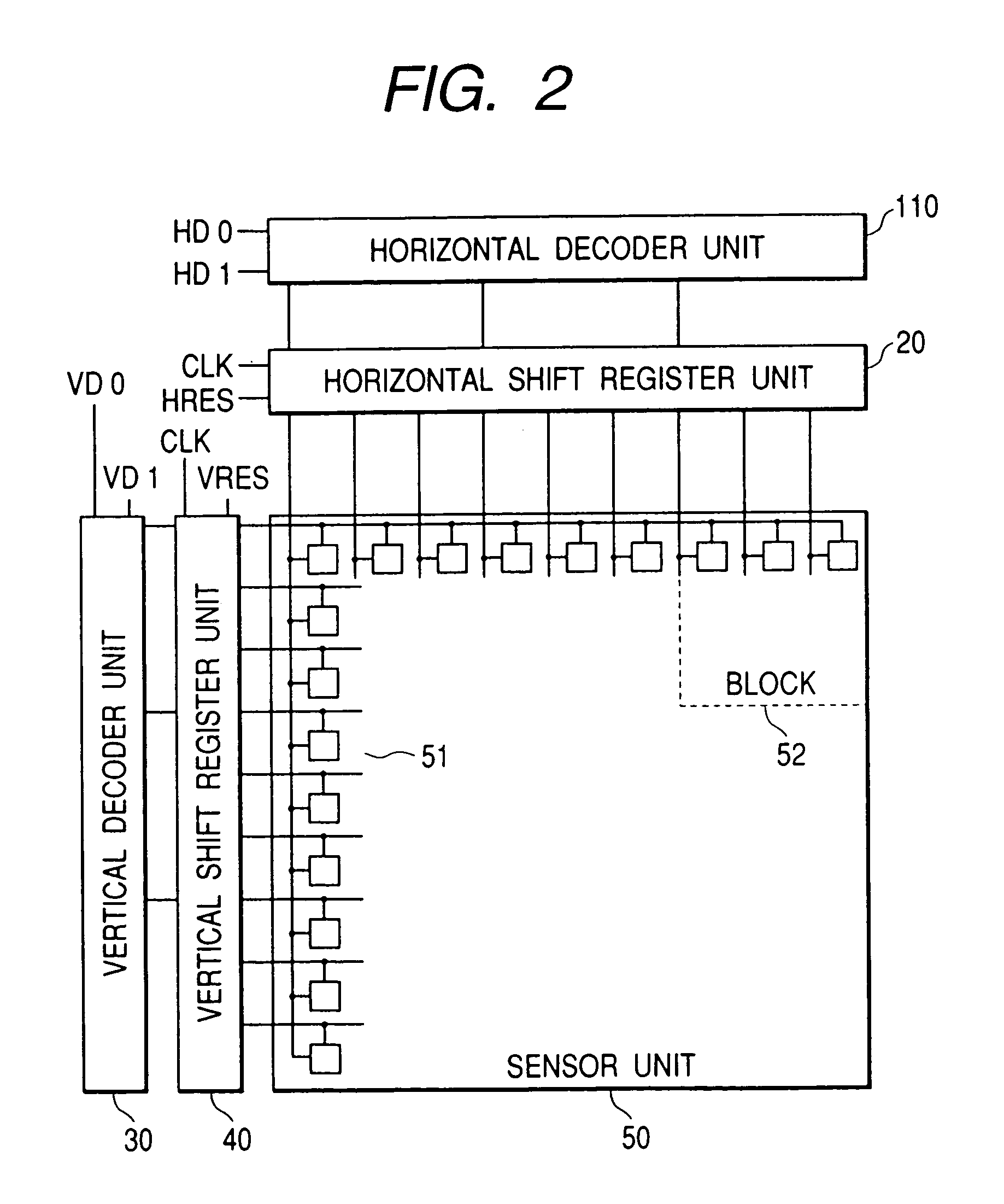

Image pickup apparatus using a selector circuit

InactiveUS7030920B1Television system detailsTelevision system scanning detailsShift registerScan circuits

A selector circuit having a shift register for sequentially outputting a select pulse and a decoder circuit for designating a desired block of a plurality of blocks divided from the scan circuit, so as to allow the scan circuit to start to output the select pulse from a head position in the designated desired block.

Owner:CANON KK

Solid-state image-pickup sensor and device

InactiveUS20050259169A1Television system detailsTelevision system scanning detailsScan circuitsPhotoelectric conversion

A solid-state image-pickup sensor comprises a plurality of vertical scan circuits, a plurality of horizontal scan circuits, a pixel section including pixels arranged in a two-dimensional array and performing photoelectric conversion, each of the pixels being connected to one of the plurality of vertical scan circuits and connected to the plurality of horizontal scan circuits, and a selection unit for controlling each of the horizontal scan circuits to independently select and output photoelectrically converted signals read from plural ones of the pixels arrayed in the horizontal direction.

Owner:OLYMPUS CORP

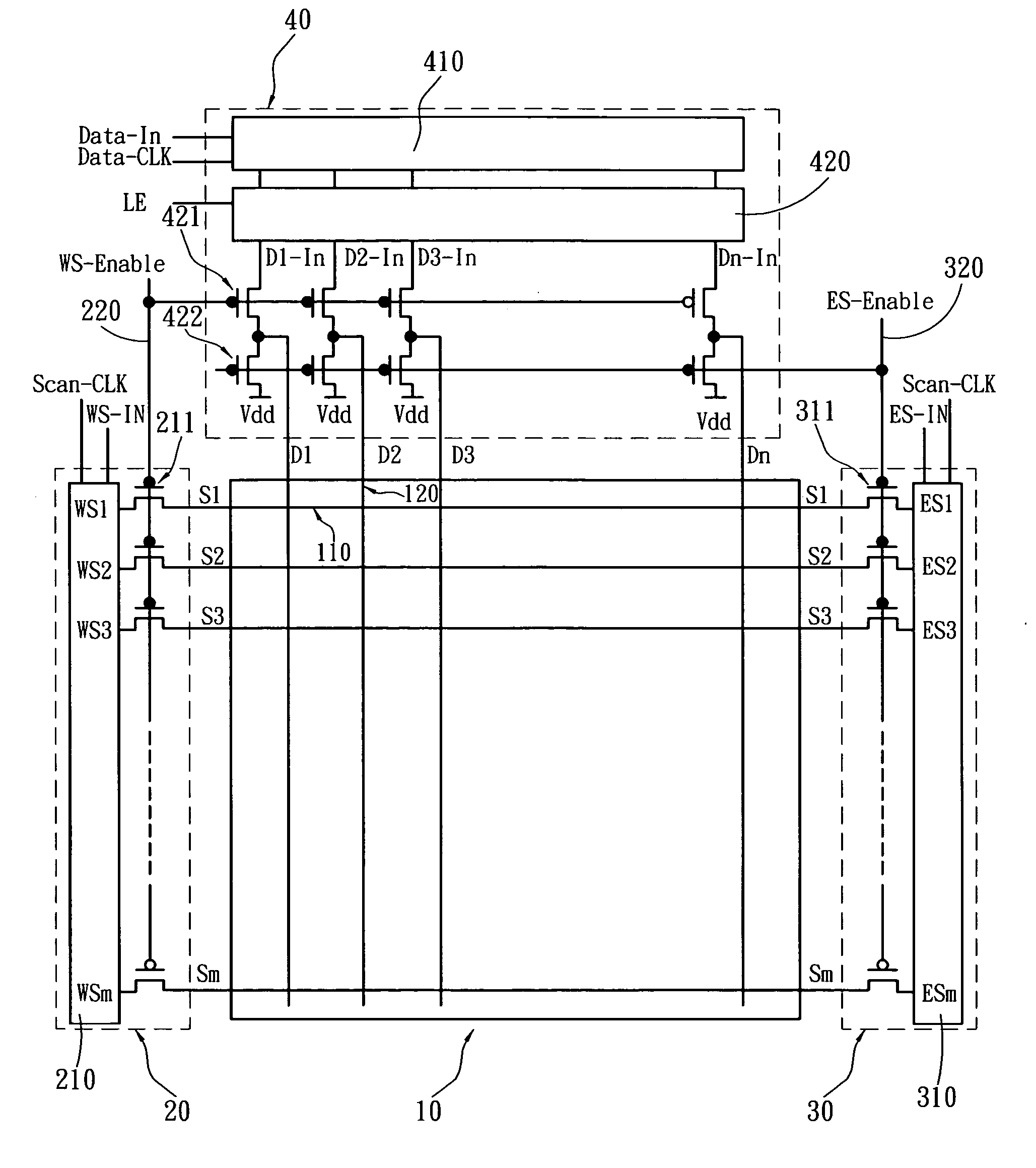

Driving apparatus for an active matrix organic light emitting display

InactiveUS20050134536A1Reduce complexityIncrease profitCathode-ray tube indicatorsInput/output processes for data processingCapacitanceActive matrix

A driving apparatus of a multiple-scanning driving circuit relating to a simple pixel structure of 2T1C (2 TFTs and 1 capacitor) includes a write-scan circuit, an erase-scan circuit and a data driving circuit. A write-enable line connected to the write-scan and the data driving circuits is used to control the signals of these two circuits. One erase-enable line connected to the erase-scan and the data driving circuits is used to control the signals of these two circuits. Thus, a circuit system of time-multiplex multiple write-scan and erase-scan is completed to solve the problems of a low time utility rate and an insufficient luminance in a digital driving AMOLED system.

Owner:WINTEK CORP

Rapid autonomous scan in FM or other receivers with parallel search strategy, and circuits, processes and systems

A wireless receiver scan circuit (10) including a low-IF de-rotator (210) with signal band and image band outputs, and search circuitry (80, 200) operable to parallelize (100) a frequency-scanning search by determination of the presence and absence of a transmission in both the signal band and the image band. Other circuits, systems and processes are also disclosed.

Owner:TEXAS INSTR INC

Semiconductor integrated circuit

InactiveUS20080010570A1Reduce in quantityElectronic circuit testingStatic storageDecision circuitInternal memory

A semiconductor integrated circuit comprises a test mode decision circuit which decides a normal operation mode or a test mode when having input a clock from a reset state and started an operation by using a scan enable signal that is used for a scan test, and retains a decision result till the decision result is reset; a scan enable mask circuit which disables the transmission of a scan enable signal to an internal scan circuit according to a decision result signal; and an access control unit which disables the access to the internal memory unit according to the decision result signal output from the test mode decision circuit. Furthermore, the semiconductor integrated circuit has a configuration of using the scan enable signal and the normal operation input signal in common.

Owner:CANON KK

Display and method for driving the same

InactiveUS20050035938A1Supply amount is increasedReduce the amplitudeStatic indicating devicesNon-linear opticsCapacitanceScan line

A display includes a pixel array, a vertical scan circuit, a horizontal drive circuit, and an auxiliary scan circuit. The pixel array includes scan lines, signal lines, pixels, and auxiliary scan lines. Each pixel includes a transistor, a pixel electrode, and an auxiliary capacitor. The auxiliary scan circuit sequentially applies auxiliary pulses, of which potential is reversed between a high level and a low level relative to a predetermined reference potential, to the auxiliary scan lines synchronously with selection pulses to control such that a potential of one electrode of each auxiliary capacitor in a selected pixel row is opposite in polarity to that of a signal written in the corresponding pixel electrode in the selected row, and further control such that the potential of the electrode of each auxiliary capacitor is returned to the reference potential when the selected row is released.

Owner:SONY CORP

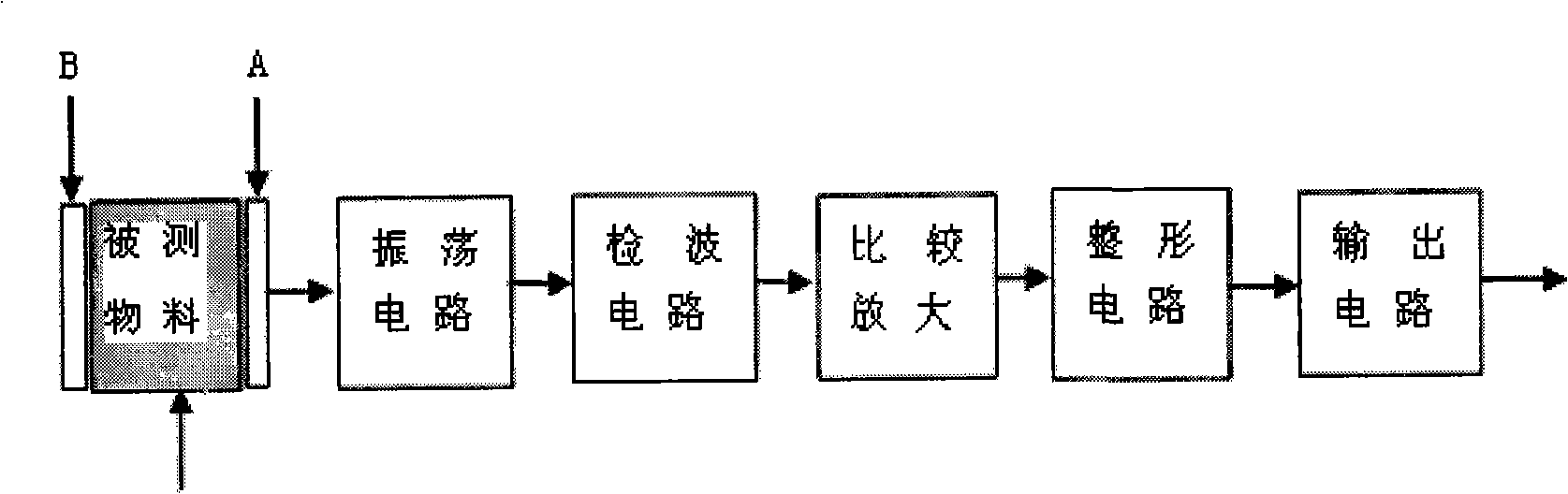

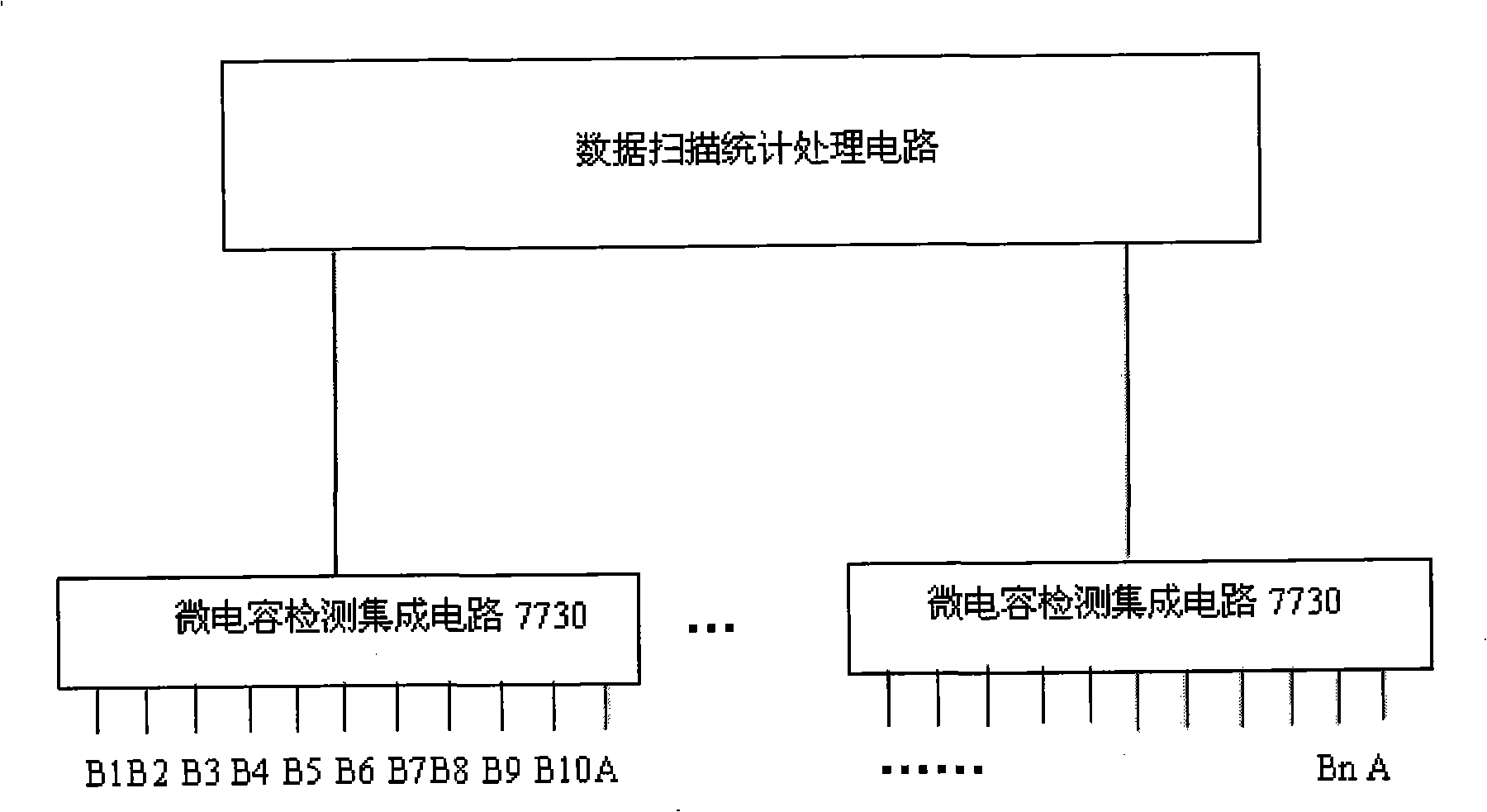

Capacitance type digital material-level sensor and its measurement method

InactiveCN101266167AImprove stabilityImprove reliabilityLevel indicators by physical variable measurementCapacitanceObservational error

The invention discloses a capacitor digital level sensor, characterized in that an electrode plate of a plurality of capacitors is formed by micro-capacitance detection integrated circuit or two or above electrode plates connected by a lead; the measuring method is that fixedly arranging the electrode plates in the detected material, two electrode plates forming a plurality of capacitors, each of which having a corresponding micro-capacitance detection circuit. Output of the electrode plates is zero or one according to alternation of the capacitance, obtaining the digital level by scanning circuit statistics. The invention is compact and reasonable in structure, convenient, rapid and accurate in use, which solves the problem of present level measurement that measuring error is greater caused by effect of factors such as temperature, humidity and capacitance value accumulation error, and enhances anti-inference capacity of the sensor greatly, and improves stability and reliability of the level measurement, in particular applied to directly digital precise measurement of powder or small particle solid, liquid.

Owner:TAIYUAN UNIV OF TECH

Solid-state imaging pickup device with vertical and horizontal driving means for a unit pixel

InactiveUS6975357B1Eliminate vertically-striped system noiseIncrease consumptionTelevision system detailsOptical wave guidanceScan circuitsCMOS

In a CMOS image pickup device in which the signal corresponding to the accumulated charge amount of each pixel is output to horizontal signal lines wired on a row basis, for example, two vertical selection transistors are provided for every horizontal signal lines, and two vertical signal lines and two vertical scan circuits are provided for every horizontal signal line, thereby separately outputting signals which are different in accumulation time and obtained by arbitrarily dividing 1 field into any number of parts on the basis of integer times of 1H.

Owner:SONY CORP

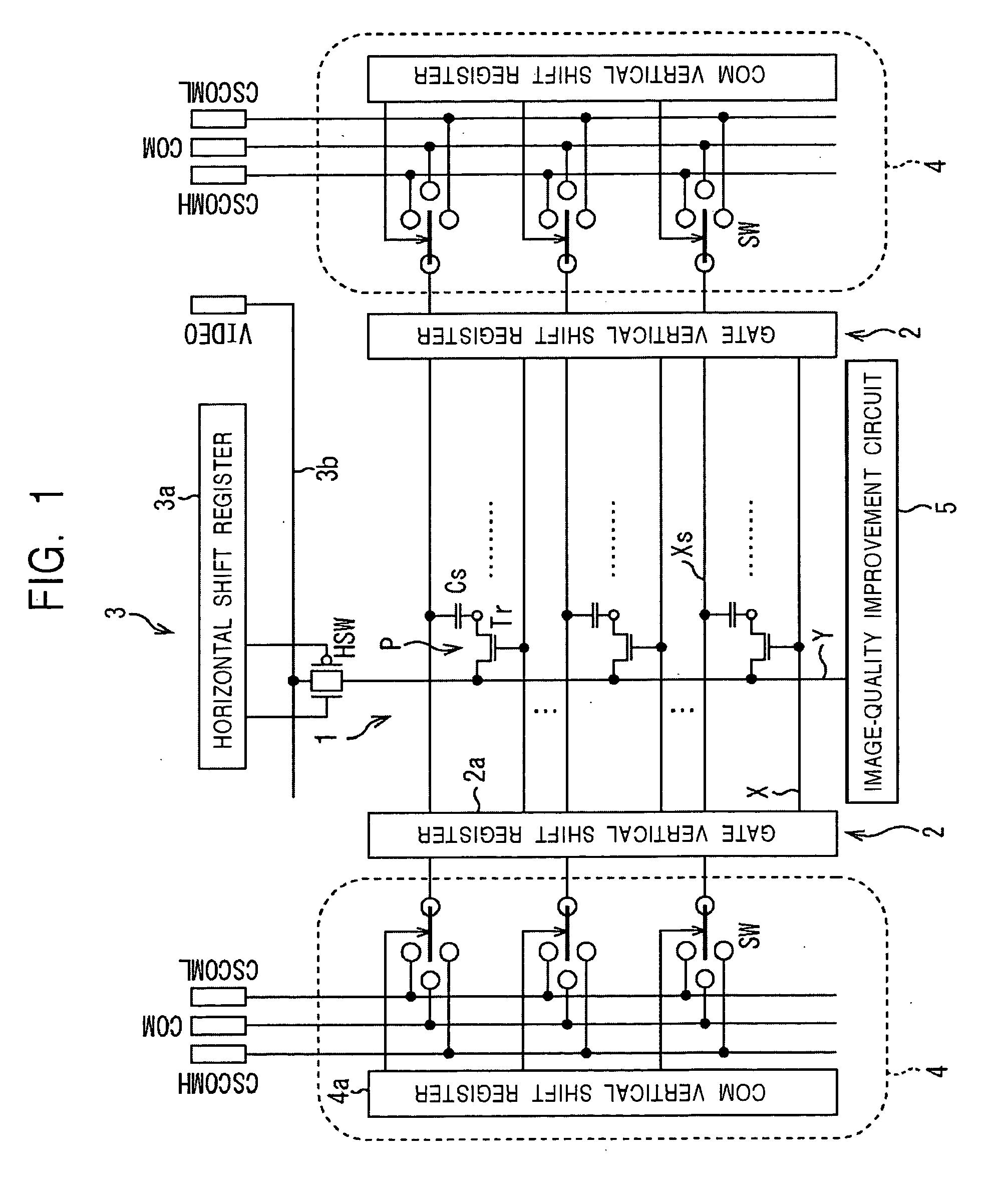

Display device and electronic apparatus

InactiveUS20040130542A1Electronic switchingCathode-ray tube indicatorsDisplay deviceBackground image

A display device enabling a superimpose display in which an image is superimposed on a background image with low power consumption is provided. By providing a switch at an input terminal of each stage of a scanning circuit which has a plurality of stages for outputting a sampling pulse or a row selection pulse, and by selecting whether or not to permit an input of a start pulse or each output pulse of a prior stage by the switch, it becomes possible to input a start pulse to an arbitrary mid-stage and output a sampling pulse or a row selection pulse from the stage. Accordingly, the pulse is outputted only to a region where a video signal needs to be updated in a display screen, and a row and a column are selected, thus a new video signal is written thereto.

Owner:SEMICON ENERGY LAB CO LTD

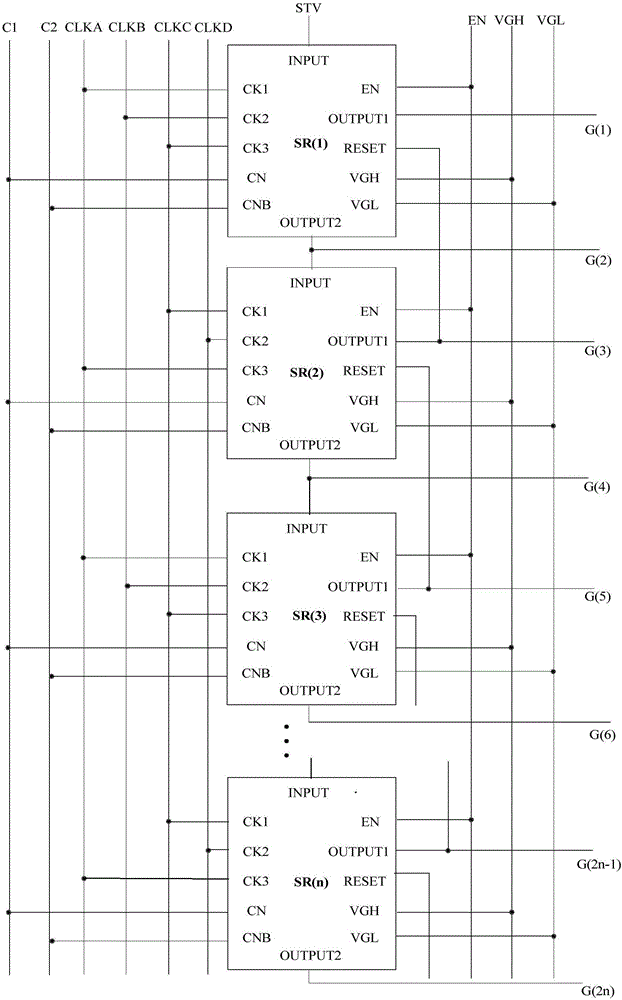

Shift register unit and grid scanning circuit

ActiveCN106128403AForward scanRealize reverse scanningStatic indicating devicesDigital storageElectricityShift register

The invention provides a shift register unit and a grid scanning circuit. In the shift register unit, the voltage of a first node is increased through a first DC voltage end when a first scanning pulse input end is at a first level; the voltage of the first node is increased through a second DC voltage end when a second scanning pulse input end is at the first level, thereby achieving the reverse scanning and enabling a shift register provided by the invention to be able to support the bidirectional scanning of a grid line. In addition, the shifting register unit at each stage is provided with two scanning pulse output ends. The second scanning pulse output end can output a grid voltage to the pixel units in an (N+1)-th row at a next time stage of the moment when the first scanning pulse output end outputs a grid drive signal to an N-th stage pixel unit, thereby achieving a purpose that the shift register at the same stage controls starting of pixels in two rows, effectively improving the display flexibility, and meeting the display demands of different states.

Owner:BOE TECH GRP CO LTD +1

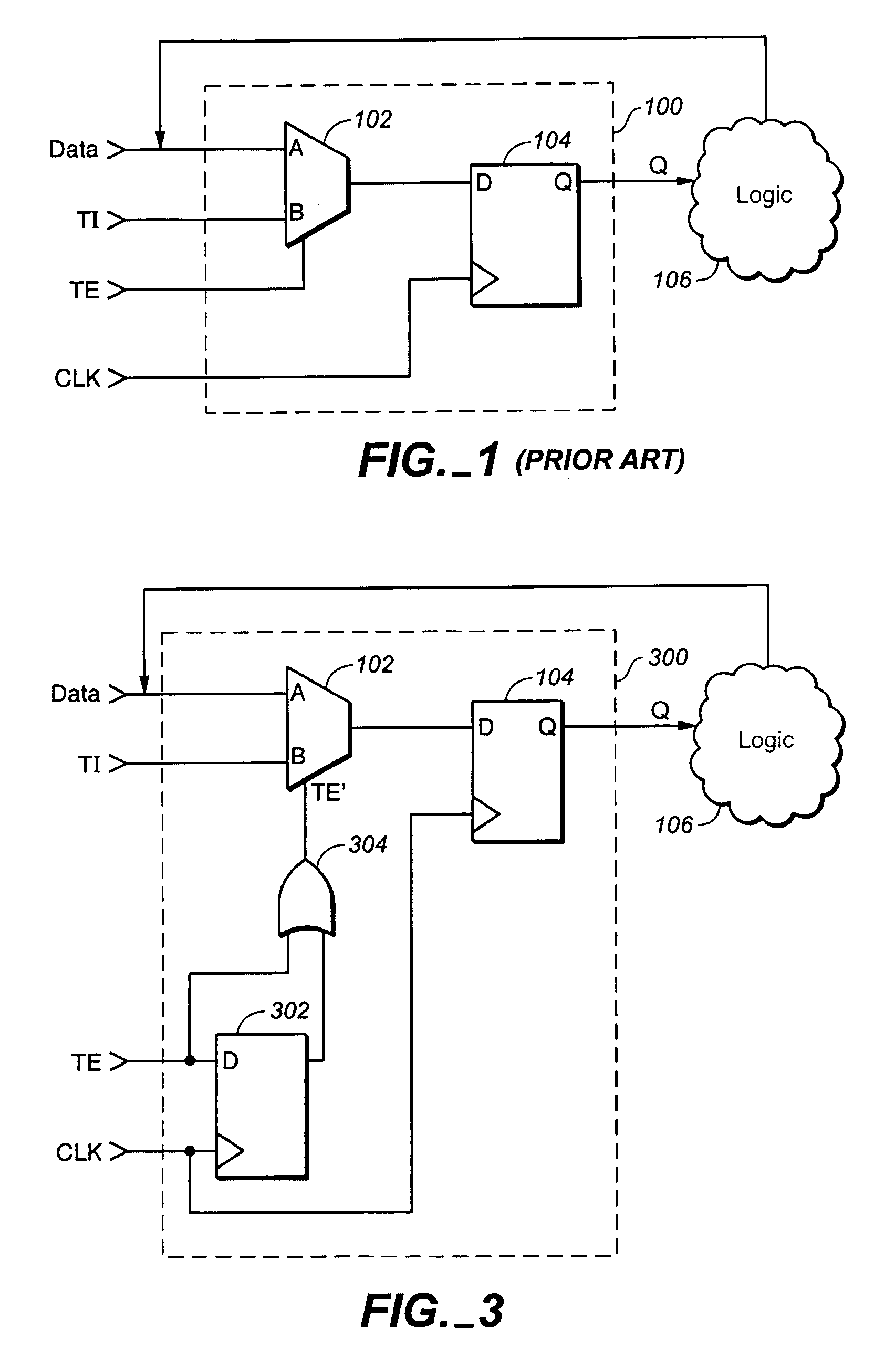

Self-timed scan circuit for ASIC fault testing

InactiveUS6972592B2Electronic circuit testingLogic circuits using elementary logic circuit componentsMultiplexingTest input

A self-timed scan circuit includes a multiplexer for selecting either a data input or a test input in response to an internal test enable signal and for generating a multiplexed output; a latch coupled to the multiplexer for generating a latched output in response to a next clock pulse; and a timing control circuit for generating the internal test enable signal in response to a global test enable signal wherein the internal test enable signal is set to logic one when the global test enable signal is set to logic one and wherein the internal test enable signal is set to logic zero in response to the next clock pulse.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

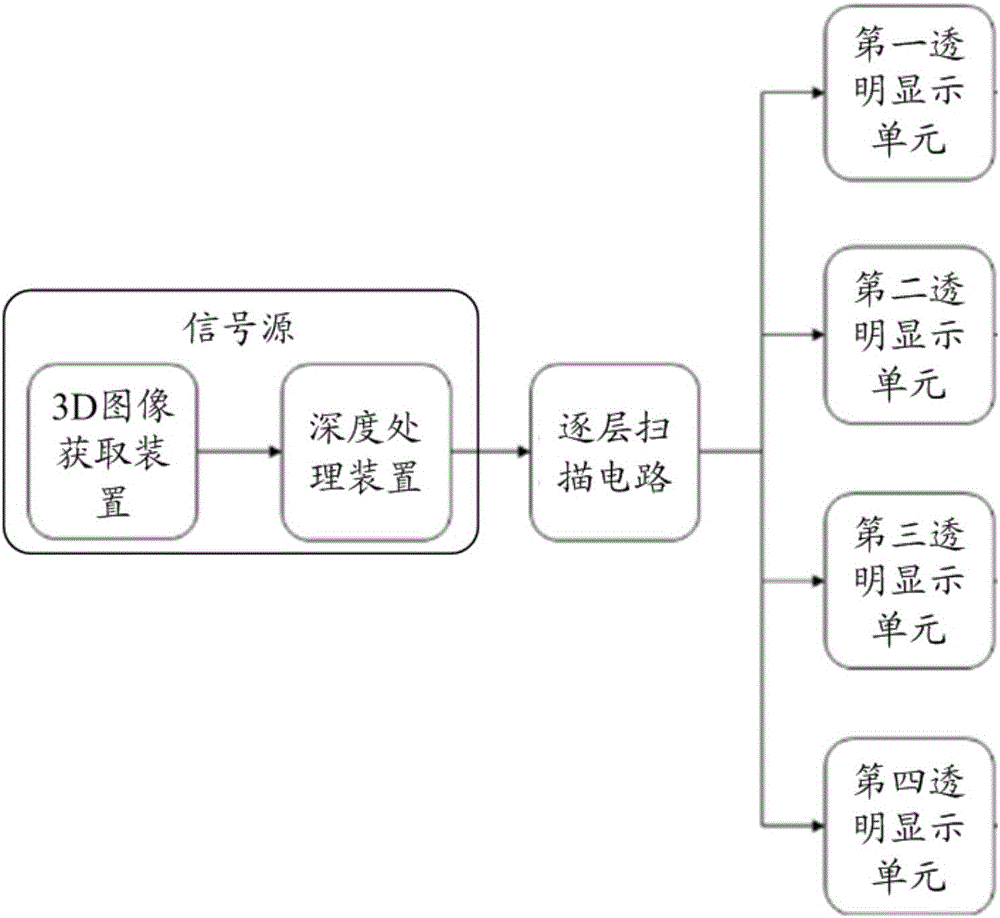

Display device and display method

InactiveCN105872520ARealize the real three-dimensional display effectRealize a real stereoscopic display effectSteroscopic systemsInstrumentsComputer hardware3d image

The invention relates to a display device and a display method. The display device comprises a signal source, a plurality of transparent display units and a layer-by-layer scanning circuit. The signal source is configured to provide a plurality of depth images based on the same 3D image, and the depth ranges of the depth images are different. The transparent display units are configured to emit imaging light rays in the same direction and are sequentially arranged at intervals in the same direction. The layer-by-layer scanning circuit is configured to input the depth images into the transparent display units respectively and control the transparent display units on the display side to be in a transparent state in the process that the transparent display units display the input depth images. The display device can reduce power consumption of 3D display.

Owner:BOE TECH GRP CO LTD +1

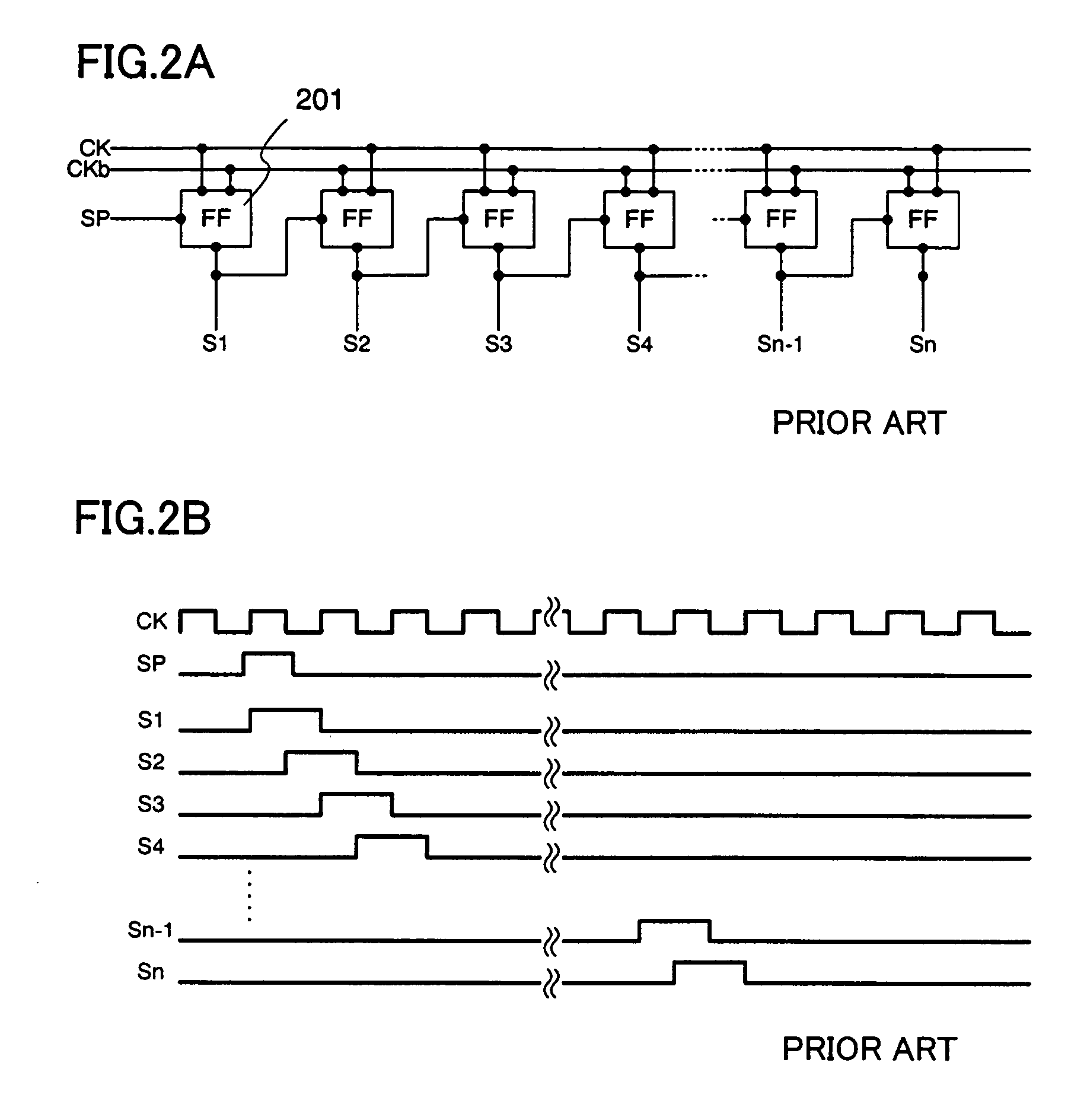

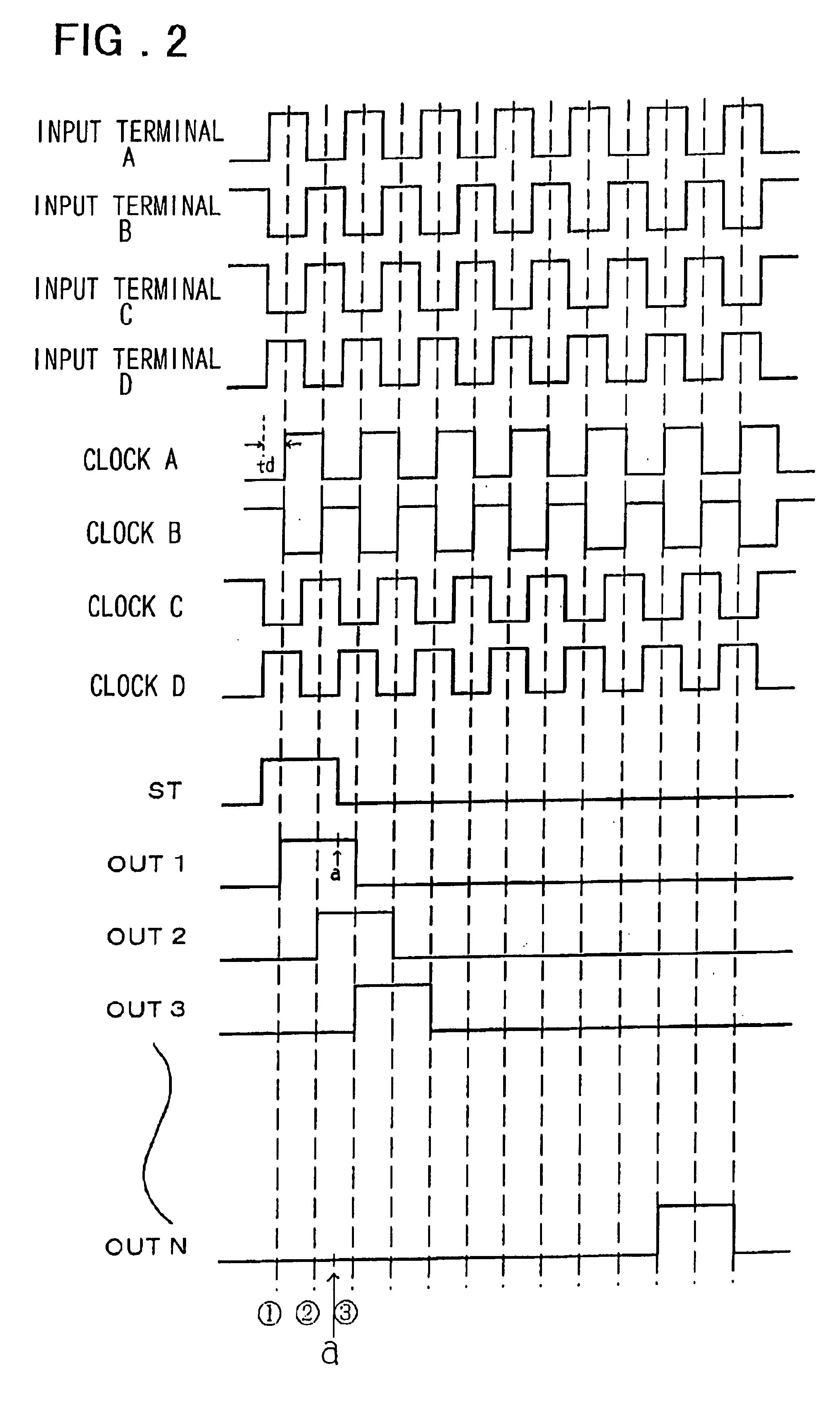

Scanning circuit

InactiveUS6876352B1High operating requirementsGuaranteed uptimeCathode-ray tube indicatorsDigital storageShift registerScan circuits

A scanning circuit having such a high operation margin for the phase deviation of clock signal that its operation is stable. The scanning circuit includes a bidirectional shift register having transfer gates of a transfer unit and a feedback circuit, the operation of which is control led by four phase clocks. The scanning circuit comprises a delay circuit (101) that delays control clocks (A, B) supplied to the transfer gates of the transfer unit (103) relative to control clocks (C, D) supplied to the feedback circuit (104).

Owner:VISTA PEAK VENTURES LLC

Masking circuit removing unknown bit from cell in scan chain

Owner:TEXAS INSTR INC

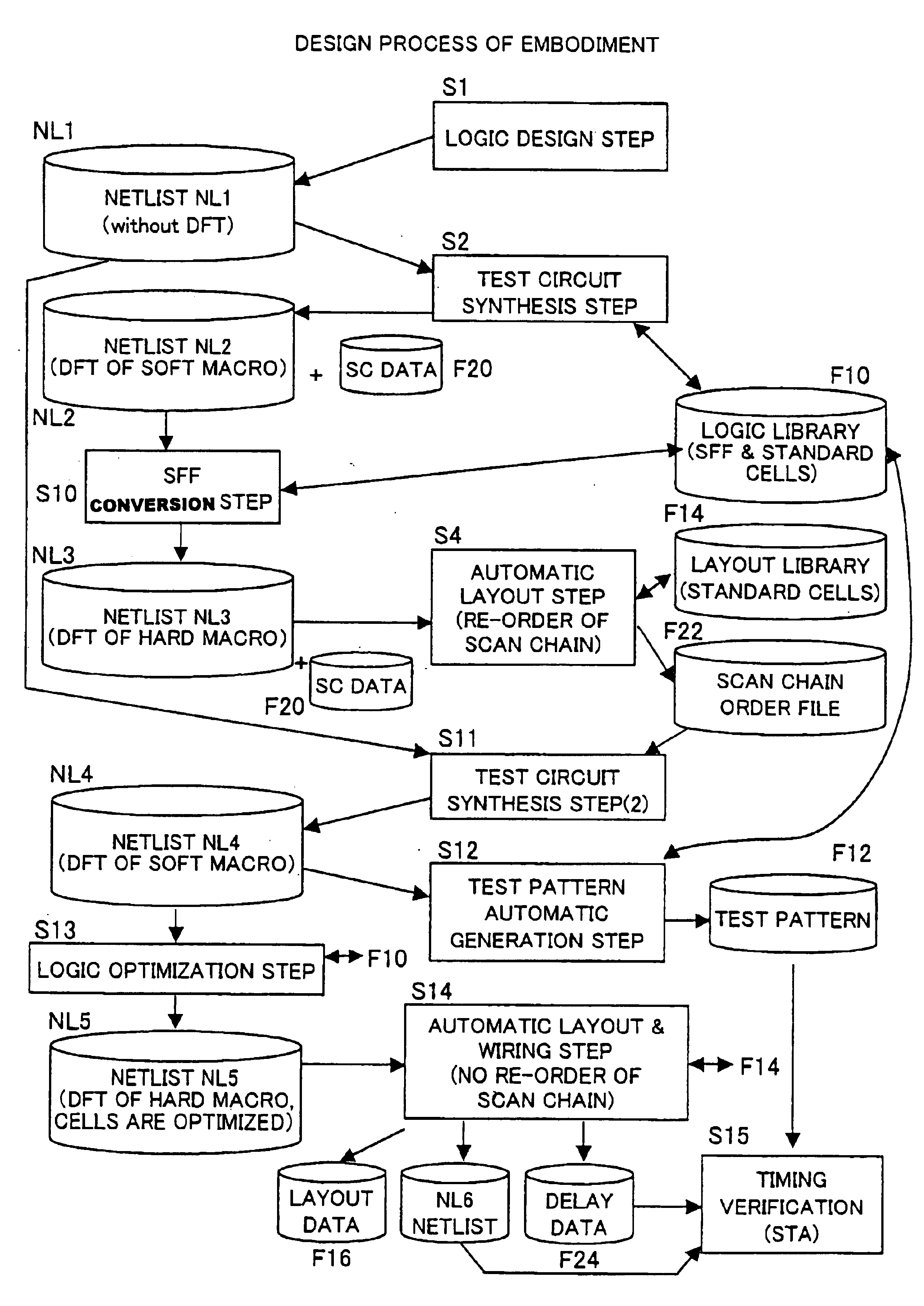

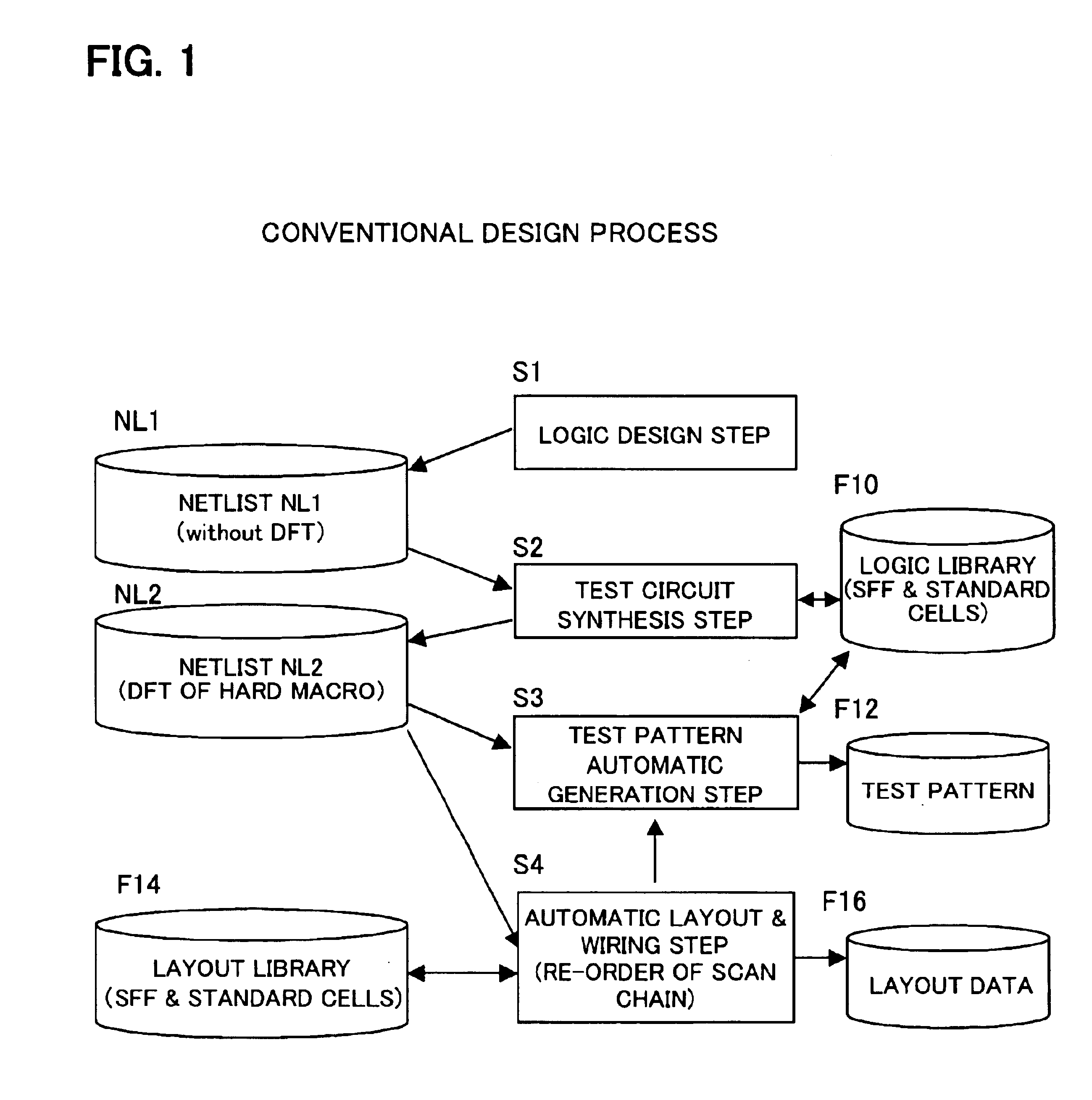

Design method for integrated circuit having scan function

InactiveUS6990642B2Small surface areaEliminate needSolid-state devicesDetecting faulty computer hardwareScan circuitsEngineering

The present invention provides a method for designing LSI including a logic circuit equipped with a scan circuit without generating a hard-macro library for the scan flip flops constituting the scan circuit. According to the method, first netlist NL1 is converted into second netlist NL2 by adding scan circuit including scan flip-flops. Order data for connecting scan chain of the scan circuit is extracted from the second netlist NL2. Such second netlist NL2 is converted into third netlist NL3 including only hard-macros, and the third netlist NL3 is laid-out by re-ordering the scan chain so that the newly generated order data for is stored temporally. Fourth netlist NL4 including scan circuit formed by scan flip-flops of soft-macros is generated on the basis of the stored order data, then the fourth netlist NL4 is converted into fifth netlist NL5 by substituting the scan flip-flops of soft-macros for standard cells of hard-macros. Finally the generated fifth netlist is laid-out without re-ordering the scan chain.

Owner:MONTEREY RES LLC

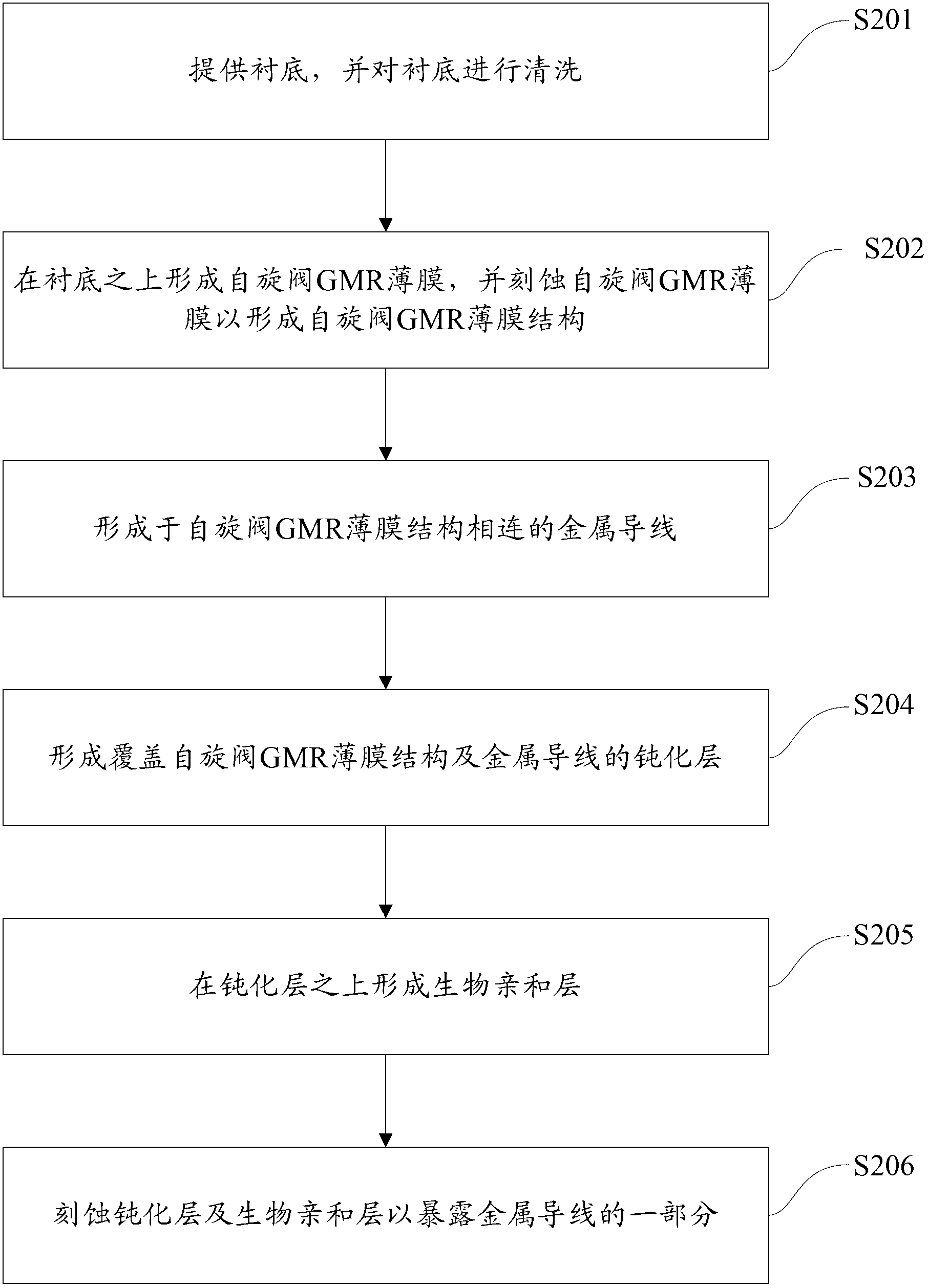

Spin valve GMR film structure, biosensor employing same and biosensor manufacturing method

InactiveCN102706954AHigh reluctanceImprove coercive forceMaterial magnetic variablesBiochemical engineeringScan circuits

The invention discloses a spin valve giant magneto resistive (GMR) film structure comprising a substrate, a buffer layer, a synthetic free layer, an isolation layer, a pinned layer, a pining layer and an overburden layer which are sequentially stacked from bottom to top, wherein the isolation layer is made from a non-magnetic material. The spin valve GMR film structure disclosed by the invention has high reluctivity and a strong coercive force, improves the detection limit of biomolecule concentration, and is suitable for volume production and application. The invention also discloses a biosensor, a biosensor manufacturing method, a multi-channel scan circuit detection system and a biological detection method.

Owner:TSINGHUA UNIV

Semiconductor memory device and data write method thereof

A semiconductor memory device includes a control circuit. The control circuit executes control to perform a verify operation with respect to only a lowest threshold voltage level of a memory cell at a time of a data write operation, and to skip the verify operation with respect to the other threshold voltage levels. The control circuit determines whether a verify pass bit number of the lowest threshold voltage level, which is counted by a bit scan circuit, is a prescribed bit number or more, and the control circuit further executes control, if the verify pass bit number is the prescribed bit number or more, to perform the verify operation with respect to only the lowest threshold voltage level and a threshold voltage level that is higher than the lowest threshold voltage level, and to skip the verify operation with respect to the other threshold voltage levels.

Owner:KIOXIA CORP

Systems for detecting electrical faults in a vehicle

ActiveUS20160202302A1Fault location by conductor typesTesting electric installations on transportElectricityScan circuits

Systems are provided to determine a location of an electrical fault in an electrical system of a vehicle. A test apparatus can include a control unit and a plurality of scan circuits. The control unit is configured to electrically couple the plurality of scan circuits to the electrical system and trigger the plurality of scan circuits to pass electrical signals to the electrical system. Each scan circuit is configured to detect a presence of an electrical fault in the electrical system based on an electrical signal passed. Each scan circuit provides information indicative of a location of the electrical fault in the electrical system, when detected, to the control unit.

Owner:GE GLOBAL SOURCING LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com