Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

189 results about "Logic network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

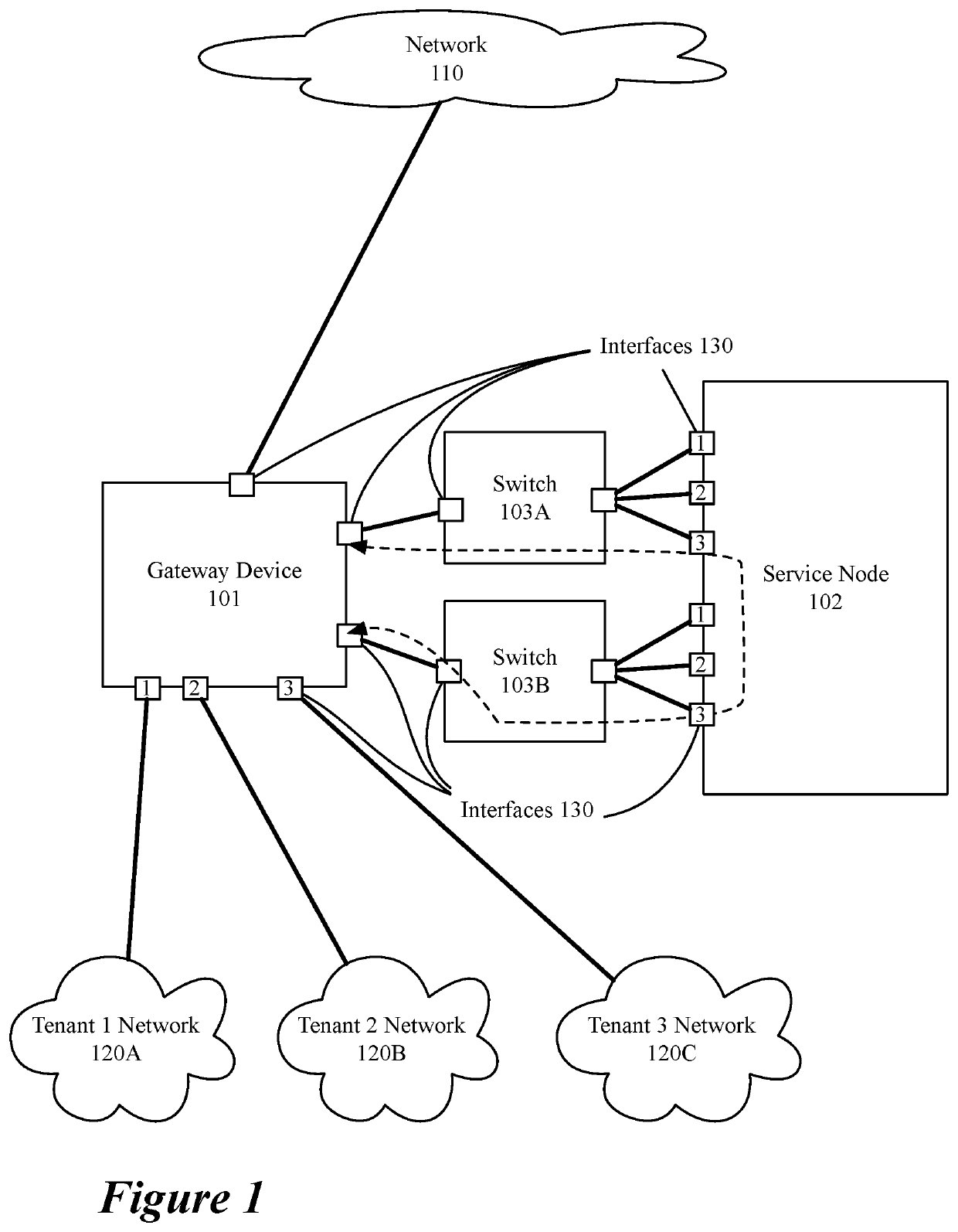

Extension of logical networks across layer 3 virtual private networks

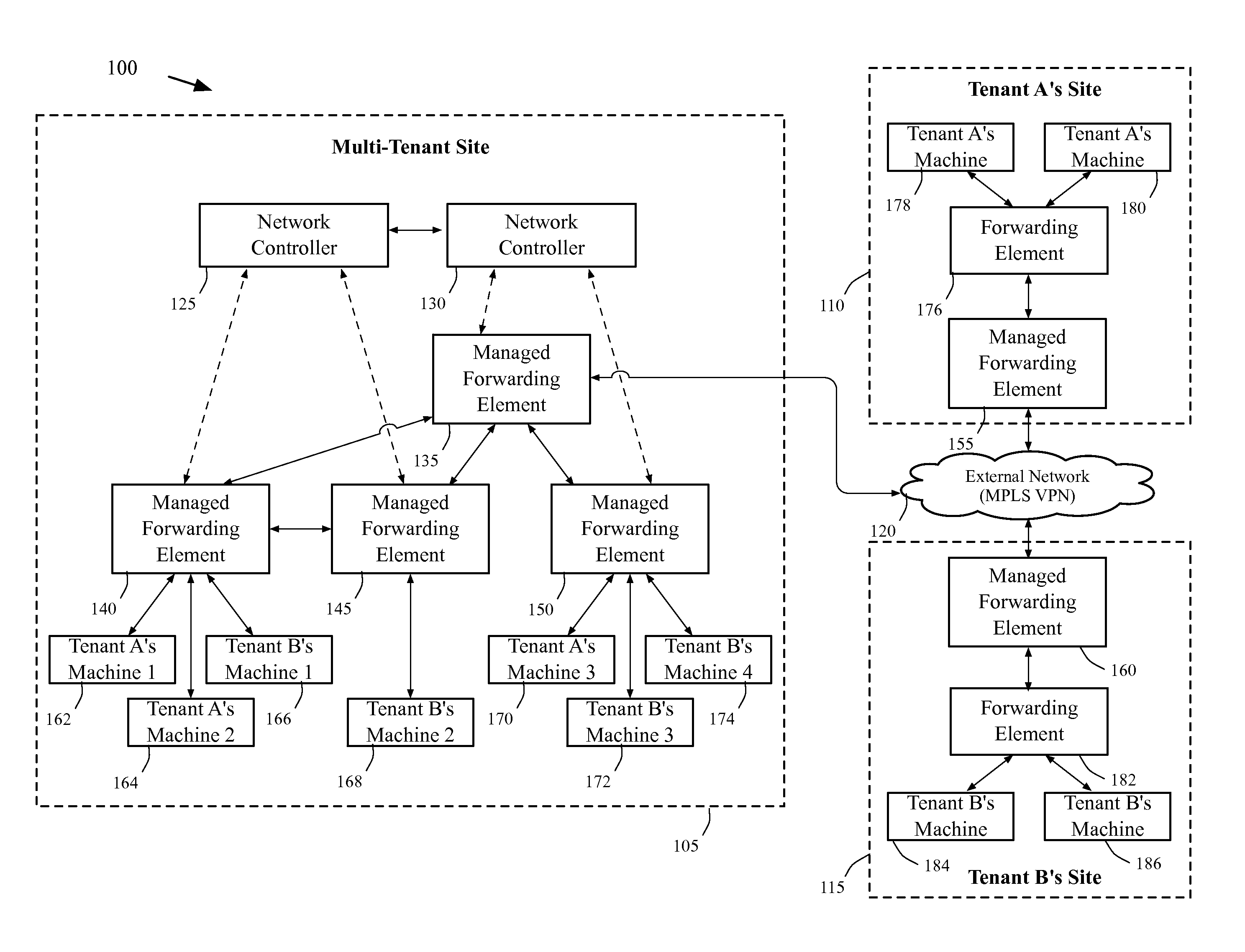

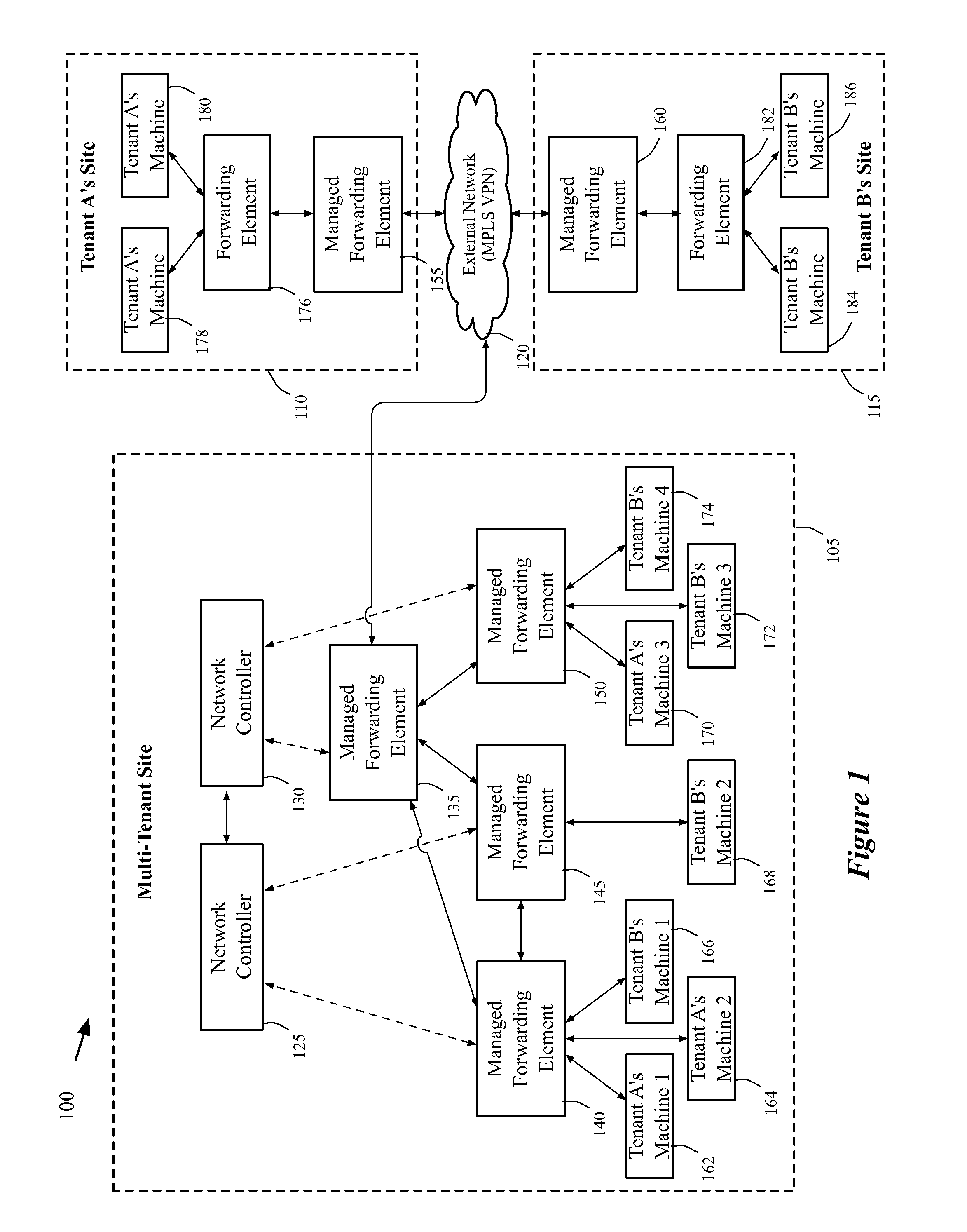

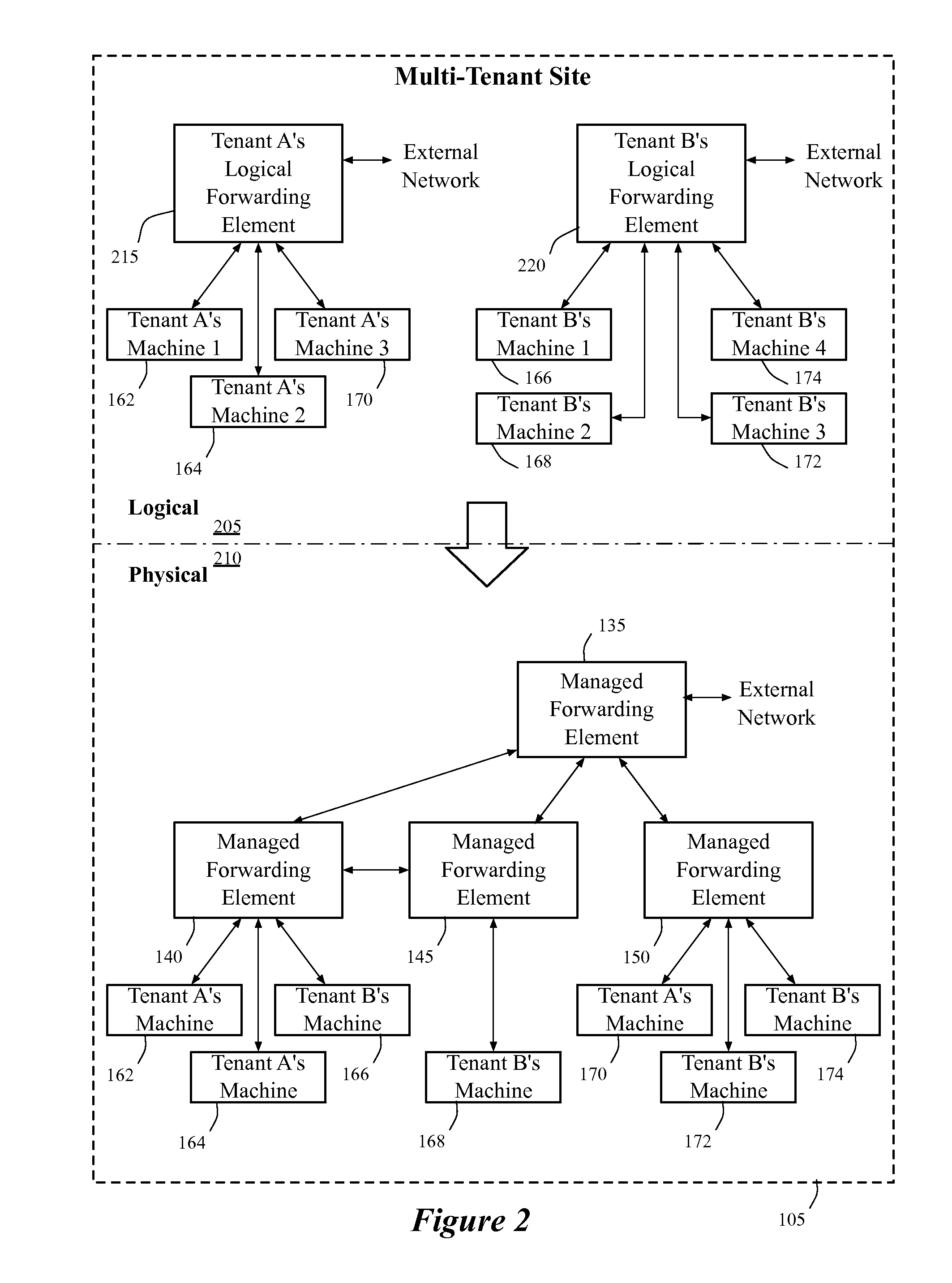

ActiveUS20130287026A1Increase heightGood serviceData switching by path configurationPrivate networkLogical network

A method of manages a set of managed forwarding elements that forward data between machines. The method configures (1) a first managed forwarding element to operate in a first network that uses first and second address spaces that at least partially overlap with each other, (2) a second managed forwarding element to operate in a second network that uses the first address space, and (3) a third managed forwarding element to operate in a third network that uses the second address space. A machine in the second network and a machine in the third network have an identical address that belongs to both the first and second address spaces. The method directs the first managed forwarding element to connect to the second and third managed forwarding elements in a manner that enables the first managed forwarding element to forward data from a machine in the first network to the machine in the second network via the second managed forwarding element.

Owner:NICIRA

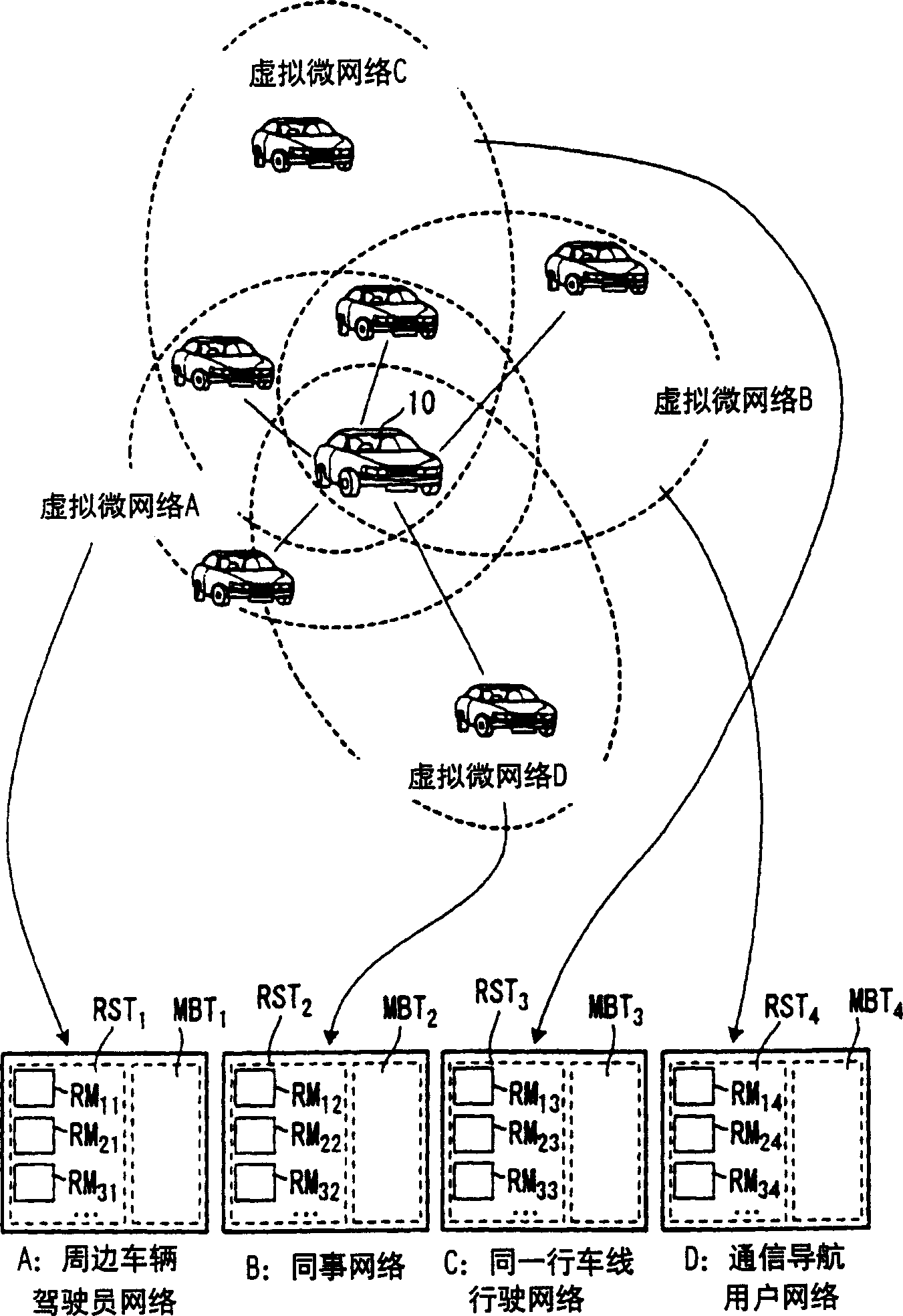

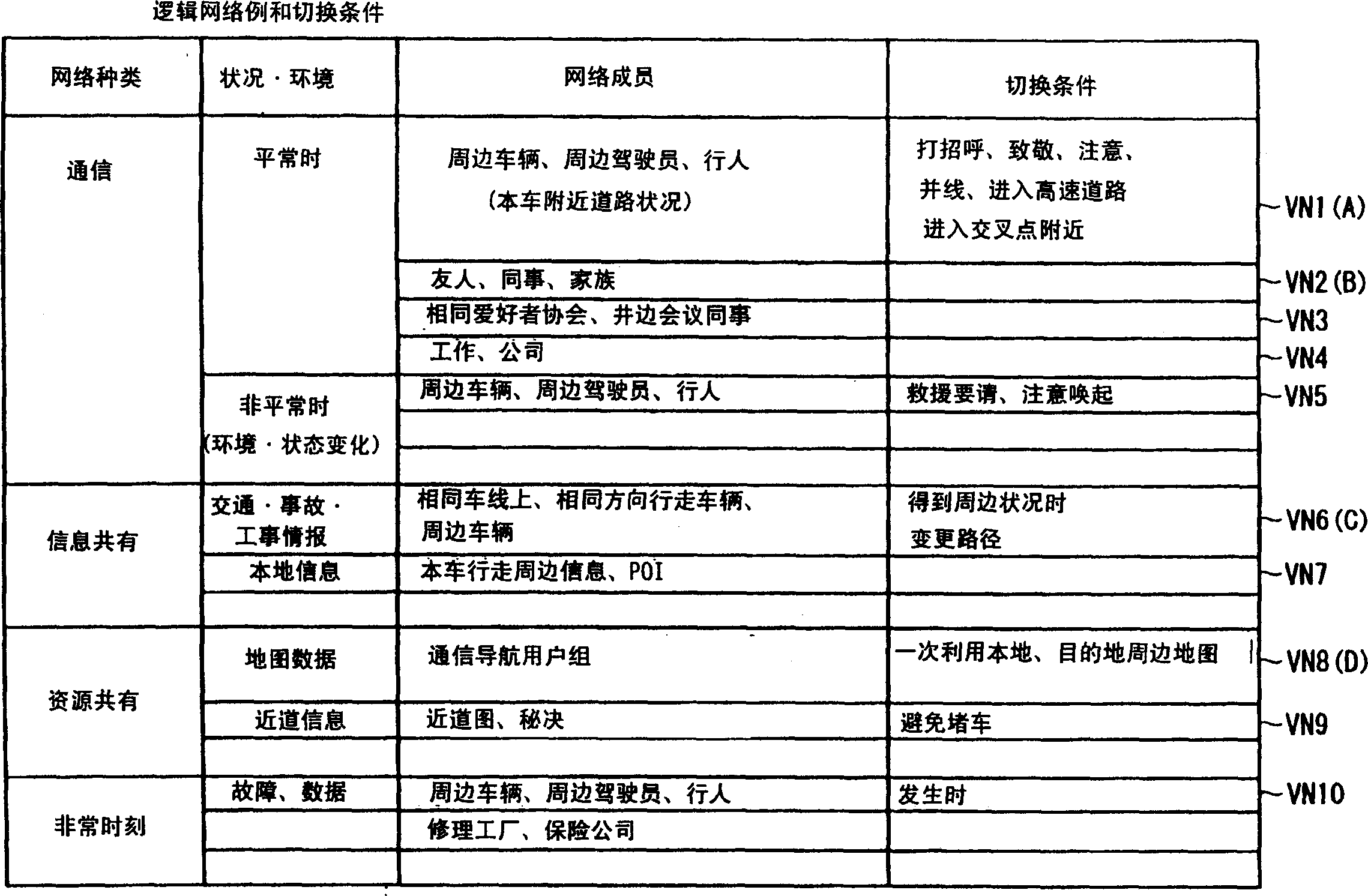

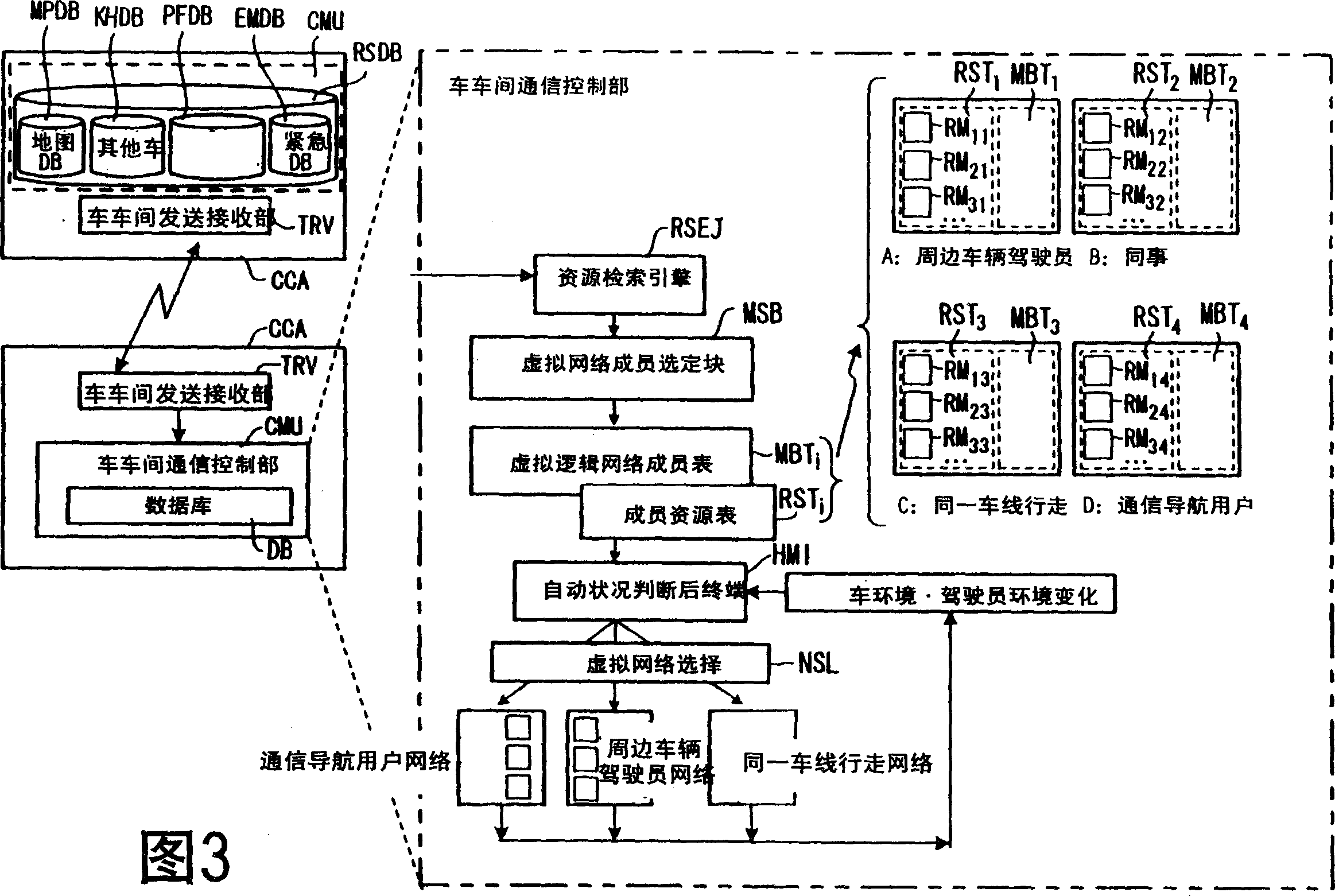

Method for communication among mobile units and vehicular communication apparatus

ActiveUS7286825B2Arrangements for variable traffic instructionsUnauthorised/fraudulent call preventionLogic networkInter vehicle communication

A method for communication among mobile units and vehicular communication apparatus make it possible to automatically establish connection with a party who can provide required information on the basis of an environment or condition change of a driver or a vehicle or in response to a driver's request so as to permit communication with the party. An inter-vehicle communication apparatus of a vehicle acquires information from other mobile units through physical networks while it is moving or stopped, and registers, in a member table, mobile units satisfying predetermined conditions on the basis of the acquired information as the members of different virtual logic networks according to the conditions. In such a state, the inter-vehicle communication apparatus selects one virtual logic network from among a plurality of virtual logic networks on the basis of an environment or condition change of a driver or a vehicle or in response to a driver's request so as to permit communication with the party. The selected virtual logic network is set as an active network to establish connection with a predetermined mobile unit in the active network thereby to request or provide required information from or to the mobile unit.

Owner:ALPINE ELECTRONICS INC

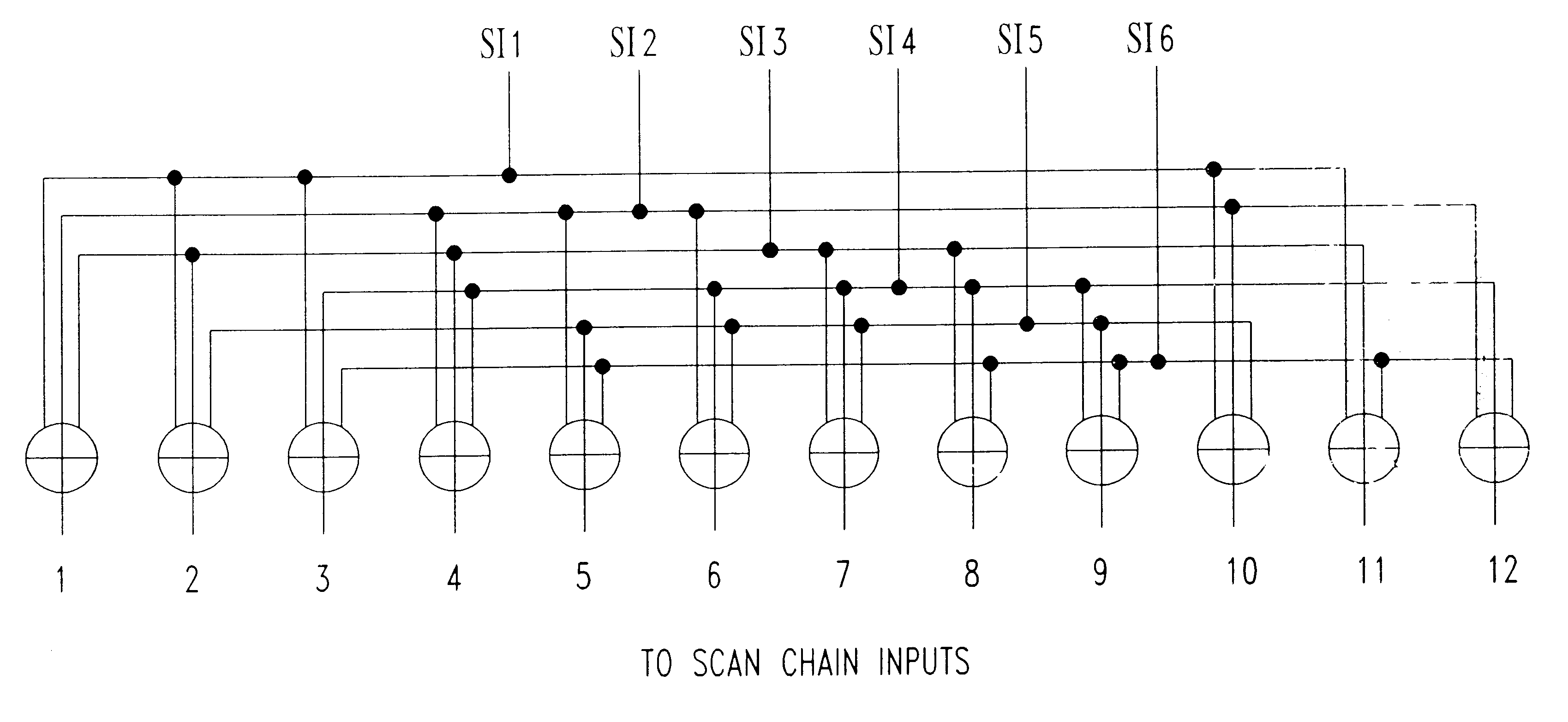

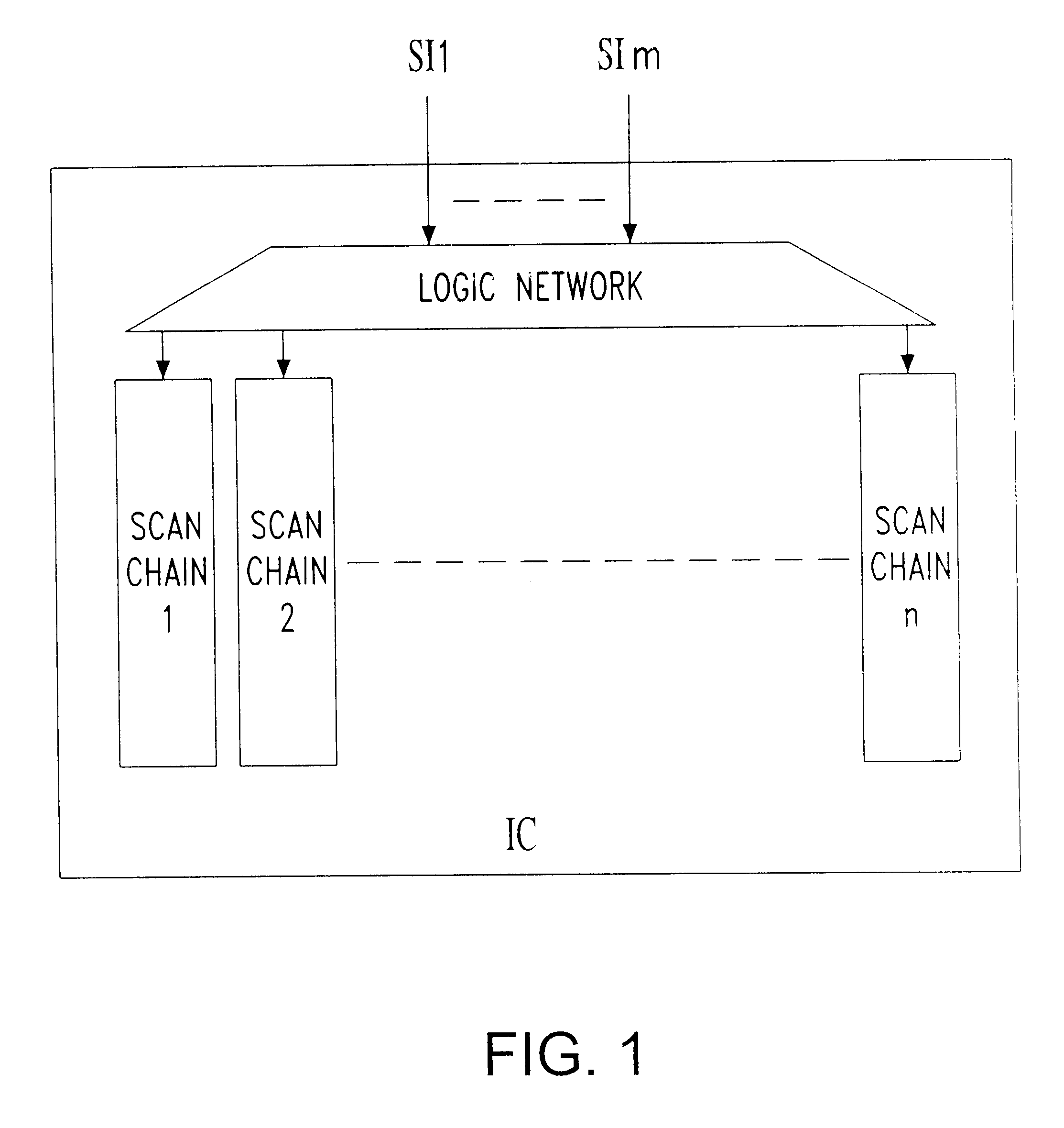

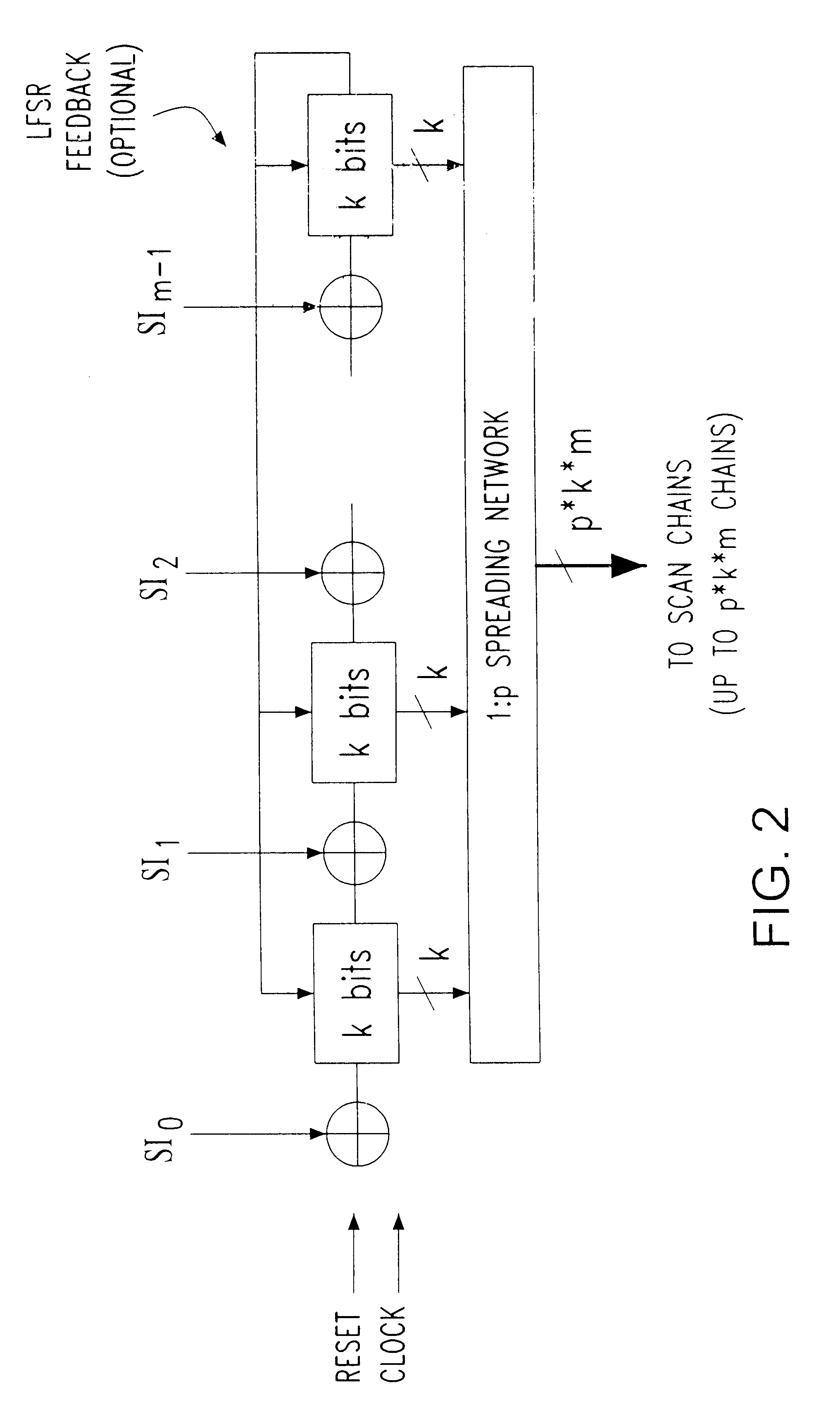

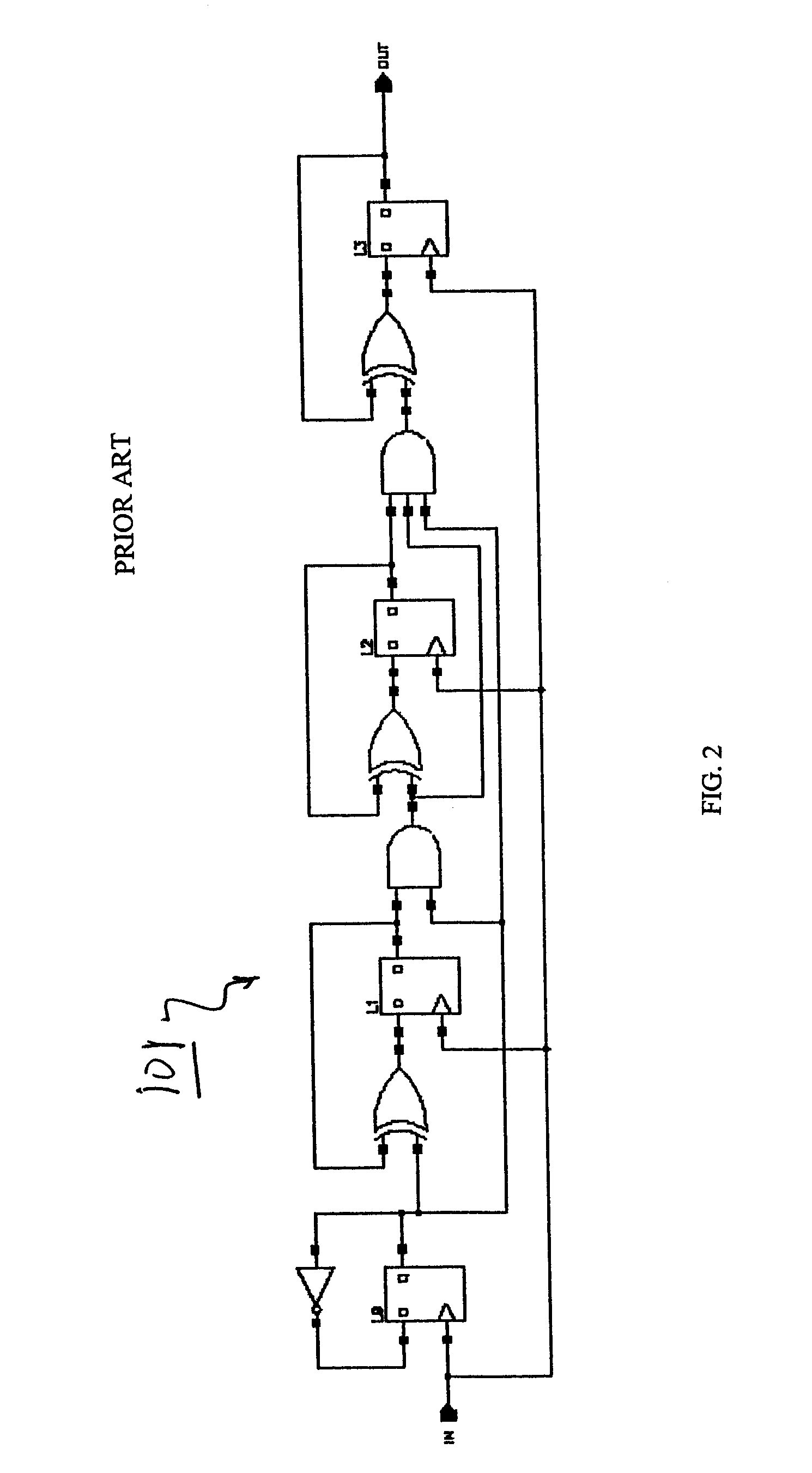

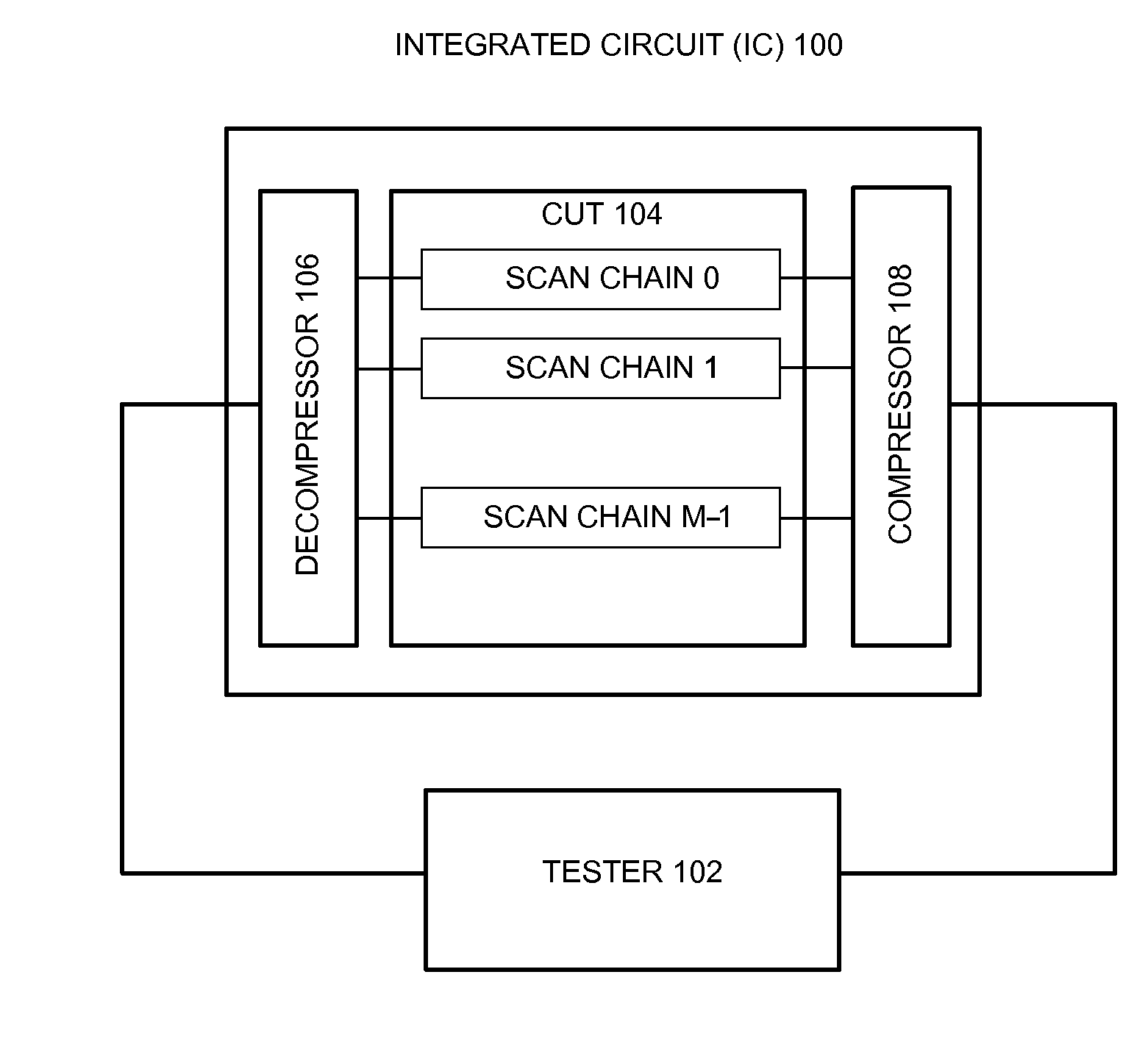

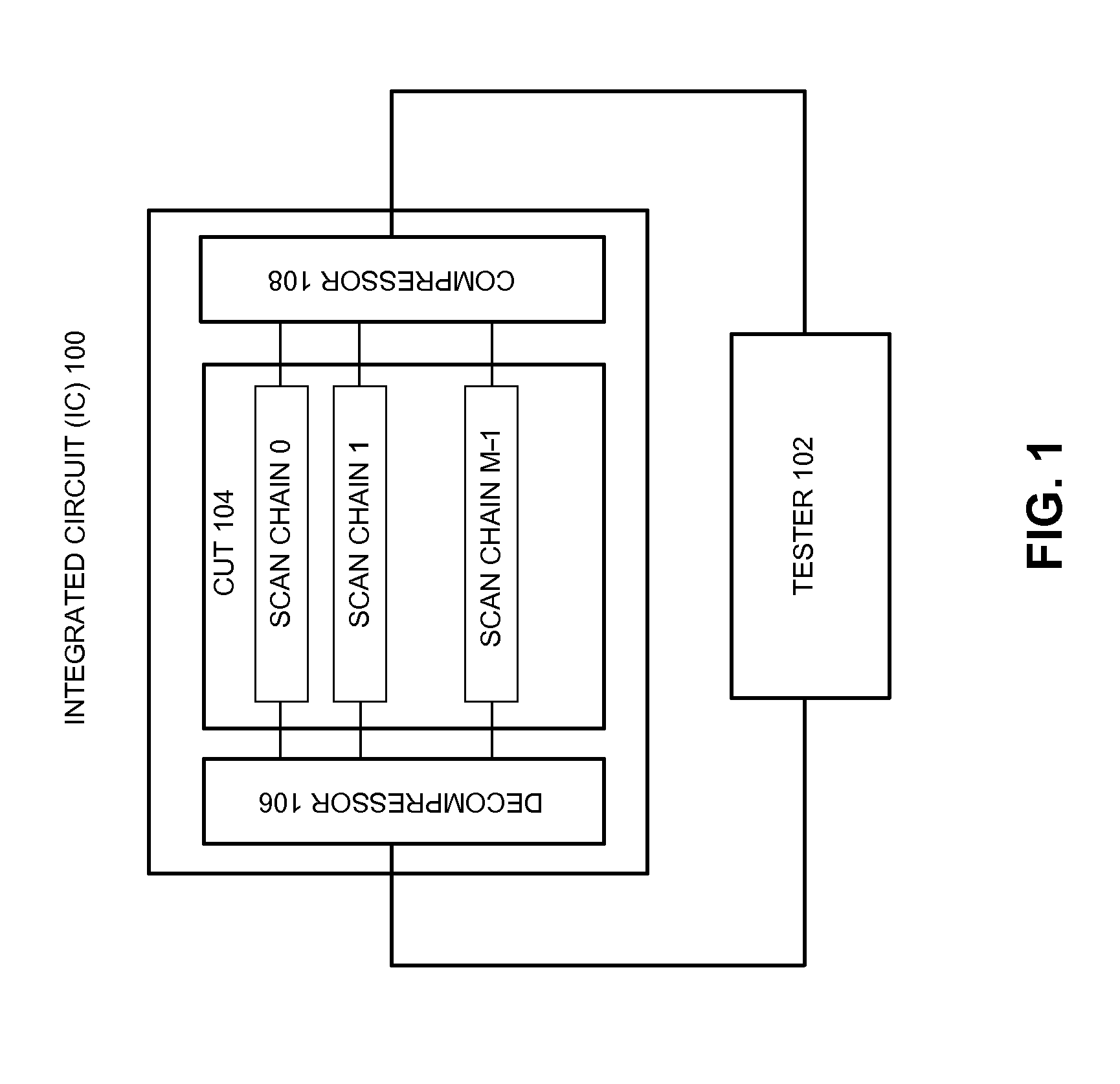

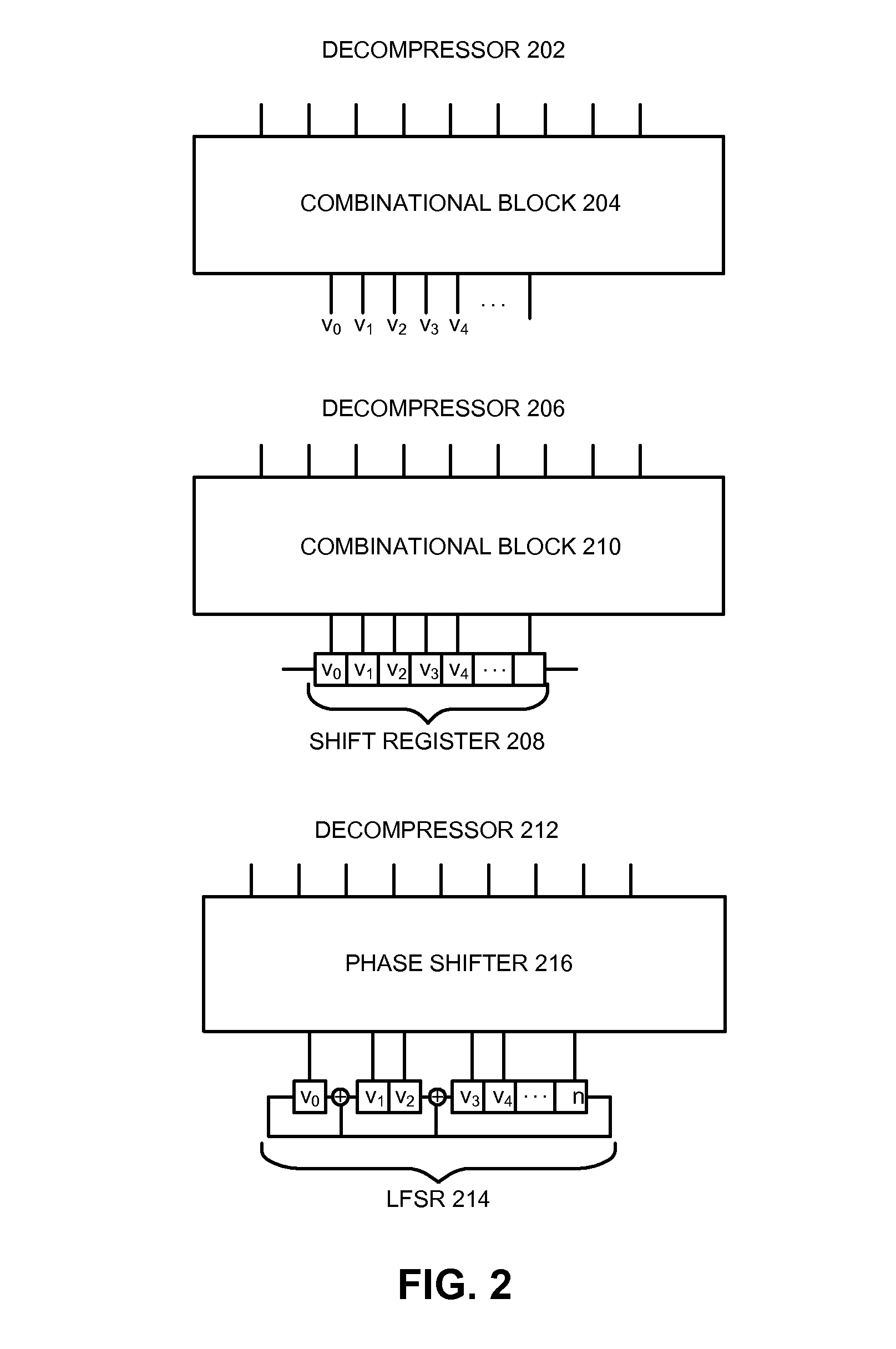

Real-time decoder for scan test patterns

InactiveUS6611933B1Cost-efficiently integratedForming accuratelyElectronic circuit testingError detection/correctionComputer hardwareTest efficiency

A method and apparatus for improving the efficiency of scan testing of integrated circuits is described. This efficiency is achieved by reducing the amount of required test stimulus source data and by increasing the effective bandwidth of the scan-load operation. The reduced test data volume and corresponding test time are achieved by integrating a real-time test data decoder or logic network into each integrated circuit chip. The apparatus, servicing a plurality of internal scan chains wherein the number of said internal scan chains exceeds the number of primary inputs available for loading data into the scan chains, includes: a) logic network positioned between the primary inputs and the inputs of the scan chains, the logic network expanding input data words having a width corresponding to the number of the primary inputs, and converting the input data words into expanded output data words having a width that corresponds to the number of the internal scan chains; and b) coupled to the internal scan chains, registers loaded with bit values provided by the expanded output data words while data previously loaded into the scan chains shifts forward within the scan chains by one bit position at a time; wherein a first plurality of the input data words supplied to the primary inputs produce a second plurality of expanded data words that are loaded into the internal scan chains to achieve an improved test coverage.

Owner:GOOGLE LLC

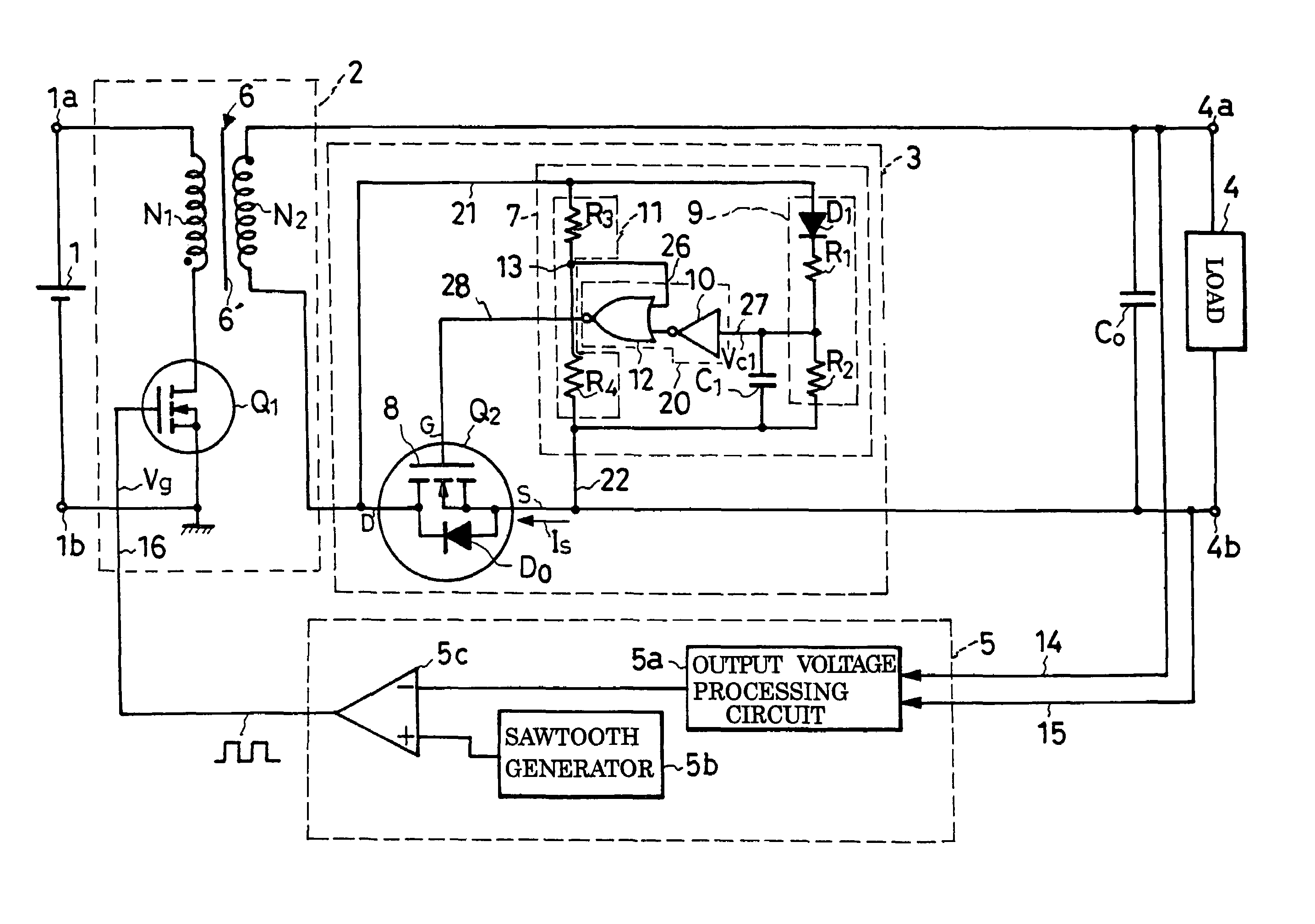

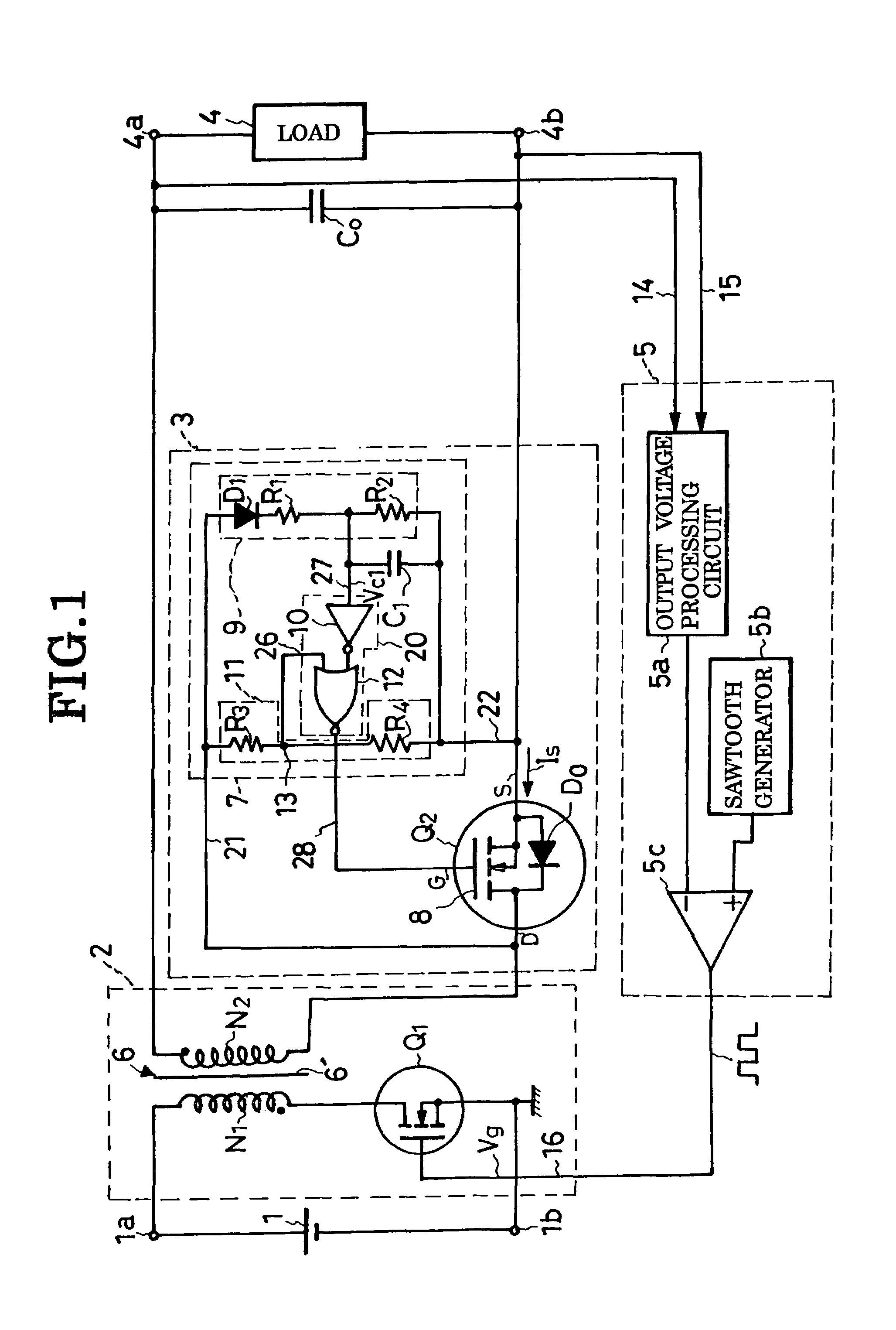

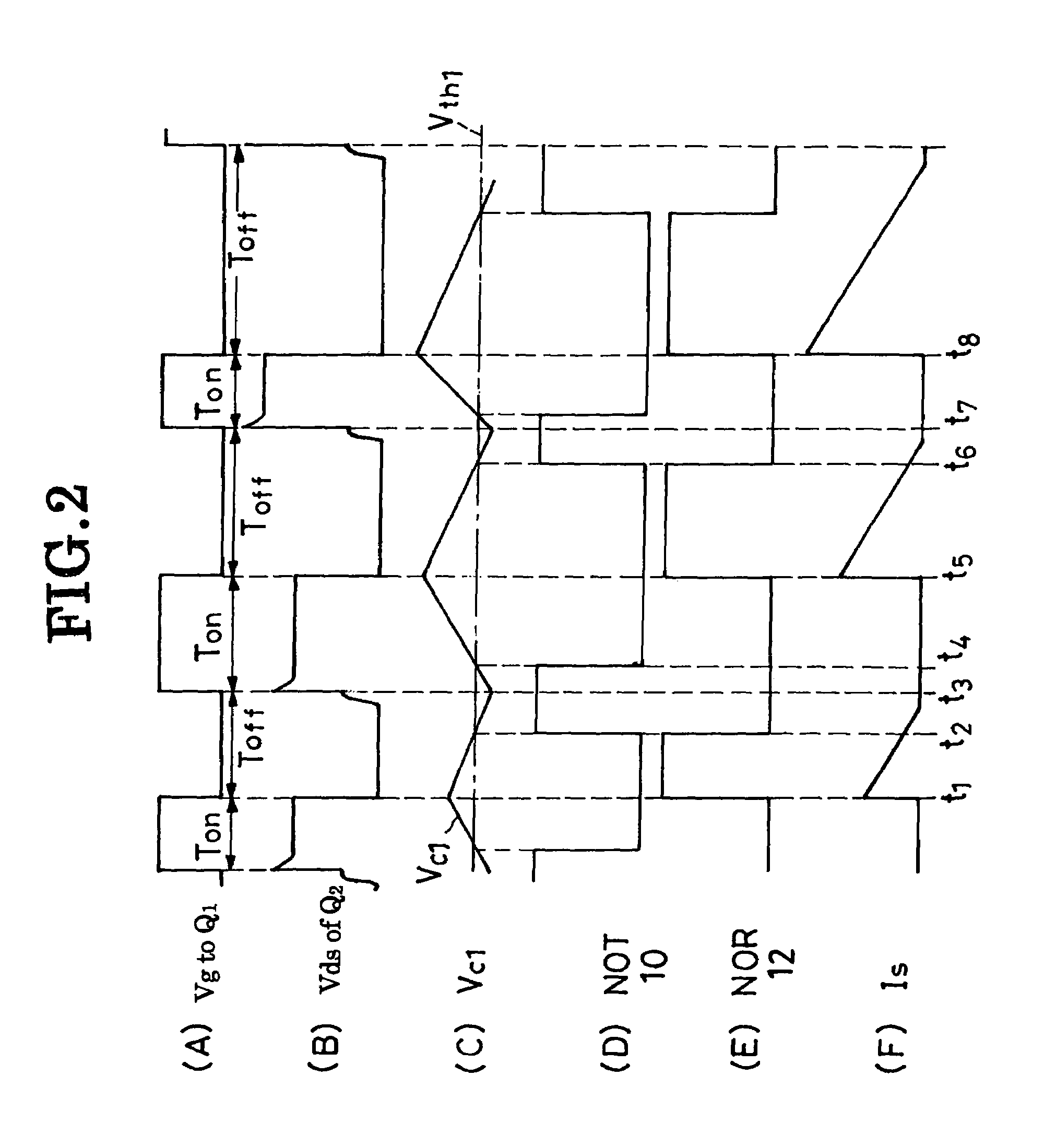

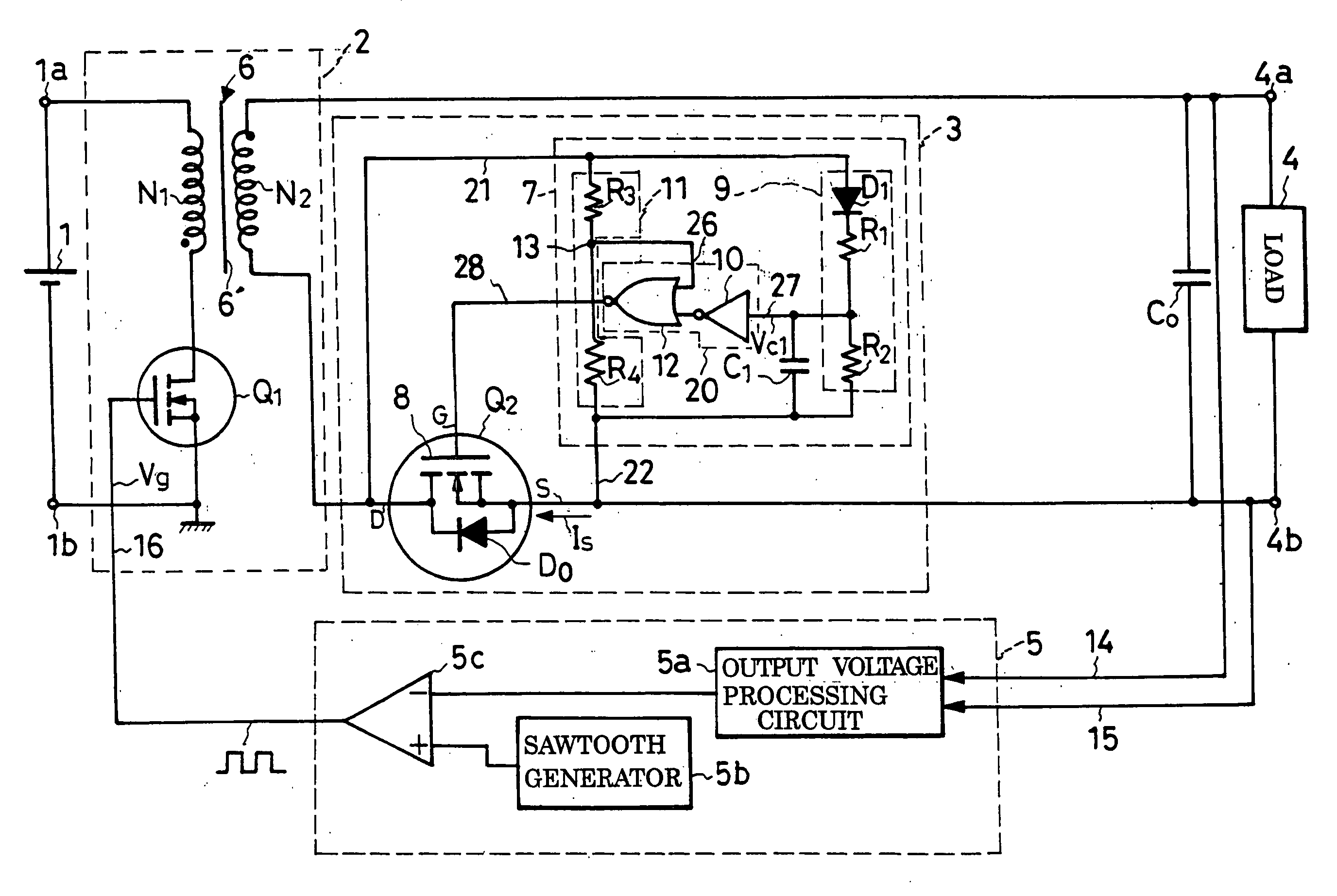

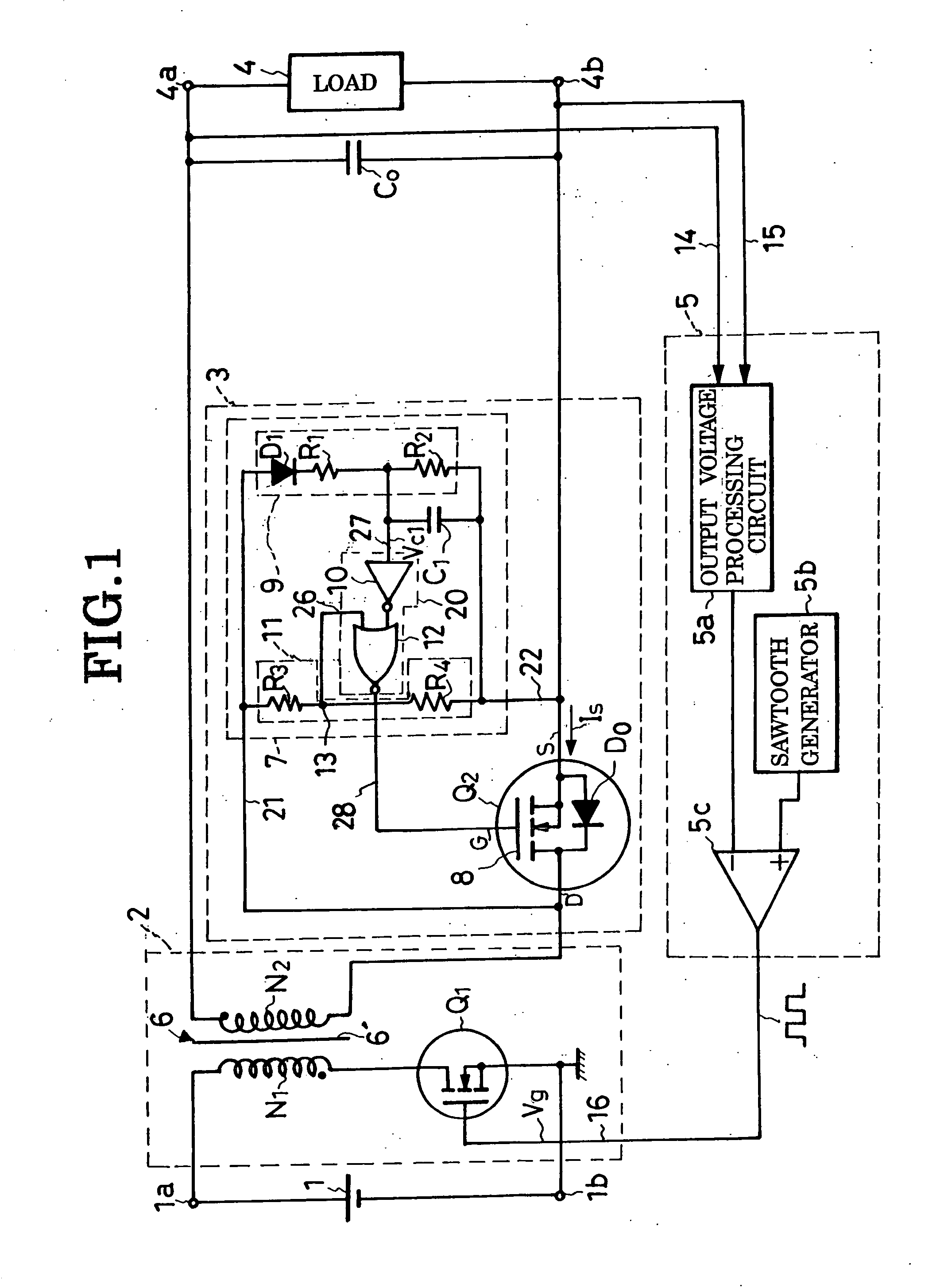

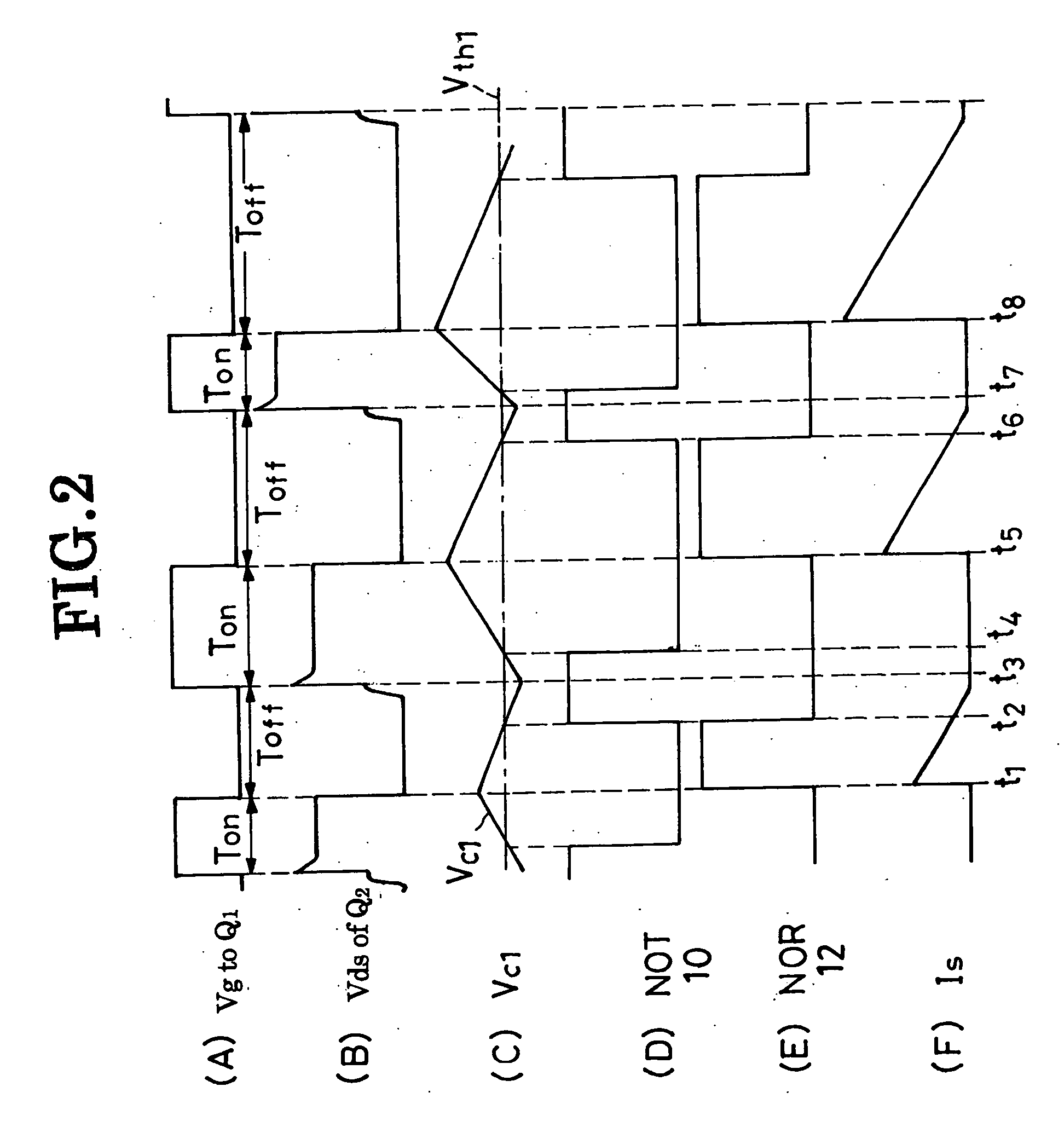

Switching-mode power supply having a synchronous rectifier

InactiveUS7120036B2Save the problemImprove efficiencyAc-dc conversion without reversalEfficient power electronics conversionCapacitor voltageFeedback circuits

A DC-to-DC converter incorporates a transformer having a primary winding connected to a pair of DC input terminals via an active switch, which turns on and off under the control of a feedback circuit, and a secondary winding connected to a pair of DC output terminals via a synchronous rectifier and a smoothing capacitor. The synchronous rectifier is a parallel connection of a synchronous rectifier switch and a diode. A synchronous rectifier control circuit is connected to the synchronous rectifier switch for causing conduction therethrough while the active switch is off. The synchronous rectifier control circuit comprises a capacitor for determination of the conducting periods of the synchronous rectifier switch, and a logic network for on / off control of the synchronous rectifier switch according to whether the active switch is on or off and whether the capacitor voltage is higher than a predefined threshold or not.

Owner:SANKEN ELECTRIC CO LTD

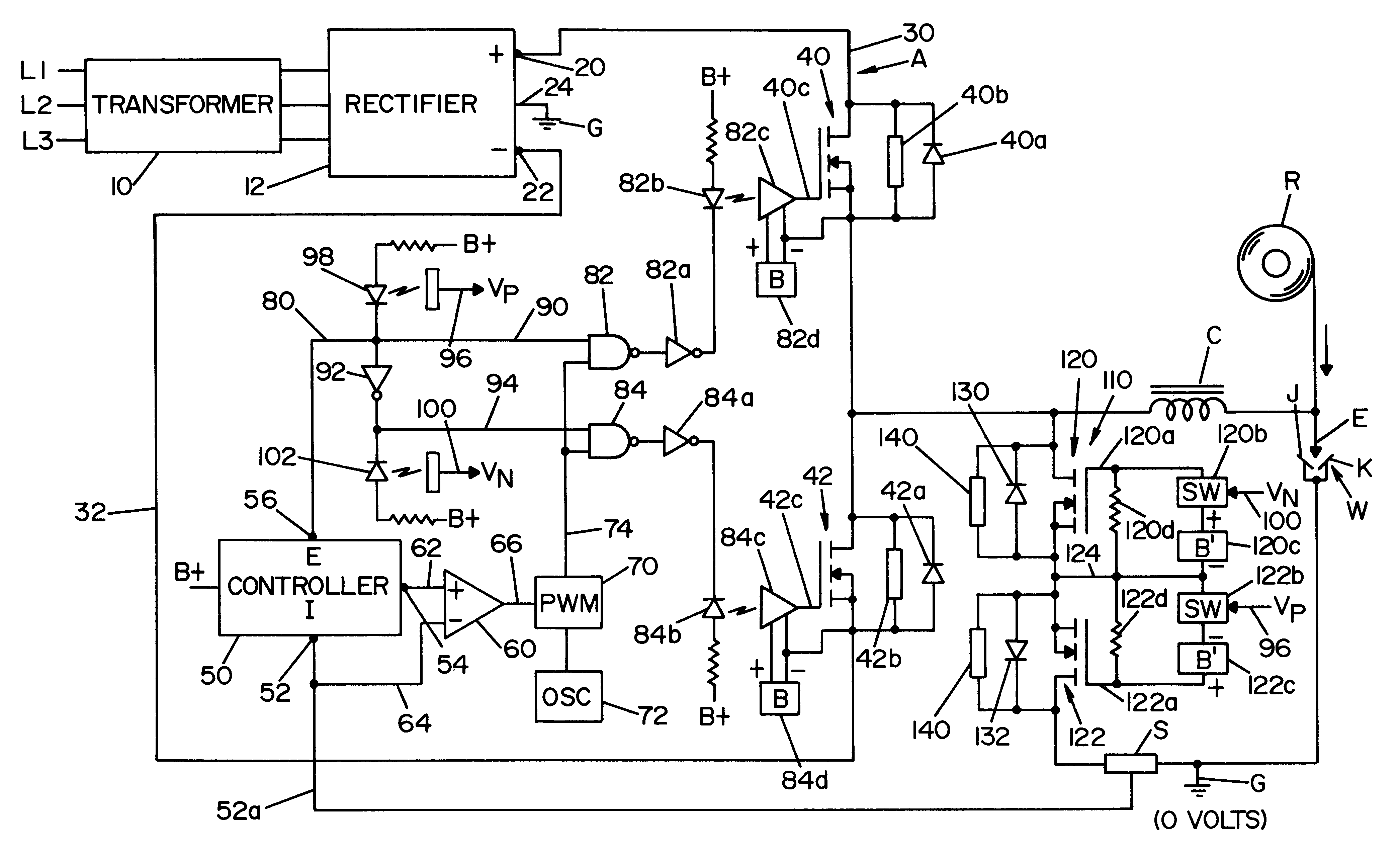

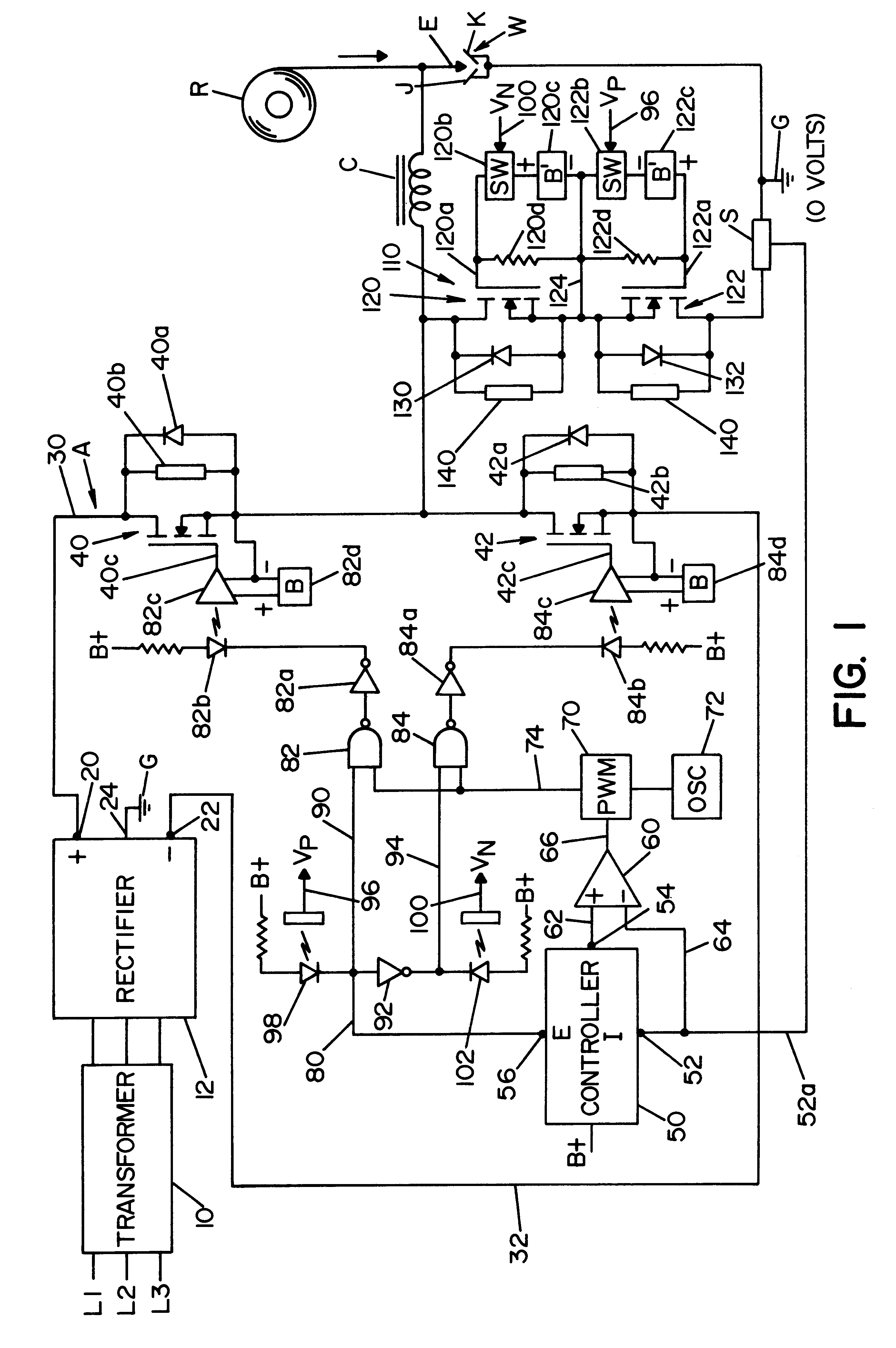

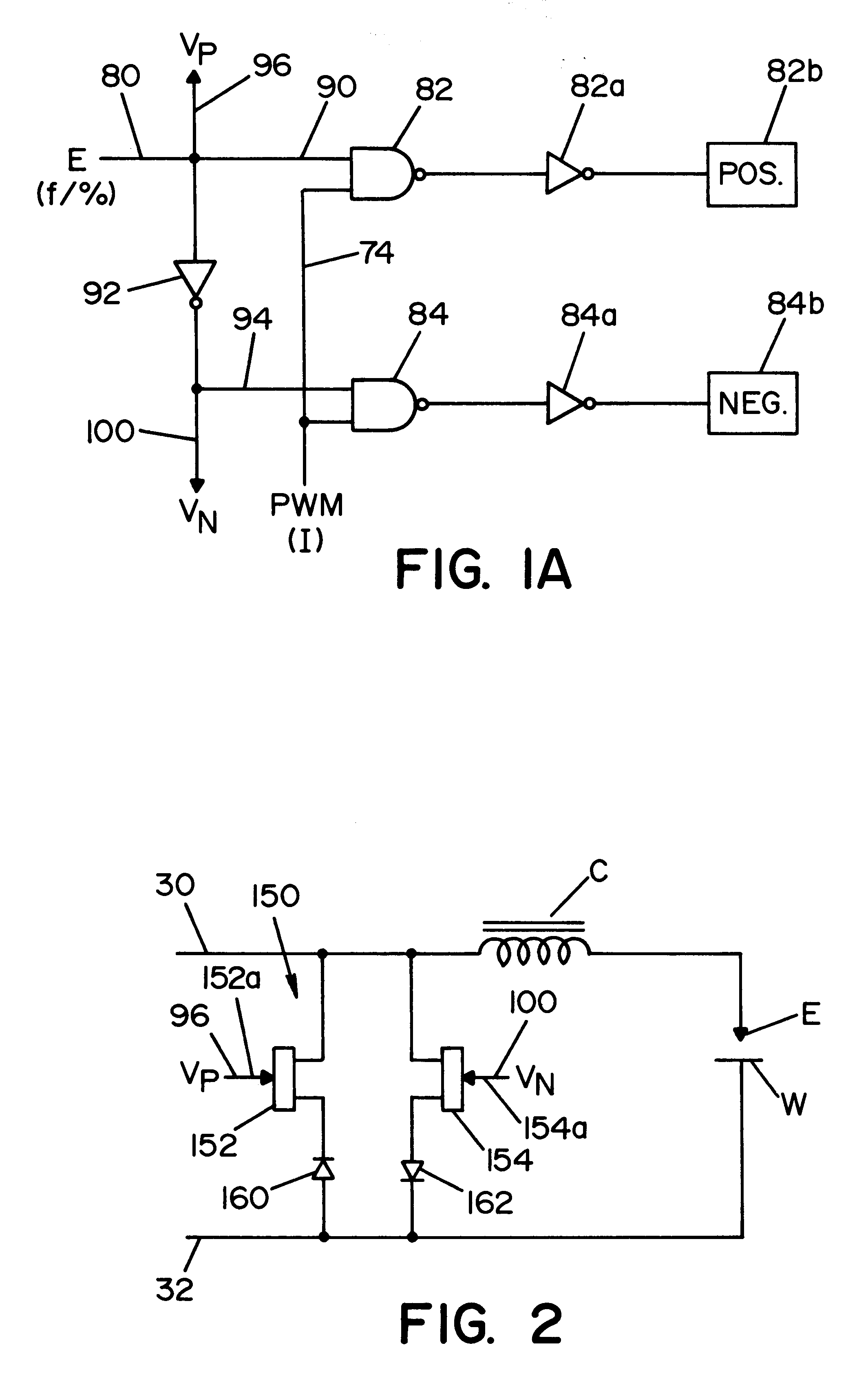

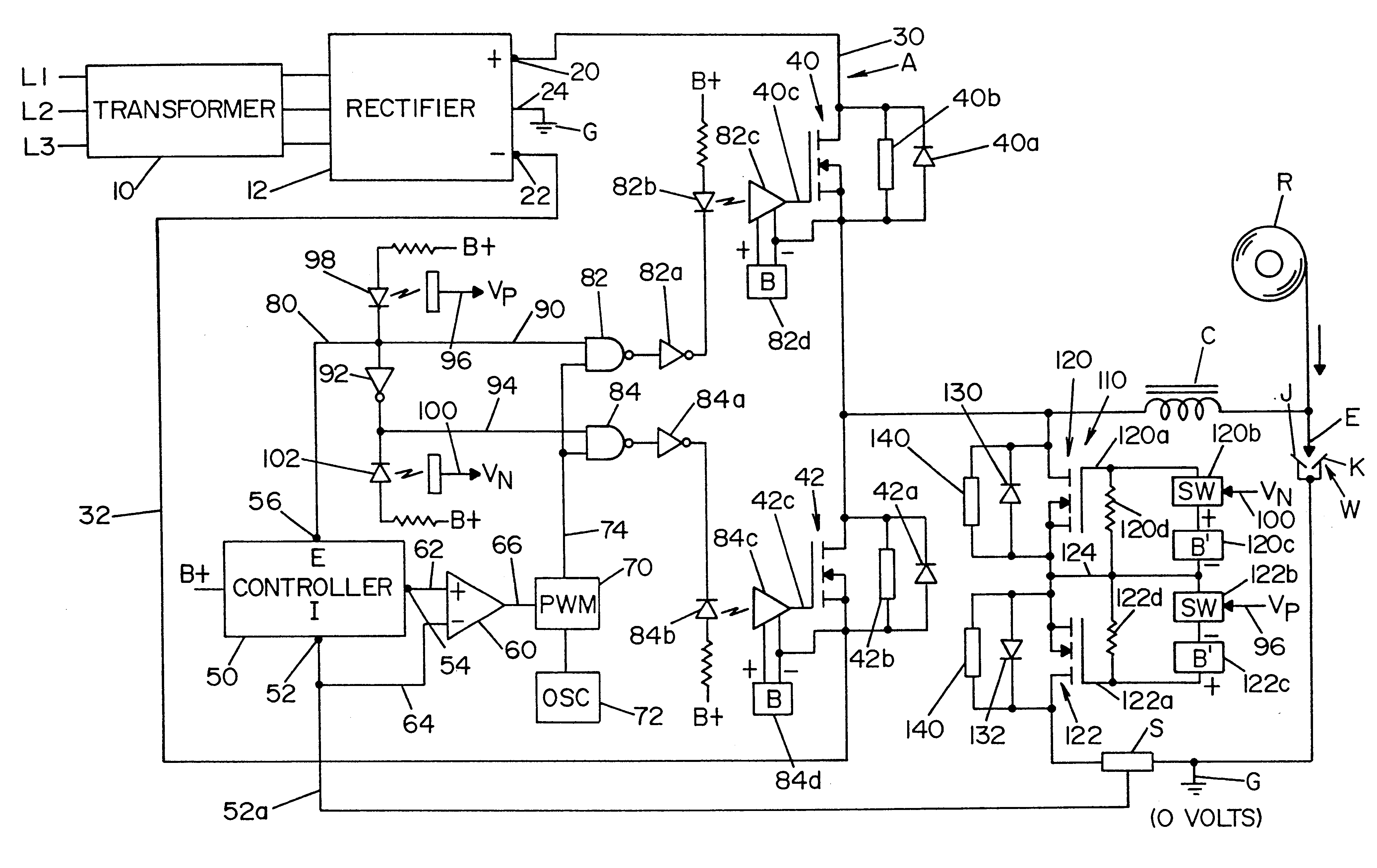

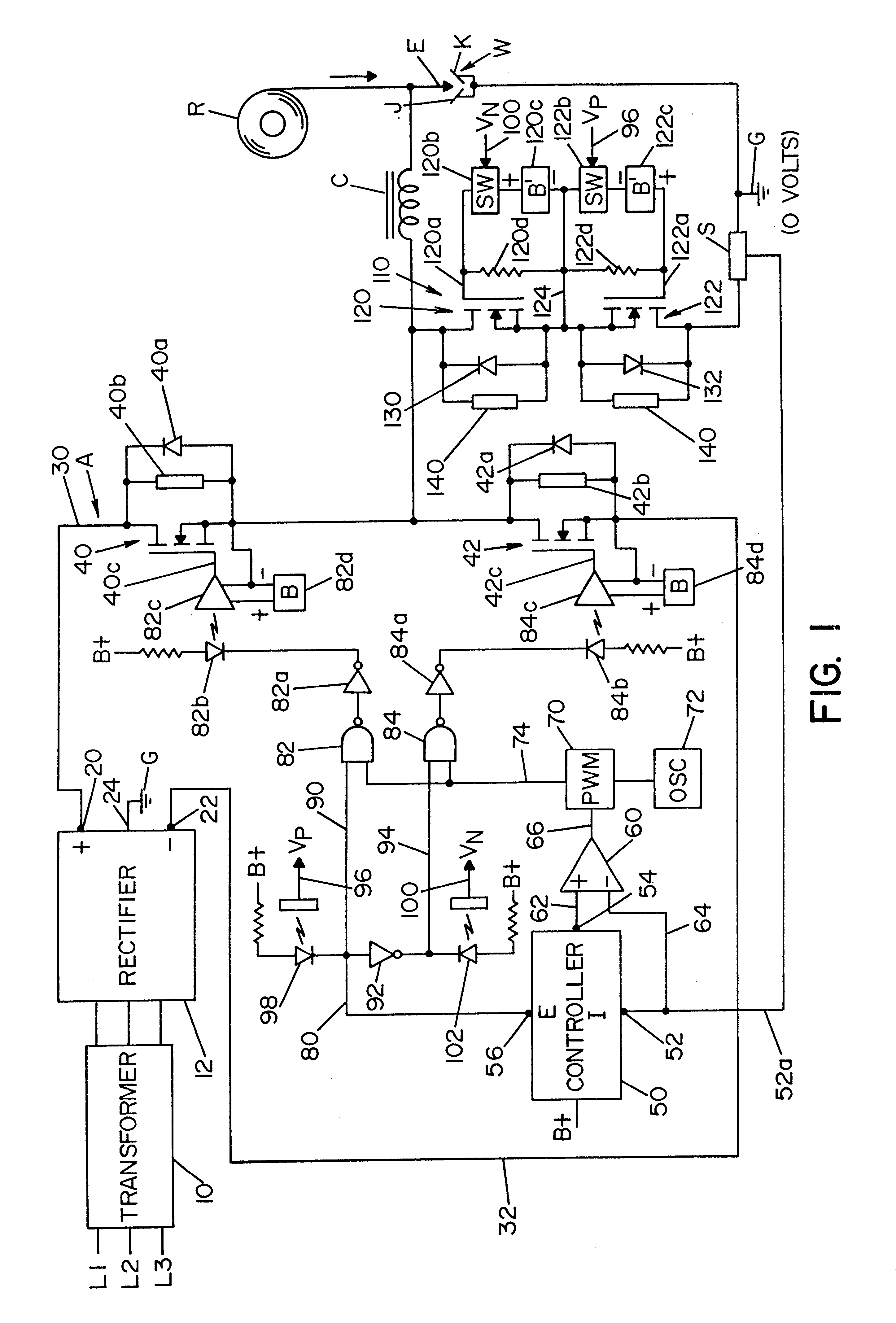

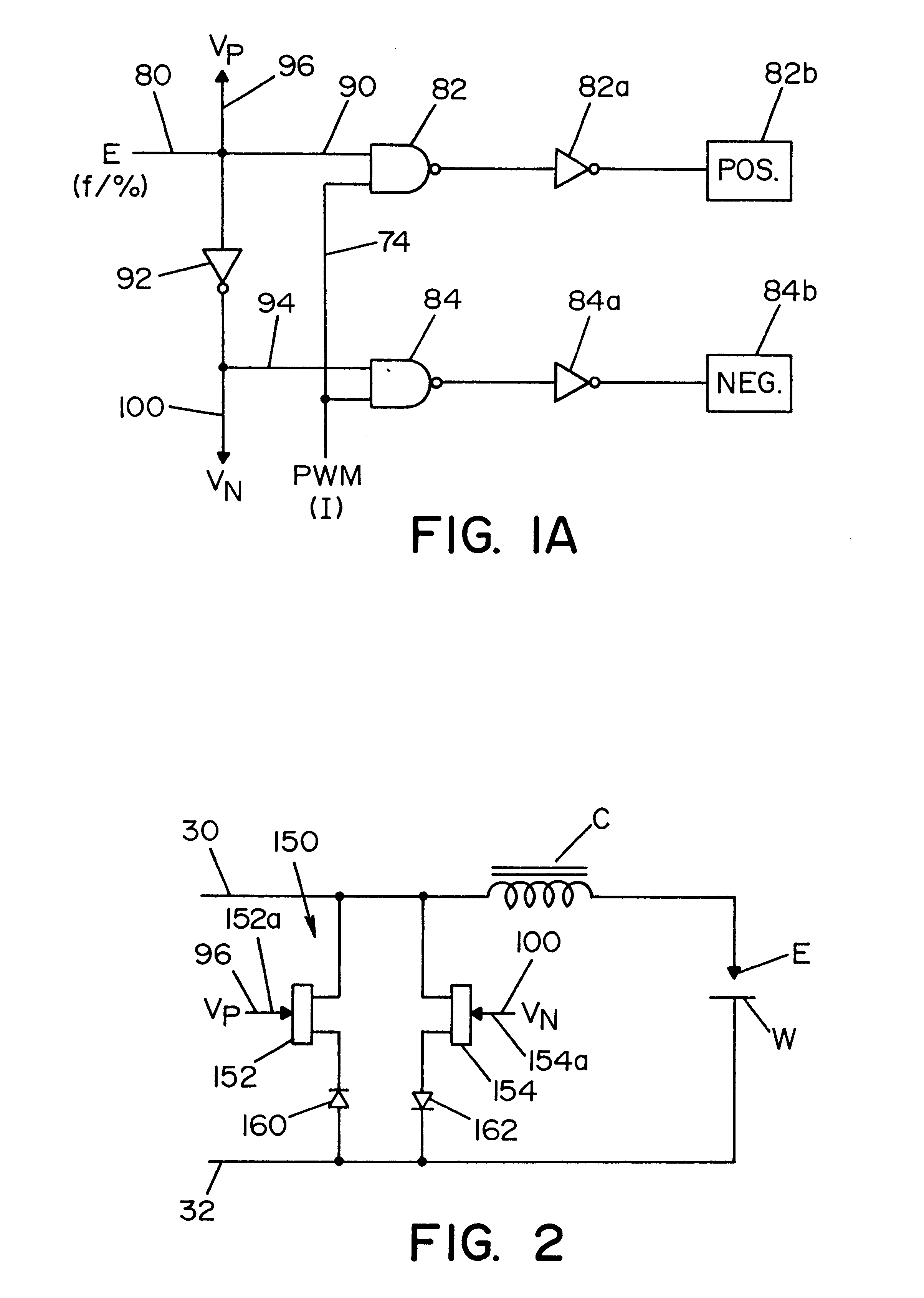

Power supply for electric arc welding

InactiveUS6365874B1Inexpensive power supplySubstantial engineeringArc welding apparatusAc-ac conversionTransformerLogic network

A power supply connectable to a source of AC line voltage for AC electric arc welding by an AC arc current across a welding gap between an electrode and a workpiece, the power supply comprises a high capacity transformer that converts said line voltage to an AC output voltage, and a rectifier that converts the AC output voltage to a DC voltage between a positive terminal and a common terminal at generally zero volts and a negative terminal and the common terminal. The power supply has a first switch that connects the positive terminal to the common terminal across the gap when a gate signal is applied to the first switch, a second switch for connecting the negative terminal to the common terminal across the gap when a gate signal is applied to the second switch and a pulse width modulator operated for generating pulses at a frequency of at least about 18 kHz. A logic network has a first circuit for directing the pulses to the first switch for a first time, a second circuit for directing the pulses to the second switch for a second time and a controller to alternately operate first and second circuits to create AC arc welding current.

Owner:LINCOLN GLOBAL INC

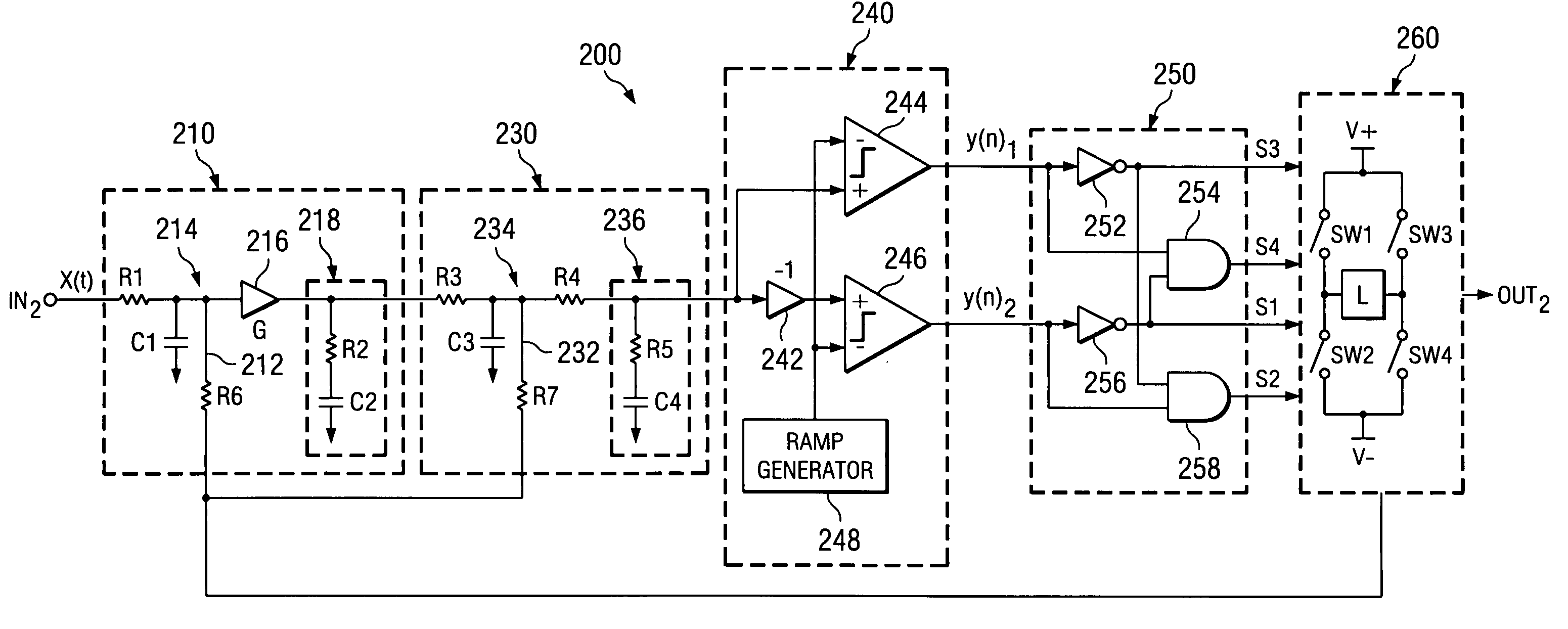

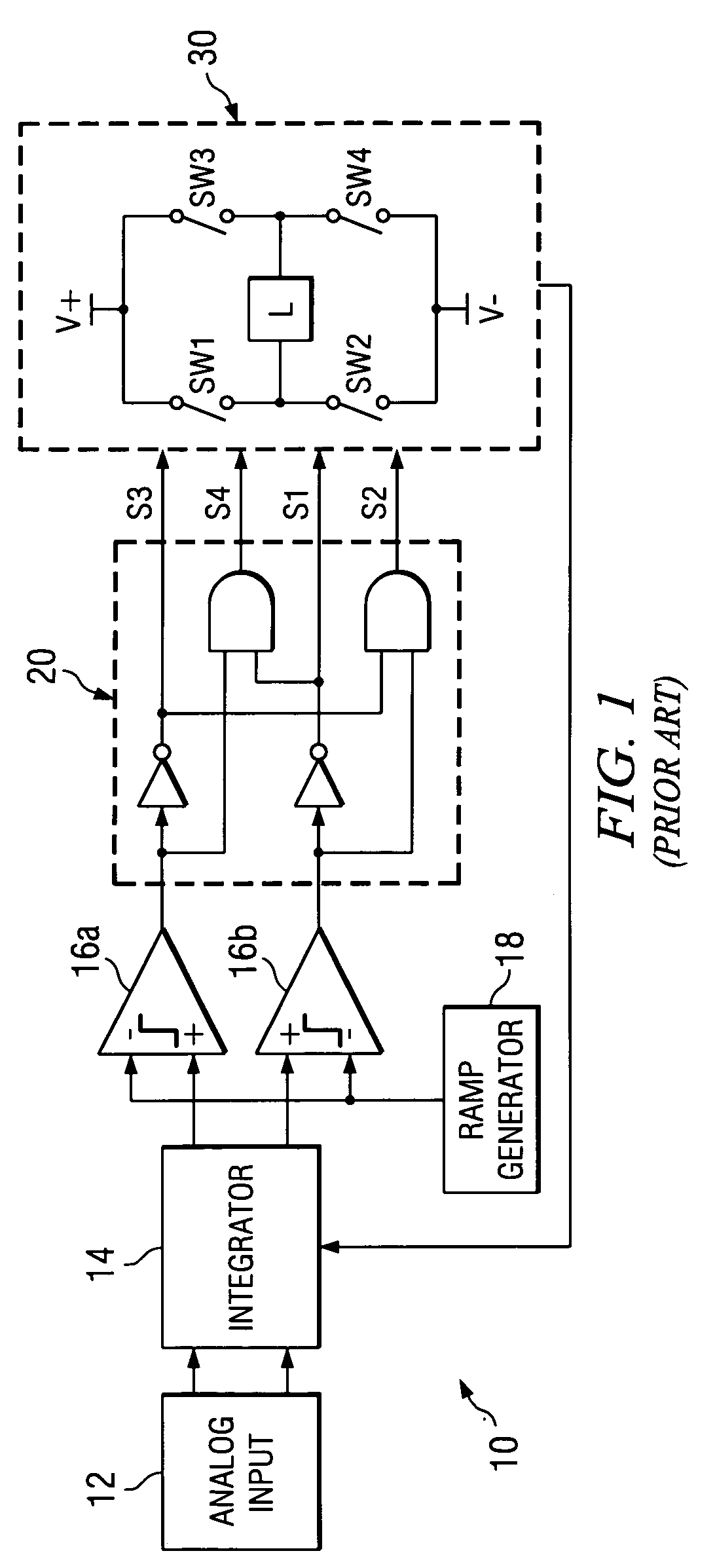

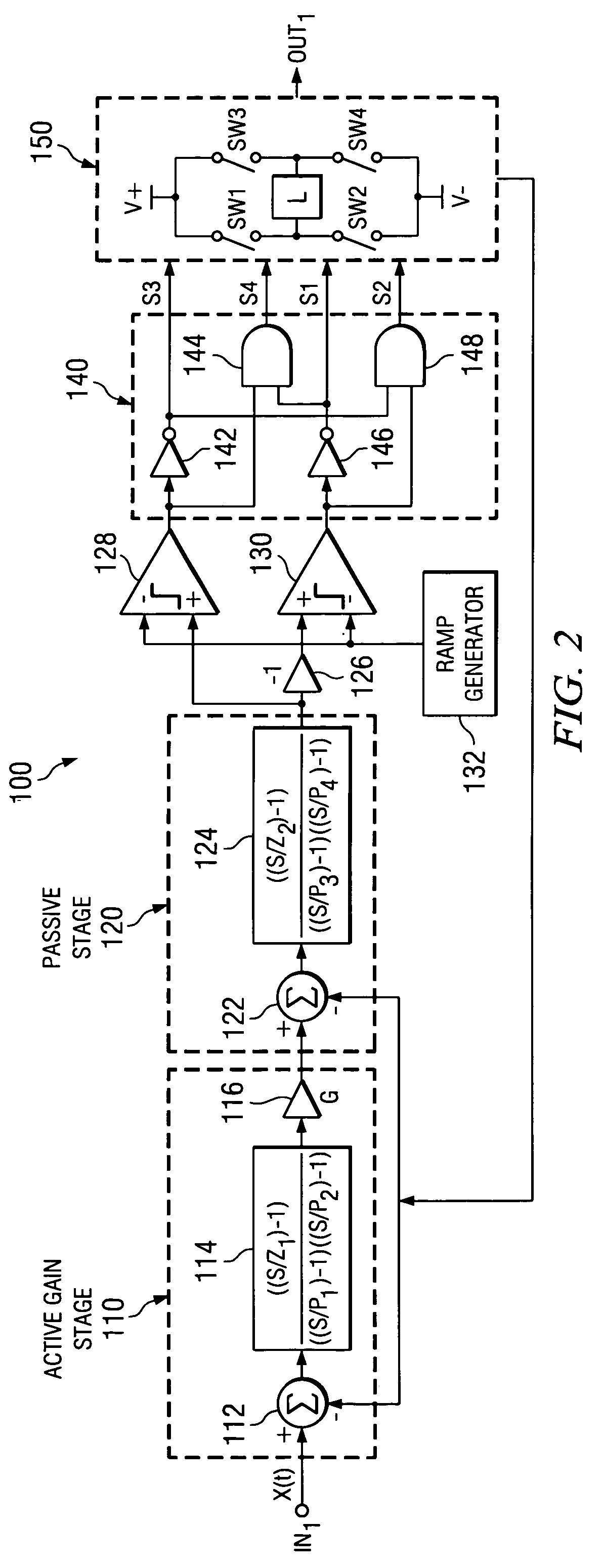

Class-D amplifier having high order loop filtering

InactiveUS20060044057A1High SNDR performanceImprove PSRRNegative-feedback-circuit arrangementsDc amplifiers with modulator-demodulatorLow-pass filterClass-D amplifier

An amplifier having an active and passive gain stage connect to a load for driving a load according to a system analog input. A first embodiment of the amplifier in accordance with the present invention includes a logic network connected between a comparator network and a switching system, wherein the comparator network connects to the passive gain stage. Specifically, the active gain stage may include an active filter connected to receive an analog or digital input and provide a difference between the analog or digital input and the feedback signal relative to the gain factor of a gain unit connected to the active filter. The passive gain stage includes a passive filter. The logic network generates at least one switching signal which controls the switching system that includes at least one switching device to selectively provide power to the load. An output signal from the switching system provides output for the amplifier and is fed back to the active gain stage. In another embodiment, the output is a two-level signal and the passive and active filters are second order low pass filters, where the gain factor is about 25 or more. In yet another embodiment, the gain factor is approximately 250. Moreover, the amplifier may include a digital delta-sigma modulator connected to supply a two level input.

Owner:TEXAS INSTR INC

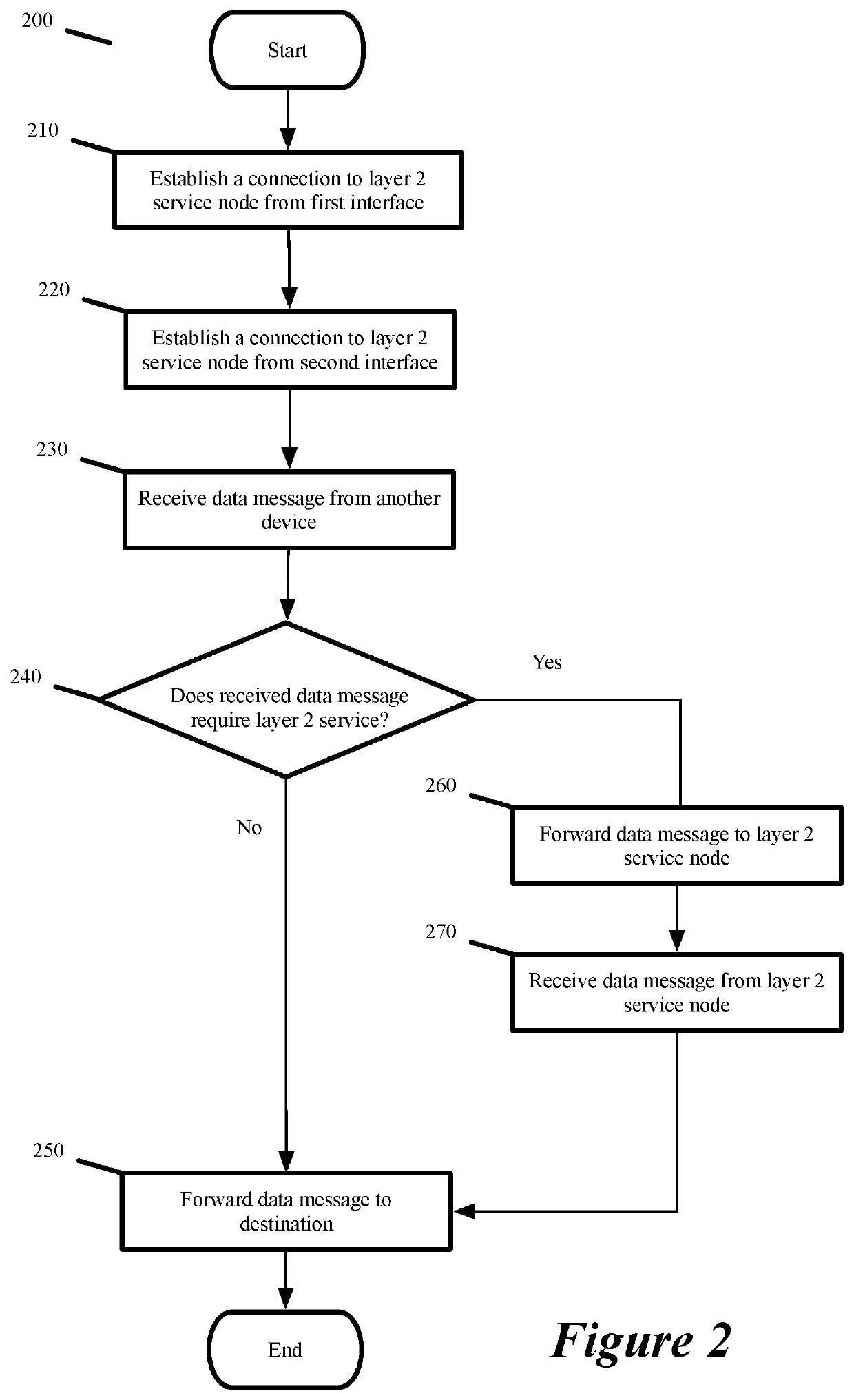

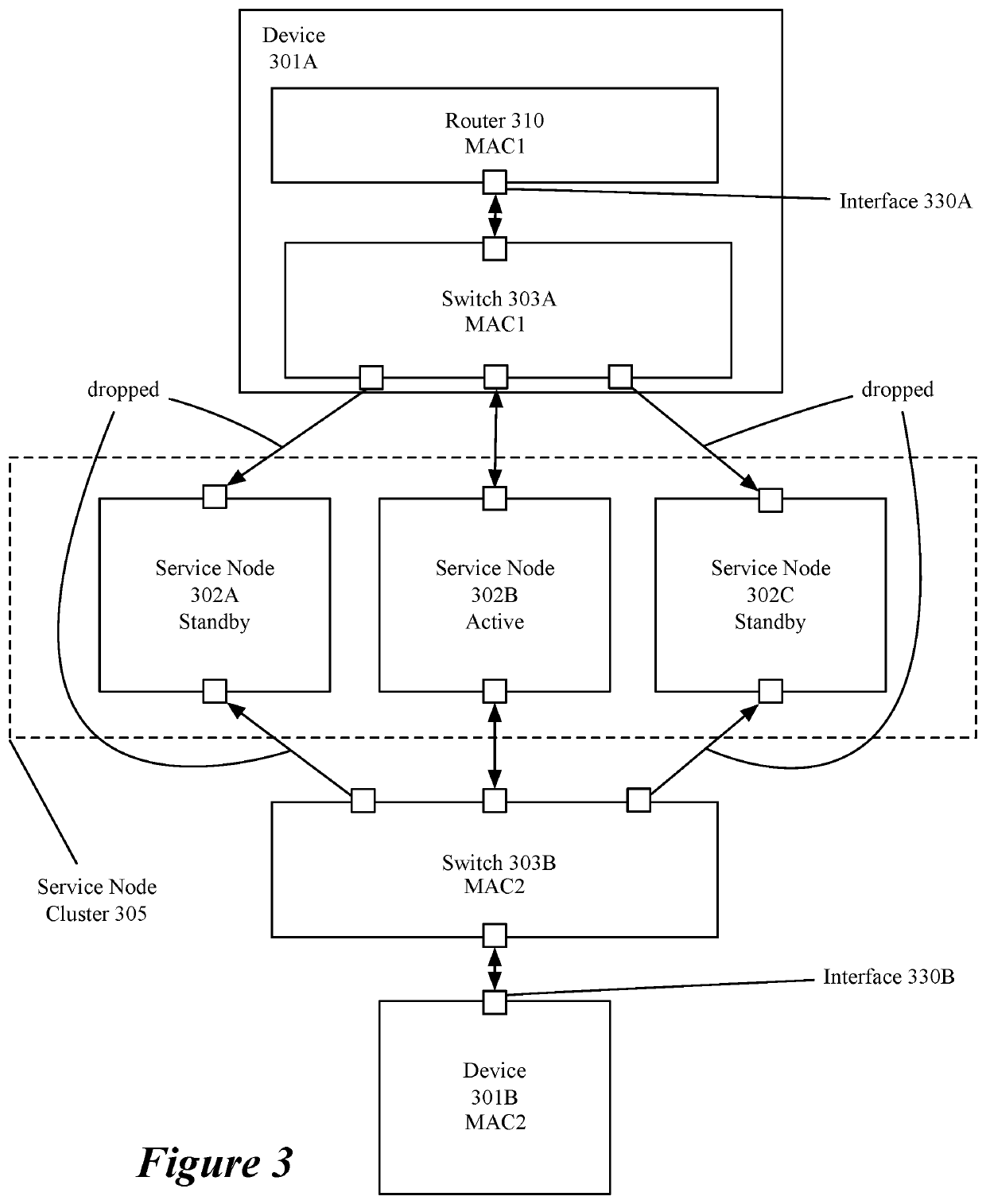

Incorporating layer 2 service between two interfaces of gateway device

ActiveUS10728174B2Shorten the timeDetect failureNetworks interconnectionNetwork connectionsEngineeringLogic network

Owner:NICIRA

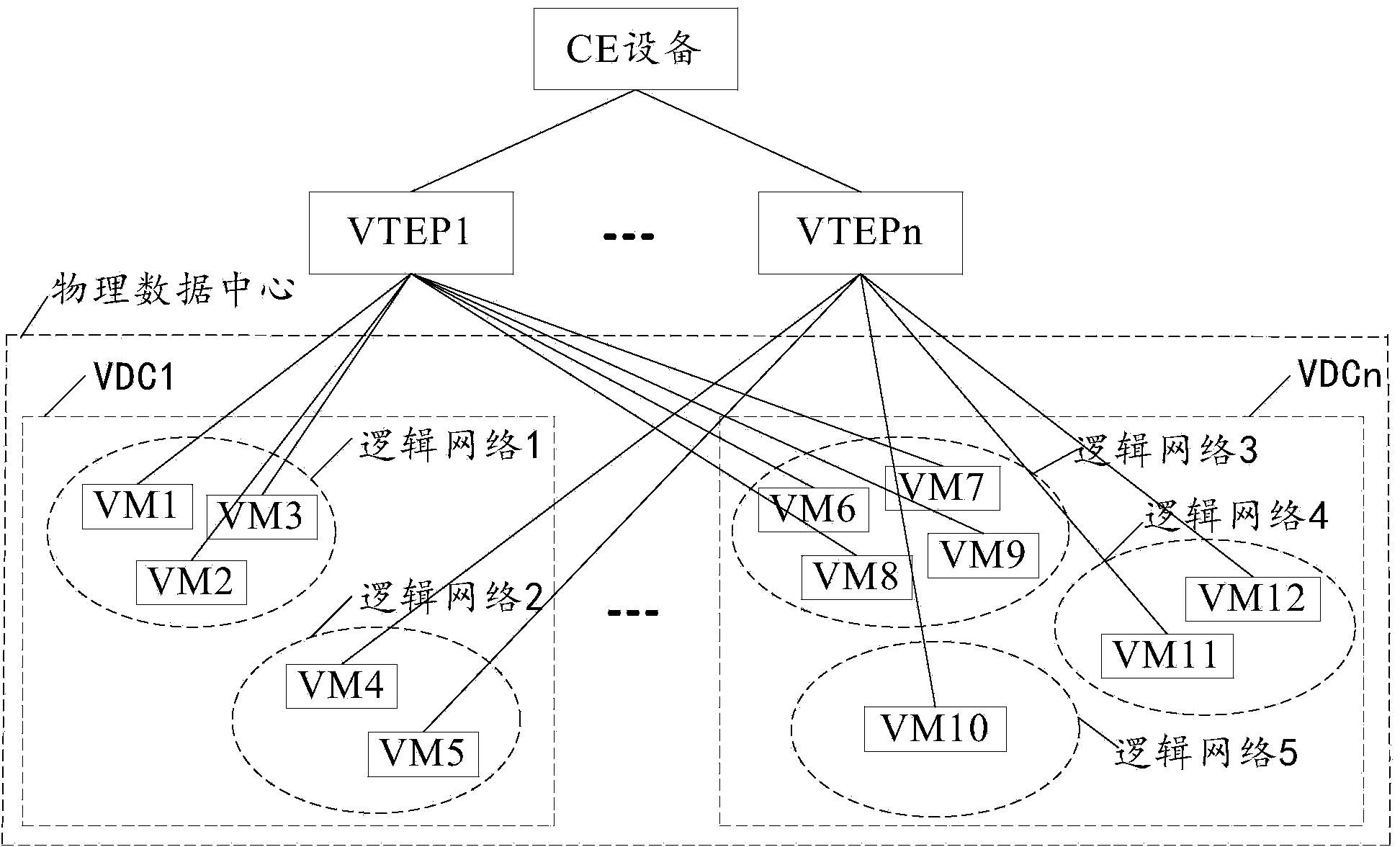

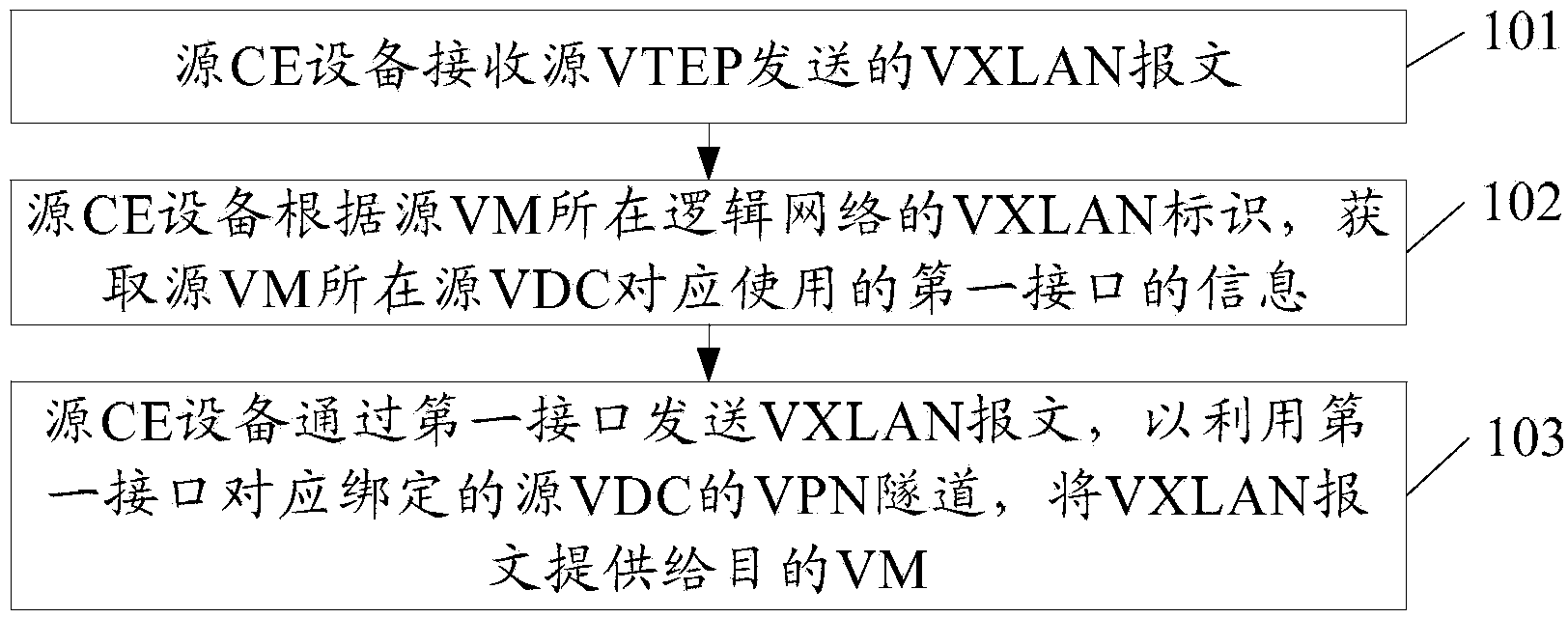

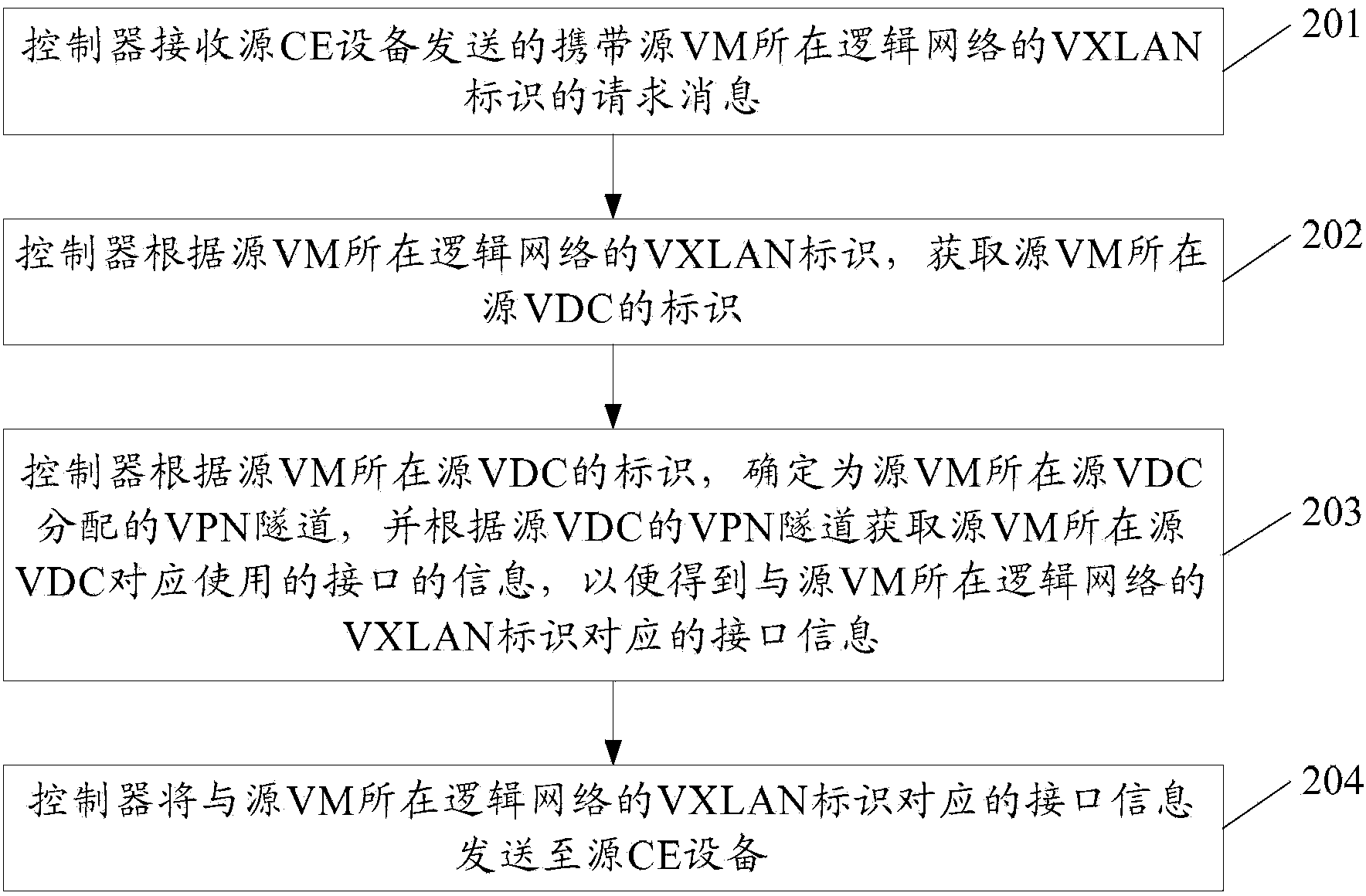

Message sending method and device

The invention discloses a message sending method and device and relates to the communication field. The message sending method and device solve the problem that due to the fact that a message located on a source VM of a certain VDC and sent to a target VM of a cross-physical data center cannot be transmitted through an exclusive VPN channel of the VDC, the QOS of the VDC cannot be guaranteed. According to the scheme, a source CE device receives a VXLAN message sent by a VTEP, wherein the VXLAN message contains an original data message to be sent to the target VM by the source VM and the VXLAN identification of a logic network where the source VM is located; the source CE device acquires the information of a first interface correspondingly used by the source VDC where the source VM is located according to the VXLAN identification of a logic network where the source VM is located; the source CE device sends the VXLAN message through the first interface to provide the VXLAN message for the target VM by utilizing the VPN channel of the source VDC correspondingly bound by the first interface. The message sending method and device are used for sending messages.

Owner:HUAWEI CLOUD COMPUTING TECH CO LTD

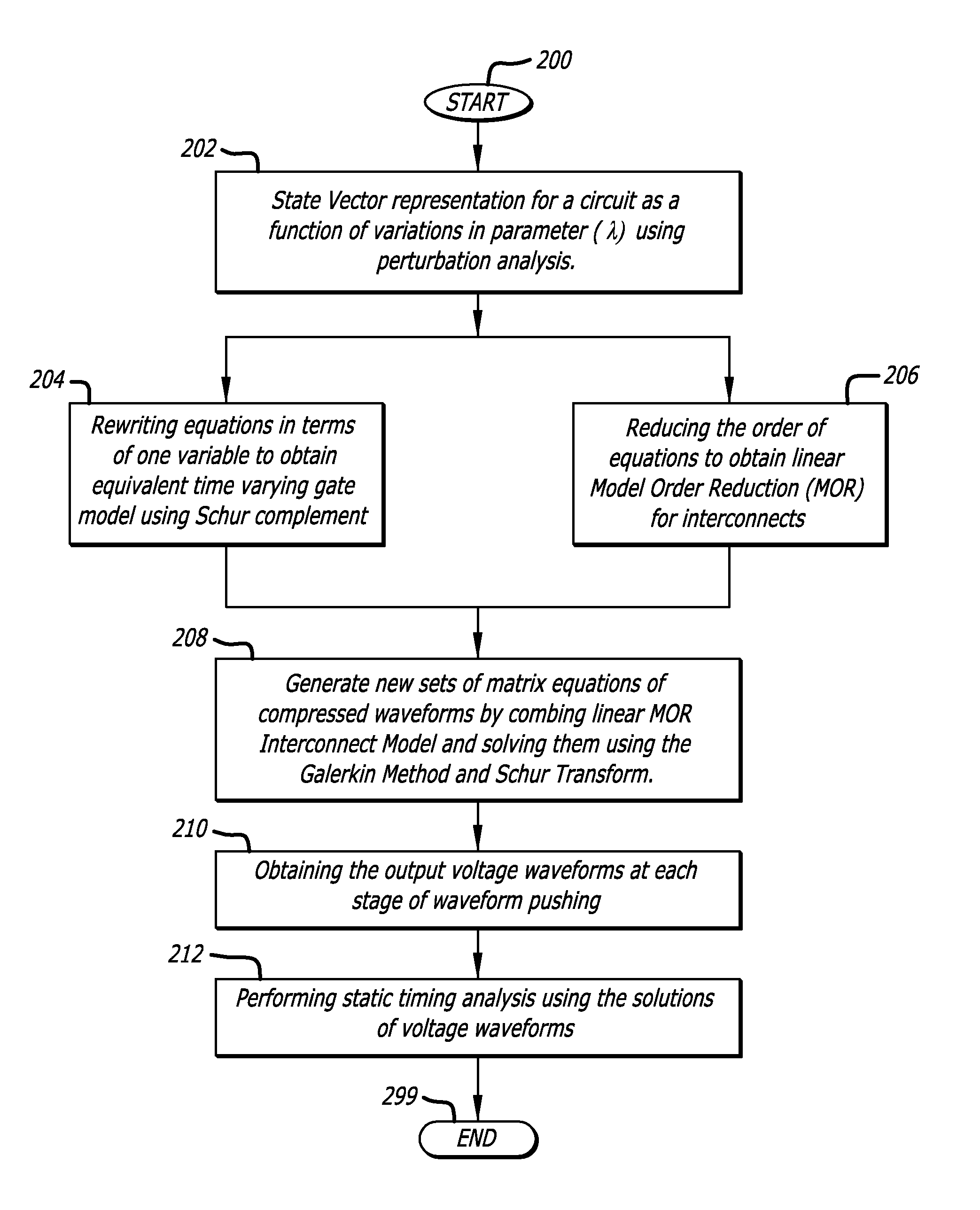

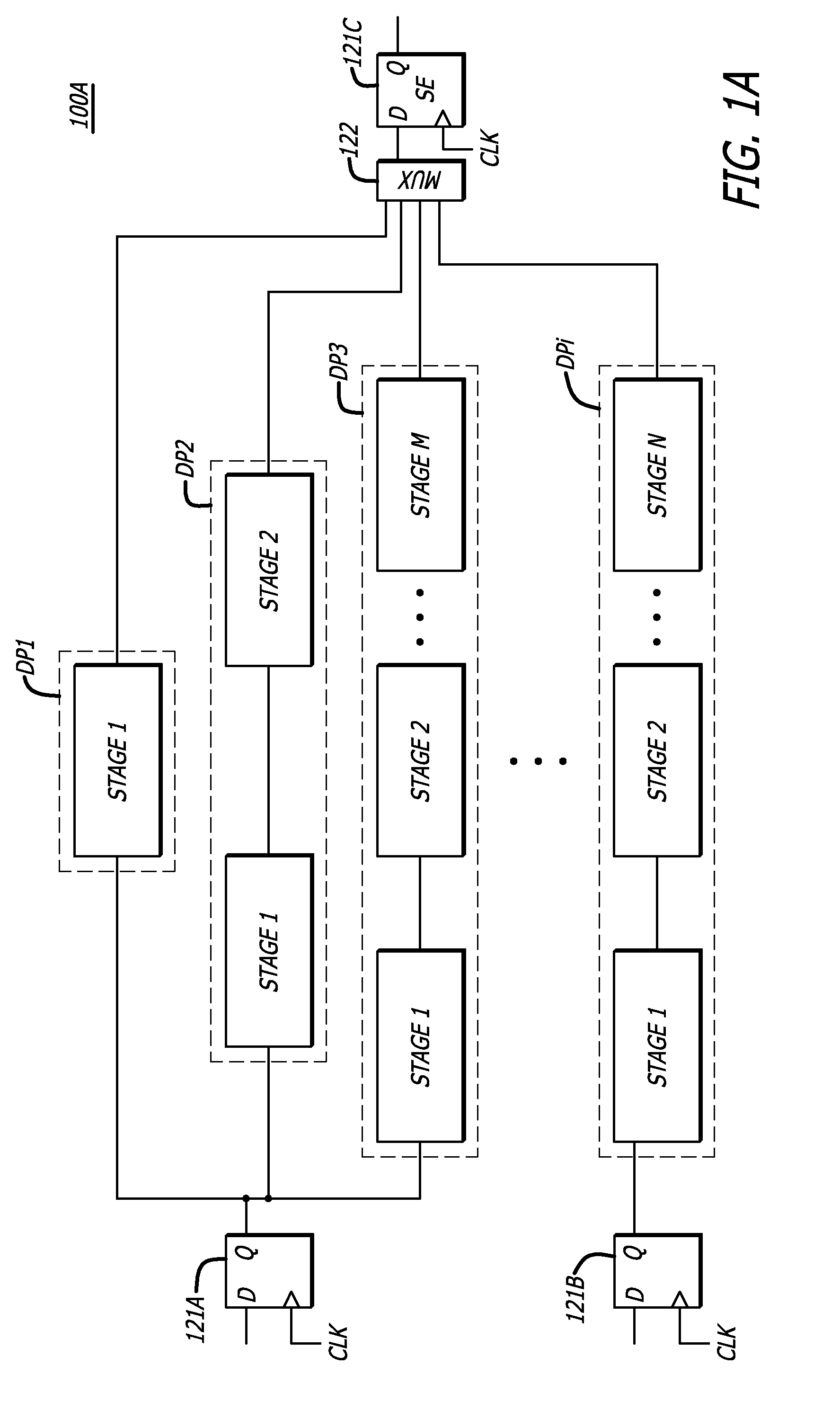

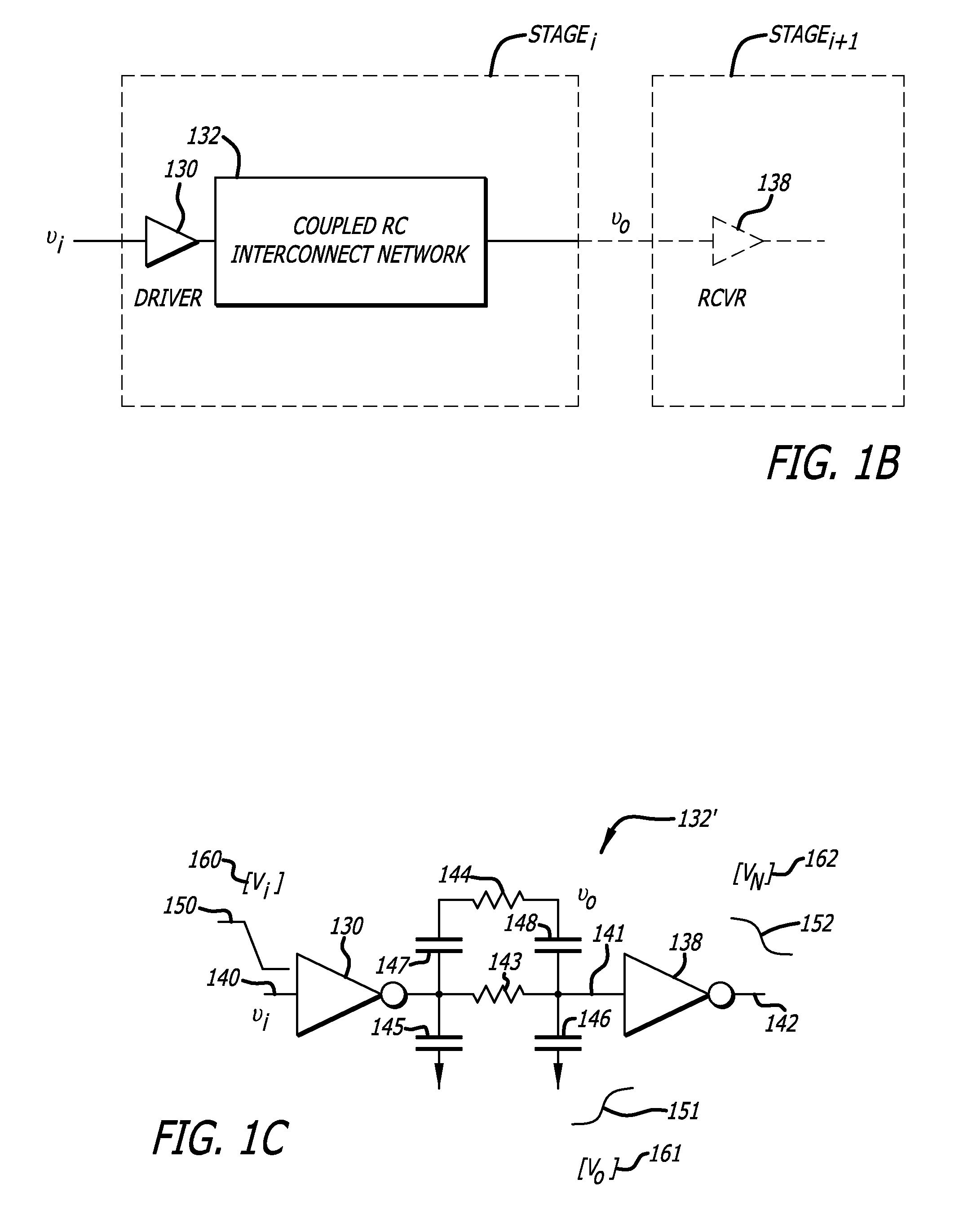

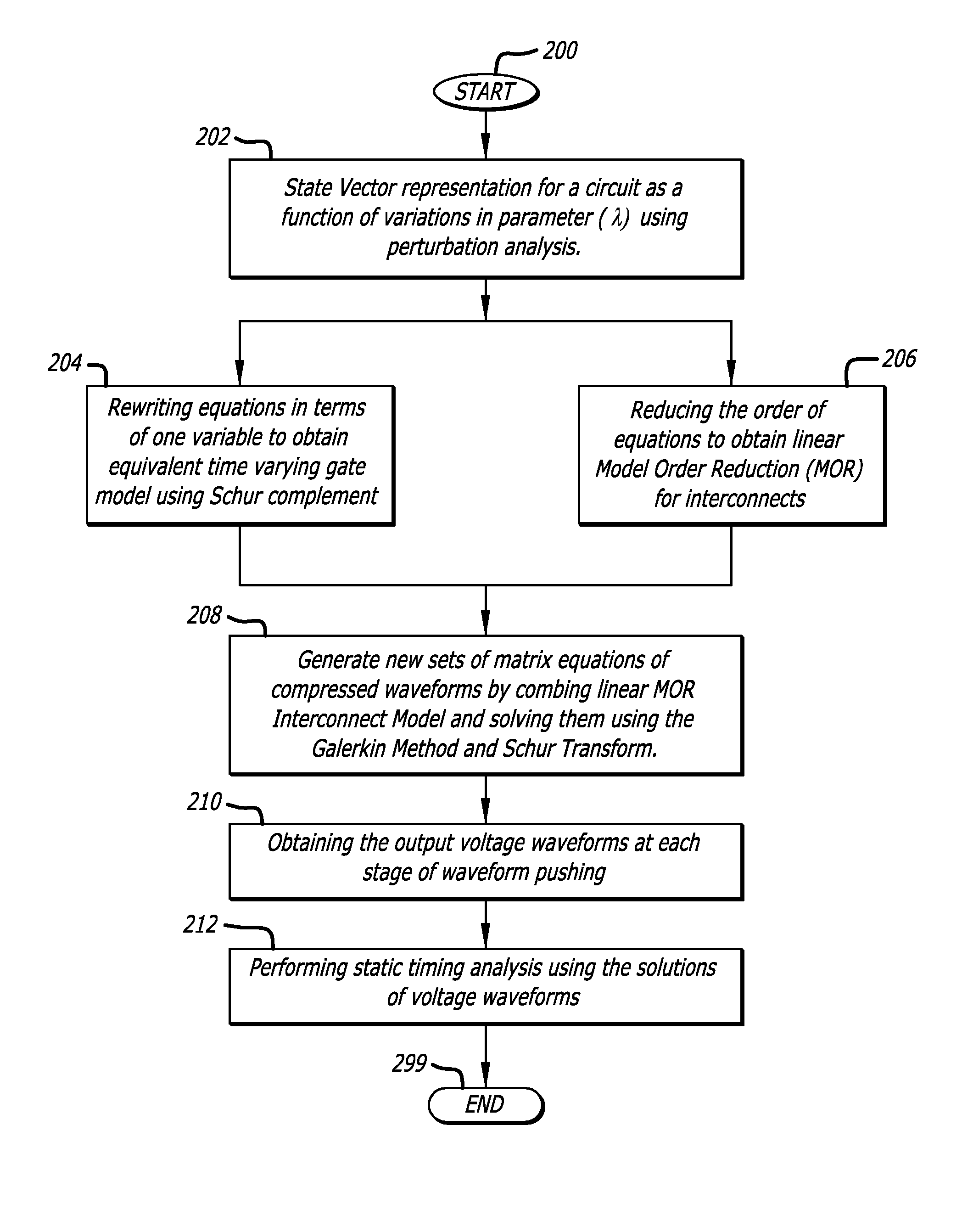

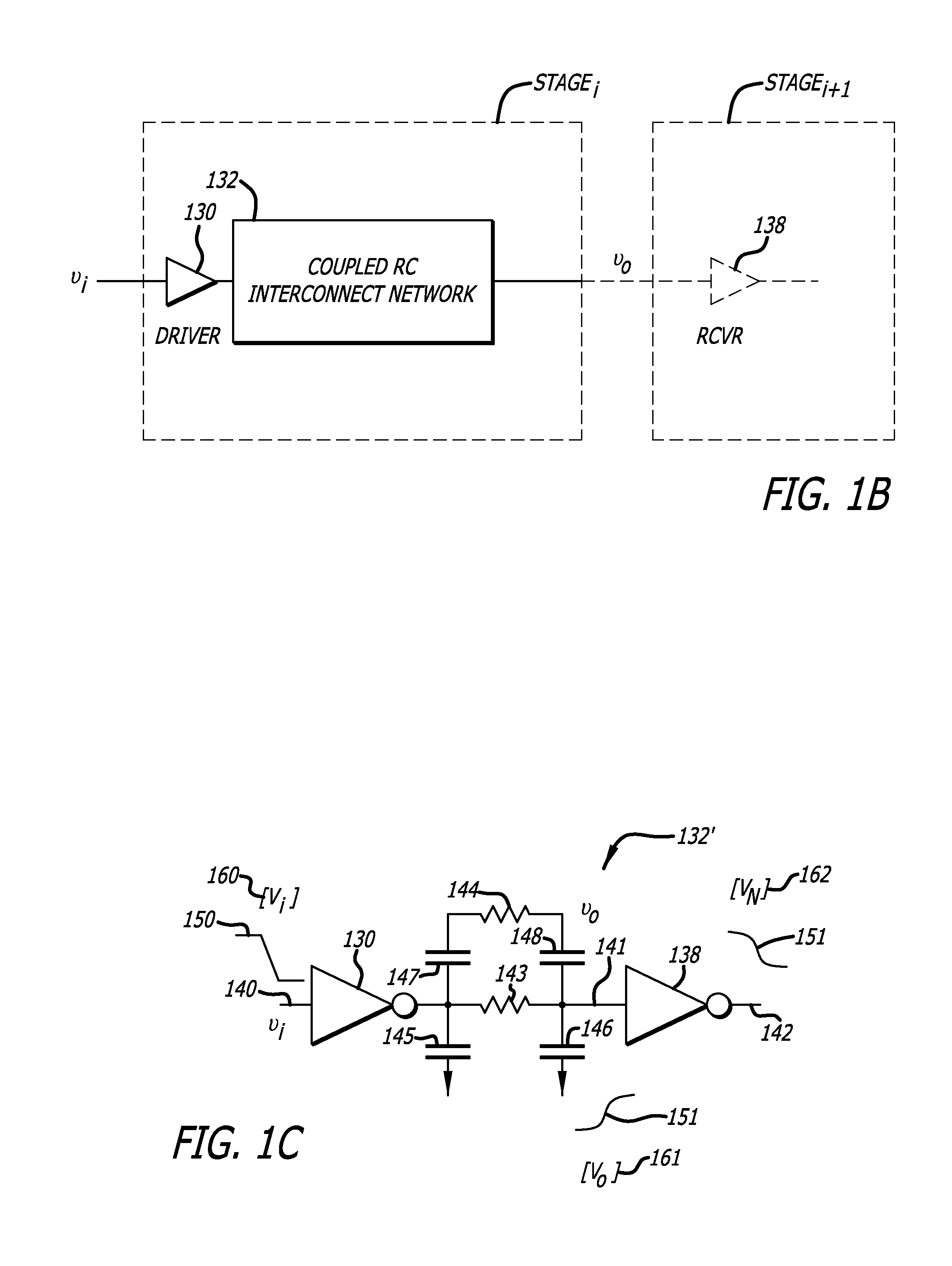

Methods and apparatus for waveform based variational static timing analysis

ActiveUS8245165B1Computer aided designSoftware simulation/interpretation/emulationLogic networkPhases of clinical research

A system and method are disclosed for waveform based variational static timing analysis. A circuit is divided into its linear circuit parts and non-linear circuit parts and modeled together, by a combination of linear modeling techniques, into linear equations that may be represented by matrices. The linear equations in matrix form may be readily solved by a computer such that an input waveform to an input pin of the circuit can be sequentially “pushed” through the various interconnects and logic networks of the circuit to an output pin. Output voltage waveforms are obtained at each stage of the waveform pushing and may be used to perform static timing analysis.

Owner:CADENCE DESIGN SYST INC

Switching-mode power supply having a synchronous rectifier

InactiveUS20060171180A1Improve efficiencySave the problemAc-dc conversion without reversalEfficient power electronics conversionCapacitanceCapacitor voltage

A DC-to-DC converter incorporates a transformer having a primary winding connected to a pair of DC input terminals via an active switch, which turns on and off under the control of a feedback circuit, and a secondary winding connected to a pair of DC output terminals via a synchronous rectifier and a smoothing capacitor. The synchronous rectifier is a parallel connection of a synchronous rectifier switch and a diode. A synchronous rectifier control circuit is connected to the synchronous rectifier switch for causing conduction therethrough while the active switch is off. The synchronous rectifier control circuit comprises a capacitor for determination of the conducting periods of the synchronous rectifier switch, and a logic network for on / off control of the synchronous rectifier switch according to whether the active switch is on or off and whether the capacitor voltage is higher than a predefined threshold or not.

Owner:SANKEN ELECTRIC CO LTD

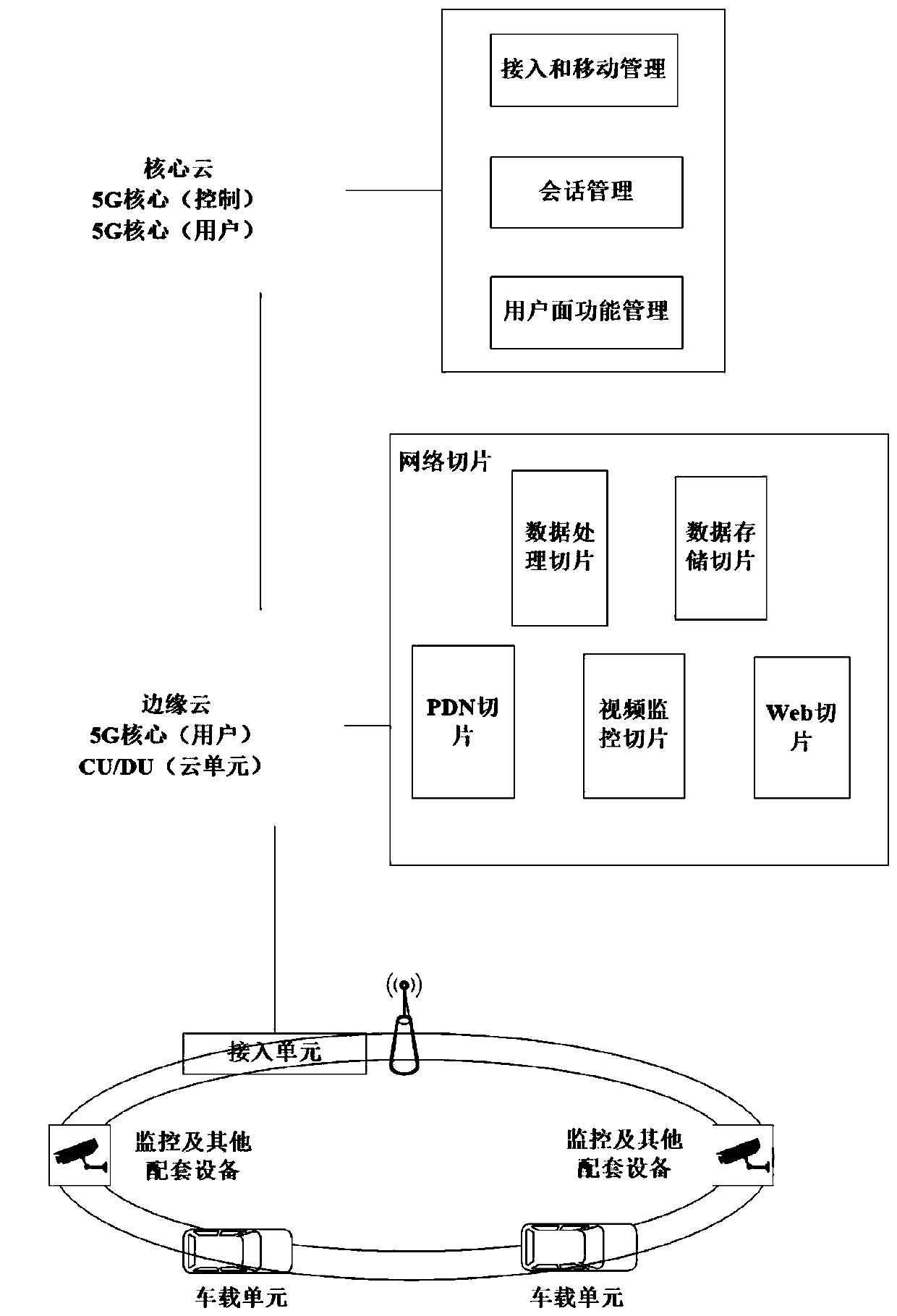

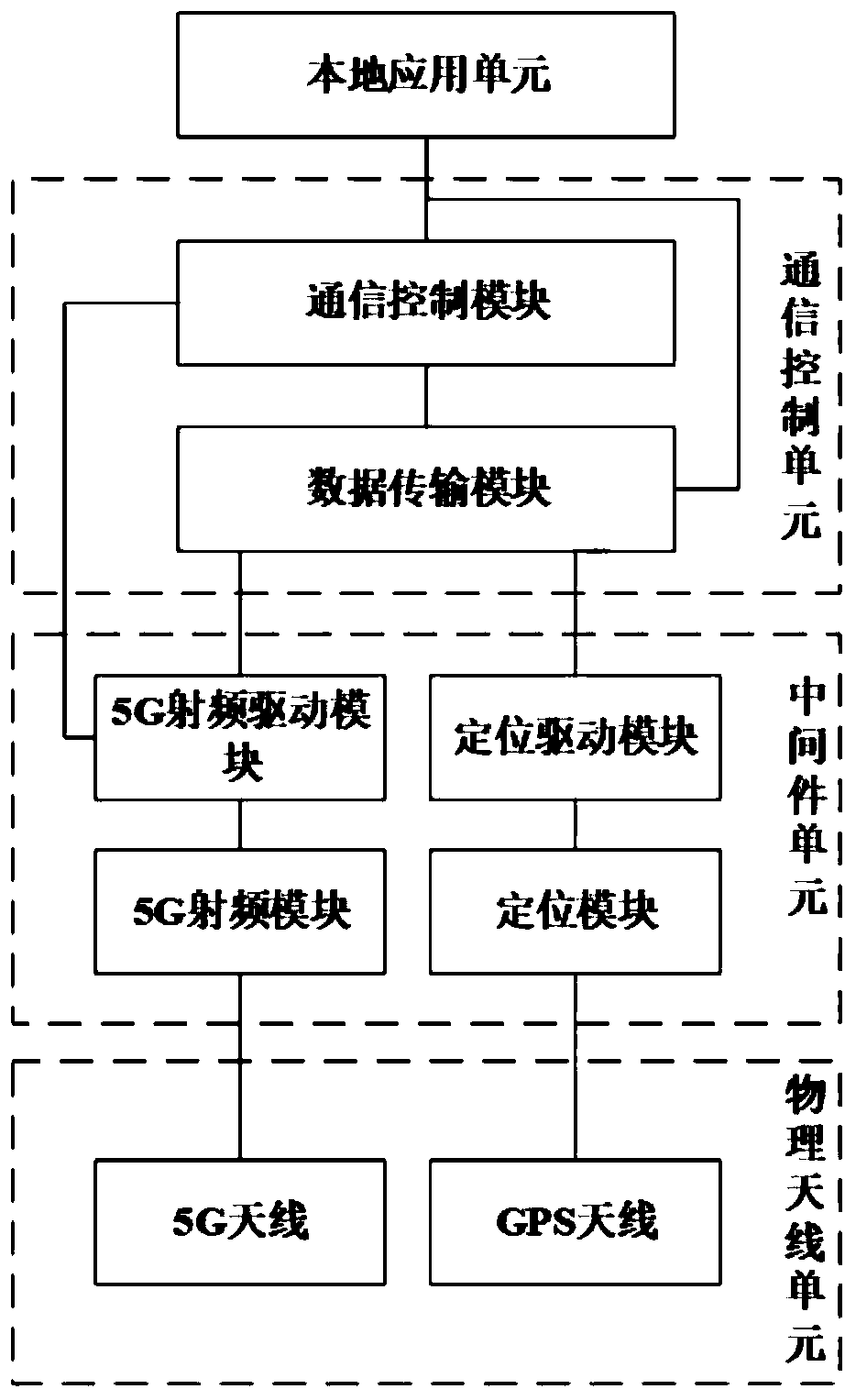

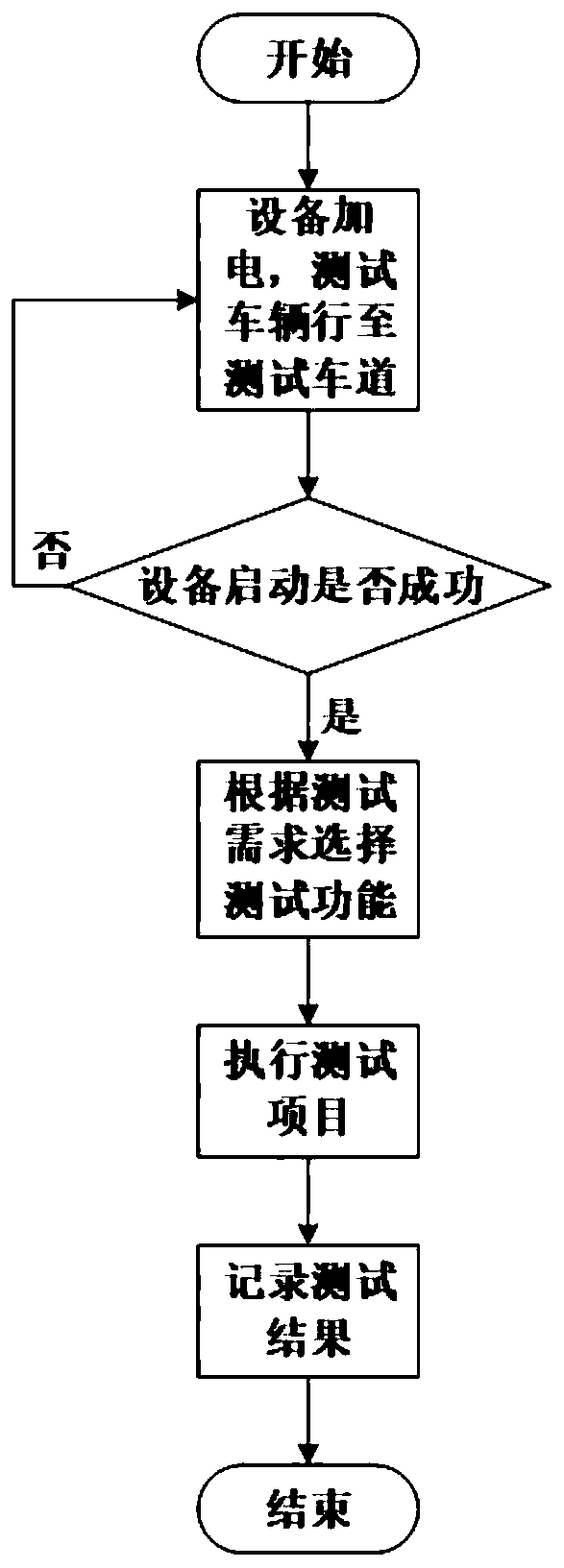

Vehicle-road communication test system and test method on 5G technology

InactiveCN109981771AReduce in quantityRealize data exchangeParticular environment based servicesVehicle-to-vehicle communicationNetwork terminationTime delays

The invention discloses a vehicle-road communication test system based on the 5G technology. A network element function is realized by adopting a virtualization and software mode; the network transmission rate can be obviously improved; concurrent network messages of dense network terminals in the Internet of Vehicles environment are ensured. the requirement of complex and huge Internet of Vehicles application on ultra-low time delay is met; the system cloud server adopts a virtualization technology. the number of servers is reduced; in a security aspect, multiple network slices are divided, asecurity isolation and height self-control special logic network is provided; network security is greatly improved, the information security of the Internet of Vehicles application and the data privacy of the user are ensured; the edge cloud server sinks a part of services to a network edge; the Internet of Vehicles application service processing speed based on roadside equipment can be remarkably increased, lower transmission delay is provided, the test platform can be used for verifying the actual effectiveness of the 5G technology applied to the Internet of Vehicles application, and support is provided for 5G-based Internet of Vehicles equipment layout and network design in a real scene.

Owner:CHANGAN UNIV

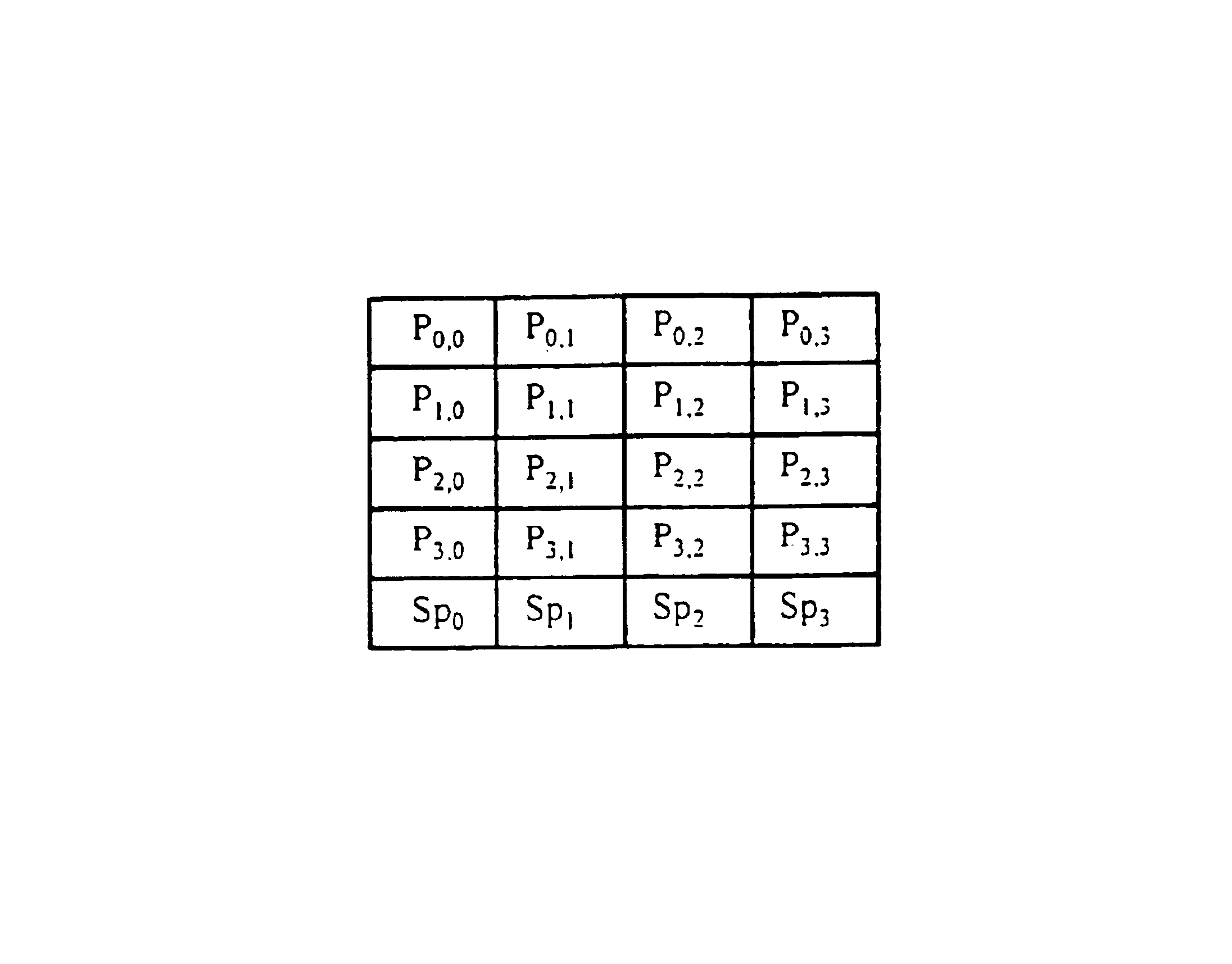

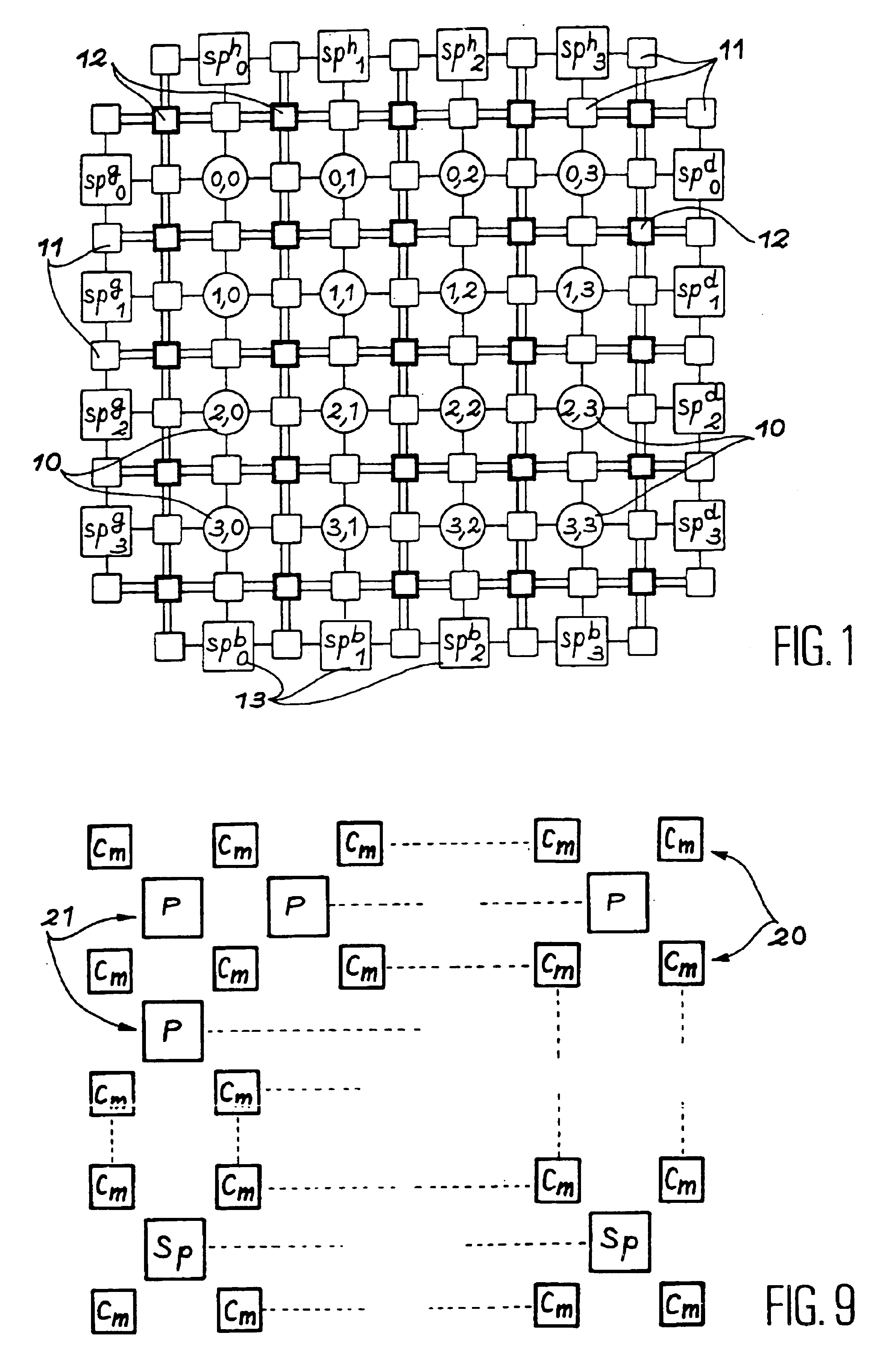

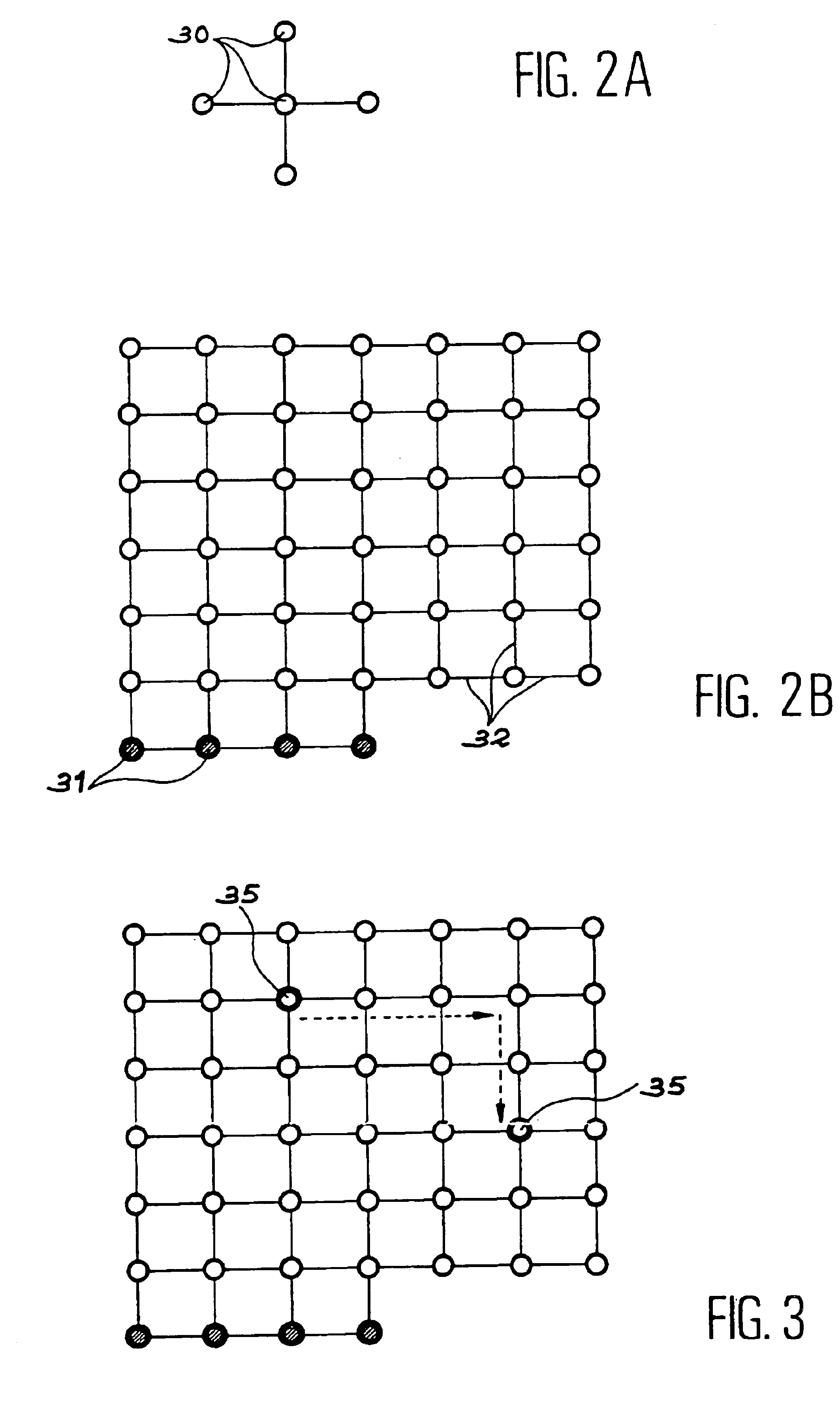

Reconfiguration method applicable to an array of identical functional elements

This invention relates to a method for reconfiguring a network of parallel functional elements tolerant to the faults of these functional elements including said basic functional elements (P), spare functional elements (Sp), interconnecting elements (Cm) of these functional elements and a control unit, said method comprising:a step of positioning the functional elements of the logic network on the physical network;a routing step of programming interconnecting elements on the physical network, by choosing a maximum number of interconnecting elements which can be passed between two neighbouring processors using a shortest track search algorithm.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

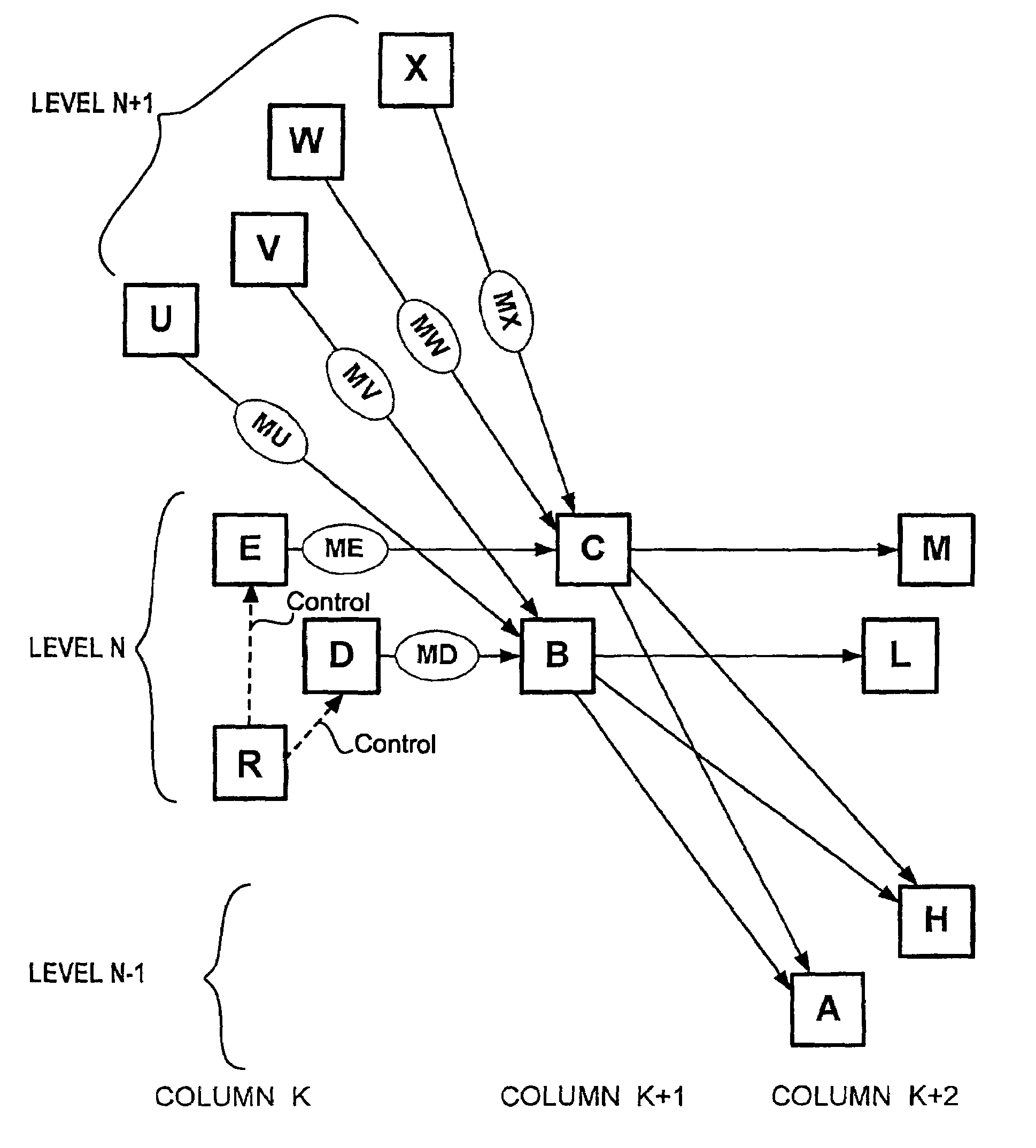

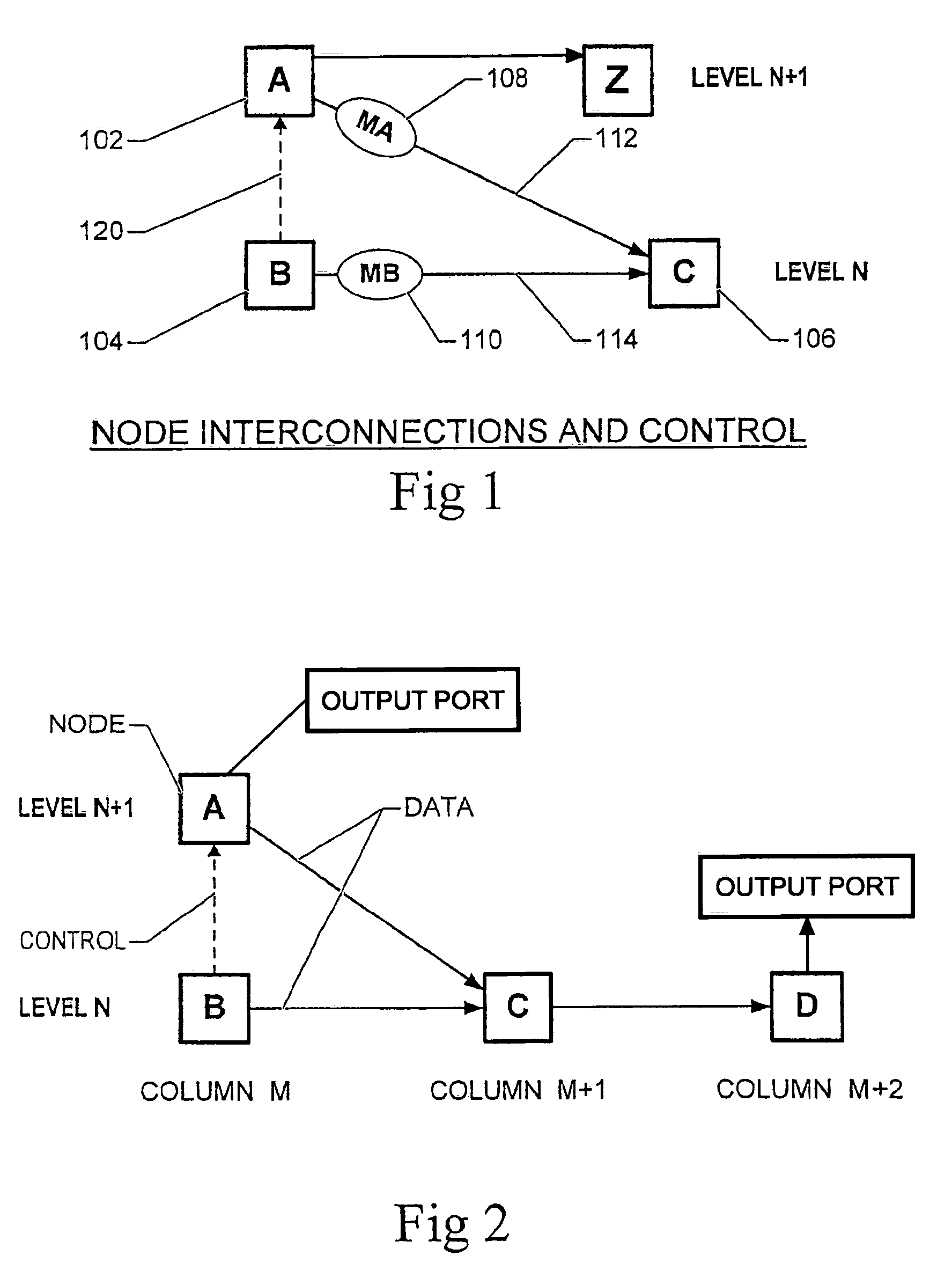

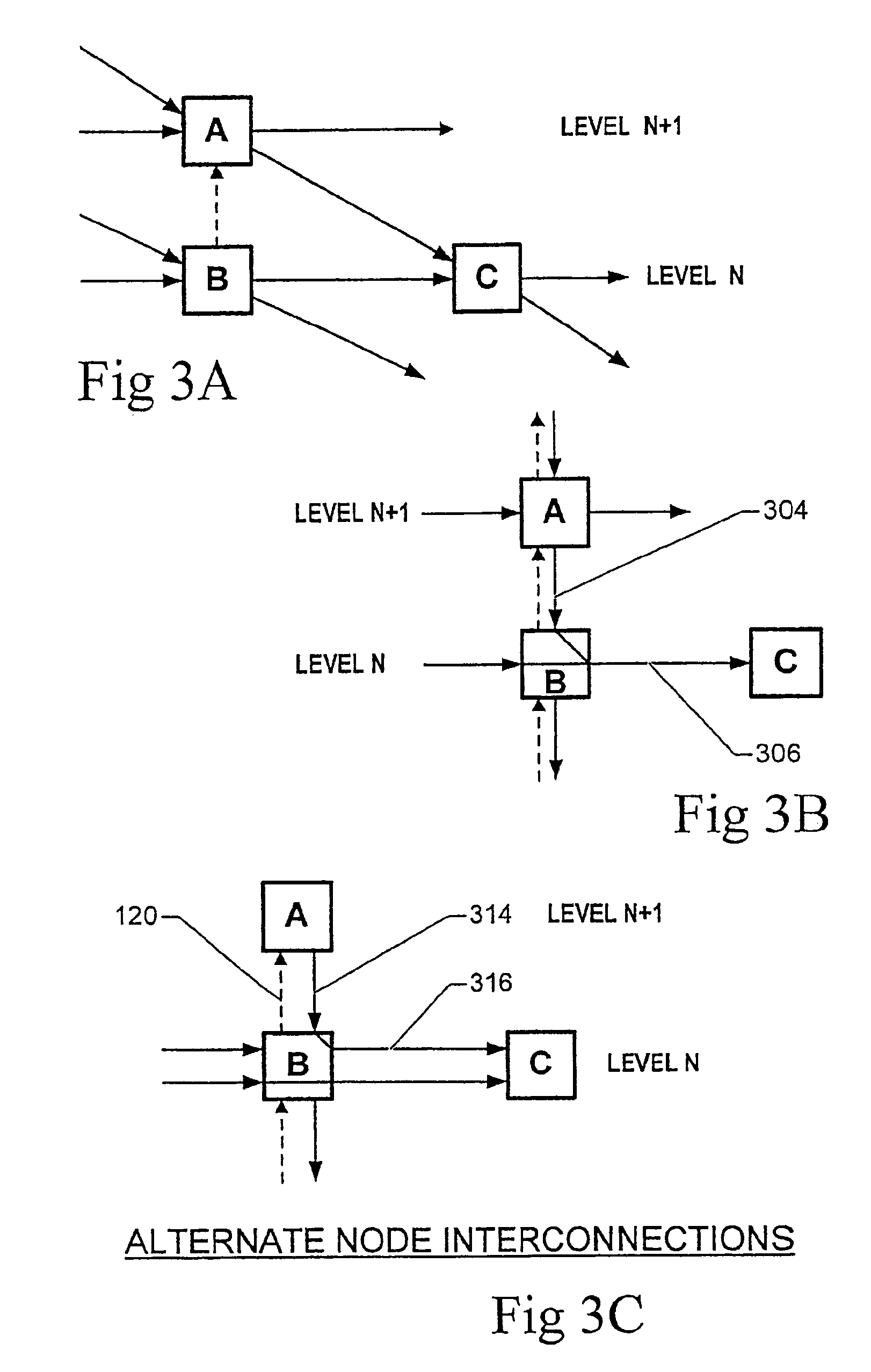

Scalable apparatus and method for increasing throughput in multiple level minimum logic networks using a plurality of control lines

InactiveUS7221677B1Information receiveImprove throughputMultiplex system selection arrangementsDigital computer detailsLevel structureControl line

A network or interconnect structure which includes a plurality of nodes which are interconnected within a hierarchical multiple level structure. The level of each node is determined by the position of the node within the structure and data messages move from node to node from a source level to a destination level. Each node within the interconnect structure is capable of receiving simultaneous data messages at its input ports from any other node and the receiving node is able to transmit each of the received data messages through its output ports to separate nodes in the interconnect structure to one or more levels below the level of the receiving node.

Owner:INTERACTIC HLDG LLC

Power supply for electric arc welding

InactiveUS6600134B2Substantial engineering and lead timeRobust and simple to constructArc welding apparatusAc-ac conversionTransformerEngineering

A power supply connectable to a source of AC line voltage for AC electric arc welding by an AC arc current across a welding gap between an electrode and a workpiece, the power supply comprises a high capacity transformer that converts said line voltage to an AC output voltage, and a rectifier that converts the AC output voltage to a DC voltage between a positive terminal and a common terminal at generally zero volts and a negative terminal and the common terminal. The power supply has a first switch that connects the positive terminal to the common terminal across the gap when a gate signal is applied to the first switch, a second switch for connecting the negative terminal to the common terminal across the gap when a gate signal is applied to the second switch and a pulse width modulator operated for generating pulses at a frequency of at least about 18 kHz. A logic network has a first circuit for directing the pulses to the first switch for a first time, a second circuit for directing the pulses to the second switch for a second time and a controller to alternately operate first and second circuits to create AC arc welding current.

Owner:LINCOLN GLOBAL INC

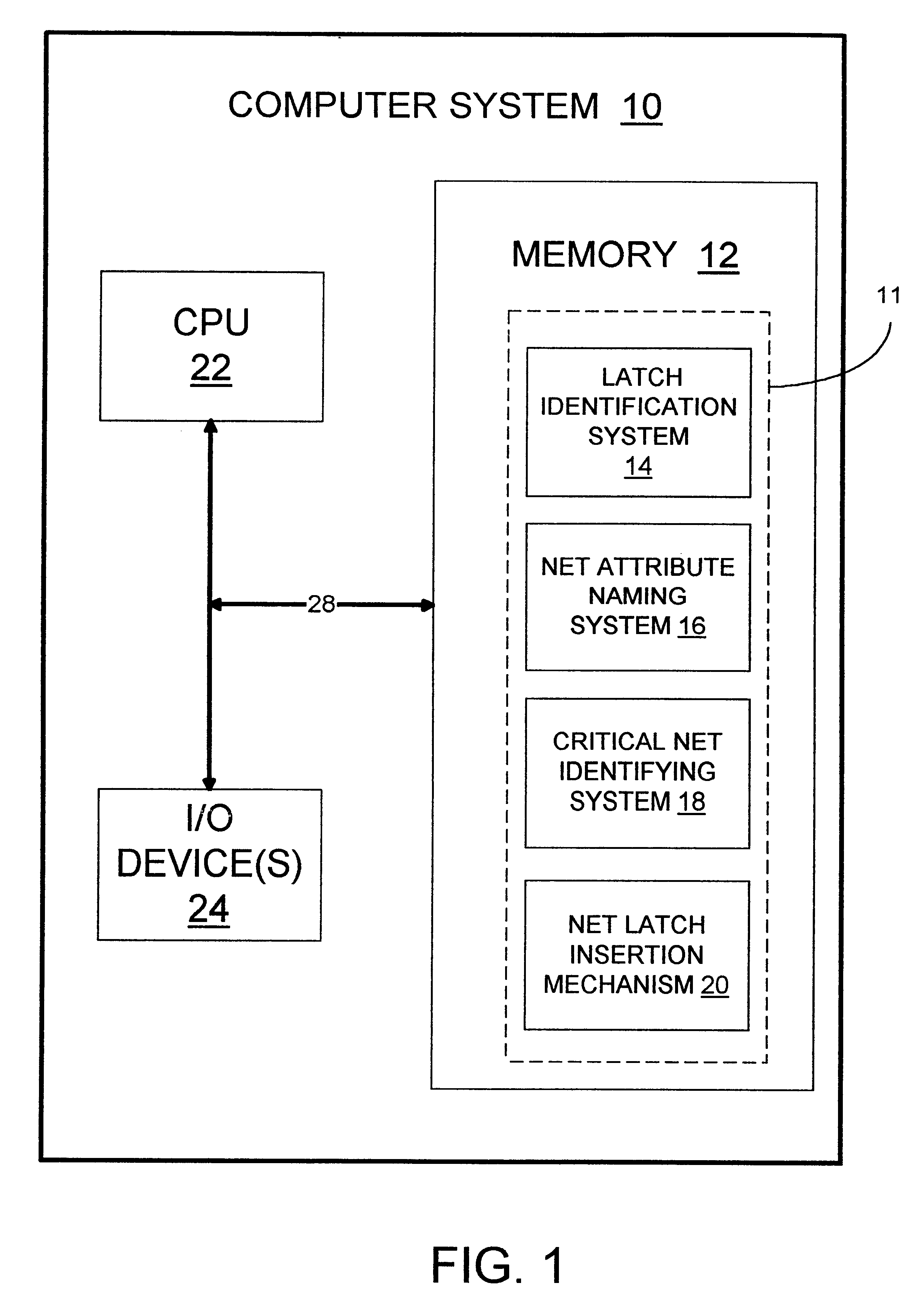

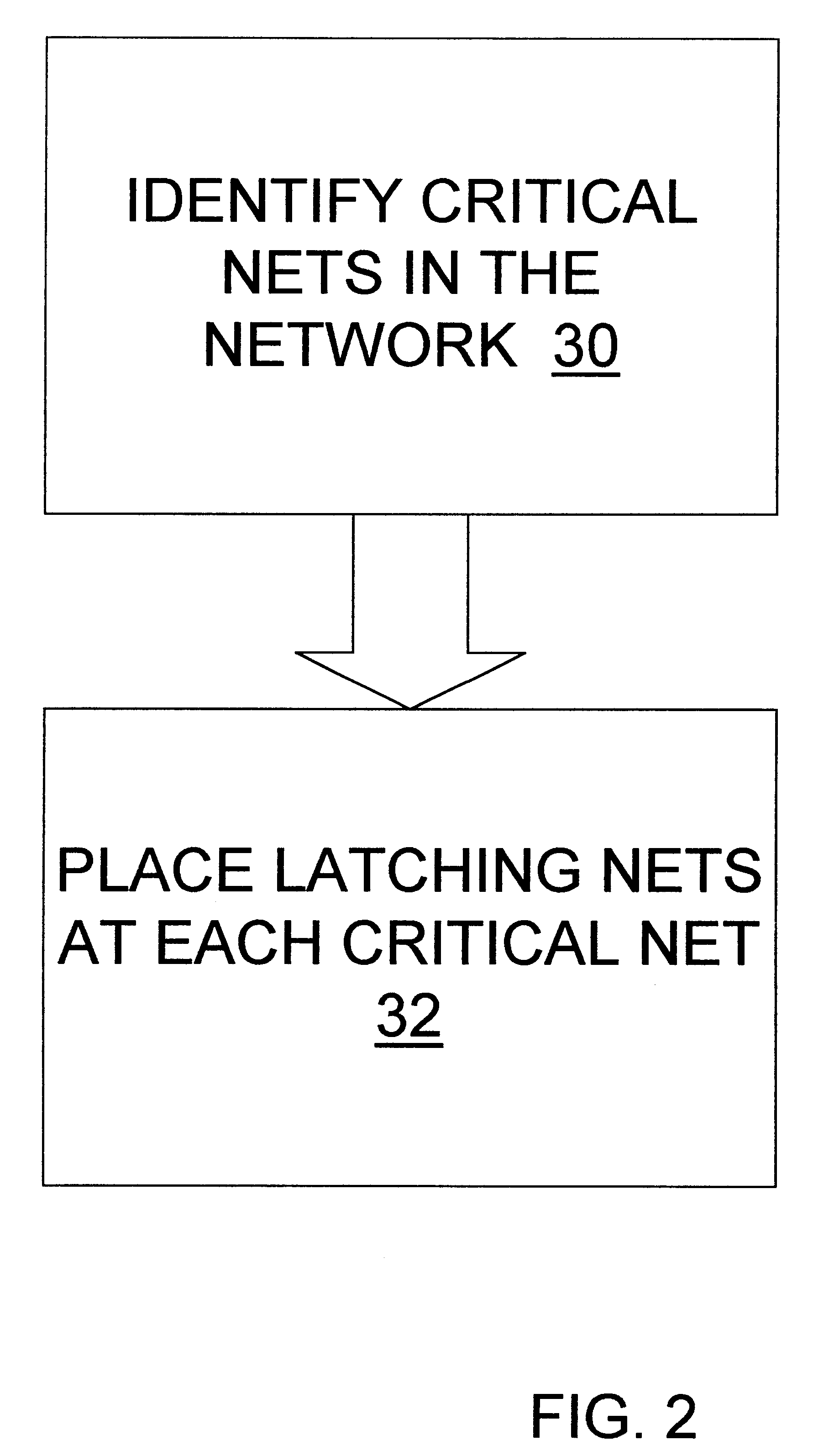

Logic power optimization algorithm

InactiveUS6658634B1Reduce wasted powerCAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic network

Disclosed is a system and method for eliminating the unnecessary toggling of logic in a logic network. The method and system can be incorporated directly into logic synthesis software, or may be implemented manually. Provided is a mechanism for identifying critical nets and then inserting net latches at the critical nets wherein each net latch is controlled by an enable signal that also controls a related output latch. Each net latch is comprised of a circuit which can on command hold static the last logic level on a given logic node.

Owner:GOOGLE LLC

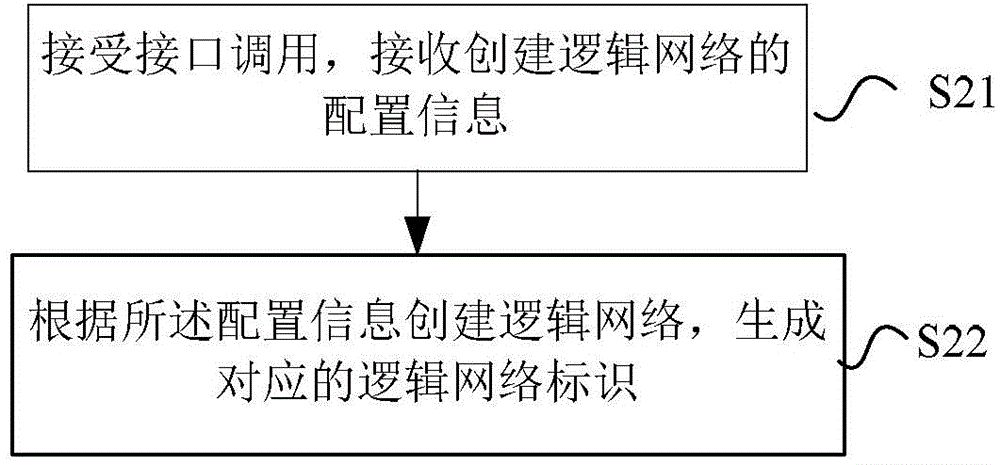

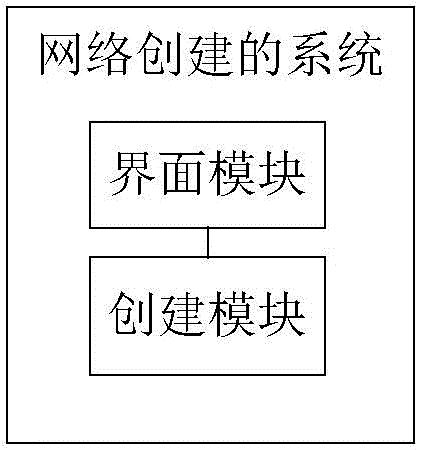

Network establishment method and system, and network control center

ActiveCN103607432AImprove automation performanceGranularityTransmissionStrategy executionNetwork control

The invention provides a network establishment method and a system, and a network control center. The method comprises the following steps of receiving configuration information used for establishing a logic network; according to the configuration information, after corresponding processing is performed, calling an assigned interface of the network control center to carry out establishment processing of the logic network. Through the method, the system and the network control center of the invention, the private and isolated logic network is established for different users; according to distribution of calculating resources owned by the user, network partition and connection are completed; network configuration is uniformly performed and strategy execution is controlled; a QOS demand needed by the user is satisfied and flexible expansion can be performed according to a need.

Owner:NANJING ZHONGXING SOFTWARE

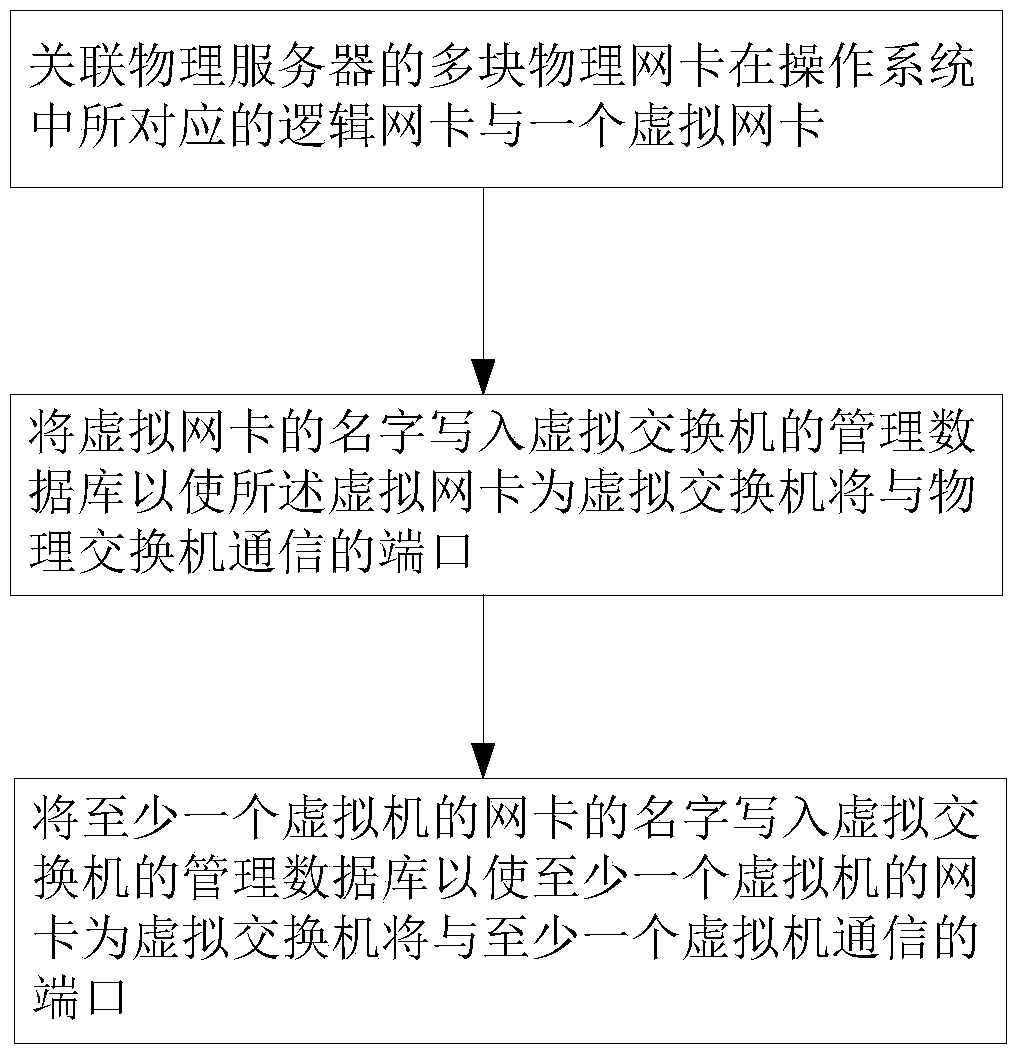

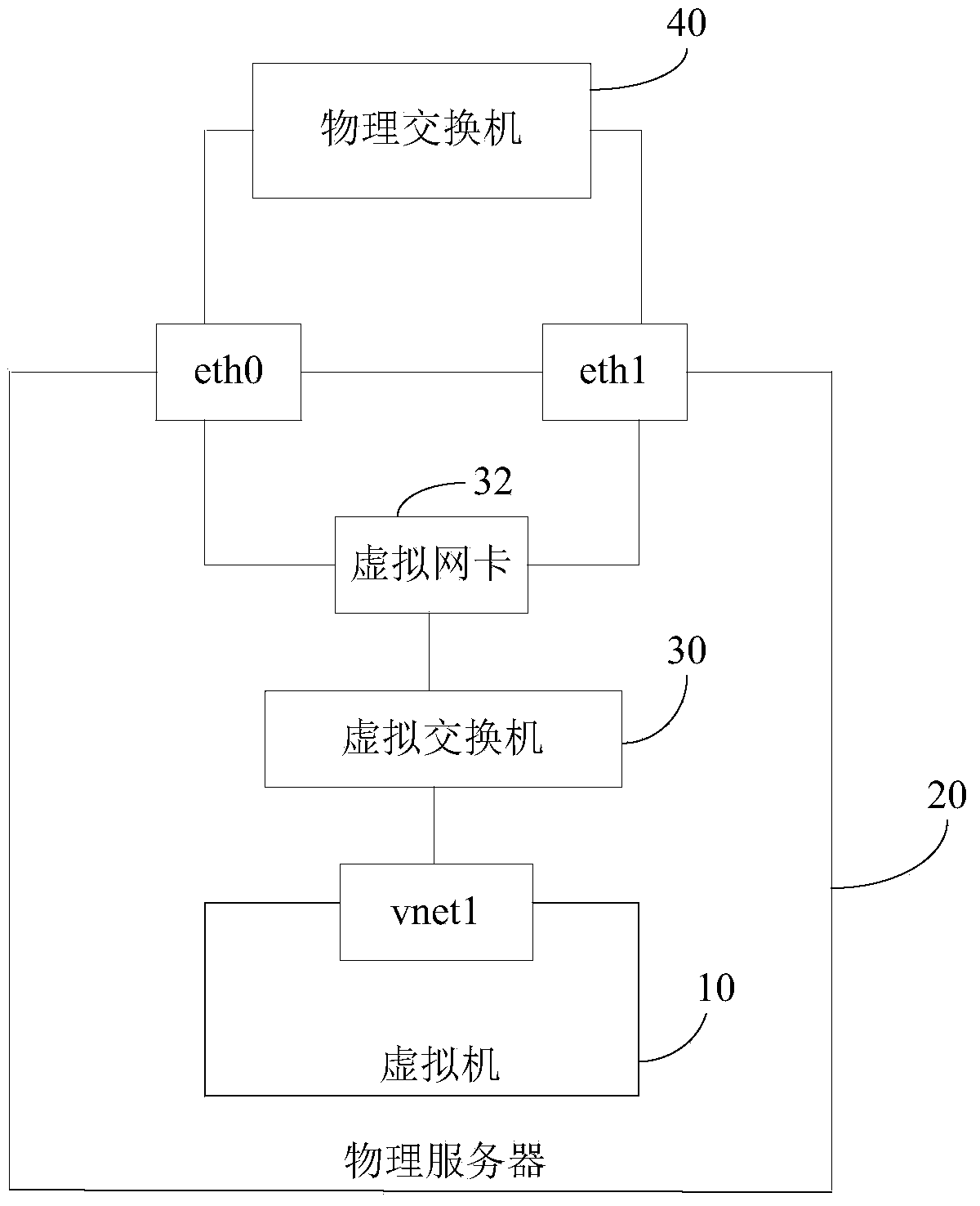

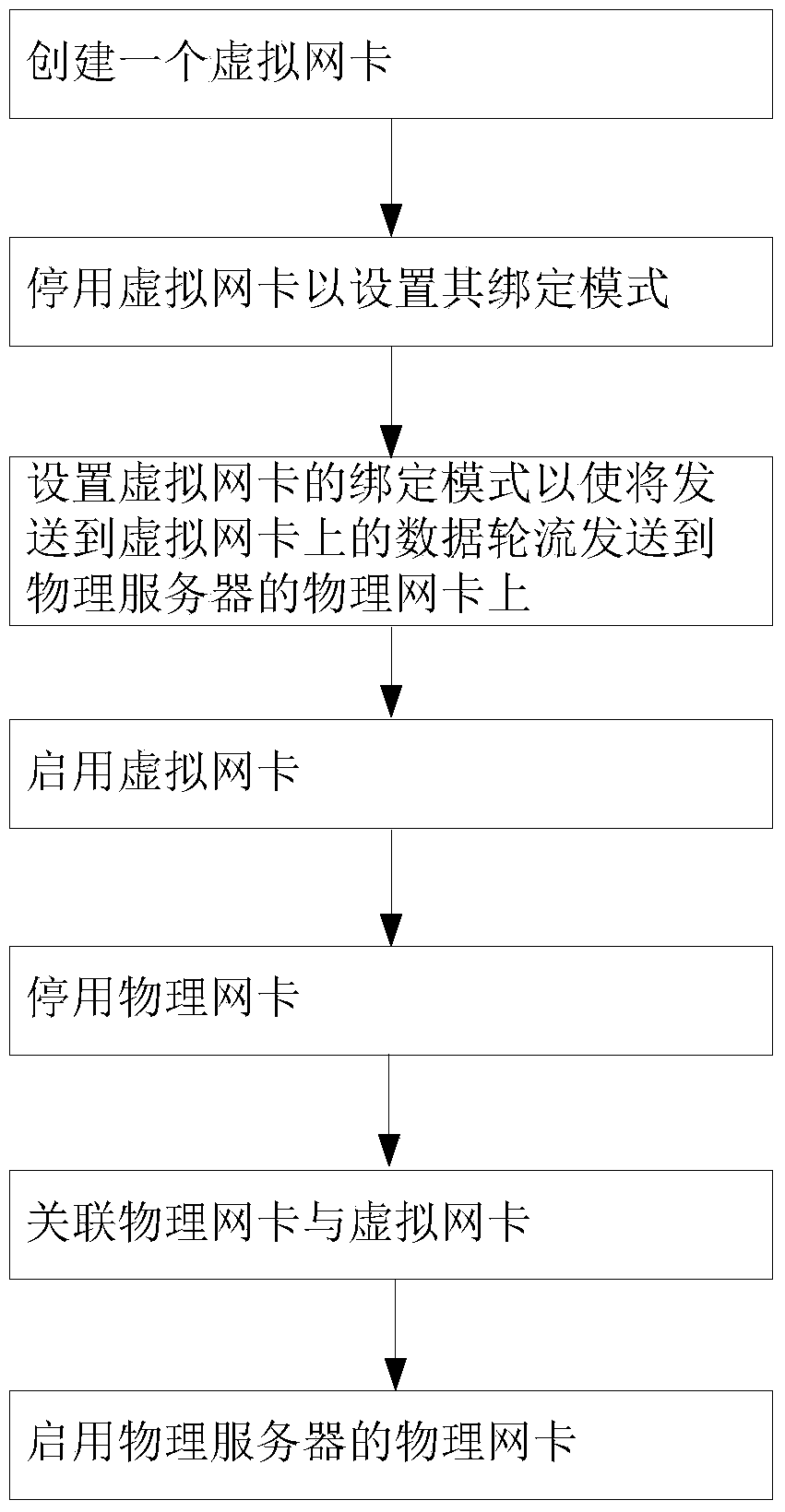

Service bandwidth expansion method in cloud computing network virtualization

The invention provides a service bandwidth expansion method in cloud computing network virtualization. The service bandwidth expansion method comprises the following steps: associating logic network cards, corresponding to a plurality of physical network cards of a physical server, in an operating system with a virtual network card; writing the name of the virtual network card into a management database of a virtual switch to enable the virtual network card to be a port for communicating the virtual switch with a physical switch; writing the name of a network card of at least one virtual machine into the management database of the virtual switch to enable the network card of at least one virtual machine to be a port for communicating the virtual switch with at least one virtual machine. According to the method, by writing the network card of the virtual machine and the virtual network card into the management database of the virtual switch, any one data stream of the virtual machine is split and is sent to the physical network cards, so that the network bandwidth can be elastically expanded by services of any protocol in the virtual machine according to the quantity of users and the change of bandwidth requirements of the users under the condition that the total bandwidth is unchanged.

Owner:WUHAN OPENKER COMPUTING

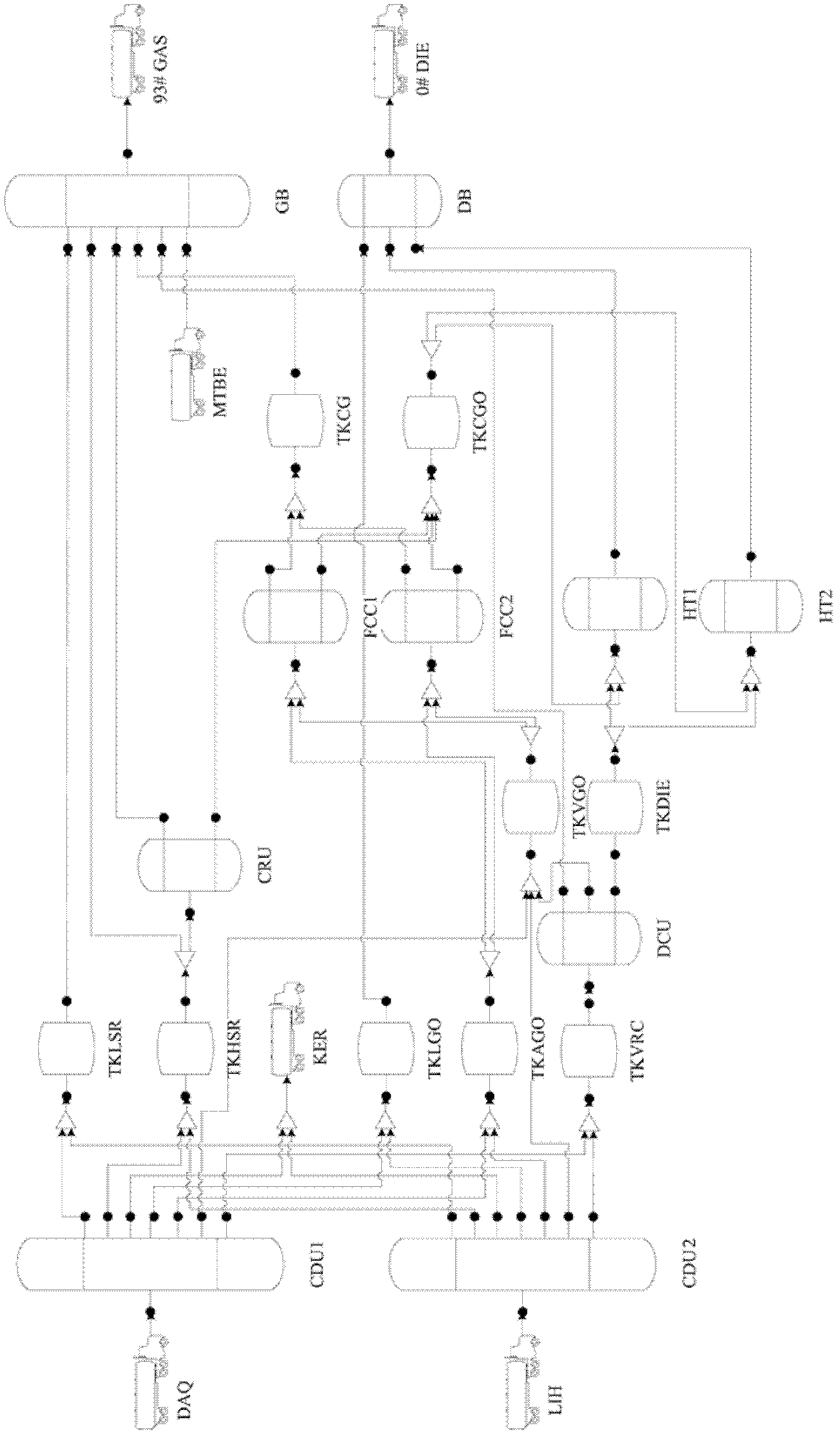

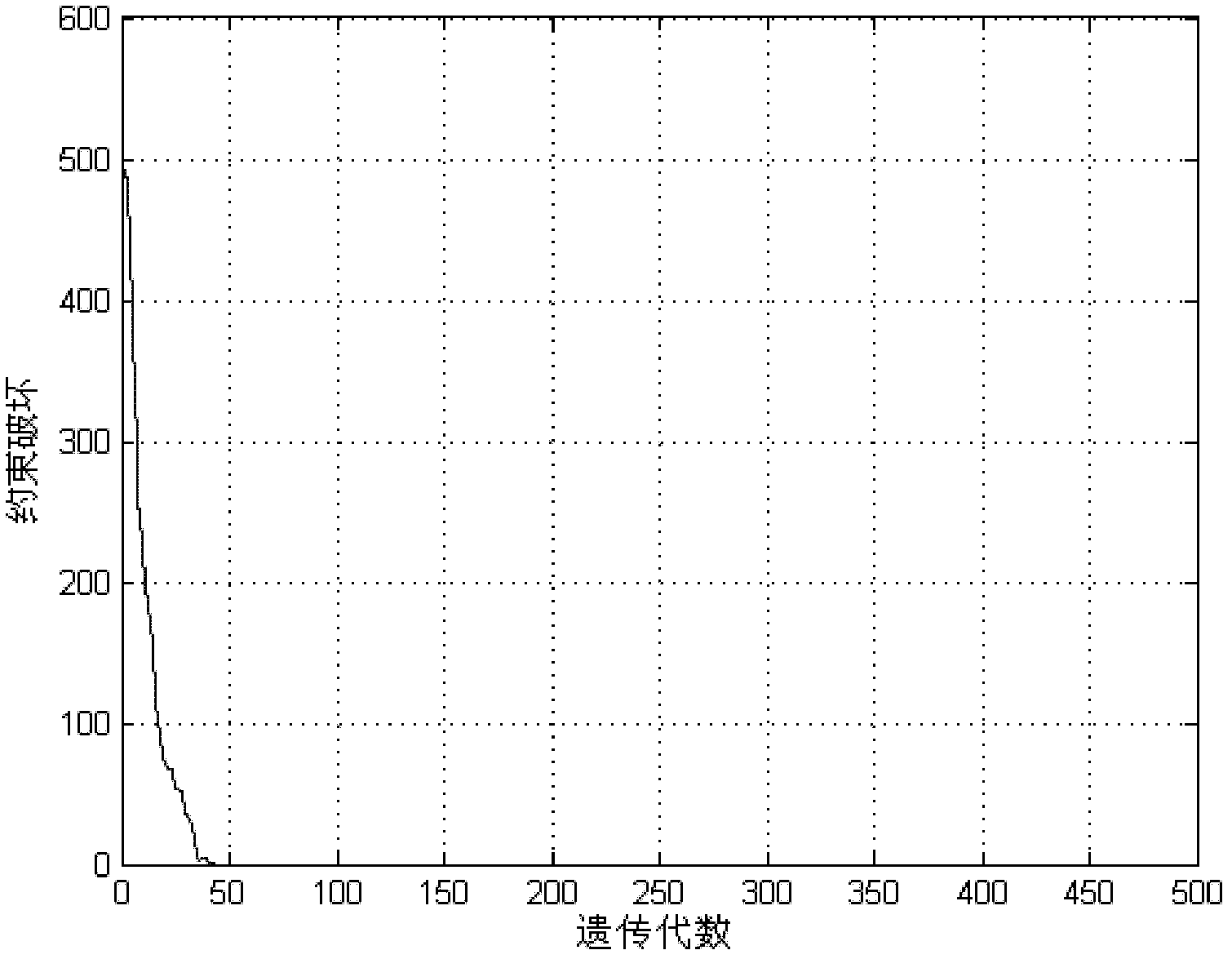

Nonlinear production plan optimization method applied to oil refineries

InactiveCN102622655AImprove global profitAvoid heavy computationForecastingProcess moduleDistillation

The invention discloses a nonlinear production plan optimization method applied to oil refineries, which includes the steps: firstly, setting up an oil refining production logic network; secondly, setting up process modules of an atmospheric and vacuum CDU (crude distillation unit) and a FCC (fluid catalytic cracking) unit; thirdly, inputting all constraint condition data and determining a target function in two-stage search; and fourthly, using the mixed searching method to optimally determine production plan decision variables. The genetic algorithm and direct search algorithm are combined on the basis of the simulation modeling technique, global profits of an oil refinery production plan can be effectively increased without destroying the constraint conditions, tremendous computation generated during solving of complex production plan problems can be avoided, and optimized solutions can be quickly obtained. The nonlinear production plan optimization method is simple in principle, convenient in implementation, high in transportability and applicable to different production plan environments.

Owner:ZHEJIANG UNIV

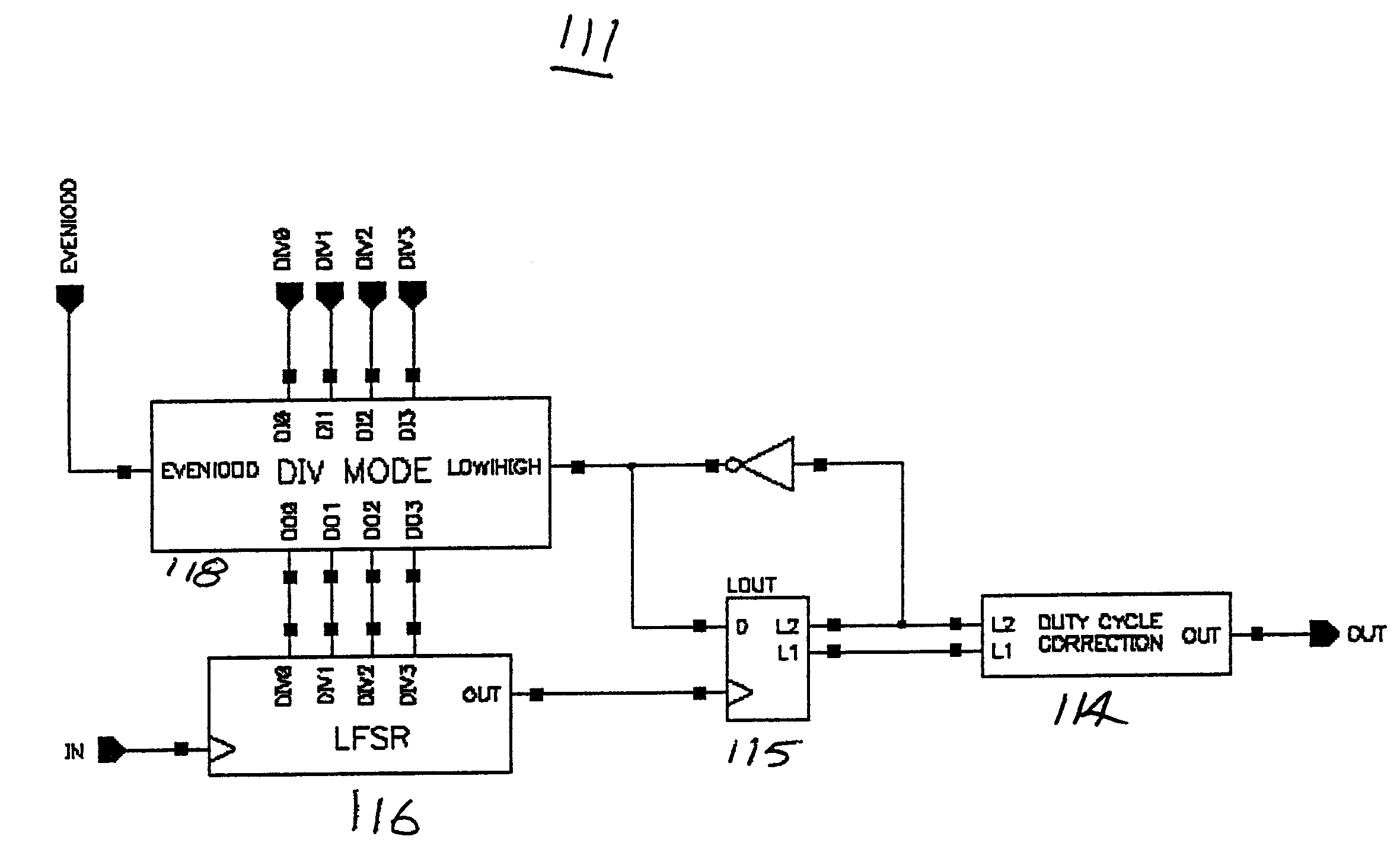

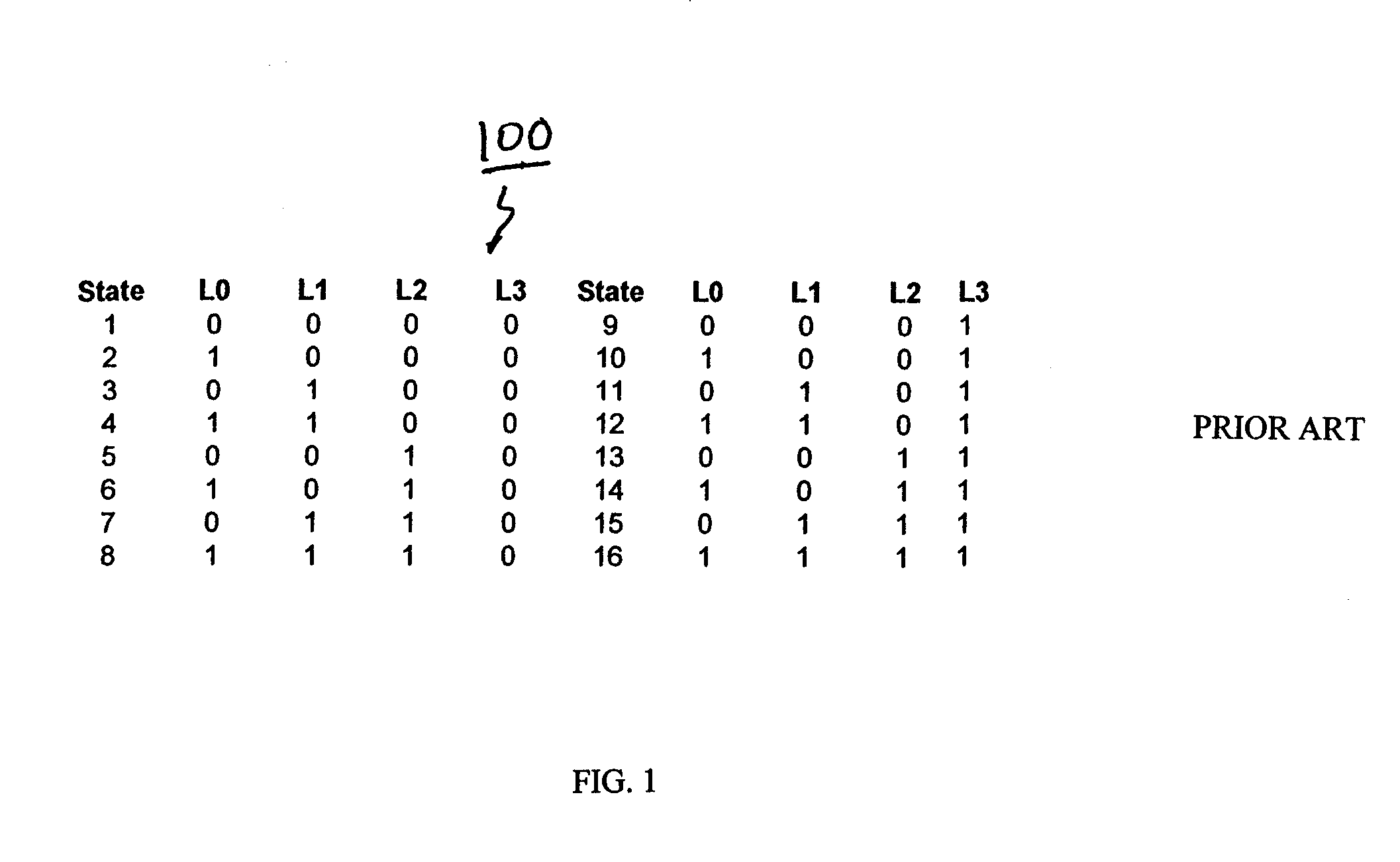

Programmable frequency divider with symmetrical output

ActiveUS6961403B1High divisor valueProvide flexibilityRandom number generatorsCounting chain pulse countersLogic networkLinear feedback shift register

A programmable frequency divider circuit with symmetrical output is disclosed. The frequency divider includes a non-symmetrical LFSR based component operated in series with a symmetrical divider component. Both the LFSR and the symmetrical divider may be programmed to provide flexibility. The frequency divider can dynamically adjust the divisor of the LFSR component to overcome limitations in the divide resolution due to the series combination of dividers, providing even and odd divisor values. The divider architecture can also provide higher level functions, including synchronization of multiple divider outputs, dynamic switching of divisor values and generation of multi-phased and spaced outputs. The linear feedback shift register (LFSR) component includes a feedback logic network decomposed into multiple stages to realize a maximum latch-to-latch operational latency of one gate delay regardless of the size of the LFSR.

Owner:MARVELL ASIA PTE LTD

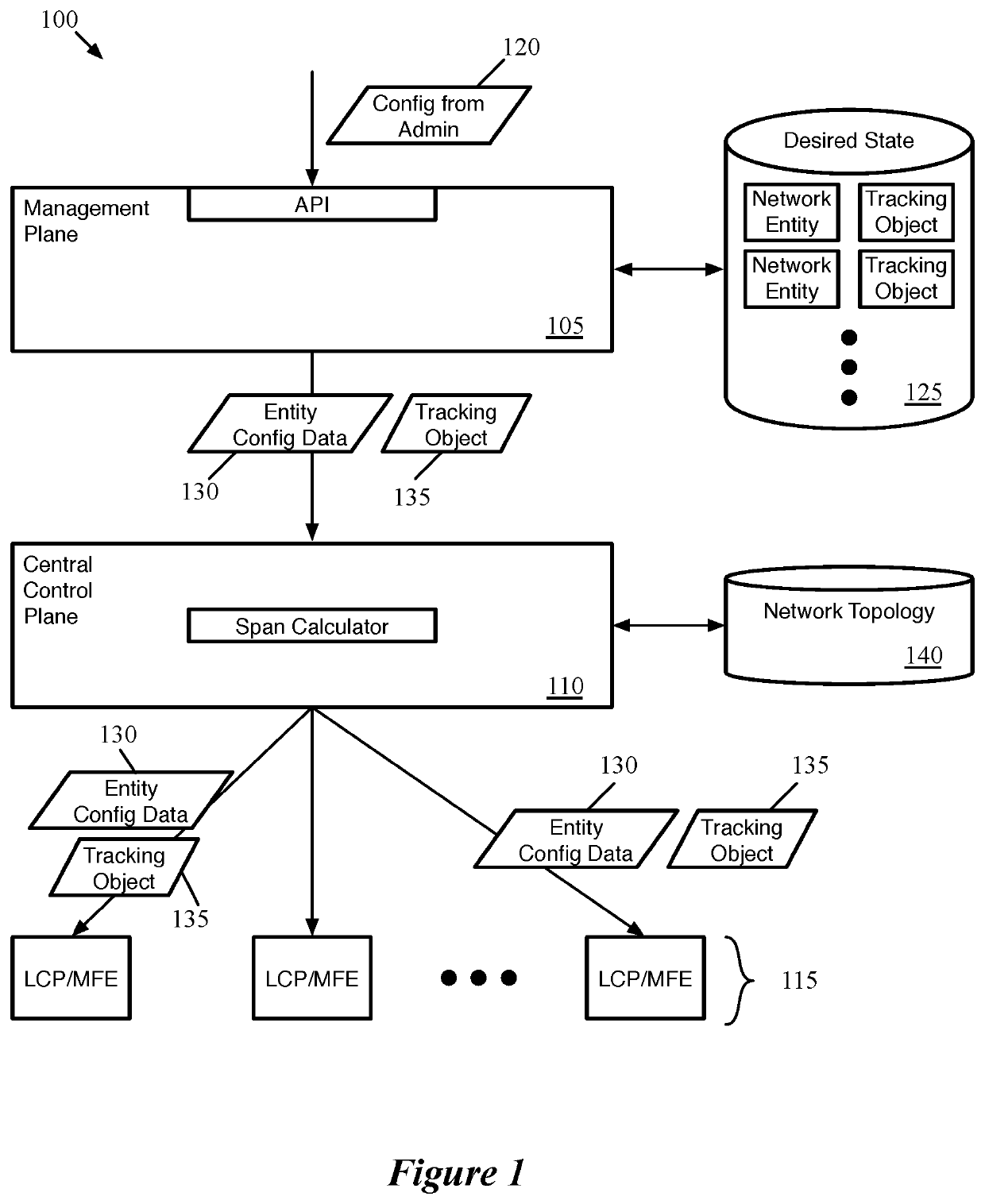

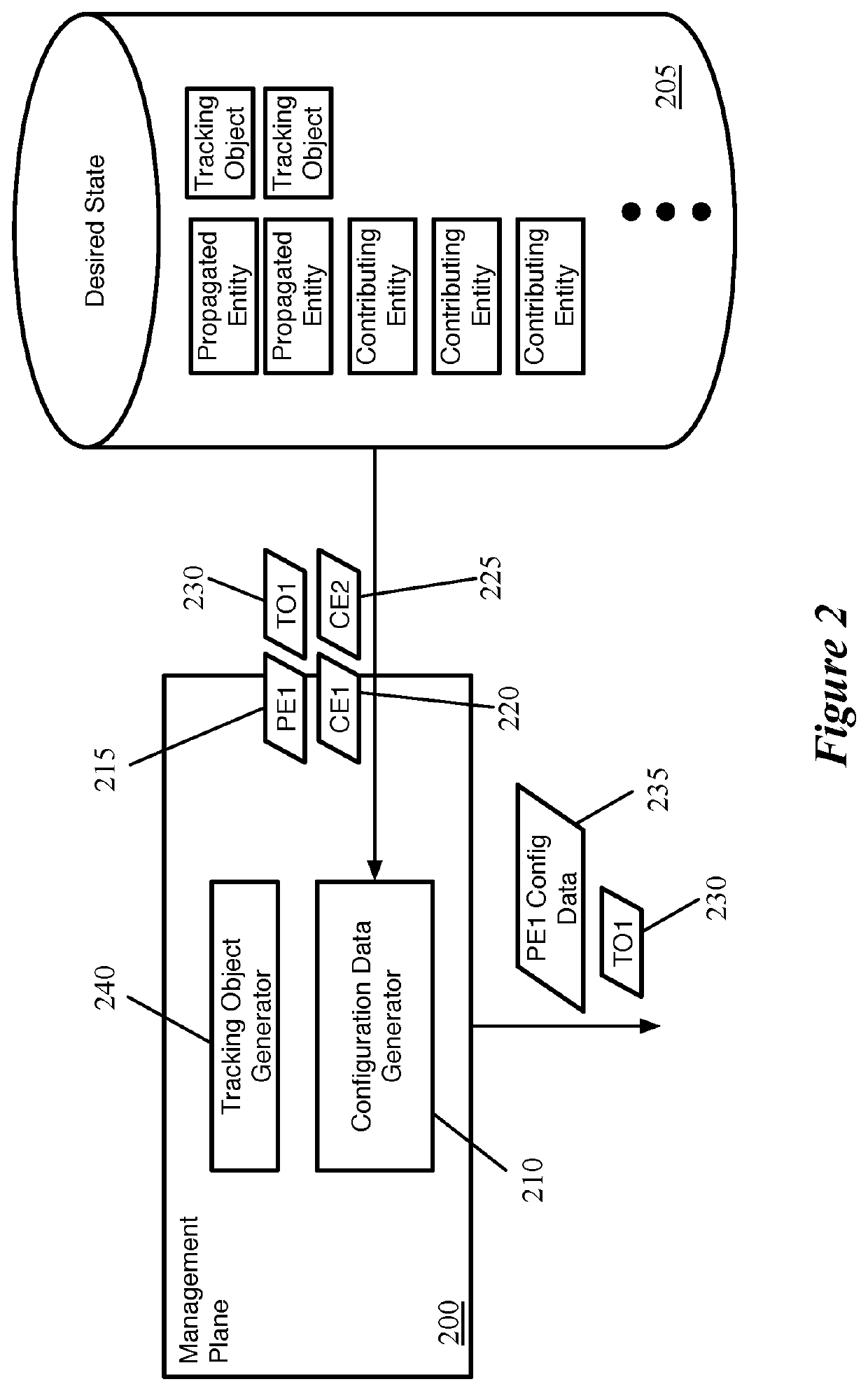

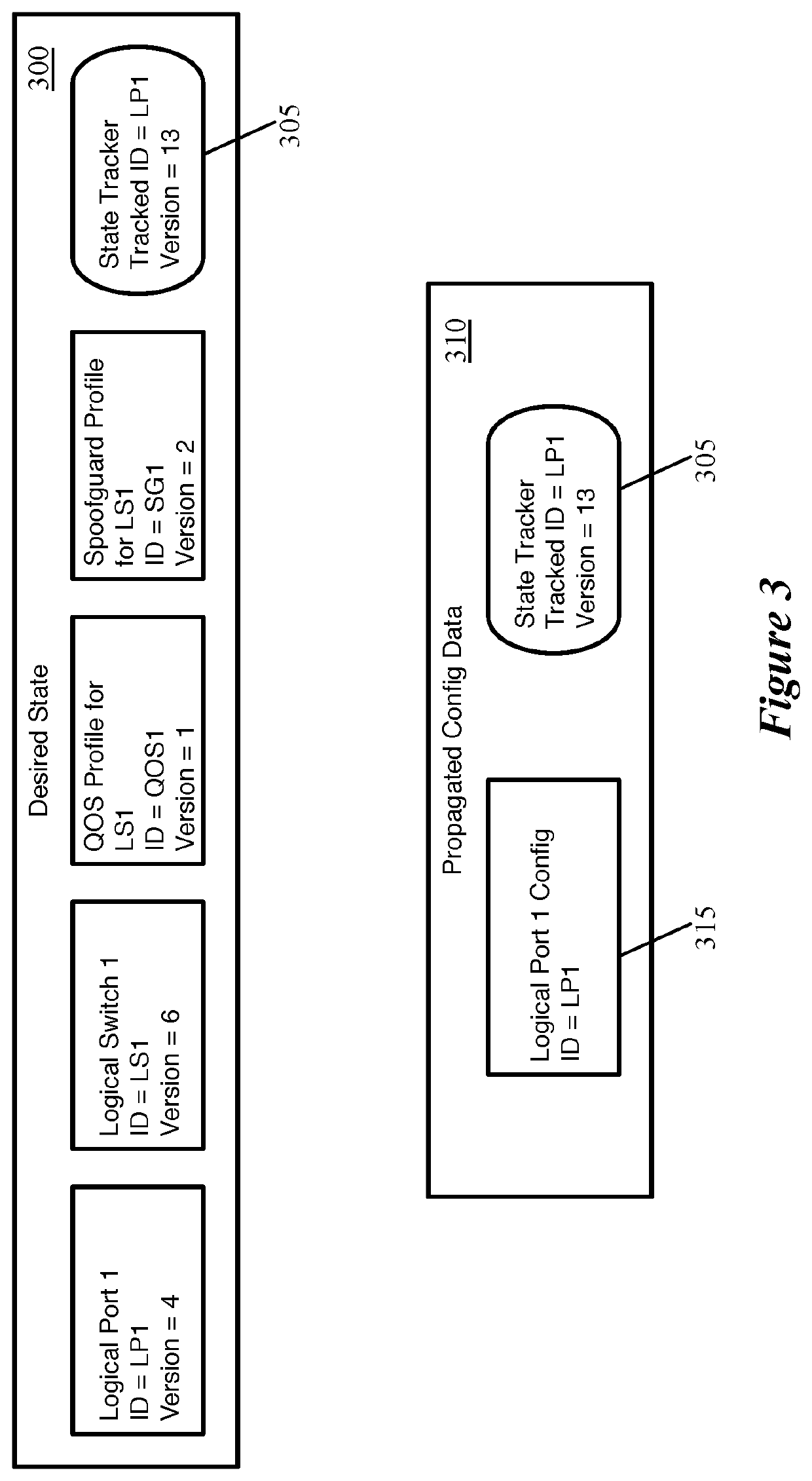

Tracking logical network entity state

Some embodiments provide a method for a central network manager that stores desired state information for multiple logical network entities for a logical network. The method stores (i) a desired state configuration for a logical network entity and (ii) a first state tracking object that identifies a version of the desired state configuration for at least the logical network entity. The method propagates to a set of managed forwarding elements (i) configuration data for the logical network entity and (ii) a second state tracking object for the logical network entity that identifies a version of the propagated configuration data. The first and second state tracking objects are compared to determine whether the propagated configuration data is based on the most recent desired state configuration.

Owner:NICIRA

Communicating method for inter-movingbodies and vehicle communicating apparatus

InactiveCN1487676AArrangements for variable traffic instructionsNetwork topologiesLogic networkInter vehicle communication

A method for communication among mobile units and vehicular communication apparatus make it possible to automatically establish connection with a party who can provide required information in response to an environment or condition change of a driver or a vehicle or in response to a driver's request so as to permit communication with the party. An inter-vehicle communication apparatus of a vehicle acquires information from other mobile units through physical networks while it is moving or stopped, and registers, in a member table, mobile units satisfying predetermined conditions on the basis of the acquired information as the members of different virtual logic networks according to the conditions. In such a state, the inter-vehicle communication apparatus selects one virtual logic network from among a plurality of virtual logic networks in response to an environment or condition change of a driver or a vehicle or in response to a driver's request so as to permit communication with the party. The selected virtual logic network is set as an active network to establish connection with a predetermined mobile unit constituting the active network thereby to request or provide required information from or to the mobile unit.

Owner:ALPINE ELECTRONICS INC

Method and apparatus for synthesizing circular decompressors

Methods and apparatuses are described for decompressing and routing test data. Some embodiments feature an integrated circuit (IC) that includes two or more shift registers configured to shift in the test data. Each of the two or more shift registers can include two or more sequential elements configured such that a scan chain in the set of scan chains receives inputs from at most one sequential element in each of the two or more shift registers. At least one shift register in the two or more shift registers can be configured as a circular shift register. The IC can also include a logic network coupled between the two or more shift registers and the set of scan chains such that the set of scan chains receives the decompressed test data from the two or more shift registers via the logic network.

Owner:SYNOPSYS INC

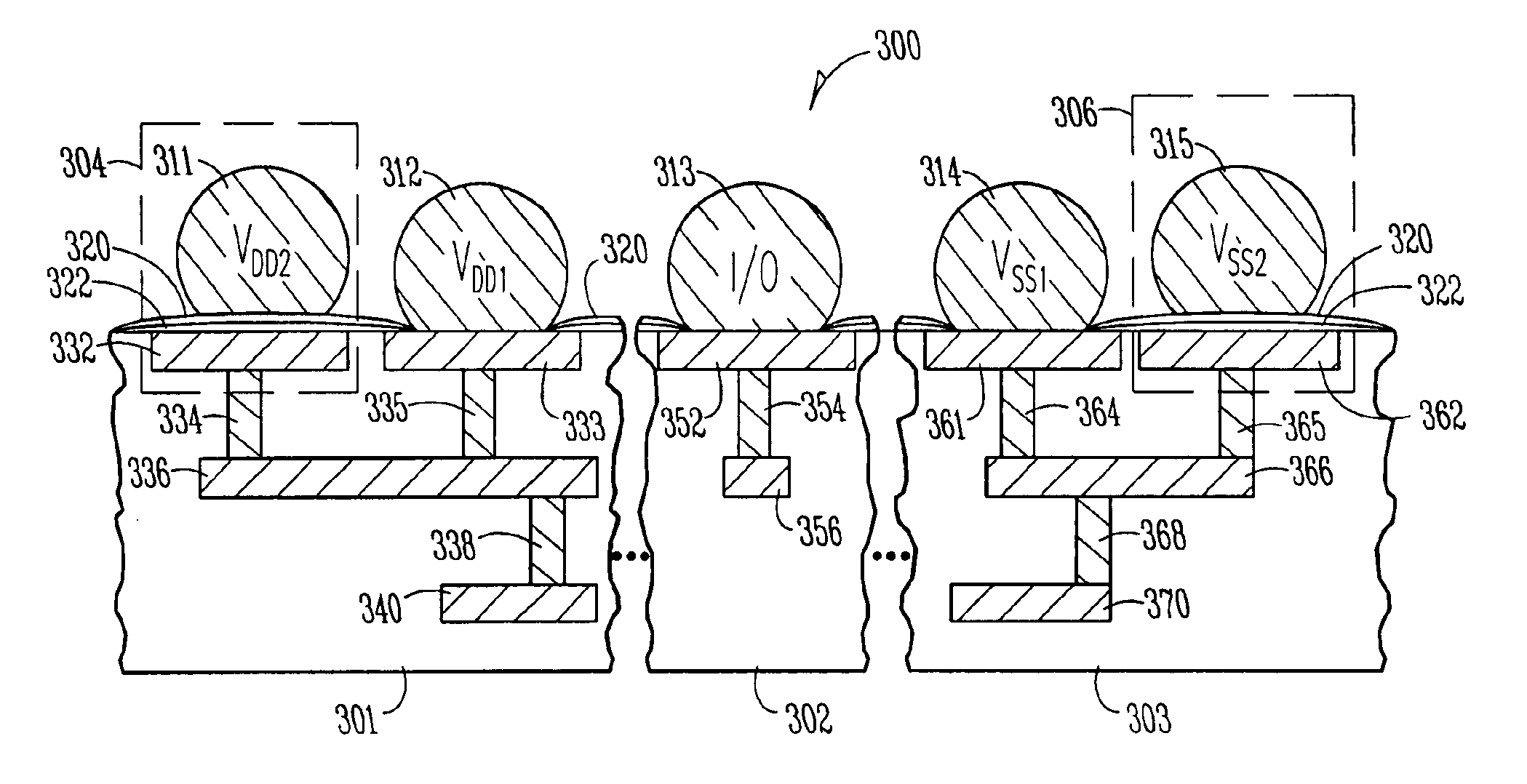

Selectable decoupling capacitors for integrated circuit and methods of use

InactiveUS6937458B2Fixed capacitor electrodesFixed capacitor dielectricElectronic systemsControl signal

Selectable capacitors are used to modify performance characteristics of functional circuit elements of an integrated circuit (IC). In one embodiment, the decoupling capacitors are implemented as additional or alternative mounting pads on a surface of the IC. At least one selectable capacitor is provided for each IC circuit element, such as a logic network, whose operational characteristic(s) is predicted to be and is actually identified as sub-optimal through IC testing, particularly following a process change, a mask shrink, operation of the IC at higher clock frequency, or the like. Expensive redesign is avoided by selectively coupling capacitors into the IC circuit element as needed, under control of selector logic that is responsive to control signals. Methods of operation, as well as application of the apparatus to an electronic assembly and an electronic system, are also described.

Owner:INTEL CORP

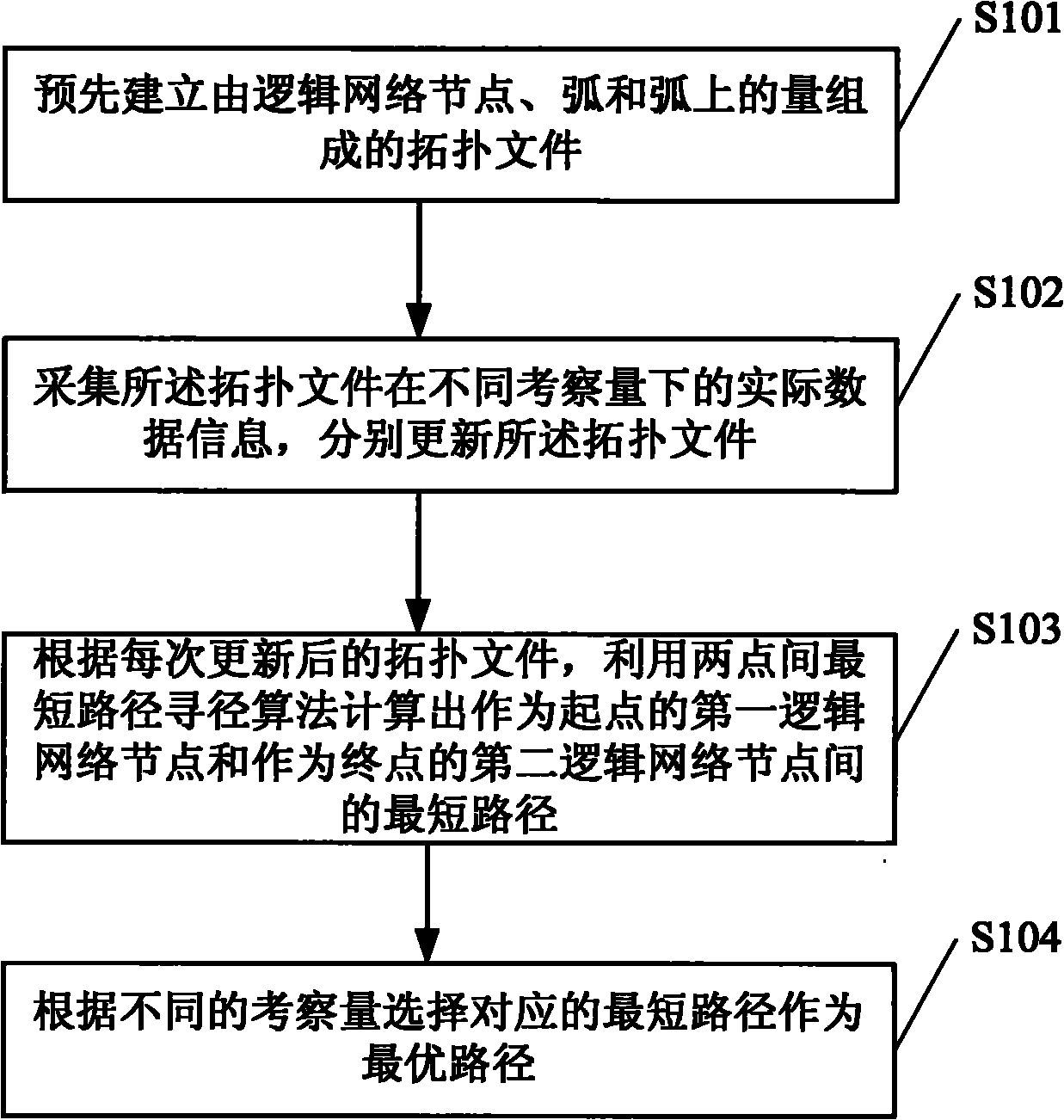

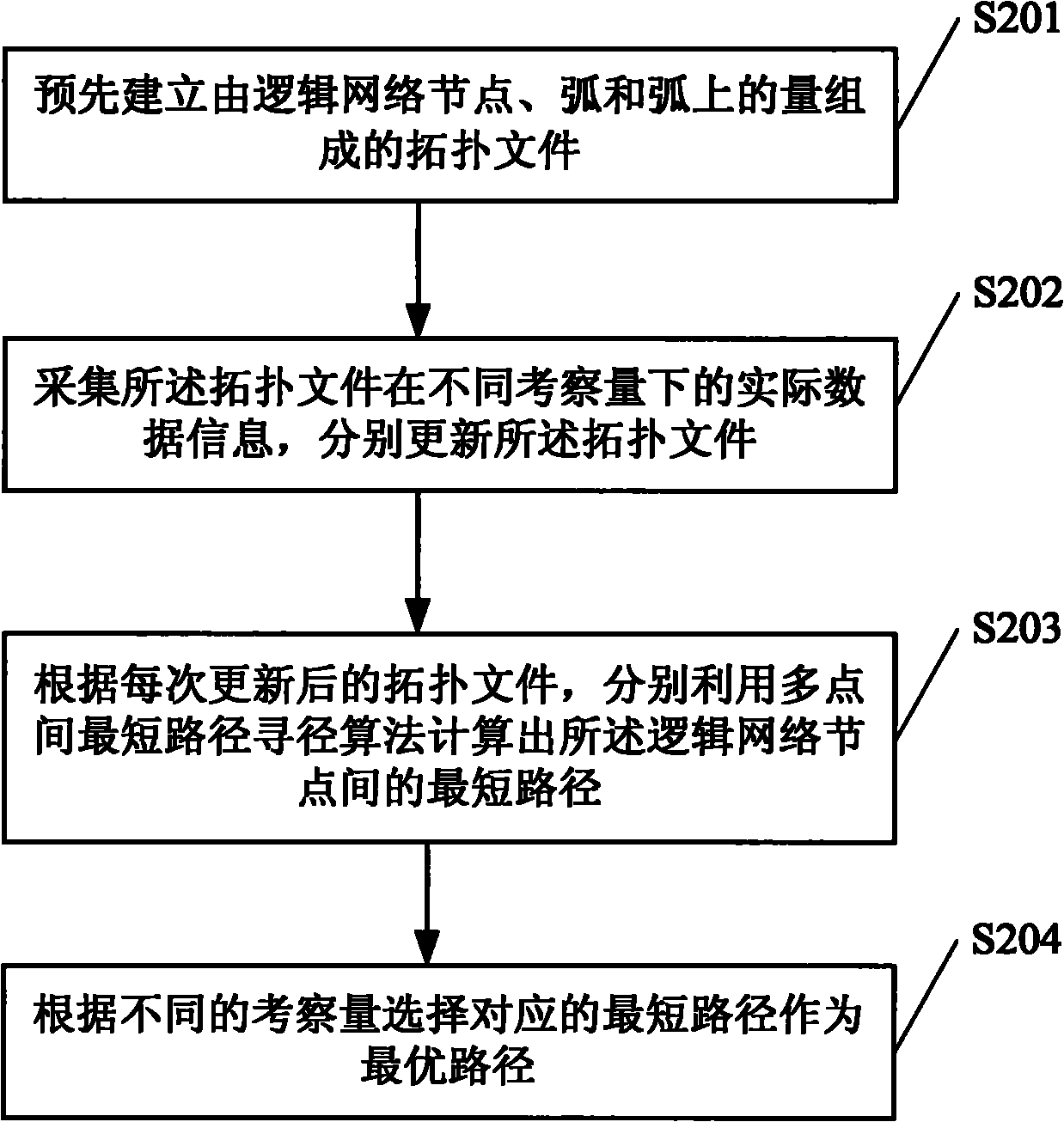

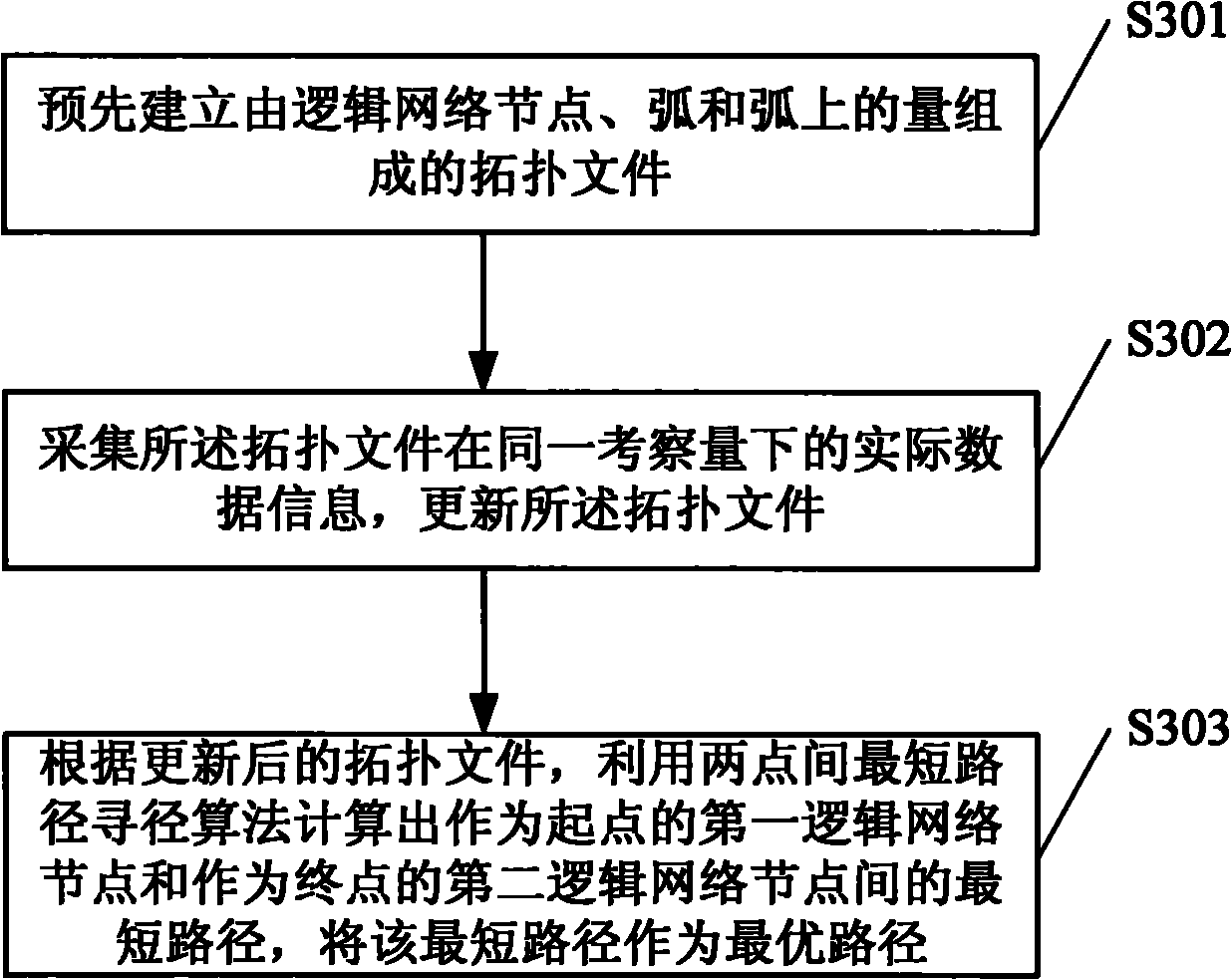

Network path finding method, optimal path selecting method and system thereof

The invention discloses a network path finding method, an optimal path selecting method and a system thereof. The method comprises the steps: pre-establishing a topology file consisting of logic network nodes, an arc and magnitudes on the arc, wherein the arc is the connecting line between the two logic network nodes and the magnitudes on the arc are weights given to the arc; collecting actual data information of the topology file with different studying magnitudes and respectively updating the topology file; figuring out the shortest path between a first logic network node as the start and a second logic network node as the end by a path finding method of the shortest path between two nodes according to the topology file after each updating; and selecting the corresponding shortest path as the optimal path according to different studying magnitudes. The method can collect actual data information of the topology file with different studying magnitudes and respectively updates the topology file, figure out the shortest path according to the topology file after each updating, and precisely work out the optimal path between the start and the end or the logic nodes.

Owner:林定伟

Methods and apparatus for waveform based variational static timing analysis

InactiveUS8341572B1Computer aided designSoftware simulation/interpretation/emulationStatic timing analysisEngineering

A system and method are disclosed for waveform based variational static timing analysis. A circuit is divided into its linear circuit parts and non-linear circuit parts and modeled together, by a combination of linear modeling techniques, into linear equations that may be represented by matrices. The linear equations in matrix form may be readily solved by a computer such that an input waveform to an input pin of the circuit can be sequentially “pushed” through the various interconnects and logic networks of the circuit to an output pin. Output voltage waveforms are obtained at each stage of the waveform pushing and may be used to perform static timing analysis.

Owner:CADENCE DESIGN SYST INC

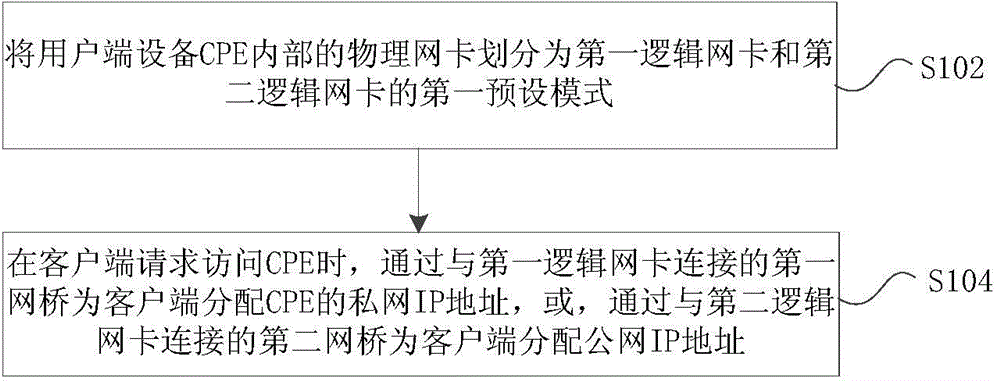

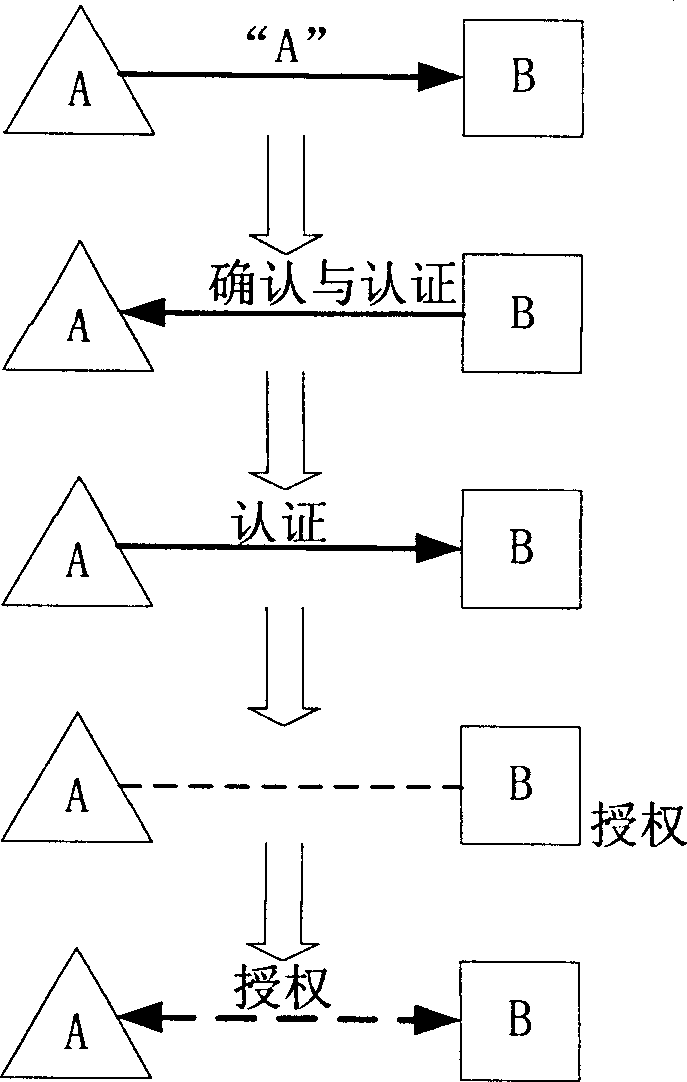

Internet protocol (IP) address allocation method and device

The invention provides an IP address allocation method and device. The method comprises: dividing a physical network card in a customer premise equipment (CPE) into a first logic network card and a second logic network card in a first preset mode; and when a client terminal requests access to the CPE, allocating a private network IP address of the CPE for a client terminal via a first network bridge connected to the first logic network card, or allocating a public network IP address to the client terminal via a second network bridge connected to the second logic network card. According to the invention, the problem in related art that when a part of client terminals only accesses a public resource, the other client terminals cannot access a resource in a router product is solved, and user experience is improved.

Owner:ZTE CORP

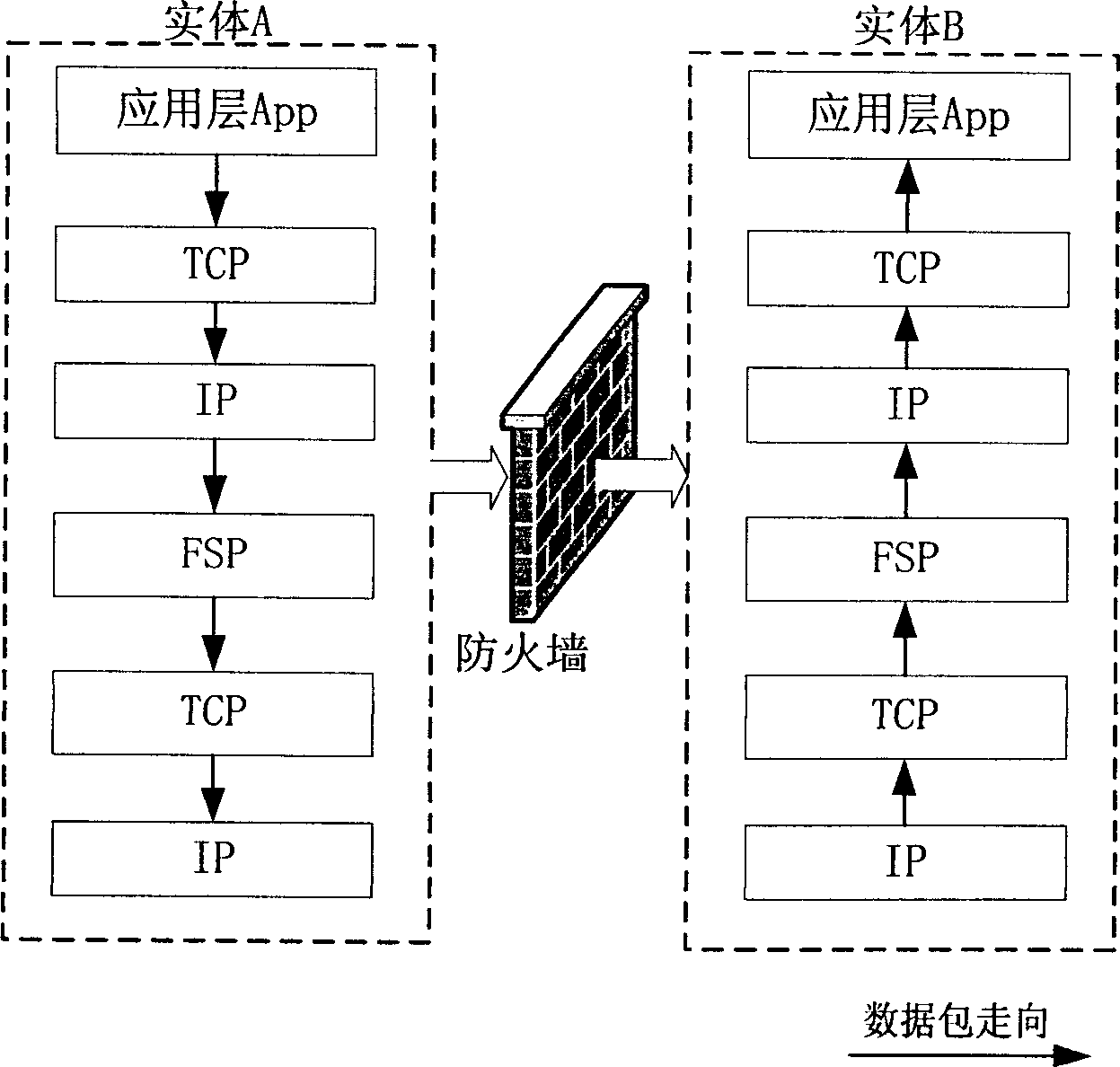

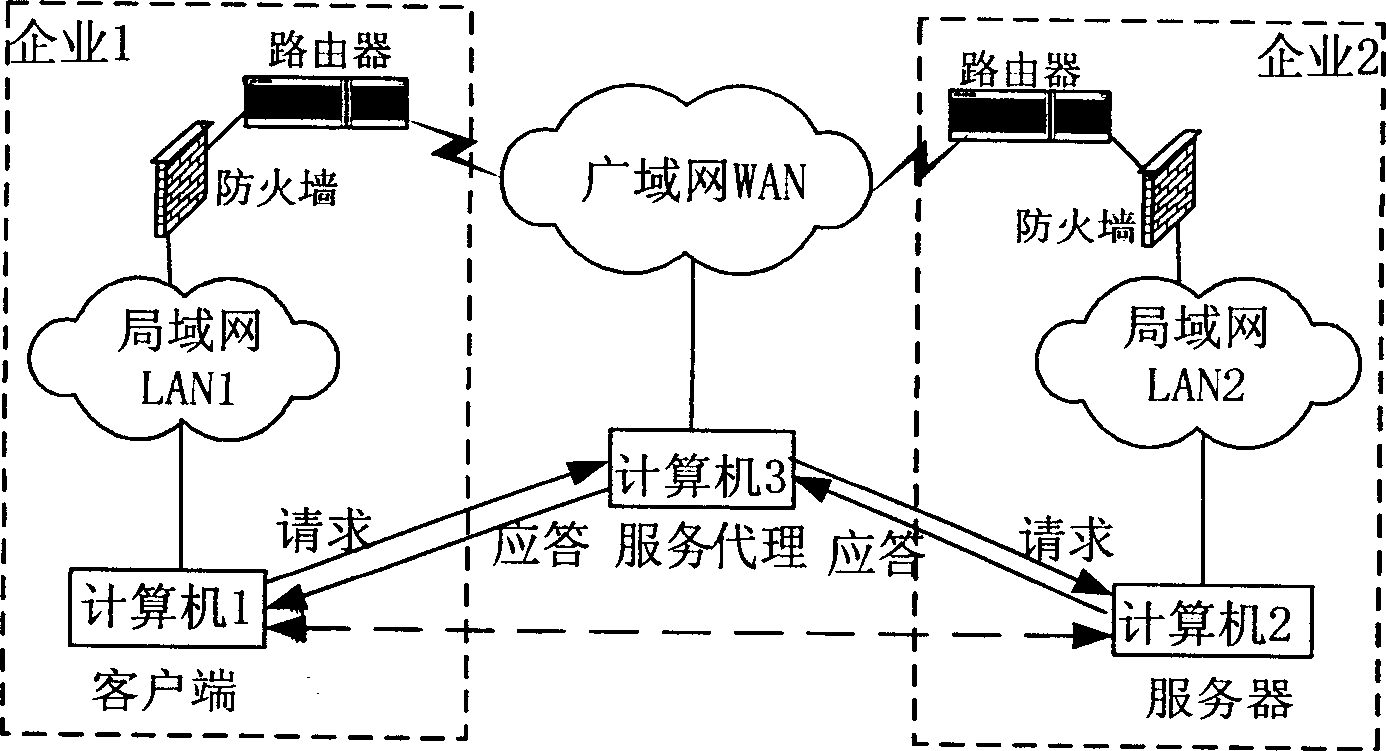

Method for realizing peer-to-peer network system architecture

InactiveCN1447256ADigital computer detailsElectric digital data processingTerminal equipmentClient-side

A peer-to-peer network is based on TCP / IP protocol to form logic network of layerless structure between abstract peer-to-peer entities in completely equal status, each entity can be a server providing service to other entities or customer end served by other entities, the concrete way of realizing and entity is specific software example operating on computer or special information terminal equipment. This method can realize centerless exchanger of no center server light burden peer-to-peer network status, any fire-proof bulkhead of NAT router, any entity log on to net can know if other coherent entities are online at once by certification and inform on-line entities about its no-line information.

Owner:CHONGQING UNIV +1

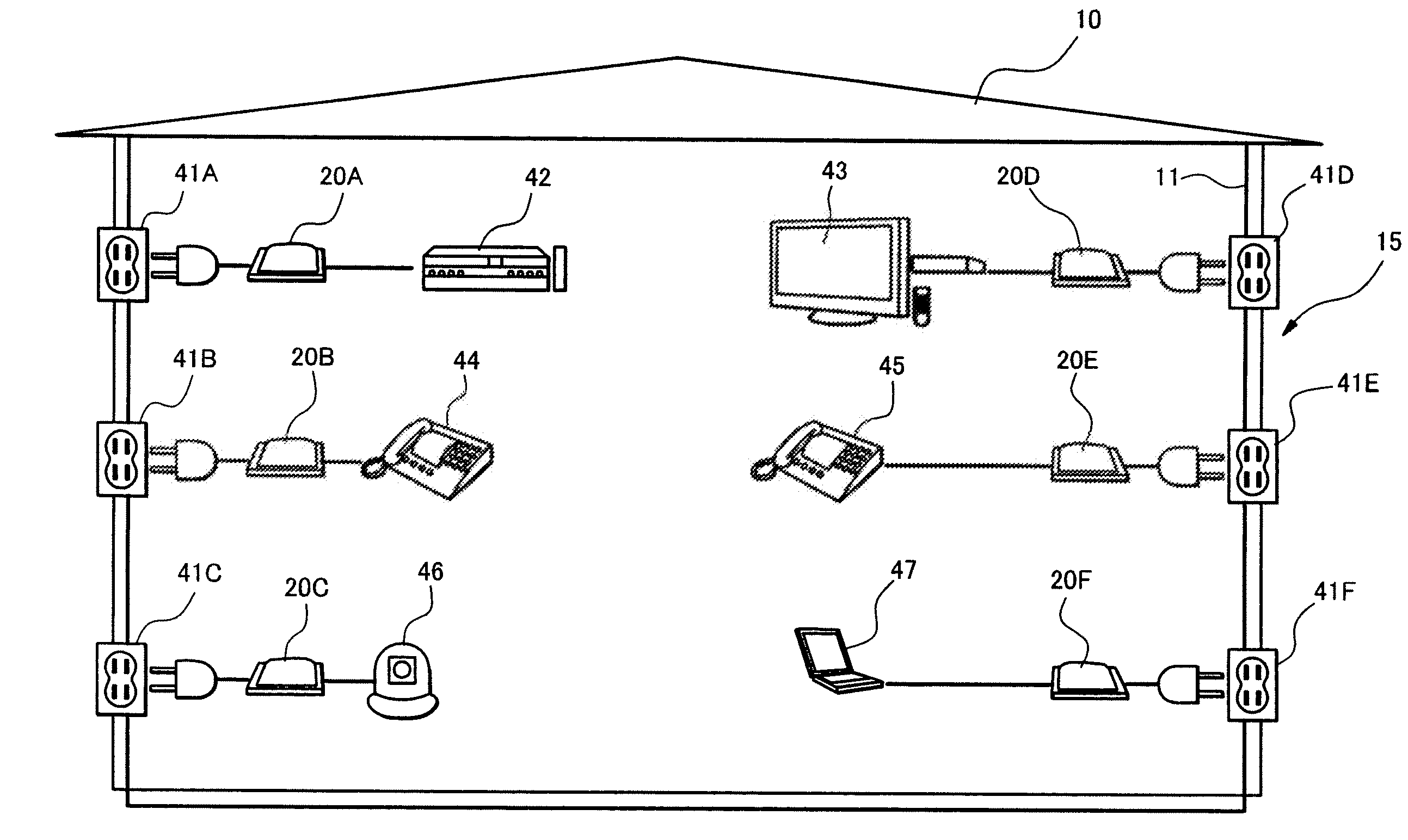

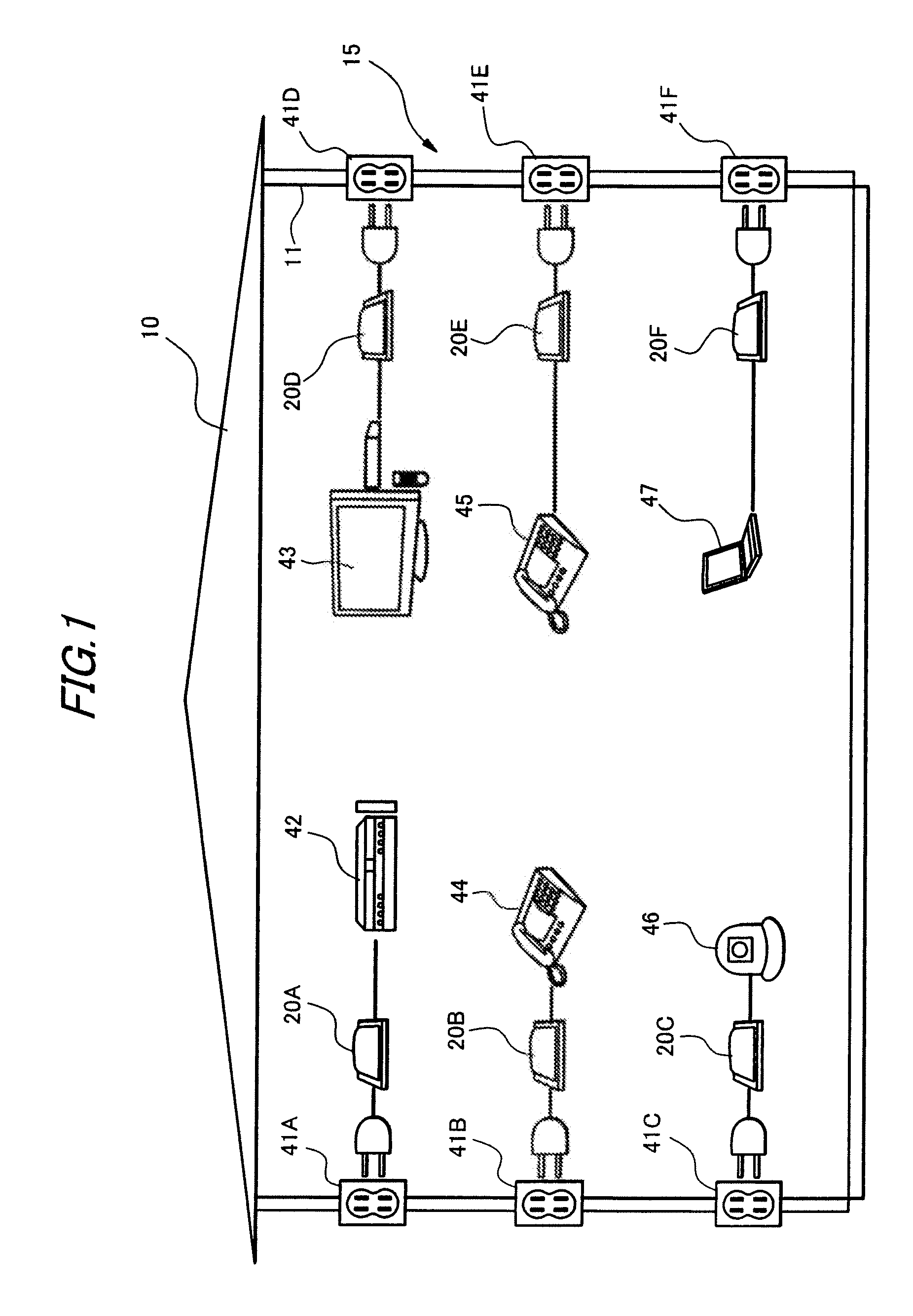

Method, apparatus and integrated circuit for controlling transmission rate

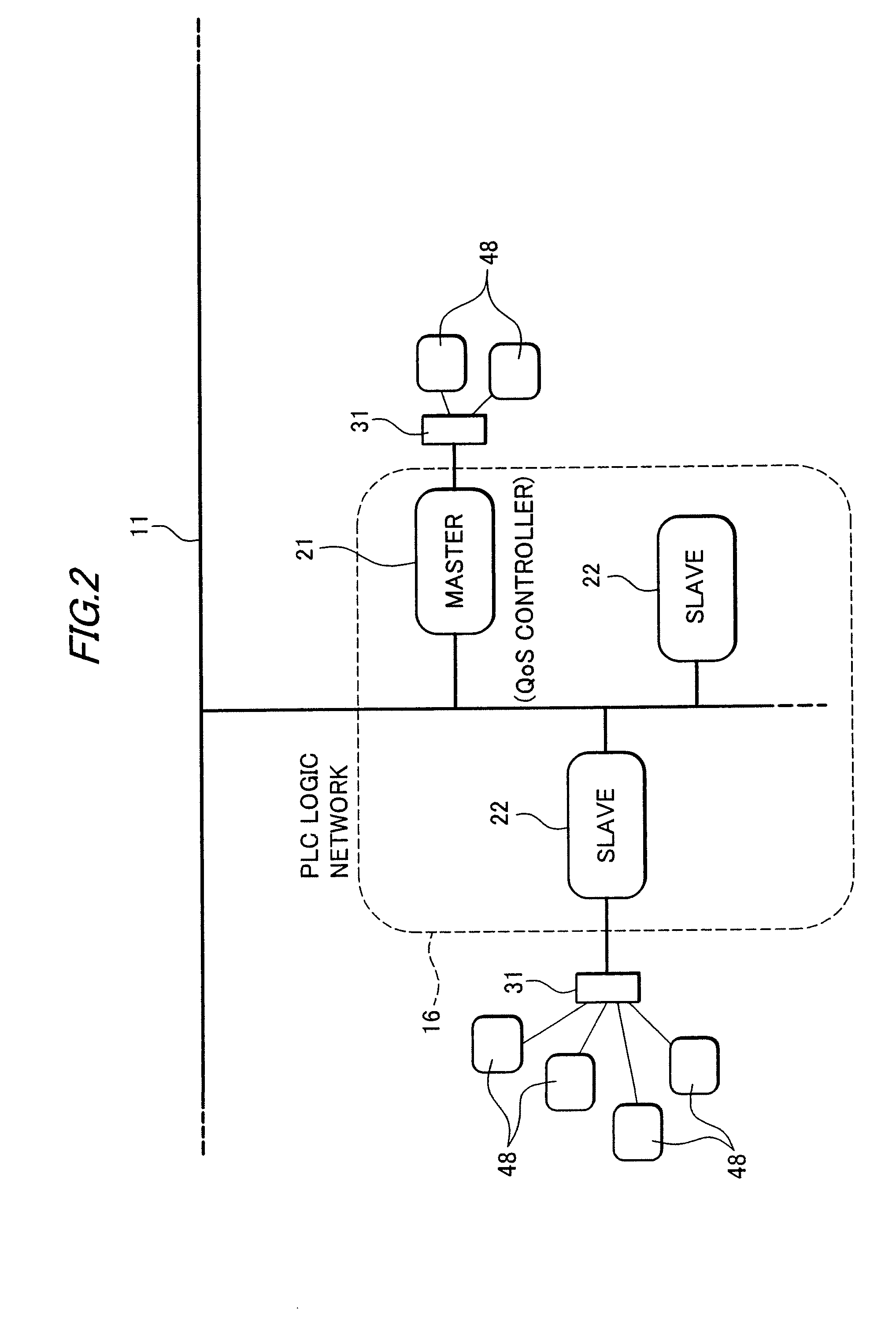

ActiveUS20090268752A1Efficient use ofError preventionFrequency-division multiplex detailsEngineeringLogic network

A plurality of PLC adapters, such as a master 21 and slaves 22, are connected to a power line 11, which forms a PLC logic network 16. Electric apparatuses 48, such as a television monitor and a video recorder, are connected to the master 21 and the slaves 22 through repeaters 31. The master 21 is a control terminal having the function of QoS controller. The master 21 allocates timeslots for transmitting data over a network, acquires information on the actual data transmission rate detected by a data receiving terminal, and modifies the timeslot allocated to target data on the basis of the acquired information on the actual data transmission rate.

Owner:PANASONIC CORP

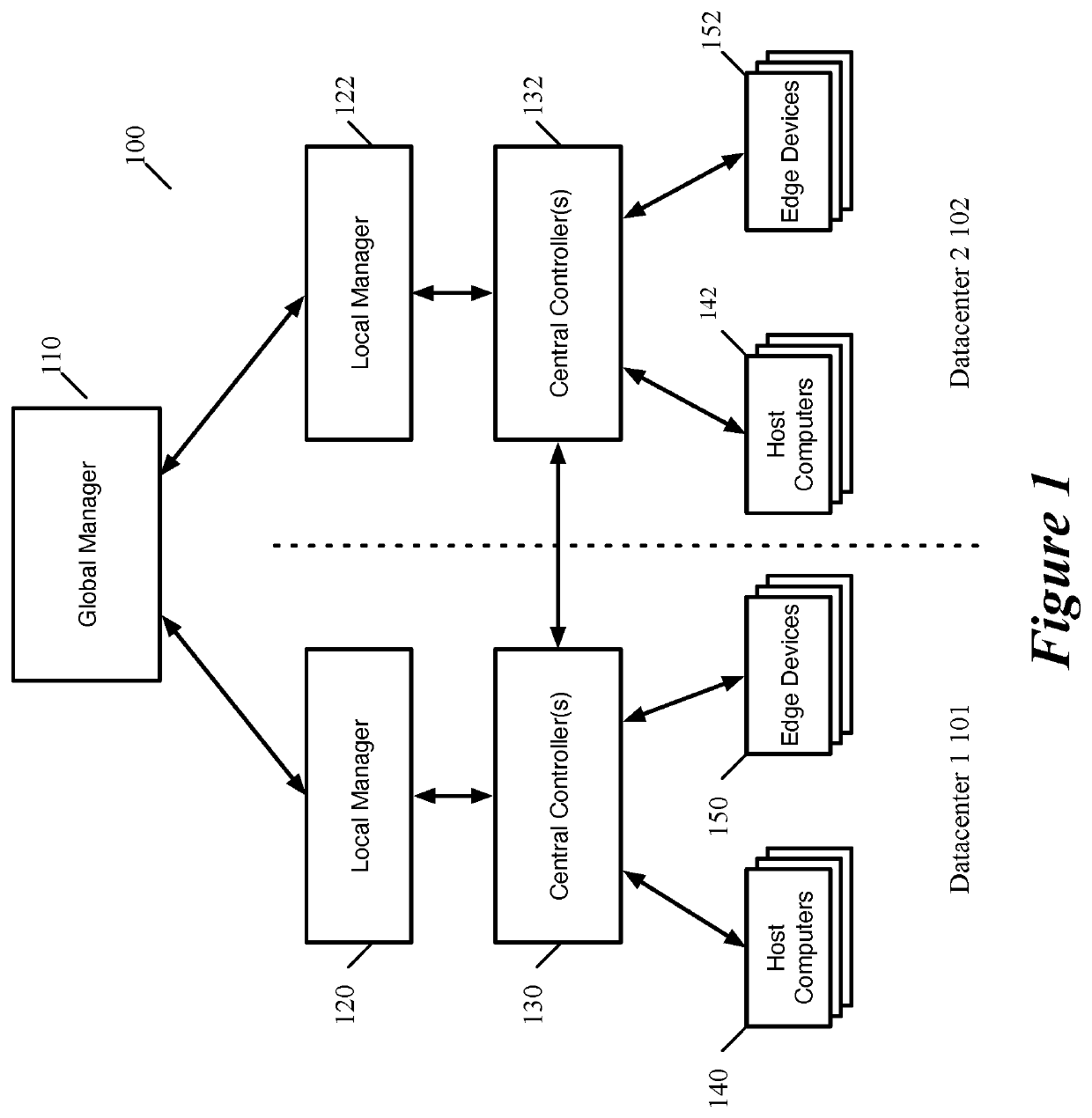

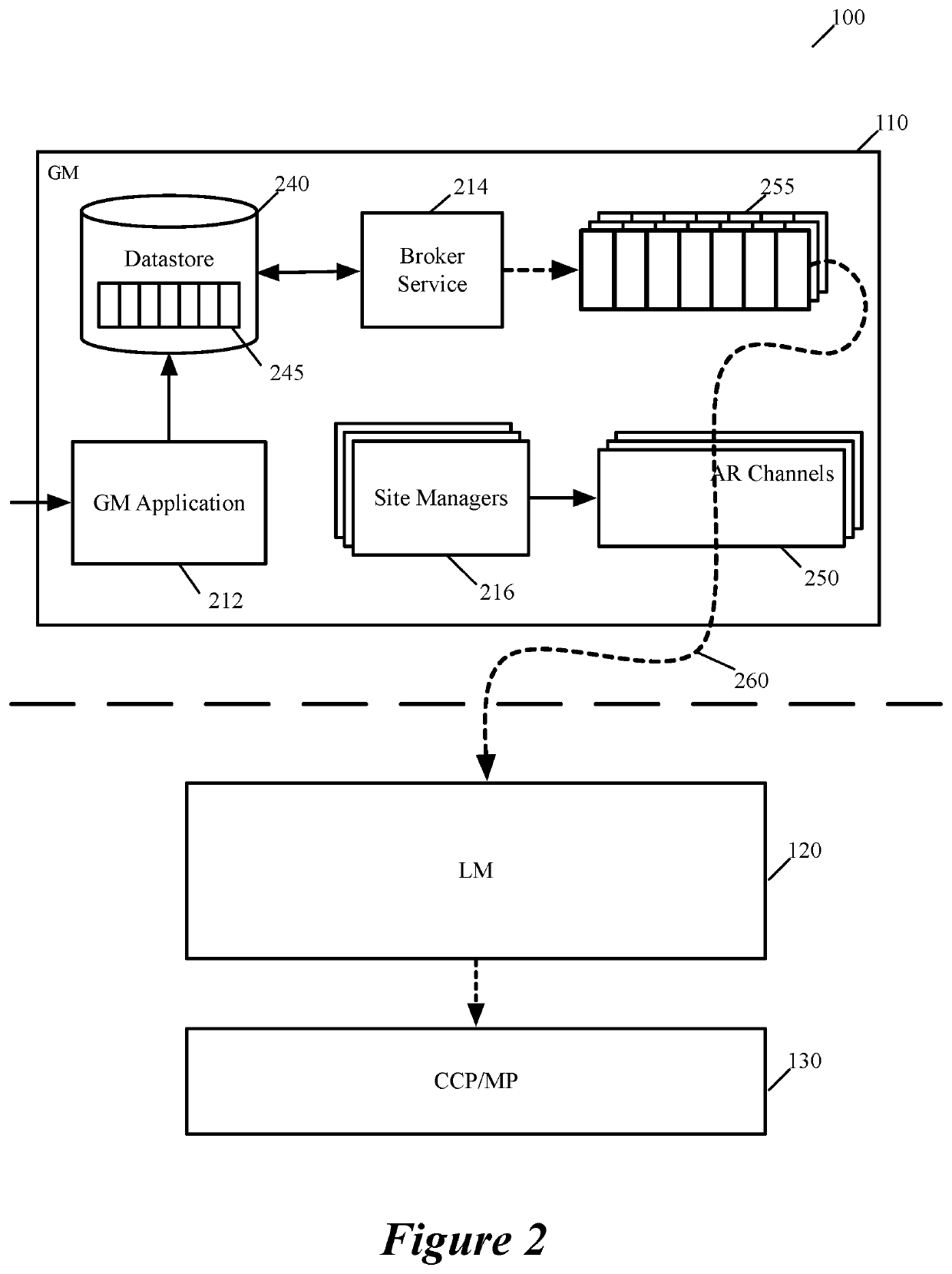

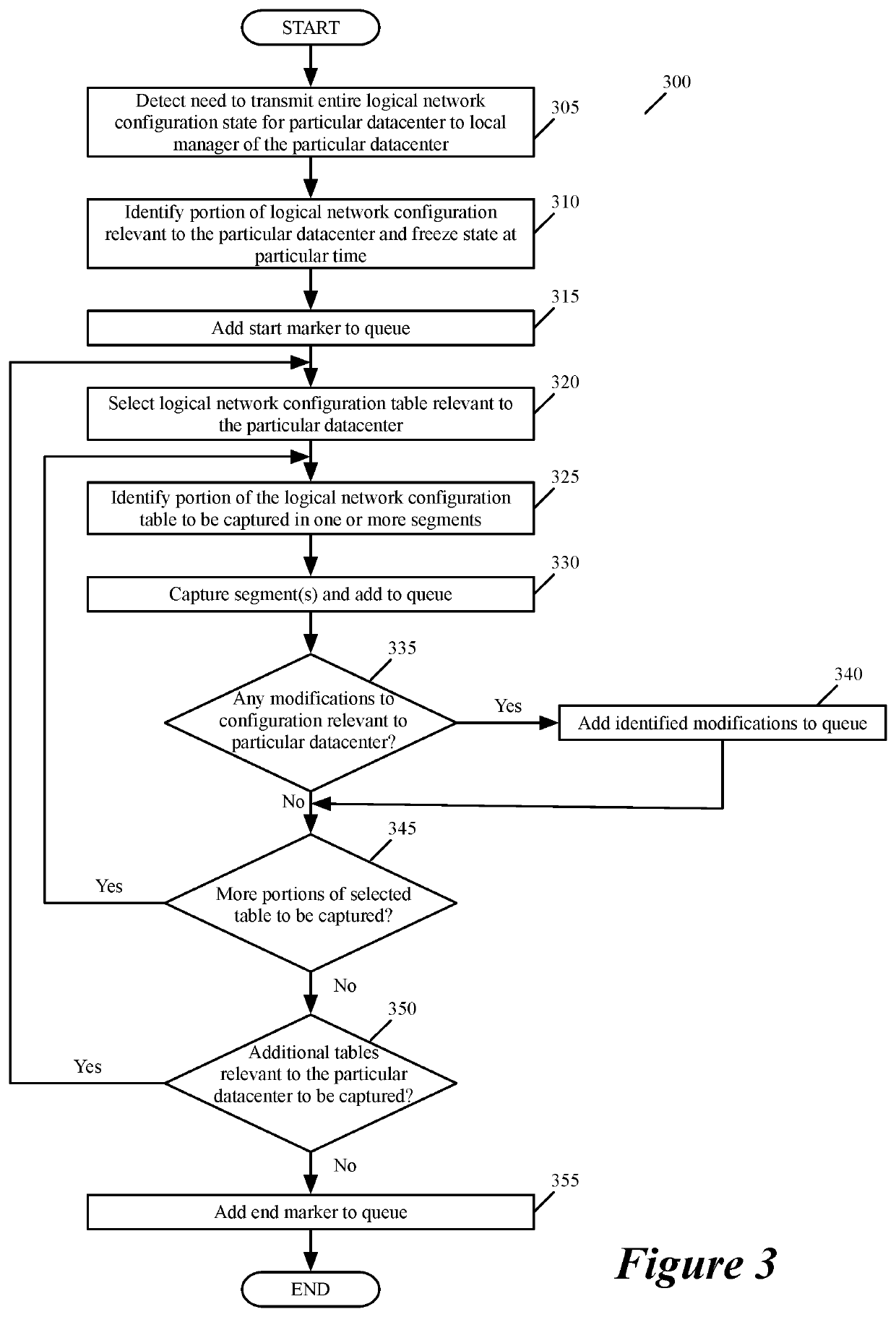

Synchronization of logical network state between global and local managers

Some embodiments provide a method for a global manager that manages a logical network configuration for multiple datacenters that each have a local manager for managing the logical network configuration within the datacenter. Based on detecting that a connection to a particular local manager of a particular datacenter has been restored after a period of unavailability, the method identifies a portion of the logical network configuration that is relevant to the particular datacenter. In a series of transactions, the method transfers the identified portion of the logical network configuration to the particular local manager. During the series of transactions, the method identifies modifications to the identified portion of the logical network configuration to be included in the series of transactions. Upon completion of the series of transactions, the method transfers a notification to the particular local manager indicating completion of the series of transactions.

Owner:VMWARE INC

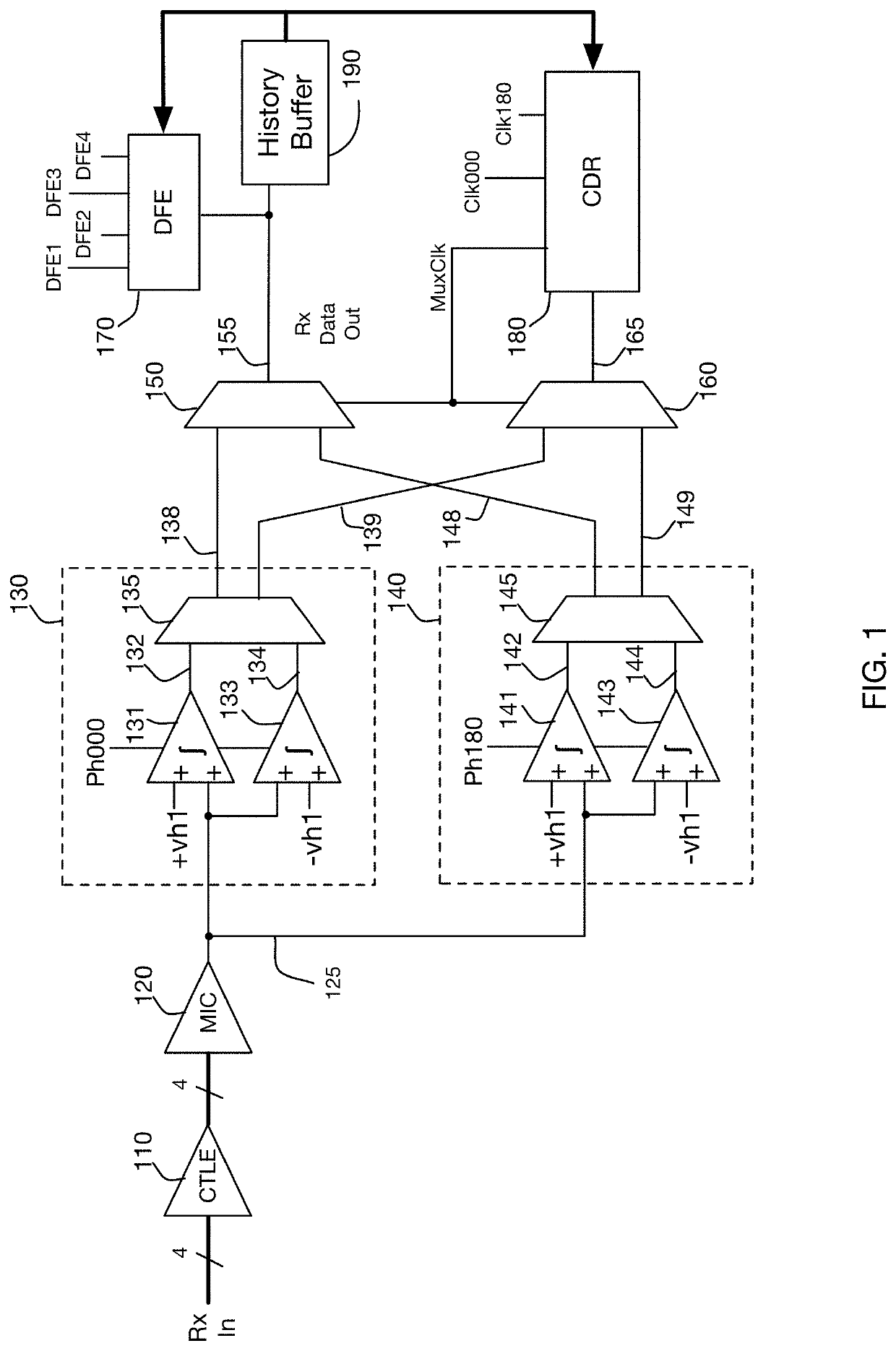

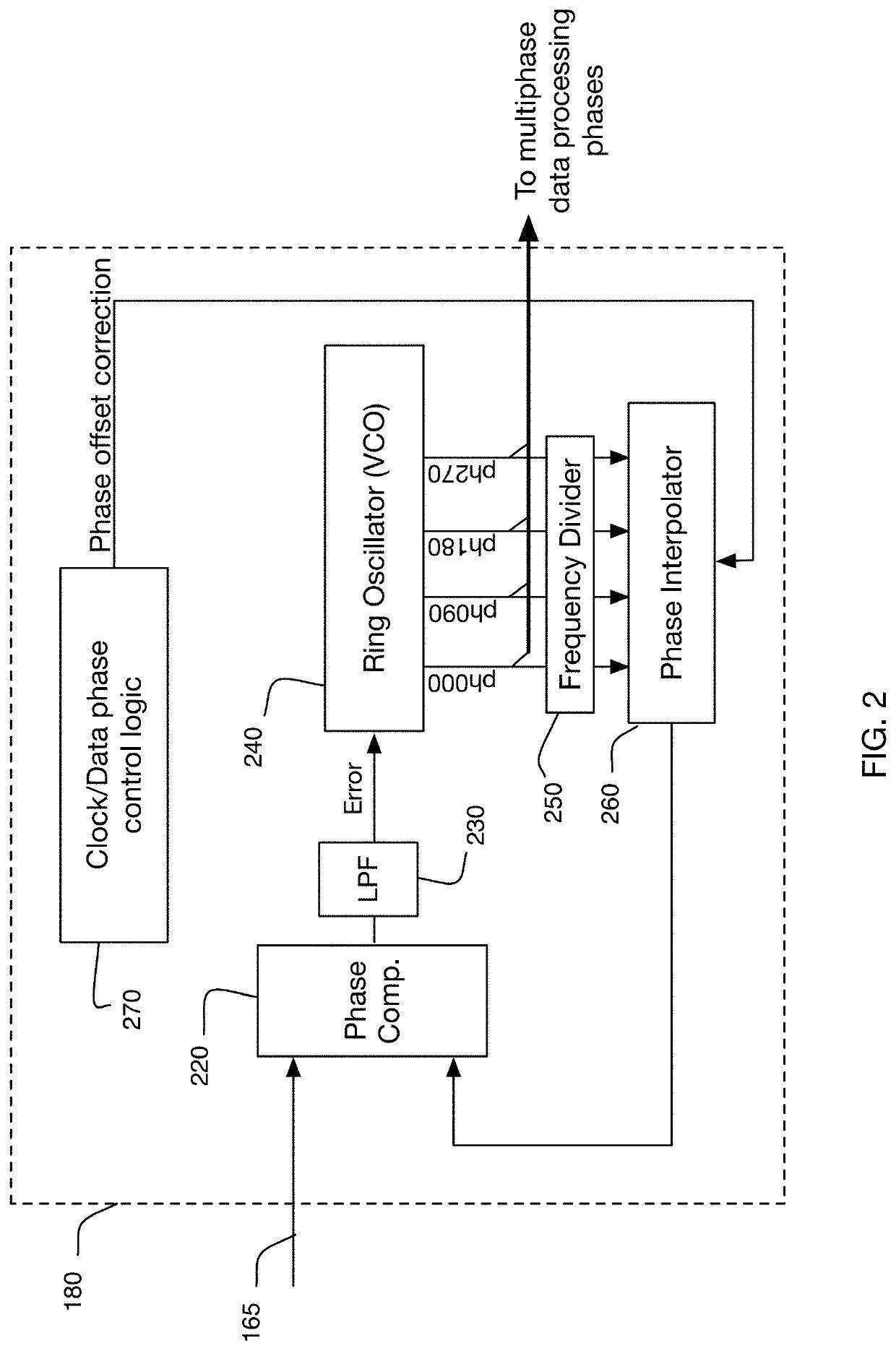

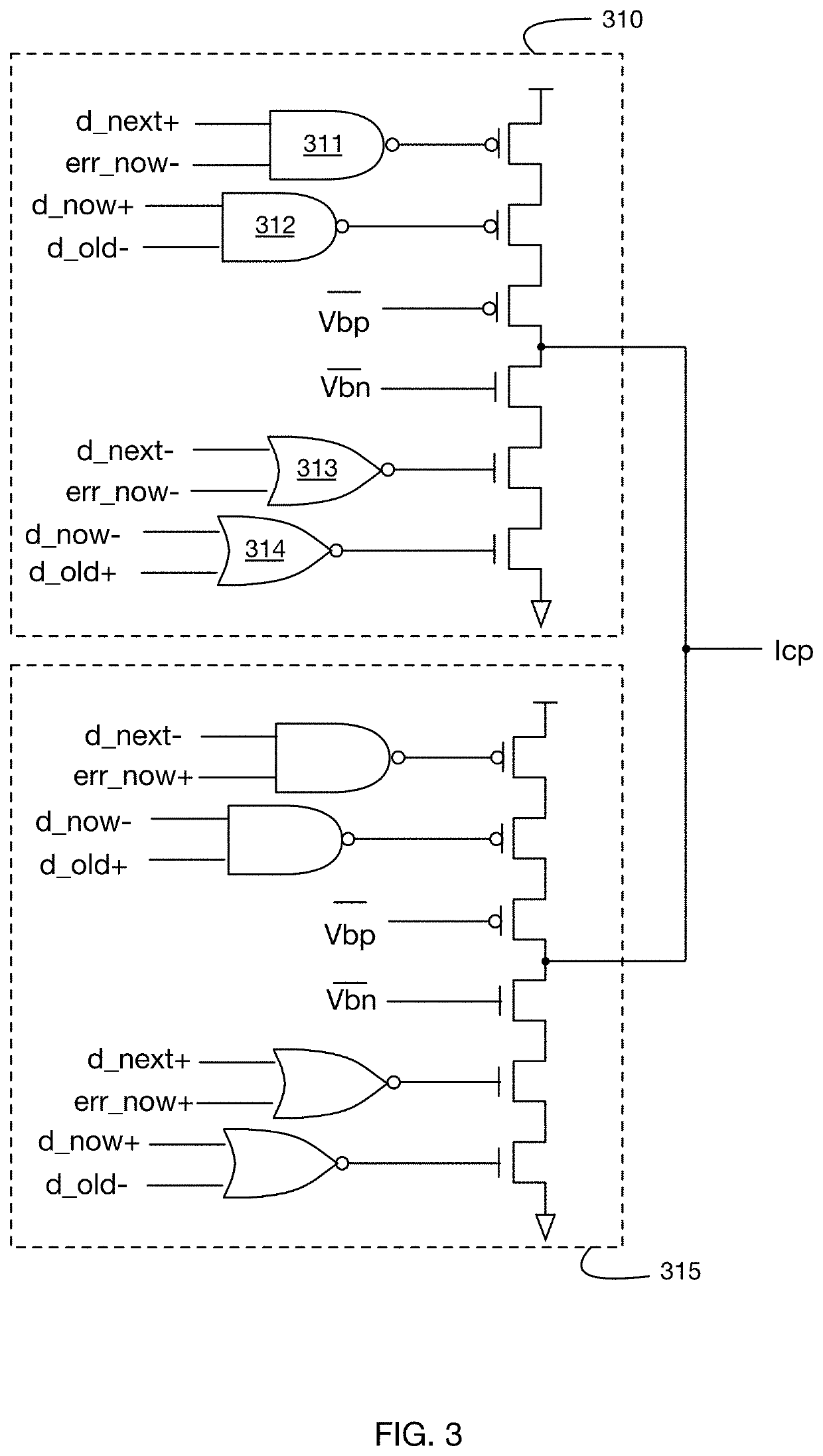

Low latency combined clock data recovery logic network and charge pump circuit

ActiveUS20190377378A1Logic circuits characterised by logic functionPulse automatic controlProportional controlCarrier signal

Methods and systems are described for obtaining a sequence of data decisions and an error signal generated by one or more samplers operating on a received input signal according to a sampling clock, applying the sequence of data decisions and the error signal to each logic branch of a set of logic branches, and responsively selecting a logic branch from the set of logic branches, the logic branch selected responsive to (i) a detection of a transitional data pattern in the sequence of data decisions and (ii) the error signal, the selected logic branch generating an output current, and providing the output current to a local oscillator controller, the output current sourcing and sinking current to a capacitor through a resistive element to adjust an input voltage of a proportional control circuit relative to a voltage on the capacitor connected to the resistive element.

Owner:KANDOU LABS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com