Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5800 results about "Integrated circuit design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

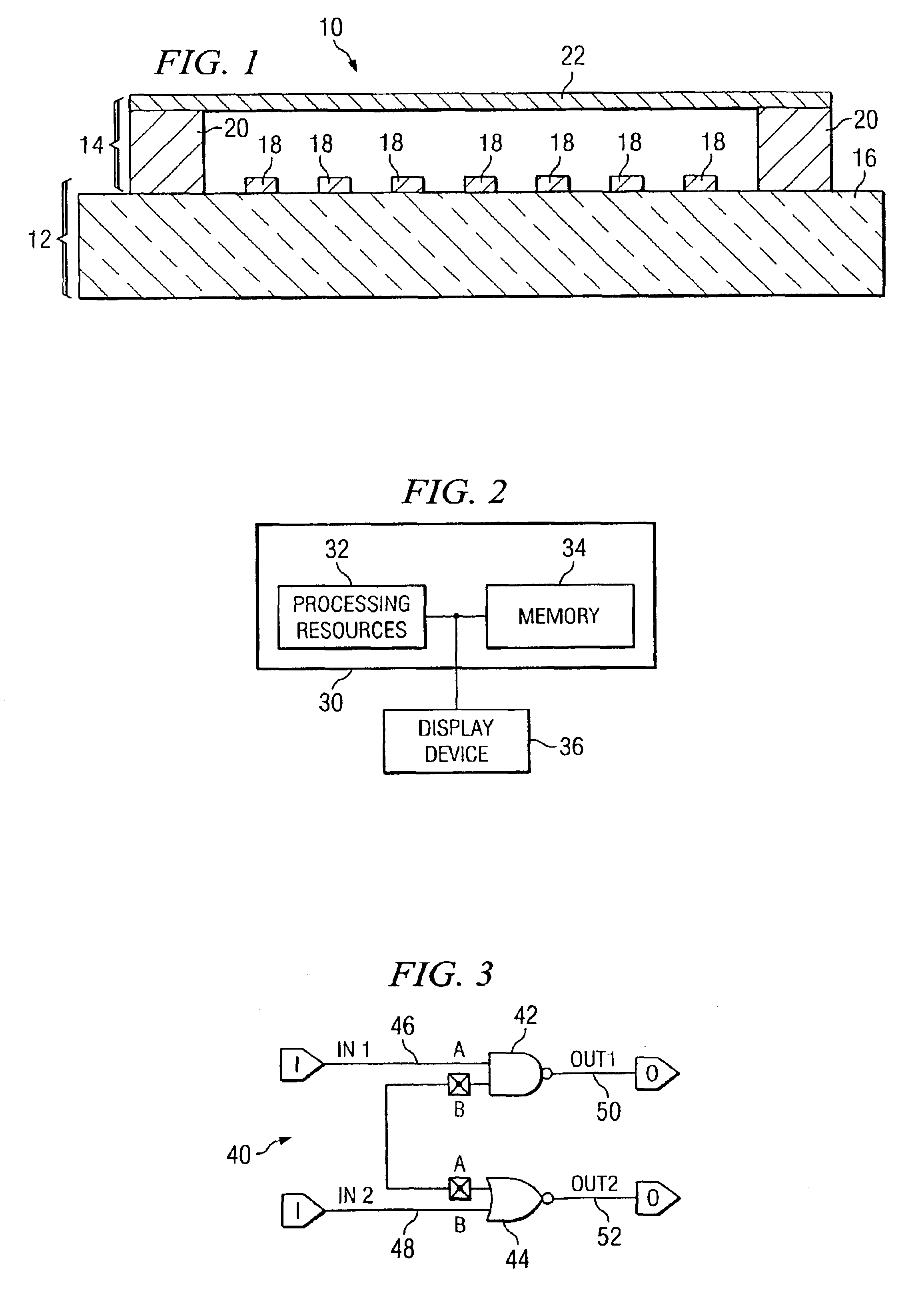

Integrated circuit design, or IC design, is a subset of electronics engineering, encompassing the particular logic and circuit design techniques required to design integrated circuits, or ICs. ICs consist of miniaturized electronic components built into an electrical network on a monolithic semiconductor substrate by photolithography.

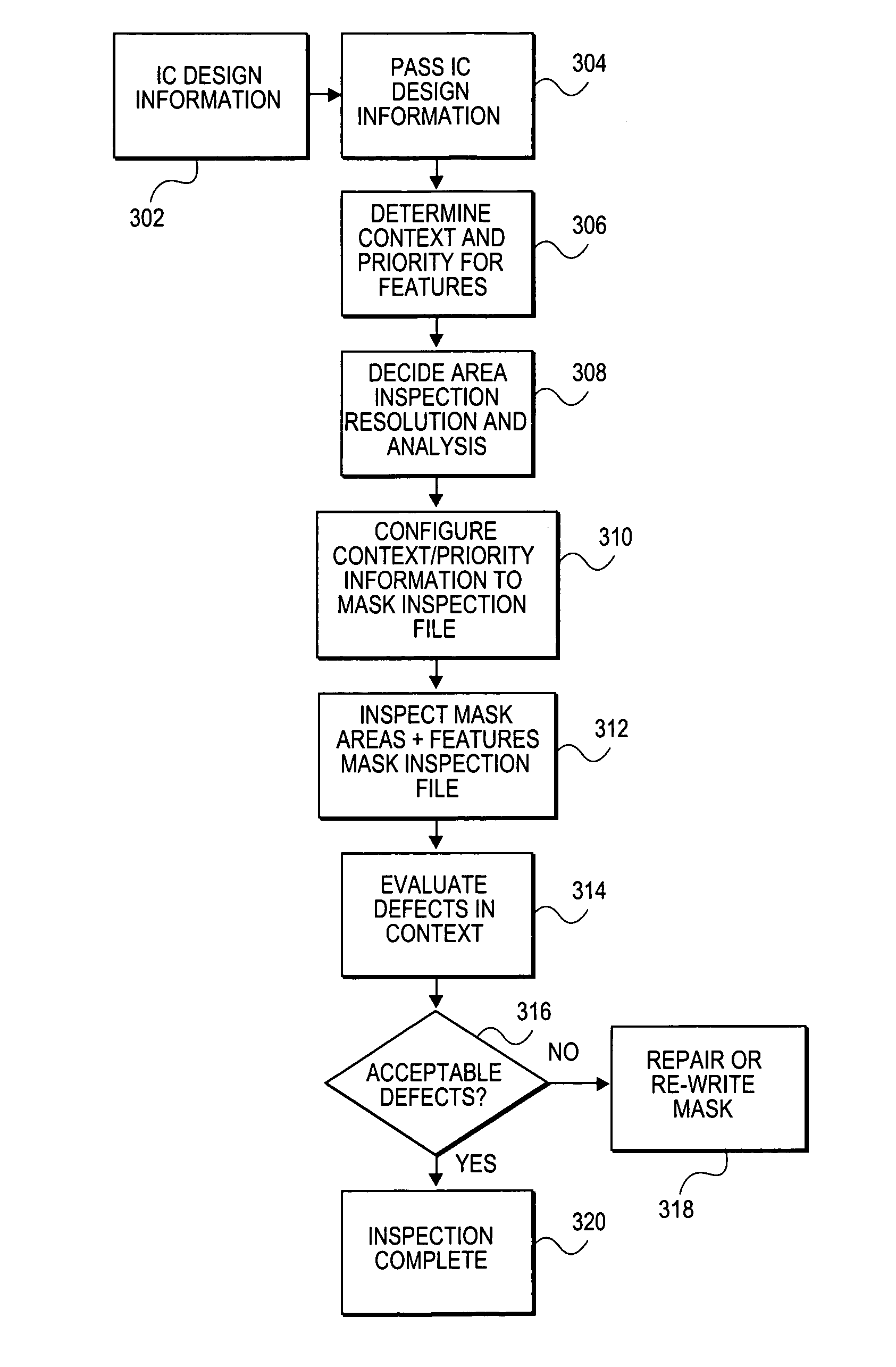

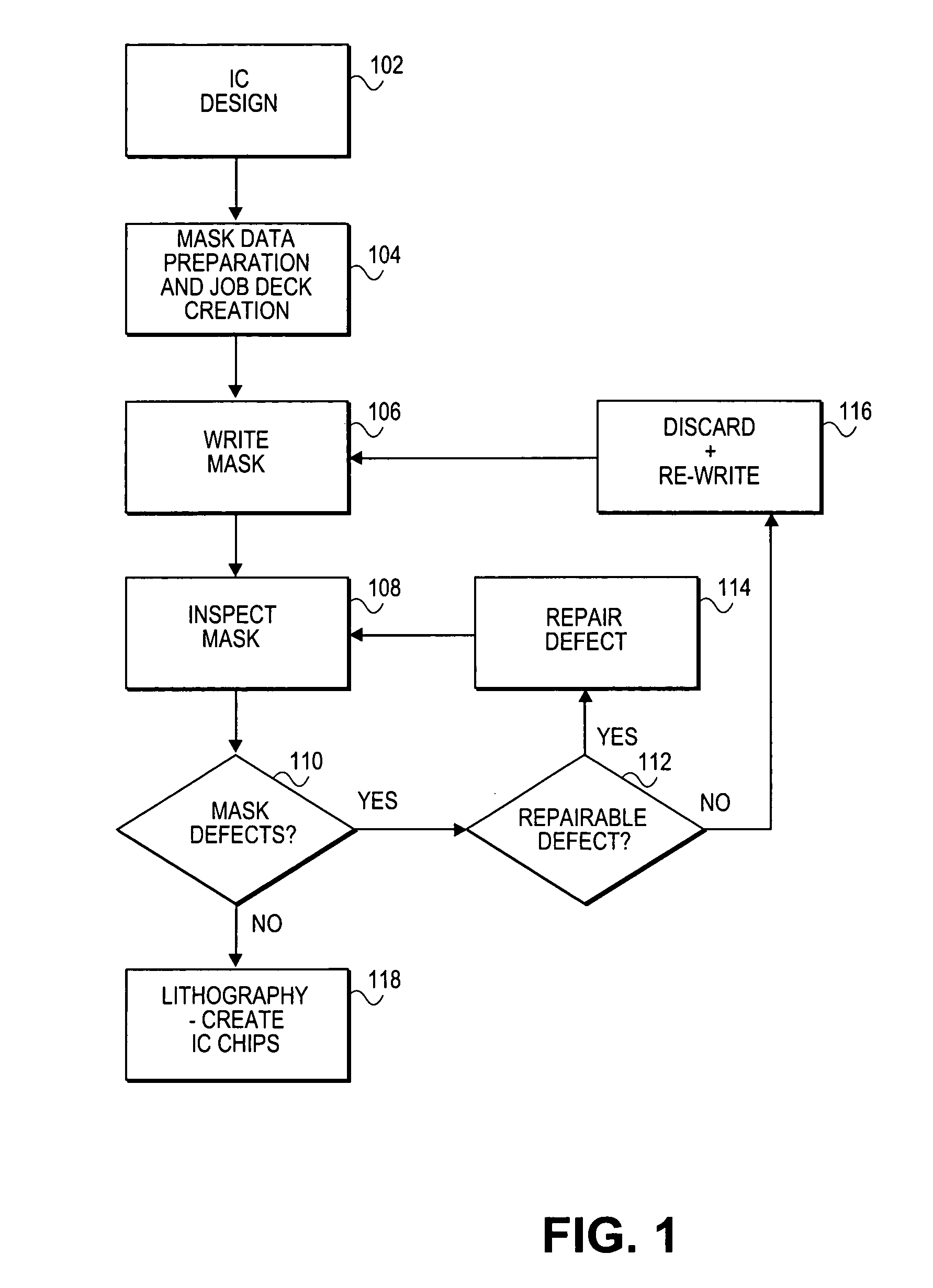

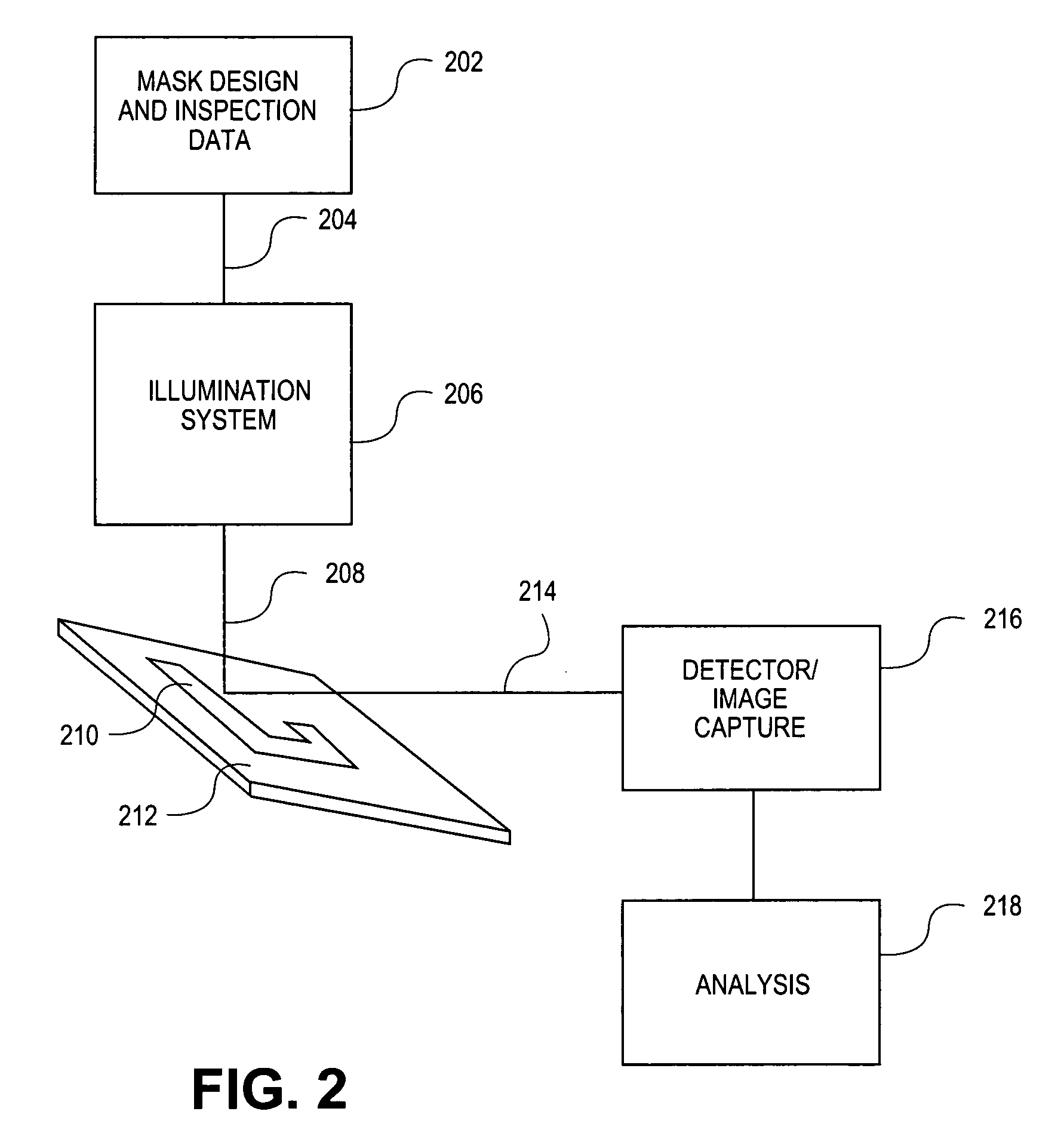

Method and system for context-specific mask inspection

InactiveUS7231628B2Electrical testingCharacter and pattern recognitionMask inspectionContext specific

A method for inspecting lithography masks includes generating integrated circuit design data and using context information from the integrated circuit design data to inspect a mask.

Owner:CADENCE DESIGN SYST INC

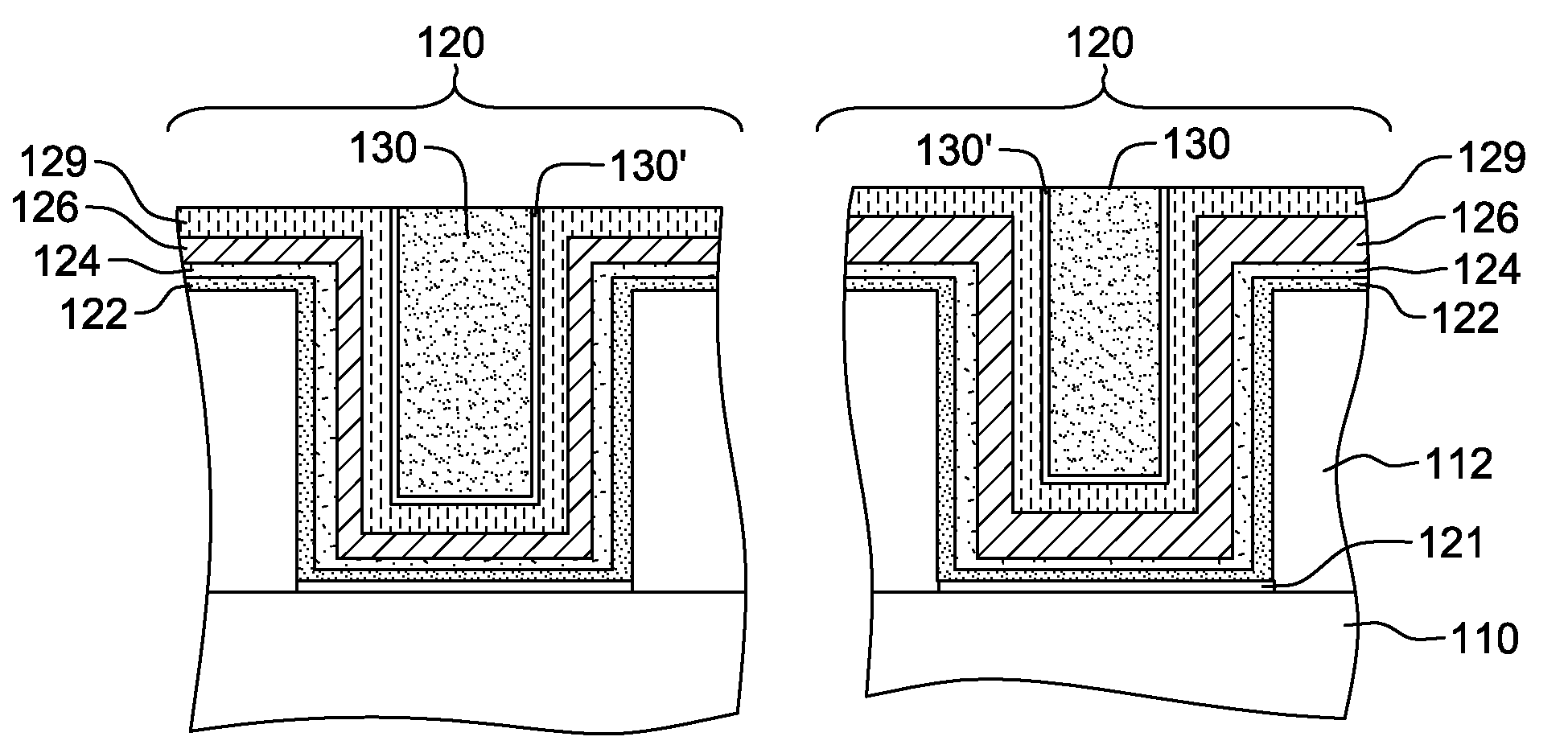

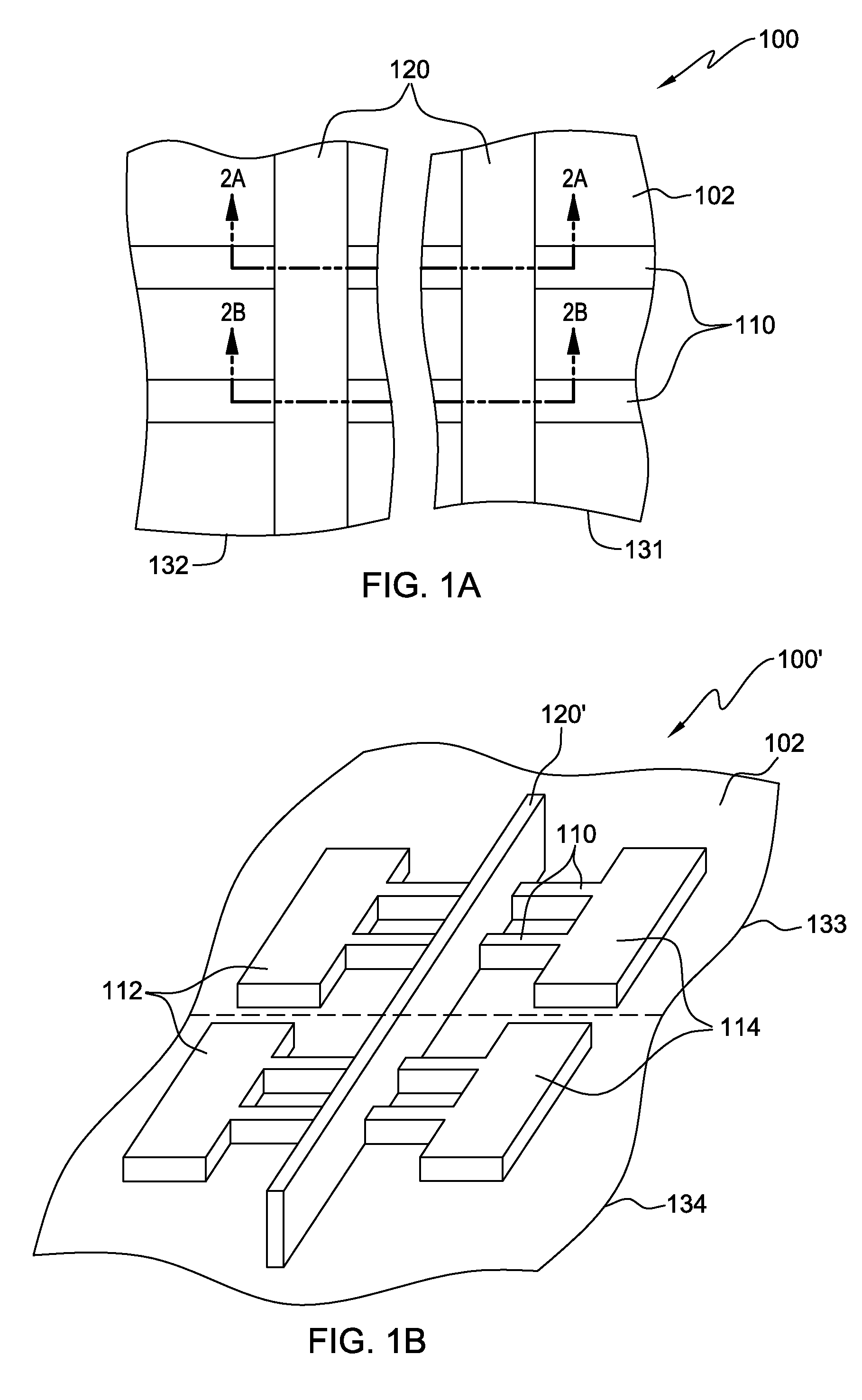

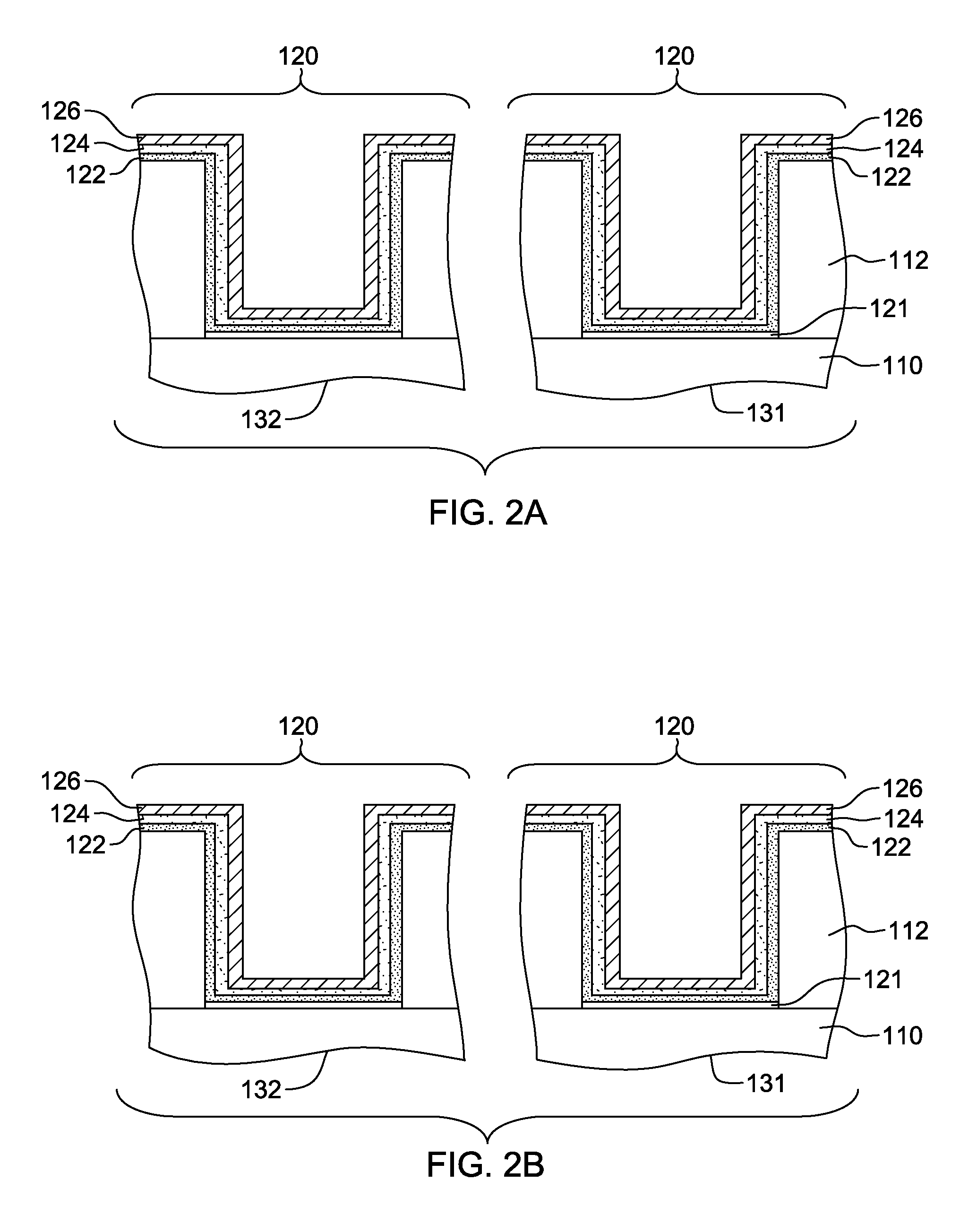

Integrated circuits with varying gate structures and fabrication methods

ActiveUS20150243658A1Overcomes shortcomingEnhanced advantageTransistorSolid-state devicesGate stackField-effect transistor

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES US INC

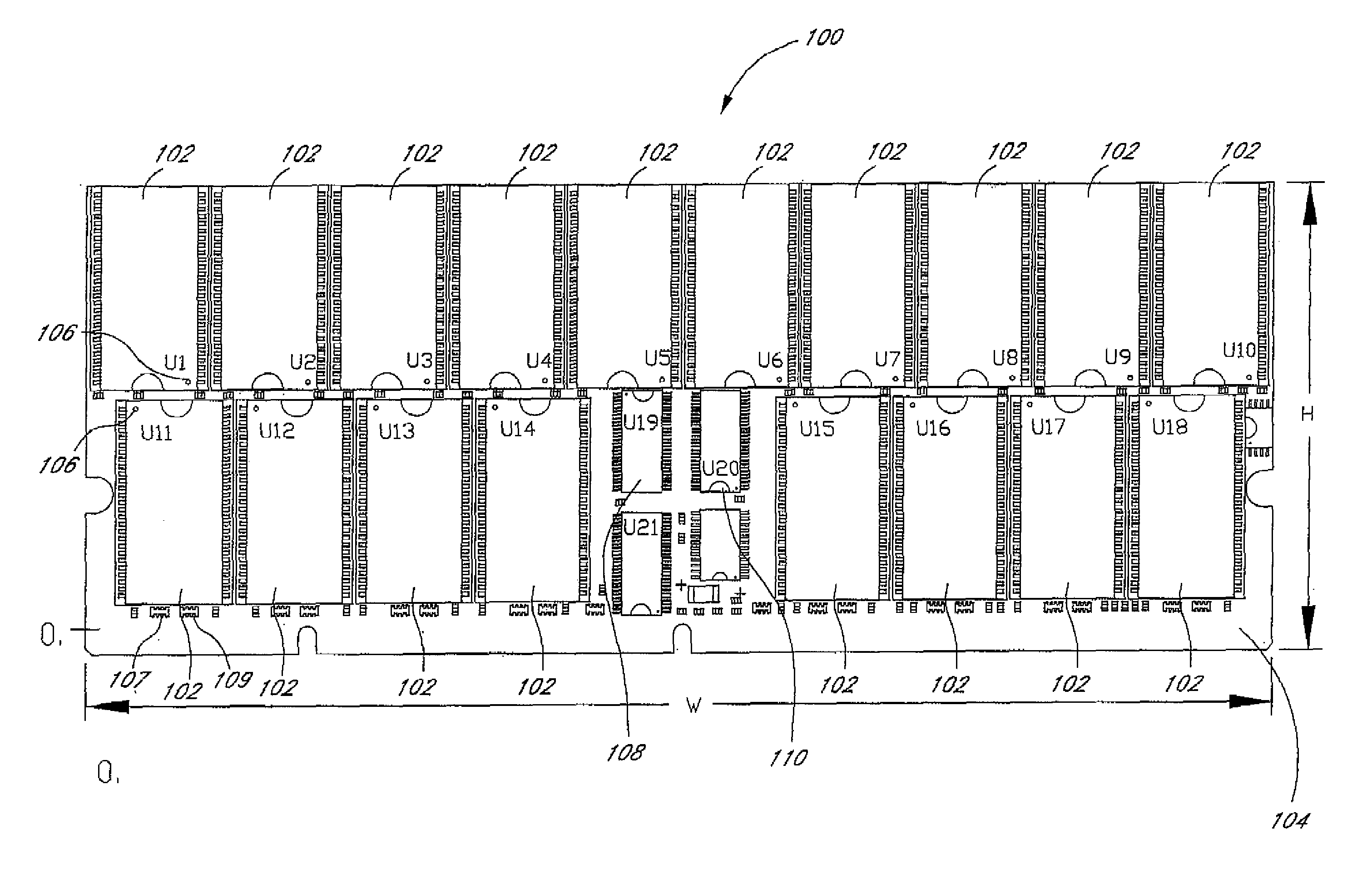

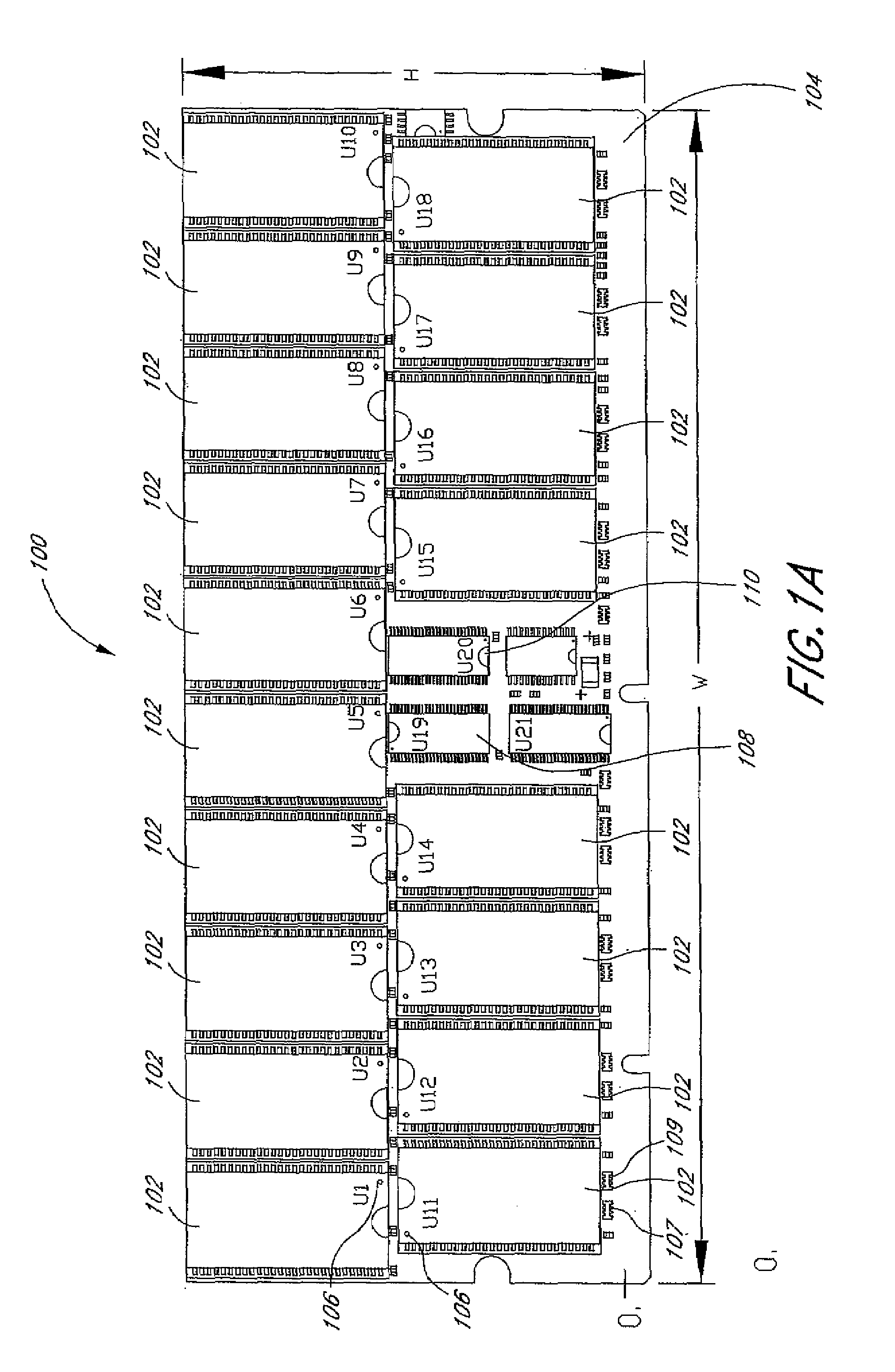

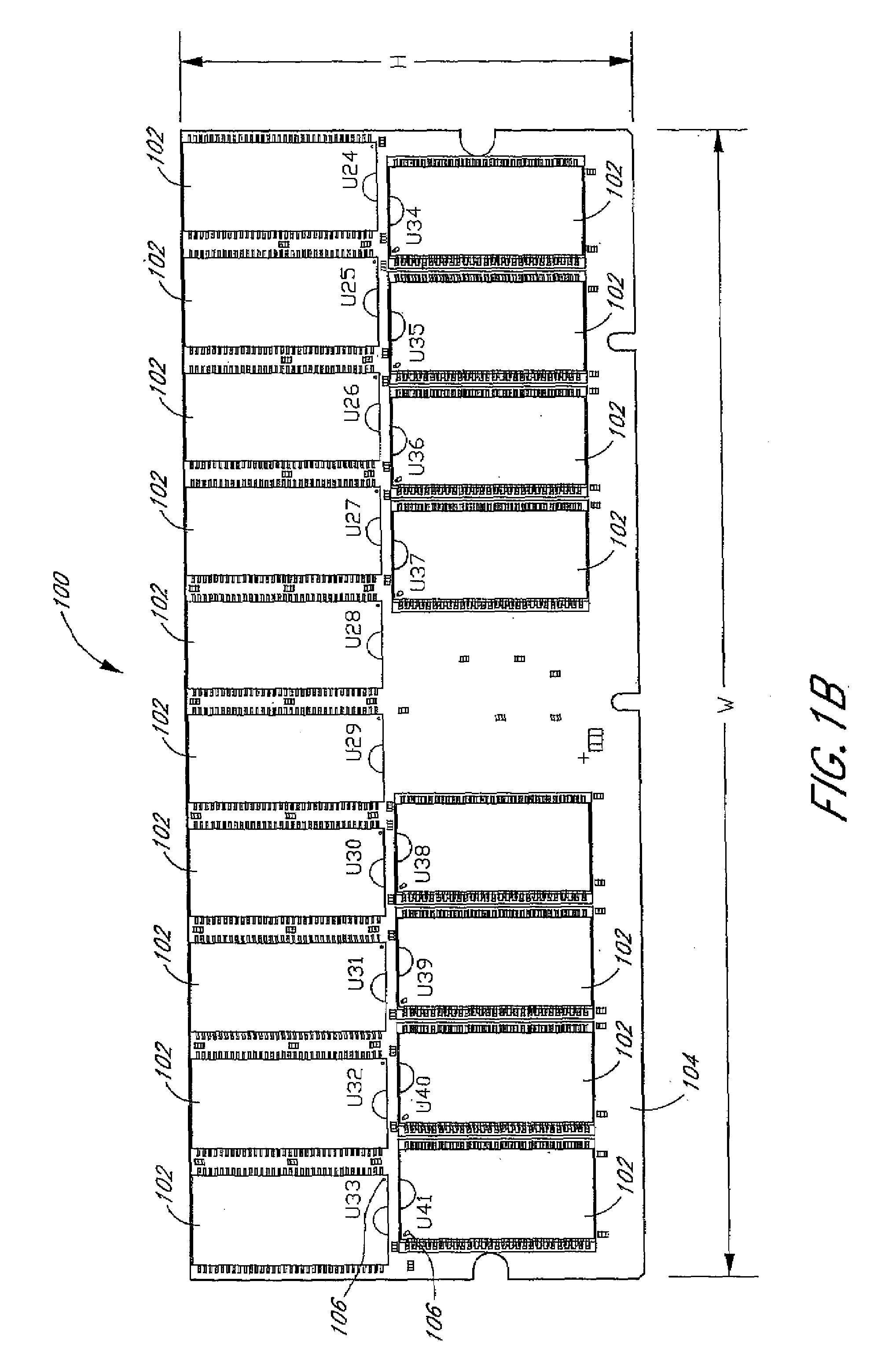

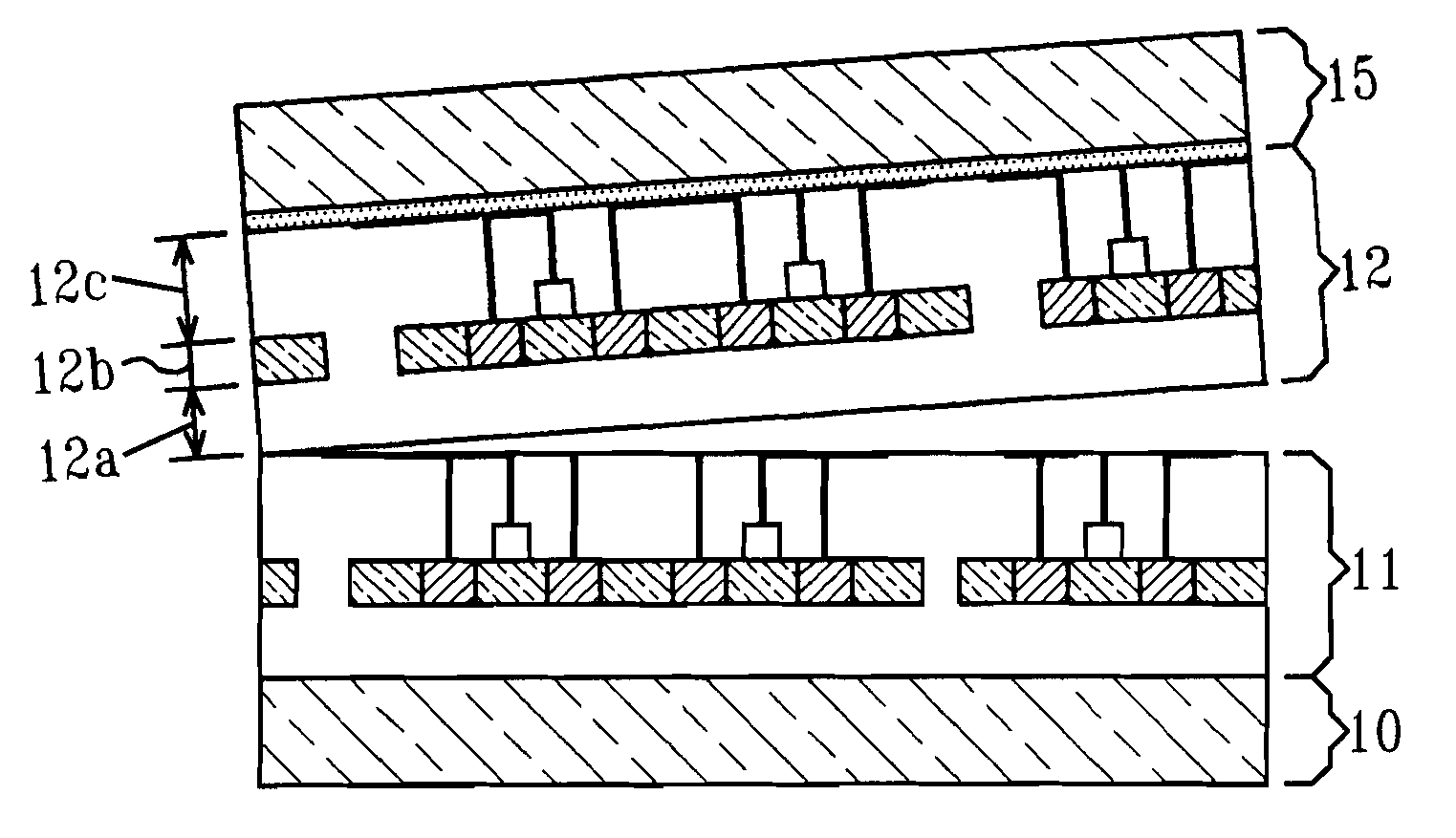

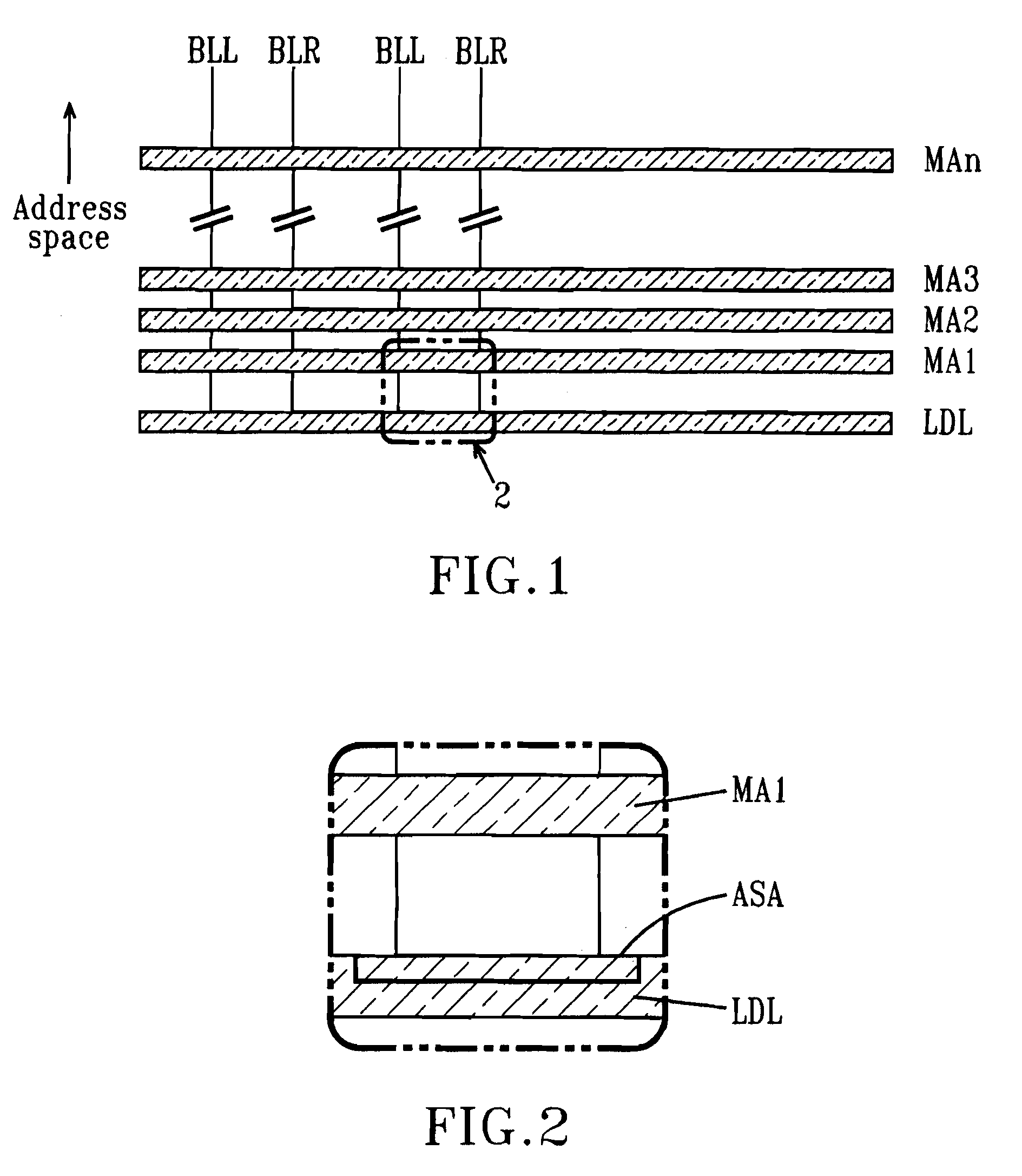

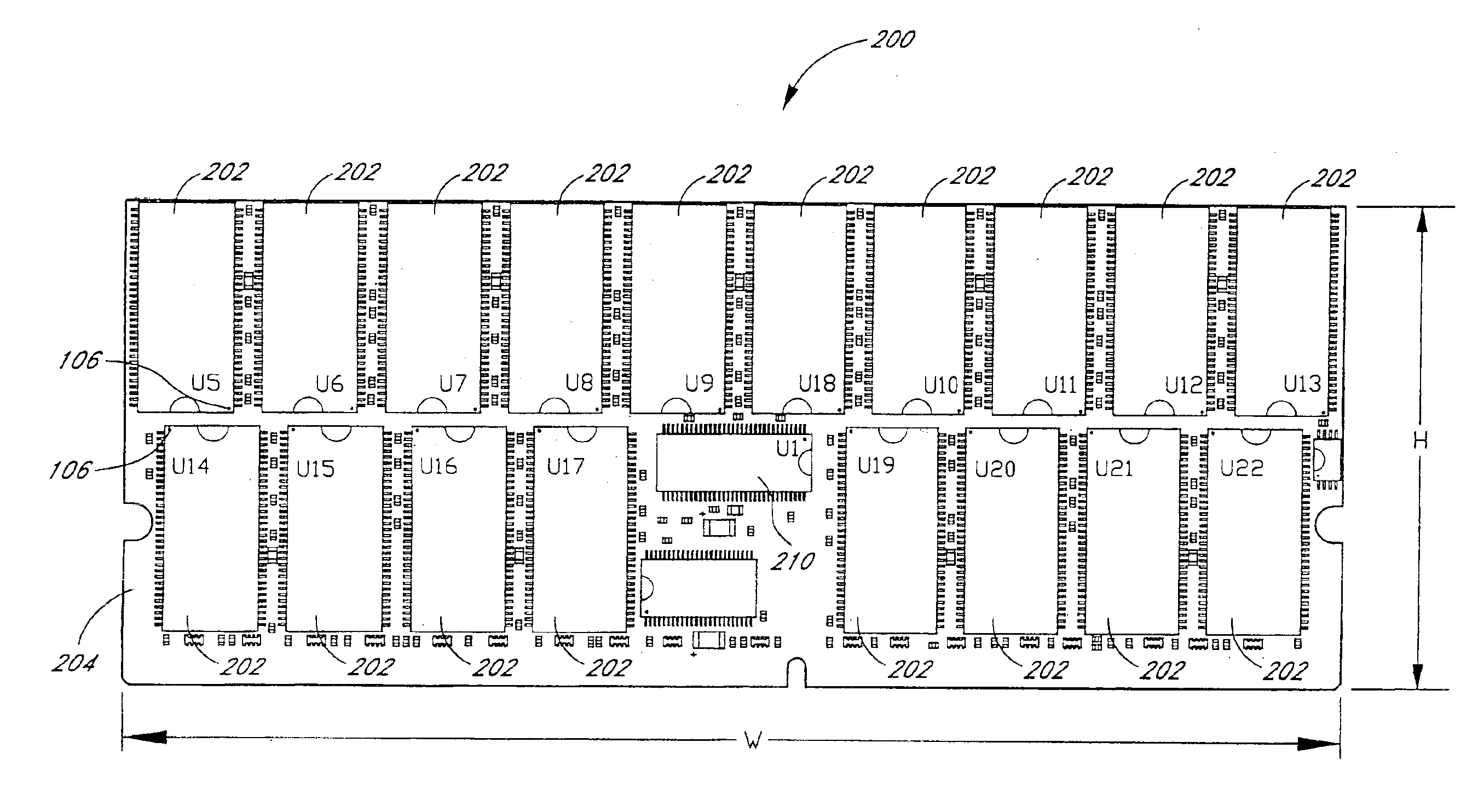

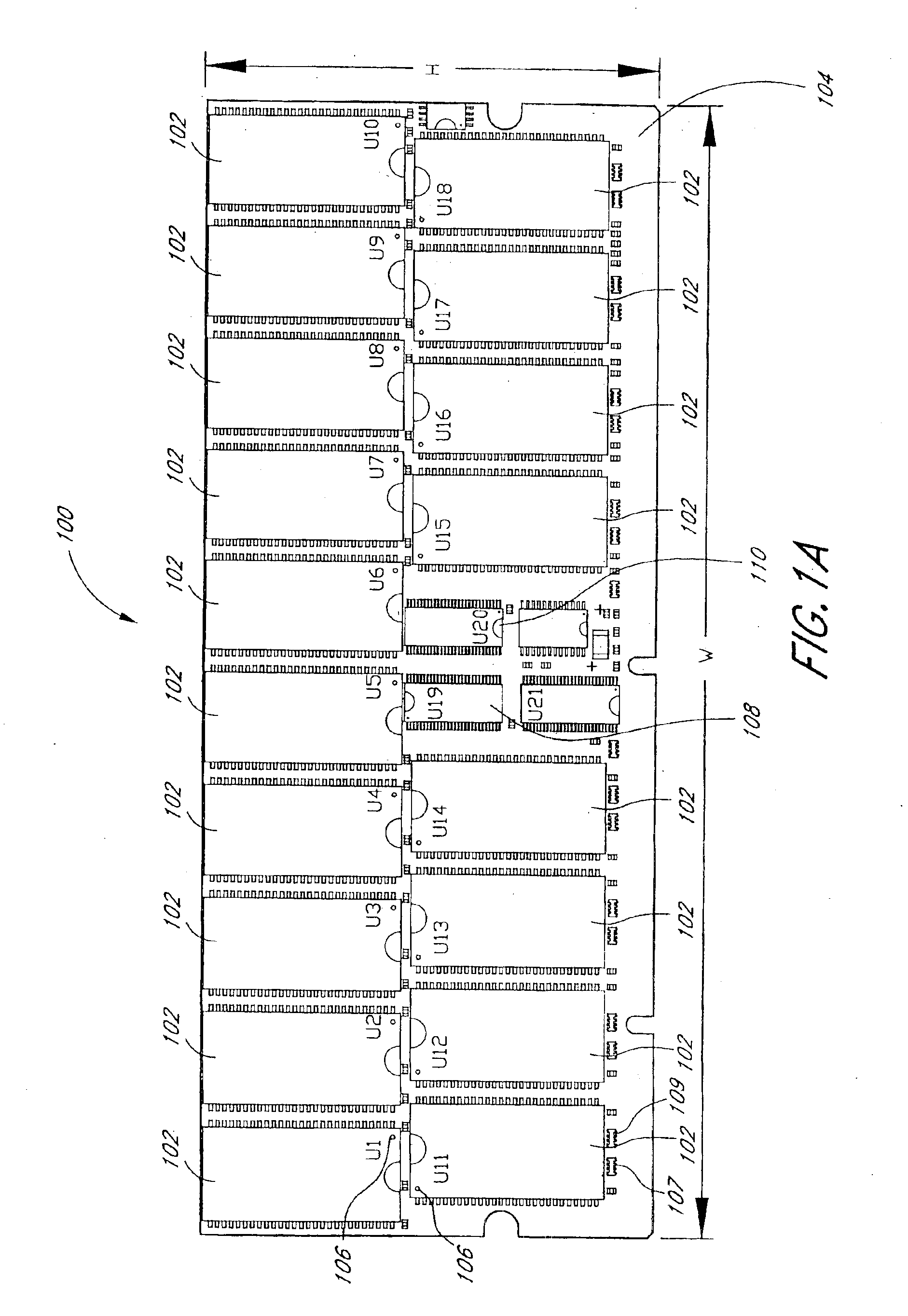

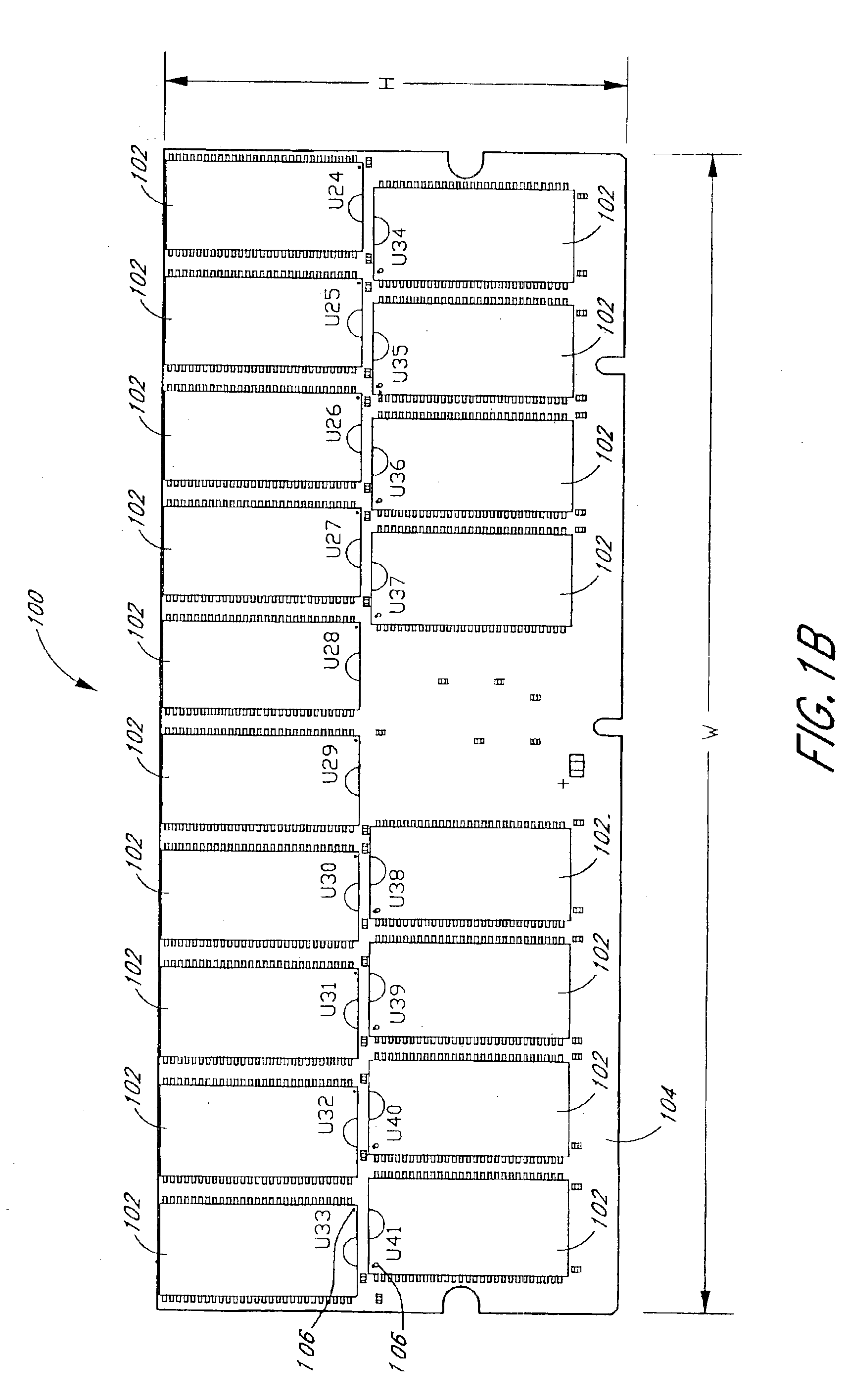

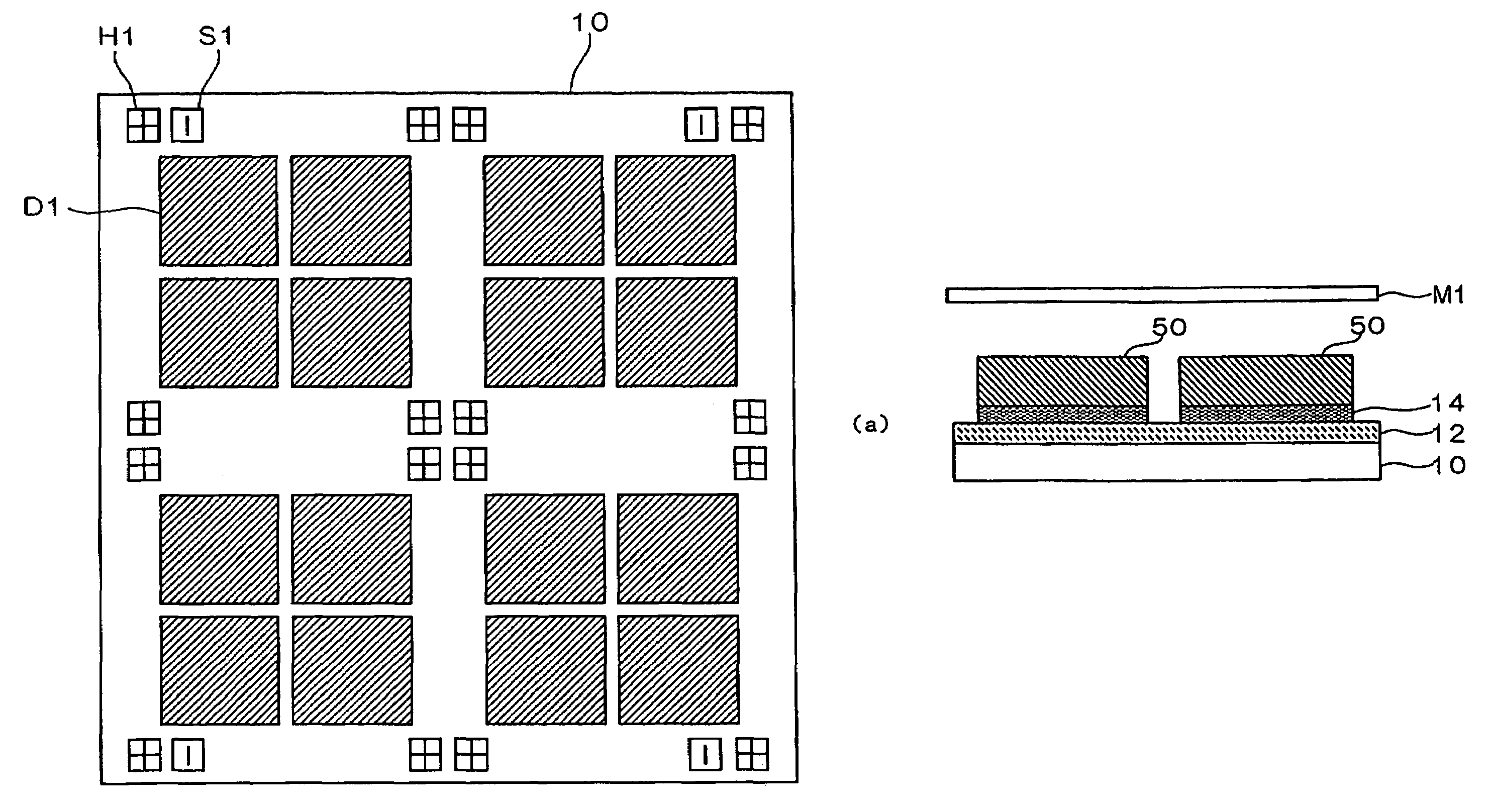

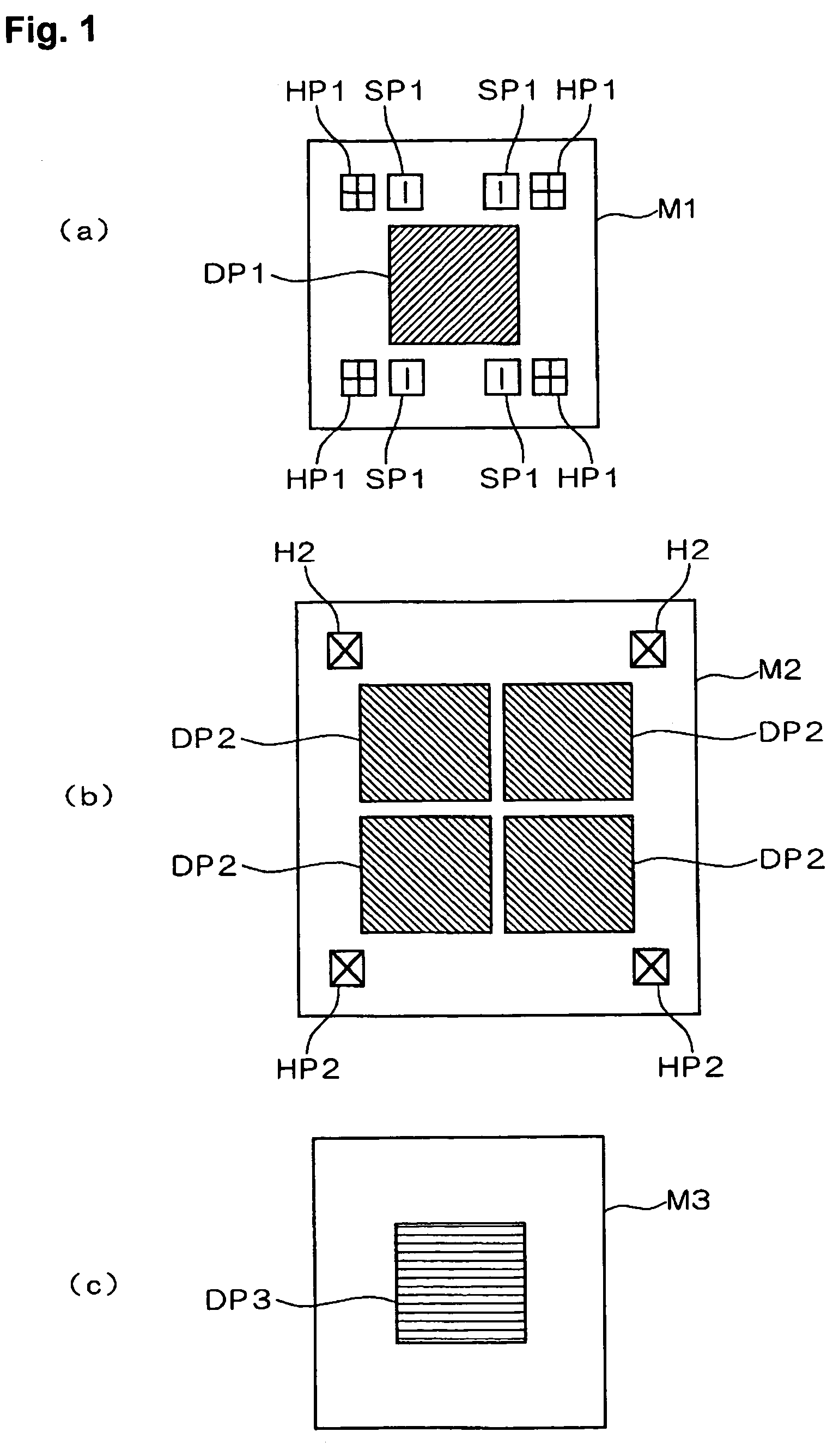

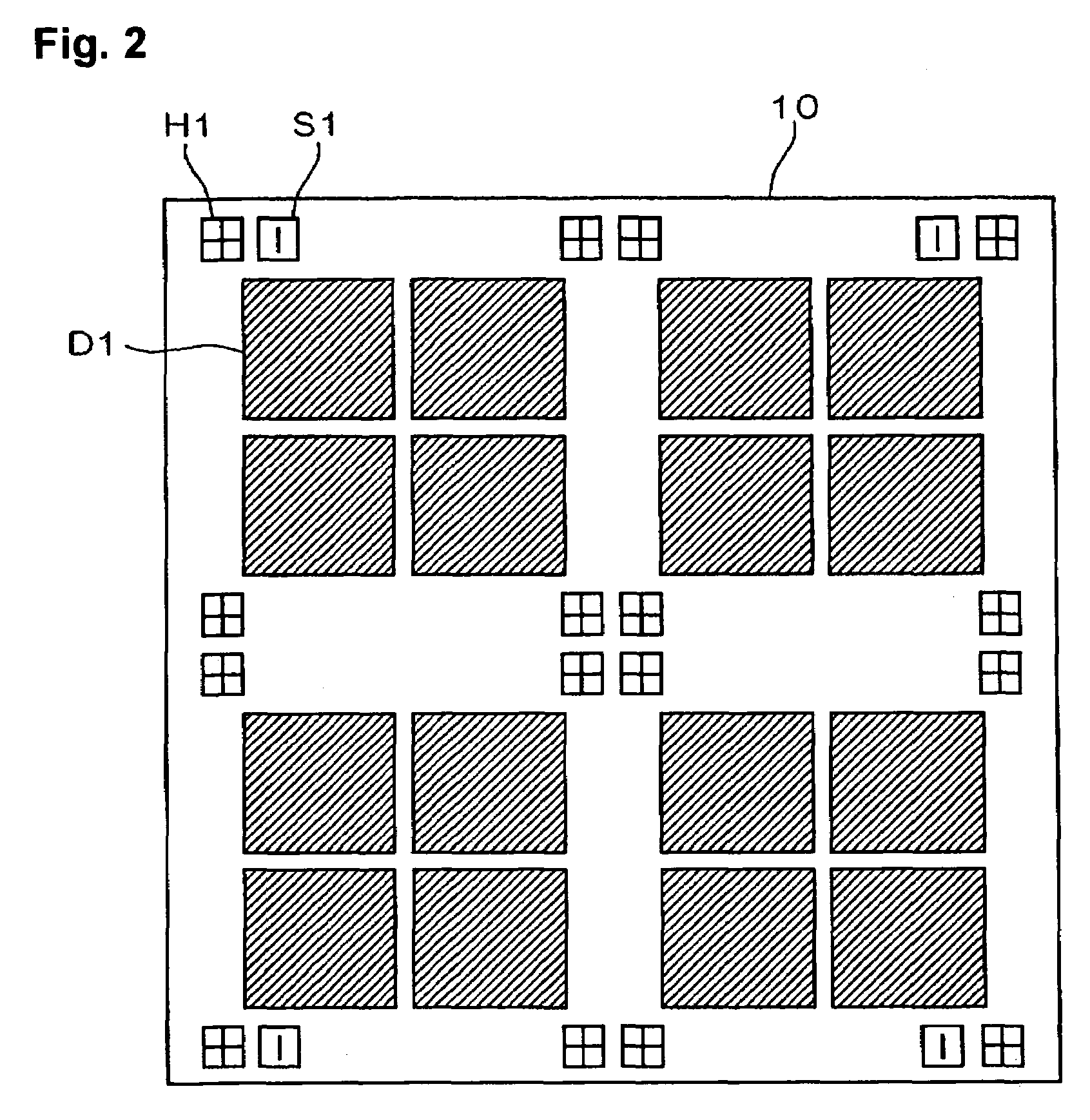

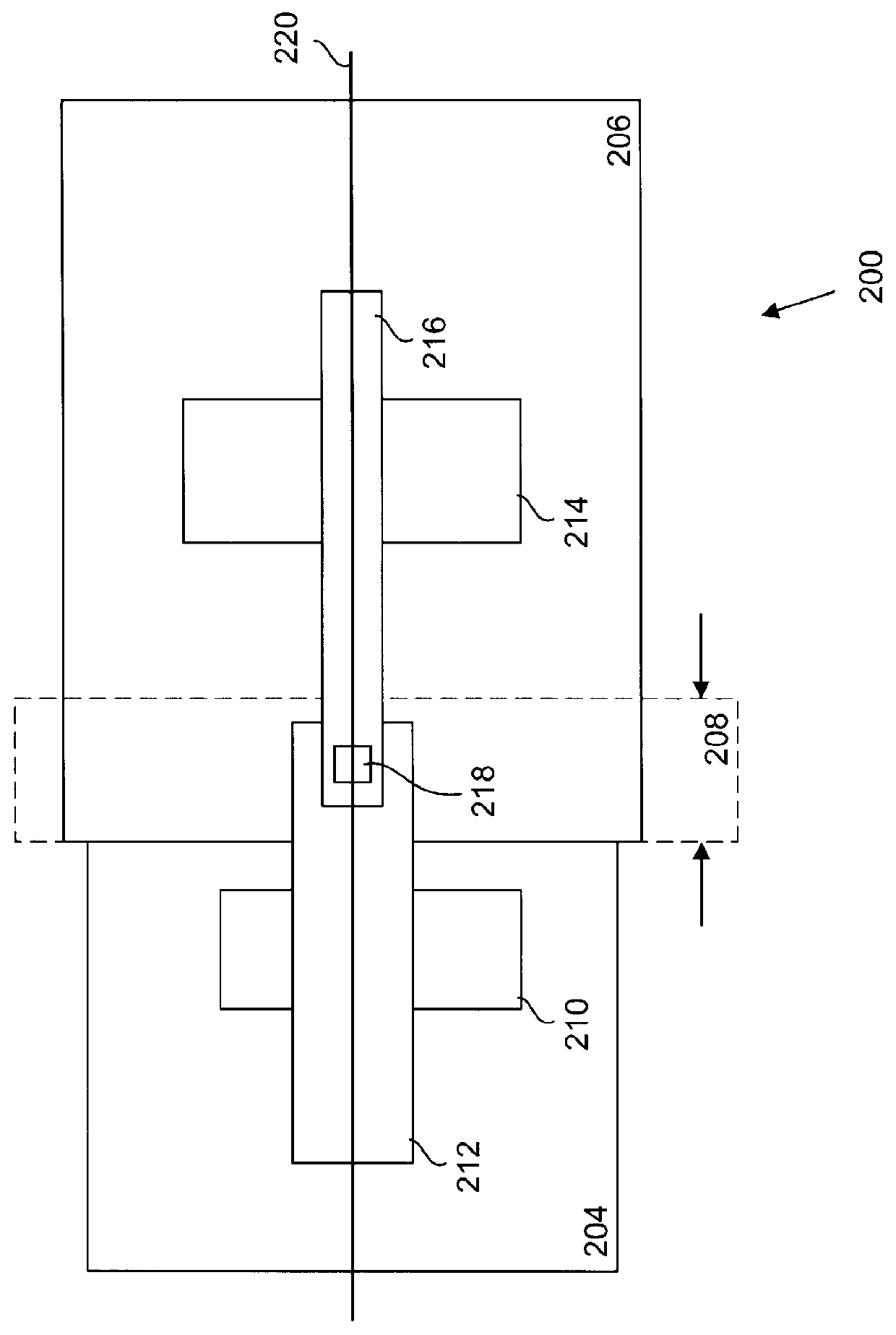

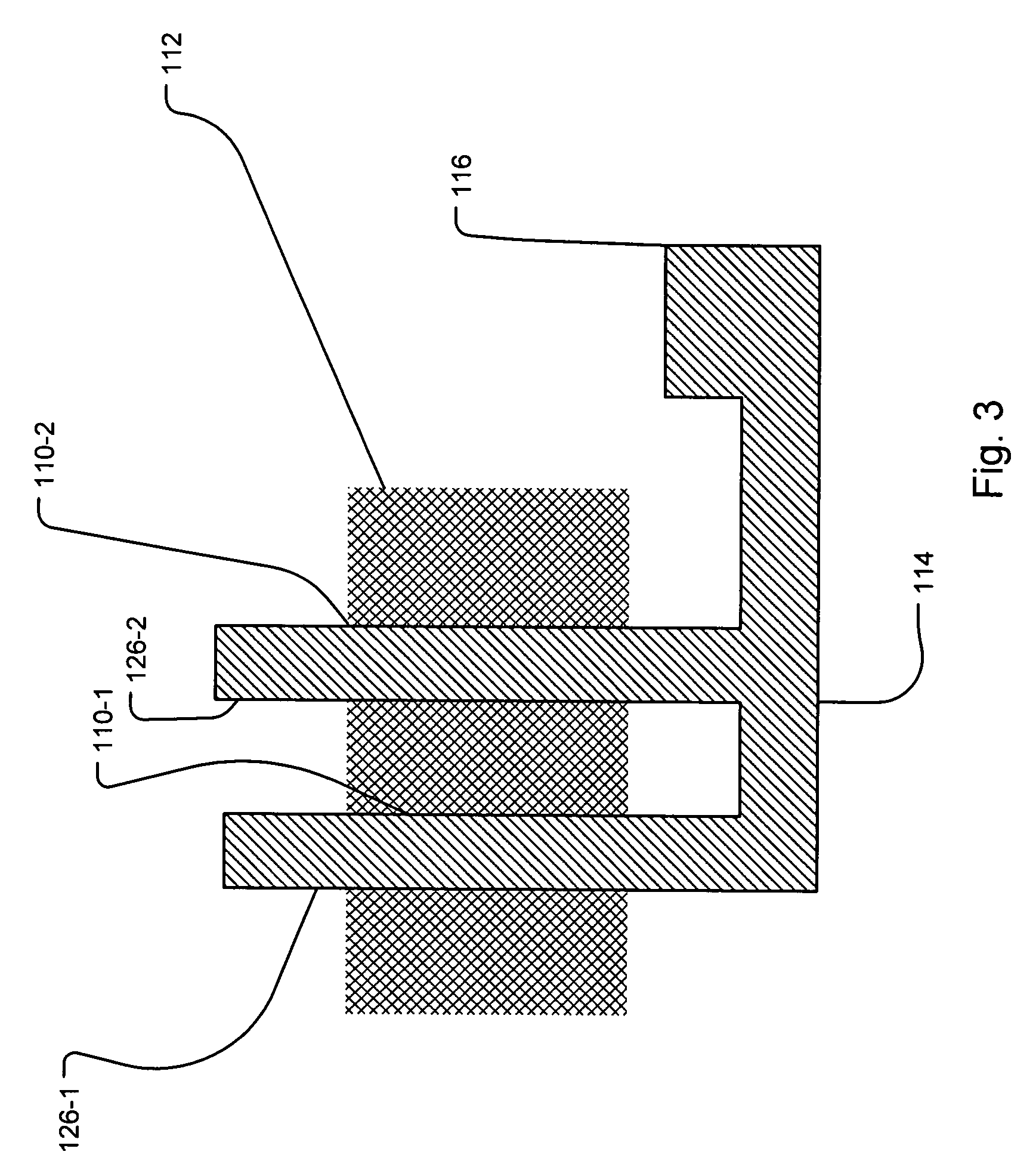

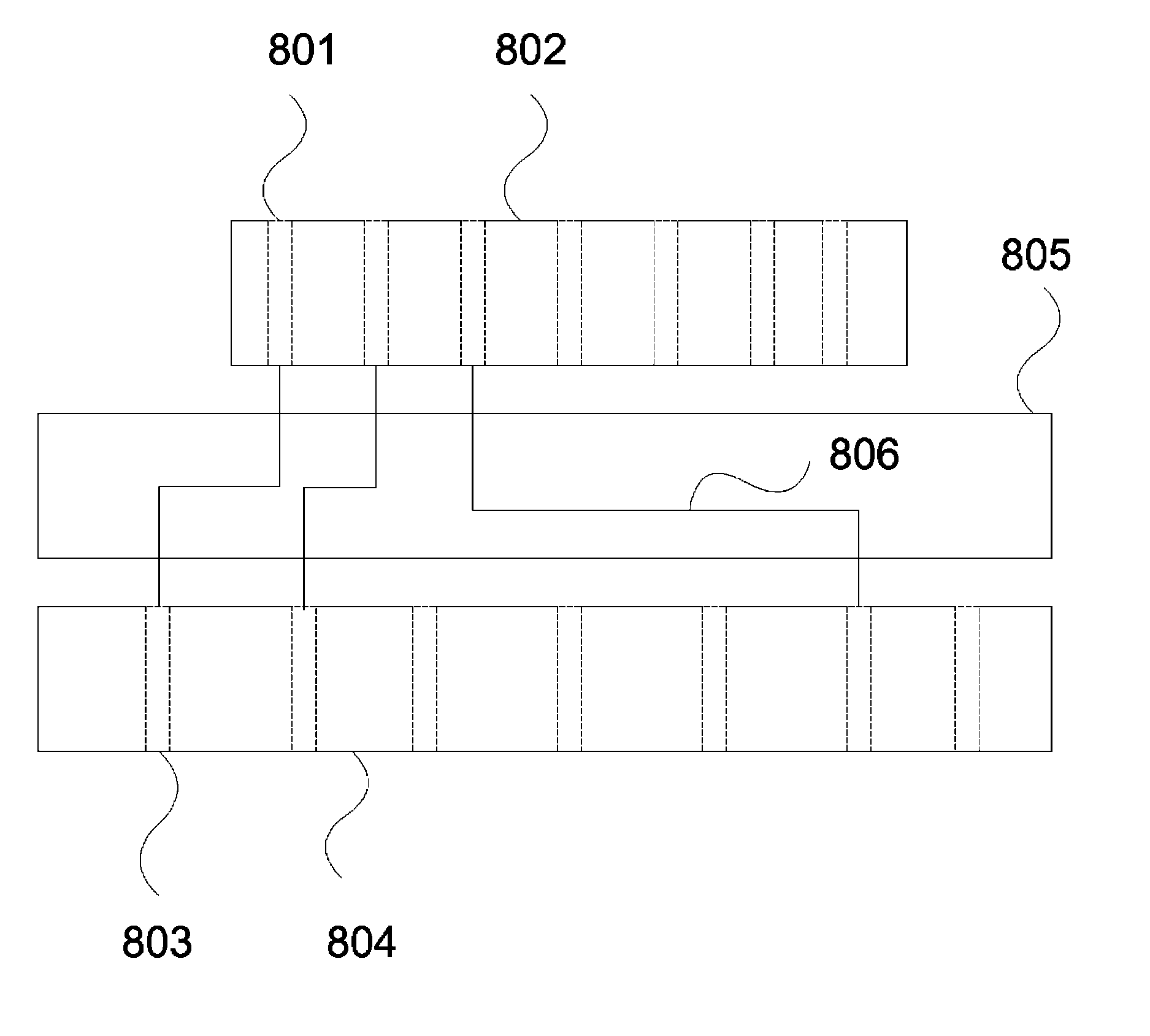

Arrangement of integrated circuits in a memory module

InactiveUS20050018495A1Final product manufactureCross-talk/noise/interference reductionGigabyteProcessor register

Abstract of the Disclosure Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of one-Gigabyte, two-Gigabyte, and four-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in the first row on a first lateral portion of the printed circuit board and in the second row on the first lateral portion are connected to a first addressing register with two register integrated circuits. The integrated circuits in the first row on the second lateral portion and in the second row on the second lateral portion are connected to a second addressing register with two register integrated circuits. Each addressing register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

Integrated circuits with varying gate structures and fabrication methods

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES U S INC

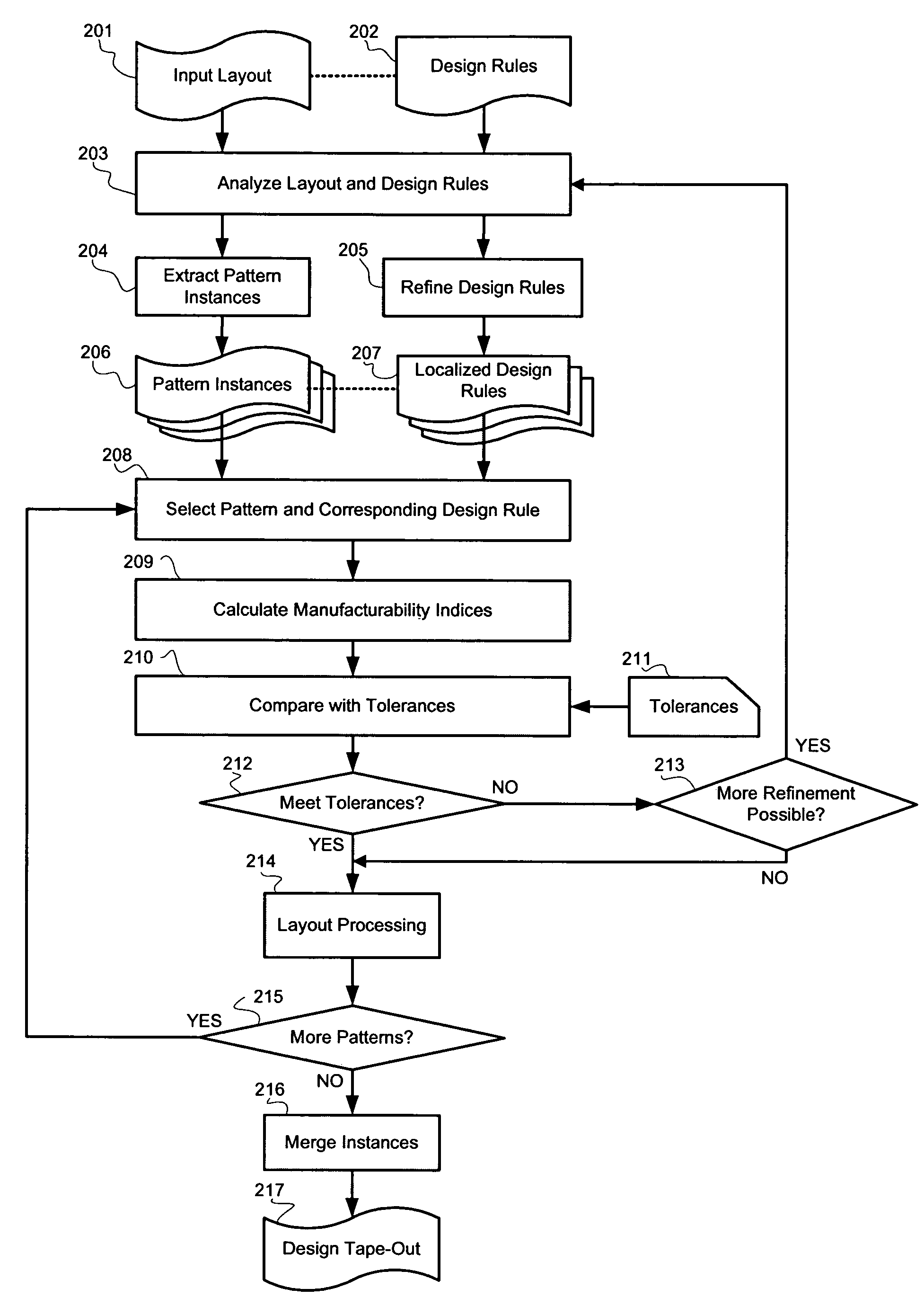

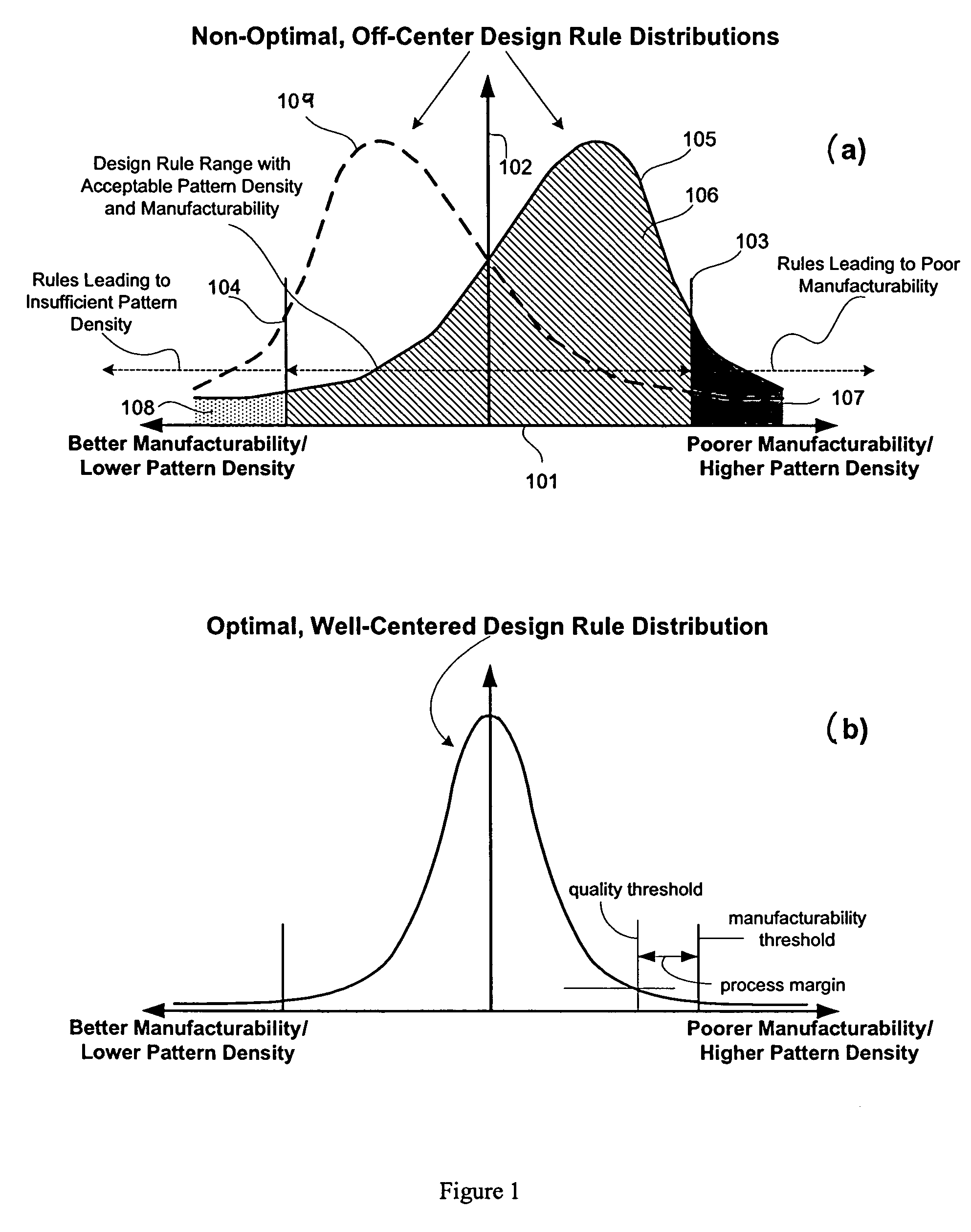

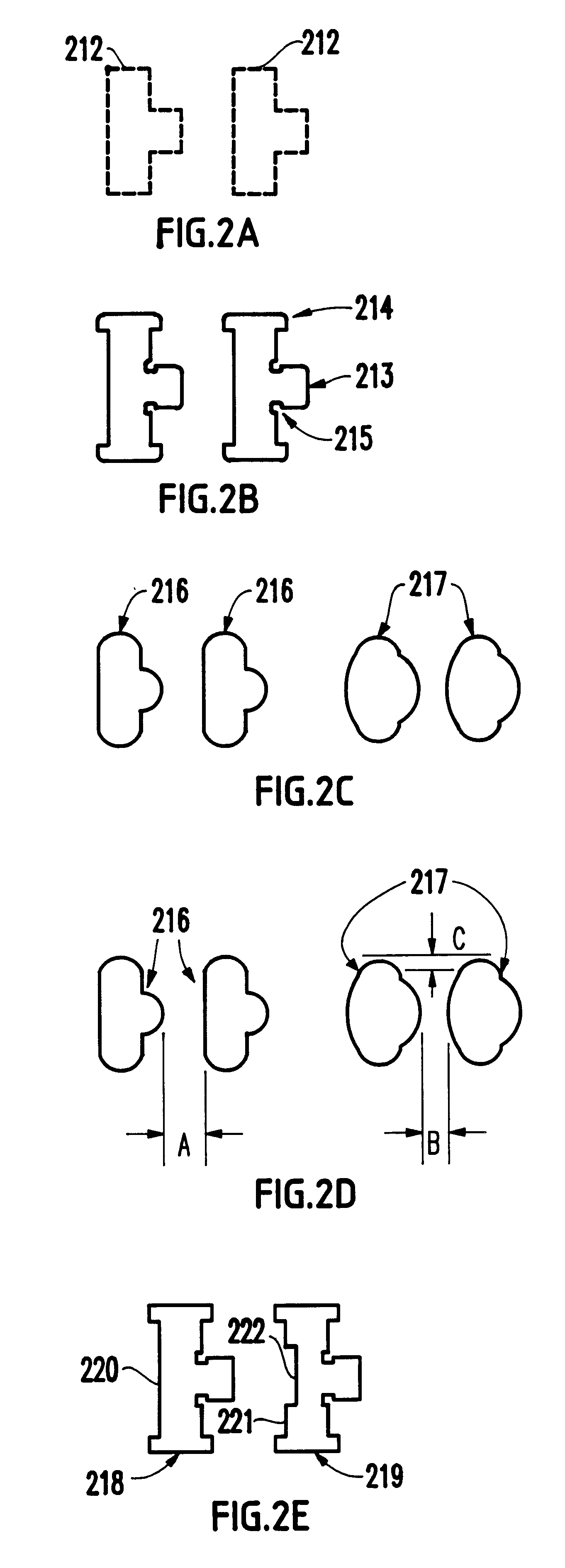

System for designing integrated circuits with enhanced manufacturability

ActiveUS7523429B2Improve manufacturabilityLittle interferencePressersMattress sewingGranularityEngineering

A system and method for integrated circuit design are disclosed to enhance manufacturability of circuit layouts through generation of hierarchical design rules which capture localized layout requirements. In contrast to conventional techniques which apply global design rules, the disclosed IC design system and method partition the original design layout into a desired level of granularity based on specified layout and integrated circuit properties. At that localized level, the design rules are adjusted appropriately to capture the critical aspects from a manufacturability standpoint. These adjusted design rules are then used to perform localized layout manipulation and mask data conversion.

Owner:APPLIED MATERIALS INC

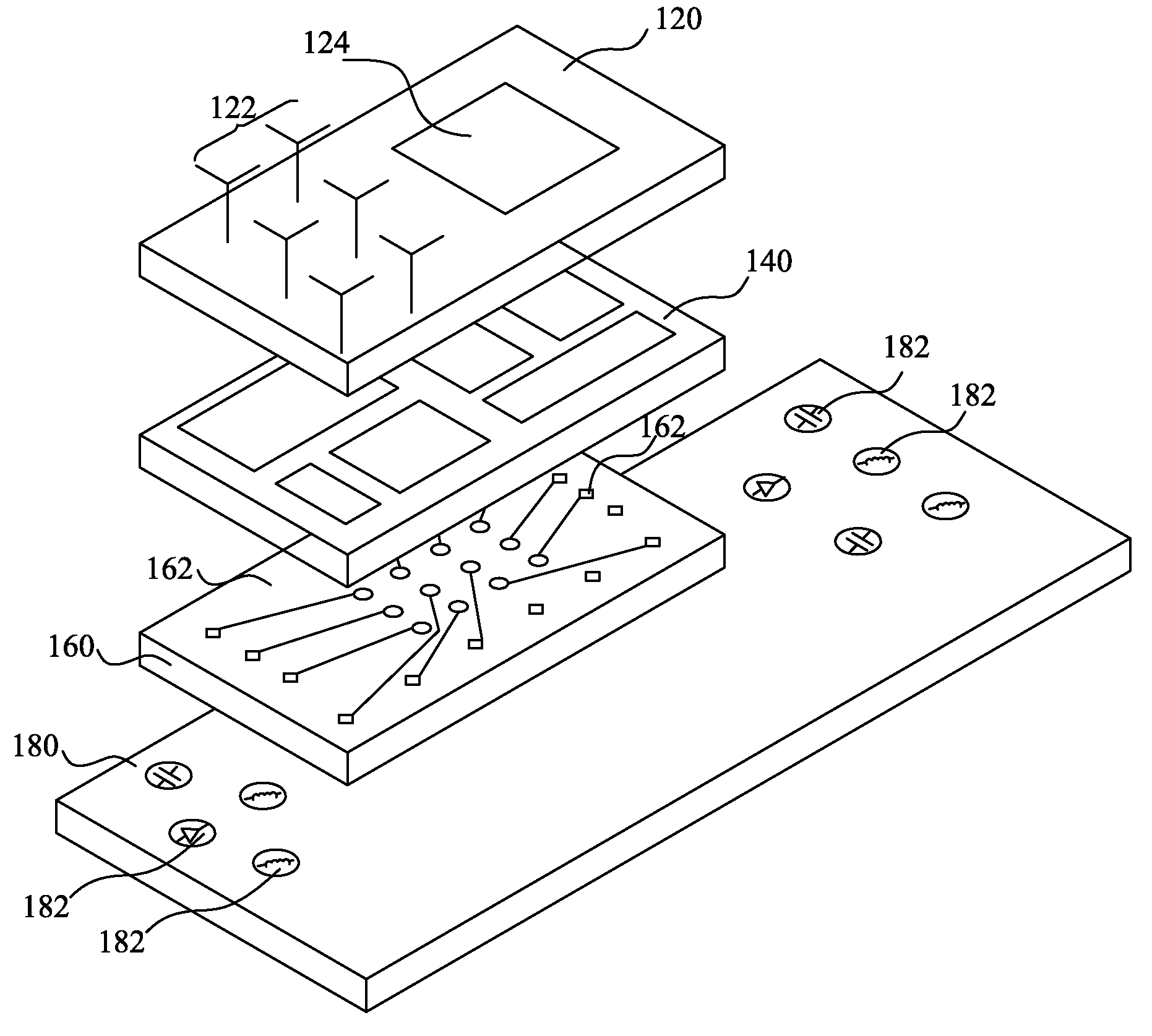

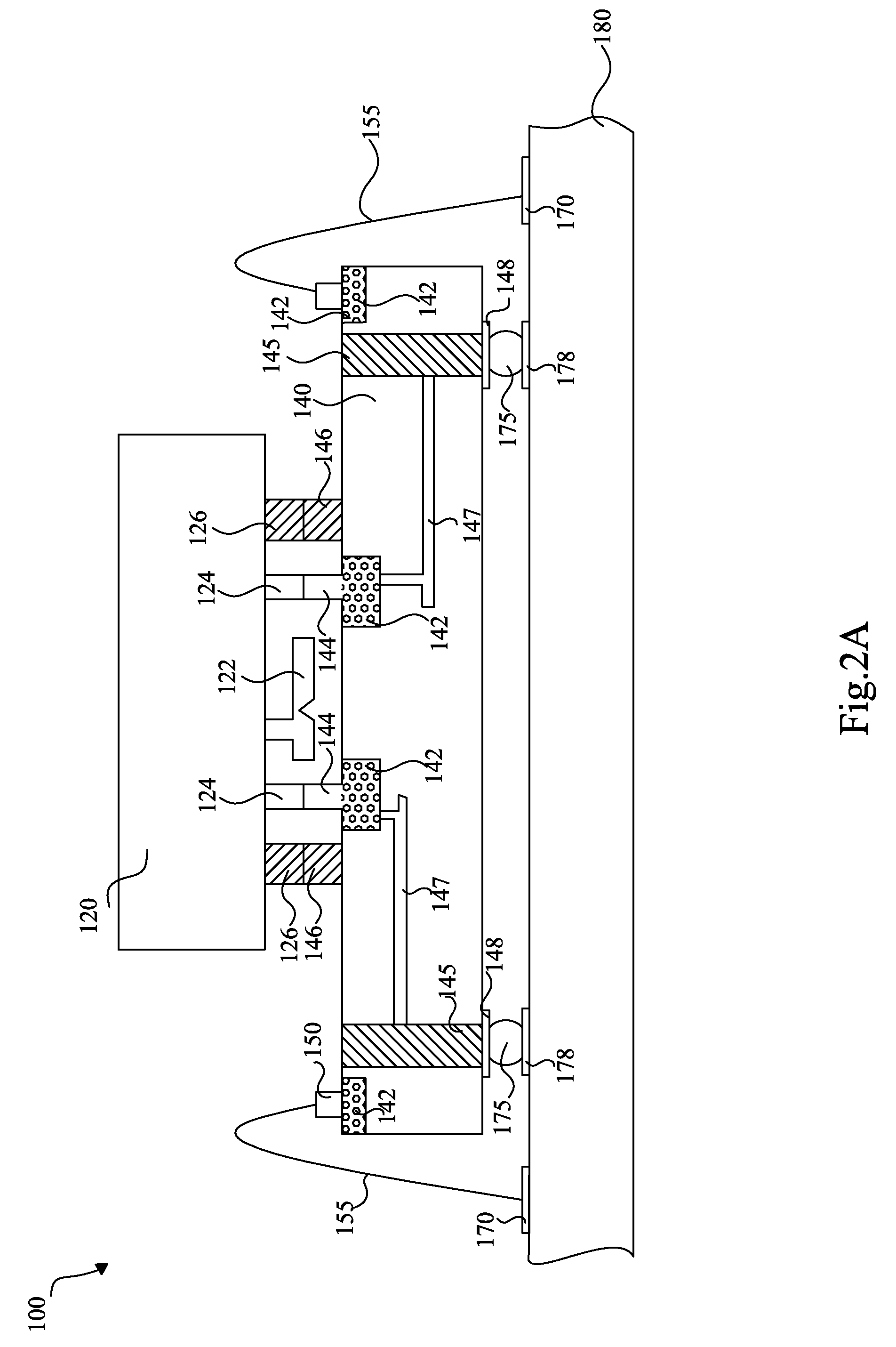

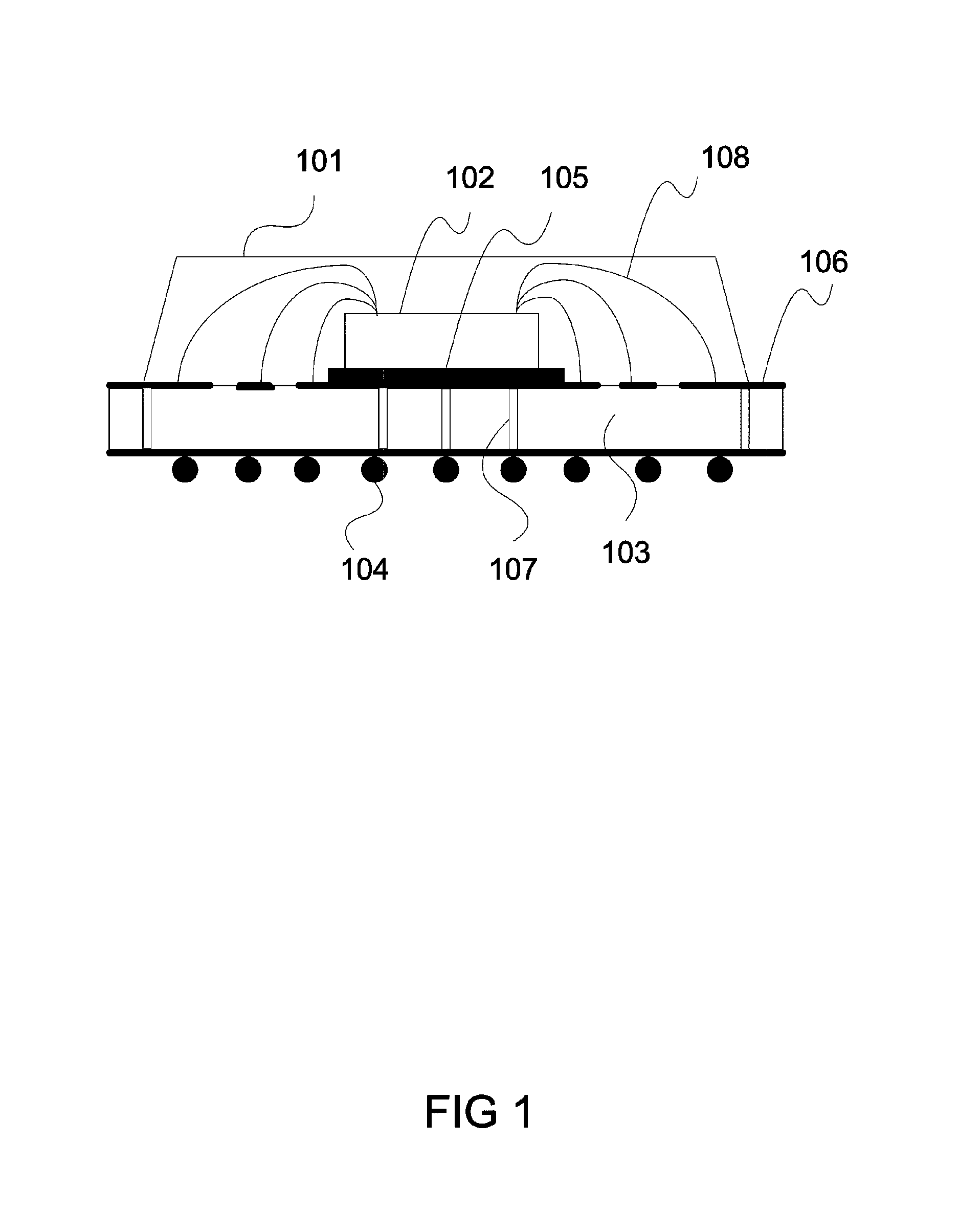

MEMS Packaging Including Integrated Circuit Dies

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

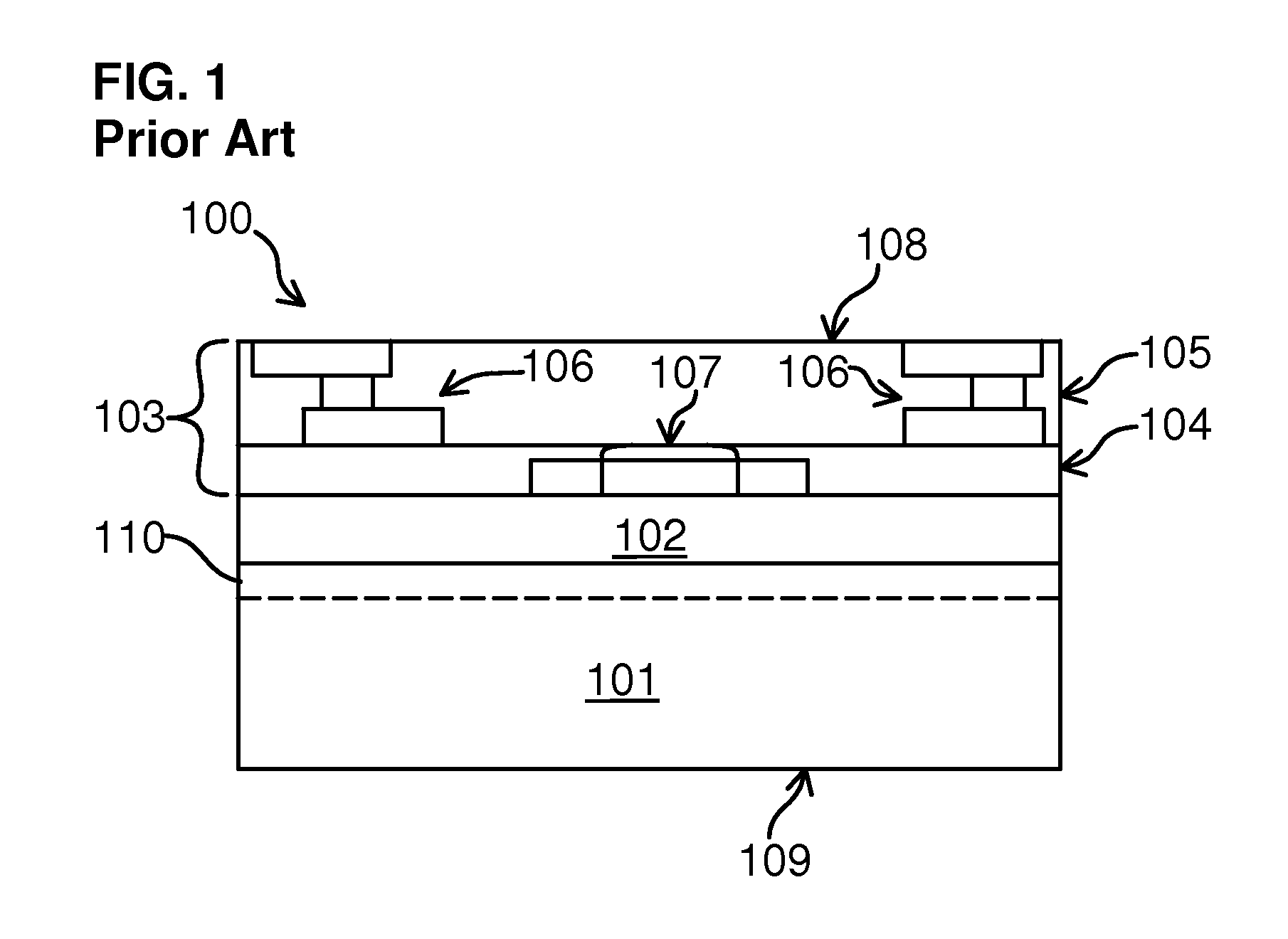

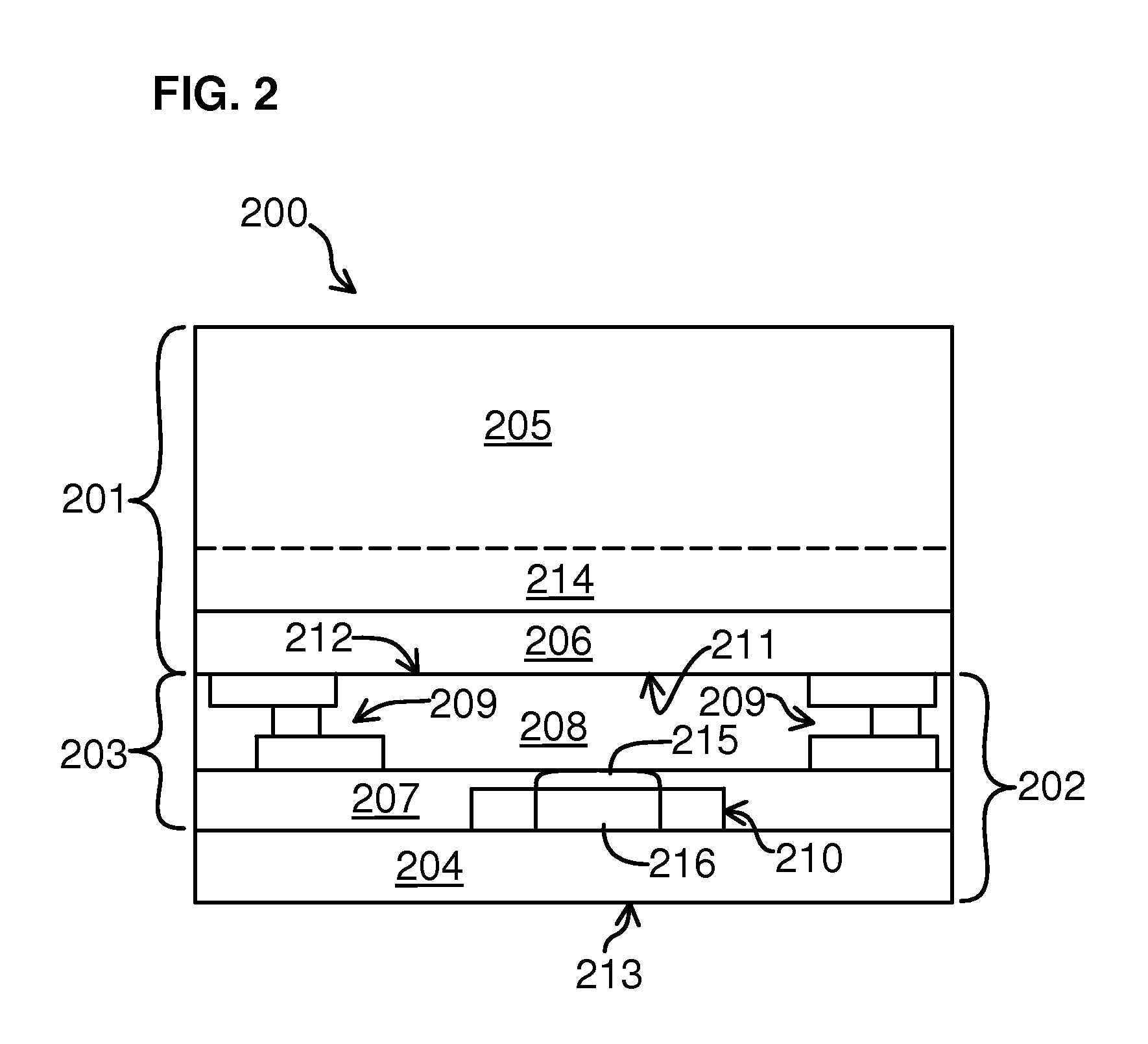

Trap Rich Layer for Semiconductor Devices

ActiveUS20120161310A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectActive layer

An integrated circuit chip is formed with an active layer and a trap rich layer. The active layer is formed with an active device layer and a metal interconnect layer. The trap rich layer is formed above the active layer. In some embodiments, the active layer is included in a semiconductor wafer, and the trap rich layer is included in a handle wafer.

Owner:QUALCOMM INC

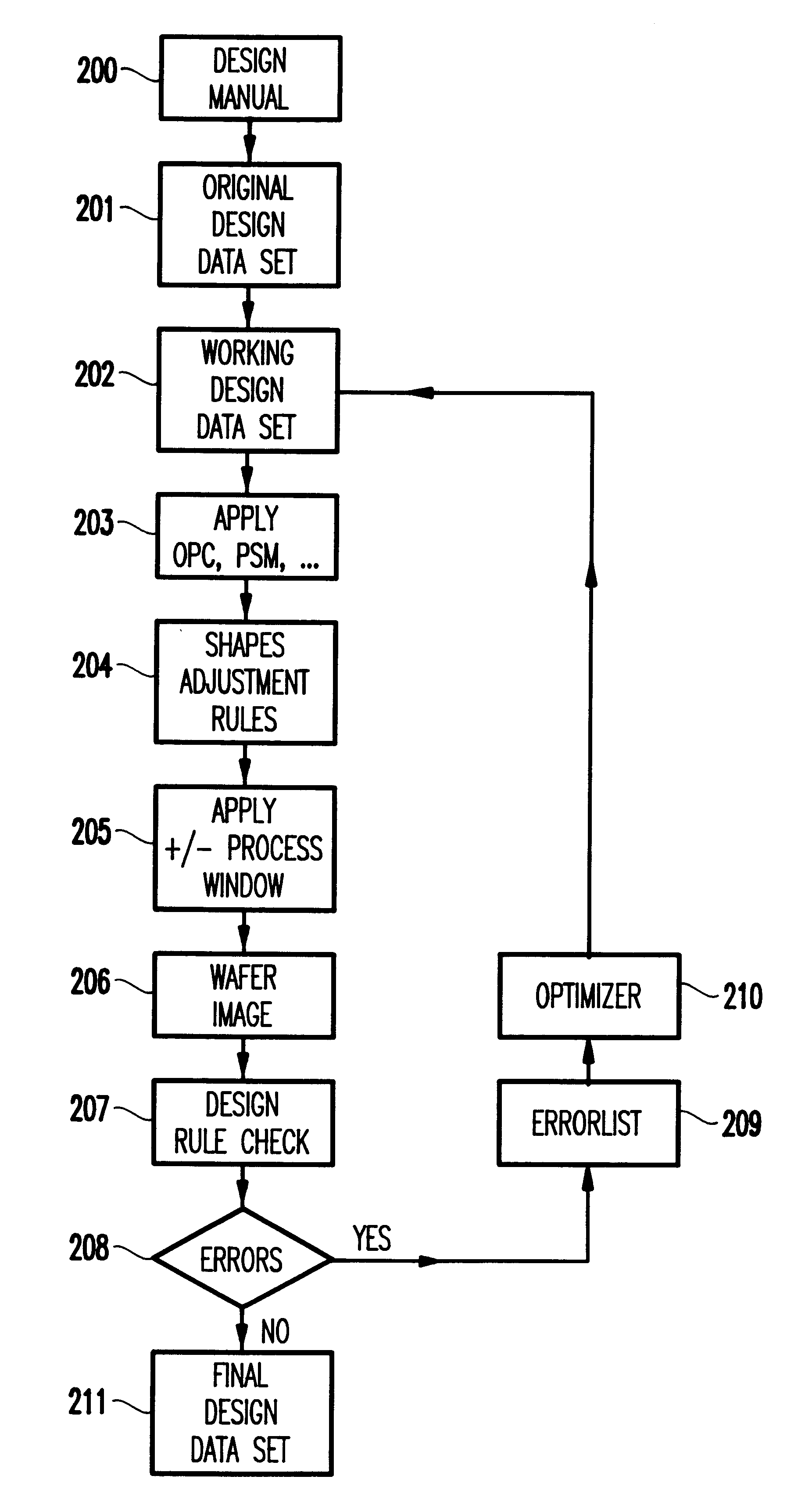

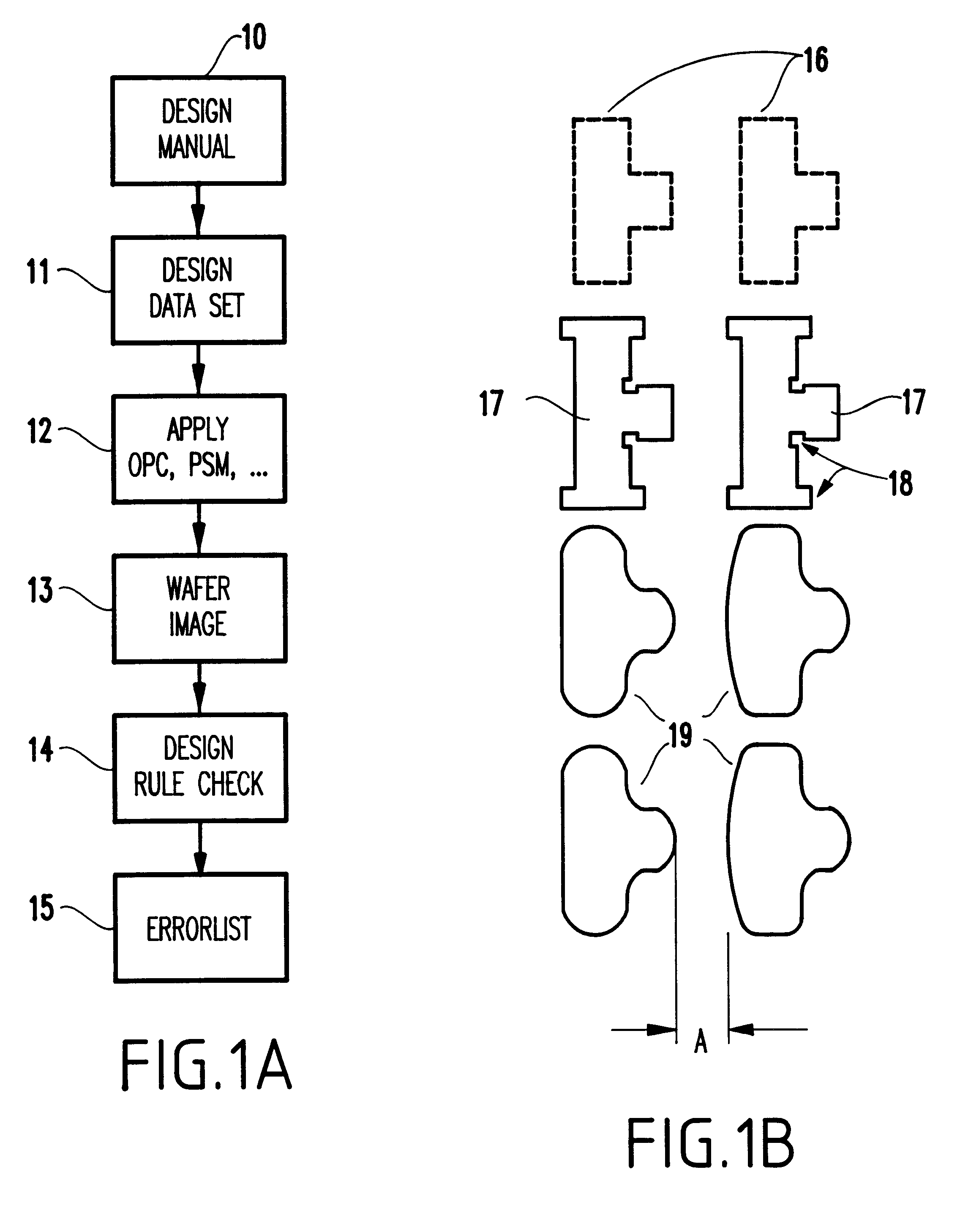

Auto correction of error checked simulated printed images

A method and computer system are provided for checking integrated circuit designs for design rule violations. The method may include generating a working design data set, creating a wafer image data set, comparing the wafer image data set to the design rules to produce an error list and automatically altering the working design data set when the comparing indicates a design rule violation. The method further automatically repeats the creating, the comparing and the automatically altering until no design rule violations occur or no solution to the errors exists.

Owner:IBM CORP

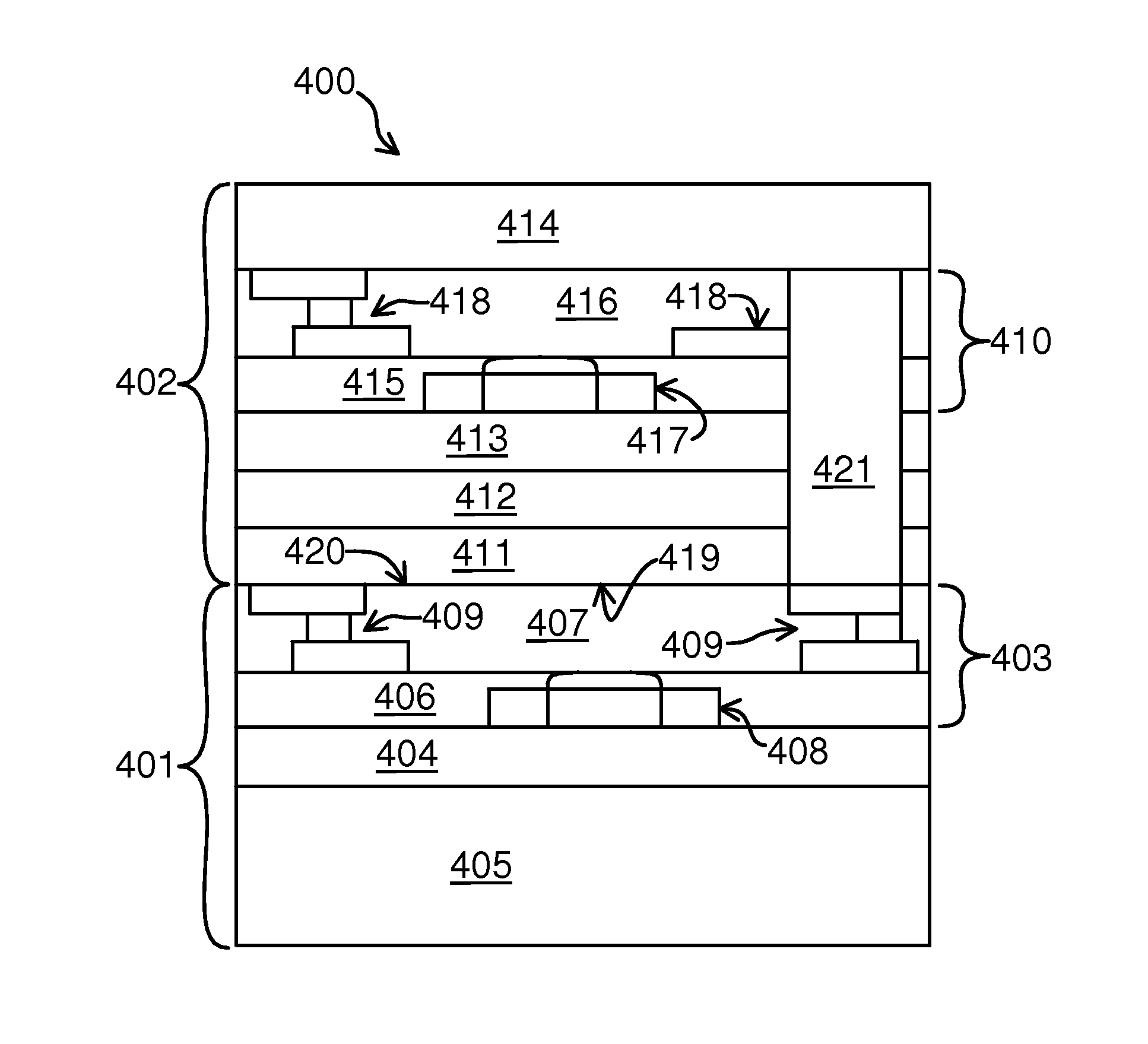

3-dimensional integrated circuit architecture, structure and method for fabrication thereof

ActiveUS20070228383A1Solid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementAudio power amplifier

An integrated circuit design, structure and method for fabrication thereof includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

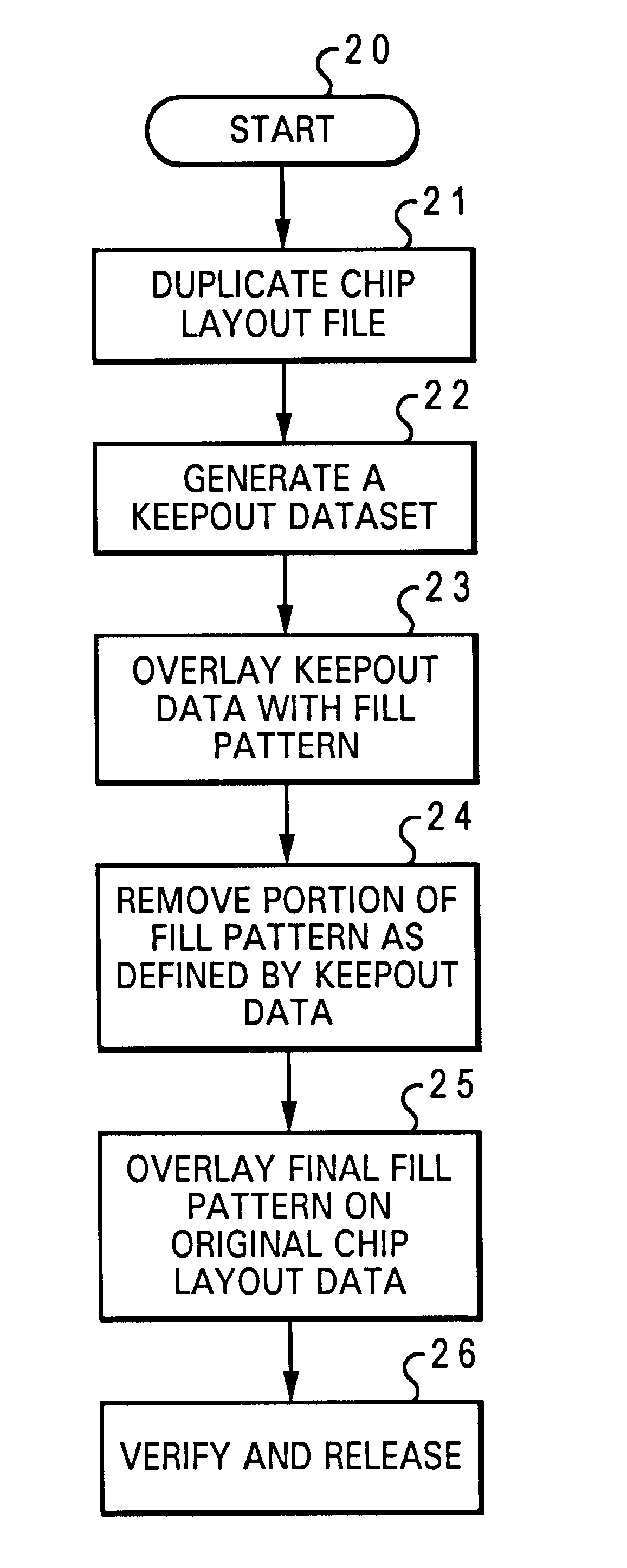

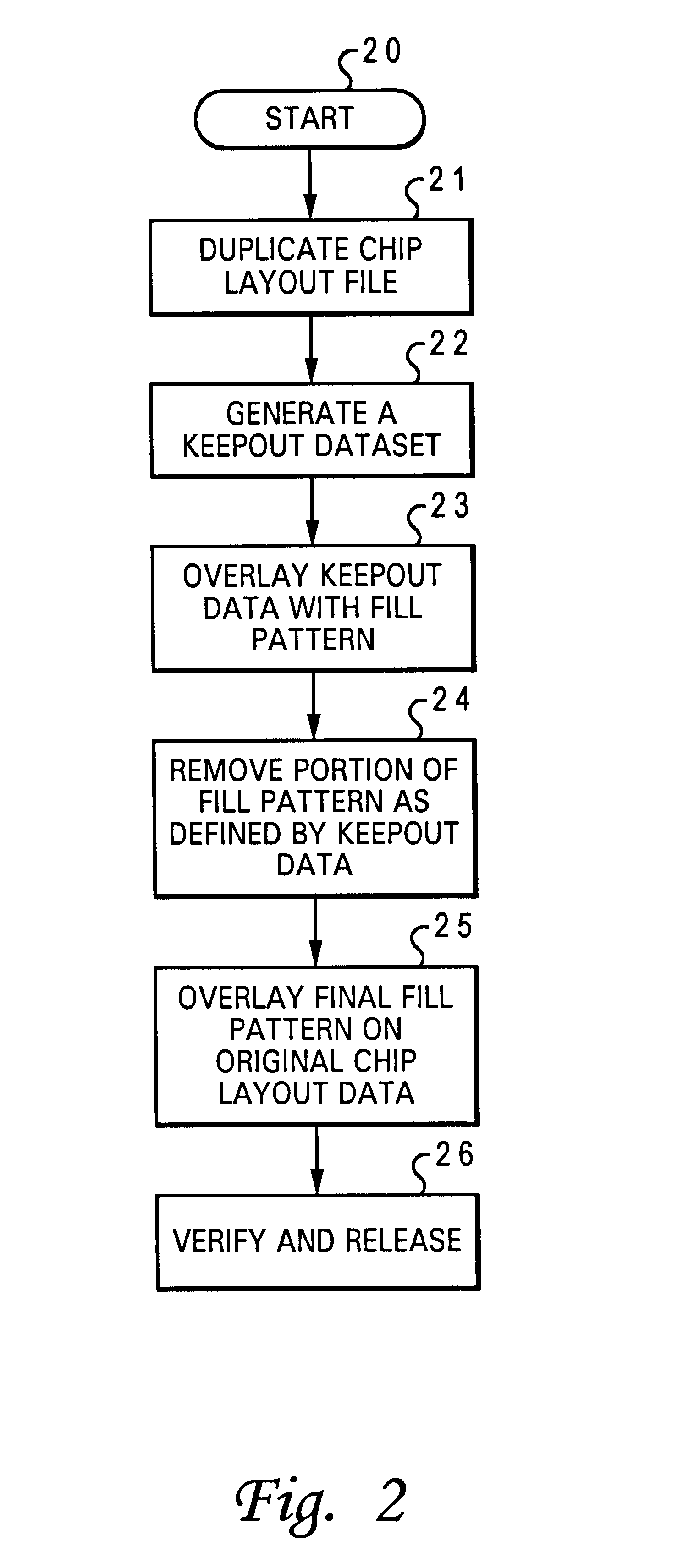

Method for providing a fill pattern for an integrated circuit design

InactiveUS6609235B2Solid-state devicesSemiconductor/solid-state device manufacturingComputer architectureIntegrated circuit design

A method for providing a fill pattern for integrated circuit designs is disclosed. A keepout file having keepout data is generated from a chip design layout file having chip design layout data. The keepout file includes a map of areas of an integrated circuit design where fill patterns cannot be placed. The map of areas from the keepout file is then overlaid with a fill pattern to yield a fill-pattern file. Fill patterns from the fill-pattern file is removed from locations that coincide with locations as defined by the keepout data to yield a final-fill file with crucial fill pattern data. The crucial fill pattern data from the final-fill file is overlaid on the design layout data in the chip design layout file to yield a complete design layout file. Finally, the design rule integrity and logical to physical correspondence of the complete design layout file is verified.

Owner:MIND FUSION LLC

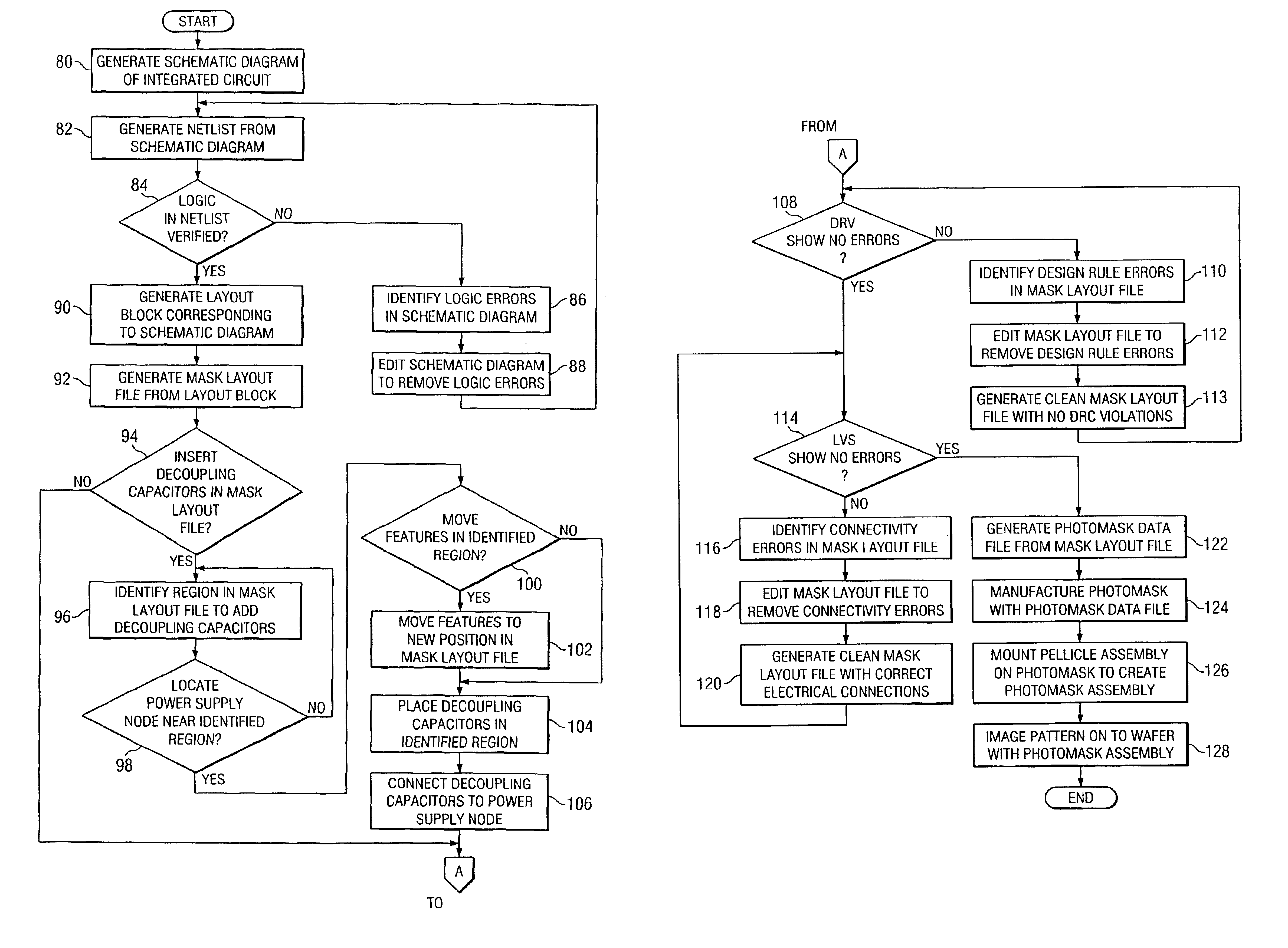

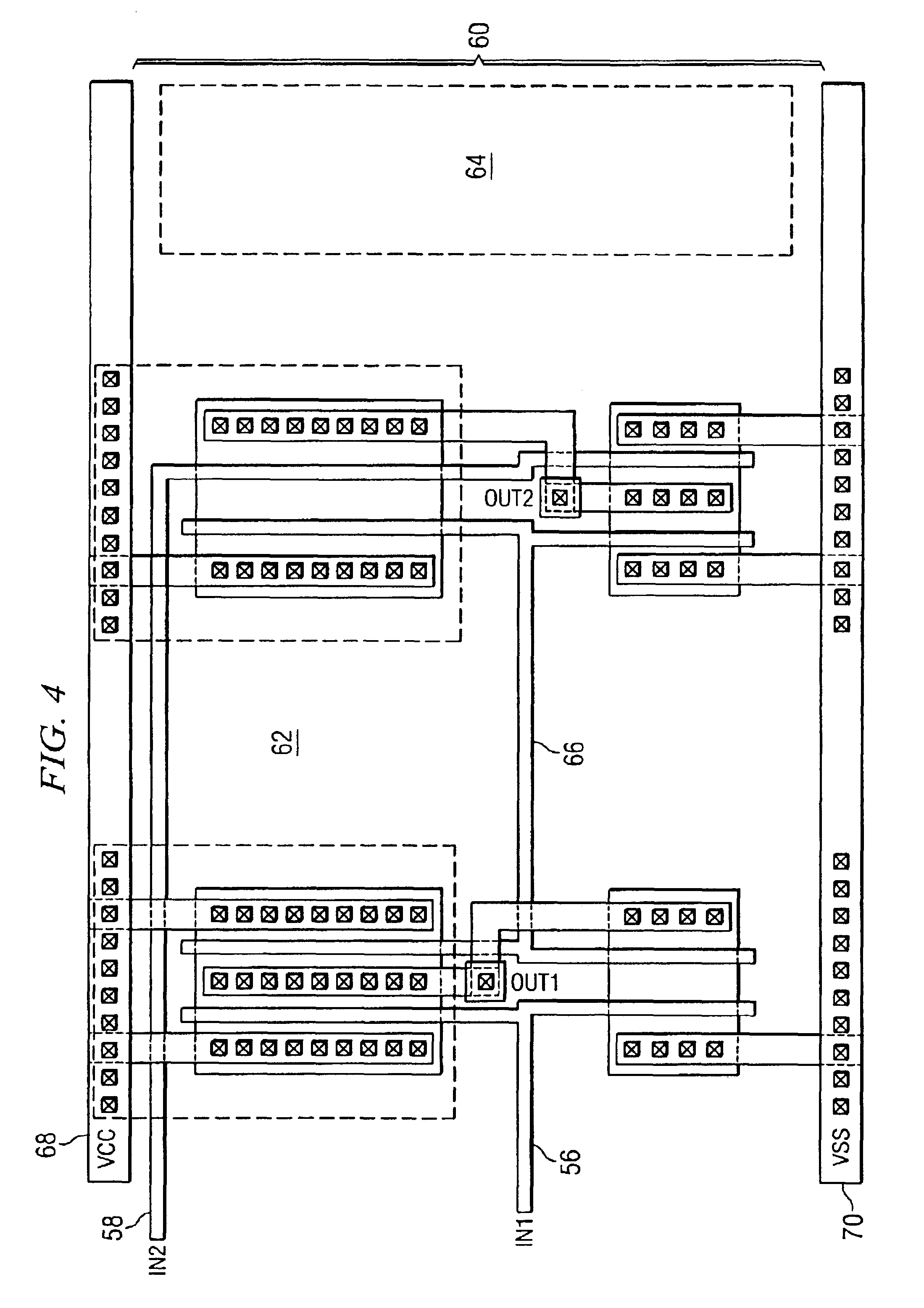

Photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured with the same

InactiveUS6904582B1Shorten the timeShorten cycle timeSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutDecoupling capacitor

A photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured by the same are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region in the pattern to add one or more decoupling capacitors. Once the region is identified, a feature located in the identified region is moved based on a design rule from a first position to a second position in the mask layout file to create a space in the identified region. The decoupling capacitors are placed in the space in the identified region.

Owner:CELERICS TECH

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

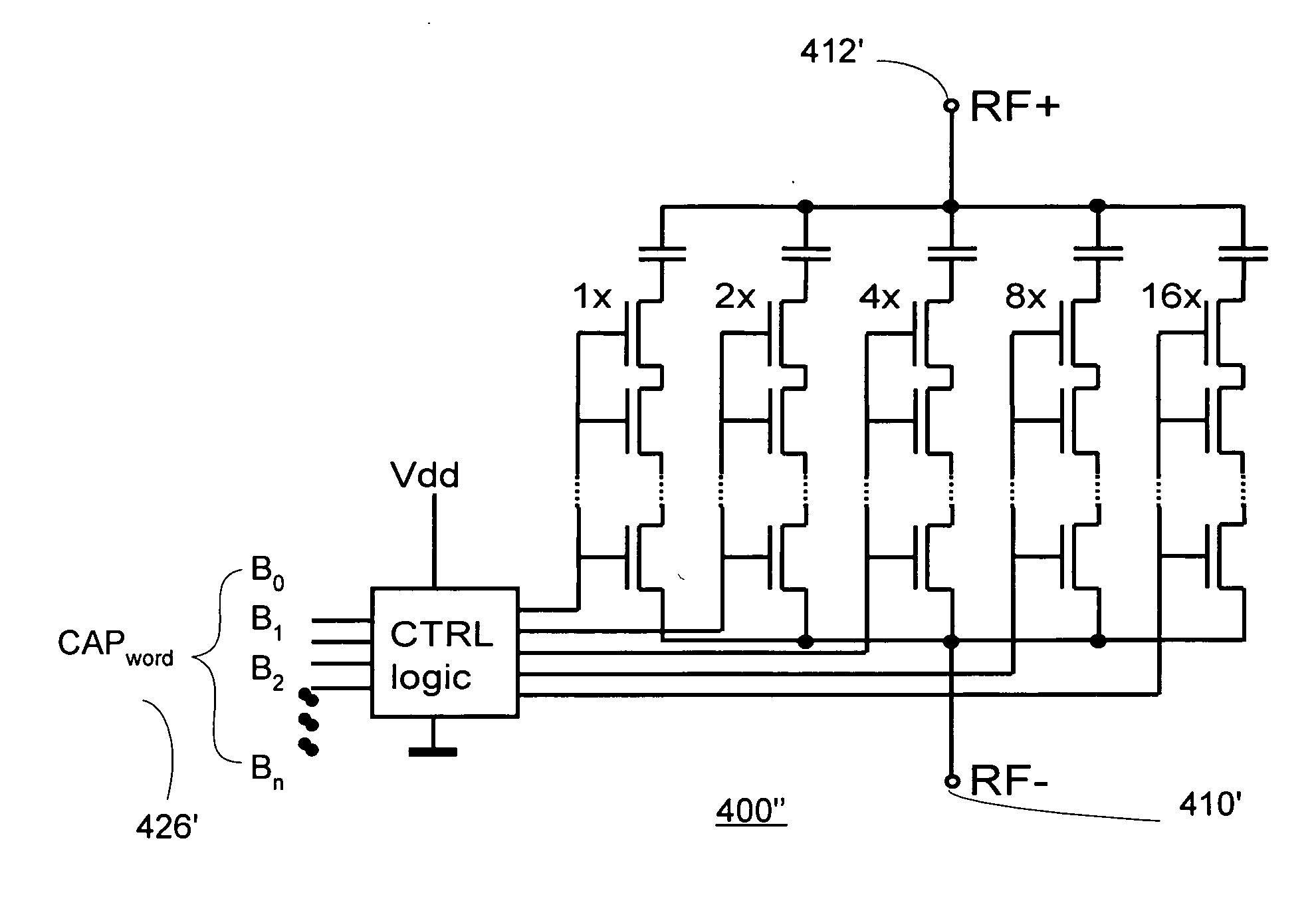

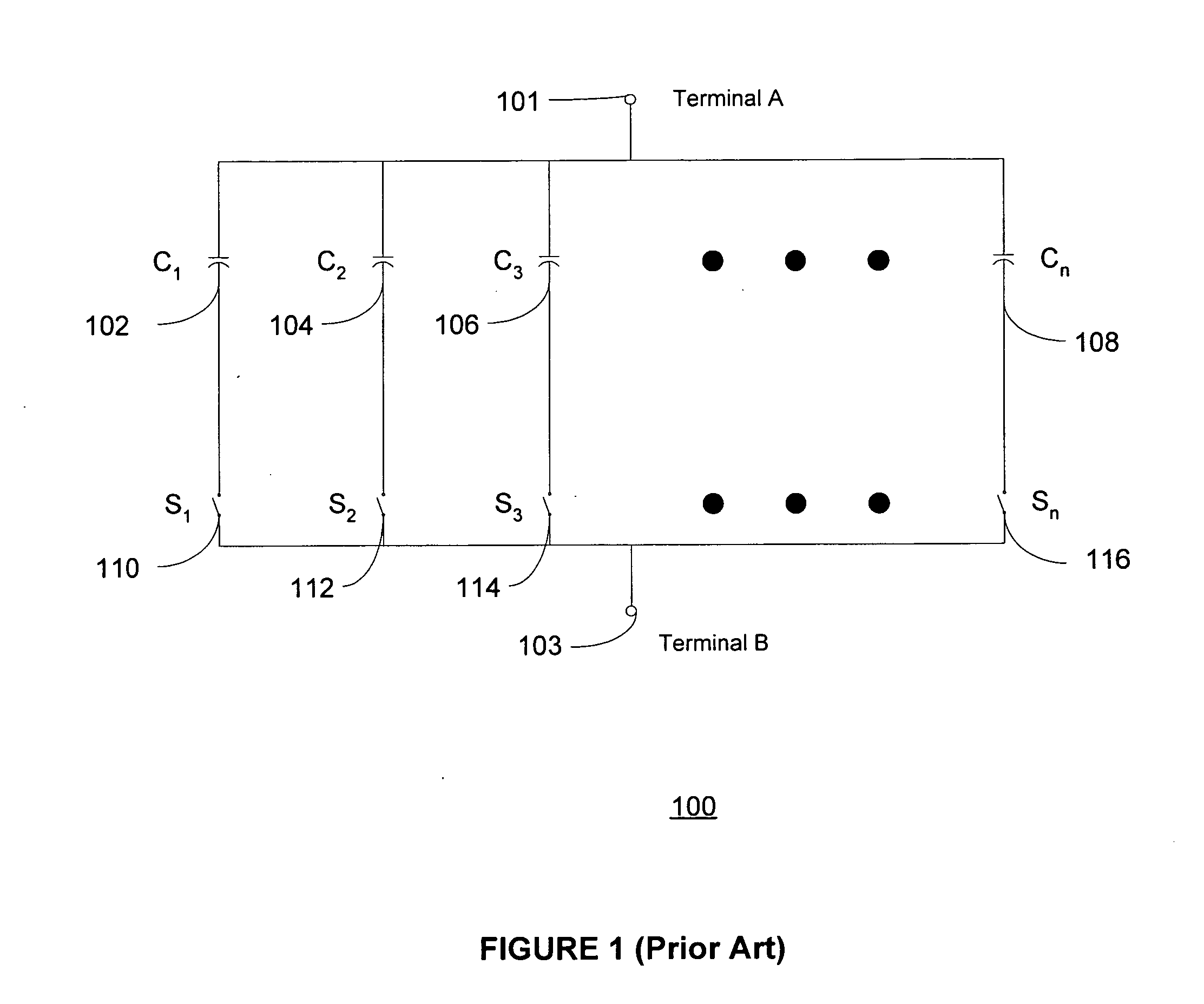

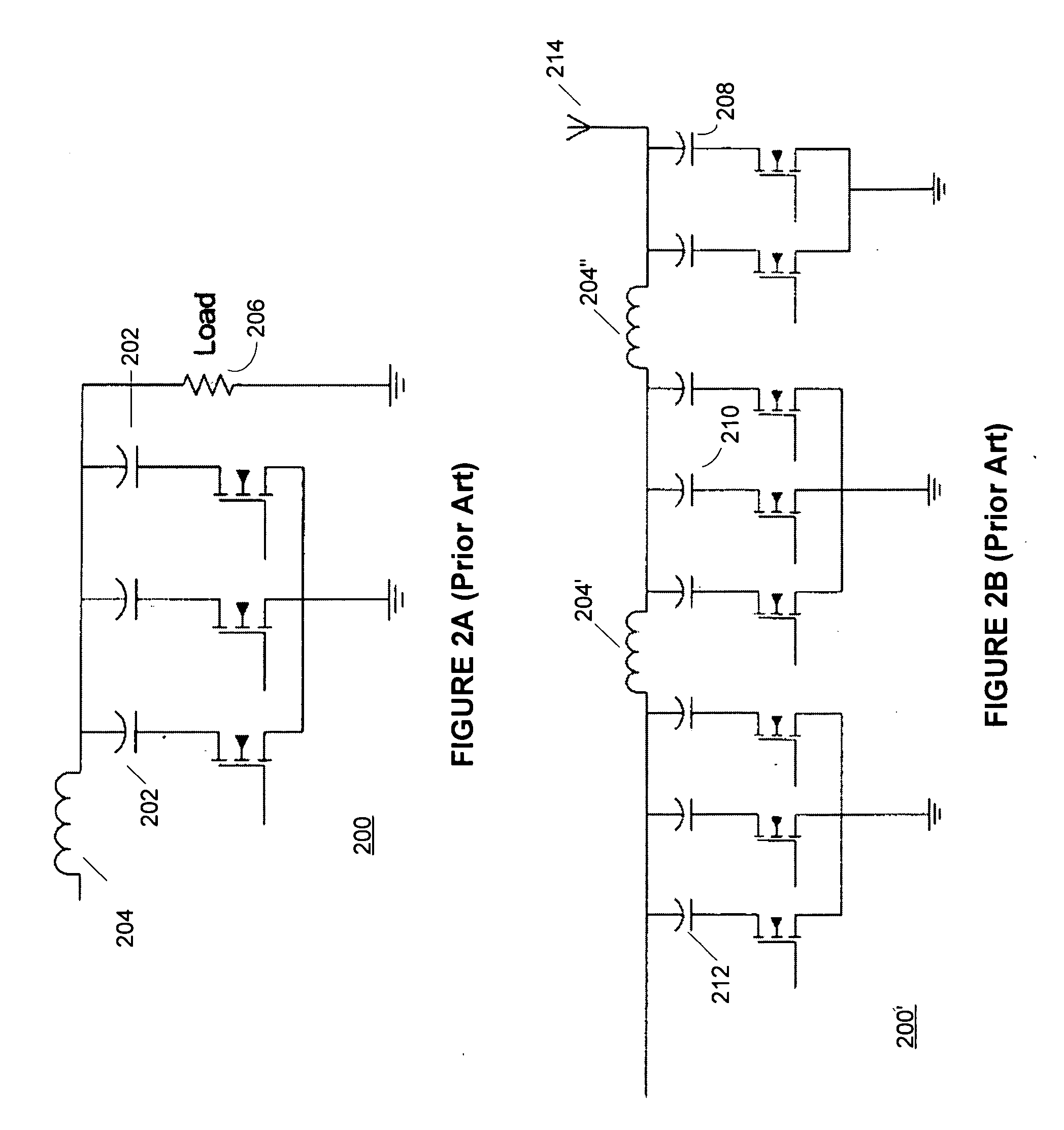

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS20110002080A1Easy to controlHigh Power Handling CapabilityAnalogue/digital conversionImpedence matching networksCapacitanceLeast significant bit

A method and apparatus for use in a digitally tuning a capacitor in an integrated circuit device is described. A Digitally Tuned Capacitor DTC is described which facilitates digitally controlling capacitance applied between a first and second terminal. In some embodiments, the first terminal comprises an FW+ terminal and the second terminal comprises an RF terminal. In accordance with some embodiments, the DTCs comprises a plurality of sub-circuits ordered in significance from least significant bit (LSB) to most significant bit (MSB) sub-circuits, wherein the plurality of significant bit sub-circuits are coupled together in parallel, and wherein each sub-circuit has a first node coupled to the first RF terminal, and a second node coupled to the second FW terminal. The DTCs further include an input means for receiving a digital control word, wherein the digital control word comprises bits that are similarly ordered in significance from an LSB to an MSB.

Owner:PSEMI CORP

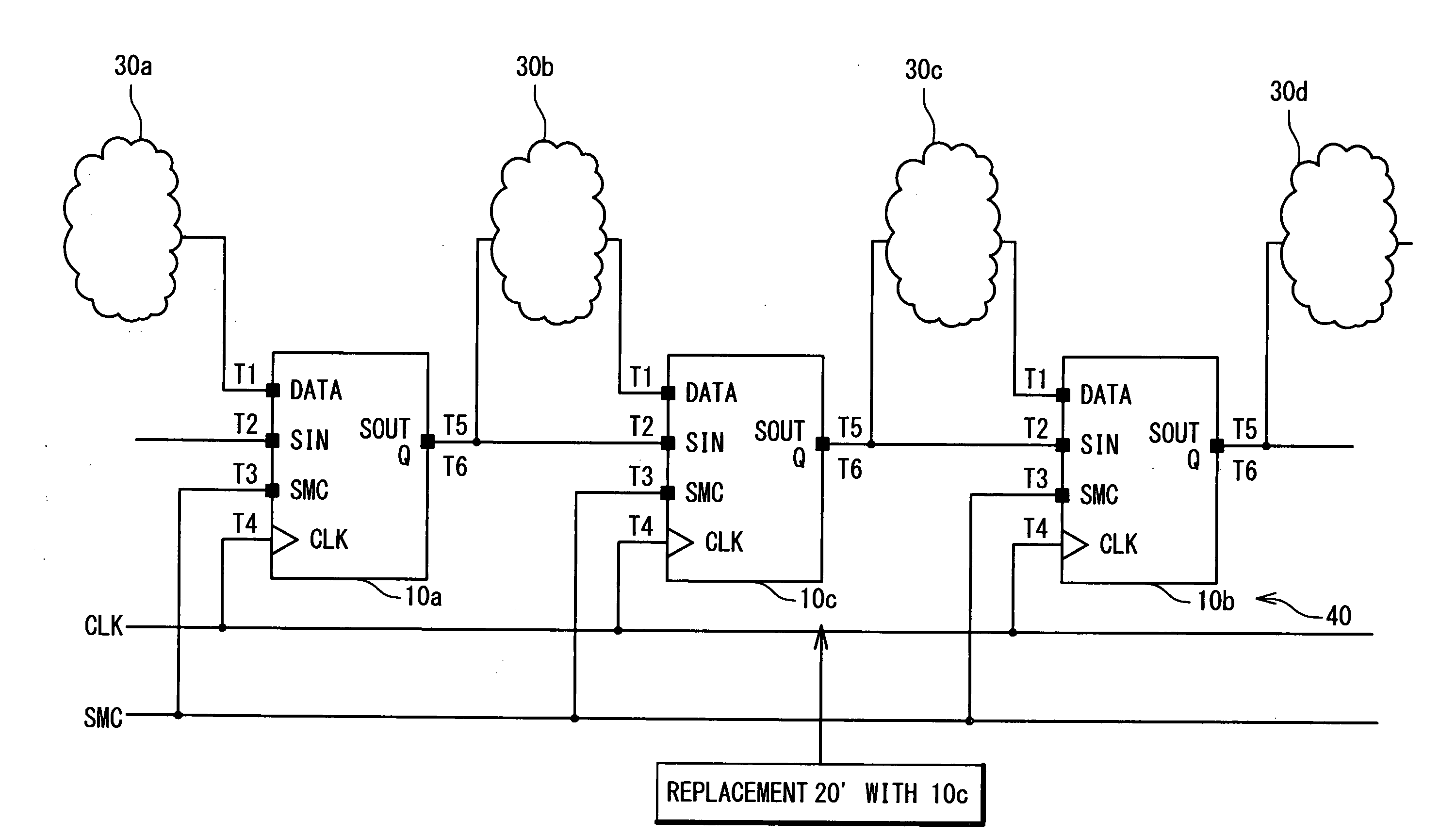

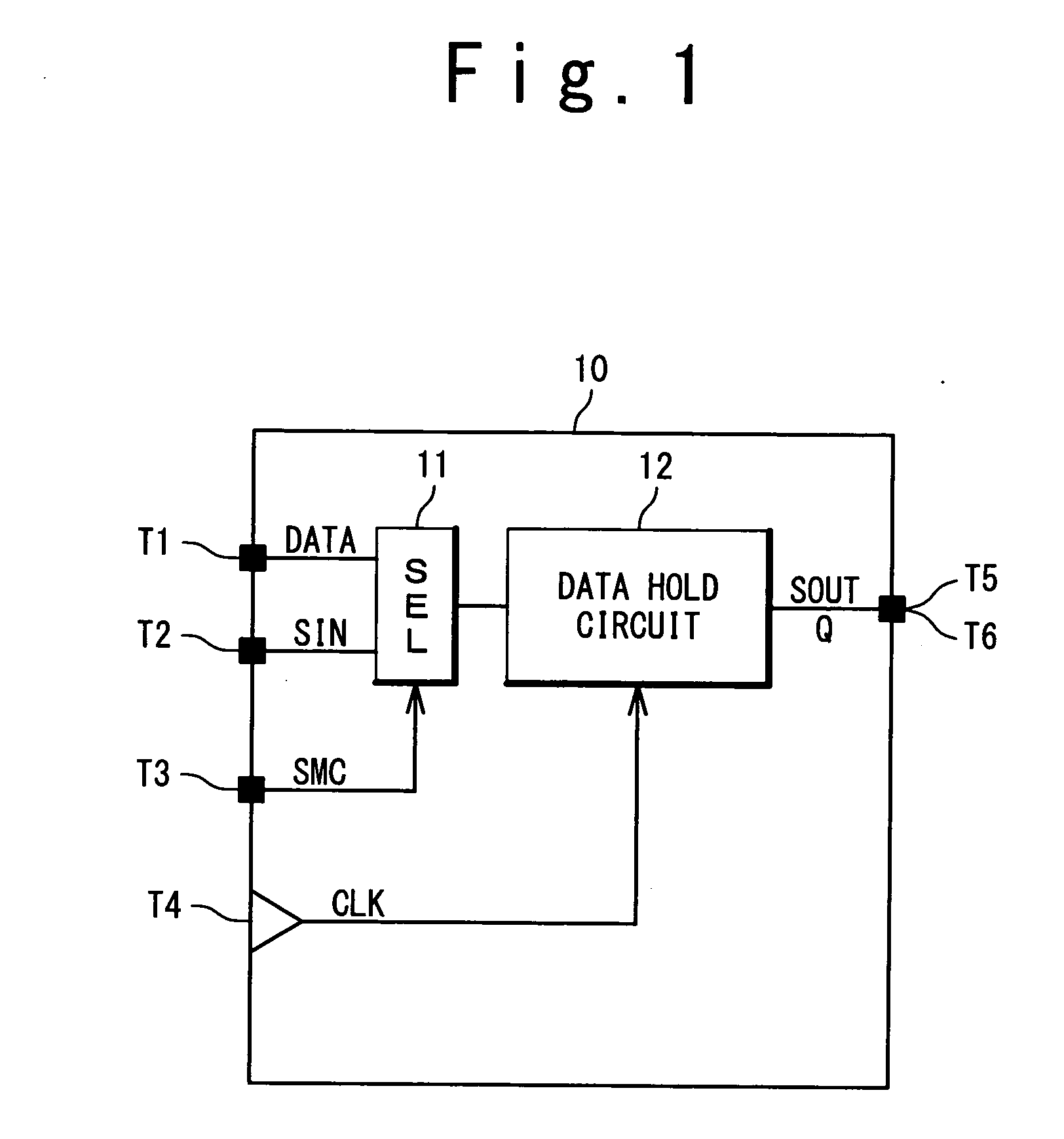

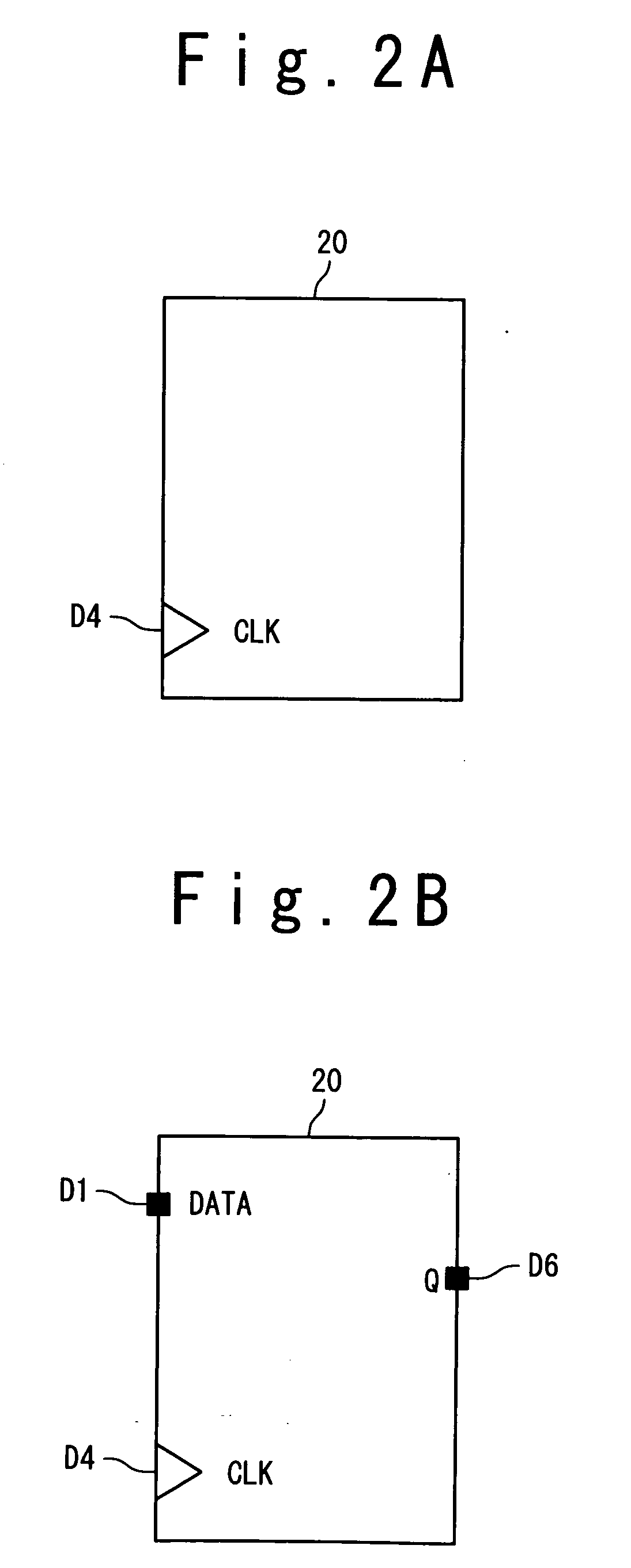

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

Method for fabricating semiconductor device, and electro-optical device, integrated circuit and electronic apparatus including the semiconductor device

InactiveUS7547589B2High resolutionDecrease productivityTransistorOther printing matterProduction rateEngineering

The invention provides a technique that enables formation of minute patterns on an uneven substrate in volume production without reducing productivity. The method for fabricating a semiconductor device includes: first patterning a semiconductor film on a substrate to form element regions, each of which will be provided with a source / drain region and a channel region, second forming a gate insulating film covering segments of the patterned semiconductor film in the respective element regions, third forming gate electrodes on the gate insulating film at predetermined positions, and fourth forming the source / drain region and the channel region in each element region. At least the gate electrodes are formed by a process including an exposure step through a holographic exposure mask in the third step, and by a process including an exposure step through a projection exposure mask, the element regions are formed in the first step, and the source / drain regions and the channel regions are formed in the fourth step.

Owner:SEIKO EPSON CORP

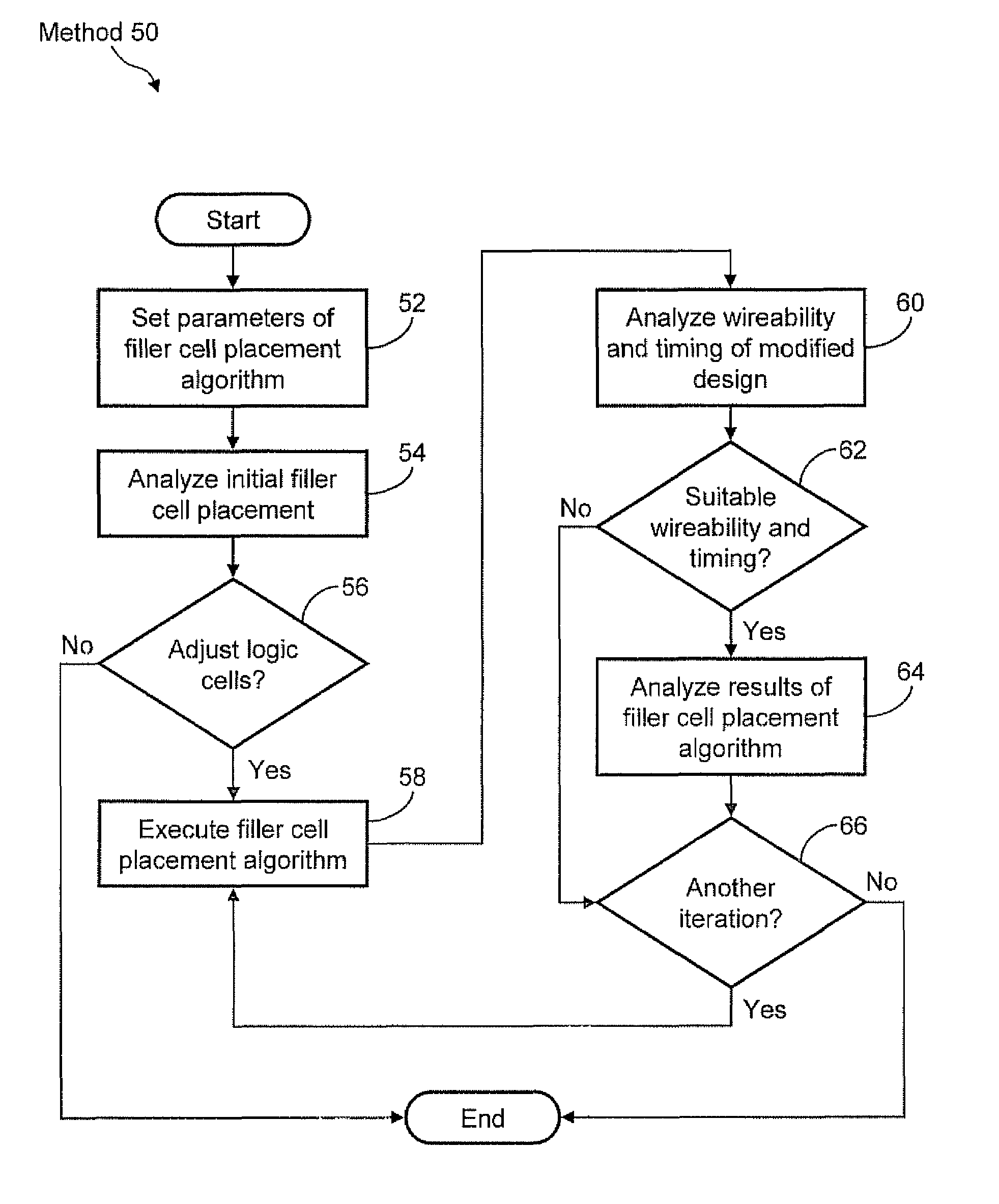

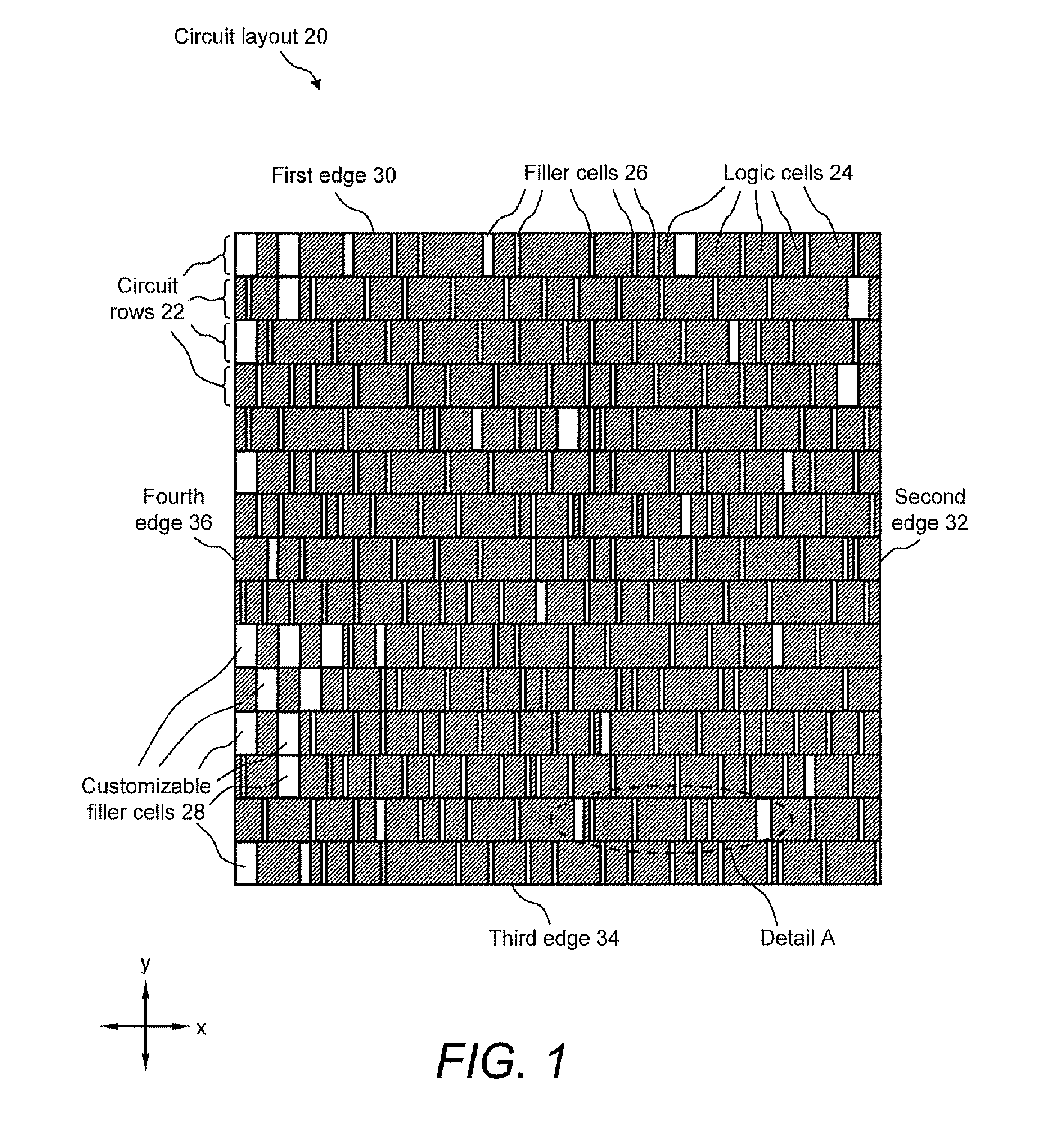

Method of optimizing customizable filler cells in an integrated circuit physical design process

ActiveUS7444609B2Computer aided designSoftware simulation/interpretation/emulationLogic cellEngineering

A system and method for optimizing customizable filler cells in an integrated circuit physical design process. In particular, a filler cell placement algorithm of the present disclosure is utilized in the method to optimize the customizable filler cells in a circuit layout. The filler cell placement algorithm performs the operation of selecting a starting point within a given circuit layout, selecting a direction in which the position of logic cells is adjusted, adjusting the position of logic cells and, thereby, combining filler cells in order to increase the accumulated area thereof; suspending the adjustment operation when a customizable filler cell is formed; and resuming the adjustment operation from the point of the newly formed customizable filler cell. Additionally, a method of optimizing the locations, number, and distribution of the customizable filler cells in an integrated circuit design by use of the filler cell placement algorithm is provided.

Owner:GLOBALFOUNDRIES U S INC

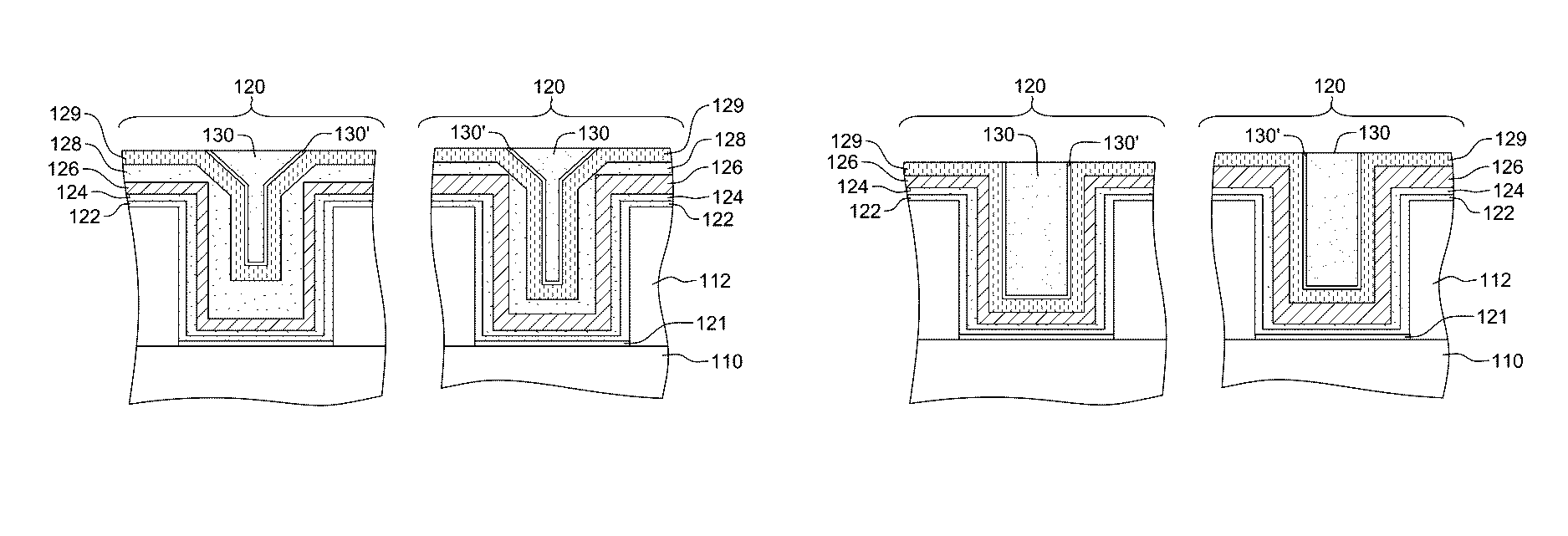

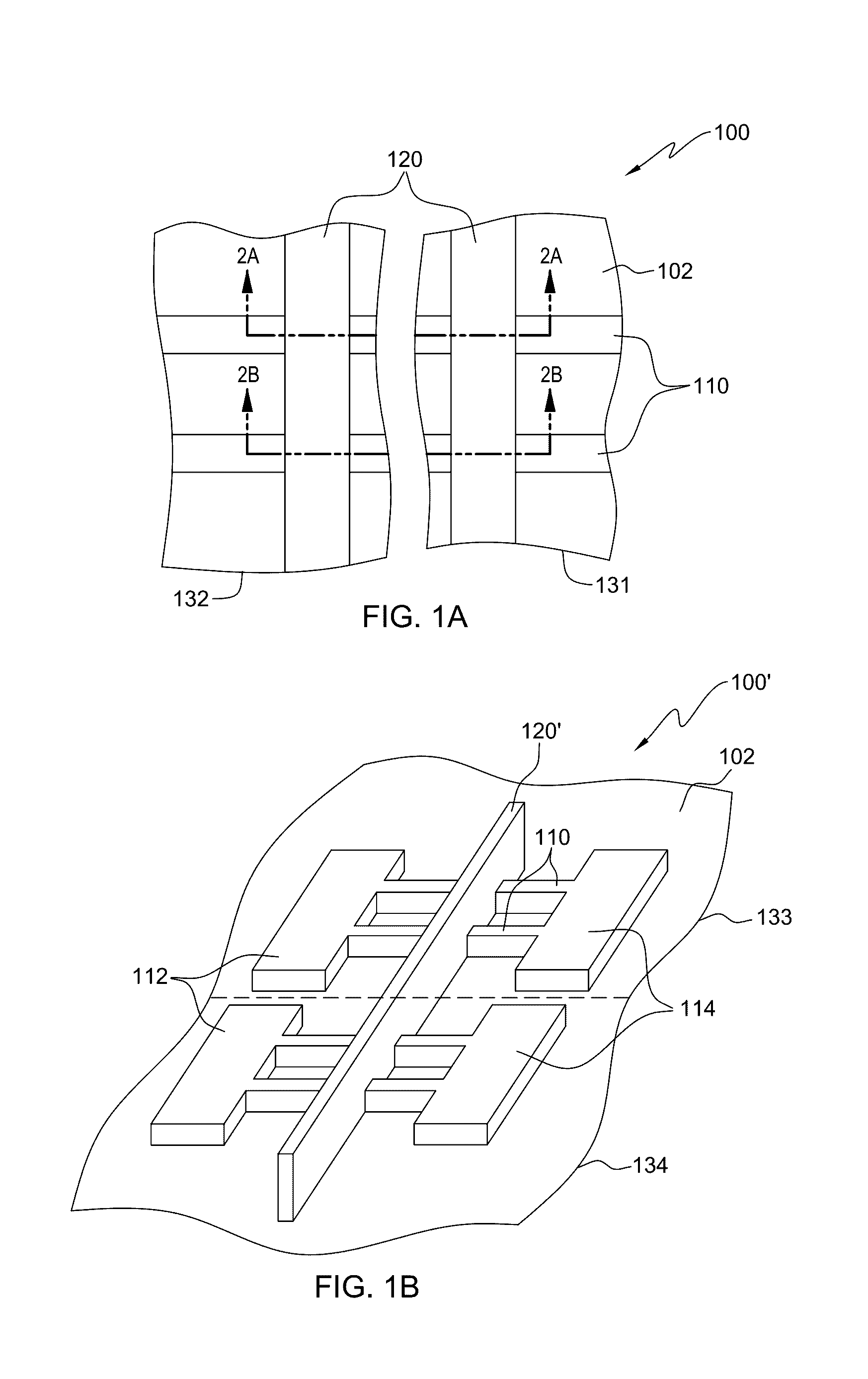

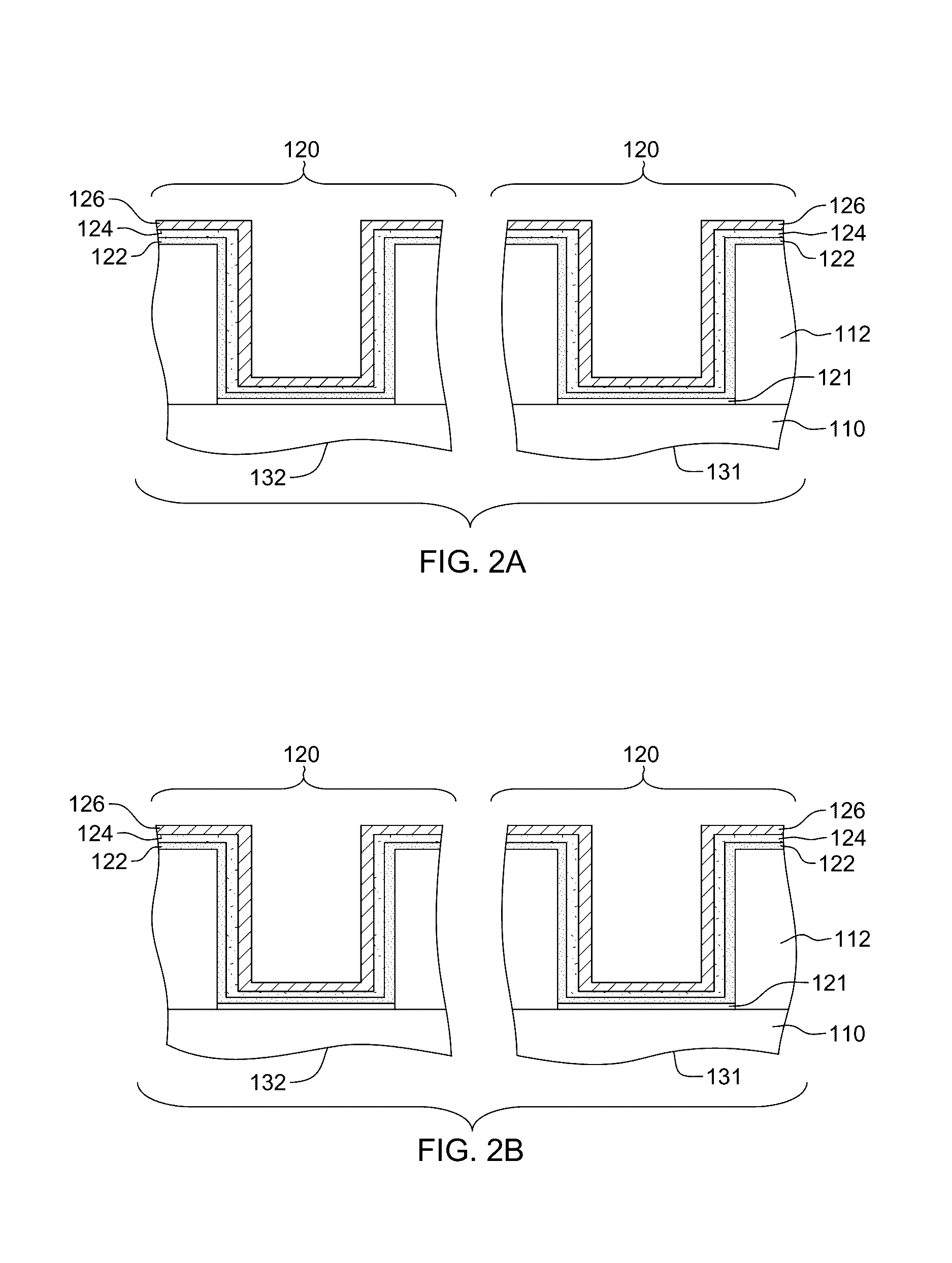

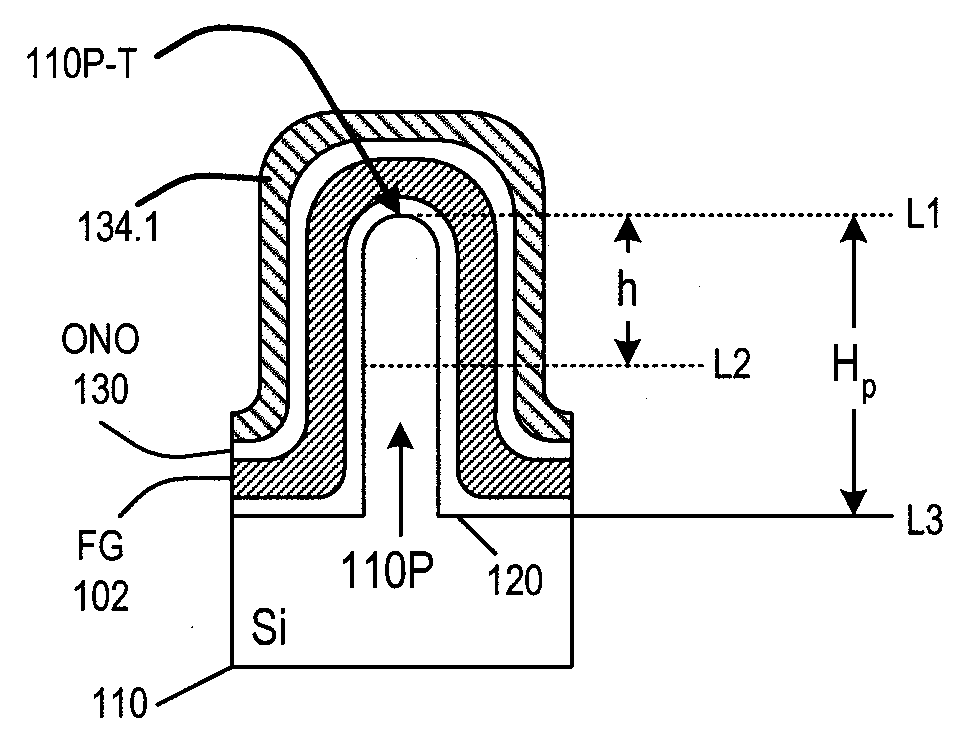

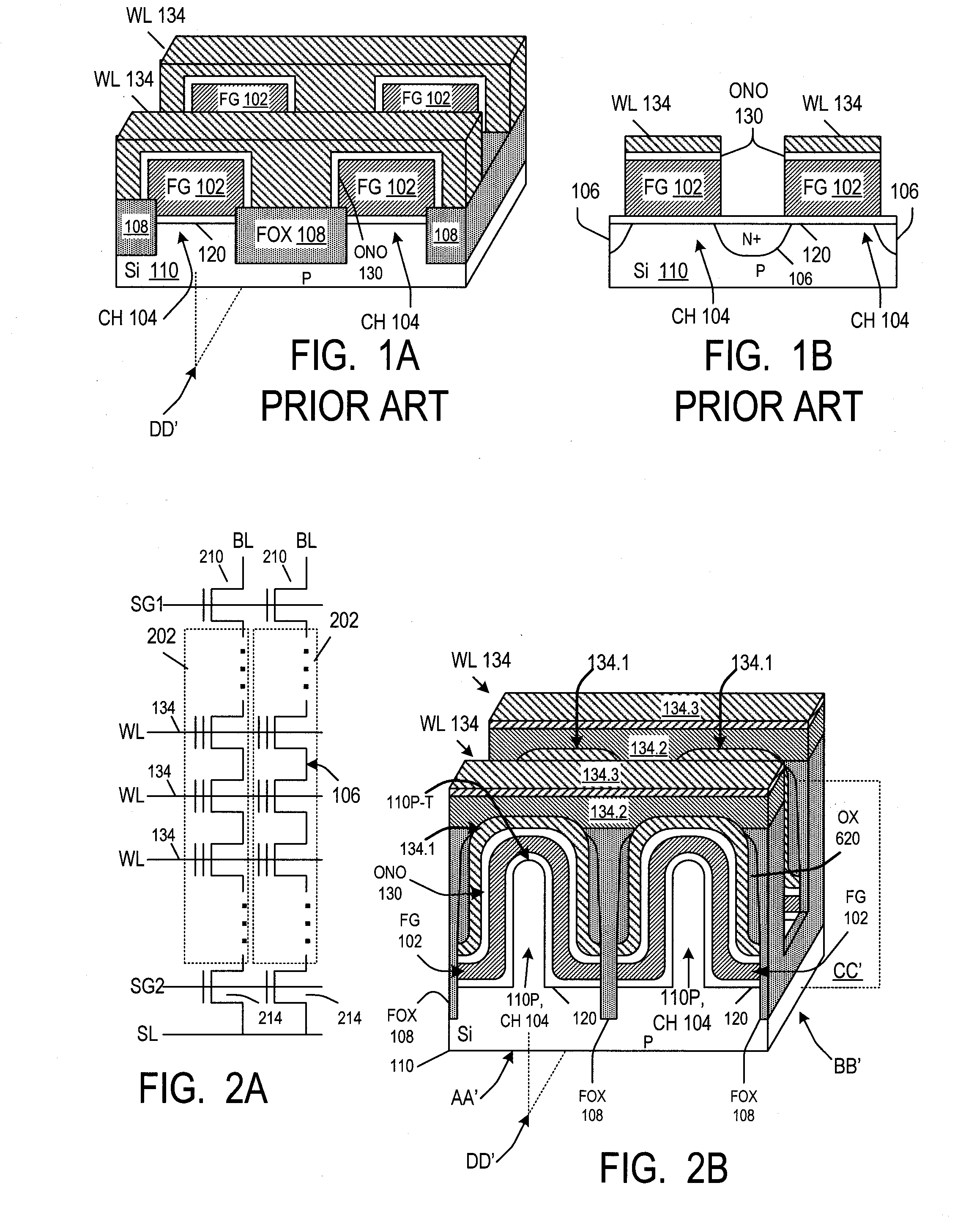

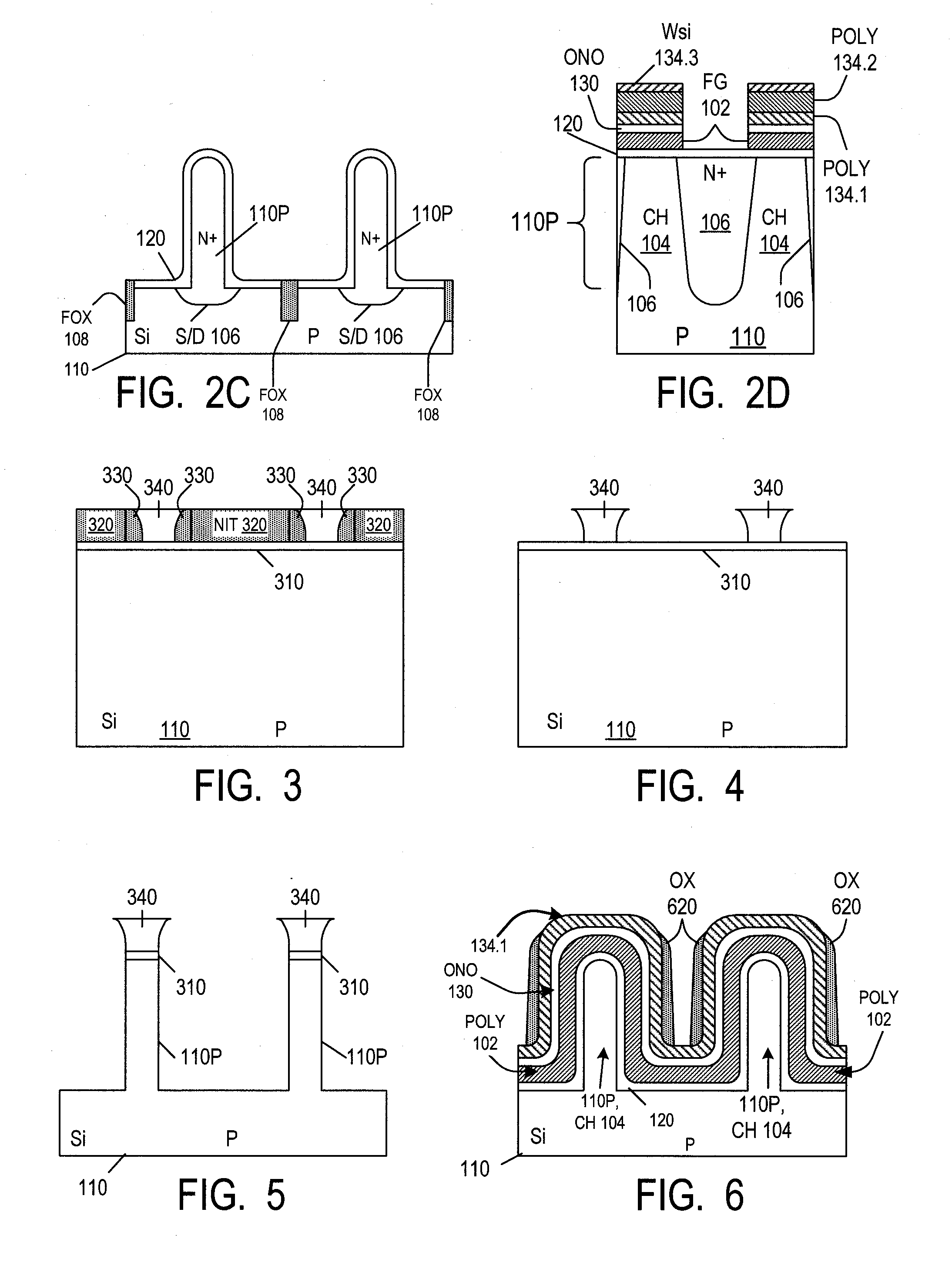

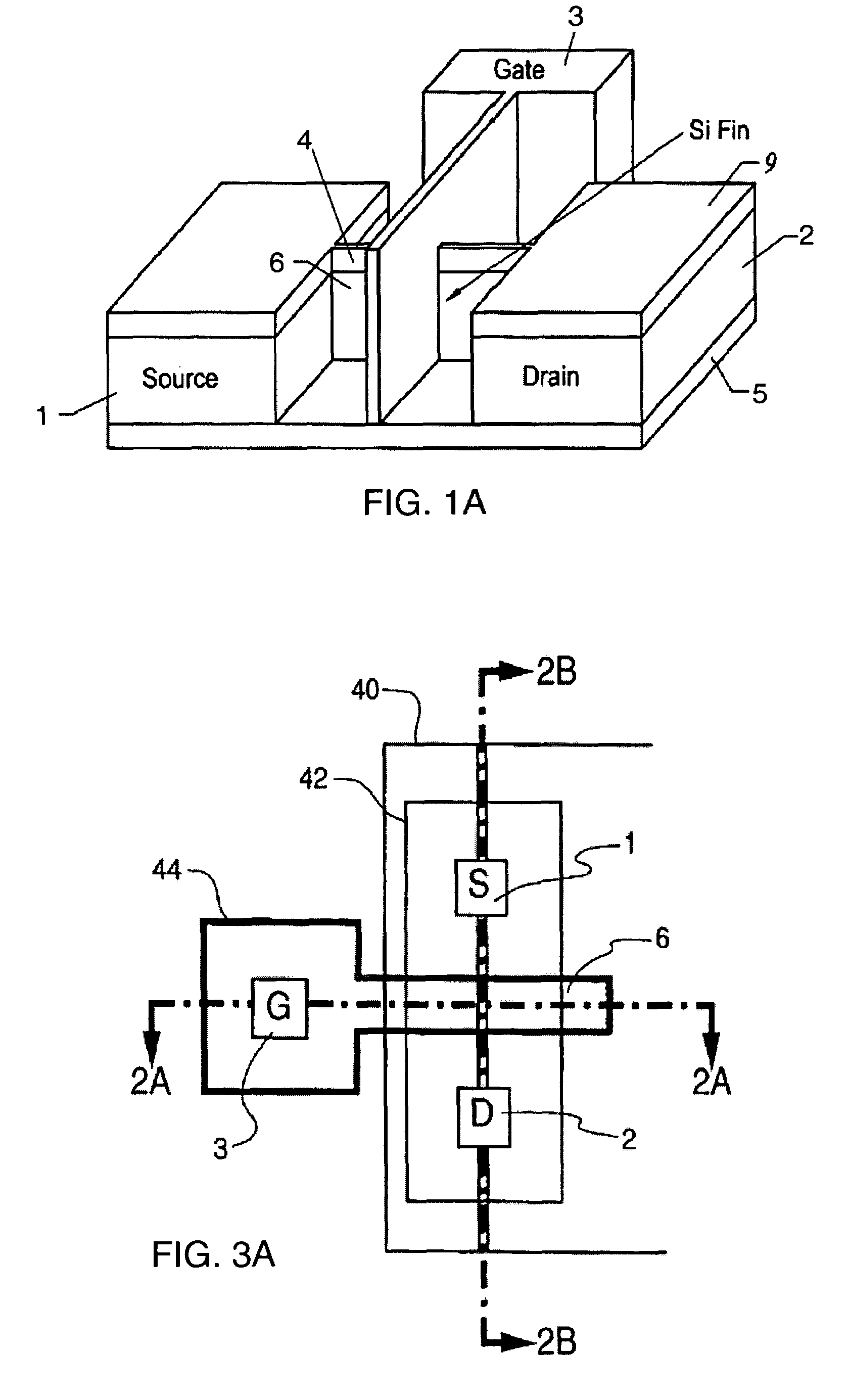

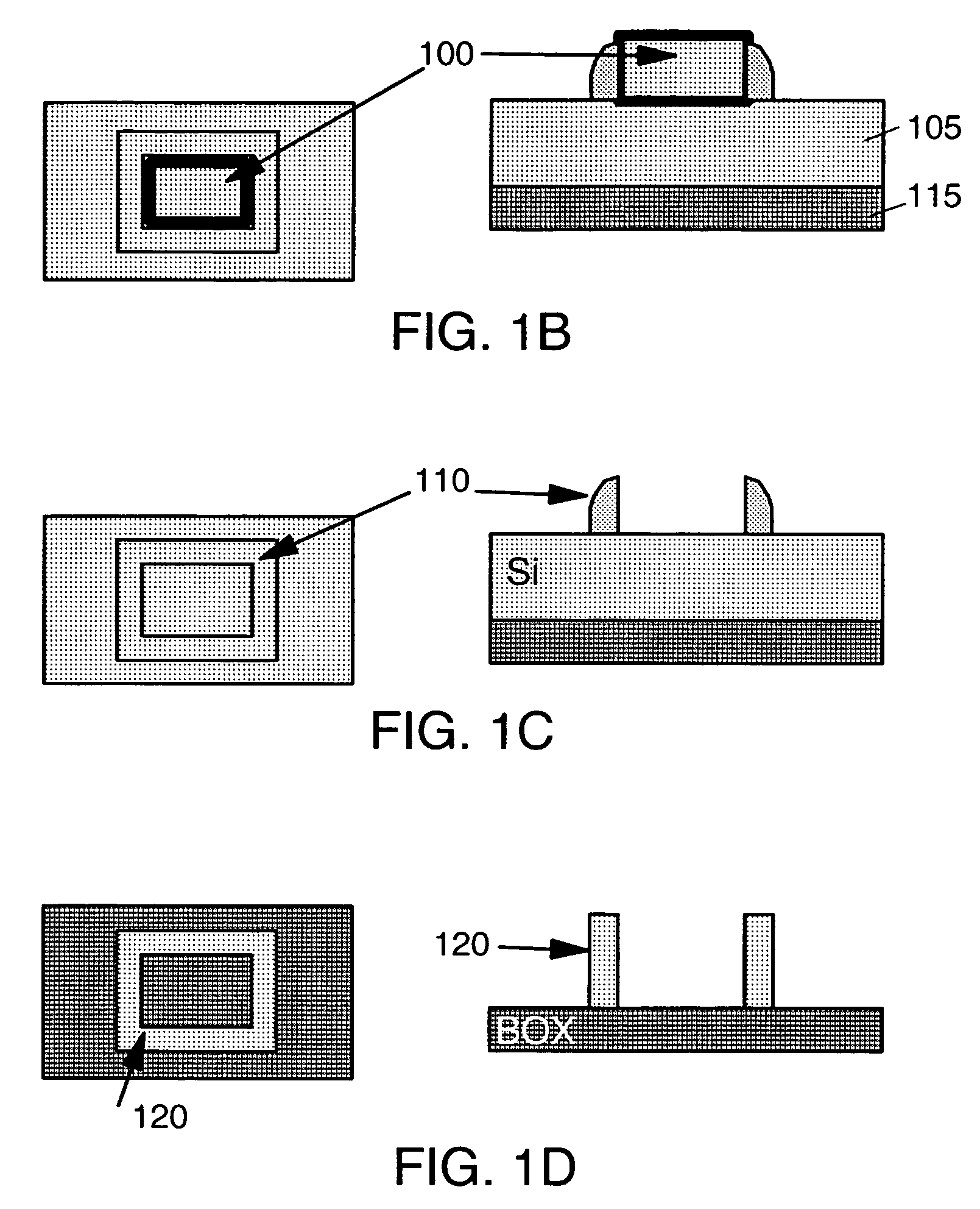

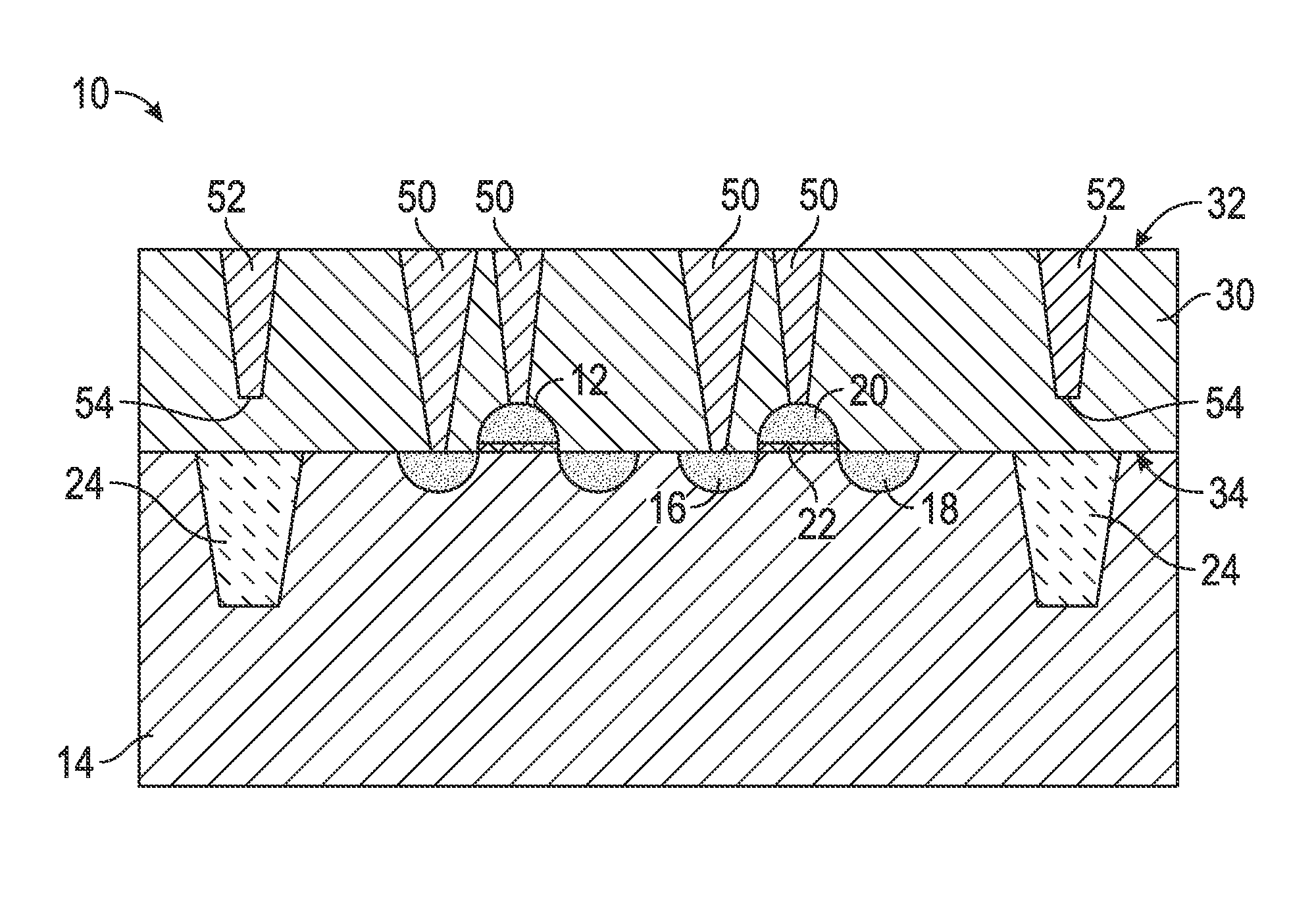

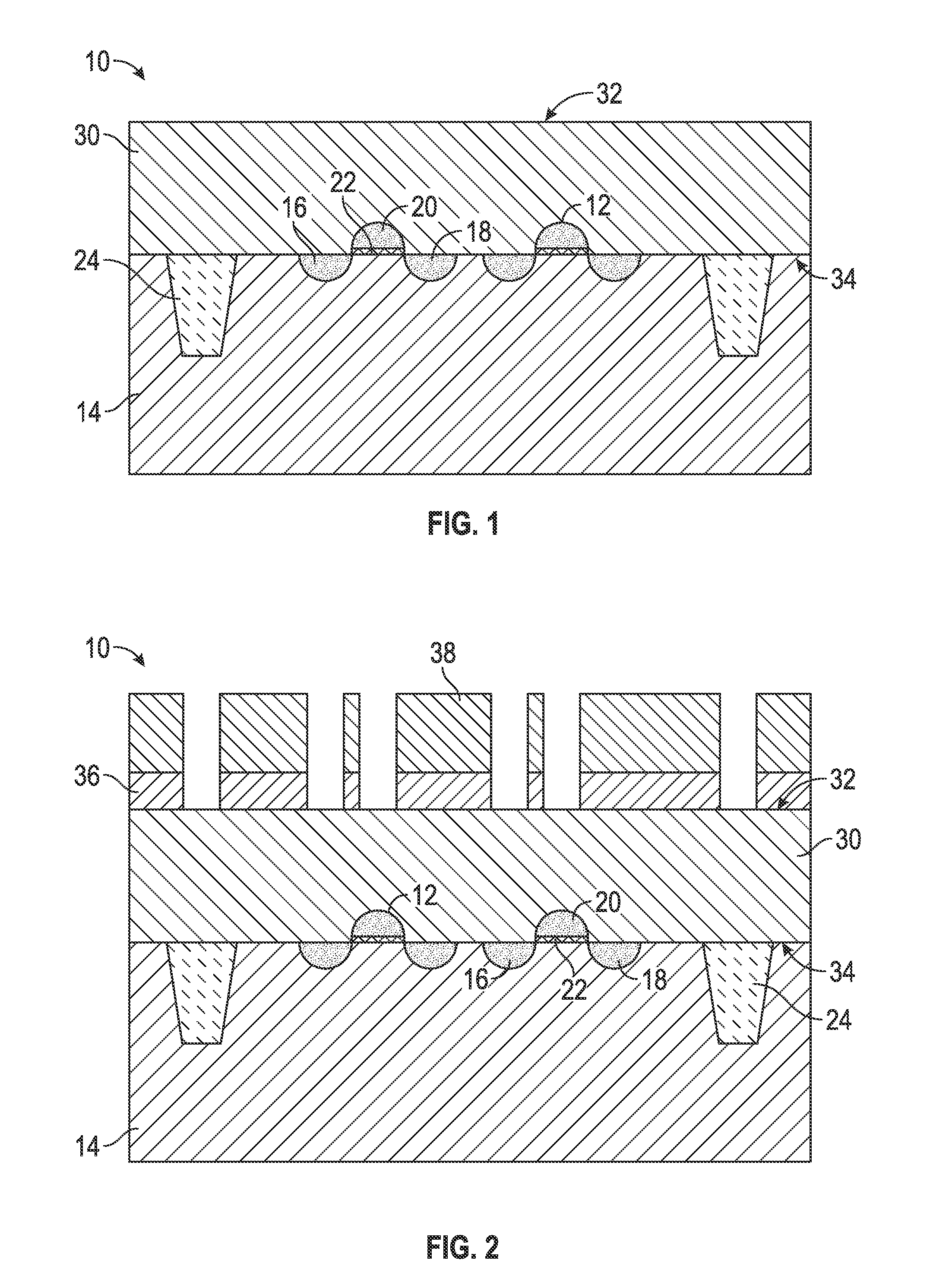

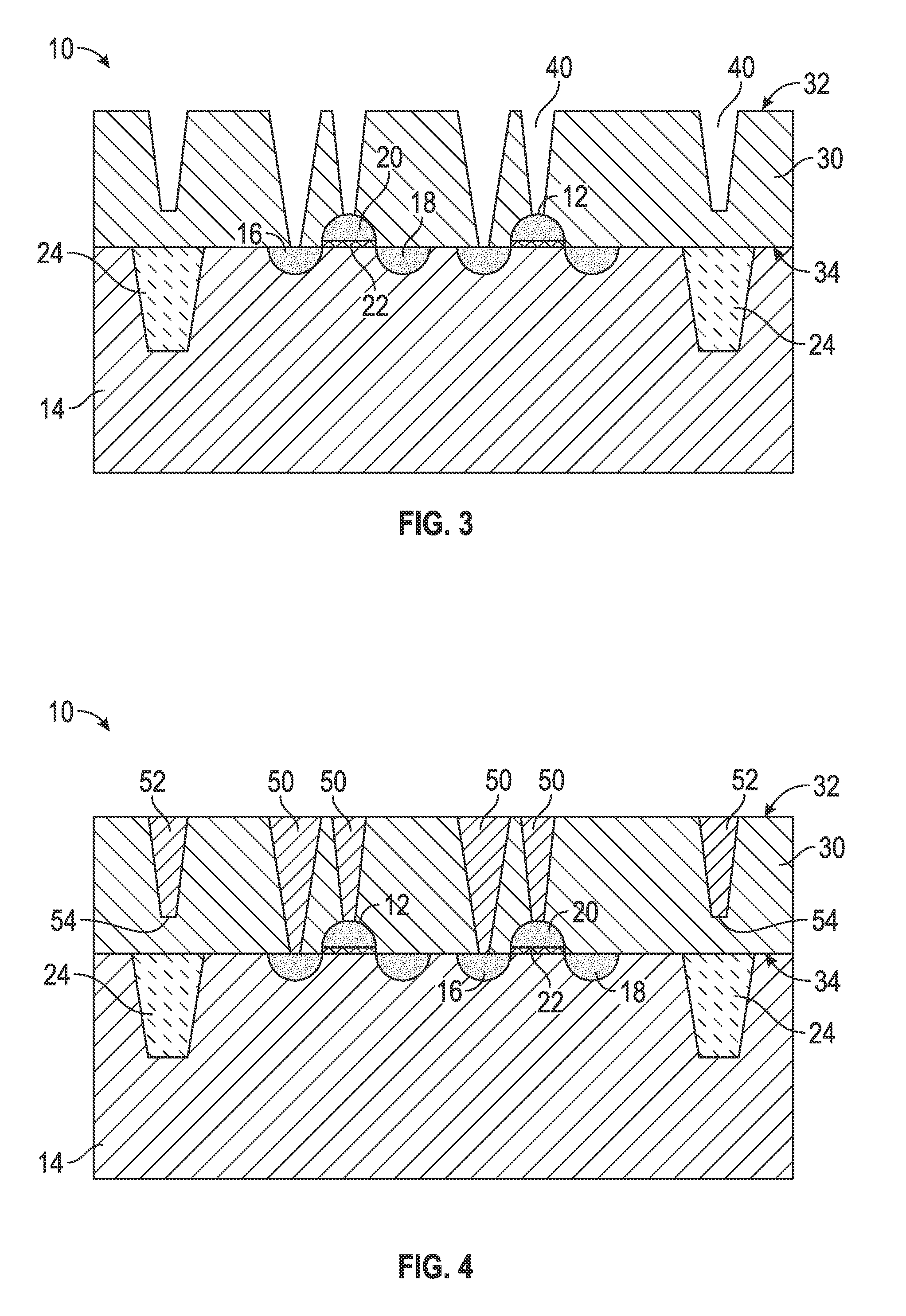

Integrated circuits with substrate protrusions, including (but not limited to) floating gate memories

ActiveUS20080265305A1Enhanced couplingIncrease currentTransistorSolid-state devicesDielectricPhotonic integrated circuit

A floating gate memory cell's channel region (104) is at least partially located in a fin-like protrusion (110P) of a semiconductor substrate. The floating gate's top surface may come down along at least two sides of the protrusion to a level below the top (110P-T) of the protrusion. The control gate's bottom surface may also comes down to a level below the top of the protrusion. The floating gate's bottom surface may comes down to a level below the top of the protrusion by at least 50% of the protrusion's height. The dielectric (120) separating the floating gate from the protrusion can be at least as thick at the top of the protrusion as at a level (L2) which is below the top of the protrusion by at least 50% of the protrusion's height. A very narrow fin or other narrow feature in memory and non-memory integrated circuits can be formed by providing a first layer (320) and then forming spacers (330) from a second layer without photolithography on sidewalls of features made from the first layer. The narrow fin or other feature are then formed without further photolithography in areas between the adjacent spacers. More particularly, a third layer (340) is formed in these areas, and the first layer and the spacers are removed selectively to the third layer. The third layer is used as a mask to form the narrow features.

Owner:PROMOS TECH INC

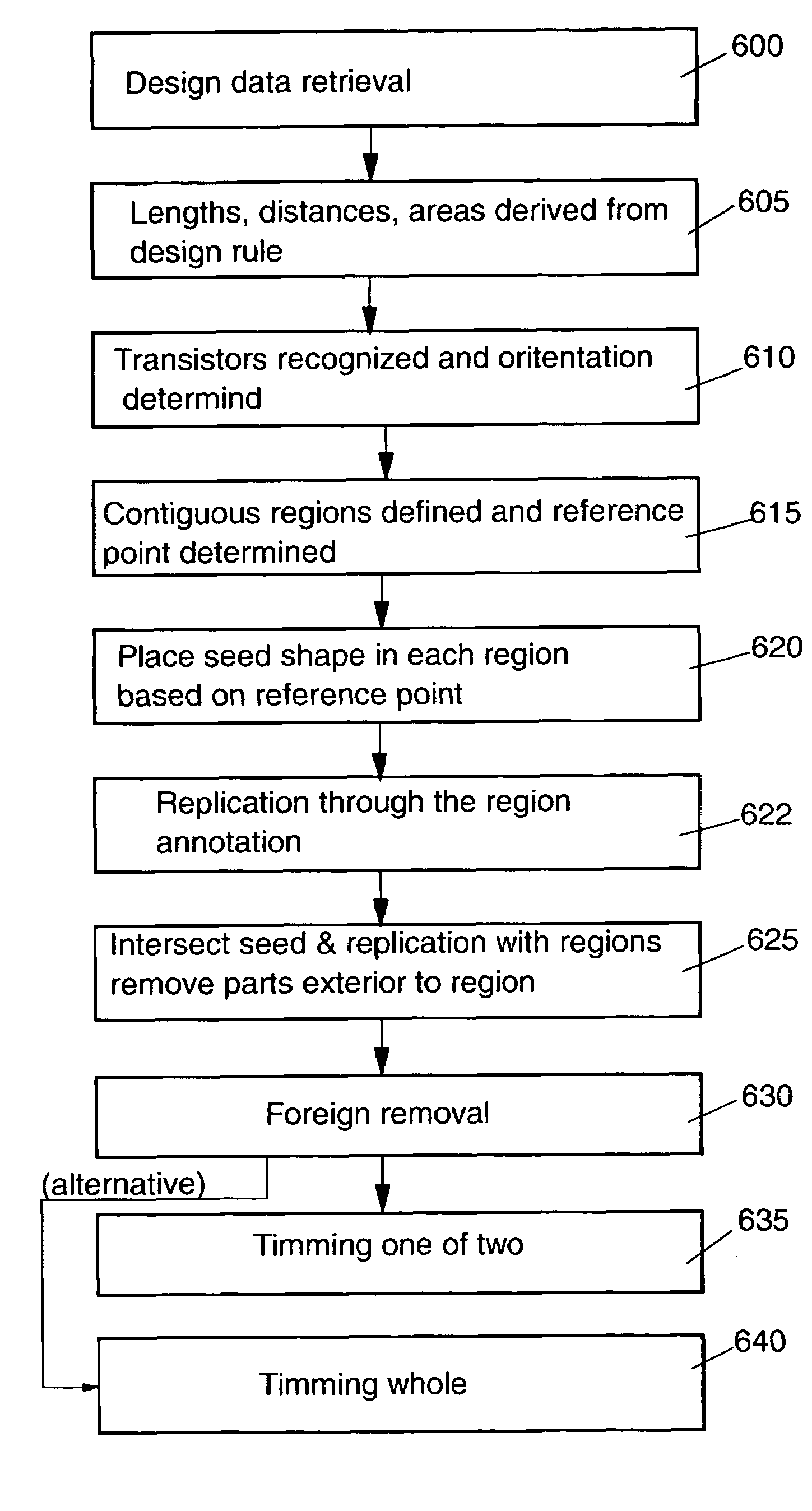

Method and device for automated layer generation for double-gate FinFET designs

InactiveUS7315994B2Reduce effortEnhance layeringTransistorSolid-state devicesEngineeringUnit structure

Owner:INT BUSINESS MASCH CORP

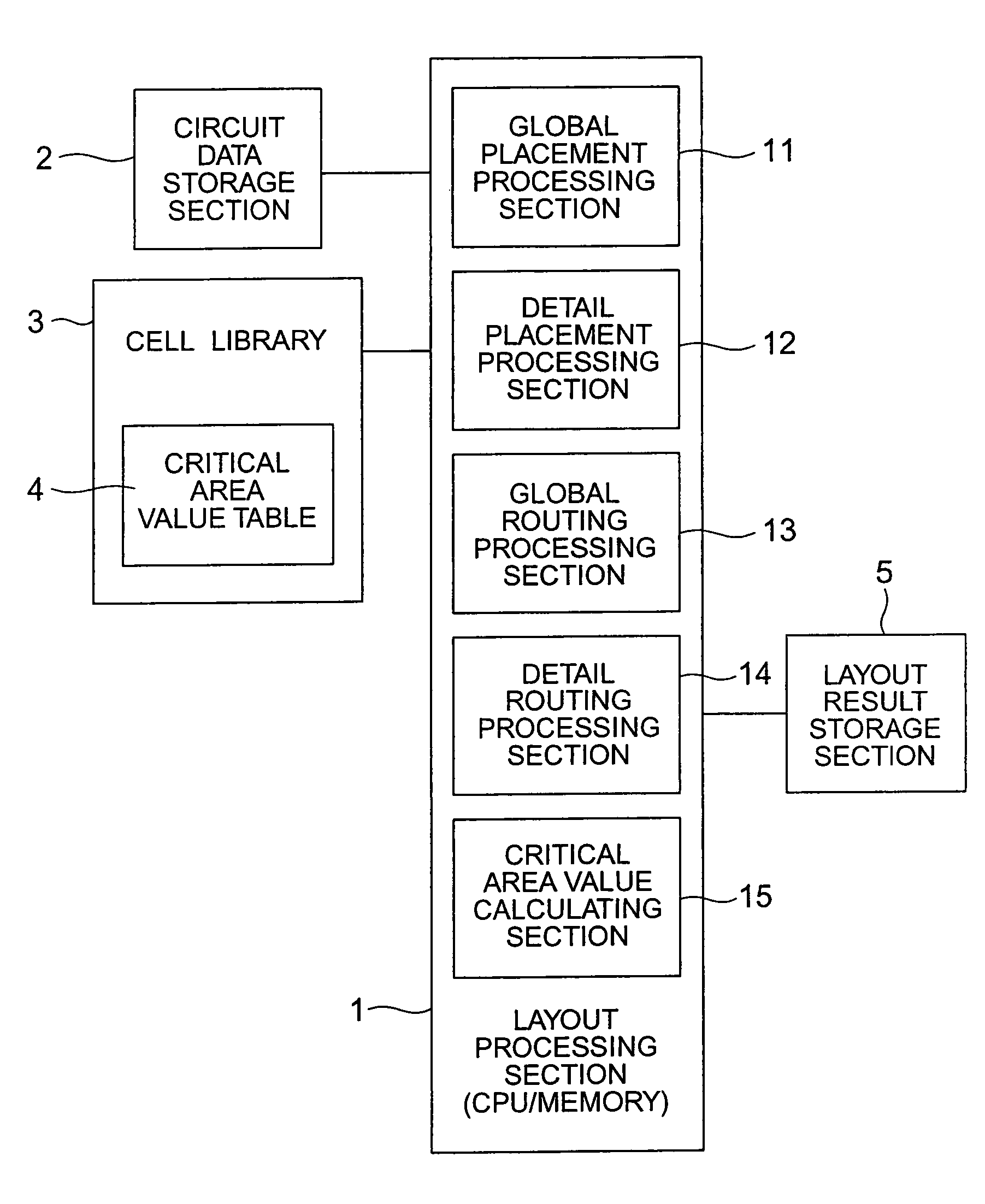

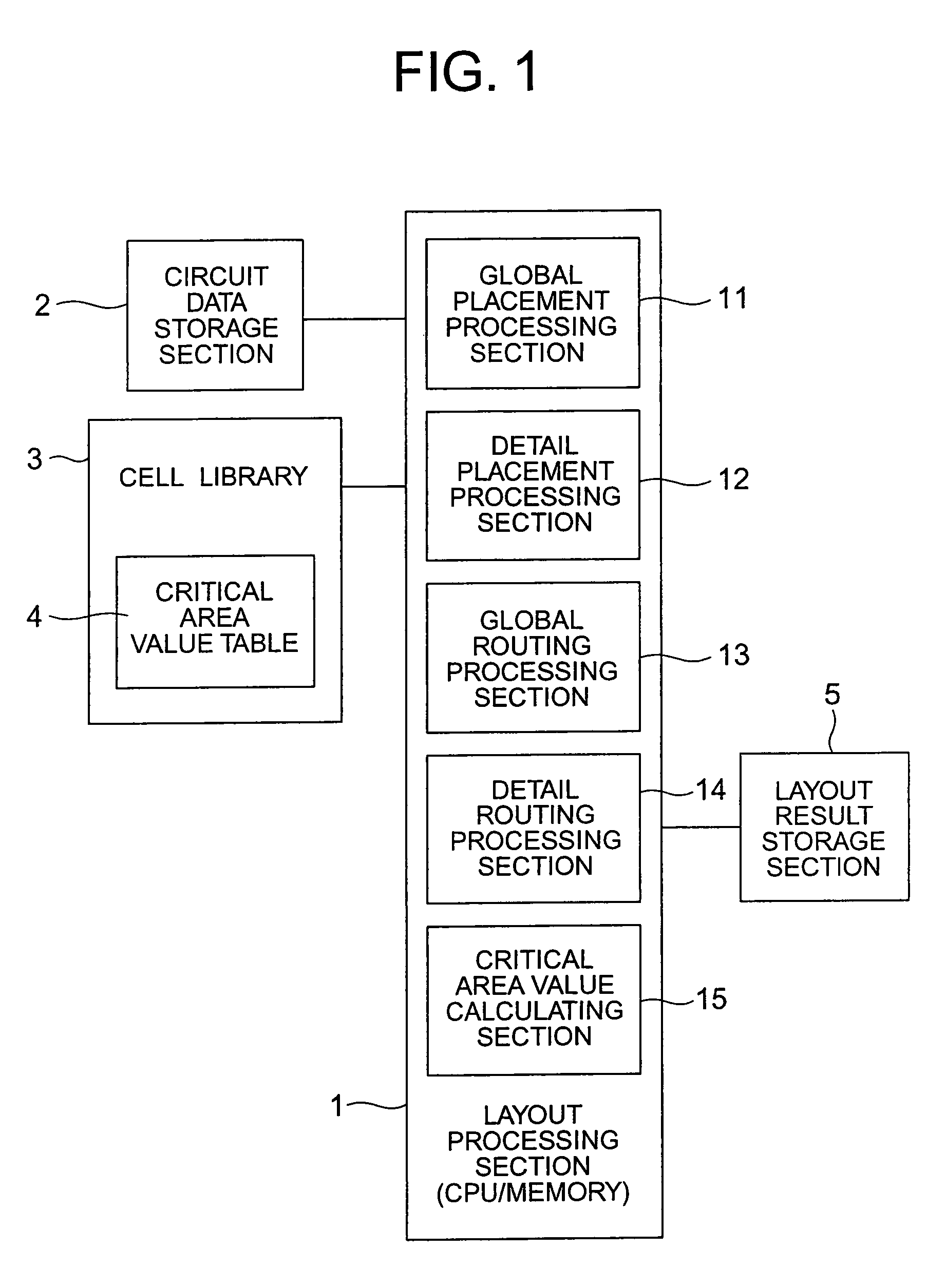

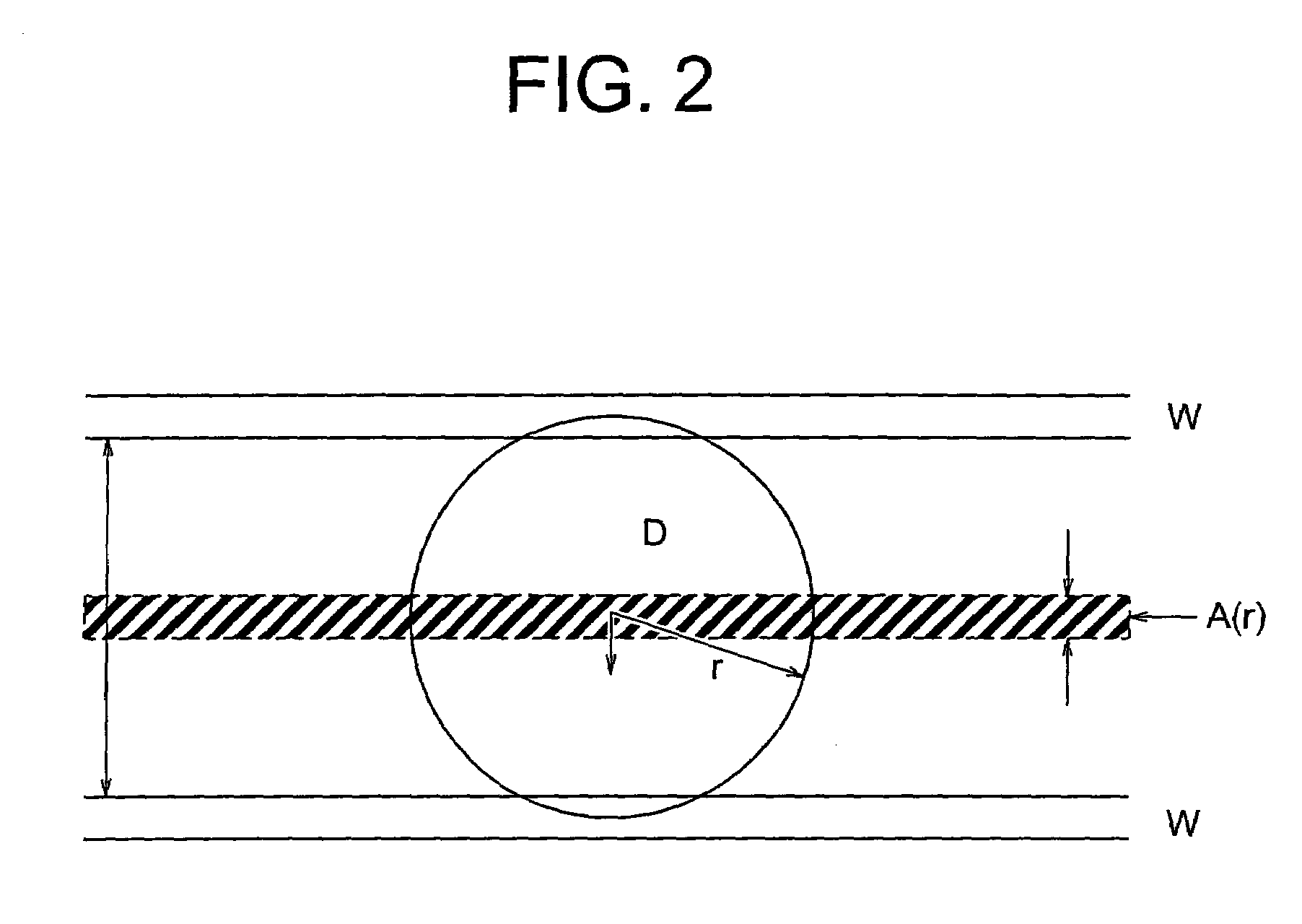

Method and apparatus for designing integrated circuit enabling the yield of integrated circuit to be improved by considering random errors

InactiveUS7512921B2Increase productionCAD circuit designSoftware simulation/interpretation/emulationIntegrated circuit layoutEngineering

A layout method in a layout apparatus for layout of an integrated circuit includes placing a plurality of cells at approximate positions according to the circuit data and placing the plurality of cells at specific positions according to the result of the placement of the plurality of cells at the approximate positions. In the placing the plurality of cells at specific positions, the plurality of cells are placed at specific positions, critical area values between cells adjacent to one another are calculated, and the specific positions of the cells are modified so as to reduce the critical area values obtained.

Owner:FUJITSU LTD

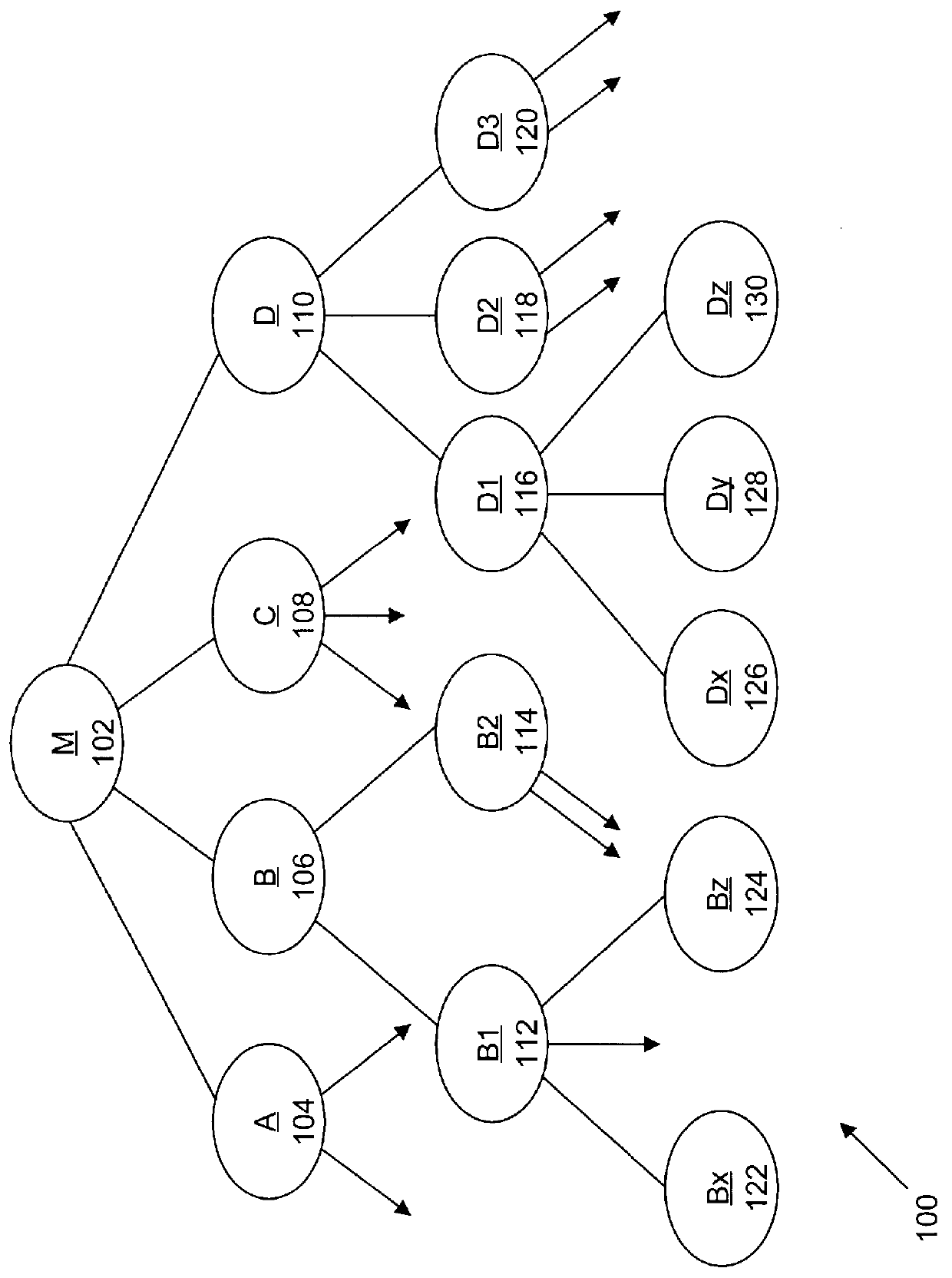

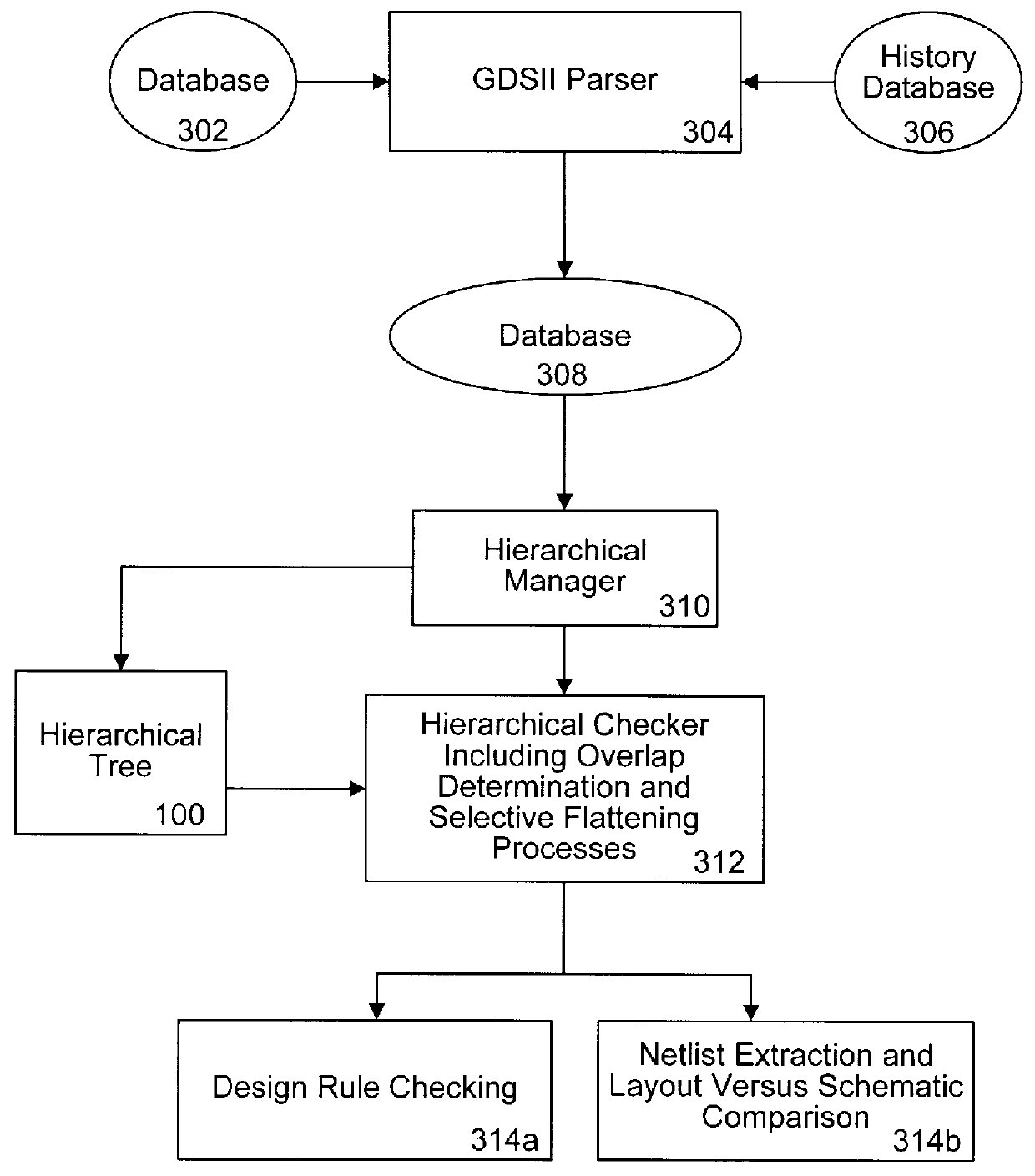

Layout overlap detection with selective flattening in computer implemented integrated circuit design

InactiveUS6011911AValid checkComputer aided designSoftware simulation/interpretation/emulationComputer architectureLayout Versus Schematic

The present invention relates to a method for efficiently performing hierarchical design rules checks (DRC) and layout versus schematic comparison (LVS) on layout areas of an integrated circuit where cells overlap or where a cell and local geometry overlap. With the present invention, a hierarchical tree describes the integrated circuit's layout data including cells having parent-child relationships and including local geometry. The present invention performs efficient layout verification by performing LVS and DRC checking on the new portions of an integrated circuit design and layout areas containing overlapping cells. When instances of cells overlap, the present invention determines the overlap area using predefined data structures that divide each cell into an array of spatial bins. Each bin of a parent is examined to determine if two or more cell instances reside therein or if a cell instance and local geometry reside therein. Once overlap is detected, the areas of the layout data corresponding to the overlap areas are selectively flattened prior to proceeding to DRC and LVS processing. During selective flattening of the overlap areas, the hierarchical tree is traversed from the top cell down through intermediate nodes to the leaf nodes. Each time geometry data is located during the traversal, it is pushes directly to the top cell without being stored in intermediate locations. This provides an effective mechanism for selective flattening.

Owner:SYNOPSYS INC

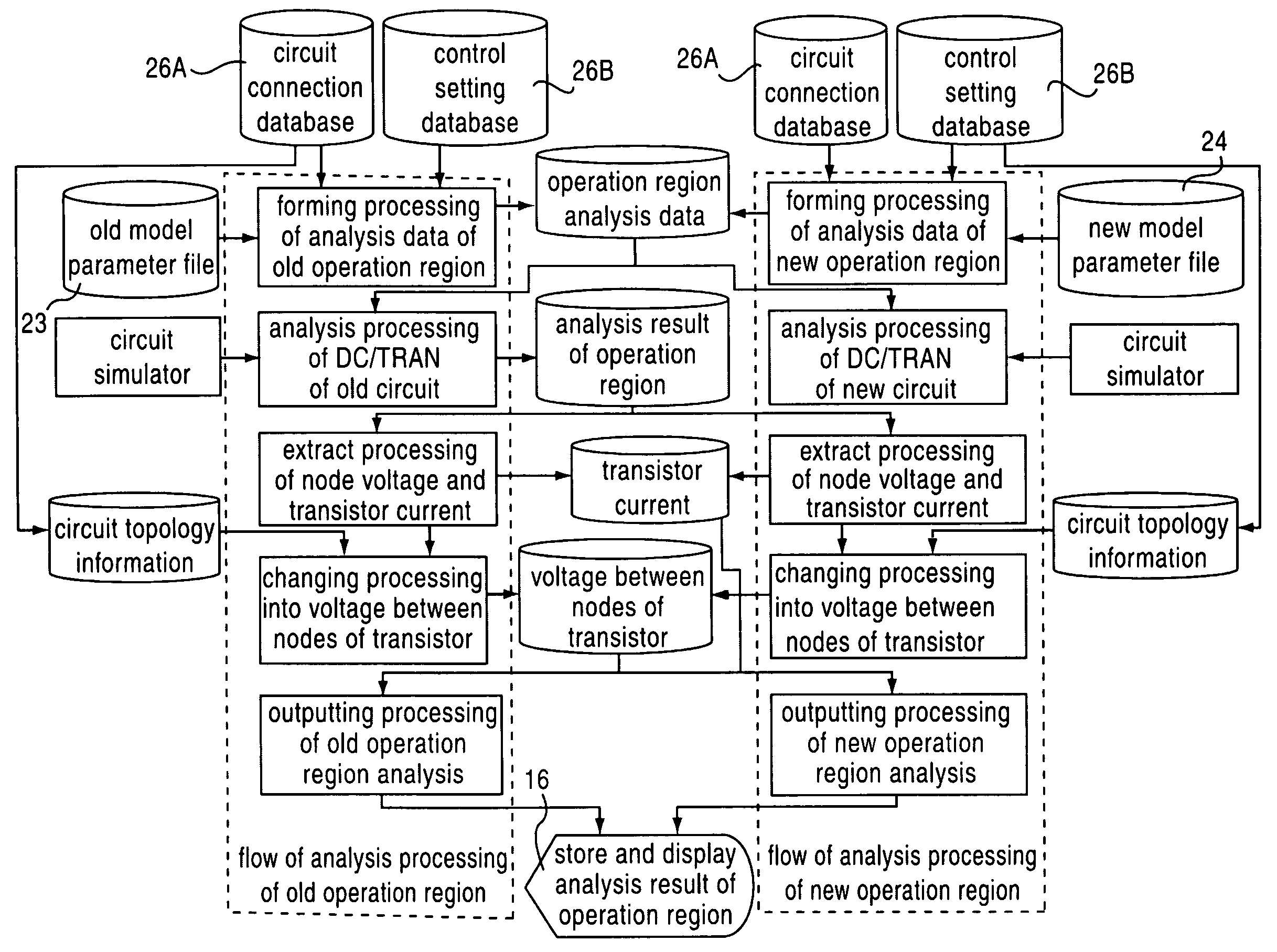

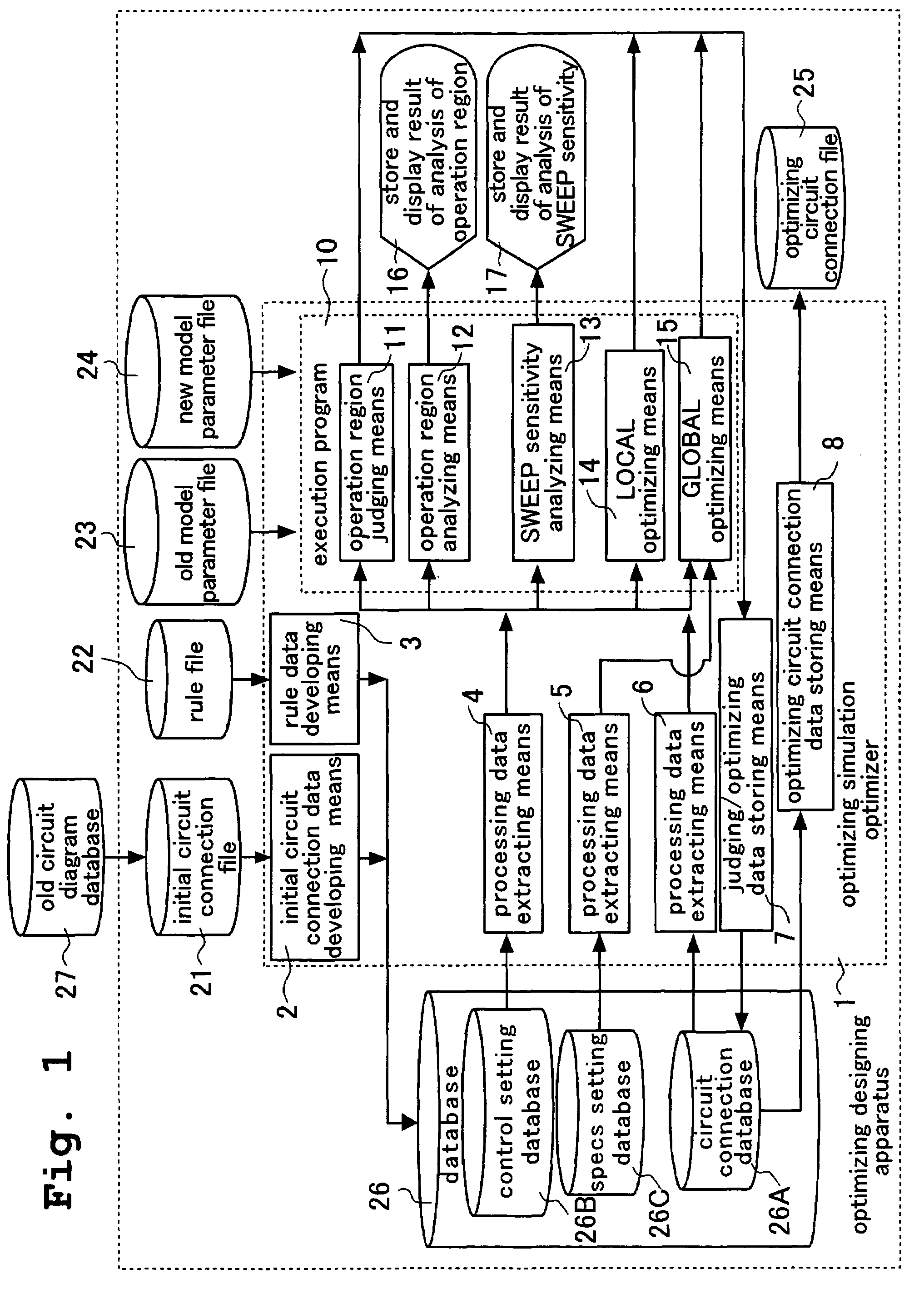

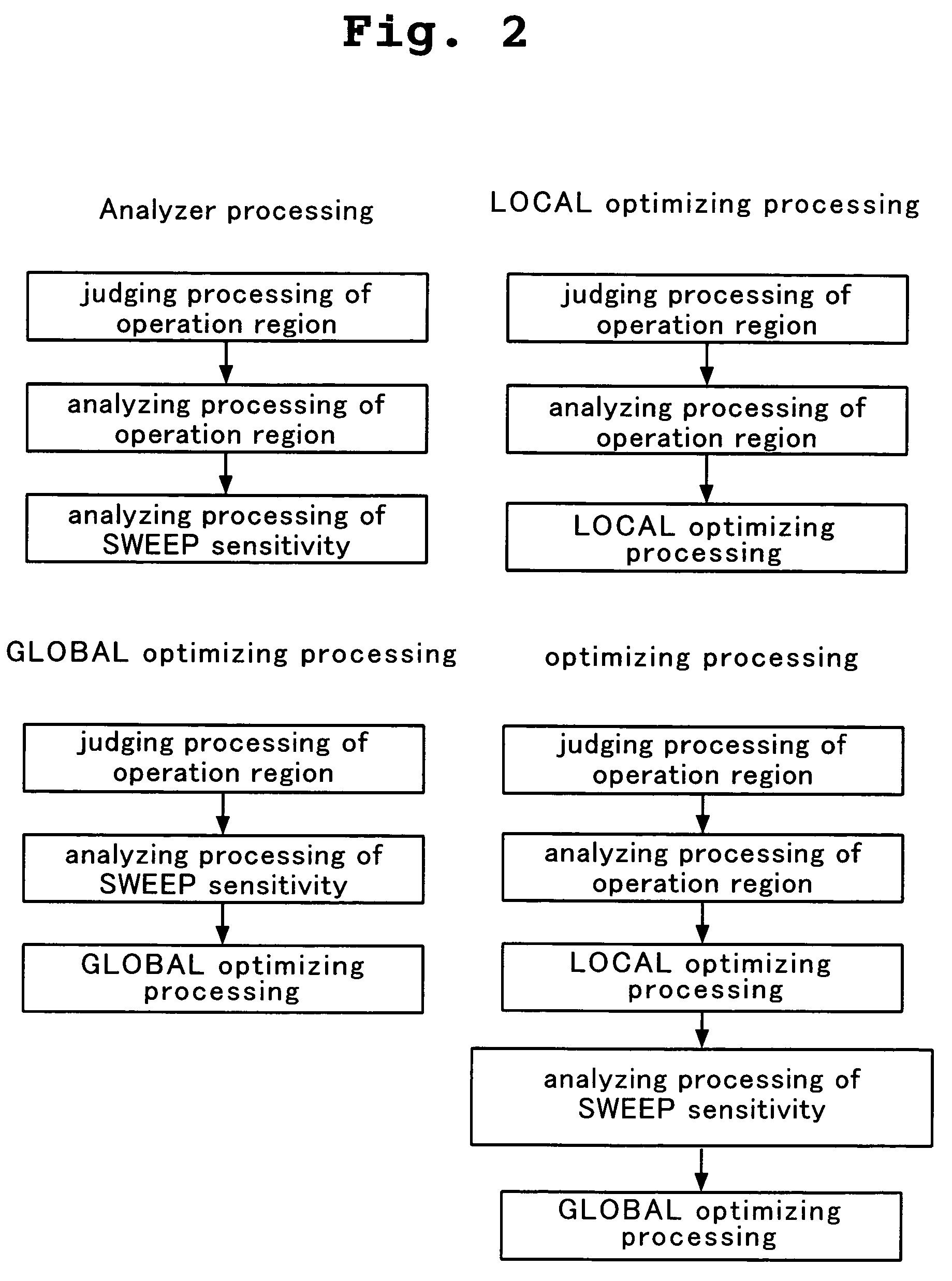

Optimizing designing apparatus of integrated circuit, optimizing designing method of integrated circuit, and storing medium in which program for carrying out optimizing designing method of integrated circuit is stored

ActiveUS7155685B2Easy to carryAnalogue computers for electric apparatusSemiconductor/solid-state device manufacturingLinear regionRegion analysis

It is an object of the present invention to provide a method, an apparatus and a program having high optimization precision and capable of obtaining an answer required by a designer in a short time by combining optimization between individual transistors and optimization as the entire circuit, or by appropriately combining judgment of an operation region, an analysis of the operation region and a SWEEP sensitivity analysis when the optimization is carried out. An optimizing designing apparatus of an integrated circuit for designing a circuit, comprises operation region judging means for adjusting an operation region (linear region, saturation region) of the circuit, operation region analysis means for displaying liner characteristics (Ids-Vgs characteristics) of the circuit and saturation characteristics (Ids-Vds characteristics) of the circuit, and SWEEP sensitivity analysis means for displaying variation in output characteristics of the circuit.

Owner:ABLIC INC

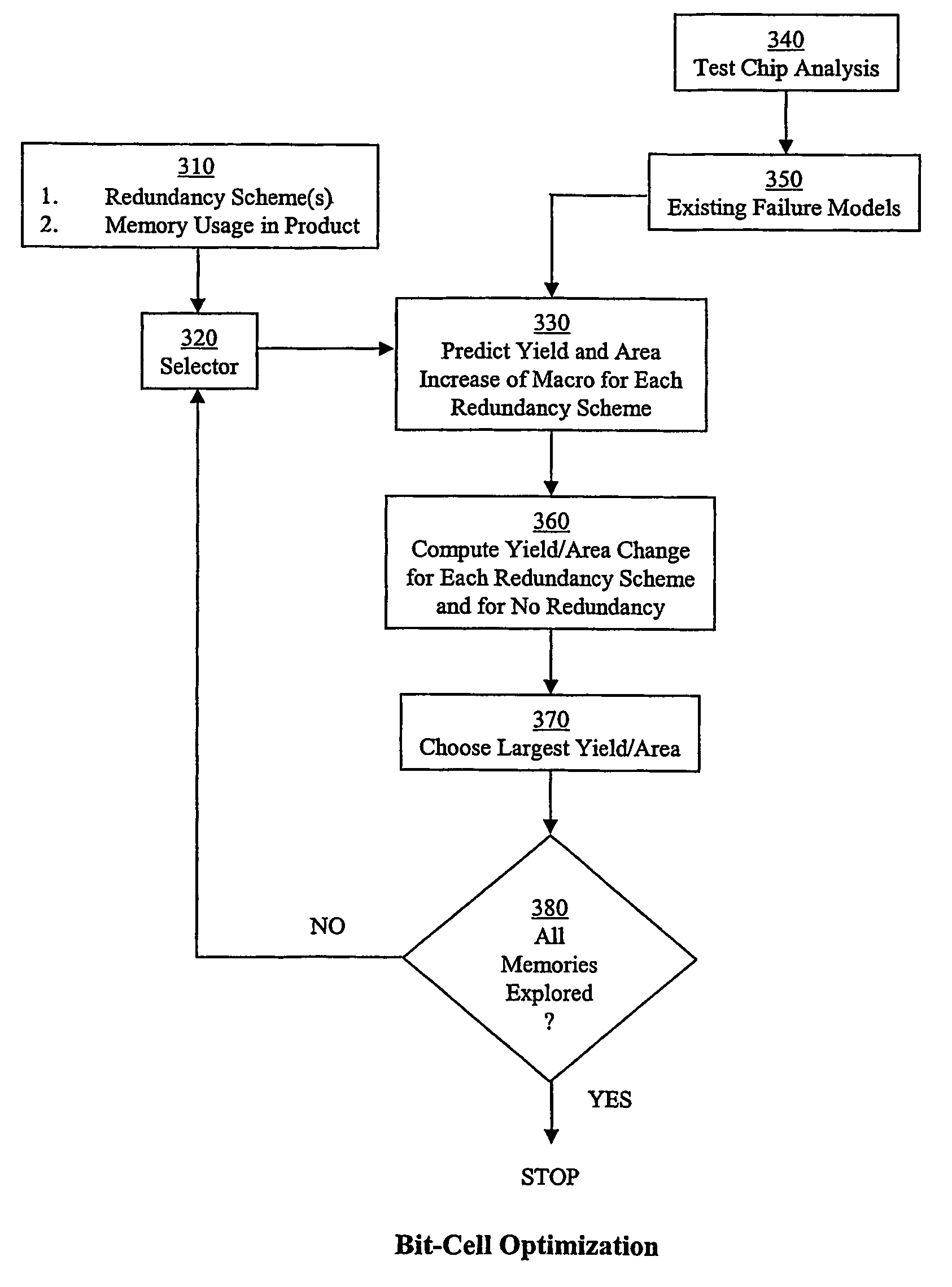

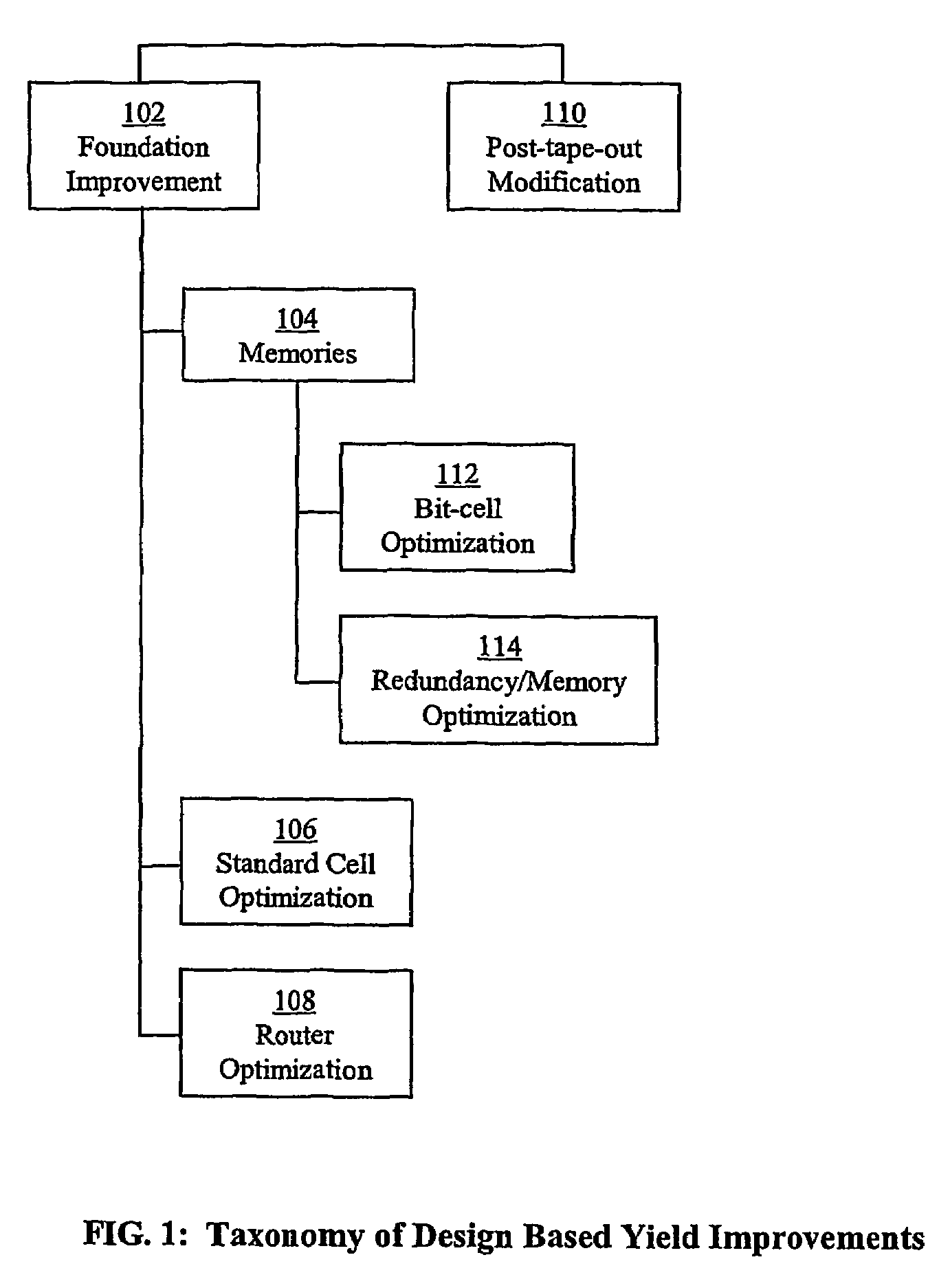

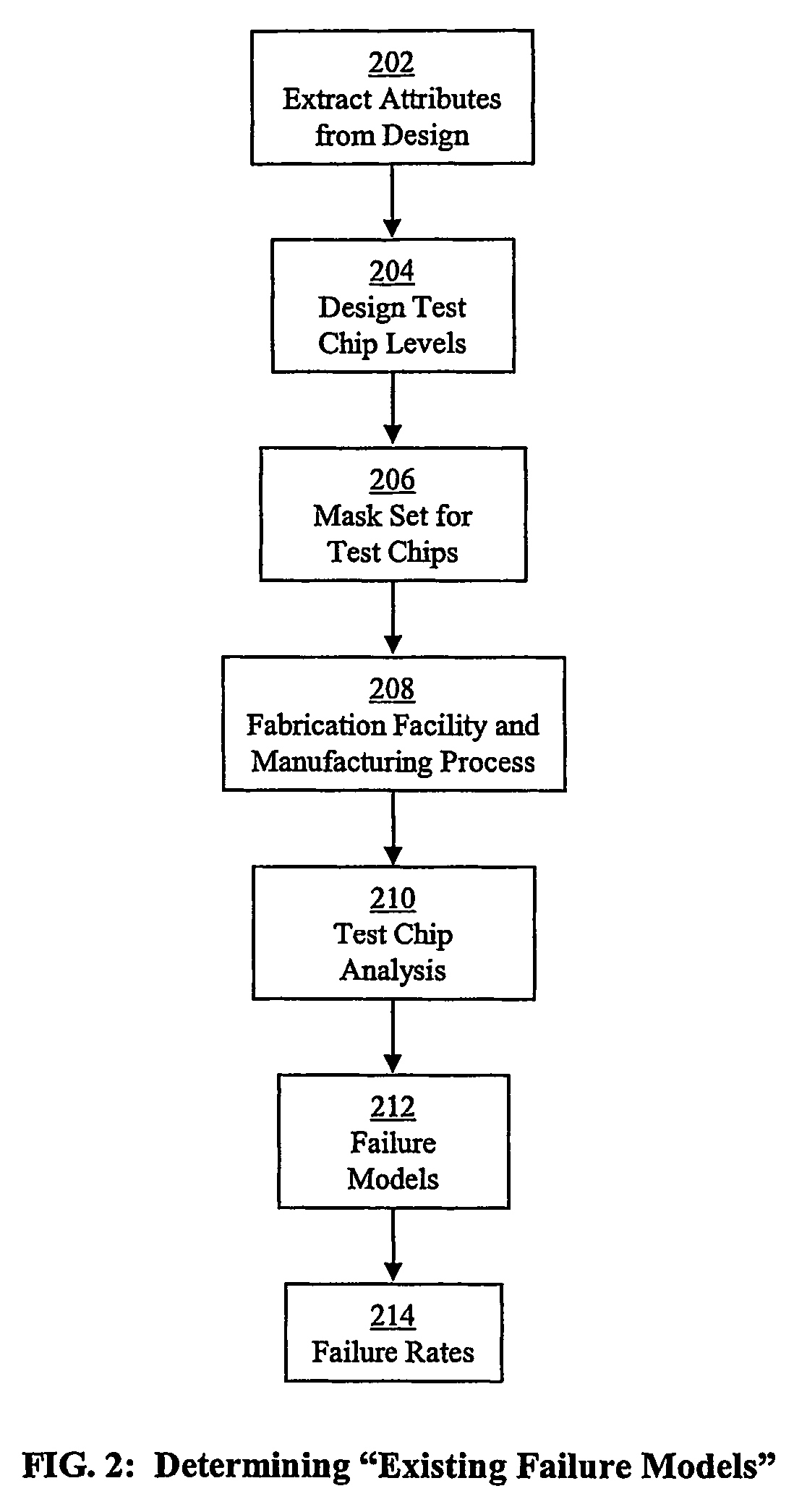

Designing an integrated circuit to improve yield using a variant design element

InactiveUS7487474B2Minimizes and eliminates relianceHigh yieldElectrical apparatusCAD circuit designIntegrated circuit layoutEngineering

An integrated circuit is designed to improve yield when manufacturing the integrated circuit, by obtaining a design element from a set of design elements used in designing integrated circuits. A variant design element is created based on the obtained design element, where a feature of the obtained design element is modified to create the variant design element. A yield to area ratio for the variant design element is determined. If the yield to area ratio of the variant design element is greater than a yield to area ratio of the obtained design element, the variant design element is retained to be used in designing the integrated circuit.

Owner:PDF SOLUTIONS INC

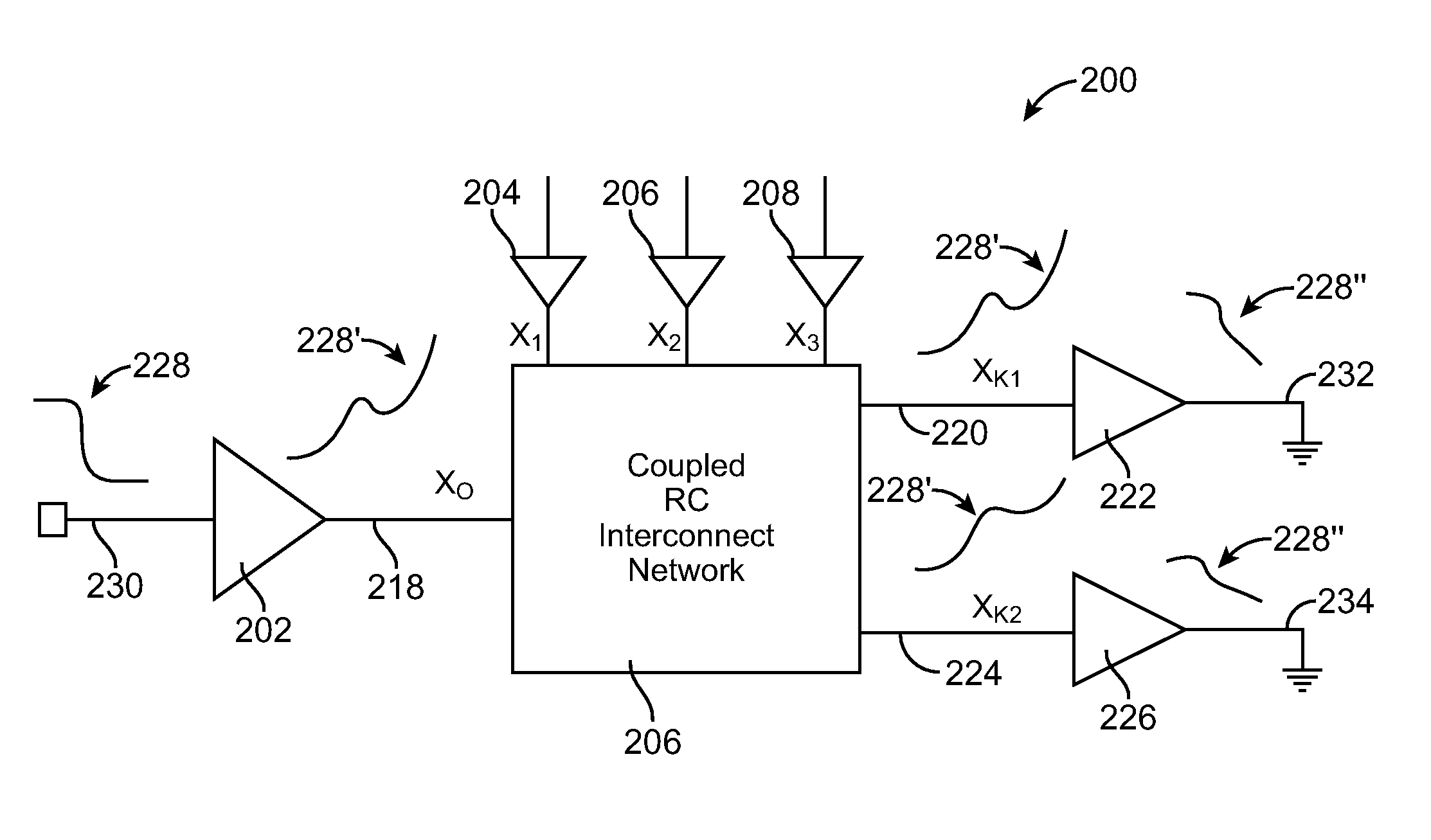

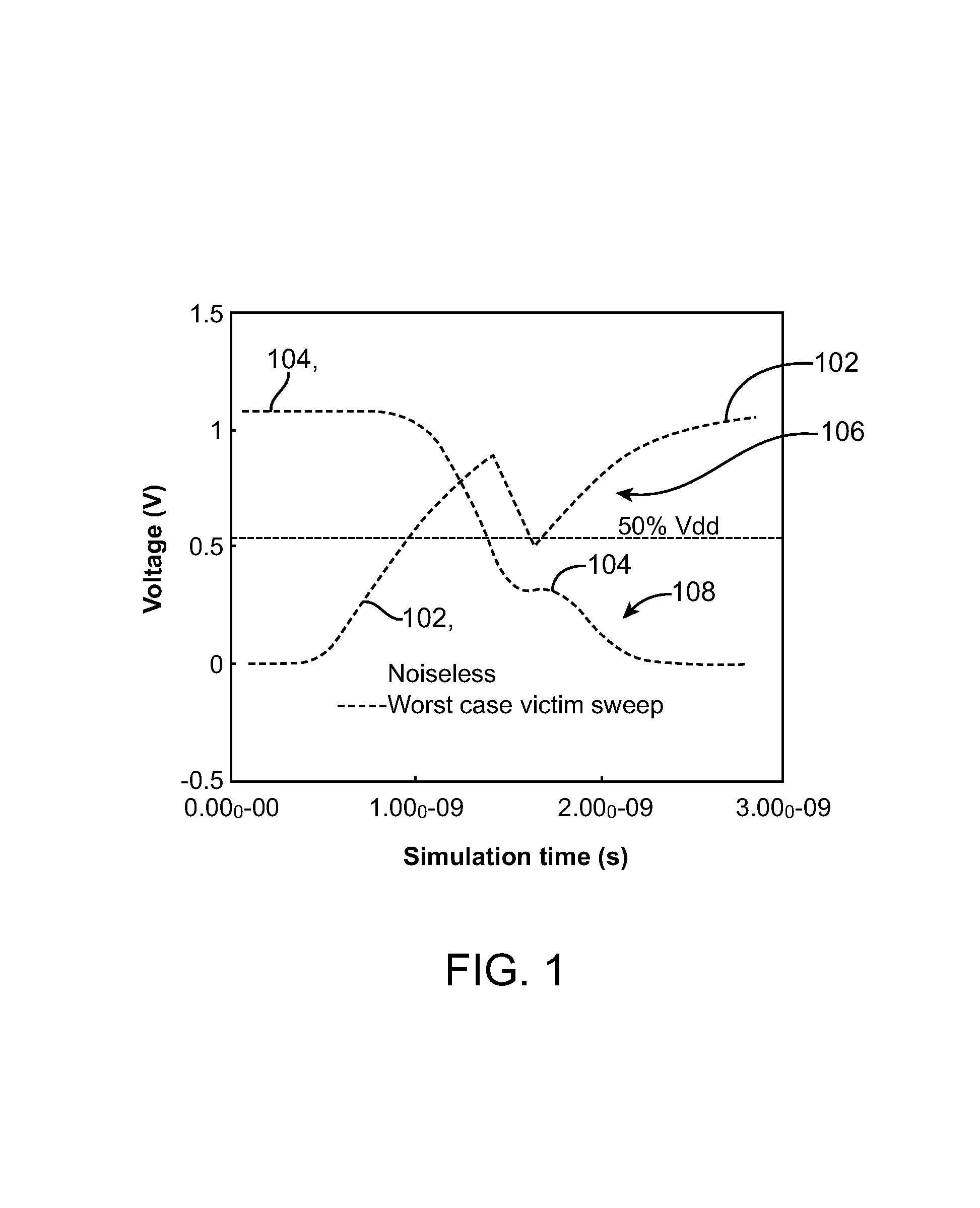

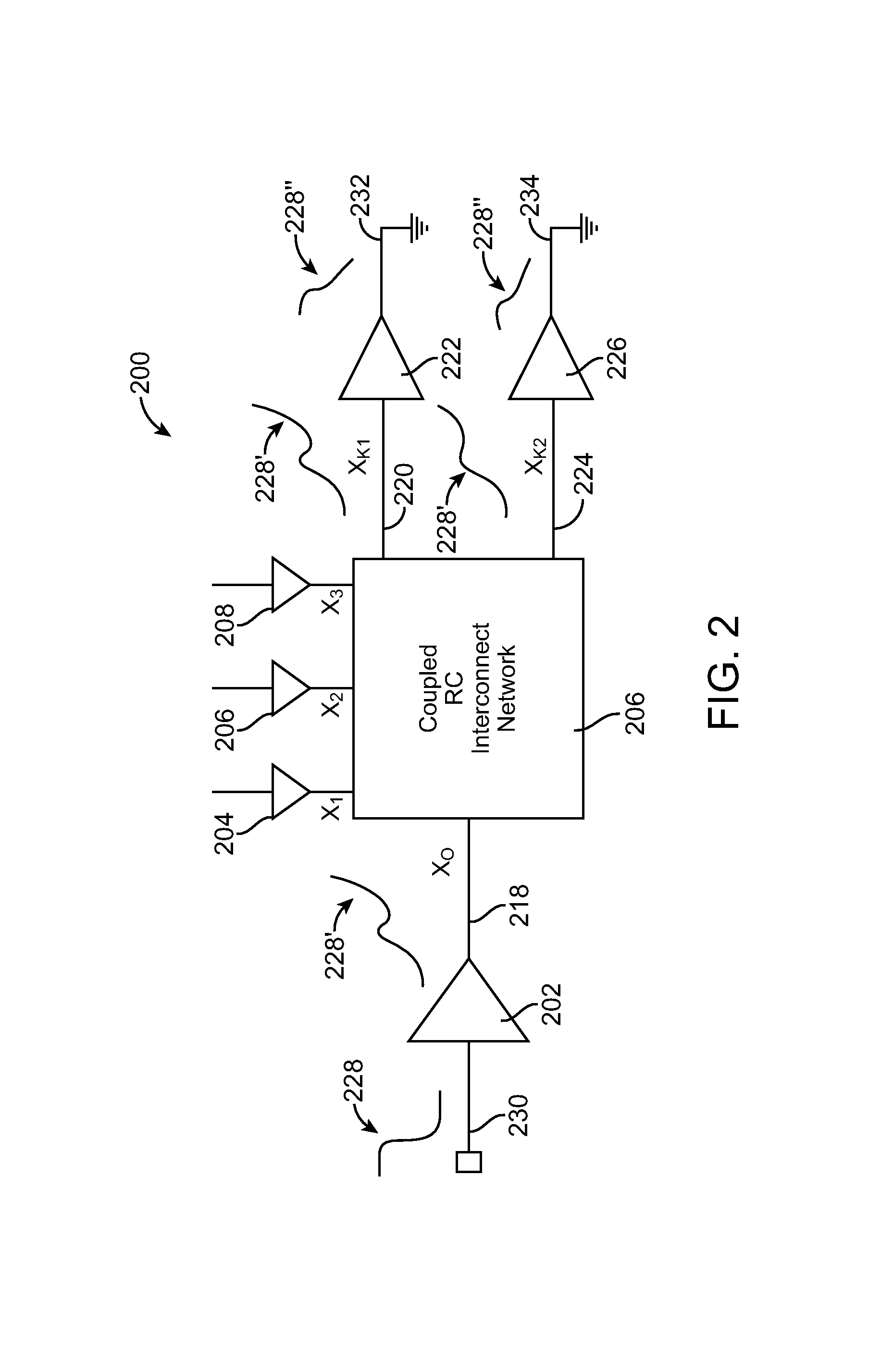

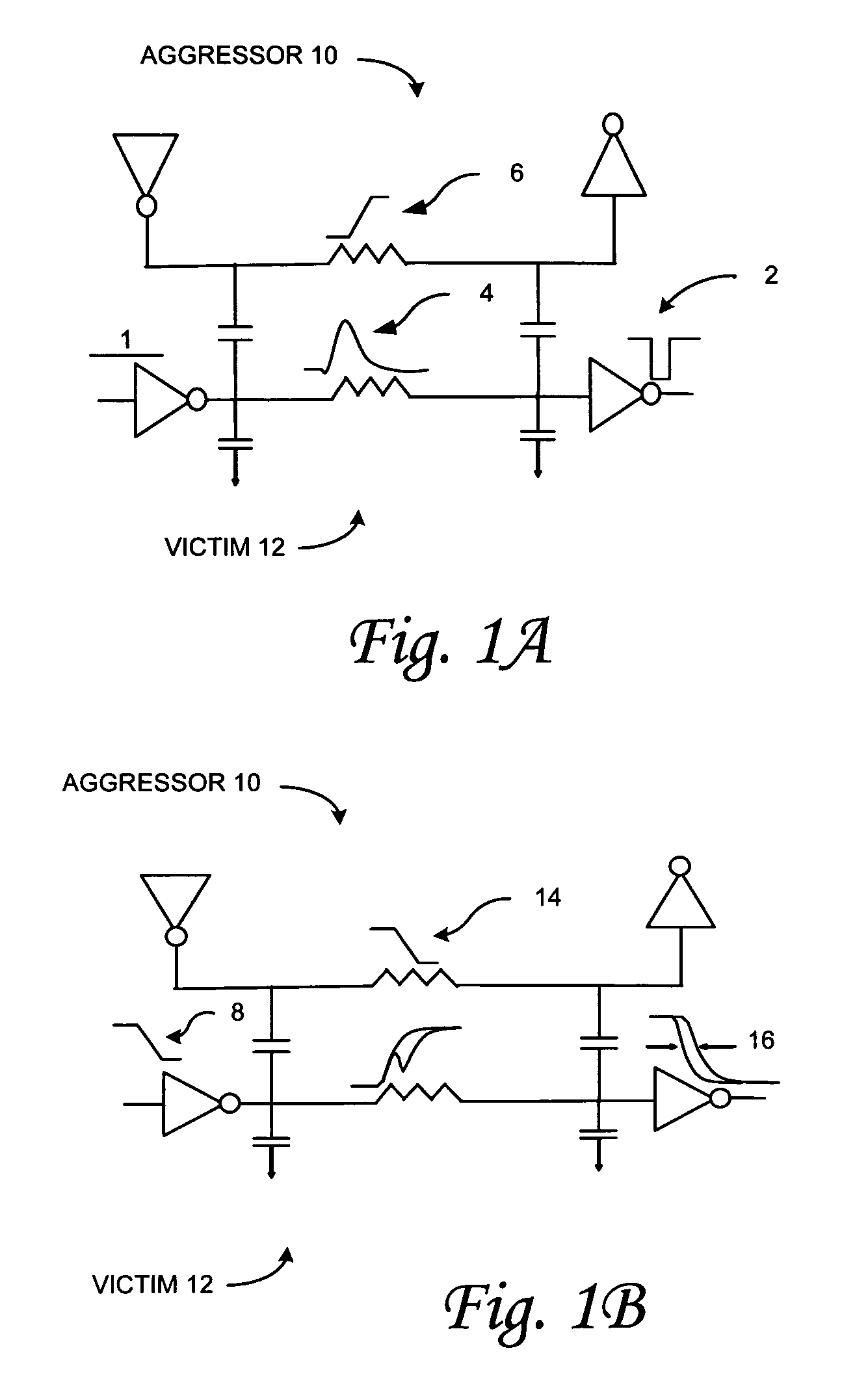

Robust calculation of crosstalk delay change in integrated circuit design

ActiveUS7359843B1Robust delay change determinationAccurate accountingComputation using non-denominational number representationComputer aided designCapacitanceCapacitive coupling

A method of delay change determination in an integrated circuit design including a stage with a victim net and one or more aggressor nets capacitively coupled thereto, the method comprising: determining a nominal (noiseless) victim net signal transition; determining a noisy victim net signal transition; and determining a delay change based upon nominal and noisy victim signal transition arrival times at a victim net receiver output.

Owner:CADENCE DESIGN SYST INC

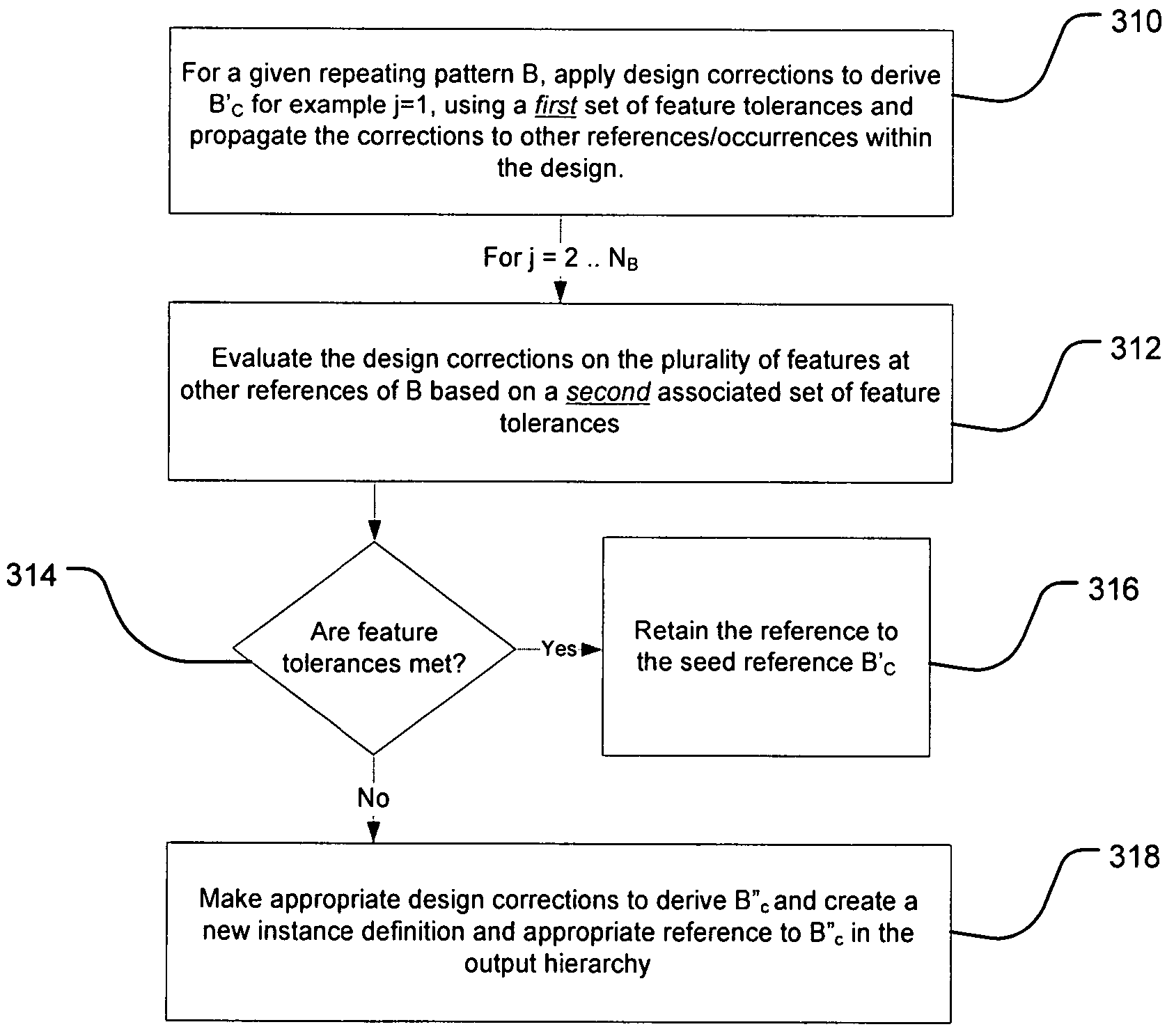

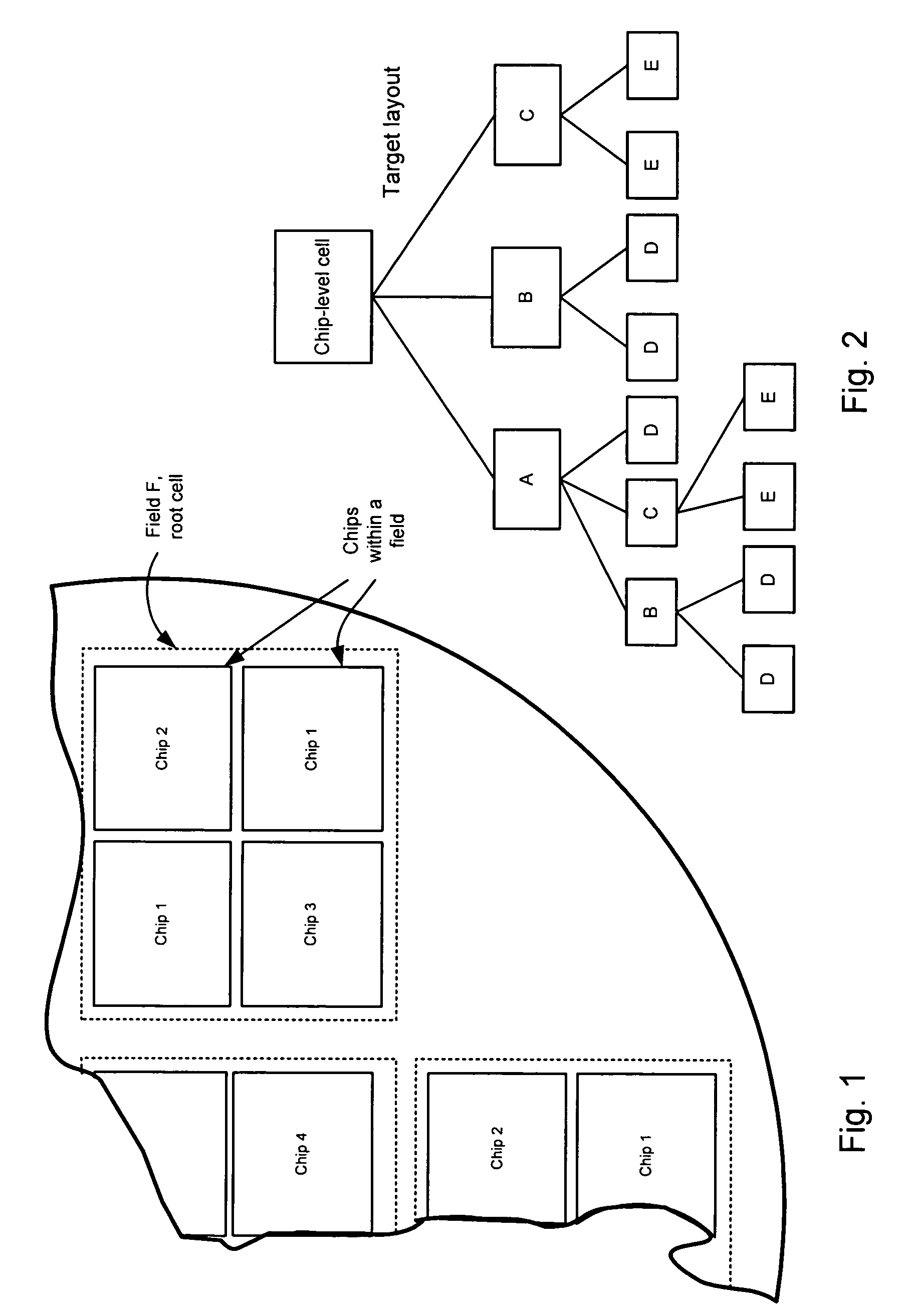

Method and system for managing design corrections for optical and process effects based on feature tolerances

ActiveUS7337421B2CAD circuit designSpecial data processing applicationsApplying knowledgeLithographic artist

Owner:CADENCE DESIGN SYST INC

Integrated circuits with dummy contacts and methods for producing such integrated circuits

InactiveUS20150171008A1Reducing density variationReduce variationSemiconductor/solid-state device detailsSolid-state devicesDielectricElectrical connection

Integrated circuits with dummy contacts and methods for fabricating such integrated circuits are provided. The method includes forming an interlayer dielectric overlying an electronic component and a substrate, wherein the interlayer dielectric has an interlayer dielectric top surface. An active contact is formed through the interlayer dielectric and forms an electrical connection with the electronic component. A dummy contact is formed within the interlayer dielectric where the dummy contact extends to a dummy contact termination point between the interlayer dielectric top surface and the substrate such that an insulator is positioned between the dummy contact termination point and the electronic component.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

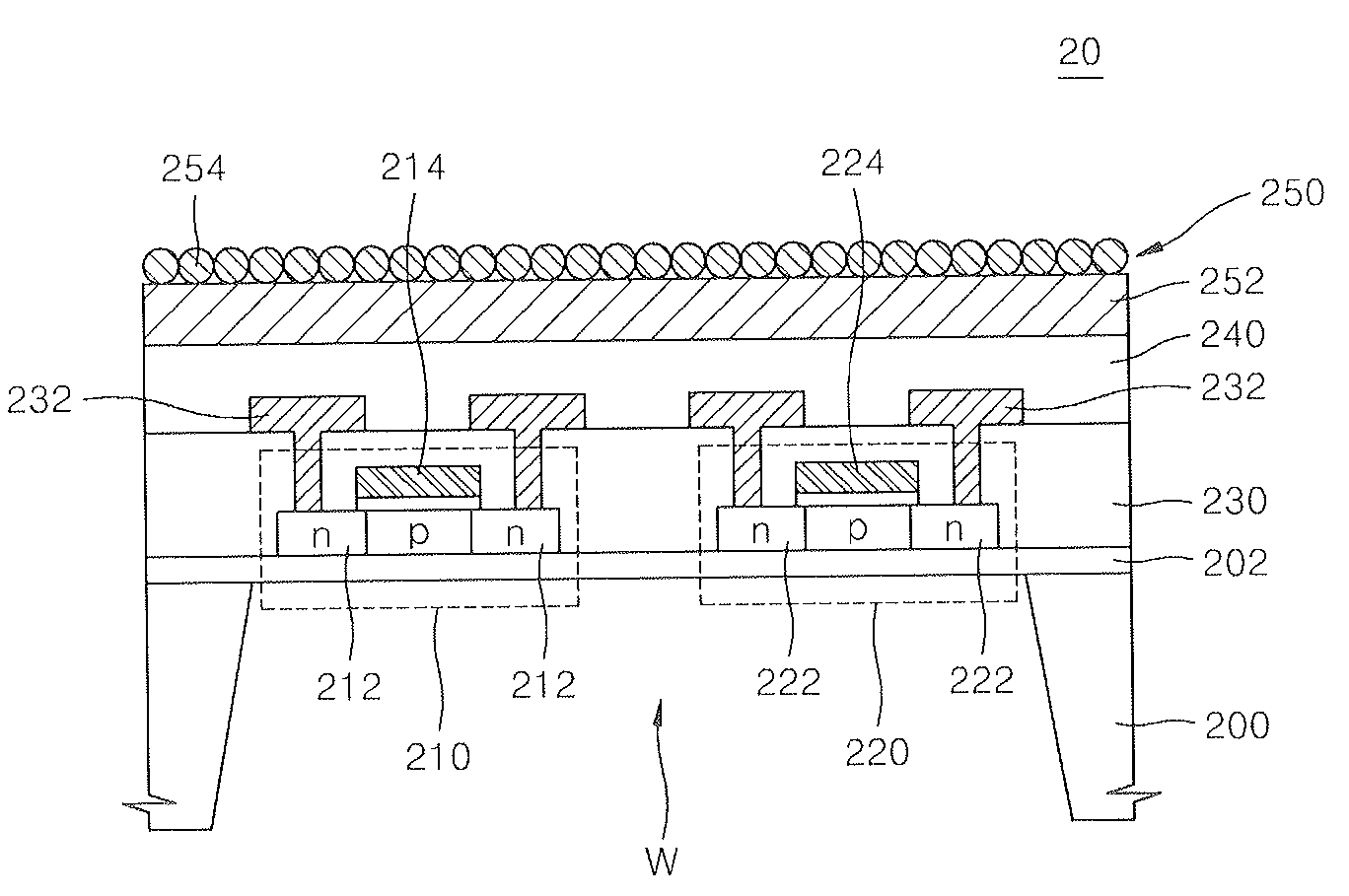

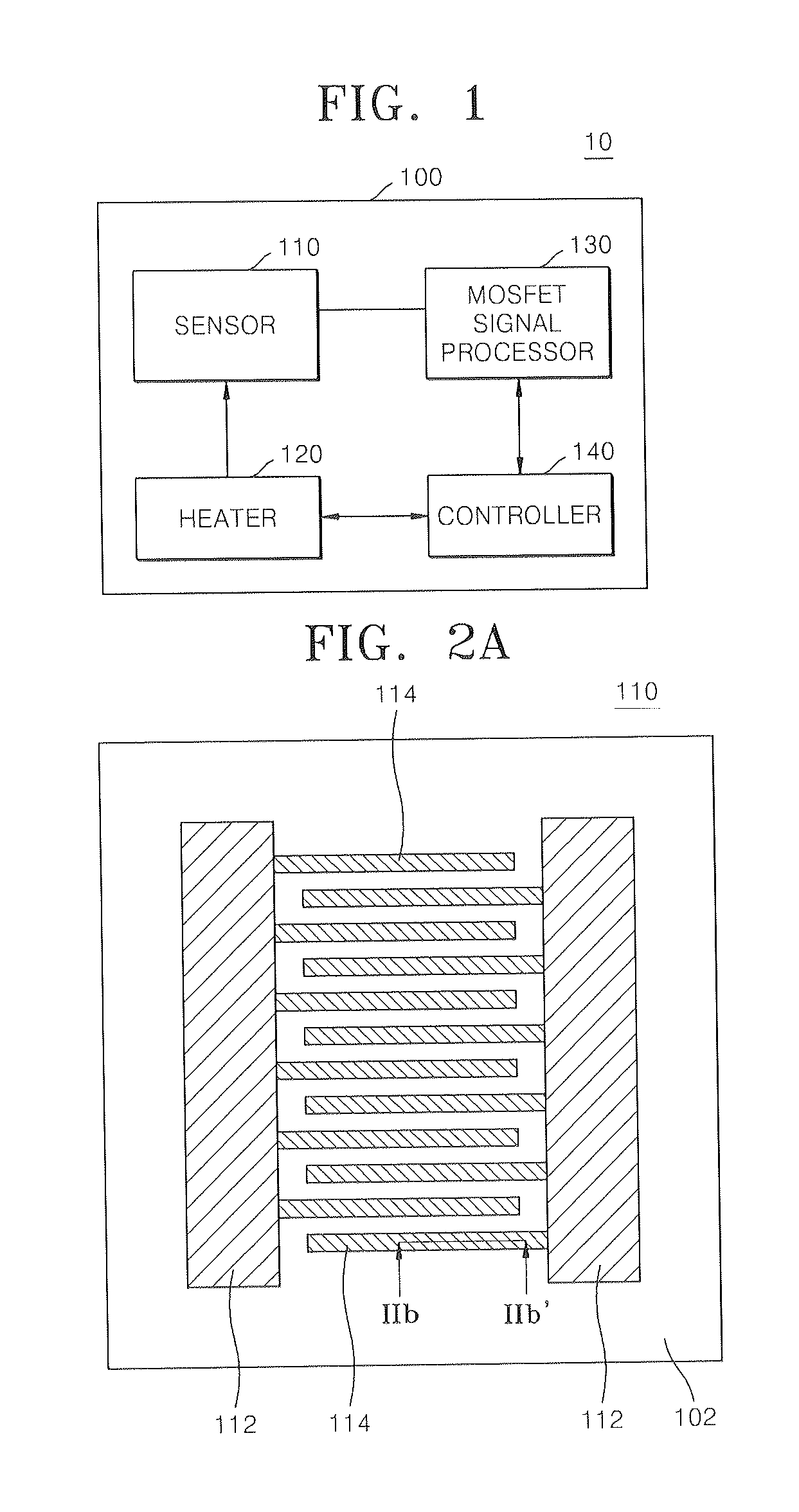

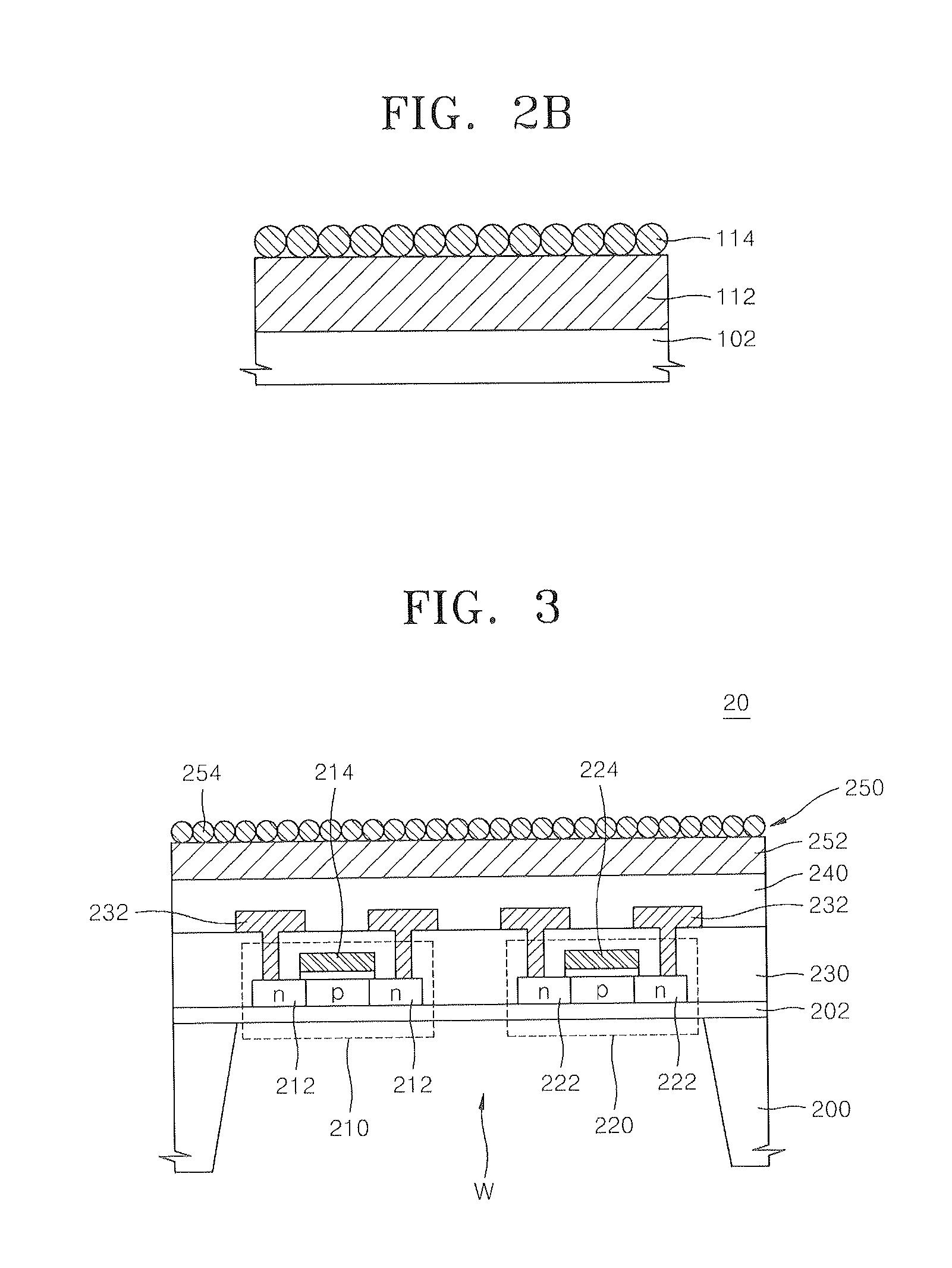

Method of forming sensor for detecting gases and biochemical materials, integrated circuit having the sensor, and method of manufacturing the integrated circuit

InactiveUS20080121946A1Characteristics degradation of an integrated circuit caused by heating the unit devices when forming the sensor can be preventedSemiconductor/solid-state device manufacturingNanosensorsMOSFETNano structuring

A method of forming a sensor for detecting gases and biochemical materials that can be fabricated at a temperature in a range from room temperature to 400° C., a metal oxide semiconductor field effect transistor (MOSFET)-based integrated circuit including the sensor, and a method of manufacturing the integrated circuit are provided. The integrated circuit includes a semiconductor substrate. The sensor for detecting gases and biochemical materials includes a pair of electrodes formed on a first region of the semiconductor substrate, and a metal oxide nano structure layer formed on surfaces of the pair electrodes. A heater is formed to perform thermal treatment to re-use the material detected in the metal oxide nano structure layer. Also, a signal processor is formed by a MOSFET to process a predetermined signal obtained from a quantity change of a current flowing through the pair of electrodes of the sensor. To form the sensor, the metal oxide nano structure layer is formed on surfaces of the pair of electrodes at a temperature in a range from room temperature to 400° C.

Owner:ELECTRONICS & TELECOMM RES INST

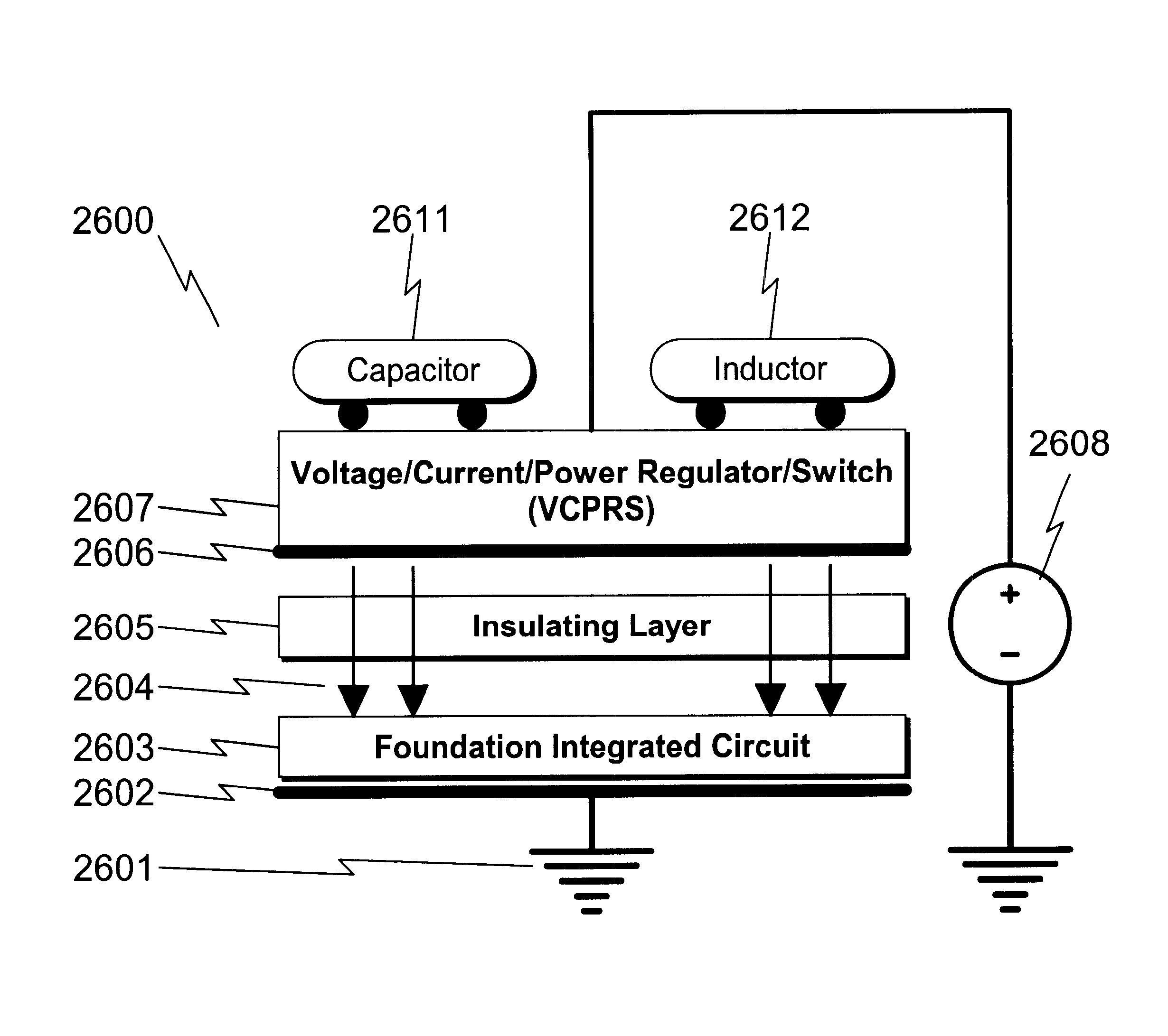

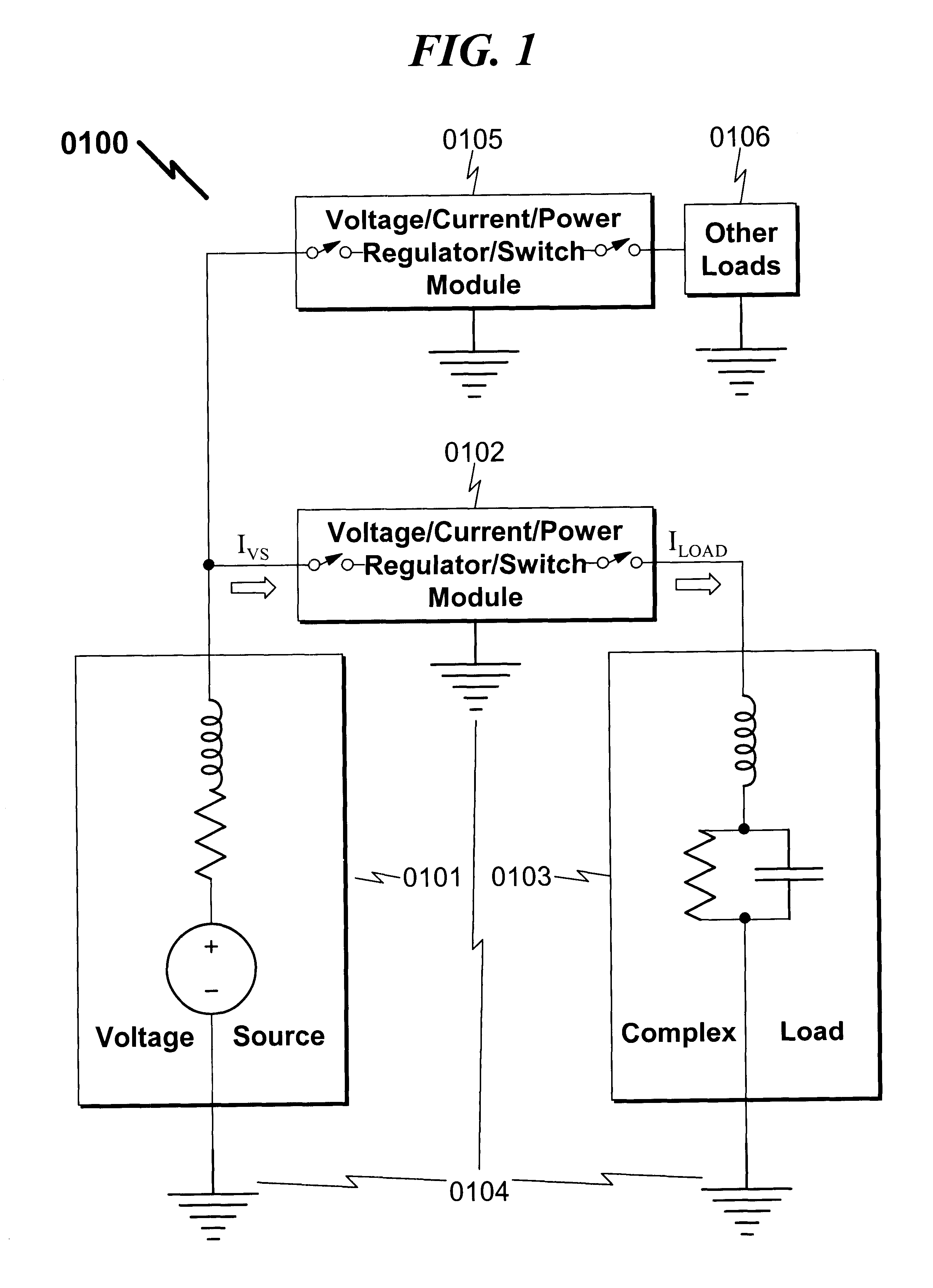

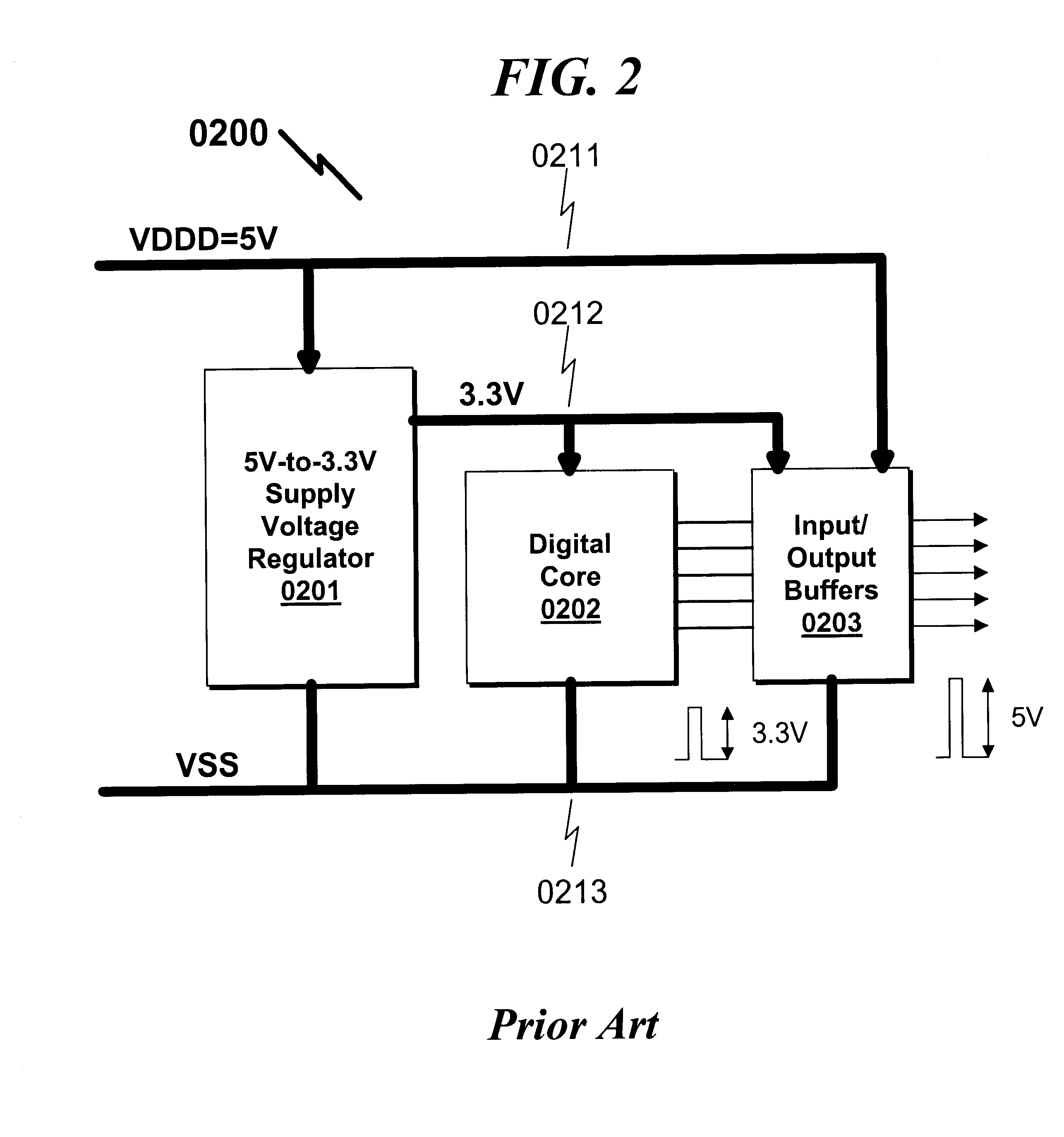

Integrated voltage/current/power regulator/switch system and method

InactiveUS6396137B1Minimal noiseGood PSRRSemiconductor/solid-state device detailsDc-dc conversionPower applicationPower capability

An integrated voltage / current / power regulator / switch (VCPRS) system and method are disclosed in which regulator / switch circuitry is vertically integrated on top of an existing integrated circuit. The present invention does not require additional integrated circuit chip area for the regulator pass device as is required in the prior art, and by virtue of its construction provides a significantly reduced on-resistance as compared to all prior art implementations. The present invention both stabilizes the power supply for large area integrated circuits and permits individual areas of the integrated circuit to have switched power capability, a highly desirable feature in low power and battery power applications. The present invention permits an increase in the power supply rejection ratio (PSRR) for digital, analog, and especially mixed-signal integrated circuit designs by permitting various circuit blocks to have localized power regulation that is obtained from a common power supply plane within the integrated circuit framework. Finally, the present invention appears to be the only economically practical method of addressing the power supply regulation requirements of modern and future integrated microprocessor designs.

Owner:KLUGHART KEVIN MARK

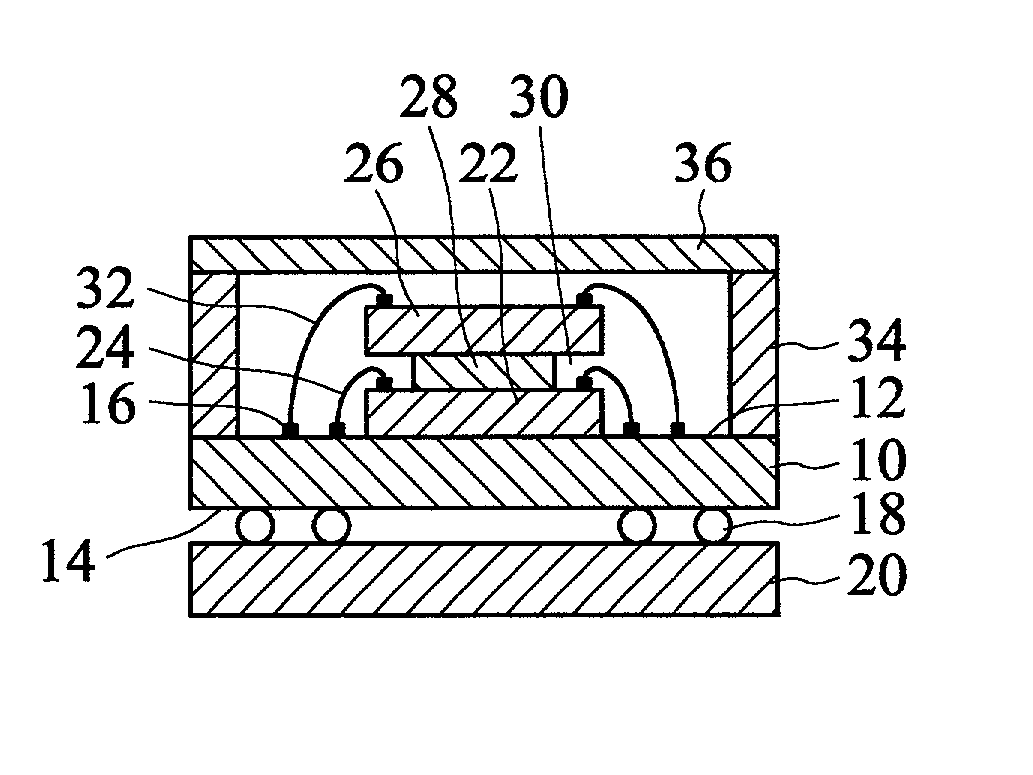

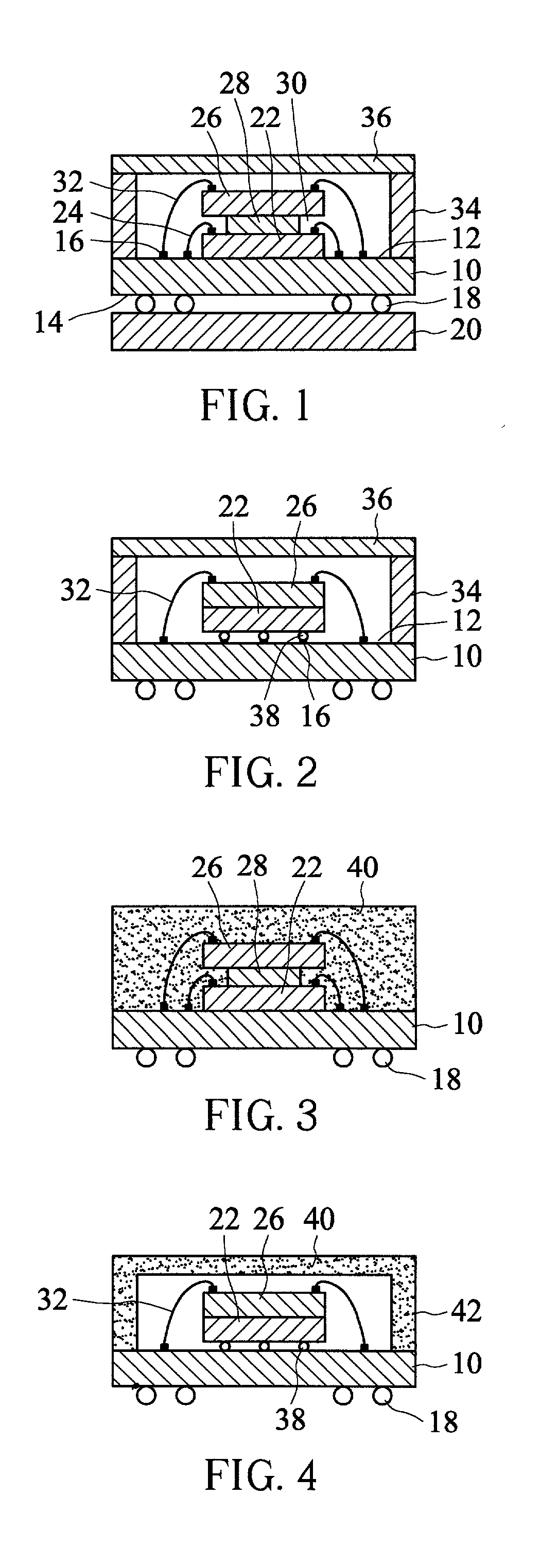

Stacked package structure of image sensor

InactiveUS20020096729A1Solid-state devicesSemiconductor/solid-state device manufacturingImage signalPrinted circuit board

A stacked package structure of an image sensor for electrically connecting to a printed circuit board includes a substrate, an integrated circuit, an image sensing chip, and a transparent layer. The substrate has a first surface and a second surface opposite to the first surface. The first surface is formed with signal input terminals. The second surface is formed with signal output terminals for electrically connecting the substrate to the printed circuit board. The integrated circuit is mounted on the first surface of the substrate and electrically connected to the signal input terminals of the substrate. The image sensing chip is located above the integrated circuit to form a stacked structure with the integrated circuit for electrically connecting to the signal input terminals of the substrate. The transparent layer covers the image sensing chip. The image sensing chip receives image signals via the transparent layer and converts the image signals into electrical signals that are to be transmitted to the substrate. Thus, the image sensing chip of the image sensing product and the integrated circuit can be integrally packaged.

Owner:KINGPAK TECH INC

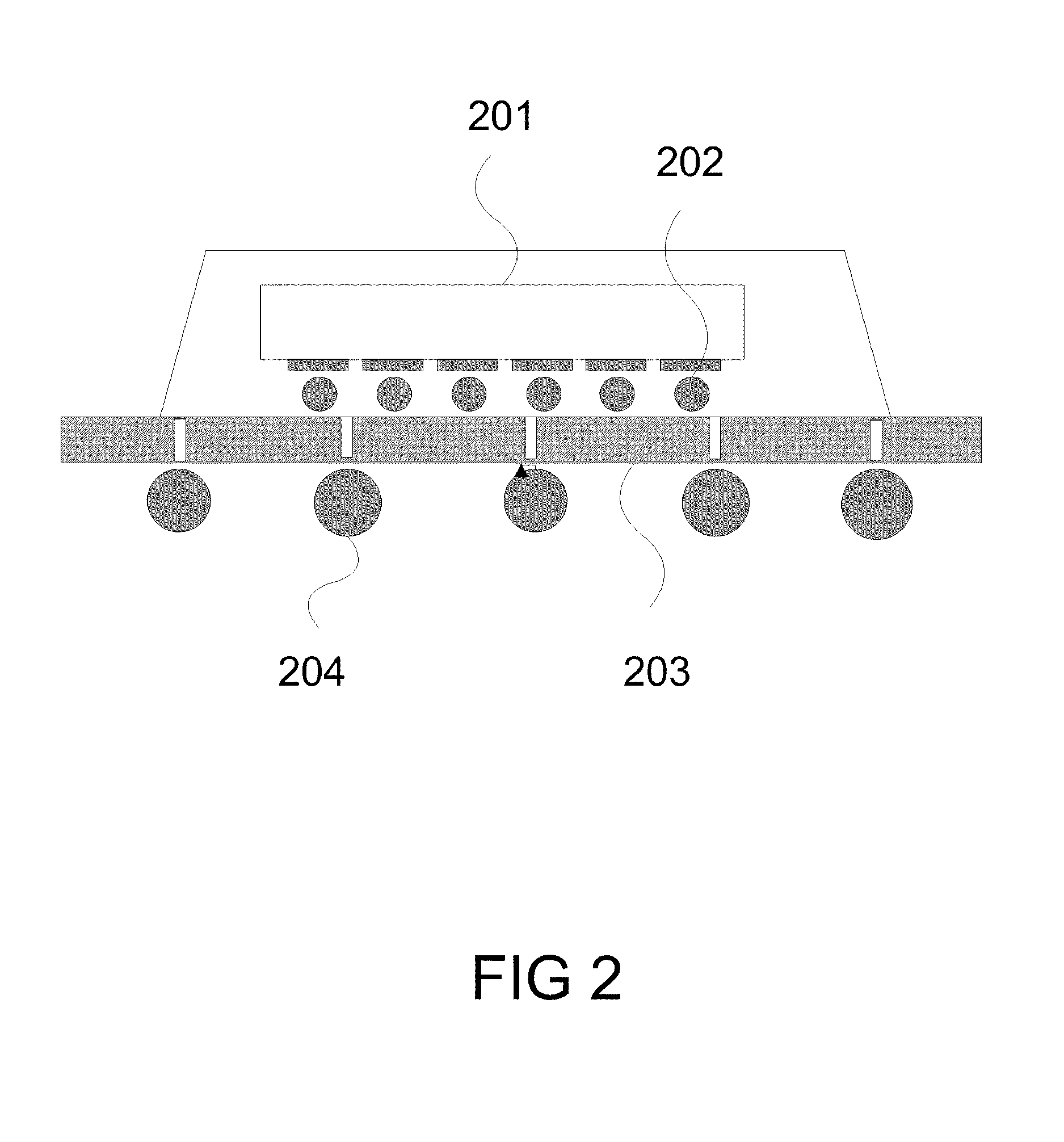

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

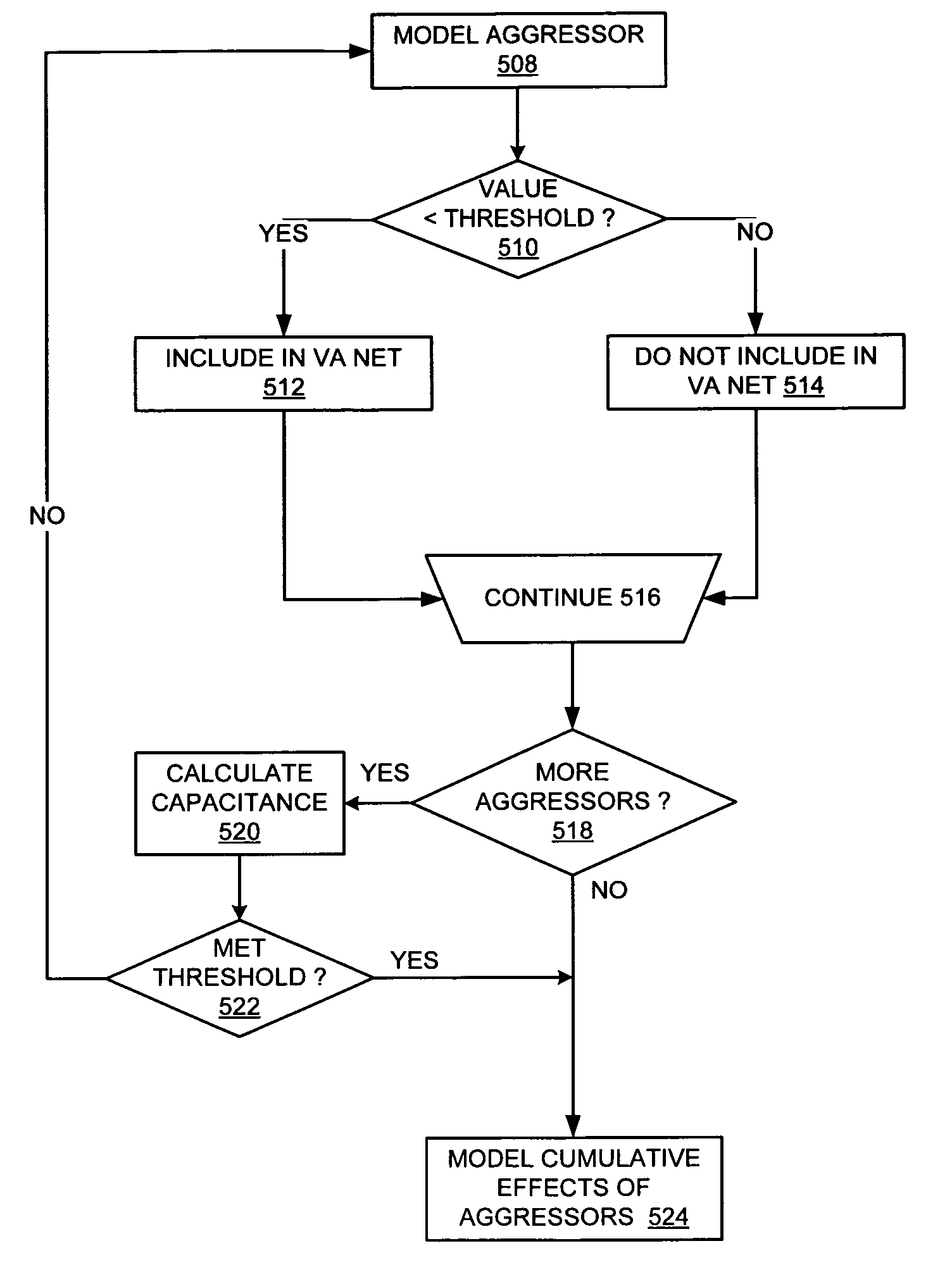

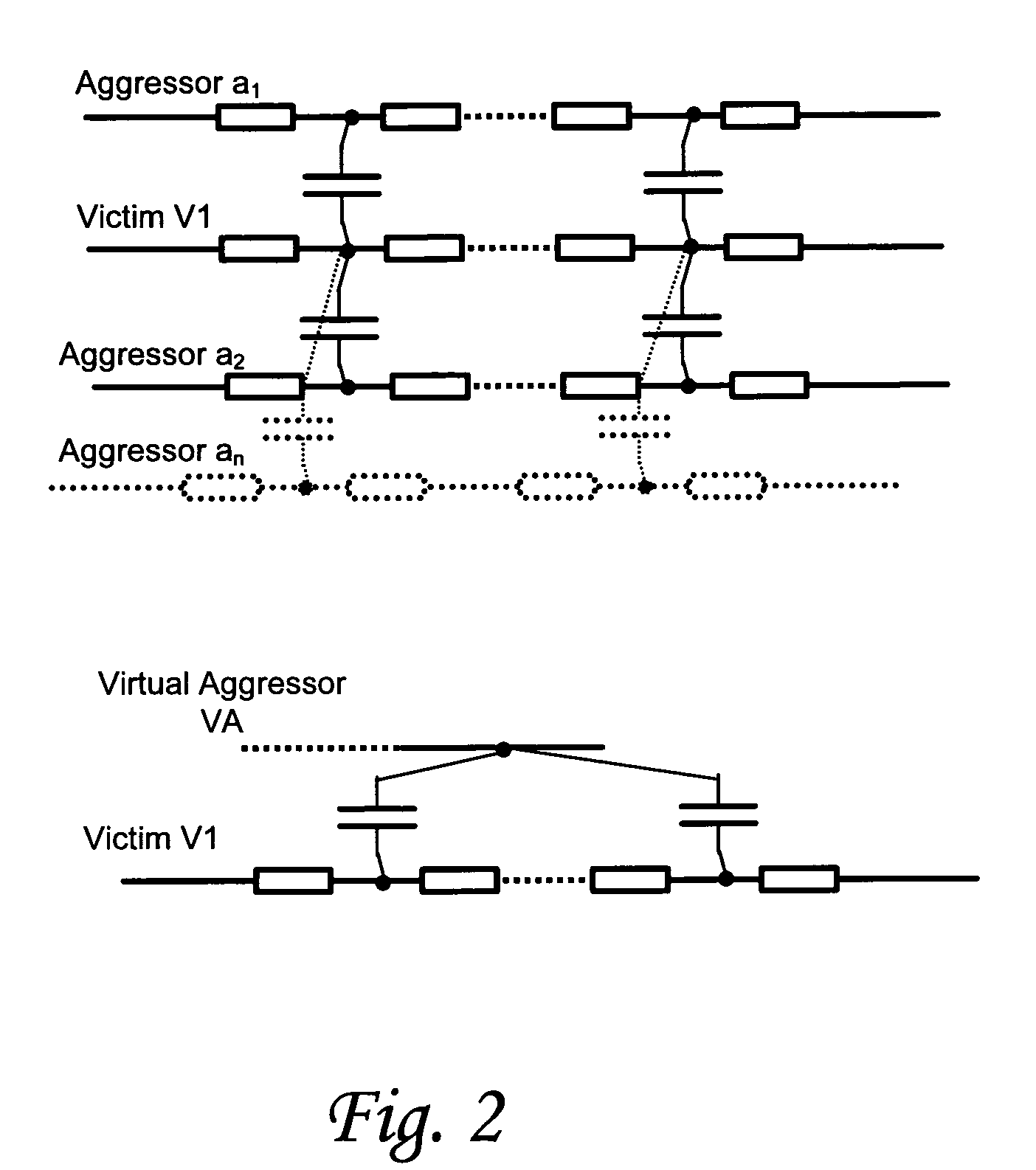

System, method and computer program product for handling small aggressors in signal integrity analysis

ActiveUS7562323B1Computation using non-denominational number representationComputer aided designCapacitanceSignal integrity analysis

A method, system and computer program product for determining aggressor-induced crosstalk in a victim net of a stage of an integrated circuit design is provided. The methodology can include combining a plurality of aggressor nets to construct a virtual aggressor net, determining a current waveform induced on the victim net by the plurality of small aggressor nets, and modeling a current waveform induced by the virtual aggressor on the victim net based on the contribution of the current waveforms determined for the plurality of small aggressor nets. In a further embodiment, the methodology can also comprise evaluating an effect of an aggressor net on a victim net; and including that aggressor net in the virtual aggressor net if its effect is below a predetermined threshold. The effect evaluated by the methodology can, for example, be the height of a glitch induced on the victim net by a transition in the aggressor net. Additionally, the aggressor net can be included in the virtual aggressor net if the height of the glitch it induces on the victim net is less than a predetermined factor of the supply voltage. Switching probability can be used to compute a 3-sigma capacitance value, and this value can be used to limit the number of small aggressors included in the virtual aggressor net. The combined currents of the aggressor in the virtual aggressor net can be modeled using a piece-wise linear analysis.

Owner:CADENCE DESIGN SYST INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com