Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30 results about "Signal integrity analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

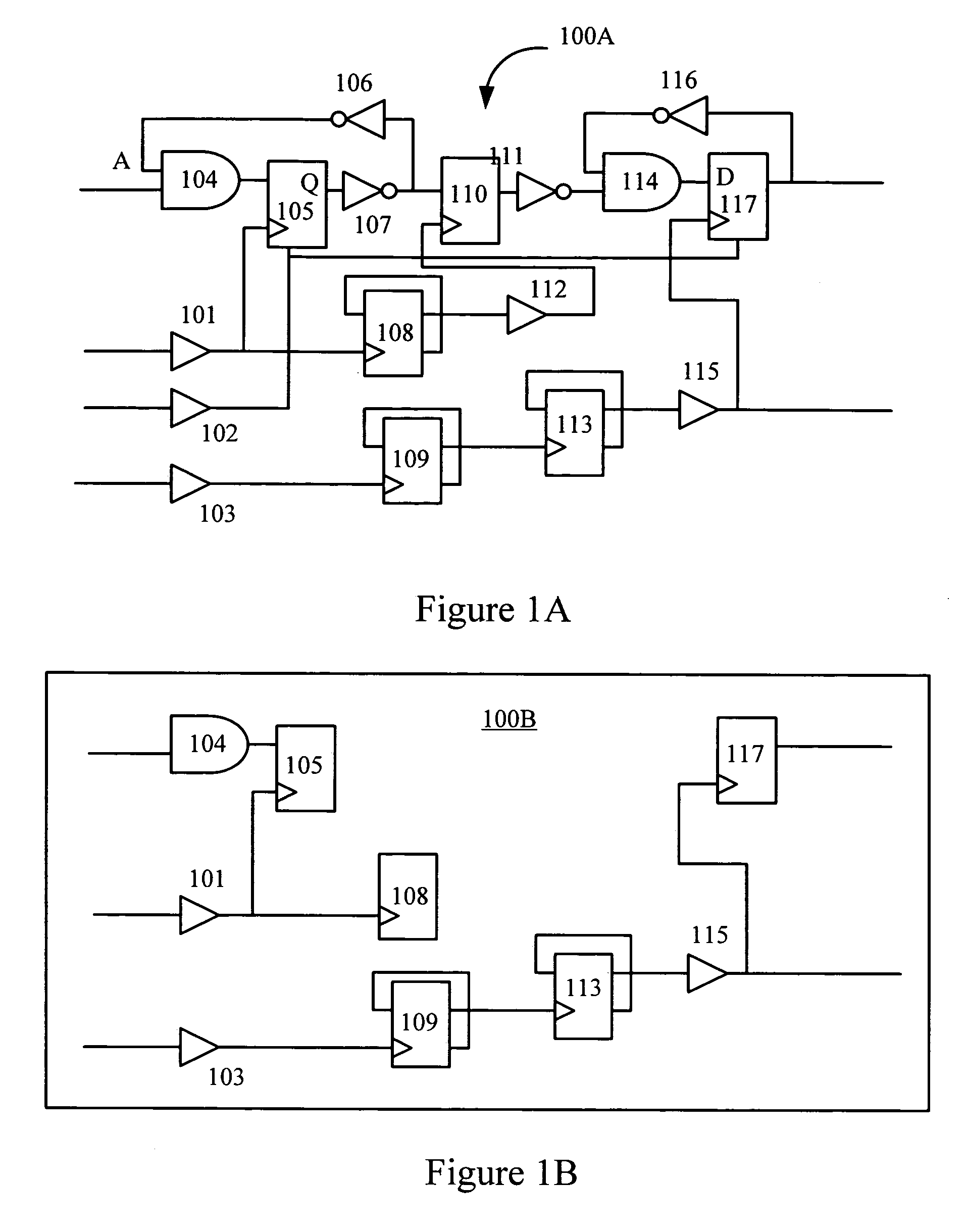

System, method and computer program product for handling small aggressors in signal integrity analysis

ActiveUS7562323B1Computation using non-denominational number representationComputer aided designCapacitanceSignal integrity analysis

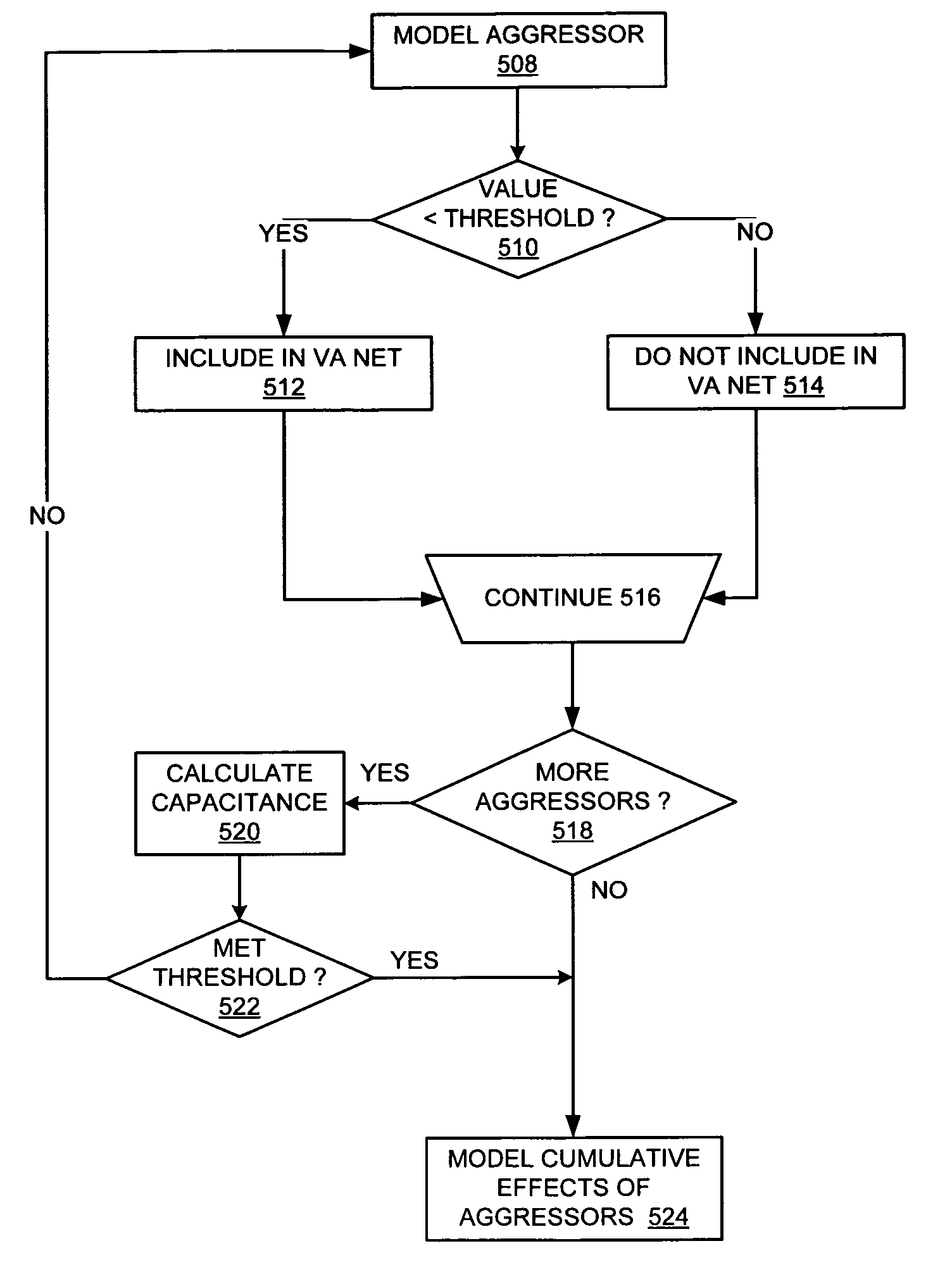

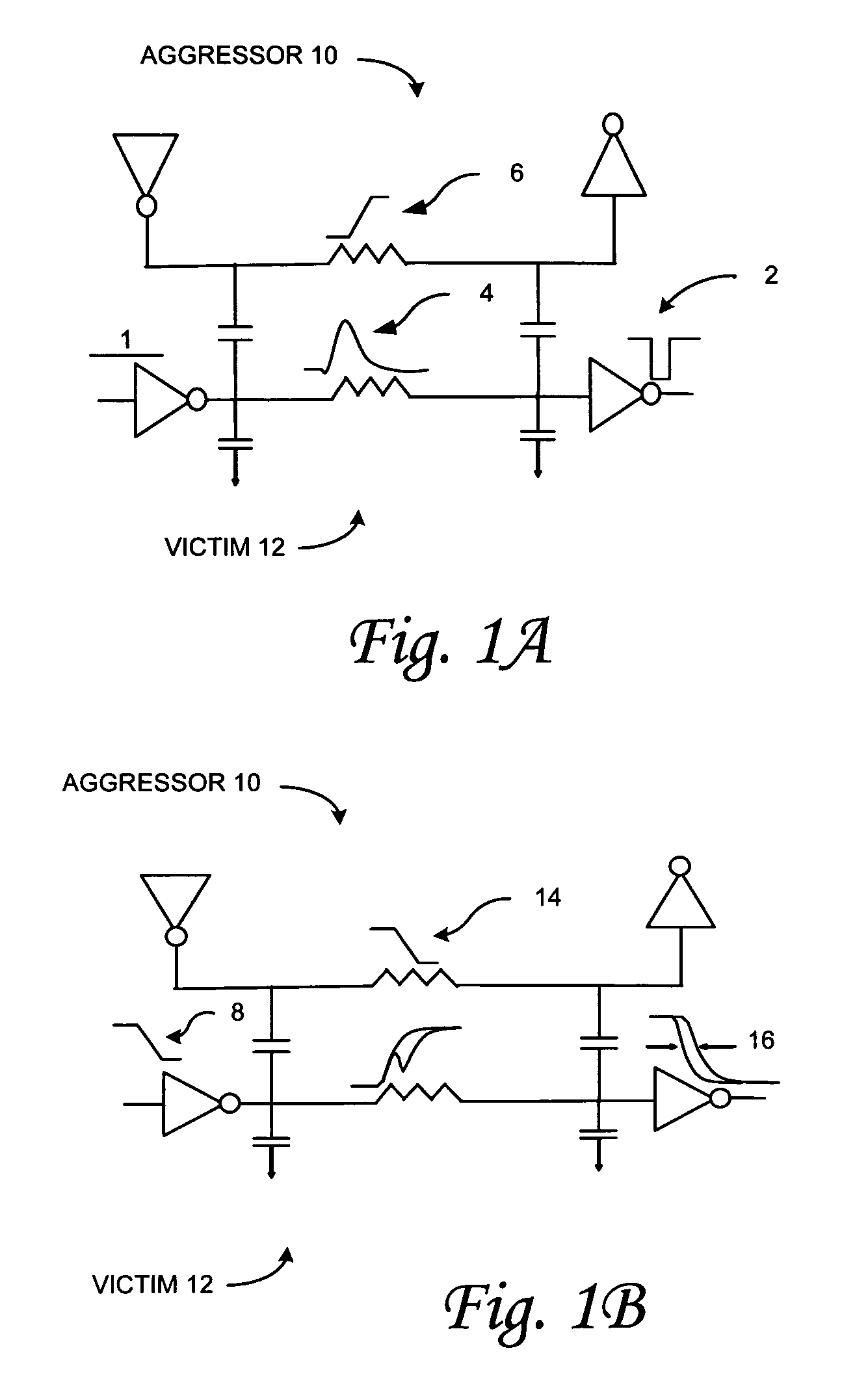

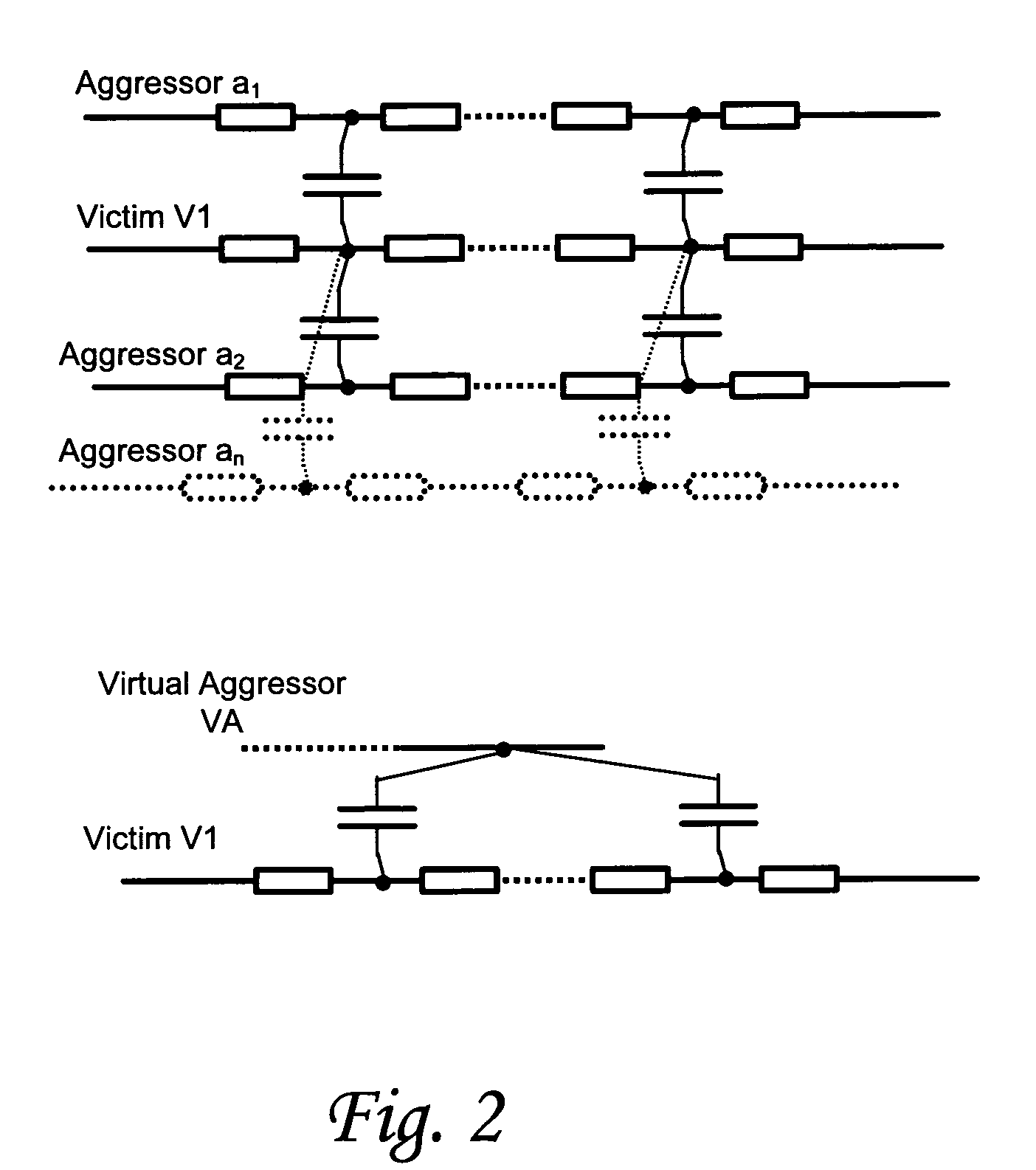

A method, system and computer program product for determining aggressor-induced crosstalk in a victim net of a stage of an integrated circuit design is provided. The methodology can include combining a plurality of aggressor nets to construct a virtual aggressor net, determining a current waveform induced on the victim net by the plurality of small aggressor nets, and modeling a current waveform induced by the virtual aggressor on the victim net based on the contribution of the current waveforms determined for the plurality of small aggressor nets. In a further embodiment, the methodology can also comprise evaluating an effect of an aggressor net on a victim net; and including that aggressor net in the virtual aggressor net if its effect is below a predetermined threshold. The effect evaluated by the methodology can, for example, be the height of a glitch induced on the victim net by a transition in the aggressor net. Additionally, the aggressor net can be included in the virtual aggressor net if the height of the glitch it induces on the victim net is less than a predetermined factor of the supply voltage. Switching probability can be used to compute a 3-sigma capacitance value, and this value can be used to limit the number of small aggressors included in the virtual aggressor net. The combined currents of the aggressor in the virtual aggressor net can be modeled using a piece-wise linear analysis.

Owner:CADENCE DESIGN SYST INC

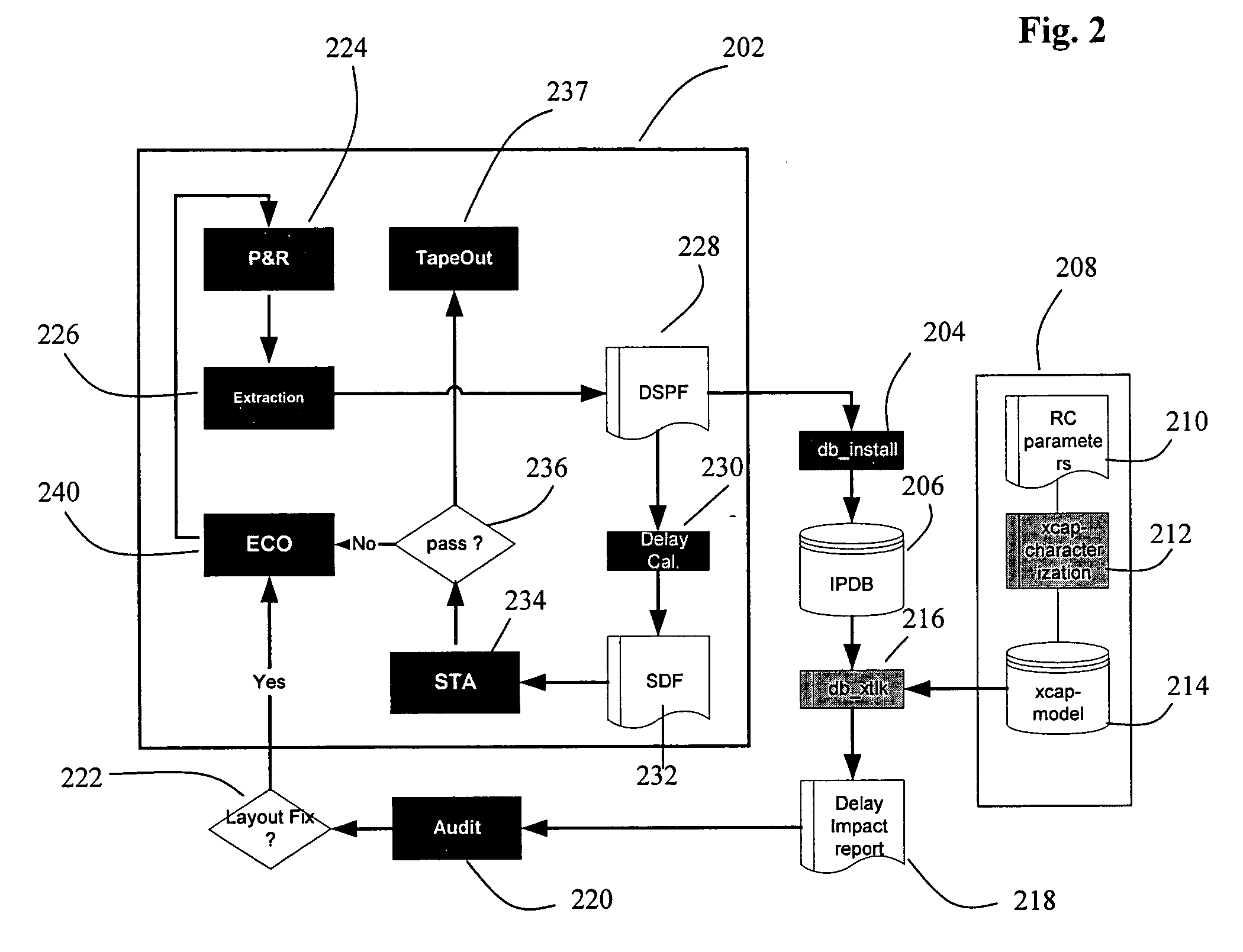

Method and system for performing crosstalk analysis

InactiveUS7549134B1Computer aided designSoftware simulation/interpretation/emulationCapacitanceSignal integrity analysis

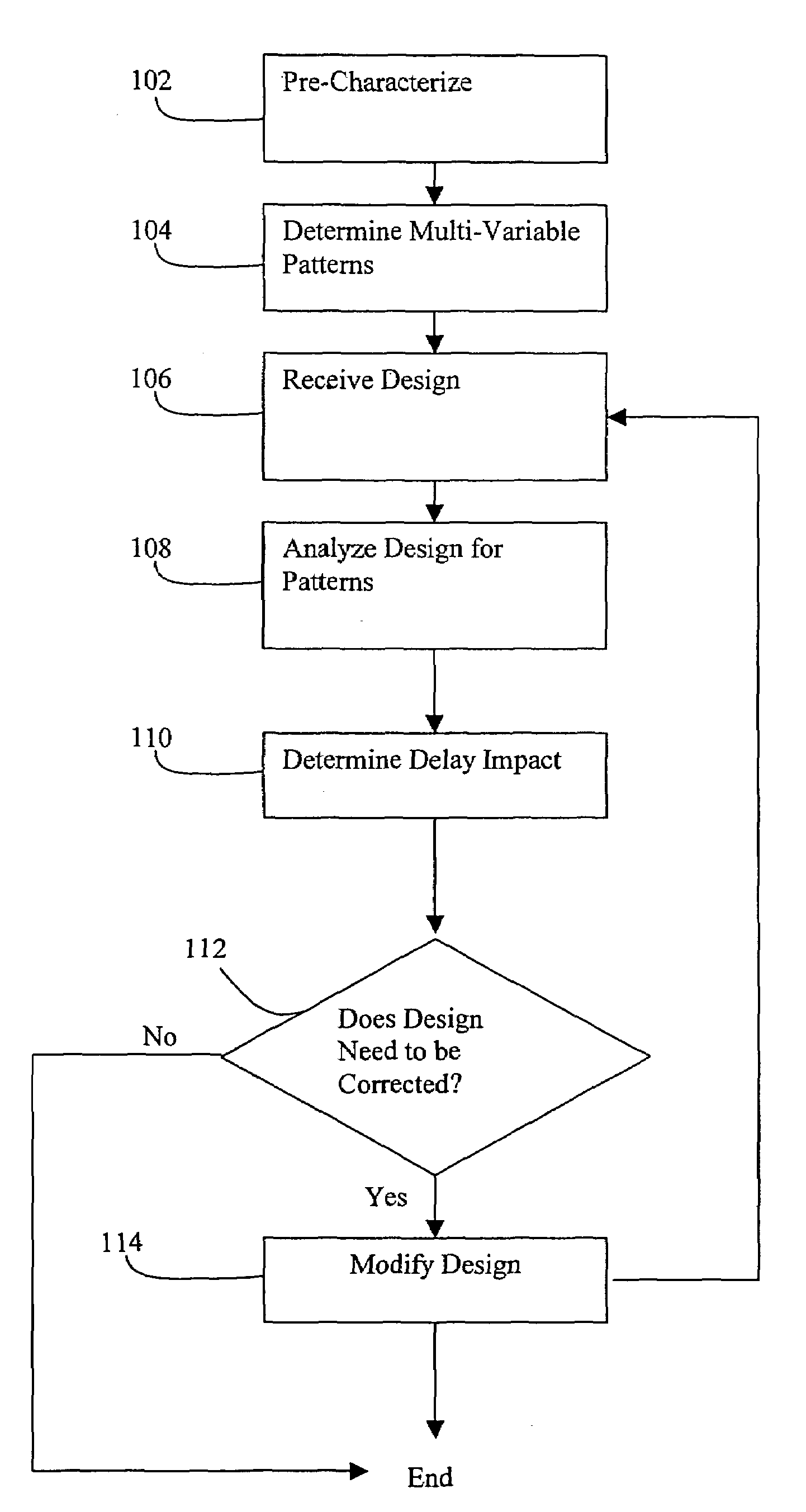

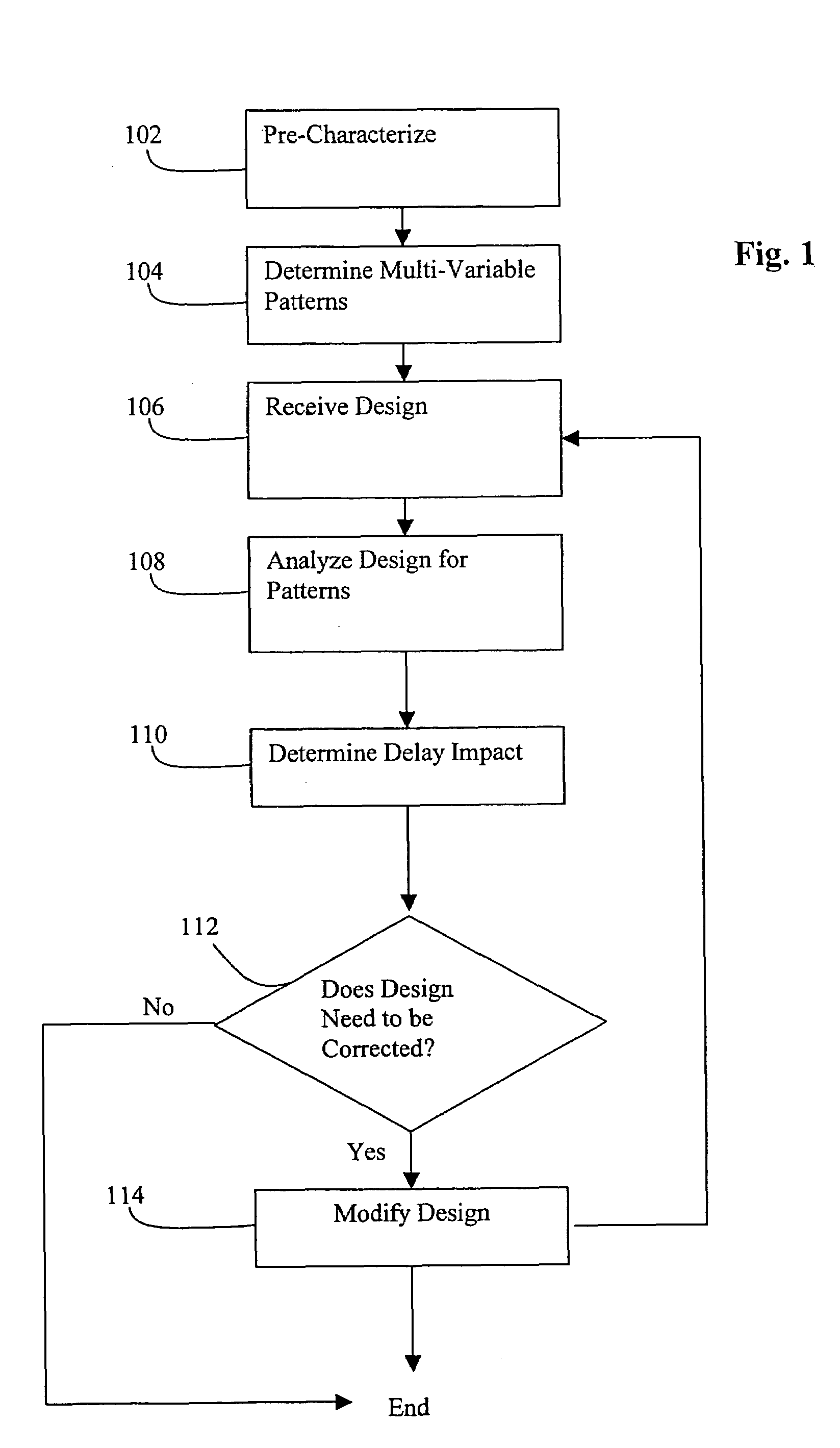

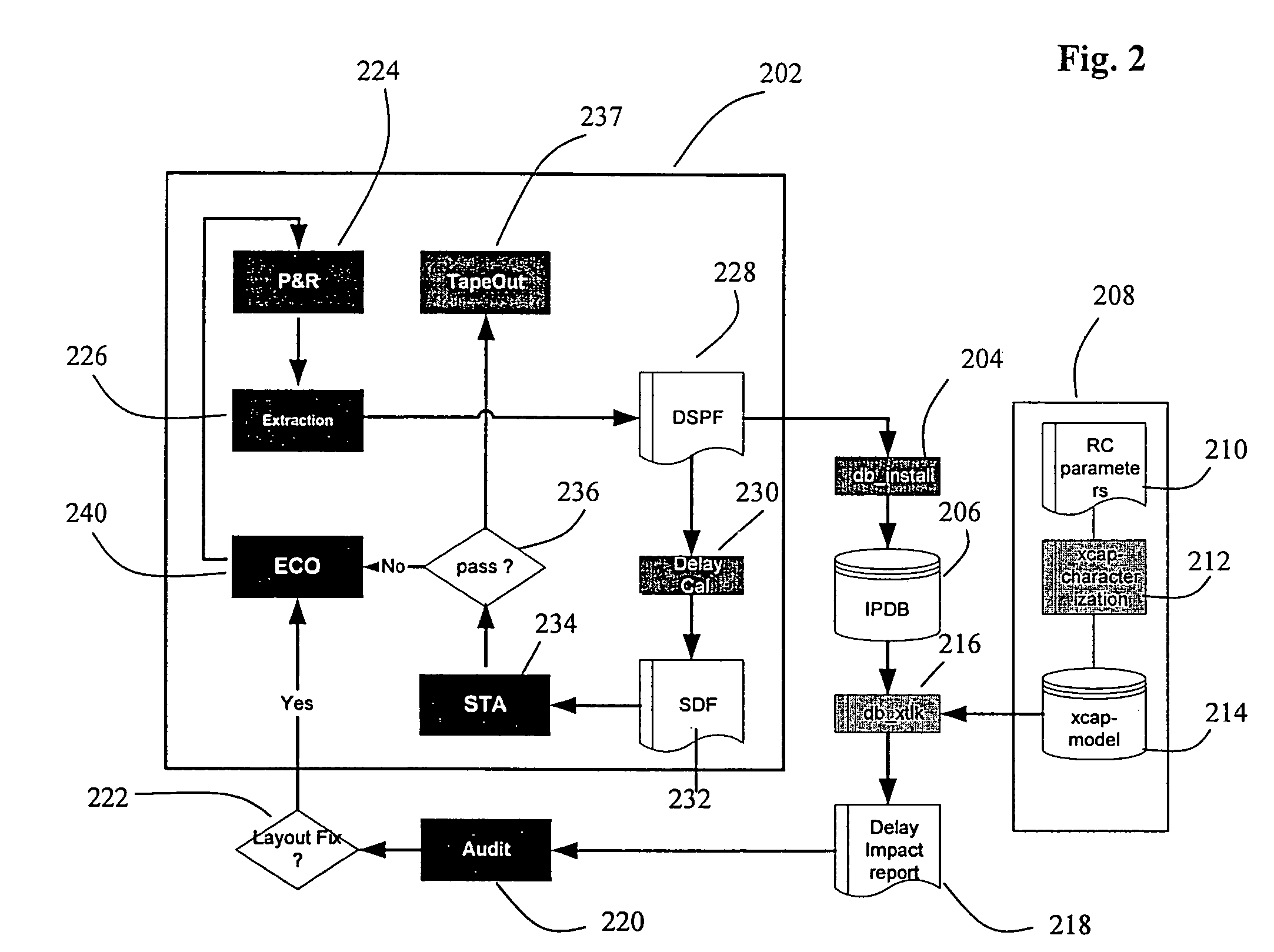

Disclosed is an improved approach for performing crosstalk and signal integrity analysis in which multiple variables are taken into account when analyzing the effects of on-chip crosstalk, such as for example coupled wire length, ratio of coupling capacitance, and aggressor and victim driver types. Rather than performing a full-chip simulation, the potential crosstalk effects can be pre-characterized by performing simulation / modeling over specific net portions by systematically changing the values of these multiple variables. A set of patterns characterized from the variables are formed from the modeling. During the analysis process, the IC design is checked of the presence of the patterns, from which is produced the expected delay impact for crosstalk in the design.

Owner:CADENCE DESIGN SYST INC

Method and system for performing crosstalk analysis

Disclosed is an improved approach for performing crosstalk and signal integrity analysis in which multiple variables are taken into account when analyzing the effects of on-chip crosstalk, such as for example coupled wire length, ration of coupling capacitance, and aggressor and victim driver types. Rather than performing a full-chip simulation, the potential crosstalk effects can be pre-characterized by performing simulation / modeling over specific net portions by systematically changing the values of these multiple variables. A set of patterns characterized from the variables are formed from the modeling. During the analysis process, the IC design is checked of the presence of the patterns, from which is produced the expected delay impact for crosstalk in the design.

Owner:CADENCE DESIGN SYST INC

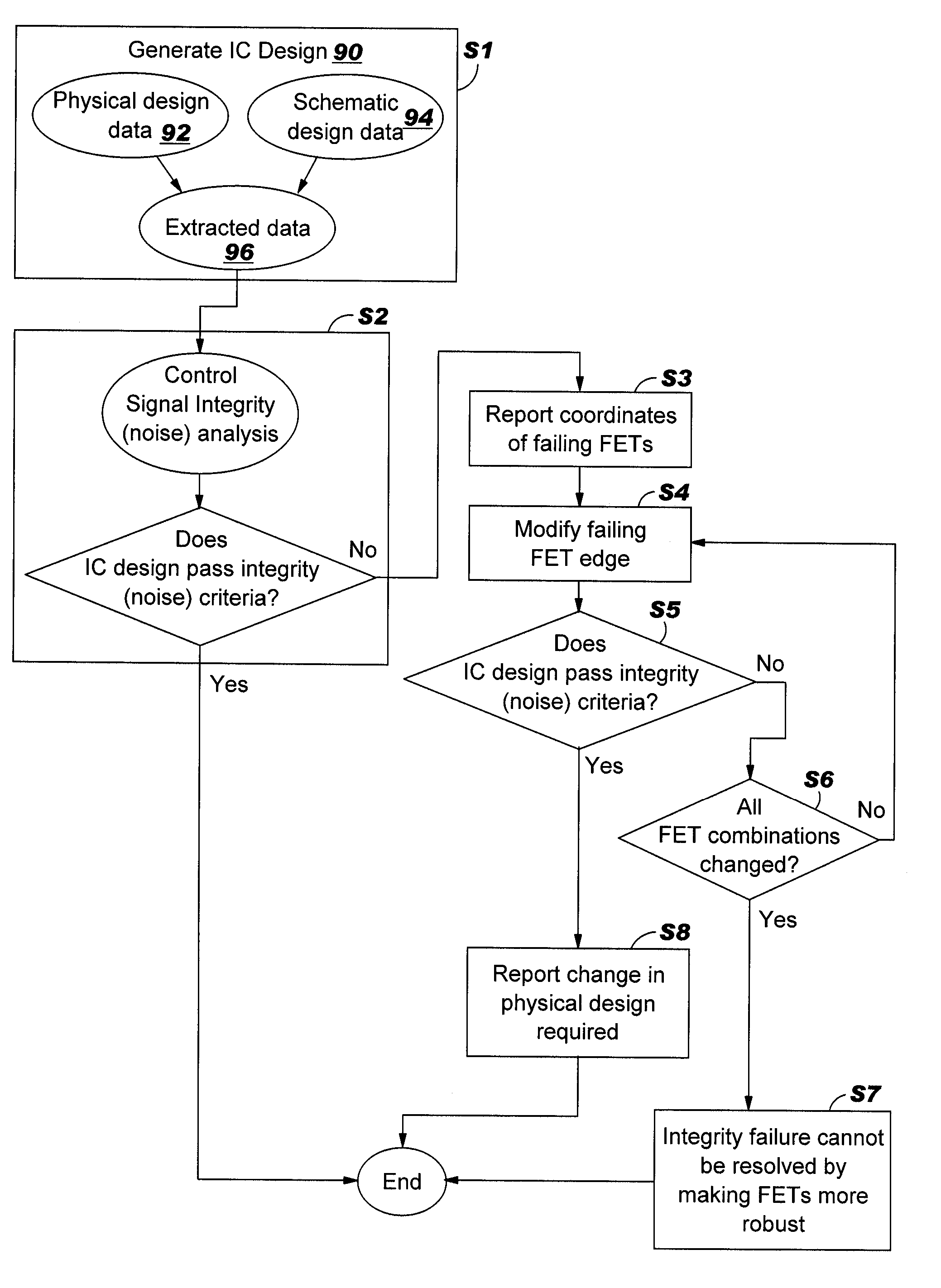

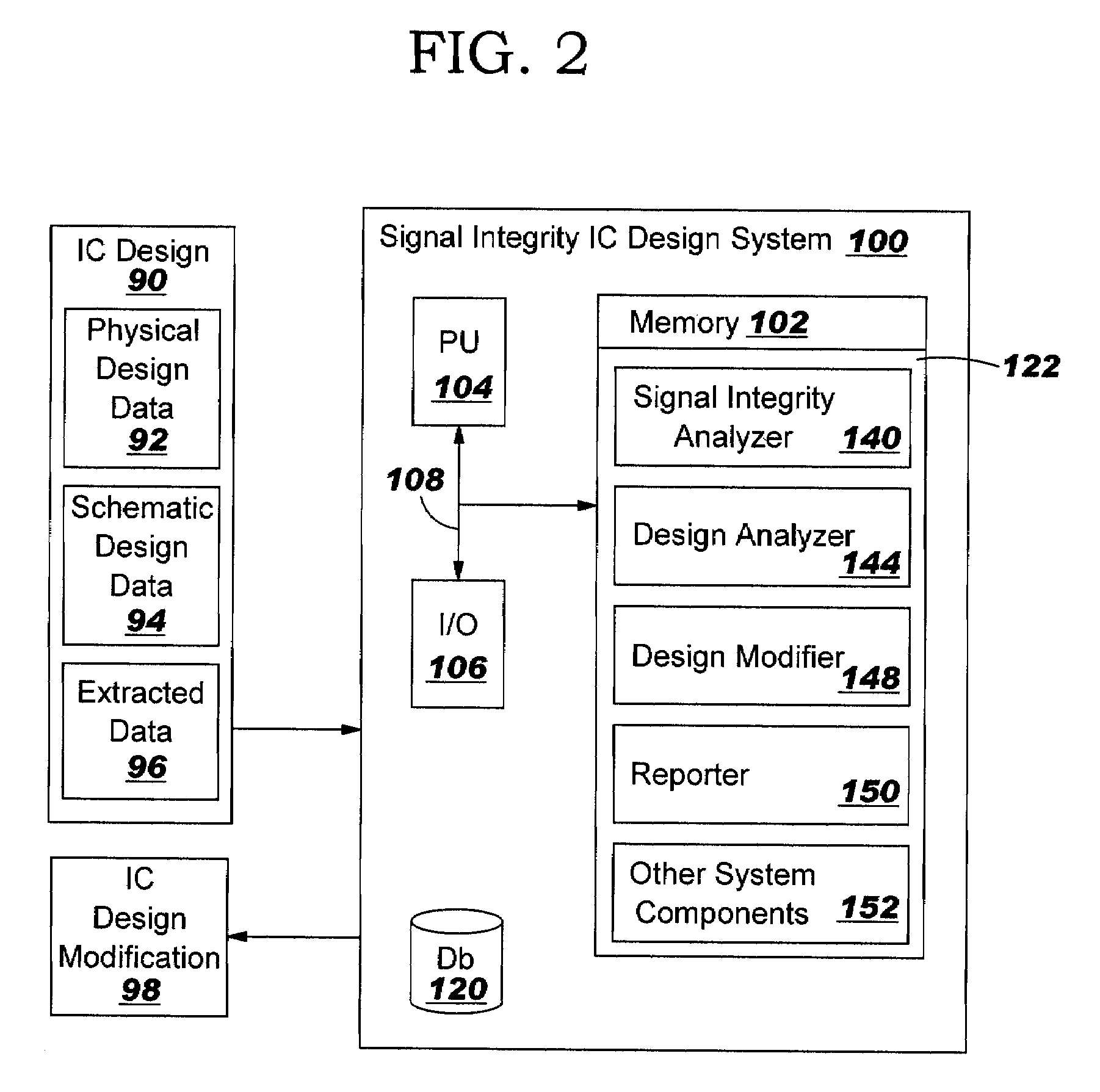

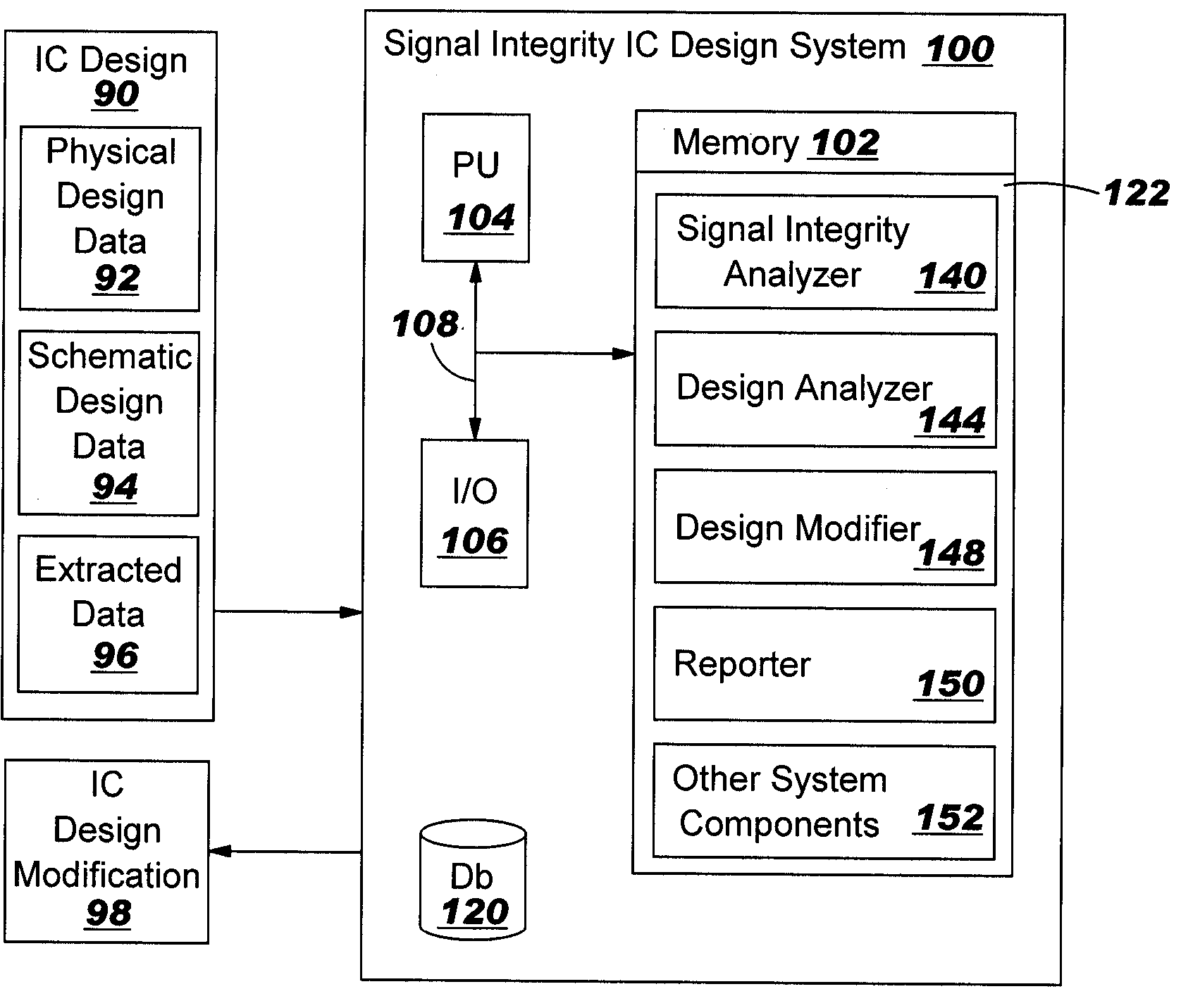

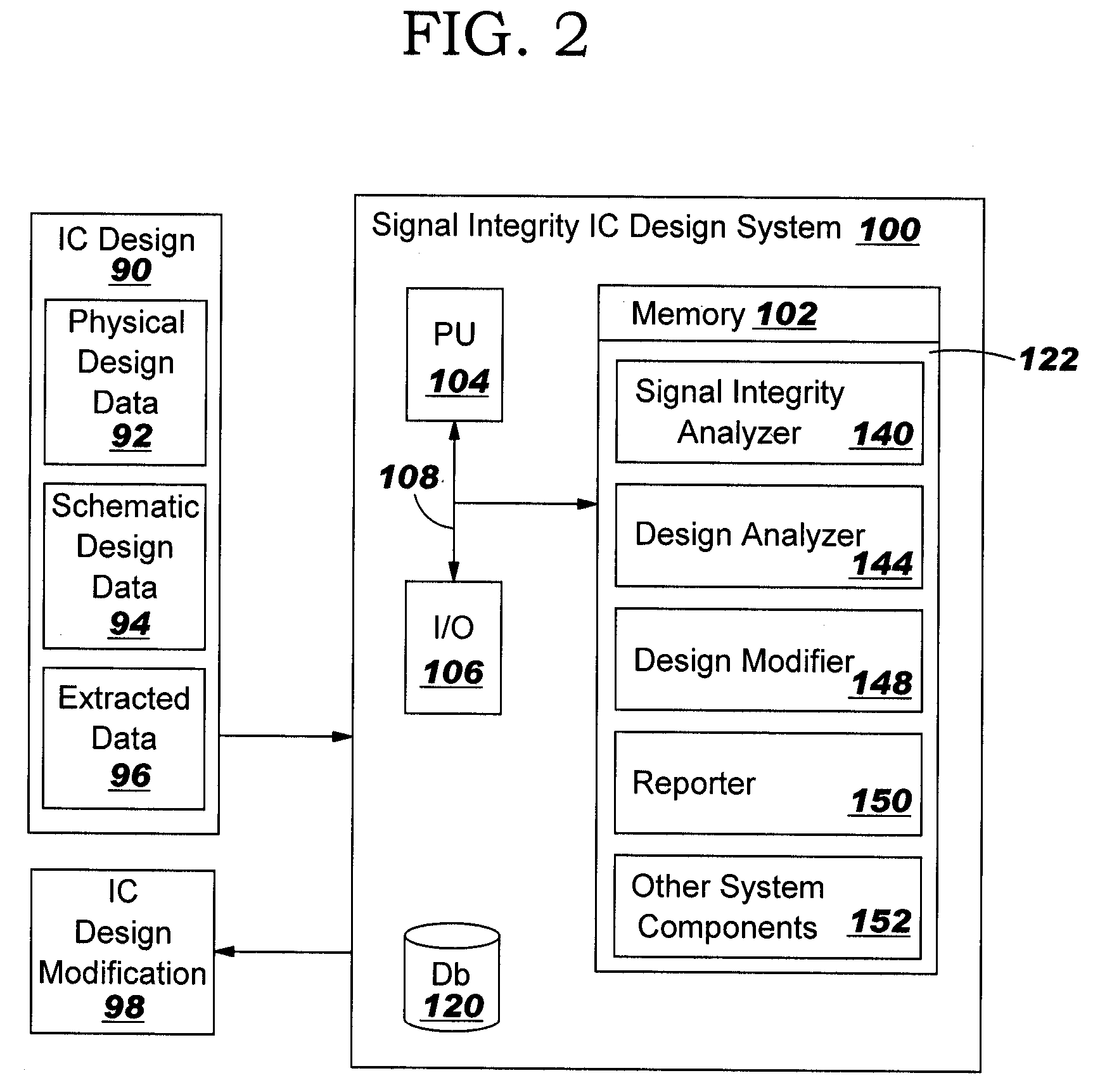

Integrated circuit design for signal integrity, avoiding well proximity effects

A method, system and program product for designing an integrated circuit (IC) for signal integrity. The invention conducts a signal integrity analysis on an IC design; identifies any field effect transistor (FET) that causes a signal integrity failure in the case that the IC design fails the signal integrity analysis; and modifies an edge of a failing FET that is closer than a threshold distance to a well edge. The invention eliminates the manual, iterative procedure for determining the device causing a signal integrity failure due to well proximity effects.

Owner:INT BUSINESS MASCH CORP

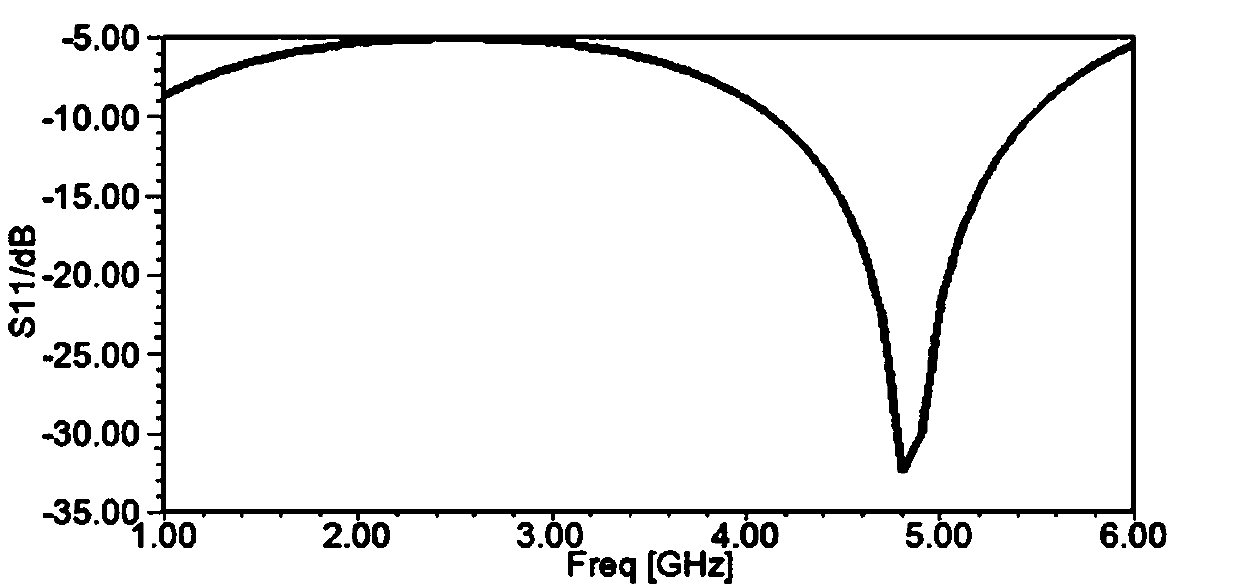

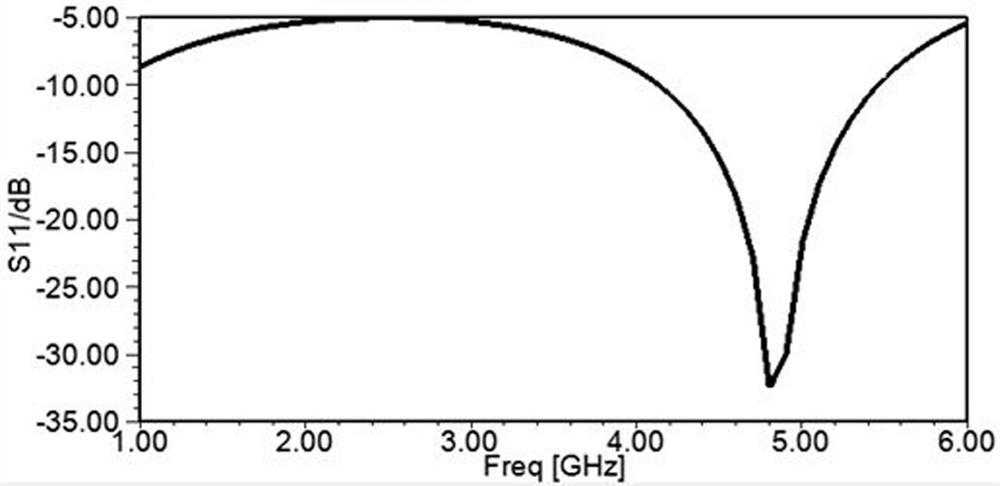

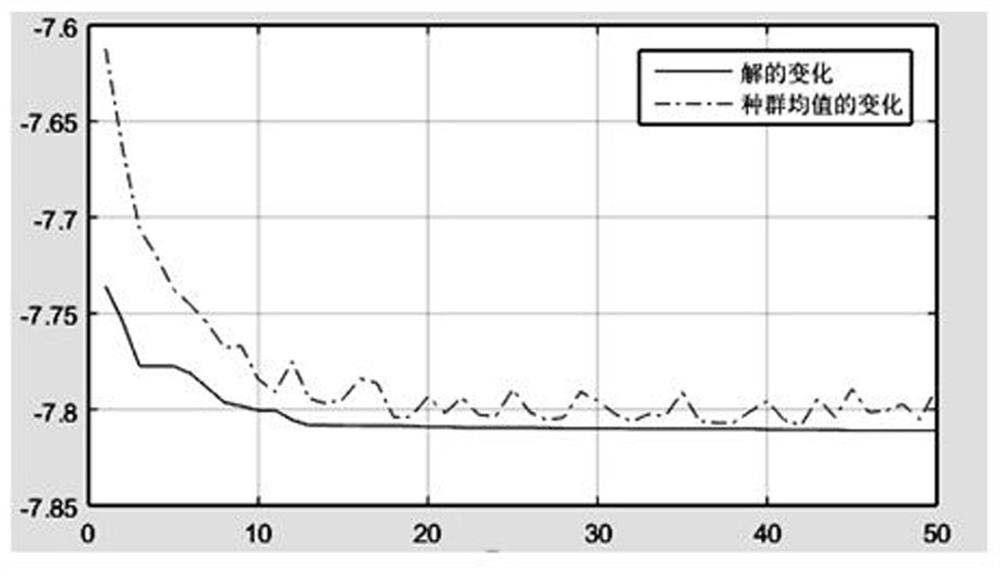

Method for optimizing BGA welding spot return loss

ActiveCN107832526ARobustSimple calculationDesign optimisation/simulationCAD circuit designGenetic algorithmEngineering

The invention discloses a method for optimizing BGA (Ball Grid Array) welding spot return loss. The method includes the steps: 1) establishing a BGA welding spot signal integrity analysis model; 2) acquiring return loss of a BGA welding spot; 3) determining an influence factor of the BGA welding spot signal integrity; 4) determining a parameter level value of the influence factor of the BGA welding spot signal integrity; 5) acquiring simulation experiment samples; 6) acquiring a functional relation between the influence factor and the return loss; 7) performing variance analysis; 8) determining the correctness of the functional relation; 9) generating an initial population; 10) acquiring a current evolution generation gen and an optimal fitness value; 11) performing interlace operation onthe population; 12) performing mutation operation on the population; 13) performing evolution reversion on the population; 14) selecting an optimal individual; and 15) performing re-determination after the population is updated. The method uses a response surface method and a genetic algorithm to optimize BGA welding spot return loss, has excellent robust Performance, and is simple in calculationprocess.

Owner:GUILIN UNIV OF ELECTRONIC TECH

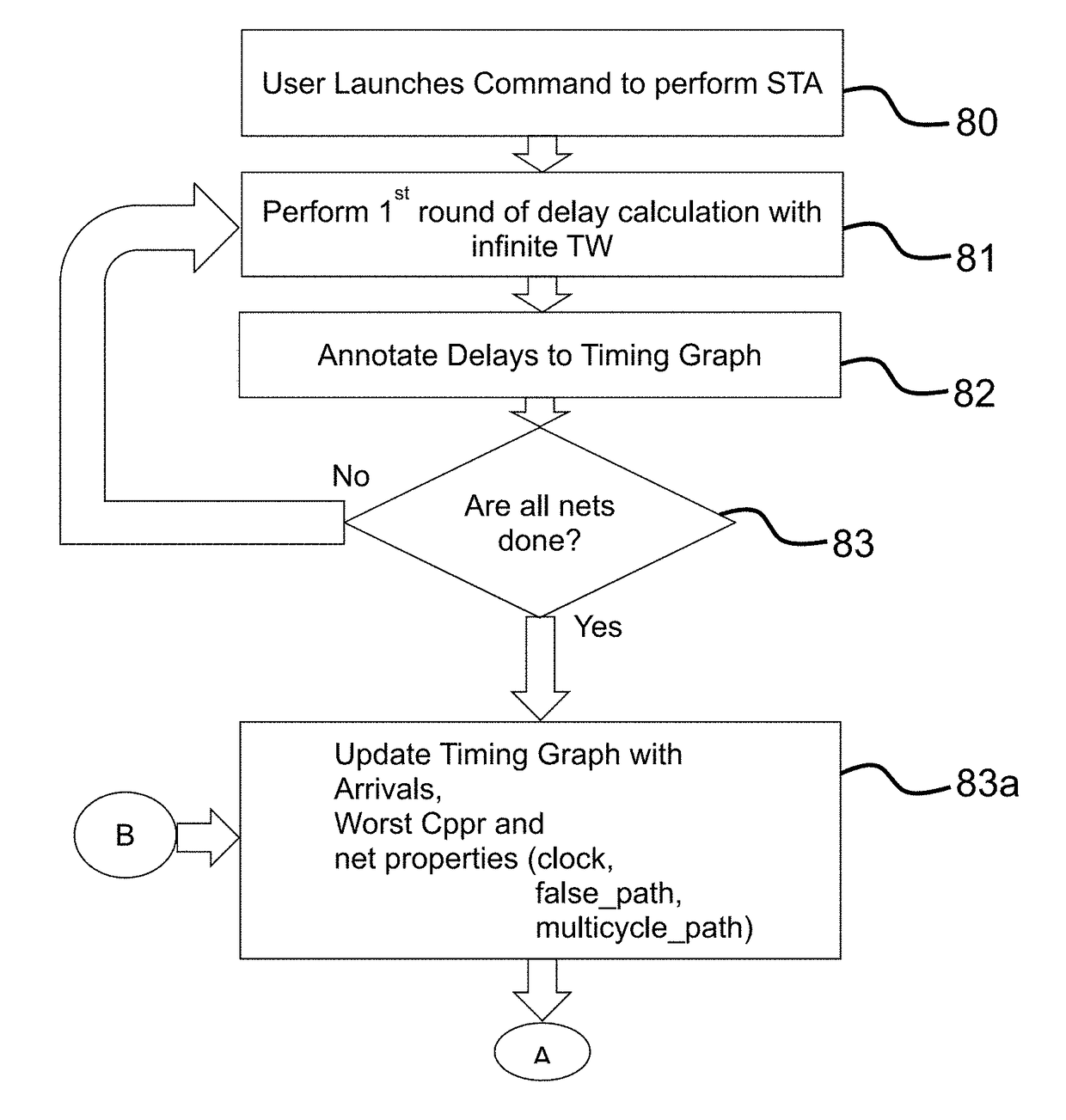

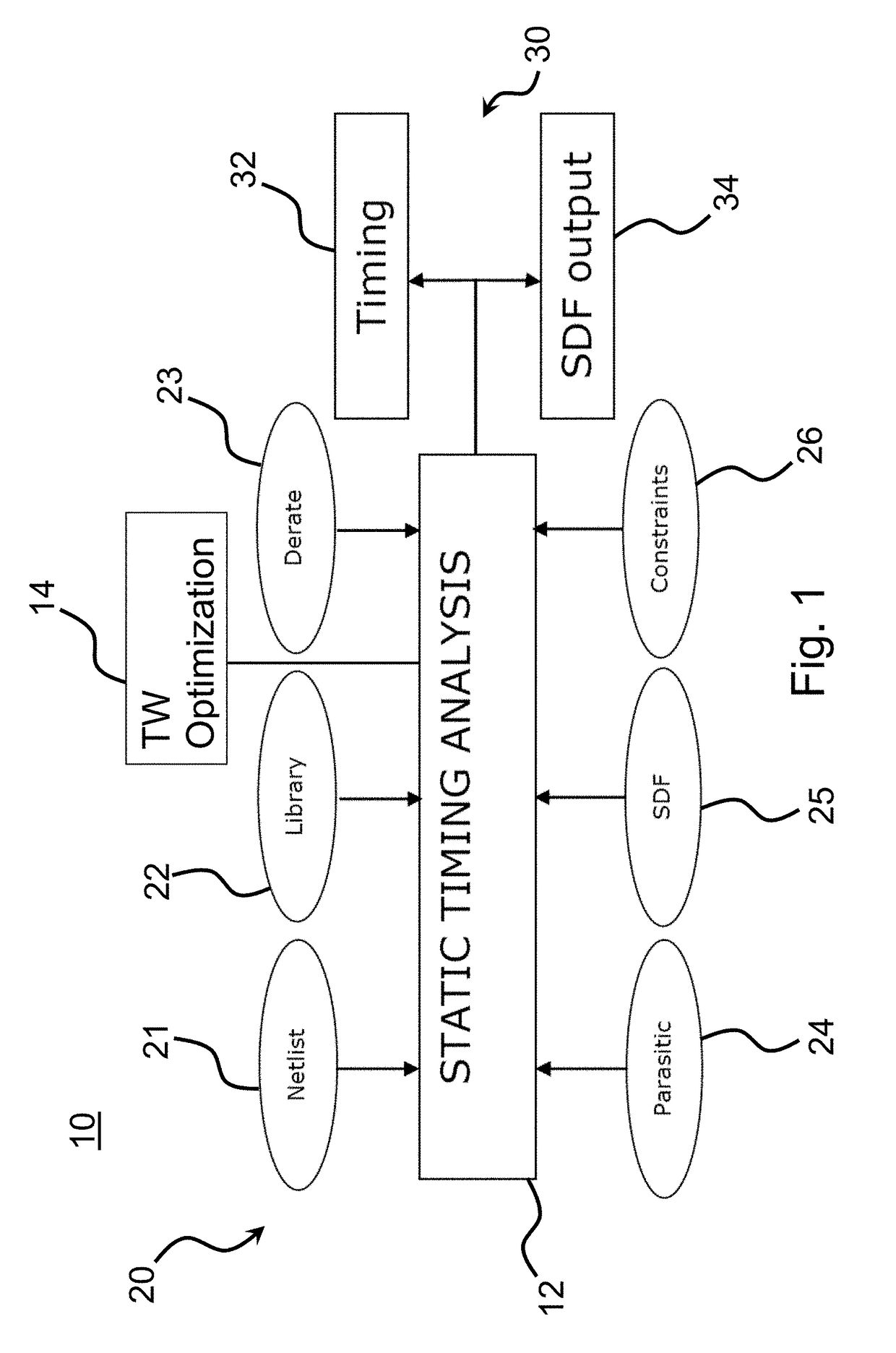

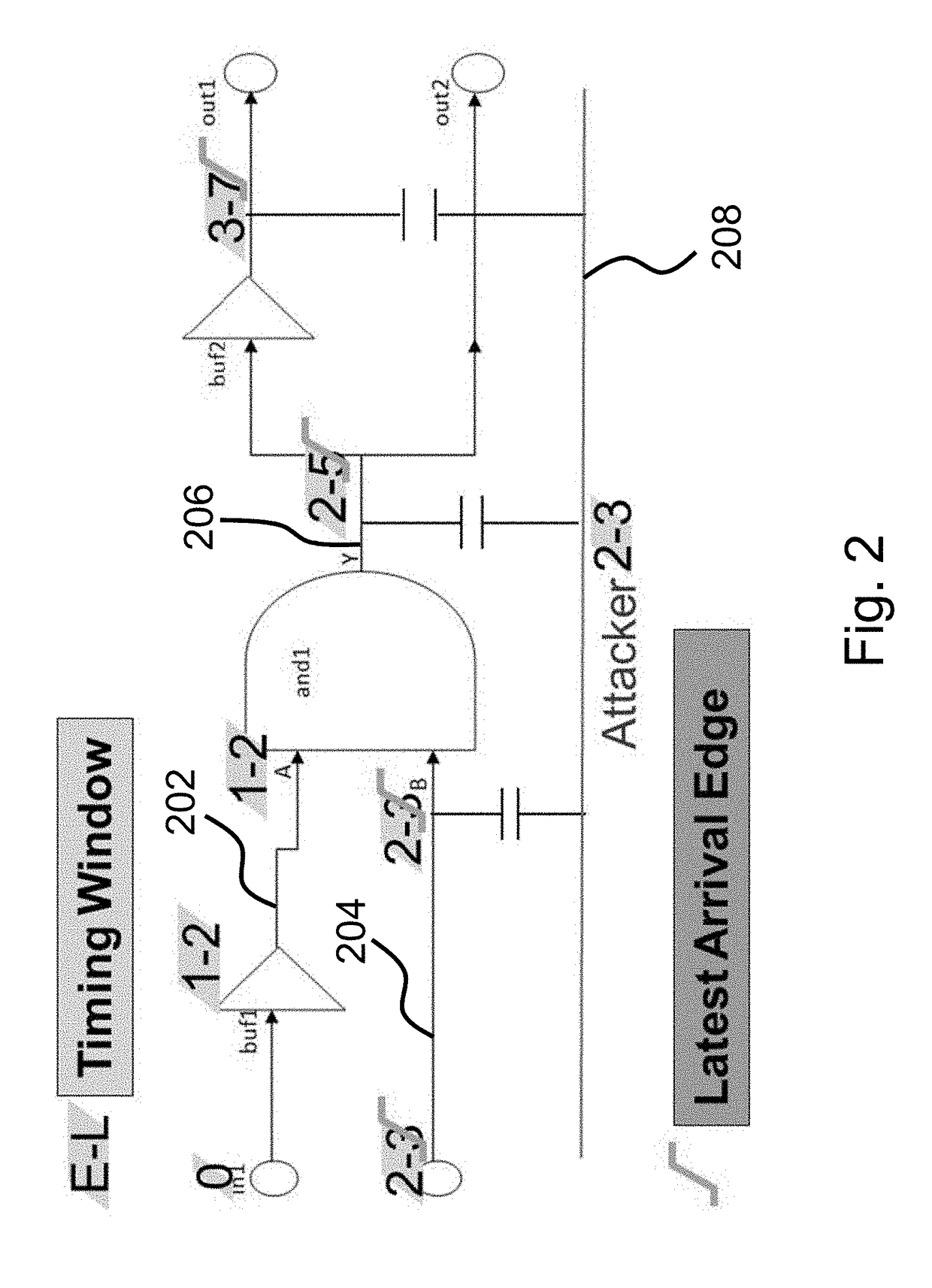

Method and system for timing analysis with adaptive timing window optimization for determining signal integrity impact

ActiveUS9881123B1Alleviates undue pessimismAlleviates optimismComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisTiming diagram

A method and system are provided for timing analysis of an electronic circuit design. A timing graph defines a plurality of timing paths through different subsections of the electronic circuit design. A timing window is defined for each of the nodes included in a timing path. At least one preliminary round of a predetermined signal integrity analysis is executed on the circuit design based on the timing windows to identify at least one pair of crosstalk-coupled victim and aggressor nodes. Each victim node's timing window is adaptively adjusted according to a predetermined timing property thereof. At least one primary round of the predetermined signal integrity analysis is executed on the electronic circuit design based in part on this adaptively adjusted timing window for each victim node to generate a delay, which is annotated to the timing graph. A predetermined static timing analysis is executed based on the delay-annotated timing graph.

Owner:CADENCE DESIGN SYST INC

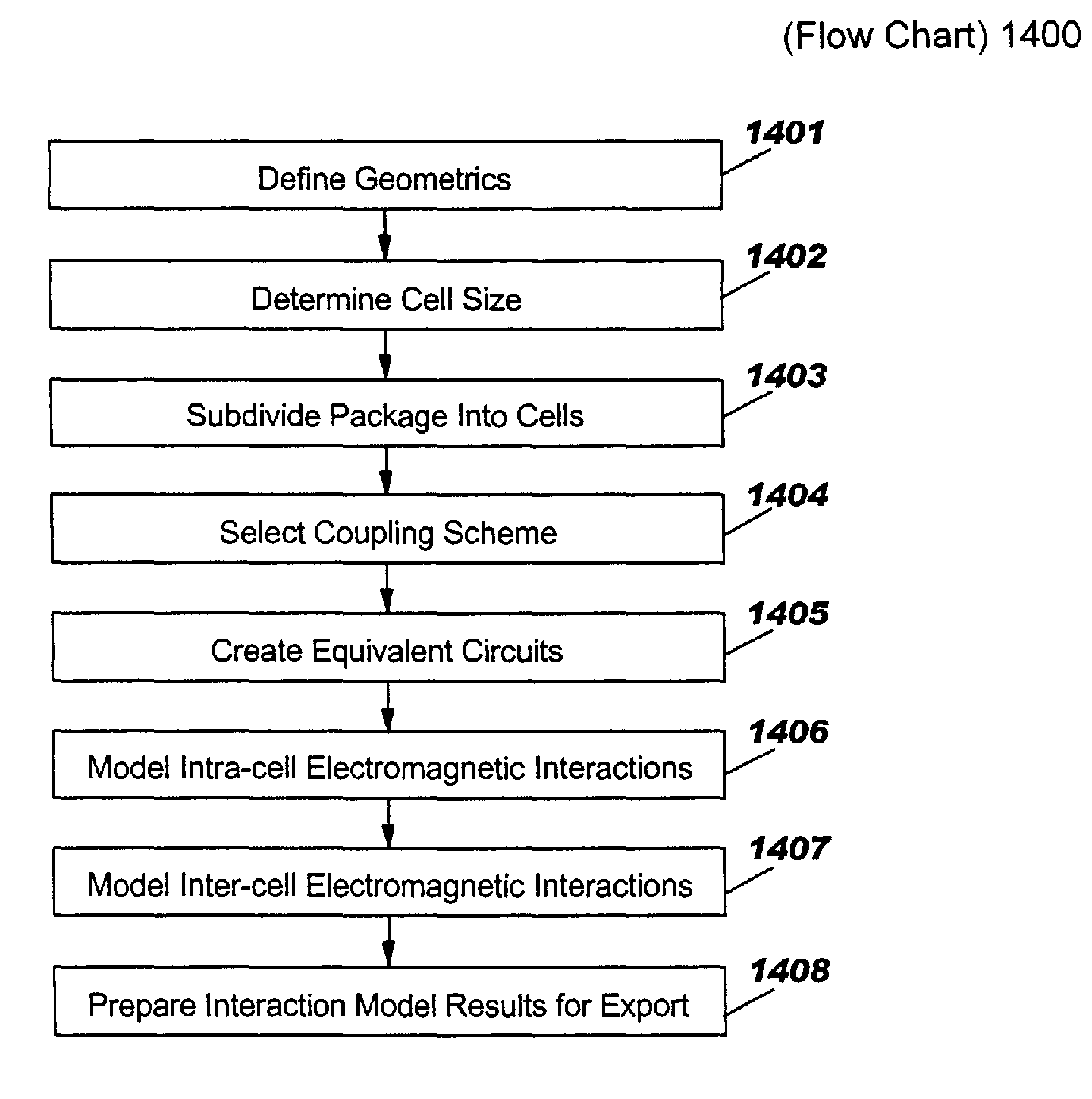

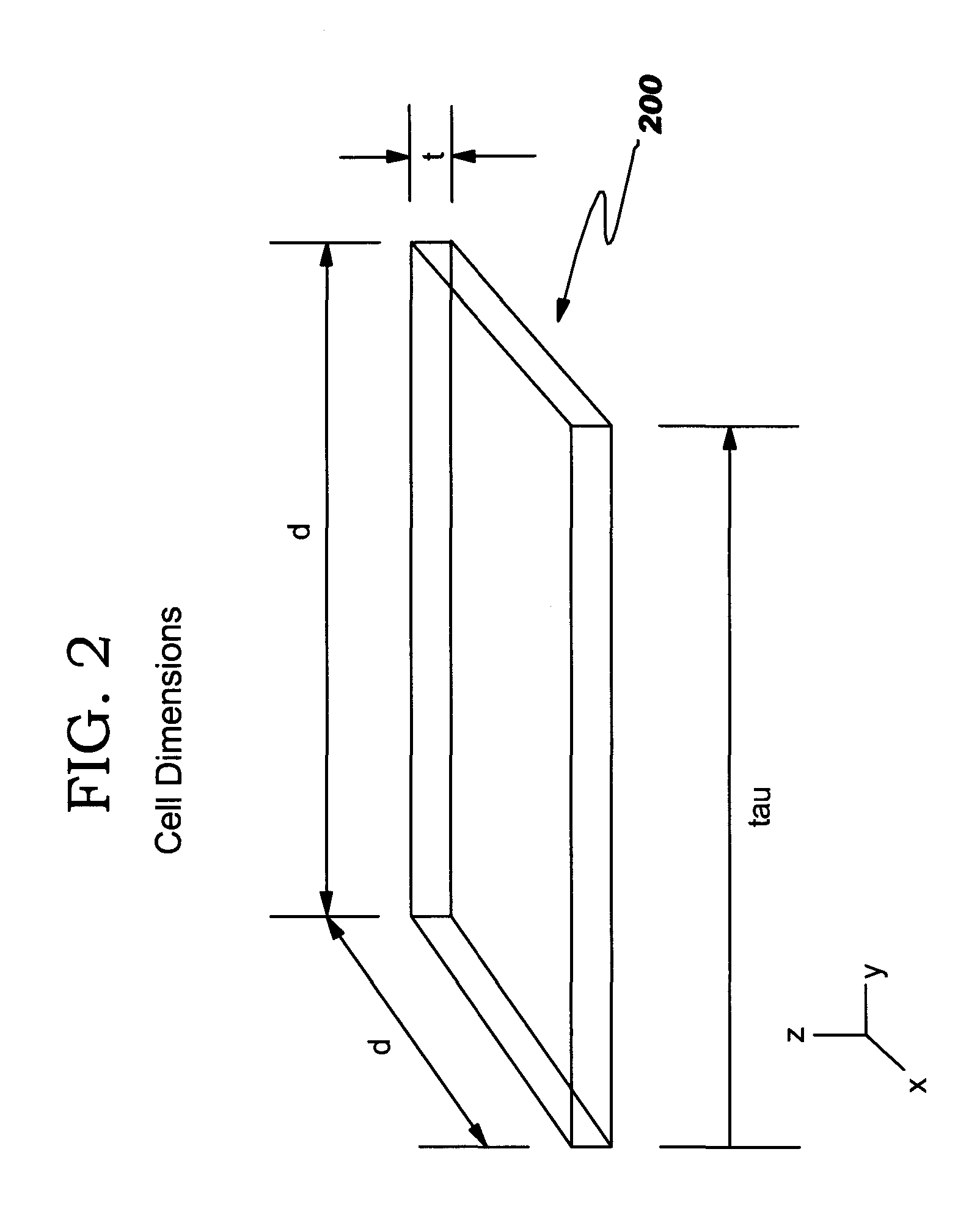

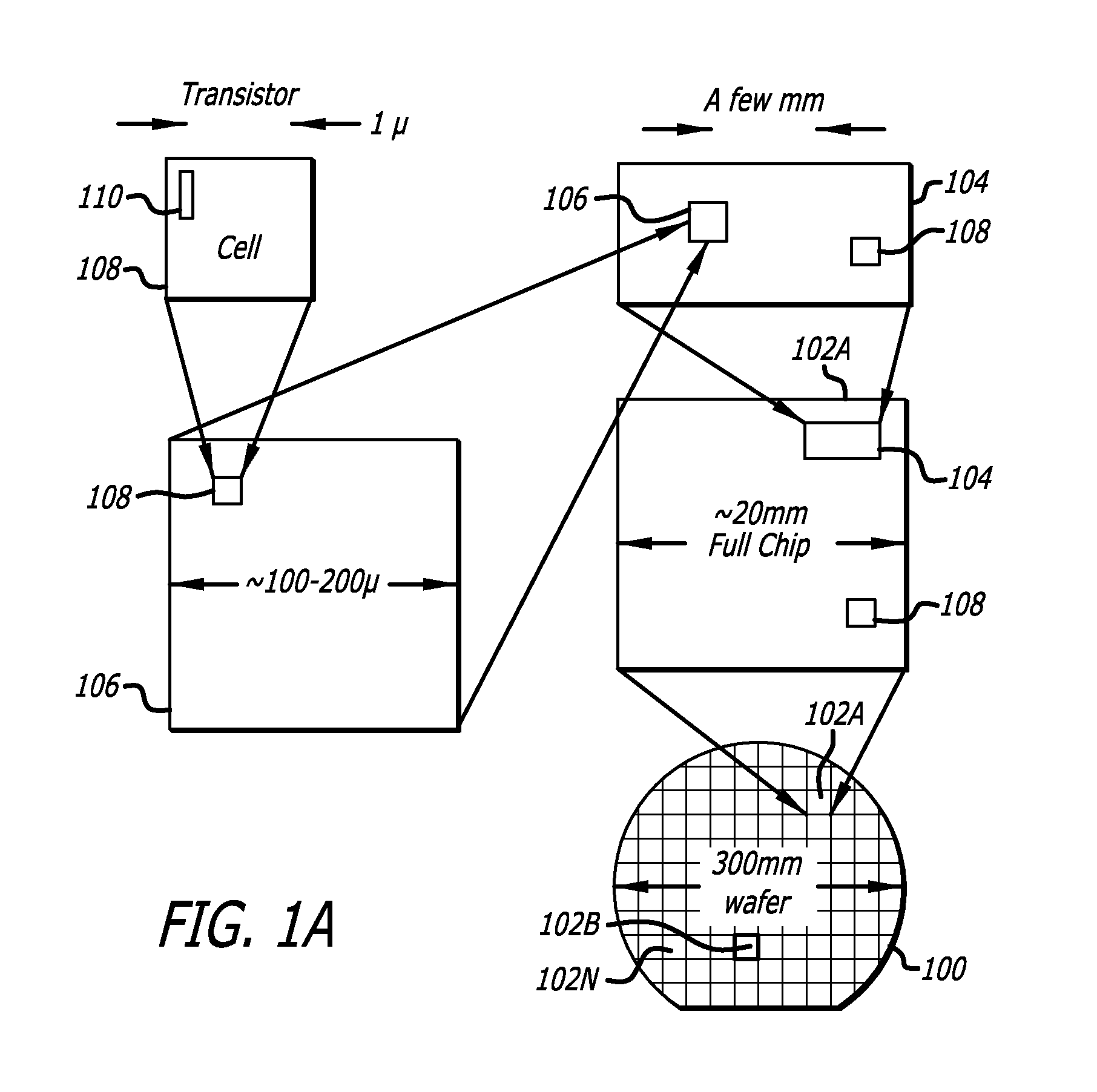

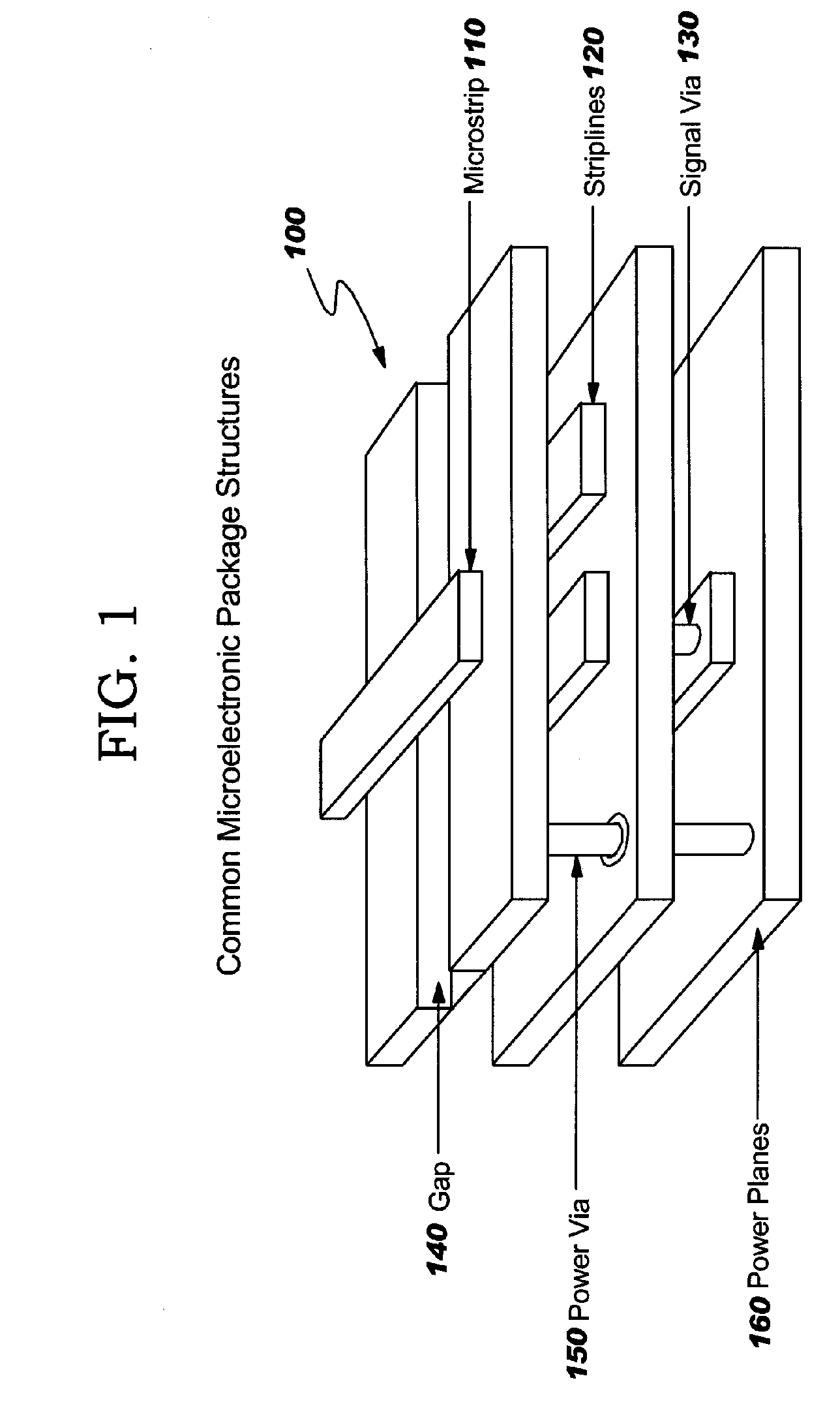

Hierarchical method of power supply noise and signal integrity analysis

InactiveUS7197446B2Reduce in quantityImprove computing efficiencyDetecting faulty computer hardwareComputation using non-denominational number representationElectricityInductor

The invention relates generally to a method of power supply noise and signal integrity analysis for creating frequency-dependent electrical models particularly related to microelectronic packages. The method discloses creation of equivalent circuits for geometries encountered in a typical chip package, including how to partition the geometry into cells which are less then 1 / 20 the minimum wavelength (λ) in size, and how to handle signal and power supply vias, signal wires, and power planes. The method also instructs how to assign values to each of the inductors, capacitors, resistors, and transmission lines in each equivalent circuit. The method further provides modeling of only those interactions which occur between adjacent cells.

Owner:IBM CORP

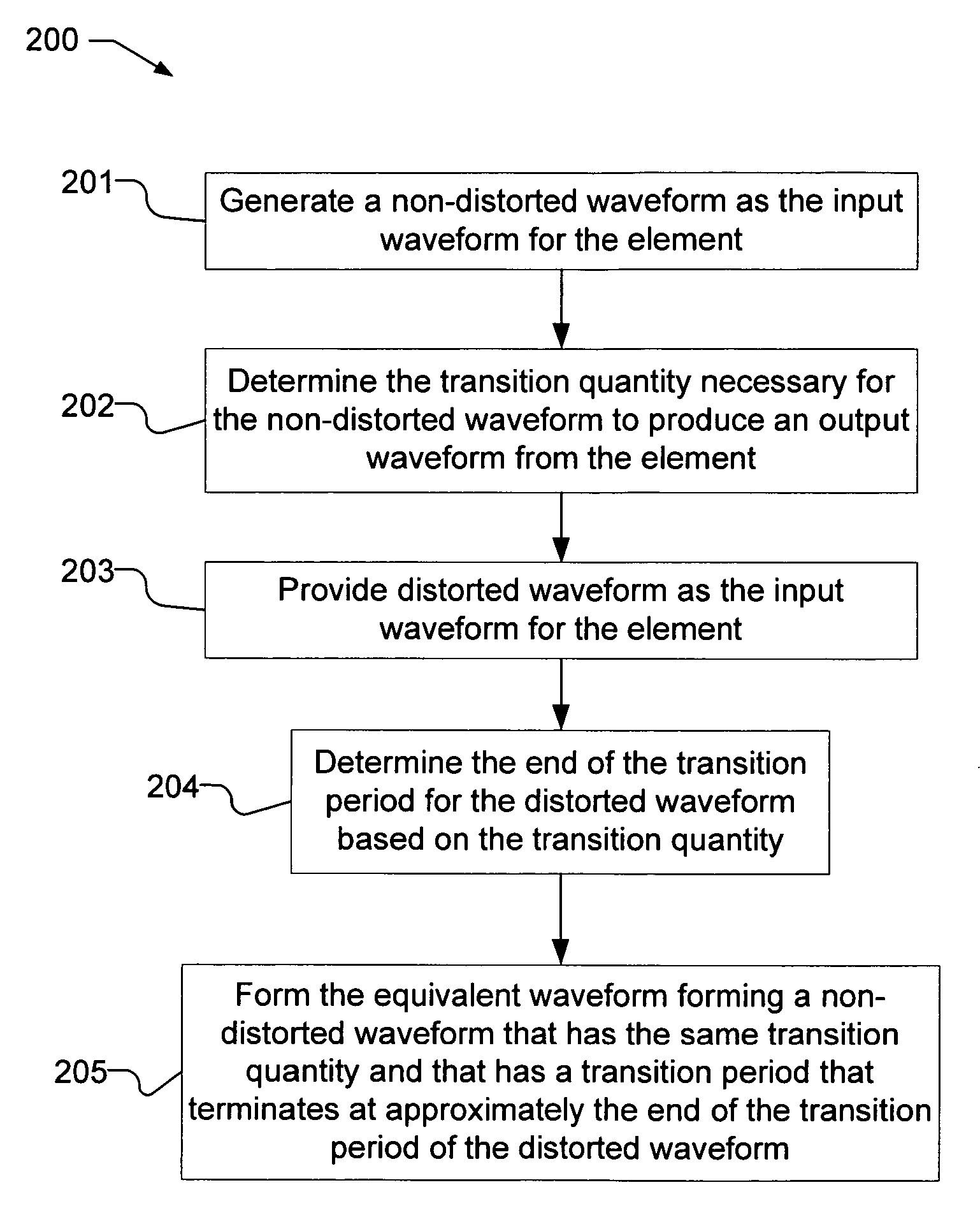

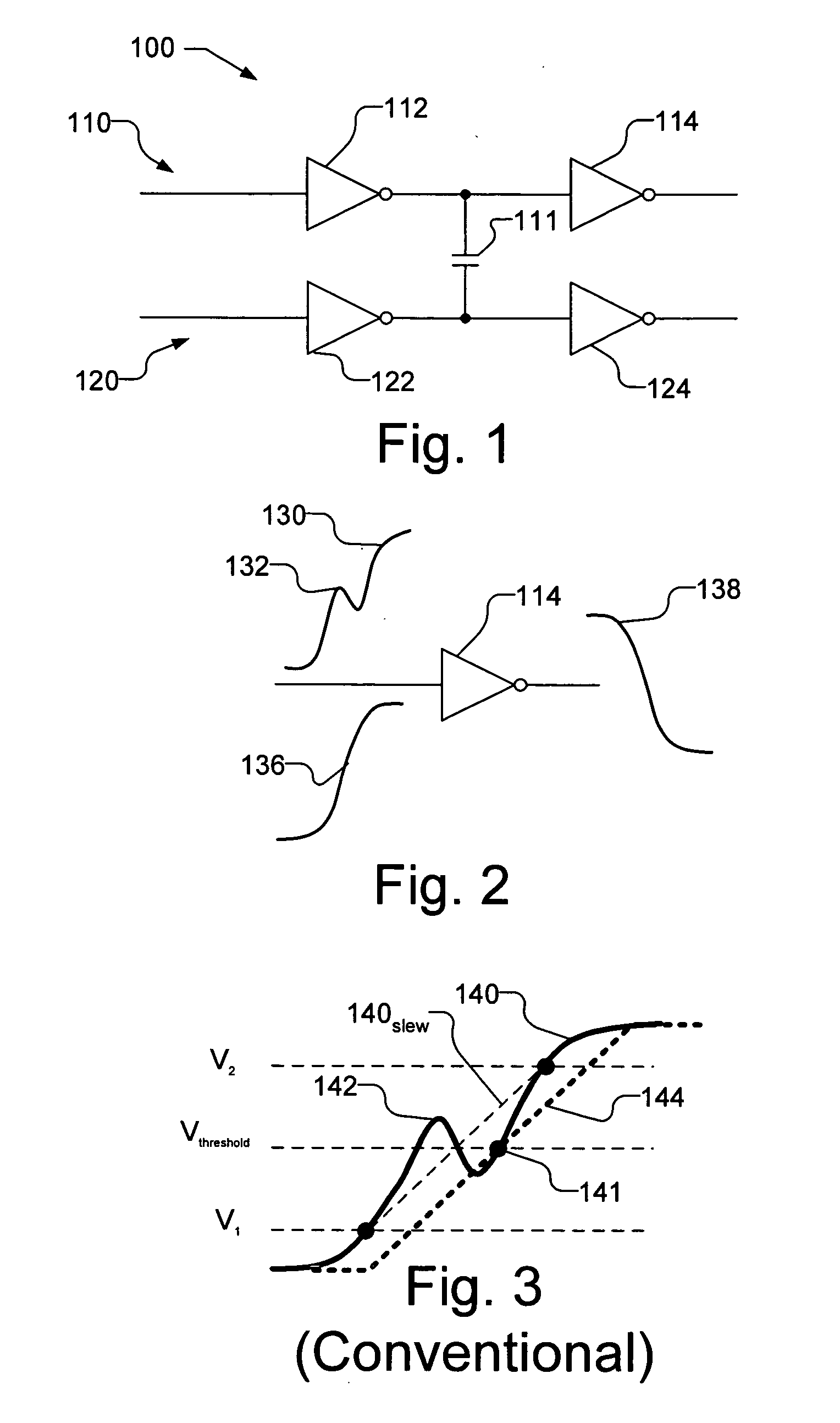

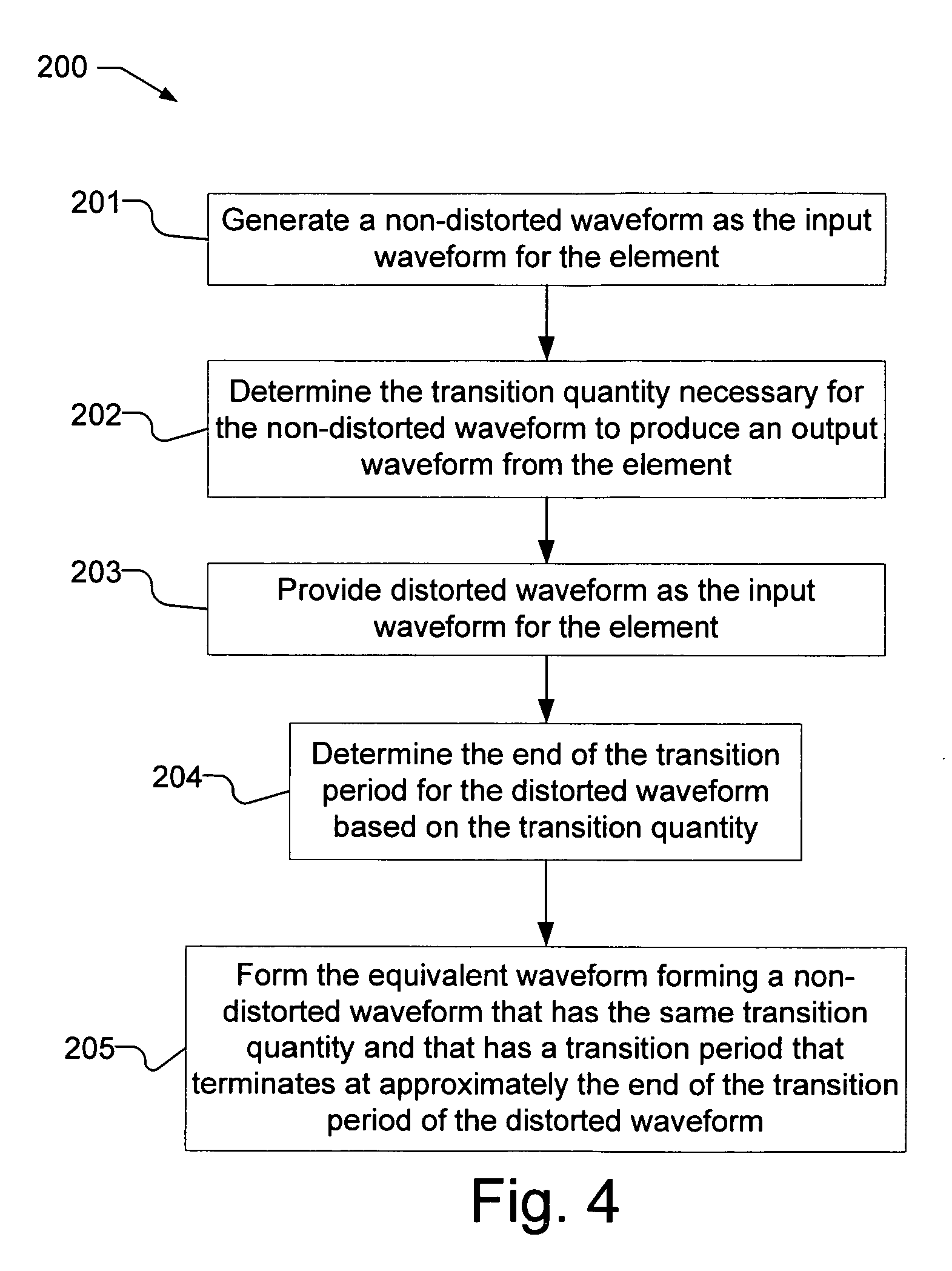

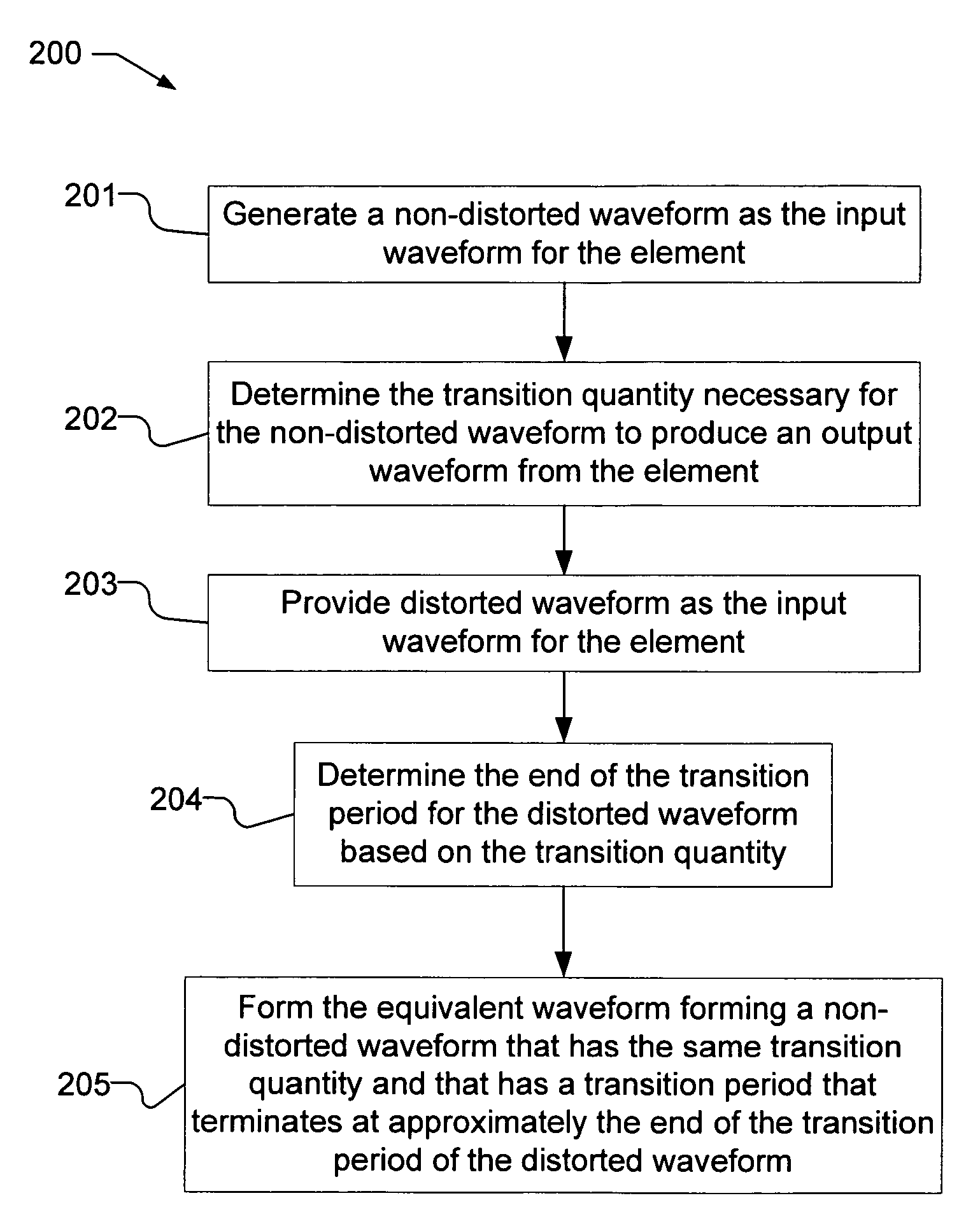

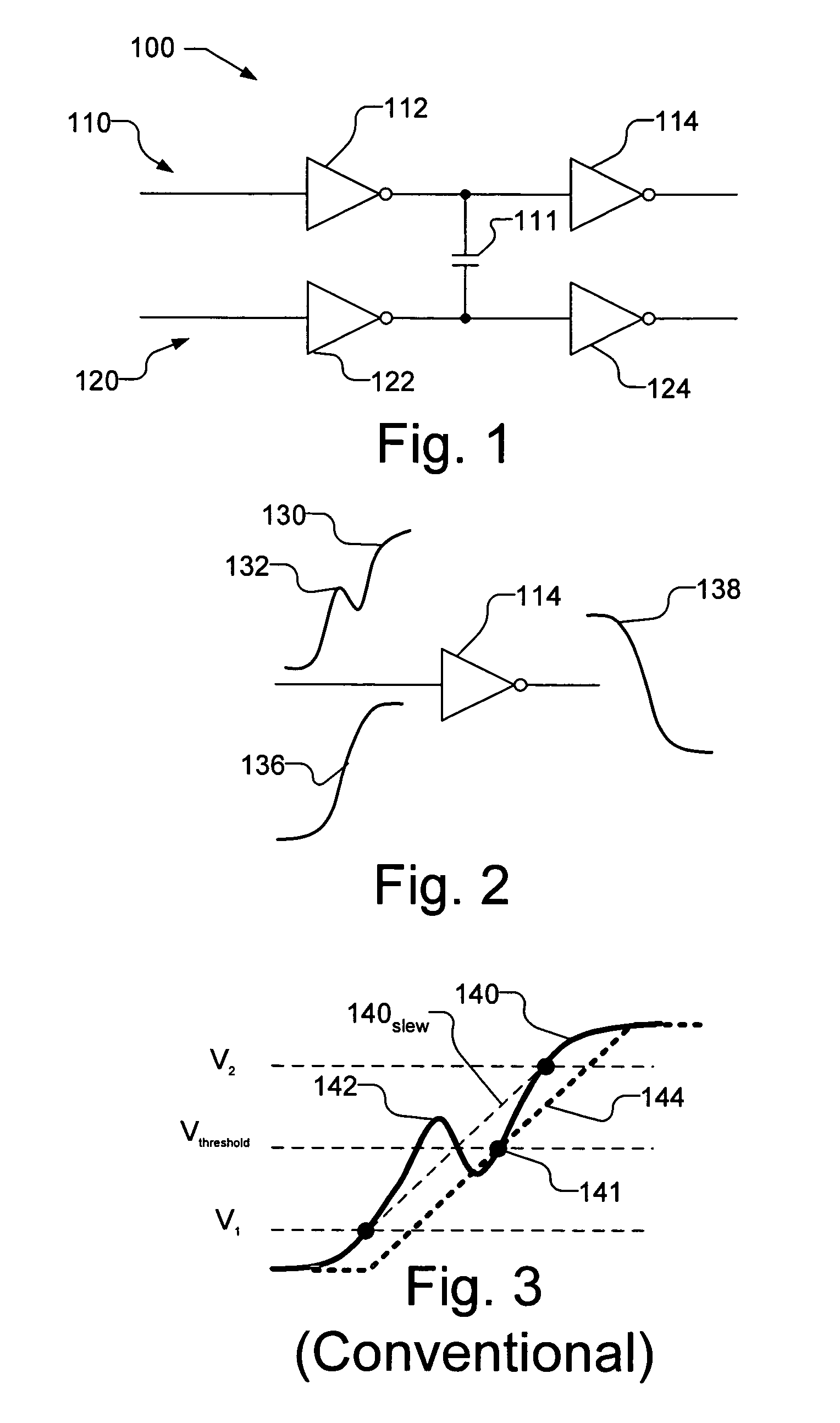

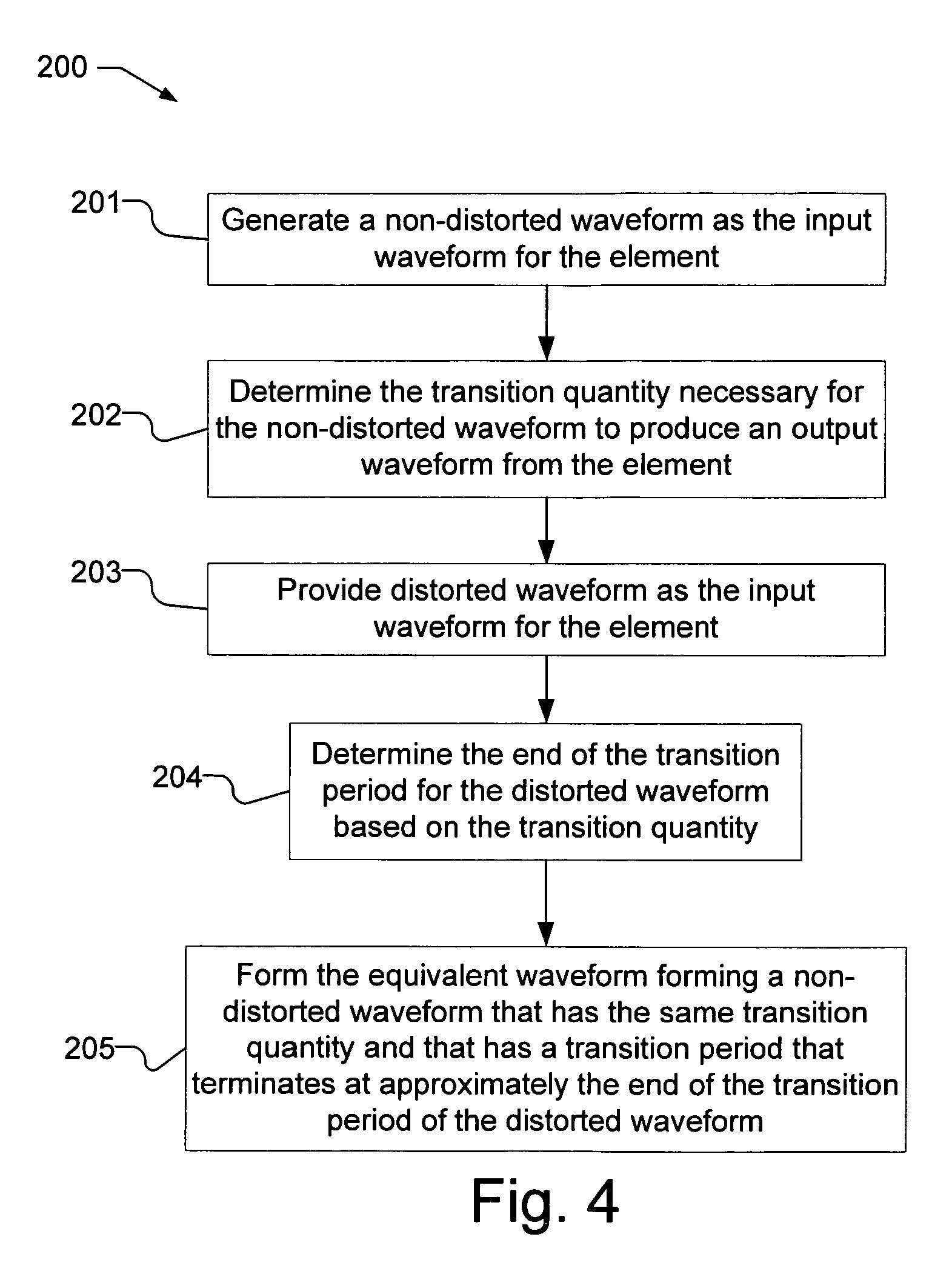

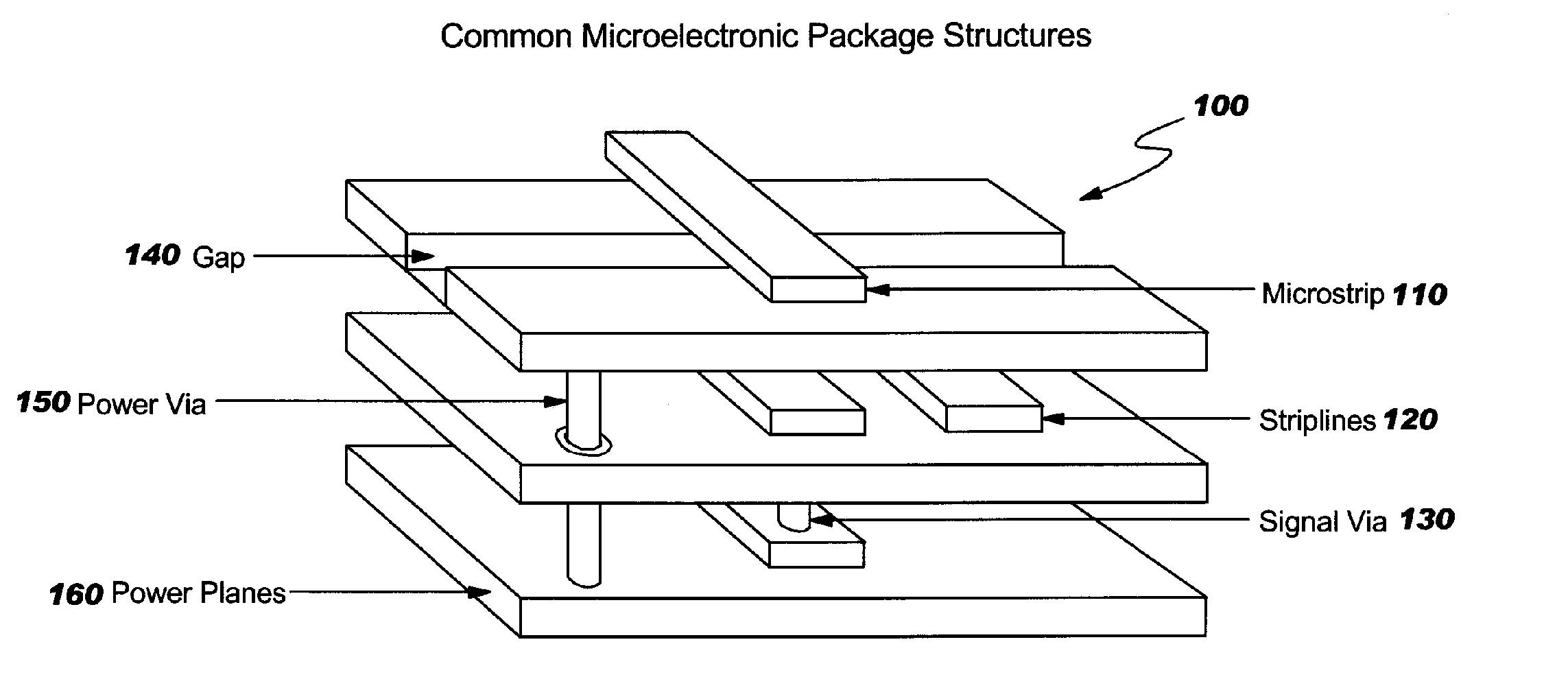

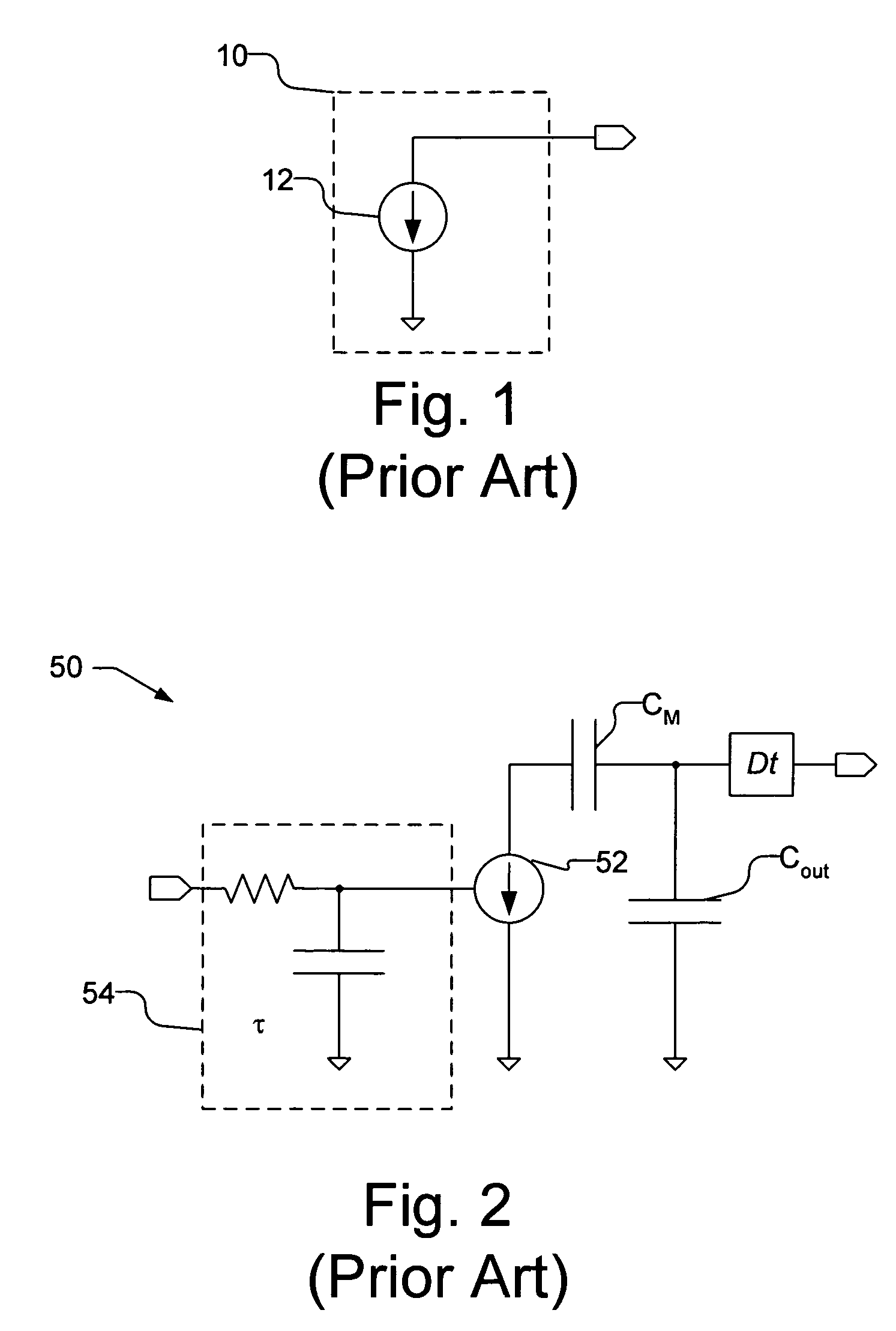

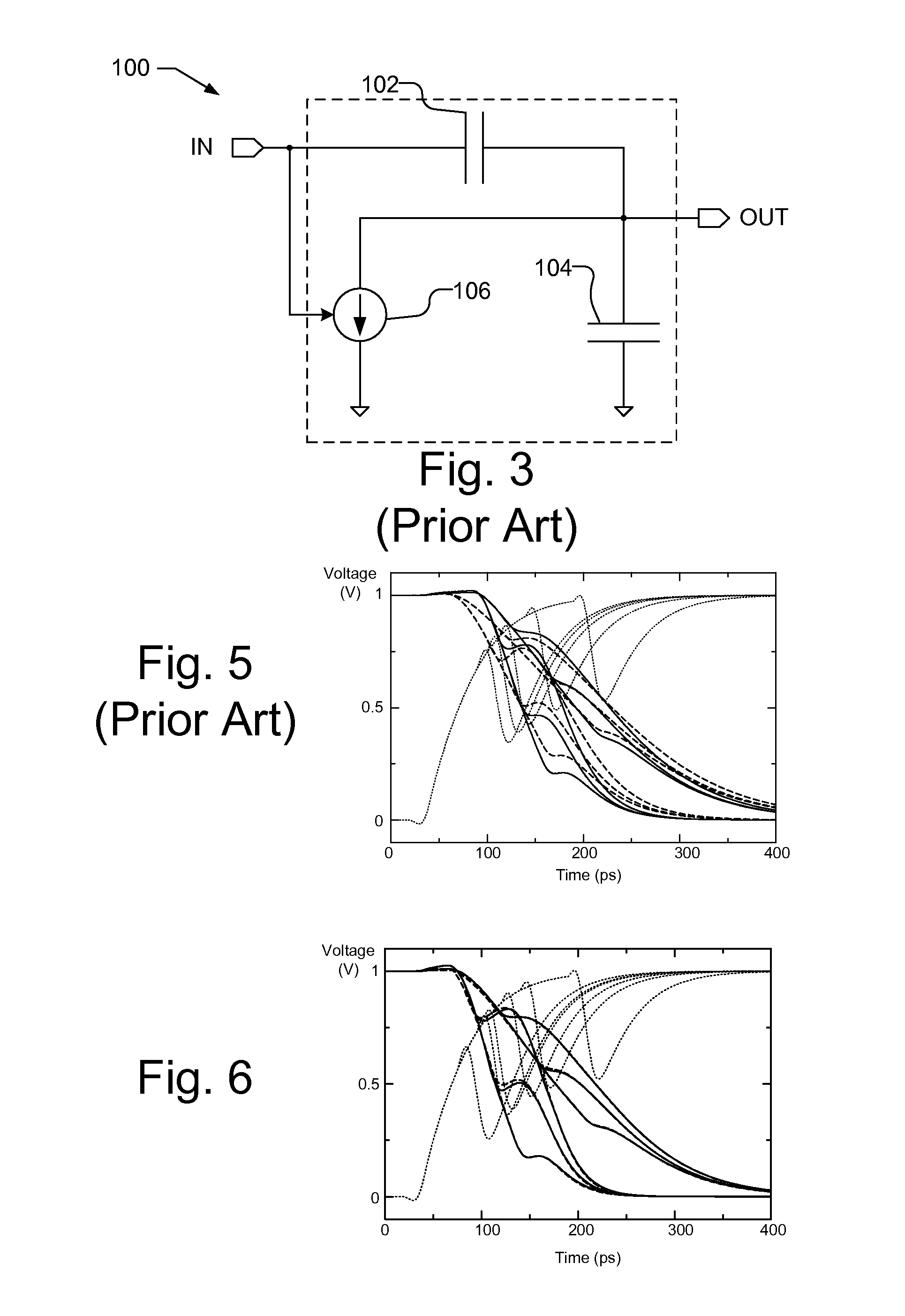

Determining equivalent waveforms for distorted waveforms

ActiveUS20060200784A1Detecting faulty computer hardwareComputer aided designEngineeringSignal integrity analysis

An equivalent waveform for a distorted waveform used in timing and signal integrity analysis in the design of an integrated circuit is automatically generated. The equivalent waveform is produced by calculating the transition quantity of a first non-distorted waveform. The transition quantity is the amount of transition of the first non-distorted waveform that is required for the cell to produce an output waveform with a predetermined end voltage. The end point of the transition period for the distorted waveform is then determined based on when the distorted waveform has accumulated the same transition quantity. The equivalent waveform can then be formed by computing a second non-distorted waveform such that the end point of the transition period for the second non-distorted waveform coincides with the end point of the transition period for the distorted waveform.

Owner:SYNOPSYS INC

Methods, systems, and apparatus for timing and signal integrity analysis of integrated circuits with semiconductor process variations

ActiveUS8631369B1Computer aided designSoftware simulation/interpretation/emulationSignal integrity analysisComputer science

Owner:CADENCE DESIGN SYST INC

Determining equivalent waveforms for distorted waveforms

ActiveUS7272807B2Detecting faulty computer hardwareComputer aided designSignal integrity analysisIntegrated circuit

An equivalent waveform for a distorted waveform used in timing and signal integrity analysis in the design of an integrated circuit is automatically generated. The equivalent waveform is produced by calculating the transition quantity of a first non-distorted waveform. The transition quantity is the amount of transition of the first non-distorted waveform that is required for the cell to produce an output waveform with a predetermined end voltage. The end point of the transition period for the distorted waveform is then determined based on when the distorted waveform has accumulated the same transition quantity. The equivalent waveform can then be formed by computing a second non-distorted waveform such that the end point of the transition period for the second non-distorted waveform coincides with the end point of the transition period for the distorted waveform.

Owner:SYNOPSYS INC

Hierarchical method of power supply noise and signal integrity analysis

InactiveUS20060047490A1Reduce in quantityImprove computing efficiencyDetecting faulty computer hardwareComputation using non-denominational number representationElectricityInductor

The invention relates generally to a method of power supply noise and signal integrity analysis for creating frequency-dependent electrical models particularly related to microelectronic packages. The method discloses creation of equivalent circuits for geometries encountered in a typical chip package, including how to partition the geometry into cells which are less then 1 / 20 the minimum wavelength (λ) in size, and how to handle signal and power supply vias, signal wires, and power planes. The method also instructs how to assign values to each of the inductors, capacitors, resistors, and transmission lines in each equivalent circuit. The method further provides modeling of only those interactions which occur between adjacent cells.

Owner:IBM CORP

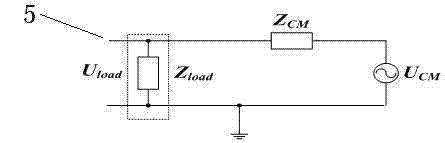

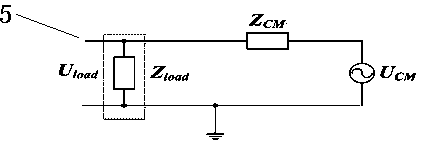

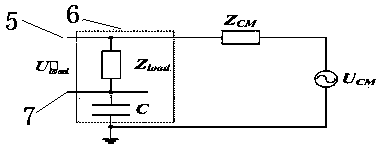

Conducted EMI (electro-magnetic interference) noise suppression method of complex electronic system

ActiveCN102769499ASuppressing Conducted EMI Noise Suppression MethodsTransmission noise suppressionCapacitanceHemt circuits

A conducted EMI noise suppression method of a complex electronic system comprises: 1) analyzing the reasons generating the conducted EMI noise: (1) crosstalk, (2) bad grounding, and (3) PCB (printed circuit board) impedance mismatch; and 2) tightly winding the live wire and the neutral wire of a crosstalk choking coil in a negative-incoming negative-outgoing manner if the conducted EMI noise is caused by crosstalk; connecting capacitors (C1 to C8) in parallel, and respectively disposing U1 and U2 between C1 and C2, and between C4 and C5 if the conducted EMI noise is caused by bad grounding, wherein U1 is equal to U2, and the capacitances of C1, C2, C3, C4, C5, C6, C7 and C8 are respectively 22muF, 22muF, 0.1muF, 0.1muF, 0.1muF, 0.1muF, 100muF, and 10pF; and calculating the characteristic impedance of the PCB circuit by using electromagnetic simulation software, and carrying out signal integrity analysis according to the frequency characteristics of the transmission signal to realize the optimum impedance match of the PCB circuit if the conducted EMI noise is caused by PCB impedance mismatch.

Owner:NANJING HUASHI ELECTRONICS SCI

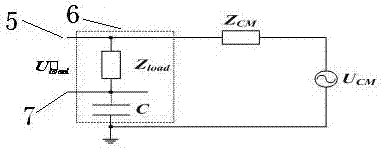

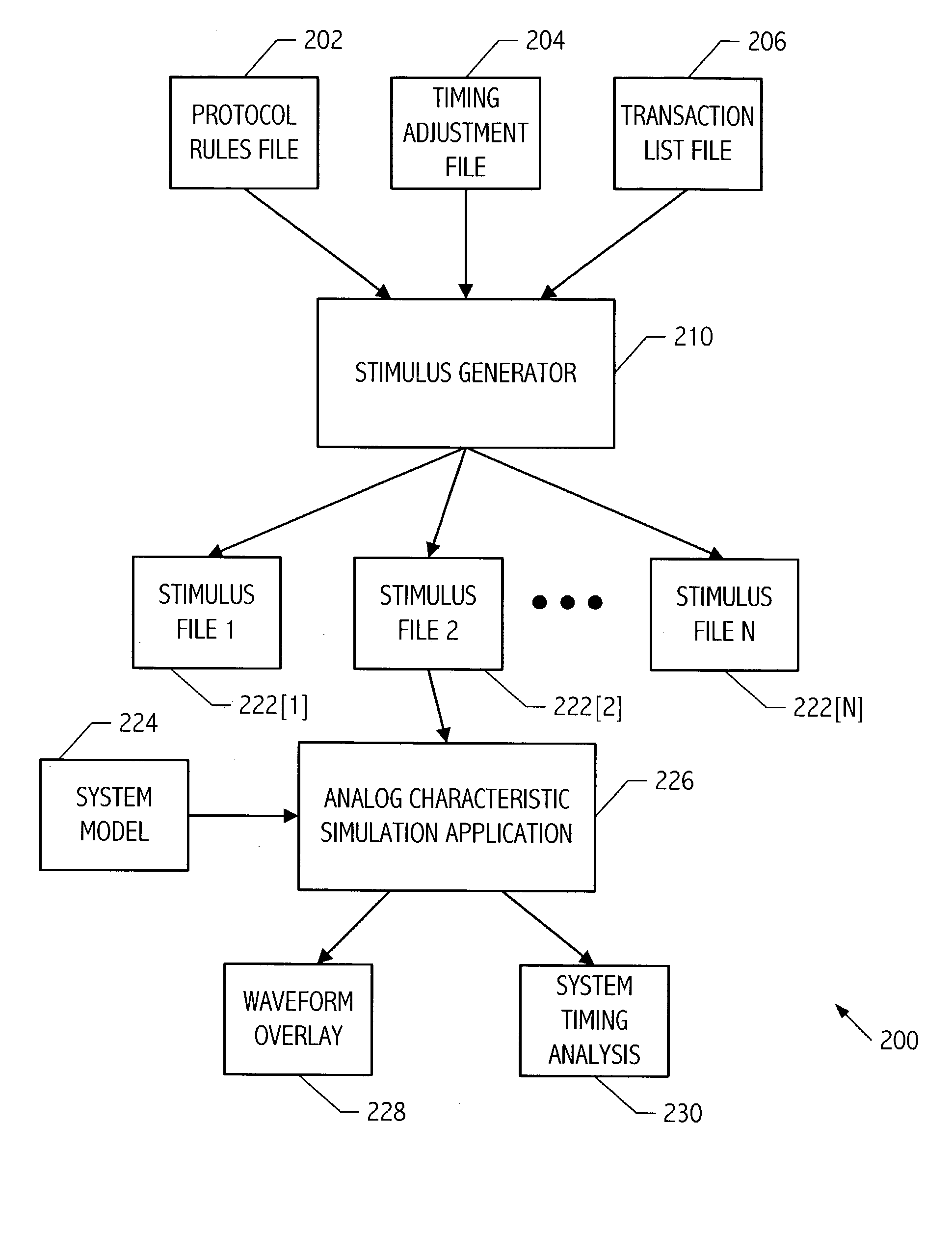

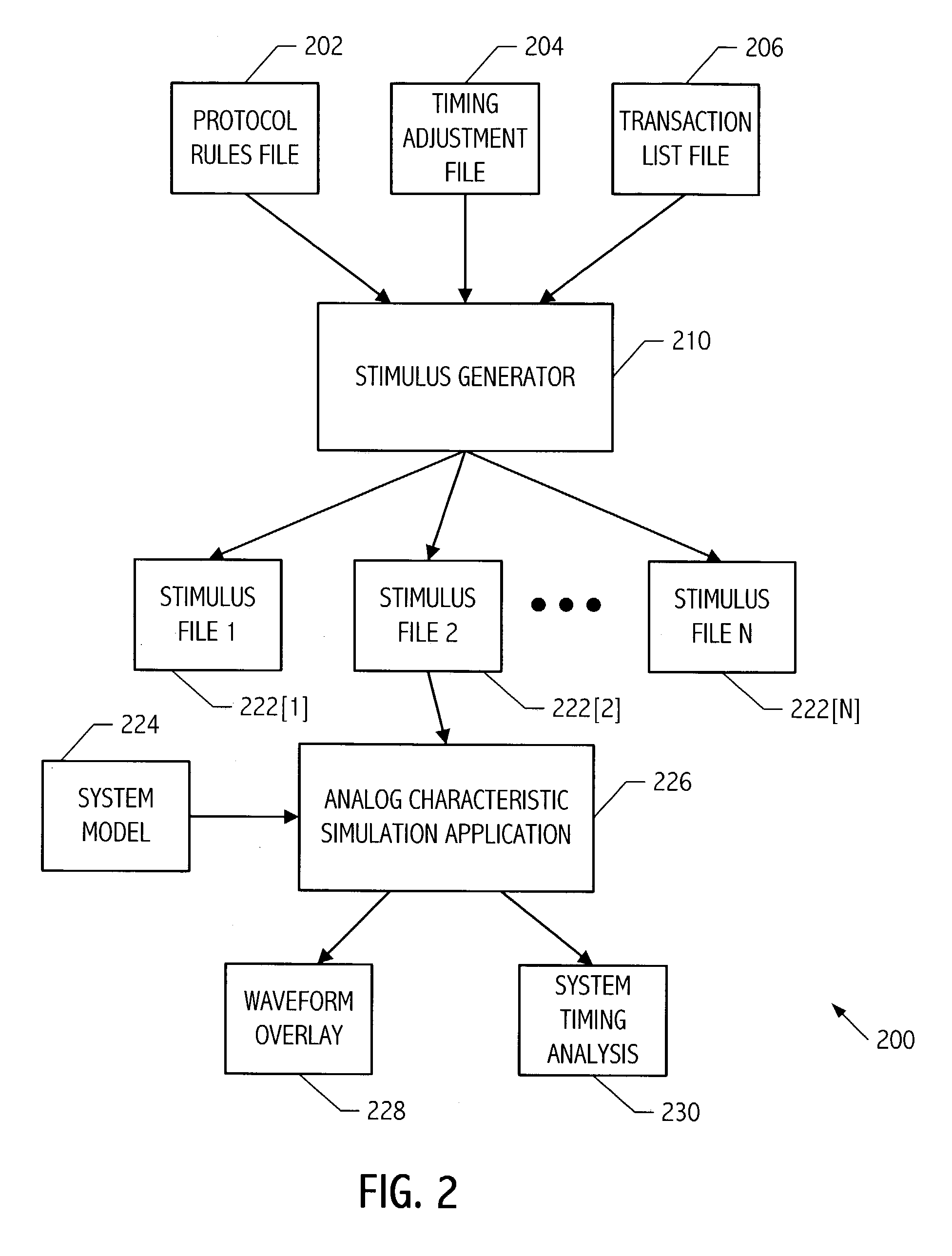

Programmable pattern generation for dynamic bus signal integrity analysis

InactiveUS7266488B1Computation using non-contact making devicesDetecting faulty computer hardwareStimulus patternPattern generation

A technique for performing signal integrity analysis of a system includes providing a stimulus pattern and a model of the system and performing analog simulation of the model utilizing the stimulus pattern. The stimulus pattern includes sequences of signal transitions with associated transition times and the sequences of signal transitions conform to a bus protocol and the associated transition times are according to characteristics of the system. The stimulus pattern is generated by initializing each of the sequences of signal transitions to an initial signal value and the associated transition times to an initial time, generating subsequent signal values and subsequent transition times by applying protocol rules and calculating timing adjustments for each of a list of transactions; the subsequent signal values and subsequent transition times to be added to the sequences of signal transitions.

Owner:GLOBALFOUNDRIES INC

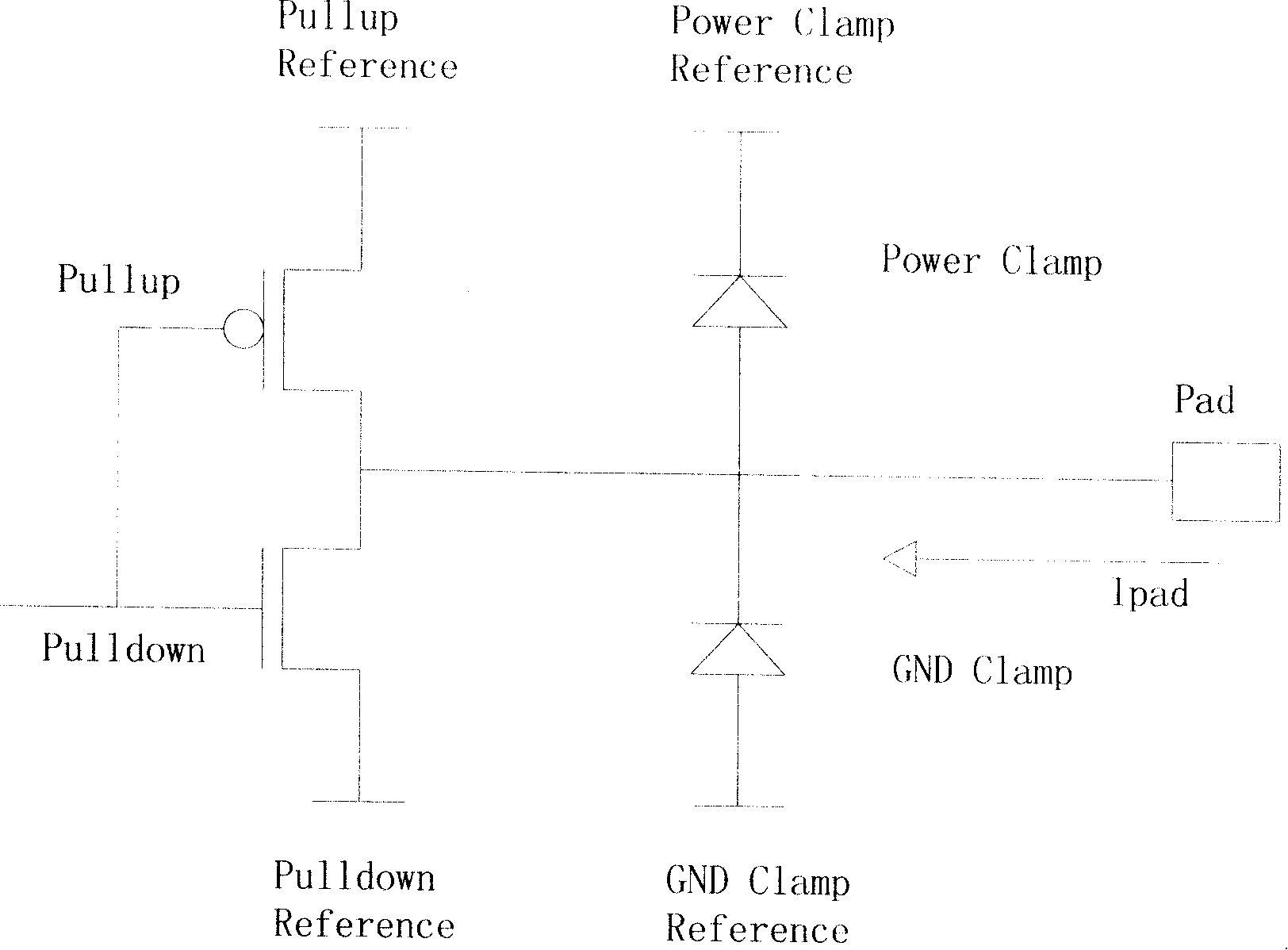

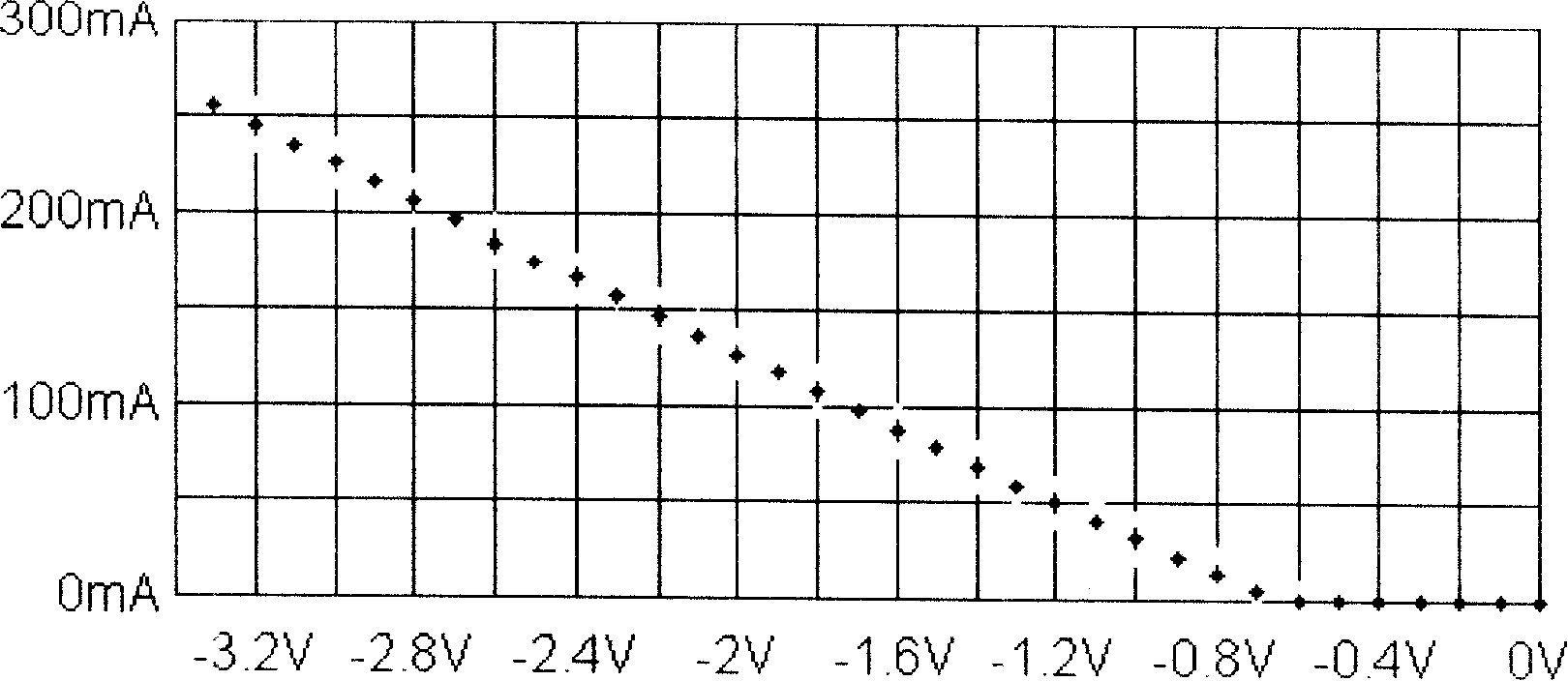

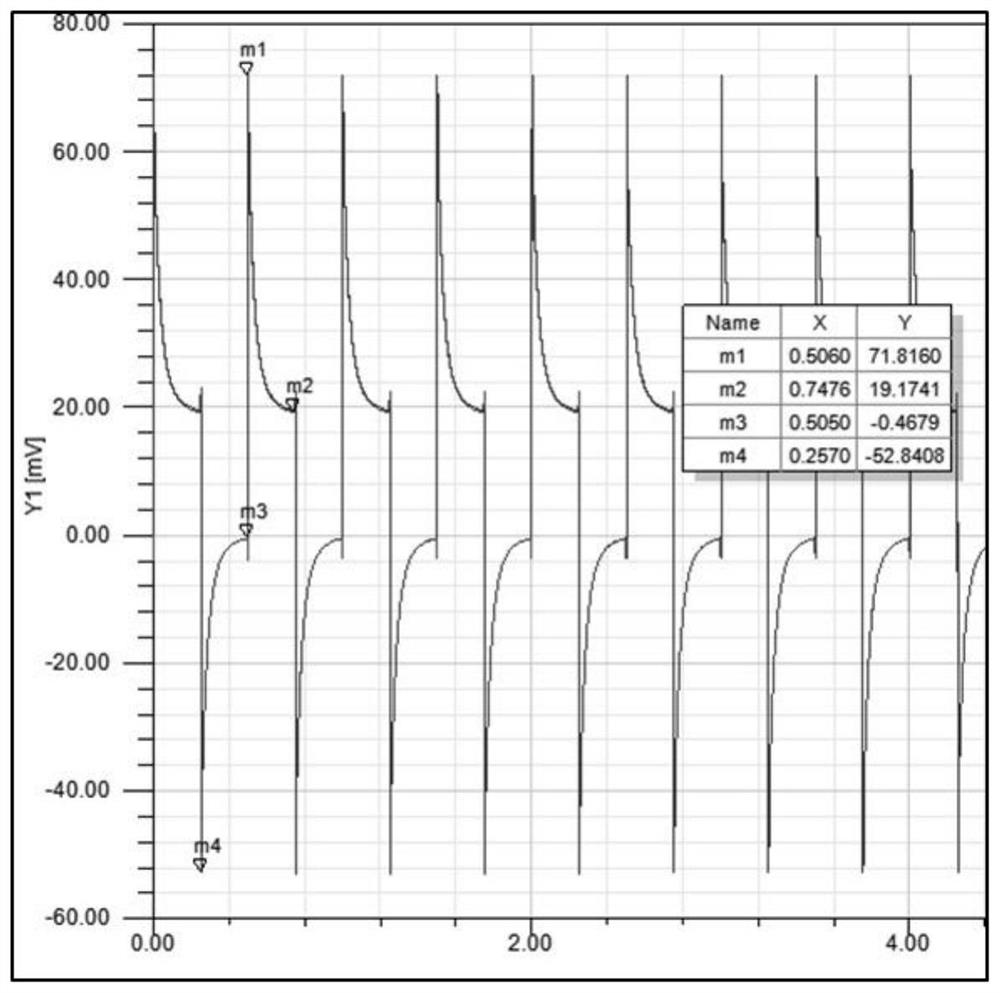

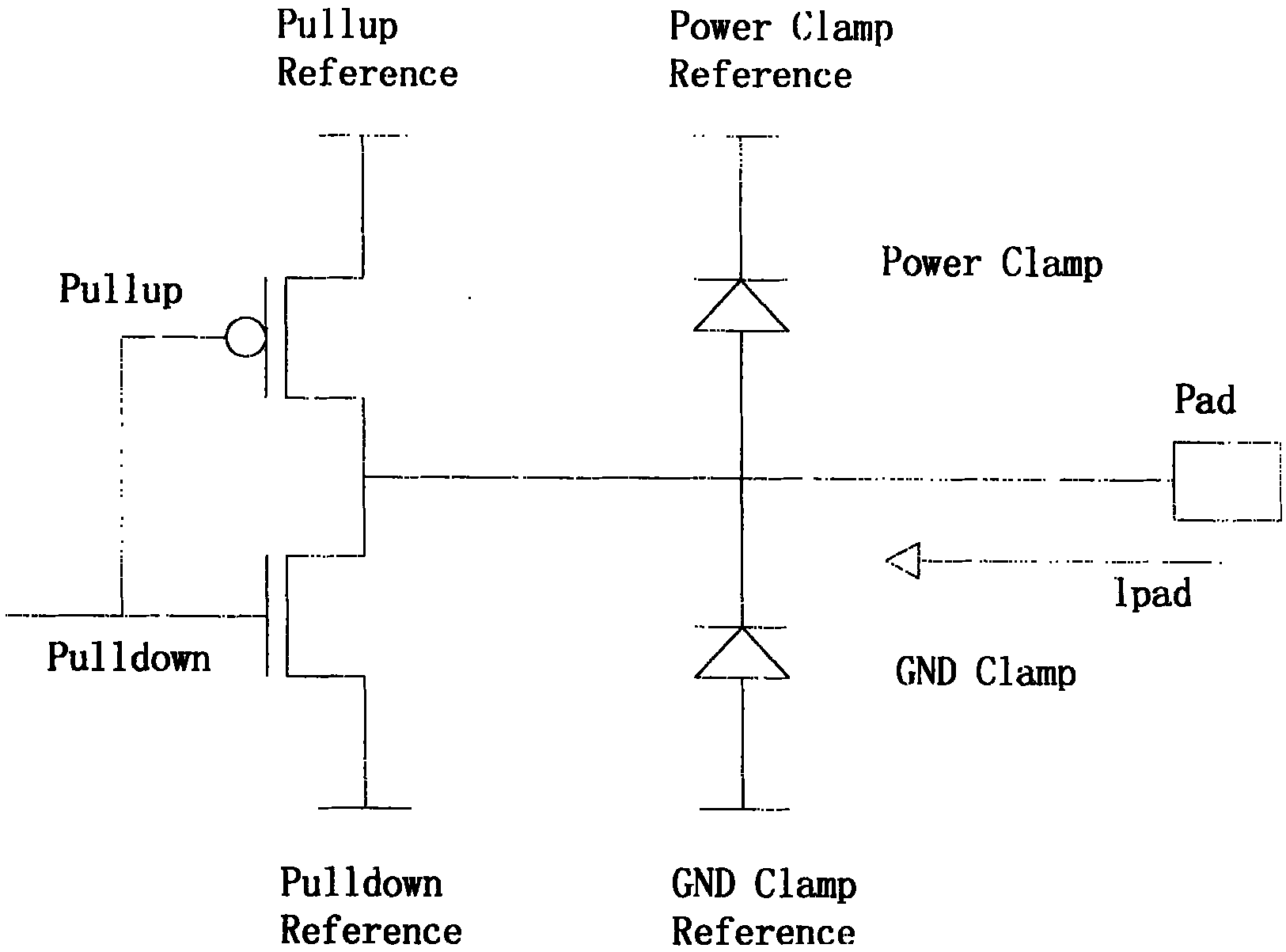

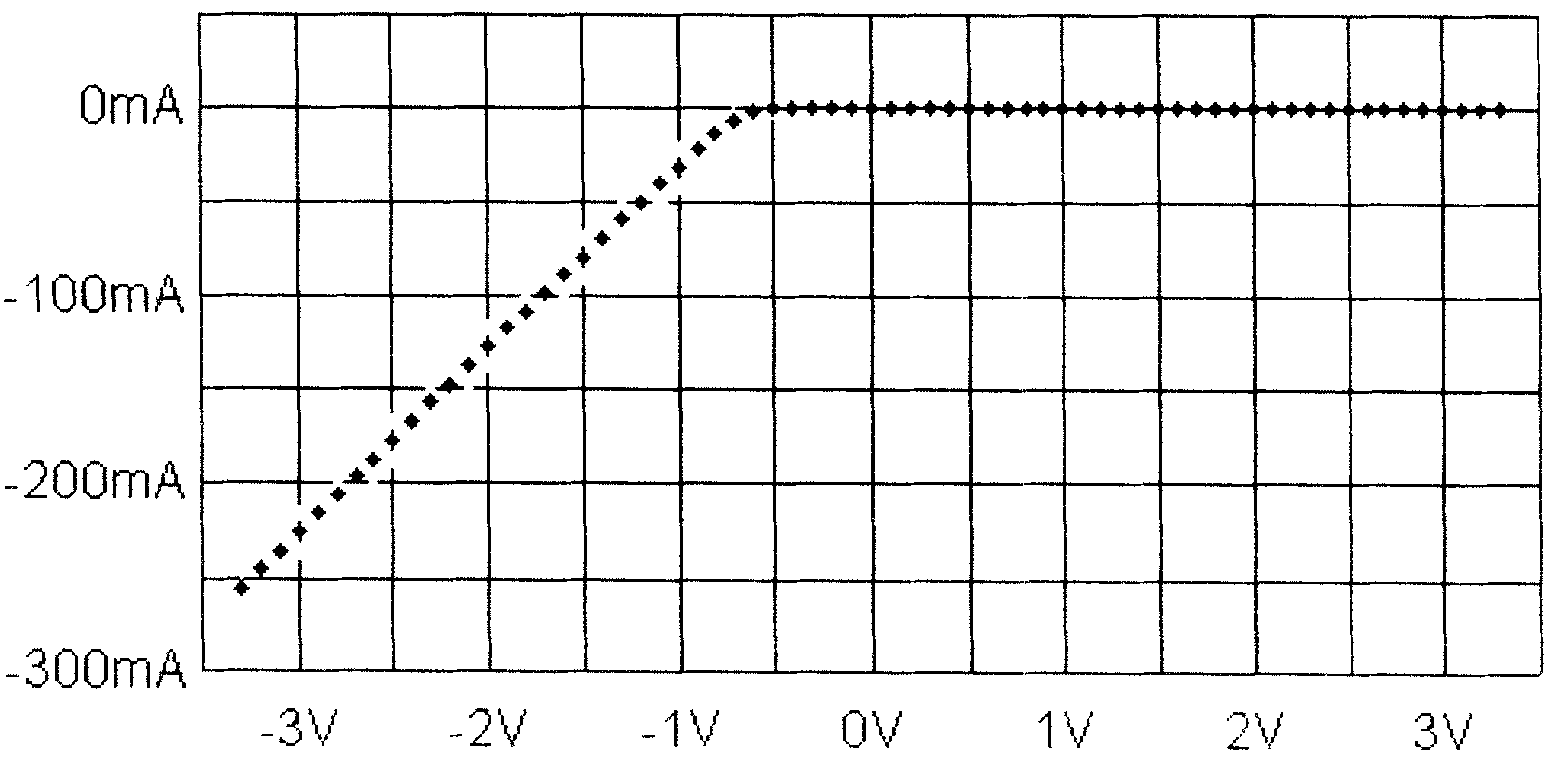

Method for reconstructing ground clamp curve and electric power clamp curve of chip IBIS model

InactiveCN101221587AIncrease credibilityIncrease authenticitySpecial data processing applicationsElectrical resistance and conductanceCurrent voltage

The invention discloses a method of reconstructing the ground clamping curve and the power clamping curve of a chip IBIS model, which reconstructs the current-voltage curve of the IBIS through a simple circuit model and is applicable to the signal integrity analysis and circuit simulation technical field. According to the characteristics showed by the power clamping curve and the ground clamping curve, proper discrete components mainly involving diodes and resistors are selected to build different equivalent circuits, and then the simulation of the equivalent circuits is carried out to obtain the accurate ground clamping curve and the power clamping curve of the IBIS model. The method which is simple and easy enables an engineer to carry out accurate simulation before obtaining the accurate IBIS model.

Owner:昆山杰得微电子有限公司

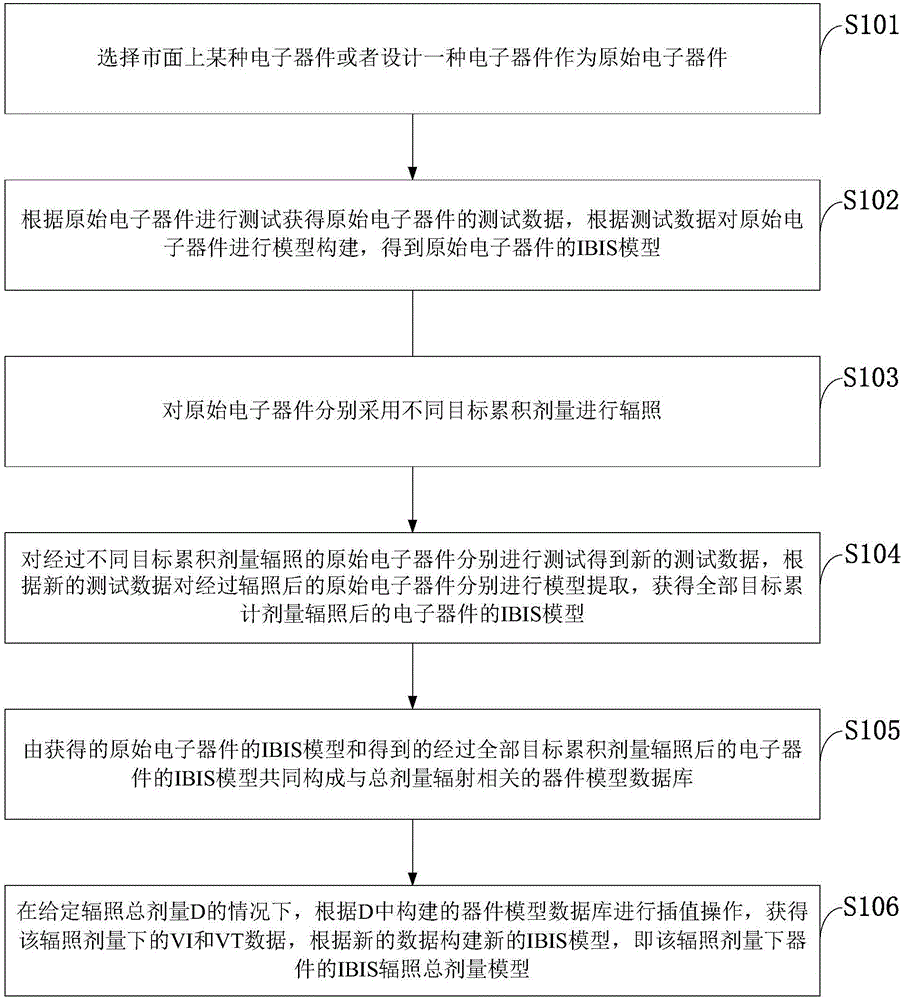

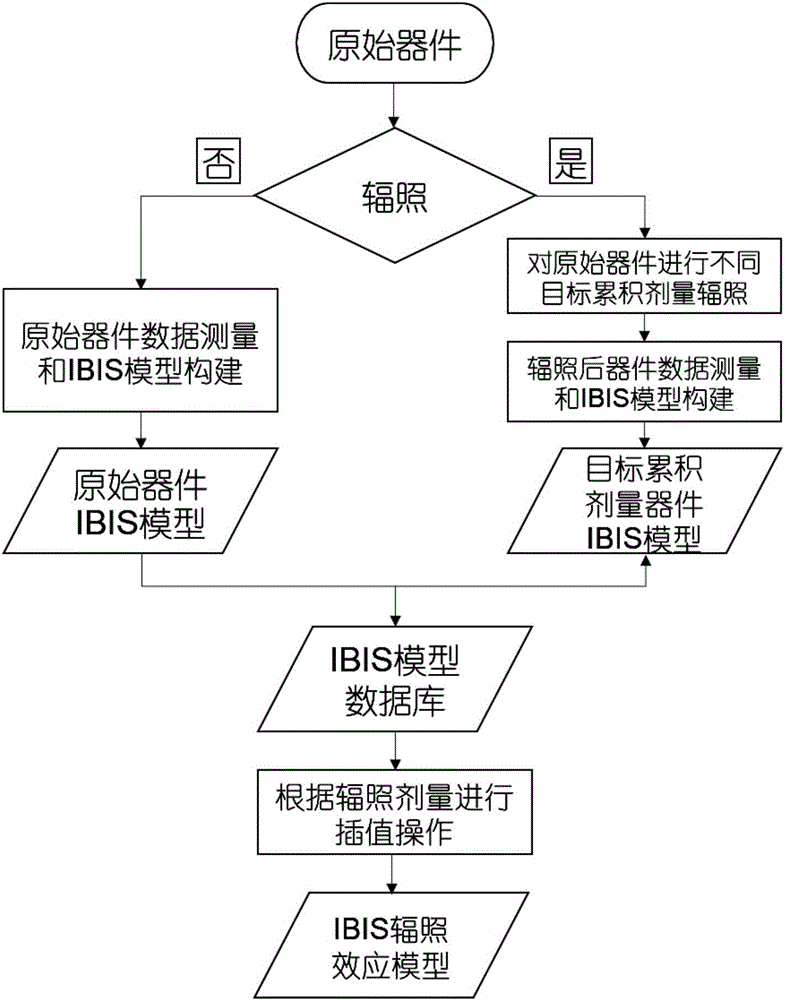

IBIS-based integrated circuit total dose effect modeling method

InactiveCN106649920ACAD circuit designSpecial data processing applicationsModel extractionSignal integrity analysis

The invention discloses an IBIS-based integrated circuit total dose effect modeling method. The IBIS-based integrated circuit total dose effect modeling method comprises the steps of performing irradiation on an original electronic device by adopting different target accumulated doses; performing data measurement and model extraction on the irradiated original electronic device, and establishing an IBIS model database of the electronic device under all the target accumulated doses; under the condition of giving a total irradiation dose D, performing interpolation operation on the established model database of the device according to the total irradiation dose D to obtain VI and VT interpolation data under the irradiation dose, and building an IBIS model according to the interpolation data, namely, an IBIS irradiation total dose effect model of the device under the irradiation dose. According to the method, the influence of irradiation conditions on PCB signal integrity is considered based on original PCB signal integrity analysis, and model support is provided for performing simulation analysis of PCB signal integrity problem under the irradiation condition.

Owner:XIDIAN UNIV

Method and apparatus for generating adaptive noise and timing models for VLSI signal integrity analysis

InactiveUS20090281781A1Speed up searchSearch processError detection/correctionComputer aided designCircuit under testSignal integrity analysis

A method, apparatus and program product are provided for performing a noise, timing, or other signal integrity simulation of a circuit under test. A simulation cache structure is accessed to retrieve cached simulation results for a first portion of the circuit under test. Simulation is performed on a second portion of the circuit under test to generate simulation results for the second portion. Simulation results are generated for the circuit under test by combining the simulation results for the second portion with the cached simulation results for the first portion.

Owner:GLOBALFOUNDRIES INC

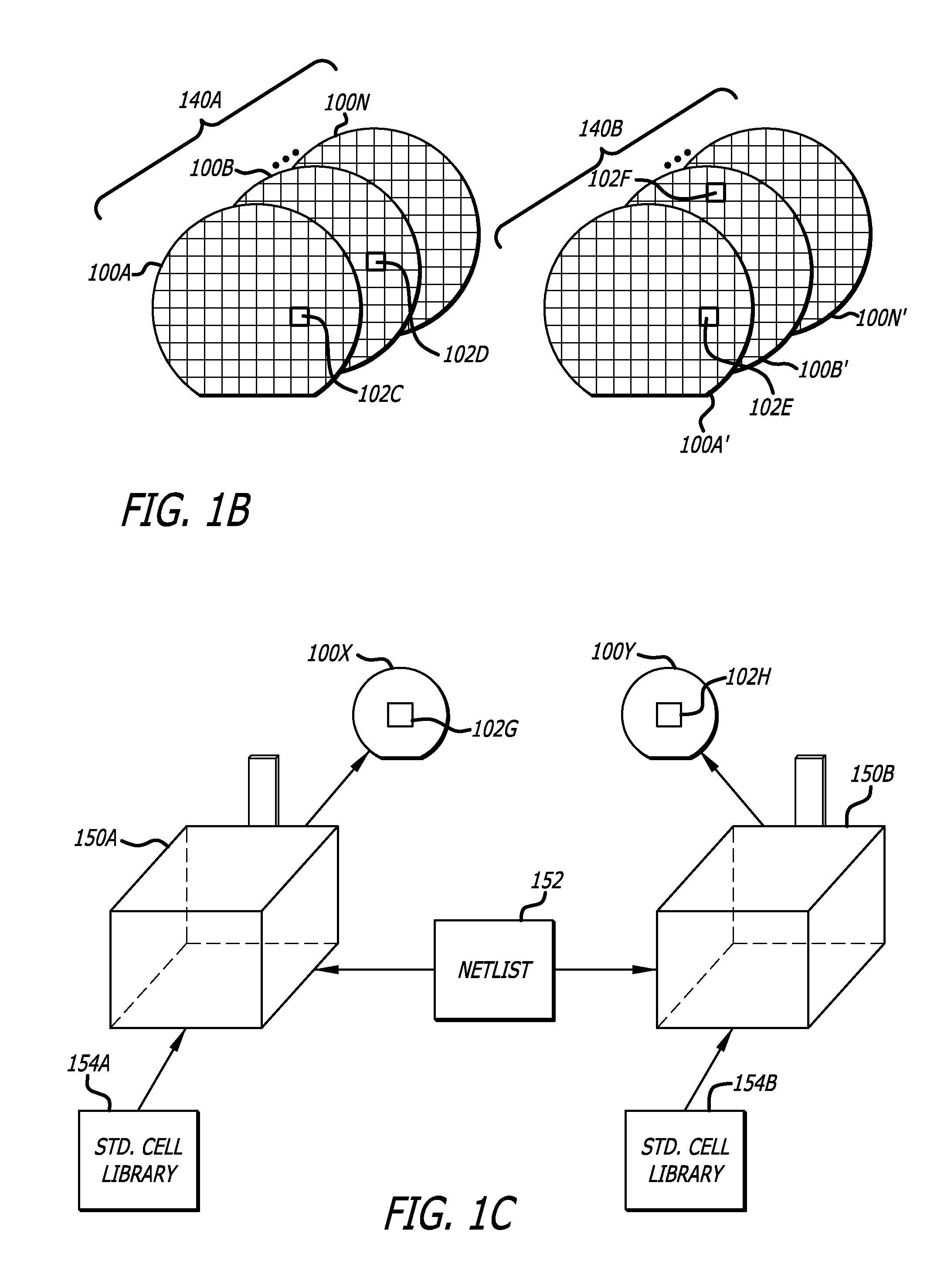

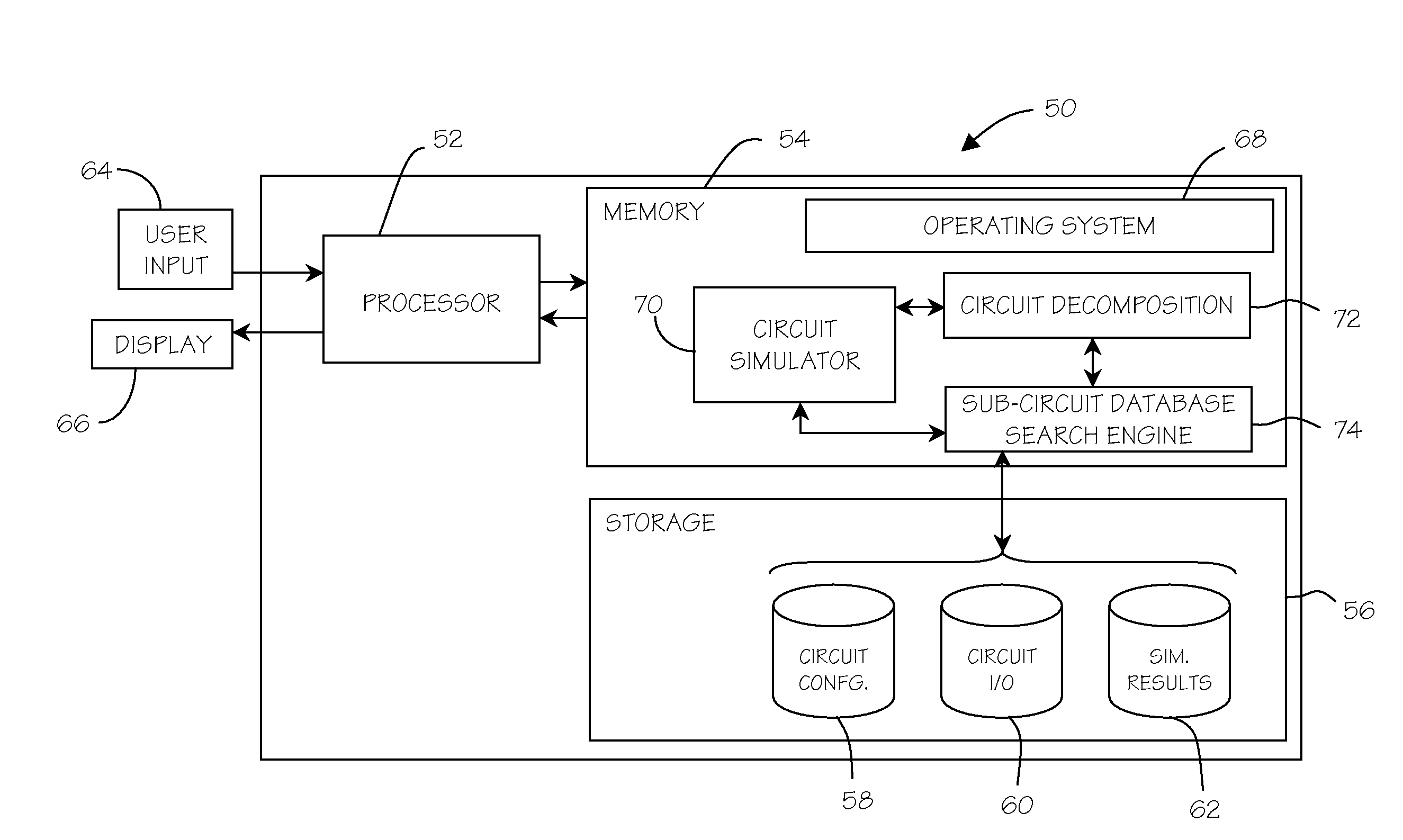

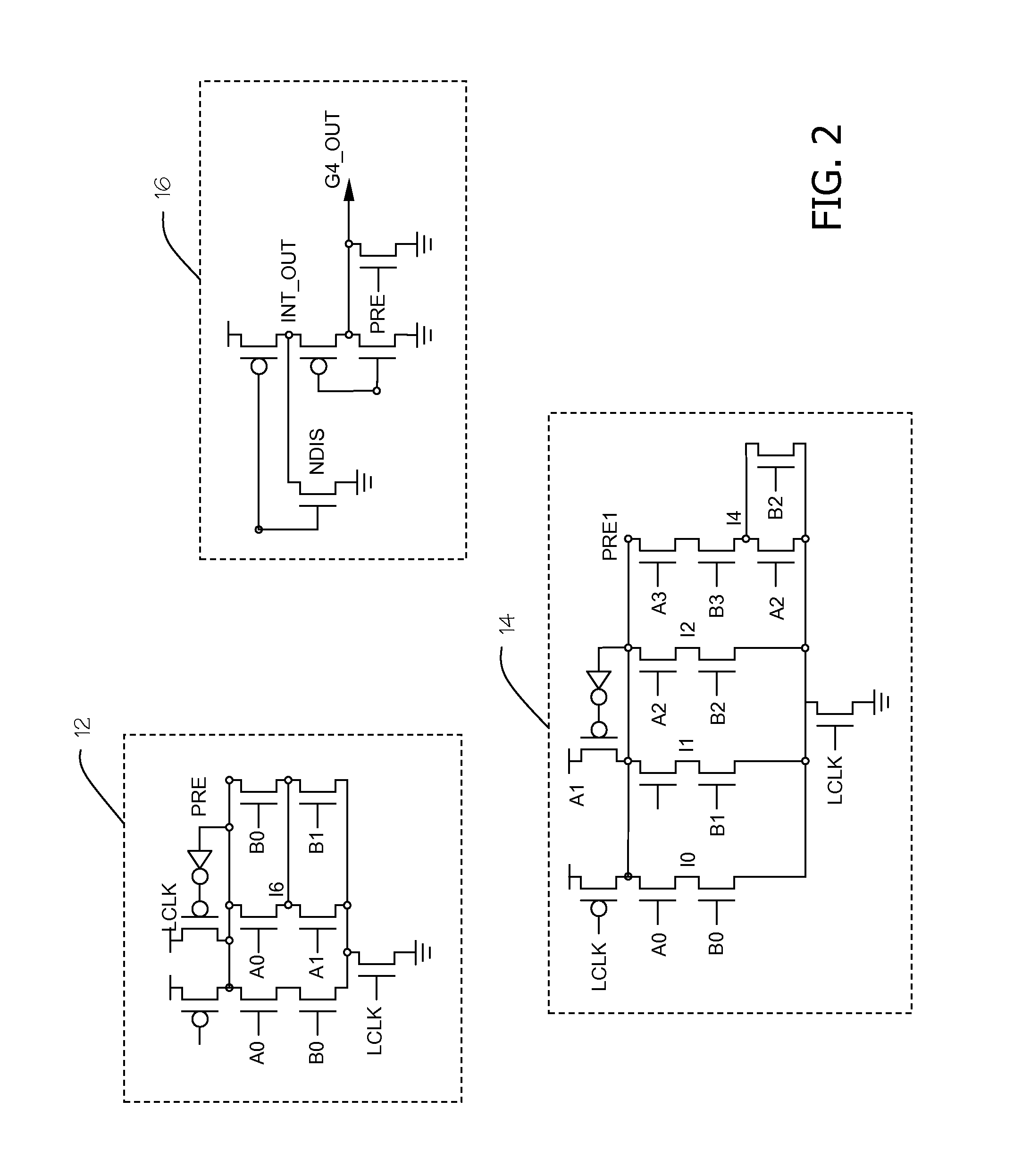

Hierarchical signal integrity analysis using interface logic models

ActiveUS7216317B2Easy to analyzeSimple interfaceCAD circuit designSoftware simulation/interpretation/emulationComputer architectureSignal integrity analysis

Performing signal integrity (SI) analysis on integrated circuit designs is becoming increasingly important as these designs increase in size and complexity. Dividing a design into blocks can simplify the resulting analysis. Additionally, such blocks can be replaced with timing models, which provide a compact means of exchanging interface timing information for the blocks. To further increase the speed and accuracy of SI analysis, enhanced interface logic models (SI-ILMs) can be used. An SI-ILM can include cells in timing paths that serve as the interface between the block and other parts of the design. The SI-ILM can also include internal nets that have cross-coupling effects on interface nets and nets outside the block. By including these internal nets, SI analysis at the top-level can be both fast and accurate.

Owner:SYNOPSYS INC

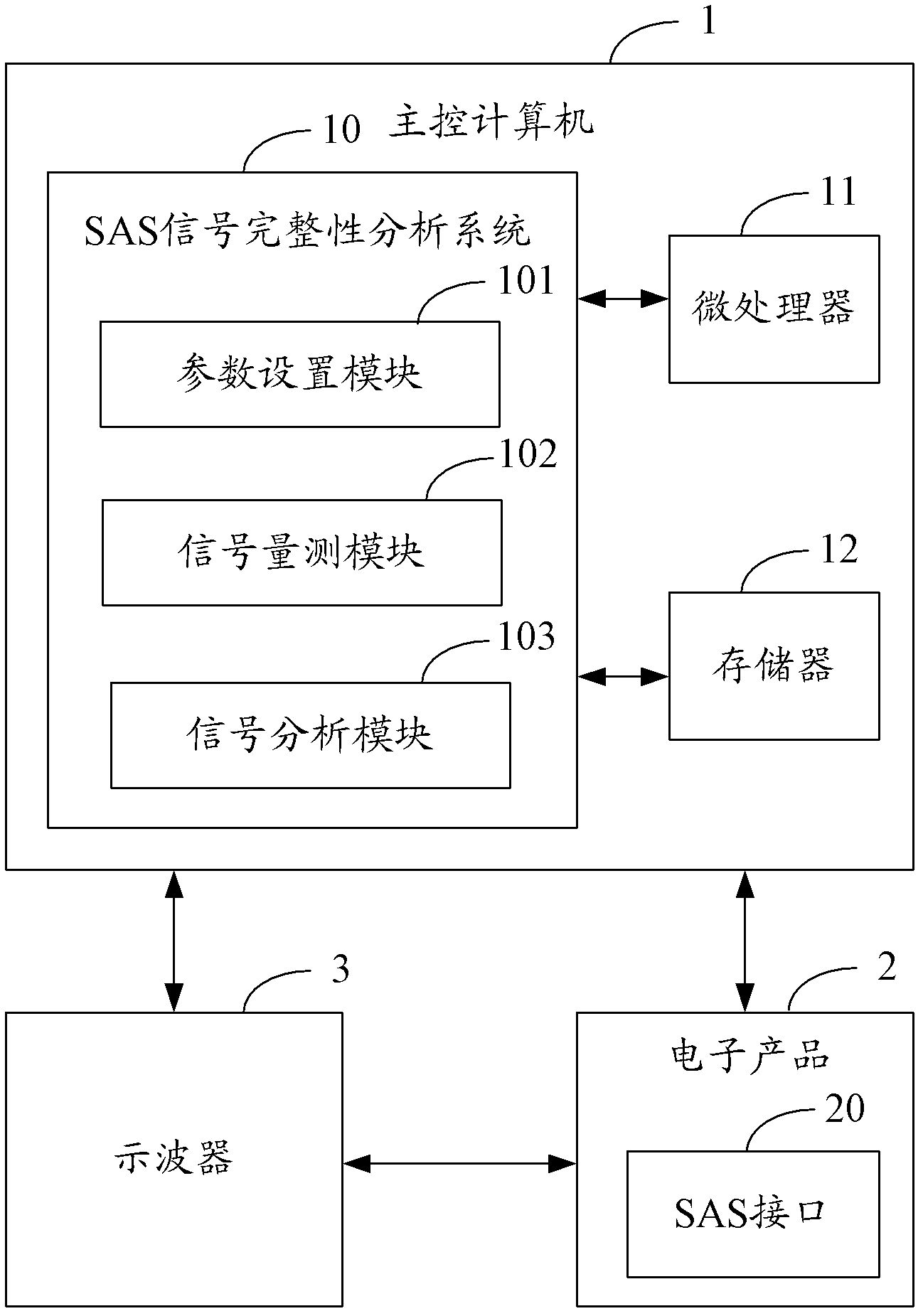

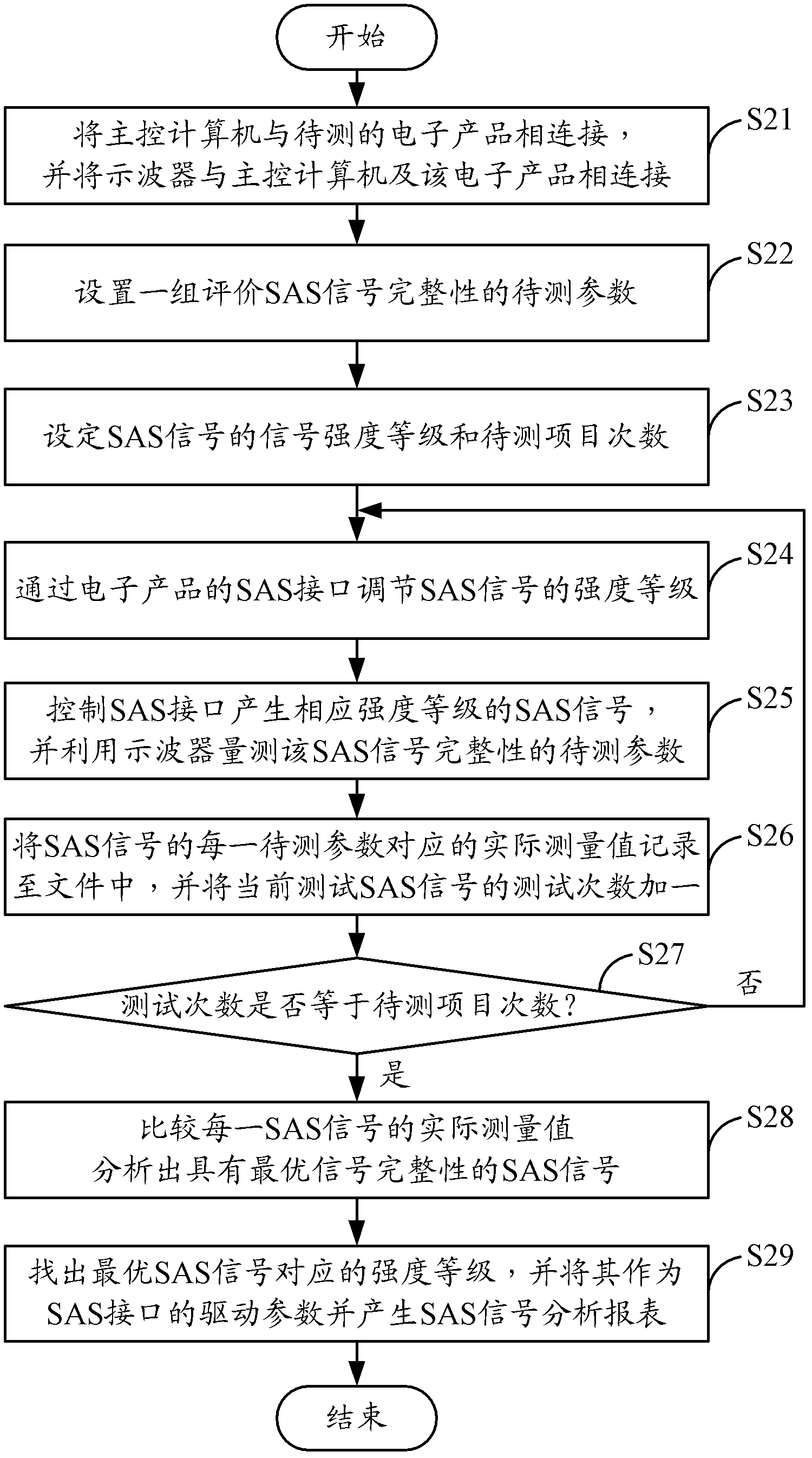

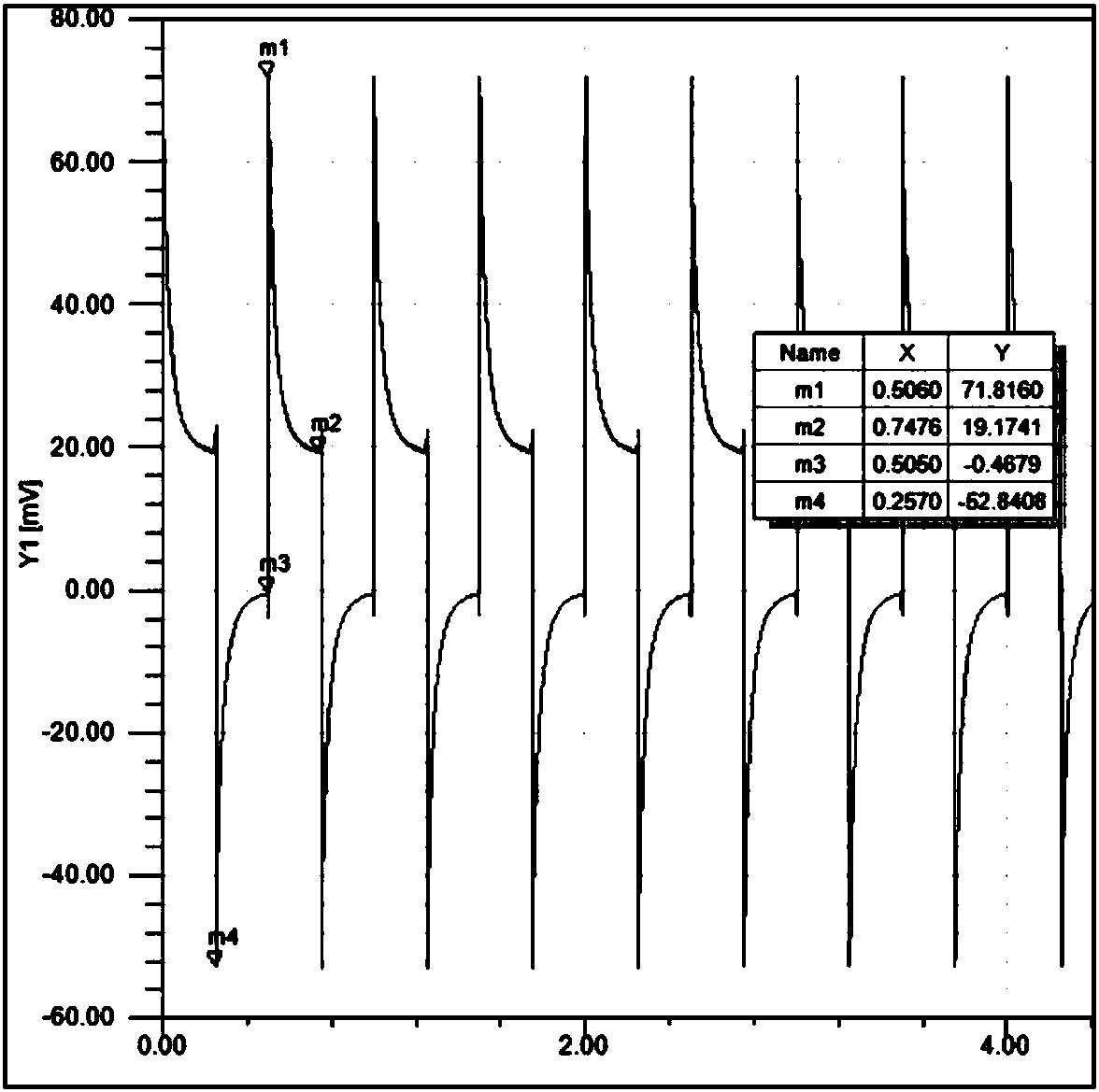

SAS signal integrity analysis system and method

Disclosed are a SAS signal integrity analysis system and a method. The system runs in a master computer, which is connected with an electronic product to be measured and an oscilloscope. The system comprises a parameter setting module, a signal measurement module and a signal analysis module. According to the method, a SAS signal can be acquired through a SAS interface of the electronic product; SAS signal integrity parameters are measured by the utilization of the oscilloscope; and a parameter corresponding to the SAS signal with optimum signal integrity is analyzed according to the SAS signal integrity parameters so as to find out a drive parameter which best fits the SAS interface.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

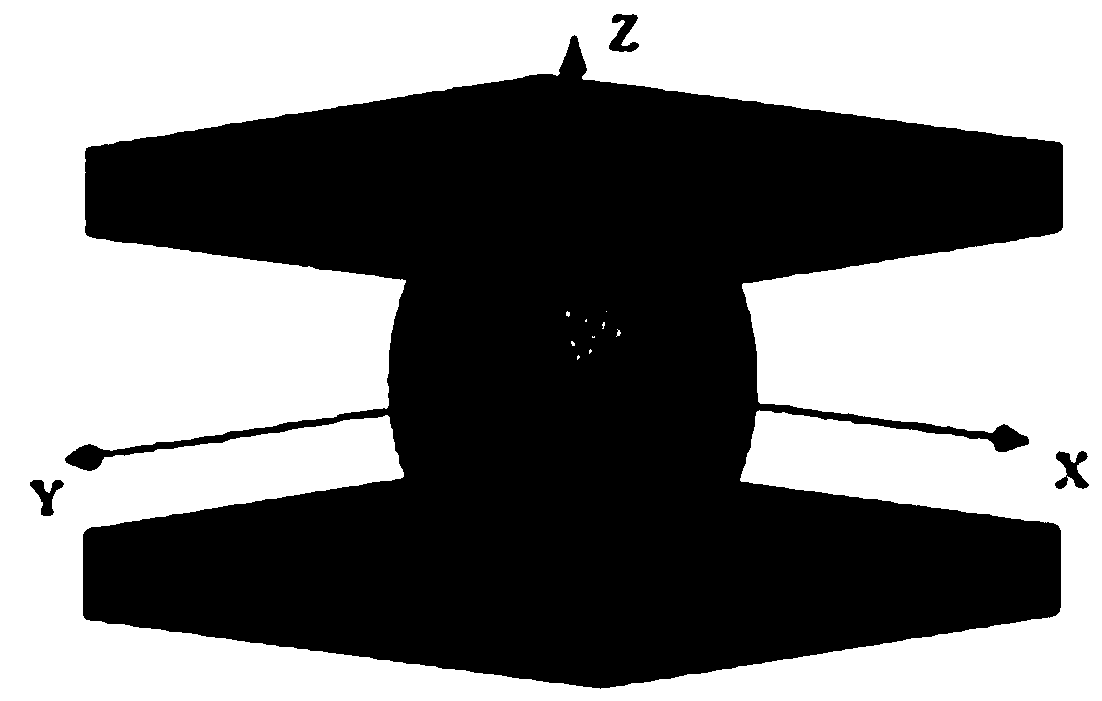

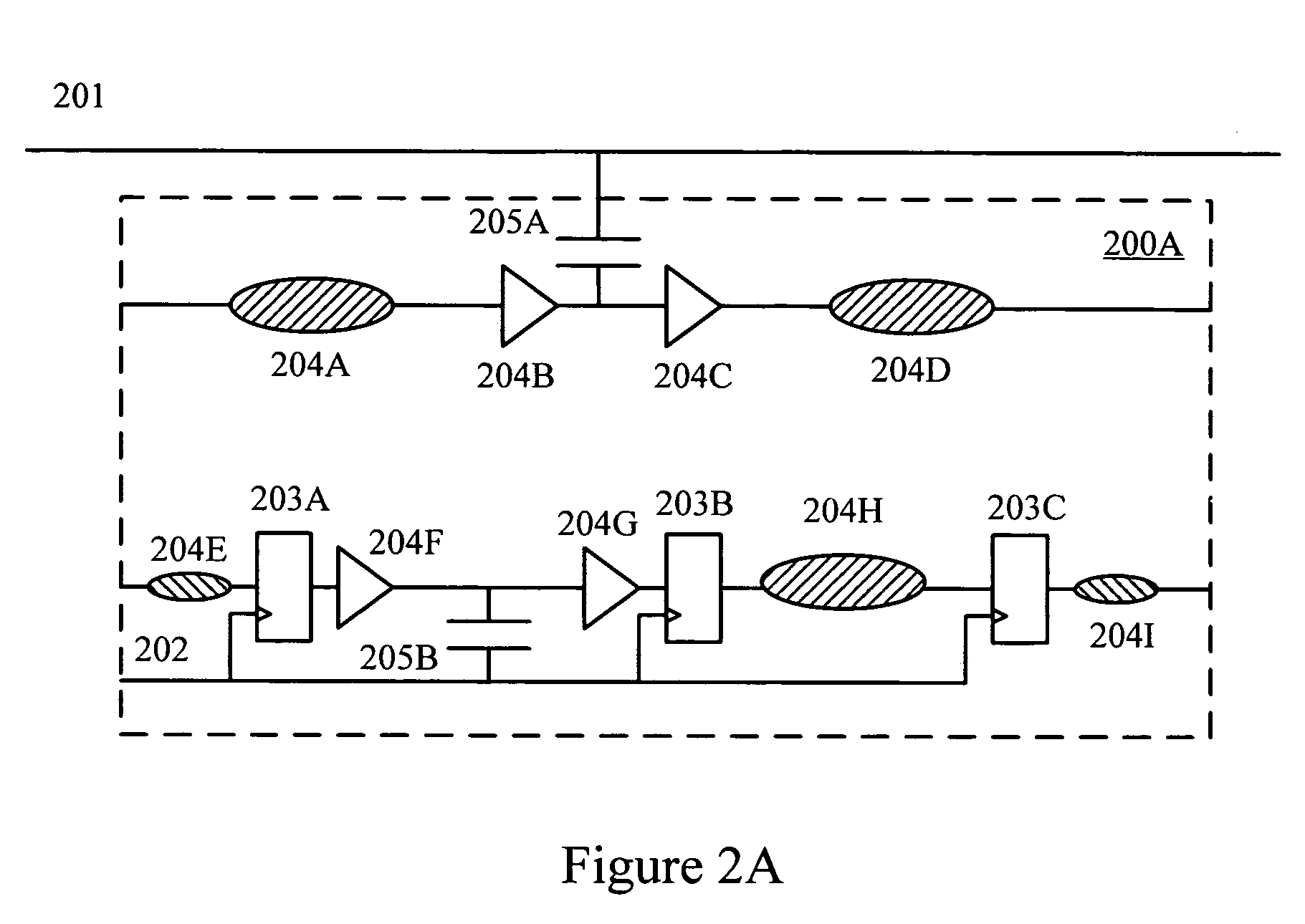

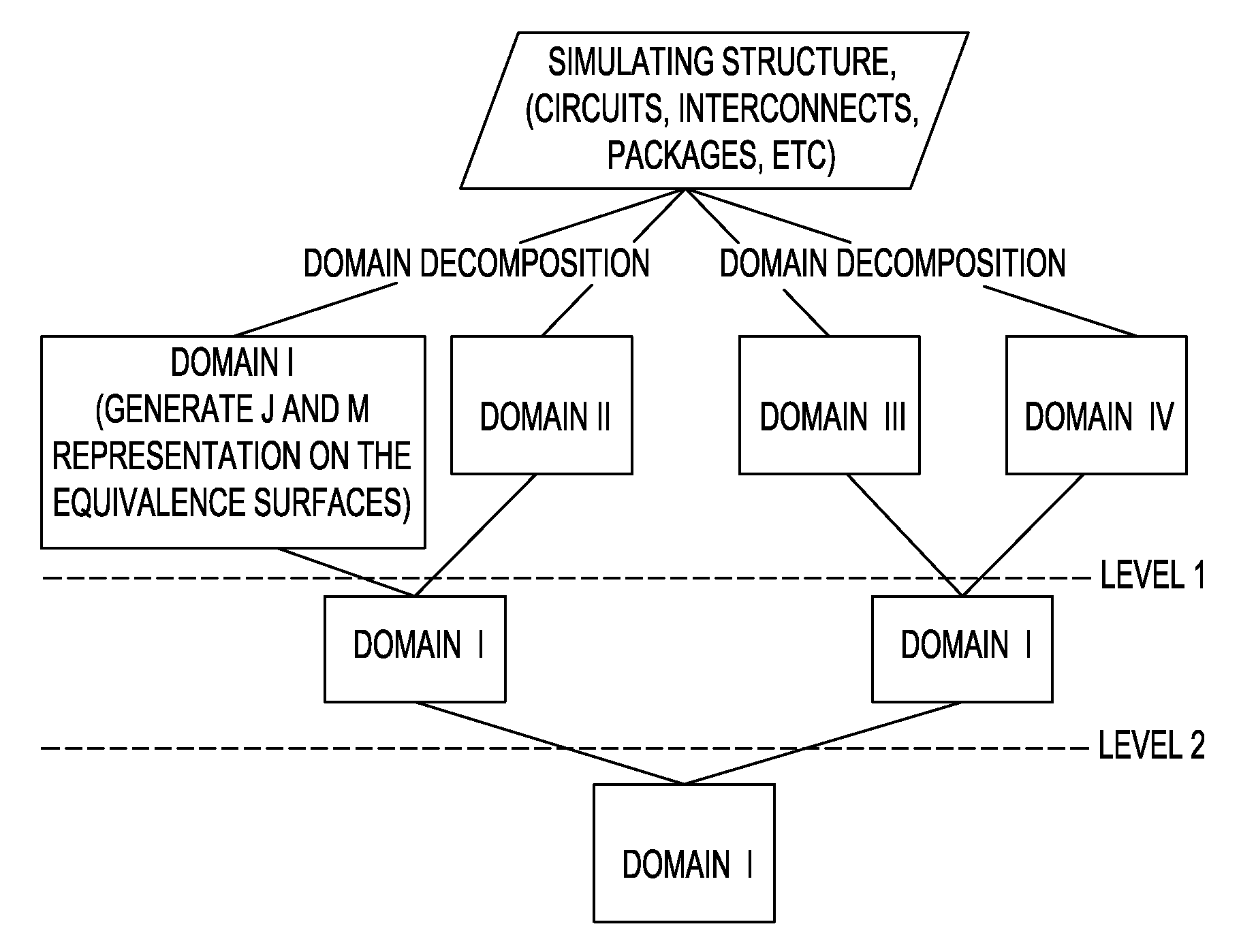

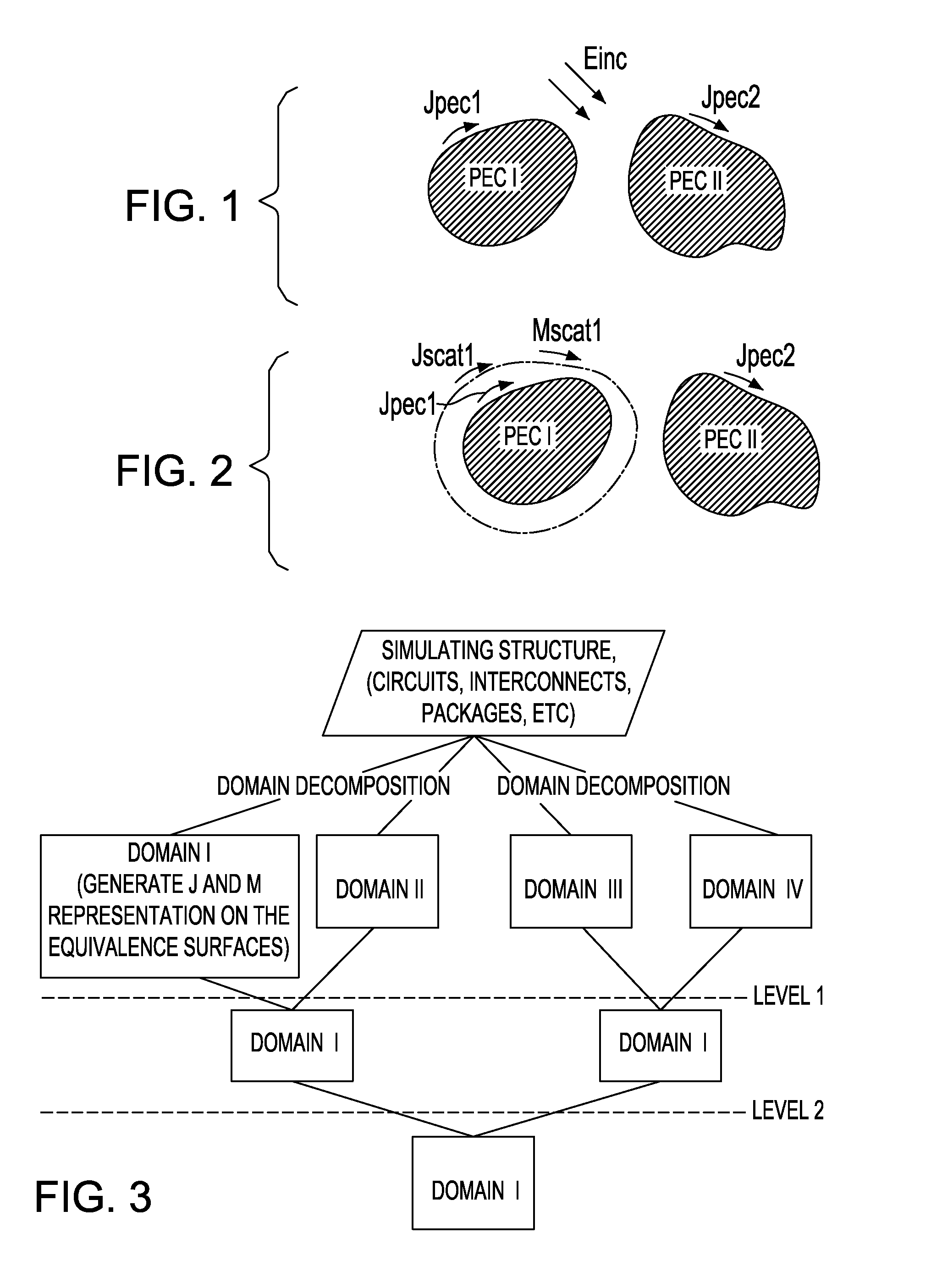

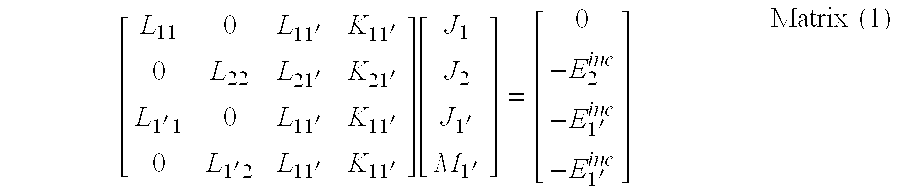

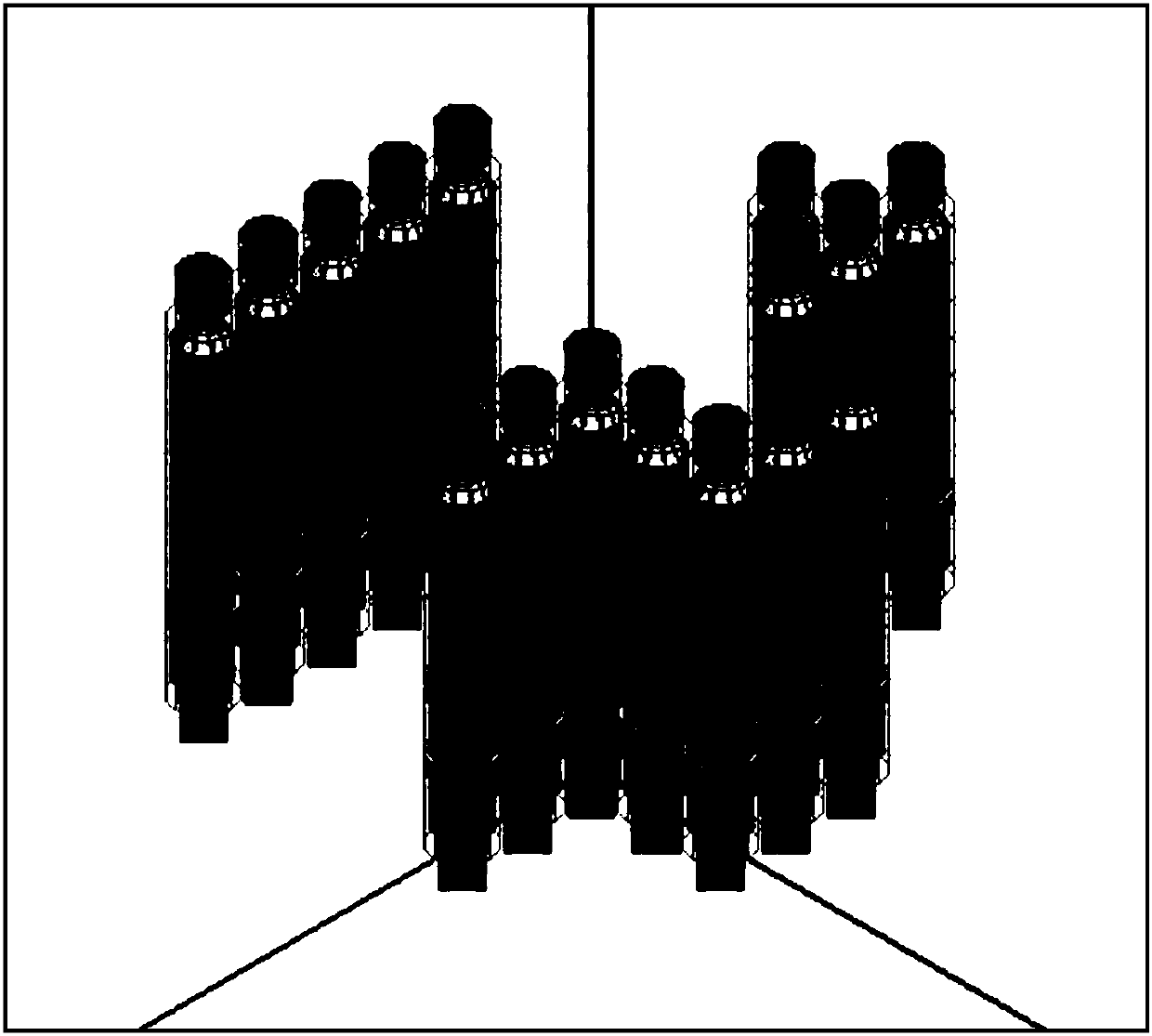

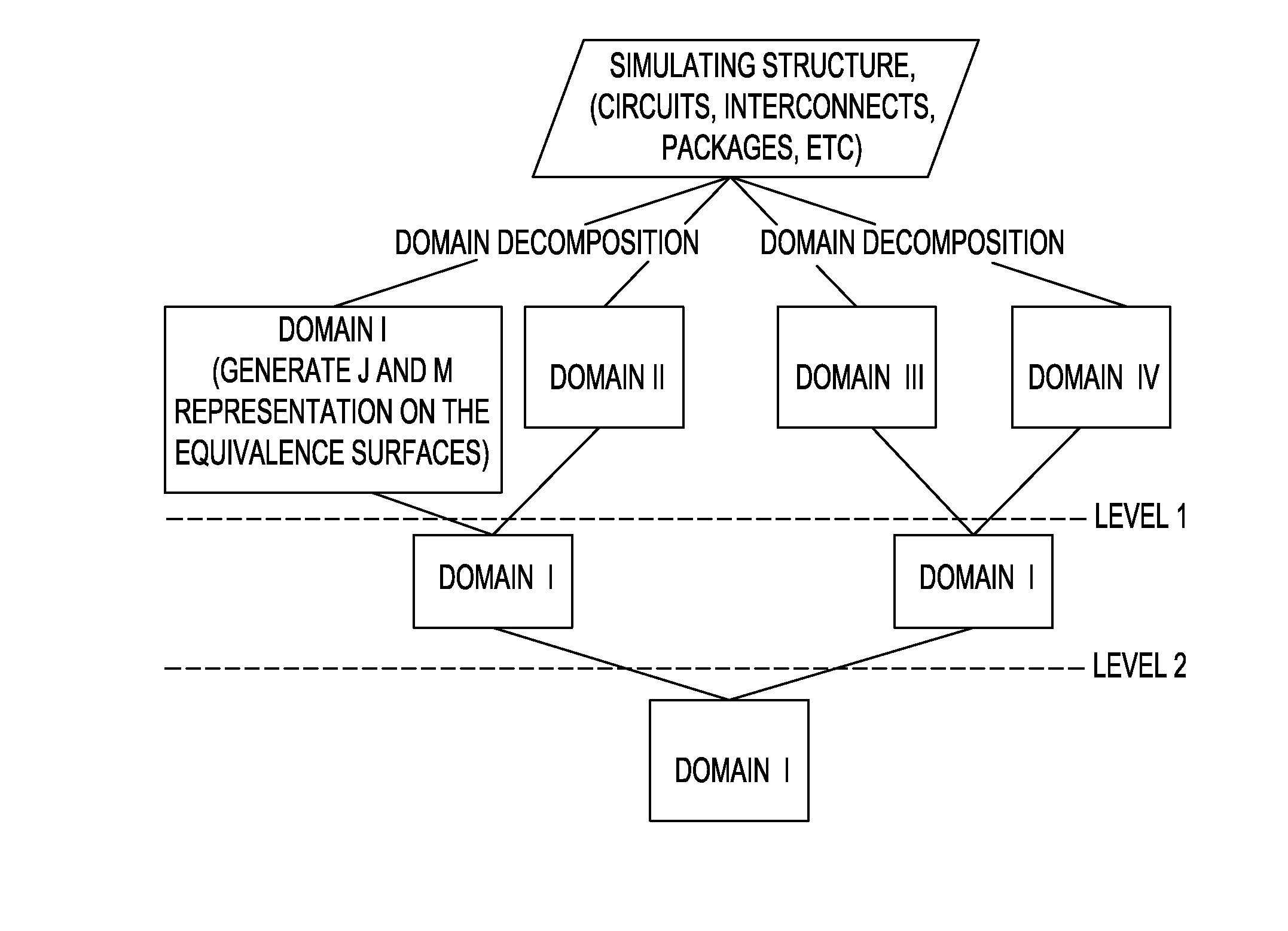

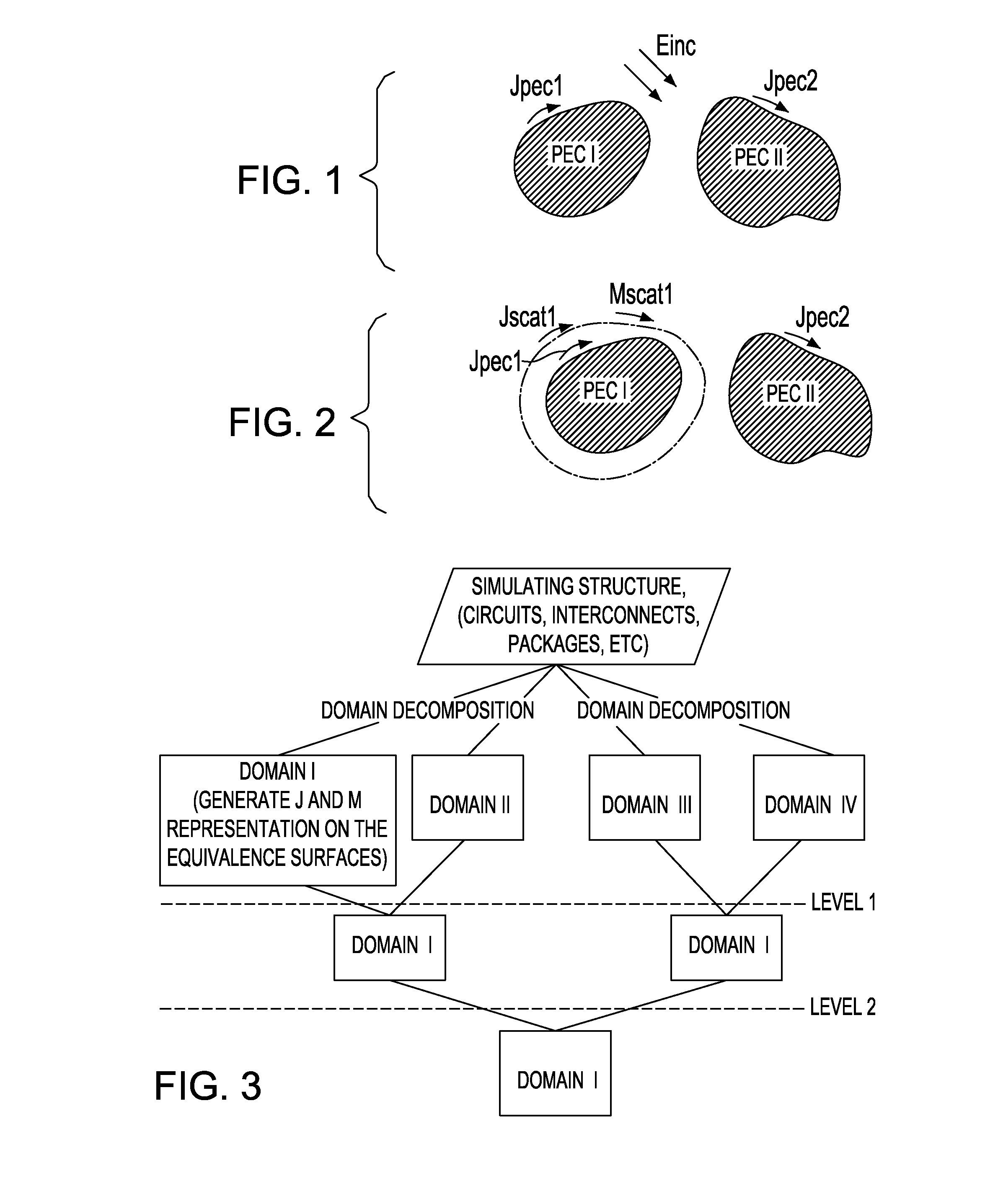

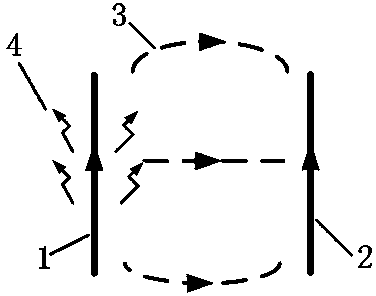

Huygens' box methodology for signal integrity analysis

InactiveUS20090089021A1Less complicated techniqueLess complicated methodDetecting faulty computer hardwareAnalogue computers for electric apparatusSignal integrity analysisEngineering

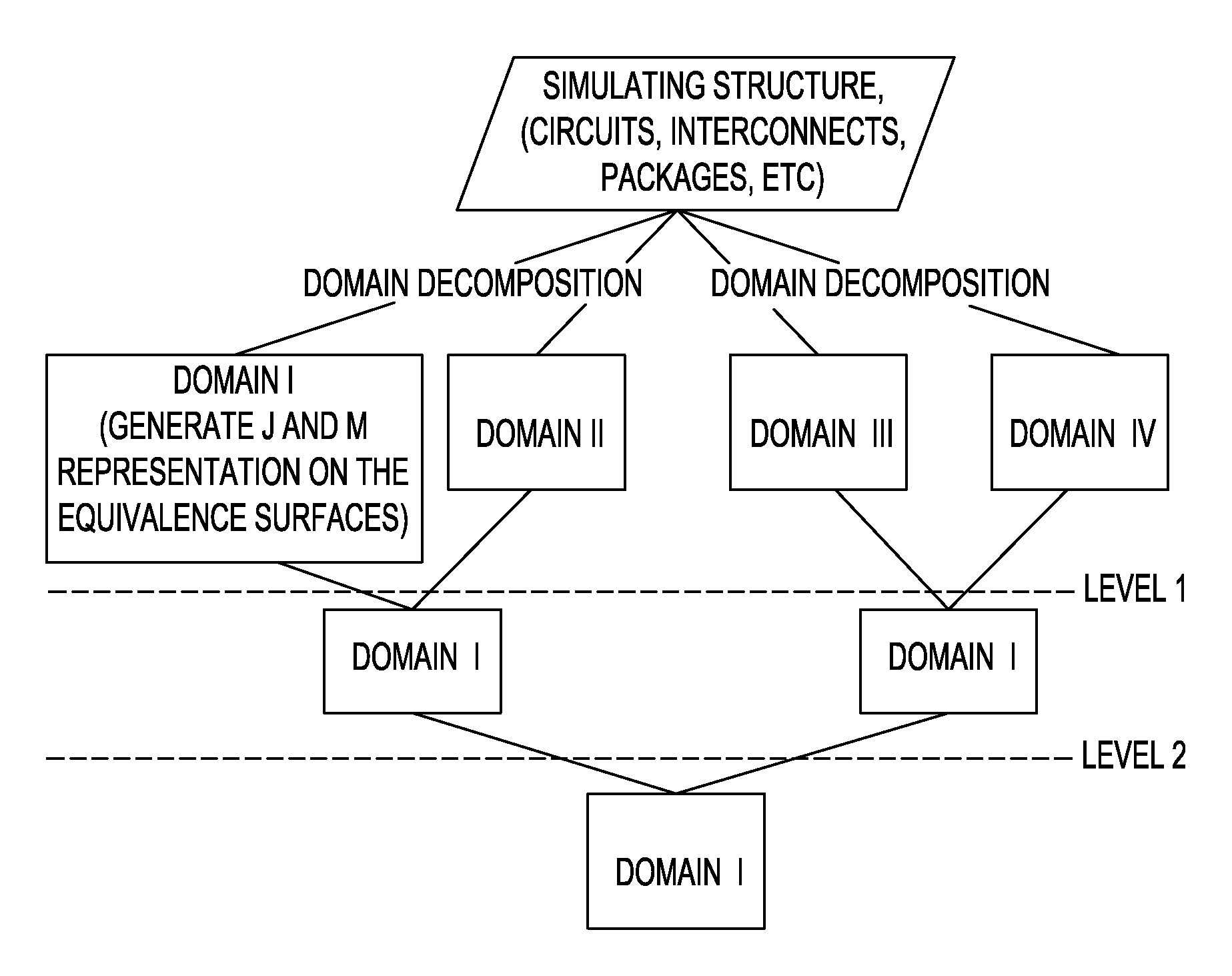

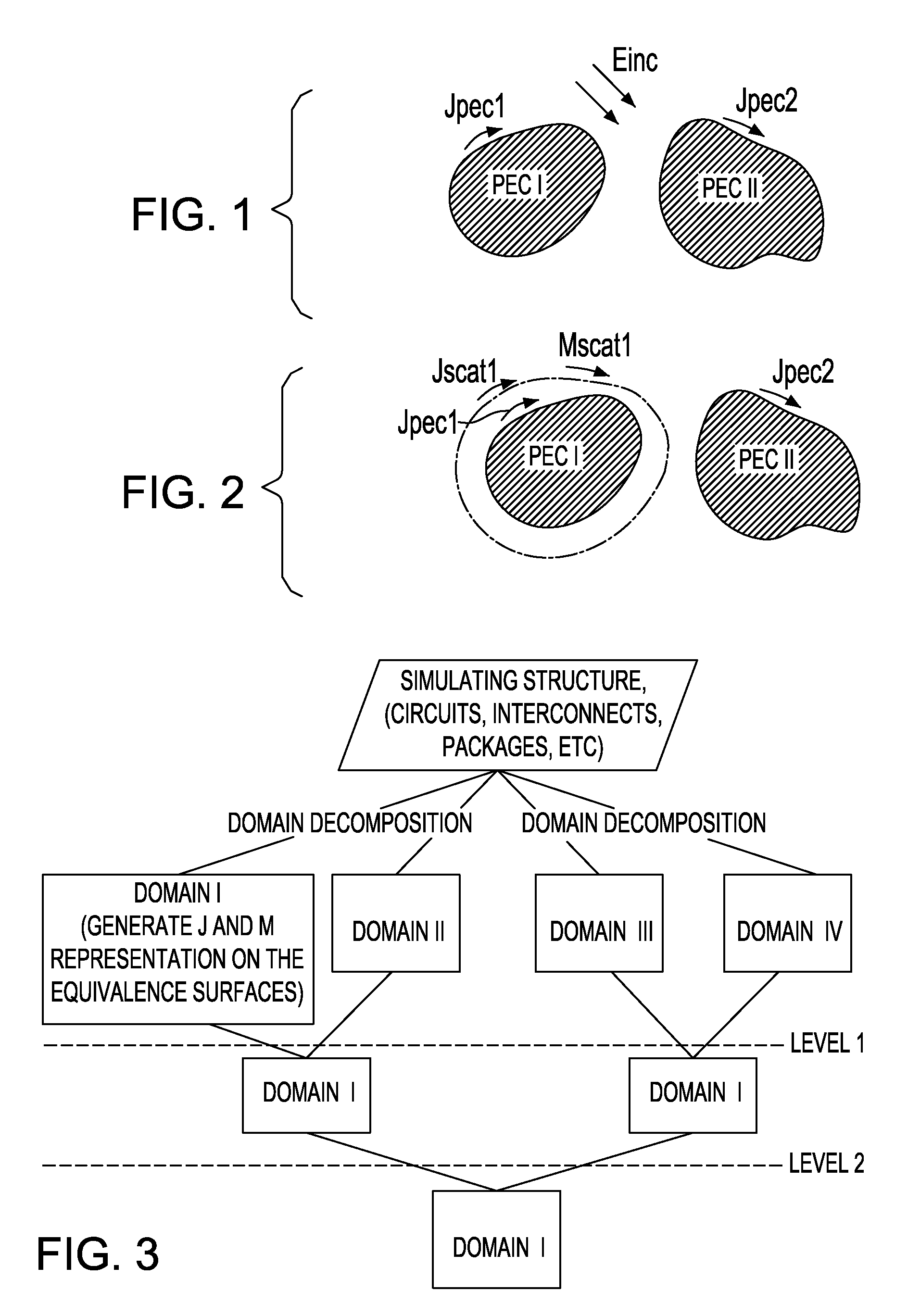

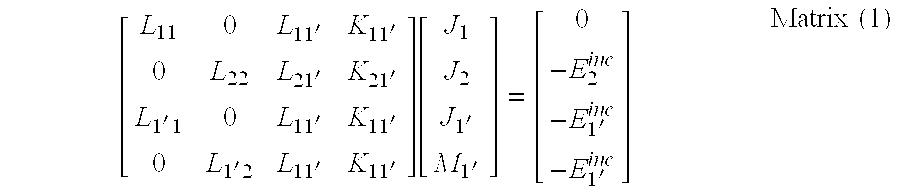

A method for performing a signal integrity analysis on an integrated circuit (IC) that includes a plurality of scatterers by dividing the scatterers into subgroups using a nested Huygens' equivalence principle algorithm and solving a set of equations realized thereby with a reduced coupling matrix. The method includes decomposing the IC design into a plurality of small non-overlapping circuit sub-domains, wherein each of the sub-domains is formed as a small, enclosed region. Each sub-domain is analyzed independently of the other sub-domains using only electric fields to represent the interactions of each sub-domains with the other sub-domains as equivalent currents on equivalent surfaces of the plurality of sub-domains. Neighboring equivalent sub-domains are grouped together to form larger sub-domains using equivalent currents on equivalent surfaces to represent the interactions of the sub-domains. The steps of analyzing and grouping the sub-domains are repeated until the grouping approaches a box comprising the entire domain, and that the domain interactions between every sub-domain have been analyzed.

Owner:IBM CORP +1

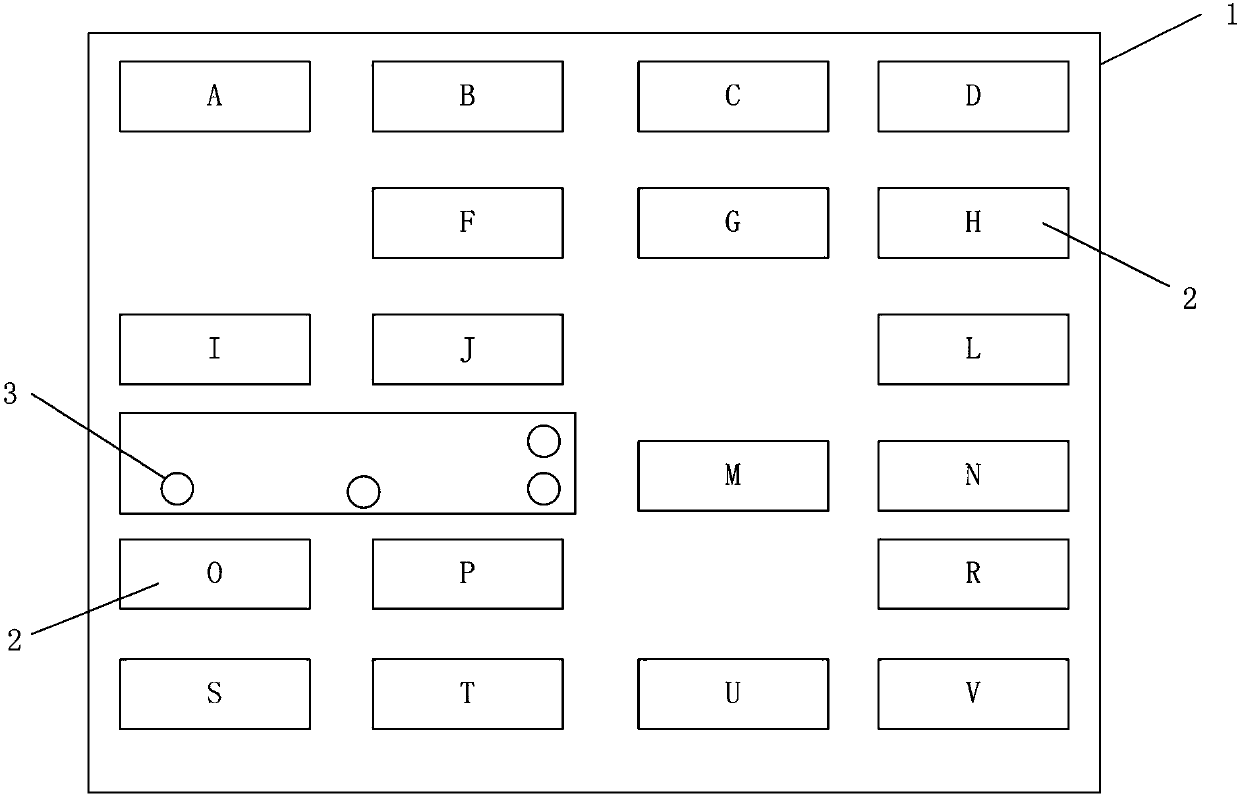

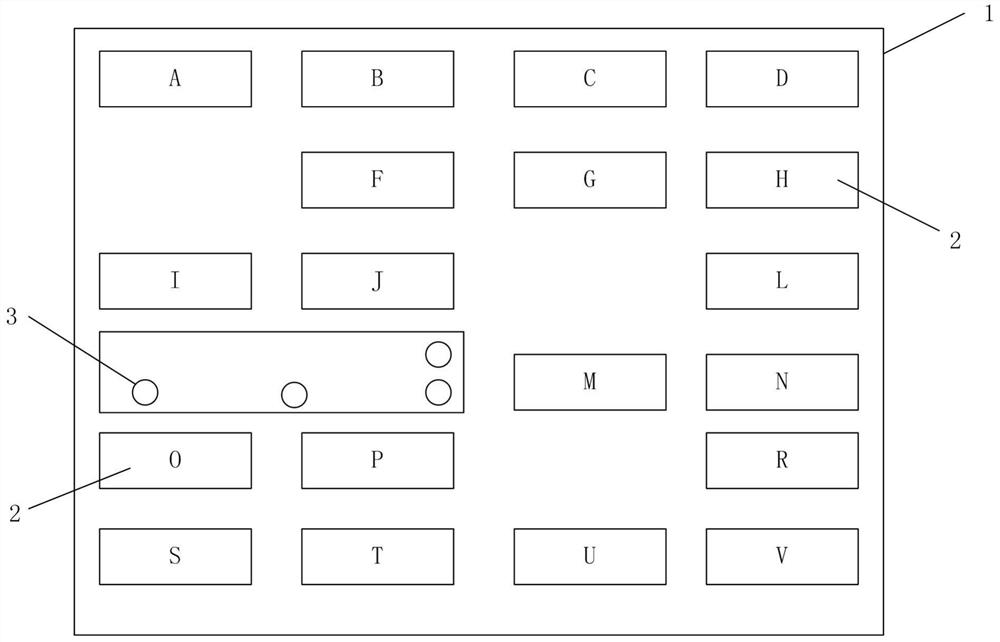

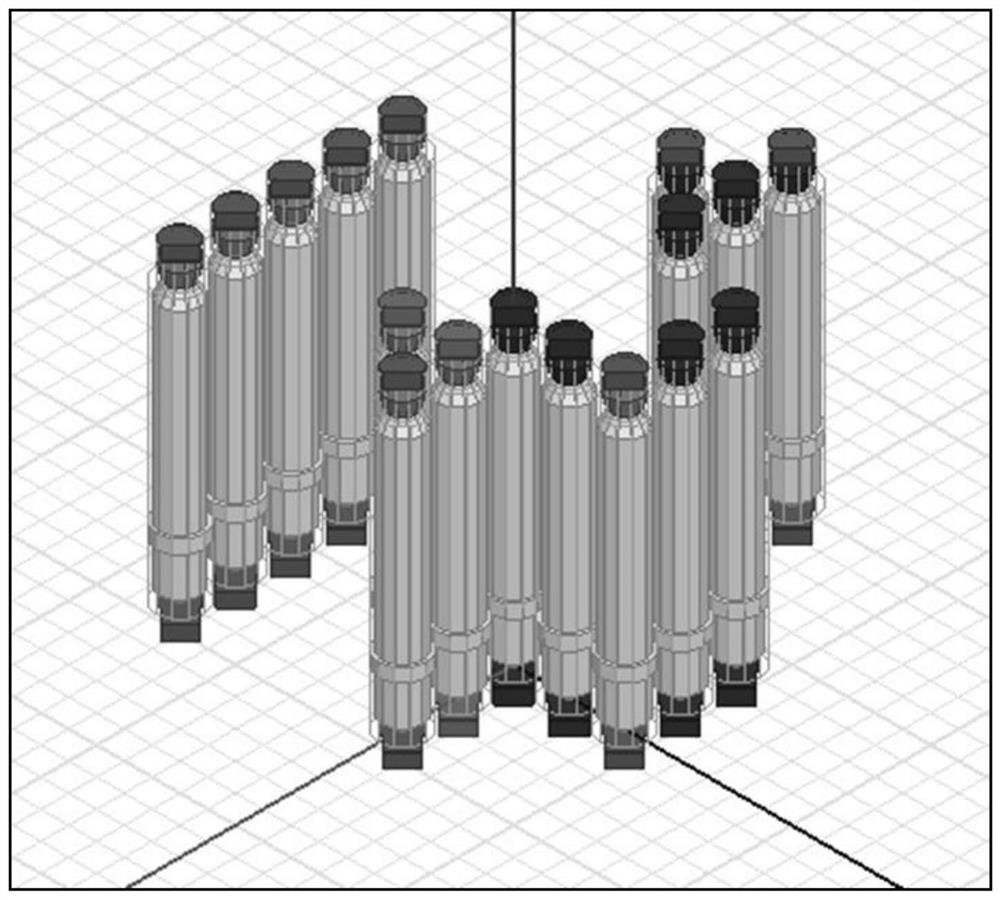

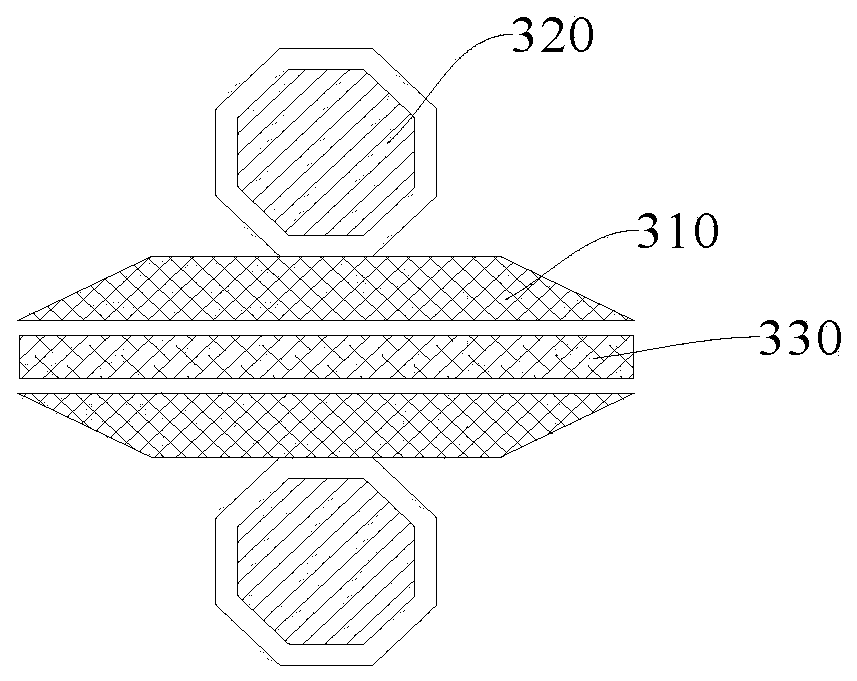

FEA simulation-based chip test socket structure design method and application thereof

ActiveCN107729581AReduce distractionsGuaranteed test accuracyElectronic circuit testingCAD circuit designSignal integrity analysisFea simulation

The invention relates to an FEA simulation-based chip test socket structure design method. The method comprises the steps of firstly in simulation software, building a 3D model of digital signal transmission; secondly according to the 3D model, building a simulation circuit model, and performing statistics on a voltage distribution condition; thirdly according to the simulation circuit model, obtaining a sampling result, and obtaining a noise equivalent distribution condition; fourthly according to the noise equivalent distribution condition, adding one or more probes to a noise position through simulative selection to form multiple probe addition schemes; and finally enabling impedance of a chip test socket circuit to reach the best match through a signal integrity analysis result, and obtaining optimal probe addition position and probe length schemes. Compared with conventional chip test method and base, a few grounded probes with the specific lengths are added for wrapping a transmitted signal, so that signal interference can be effectively reduced; and the proper probes and the probe positions are selected through an FEA simulation tool, and an optimal chip test socket is designed, so that the test cost is reduced to the maximum extent and the chip test precision is ensured.

Owner:SUZHOU TAOSHENG ELECTRONICS TECH CO LTD

Huygens' box methodology for signal integrity analysis

InactiveUS20100161293A1Easy to parallelizeAnalogue computers for electric apparatusDetecting faulty computer hardwareEngineeringSignal integrity analysis

A method for performing a signal integrity analysis on an integrated circuit (IC) that includes a plurality of scatterers by dividing the scatterers into subgroups using a nested Huygens' equivalence principle algorithm and solving a set of equations realized thereby with a reduced coupling matrix. The method includes decomposing the IC design into a plurality of small non-overlapping circuit sub-domains, wherein each of the sub-domains is formed as a small, enclosed region. Each sub-domain is analyzed independently of the other sub-domains using only electric fields to represent the interactions of each sub-domains with the other sub-domains as equivalent currents on equivalent surfaces of the plurality of sub-domains. Neighboring equivalent sub-domains are grouped together to form larger sub-domains using equivalent currents on equivalent surfaces to represent the interactions of the sub-domains. The steps of analyzing and grouping the sub-domains are repeated until the grouping approaches a box comprising the entire domain, and that the domain interactions between every sub-domain have been analyzed.

Owner:INT BUSINESS MASCH CORP

Integrated circuit design for signal integrity, avoiding well proximity effects

InactiveUS20050210431A1Solid-state devicesComputer aided designSignal integrity analysisField-effect transistor

A method, system and program product for designing an integrated circuit (IC) for signal integrity. The invention conducts a signal integrity analysis on an IC design; identifies any field effect transistor (FET) that causes a signal integrity failure in the case that the IC design fails the signal integrity analysis; and modifies an edge of a failing FET that is closer than a threshold distance to a well edge. The invention eliminates the manual, iterative procedure for determining the device causing a signal integrity failure due to well proximity effects.

Owner:IBM CORP

Conducted EMI (electro-magnetic interference) noise suppression method of complex electronic system

ActiveCN102769499BSuppressing Conducted EMI Noise Suppression MethodsTransmission noise suppressionCapacitanceHemt circuits

A conducted EMI noise suppression method of a complex electronic system comprises: 1) analyzing the reasons generating the conducted EMI noise: (1) crosstalk, (2) bad grounding, and (3) PCB (printed circuit board) impedance mismatch; and 2) tightly winding the live wire and the neutral wire of a crosstalk choking coil in a negative-incoming negative-outgoing manner if the conducted EMI noise is caused by crosstalk; connecting capacitors (C1 to C8) in parallel, and respectively disposing U1 and U2 between C1 and C2, and between C4 and C5 if the conducted EMI noise is caused by bad grounding, wherein U1 is equal to U2, and the capacitances of C1, C2, C3, C4, C5, C6, C7 and C8 are respectively 22muF, 22muF, 0.1muF, 0.1muF, 0.1muF, 0.1muF, 100muF, and 10pF; and calculating the characteristic impedance of the PCB circuit by using electromagnetic simulation software, and carrying out signal integrity analysis according to the frequency characteristics of the transmission signal to realize the optimum impedance match of the PCB circuit if the conducted EMI noise is caused by PCB impedance mismatch.

Owner:NANJING HUASHI ELECTRONICS SCI

A method for optimizing the return loss of bga solder joints

ActiveCN107832526BRobustSimple calculationDesign optimisation/simulationCAD circuit designAlgorithmComputation process

The invention discloses a method for optimizing BGA (Ball Grid Array) welding spot return loss. The method includes the steps: 1) establishing a BGA welding spot signal integrity analysis model; 2) acquiring return loss of a BGA welding spot; 3) determining an influence factor of the BGA welding spot signal integrity; 4) determining a parameter level value of the influence factor of the BGA welding spot signal integrity; 5) acquiring simulation experiment samples; 6) acquiring a functional relation between the influence factor and the return loss; 7) performing variance analysis; 8) determining the correctness of the functional relation; 9) generating an initial population; 10) acquiring a current evolution generation gen and an optimal fitness value; 11) performing interlace operation onthe population; 12) performing mutation operation on the population; 13) performing evolution reversion on the population; 14) selecting an optimal individual; and 15) performing re-determination after the population is updated. The method uses a response surface method and a genetic algorithm to optimize BGA welding spot return loss, has excellent robust Performance, and is simple in calculationprocess.

Owner:GUILIN UNIV OF ELECTRONIC TECH

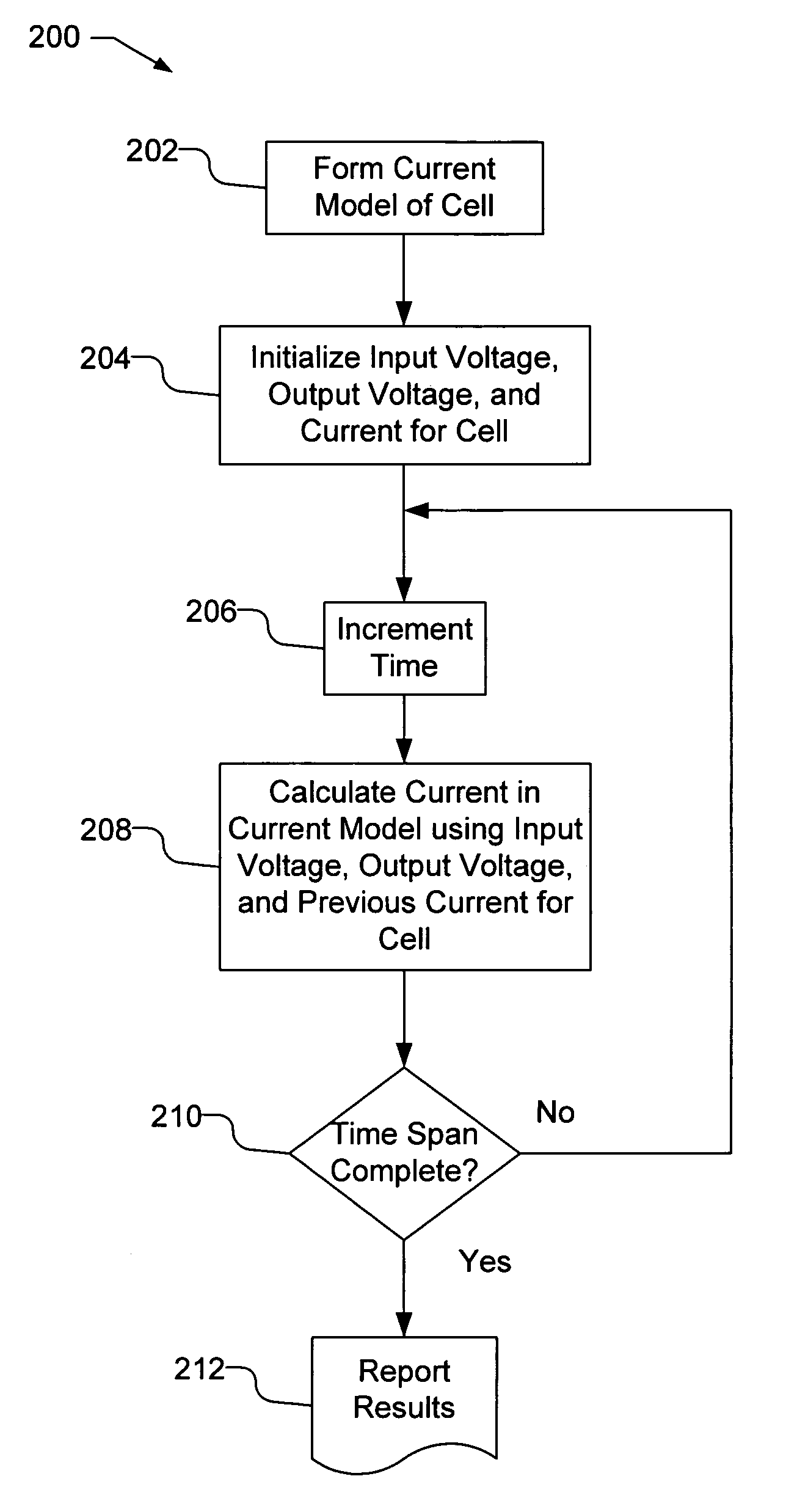

Modeling circuit cells for waveform propagation

ActiveUS8478573B2Computer aided designSpecial data processing applicationsSignal integrity analysisGate current

A model for a circuit cell used in timing and signal integrity analysis in an integrated circuit design is automatically generated. A behavioral model, such as a gate current model is used in which the current in the circuit cell is determined as a function of the input voltage and the output voltage of the circuit cell as well as the history of at least one of the current, voltage, and charge values of the circuit cell. For example, the current in the circuit cell may be a function of the history of the current, which may be calculated incrementally using recursive convolution at each time step when using the model.

Owner:SYNOPSYS INC

A method and application of chip test socket structure design based on fea simulation

ActiveCN107729581BReduce distractionsGuaranteed test accuracyElectronic circuit testingCAD circuit designSimulationHemt circuits

The invention relates to a method for designing a structure of a chip test socket based on FEA simulation. First, a 3D model of digital signal transmission is established in simulation software, then a simulation circuit model is built according to the 3D model, voltage distribution is counted, and sampling results are obtained according to the simulation circuit model again. , obtain the equivalent distribution of noise, according to the equivalent distribution of noise, simulate and choose to add one or more probes at the noise position to form multiple probe addition schemes, and finally make the impedance of the chip test socket circuit through the signal integrity analysis results. To achieve the best match, get the best probe adding position and probe length scheme. Compared with the traditional chip testing method and base, the invention adds some grounding probes of specific length to wrap the transmission signal, which can effectively reduce the interference of the signal, select the appropriate probe and probe position through the FEA simulation tool, and design the optimal chip Test sockets can save test costs to the greatest extent and ensure chip test accuracy.

Owner:SUZHOU TAOSHENG ELECTRONICS TECH CO LTD

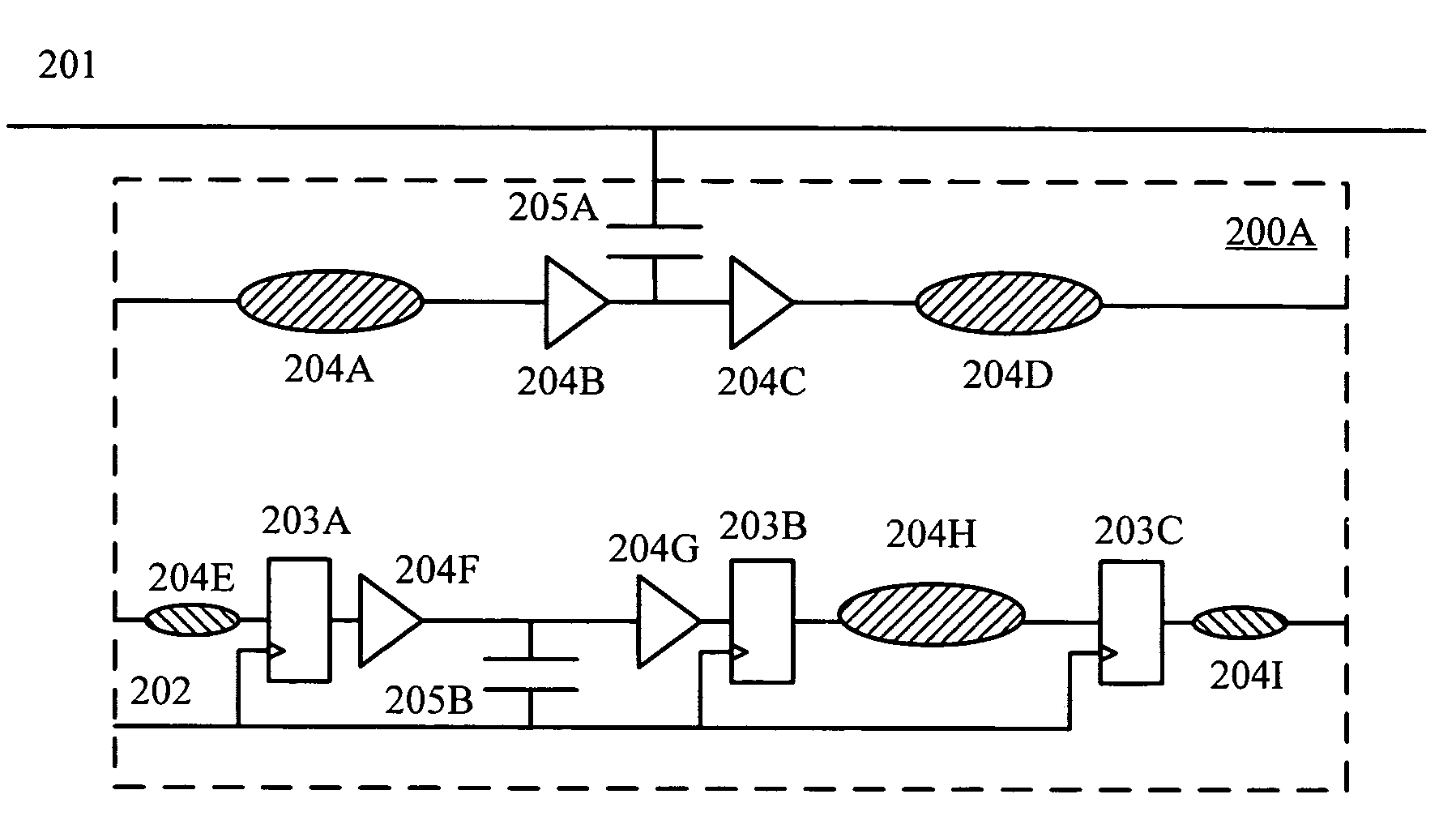

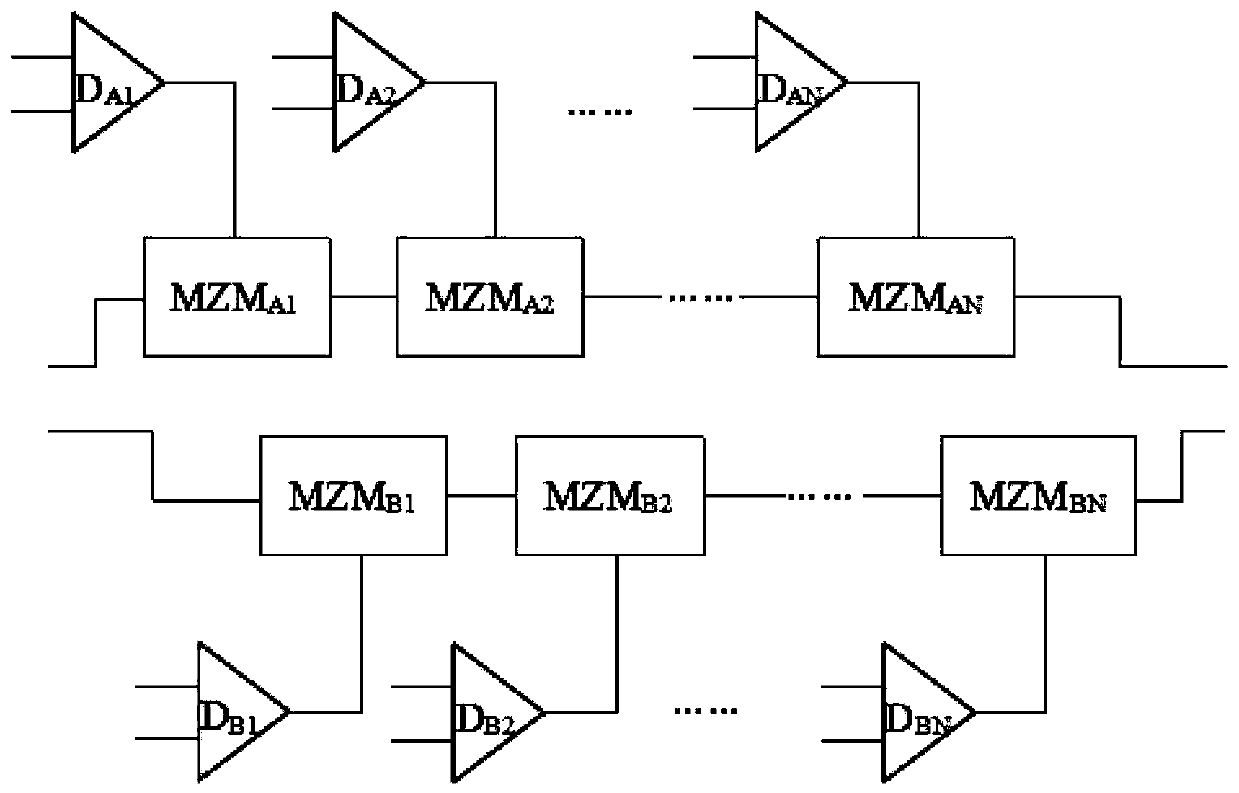

Optoelectronic modulator and optoelectronic interconnection interface

InactiveCN110350979AOptical Speed MatchingShorten the lengthElectromagnetic transmissionNon-linear opticsElectricitySignal integrity analysis

The invention provides a photoelectric modulator and a photoelectric interconnection interface. The photoelectric modulator comprises an optical beam splitter, an optical beam combiner and two opticalmodulation branches connected in parallel. The light beam splitter is provided with two output ends, one output end is connected with the input end of one light modulation branch, and the other output end is connected with the input end of the other light modulation branch; the light beam combiner is provided with two input ends, one input end is connected with the output end of one light modulation branch, and the other input end is connected with the output end of the other light modulation branch; and each light modulation branch comprises a plurality of Mach-Zehnder modulators which are connected in series. According to the invention, the requirement on the driving capability of the electric driver is reduced, so that the electric signal (driving signal) does not need to be remotely transmitted, the complexity of signal integrity analysis is reduced, and the propagation loss of the electric signal (driving signal) is reduced.

Owner:SHANGHAI JIAO TONG UNIV

Method for reconstructing ground clamp curve and electric power clamp curve of chip IBIS model

InactiveCN101221587BIncrease credibilityIncrease authenticitySpecial data processing applicationsElectrical resistance and conductanceCurrent voltage

The invention discloses a method of reconstructing the ground clamping curve and the power clamping curve of a chip IBIS model, which reconstructs the current-voltage curve of the IBIS through a simple circuit model and is applicable to the signal integrity analysis and circuit simulation technical field. According to the characteristics showed by the power clamping curve and the ground clamping curve, proper discrete components mainly involving diodes and resistors are selected to build different equivalent circuits, and then the simulation of the equivalent circuits is carried out to obtainthe accurate ground clamping curve and the power clamping curve of the IBIS model. The method which is simple and easy enables an engineer to carry out accurate simulation before obtaining the accurate IBIS model.

Owner:昆山杰得微电子有限公司

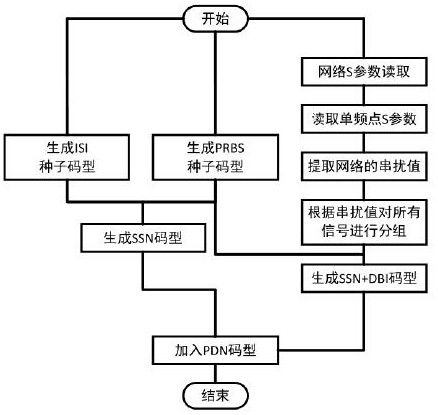

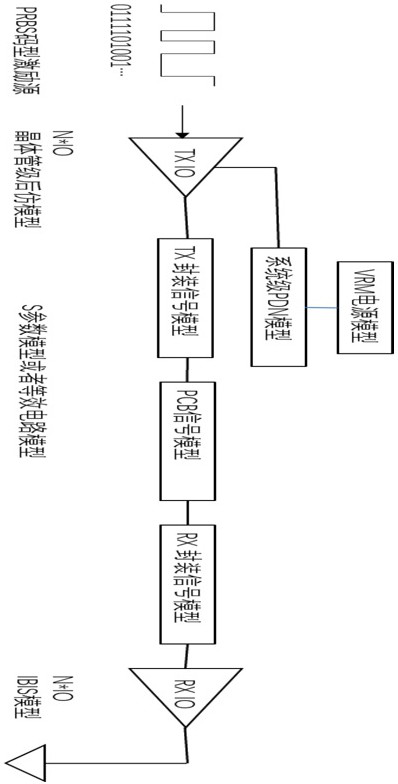

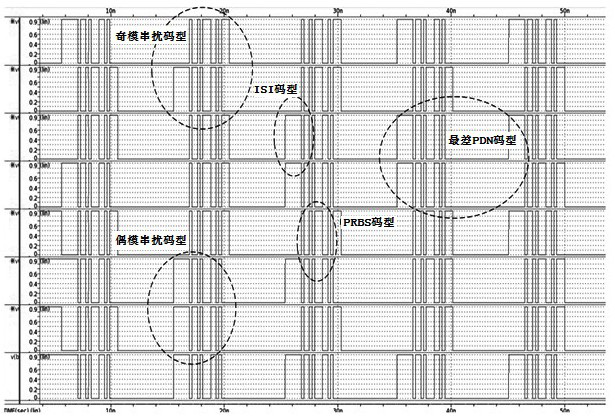

Method for generating code pattern for signal integrity analysis

PendingCN112329372AIncrease the lengthIntegrity Simulation Acceptance Design Efficiency ImprovementComputer aided designSpecial data processing applicationsProgramming languageSignal quality

The invention discloses a method for generating a code pattern for signal integrity analysis, which comprises the following steps of reading a signal full-link S parameter model, determining a crosstalk sequence of bits in each high-speed interface, and determining an attacked person corresponding to each signal line according to the maximum number of attacked persons of a victim signal, generating a PRBS seed code pattern to enable the PRBS seed code pattern to contain the worst inter-code interference effect, and rewriting the PRBS seed code pattern into a code pattern a, taking the code pattern a as a seed code pattern, and generating a code pattern b containing crosstalk of each signal, and reading the S parameter model or the PDN impedance resonant frequency of the PDN link, and carrying out post-processing on the code pattern b to generate a code pattern c comprising worst power supply noise. According to the method, the worst result of the PRBS code pattern theory can be simulated, the signal quality of the full link of the high-speed interface can also be accurately simulated, the defects that power supply noise cannot be considered and the precision problem exists in a traditional method are overcome, the acceptance design basis of the full link of the high-speed interface is more reliable, over-design or under-design is avoided, and the design cost is saved.

Owner:南京蓝洋智能科技有限公司

Huygens' box methodology for signal integrity analysis

InactiveUS7707527B2Easy to parallelizeDetecting faulty computer hardwareAnalogue computers for electric apparatusSignal integrity analysisEngineering

A method for performing a signal integrity analysis on an integrated circuit (IC) that includes a plurality of scatterers by dividing the scatterers into subgroups using a nested Huygens' equivalence principle algorithm and solving a set of equations realized thereby with a reduced coupling matrix. The method includes decomposing the IC design into a plurality of small non-overlapping circuit sub-domains, wherein each of the sub-domains is formed as a small, enclosed region. Each sub-domain is analyzed independently of the other sub-domains using only electric fields to represent the interactions of each sub-domains with the other sub-domains as equivalent currents on equivalent surfaces of the plurality of sub-domains. Neighboring equivalent sub-domains are grouped together to form larger sub-domains using equivalent currents on equivalent surfaces to represent the interactions of the sub-domains. The steps of analyzing and grouping the sub-domains are repeated until the grouping approaches a box comprising the entire domain, and that the domain interactions between every sub-domain have been analyzed.

Owner:IBM CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com