Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

87949results about How to "Easy to carry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

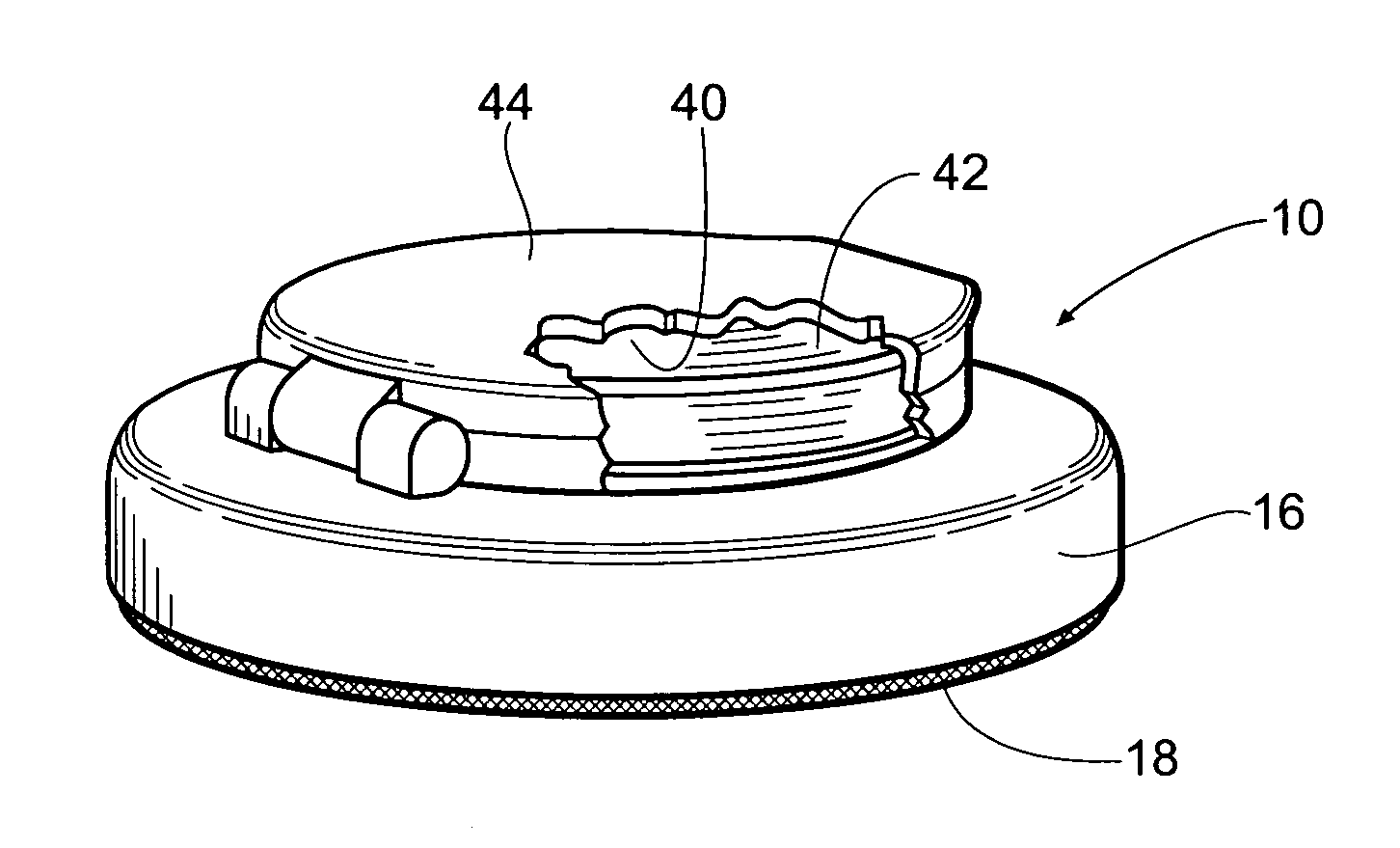

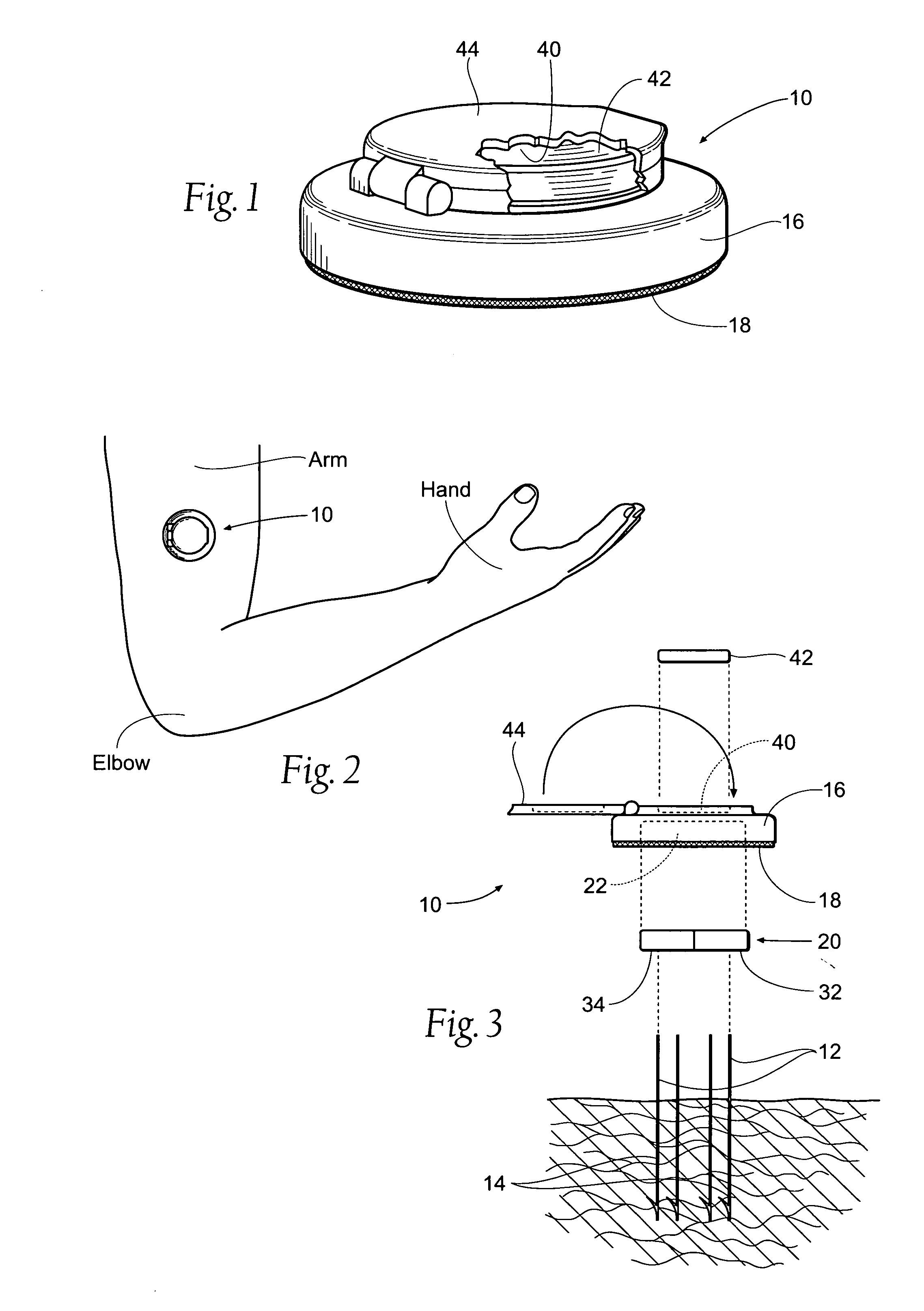

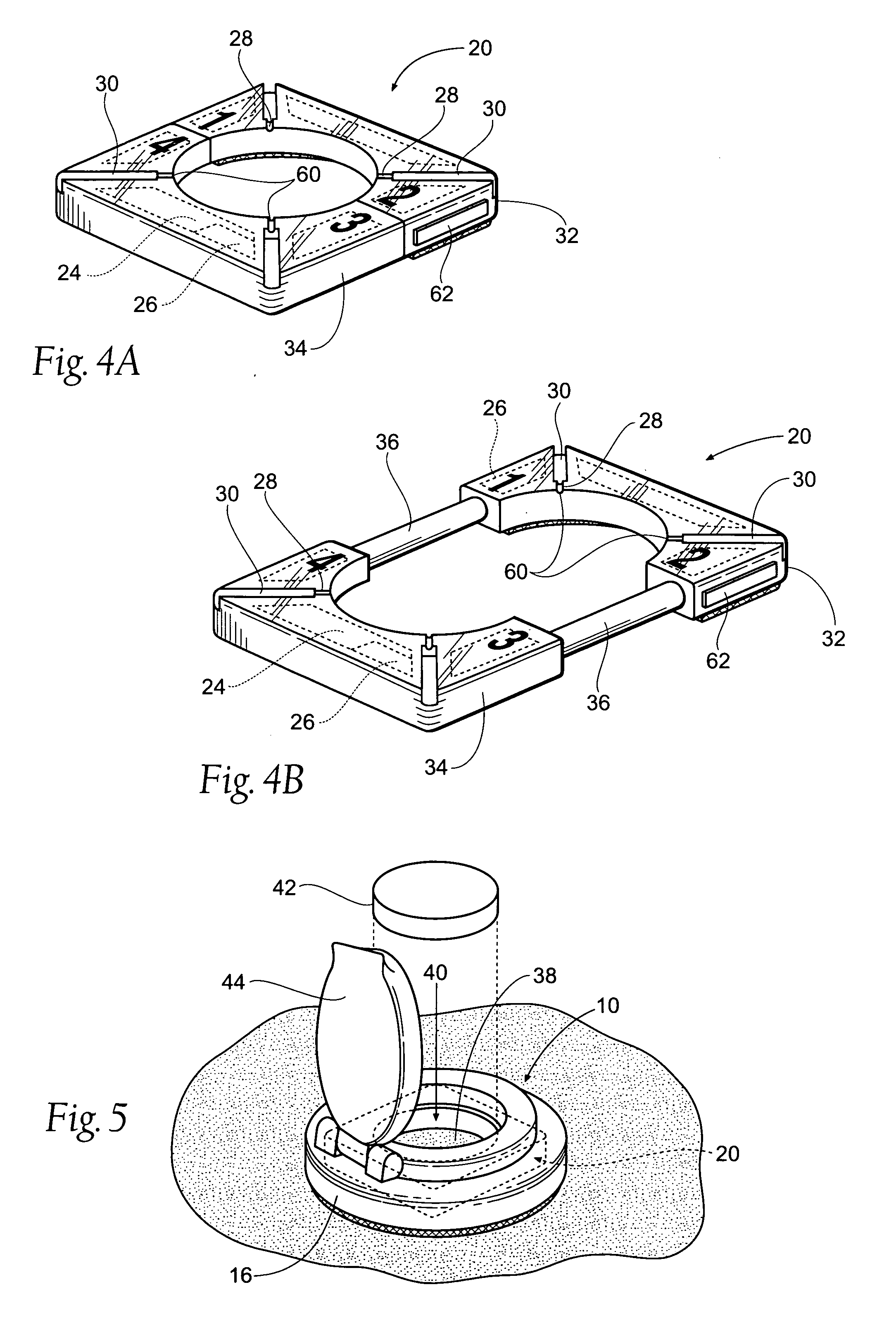

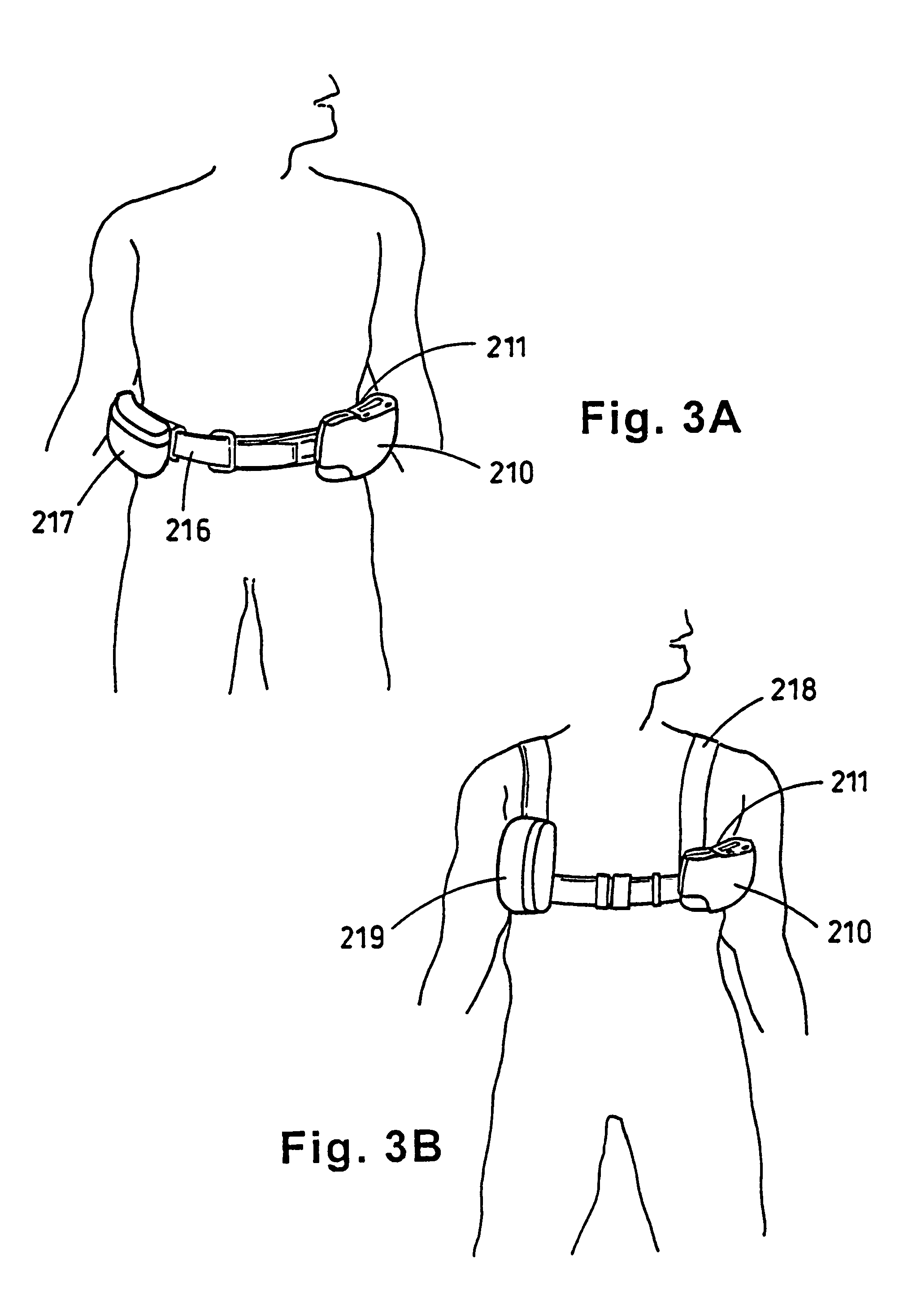

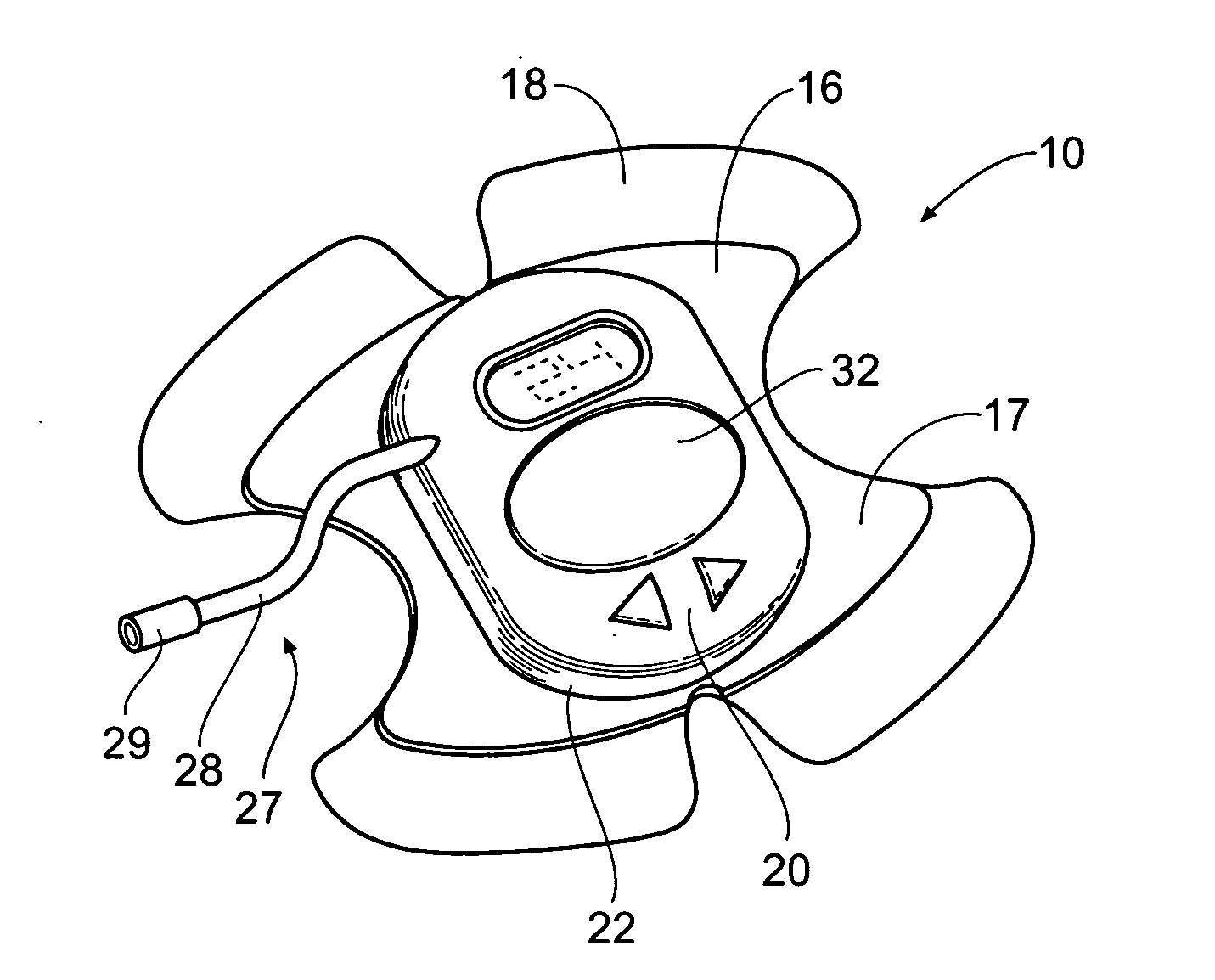

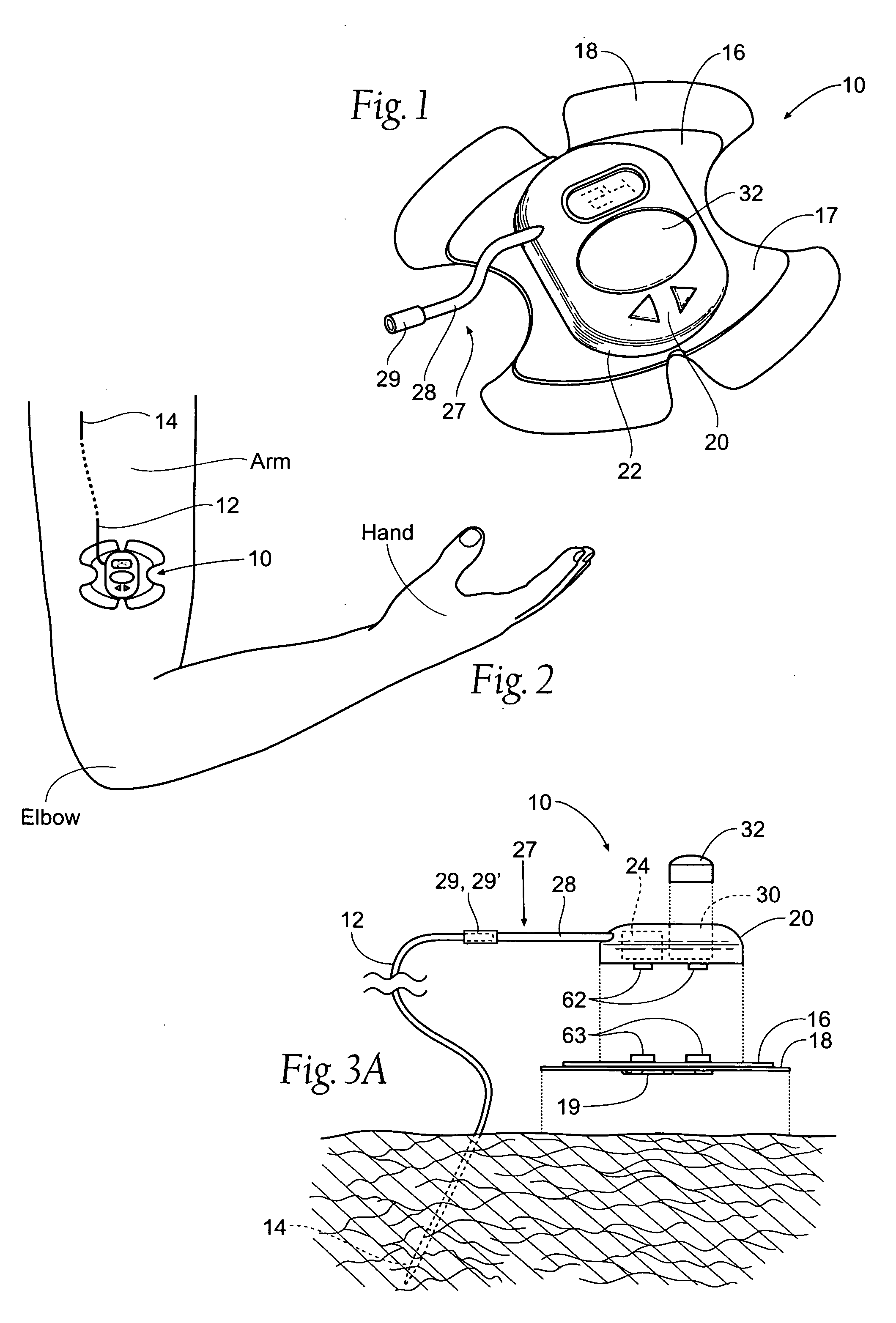

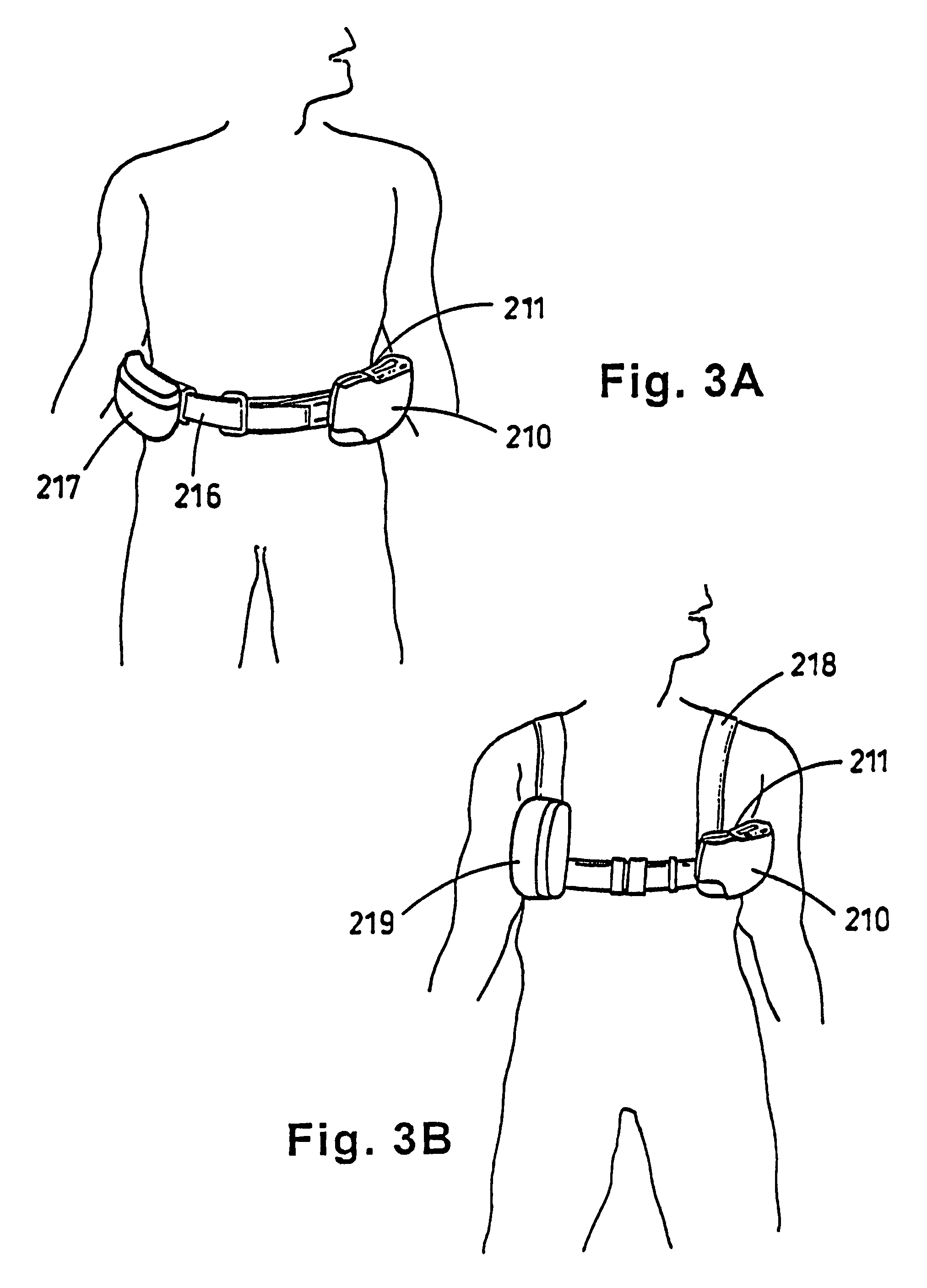

Portable assemblies, systems and methods for providing functional or therapeutic neuromuscular stimulation

InactiveUS20080154335A1Easy to carryNo discomfortSpinal electrodesExternal electrodesElectricityMedicine

Neuromuscular stimulation assemblies, systems, and methods make possible the providing of short-term therapy or diagnostic testing by providing electrical connections between muscles or nerves inside the body and stimulus generators or recording instruments mounted on the surface of the skin outside the body. Neuromuscular stimulation assemblies, systems, and methods may include a steerable introducer that defines an interior lumen sized and configured to shield a percutaneous electrode from contact with tissue during advancement to a desired position within tissue.

Owner:NDI MEDICAL LLC - CHARTER NO 1766209

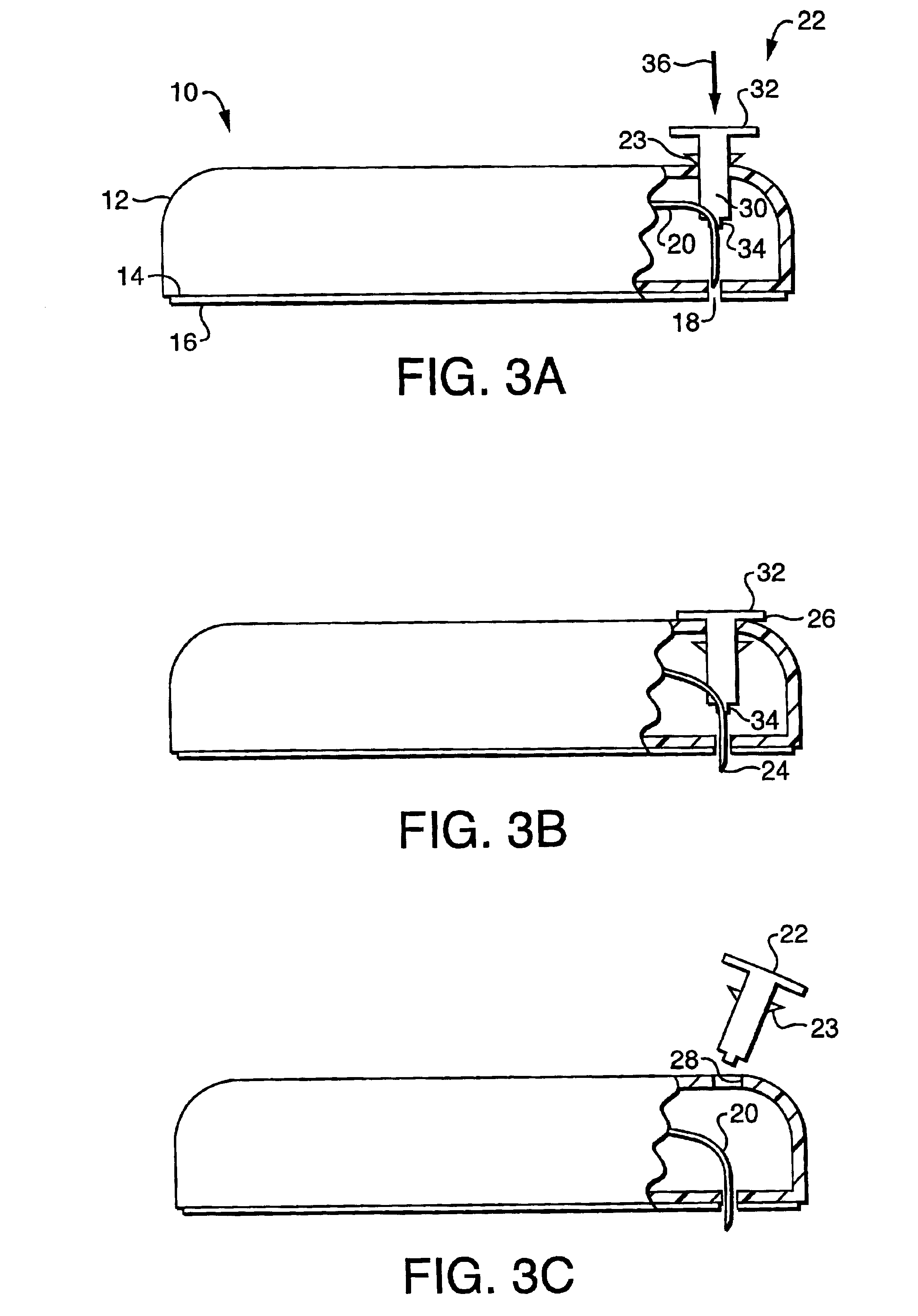

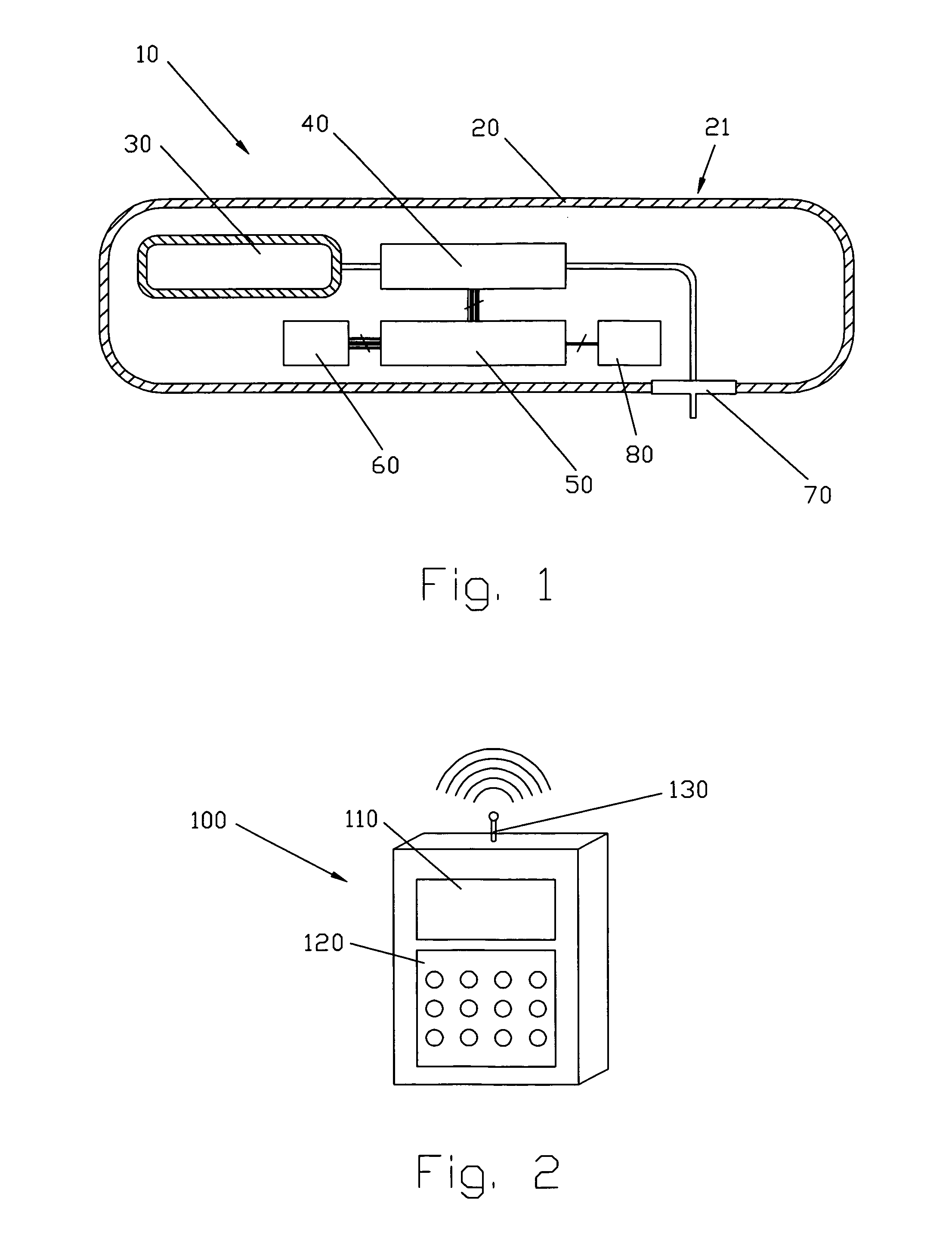

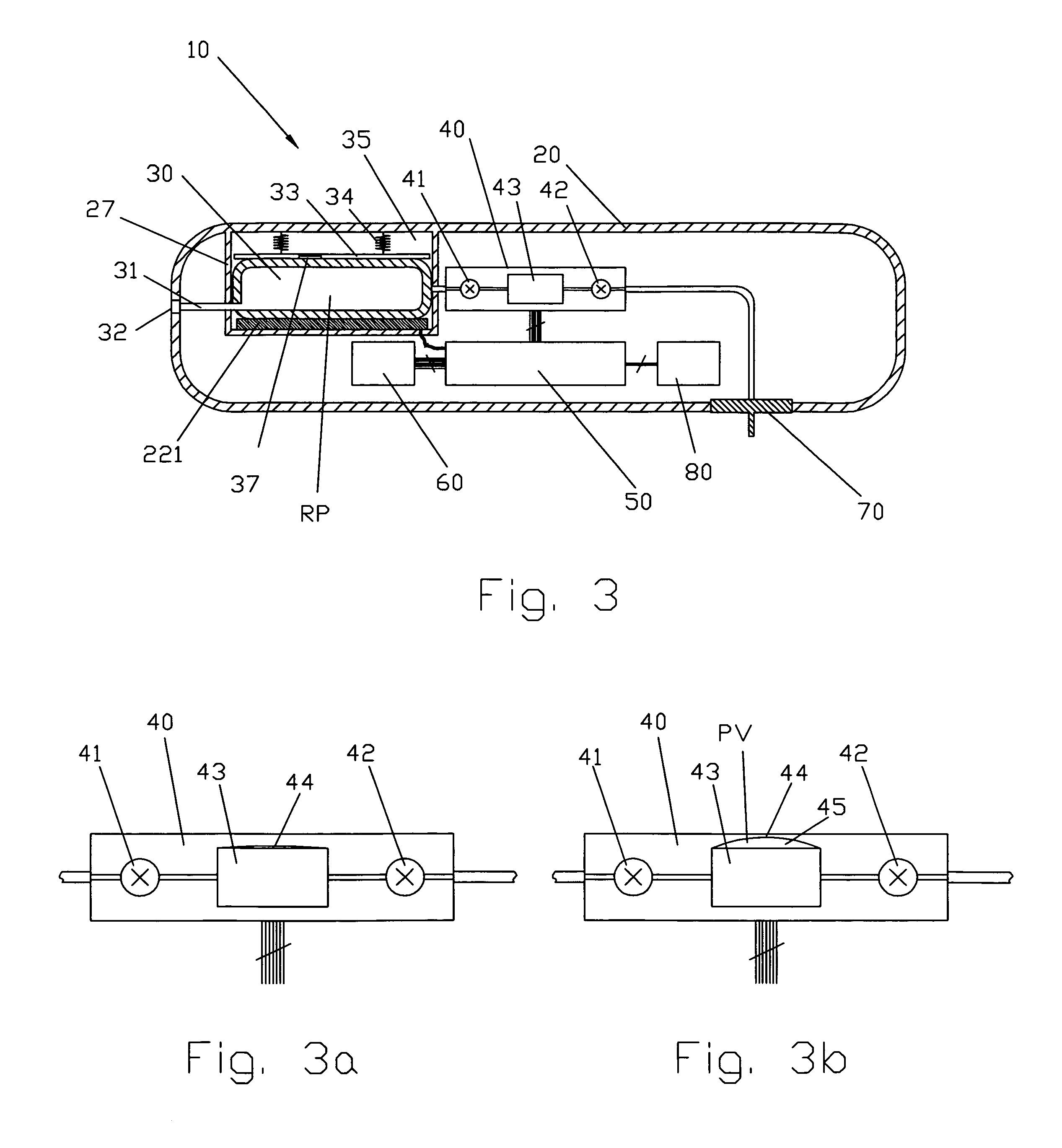

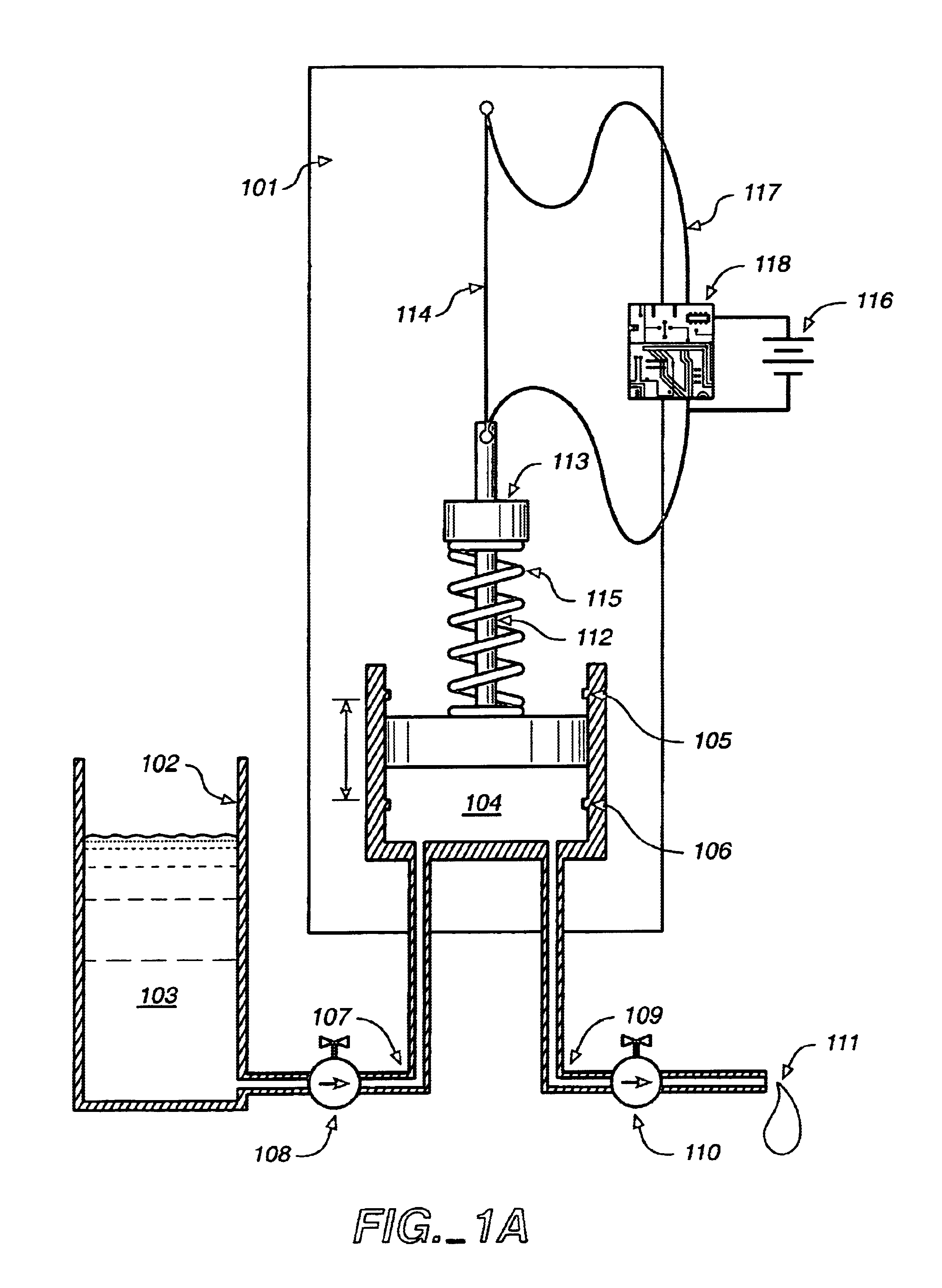

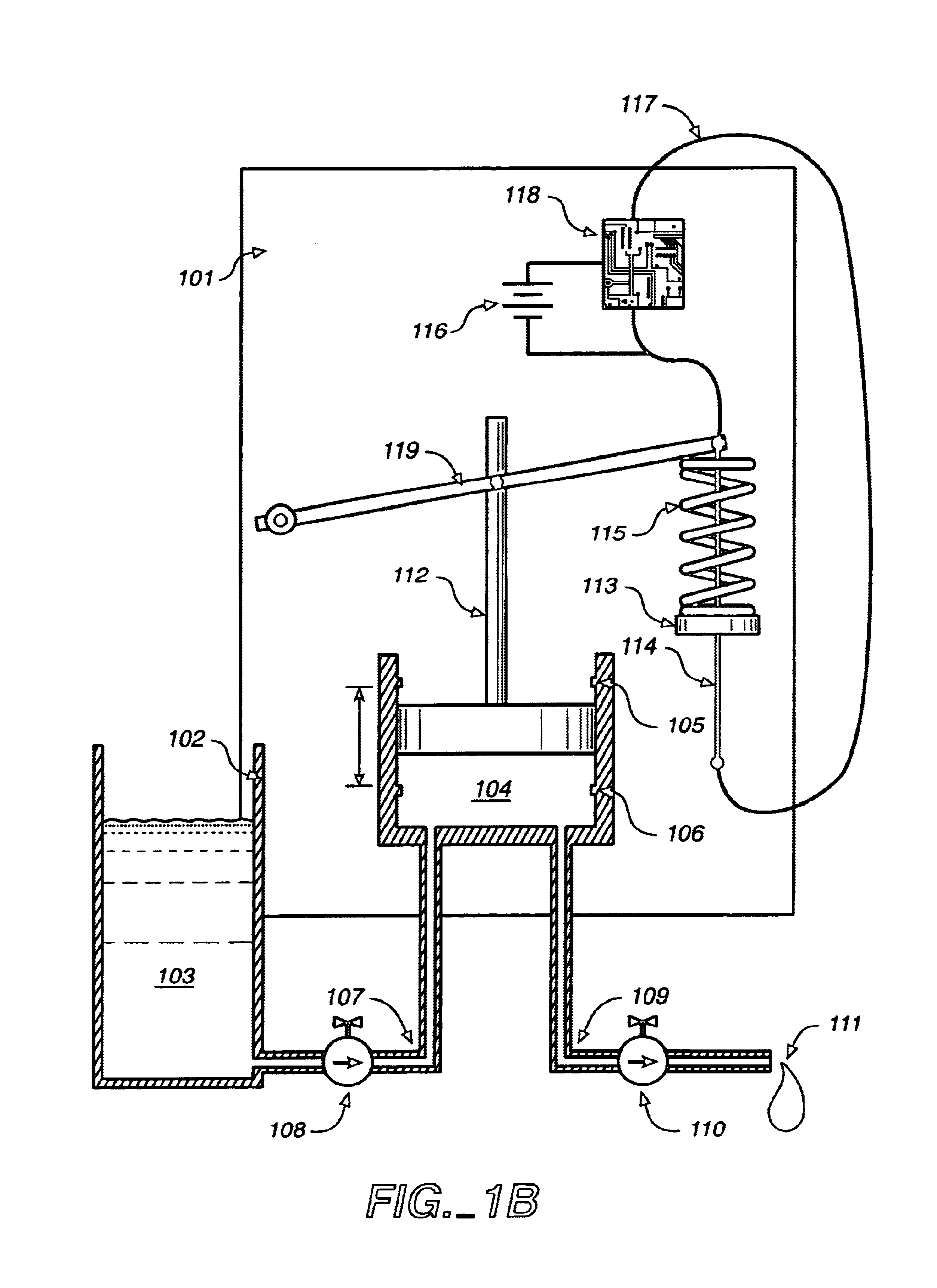

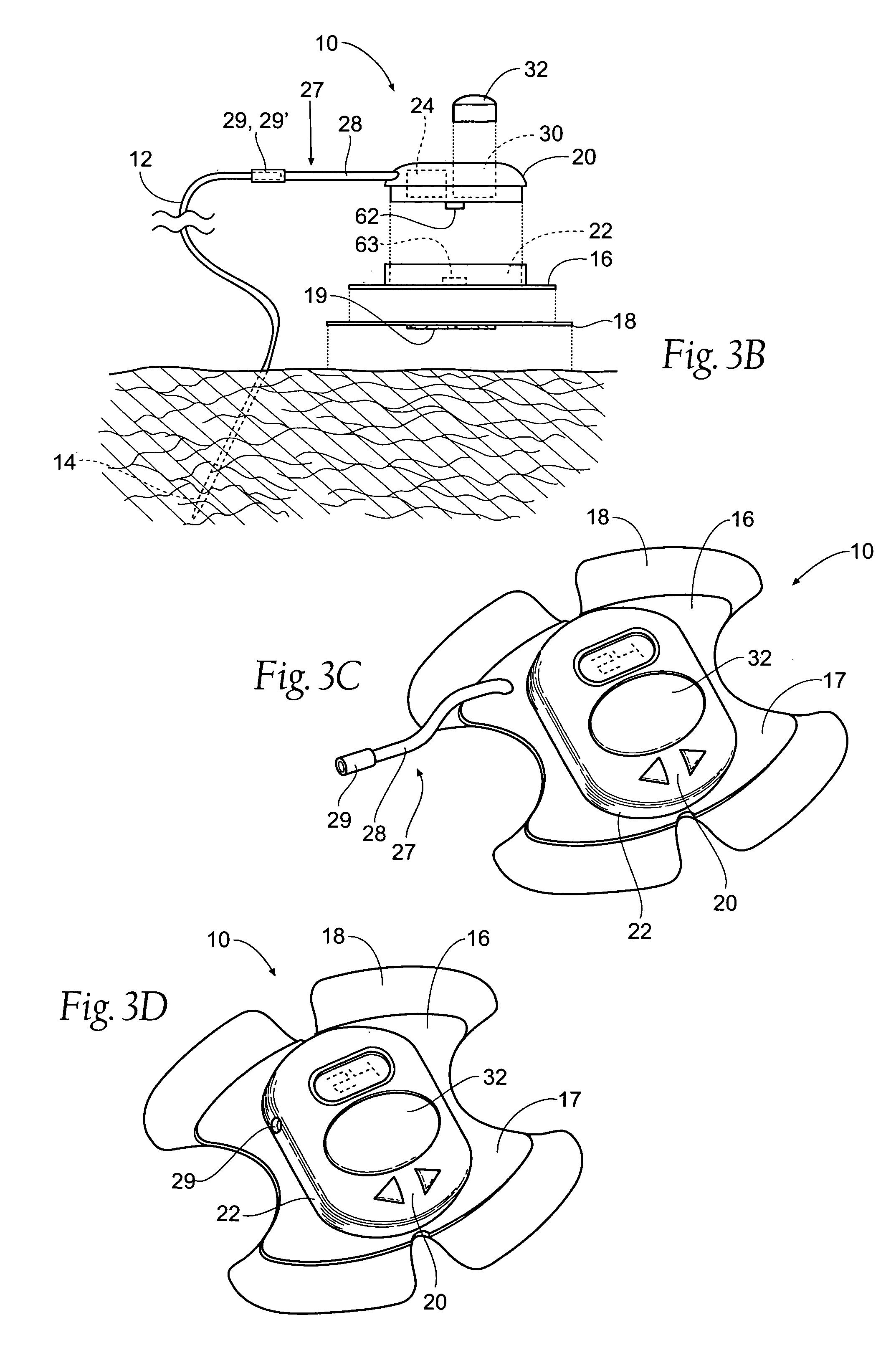

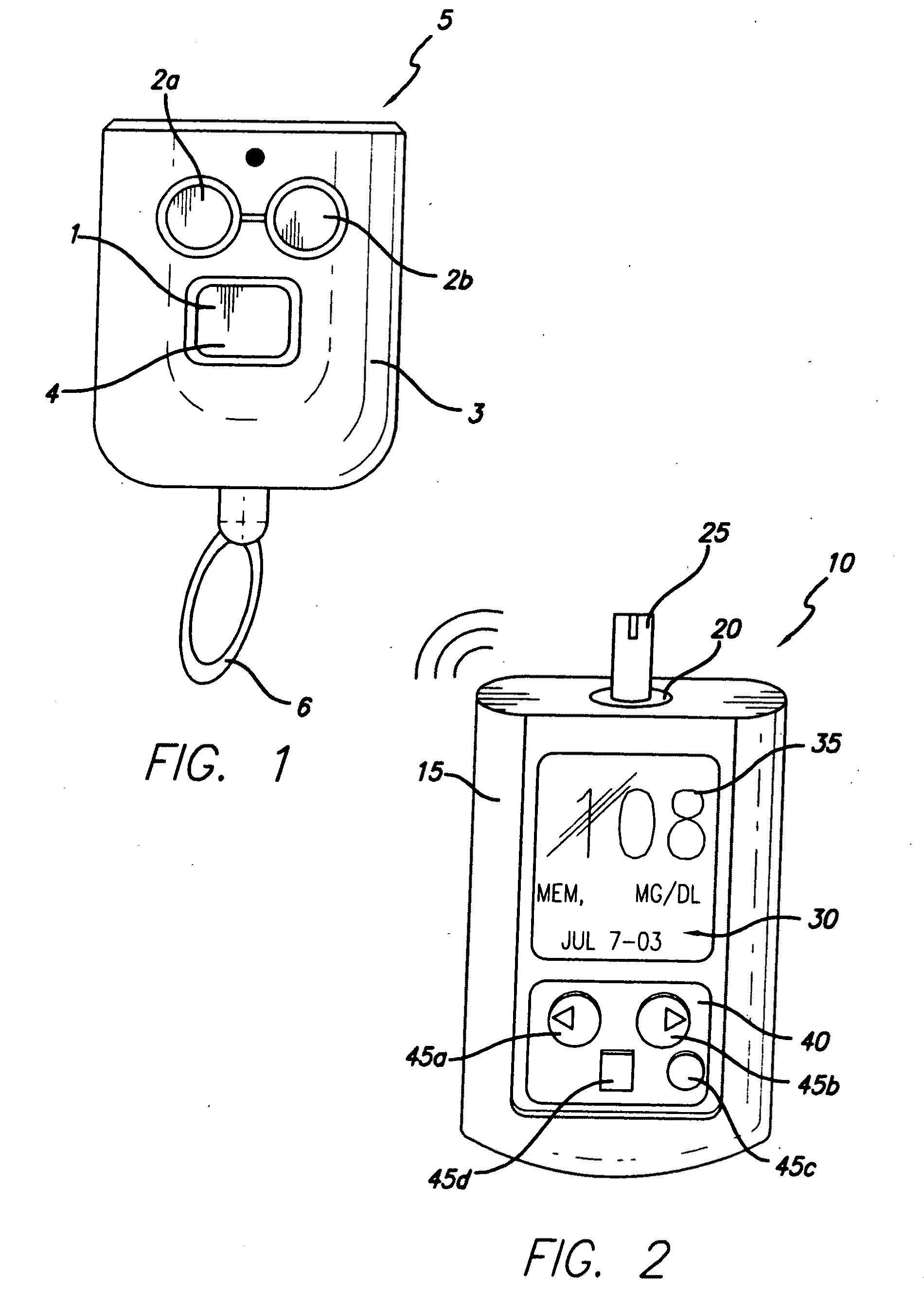

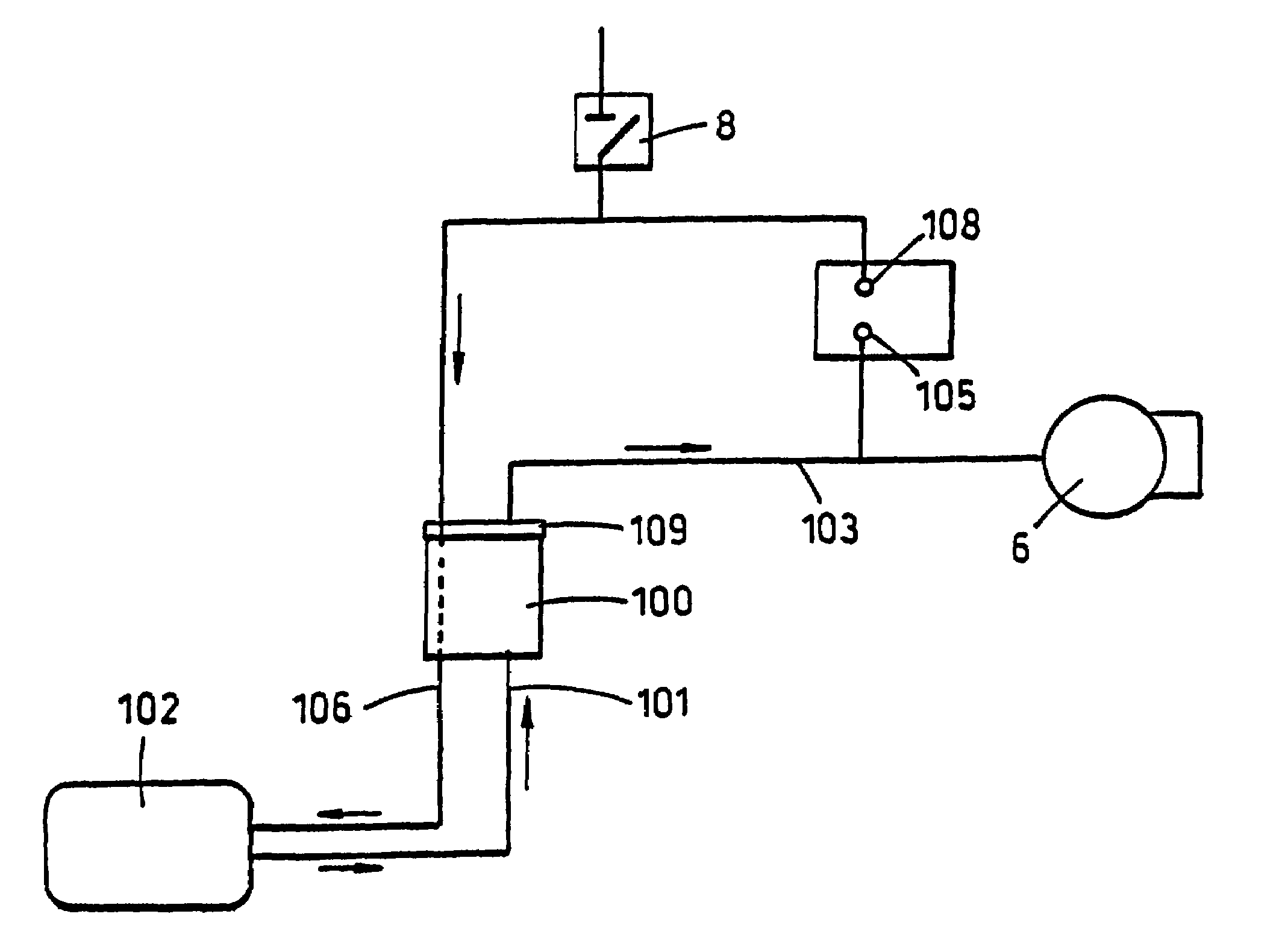

Transcutaneous fluid delivery system

InactiveUS6960192B1Avoiding general upkeep and maintenanceEasy to carryAutomatic syringesMedical devicesFluid transportBiological activation

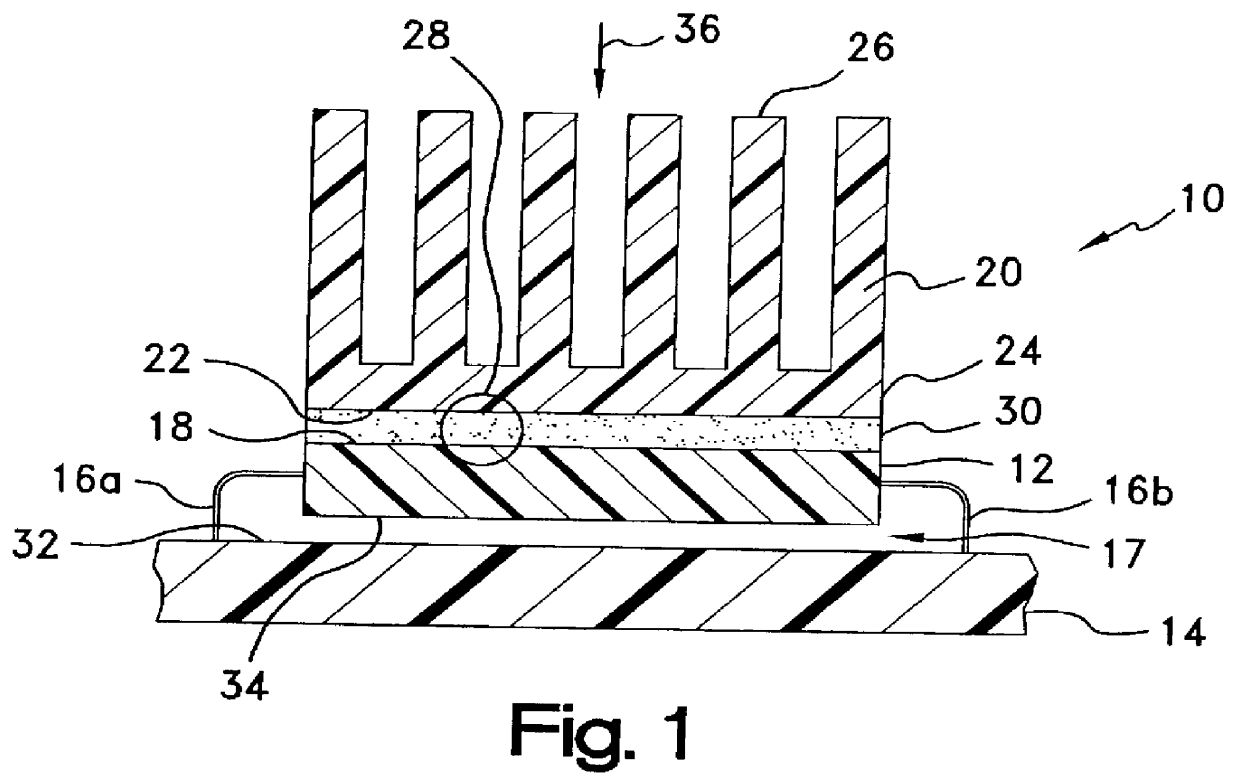

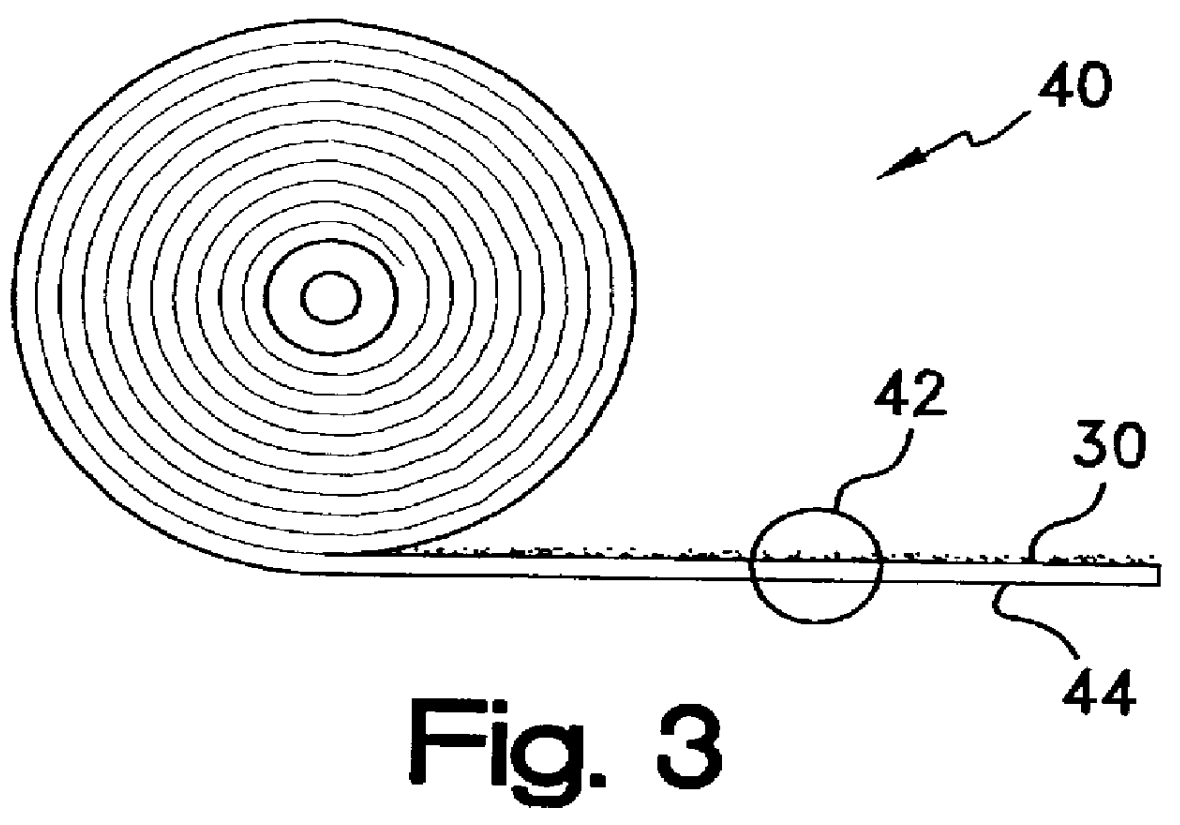

A device for delivering fluid to a person includes a reservoir for containing a fluid to be delivered to the person; a fluid transport device for dispensing fluid from the reservoir to the person, the fluid transport device including a proximal end in fluid communication with the reservoir and a distal end having a penetrating member for piercing the skin of the person to facilitate the delivery of fluid to the person through the fluid transport device; a housing containing the reservoir and the fluid transport device, the housing including an exit port for receiving the distal end of the fluid transport device upon injection of the distal end into the person and means for securing a first wall of the housing to the skin of the person; and an injection activation device including a driving mechanism contacting the fluid transport device for driving the penetrating member from a first position within the housing, through the exit port to a second position, external to the housing and into the skin of the person.

Owner:INSULET CORP

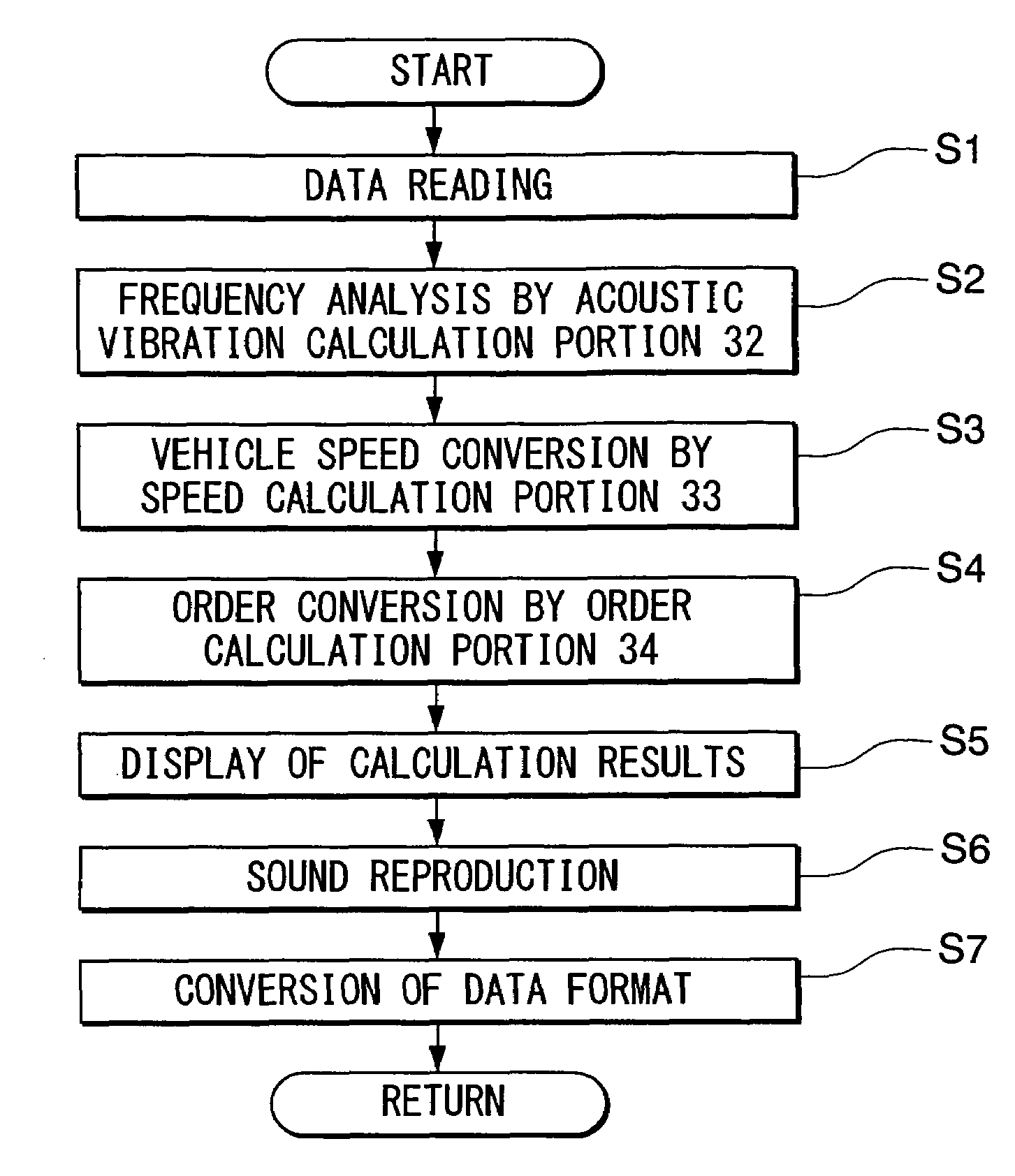

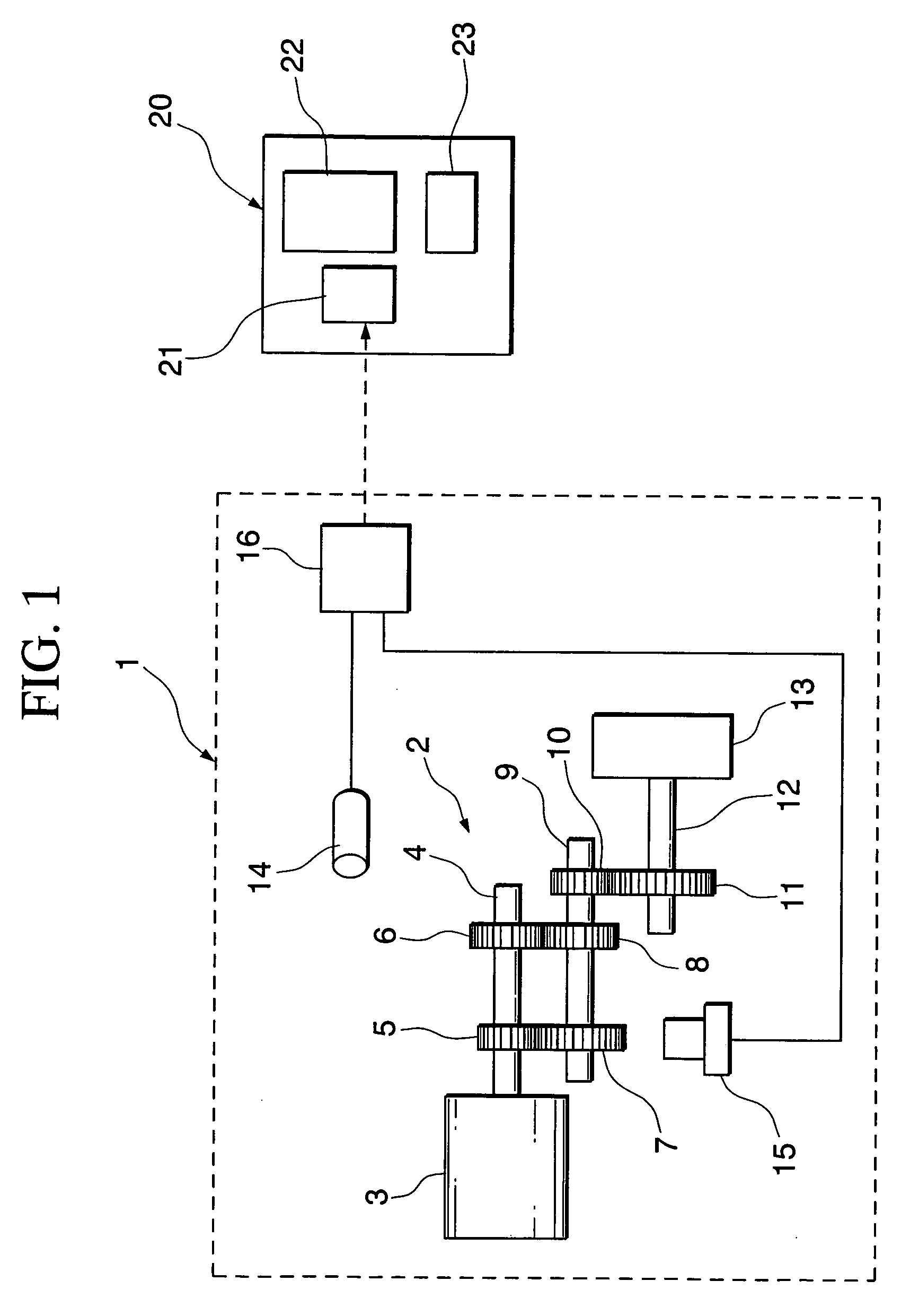

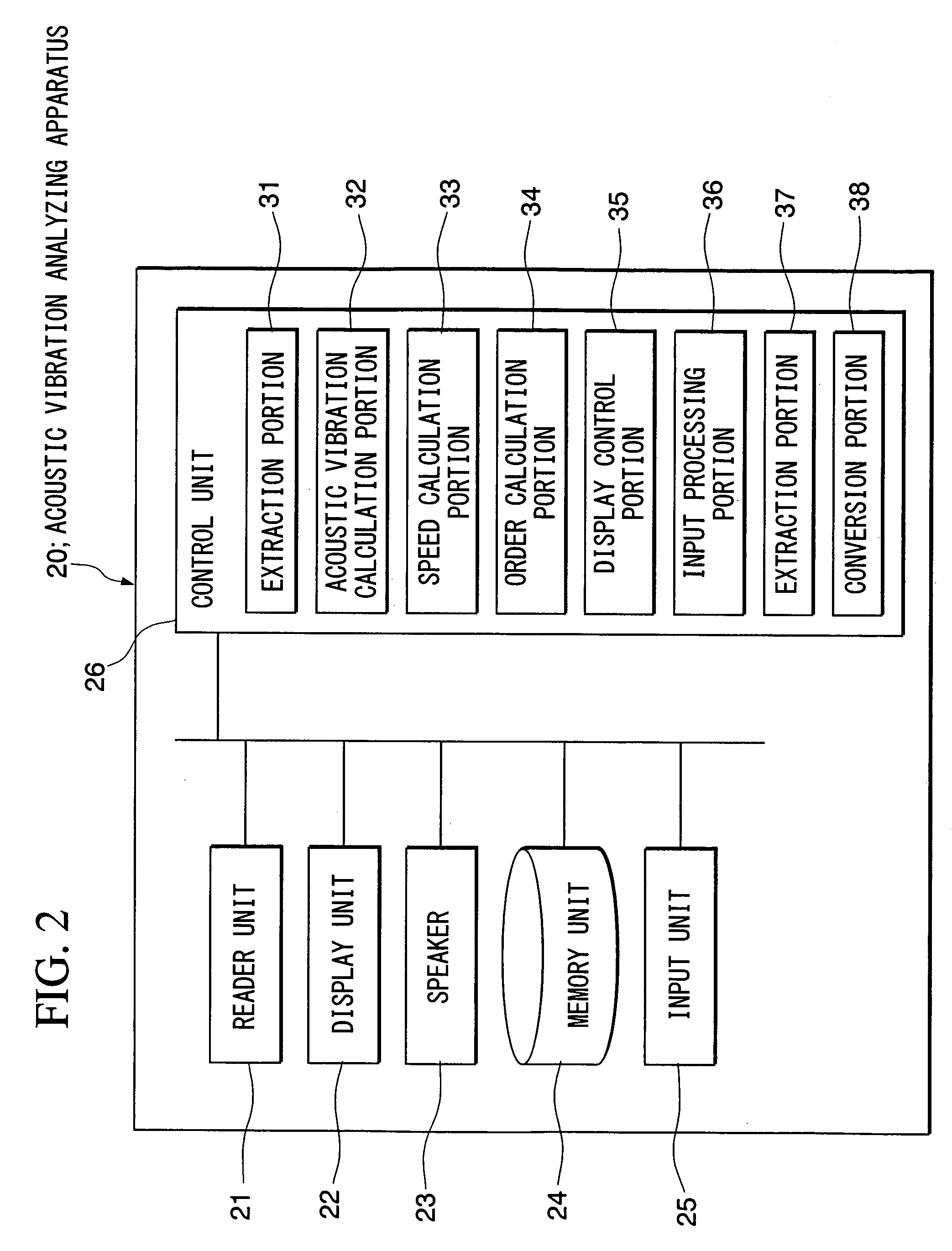

Acoustic vibration analyzing apparatus and acoustic vibration analyzing method, program for analyzing acoustic vibration, and recording medium, readable by computer, on which program for analyzing acoustic vibration is stored

ActiveUS7401000B2Easy to carryReduce in quantityVibration measurement in solidsVehicle testingAnalysis methodAcoustics

The present invention provides an acoustic vibration analyzing apparatus for carrying out acoustic vibration analysis by picking up data of sounds generated due to rotation of a plurality of gears and data of the number of revolutions of a gear selected from a plurality of gears when a transmission of a vehicle having the plurality of gears operates. The acoustic vibration analyzing apparatus comprises an acoustic vibration calculation portion for analyzing acoustic data in terms of frequency, an order calculation portion for calculating an order in compliance with the specifications of a plurality of gears, a speed calculation portion for calculating the speed of a vehicle, and a display unit for displaying acoustic pressure levels with the order and vehicle speed associated therewith.

Owner:HONDA MOTOR CO LTD

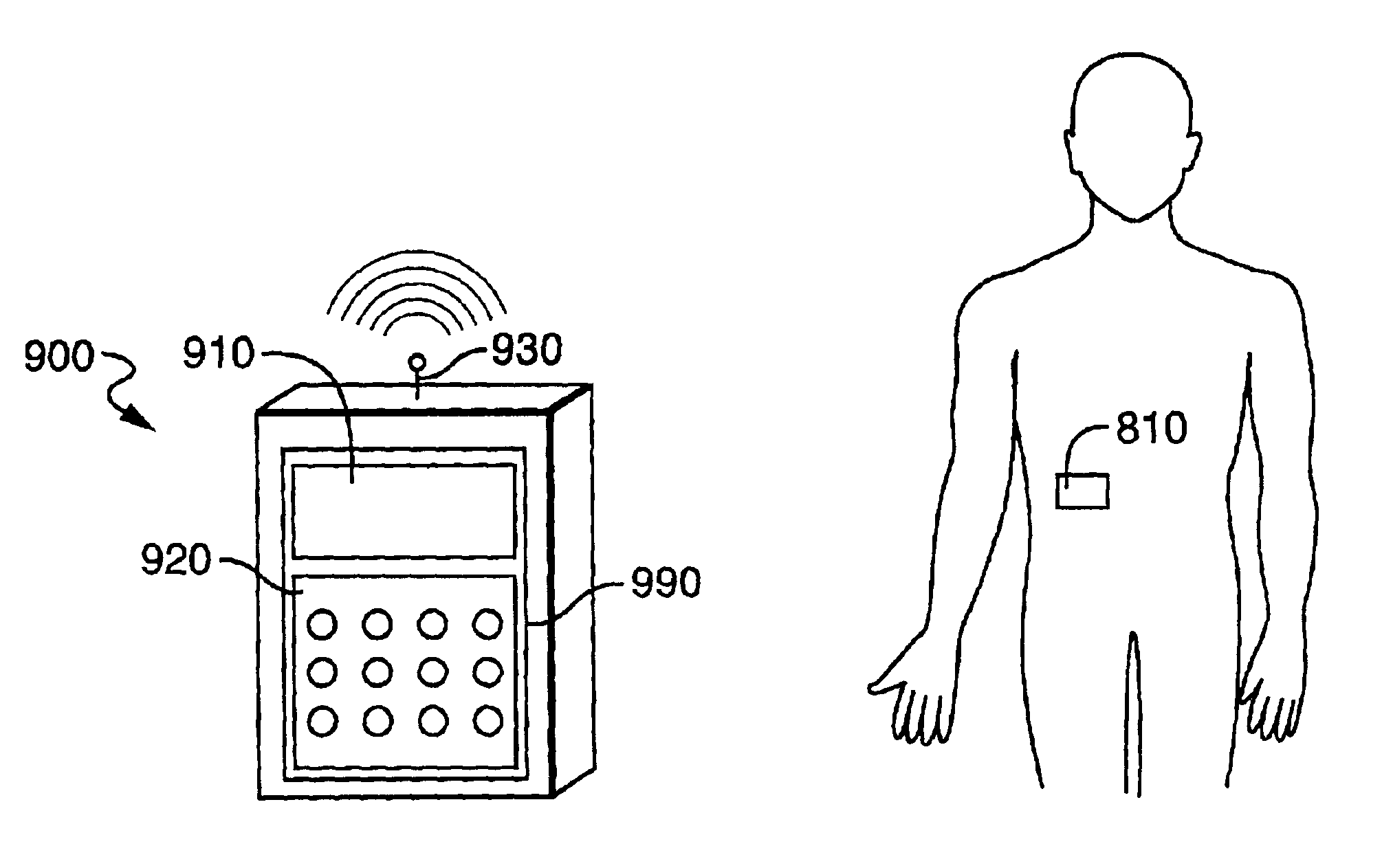

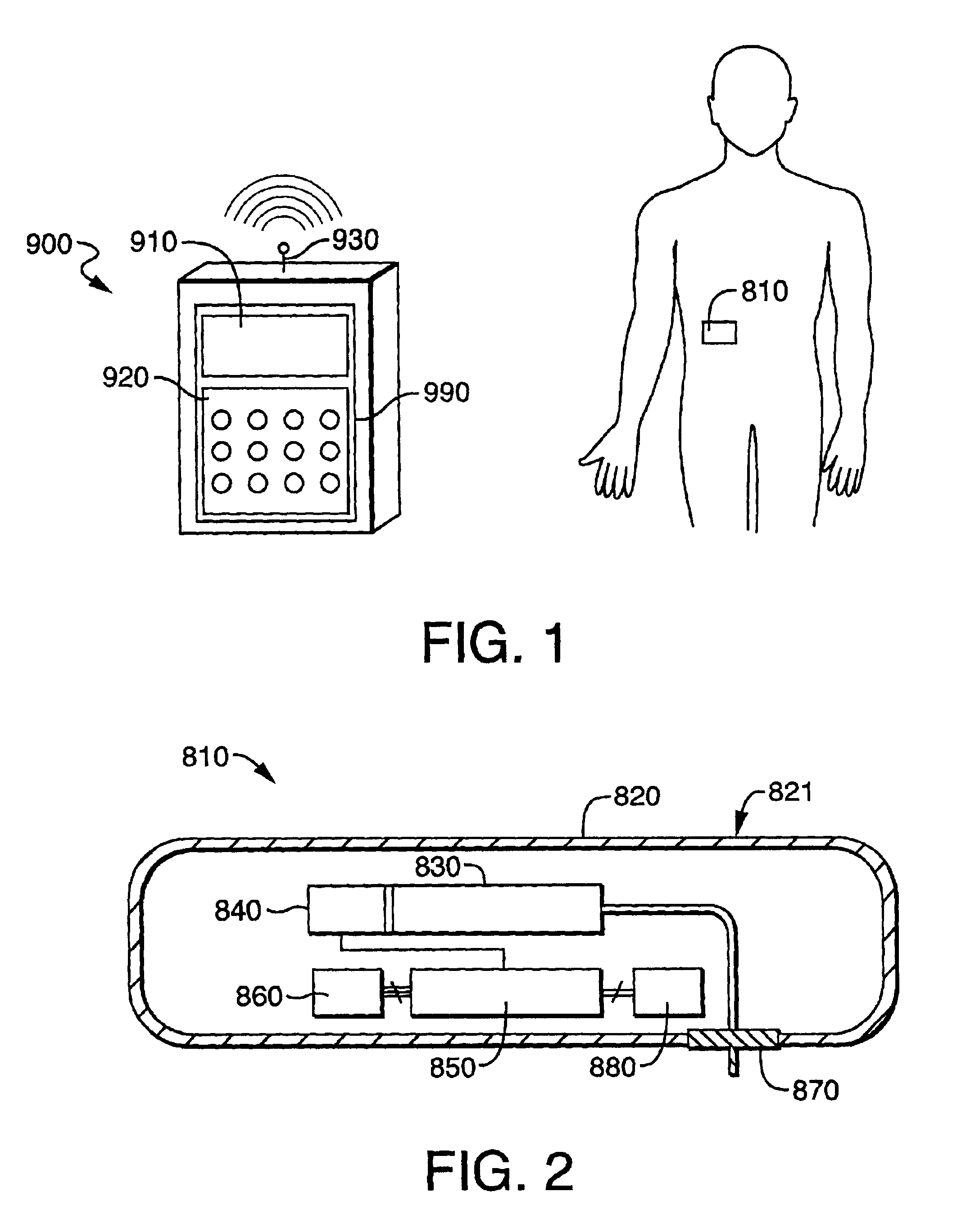

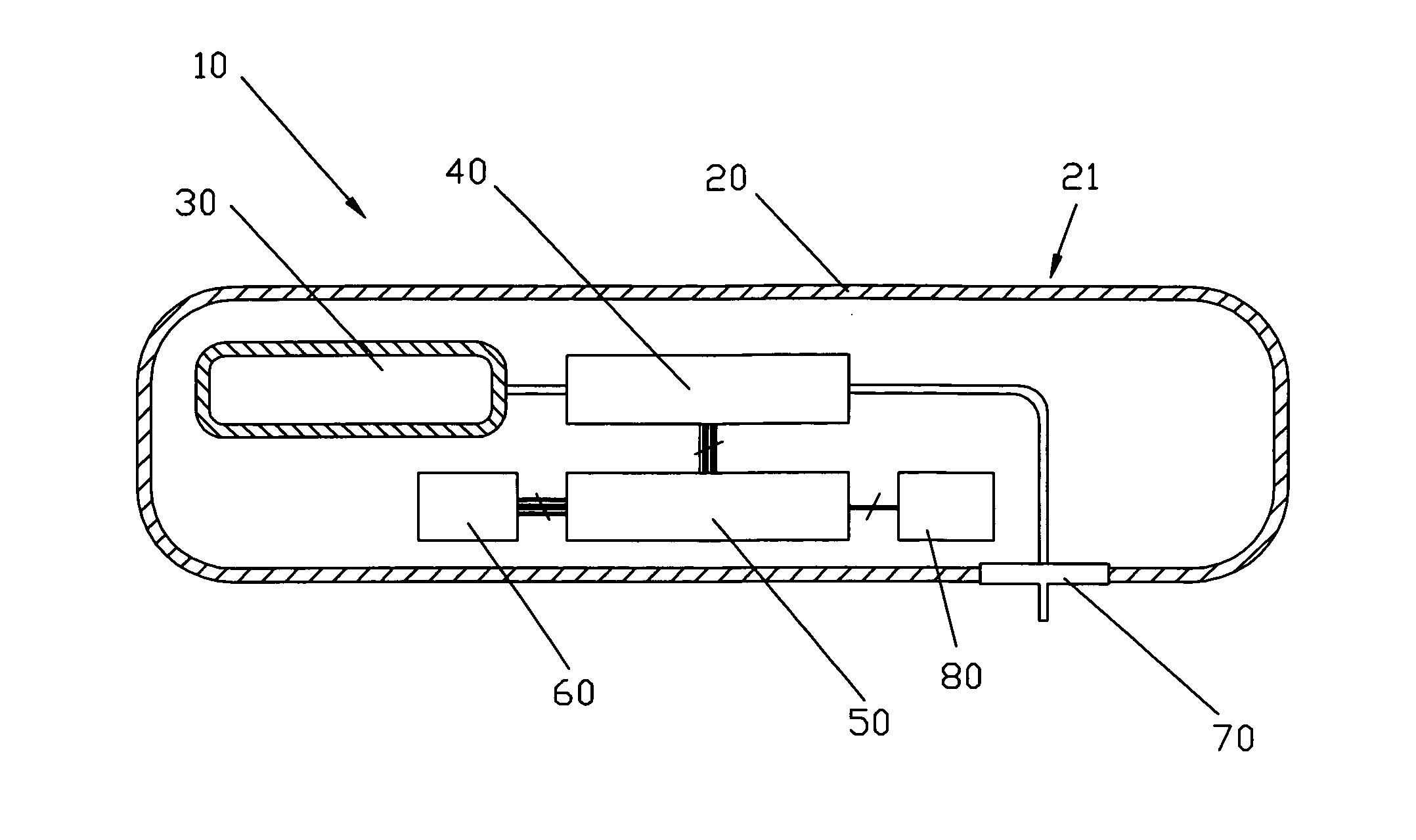

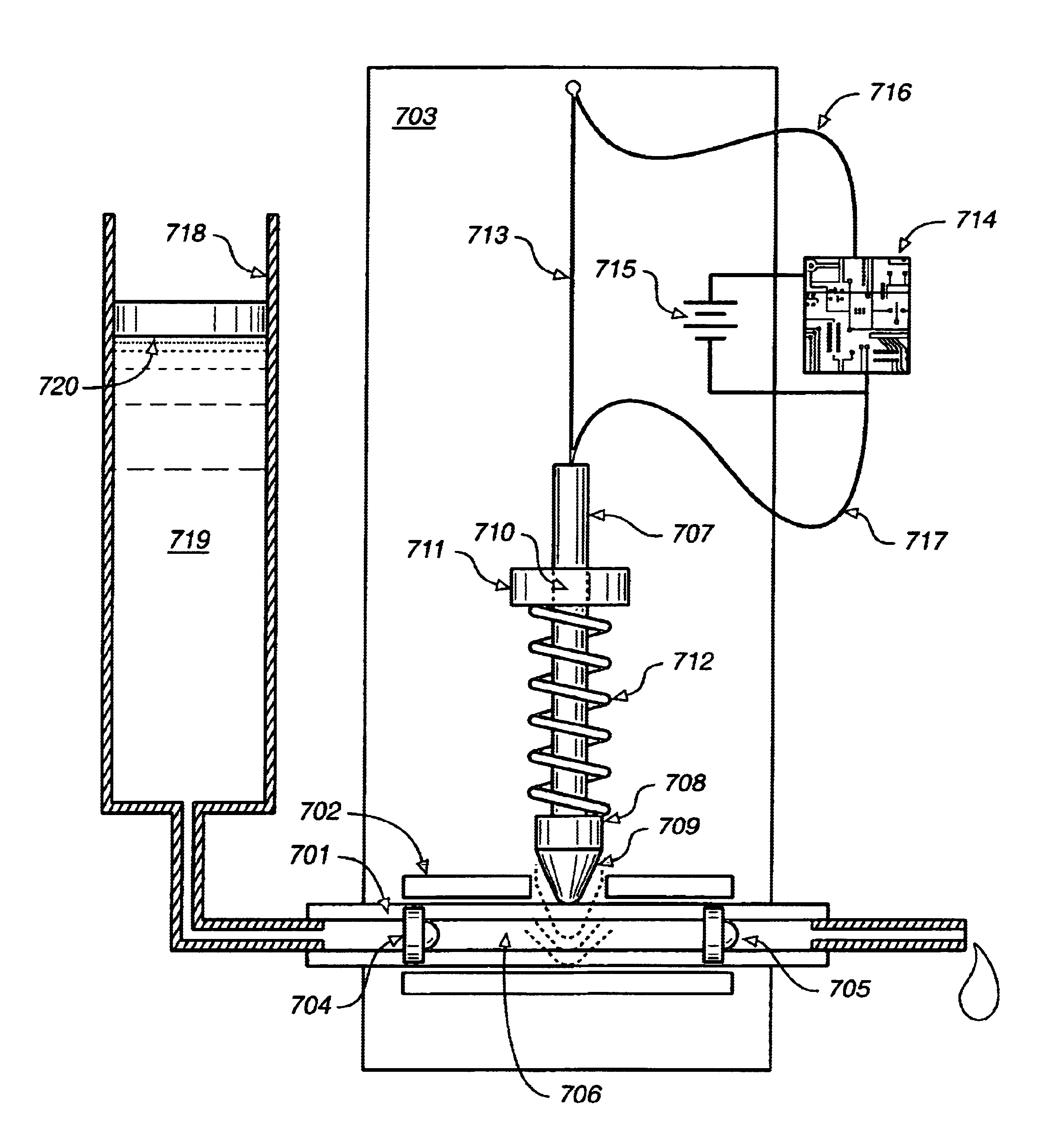

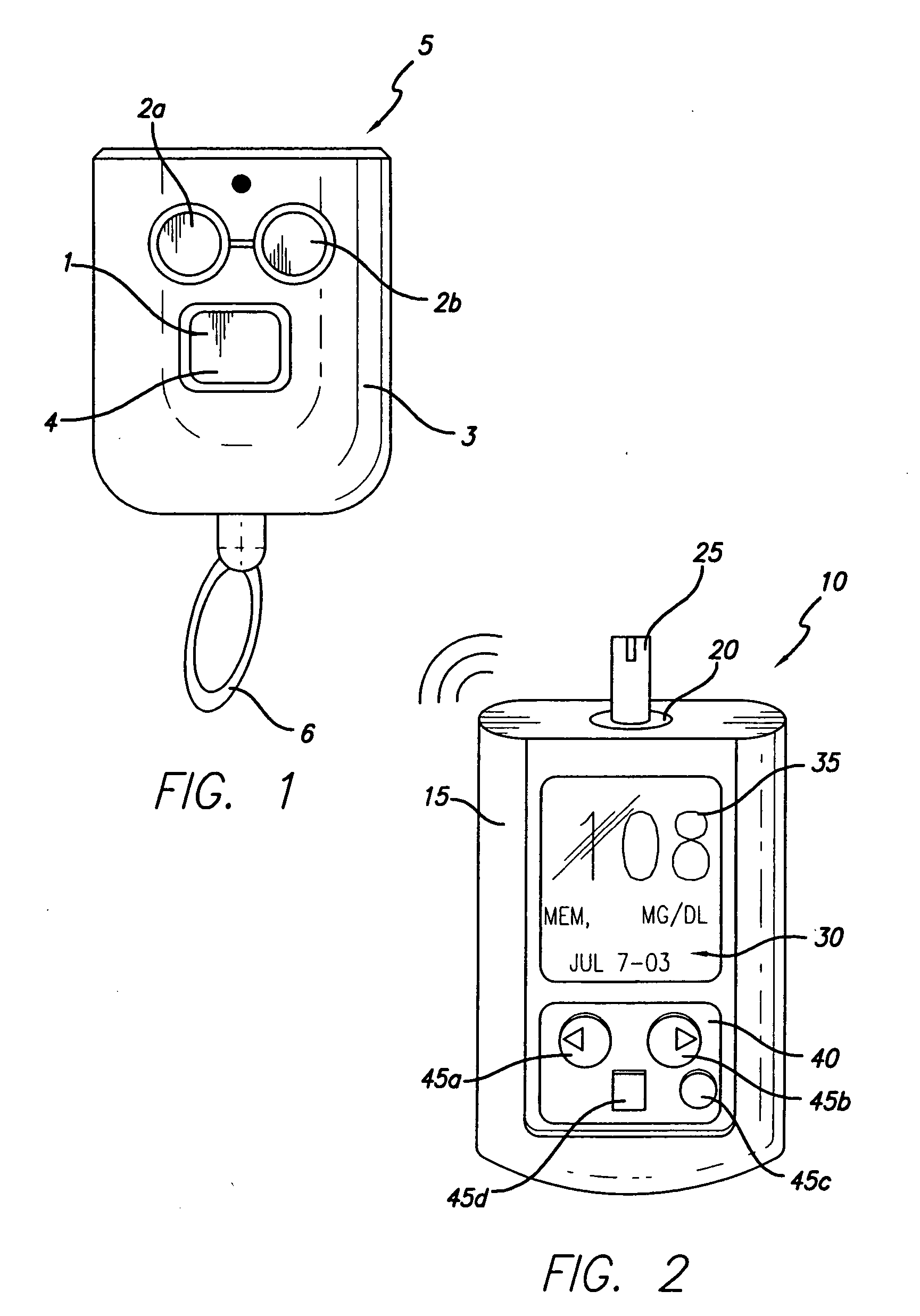

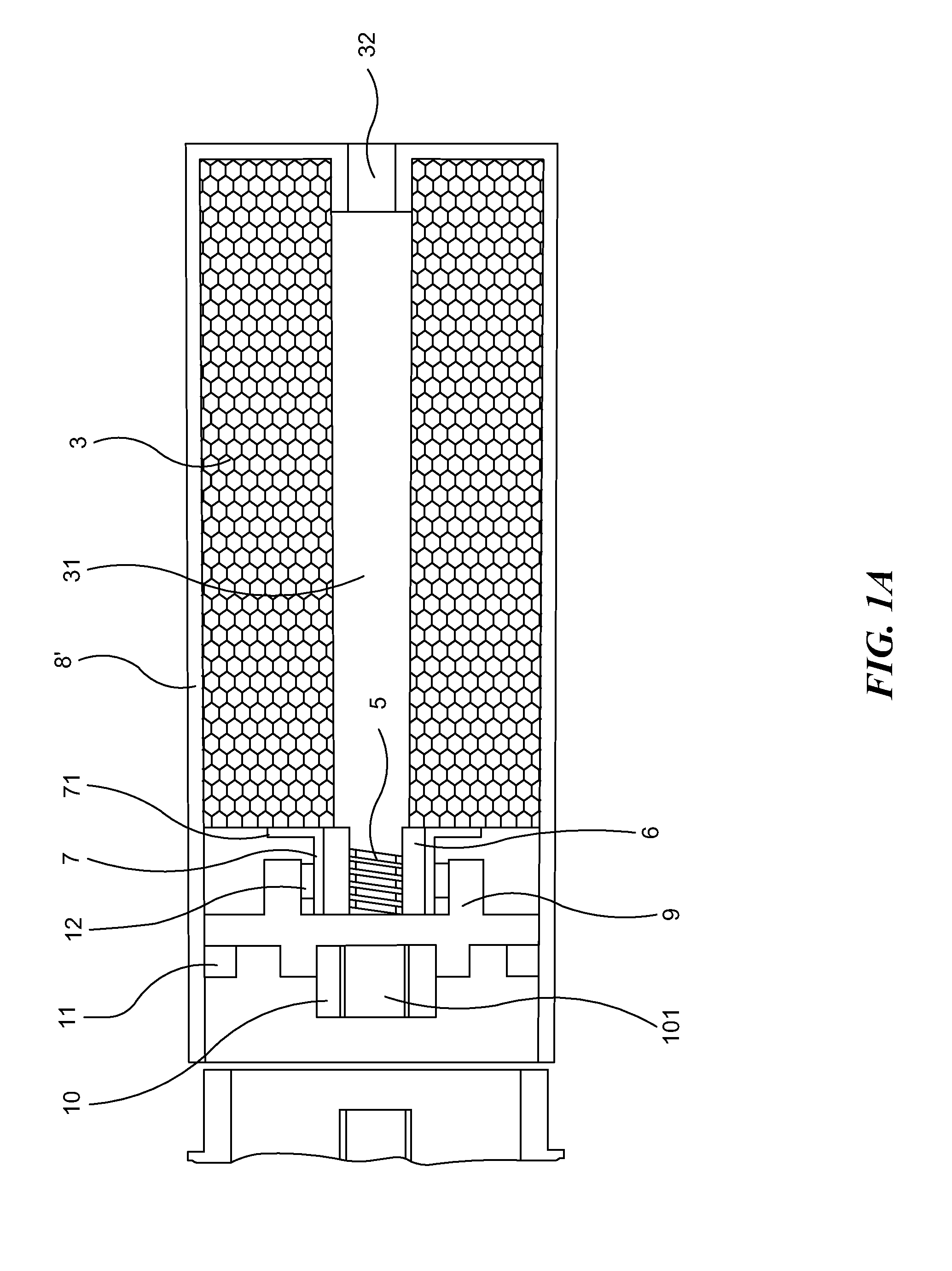

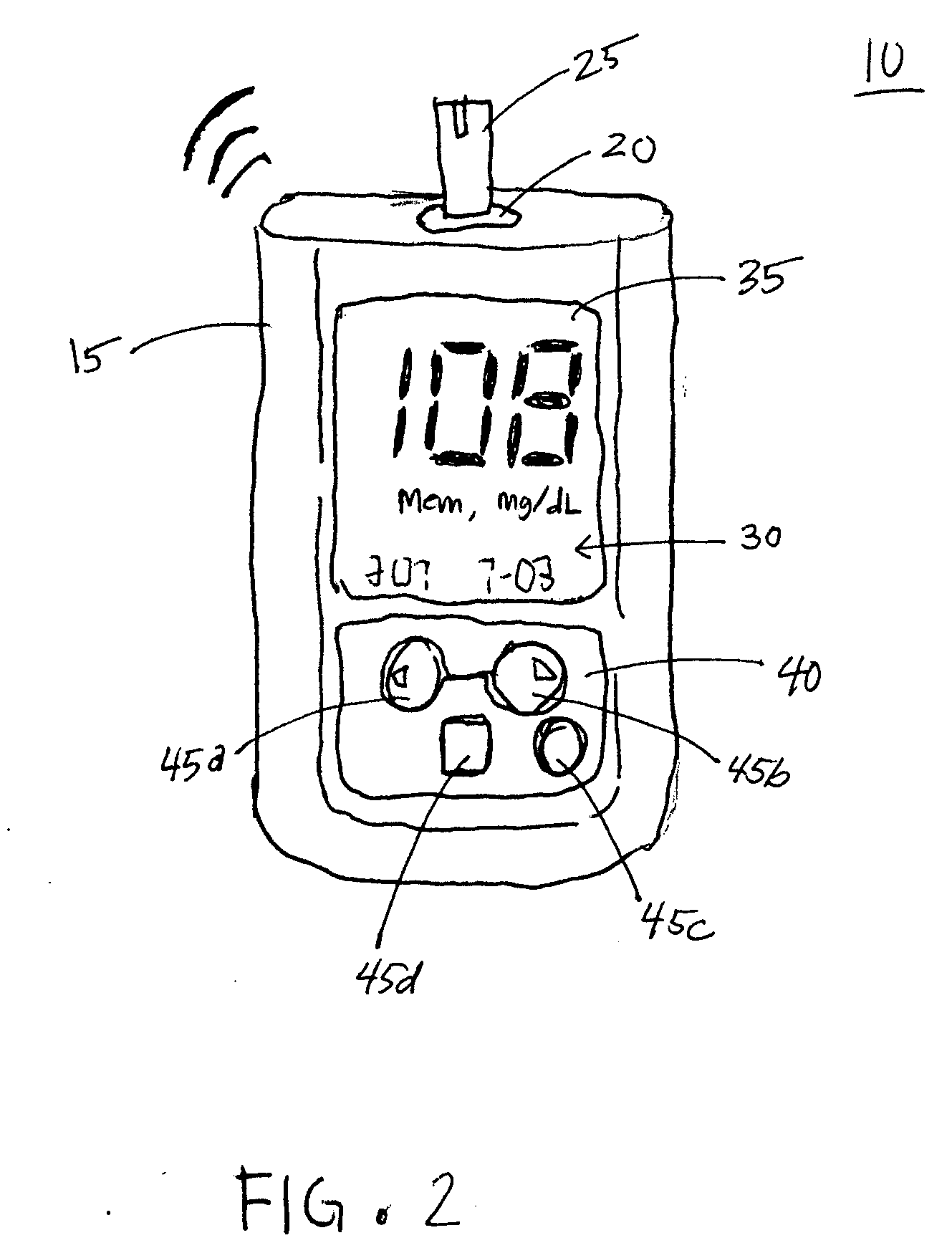

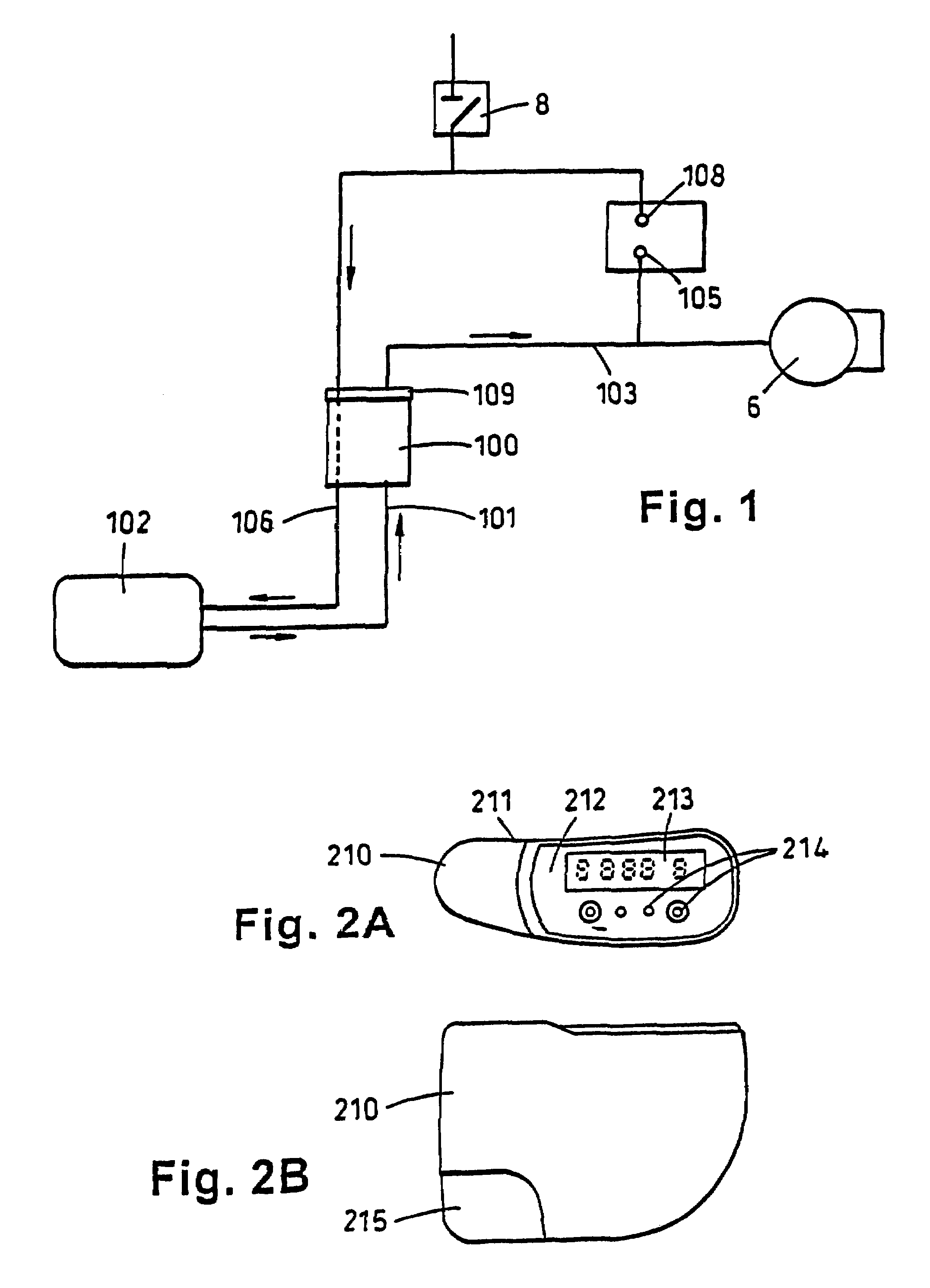

Devices, systems and methods for patient infusion

InactiveUS7029455B2Easy to carryReduce financial burdenDrug and medicationsPharmaceutical delivery mechanismUser inputRemote control

A device for delivering a fluid to a patient, including an exit port, a dispenser for causing fluid from a reservoir to flow to the exit port, a local processor programmed to cause a flow of fluid to the exit port based on flow instructions from a separate, remote control device, and a wireless receiver connected to the local processor for receiving the flow instructions. The device also includes a housing free of user input components for providing flow instructions to the local processor, in order to reduce the complexity and costs of the device so that the device lends itself to being disposable in nature. A system and a kit are also described that include the fluid delivery device, a separate, remote control device, and accessories for transcutaneous delivery of fluid medications. Methods of utilizing the fluid delivery device to infuse fluid medications are additionally disclosed.

Owner:INSULET CORP

Device and method employing shape memory alloy

InactiveUS6916159B2Low costSmall size and weightTesting/calibration apparatusVolume/mass flow measurementShape-memory alloyEngineering

Owner:THERASENSE

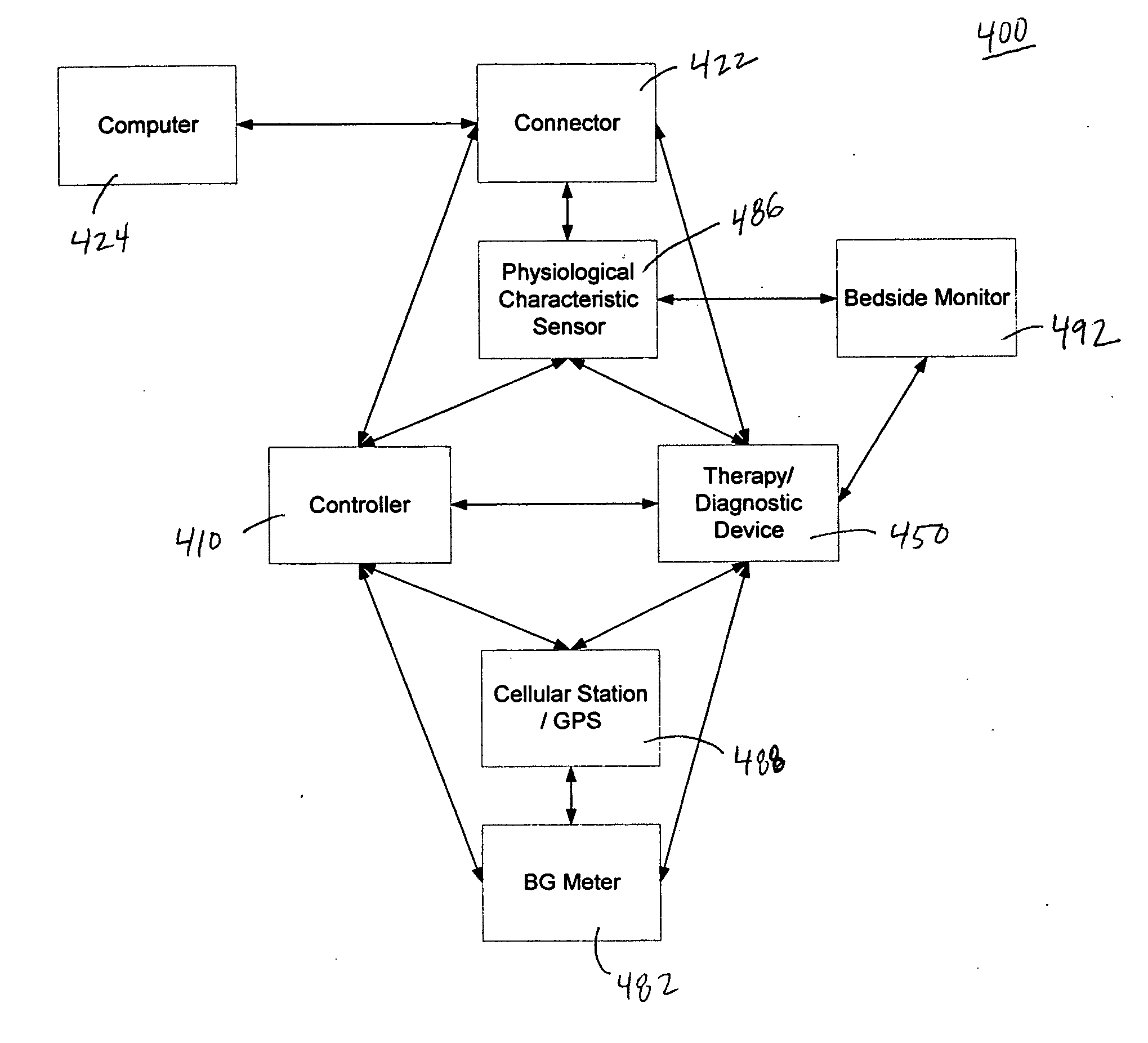

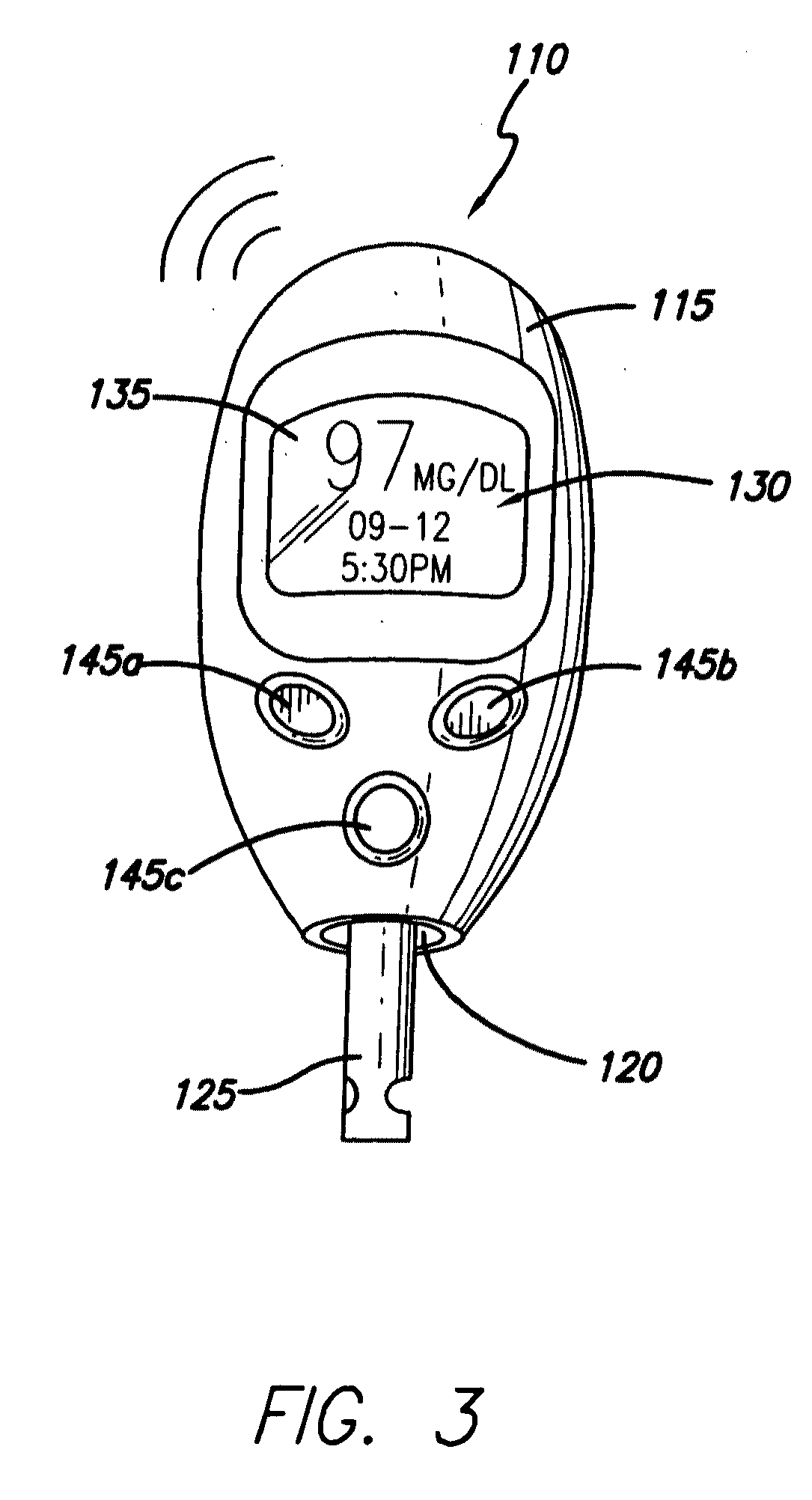

Watch controller for a medical device

InactiveUS20070093786A1Minimizes potential for errorEasy to watchMedical devicesPharmaceutical delivery mechanismCommunications systemMonitoring and control

An infusion system that includes a watch controller device and a communication system to transmit the communications from the watch controller device to an infusion device pump that controls delivery of fluids to the user's body. More particularly, these apparatuses and methods are for providing convenient monitoring and control of the infusion pump device in determining the appropriate amount of insulin to deliver.

Owner:MEDTRONIC MIMIMED INC

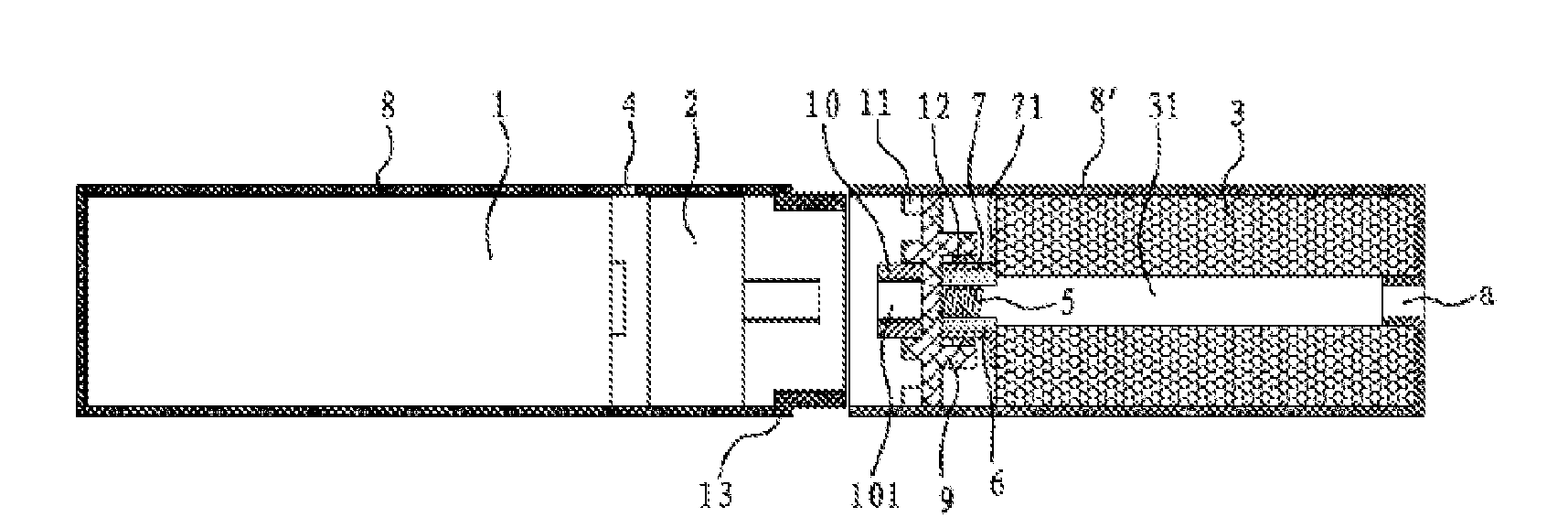

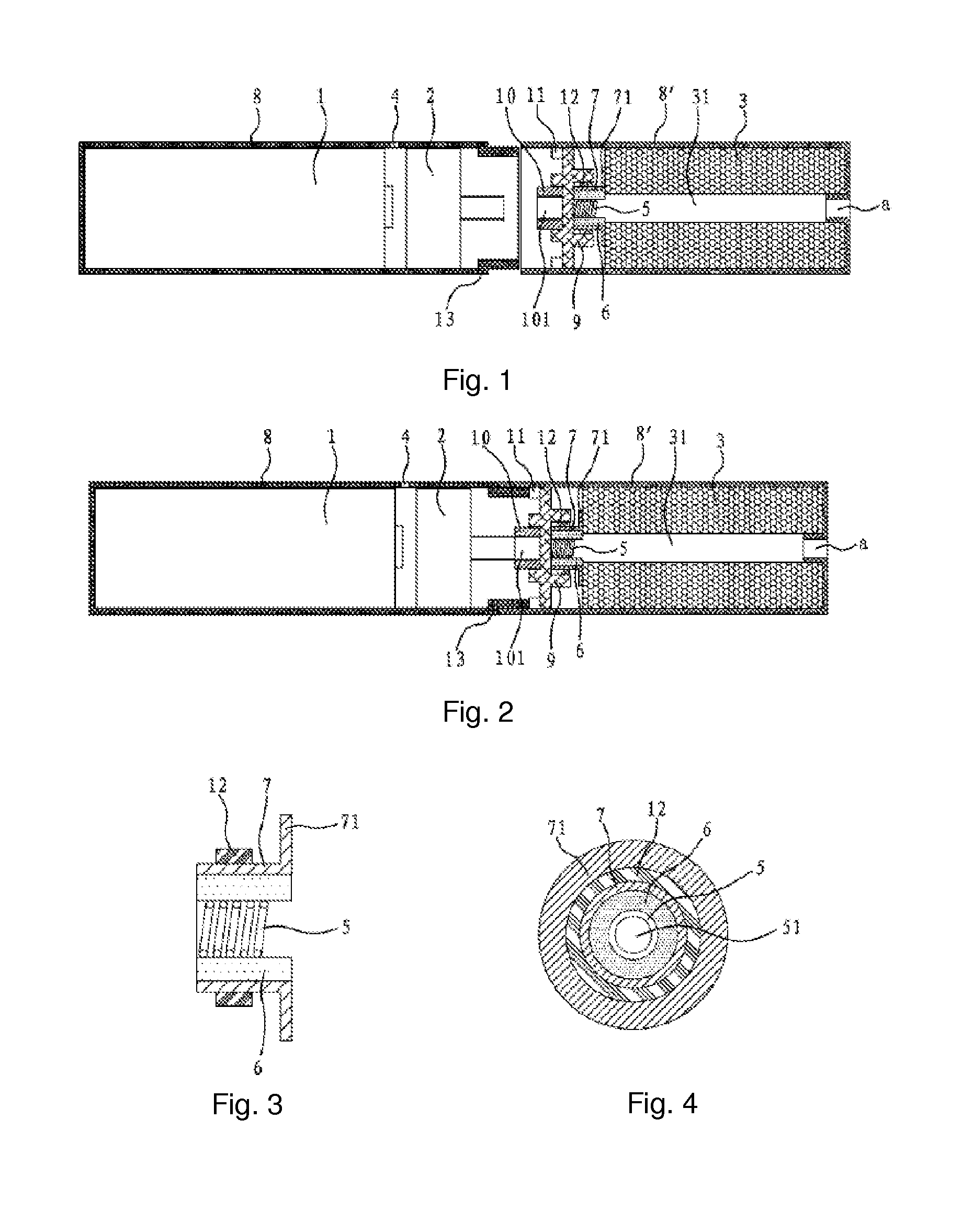

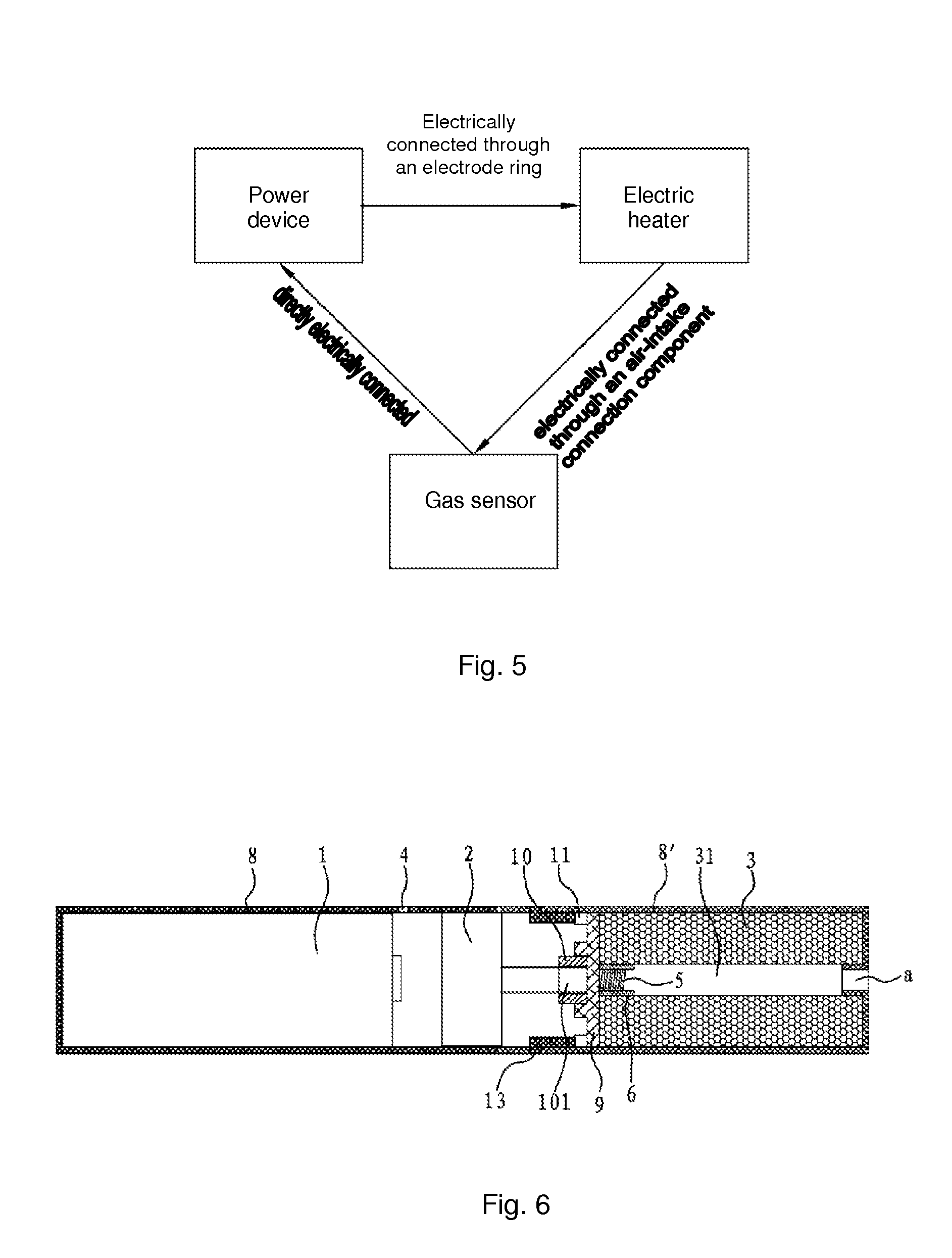

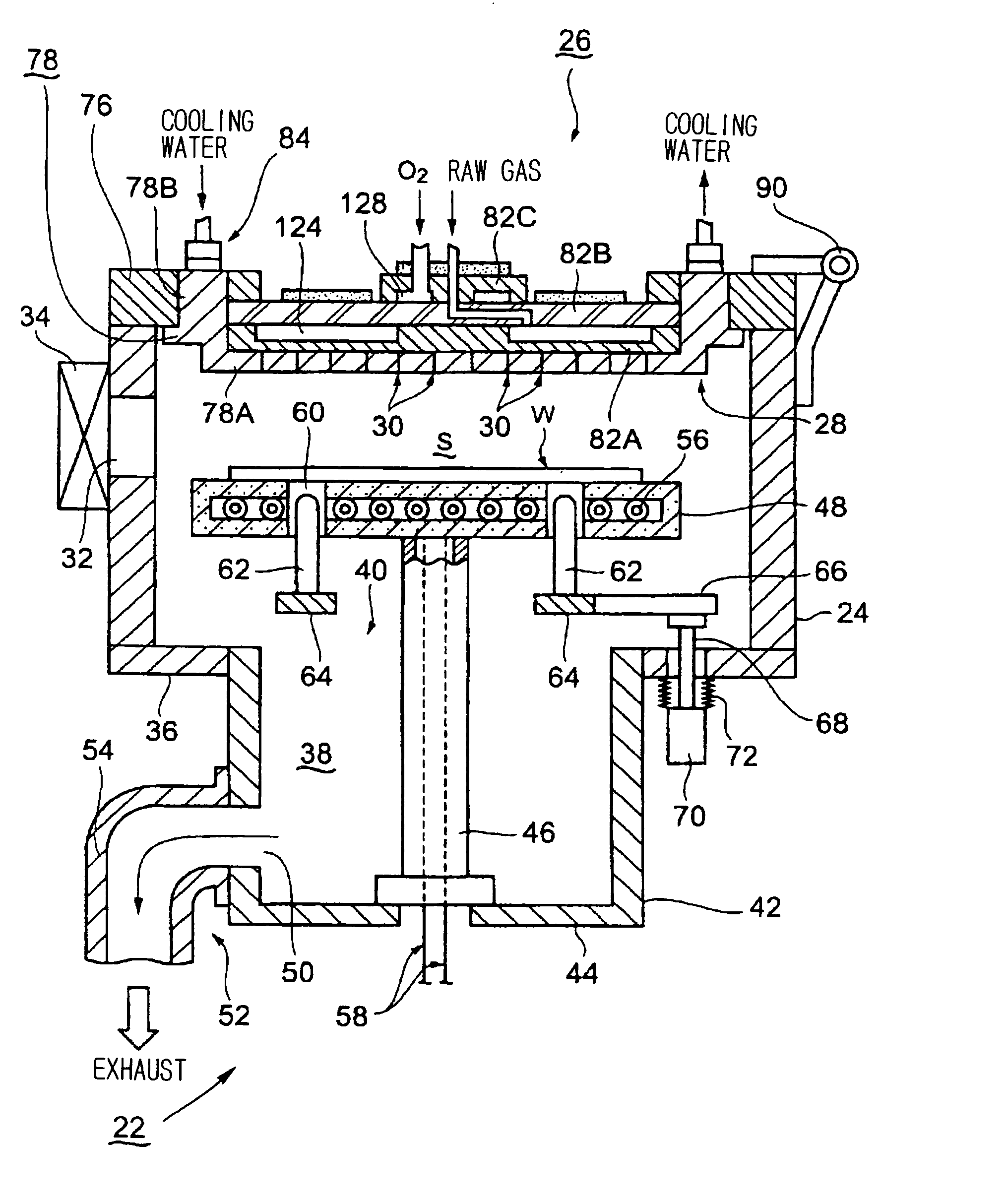

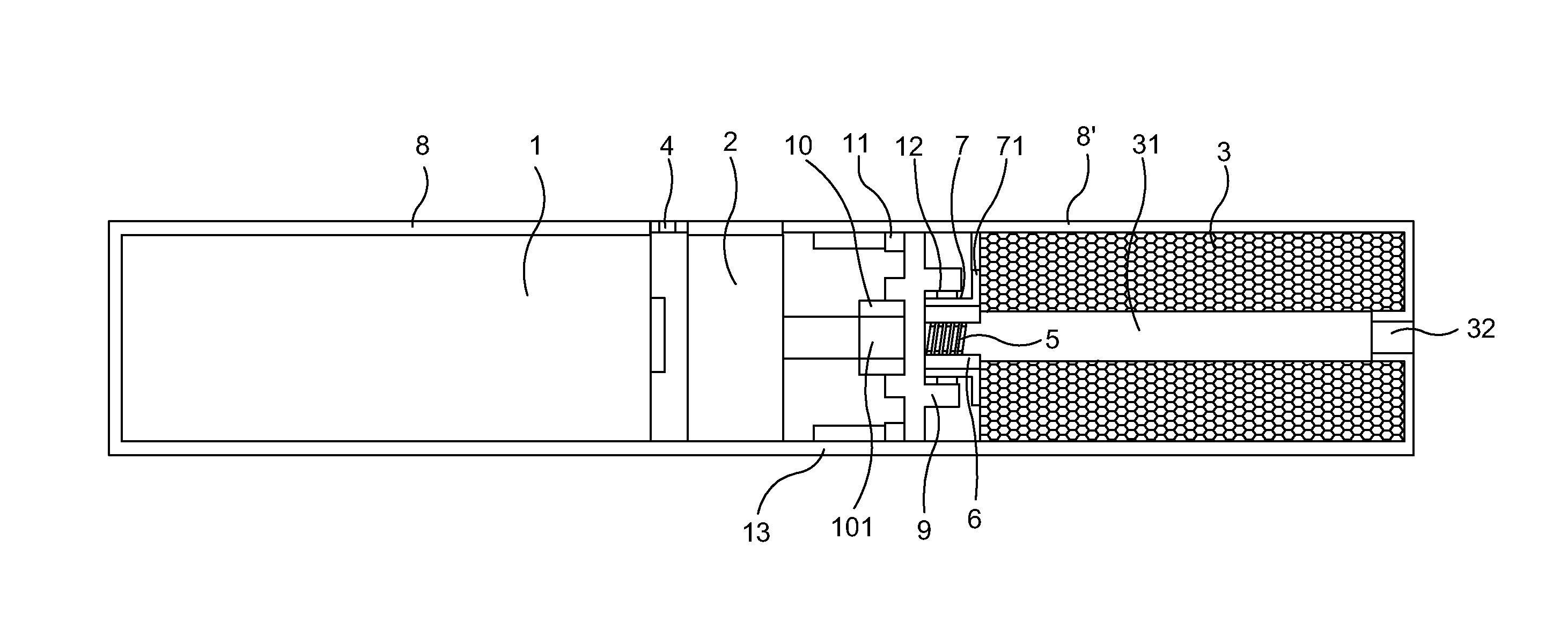

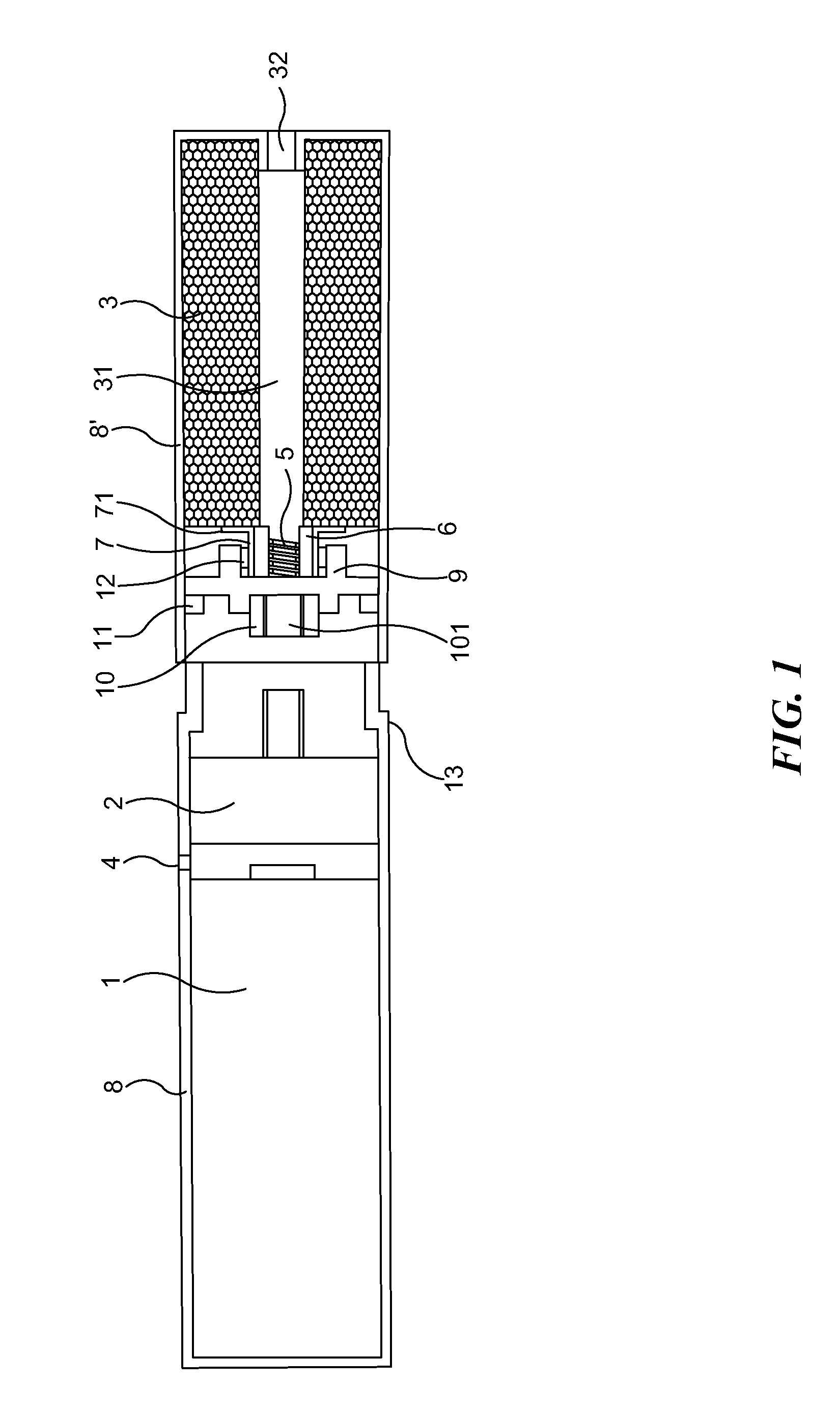

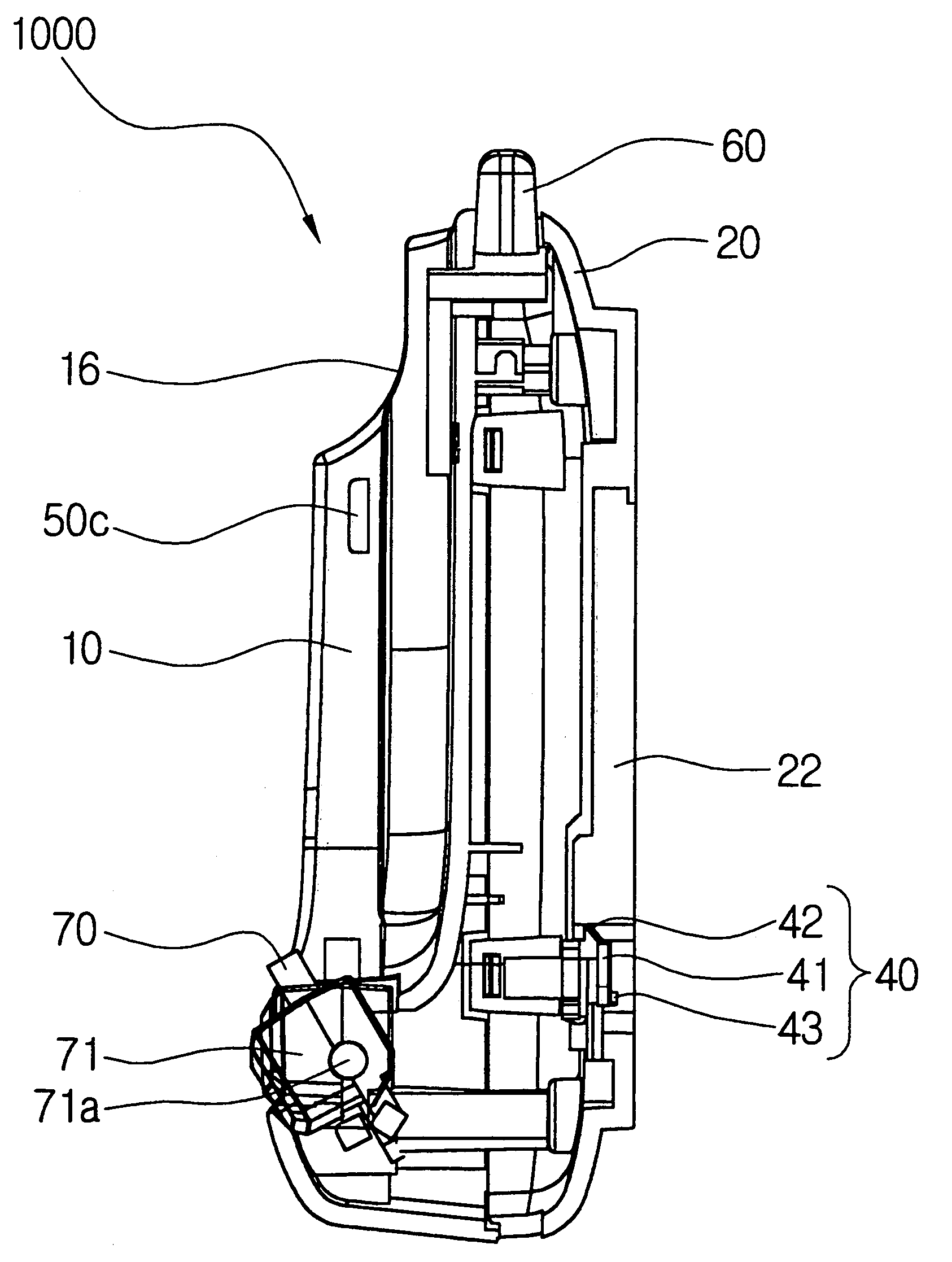

Atomizing electronic cigarette

InactiveUS20120111347A1Promote atomizationFully atomizedRespiratorsHeater elementsCore componentElectronic cigarette

An electronic cigarette has a power device (1), a sensor (2), an atomizing core component and a liquid storage component (3). The atomizing core component includes an electric heater (5) and a liquid permeating component (6). The electric heater (5) has a through hole (51), the liquid storage component (3) has a channel (31), and the sensor (2) is connected with the through hole (51) and the channel (31) to form an airflow loop by the auxiliary air inlet. The liquid permeating component (6) is directly sleeved on the electric heater (5), so that the cigarette can adequately heat gasified smoke with uniform small drops. The electric heater (5) and the liquid storage component (3) are connected with the through hole (51) and the channel (31), so that the vapor generated by the atomizing process can be cooled.

Owner:FONTEM HLDG 1

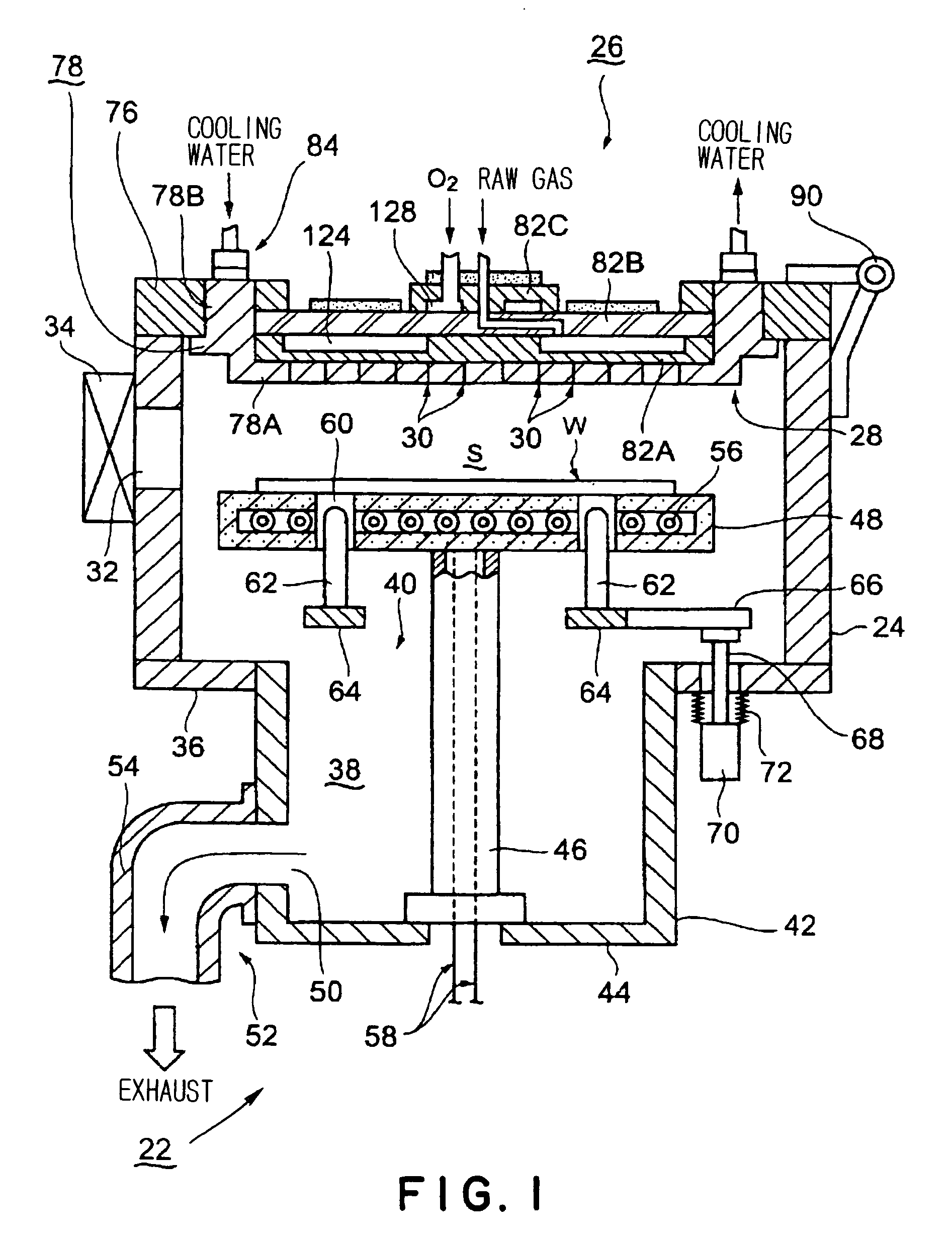

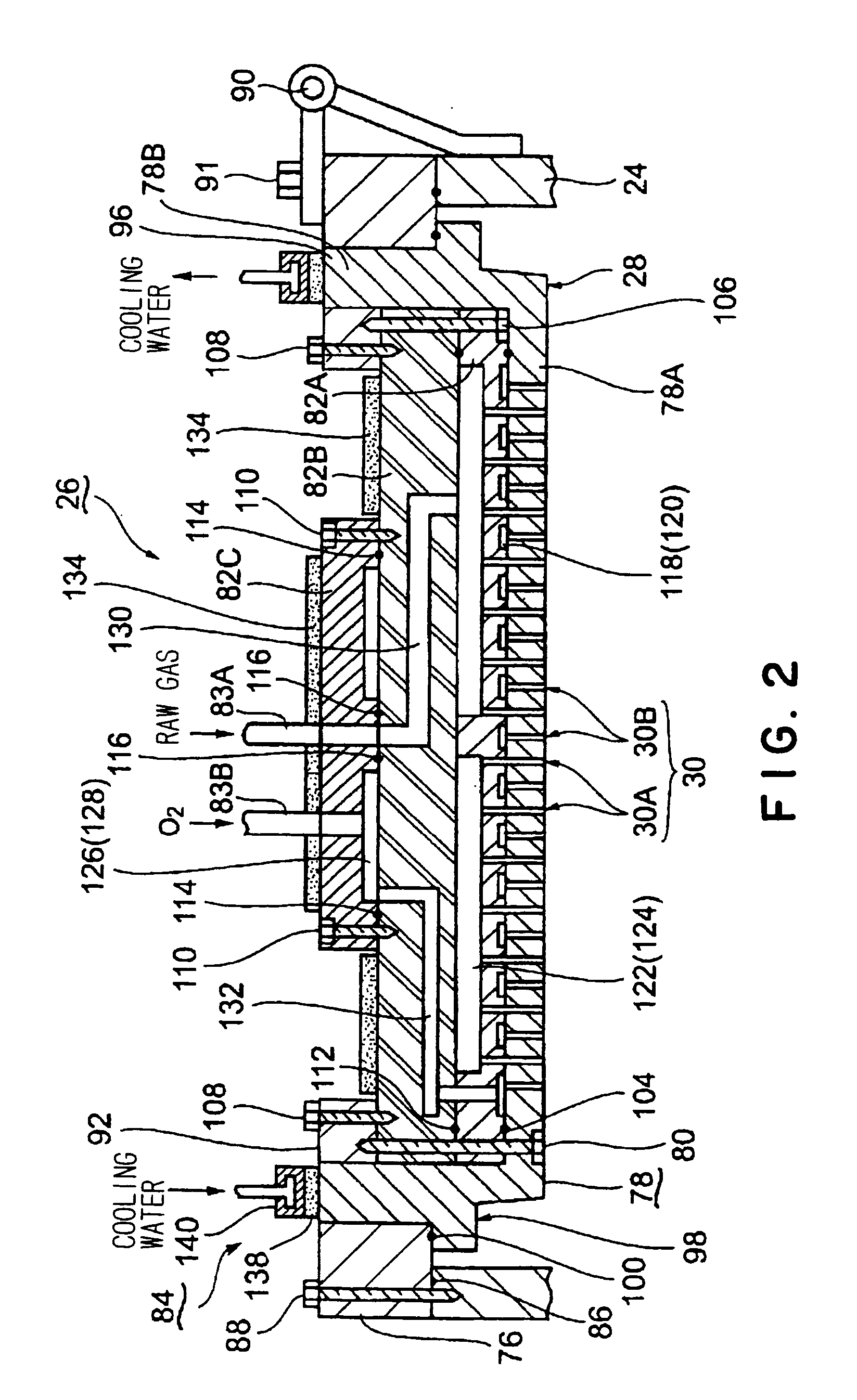

Processing apparatus

InactiveUS20070158026A1High temperature controllabilityEasy maintenanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringMechanical engineering

A shower head structure (26) includes a shower head main body (78) of a one-piece structure formed in a generally cup shape and having a bottom wall (78A) provided with a plurality of gas injection holes (30A, 30B) formed therein and a side wall (78B) rising from a peripheral portion of the bottom wall. A plurality of gas diffusion chamber forming plates (82A-82C) are housed in the shower head main body (78). A through-hole is formed in a head mounting frame (76) disposed on a ceiling of a processing vessel (24). An upper portion of the side wall (78B) of the shower head main body (78) is inserted into the through-hole, so that a part of the side wall (78B) is exposed to the exterior of the processing vessel. A cooling mechanism (84) is disposed at the upper end portion of the side wall (78B). Heat transfer between the cooling mechanism (84) and the bottom wall (78A) is enhanced, so that the temperature of the bottom wall (78A) can be controlled at a proper value, thereby preventing any adhesion of an unnecessary film onto the bottom wall (78A).

Owner:TOKYO ELECTRON LTD

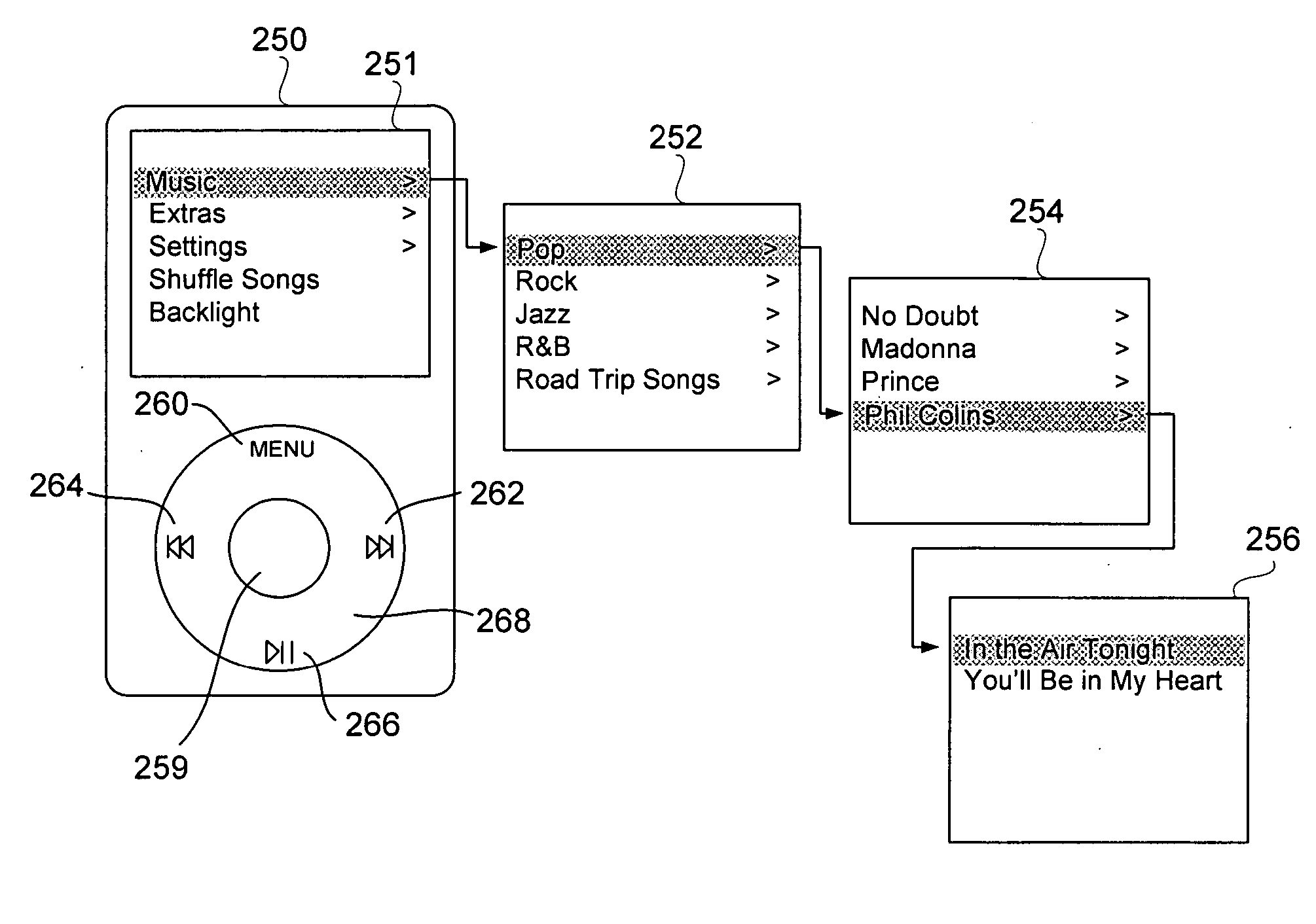

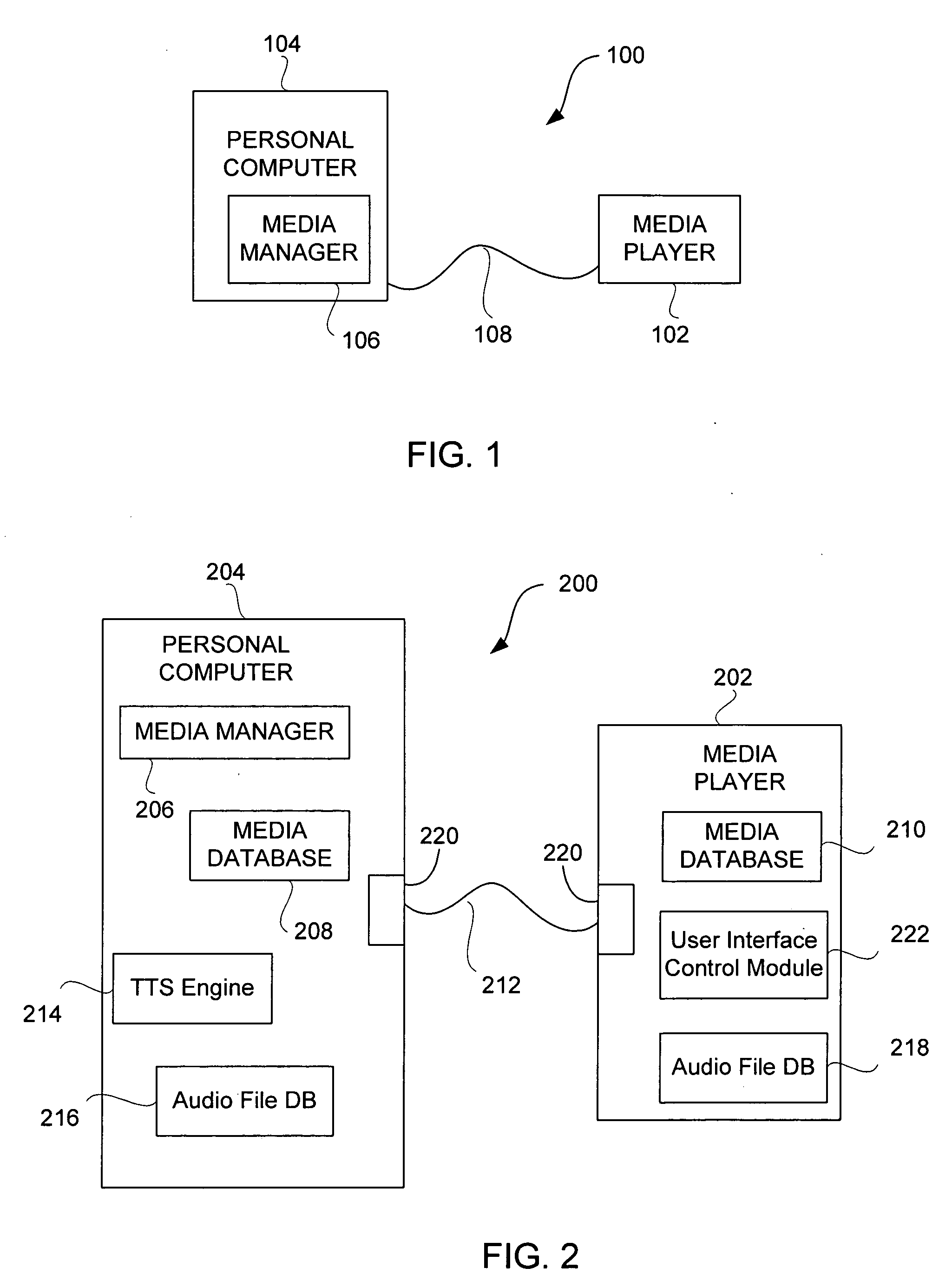

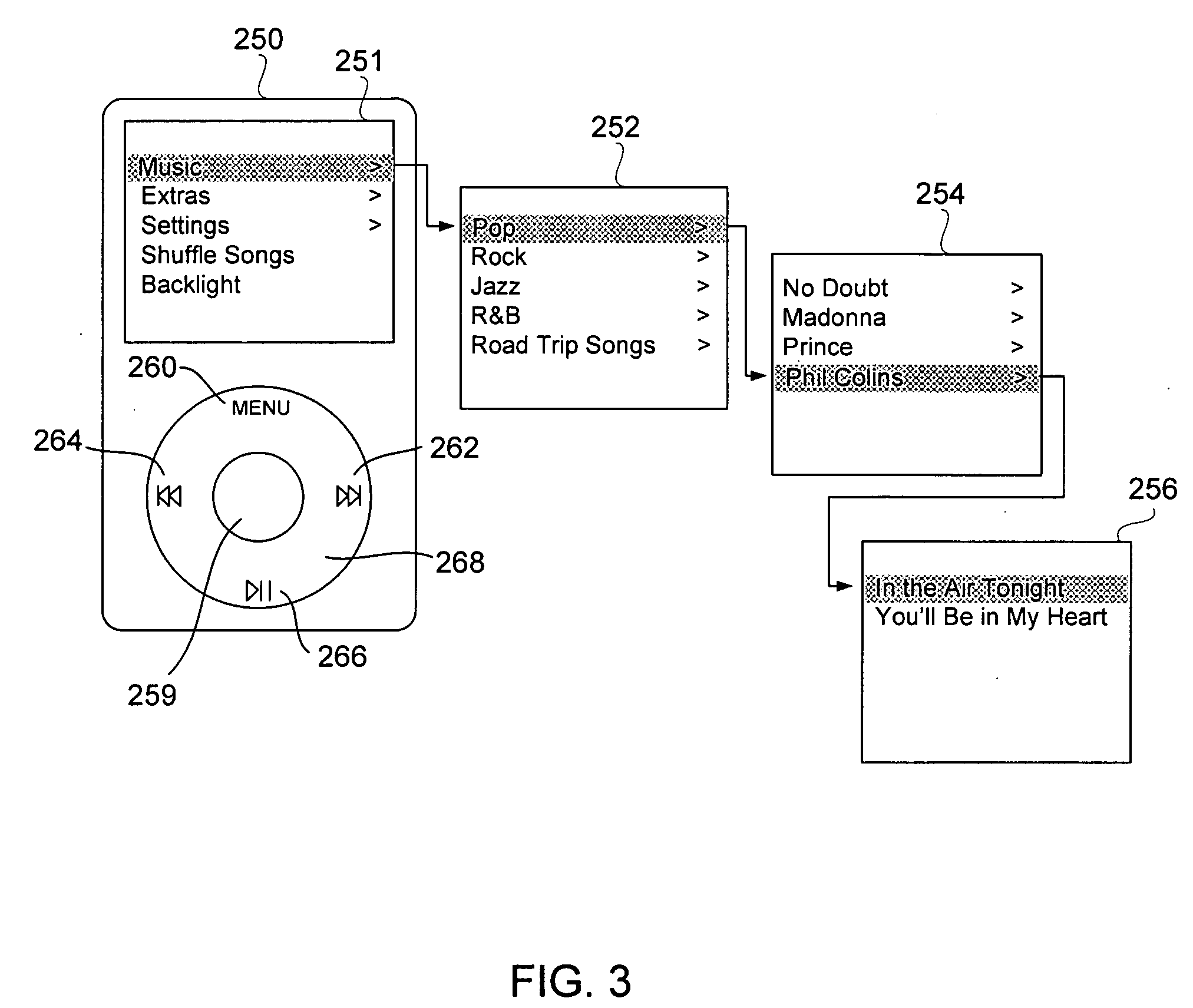

Audio user interface for computing devices

ActiveUS20060095848A1Easy to carryEfficient leveragingRecord information storageCarrier indicating arrangementsHand heldHand held devices

An audio user interface that generates audio prompts that help a user interact with a user interface of a device is disclosed. One aspect of the present invention pertains to techniques for providing the audio user interface by efficiently leveraging the computing resources of a host computer system. The relatively powerful computing resources of the host computer can convert text strings into audio files that are then transferred to the computing device. The host system performs the process intensive text-to-speech conversion so that a computing device, such as a hand-held device, only needs to perform the less intensive task of playing the audio file. The computing device can be, for example, a media player such as an MP3 player, a mobile phone, or a personal digital assistant.

Owner:APPLE INC

Electronic cigarette

ActiveUS20120279512A1Promote atomizationEfficient productionRespiratorsHeater elementsEngineeringElectronic cigarette

Owner:FONTEM VENTURES

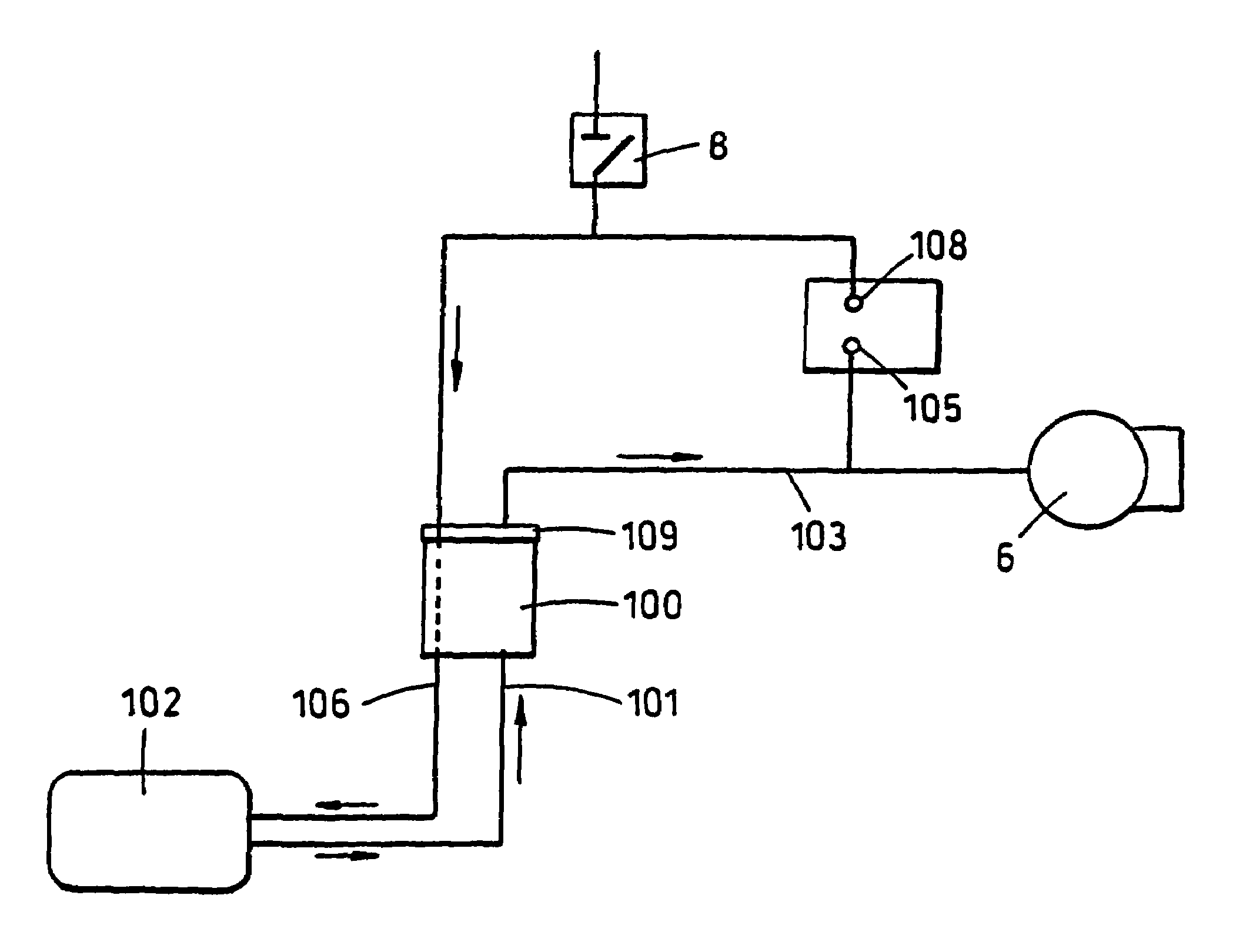

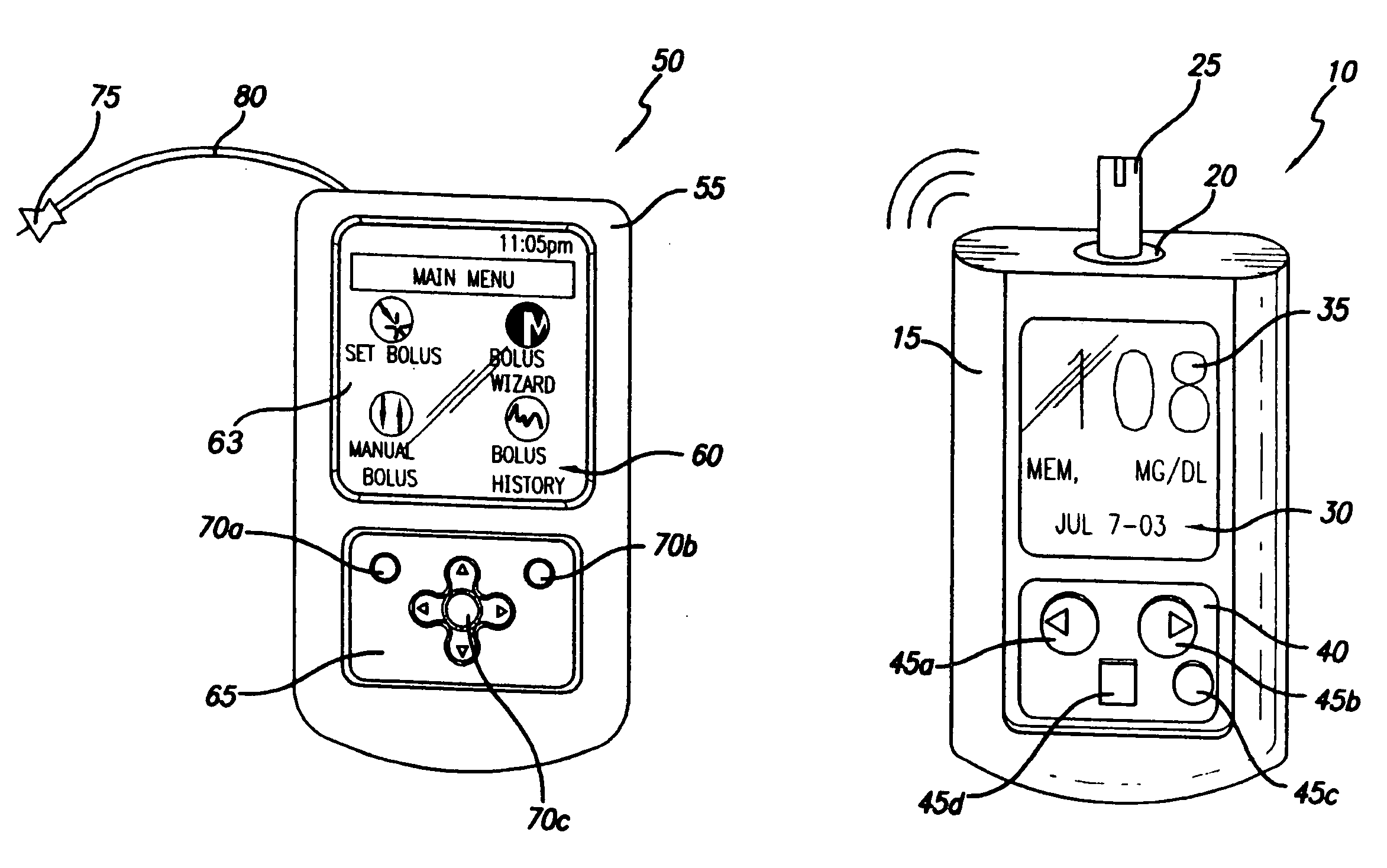

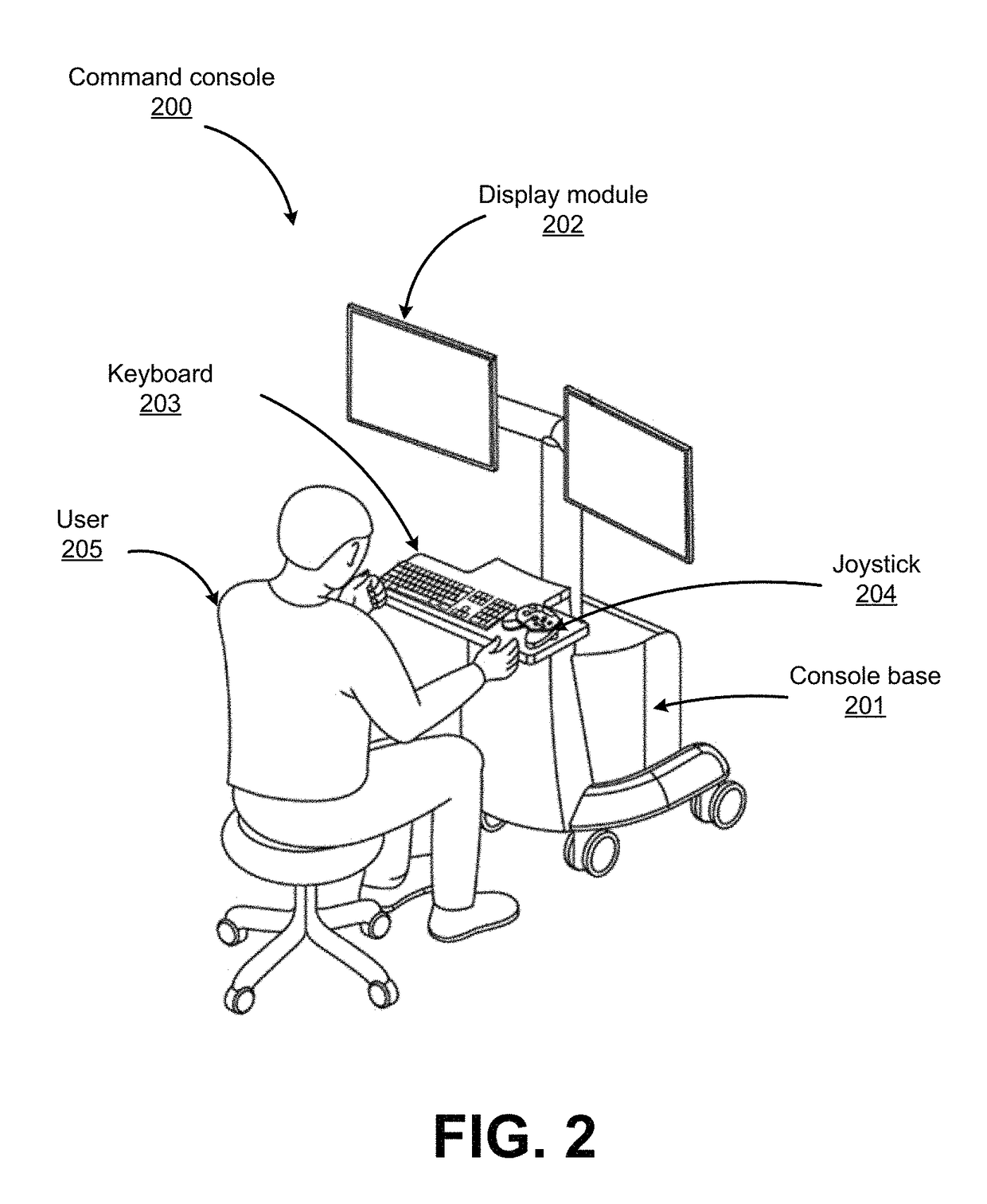

Controller device for an infusion pump

InactiveUS20070060869A1Avoid interferenceMinimizes potential for errorMedical devicesIntravenous devicesCommunications systemEngineering

An infusion system that includes a controller device and a communication system to transmit the communications from the controller device to an infusion device pump that controls delivery of fluids to the user's body. More particularly, these apparatuses and methods are for providing convenient monitoring and control of the infusion pump device in determining the appropriate amount of insulin to deliver.

Owner:MEDTRONIC MIMIMED INC

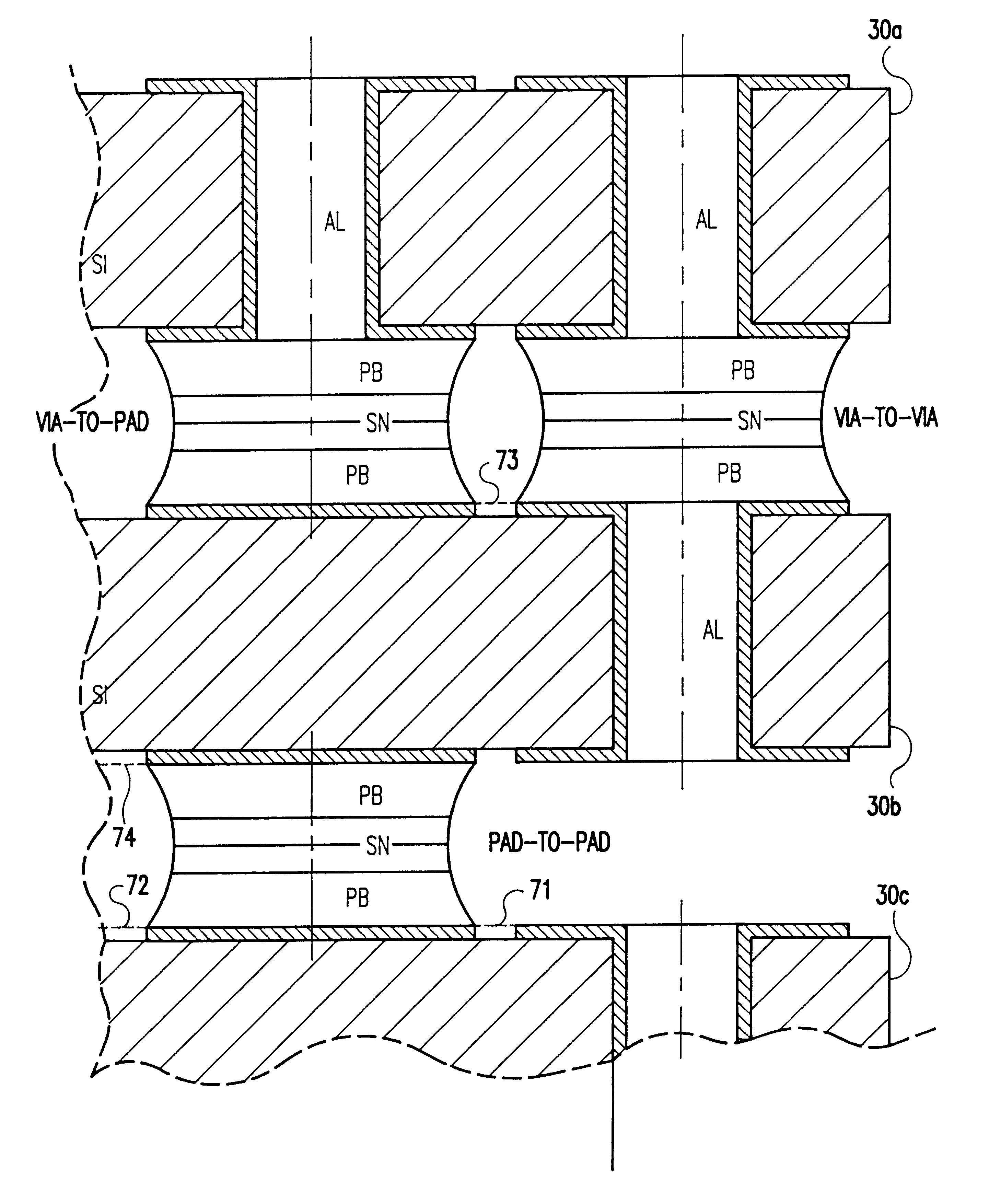

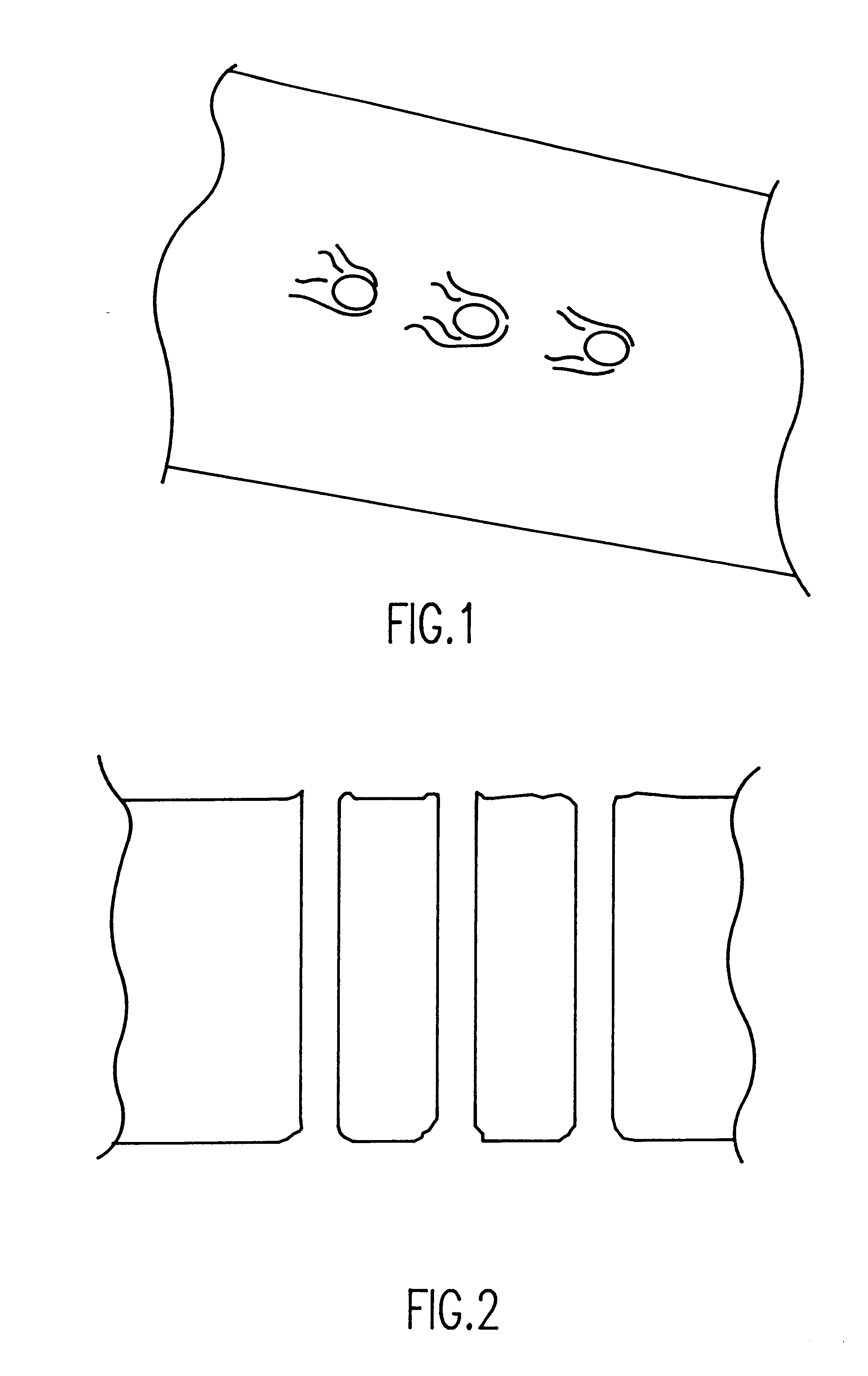

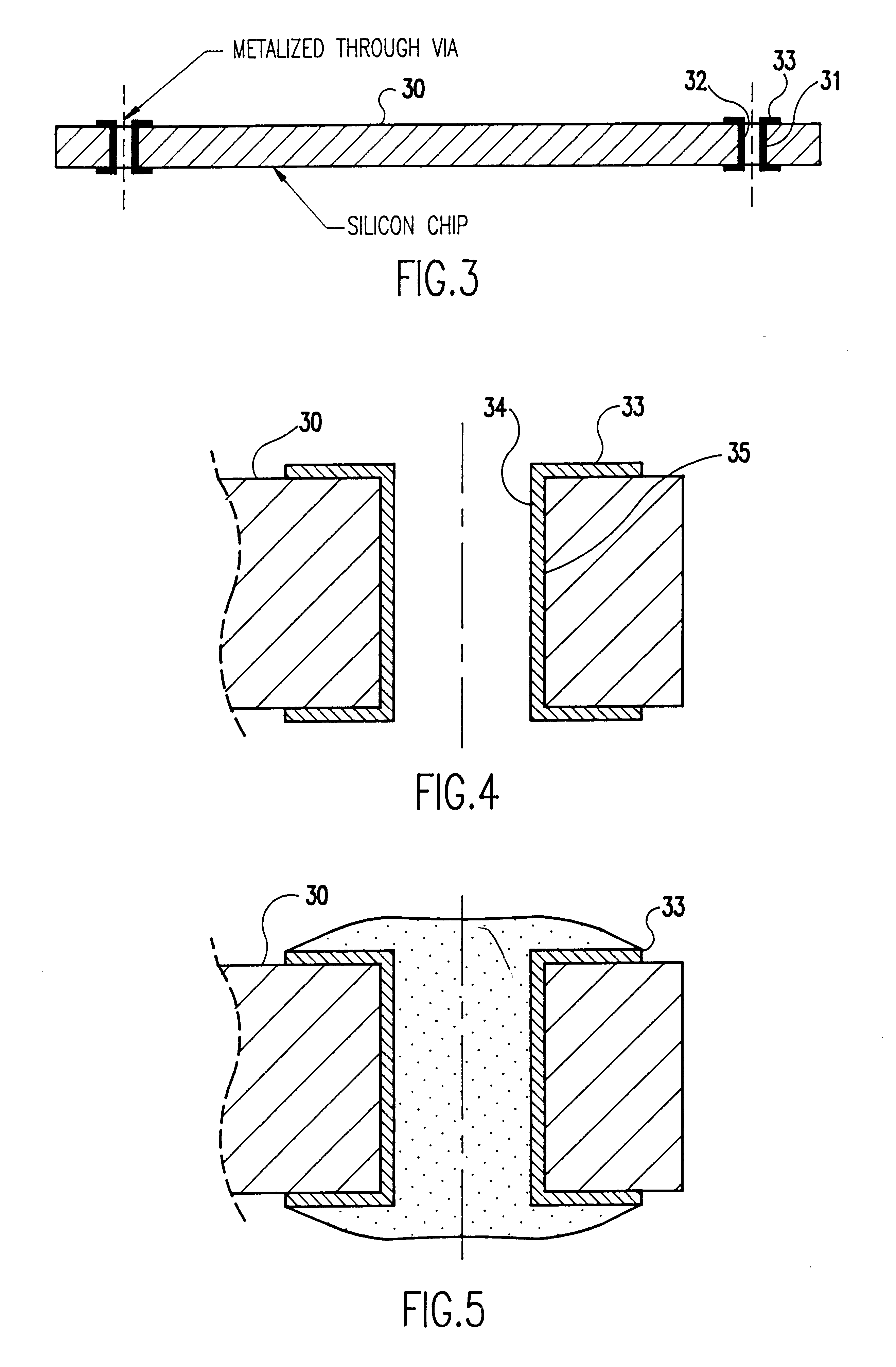

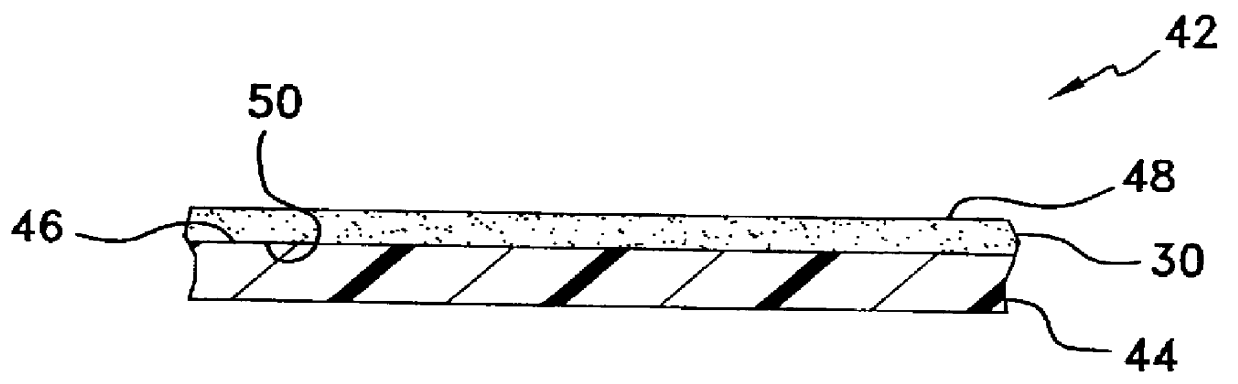

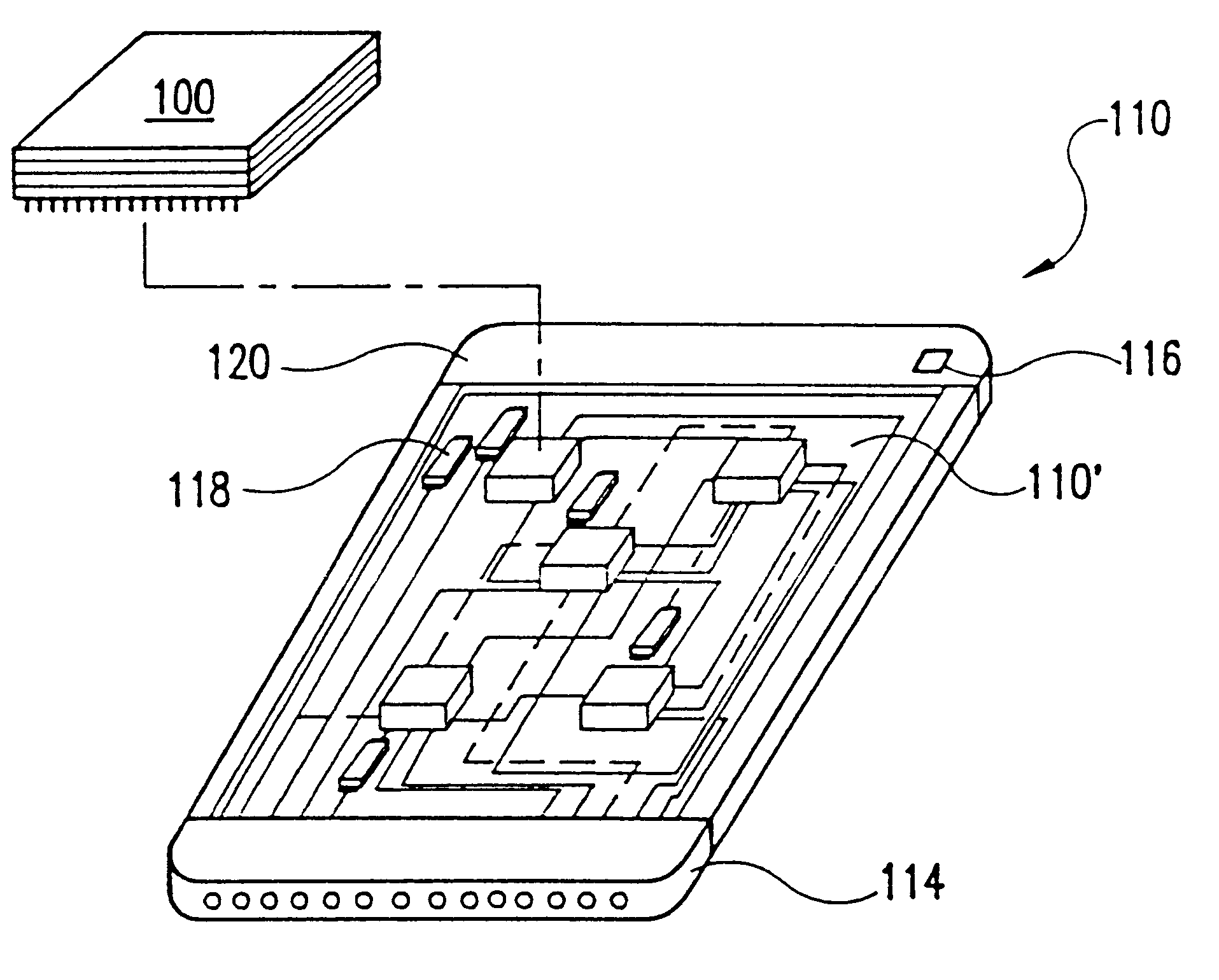

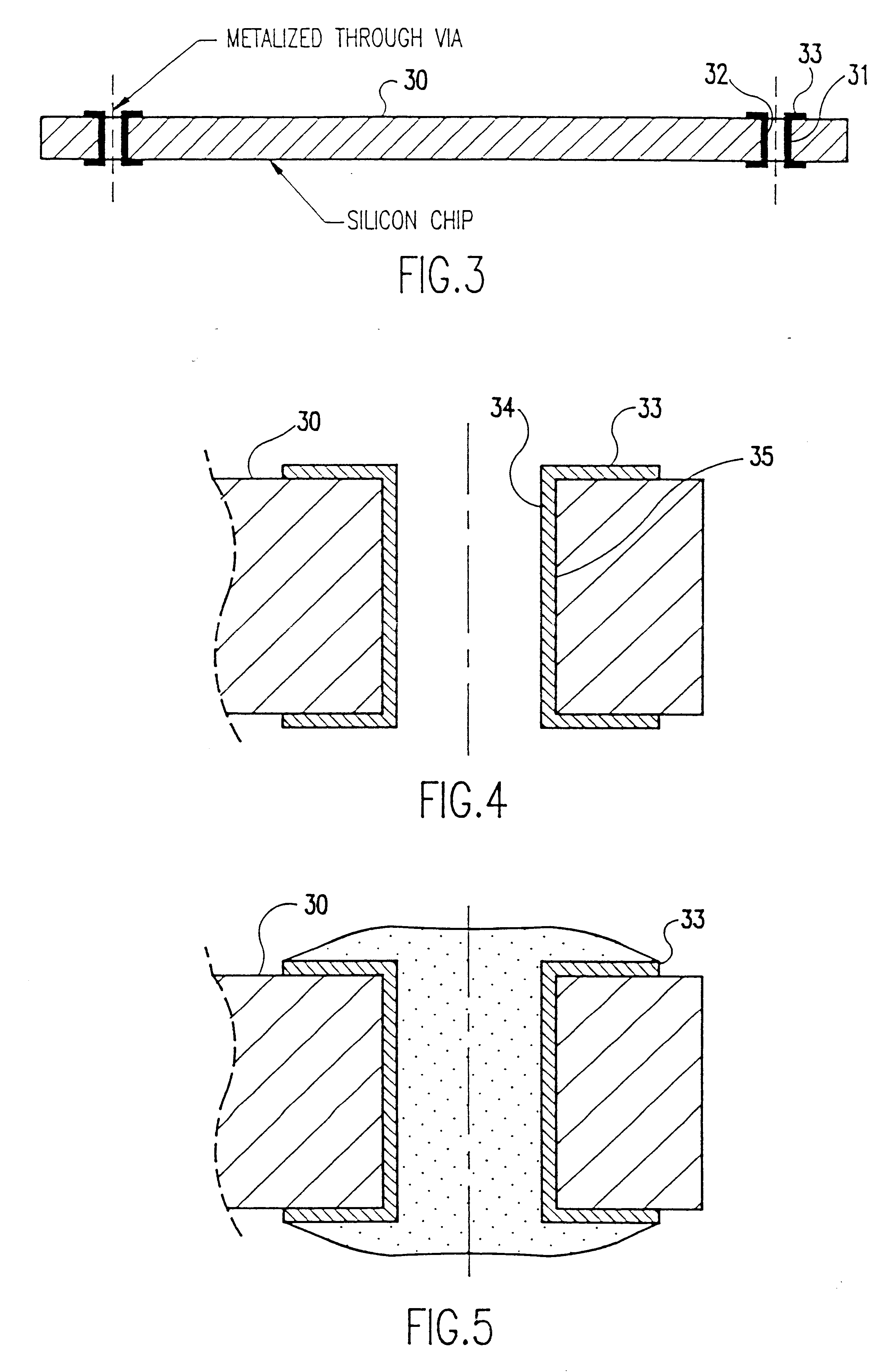

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

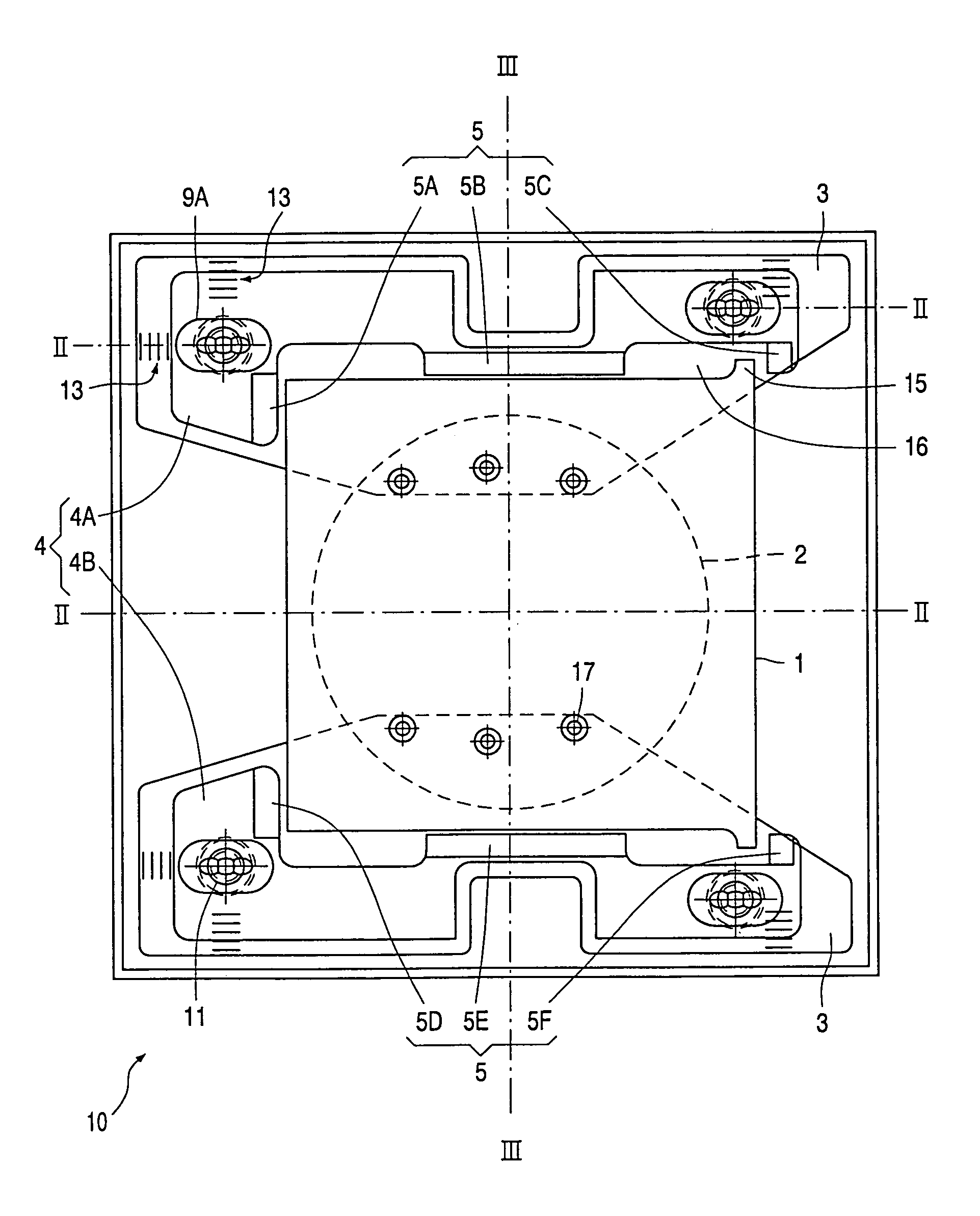

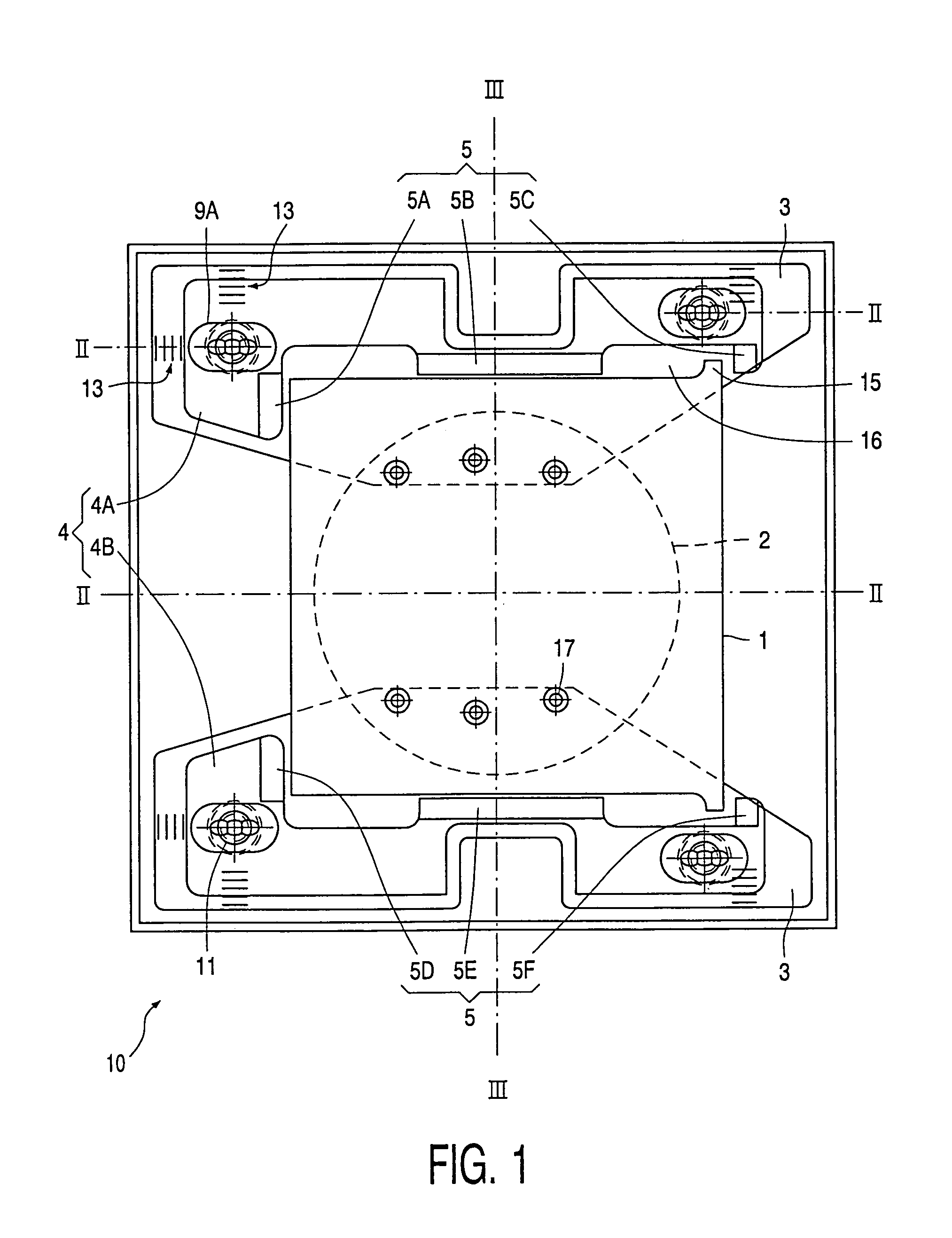

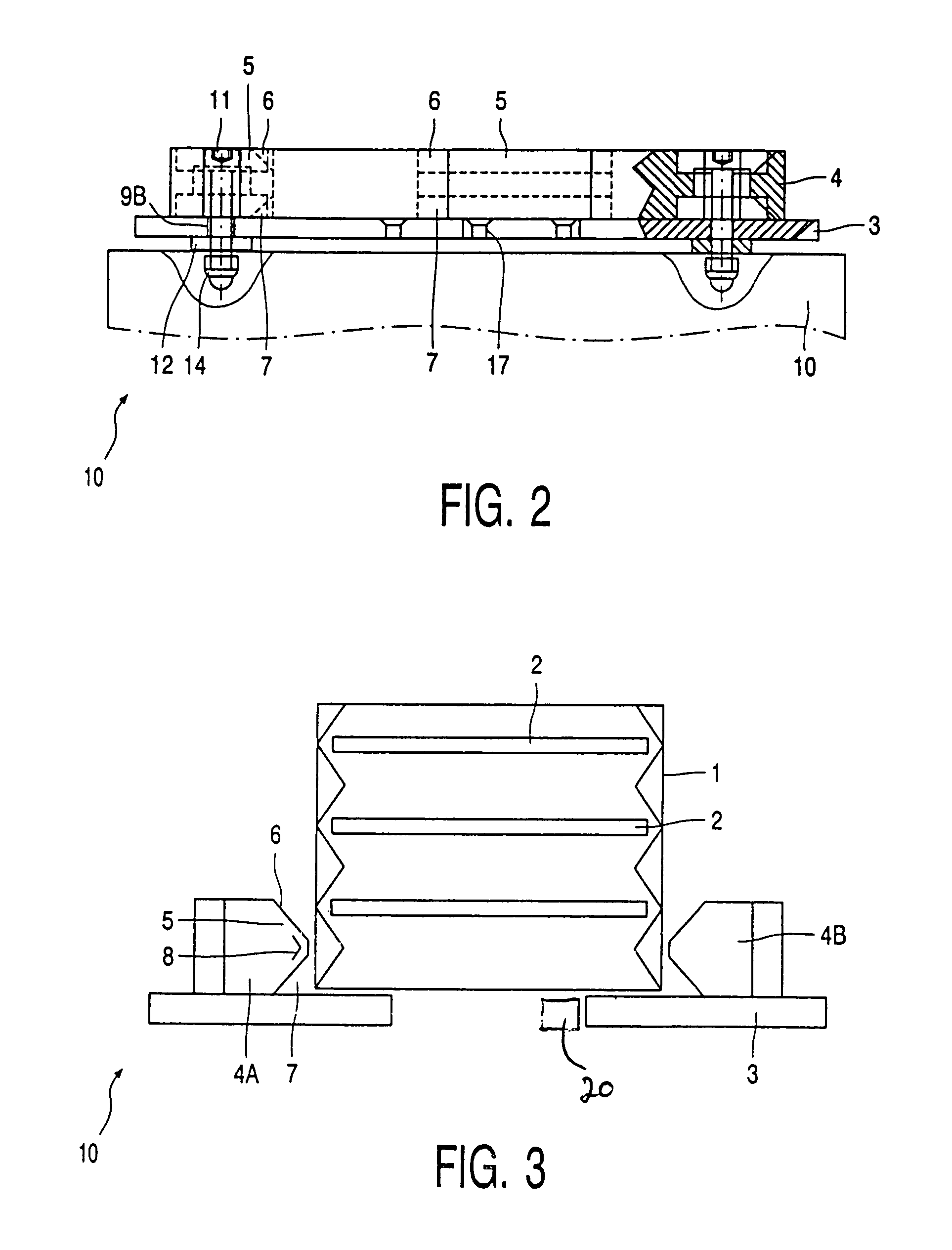

Holder for a substrate cassette and device provided with such a holder

InactiveUS7070178B2Easy and economical to manufactureEasy to manufactureSemiconductor/solid-state device manufacturingPositioning apparatusMechanical engineeringSemiconductor

A holder is disclosed for a cassette for substrates. The holder includes a base plate on which a guide member provided with at least two guides is secured. The cassette is to be positioned between the guides, which enable the cassette to be aligned with respect to the base plate, and the side of which facing the base plate tapers inwards and downwards. The application of such a holder in an apparatus for manufacturing semiconductor devices is still hampered as a result of incorrectly positioning the holder in the apparatus. This can lead to damage to the substrates and a lower yield of the manufacturing process. The side of the guide member tapers inwards and upwards. By virtue of this structure, the cassette can be positioned more accurately and reproducibly into the holder. In this way, damage to substrates is avoided and the yield is high. The guide member may be mirror symmetrical and can include two separate guide members, which are mirror symmetrical as well. As a result, the holder can be mounted, adjusted and manufactured in a simple and inexpensive manner.

Owner:NXP BV

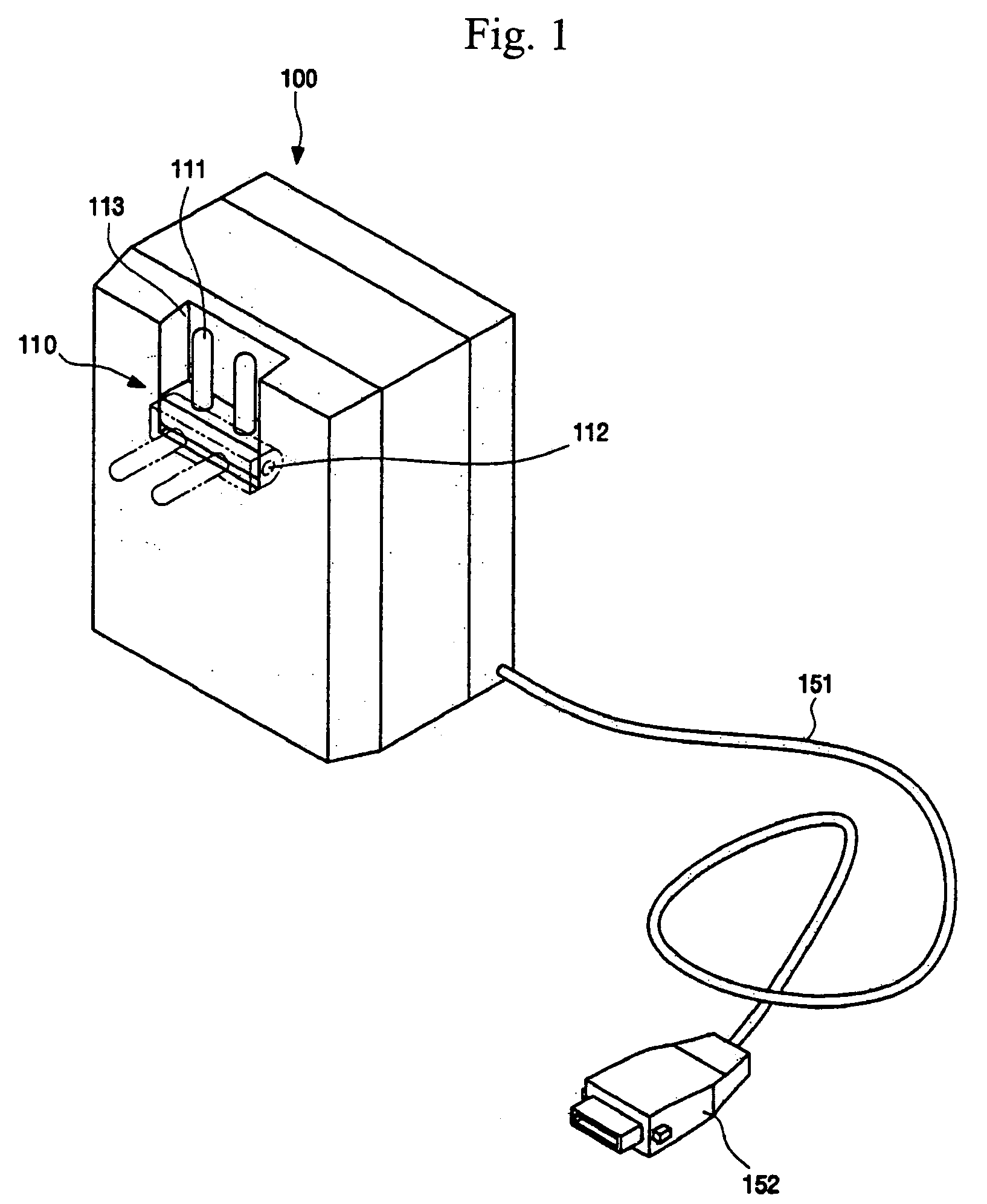

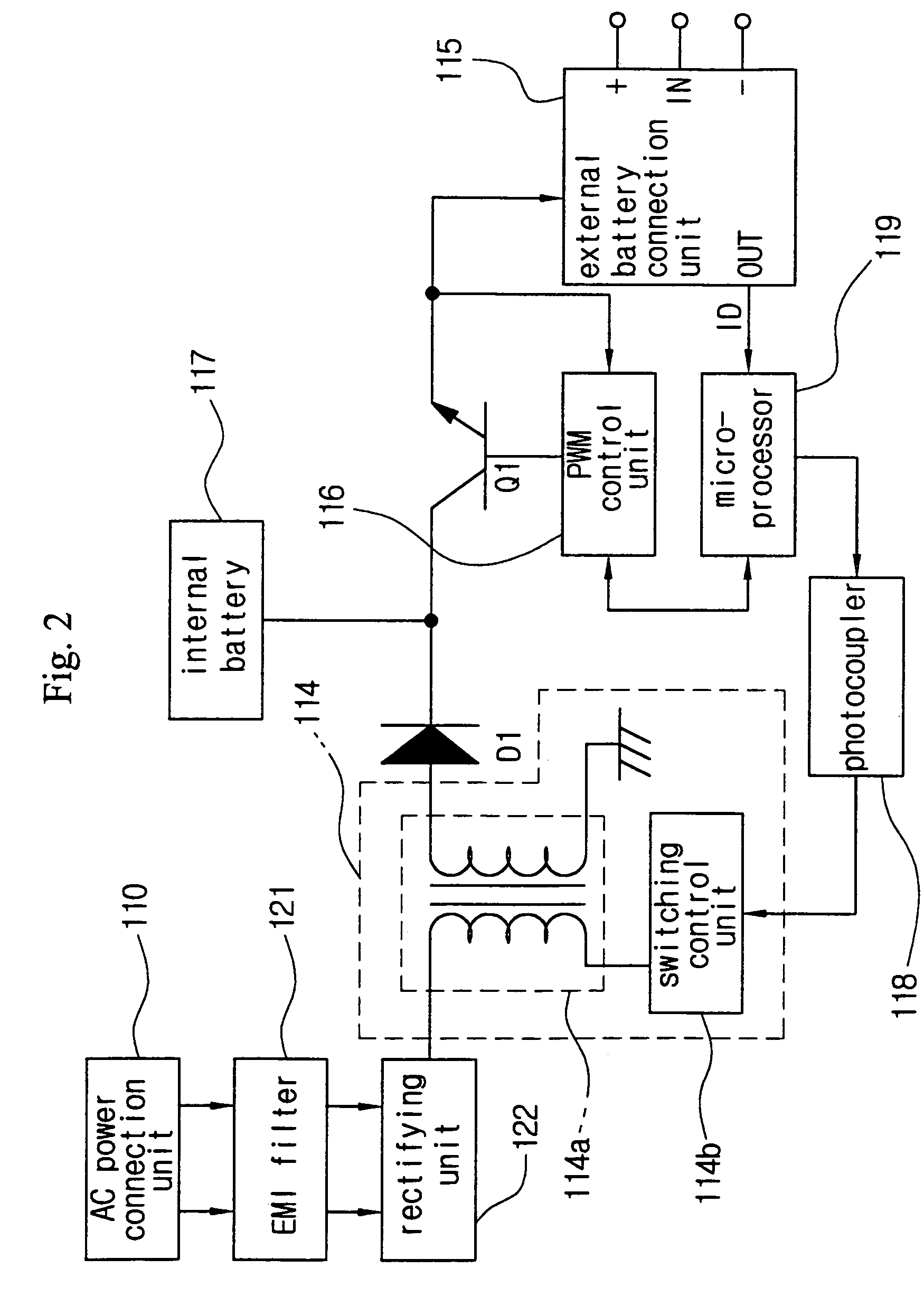

Portable charger for mobile phone

InactiveUS7166987B2Easy to carryGood adhesionTravelling carriersHoldersCapacitanceElectrical battery

Owner:R F TECH

Portable wound treatment apparatus

A portable wound treatment apparatus, for stimulating the healing of superficial wounds, comprises a housing containing a suction pump and a canister for containing fluids drawn from the wound. The housing is supported on a harness or belt worn by the patient. The canister is connected to a porous wound dressing at the wound site via a plurality of tubes, a multi-lumen tube or a combination thereof. A rechargeable battery pack may be incorporated within the housing or externally thereto. The external battery pack may be shaped to balance the housing on the harness or belt. Pressure transducers are provided to monitor and report pressures at the wound site or internal to the canister. Monitored pressures may also be utilized to determine the filled state of the canister and, thereafter, either report this state to the operator or automatically discontinue suction from the wound, or both.

Owner:KCI LICENSING INC

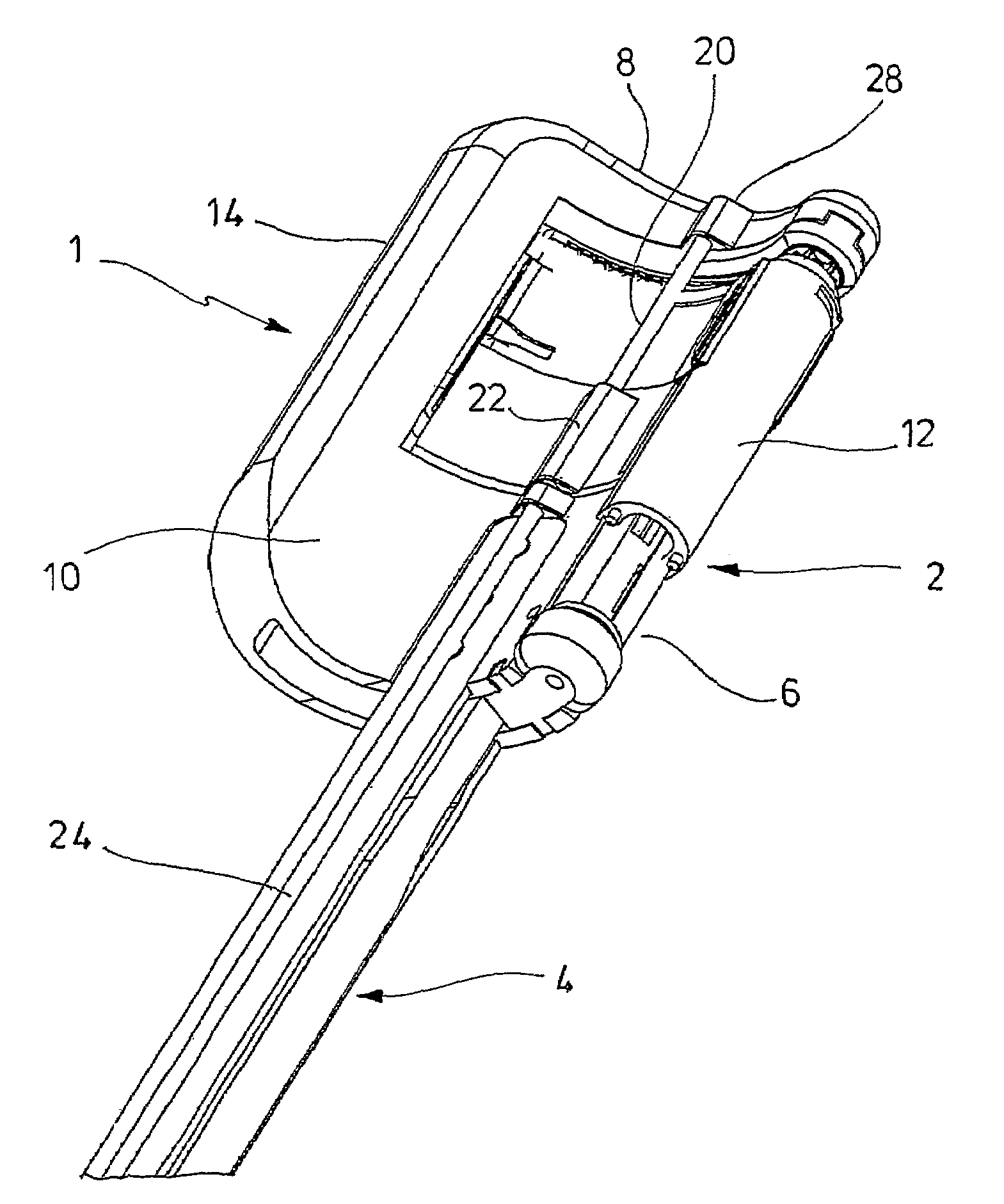

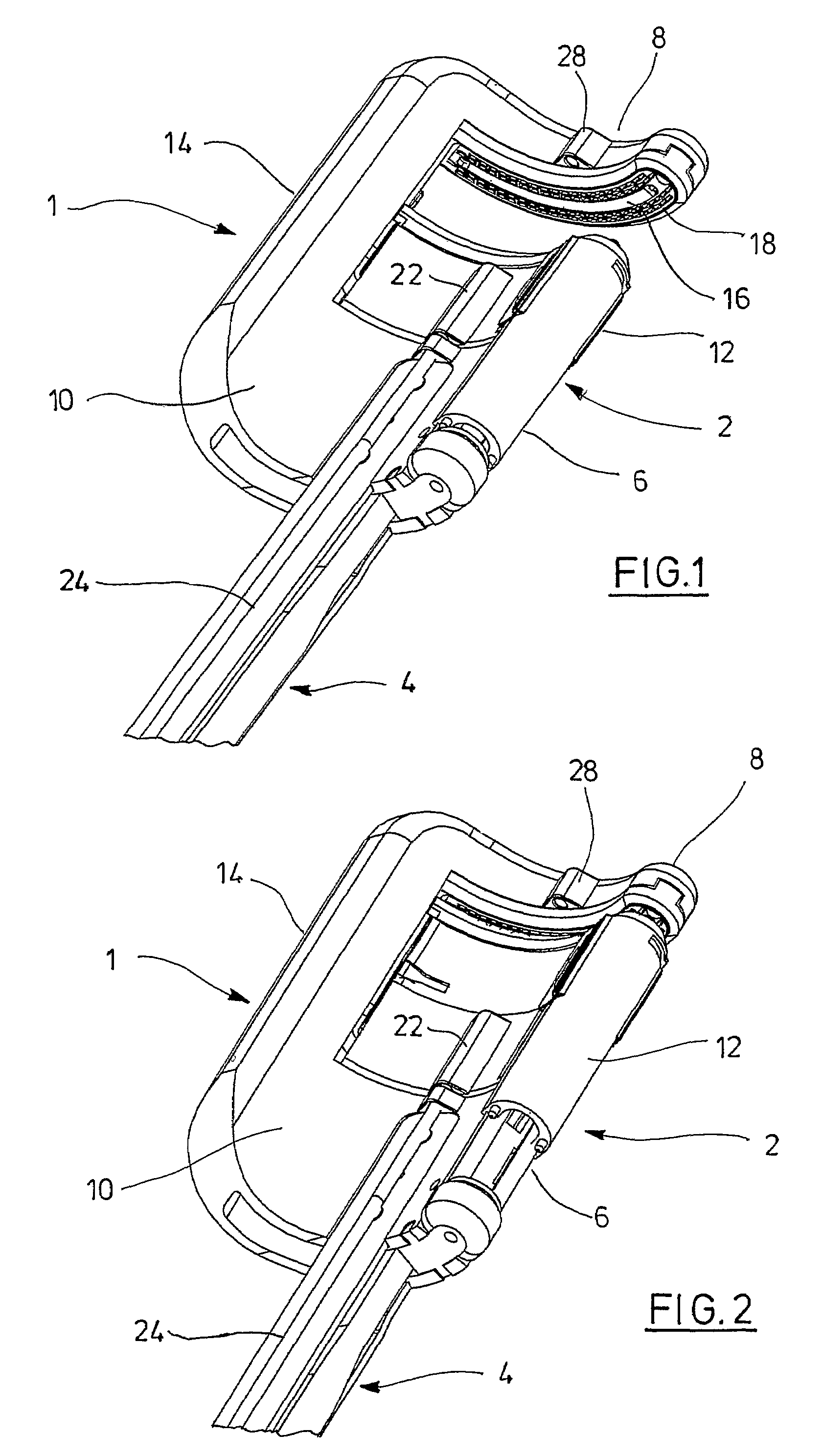

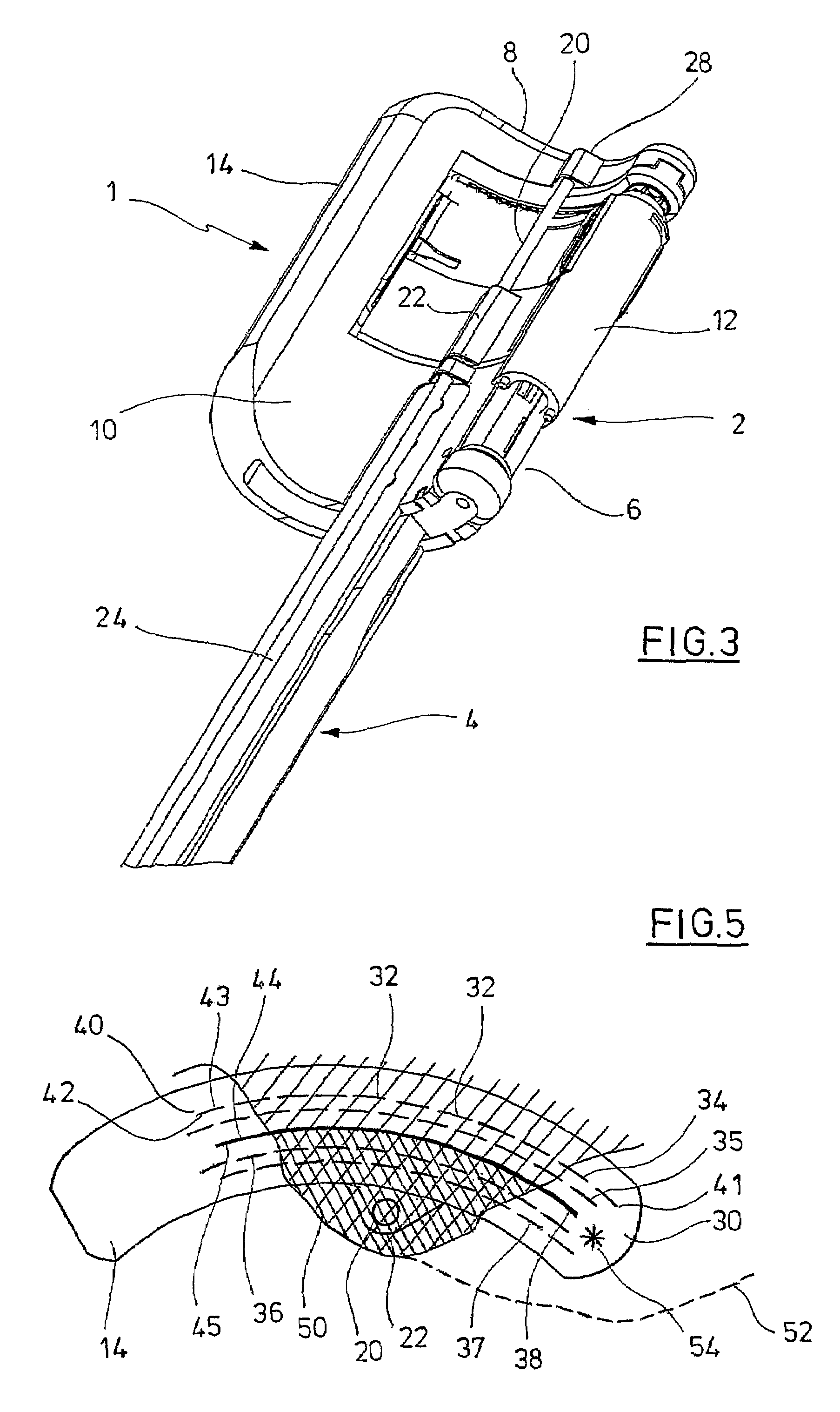

Surgical stapling instrument

A surgical stapling instrument having a staple fastening assembly including a curved cartridge device. The device has at least one curved open row of staples having a first and second ends and having a concave side and a convex side. Opposite to the cartridge device there is a curved anvil for forming the ends of the staples. The instrument also includes a moving device adapted to move the anvil with respect to the cartridge device in a parallel relationship. The instrument also includes a staple driving device adapted to drive the staples out of the cartridge device towards the anvil, and a knife. The knife has opposing first and second sides and is contained in the cartridge device. There is also a knife actuating device adapted to move the knife towards the anvil. The instrument includes staple fastening assembly having a retaining pin which moves between the cartridge device to align them. The retaining pin is located on the second side of the knife in an intermediate region between the first end and second ends of the curved row of staples.

Owner:CILAG GMBH INT

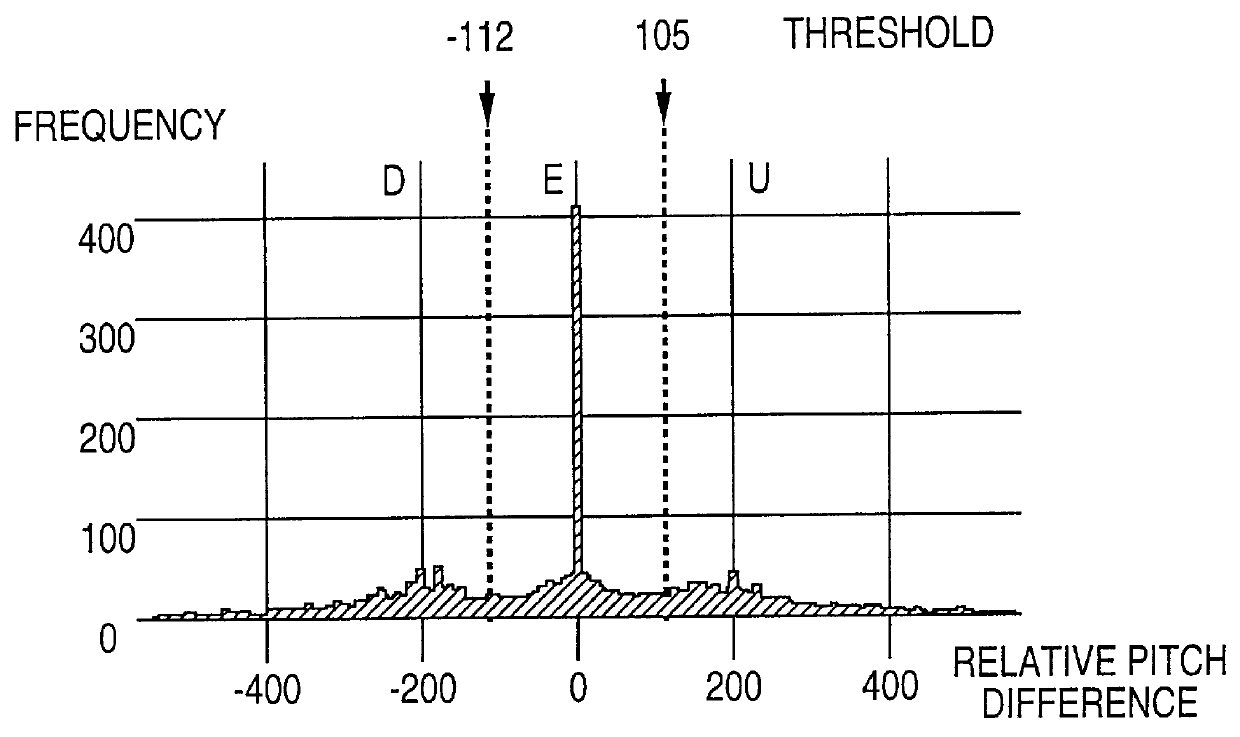

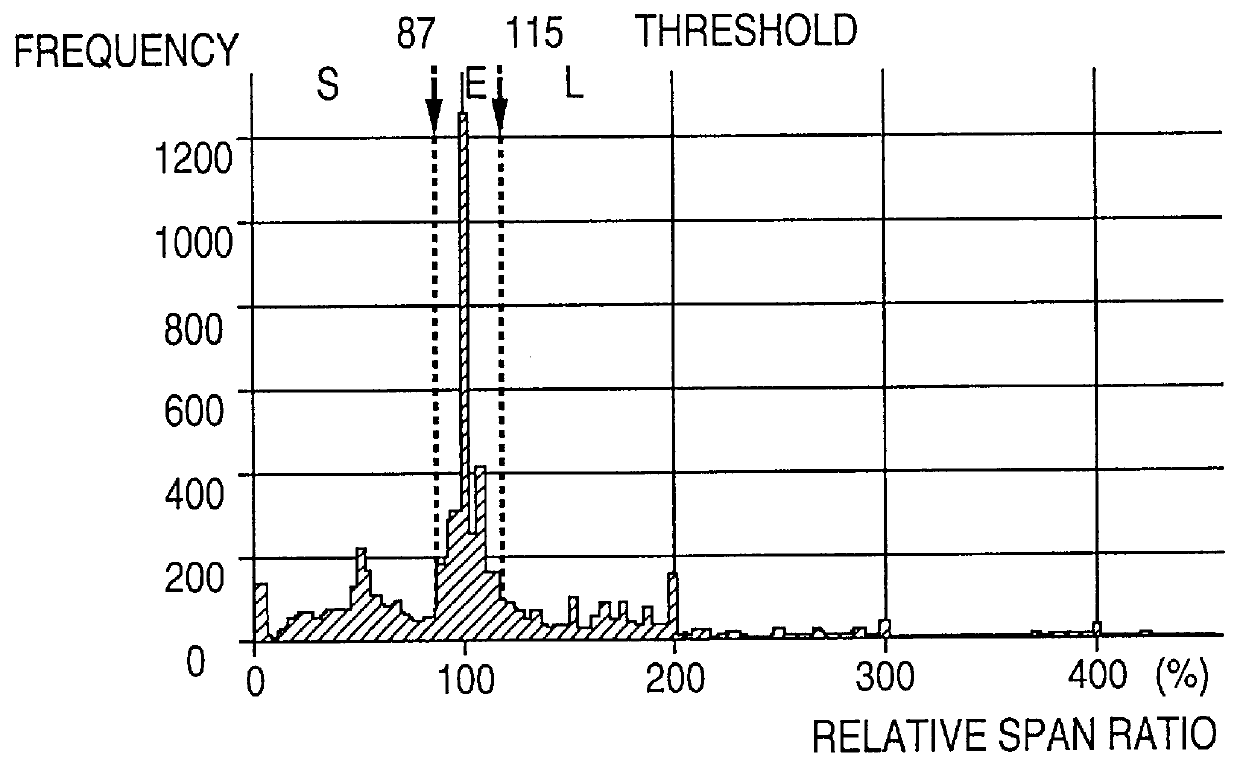

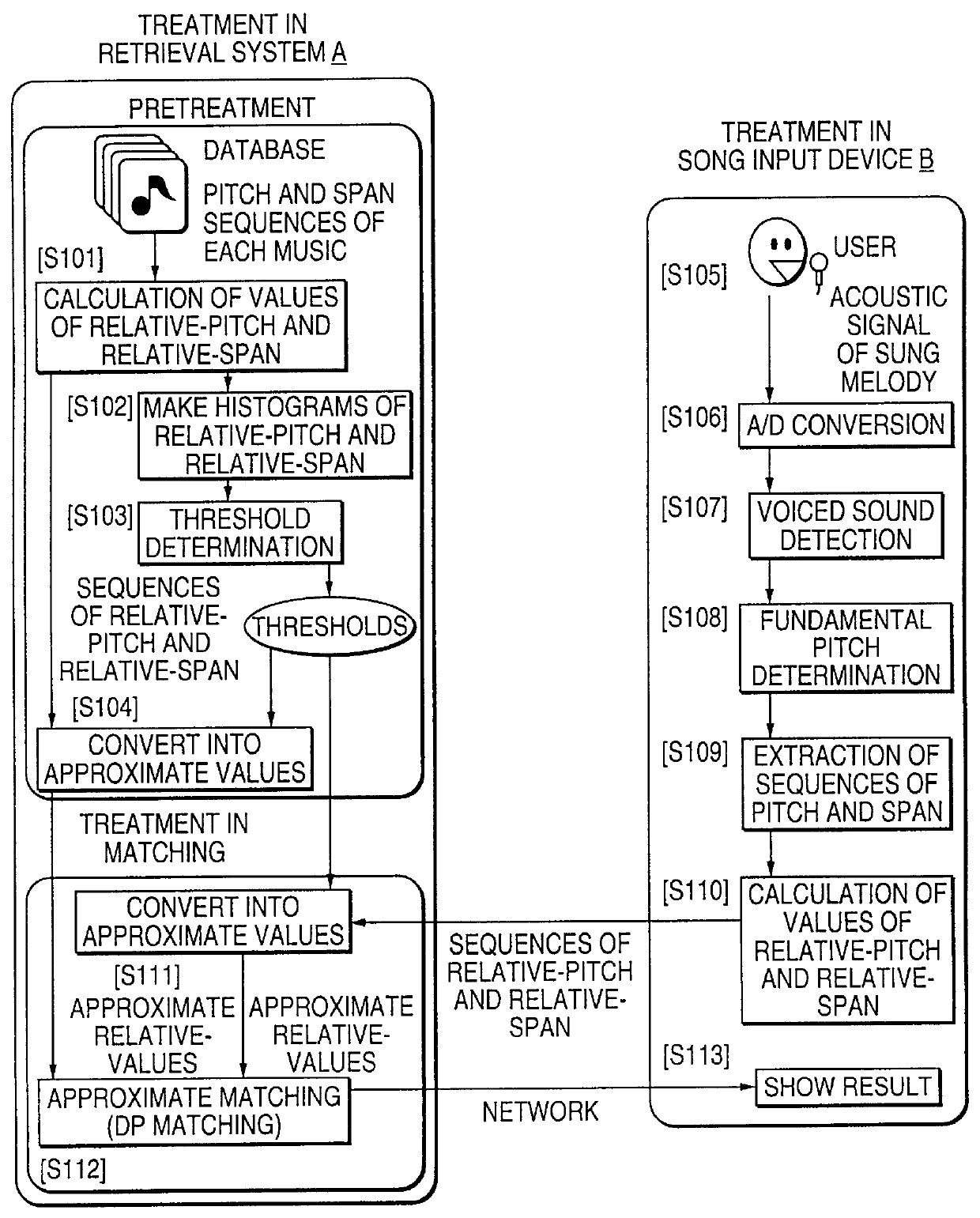

World Wide Web-based melody retrieval system with thresholds determined by using distribution of pitch and span of notes

InactiveUS6121530AReduce in quantityEasy to carryGearworksMusical toysInformation quantityData library

A World Wide Web-based melody retrieval system takes a sung melody as a query and retrieves the song's title or other information from a music database over a WWW network which comprises a method of obtaining search clues with the maximum quantity of information from pitch and span (dynamic threshold determination) and a method of effectively reducing the number of answer candidates (coarse-to-fine matching), thus increasing the matching accuracy, and it is characterized in that a user can retrieve music or media with music by singing.

Owner:SONODA TOMONARI

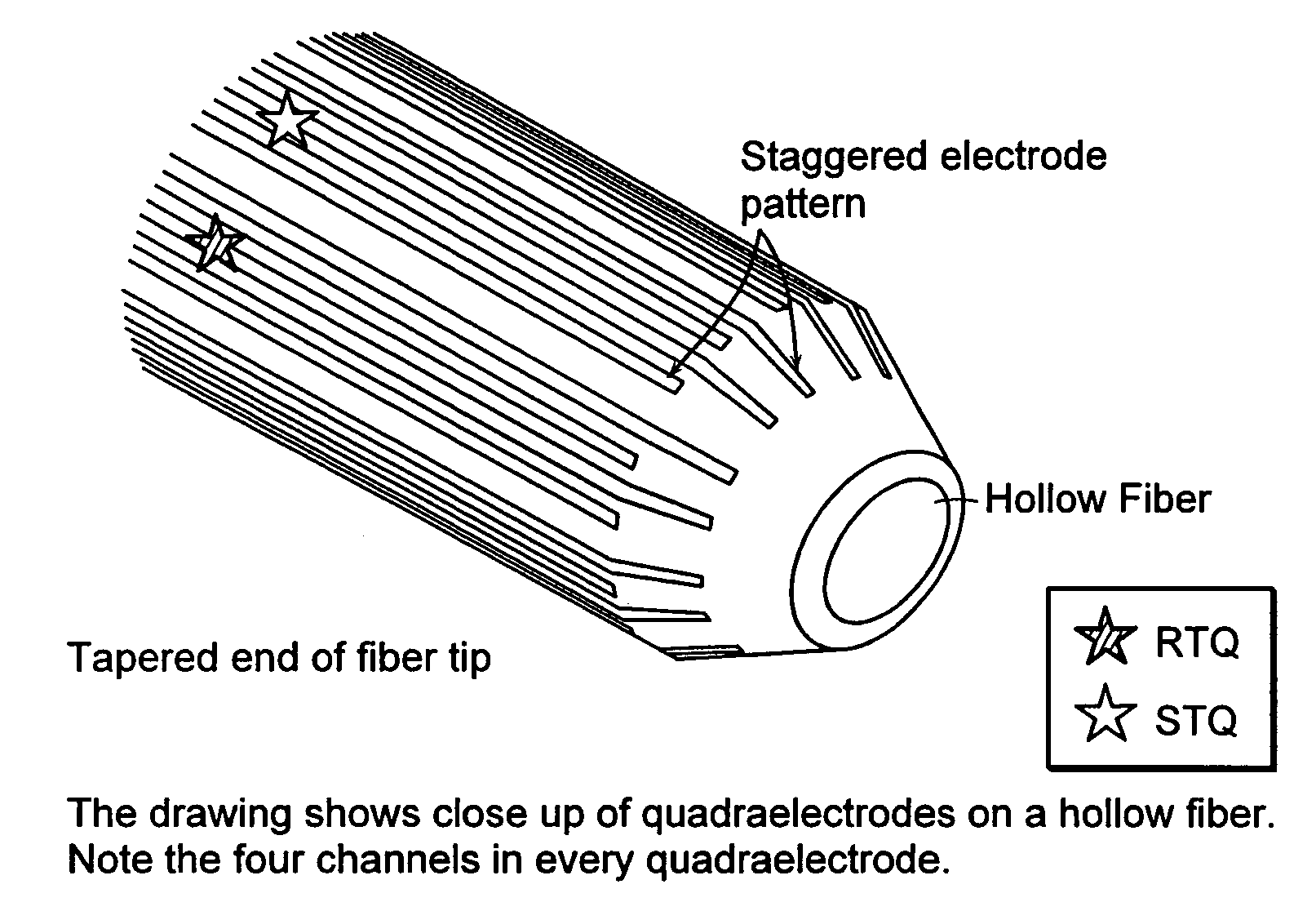

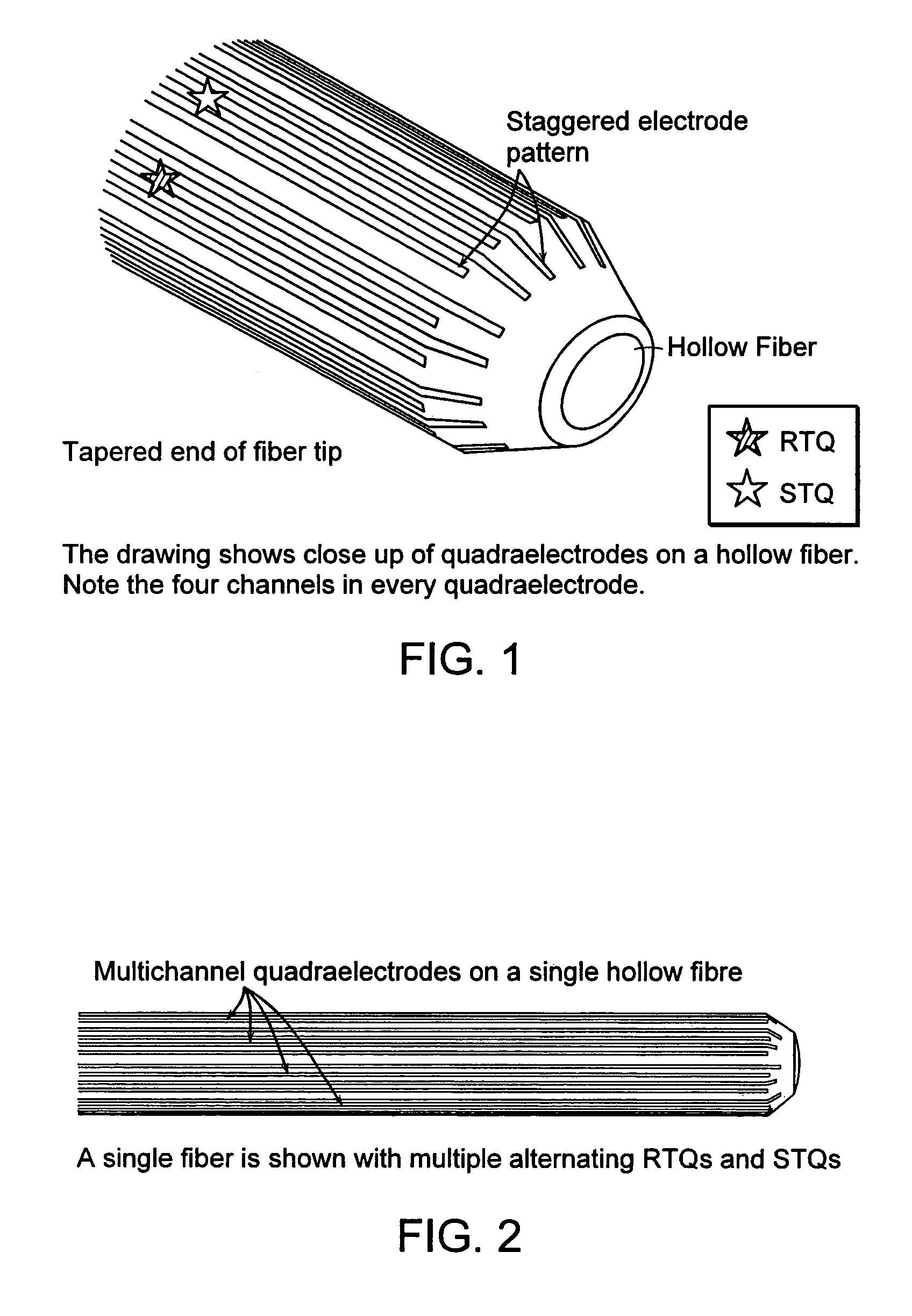

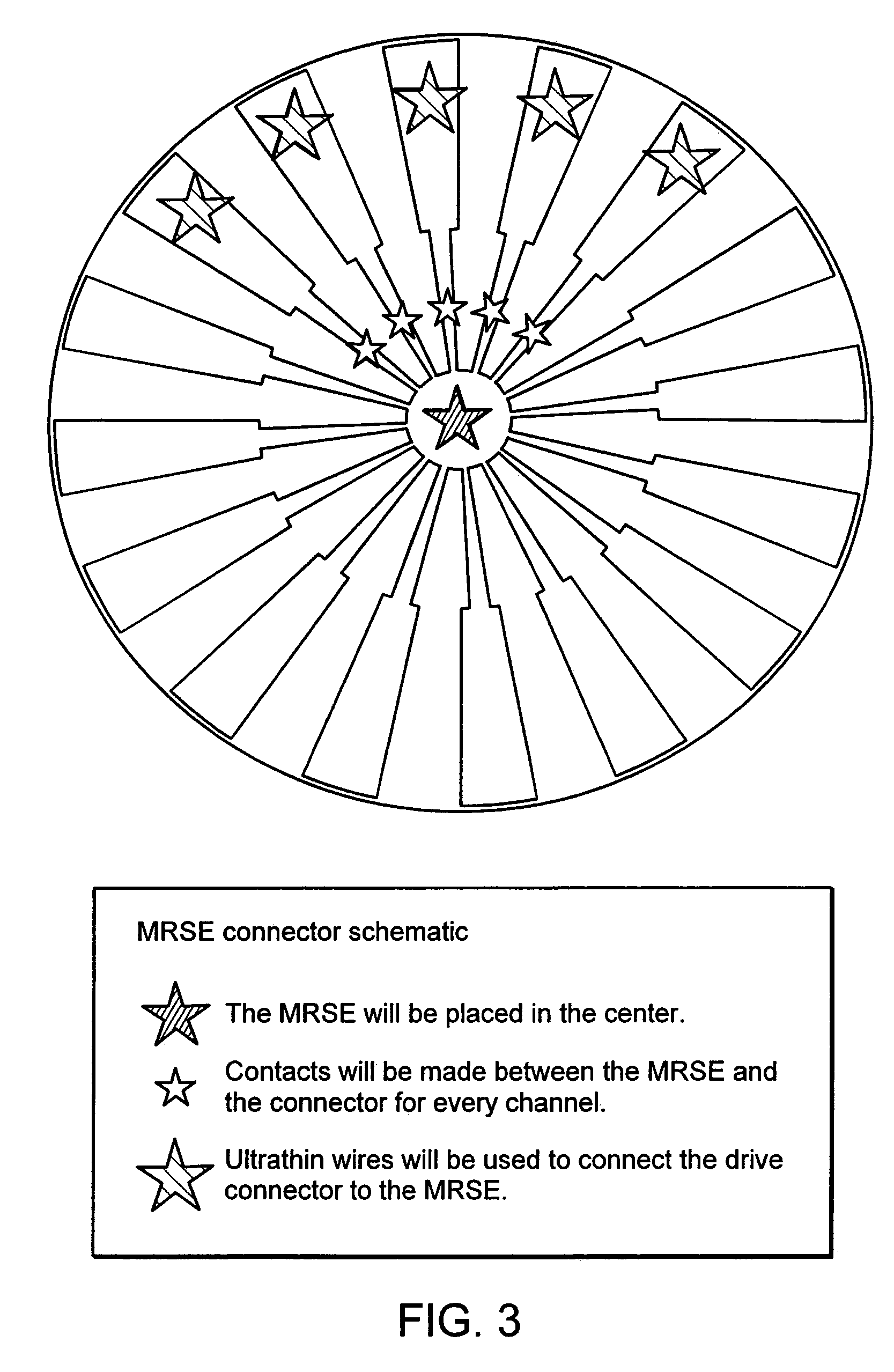

Multichannel electrode and methods of using same

InactiveUS7010356B2Good light transmissionEnhance the imageSpinal electrodesHead electrodesMedicineData acquisition

The invention provides a multichannel electrode (“MC electrode”) which can perform multiple functions such as recording, stimulating and lesioning simultaneously or sequentially upon a single insertion into a target site. In one aspect, the MC electrode further provides imaging and drug delivery capabilities. The invention also provides interface connectors for connecting the MC electrode to external units such as data acquisition and / or stimulation systems. Although the MC electrode and associated connectors and system(s) provide an optimal way to perform deep brain surgical procedures, the MC electrode and associated connectors and system(s) are useful generally in any technique which relies on recording, activating, and / or inhibiting electrical signals produced by cells.

Owner:LONDON HEALTH SCI CENT RES +1

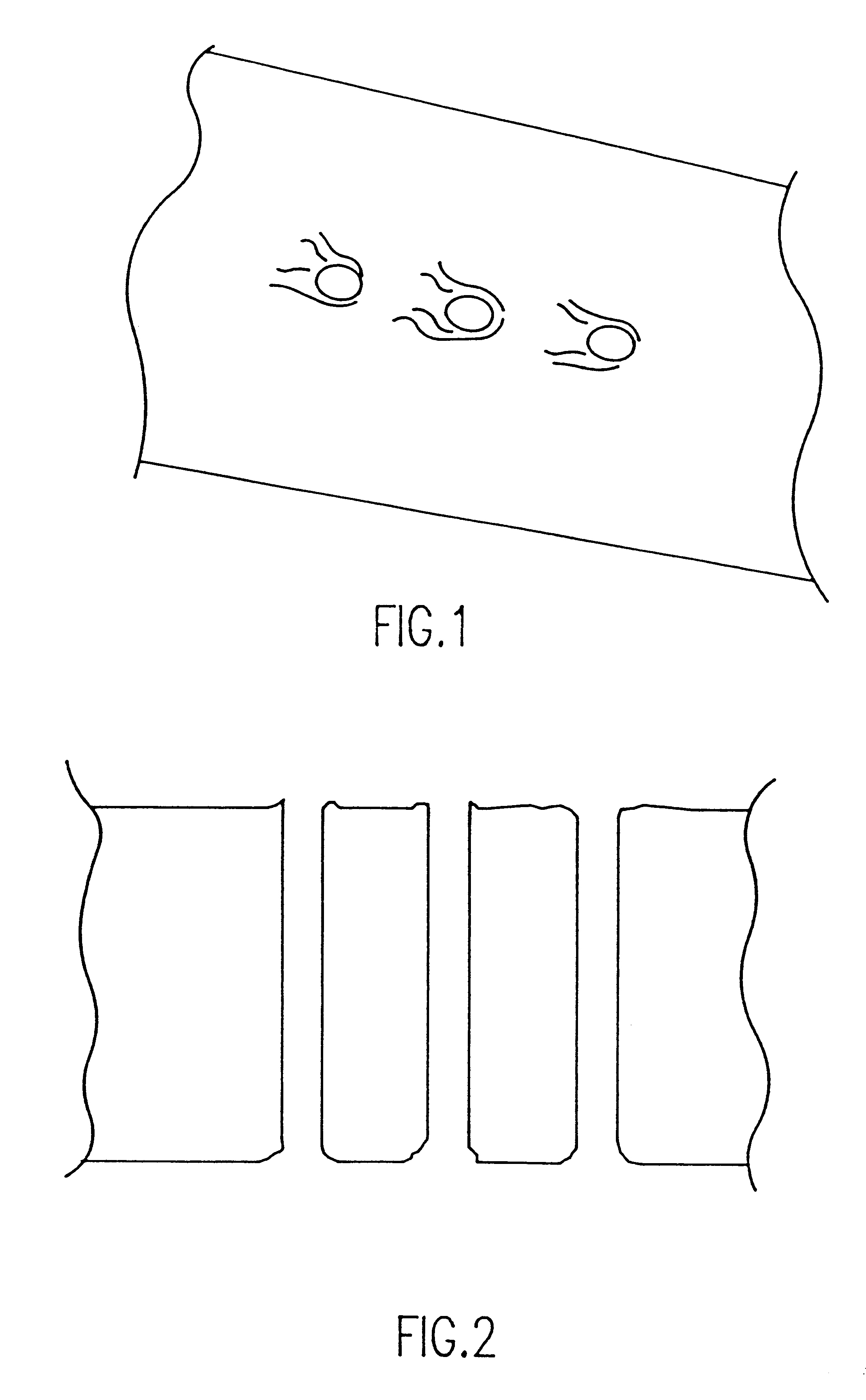

Conformal thermal interface material for electronic components

InactiveUS6054198AOptimize allocationReadily apparentSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureConductive materials

A thermally-conductive interface for conductively cooling a heat-generating electronic component having an associated thermal dissipation member such as a heat sink. The interface is formed as a self-supporting layer of a thermally-conductive material which is form-stable at normal room temperature in a first phase and substantially conformable in a second phase to the interface surfaces of the electronic component and thermal dissipation member. The material has a transition temperature from the first phase to the second phase which is within the operating temperature range of the electronic component.

Owner:PARKER INTANGIBLES LLC

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

Portable assemblies, systems, and methods for providing functional or therapeutic neurostimulation

ActiveUS20070123952A1Simplifies meeting power demandSimple prescriptionSpinal electrodesHead electrodesElectricitySkin surface

Neurostimulation assemblies, systems, and methods make possible the providing of short-term therapy or diagnostic testing by providing electrical connections between muscles or nerves inside the body and stimulus generators or recording instruments mounted on the surface of -the skin or carried outside the body. Neurostimulation assemblies, systems, and methods may include a carrier and a removable electronics pod, the electronics pod including stimulation generation circuitry, a power input bay to hold a disposable power source, and user interface components. The assemblies, systems, and methods are adapted to provide coordinated neurostimulation to multiple regions of the body.

Owner:SPR THERAPEUTICS

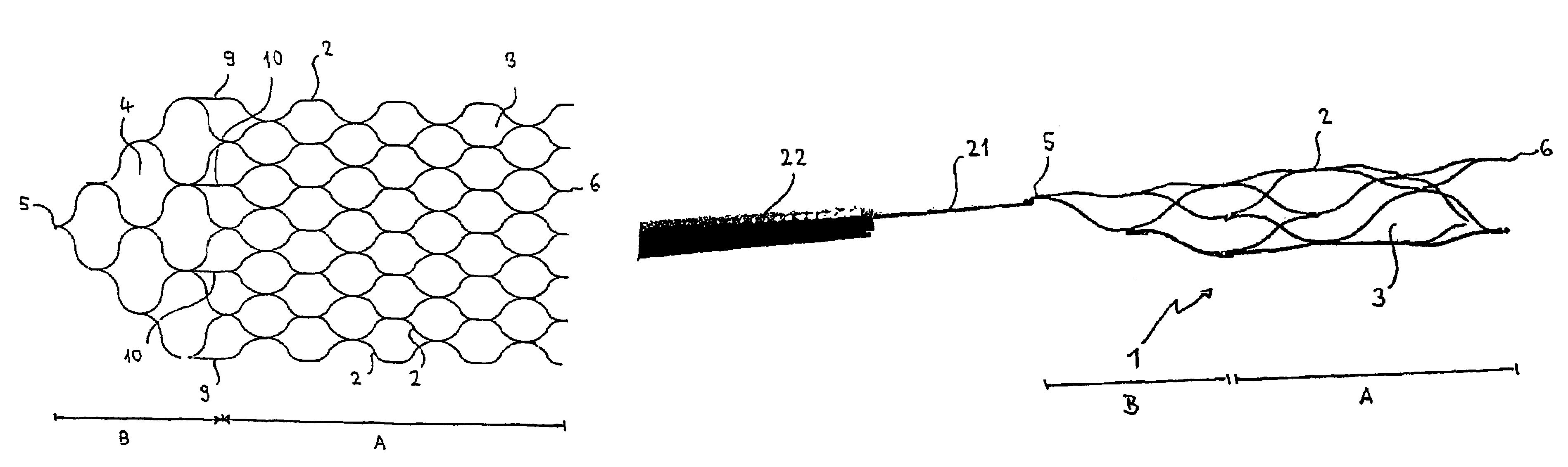

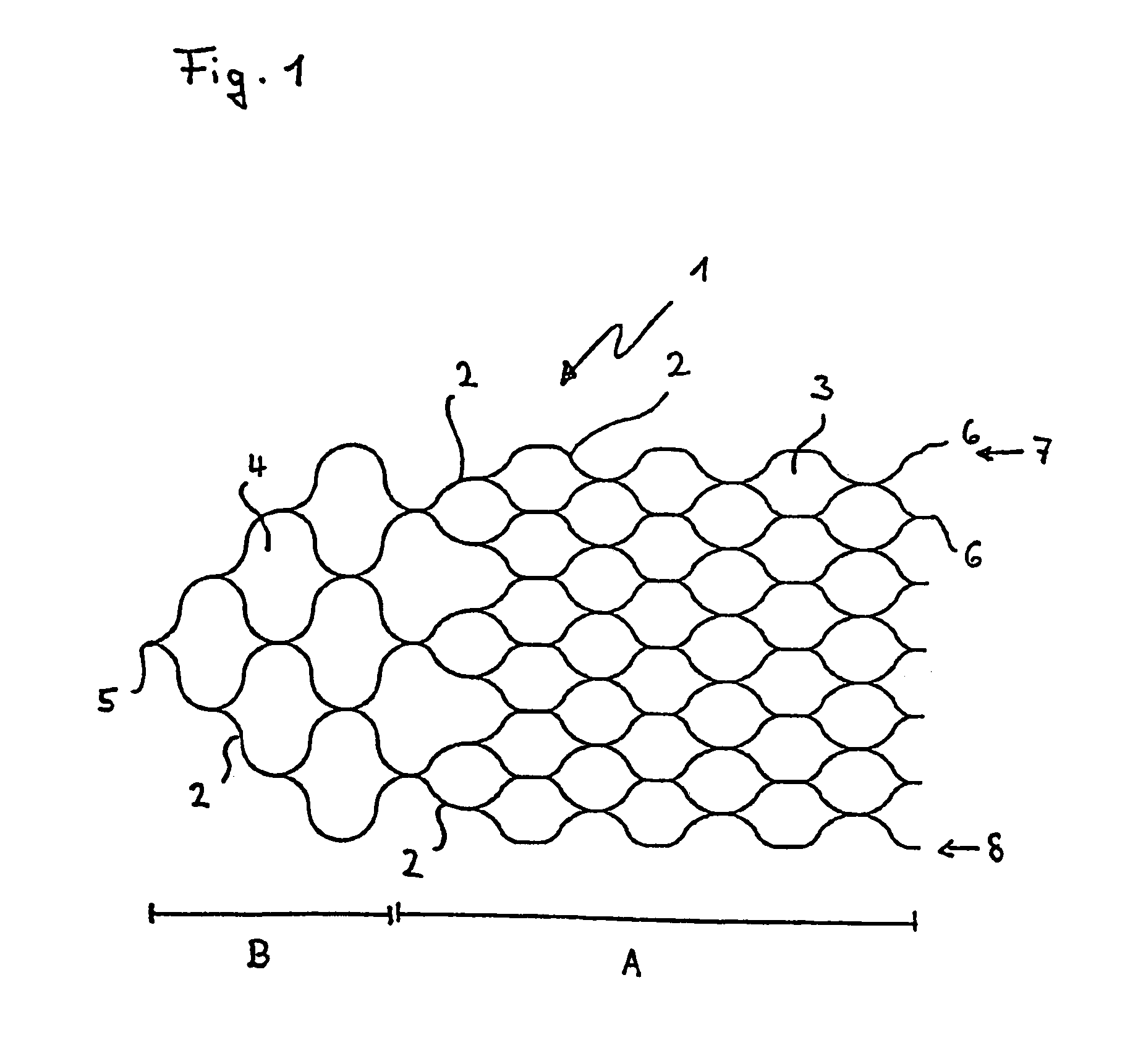

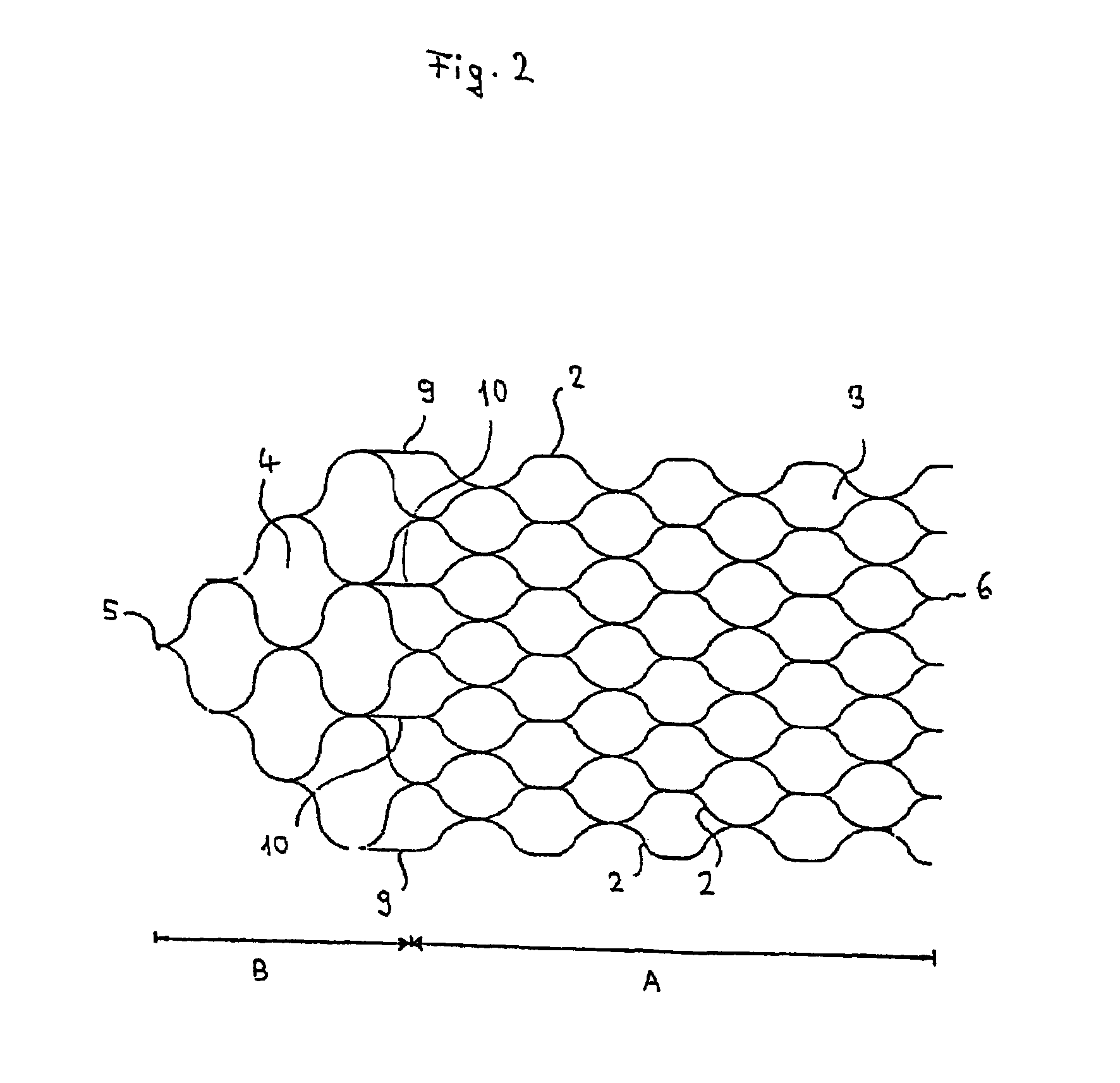

Medical implant having a curlable matrix structure

InactiveUS7300458B2Reduce the overall diameterEasy to slideStentsCatheterReticular formationGuide wires

A medical implant, having a proximal and a distal end, that is preformed to assume a superimposed structure at an implantation site but can be made to take on a volume-reduced form making it possible to introduce it with a micro-catheter and a guide wire arranged at the proximal end, with the implant in its superimposed structure assuming the form of a longitudinally open tube and having a mesh structure of interconnected strings or filaments. The implant has a tapering structure at its proximal end where the strings or filaments converge at a connection point.

Owner:USSC MEDICAL GMBH

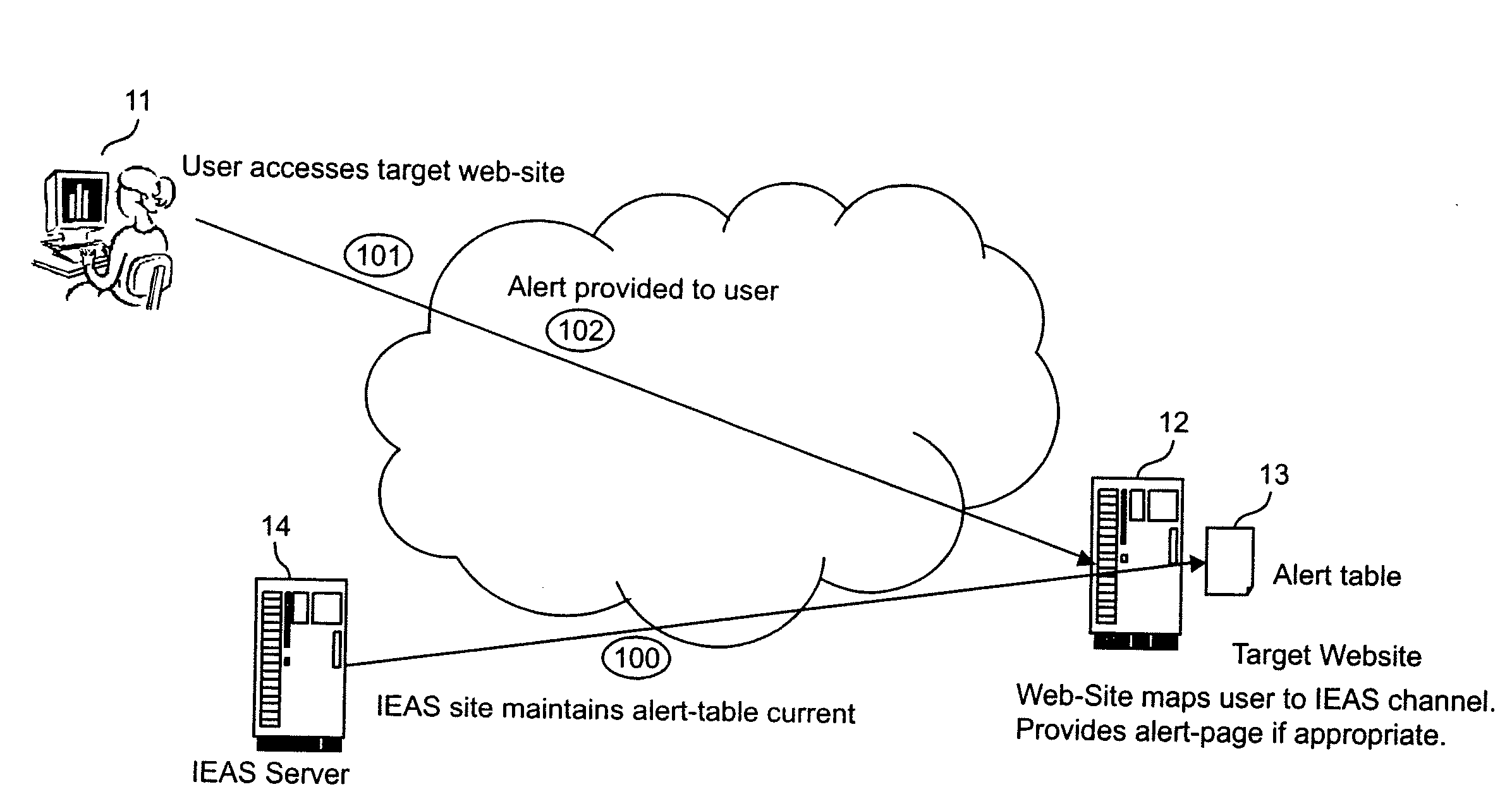

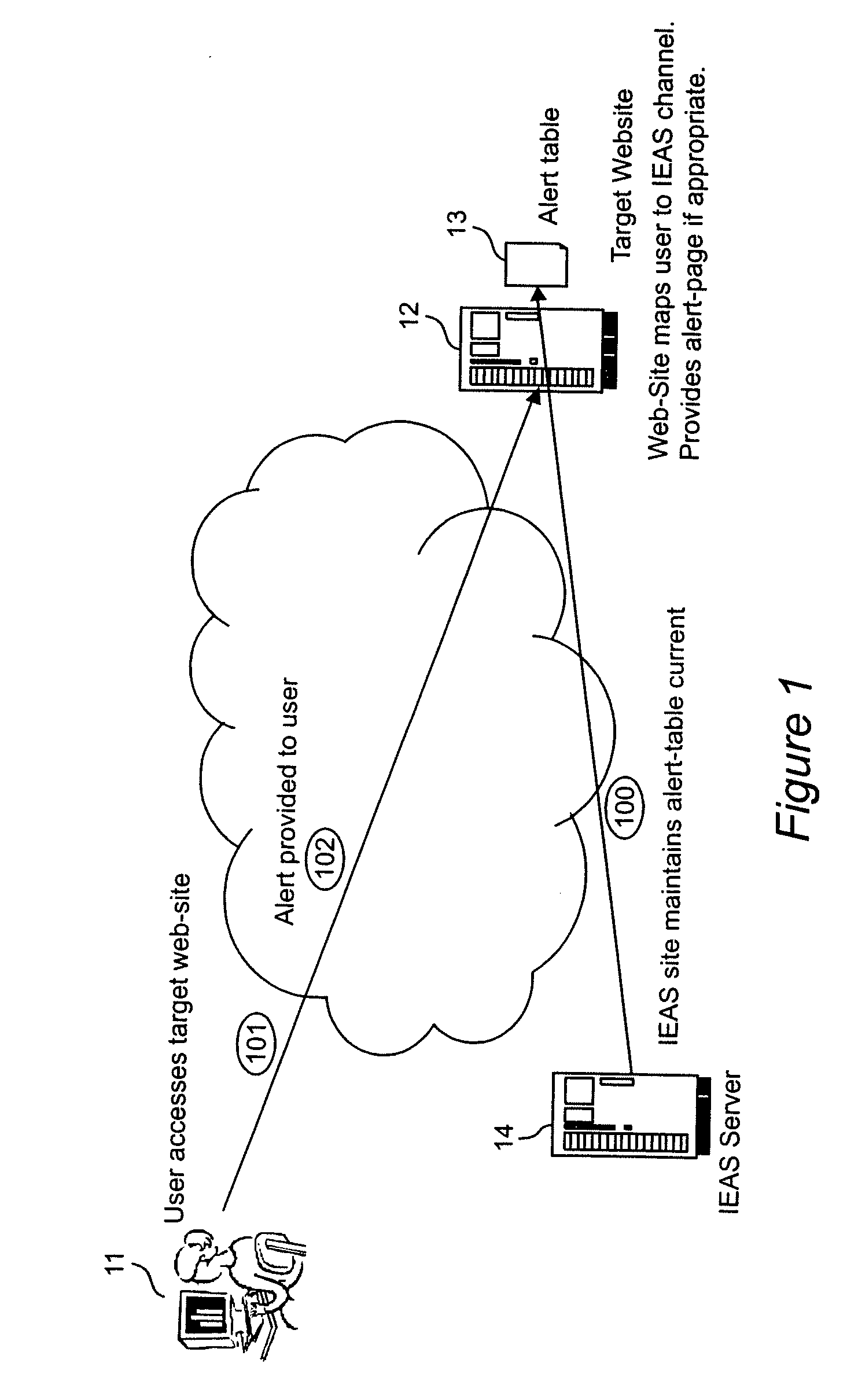

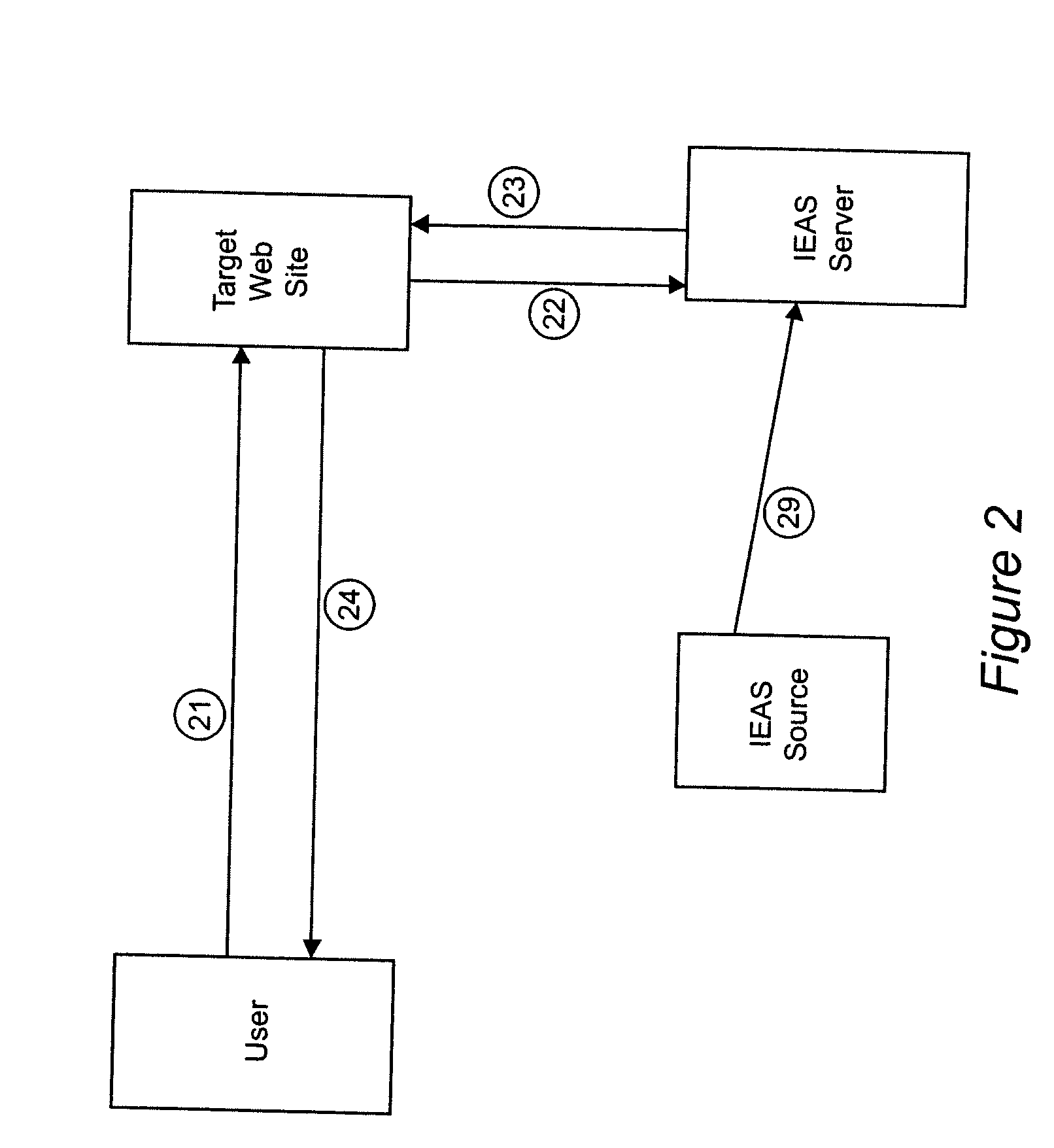

Method and system for rapid dissemination of public announcements

InactiveUS20080162667A1Spread quicklyEasy to carryMultiple digital computer combinationsOffice automationIp addressGeolocation

Owner:VERMA DINESH CHANDRA +1

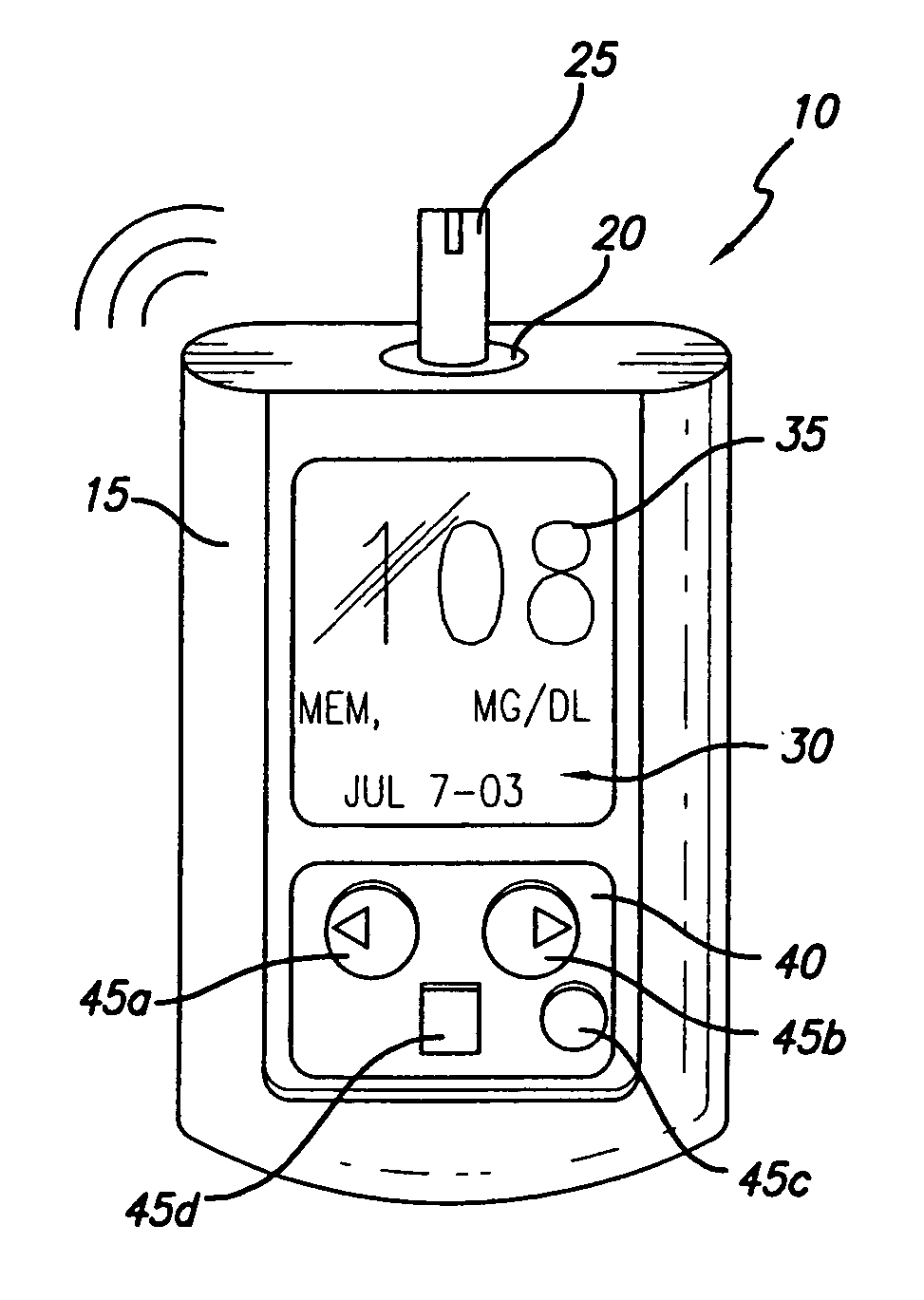

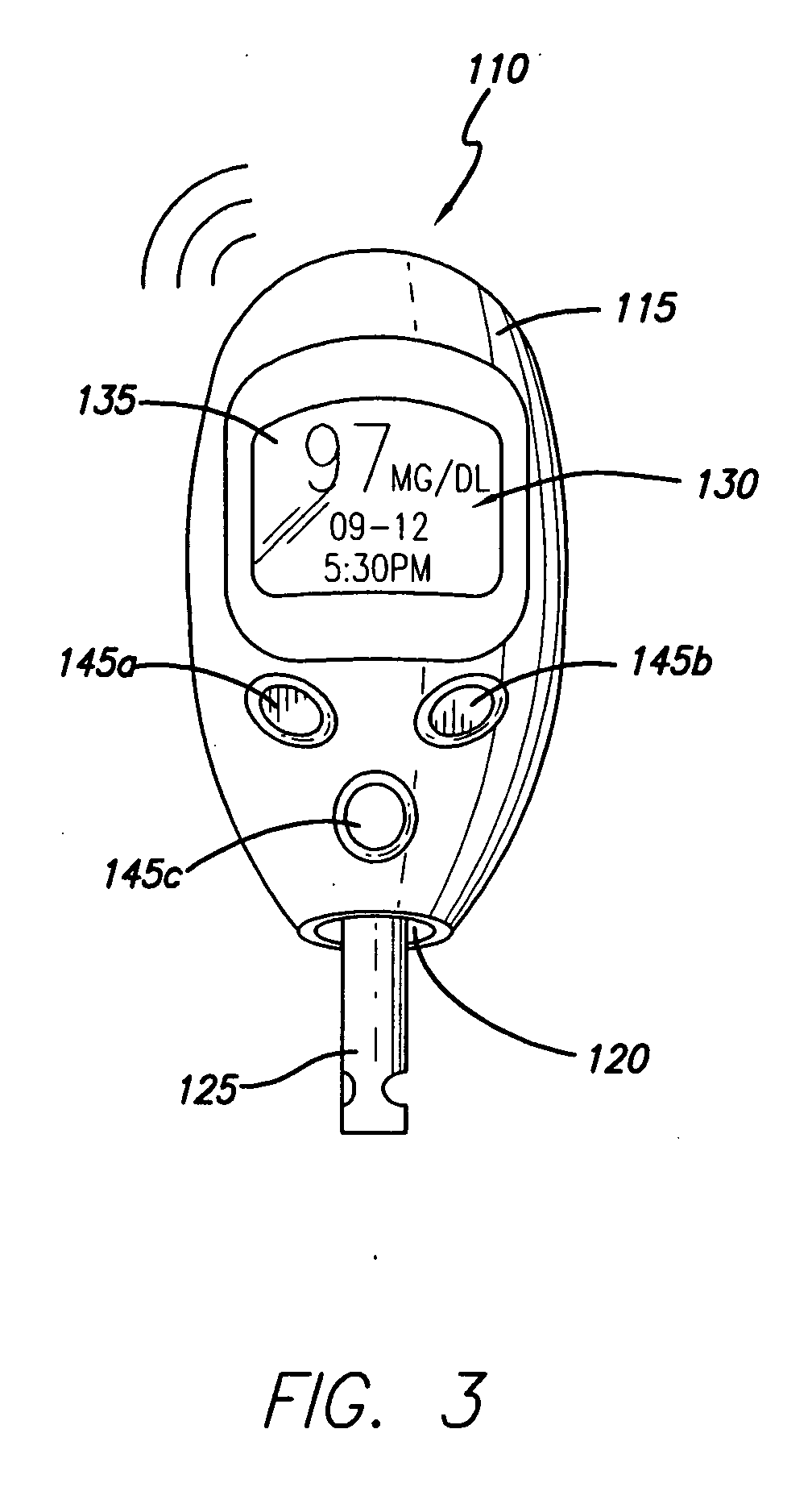

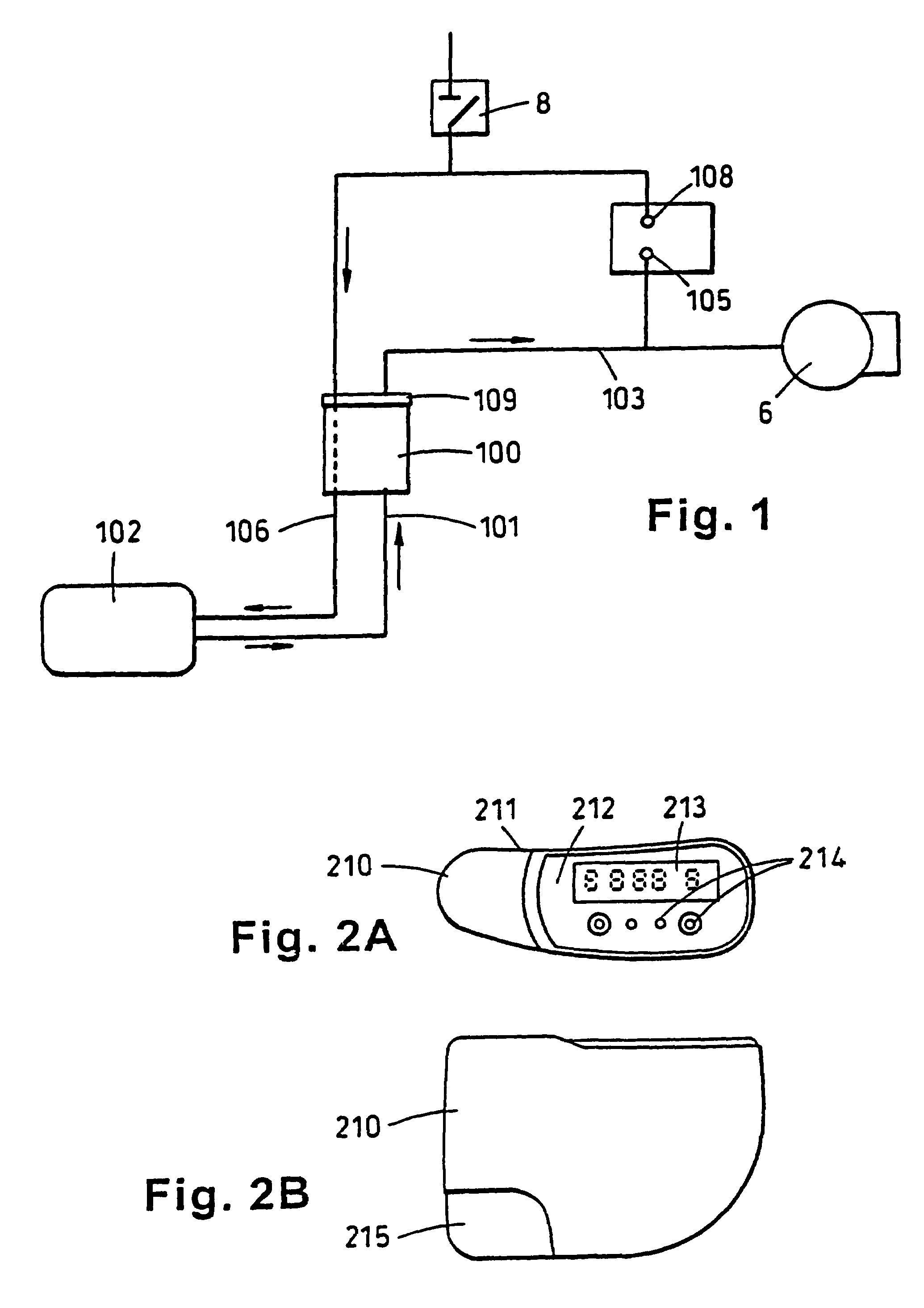

Controller device for an infusion pump

InactiveUS20090227855A1Minimizes potential for errorEasy to watchDrug and medicationsMedical devicesEngineeringInfusion pump

An infusion system that includes a controller device and a communication system to provide for two-way communication between the controller device and an infusion device that controls delivery of fluids to a user's body. Either the controller device or the infusion device may be integrated with a characteristic determining device in a single housing. The housing, in turn, may include a test-strip receptacle and an illuminator disposed so as to illuminate an area covering the receptacle and a test-strip inserted therein. The illuminator may be configured to be activated automatically when a test strip is inserted into the receptacle, selectively by the user via a button, key, or similar mechanism, and / or when the ambient light level, measured, e.g., with a light sensor, falls below a predetermined intensity. The illuminator may be a LED emitting white light, and may provide illumination at various levels of intensity.

Owner:MEDTRONIC MIMIMED INC

Process for percutaneous operations

A method is described for performing a percutaneous operation on a patient to remove an object from a cavity within the patient. The method includes advancing a first alignment sensor into the cavity through a patient lumen. The first alignment sensor provides its position and orientation in free space in real time. The alignment sensor is manipulated until it is located in proximity to the object. A percutaneous opening is made in the patient with a surgical tool, where the surgical tool includes a second alignment sensor that provides the position and orientation of the surgical tool in free space in real time. The surgical tool is directed towards the object using data provided by both the first and the second alignment sensors.

Owner:AURIS HEALTH INC

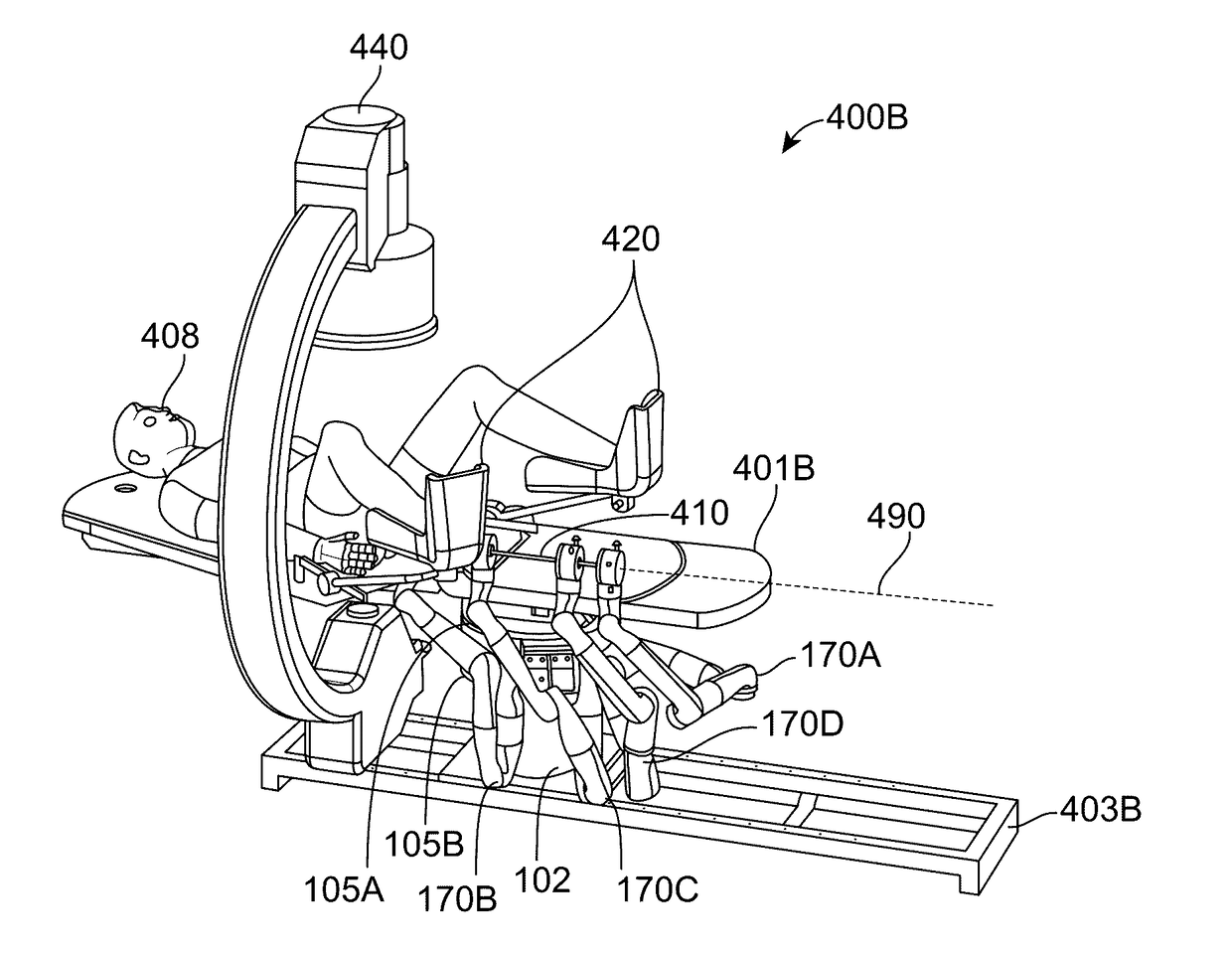

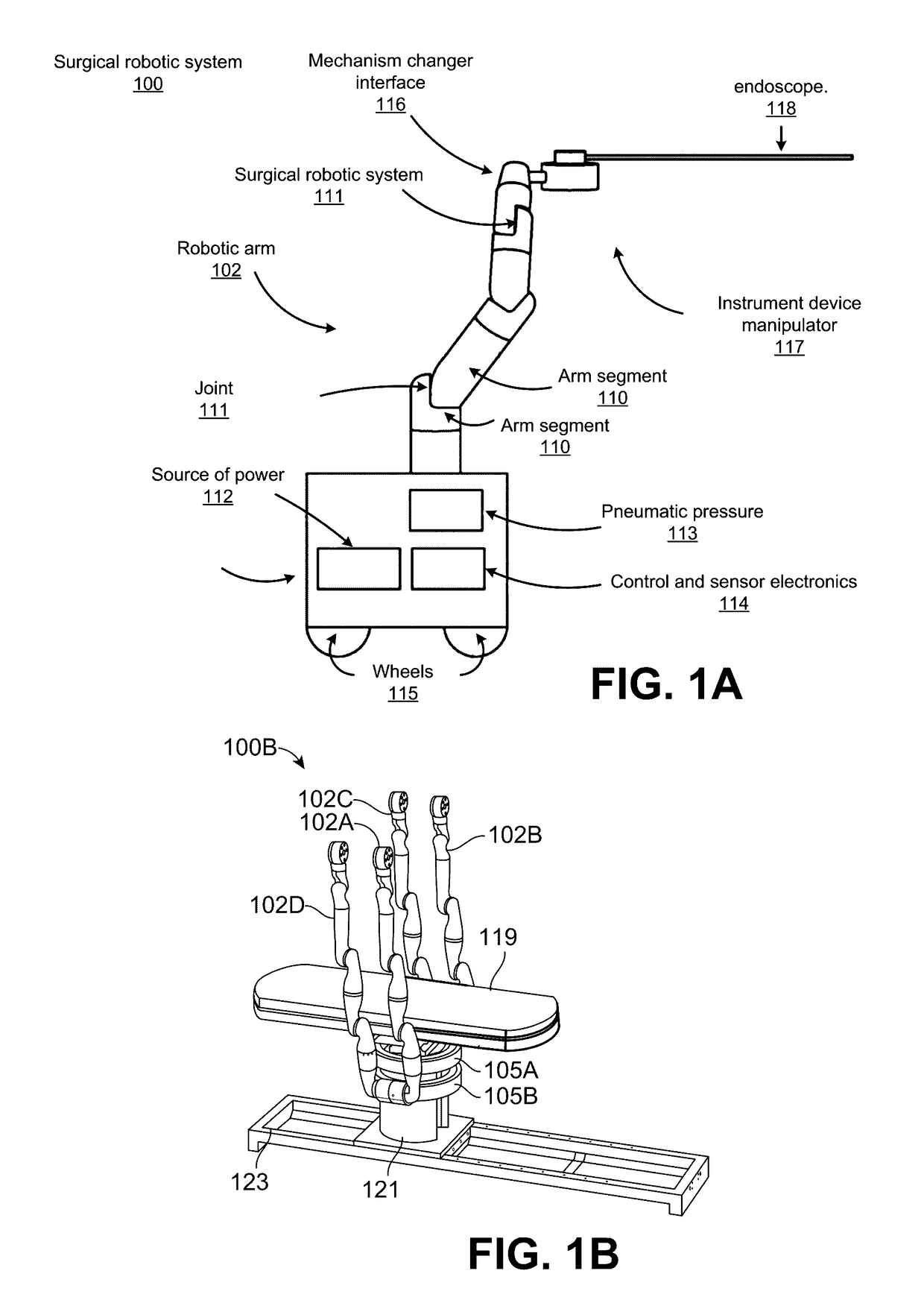

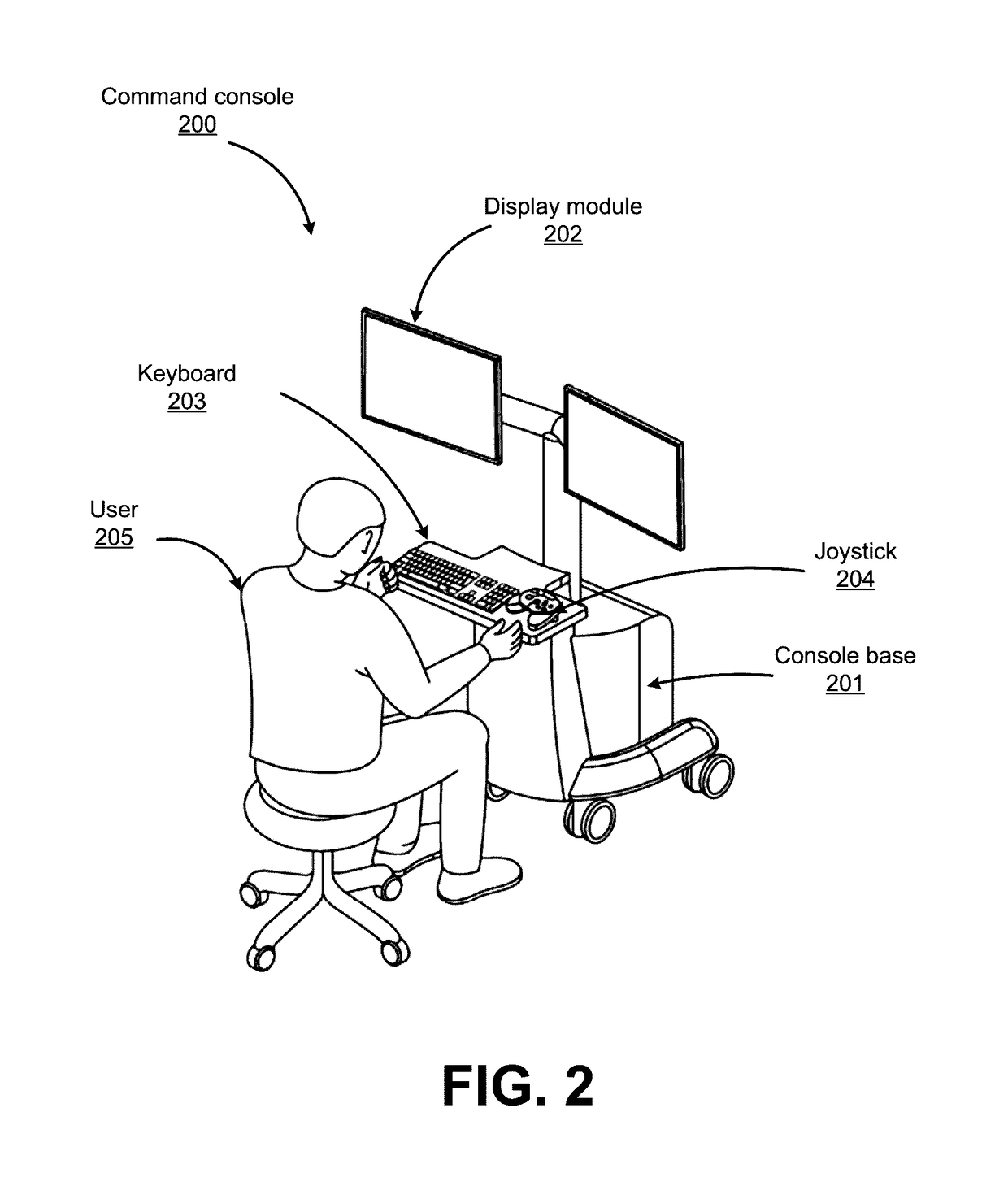

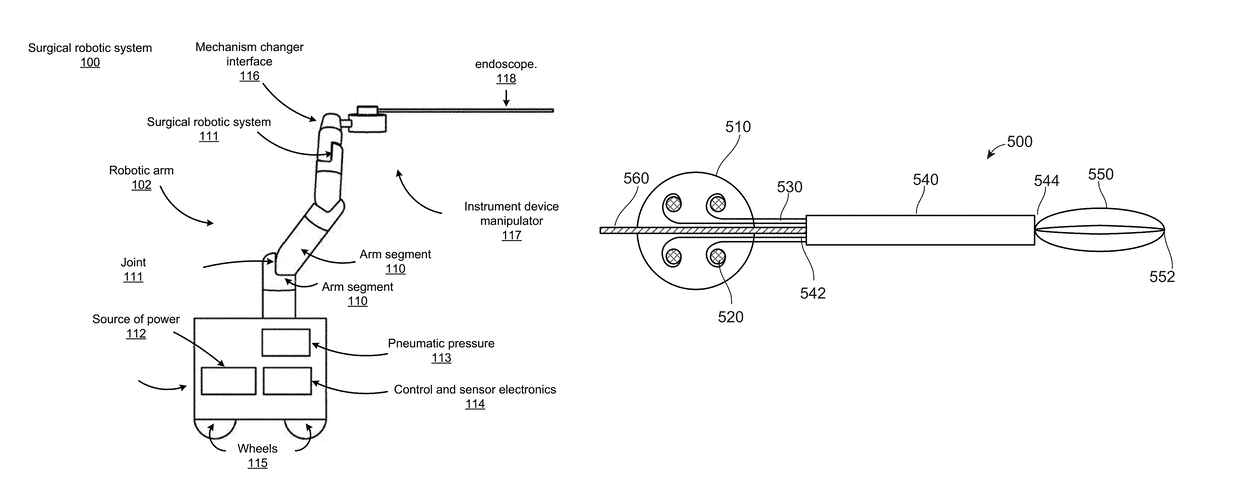

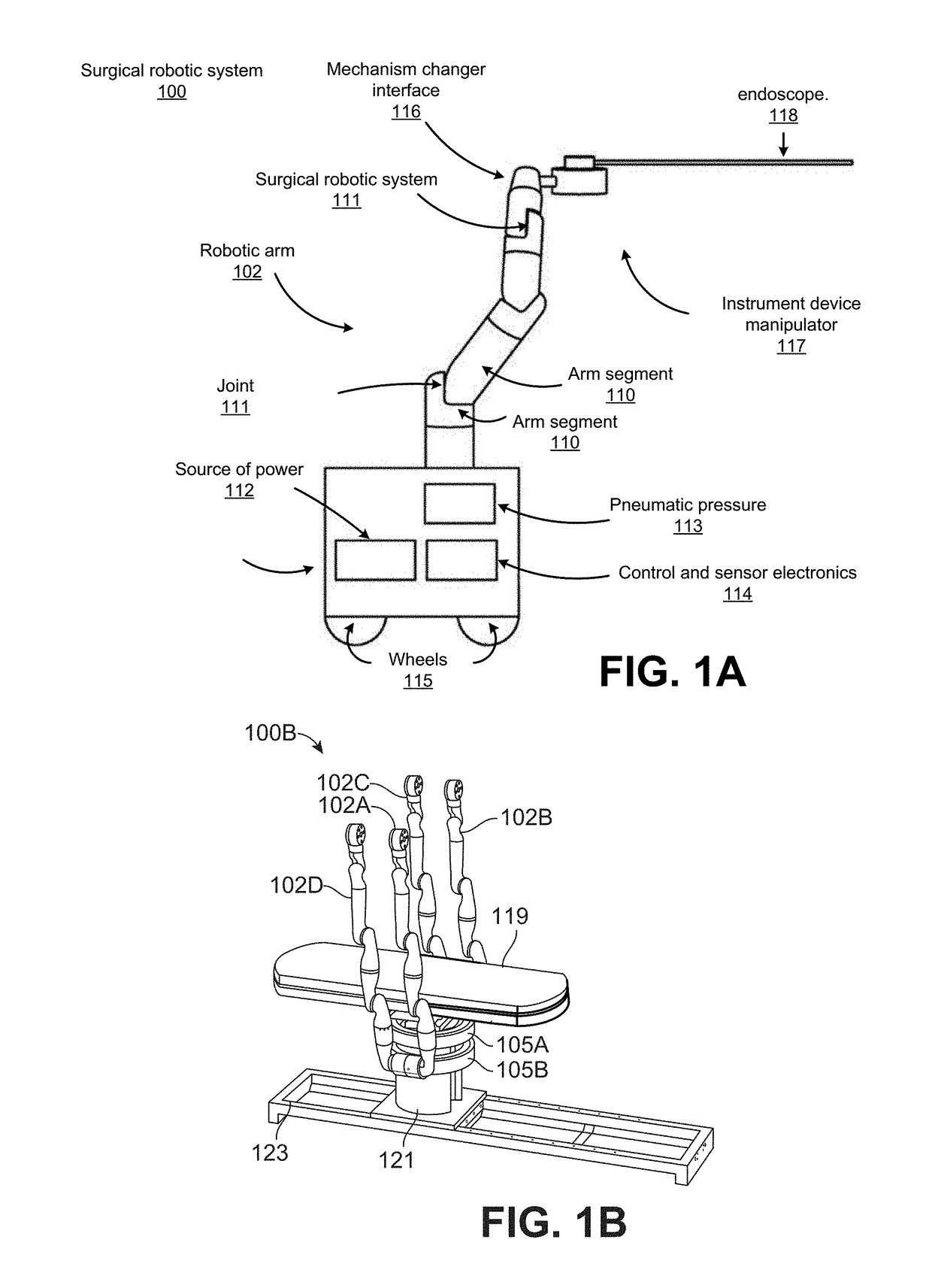

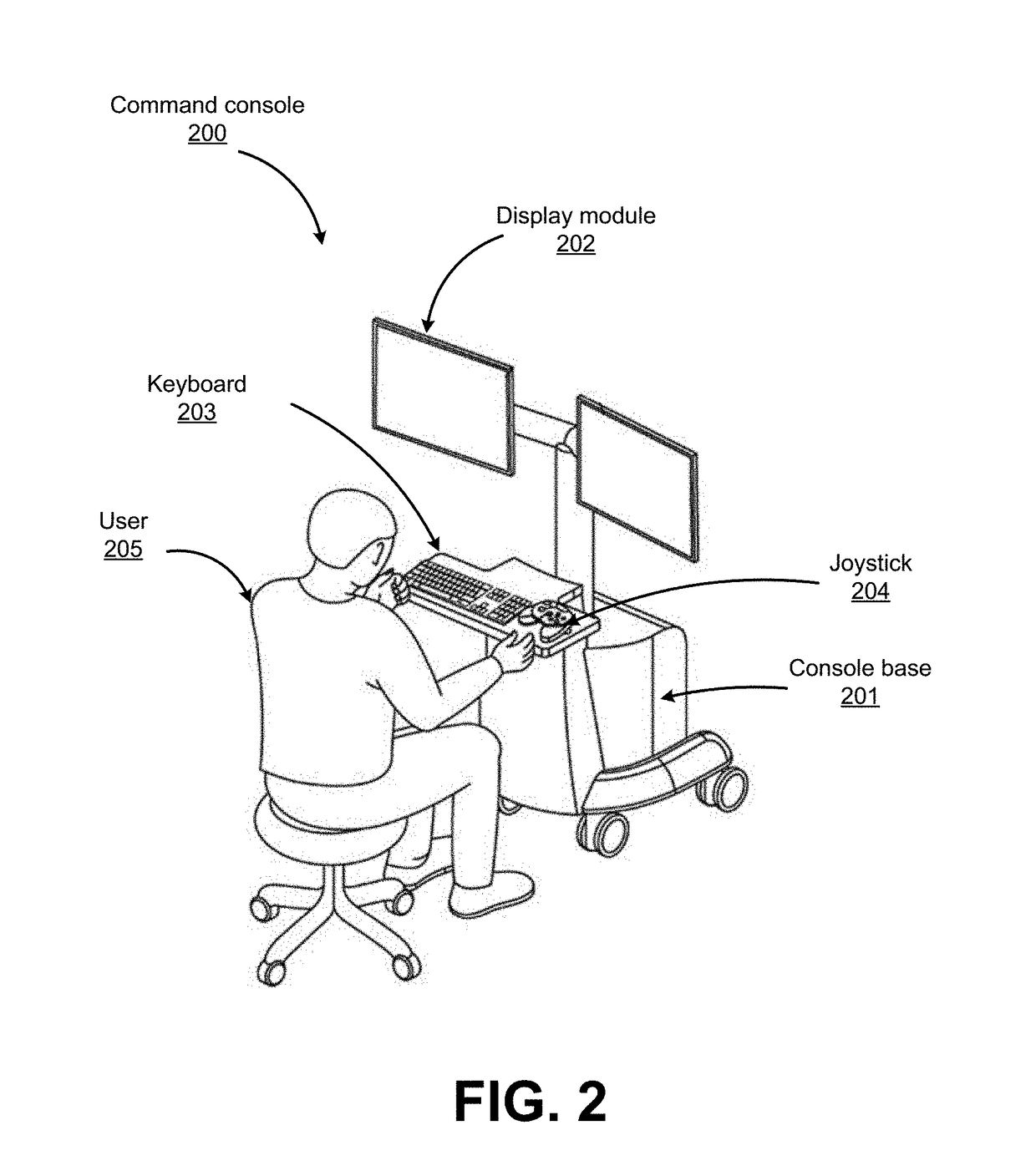

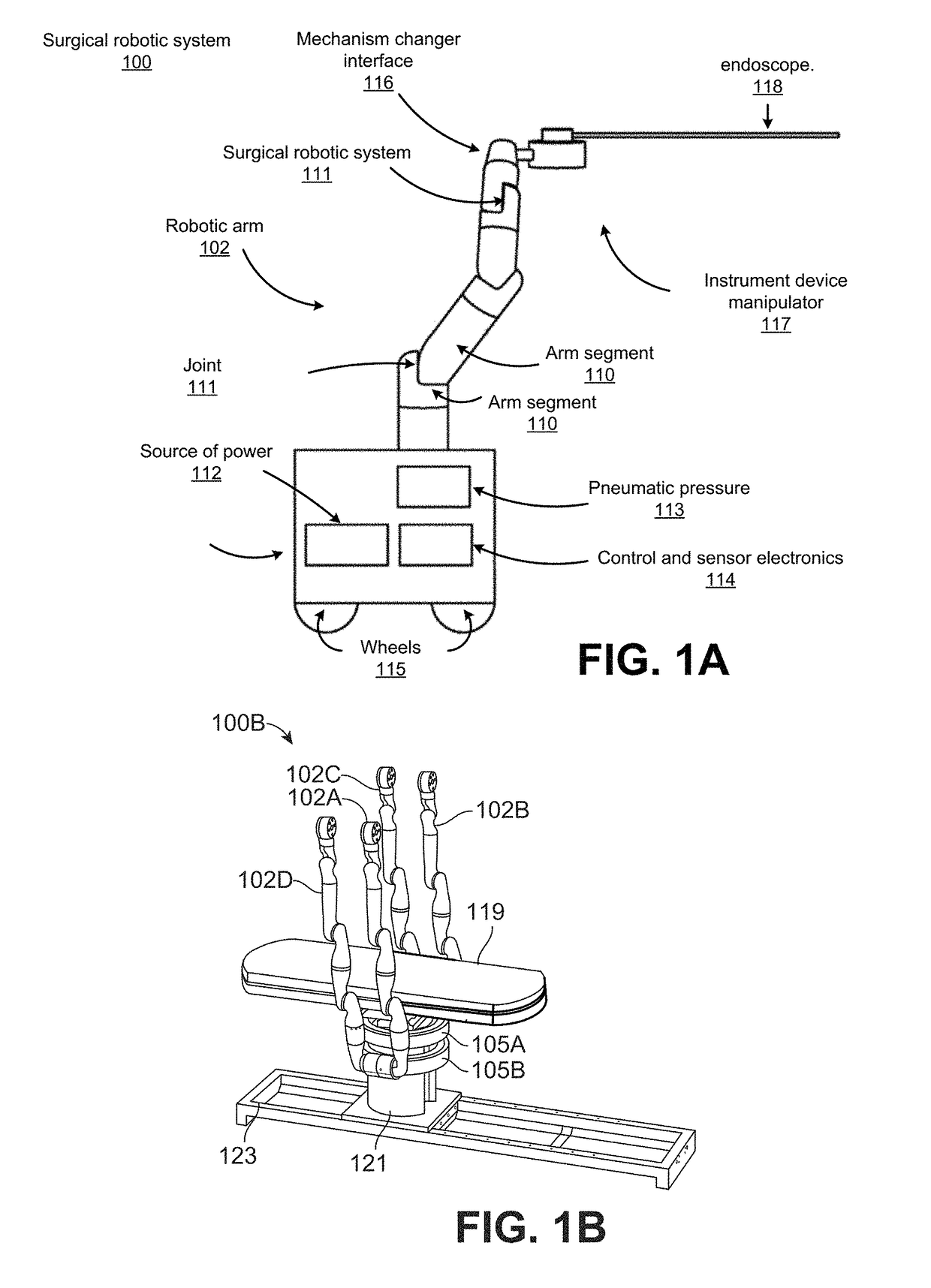

Object capture with a basket

ActiveUS9949749B2Easy to carryEasy to catchEndoscopesSurgical instrument detailsURETEROSCOPERobotic arm

Owner:AURIS HEALTH INC

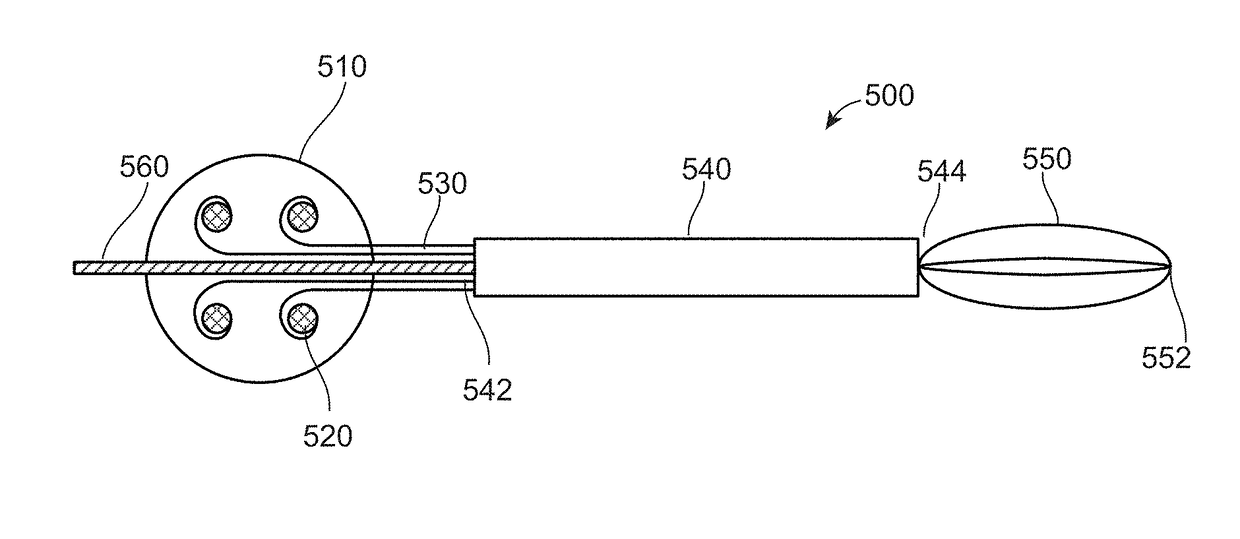

Basket apparatus

ActiveUS9955986B2Easy to carryEasy to catchEndoscopesSurgical systems user interfaceMechanical engineeringEndoscope

A basket apparatus is described that assists in removing objects from within a patient. The apparatus includes a number of pull wires, each pull wire physically coupled to a different capstan that individually actuates one of the pull wires. The apparatus also includes an outer support shaft itself including a number of channels through which the pull wires traverse. The portions of the pull wires extending out of the outer support shaft form a basket of adjustable size, shape, and position. The pull wires are attached together at a tip located at a distal end of the basket apparatus. By controlling the actuation of the various pull wires, the basket's shape, position size can be manipulated to reposition the basket around an object located within a patient, independent of or in conjunction with motion of the remainder of the apparatus or an associated endoscope.

Owner:AURIS HEALTH INC

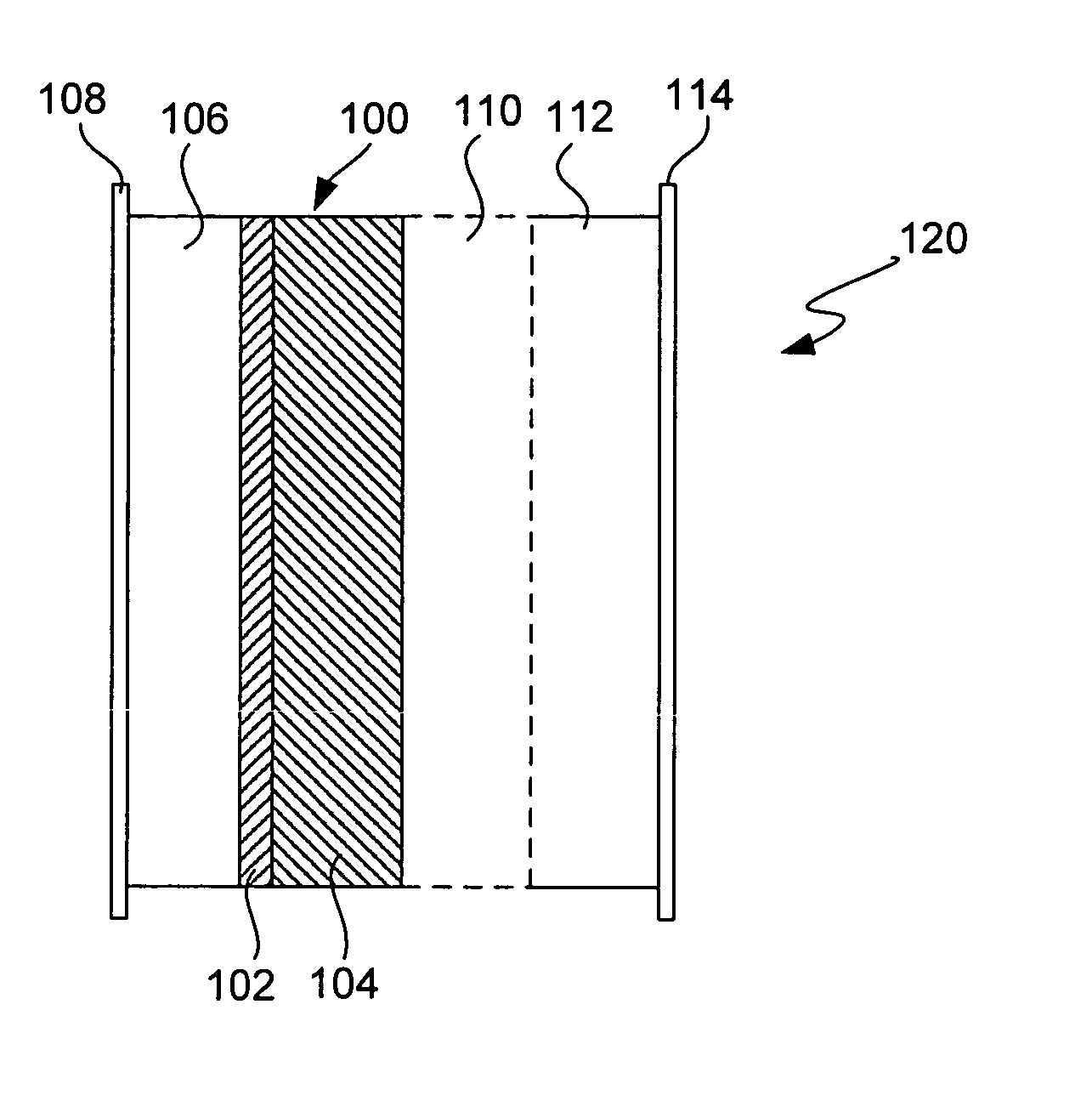

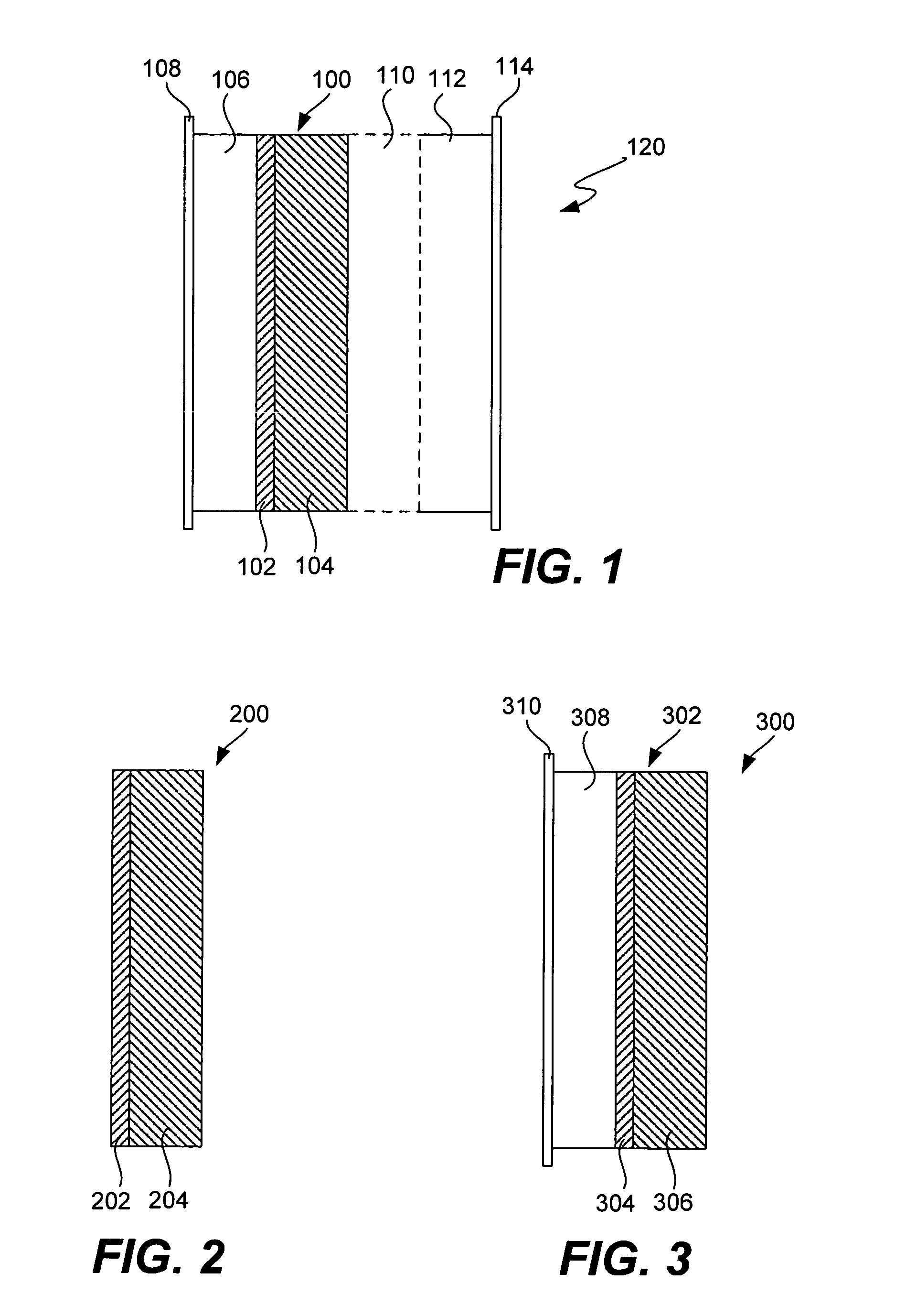

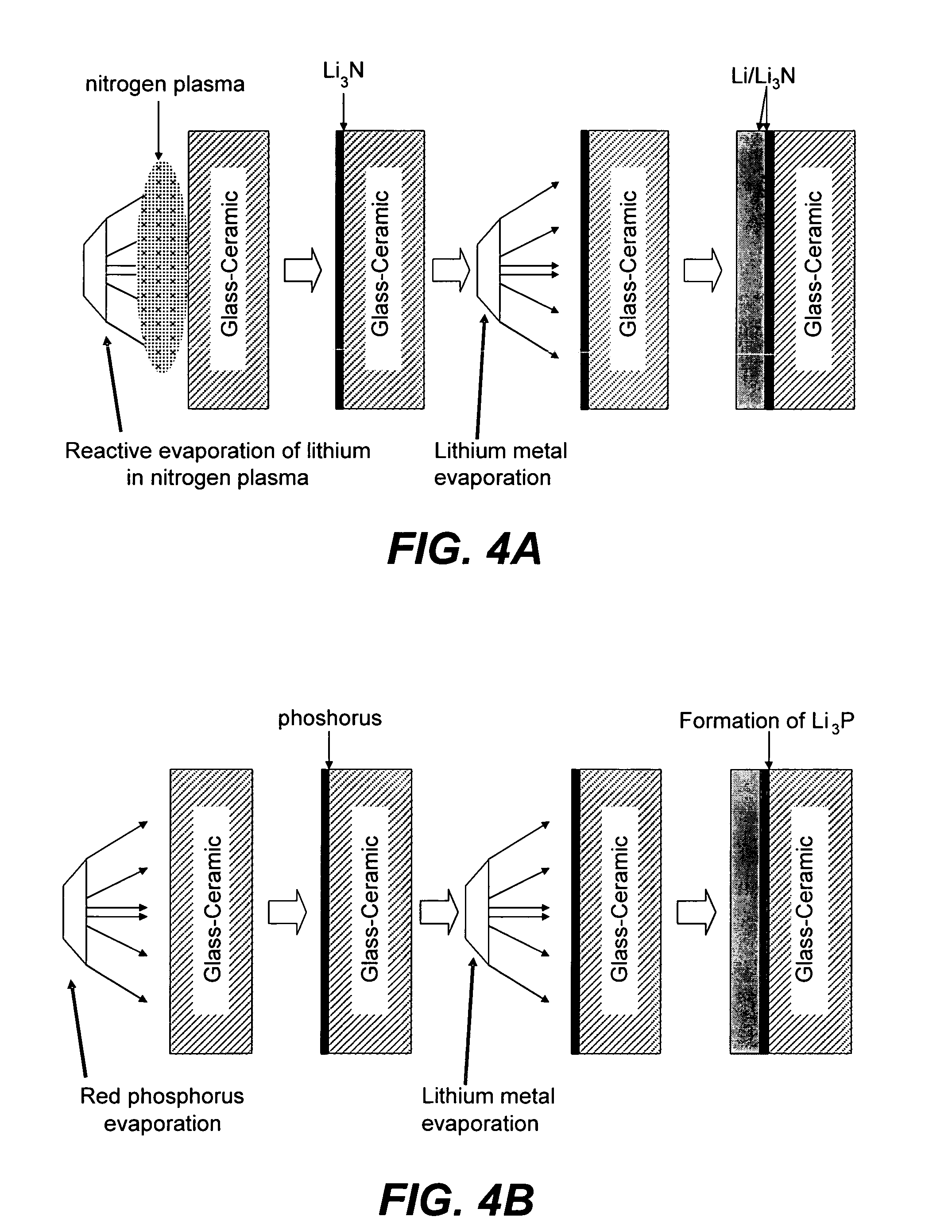

Ionically conductive composites for protection of active metal anodes

ActiveUS7282296B2Easy to manufactureImprove battery performanceFinal product manufactureElectrode carriers/collectorsChemical stabilityIonic conductivity

Disclosed are ionically conductive composites for protection of active metal anodes and methods for their fabrication. The composites may be incorporated in active metal negative electrode (anode) structures and battery cells. In accordance with the invention, the properties of different ionic conductors are combined in a composite material that has the desired properties of high overall ionic conductivity and chemical stability towards the anode, the cathode and ambient conditions encountered in battery manufacturing. The composite is capable of protecting an active metal anode from deleterious reaction with other battery components or ambient conditions while providing a high level of ionic conductivity to facilitate manufacture and / or enhance performance of a battery cell in which the composite is incorporated.

Owner:POLYPLUS BATTERY CO INC

Portable wound treatment apparatus having pressure feedback capabilities

InactiveUS7670323B2Easy to remove and replaceLess-easy to determineWound drainsSurgeryWound sitePressure feedback

A reduced pressure treatment apparatus includes a drape for positioning over the wound site to create and maintain a substantially air-tight cavity between the wound site and the drape. A multi-lumen suction tube is provided to be attached to a reduced pressure source. The multi-lumen suction tube includes a center lumen and at least one outer lumen and is configured to deliver reduced pressure beneath the drape to the substantially air-tight cavity. The multi-lumen suction tube is adapted to allow fluid to be drawn from the wound site through the center lumen and pressure to be monitored at the wound site through the at least one outer lumen.

Owner:KCI LICENSING INC

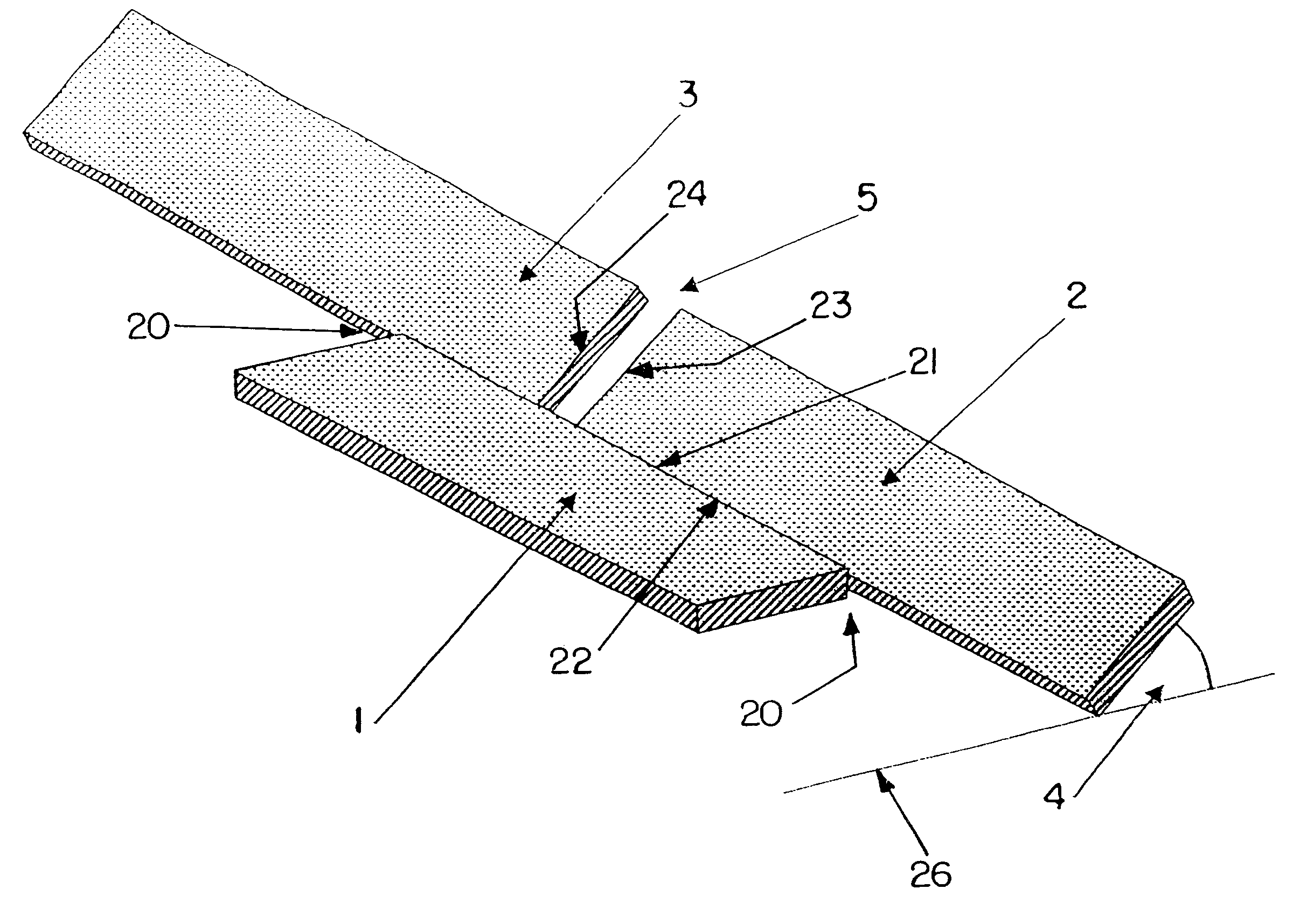

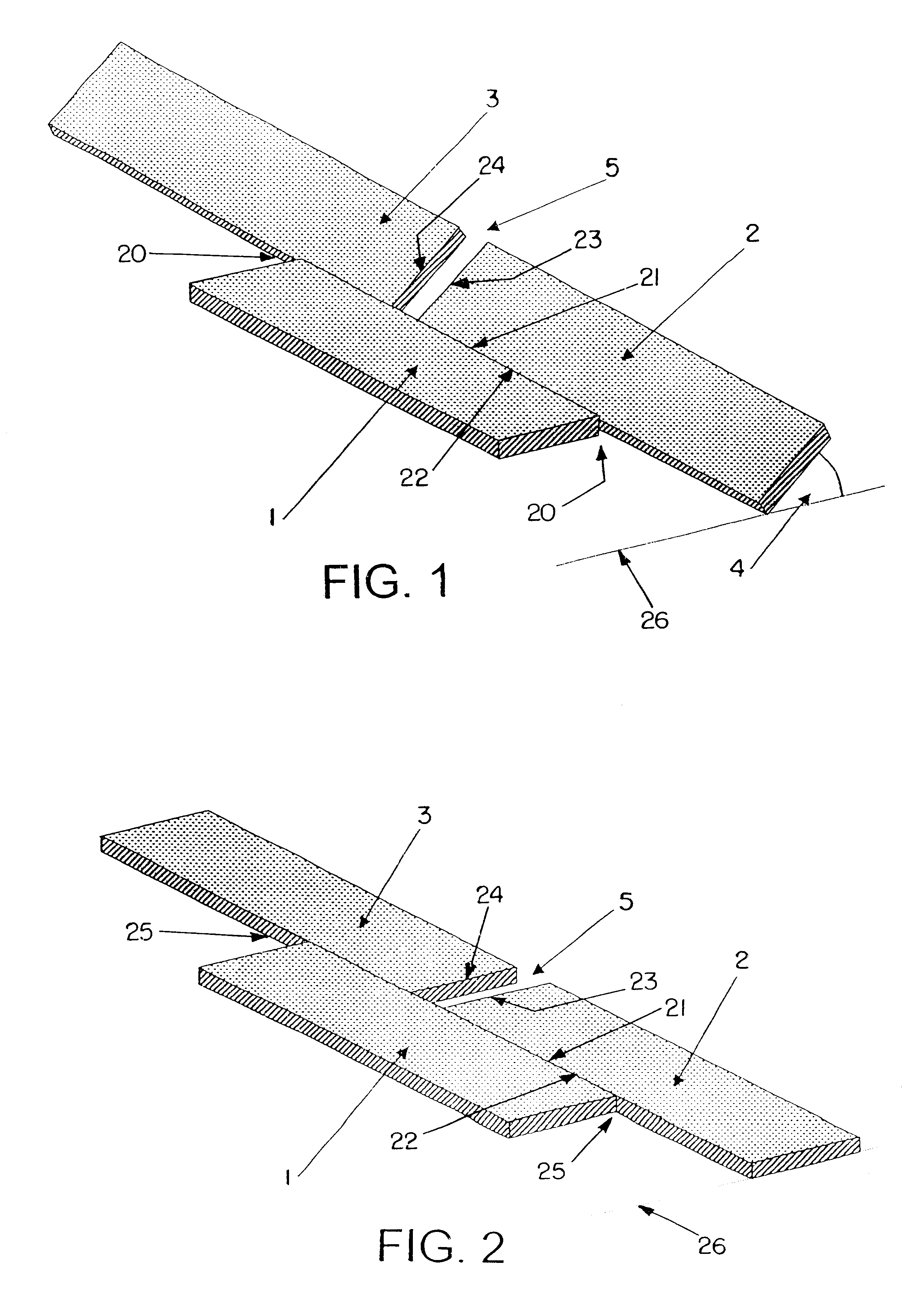

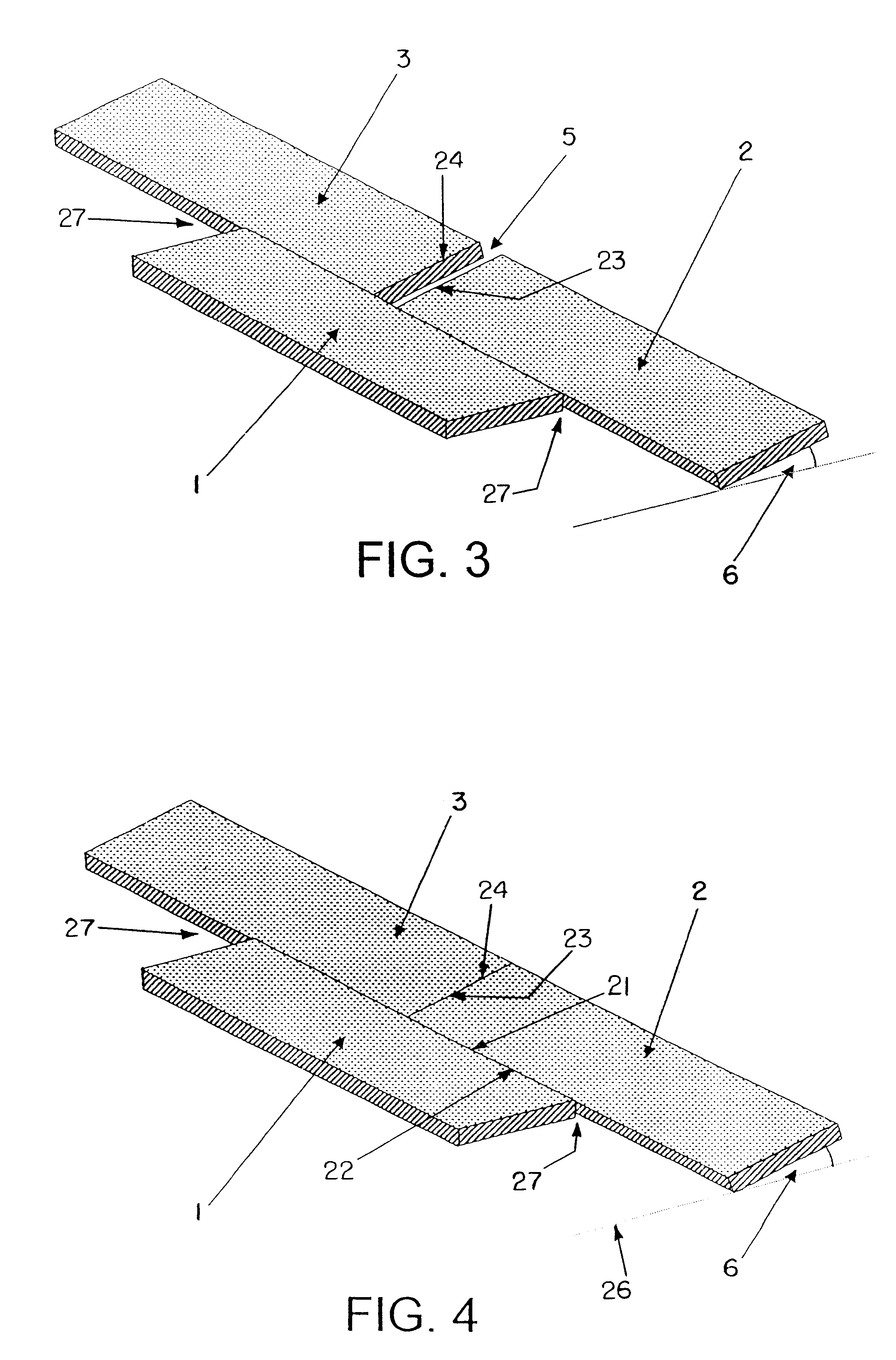

Method of laying panels

InactiveUS6546691B2Increase displacementAvoid the needRoof covering using tiles/slatesWallsEngineeringMutual position

The present invention provides a method of laying and mechanically joining panels, especially floor panels. In a first step a first panel is already located in a first row. A second panel is positioned in a second row in a first position in relation to the first panel. A third panel is now brought into the second row and into the first position in relation to the first panel. In this position, there is a mutual distance between the adjacent edges of the second and third panel. In a second step the second and third panel are angled into the third mutual position in relation to the first panel. Thereby, the second and third panel each achieve the possibility of easy displacement in the third direction in relation to the first panel. In a third step one or both of the second and third panel are moved in relation to the first panel. By this displacement the second and third panel get in a second position in relation to each other. An additional intermediate step may be employed between the first and the second step. In this intermediate step the second and third panel are angled down into the second mutual position in relation to the first panel.

Owner:KRONOSPAN TECHN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com