Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2228 results about "Logic cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

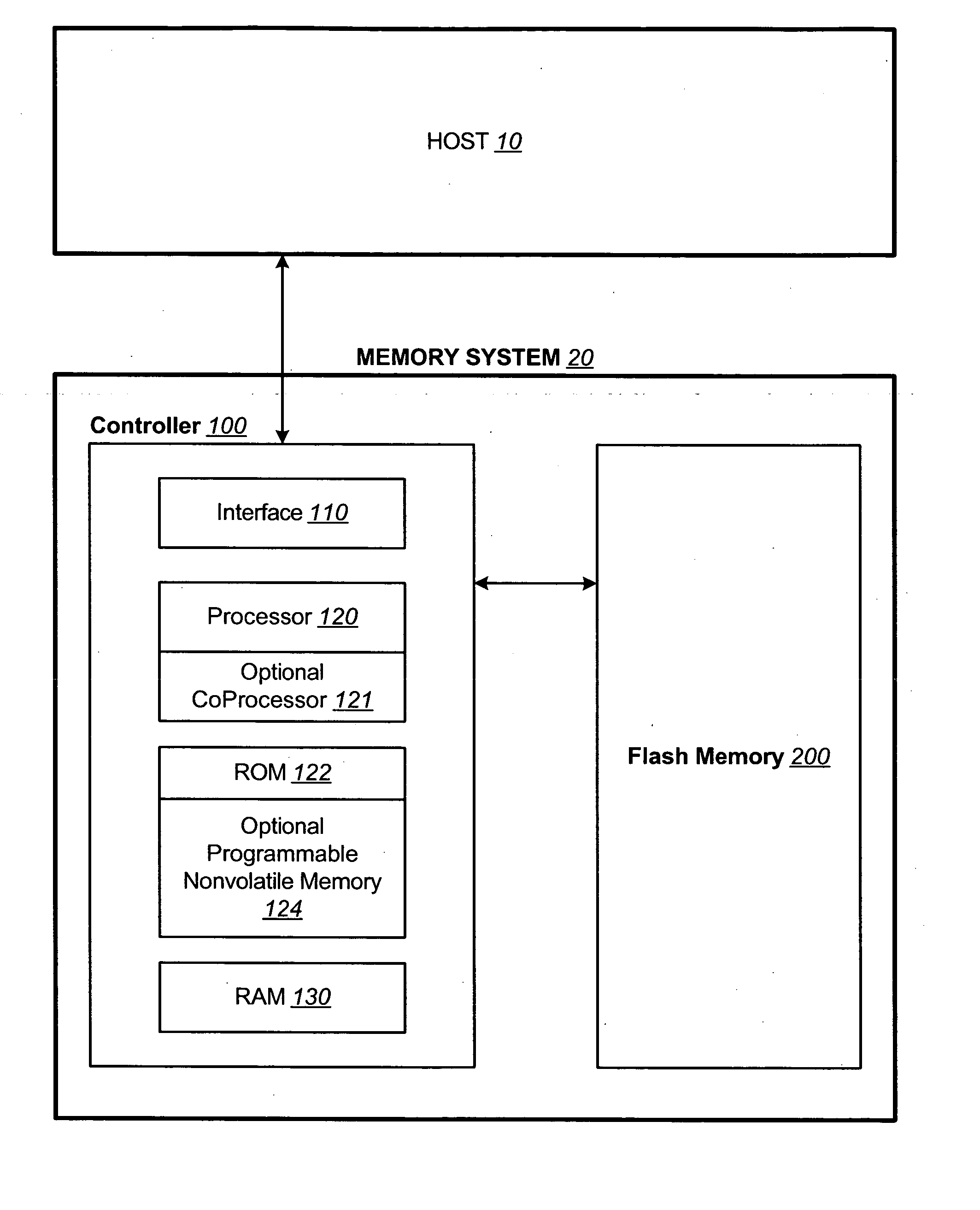

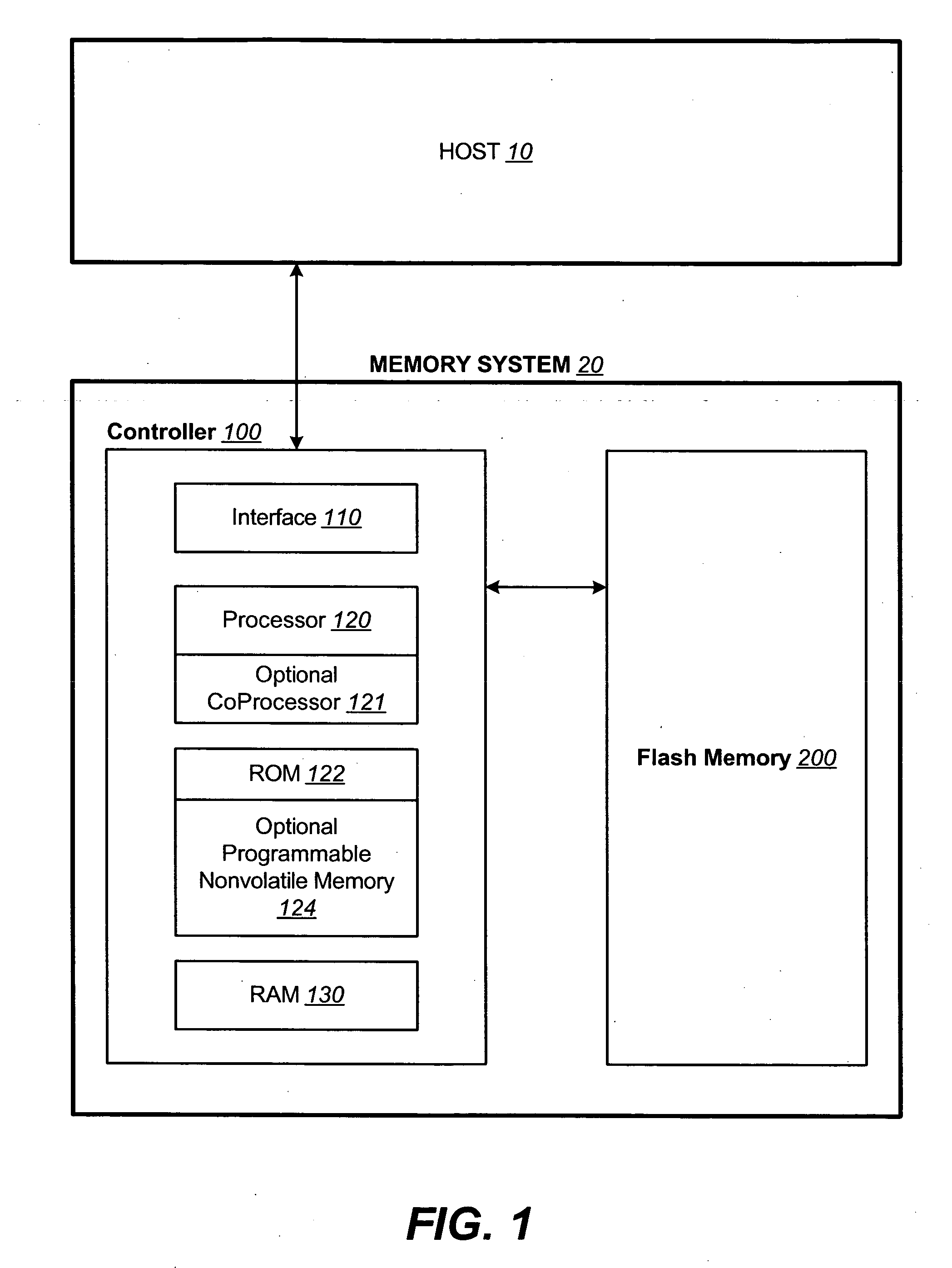

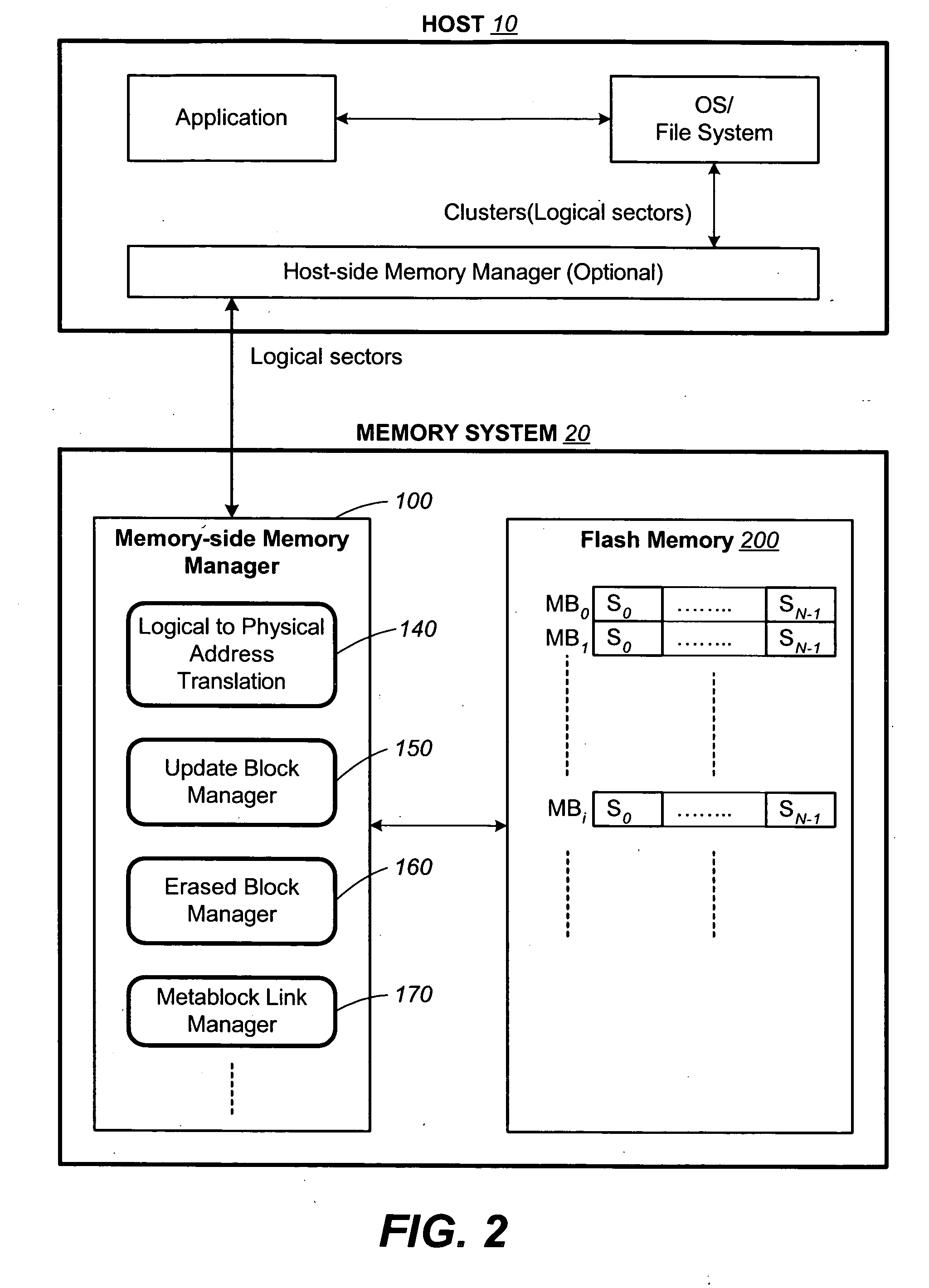

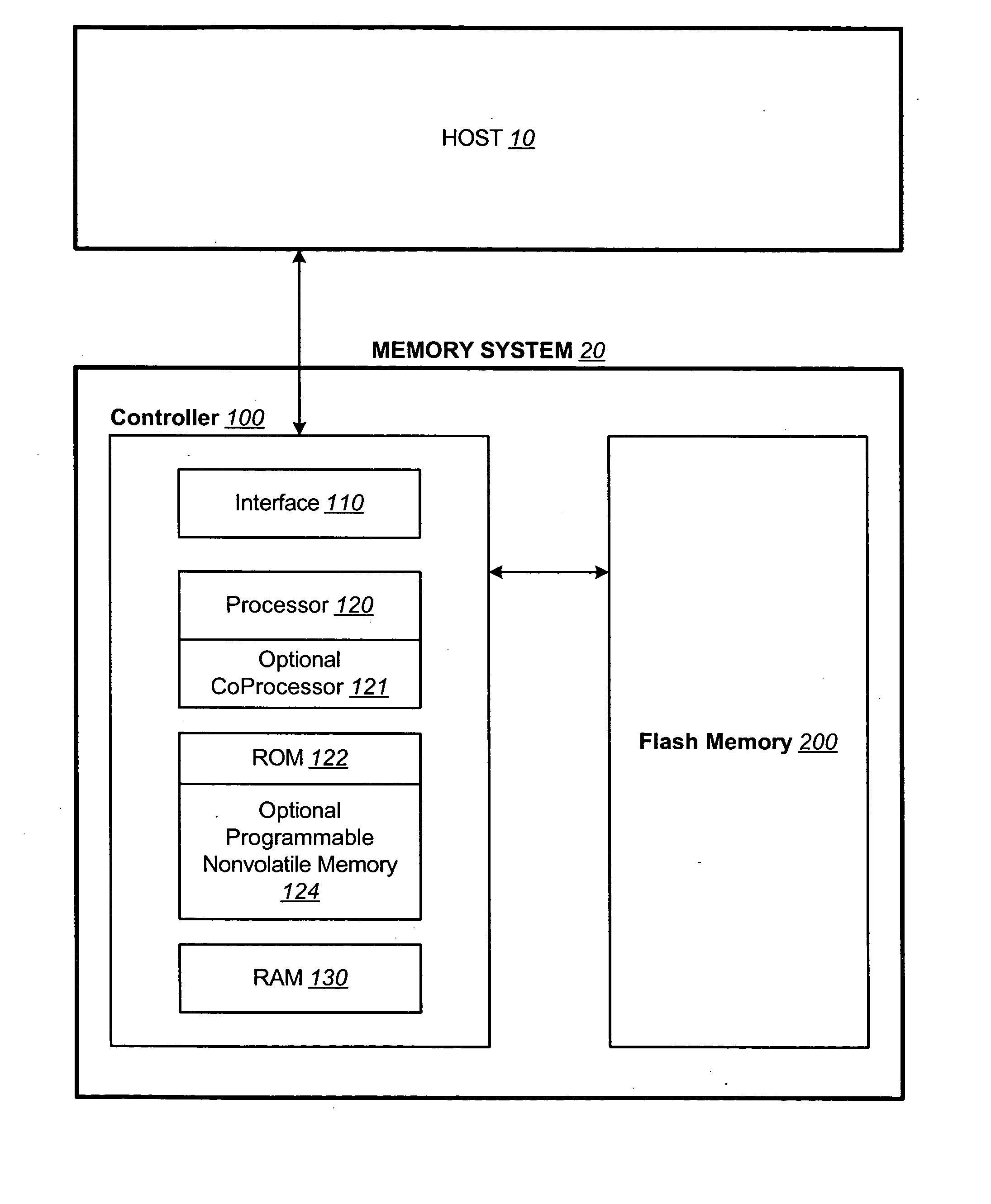

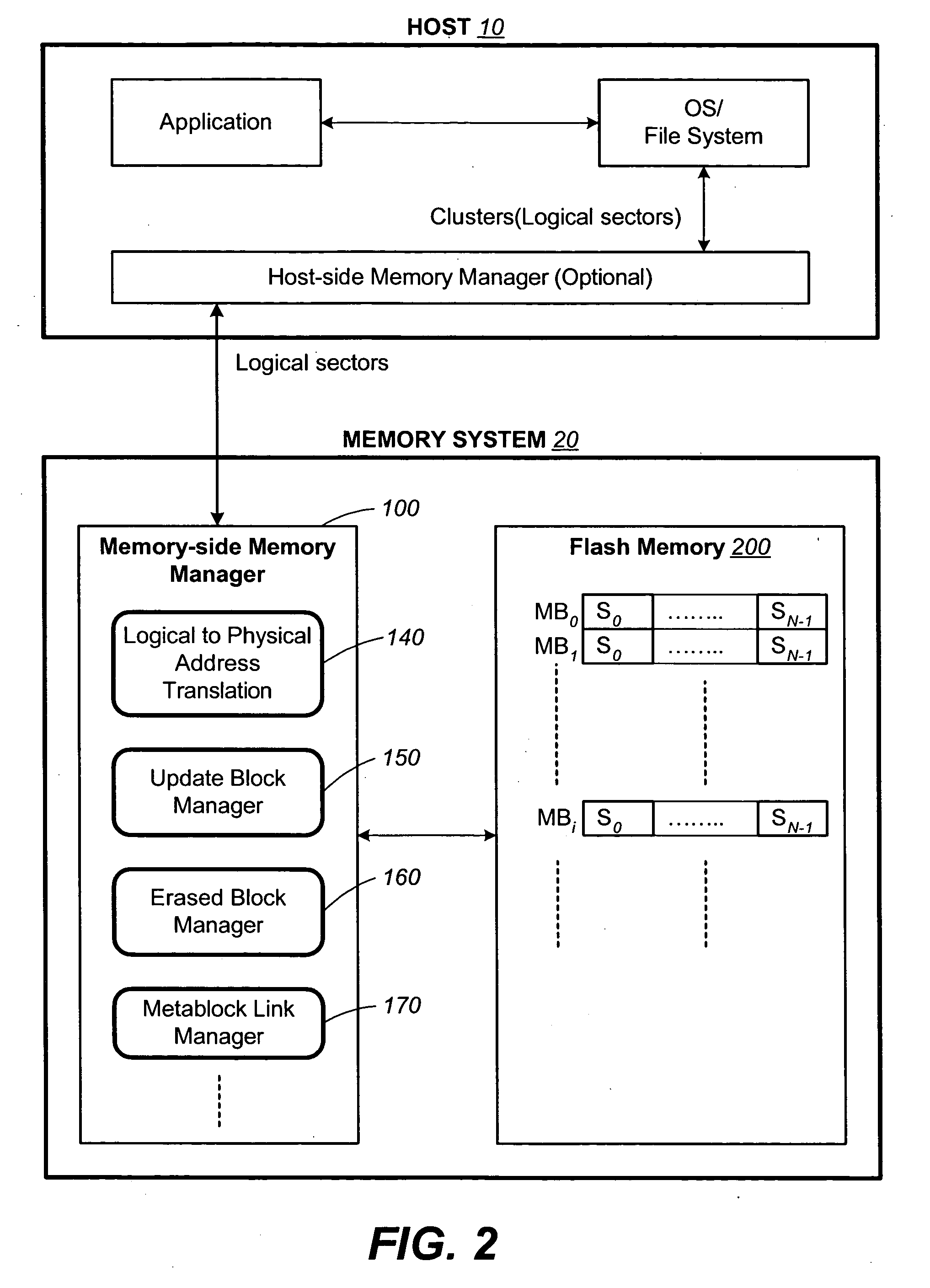

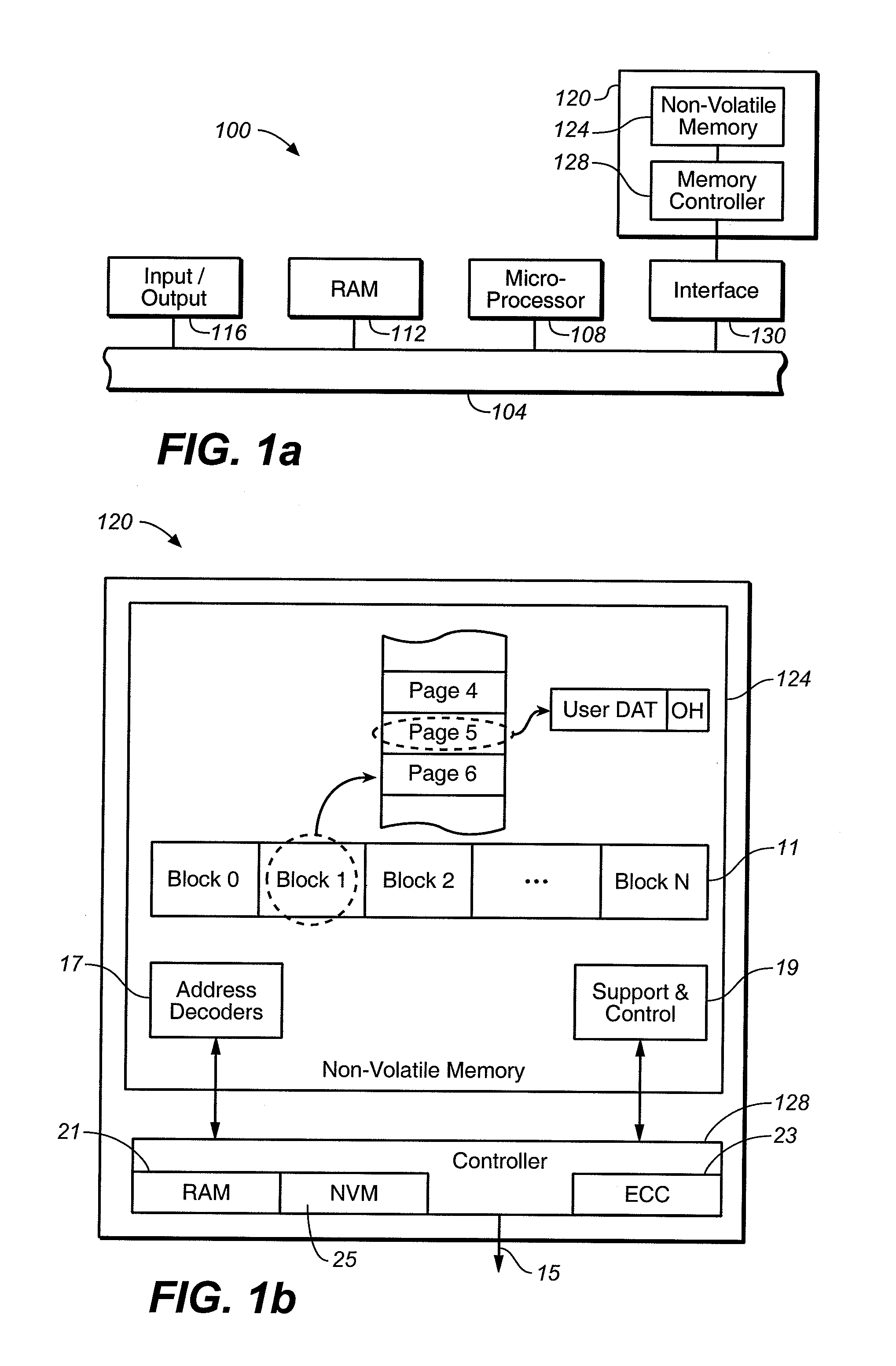

Non-volatile memory and method with non-sequential update block management

InactiveUS20050141312A1Good ECCExtra level of reliabilityMemory architecture accessing/allocationMemory adressing/allocation/relocationLogic cellOperating system

In a nonvolatile memory with block management system that supports update blocks with non-sequential logical units, an index of the logical units in a non-sequential update block is buffered in RAM and stored periodically into the non-volatile memory. In one embodiment, the index is stored in a block dedicated for storing indices. In another embodiment, the index is stored in the update block itself. In yet another embodiment, the index is stored in the header of each logical unit. In another aspect, the logical units written after the last index update but before the next have their indexing information stored in the header of each logical unit. In this way, after a power outage, the location of recently written logical units can be determined without having to perform a scanning during initialization. In yet another aspect, a block is managed as partially sequential and partially non-sequential, directed to more than one logical subgroup.

Owner:SANDISK TECH LLC

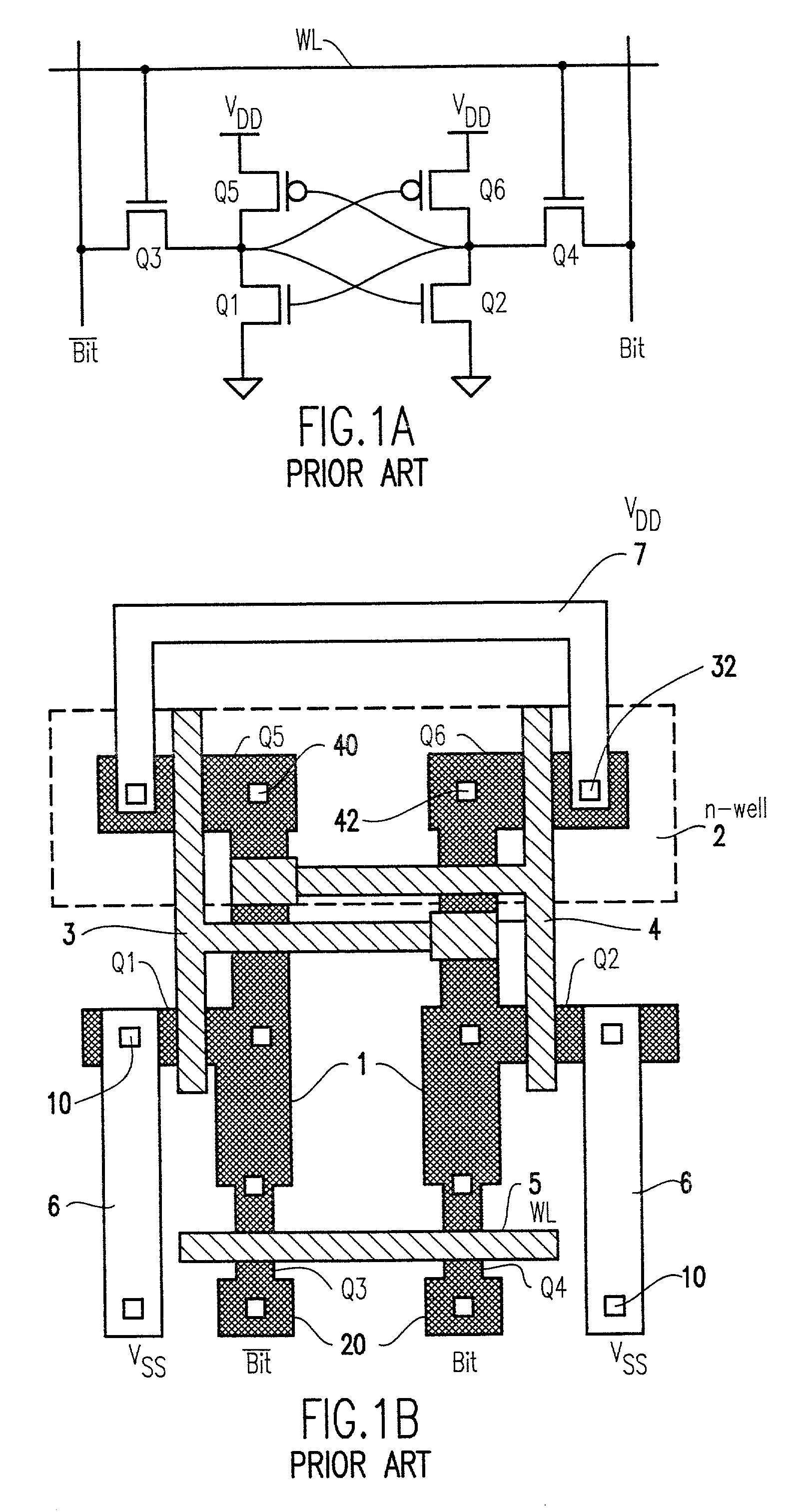

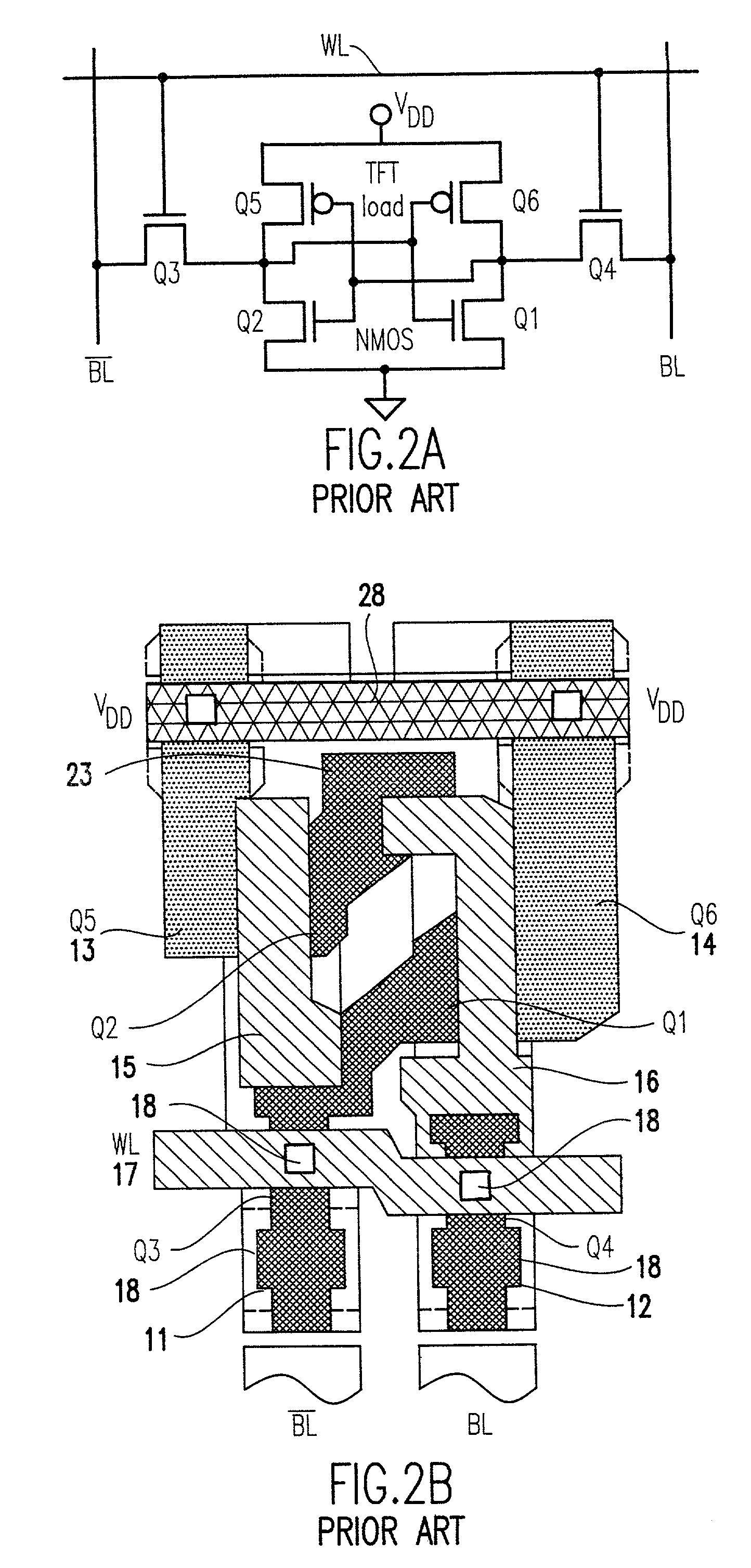

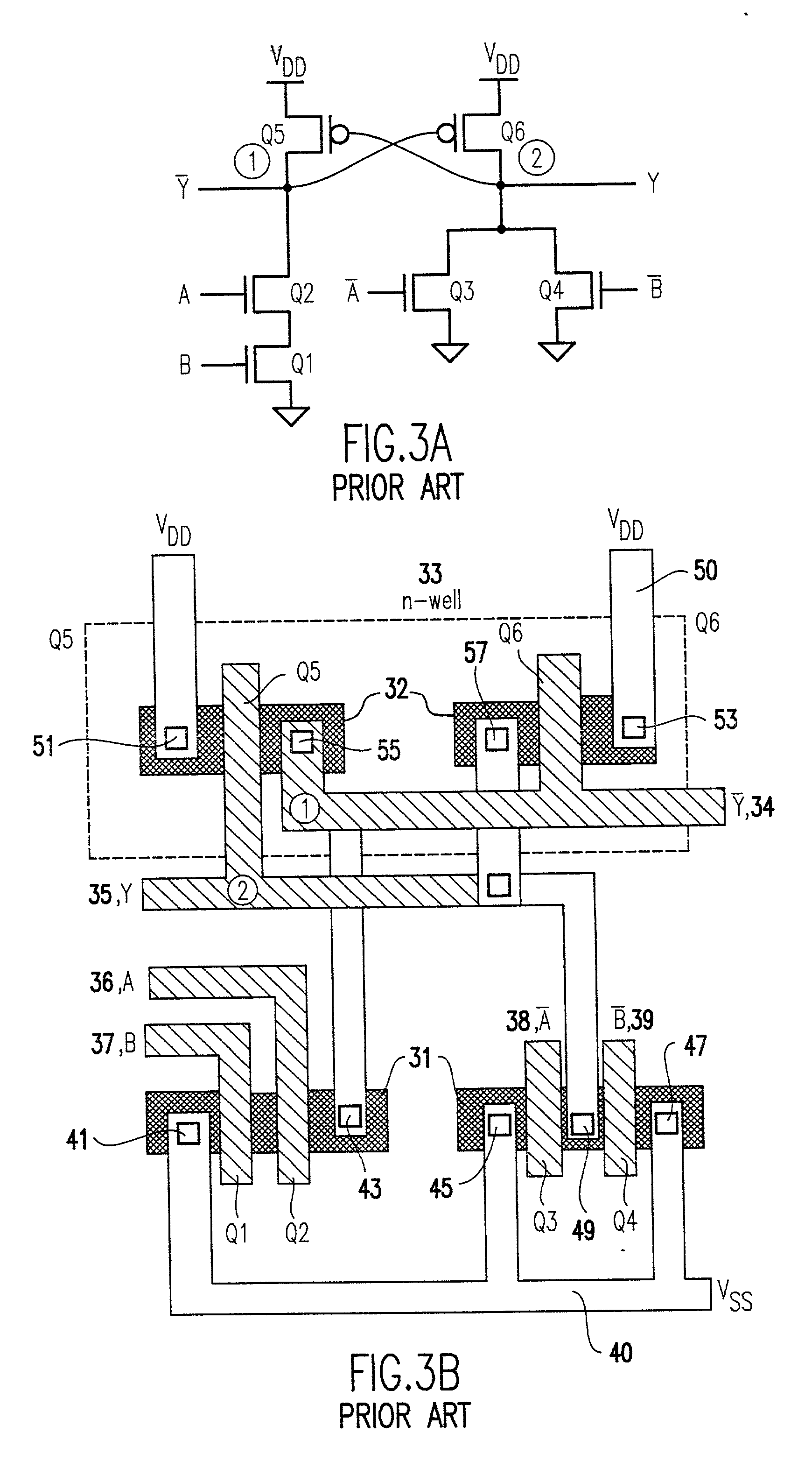

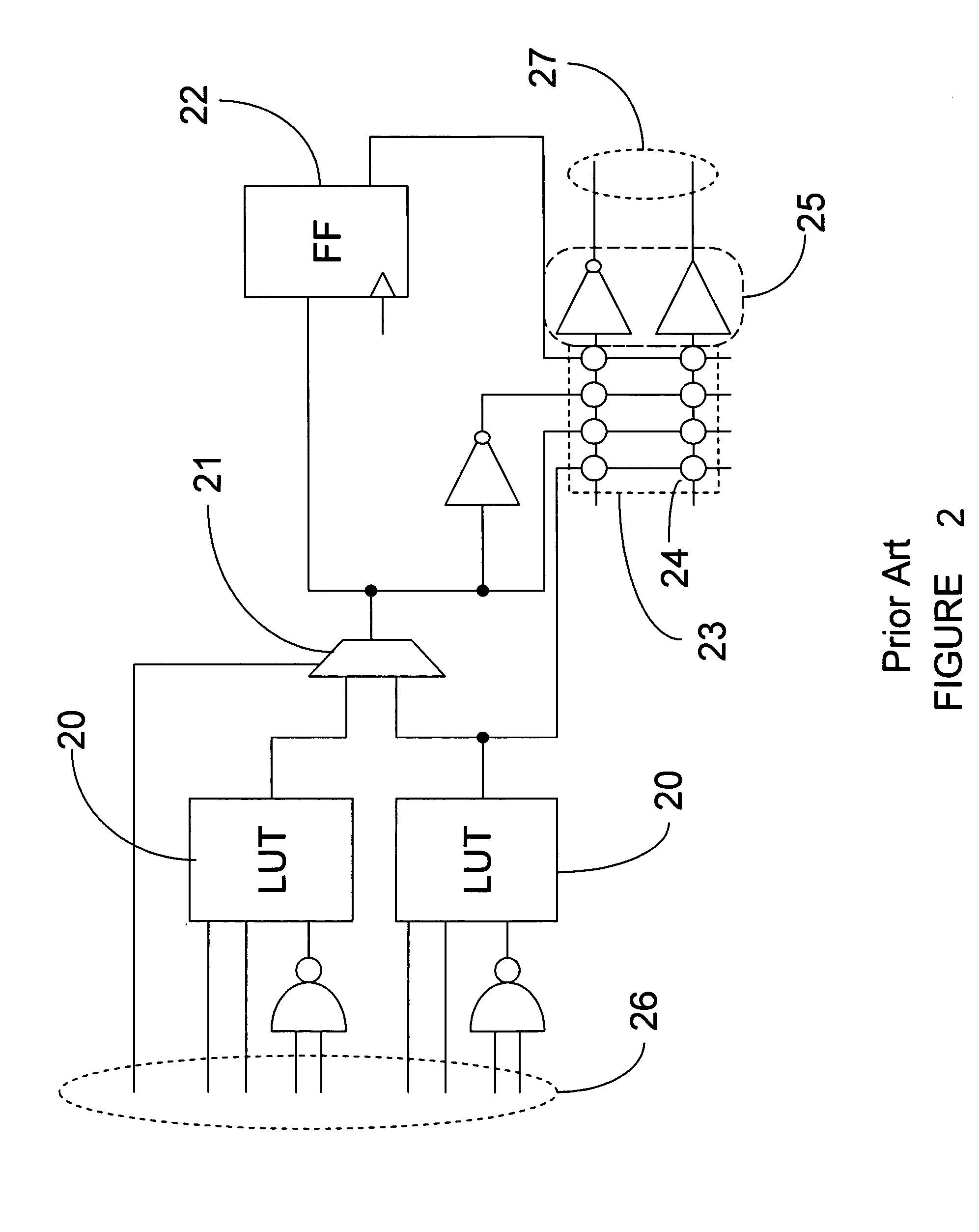

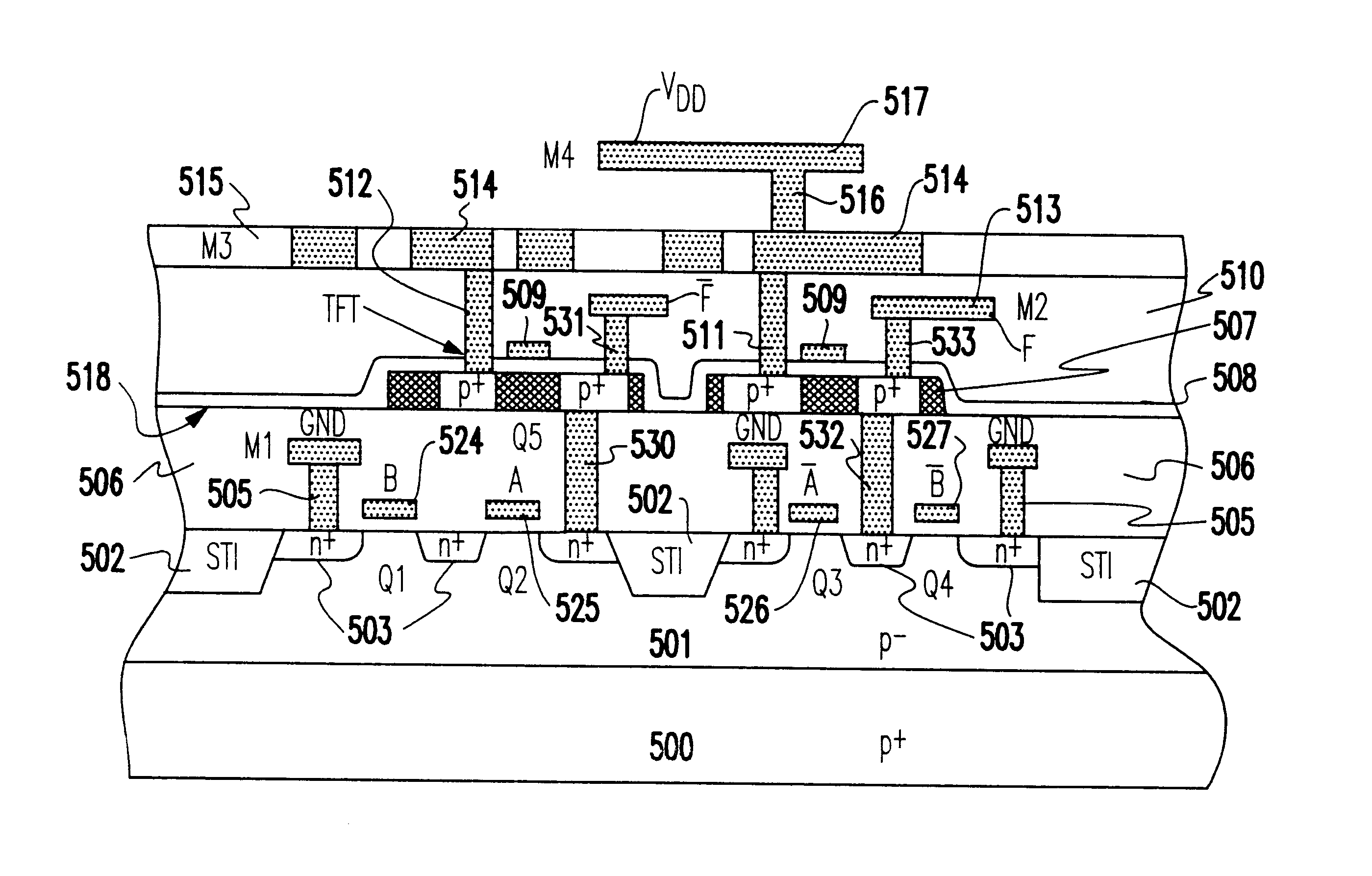

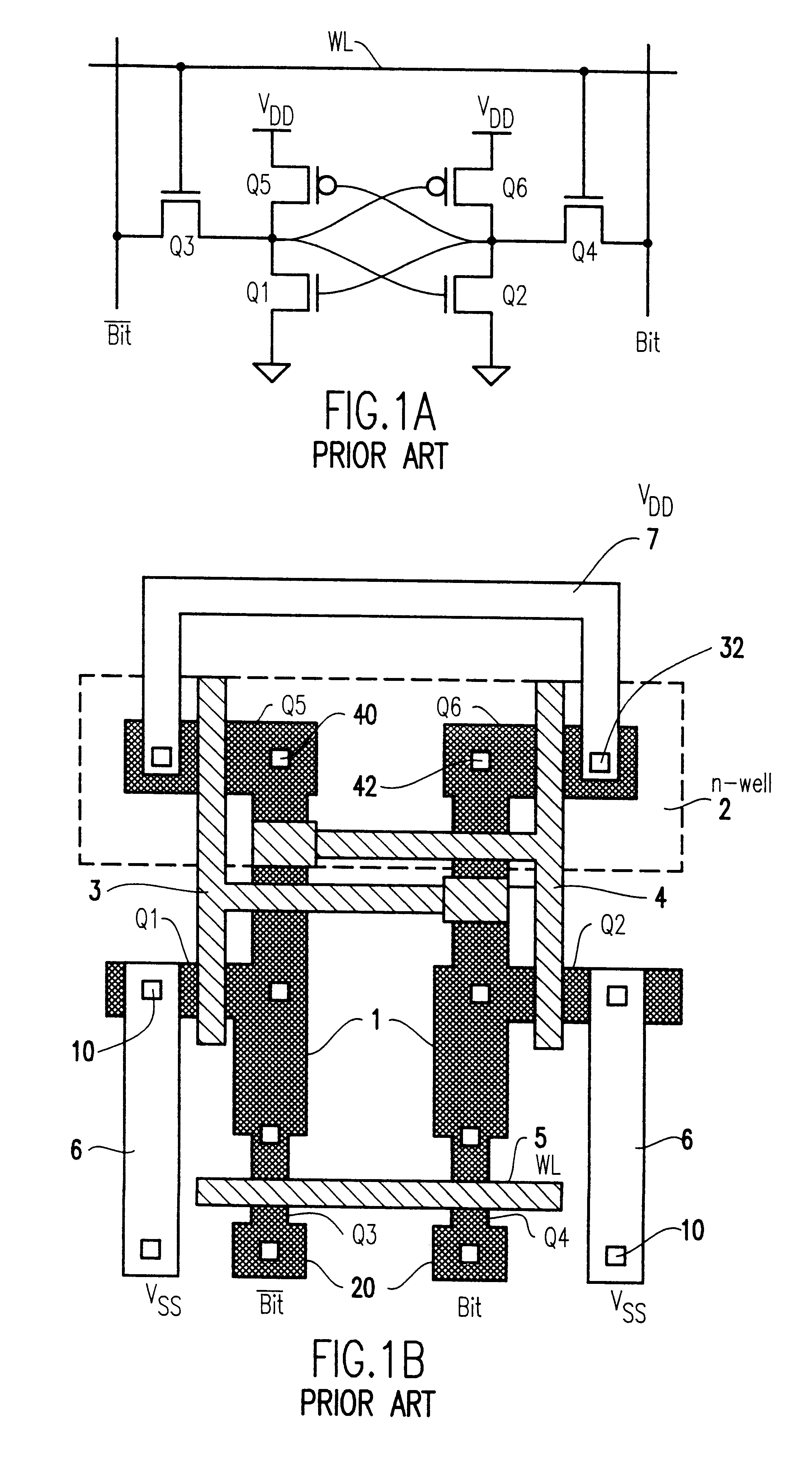

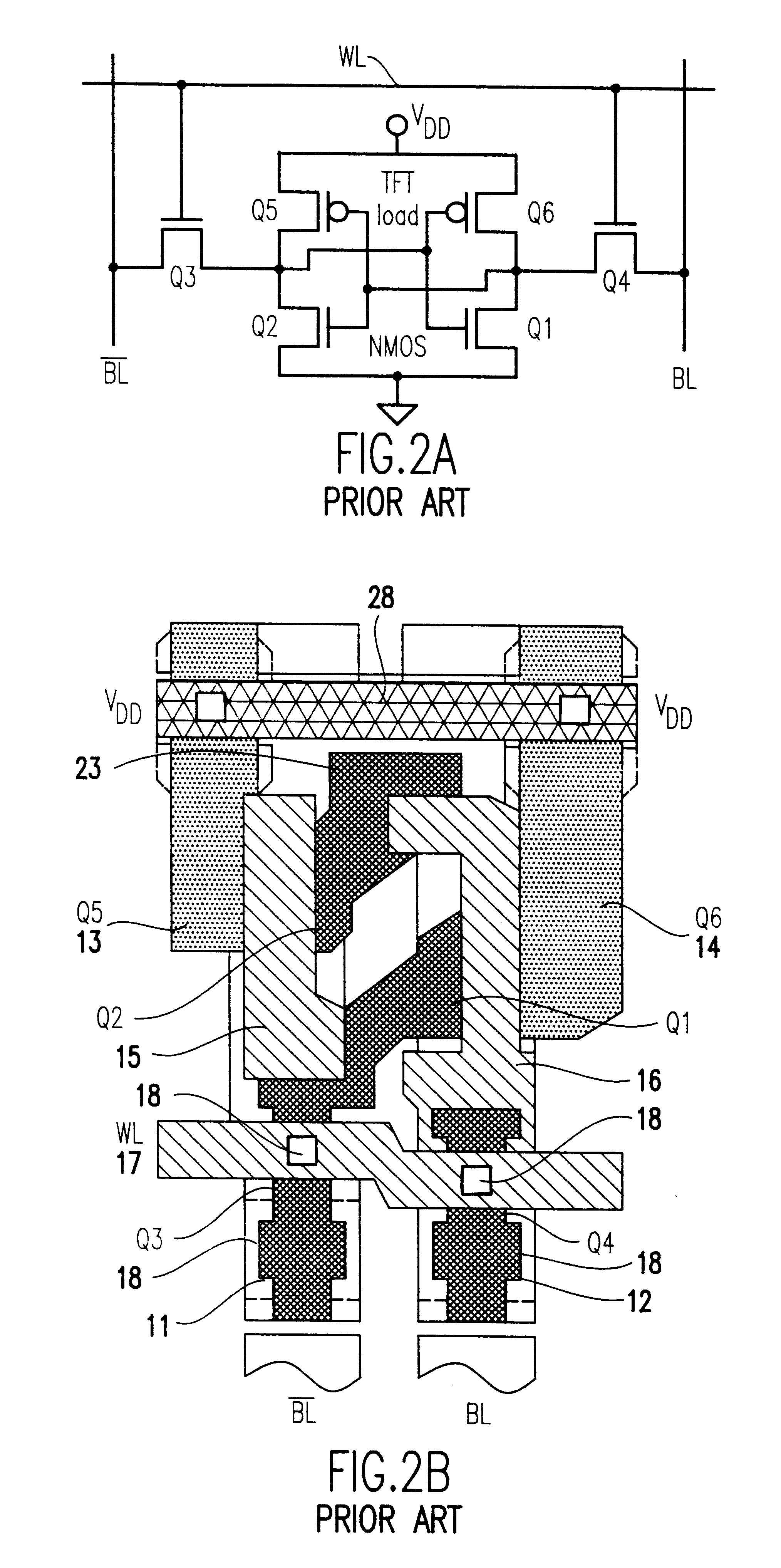

Merged logic and memory combining thin film and bulk Si transistors

InactiveUS20010028059A1Compact and economicalTransistorSolid-state devicesHigh densitySingle process

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

Non-volatile memory and method with memory planes alignment

InactiveUS20050141313A1Good ECCExtra level of reliabilityMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer architectureLogic cell

A non-volatile memory is constituted from a set of memory planes, each having its own set of read / write circuits so that the memory planes can operate in parallel. The memory is further organized into erasable blocks, each for storing a logical group of logical units of data. In updating a logical unit, all versions of a logical unit are maintained in the same plane as the original. Preferably, all versions of a logical unit are aligned within a plane so that they are all serviced by the same set of sensing circuits. In a subsequent garbage collection operation, the latest version of the logical unit need not be retrieved from a different plane or a different set of sensing circuits, otherwise resulting in reduced performance. In one embodiment, any gaps left after alignment are padded by copying latest versions of logical units in sequential order thereto.

Owner:SANDISK TECH LLC

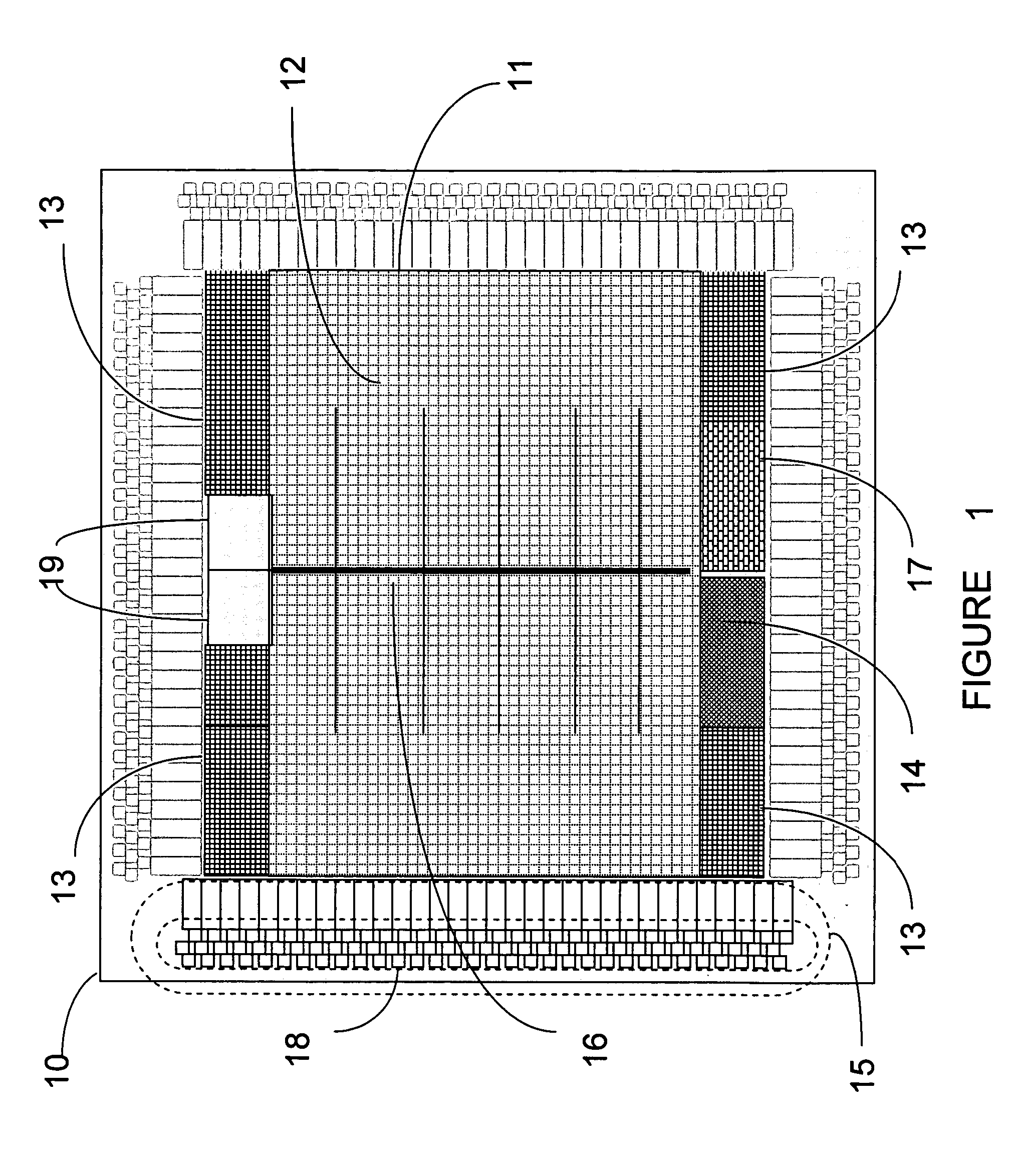

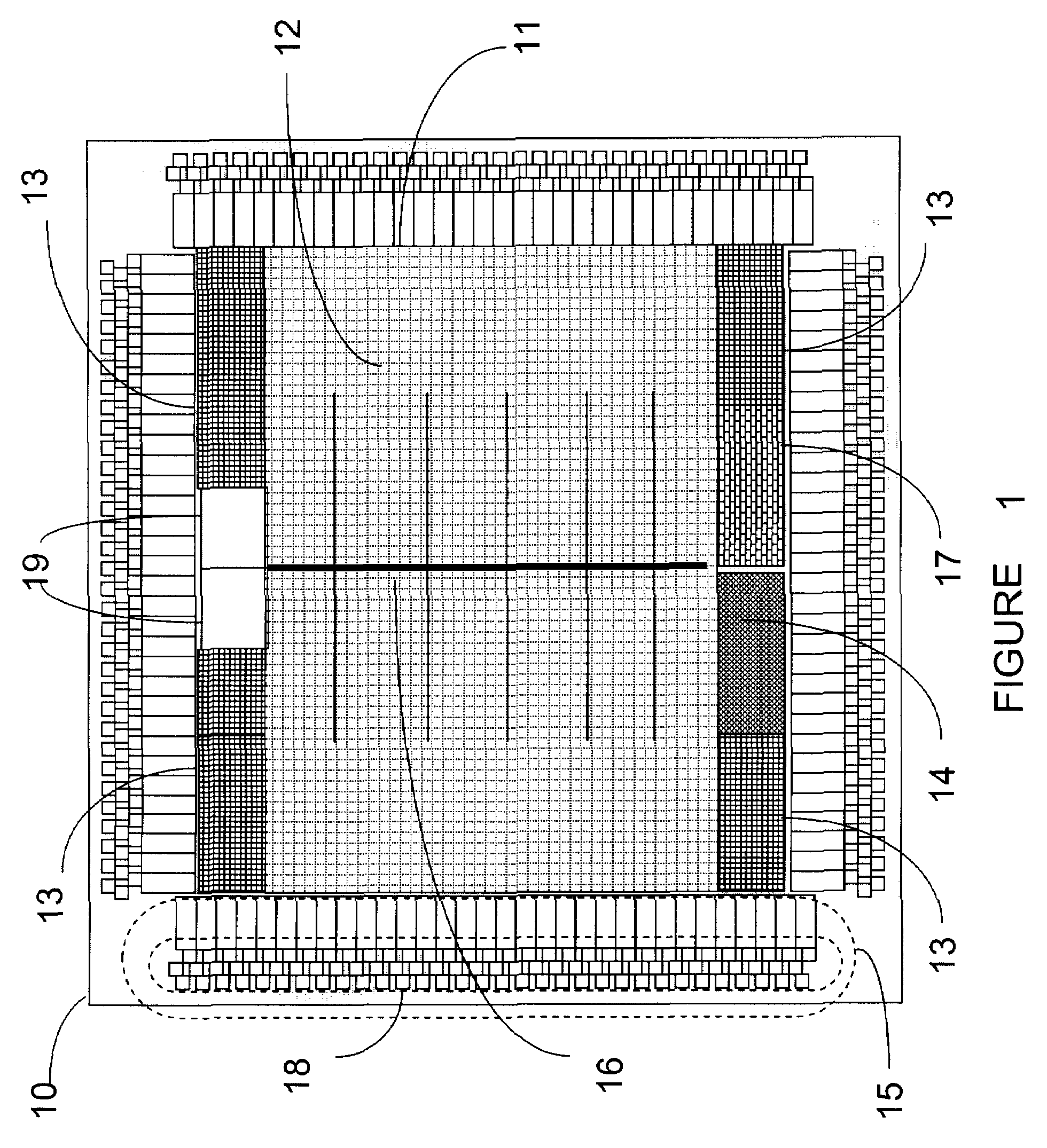

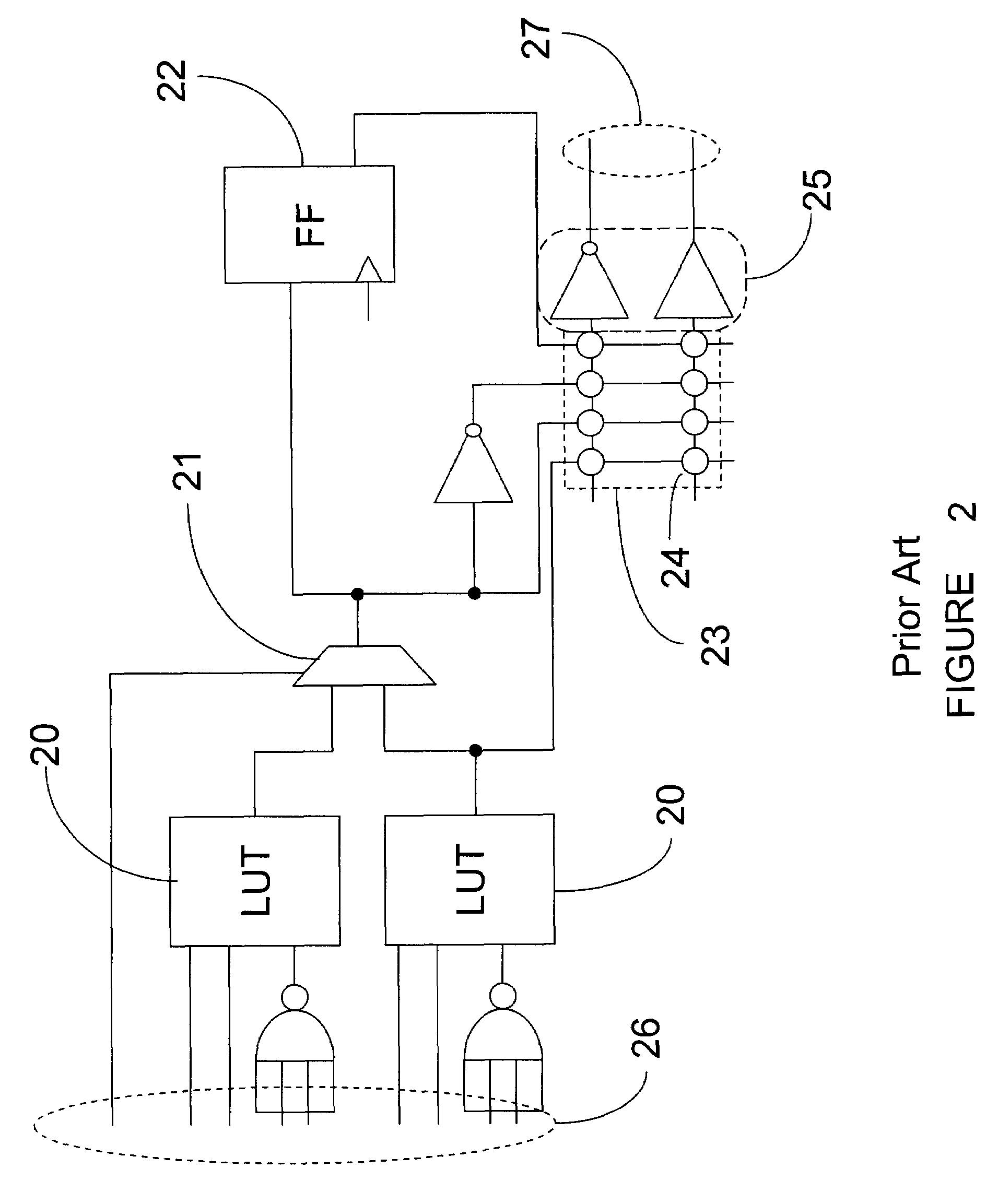

Structured integrated circuit device

InactiveUS7514959B2Solid-state devicesLogic circuits using elementary logic circuit componentsLogic cellMetal

A configurable logic array may include: a multiplicity of logic cells, containing look-up tables; customizable metal and via connection layers overlying the multiplicity of logic cells; a multiplicity of device customizable I / O cells; a multiplicity of configuration customizable RAM blocks; a ROM block with customizable contents; and a microprocessor with customizable I / O for configuring and testing the array, where the customizations are all done on a single via layer.

Owner:TAHOE RES LTD

Structured integrated circuit device

ActiveUS7463062B2Solid-state devicesLogic circuits using elementary logic circuit componentsLogic cellComputer science

A configurable logic array may include: a multiplicity of logic cells, containing look-up tables; customizable metal and via connection layers overlying the multiplicity of logic cells; a multiplicity of device customizable I / O cells; a multiplicity of configuration customizable RAM blocks; a ROM block with customizable contents; and a microprocessor with customizable I / O for configuring and testing the array, where the customizations may all be done on a single via layer.

Owner:TAHOE RES LTD

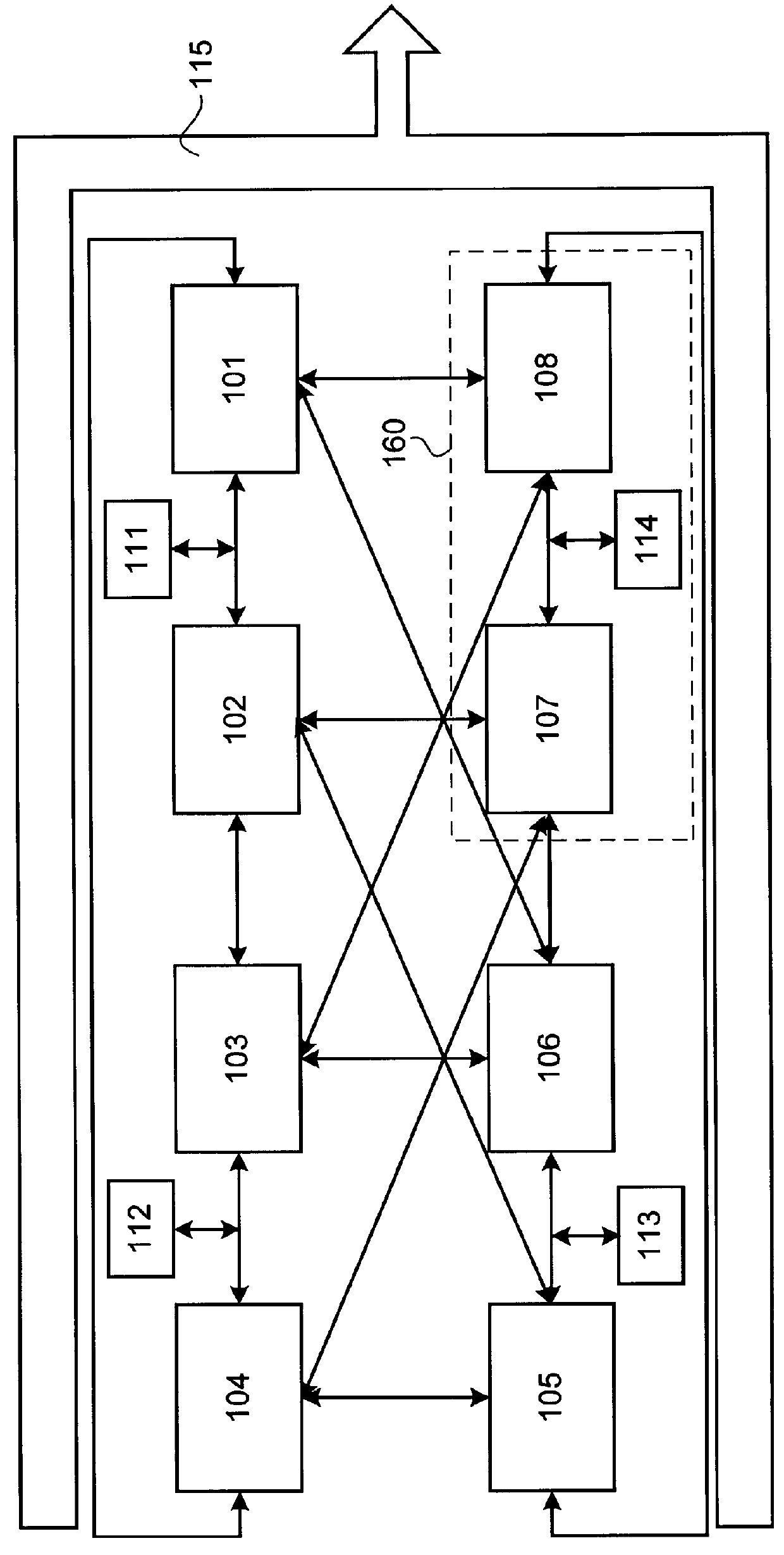

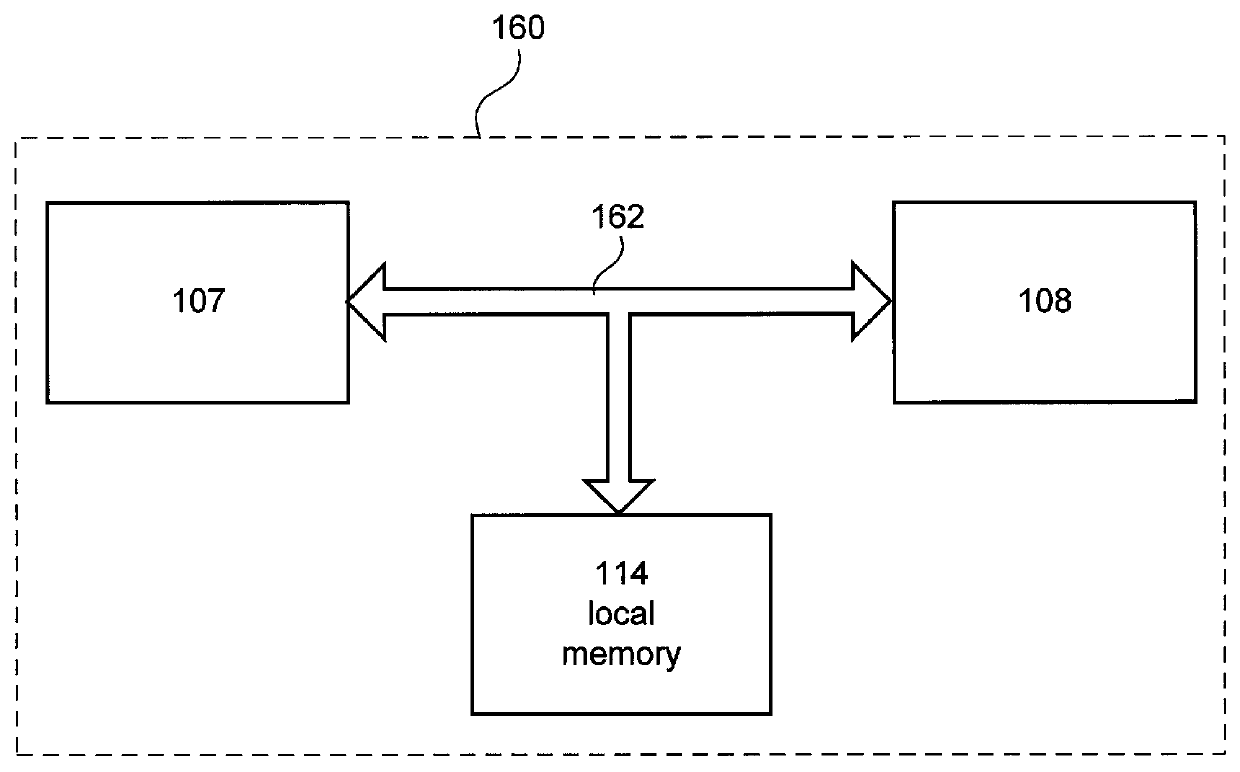

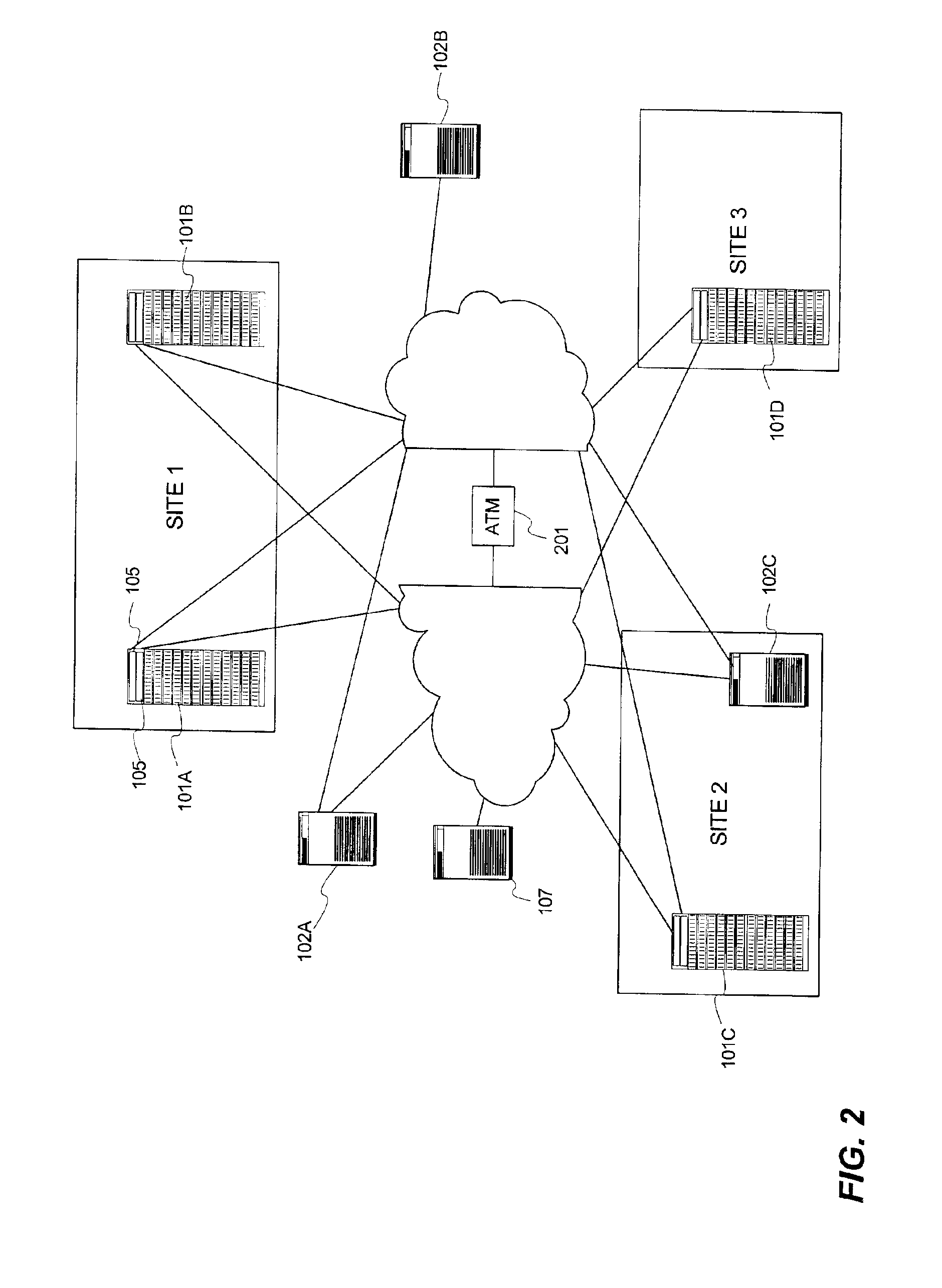

Reconfigurable computer architecture using programmable logic devices

A method and system for computing using reconfigurable computer architecture utilizing logic devices is disclosed. The computing may be accomplished by configuring a first programmable logic unit as a system controller. The system controller directs the implementation of an algorithm in a second one of the programmable logic units concurrently with reconfirguring a third one of the programmable logic units. In another aspect, the computing system may include a pair of independent, bi-directional busses each of which is arranged to electrically interconnect the system controller and the plurality of programmable logic devices. With this arrangement, a first bus may be used to reconfigure a selected one of the programmable logic devices as directed by the system controller while the second bus is used by an operational one of the programmable logic devices.

Owner:ALTERA CORP

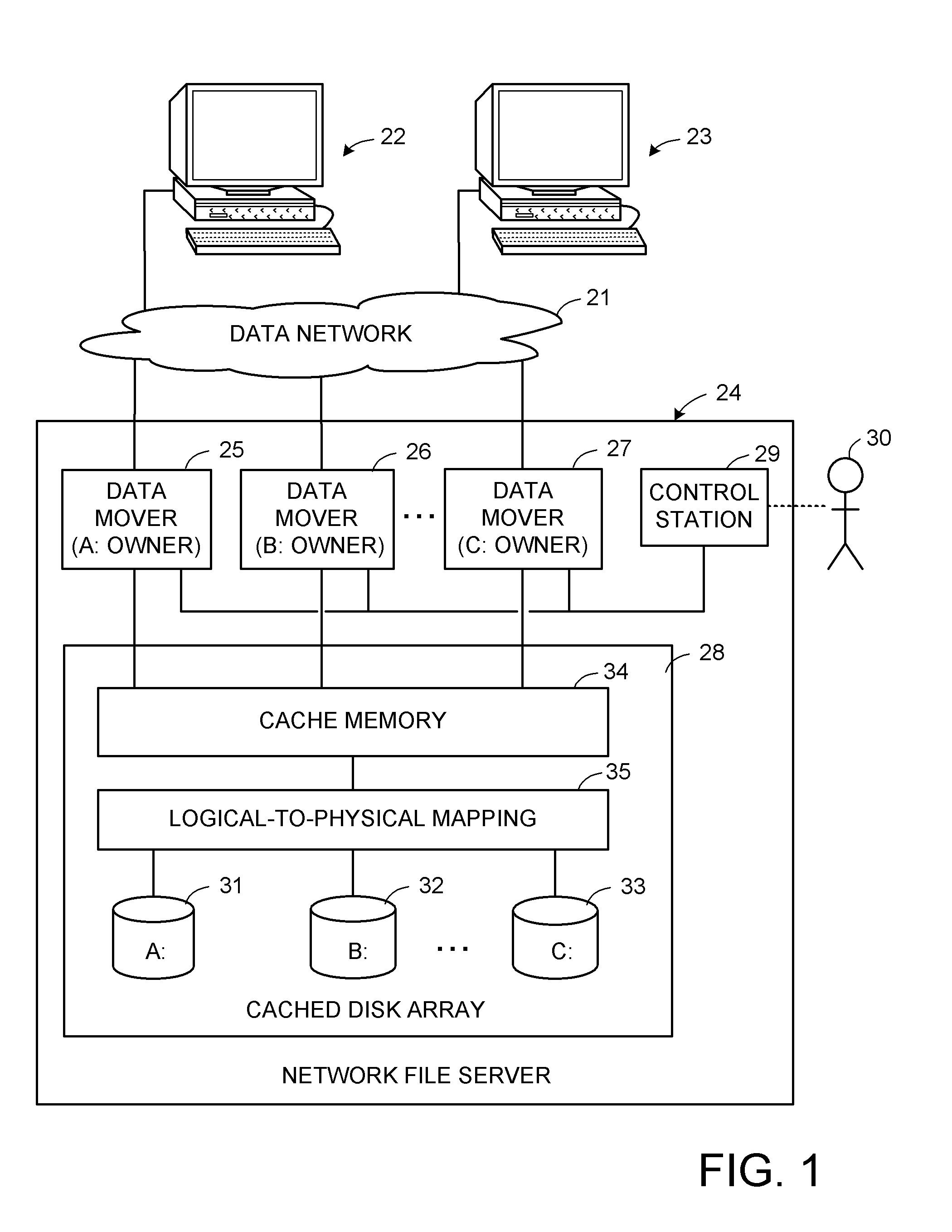

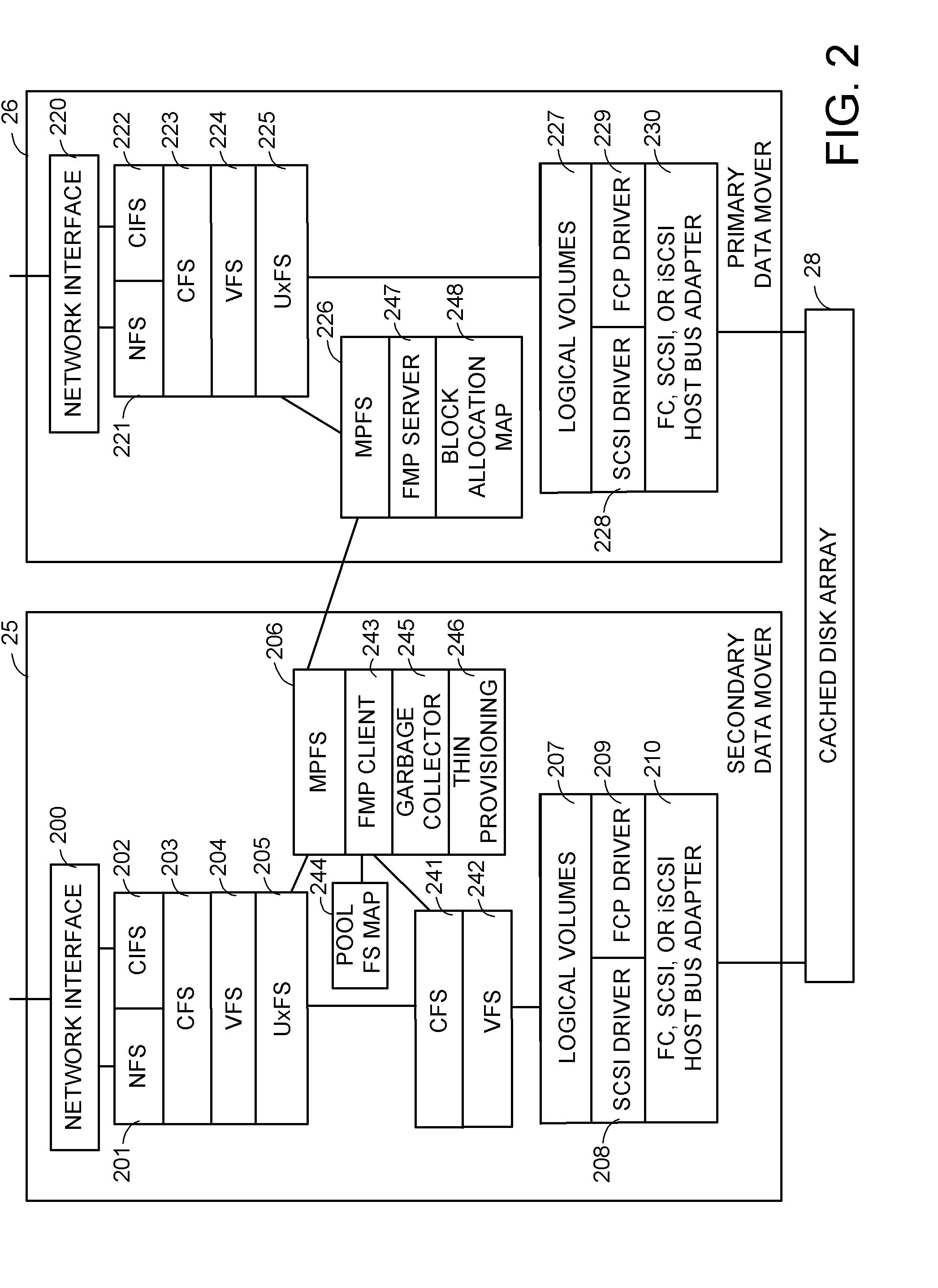

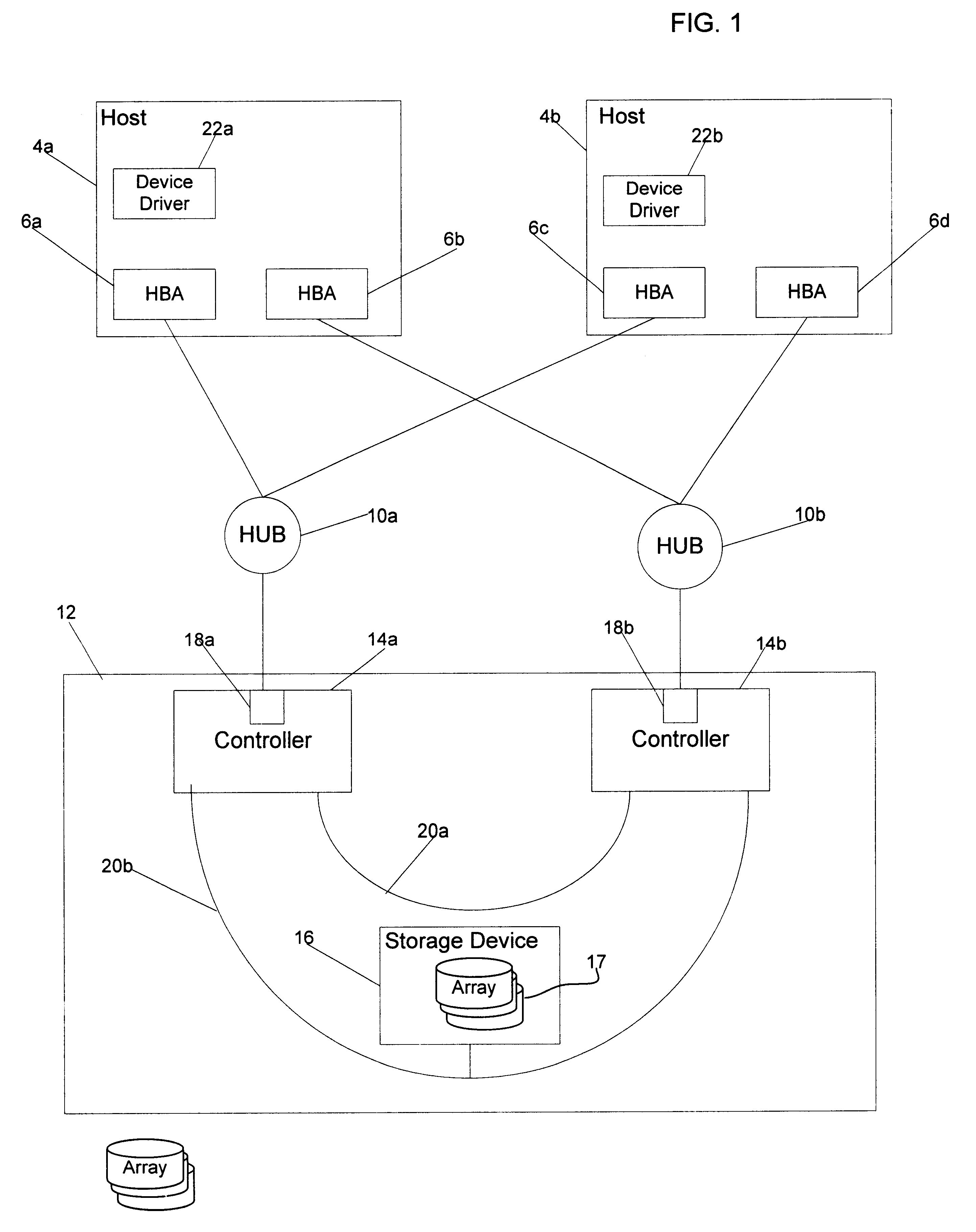

Storage array virtualization using a storage block mapping protocol client and server

A cached disk array includes a disk storage array, a global cache memory, disk directors coupling the cache memory to the disk storage array, and front-end directors for linking host computers to the cache memory. The front-end directors service storage access requests from the host computers, and the disk directors stage requested data from the disk storage array to the cache memory and write new data to the disk storage. At least one of the front-end directors or disk directors is programmed for block resolution of virtual logical units of the disk storage, and for obtaining, from a storage allocation server, space allocation and mapping information for pre-allocated blocks of the disk storage, and for returning to the storage allocation server requests to commit the pre-allocated blocks of storage once data is first written to the pre-allocated blocks of storage.

Owner:EMC IP HLDG CO LLC

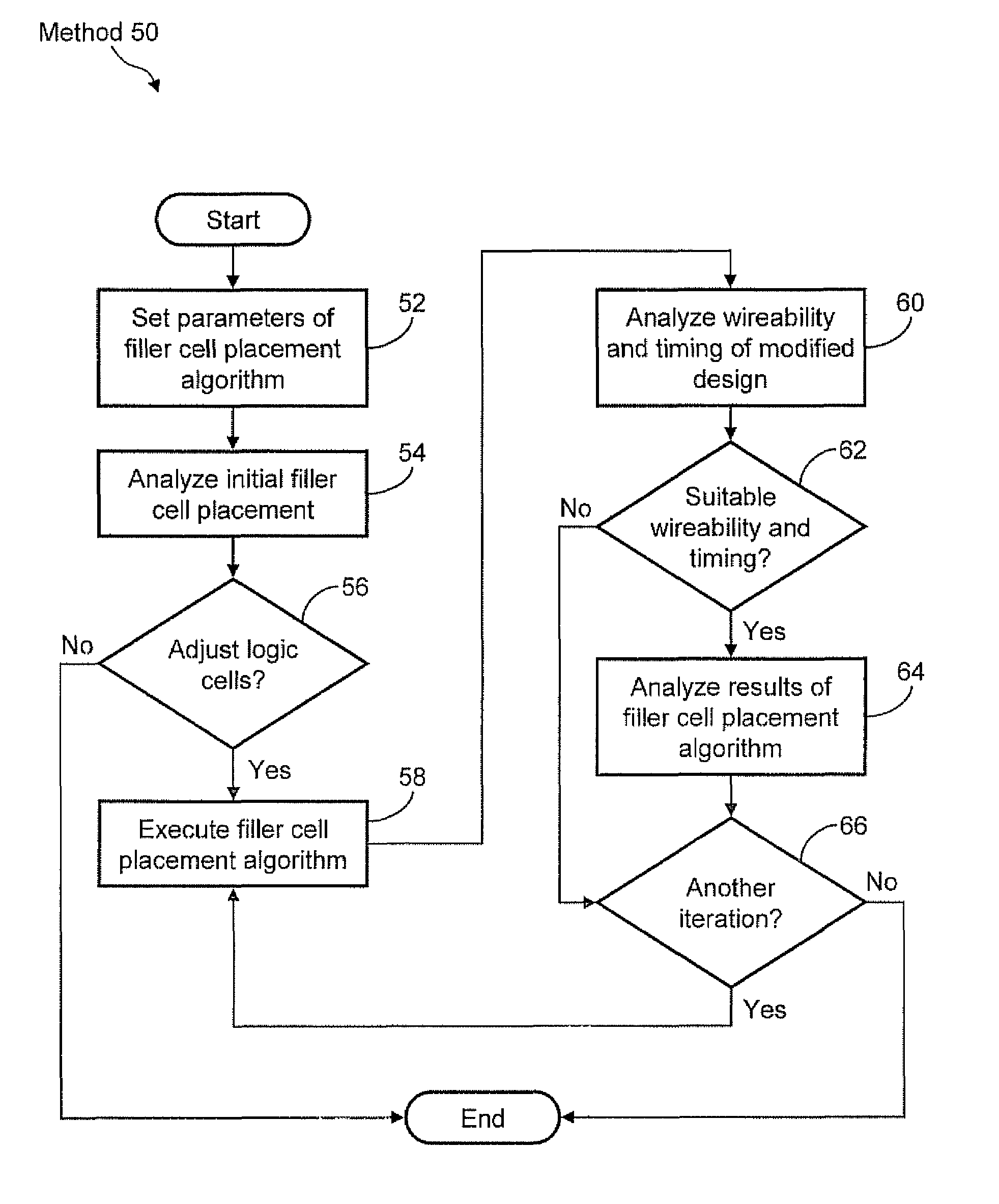

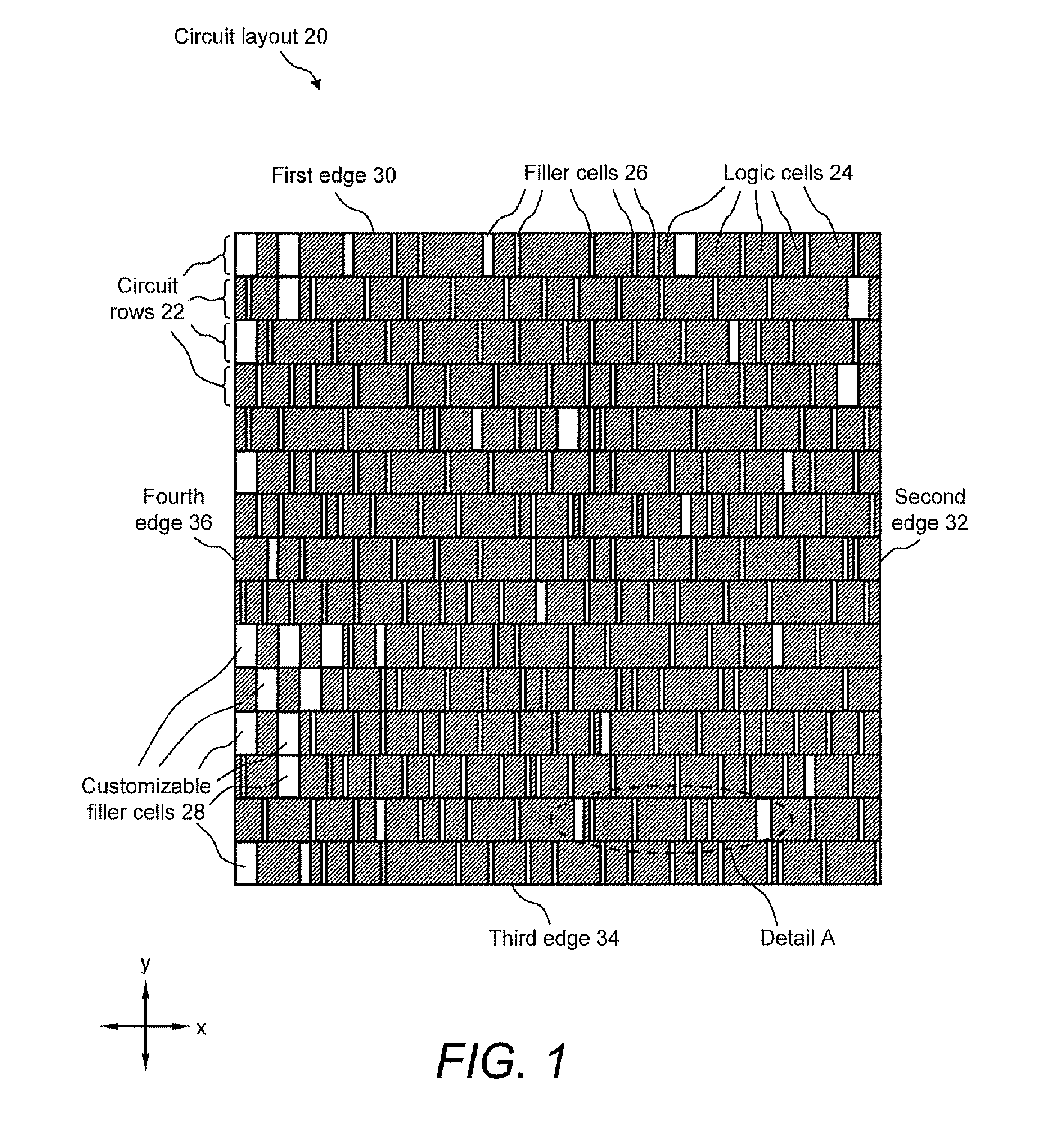

Method of optimizing customizable filler cells in an integrated circuit physical design process

ActiveUS7444609B2Computer aided designSoftware simulation/interpretation/emulationLogic cellEngineering

A system and method for optimizing customizable filler cells in an integrated circuit physical design process. In particular, a filler cell placement algorithm of the present disclosure is utilized in the method to optimize the customizable filler cells in a circuit layout. The filler cell placement algorithm performs the operation of selecting a starting point within a given circuit layout, selecting a direction in which the position of logic cells is adjusted, adjusting the position of logic cells and, thereby, combining filler cells in order to increase the accumulated area thereof; suspending the adjustment operation when a customizable filler cell is formed; and resuming the adjustment operation from the point of the newly formed customizable filler cell. Additionally, a method of optimizing the locations, number, and distribution of the customizable filler cells in an integrated circuit design by use of the filler cell placement algorithm is provided.

Owner:GLOBALFOUNDRIES U S INC

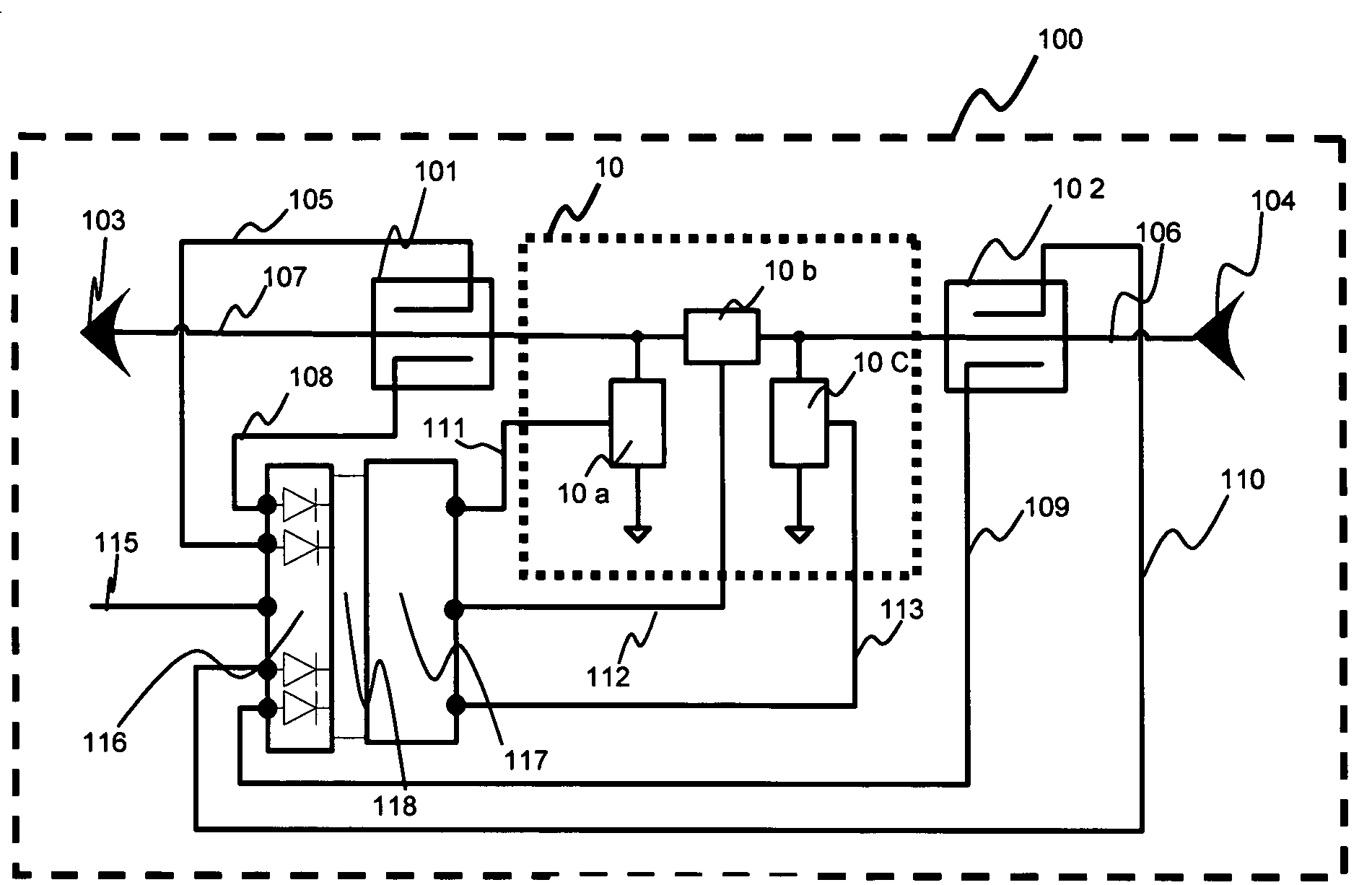

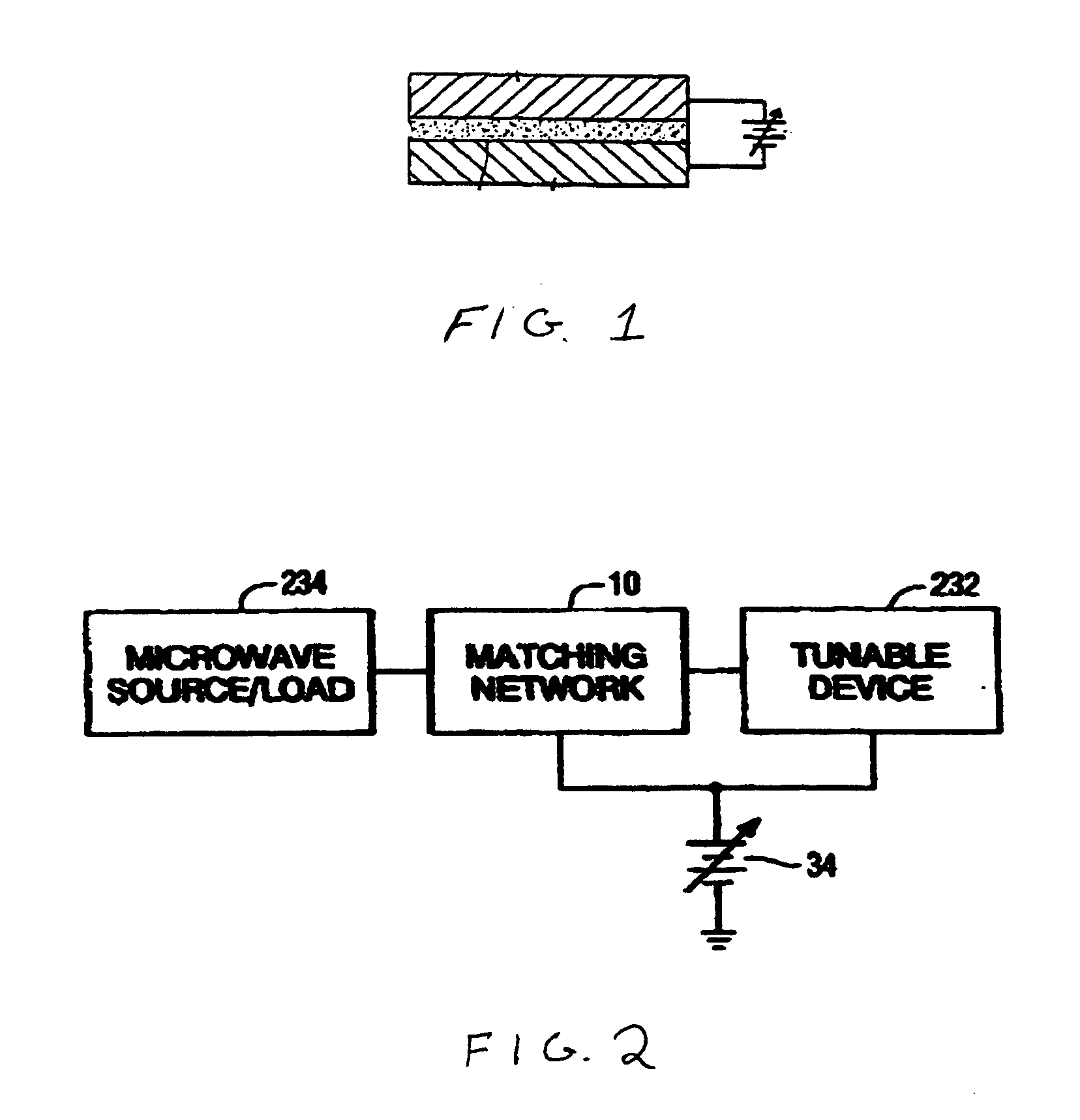

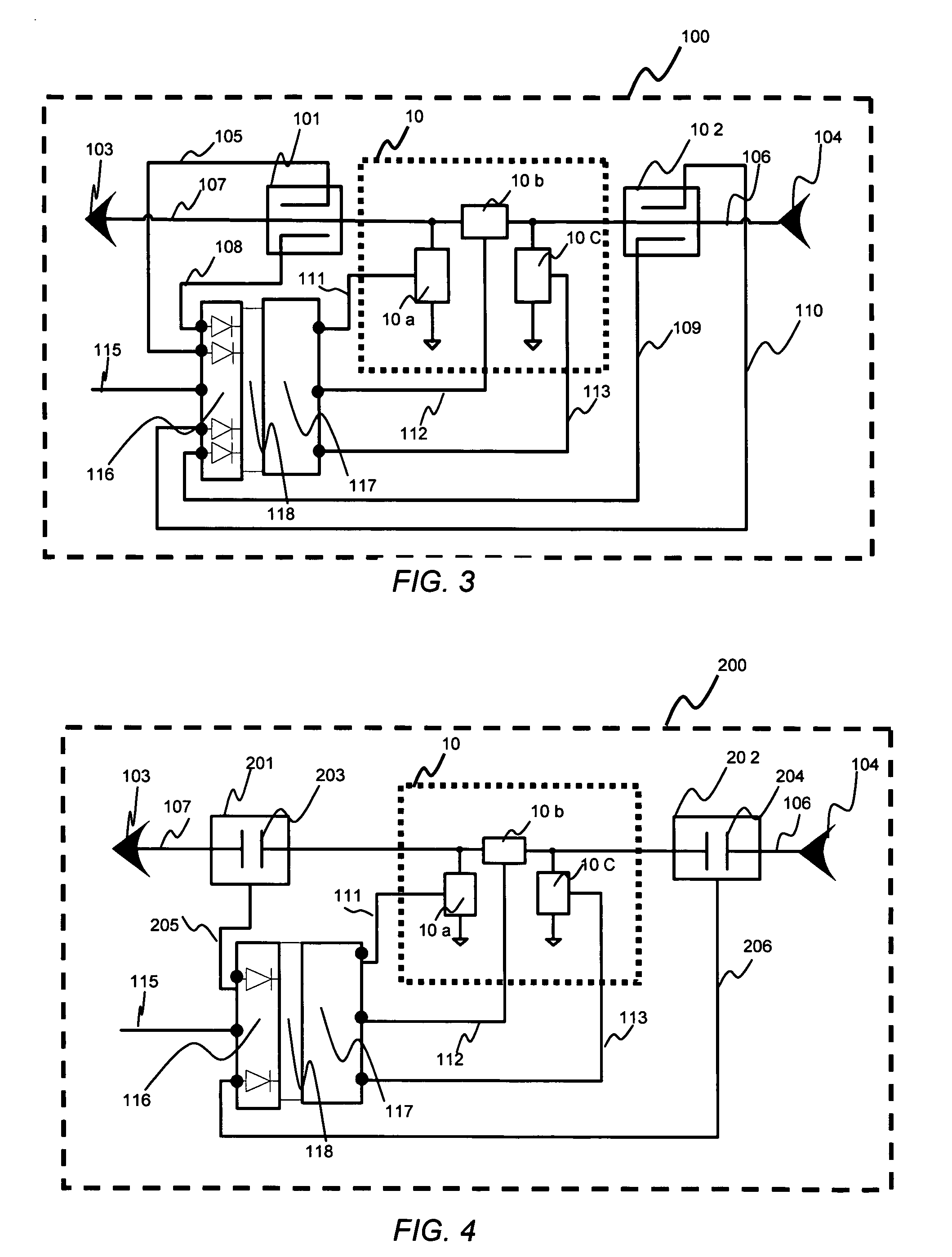

Tunable microwave devices with auto-adjusting matching circuit

ActiveUS20060160501A1Realize automatic adjustmentMultiple-port networksResonant long antennasEngineeringHigh pressure

An embodiment of the present invention provides an apparatus, comprising an input port and a dynamic impedance matching network capable of determining a mismatch at the input port and dynamically changing the RF match by using at least one matching element that includes at least one voltage tunable dielectric capacitor. The matching network may be a “Pi”, a “T”, or “ladder” type network and the apparatus may further comprise at least one directional coupler capable of signal collection by sampling a portion of an incident signal, a reflected signal or both. In an embodiment of the present invention, the apparatus may also include a control and power control & logic unit (PC LU) to convert input analog signals into digital signals and sensing VSWR phase and magnitude and processing the digital signals using an algorithm to give it a voltage value and wherein the voltage values may be compared to values coming from the coupler and once compared and matched, the values may be passed to a Hi Voltage Application Specific Integrated Circuit (HV ASIC) to transfer and distribute compensatory voltages to the matching network elements.

Owner:NXP USA INC

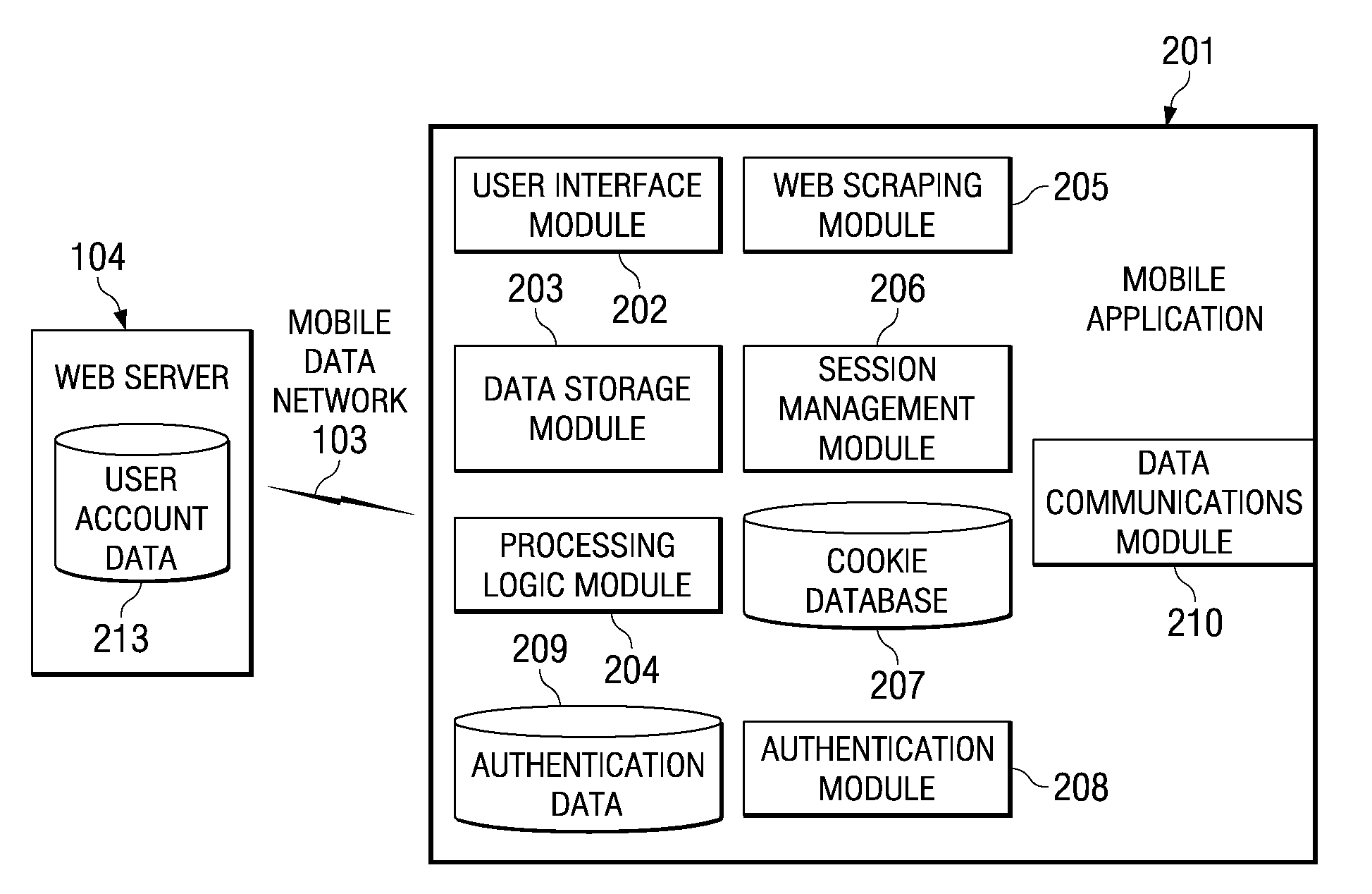

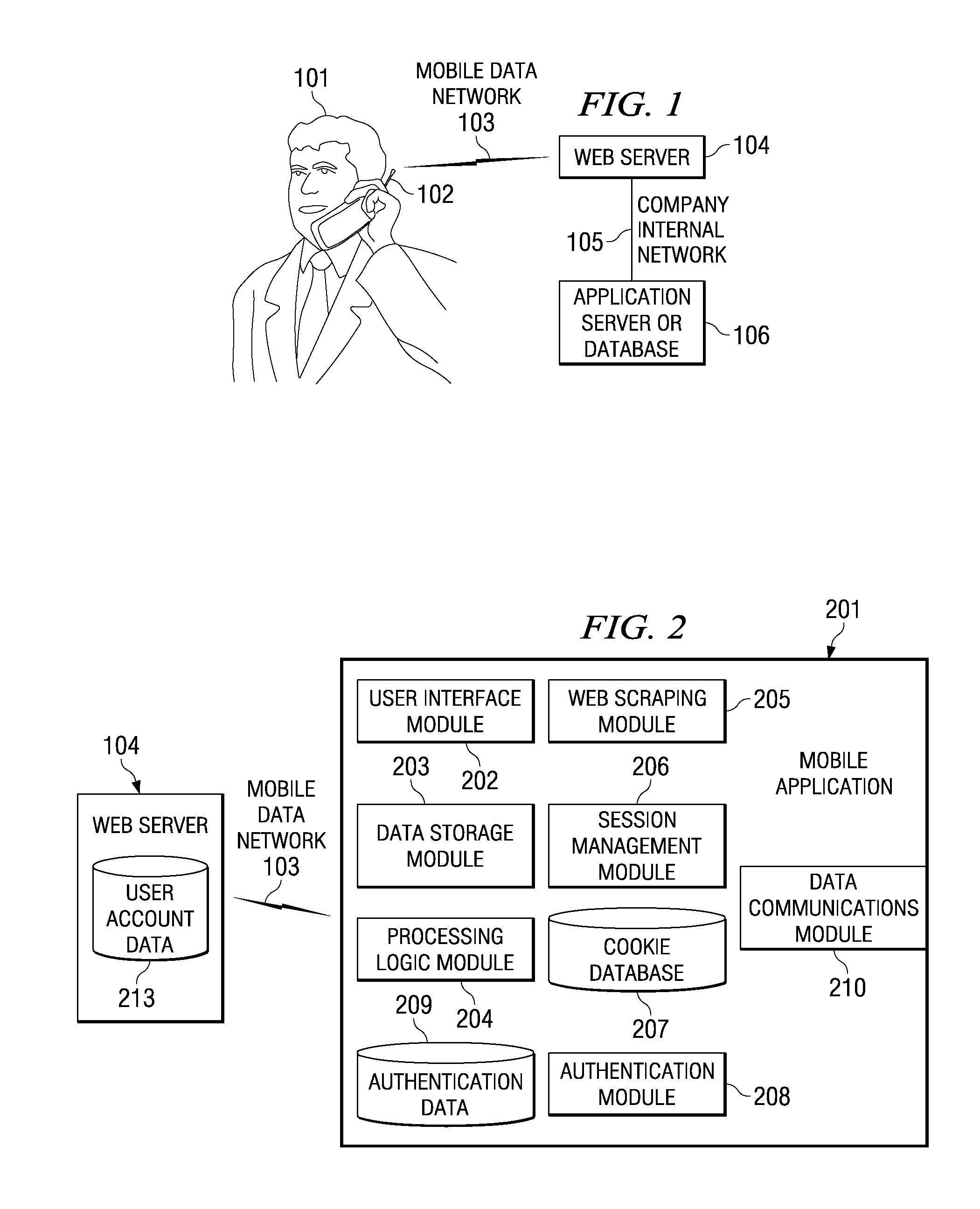

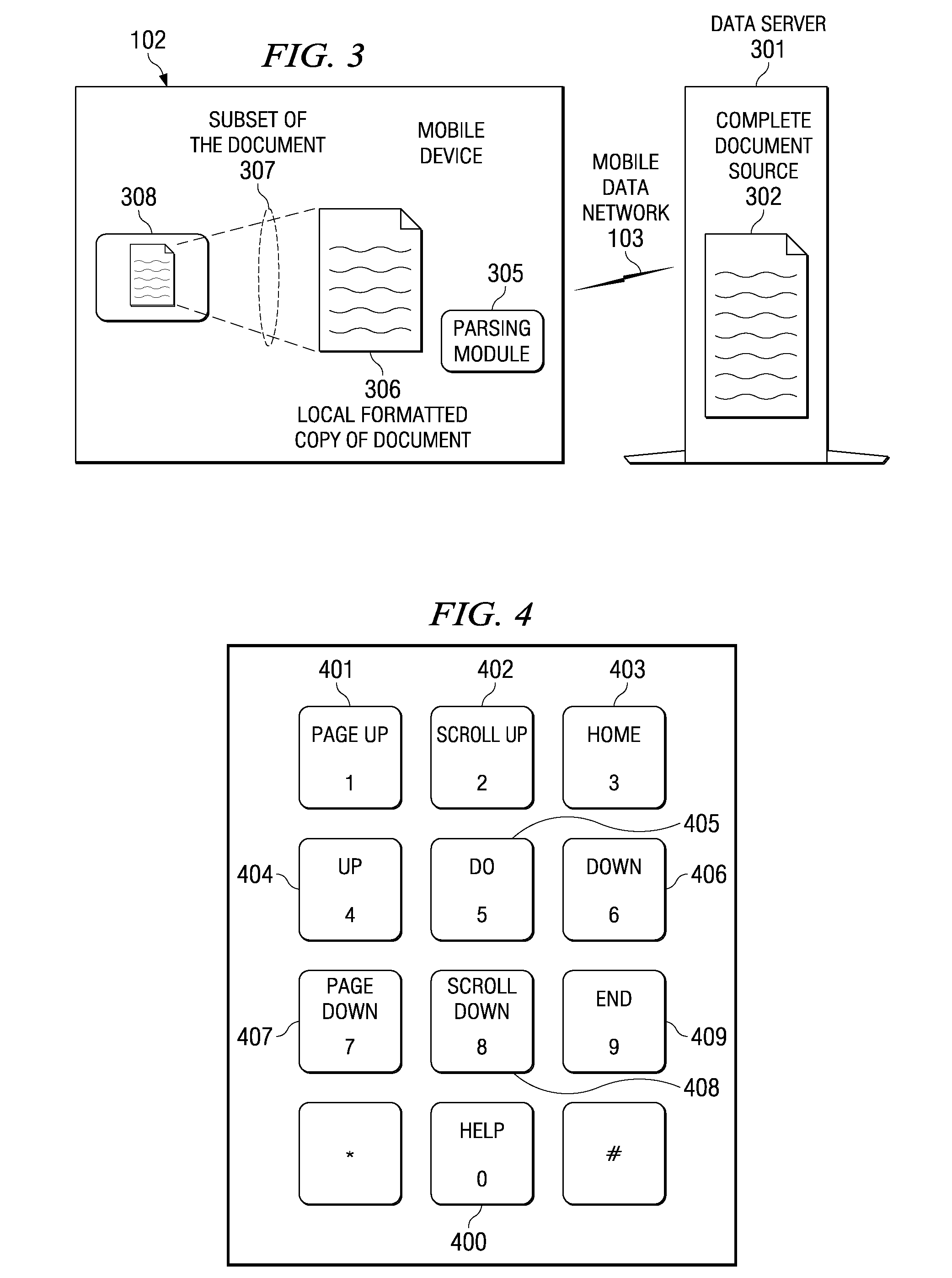

System and method for presenting and inputting information on a mobile device

InactiveUS20070250711A1Perceived latencyProviding user controlUser identity/authority verificationInformation formatSession managementWeb service

Disclosed are combinations of authentication, session management and web scraping implemented on a mobile device to support a rich mobile application using secure connections to existing websites to access data sources. The mobile application presents information in logical units rather than screen by screen, and fetches data in the background for low perceived delay. The mobile application provides consistent navigation using the 12-key or QWERTY keypad. The mobile application maintains a history of screens, allowing the user to easily return to a prior screen. A web server allows phrases to be configured on-line by an individual user and downloaded to that user's mobile device to simplify data entry on the mobile device. A method of embedding user profile information in a signed application executable file that allows applications to be pre-configured per user. A licensing mechanism that supports multiple distribution channels.

Owner:PHONIFIED

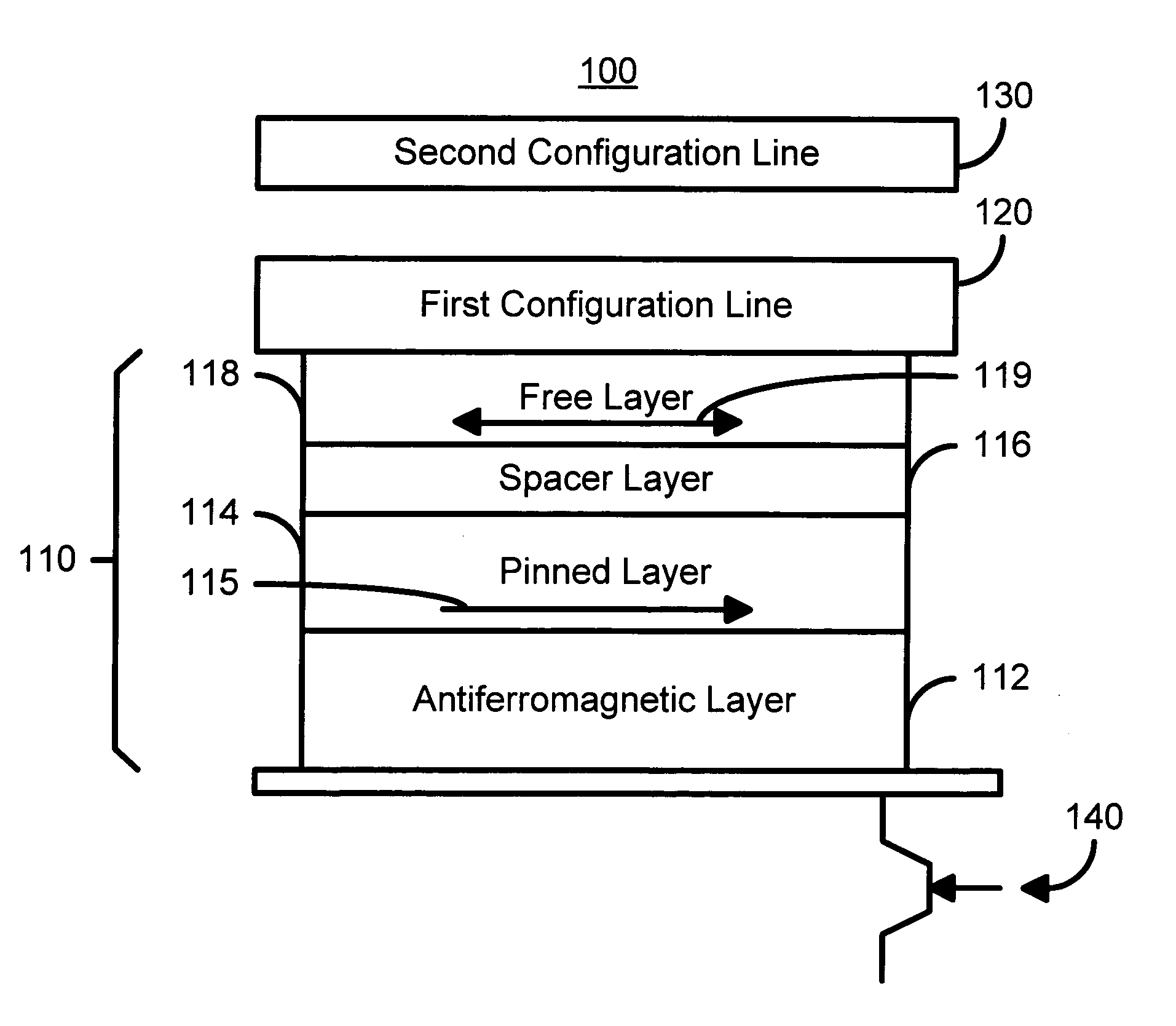

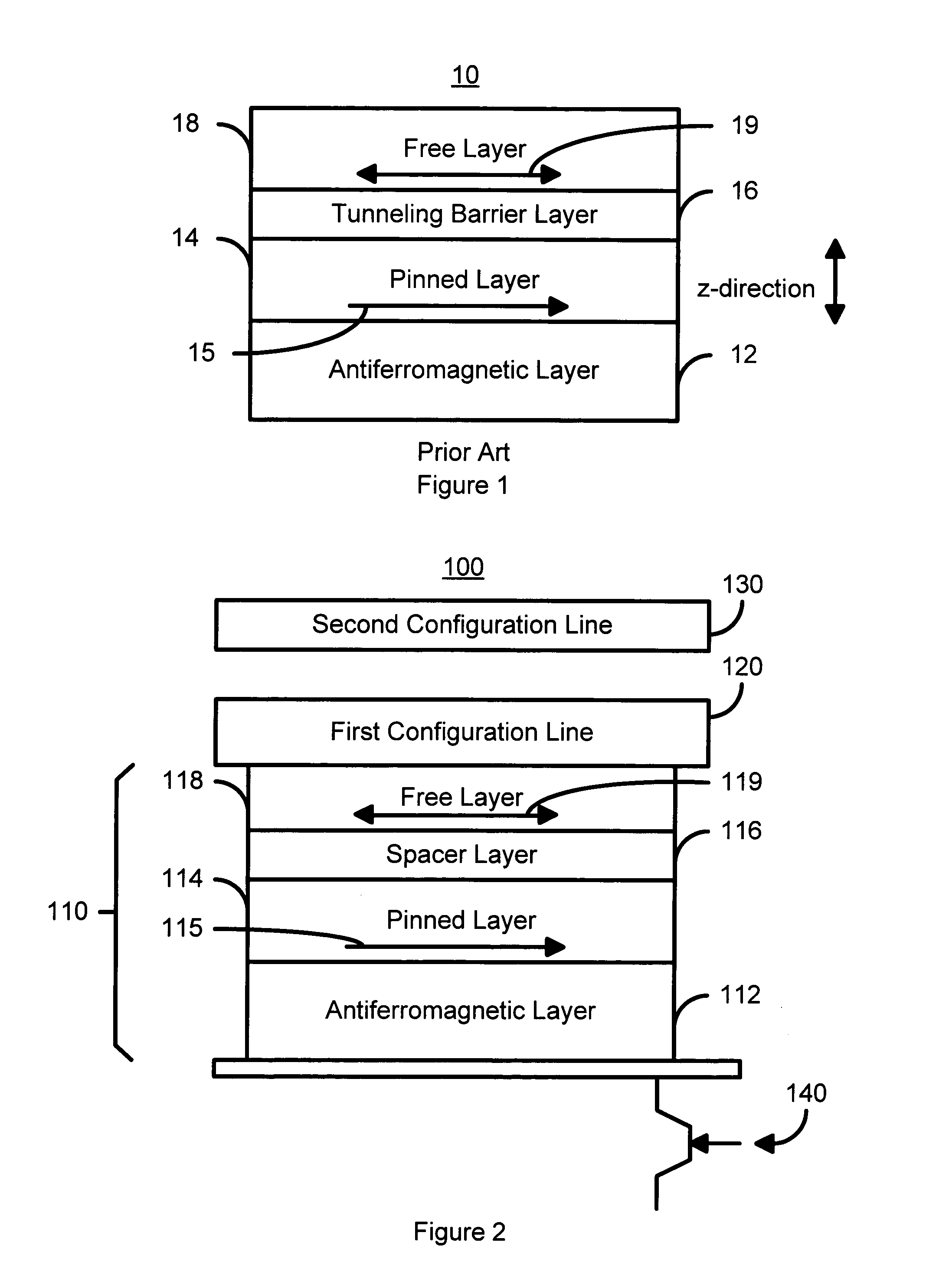

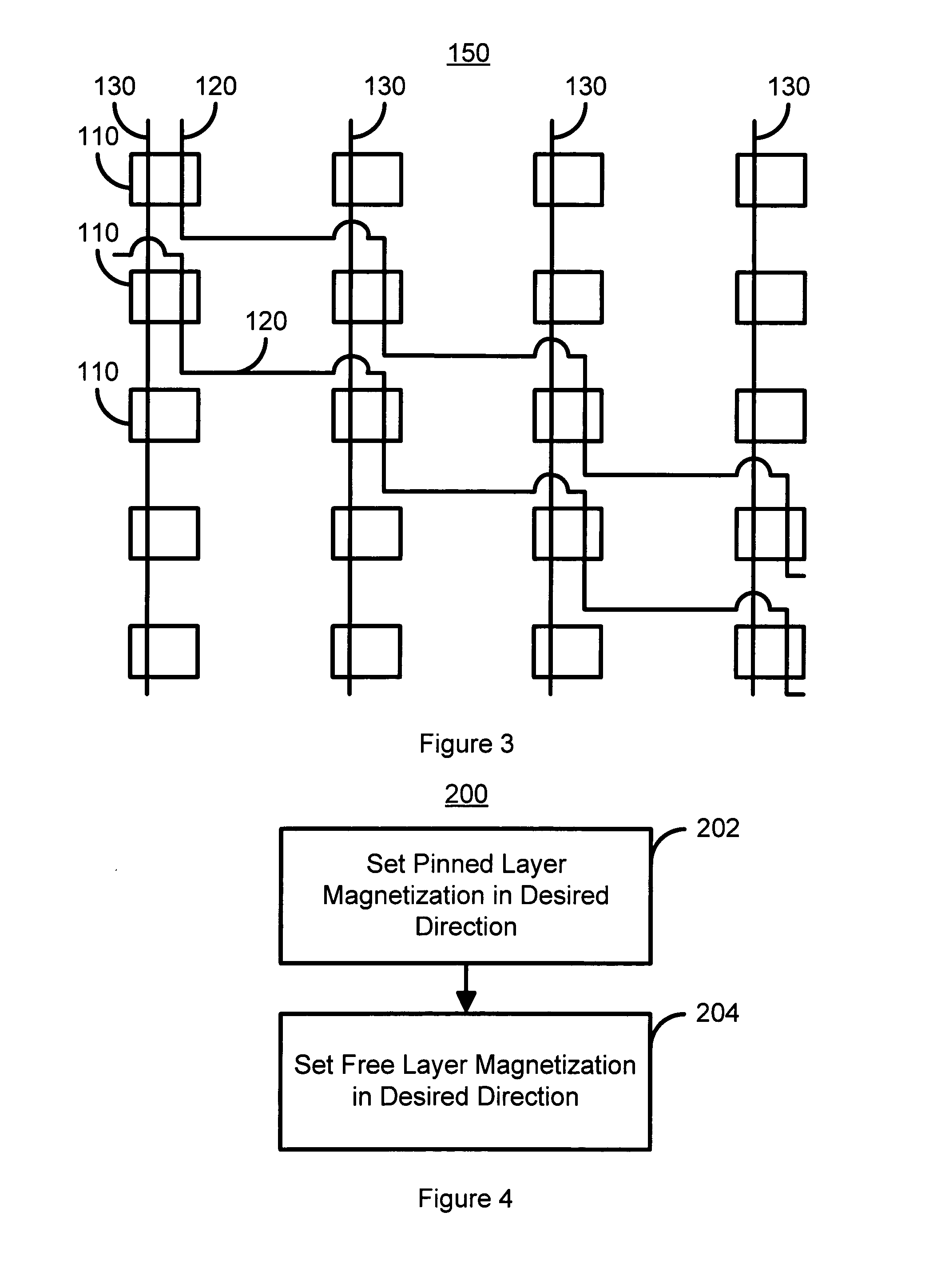

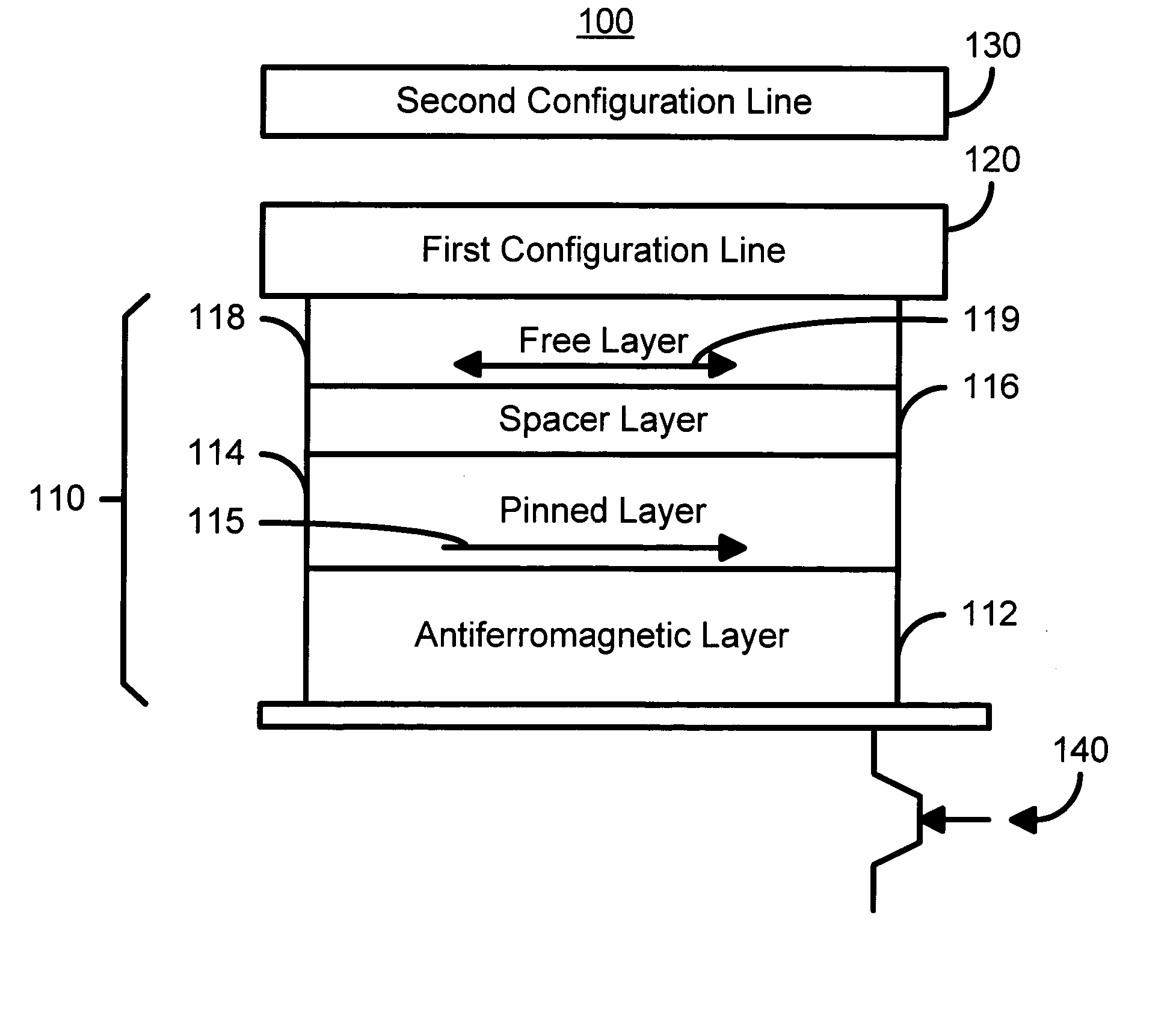

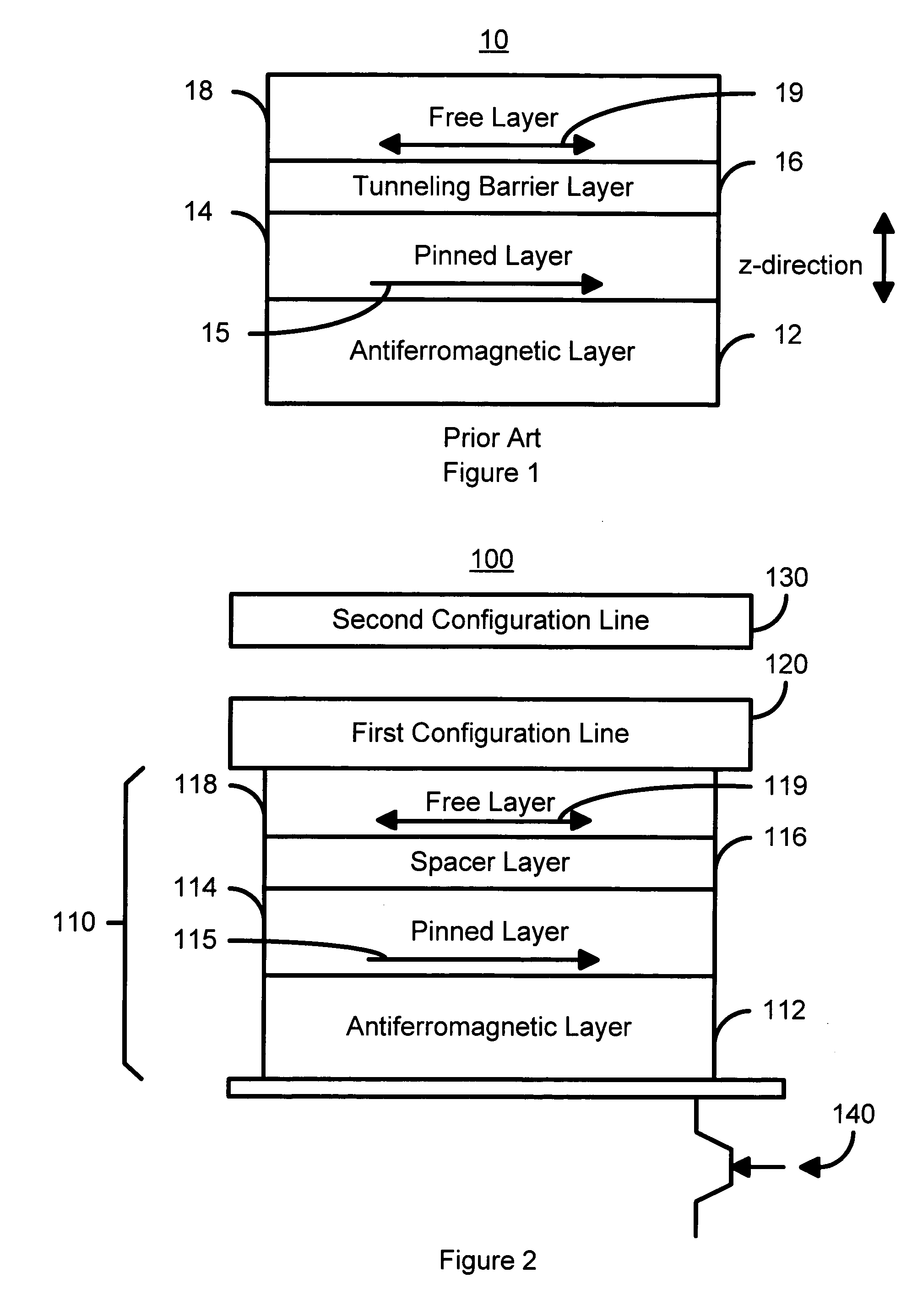

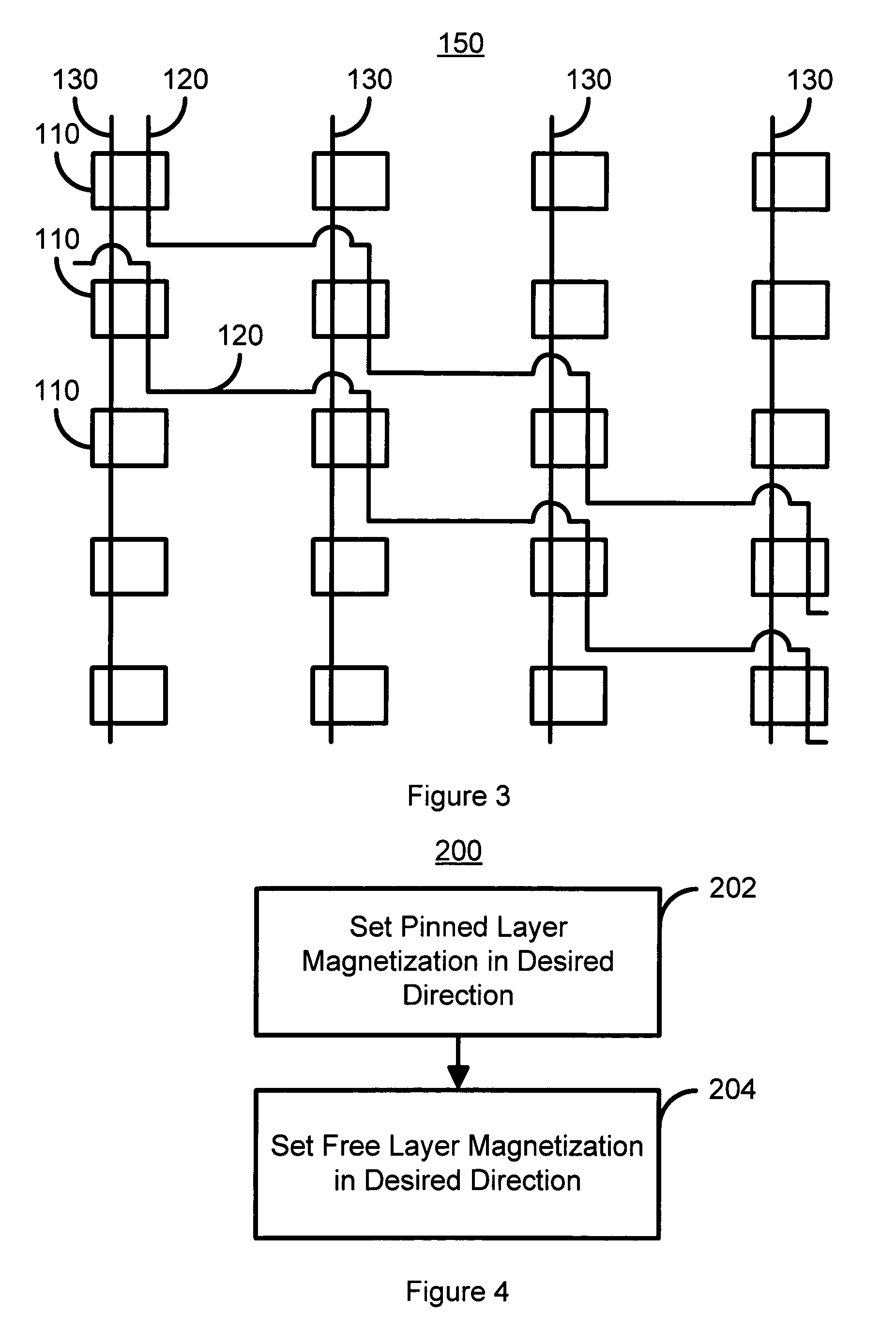

Re-configurable logic elements using heat assisted magnetic tunneling elements

A magnetic logic cell includes a magnetic element having a pinned layer, a free layer, and a spacer layer. The pinned and free layers have pinned and free layer magnetizations. The spacer layer resides between the pinned and free layers. In one aspect, the magnetic logic cell includes a first configuration line that is electrically connected to the magnetic element and carries a first current and a second configuration line electrically that is insulated from the magnetic element and the first configuration line and carries a second current. The first or second current alone cannot switch the free layer magnetization. The first and second currents together can switch the free layer magnetization. When the first current is driven through the magnetic element and the second current is provided, the combination sets the pinned layer magnetization direction. In one aspect, the pinned layer magnetization is set by heating the AFM layer to approximately at or above the blocking temperature. In order to configure the logic cell, an initial direction for the free layer magnetization is also set.

Owner:SAMSUNG SEMICON

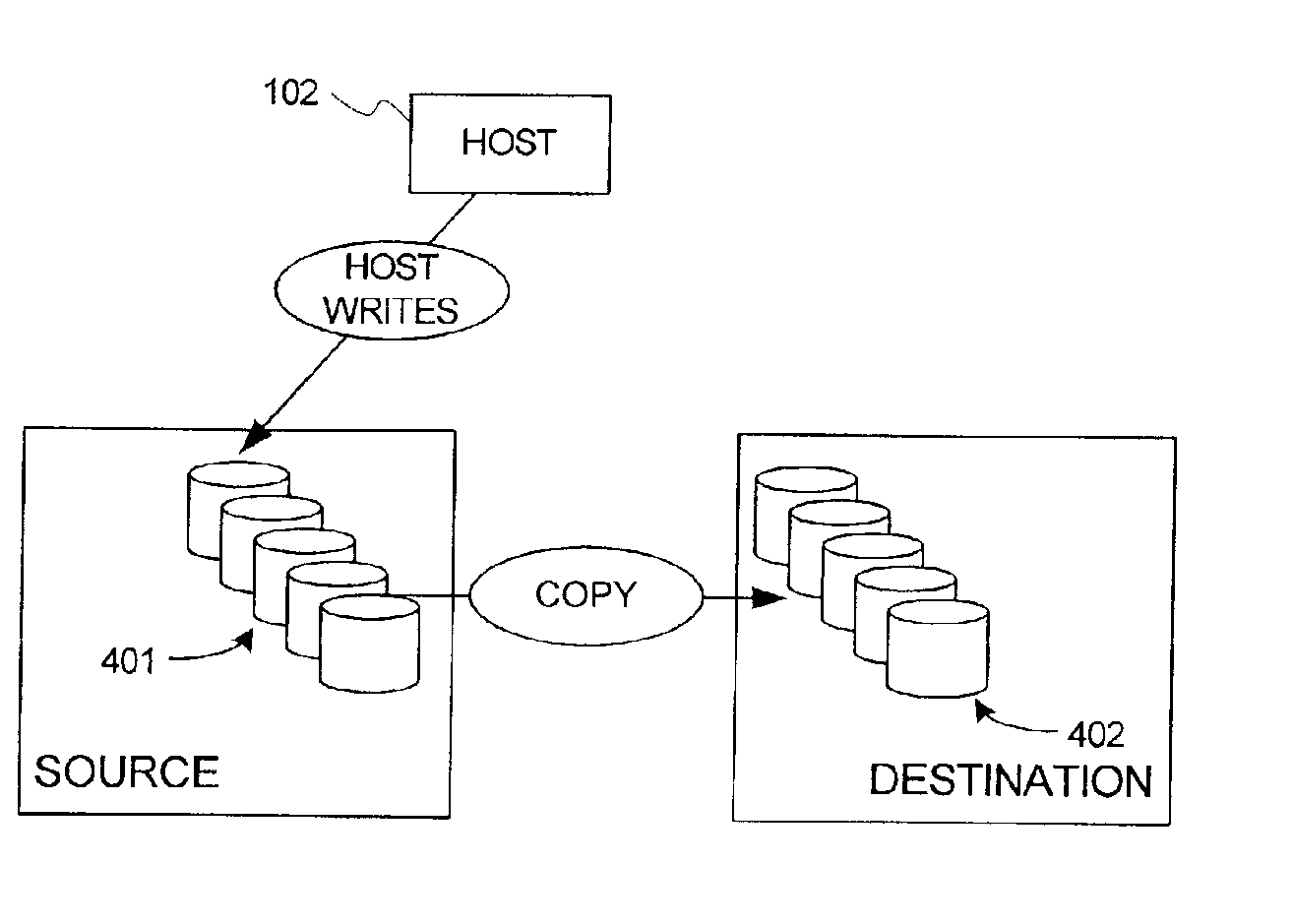

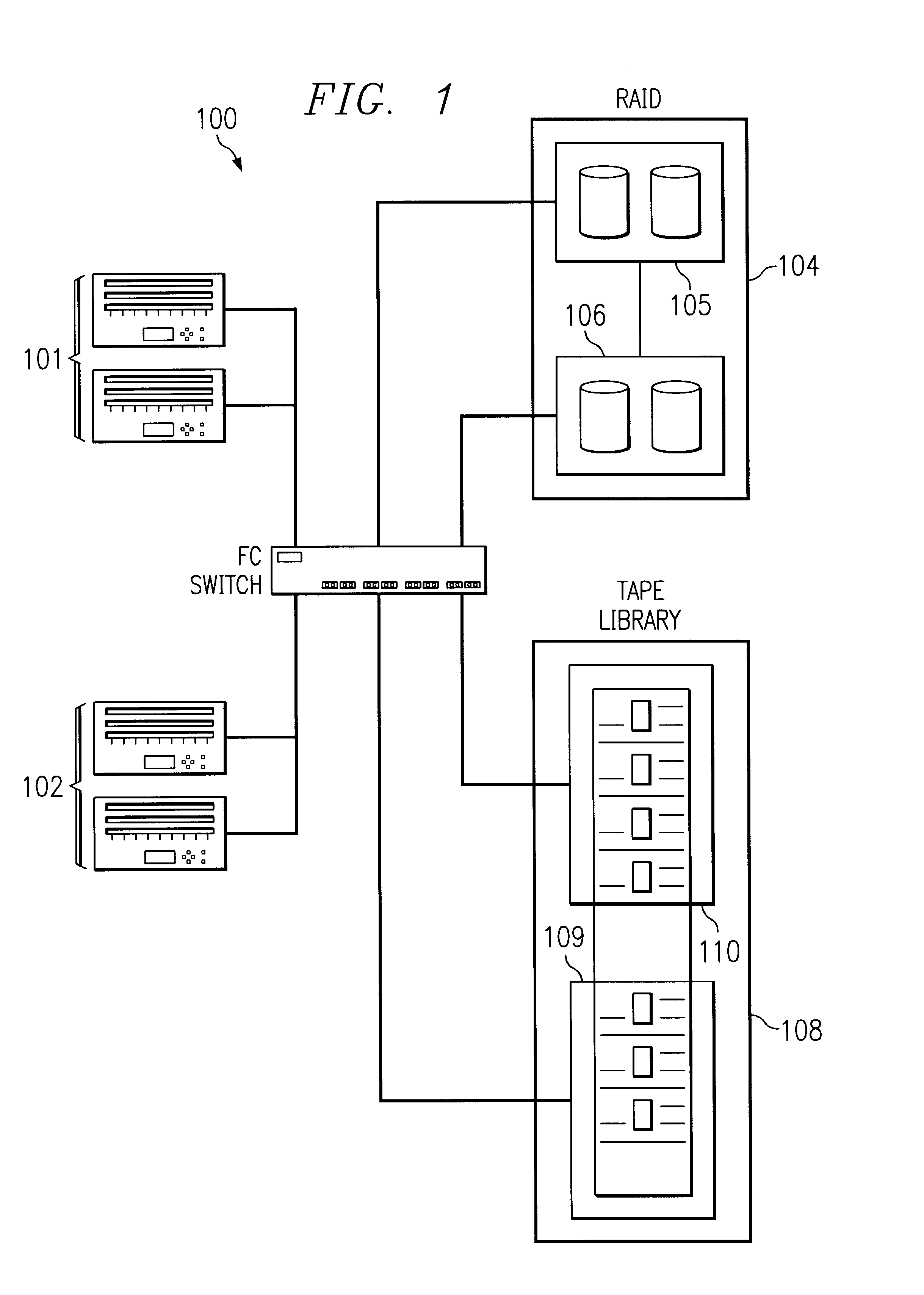

Method for transaction log failover merging during asynchronous operations in a data storage network

InactiveUS7111189B1Easily exposedPromote recoveryError detection/correctionLogic cellAsynchronous operation

A disaster-tolerant data backup and remote copy system which is implemented as a controller-based replication of one or more LUNs (logical units) between two remotely separated pairs of array controllers connected by redundant links. In the situation wherein an array controller fails during an asynchronous copy operation, the partner array controller uses a ‘micro log’ stored in mirrored cache memory to recover transactions, in order, which were ‘missed’ by the backup storage array when the array controller failure occurred.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

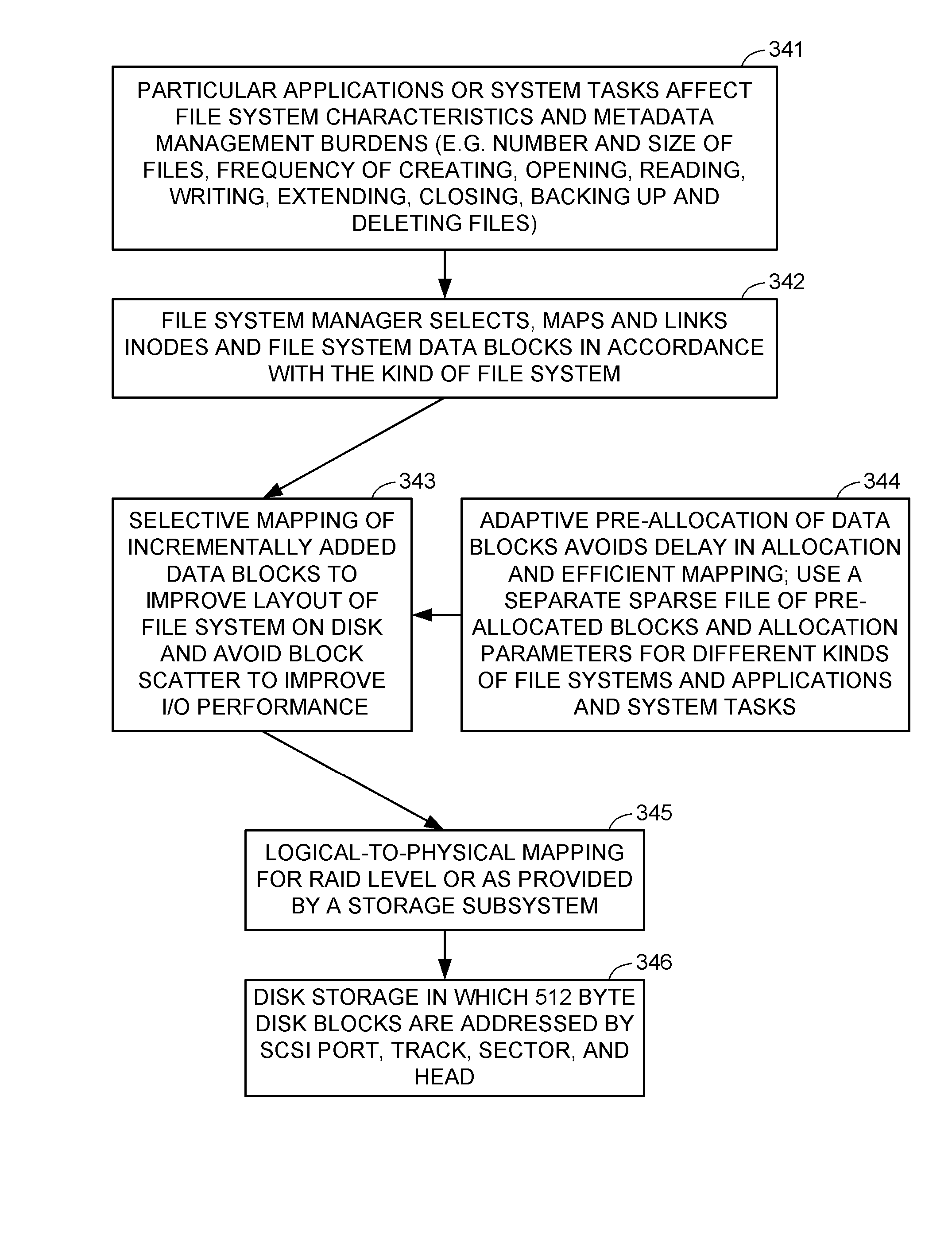

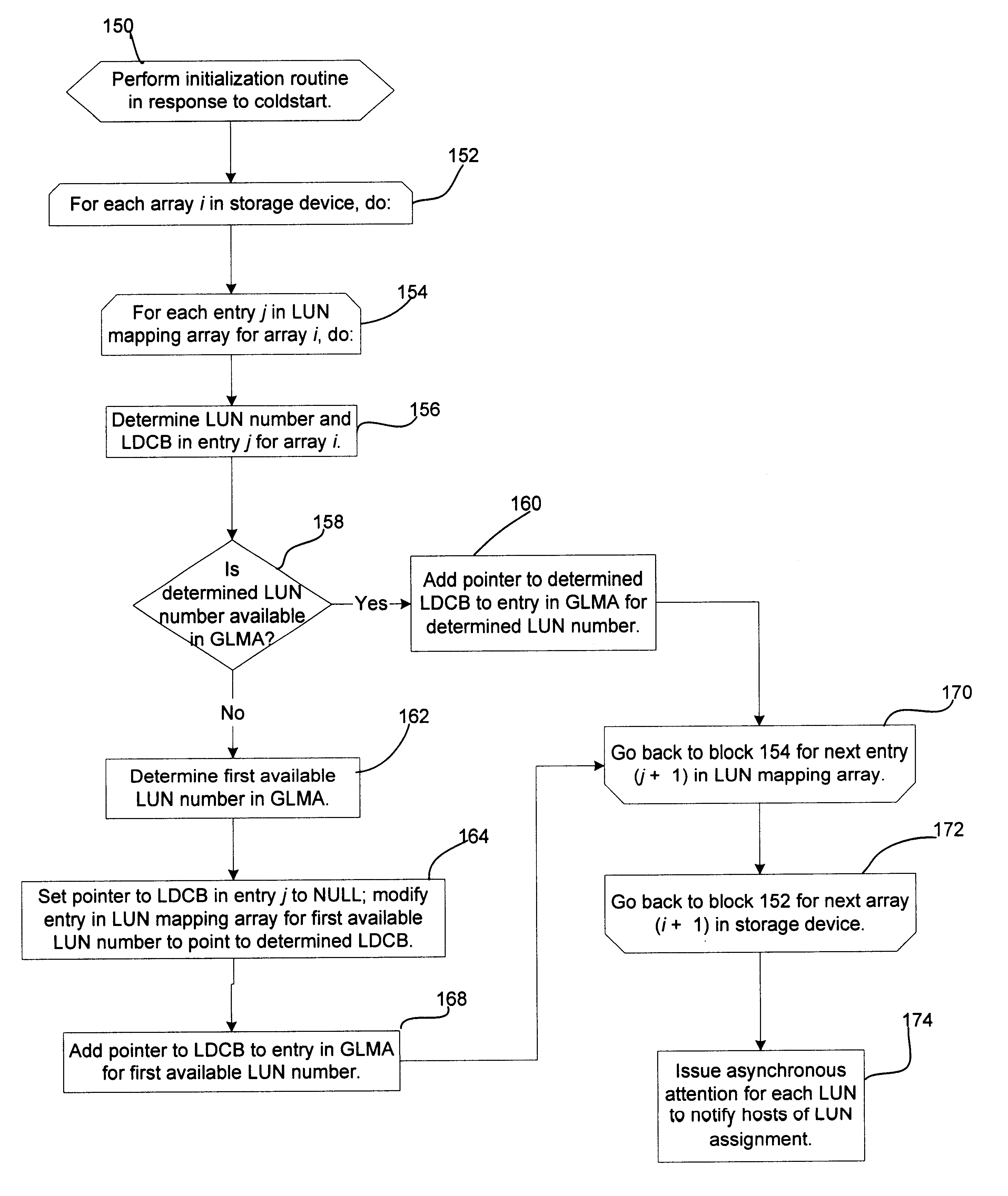

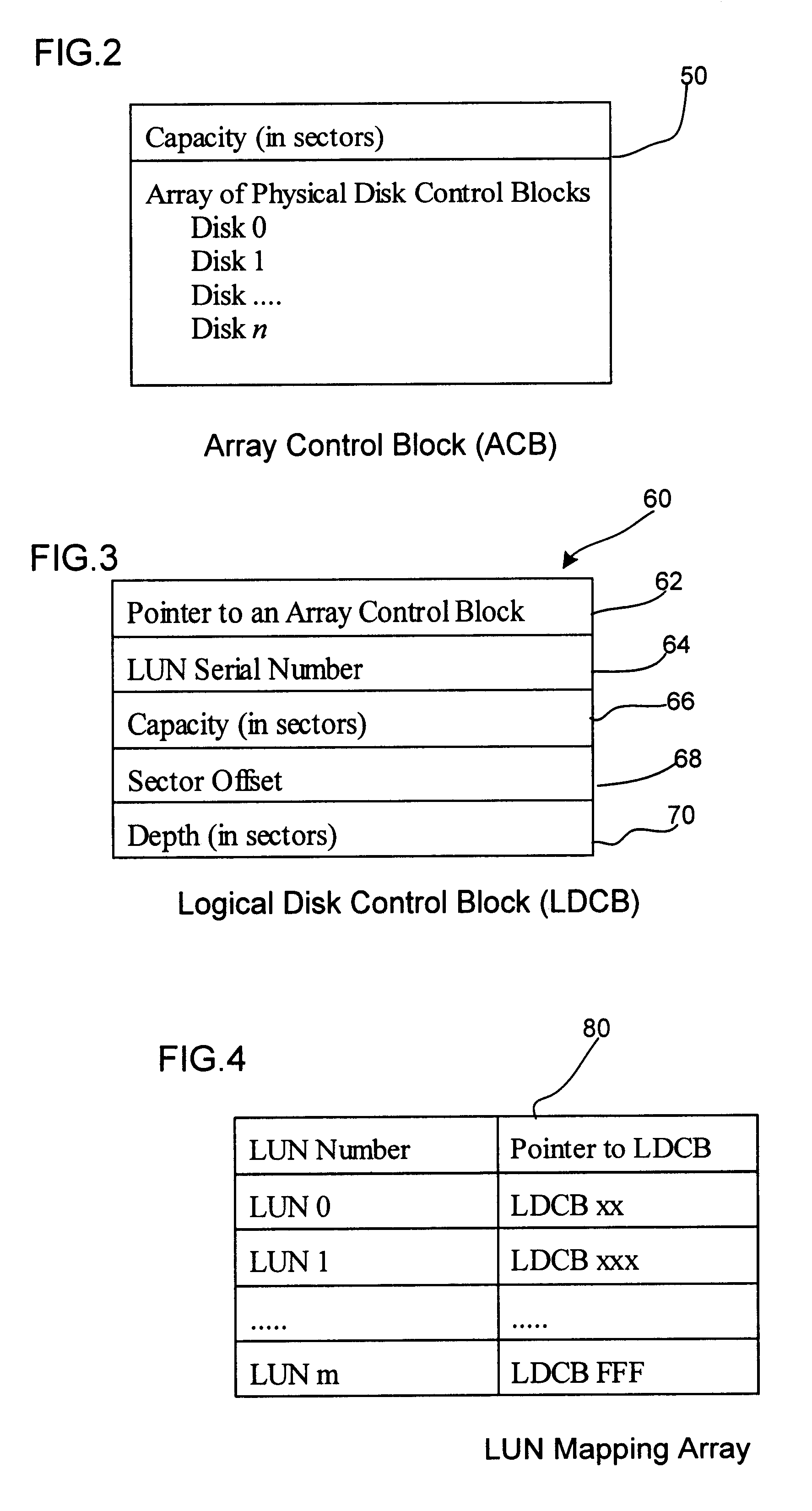

Method, system, program, and data structures for mapping logical units to a storage space comprises of at least one array of storage units

InactiveUS6618798B1Input/output to record carriersMemory systemsHard disc driveComputer architecture

Disclosed is a method, system, program, and data structures for mapping logical units, such as logical unit numbers (LUNs), to a storage space comprised of at least one array of storage units, e.g., hard disk drives. Configuration information stored in one array indicating a first mapping of logical units to storage locations in the array is read. A second mapping of logical units to storage locations in multiple arrays is generated using the configuration information read from the array. Each logical unit is assigned to only one of the arrays.

Owner:IBM CORP

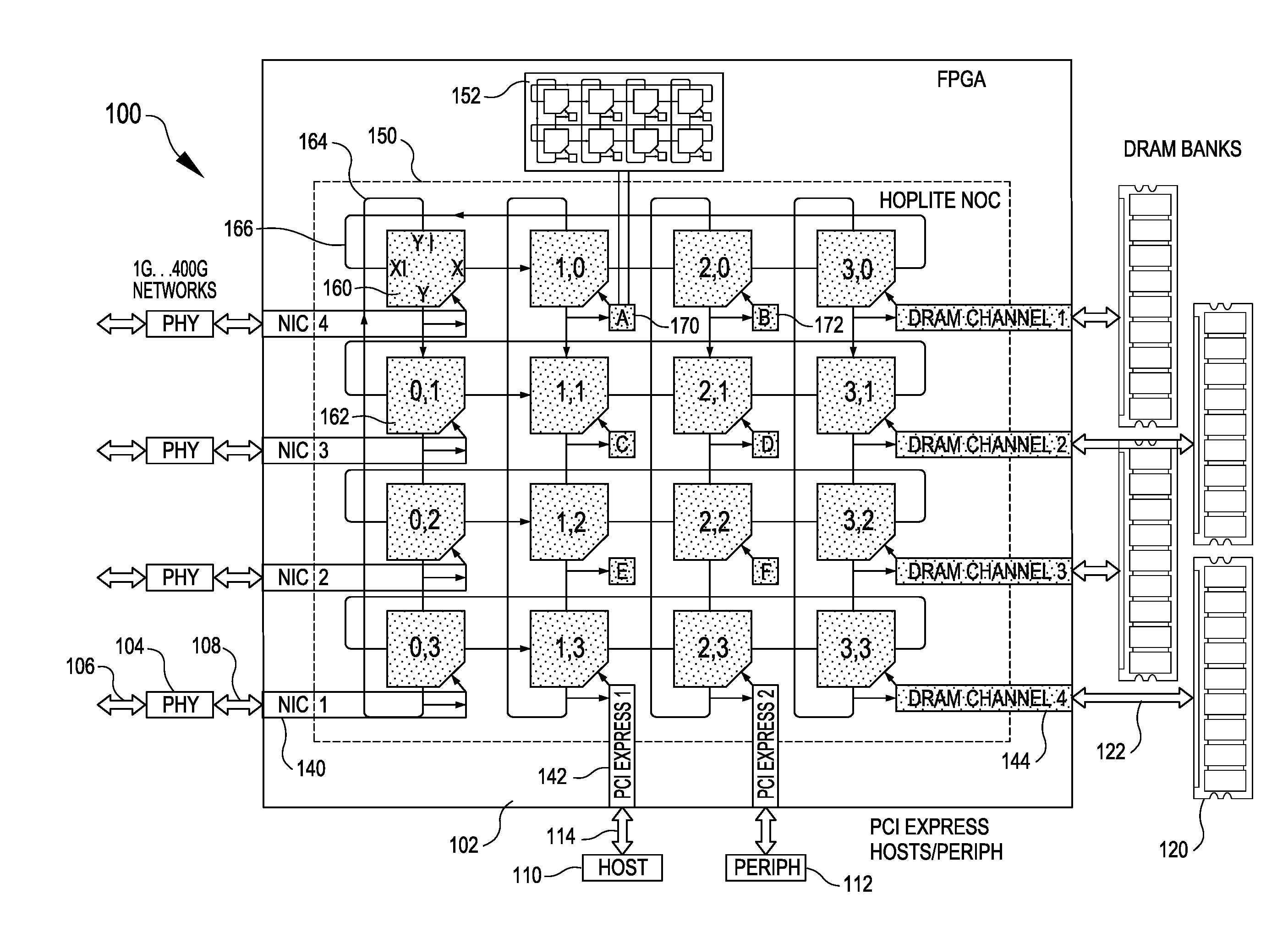

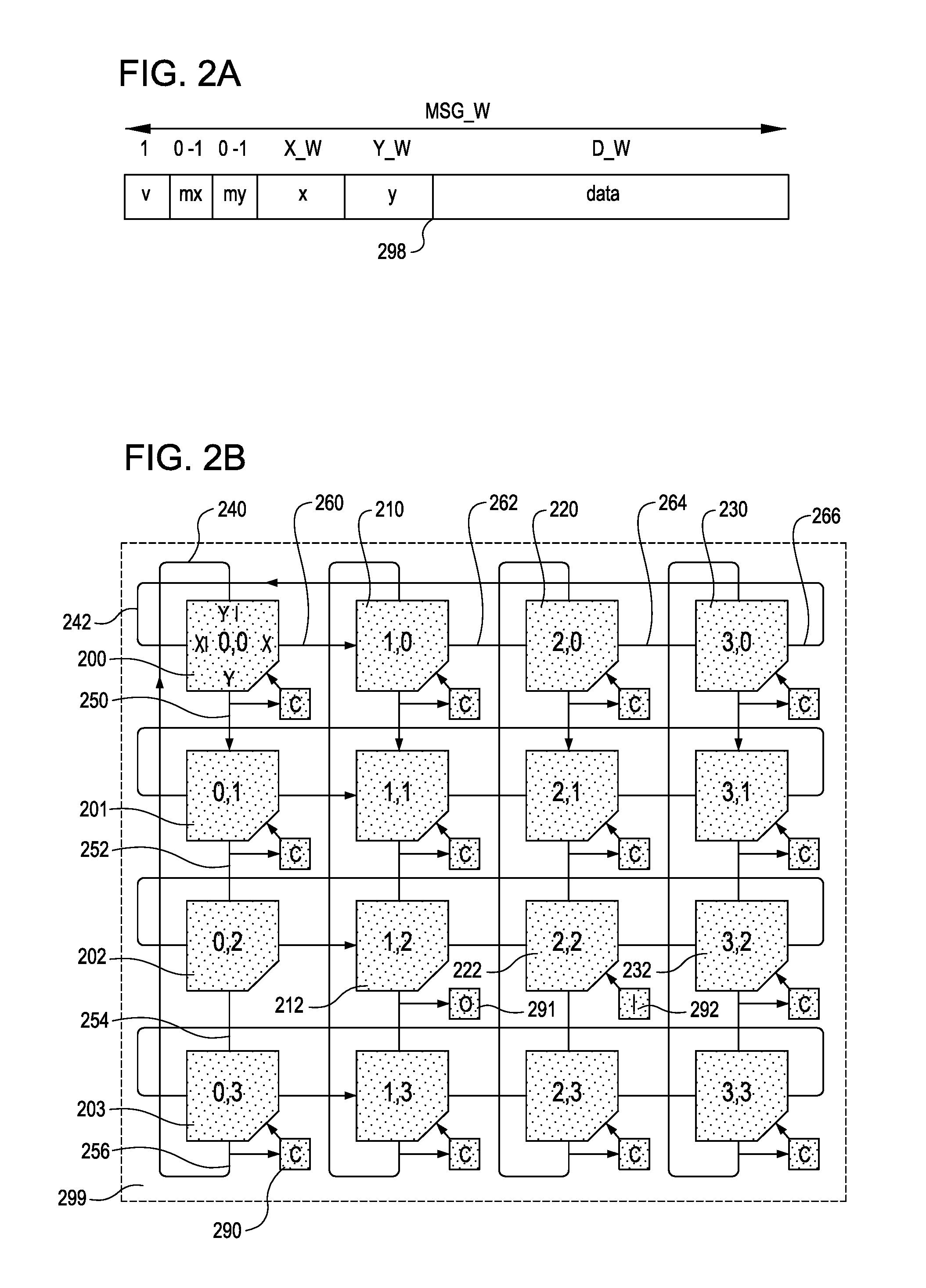

Directional two-dimensional router and interconnection network for field programmable gate arrays, and other circuits and applications of the router and network

ActiveUS20160344629A1Reduce switching delayLower latencyData switching networksNetwork sizeFpga implementations

A configurable directional 2D router for Networks on Chips (NOCs) is disclosed. The router, which may be bufferless, is designed for implementation in programmable logic in FPGAs, and achieves theoretical lower bounds on FPGA resource consumption for various applications. The router employs an FPGA router switch design that consumes only one 6-LUT or 8-input ALM logic cell per router per bit of router link width. A NOC comprising a plurality of routers may be configured as a directional 2D torus, or in diverse ways, network sizes and topologies, data widths, routing functions, performance-energy tradeoffs, and other options. System on chip designs may employ a plurality of NOCs with different configuration parameters to customize the system to the application or workload characteristics. A great diversity of NOC client cores, for communication amongst various external interfaces and devices, and on-chip interfaces and resources, may be coupled to a router in order to efficiently communicate with other NOC client cores. The router and NOC enable feasible FPGA implementation of large integrated systems on chips, interconnecting hundreds of client cores over high bandwidth links, including compute and accelerator cores, industry standard IP cores, DRAM / HBM / HMC channels, PCI Express channels, and 10G / 25G / 40G / 100G / 400G networks.

Owner:GRAY RES LLC

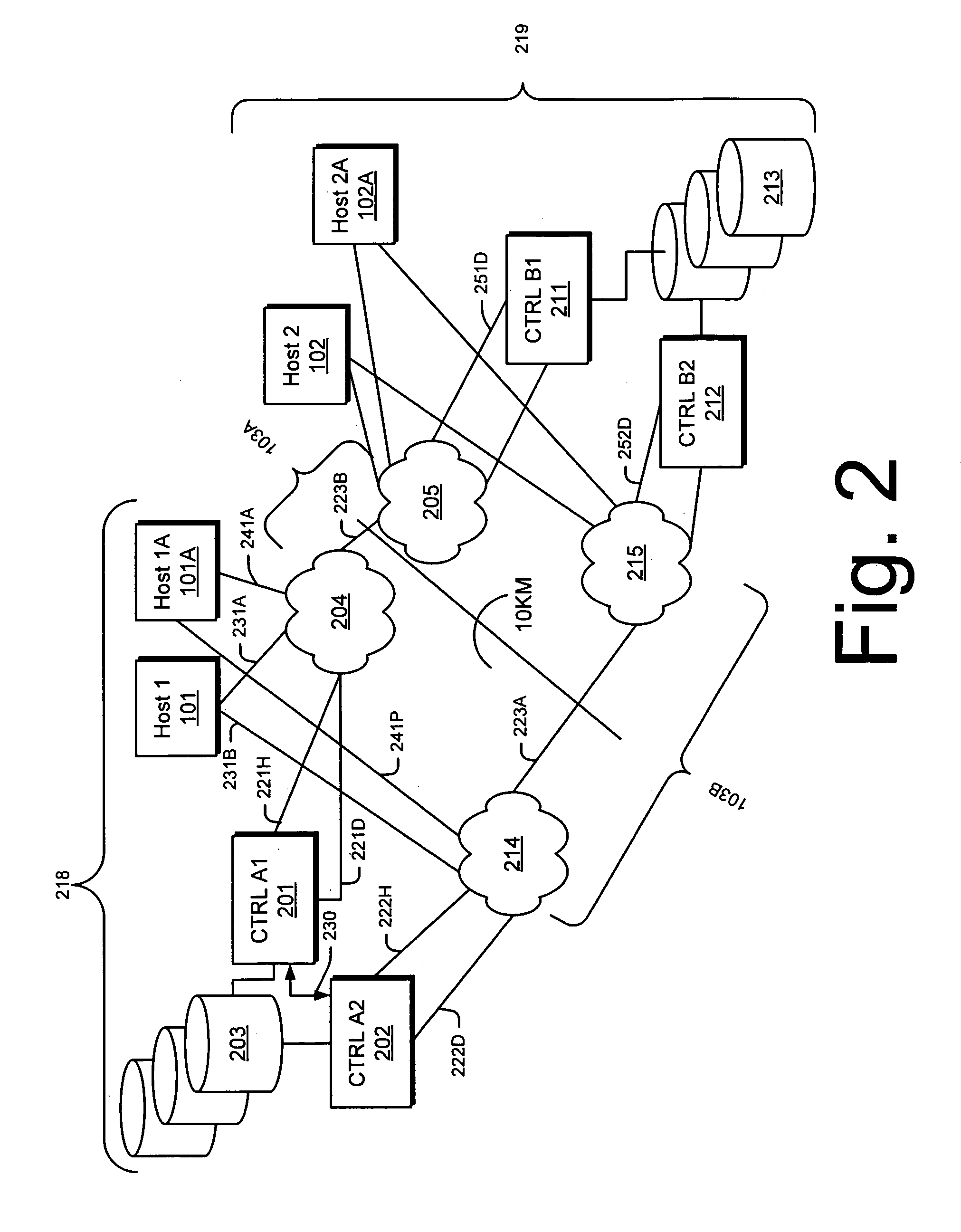

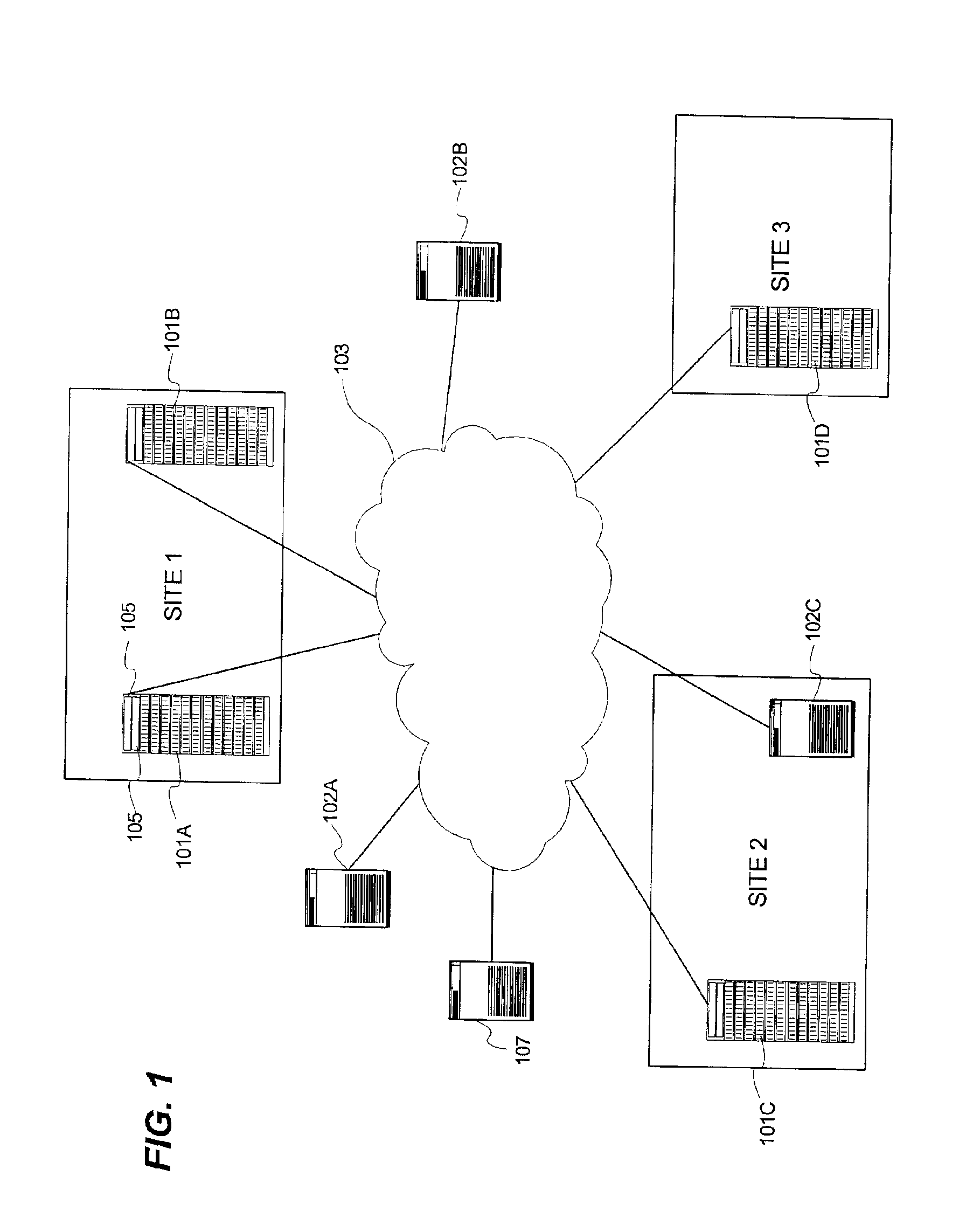

Storage area network, data replication and storage controller, and method for replicating data using virtualized volumes

A storage area network (SAN) controller and method for storing and replicating data between sites in a storage area network in which storage controllers at each site implement storage virtualization. A storage cell is implemented at each site comprising at least one storage controller and a pool of physical storage coupled to the controller. A copy set comprising a logical unit (LUN) of storage, referred to as a member, in each of the storage cells is defined. As operational data transactions are performed against one of the members of a copy set, they are replicated, immediately or after a delay, in each other member of the copy set. As changes are made to dependent attributes such as size of one member of the copy set, the change is replicated in each other member of the copy set automatically. Changes can be made in the independent attributes such as size of each member of the copy set independently of other members of the copy set.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

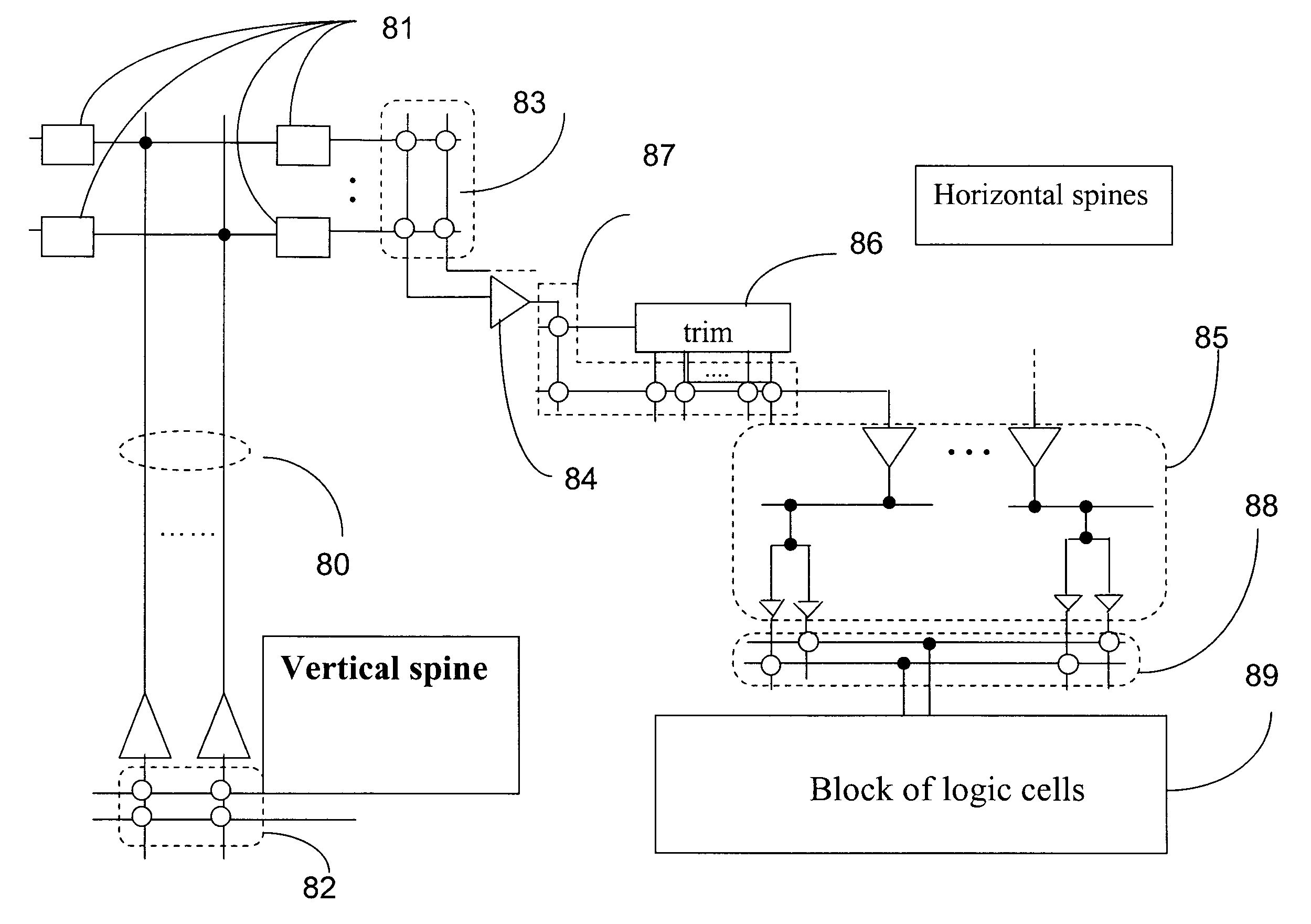

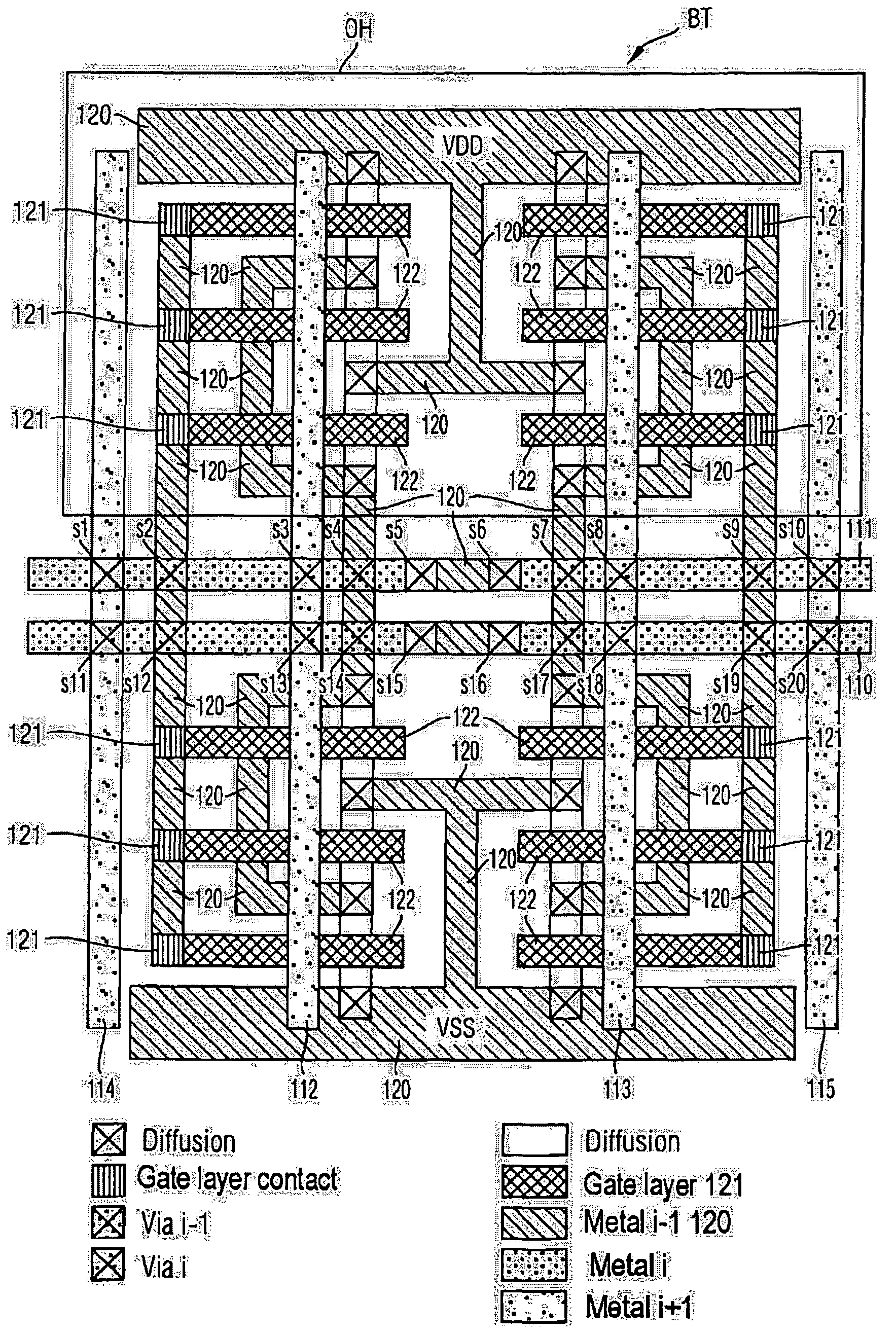

Architecture of function blocks and wirings in a structured ASIC and configurable driver cell of a logic cell zone

ActiveUS7755110B2Cost effective productionEfficient configuration and allocationSemiconductor/solid-state device detailsSolid-state devicesLogic cellEngineering

An integrated semiconductor circuit has a regular array of logic function blocks (L) and a regular array of wiring zones (X) corresponding thereto. The wiring lines in at least one wiring layer of a wiring zone (X) are realized as line segments that are continuous within the wiring zone and are interrupted at zone boundaries. Furthermore, the semiconductor circuit comprises driver cells that surround a logic cell of the logic function block in an L-shaped manner.

Owner:INFINEON TECH AG

Apparatus, system, and method for rapid wireless network association

ActiveUS20060189311A1Fast internetAssess restrictionRadio/inductive link selection arrangementsTelecommunicationsFrequency spectrum

An apparatus, system, and method are disclosed for rapid wireless network association. The apparatus includes a logic unit containing a plurality of modules configured to functionally execute the necessary steps of conducting a preliminary full band search on a predefined frequency spectrum to identify the frequency of an active communication channel, investigate the availability of the active communication channels identified during the preliminary search, and associate with a wireless network device on the available active communication channel. These modules in the described embodiments include a search module, an investigation module, and an association module. Beneficially such an apparatus, system, and method provide for more efficient searching, scanning, and association than typically found in wireless networks.

Owner:LENOVO PC INT

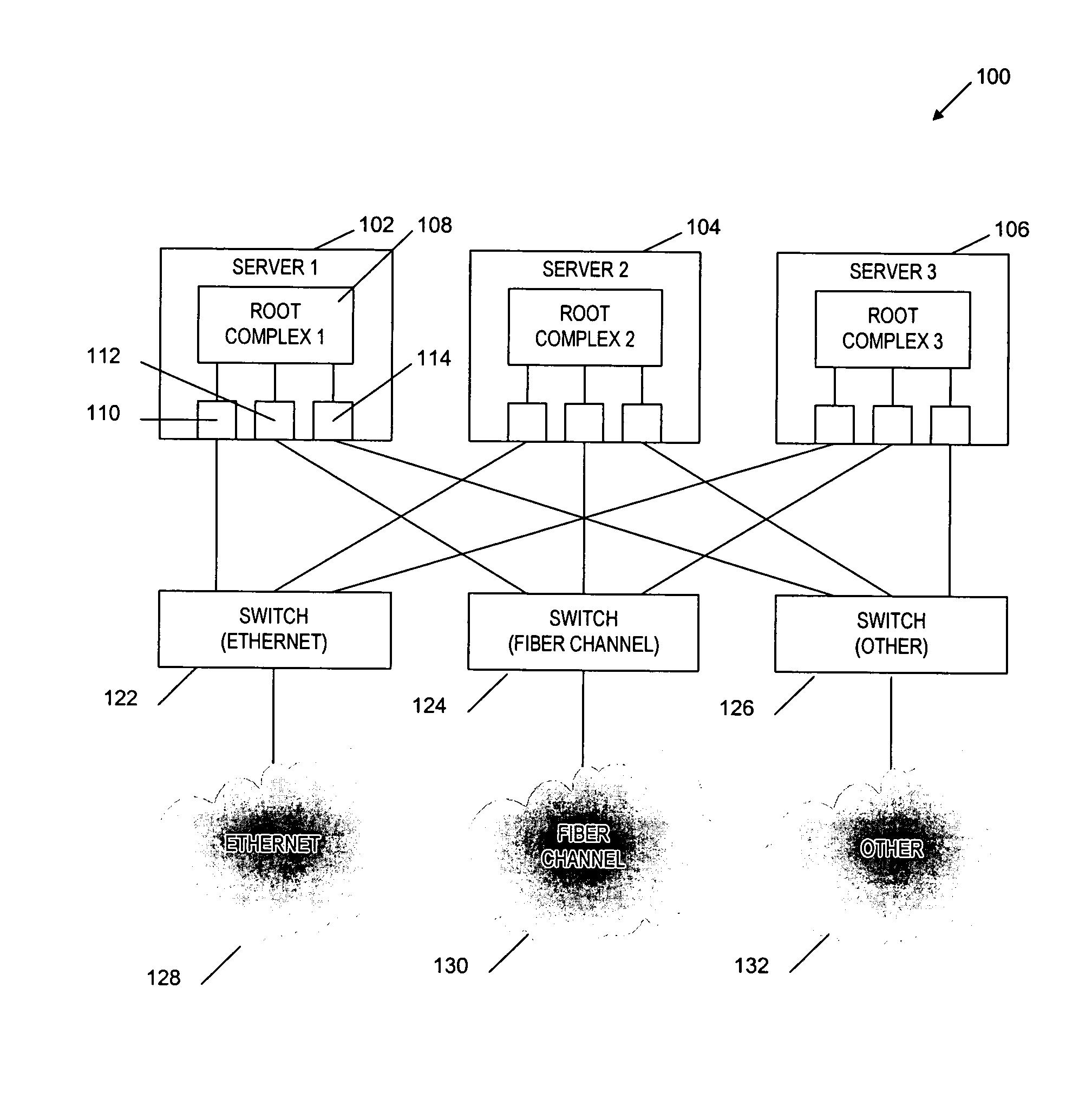

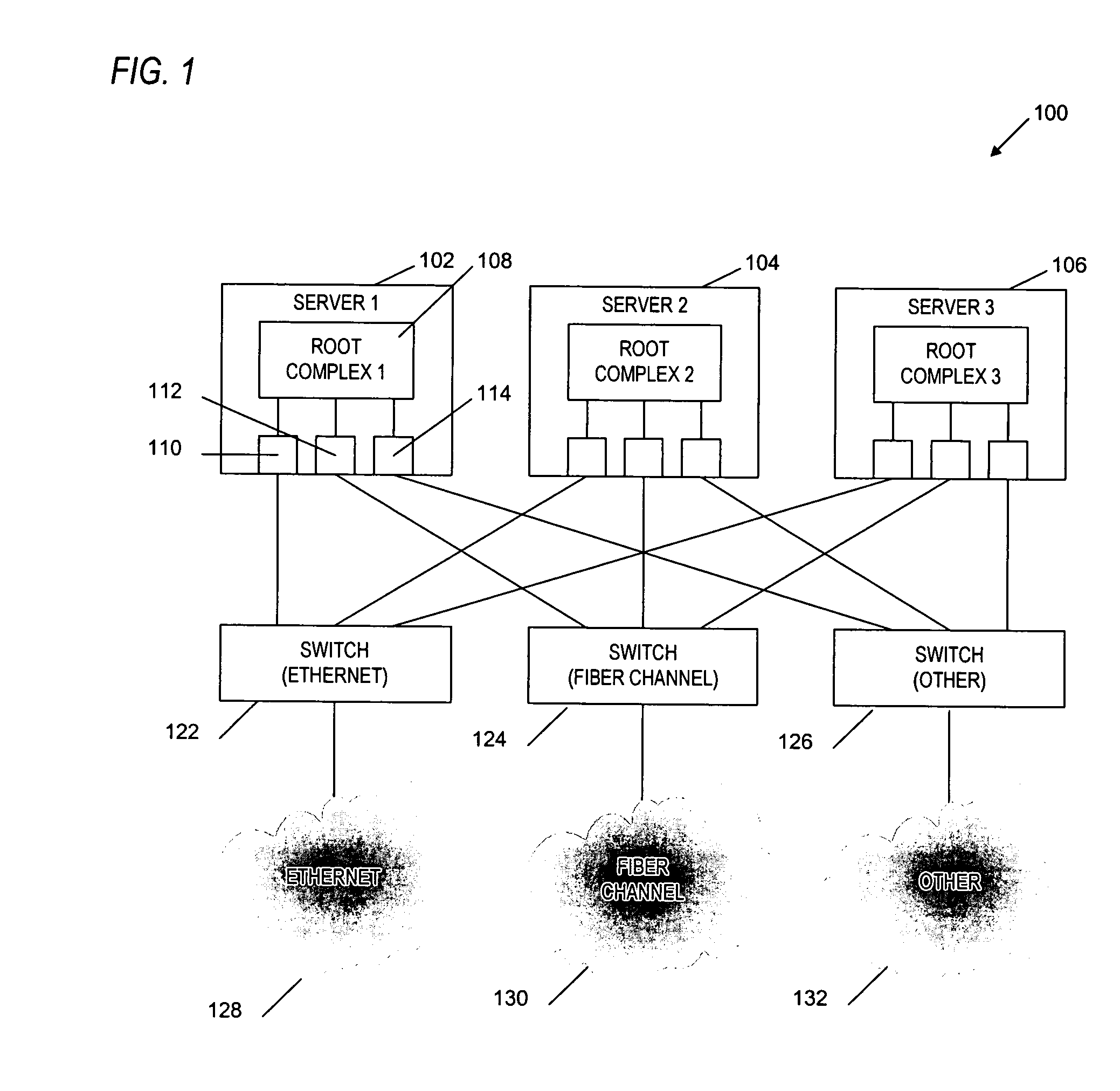

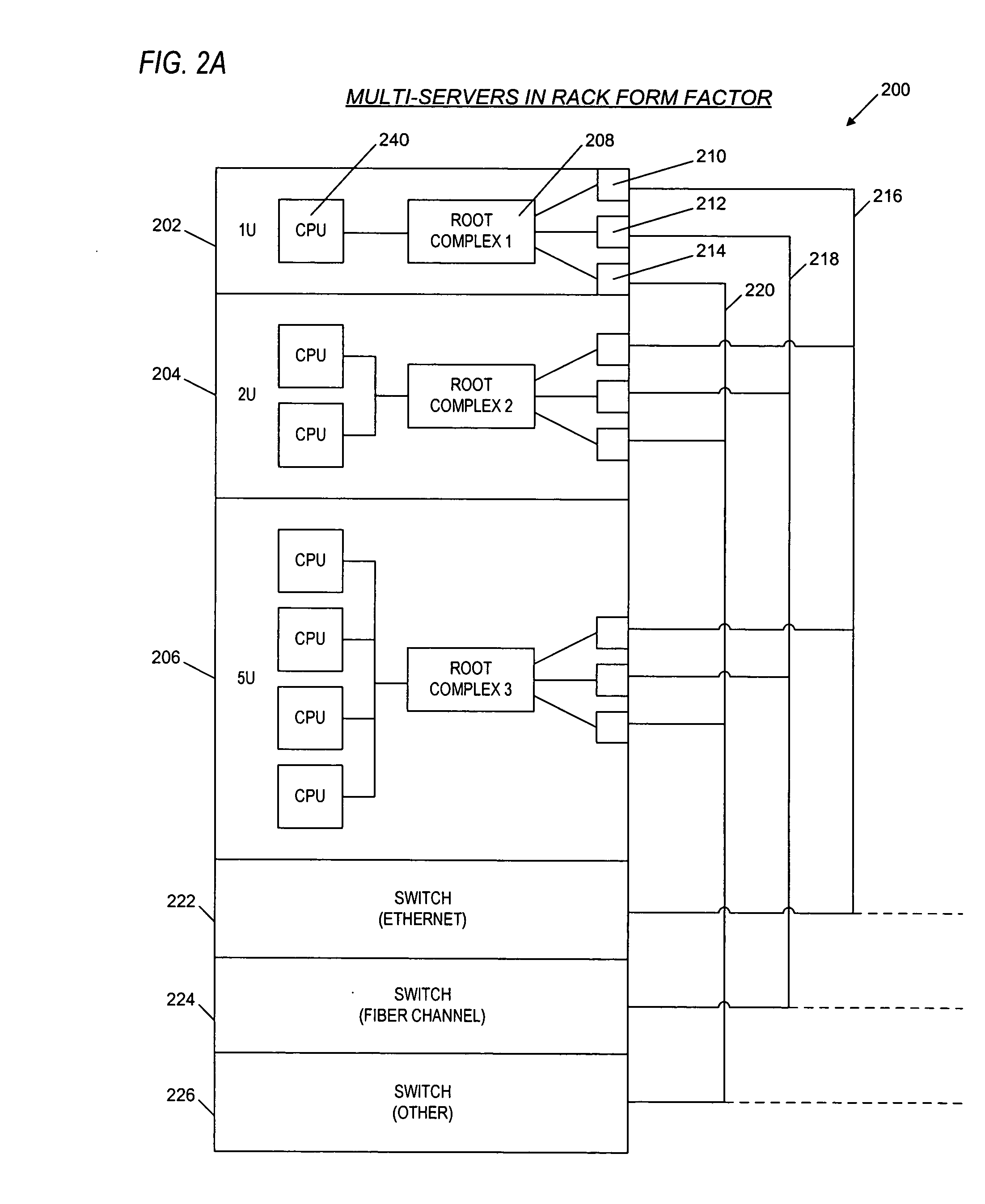

Apparatus and method for port polarity initialization in a shared I/O device

InactiveUS20050147117A1Multiplex system selection arrangementsData switching by path configurationOperational systemLogic cell

An apparatus and method are provided that enable I / O devices to be shared among multiple operating system domains. The apparatus includes a first plurality of I / O ports, a second I / O port, and a plurality of port initialization logic elements. The first plurality of I / O ports is coupled to a plurality of operating system domains through a load-store fabric. Each of the first plurality of I / O ports routes transactions between the plurality of operating system domains and the switching apparatus. The second I / O port is coupled to a first shared input / output endpoint. The first shared input / output endpoint is configured to request / complete the transactions for each of the plurality of operating system domains. One of the plurality of port initialization logic elements is coupled to the second I / O port and remaining ones of the plurality of port initialization logic elements are each coupled to a corresponding one of the first plurality of I / O ports. The plurality of port initialization logic elements is configured to initialize corresponding links between each of the plurality of operating system domains and the switching apparatus, and between the first shared input / output endpoint and the switching apparatus, to support the transactions, where each of the plurality of port initialization logic elements automatically configures a corresponding polarity for each of the first plurality of I / O ports and the second I / O port, and where the corresponding polarity is in a default polarity prior to being configured.

Owner:AVAGO TECH INT SALES PTE LTD

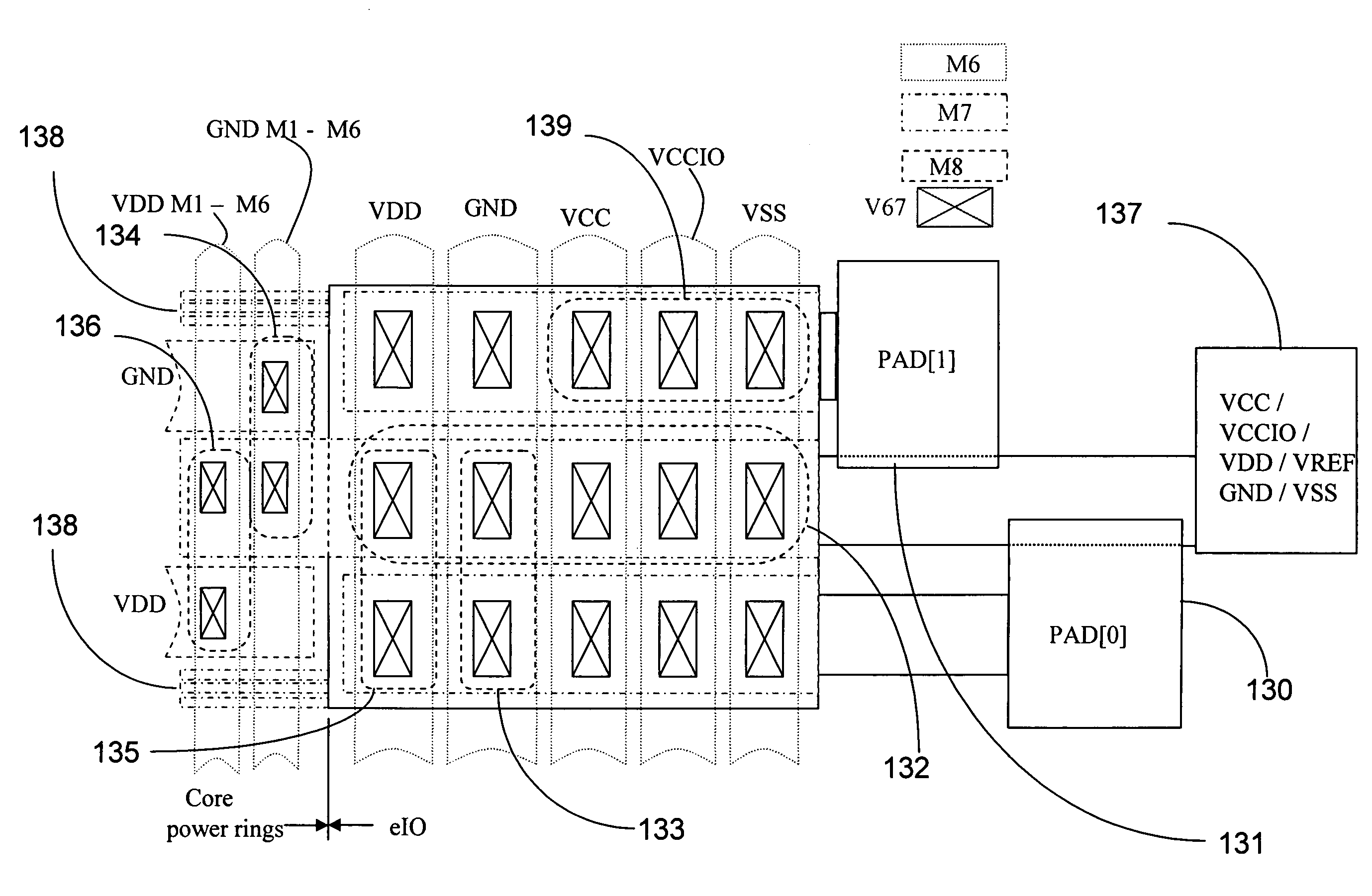

Semiconductor device and method of fabricating the same

InactiveUS20080180132A1Suppress power noiseSemiconductor/solid-state device detailsSolid-state devicesPower noiseLogic cell

This invention efficiently suppresses the power noise of an LSI. A semiconductor device includes first and second interconnection layers. The first interconnection layer has a source voltage supply line of a first potential positioned to extend along logic cells in a first direction. The second interconnection layer lies on an upper layer than the first interconnection layer and has plural source voltage supply lines of a second potential arranged adjacent to each other to form a group and positioned to extend in a second direction which is different from the first direction of interconnection. An interconnection line of the second potential is positioned on an upper layer than the first interconnection layer and interconnects at least two of the plurality of source voltage supply lines of the second potential. The interconnection line of the second potential is positioned to overlap the source voltage supply line of the first potential, to form a capacitor with the source voltage supply line of the first potential.

Owner:NEC ELECTRONICS CORP

Re-configurable logic elements using heat assisted magnetic tunneling elements

A magnetic logic cell includes a magnetic element having a pinned layer, a free layer, and a spacer layer. The pinned and free layers have pinned and free layer magnetizations. The spacer layer resides between the pinned and free layers. In one aspect, the magnetic logic cell includes a first configuration line that is electrically connected to the magnetic element and carries a first current and a second configuration line electrically that is insulated from the magnetic element and the first configuration line and carries a second current. The first or second current alone cannot switch the free layer magnetization. The first and second currents together can switch the free layer magnetization. When the first current is driven through the magnetic element and the second current is provided, the combination sets the pinned layer magnetization direction. In one aspect, the pinned layer magnetization is set by heating the AFM layer to approximately at or above the blocking temperature. In order to configure the logic cell, an initial direction for the free layer magnetization is also set.

Owner:SAMSUNG SEMICON

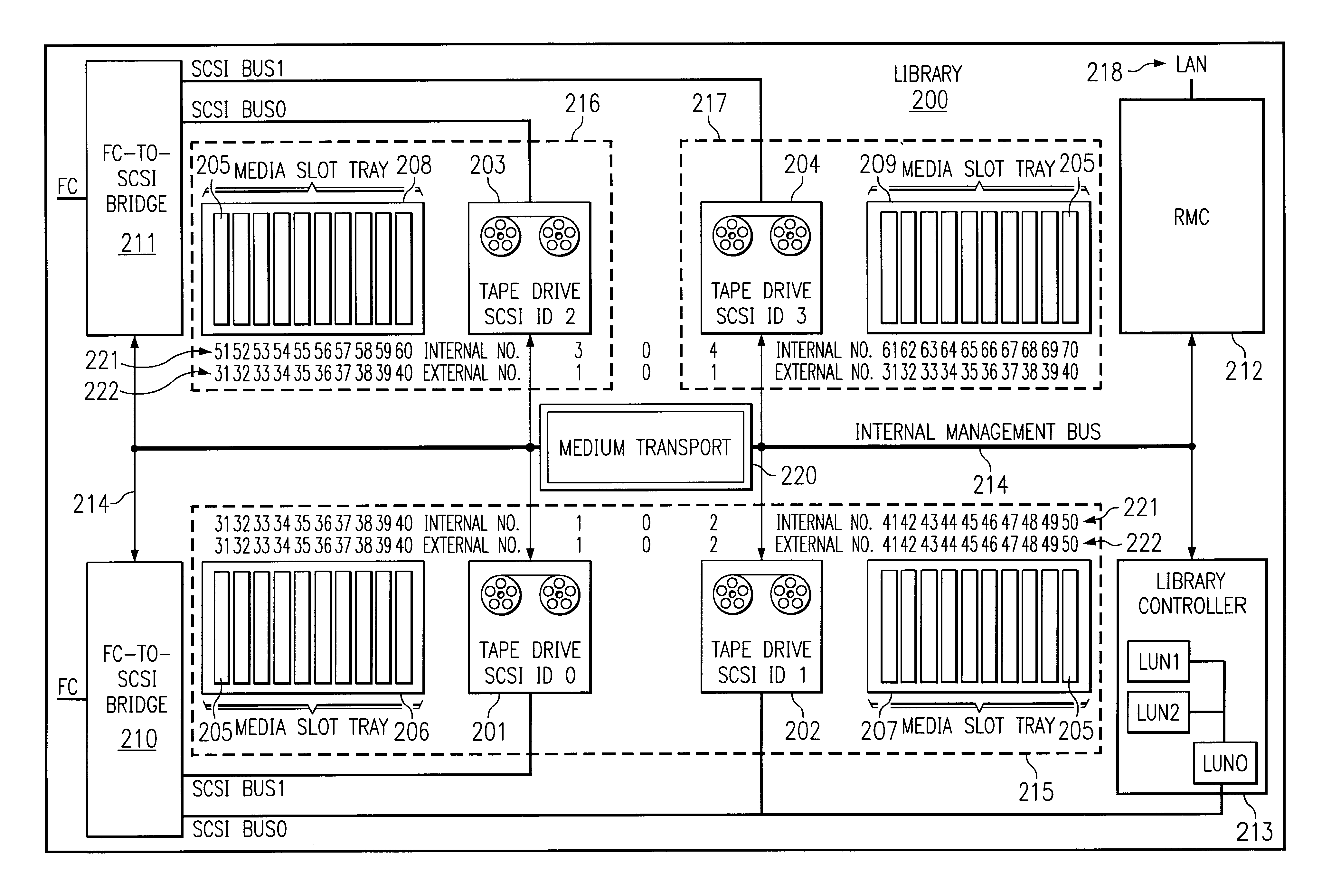

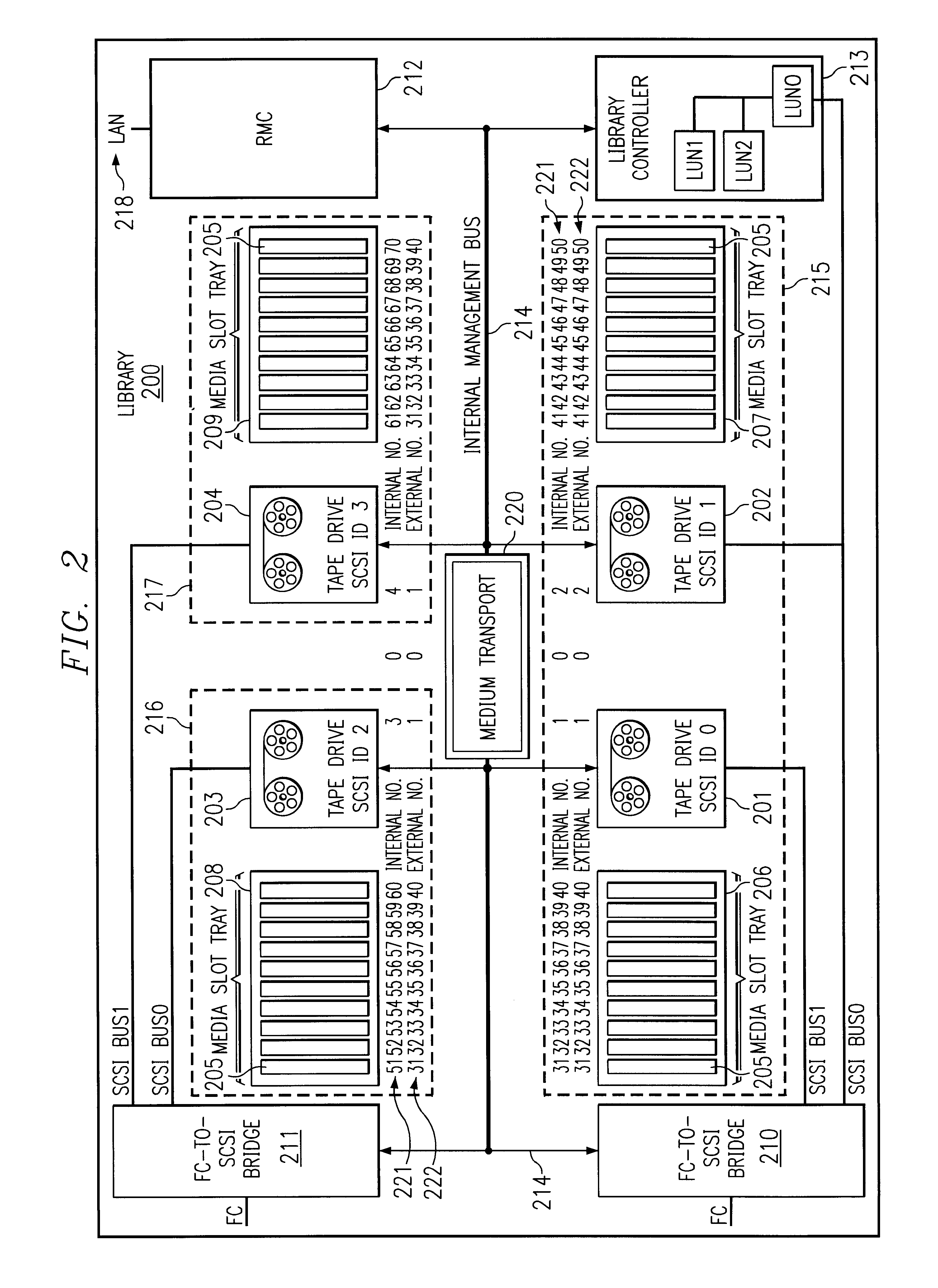

System and method for partitioning a storage area network associated data library employing element addresses

InactiveUS6839824B2Flat record carrier combinationsInput/output to record carriersStorage area networkLogic cell

A data library comprising a plurality of partitions, at least one data transfer element, each of the data transfer elements assigned to one of the partitions and assigned an internally unique element address, a plurality of data storage element slots, each of the slots assigned to a partition and assigned an internally unique element address, at least one media transport element shared by the partitions to move media between the slots and the at least one data transfer elements, the transport assigned an internally unique element address, and a library controller that assigns a different logical unit designation to each of the partitions and that assigns external element addresses to the transport, the data transfer elements, and the slots for each of the partitions and maps the internally unique addresses to the external addresses, the controller restricting movement of media to and from the slots assigned to a same of the partitions.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

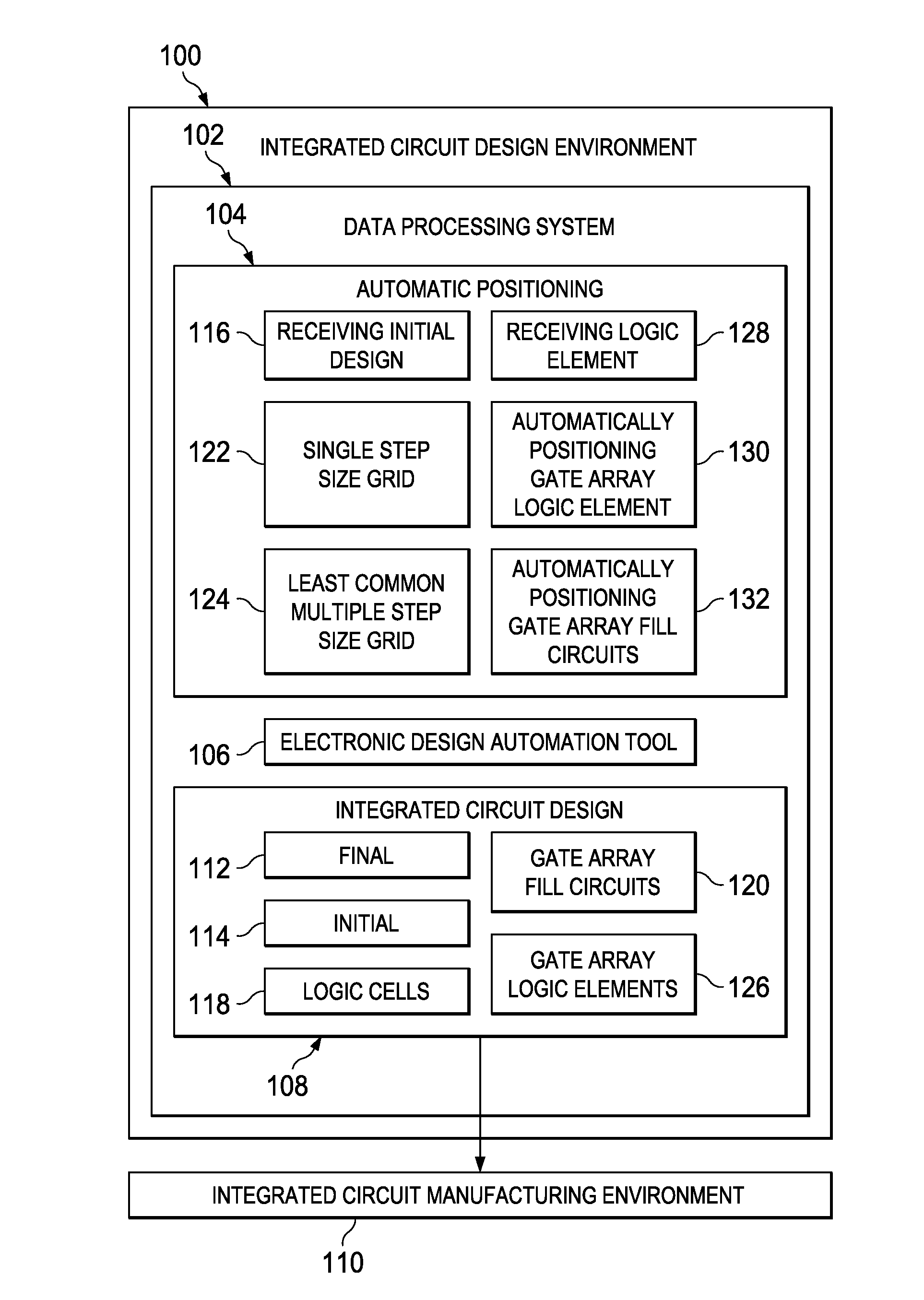

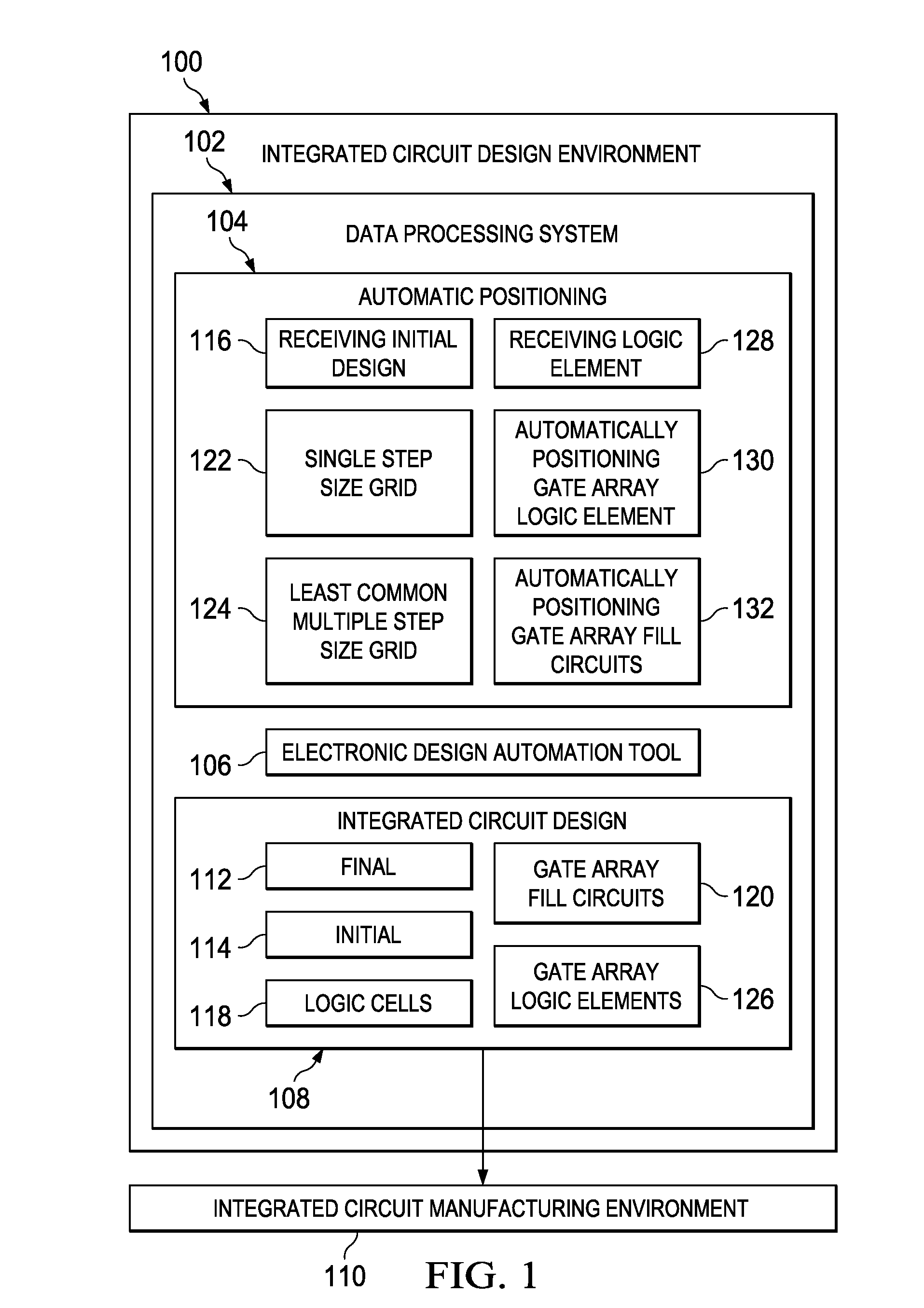

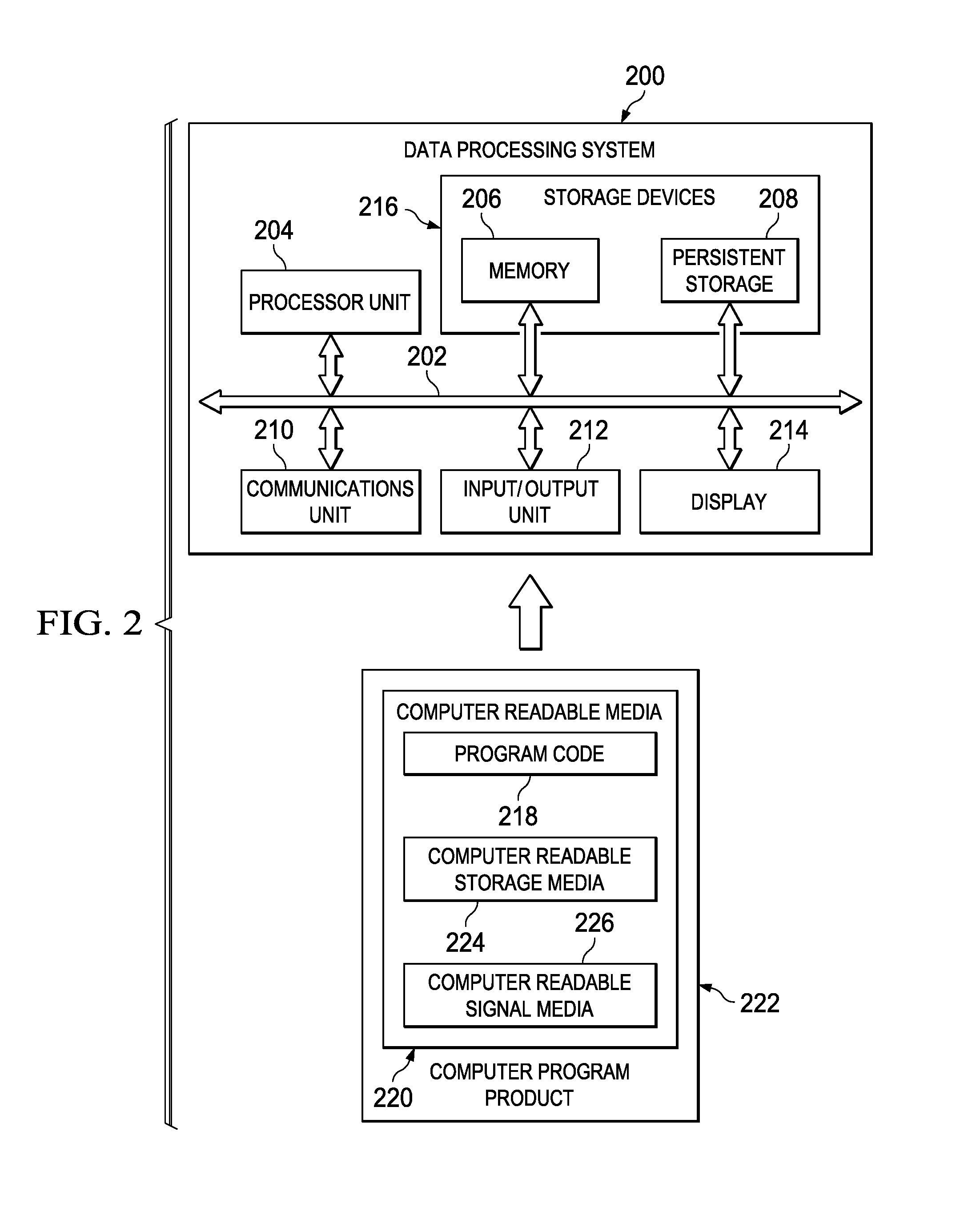

Automatic Positioning of Gate Array Circuits in an Integrated Circuit Design

ActiveUS20110072407A1Computer programmed simultaneously with data introductionComputer aided designLogic cellGate array

An automated method and apparatus for positioning gate array circuits in an integrated circuit design. An initial integrated circuit design includes logic cells and gate array fill circuits positioned thereon. The gate array fill circuits are positioned in available space between the adjacent logic cells so as to fill the available space with the maximum gate array fill circuits. A gate array logic element to be positioned in the integrated circuit design, such as may be required by an engineering change to the circuit design, is automatically positioned between adjacent logic cells so as to allow for full utilization of any space remaining between the adjacent logic cells by gate array fill circuits.

Owner:GLOBALFOUNDRIES US INC

Merged logic and memory combining thin film and bulk Si transistors

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

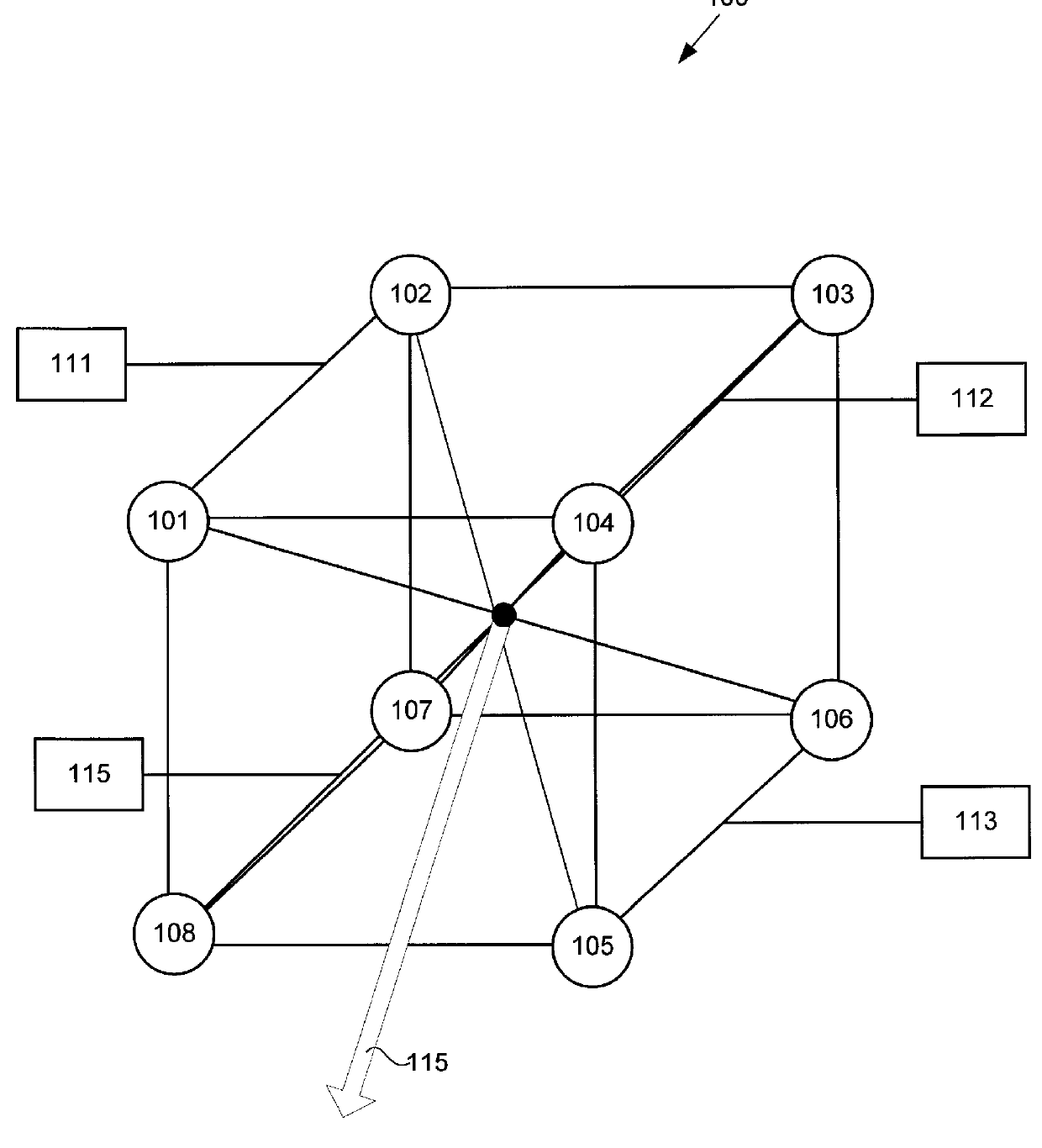

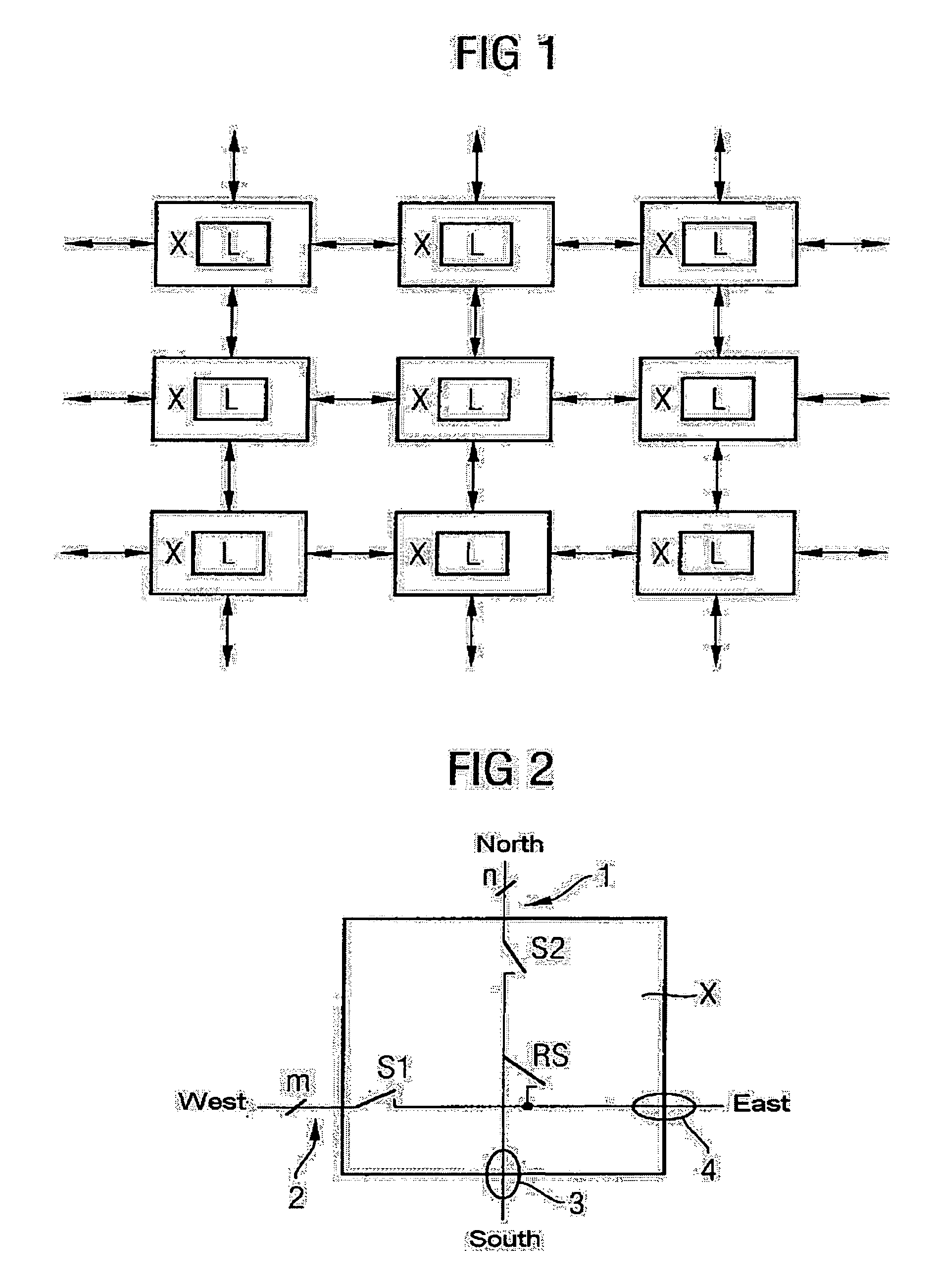

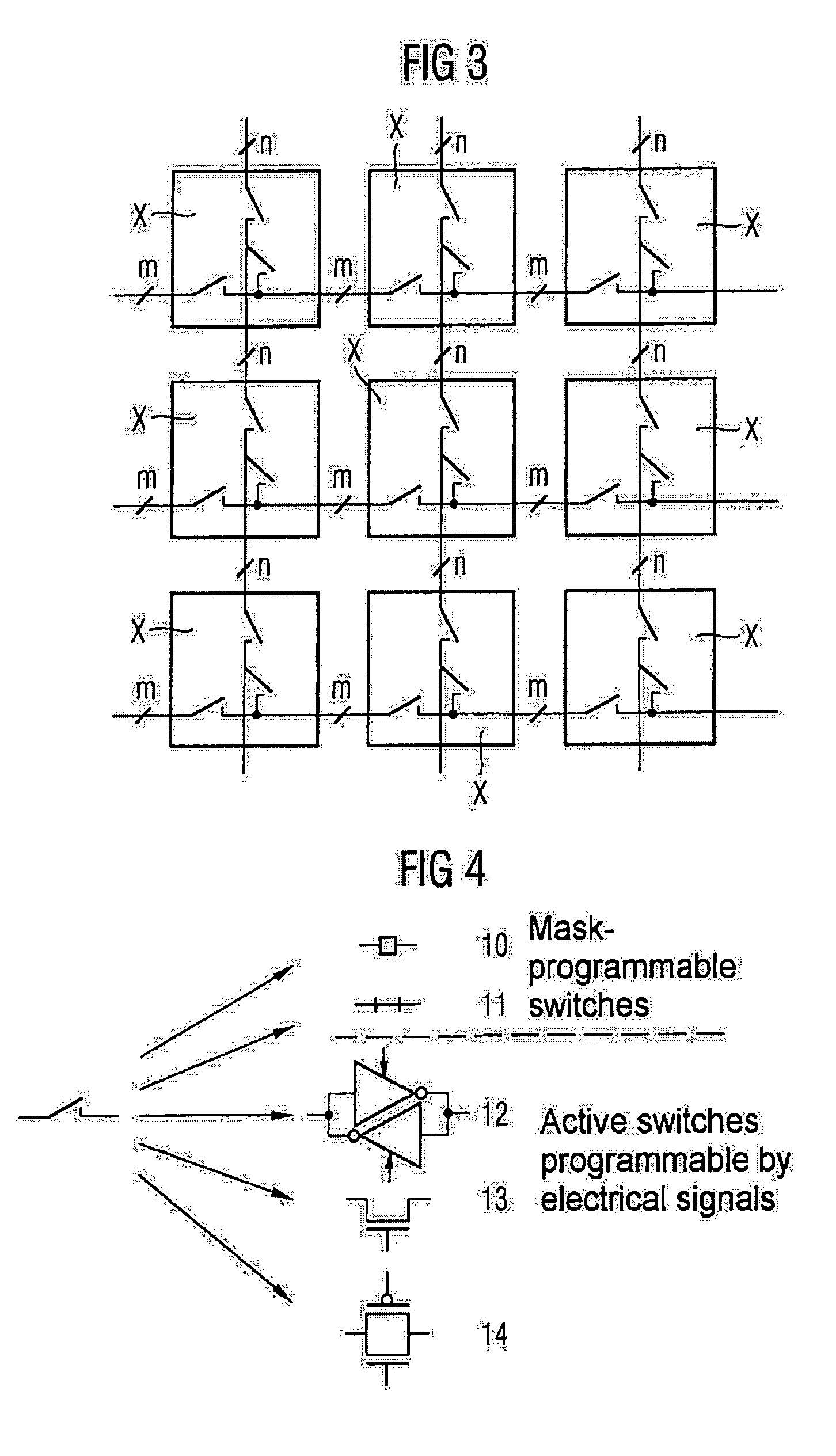

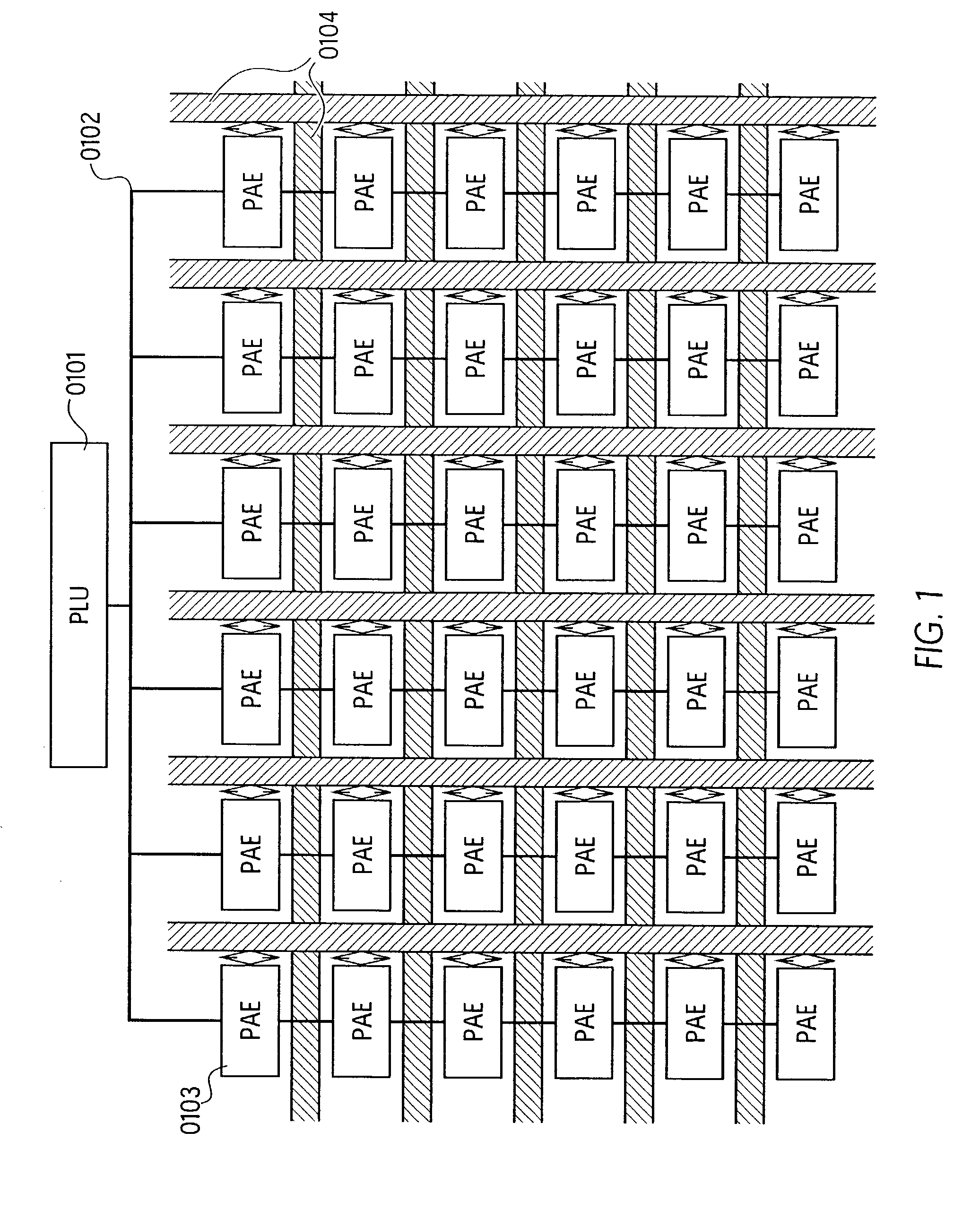

Method for the automatic address generation of modules within clusters comprised of a plurality of these modules

InactiveUS6038650AConcurrent instruction executionArchitecture with single central processing unitLogic cellComputer module

A method of automatic address generation by units within clusters of a plurality of such units in which individual configurable elements of a unit can be addressed. It is thus possible to address the individual elements directly for reconfiguration. This is a prerequisite for being able to reconfigure parts of the unit by an external primary logic unit without having to change the entire configuration of the unit. In addition, the addresses for the individual elements of the units are automatically generated in the X and Y directions, so that the addressing scheme represents the actual arrangement of units and configurable elements. Furthermore, manual allocation of addresses is not necessary due to automatic address generation. In accordance with the present invention, a cluster is provided with a number of configurable units, each having two inputs for receiving the X address of the last element of the preceding unit in the X direction (row) and the Y address of the last element of the preceding unit in the Y direction (column) and having two outputs to relay to the next unit the position of the last element of the unit in the X direction and in the Y direction.

Owner:SCIENTIA SOL MENTIS AG

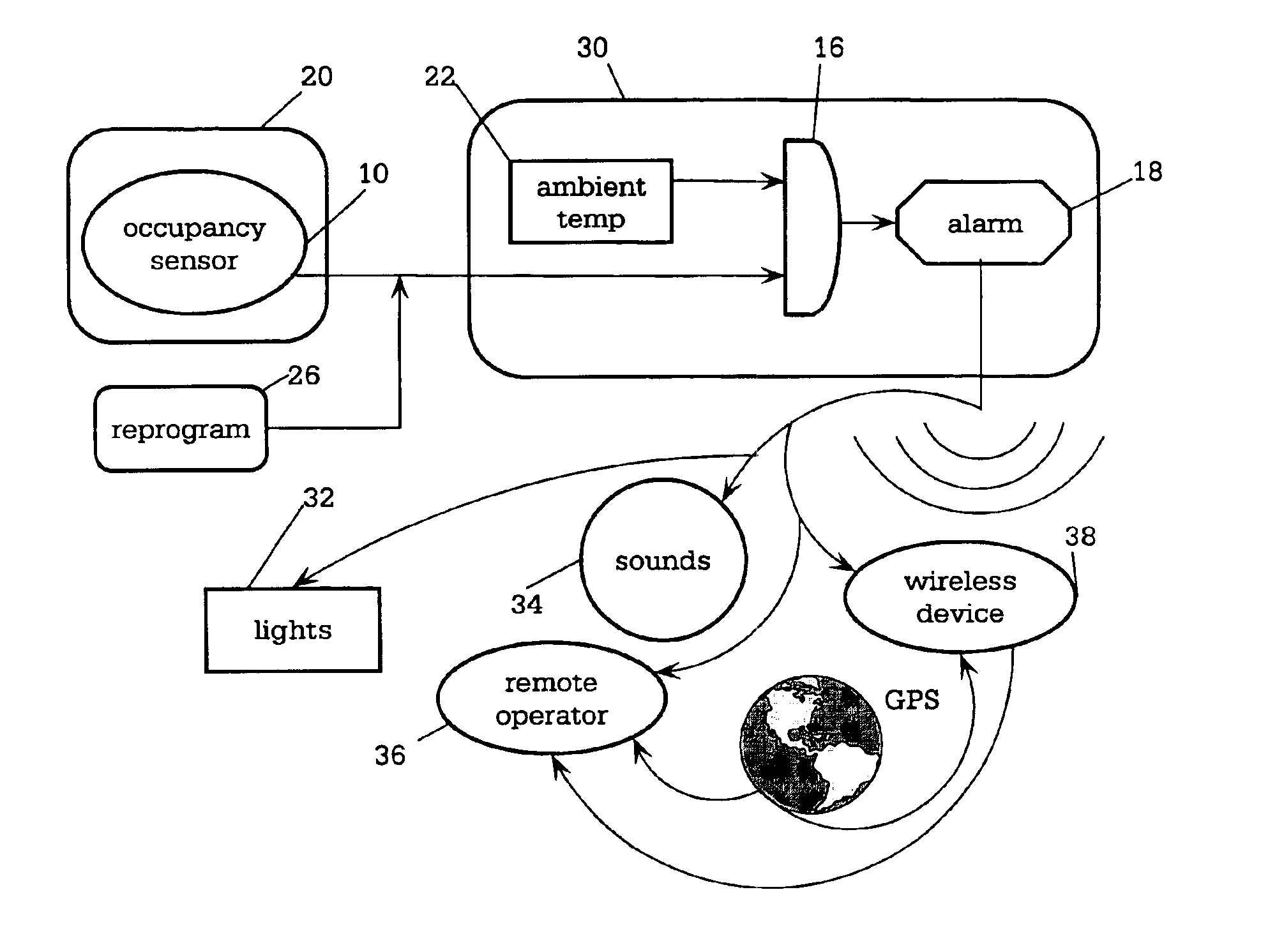

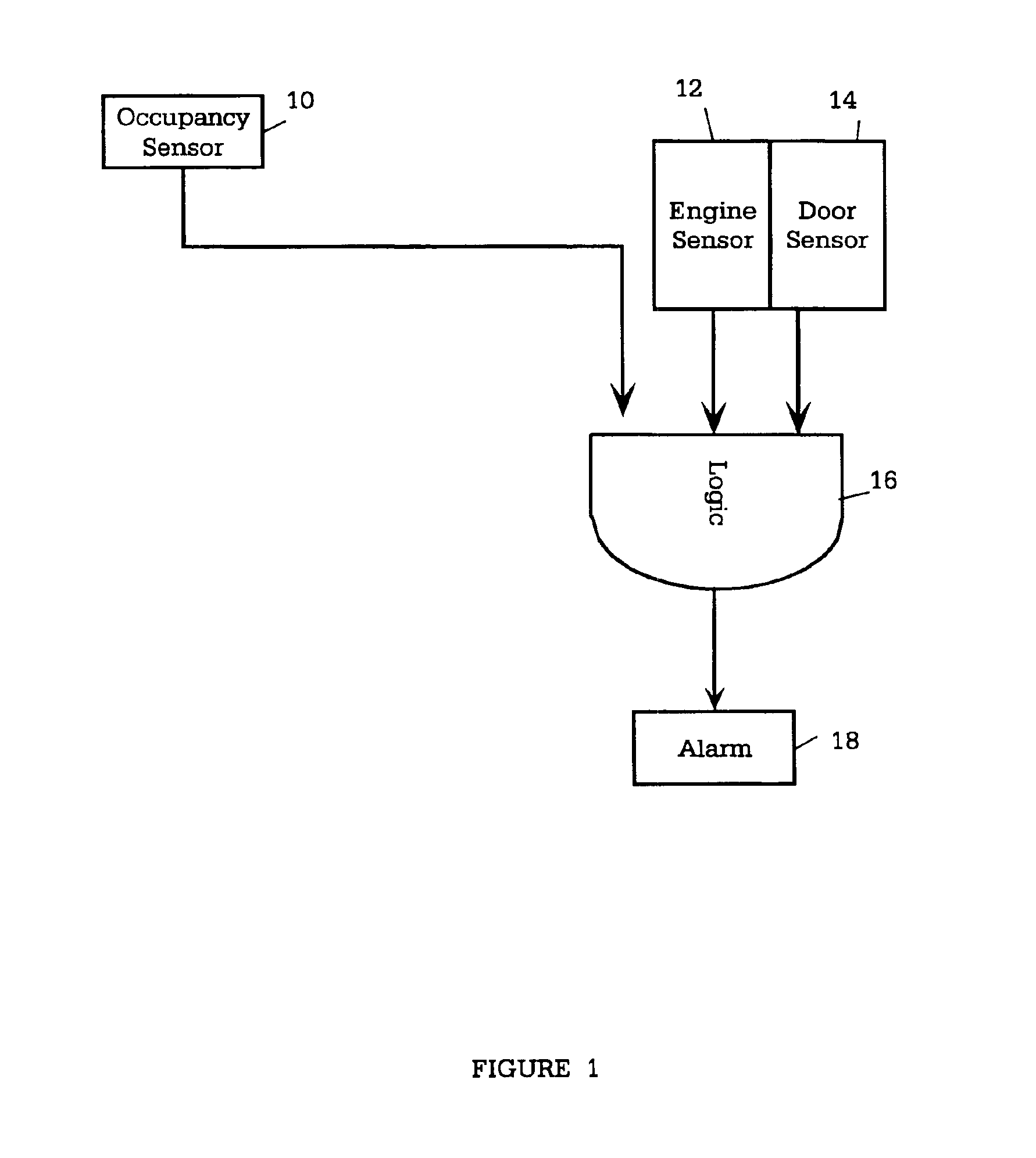

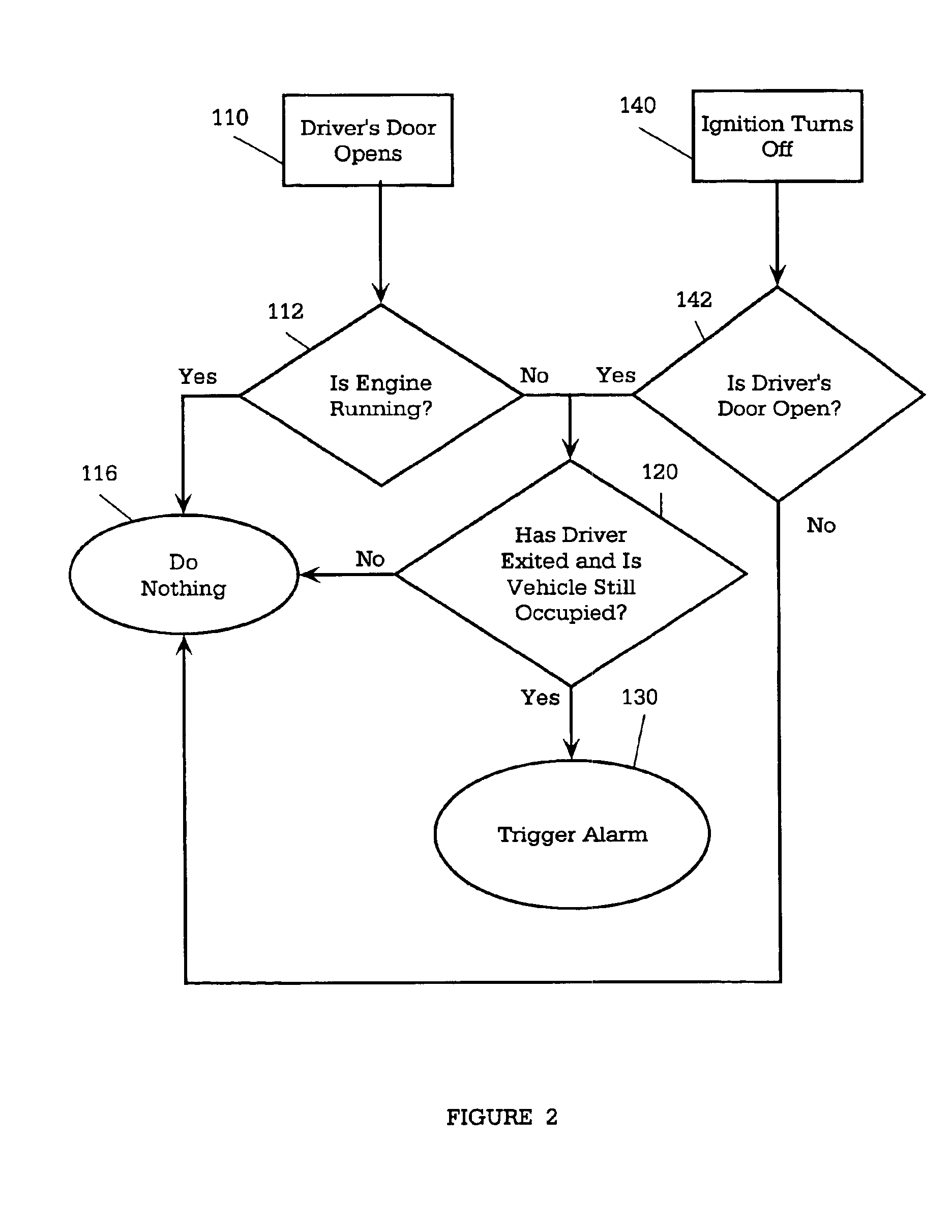

Smart occupant alarm system

An occupancy alarm system can be integrated into a motor vehicle or can be portable. The occupancy alarm system may be programmed to communicate with a program within a logic unit of the on-board computer within the vehicle or a cellular telephone or other wireless logic device so that if the driver's door is open and the engine is turned off but there still is an occupant in the motor vehicle, an alarm is immediately triggered. The GPS coordinates of the motor vehicle or the cellular telephone or other wireless device may be communicated to a remote location service or a local emergency center as part of the alarm. The occupancy sensor may be mounted on the occupant or on the restraint system, and may interact with an ambient temperature sensor and an alarm, both of which may be integrated into a motor vehicle, to indicate that a dangerous condition exists for an occupant within the motor vehicle. The occupancy sensor, the ambient temperature monitor, and the alarm may further be integrated together for a portable alarm system or may be mounted or otherwise integrated onto a portable restraint system. The occupancy alarm system may provide an interface and an override such that when the occupant remains in a potentially hazardous environment, that state is communicated via the interface and, if monitored by a responsible adult, the alarm can be overridden.

Owner:SLINGSHOT IOT LLC

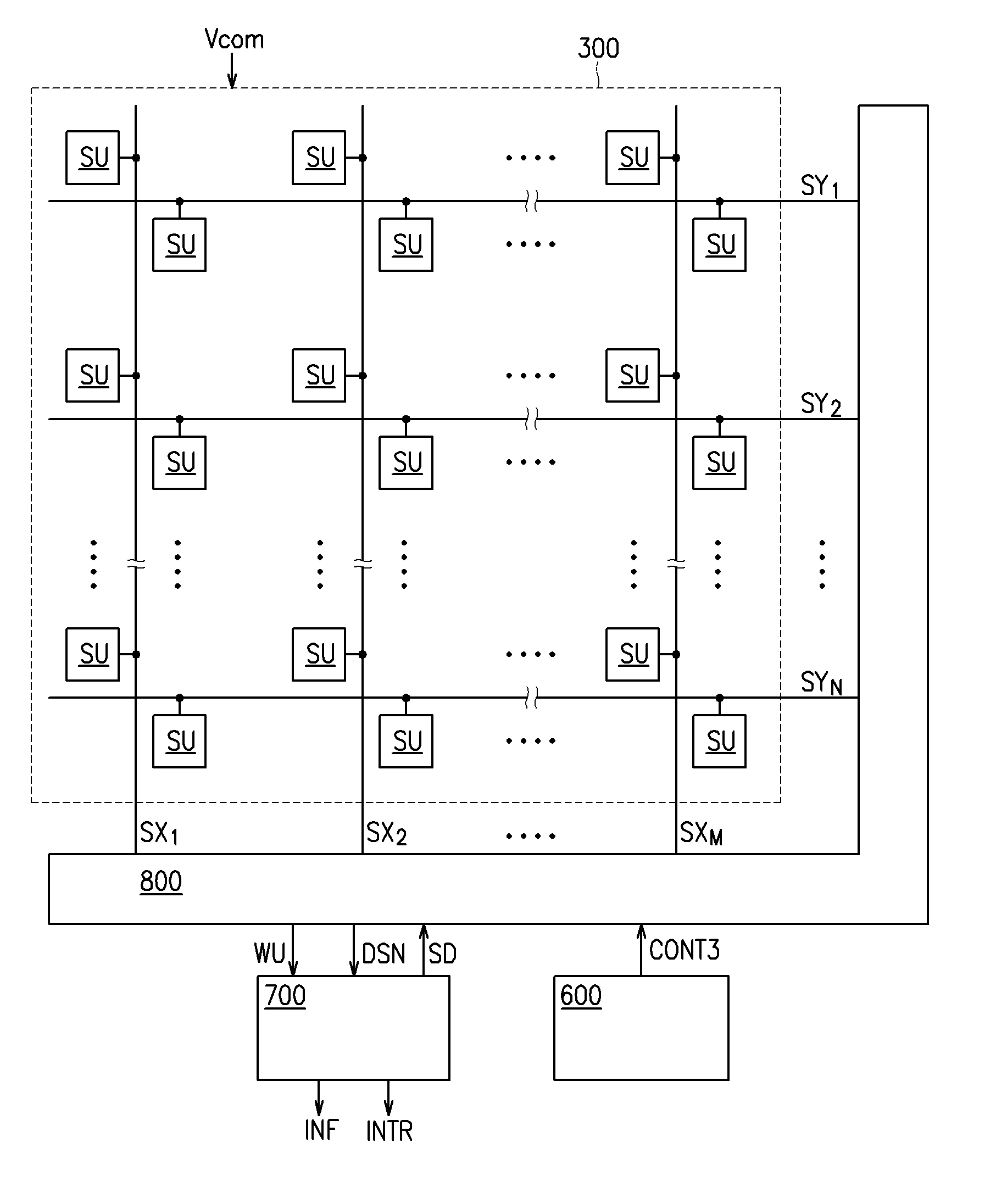

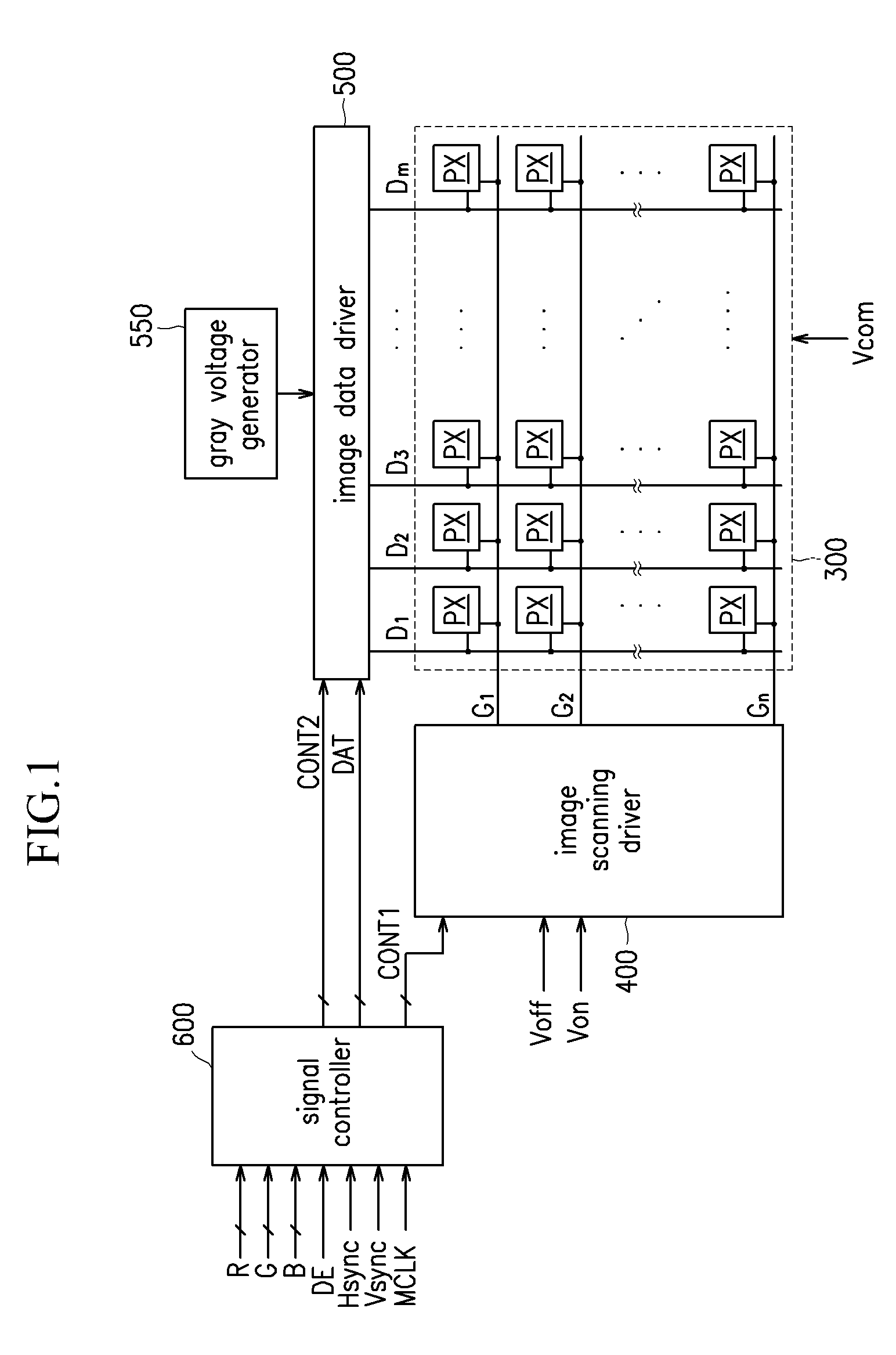

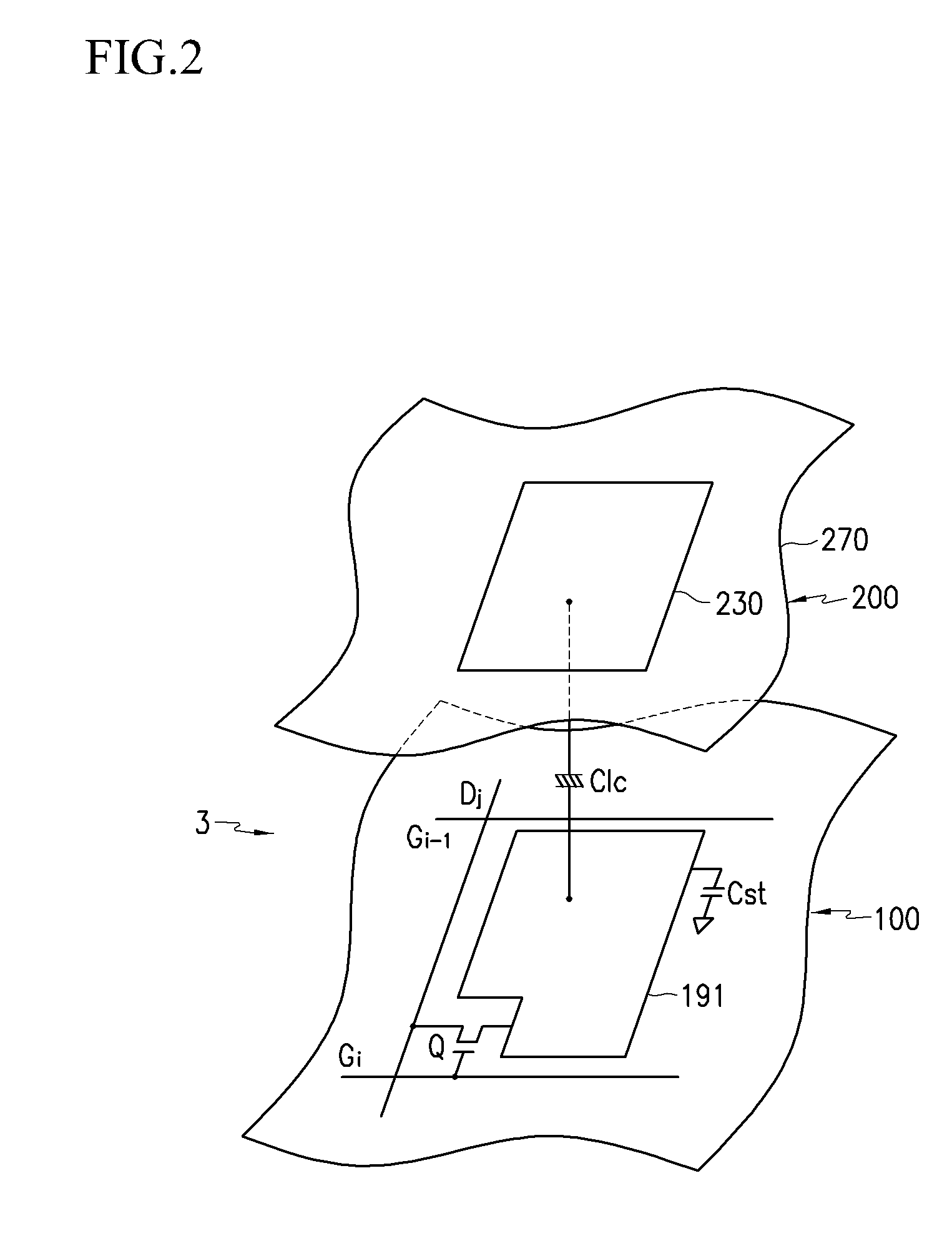

Touch sensitive display device and driving apparatus and method thereof

ActiveUS20070063991A1Digital data processing detailsCathode-ray tube indicatorsLogic cellDisplay device

A display device includes a display panel, a plurality of pixels formed on the display panel, a plurality of sensing units formed on the display panel and generating sensor output signals in response to a touch exerted on the display panel, a sensing signal processor receiving and processing an analog sensor data signal originated from the sensor output signals to generate a digital sensor data signal, a first touch-determination unit detecting whether a touch exists based on the digital sensor data signal for a plurality of frames, and operating in a power saving mode, and a second touch-determination unit detecting whether and where a touch exists based on the digital sensor data signal for the plurality of frames, and operating in a normal mode. The display device includes hardwired logic units for detecting the touch, it detects the touch using the hardwired logic units in the power saving mode and converts the operation mode to the normal mode when the touch is detected, thus reducing power consumption.

Owner:SAMSUNG DISPLAY CO LTD

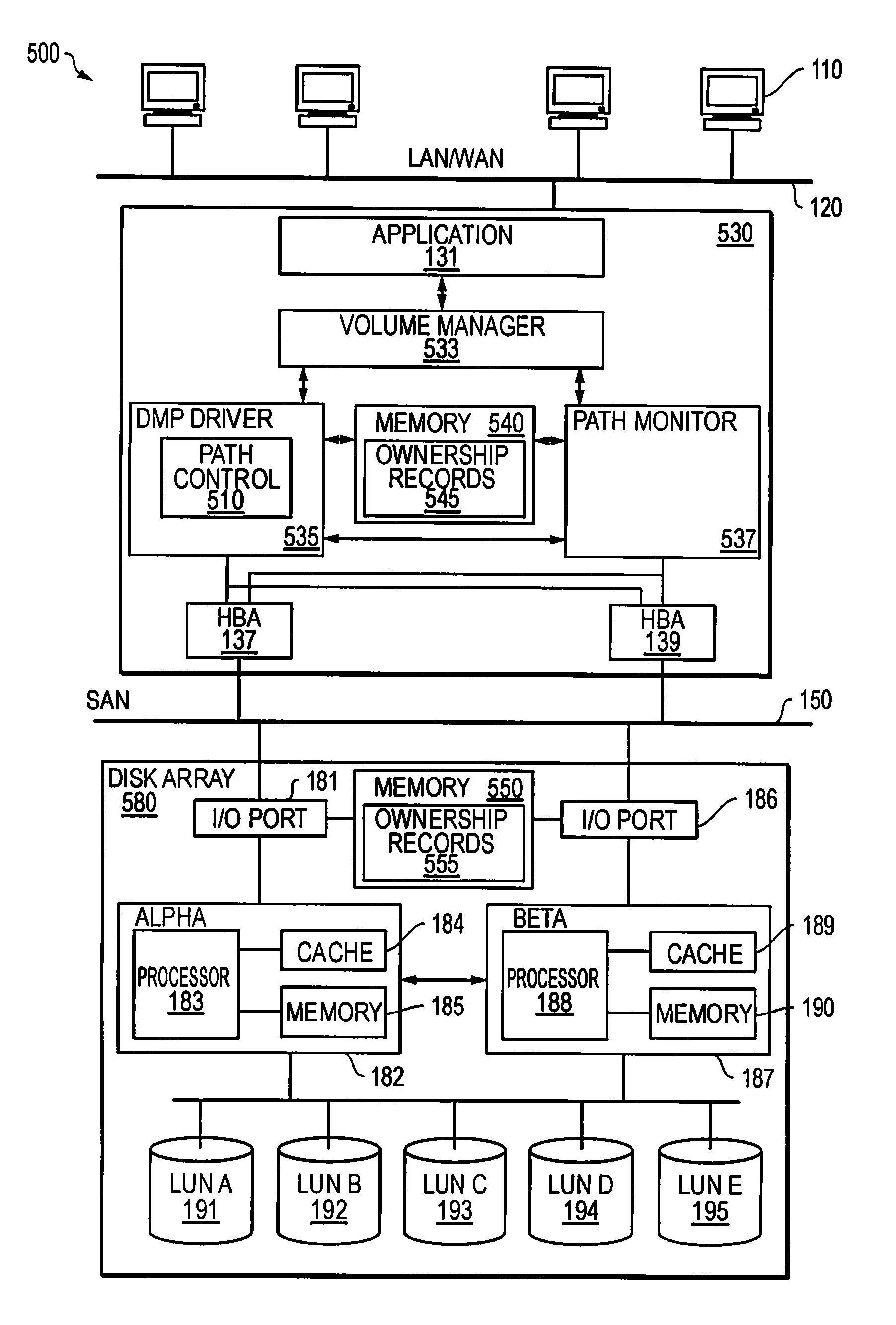

Preventing undesired trespass in storage arrays

InactiveUS7730274B1Avoid undesired trespassAvoiding undesired trespassesError detection/correctionMemory systemsFailoverLogic cell

Procedures and systems for avoiding undesired trespass may be deployed in host processors that use storage arrays with automated fail-back and fail-over functions. In one embodiment, a method may synchronize path records in a storage array with path records in a host processor. The method may detect a failure of a first data path through a first controller on the storage array to a logical unit (LUN) on the storage array. In response to the failure, the host processor may initiate a failover on the storage array of the LUN, so that the LUN is accessed through a backup controller on the storage array. The host processor may also issue commands to pin the failed-over LUN to the backup controller. For example, the host processor may issue commands to set the default owner of the LUN to be the backup controller.

Owner:VERITAS TECH

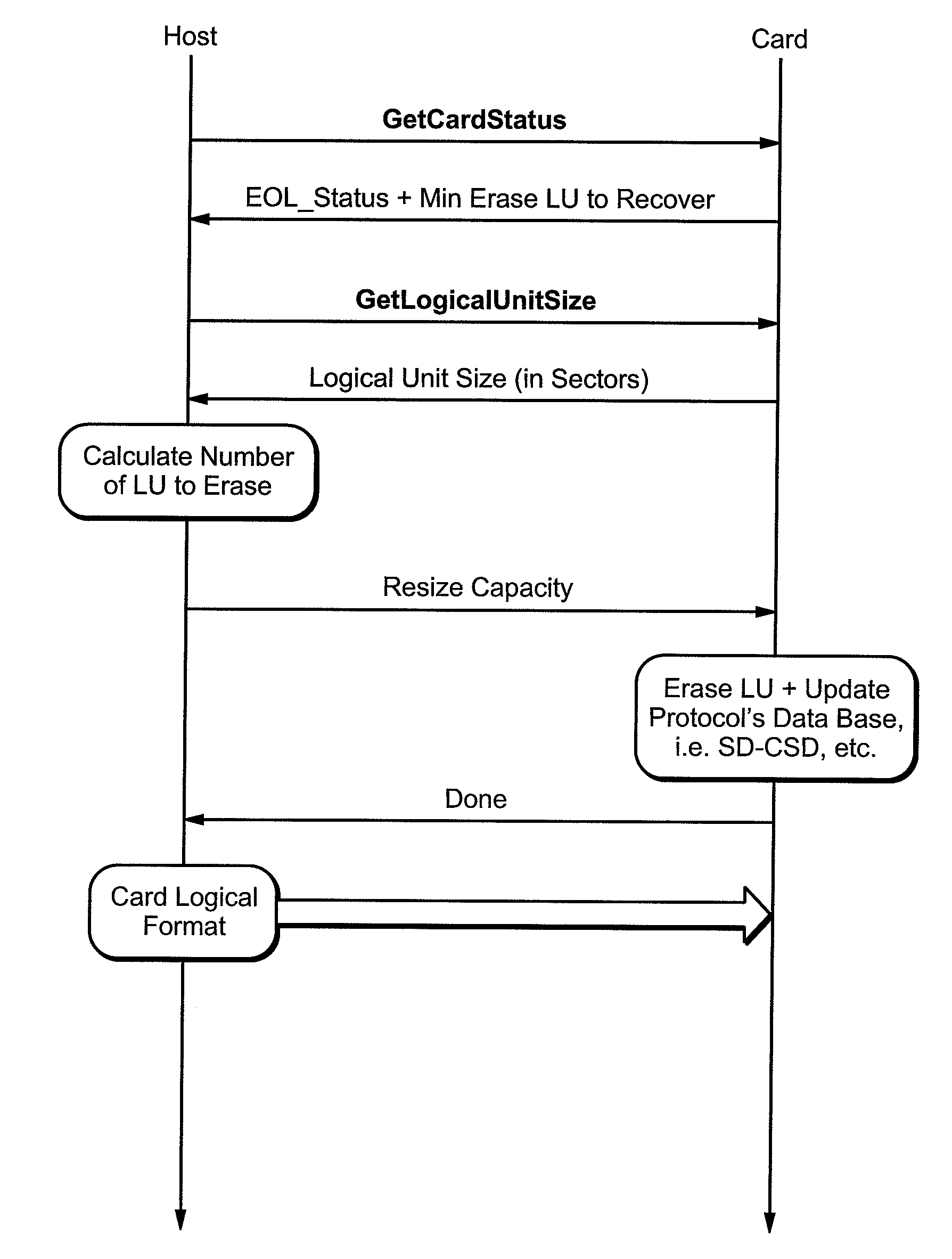

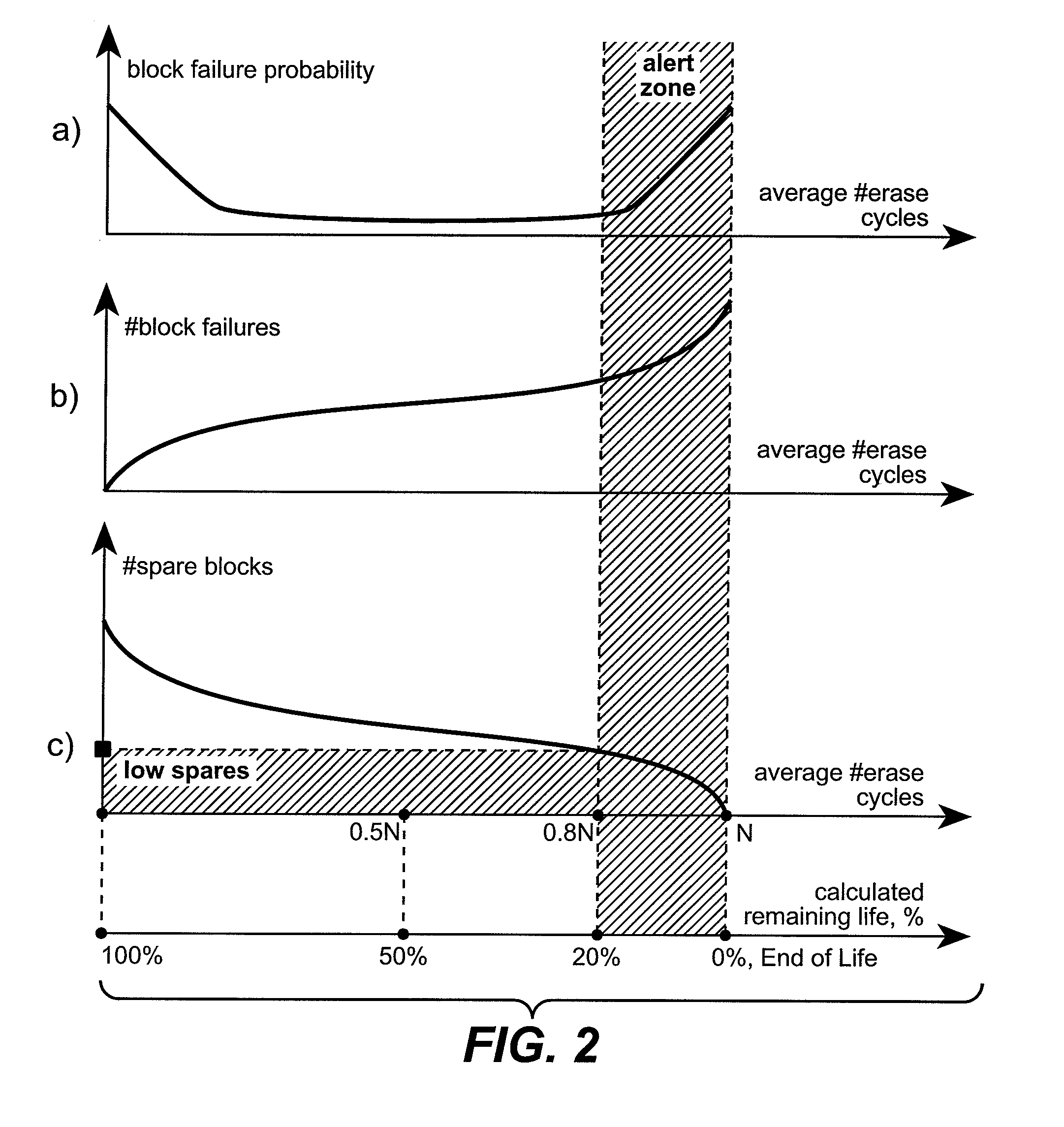

Memory Cards with End of Life Recovery and Resizing

A system and methods are given for providing information on the amount of life remaining for a memory having a limited lifespan, such as a flash memory card. For example, it can provide a user with the amount of the memory's expected remaining lifetime in real time units or as a percentage of estimated initial life. An end of life warning can also be provided. The memory device can be resized by host command. In an exemplary embodiment, a host can send a request to the memory device obtain its status and the size of logical units with which it operates. Based on this information, portions of the memory device can be erased, after which it can be reformatted and operated with a reduce capacity.

Owner:SANDISK TECH LLC

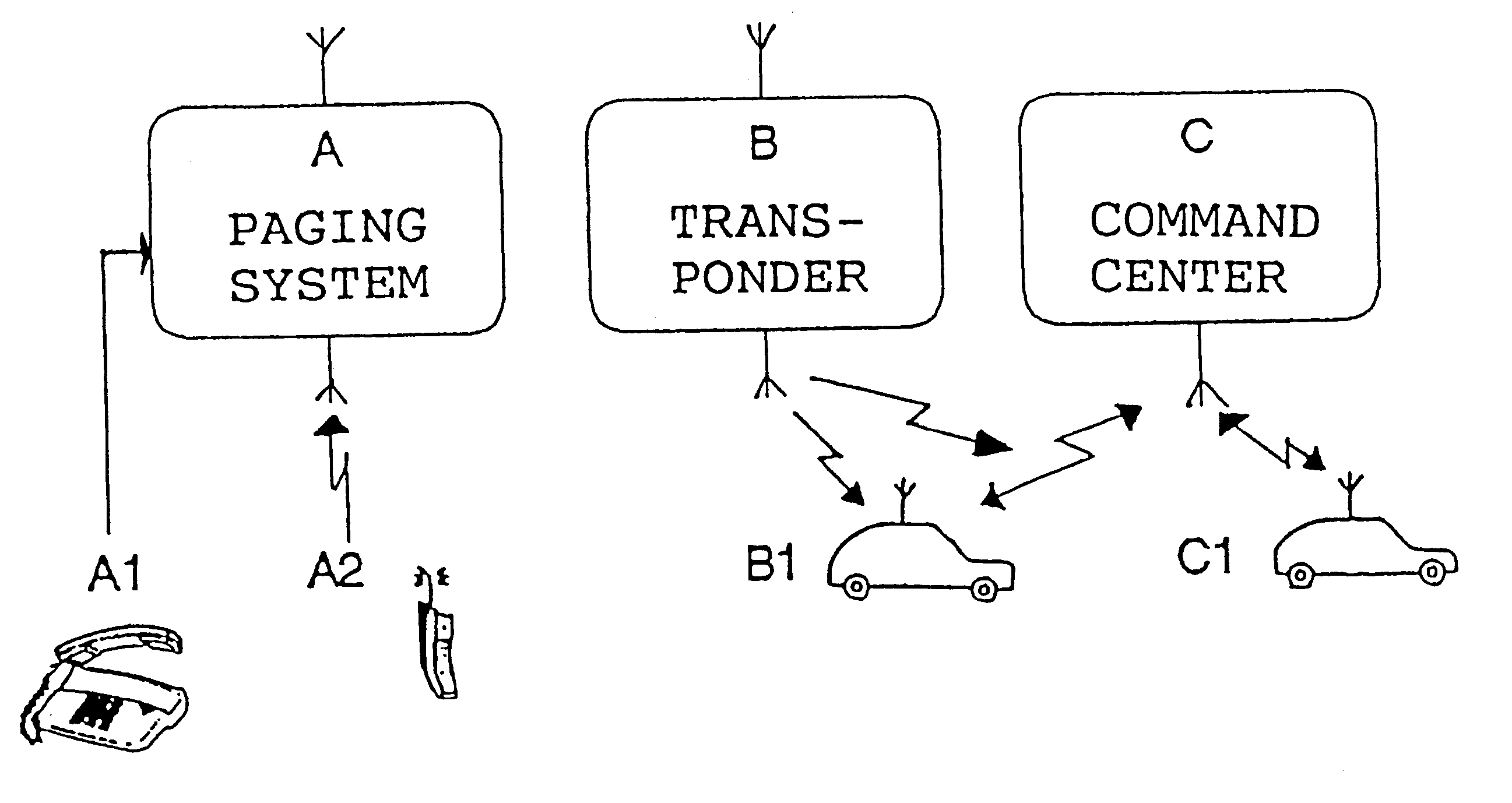

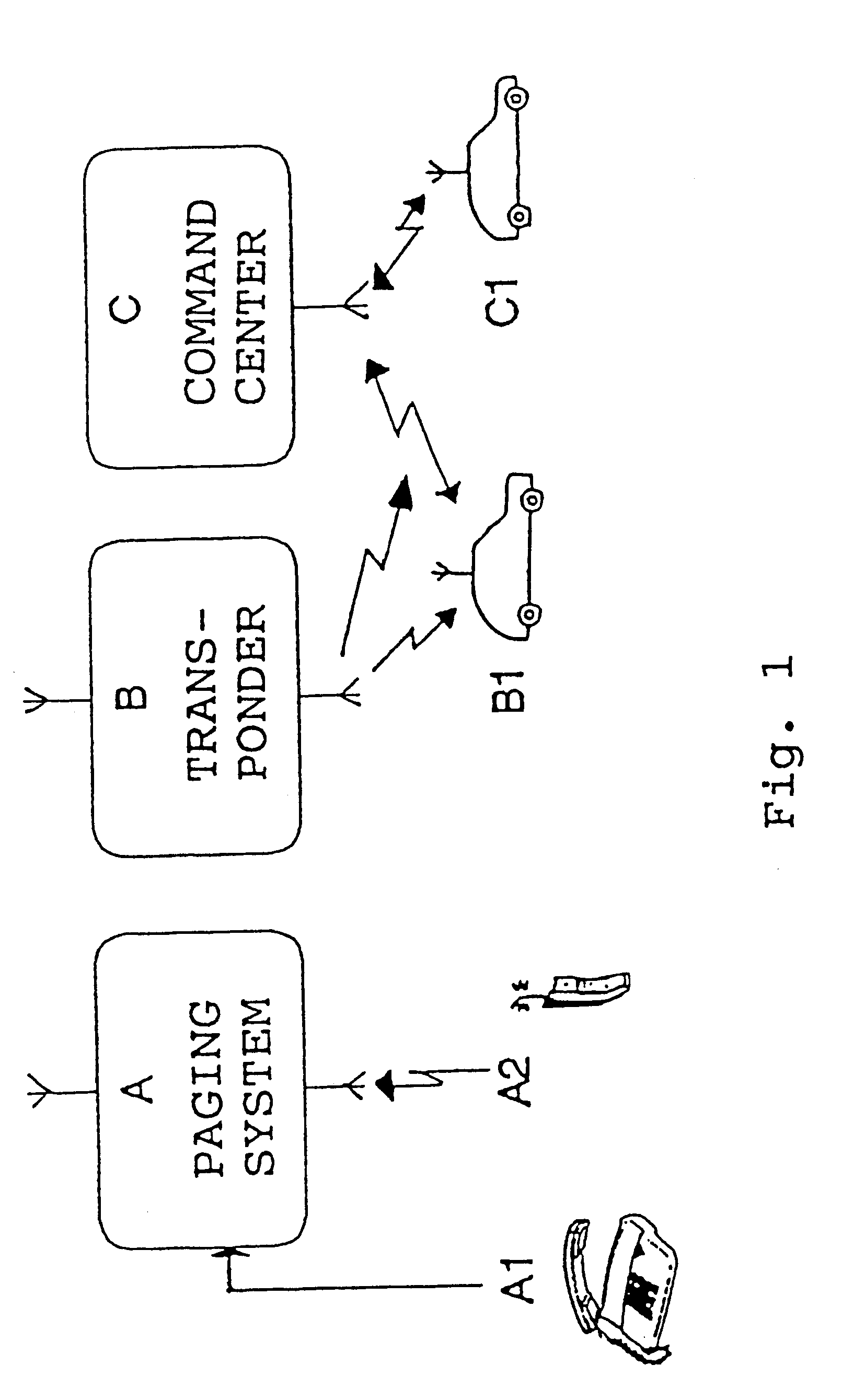

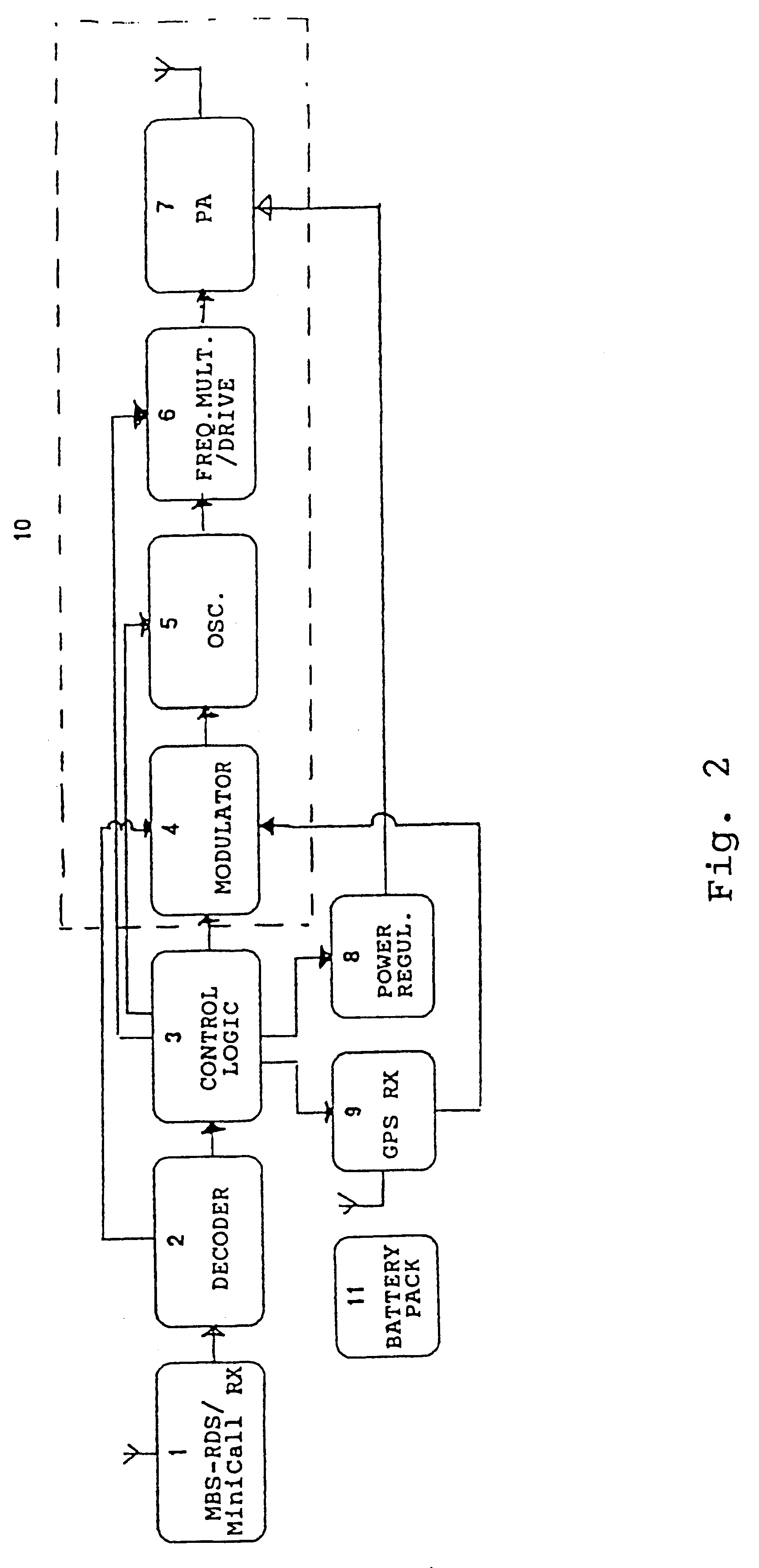

Transponder system for localization of an object

InactiveUS6236836B1Easily mobileEasily portableDirection finders using radio wavesFrequency-division multiplex detailsSpecific functionTransmitted power

A transponder system is provided which presents a light weight portable or mobile system for localization of movable objects, e.g., for surveillance of valuable transports and the like. The small unit constituting the transponder contains a receiver (1) of paging type, a decoder (2), a logic unit (3), a transmitter portion (10), a built-in antenna and power supply (11). The system is controllable by an existing tested radio system for paging. One advantage of utilizing an already existing paging system is that functionality is well tested and a general covering range is obtained. In addition, costs for building up and operation of a paging system are eliminated. Control information being sent to the transponder includes a number of symbols defining a certain basic function for the built-in marker transmitter (10) and symbols which constitute control code and control data for the specific function. Consequently at least the frequency, transmit power and transmitting sequences of the marker transmitter are controllable.

Owner:WESTMAN TONY +1

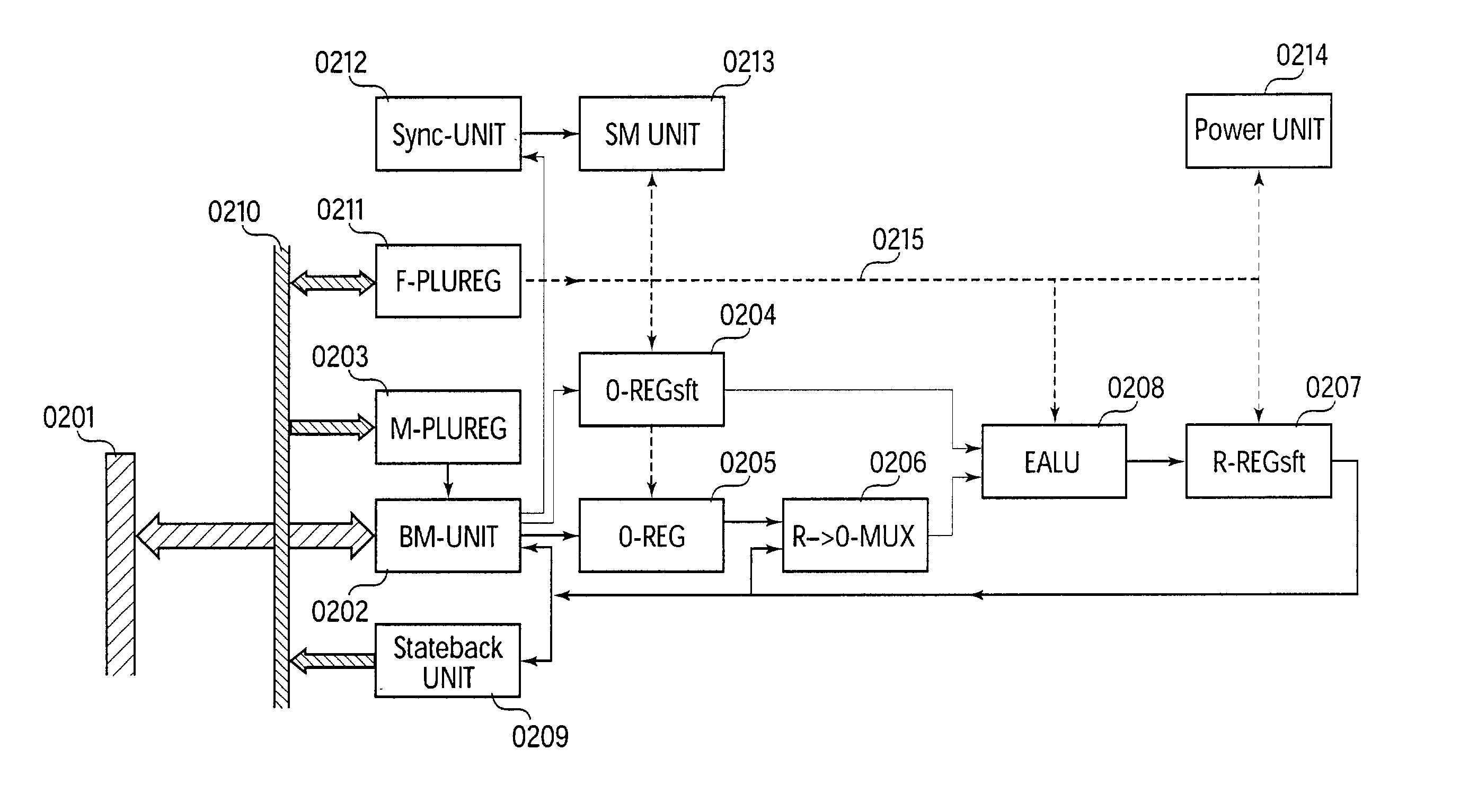

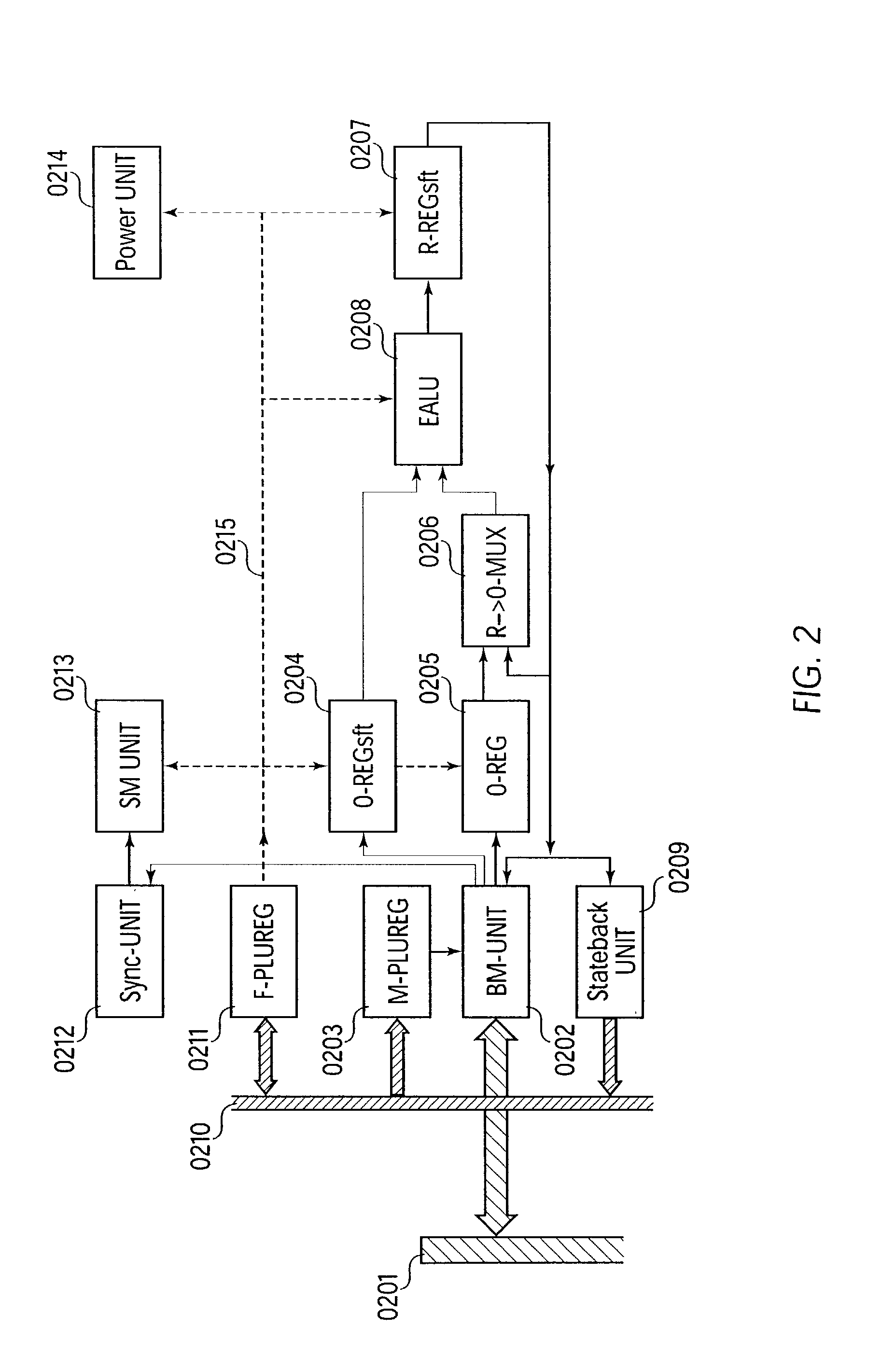

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com