Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

203 results about "And logic unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

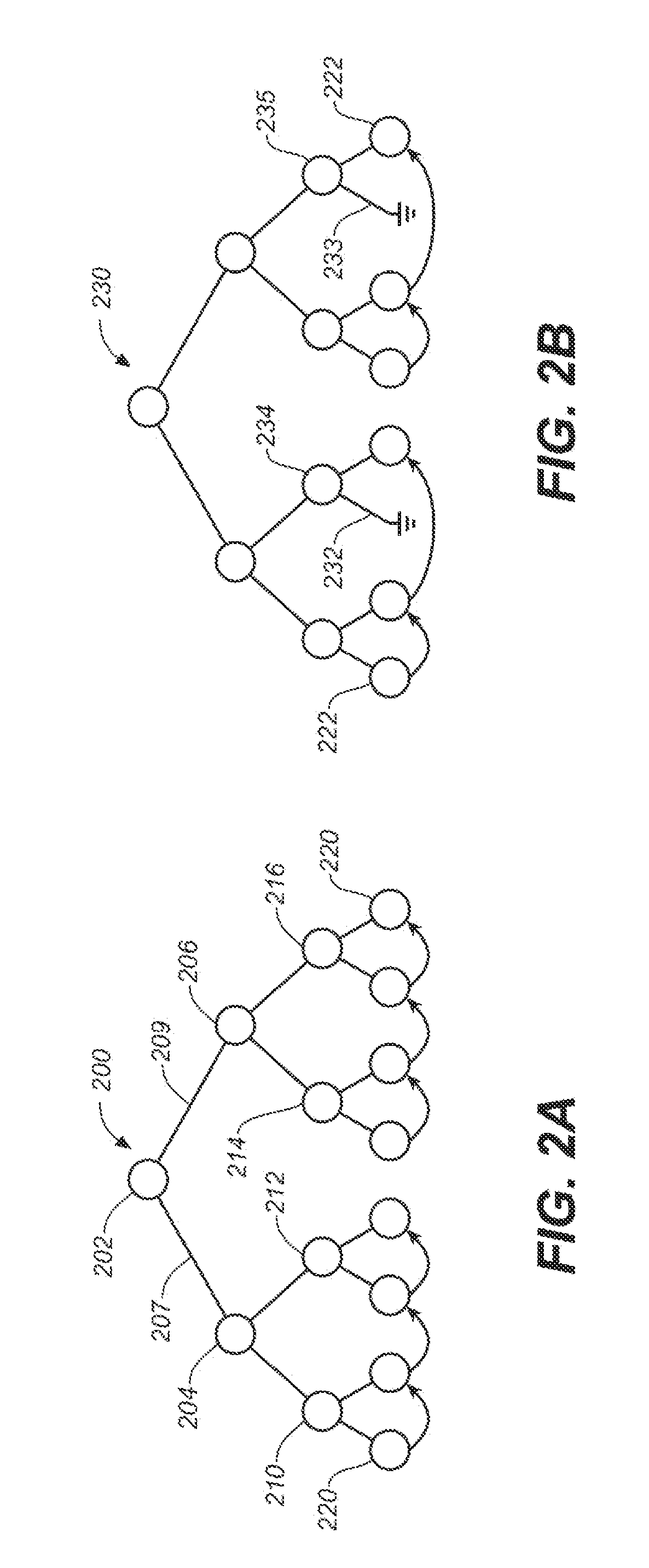

Method and apparatus for communications using turbo like codes

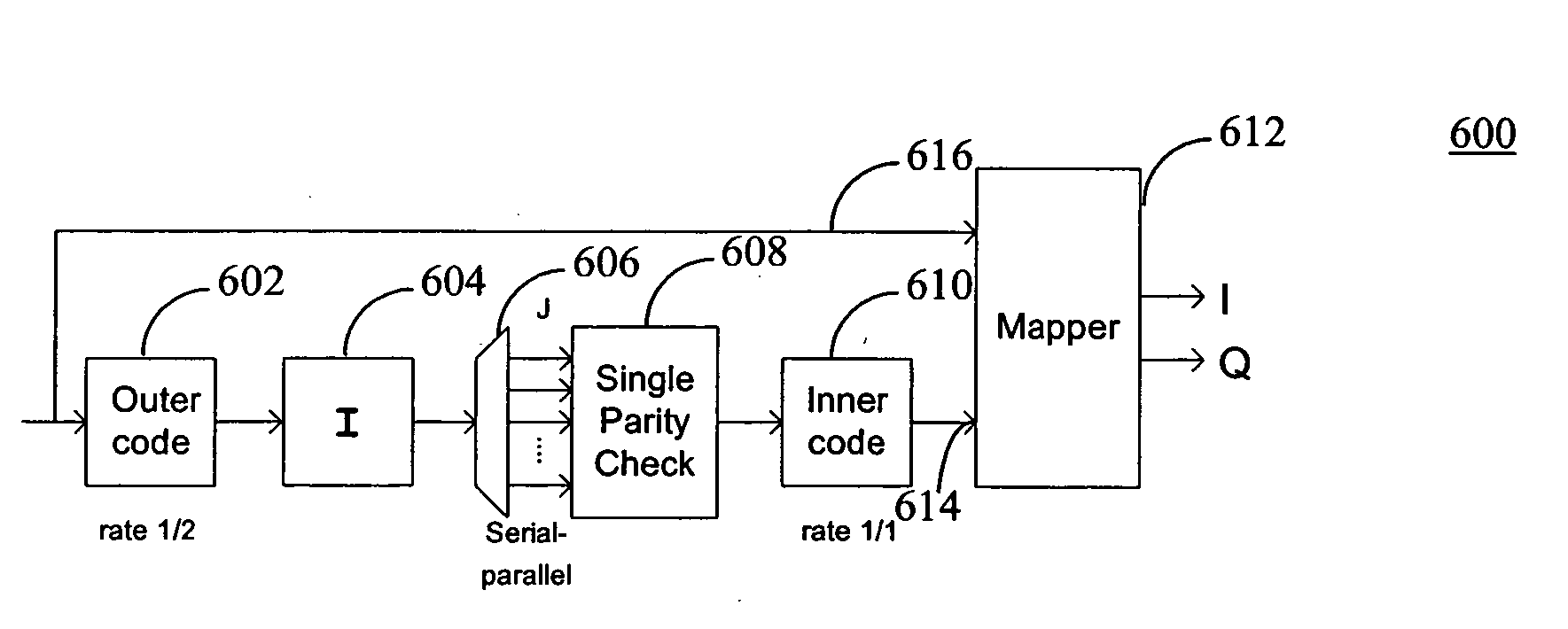

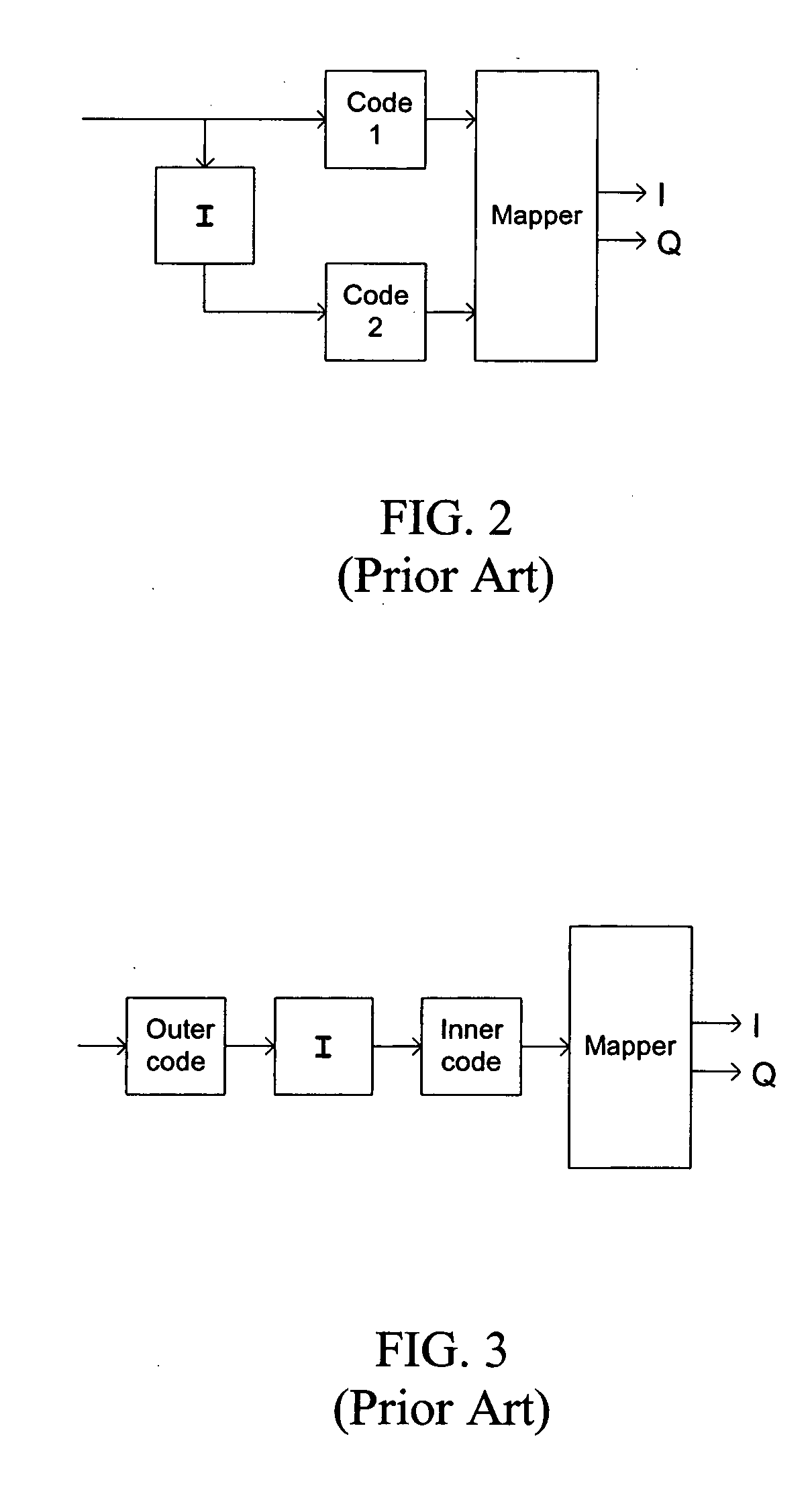

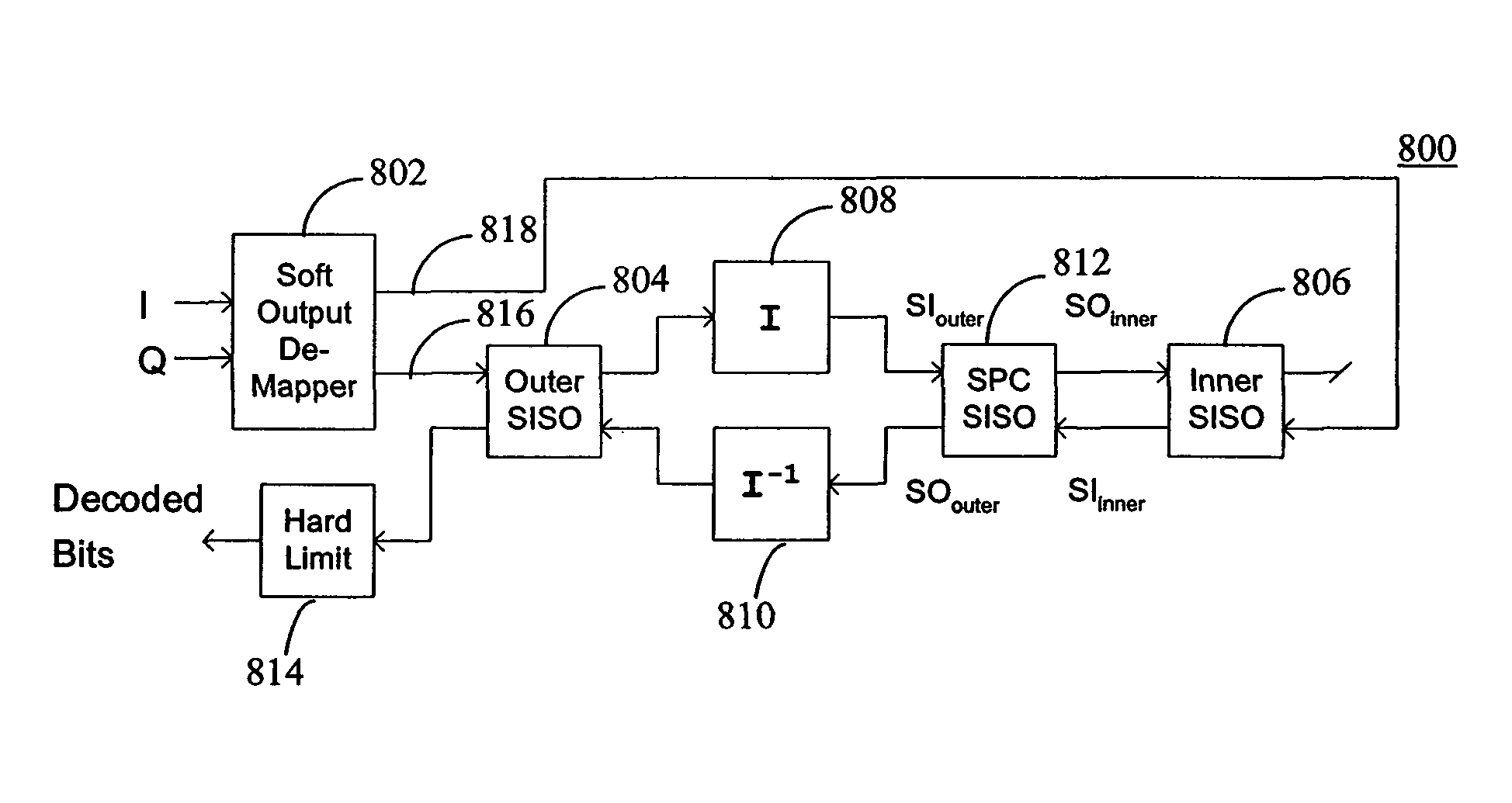

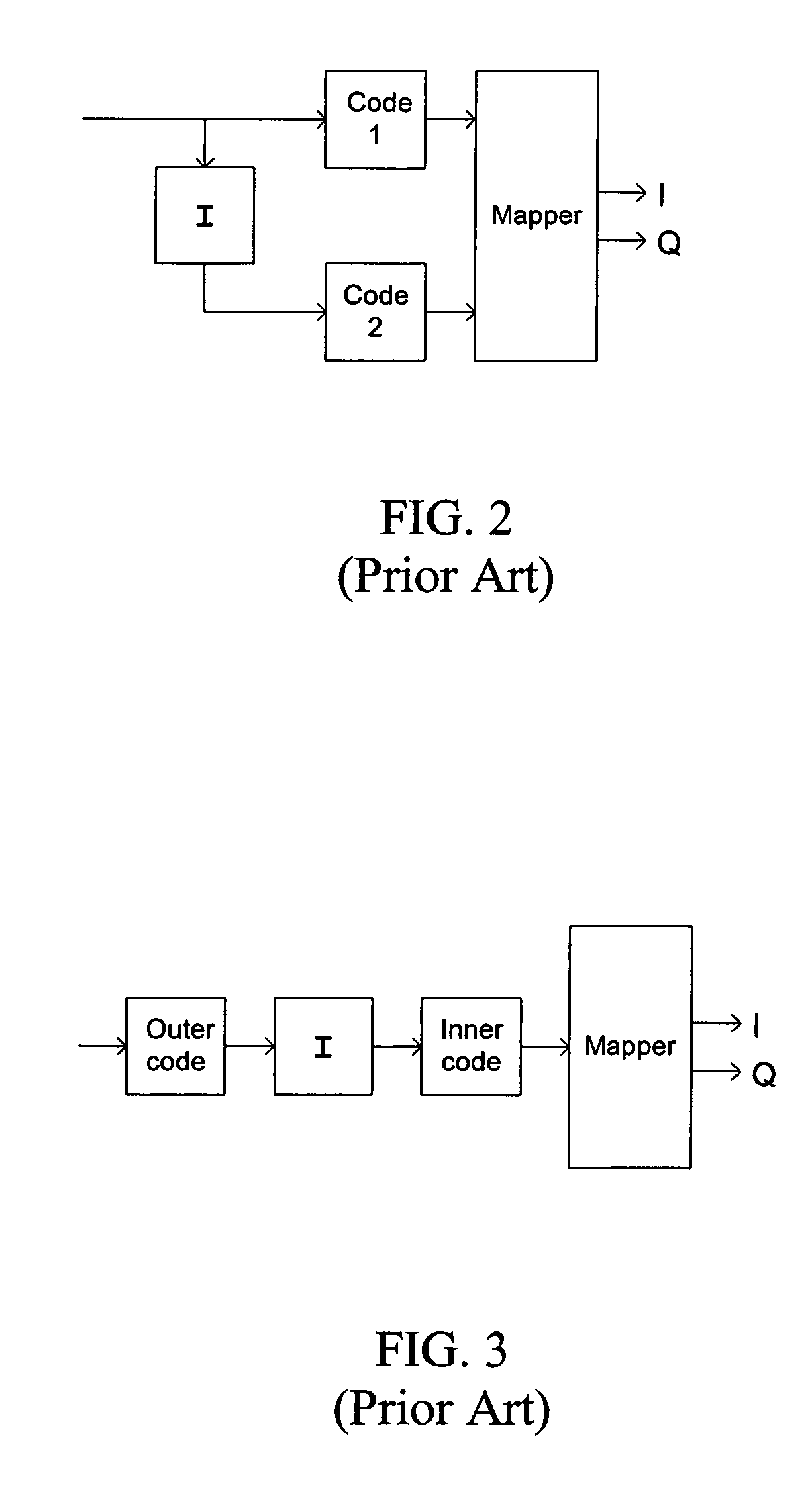

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

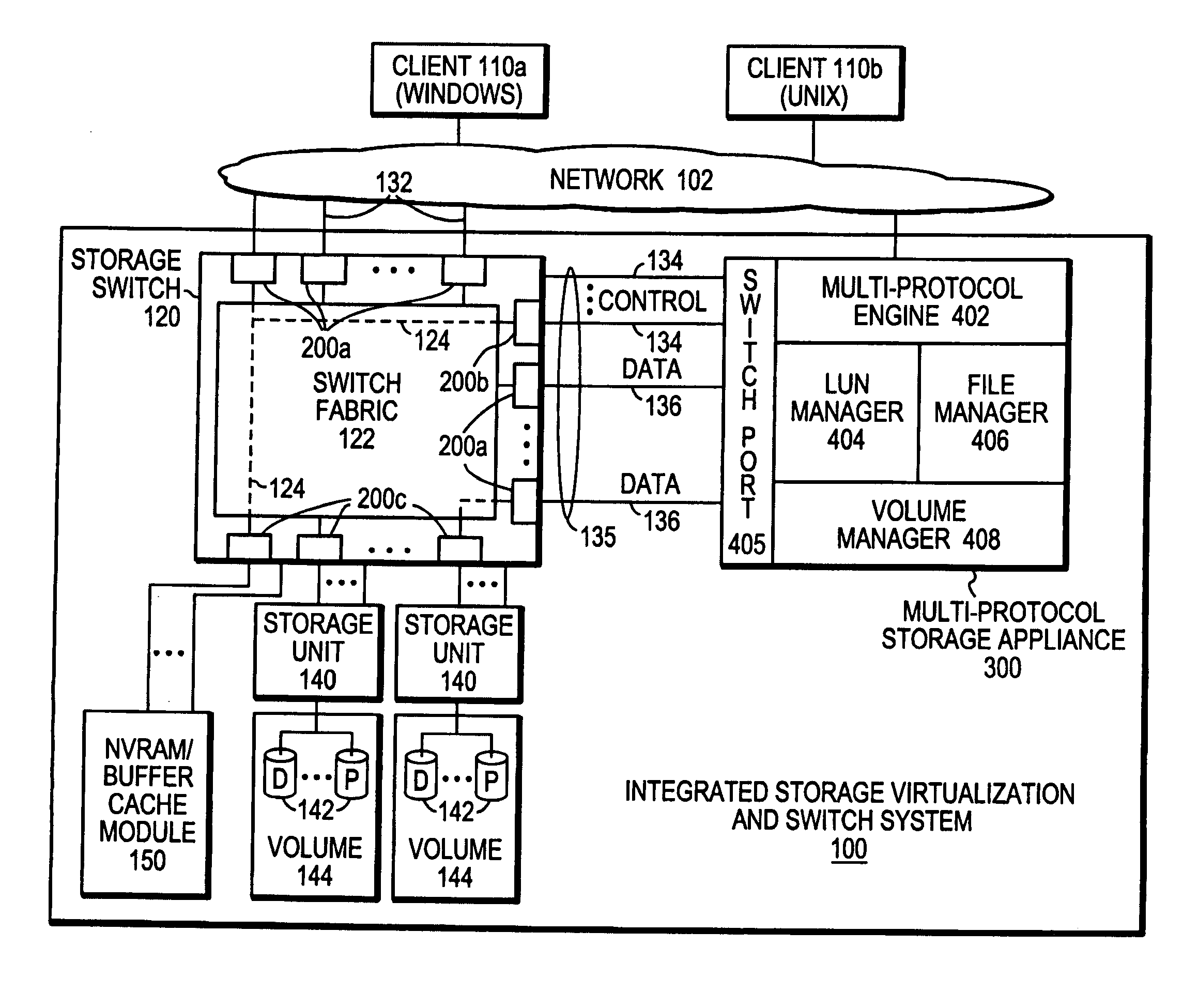

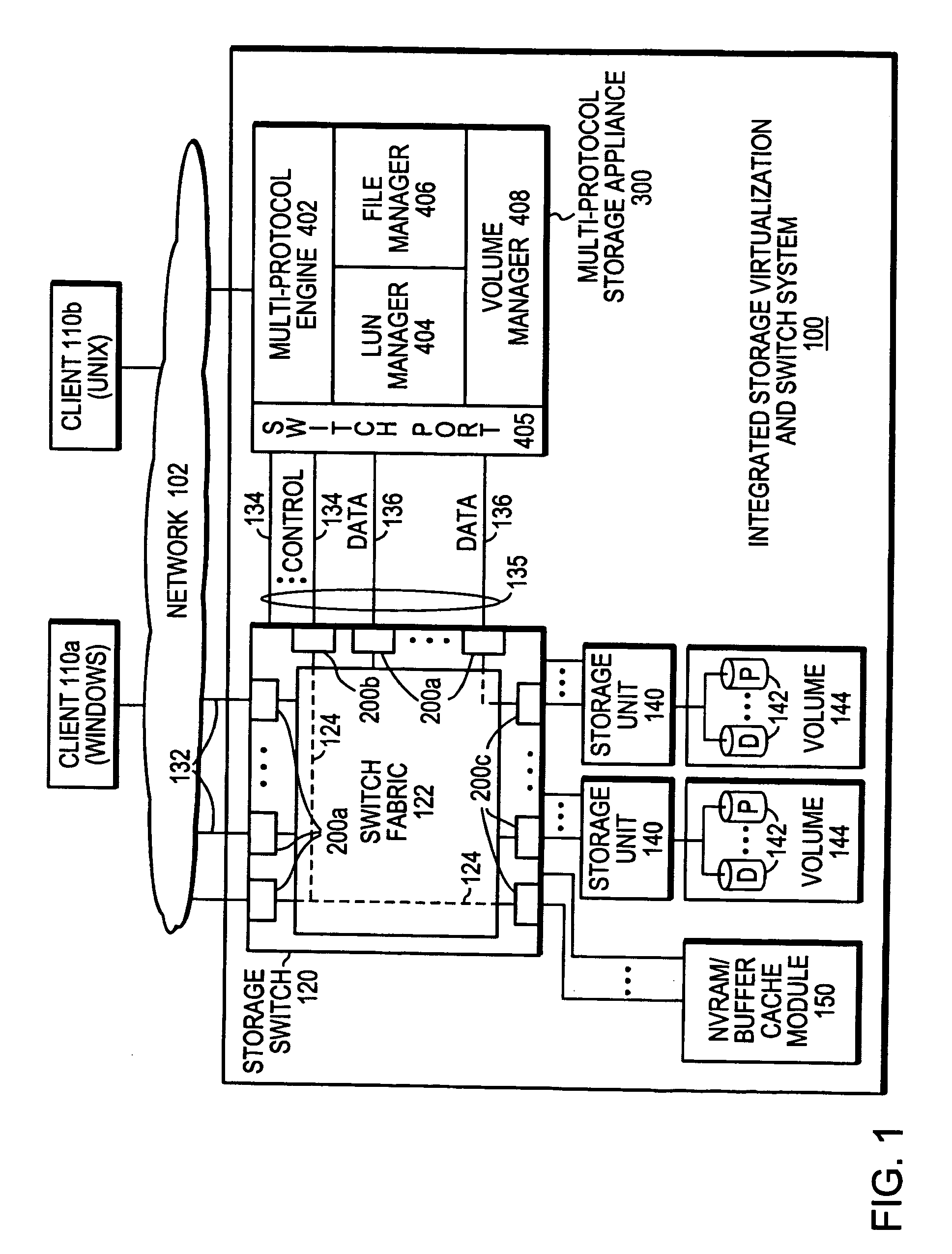

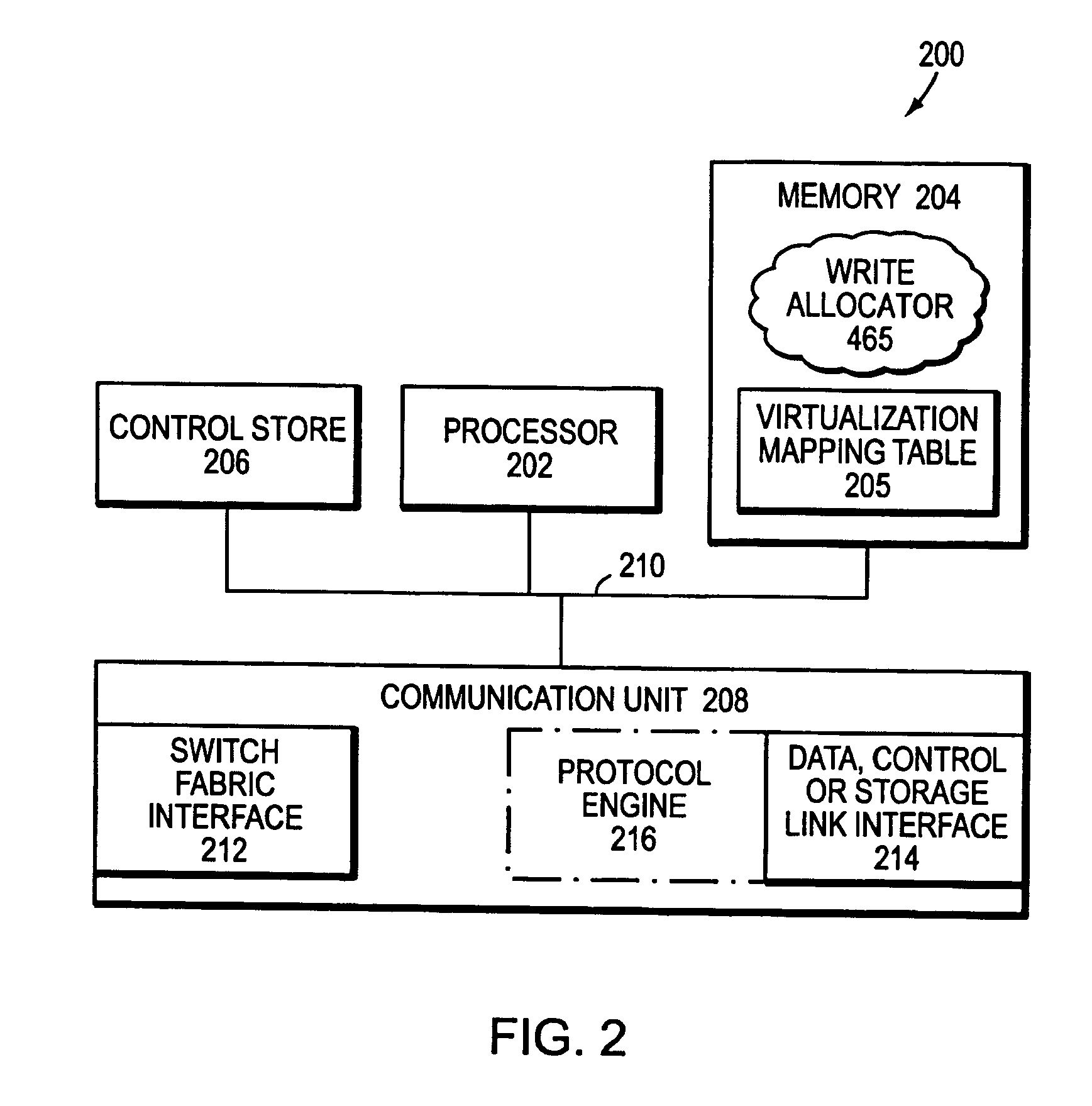

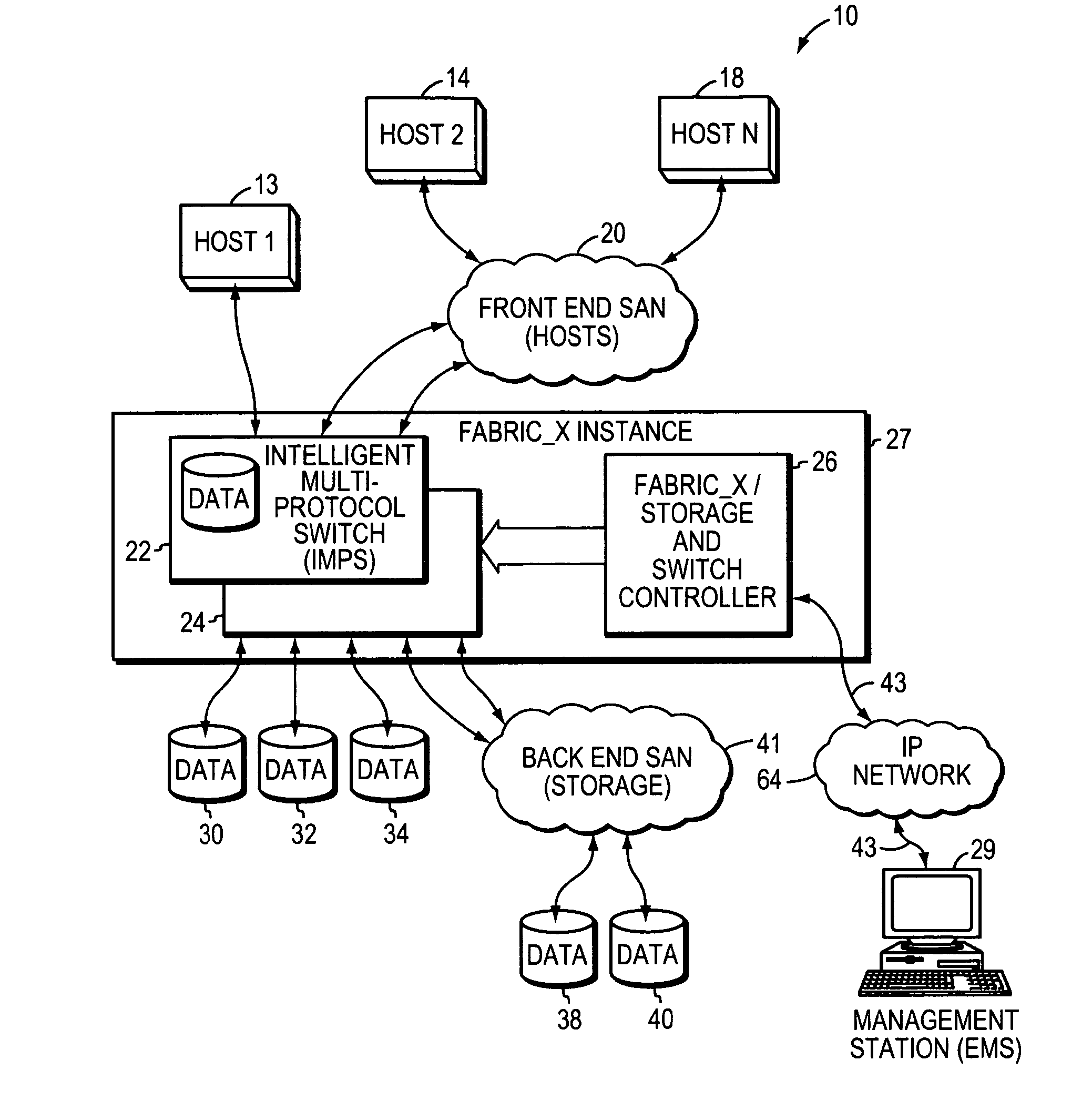

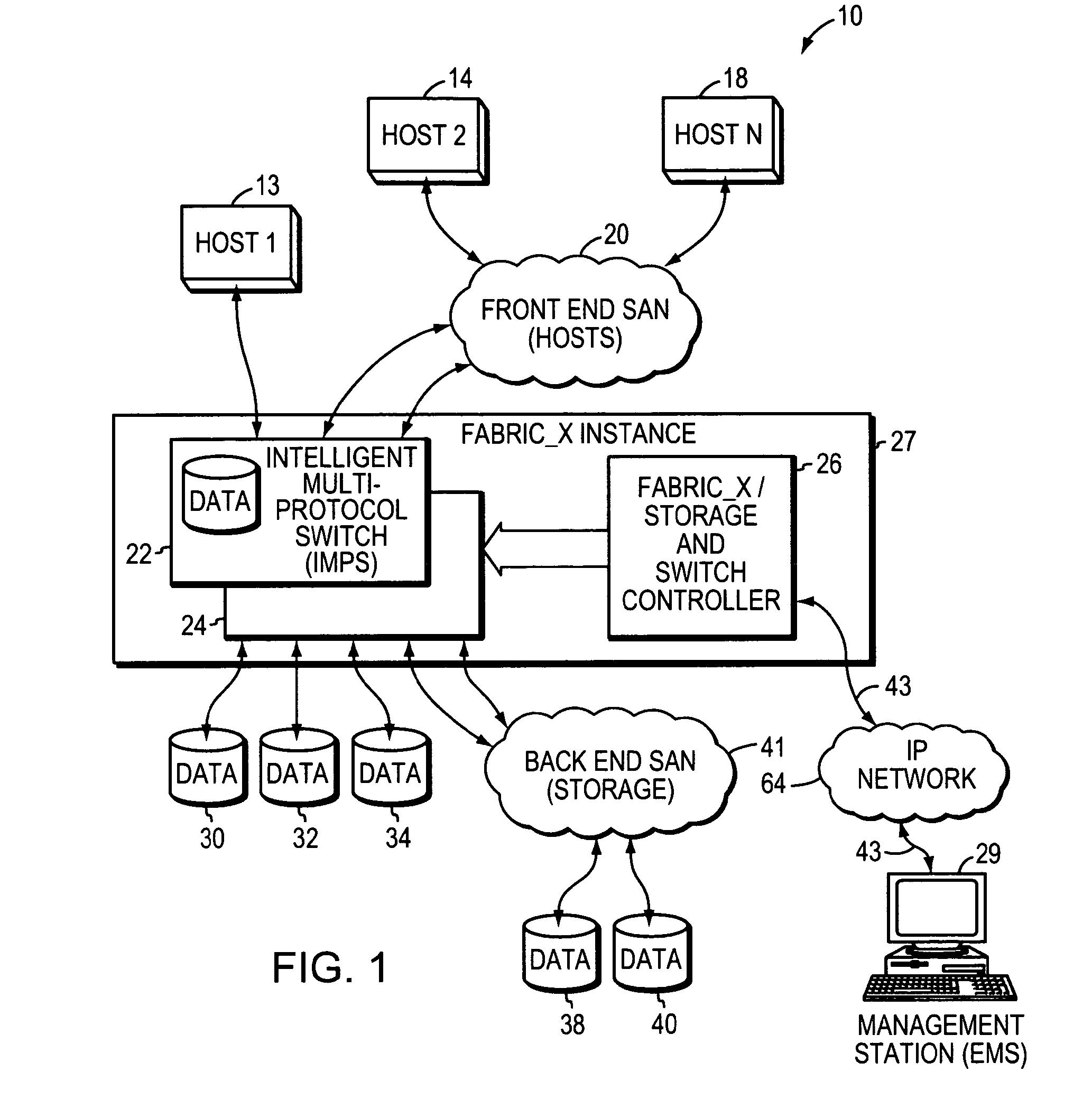

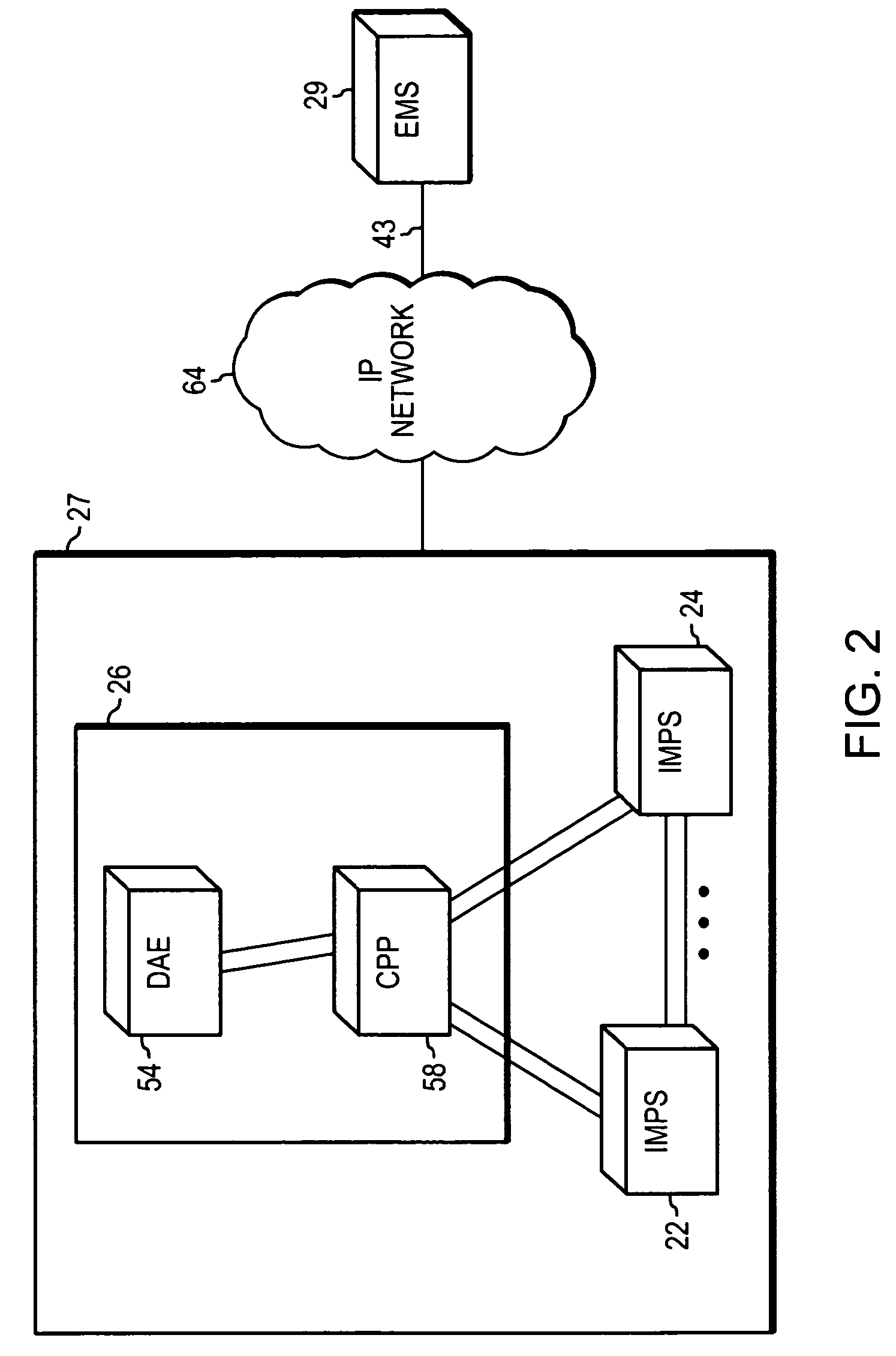

Integrated storage virtualization and switch system

ActiveUS20060206603A1Reduce sizeImprove connectivityDigital computer detailsTransmissionOperational systemFile system

A system integrates an intelligent storage switch with a flexible virtualization system to enable efficient service of file and block protocol data access requests for information stored on the system. A storage operating system executing on a storage system coupled to the switch implements the virtualization system to provide a unified view of storage to clients by logically organizing the information as named files, directories and logical unit numbers. The virtualization system is illustratively embodied as a file system having a write allocator configured to provide a flexible block numbering policy that addresses volume management capabilities, such as storage virtualization, at a finer granularity (e.g., a single block) than that of previous non-flexible storage virtualization schemes. The flexible block numbering policy also yields substantial benefits in terms of increased write efficiency and elimination of storage “hot spots”, as well as a compelling point-in-time read-only data image (snapshot) mechanism.

Owner:NETWORK APPLIANCE INC

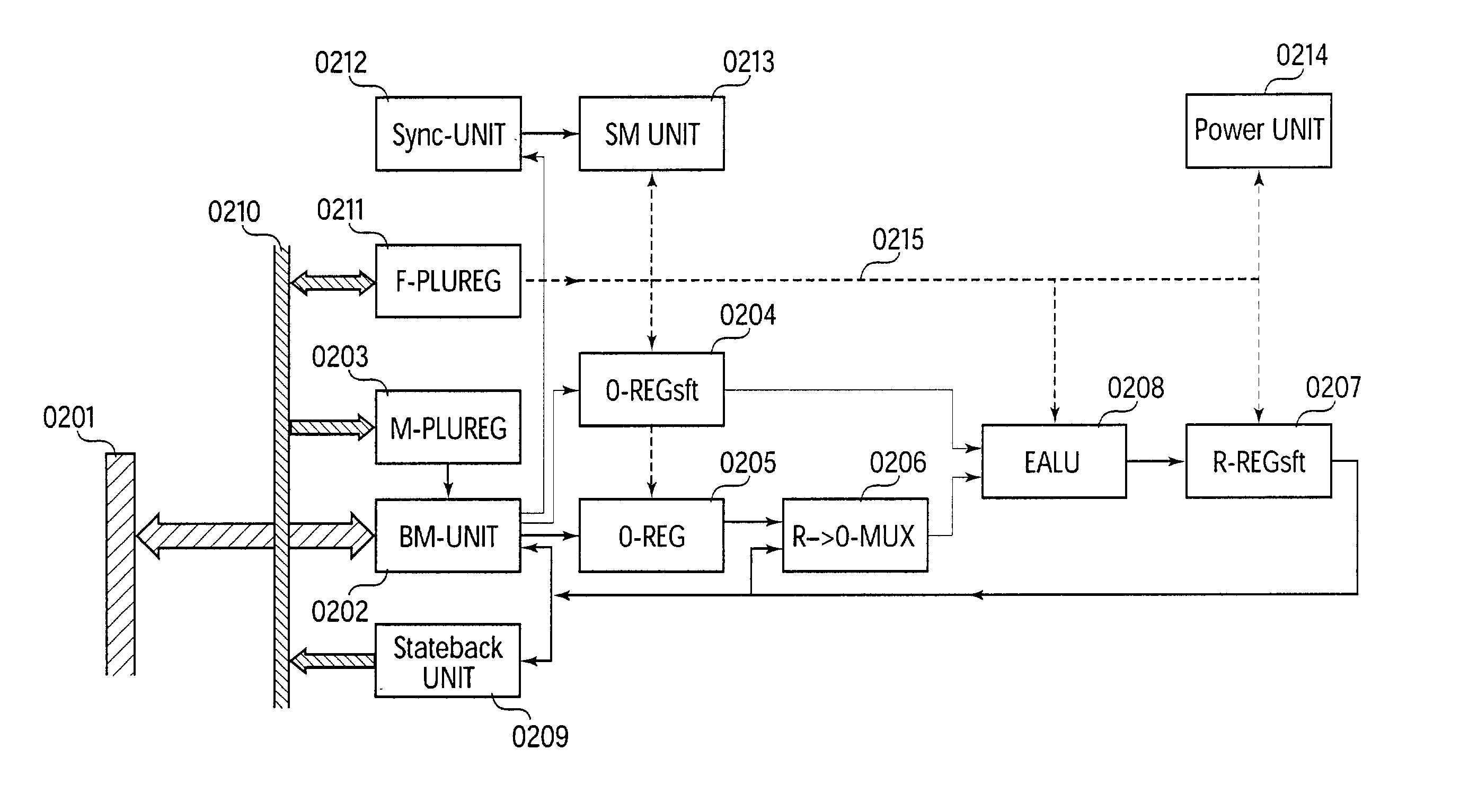

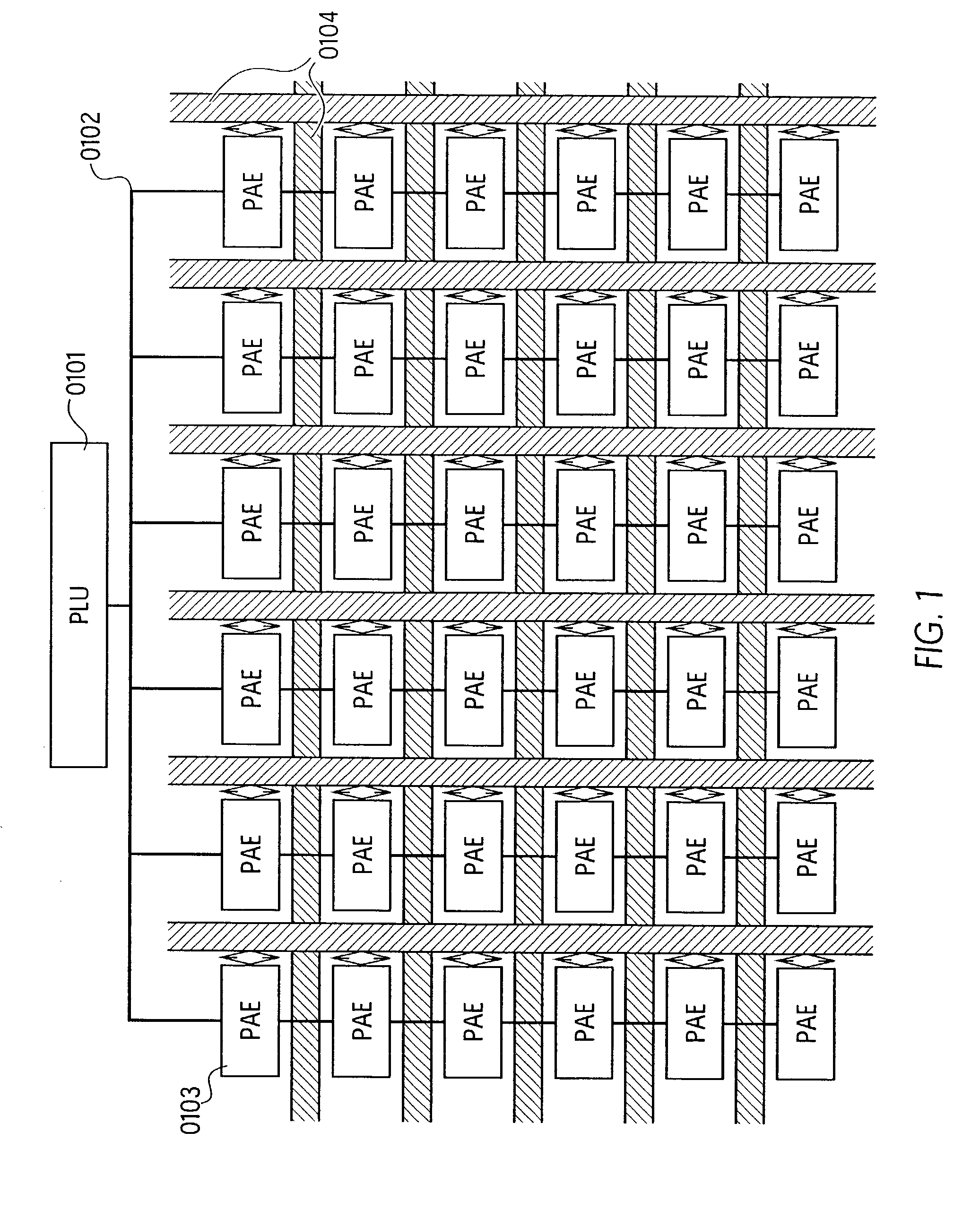

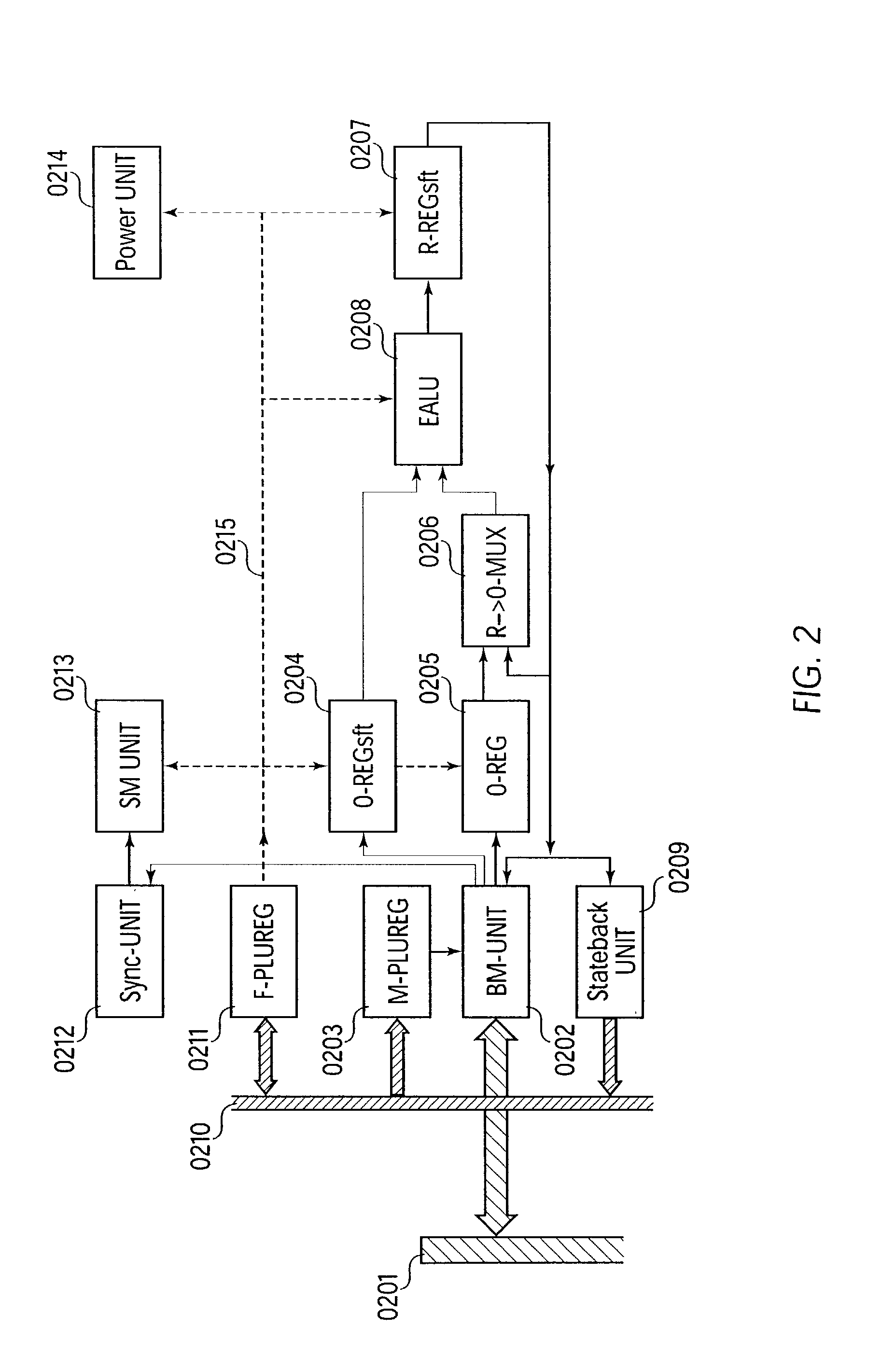

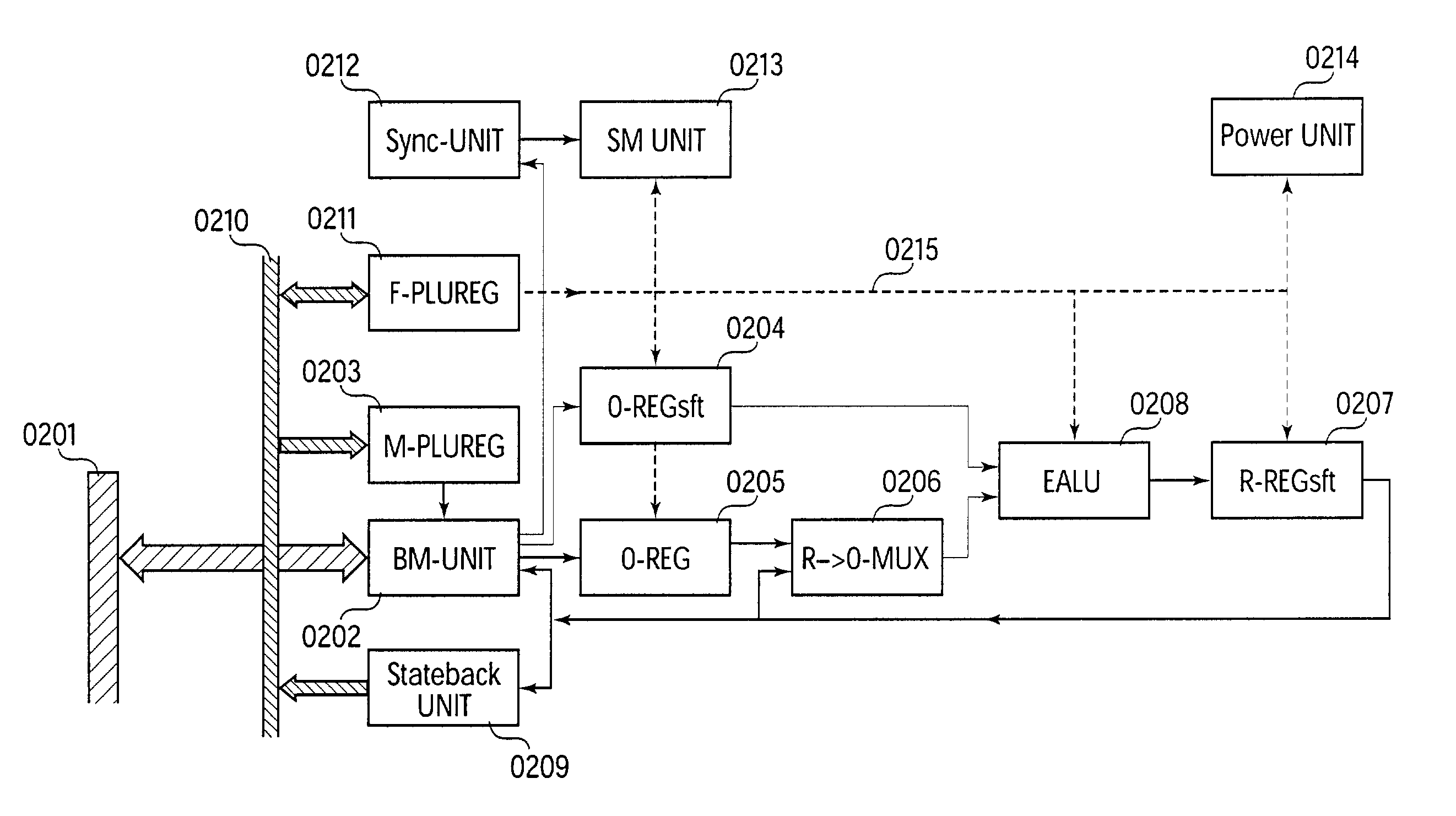

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

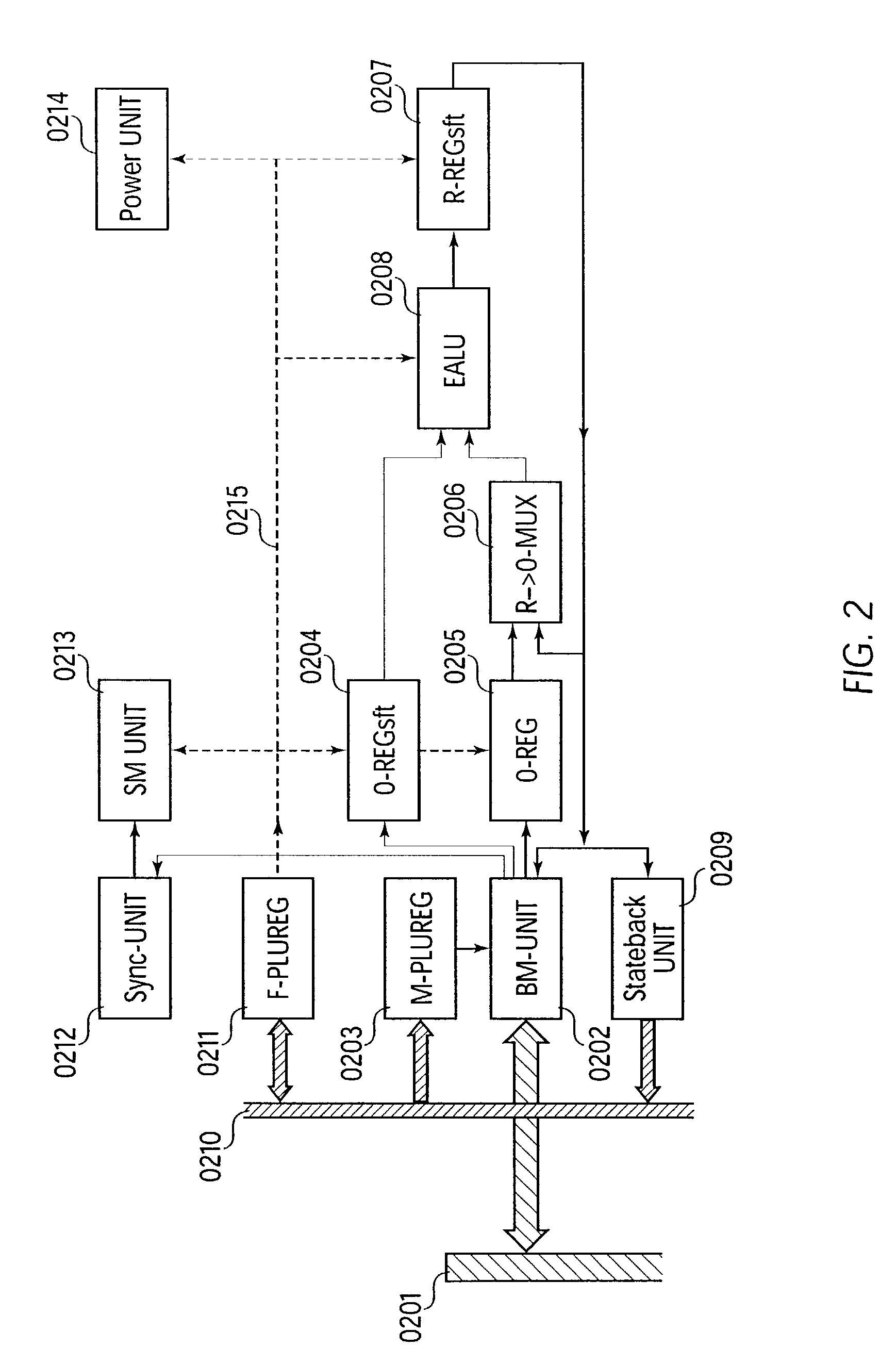

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

Method and apparatus for communications using turbo like codes

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

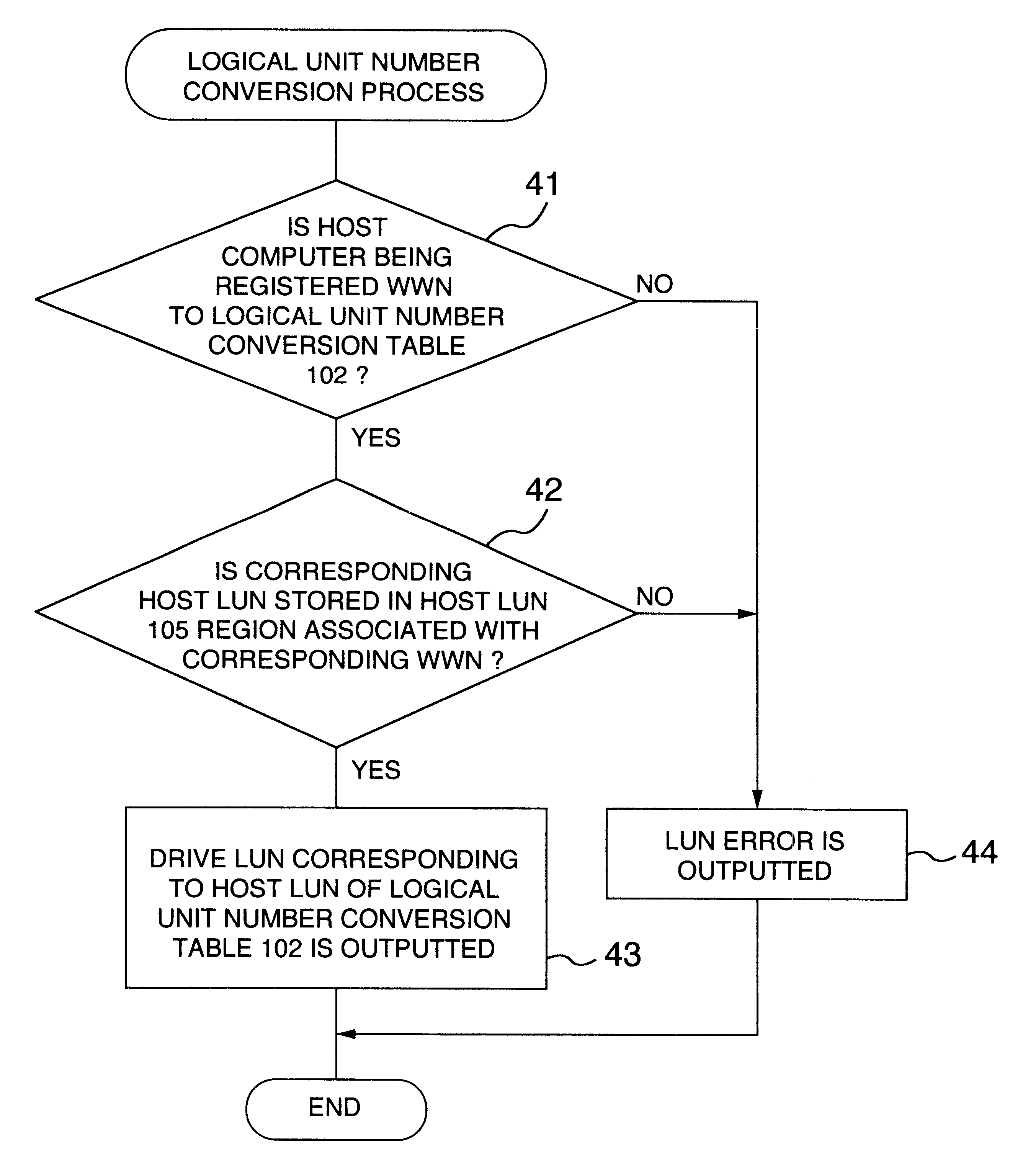

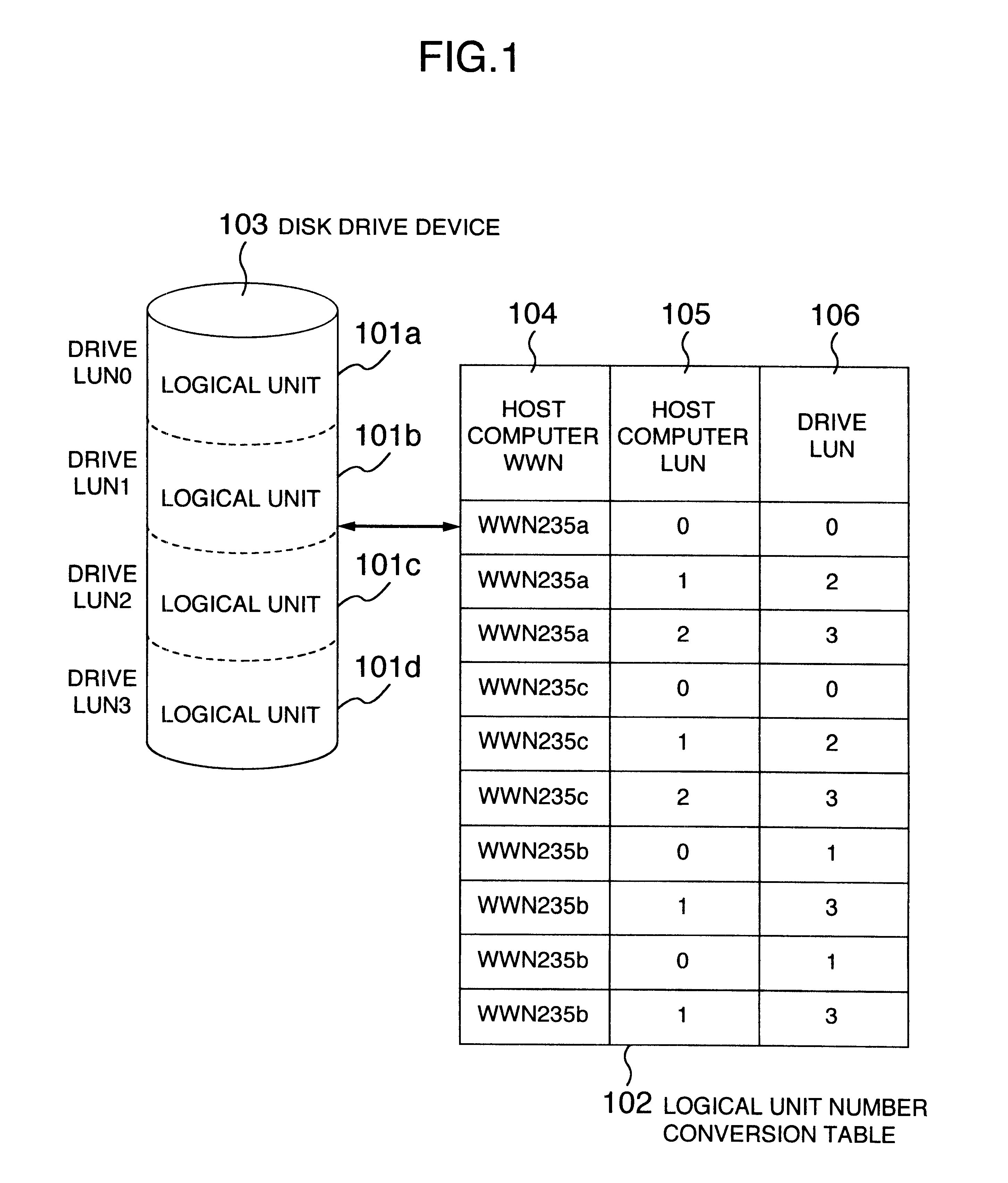

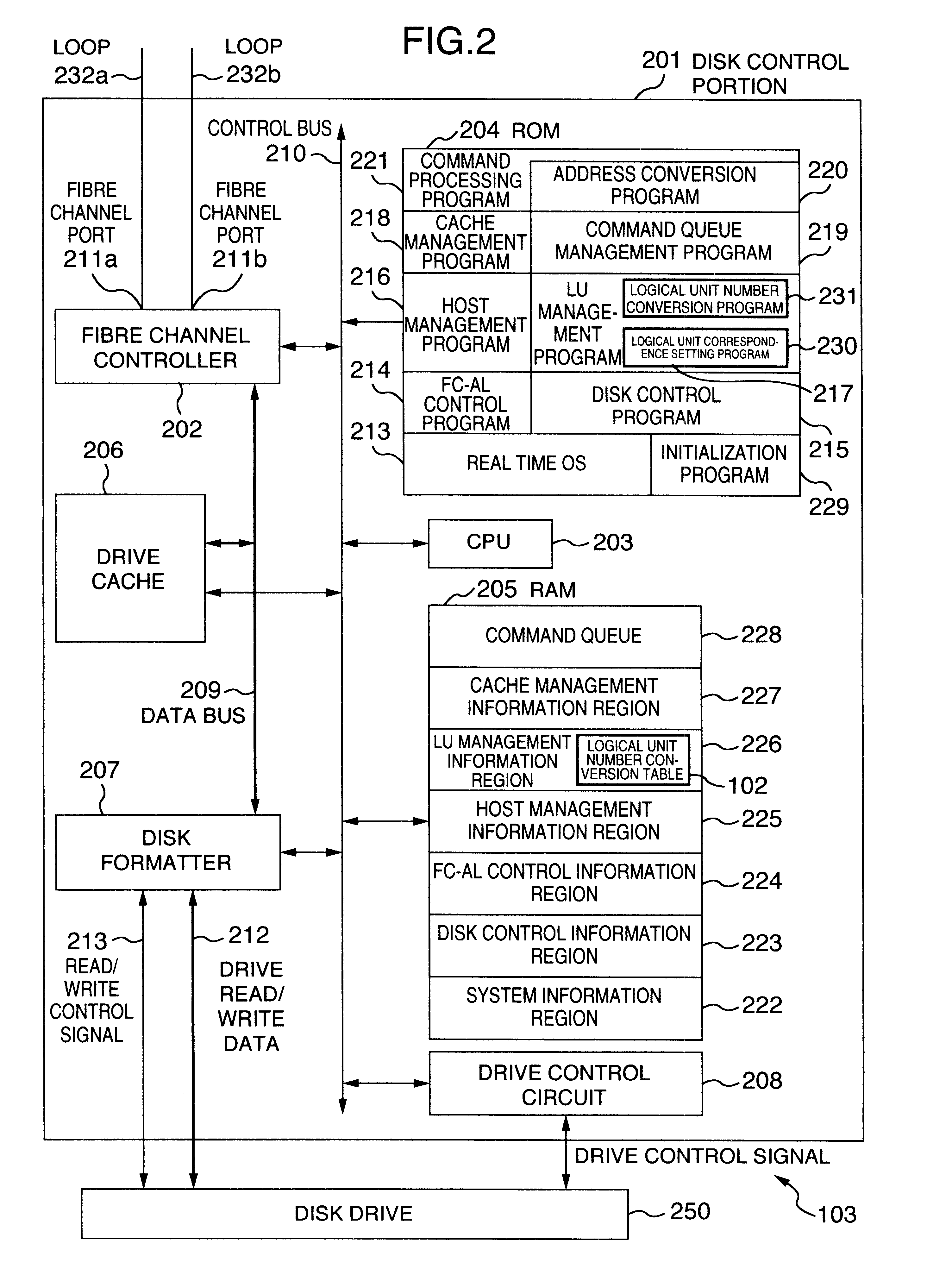

Magnetic disk apparatus

A disk storage apparatus includes a logical unit number correspondence memory for storing the correspondence and the logical unit number designated by a host computer and the logical unit number of the disk storage apparatus, a logical unit number conversion program for converting the logical unit number designated by the host computer to the logical unit number of the disk storage apparatus, and a logical unit correspondence setting program for storing the correspondence of the logical unit number designated by the host computer to the logical unit number of the disk storage in the logical unit number correspondence memory thereby, a plurality of host computers sharing at least one disk storage apparatus.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD

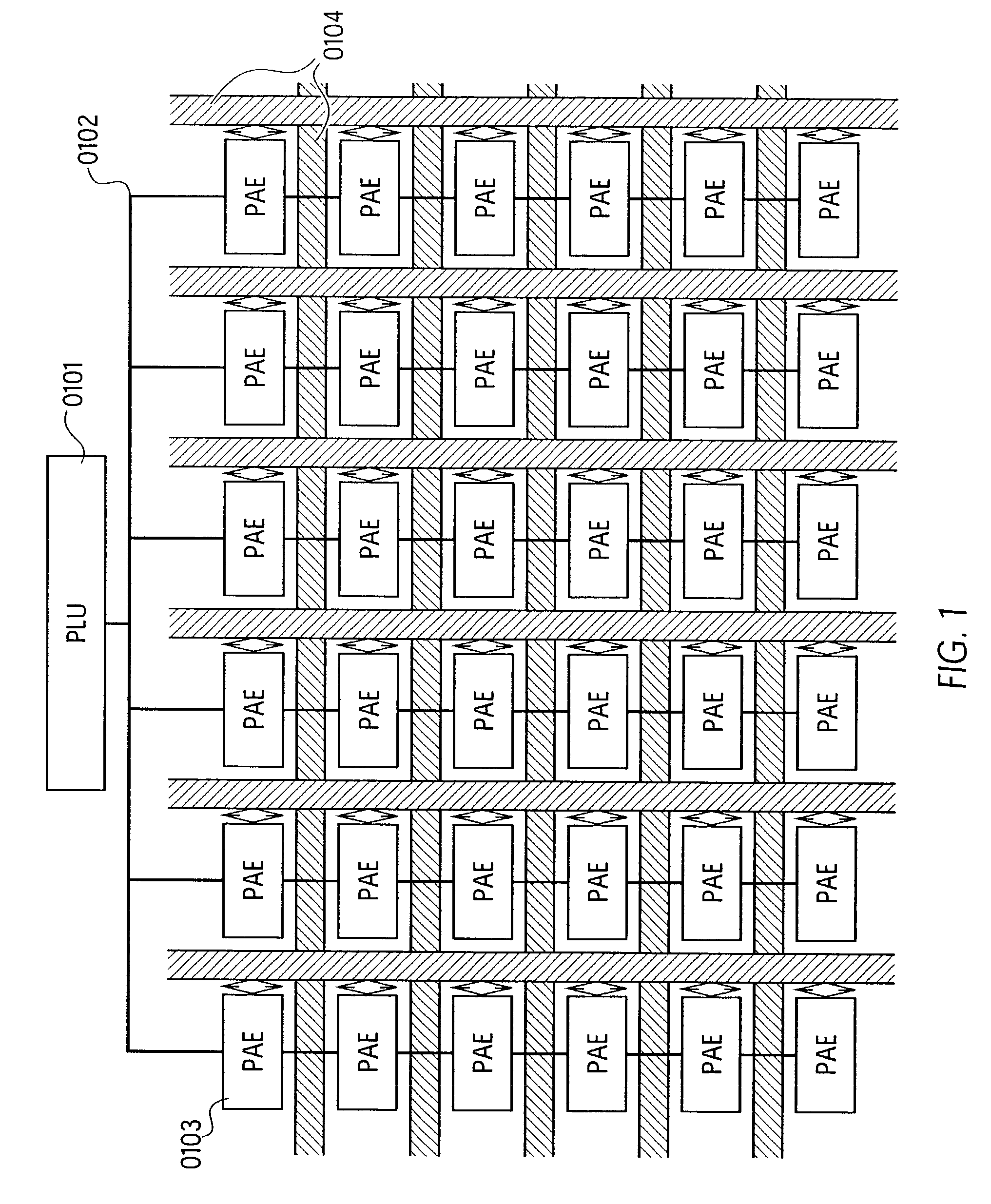

Reconfigurable multidimensional array processor allowing runtime reconfiguration of selected individual array cells

InactiveUS7237087B2Small volumeEffects spaceEnergy efficient ICTMultiple digital computer combinationsClock rateAnd logic unit

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

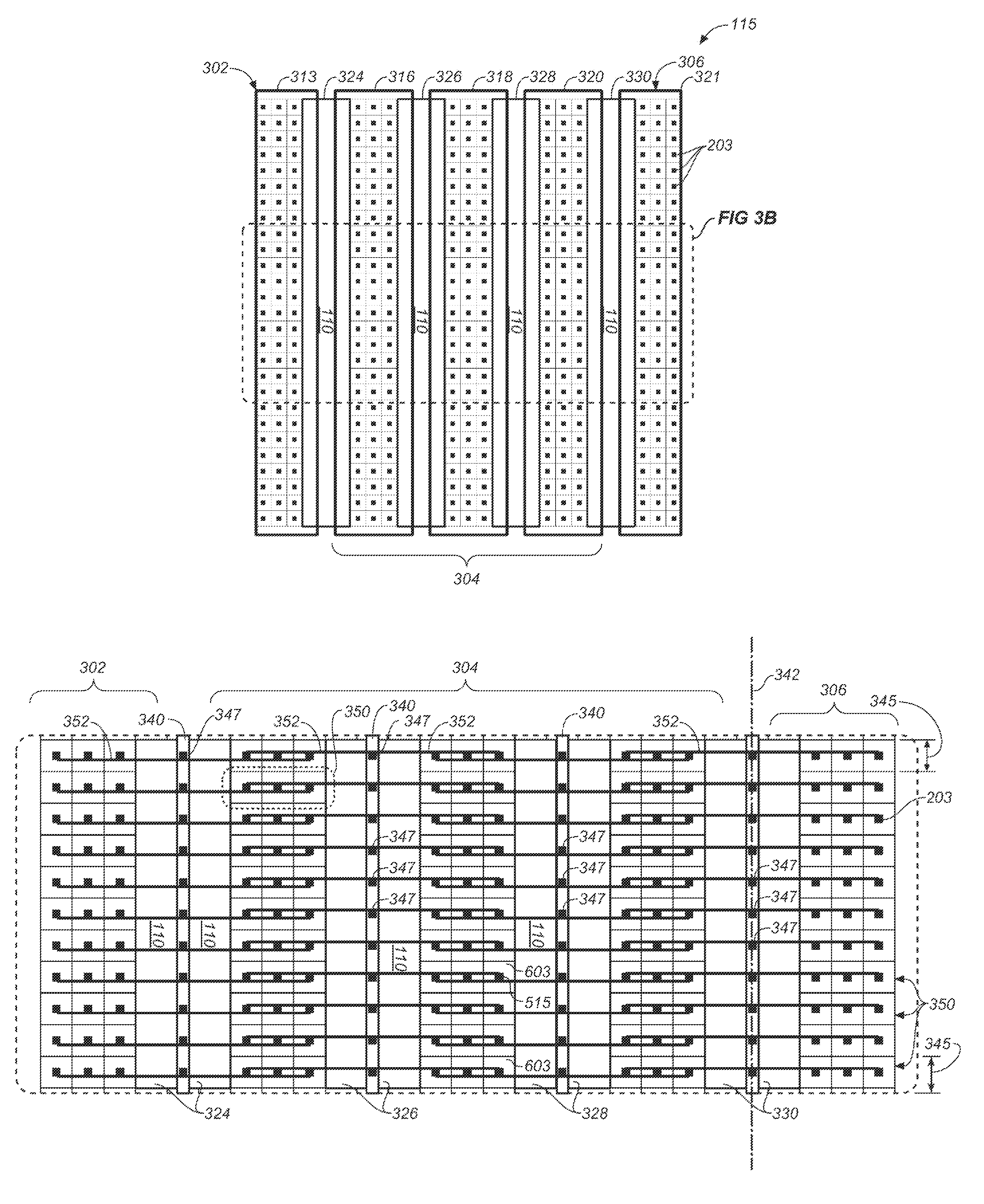

Aligned logic cell grid and interconnect routing architecture

ActiveUS20060195810A1Eliminate misalignmentCAD circuit designSpecial data processing applicationsLogic cellAnd logic unit

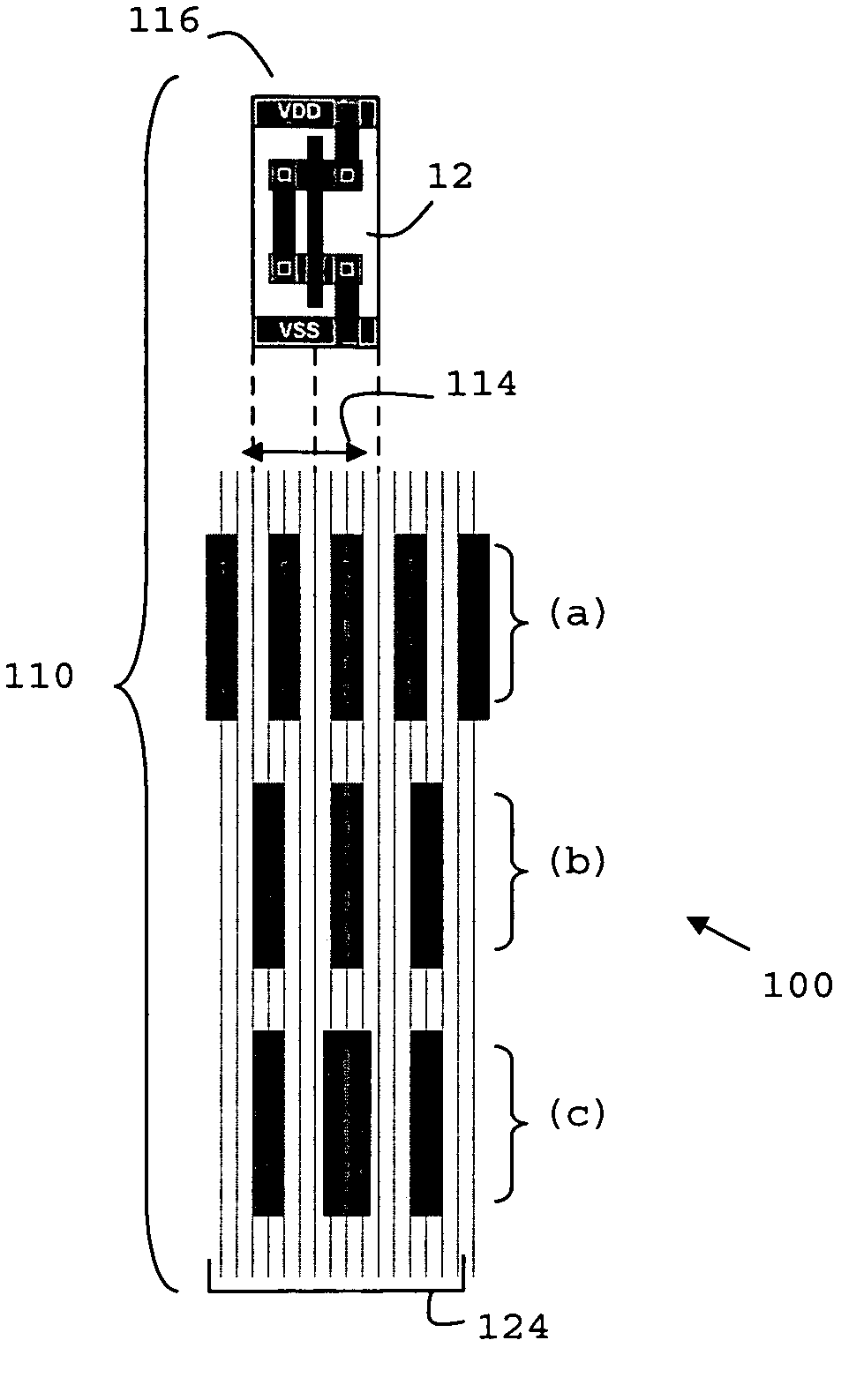

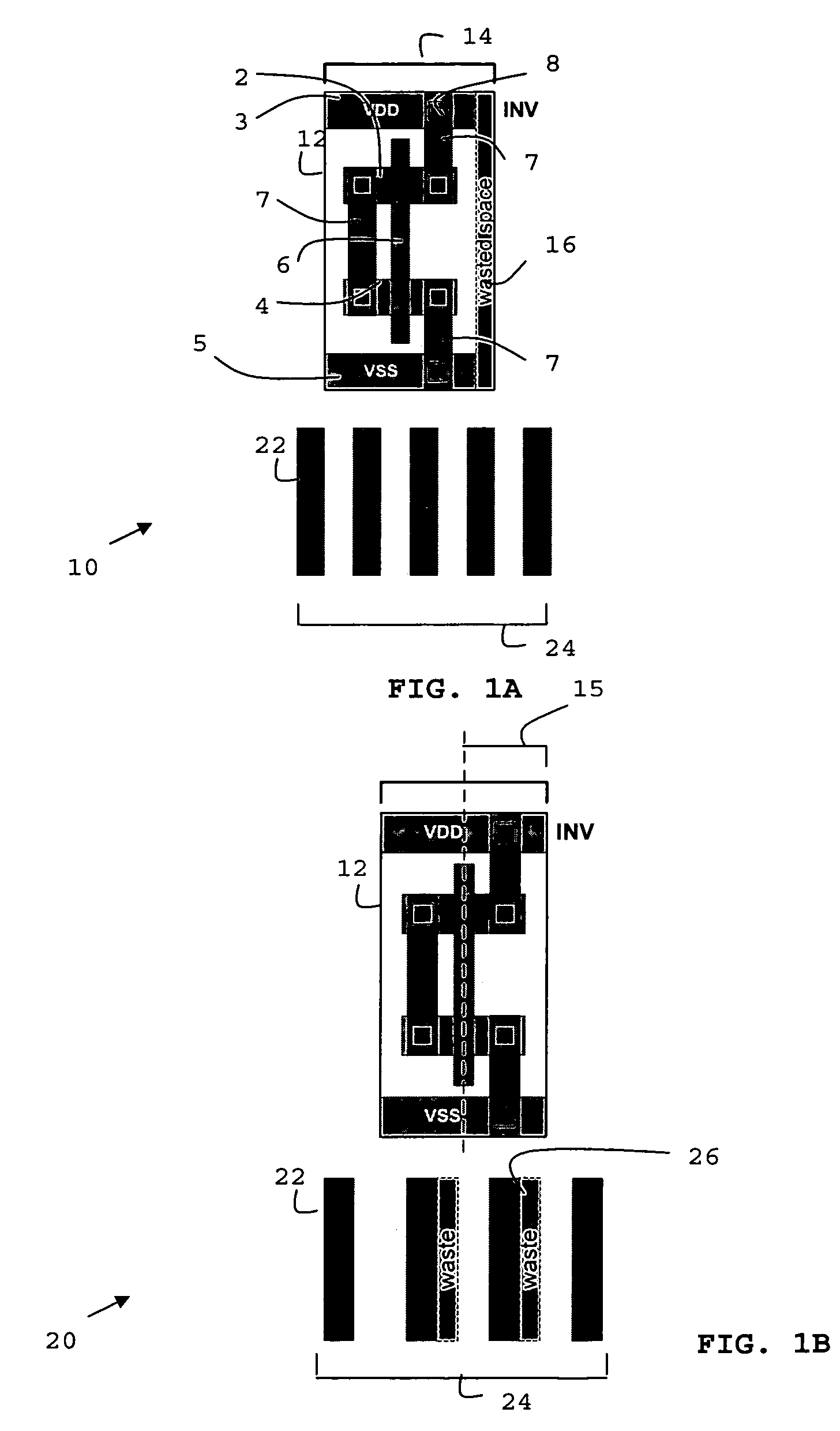

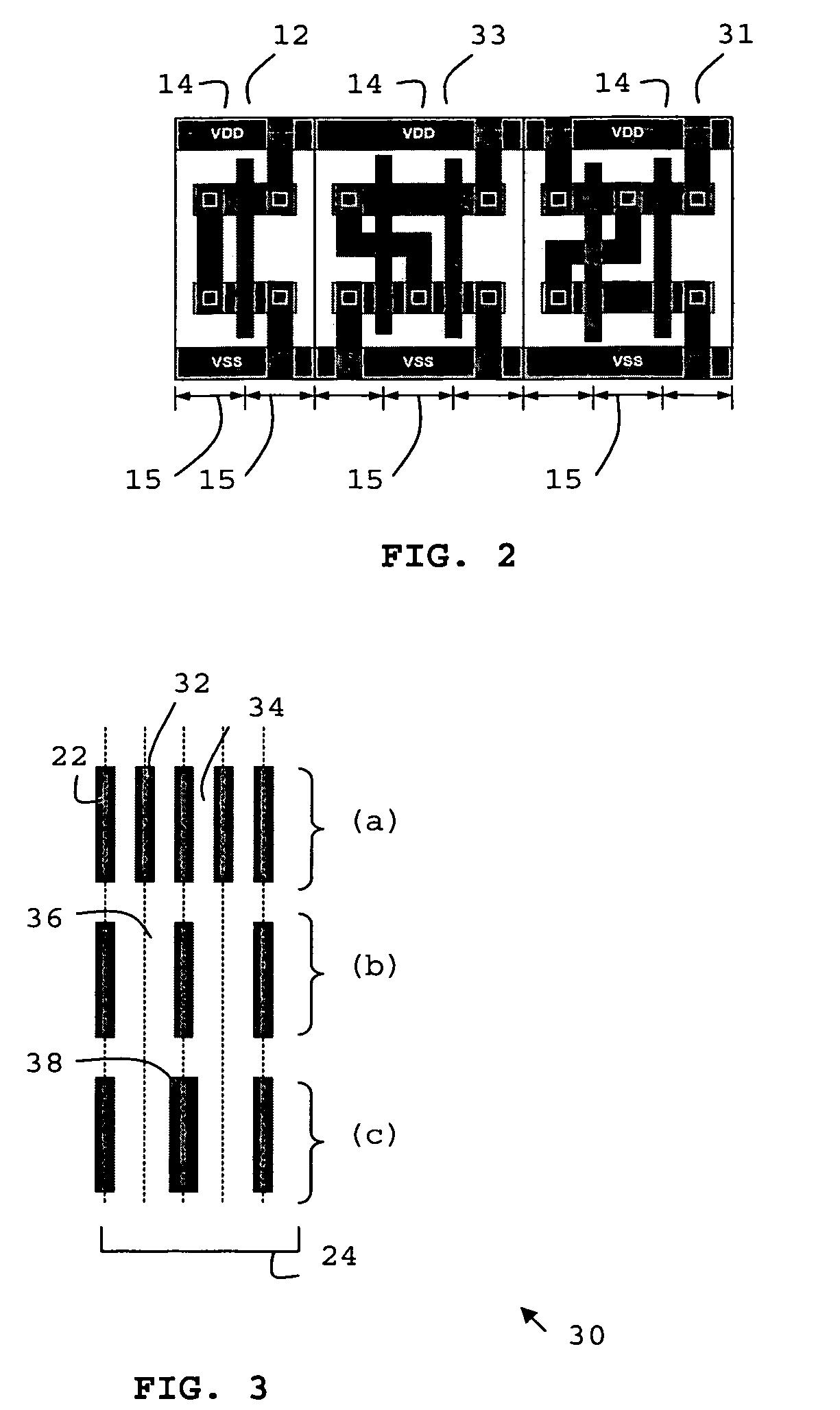

A method (150) for defining an aligned logic cell grid and interconnect layout of a semiconductor integrated circuit having a logic cell (12) is disclosed. The interconnect layout is resized in accordance with a highest common denominator of an initial routing pitch (24) of the interconnect layout and a transistor pitch (14) of the logic cell. The cell grid is aligned with the resized routing pitch (124) which provides efficient routing density and transistor performance, minimises excess transistor area and wire routing waste while maximising cell packing density.

Owner:ICERA INC

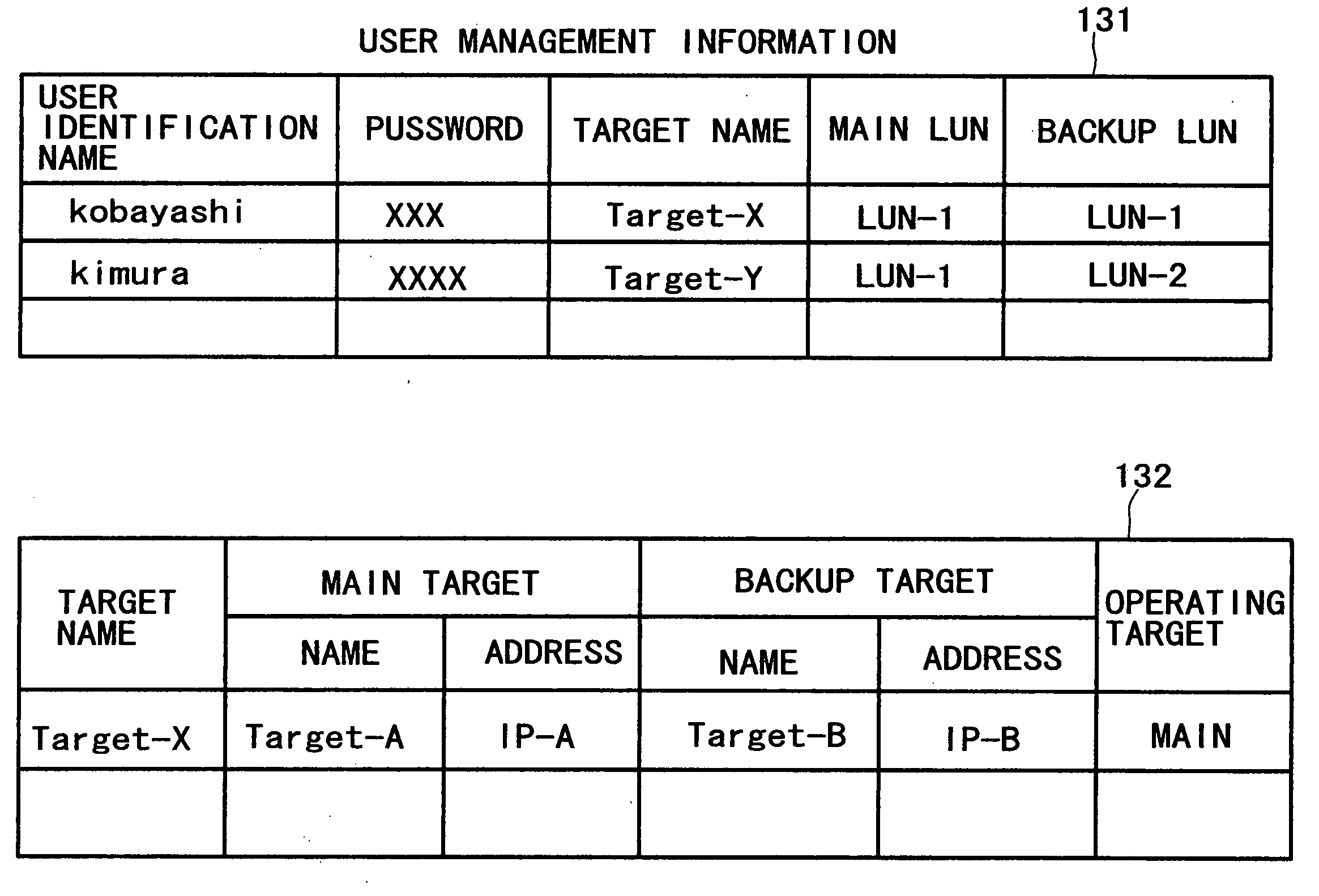

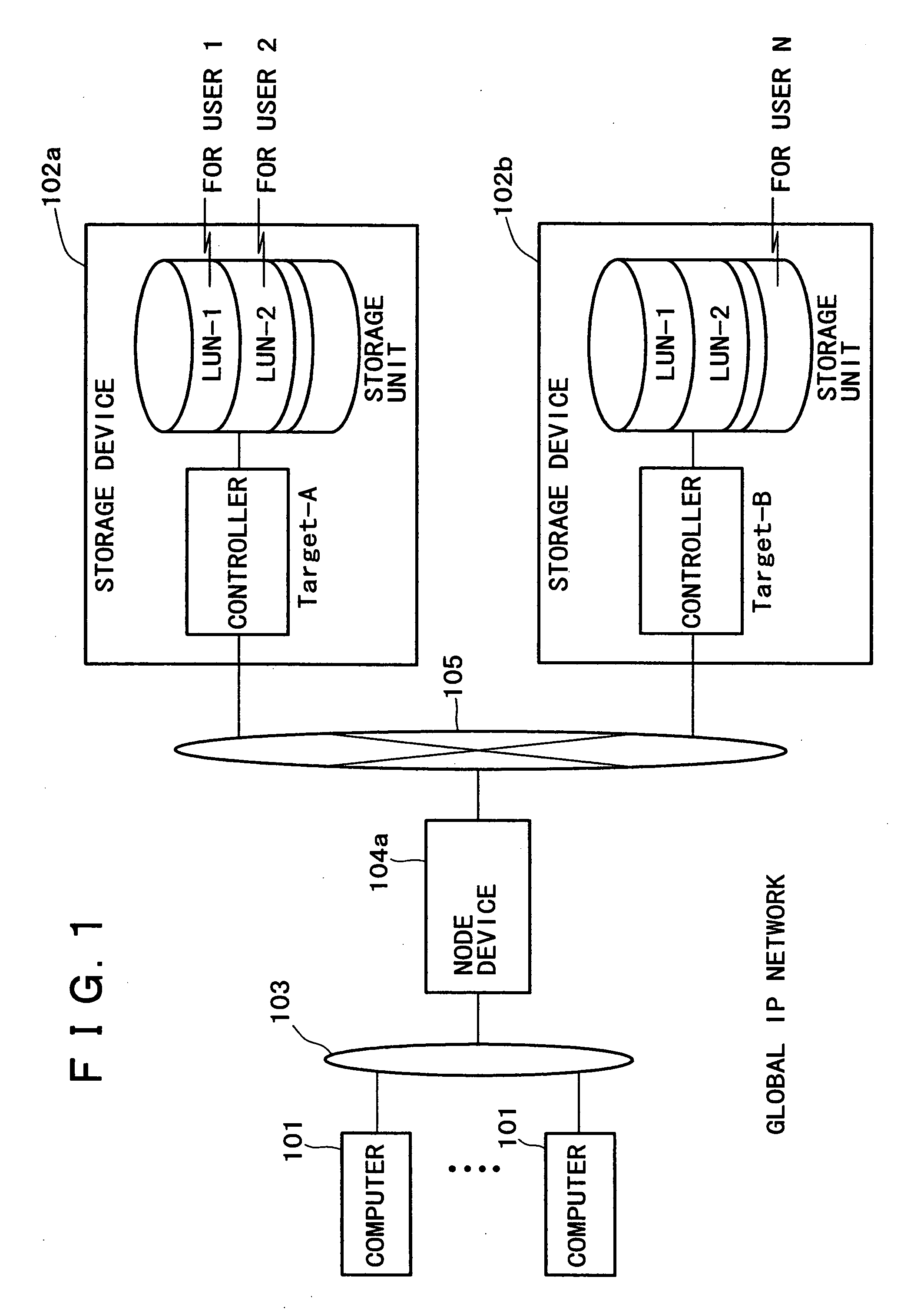

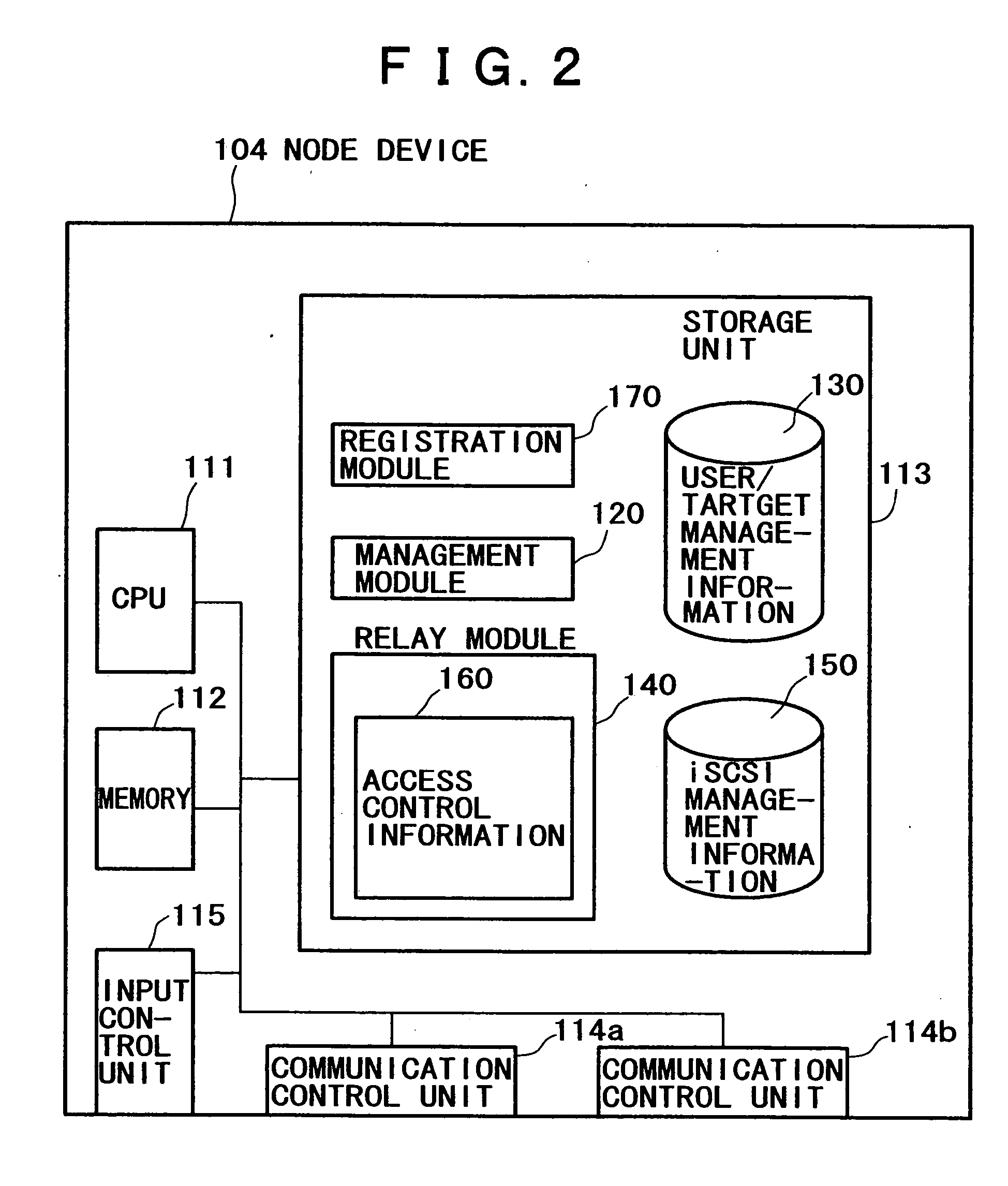

Computer system that a plurality of computers share a storage device

InactiveUS20050091333A1Reduce access loadEliminate delaysInput/output to record carriersUnauthorized memory use protectionPasswordAnd logic unit

A computer system includes: means for centrally managing user identification names and passwords that are assigned to users, target names of storage devices, addresses, and logical units; means for acquiring target names of storage devices and logical unit names from the user identification names and passwords; means for obtaining the addresses of the storage devices from the user identification names, passwords, and target names; and means for dynamically creating access control information of the logical units for each session in iSCSI session establishment processing.

Owner:HITACHI LTD

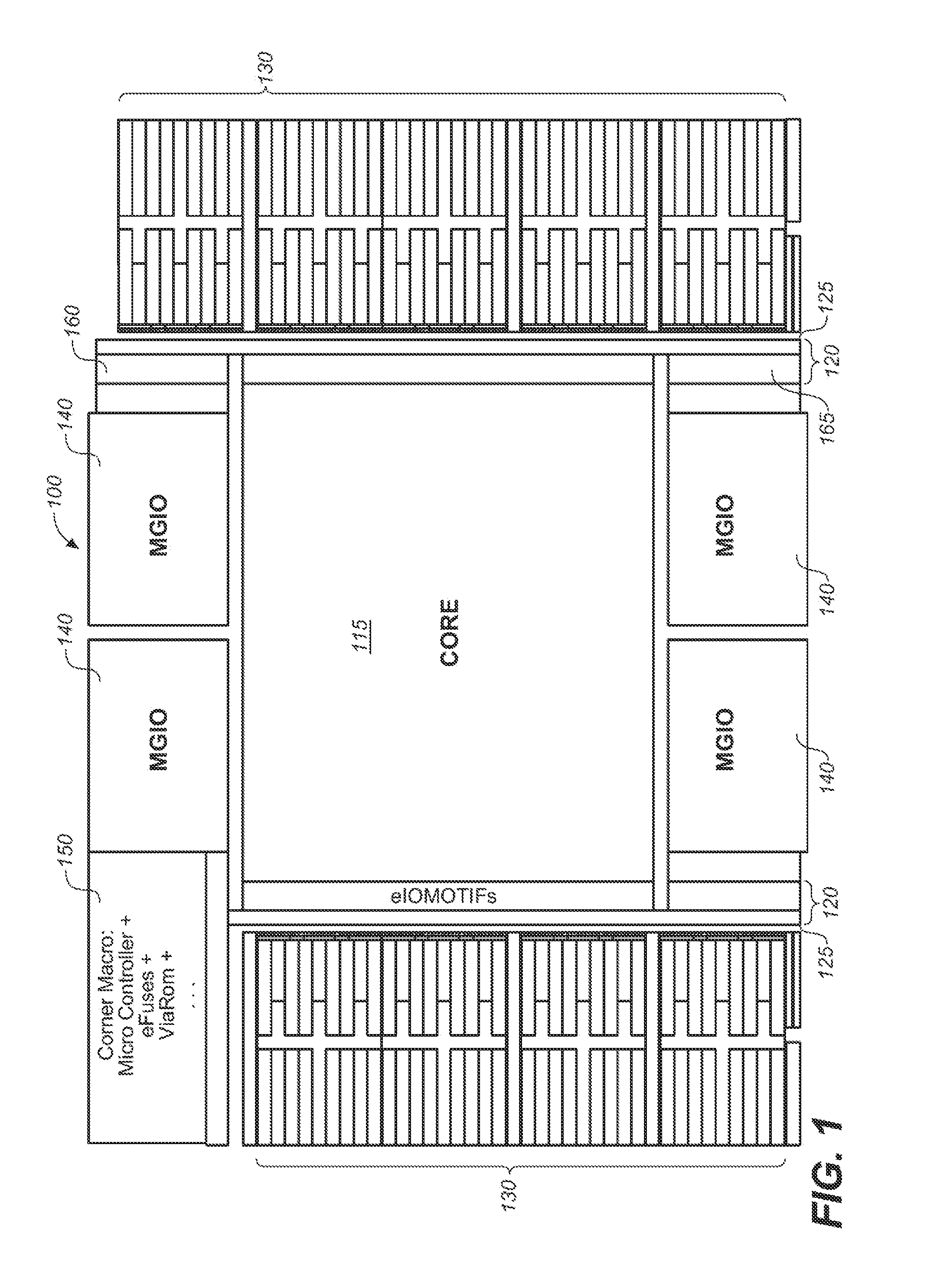

Clock network fishbone architecture for a structured ASIC manufactured on a 28 NM CMOS process lithographic node

InactiveUS8629548B1Low levelEasy constructionPower reduction in field effect transistorsPower reduction by control/clock signalLogic cellAnd logic unit

A clock architecture for a Structured ASIC chip, manufactured using a CMOS process is shown. A via-configurable logic block (VCLB) architecture in the Structured ASIC has a core region containing memory and logic cells arranged in columns that are supplied by a clock network having a global clock network tree and a low-level clock mesh to distribute the global clock signal in a repeating pattern. The clock mesh has a fishbone configuration in outline and allows for scalable expansion of the clock network. In one embodiment 36 global clocks may be provided to the Structured ASIC, with four clocks per logic cell. The VCLB Structured ASIC chip is manufactured on a 28 nm CMOS process lithographic node, having several metal layers but preferably is programmable on a single via layer.

Owner:INTEL CORP

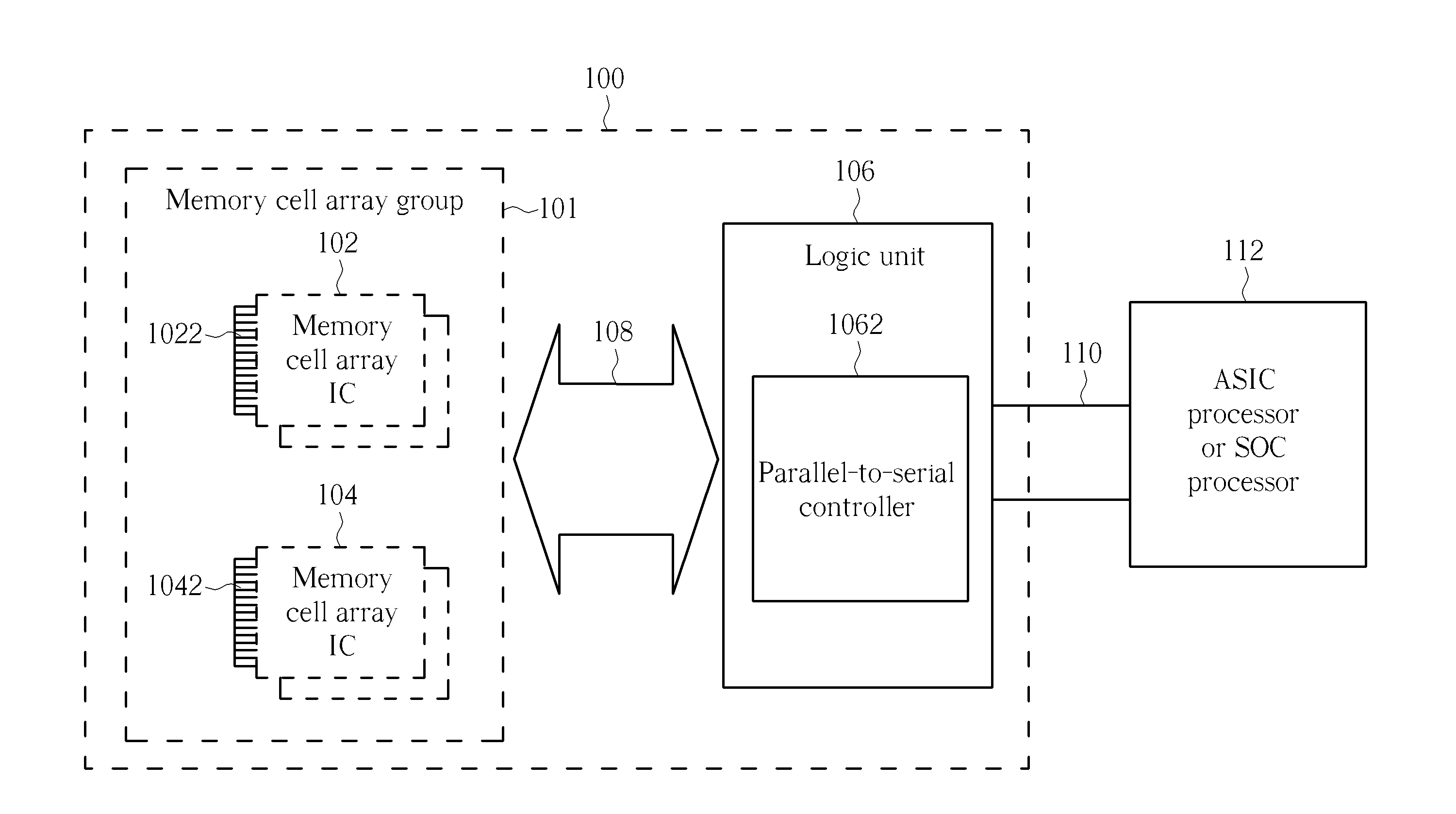

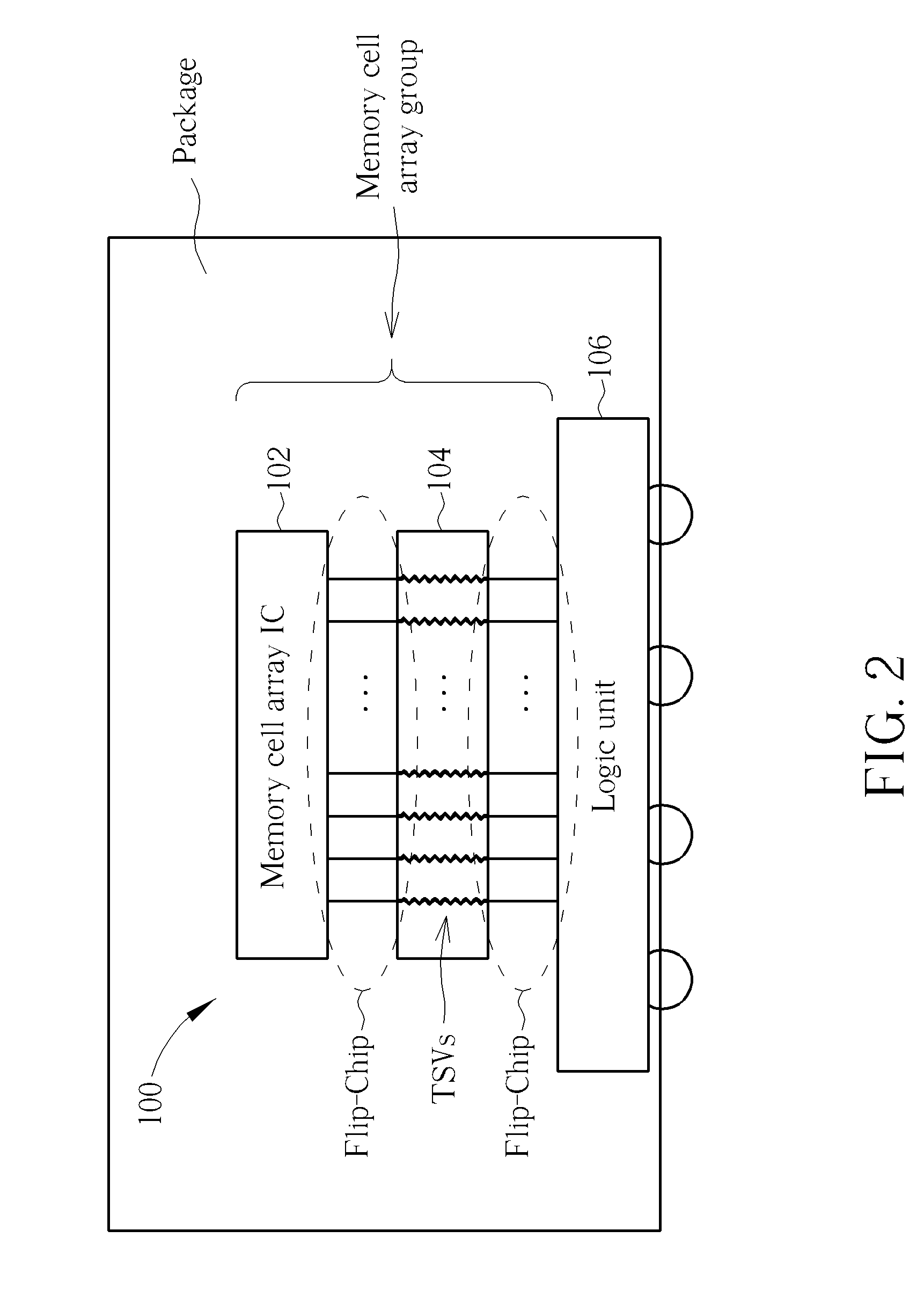

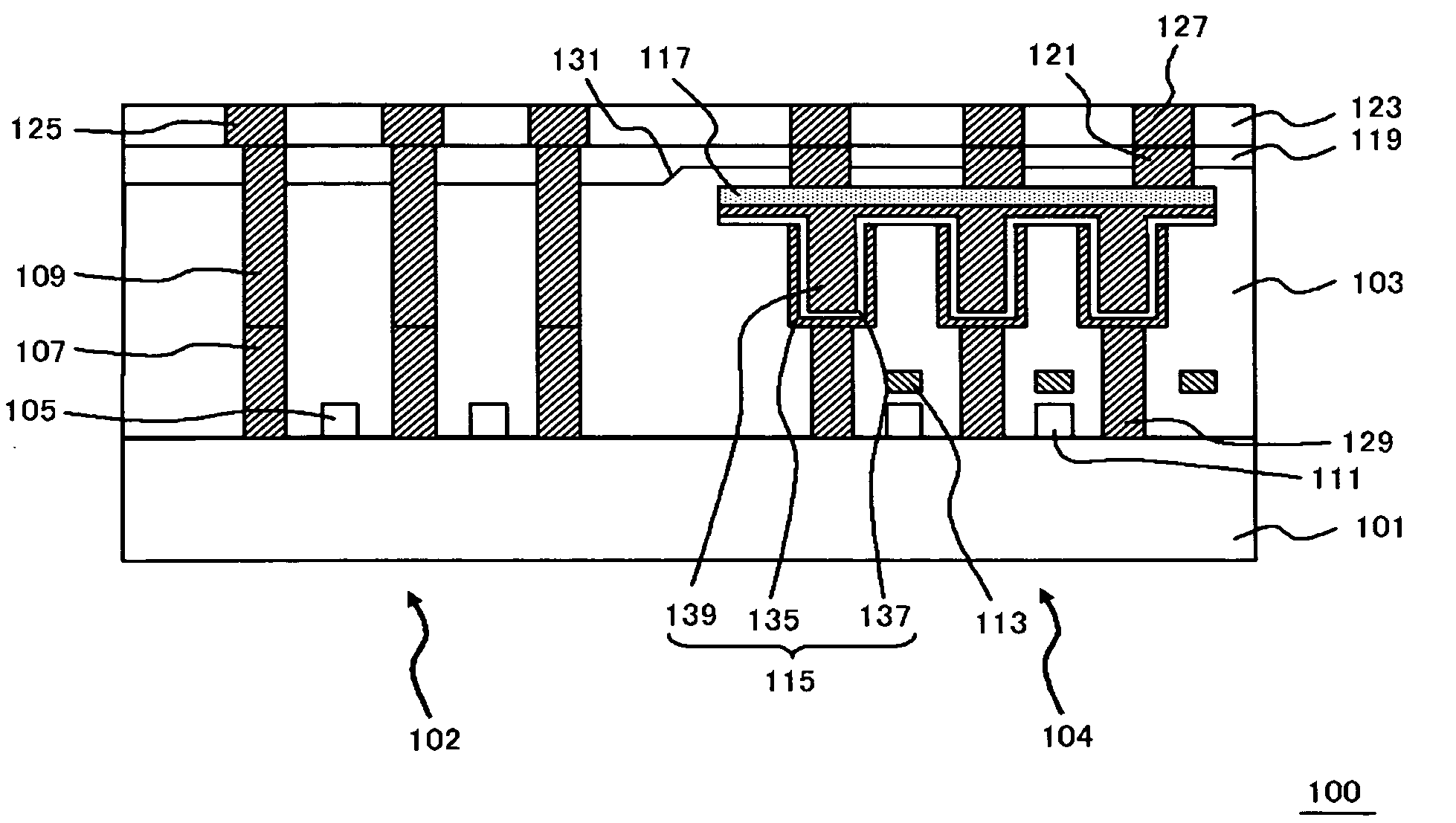

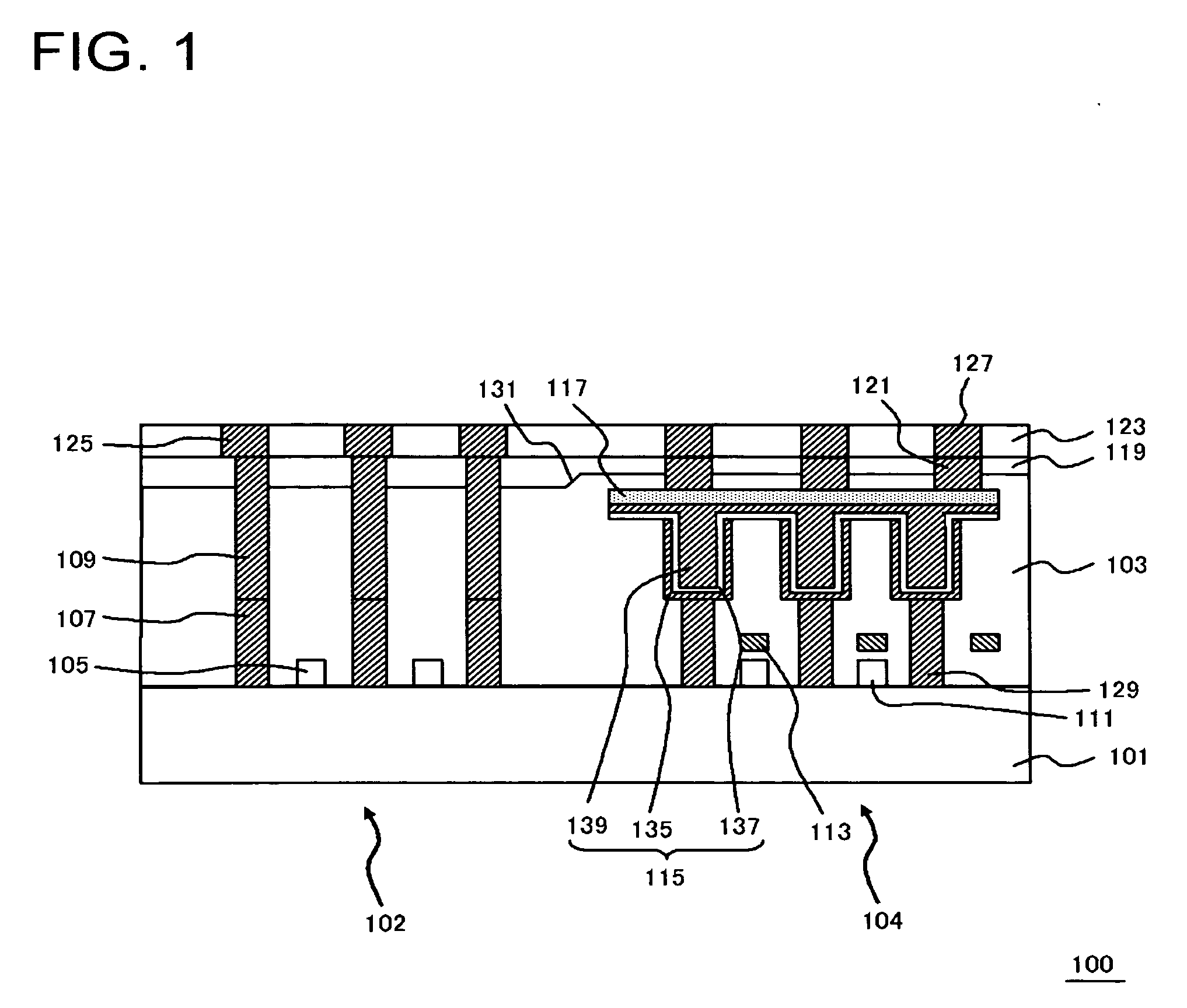

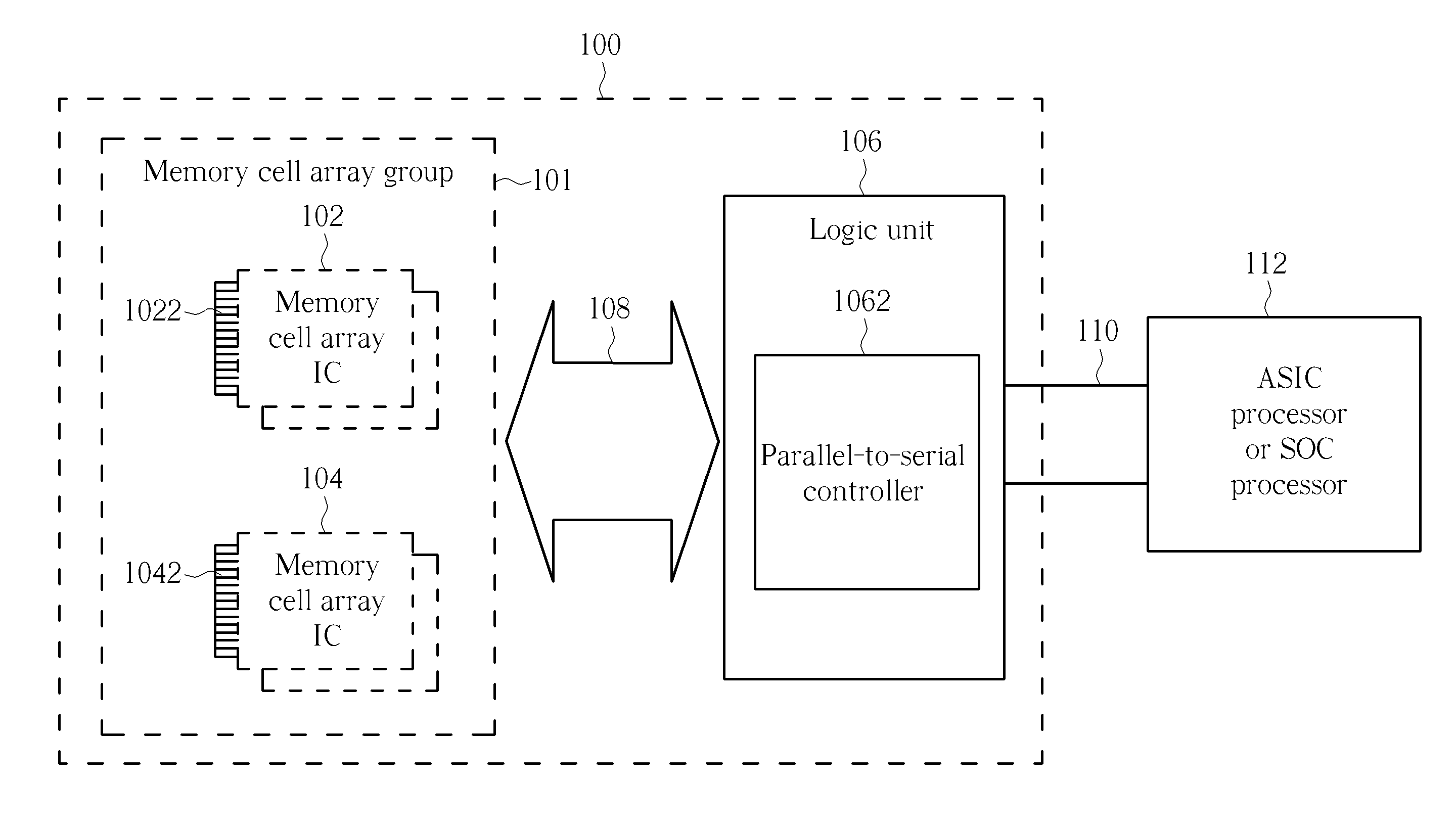

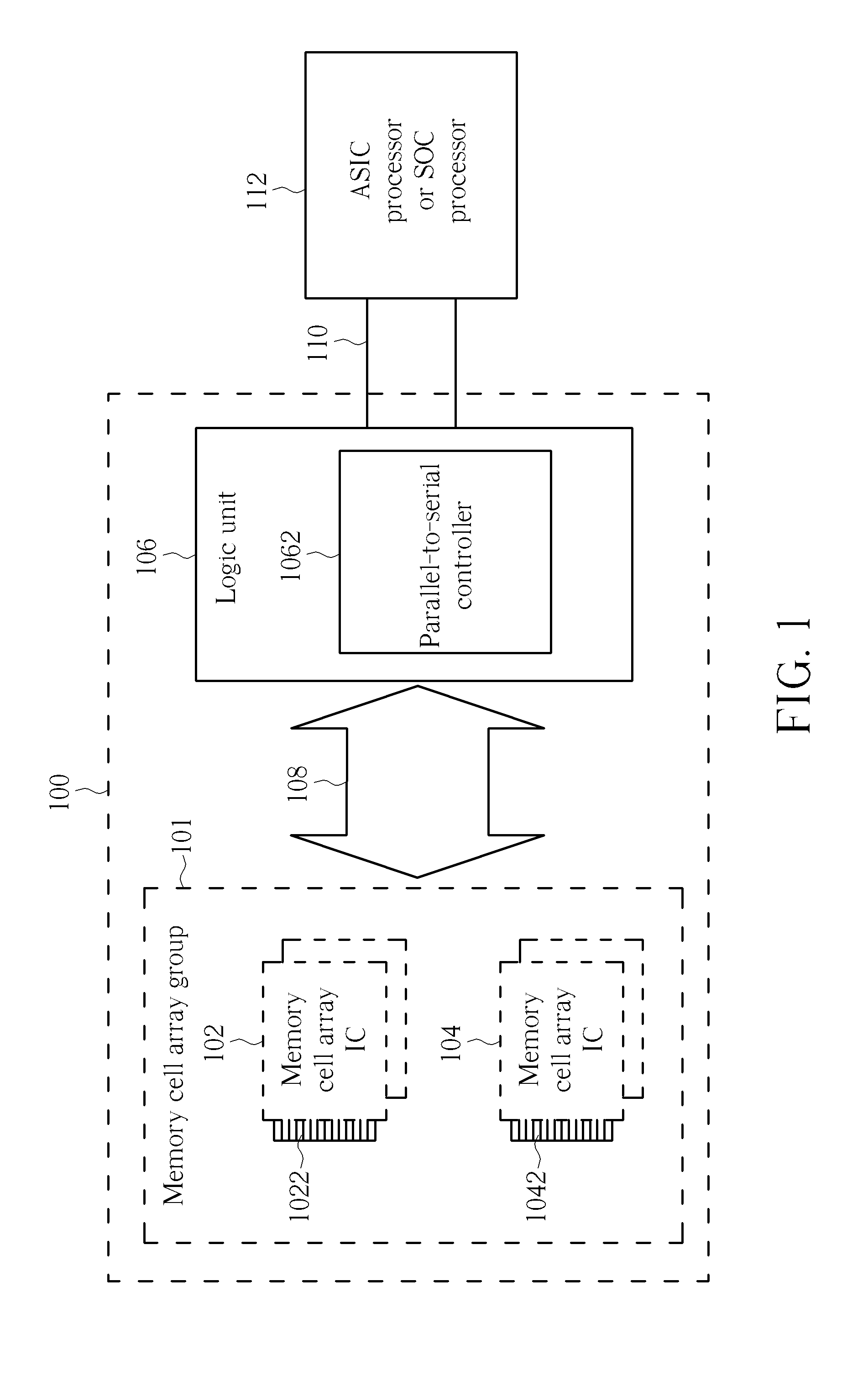

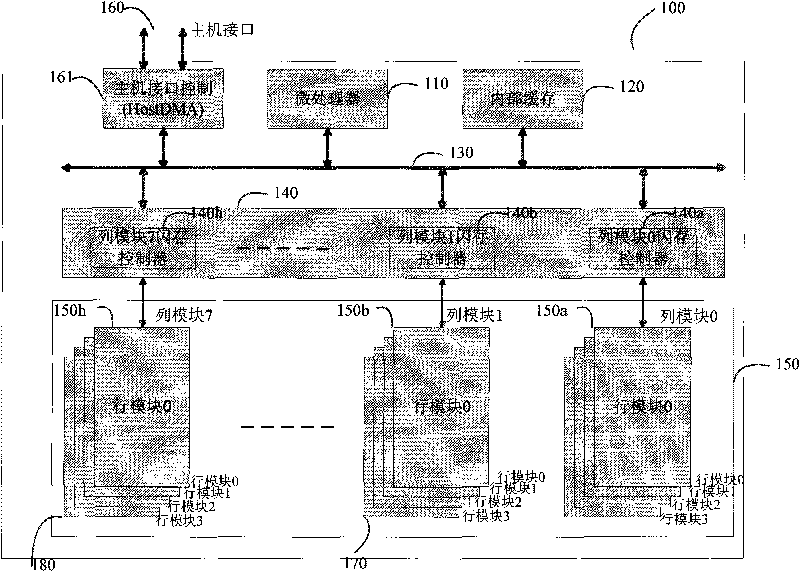

Reconfigurable high speed memory chip module and electronics system device

ActiveUS20130091312A1Improve shielding effectImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesElectronic systemsHigh speed memory

A reconfigurable high speed memory chip module includes a type of memory cell array group, a first transmission bus, and a logic unit. The type memory cell array group includes multiple memory cell array integrated circuits (ICs). The first transmission bus coupled to the type memory cell array group has a first programmable transmitting or receiving data rate, a first programmable transmitting or receiving signal swing, a first programmable bus width, and a combination thereof. The logic unit is coupled to the first transmission bus for accessing the type memory cell array group through the first transmission bus.

Owner:ETRON TECH INC

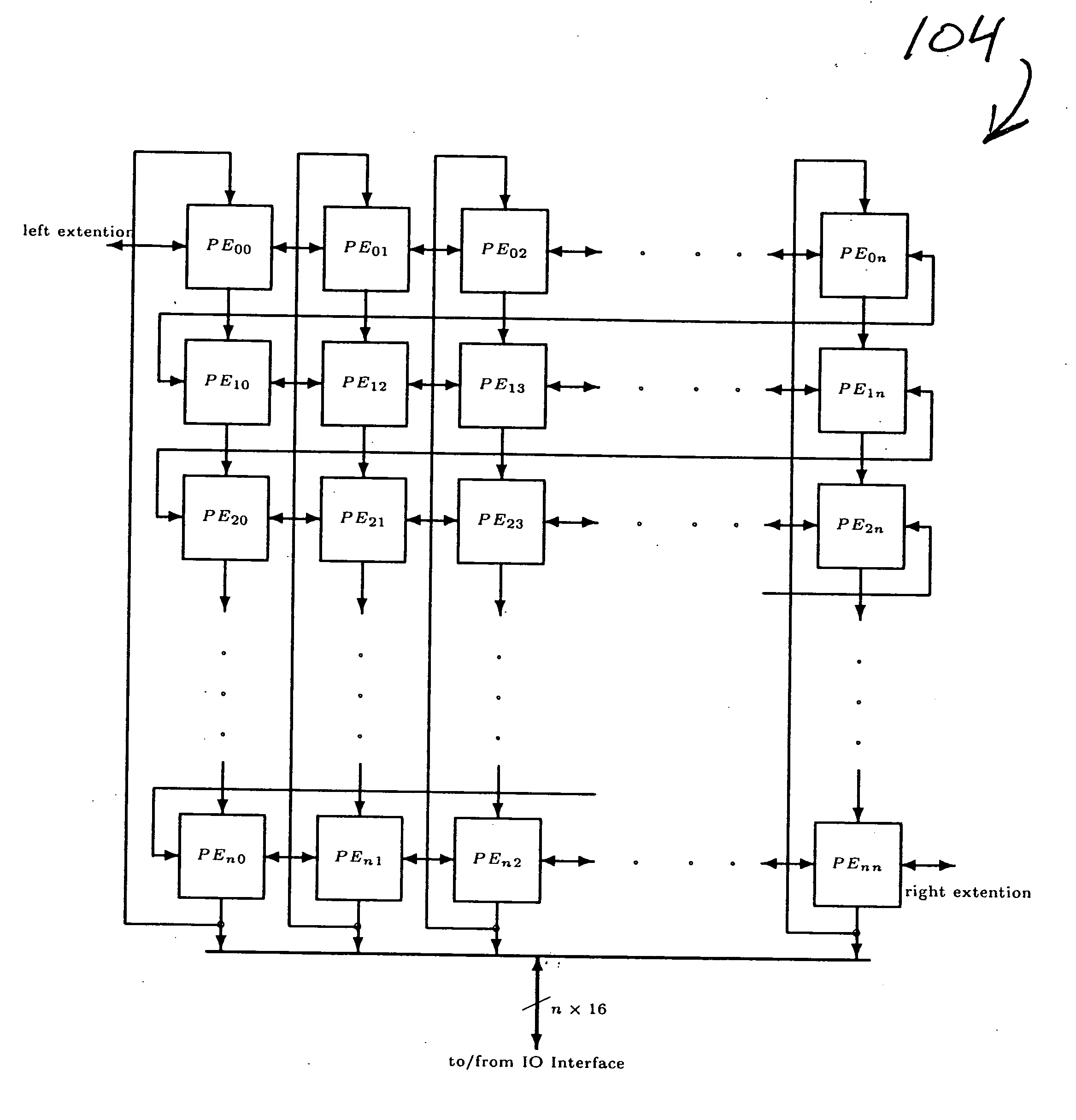

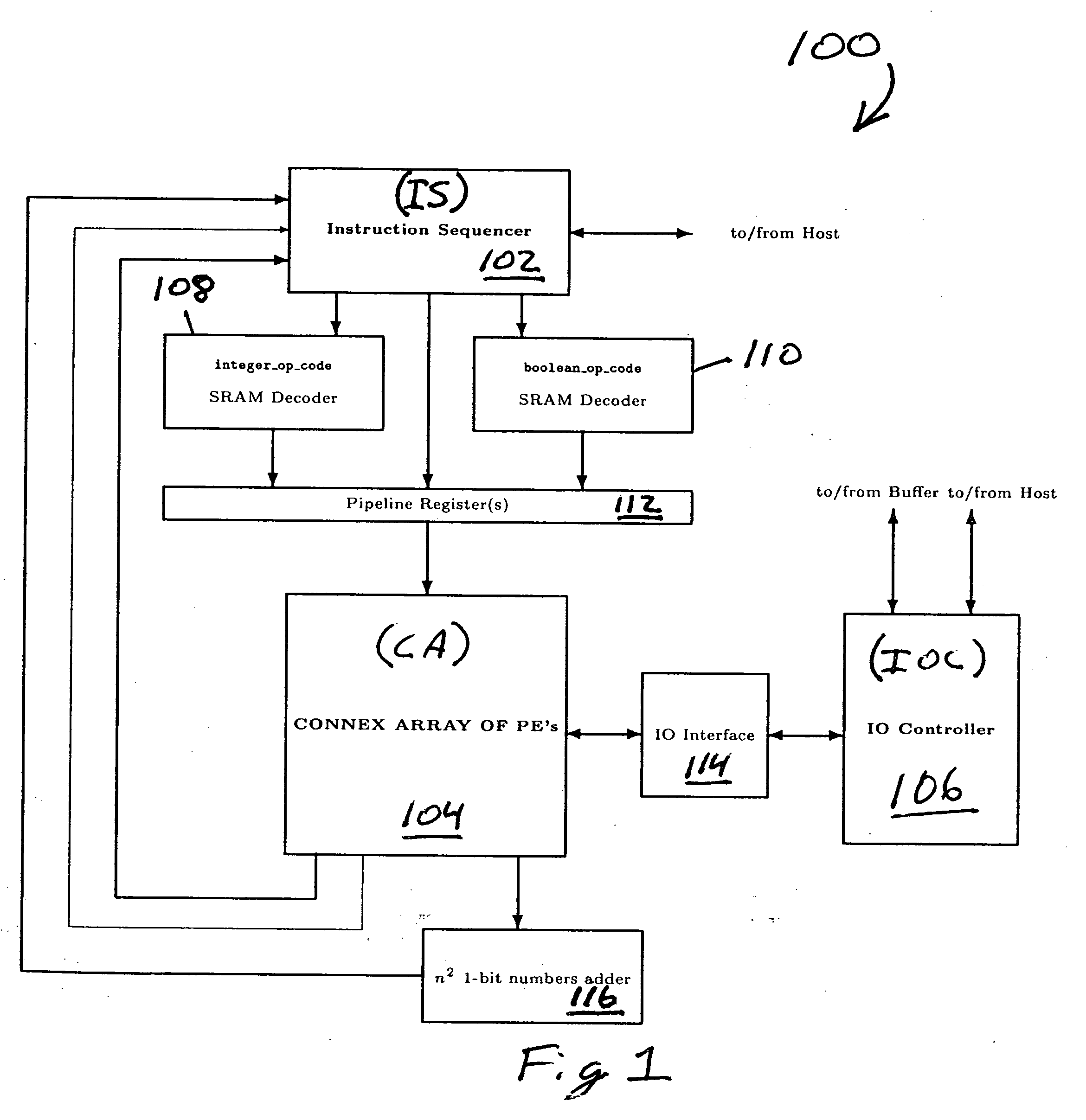

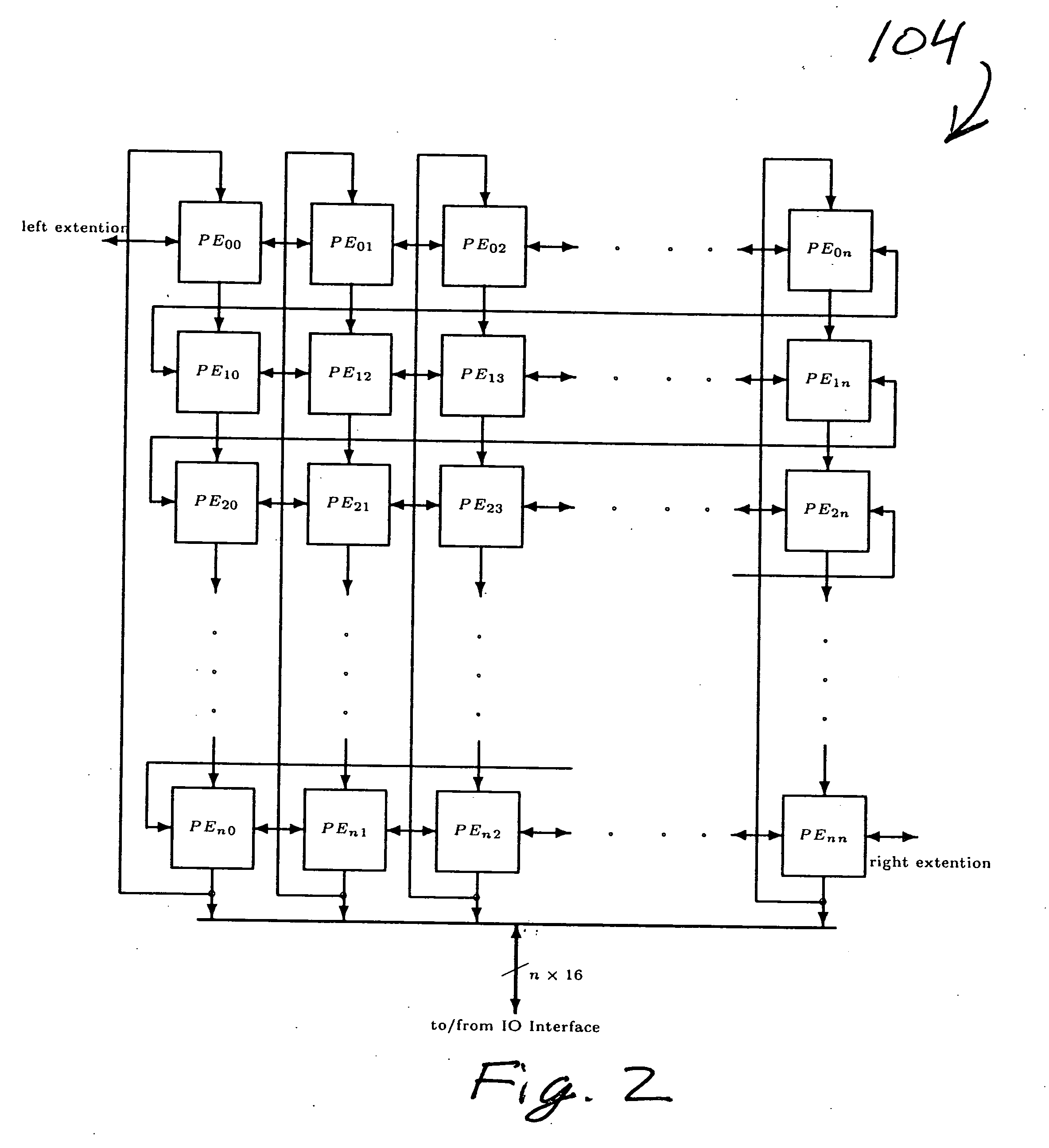

Integrated processor array, instruction sequencer and I/O controller

InactiveUS20070130444A1Single instruction multiple data multiprocessorsSpecific program execution arrangementsInformation processingLogic state

A computer processor having an integrated instruction sequencer, array of processing engines, and I / O controller. The instruction sequencer sequences instructions from a host, and transfers these instructions to the processing engines, thus directing their operation. The I / O controller controls the transfer of I / O data to and from the processing engines in parallel with the processing controlled by the instruction sequencer. The processing engines themselves are constructed with an integer arithmetic and logic unit (ALU), a 1-bit ALU, a decision unit, and registers. Instructions from the instruction sequencer direct the integer ALU to perform integer operations according to logic states stored in the 1-bit ALU and data stored in the decision unit. The 1-bit ALU and the decision unit can modify their stored information in the same clock cycle as the integer ALU carries out its operation. The processing engines also contain a local memory for storing instructions and data.

Owner:ALLSEARCH SEMI

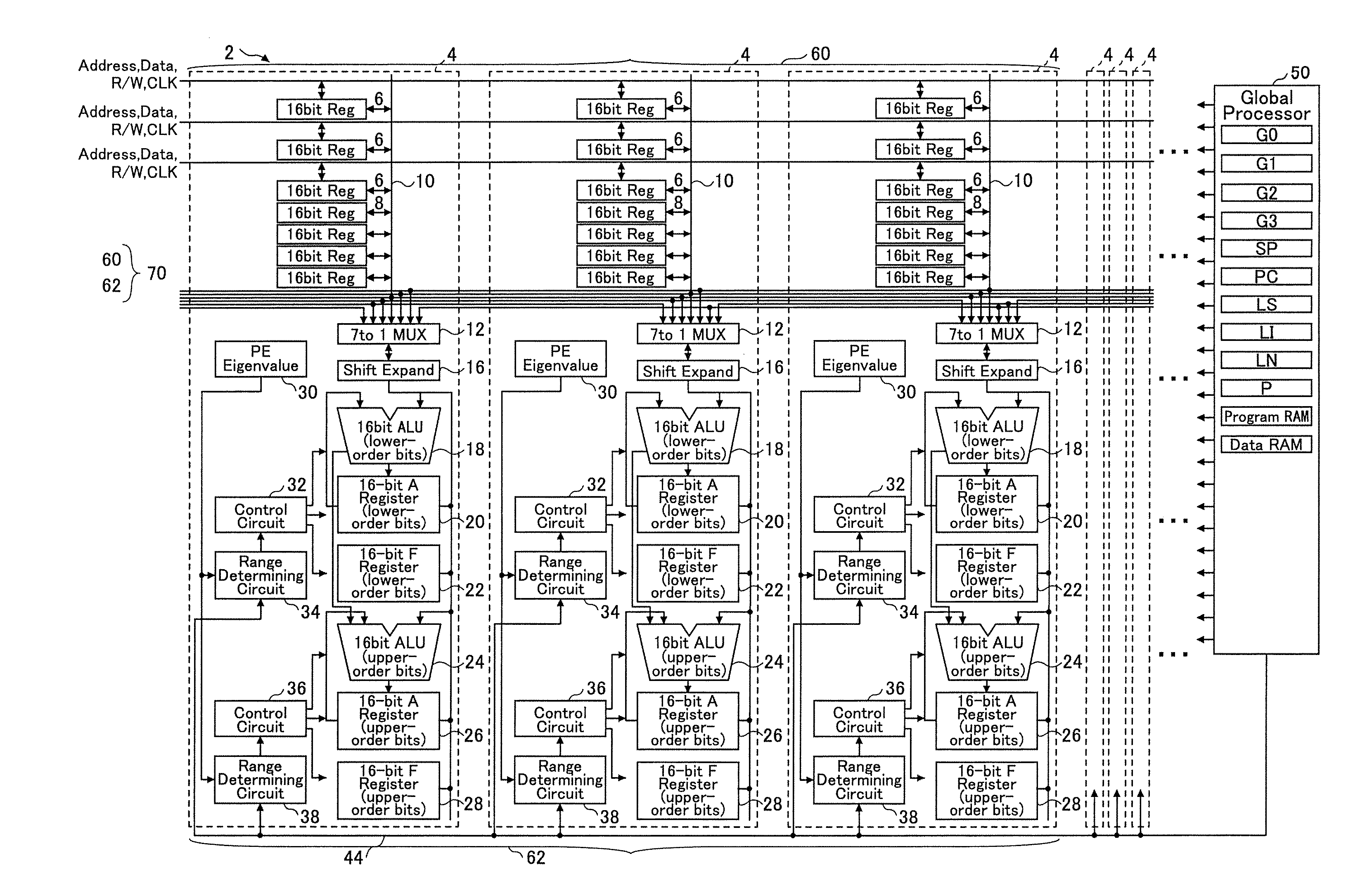

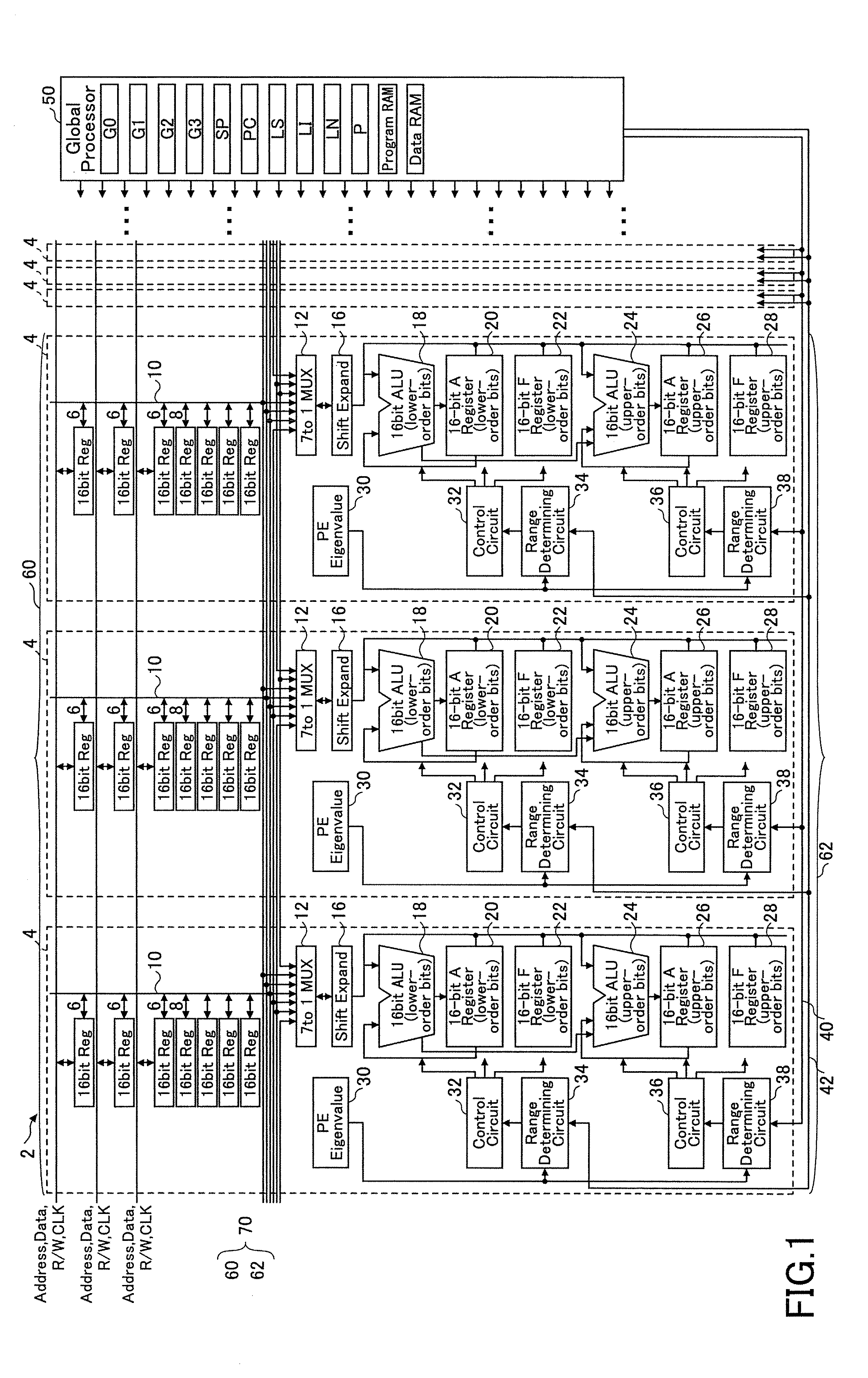

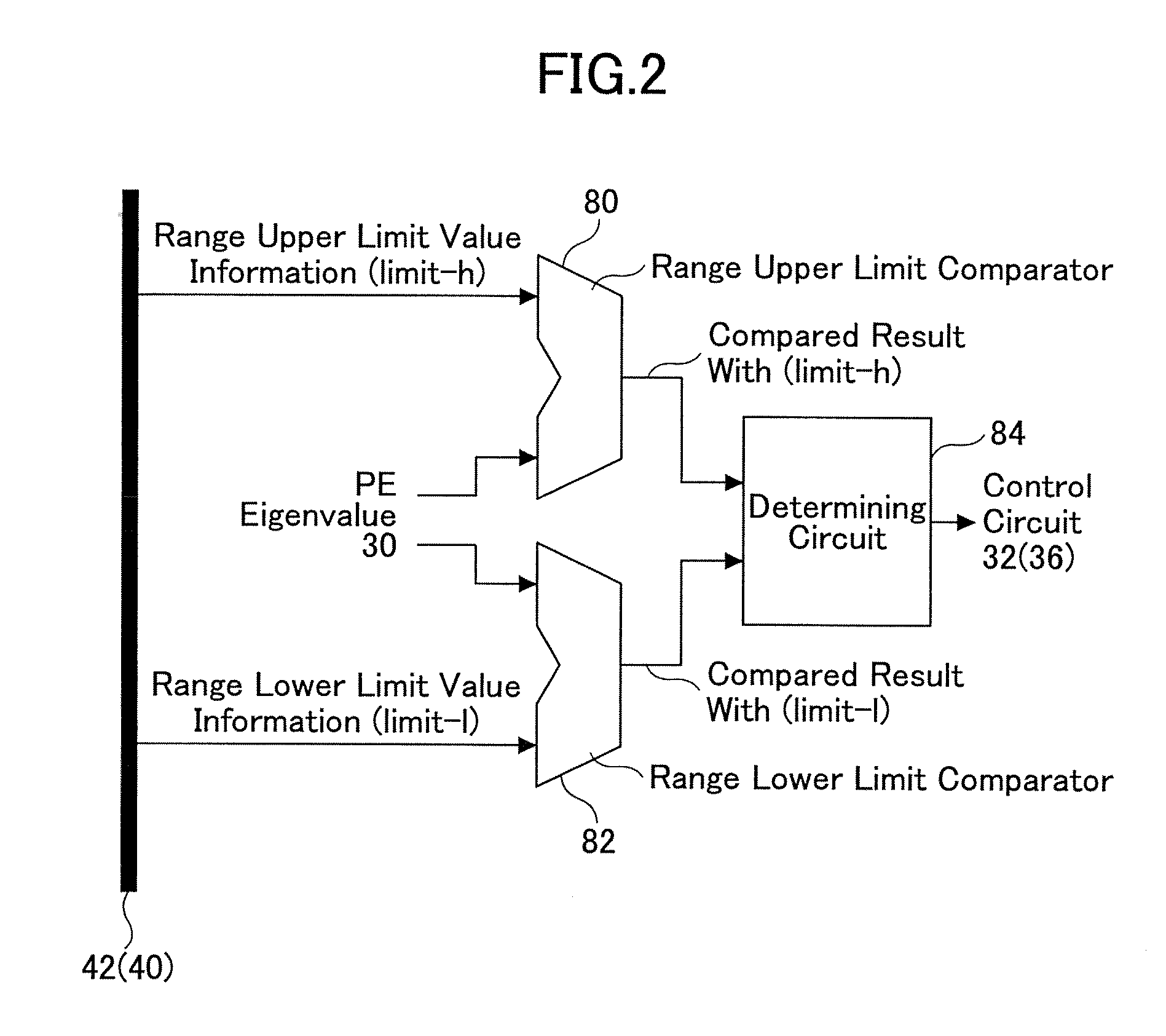

SIMD type microprocessor having processing elements that have plural determining units

InactiveUS8219783B2General purpose stored program computerSpecific program execution arrangementsProcessor elementAnd logic unit

An SIMD type microprocessor is disclosed. The SIMD type microprocessor includes plural PEs (processor elements) each of which provides an ALU (arithmetic and logic unit) for lower-order bits, an ALU for upper-order bits, a control circuit for lower-order bits, a control circuit for upper-order bits, a range determining circuit for lower-order bits, and a range determining circuit for upper-order bits. The SIMD type microprocessor further includes a global processor, a range designation bus for lower-order bits which connects the global processor to the range determining circuit for lower-order bits, and a range designation bus for upper-order bits which connects the global processor to the range determining circuit for upper-order bits. The global processor instructs the range determining circuits to designate corresponding ranges to be operated on by the corresponding ALUs via the corresponding range designation buses so that the ALU for lower-order bits and the ALU for upper-order bits can be operated separately.

Owner:RICOH KK

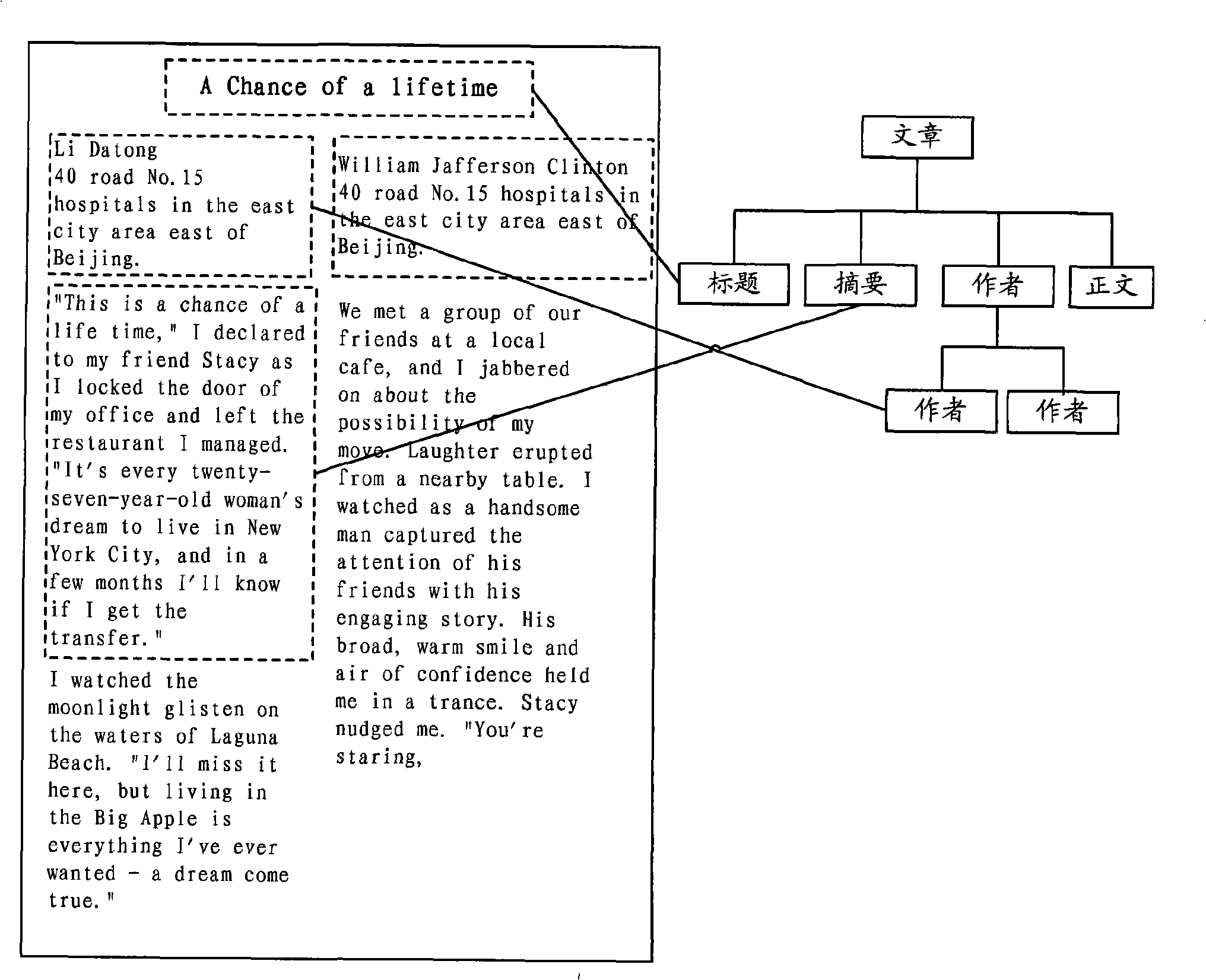

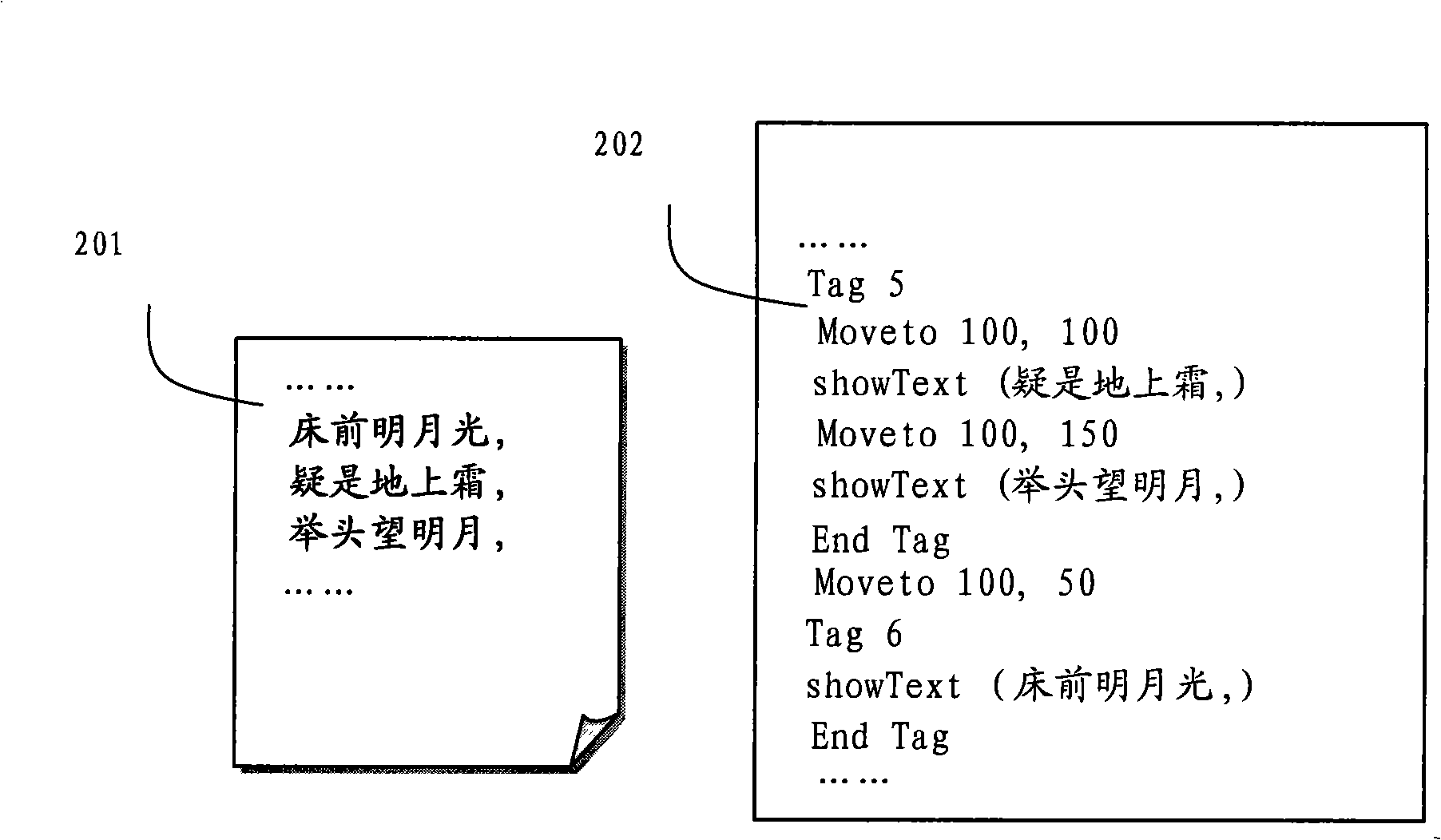

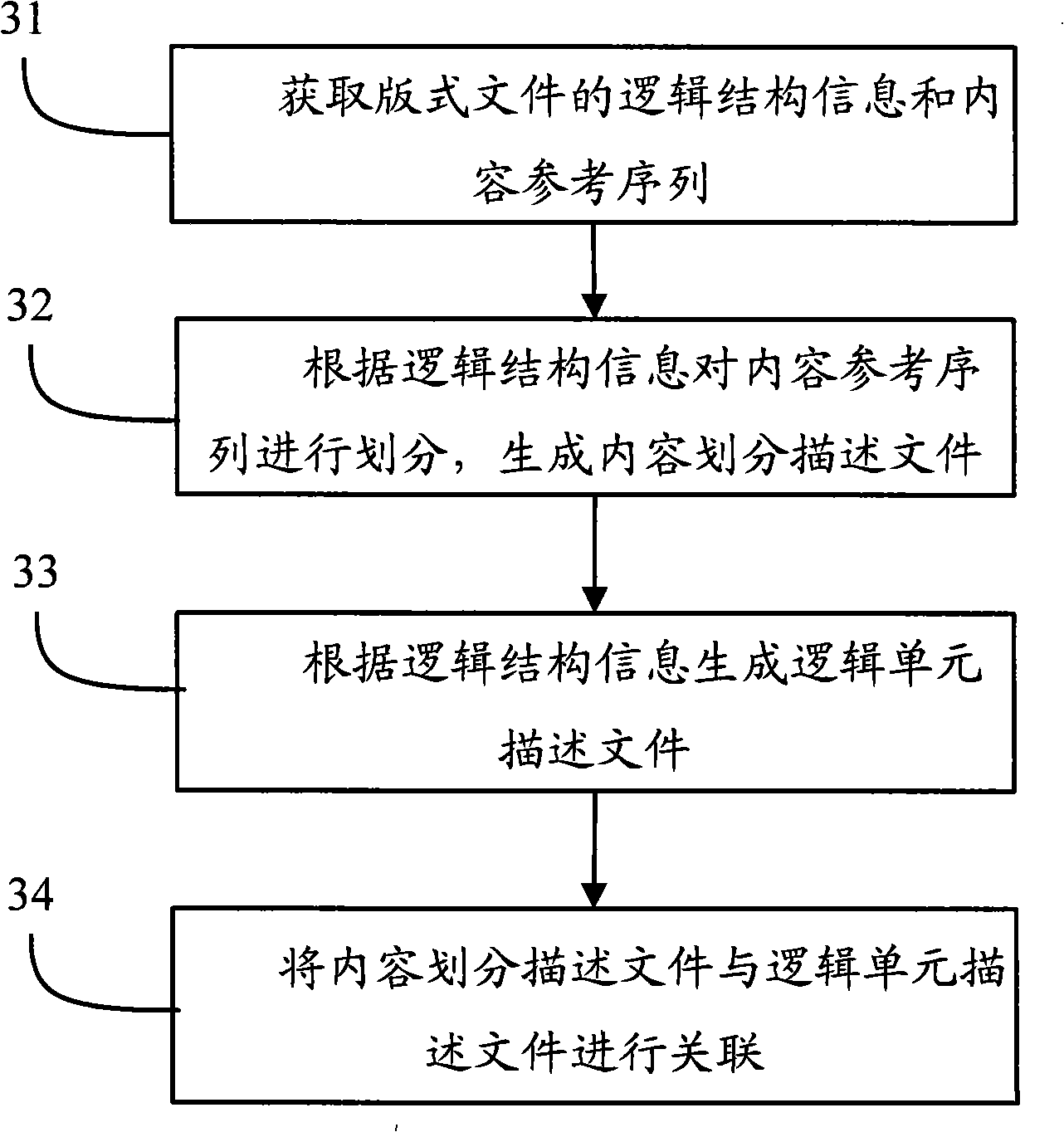

Representation method and system of layout file logical structure information

ActiveCN101271463AIndicates flexibilityAccurate descriptionNatural language data processingSpecial data processing applicationsInformation processingAfter treatment

The present invention discloses an expressing method and a system of layout file logical structure information, which relates to an information expressing method and a system of layout file in the computer information processing technology. The present invention obtains the layout file logical structure information and the content reference sequence; divides the content reference sequence into a plurality of content reference sub-sequences according to the logical structure information and generates the corresponding content division descriptive files; generates the descriptive file of a logical unit according to the logical structure information; divides the content into the descriptive file and the descriptive file of the logical unit for association; and performing file treatment to the layout file after treatment according to the association of the content division descriptive file and logic unit descriptive file. The present invention has the advantages that the method can effectively and flexibly express the layout file logical structure information, flexibly treat the layout file structure and meet user demand.

Owner:NEW FOUNDER HLDG DEV LLC +2

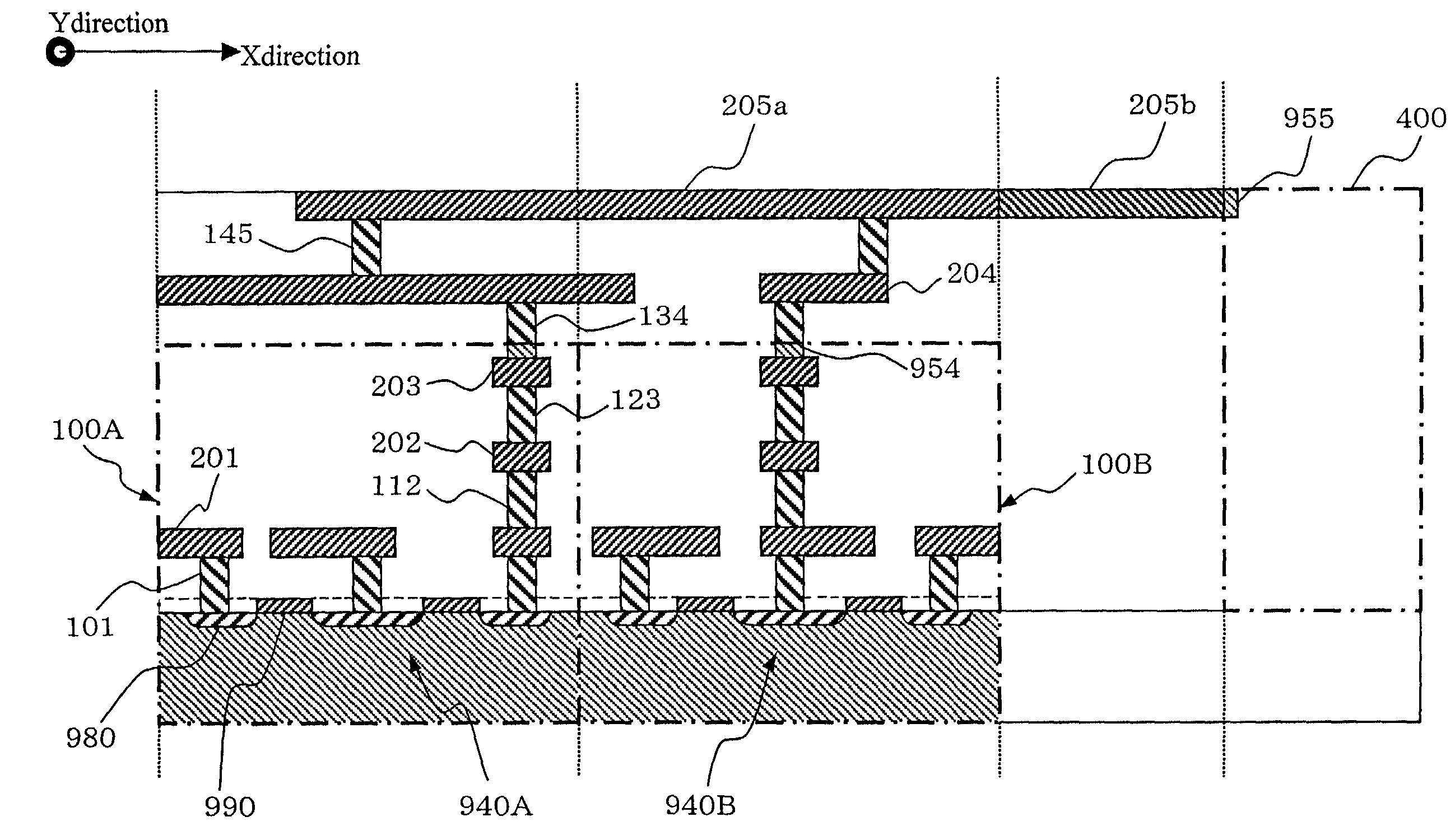

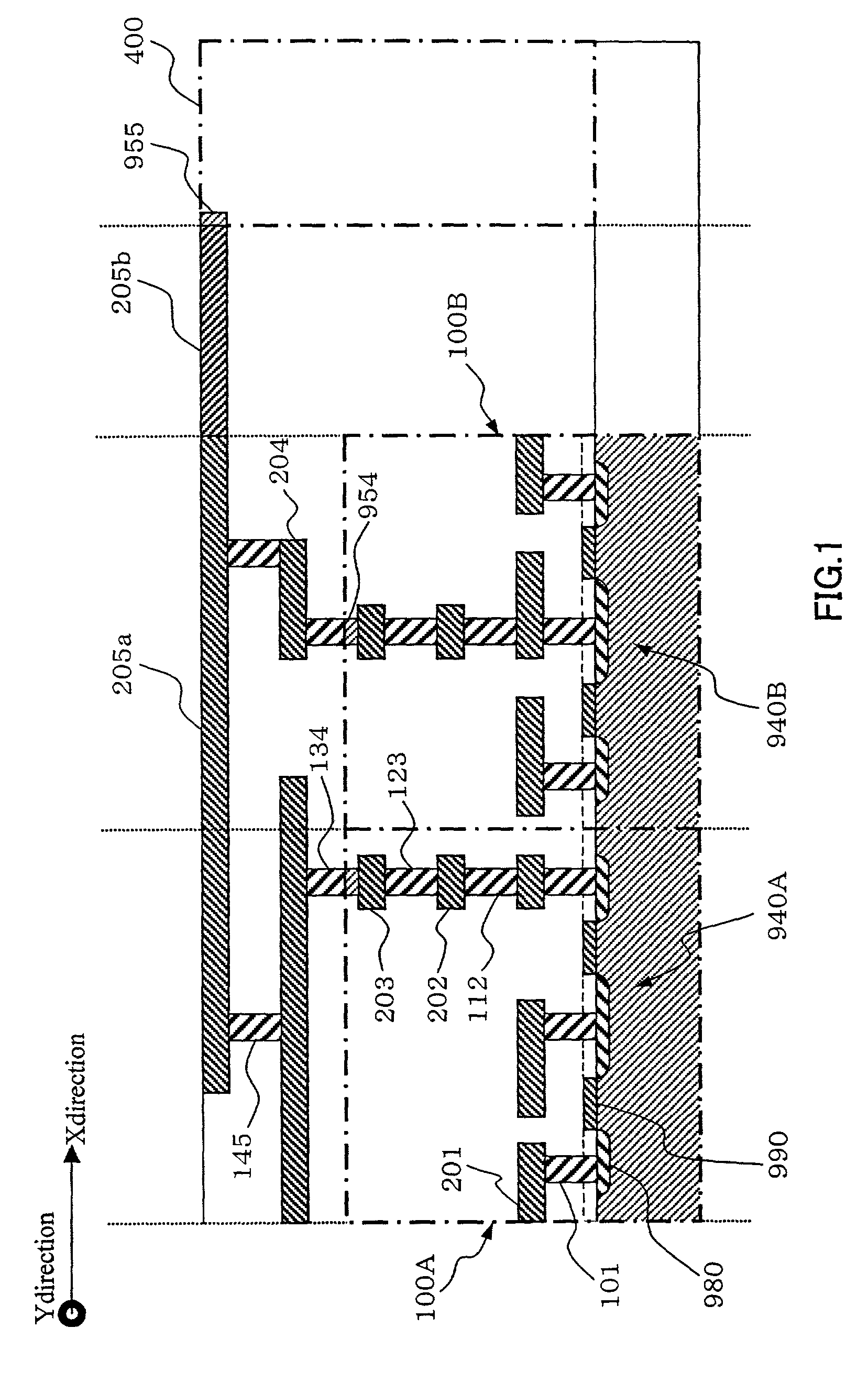

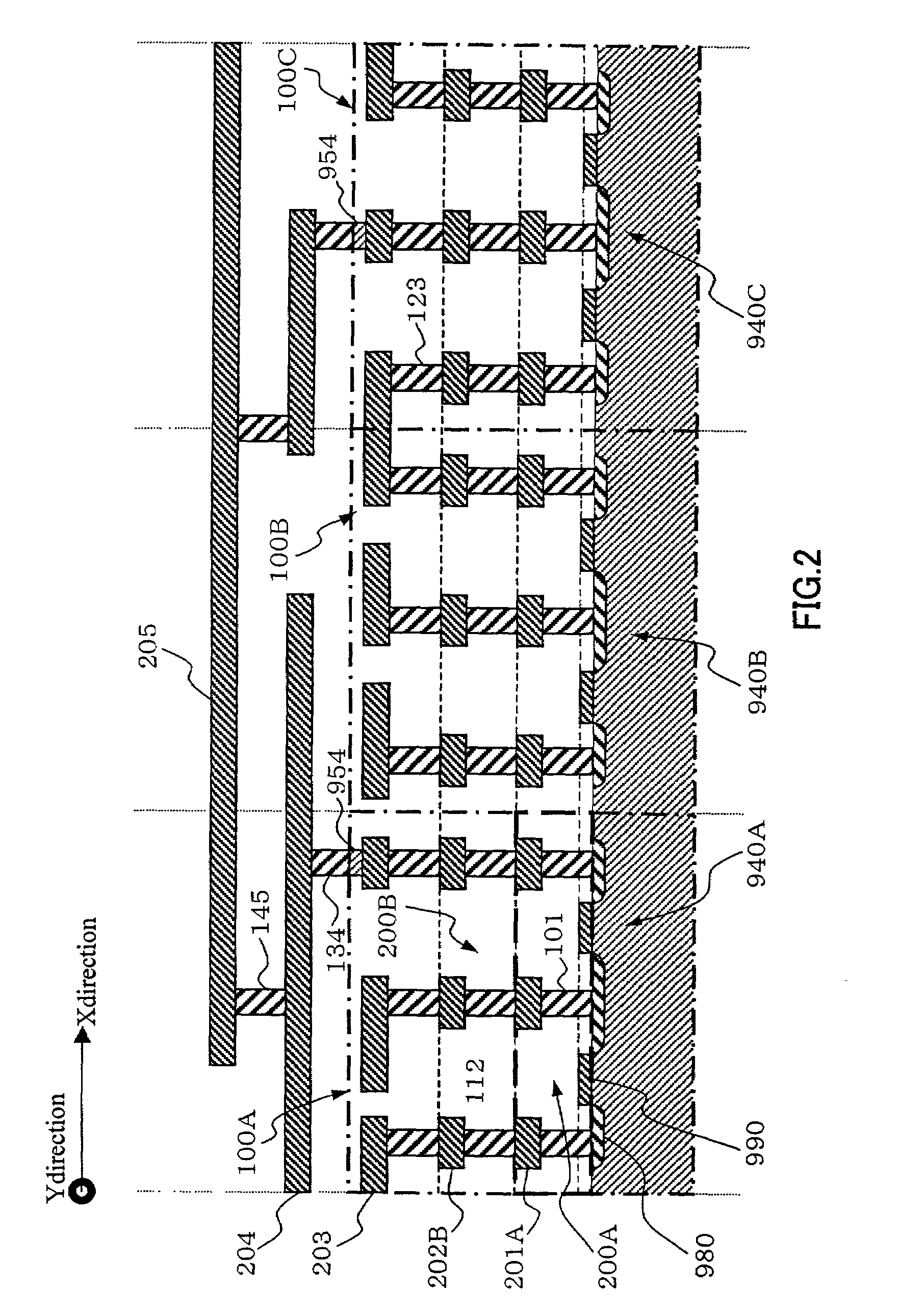

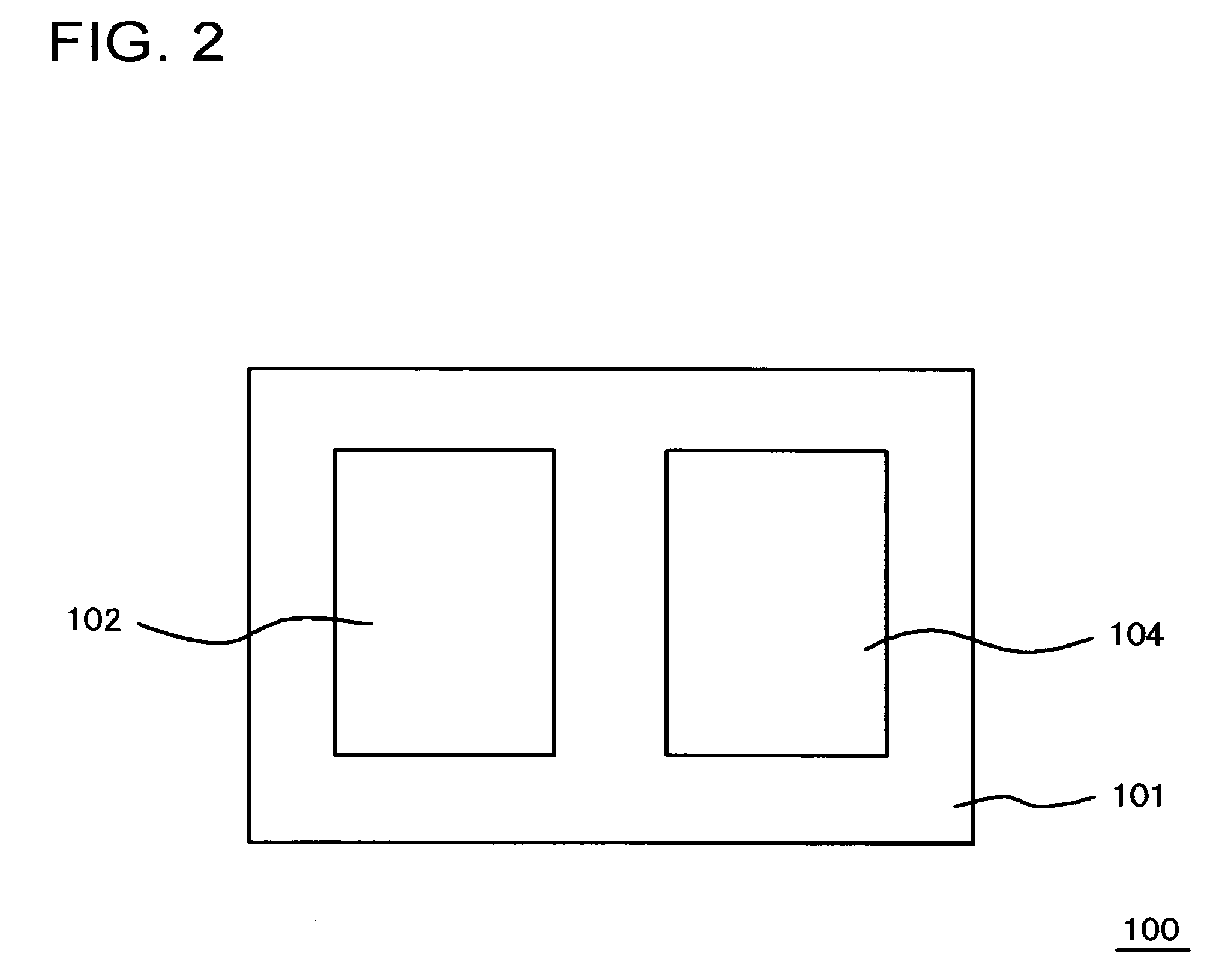

Semiconductor integrated circuit device and method of producing the same

InactiveUS7170115B2Shorten the overall cycleReduce development costsTransistorThyristorCMOSGate array

A semiconductor integrated circuit device has a plurality of CMOS-type base cells arranged on a semiconductor substrate and m wiring layers, and gate array type logic cells are composed of the base cells and the wiring layers. Wiring within and between the logic cells is constituted by using only upper n (n<m) wiring layers. It becomes possible to shorten a development period and reduce a development cost when a gate array type semiconductor integrated circuit device becomes large in scale.

Owner:PANASONIC CORP

A semiconductor device including a memory unit and a logic unit

InactiveUS20070035984A1Improved degree flexibilitySimple structureSolid-state devicesDigital storageDevice materialAnd logic unit

In a semiconductor device including a memory unit and a logic unit, a generation of a step in a terminal end surface of an electroconductive plug in a region above a capacitor element is inhibited. Such semiconductor device includes an insulating layer provided on the semiconductor substrate extending from the memory unit to the logic unit; a plurality of second interconnect connecting plugs embedded in the interlayer insulating film and the interlayer insulating film in the logic unit; capacitor elements embedded in the interlayer insulating film in memory unit; and dummy plugs, embedded in the interlayer insulating film and the interlayer insulating film in a region above a region that is provided with the capacitor element in the memory unit, and insulated from the capacitor element. A plurality of second interconnect connecting plugs and the dummy plug are terminated in the top surface of the interlayer insulating film.

Owner:RENESAS ELECTRONICS CORP

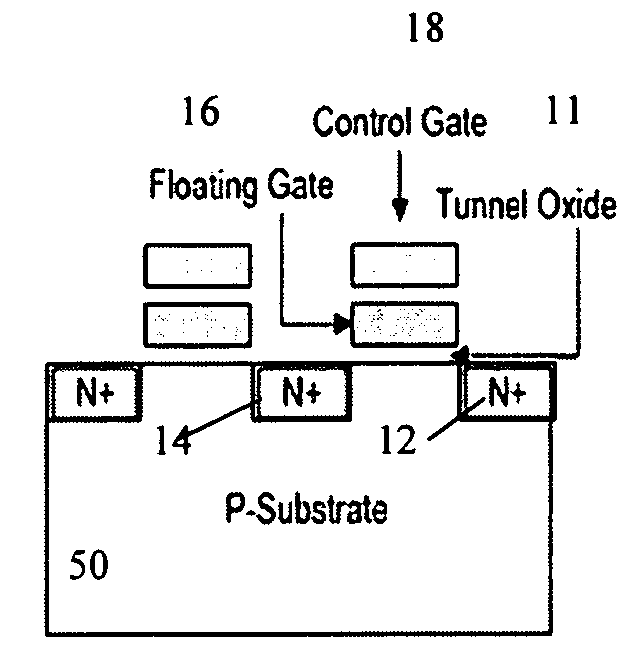

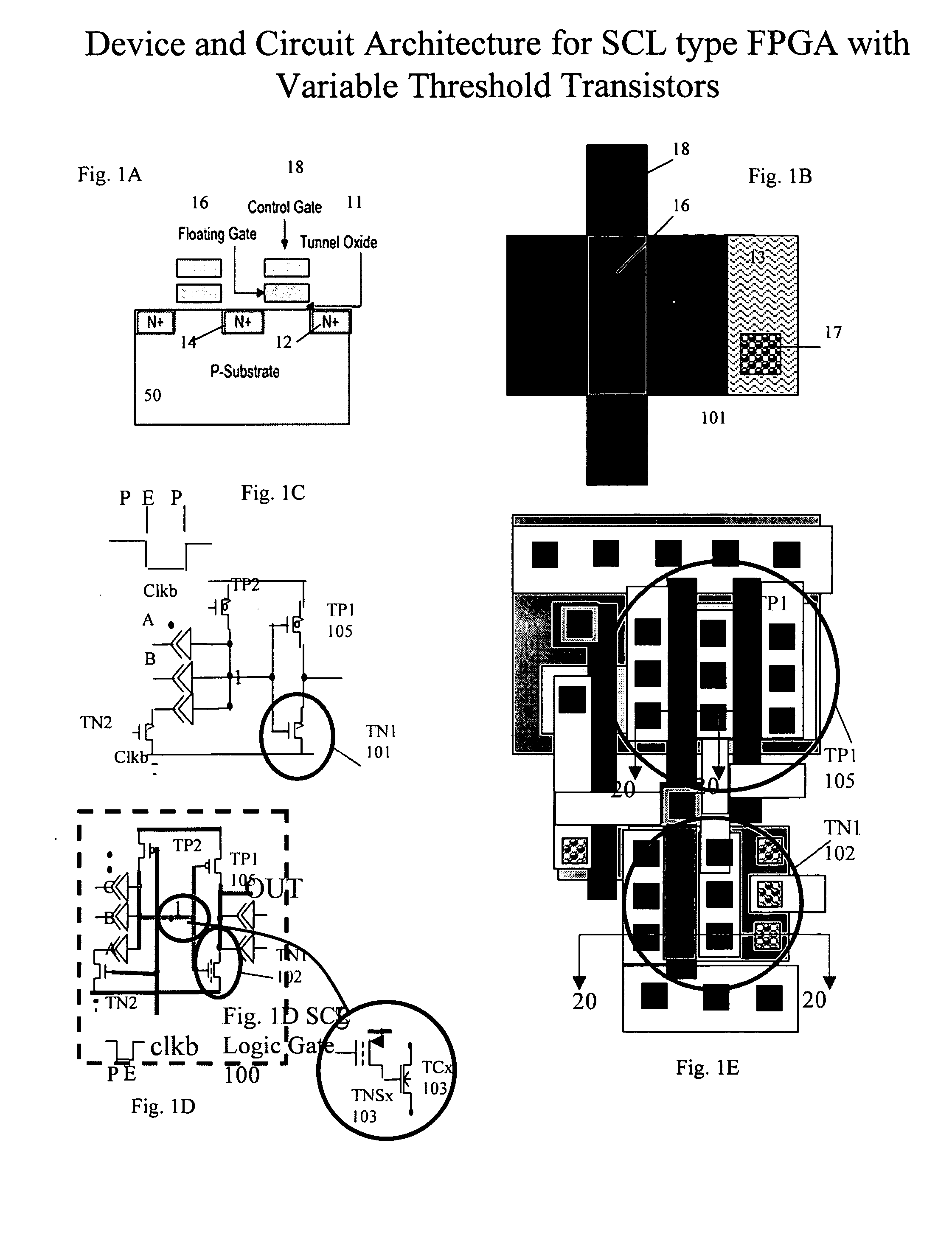

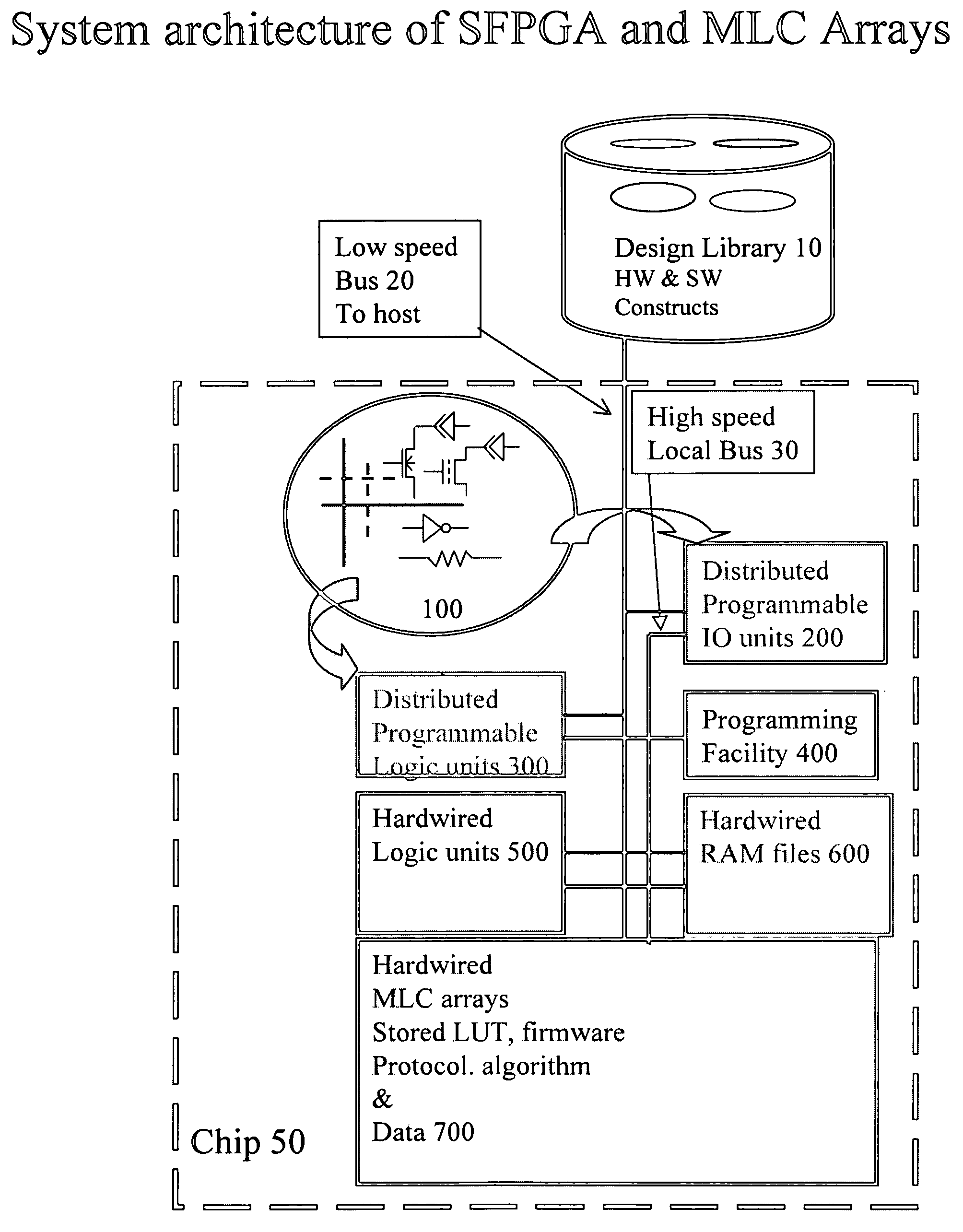

SCL type FPGA with multi-threshold transistors and method for forming same

InactiveUS20050231237A1Low powerImprove performanceMultistate logicSolid-state devicesDigital converterDigital device

A new scheme of Schottky FPGA (SFPGA) IC solution is proposed. The chip is organized by embedded analog, memory, and logic units with on chip apparatus and software means to partitioning, altering selected portions of hardware. The process means is based on the combined Schottky CMOS (SCMOS, U.S. Pat. No. 6,590,800) and Flash technology. The circuit means is based on SCMOS-DTL gate arrays. Software means is based on the C++ procedures with levels of LUT. The SFPGA device supports GHz low power ASIC mixed signal product applications with embedded analog, logic, and memory array units. Several multiplexing schemes are disclosed, which accommodate tasks to vary the Vt and transmission line transmission of selected transistor or IO nets, and therefore their analog and digital device properties. A voltage doubler and supply booster and a Digital-Analog-Digital-Translator (DADT) apparatus are also disclosed in accordance with the present invention. Accordingly, the present invention includes control schemes to field program basic circuit element or any critical nets, and to alter the functionality of certain predetermined circuit units, and update array interconnections, accessing stored protocols, algorithms in all chips in the embodiment subsystem of a SFPGA chip sets.

Owner:SUPER TALENT ELECTRONICS

Architecture for virtualization of networked storage resources

InactiveUS7984253B1Multiple digital computer combinationsTransmissionVirtualizationStorage area network

An architecture for managing a plurality of storage area networks including a plurality of data storage volumes and one or more hosts, wherein the volumes are in a switched storage network in the storage area networks the architecture comprising one or more processors in communication with switching capability for the switched storage network, wherein the one or more processors include program logic for embodying logical constructions of a storage presentation layer including target virtualization and logical unit (LU) virtualization; and a volume presentation layer including volume virtualization for replication of data.

Owner:EMC IP HLDG CO LLC

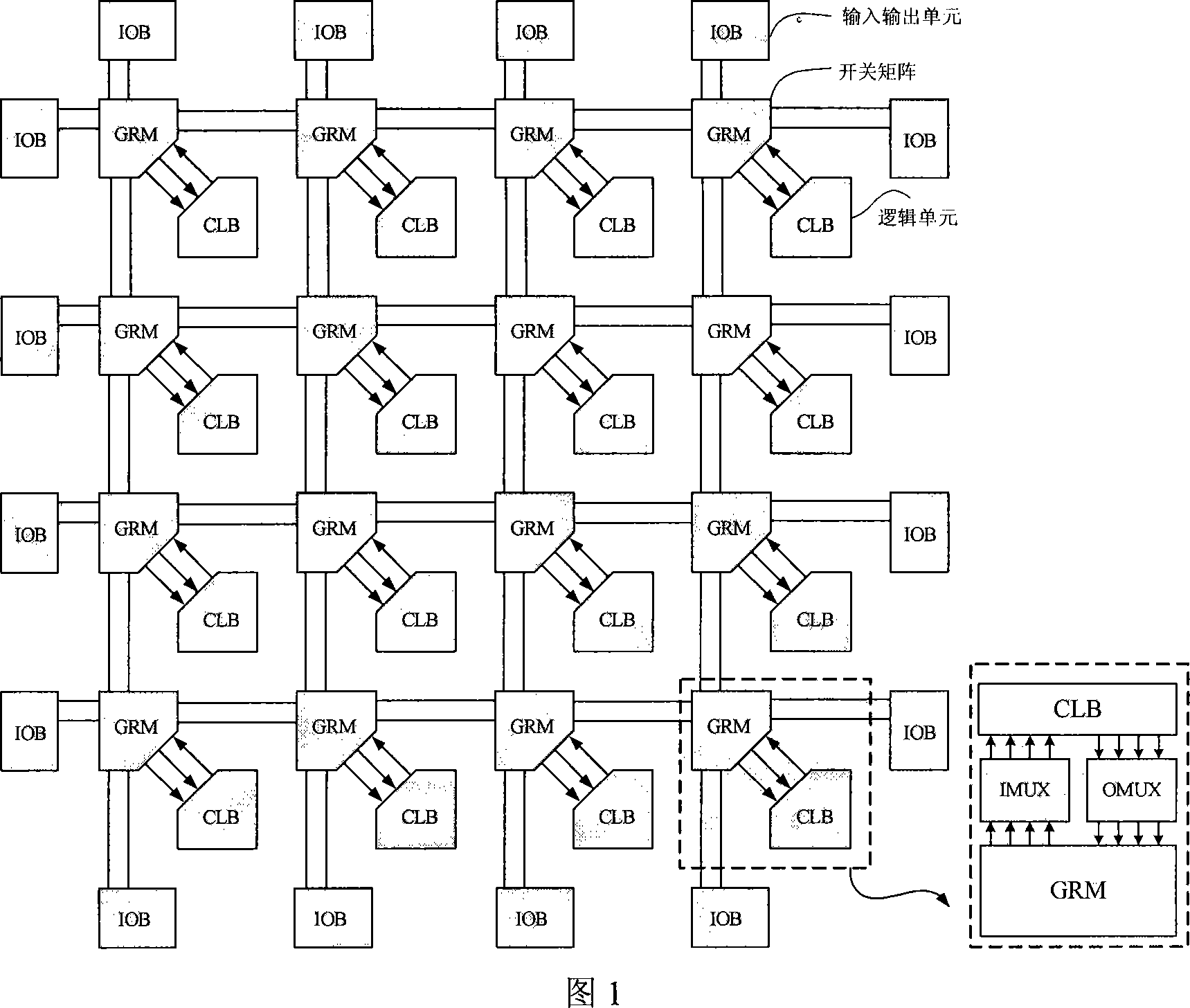

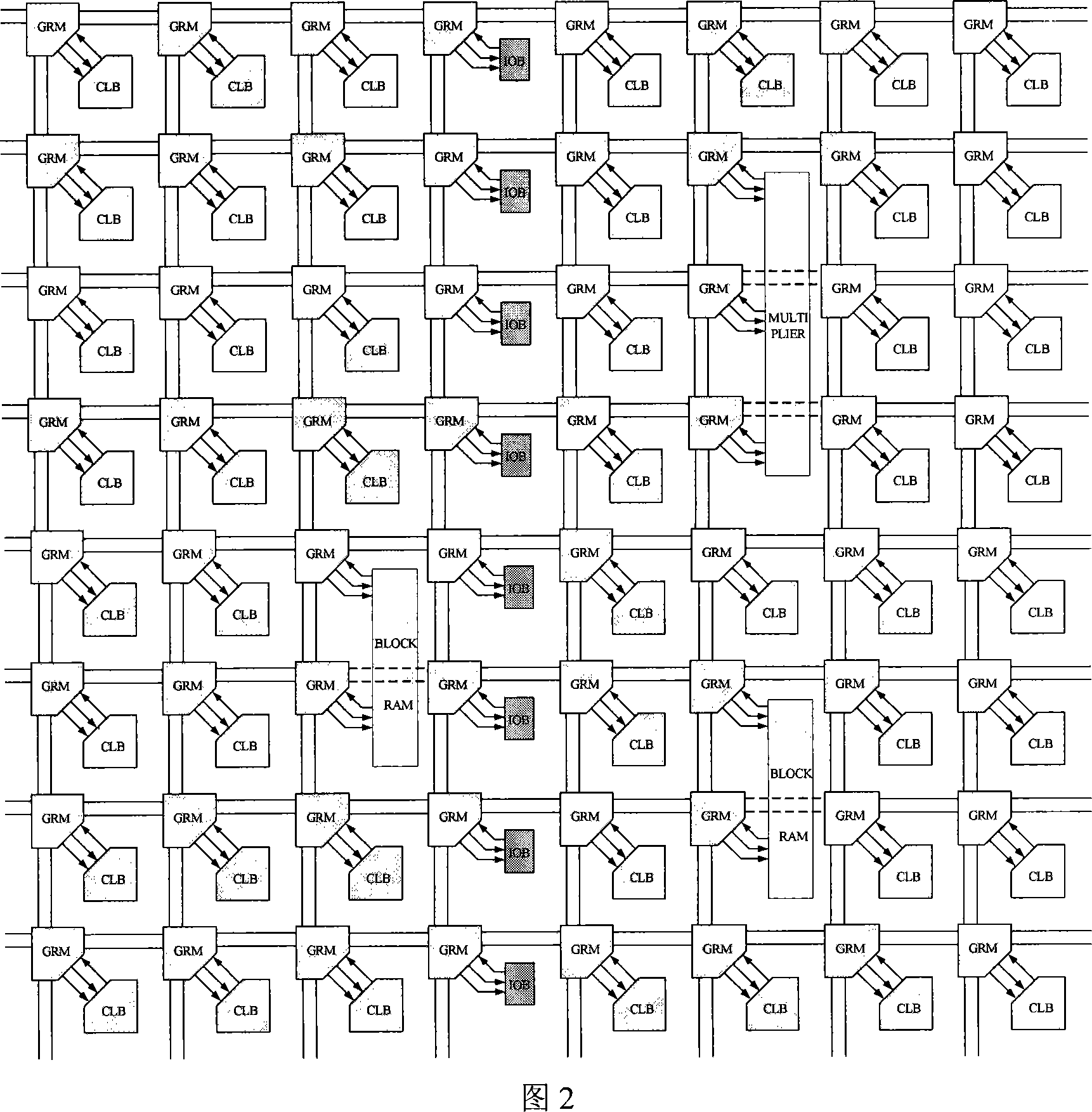

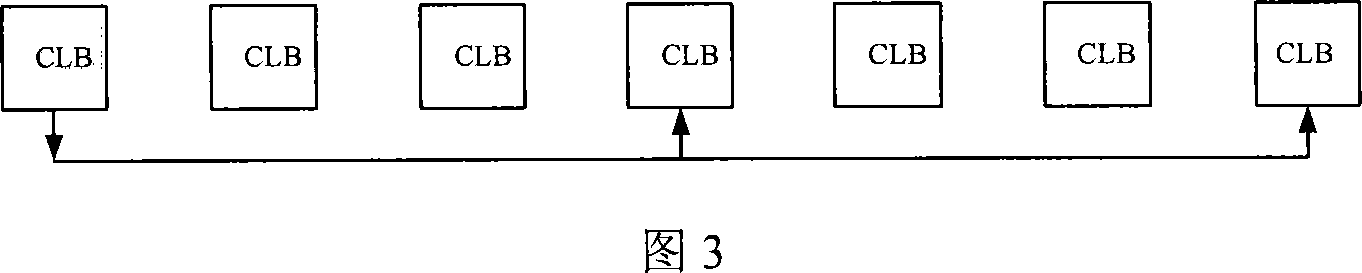

Field programmable logical array wiring resource structure and its modeling approach thereof

ActiveCN101043213AReduce duplicationFlexible descriptionLogic circuits using elementary logic circuit componentsAnd logic unitMulti path

The invention belongs to programmable component structure technology field, specially a local programmable logic array wiring resource structure and modeling method which supports the crutch line. The wiring resource structure of the invention includes: programmable interconnected line, uniform switch matrix, input and output multi path selector array and logic unit. It breaks the limit of level and uprightness interlinkage resource, introduces the concept of crutch line, makes the wiring path not pass the programmable switch, it gives attention to speed and agility. The description of wiring line resource, the interconnected line is distributed to the repeated unit then integral interconnected resource is described by describing an interconnected line resource in a repeated unit. This describing method is very flexible, the kind, amount, proportion of interconnected resource can be changed conveniently, and any switch array can be generated.

Owner:FUDAN UNIV

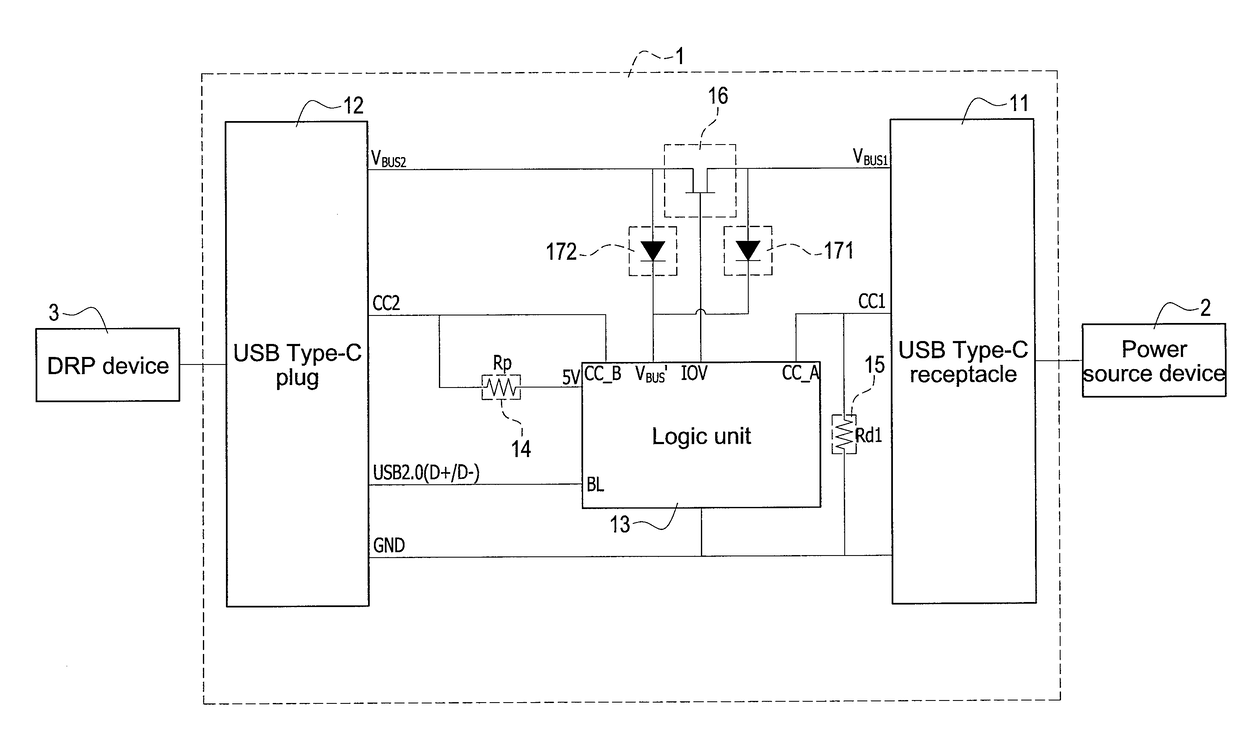

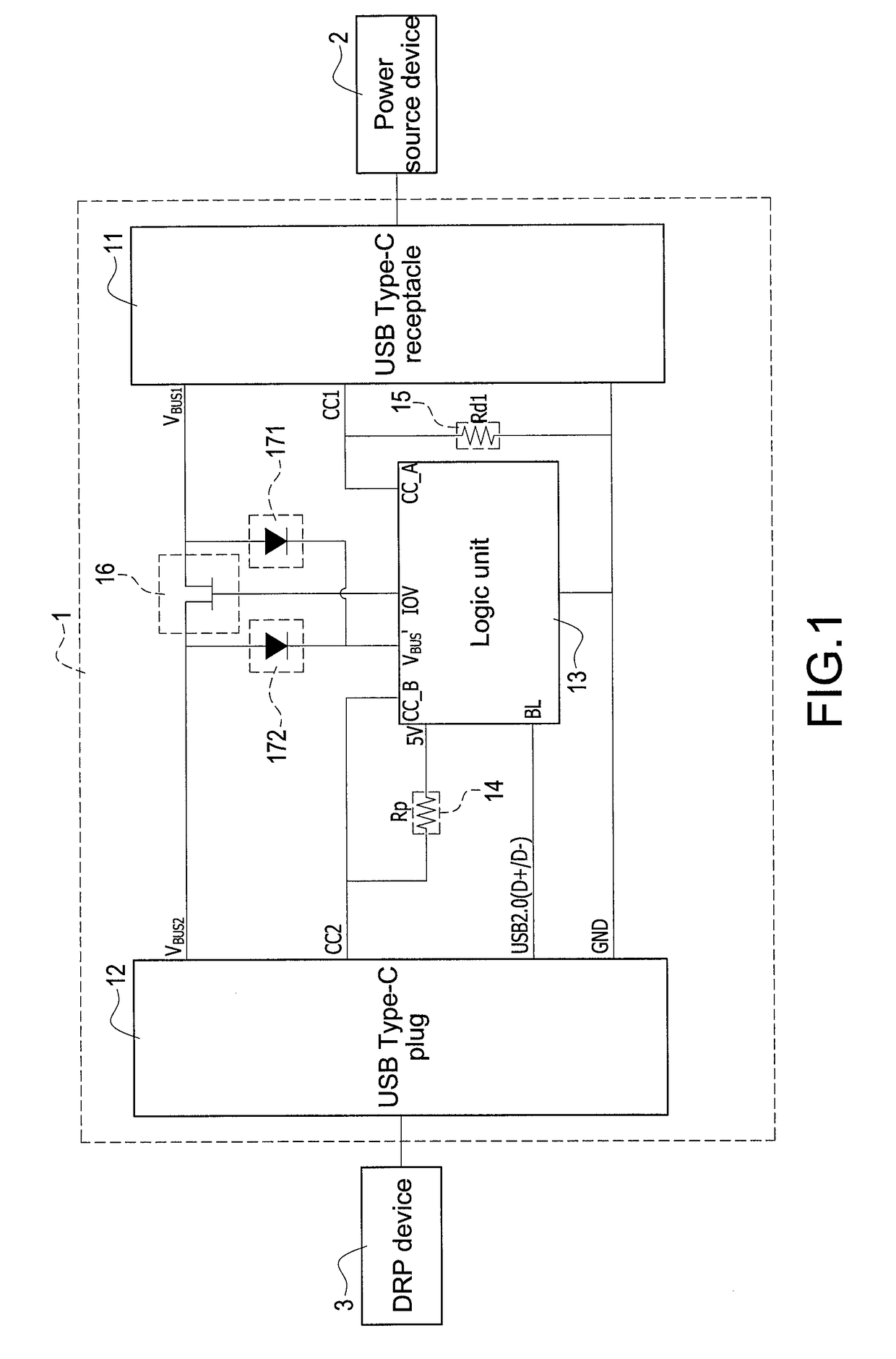

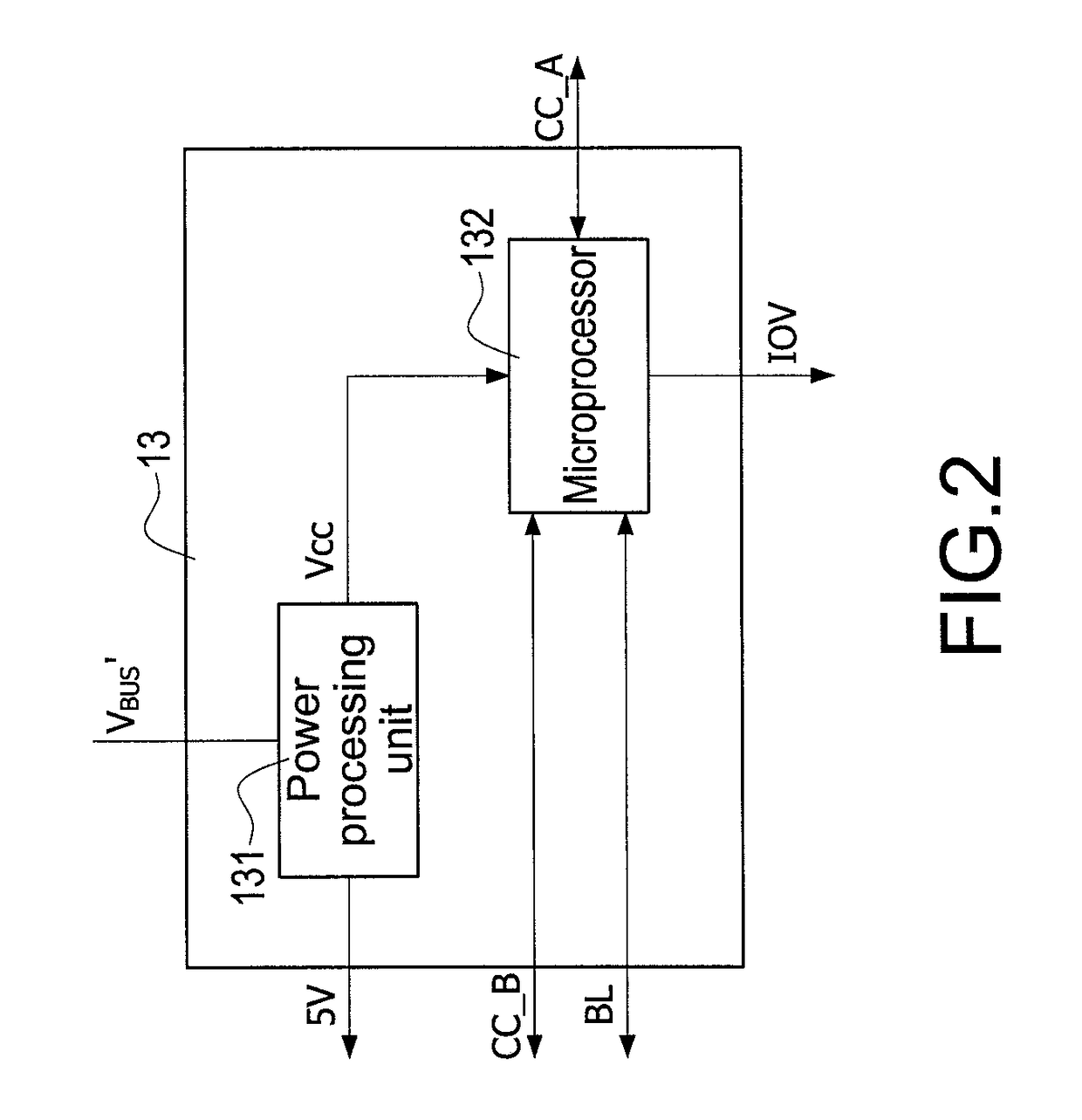

USB type-c adapter module and activating method for the same

ActiveUS20170351638A1Easy to updateOvercome problemsCoupling device detailsEnergy efficient computingElectrical resistance and conductanceAnd logic unit

A module comprising a USB Type-C receptacle, a USB Type-C plug and a logic unit is disclosed. A power pin of the receptacle is connected with another power pin of the plug via a switch. A CC pin of the receptacle is connected to ground through a pull-down resistance. Another CC pin of the plug is connected to the logic unit through a pull-up resistance. The module connects with a power source device being a power sink-role in order to receive a source capability of the power source device, then turns on the switch and transforms itself to a power source-role. The module connects to a DRP device afterward being the power source-role to act for the power source device and perform a USB PD communication with the DRP device.

Owner:DELTA ELECTRONICS INC

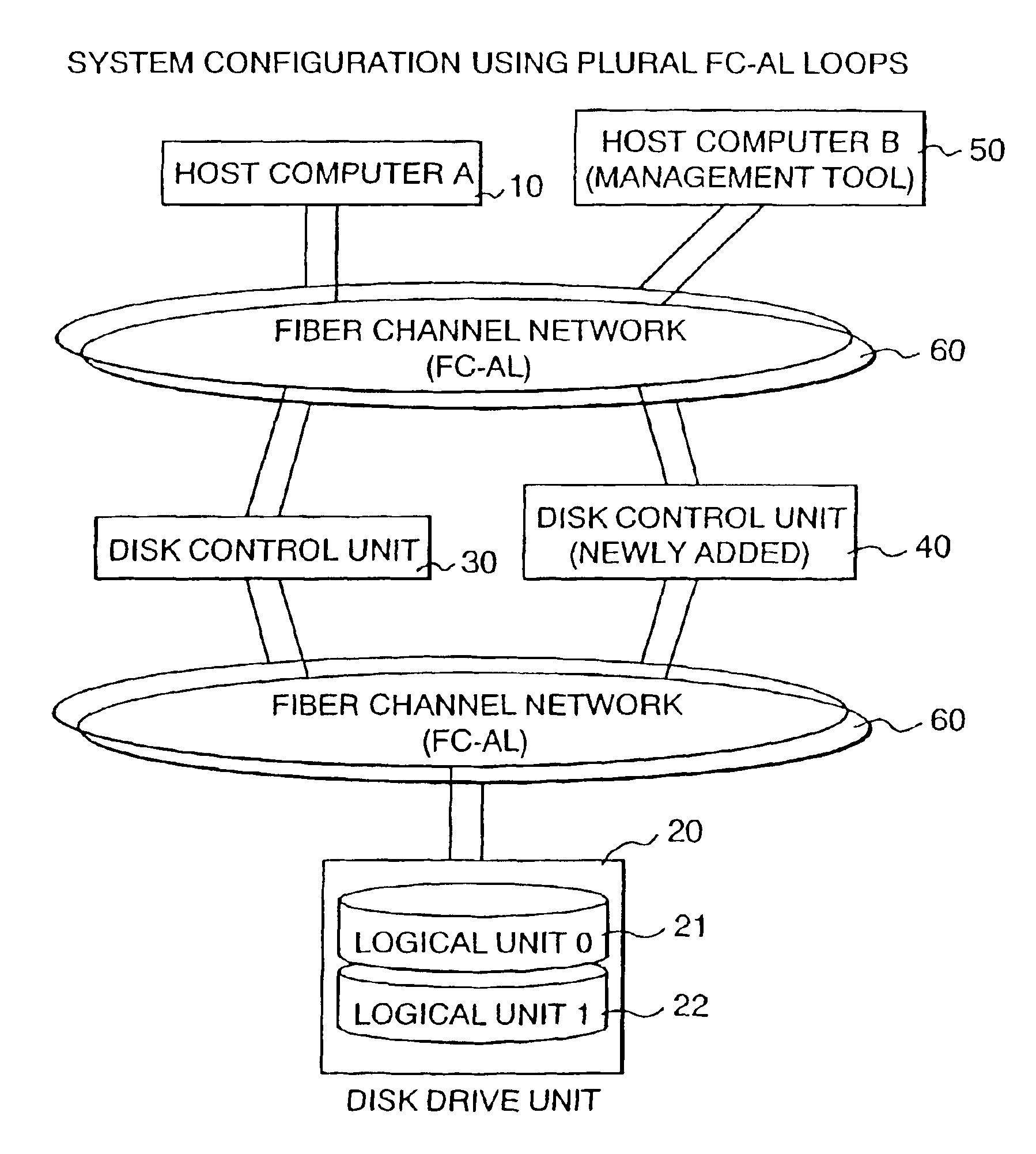

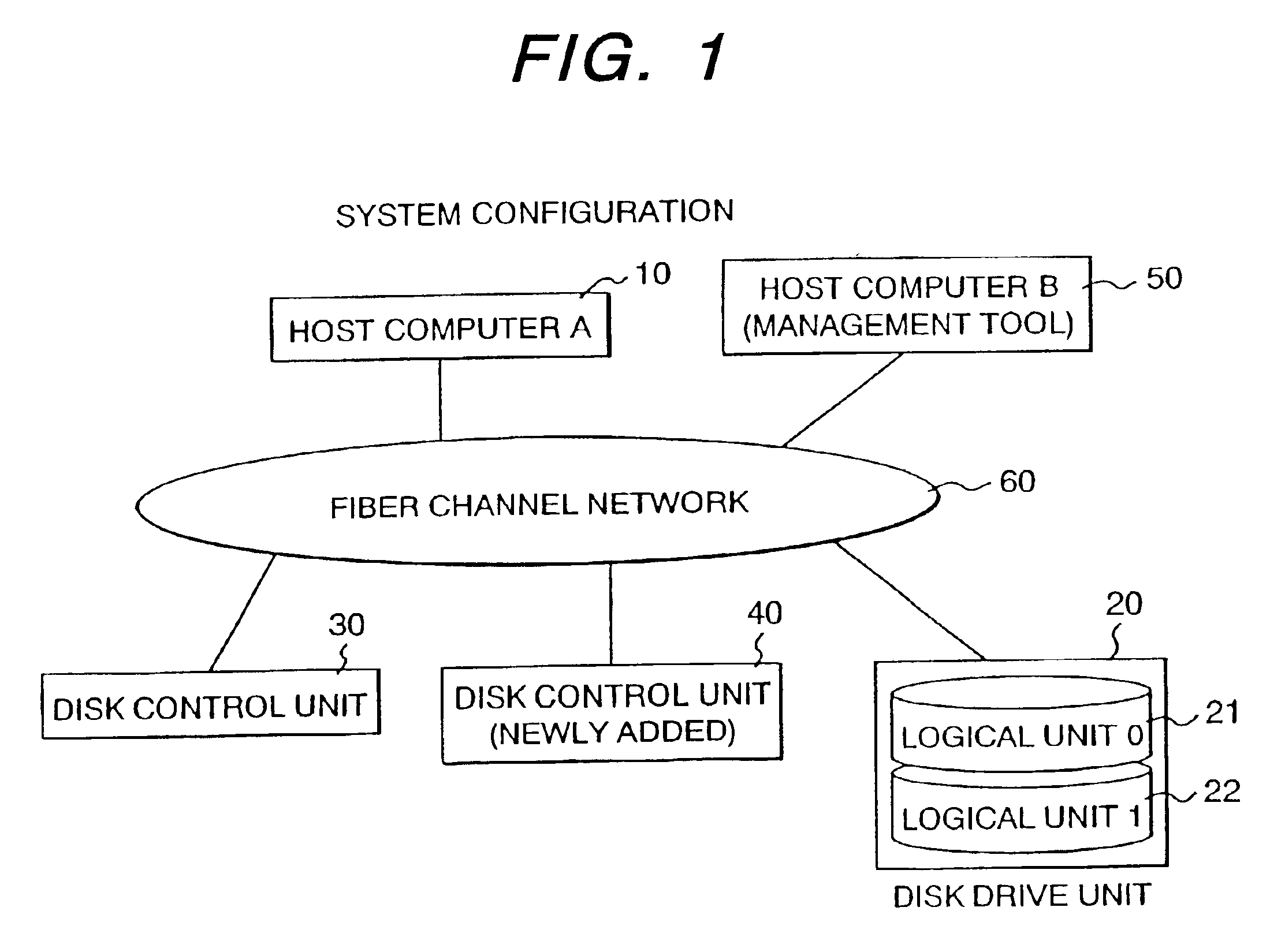

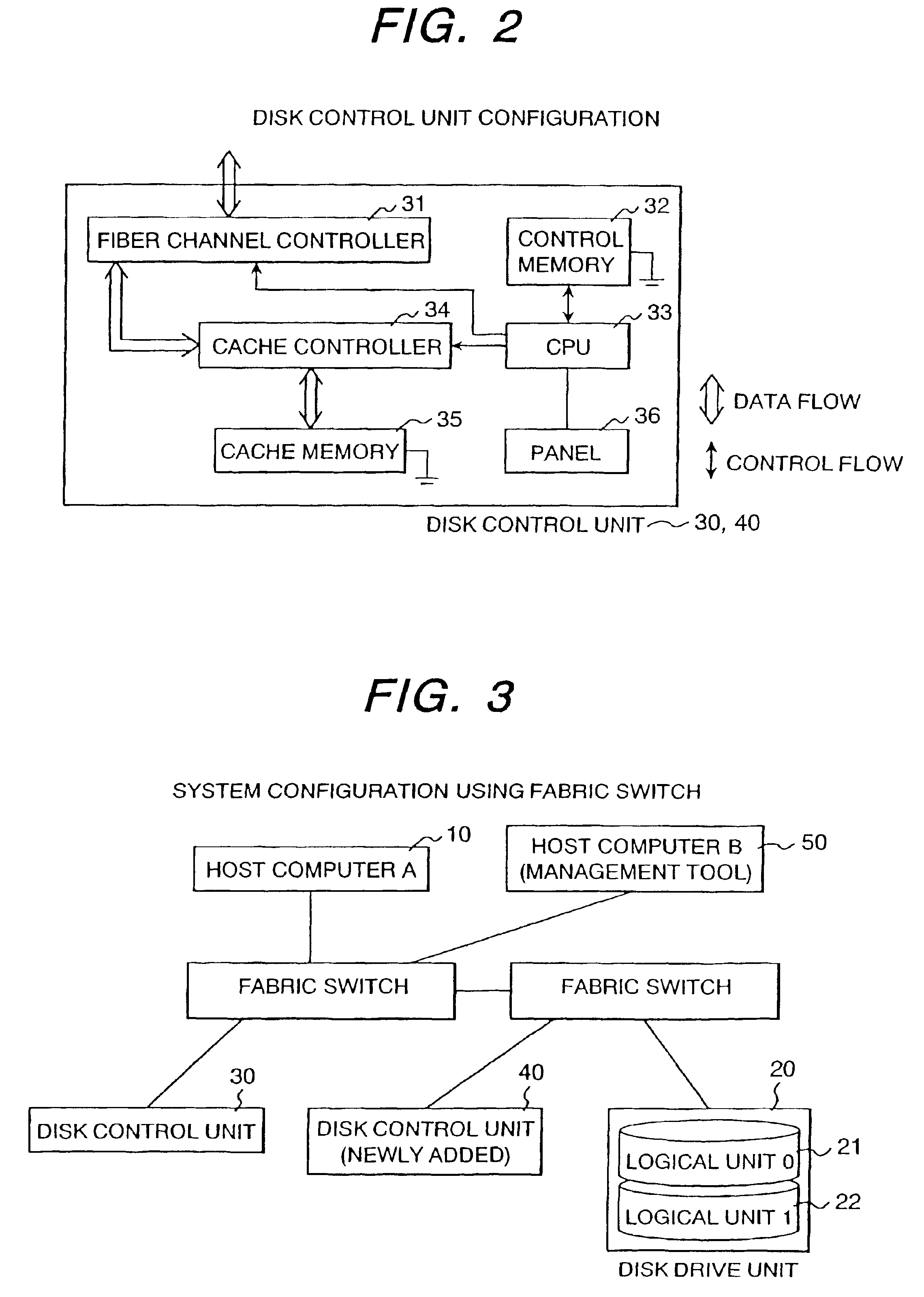

Storage control unit and method for handling data storage system using thereof

InactiveUS6889286B2To achieve load distributionInput/output to record carriersMemory adressing/allocation/relocationFiberLogic cell

For providing a storage control unit to be connected to a fiber channel, in which a new storage control unit is added onto the fiber channel network during on-line operation and succeeds control information of a logical unit from the storage control unit which has been existing before, so as to be in charge of a process request issued to that logical unit from a host computer thereafter, wherein a control memory being able to memorize the control information is provided in each of the storage control units 30 and 40, which information is necessary when succeeding or taking over the logical unit and is represented by such as construction information of a magnetic disk drive within a disk drive unit 20 and construction information of the logical unit, so on. The contents of the control memory within the storage control unit 30 is copied into the control memory of the storage control unit 40 when the new storage control unit 40 is added onto the fiber channel network.

Owner:HITACHI LTD

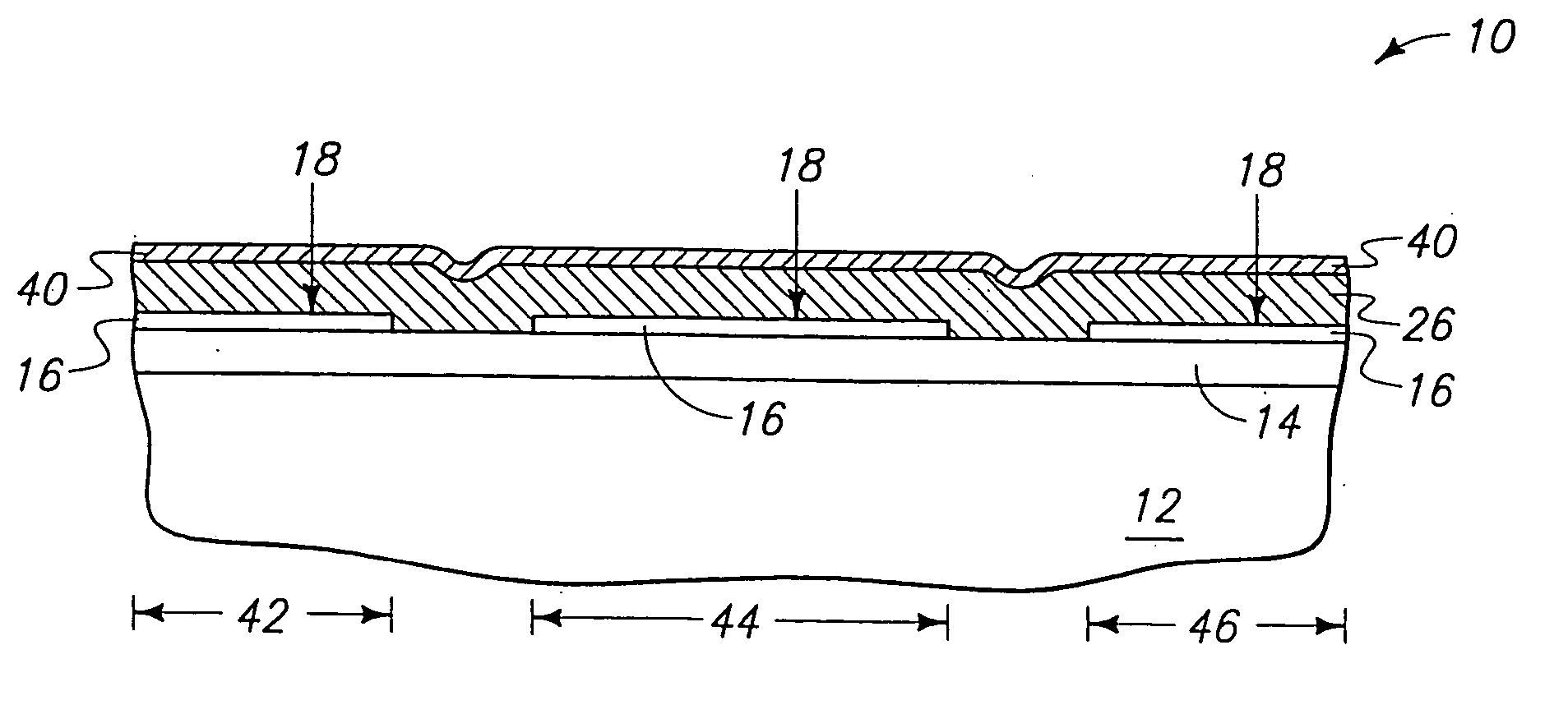

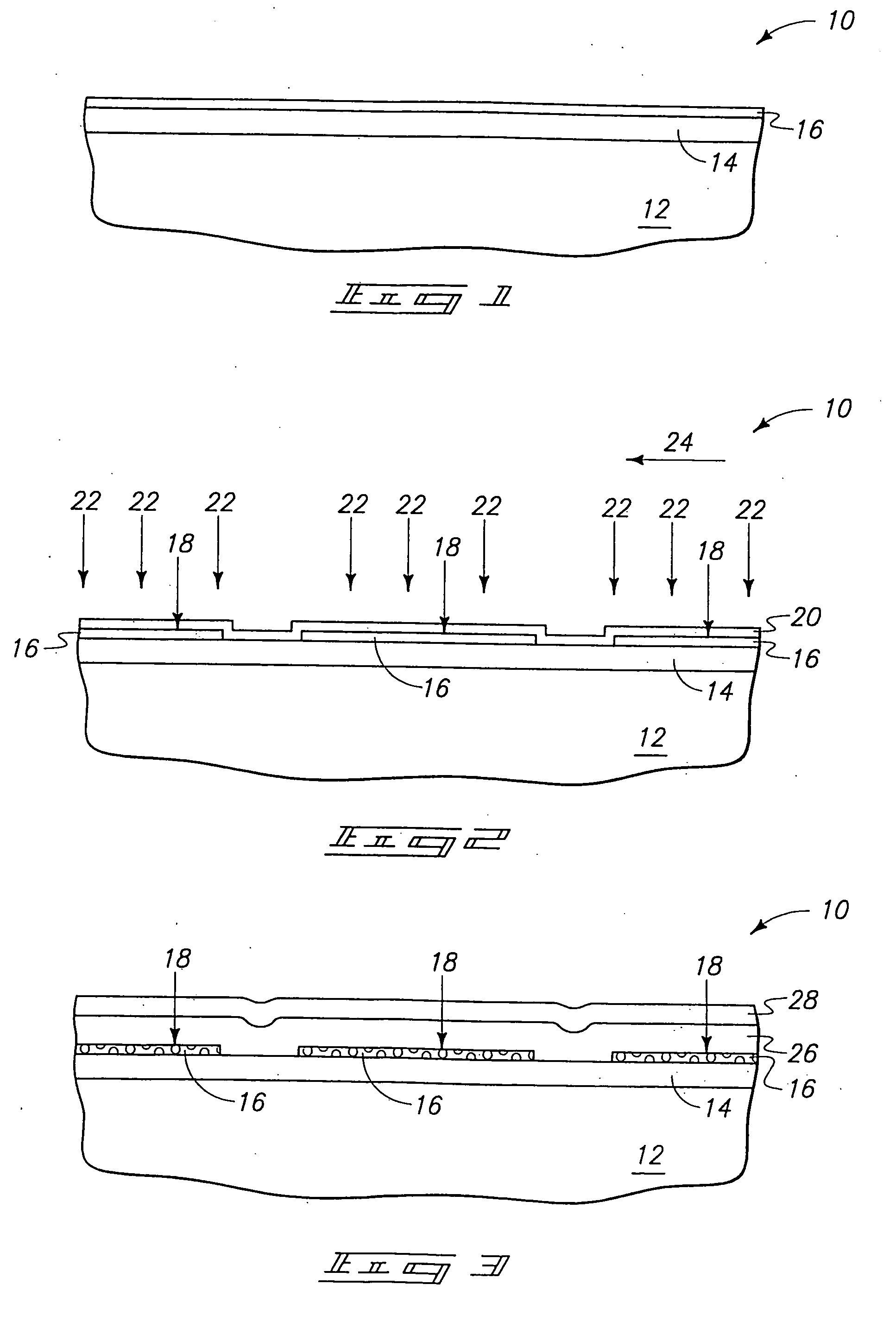

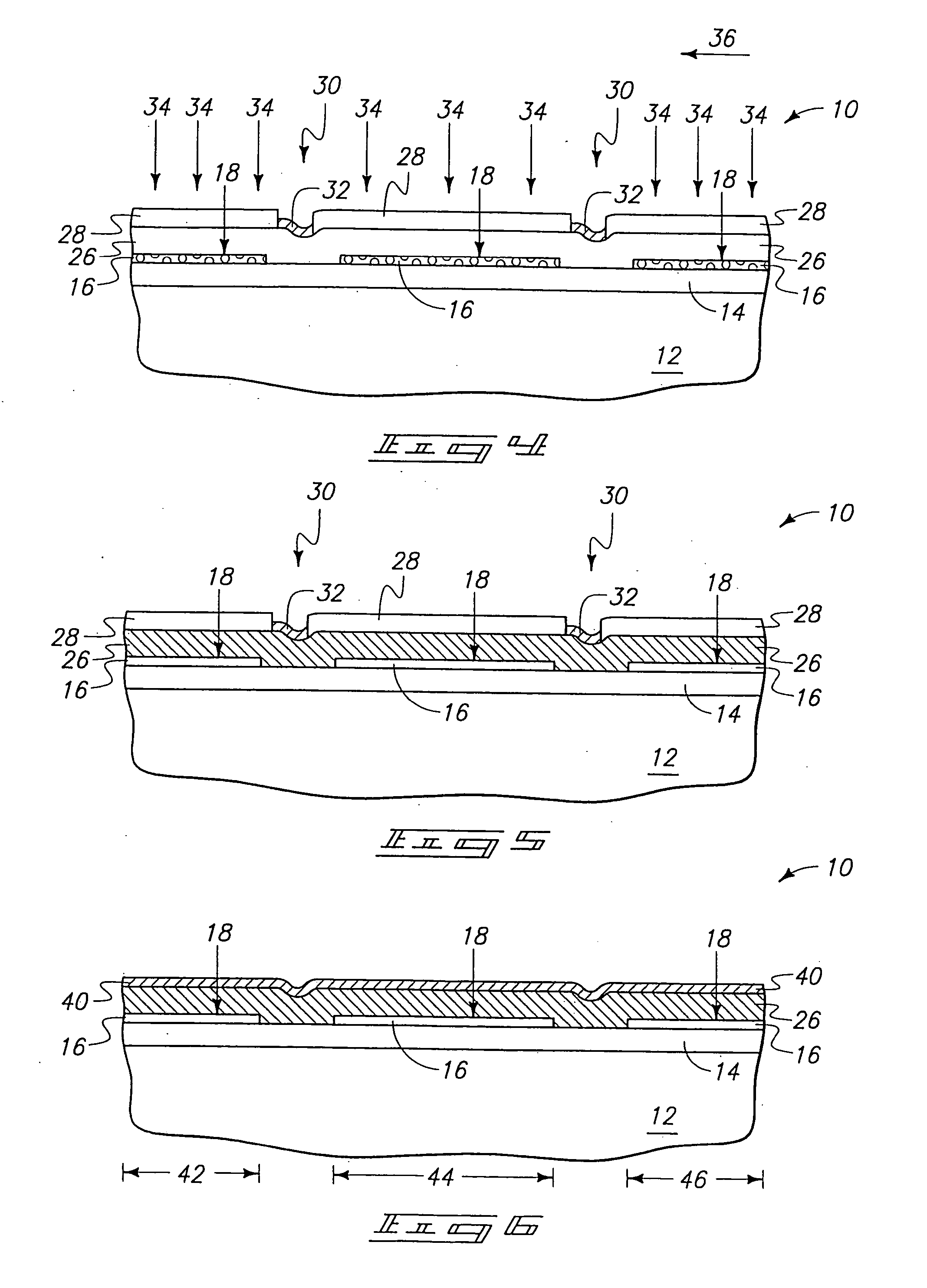

Methods of forming semiconductor constructions and integrated circuits

The invention includes a TFT-based logic circuit construction. Such construction includes a pair of first transistor devices, and a pair of second transistor devices over the first transistor devices. The first transistor devices have first active regions extending into a first semiconductive material, and the second transistor devices have second active regions extending into a second semiconductive material. At least one of the first and second semiconductive materials can comprise crystalline Si / Ge. The logic construction can comprise NOR circuitry and / or NAND circuitry, as well as higher level logic cells, such as latches. Further, the logic circuit construction can be associated with a semiconductor-on-insulator structure, and on versatile substrates. The invention includes three-dimensional logic cell layout configurations for enhanced wireability and logic cell density, which can lead to enhanced performance.

Owner:MICRON TECH INC

SCL type FPGA with multi-threshold transistors and method for forming same

A new scheme of Schottky FPGA (SFPGA) IC solution is proposed. The chip is organized by embedded analog, memory, and logic units with on chip apparatus and software means to partitioning, altering selected portions of hardware. The process means is based on the combined Schottky CMOS (SCMOS, U.S. Pat. No. 6,590,800) and Flash technology. The circuit means is based on SCMOS-DTL gate arrays. Software means is based on the C++ procedures with levels of LUT. The SFPGA device supports GHz low power ASIC mixed signal product applications with embedded analog, logic, and memory array units. Several multiplexing schemes are disclosed, which accommodate tasks to vary the Vt and transmission line transmission of selected transistor or IO nets, and therefore their analog and digital device properties. A voltage doubler and supply booster and a Digital-Analog-Digital-Translator (DADT) apparatus are also disclosed in accordance with the present invention.Accordingly, the present invention includes control schemes to field program basic circuit element or any critical nets, and to alter the functionality of certain predetermined circuit units, and update array interconnections, accessing stored protocols, algorithms in all chips in the embodiment subsystem of a SFPGA chip sets.

Owner:SUPER TALENT ELECTRONICS

High speed memory chip module and electronics system device with a high speed memory chip module

ActiveUS20130091315A1Easy to optimizeReduce power consumptionSolid-state devicesDigital storageMOSFETElectronic systems

A high speed memory chip module includes a type of memory cell array group and a logic unit. The type memory cell array group includes multiple memory cell array integrated circuits (ICs), and each of the memory cell array ICs has a data bus and at least one memory cell array, and corresponds to first metal-oxide-semiconductor field-effect transistor (MOSFET) gate length corresponding to a first MOSFET process. The logic unit accesses the type of memory cell array group through a first transmission bus, where bus width of the first transmission bus is wider than bus width of the data bus of each of the memory cell array ICs. Corresponding to a second MOSFET process, the logic unit has a second MOSFET gate length which is shorter than the first MOSFET gate length.

Owner:ETRON TECH INC

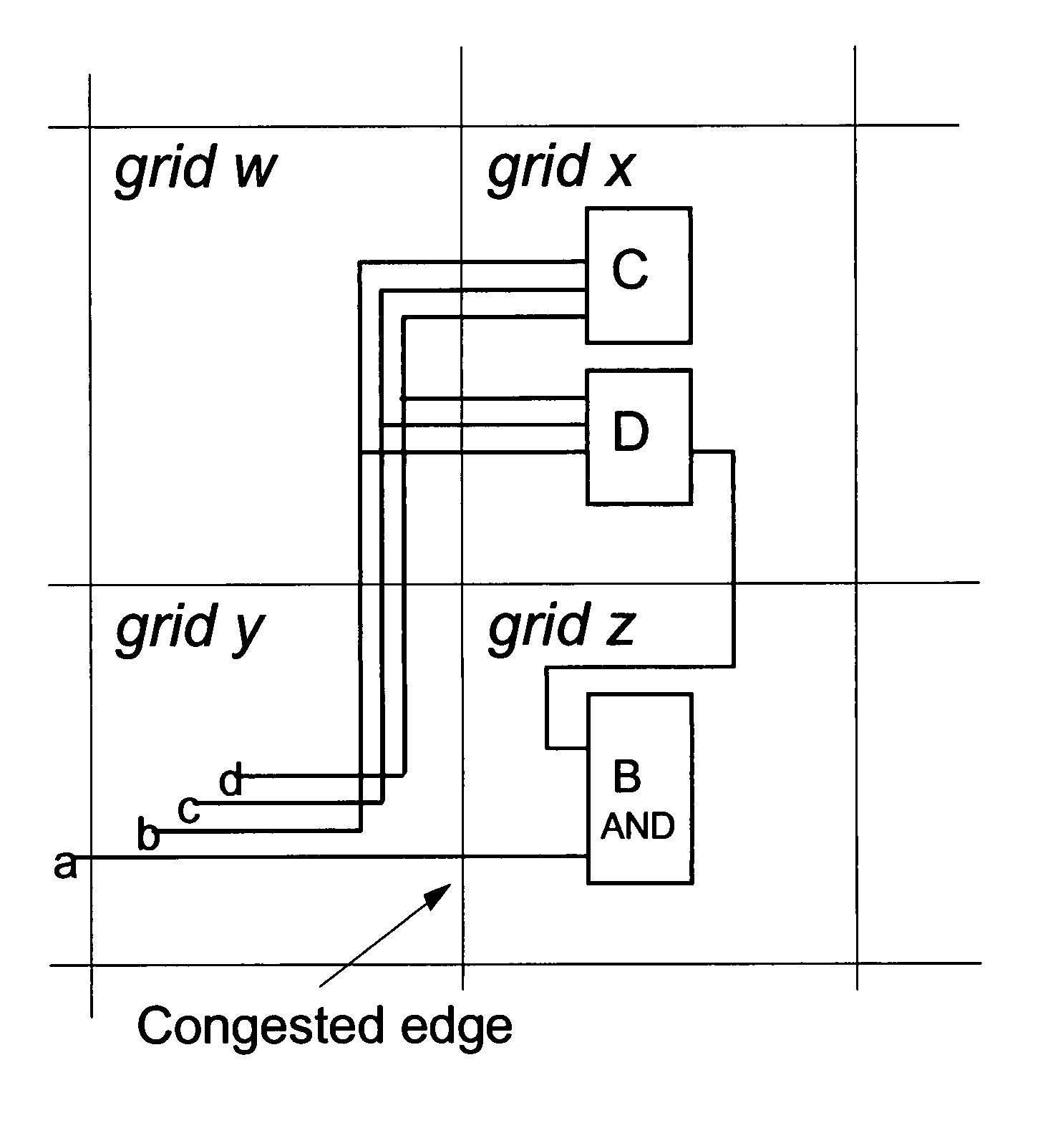

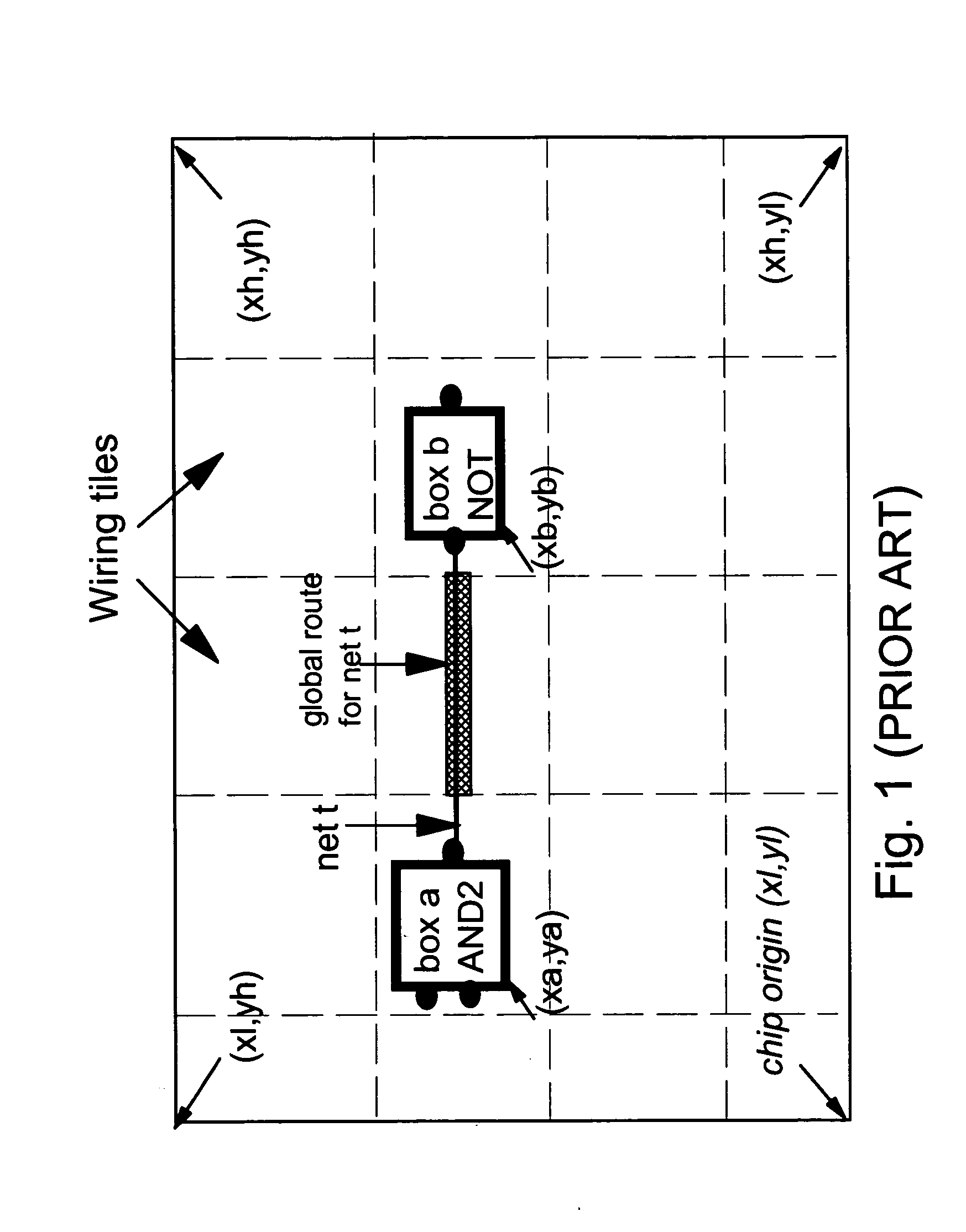

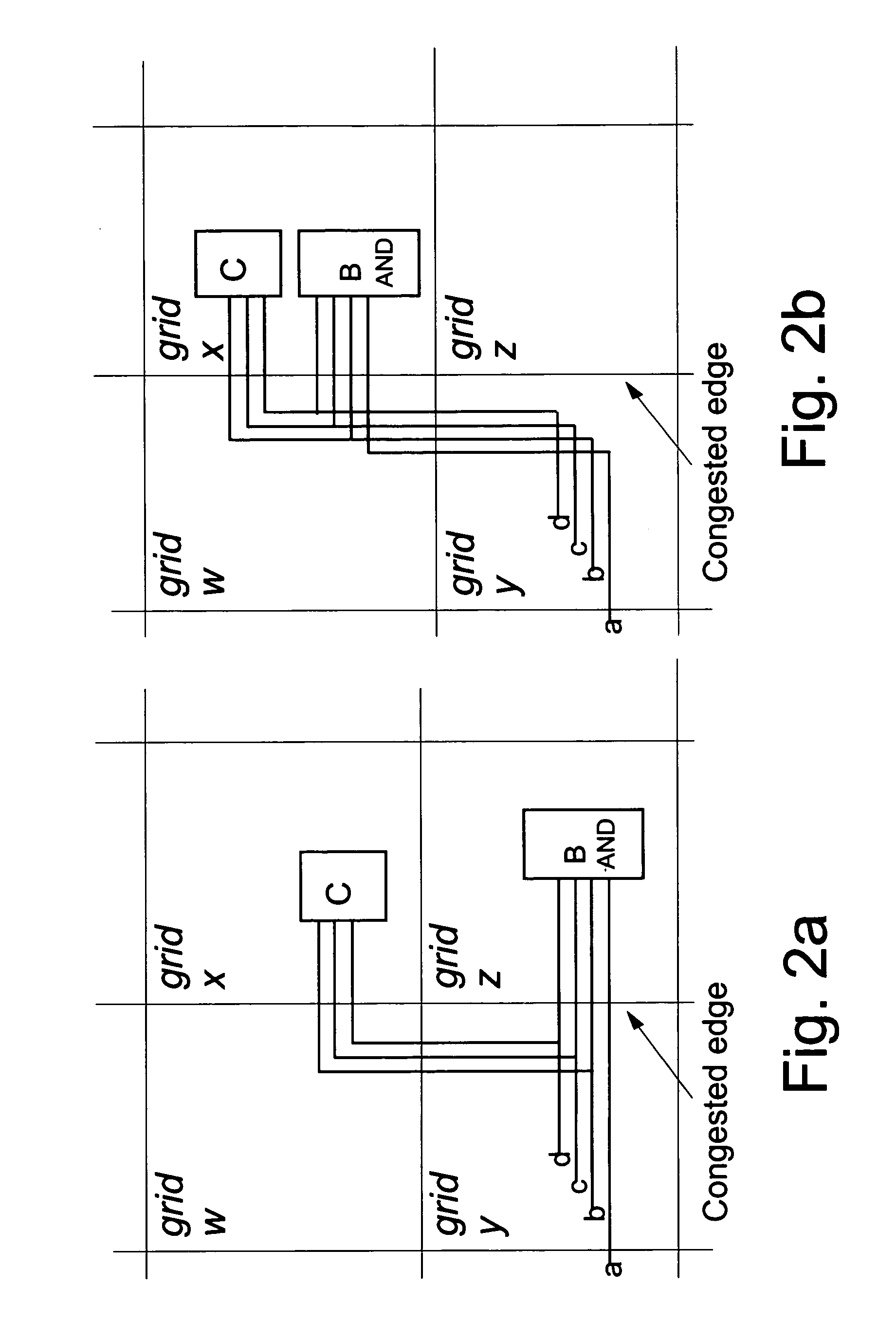

Method for reducing wiring congestion in a VLSI chip design

InactiveUS20050151258A1Reduced wiring areaReduce congestionSemiconductor/solid-state device detailsSolid-state devicesLogic cellAnd logic unit

A system and method for correcting wiring congestion in a placed and partially or fully globally-routed VLSI chip design while avoiding adding new timing or electrical violations or other design constraints. Globally-congested areas are identified along with determining terminated and non-terminated wires in the congested areas. The process includes optimizing the identified congestion areas, incrementally rerouting affected nets, testing the resultant design legality and congestion metrics, and committing or reversing the optimizations and reroutings. The optimizations further includes the movement of logic cells and decomposition, recomposition or any other modification of logic cell structures (possibly combined with cell movement) to move terminated wires to less congested grid edges, rearrangement of commutative connections within or between cells, or addition of buffers to cause reroutes of feedthrough wires.

Owner:IBM CORP

Method and apparatus for device discovery

InactiveUS7103686B1Return quicklyEfficiently provideData switching by path configurationMultiple digital computer combinationsFiberComputer network

An invention is disclosed that provides device information using a Fibre Channel network. Initially, device information is obtained for a device coupled to a Fibre Channel based network, and an address database is constructed that includes a device entry for the device. Preferably, the device entry includes a port target identifier and a logical unit identifier for the device, and associates the previously obtained device information with the port target identifier and the logical unit identifier. A request is then received for the device information that typically includes the port target identifier and the logical unit identifier. The device information associated with the port target identifier and the logical unit identifier is then returned in response to the request.

Owner:PMC-SIERRA

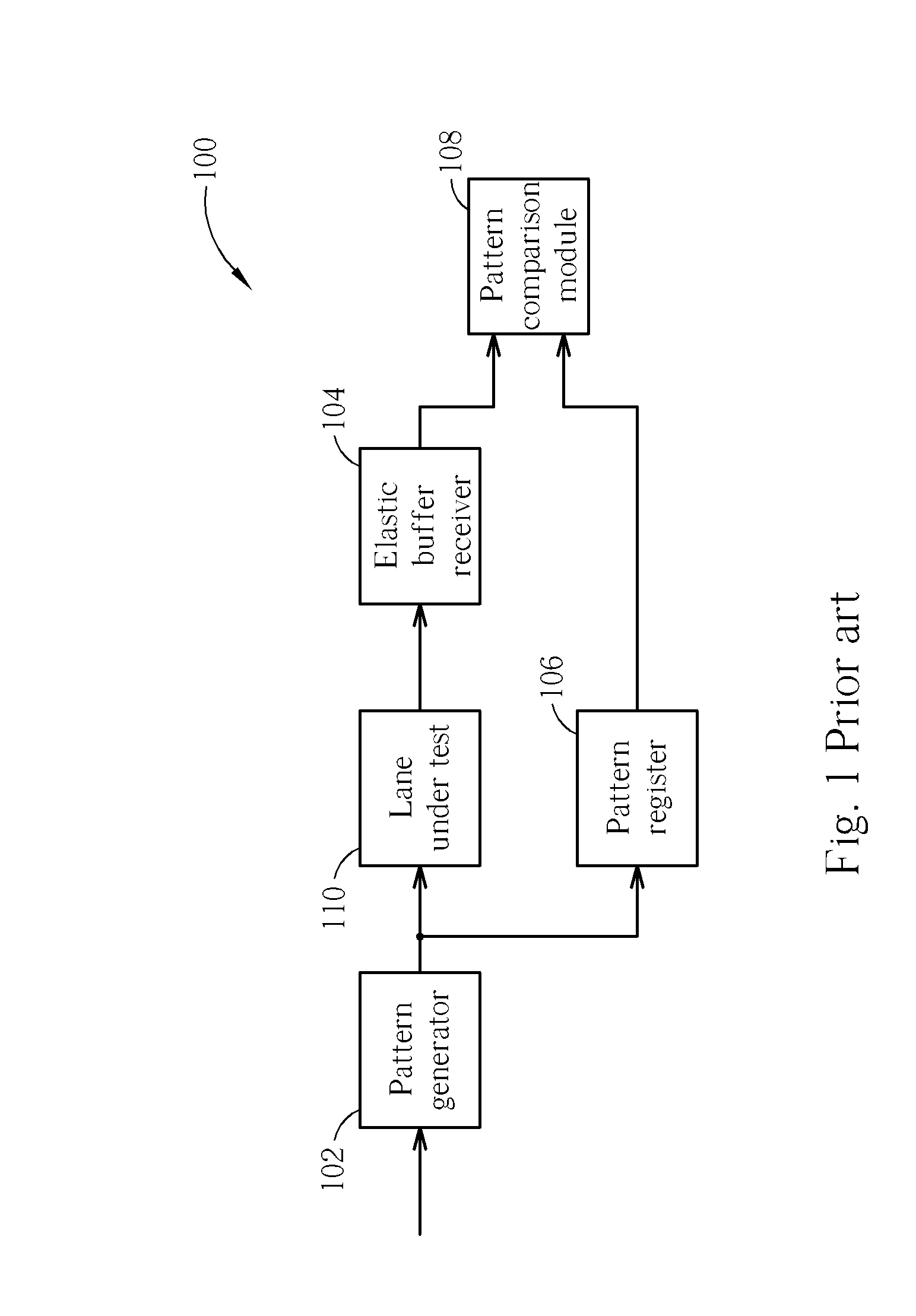

PCI Express Physical Layer Built-In Self Test Architecture

ActiveUS20060123298A1Correct operation testingElectronic circuit testingAnd logic unitPhysical layer

Owner:VIA LABS INC

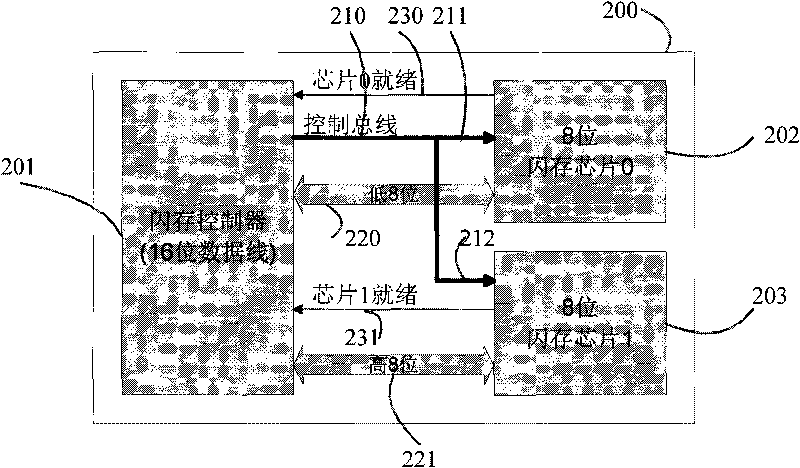

Method for protecting the safety of storing data in flash memory storing device

The present invention discloses a method for protecting the safety of storing data in a flash memory storing device, which comprises the following steps: a controlling bus and a data order bus of a flash memory controller are connected with a 0 chip and a 1 chip at the same time; 8 bits in a 16-bit data bus are connected with the 0 chip, and the rest 8 bits are connected with a 1 chip of the same storing unit; and a data repeating unit is in the flash memory controller. When a data managing table is written, the 0 chip and the 1 chip receive orders at the same time, a data repeating and logic unit is started, and the data managing table can be written in the 0 chip and the 1 chip at the same time. When the data managing table is read out, if the reading is failure, another chip in the same storing unit is used for reading. The method for protecting the safety of storing data in a flash memory storing device reduces the damage rate of the data managing table, protects the safety of stored data, and can provide the reliability of the flash memory controller.

Owner:BRITE SEMICON SHANGHAI CORP

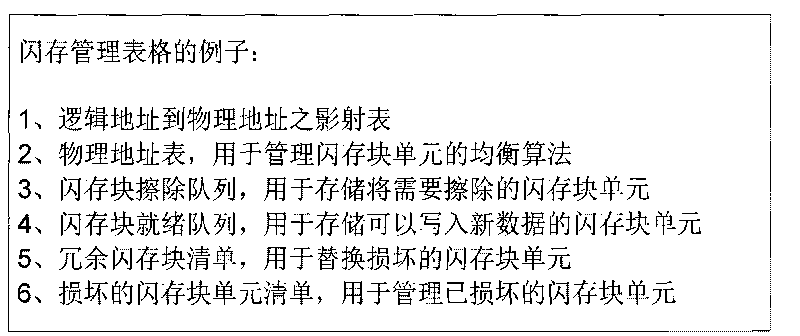

Semiconductor device and driving method thereof

InactiveUS20080277707A1Guaranteed ease of operationTransistorSolid-state devicesAnd logic unitDevice material

It is an object of the invention to provide a digital circuit which can operate normally regardless of binary potentials of an input signal. A semiconductor device having a correcting unit and a logic unit wherein the correcting unit includes a capacitor, first and second switches, wherein the first electrode of the capacitor is connected to the input terminal and the second electrode of the capacitor is connected to the gate of the transistor in the logic circuit, wherein the first switch controls the connection between a gate and drain of the transistor and the second switch controls the potential to be supplied to the drain of the transistor is provided.

Owner:SEMICON ENERGY LAB CO LTD

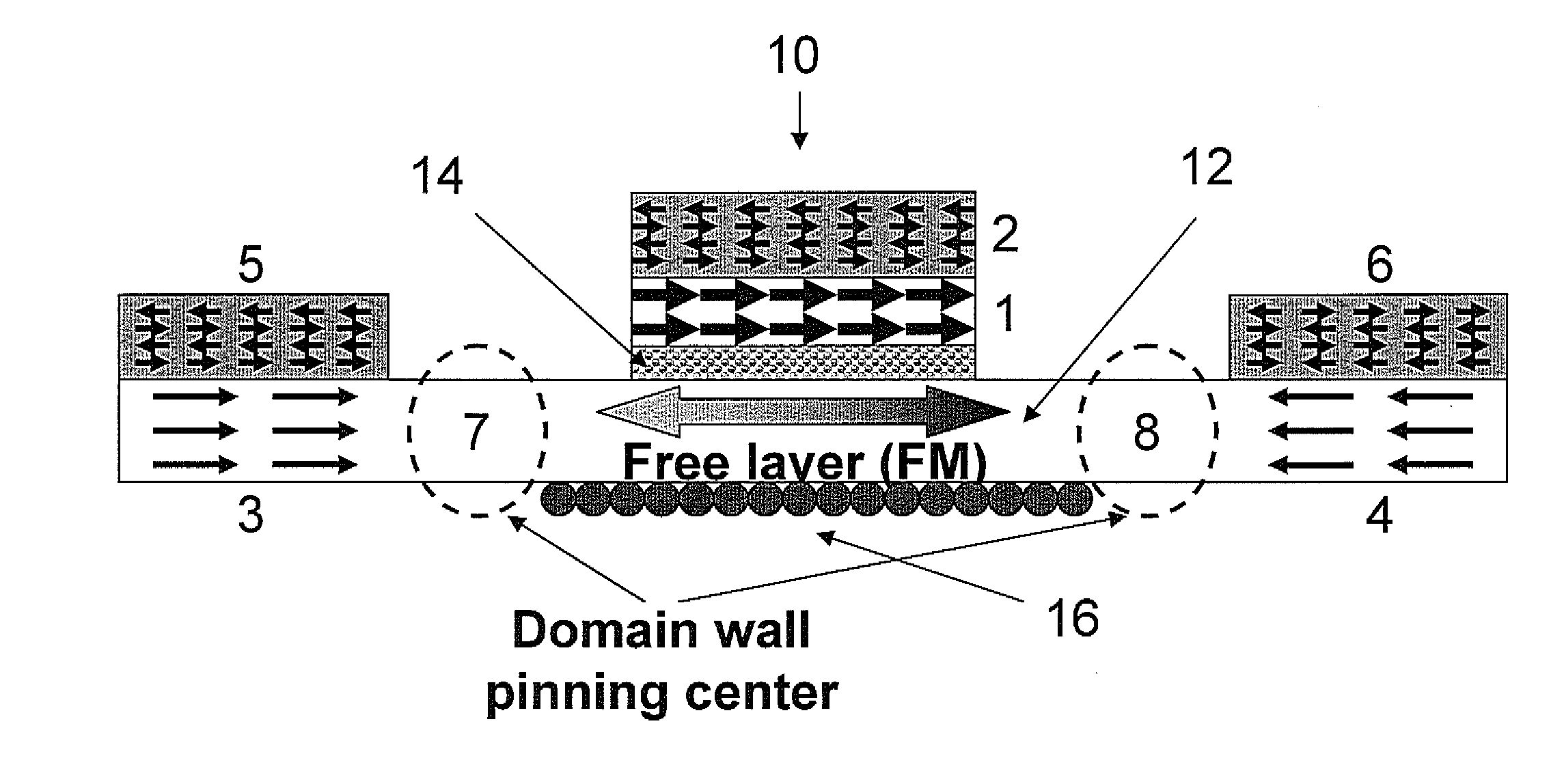

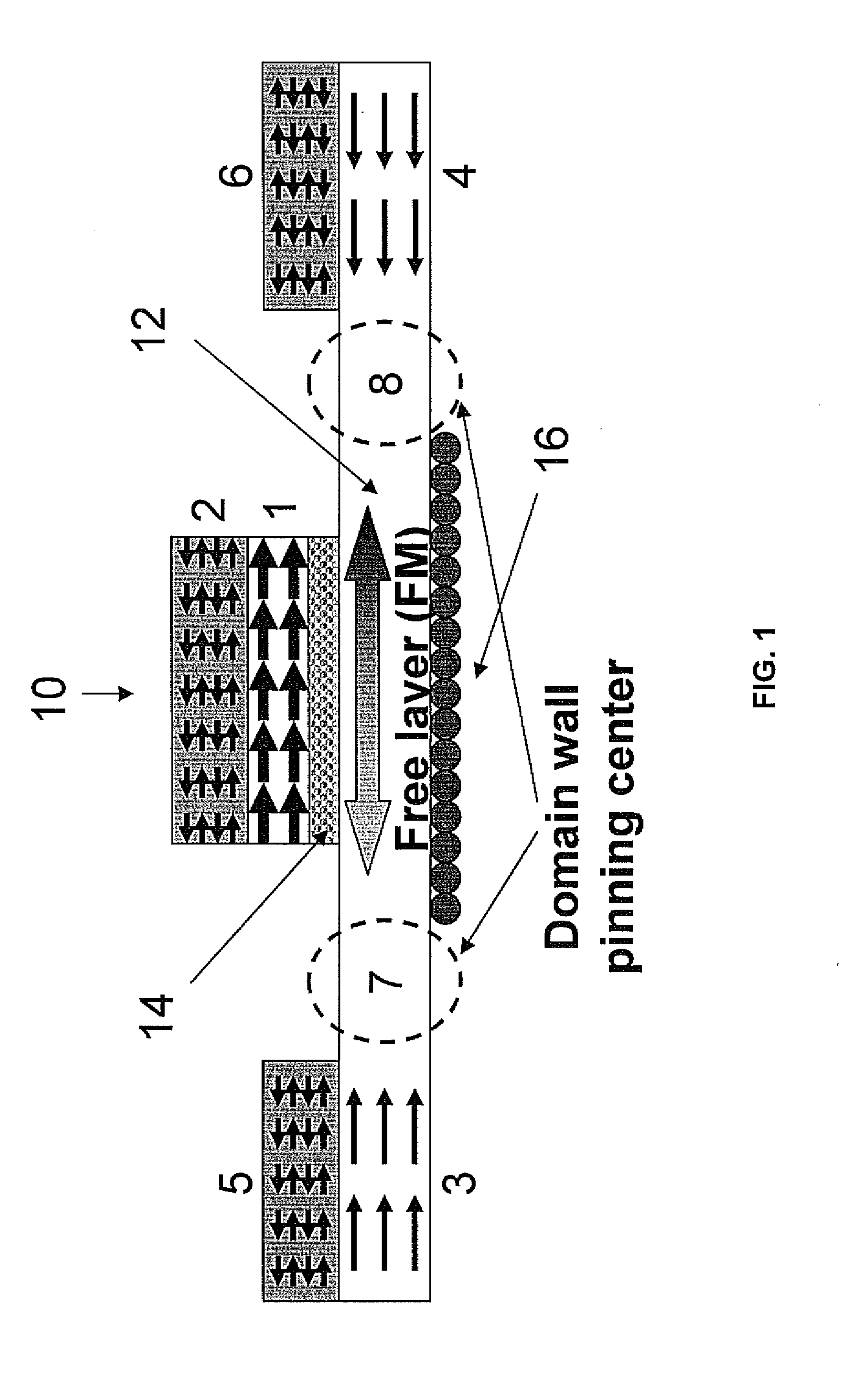

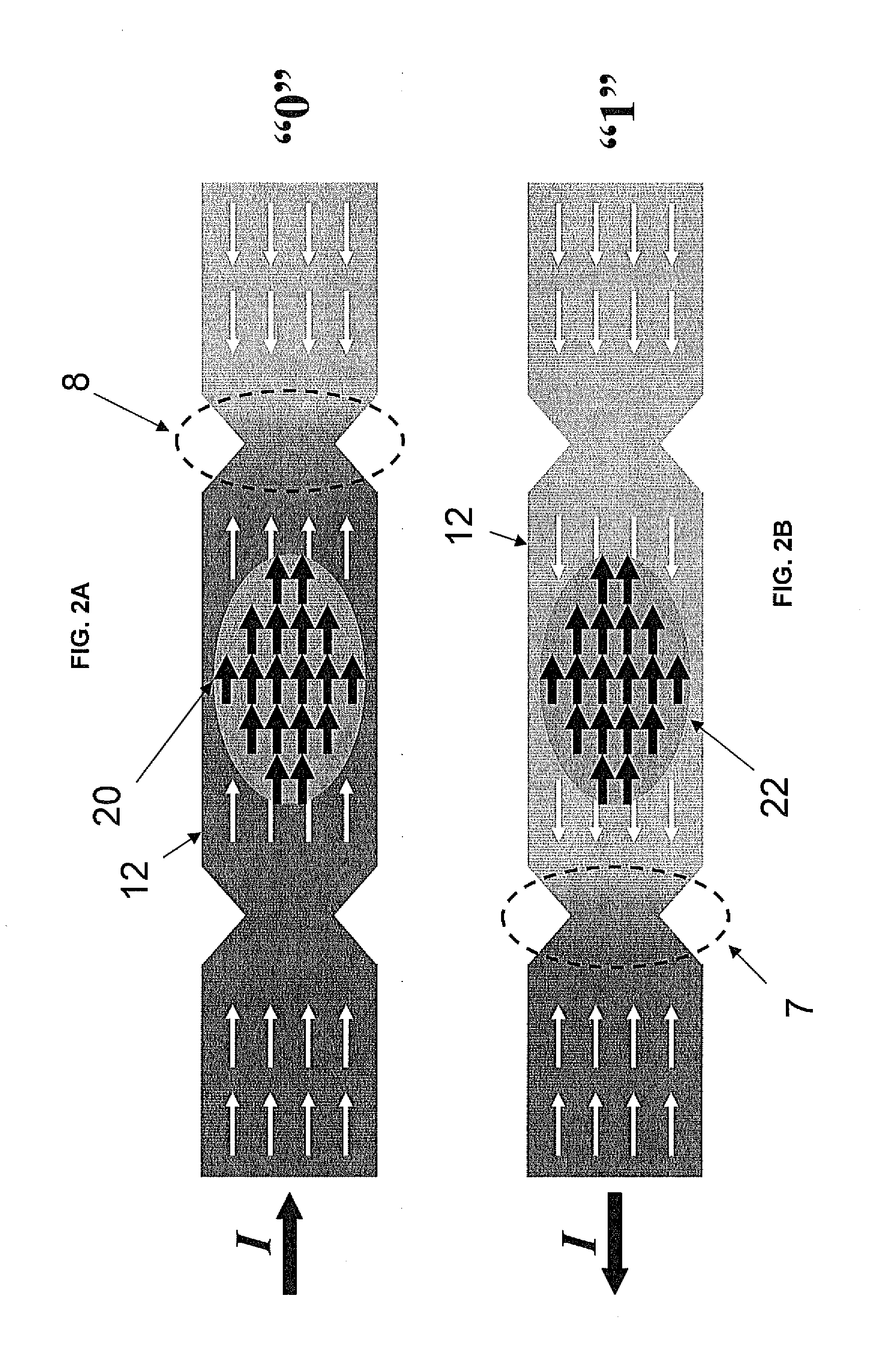

Switching mechanism of magnetic storage cell and logic unit using current induced domain wall motions

InactiveUS20140062530A1Magnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingLogic cellAnd logic unit

A magnetic memory cell is provided that includes a free layer that is pinned on both of its sides to form one or more domain wall structures. The one or more domain wall structures define one or more logic states by controlling the motion of the one or more domain wall structures.

Owner:MASSACHUSETTS INST OF TECH

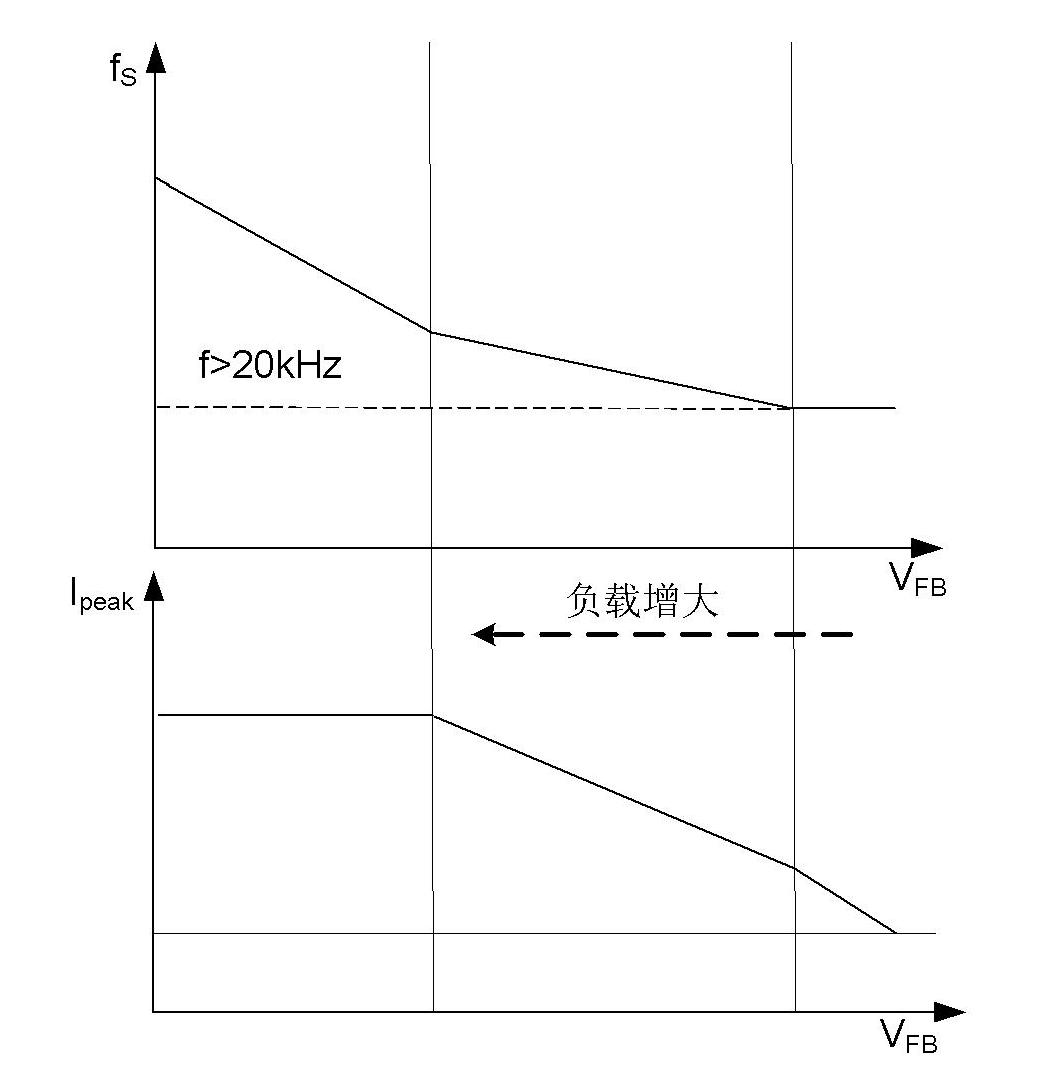

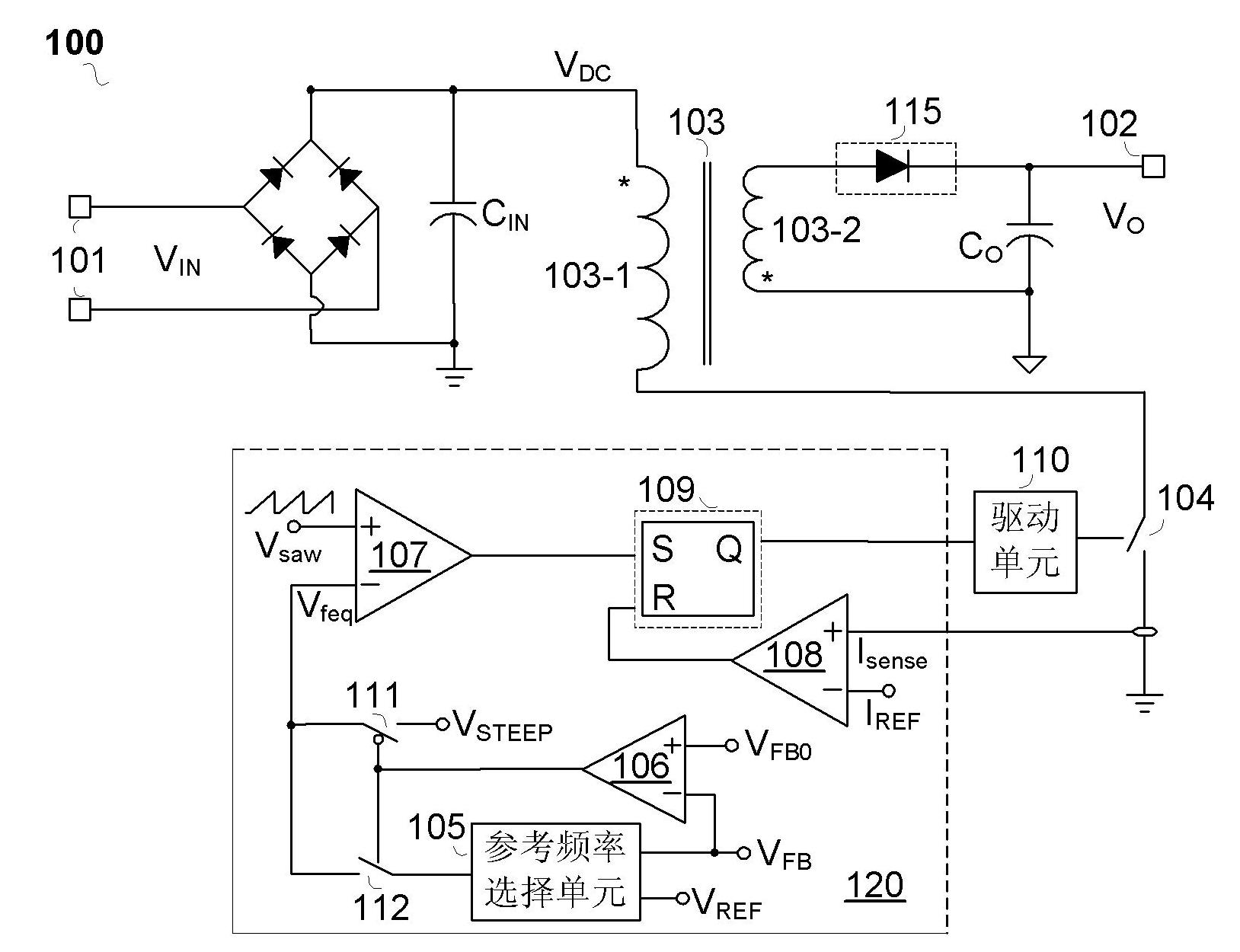

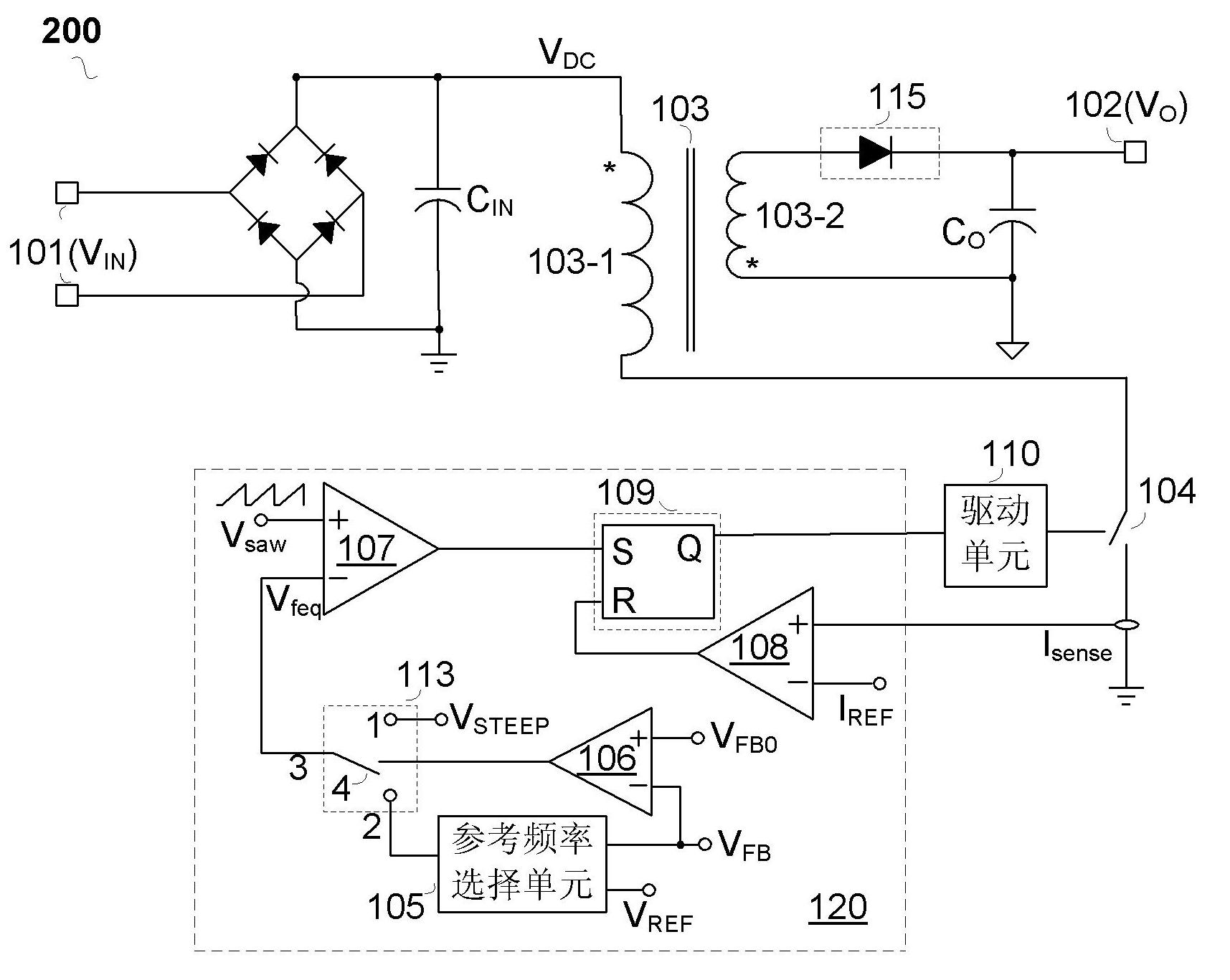

Switching voltage stabilizing circuit and control circuit and method thereof

ActiveCN102647073AAvoid switching frequency increaseAvoid power lossEfficient power electronics conversionDc-dc conversionAnd logic unitEngineering

The invention discloses a switching voltage stabilizing circuit and a control circuit and method thereof. The switching voltage stabilizing circuit comprises an input port, an output port, an energy storage element, a main switch, a reference frequency selection unit, a load state detection unit, a first comparator, a current comparator and a logic unit. The switching frequency of the switching voltage stabilizing circuit is quickly improved to be the maximum when the load is the maximum, the continuous improvement of the switching frequency at this time is prevented, so that the continuous improvement of power loss is prevented, and the heat problem is relieved. According to the embodiment of the invention, when the switching voltage stabilizing circuit works under the maximum load, the heat problem is further solved through a continuous time setting unit, so that the performance of a system is better.

Owner:CHENGDU MONOLITHIC POWER SYST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com