Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

259 results about "Processor element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Element Processor. Is an item created by Structure Traders. This item is used in the Stage 2 of the Refining Process. This item, when used with one Enzyme Element and one Element Processing Canister will then create one Processed Enzyme Element.

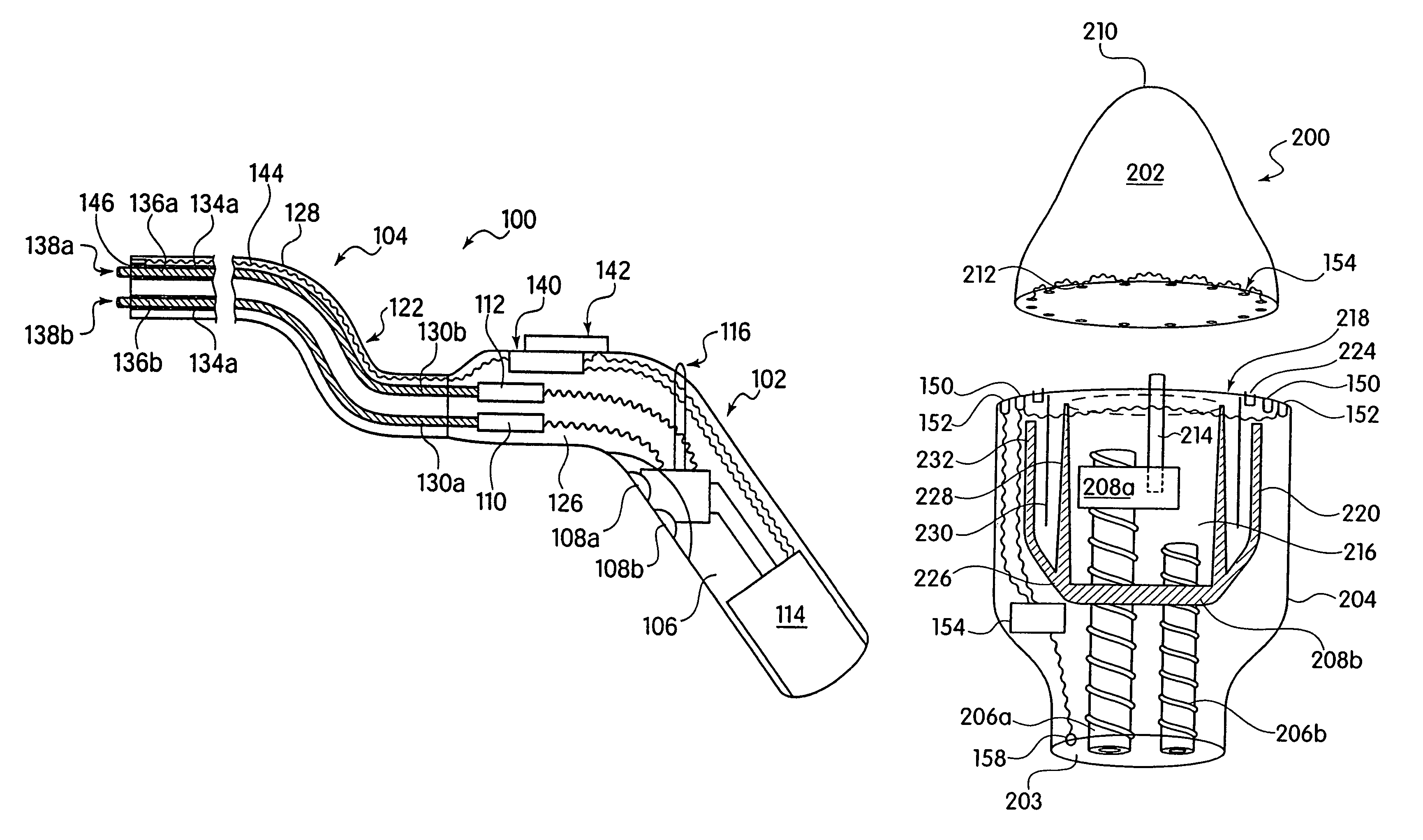

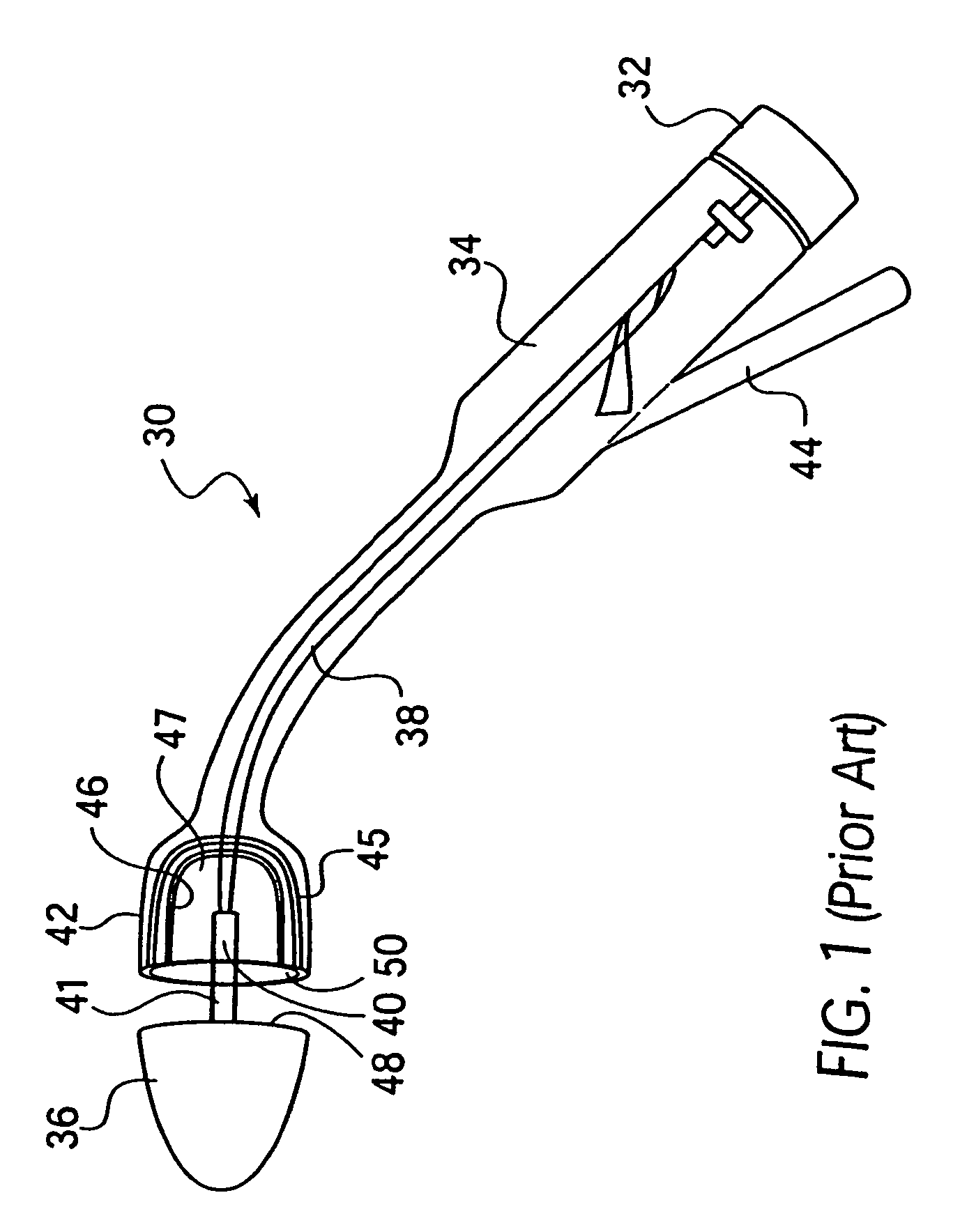

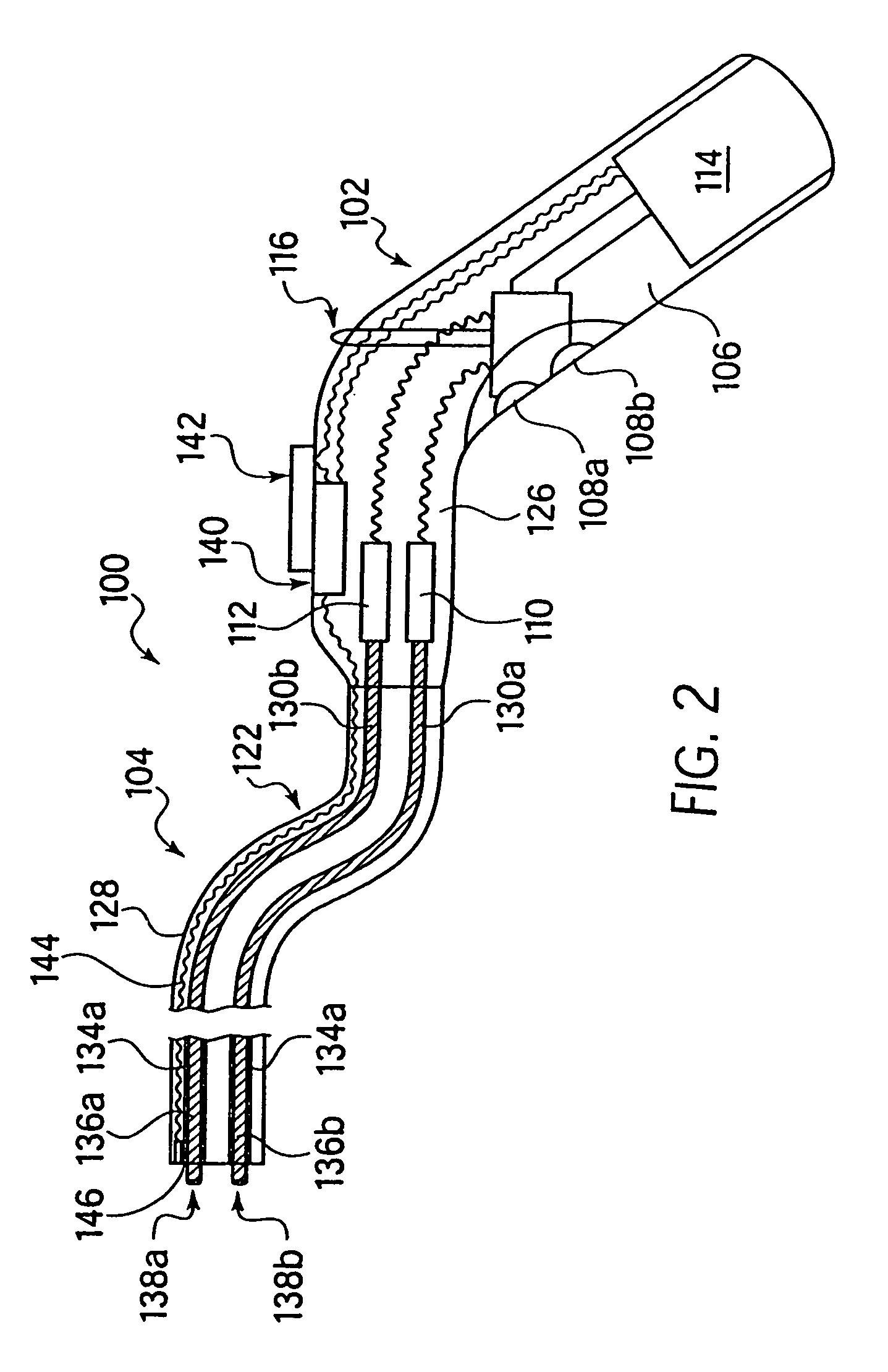

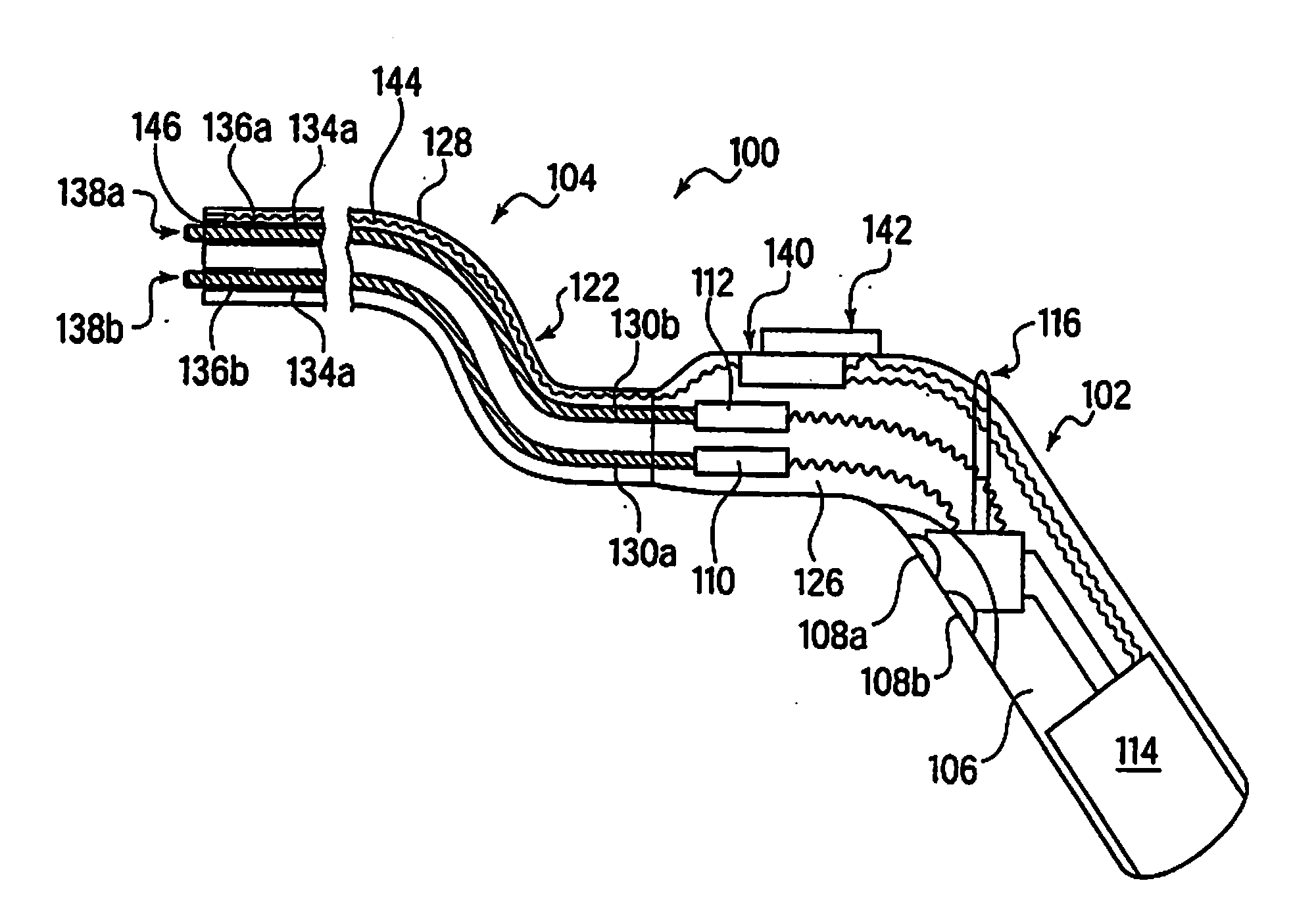

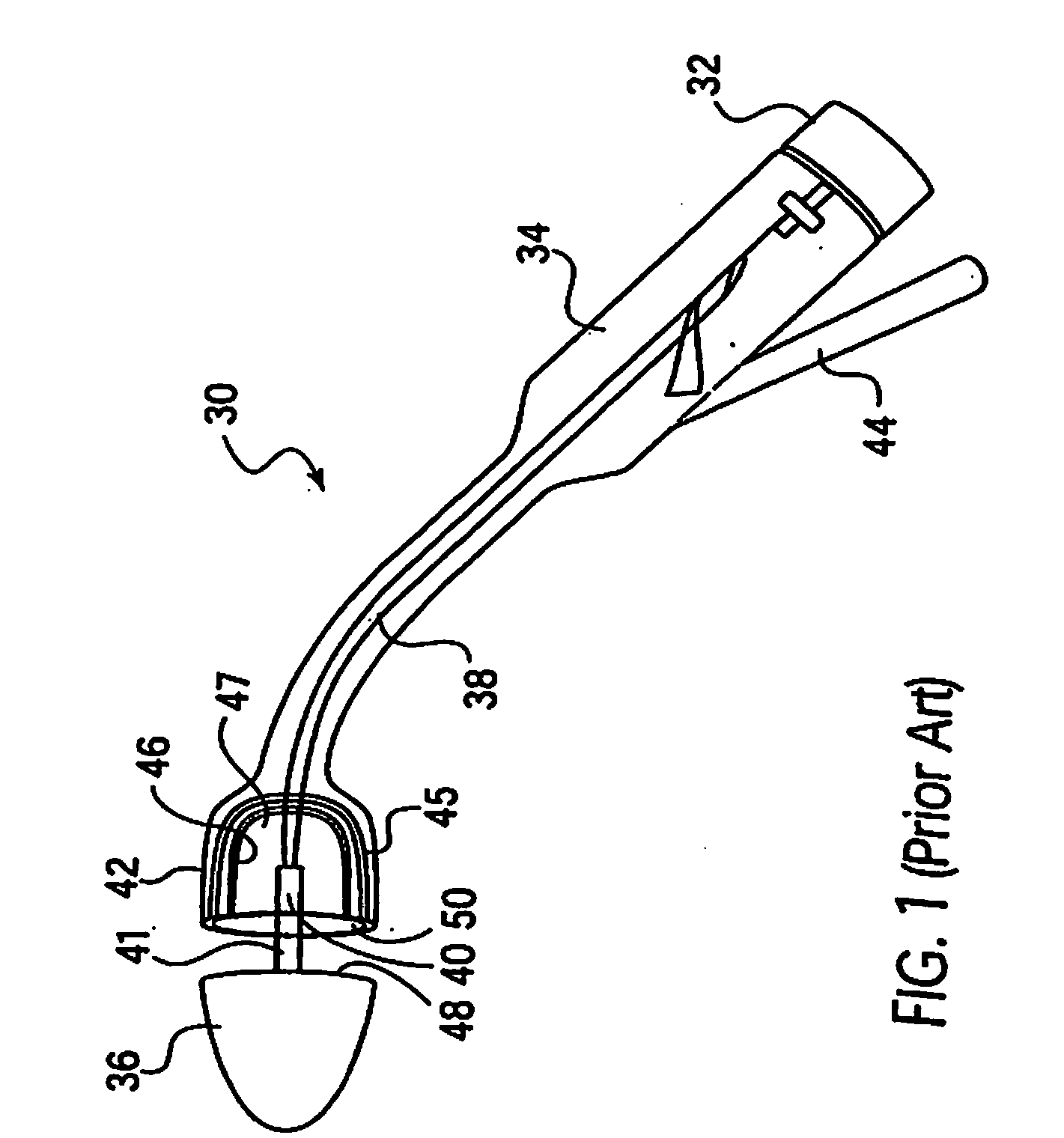

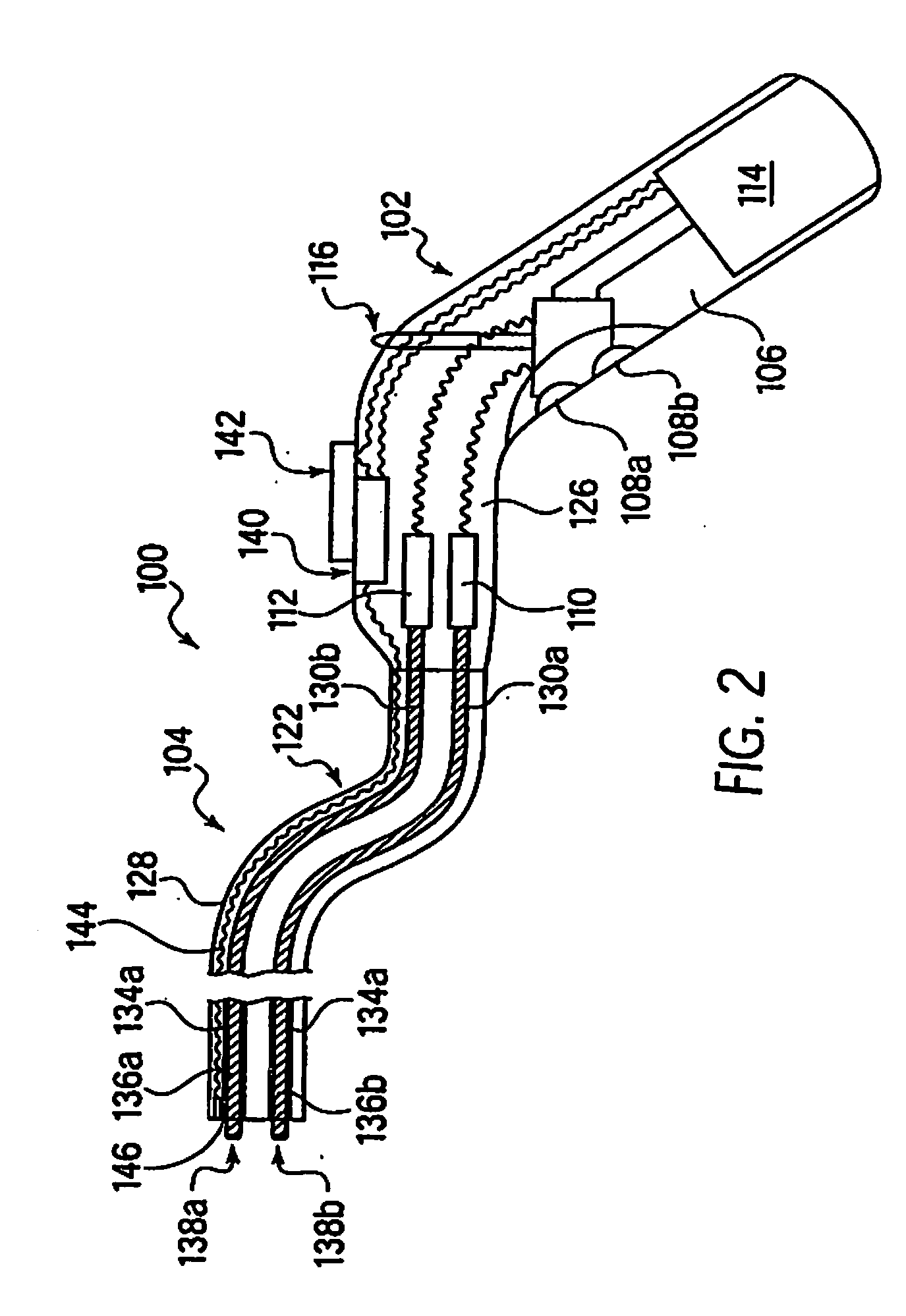

Electromechanical driver and remote surgical instrument attachment having computer assisted control capabilities

A medical tool comprising an electromechanical driver and a surgical instrument attachment for use in invasive surgery, including a handle coupled to a flexible sheath which is in turn coupled to a surgical attachment. The handle of the driver includes the electromechanical driver and at least one processor element which controls the actions of the electromechanical driver, and therefore the application elements of the surgical attachment, based on information relayed between the processor element and remotely activatable sensor assemblies in the surgical instrument attachment.

Owner:COVIDIEN LP

Electromechanical driver and remote surgical instrument attachment having computer assisted control capabilities

A medical tool comprising an electromechanical driver and a surgical instrument attachment for use in invasive surgery, including a handle coupled to a flexible sheath which is in turn coupled to a surgical attachment. The handle of the driver includes the electromechanical driver and at least one processor element which controls the actions of the electromechanical driver, and therefore the application elements of the surgical attachment, based on information relayed between the processor element and remotely activateable sensor assemblies in the surgical instrument attachment.

Owner:COVIDIEN LP

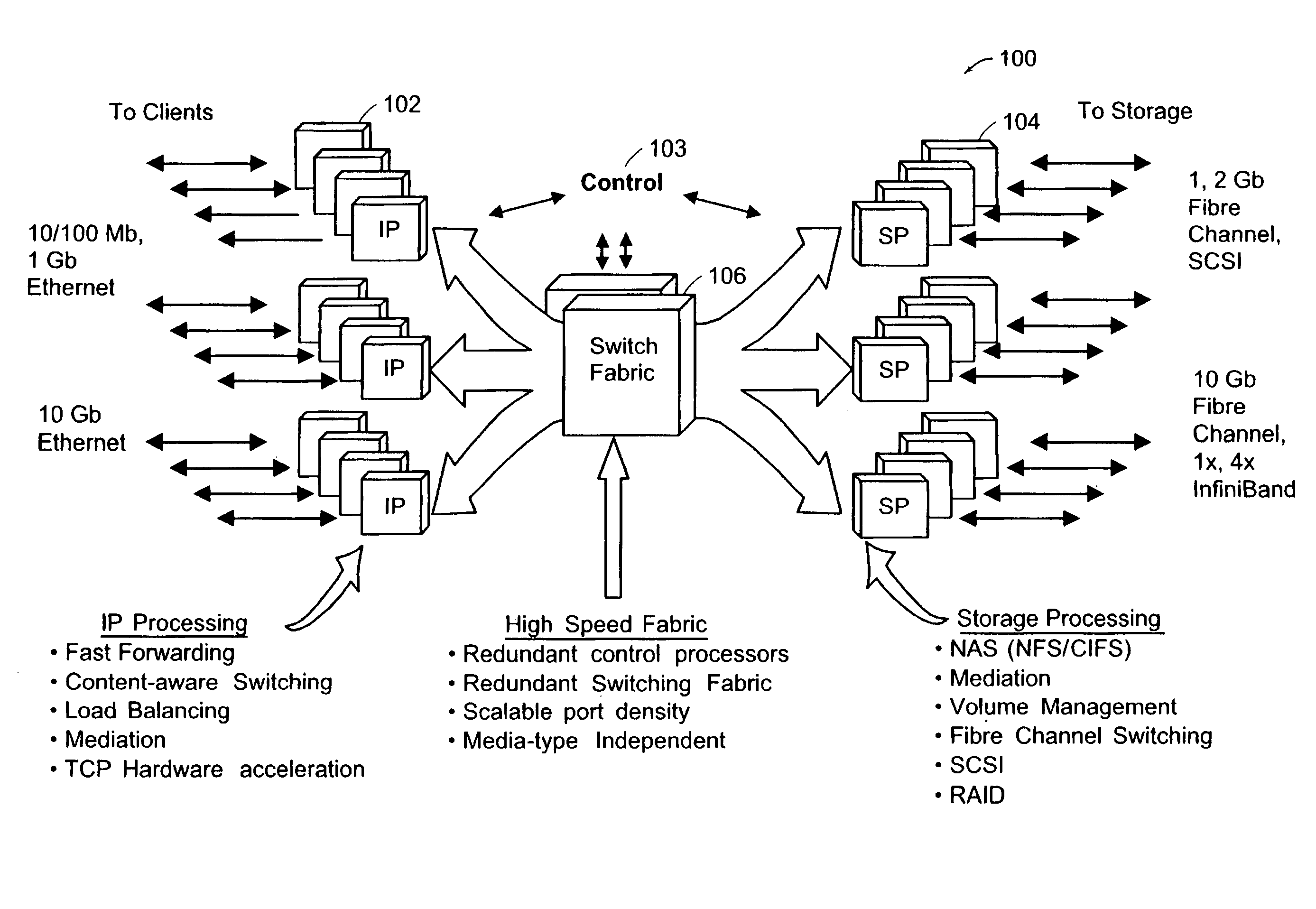

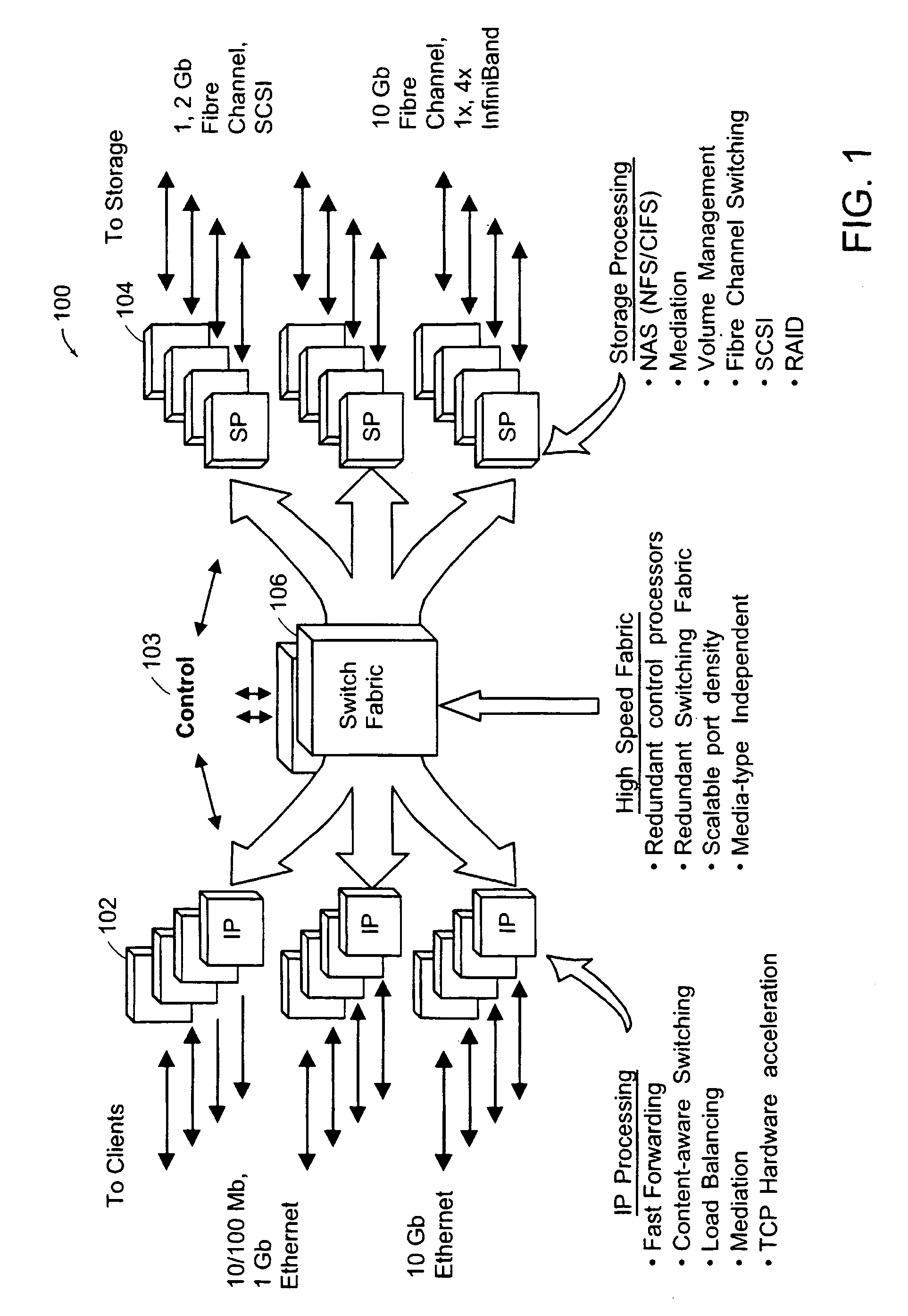

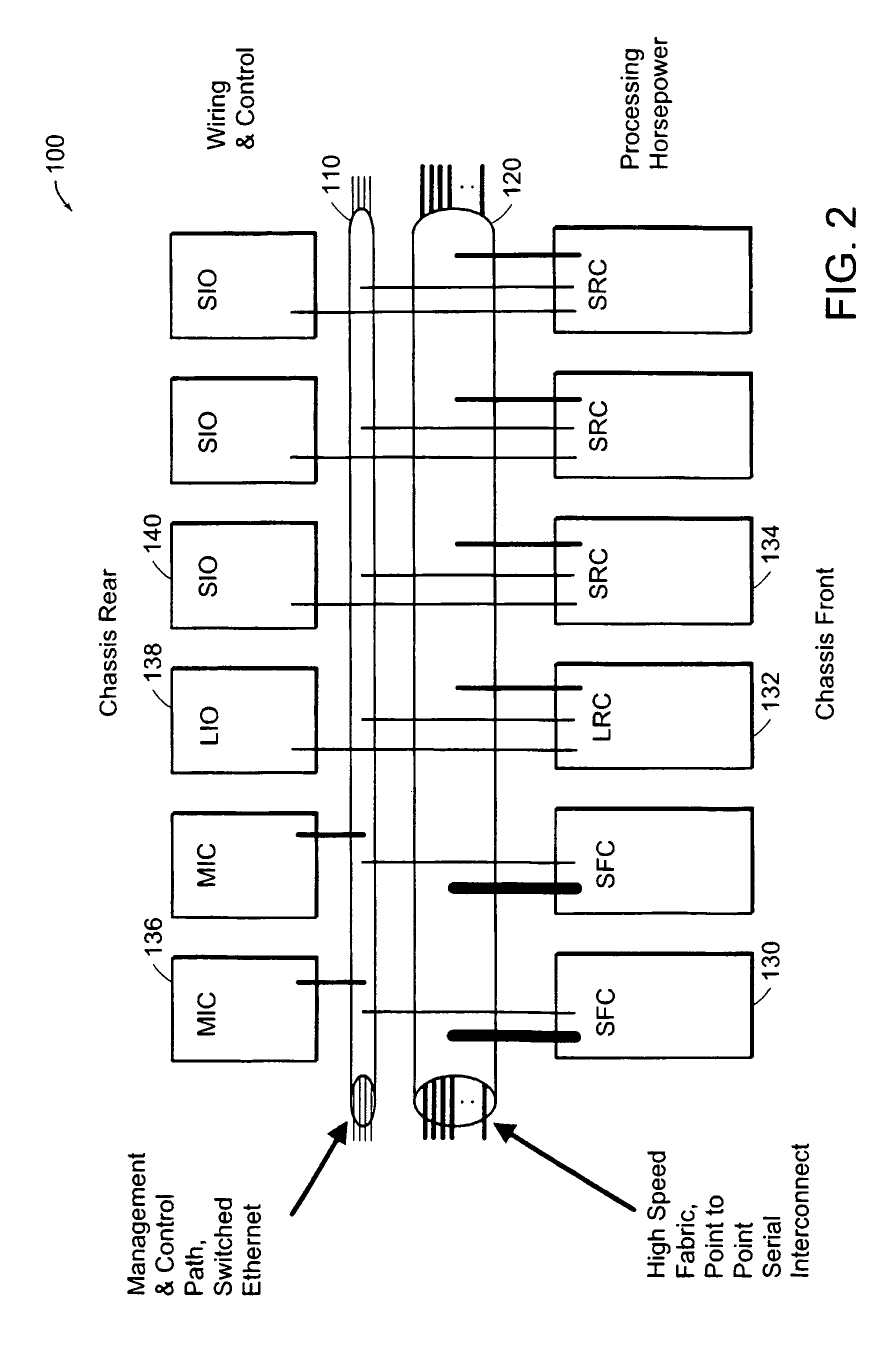

Switching system

ActiveUS7313614B2Accelerates TCP processingRobust systemInput/output to record carriersError detection/correctionProcessor elementComputer architecture

A system and method for provided a switch system (100) having a first configurable set of processor elements (102) to process storage resource connection requests (104), a second configurable set of processor elements capable of communications with the first configurable set of processor elements (102) to receive, from the first configurable set of processor elements, storage connection requests representative of client requests, and to route the requests to at least one of the storage elements (104), and a configurable switching fabric (106) interconnected between the first and second sets of processor elements (102), for receiving at least a first storage connection request (104) from one of the first set of processor elements (102), determining an appropriate one of the second set of processors for processing the storage connection request (104), automatically configuring the storage connection request in accordance with a protocol utilized by the selected one of the second set of processors, and forwarding the storage connection request to the selected one of the second set of processors for routing to at least one of the storage elements.

Owner:ORACLE INT CORP

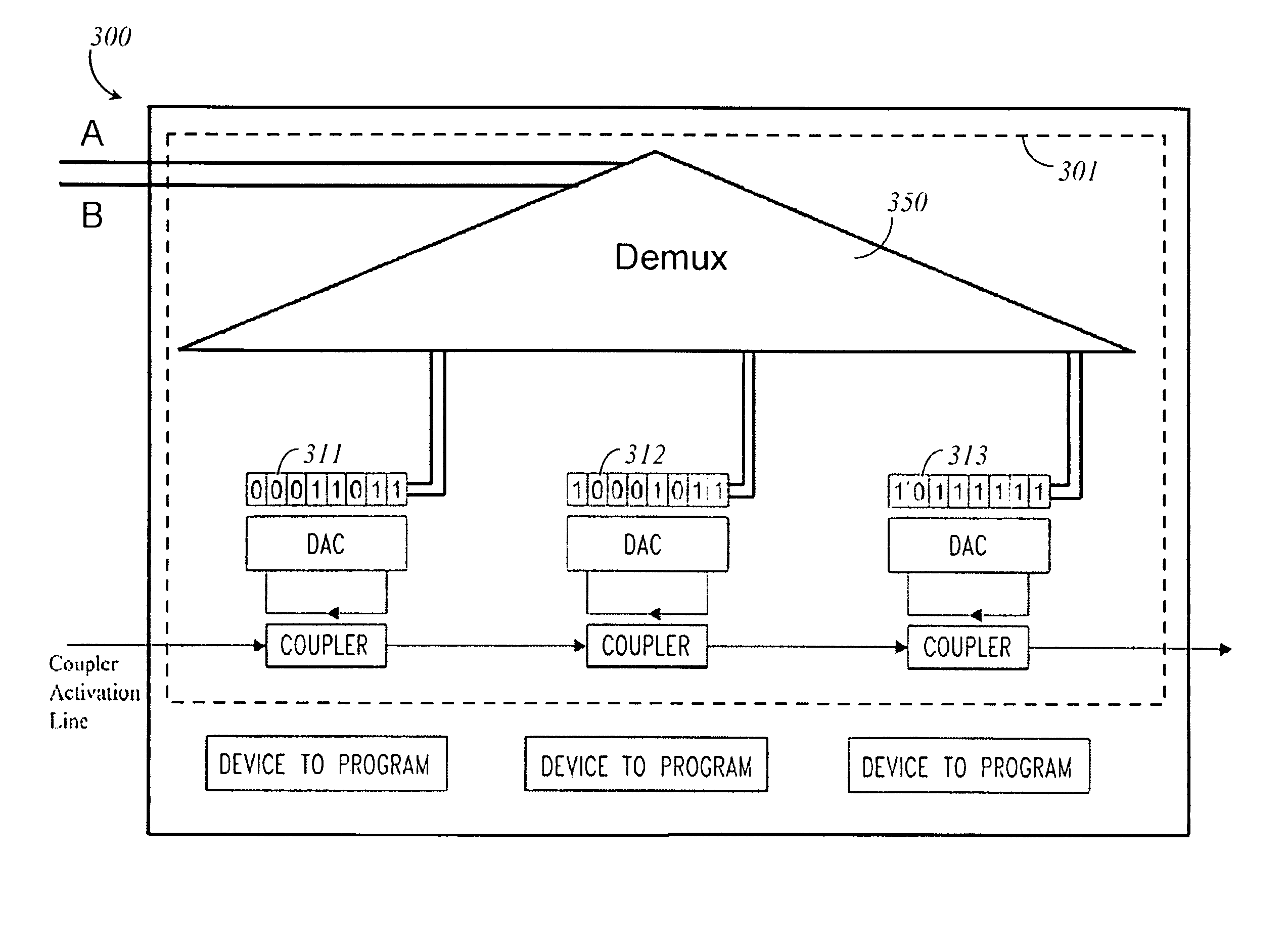

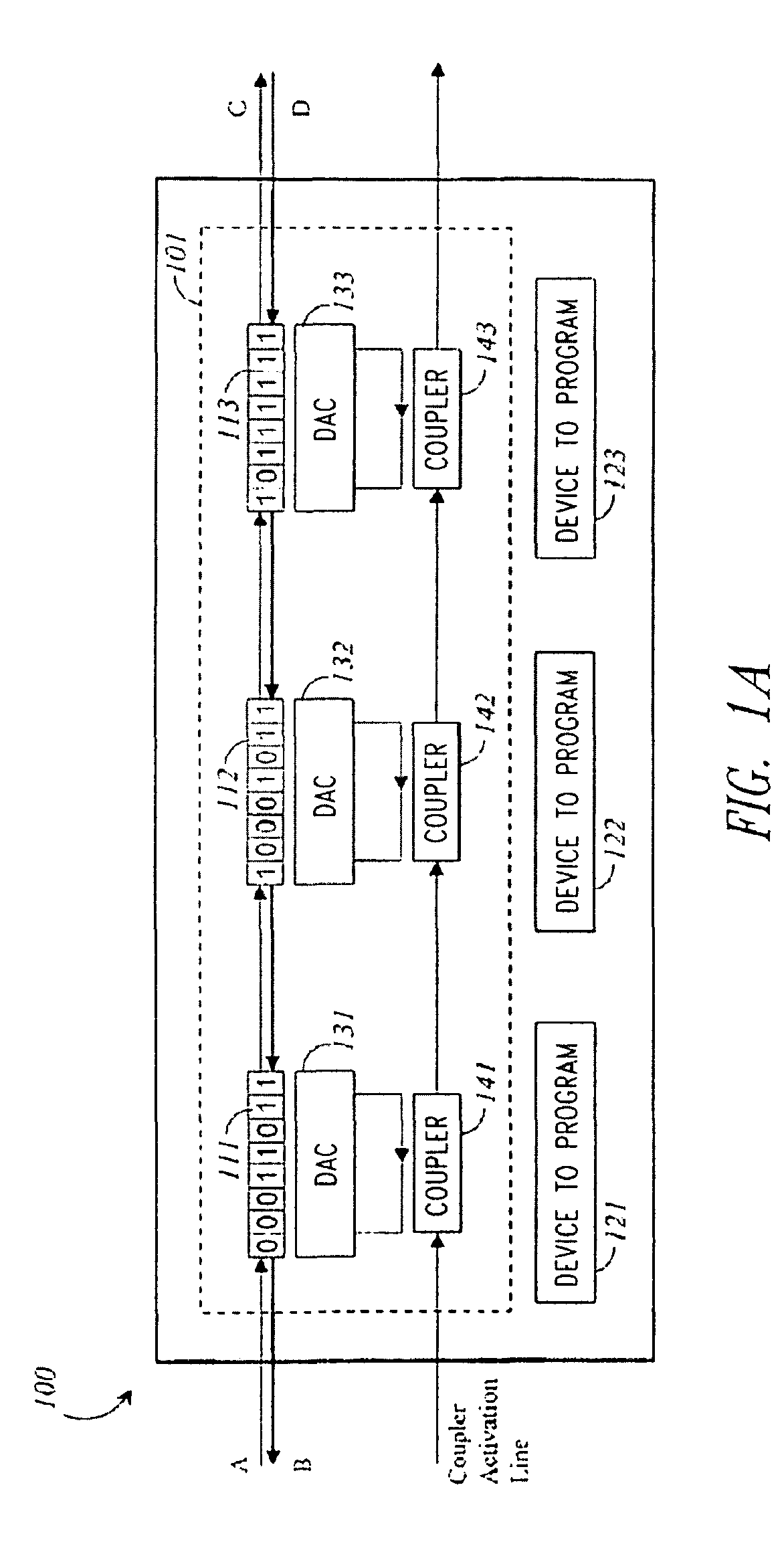

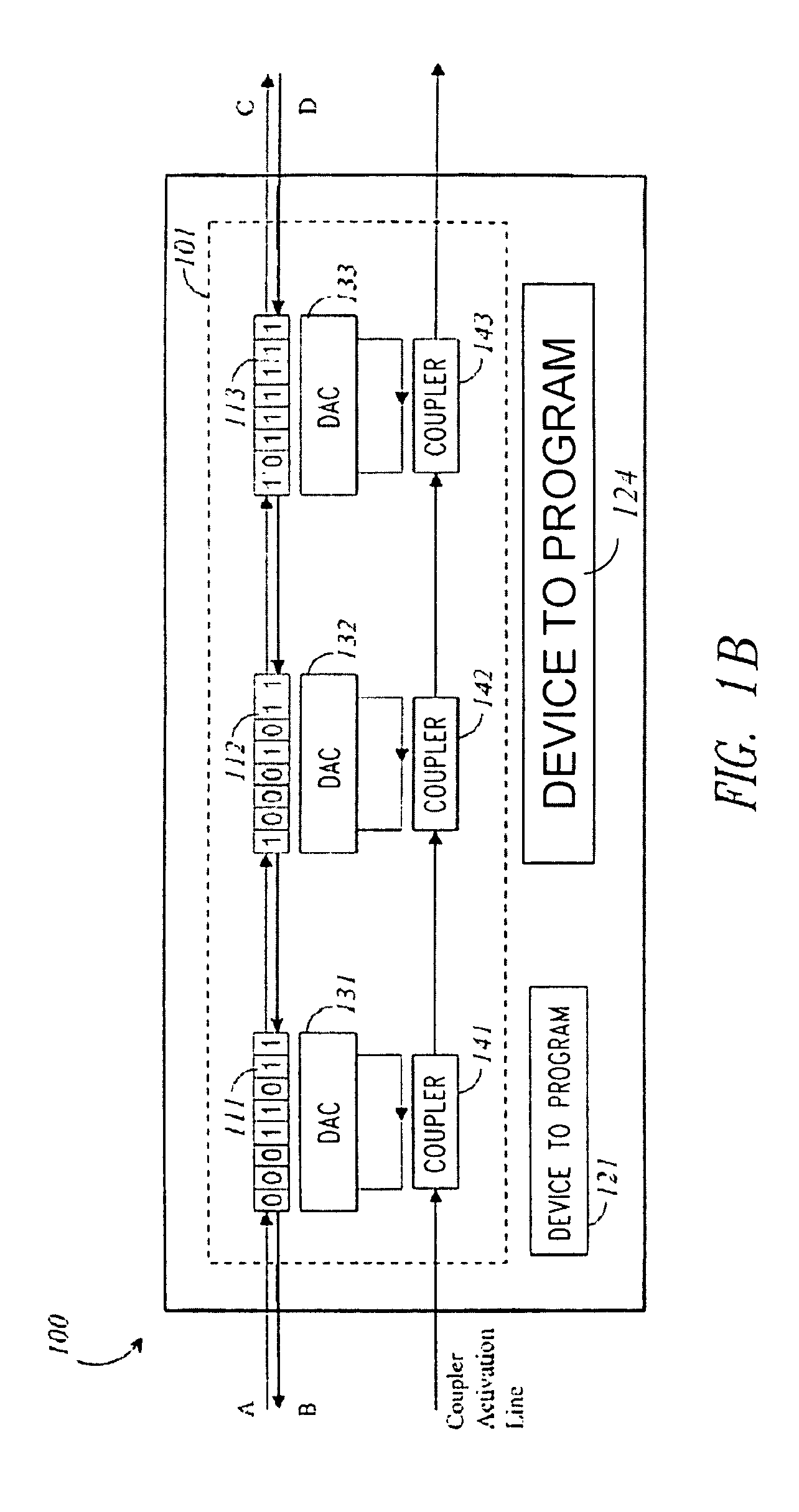

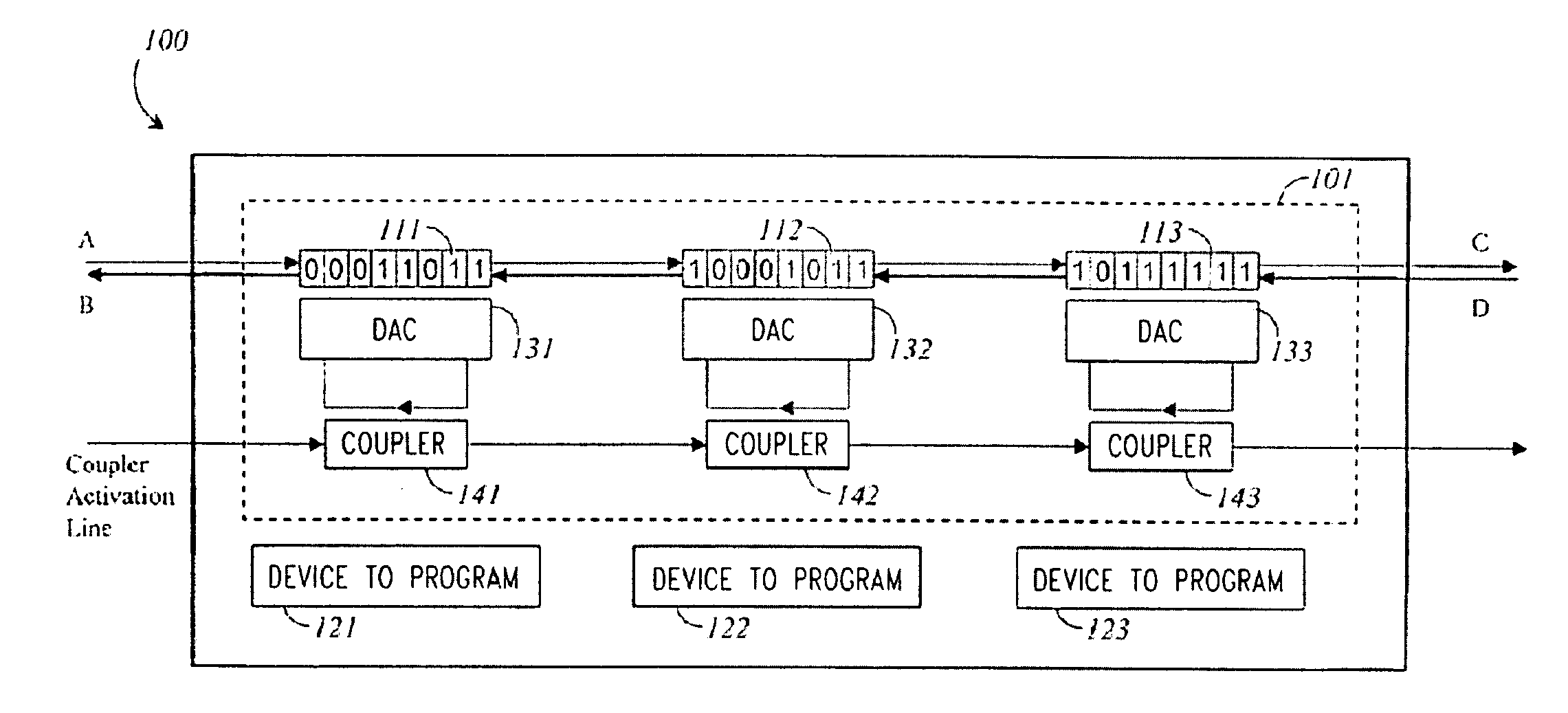

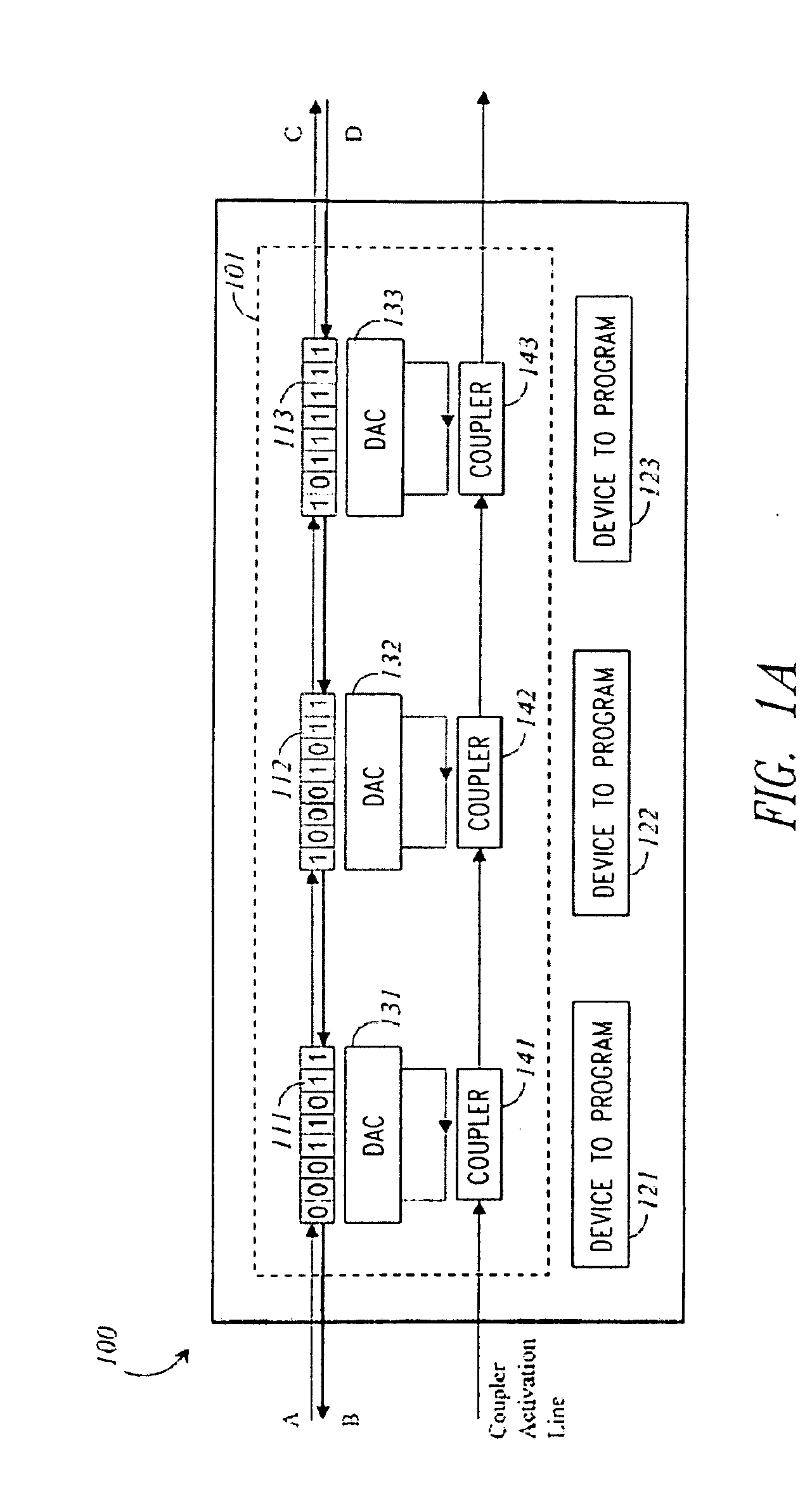

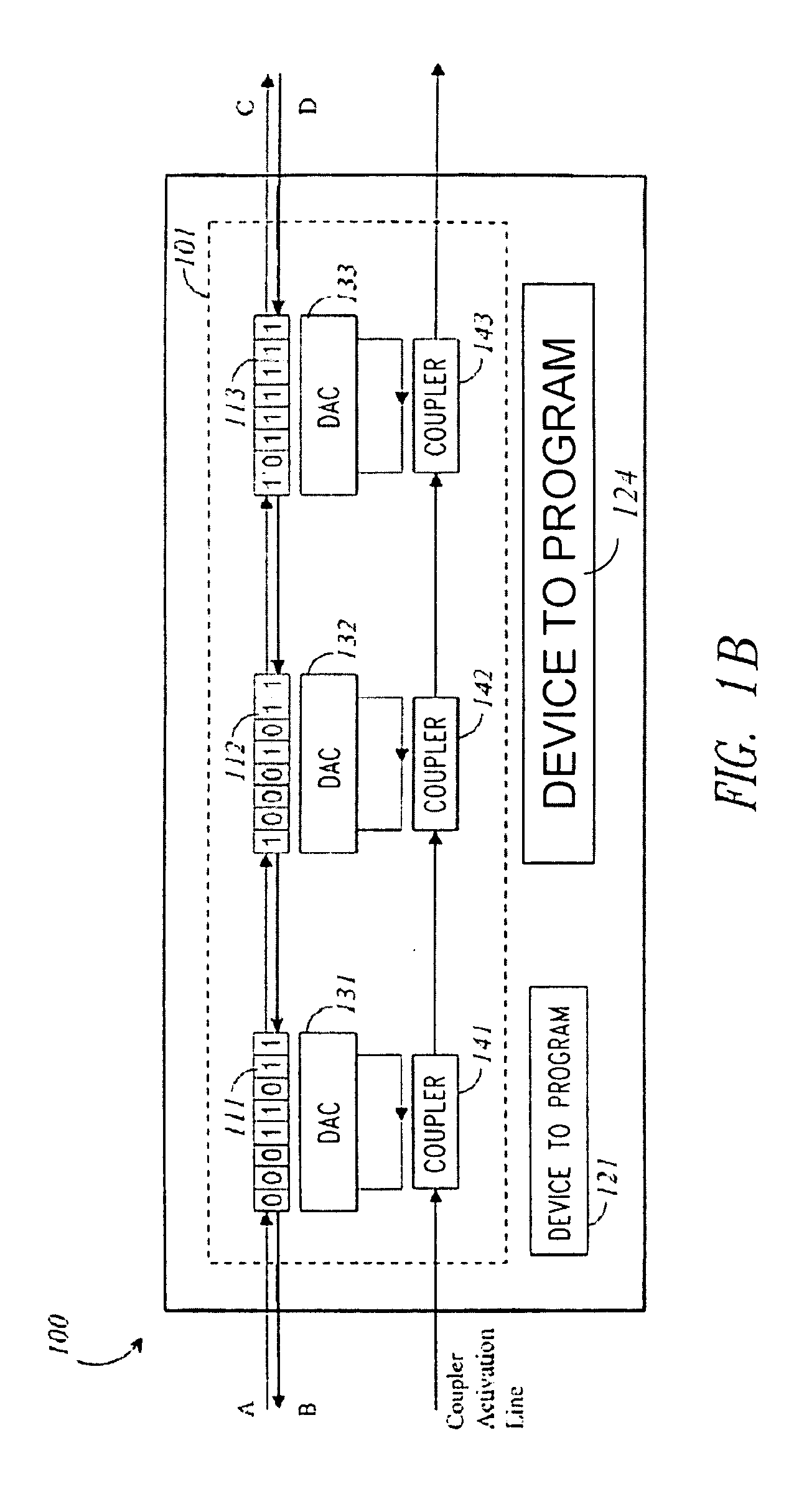

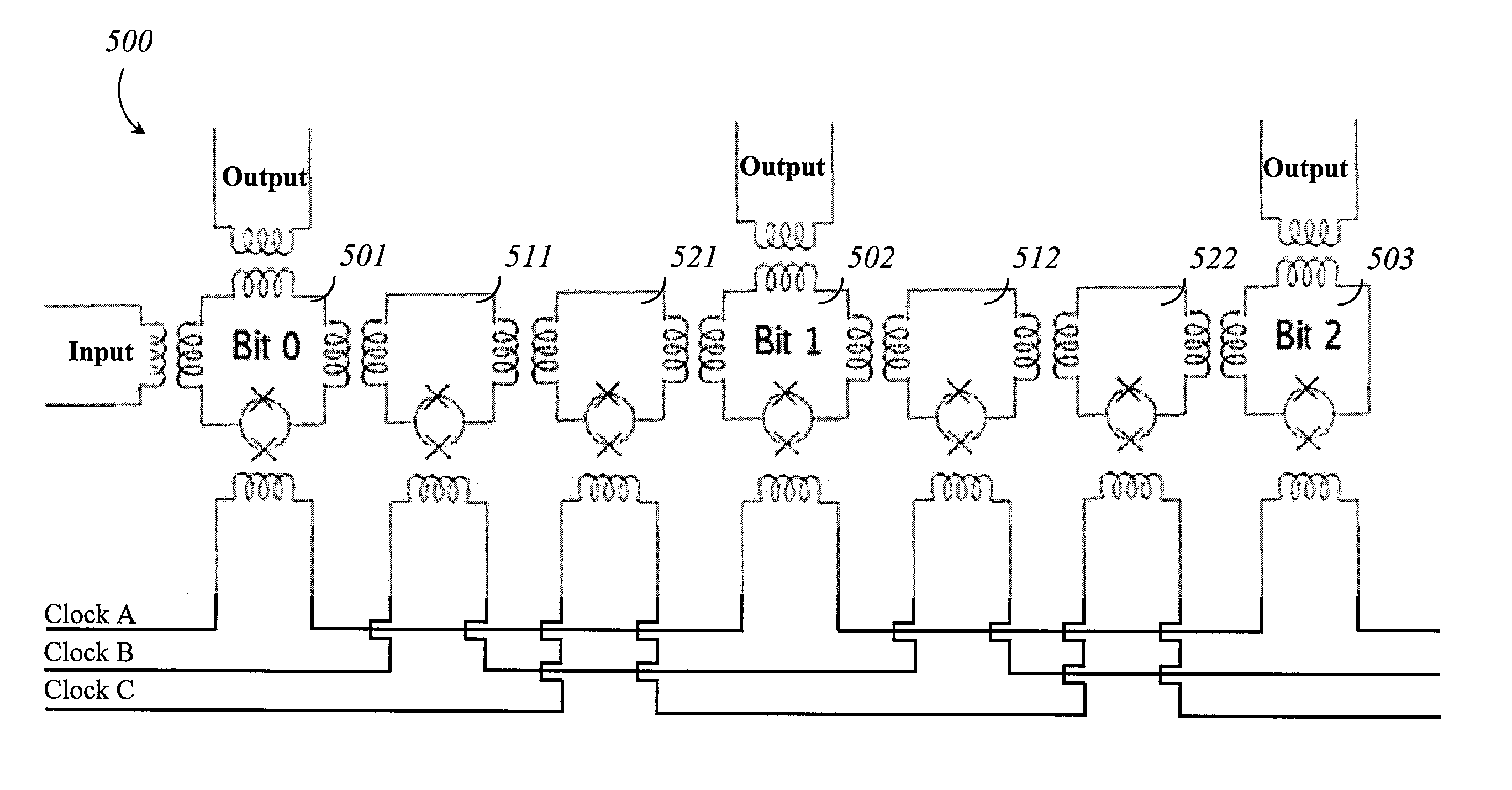

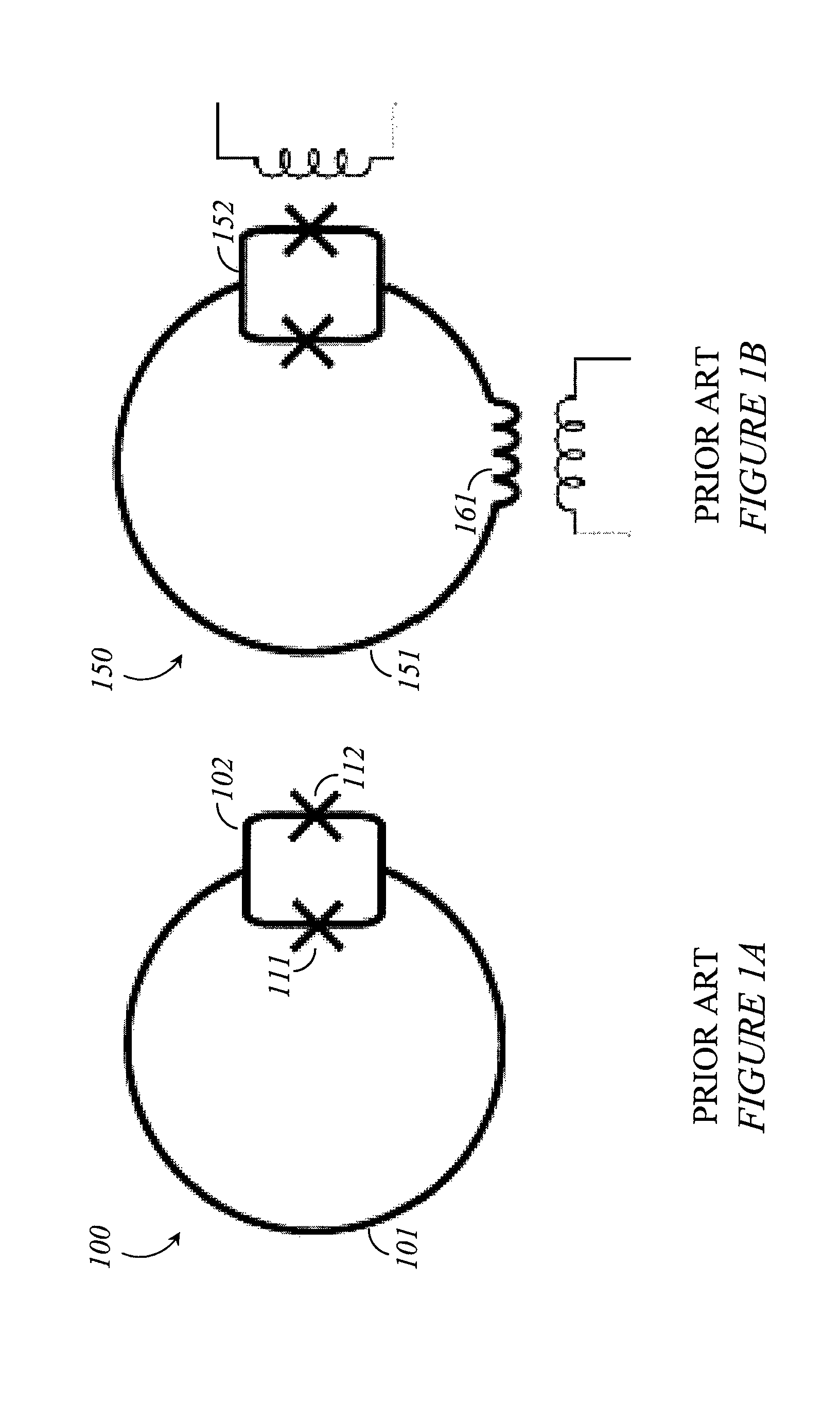

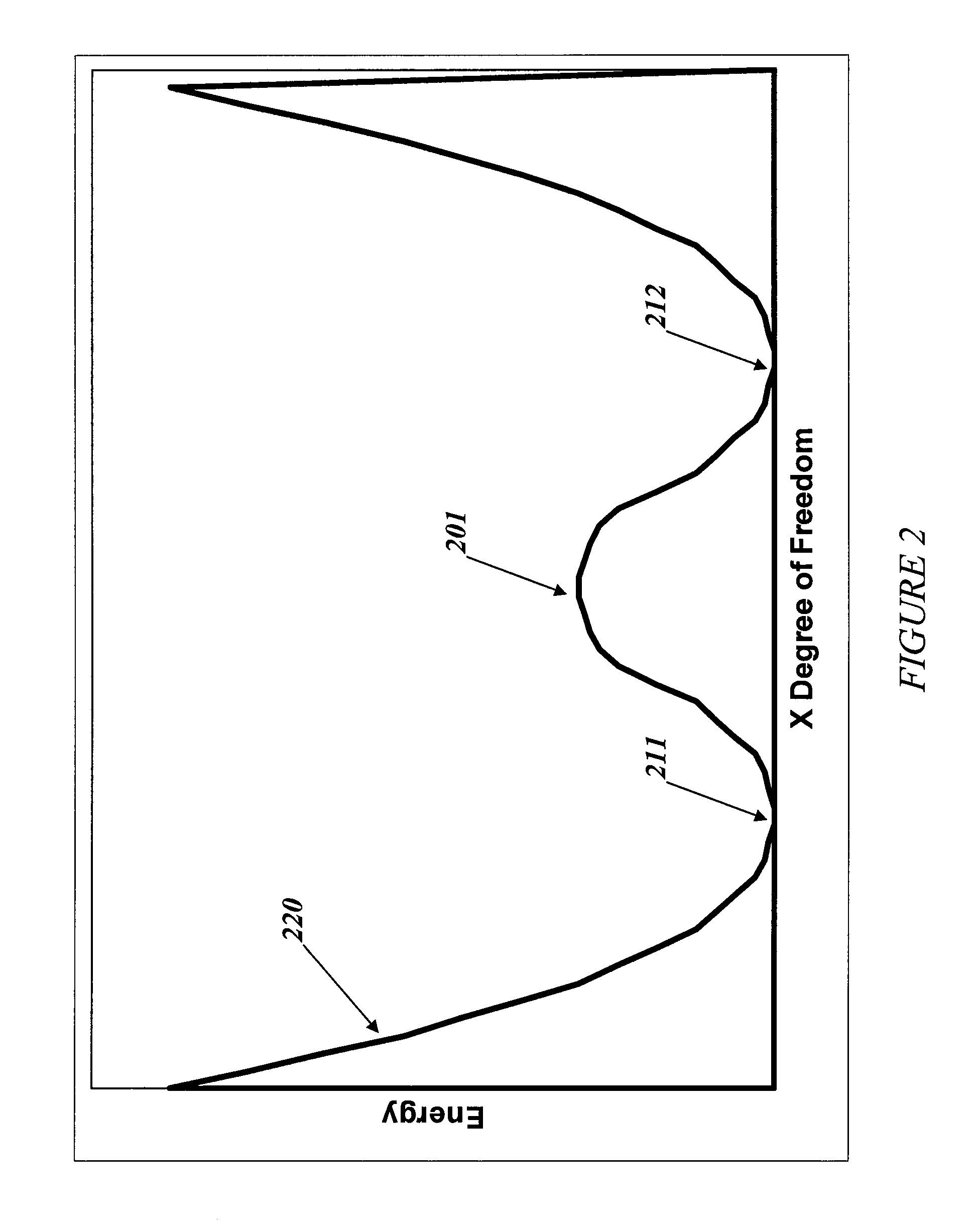

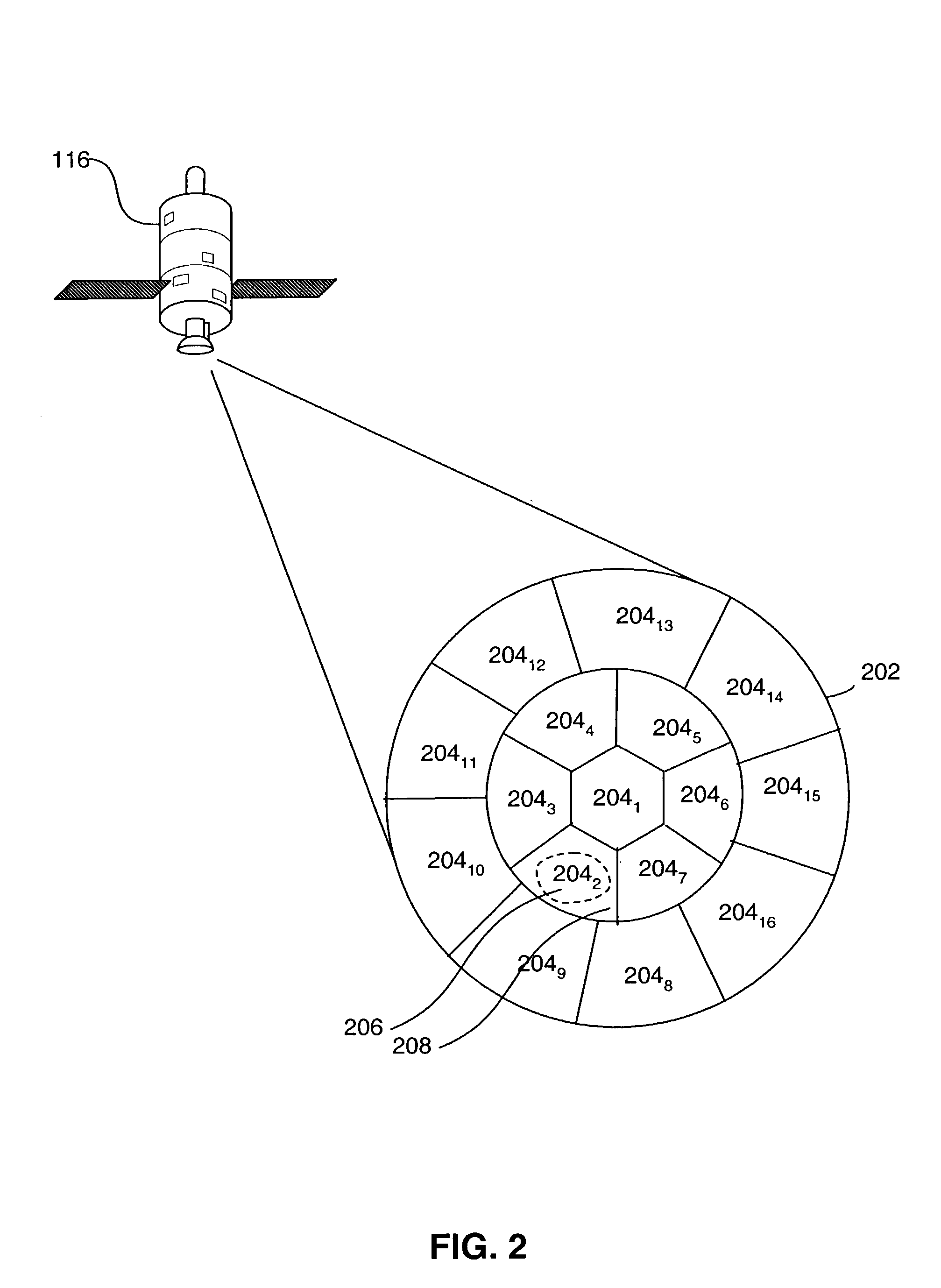

Systems, methods and apparatus for local programming of quantum processor elements

Systems, methods and apparatus for a scalable quantum processor architecture. A quantum processor is locally programmable by providing a memory register with a signal embodying device control parameter(s), converting the signal to an analog signal; and administering the analog signal to one or more programmable devices.

Owner:D WAVE SYSTEMS INC

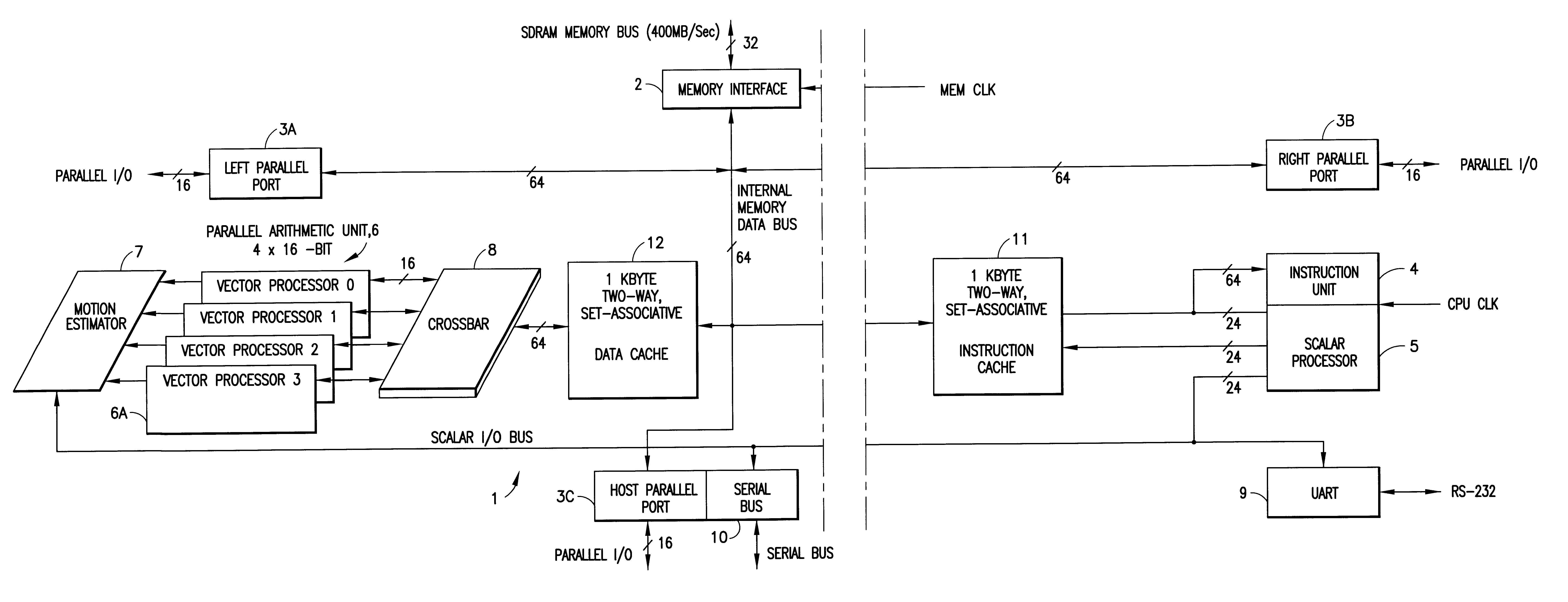

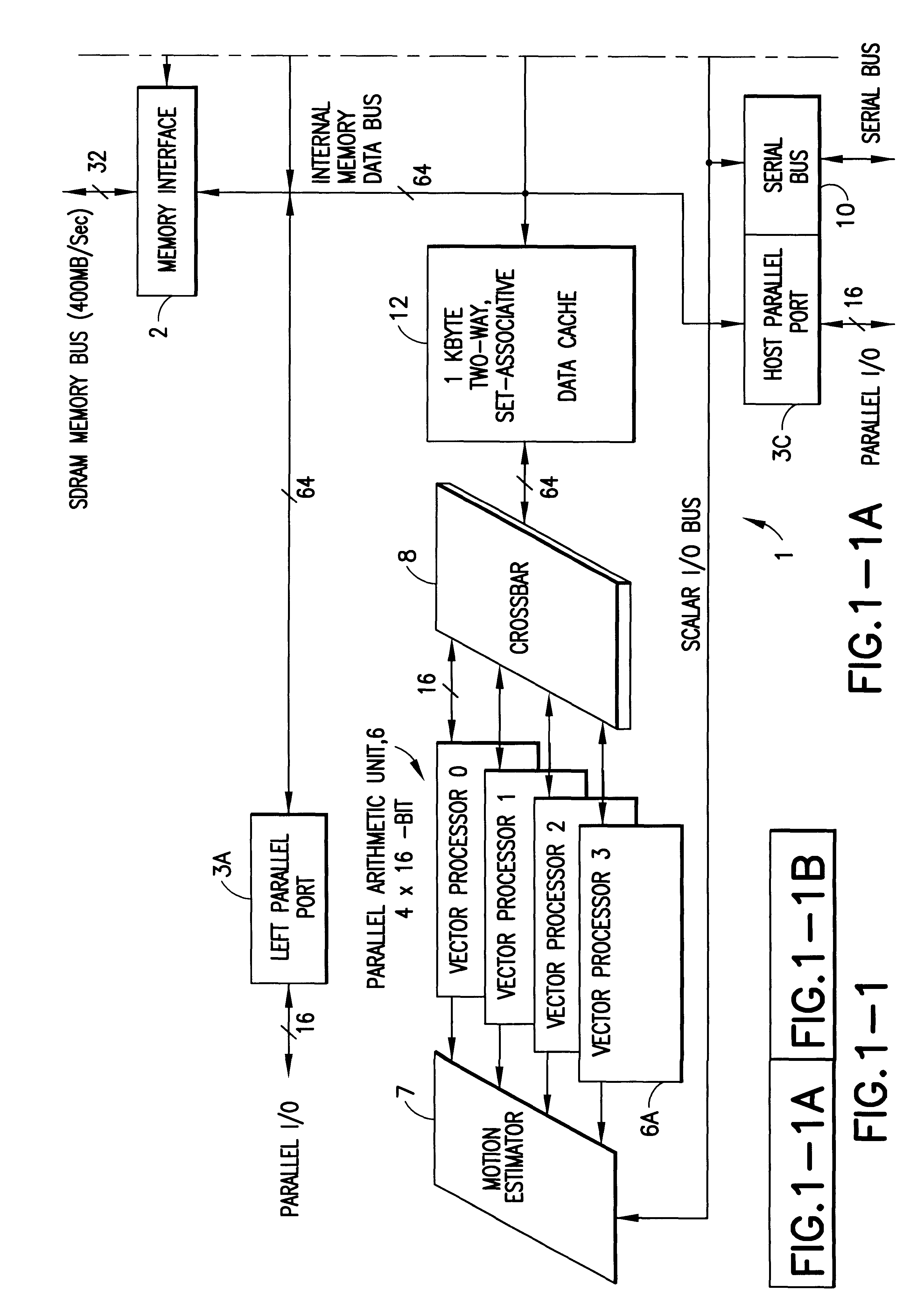

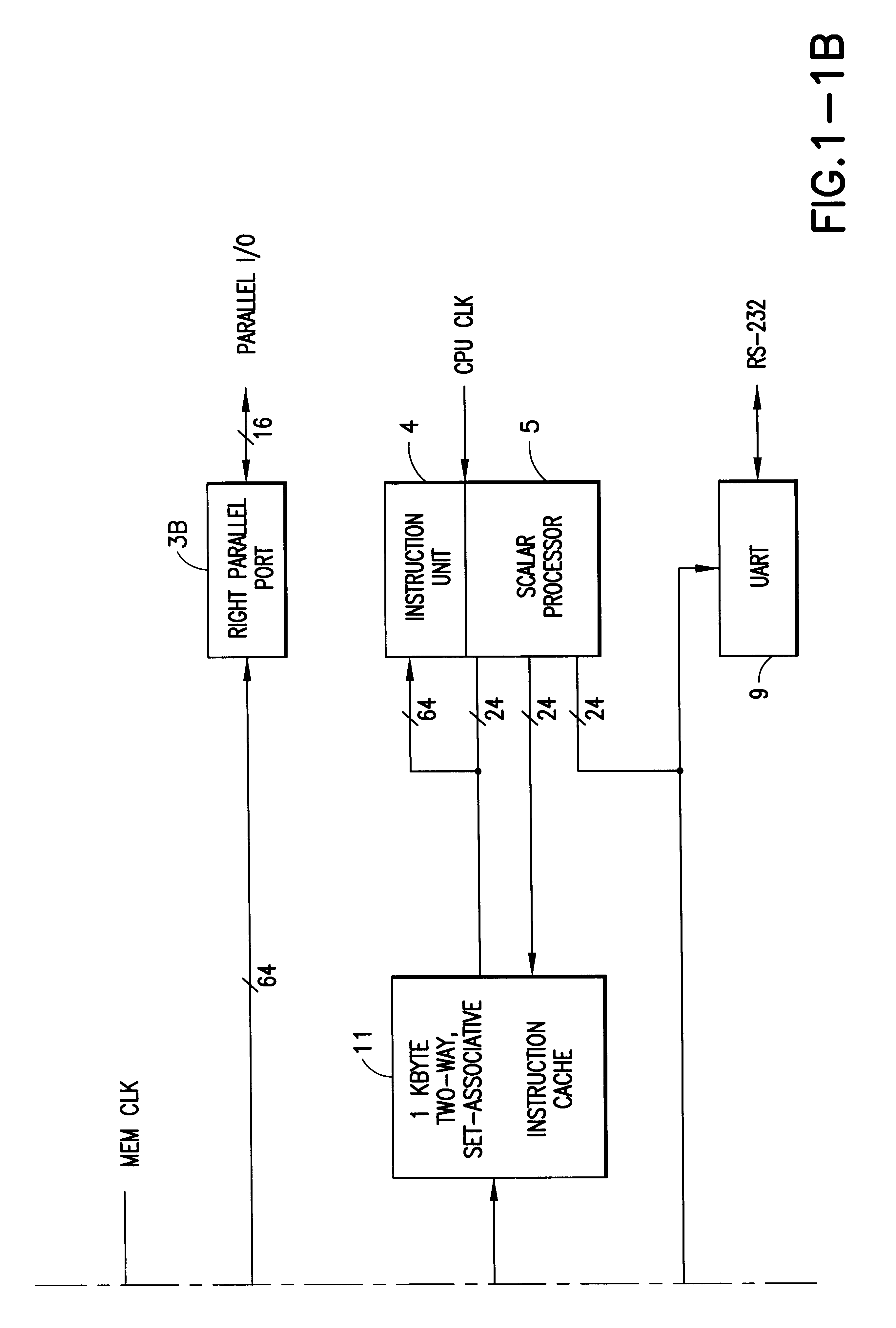

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

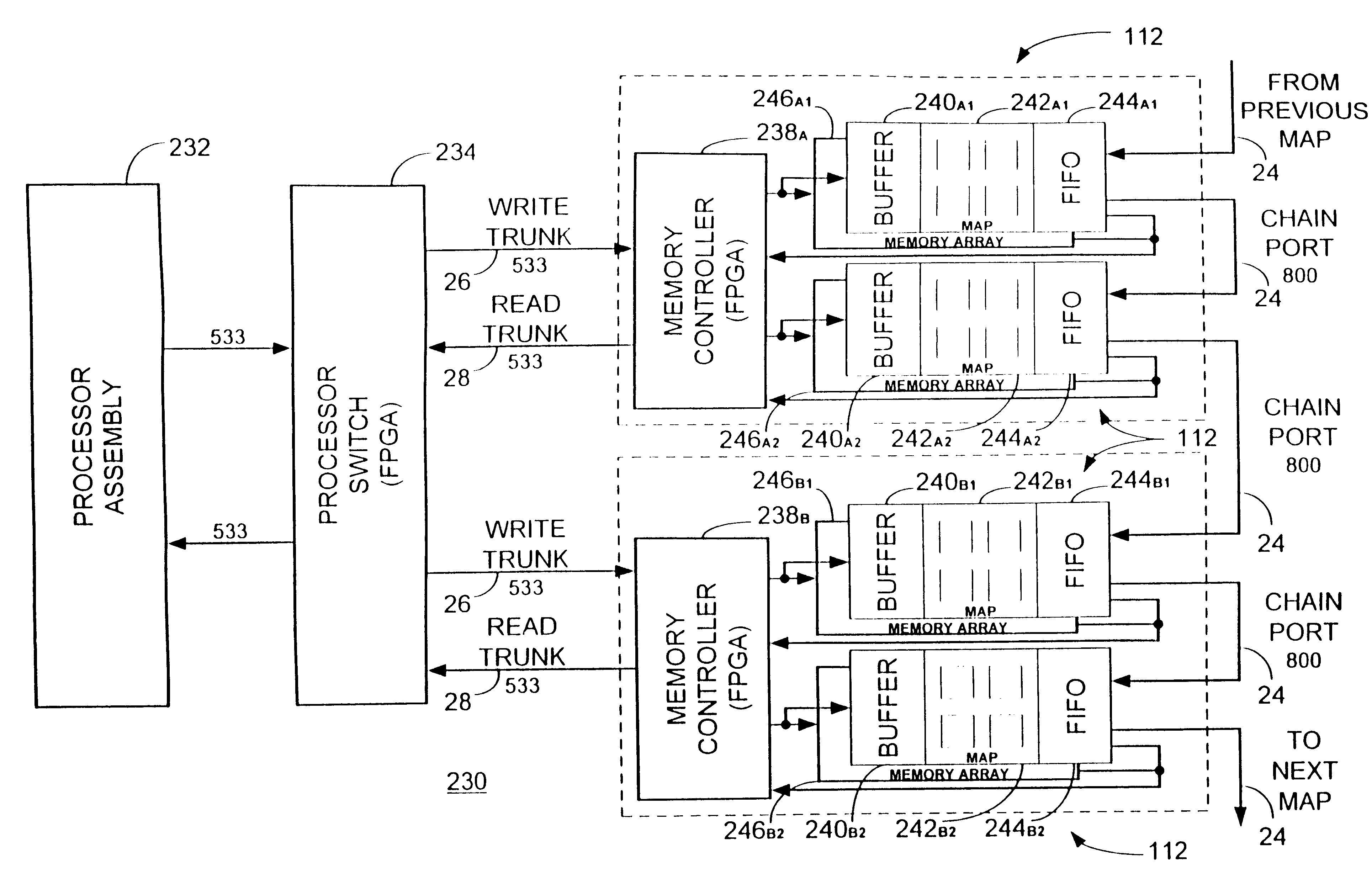

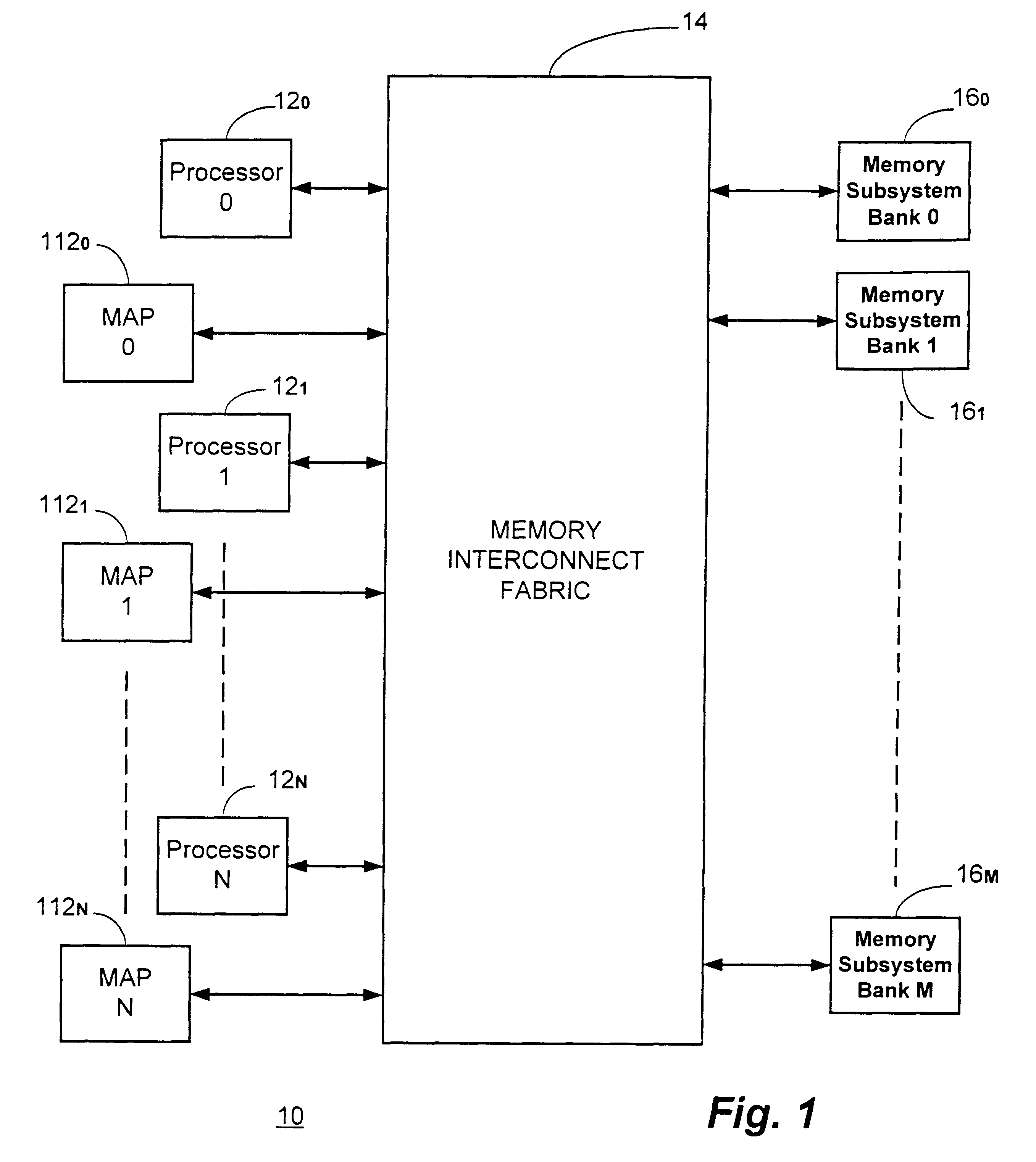

Multiprocessor with each processor element accessing operands in loaded input buffer and forwarding results to FIFO output buffer

InactiveUS6339819B1Perform operationPotential utilitySingle instruction multiple data multiprocessorsMemory adressing/allocation/relocationProcessor elementMulti processor

An enhanced memory algorithmic processor ("MAP") architecture for multiprocessor computer systems comprises an assembly that may comprise, for example, field programmable gate arrays ("FPGAs") functioning as the memory algorithmic processors. The MAP elements may further include an operand storage, intelligent address generation, on board function libraries, result storage and multiple input / output ("I / O") ports. The MAP elements are intended to augment, not necessarily replace, the high performance microprocessors in the system and, in a particular embodiment of the present invention, they may be connected through the memory subsystem of the computer system resulting in it being very tightly coupled to the system as well as being globally accessible from any processor in a multiprocessor computer system.

Owner:SRC COMP

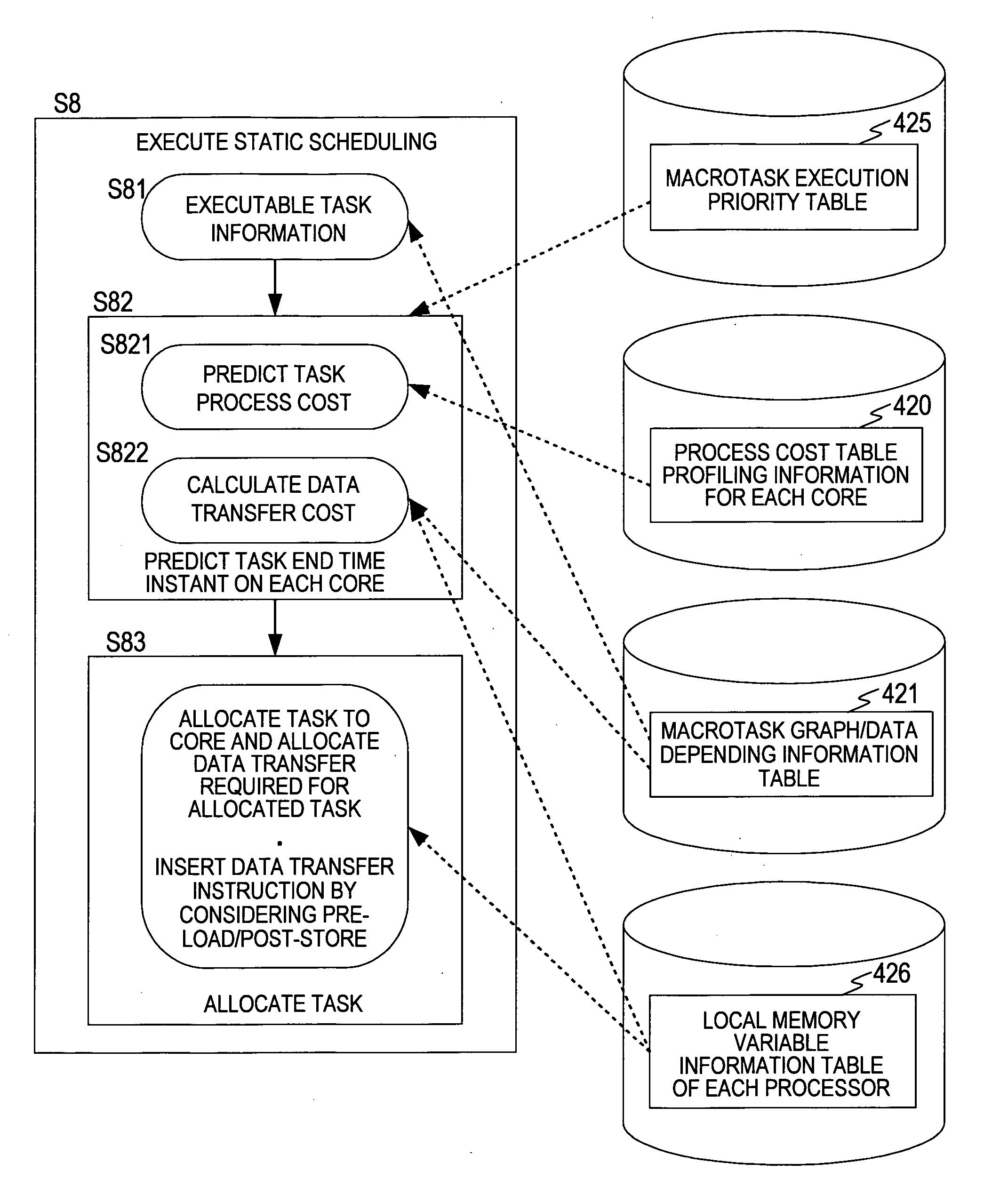

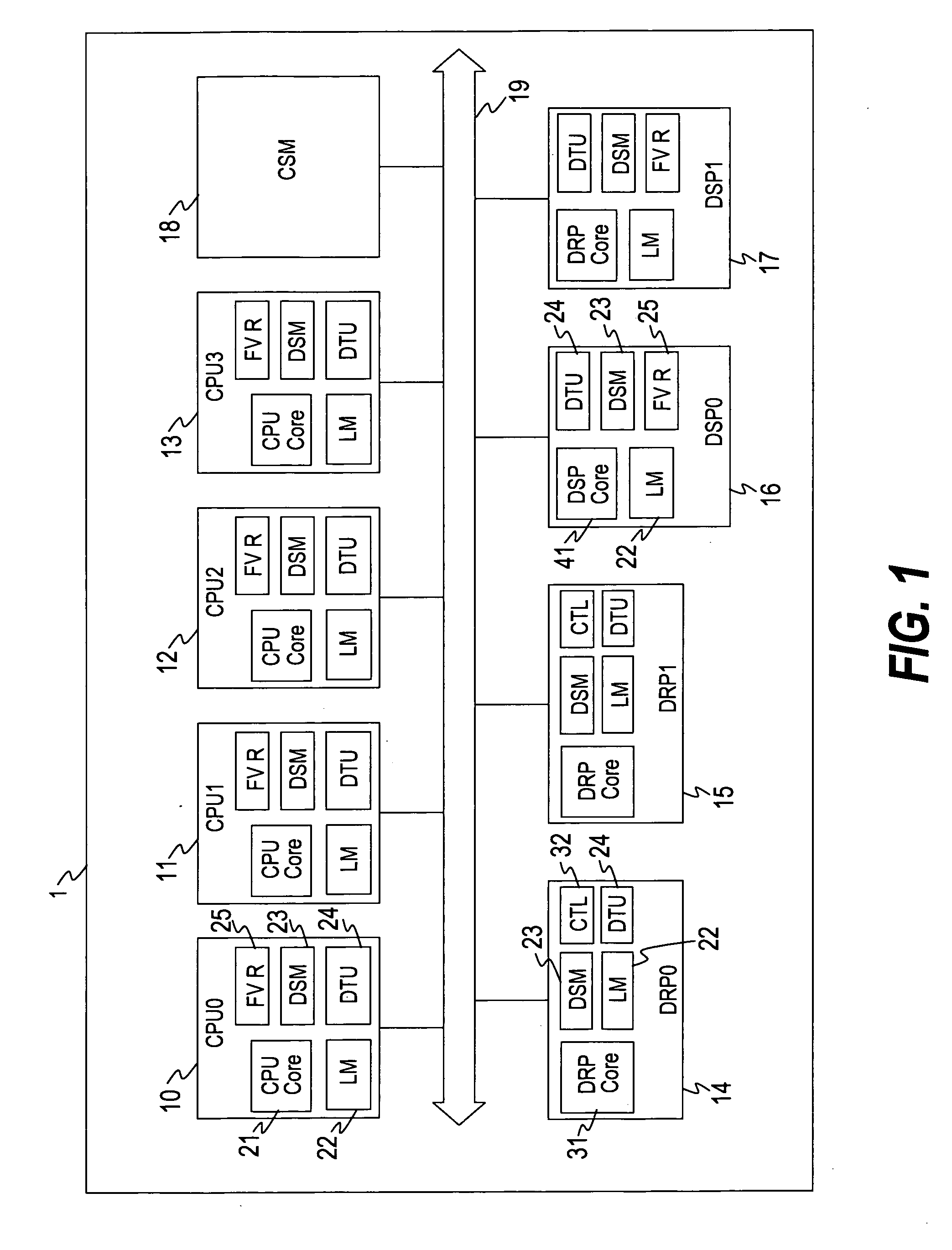

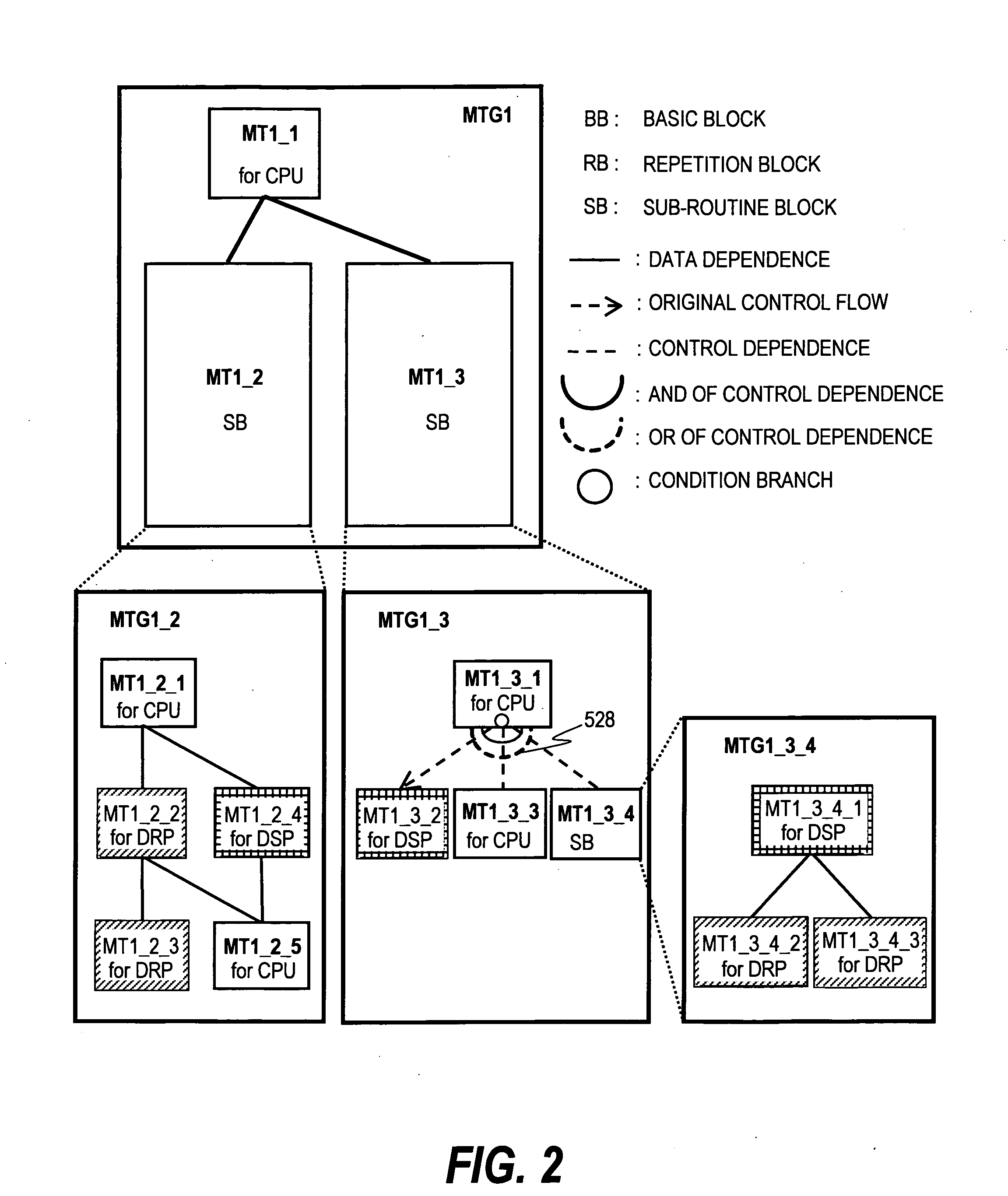

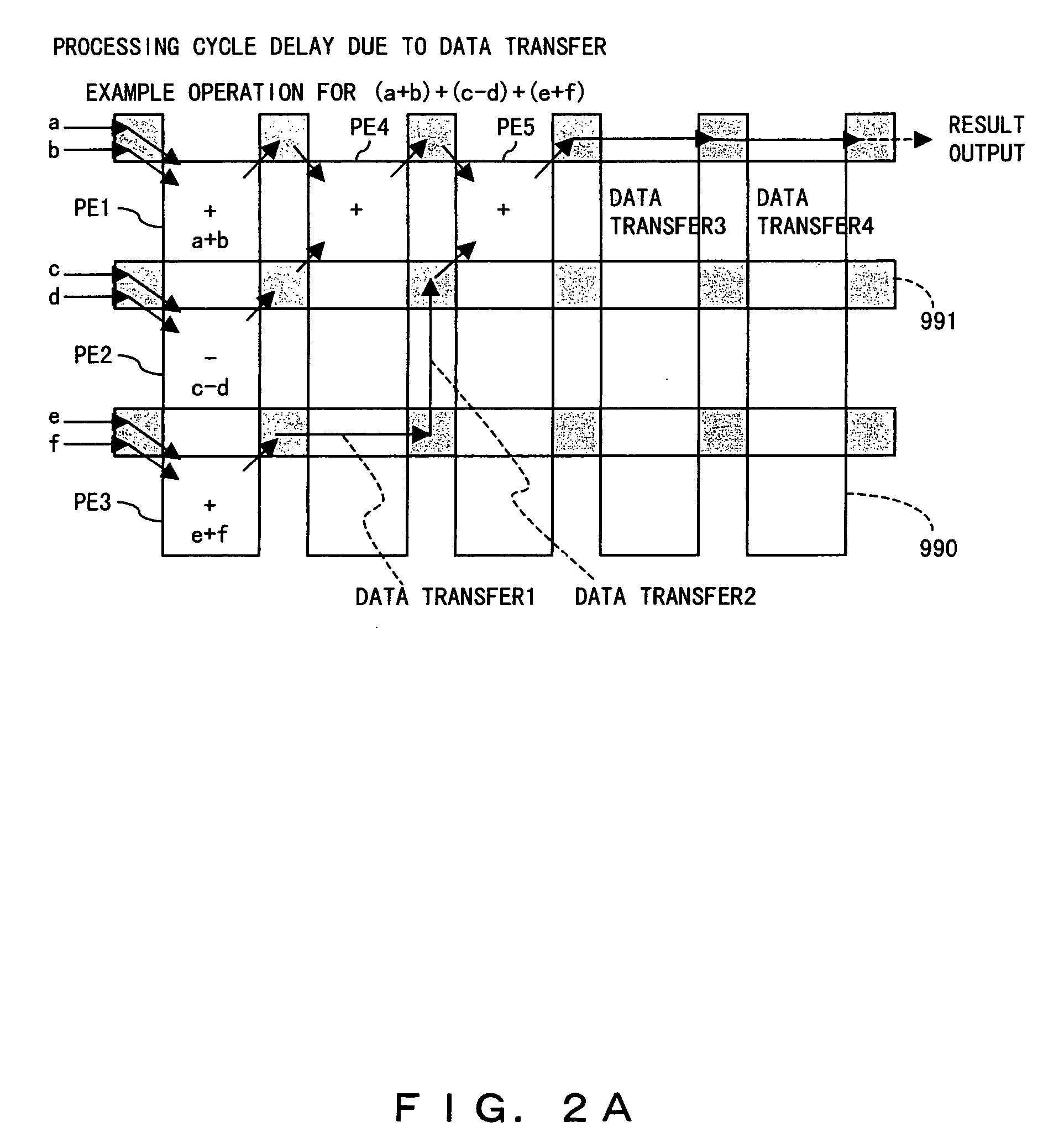

Method for controlling heterogeneous multiprocessor and multigrain parallelizing compiler

ActiveUS20070283358A1Improve efficiencyOverhead required can be suppressedEnergy efficient ICTResource allocationGeneral purposeCost comparison

A heterogeneous multiprocessor system including a plurality of processor elements having mutually different instruction sets and structures avoids a specific processor element from being short of resources to improve throughput. An executable task is extracted based on a preset depending relationship between a plurality of tasks, and the plurality of first processors are allocated to a general-purpose processor group based on a depending relationship among the extracted tasks. A second processor is allocated to an accelerator group, a task to be allocated is determined from the extracted tasks based on a priority value for each of tasks, and an execution cost of executing the determined task by the first processor is compared with an execution cost of executing the task by the second processor. The task is allocated to one of the general-purpose processor group and the accelerator group that is judged to be lower as a result of the cost comparison.

Owner:WASEDA UNIV

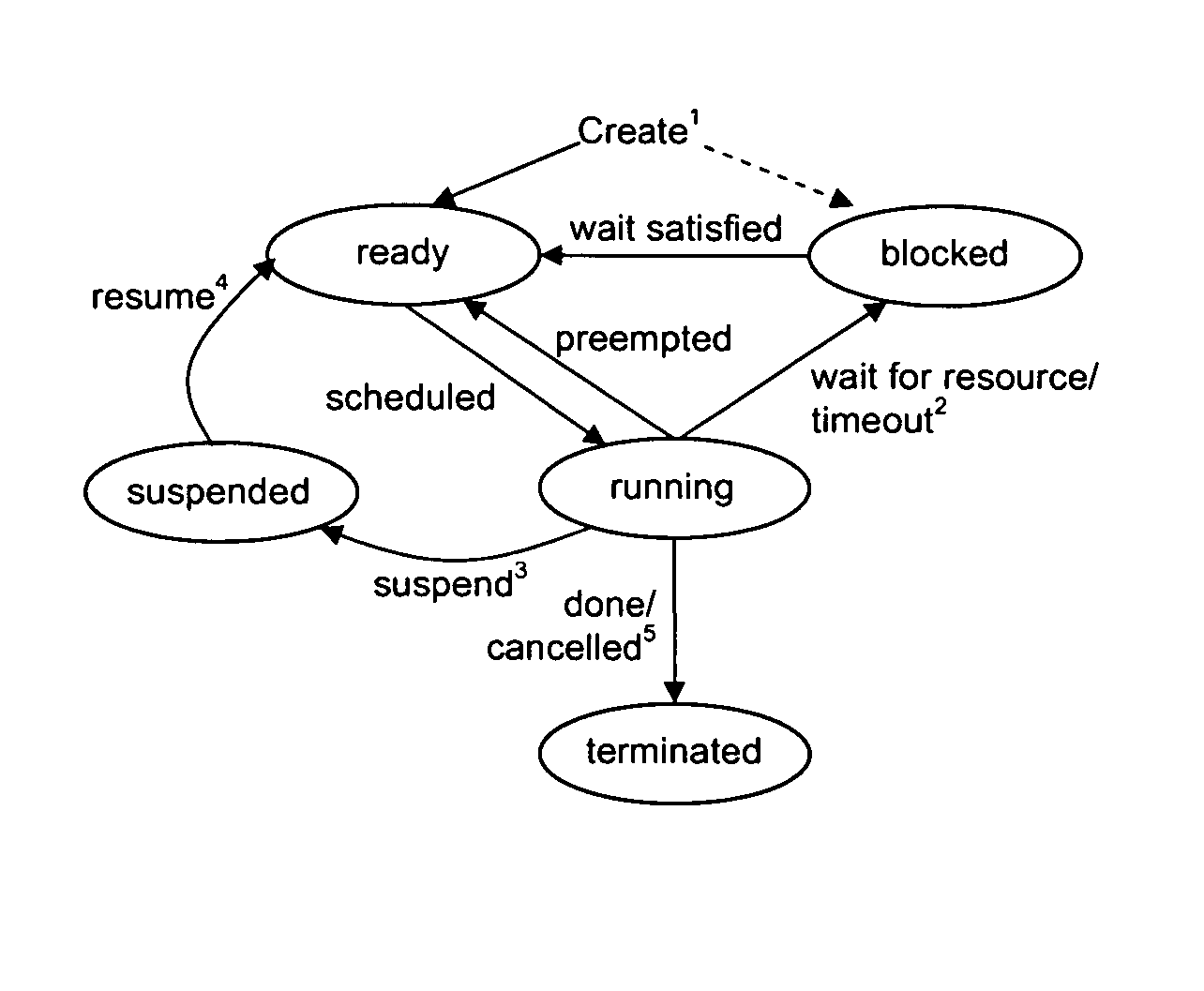

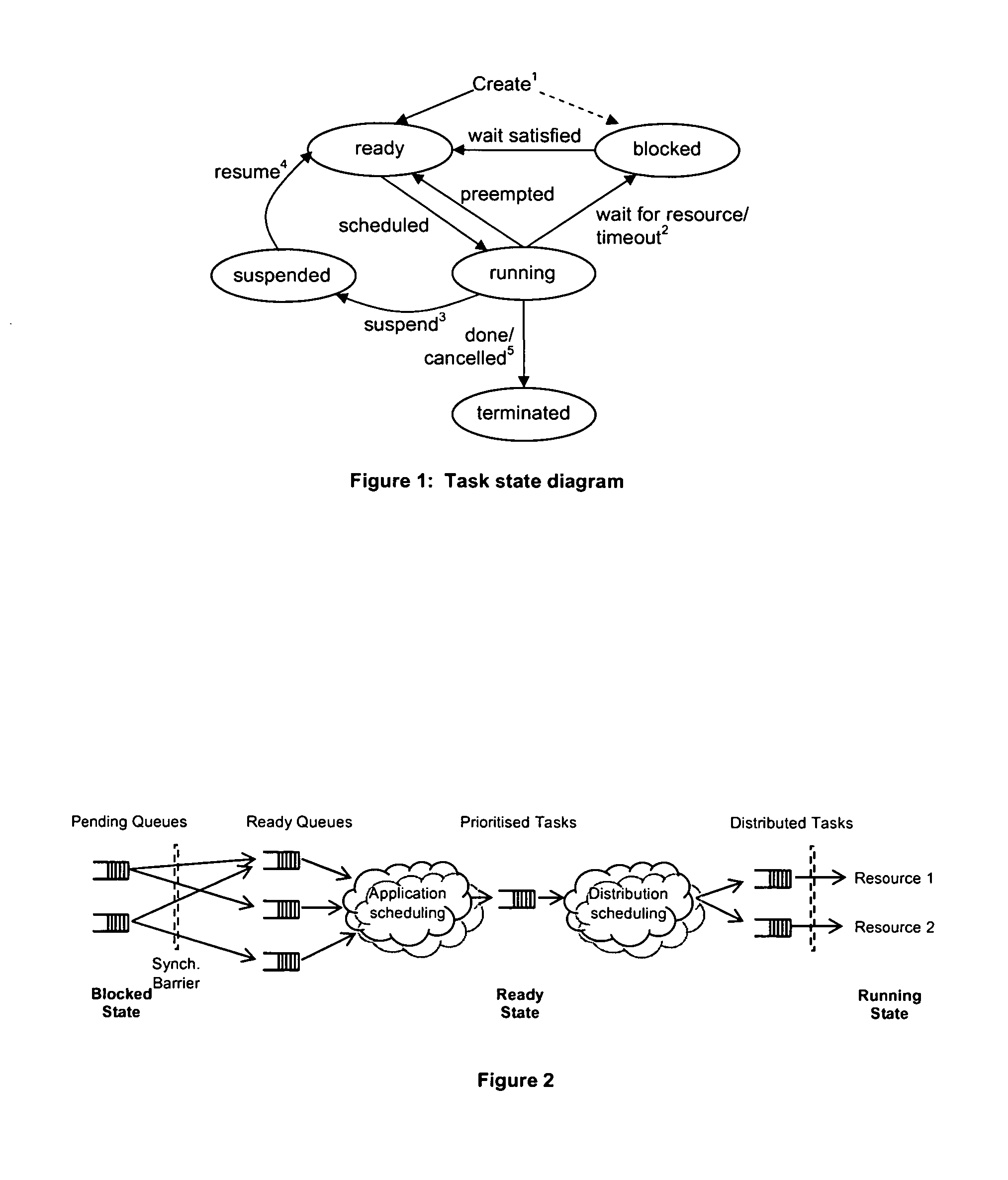

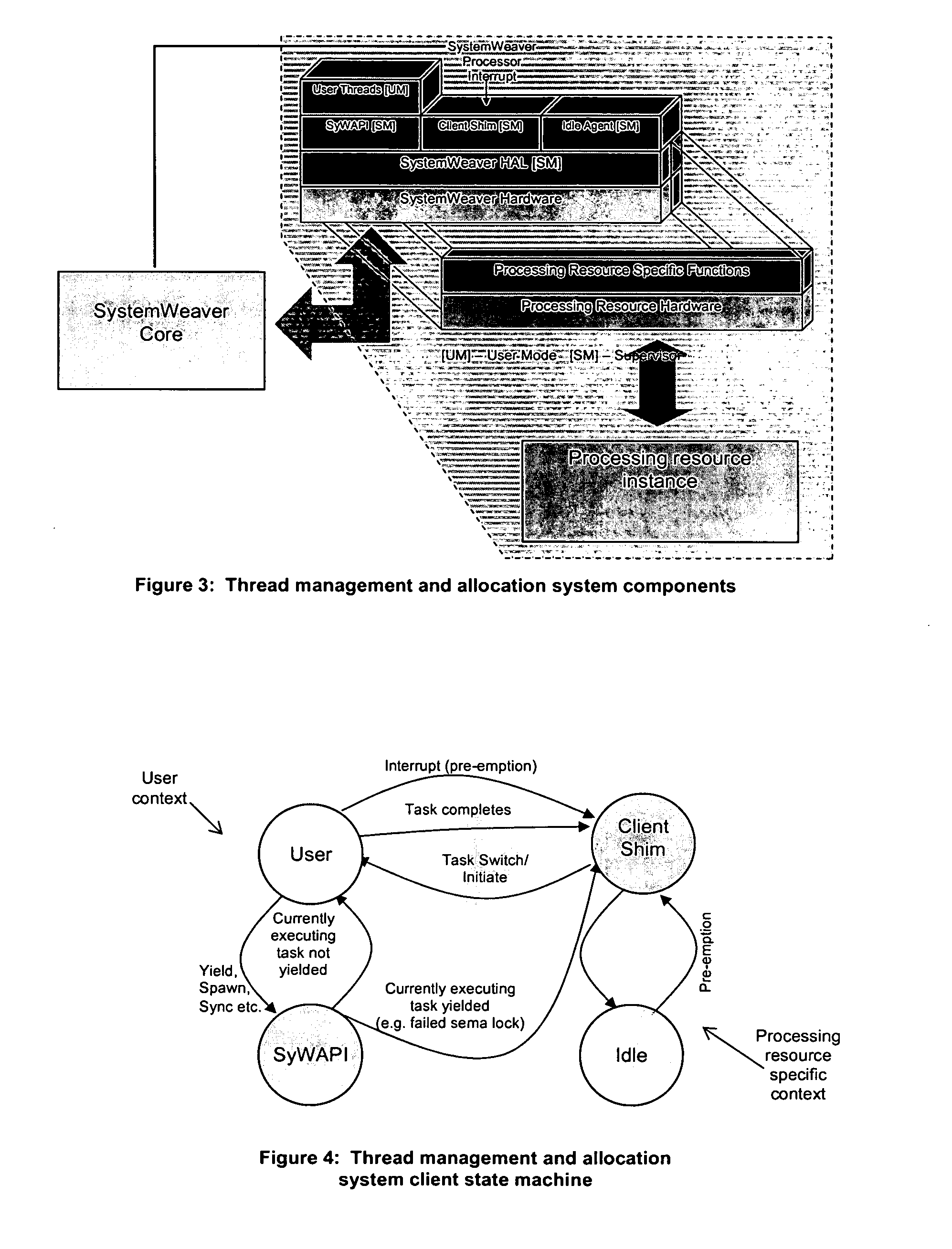

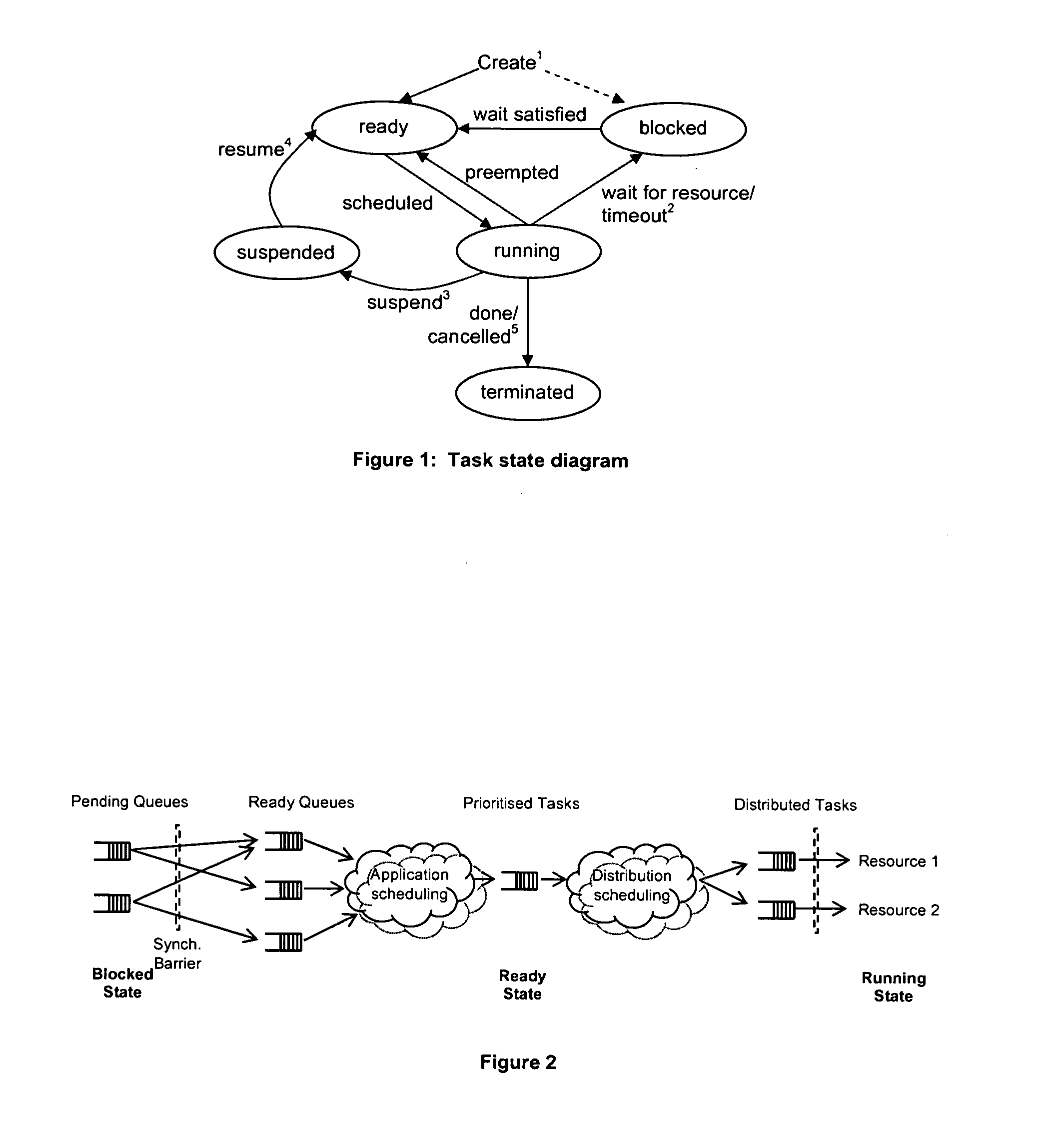

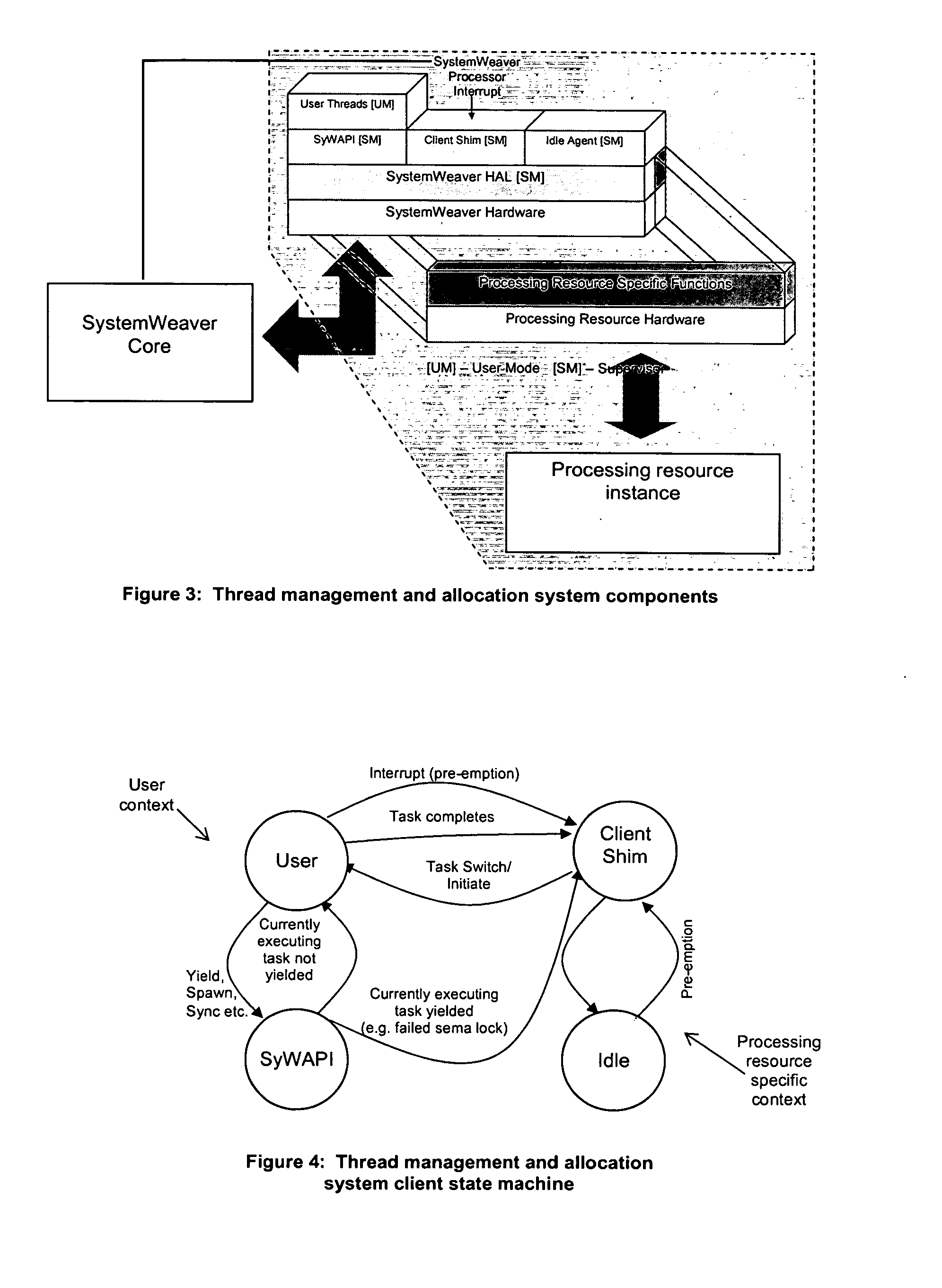

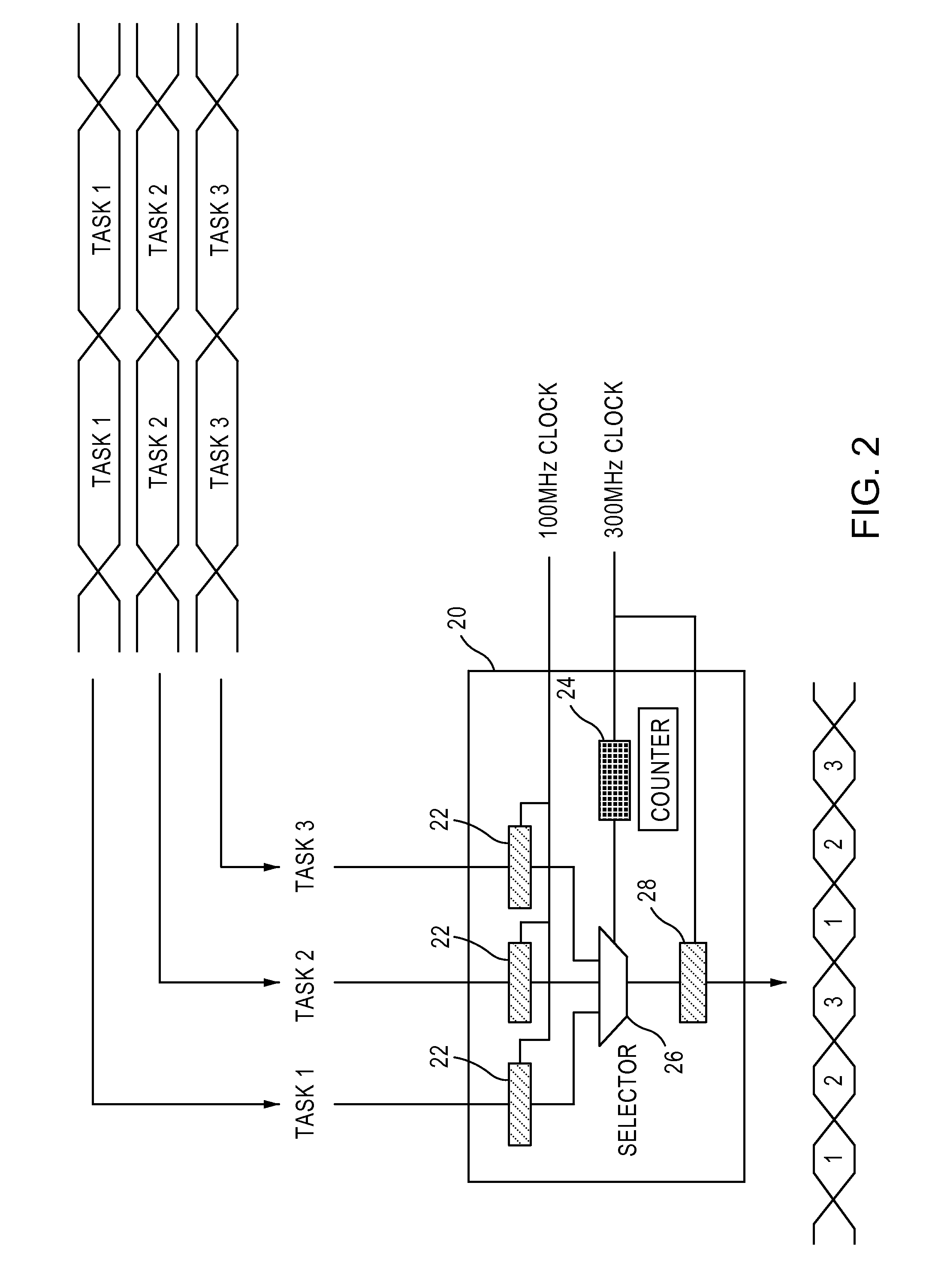

Scheduling in a multicore processor

ActiveUS20070220517A1Improve application performanceIncrease speedEnergy efficient ICTConcurrent instruction executionProcessor elementMulti-core processor

A method and computer-usable medium including instructions for performing a method for scheduling executable transactions within a multicore processor comprising a plurality of processor elements. The method includes listing, using at least one distribution queue, a portion of the executable transactions in order of eligibility for execution. A plurality of executable transaction schedulers are provided, wherein each executable transaction scheduler includes a scheduling process for determining a most eligible executable transaction for execution from at least one candidate executable transaction ready for execution. The executable transaction schedulers are linked together to provide a multilevel scheduler. The most eligible executable transaction is output from the multilevel scheduler to the at least one distribution queue.

Owner:SYNOPSYS INC +1

Systems, methods and apparatus for local programming of quantum processor elements

Systems, methods and apparatus for a scalable quantum processor architecture. A quantum processor is locally programmable by providing a memory register with a signal embodying device control parameter(s), converting the signal to an analog signal; and administering the analog signal to one or more programmable devices.

Owner:D WAVE SYSTEMS INC

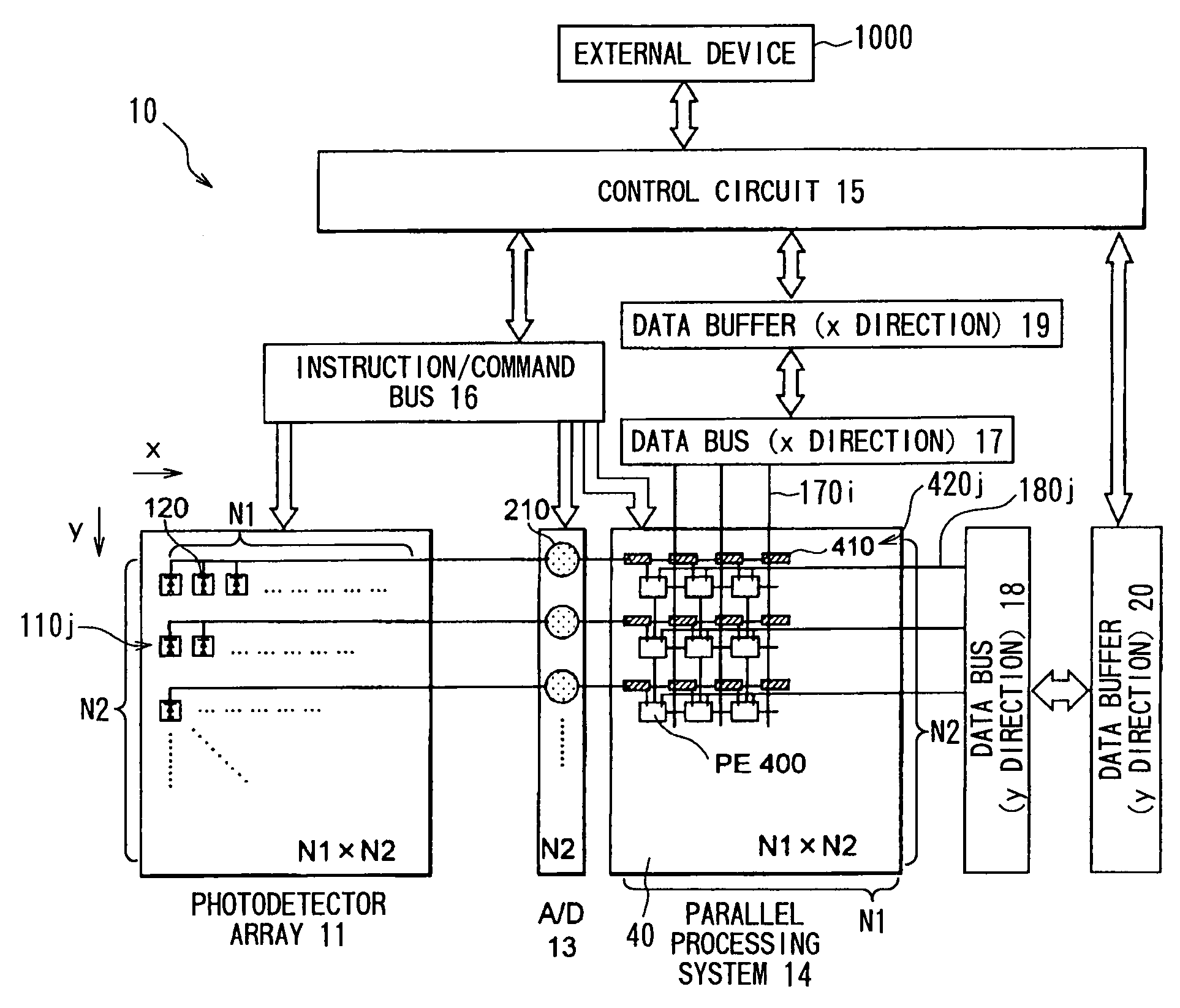

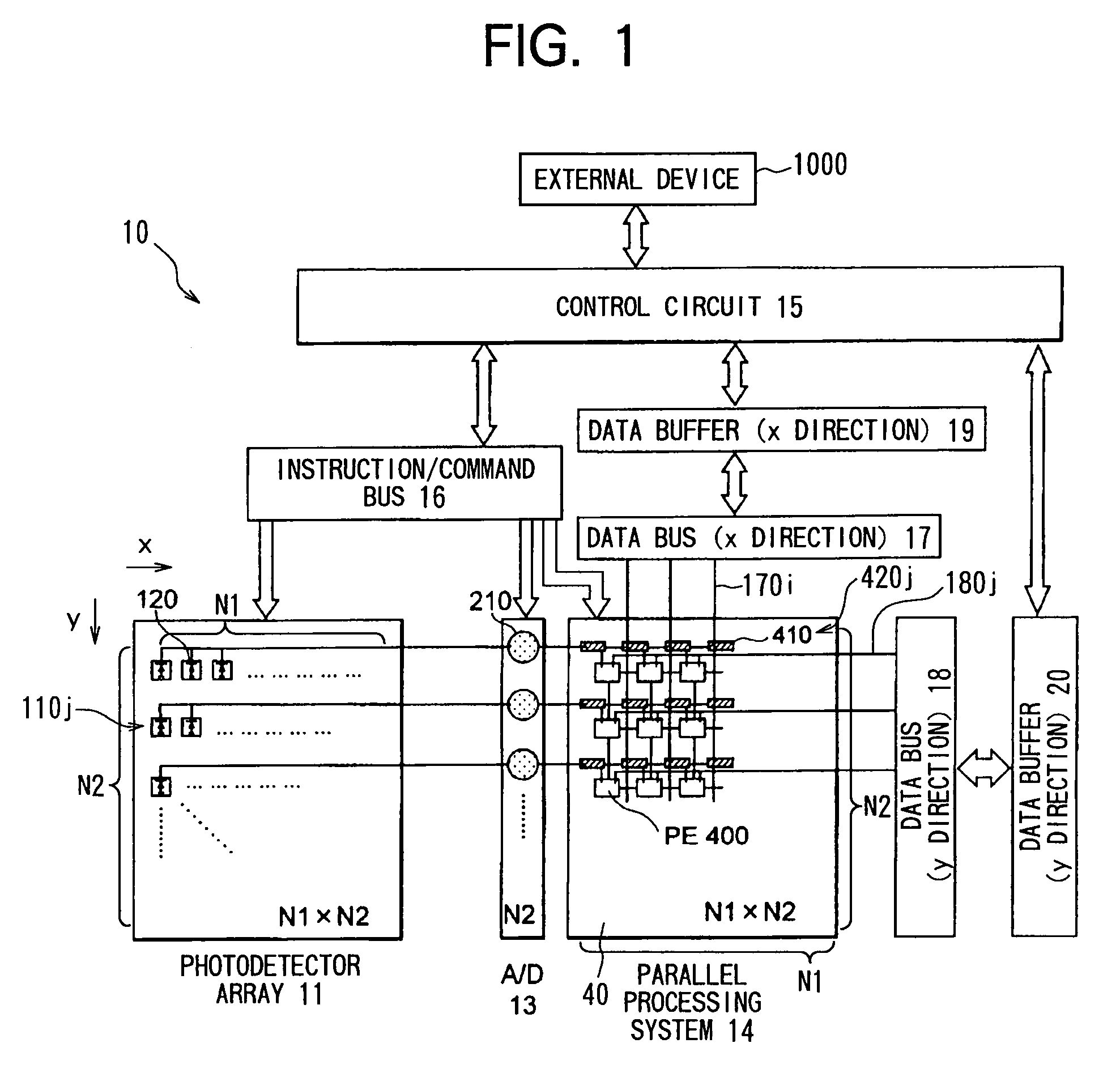

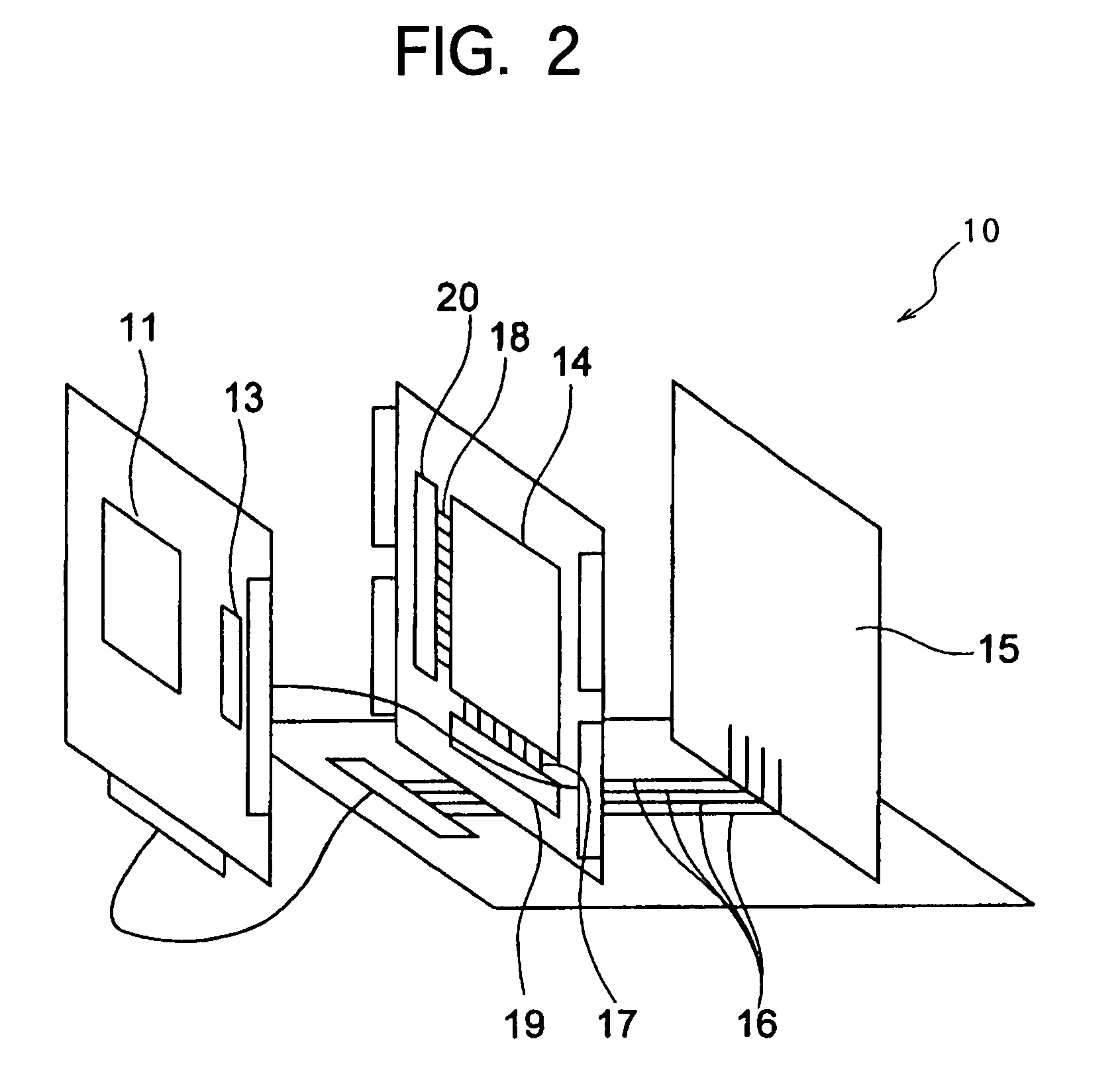

High-speed vision sensor with image processing function

InactiveUS6970196B1Simple circuit structureIncrease speedProgramme controlTelevision system detailsShift registerHigh rate

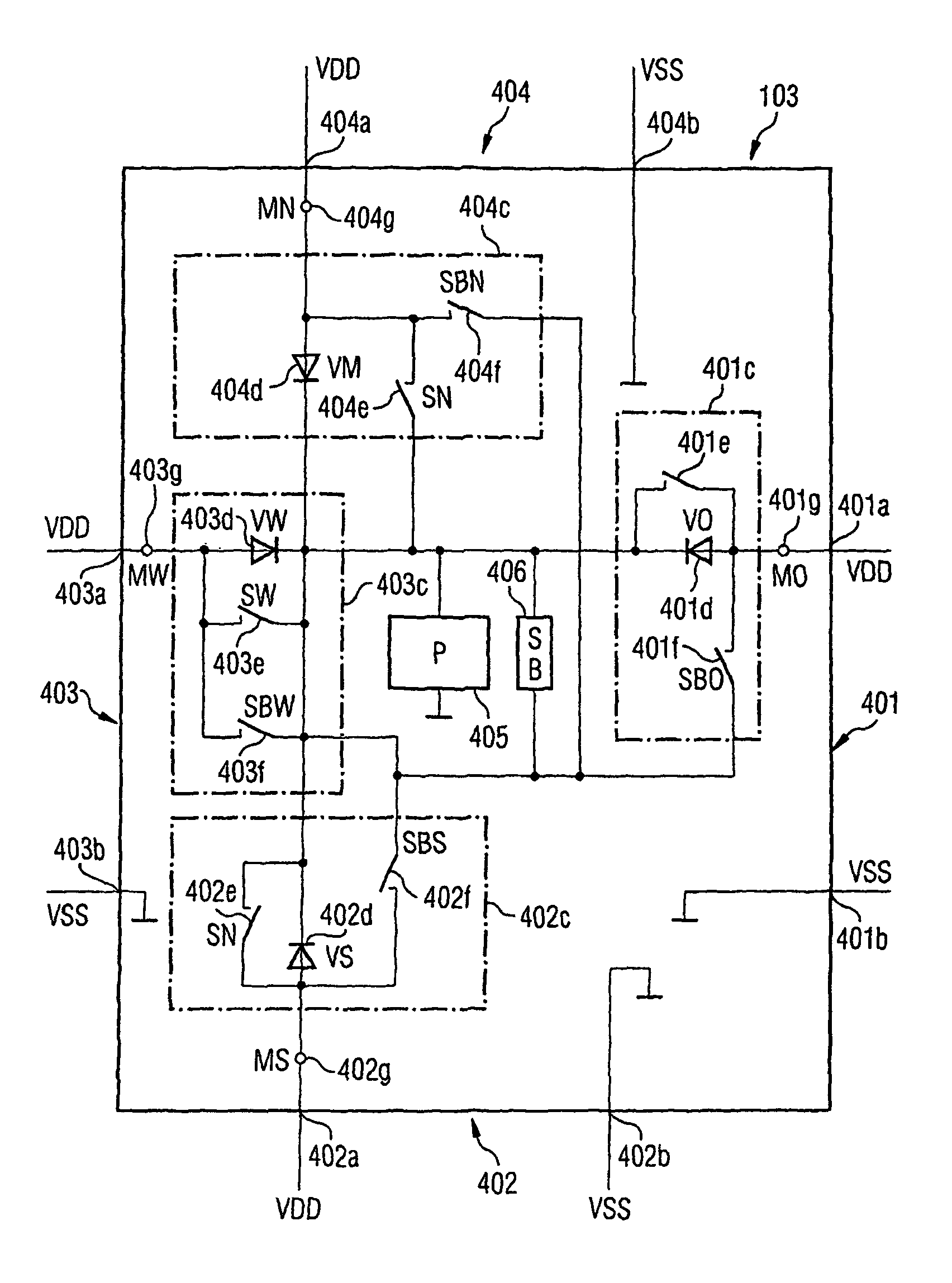

A high-speed vision sensor includes: an analog-to-digital converter array 13, in which one analog-to-digital converter 210 is provided in correspondence with all the photodetector elements 120 that are located on each row in a photodetector array 11; a parallel processing system 14 that includes processor elements 400 and shift registers 410, both of which form a one-to-one correspondence with the photodetector elements 120; and data buses 17, 18 and data buffers 19 and 20 for data transfer to processing elements 400. The processing elements 400 perform high-speed image processing between adjacent pixels by parallel processings. By using the data buses 17, 18, it is possible to attain, at a high rate of speed, such calculation processing that requires data supplied from outside.

Owner:HAMAMATSU PHOTONICS KK

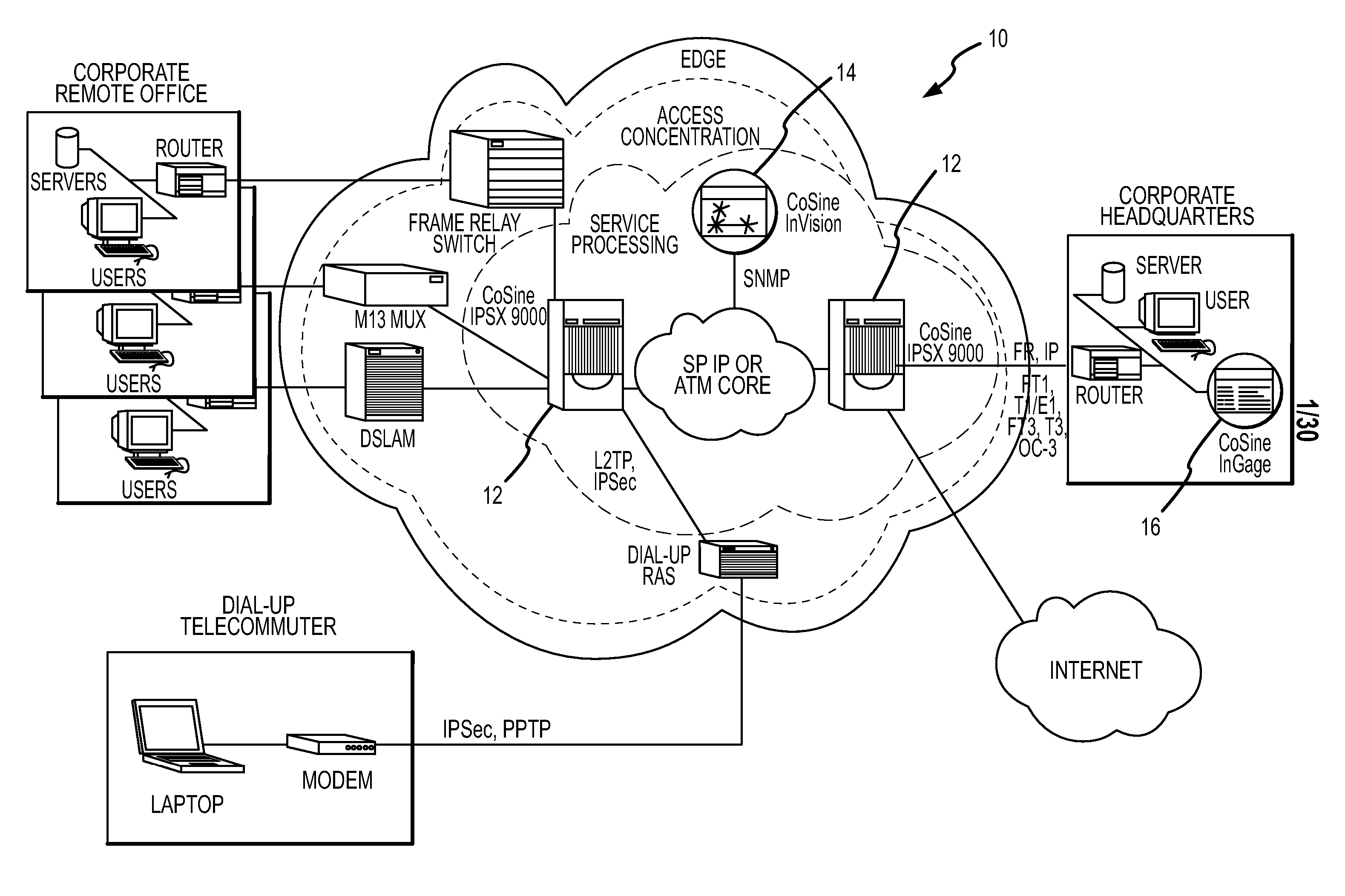

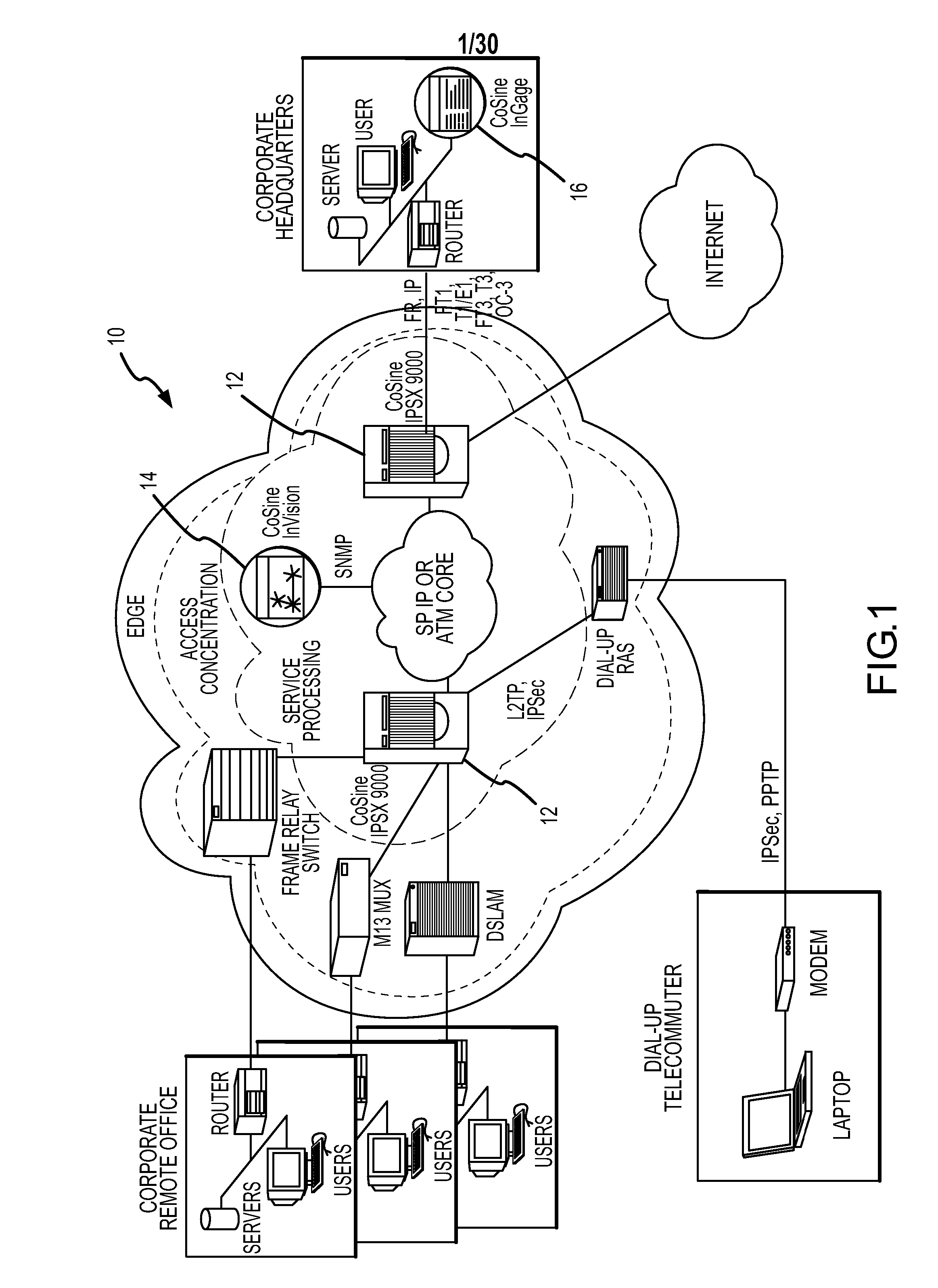

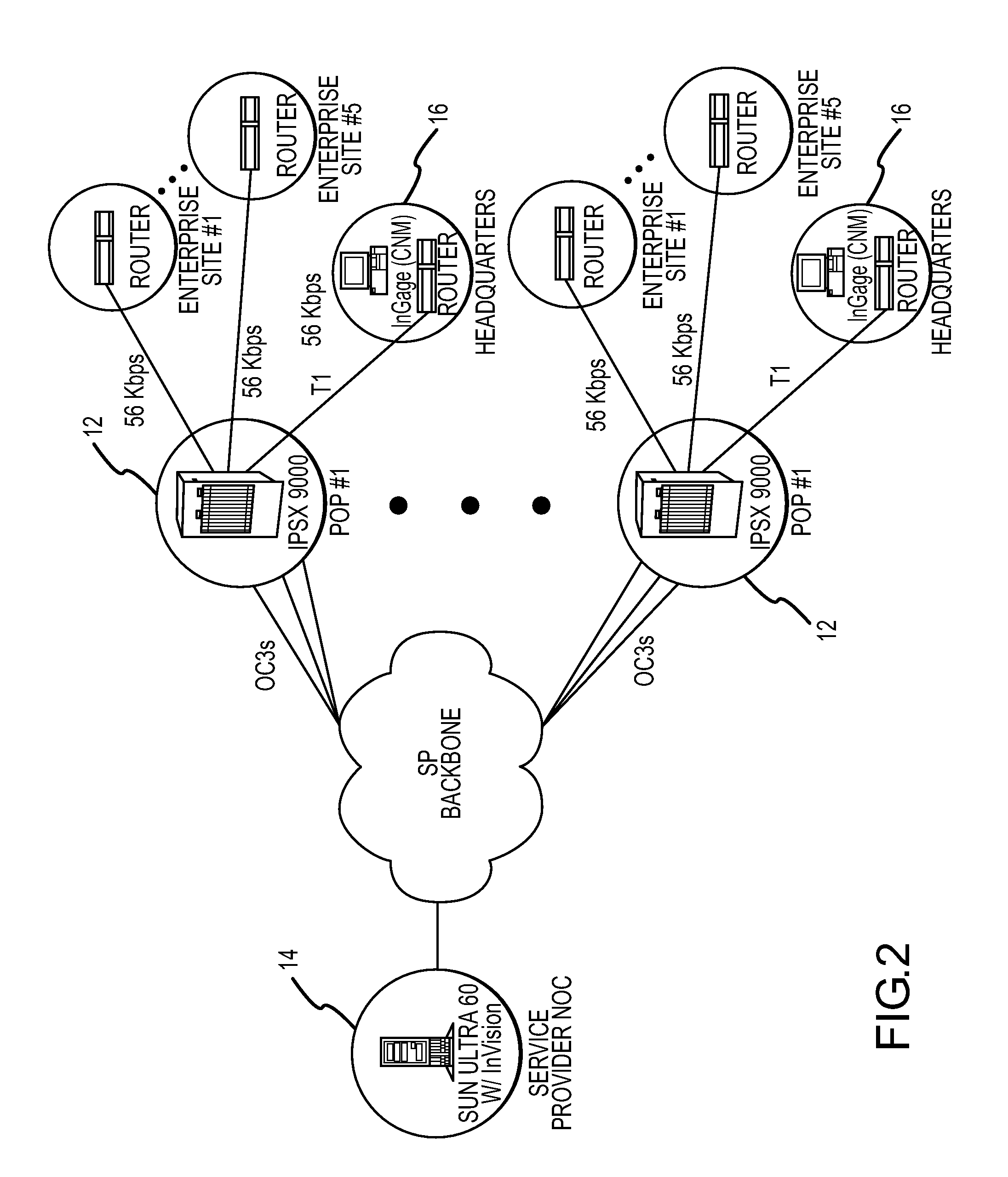

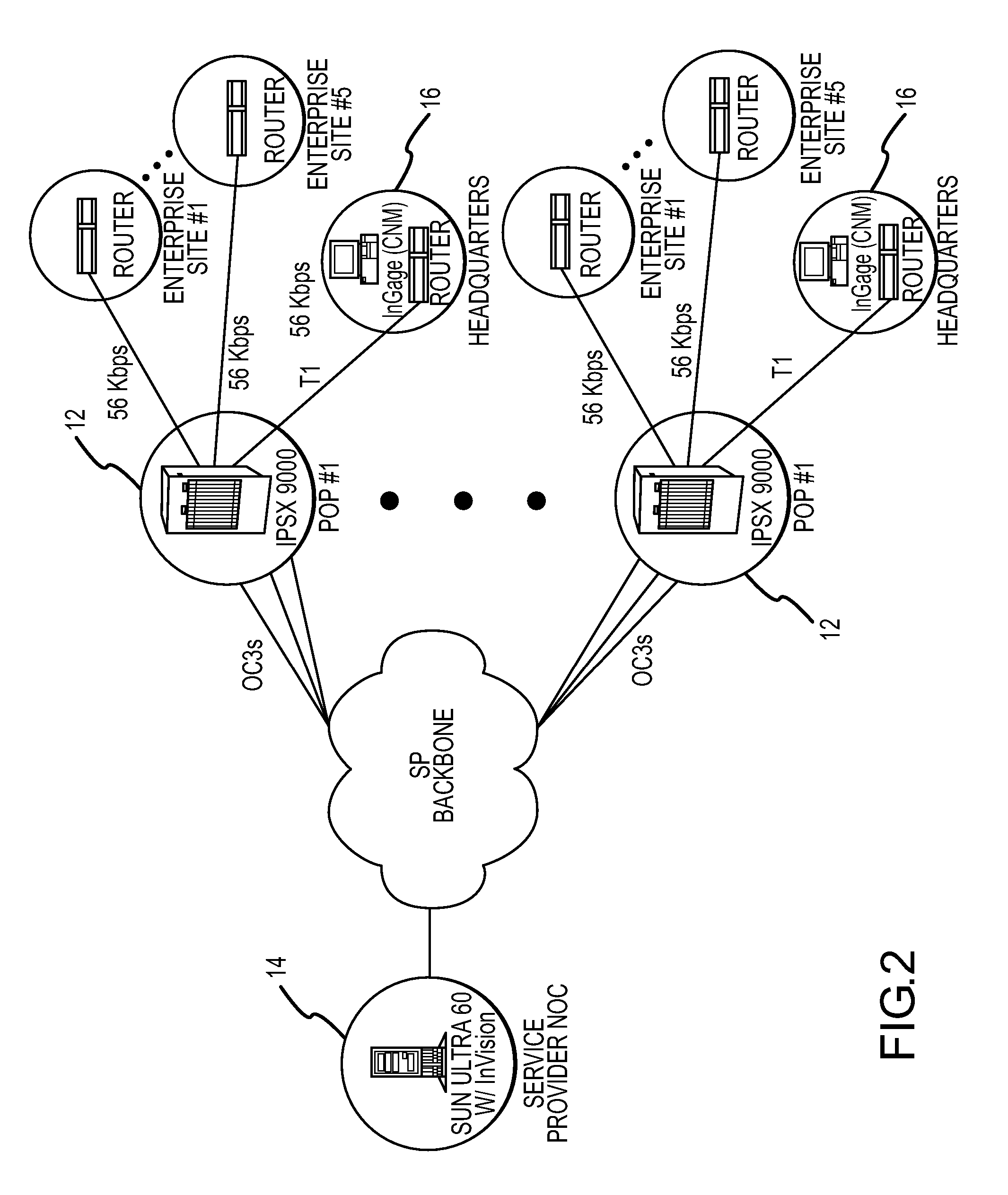

Switch management system and method

ActiveUS20070083528A1TransmissionSpecial data processing applicationsOperational systemProcessor element

A system and method of managing a switch includes installing a switch having a plurality of processor elements, installing an operating system on each processor element, creating a system virtual router and configuring the processor elements from the system virtual router.

Owner:CISCO TECH INC

Architecture for local programming of quantum processor elements using latching qubits

Owner:D WAVE SYSTEMS INC

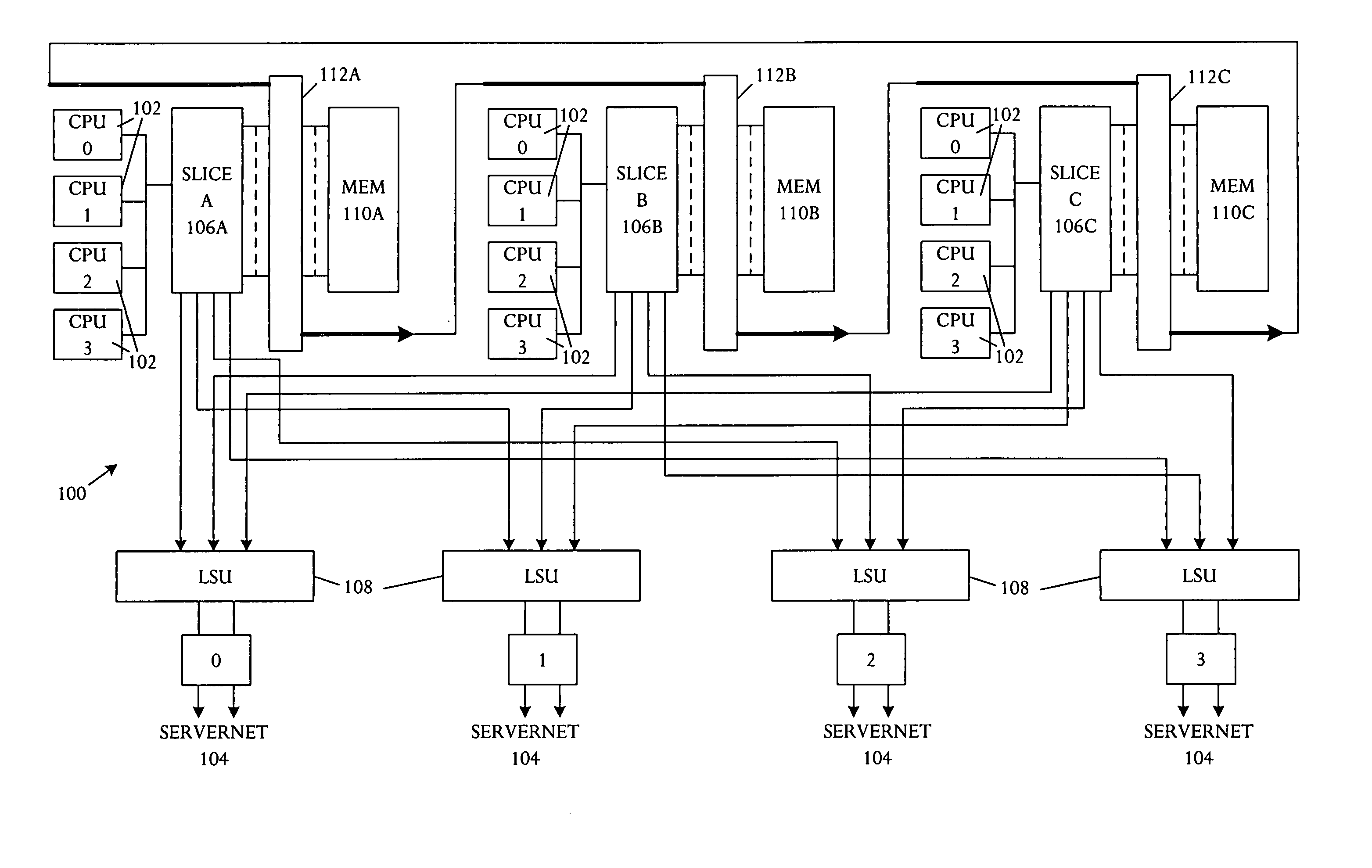

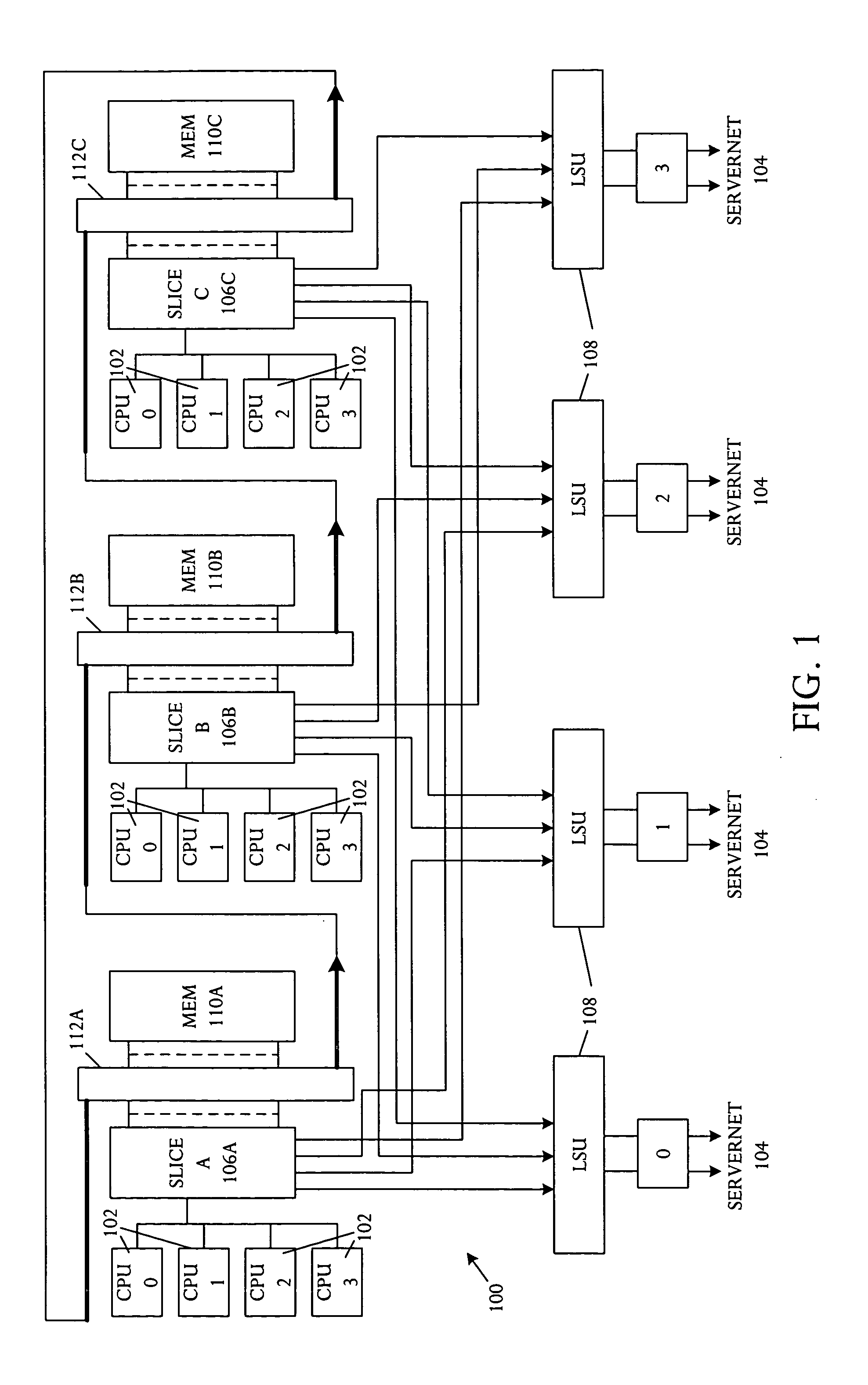

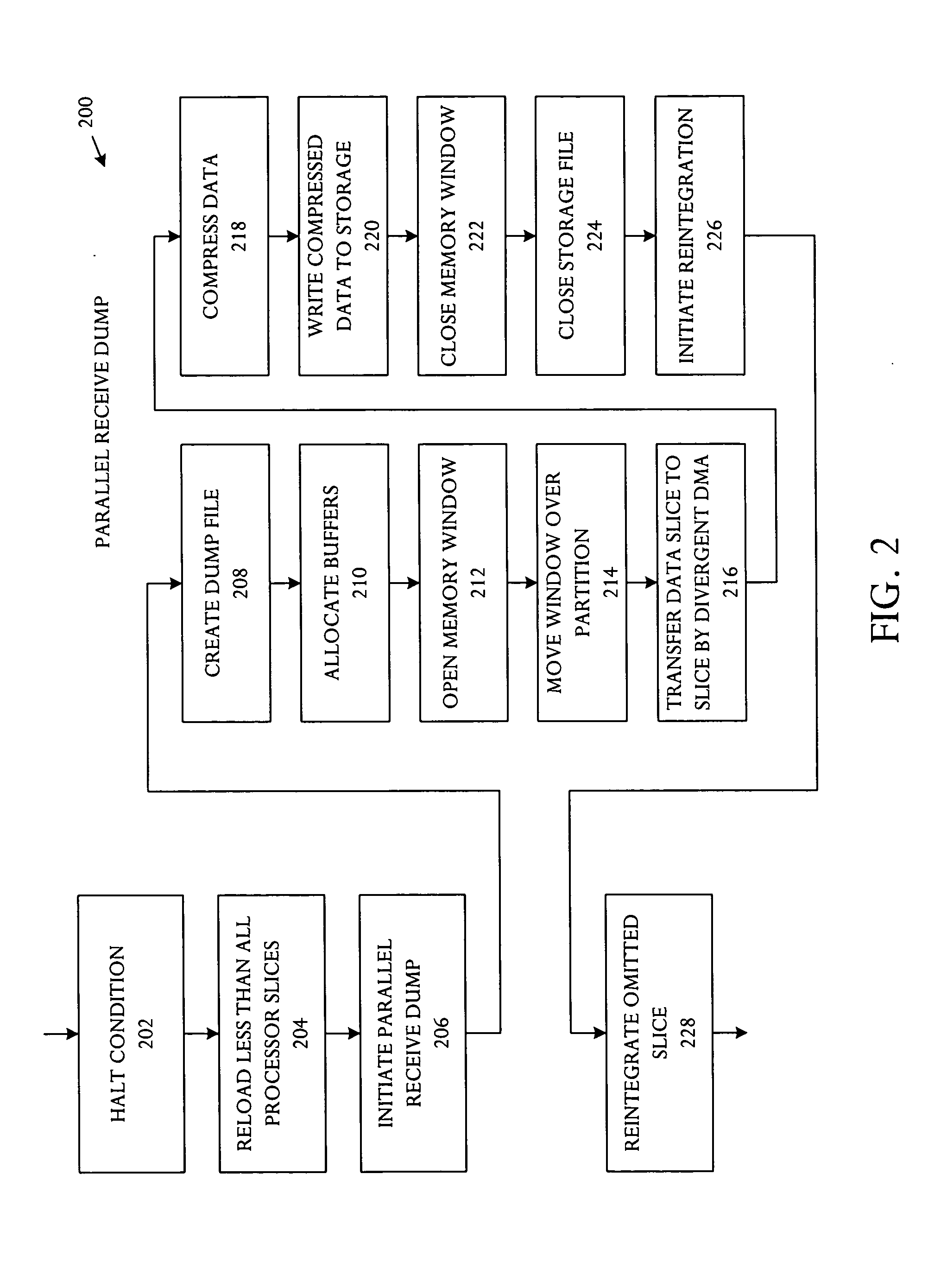

Diagnostic memory dump method in a redundant processor

Owner:HEWLETT PACKARD DEV CO LP

Debug in a multicore architecture

According to a first aspect of the present invention, there is provided a method of monitoring thread execution within a multicore processor architecture which comprises a plurality of interconnected processor elements for processing the threads, the method comprising receiving a plurality of thread parameter indicators indicative of one or more parameters relating to the function and / or identity of a thread or threads comparing at least some of the thread parameter indicators with a first plurality of predefined criteria each representative of an indicator of interest and generating an output consequential upon thread parameter indicators which have been identified to be of interest as a result of the said comparison.

Owner:FUJITSU SEMICON LTD +1

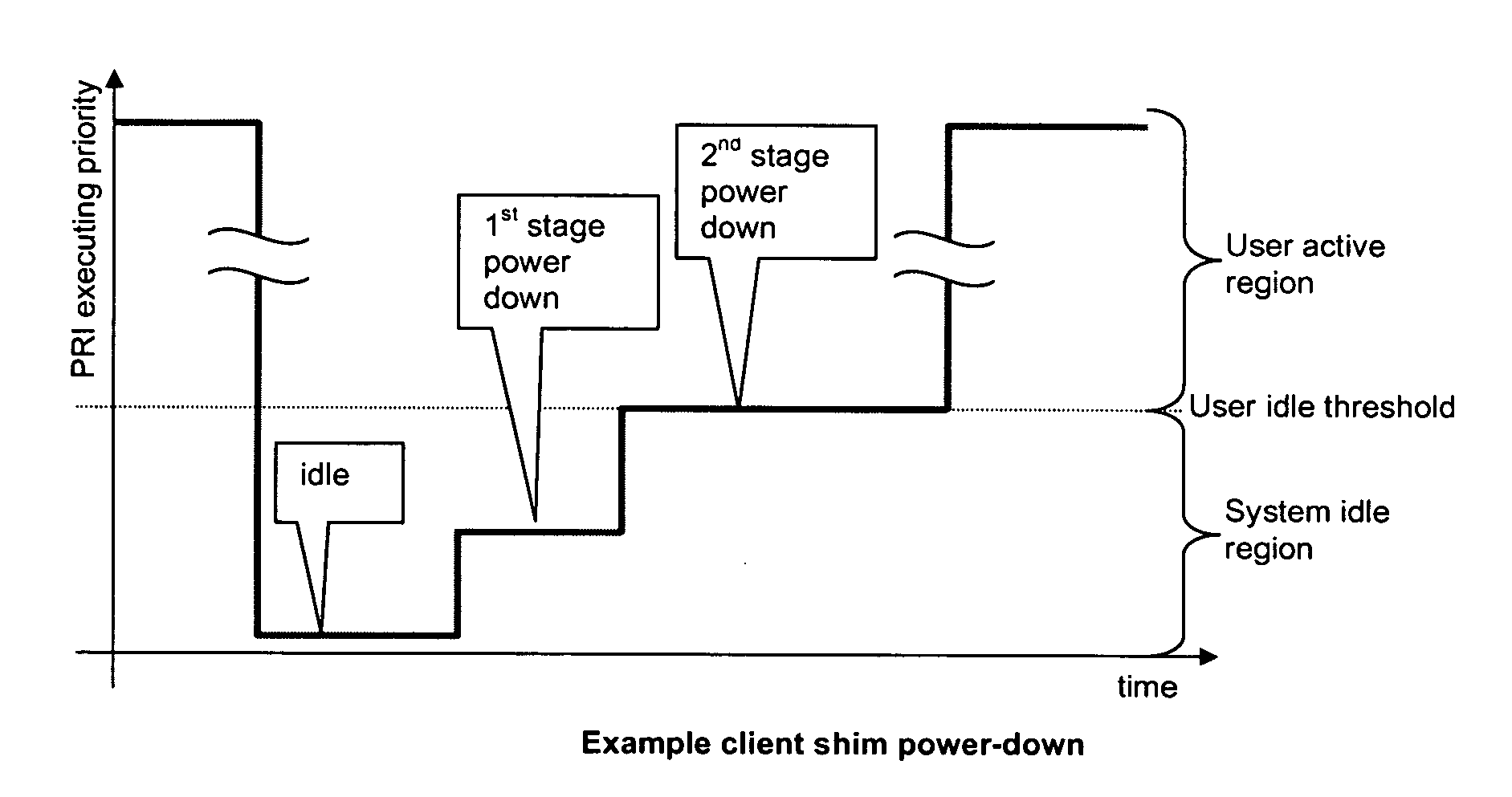

Managing power consumption in a multicore processor

ActiveUS20070220294A1Improve application performanceIncrease speedEnergy efficient ICTVolume/mass flow measurementProcessor elementMulti-core processor

A method and computer-usable medium including instructions for performing a method of managing power consumption in a multicore processor comprising a plurality of processor elements with at least one power saving mode. The method includes listing, using at least one distribution queue, a portion of the executable transactions in order of eligibility for execution. A plurality of executable transaction schedulers are provided. The executable transaction schedulers are linked together to provide a multilevel scheduler. The most eligible executable transaction is output from the multilevel scheduler to the at least one distribution queue. One or more of the plurality of processor elements are placed into a first power saving mode when a number of executable transactions allocated to the plurality of processor elements is such that only a portion of available processor elements are used to execute executable transactions.

Owner:FUJITSU SEMICON LTD +1

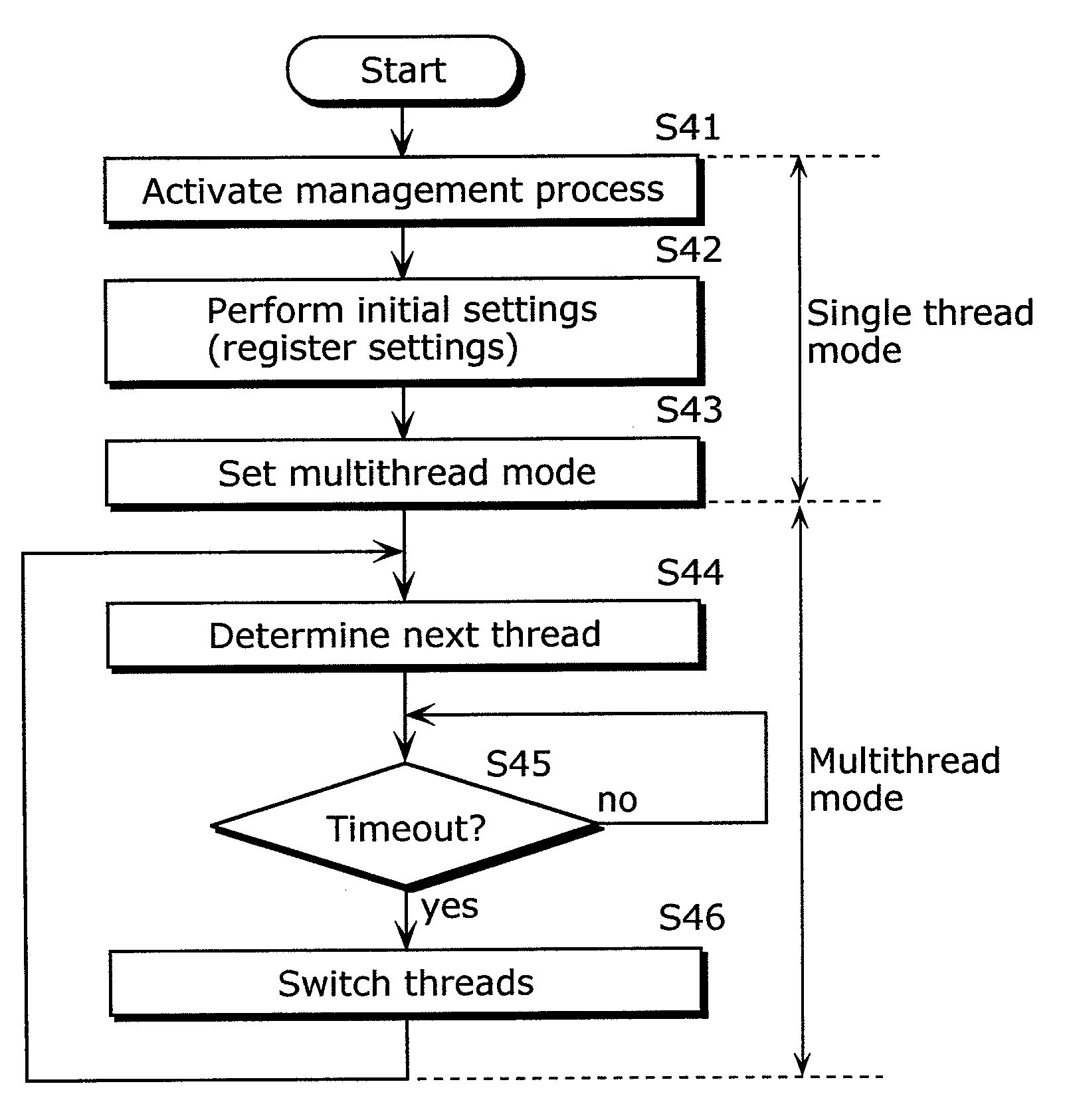

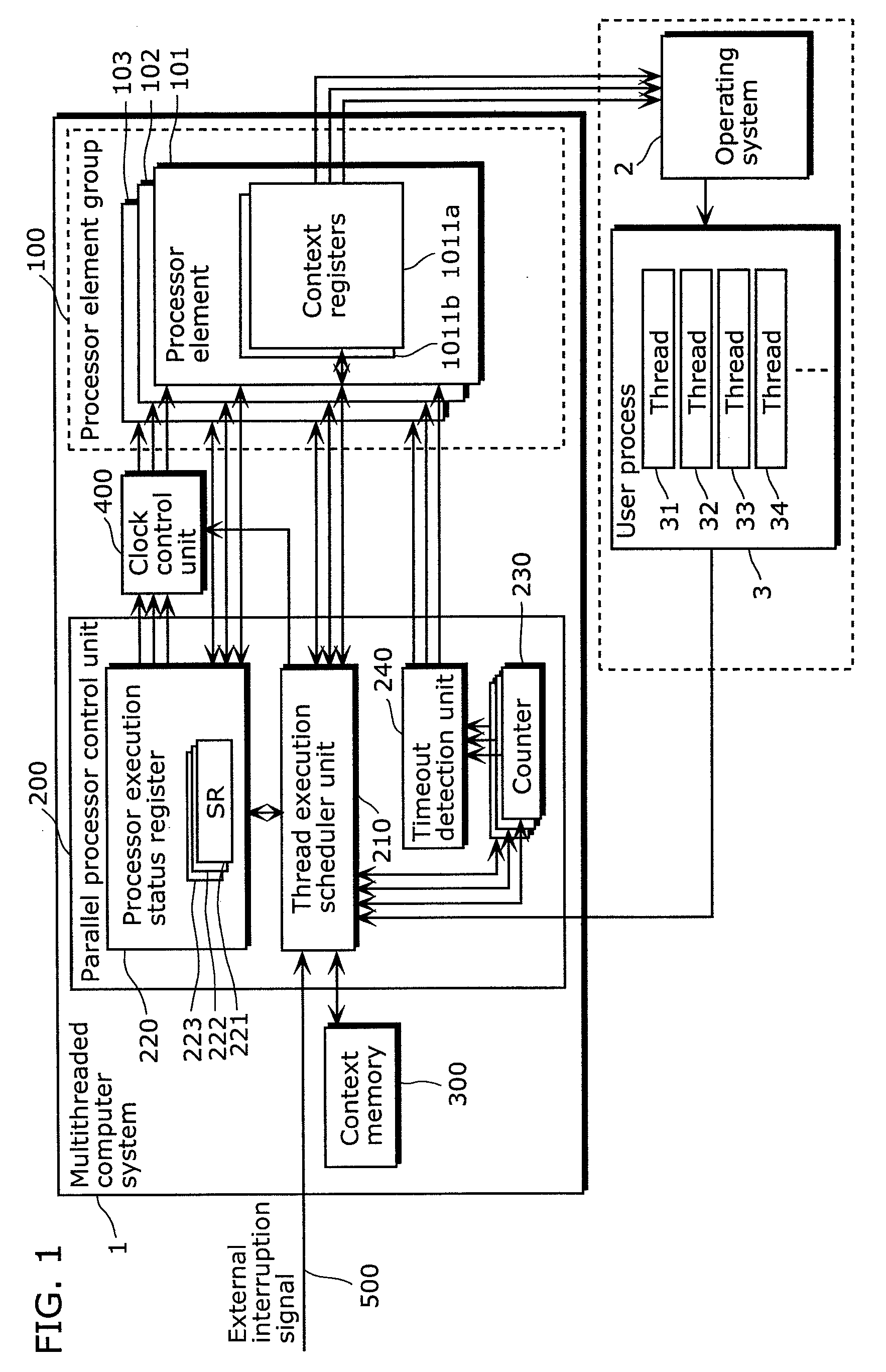

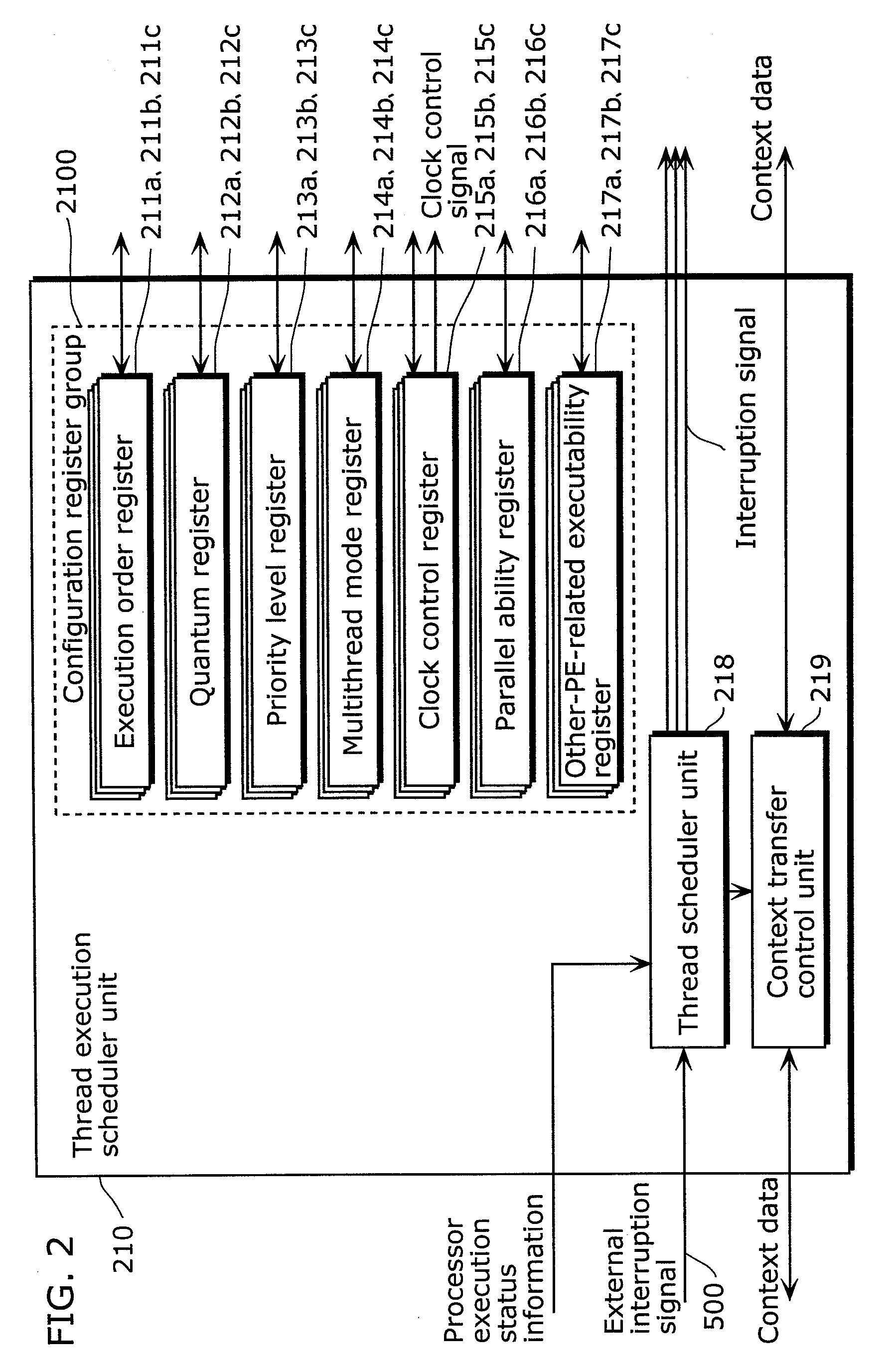

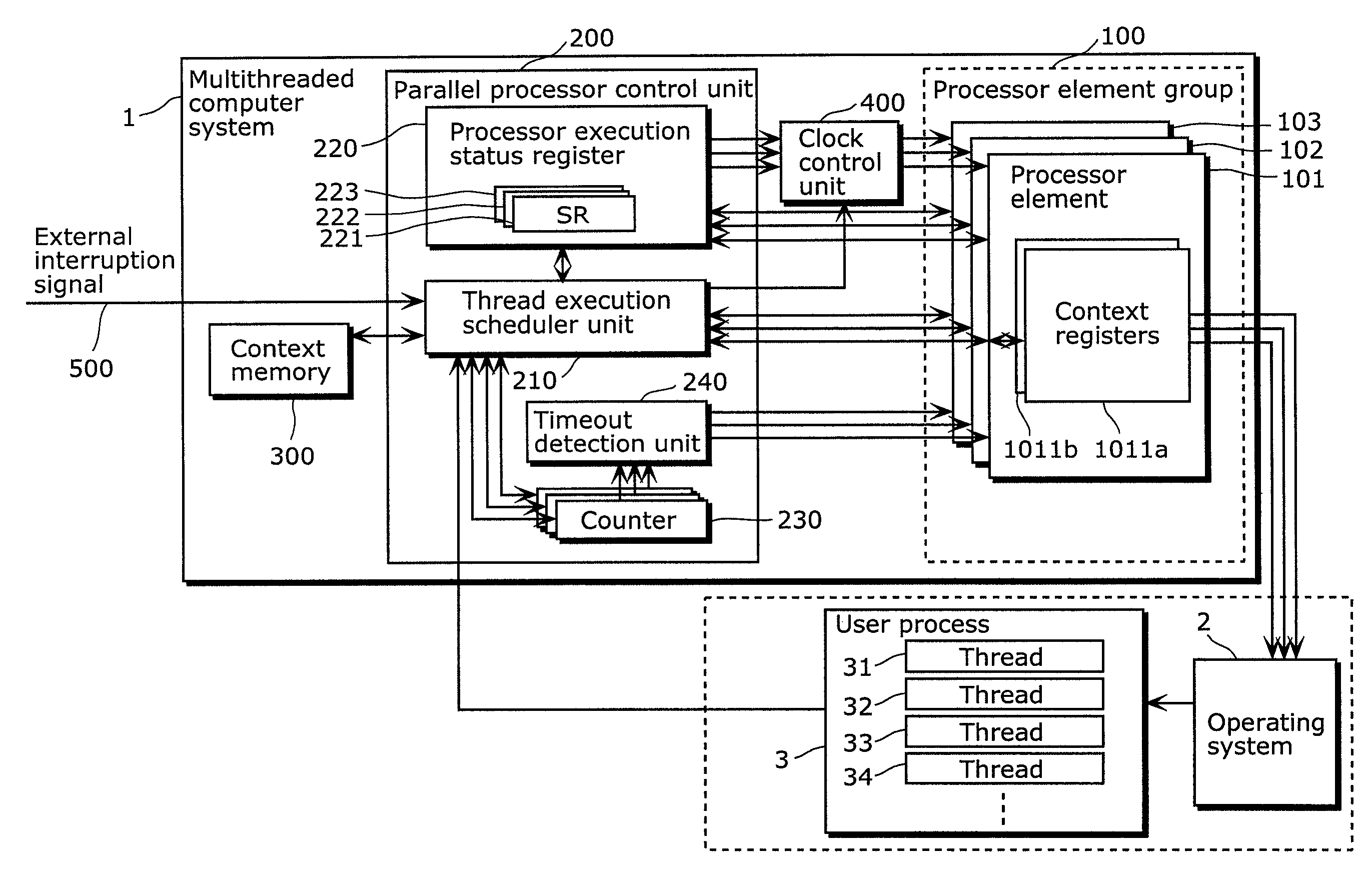

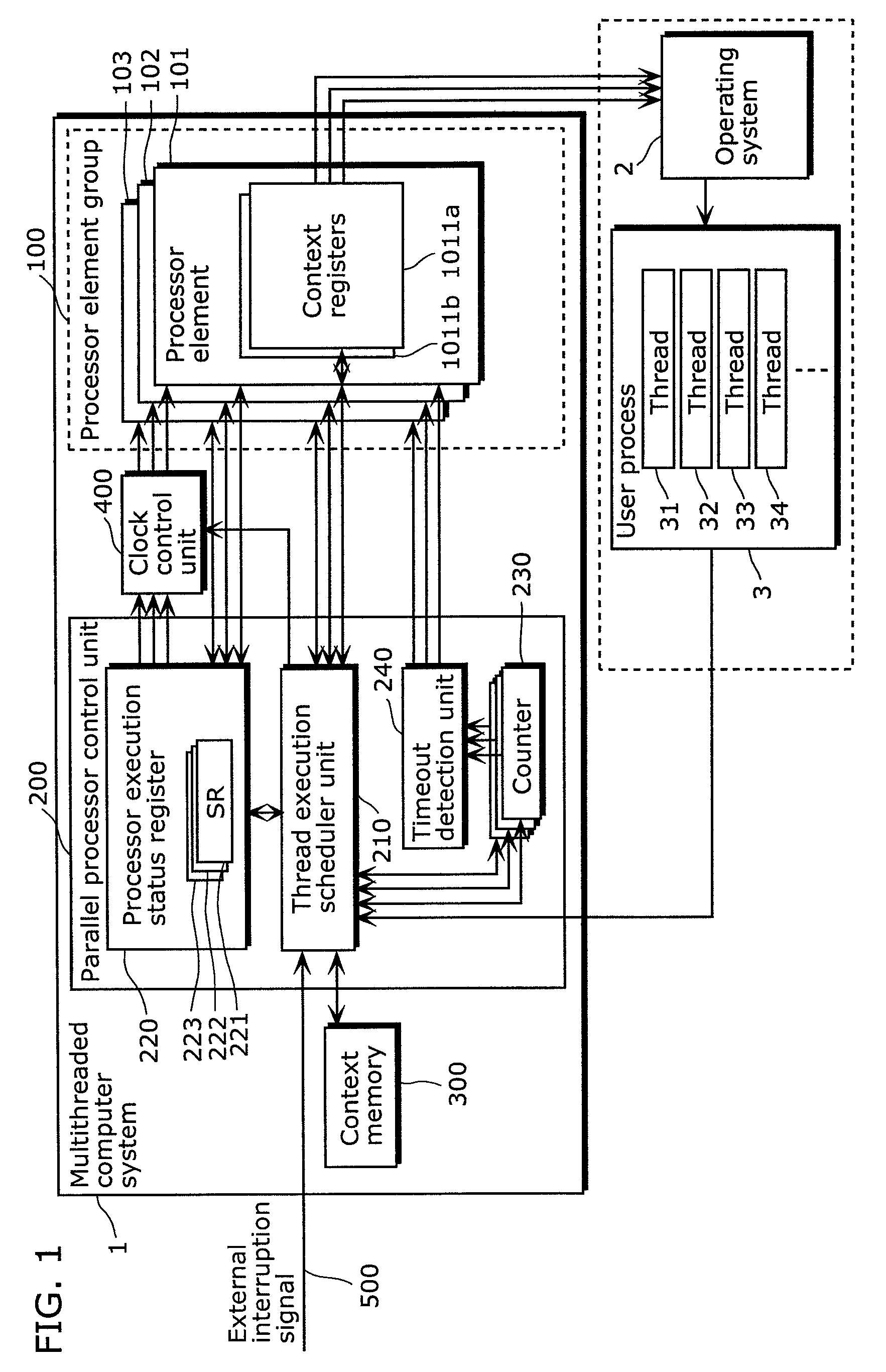

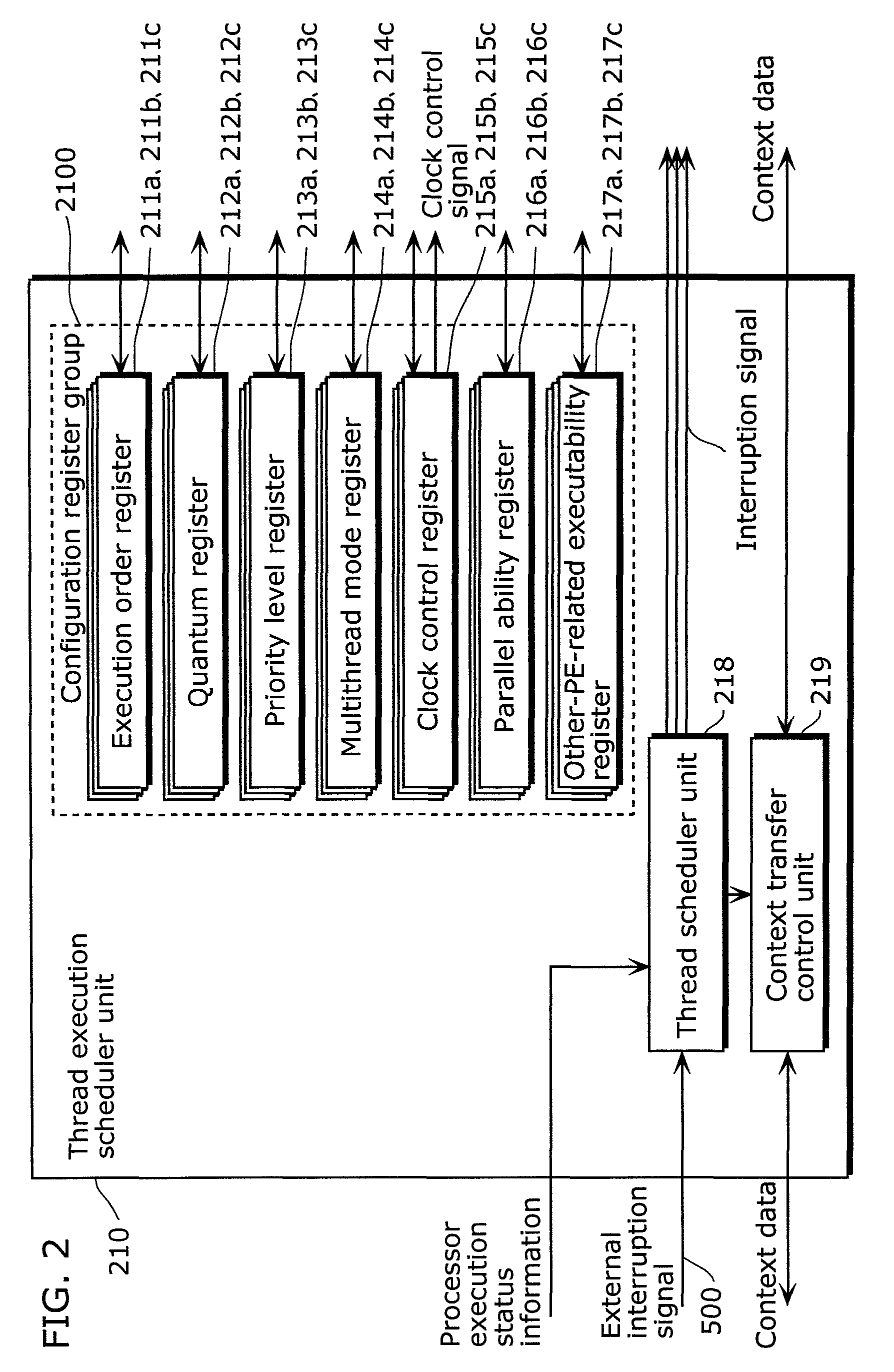

Multithreaded computer system and multithread execution control method

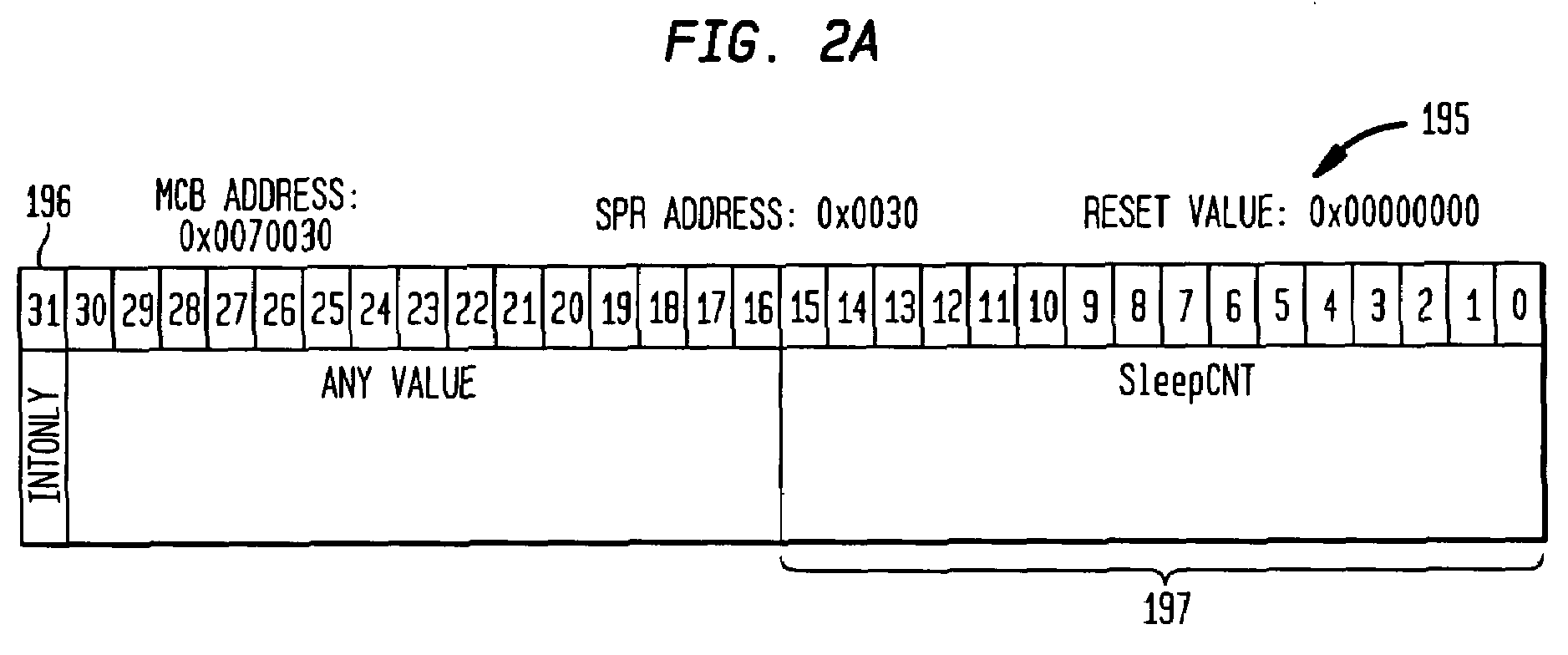

ActiveUS20070266387A1Improve usabilityEnhancing substantial availabilityEnergy efficient ICTDigital computer detailsProcessor elementProcessor register

A multithreaded computer system of the present invention includes a plurality of processor elements (PEs) 101 to 103, and a parallel processor control unit 200, which switches threads in each PE, and the parallel processor control unit 200 includes: a plurality of execution order registers, which hold, for each processor element, an execution order of threads to be executed; a plurality of counters 230, which count an execution time for a thread that is being executed by each processor element and generate a timeout signal when the counted time reaches a limit assigned to the thread; and a thread execution scheduler unit 210, which switches the thread that is being executed to the thread to be executed by each processor element based on the execution order held in said execution order register and the timeout signal.

Owner:BEIJING ESWIN COMPUTING TECH CO LTD

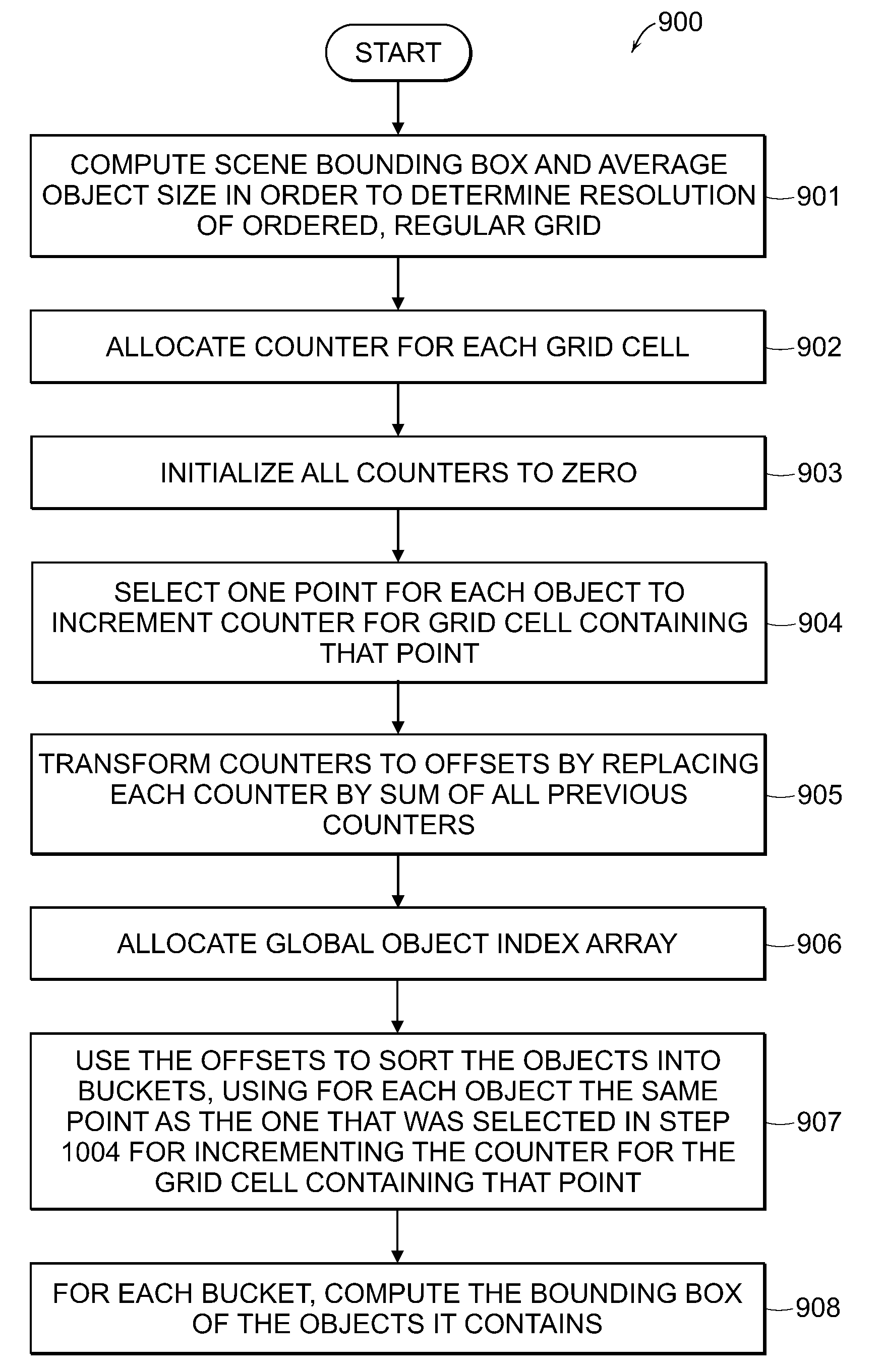

Accelerated ray tracing

ActiveUS20090256845A1Computationally efficientEfficiently compute collision detection3D-image renderingLinear motionProcessor element

Methods, systems and computer program code (software) products executable in a computer processor element include computing, in the processor element, a minimal axis-aligned bounding box of the intersection of a given axis-aligned bounding box and a triangle under linear motion, and / or traversing, in the processor element, a ray tracing acceleration hierarchy for a given set of rays, wherein the traversing includes computing decisions for a representative form of the rays, without requiring a traversing of all rays in turn.

Owner:NVIDIA CORP

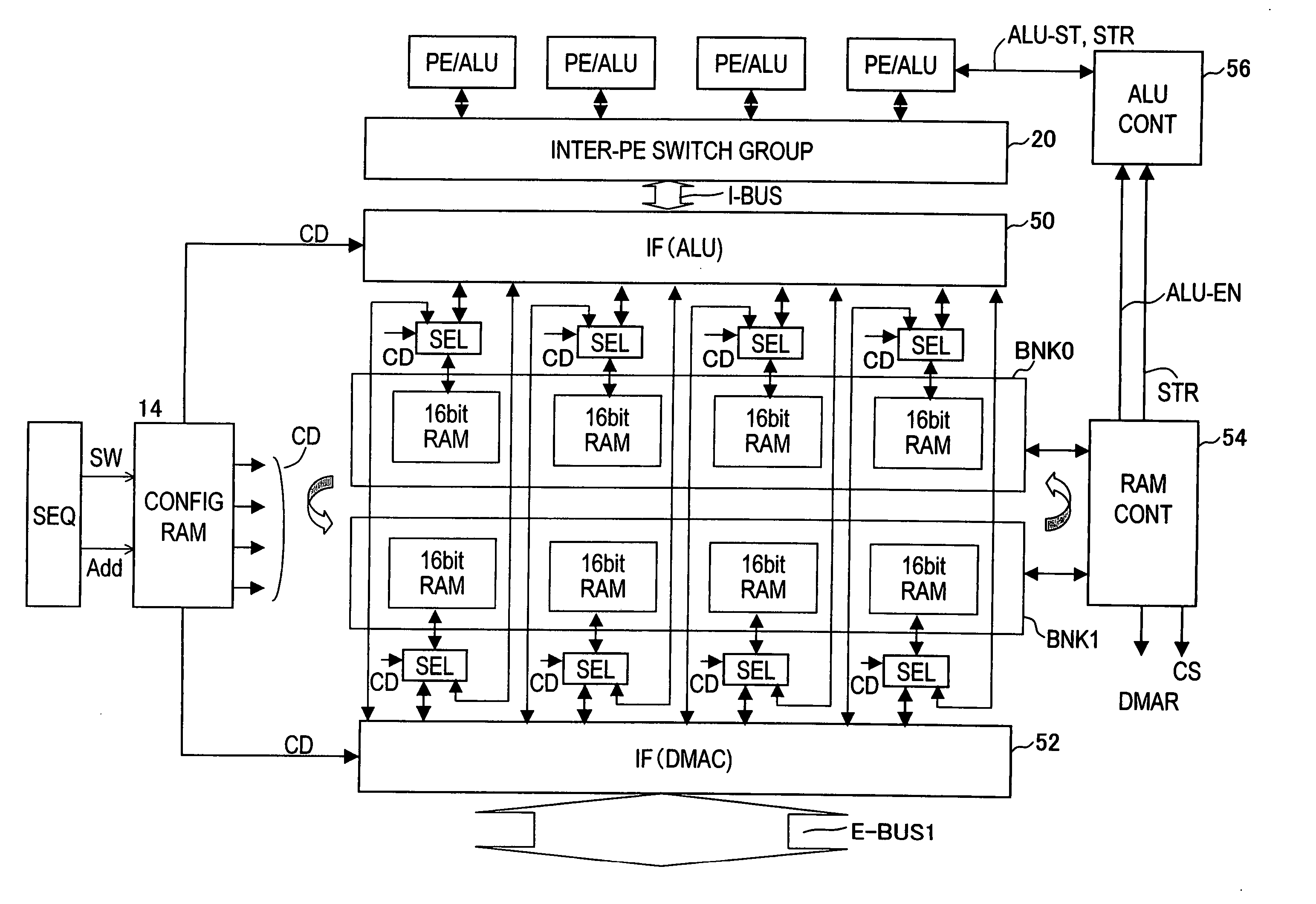

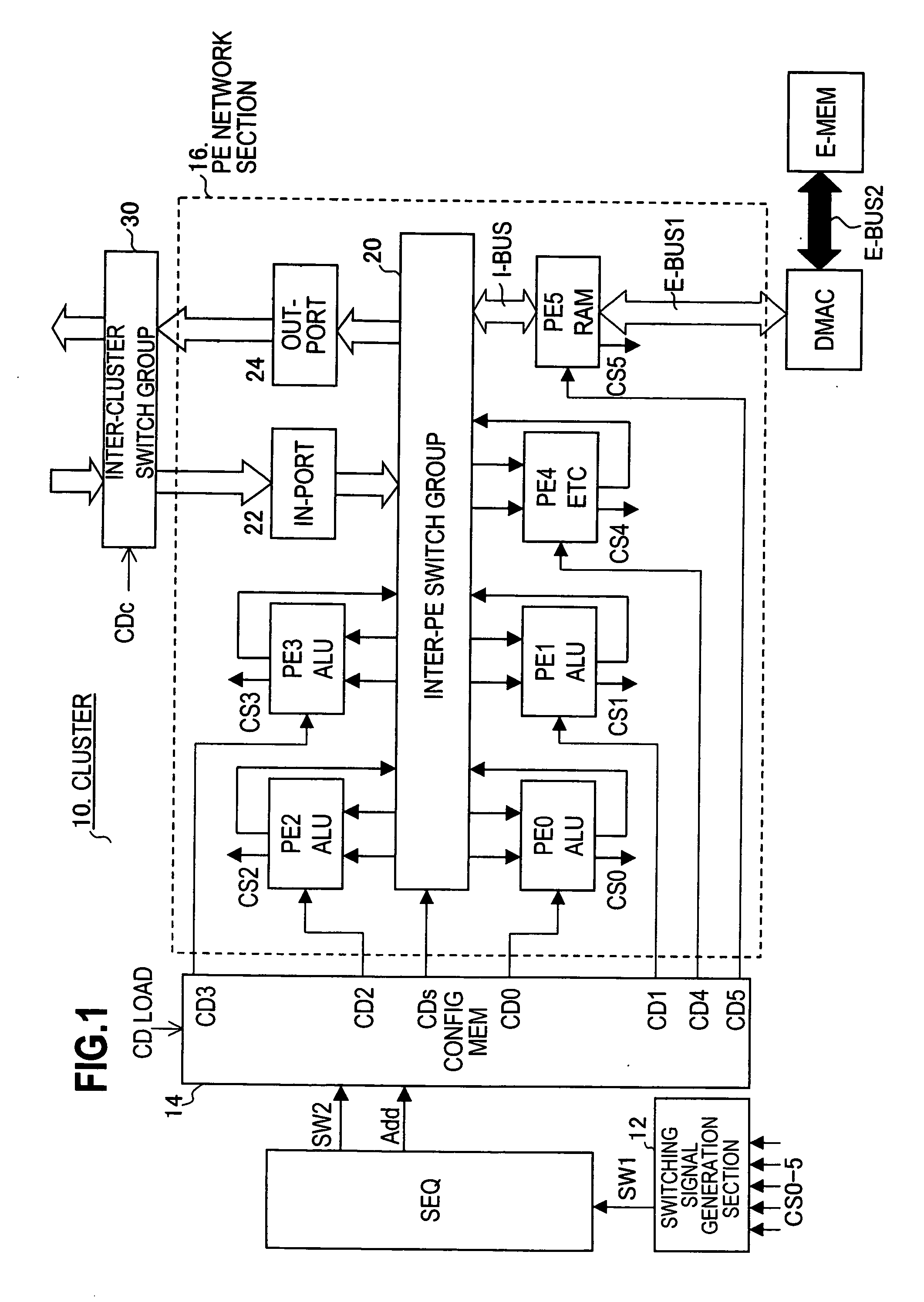

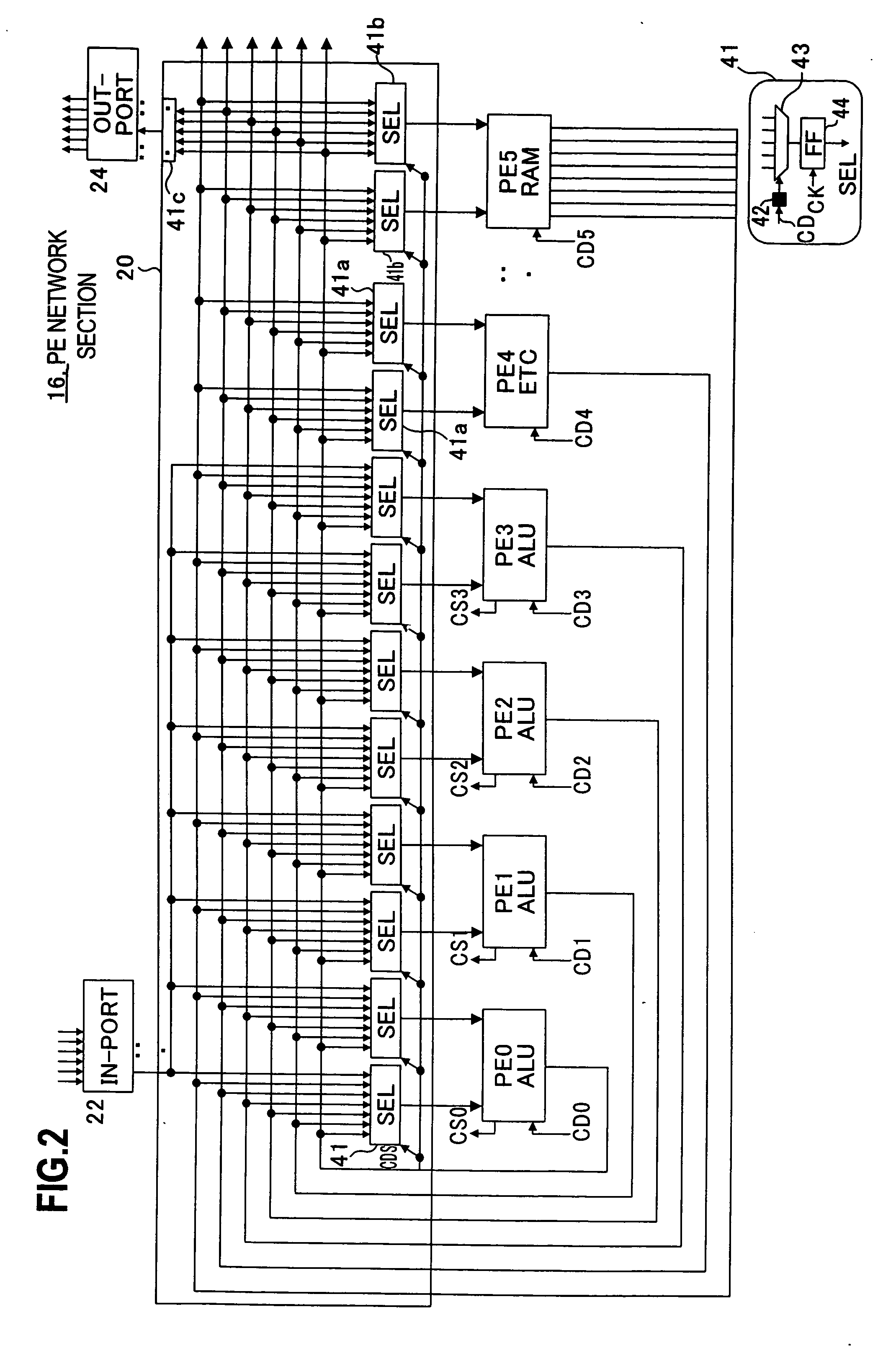

Reconfigurable integrated circuit device

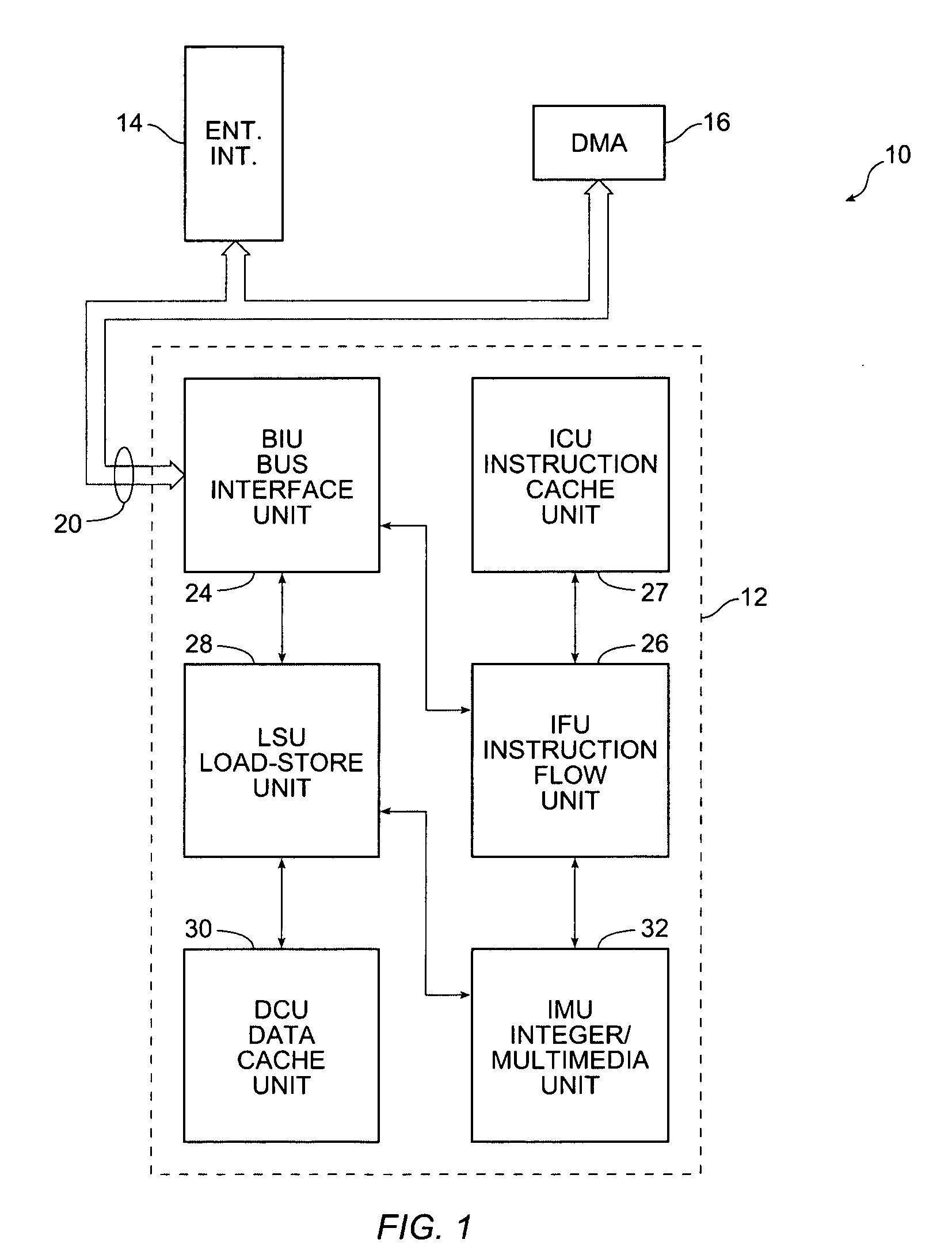

InactiveUS20070033369A1Configuration highHigh operating requirementsSingle instruction multiple data multiprocessorsMemory systemsExternal storageDirect memory access

A reconfigurable integrated circuit device which is dynamically constructed to be an arbitrary operation status based on a configuration data, has a plurality of clusters including operation processor elements, a memory processor element, and an inter-processor element switch group for connecting the elements in an arbitrary status; an inter-cluster switch group for constructing data paths between the clusters in an arbitrary status; and an external memory bus. A direct memory access control section, for executing the data transfer between the memory processor element and the external memory by direct memory access responding to an access request from the memory processor elements of the plurality of clusters, is further provided.

Owner:FUJITSU SEMICON LTD

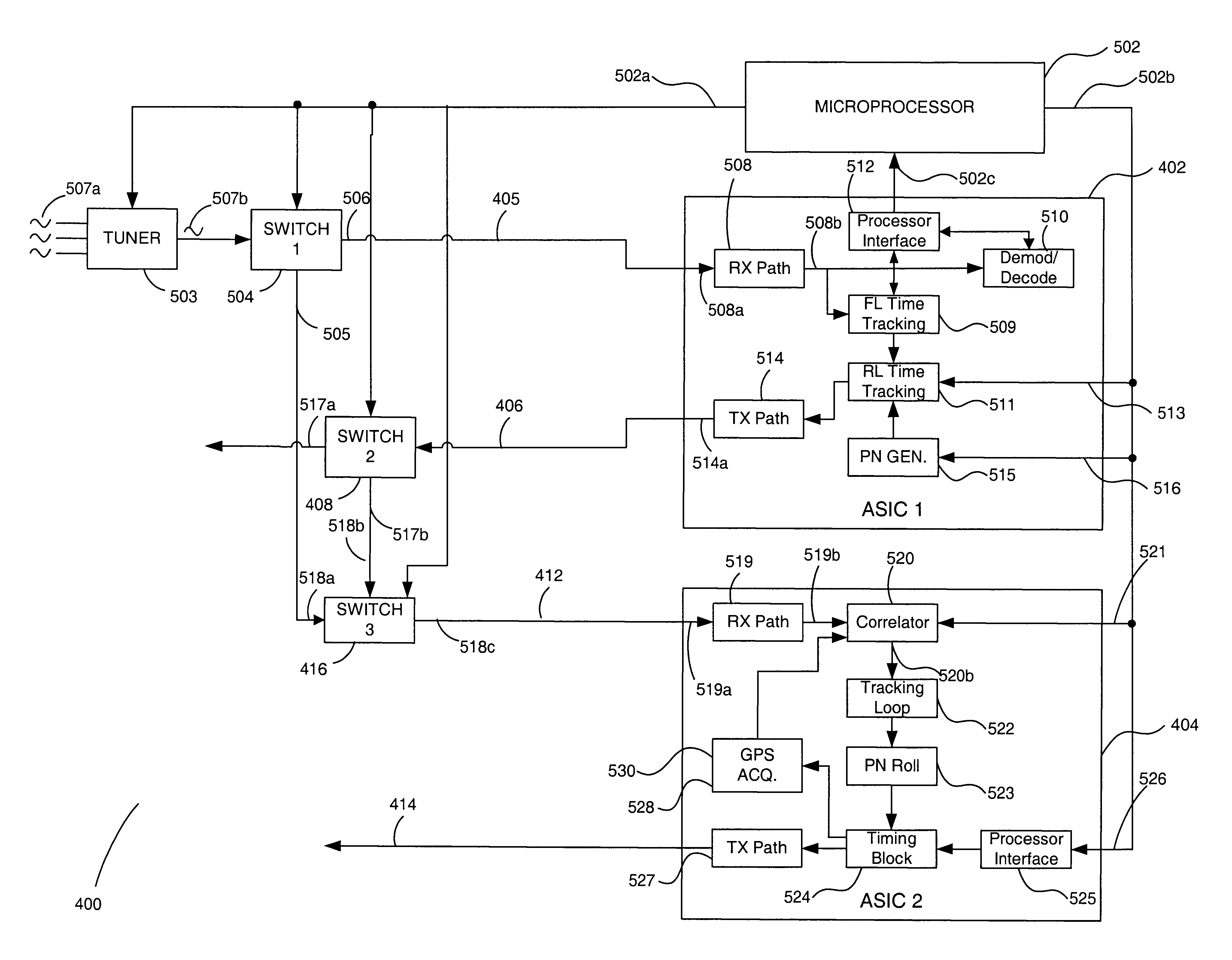

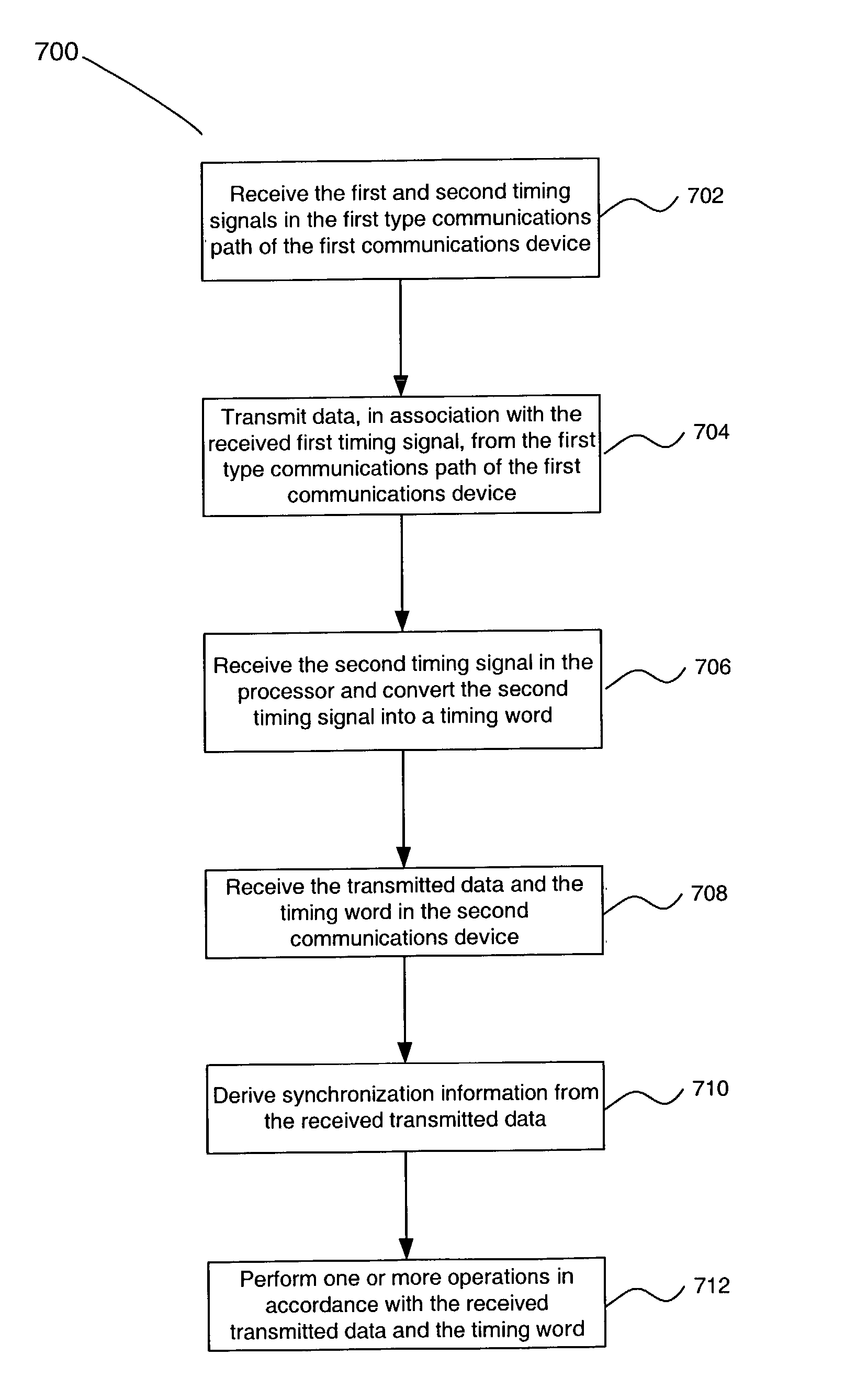

Synchronizing timing between multiple air link standard signals operating within a communications terminal

InactiveUS6836506B2Minimize frequencyAcquisition of of quickly and accuratelySynchronisation arrangementCode division multiplexProcessor elementComputer terminal

Owner:QUALCOMM INC

Synchronized backup of an object manager global database as part of a control blade redundancy service

InactiveUS20070073733A1TransmissionSpecial data processing applicationsProcessor elementOperational system

A system and method of managing a switch includes installing a switch having a plurality of processor elements, installing an operating system on each processor element, creating a system virtual router and configuring the processor elements from the system virtual router.

Owner:CISCO TECH INC

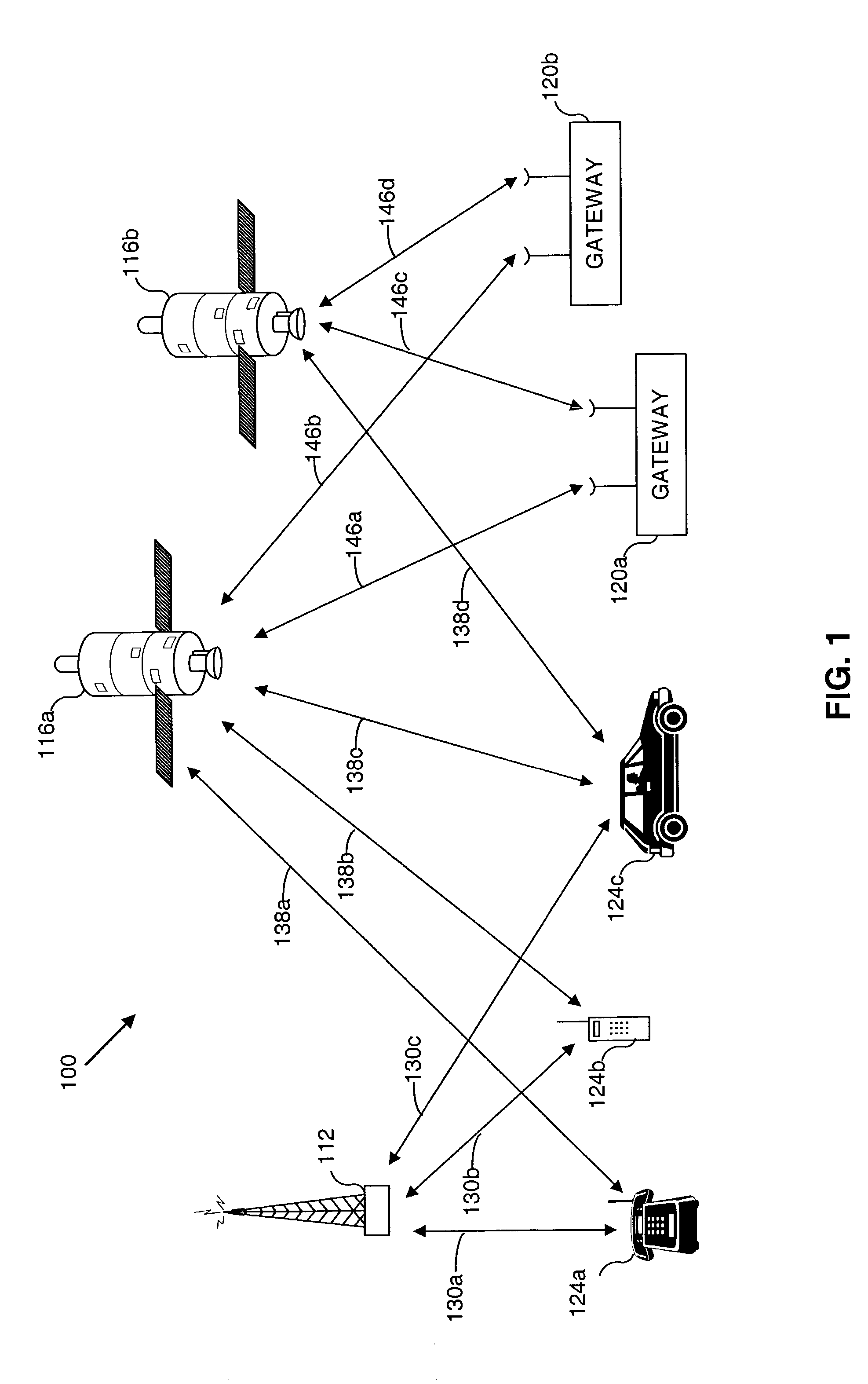

Synchronizing timing between multiple air link standard signals operating within a communications terminal

InactiveUS20040042576A1Minimize frequencyAcquisition of of quickly and accuratelySynchronisation arrangementCode division multiplexProcessor elementComputer terminal

A system and method for synchronizing a number of specialized circuits or application-specific integrated circuits to a common timing standard is provided. The system includes a first communications device including at least first and second type communication paths which is configured to receive first and second timing signals in the first type communications path and to transmit data on the second type communications path. The data is transmitted in association with the received first timing signal. A controller or signal processor element is coupled to the first device and configured to receive the second timing signal and produce a timing word therefrom. A second communications device is coupled to the processor and configured to receive the second timing signal and produce a timing word therefrom. The second communications. device receives the timing word and the transmitted data and derives synchronization information therefrom. The derived synchronization information is related to the first timing signal. The second communications device performs one or more operations in accordance with the received second timing signal and the derived synchronization information.

Owner:QUALCOMM INC

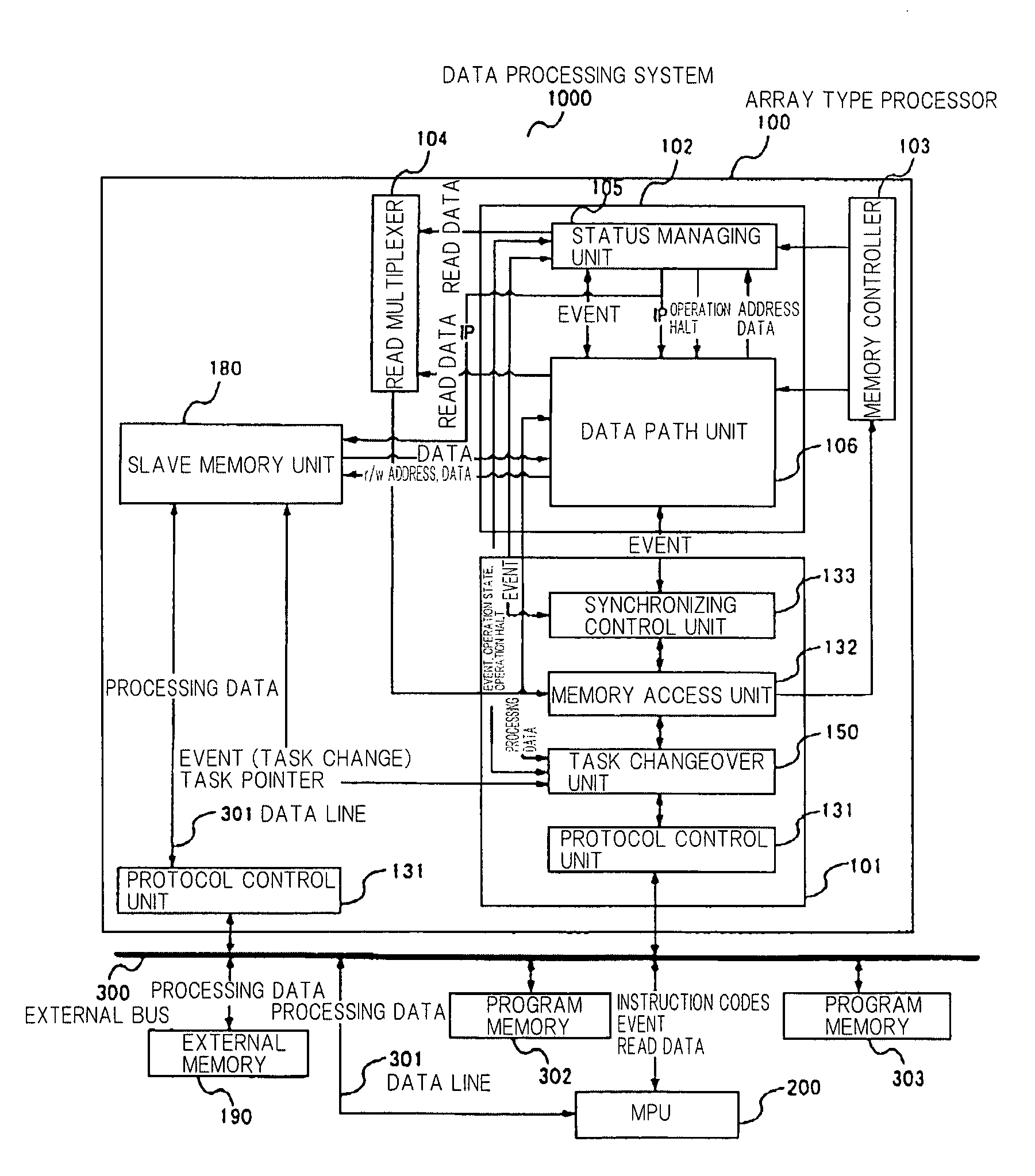

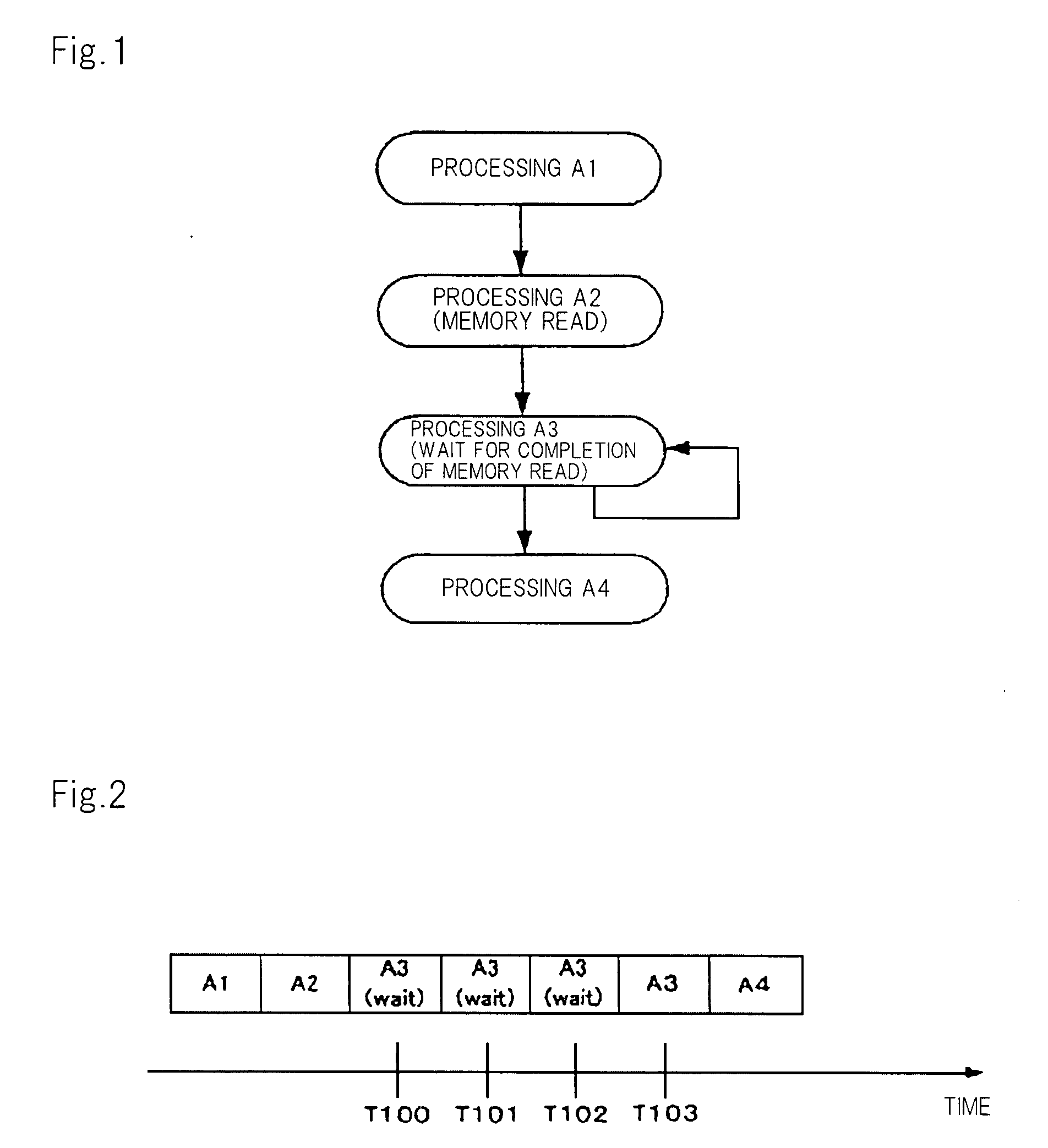

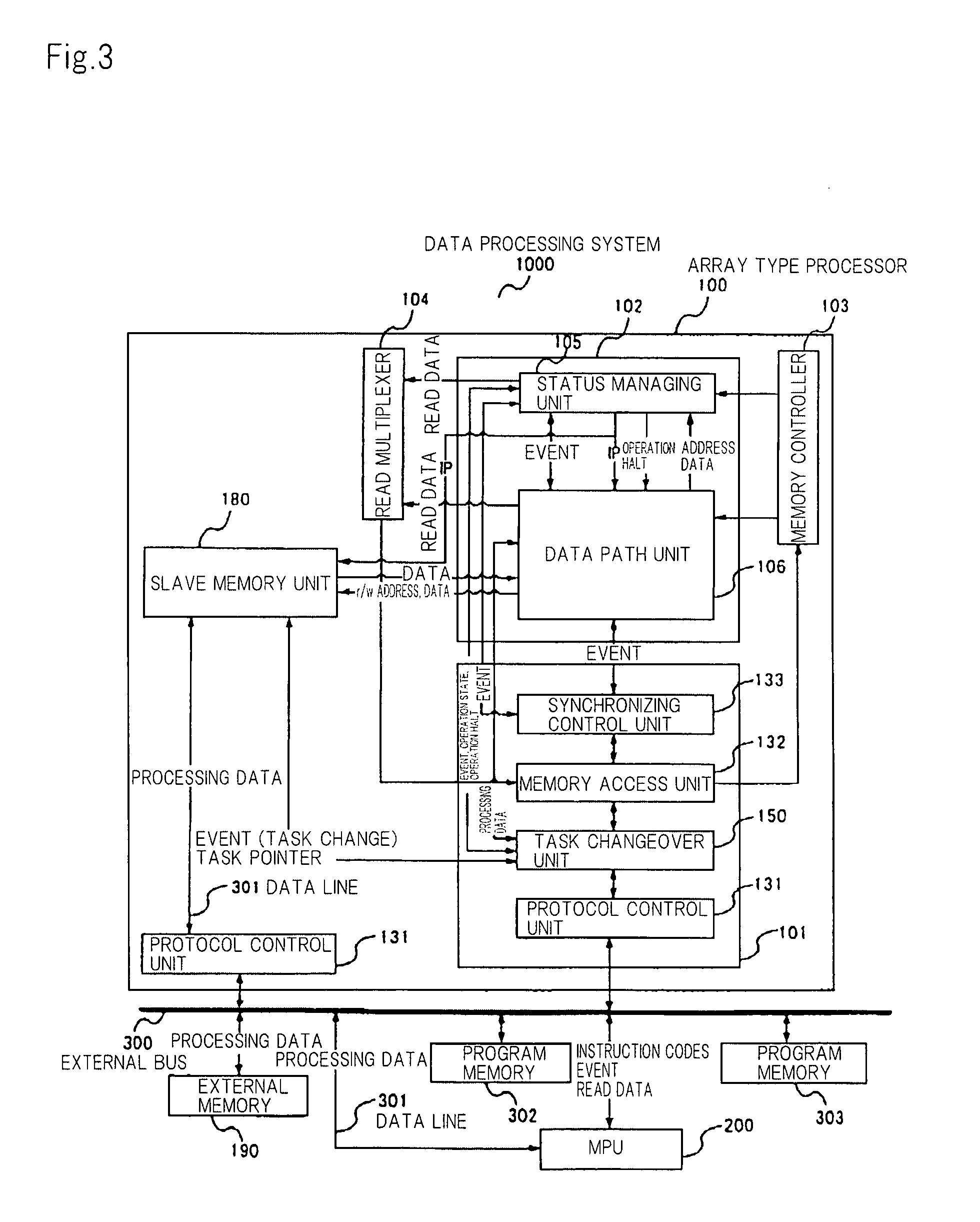

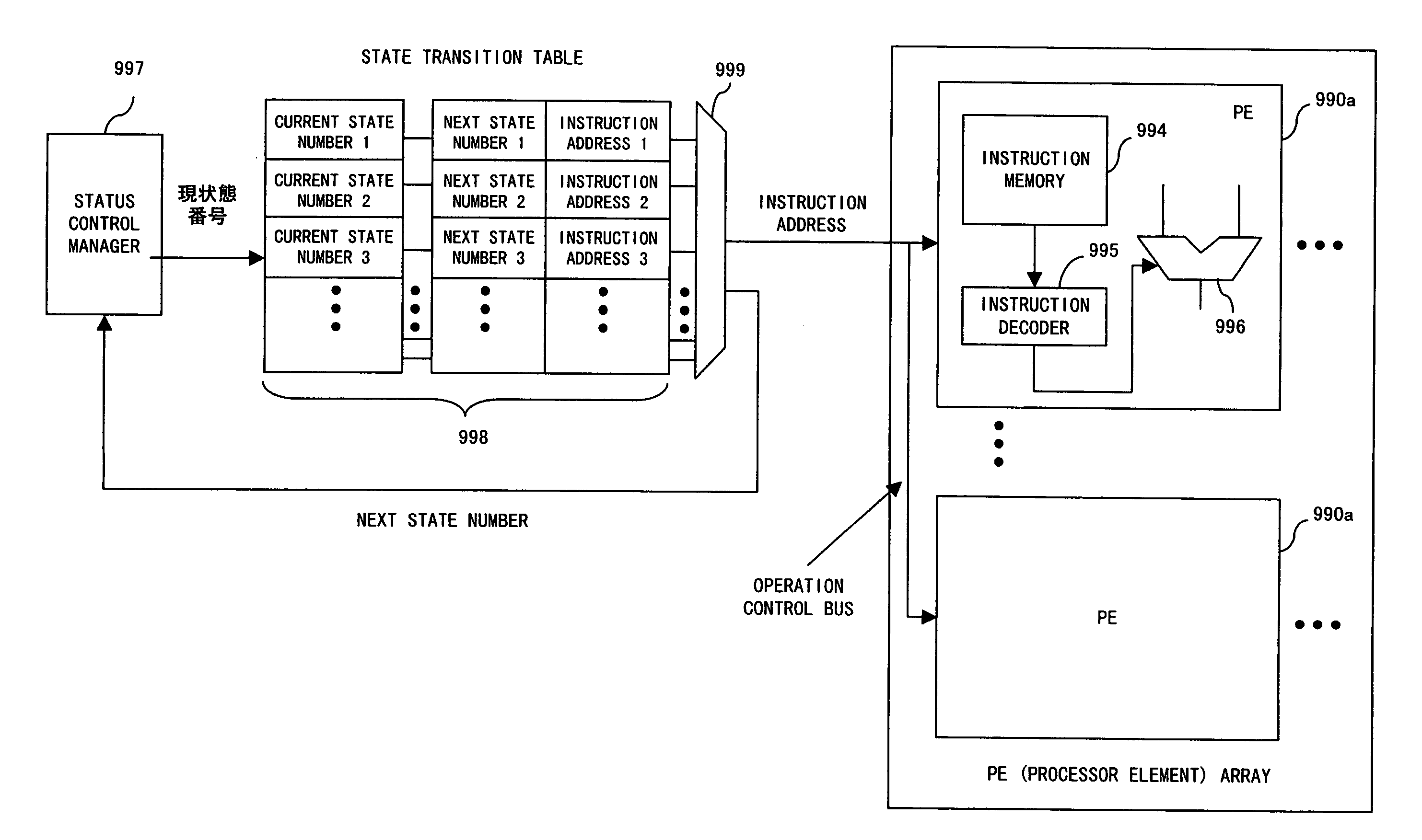

Array type processor and data processing system

InactiveUS20090300324A1Low availability rateReduce impactGeneral purpose stored program computerMemory systemsData processing systemExternal storage

In data path means, processor elements individually execute data processing in accordance with command codes described in a computer program, and switching elements individually control a connection relationship to switch among a plurality of processor elements in accordance with the command codes. When an access to an external memory is made from the data path means, slave memory means generates event data indicative of a task change while temporarily holding access information for executing the access with a delay, and executes the access in place of the data path means. Task changing means changes a task to be executed by the data path means when event data indicative of a task change is generated by the slave memory means.

Owner:NEC CORP

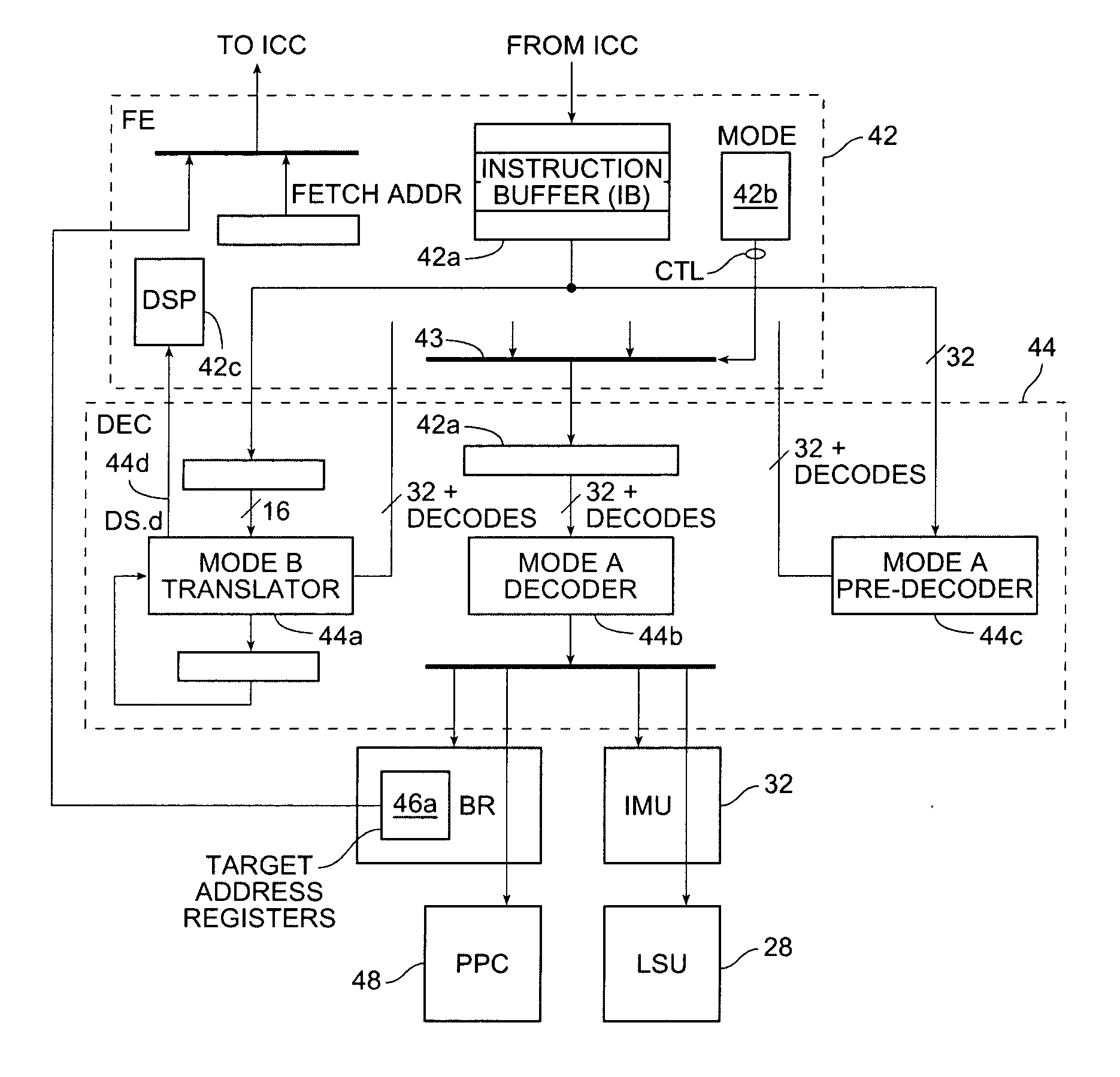

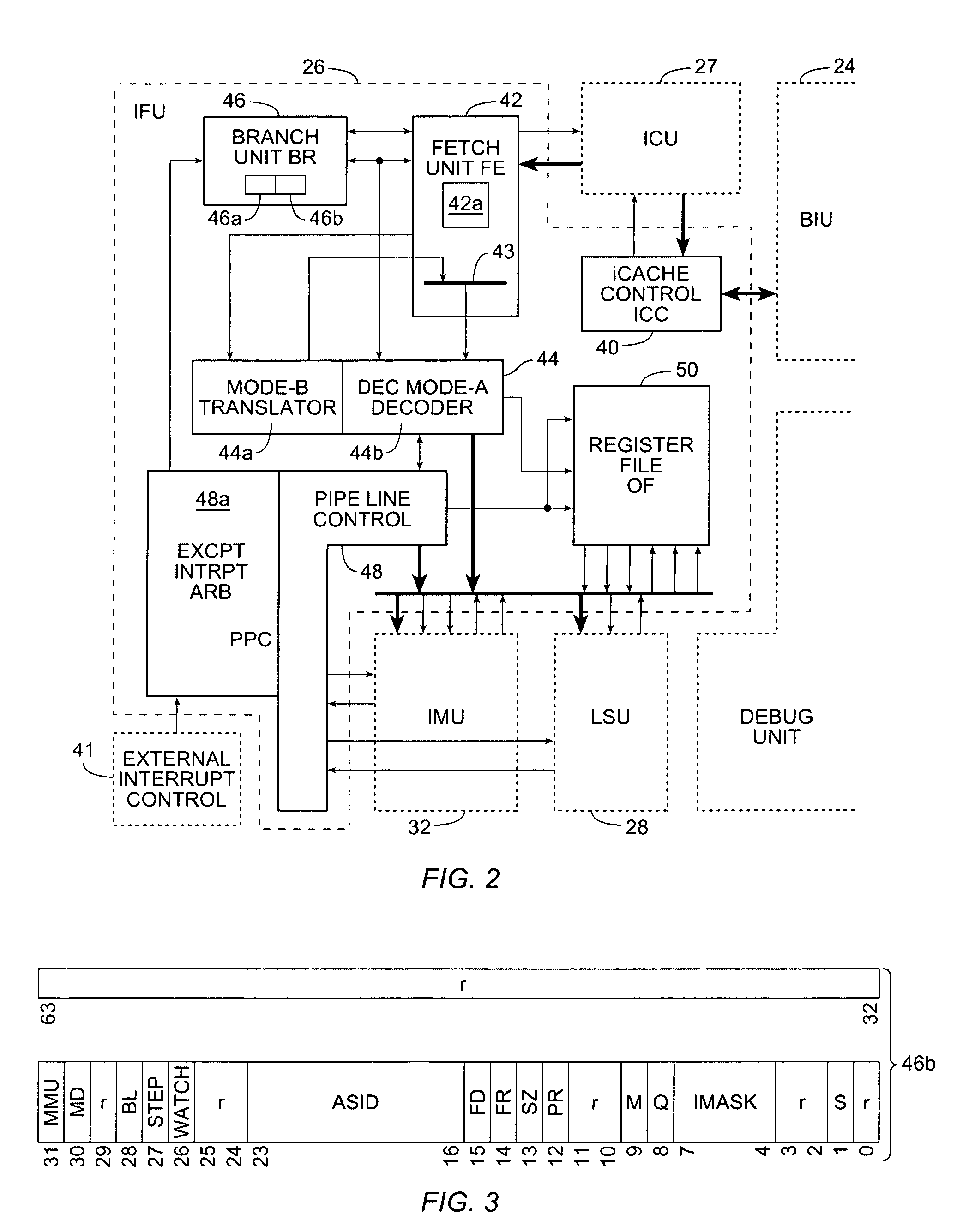

Processor architecture for executing two different fixed-length instruction sets

InactiveUS20050262329A1High simulationSave memory spaceDigital computer detailsNext instruction address formationProcessor elementLeast significant bit

A processor element, structured to execute a 32-bit fixed length instruction set architecture, is backward compatible with a 16-bit fixed length instruction set architecture by translating each of the 16-bit instructions into a sequence of one or more 32-bit instructions. Switching between 16-bit instruction execution and 32-bit instruction execution is accomplished by branch instructions that employ a least significant bit position of the address of the target of the branch to identify whether the target instruction is a 16-bit instruction or a 32-bit instruction.

Owner:HITACHI LTD

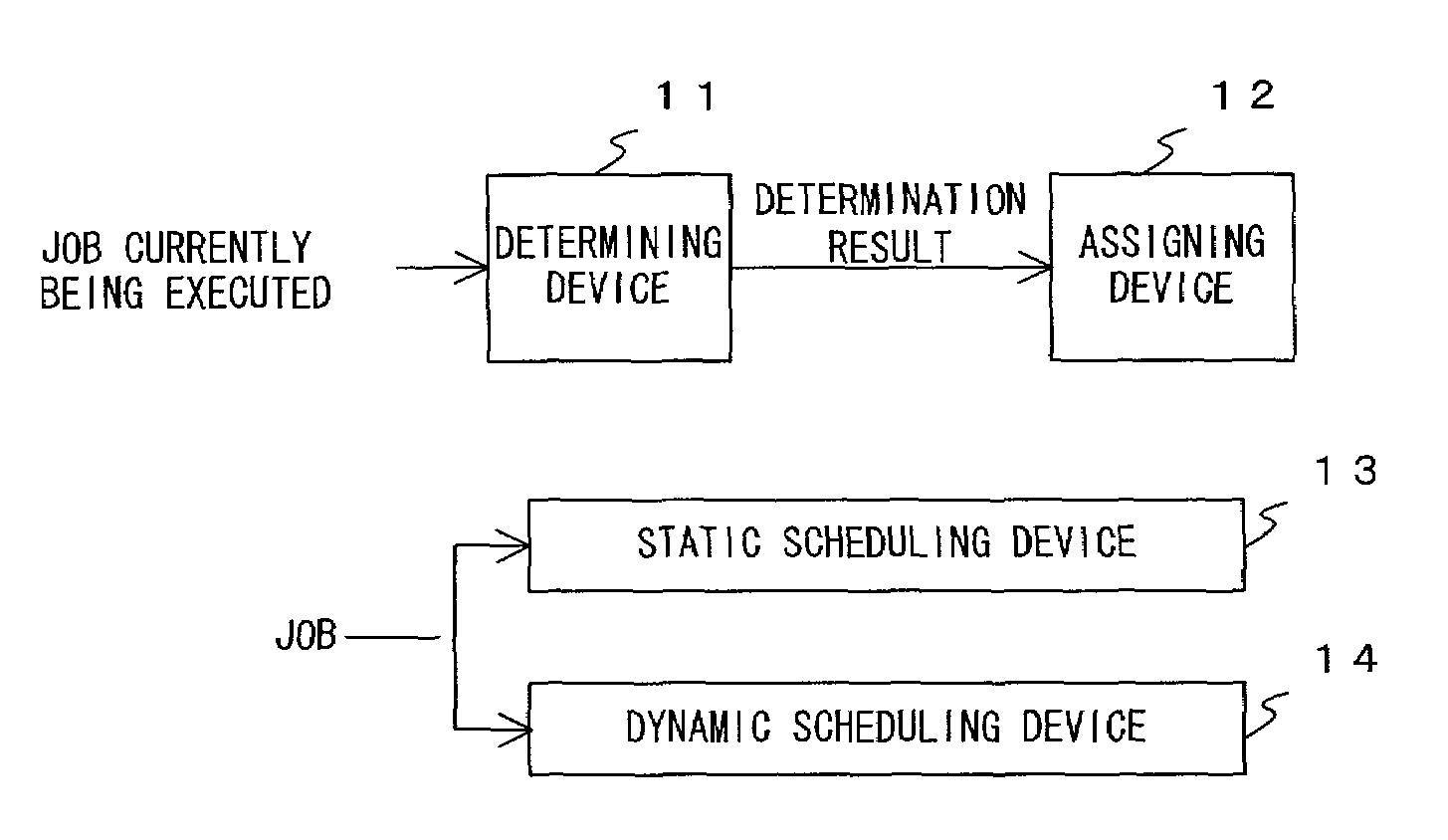

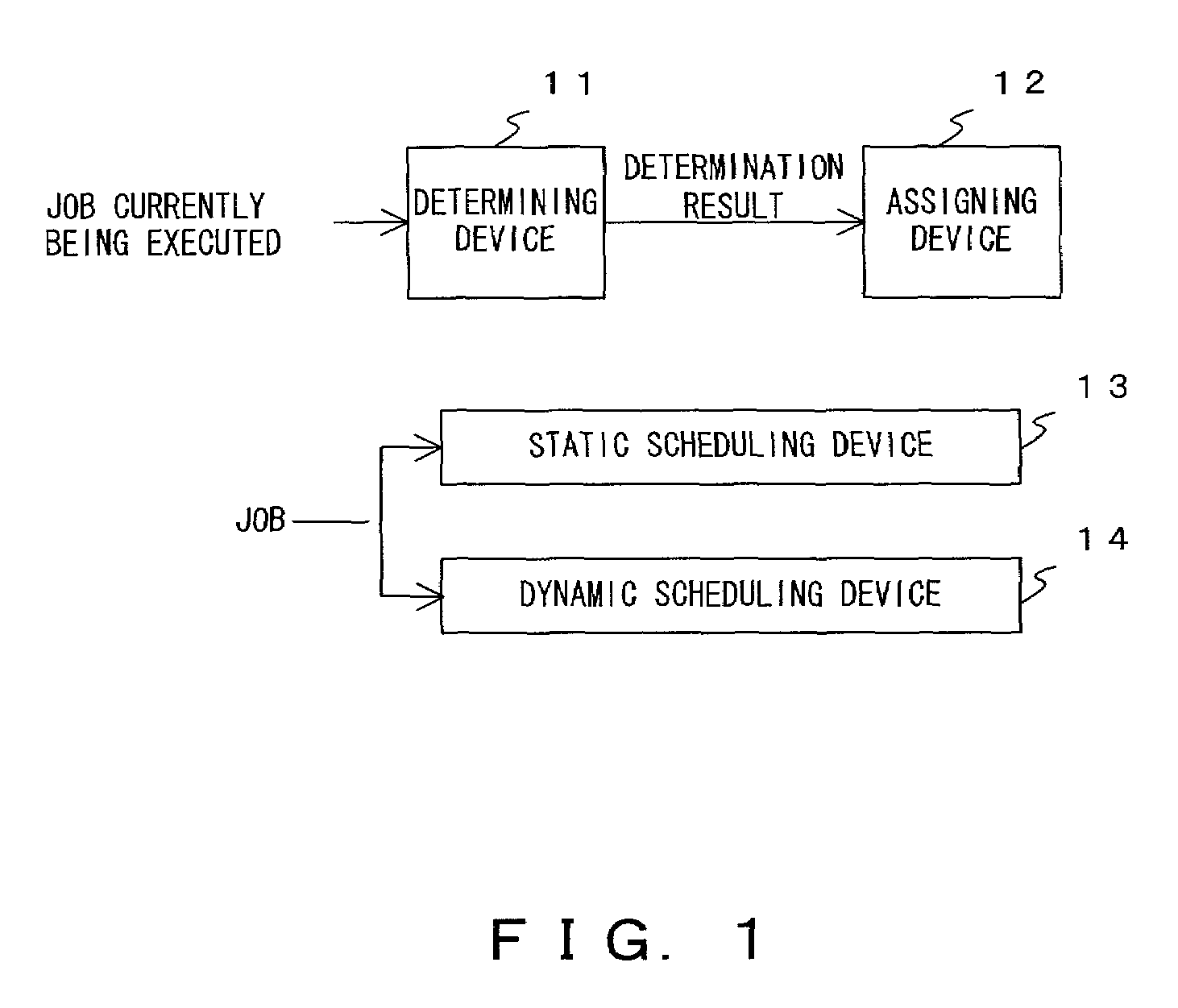

Scheduling apparatus performing job scheduling of a parallel computer system

InactiveUS7024671B2Reduce errorsImprove efficiencyResource allocationDigital computer detailsProcessor elementJob shop scheduling

A job entered into a processor element (PE) of a parallel computer system is moved to a different PE, or written to an external auxiliary storage device by being frozen, with dynamic scheduling. A scheduler estimates the remaining time of execution of each job, compares with a migration / freezing cost, and determines a job to be moved / frozen.

Owner:FUJITSU LTD

Method and apparatus for fault tolerant execution of computer programs

InactiveUS6434712B1Maximum countEconomically manufacturedRedundant hardware error correctionArithmetic logic unitProcessor element

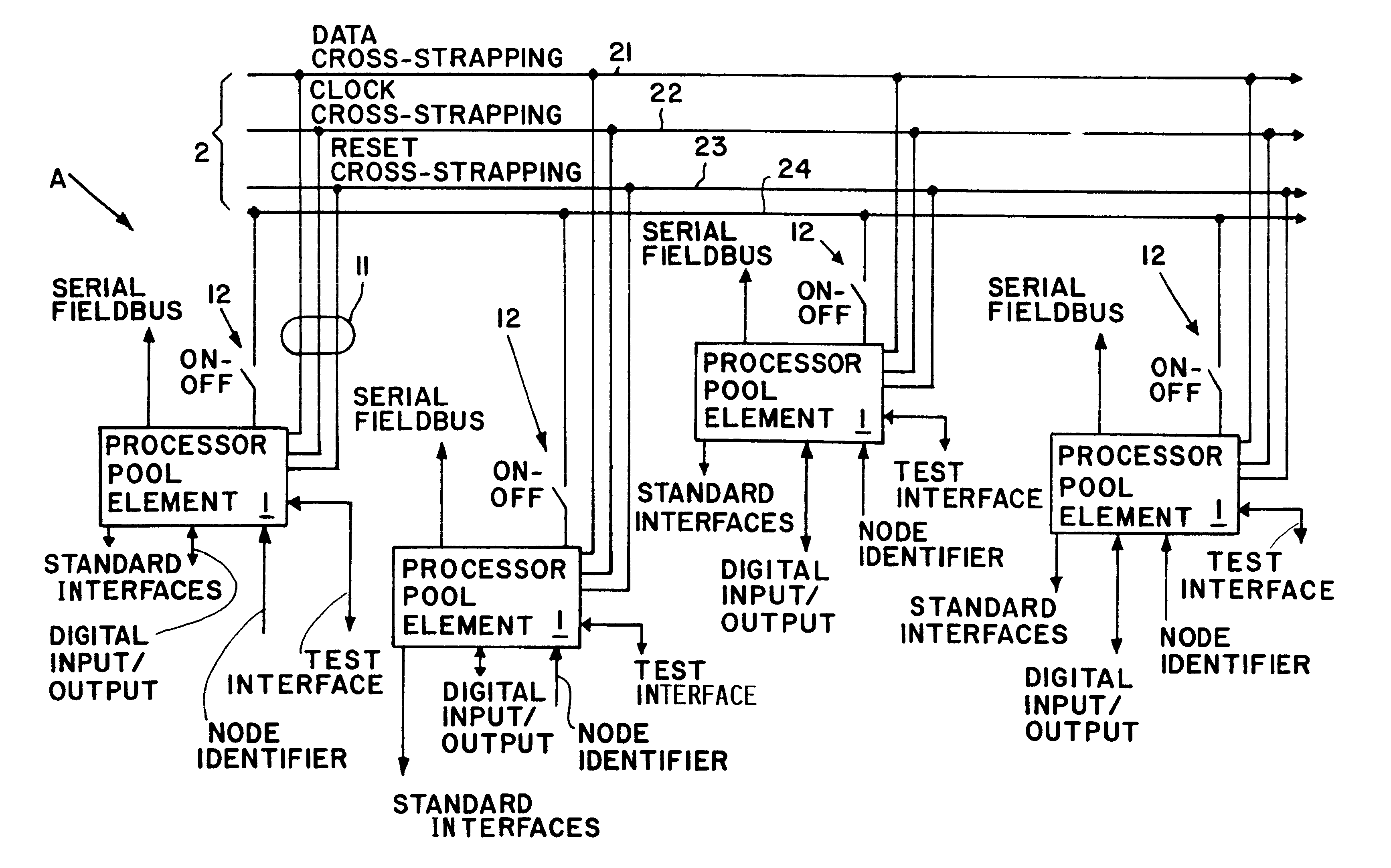

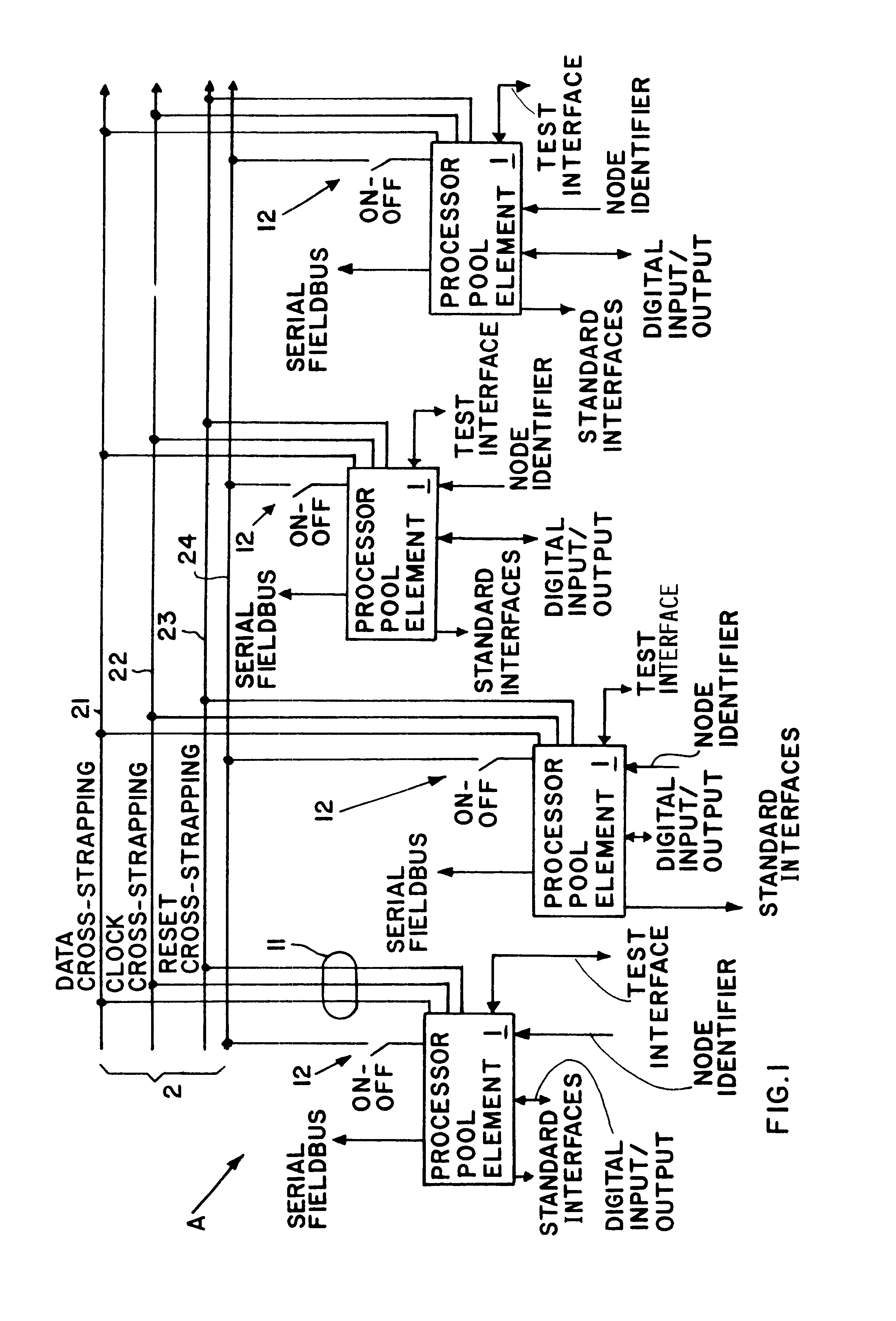

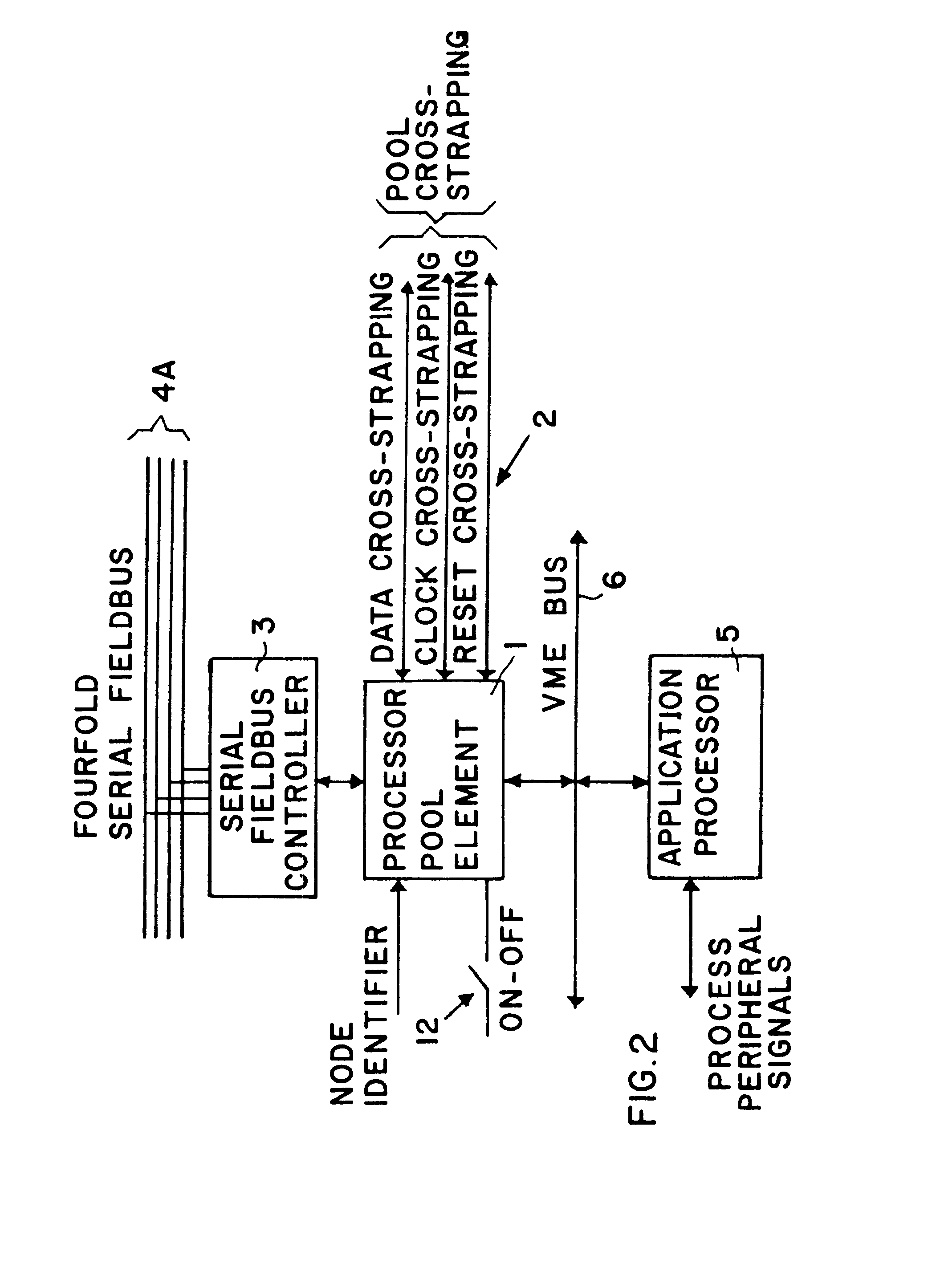

A circuit arrangement for the fault tolerant execution of digital computer programs includes a plurality of arithmetic logic units embodied as processor pool elements connected together so that they can each execute the program in parallel. The processor elements are connected to each other through respective data, clock and reset cross-strapping interconnect lines, and are each connected to one or more serial field buses. Each processor element includes at least one microprocessor controller for controlling the functions of the processor element in such a manner that any selected number of the processor elements can be automatically actuated at any time to simultaneously execute the program in parallel and thereby achieve a prescribed degree of redundancy in the circuit arrangement. The data cross-strapping line transmits data among the several processor elements, the clock signal cross-strapping line achieves a compelled synchronization of all of the processor elements, and the reset cross-strapping line carries out the deactivation of any processor element that is recognized as carrying out a faulty execution of the program or that is not necessary for achieving the required degree of redundancy. A deactivated processor element may later be reactivated to again participate in the parallel execution of the program.

Owner:DAMELERKLESLER AVIATION

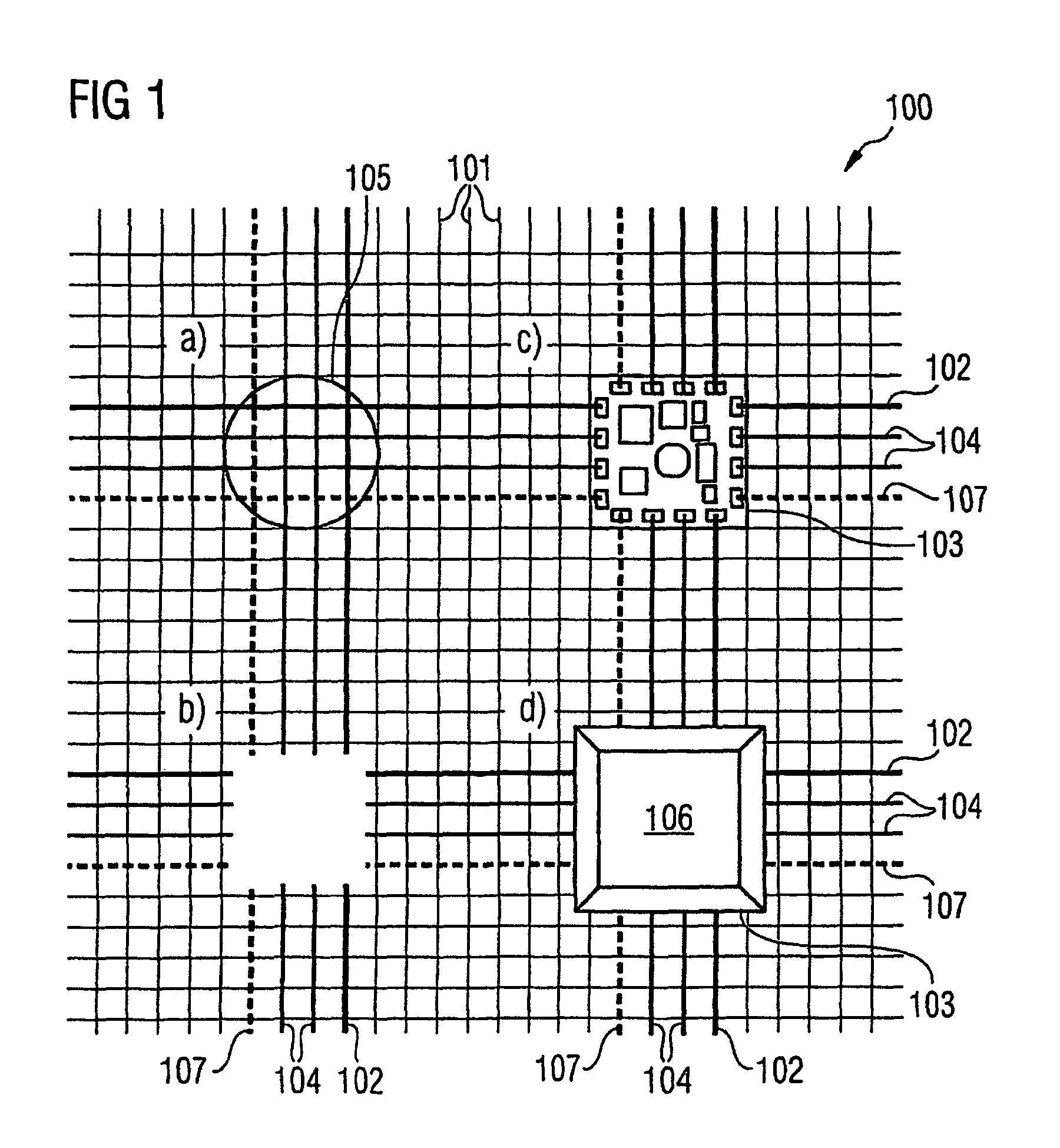

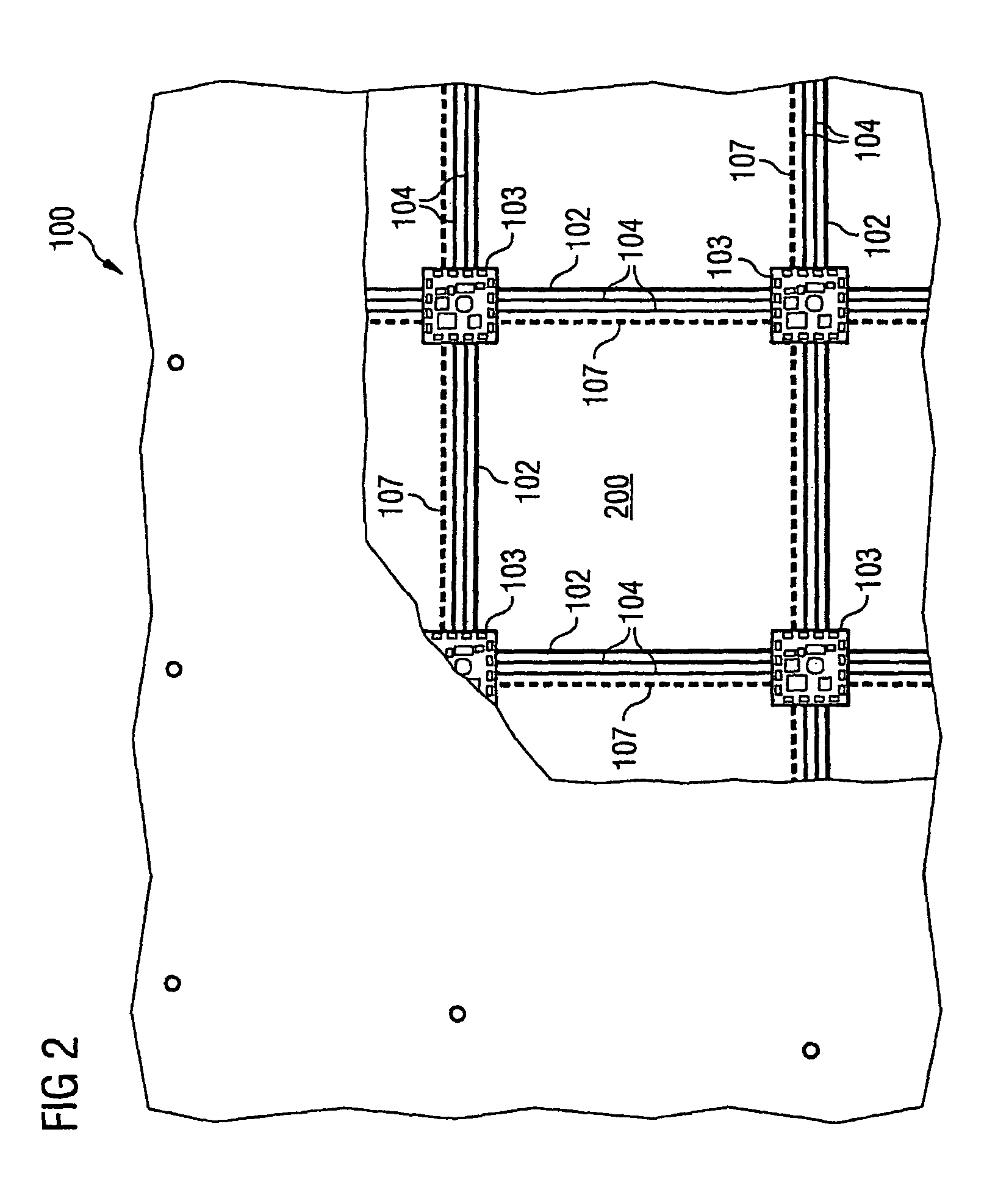

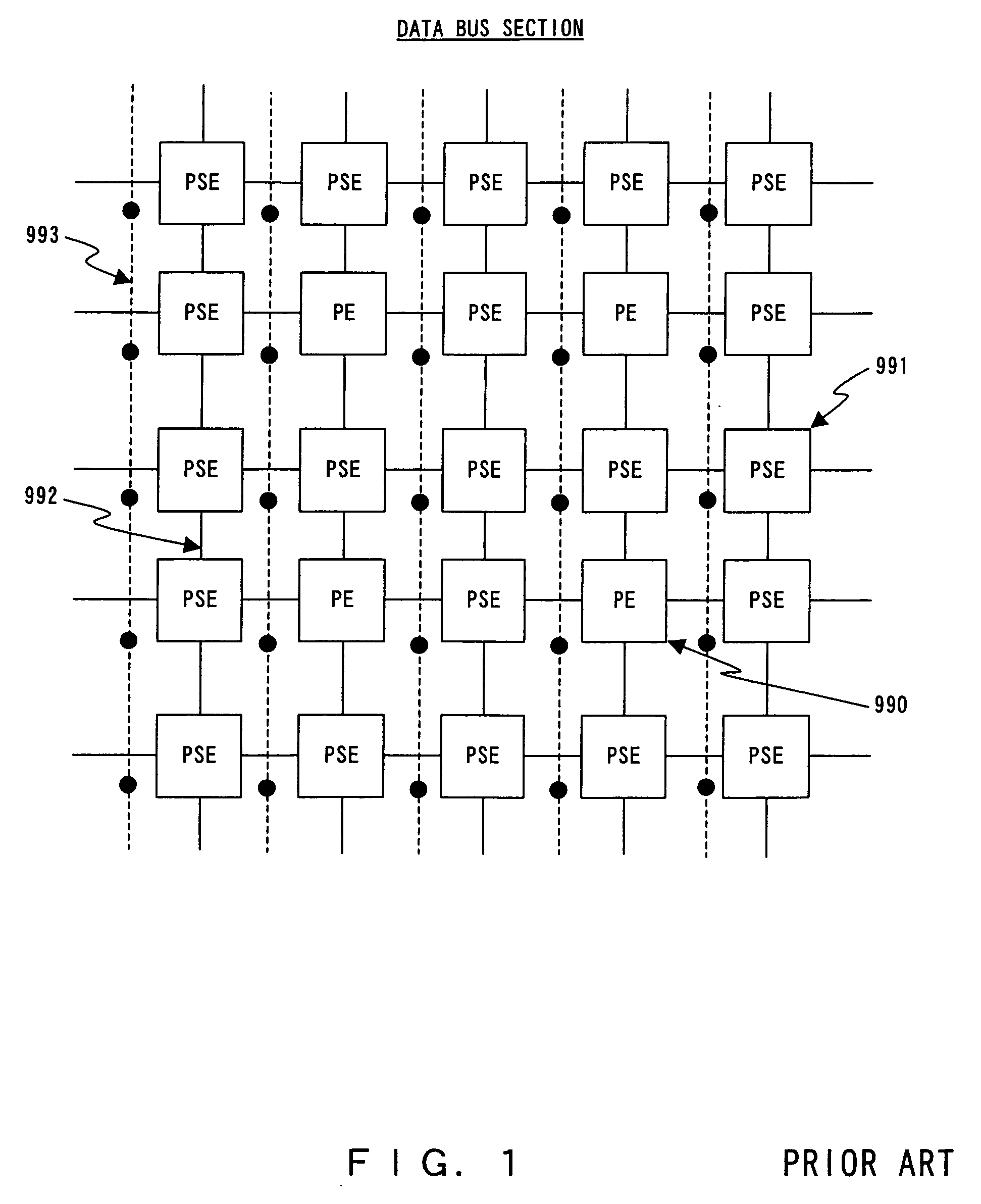

Processor array having a multiplicity of processor elements and method of transmitting electricity between processor elements

InactiveUS7941676B2Avoid failureCovering/liningsOrnamental textile articlesElectricityProcessor element

Disclosed is a processor element including a plurality of power supply interfaces, a plurality of power supply switches, and a fault-testing unit for testing whether a short-circuit to a connected adjacent processor element has occurred at a power supply interface. The respective power supply switch is closed in case no short-circuit has occurred such that electricity can be fed to the respective power supply interface.

Owner:INFINEON TECH AG

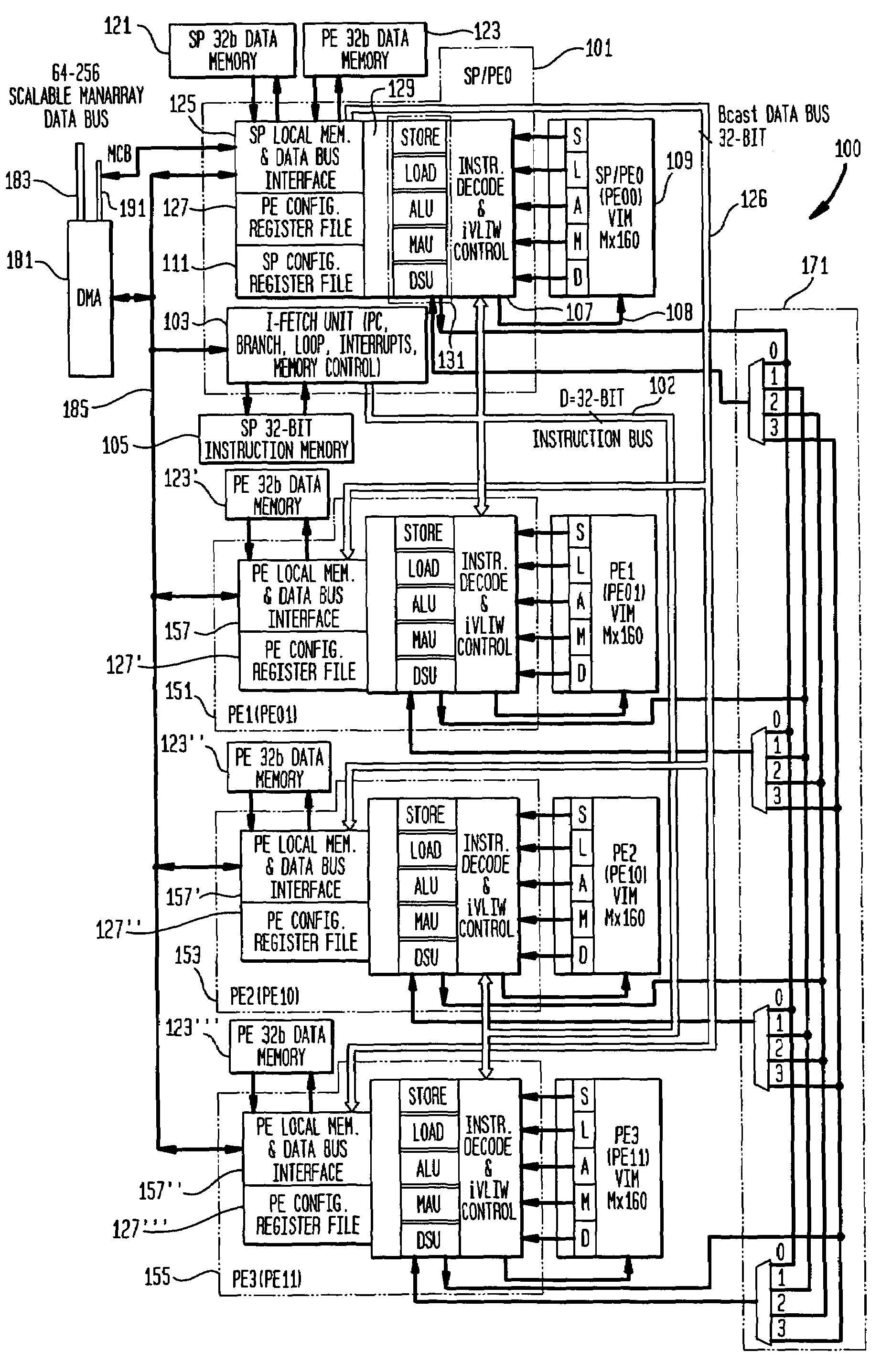

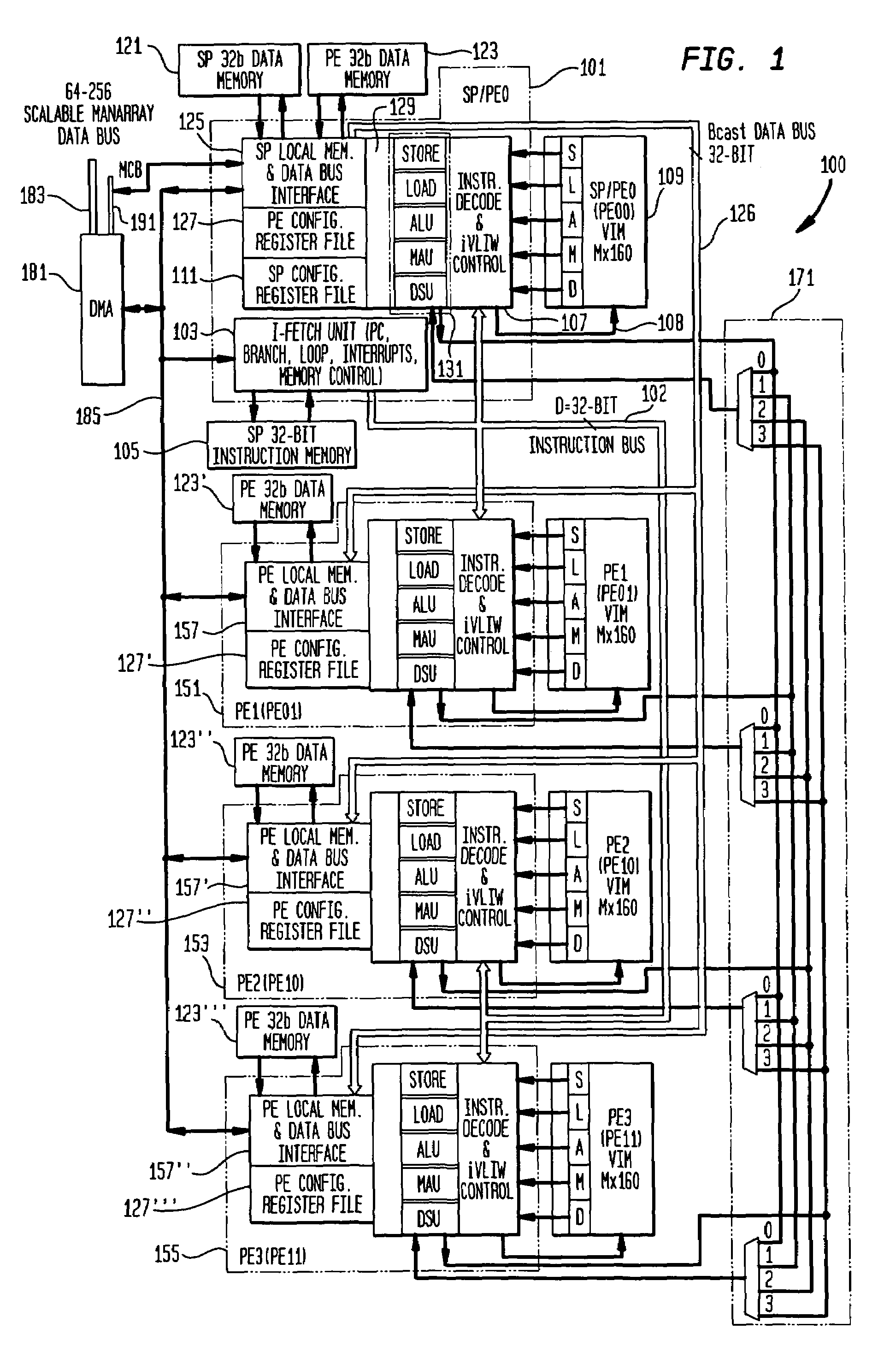

Methods and apparatus for power control in a scalable array of processor elements

InactiveUS7263624B2Reduce the required powerEnergy efficient ICTVolume/mass flow measurementSequence processingProcessor element

Low power architecture features and techniques are provided in a scalable array indirect VLIW processor. These features and techniques include power control of a reconfigurable register file, conditional power control of multi-cycle operations and indirect VLIW utilization, and power control of VLIW-based vector processing using the ManArray register file indexing mechanism. These techniques are applicable to all processing elements (PEs) and the array controller sequence processor (SP) to provide substantial power savings.

Owner:ALTERA CORP

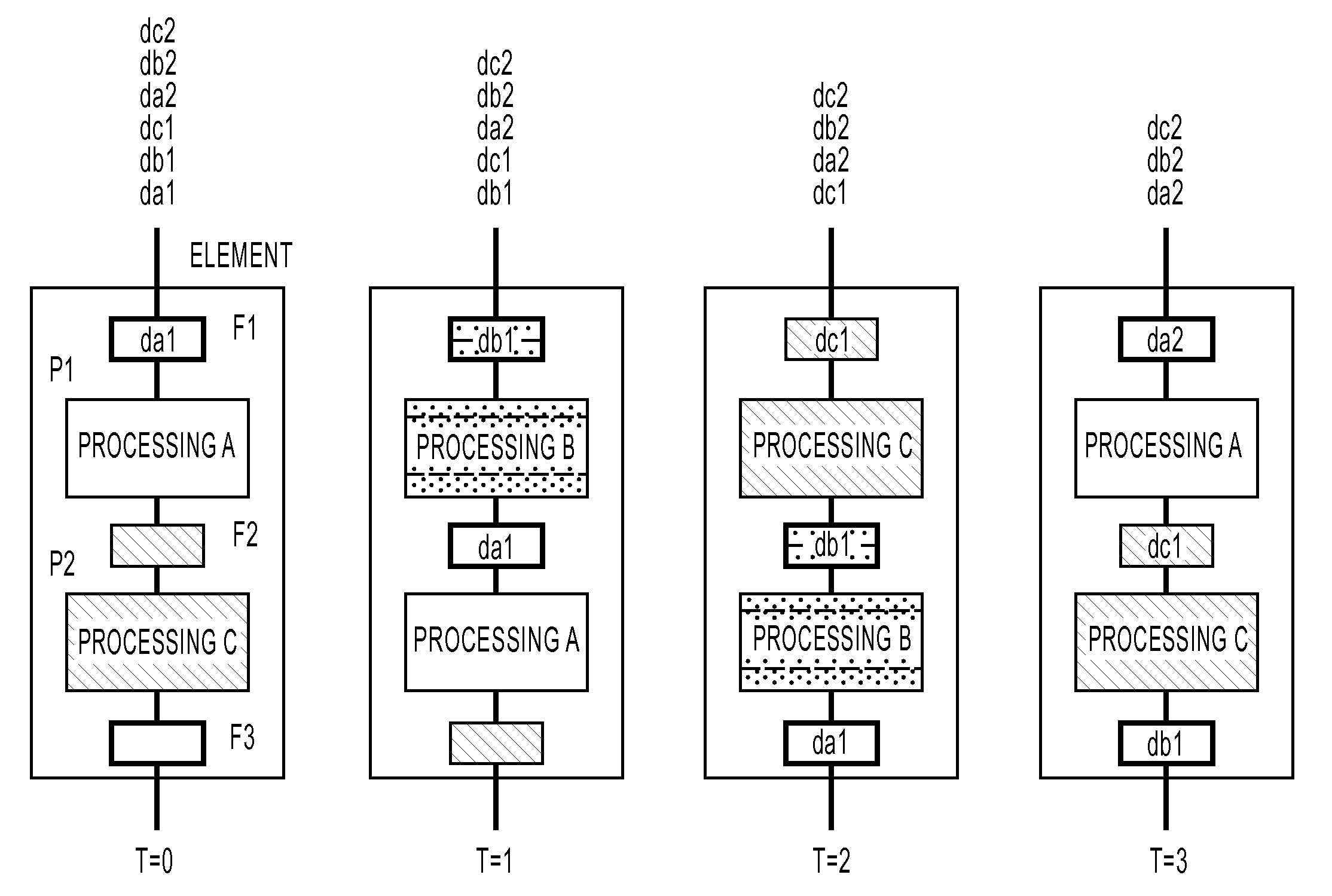

Reconfigurable circuit having a pipeline structure for carrying out time division multiple processing

ActiveUS8055880B2Loss of timeReduce data latencySingle instruction multiple data multiprocessorsSpecific program execution arrangementsProcessor elementTime-division multiplexing

The reconfigurable circuit of the present invention in which time division multiple processing is possible has a pipeline structure with the number of stages of an integral multiple of a given number, and comprises a plurality of processor elements having a processing unit whose configuration is variable according to first configuration data to be supplied, a network in which all inputs and outputs of a plurality of said processor elements are connected and which transfers data by one clock between the input and output according to second configuration data to be supplied, and a switching unit which cyclically switches by one clock and supplies the first and second configuration data prepared for the given number of tasks to each of the processing units.

Owner:FUJITSU LTD

Multithreaded computer system and multithread execution control method

ActiveUS8001549B2Enhancing substantial availabilityReduce switching overheadEnergy efficient ICTDigital computer detailsProcessor elementProcessor register

A multithreaded computer system of the present invention includes a plurality of processor elements (PEs) and a parallel processor controller which switches threads in each PE. The parallel processor controller includes a plurality of execution order registers which hold, for each processor element, an execution order of threads to be executed; a plurality of counters which count an execution time for a thread that is being executed by each processor element and generate a timeout signal when the counted time reaches a limit assigned to the thread; and a thread execution scheduler which switches the thread that is being executed to the thread to be executed by each processor element based on an execution order held in the execution order register and the timeout signal.

Owner:BEIJING ESWIN COMPUTING TECH CO LTD

Reconfigurable operation apparatus

InactiveUS20060010306A1Improve processing effectivenessQuickly reconfiguredSingle instruction multiple data multiprocessorsSpecific program execution arrangementsExternal storageProcessor element

A reconfigurable operation apparatus consists of a plurality of operation units capable of reconfiguring themselves by using a piece of given first configuration data and of operating simultaneously with one another; RAMs; diverse processor elements required for constituting an operation apparatus; an inter-resource network interconnecting the operation units, the RAMs and the diverse processor elements, performing data transfers between resources connected thereto in a uniform transfer time independent of positions and kinds of the resources, and being reconfigurable by using a given second configuration data; and a configuration memory storing the first and the second configuration data. Configuration data is loaded from an external storage apparatus onto the configuration memory, and the first and the second configuration data are supplied to the reconfigurable processor resources in appropriate sequence and timing based on data available from a plurality of operation units.

Owner:FUJITSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com