Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

709 results about "PCI Express" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

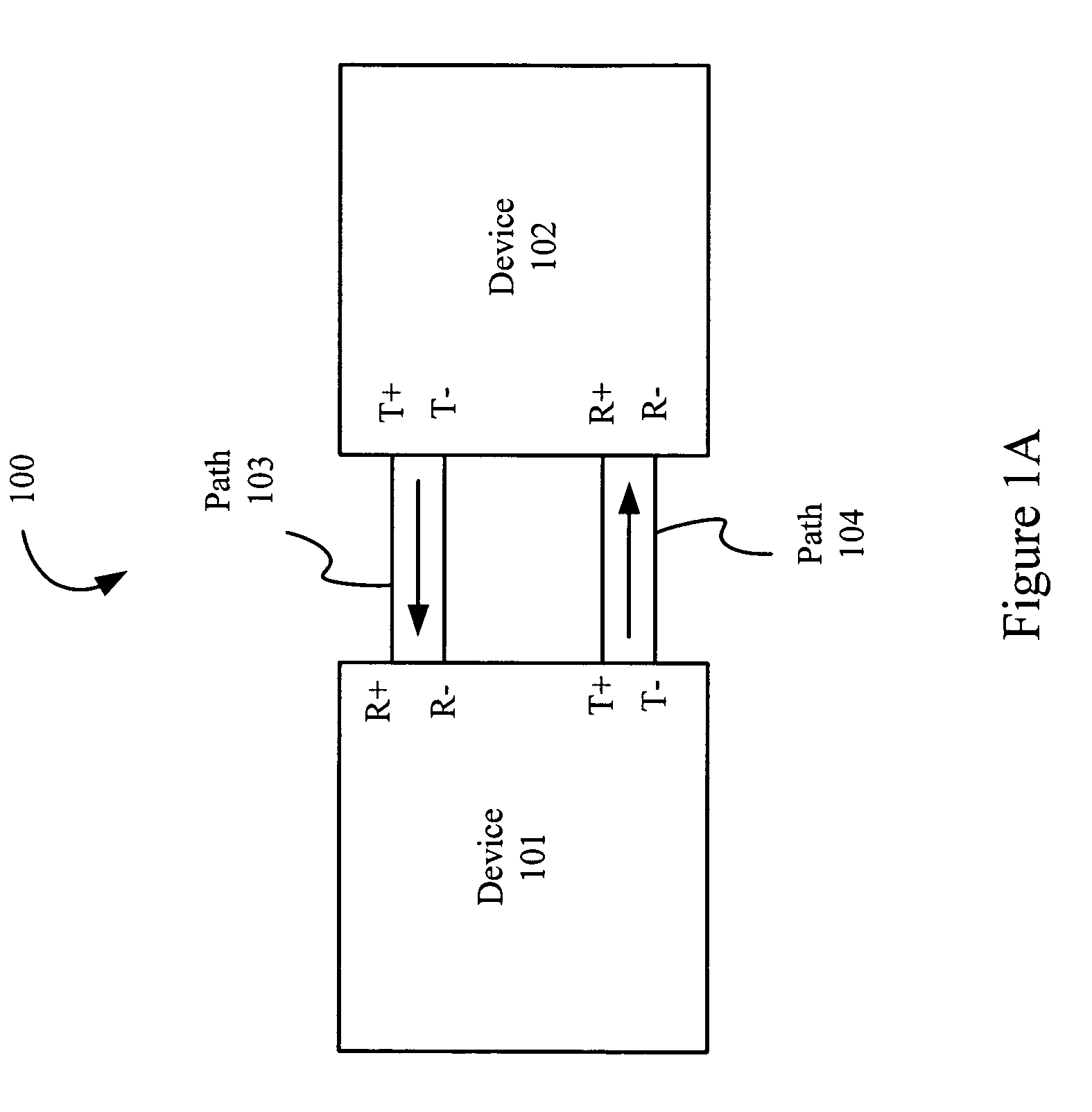

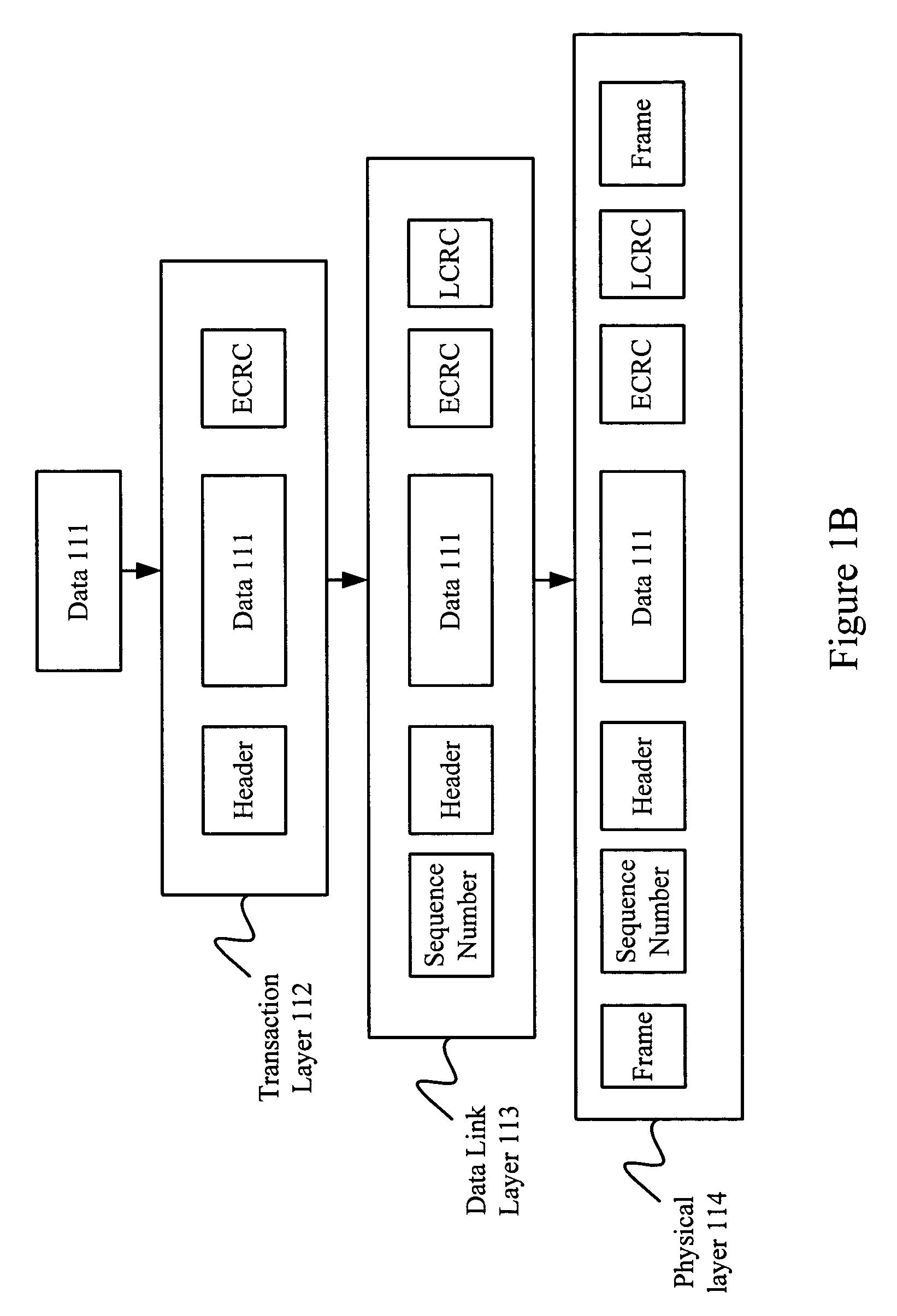

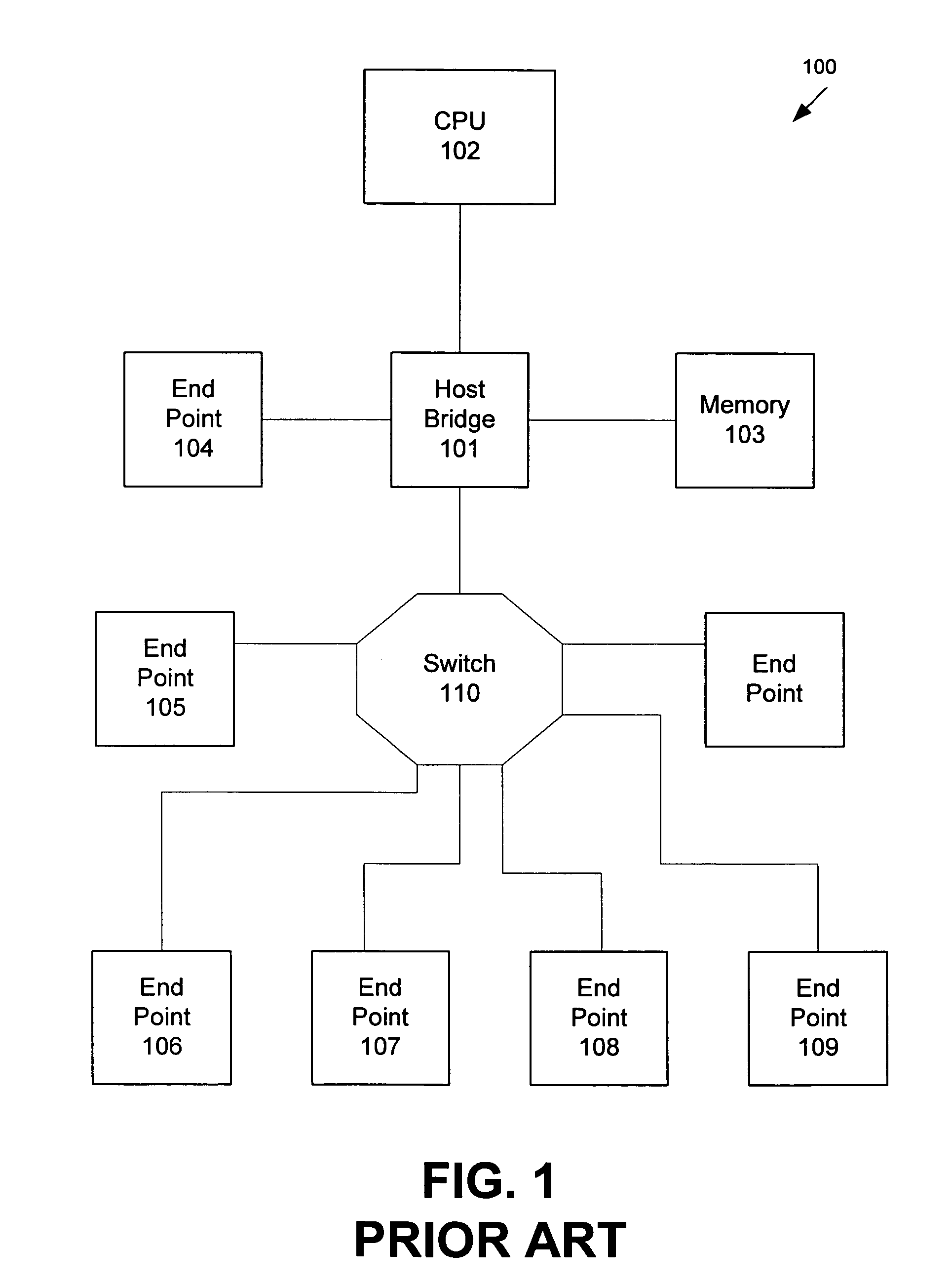

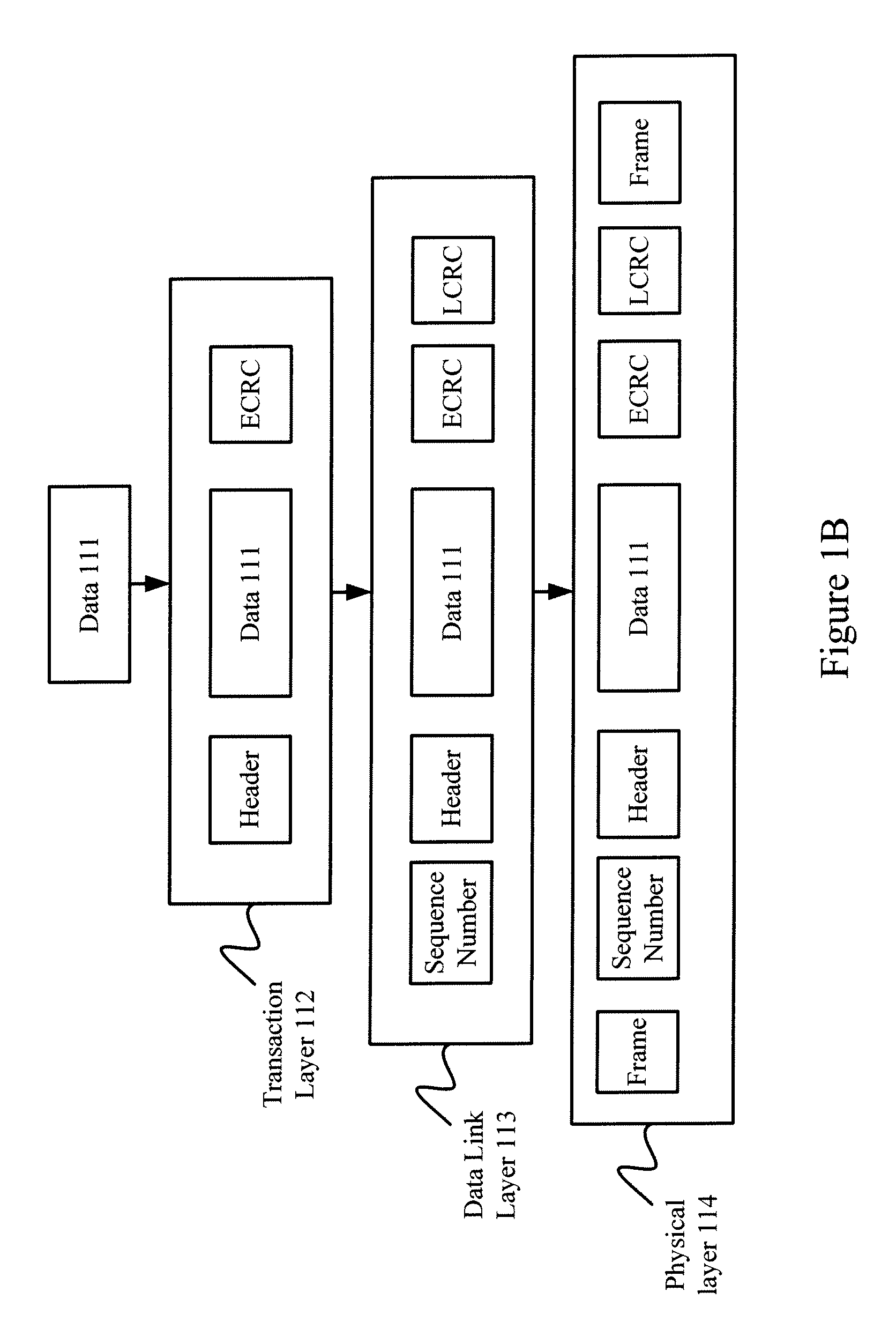

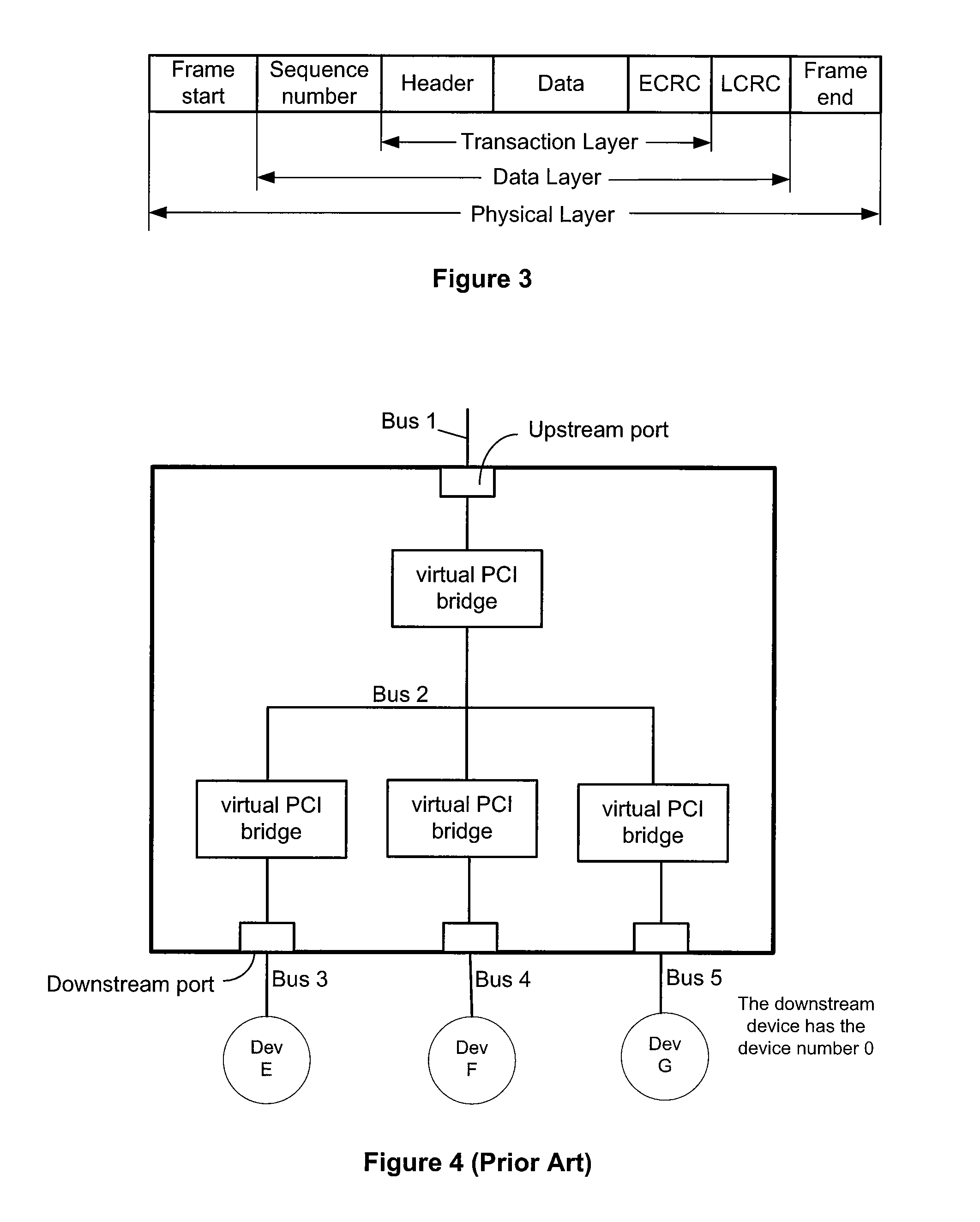

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard drives, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization.

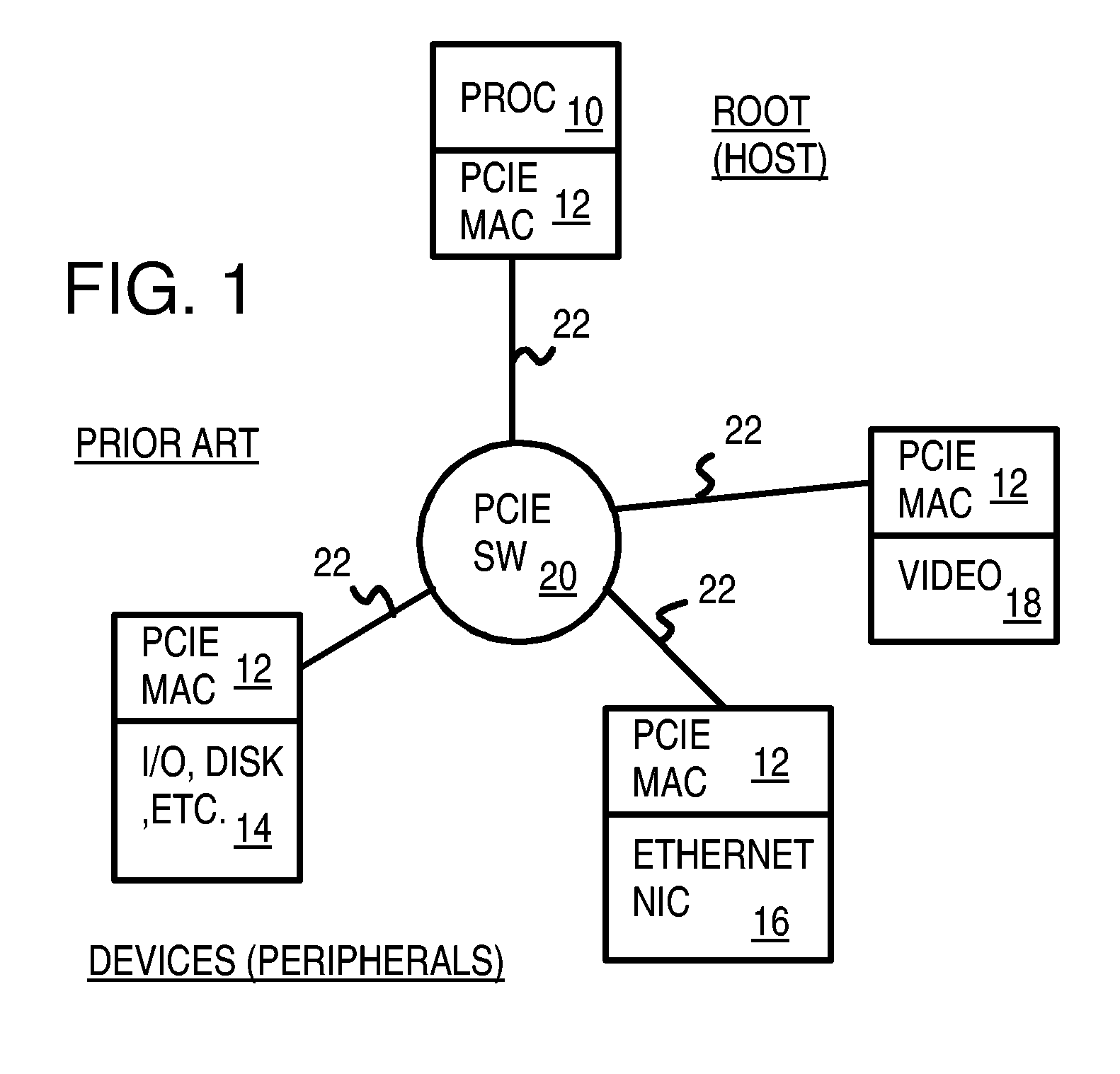

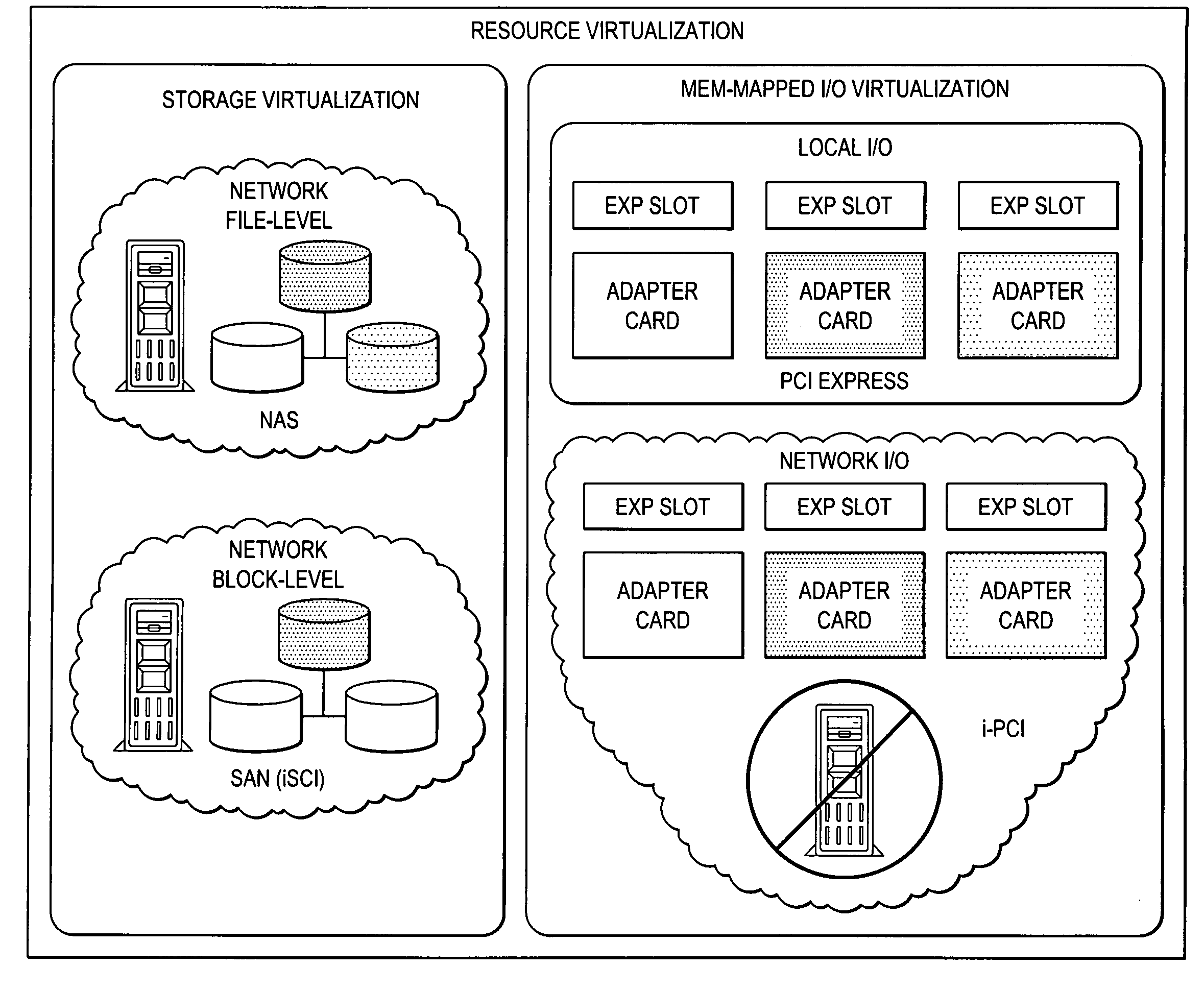

Resource virtualization switch

ActiveUS7502884B1Error detection/correctionData switching by path configurationResource virtualizationPCI Express

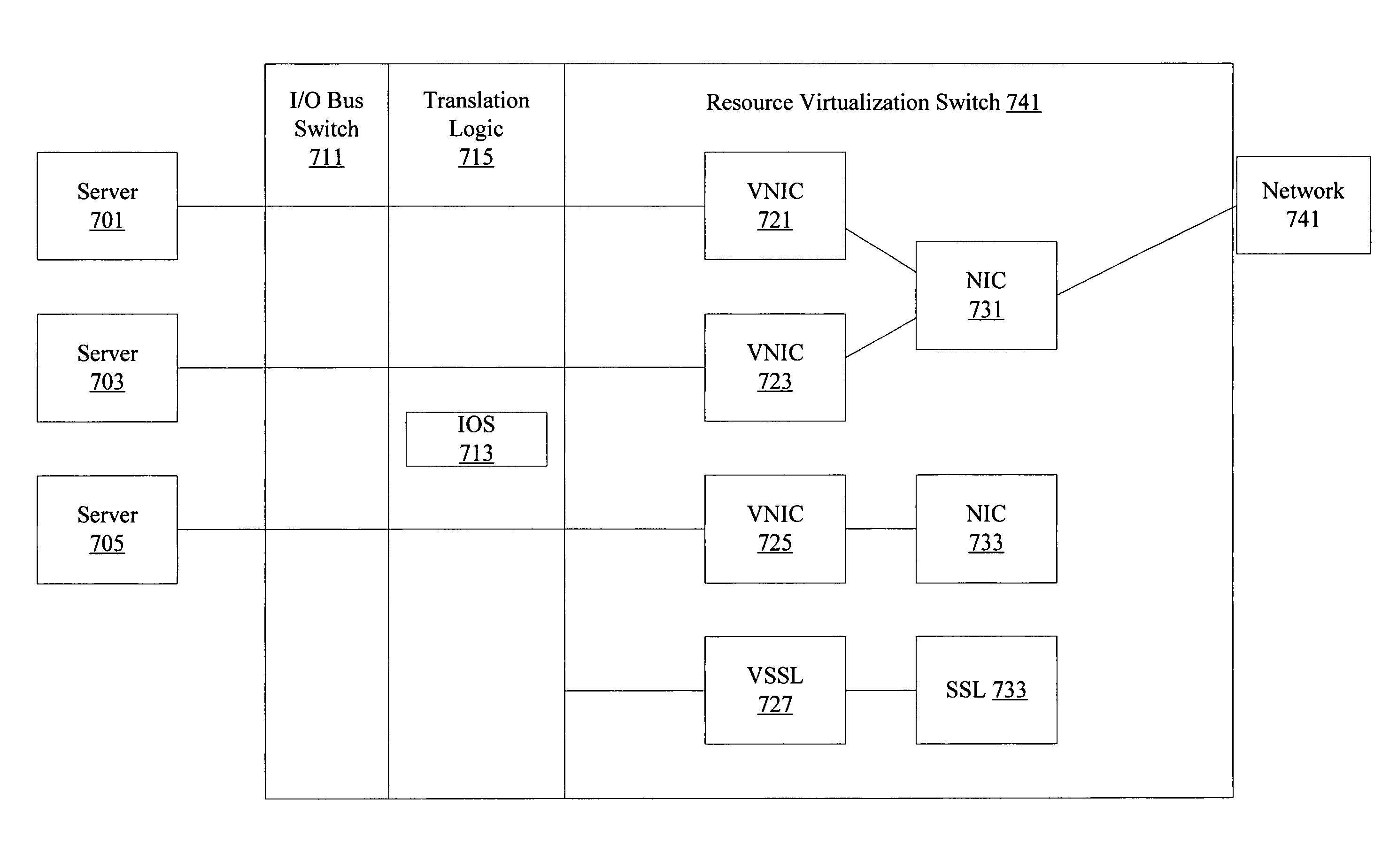

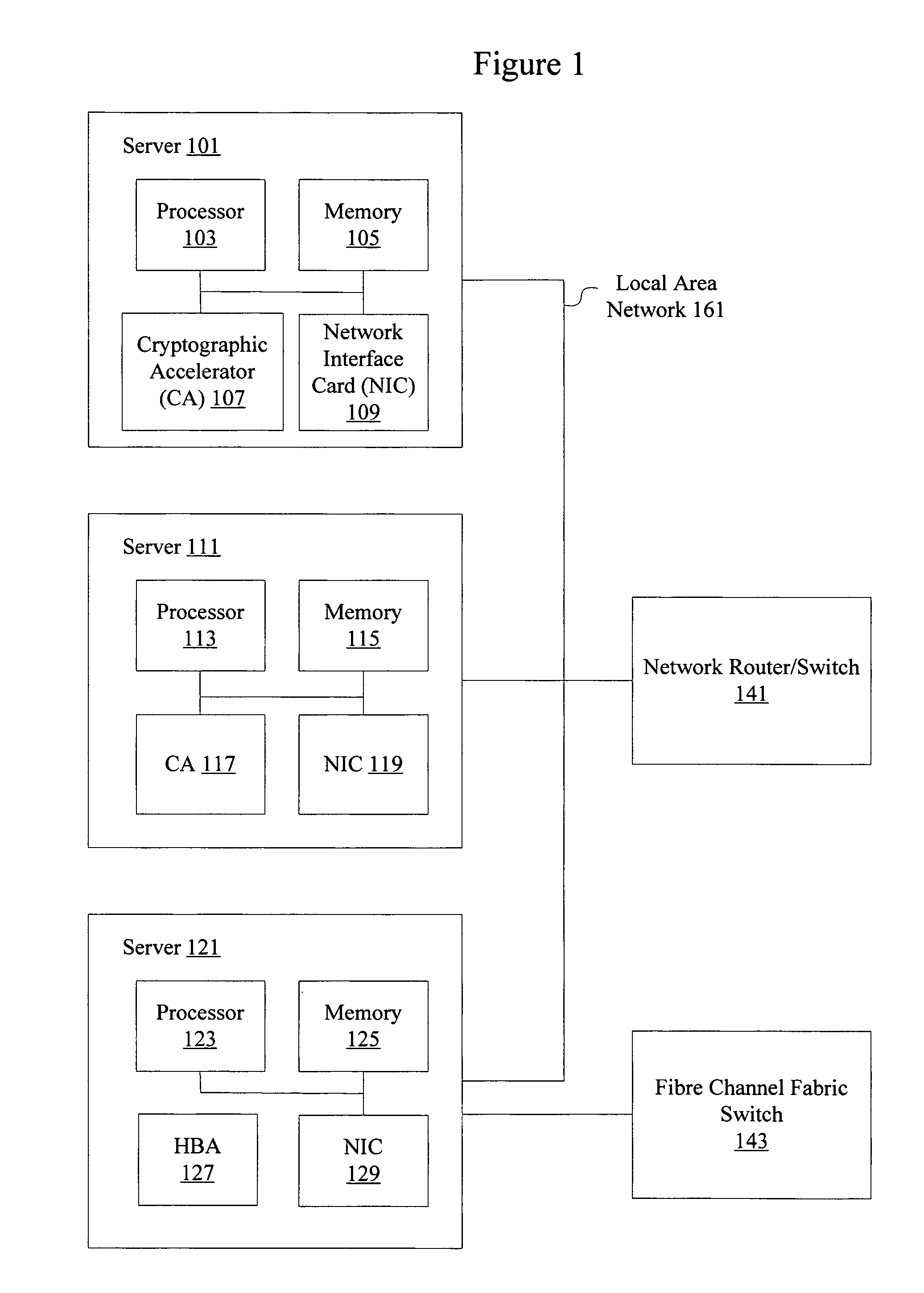

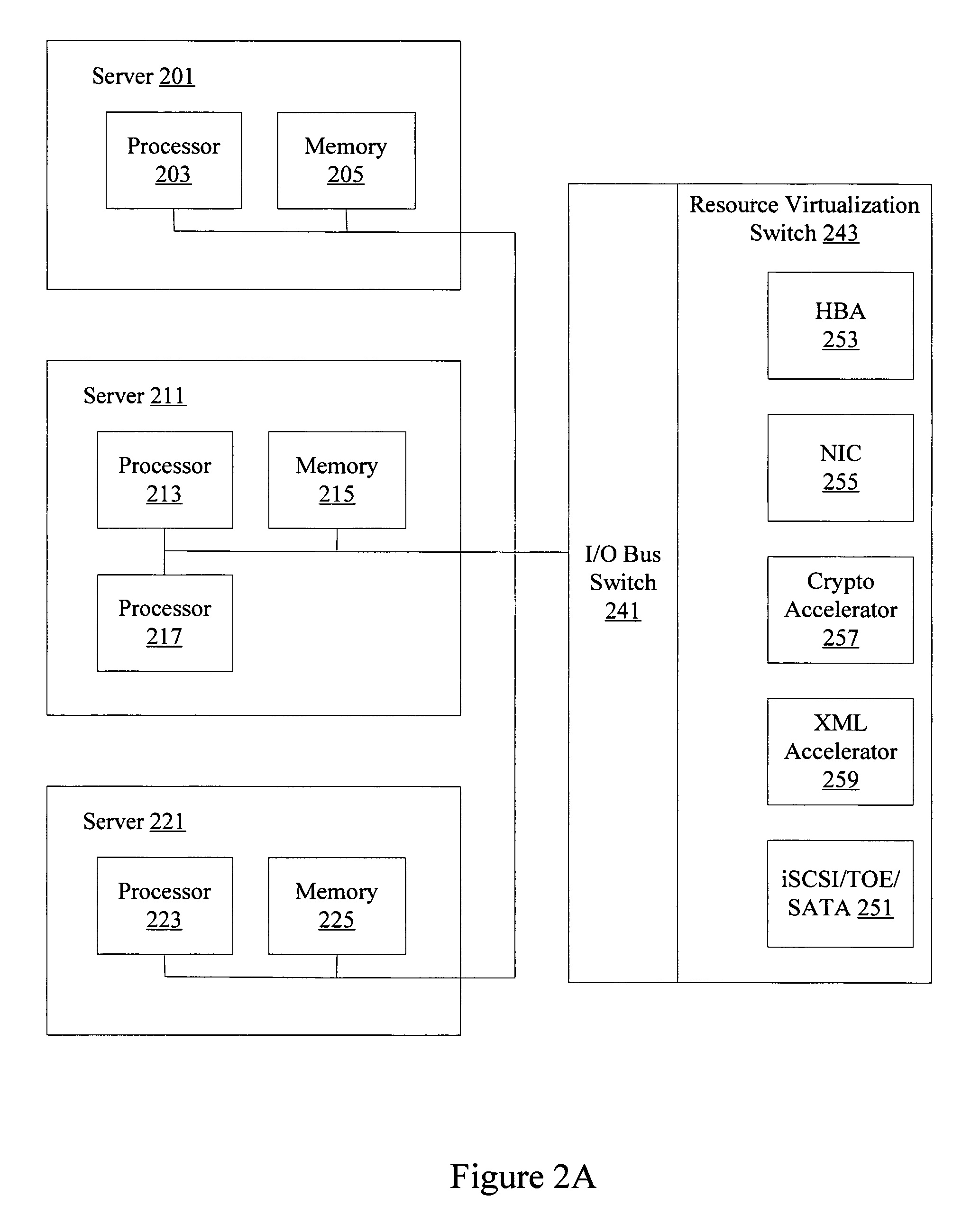

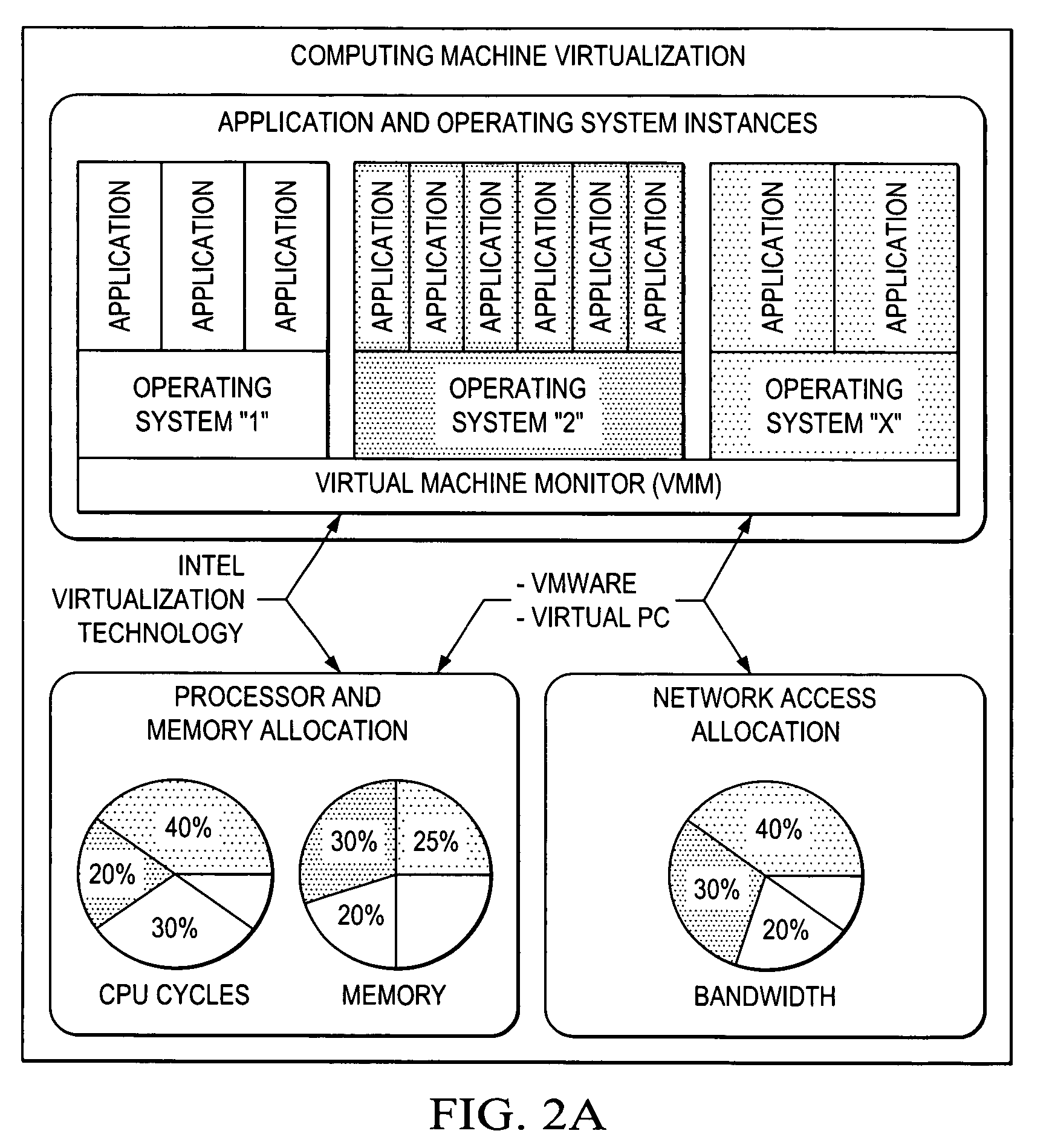

Methods and apparatus are provided for virtualizing resources including peripheral components and peripheral interfaces. Peripheral component such as hardware accelerators and peripheral interfaces such as port adapters are offloaded from individual servers onto a resource virtualization switch. Multiple servers are connected to the resource virtualization switch over an I / O bus fabric such as PCI Express or PCI-AS. The resource virtualization switch allows efficient access, sharing, management, and allocation of resources.

Owner:ORACLE INT CORP

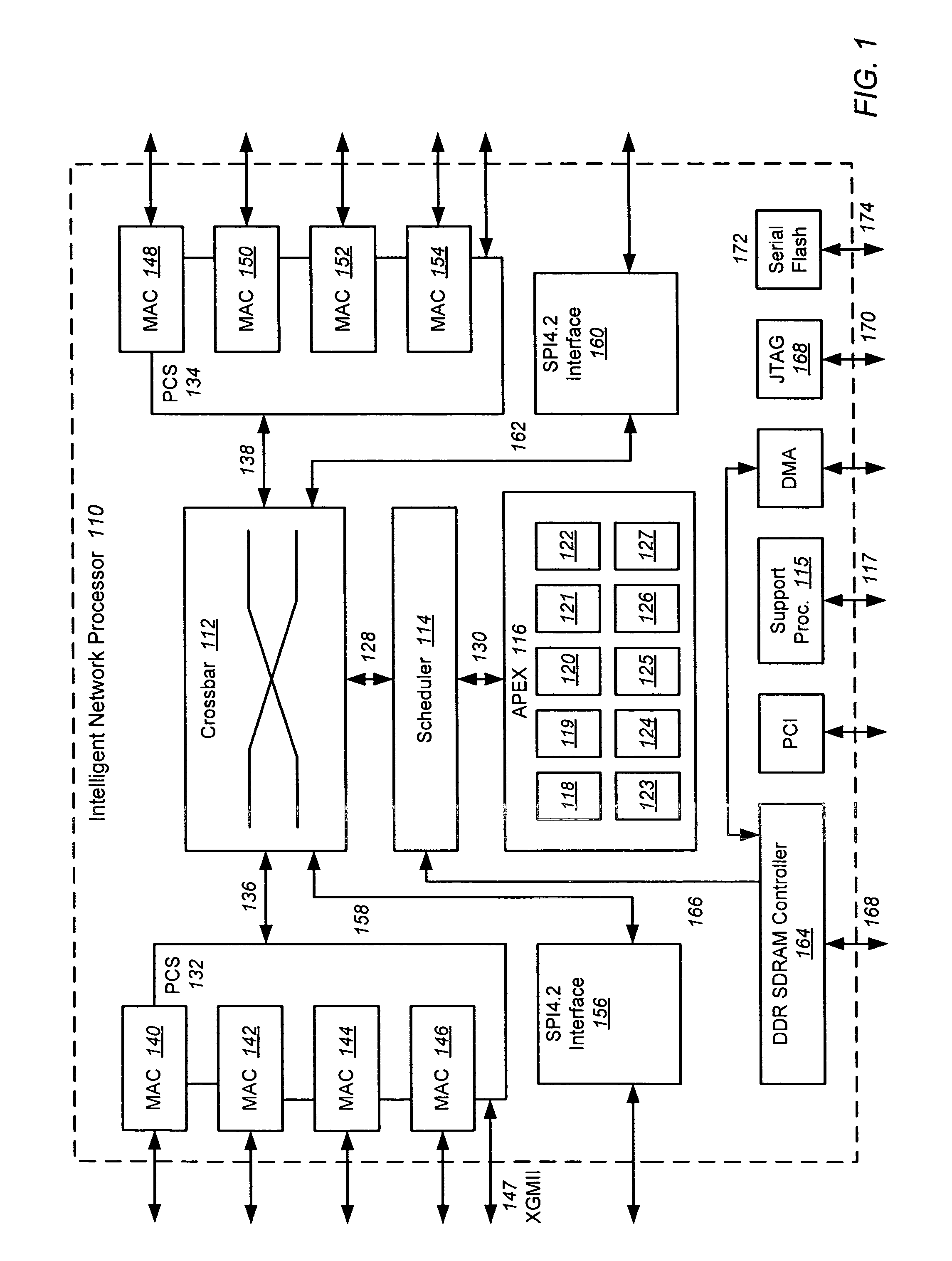

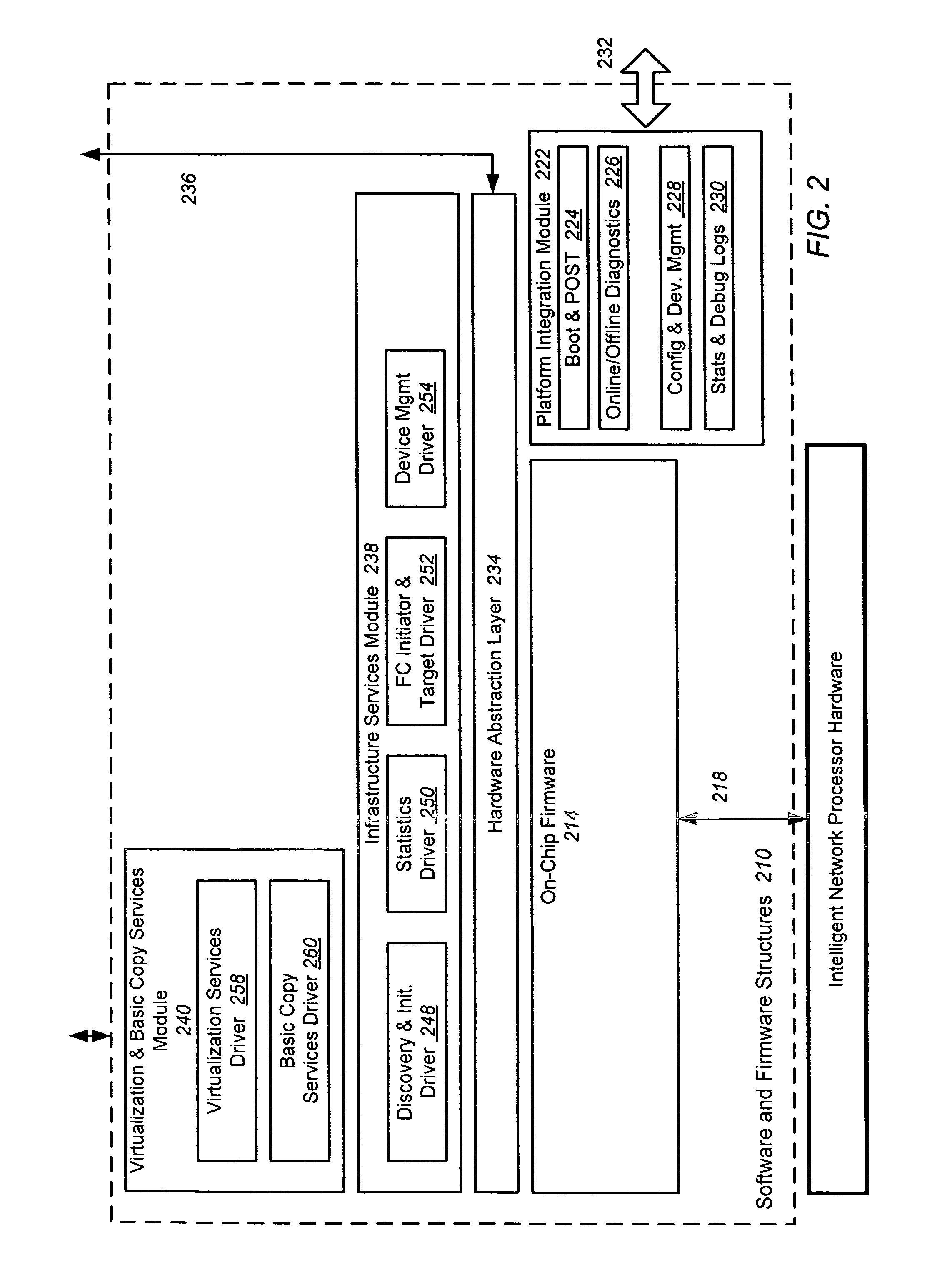

Intelligent network processor and method of using intelligent network processor

ActiveUS20070266179A1Efficient accessImprove creditMultiple digital computer combinationsData switching networksIntelligent NetworkPCI Express

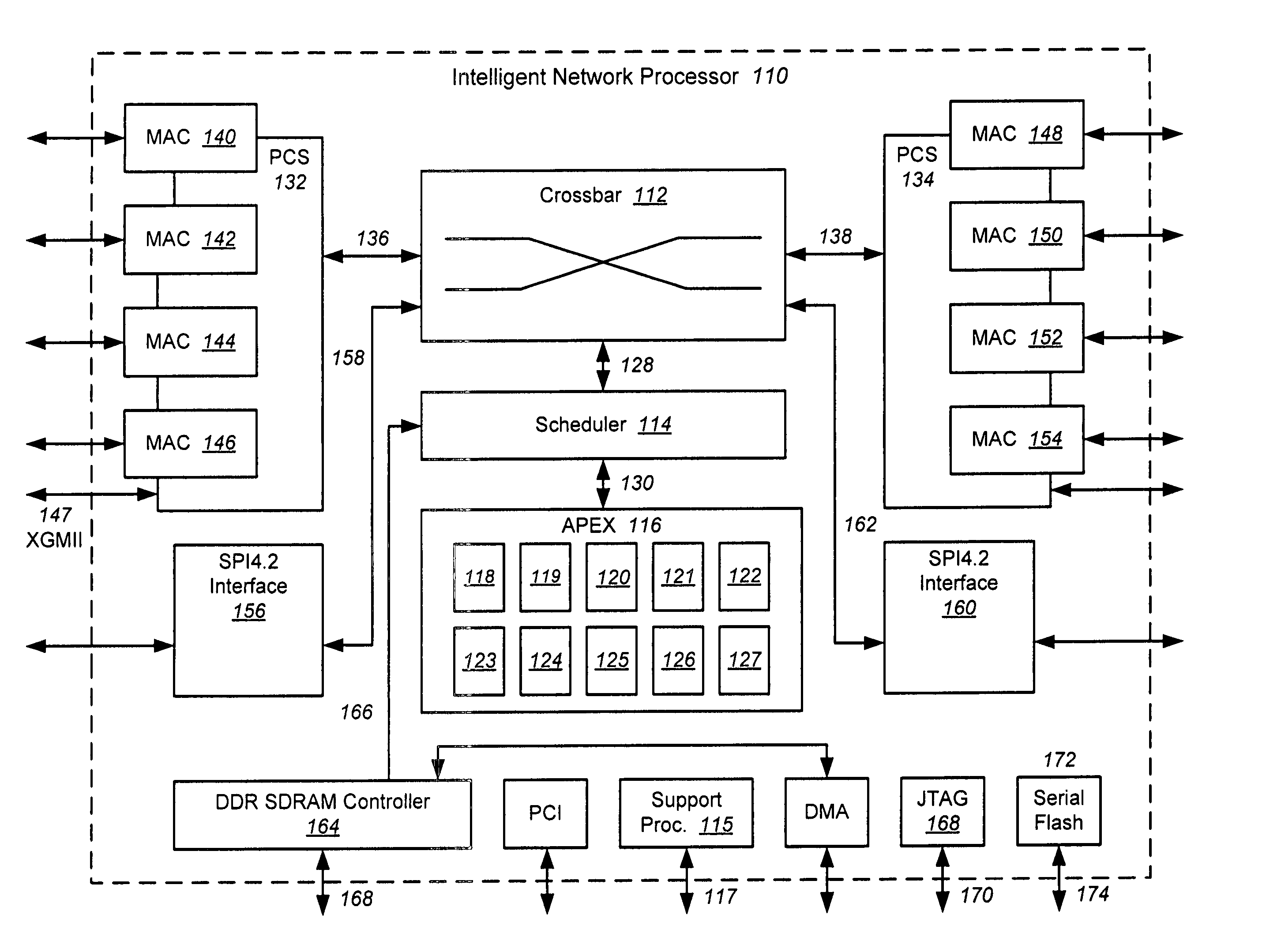

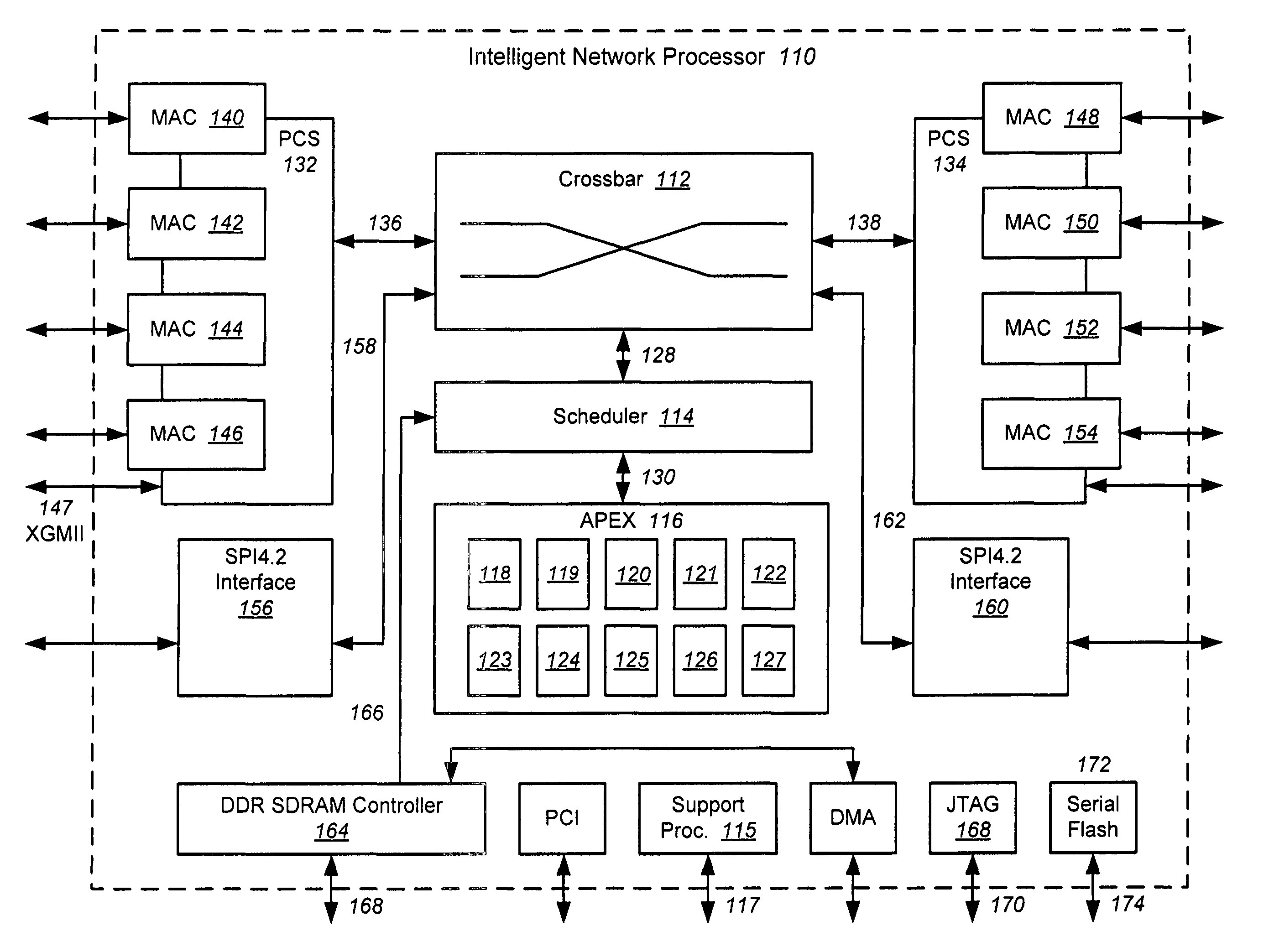

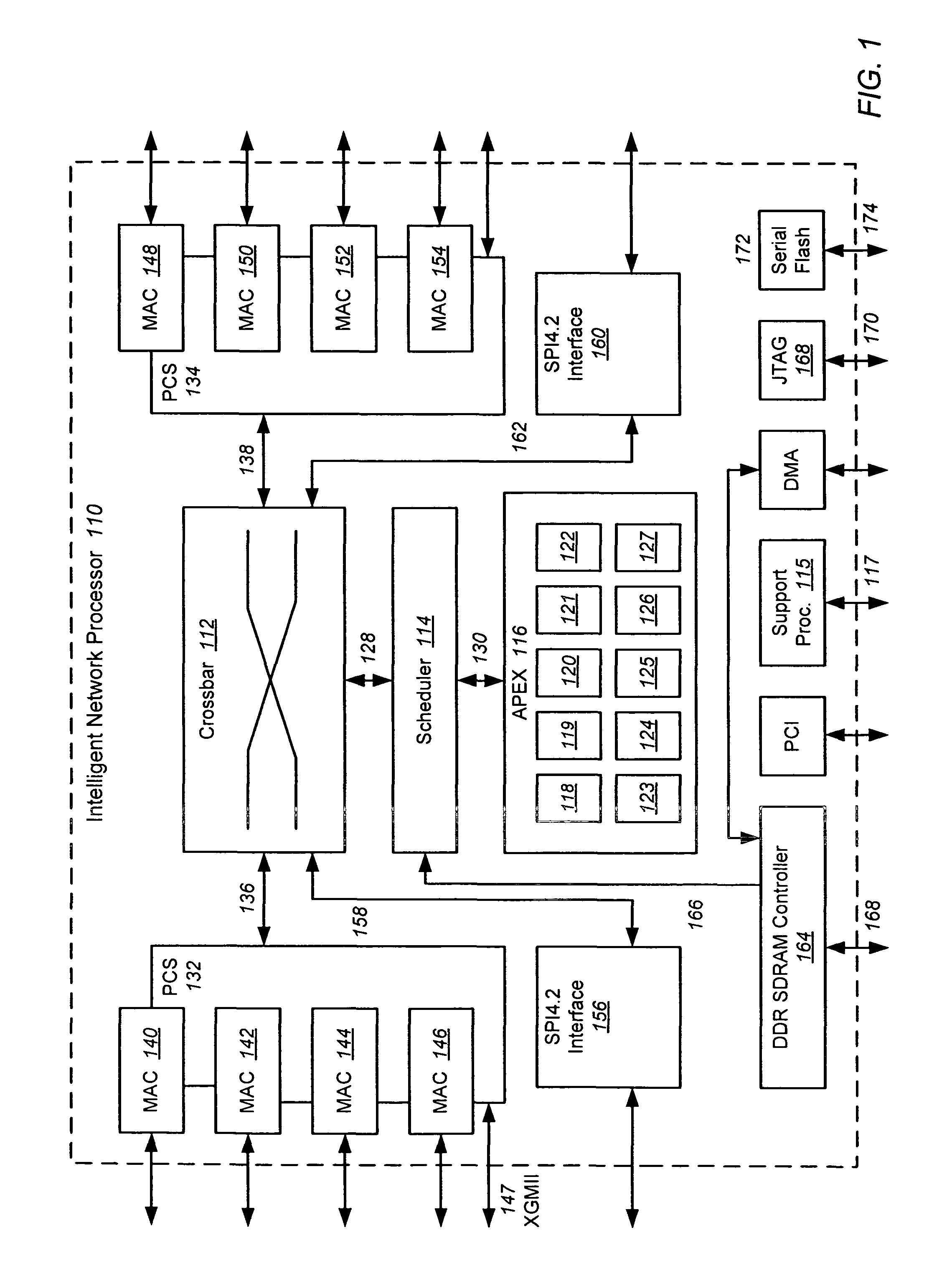

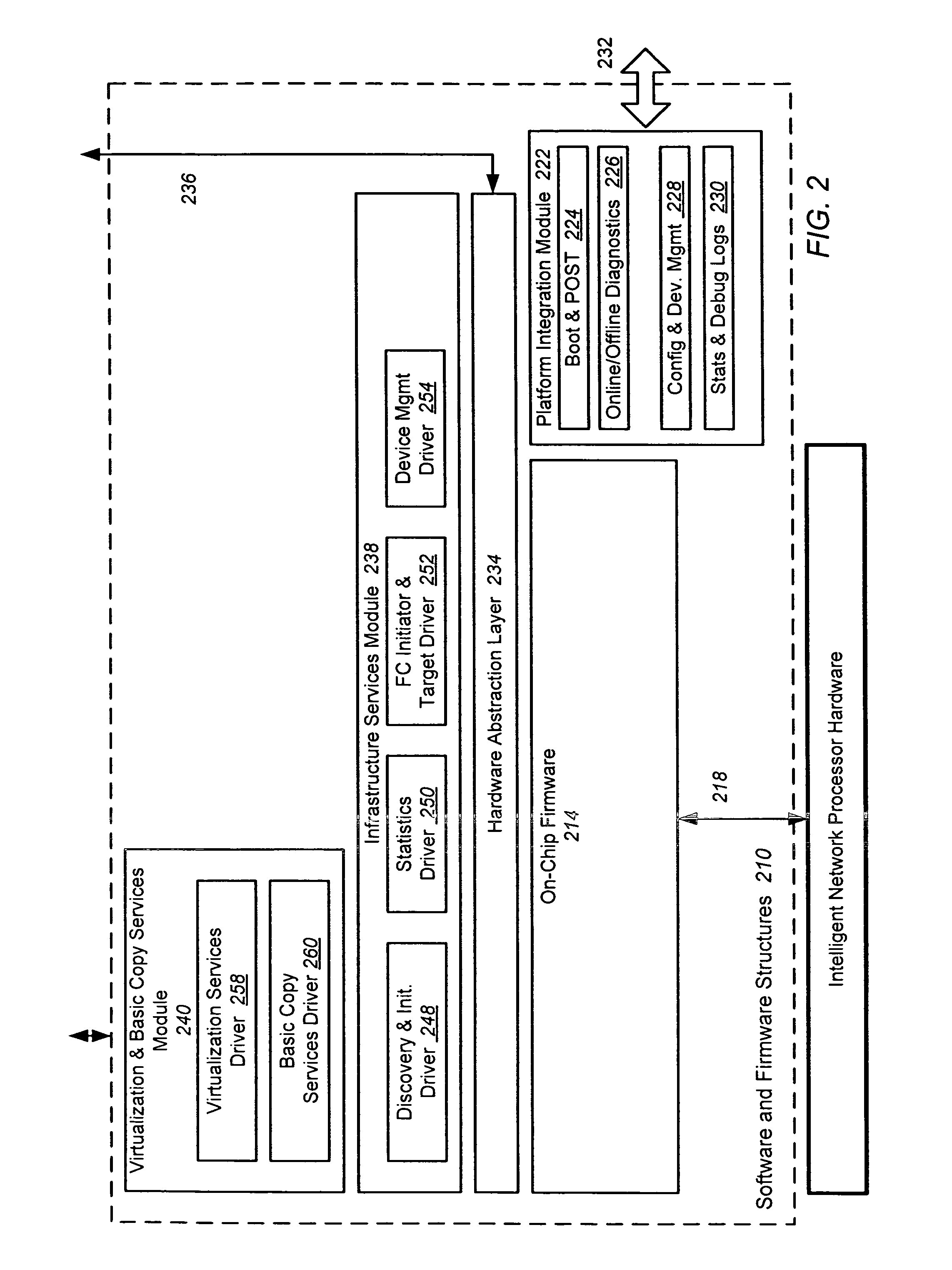

An intelligent network processor is disclosed that provides a PCI express (PCIe) host bus adapter with firmware selectable hardware capabilities and firmware enabled emulation of capabilities not supported by hardware. Support for Fibre Channel (FC) and Gigabit Ethernet (GbE) protocols are provided through the same fabric ports, including multiple port trunking for both protocols. On chip protocol conversion is provided for switching and routing between FC and GbE ports. Switching using the same crossbar module is provided for both FC and GbE protocols. The crossbar module is coupled to directly access external DDR memory so that messages from FC, GbE, and PCIe interfaces may be switched directly to the DDR memory.

Owner:EMULEX COMM CORP

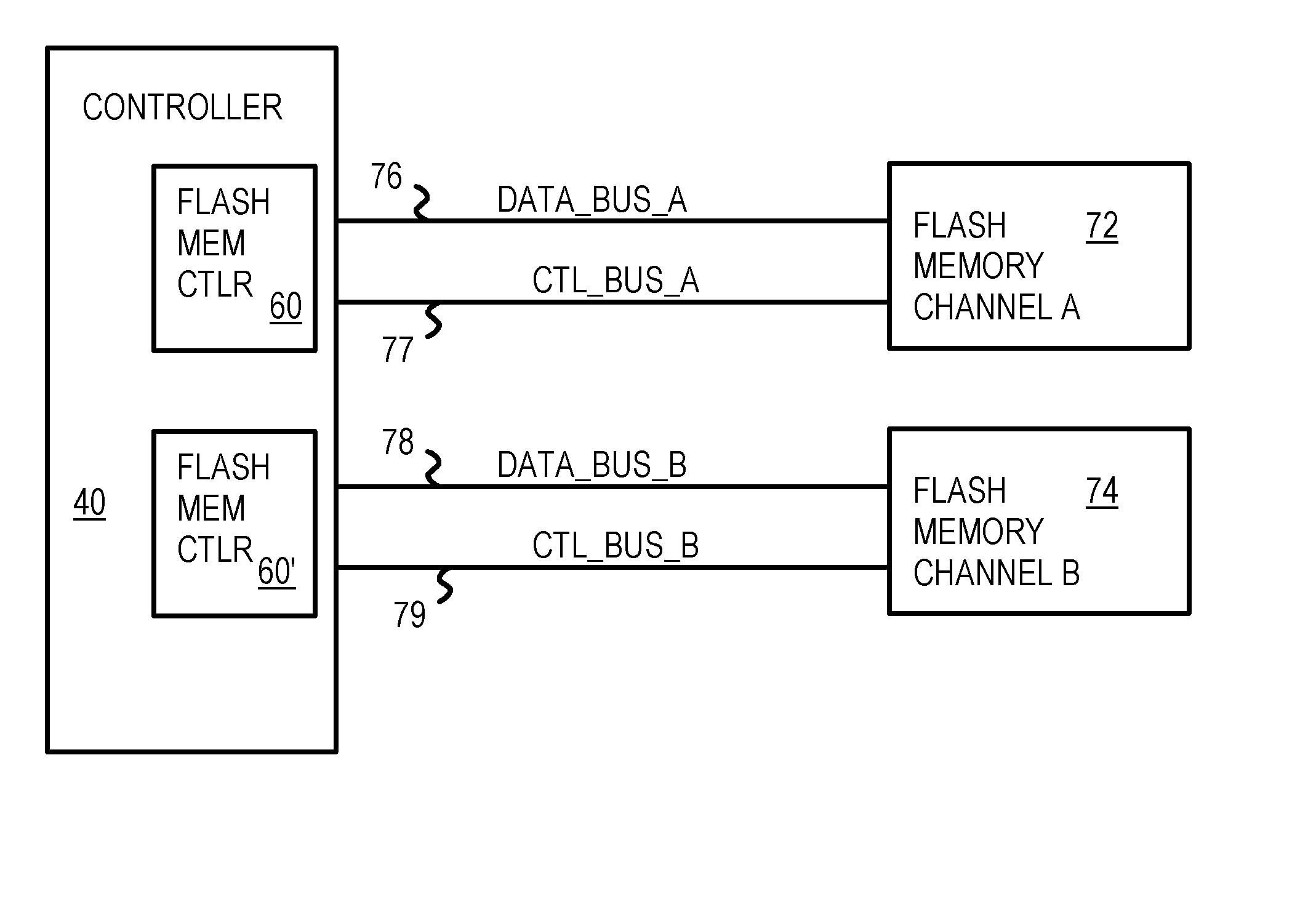

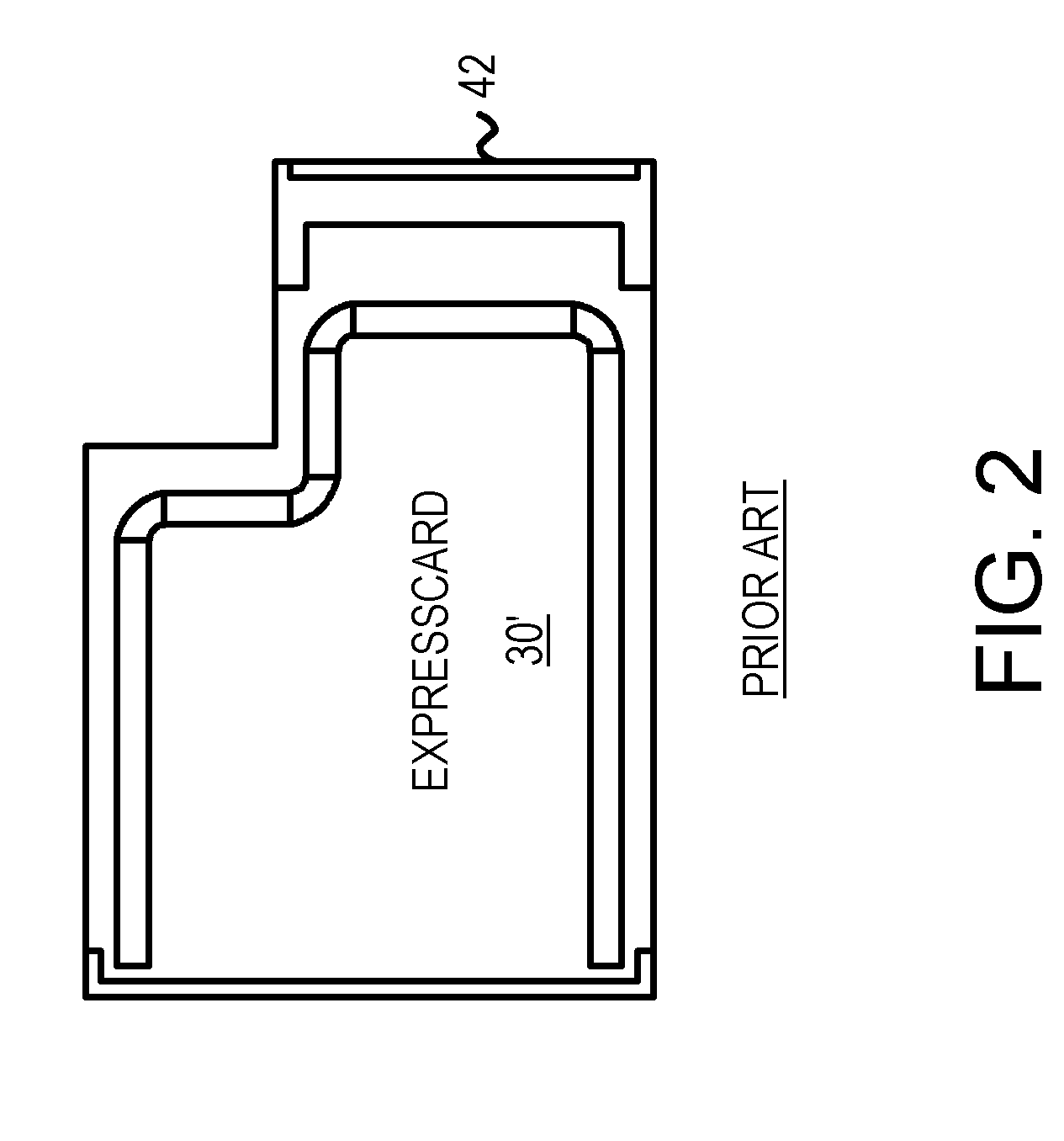

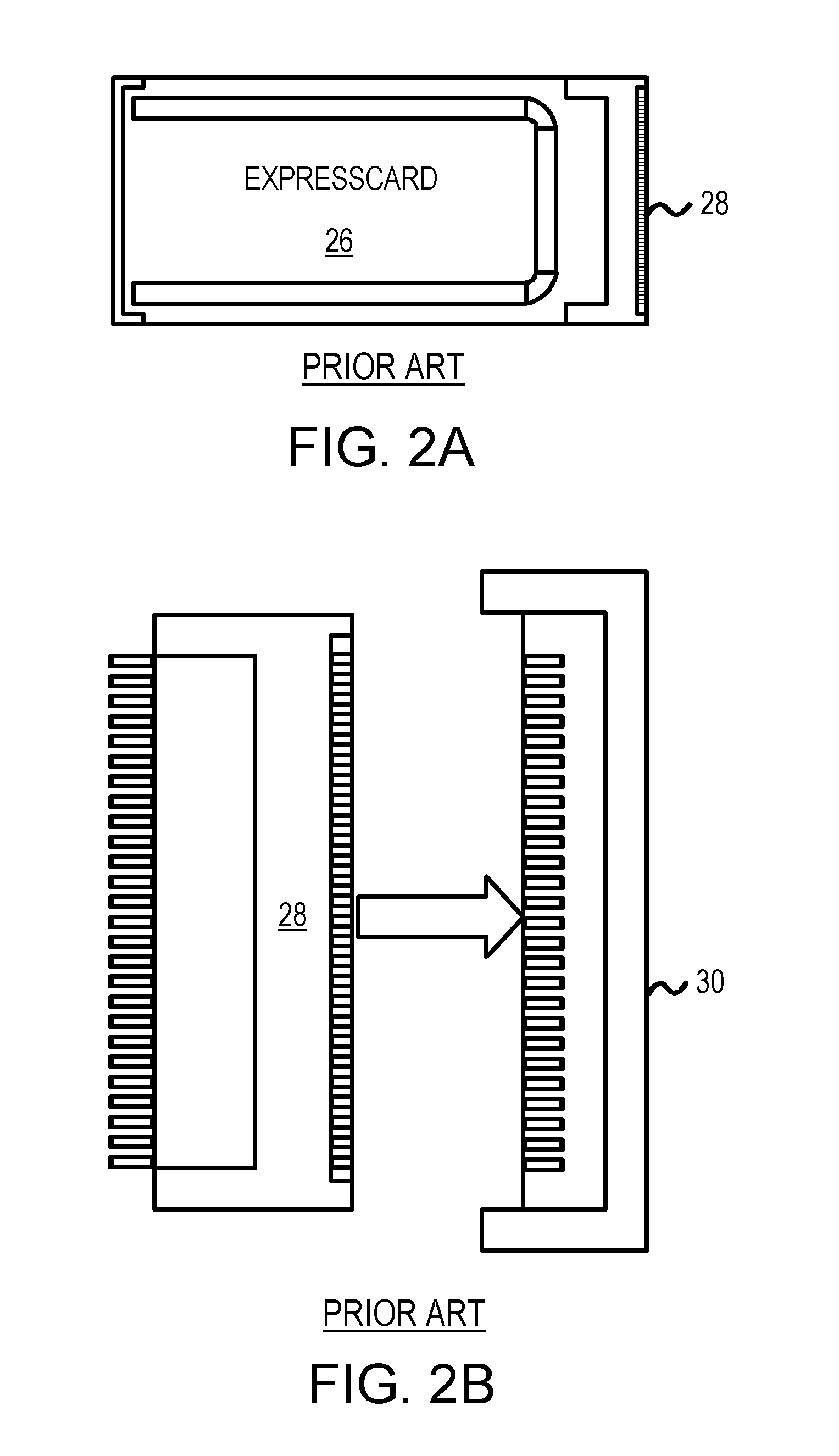

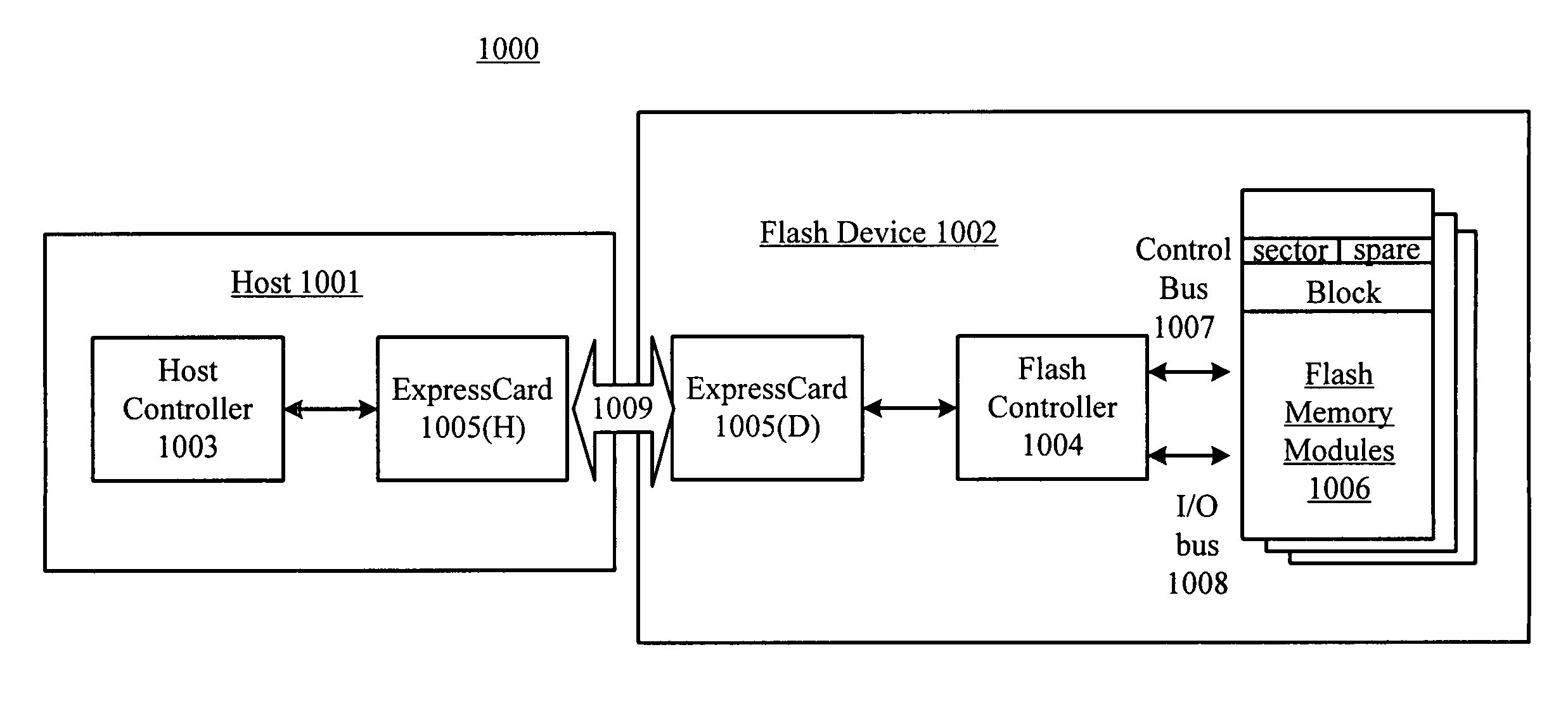

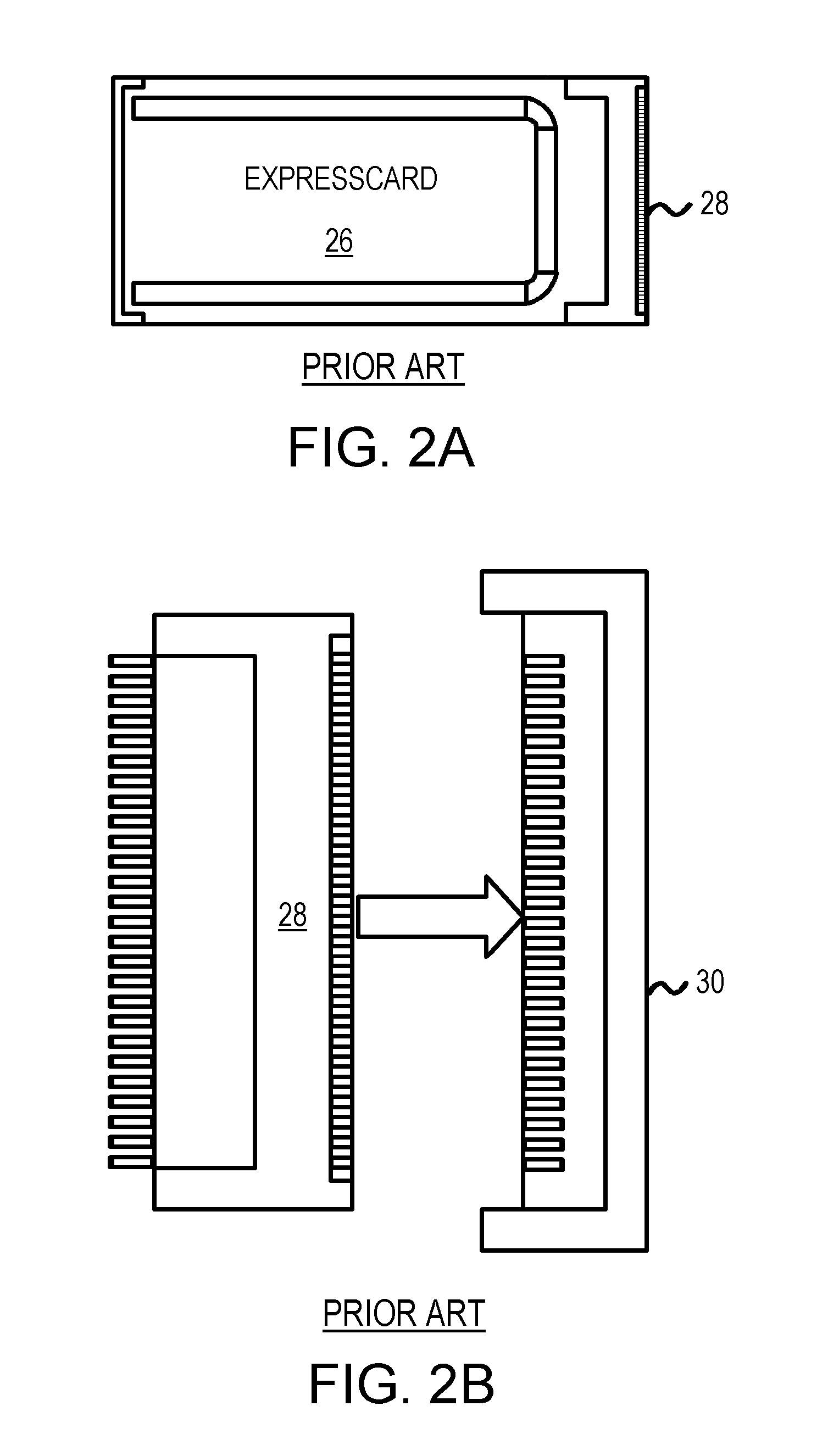

ExpressCard with On-Card Flash Memory with Shared Flash-Control Bus but Separate Ready Lines

An ExpressCard contains flash memory. The ExpressCard has an ExpressCard connector that plugs into a host, such as a personal computer, digital camera, or personal digital assistant (PDA). A controller chip on the ExpressCard uses a pair of differential Universal-Serial-Bus (USB) data lines in the connector to communicate with the USB host, or can use PCI Express, Firewire, or other protocols. One or more flash-memory chips on the ExpressCard are controlled by a flash-memory controller in the controller chip. Two or more channels of a flash bus have a shared control bus but separate ready lines. The separate ready lines allow flash-memory chips in the two channels to finish operations at different times.

Owner:SUPER TALENT ELECTRONICS

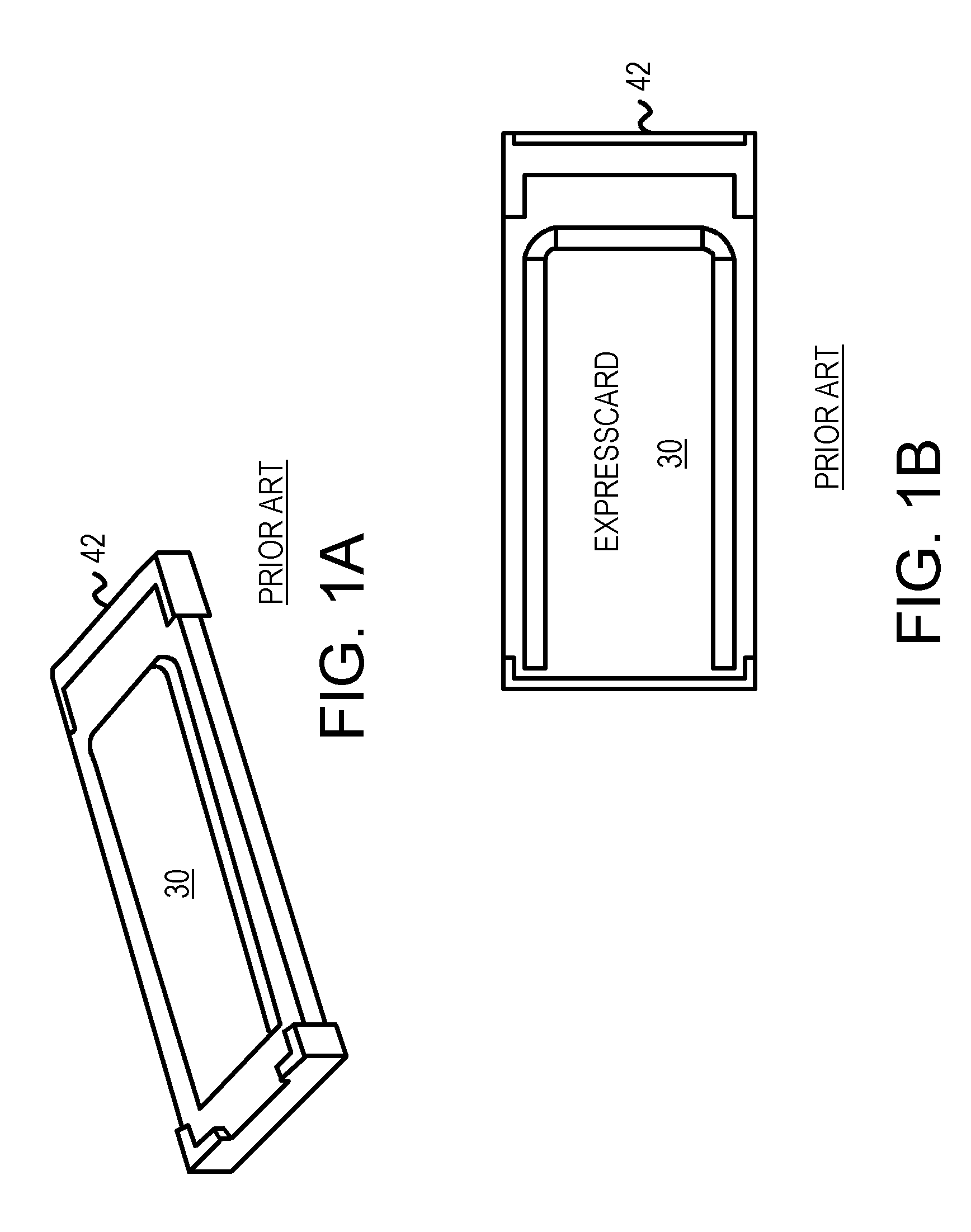

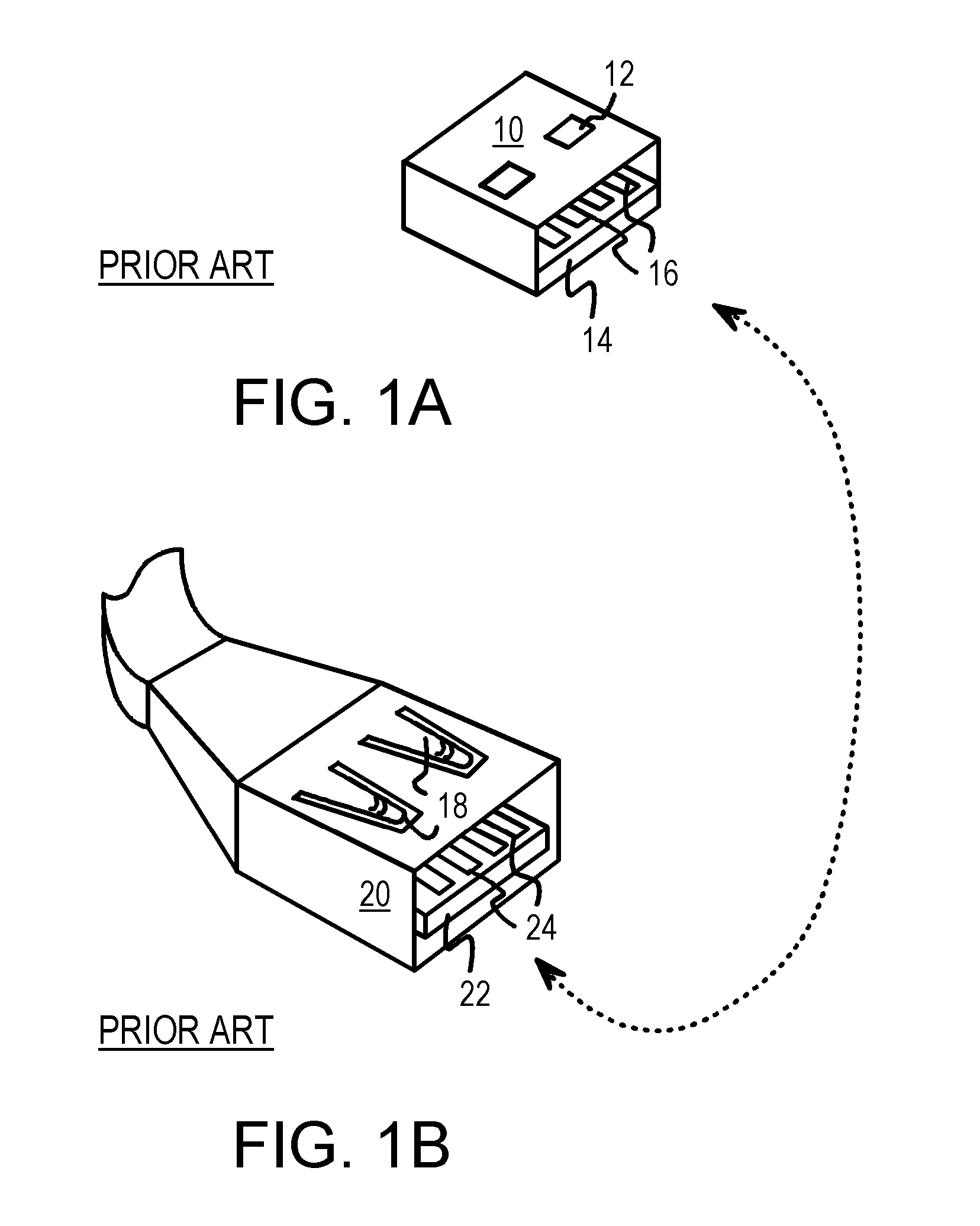

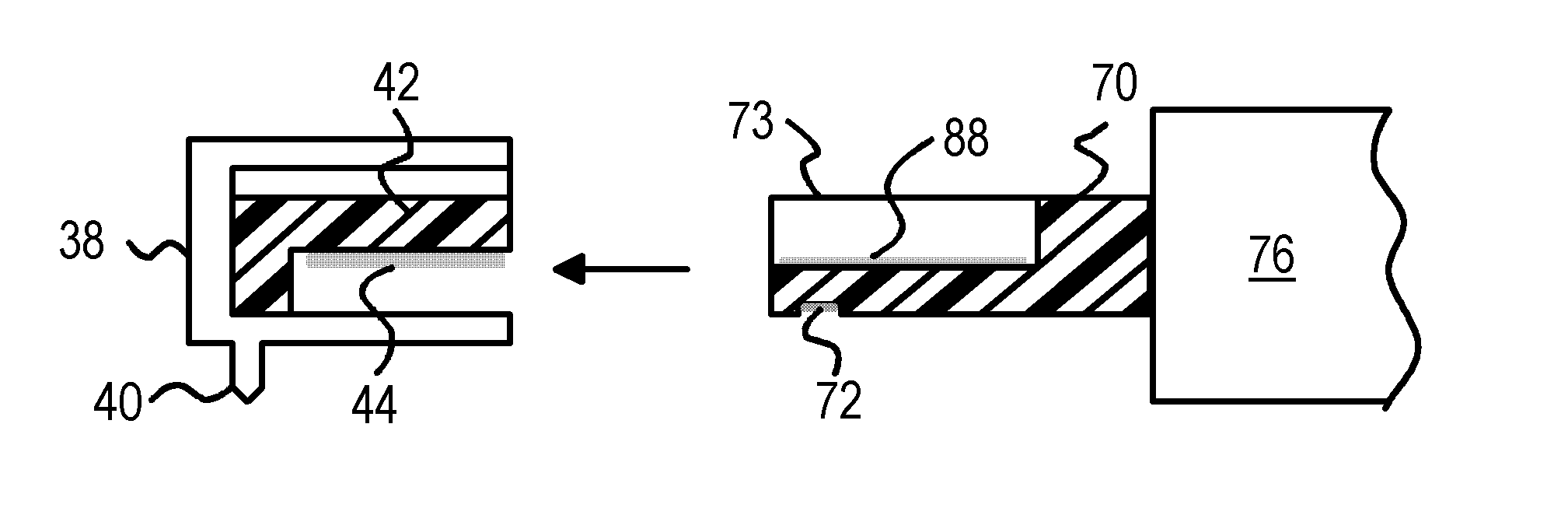

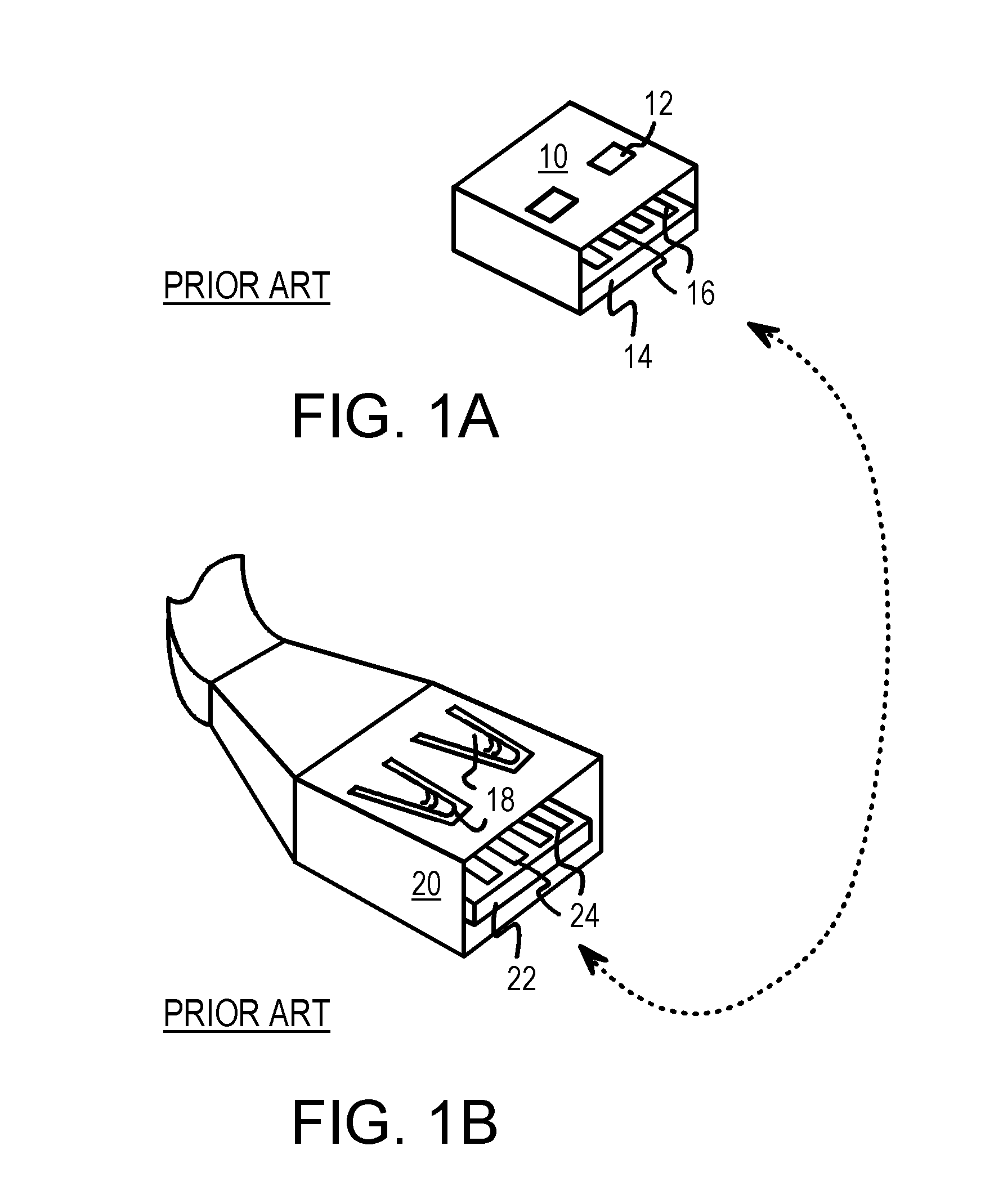

Dual-personality extended-USB plug and receptacle with PCI-Express or Serial-At-Attachment extensions

An extended Universal-Serial-Bus (USB) connector plug and socket each have a pin substrate with one surface that supports the four metal contact pins for the standard USB interface. An extension of the pin substrate carries another 8 extension metal contact pins that mate when both the connector plug and socket are extended. The extension can be an increased length of the plug's and socket's pin substrate or a reverse side of the substrate. Standard USB connectors do not make contact with the extension metal contacts that are recessed, retracted by a mechanical switch, or on the extension of the socket's pin substrate that a standard USB connector cannot reach. Standard USB sockets do not make contact with the extension metal contacts because the extended connector's extension contacts are recessed, or on the extension of the connector pin substrate that does not fit inside a standard USB socket.

Owner:SUPER TALENT TECH CORP

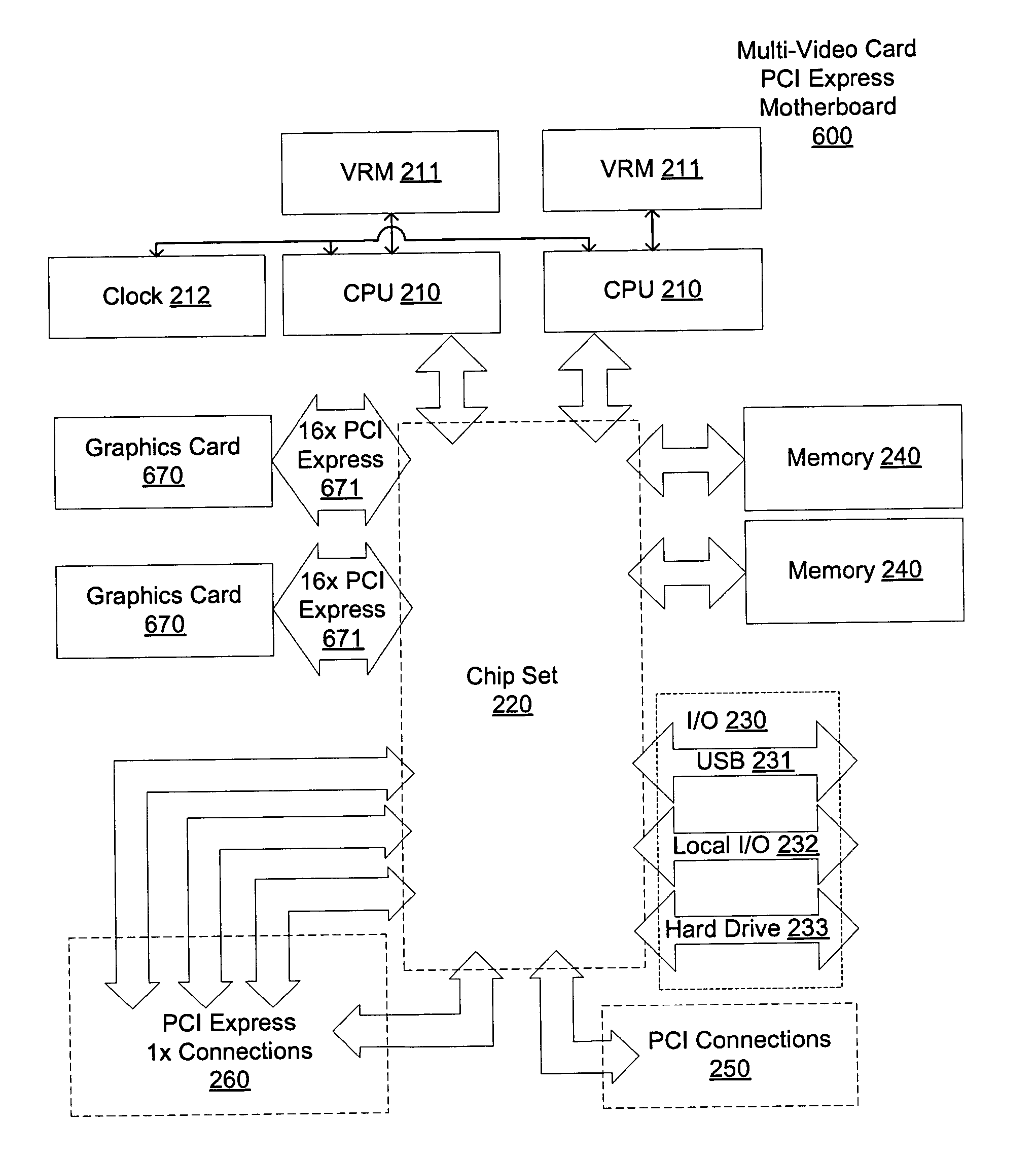

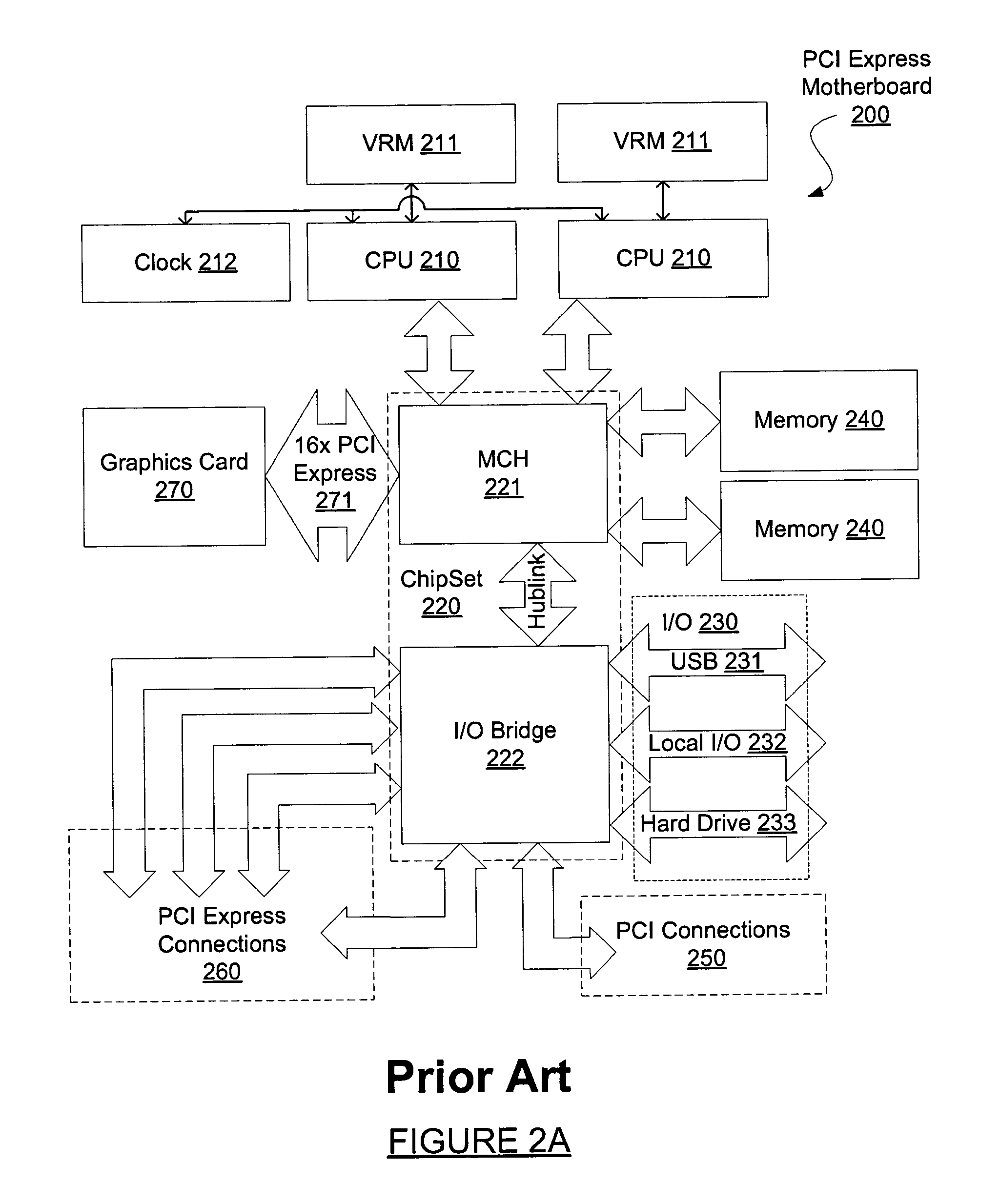

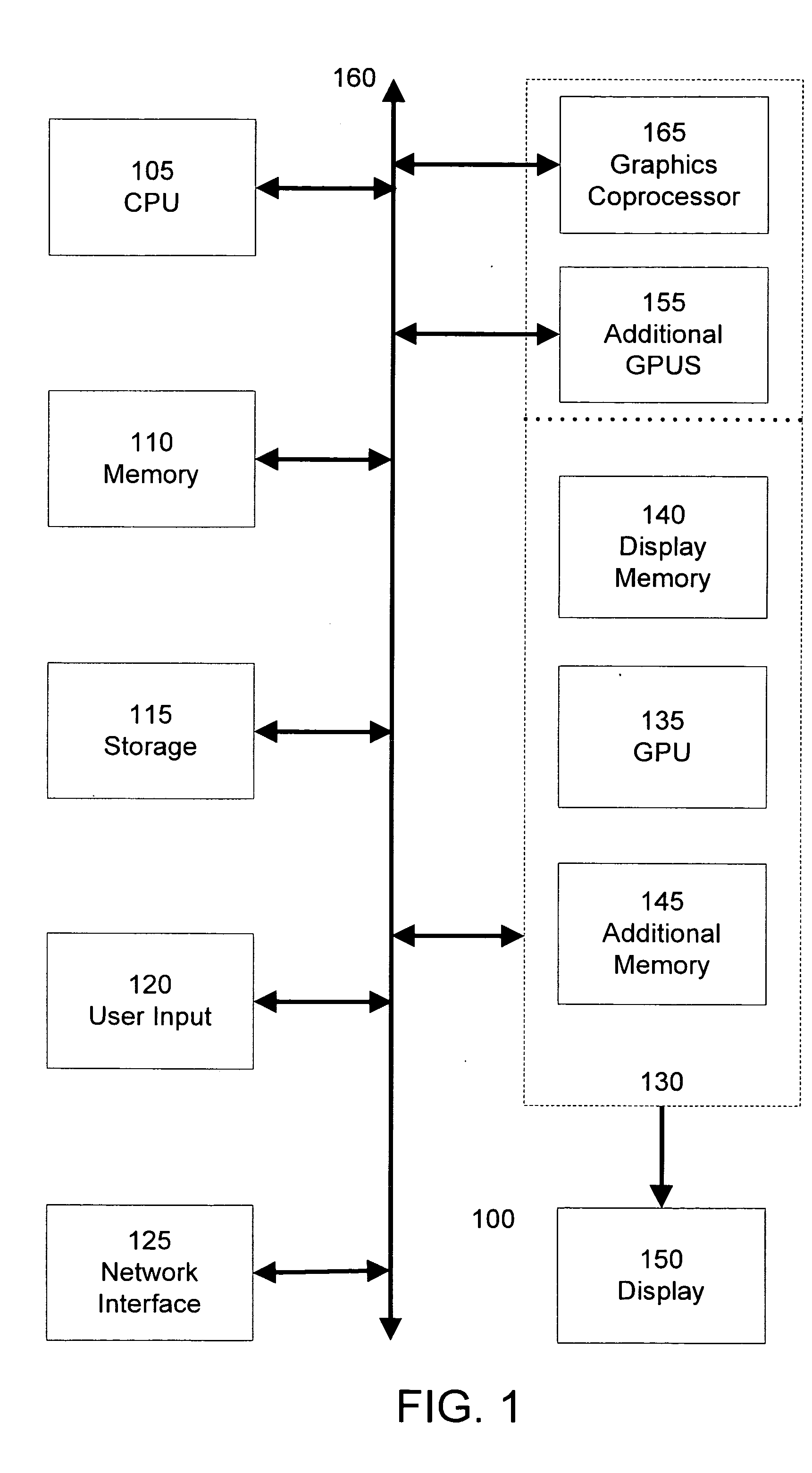

Motherboard for supporting multiple graphics cards

ActiveUS20050088445A1Cathode-ray tube indicatorsMultiple digital computer combinationsGraphicsScalable system

The present invention provides a motherboard that uses a high-speed, scalable system bus such as PCI Express® to support two or more high bandwidth graphics slots, each capable of supporting an off-the-shelf video controller. The lanes from the motherboard chipset may be directly routed to two or more graphics slots. For instance, the chipset may route (1) thirty-two lanes into two ×16 graphics slots; (2) twenty-four lanes into one ×16 graphics slot and one ×8 graphics slot (the ×8 slot using the same physical connector as a ×16 graphics slot but with only eight active lanes); or (3) sixteen lanes into two ×8 graphics slots (again, physically similar to a ×16 graphics slot but with only eight active lanes). Alternatively, a switch can convert sixteen lanes coming from the chipset root complex into two ×16 links that connect to two ×16 graphics slots. Each and every embodiment of the present invention is agnostic to a specific chipset.

Owner:DELL MARKETING

Flash / Phase-Change Memory in Multi-Ring Topology Using Serial-Link Packet Interface

A multi-ring memory controller sends request packets to multiple rings of serial flash-memory chips. Each of the multiple rings has serial flash-memory chips with serial links in a uni-directional ring. Each serial flash-memory chip has a bypassing transceiver with a device ID checker that bypasses serial packets to a clock re-synchronizer and bypass logic for retransmission to the next device in the ring, or extracts the serial packet to the local device when an ID match occurs. Serial packets pass through all devices in the ring during one round-trip transaction from the controller. The average latency of one round is constant for all devices on the ring, reducing data-dependent performance, since the same packet latency occurs regardless of the data location on the ring. The serial links can be a Peripheral Component Interconnect (PCI) Express bus. Packets have modified-PCI-Express headers that define the packet type and data-payload length.

Owner:SUPER TALENT ELECTRONICS

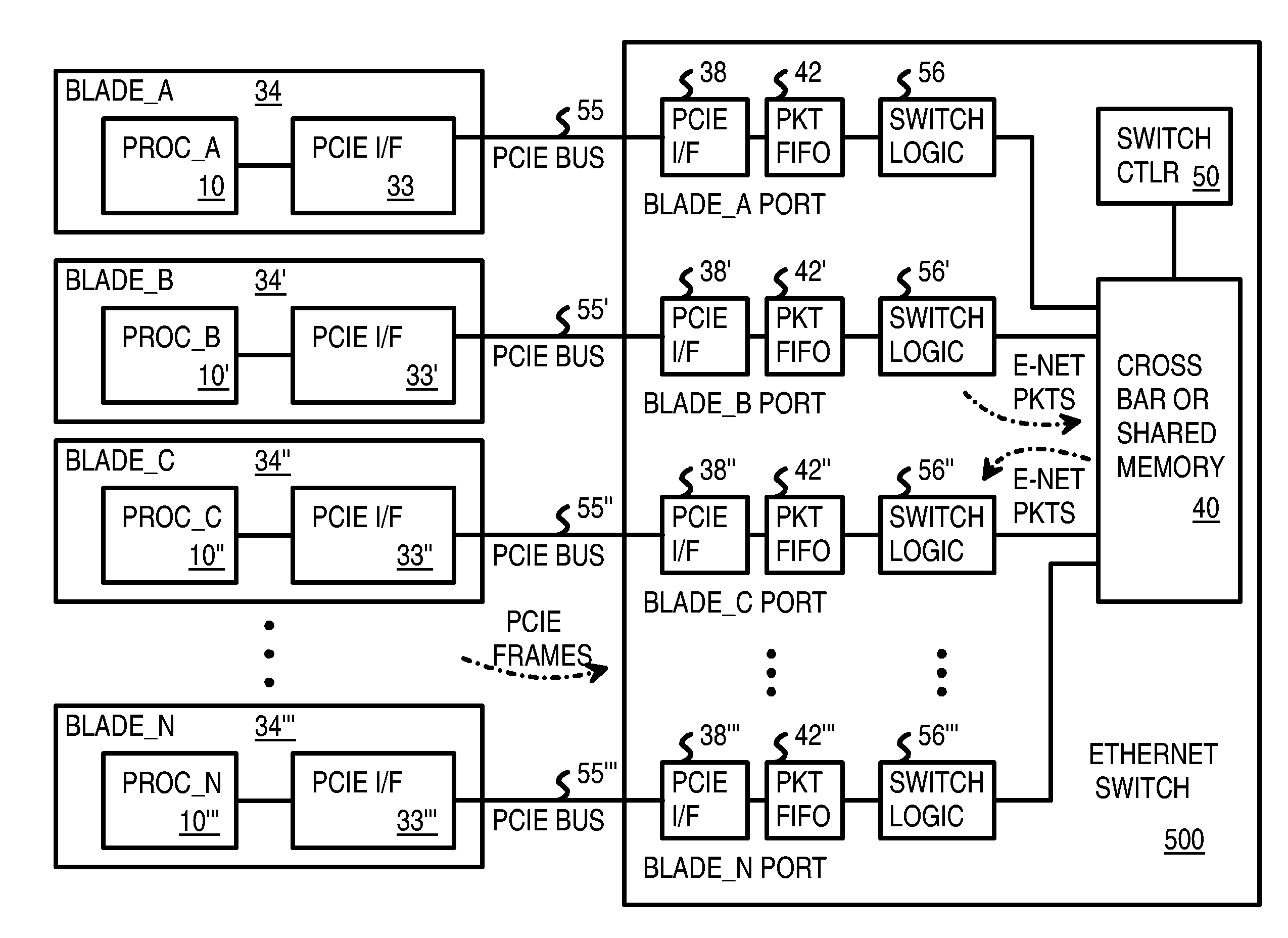

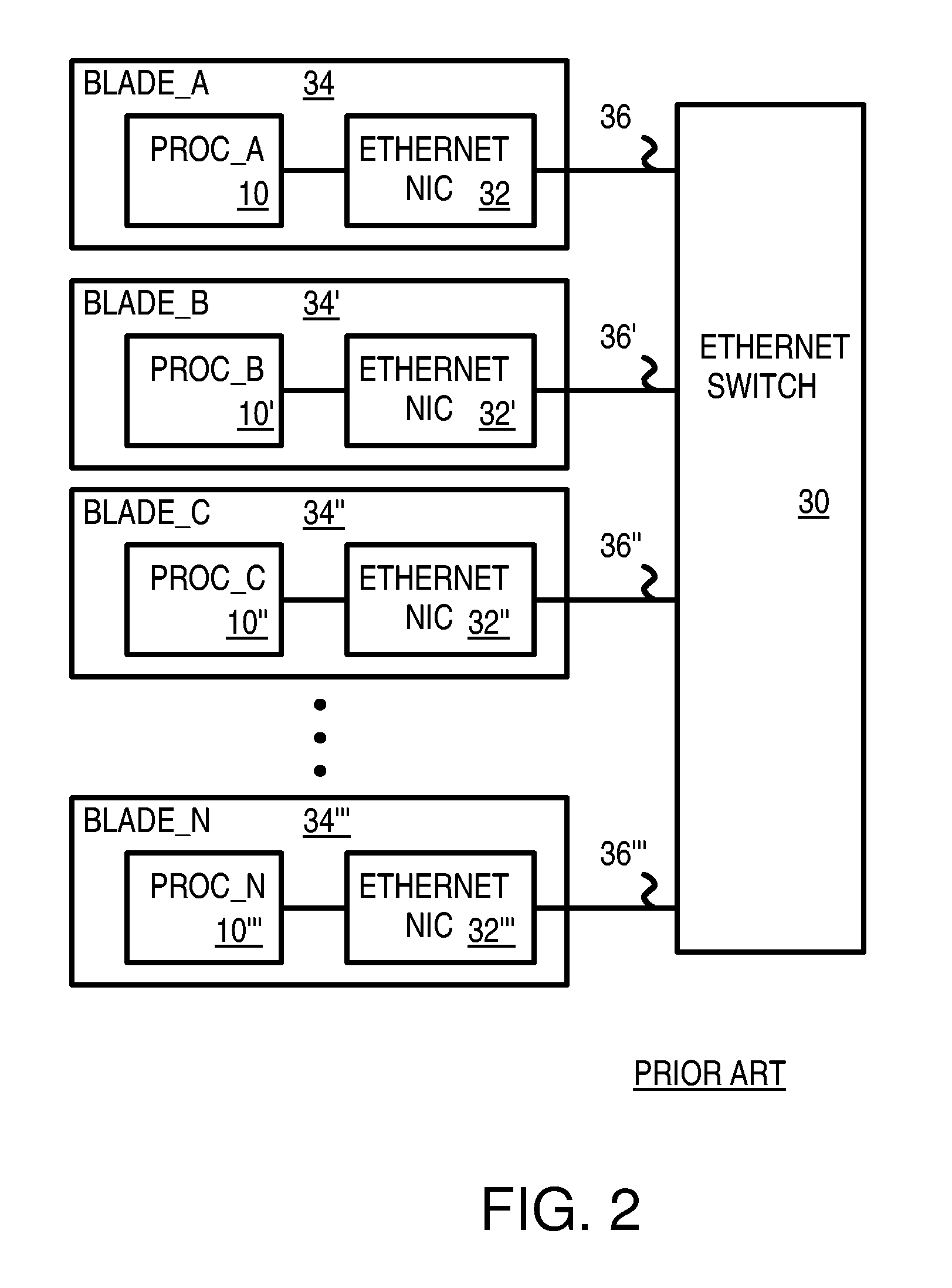

Pseudo-ethernet switch without ethernet media-access-controllers (MAC's) that copies ethernet context registers between PCI-express ports

A Pseudo-Ethernet switch has a routing table that uses Ethernet media-access controller (MAC) addresses to route Ethernet packets through a switch fabric between an input port and an output port. However, the input port and output port have Peripheral Component Interconnect Express (PCIE) interfaces that read and write PCI-Express packets to and from host-processor memories. When used in a blade system, host processor boards have PCIE physical links that connect to the PCIE ports on the Pseudo-Ethernet switch. The Pseudo-Ethernet switch does not have Ethernet MAC and Ethernet physical layers, saving considerable hardware. The switch fabric can be a cross-bar switch or can be a shared memory that stores Ethernet packet data embedded in the PCIE packets. Write and read pointers for a buffer storing an Ethernet packet in the shared memory can be passed from input to output port to perform packet switching.

Owner:DIODES INC

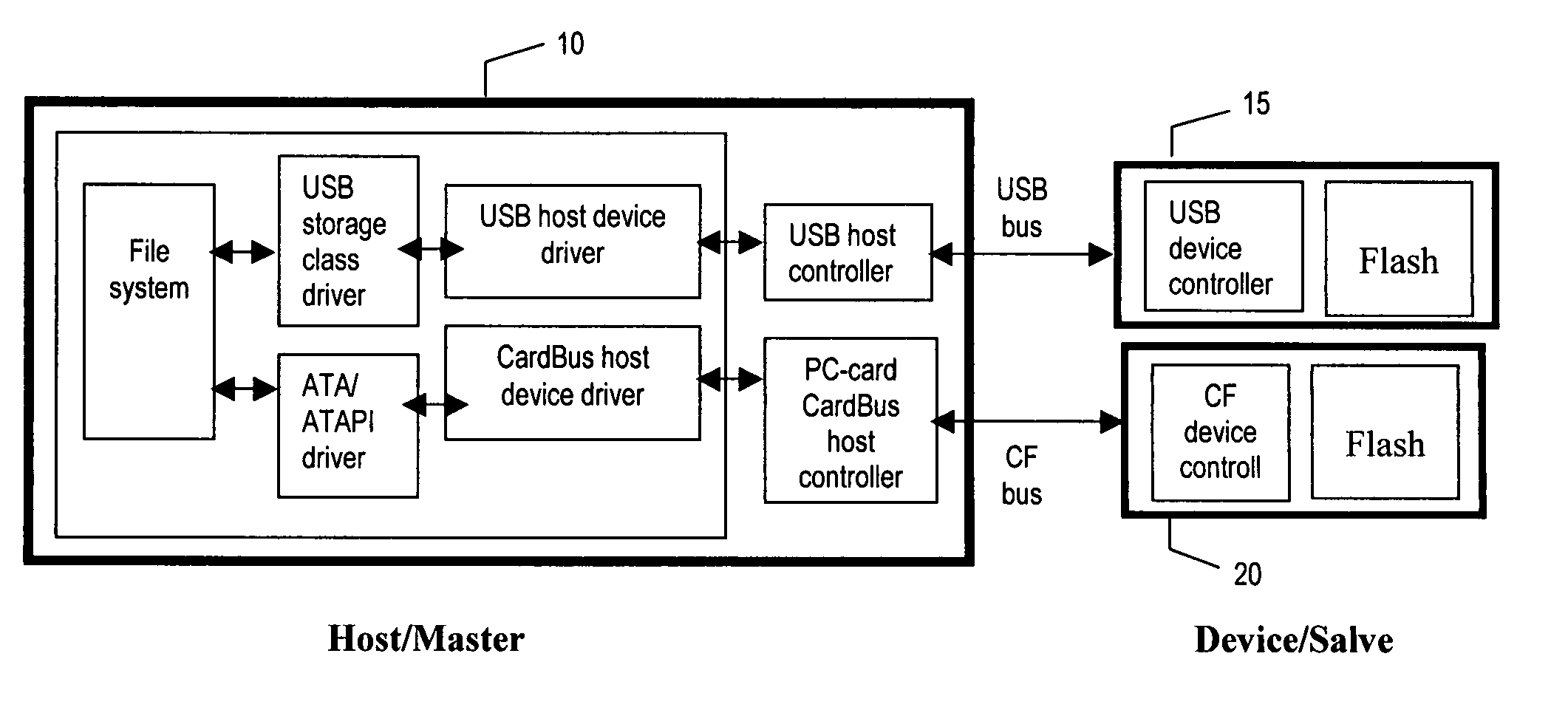

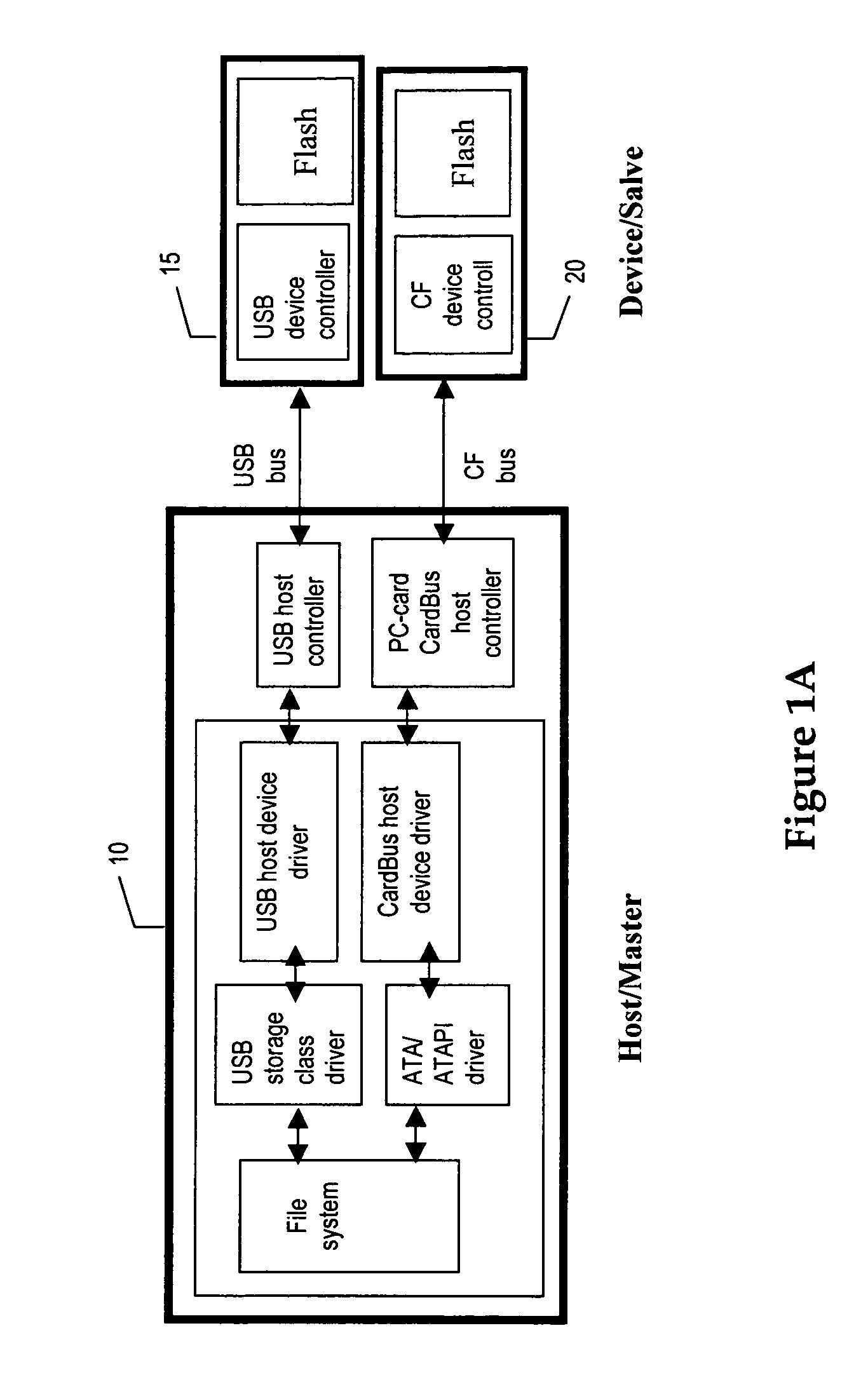

Flash memory device with ATA/ATAPI/SCSI or proprietary programming interface on PCI express

InactiveUS20050240713A1Easy to useOvercome difficultiesInput/output to record carriersSCSIComputer compatibility

A storage device made of flash memory module(s) and a storage device controller and a PCI Express interface unit, is implemented to be compatible with (1) either ATA, ATAPI, SCSI or proprietary specification, and (2) PCI Express platform such as, with then, ExpressCard Standard or PCI Express Card Specification or PCI Express Mini Card Specification. The device includes memory module(s), which can accept data transfer and configuration and status report to / from non-volatile solid-state memory herein referred to as flash memory module(s). The storage device controller and the PCI Express interface unit work together to provide (A) PCI Express interface functionality and compatibility, and (B) ATA, ATAPI or SCSI or proprietary programming interface functionality and compatibility, alone with common flash memory operations such as programming reading, writing, erasing, and data transferring from / to PCI Express host platform.

Owner:V TECH CO LTD

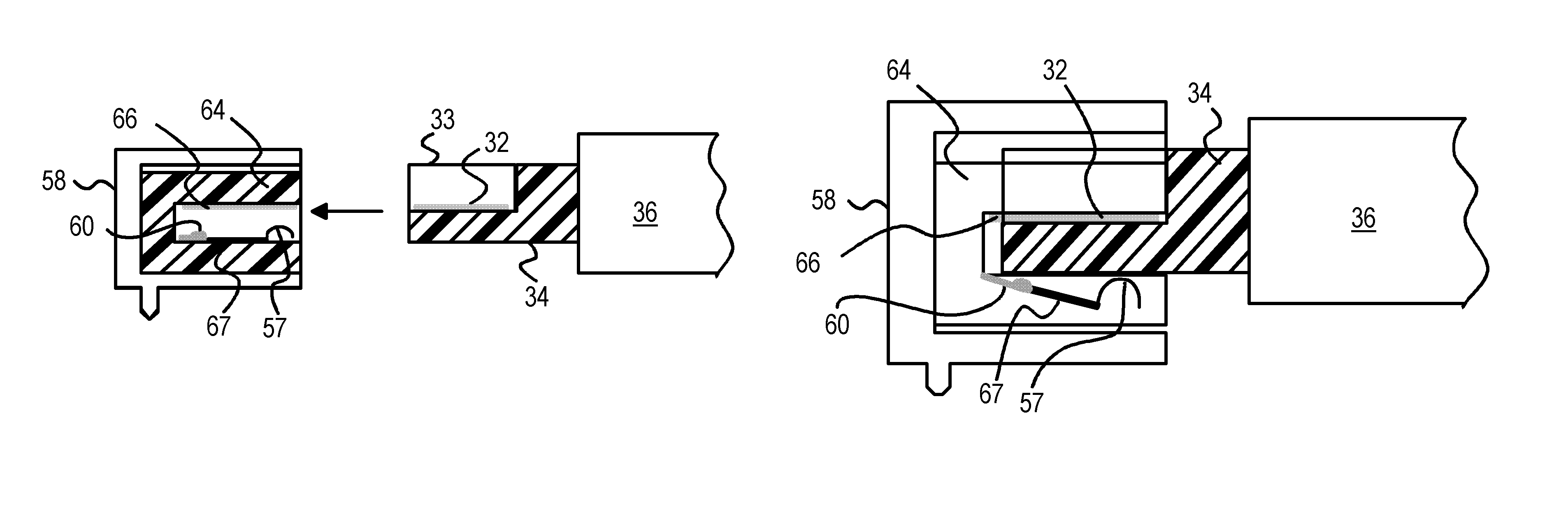

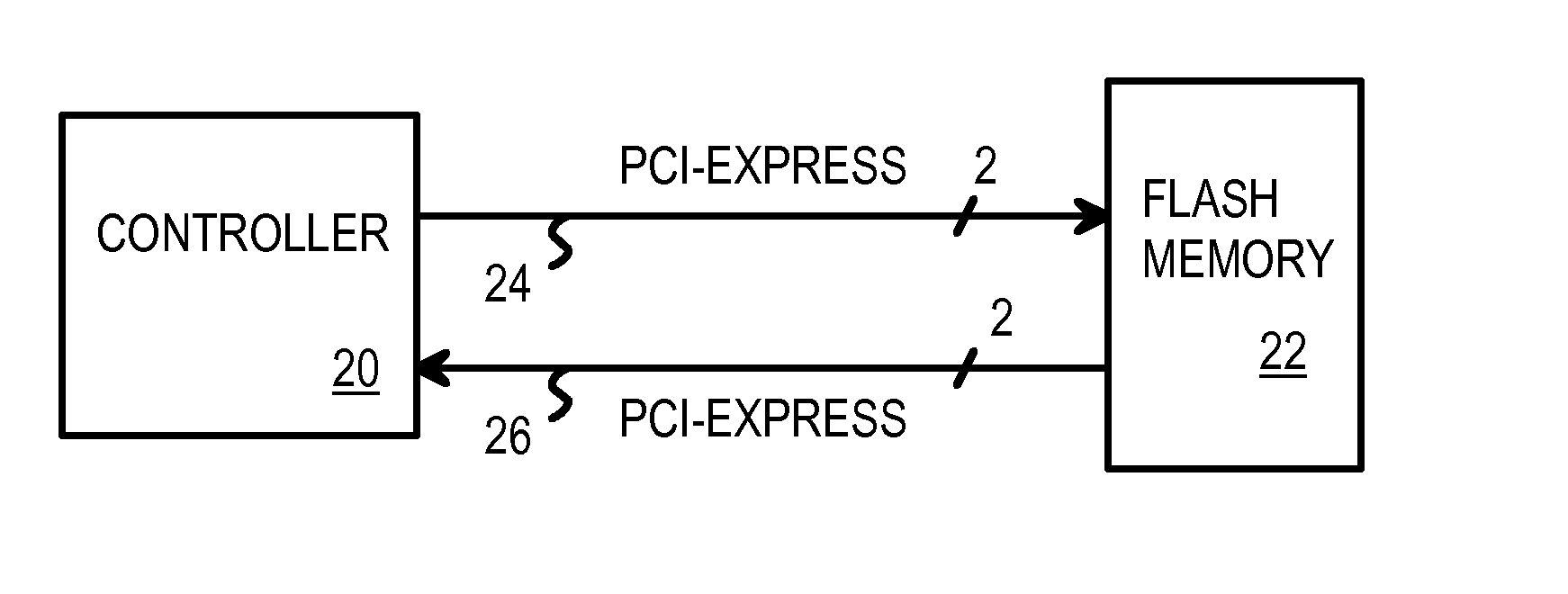

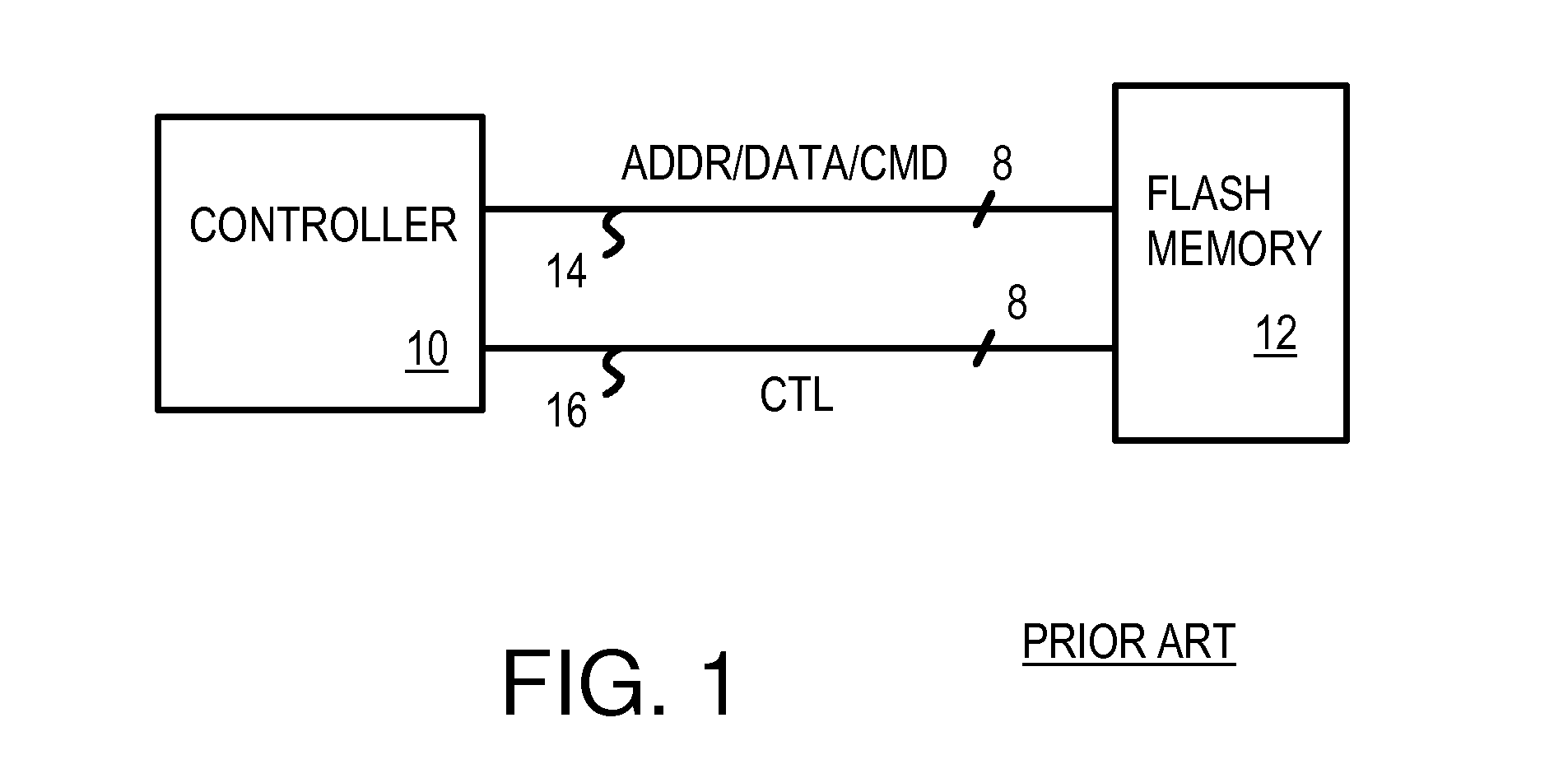

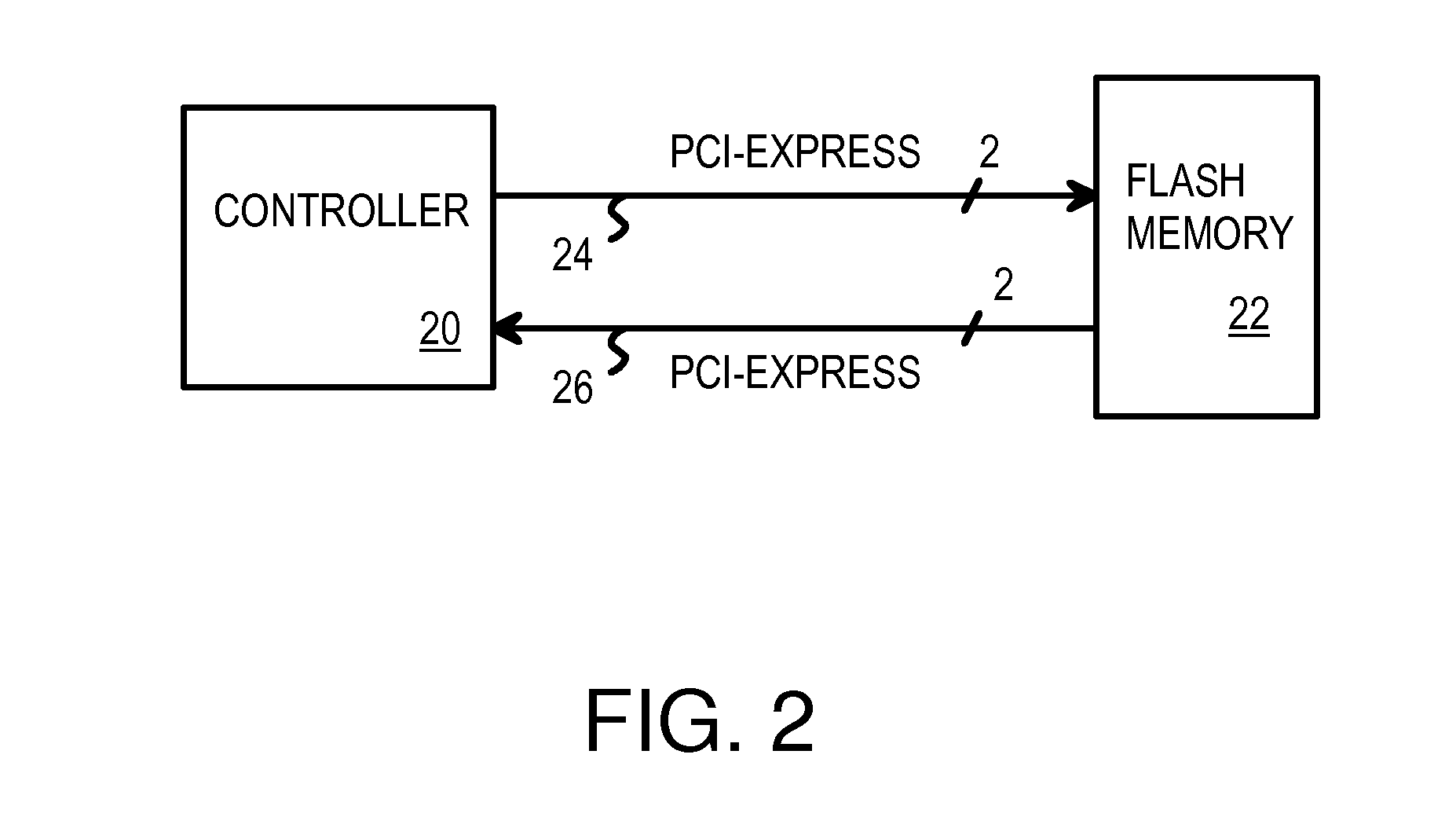

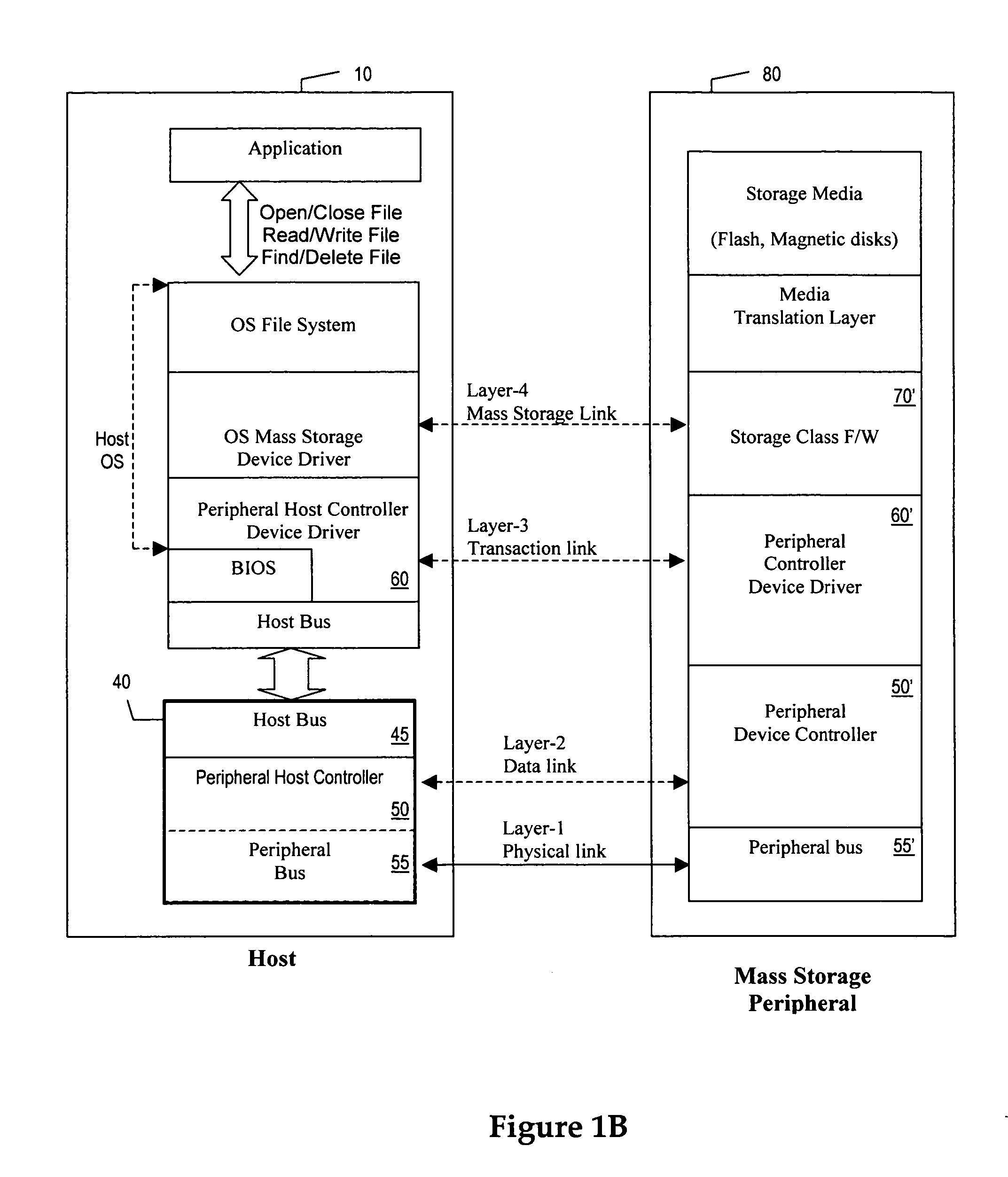

PCI express-compatible controller and interface for flash memory

InactiveUS7457897B1Improve performanceFacilitates optimal serviceabilityRead-only memoriesDigital storagePCI ExpressSystem bus

A PCI Express-compatible flash device can include one or more flash memory modules, a controller, and an ExpressCard interface. The controller can advantageously provide PCI Express functionality as well as flash memory operations, e.g. writing, reading, or erasing, using the ExpressCard interface. A PIO interface includes sending first and second memory request packets to the flash device. The first memory request packet includes a command word setting that prepares the flash device for the desired operation. The second memory request packet triggers the operation and includes a data payload, if needed. A DMA interface includes sending the second memory request from the flash device to the host, thereby triggering the host to release the system bus for the DMA operation.

Owner:SUPER TALENT TECH CORP

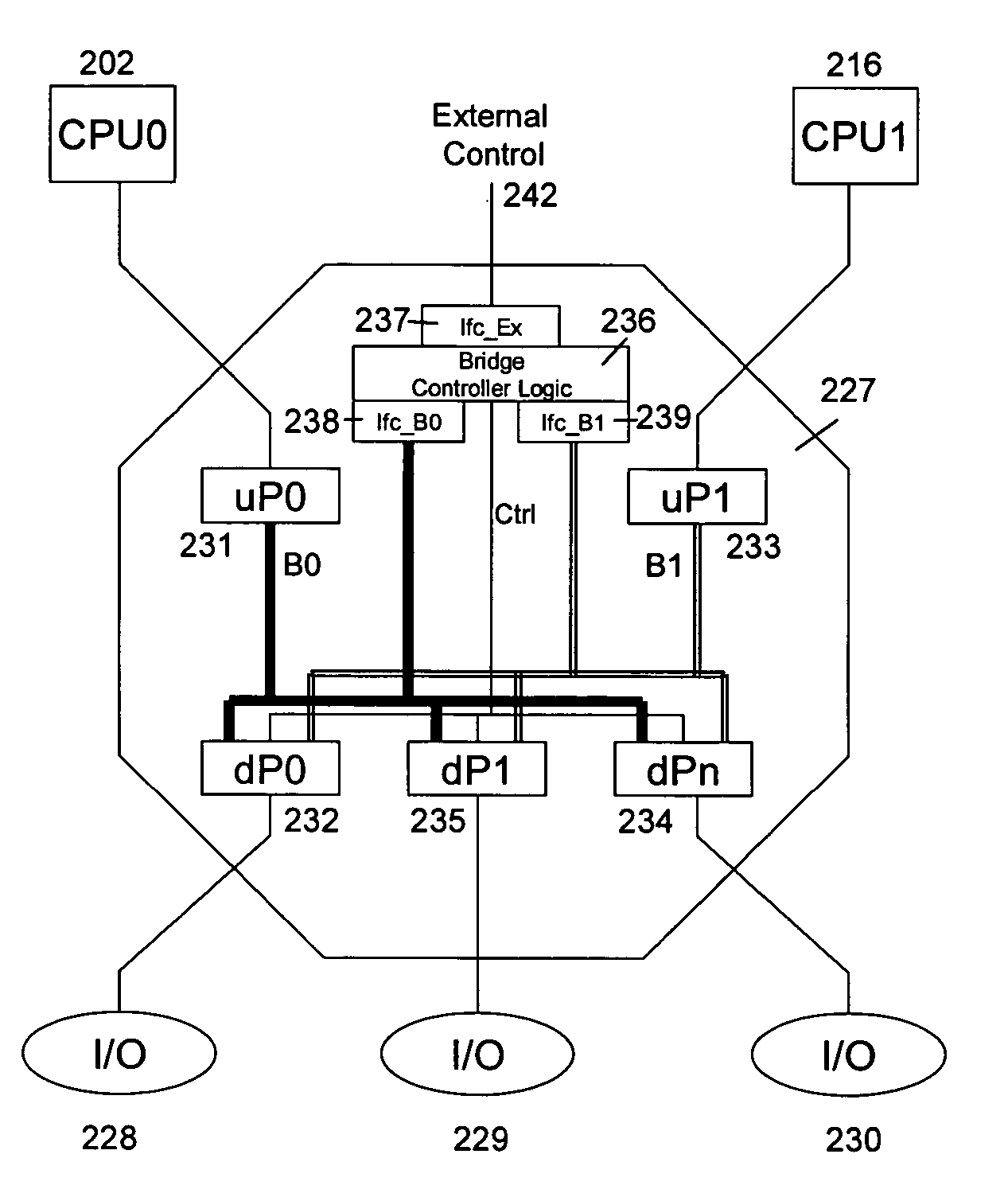

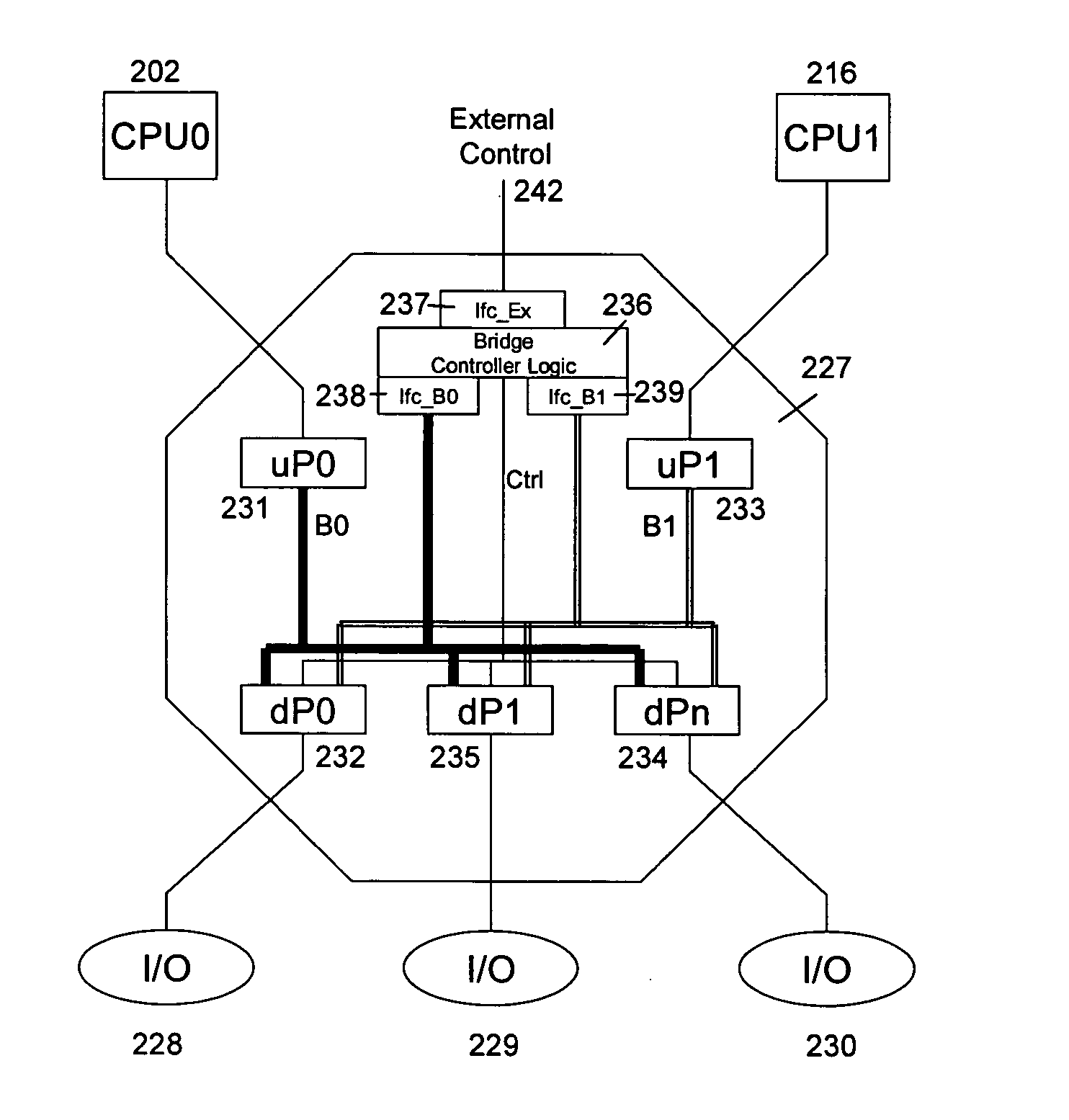

Configurable PCI express switch which allows multiple CPUs to be connected to multiple I/O devices

A configurable switch that enables multiple CPUs to be connected to multiple I / O devices through a single switch. The switches can be cascaded to enable more CPUs and / or more I / O devices in the tree. The configuration is transparent to the enumeration of the bus and endpoint devices. A simple management input such as SMBus or hardware strapping is used to set up the assignation of devices to CPUs. Utilization of a manager and the PCI Express hot plug controller registers enable hot-plug reconfiguration of the device tree as devices a switched between CPUs via PCI buses within the switch.

Owner:MICROSOFT TECH LICENSING LLC

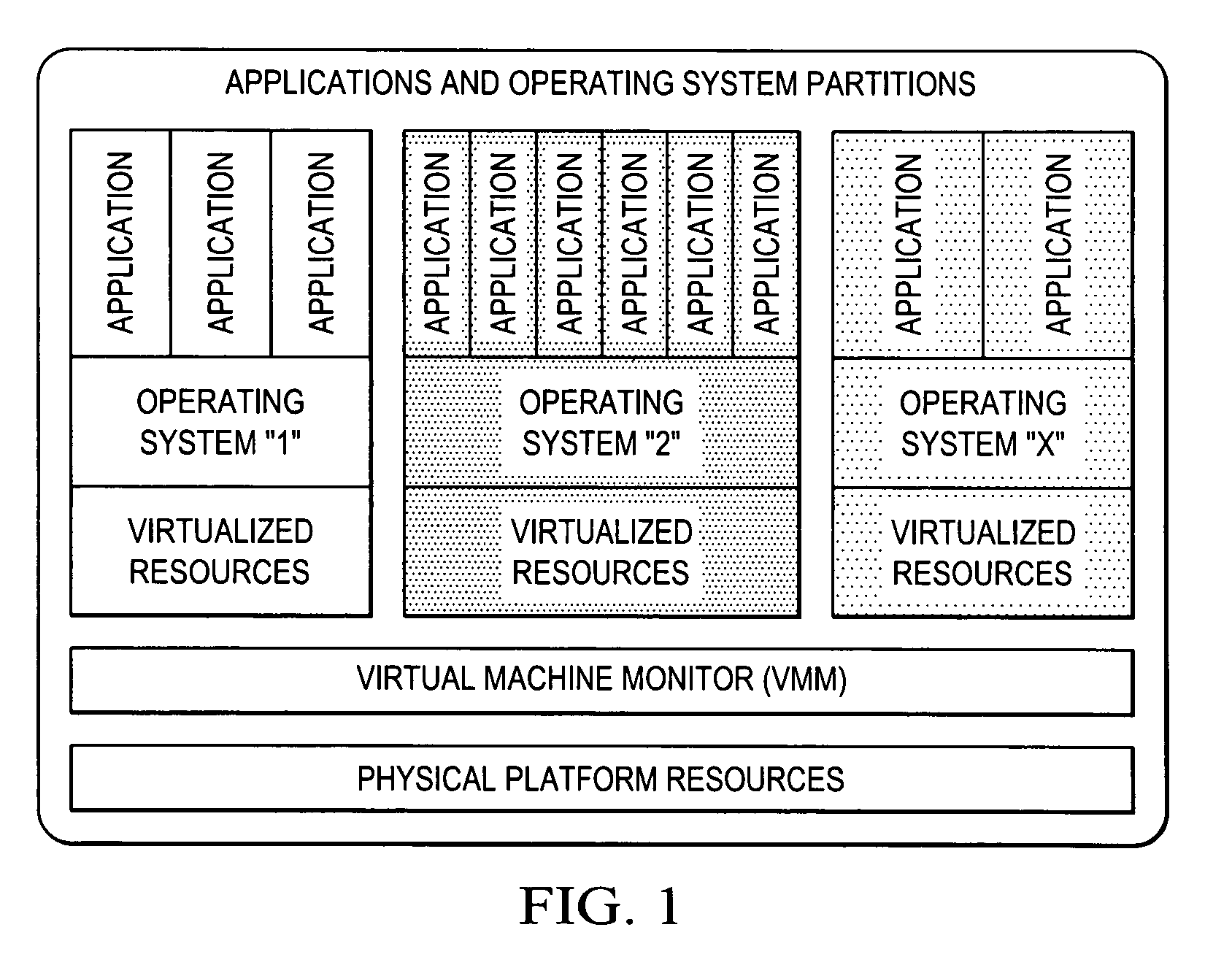

Method and system for native virtualization on a partially trusted adapter using adapter bus, device and function number for identification

A method, computer program product, and distributed data processing system that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to use a PCI adapter identifier to associate its resources to a system image and isolate them from other system images thereby providing I / O virtualization is provided. Specifically, the present invention is directed to a mechanism for sharing among multiple system images a conventional PCI (Peripheral Component Interconnect) I / O adapters, PCI-X I / O adapters, PCI-Express I / O adapters, and, in general, any I / O adapter that uses a memory mapped I / O interface for communications. A mechanism is provided that allows a single physical I / O adapter, such as a PCI, PCI-X, or PCI-E adapter, to use a PCI adapter identifier to associate its resources to a system image and isolate them from other system images, thereby providing I / O virtualization.

Owner:IBM CORP

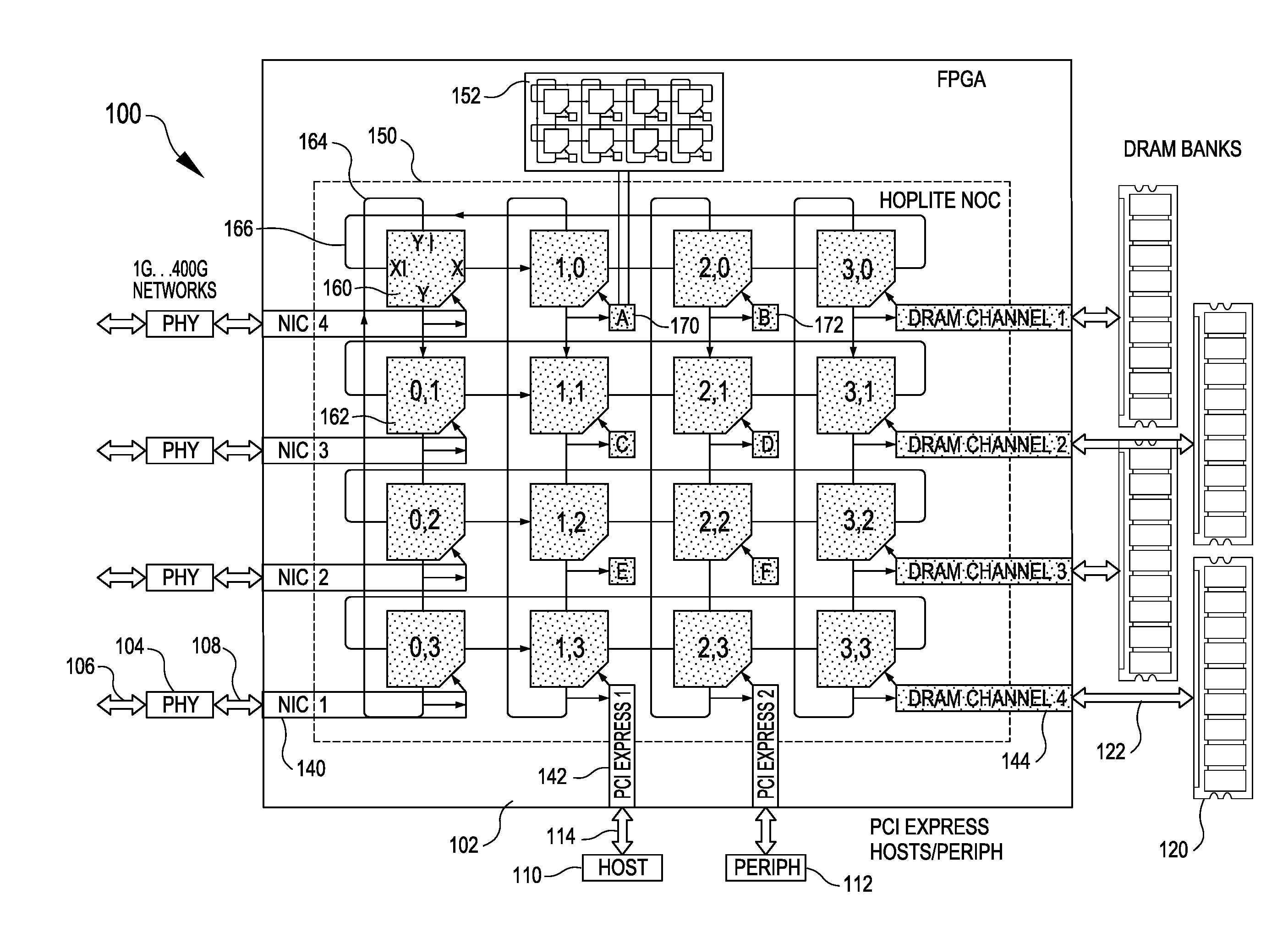

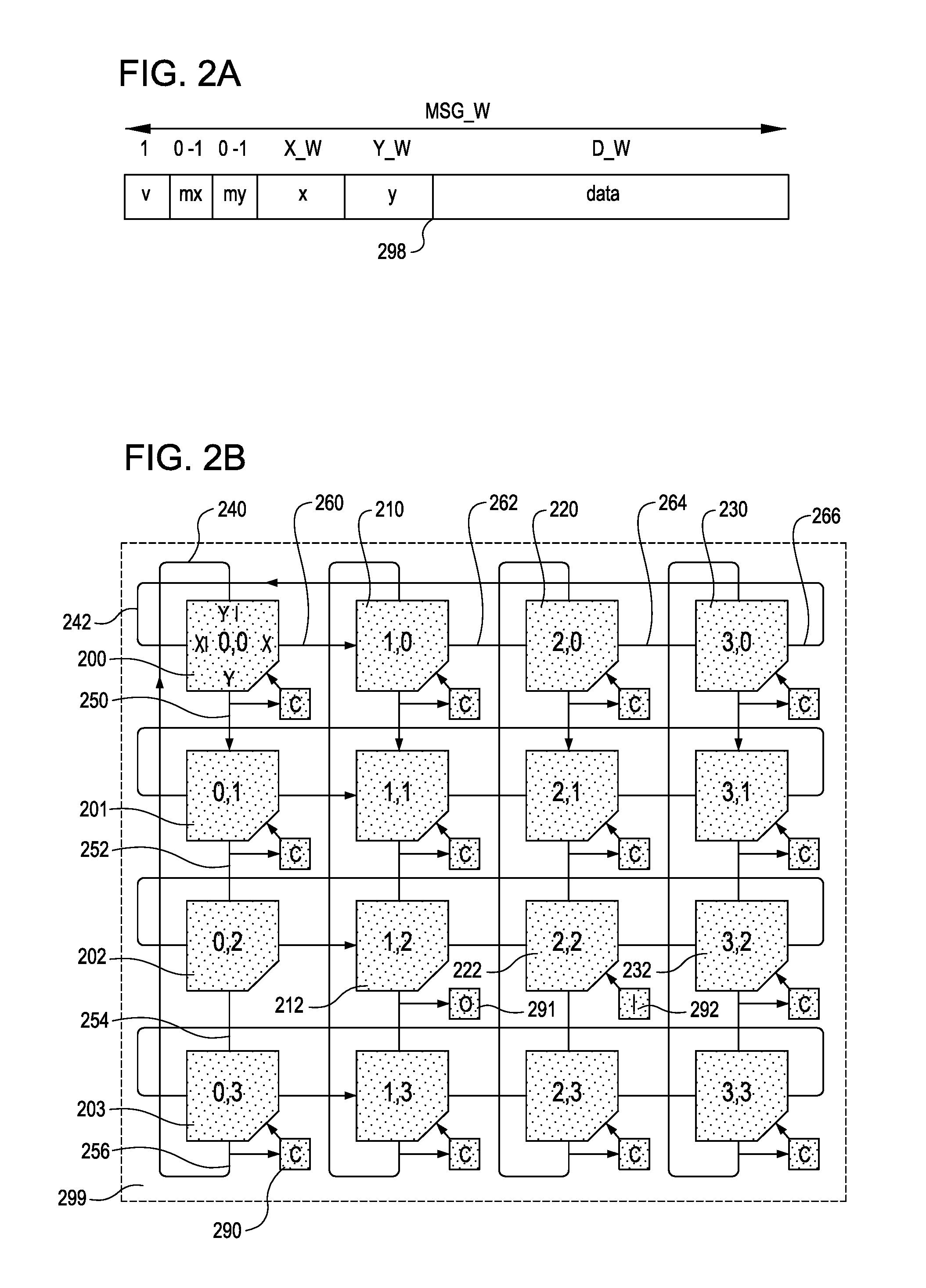

Directional two-dimensional router and interconnection network for field programmable gate arrays, and other circuits and applications of the router and network

ActiveUS20160344629A1Reduce switching delayLower latencyData switching networksNetwork sizeFpga implementations

A configurable directional 2D router for Networks on Chips (NOCs) is disclosed. The router, which may be bufferless, is designed for implementation in programmable logic in FPGAs, and achieves theoretical lower bounds on FPGA resource consumption for various applications. The router employs an FPGA router switch design that consumes only one 6-LUT or 8-input ALM logic cell per router per bit of router link width. A NOC comprising a plurality of routers may be configured as a directional 2D torus, or in diverse ways, network sizes and topologies, data widths, routing functions, performance-energy tradeoffs, and other options. System on chip designs may employ a plurality of NOCs with different configuration parameters to customize the system to the application or workload characteristics. A great diversity of NOC client cores, for communication amongst various external interfaces and devices, and on-chip interfaces and resources, may be coupled to a router in order to efficiently communicate with other NOC client cores. The router and NOC enable feasible FPGA implementation of large integrated systems on chips, interconnecting hundreds of client cores over high bandwidth links, including compute and accelerator cores, industry standard IP cores, DRAM / HBM / HMC channels, PCI Express channels, and 10G / 25G / 40G / 100G / 400G networks.

Owner:GRAY RES LLC

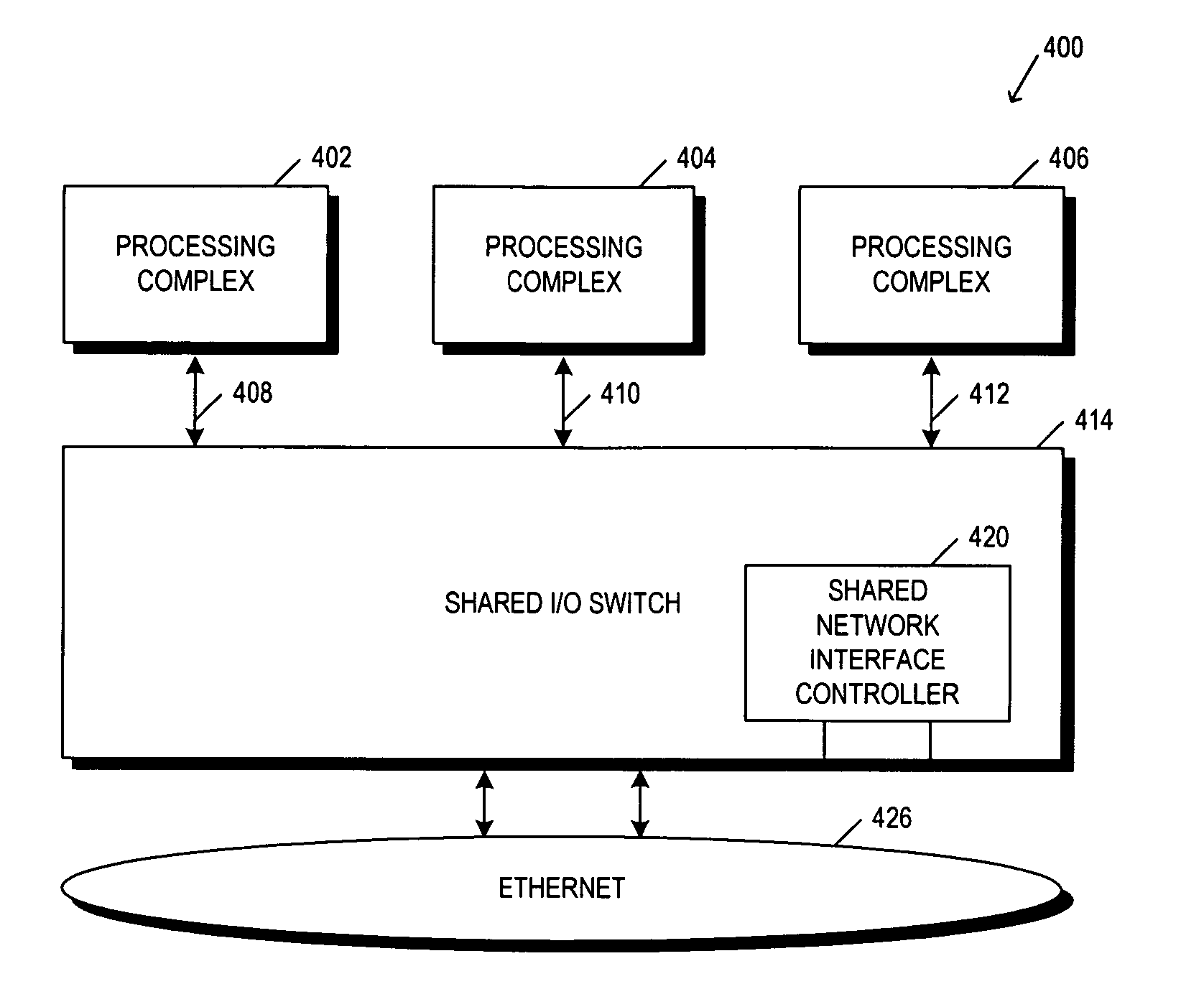

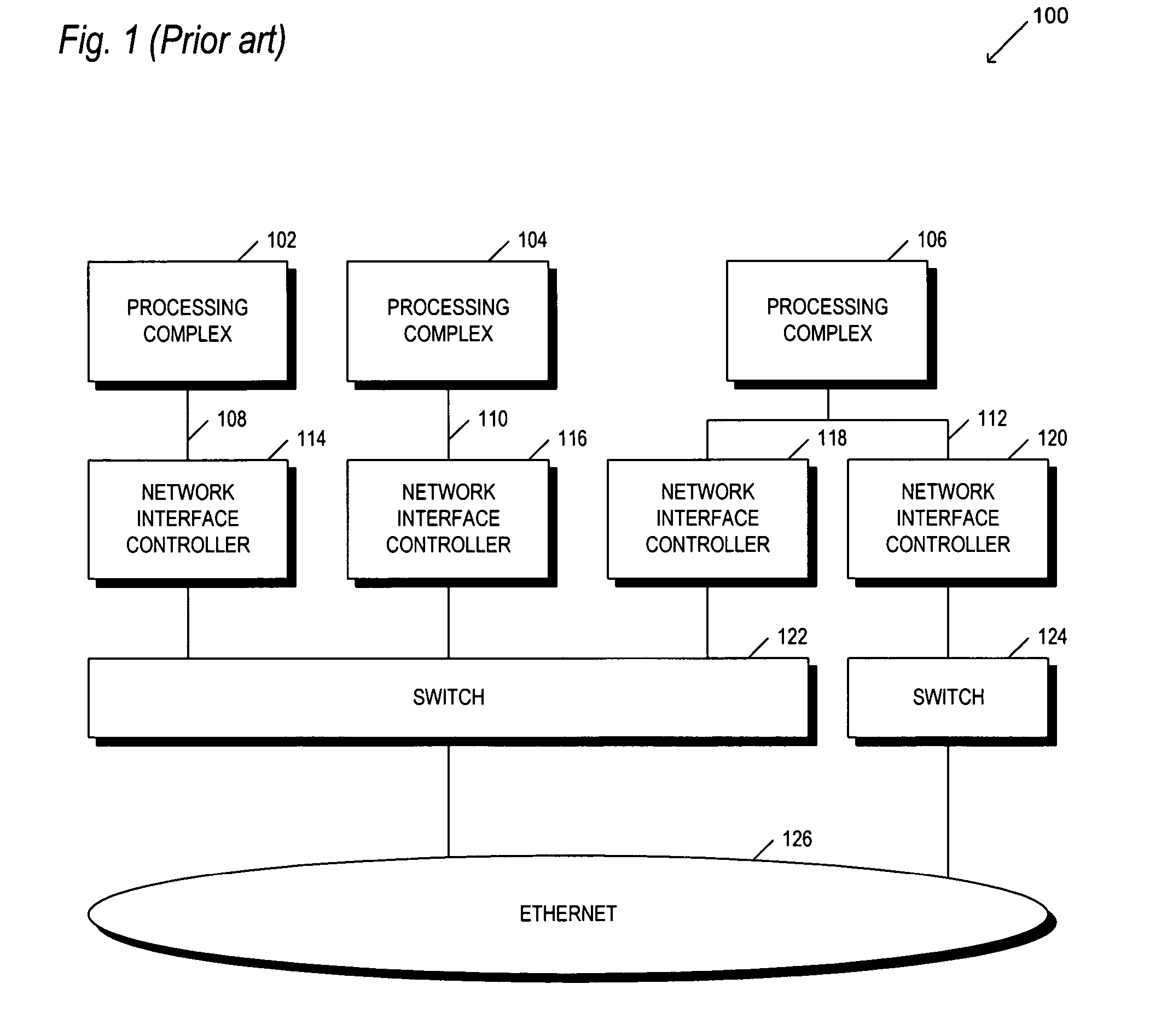

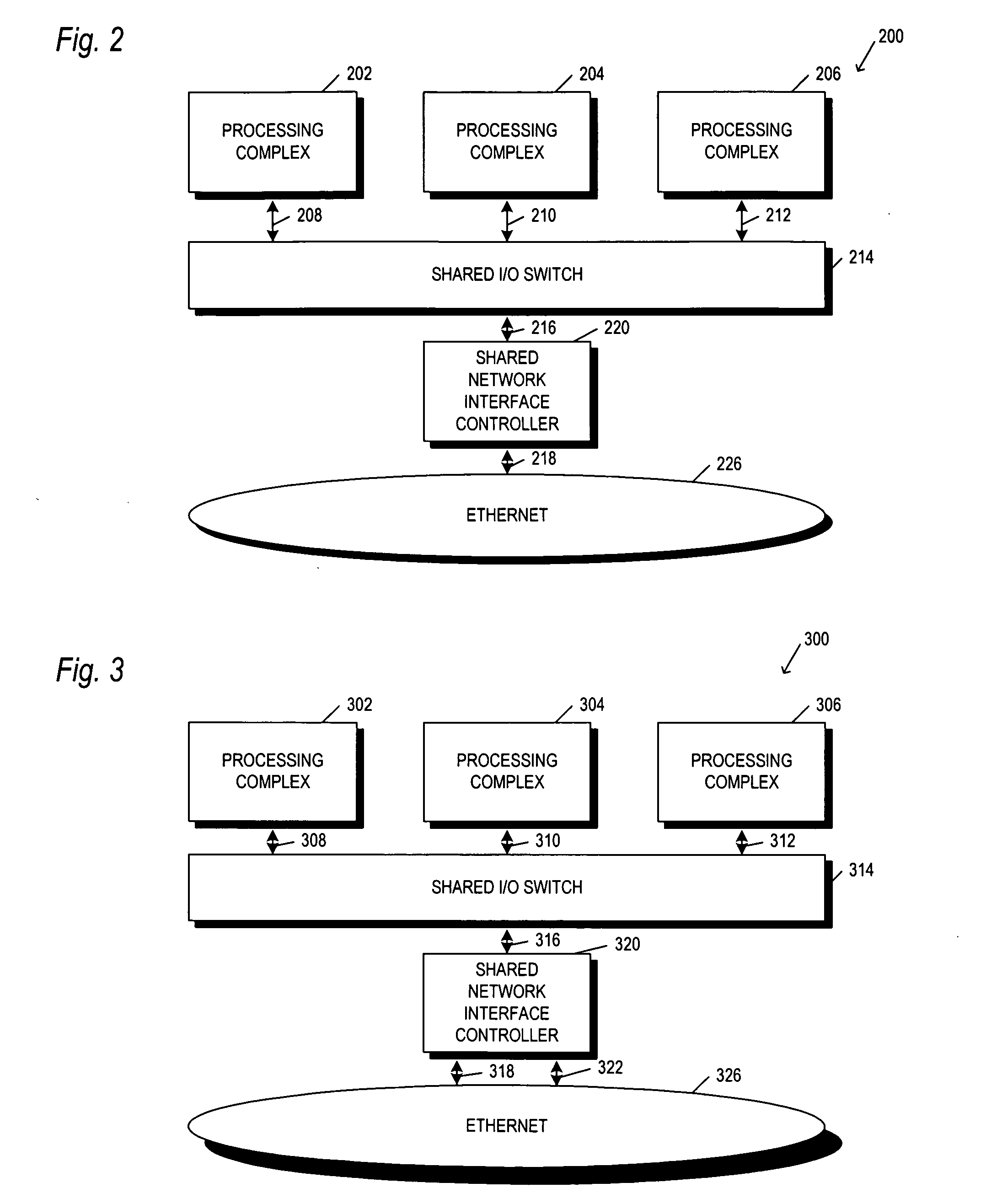

Method and apparatus for a shared I/O network interface controller

ActiveUS20050053060A1Multiplex system selection arrangementsData switching by path configurationTransient storagePCI Express

An apparatus and method is provided for interfacing a number of computer servers (or operating system domains) to a network such as Ethernet through a shared network interface controller (NIC) which is part of the load-store architecture of the operating system domains. The network interface controller includes a bus interface to couple the controller to a load-store domain bus (such as PCI-Express), the bus including header information to associate data on the bus with an originating operating system domain. The controller also includes transmit / receive logic to connect it to the network. In between the bus interface and the transmit / receive logic is buffering to temporarily store data coming either from the operating system domains or the network. The buffered data is tagged within an identifier to associate it with one or more of the operating system domains. Association logic is further provided to allow the controller to designate, and later lookup which destination MAC address (on the Ethernet side) is associated with which operating system domain. Control Status Registers (CSR's) specific to an operating system domain are duplicated and made available for each domain. Descriptor Register files are also duplicated for each operating system domain. A number of direct memory access (DMA) engines are provided to improve throughput. And, packet replication logic, along with filters (perfect and hash) and VLAN tables are used for looping back packets originating from one of the operating system domains to one or more of the other operating system domains, for server to server communication, multicast and broadcast operations.

Owner:MELLANOX TECHNOLOGIES LTD

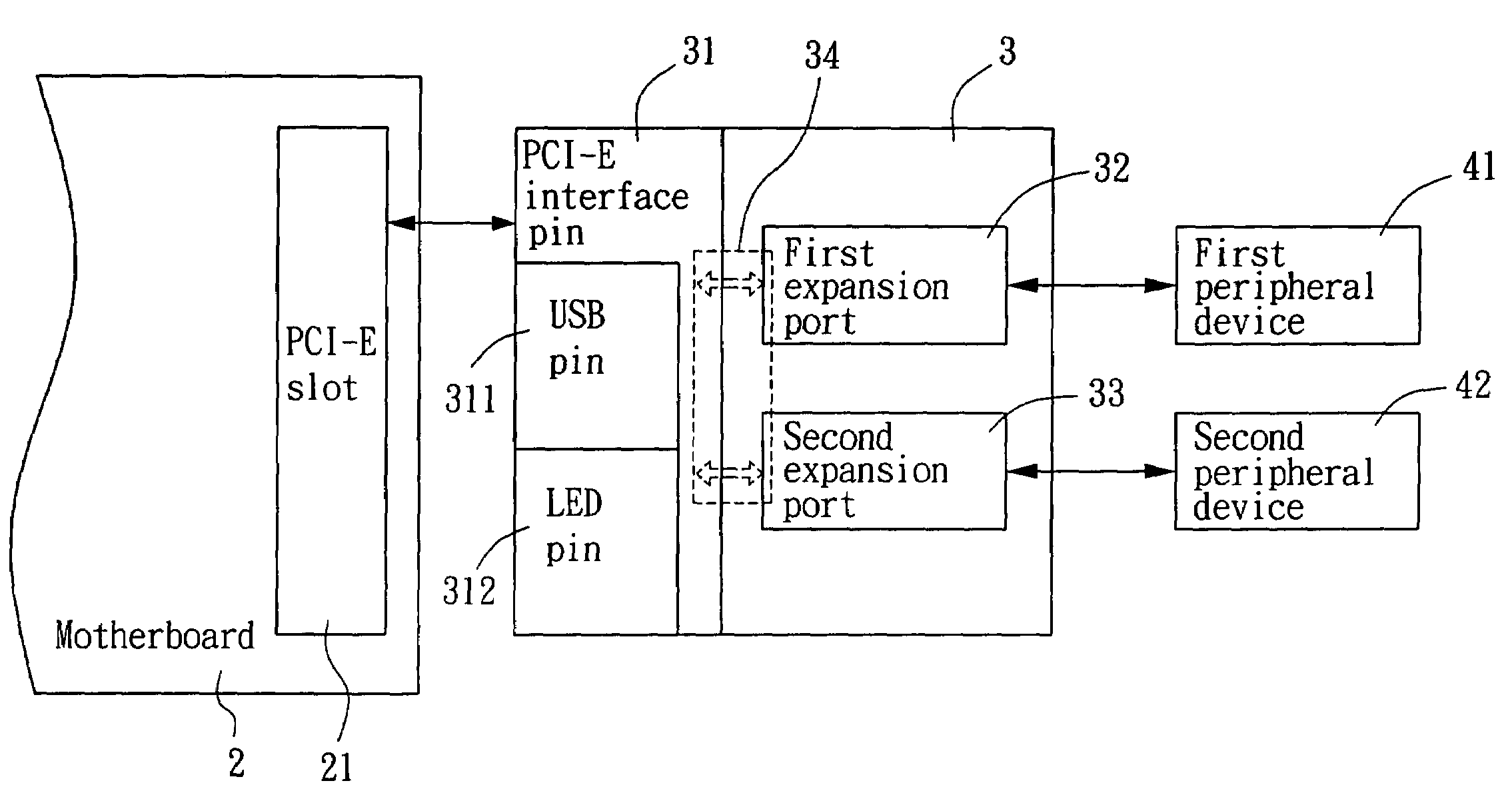

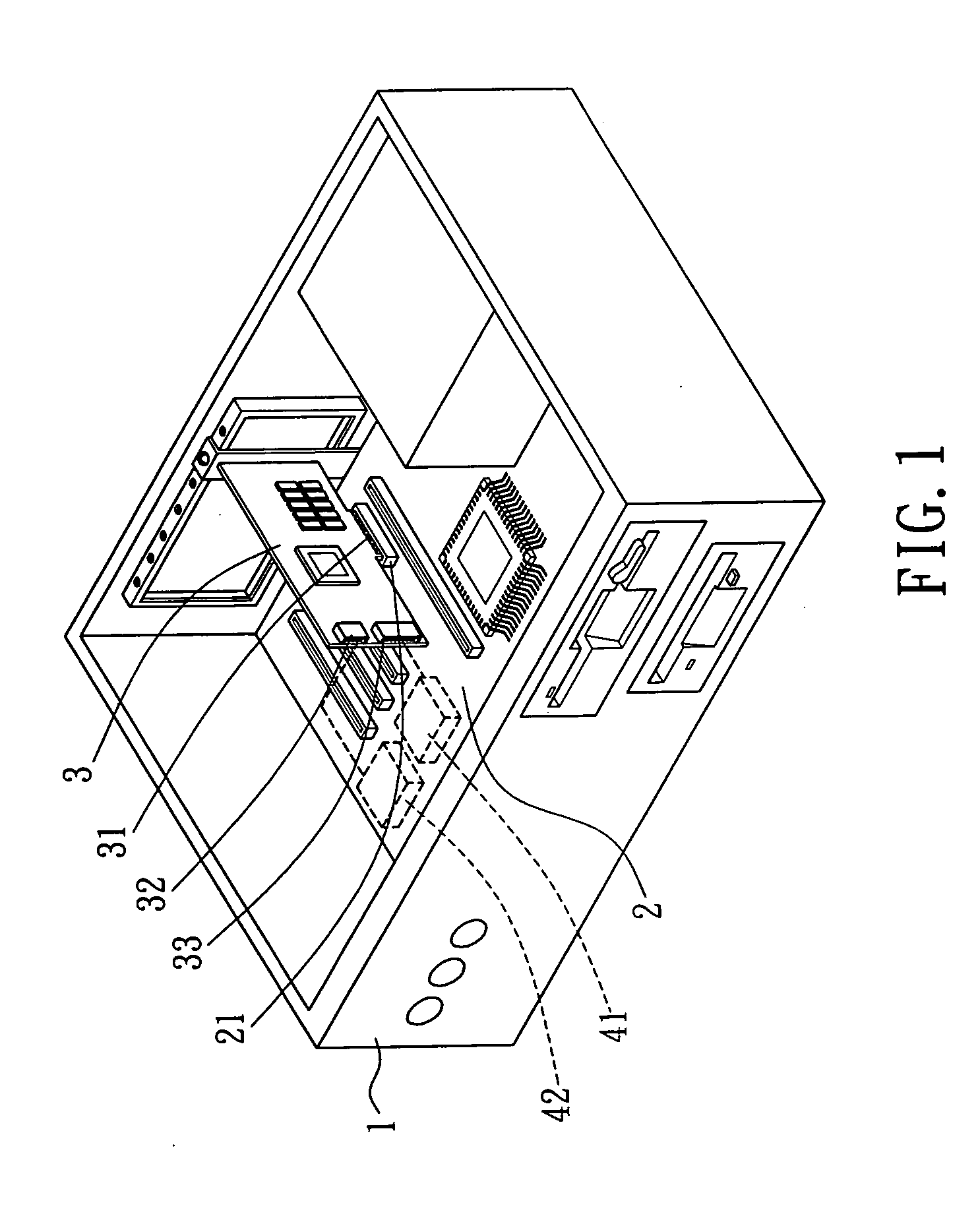

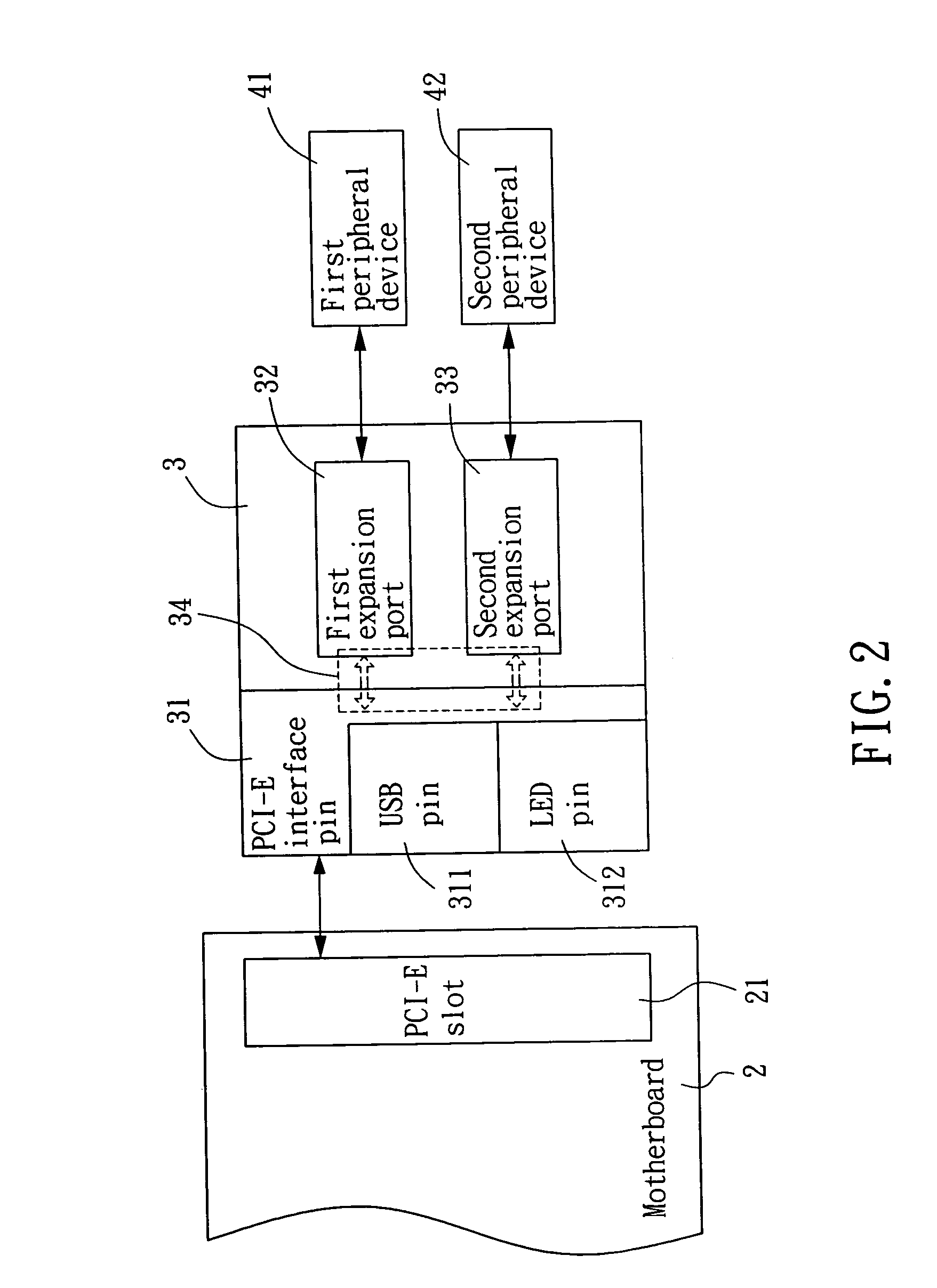

PCI-Express multimode expansion card and communication device having the same

InactiveUS20080065805A1Achieve effectDigital data processing detailsComponent plug-in assemblagesExpansion cardExtensibility

The present invention discloses a PCI-Express multimode expansion card comprising a PCI-Express interface port for insertion into a PCI-Express slot of a motherboard, a PCI-Express expansion port, a USB expansion port, and a jumper circuit connecting the PCI-Express interface port and the two expansion ports. The PCI-Express expansion port provides expandability by allowing the attachment of a PCI-Express interfaced peripheral device, and the USB expansion port provides expandability by allowing the attachment of a USB-interfaced peripheral device. As such, a single PCI-Express multimode expansion card inserted into a PCI-Express slot configured on the motherboard can be used to attach two peripheral devices with different interface, thereby achieving the function of multimode expansion.

Owner:CAMEO COMM

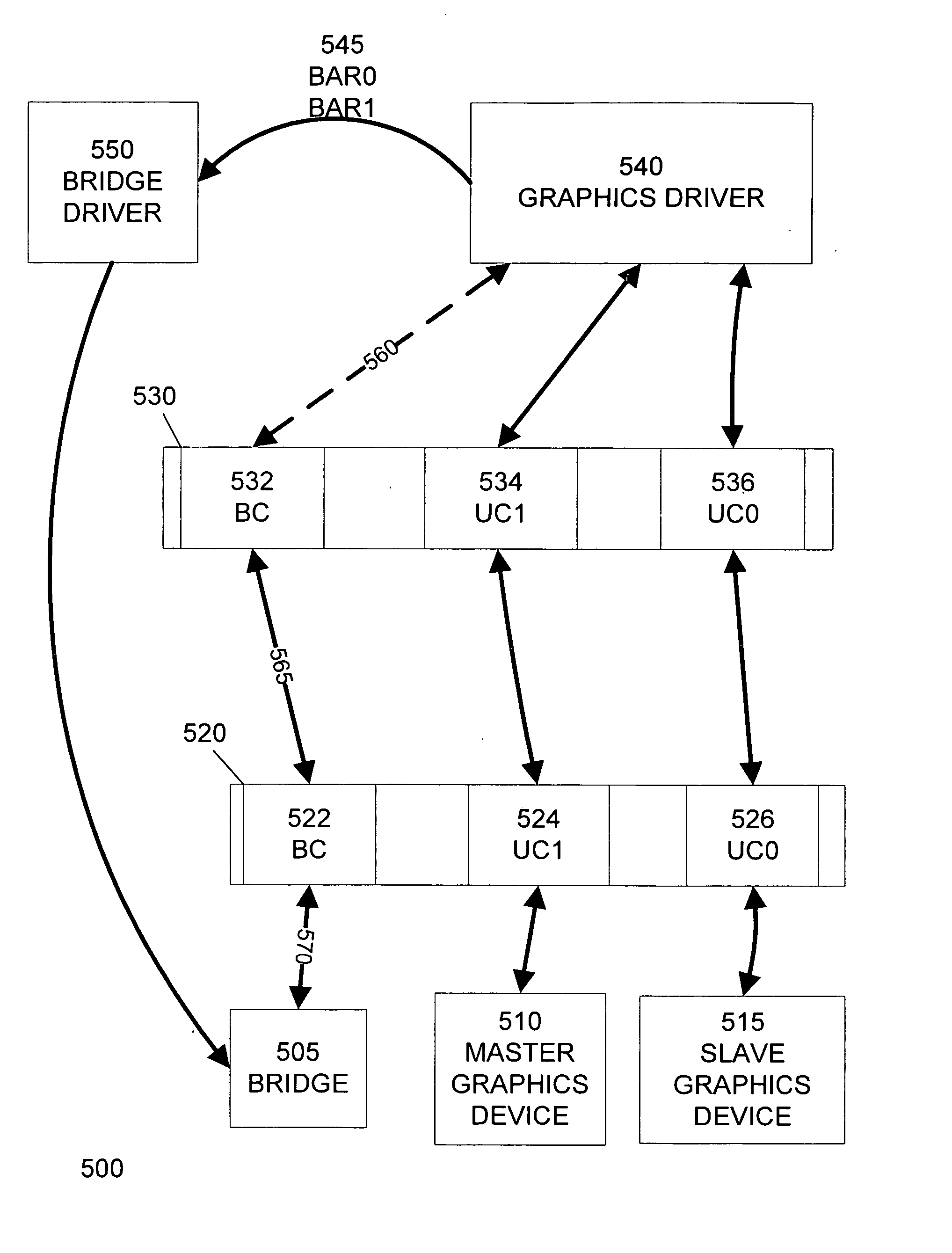

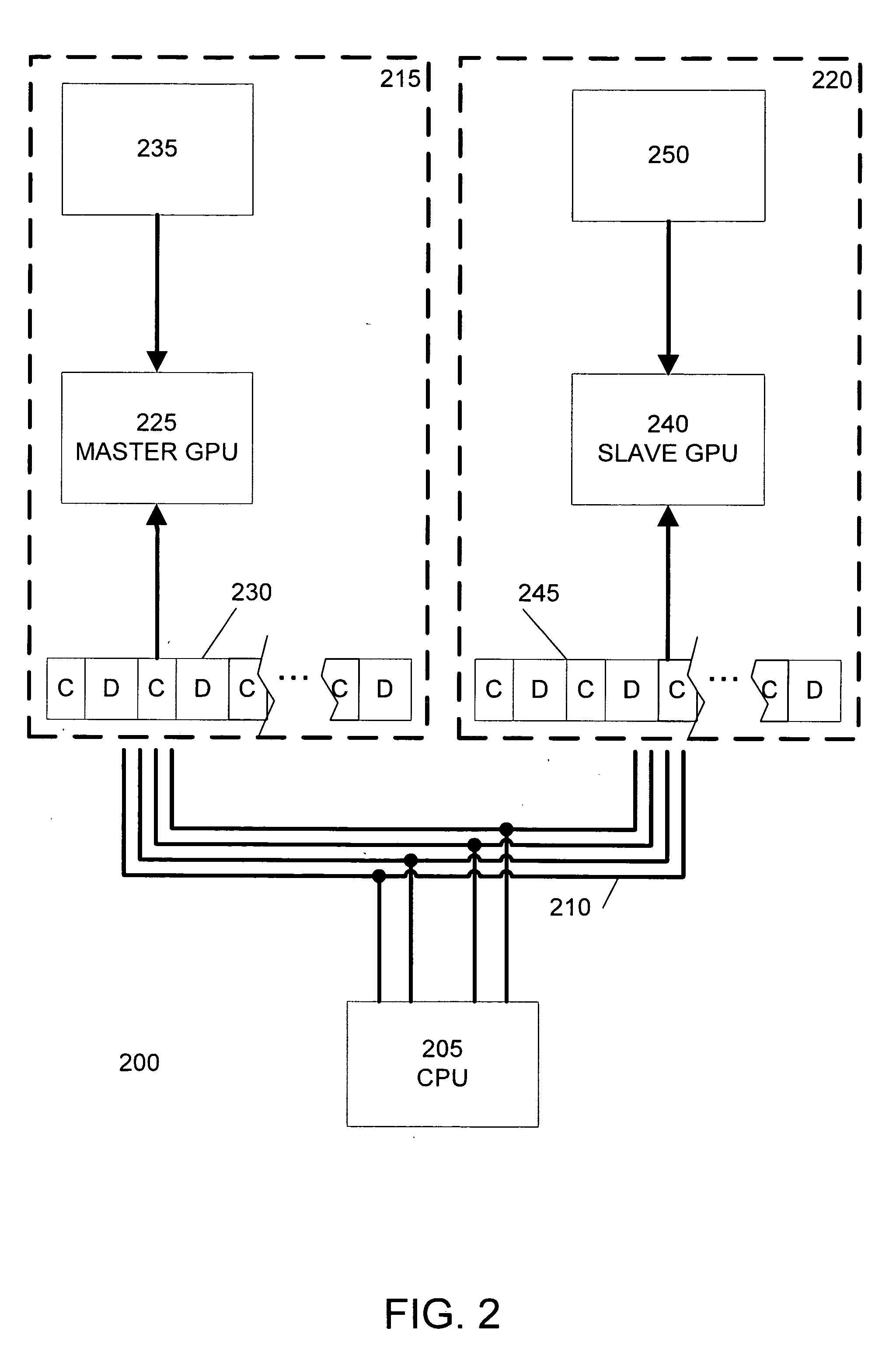

Graphics device clustering with PCI-express

ActiveUS20050190190A1Easy transferImprove performanceCathode-ray tube indicatorsMultiple digital computer combinationsGraphicsAlternate frame rendering

A bridge associated with a broadcast aperture facilitates the transfer of rendering commands and data between a processor and multiple graphics devices. The bridge receives data written by the processor to the broadcast aperture and forwards it to multiple graphics devices, eliminating the need for the processor to perform duplicative(?) write operations. During system initialization, a broadcast aperture is allocated to the bridge in address space based on an aperture size value set using a system configuration utility and stored in system configuration memory. A graphics driver activates the broadcast aperture by sending unicast aperture parameters associated with the multiple graphics devices to the bridge via a bridge driver. Upon activating the broadcast aperture, multiple graphics devices can be operated in parallel to improve rendering performance. Parallel rendering techniques include split-frame, alternate frame, and combined split- and alternate frame rendering.

Owner:NVIDIA CORP

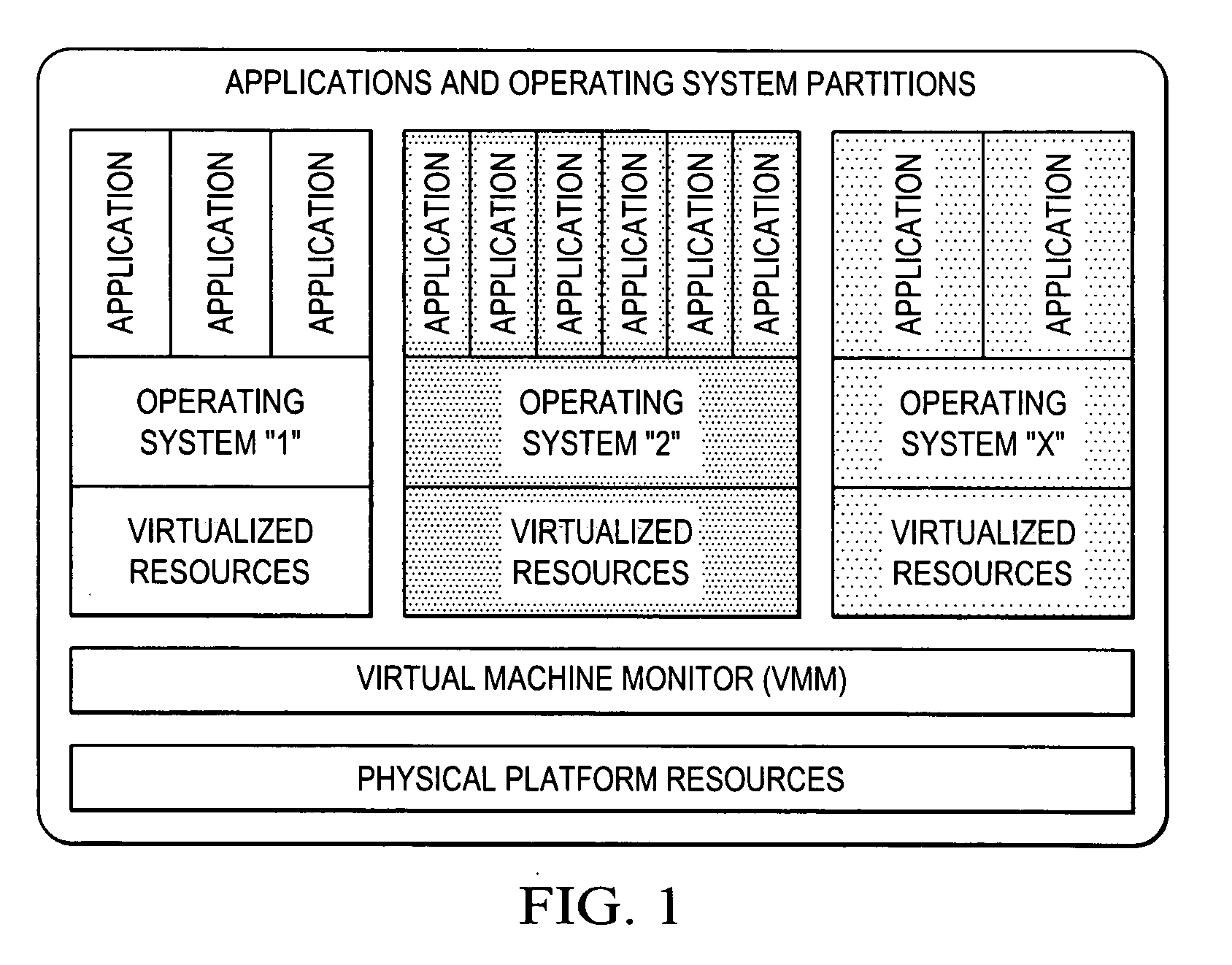

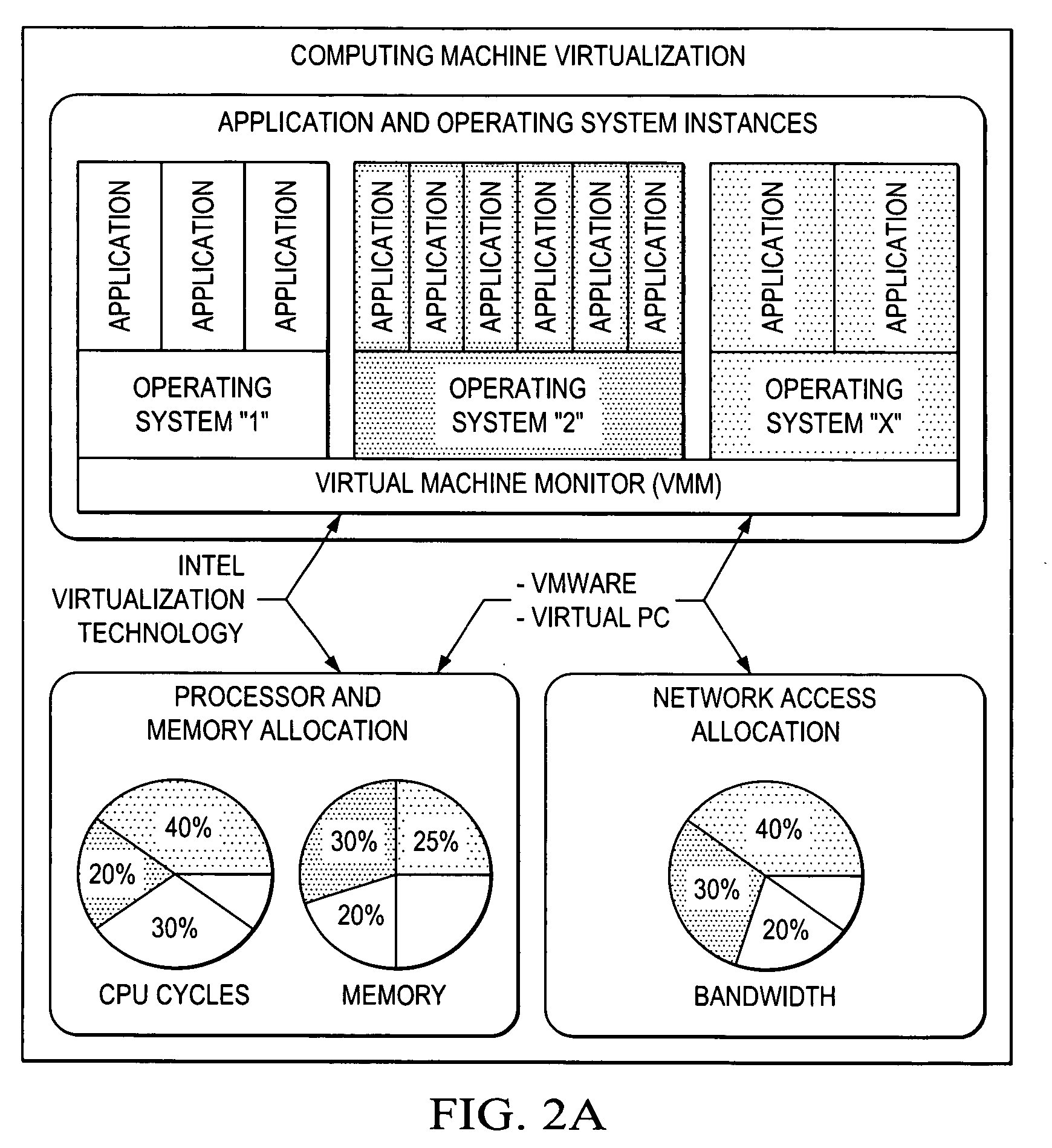

Virtualization of a host computer's native I/O system architecture via the internet and LANs

InactiveUS20090006710A1Unprecedented reachUnprecedented flexibilityTime-division multiplexMultiple digital computer combinationsVirtualizationTTEthernet

Owner:NUON

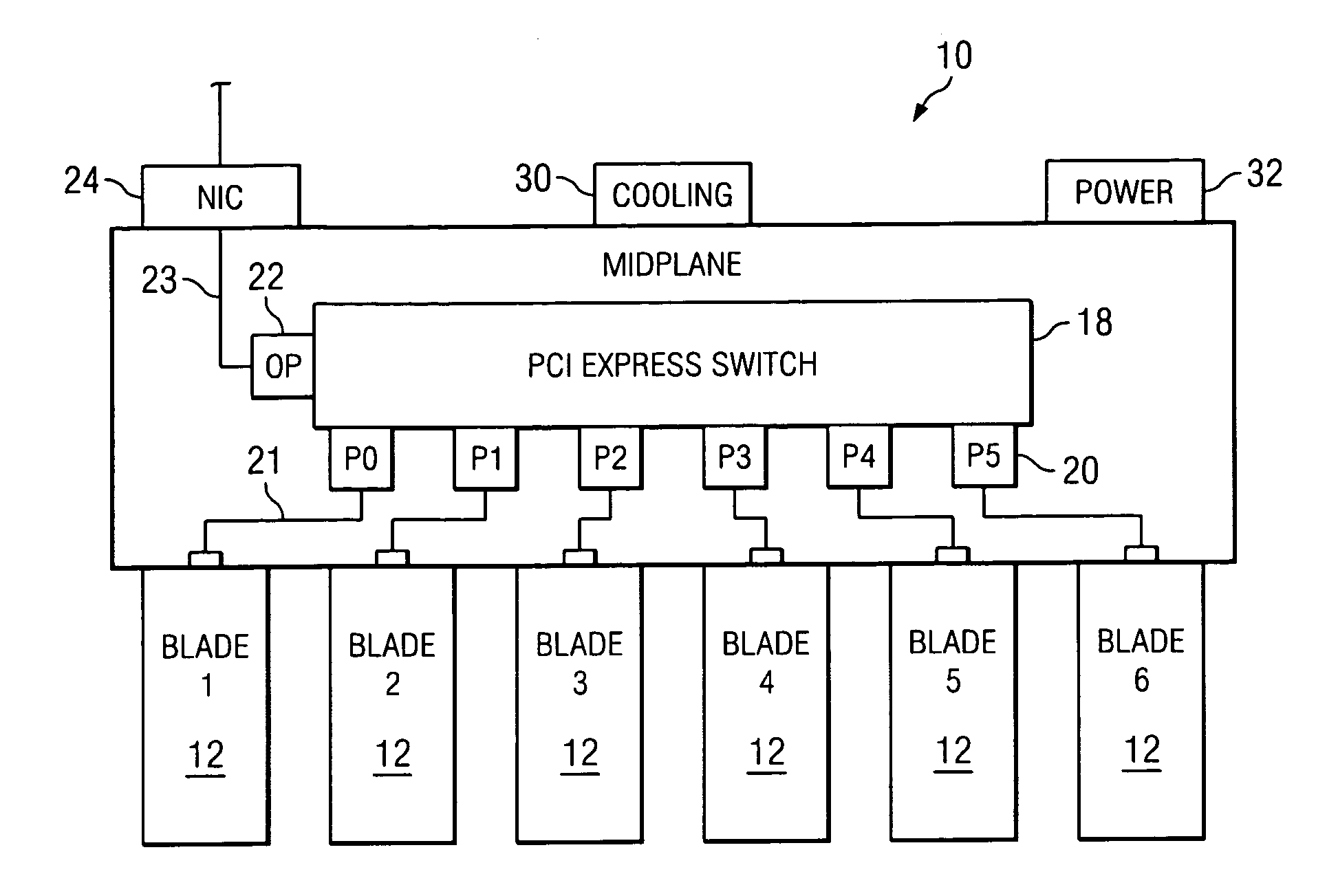

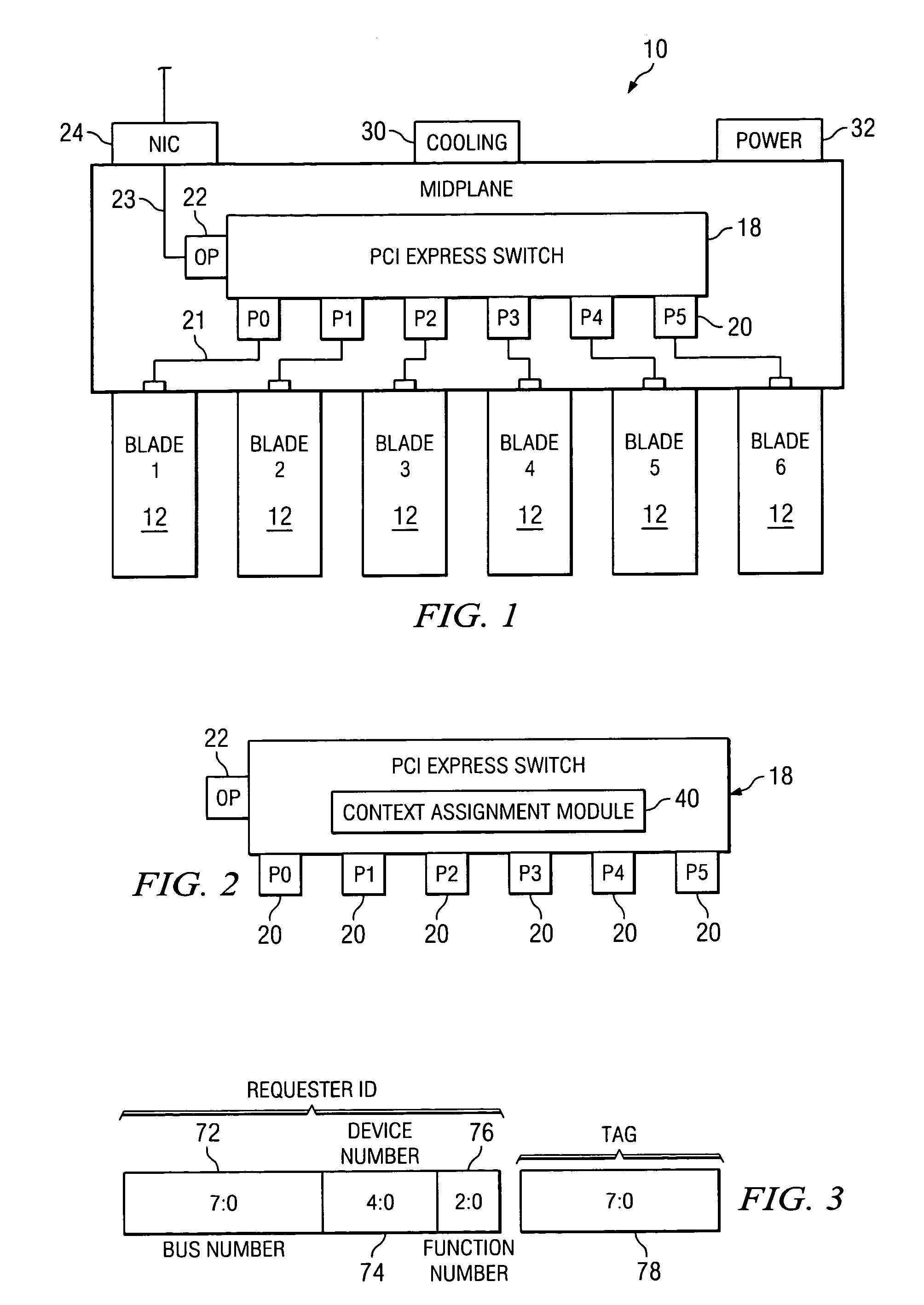

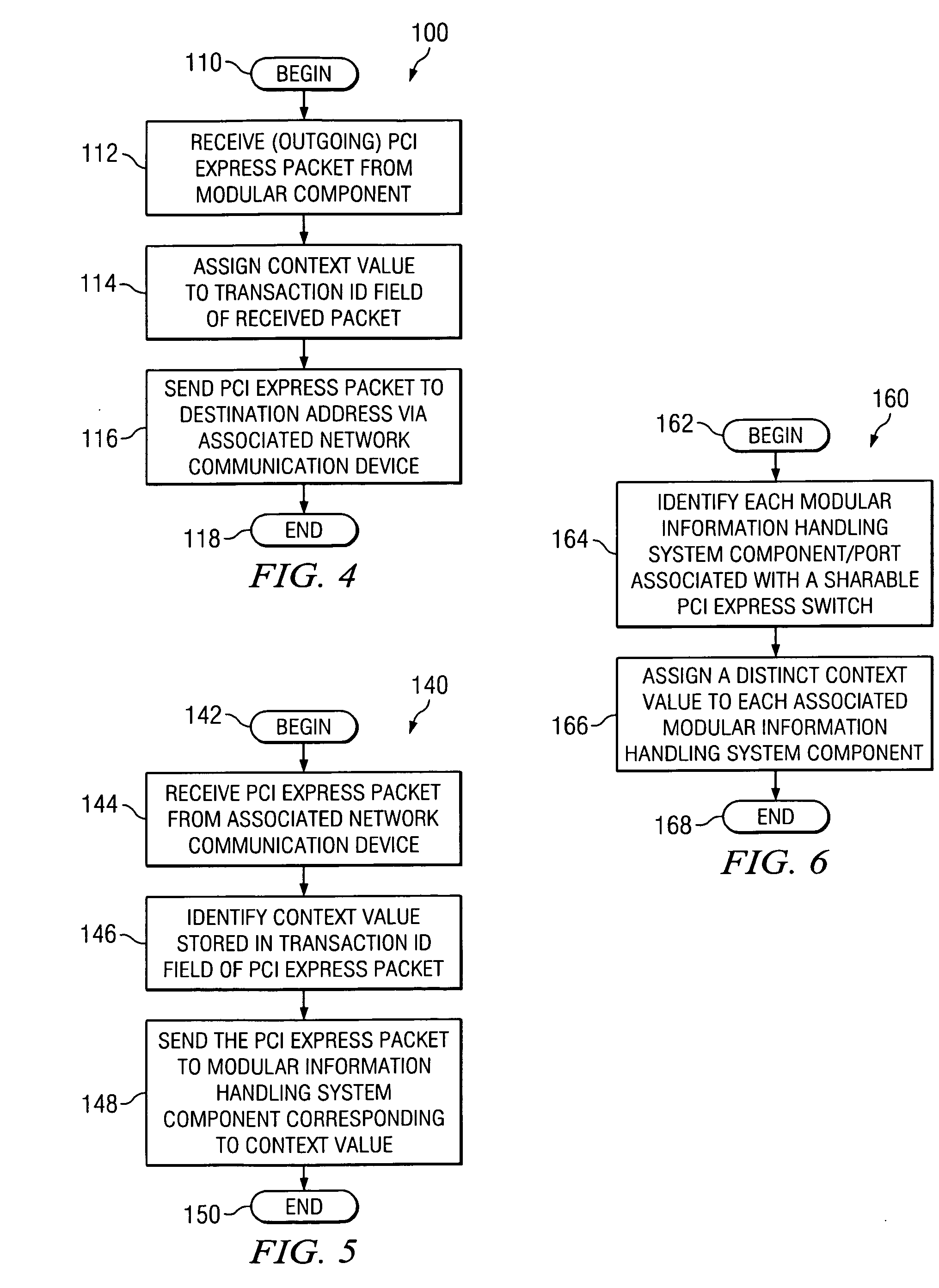

System and method for providing a shareable input/output device in a PCI express environment

The midplane of a modular information handling system includes a sharable PCI Express switch that is serially connect with each associated modular information handling system component and a network communication device. The shareable PCI Express switch acts to receive PCI Express packets from associated information handling system components, with each packet including a Transaction ID field. The shareable PCI Express switch assigns a context value that identifies a particular modular information handling system component within the Transaction ID field of each PCI Express packet received from the connected modular information handling system component.

Owner:DELL PROD LP

Dual-Personality Extended-USB Plug and Receptacle with PCI-Express or Serial-AT-Attachment Extensions

An extended Universal-Serial-Bus (USB) connector plug and socket each have a pin substrate with one surface that supports the four metal contact pins for the standard USB interface. An extension of the pin substrate carries another 8 extension metal contact pins that mate when both the connector plug and socket are extended. The extension can be an increased length of the plug's and socket's pin substrate or a reverse side of the substrate. Standard USB connectors do not make contact with the extension metal contacts that are recessed, retracted by a mechanical switch, or on the extension of the socket's pin substrate that a standard USB connector cannot reach. Standard USB sockets do not make contact with the extension metal contacts because the extended connector's extension contacts are recessed, or on the extension of the connector pin substrate that does not fit inside a standard USB socket.

Owner:SUPER TALENT TECH CORP

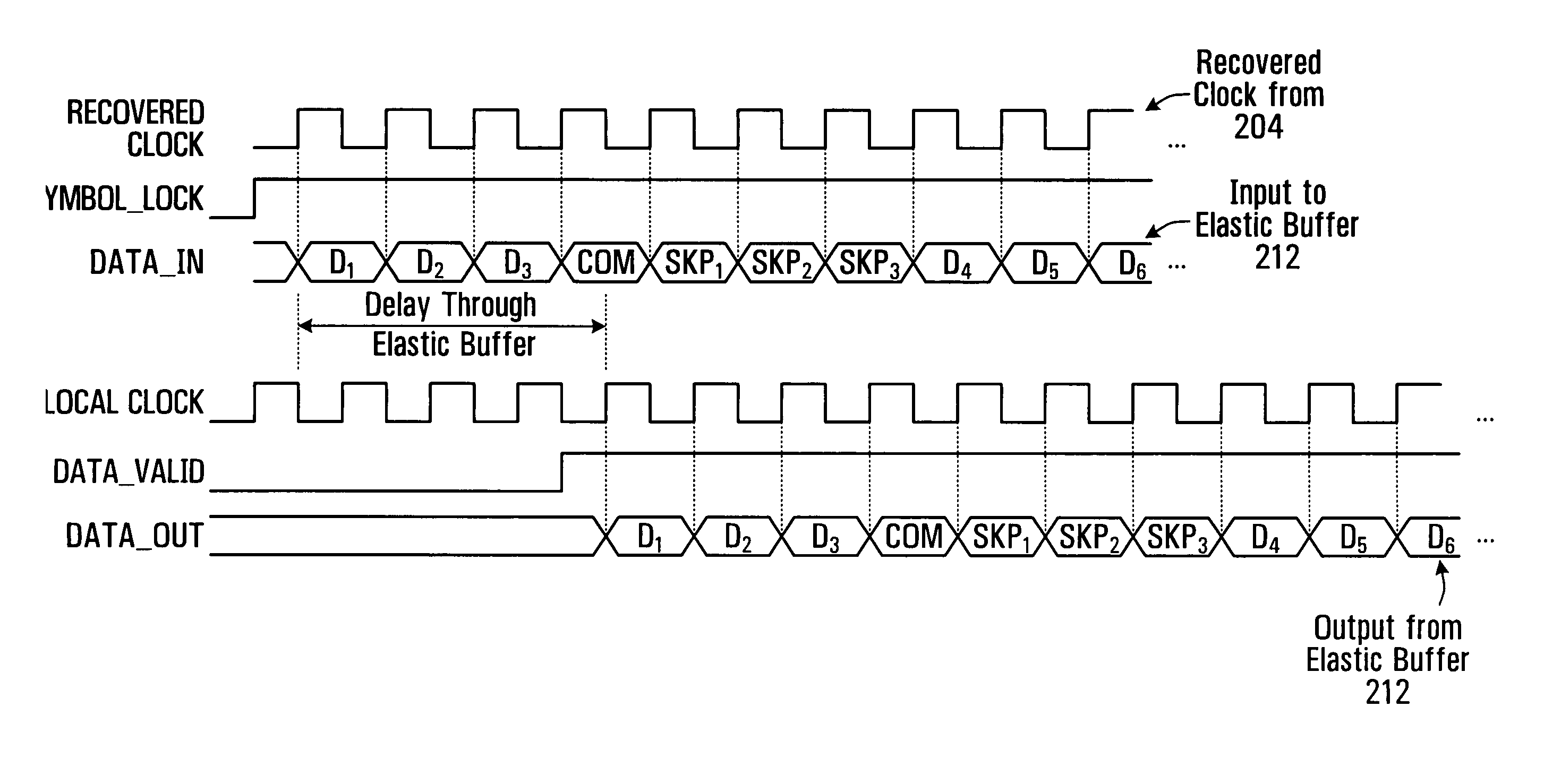

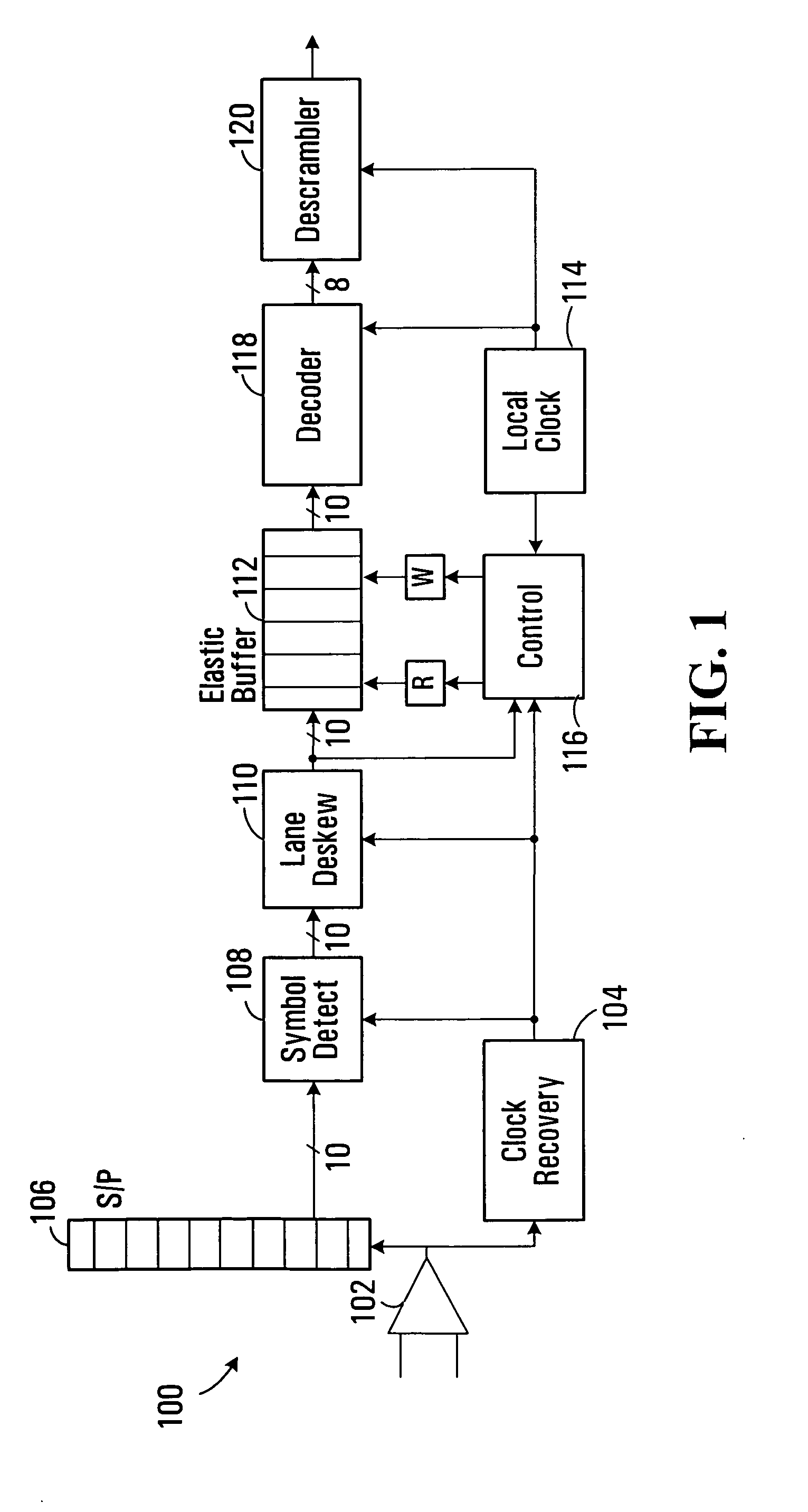

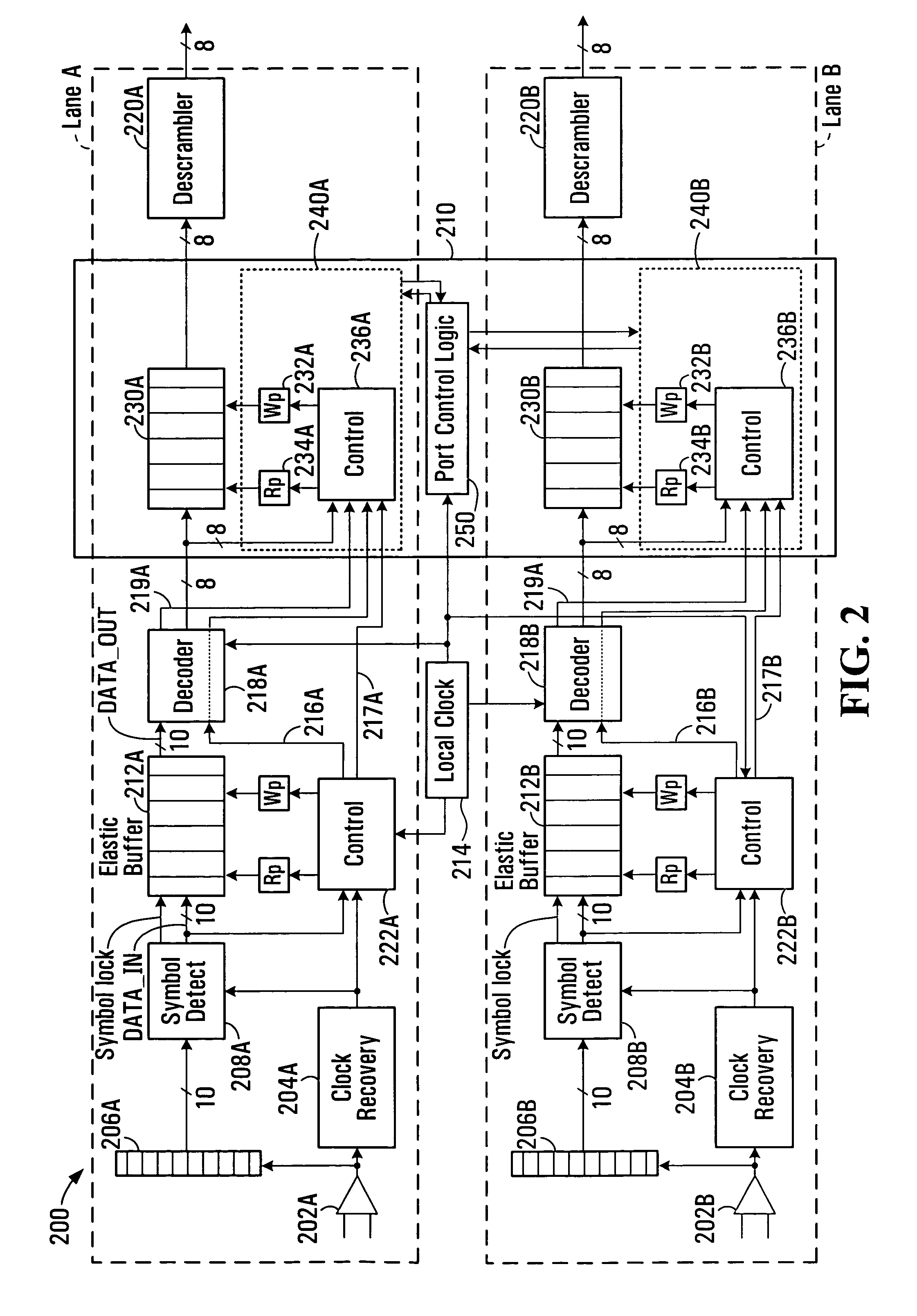

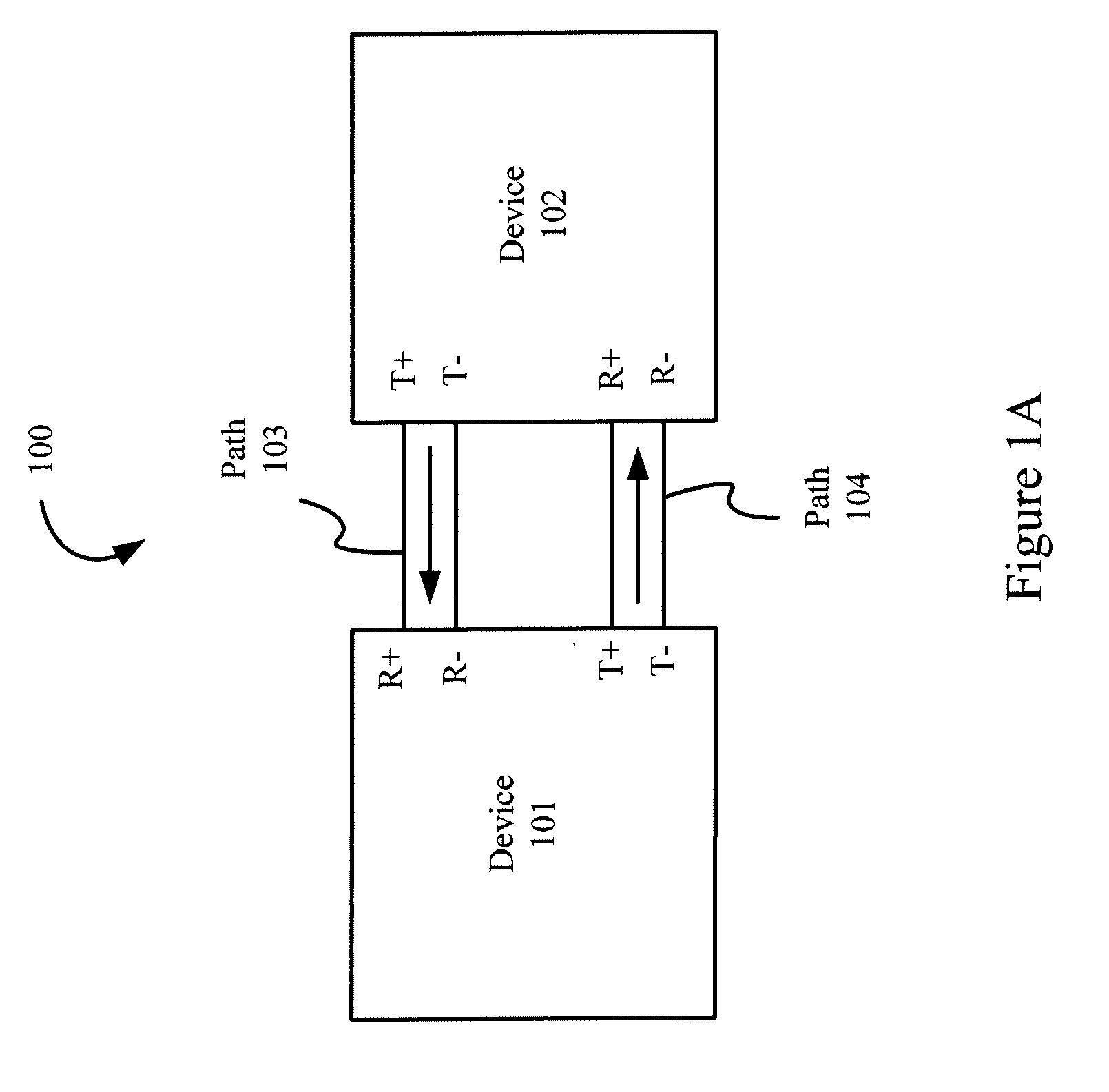

Receiver and method for synchronizing and aligning serial streams

ActiveUS20070177701A1Avoid the needAvoid storage problemsTime-division multiplexSynchronising arrangementClock ratePCI Express

A receiver for receiving a stream of symbols clocked at a first rate, and providing the symbols at a second clock rate uses two buffers. Incoming symbols are written to a first dual clock buffer at the first rate, and read from the first and second buffer, at the second rate. Underflow of the first buffer is signaled to the second buffer, thereby avoiding the need to insert defined clock compensation symbols at the second rate. Symbols received at the second buffer while underflow is signaled may be ignored. Conveniently, the second buffer may also be used to align symbol data across multiple symbol streams using periodic alignment symbols. An exemplary embodiment conforms to the PCI Express standard.

Owner:ATI TECH INC

PCI Express-Compatible Controller And Interface For Flash Memory

InactiveUS20090049222A1Improve performanceImprove scalabilityRead-only memoriesDigital storageFlash memory controllerPCI Express

A PCI Express-compatible flash device can include one or more flash memory modules, a controller, and an ExpressCard interface. The controller can advantageously provide PCI Express functionality as well as flash memory operations, e.g. writing, reading, or erasing, using the ExpressCard interface. A PIO interface includes sending first and second memory request packets to the flash device. The first memory request packet includes a command word setting that prepares the flash device for the desired operation. The second memory request packet triggers the operation and includes a data payload, if needed. A DMA interface includes sending the second memory request from the flash device to the host, thereby triggering the host to release the system bus for the DMA operation.

Owner:SUPER TALENT TECH CORP

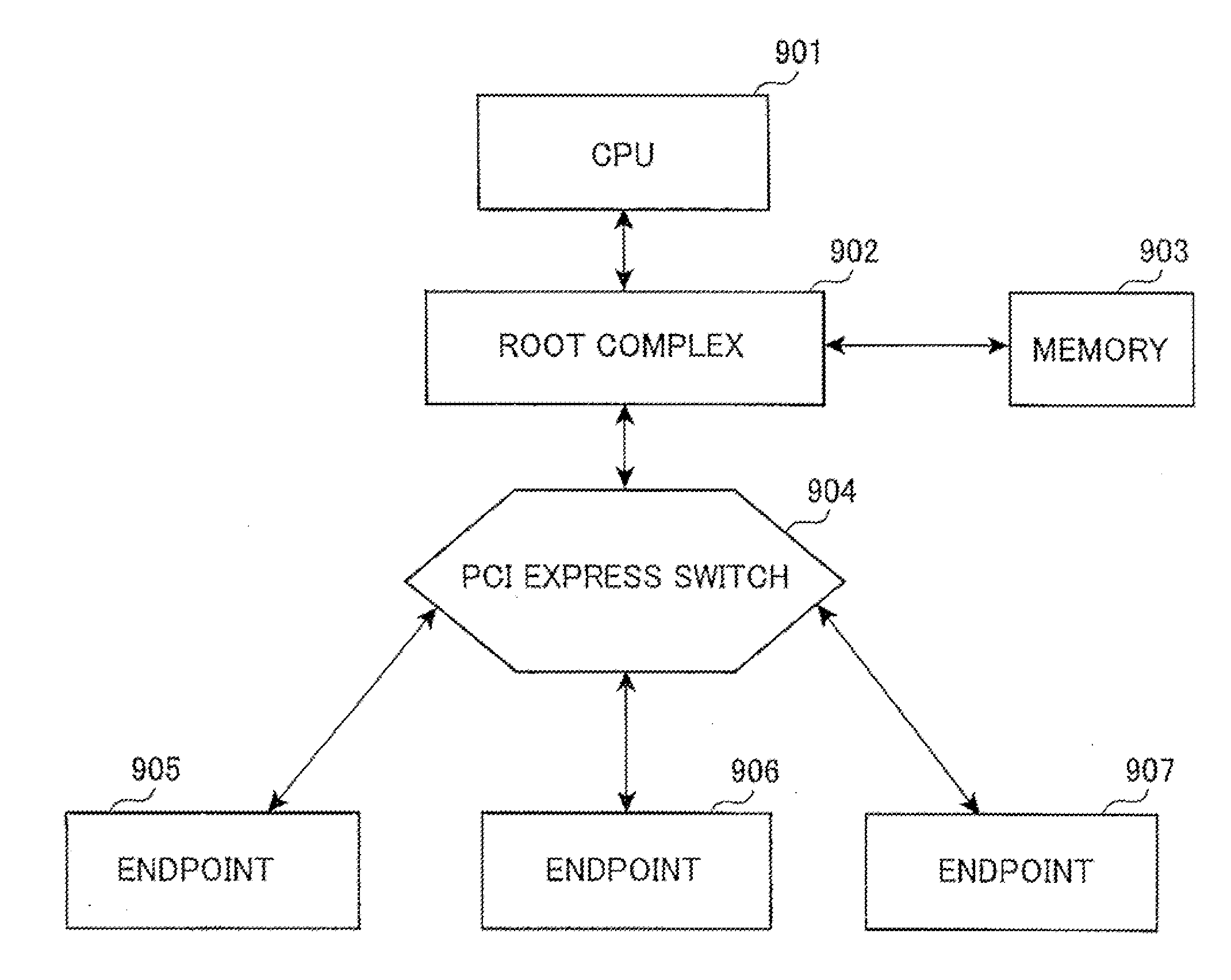

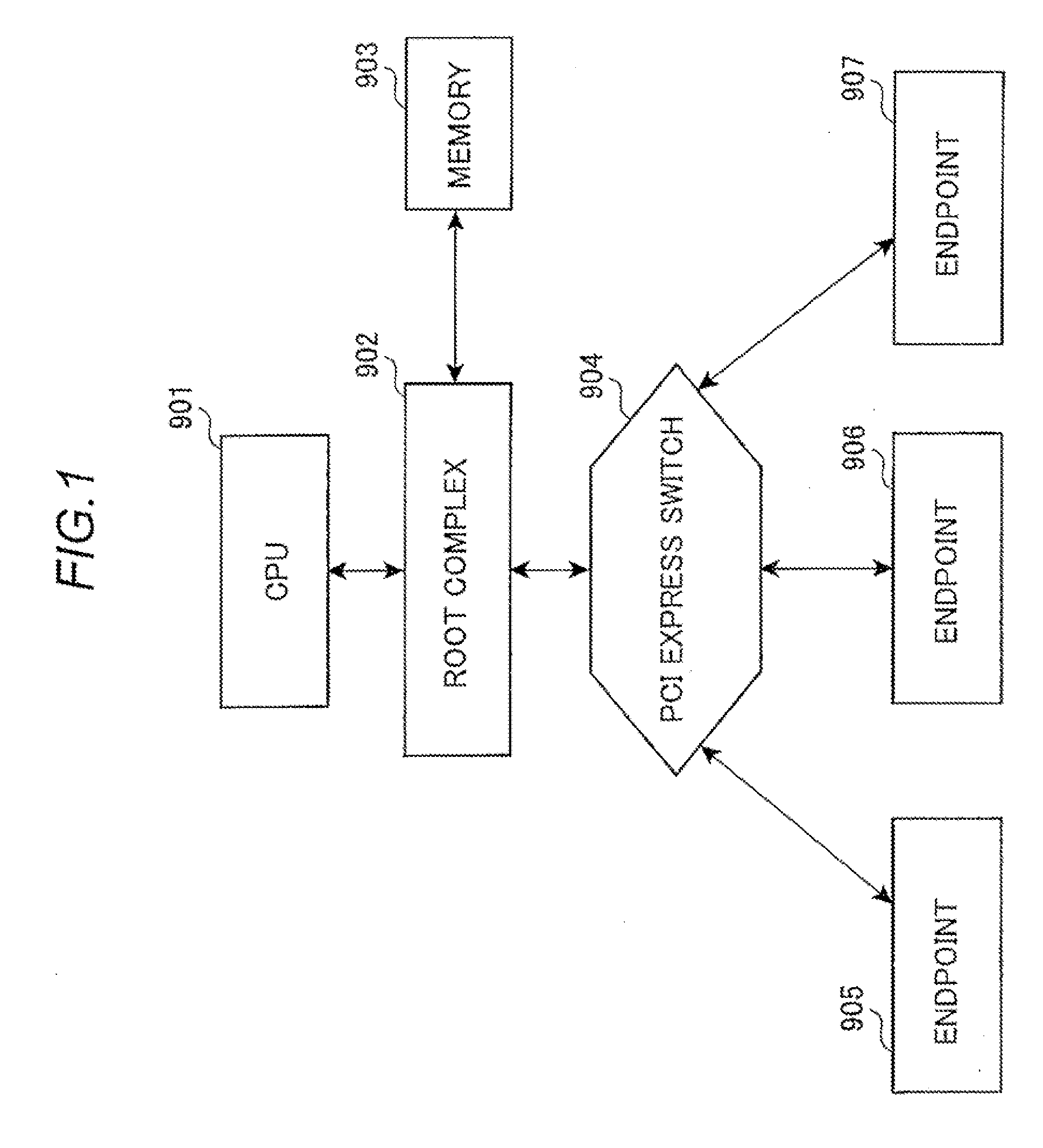

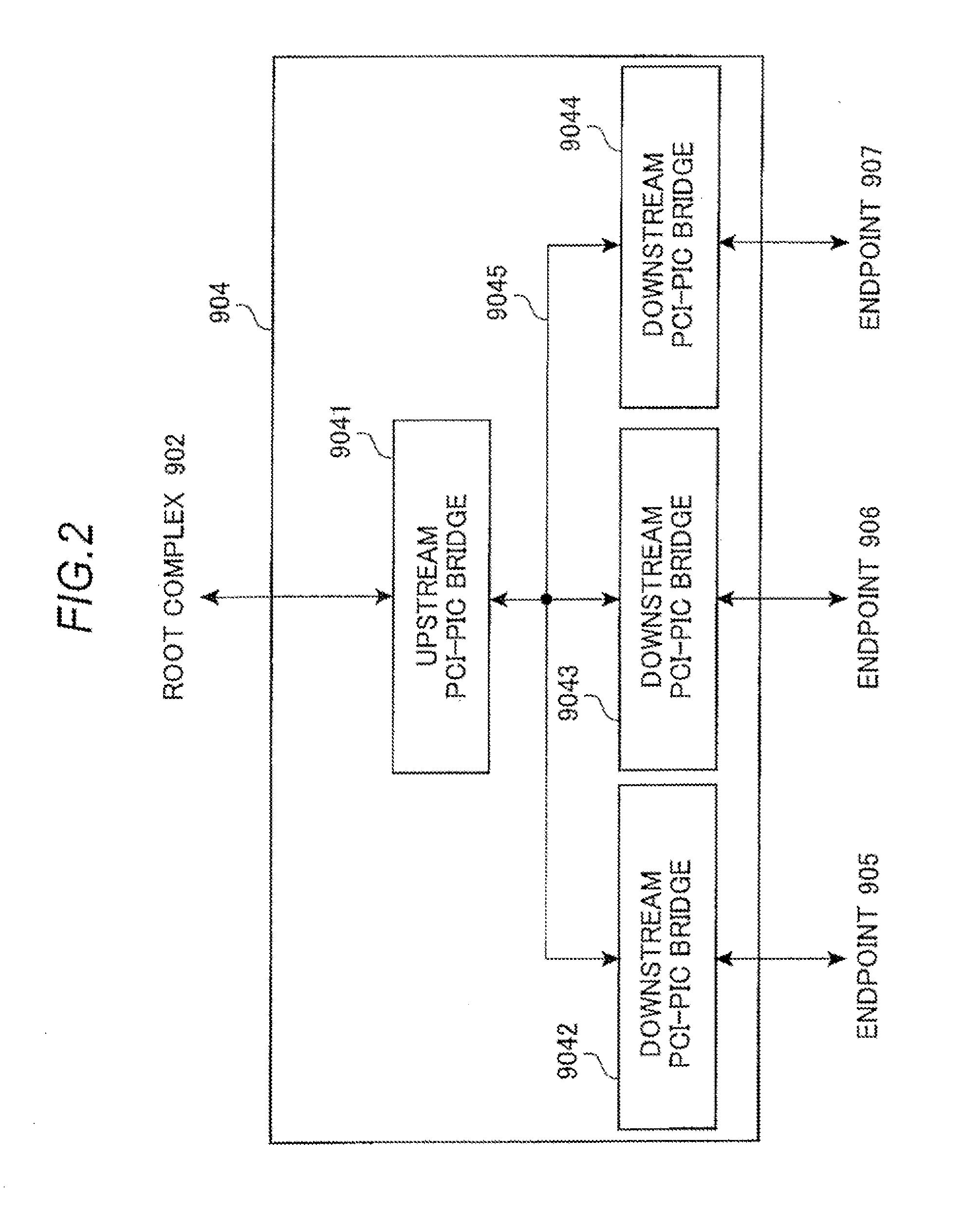

PCI express switch, PCI express system, and network control method

ActiveUS20110064089A1Reduce the overall heightData switching by path configurationElectric digital data processingRoot complexNetwork control

Provided are a first PCI-PCI bridge that handles Multi Root to connect to a plurality of root complexes; a second PCI-PCI bridge that connects to an endpoint; a virtual PCI Express switch that performs a switching process between the first and second PCI-PCI bridges; and a network control device that transfers data that is to be processed in the virtual PCI Express switch to an external switch through a network without passing through a PCI-PCI bridge.

Owner:NEC CORP

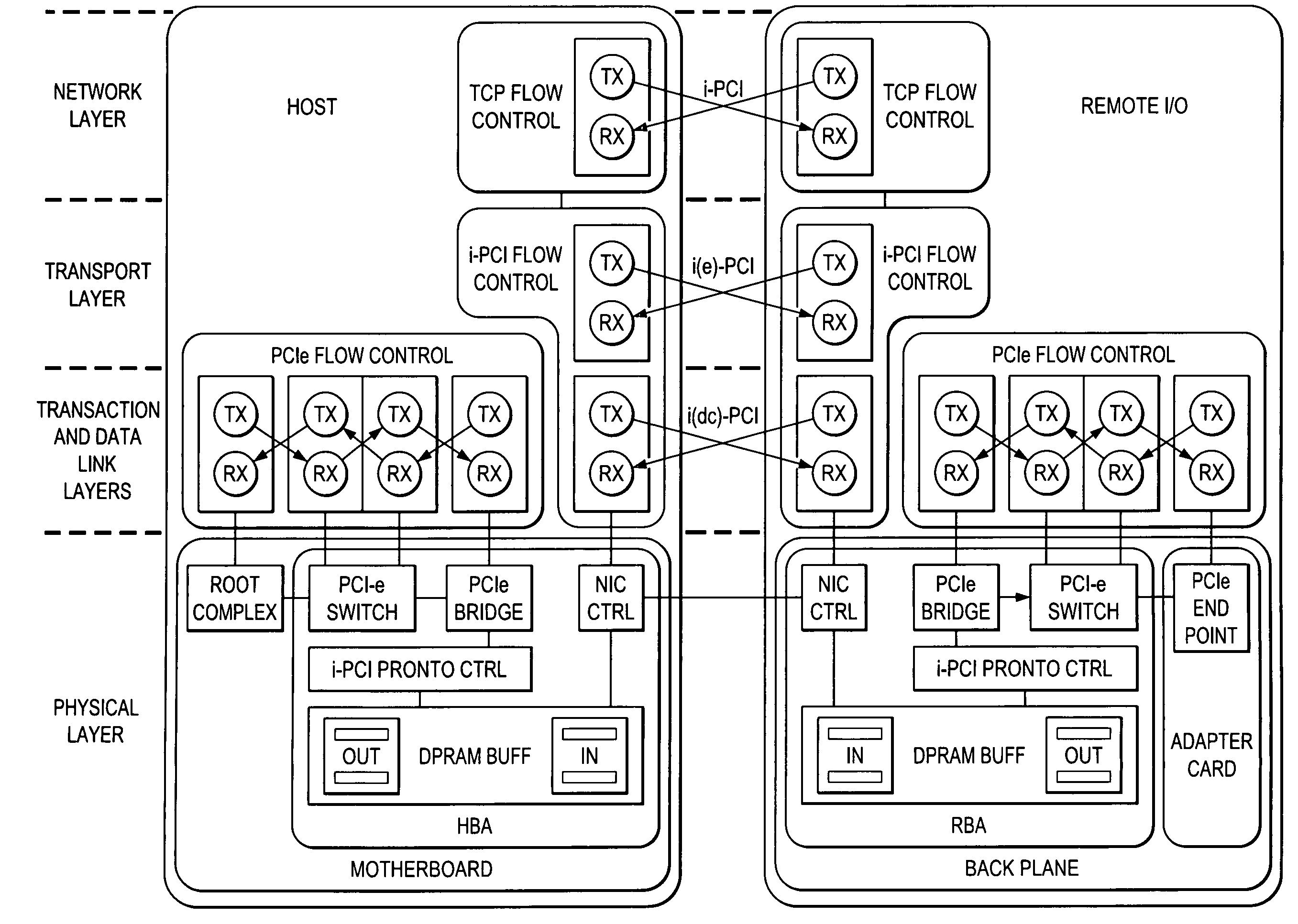

Virtualization of a host computer's native I/O system architecture via the internet and LANs

InactiveUS7734859B2Unprecedented reachUnprecedented flexibilityTime-division multiplexMultiple digital computer combinationsVirtualizationTTEthernet

A hardware / software system and method that collectively enables virtualization of the host computer's native I / O system architecture via the Internet and LANs. The invention includes a solution to the problems of the relatively narrow focus of iSCSI, the direct connect limitation of PCI Express, and the inaccessibility of PCI Express for expansion in blade architectures.

Owner:NUON

System and method for virtualizing PCIe devices

ActiveUS7743197B2Efficient accessImprove creditMultiple digital computer combinationsData switching networksCrossbar switchIntelligent Network

An intelligent network processor is disclosed that provides a PCI express (PCIe) host bus adapter with firmware selectable hardware capabilities and firmware enabled emulation of capabilities not supported by hardware. Support for Fibre Channel (FC) and Gigabit Ethernet (GbE) protocols are provided through the same fabric ports, including multiple port trunking for both protocols. On chip protocol conversion is provided for switching and routing between FC and GbE ports. Switching using the same crossbar module is provided for both FC and GbE protocols. The crossbar module is coupled to directly access external DDR memory so that messages from FC, GbE, and PCIe interfaces may be switched directly to the DDR memory.

Owner:EMULEX COMM CORP

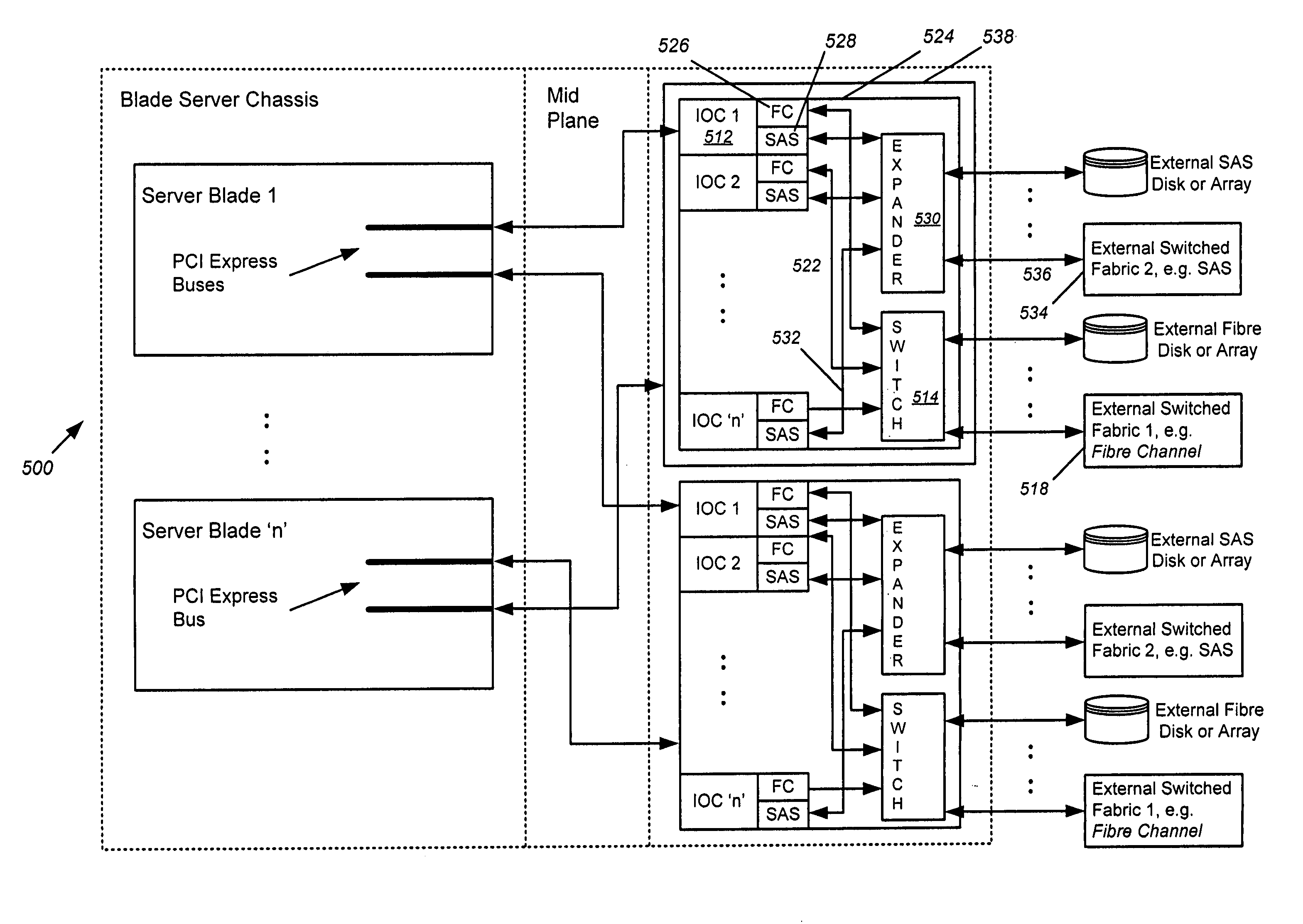

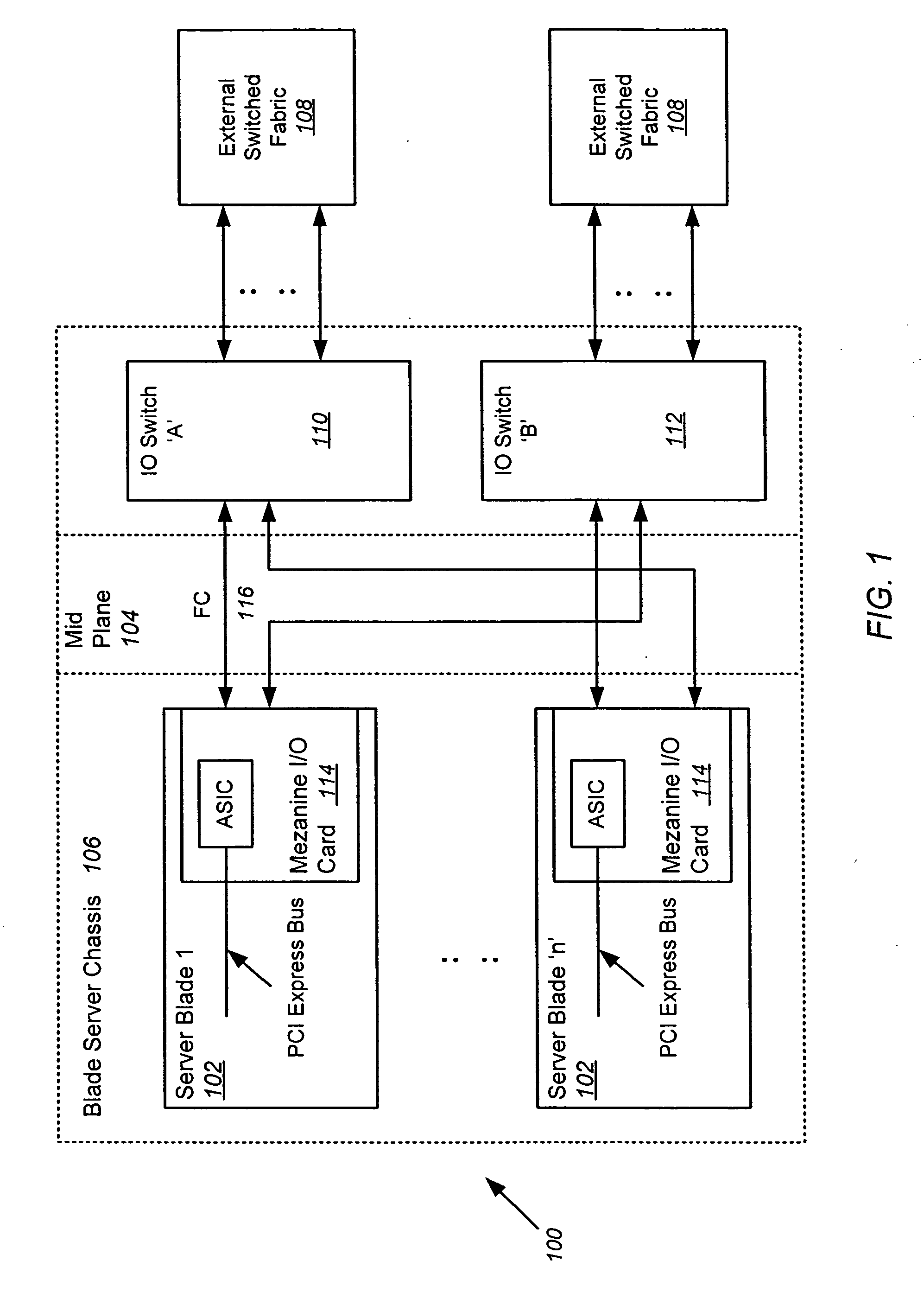

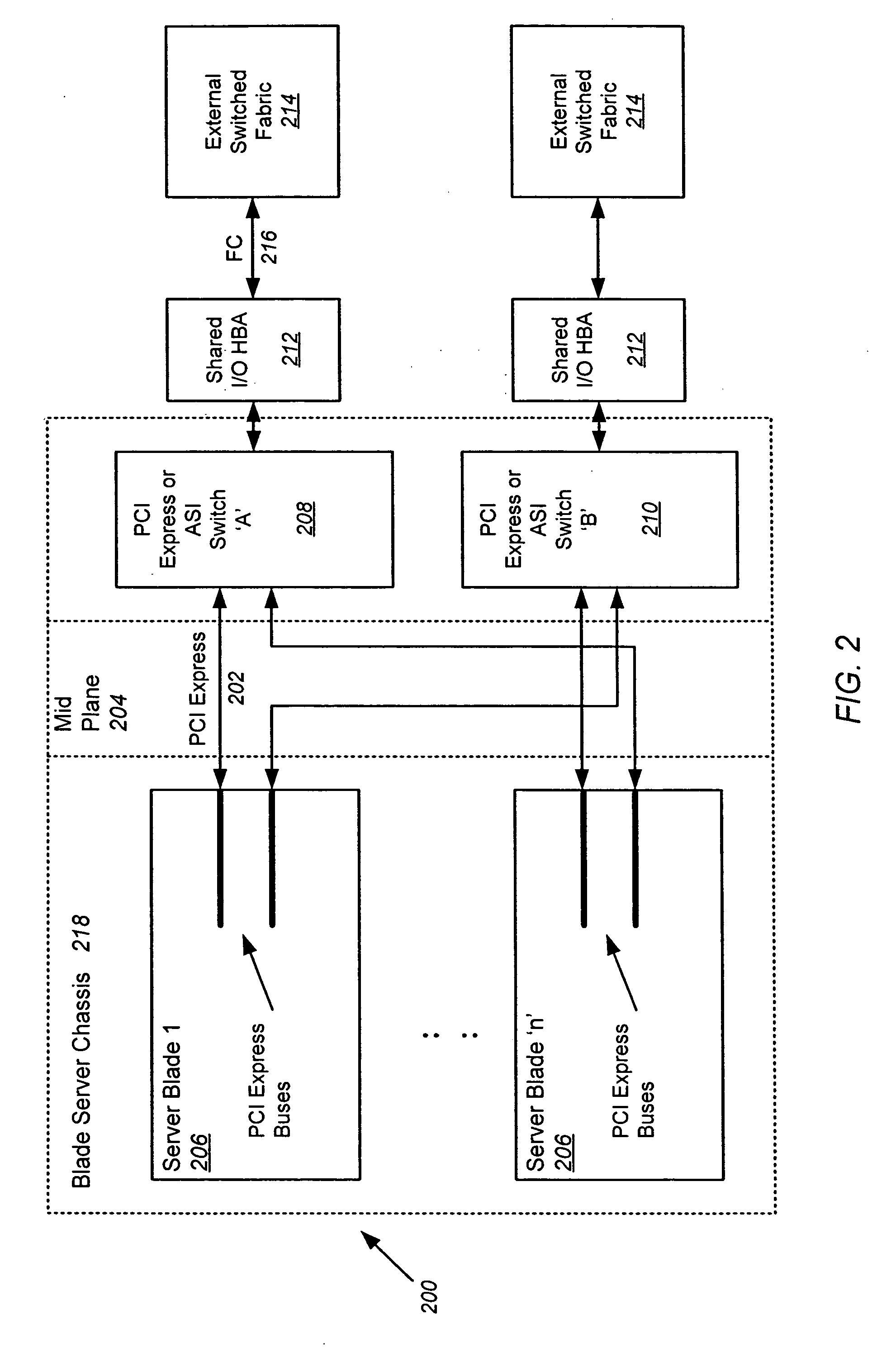

Input/output router for storage networks

ActiveUS20070047536A1Multiplex system selection arrangementsTime-division multiplexVirtualizationComputer compatibility

A blade server is disclosed, comprised of multiple server blades that plug into a midplane from the front, and an I / O router including multiple IOCs (one for each server blade) and an embedded switch that plugs into the midplane from the back. The midplane carries PCI Express lanes for connecting the server blades to the I / O router. Each of the IOCs is physically couplable to a server blade over a separate PCI Express connection in the midplane, preserving existing driver compatibility, and is coupled to the embedded switch via an internal FC link within the I / O router. Each embedded switch may contain full fabric services ports. Alternatively, the full fabric services may be left out, and N_PORT virtualization or FC_AL stealth mode may be employed to allow the embedded switch to interoperate transparently with the external fabric switch and eliminate the third hop in the blade server chassis.

Owner:AVAGO TECH INT SALES PTE LTD

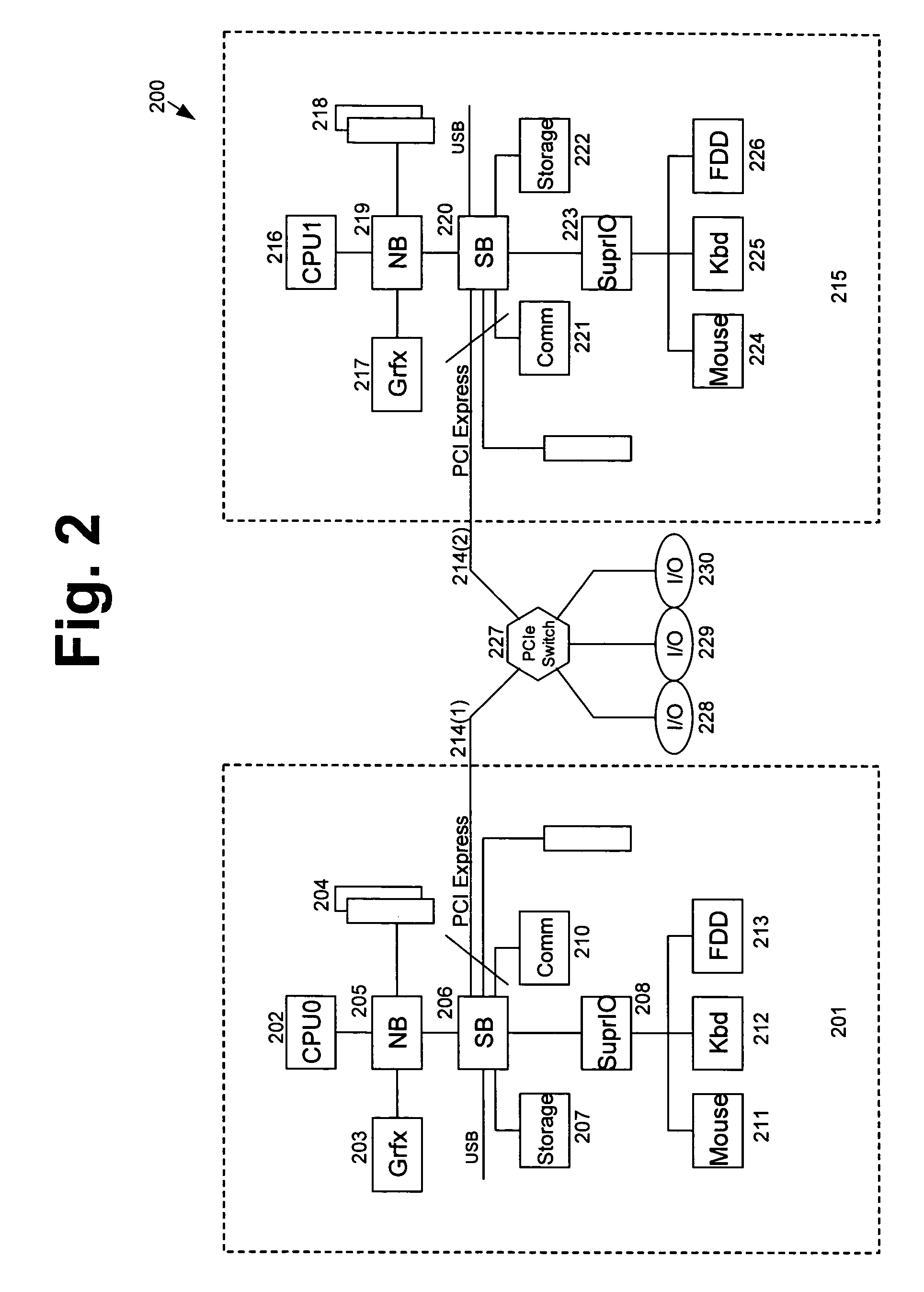

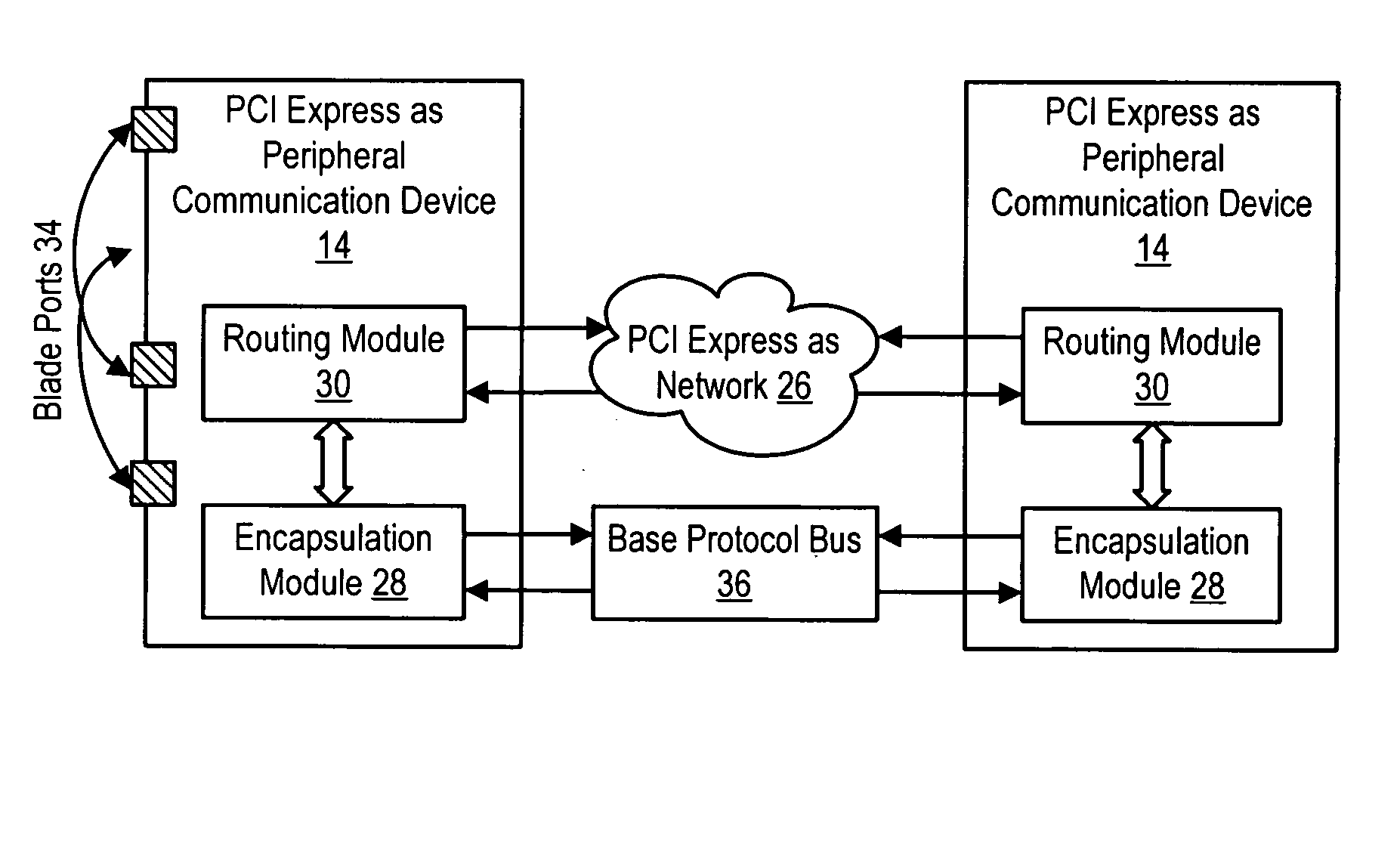

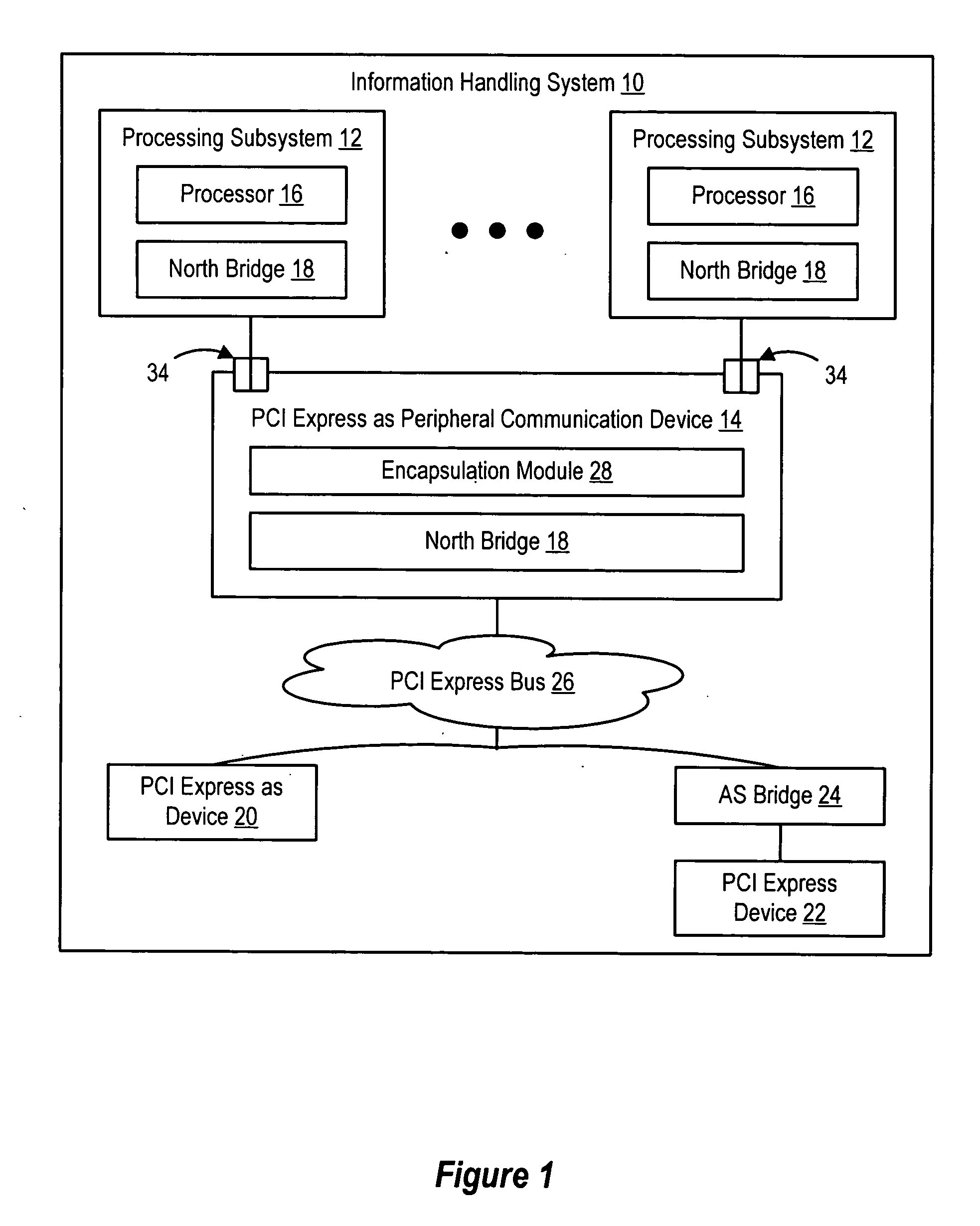

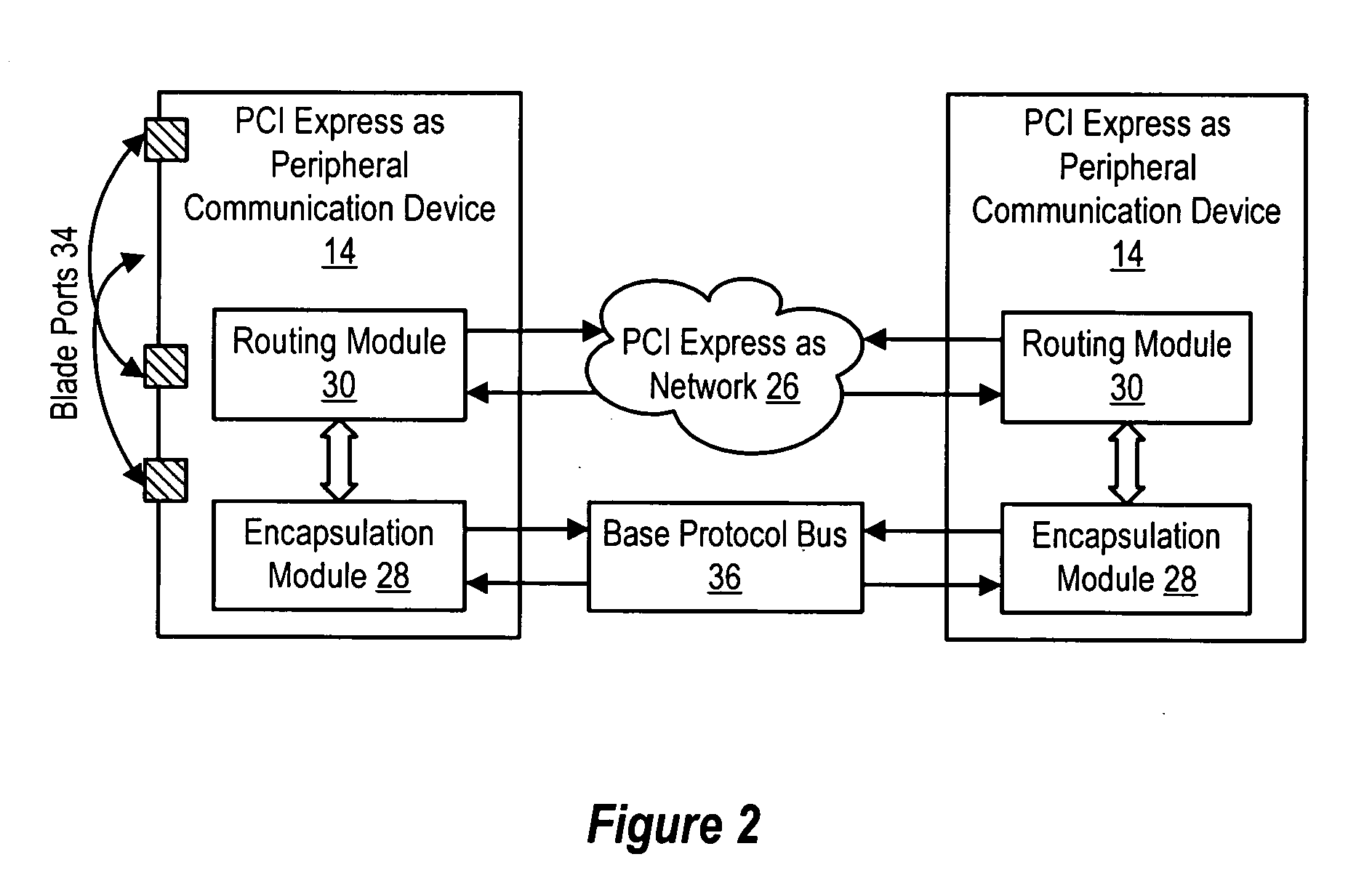

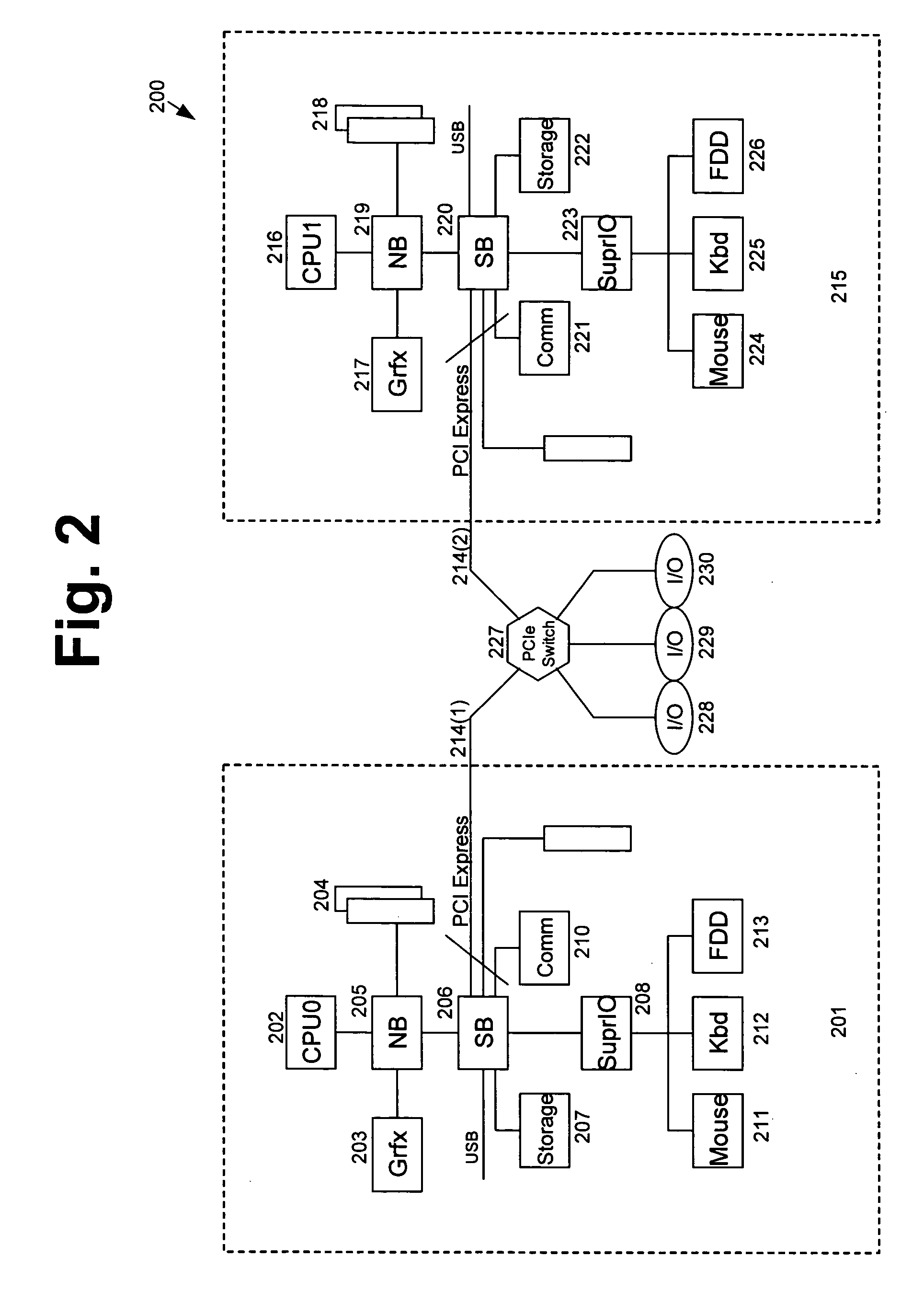

System and method for information handling system PCI express advanced switching

InactiveUS20050262269A1Simple processReduce disadvantagesConcurrent instruction executionMultiple digital computer combinationsInformation processingData pack

Plural processing subsystems of an information handling system, such as plural blades of a blade server, communicate through a base protocol, such as PCI Express, to a peripheral communication device with each processing subsystem interfaced through a port of the peripheral communication device. An encapsulation module of the peripheral communication device encapsulates the base protocol in an advanced switching packet, such as a packet formed with the PCI Express Advanced Switching protocol. A routing module of the peripheral communication device routes the packets through a bus, such as a blade server backplane bus, for use of the information by a selected peripheral. Peripherals communicate with selected processing subsystems by sending advanced switching packets to the routing module for the encapsulation module to extract the peripheral information from the packets and send the peripheral information to the port associated with the selected processing subsystem.

Owner:DELL PROD LP

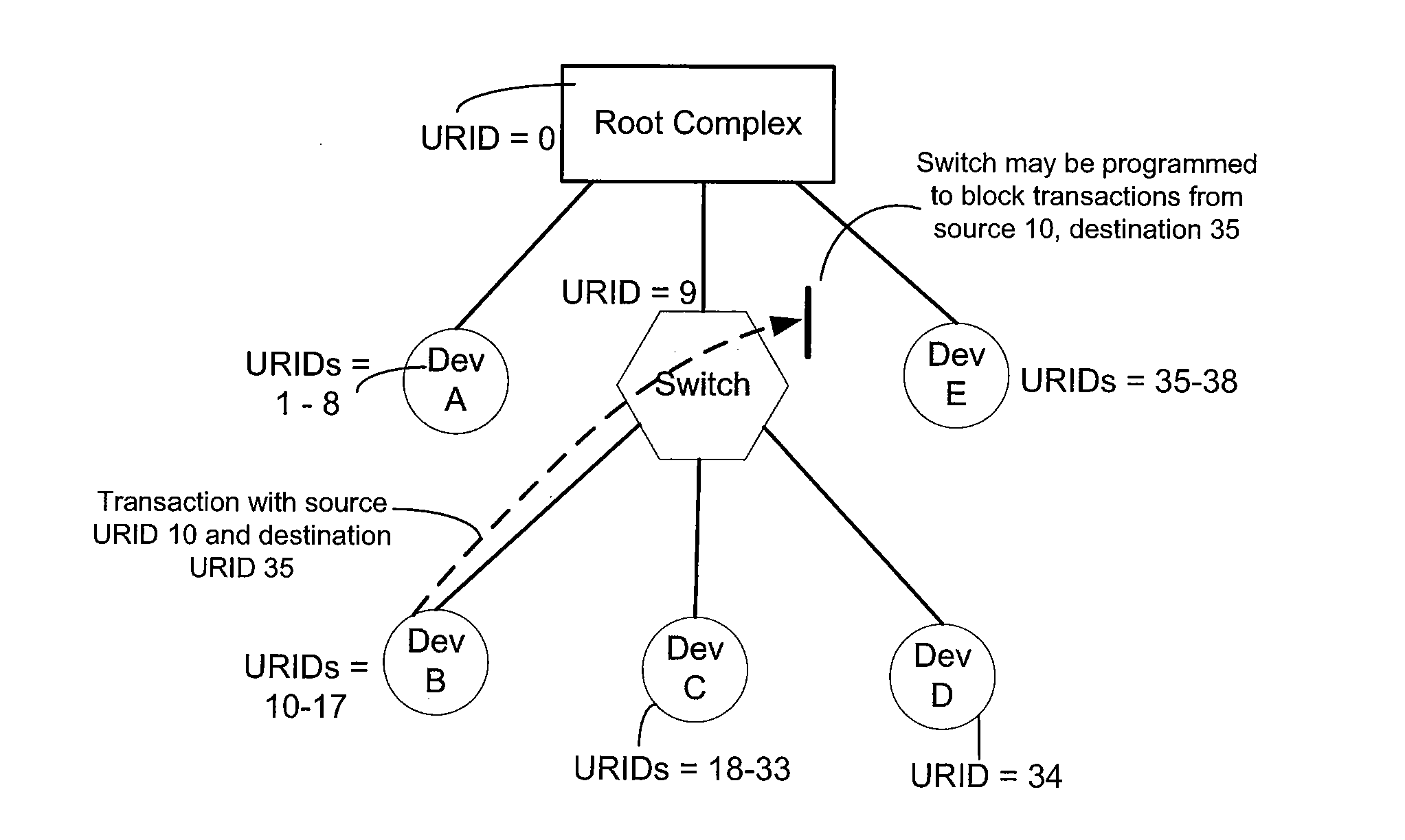

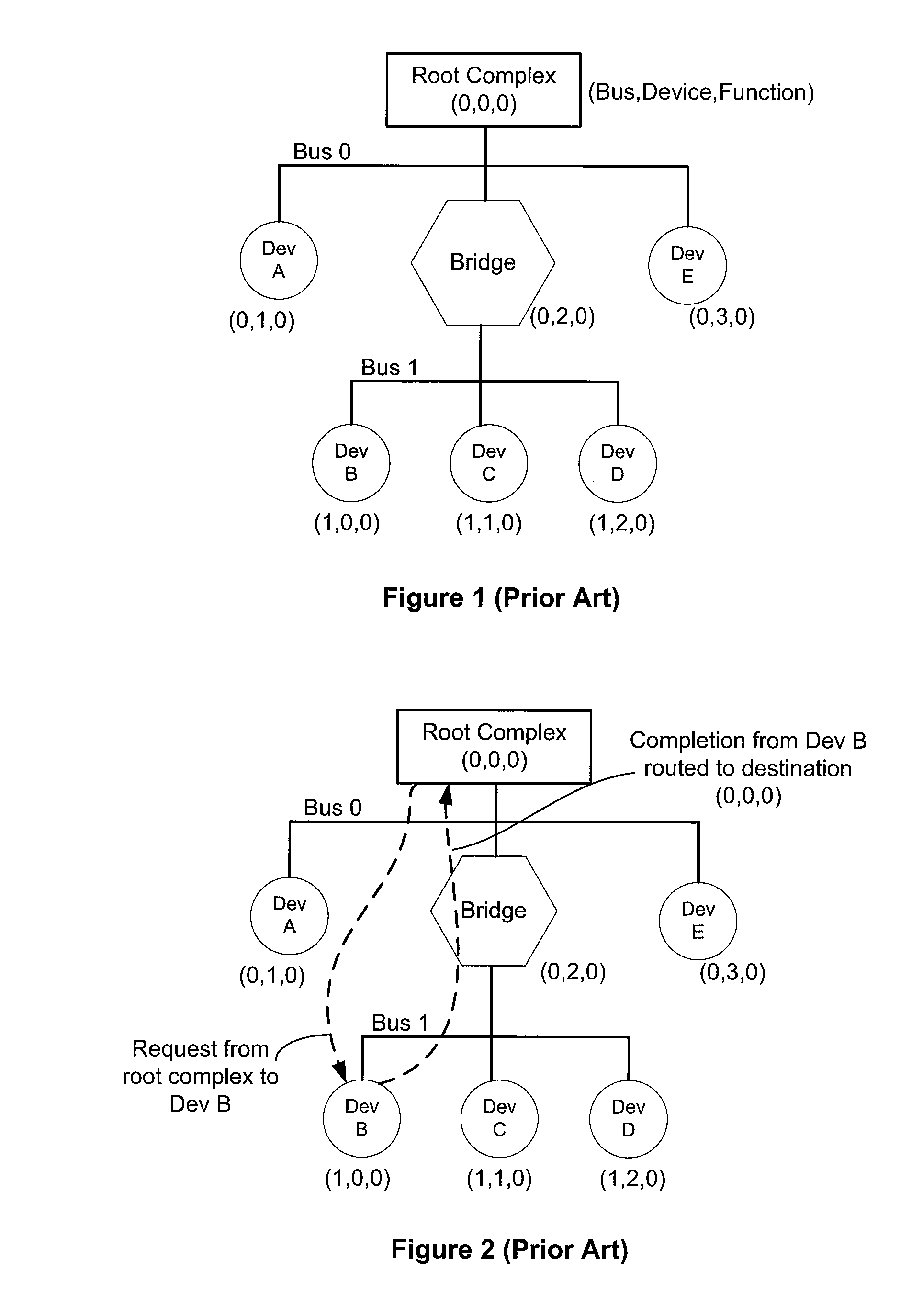

Universal routing in pci-express fabrics

ActiveUS20090164694A1Verifies the validity of the source IDImprove performanceInput/output processes for data processingFunctional spacePCI Express

A universal routing identifier (URID) is provided to extend the function space in PCI-Express fabrics. Methods and systems based on the URID are provided for configuring URID capable devices and upgrading PCI-Express bridges and switches having lookup tables with access control functionality. The lookup table entry contains URIDs of destination ports, backup ports, acceptance ports, and permitted ports for downstream and upstream filtering, routing and arbitrating of transaction packets. URID capable devices can be incrementally added to current PCI-Express bridges and switches. A configuration mechanism is added to the current PCI / PCI-Express enumeration software. The URID capabilities can be disabled to maintain system compatibility. A URID capable PCI-Express system is able to address ten of thousands single-function devices. A URID capability segment field is provided in the current PCI-Express configuration space. Each URID capable device contains the URID capability segment implemented in its own set of configuration space registers.

Owner:SANDISK TECH LLC

Method and aparatus for plug-and-play webserver

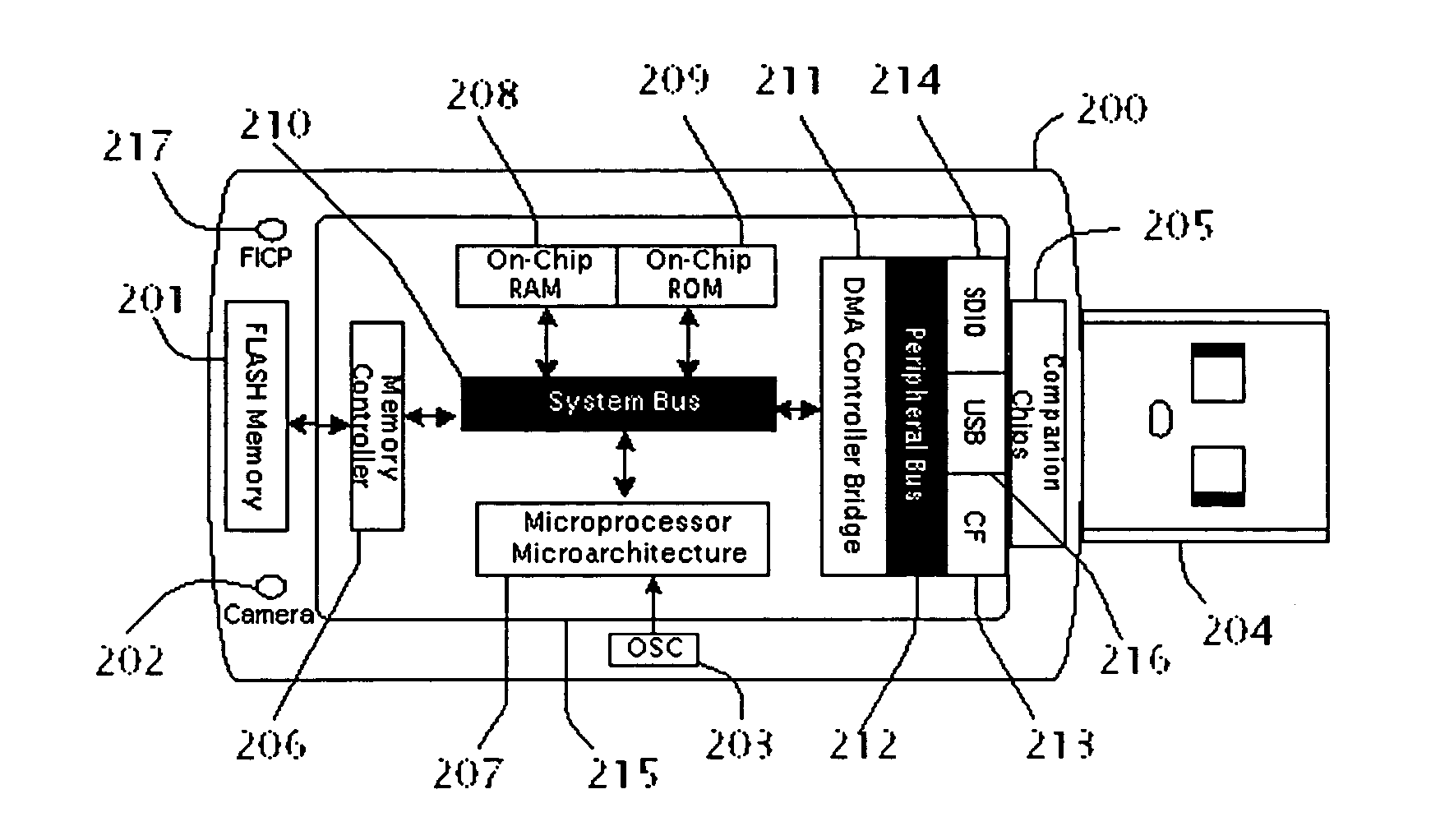

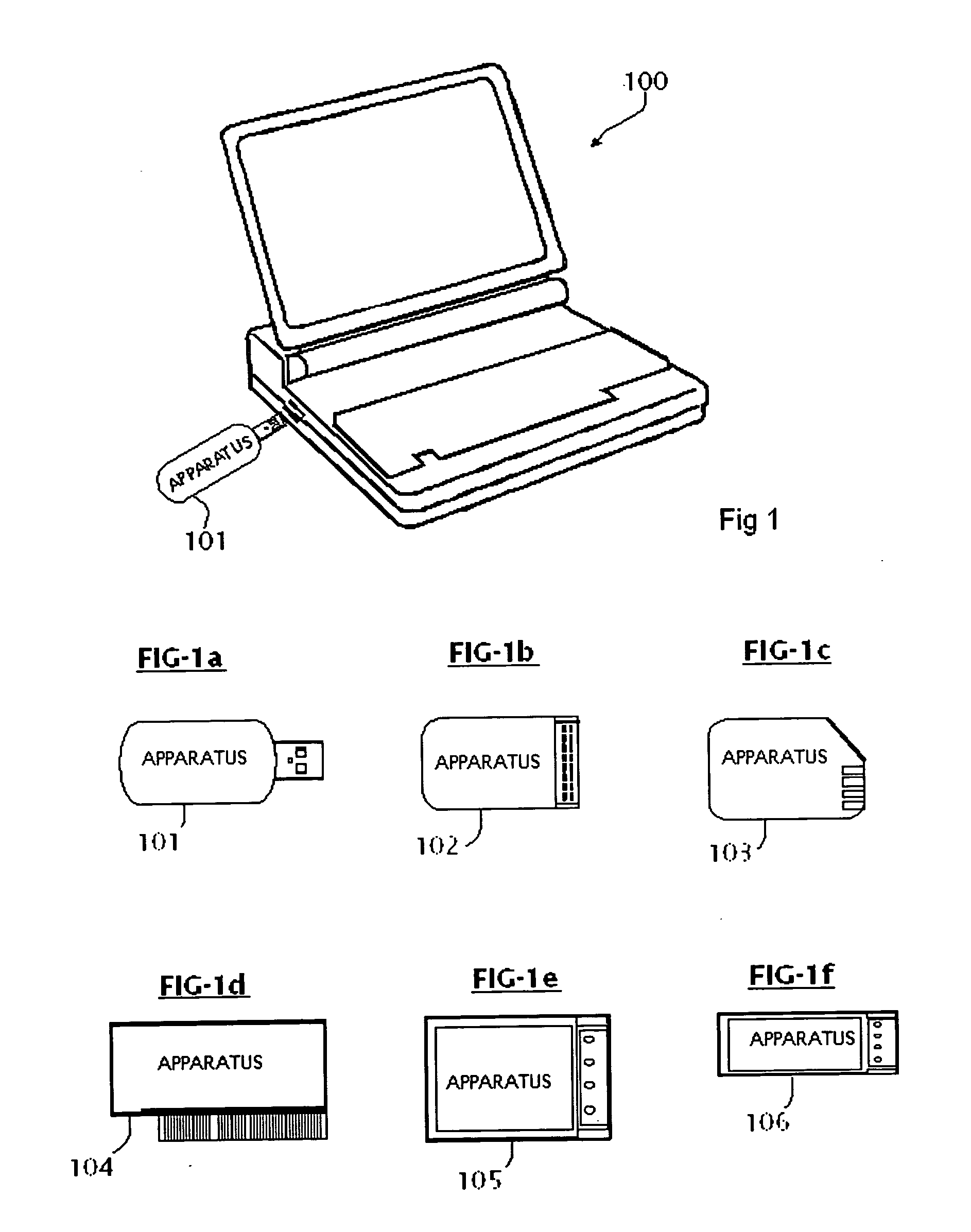

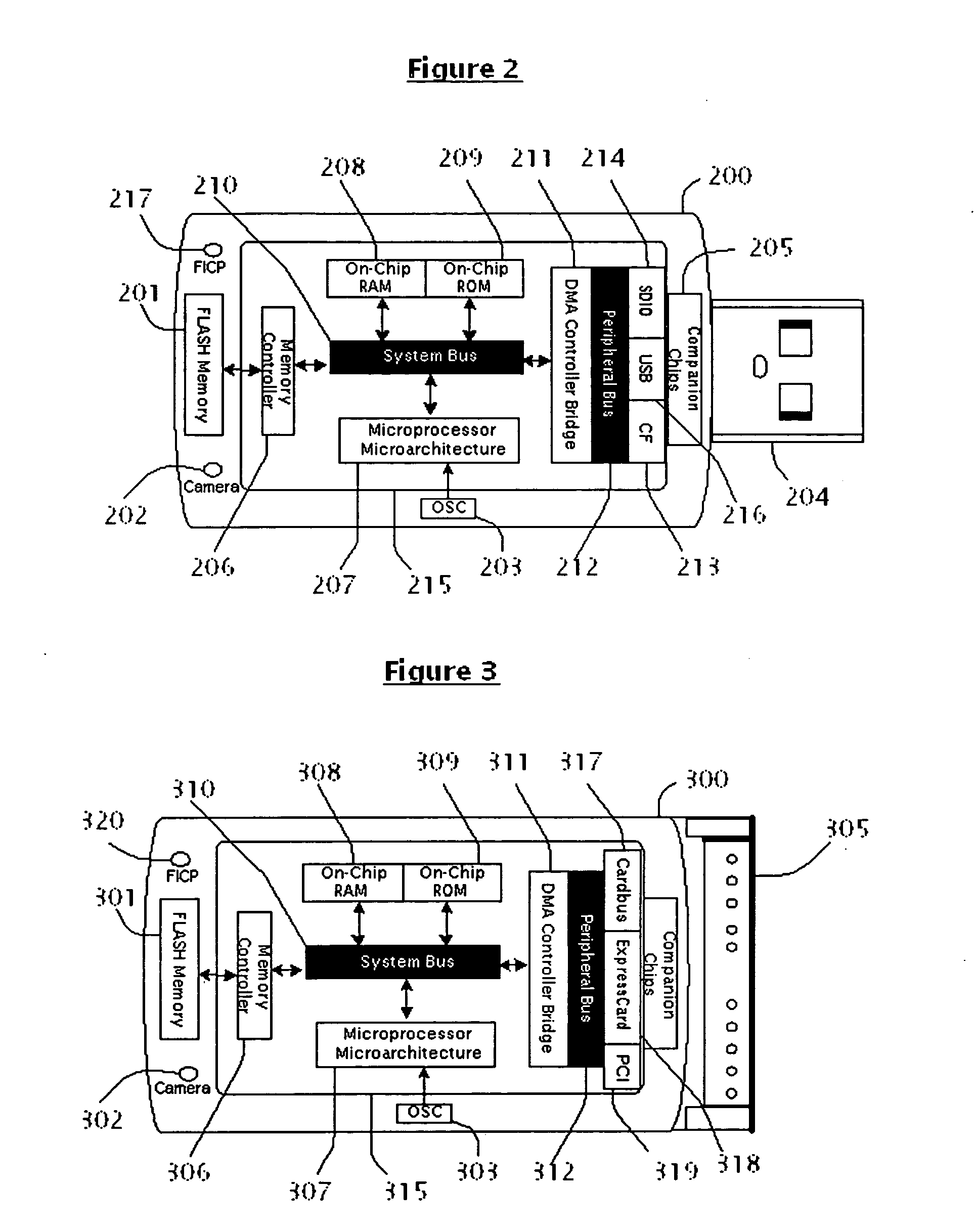

InactiveUS20060075174A1Simplify the development processEasy to adaptComponent plug-in assemblagesProgram loading/initiatingPCI ExpressUSB

A system, method and computer program for an apparatus is described. An apparatus is a very convenient, plug-and-play, ultra small, smart device that lets the end-users to host their websites at computer peripheral port. When said device is plugged in one of the computer peripheral ports: Universal Serial Bus (USB), Secure Digital Input and Output (SDIO), Compact Flash (CF), Cardbus, Peripheral Component Interconnect (PCI), PCI-Express and ExpressCard; it shall function as a dedicated web hosting device powerful and robust enough to handle web hosting functions for Personal Home Page, File Transfer Protocol (FTP) Files Server, Streaming media, Common Gate Interface (CGI) scripts, Active Server Pages, or Game Server.

Owner:MR VUONG CORY THANG

Configurable PCI express switch

ActiveUS20050246460A1Energy efficient ICTData switching by path configurationPCI ExpressComputer science

A configurable switch that enables multiple CPUs to be connected to multiple I / O devices through a single switch. The switches can be cascaded to enable more CPUs and / or more I / O devices in the tree. The configuration is transparent to the enumeration of the bus and endpoint devices. A simple management input such as SMBus or hardware strapping is used to set up the assignation of devices to CPUs. Utilization of a manager and the PCI Express hot plug controller registers enable hot-plug reconfiguration of the device tree as devices a switched between CPUs via PCI buses within the switch.

Owner:MICROSOFT TECH LICENSING LLC

Computing device with flexibly configurable expansion slots, and method of operation

ActiveUS20060271713A1Component plug-in assemblagesElectric digital data processingExpansion cardGraphics

A computing device that allows for a flexible allocation of bandwidth among peripheral devices using a peripheral bus is disclosed. The computing device includes a peripheral bus and at least two slots. The computing device may be used with a single peripheral card or multiple peripheral cards. In a multi-card configuration the invention allows the bandwidth on the peripheral bus to be shared by all the cards. In a single-card configuration, the computing device allows available bandwidth on the peripheral bus to be used by a single card. The device is particularly useful with PCI express compliant expansion cards, such as graphics adapters.

Owner:ATI TECH INC

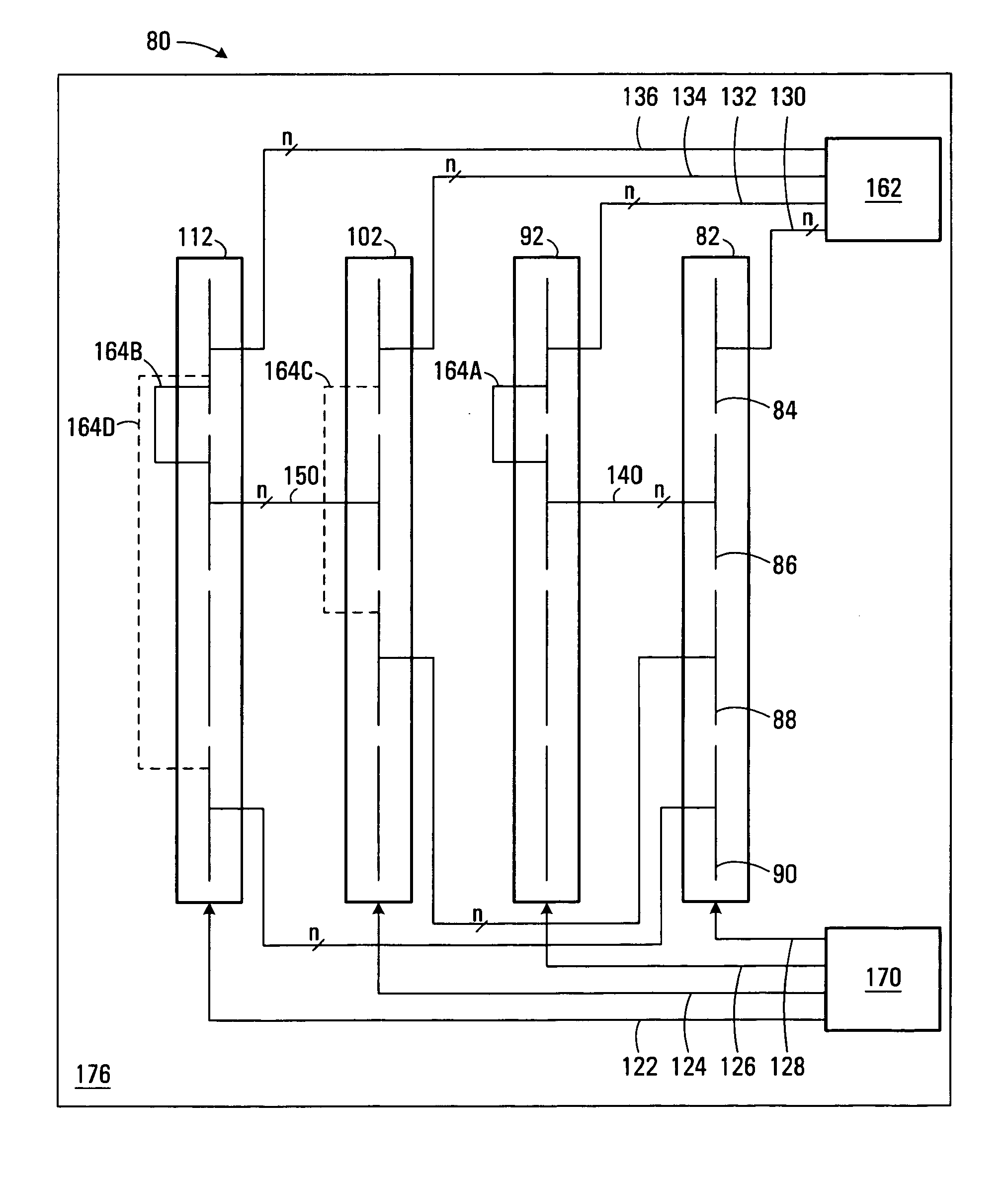

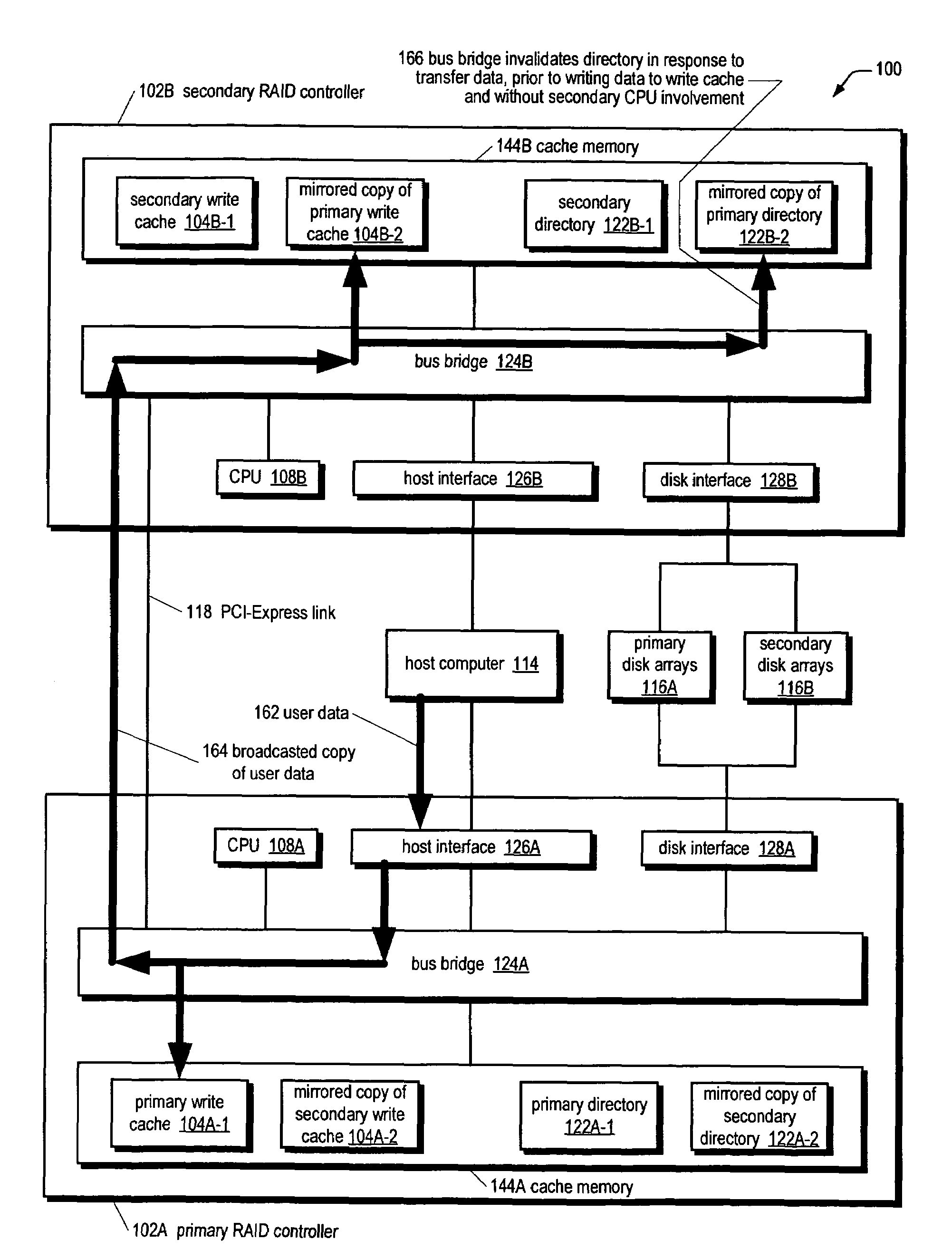

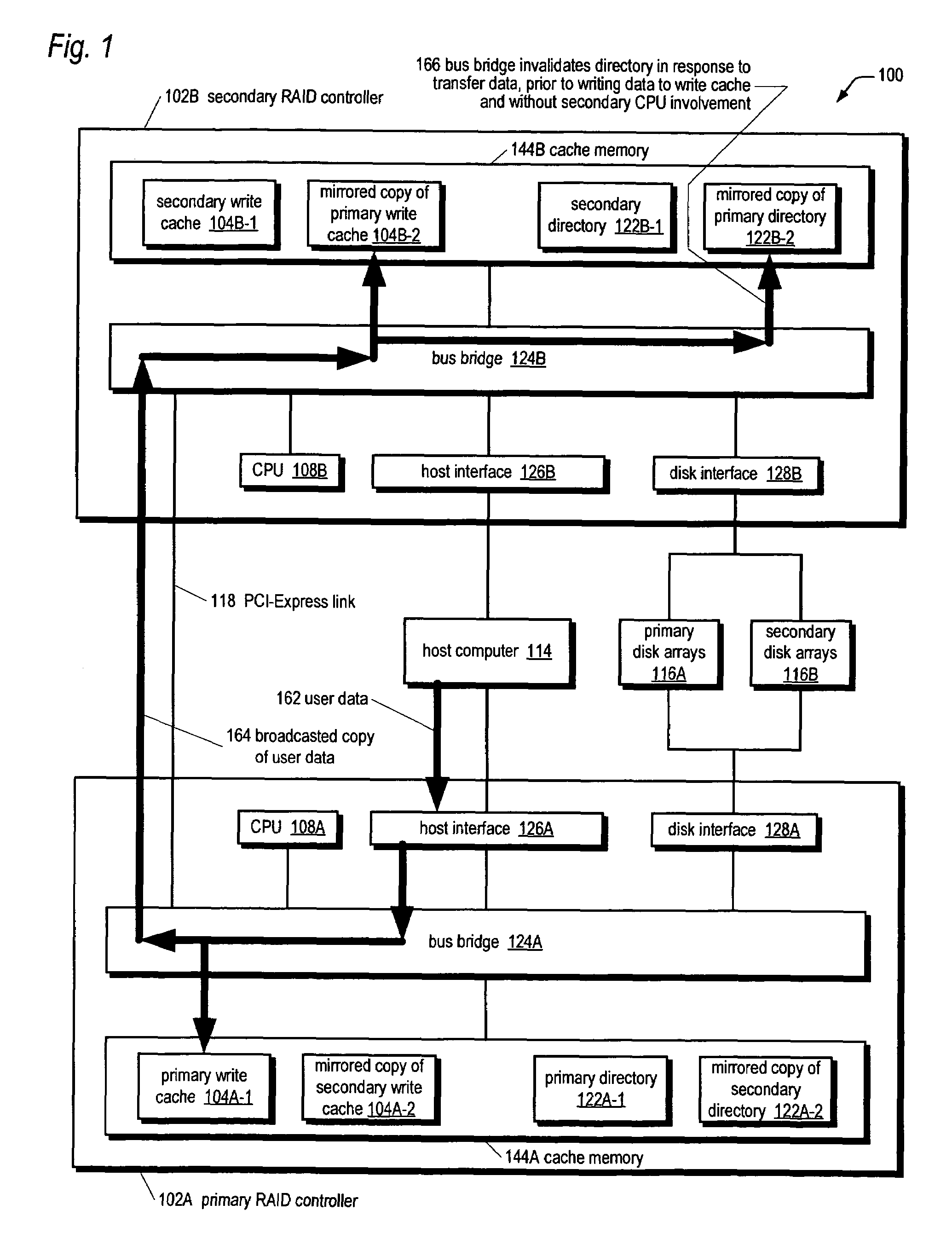

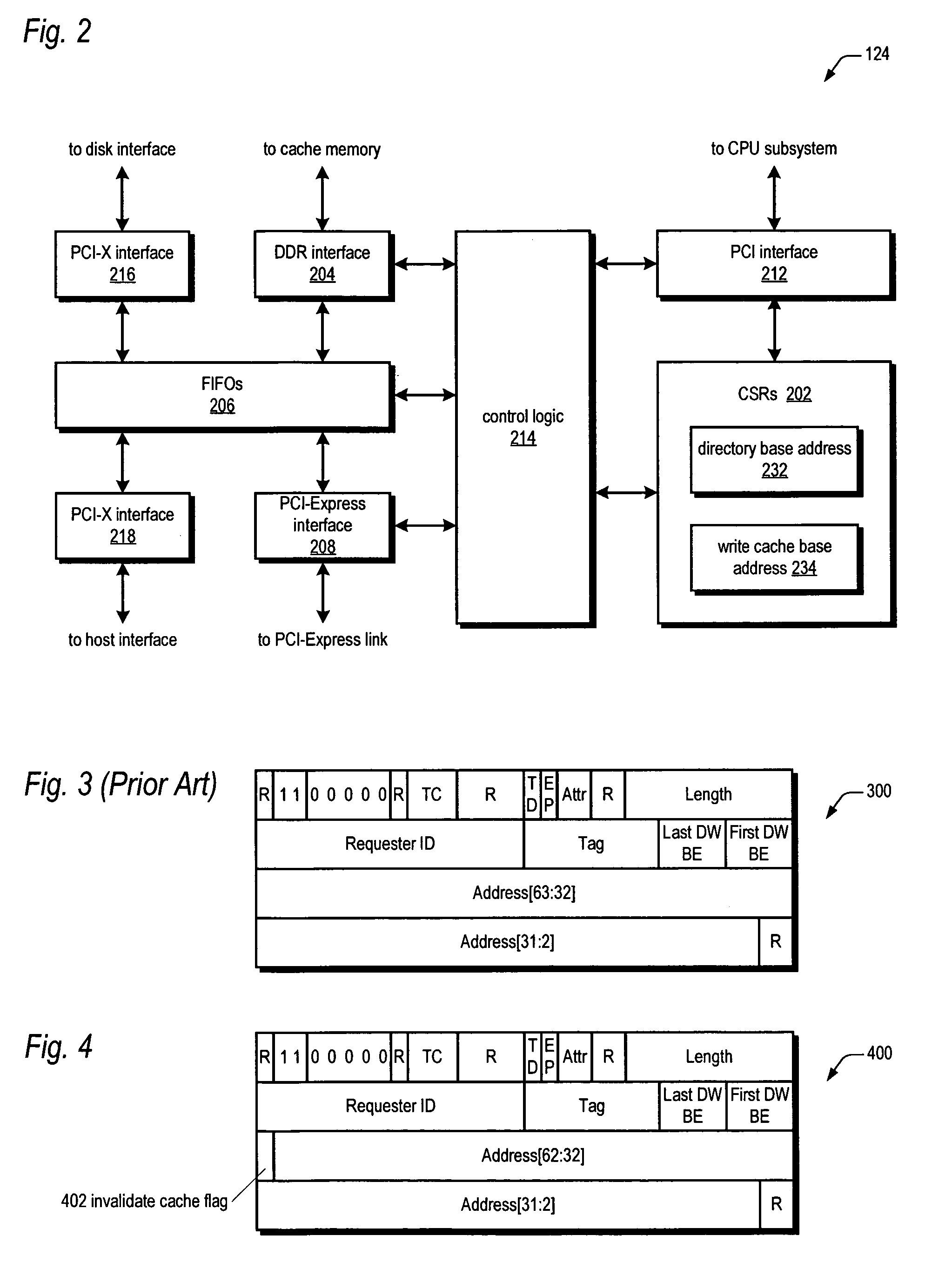

RAID system for performing efficient mirrored posted-write operations

InactiveUS7340555B2Reduce needMemory architecture accessing/allocationError detection/correctionRAIDPCI Express

A bus bridge on a primary RAID controller receives user write data from a host and writes the data to its write cache and also broadcasts the data over a high speed link (e.g., PCI-Express) to a secondary RAID controller's bus bridge, which writes the data to its mirroring write cache. However, before writing the data, the second bus bridge automatically invalidates the cache buffers to which the data is to be written, which alleviates the primary controller's CPU from sending a message to the secondary controller's CPU to instruct it to invalidate the cache buffers. The secondary controller CPU programs its bus bridge at boot time with the base address of its mirrored write cache to enable it to detect that the cache buffer needs invalidating in response to the broadcast write, and with the base address of its directory that includes the cache buffer valid bits.

Owner:DOT HILL SYST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com