Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2973 results about "Integrated circuit layout" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Integrated circuit layout, also known IC layout, IC mask layout, or mask design, is the representation of an integrated circuit in terms of planar geometric shapes which correspond to the patterns of metal, oxide, or semiconductor layers that make up the components of the integrated circuit. Originally the overall process was called tapeout as historically early ICs used graphical black crepe tape on mylar media for photo imaging (erroneously believed to reference magnetic data--the photo process greatly predated magnetic media).

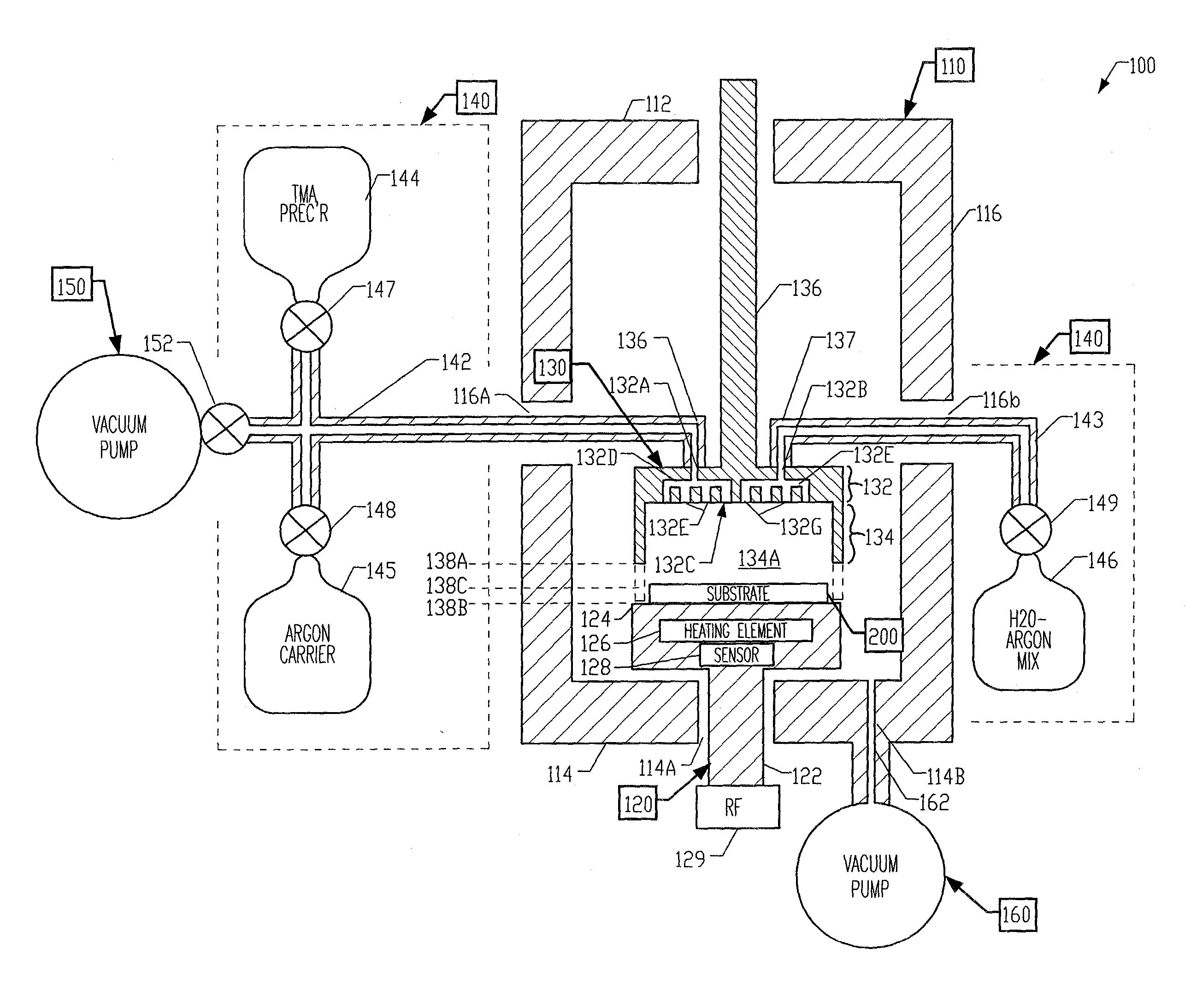

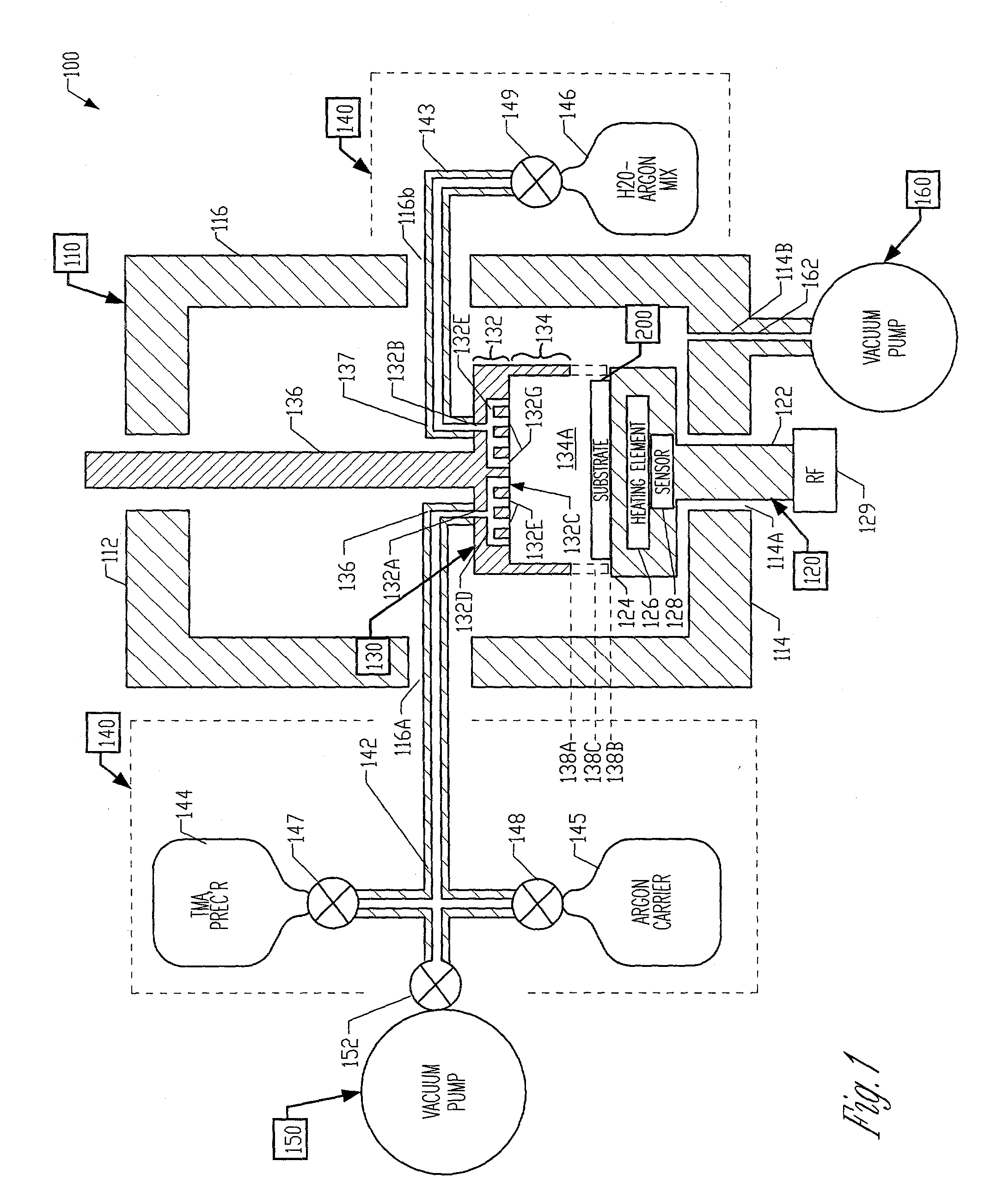

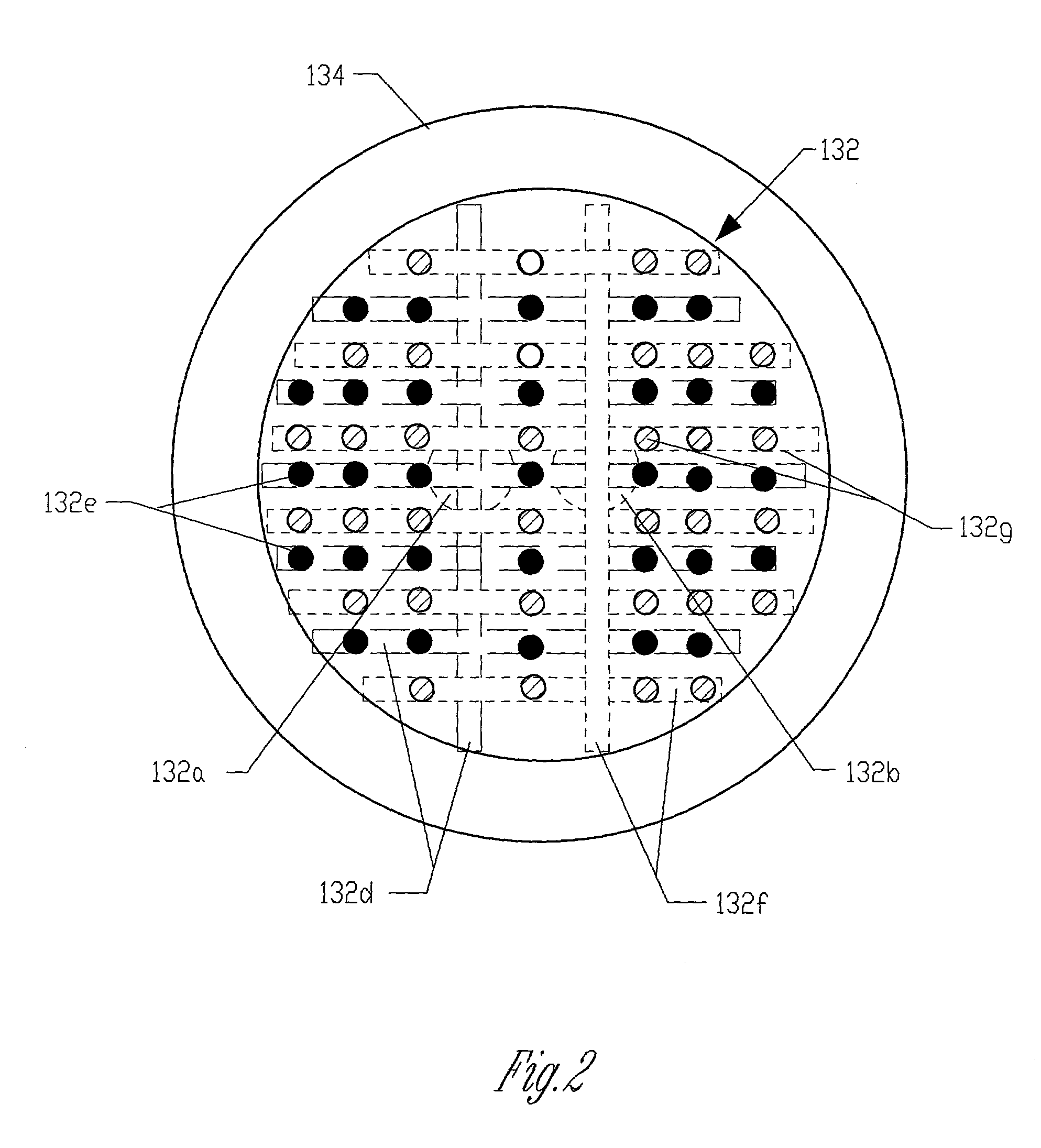

Methods, systems, and apparatus for atomic-layer deposition of aluminum oxides in integrated circuits

InactiveUS20030207032A1Small volumeConsumes less gasPretreated surfacesChemical vapor deposition coatingProduct gasIntegrated circuit layout

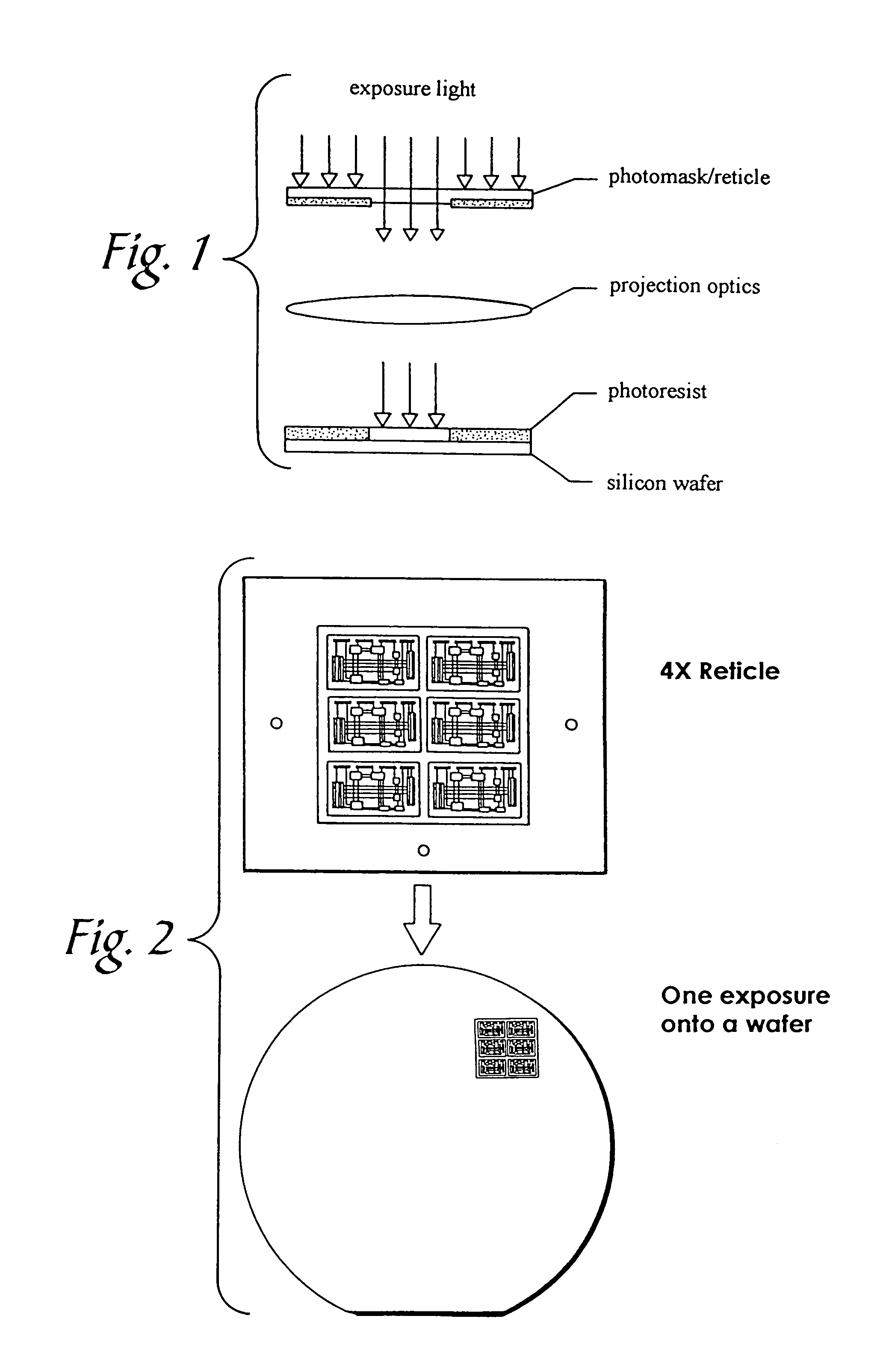

Integrated circuits, the key components in thousands of electronic and computer products, are generally built layer by layer on a silicon substrate. One common layer-formation technique, known as chemical-vapor deposition (CVD), produces uneven layers and covers vertical surfaces poorly. An emergent technique, atomic-layer deposition, overcomes these shortcomings, but has others, such as slow deposition rates and longer than desirable cycle times, particularly as applied to deposition of aluminum oxide. Accordingly, the inventors devised unique atomic-layer deposition systems, methods, and apparatus suitable for aluminum-oxide deposition. One exemplary system includes an outer chamber, a substrate holder, and a gas-distribution fixture that engages or cooperates with the substrate holder to form an inner chamber within the outer chamber. The inner chamber has a smaller volume than the outer chamber, which ultimately requires less time to fill and purge and thus promises to reduce cycle times for deposition of materials, such as aluminum oxide.

Owner:MICRON TECH INC

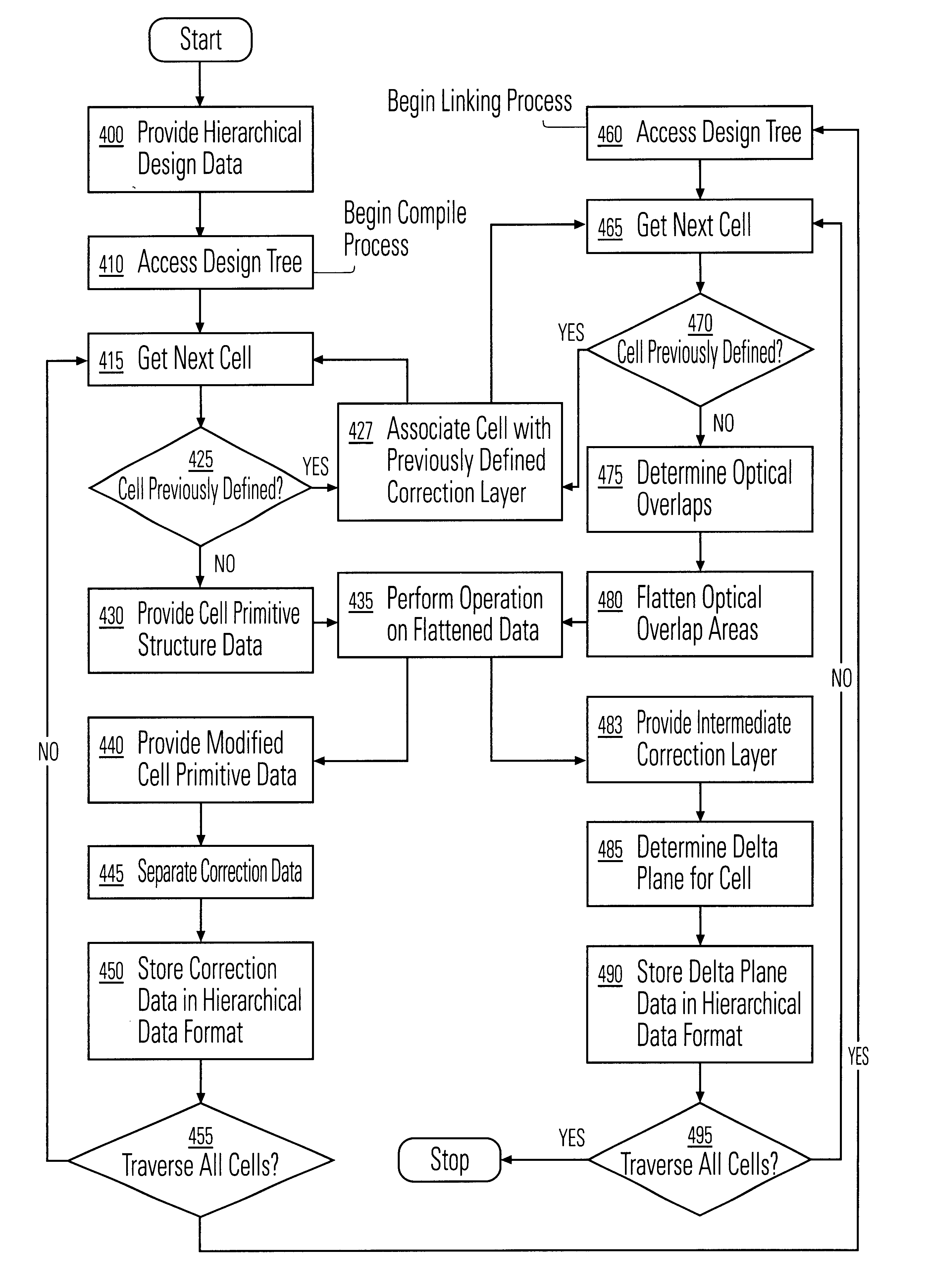

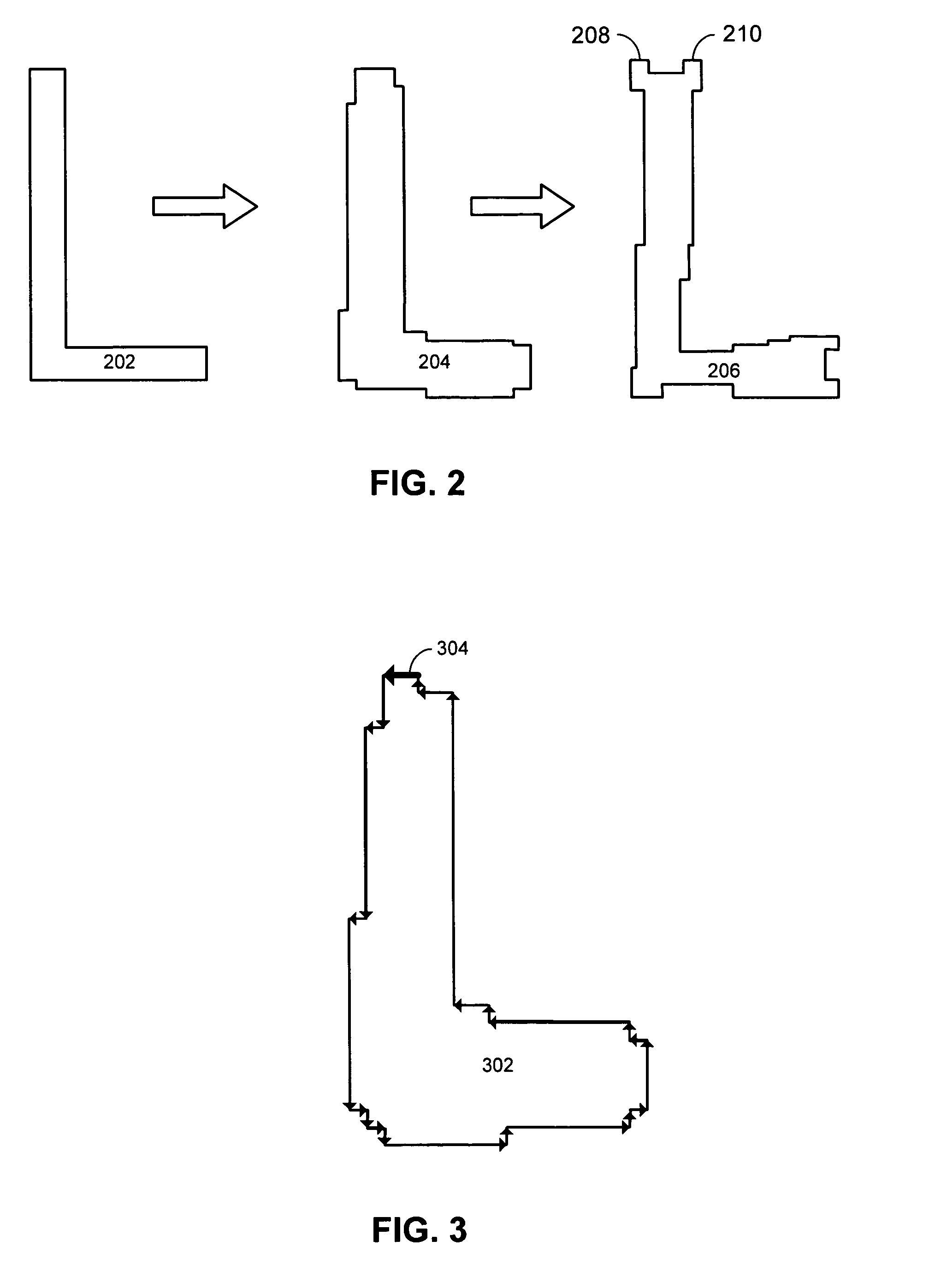

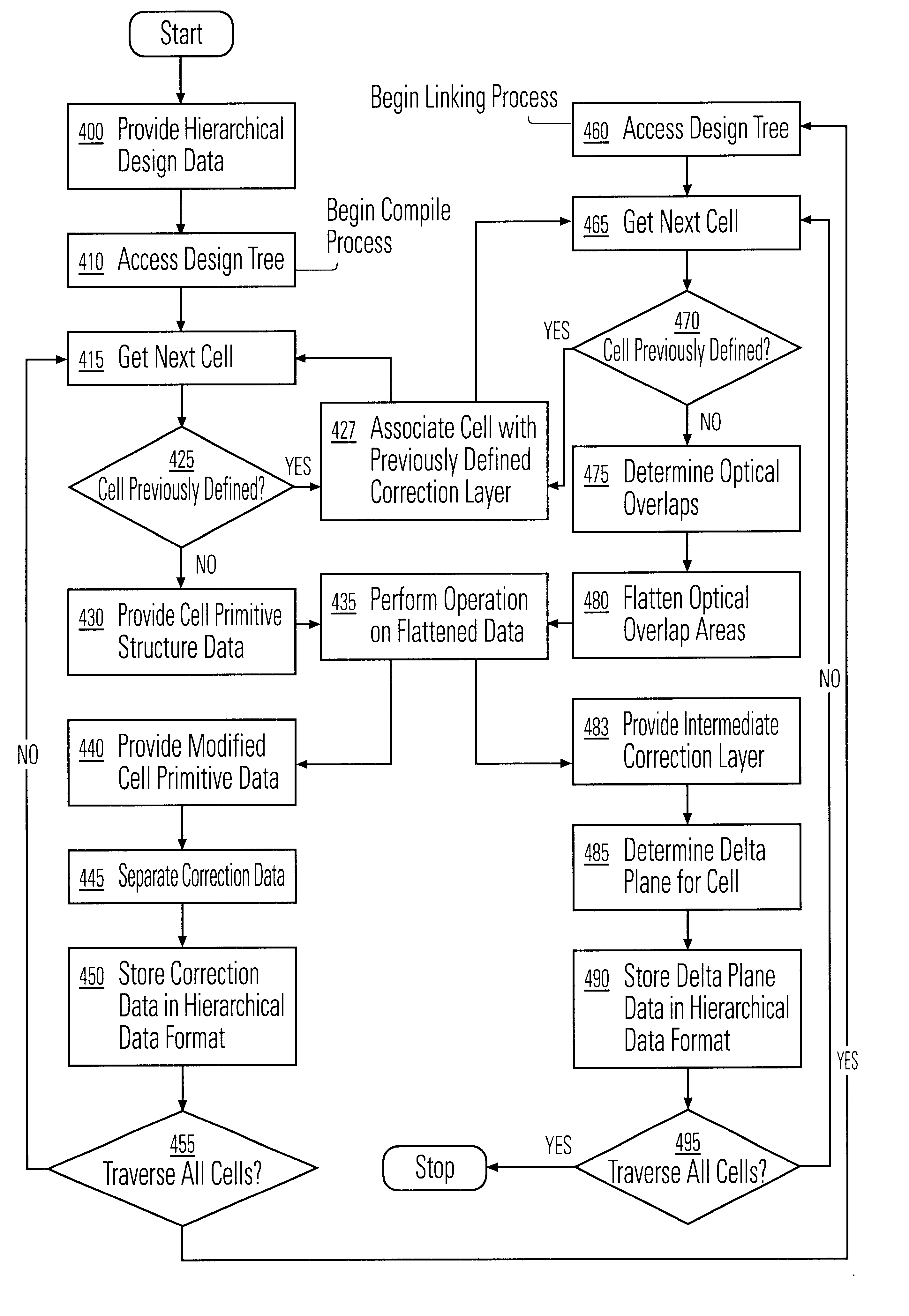

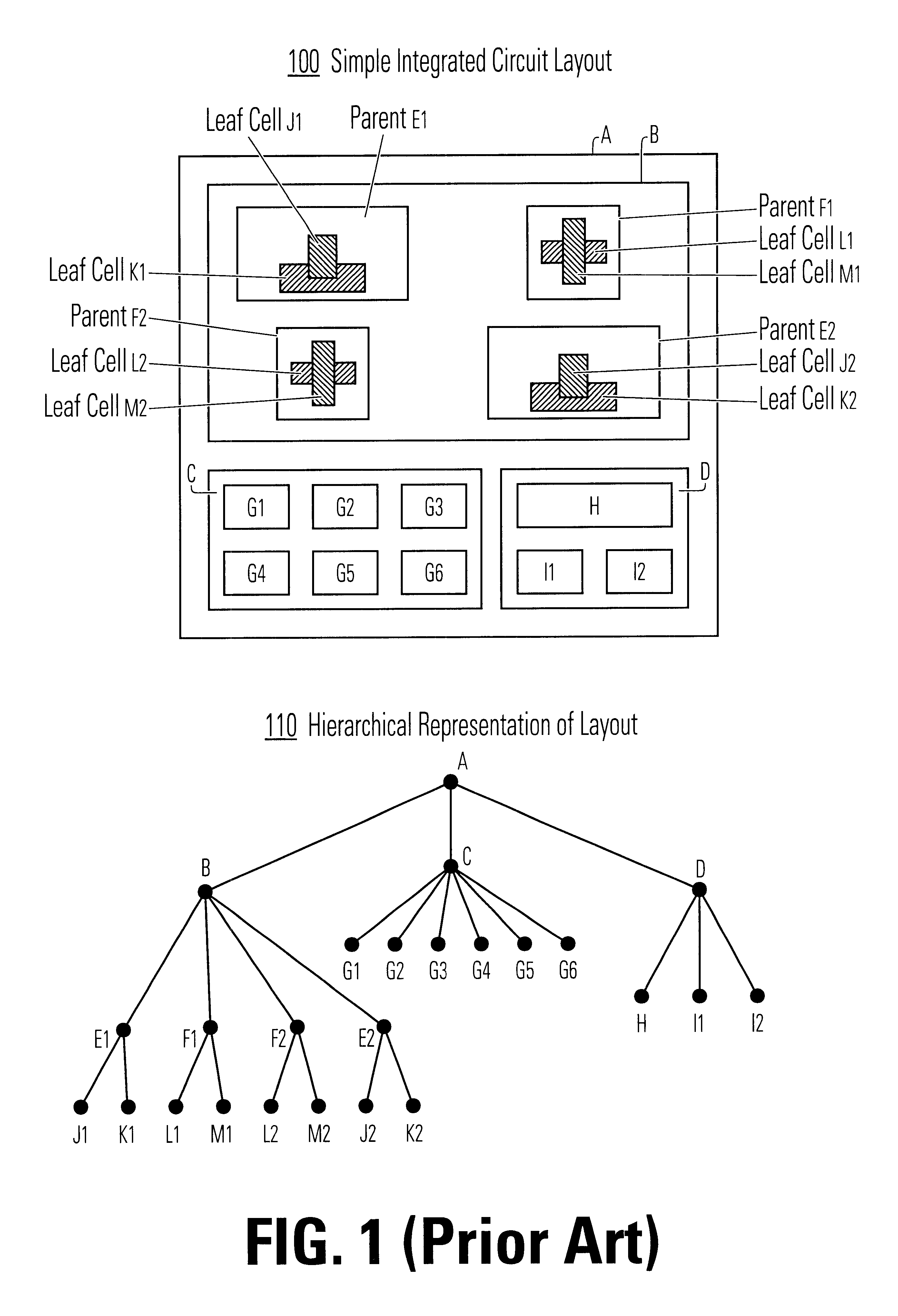

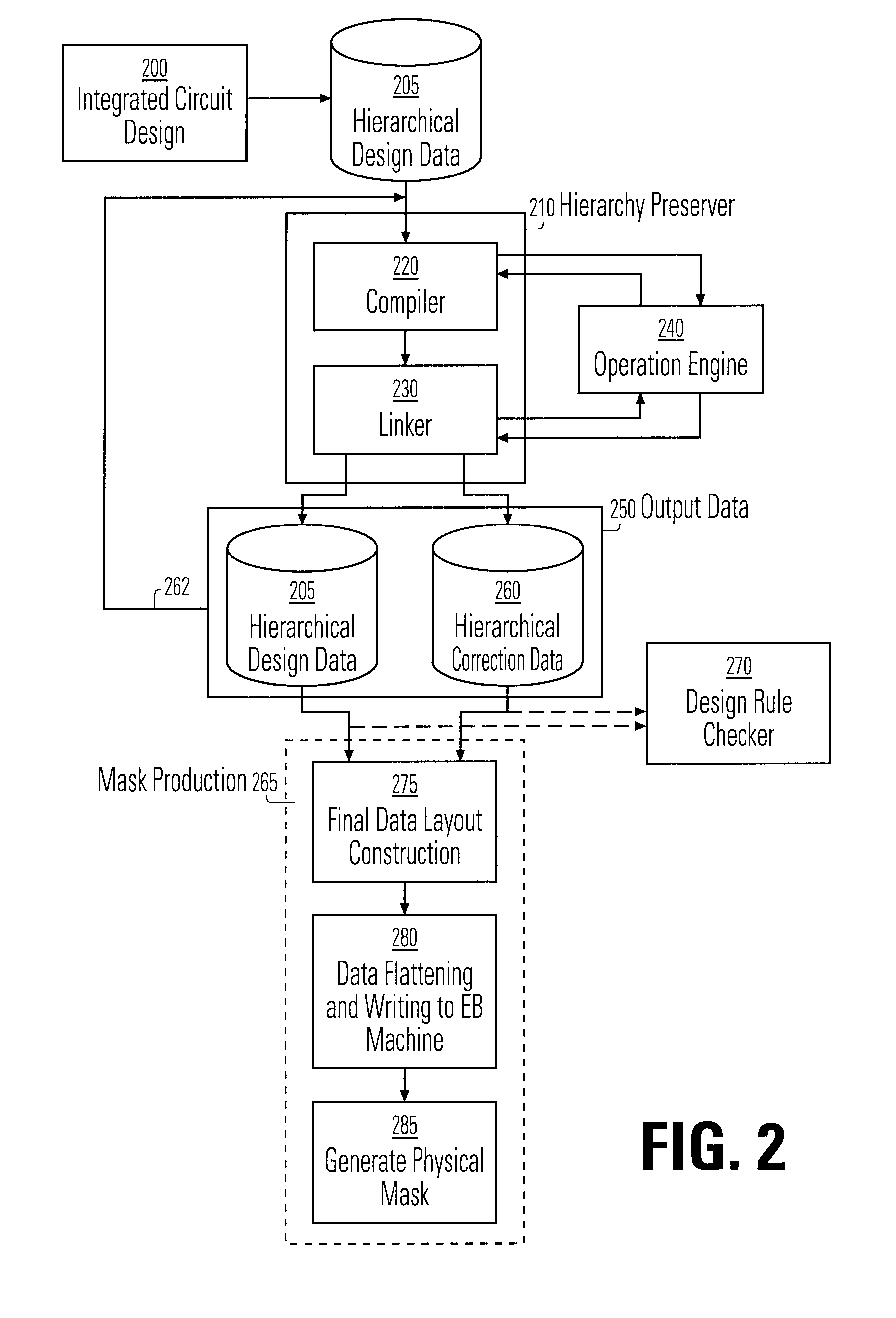

Data hierarchy layout correction and verification method and apparatus

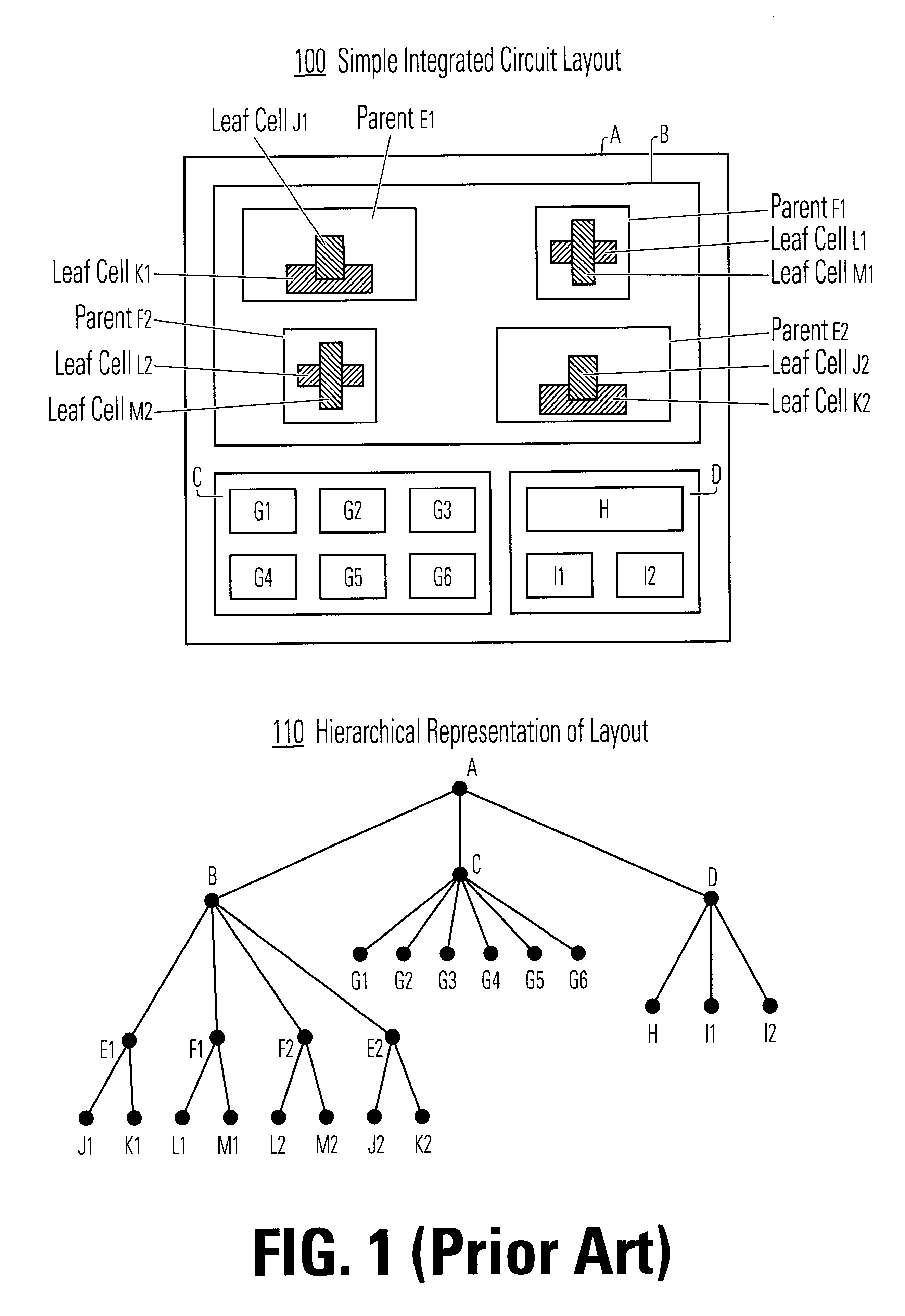

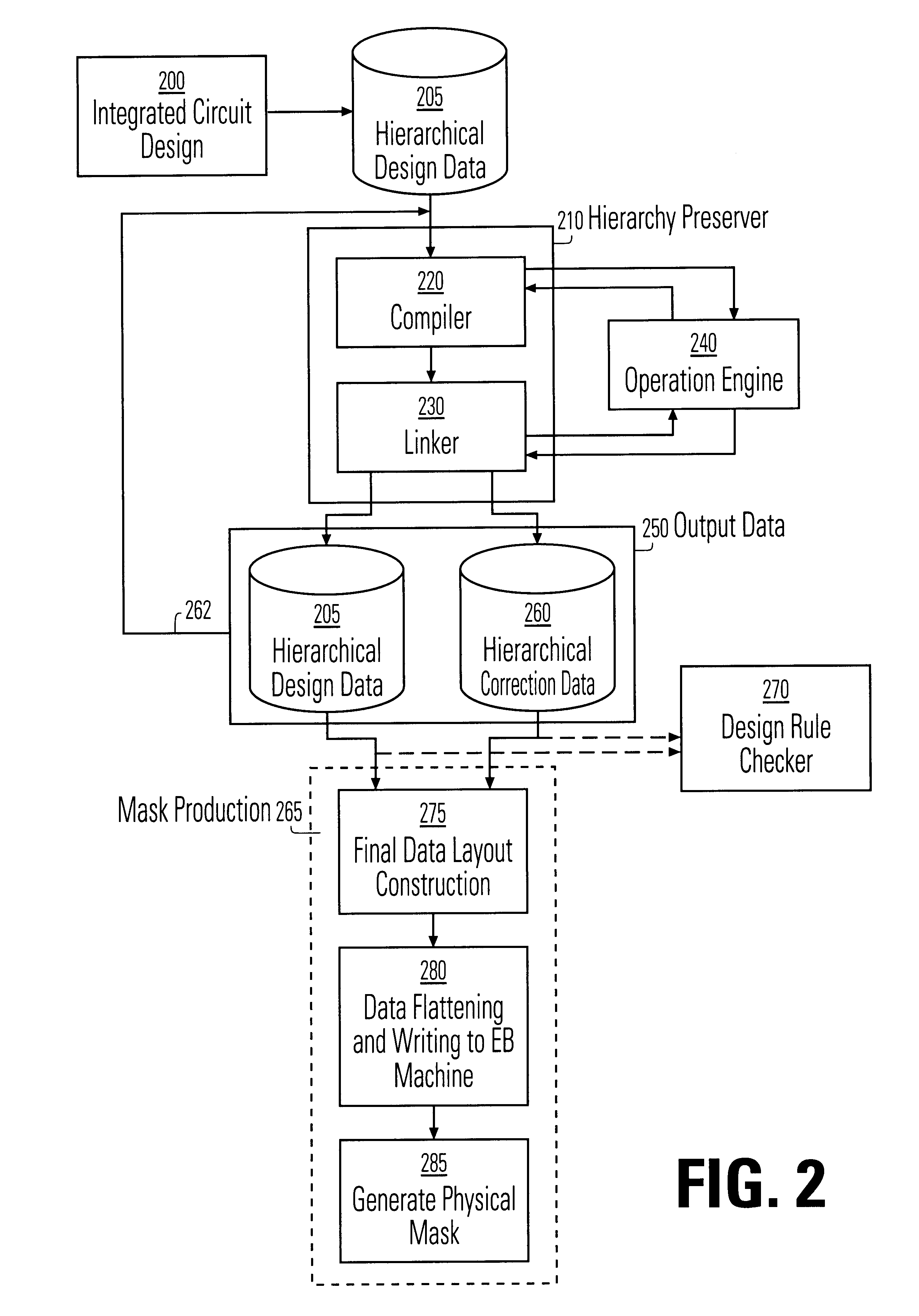

InactiveUS6370679B1Computation using non-denominational number representationOriginals for photomechanical treatmentComputer architectureValidation methods

A method and apparatus for the correction of integrated circuit layouts for optical proximity effects which maintains the original true hierarchy of the original layout is provided. Also provided is a method and apparatus for the design rule checking of layouts which have been corrected for optical proximity effects. The OPC correction method comprises providing a hierarchically described integrated circuit layout as a first input, and a particular set of OPC correction criteria as a second input. The integrated circuit layout is then analyzed to identify features of the layout which meet the provided OPC correction criteria. After the areas on the mask which need correction have been identified, optical proximity correction data is generated in response to the particular set of correction criteria. Finally, a first program data is generated which stores the generated optical proximity correction data in a hierarchical structure that corresponds to the hierarchical structure of the integrated circuit layout. As the output correction data is maintained in true hierarchical format, layouts which are OPC corrected according to this method are able to be processed through conventional design rule checkers with no altering of the data.

Owner:SYNOPSYS INC

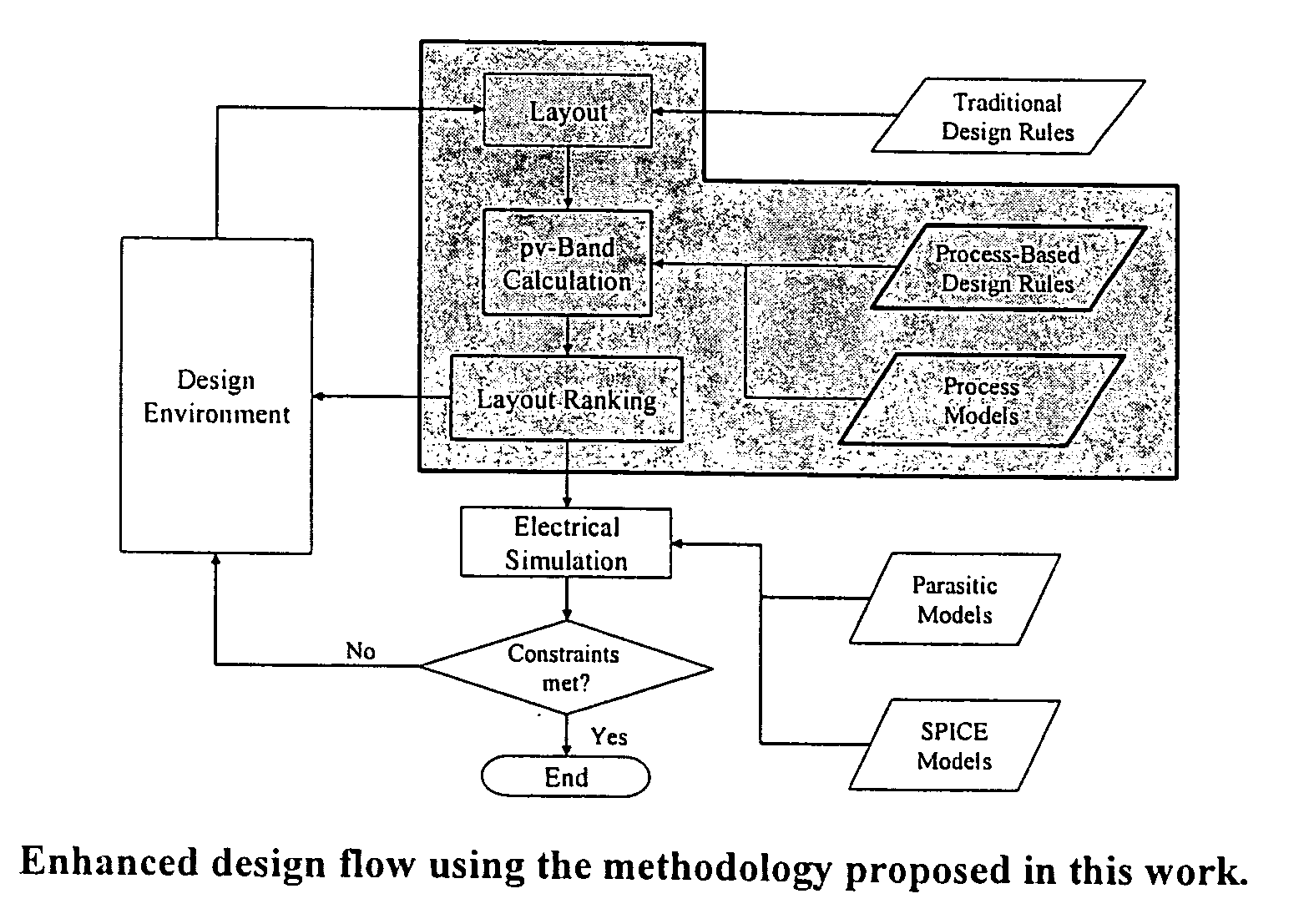

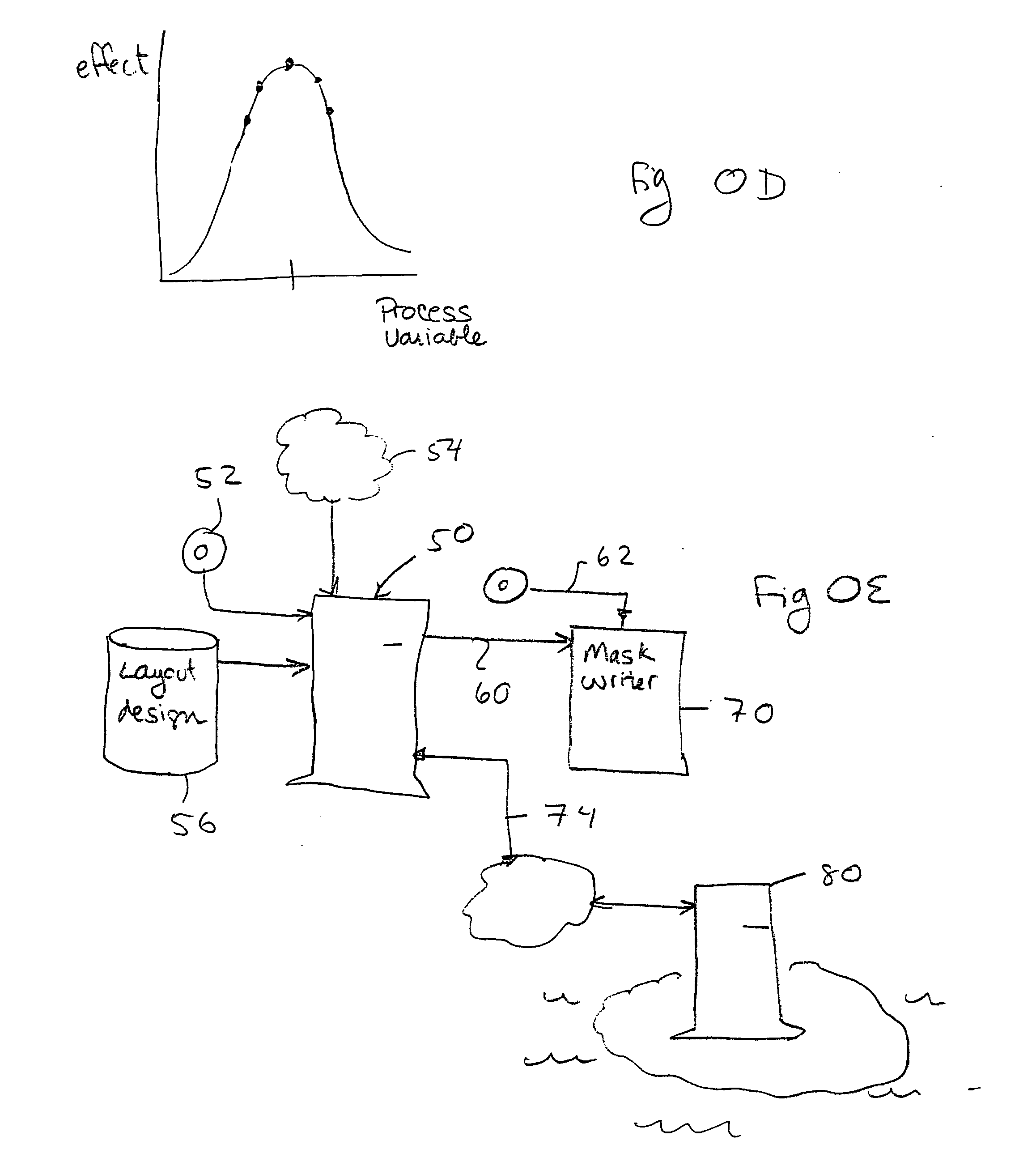

Integrated circuit layout design methodology with process variation bands

ActiveUS20050251771A1Constraint-based CADCAD circuit designSystems analysisIntegrated circuit layout

A system for analyzing IC layouts and designs by calculating variations of a number of objects to be created on a semiconductor wafer as a result of different process conditions. The variations are analyzed to determine individual feature failures or to rank layout designs by their susceptibility to process variations. In one embodiment, the variations are represented by PV-bands having an inner edge that defines the smallest area in which an object will always print and an outer edge that defines the largest area in which an object will print under some process conditions.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

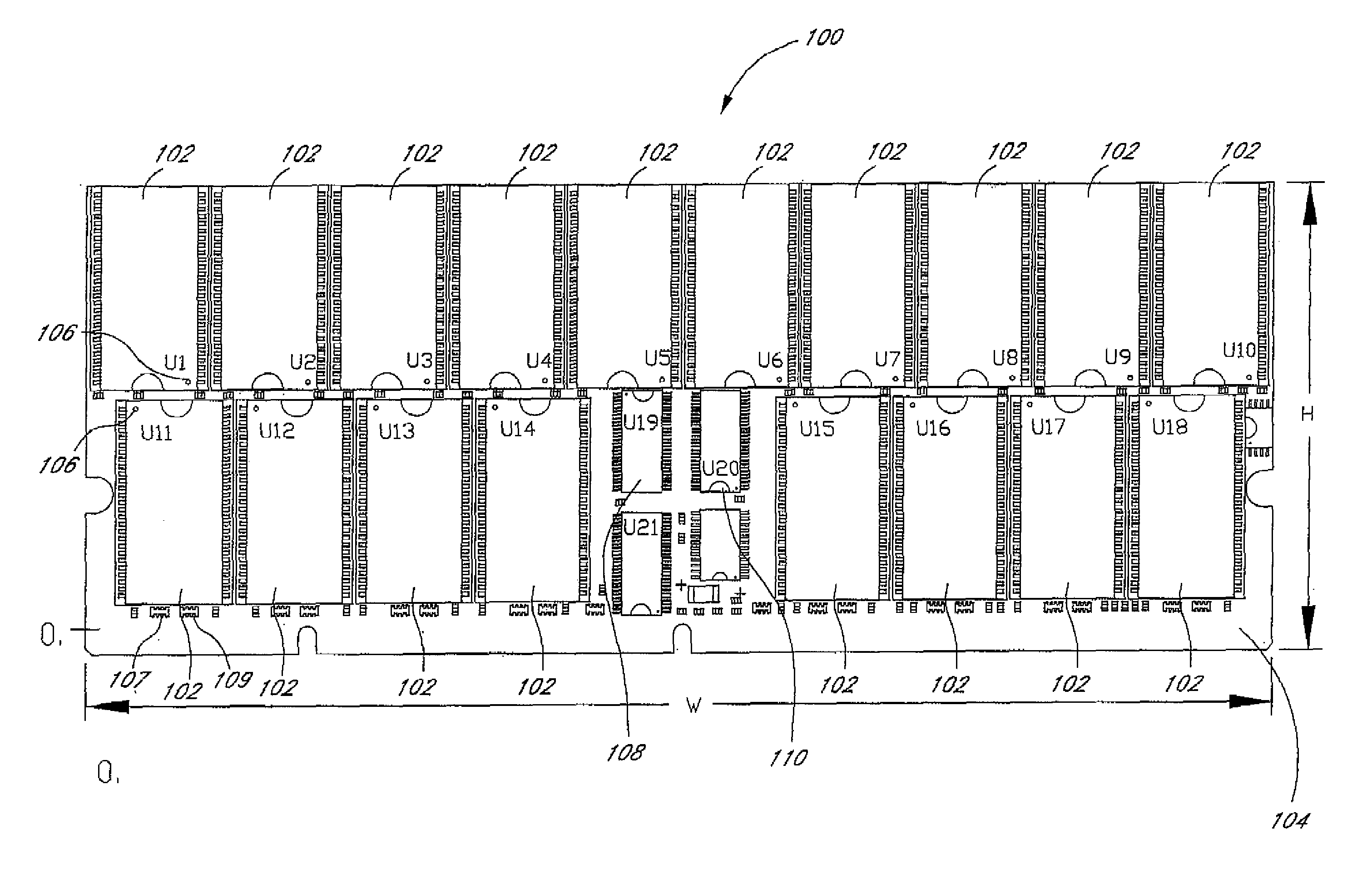

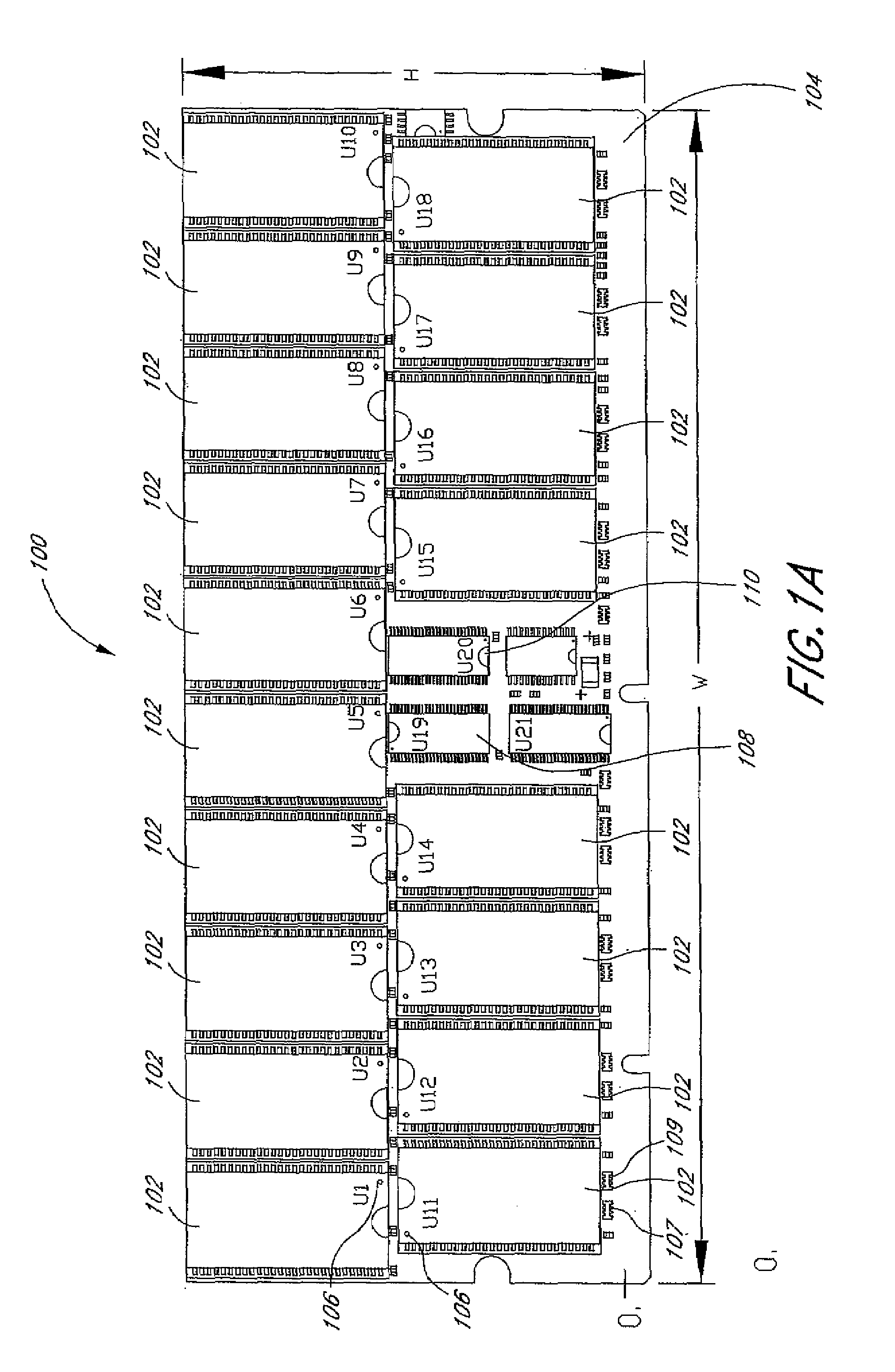

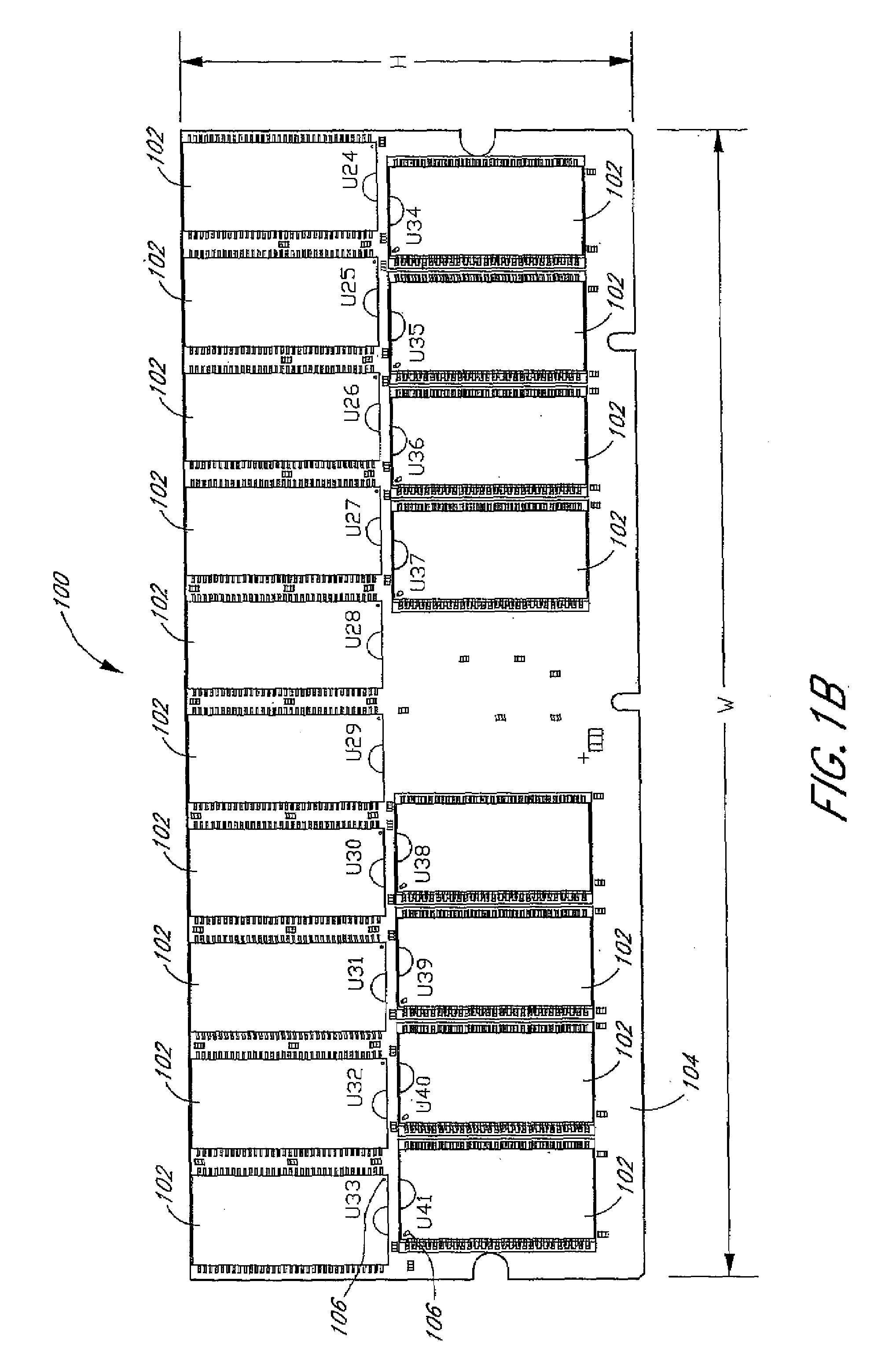

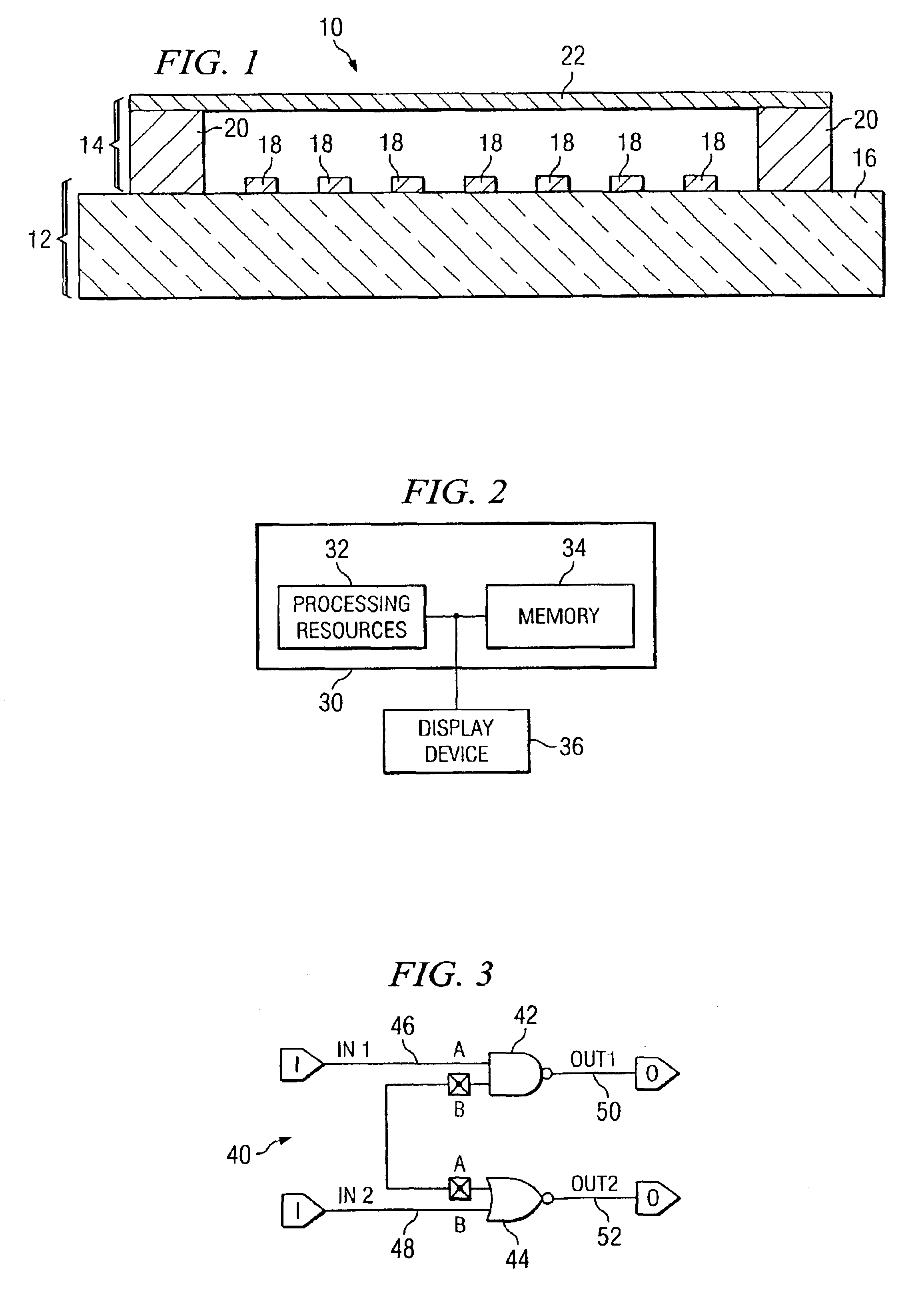

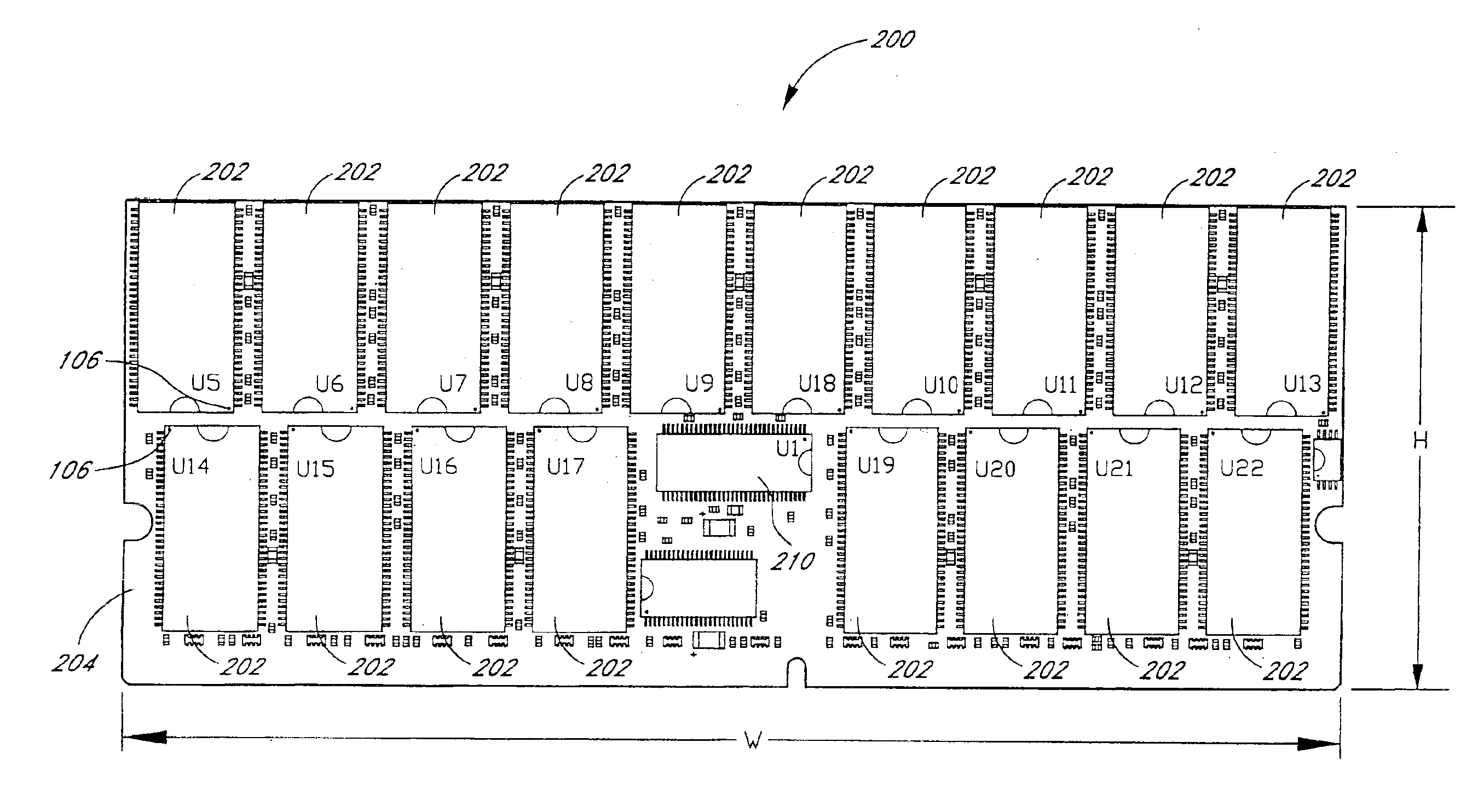

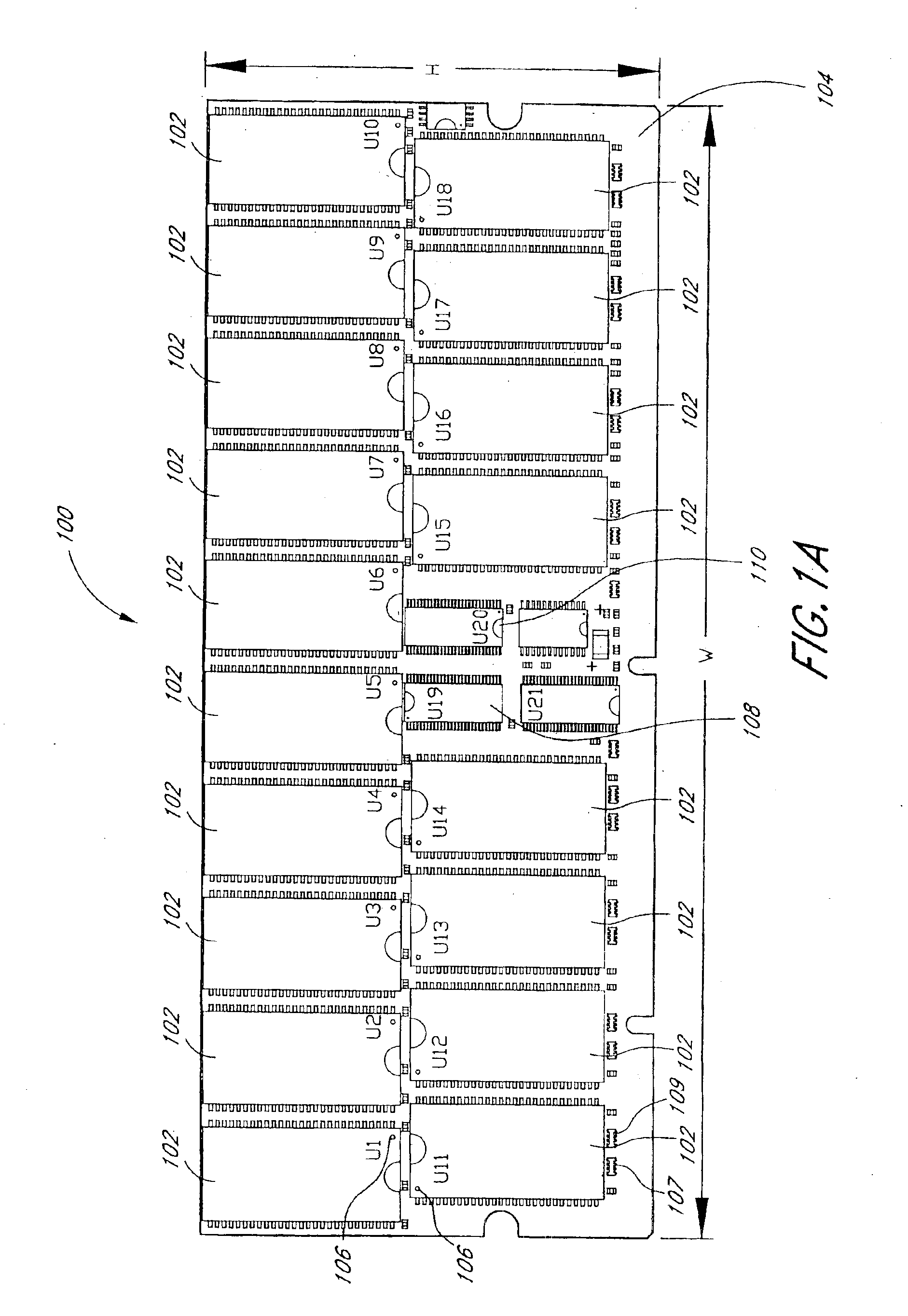

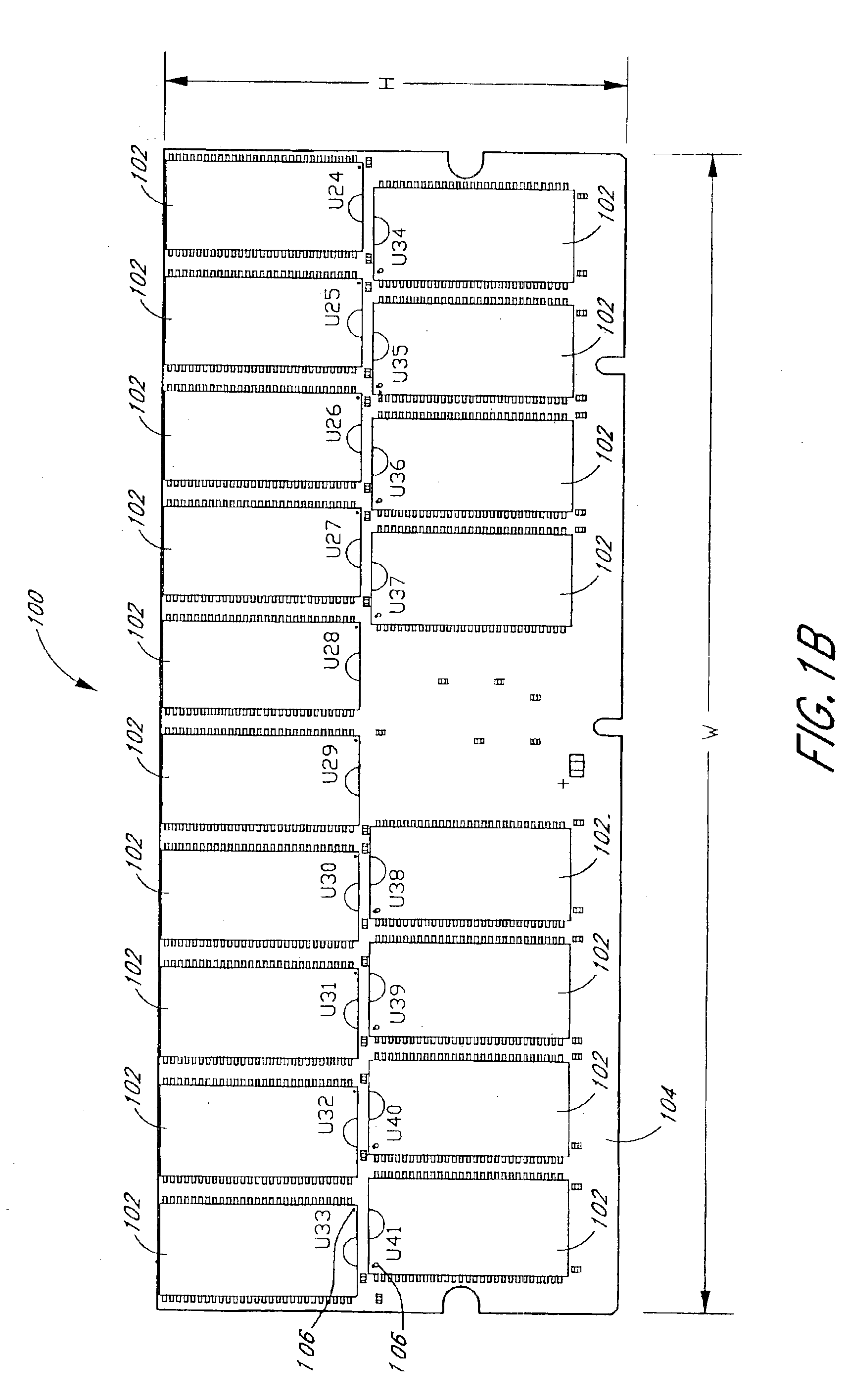

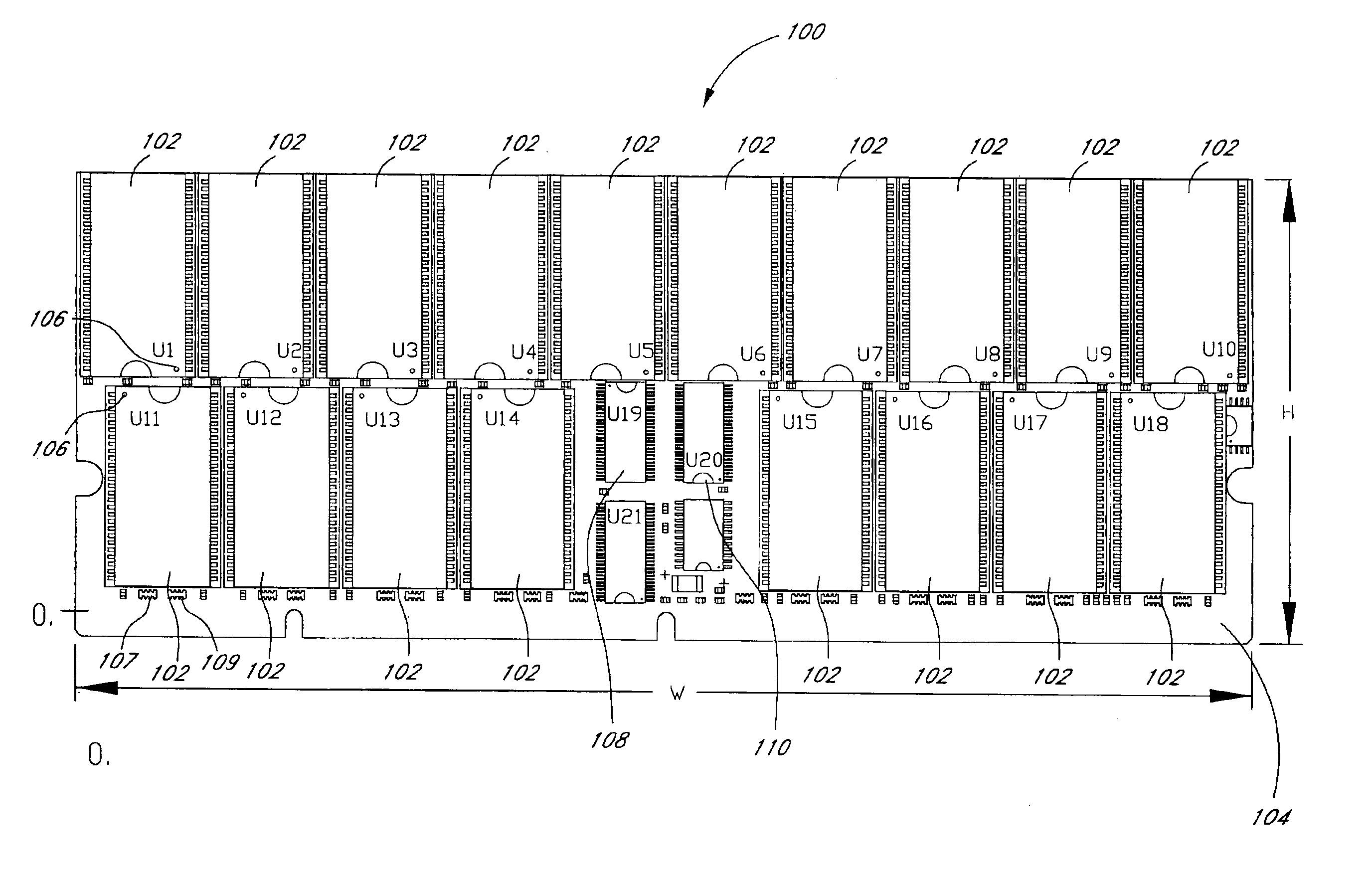

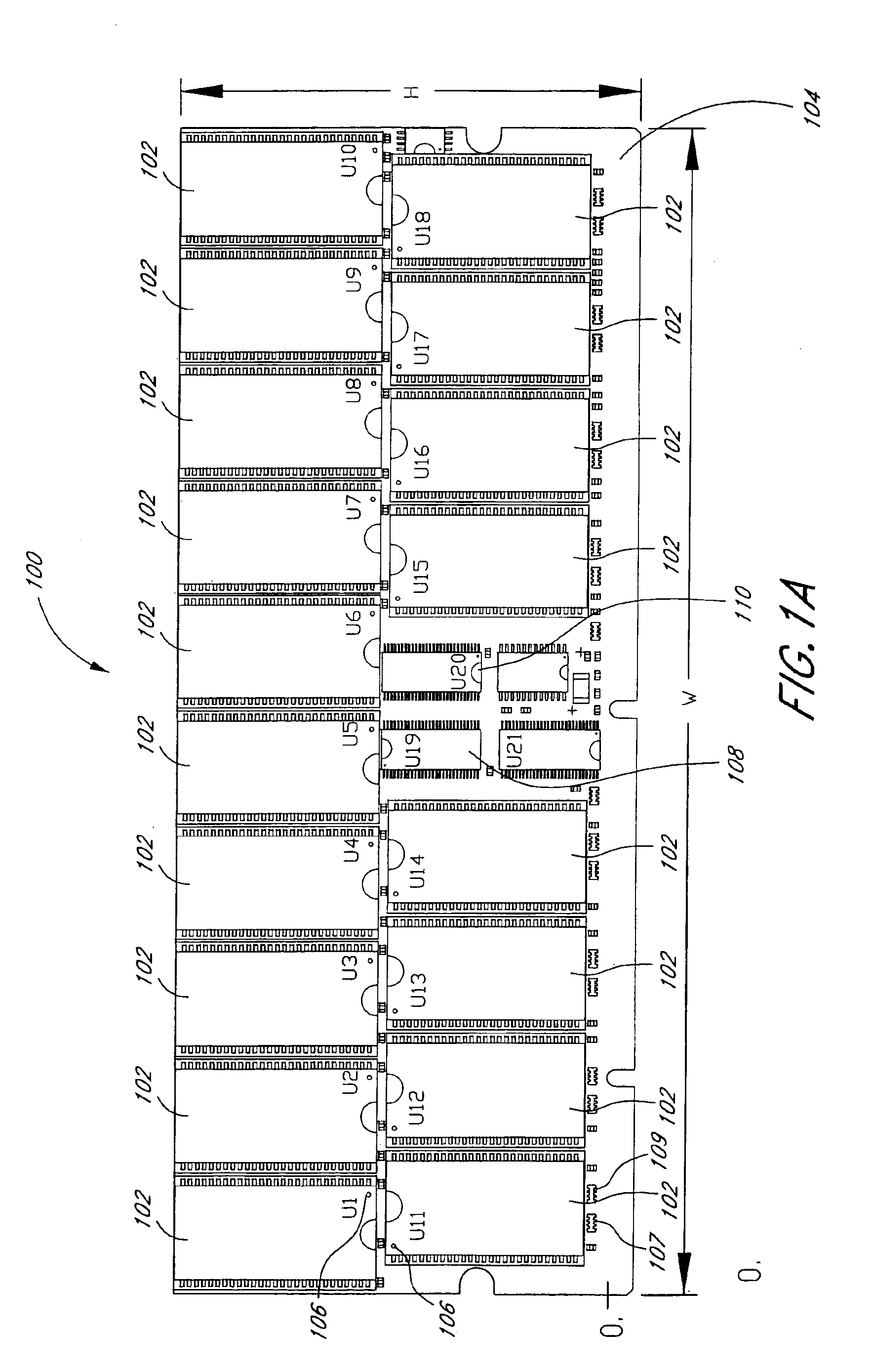

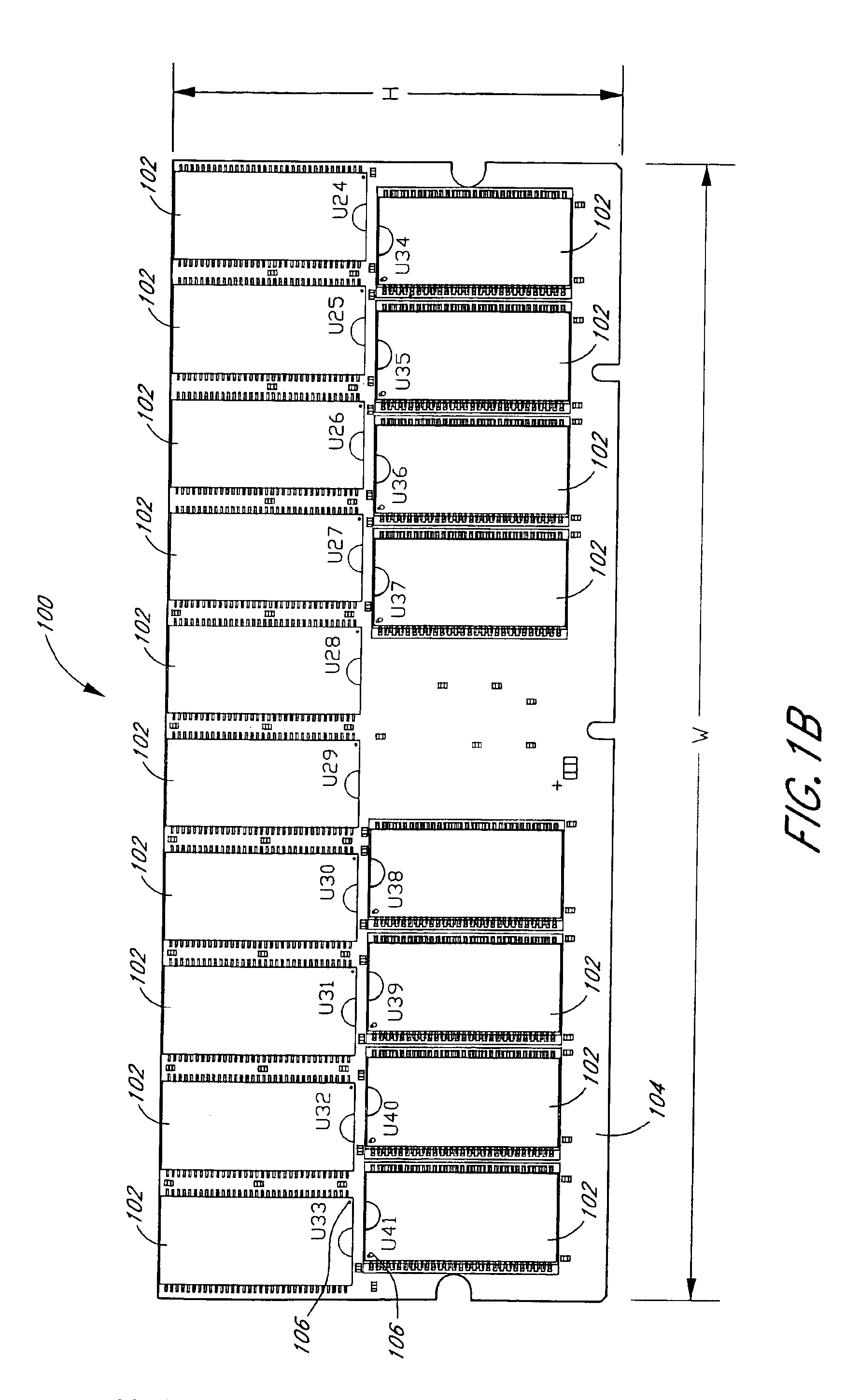

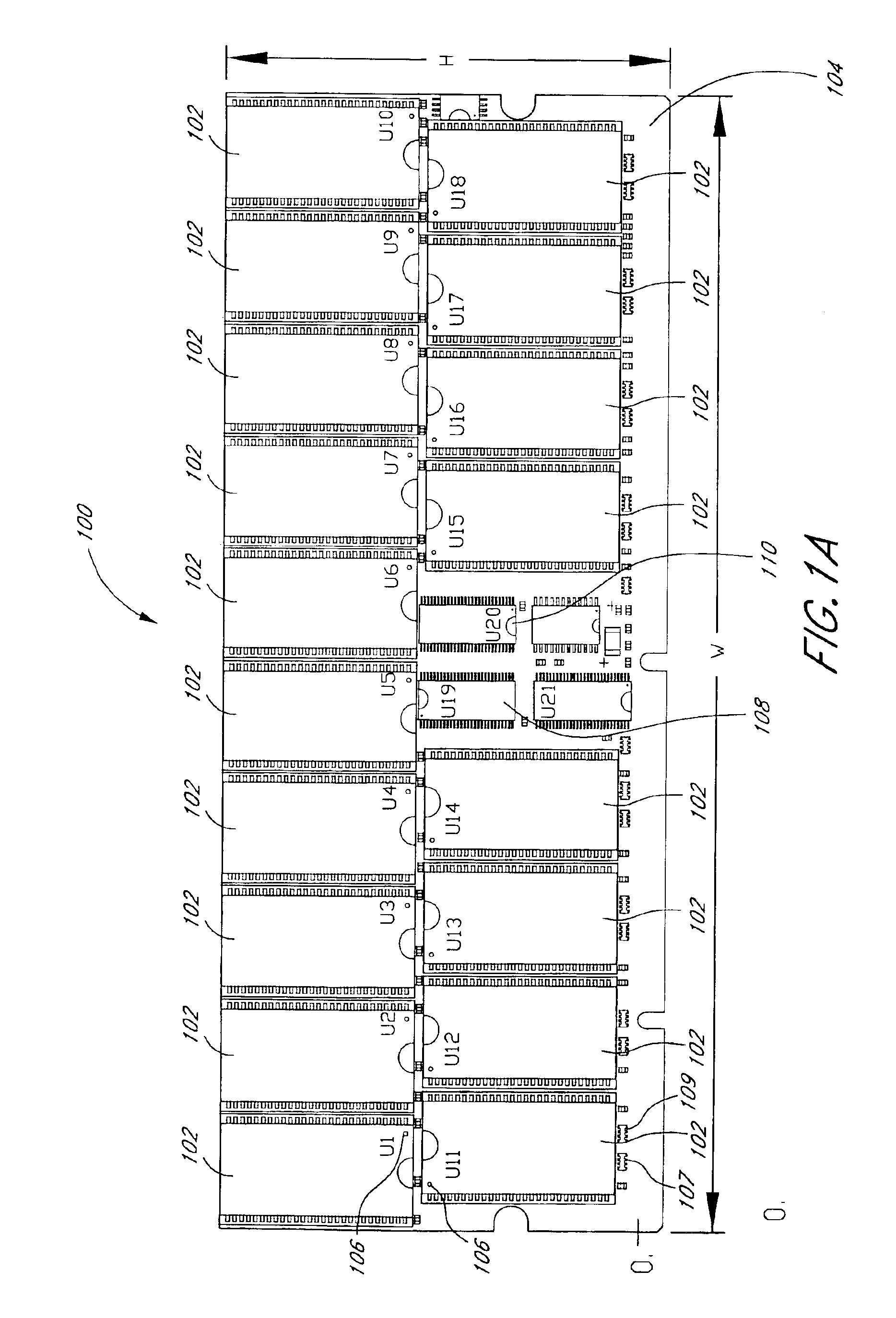

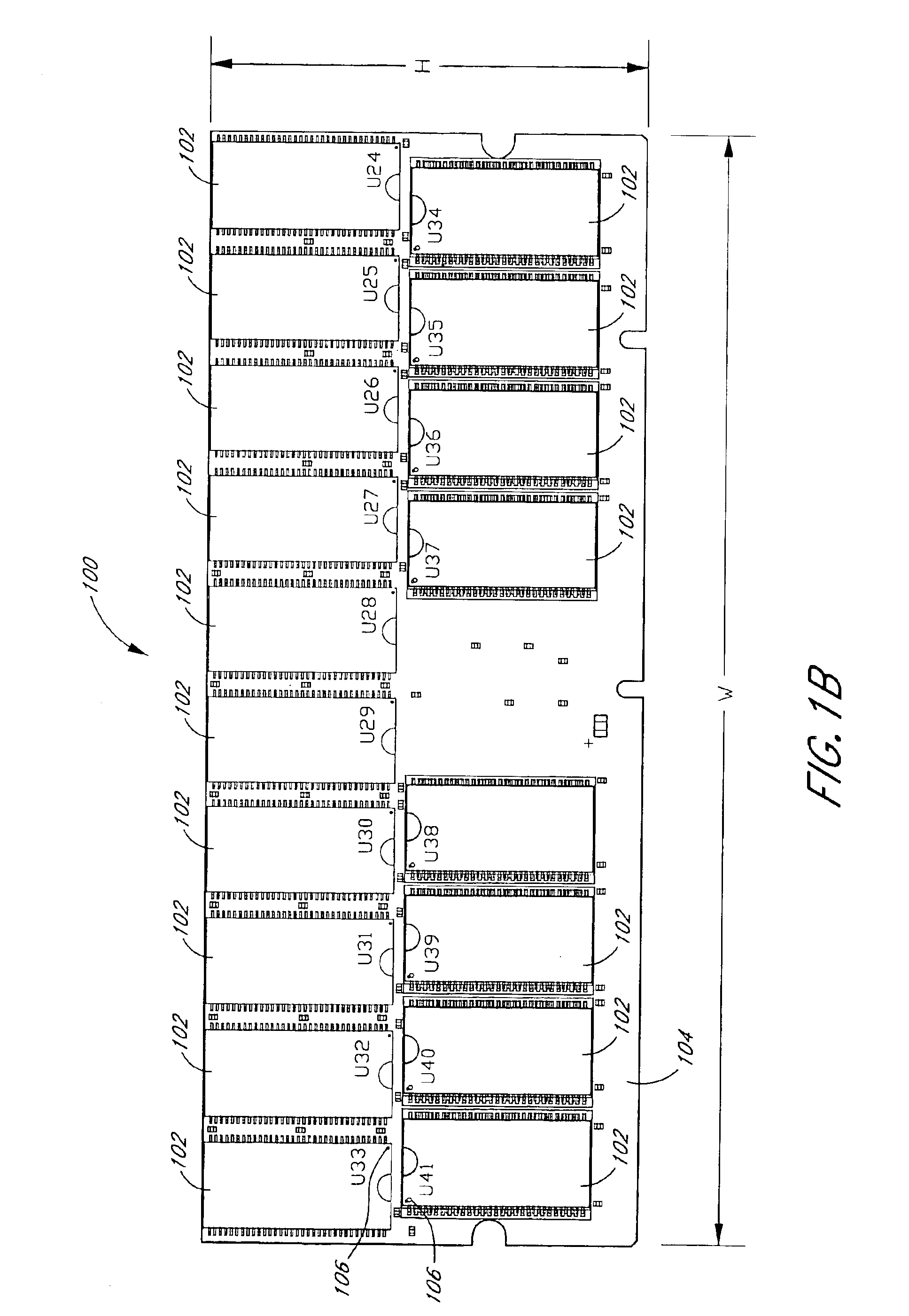

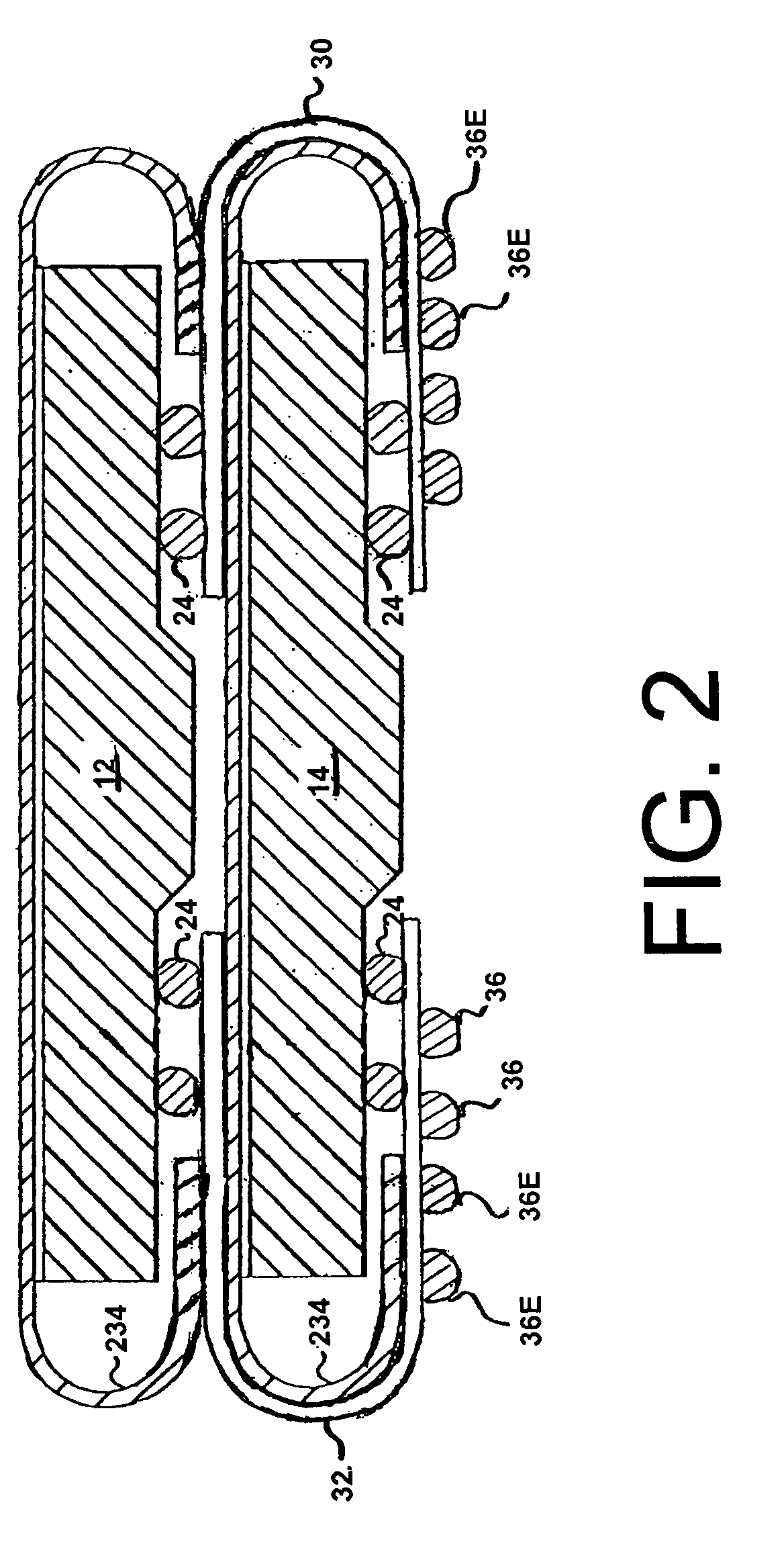

Arrangement of integrated circuits in a memory module

InactiveUS20050018495A1Final product manufactureCross-talk/noise/interference reductionGigabyteProcessor register

Abstract of the Disclosure Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of one-Gigabyte, two-Gigabyte, and four-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in the first row on a first lateral portion of the printed circuit board and in the second row on the first lateral portion are connected to a first addressing register with two register integrated circuits. The integrated circuits in the first row on the second lateral portion and in the second row on the second lateral portion are connected to a second addressing register with two register integrated circuits. Each addressing register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

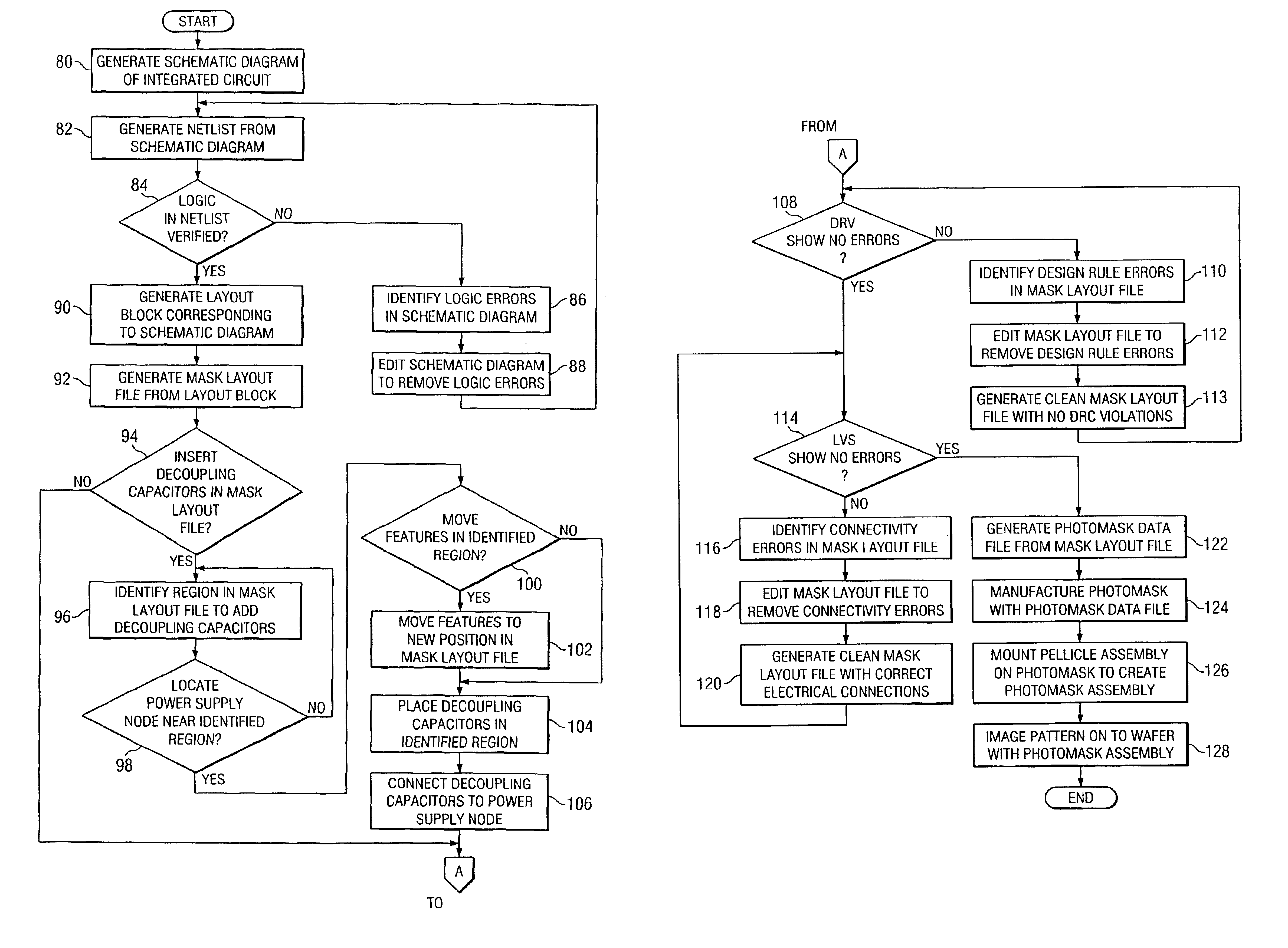

Photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufacture with same

InactiveUS6978437B1Increase antenna ratioRaise the ratioSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

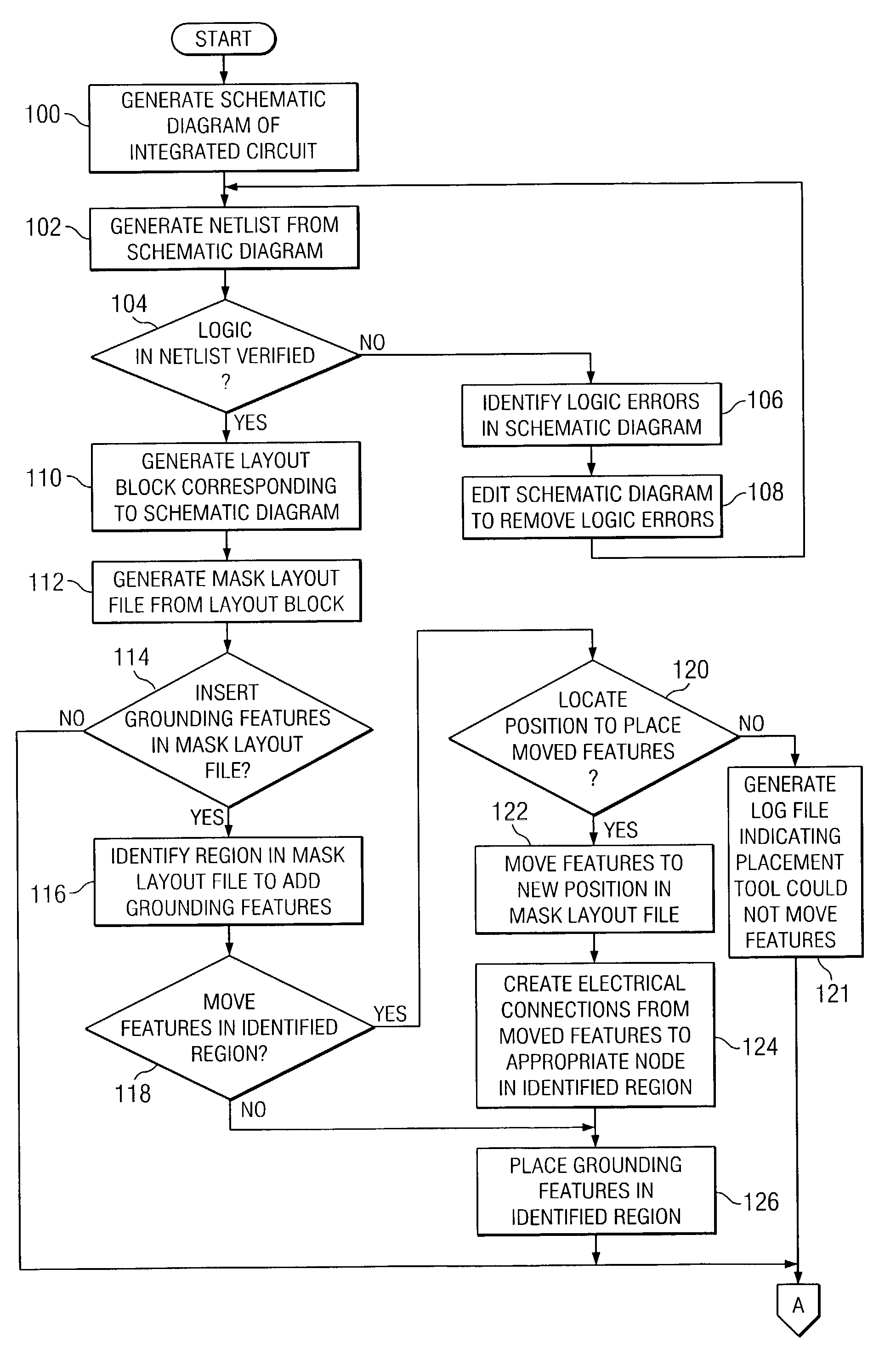

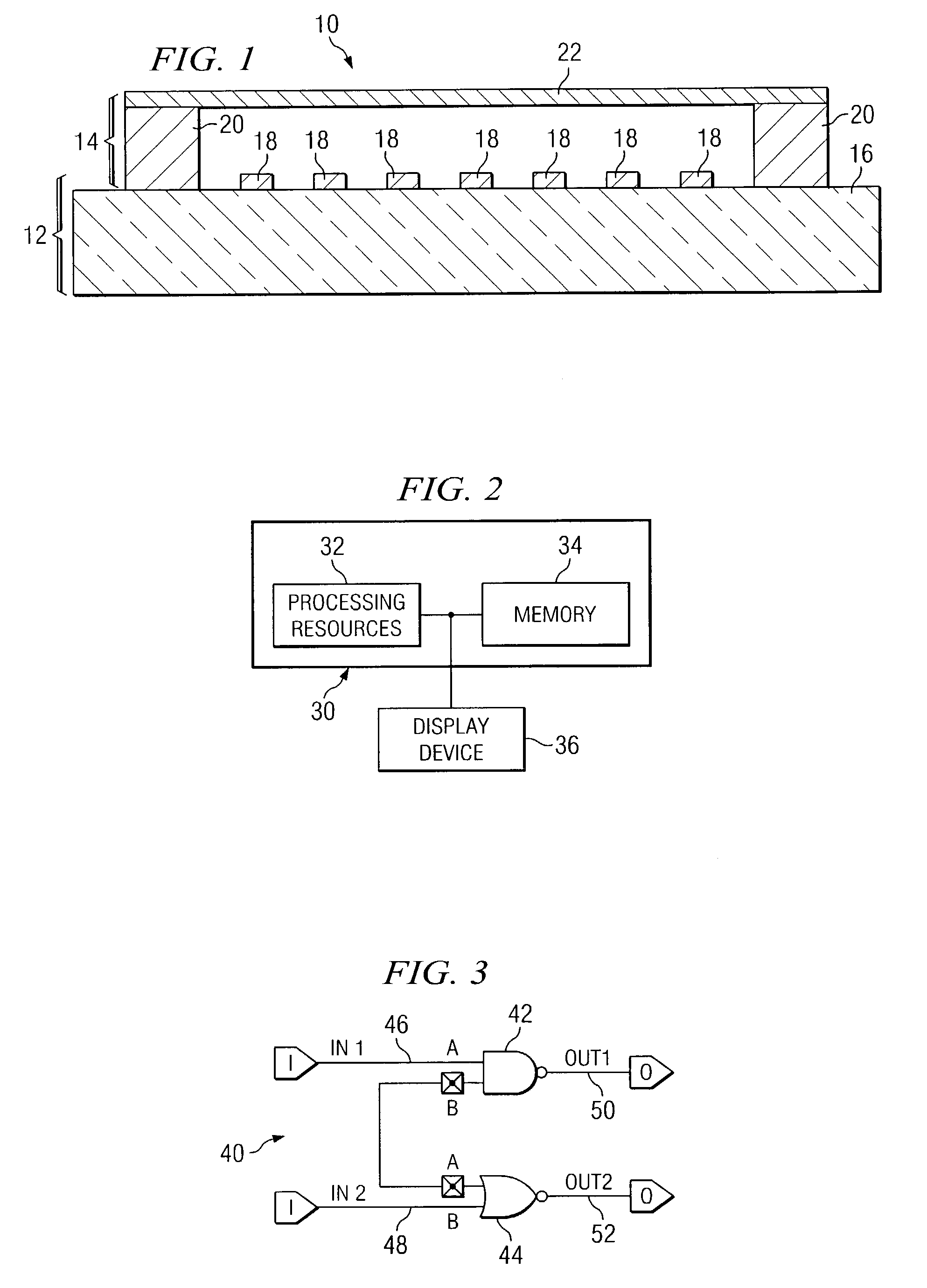

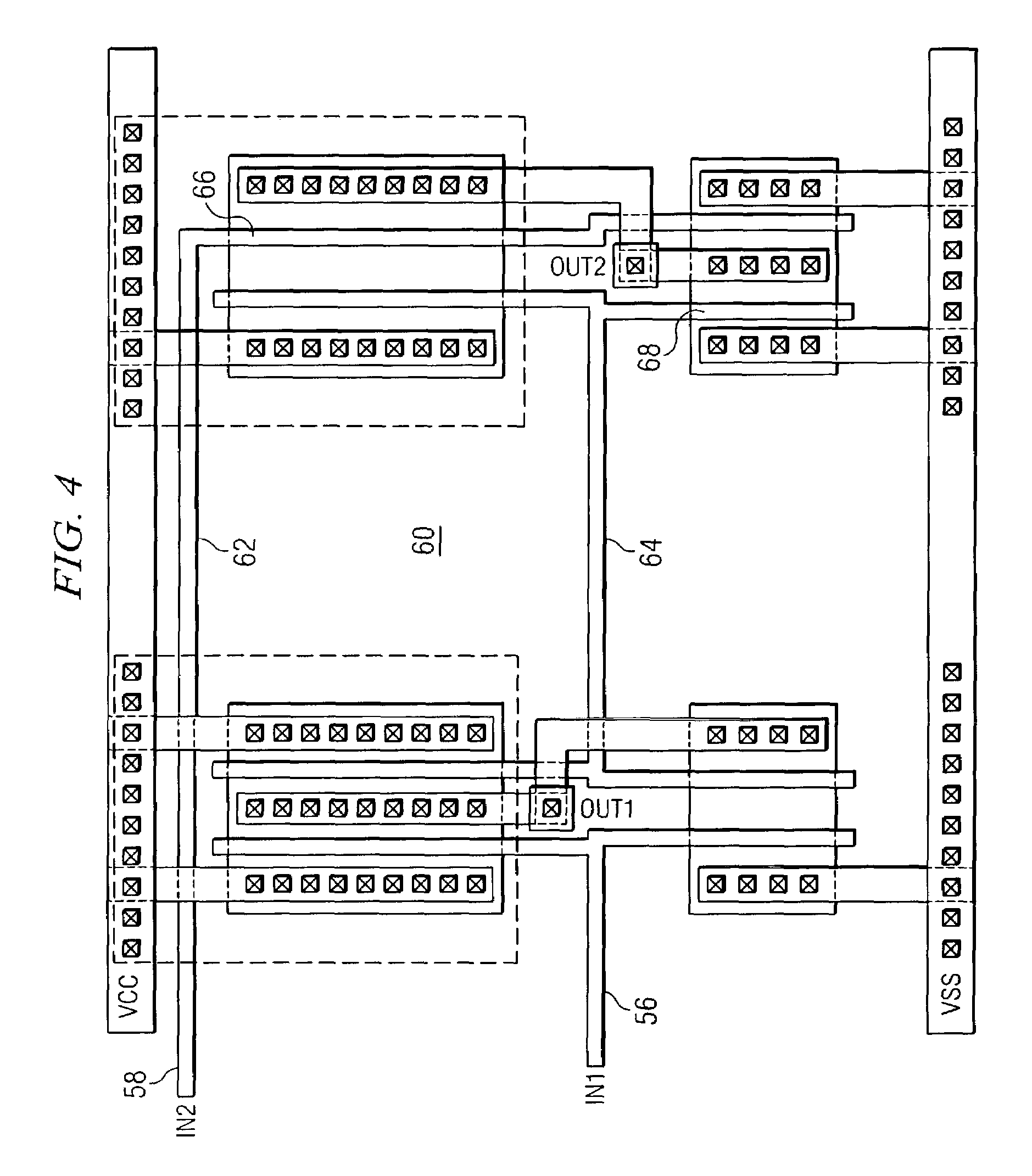

A photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufactured with the photomask are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region including an antenna ratio less than a first design rule. A feature located in the identified region is moved based on a second design rule from a first position to a second position in the mask layout file to create a space in the identified region. A grounding feature is placed in the space and automatically connected to a gate feature in the mask layout file such that the antenna ratio is increased to greater than or approximately equal to the first design rule.

Owner:CELERICS TECH

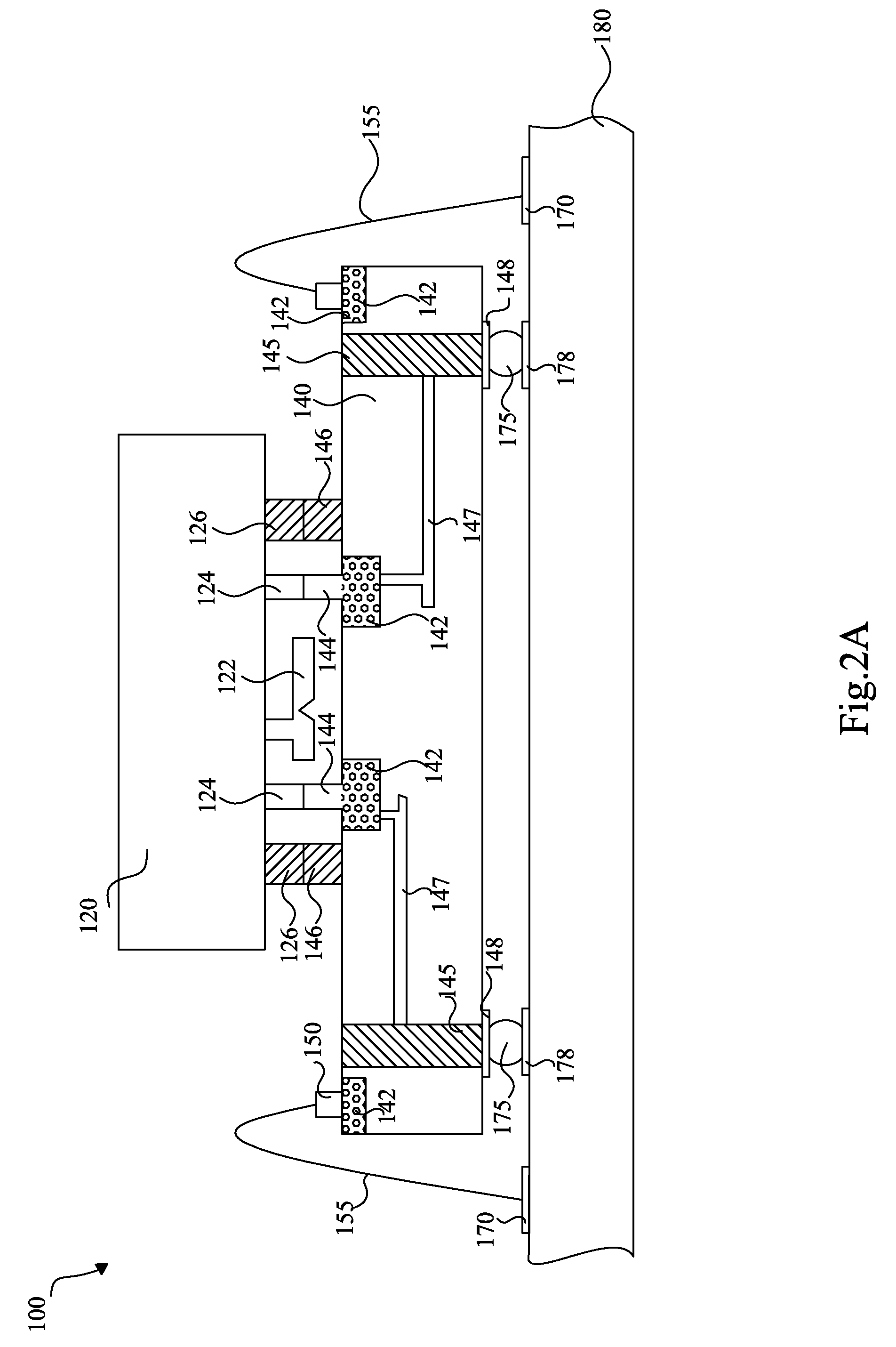

MEMS Packaging Including Integrated Circuit Dies

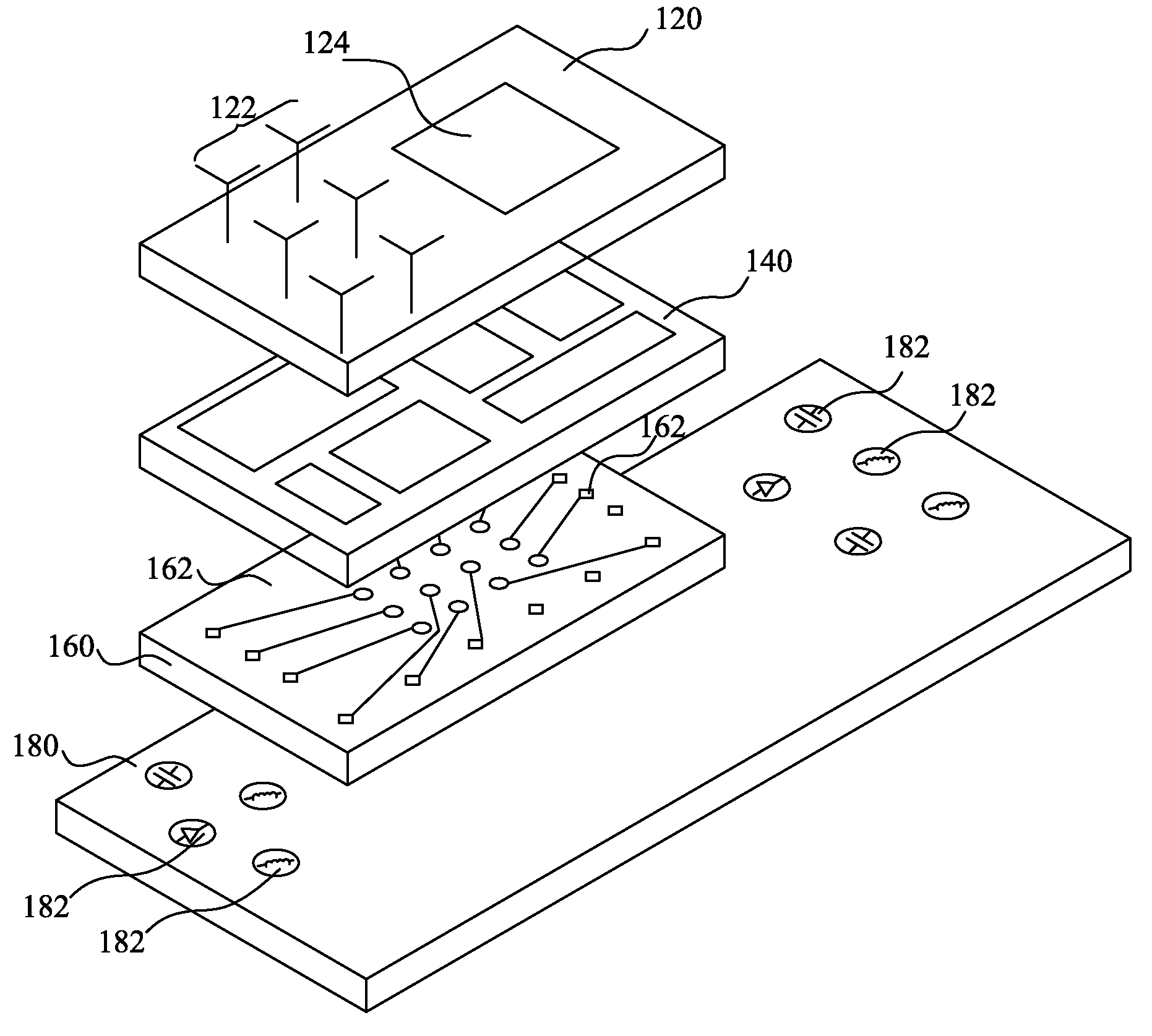

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

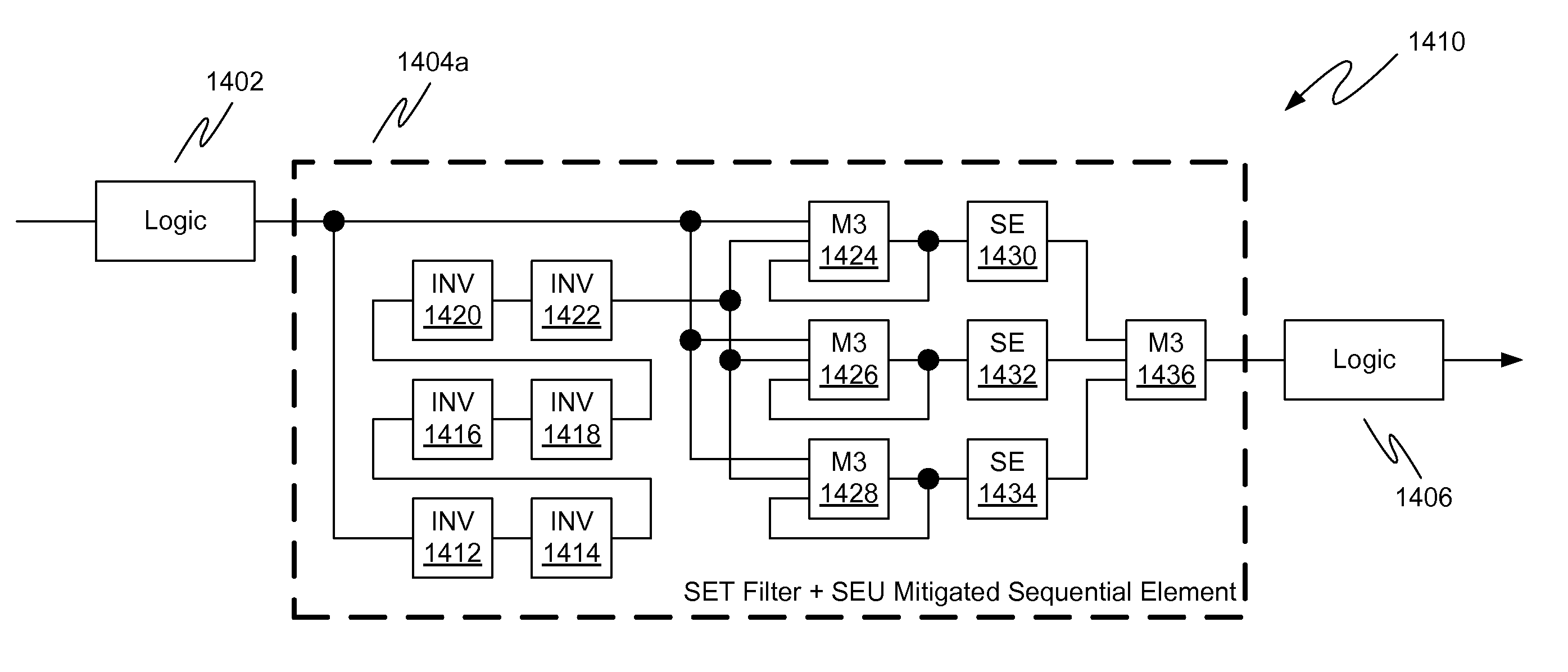

Single event transient mitigation and measurement in integrated circuits

ActiveUS20090204933A1Fail-safe circuitsDetecting faulty computer hardwareIntegrated circuit layoutComputer science

A method for single event transient filtering in an integrated circuit device is described. The device comprises three sequential elements, each having a data input and a data output with each of the three data outputs coupled to one of three inputs of a voting gate. The method comprises generating first and second nominally equivalent logic signals in first and second SET domains, converting the first and second nominally equivalent logic signals into first, second and third nominally equivalent data channels, and transmitting the first, second and third nominally equivalent data channels to the data inputs of the first, second and third sequential elements. Provision is made for applying the method to logic designs implemented in programmable logic integrated circuit devices.

Owner:MICROSEMI SOC

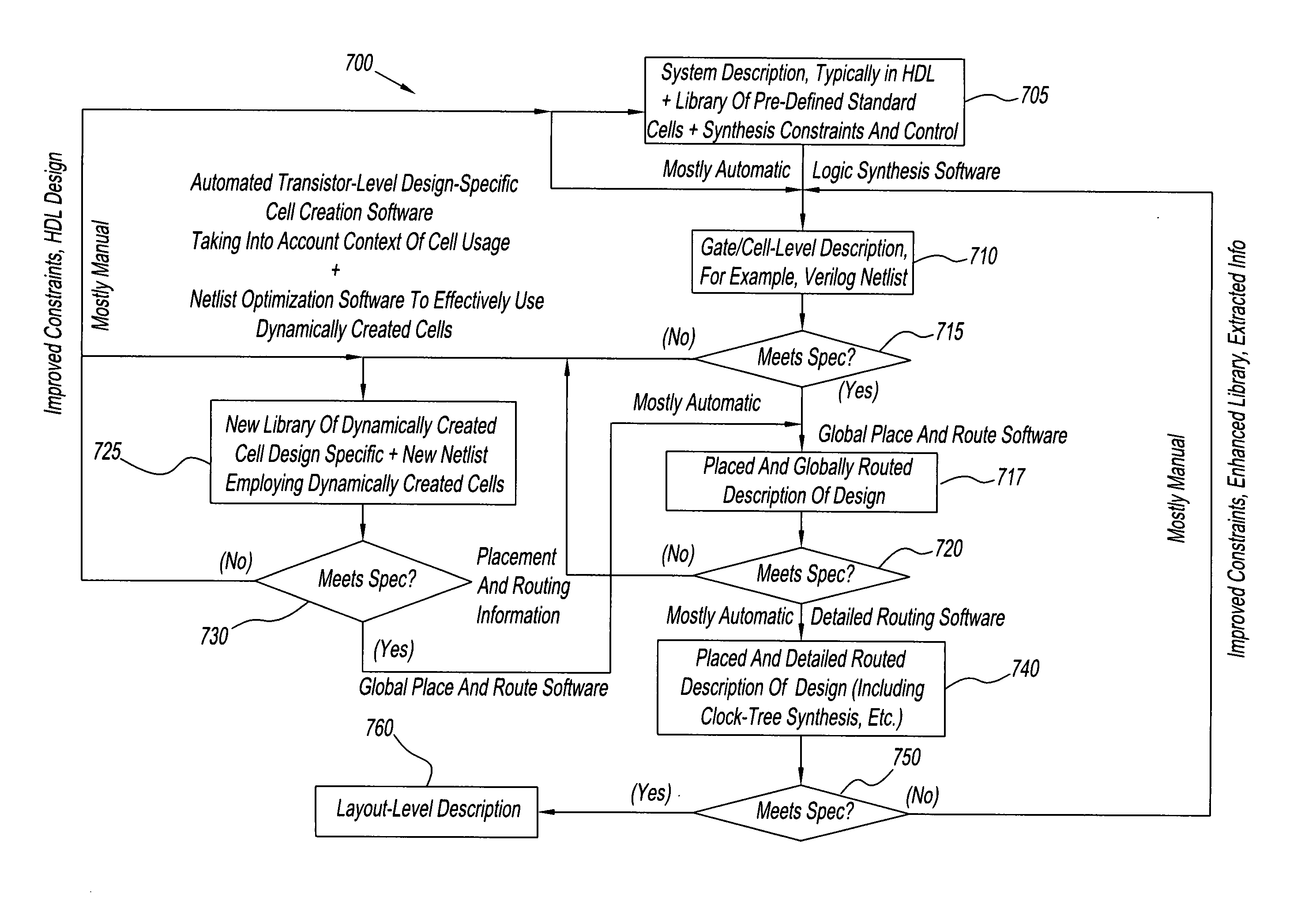

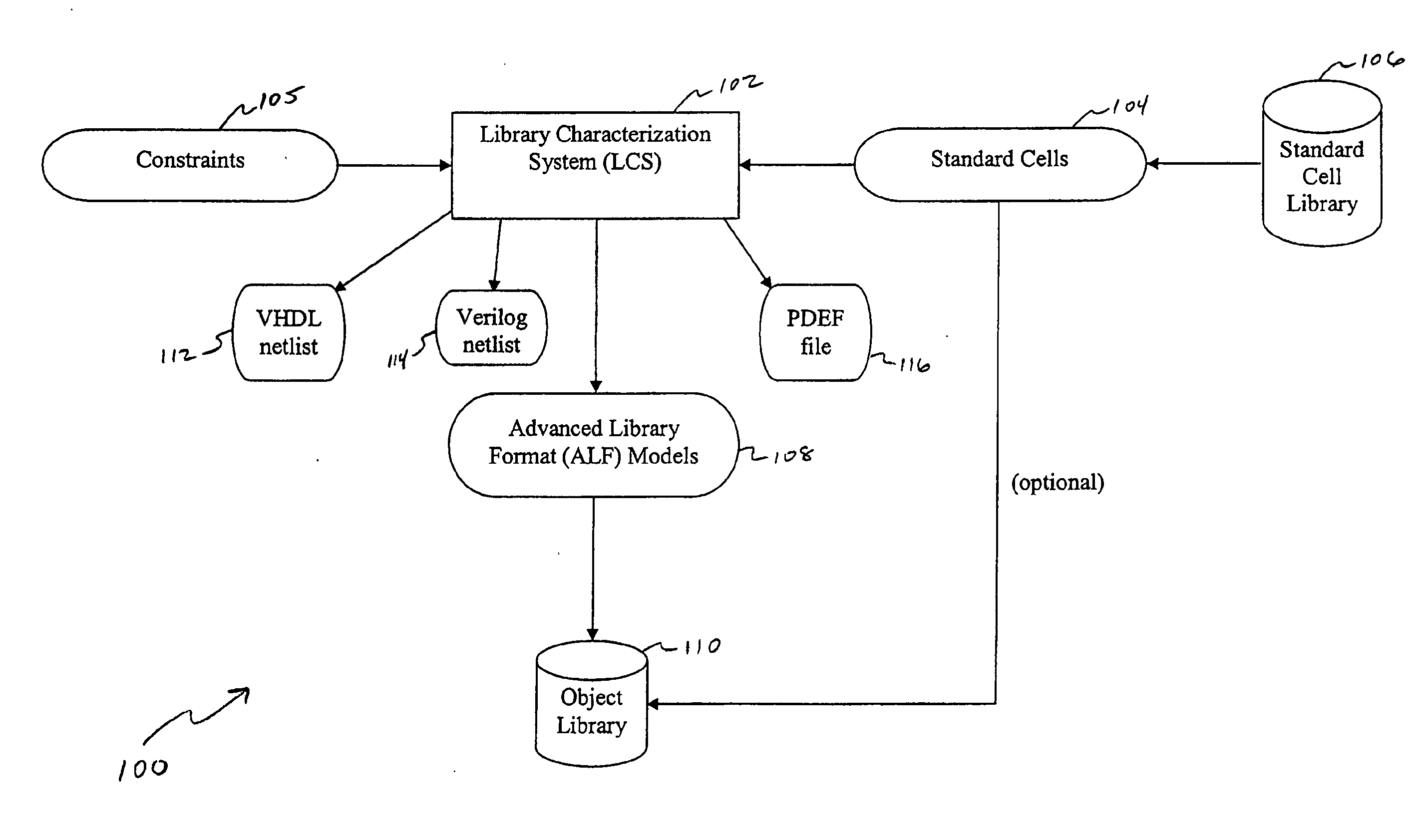

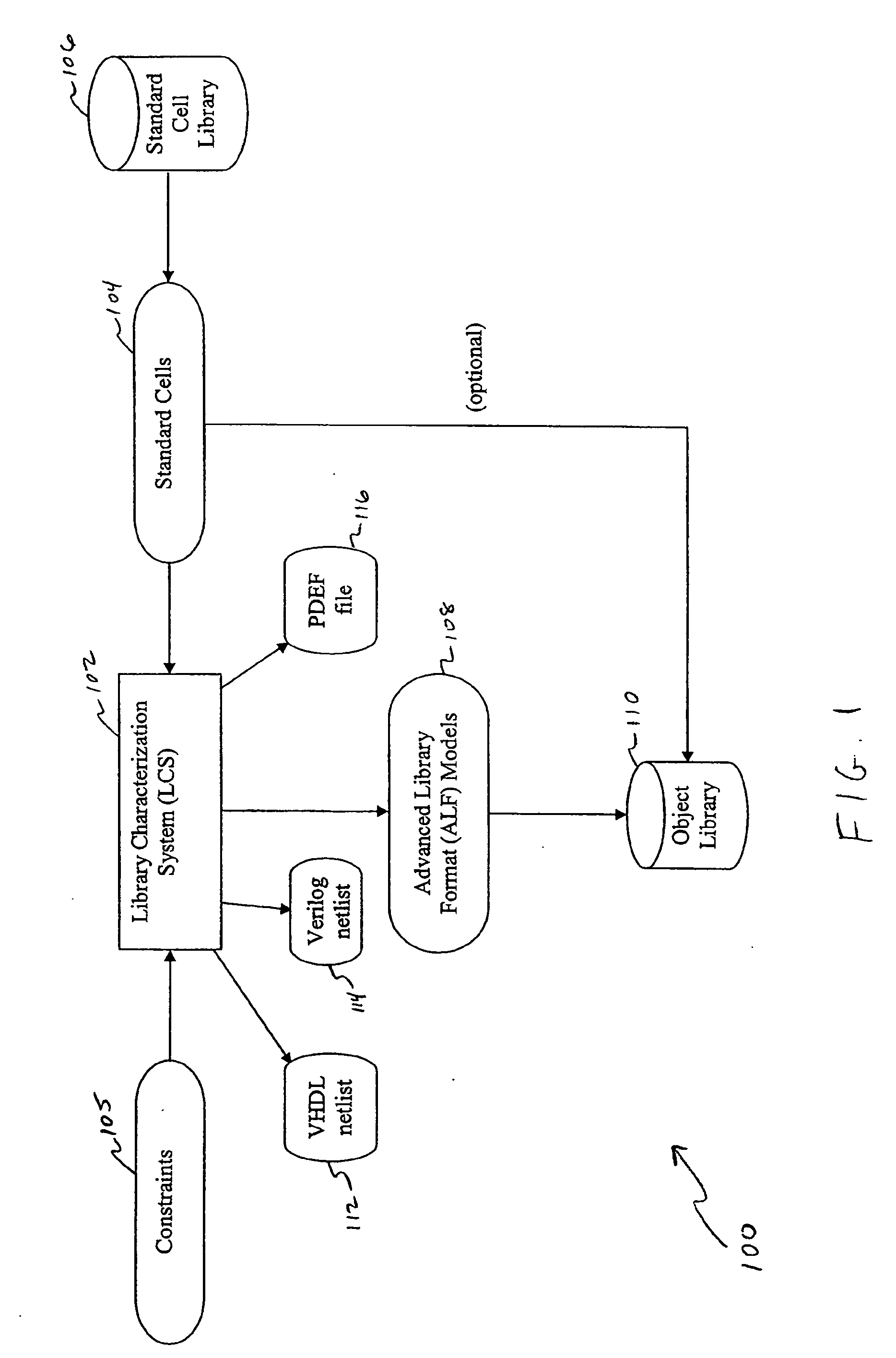

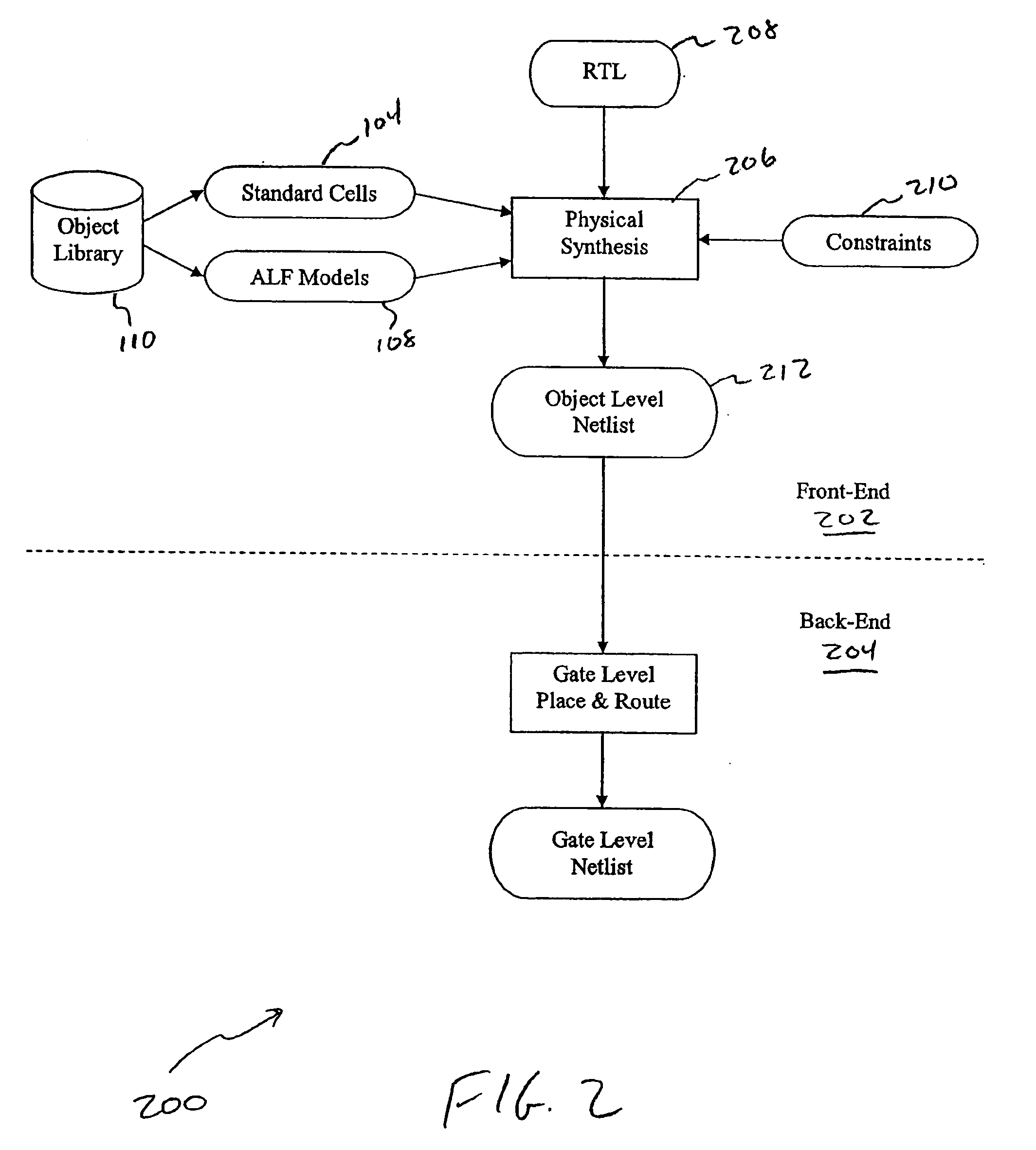

Method for automated design of integrated circuits with targeted quality objectives using dynamically generated building blocks

InactiveUS7225423B2Improve propertiesMinimize the numberCAD circuit designSoftware simulation/interpretation/emulationTarget analysisComputer architecture

A system and method for designing ICs, including the steps of: analyzing and optimizing a target IC design based on design-specific objectives; partitioning the optimized target IC design into pre-defined standard-cells from one or more libraries and creating design-specific cells specifically having unique functionality and characteristics not found amongst the standard-cells; identifying and determining a minimal subset of the standard-cells and design-specific cells, the interconnection of which represents the target IC design; generating the necessary views, including layout and characterizing of the design-specific cells included in a unique, minimal subset, wherein the IC design is subject to objectives and constraints of the target IC.

Owner:OPEN-SILICON

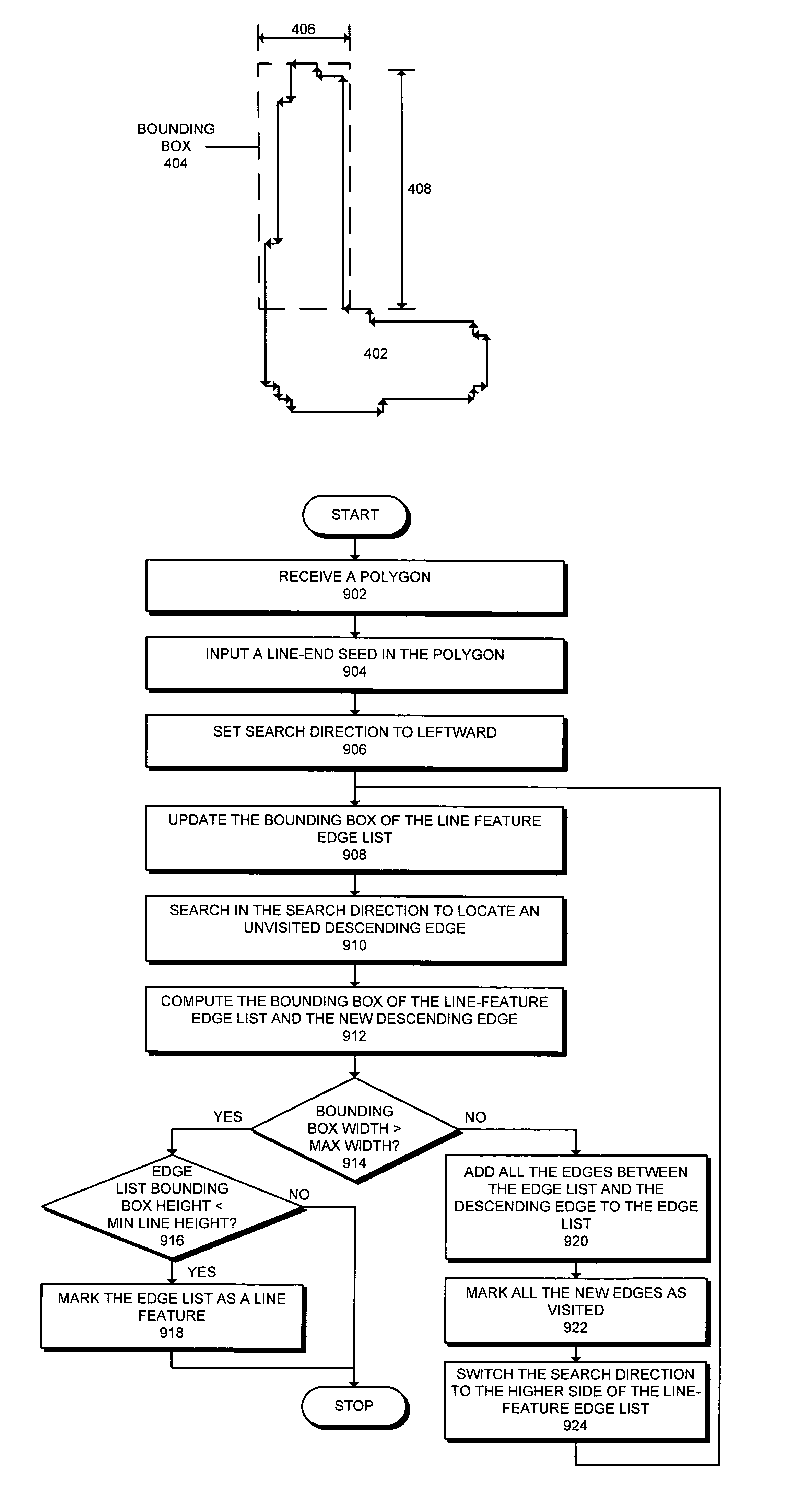

Method and apparatus for identifying line-end features for lithography verification

ActiveUS7194712B2Facilitates identifying line-end featureComputer aided designSpecial data processing applicationsLithographic artistEngineering

One embodiment of the invention provides a system that facilitates identifying line-end features in a layout for an integrated circuit. The system operates by first receiving the layout for the integrated circuit. Next, the system selects a polygon from the layout and marks a line-end seed on the polygon. The system then determines if the line-end seed is associated with a line feature, and if so, the system marks the line-end feature inside the line feature.

Owner:SYNOPSYS INC

Photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured with the same

InactiveUS6904582B1Shorten the timeShorten cycle timeSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutDecoupling capacitor

A photomask for reducing power supply voltage fluctuations in an integrated circuit and integrated circuit manufactured by the same are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region in the pattern to add one or more decoupling capacitors. Once the region is identified, a feature located in the identified region is moved based on a design rule from a first position to a second position in the mask layout file to create a space in the identified region. The decoupling capacitors are placed in the space in the identified region.

Owner:CELERICS TECH

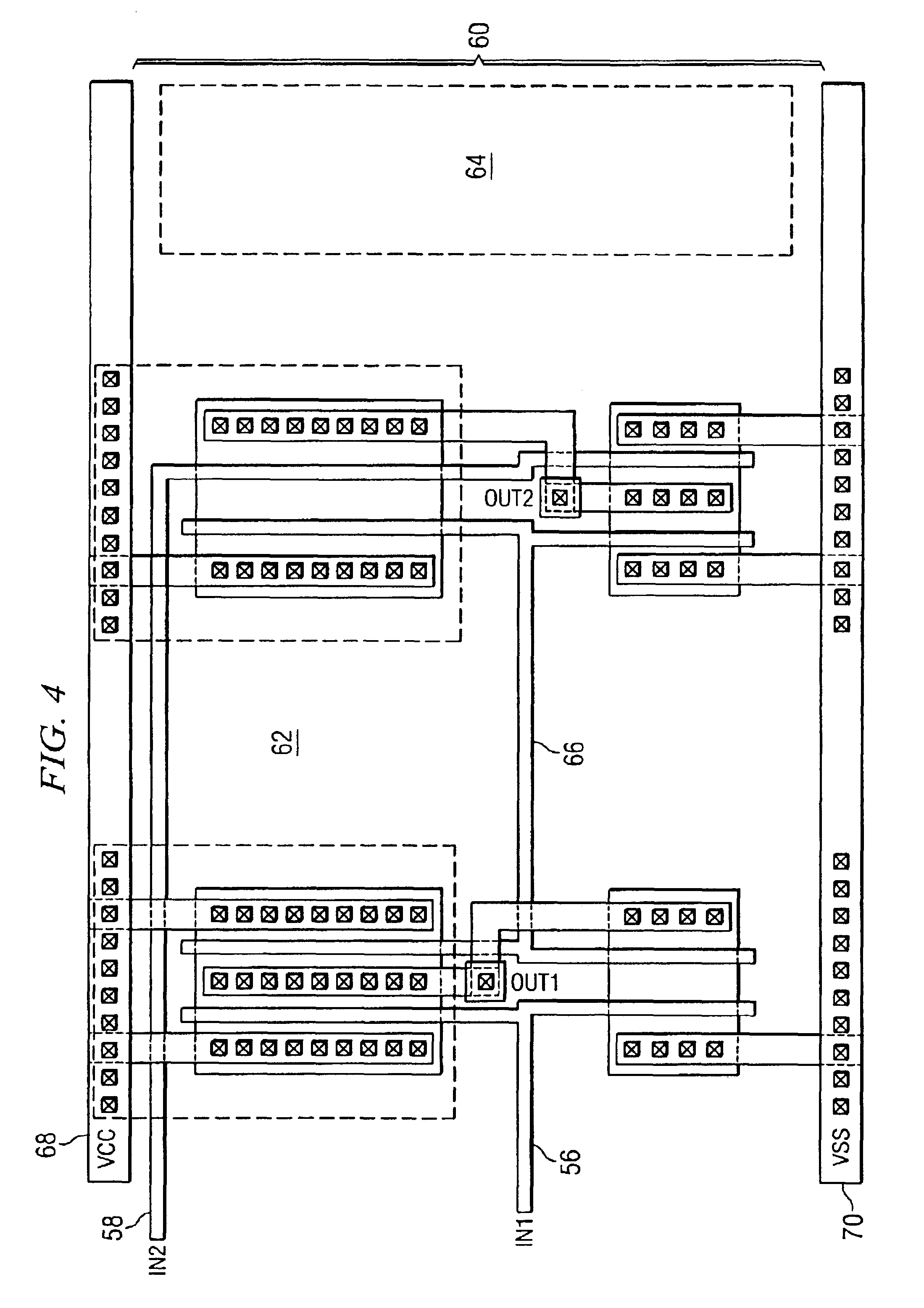

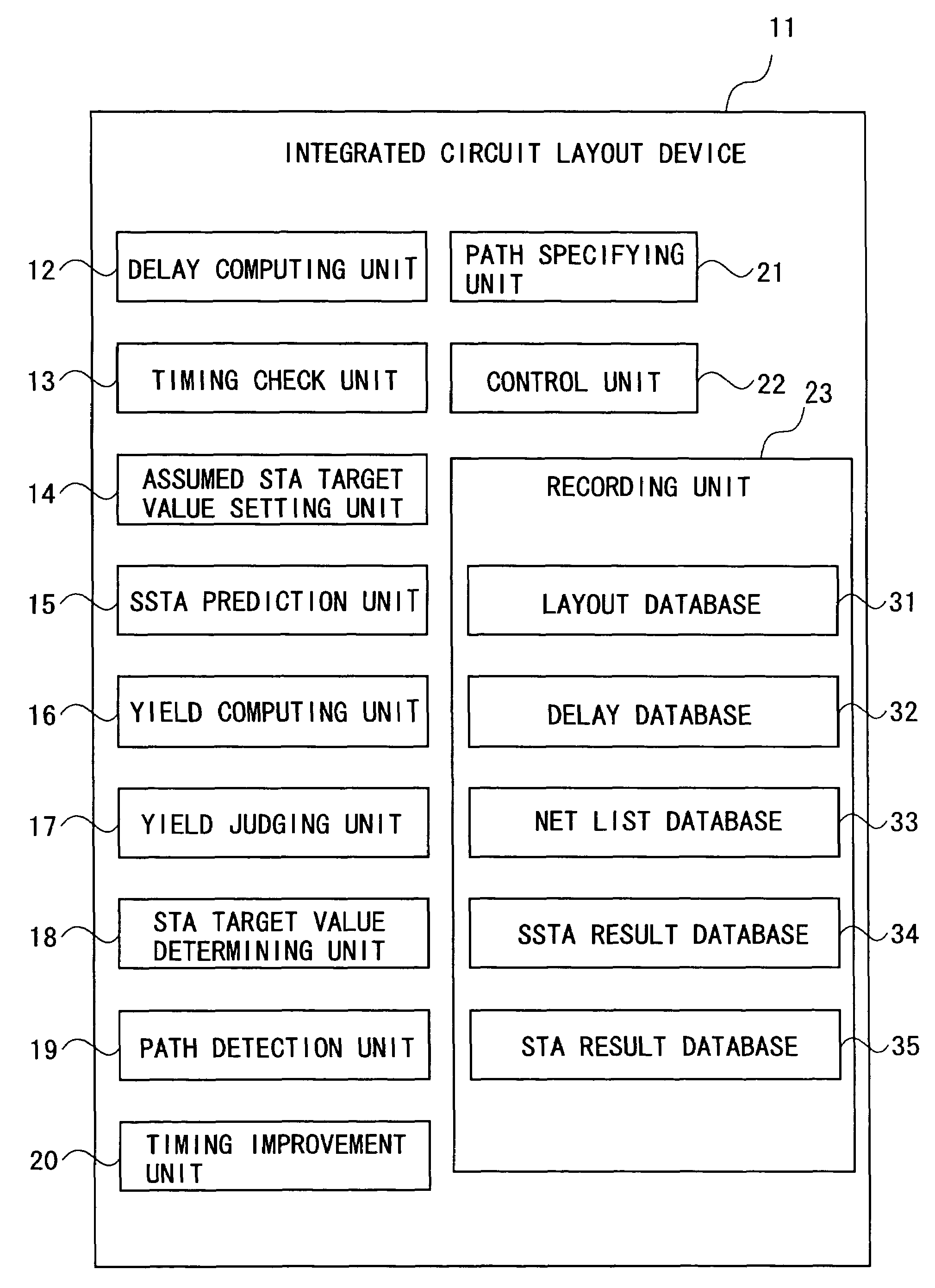

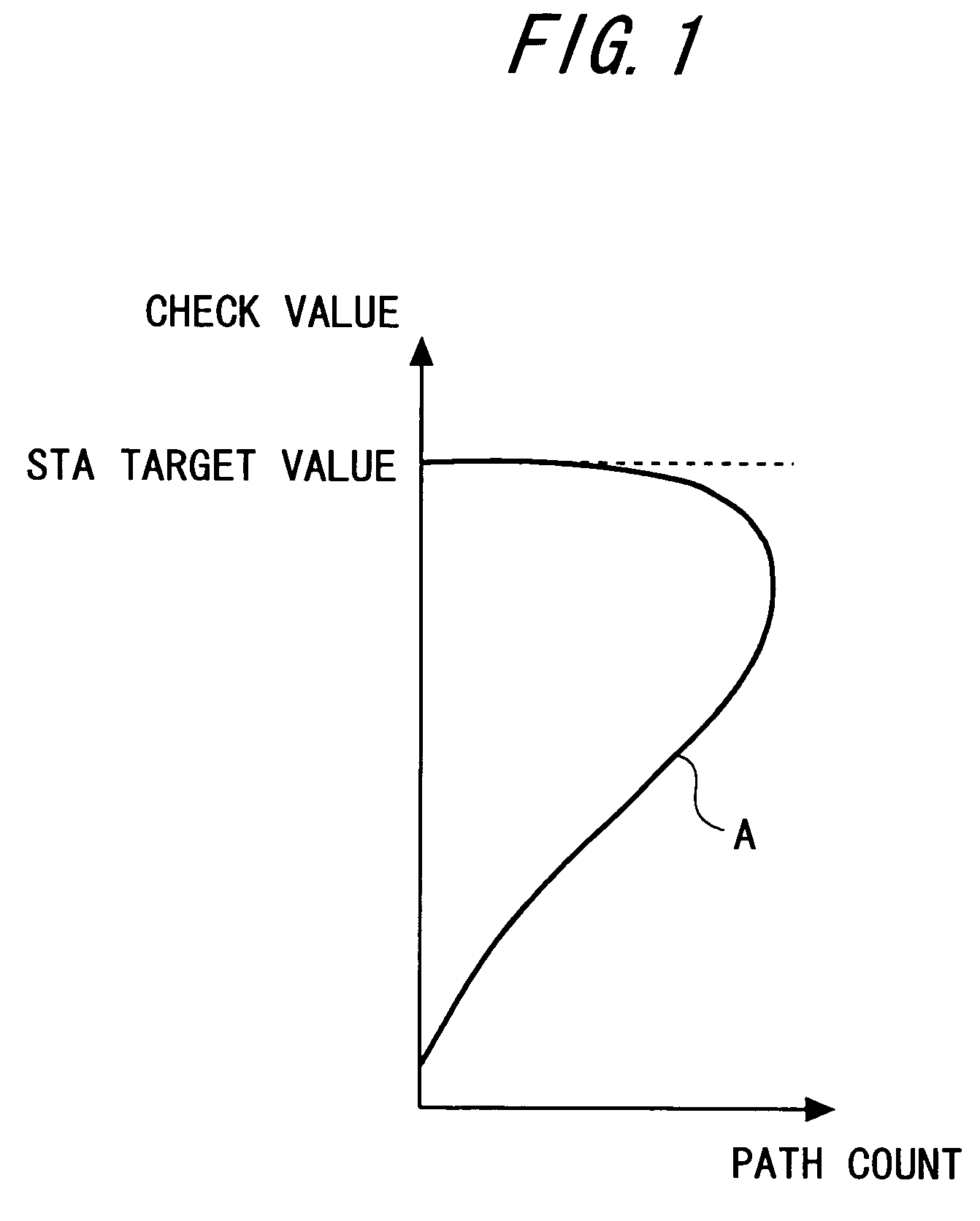

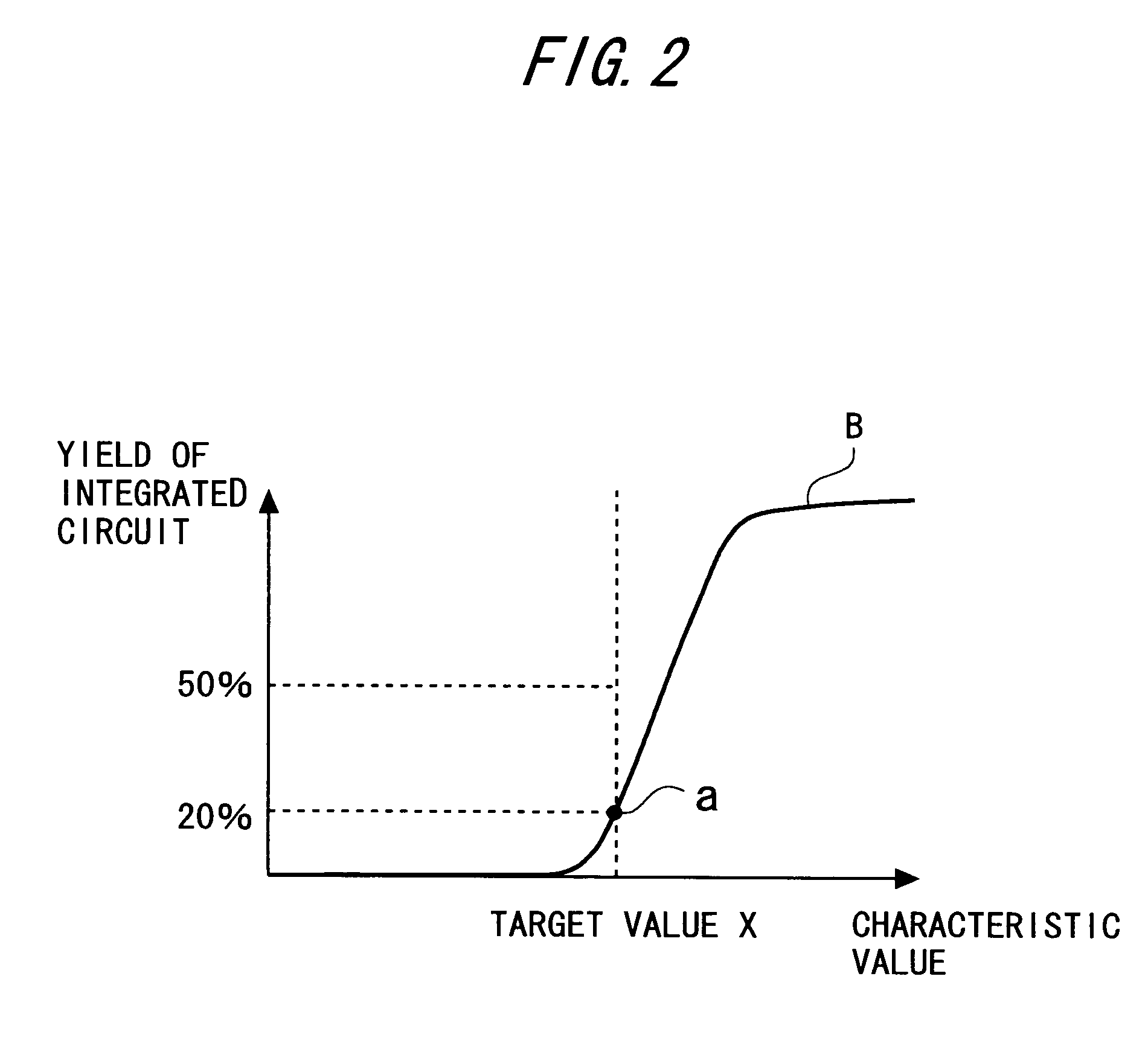

Integrated circuit layout device, method thereof and program thereof

InactiveUS7424694B2Improve timing errorExtension of timeComputer aided designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit layout

A layout device for an integrated circuit executes calculating a timing value with respect to each wiring path by a analysis based on connection information and delay information of wirings, determining a target value serving as an improvement target of the wiring path, detecting an error wiring path exhibiting the timing value larger than the target value, changing the wiring connection so that the error wiring path shows a timing value smaller than the target value, updating these piece of information into connection information and delay information of the wirings after changing the wiring connection, calculating a distribution about each wiring path by the analysis based on the post-updating connection information and the post-updating delay information of the wirings and a fluctuation factor, calculating a yield of the integrated circuit from the distribution, and judging whether or not the yield is within an allowable range of a predetermined value.

Owner:FUJITSU LTD

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

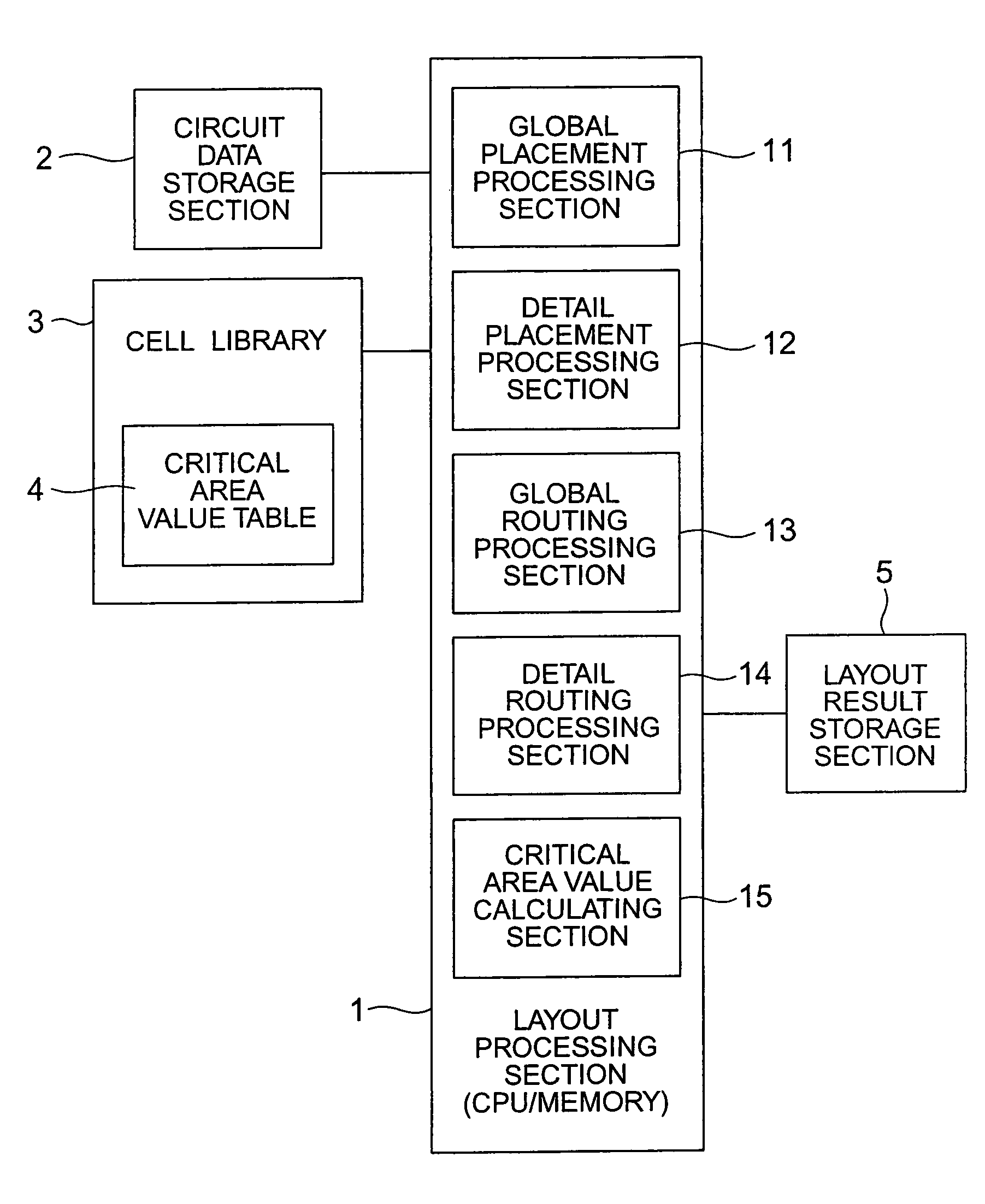

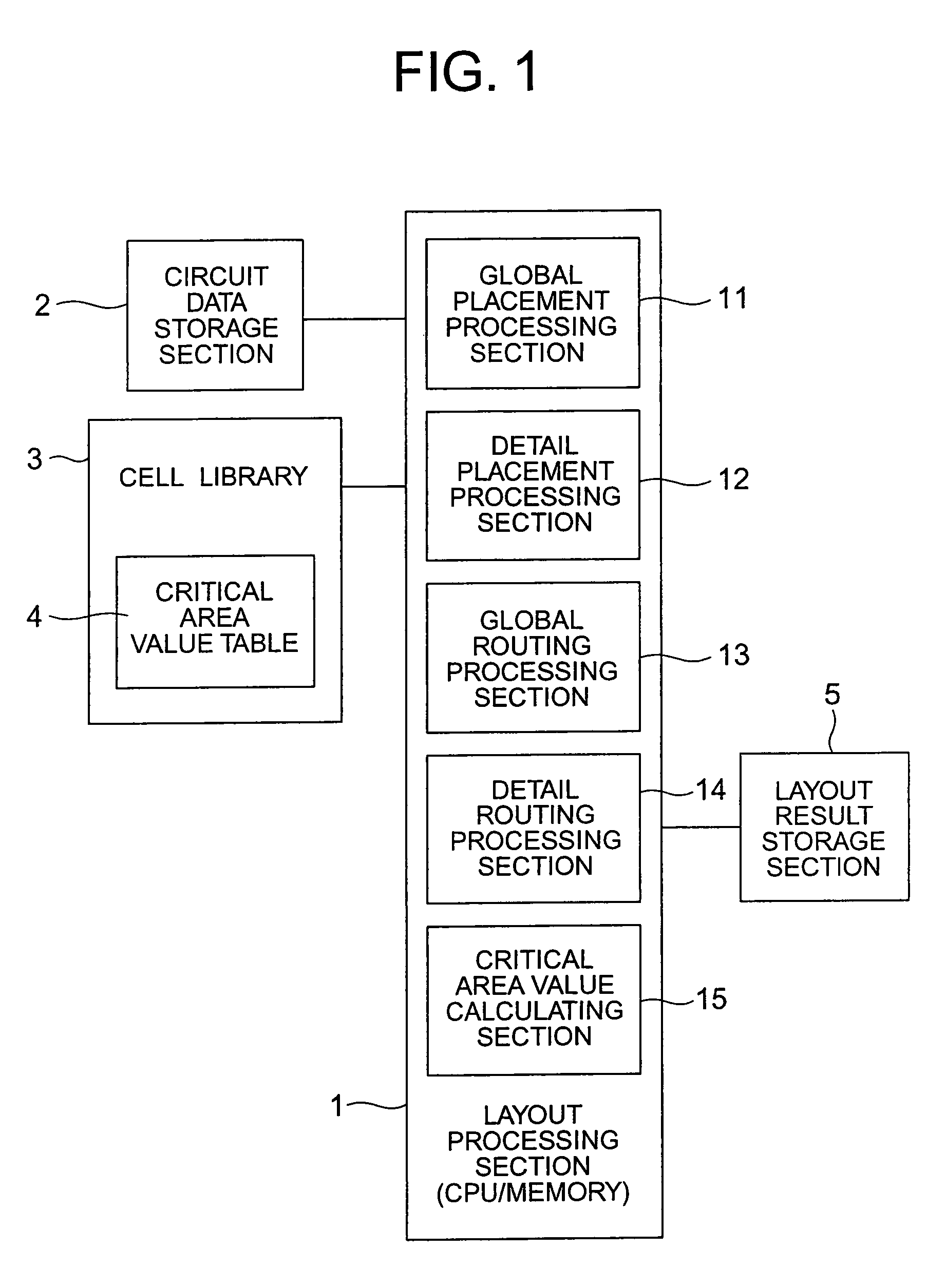

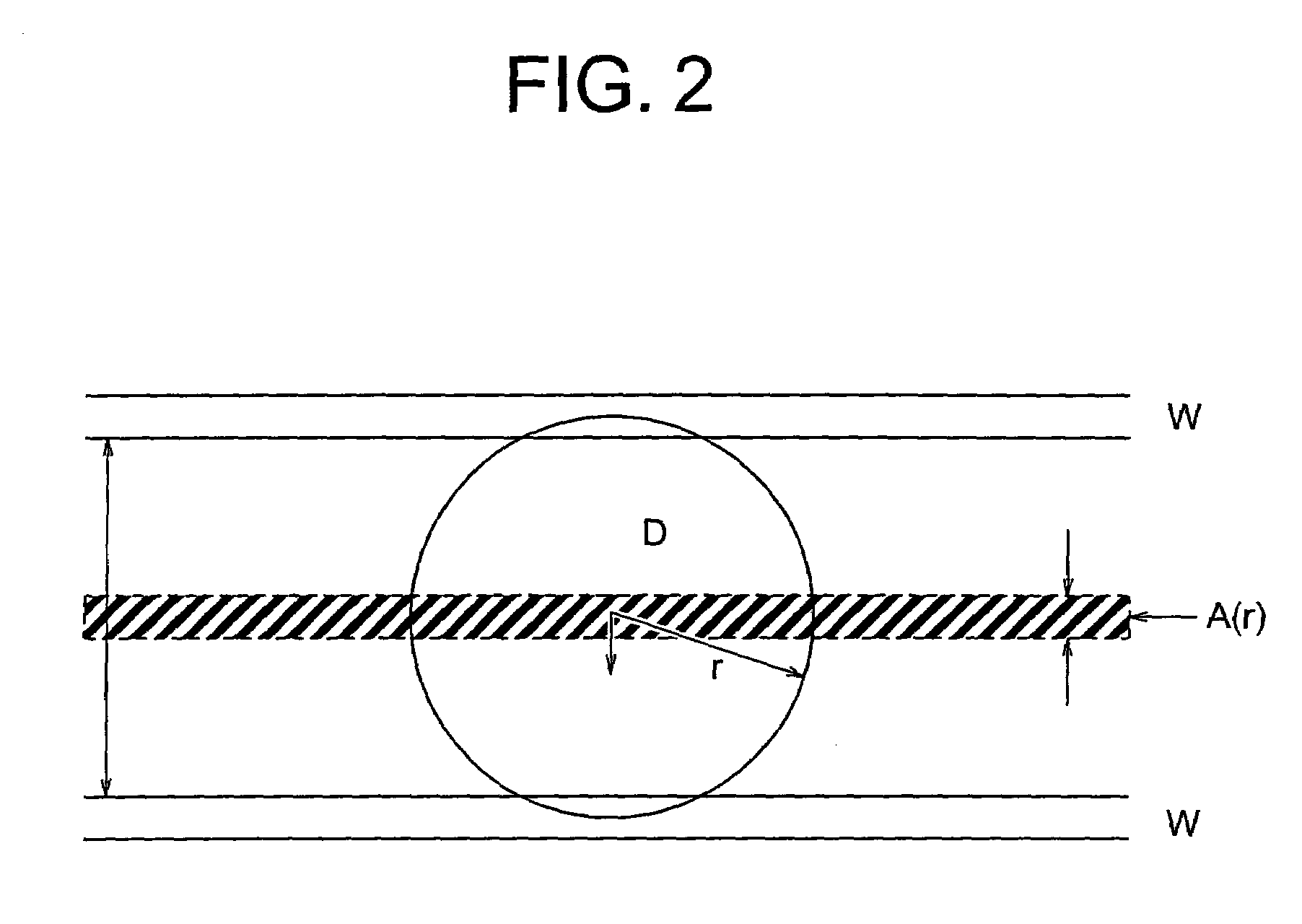

Method and apparatus for designing integrated circuit enabling the yield of integrated circuit to be improved by considering random errors

InactiveUS7512921B2Increase productionCAD circuit designSoftware simulation/interpretation/emulationIntegrated circuit layoutEngineering

A layout method in a layout apparatus for layout of an integrated circuit includes placing a plurality of cells at approximate positions according to the circuit data and placing the plurality of cells at specific positions according to the result of the placement of the plurality of cells at the approximate positions. In the placing the plurality of cells at specific positions, the plurality of cells are placed at specific positions, critical area values between cells adjacent to one another are calculated, and the specific positions of the cells are modified so as to reduce the critical area values obtained.

Owner:FUJITSU LTD

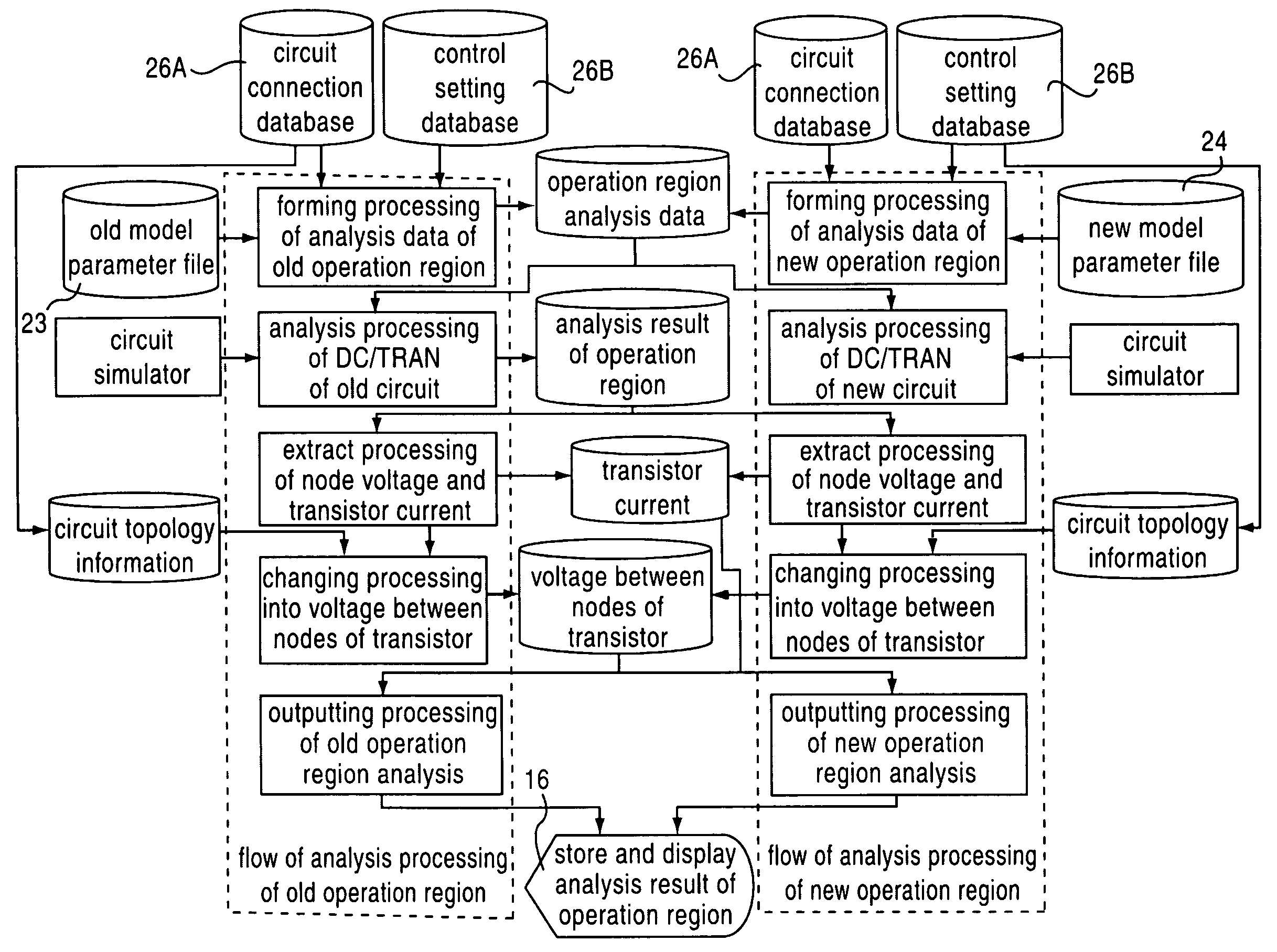

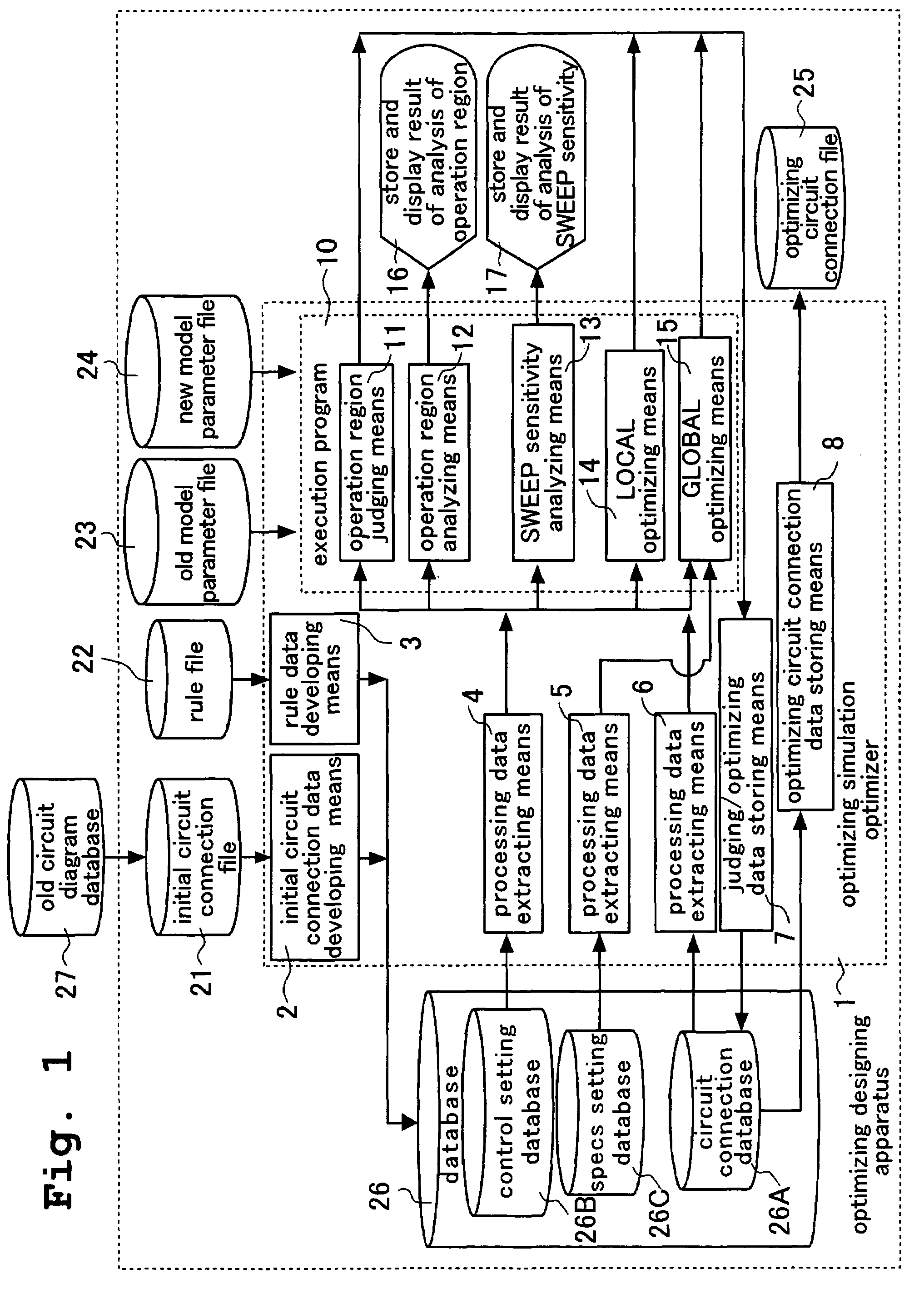

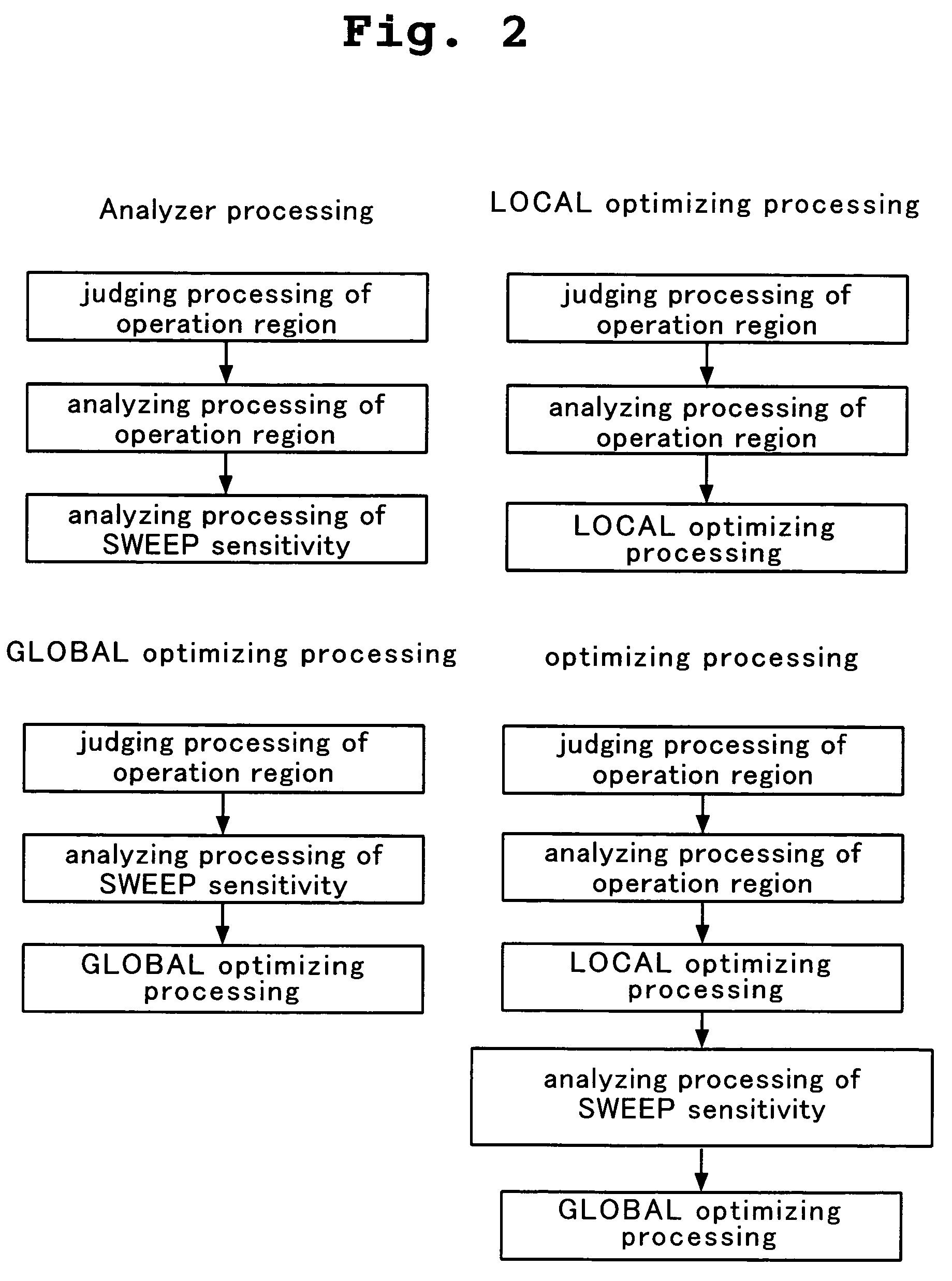

Optimizing designing apparatus of integrated circuit, optimizing designing method of integrated circuit, and storing medium in which program for carrying out optimizing designing method of integrated circuit is stored

ActiveUS7155685B2Easy to carryAnalogue computers for electric apparatusSemiconductor/solid-state device manufacturingLinear regionRegion analysis

It is an object of the present invention to provide a method, an apparatus and a program having high optimization precision and capable of obtaining an answer required by a designer in a short time by combining optimization between individual transistors and optimization as the entire circuit, or by appropriately combining judgment of an operation region, an analysis of the operation region and a SWEEP sensitivity analysis when the optimization is carried out. An optimizing designing apparatus of an integrated circuit for designing a circuit, comprises operation region judging means for adjusting an operation region (linear region, saturation region) of the circuit, operation region analysis means for displaying liner characteristics (Ids-Vgs characteristics) of the circuit and saturation characteristics (Ids-Vds characteristics) of the circuit, and SWEEP sensitivity analysis means for displaying variation in output characteristics of the circuit.

Owner:ABLIC INC

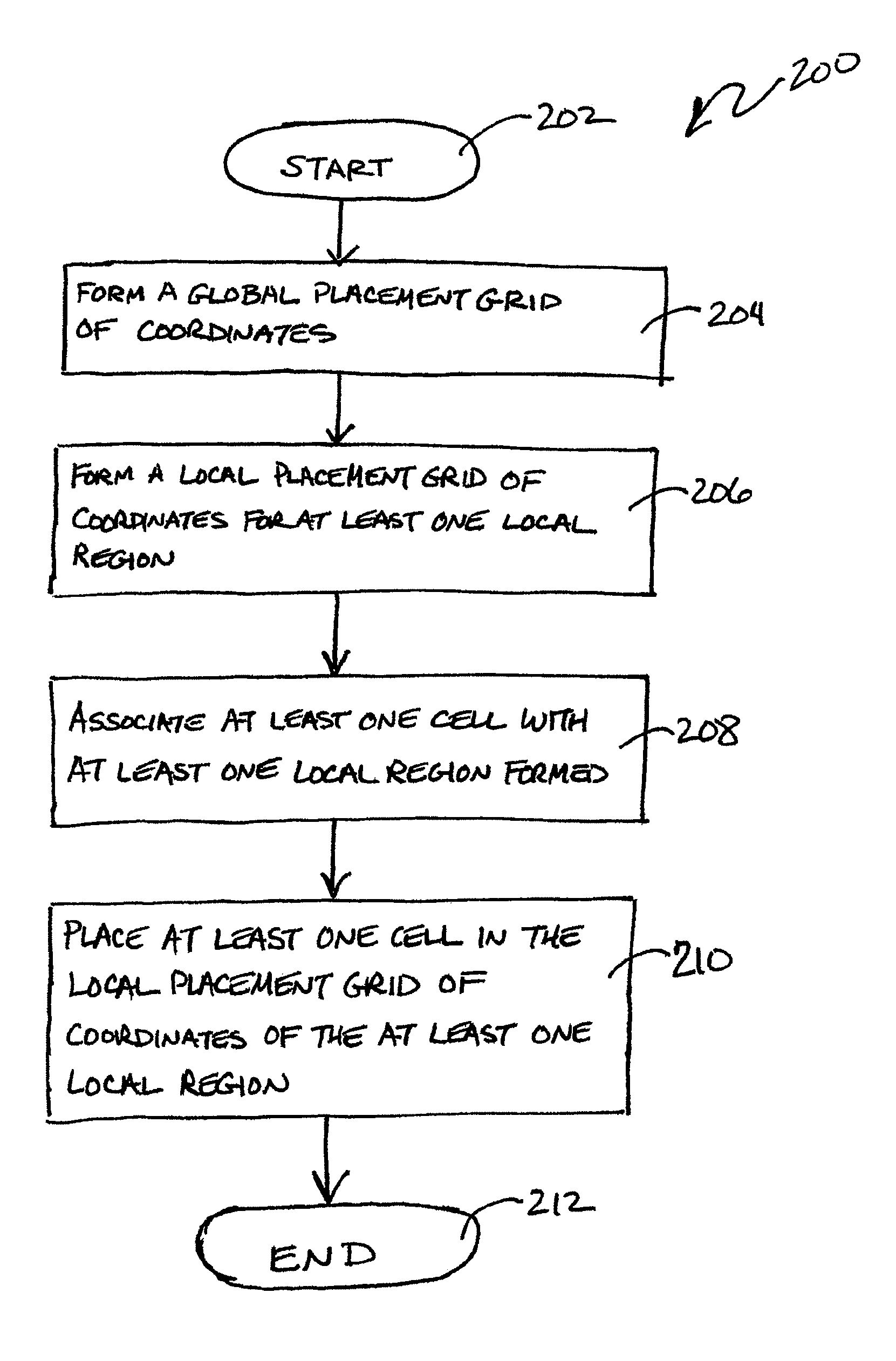

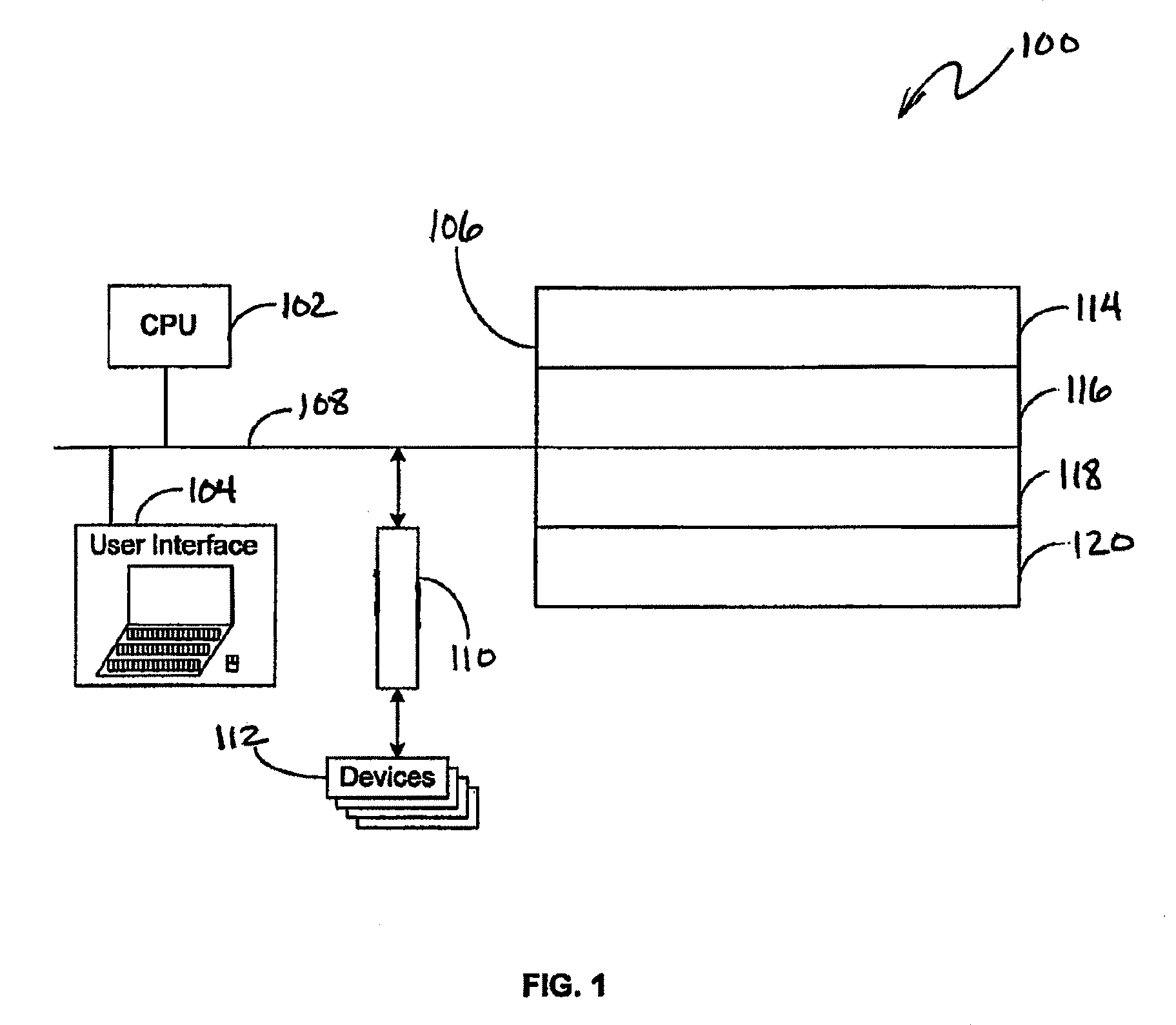

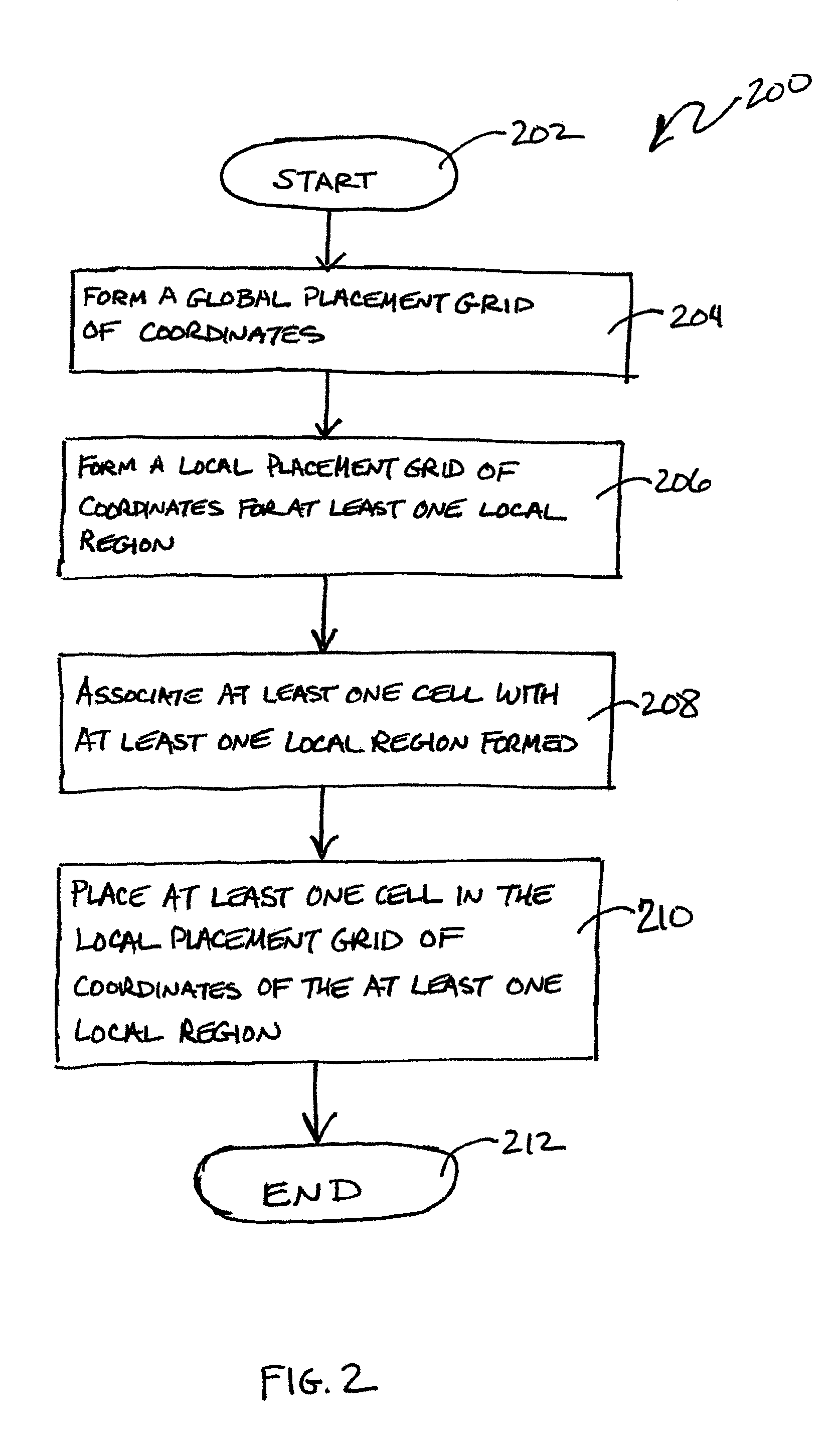

Flat placement of cells on non-integer multiple height rows in a digital integrated circuit layout

ActiveUS7802219B2Reduce the amount requiredExtension of timeComputer programmed simultaneously with data introductionComputer aided designIntegrated circuit layoutHorizontal and vertical

The various embodiments of the present invention generally relate to systems, methods, and computer program products for placement of at least one cell in a digital integrated circuit layout. A global placement grid of coordinates is formed, where the coordinates represent horizontal and vertical directions. A local placement grid of coordinates is also formed for at least one local region, where the local placement grid of coordinates represent horizontal and vertical directions, and where the at least one local region is adapted to support non-integer multiple height rows. At least one cell is associated with the at least one local region formed, and the cell can be placed in the local placement grid of the local region.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for data hierarchy maintenance in a system for mask description

InactiveUS6453452B1Data augmentationReduce processing speedCAD circuit designProgram controlComputer architectureLogical operations

A method and apparatus for performing an operation on hierarchically described integrated circuit layouts such that the original hierarchy of the layout is maintained is provided. The method comprises providing a hierarchically described layout as a first input and providing a particular set of operating criteria corresponding to the operation to be performed as a second input. The mask operation, which may include operations such as OPC and logical operations such as NOT and OR, is then performed on the layout in accordance with the particular set of operating criteria. A first program data comprising hierarchically configured correction data corresponding to the hierarchically described layout is then generated in response to the layout operation such that if the first program data were applied to the flattened layout an output comprising data representative of the result of performing the operation on the layout would be generated. As the first program data is maintained in a true hierarchical format, layouts which are operated upon in accordance with this method are able to be processed through conventional design rule checkers. Further, this method is capable of being applied to all types of layouts including light and dark field designs and phase shifting layouts.

Owner:SYNOPSYS INC

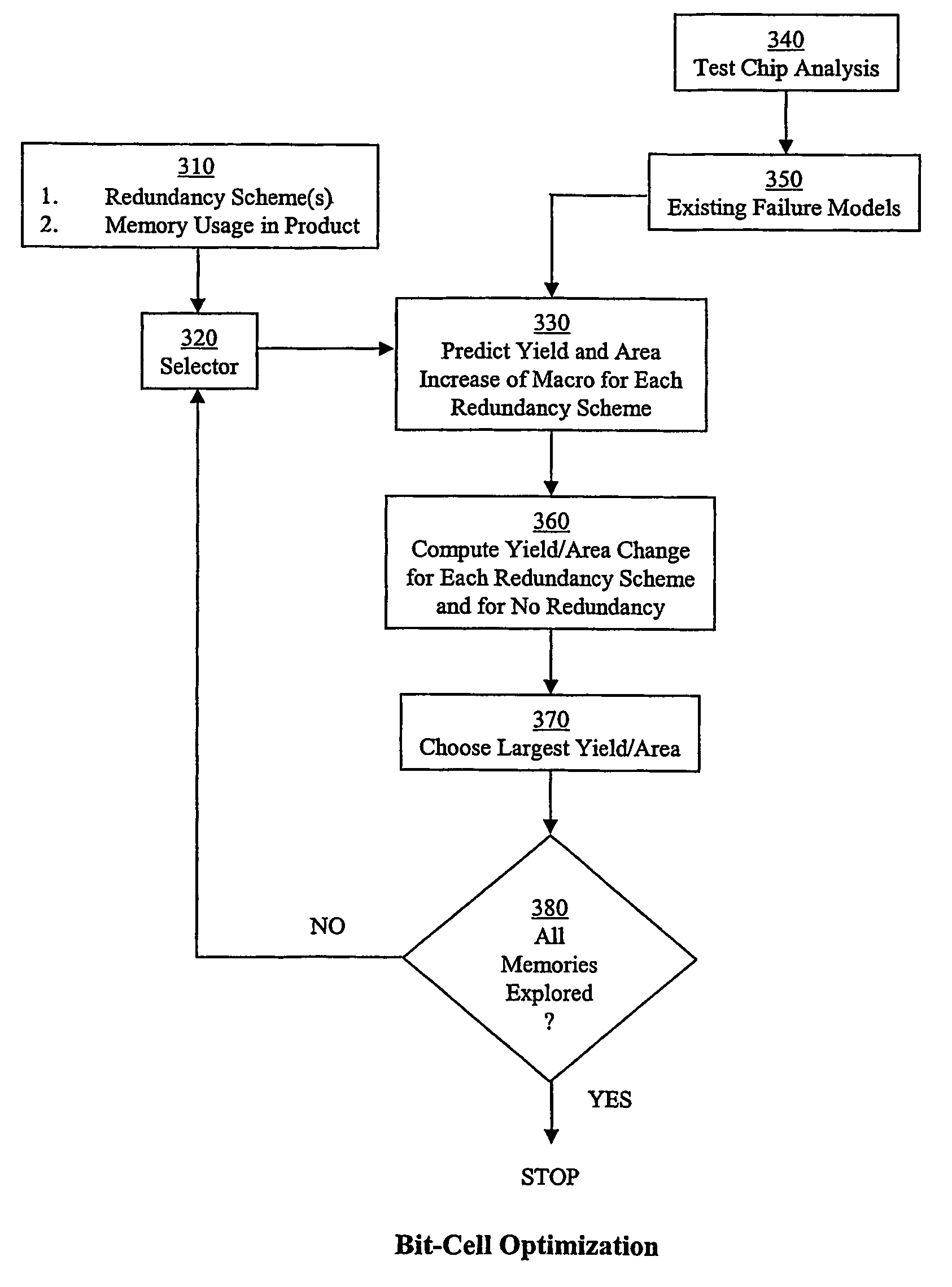

Designing an integrated circuit to improve yield using a variant design element

InactiveUS7487474B2Minimizes and eliminates relianceHigh yieldElectrical apparatusCAD circuit designIntegrated circuit layoutEngineering

An integrated circuit is designed to improve yield when manufacturing the integrated circuit, by obtaining a design element from a set of design elements used in designing integrated circuits. A variant design element is created based on the obtained design element, where a feature of the obtained design element is modified to create the variant design element. A yield to area ratio for the variant design element is determined. If the yield to area ratio of the variant design element is greater than a yield to area ratio of the obtained design element, the variant design element is retained to be used in designing the integrated circuit.

Owner:PDF SOLUTIONS INC

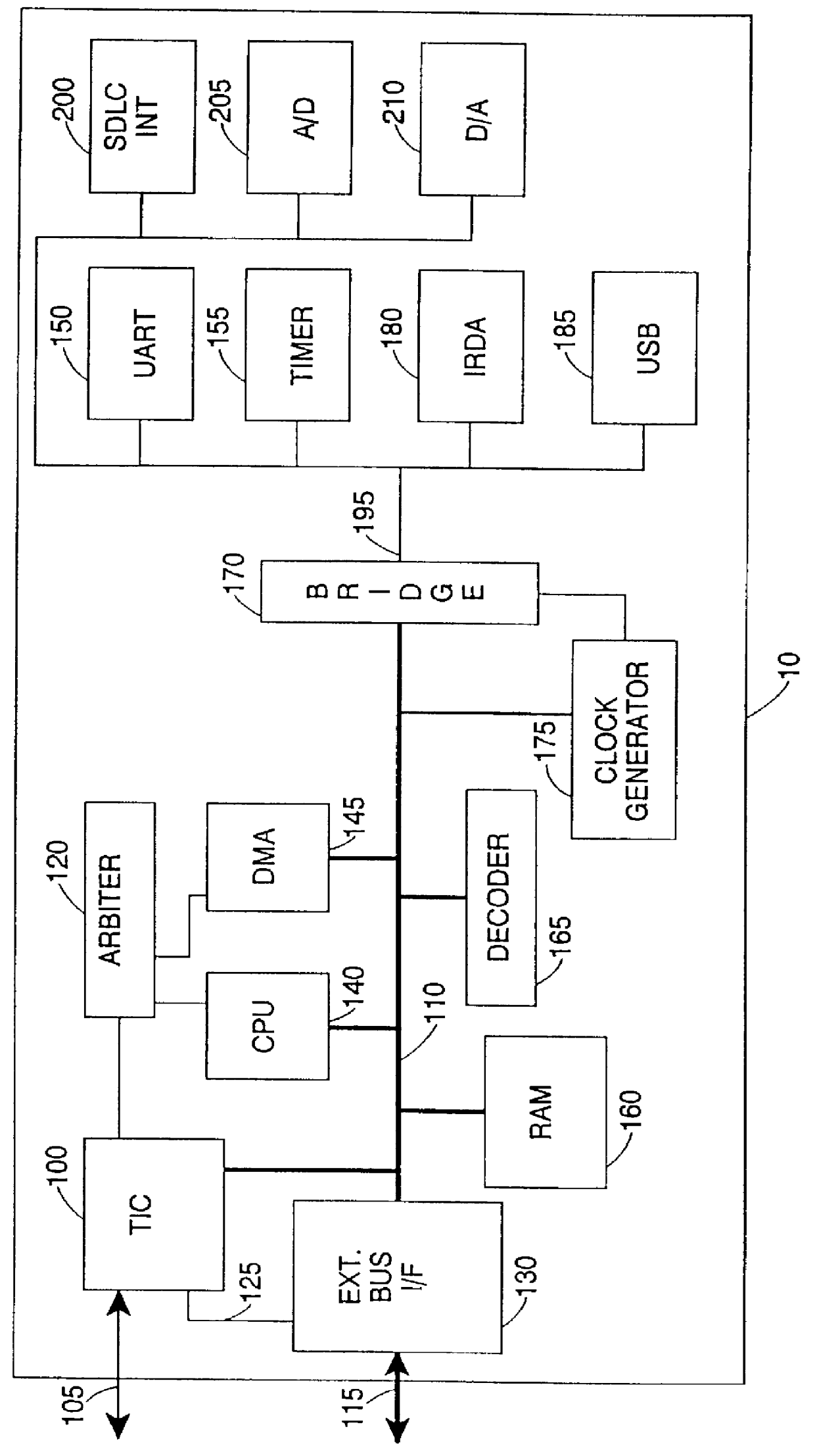

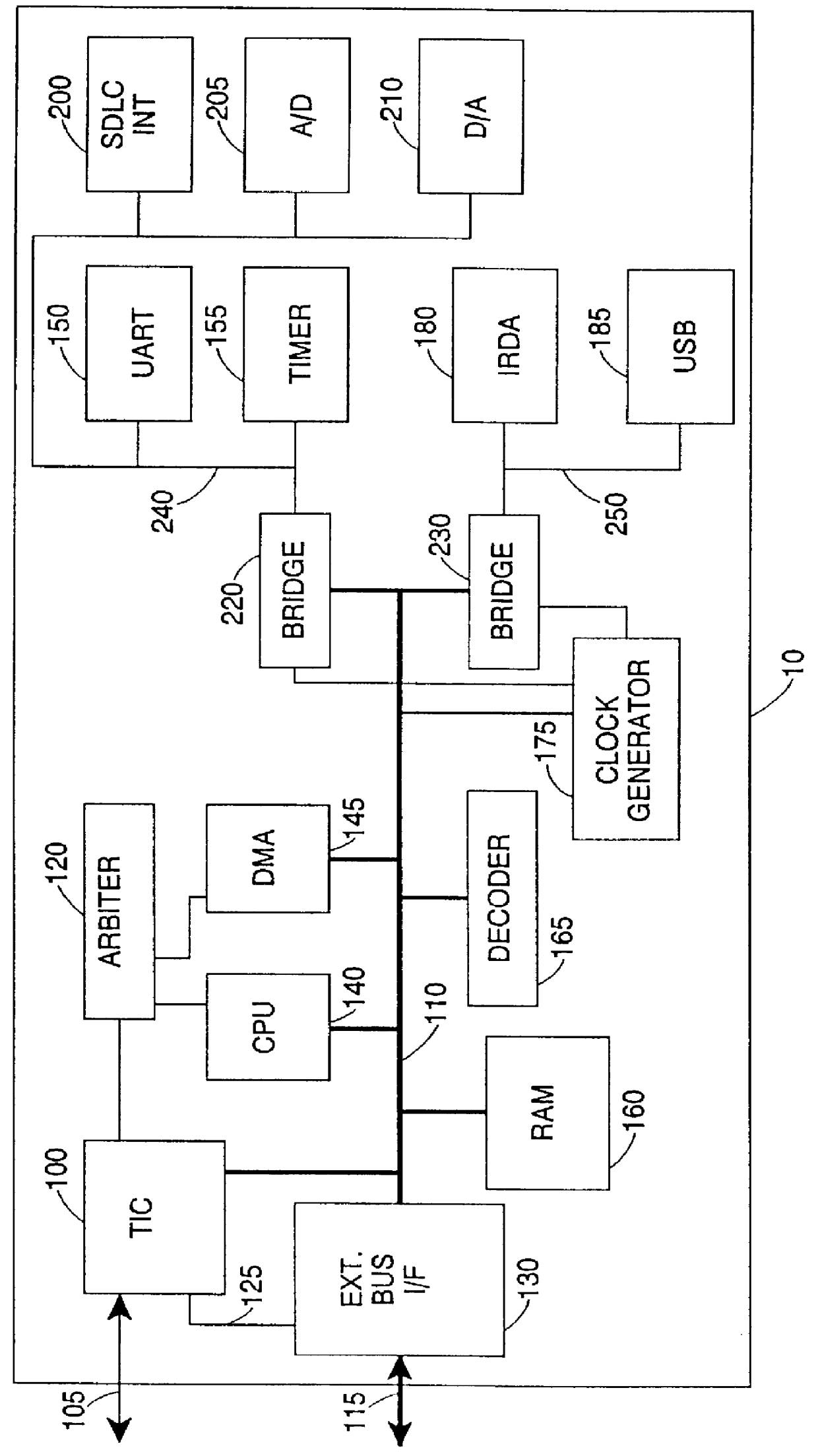

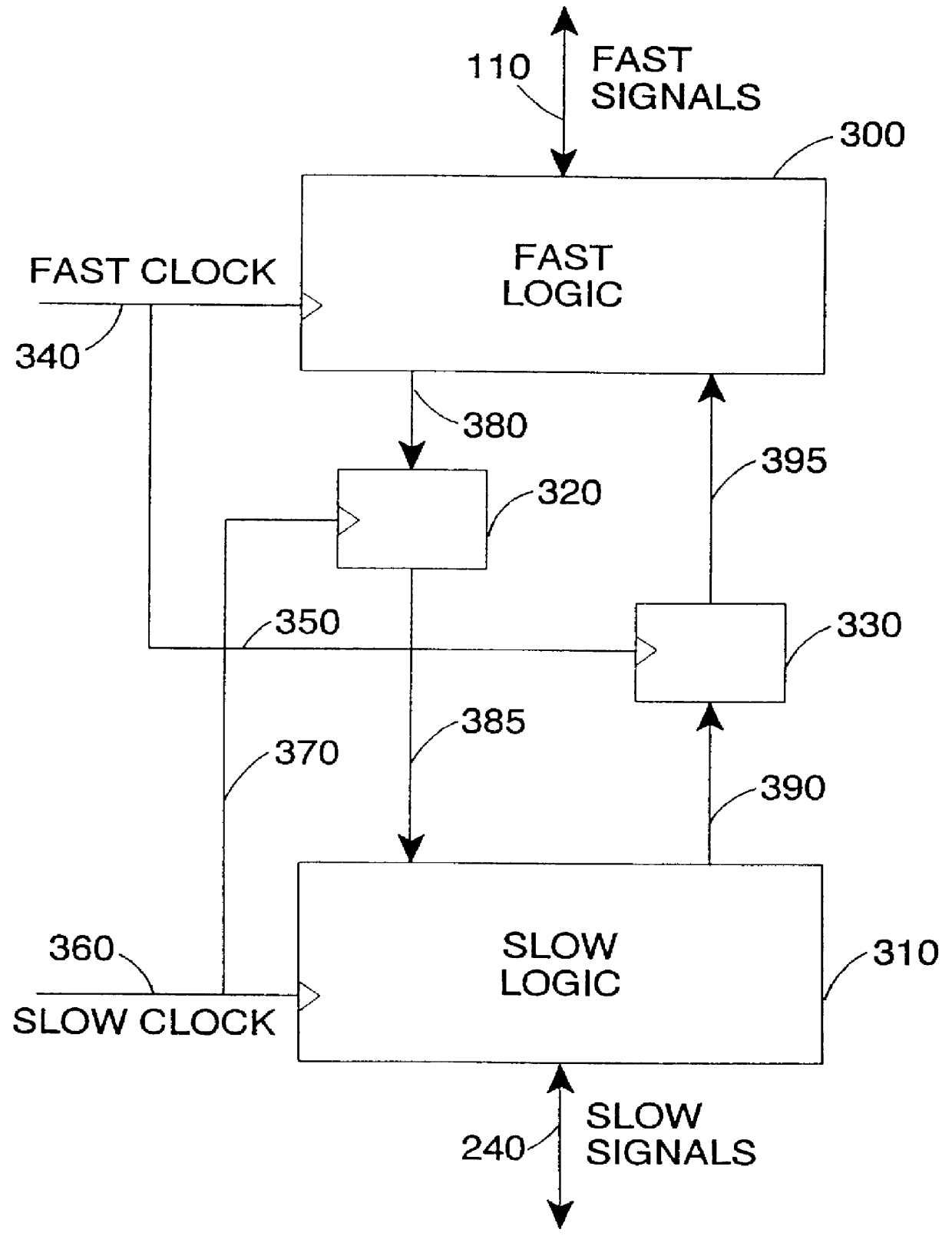

Peripheral buses for integrated circuit

InactiveUS6064626AReduce power consumptionAverage power consumptionEnergy efficient ICTDigital storageCapacitanceClock rate

The present invention provides an integrated circuit comprising a system bus to which a processor is connectable, and first and second peripheral buses to which peripheral units used by said processor are connected, the first peripheral bus operating at a higher clock speed than the second peripheral bus. Further, the integrated circuit comprises bridge logic for providing an interface between the system bus and the peripheral buses to enable signals to be passed between the system bus and the peripheral buses, the bridge logic comprising clock resynchronisation logic for synchronising the system bus and the peripheral buses. Through the provision of first and second peripheral buses operating at different clock speeds, the integrated circuit of the present invention provides a great deal of flexibility for reducing the power consumption of the integrated circuit as compared with a similar integrated circuit having only one peripheral bus. Since the power consumption of each peripheral bus is proportional to the clock frequency and capacitance, significant power consumption savings can be realised by ensuring that each peripheral unit is connected to the slowest peripheral bus appropriate for that peripheral unit.

Owner:ARM LTD

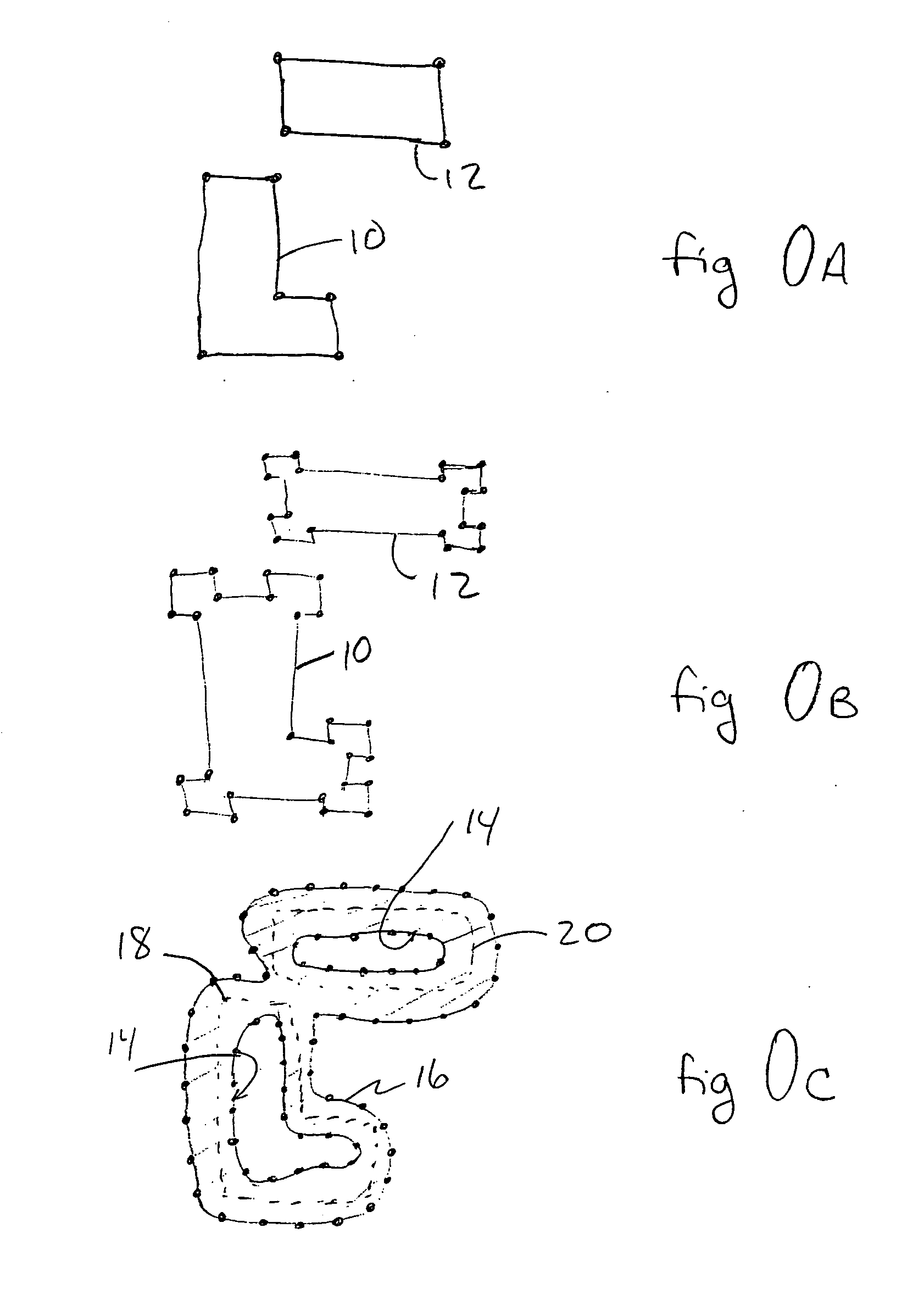

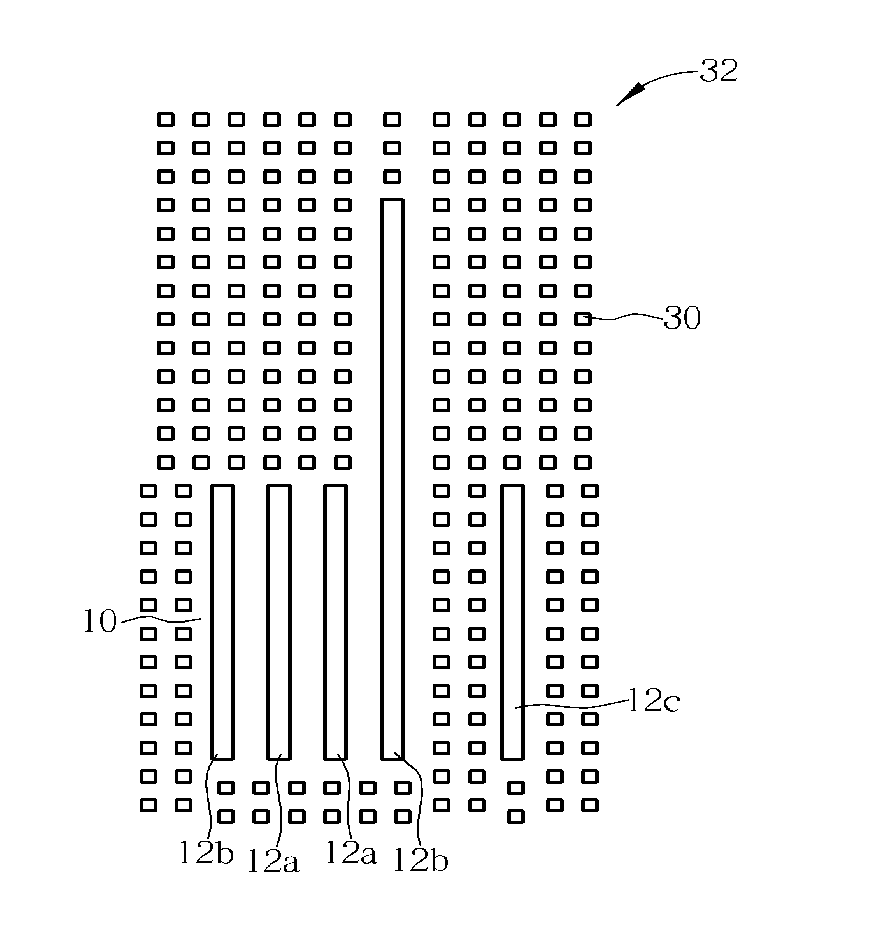

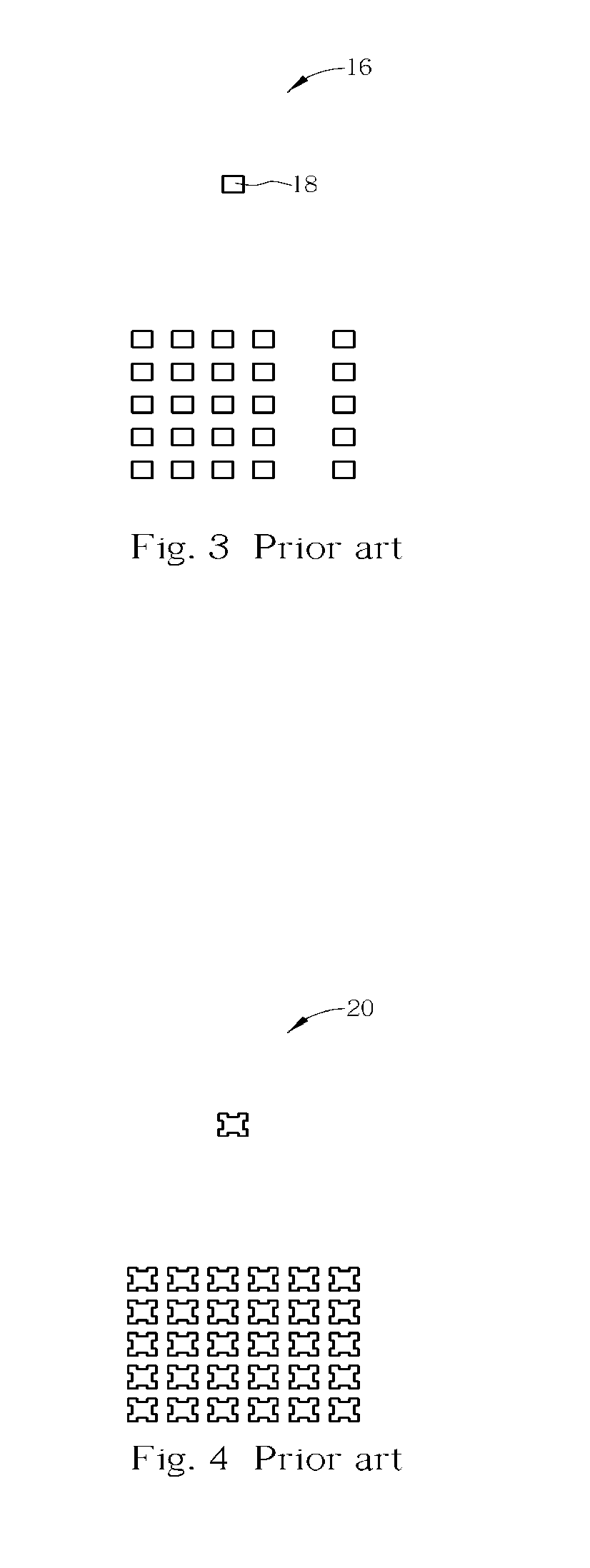

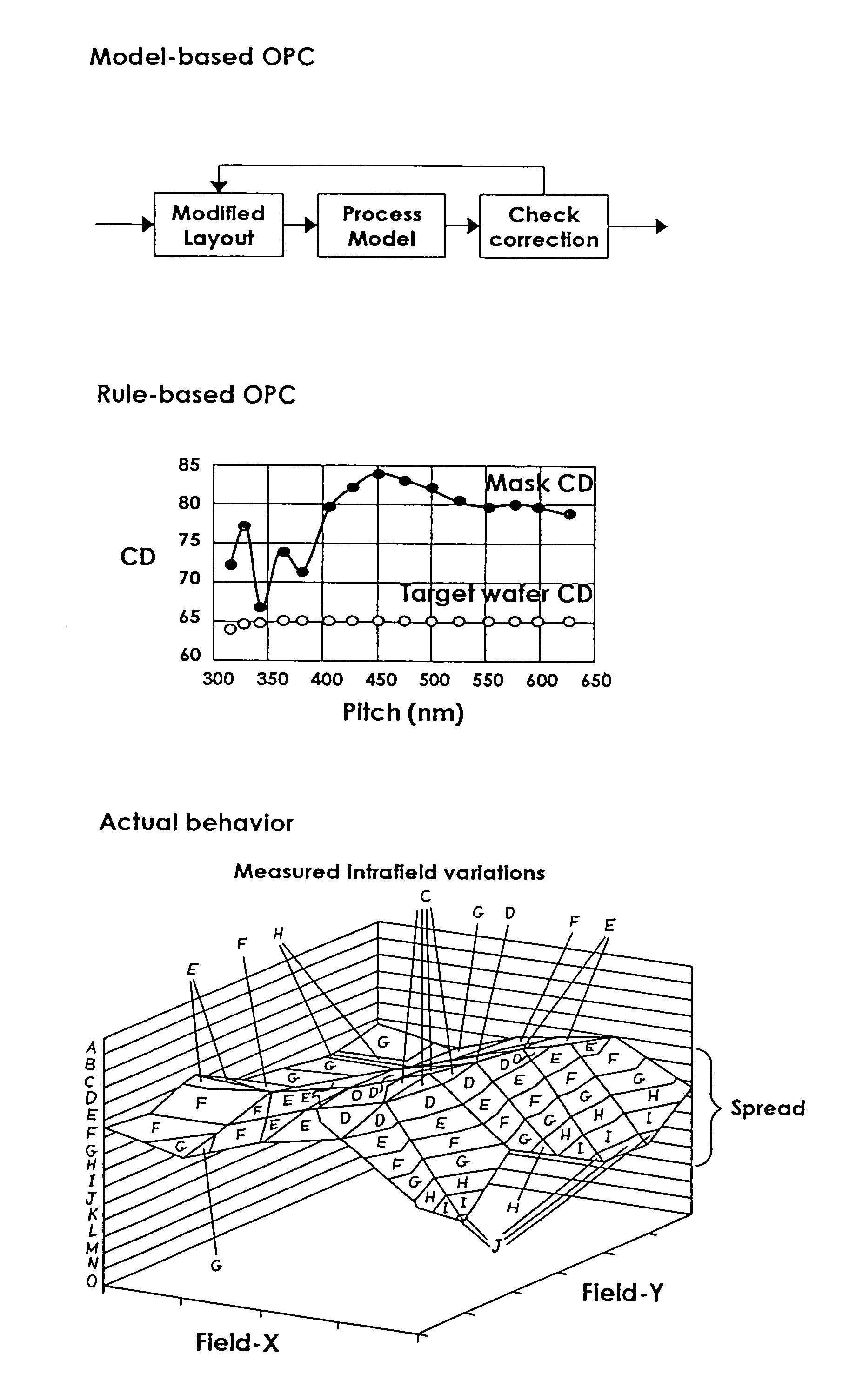

Optical proximity correction method

InactiveUS20050009344A1Reduce the differenceEasy to operateSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentGraphicsPhase difference

An integrated circuit layout includes dense figures and at least one isolated figure. A plurality of dummy patterns are formed to surround the isolated figure, so as to reduce the difference in pattern density of the integrated circuit layout. A transmitted light of the dummy patterns provides a phase difference of 0 or 180 degrees relative to a transmitted light of the integrated circuit layout. The integrated circuit layout and the plurality of dummy patterns are formed on a photo-mask.

Owner:UNITED MICROELECTRONICS CORP

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

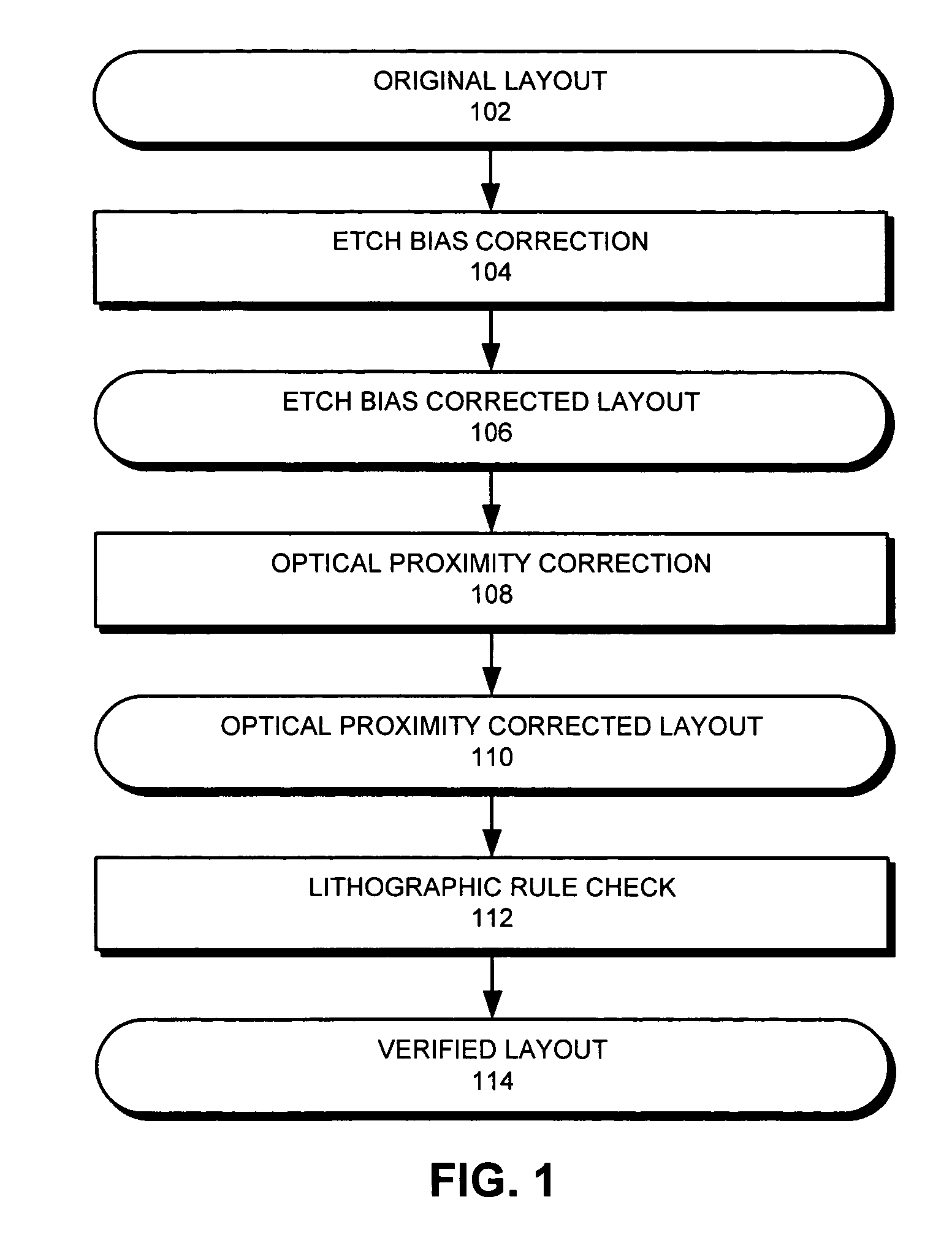

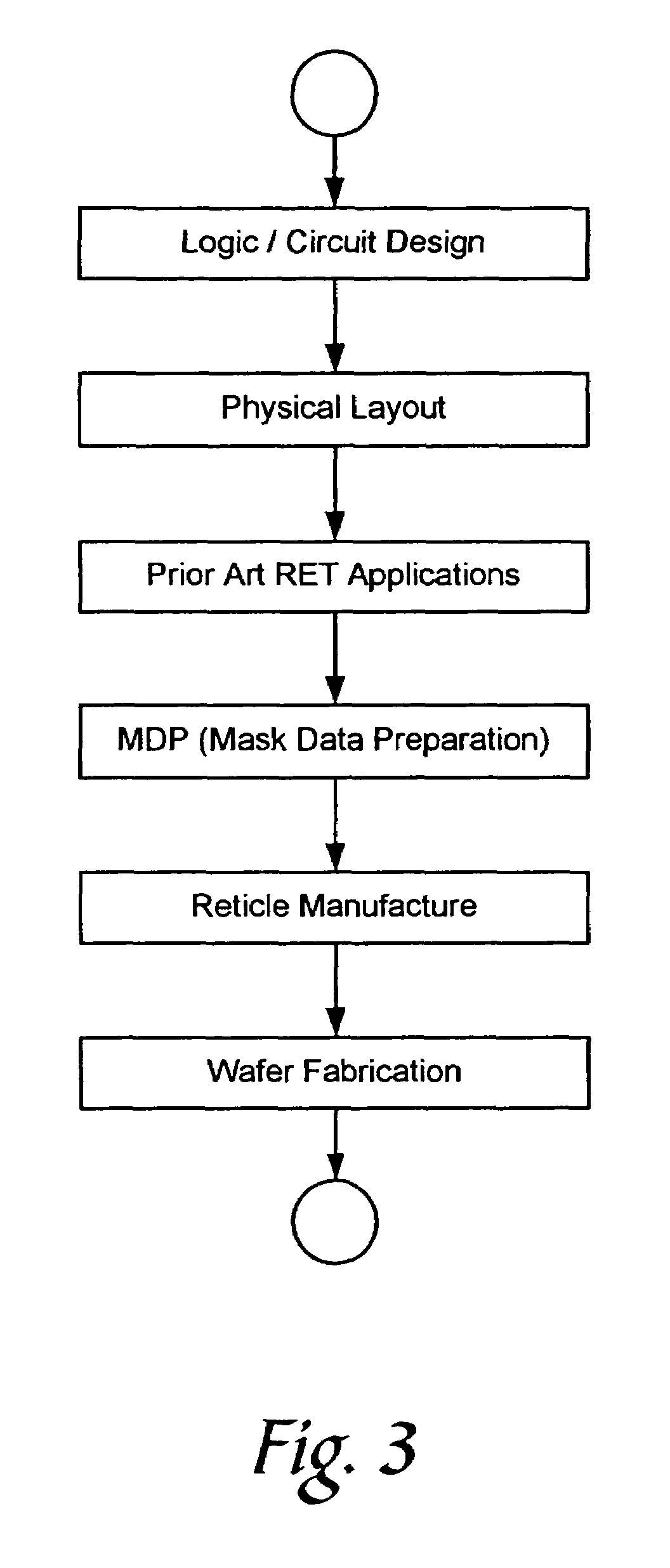

System and method for reducing patterning variability in integrated circuit manufacturing through mask layout corrections

ActiveUS7318214B1Improve accuracyImprove fidelityPhotomechanical apparatusOriginals for photomechanical treatmentIntegrated circuit manufacturingEngineering

The present invention provides a system and method of modifying the mask layout shapes of an integrated circuit layout design to compensate for reticle field location-specific systematic CD variations resulting from mask writing process variations, lens imperfections in lithographic patterning, and photoresist process variations. Called PLC (Process-optimized Layout Compensation), each set of compensation rules according to the present invention is specifically tailored for a particular mask-writer-patterning-tools-and-resist-process combination, and are performed on a reticle-wide basis. Furthermore, for each geometric shape in the mask layout, the amount of modification is determined based on a categorization of the type of the shape, the specific location in the reticle field the particular shape falls in, its context (i.e., surrounding patterns, orientation, etc.), as well as certain photoresist parameters to be used in the patterning process.

Owner:CADENCE DESIGN SYST INC

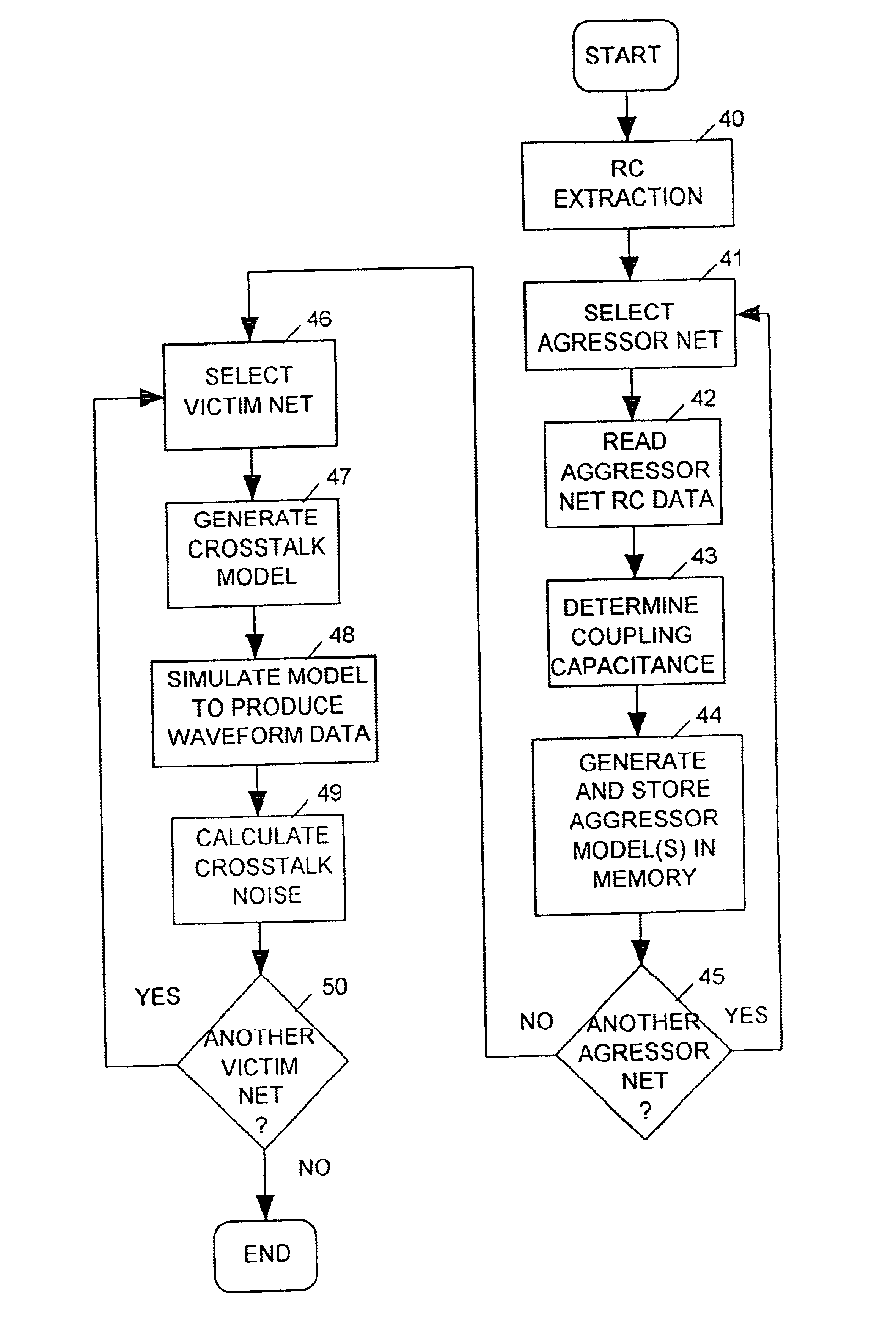

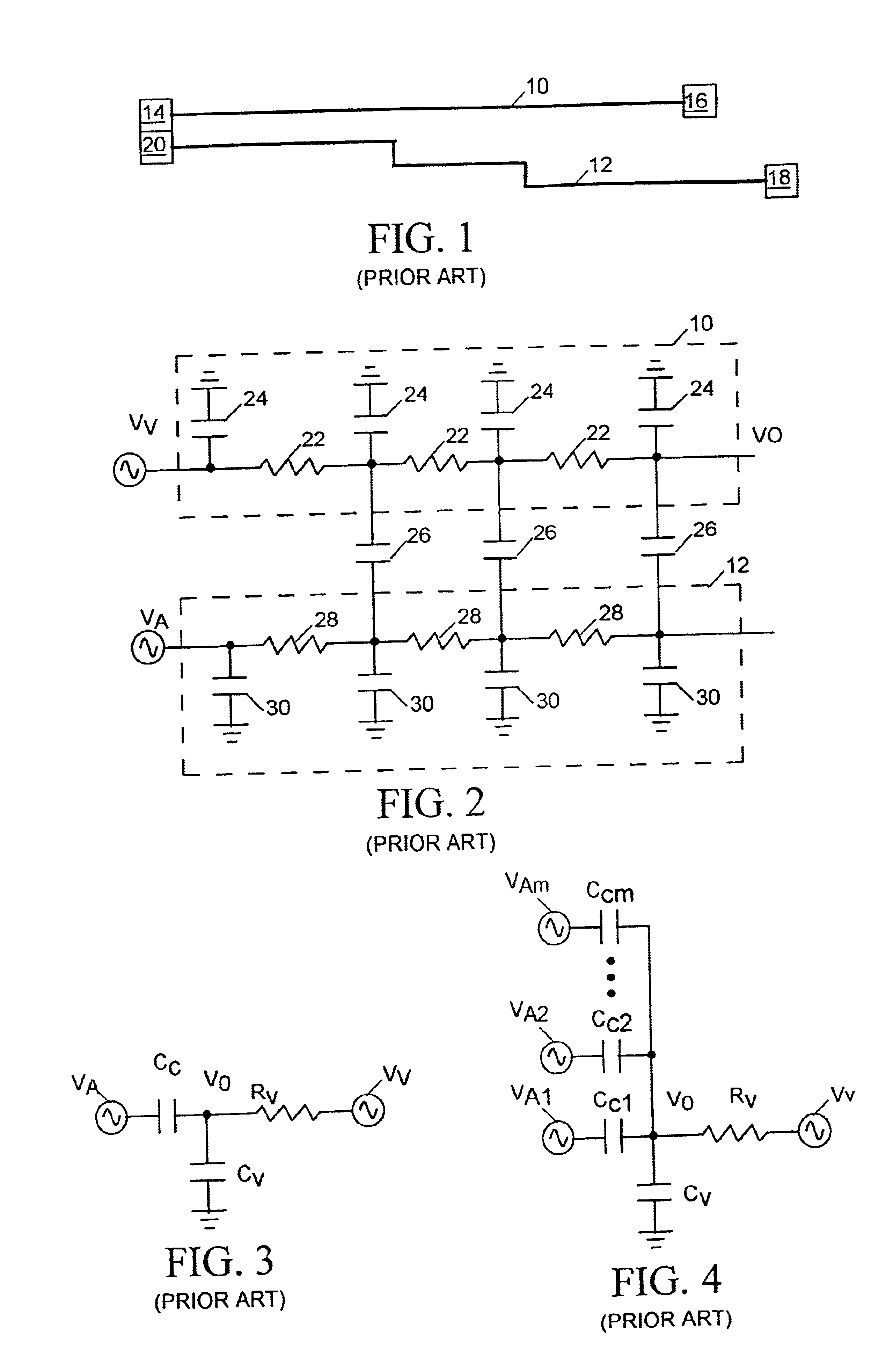

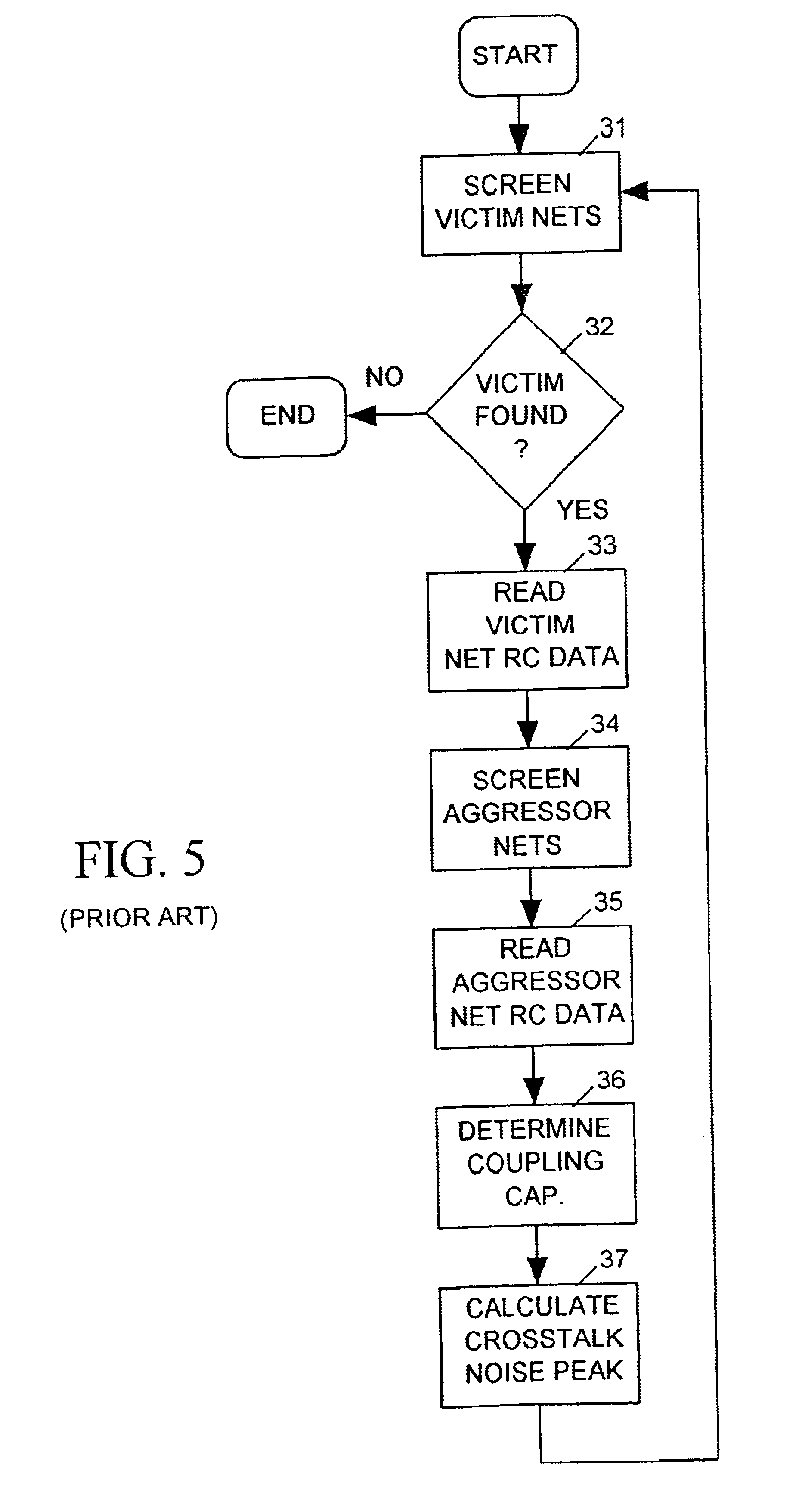

Method for estimating peak crosstalk noise based on separate crosstalk model

InactiveUS6971076B2Computer aided designSpecial data processing applicationsCapacitanceElectrical resistance and conductance

Crosstalk noise peaks in output signals of nets of an integrated circuit layout design are estimated by first processing the design to estimate resistances and capacitances of the nets. The design is then processed to identify each aggressor net having at least one section that is proximate to a section of a victim net. A separate aggressor model is then generated for each proximate aggressor net section, the aggressor model including a current source and a capacitor. The design is then processed to identify each victim net that is proximate any aggressor net and a separate crosstalk model is generated for each identified victim net. The crosstalk model for each victim net includes the victim net's estimated resistances and capacitances and incorporates the aggressor model of each aggressor net section that is proximate to a section of the identified victim net. The crosstalk model for each identified victim net is then evaluated to determine a response to a signal applied as input to the victim net of a victim net output signal. The peak crosstalk noise in each identified victim net is estimated based on the response of the net's output signal.

Owner:CADENCE DESIGN SYST INC

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

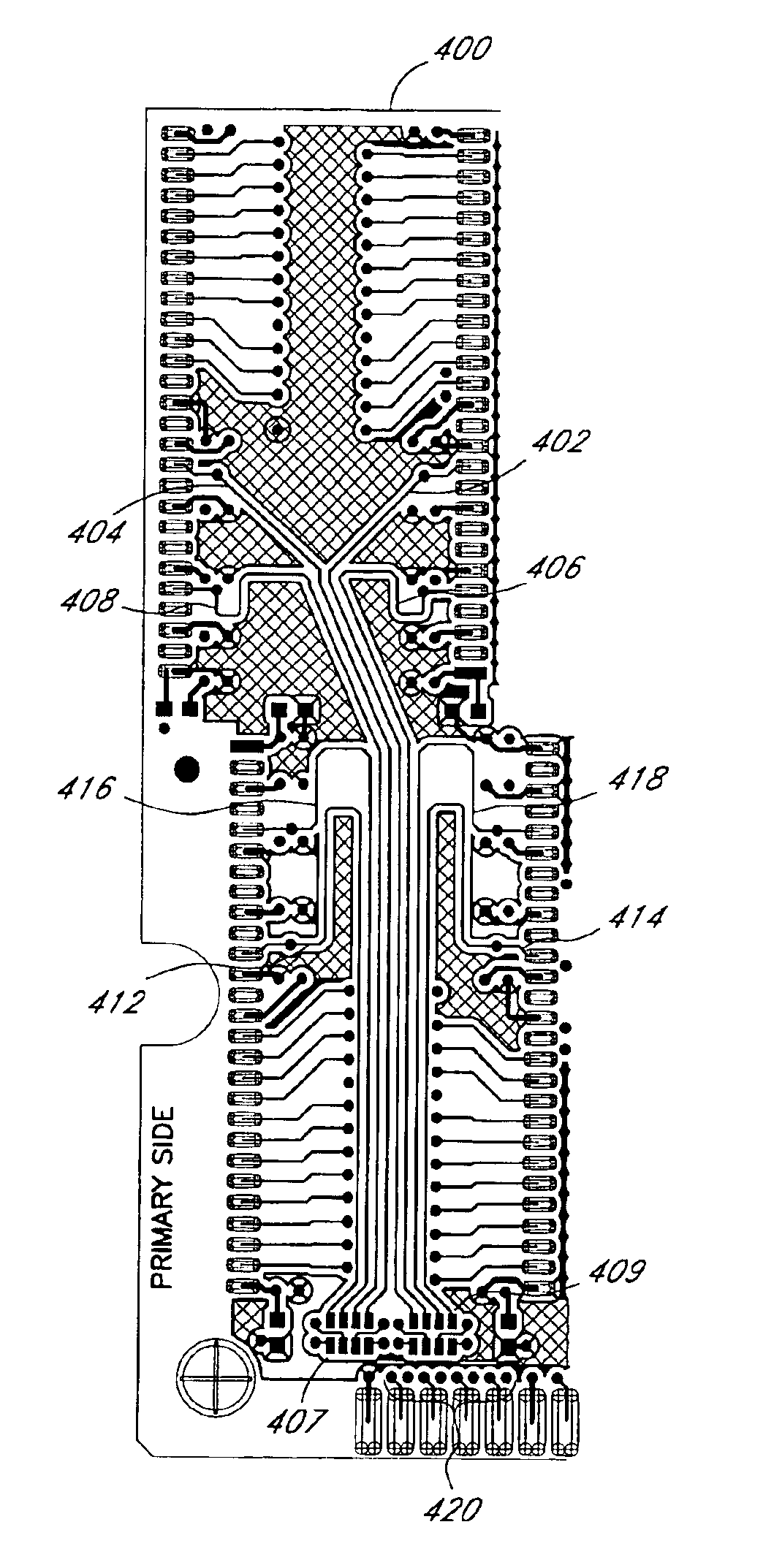

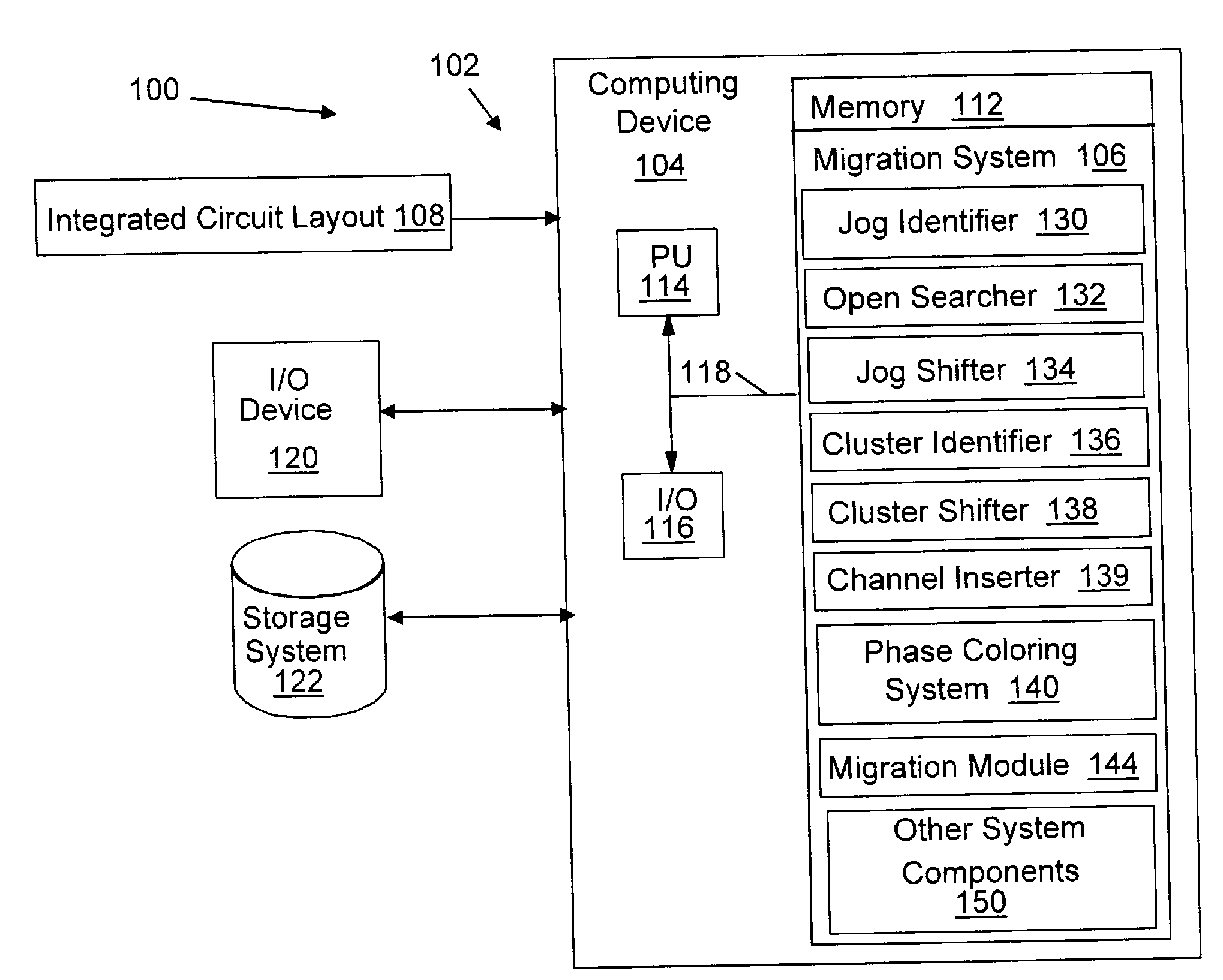

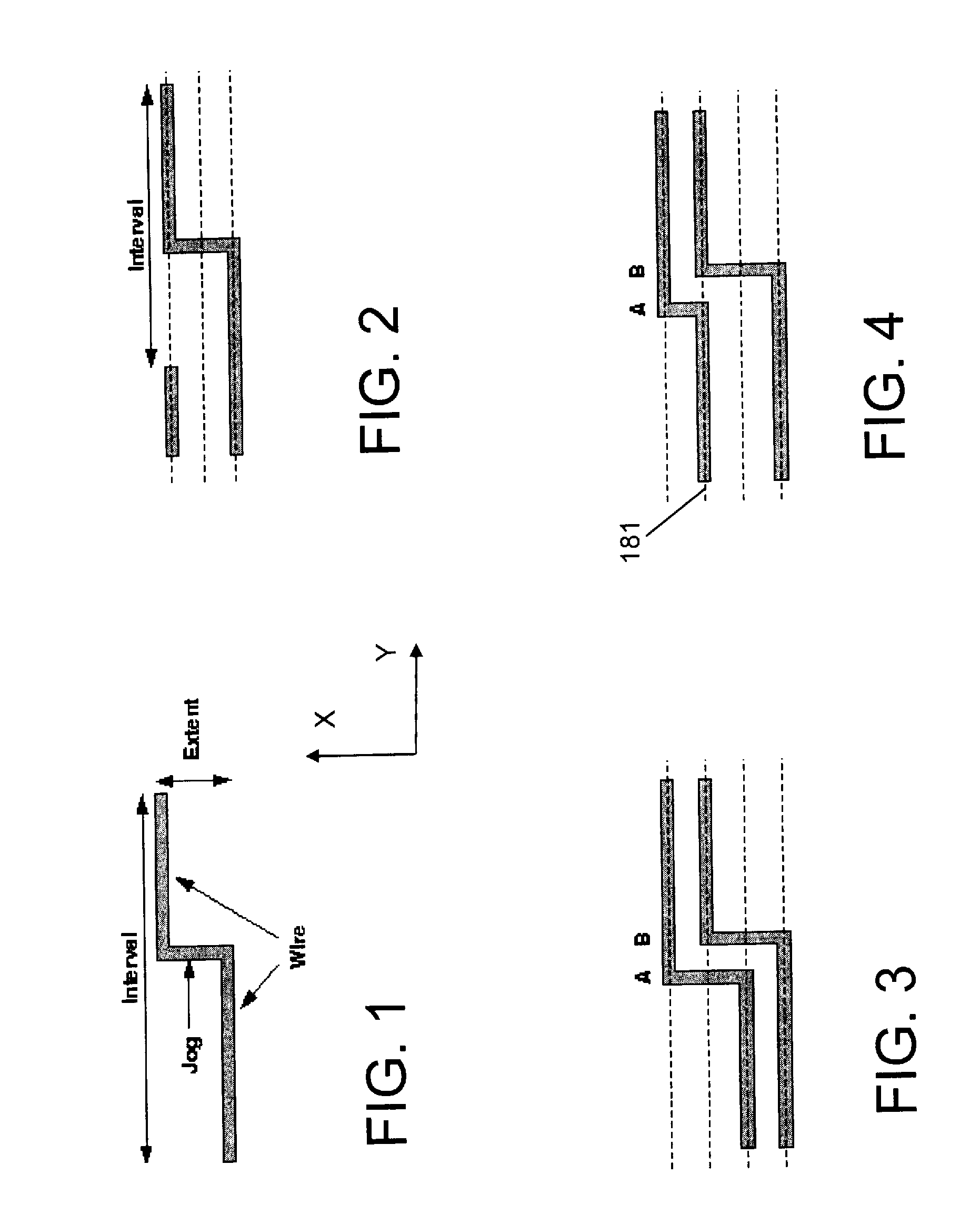

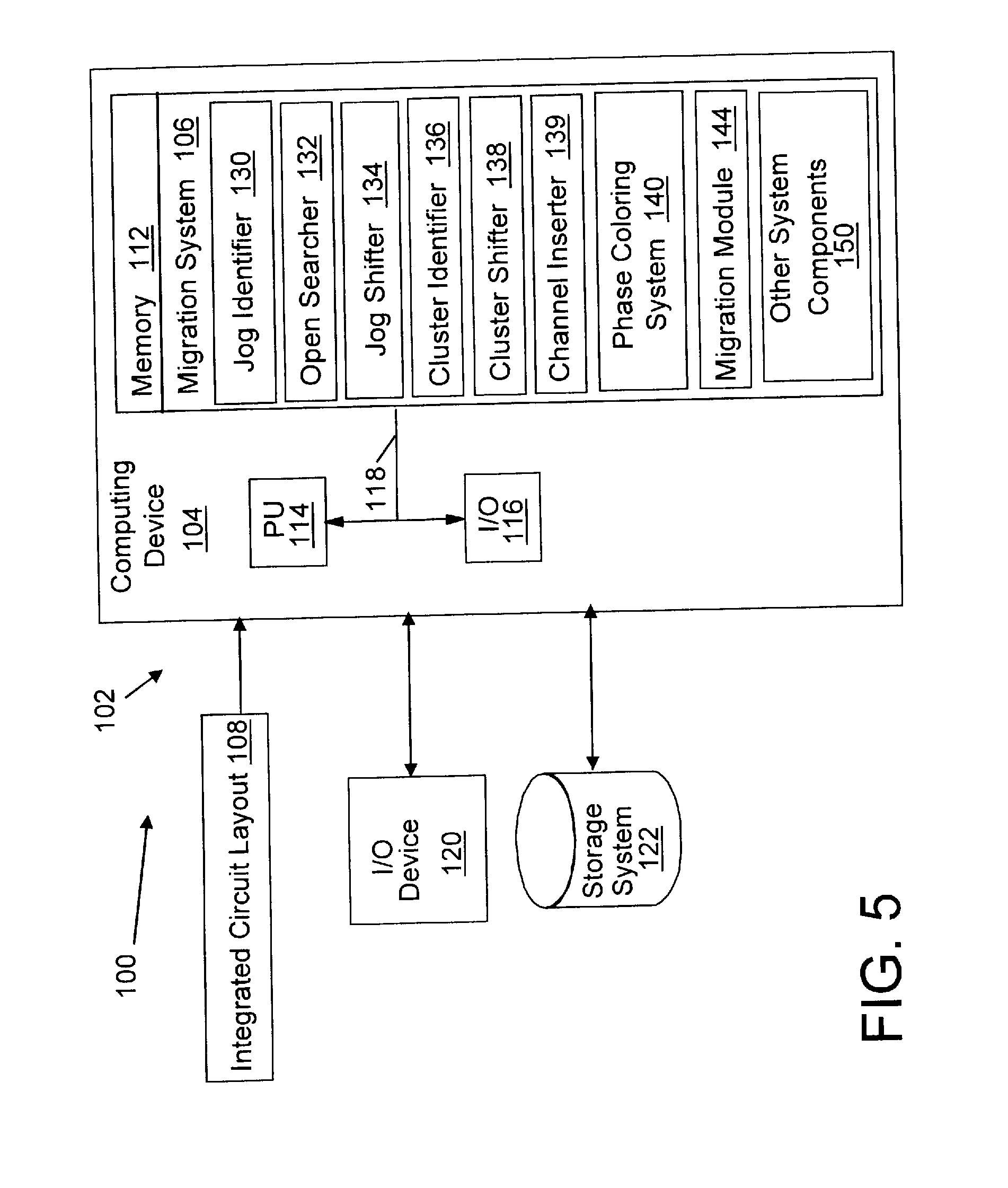

Migration of integrated circuit layout for alternating phase shift masks

InactiveUS20080244494A1Space is requiredCAD circuit designOriginals for photomechanical treatmentPhase shiftedProbable Case

Method, system and program product for migrating an integrated circuit (IC) layout for, for example, alternating aperture phase shift masks (AltPSM), are disclosed. In order to migrate a layout to phase compliance, jogs are identified on a first (AltPSM) layer and shifted to another second layer. Isolated or clustered jogs are shifted into an open channel portions on the second layer where possible. Remaining clustered jogs are shifted into as few new channels as possible on the second layer. The jog removal process leaves unidirectional wires that can be trivially phase colored. Standard technology migration techniques are then used to legalize the results on the layers.

Owner:IBM CORP

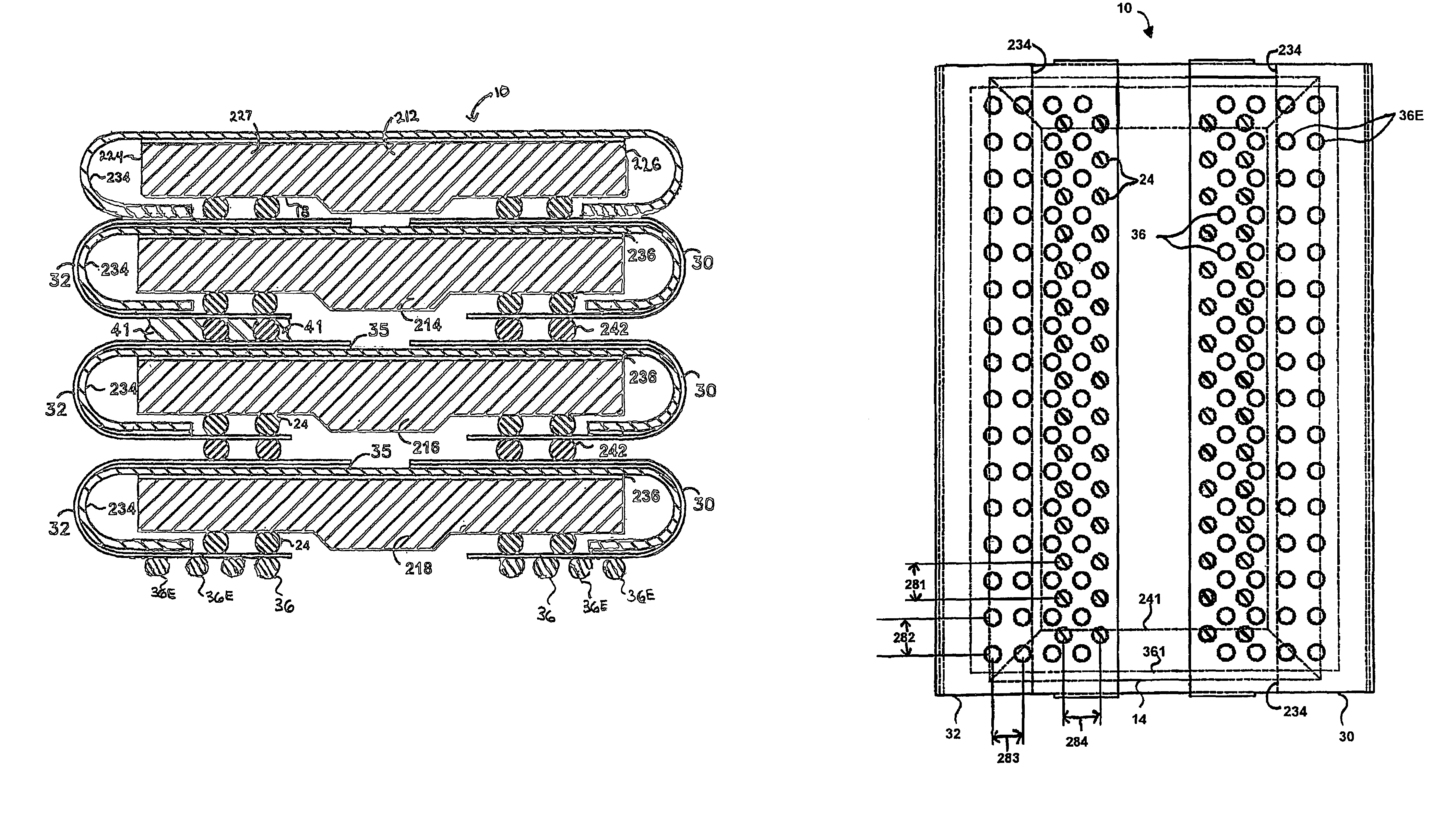

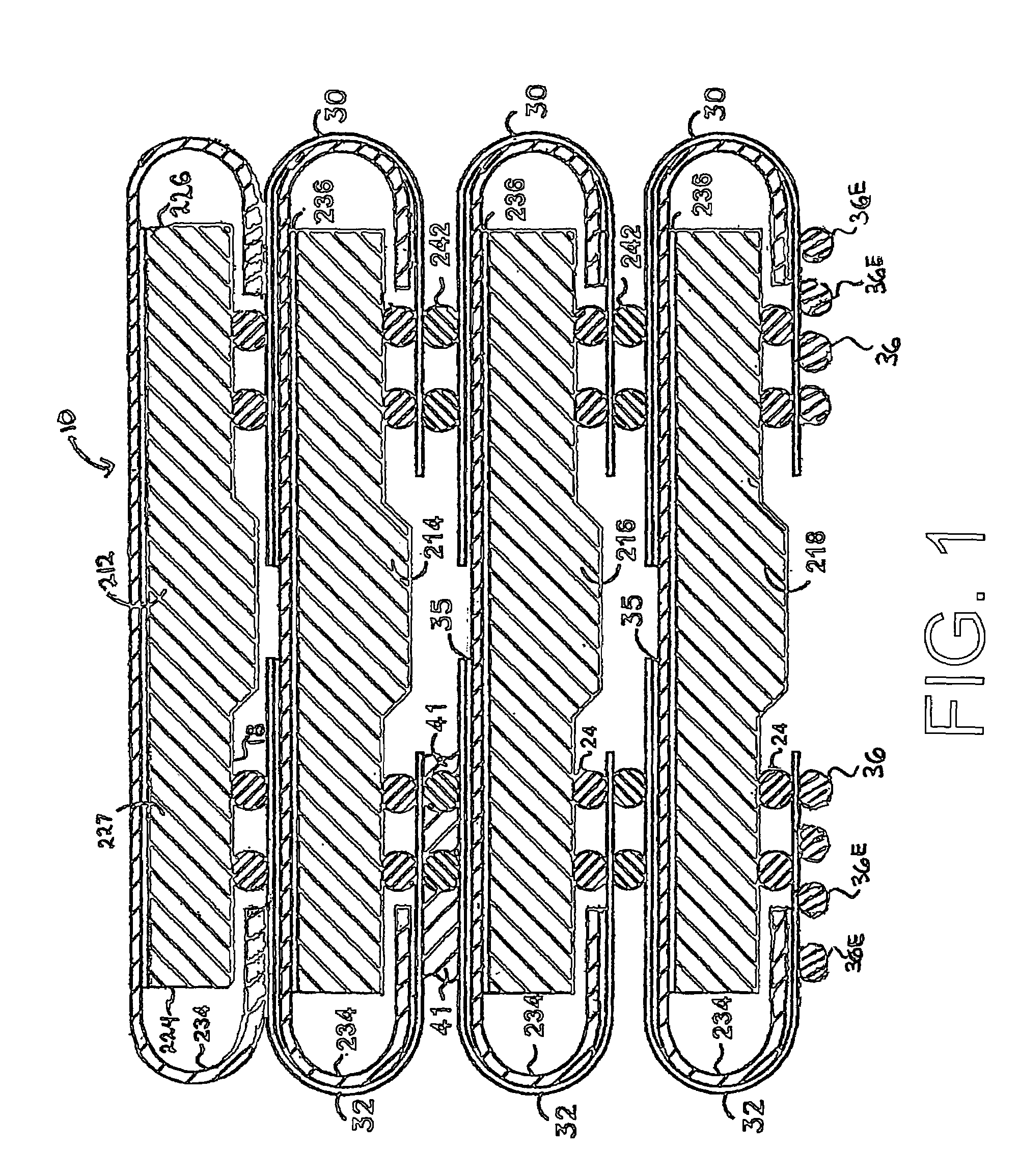

Pitch change and chip scale stacking system

InactiveUS7053478B2Printed circuit assemblingSemiconductor/solid-state device detailsHigh densityFlexible circuits

The present invention stacks integrated circuits into modules that conserve board surface area. In a two-high stack or module devised in accordance with a preferred embodiment of the present invention, a pair of integrated circuits is stacked, with one integrated circuit above the other. The two integrated circuits are connected with a pair of flexible circuit structures. Each of the pair of flexible circuit structures is partially wrapped about a respective opposite lateral edge of the lower integrated circuit of the module. The flex circuit pair connects the upper and lower integrated circuits and provides a thermal and electrical path connection path between the module and its application environment. The module has a ballout pattern with a different pitch and / or supplemental module contacts devised to allow combined signaling to the integrated circuits through contacts having a desired ballout footprint. The present invention may be employed to advantage in numerous configurations and combinations of integrated circuits in modules provided for high-density memories or high capacity computing.

Owner:TAMIRAS PER PTE LTD LLC

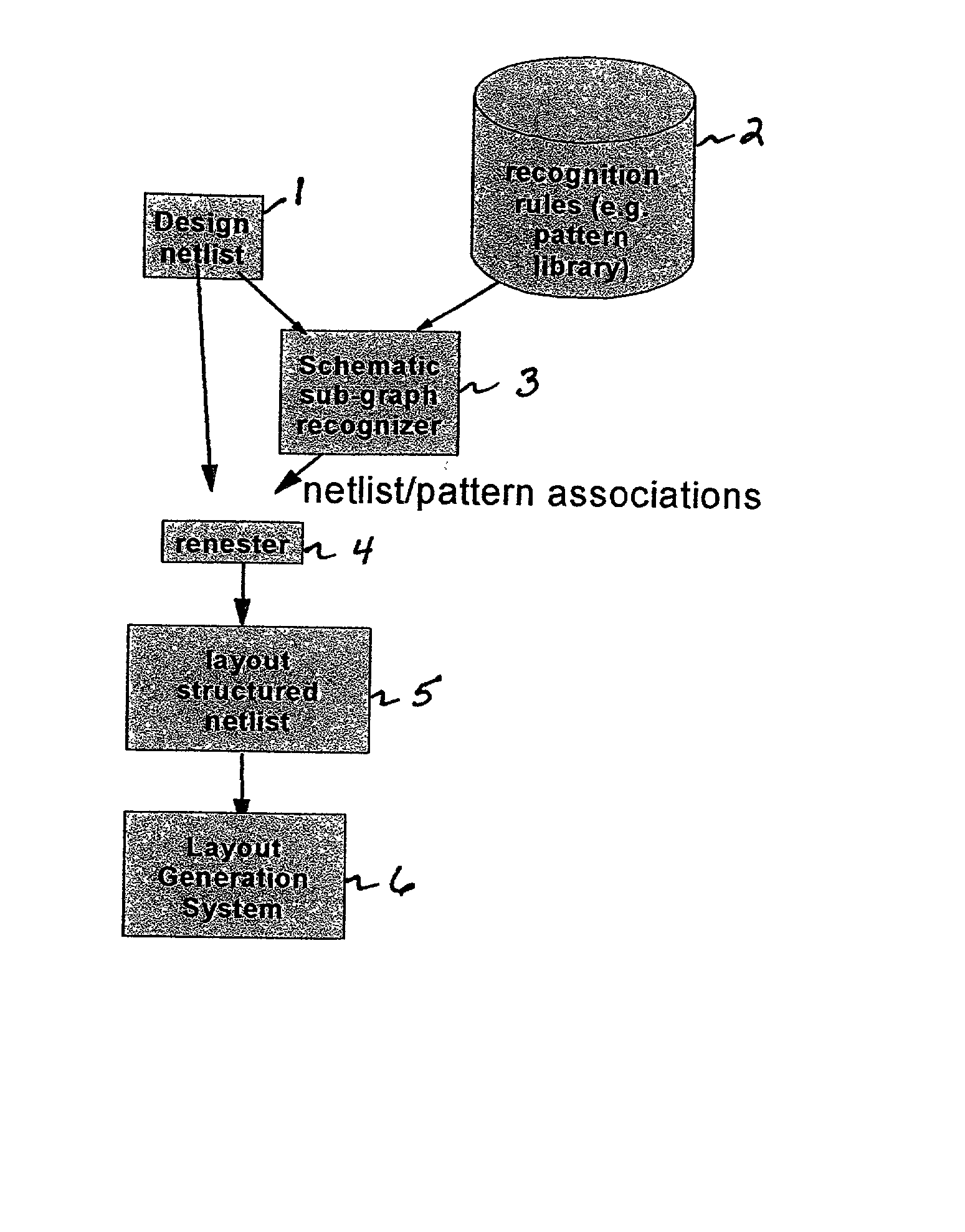

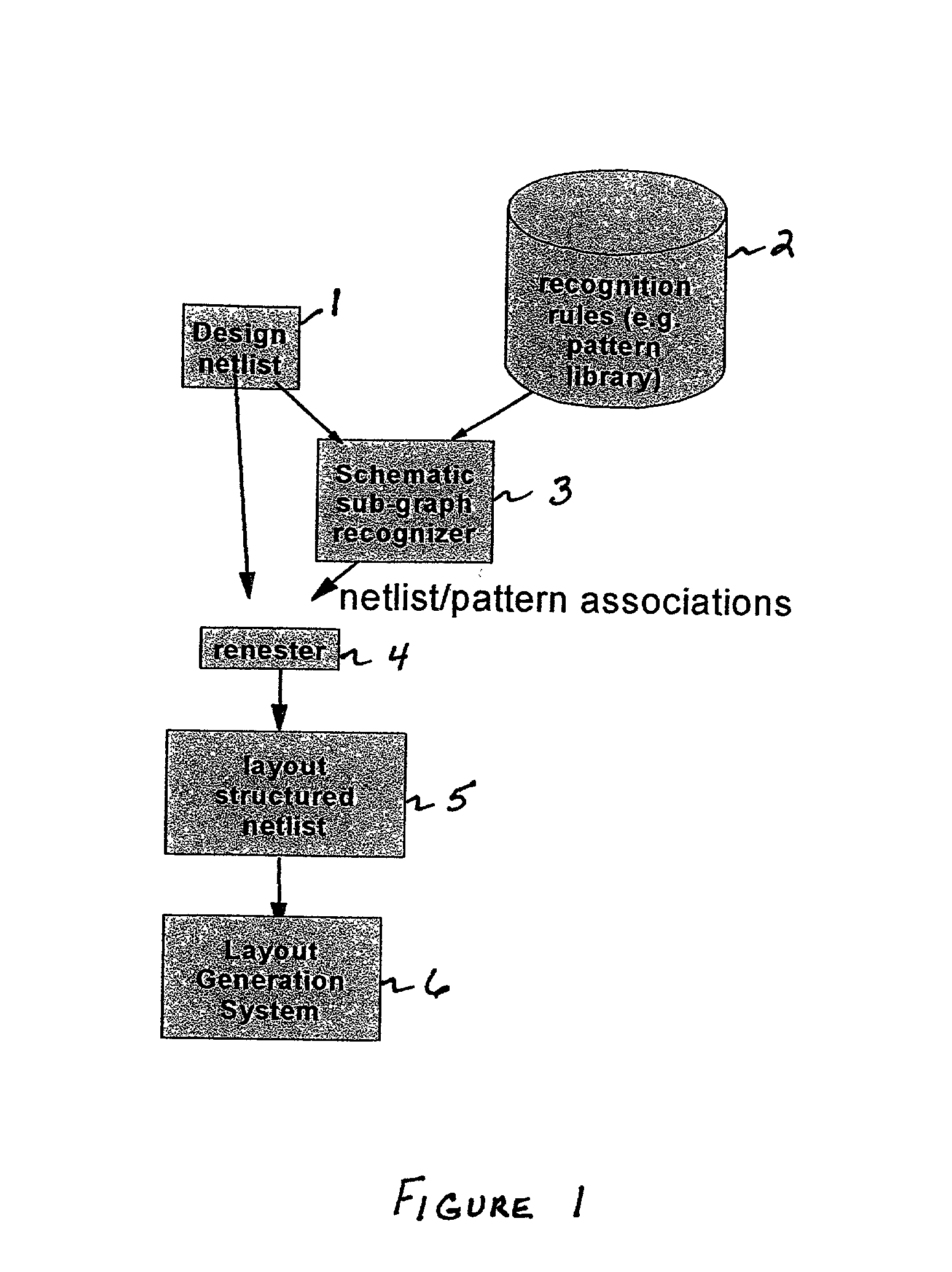

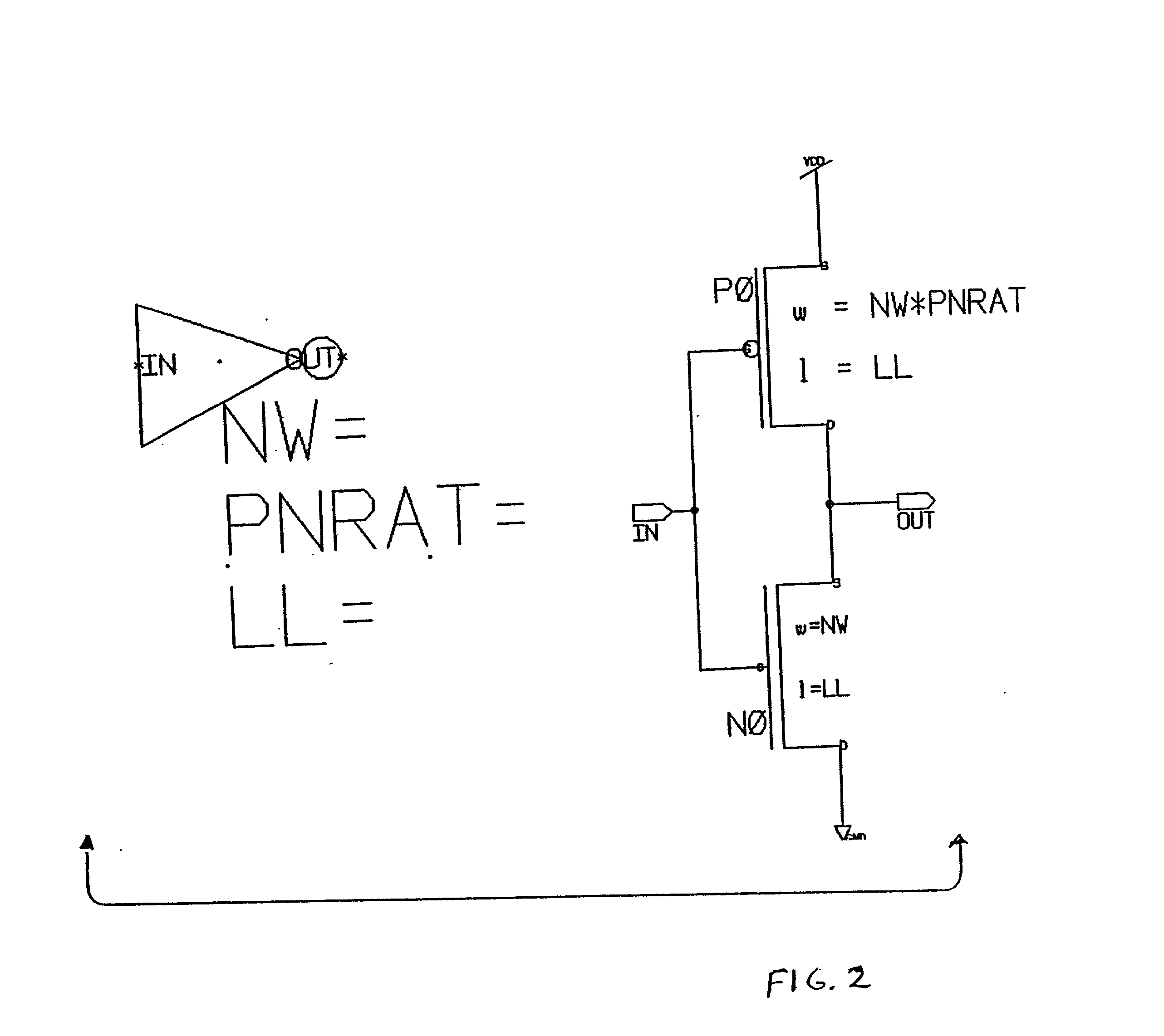

Hierarchical layout method for integrated circuits

InactiveUS20020194575A1Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

A method for hierarchical layout of an electronic design using an electronic computer aided design system, wherein the method includes generating a parameterized pattern library and using an existing netlist and analyze in a pattern recognizer, from which a list of associations between the pattern library and the netlist is created. Renesting then occurs wherein the netlist using the list of associations is used for generating a hierarchical layout of the electronic components in the design.

Owner:IBM CORP

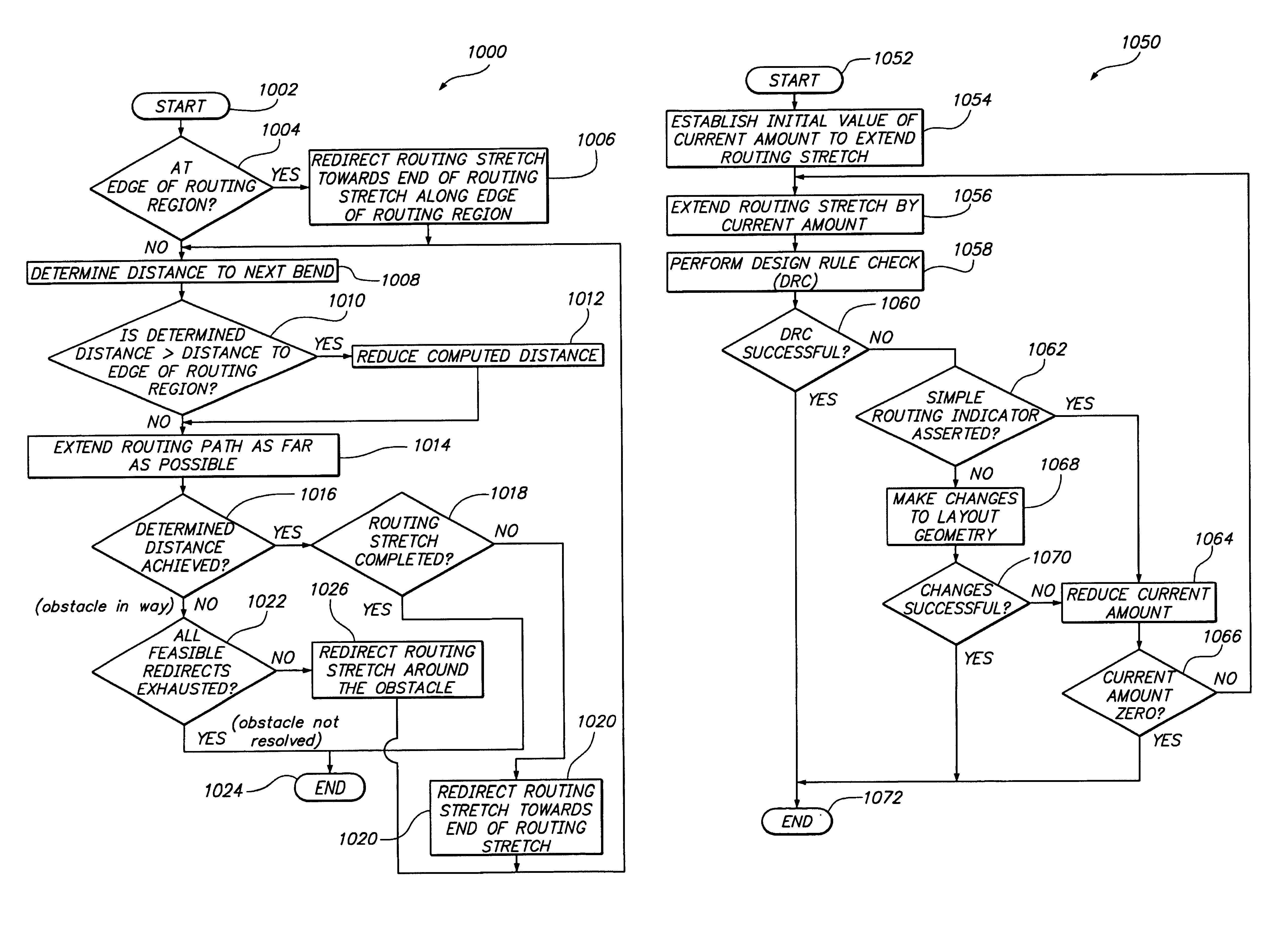

Approach for routing an integrated circuit

InactiveUS7065729B1Computer aided designSpecial data processing applicationsGraphicsImage resolution

A computer-implemented approach for routing an integrated circuit using non-orthogonal routing is accomplished during two phases: a global routing phase and a detailed routing phase. During global routing, routing indicators, in the form of hint polygons, are added to the integrated circuit layout and strategy lists, that include bias directions and straying limits, are generated for the new wires to be added. The hint polygons and strategy lists are used during detailed routing to aid in placing the new wires. If obstacle conflicts or insufficient space problems prevent the detailed routing of a new wire, then an obstacle resolution portion of global routing is used to resolve the obstacle conflict and / or provide additional space in the integrated circuit layout to route the new wires. Obstacle resolution includes, without limitation, moving or changing layout geometry, changing or add hint polygons, changing the routing strategy by changing the bias direction and / or adjusting straying limits, inserting one or more layer changes, instructing the detailed router to backup and insert a bend, ripping-up and rerouting one or more wires, or routing the wire from the destination connection point. Also, a tight routing approach may be employed to accommodate constructing routing paths in tight layout areas. Object specific design rule checks are employed to increase routing flexibility optimize routing performance. “On-the-fly” design rule checks are performed on portions of routing paths as the routing paths are being constructed.

Owner:CHAPMAN DAVID C

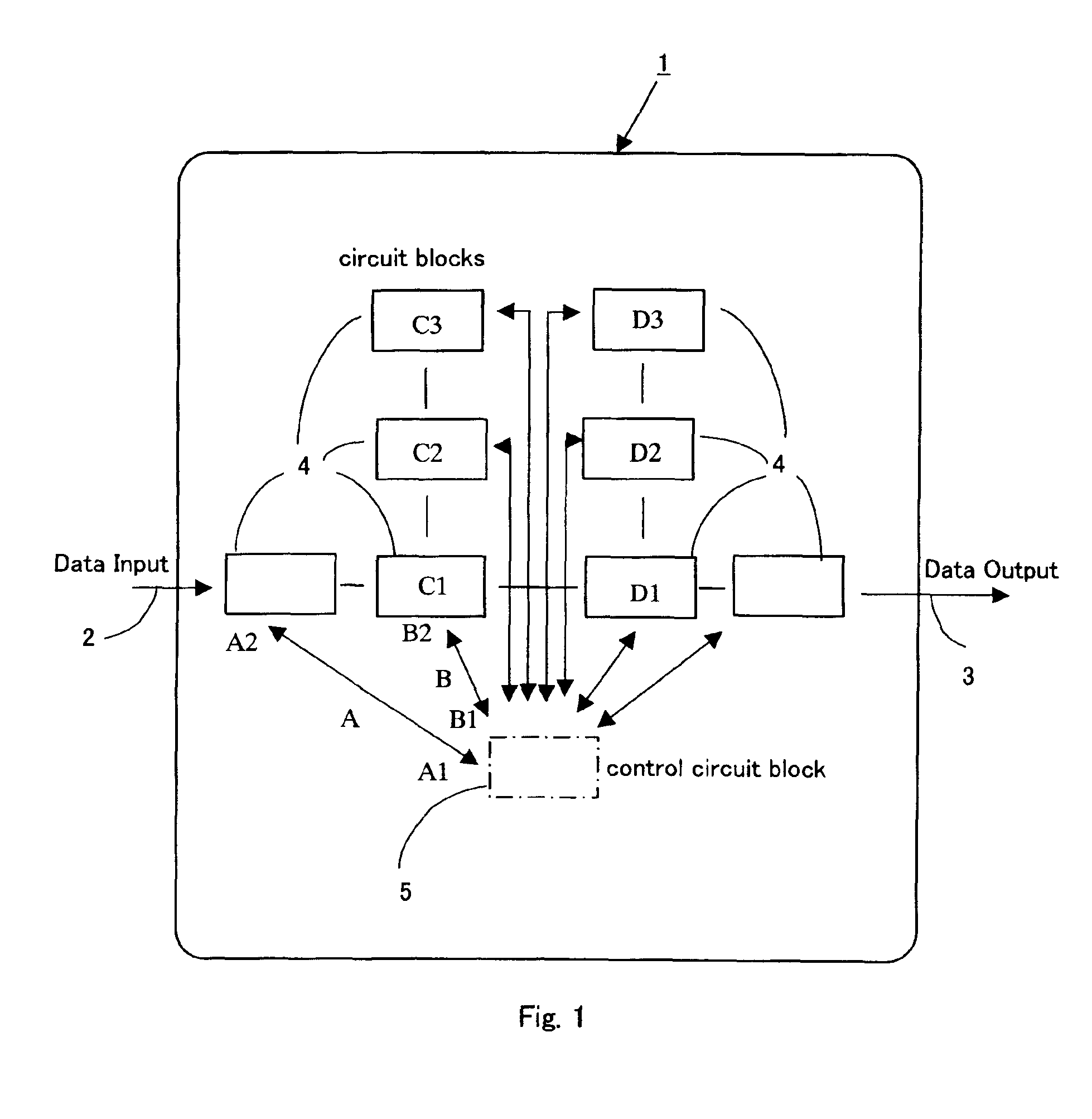

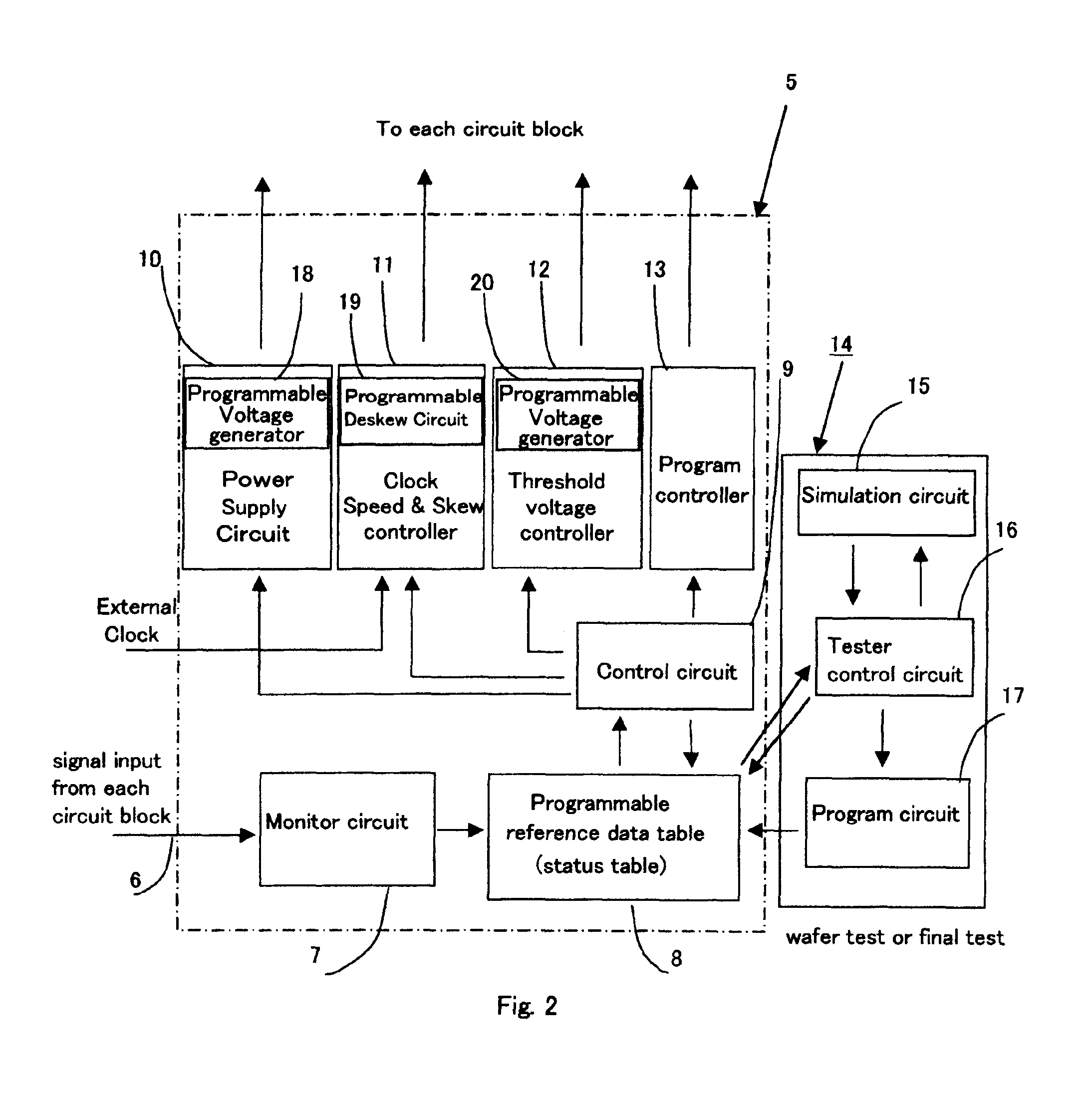

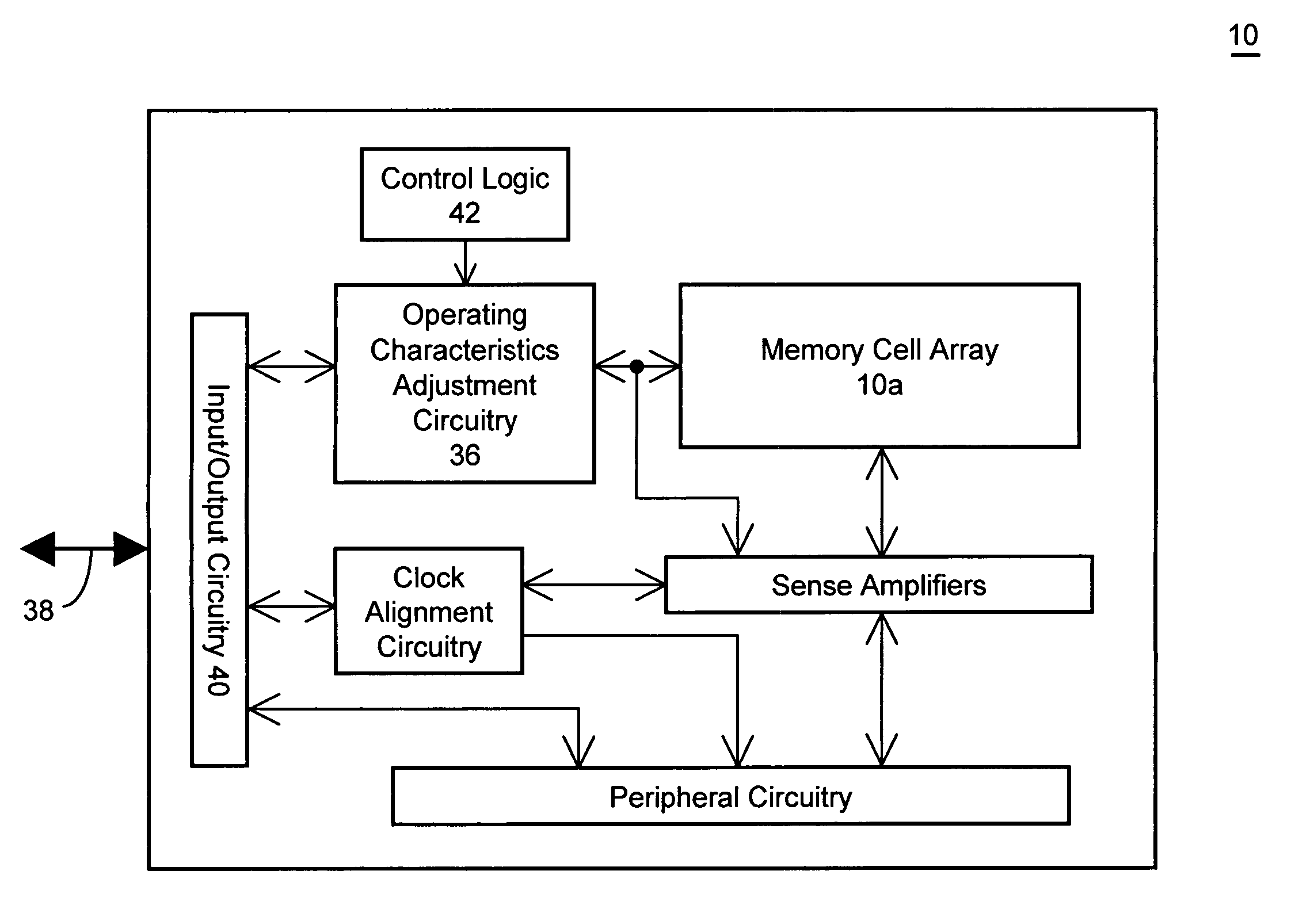

Integrated circuits having post-silicon adjustment control

InactiveUS6957163B2Double program execution timeReduce power consumptionThermometer detailsDigital circuit testingControl systemIntegrated circuit layout

An integrated circuit system has a reference data table for holding information that is used to control at least one circuit block in the system and also has a power supply circuit, a body bias control circuit, a clock delivery circuit, a temperature monitor circuit, and / or a configuration control circuit. The performance of the system is improved by obtaining system performance data by testing the system at different supply voltages, different body-bias voltages, different clock speeds, and / or different temperatures. Values based on the data are entered into the reference data table. The power supply circuit, the body bias control circuit, the clock delivery circuit, and / or the temperature monitor circuit data is adjusted using the entered values.

Owner:RPX CORP

Rule-based design consultant and method for integrated circuit design

InactiveUS20050268258A1Accurate and useful diagnosisComputer programmed simultaneously with data introductionCAD circuit designGraphicsComputer architecture

A rule-based design consultant and analysis method for an integrated circuit (“IC”) layout design compares an IC design against a list of rules. The IC design information may be included in a set of databases, including a database containing physical implementation and technology specific timing and area information. The consultant and method can be used with a graphical user interface that displays a report of the rules run on the IC design. Cross-probing may be incorporated to display at least one diagram of an object that is not compliant with a particular rule, as well as relevant source code for the object.

Owner:MAGMA DESIGN AUTOMATION

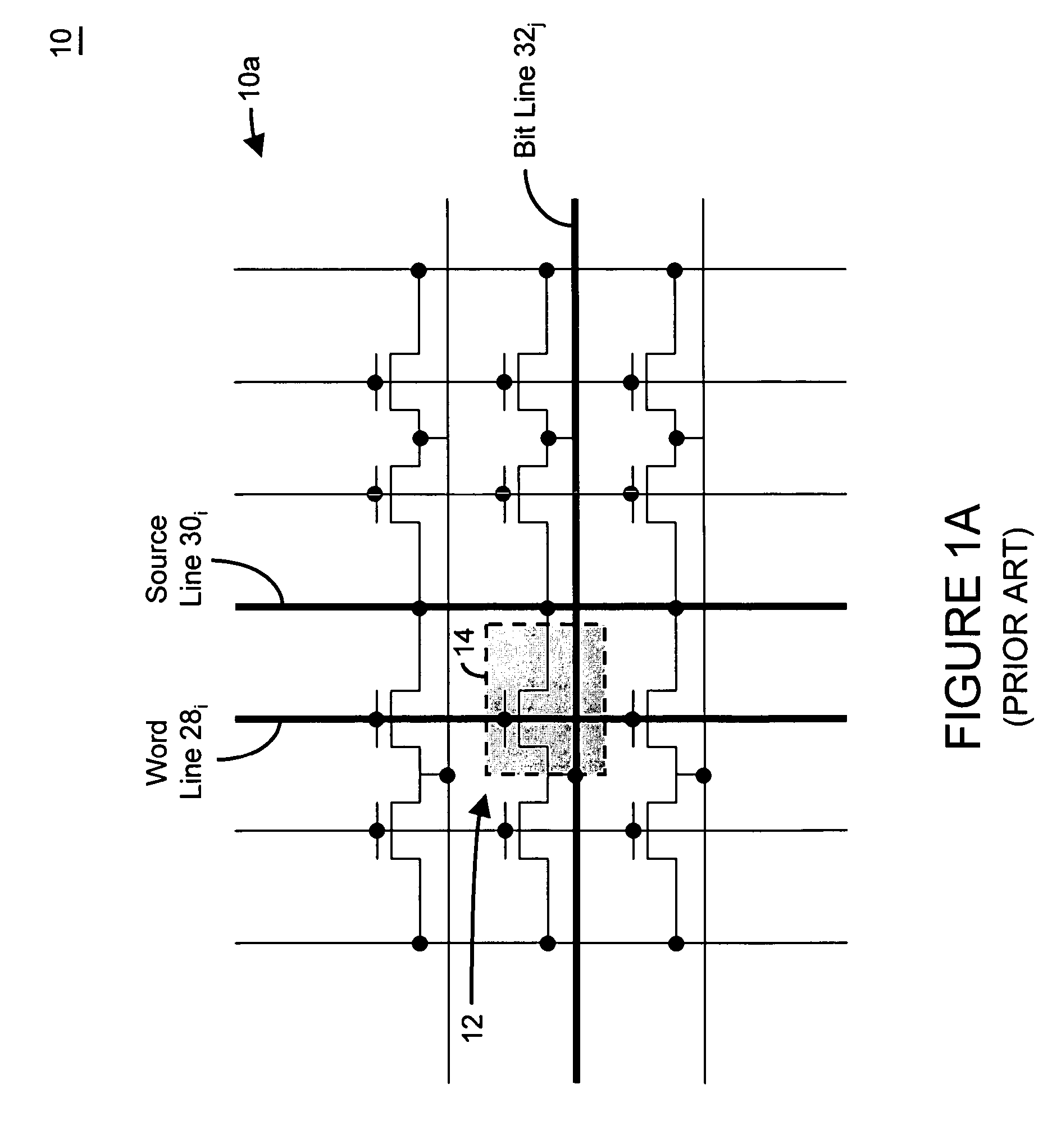

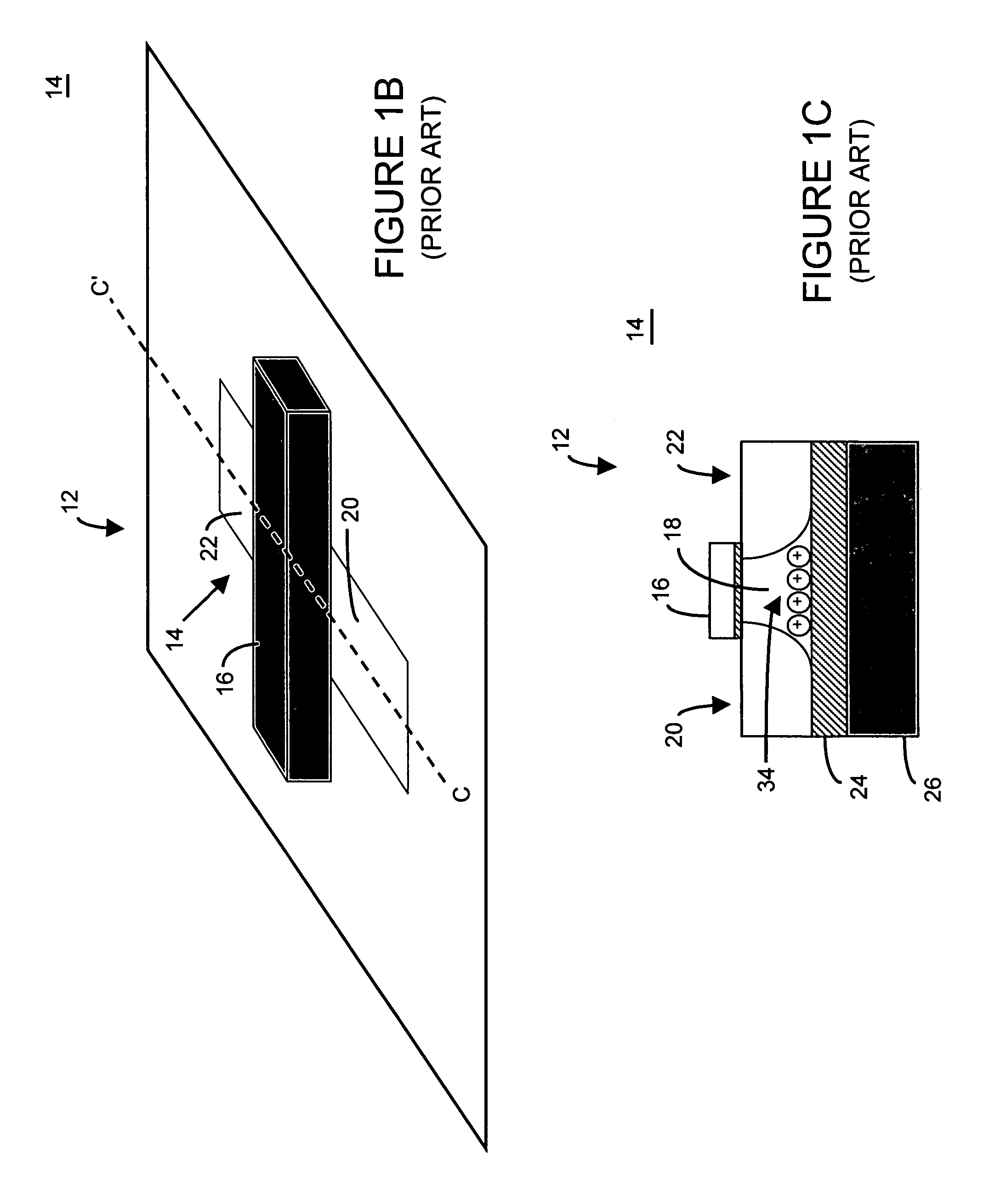

Circuitry for and method of improving statistical distribution of integrated circuits

ActiveUS7251164B2Enhance uniformity of operation and responseRead-only memoriesDigital storageElectricityArray data structure

An integrated circuit device comprising a memory cell array including a plurality of memory cells wherein each memory cell includes at least one electrically floating body transistor having source, drain and a body regions, wherein the body region is electrically floating and disposed between the source and drain regions; a gate is disposed over the body region. Each memory cell includes a first data state representative of a first charge in the body region and a second data state representative of a second charge in the body region. The integrated circuit device further includes operating characteristics adjustment circuitry, coupled to the memory cell array, to adjust one or more operating or response characteristics of one or more memory cells to improve the uniformity of operation / response characteristics of the memory cells of the memory cell array relative to the other memory cells of the array.

Owner:MICRON TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com