Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

280results about "Fail-safe circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

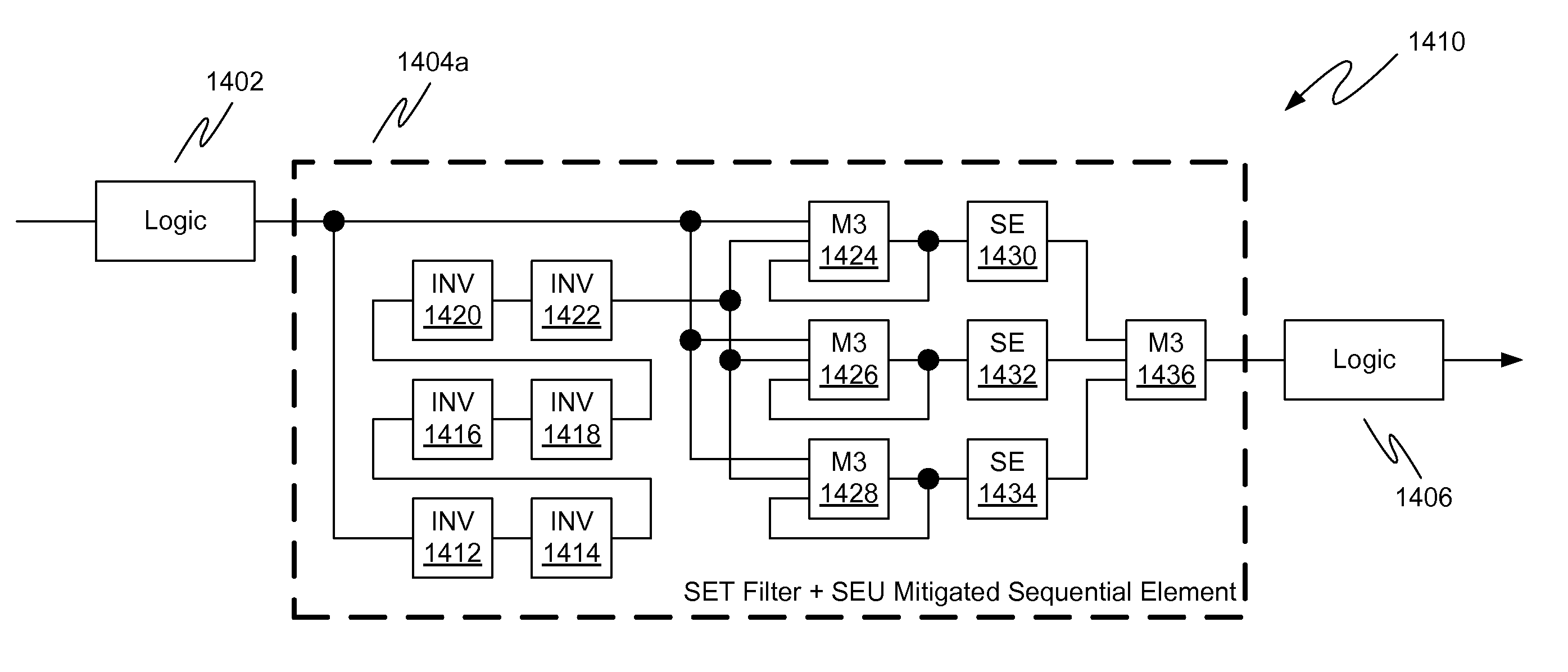

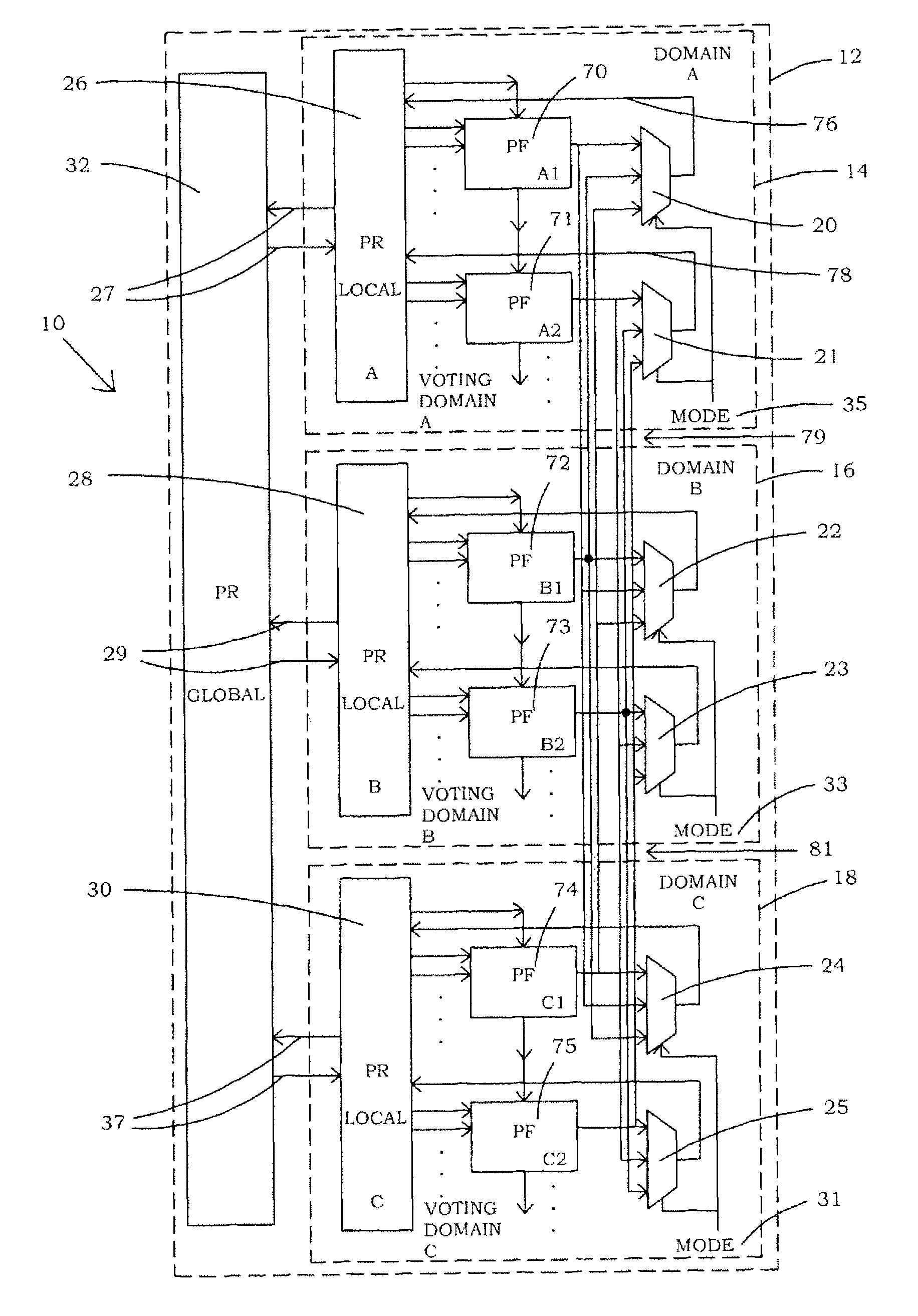

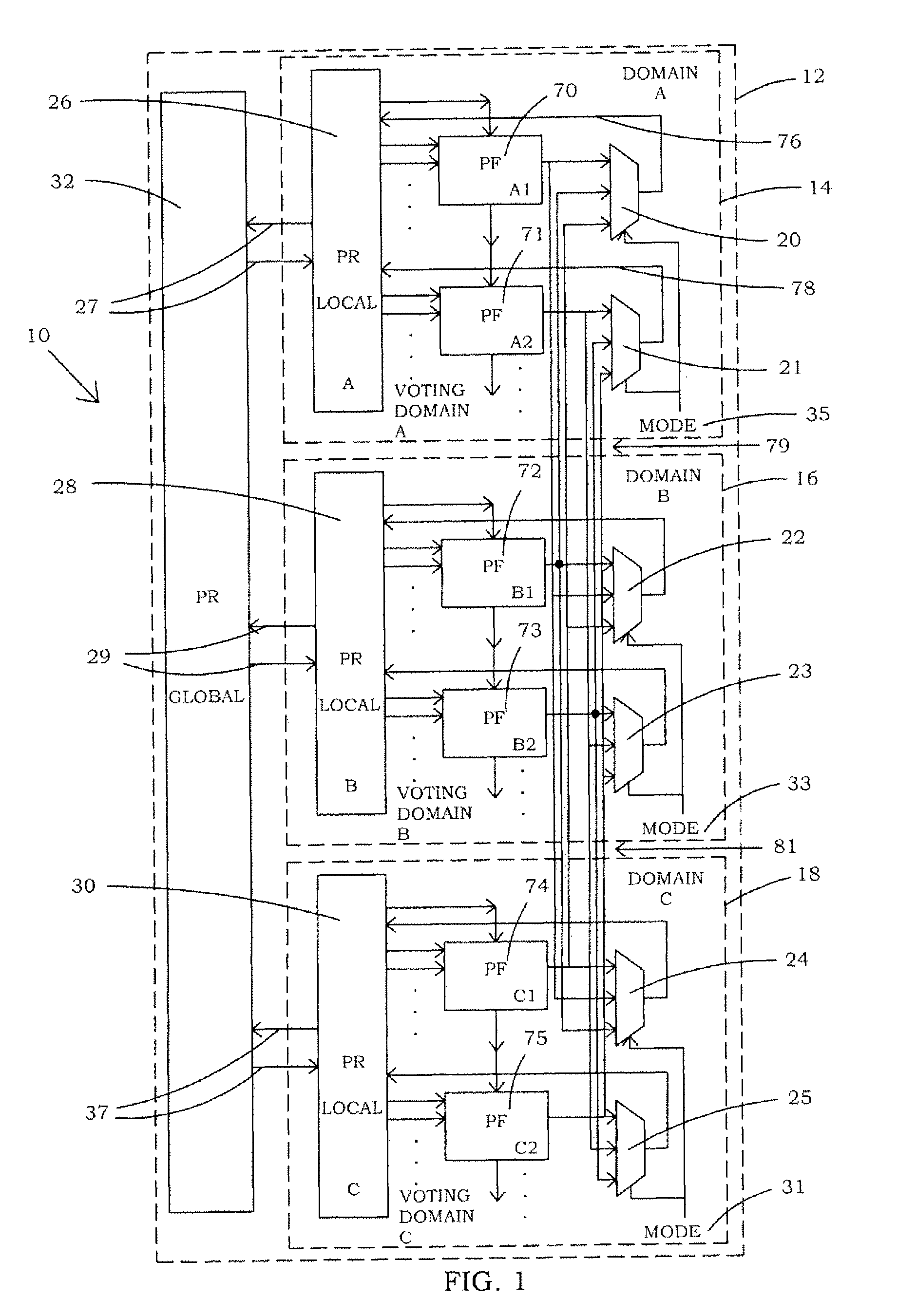

Single event transient mitigation and measurement in integrated circuits

ActiveUS20090204933A1Fail-safe circuitsDetecting faulty computer hardwareIntegrated circuit layoutComputer science

A method for single event transient filtering in an integrated circuit device is described. The device comprises three sequential elements, each having a data input and a data output with each of the three data outputs coupled to one of three inputs of a voting gate. The method comprises generating first and second nominally equivalent logic signals in first and second SET domains, converting the first and second nominally equivalent logic signals into first, second and third nominally equivalent data channels, and transmitting the first, second and third nominally equivalent data channels to the data inputs of the first, second and third sequential elements. Provision is made for applying the method to logic designs implemented in programmable logic integrated circuit devices.

Owner:MICROSEMI SOC

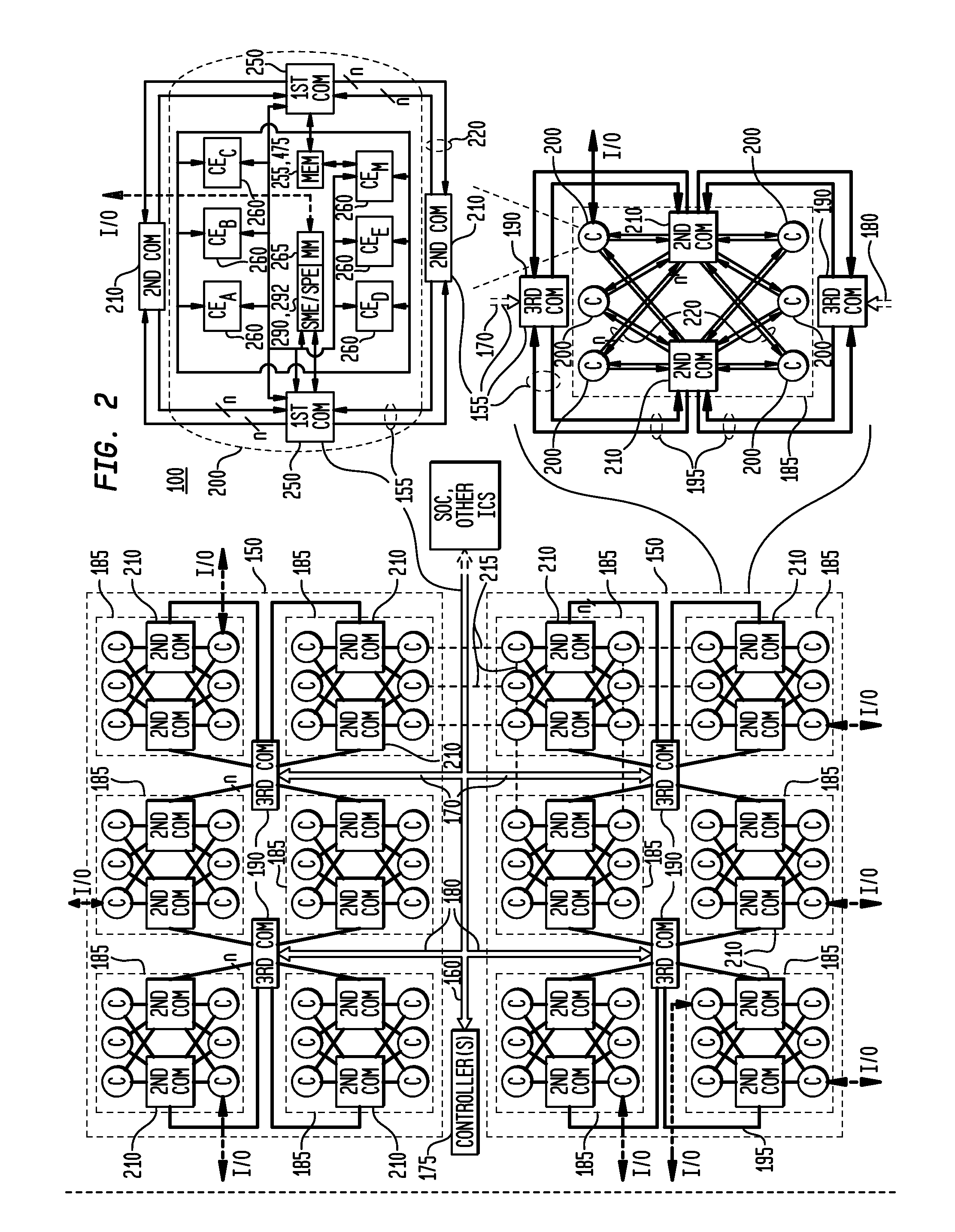

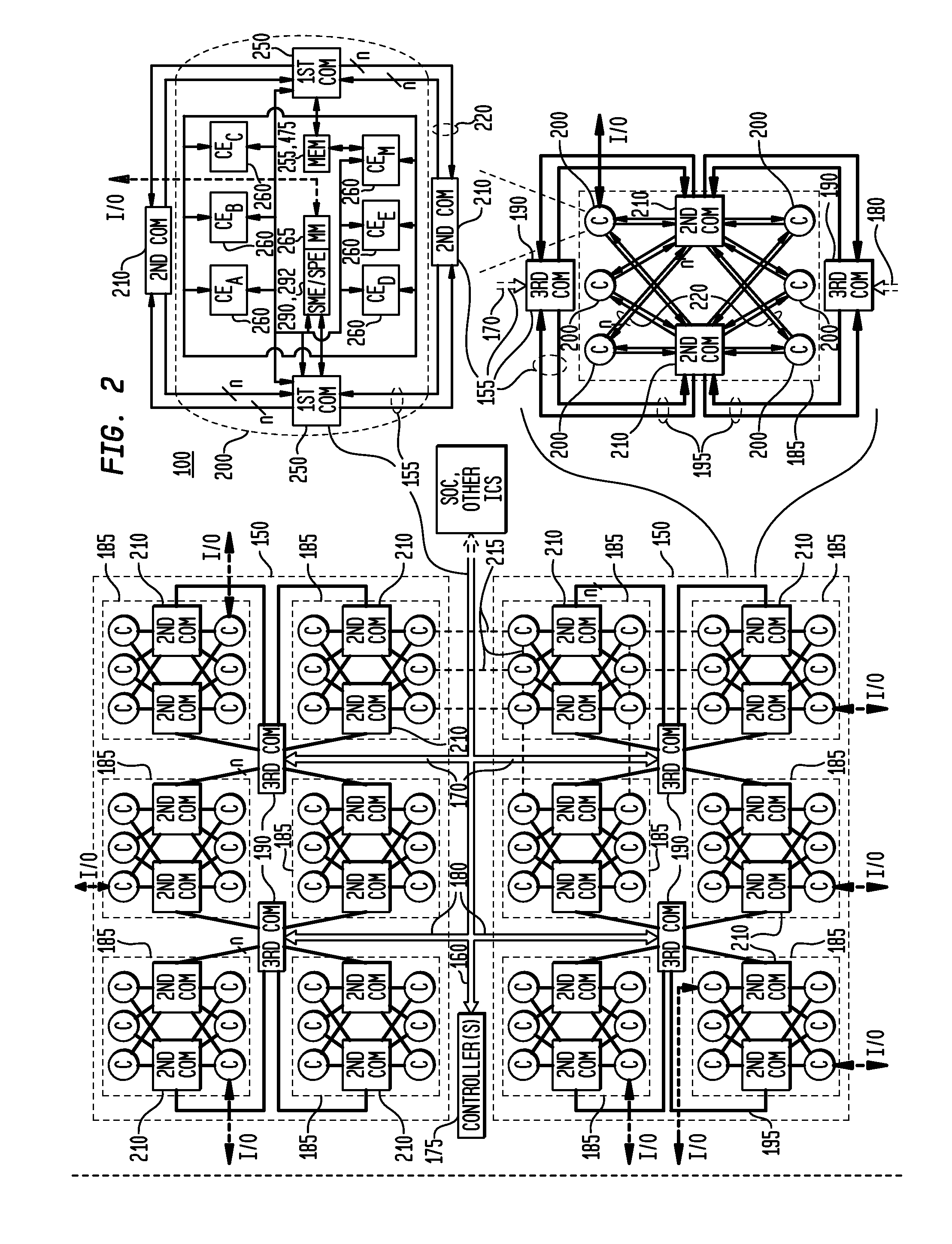

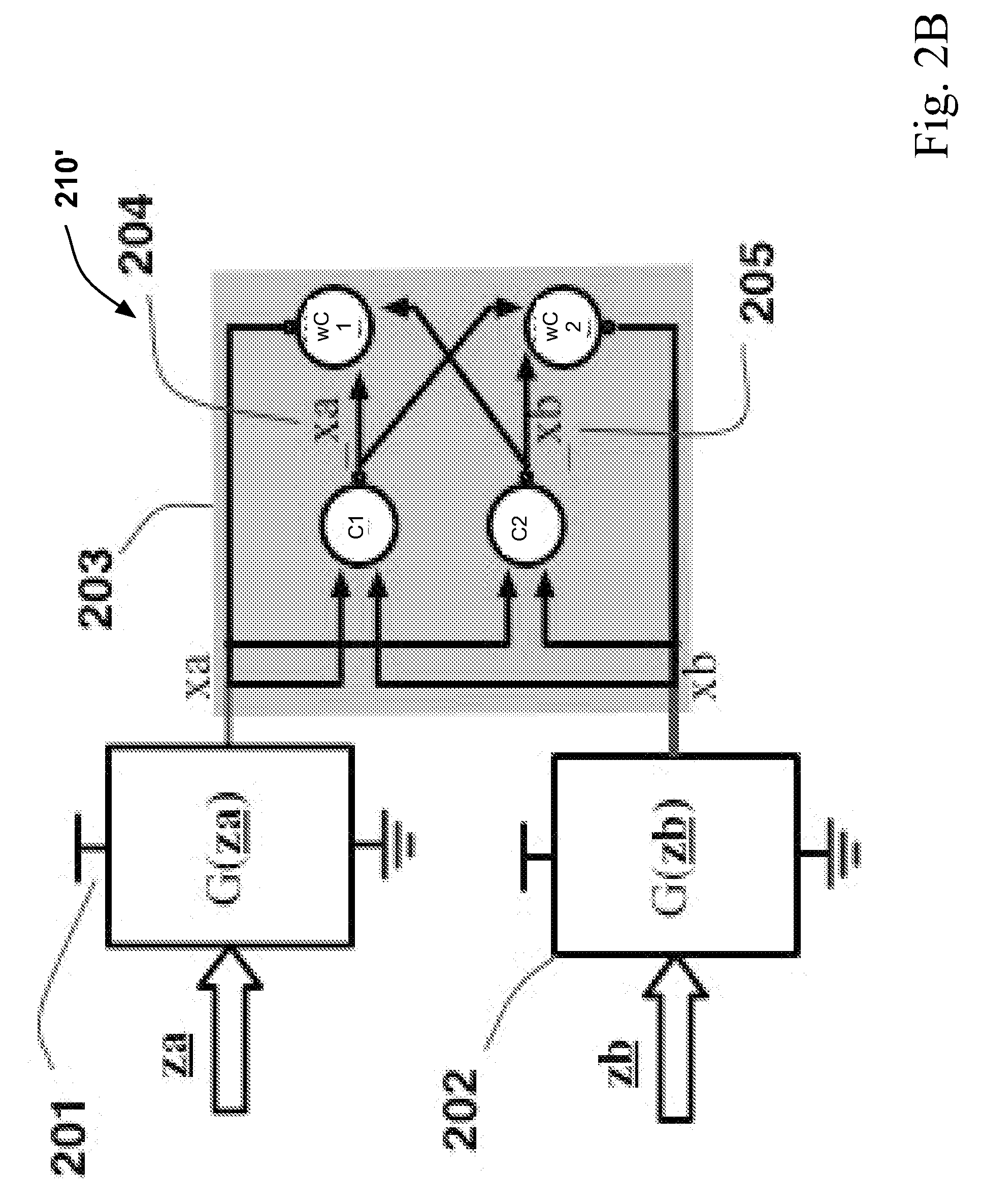

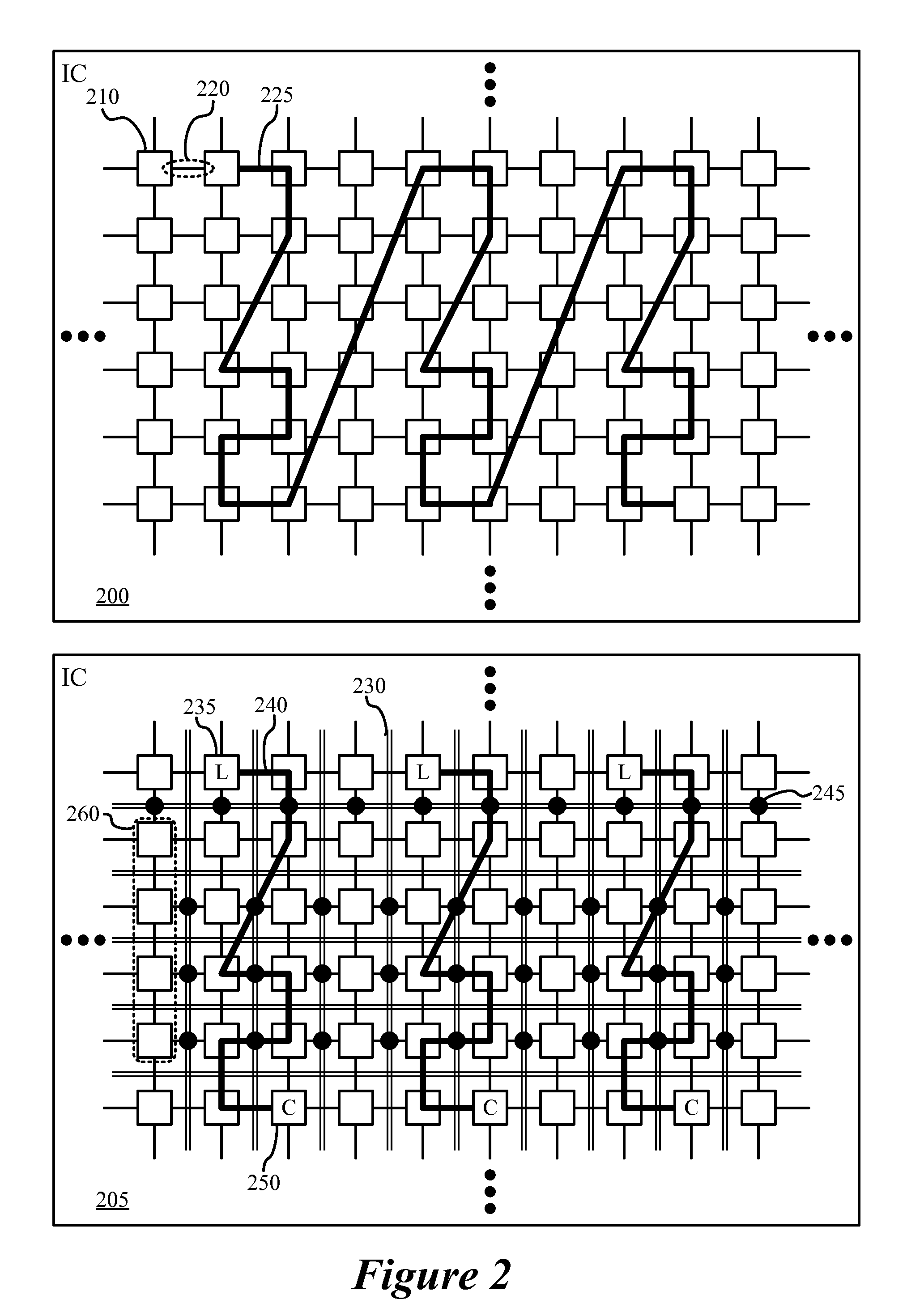

Data-Driven Integrated Circuit Architecture

InactiveUS20120126851A1Significant resiliencyReliability increasing modificationsError detection/correctionMultiple contextComputer architecture

The exemplary embodiments provide a reconfigurable integrated circuit architecture comprising: a configurable circuit element configurable for a plurality of data operations, each data operation corresponding to a context of a plurality of contexts; a plurality of input queues; a plurality of output queues; one or more configuration and control registers to store, for each context of the plurality of contexts, a plurality of configuration bits, a run status bit, and a plurality of bits designating at least one data input queue and at least one data output queue; and an element controller coupled to the configurable circuit element and to the one or more configuration and control registers, the element controller to allow loading of a context configuration and execution of a data operation upon the arrival of input data in the context-designated data input queue when the context run status is enabled and the context-designated data output queue has a status to accept output data.

Owner:ELEMENT CXI

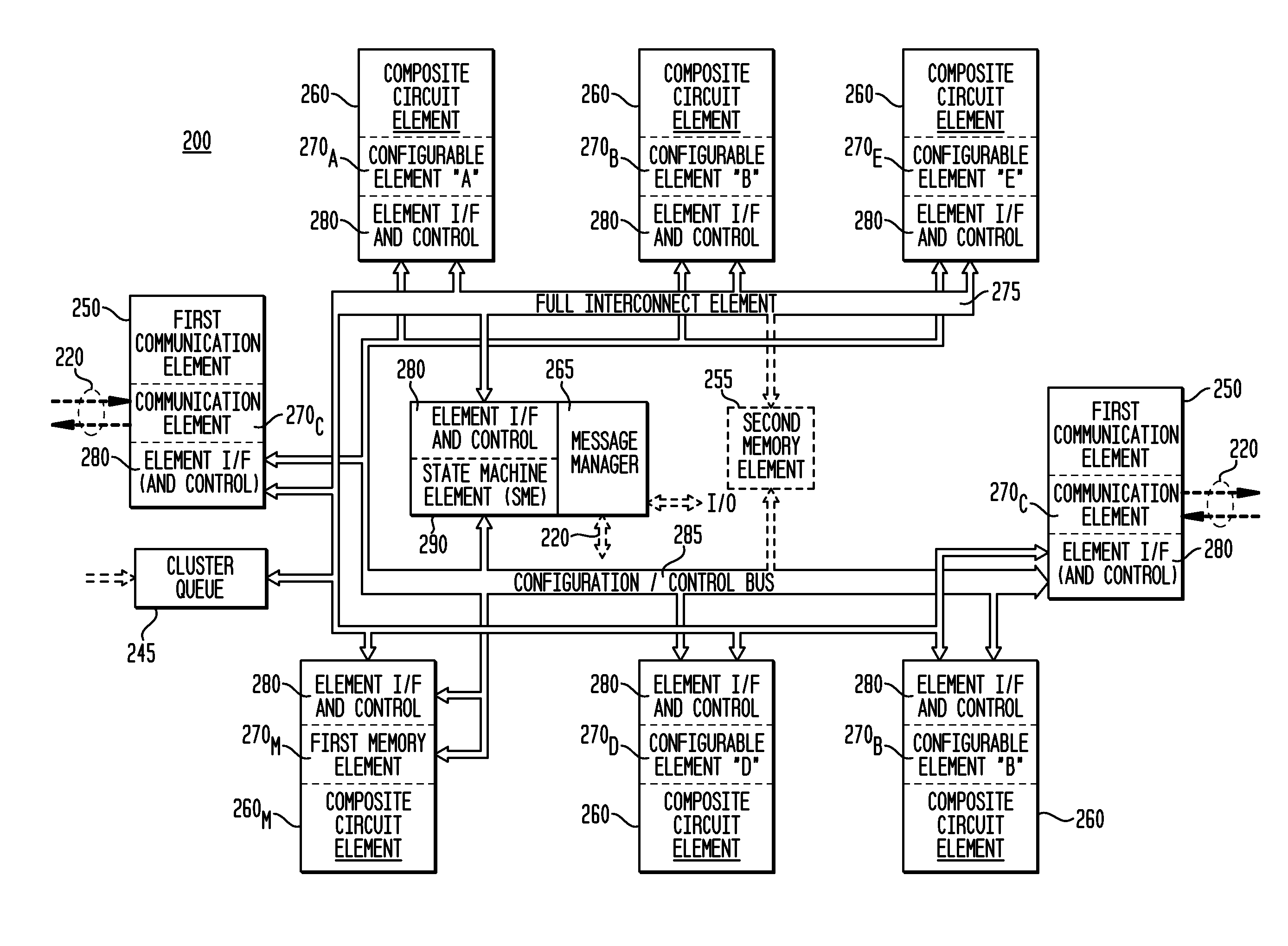

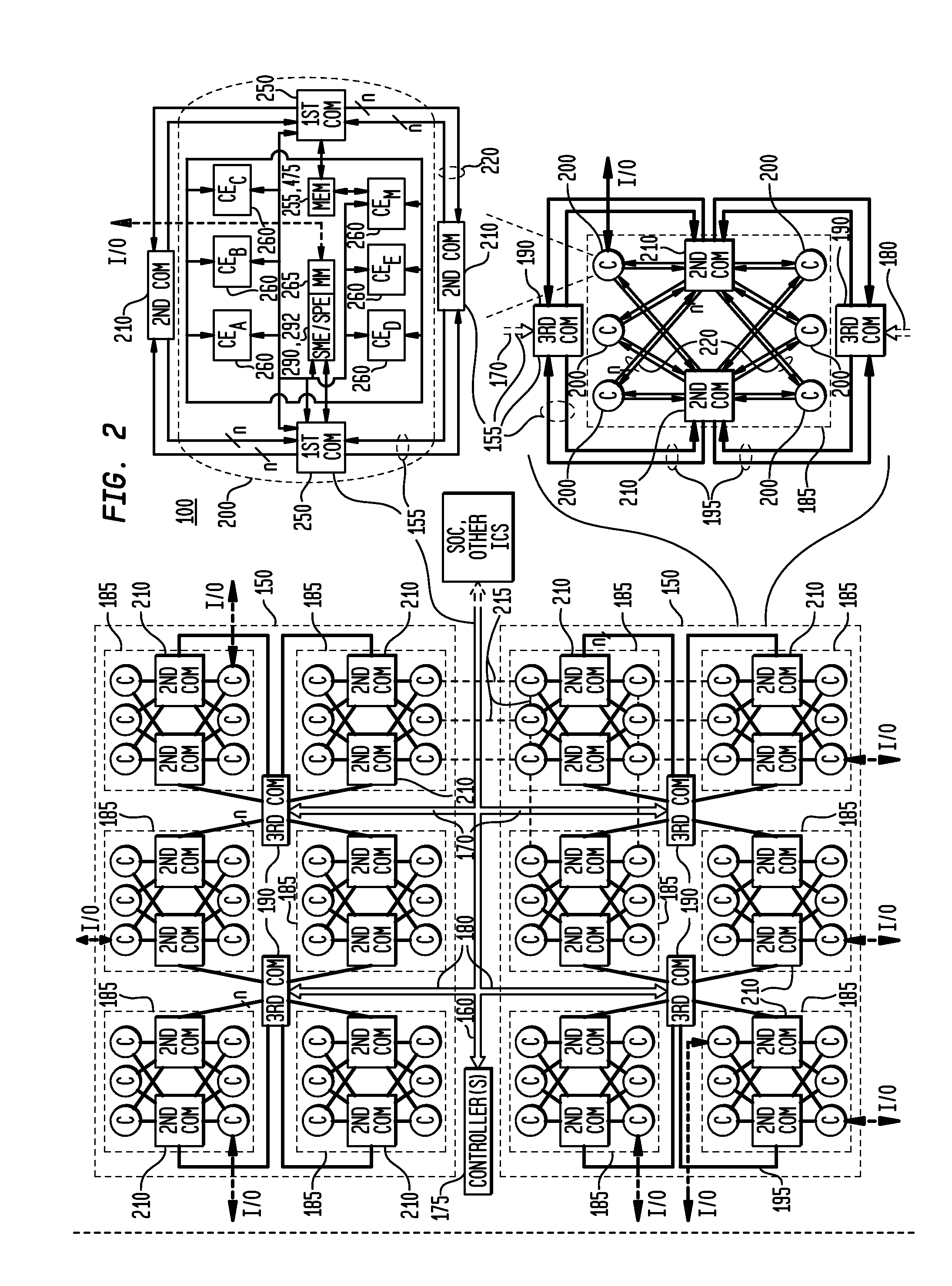

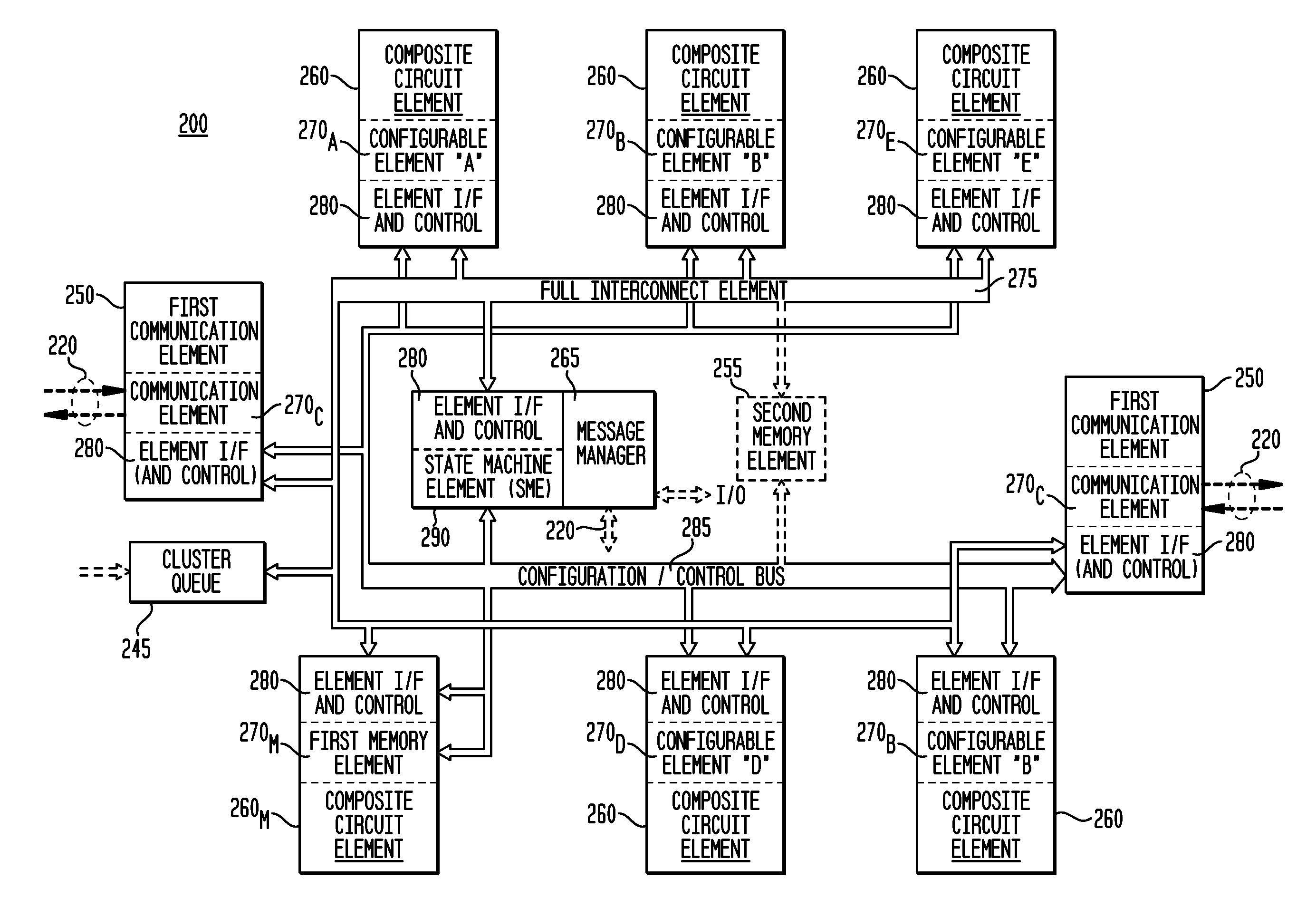

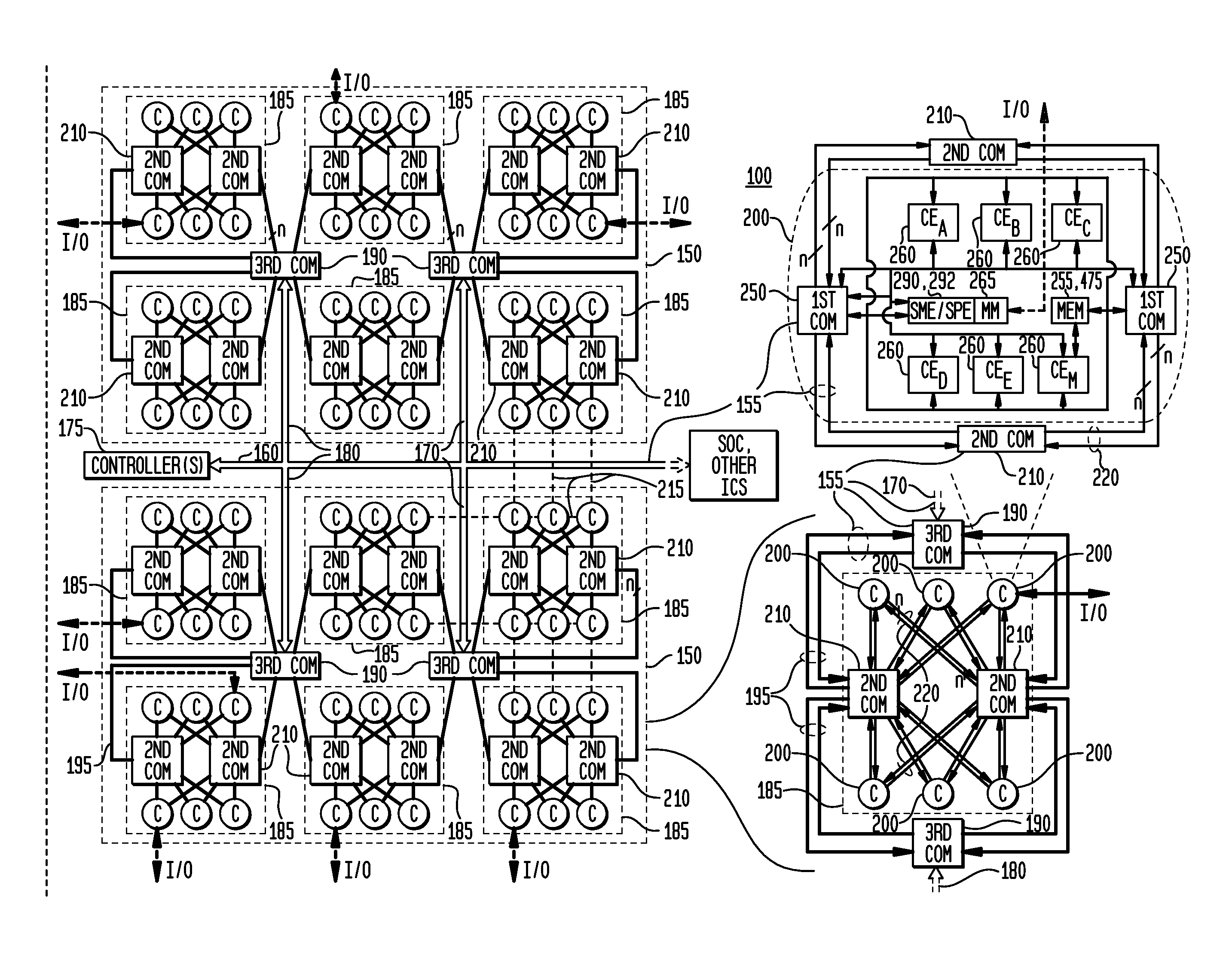

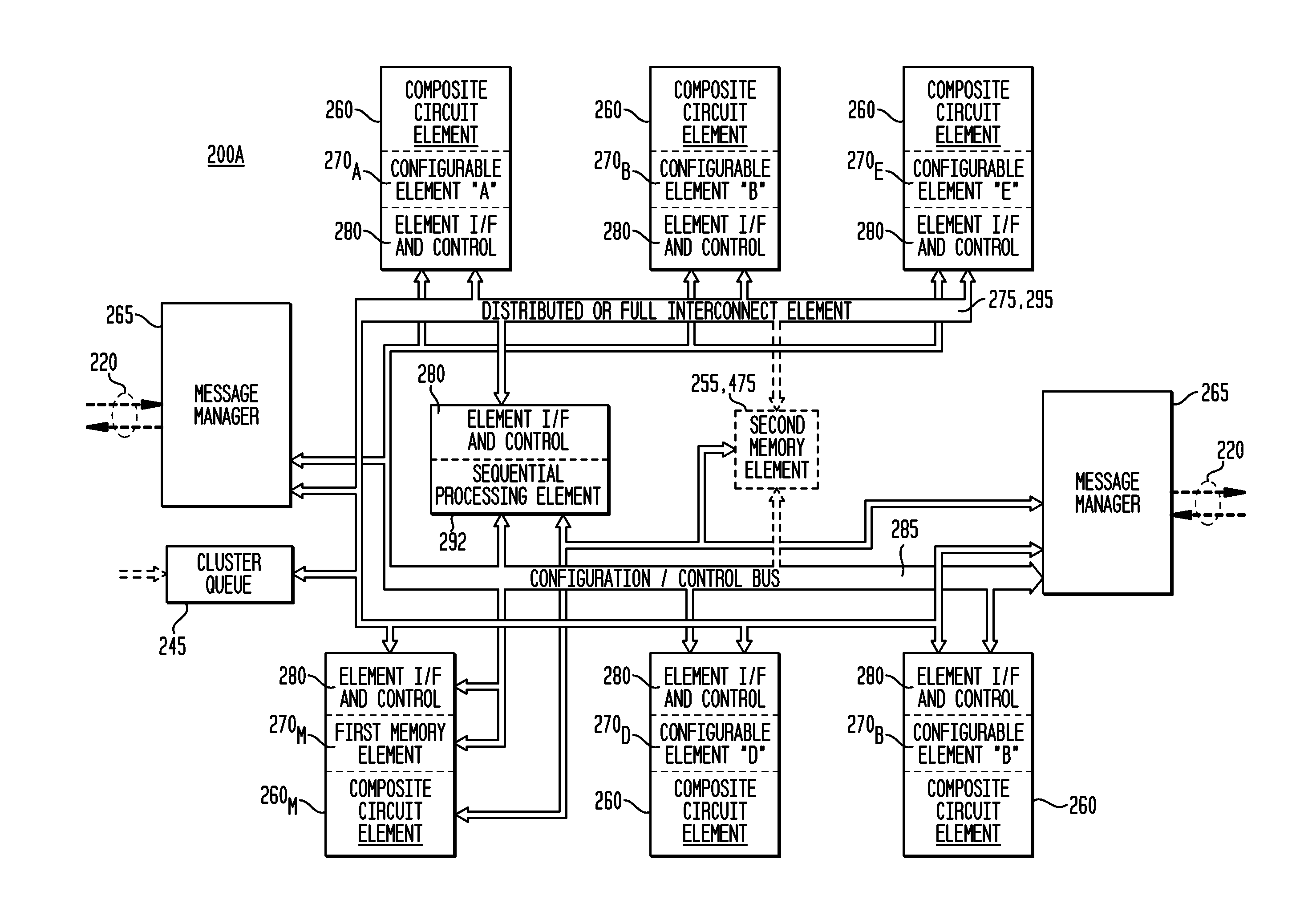

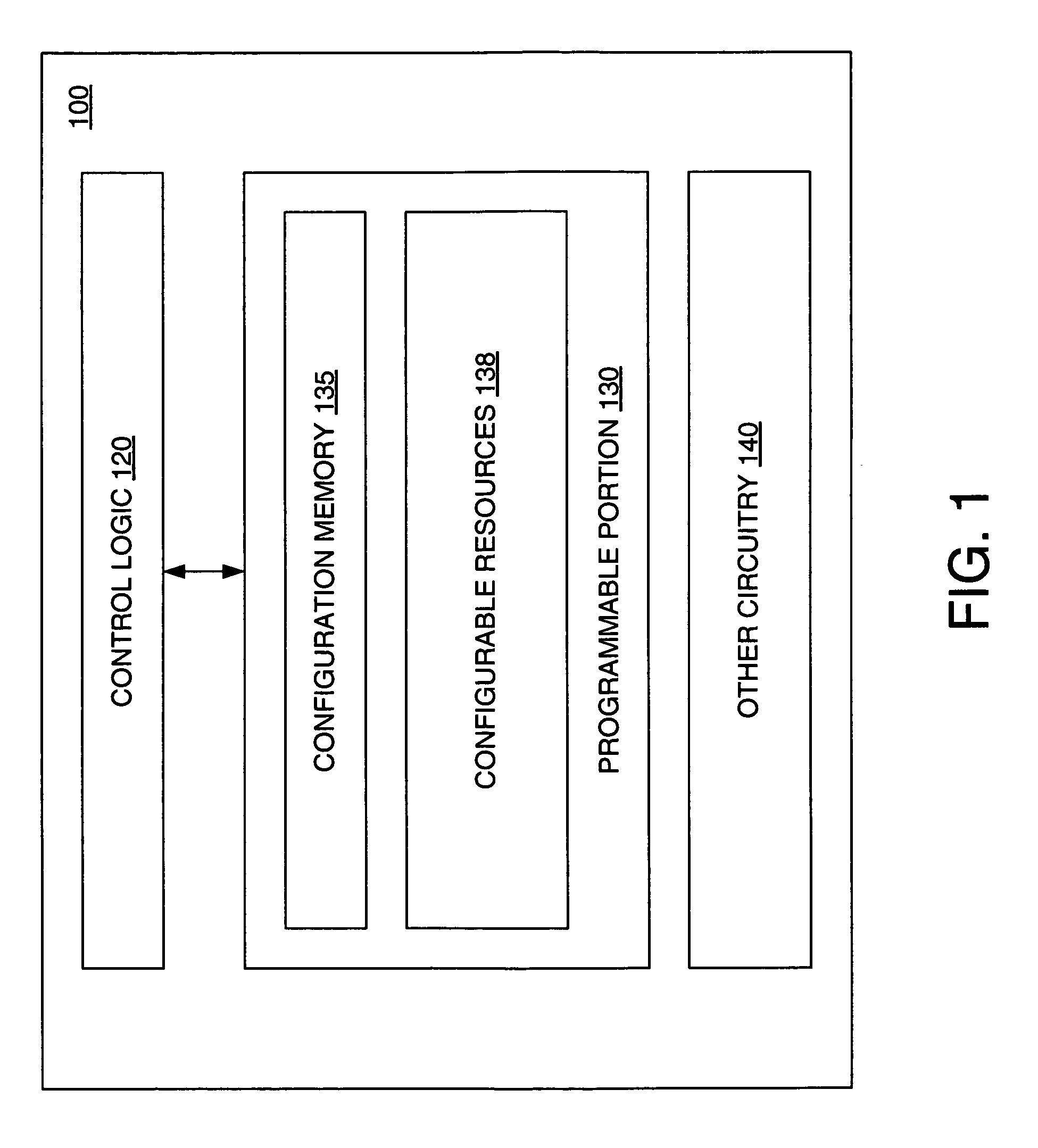

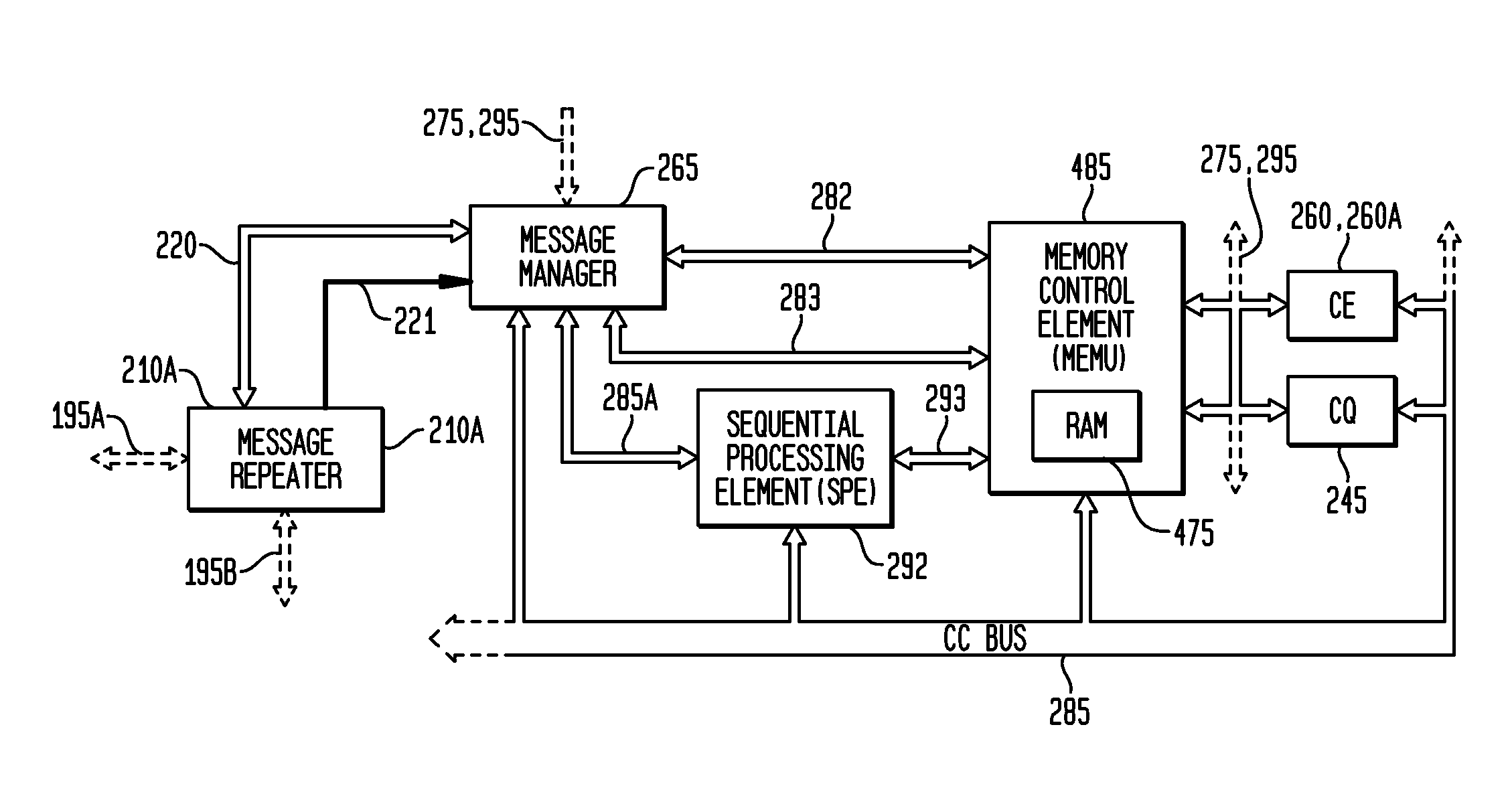

Reconfigurable Integrated Circuit Architecture With On-Chip Configuration and Reconfiguration

InactiveUS20120131288A1Significant resiliencyError detection/correctionFail-safe circuitsComputer architectureProcessor register

The exemplary embodiments provide a reconfigurable integrated circuit capable of on-chip configuration and reconfiguration, comprising: a plurality of configurable composite circuit elements; a configuration and control bus; a memory; and a sequential processor. Each composite circuit element comprises: a configurable circuit; and an element interface and control circuit, the element interface and control circuit comprising an element controller and at least one configuration and control register to store one or more configuration and control words. The configuration and control bus is coupled to the plurality of configurable composite circuit elements, and comprises a plurality of address and control lines and a plurality of data lines. The sequential processor can write configurations to the configuration and control registers of an addressed configurable composite circuit element to configure or reconfigure the configurable circuit.

Owner:ELEMENT CXI

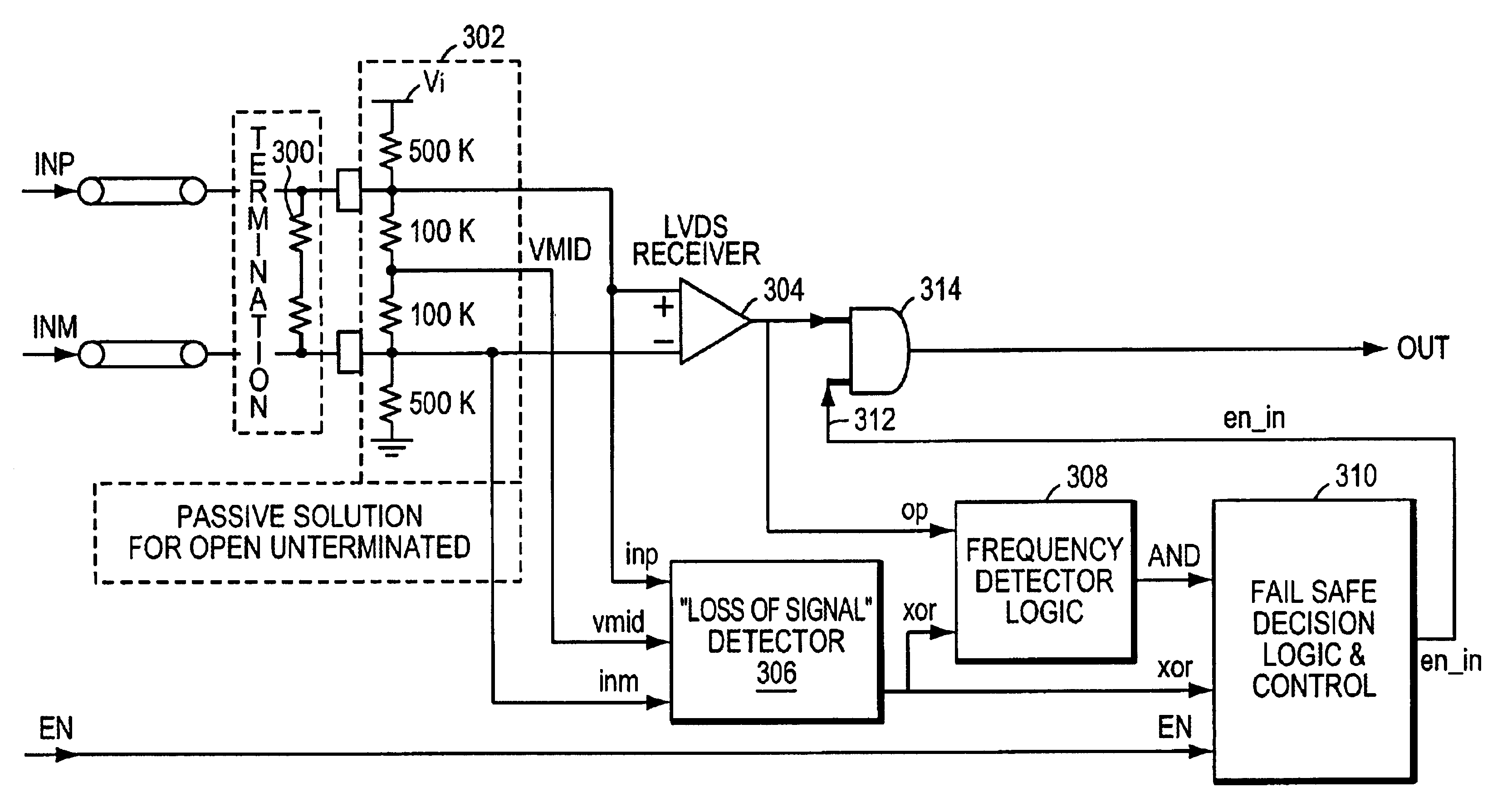

Failsafe differential amplifier circuit

InactiveUS6781456B2Not affect high-frequency performance of receiverFail-safe circuitsAmplifier combinationsAudio power amplifierSafety status

Differential input fail safe circuitry is disclosed that detects missing or too low differential signals combined with a frequency lower than a frequency limit where a final safe condition is detected and signaled. The output signal form the fail safe circuitry is held in a given state that is an invalid representation of the differential input signal. A frequency detector, complementary offsetting auxiliary amplifiers with limit frequency roll offs are used to detect the fail safe condition. In addition a delay circuit is used that requires the fail safe condition to exist for some time before the fail safe circuit is active. Initialization circuitry ensures a proper power up conditions where the circuitry is enabled to detect the fail safe conditions and guarantees a reliable fail safe irrespective of the previous state of the signal.

Owner:SEMICON COMPONENTS IND LLC

Multi-Context Configurable Memory Controller

InactiveUS20120131257A1Significant resiliencyFail-safe circuitsMemory adressing/allocation/relocationMultiple contextMemory address

The exemplary embodiments provide a multi-context configurable memory controller comprising: an input-output data port array comprising a plurality of input queues and a plurality of output queues; at least one configuration and control register to store, for each context of a plurality of contexts, a plurality of configuration bits; a configurable circuit element configurable for a plurality of data operations, each data operation corresponding to a context of a plurality of contexts, the plurality of data operations comprising memory address generation, memory write operations, and memory read operations, the configurable circuit element comprising a plurality of configurable address generators; and an element controller, the element controller comprising a port arbitration circuit to arbitrate among a plurality of contexts having a ready-to-run status, and the element controller to allow concurrent execution of multiple data operations for multiple contexts having the ready-to-run status.

Owner:ELEMENT CXI

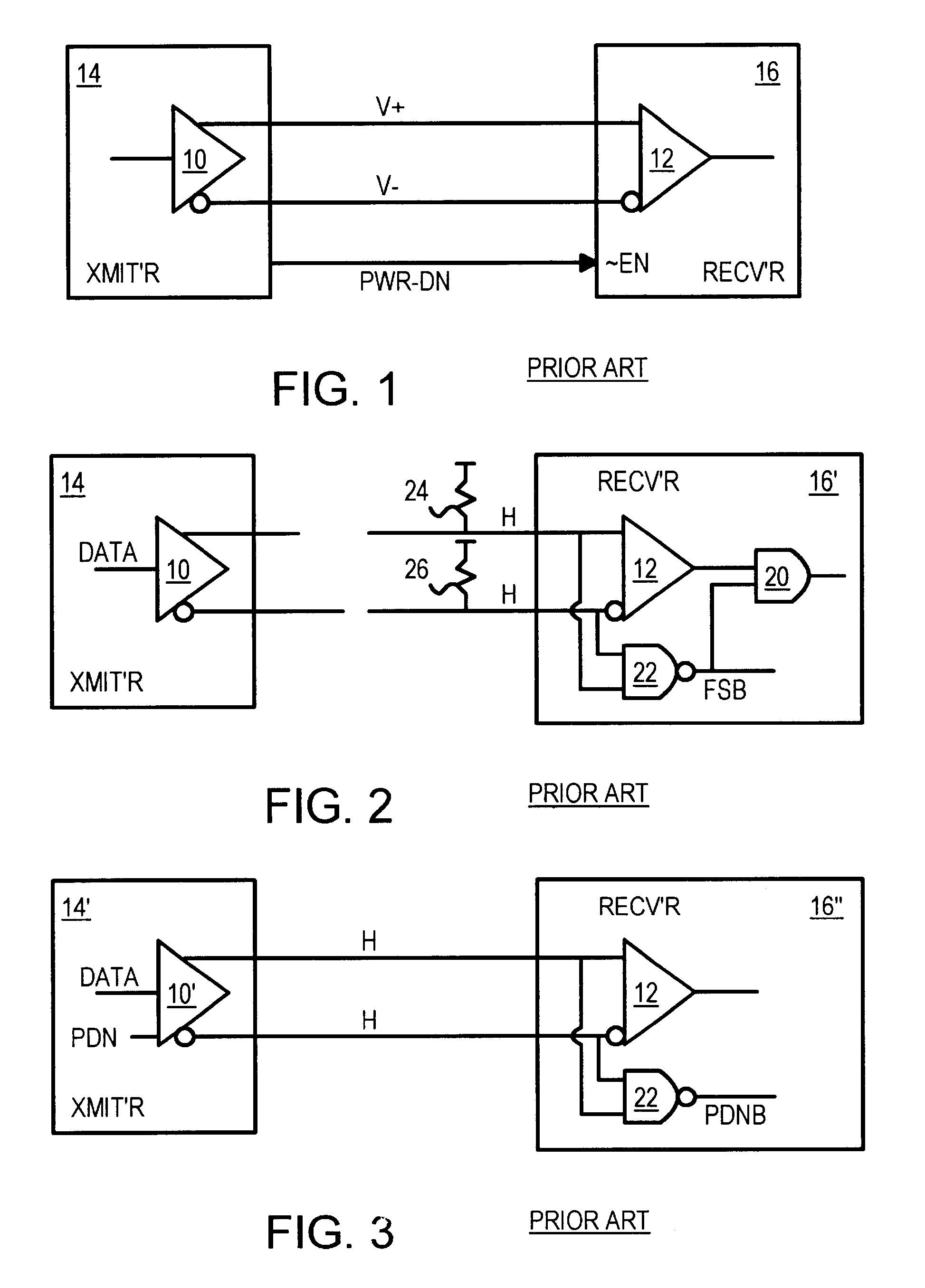

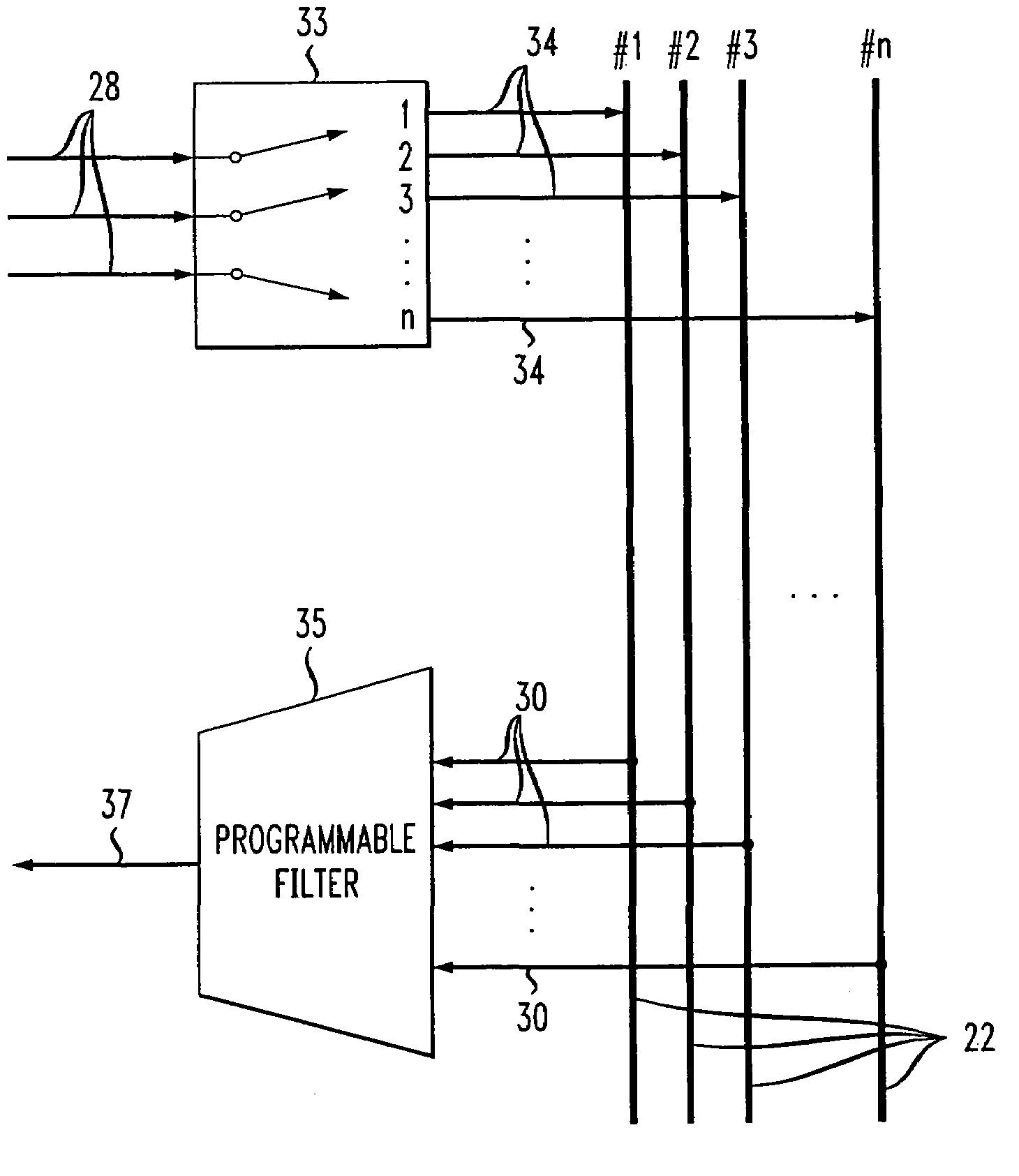

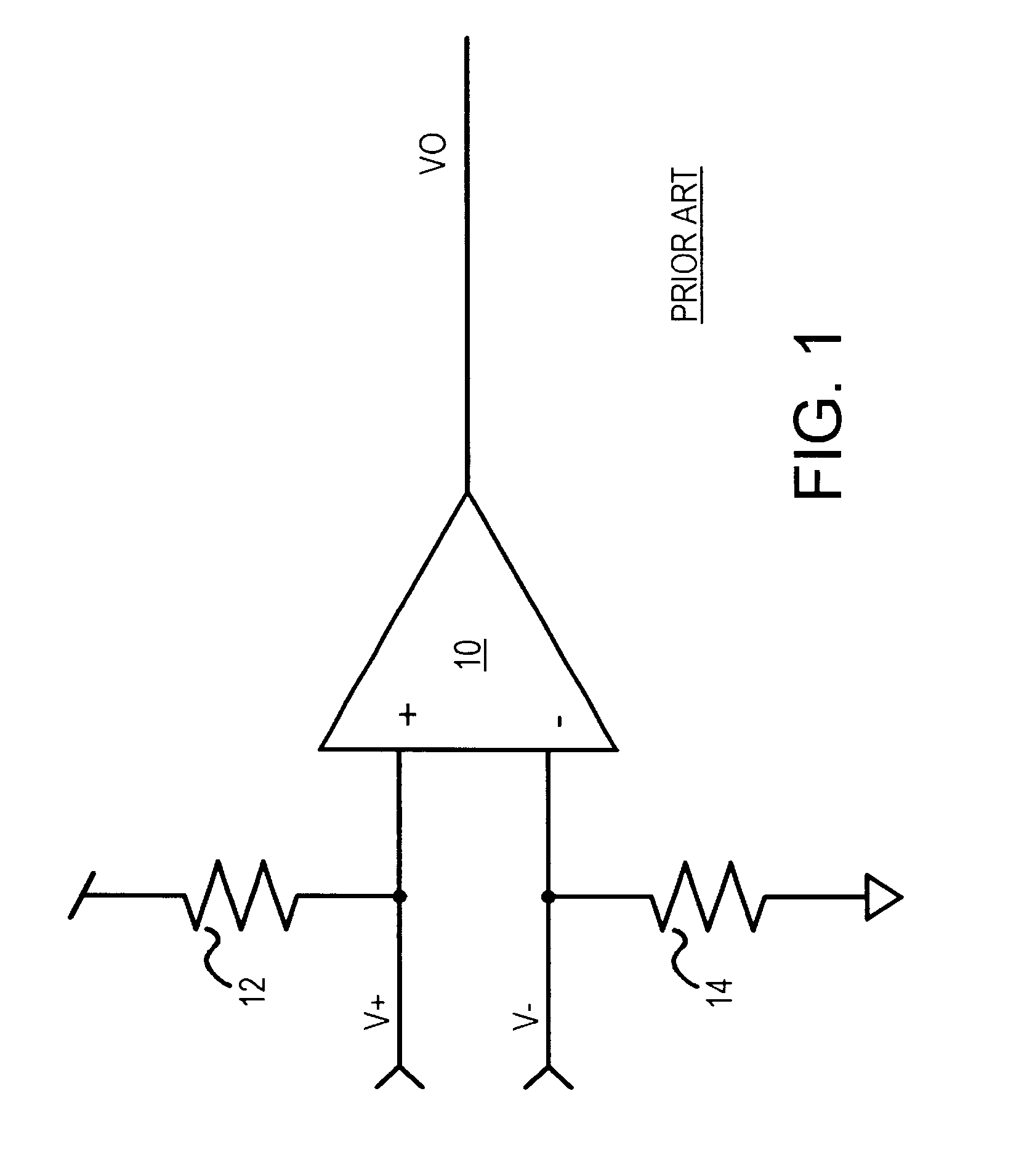

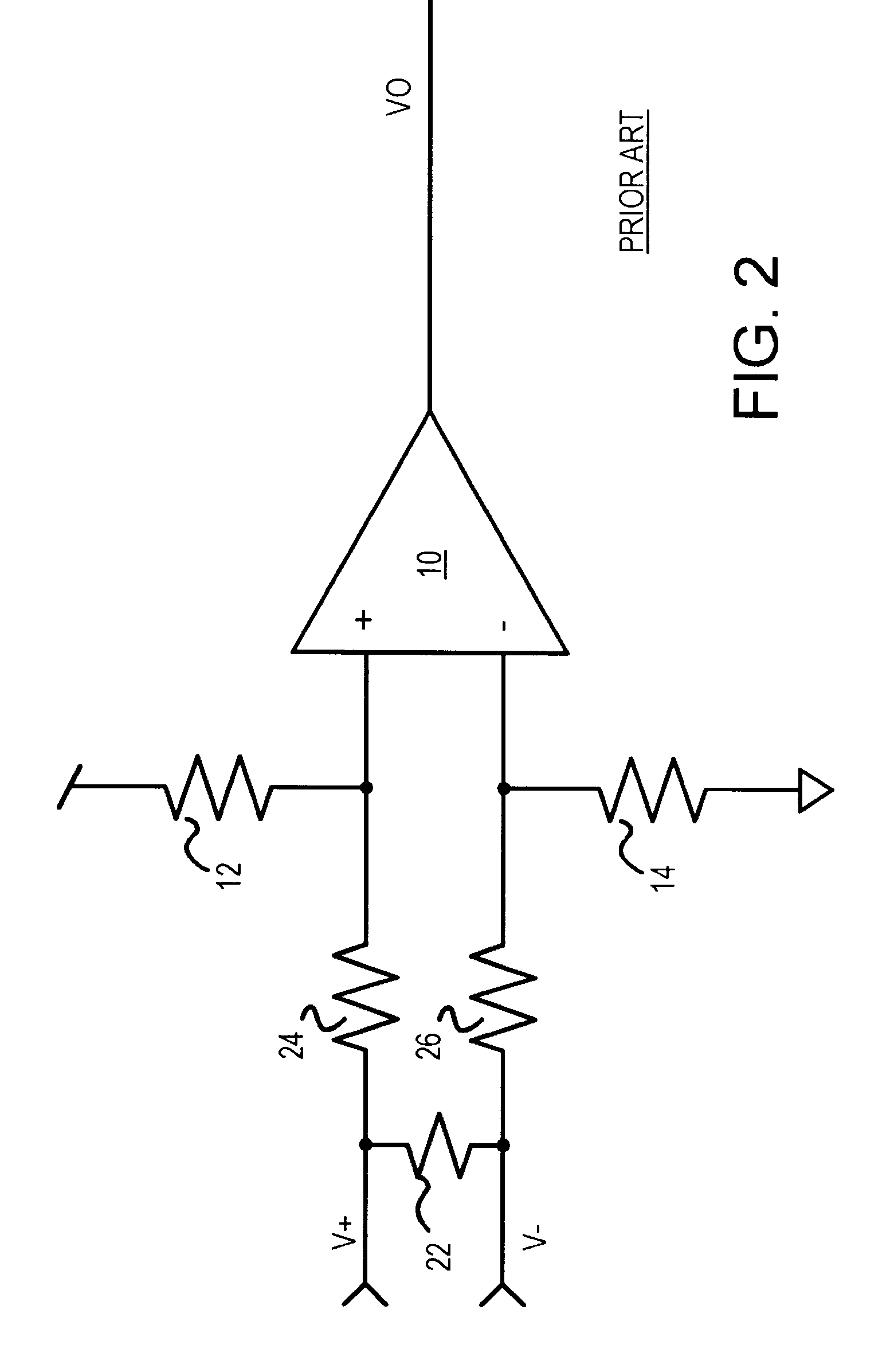

Power down mode signaled by differential transmitter's high-Z state detected by receiver sensing same voltage on differential lines

InactiveUS6593801B1Energy efficient ICTMultiple input and output pulse circuitsElectricityDifferential line

A power-down signal is encoded into a differential pair of lines between two chips. When the differential transmitter powers down, it enters a high-impedance state and floats the differential lines A shunt resistor between a pair of differential lines equalize the voltages on the differential lines so they float to a same voltage when a differential transmitter is disabled and enters a high-impedance state. The condition of equal voltages on the differential lines is detected by an equal-voltage detector that generates a power-down signal when the differential lines are at equal voltages for a period of time. The period of time can be greater than the cross-over time during normal switching to prevent false power-downs during normal switching. Standard differential drivers can signal power-down using the high-impedance state, which is detected by equal voltages on the differential lines. A sensitive dual-differential amplifier and a simpler detector are disclosed.

Owner:DIODES INC

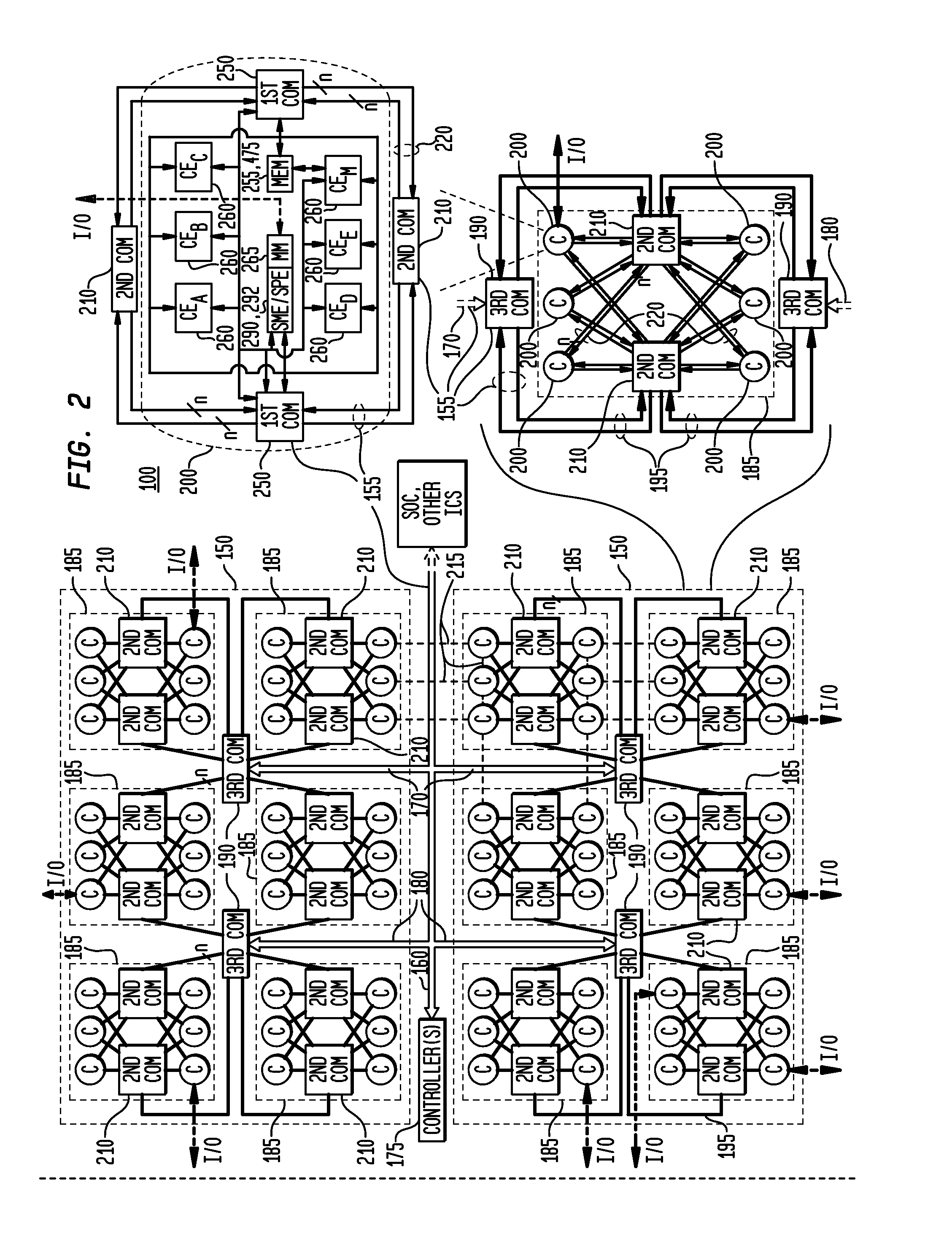

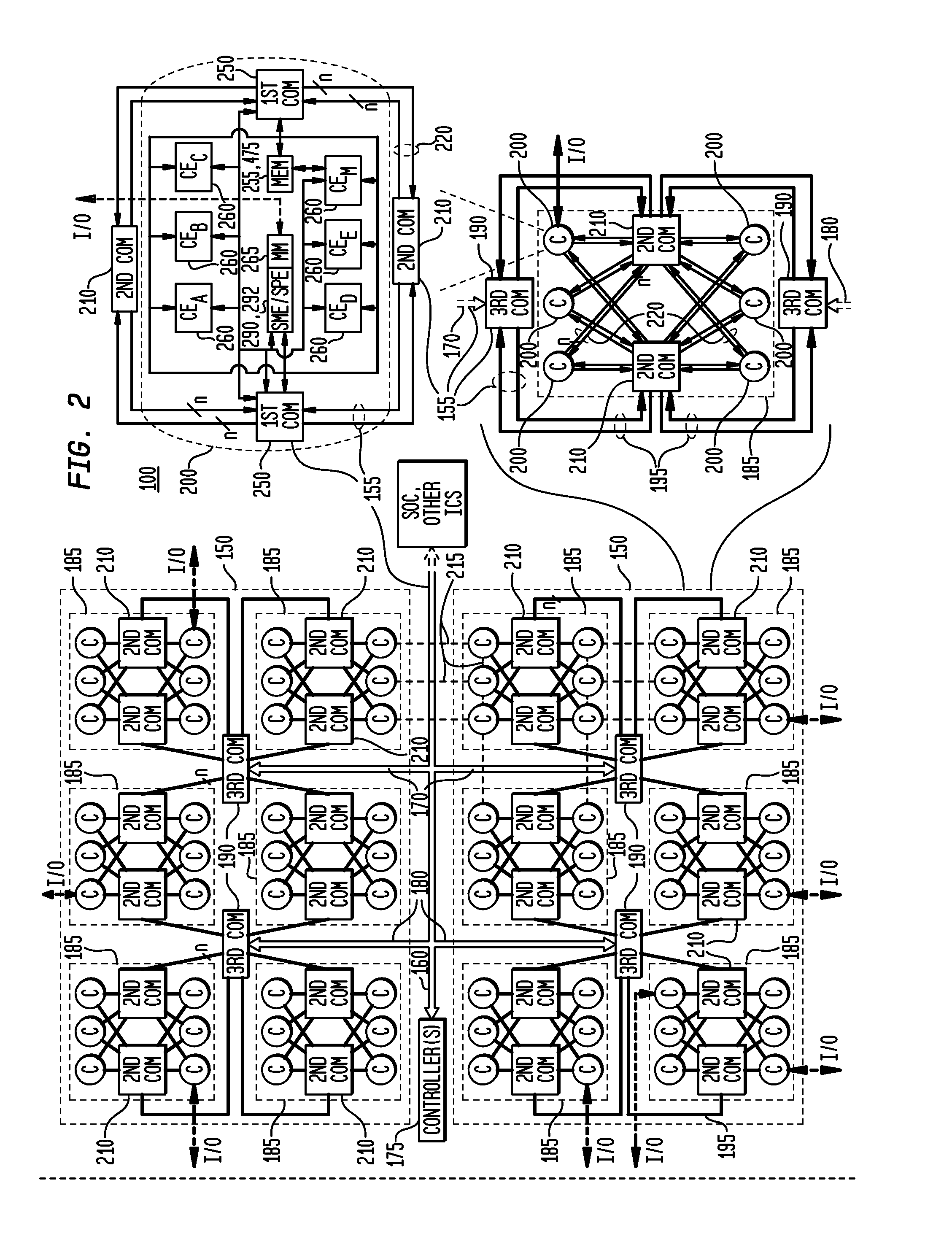

Hierarchically-Scalable Reconfigurable Integrated Circuit Architecture With Unit Delay Modules

InactiveUS20120126850A1Significant resiliencyError detection/correctionFail-safe circuitsData operationsTime delays

The exemplary embodiments provide a reconfigurable integrated circuit architecture having a predetermined, unit timing increment (or delay) for both data operations and data word transfers within every zone and between zones, which are independent of application placement and routing. An exemplary IC comprises a plurality of circuit zones, with each zone comprising: a plurality of composite circuit elements, a plurality of cluster queues, and a full interconnect bus. Each composite circuit element comprises: a configurable circuit element circuit and an element interface and control circuit, with the element interface and control circuit comprising an input queue and an output queue. Each cluster queue comprises an element interface and control having an input queue and an output queue. The full interconnect bus couples every output queue within the zone to every input queue within the zone. Any data operation performed by a composite circuit element, any data word transfer through a cluster queue, and any data word transfer over the first full interconnect bus, is completed within a predetermined unit time delay which is independent of application placement and application data routing on the reconfigurable IC.

Owner:ELEMENT CXI

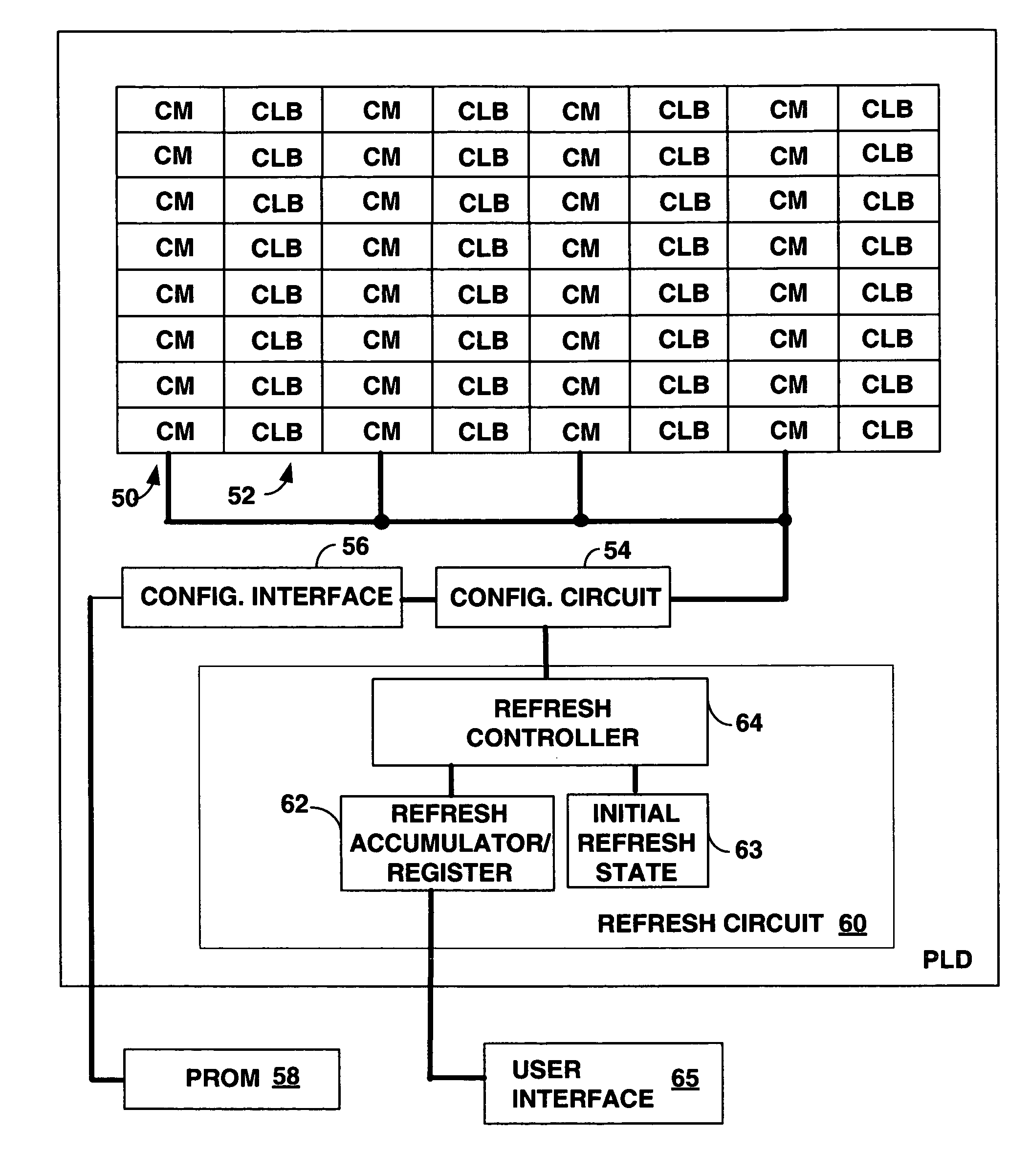

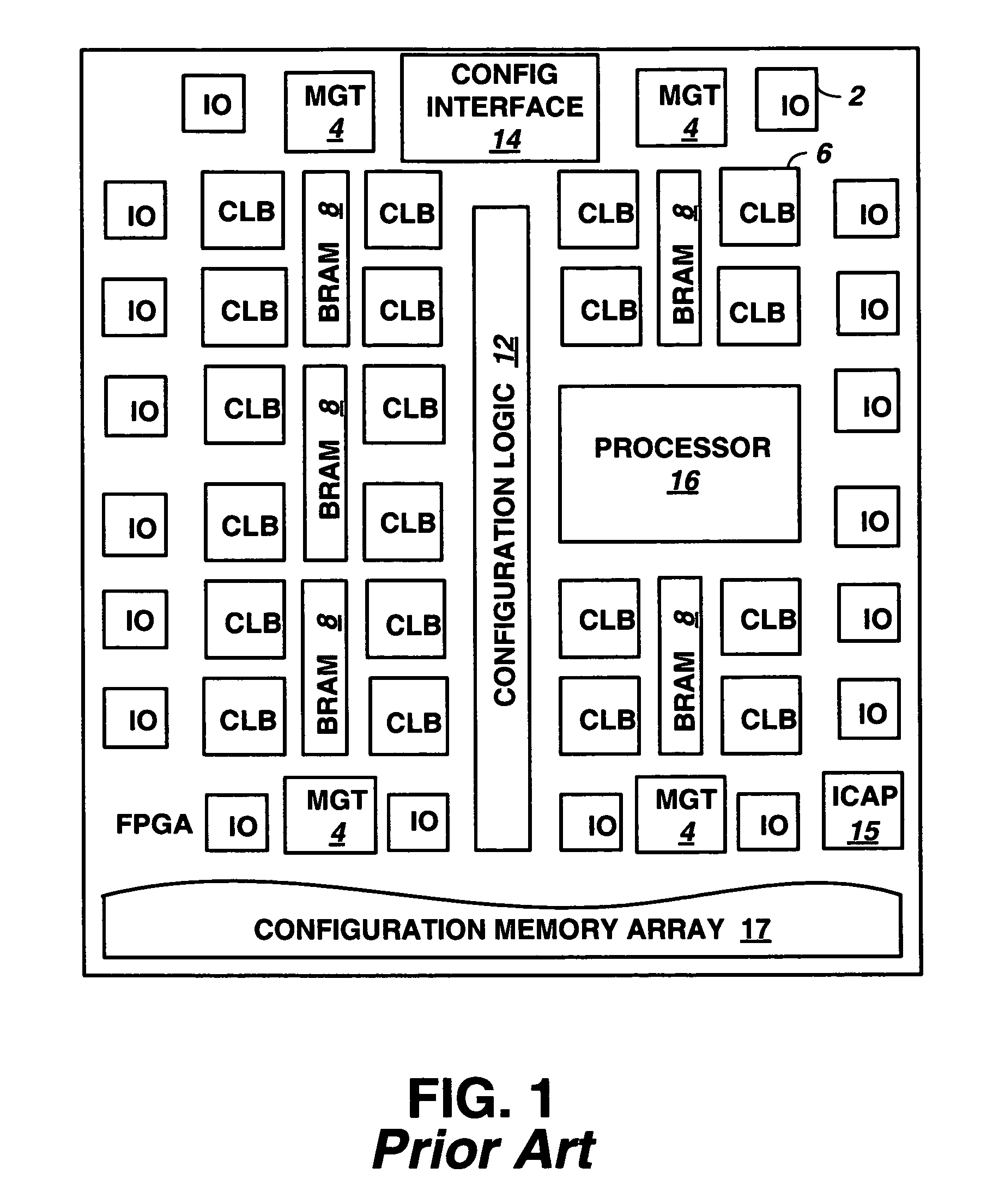

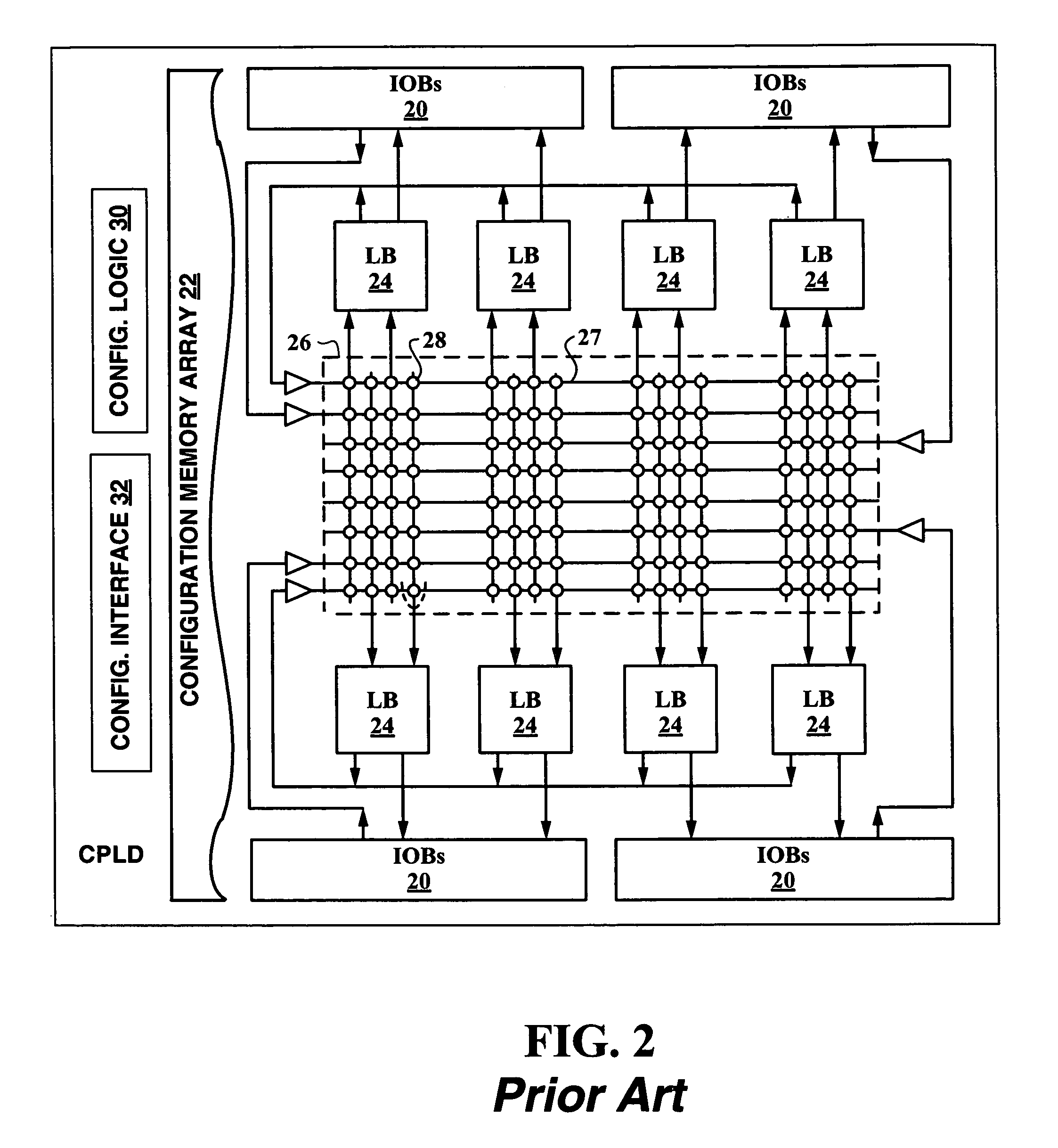

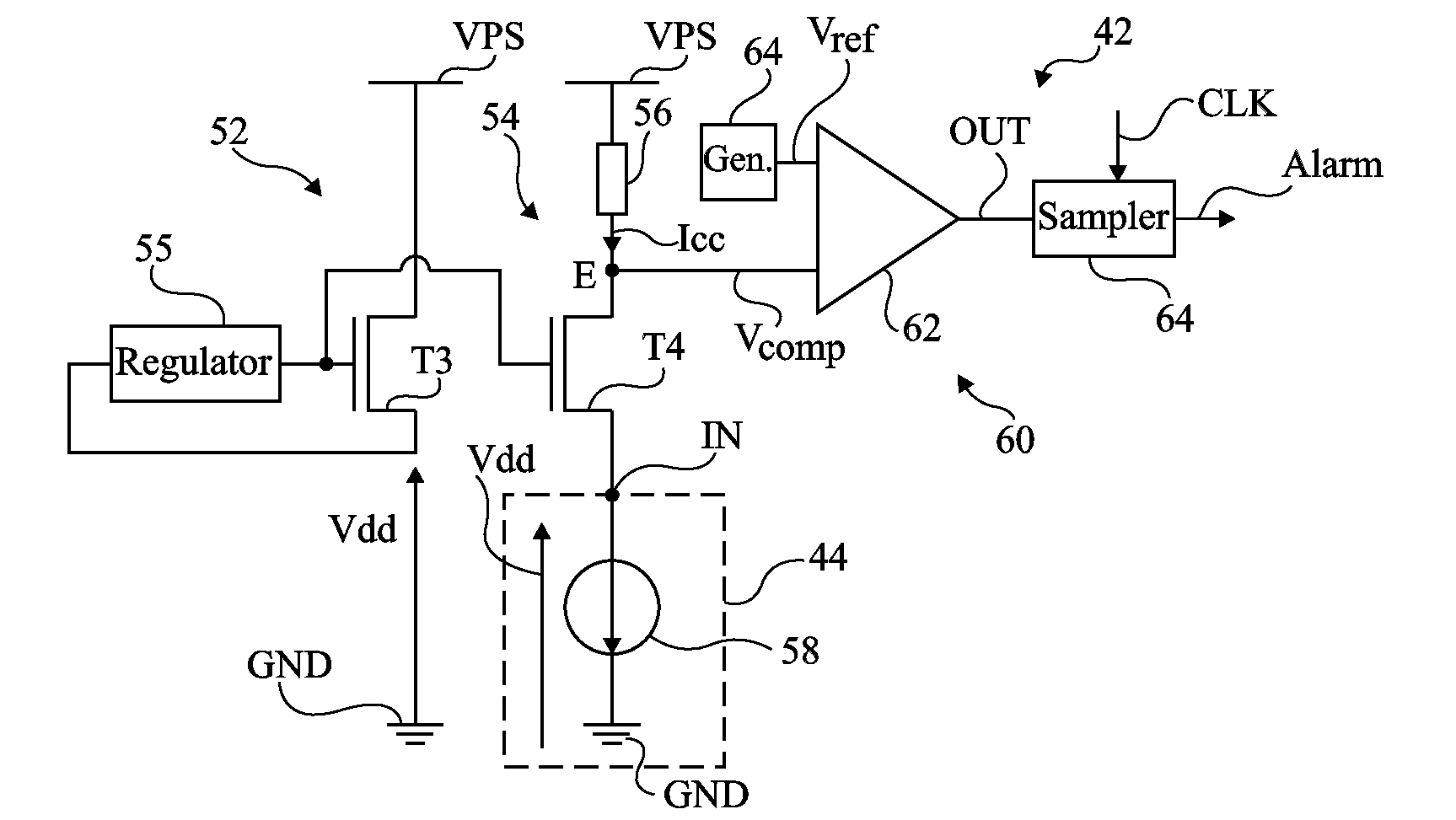

Programmable logic device (PLD) with memory refresh based on single event upset (SEU) occurrence to maintain soft error immunity

ActiveUS7764081B1Reduce memory cell densityMinimized circuitReliability increasing modificationsFail-safe circuitsProgrammable logic deviceSingle event upset

A Programmable Logic Device (PLD) is provided with configuration memory cells displaying a superior soft error immunity by combating single event upsets (SEUs) as the configuration memory cells are regularly refreshed from non-volatile storage depending on the rate SEUs may occur. Circuitry on the PLD uses a programmable timer to set a refresh rate for the configuration memory cells. Because an SEU which erases the state of a small sized memory cell due to collisions with cosmic particles may take some time to cause a functional failure, periodic refreshing will prevent the functional failure. The configuration cells can be DRAM cells which occupy significantly less space than the SRAM cells. Refresh circuitry typically provided for DRAM cells is reduced by using the programming circuitry of the PLD. Data in the configuration cells of the PLD are reloaded from either external or internal soft-error immune non-volatile memory.

Owner:XILINX INC

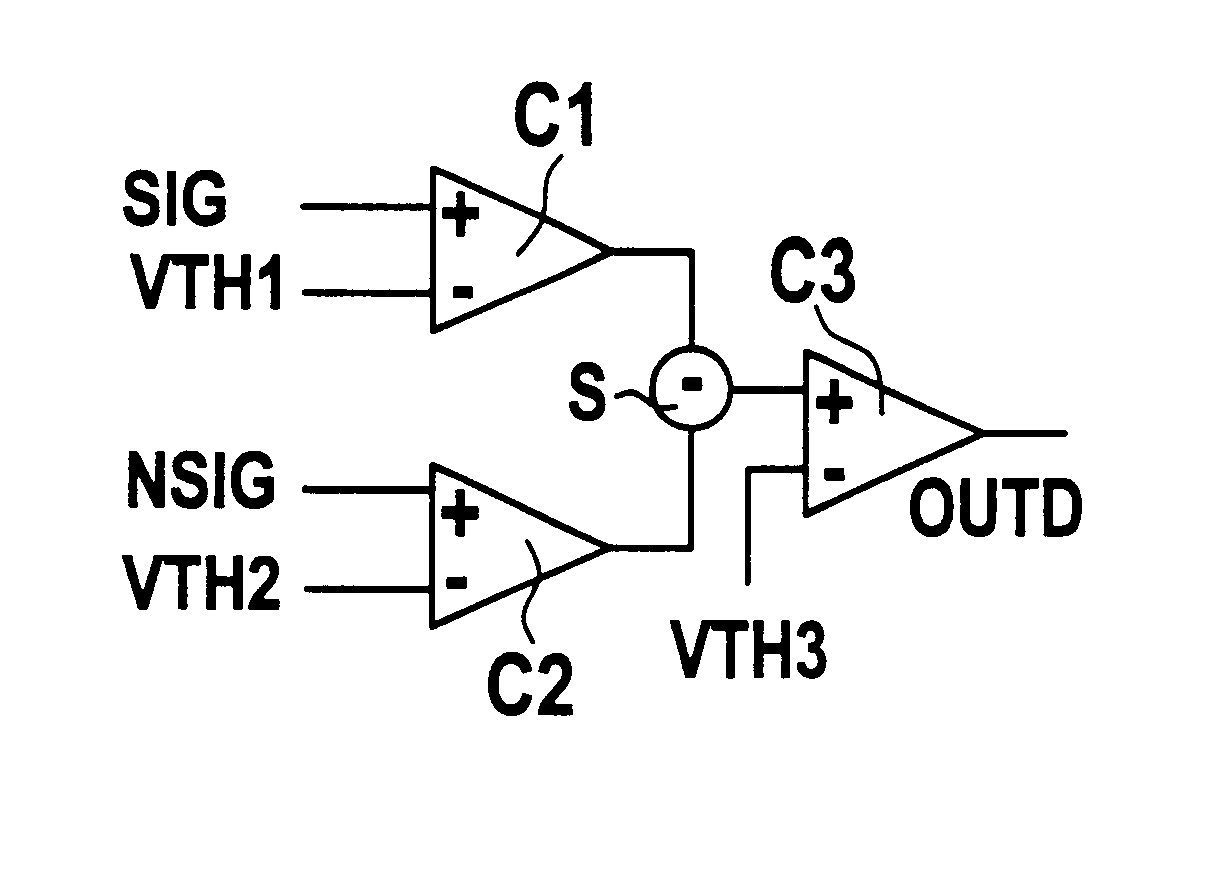

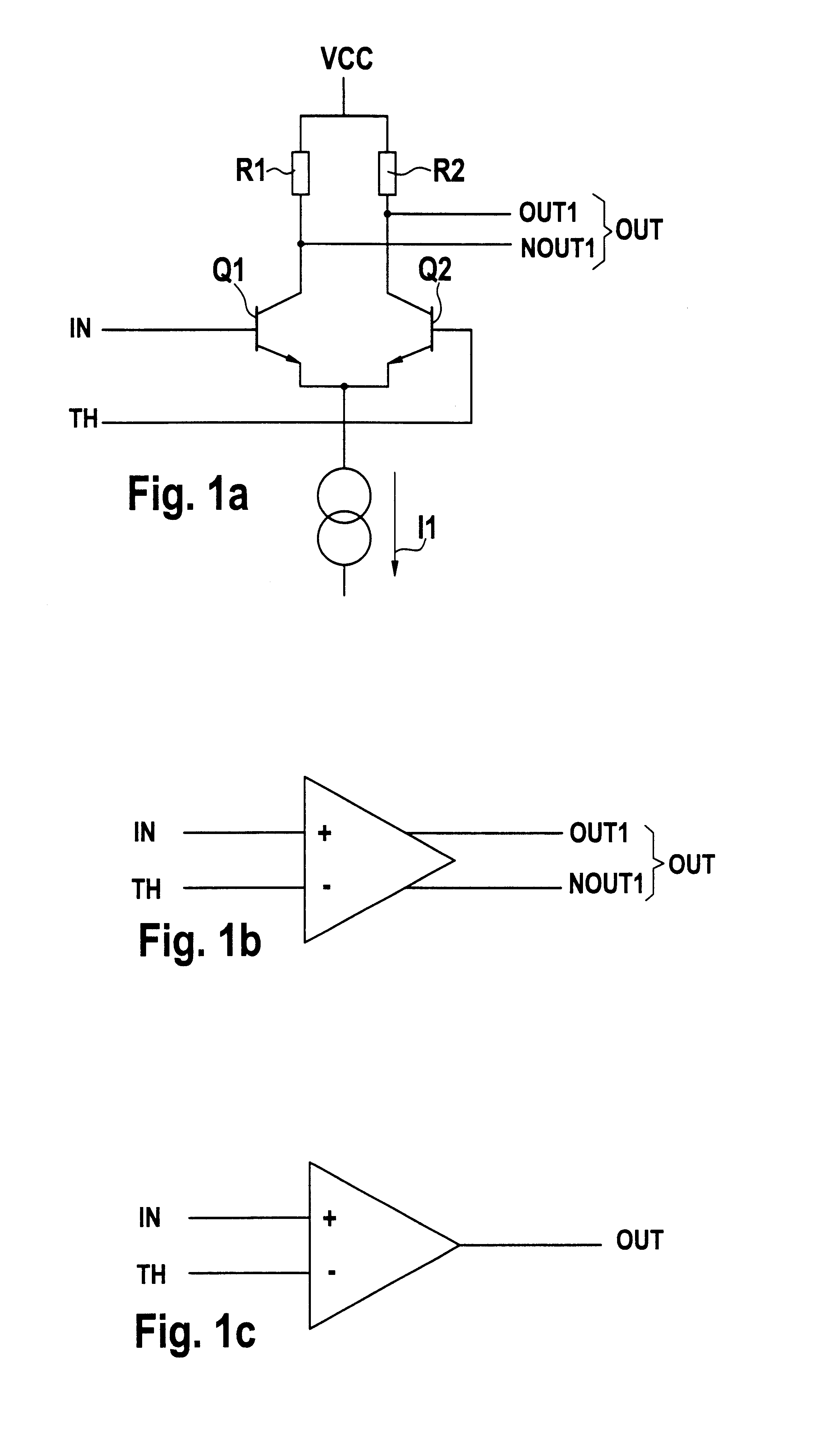

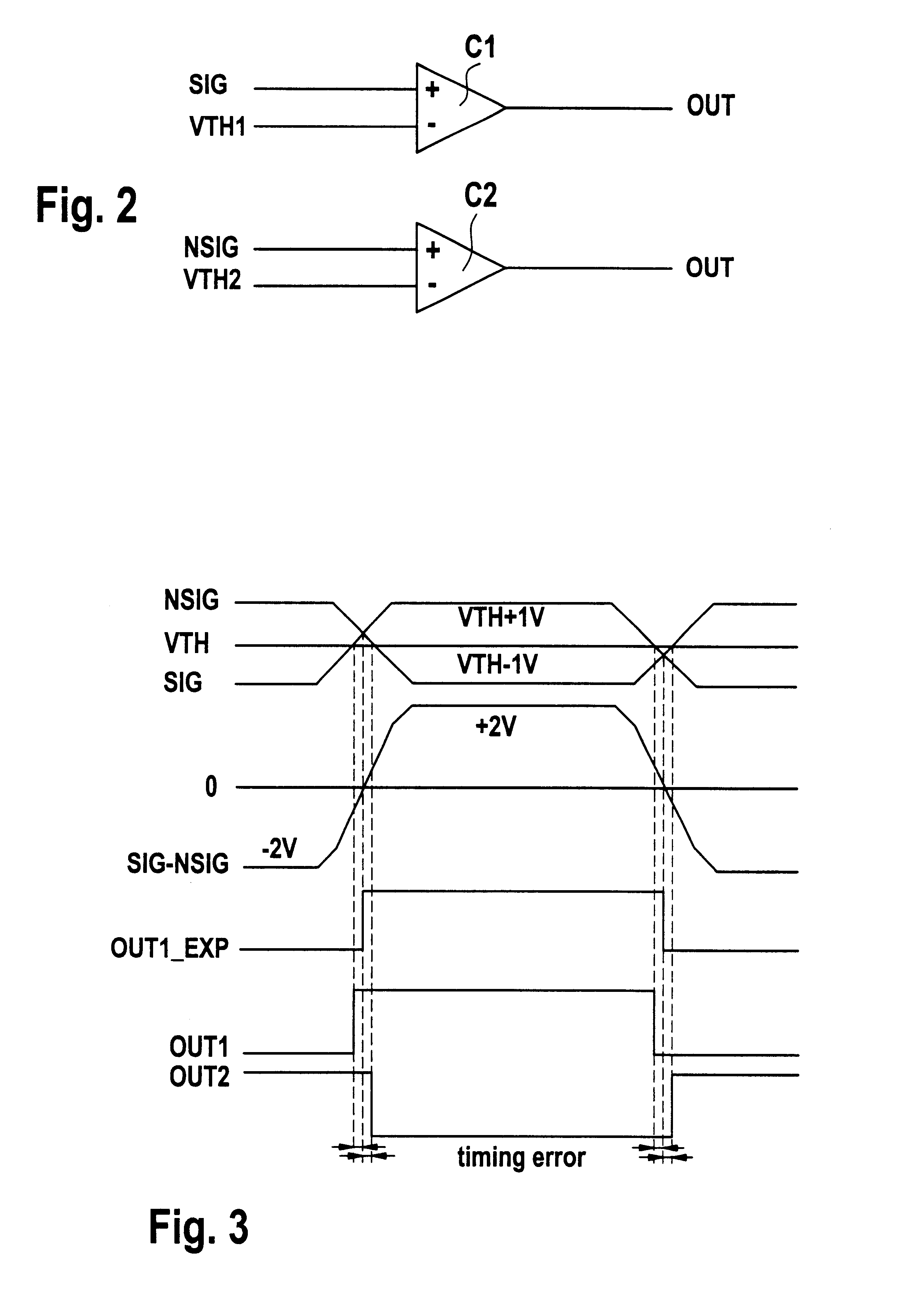

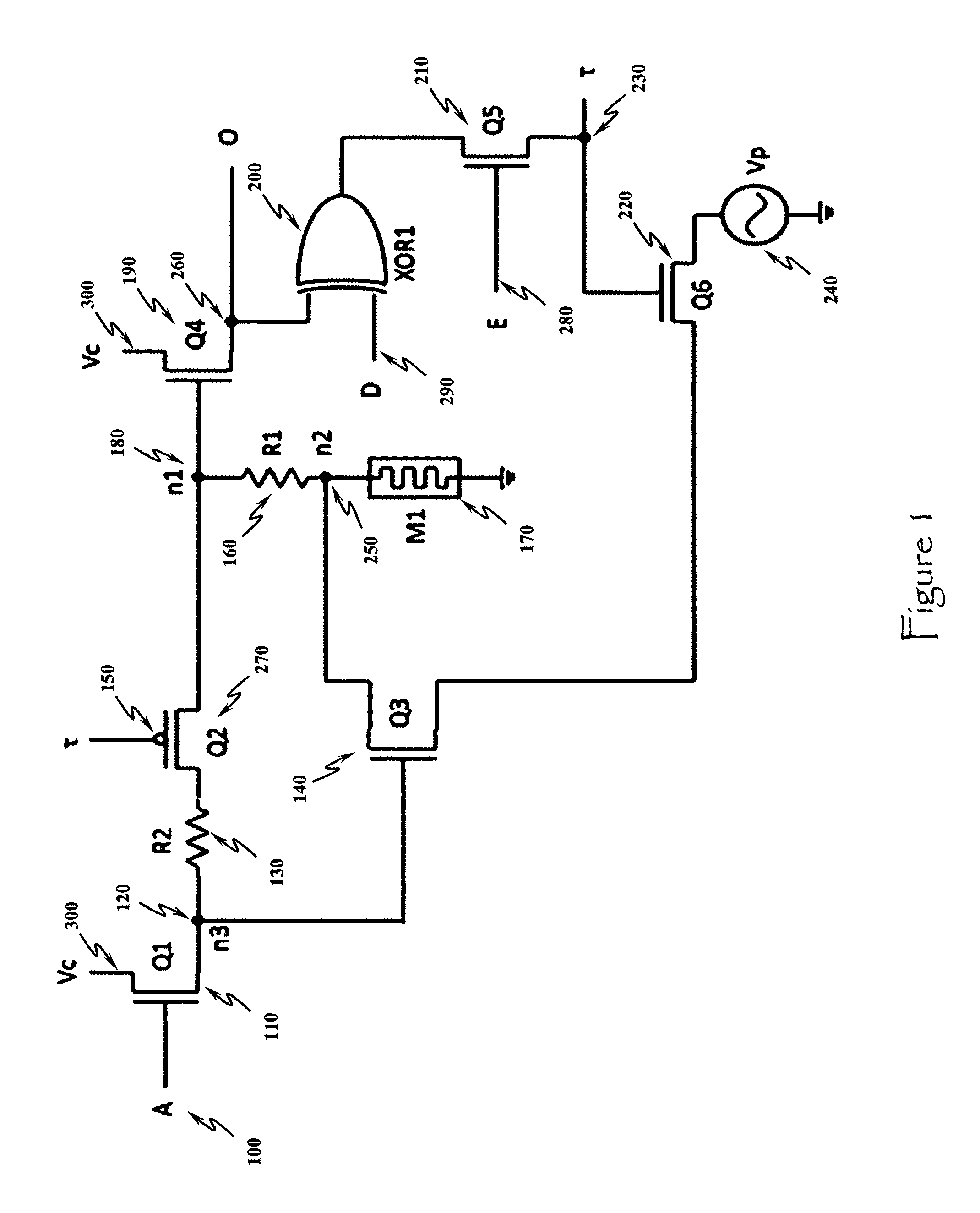

Circuit for providing a logical output signal in accordance with crossing points of differential signals

InactiveUS6448806B1Increase currentMinimal numberMultiple input and output pulse circuitsDigital circuit testingAudio power amplifierDifferential signaling

A circuit provides an output signal in accordance with crossing points of a differential signal, which includes a normal input signal and a complementary input signal. The circuit includes a first amplifier for amplifying a first signal difference between the normal input signal and a first threshold value, and for providing as a first output signal the amplified first signal difference. The circuit includes a second amplifier for amplifying a second signal difference between the complementary input signal and a second threshold value, and for providing as a second output signal the amplified second signal difference. The circuit also includes a first comparator for providing a first logical level when a third signal difference between the first output signal and the second output signal is greater than a third threshold value, and for providing a second logical level when the third signal difference is smaller than the third threshold value.

Owner:ADVANTEST CORP

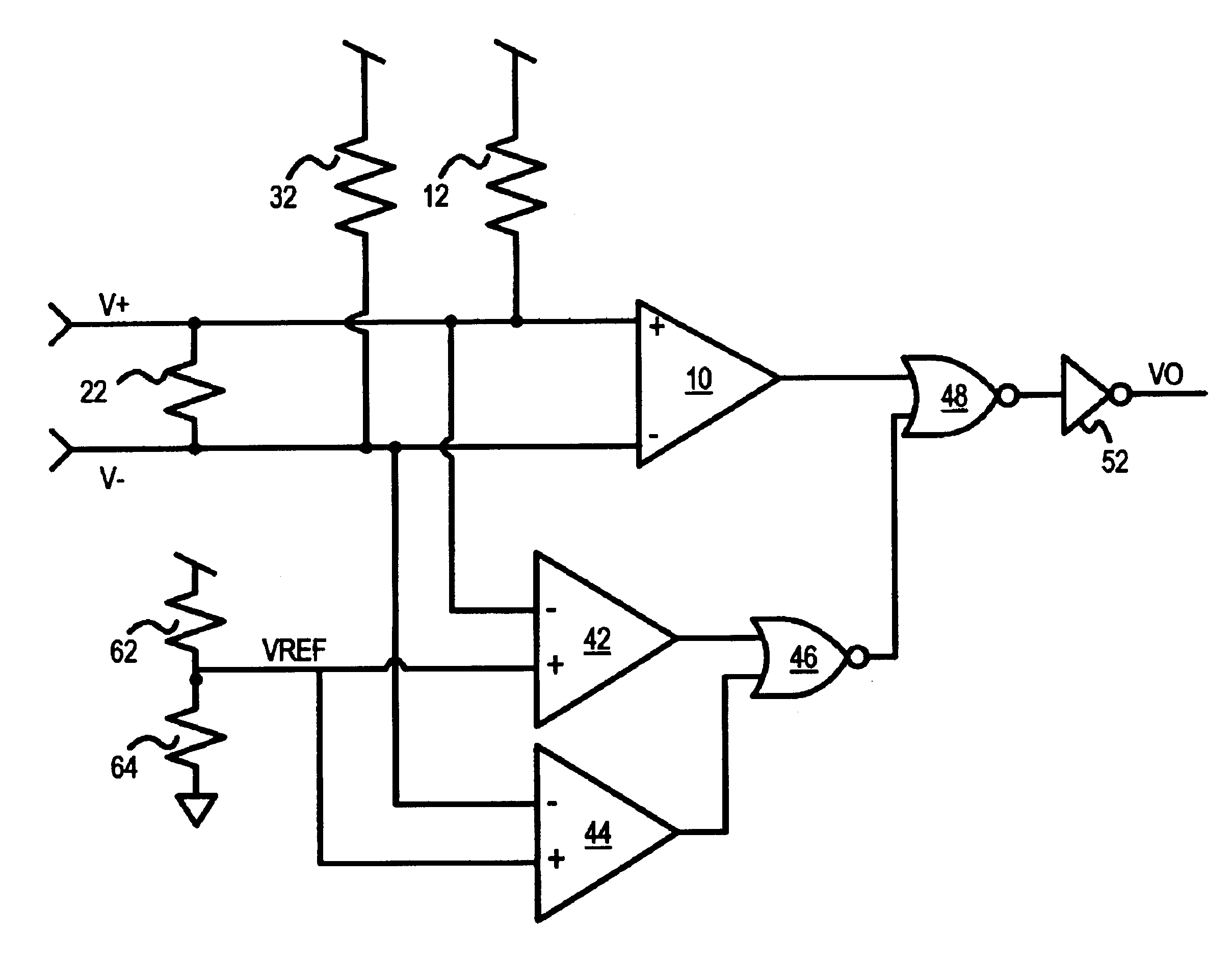

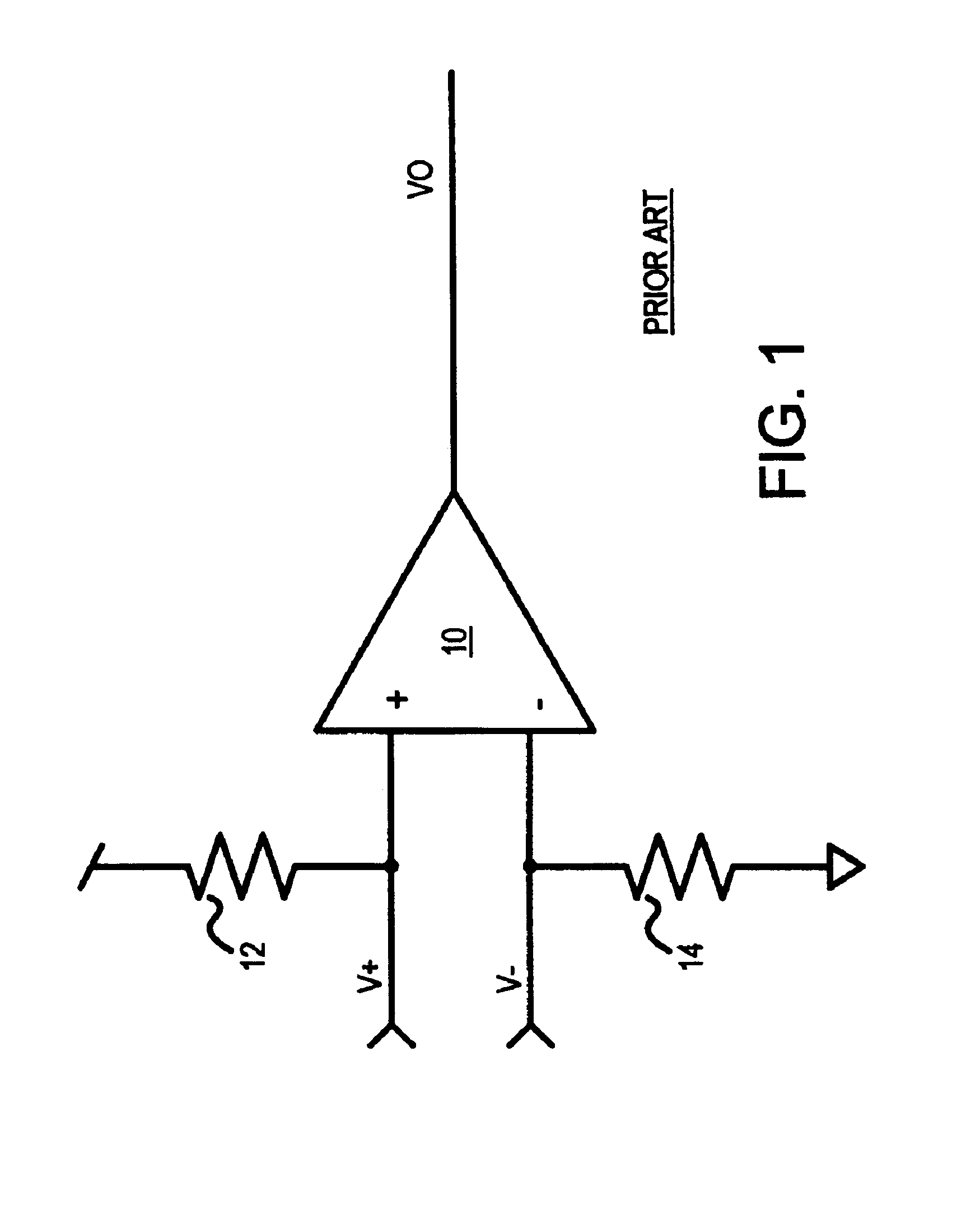

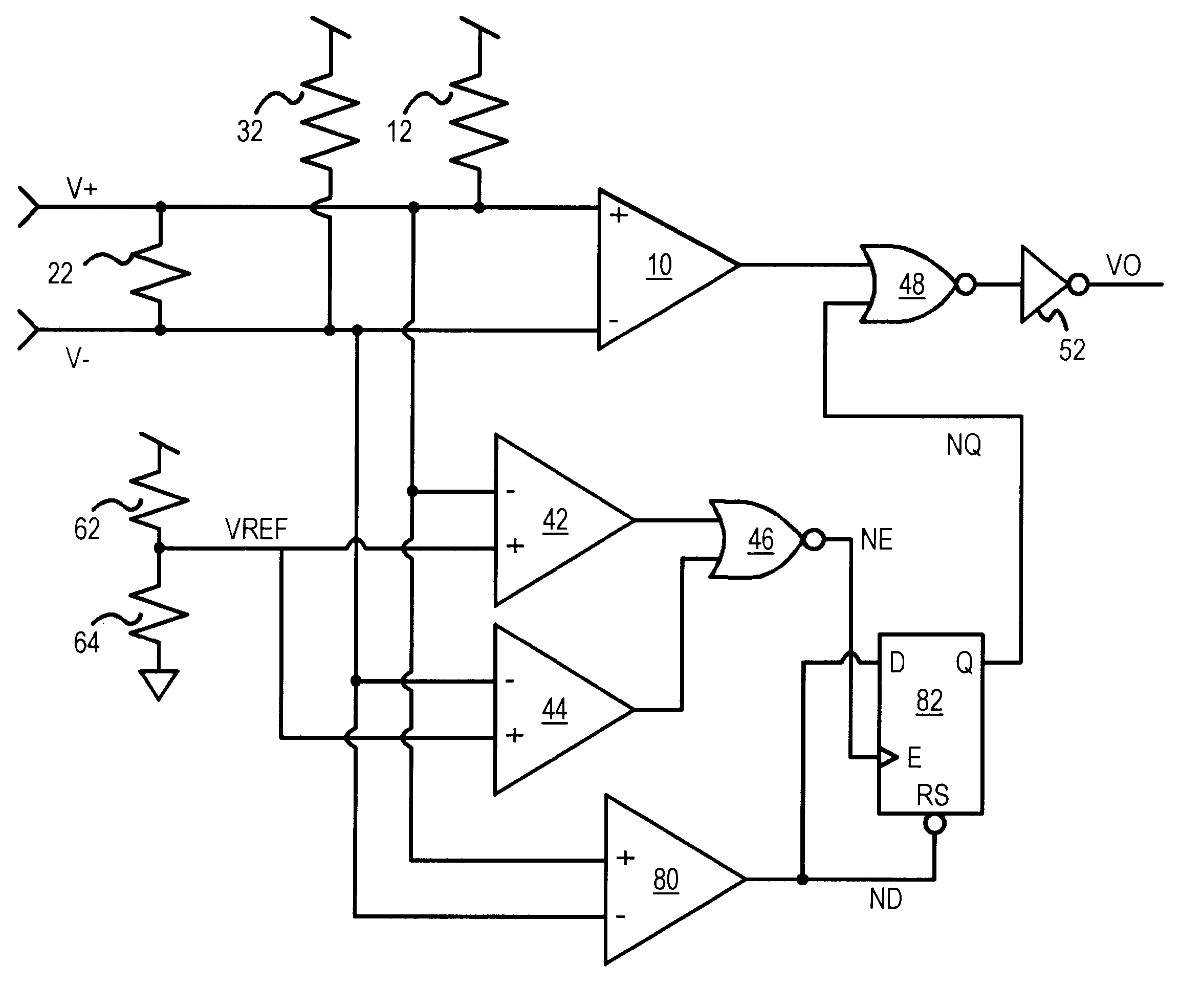

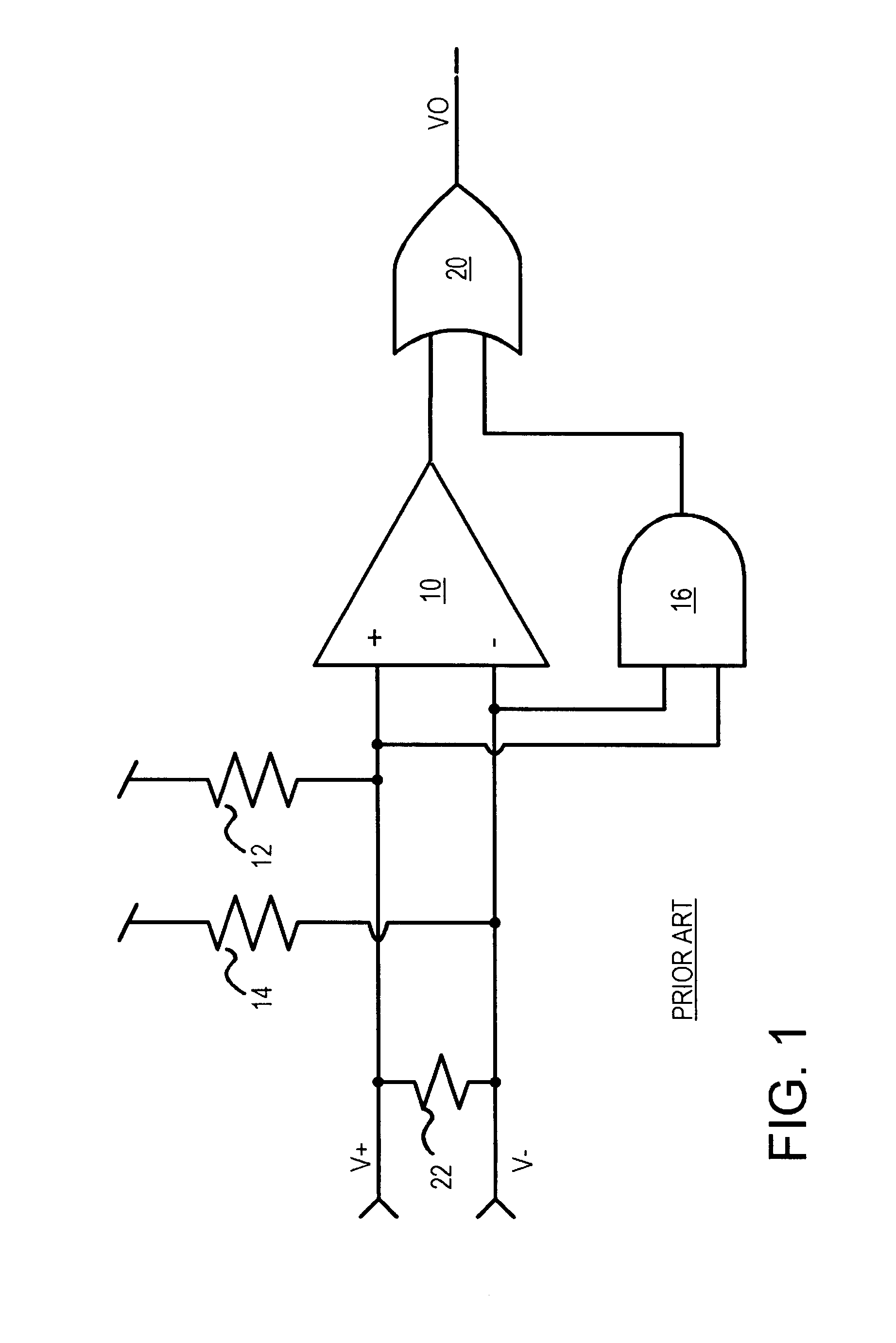

Active fail-safe detect circuit for differential receiver

InactiveUS6288577B1Multiple input and output pulse circuitsFail-safe circuitsNOR gateDifferential signaling

A fail-safe circuit for a differential receiver can tolerate high common-mode voltages. An output from a differential amplifier that receives a V+ and a V- differential signal can be blocked by a NOR gate when the fail-safe condition is detected, such as when the V+, V- lines are open. Pullup resistors pull V+, V- to Vcc when an open failure occurs. A pair of comparators receive a reference voltage on the non-inverting input. Once comparator outputs a high when the V+ line is above the reference voltage, and the other comparator outputs a high when the V- line is above the reference voltage. When both V+ and V- are above the reference voltage, the NOR gate blocks the output from the differential amplifier, providing a fail-safe. Since the reference voltage is very close to Vcc, a high common-mode bias can exist on V+, V- without falsely activating the fail-safe circuit.

Owner:DIODES INC

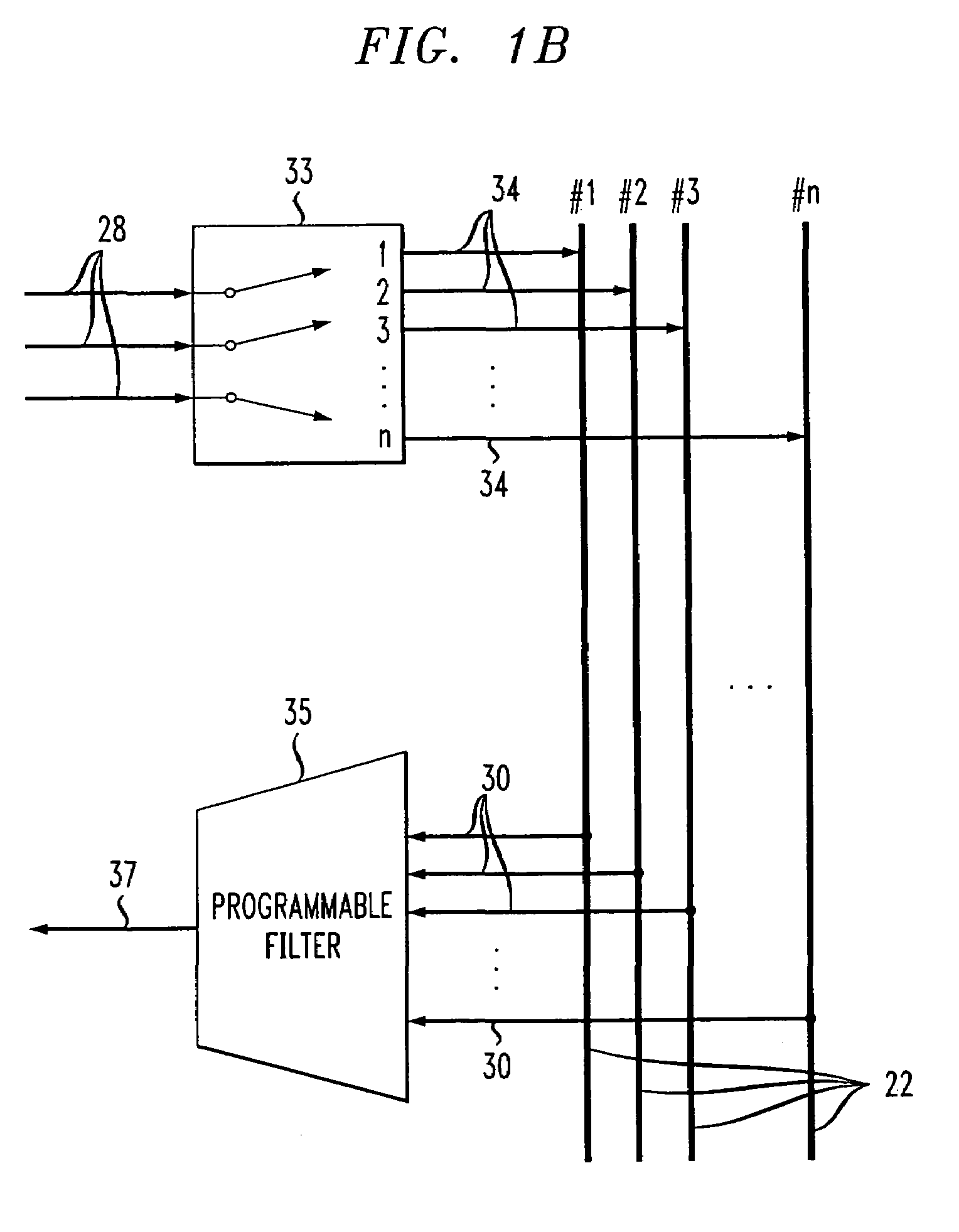

Modular switch with dynamic bus

InactiveUS7085875B1Simplify the management processRaise the possibilityError preventionTransmission systemsModularityEngineering

A modular switch, comprising a plurality of backplane sub-buses; a plurality of cards which are each allocated one or more of the backplane sub-buses; and a controller which dynamically allocates the backplane sub-buses to the plurality of cards, based on the bandwidth needs of the cards. Preferably, the bandwidth capacity of substantially all the backplane sub-buses is less than the sum of the maximal transmission bandwidth capacities of the cards.

Owner:LUCENT TECH NETWORKS +1

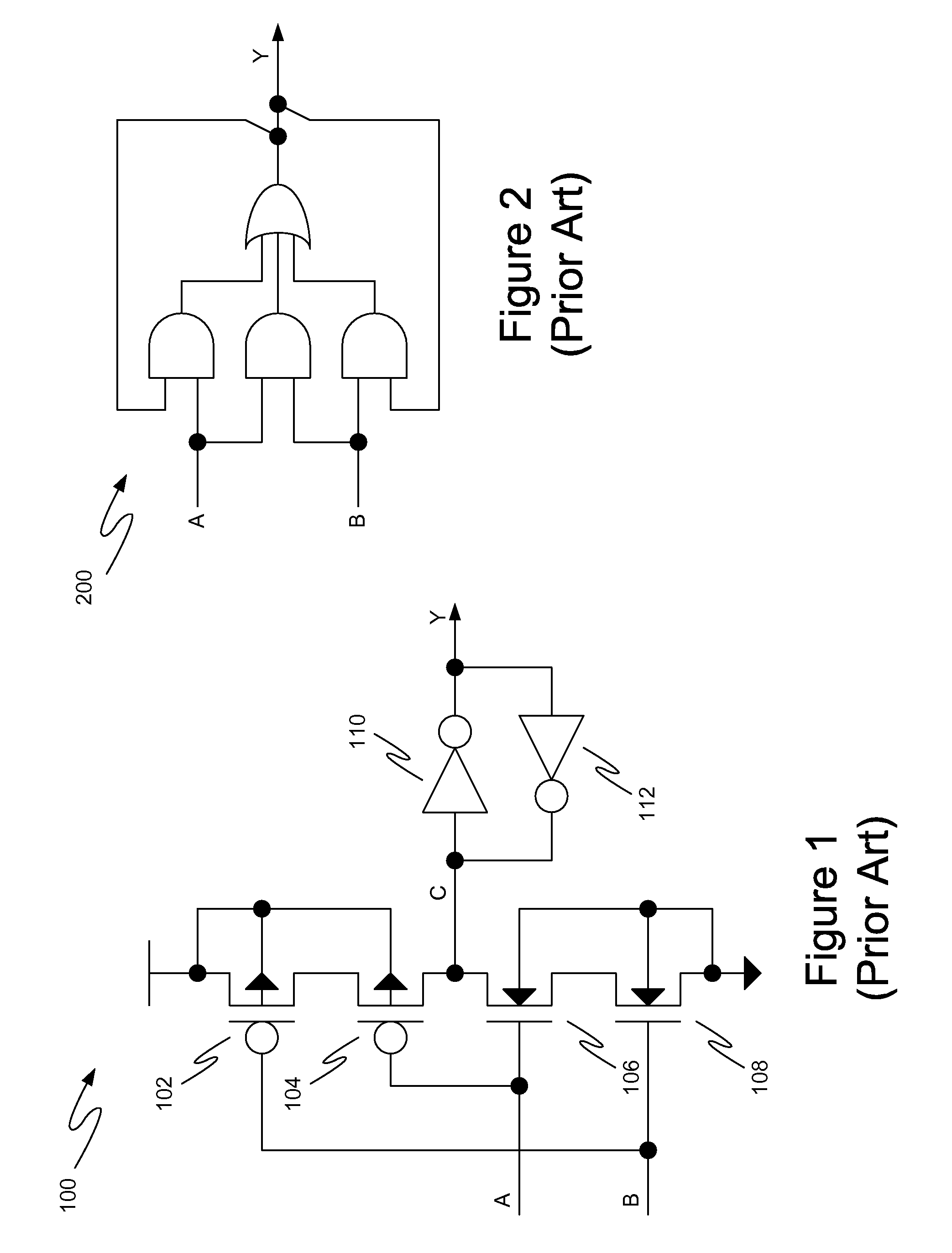

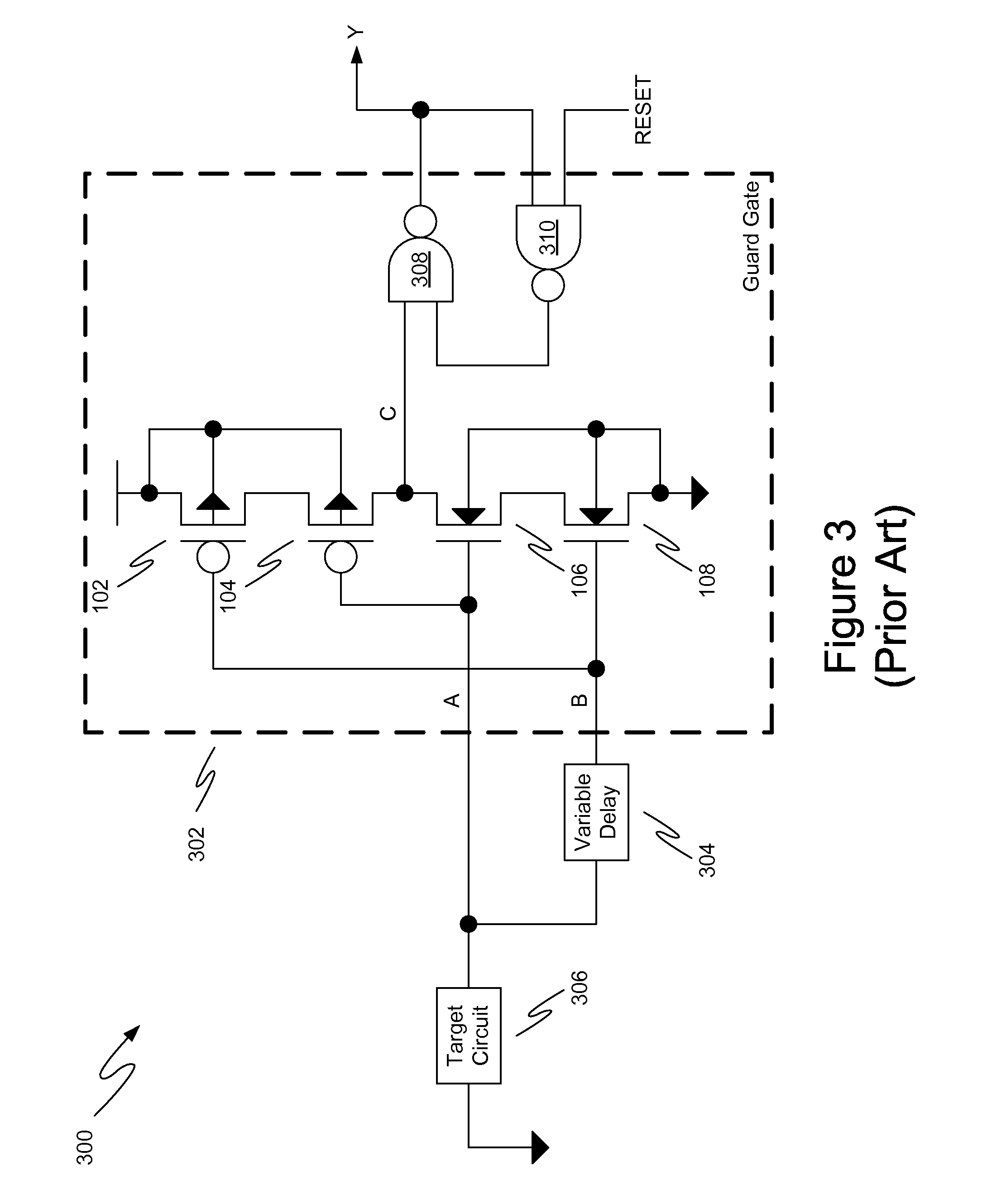

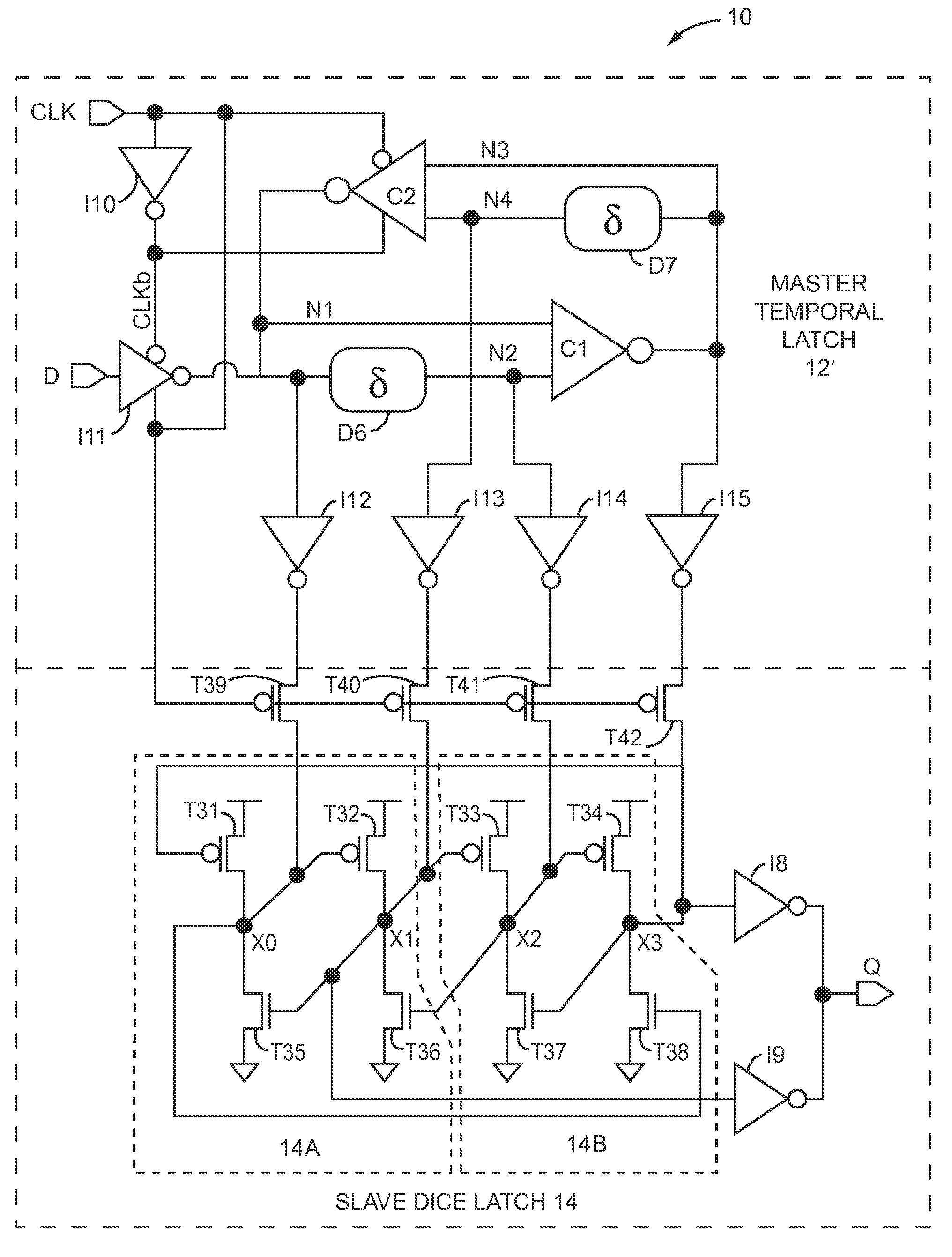

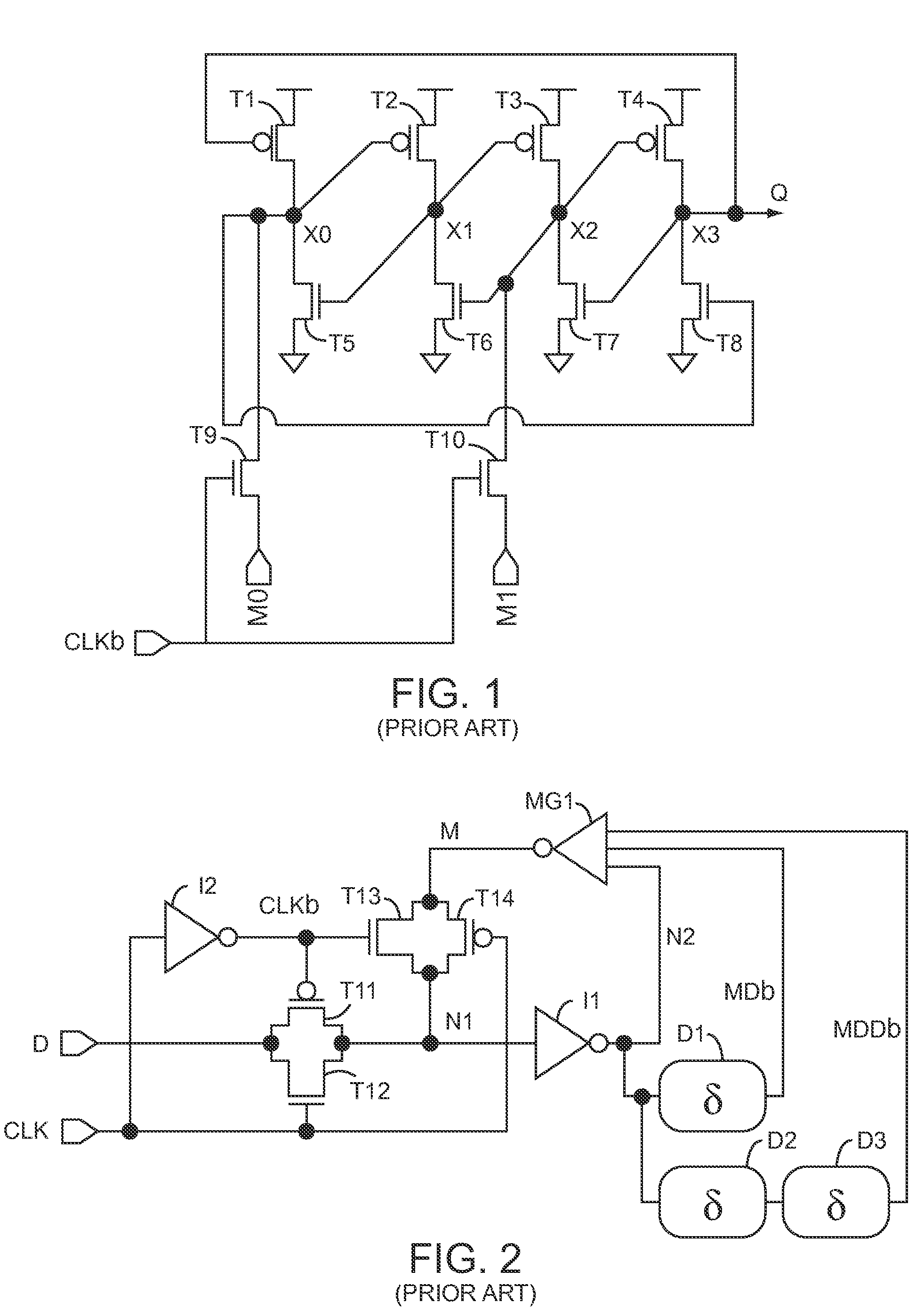

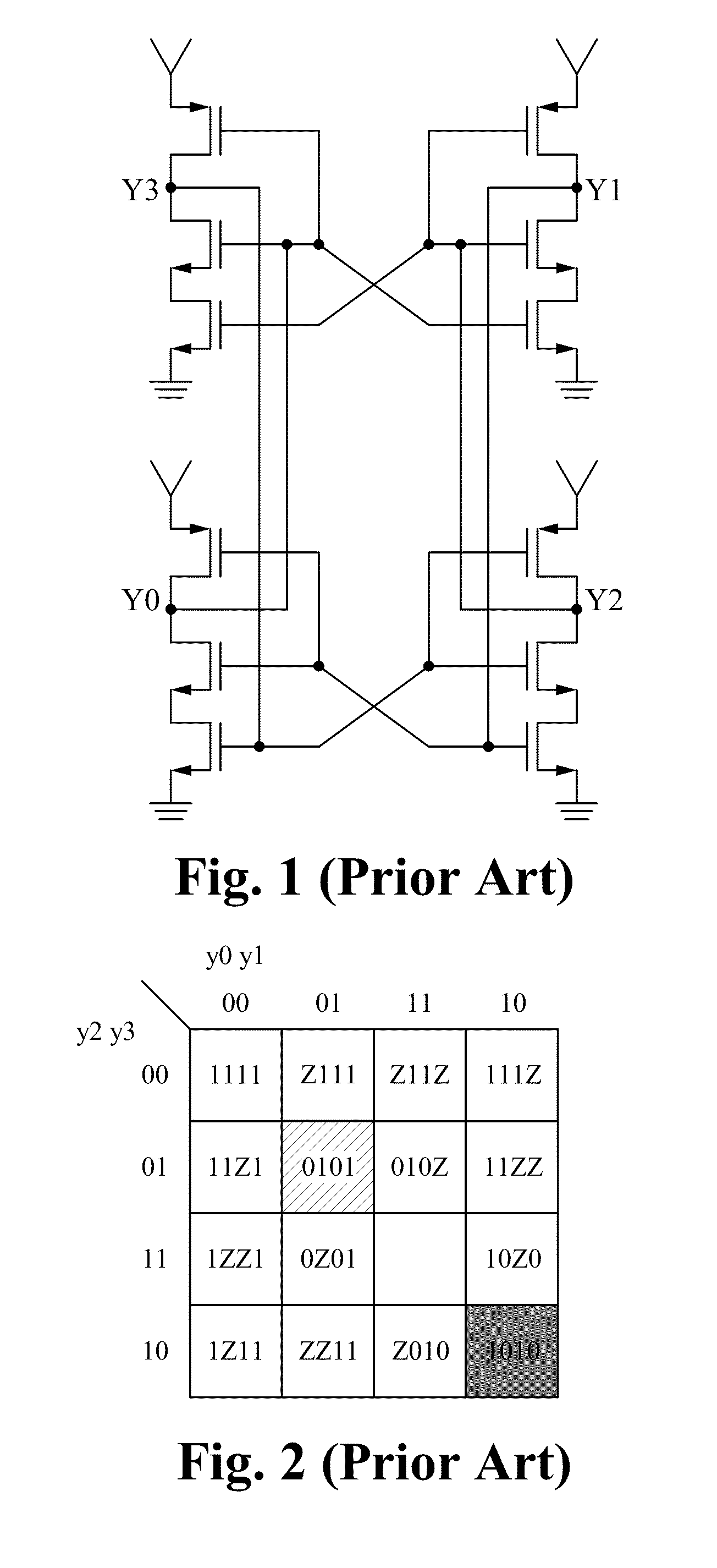

Radiation hardened master-slave flip-flop

InactiveUS7719304B1Increase radiation hardeningCompact layoutReliability increasing modificationsFail-safe circuitsStorage cellCross coupled

The present invention provides a radiation hardened flip-flop formed from a modified temporal latch and a modified dual interlocked storage cell (DICE) latch. The temporal latch is configured as the master latch and provides four output storage nodes, which represent outputs of the temporal latch. The DICE latch is configured as the slave latch and is made of two cross-coupled inverter latches, which together provide four DICE storage nodes. The four outputs of the temporal latch are used to write the four DICE storage nodes of the DICE latch. The temporal latch includes at least one feedback path that includes a delay element, which provides a delay.

Owner:ARIZONA STATE UNIVERSITY

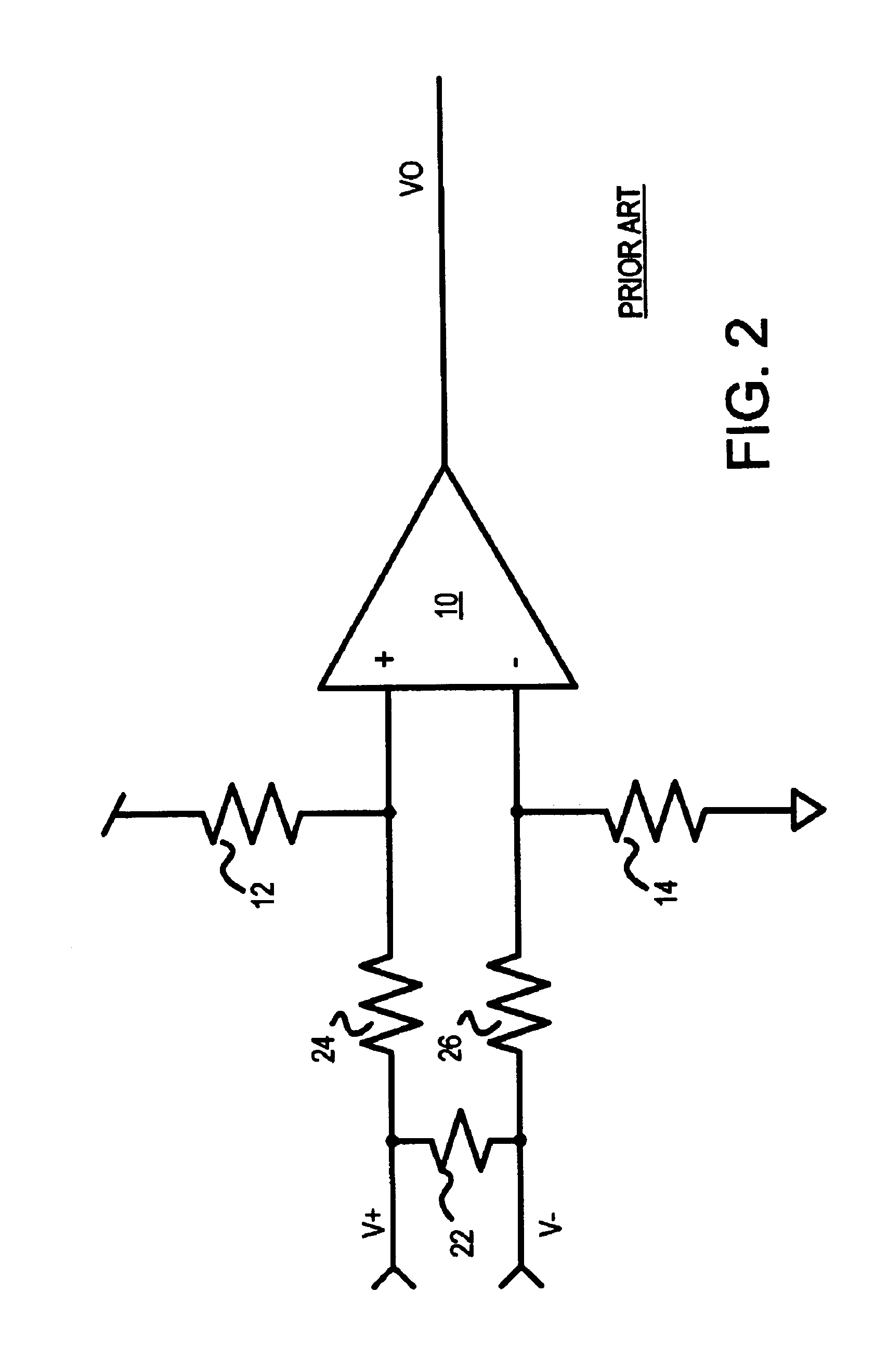

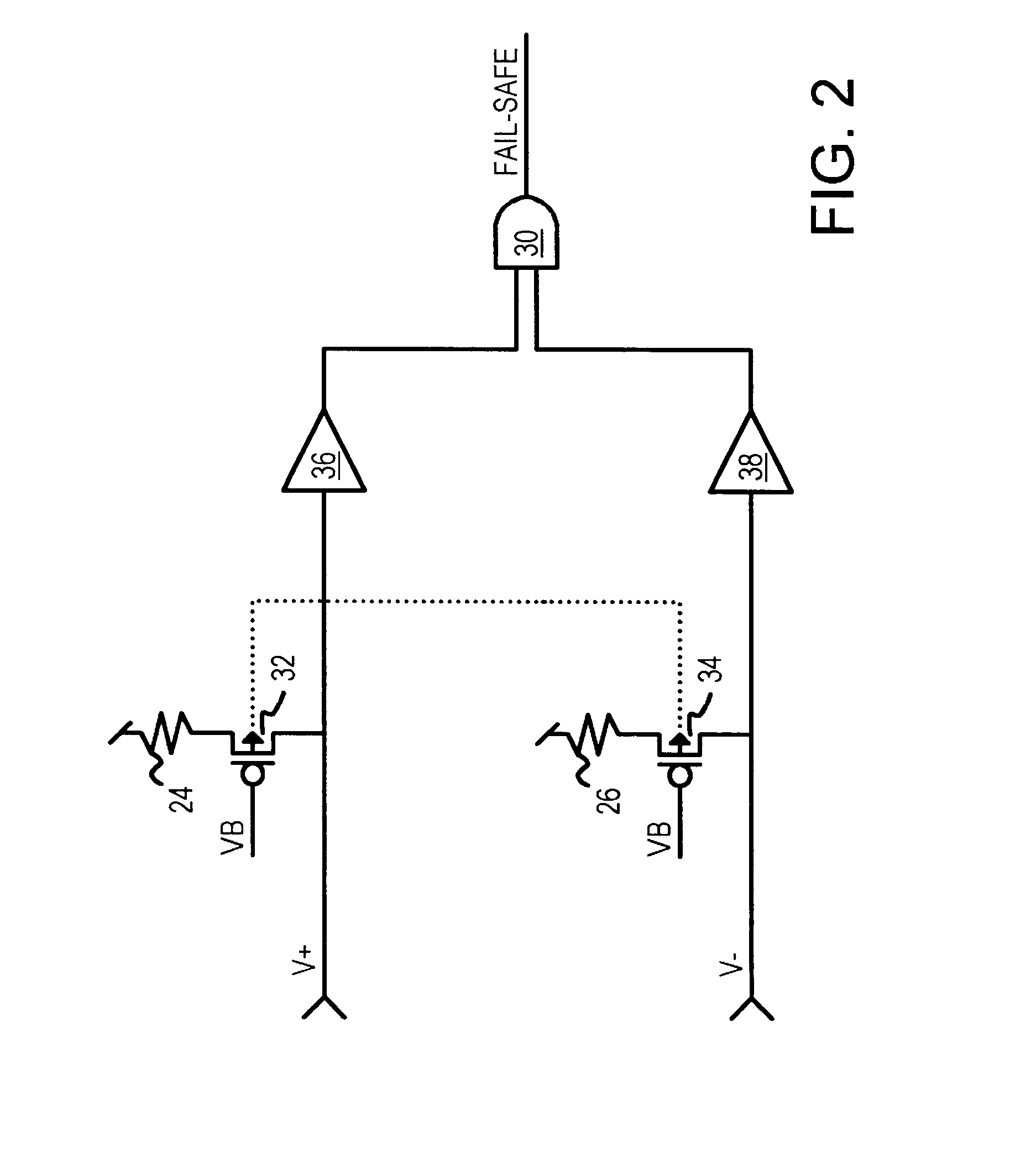

Latched active fail-safe circuit for protecting a differential receiver

InactiveUS6650149B1Multiple input and output pulse circuitsFail-safe circuitsAudio power amplifierEngineering

A fail-safe circuit for a differential receiver can tolerate noise. A latch is enabled when both differential inputs V+, V- rise above a reference voltage that is close to Vcc. The latch, once enabled, is set by an offset amplifier, signaling the fail-safe condition. The offset amplifier sets the latch when V+ is above or equal to V-. The differential amplifier has a small offset voltage to allow the latch to remain set when V+ and V- are equal in voltage. An output from a differential amplifier receiving V+ and V- can be blocked by a gate when the fail-safe condition is latched. Pullup resistors pull V+, V- to Vcc when an open failure occurs. The latch remains set when common-mode noise occurs on V+, V-, preventing noise from prematurely disabling the fail-safe condition. Such noise coupled into a broken cable is usually common-mode.

Owner:DIODES INC

Reconfigurable electronic circuit

InactiveUS7902857B1Reduce power consumptionEliminate needFail-safe circuitsDigital storageElectrical resistance and conductanceEngineering

An apparatus and method provides the foundation for designing reconfigurable electronic computing systems. The invention relies on an ability to change the resistance state of a memristor device to achieve an optimal voltage at specific circuit nodes, whereby this dynamically and autonomously causes the circuit to reconfigure itself and produce a different output for the same input relative to the circuit's initial state. The circuit's state remains constant until the memristor's resistance is changed, at which point the circuit's function is “reprogrammed”.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

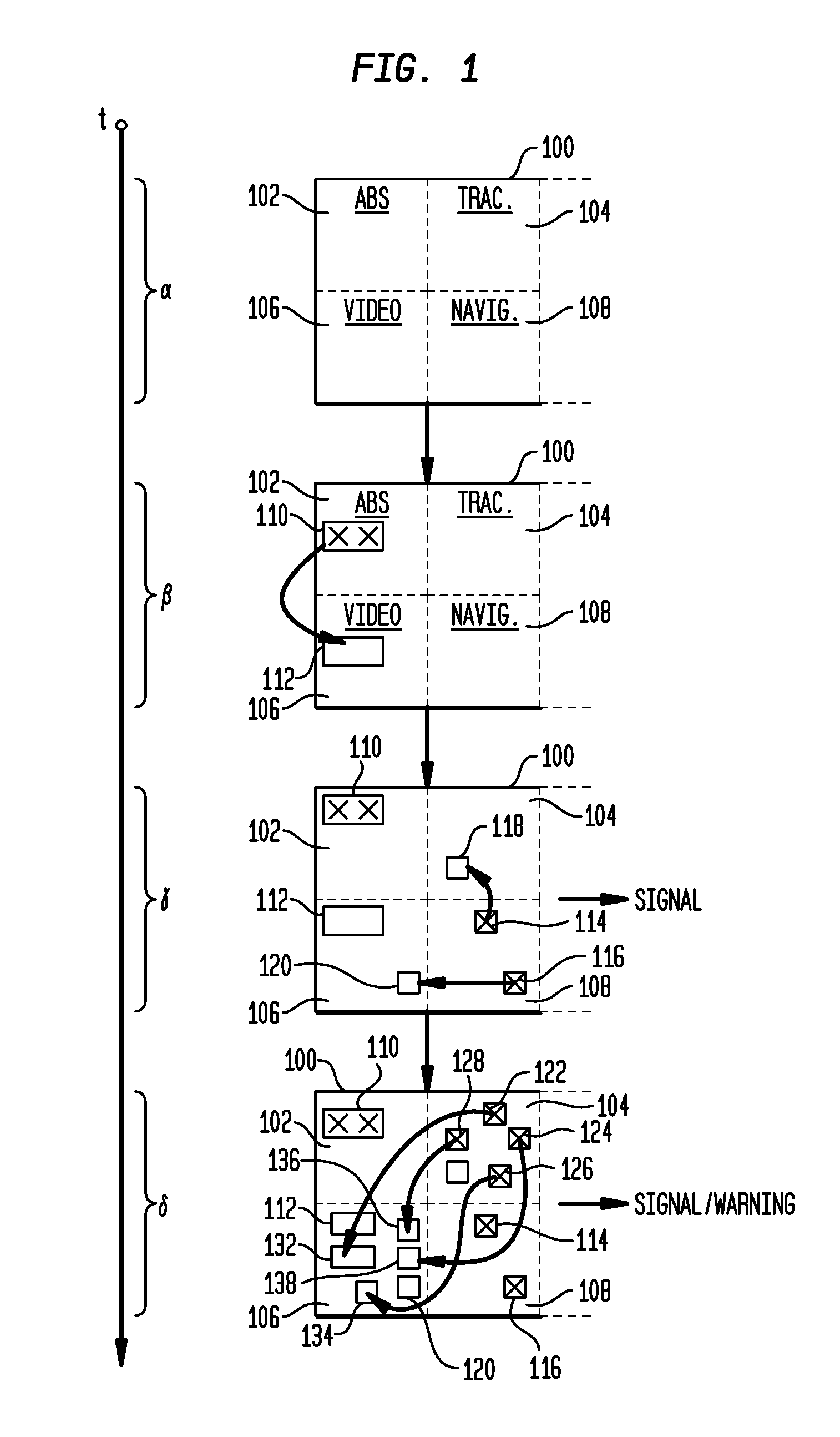

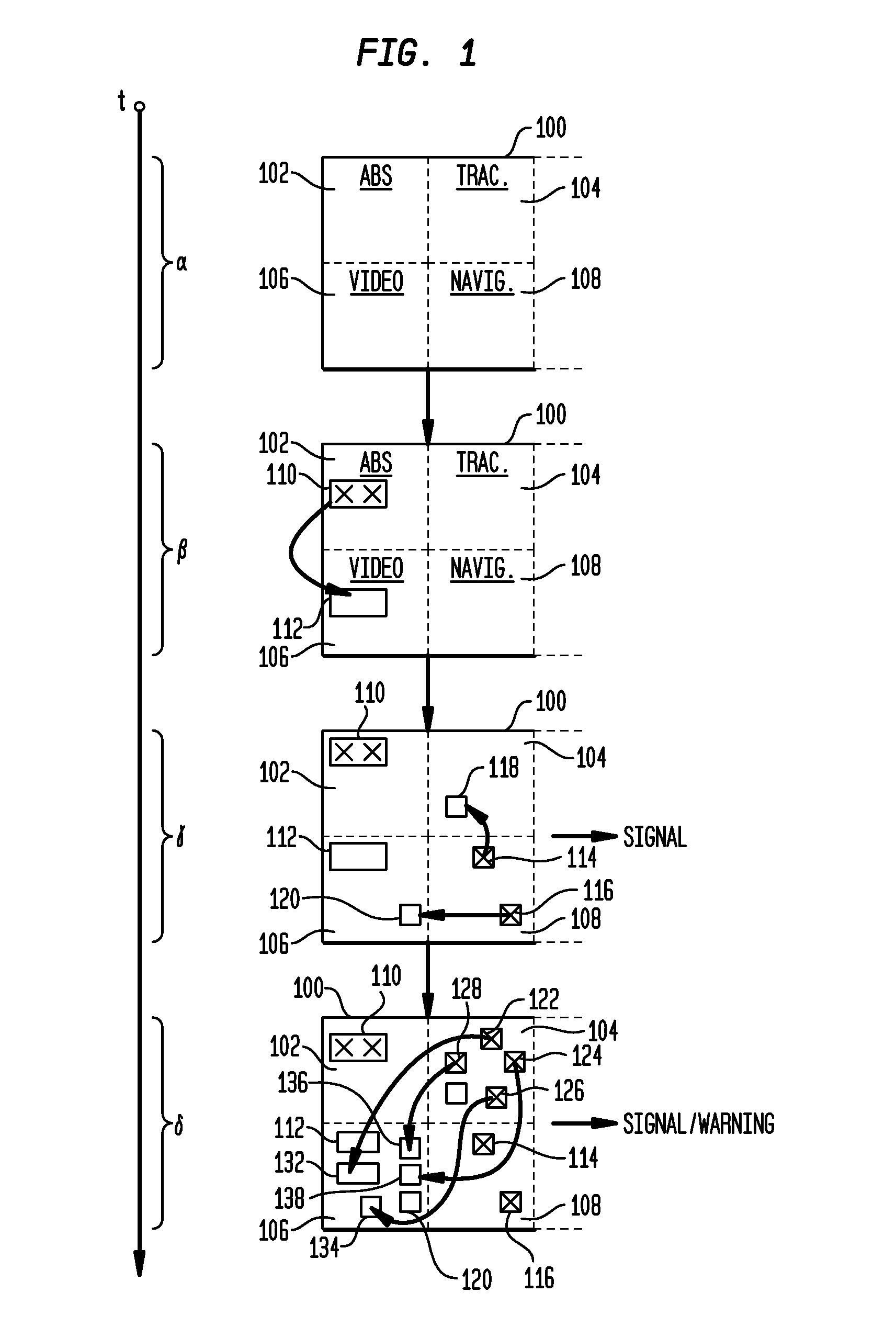

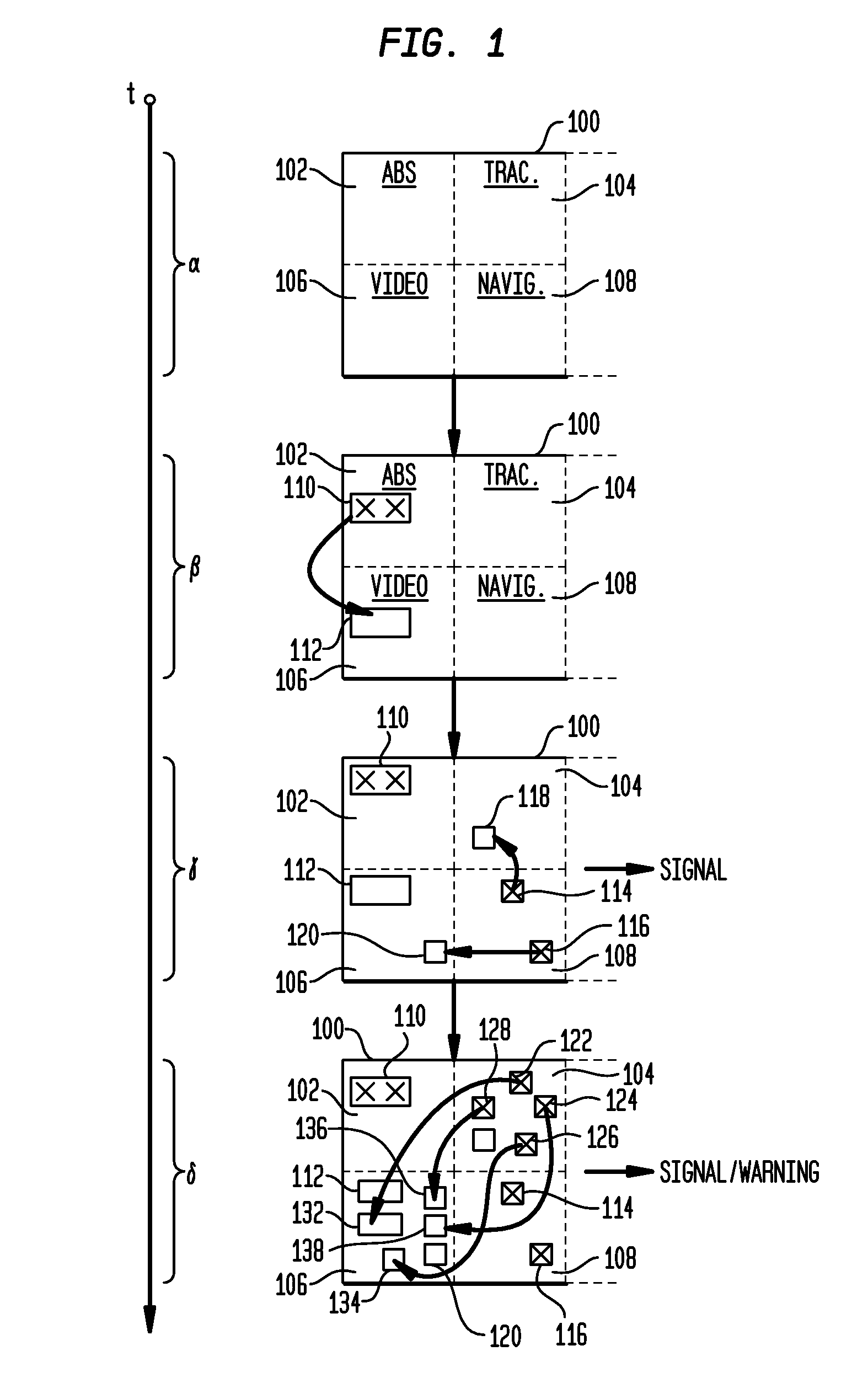

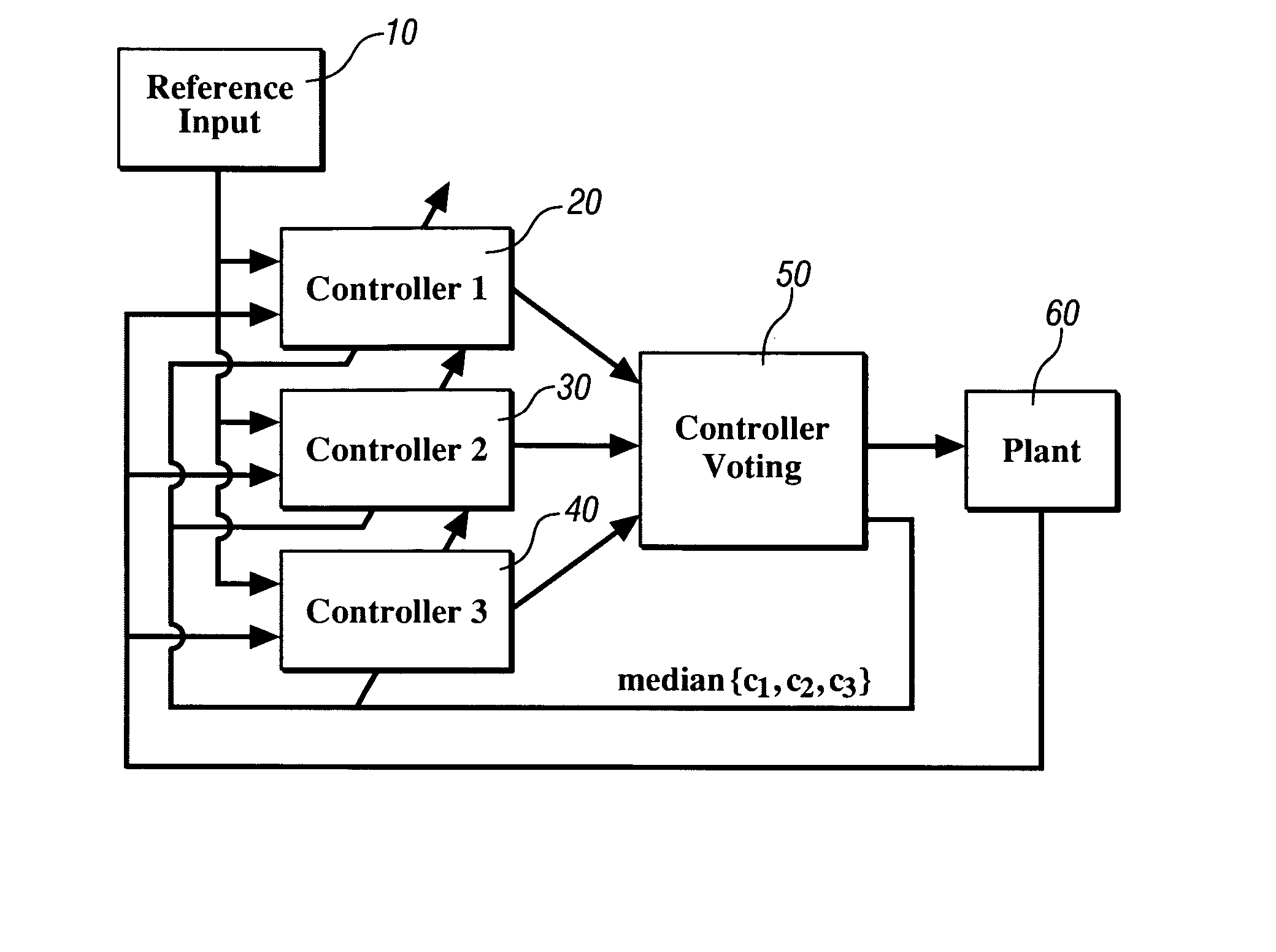

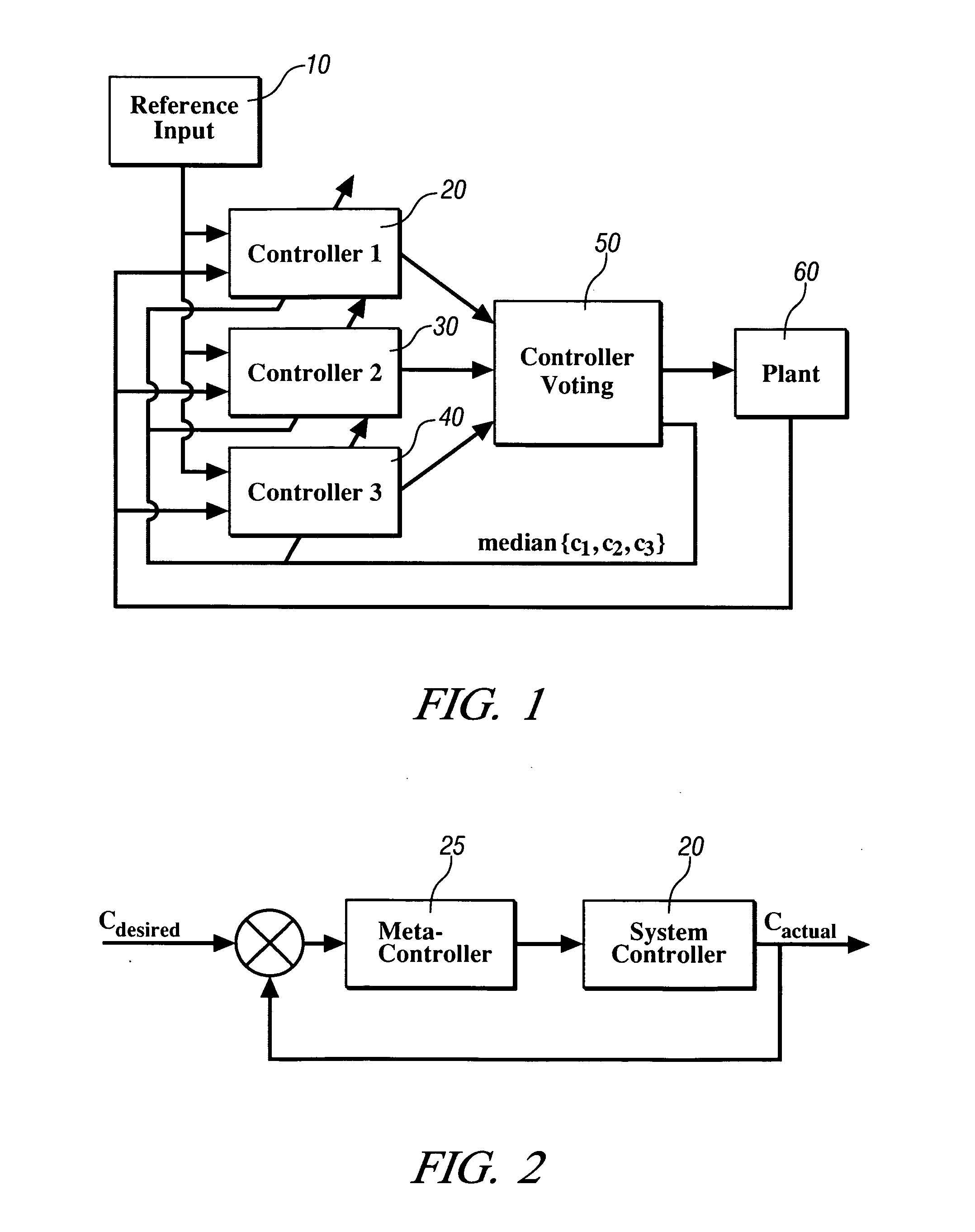

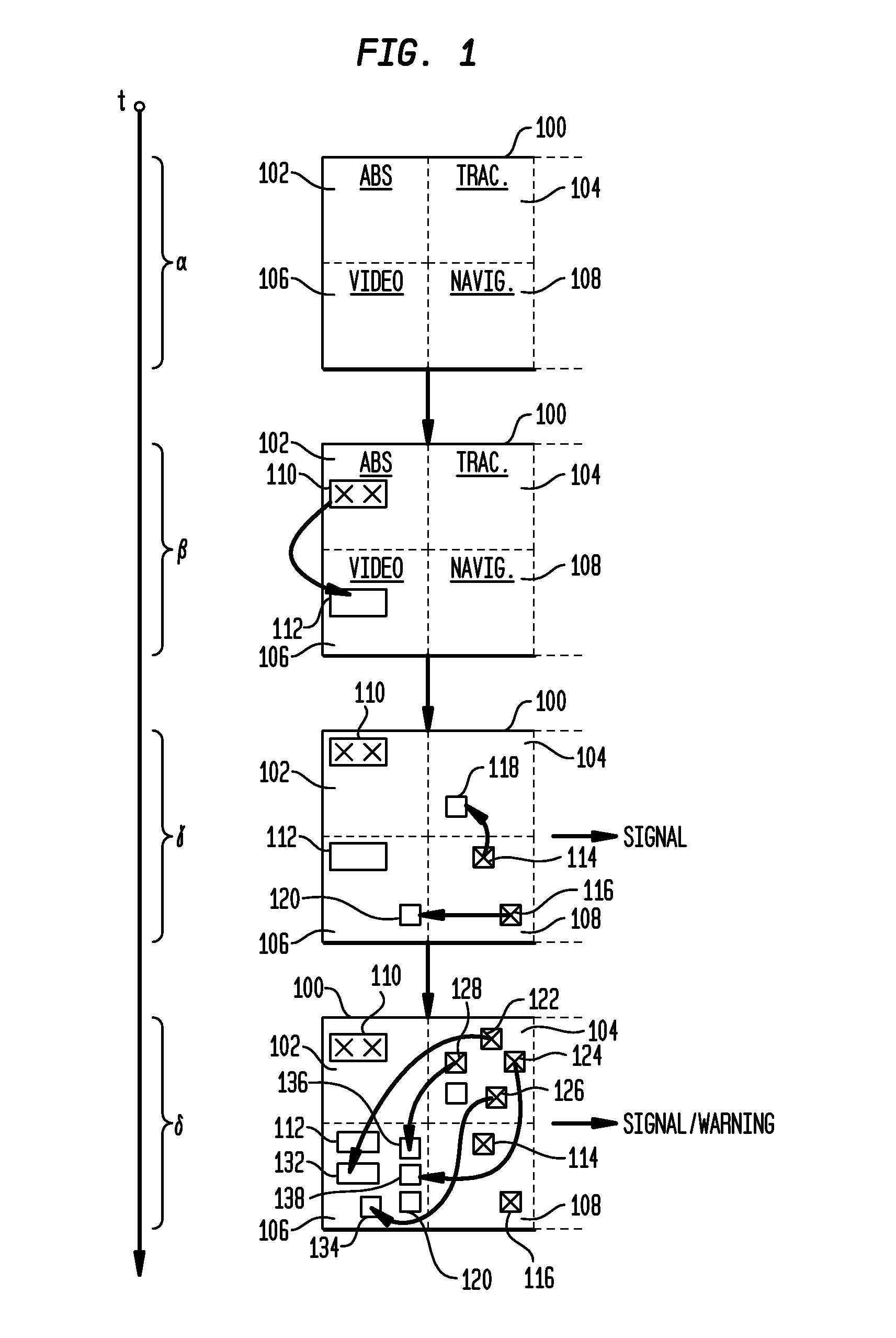

Method for synchronization of a controller

InactiveUS20070250183A1Reducing additional fault scenariosVehicle testingReliability increasing modificationsSynchronous controlOperation mode

A system and method for reintegration of a redundant controller after occurrence of a fault is provided, comprising synchronizing outputs of a primary controller with outputs of secondary controllers. The controller is placed in a different mode of operation in which its output is not used in system control. A meta-controller is activated to drive the primary controller to the same states at which the secondary or redundant controllers operate. A voting mechanism is used to determine a fault in an output to a controlled device. Control of the device using the secondary outputs is effected. The primary controller recalculates the primary output, based upon the primary output; a feedback signal; and, the secondary outputs. Control using the primary output is permitted when the primary output is within an allowable range of the secondary outputs.

Owner:GM GLOBAL TECH OPERATIONS LLC

Fault tolerant asynchronous circuits

ActiveUS20070262786A1Reliability increasing modificationsFail-safe circuitsAsynchronous circuitMemory circuits

New and improved methods and circuit designs for asynchronous circuits that are tolerant to transient faults, for example of the type introduced through radiation or, more broadly, single—event effects. SEE-tolerant configurations are shown and described for combinational logic circuits, state-holding logic circuits and SRAM memory circuits.

Owner:ACHRONIX SEMICON CORP

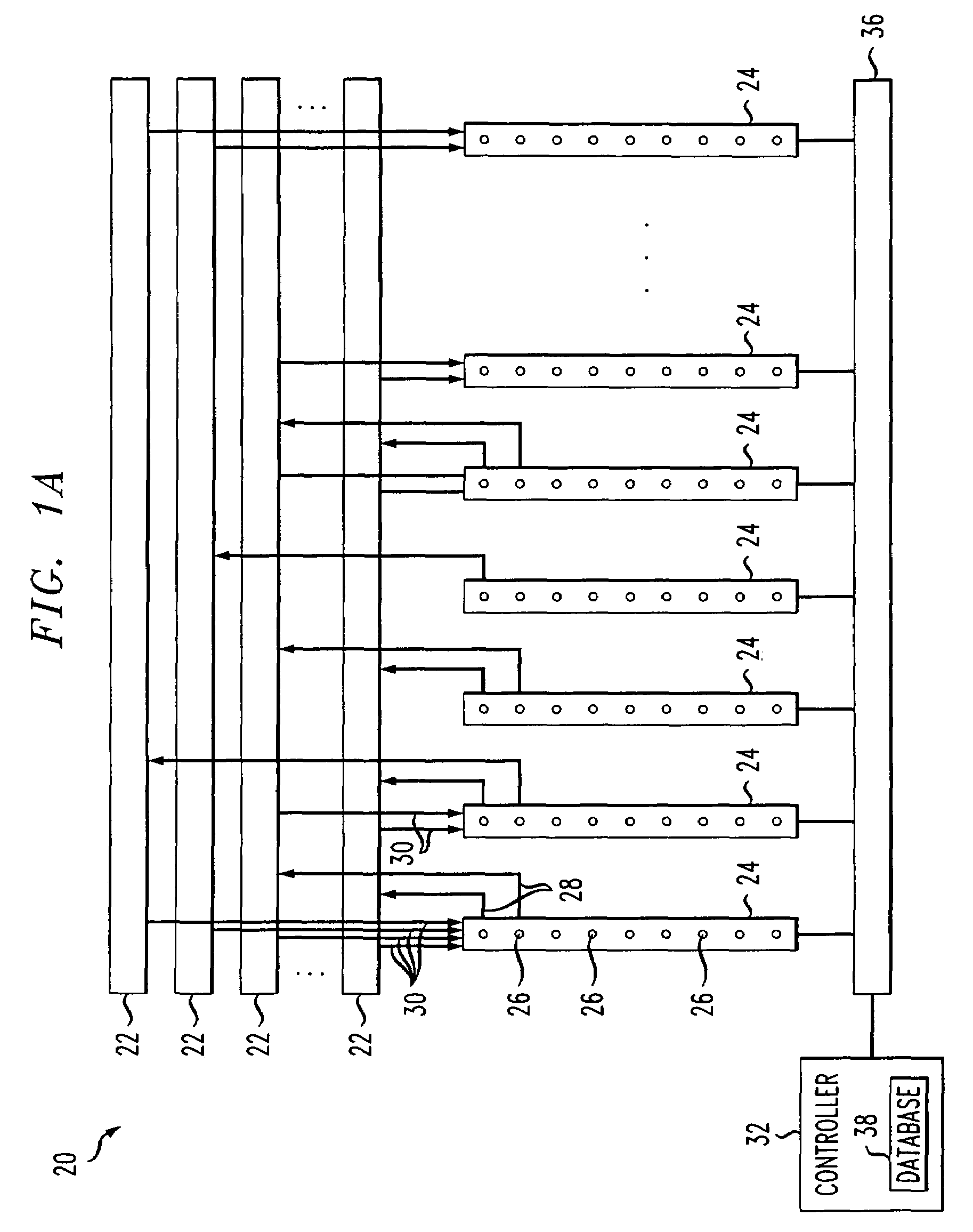

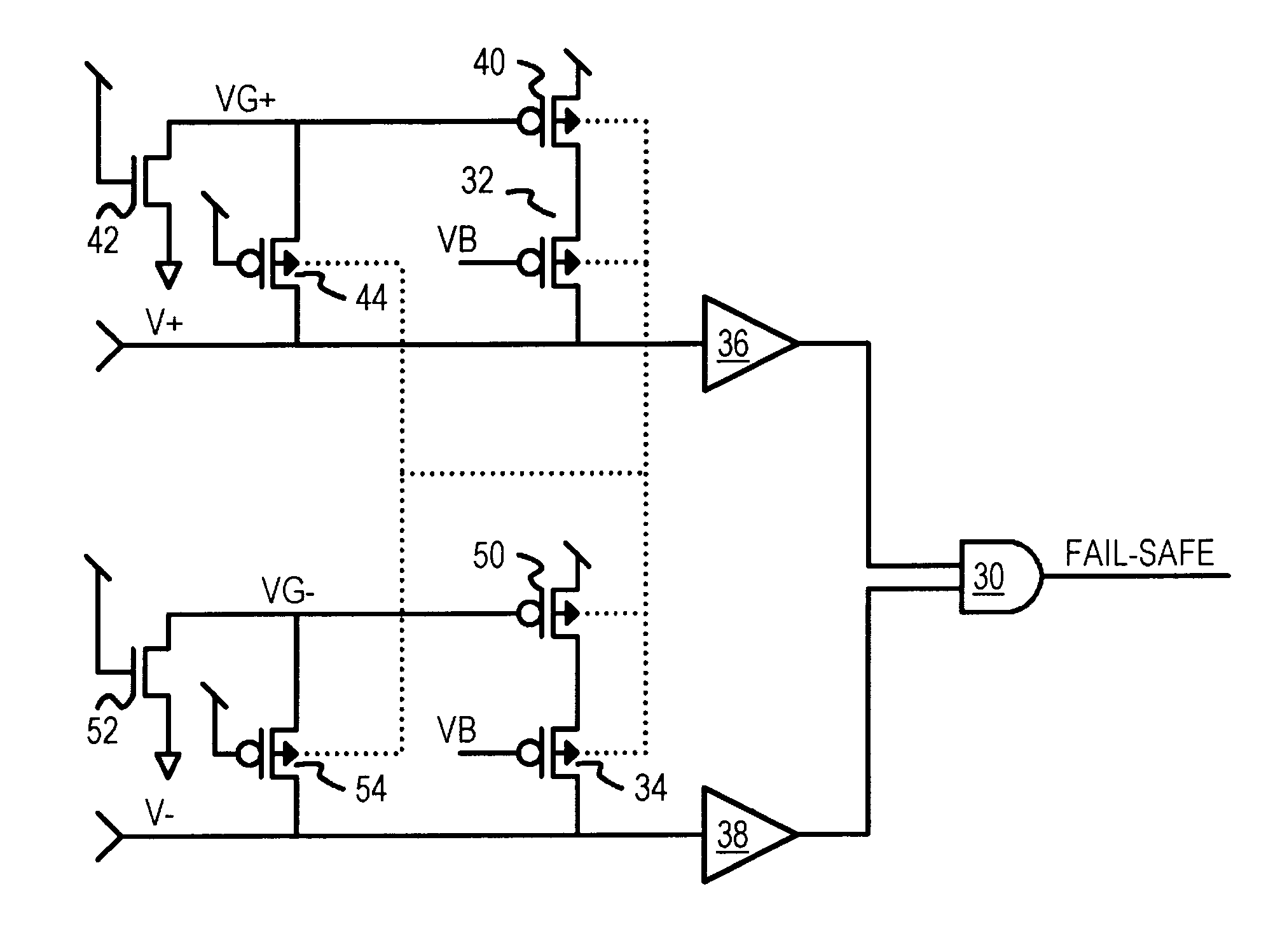

Fail-safe circuit with low input impedance using active-transistor differential-line terminators

InactiveUS6525559B1Reliability increasing modificationsFail-safe circuitsEngineeringPull-up resistor

A fail-safe circuit for a pair of differential input lines detects when one or both lines are open. Each line has a pull-up of a switched p-channel transistor in series with a resistor or another p-channel transistor that has its effective resistance controlled by a gate bias. The gate of the switched p-channel transistor is driven to ground when power is applied to the gate of a grounding n-channel transistor. When power is off, a p-channel connecting transistor charges the gate node from the differential input line when a positive voltage is applied to the input line, such as during a leakage test. Charging the gate node prevents the switched p-channel transistor from turning on, blocking a leakage current path through the pull-up. An N-well bias circuit can be added, which connects the N-well under p-channel transistors to power or the gate node or the input line.

Owner:DIODES INC

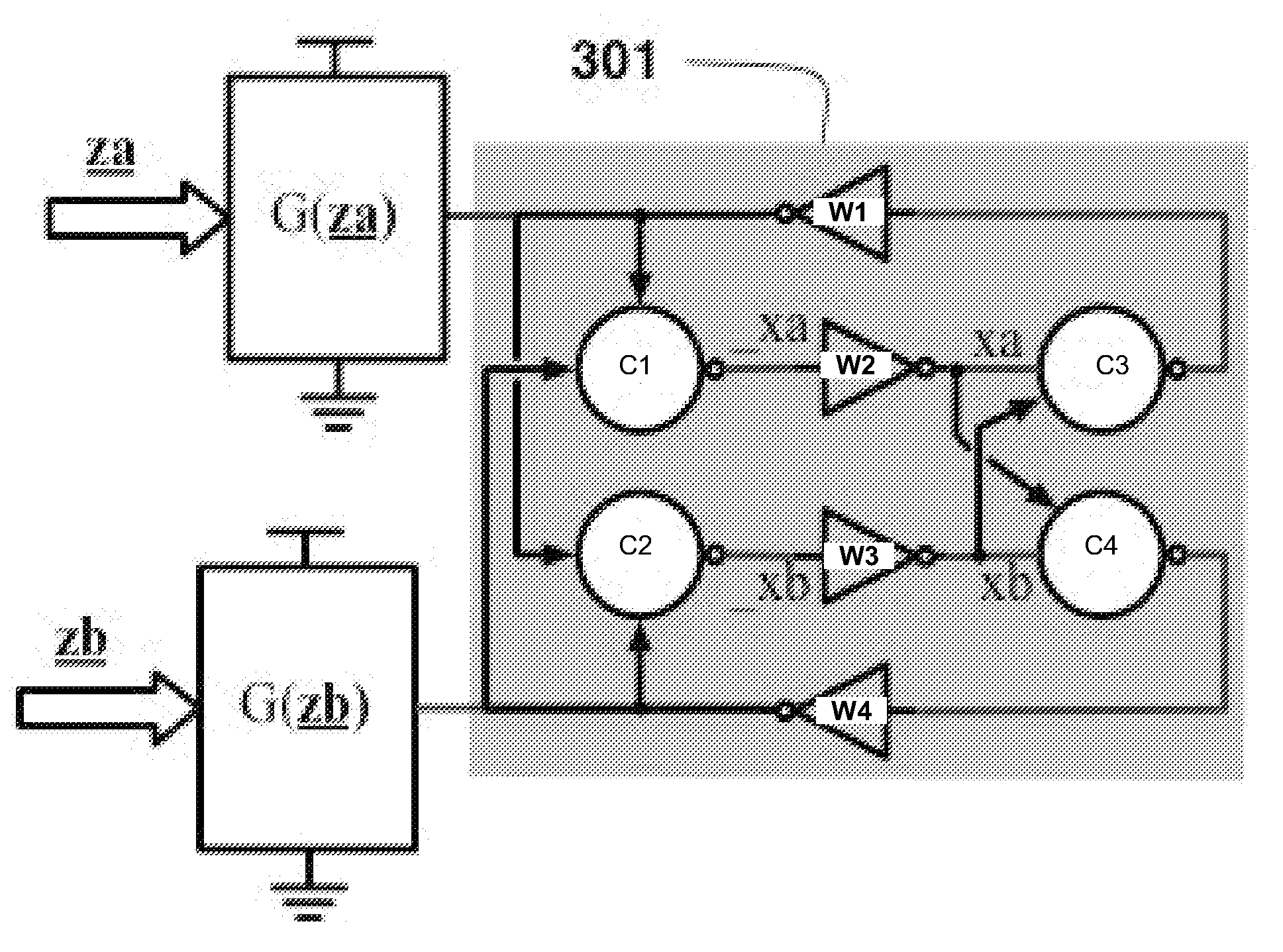

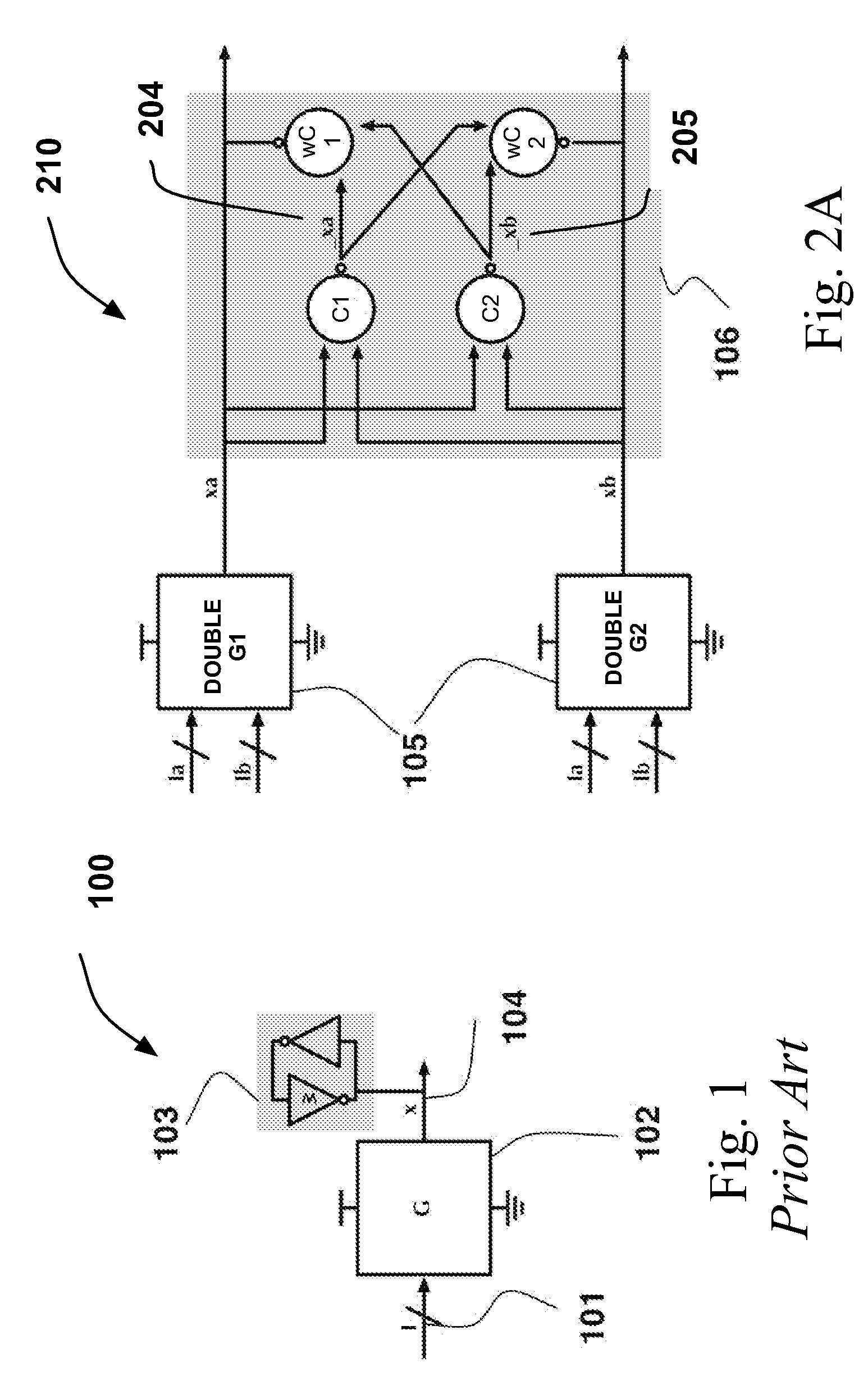

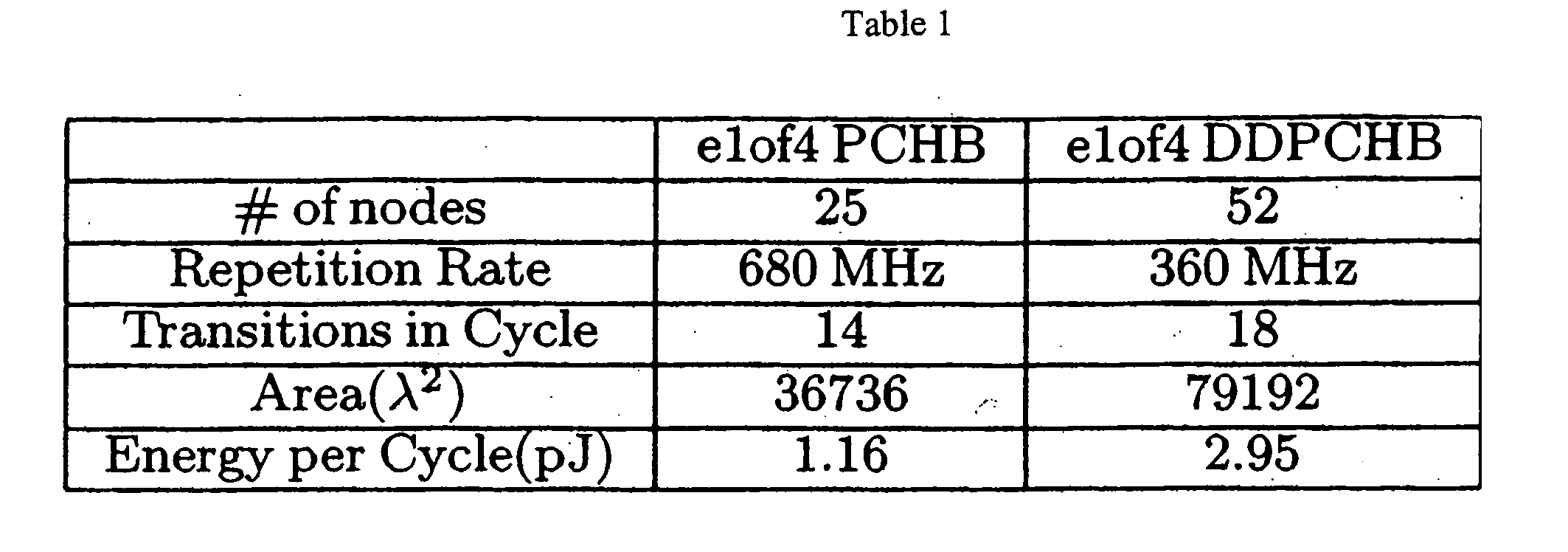

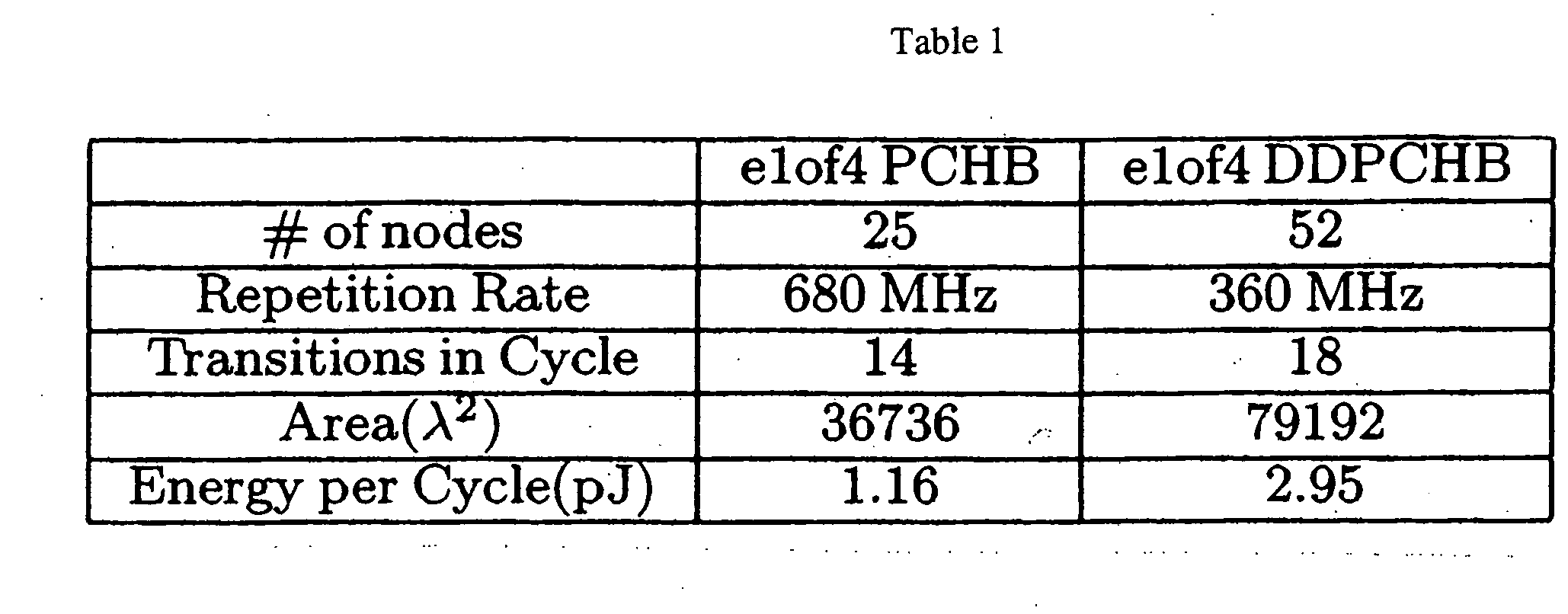

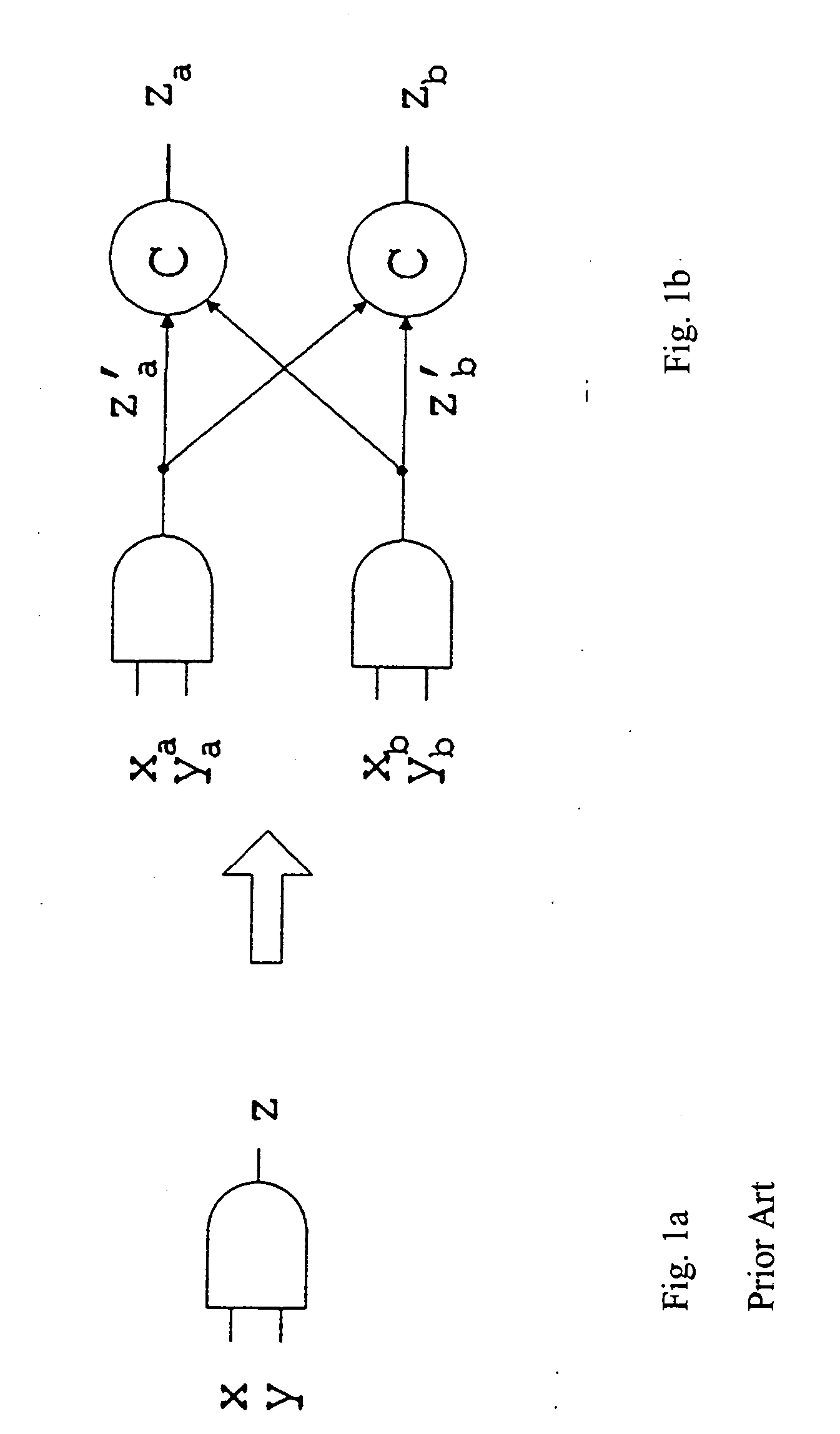

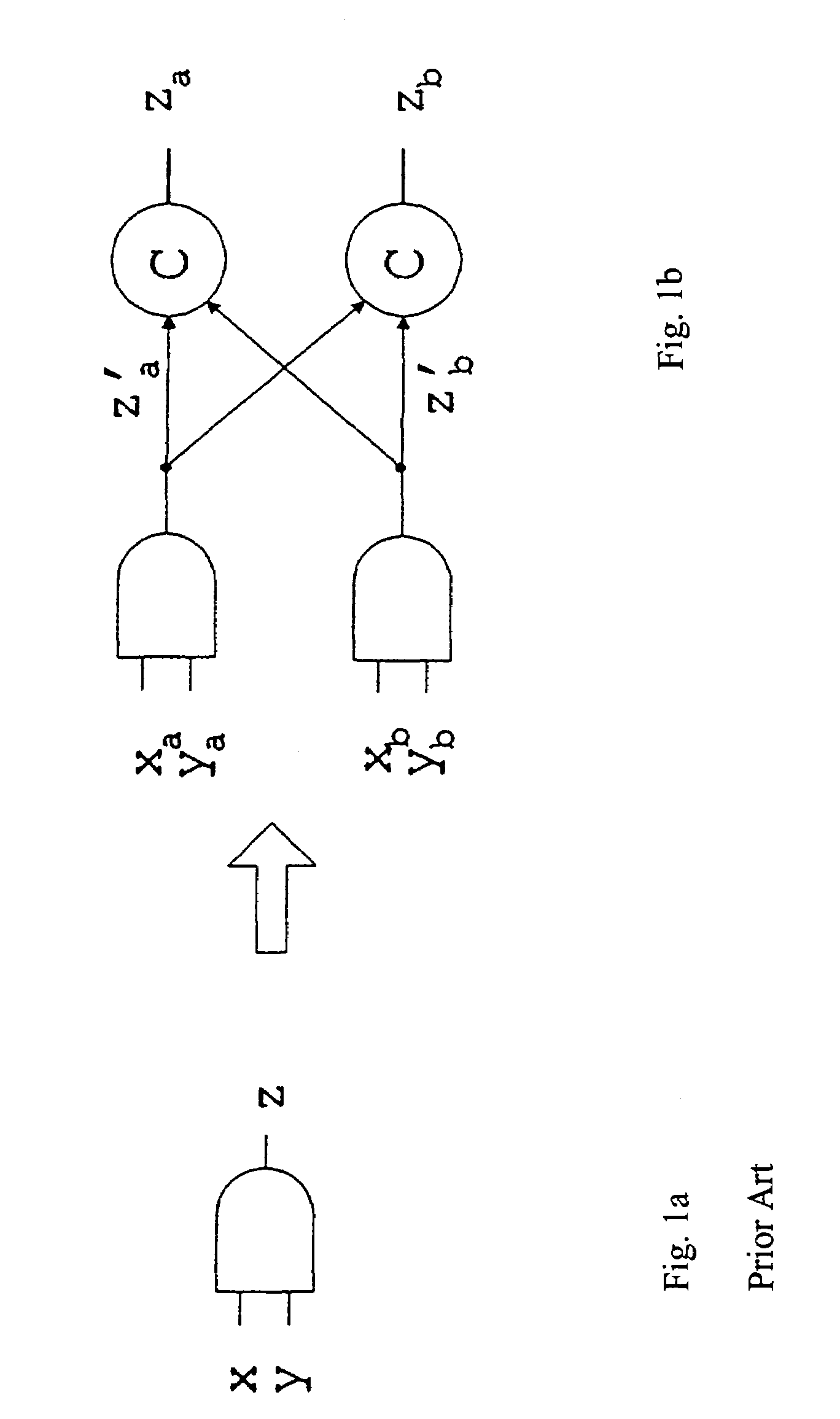

Duplicated double checking production rule set for fault-tolerant electronics

InactiveUS20070016823A1Reduce soft errorsEliminating soft errorReliability increasing modificationsError detection/correctionElectronic systemsHemt circuits

Systems and methods for mitigating the effects of soft errors in asynchronous digital circuits. Circuits are constructed using stages comprising doubled logic elements which are connected to c-elements that compare the output states of the double logic elements. The inputs of logic elements in a stage are inhibited from changing until the outputs of the c-elements of that stage are enabled. The c-elements inhibit the propagation of a soft error by halting the operation of the circuit until the temporary effects of the soft error pass.

Owner:CALIFORNIA INST OF TECH

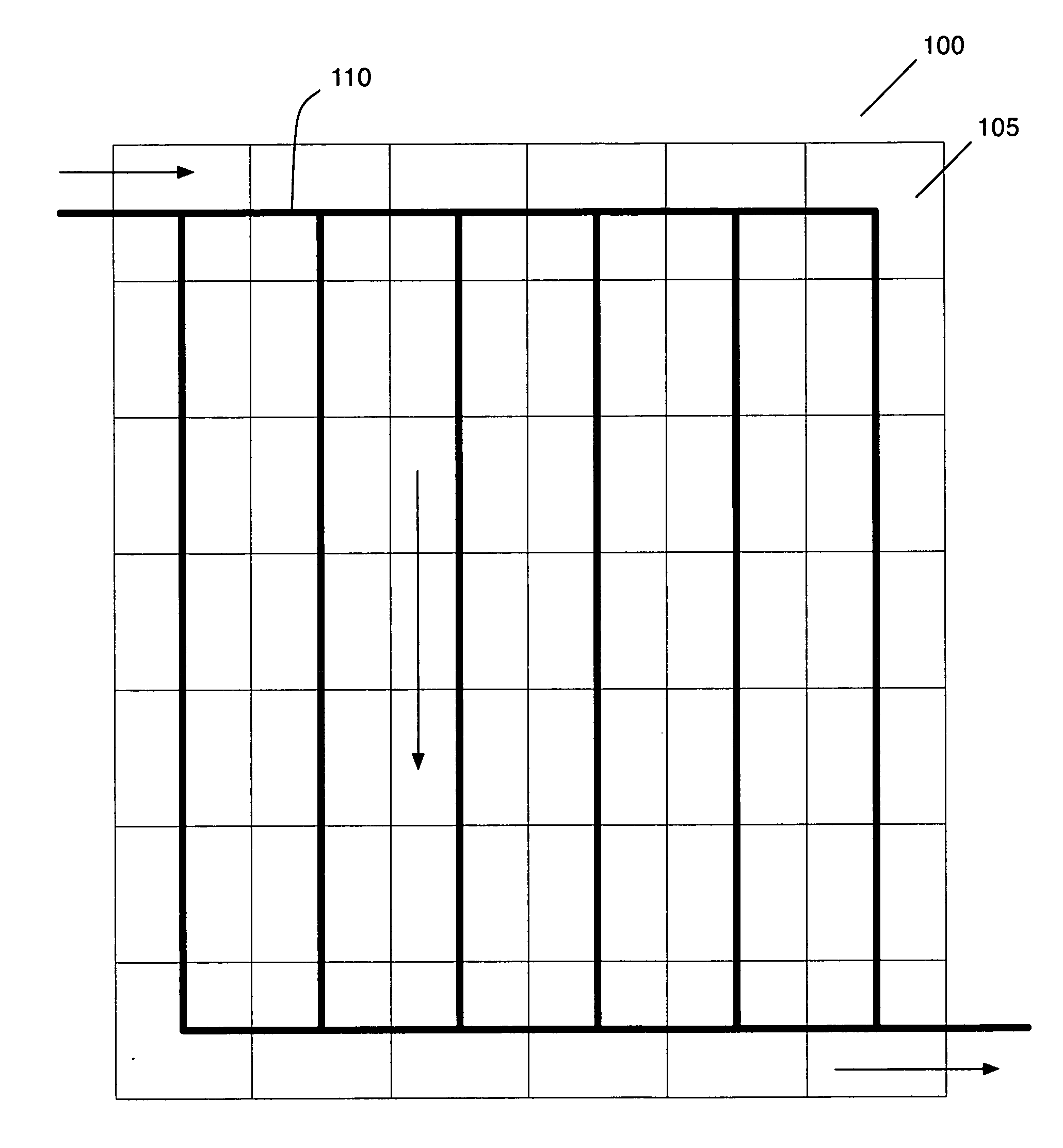

Micro-granular delay testing of configurable ICs

ActiveUS8072234B2Delay in testingEnsure correct executionReliability increasing modificationsFail-safe circuitsComputer hardwarePerformance limit

A method for testing a set of circuitry in an integrated circuit (IC) is described. The IC includes multiple configurable circuits for configurably performing multiple operations. The method configures the IC to operate in a user mode with a set of test paths that satisfies a set of evaluation criteria. Each test path includes a controllable storage element for controllably storing a signal that the storage element receives. The method operates the IC in user mode. The method reads the values stored in the storage elements to determine whether the set of circuitry is operating within specified performance limits.

Owner:ALTERA CORP

Micro-Granular Delay Testing of Configurable ICs

ActiveUS20110068820A1Ensure correct executionReduce minimum testable durationReliability increasing modificationsFail-safe circuitsComputer hardwarePerformance limit

A method for testing a set of circuitry in an integrated circuit (IC) is described. The IC includes multiple configurable circuits for configurably performing multiple operations. The method configures the IC to operate in a user mode with a set of test paths that satisfies a set of evaluation criteria. Each test path includes a controllable storage element for controllably storing a signal that the storage element receives. The method operates the IC in user mode. The method reads the values stored in the storage elements to determine whether the set of circuitry is operating within specified performance limits.

Owner:ALTERA CORP

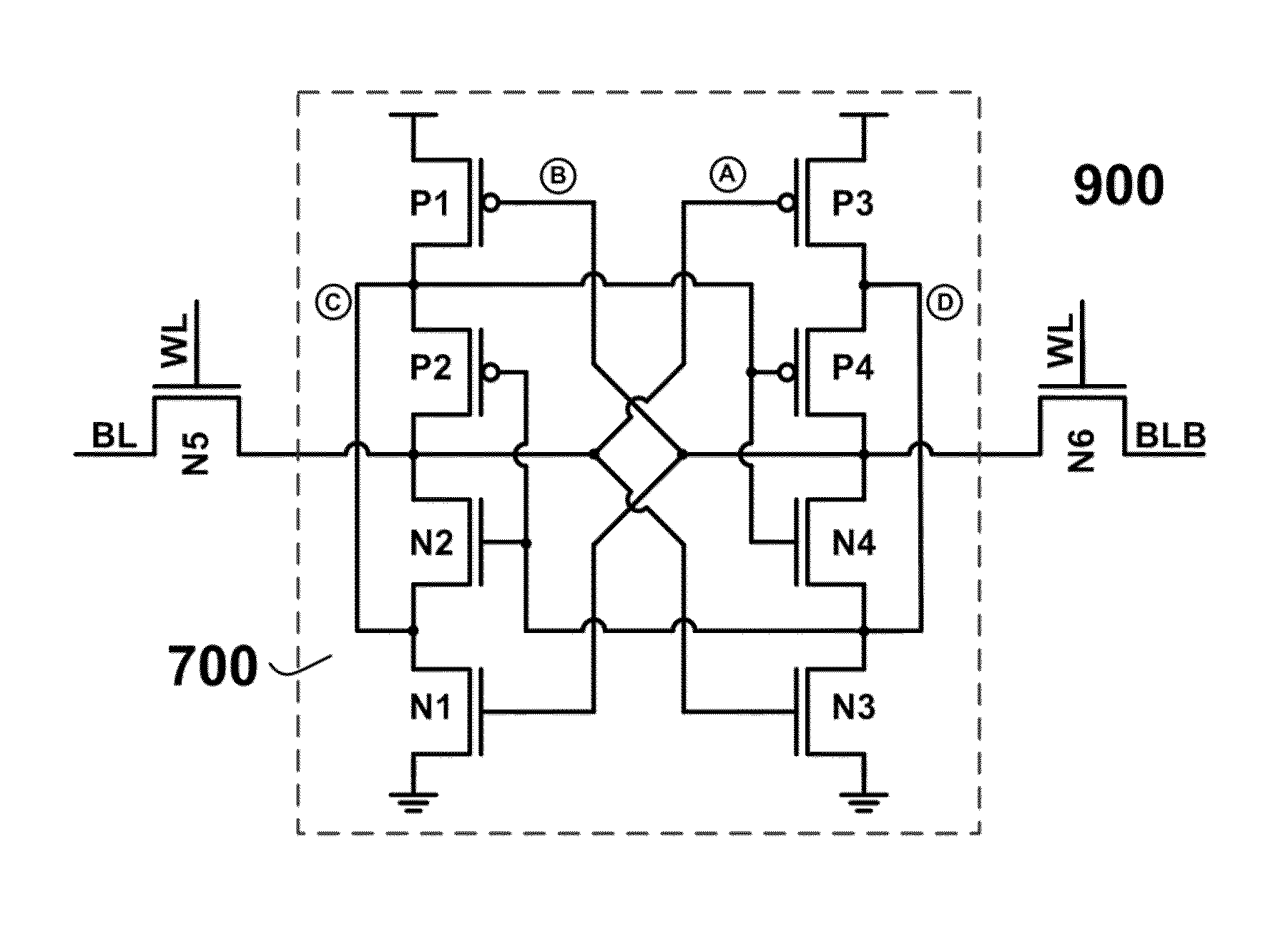

Eight transistor soft error robust storage cell

Owner:NYTELL SOFTWARE LLC

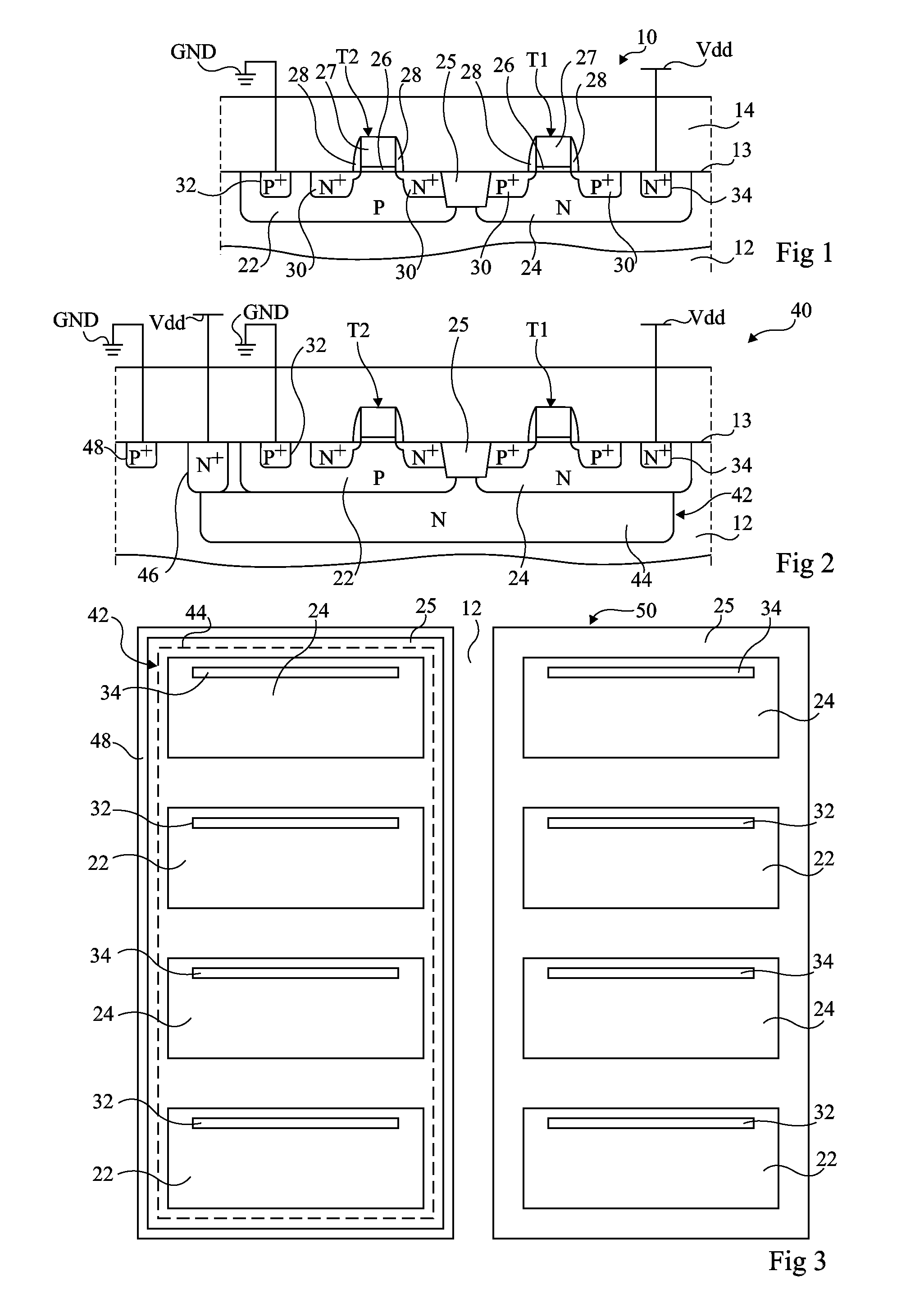

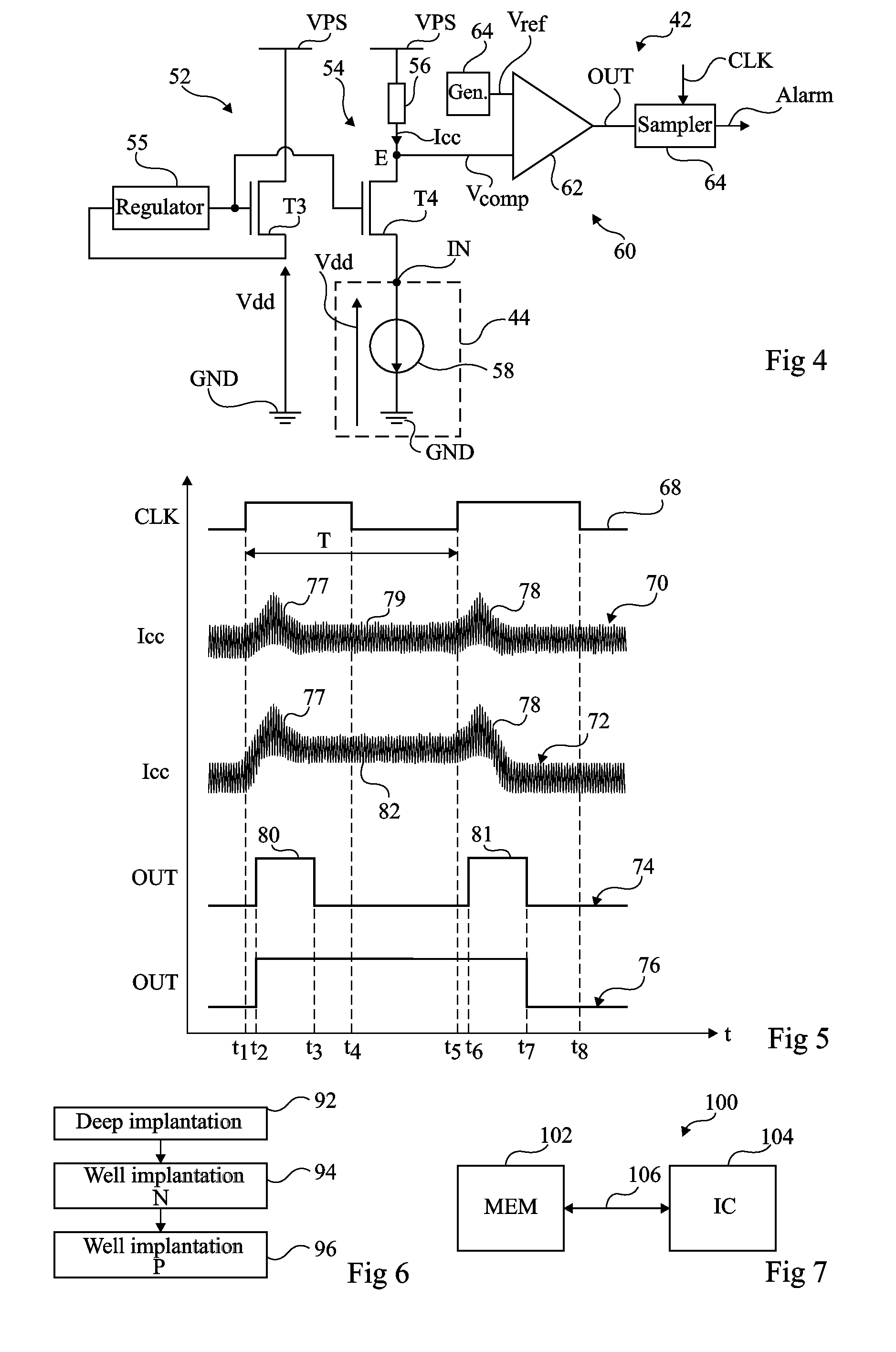

Device for protecting an integrated circuit against a laser attack

InactiveUS20090251168A1Reliability increasing modificationsFail-safe circuitsSemiconductor materialsLaser

An integrated circuit including a substrate of a semiconductor material having first and second opposite surfaces and including active areas leveling the first surface. The integrated circuit includes a device of protection against laser attacks, the protection device includes at least one first doped region extending between at least part of the active areas and the second surface, a device for biasing the first region, and a device for detecting an increase in the current provided by the biasing device.

Owner:STMICROELECTRONICS (ROUSSET) SAS

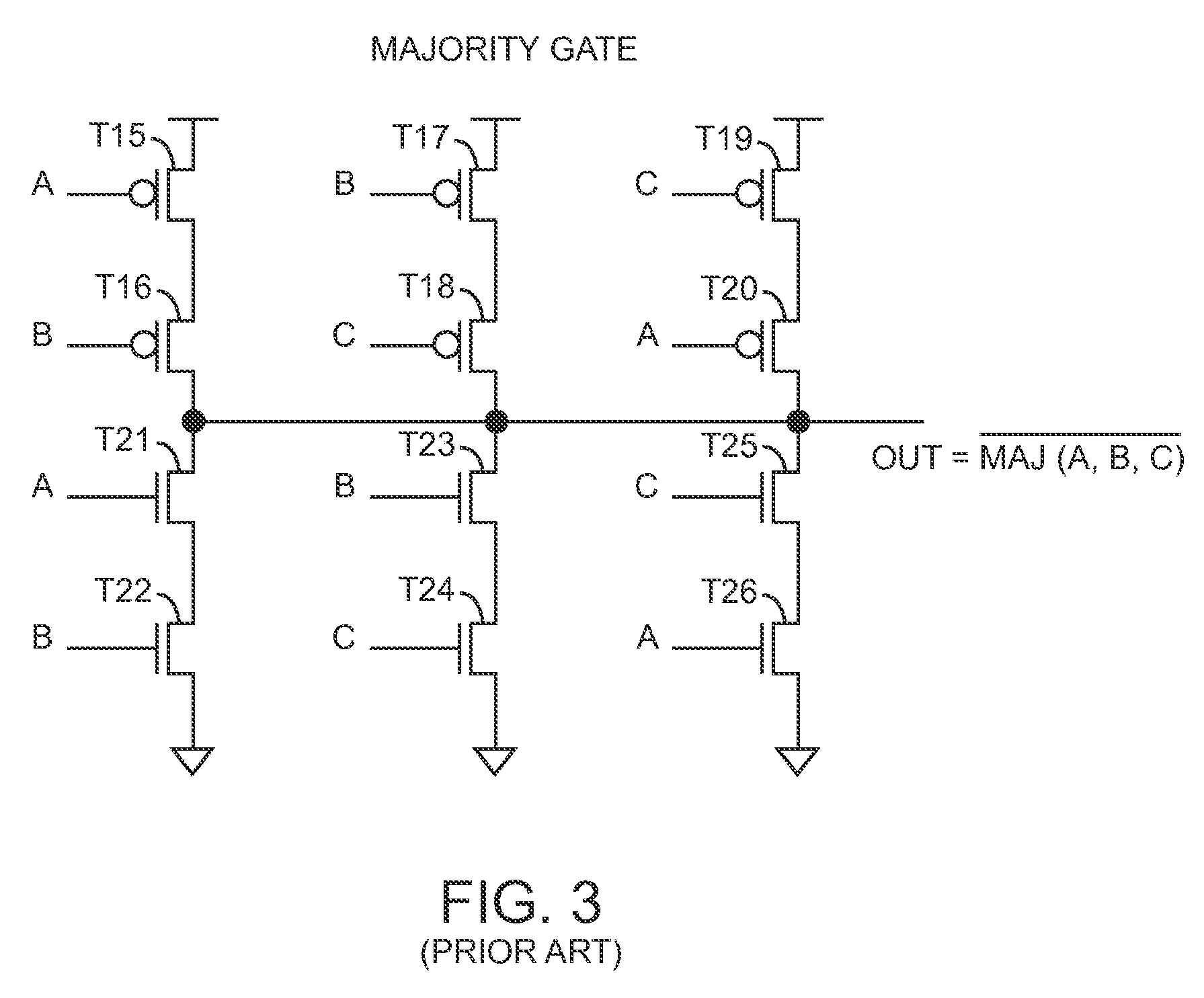

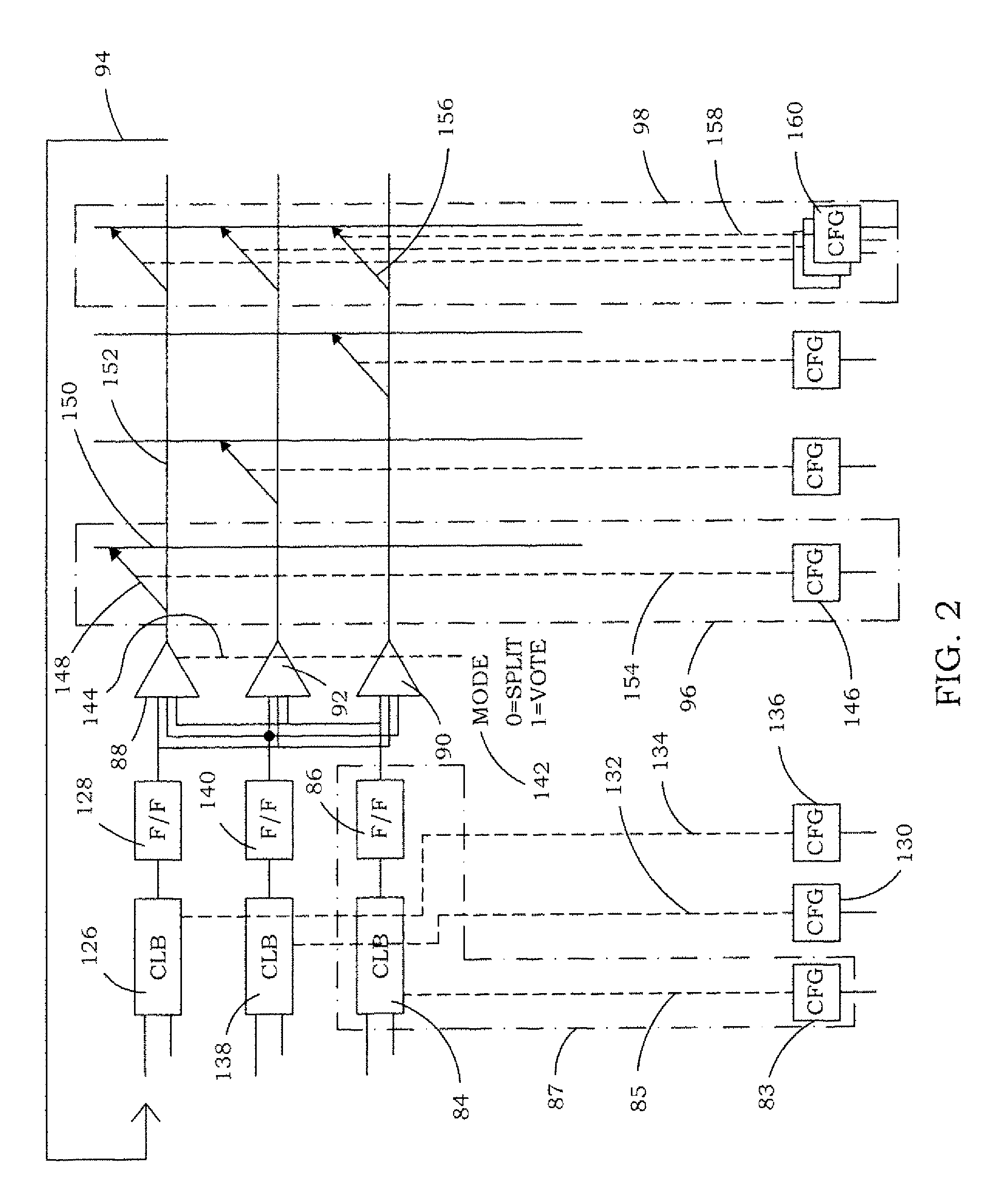

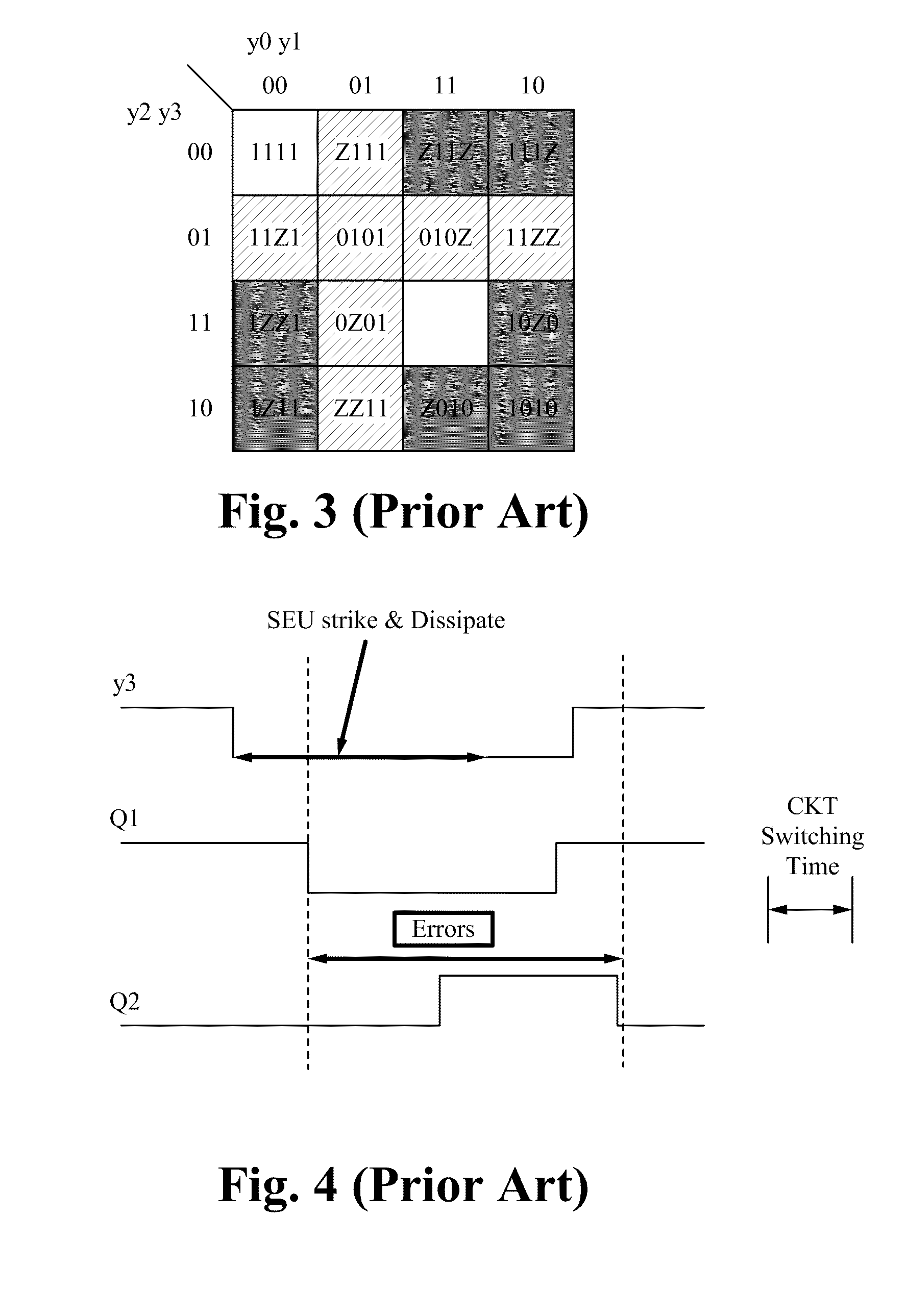

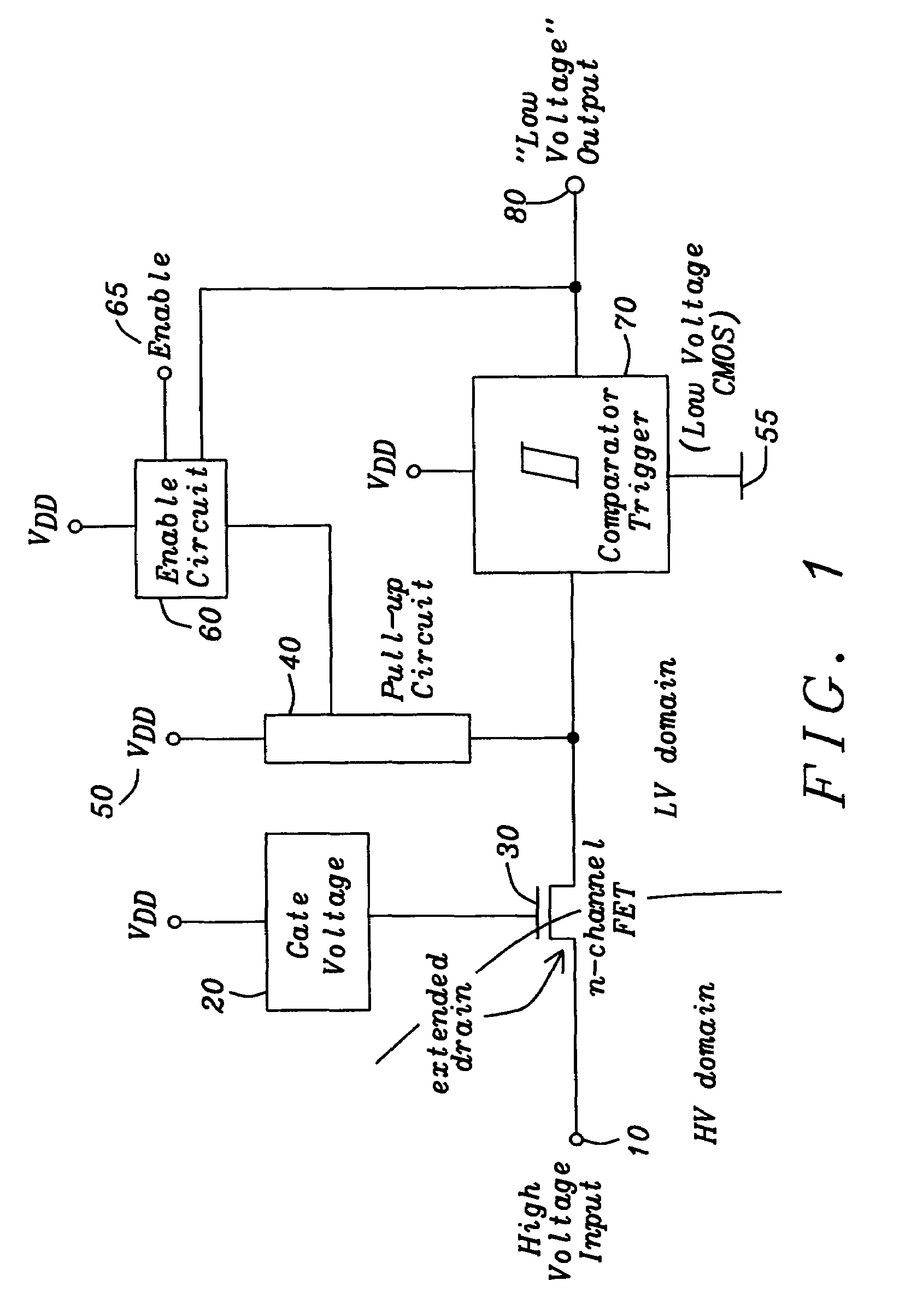

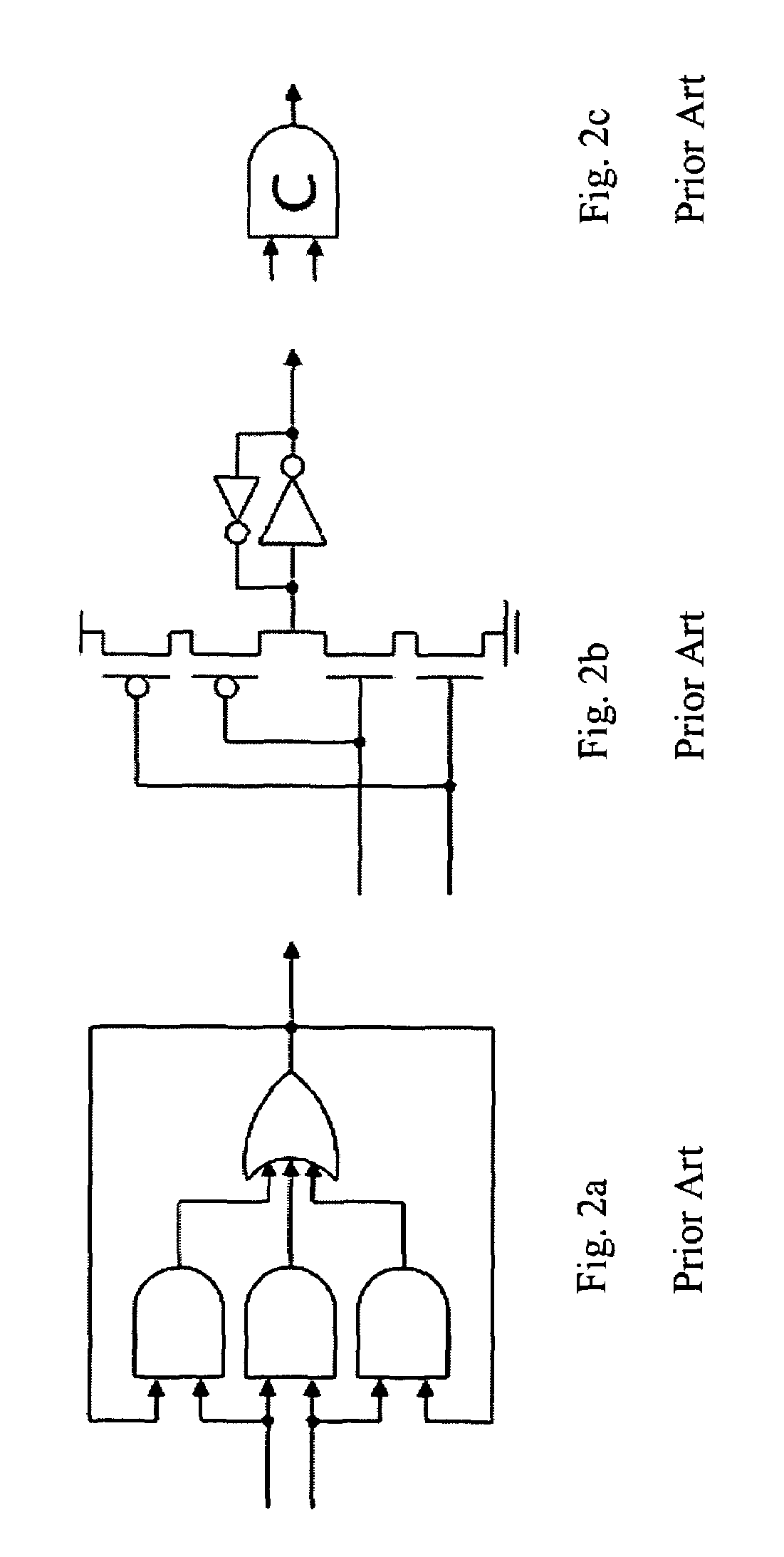

Methods and circuitry for reconfigurable SEU/SET tolerance

InactiveUS7859292B1Large capacityQuicklyMajority/minority circuitsWave amplification devicesComputer scienceMajority voter

Owner:NASA

Design security for configurable devices

ActiveUS7345502B1Fail-safe circuitsElectrical testingProgrammable logic deviceComplex programmable logic device

Methods and structures for design security in configurable devices are described. In some embodiments, a configurable device may be placed in an unsecured mode allowing for access to configuration data and other diagnostic functions during development and production phases. Once the device is finalized, it may be placed in a secure mode that disables a configuration path and enables a bypass path, thereby securing the configuration data. In some embodiments, the configurable device may be a programmable logic device, such as a complex programmable logic device.

Owner:XILINX INC

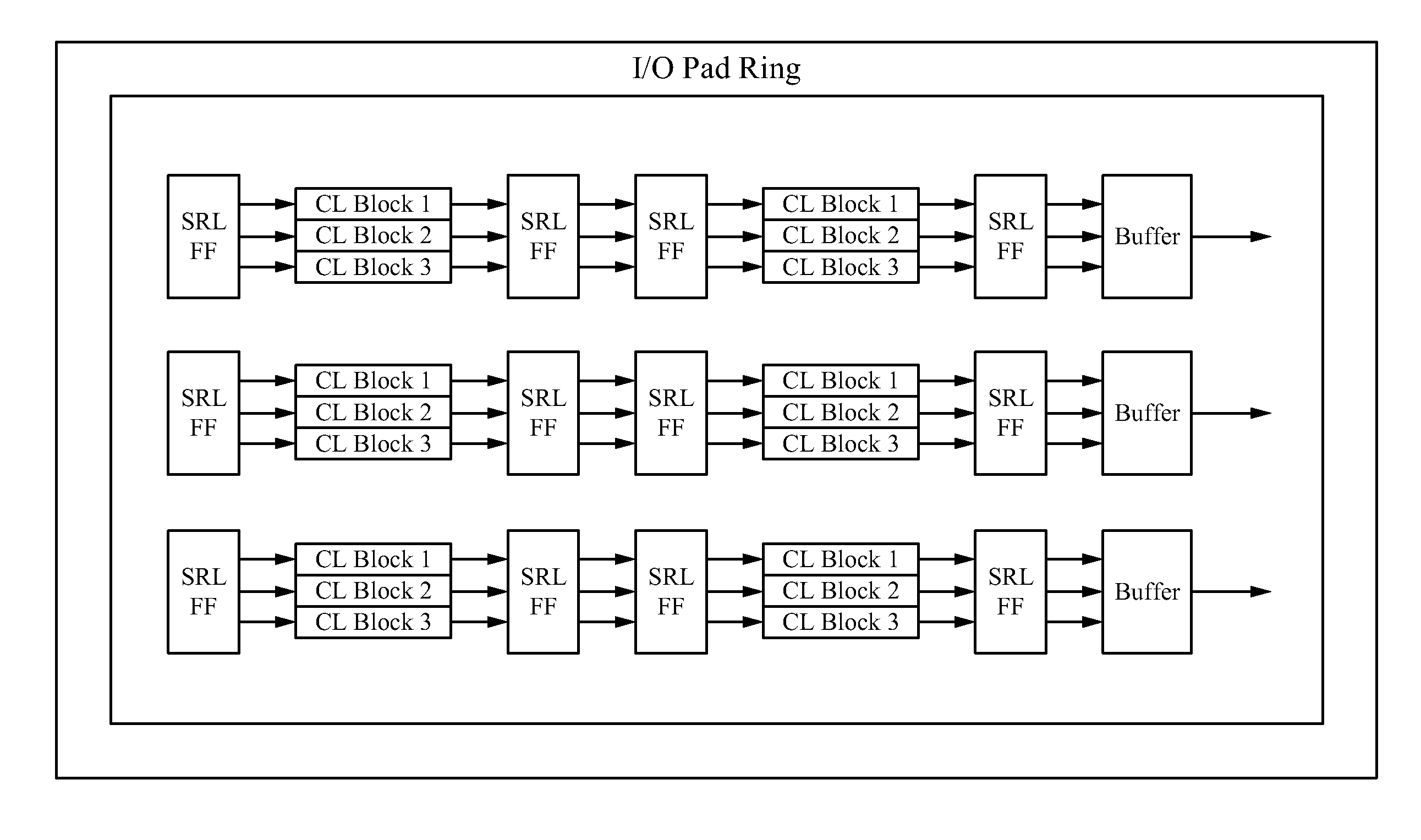

Self restoring logic

Self Restoring Logic (SRL) provides for SEU tolerance in high speed circuits. An SRL cell is designed to be stable in one of two internal states. Upon an SEU event, the SRL cell will not transition between the internal stable states and recover from an SEU. SRL circuits are realized with SRL storage cells driving succeeding SRL storage cells directly or through combinational logic such that the corruption of any one internal state variable in the driving SRL cell and it's the associated combinational output logic can affect at most one internal state variable of the succeeding SRL cell. An SRL circuit does not allow propagation of single SEU faults.

Owner:ICS LLC

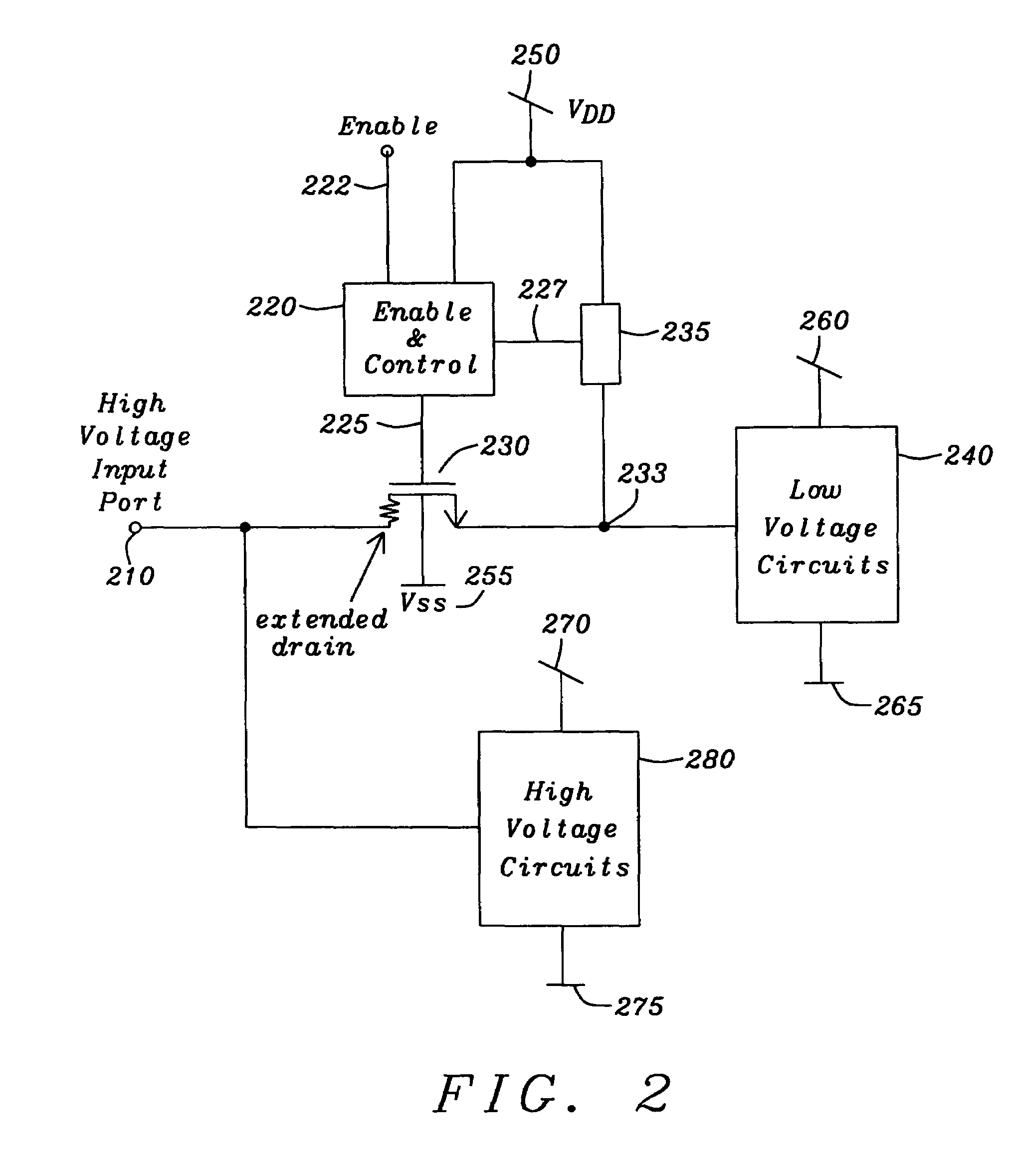

Digital CMOS-input with N-channel extended drain transistor for high-voltage protection

ActiveUS7236002B2Low costFail-safe circuitsReliability increase in field effect transistorsCMOSElectronic systems

A circuit and a method are given, to realize an electronic system for combined usage at differing voltage ranges as defined by a low-voltage range for operating standard CMOS devices and a high-voltage range exceeding said standard CMOS low-voltage operating range significantly by multiples and thus necessarily utilizing input ports with an intrinsic high-voltage protection feature. Said circuit and method are designed in order to be implemented with a very economic number of components, capable to be realized with standard modern integrated circuit technologies in CMOS technology.

Owner:DIALOG SEMICONDUCTOR GMBH

Reconfigurable integrated circuit architecture with on-chip configuration and reconfiguration

InactiveUS8390325B2Significant resiliencyError detection/correctionFail-safe circuitsComputer architectureProcessor register

The exemplary embodiments provide a reconfigurable integrated circuit capable of on-chip configuration and reconfiguration, comprising: a plurality of configurable composite circuit elements; a configuration and control bus; a memory; and a sequential processor. Each composite circuit element comprises: a configurable circuit; and an element interface and control circuit, the element interface and control circuit comprising an element controller and at least one configuration and control register to store one or more configuration and control words. The configuration and control bus is coupled to the plurality of configurable composite circuit elements, and comprises a plurality of address and control lines and a plurality of data lines. The sequential processor can write configurations to the configuration and control registers of an addressed configurable composite circuit element to configure or reconfigure the configurable circuit.

Owner:ELEMENT CXI

Configurable IC with trace buffer and/or logic analyzer functionality

InactiveUS20080191733A1Quick configurationEasy to operateReliability increasing modificationsFail-safe circuitsHemt circuitsLogic analyzer

Some embodiments of the invention provide a configurable integrated circuit (IC) that includes several configurable circuits for configurably performing different operations and several user design state (UDS) circuits for storing user-design state values. The IC further includes a trace buffer for storing user-design state values associated with an operational trigger event of the IC. In some embodiments, the configurable circuits, UDS circuits, and tracer buffer are on a single IC die.

Owner:TAHOE RES LTD

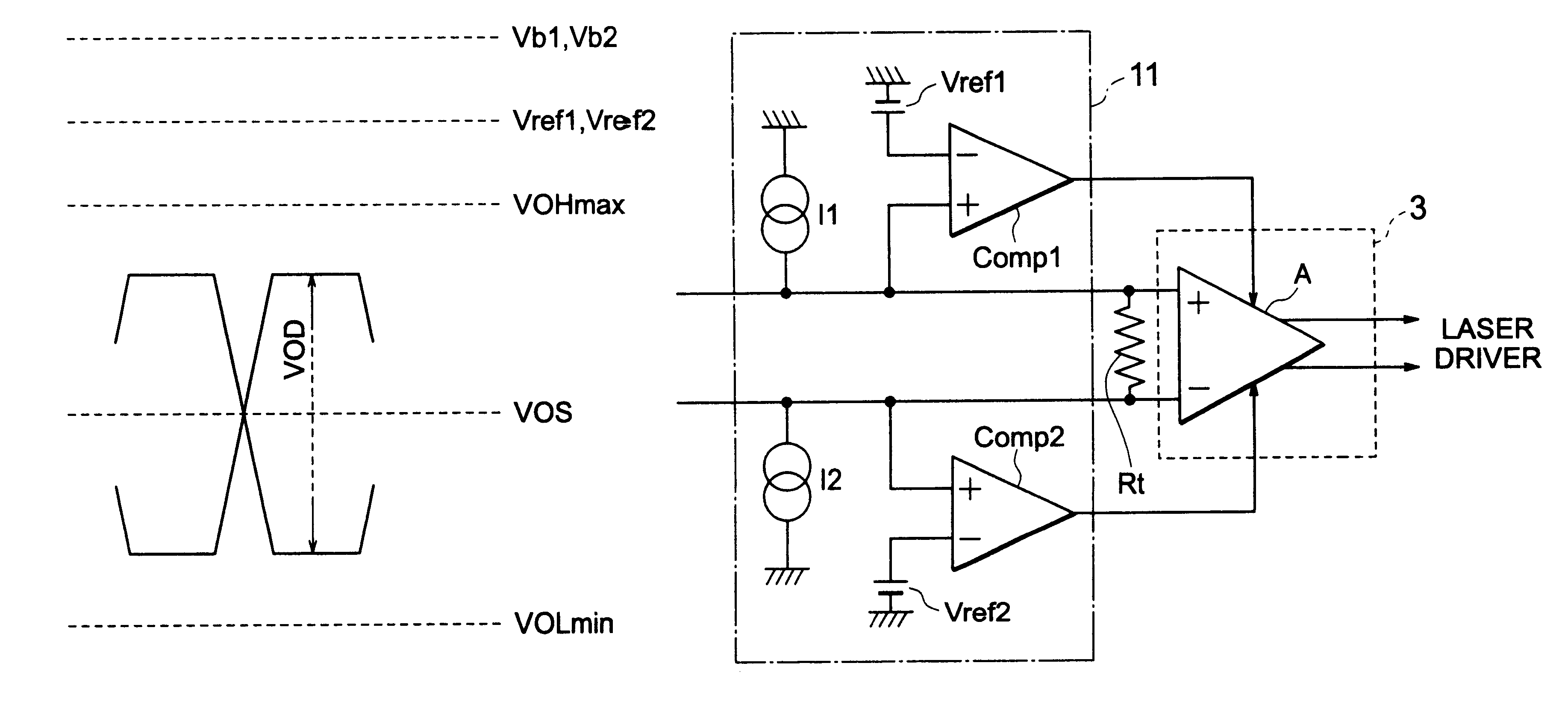

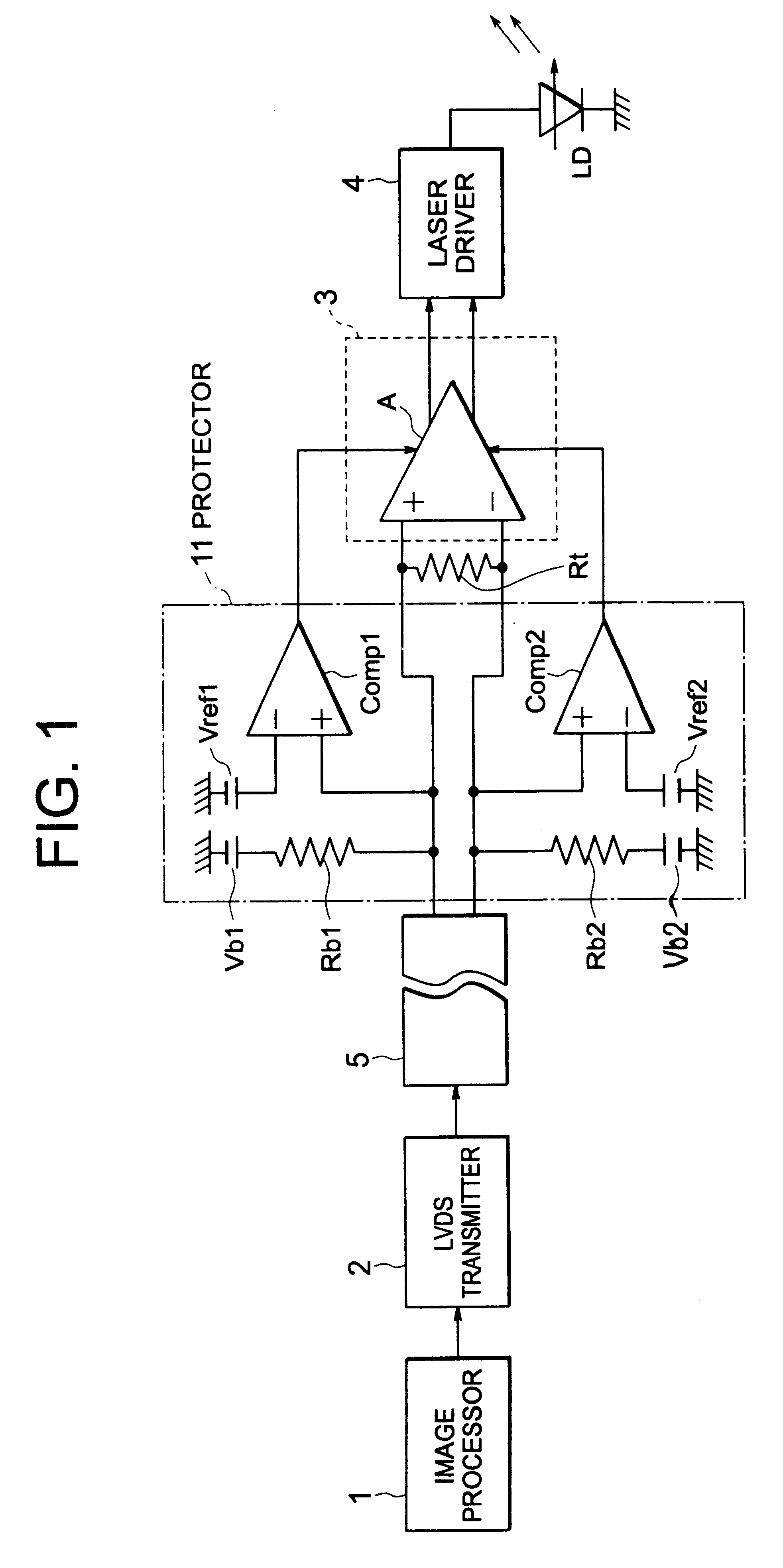

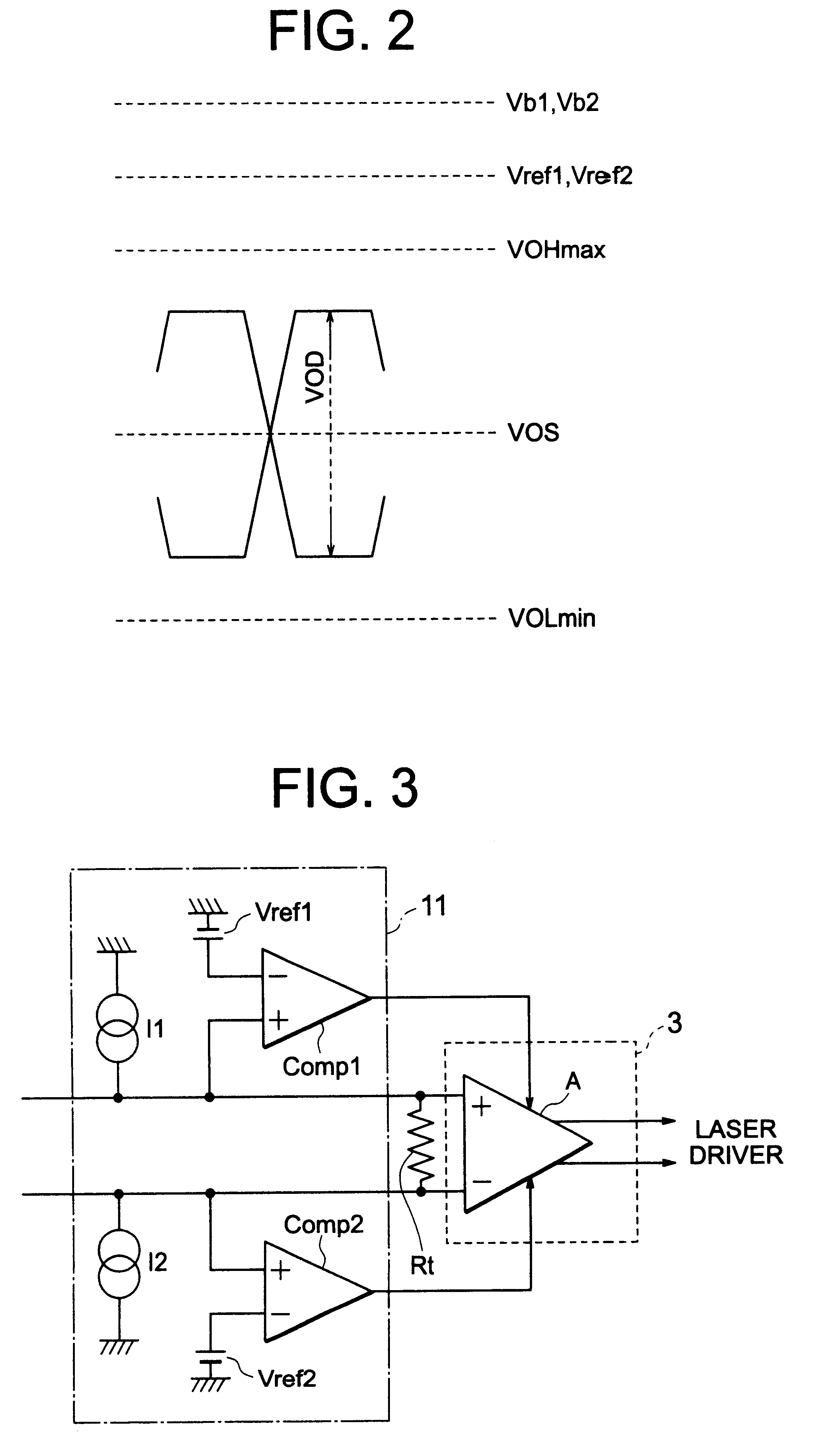

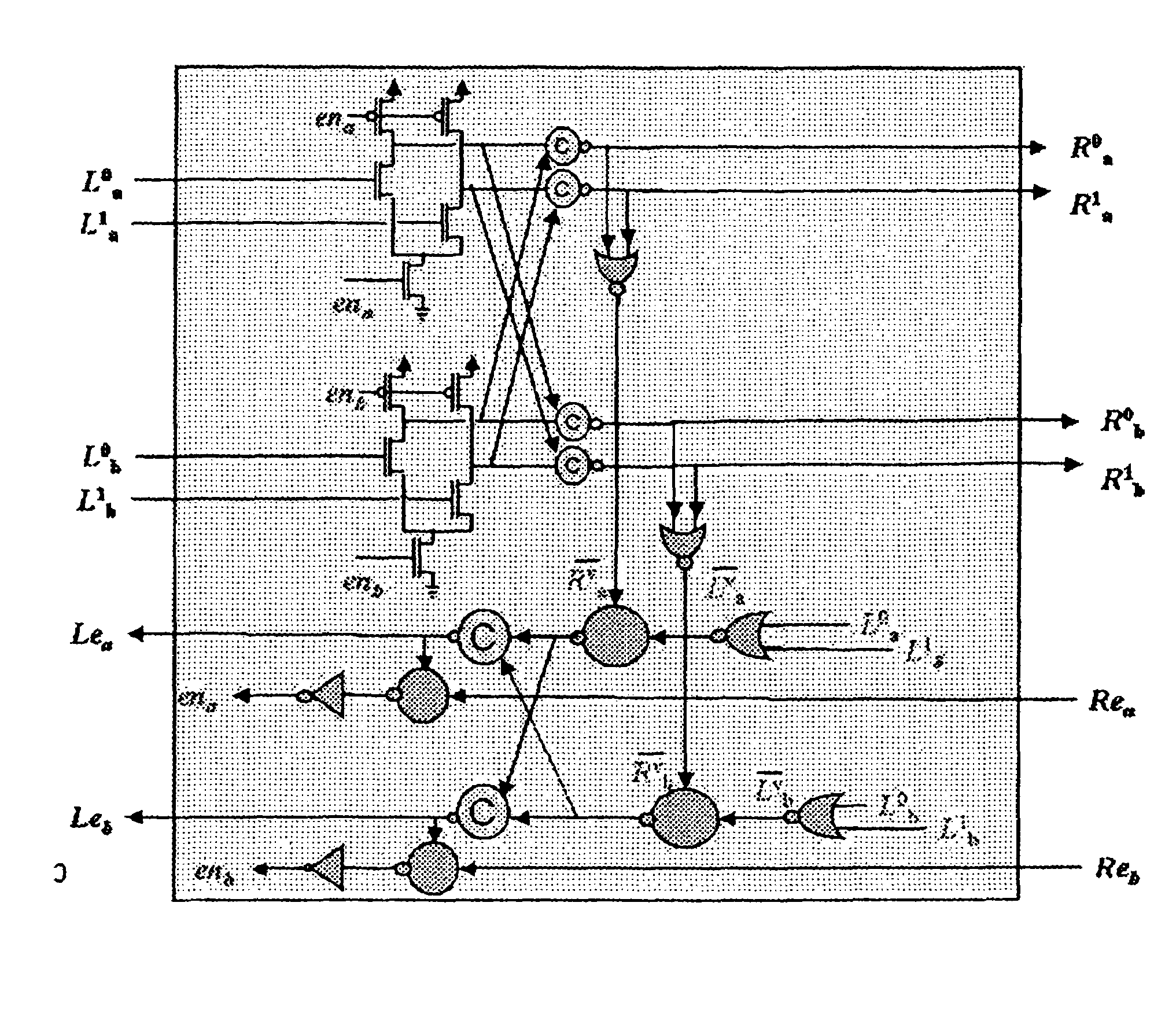

Protecting unit

InactiveUS6486695B1Reliability increasing modificationsMultiple input and output pulse circuitsDifferential signalingEngineering

A protecting unit is provided. The protecting unit can prevent accidents from occurring that become problems when data are transmitted due to for instance LVDS and for instance laser light is emitted based on the data. The protecting unit is applied in an instrument comprising an input end to which differential signal is transmitted, the input end being attachable to and detachable from an input line. Here, the voltage at the input end when the input line is not connected is set to a voltage different from that generated at the input end when the input line is connected, variation of the voltage at the input end is transmitted to an input terminal of a differential input / output circuit, and the voltage at the input end or a portion corresponding thereto is compared with a prescribed voltage to fix a state of output of the differential input / output circuit to a prescribed state based on the compared results.

Owner:KK TOSHIBA

Duplicated double checking production rule set for fault-tolerant electronics

InactiveUS7301362B2Reduce soft errorsEliminating soft errorReliability increasing modificationsFail-safe circuitsElectronic systemsHemt circuits

Systems and methods for mitigating the effects of soft errors in asynchronous digital circuits. Circuits are constructed using stages comprising doubled logic elements which are connected to c-elements that compare the output states of the double logic elements. The inputs of logic elements in a stage are inhibited from changing until the outputs of the c-elements of that stage are enabled. The c-elements inhibit the propagation of a soft error by halting the operation of the circuit until the temporary effects of the soft error pass.

Owner:CALIFORNIA INST OF TECH

Popular searches

Electronic switching Radiation hardening Software simulation/interpretation/emulation Special data processing applications Memory systems Digital computer details Program control Logic circuits using elementary logic circuit components Computation using denominational number representation Differential amplifiers

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com