Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

484 results about "Test path" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

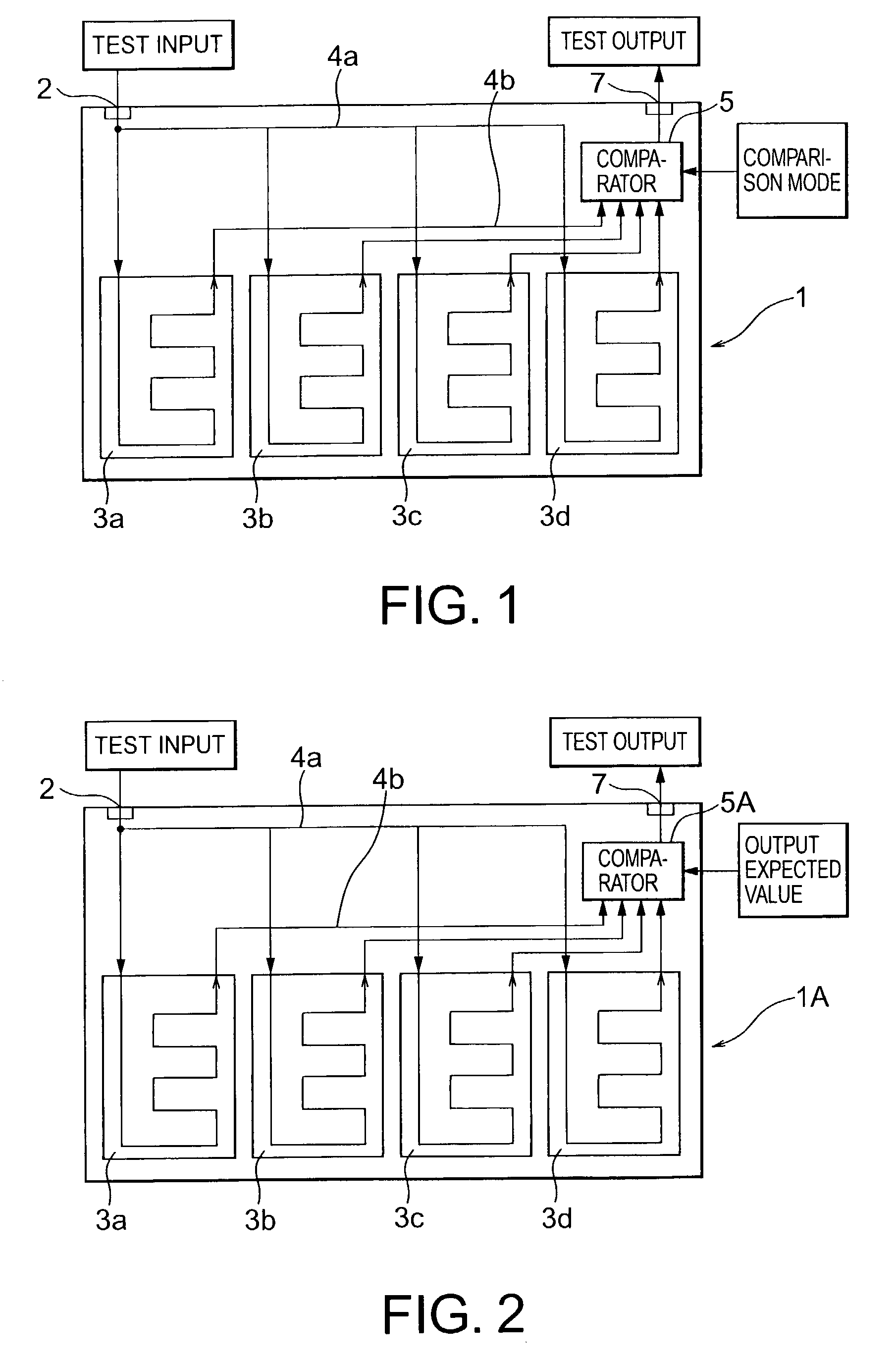

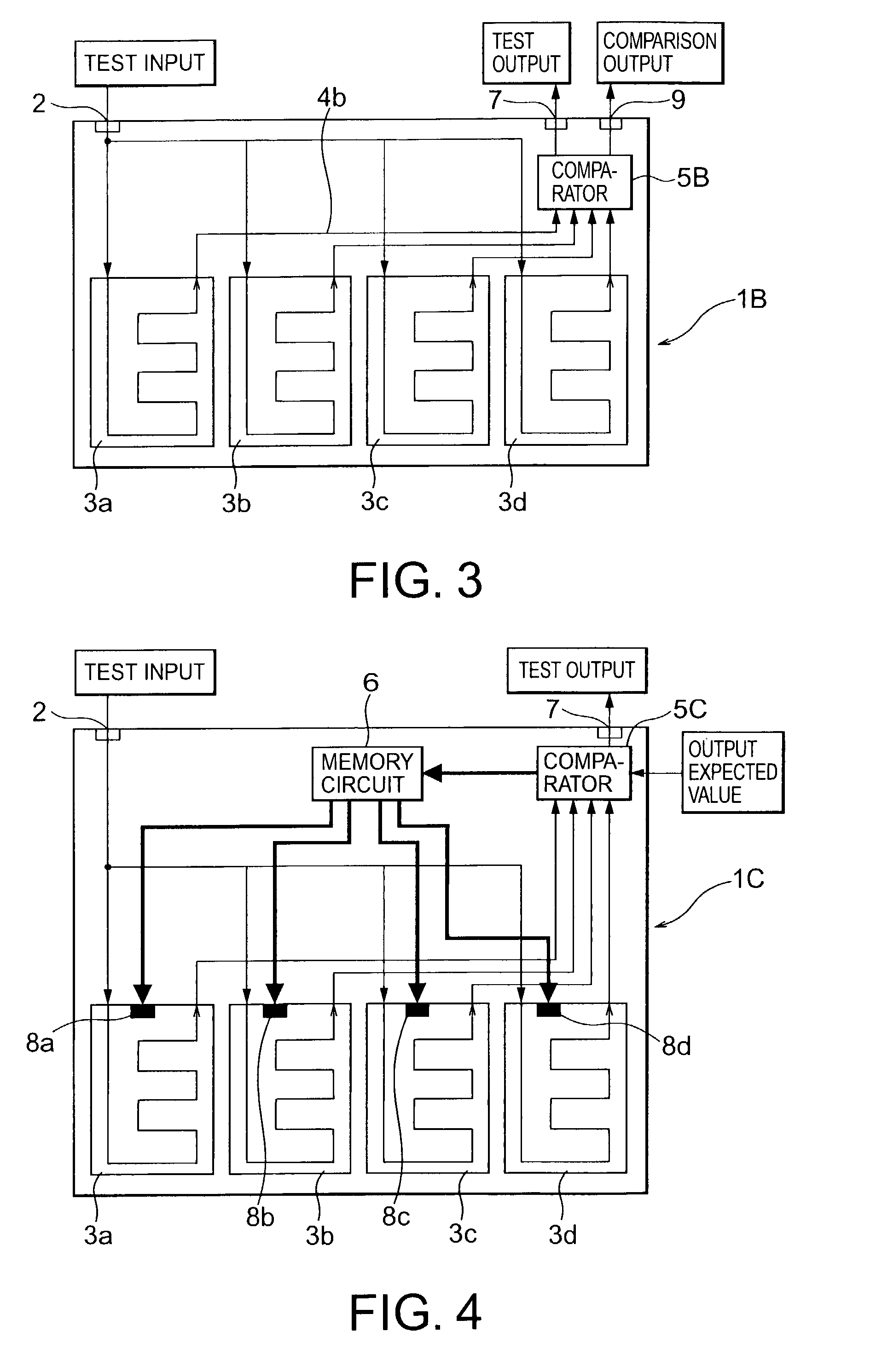

Semiconductor integrated circuit

InactiveUS20030061555A1Semiconductor/solid-state device testing/measurementElectronic circuit testingComparative testSemiconductor

A semiconductor integrated circuit includes: a plurality of circuits to be tested, each having the same structure; test paths each provided for one of the circuits to be tested; and a comparator receiving, via the test paths, test outputs sent from the circuits to be tested, comparing the test outputs, and determining whether the test outputs match with each other or not.

Owner:KK TOSHIBA

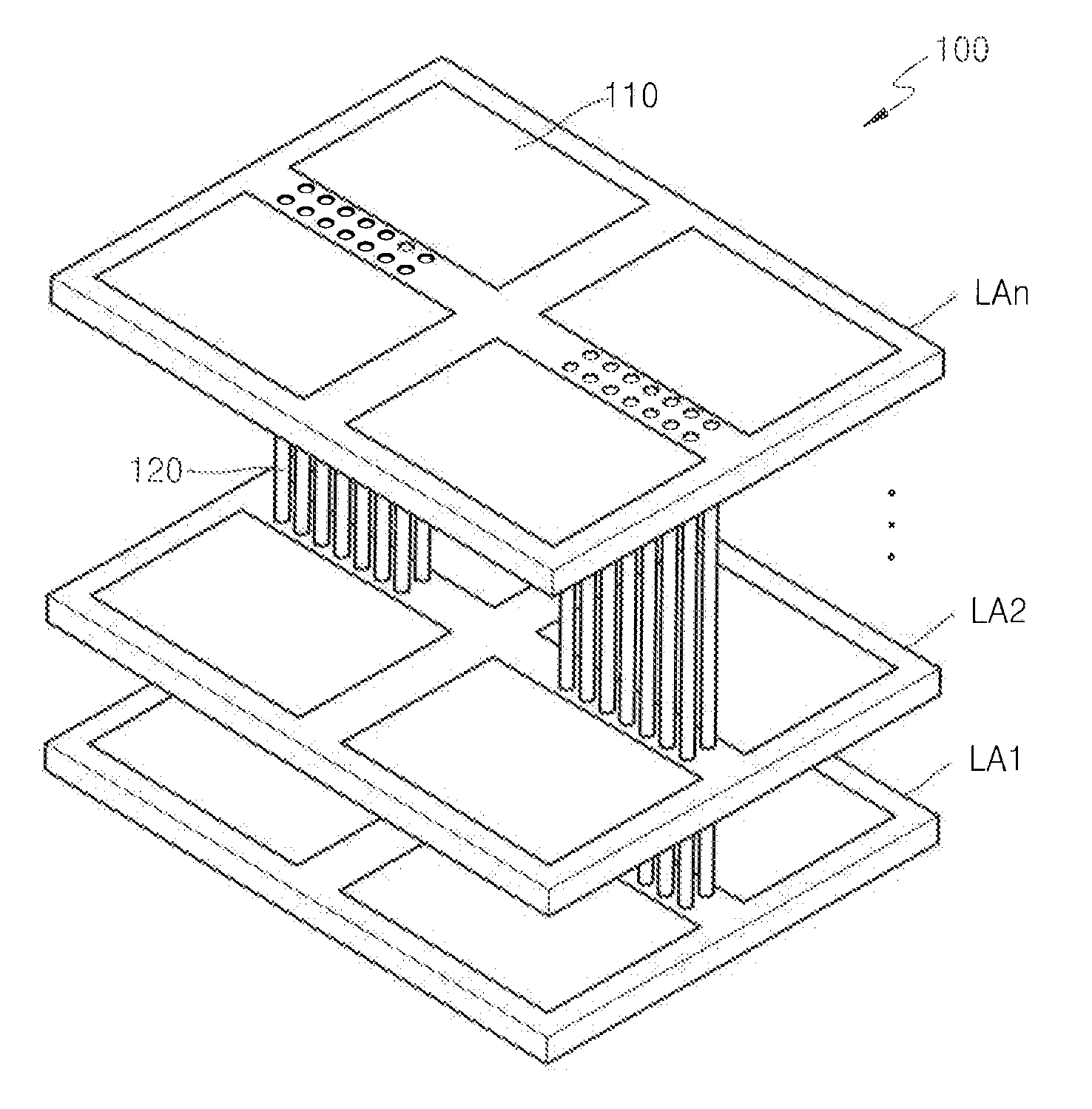

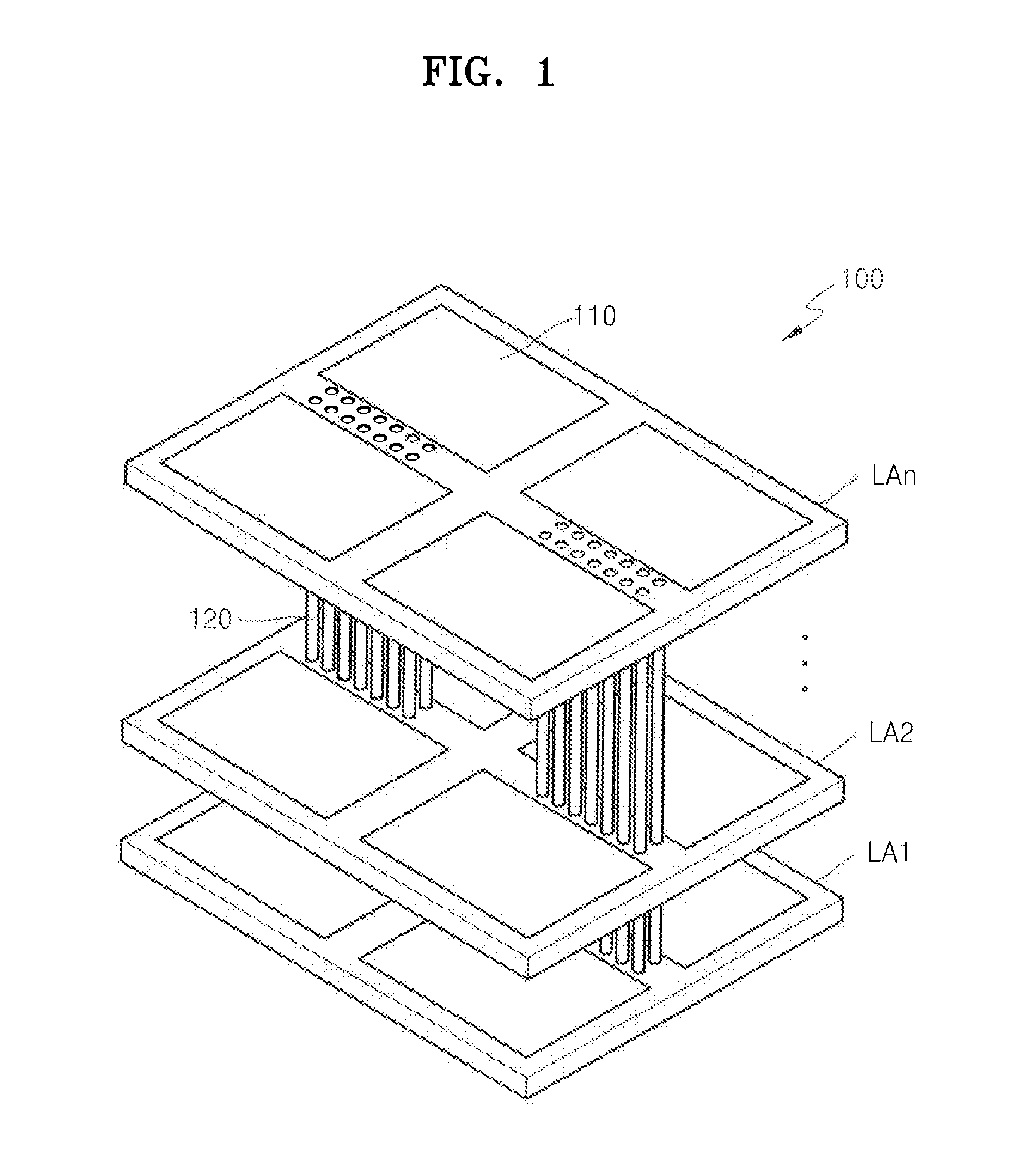

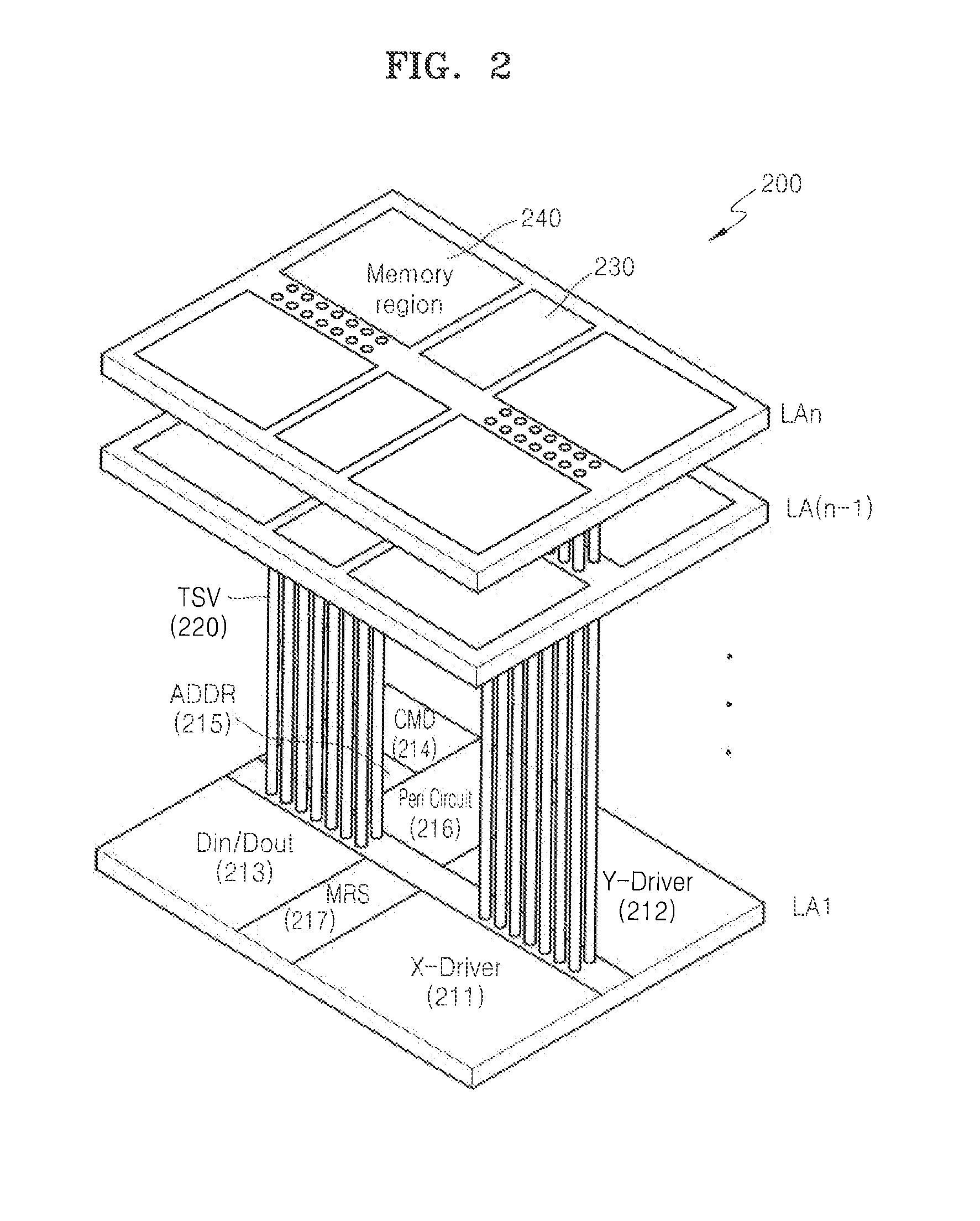

Semiconductor device having stacked structure including through-silicon-vias and method of testing the same

InactiveUS20120138927A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsPower semiconductor deviceElectrical conductor

A semiconductor device having a stacked structure including through-silicon-vias (TSVs) and a method of testing the semiconductor device. The semiconductor device includes a first semiconductor layer, one or more second semiconductor layers stacked on the first semiconductor layer, and a plurality of input through-silicon-vias (TSVs) to transmit signals from a plurality of input pads, respectively. In a test mode, a test signal from the plurality of input pads is transmitted through at least two test paths, and the test signal transmitted through each of the test paths is output as a test result with respect to each of the plurality of input TSVs through an output pad.

Owner:SAMSUNG ELECTRONICS CO LTD

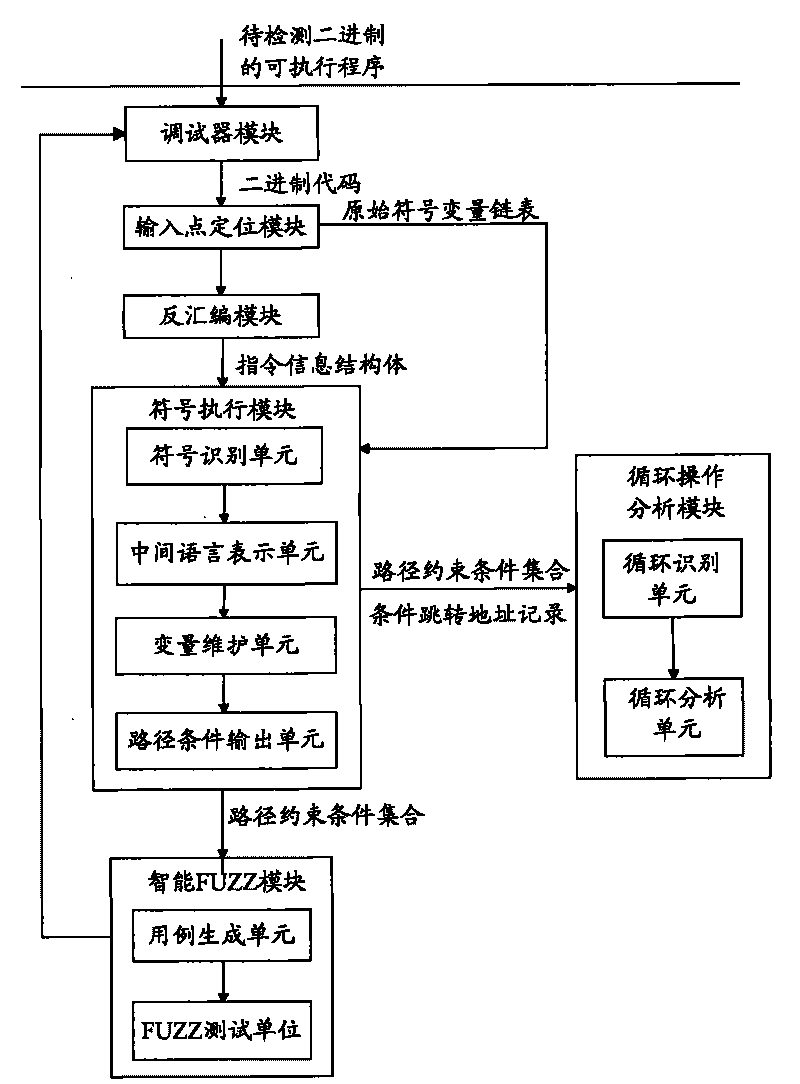

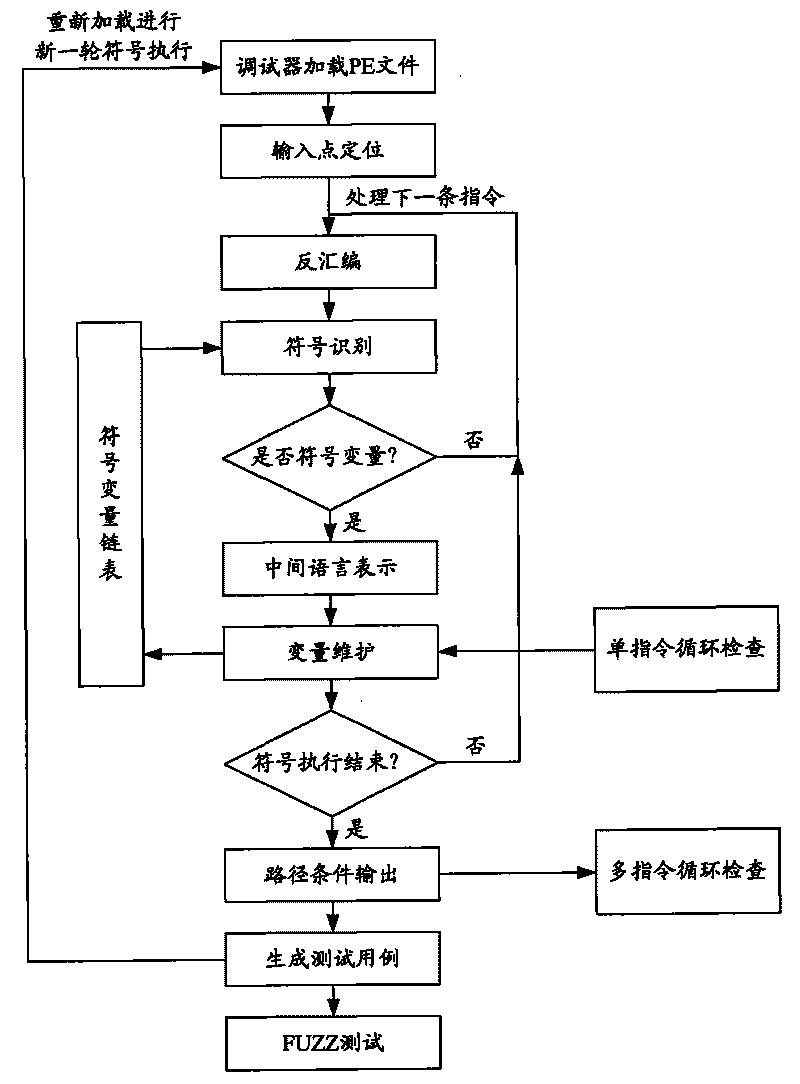

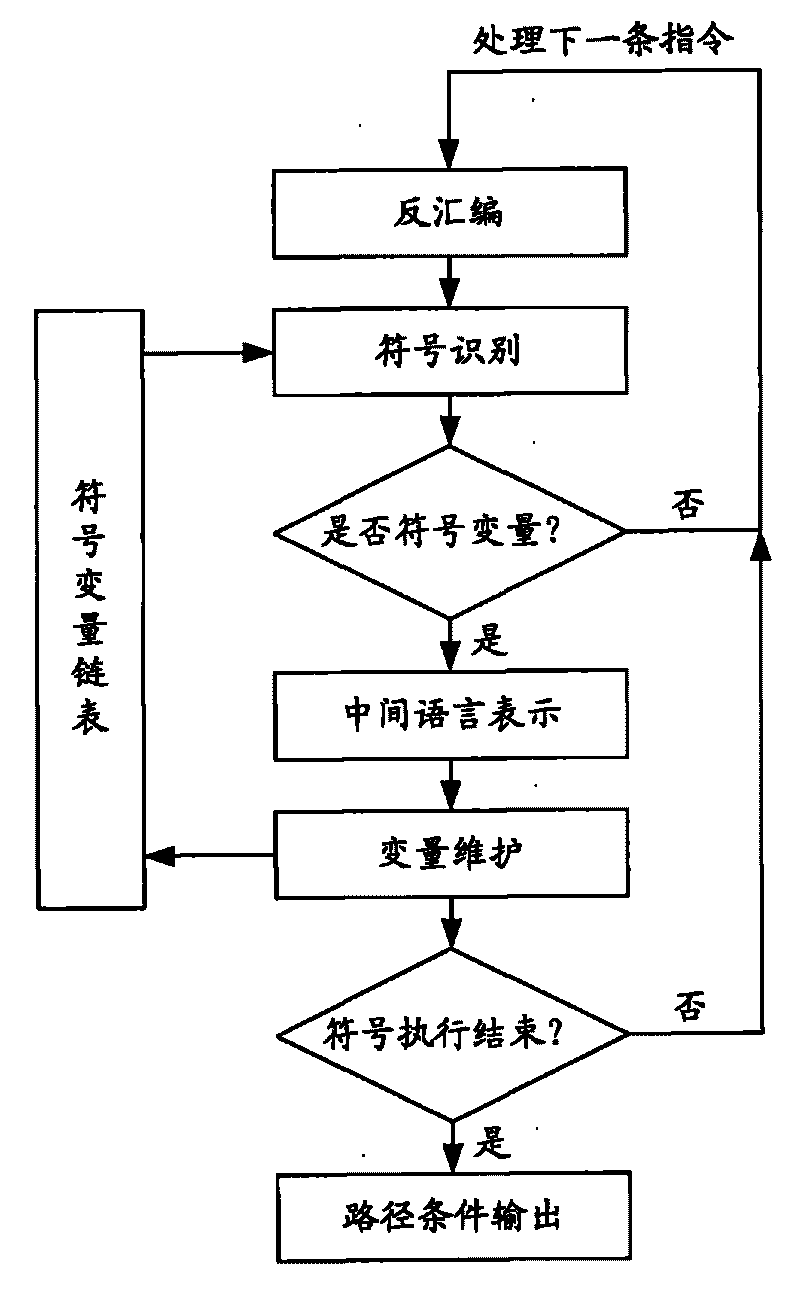

Detector for binary-code buffer-zone overflow bugs, and detection method thereof

InactiveCN101714118AGuaranteed feasibilityGuaranteed accuracyMultiprogramming arrangementsSoftware testing/debuggingBuffer overflowSource code

The invention provides a detector for binary-code buffer-zone overflow bugs, and a detection method thereof. The detector comprises six functional modules, namely a debugger module, an input point positioning module, a disassembling module, a symbolic execution module, a loop operation analysis module and an intelligent FUZZ test module. Differing from static symbolic execution, the detection method dynamically loads programs through the self-developed debugger module to synchronously performing symbolic execution and single-step practical execution, and then applies a model to solve each difficulty in binary code analysis so as to test path coverage and detect overflow bugs in accordance with all executable programs of PE format under a Windows platform. The detection can also provide propagation paths of input data and other important information related to bug formation cause while positioning the bugs, only analyzes the selves of the executable programs, needs no source codes, is unrelated to the species of source codes and development tools, and is extensive in applicable occasions, so the detection method has good prospects for popularization and application.

Owner:BEIJING UNIV OF POSTS & TELECOMM

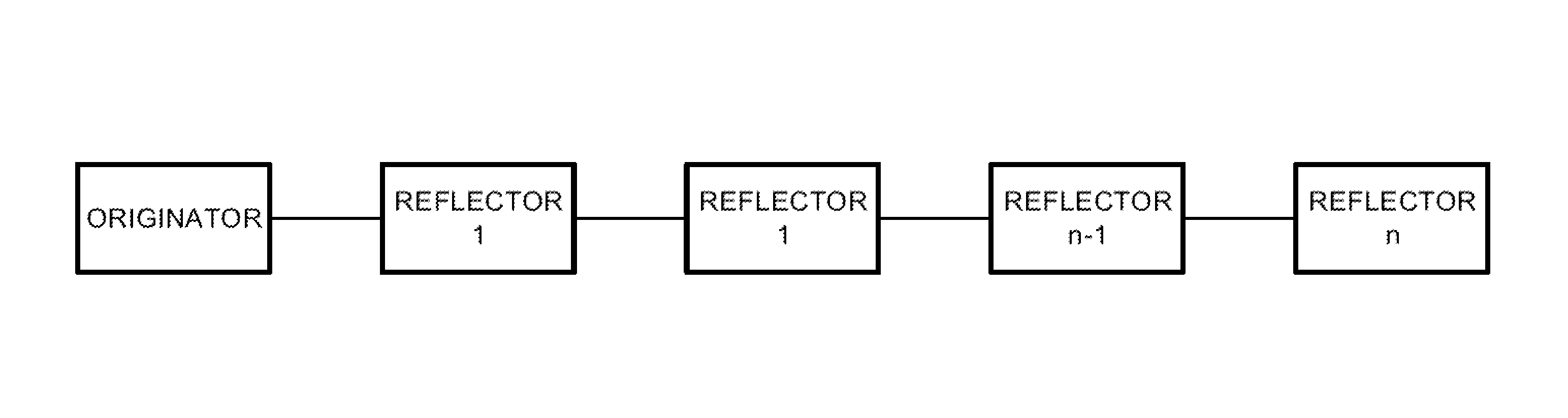

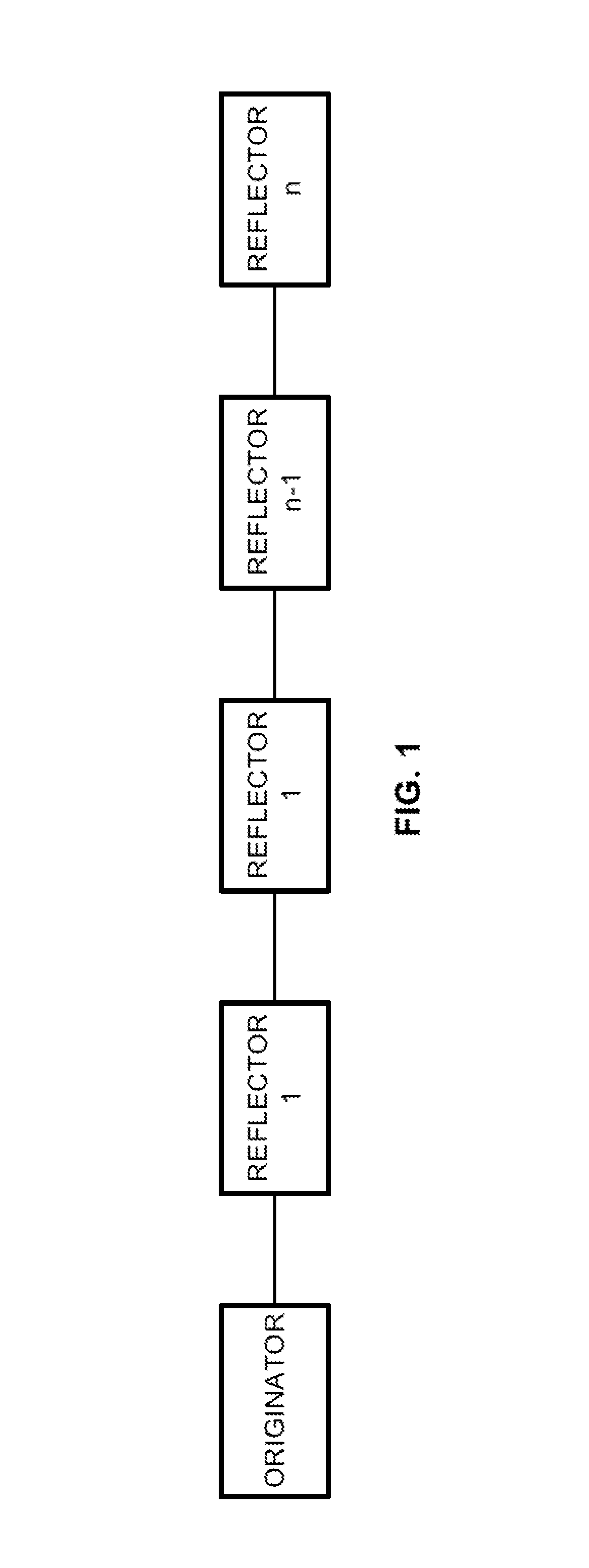

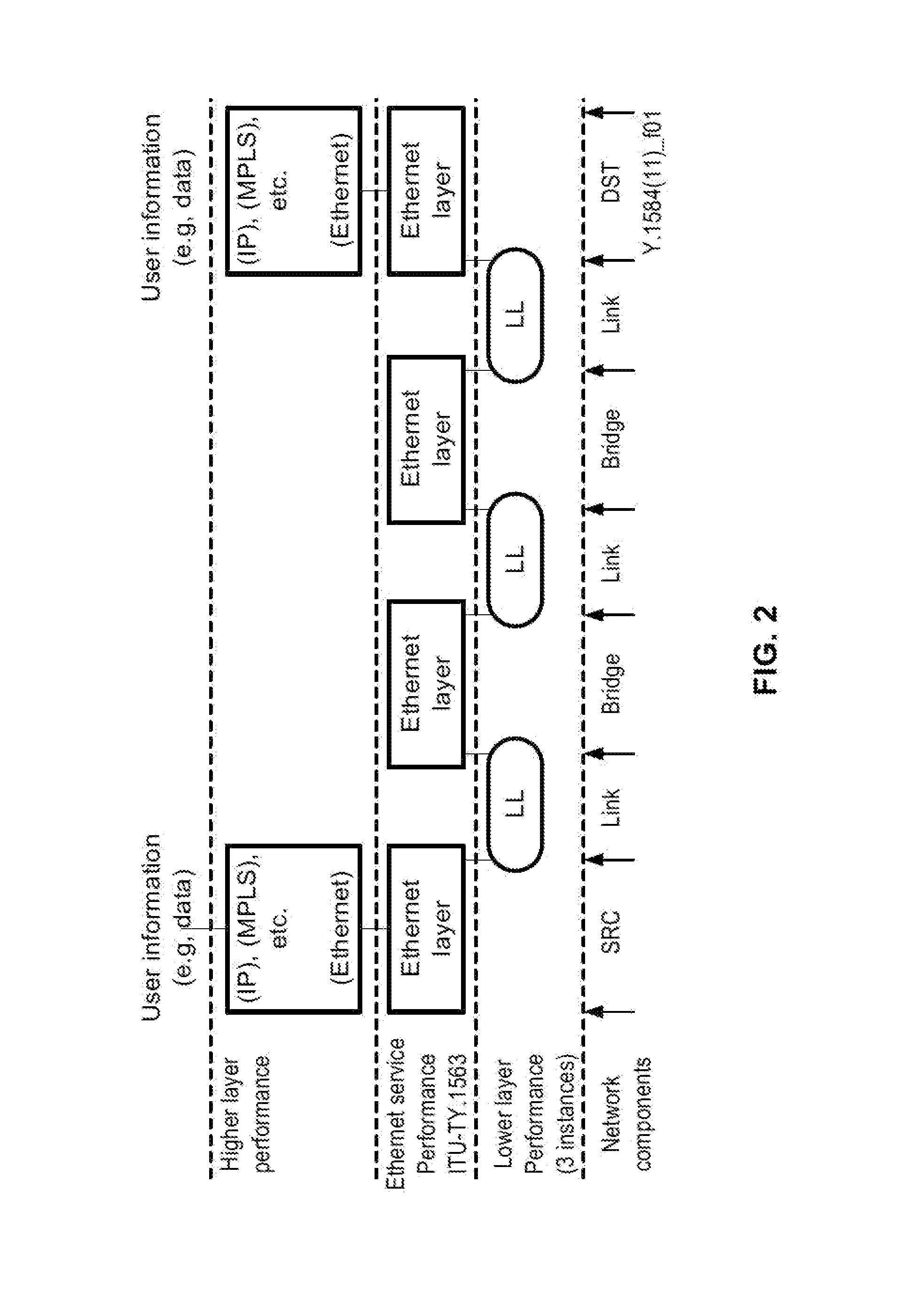

Multi-hop reflector sessions

A method for measuring and reporting performance parameters in a network having at least one originator for generating test protocol data units, and multiple reflectors for relaying the test protocol data units along successive segments of a test path in the network. The method generates the test protocol data units at the originator and transmits the test protocol data unit along a test path that includes multiple reflectors. Each reflector relays the test protocol data unit to the next reflector along the test path. Measurements of performance parameters are collected from the multiple reflectors in the test protocol data unit by inserting timestamps into the test protocol data unit at the originator and each of the reflectors to identify the departure and arrival times for each test protocol data unit at the originator and each of the reflectors in both the downstream and upstream directions along the test path.

Owner:ACCEDIAN NETWORKS

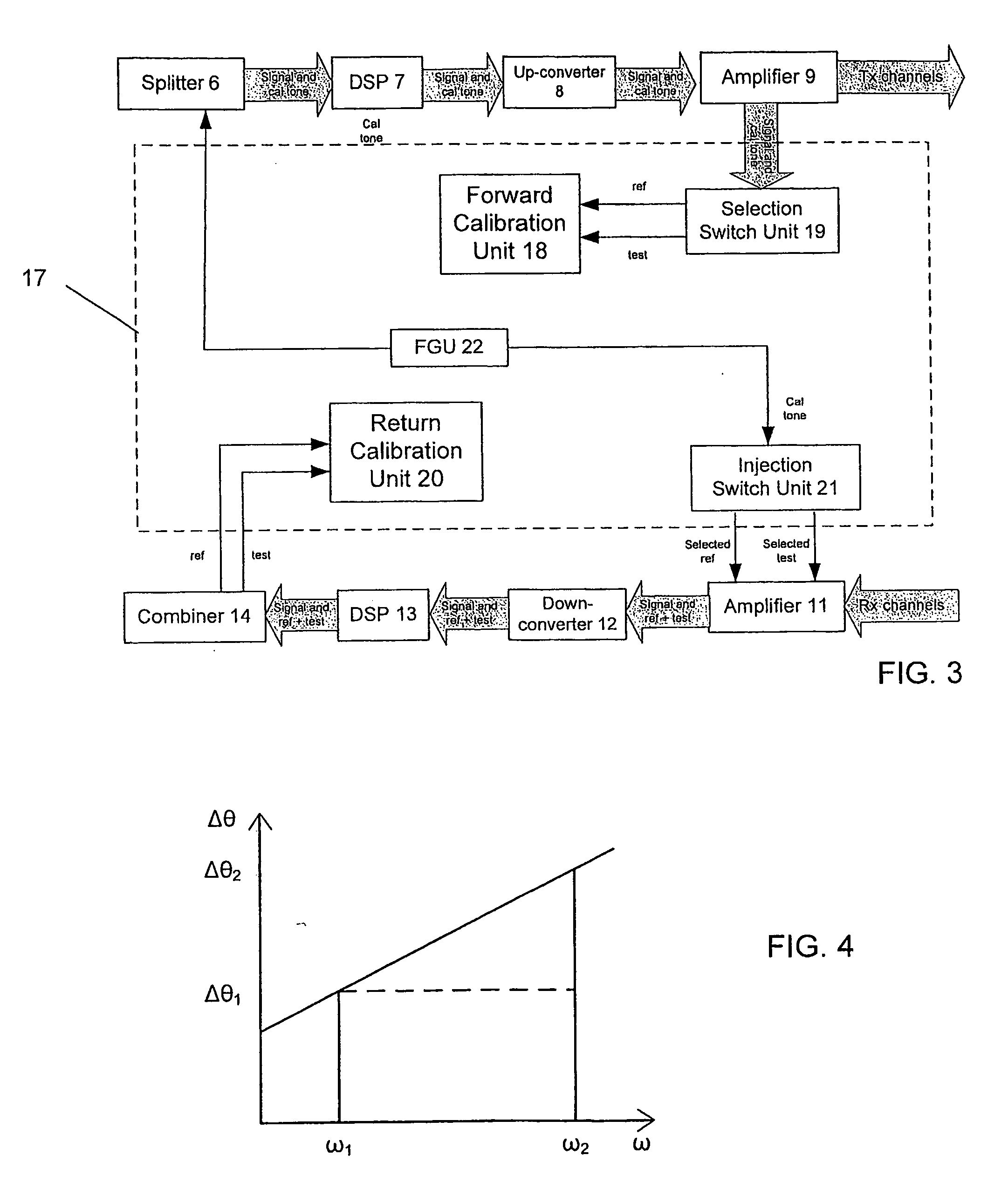

Calibration apparatus and method

ActiveUS20100164782A1Wave based measurement systemsReceivers monitoringMulti beamOperating frequency

There is provided an apparatus for calibrating a multi-beam satellite system comprising a beam forming network providing a plurality of signal paths, the apparatus comprising a calibration processor for determining the phase and amplitude shift of a test path of the plurality of signal paths by correlating a calibration tone extracted from the test path with a reference calibration signal, the calibration processor being configured to determine the phase and amplitude shifts of the test path for at least two calibration tones of at least two different frequencies. The apparatus also comprises means for applying a correction based on the determined phase and amplitude shift to the test path in the beam forming network. The two calibration tones of at least two different frequencies may be calibration tones injected at two different frequencies but also calibration tones translated into two different frequencies by the beam forming network. The invention allows a phase and amplitude shift for any path through the beam forming network to be calculated for any frequency in an operational frequency range of the multi-beam satellite system and corrections to be applied to form or interpret the required downlink or uplink beams of the multi-beam satellite system.

Owner:ASTRIUM LTD

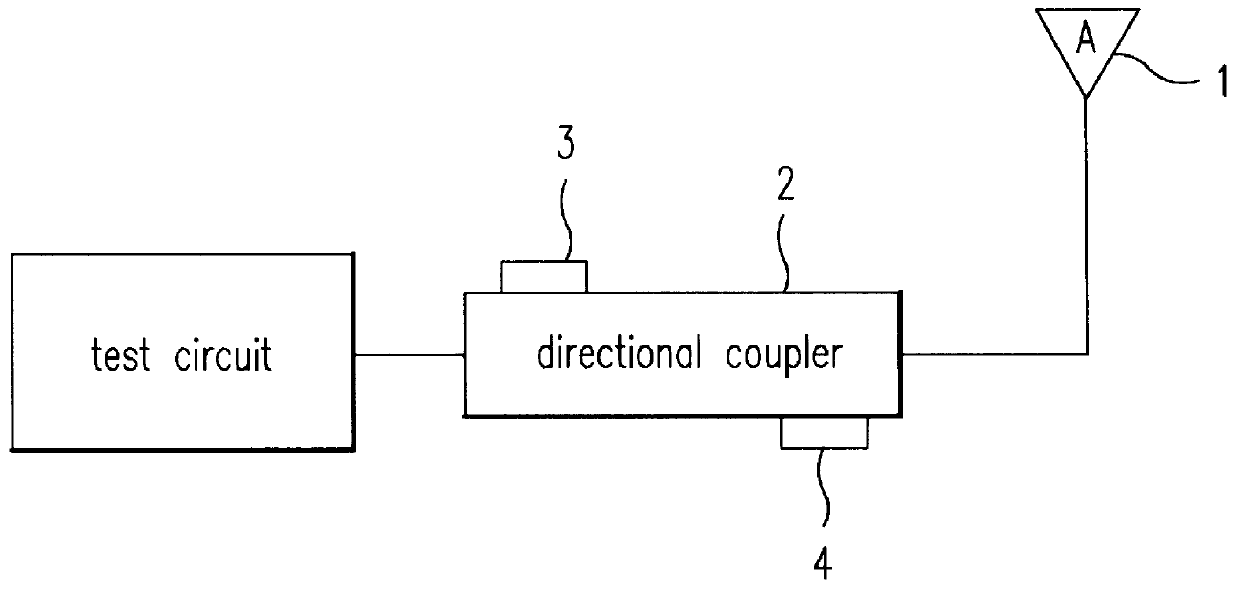

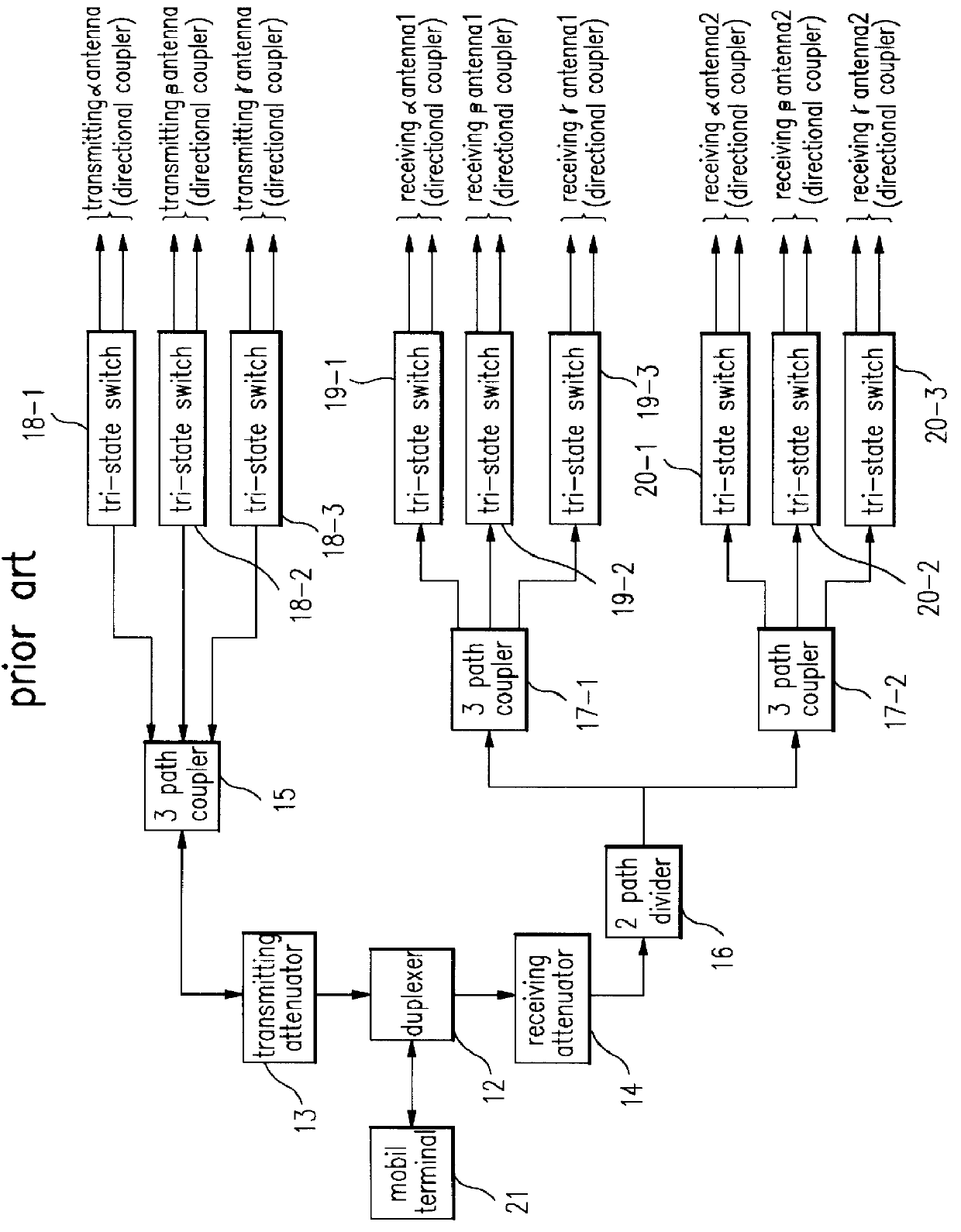

Test circuit of base station for mobile radio communication system

InactiveUS6128474AReceivers monitoringTransmission systemsCommunications systemRadio frequency signal

A test circuit of a base station for use of a mobile radio communication system includes a terminal simulator for analyzing radio frequency signals provided from the base station and outputting the analyzed signals to an exam controller; a radio frequency signal path adjuster connected to the terminal simulator, for adjusting a combination and division of radio frequency signals, and a selection of a test path and a level of signals; and the exam controller connected with the radio frequency signal path adjuster, the terminal simulator and an upper level controller, the exam controller being for operating according to a test instruction of the upper level controller or controlling the radio frequency signal path adjuster and the terminal simulator to thereby execute a test and inform the upper level controller of the test result; whereby enabling the test circuit to be performed in a mutual test between sectors of the base station and an unmanned automation test.

Owner:LG ERICSSON

Bundled probe apparatus for multiple terminal contacting

InactiveUS7064564B2Resistance/reactance/impedenceElectronic circuit testingElectrical resistance and conductanceContact test

A probe apparatus having probe groups comprising two or three probes that independently contact single terminals of tested chips. As a result, the probe apparatus is capable of recognizing voltage drops of a test signal applied prior to the chip testing onto a test path along two or three probes contacting, the terminal and the interfaces between them. The test path does not pass through the chip. An electronic circuit measures the voltage drops and compensated accordingly operational signals passing through the terminals, the probes and the interfaces during the chip testing. A first embodiment comprises two probes per group. A second embodiment comprises three probes per group. In the second embodiment, the variable resistance component of three resistance measurements of first / second, first / third and second / third resistance paths are compared by the electronic circuit, in order to determine absolute resistance values for each of the three signal paths. Consequently, in the second embodiment, the voltage drops may be individually adjusted for each of the three operational signal paths.

Owner:INTERCONNECT DEVICES

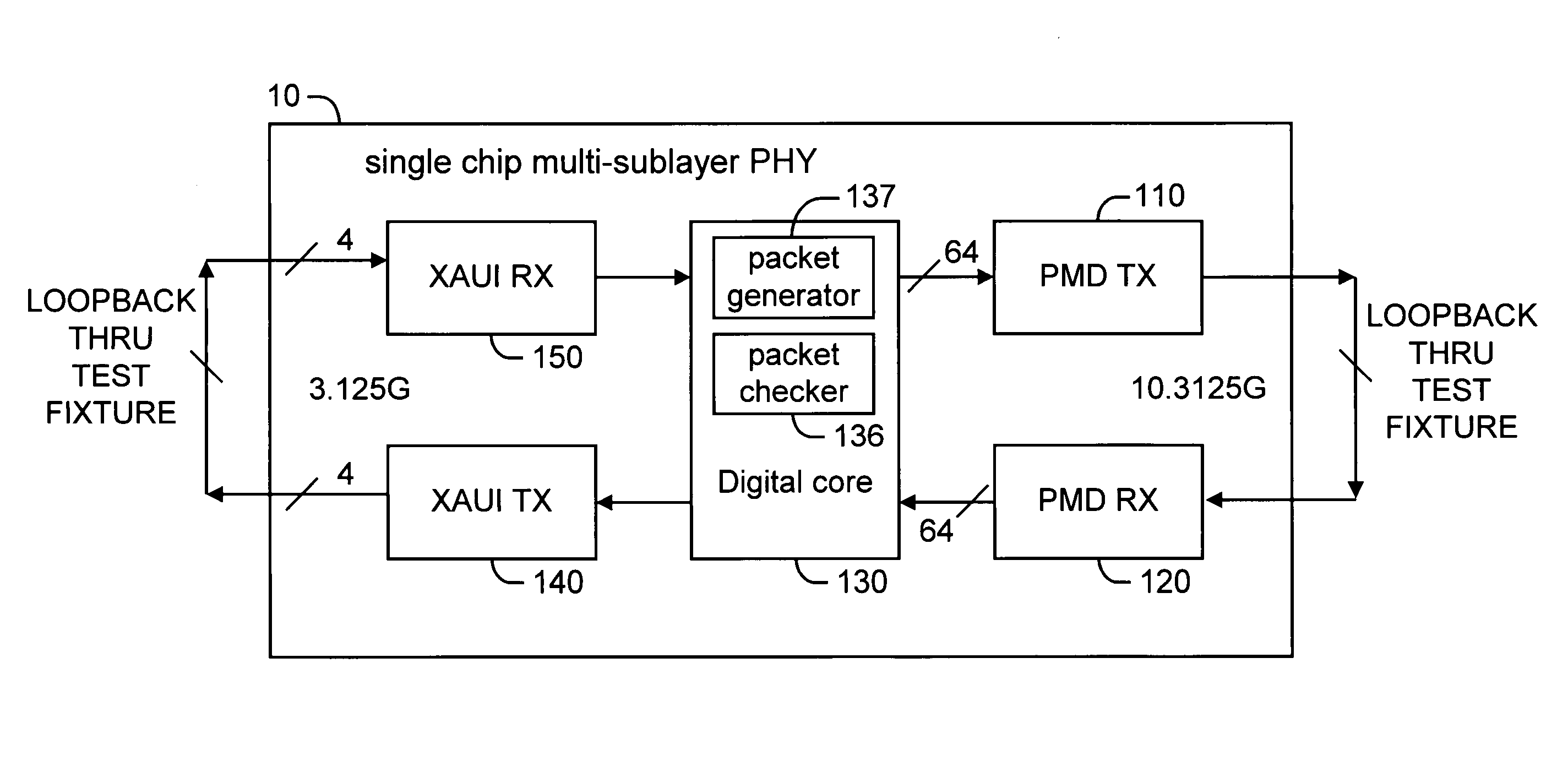

On-chip standalone self-test system and method

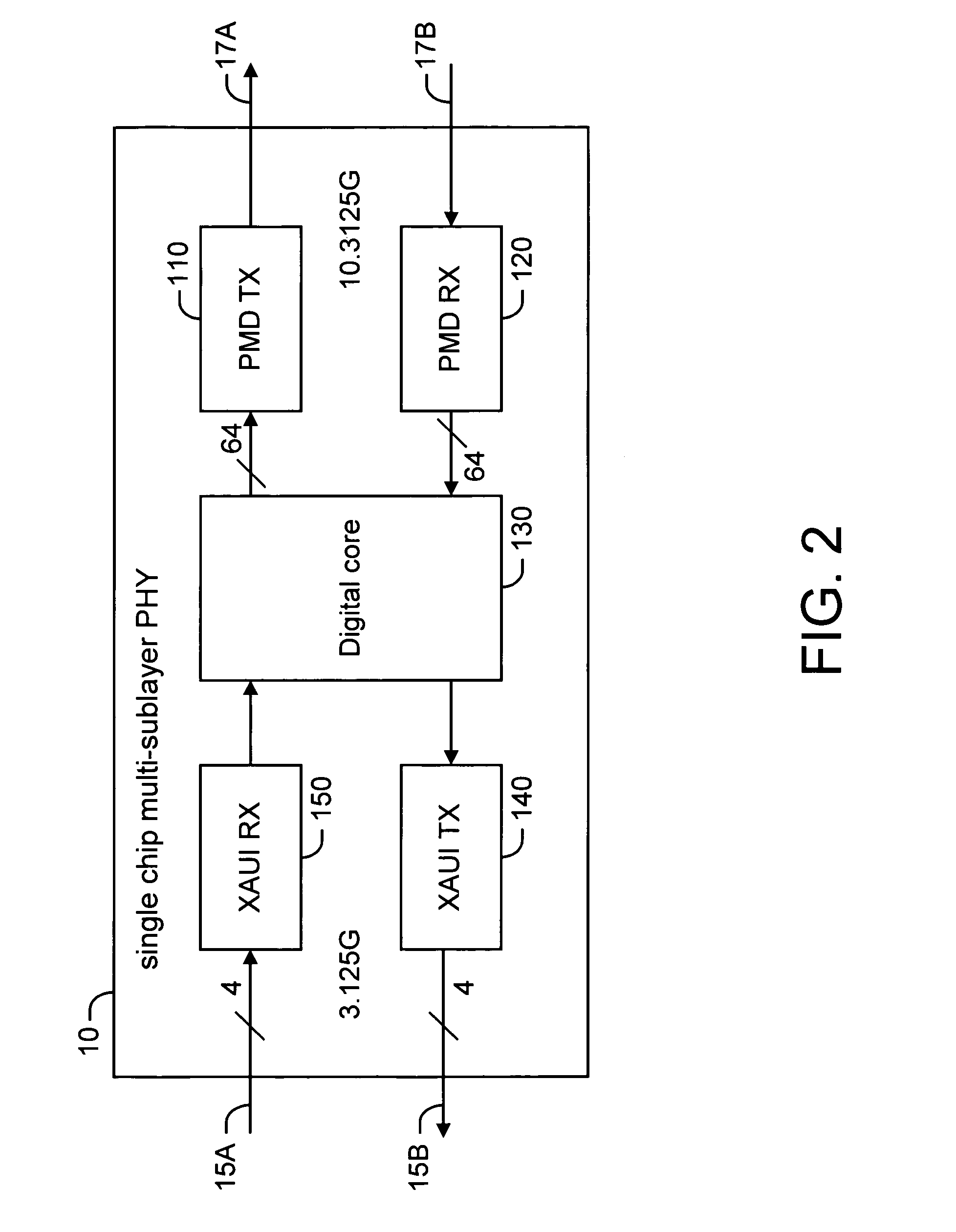

A method and system are disclosed for providing standalone built-in self-testing of a transceiver chip. The transceiver chip includes packet generators for generating test packets and packet checkers for comparing received packets with expected packets. The transceiver chip may be configured for testing through at least two wraparound test paths—a first test path that includes an elastic FIFO of a transmit path of the transceiver chip, and a second test path that includes an elastic FIFO of a receive path of the transceiver chip. During testing, the test packets are generated by packet generators within the transceiver chip and routed through the at least two wraparound test paths to packet checkers within the same transceiver chip. The packet checkers compare the returned packets to the expected packets. If the returned packets are inconsistent with the expected packets, the transceiver chip is defective.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Method for automating unit test development

InactiveUS20060248405A1Highly effectiveEfficient and effectiveError detection/correctionControl flowTest suite

A method and software product for capturing decision data and generating JUnit / NUnit tests for each of a JAVA or C# code unit basis paths. The present software erects a user-interface for guiding a user through the basis paths in their source code and assisting them in creating the test data necessary to exercise each of those paths. At each decision in a given path, the software tells the user that the decision must evaluate either true or false to follow the current path, and it allows them to specify, select, or construct test data that will satisfy this condition. After the user has specified test data for all test paths, the software creates a new class containing a rewritten version of the user's original source code that allows test data to be injected at each decision while still preserving the overall control flow of the original code. The software then creates a complete JUnit or NUnit test suite to test each basis path from the original class in the new class by injecting the test data specified by the user.

Owner:PONCZAK JOSEPH M +1

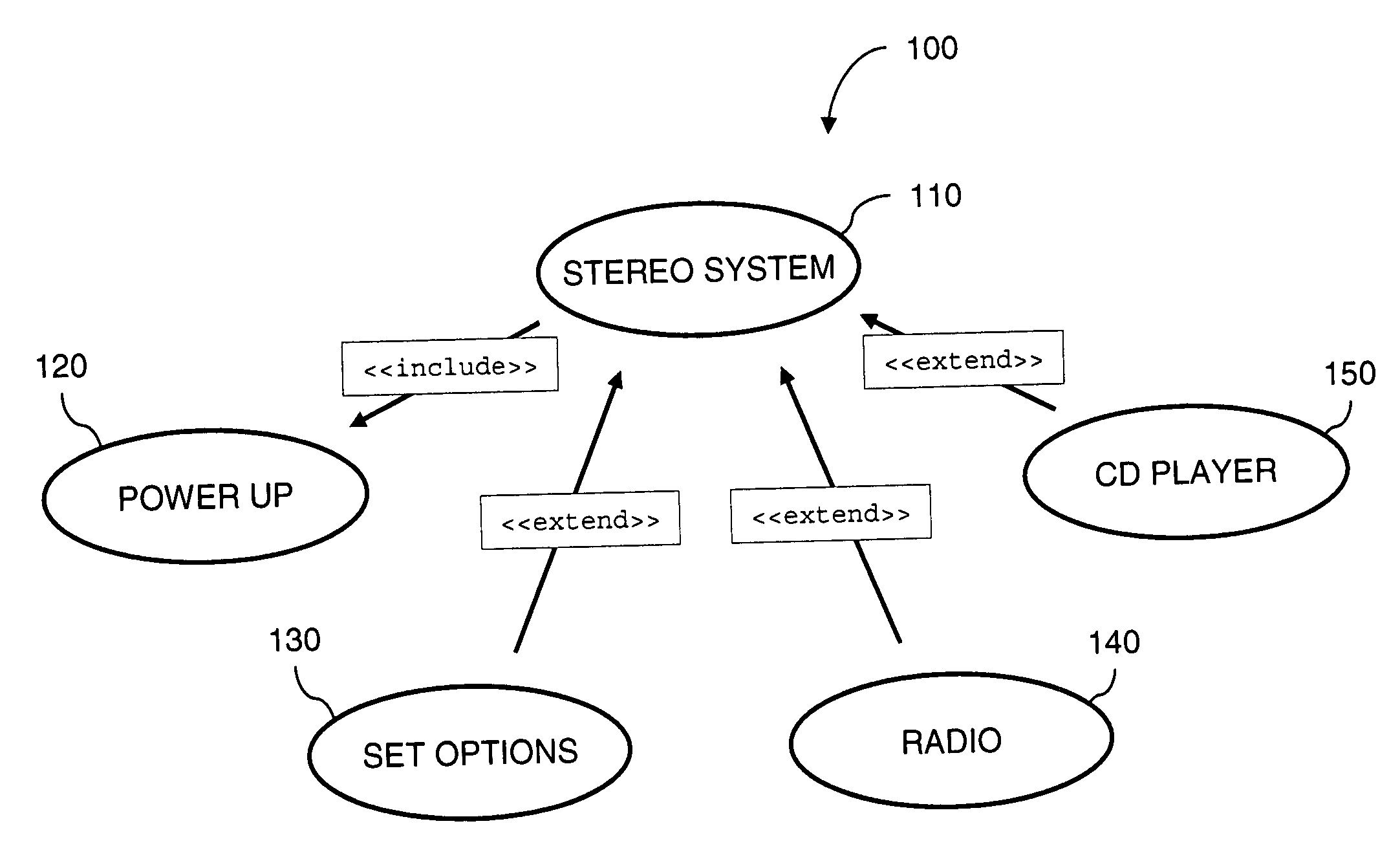

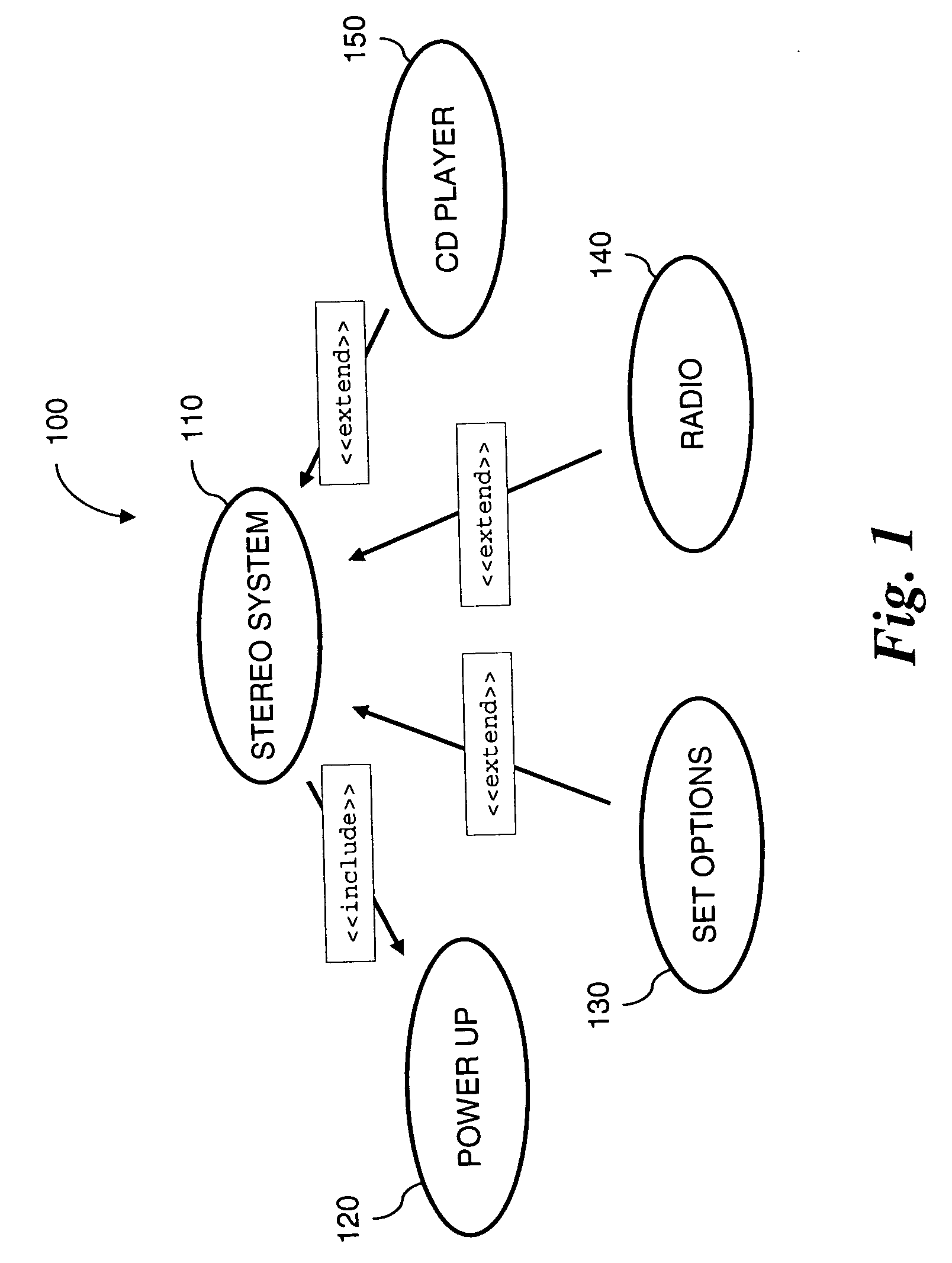

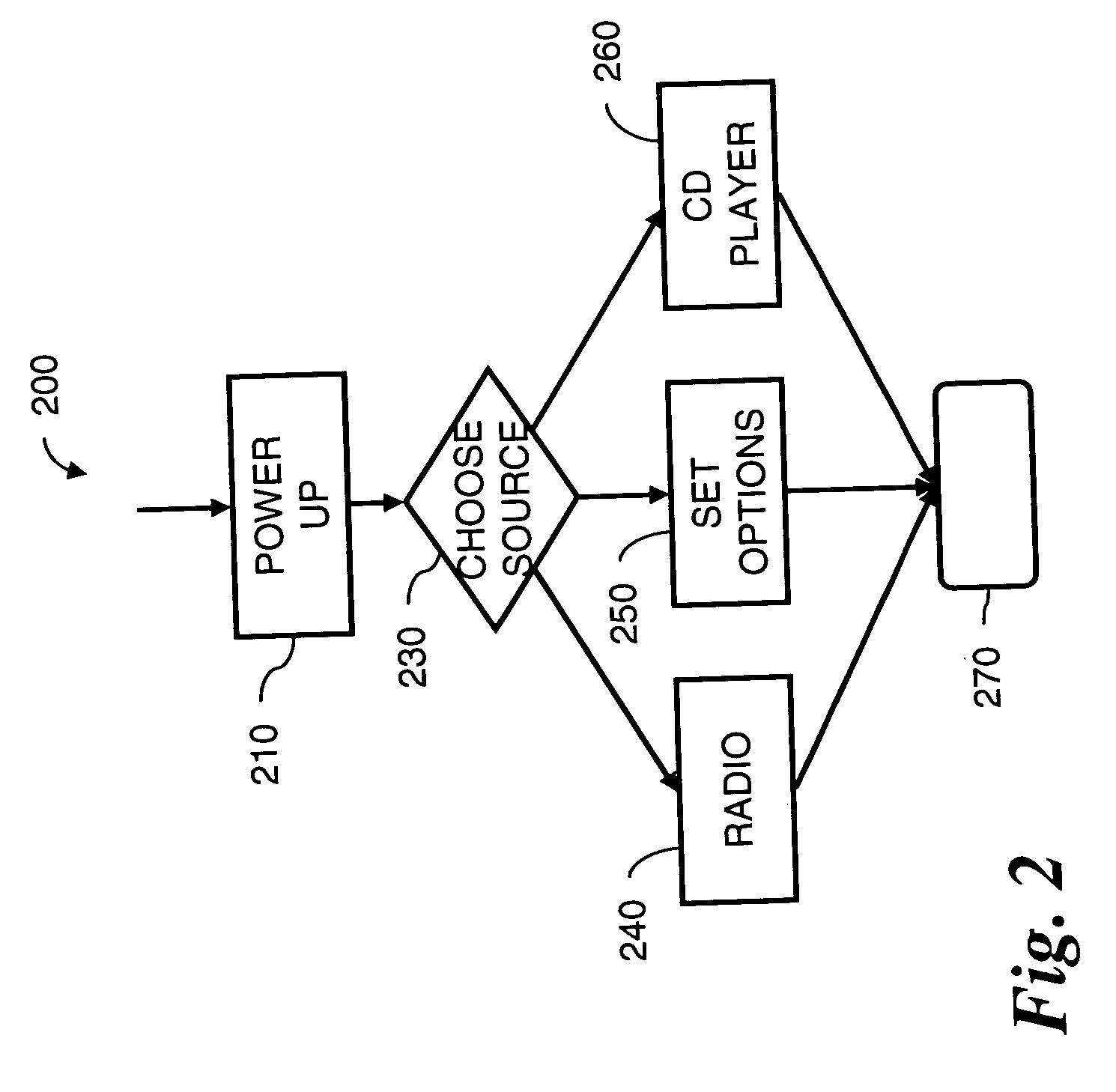

Generating performance tests from UML specifications using markov chains

InactiveUS20060253839A1Error detection/correctionSpecific program execution arrangementsSoftware development processMarkov chain

An automated approach to generating test cases for performance testing may be used for test case planning, early in the software development process, when a UML use case model and its activity diagram refinement are specified. The planned performance tests are executed later in the software development process, after the system is developed. The use case model is annotated with operation arrival rates and departure rates. Deterministic state testing (DST) generation and execution are applied for performance test generation and execution. In addition, a technique is described to generate the most likely test scenarios, labeling each arch in the activity diagram with transition probabilities and applying a breadth first search algorithm to select the most likely paths to be tested for each state generated by the DST algorithm.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

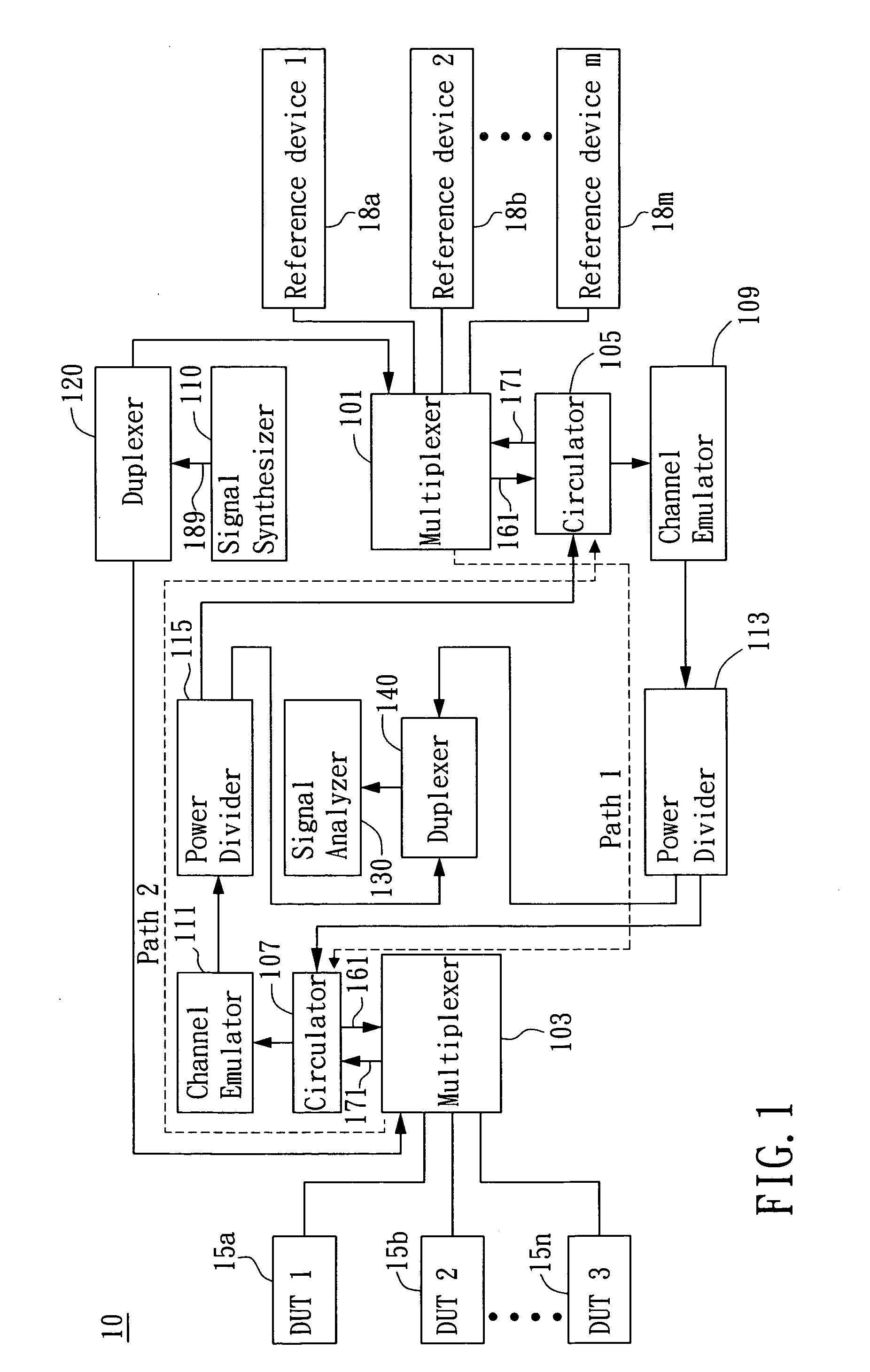

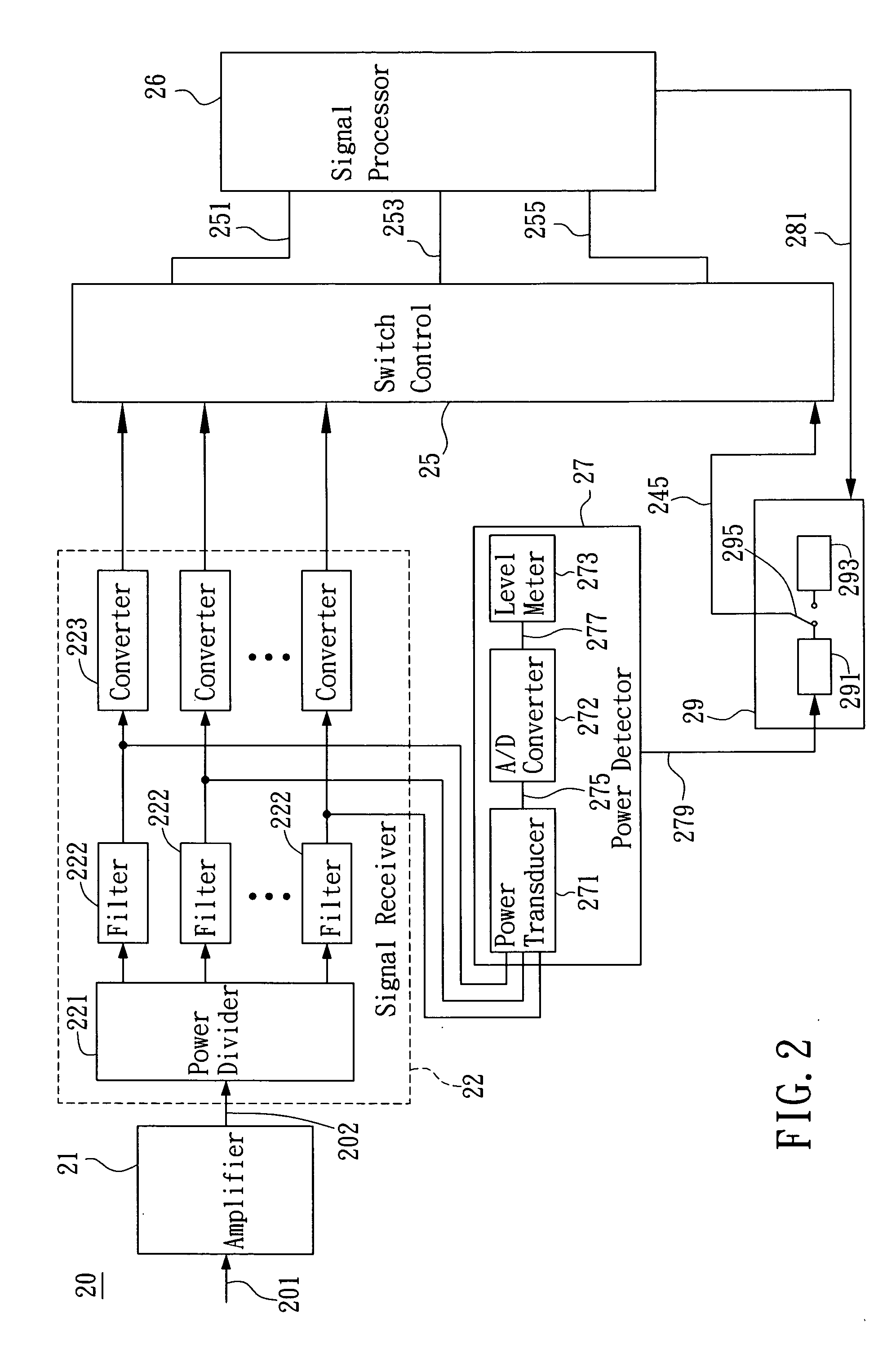

Signal testing system

InactiveUS20060252419A1Radio/inductive link selection arrangementsTransmission monitoringWireless transmissionMultiplexer

A signal testing system is disclosed, which is capable of achieving a bi-directional wireless transmission measurement enabling mutual testing between device-under-tests and reference devices by configuring a symmetrical structure with circulators and multiplexers. Moreover, the signal testing system not only is capable of fetching signal out of a test path by the use of power dividers and then transmitting the fetched signal to a signal analyzer to be analyzed so as to enable the system to support multiple testing, but also is capable of generating a signal used for referencing by a signal synthesizer so as to enable the system to support numerous tests. In addition, both the signal analyzer and the signal synthesizer have a switch control integrated therein, which enables the signal analyzer to perform analysis on signals of different frequency bandwidth, and enables the signal synthesizer to generate signals of different frequency bandwidth as require.

Owner:ARCADYAN

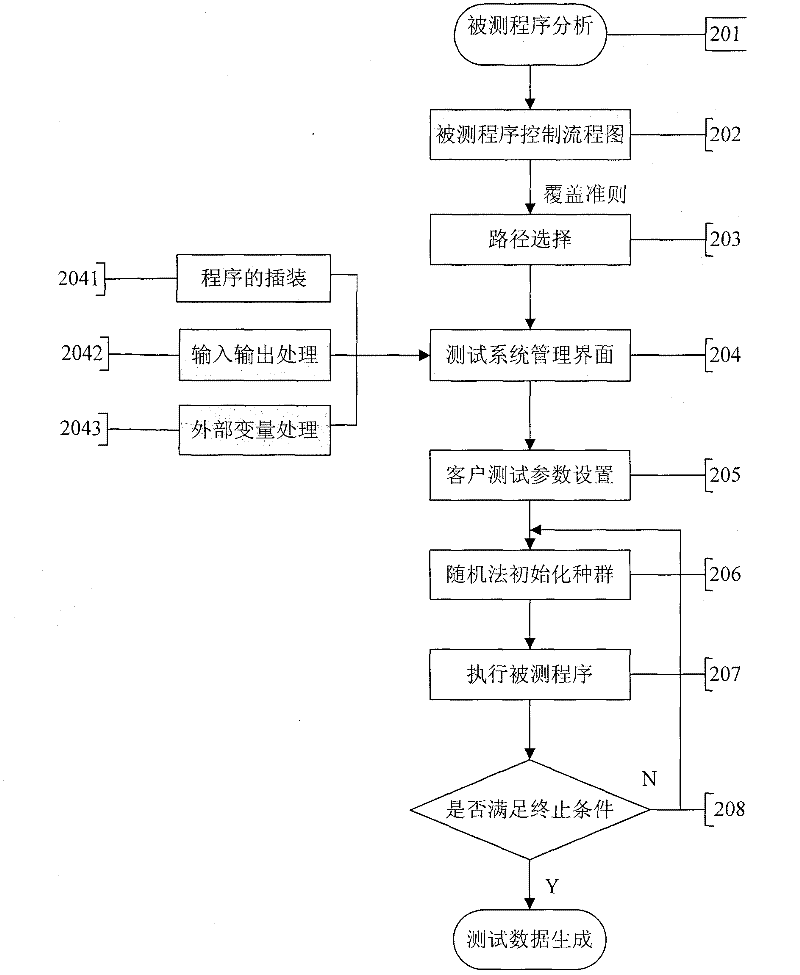

Software test data evolution generation system facing path

InactiveCN102331966AImprove test efficiencySave resourcesSoftware testing/debuggingRandom methodSoftware development

The invention develops a software test data evolution generation system facing a path, which has the advantages that the test data passing a target path can be automatically generated by using a genetic algorithm according to the test path selected by users, in addition, various optional genetic algorithm individual coding modes, adaptive value calculation methods, selection modes, crossing modes, variation modes and the like can be provided in the process of generating test data by using the genetic algorithm, and users can conveniently select different test data generation methods according to the tested program in different types. In addition, the system also provides the traditional random method test data generation method as the comparison, and the automation generation of the software test data is really realized. When the system disclosed by the invention is utilized, the software test efficiency is greatly improved, a large number of software development resources are also saved, the technical support is provided for the credible software research and development of the national relevant plan and the engineering, and the development of software industry in China is promoted.

Owner:CHINA UNIV OF MINING & TECH

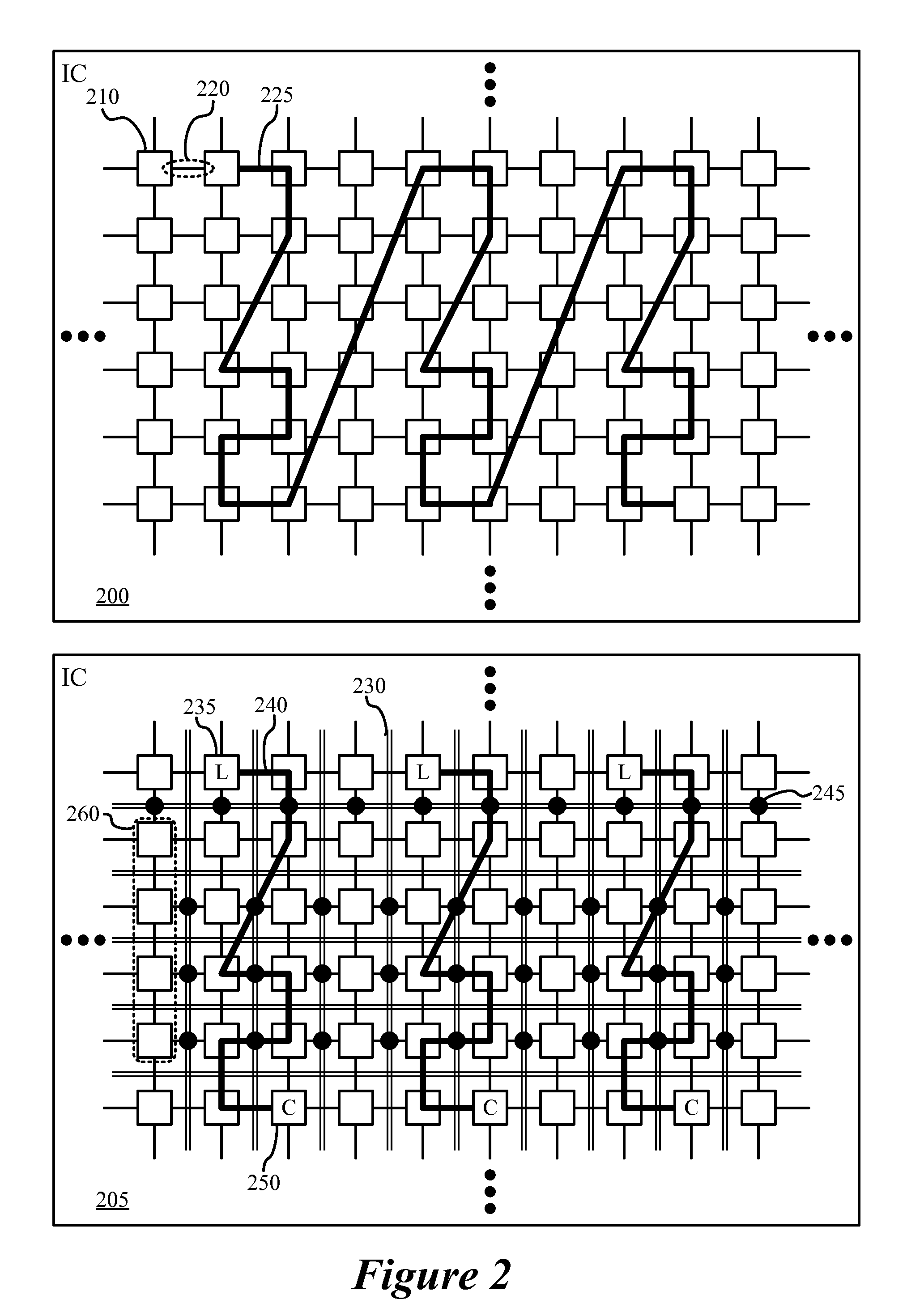

Micro-granular delay testing of configurable ICs

ActiveUS8072234B2Delay in testingEnsure correct executionReliability increasing modificationsFail-safe circuitsComputer hardwarePerformance limit

A method for testing a set of circuitry in an integrated circuit (IC) is described. The IC includes multiple configurable circuits for configurably performing multiple operations. The method configures the IC to operate in a user mode with a set of test paths that satisfies a set of evaluation criteria. Each test path includes a controllable storage element for controllably storing a signal that the storage element receives. The method operates the IC in user mode. The method reads the values stored in the storage elements to determine whether the set of circuitry is operating within specified performance limits.

Owner:ALTERA CORP

Micro-Granular Delay Testing of Configurable ICs

ActiveUS20110068820A1Ensure correct executionReduce minimum testable durationReliability increasing modificationsFail-safe circuitsComputer hardwarePerformance limit

A method for testing a set of circuitry in an integrated circuit (IC) is described. The IC includes multiple configurable circuits for configurably performing multiple operations. The method configures the IC to operate in a user mode with a set of test paths that satisfies a set of evaluation criteria. Each test path includes a controllable storage element for controllably storing a signal that the storage element receives. The method operates the IC in user mode. The method reads the values stored in the storage elements to determine whether the set of circuitry is operating within specified performance limits.

Owner:ALTERA CORP

Method for testing DSL capability of telephone lines

ActiveUS20070230667A1Supervisory/monitoring/testing arrangementsSubstation equipmentDiagnostic testService provision

A system and method for performing DSL assessments of a telephone line along a prescribed test path is disclosed. The disclosed system includes a loop diagnostic test unit adapted for testing said telephone line using narrow-band and mid-band frequency test signals; a test system controller and a test system server to provide the DSL assessments to a user via an appropriate interface. In addition, the disclosed methods include the basic steps of: accessing the telephone line along the test path that includes selected hardware such as a voice switch test bus, central office splitter, service provider instruments and terminations; ascertaining various line characteristics along the test path using mid-band and narrow-band frequency signals; analyzing the line characteristics to identify line conditions that affect DSL service; and determining the impact of the line conditions on DSL service.

Owner:TOLLGRADE COMM INC

Method and Apparatus for Providing Requirement Driven Static Analysis of Test Coverage for Web-Based, Distributed Processes

InactiveUS20090019427A1Improve test coverageEasy to testError detection/correctionSpecific program execution arrangementsSpecific testTest case

A method (which can be computer implemented) for analyzing test coverage of distributed processes includes the steps of identifying at least one of the processes that is invoked by a test case, mapping at least a portion of the test case to a plurality of specific test paths in the at least one of the processes, and identifying given ones of the test paths as possibly relevant in at least one of the processes, if the test paths are not infeasible.

Owner:IBM CORP

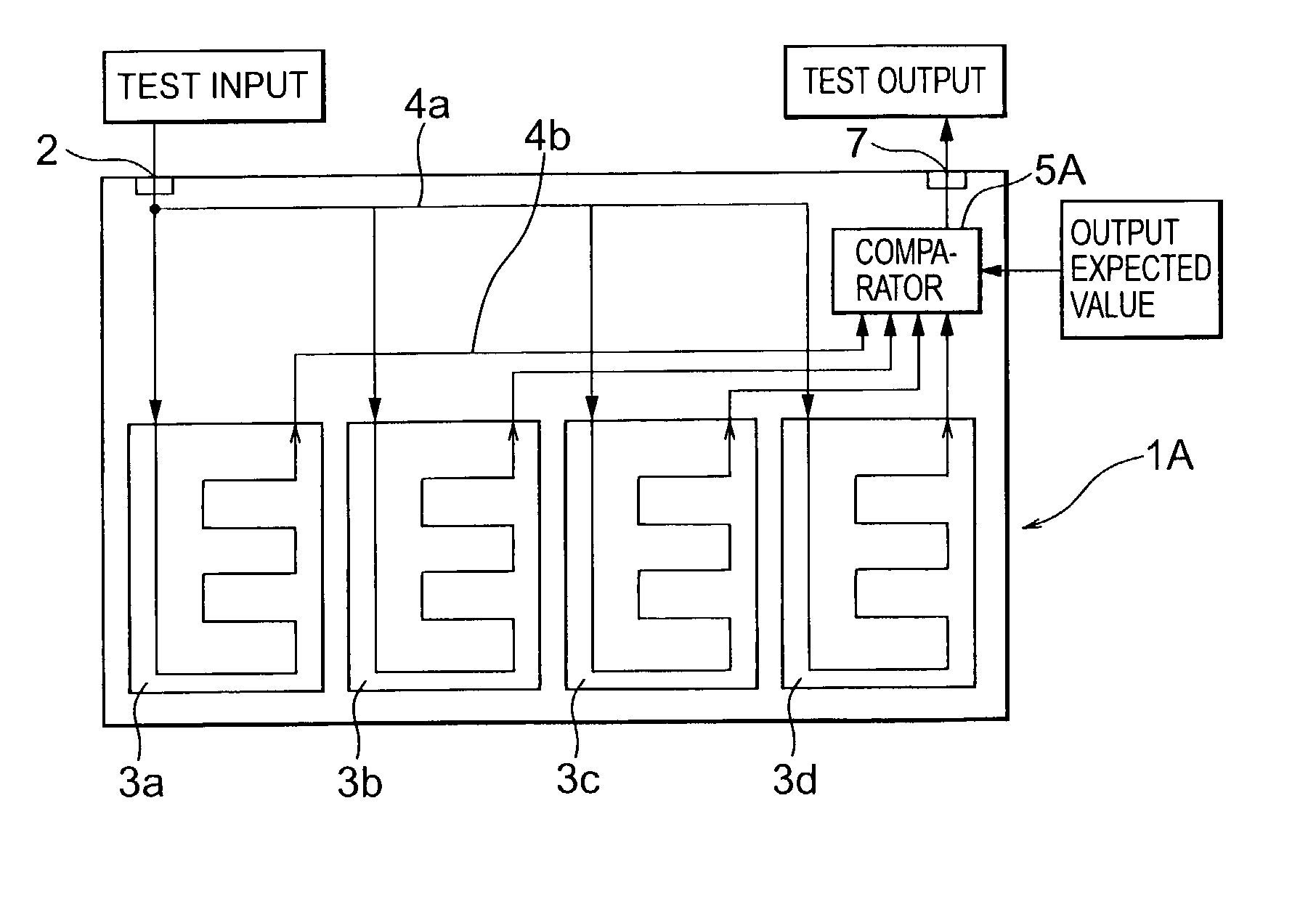

Semiconductor integrated circuit

A semiconductor integrated circuit includes: a logic circuit to be tested; a memory connected the logic circuit to be tested; a BIST circuit for testing the memory; and a bypass circuit connected between the memory and the logic circuit and between the memory and the BIST circuit, the bypass circuit has a parallel test path for testing the logic circuit and the memory in parallel, and a signal line test path for testing non-tested signal lines in the parallel test path, and the bypass circuit selectively switches the parallel test path and the signal line test path.

Owner:KK TOSHIBA

Semiconductor device on device interface board and test system using the same

InactiveUS20140253099A1Easy to operateSemiconductor/solid-state device testing/measurementElectronic circuit testingPower semiconductor deviceElectricity

A semiconductor device, which is mounted on a device interface board to interface an electrical measuring signal between automated test equipment (ATE) and a device under test (DUT), includes an AC test unit, a DC test unit, a first input / output (I / O) interface unit, and a second I / O interface unit. The AC test unit tests an AC characteristic of the DUT. The DC test unit provides a DC test path according to attributes of I / O terminals of the DUT. The first I / O interface unit selectively connects the AC test unit or the DC test unit to the ATE in response to a mode control signal. The second I / O interface unit selectively connects the AC test unit or the DC test unit to the DUT in response to the mode control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Acute angle avoidance during routing

InactiveUS7174529B1Computer aided designSpecial data processing applicationsAcute angleReal-time computing

Determining a route between a start to the target geometry by producing potential route segments and testing the segments to determine whether they create acute angles in the route. If a potential route segment produces an acute angle in the route, it is prevented from being included in the route. Some embodiments define at least one border region about each start or target geometry. Associated with each border region are one or more routing rules that specify valid routing configuration that do not produce acute angles in the route within the border region. To avoid acute angles in the routing pathway between the start and target geometries, some embodiments test for acute angles at connection points between route segments using pretabulated tables that define connection configurations between route segments that do not contain acute angles.

Owner:CADENCE DESIGN SYST INC

Fault-tolerant unit and method for through-silicon via

ActiveUS20120248438A1Unnecessary additionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsTest statusComputer science

A fault-tolerant unit and a fault-tolerant method for through-silicon via (TSV) are provided. The fault-tolerant unit includes TSV structures TSV1˜TSVn, nodes N11˜N1n, nodes N21˜N2n and a switching module. The TSV structure TSVi is connected between the node N11 of the first chip and the node N2i of the second chip, wherein 1≦i≦n. The switching module is connected between the nodes N21˜N2n of the second chip and a test path of the second chip. In normal operation state, the switching module disconnects the test path and the nodes N21˜N2n when the TSV structures TSV1˜TSVn are valid. The switching module connects the node N2i to at least another one of the nodes N21˜N2n when the TSV structure TSVi is faulty in the normal operation state. In test status, the switching module connects the test path to the nodes N21˜N2n.

Owner:IND TECH RES INST

Method for assessing DSL capability of telephone lines

ActiveUS20060109979A1Interconnection arrangementsSupervisory/monitoring/testing arrangementsDiagnostic testExternal data

A test system and method for performing DSL assessments of a telephone line along a prescribed test path is disclosed. The disclosed test system and method includes a loop diagnostic test unit adapted for testing said telephone line using narrow-band and mid-band frequency test signals; a test system controller and a test system server to provide the DSL assessments to a user via an appropriate interface. In addition, the disclosed analysis methods utilize primary line condition information, secondary line condition information, historical line information, together with real-time measurements and external data inputs to perform line imbalance analysis, fault identification analysis, trend analysis, and jurisdictional analysis all of which have relevance to quality, performance and assurance of DSL service through the telephone line.

Owner:TOLLGRADE COMM INC

Circuit board having boundary scan self-testing function

A circuit board with a boundary scan self-testing function comprises a substrate, a plurality of devices under test and an active testing device. The active testing device mounted the substrate can conduct circuit testing on the plurality of devices under test, and self-testing is allowed without employing any external testing equipment. The testing data of the active testing device is transmitted through a predetermined test route on the circuit board. Each of the devices under test is completely tested of all designated functions in either series connection or parallel connection with each other. The testing can help find out whether the devices have any defects.

Owner:LEADTEK

Device for receiving a test sample

The invention relates to a device for receiving a test sample, particularly sample holders for combined examination of the test sample by a test procedure combined with another test procedure, which differs from the first test procedure, with a planar preparation component (1) in a transparent material with a preparation surface on which the test sample can be prepared, wherein a test path for the introduction of a test facility for carrying out the test procedure is formed on one side of the preparation component (1) and another test path for the introduction of a test facility for carrying out the other test procedure on the test sample is formed on an opposite side of the preparation component (1), wherein a supporting and covering element (3a) which has an aperture (5) through which the test path is formed is pressed against the preparation component (1) on one side (FIG. 1).

Owner:BRUKER NANO INC +1

Loop back testing for multi-protocol hybrid networks

A hybrid network (100) includes a plurality of network elements (102, 106, 110, 114) that are coupled together by communication links (116, 118, 120, 122, 124). The network elements operate on different communications protocols. A loop back test message traverses a path (140) across network elements to test the integrity and quality of the path. Each network element that receives the loop back message modifies the message in a predetermined manner. The originator of the message verifies that the message was modified in an appropriate manner and in an appropriate time frame to determine integrity and quality.

Owner:LUCENT TECH INC

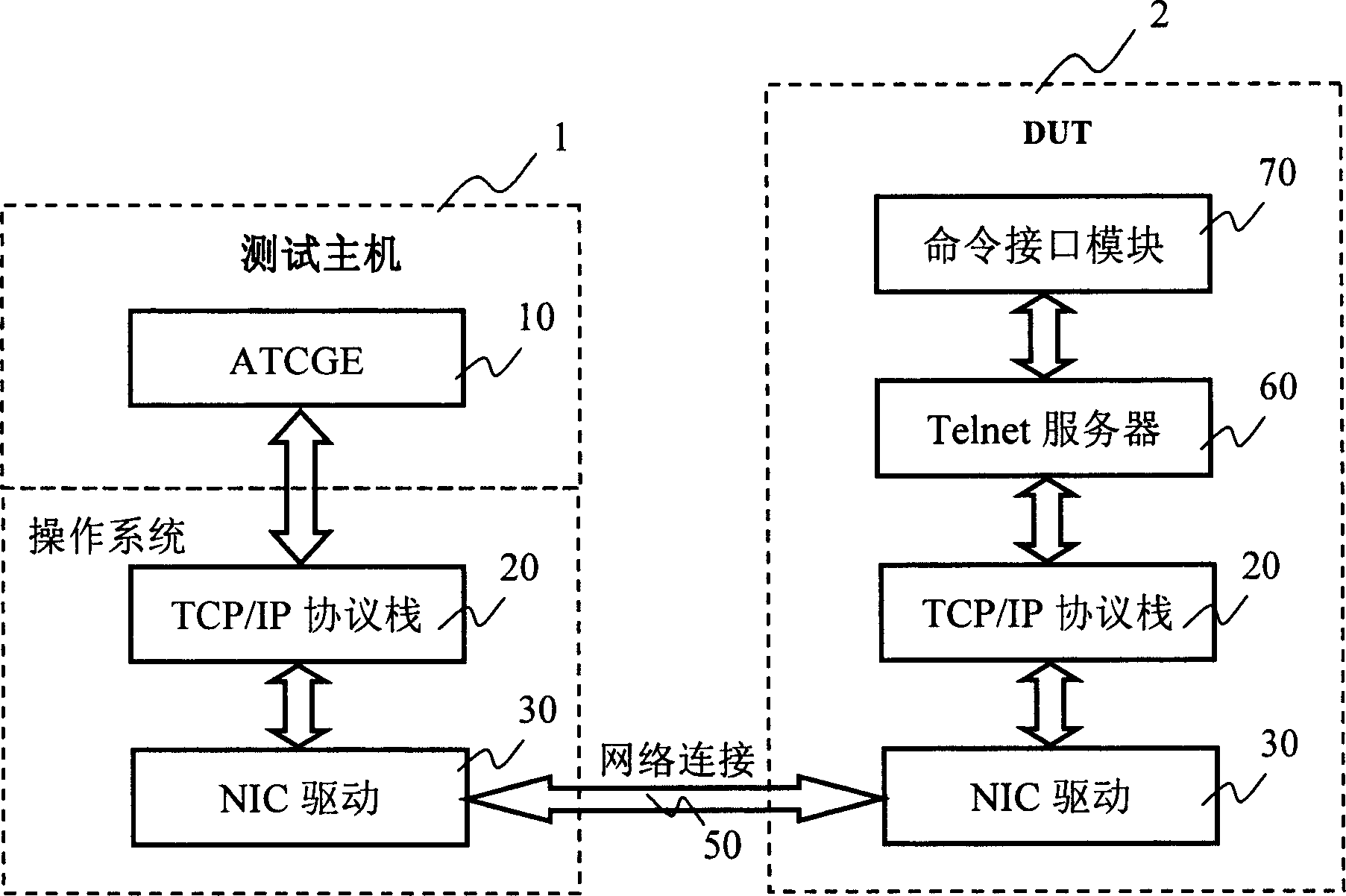

Automatic testing system and method for command of command line interface of data communication apparatus

This invention relates to an automatic test system and a method for data communication device command line interface instructions, which constructs a man-machine command character string analysis process software module on a communication protocol software layer of a test host containing a test example automatic generation and executing system and an operation system, automatically generates gateway command node tree data structure and takes it as the basis to utilize software to realize automatic structure, generation and execution of network command test example to realize automatic test of command line interface command to a tested device.

Owner:ZTE CORP

Method and system for testing machine top box based on serial port communication

InactiveCN101646100AImprove performanceImprove stabilityTelevision system detailsColor television detailsKey pressingAutomatic testing

The invention relates to a method and a system for testing a machine top box based on serial port communication. The method comprises the following steps: (a) constructing an independent monitoring line range; (b) constructing annular queues which are connected from the beginning to the end and storing the input testing information; (c) starting a machine top box, initializing and communicating with a computer by a serial port; (d) referring the serial port to output aid prompting information, setting a testing item by operating a remote controller, recording the input key value and the inputkey time by the monitoring line range of the serial port and forming a testing path which is placed in the annular queues; (e) inputting a command of 'starting automatic testing' by the serial port, carrying out sequence circulation scanning on each node of the whole queue after receiving and affirming the command by the monitoring line range, and delivering the scanned key value sequentially intothe system of the machine top box according to the calculated time interval; (f) monitoring the testing information input by keys by the system of the machine top box and running a corresponding function module to the testing path set by the testing personnel by different received testing information; and (g) outputting a testing result to a computer screen by the serial port. The invention can carry out automatic testing, has simple operation and is beneficial to discovering a latent defect existing in software and enhancing the stability of a product.

Owner:SHENZHEN SKYWORTH DIGITAL TECH CO LTD

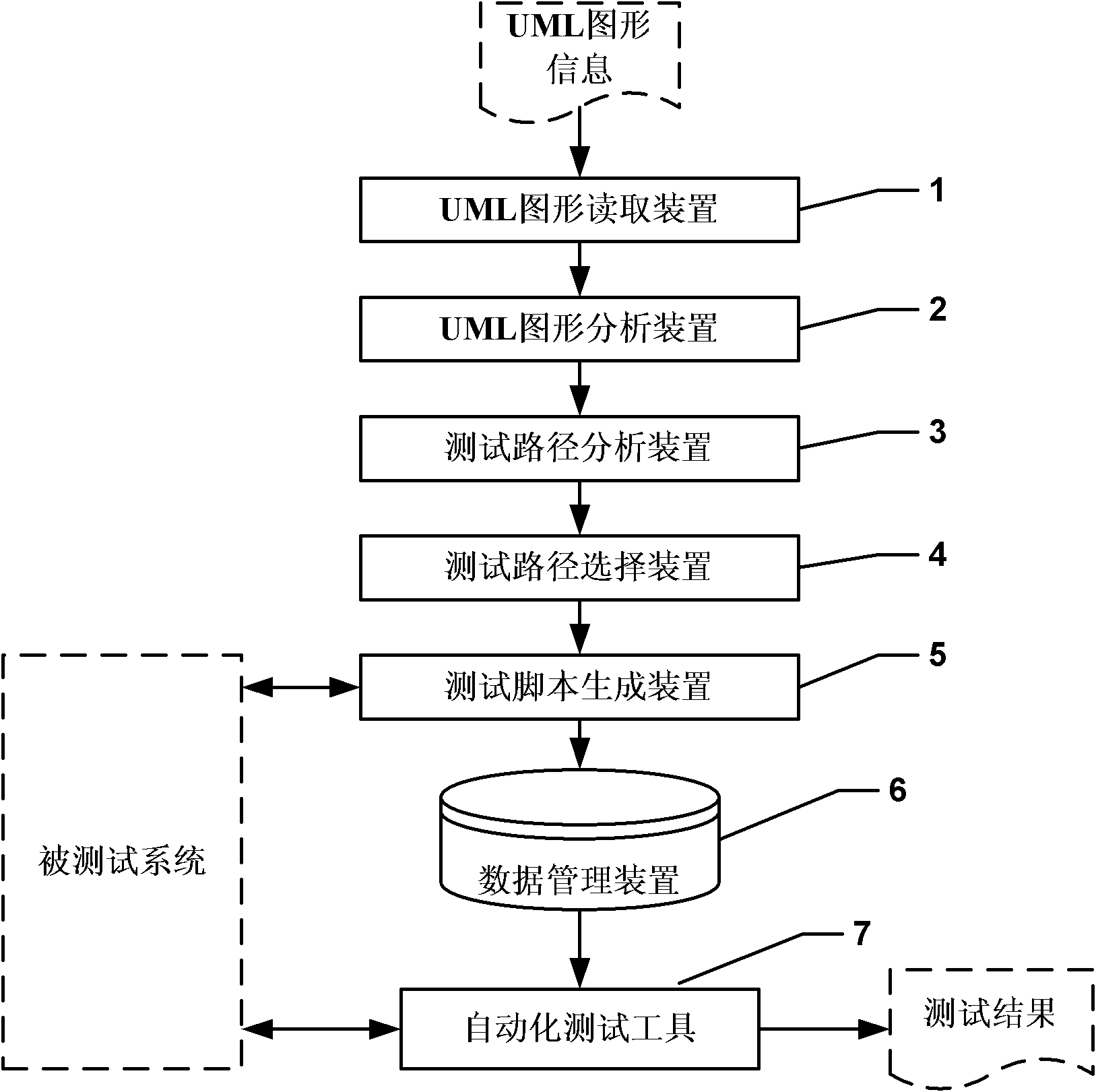

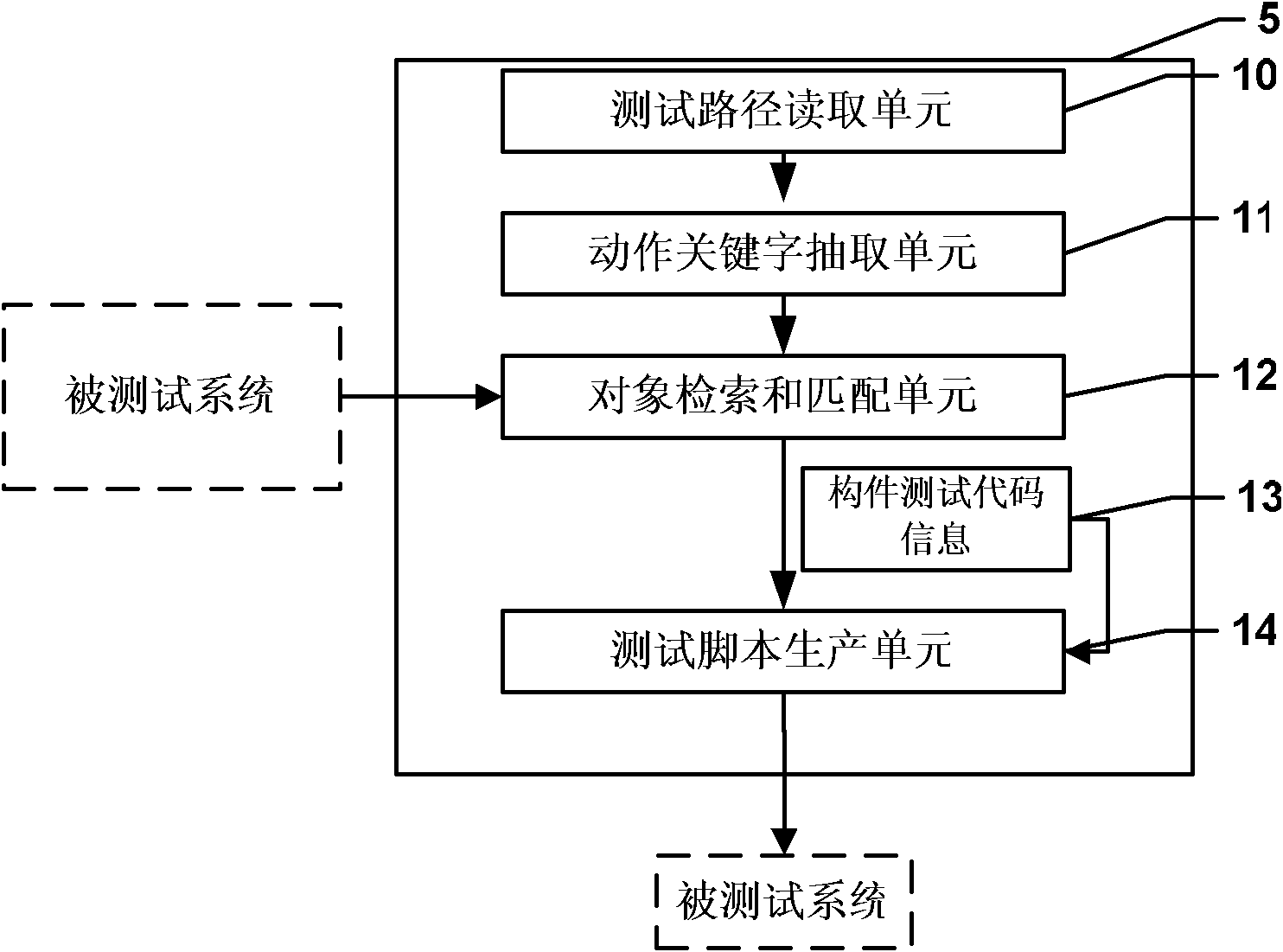

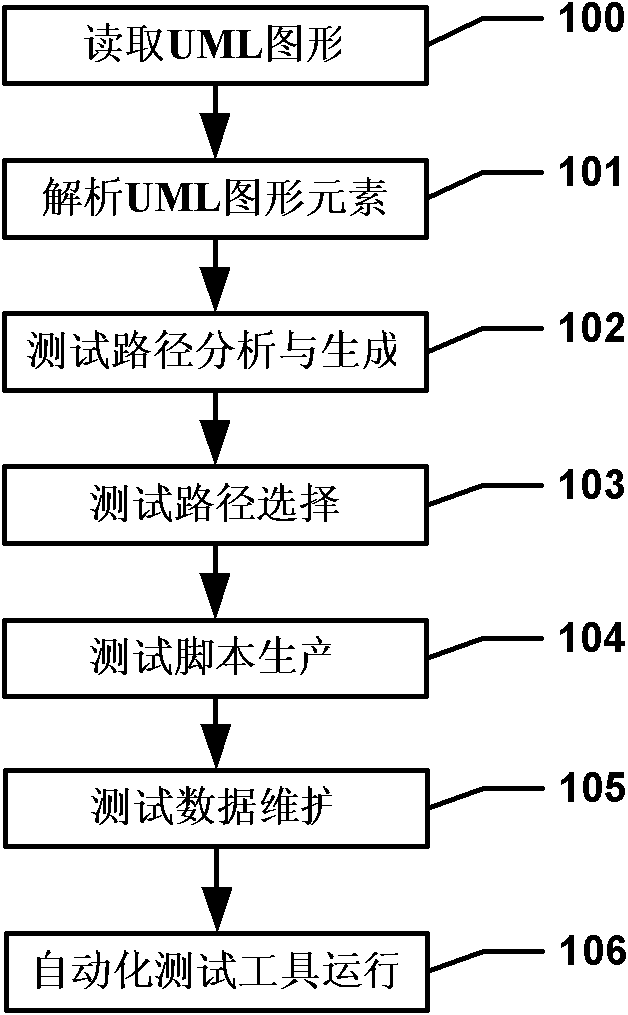

Device and method for automatically testing software based on UML (unified modeling language) graphs

InactiveCN102053912AImprove test efficiencyImprove test qualitySoftware testing/debuggingTest efficiencyGraphics

The invention discloses a device and method for automatically testing software based on UML (unified modeling language) graphs. The device comprises a UML graph reading device, a UML graph analyzing device, a testing route analyzing device, a testing route choosing device, a testing script generating device, a data management device and an automatic testing tool which are connected in sequence. The device realizes automatic testing of the software by analyzing UML graphs and generating a test script according to the content of the UML graphs. Through the device and method provided by the invention, the problems that the frequently repeated transcribing process and testing script modifying process required by the traditional process of automatic testing result in low testing efficiency, low accuracy and low coverage rate are solved.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

Program testing method and device

ActiveCN105975394AImprove accuracyReduce testing costsSoftware testing/debuggingComputer hardwareProgram testing

The invention provides a program testing method and device. The method comprises the following steps: loading a program to be tested, and outputting various test scenes corresponding to the program to be tested; according to a selection instruction input by aiming at various test scenes, determining a target test scene, wherein the target test scene comprises a target test path; obtaining target test data corresponding to the target test path; and on the basis of the target test data, carrying out a test and outputting a test result. The embodiment of the invention carries out the test on a mobile type application program on the basis of various test scenes so as to improve test accuracy, lower test cost and shorten test duration.

Owner:HONOR DEVICE CO LTD

Signal testing system

InactiveUS7395060B2Radio/inductive link selection arrangementsTransmission monitoringWireless transmissionMultiplexer

A signal testing system is disclosed, which is capable of achieving a bi-directional wireless transmission measurement enabling mutual testing between device-under-tests and reference devices by configuring a symmetrical structure with circulators and multiplexers. Moreover, the signal testing system not only is capable of fetching signal out of a test path by the use of power dividers and then transmitting the fetched signal to a signal analyzer to be analyzed so as to enable the system to support multiple testing, but also is capable of generating a signal used for referencing by a signal synthesizer so as to enable the system to support numerous tests. In addition, both the signal analyzer and the signal synthesizer have a switch control integrated therein, which enables the signal analyzer to perform analysis on signals of different frequency bandwidth, and enables the signal synthesizer to generate signals of different frequency bandwidth as require.

Owner:ARCADYAN

Source code change influence analyzing and testing method for software units and components with combination of phase

InactiveCN102880547AImprove test efficiencySystematicSoftware testing/debuggingNODALParallel computing

The invention discloses a source code change influence analyzing and testing method for software units and components with combination of phase. The analysis and test on unit grade source code change influence comprise the following steps of: constructing a program unit flow graph; establishing a linear independent test route set; checking a node of a modified code in the flow graph and determining the node as a change point; using a route selector to select a route containing the change point from the linear independent test route set so as to form a influenced route set; executing the route in the influenced route set; and comparing the execution result with expected results. The analysis and test on component grade source code change influence comprise the following steps of: establishing a program scheduling graph, wherein the scheduling graph uses a scheduling structure of nodes and boundary description programs; establishing a linear independent test sub-tree set; confirming a unit at which the modified code is located and taking the unit as the change point; using a sub-tree selector to select a sub-tree from the linear independent test sub-tree set which contains the change point so as to form an influenced sub-tree set; executing the sub-tree in the influenced sub-tree set; and comparing the execution result with expected results.

Owner:JIANGNAN INST OF COMPUTING TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com