Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5501 results about "Mode control" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

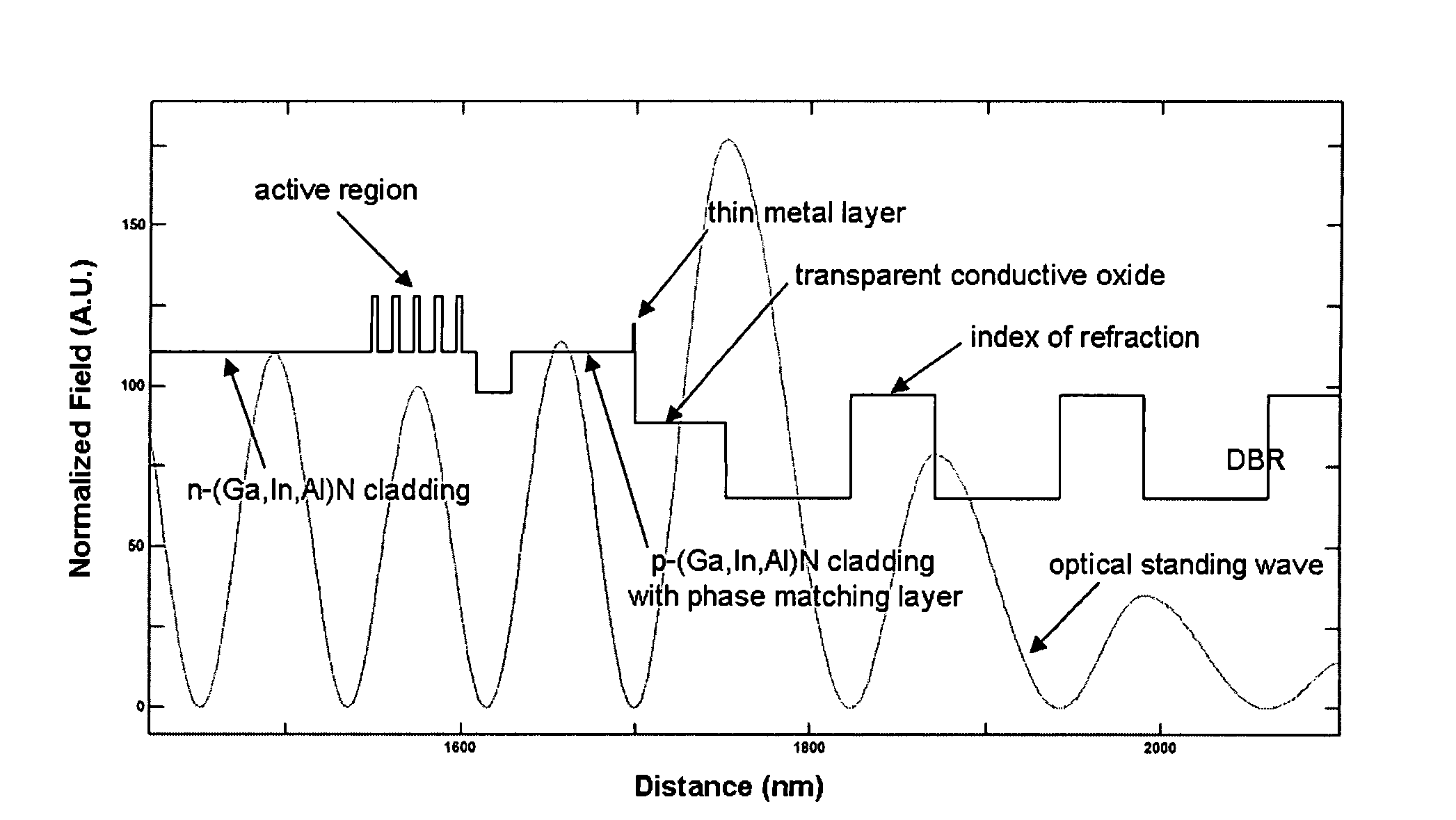

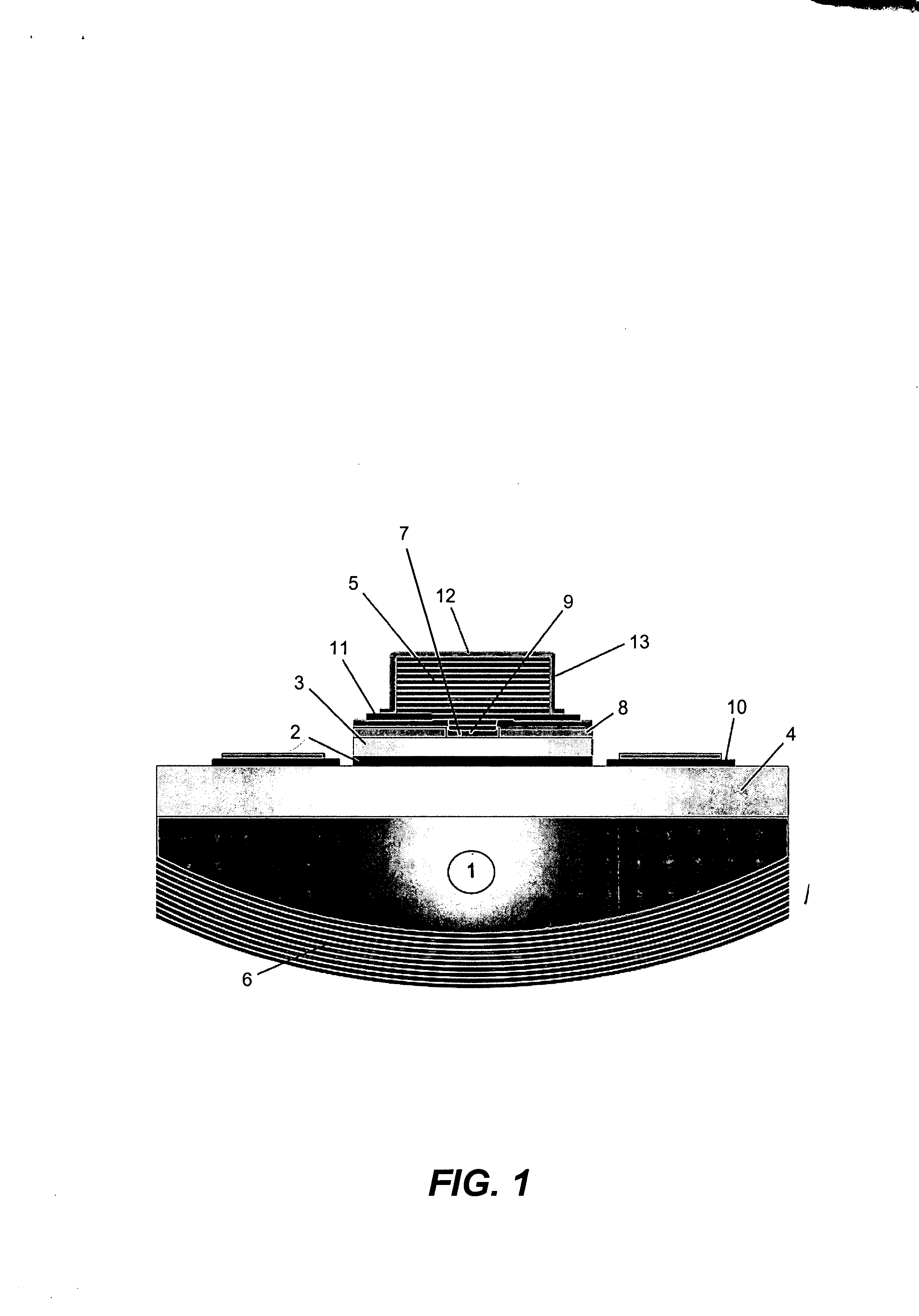

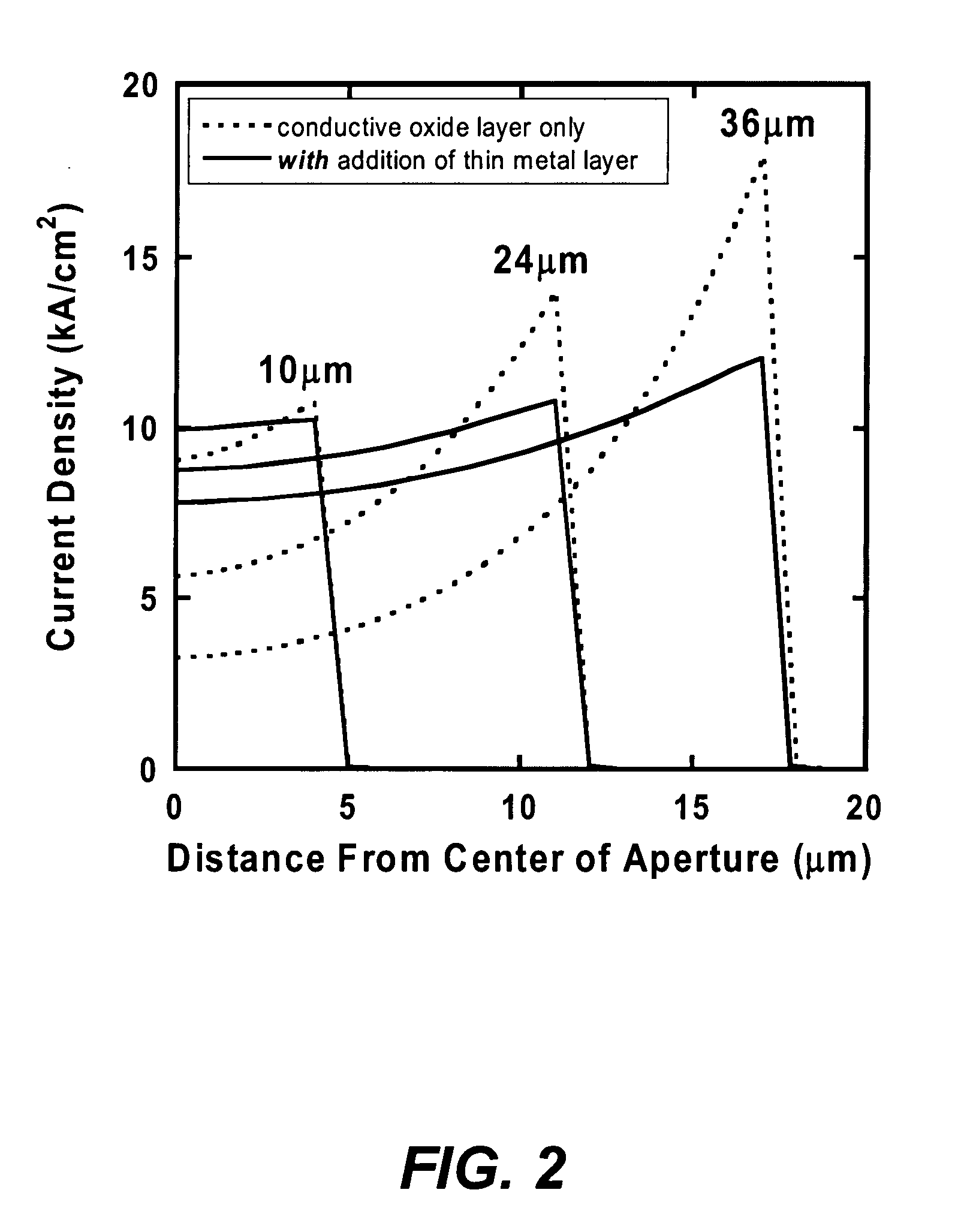

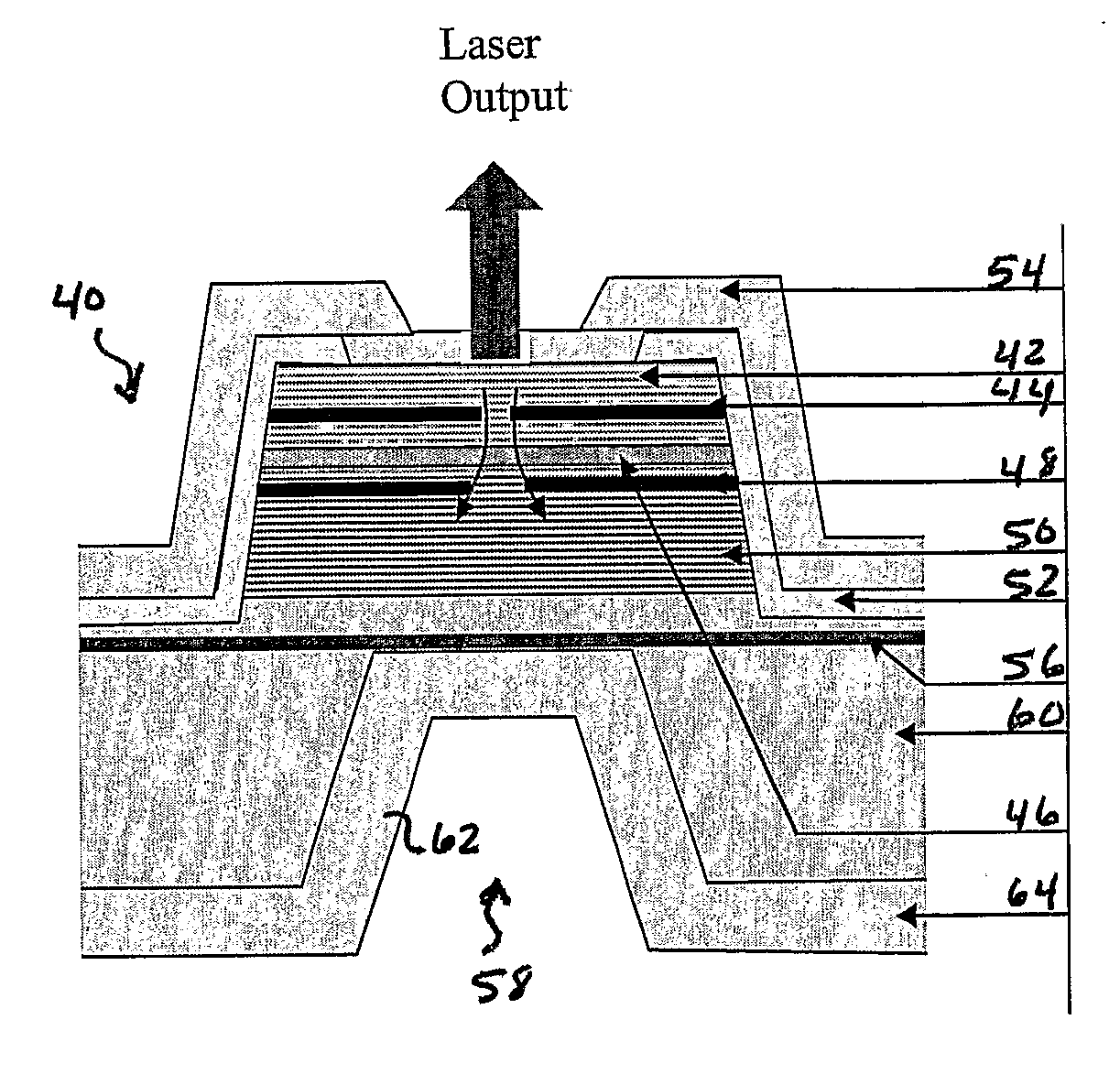

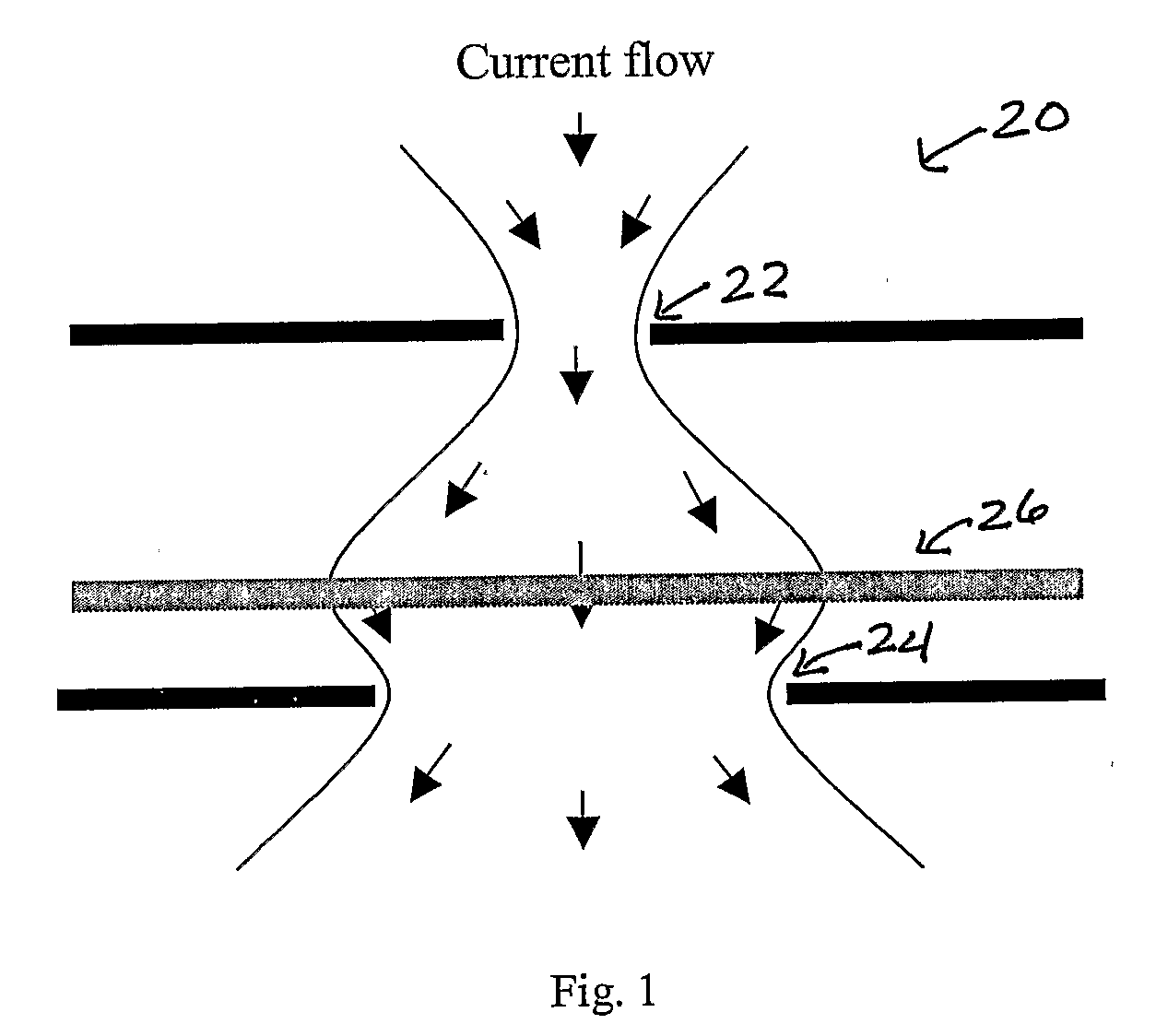

Electrically-pumped (Ga,In,Al)N vertical-cavity surface-emitting laser

InactiveUS20070280320A1Good ohmic contactOptical resonator shape and constructionSemiconductor lasersThin metalVertical-cavity surface-emitting laser

A vertical-cavity surface-emitting laser (VCSEL) comprising a low-loss thin metal contact and current spreading layer within the optical cavity that provides for improved ohmic contact and lateral current distribution, a substrate including a plano-concave optical cavity, a (Ga,In,Al)N multiple quantum well (MQW) active region contained within the optical cavity that generates light when injected by an electrical current, and an integrated micromirror fabricated onto the substrate that provides for optical mode control of the light generated by the active region. A relatively simple process is used to fabricate the VCSEL.

Owner:RGT UNIV OF CALIFORNIA

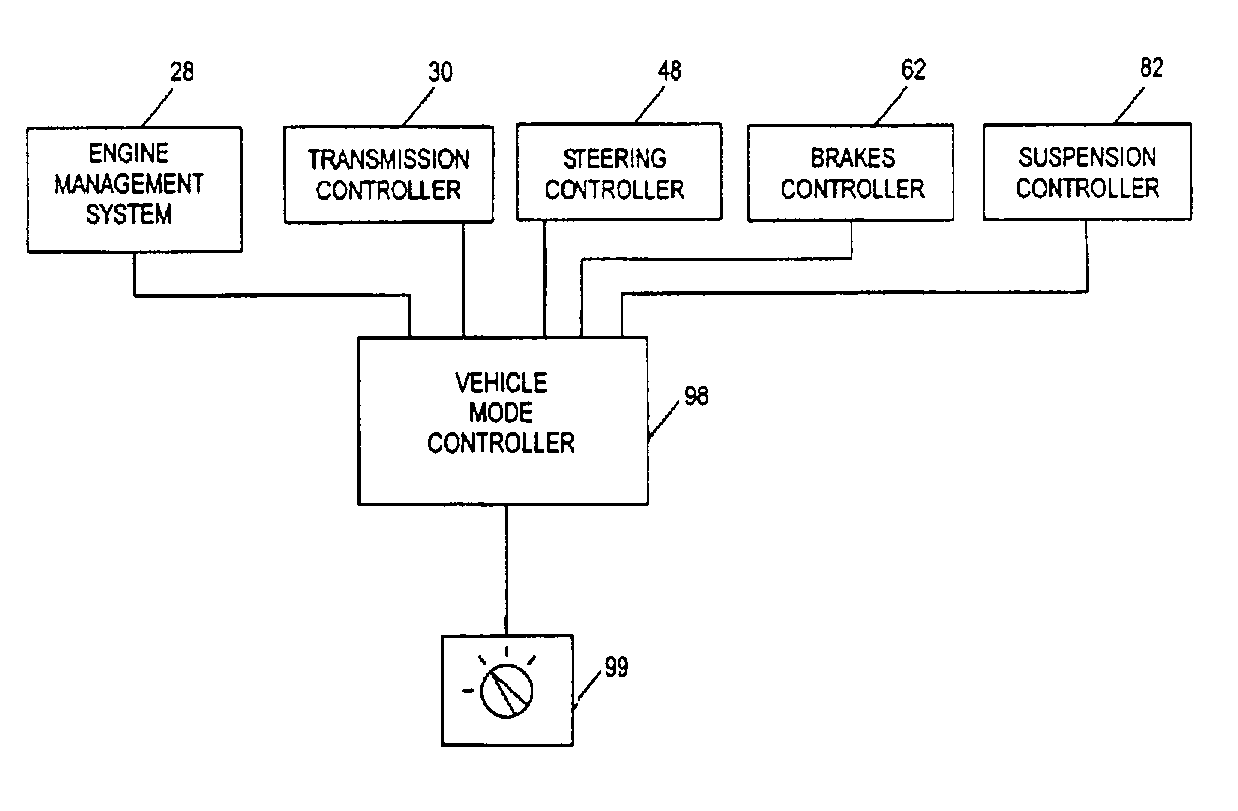

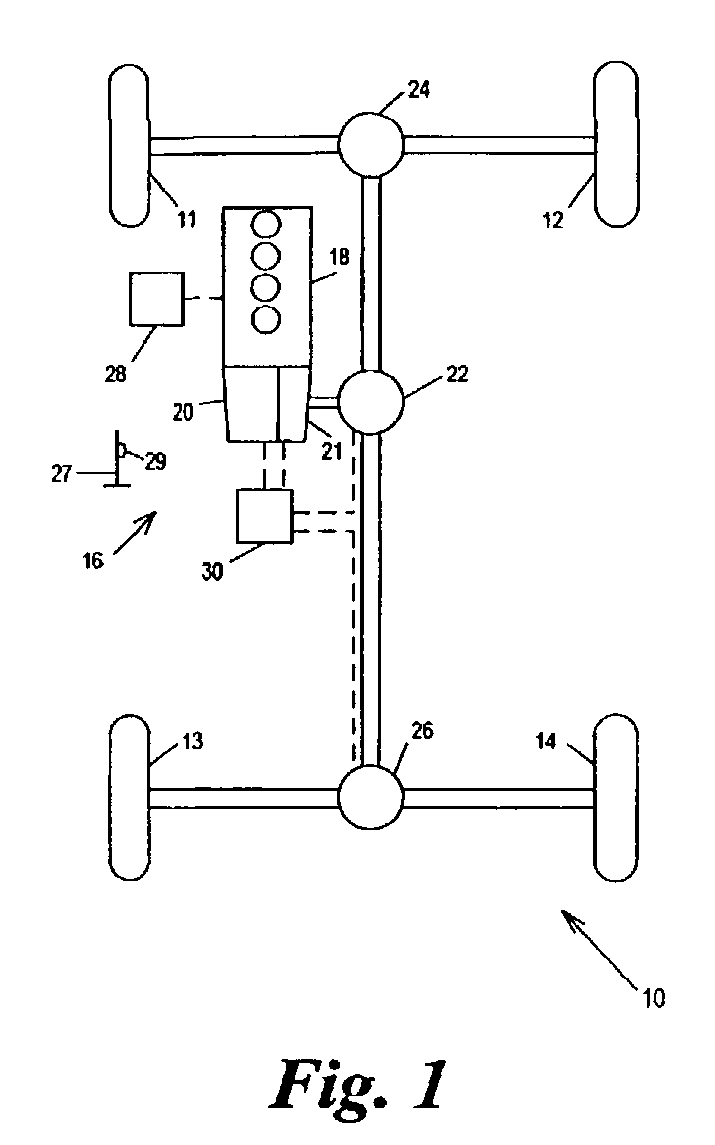

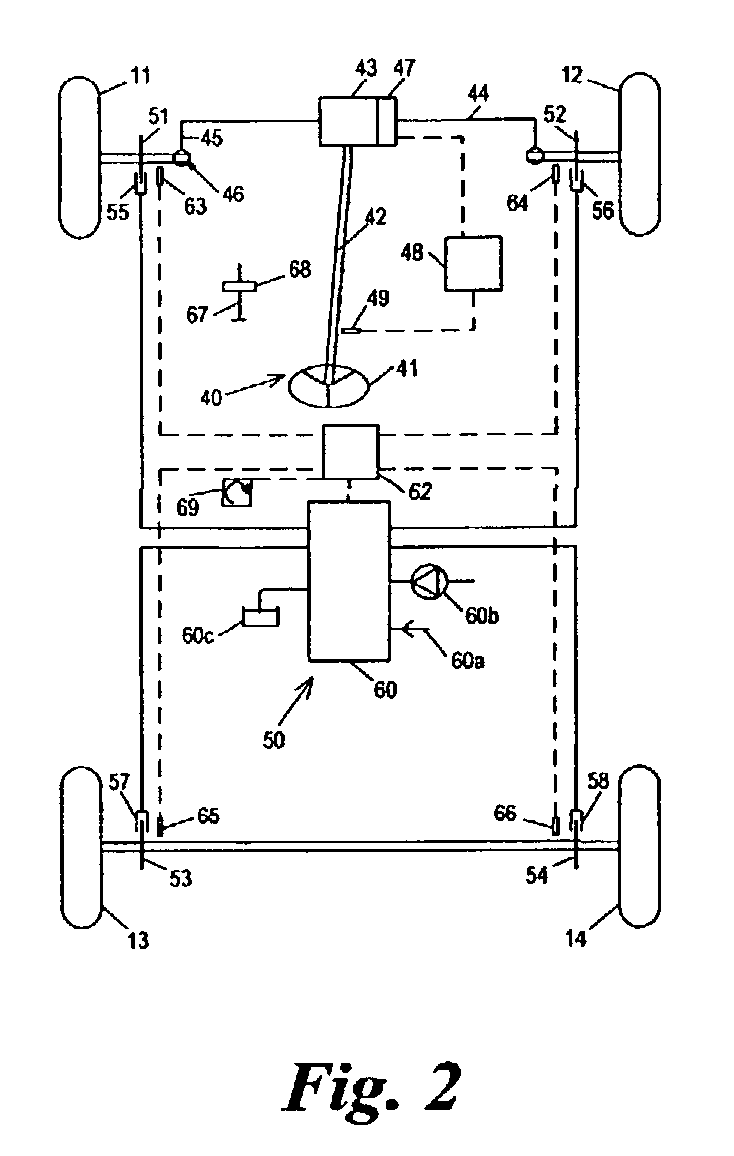

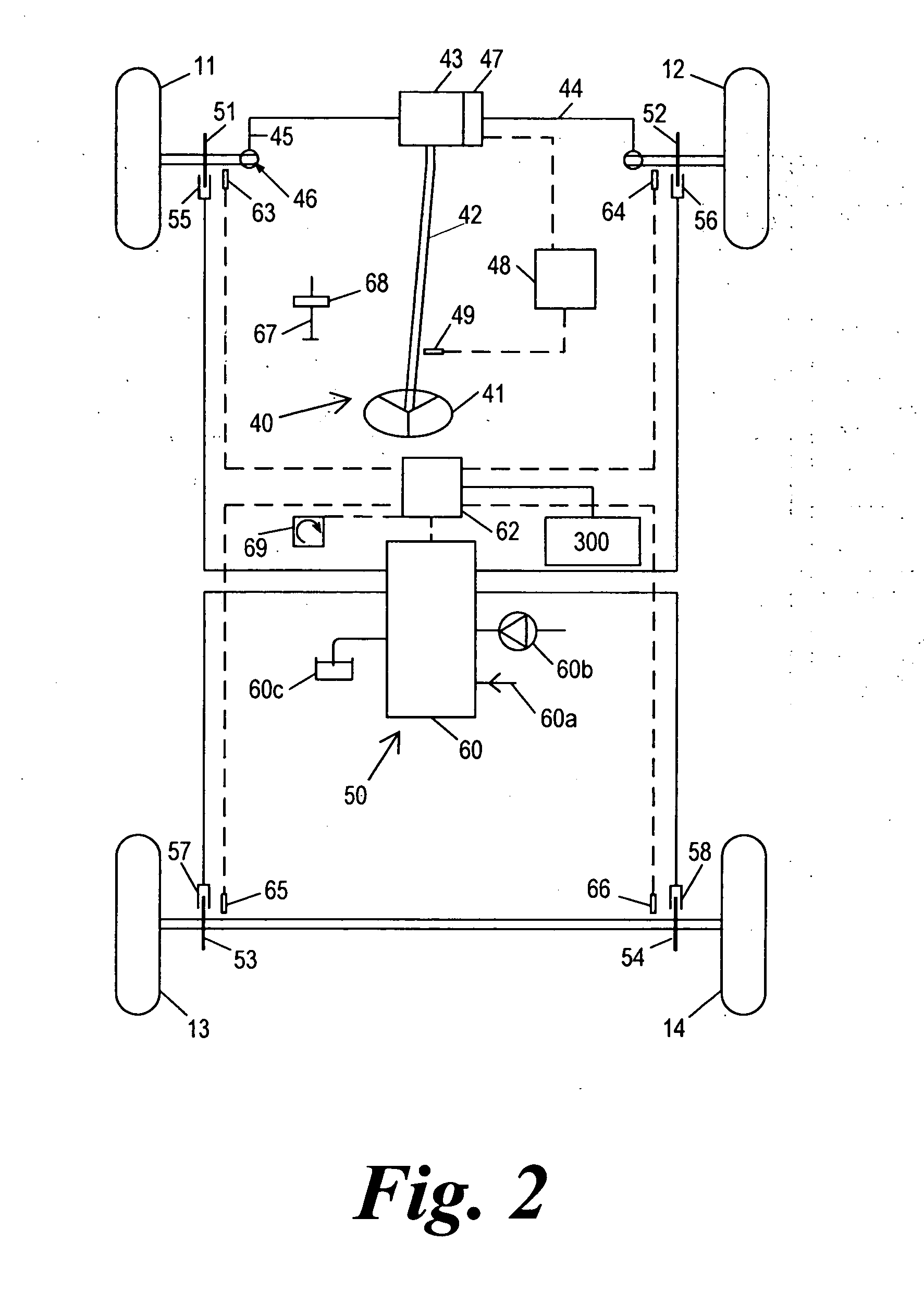

Vehicle control

ActiveUS7349776B2Improved vehicle controlEasy to controlBrake system interactionsDigital data processing detailsControl systemMode control

A vehicle control system has a plurality of subsystem controllers including an engine management system 28, a transmission controller 30, a steering controller 48, a brakes controller 62 and a suspension controller 82. These subsystem controllers are each operable in a plurality of subsystem modes, and are all connected to a vehicle mode controller 98 which controls the modes of operation of each of the subsystem controllers so as to provide a number of driving modes for the vehicle. Each of the modes corresponds to a particular driving condition or set of driving conditions, and in each mode each of the functions is set to the function in mode most appropriate to those conditions.

Owner:JAGUAR LAND ROVER LTD

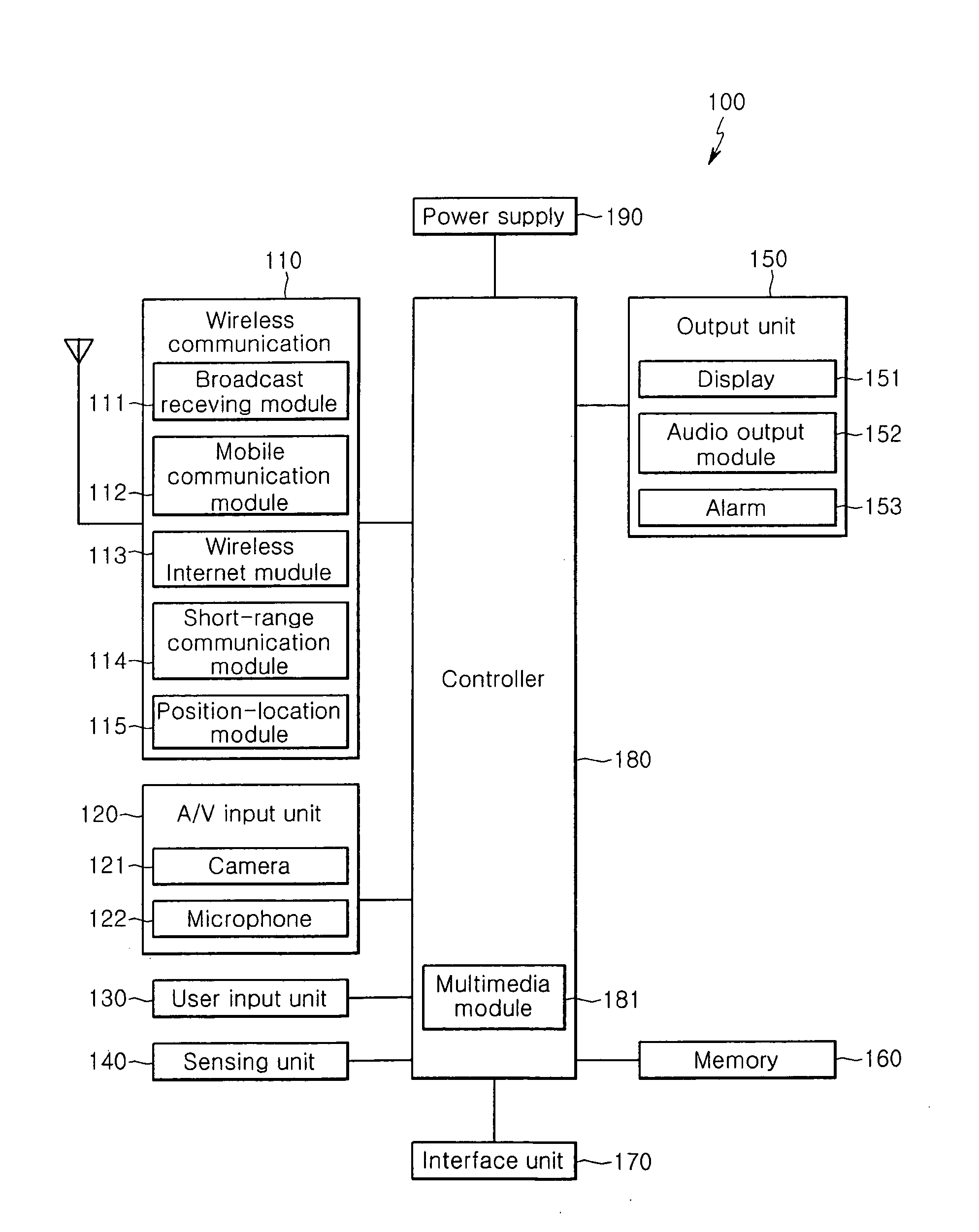

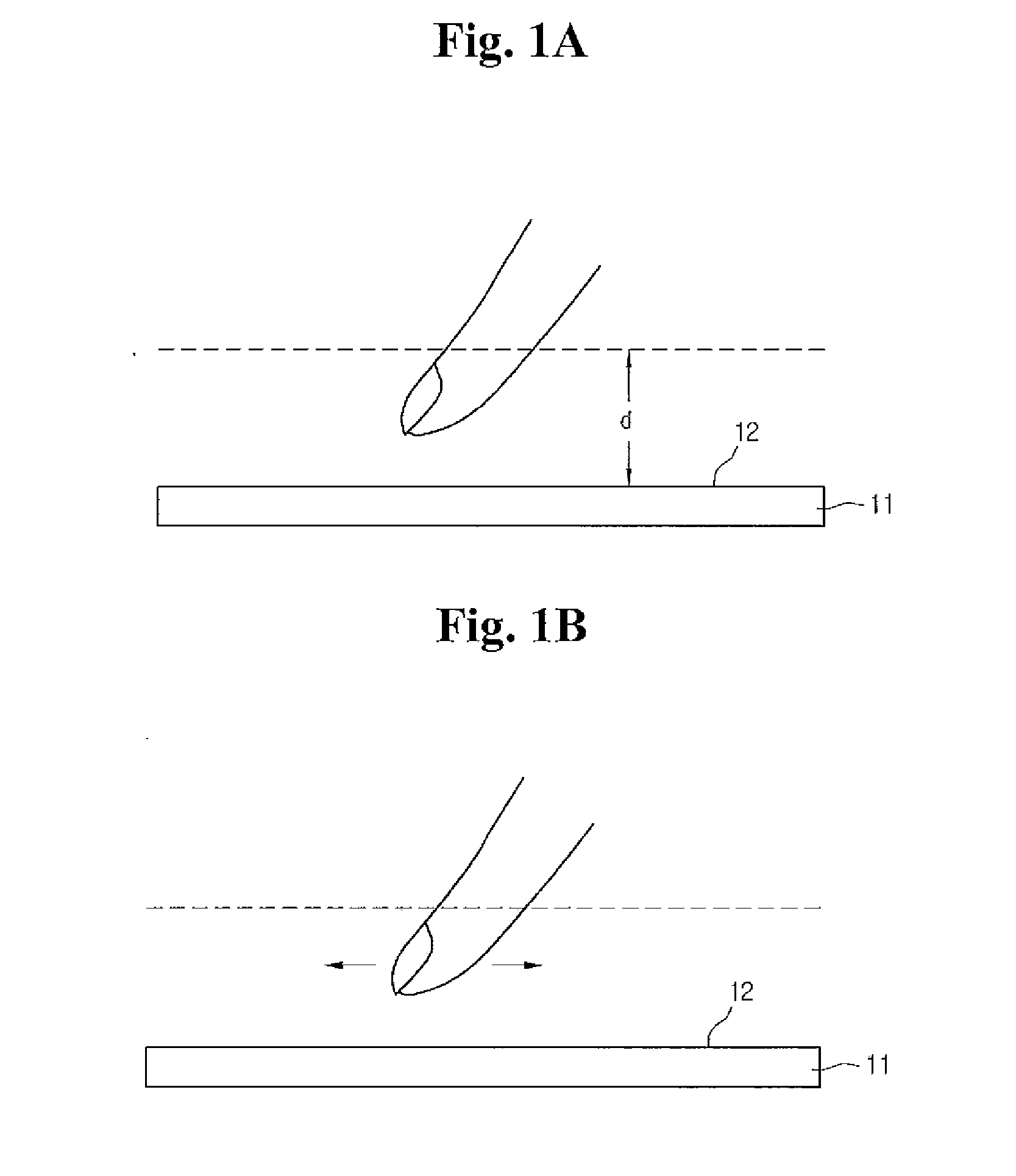

User interface for a mobile device using a user's gesture in the proximity of an electronic device

InactiveUS20090265670A1Cathode-ray tube indicatorsInput/output processes for data processingMode controlDisplay device

An electronic device having a user interface on a display and method for controlling the device, the method including: detecting a proximity of an object to the display; detecting a two-dimensional motion pattern of the object; and controlling the user interface according to the detected two-dimensional motion pattern. Also, a method including: detecting an object in a space over a border between first and second zones of a plurality of touch-sensitive zones and outputting a detection signal; and simultaneously displaying first and second information elements corresponding to the first and second zones in response to the detection signal.

Owner:LG ELECTRONICS INC

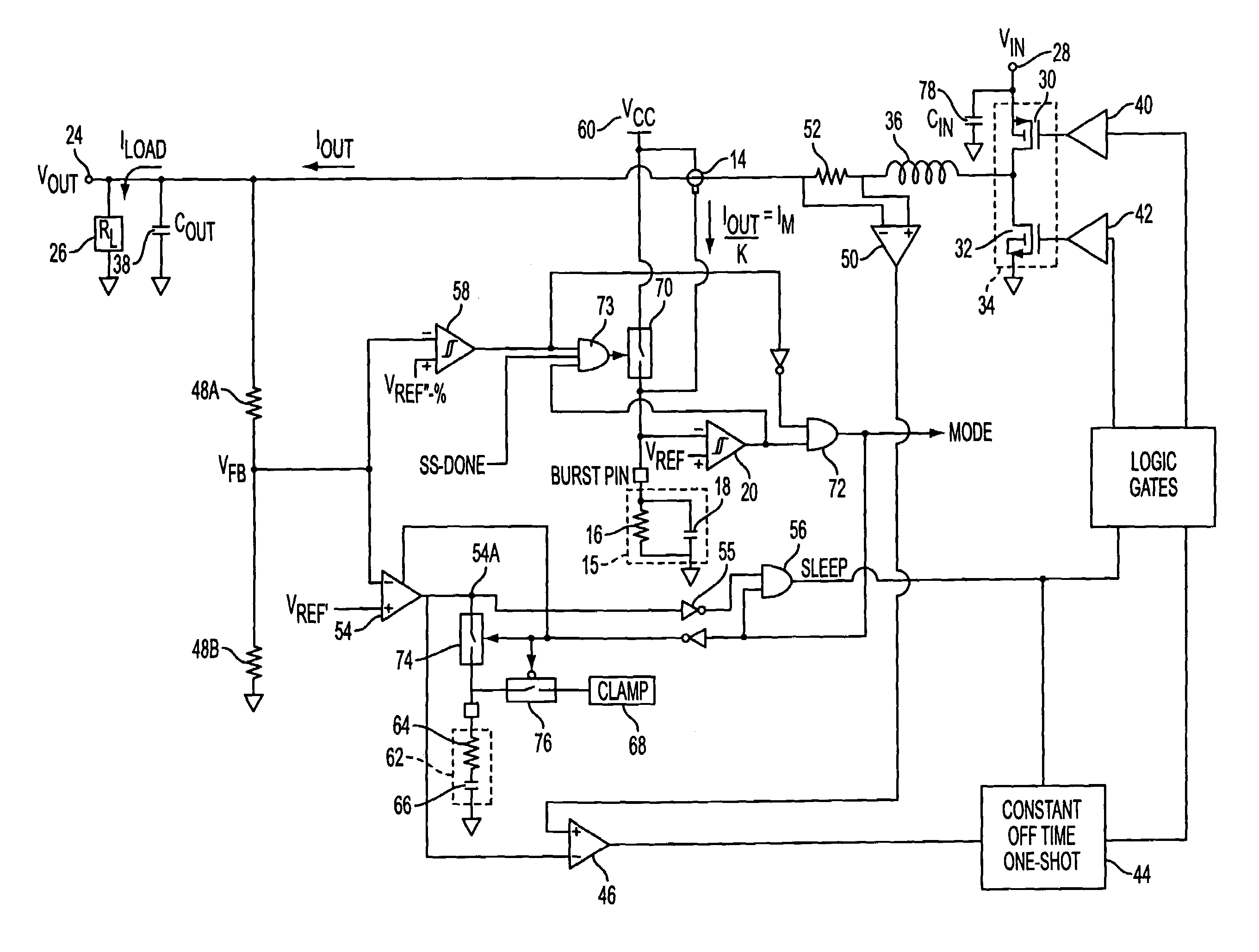

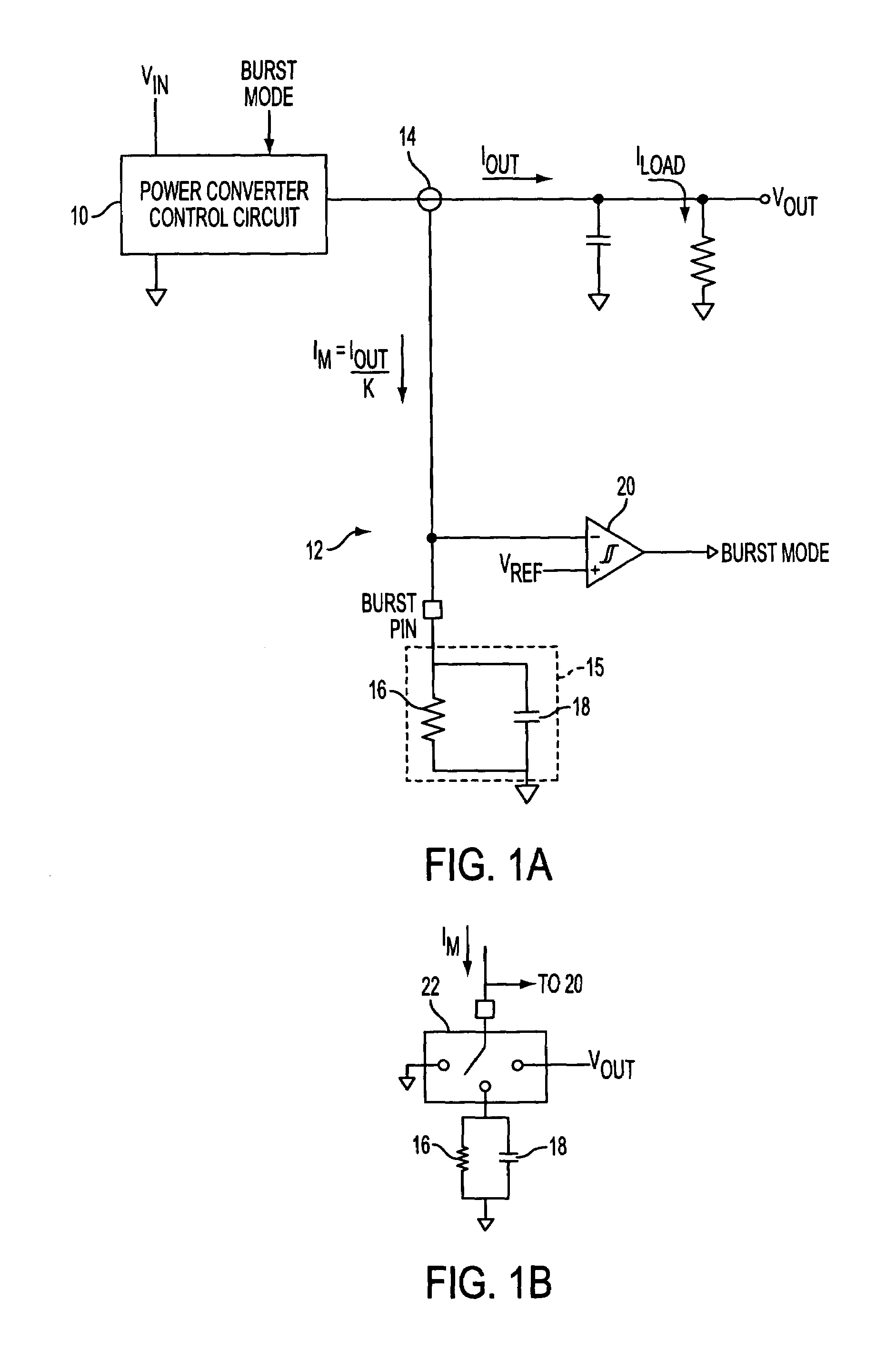

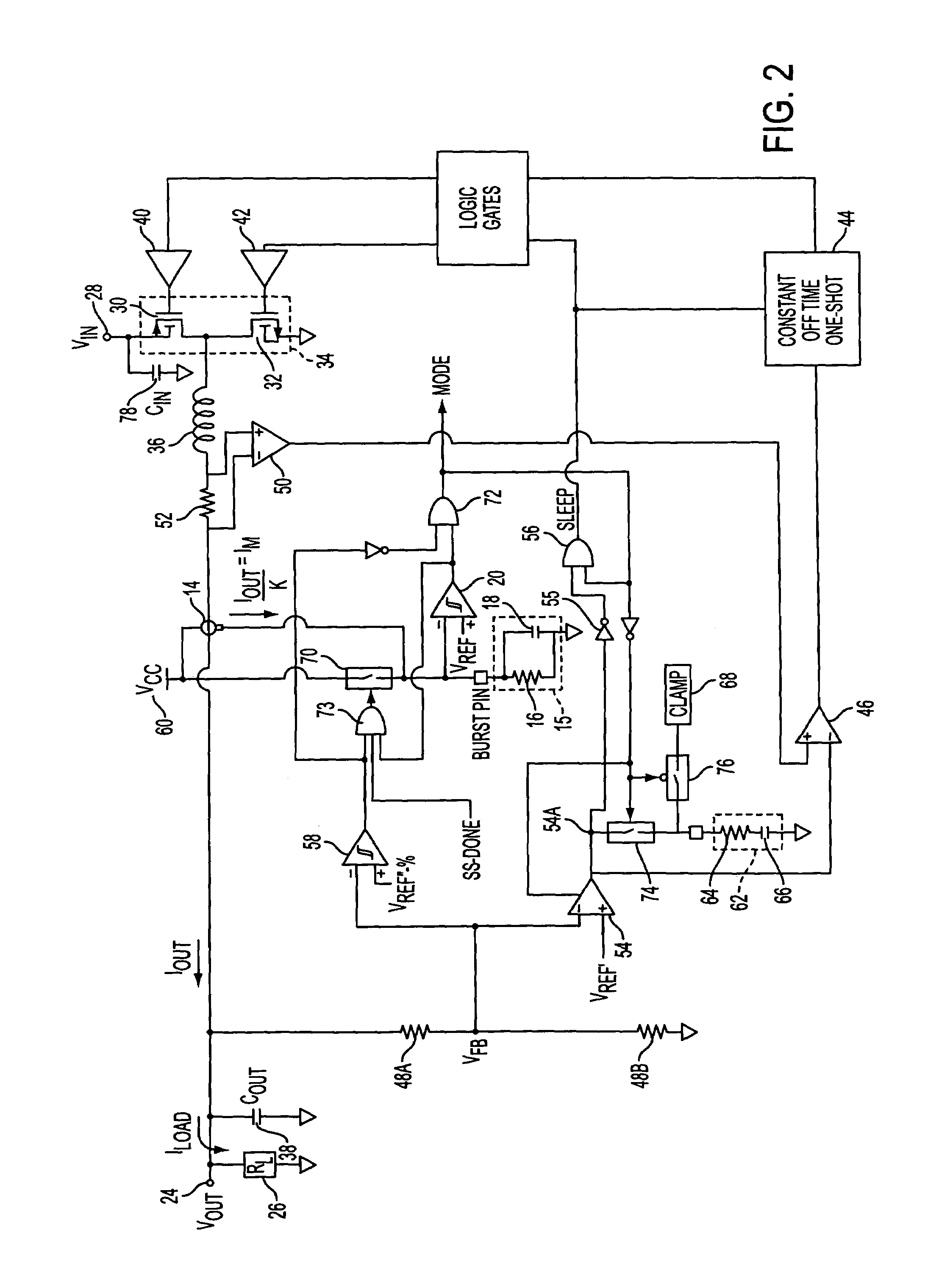

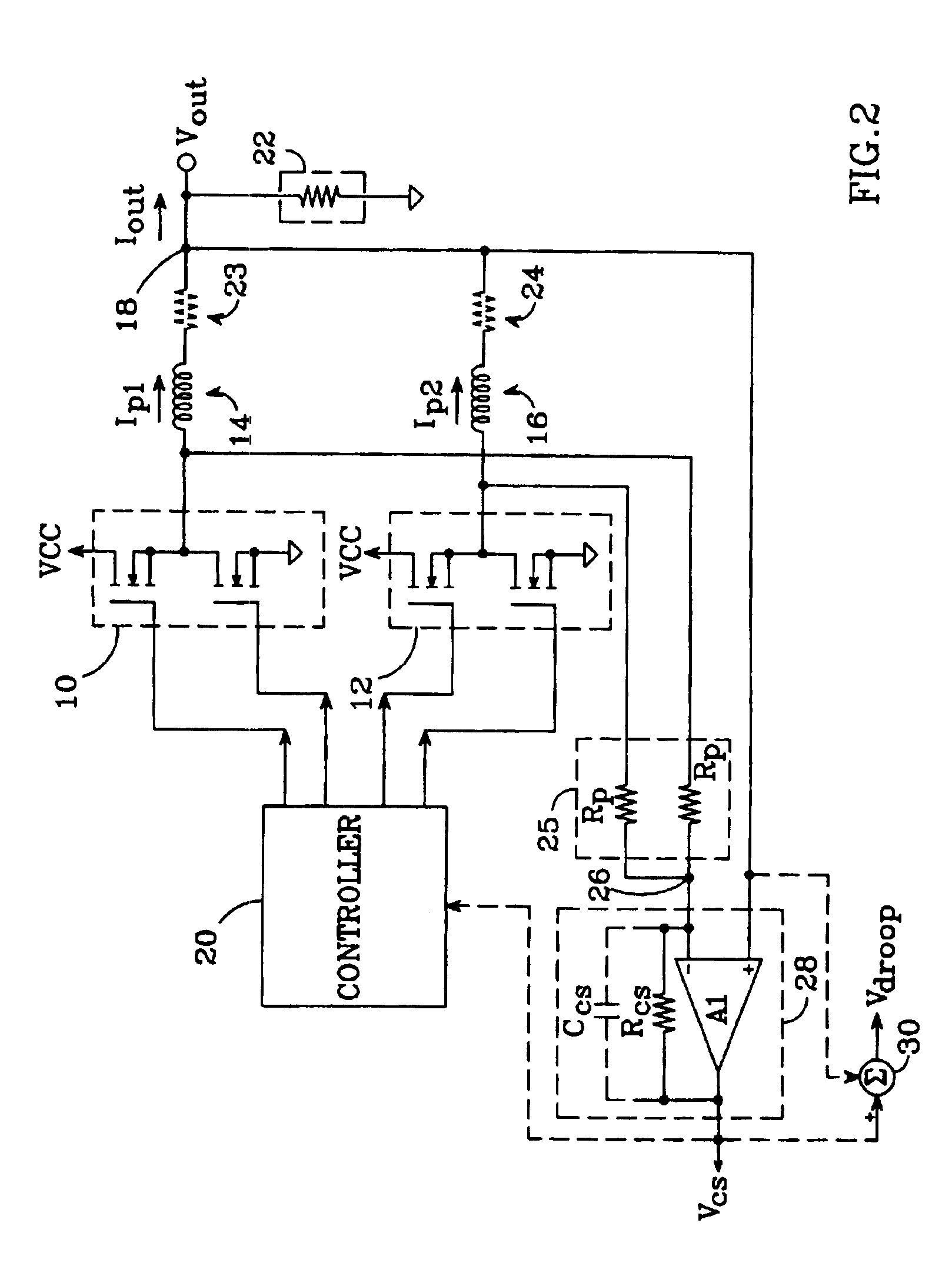

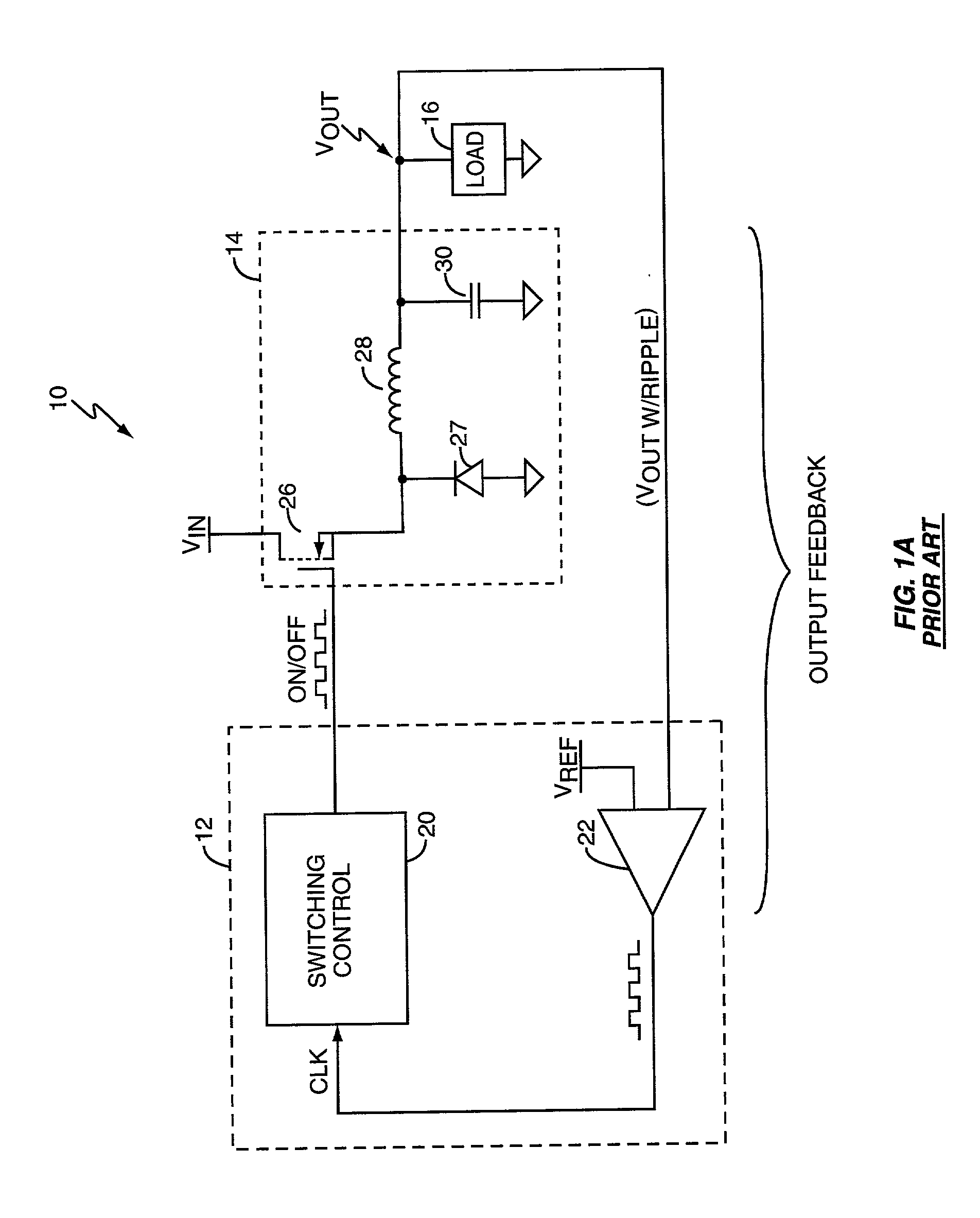

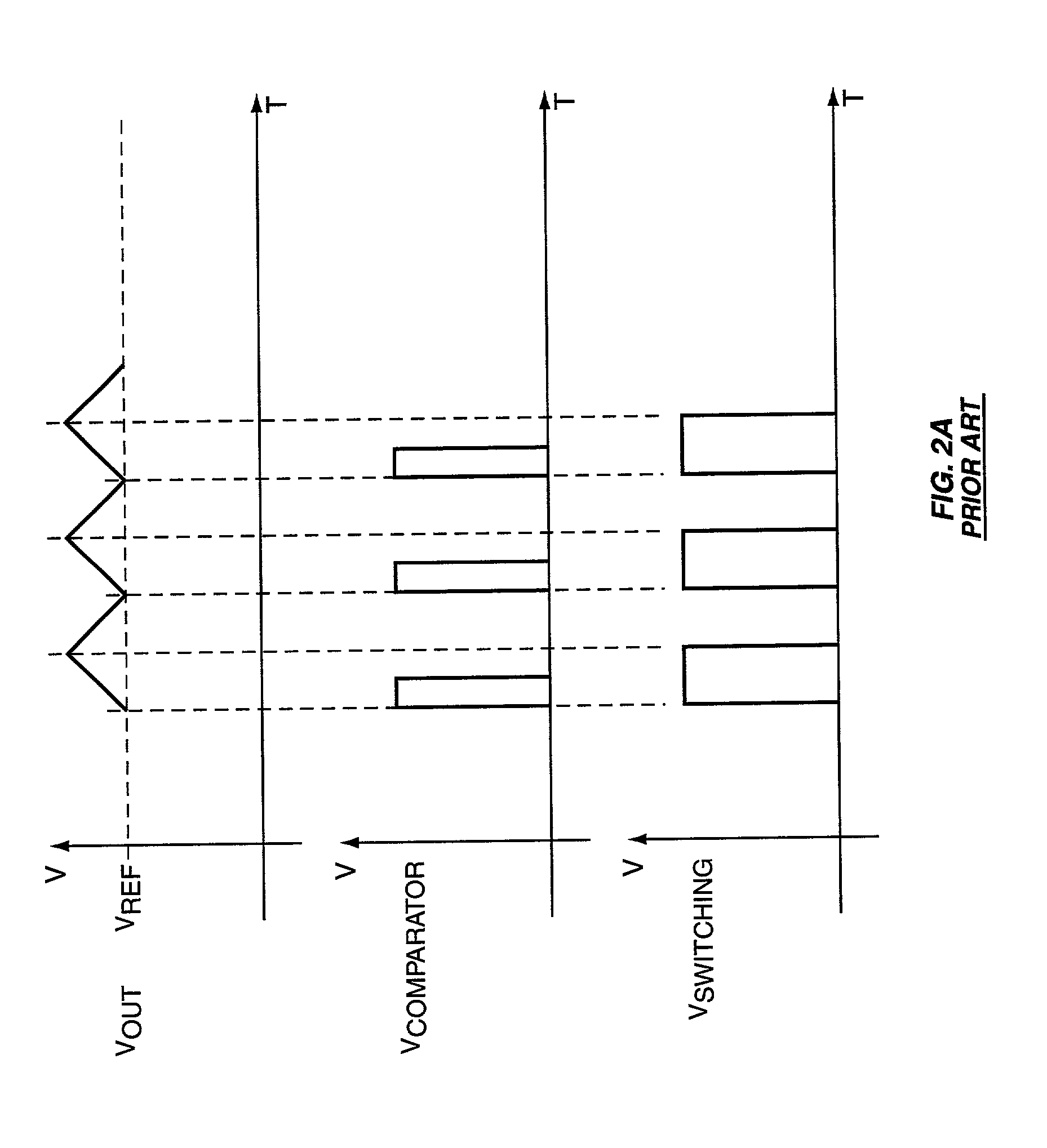

Methods and circuits for programmable automatic burst mode control using average output current

ActiveUS7030596B1Smooth and repeatable transitionEasy programmingEfficient power electronics conversionDc-dc conversionMode controlTransverter

The present invention comprises a user-programmable control circuit for use in a power converter to automatically transition the converter into BURST mode when load current demand is low. The control circuit senses load current demand by monitoring the output current of the converter, and generating a signal representative of the monitored output current. The control circuit may automatically transition the converter into BURST mode when the signal indicative of the average monitored output current decreases below a user-programmable threshold. BURST mode may increase overall converter efficiency by turning OFF a plurality of electronic components, and maintaining the converter's output voltage at a regulated level by energy stored in an output capacitor.

Owner:ANALOG DEVICES INT UNLTD

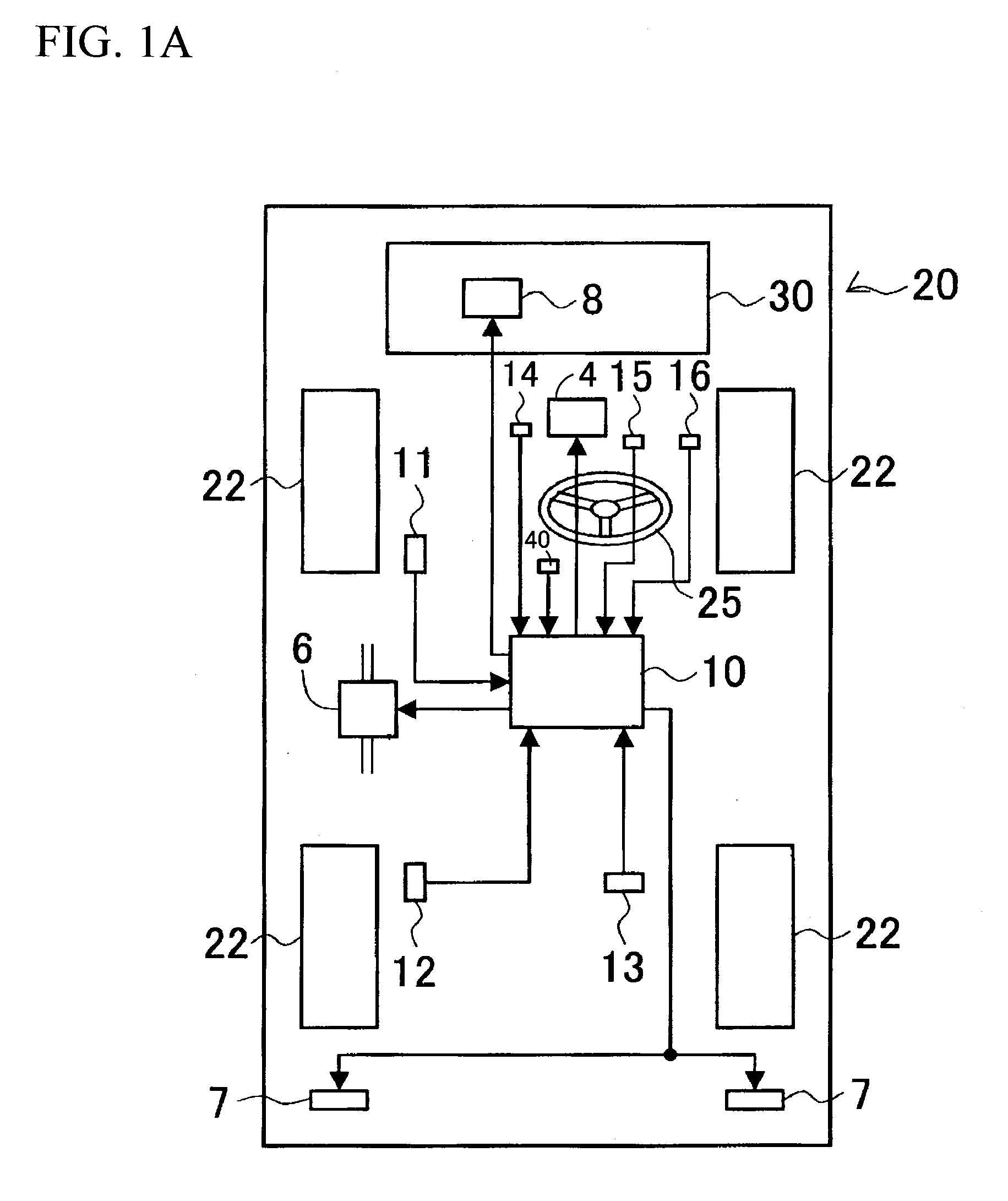

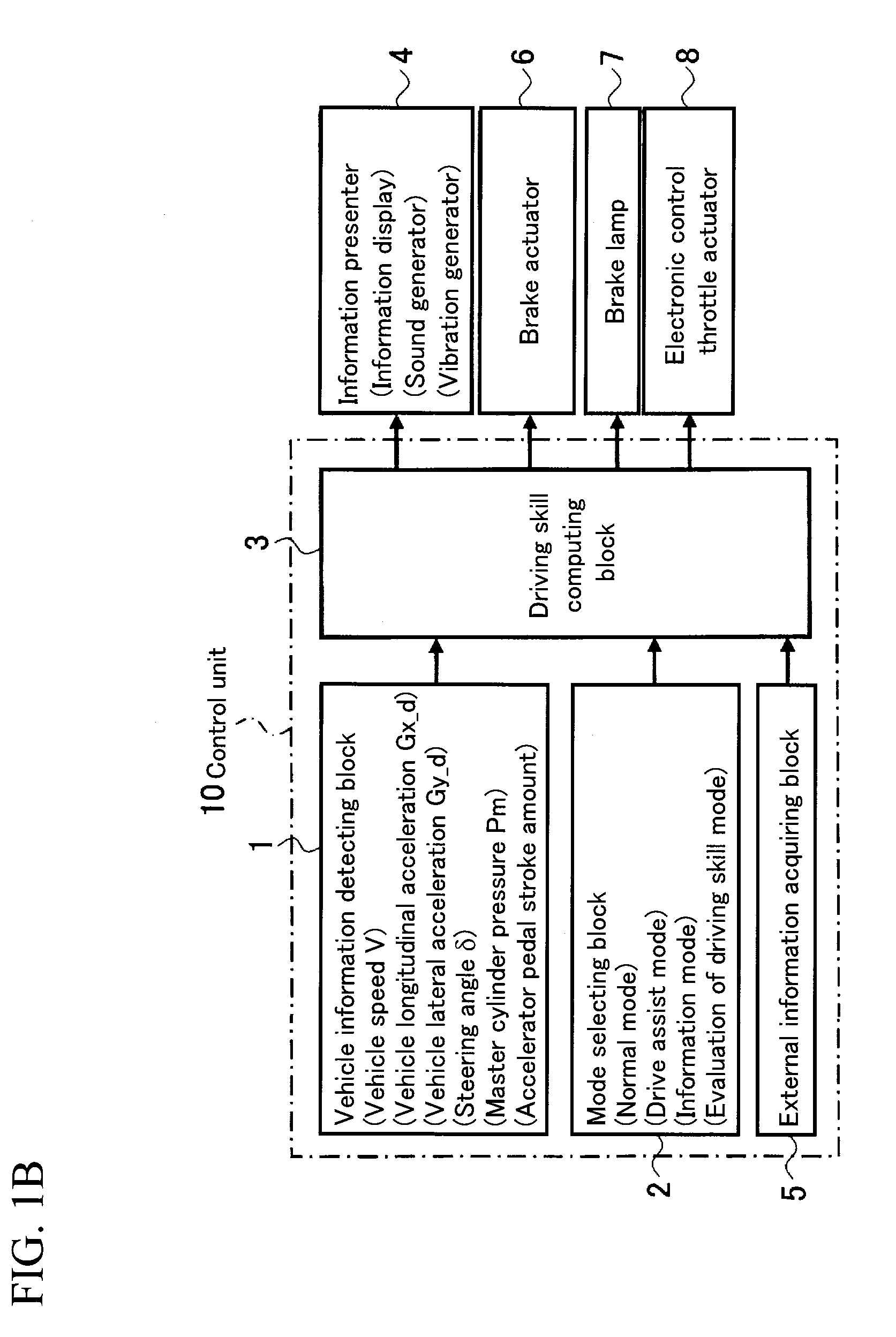

Driving Skill Improvement Device and Driving Skill Improvement Method

InactiveUS20100055649A1Increase awarenessInformation obtainedCosmonautic condition simulationsPedestrian/occupant safety arrangementDriver/operatorMode control

Owner:HITACHI LTD

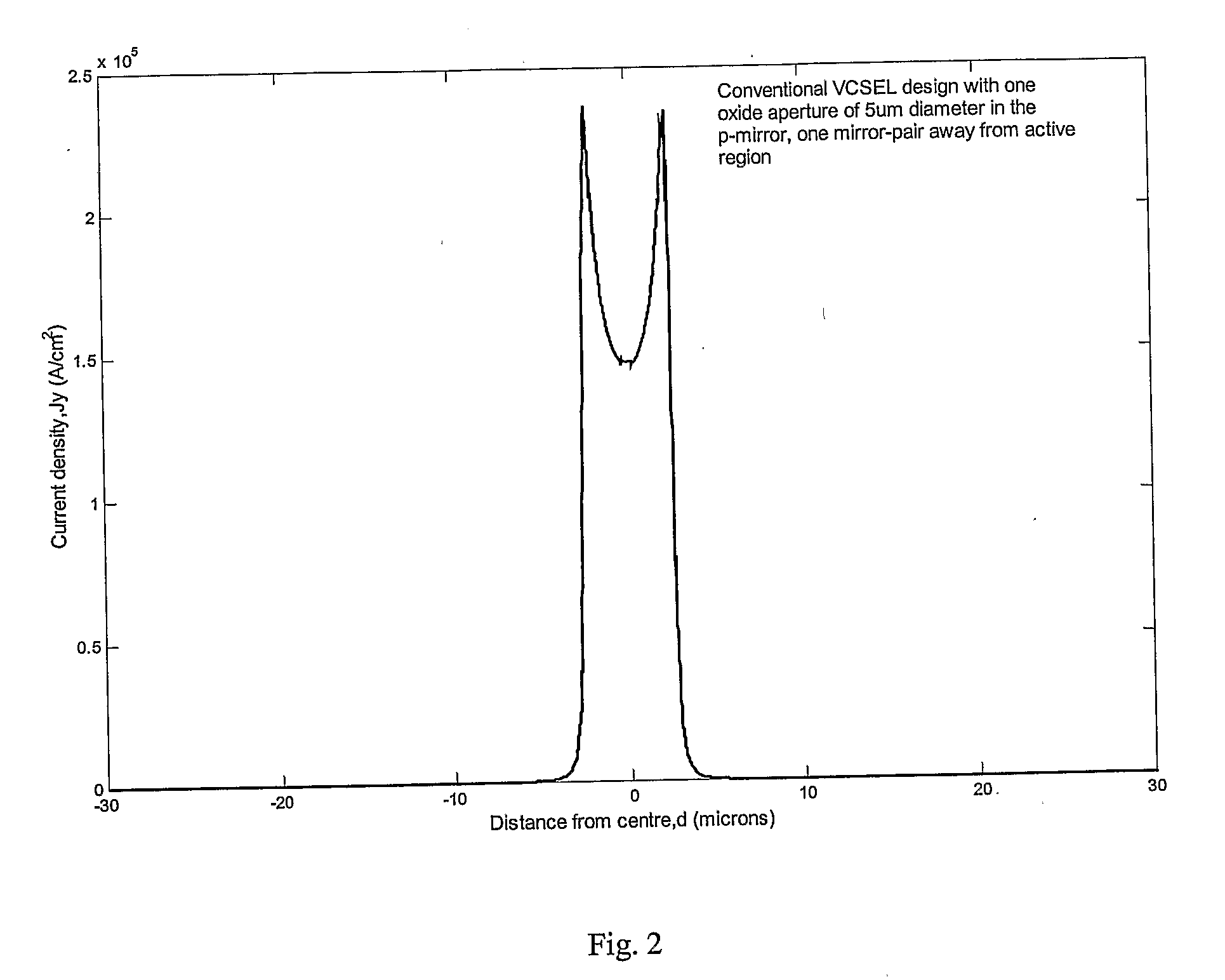

High Power Vcsels With Transverse Mode Control

InactiveUS20070242716A1High yieldSimple designLaser detailsSemiconductor lasersHigh power lasersMode control

A single mode high power laser device such as a VCSEL is formed with two oxide apertures, one on each side of the active region or cavity. The sizes of the apertures and the distances from the apertures to the cavity center are chosen or optimum, near-Gaussian current density distribution. The high power of a VCSEL thus formed is improved still more by good heat removal by either formation of a via through the substrate and gold plating on top and bottom of the VCSEL (including the via) or by lifting the VCSEL structure from the substrate and locating it on a heat sink.

Owner:ARIZONA STATE UNIVERSITY

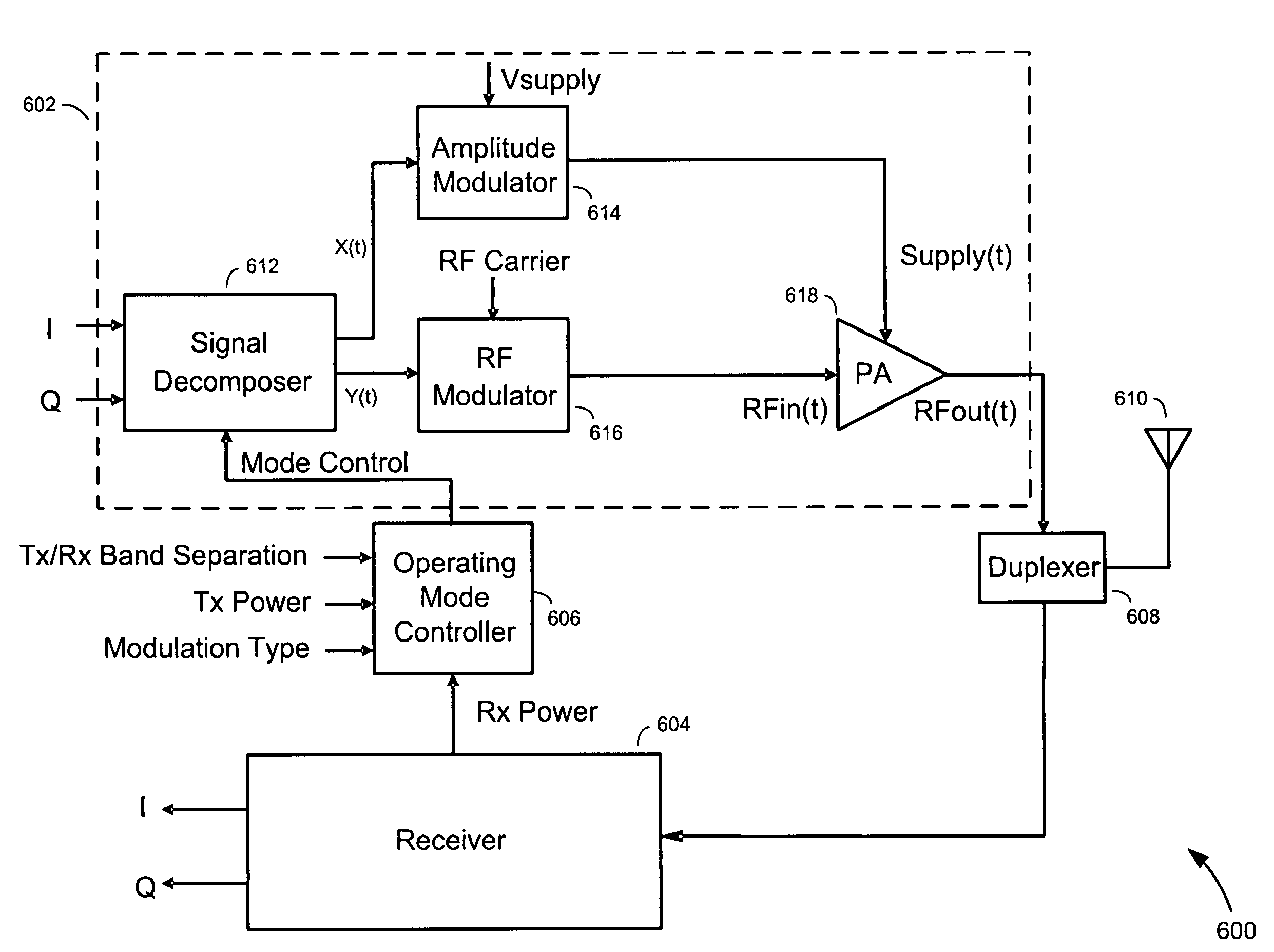

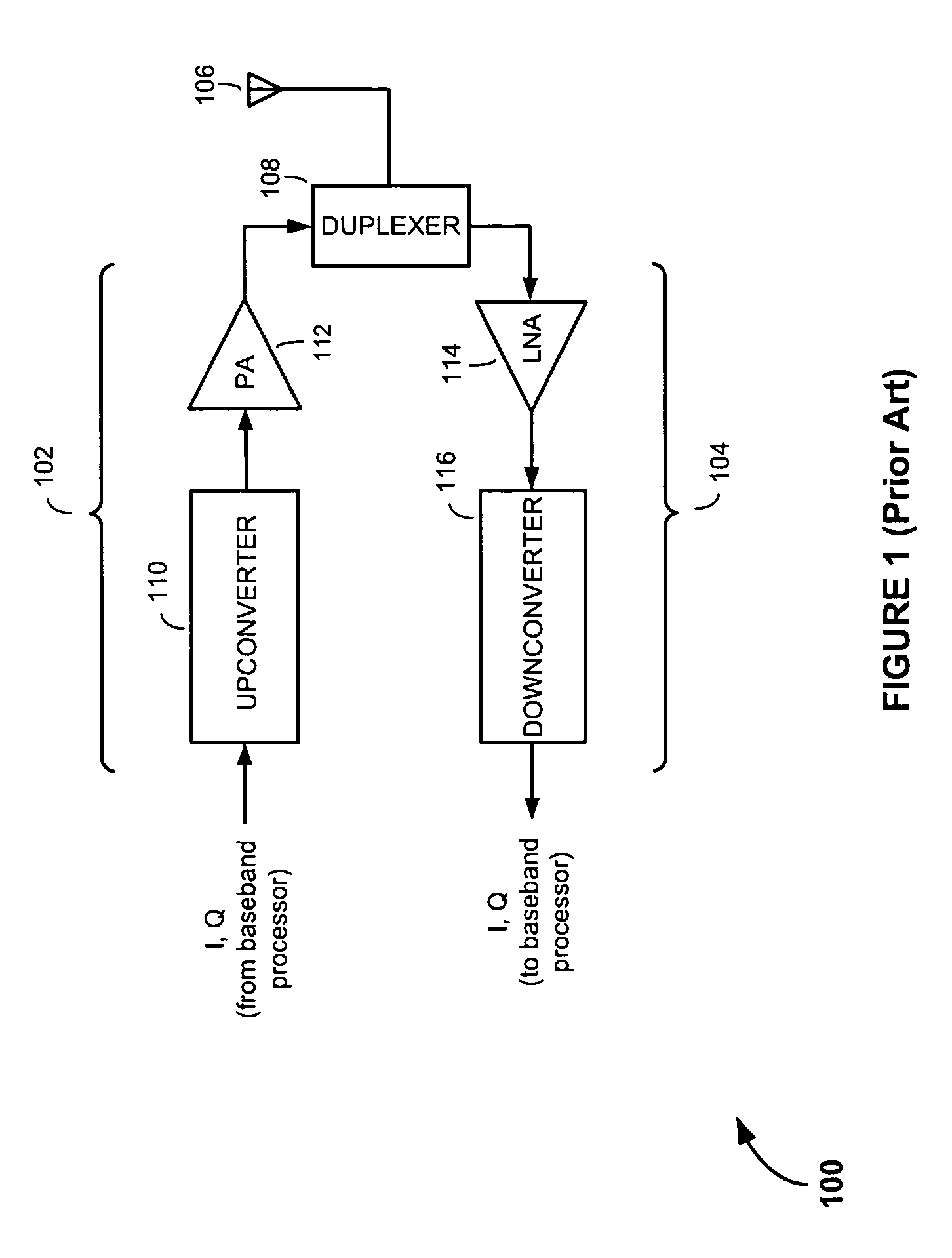

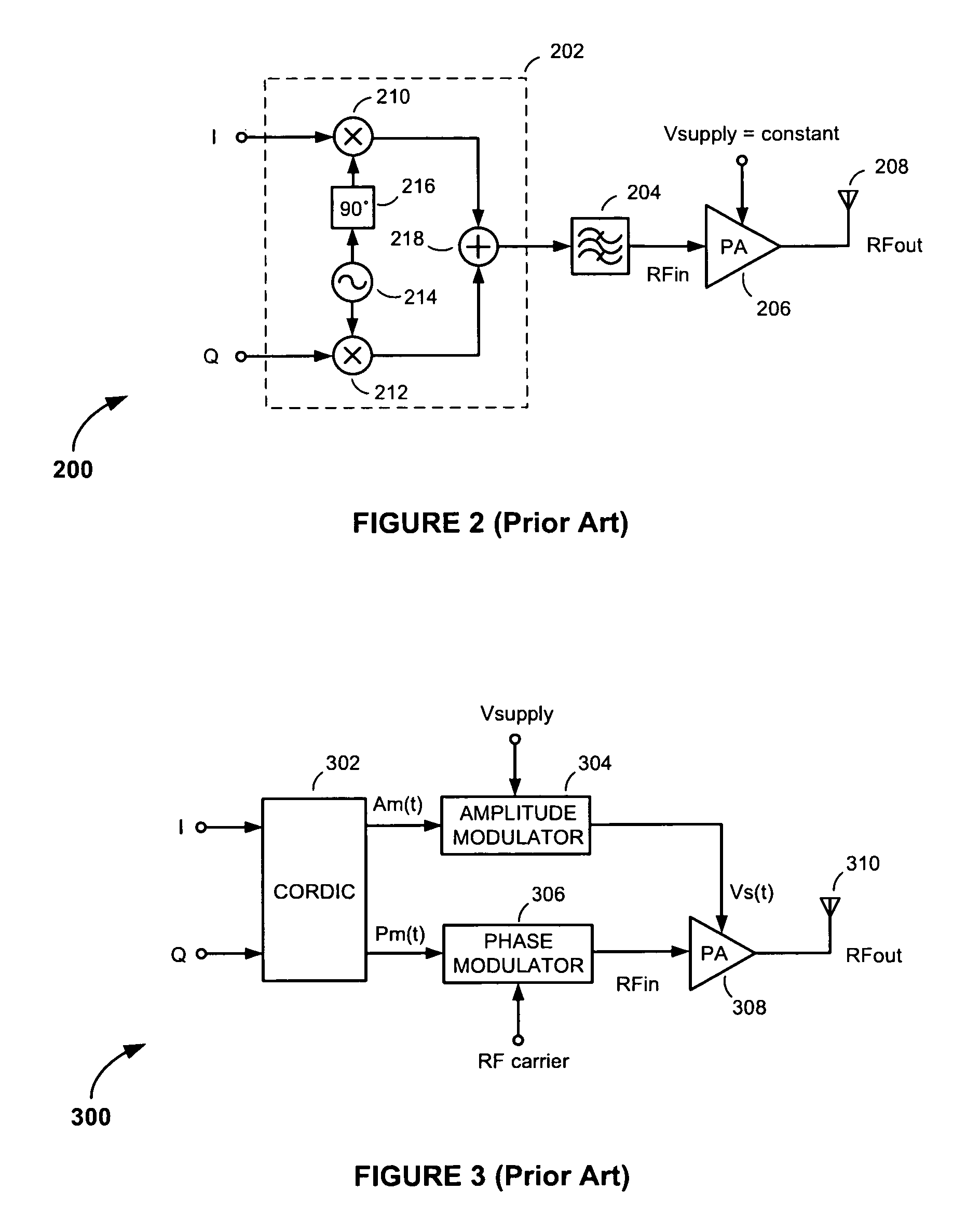

Multi-mode transmitter having adaptive operating mode control

ActiveUS8095093B2Improve power efficiencyPower efficiency and noiseResonant long antennasPower amplifiersPower efficientTransceiver

Methods and apparatus for transmitting communications signals that are both power efficient and effective at avoiding or reducing transmitter-generated receive band noise. An exemplary transceiver apparatus includes a multi-mode transmitter that is configurable to operate in a plurality of operating modes (e.g., a polar mode, a quadrature mode and a hybrid mode), a receiver, and an operating mode controller. The operating mode controller is configured to control which operating mode the transmitter is to operate, depending on one or more of a transmit (Tx) power, receive (Rx) power, the Tx power relative to the Rx power, a level of frequency separation between a Tx frequency band and a Rx frequency band (Tx / Rx band separation), and modulation type employed by the transmitter.

Owner:APPLE INC

Waypoint navigation

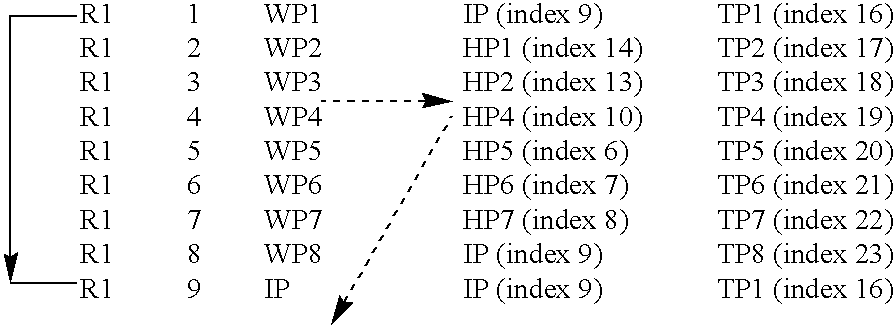

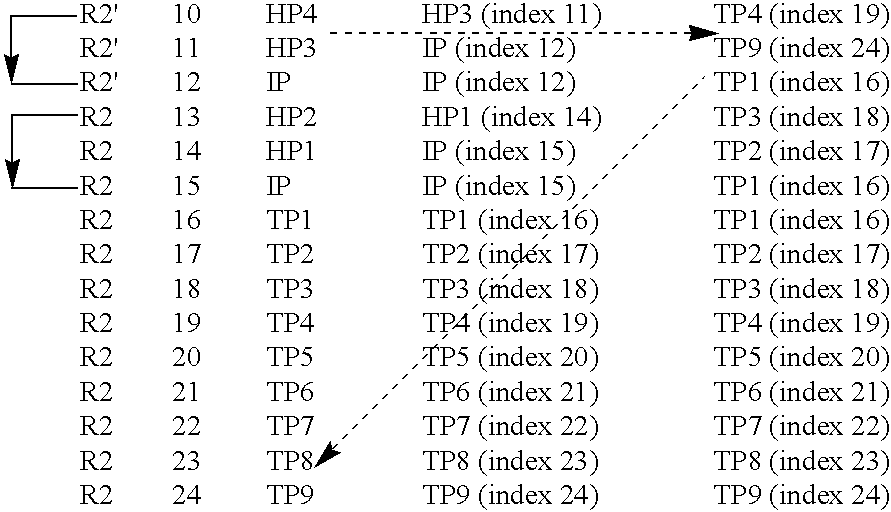

ActiveUS20040193334A1Reduce riskDigital data processing detailsHeight/levelling measurementMode controlRemote control

The invention relates to remote control of an unmanned aerial vehicle, UAV, (100) from a control station (110) by means of a wireless command link (115). The UAV (100) may be controlled in an autonomous mode wherein it flies according to a primary route (R1, R1') defined by a first set of predefined waypoints (WP1-WP8, IP). The UAV (100) may also be controlled in a manual mode wherein it flies according to an alternative primary route (R1') defined in real-time by control commands received via the wireless command link (115). Flight control parameters are monitored in both modes, and in case a major alarm condition occurs, the UAV (100) is controlled to follow an emergency route (R2') defined by a second set of predefined waypoints (HP1-HP7, TP1-TP9, IP). Particularly, a major alarm condition is activated if an engine failure is detected. Then, the emergency route (R2') involves flying the UAV (100) to an air space above a termination waypoint (TP9) on the ground at which it is estimated that the vehicle's (100) flight may be ended without injuring any personnel or causing uncontrolled material damages.

Owner:SAAB AB

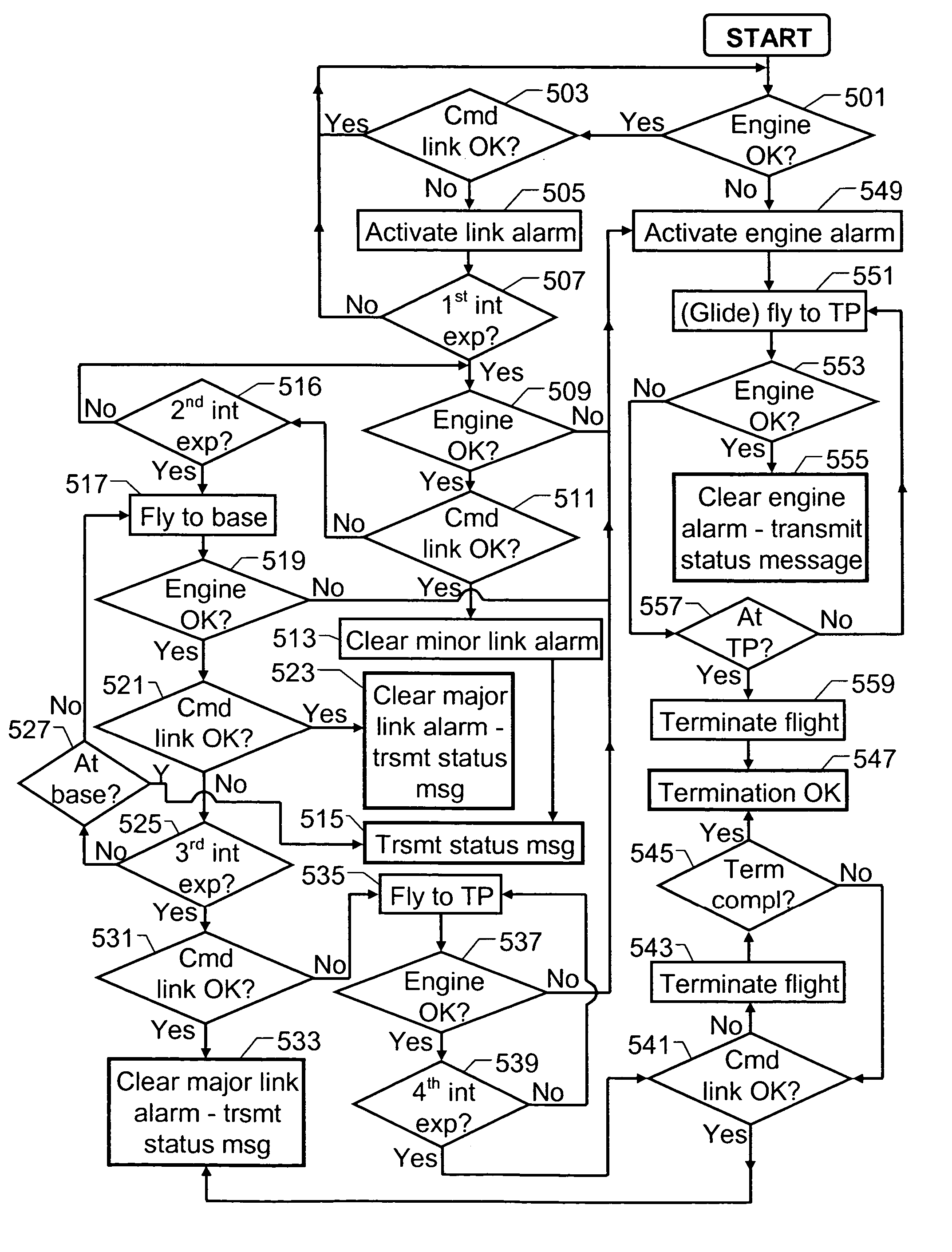

Method, apparatus and system for access mode control of a device

ActiveUS20120023573A1Digital data processing detailsUnauthorized memory use protectionMode controlAccess control

A method, apparatus, and system for accessing at least a portion of a device based upon an access input. An access input is received. The access input includes information for gaining access to one or more functions of the device. A user access mode of the device is changed from a first access mode to a second access mode based upon at least in part on the access input. An application is selected in the device in response to changing from the first access mode to the second access mode. At least a portion of the output of the selected application is provided.

Owner:APPLE INC

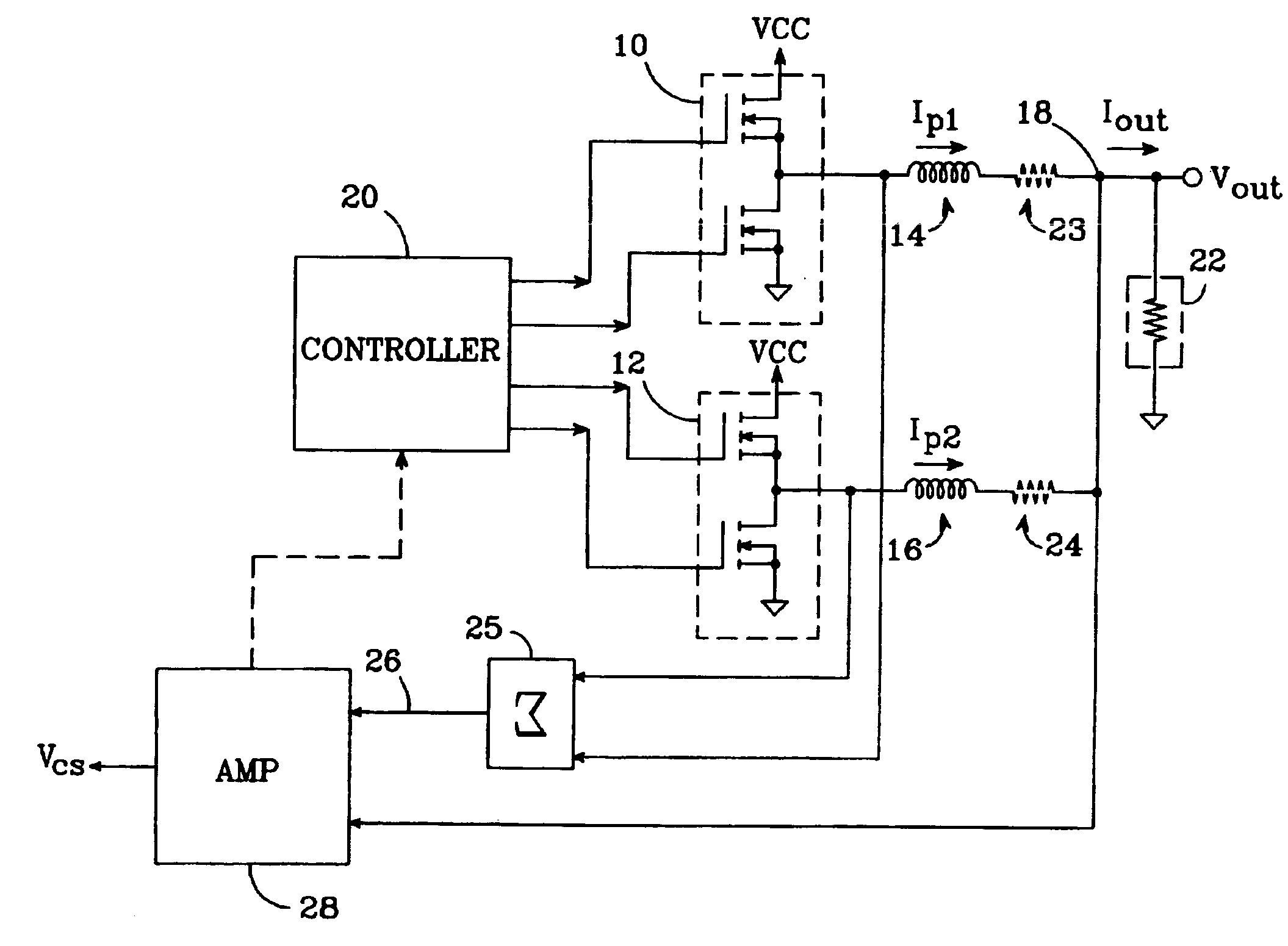

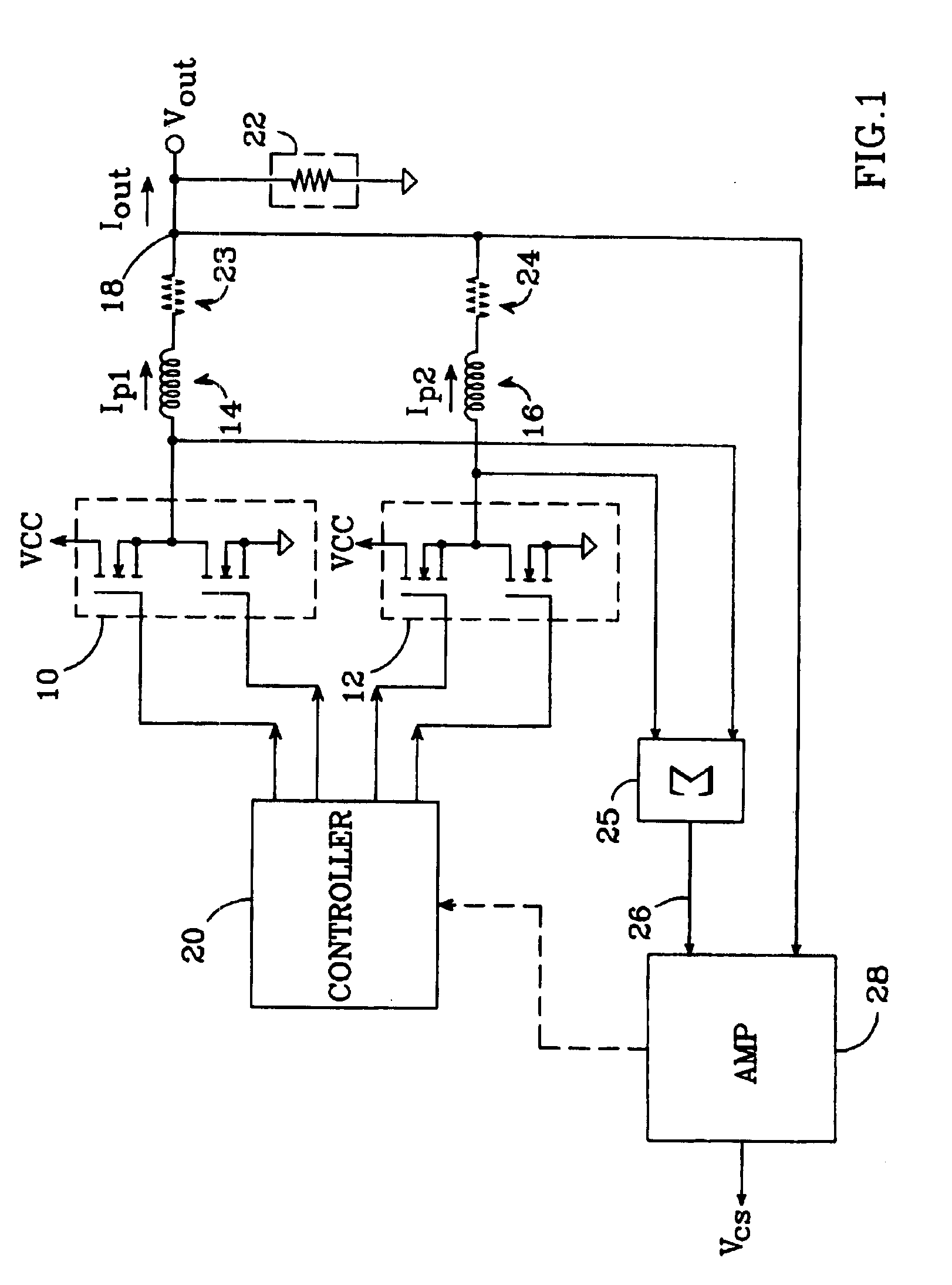

Multi-phase switching regulator

InactiveUSRE39976E1Overcome problemsEasy to controlDc-dc conversionElectric variable regulationPhase currentsAudio power amplifier

An N-phase switching voltage regulator includes N current sensing elements which carry respective phase currents. The voltages present at the switch node sides of the sensing elements are summed and presented to an amplifier which also receives the regulator's output voltage, to produce an output which is proportional to the regulator's total output current Iout. The invention also provides a means for direct insertion of total inductor output current information into a regulator's voltage-mode control loop, to provide active voltage positioning (AVP) for the output voltage. A voltage based on total inductor output current is summed with the regulator's reference voltage; this sum and Vout are applied to the voltage control error amplifier, the output of which is processed to operate the regulator's switches. This enables the regulator's output to have a desired droop impedance and to provide AVP of Vout as a function of total filtered inductor output current Iout(fltr).

Owner:ANALOG DEVICES INC

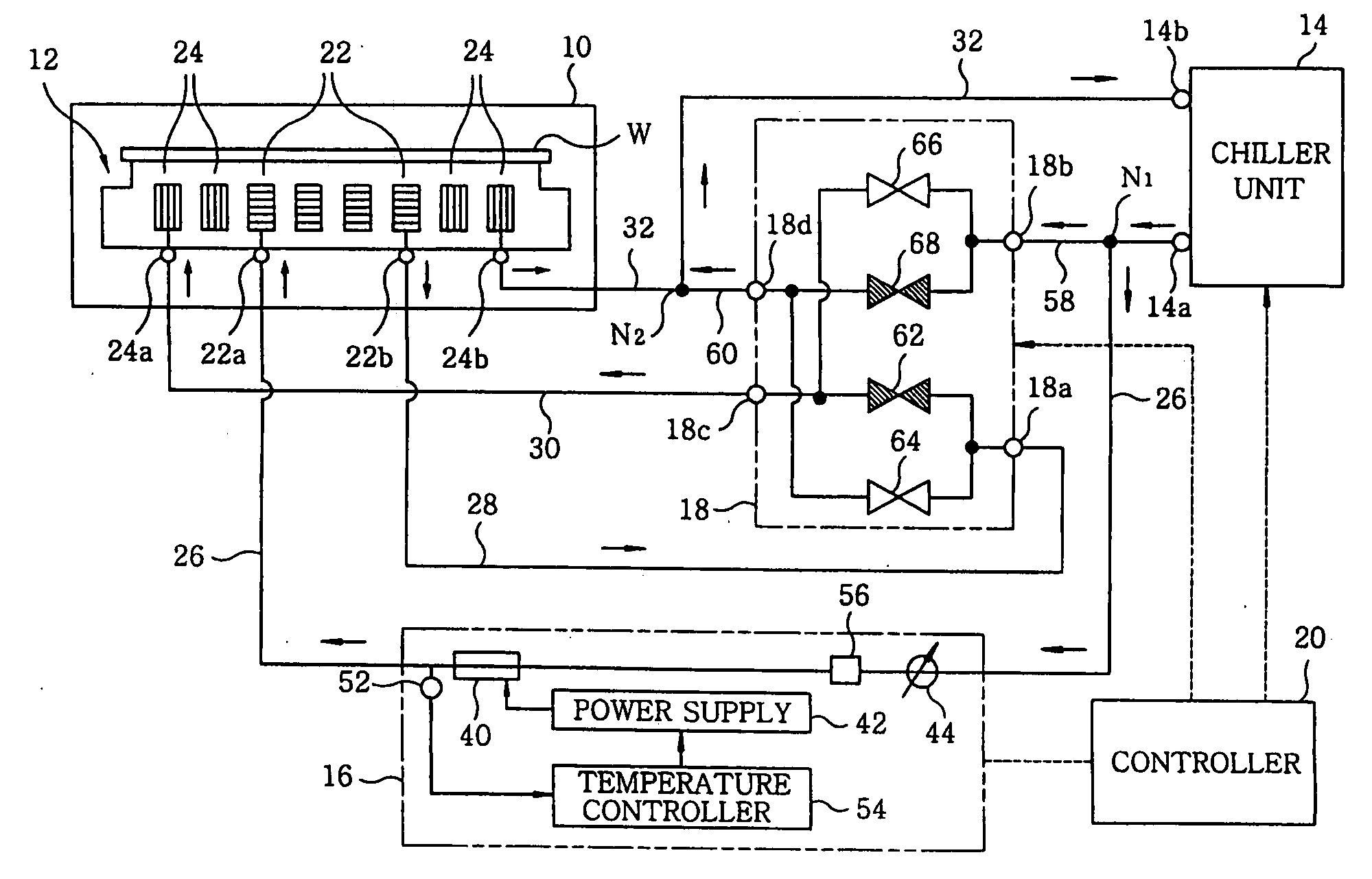

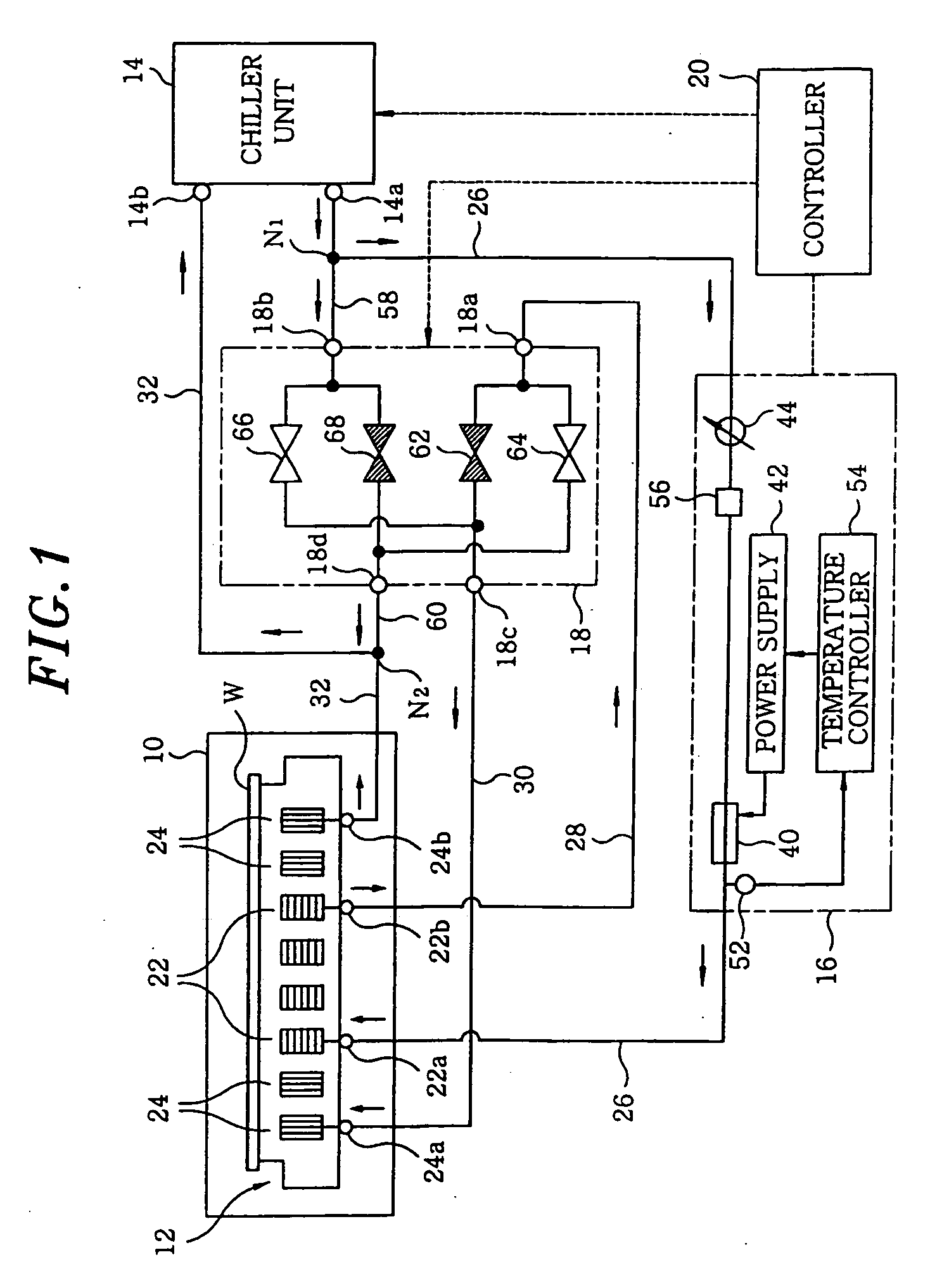

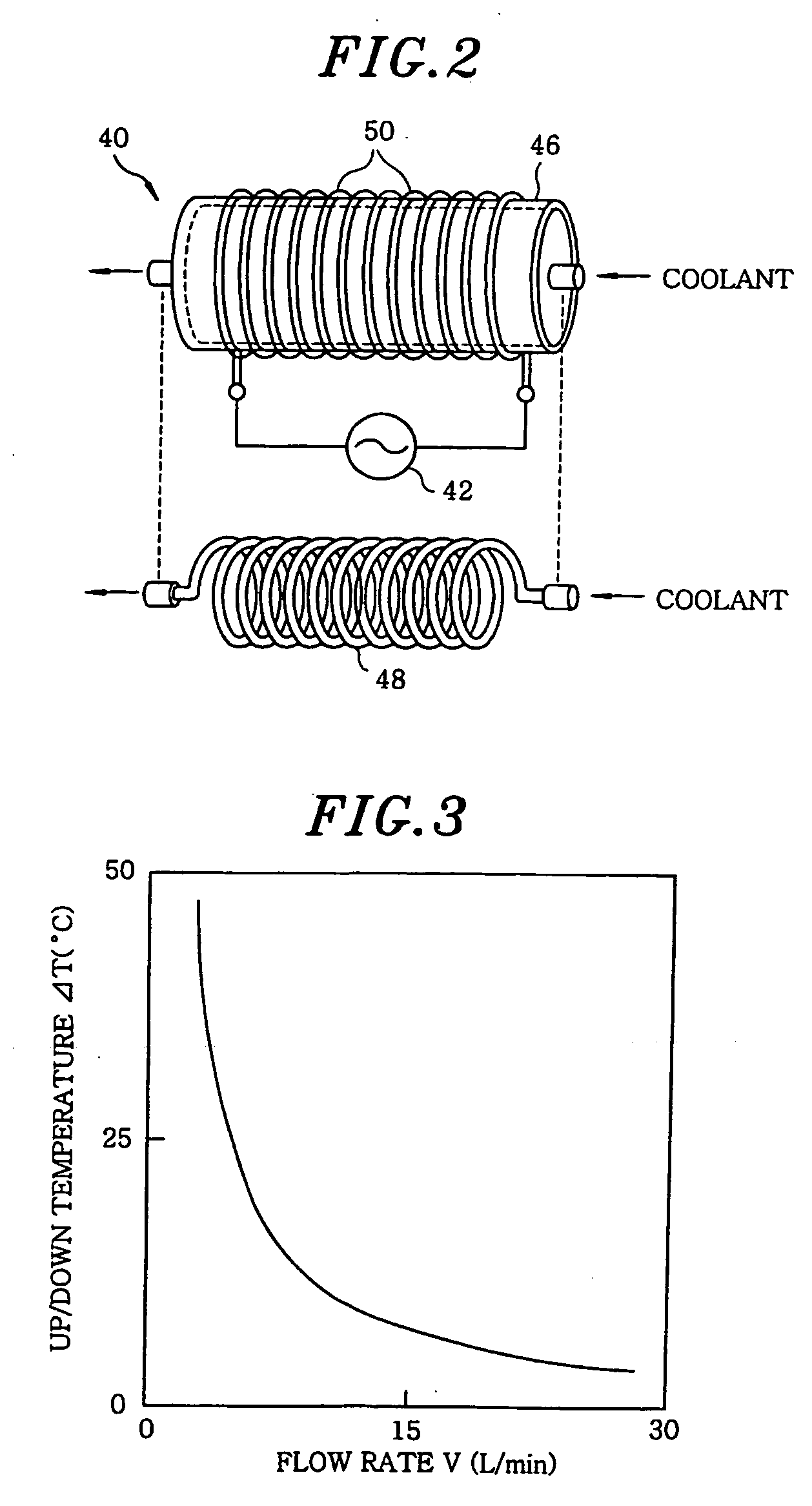

Device and method for controlling temperature of a mounting table, a program therefor, and a processing apparatus including same

ActiveUS20060219360A1Small-scaledImprove accuracyElectric discharge tubesTemperatue controlTemperature controlMode control

A device for controlling a temperature of a mounting table for mounting thereon a target object includes a first and a second coolant passageway provided at the mounting table, a coolant circulator for circulating a coolant in the first and the second coolant passageway, channels, a coolant temperature controller for raising or lowering the temperature of the coolant, a channel switching unit for connecting, blocking and changing the channels among a first to a fourth port; and a channel controller. Various modes for controlling a temperature of the mounting table can be obtained by combining an ON / OFF state of the heating operation in the coolant temperature controller with ON / OFF states of opening / closing valves in the channel switching unit under the control of the channel controller.

Owner:TOKYO ELECTRON LTD

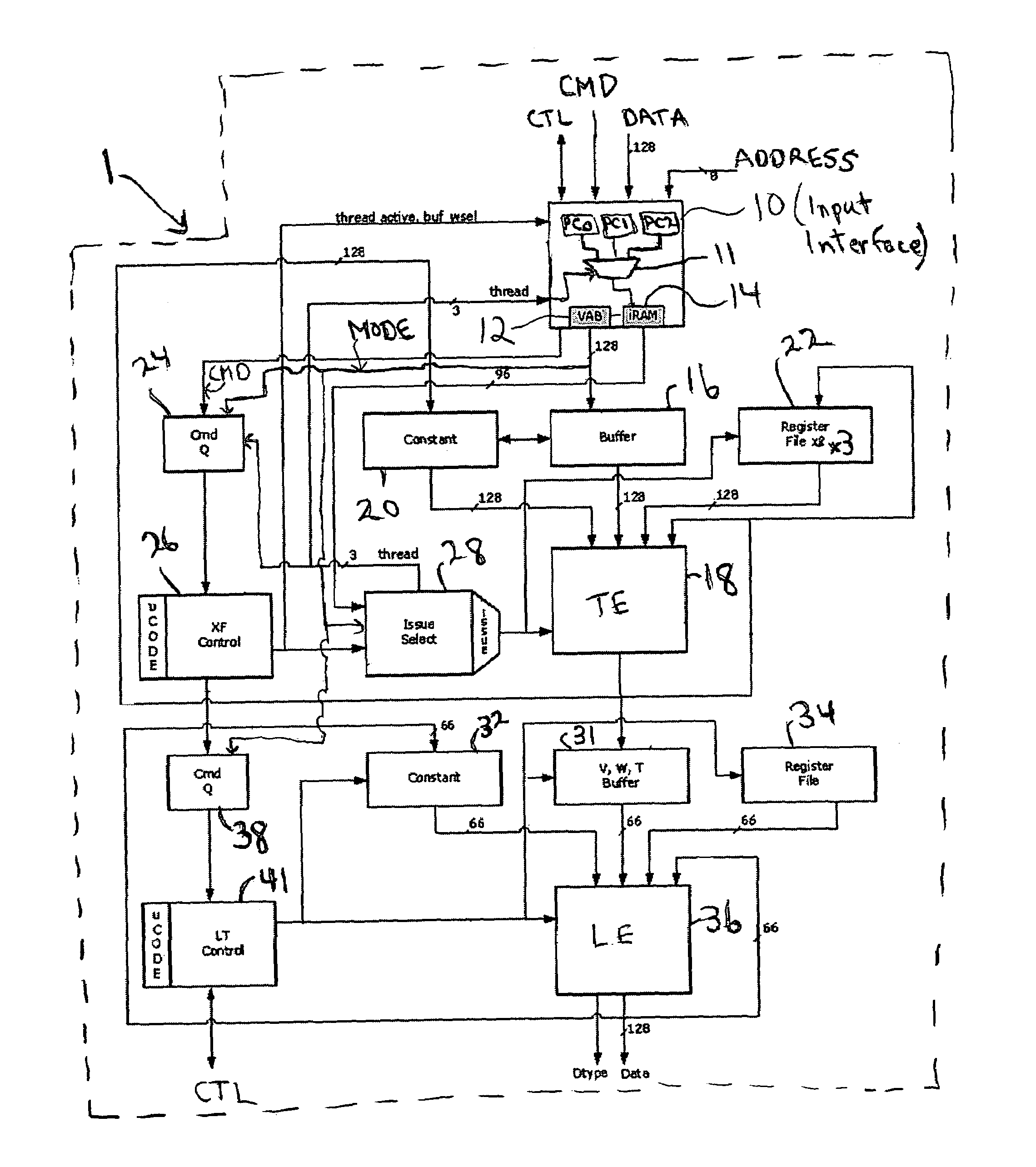

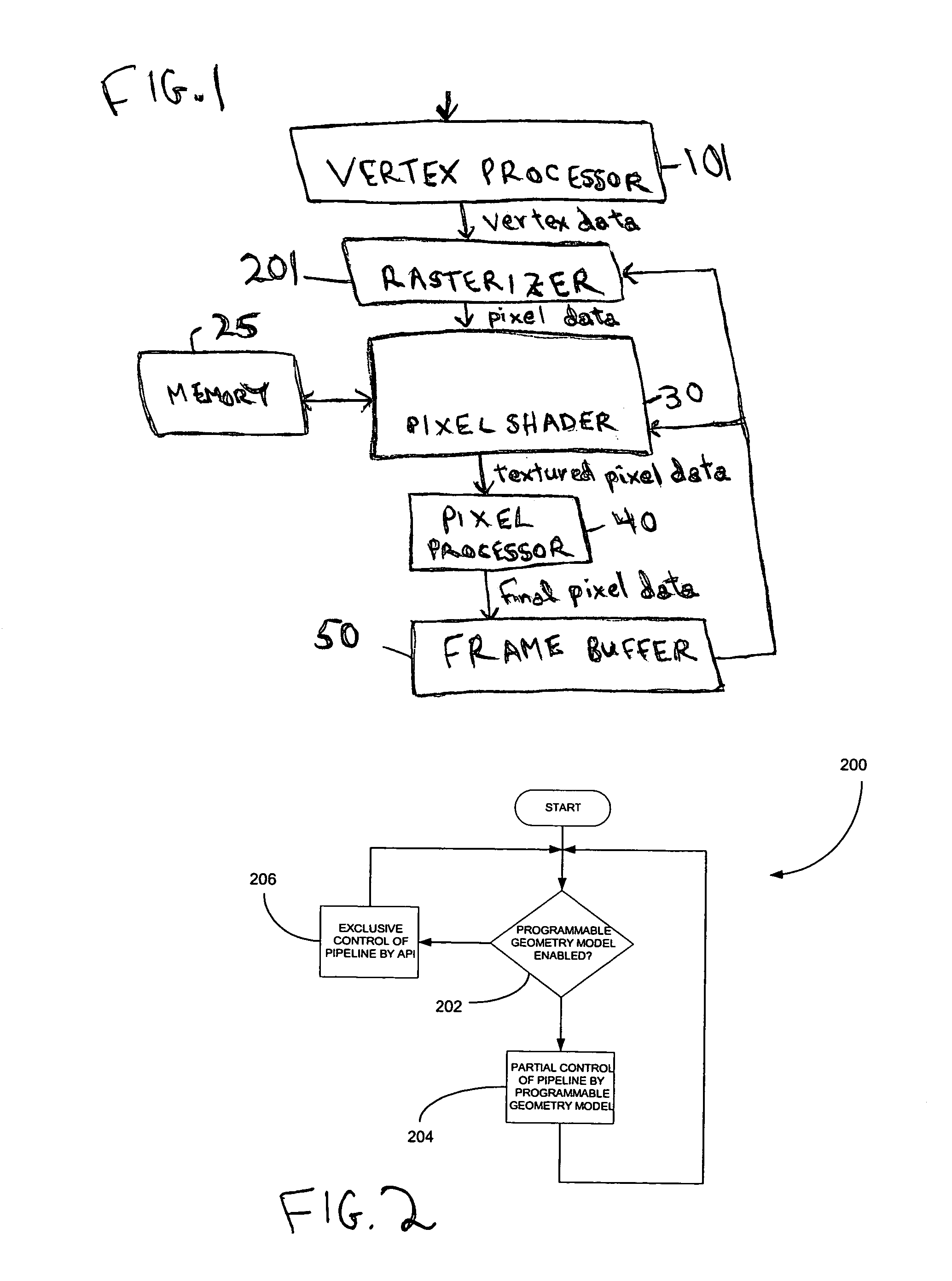

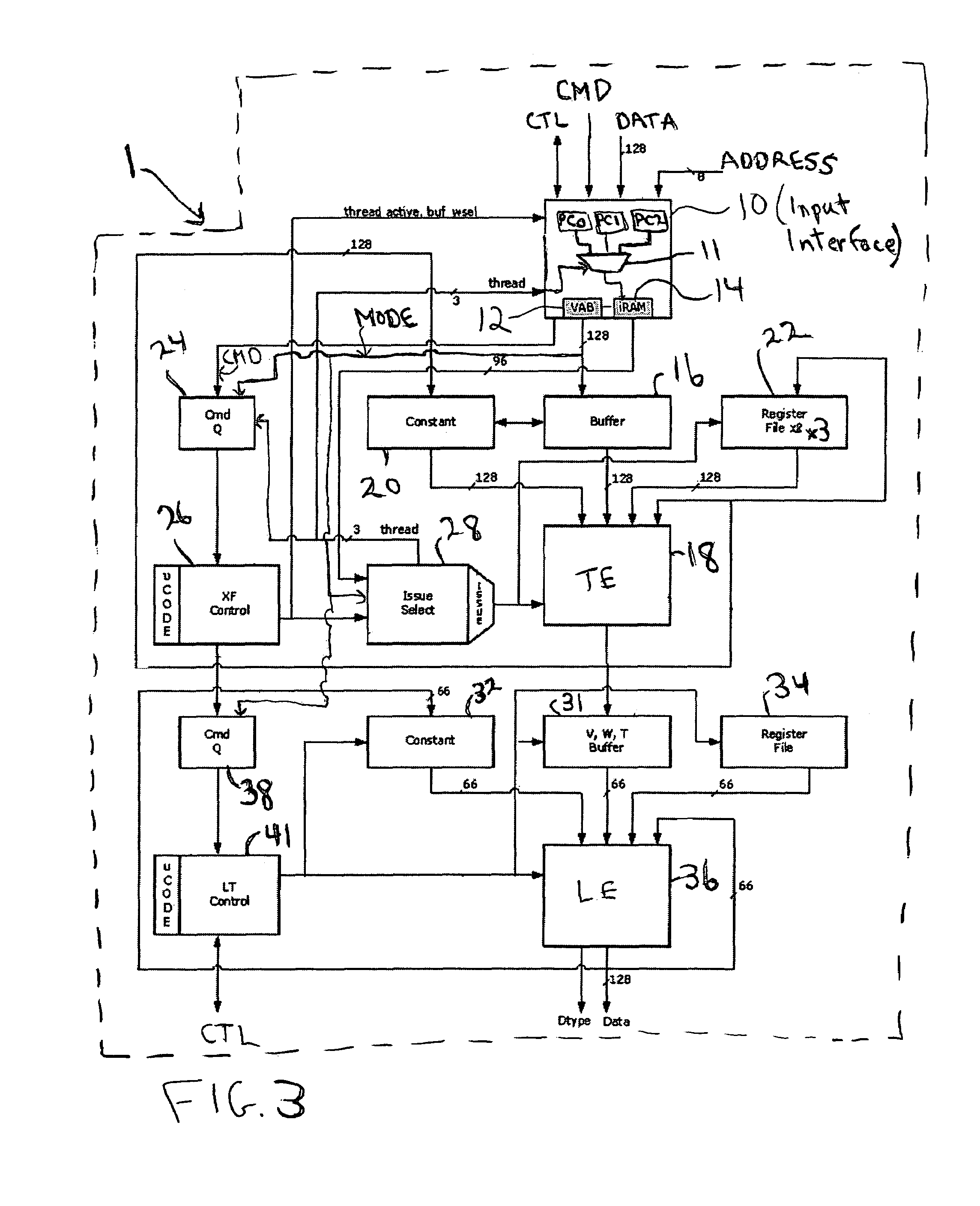

Method and system for programmable pipelined graphics processing with branching instructions

InactiveUS6947047B1Avoid confictMultiple digital computer combinationsProcessor architectures/configurationGraphicsMode control

A programmable, pipelined graphics processor (e.g., a vertex processor) having at least two processing pipelines, a graphics processing system including such a processor, and a pipelined graphics data processing method allowing parallel processing and also handling branching instructions and preventing conflicts among pipelines. Preferably, each pipeline processes data in accordance with a program including by executing branch instructions, and the processor is operable in any one of a parallel processing mode in which at least two data values to be processed in parallel in accordance with the same program are launched simultaneously into multiple pipelines, and a serialized mode in which only one pipeline at a time receives input data values to be processed in accordance with the program (and operation of each other pipeline is frozen). During parallel processing mode operation, mode control circuitry recognizes and resolves branch instructions to be executed (before processing of data in accordance with each branch instruction starts) and causes the processor to operate in the serialized mode when (and preferably only for as long as) necessary to prevent any conflict between the pipelines due to branching. In other embodiments, the processor is operable in any one of a parallel processing mode and a limited serialized mode in which operation of each of a sequence of pipelines (or pipeline sets) pauses for a limited number of clock cycles. The processor enters the limited serialized mode in response to detecting a conflict-causing instruction that could cause a conflict between resources shared by the pipelines during parallel processing mode operation.

Owner:NVIDIA CORP

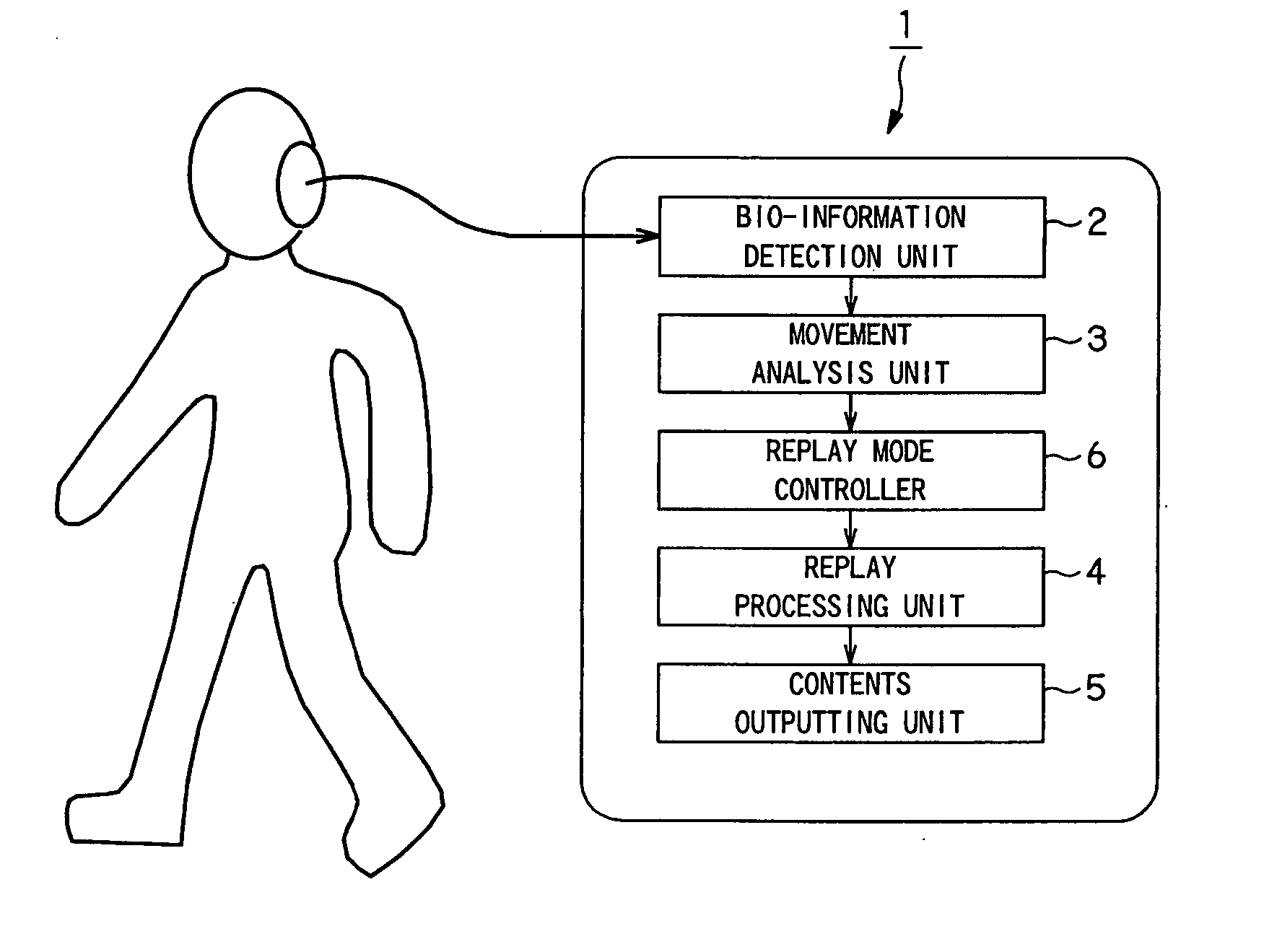

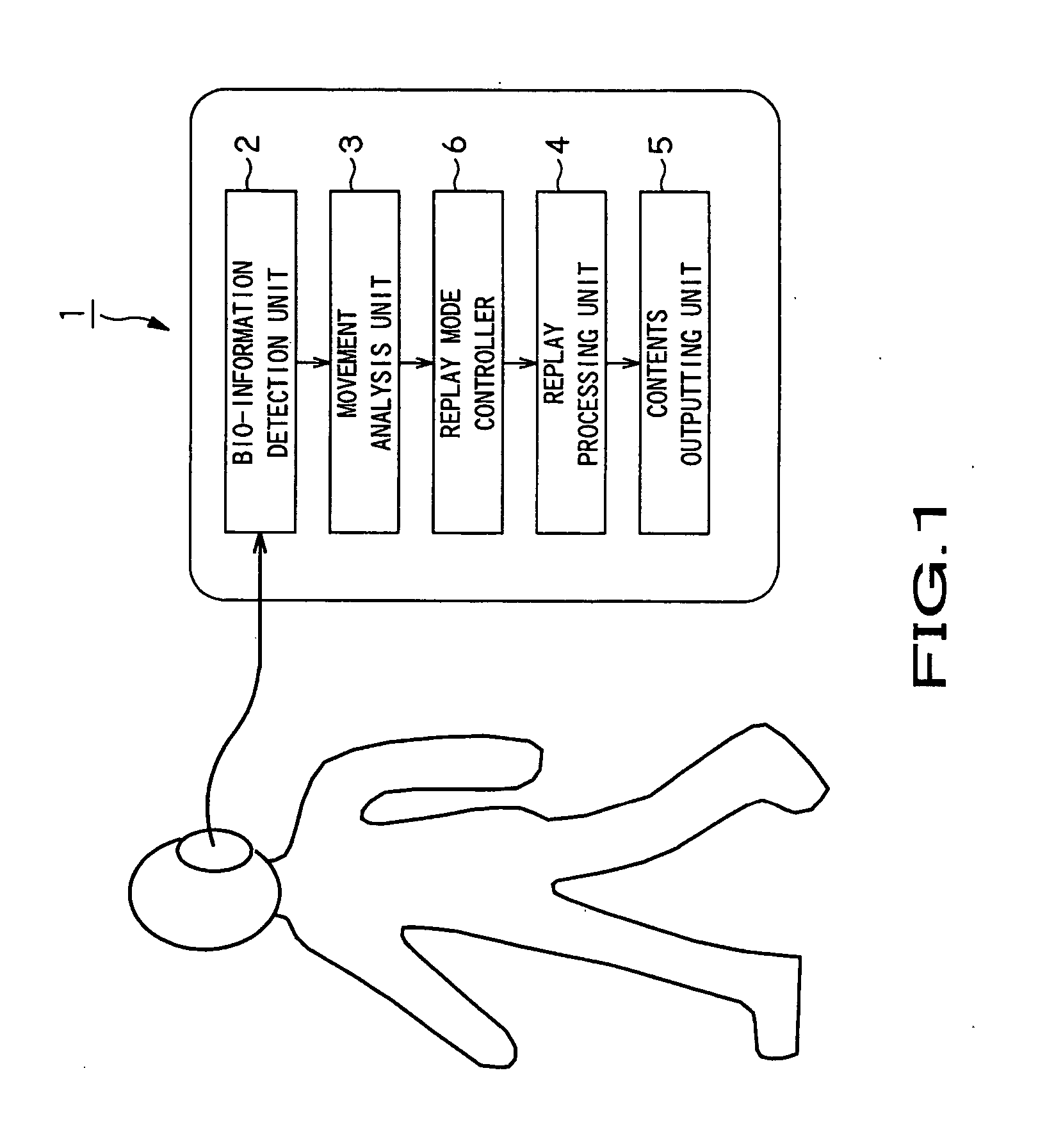

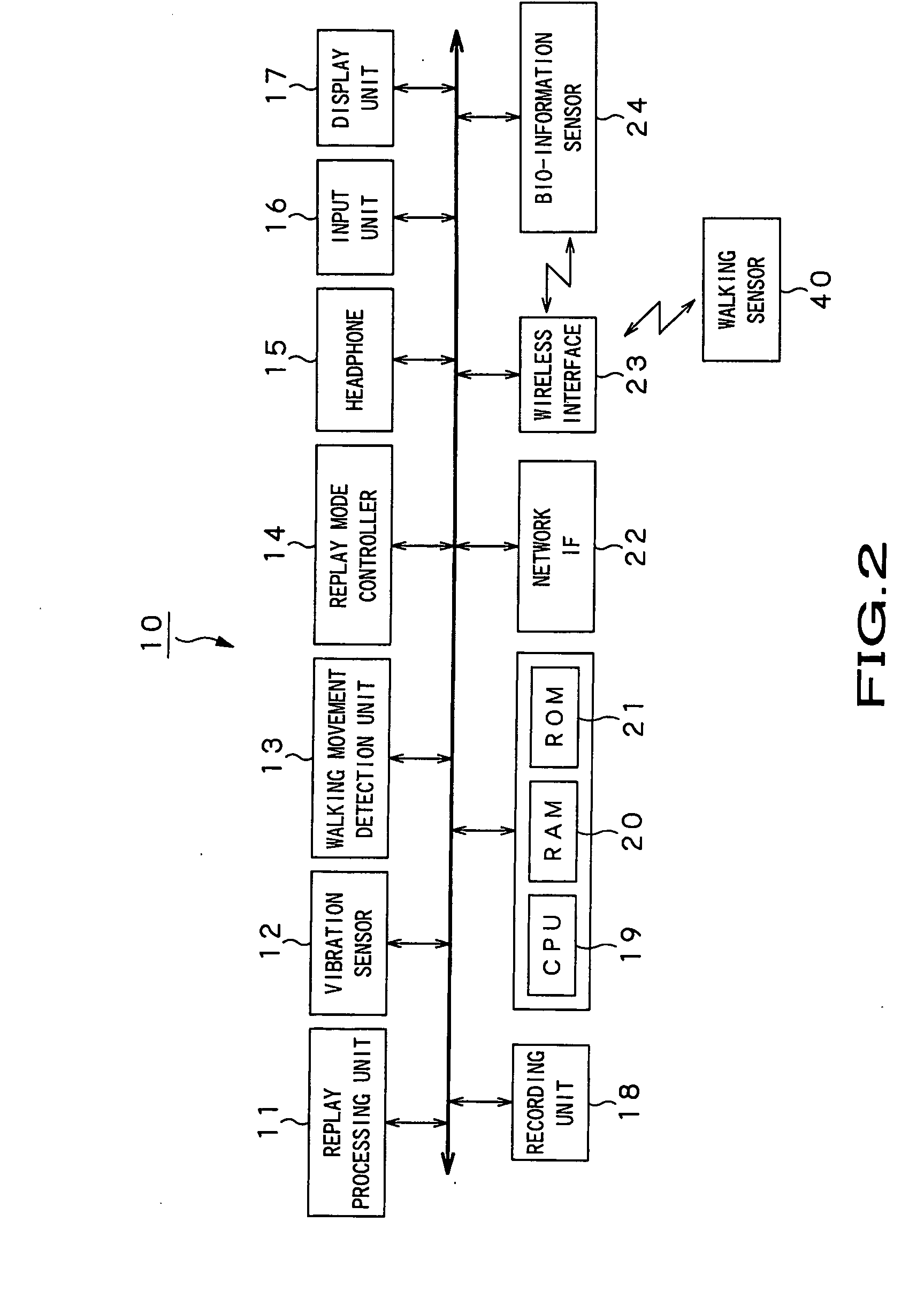

Playback mode control device and playback mode control method

InactiveUS20050126370A1Highly variegatedIncrease contentElectrophonic musical instrumentsDigital data information retrievalMode controlHeadphones

A replay mode control device in which the replay mode in reproducing music or video contents is controlled so as to be suitable for a user. A headphone of a mobile music reproducing device is provided with a vibration sensor for detecting movements of the user in the up-and-down direction. A walking movement detection unit detects the walking interval of the user based on an output of the vibration sensor. A replay mode controller manages control to adjust the replay rate of music contents to the walking interval of the user.

Owner:SONY CORP

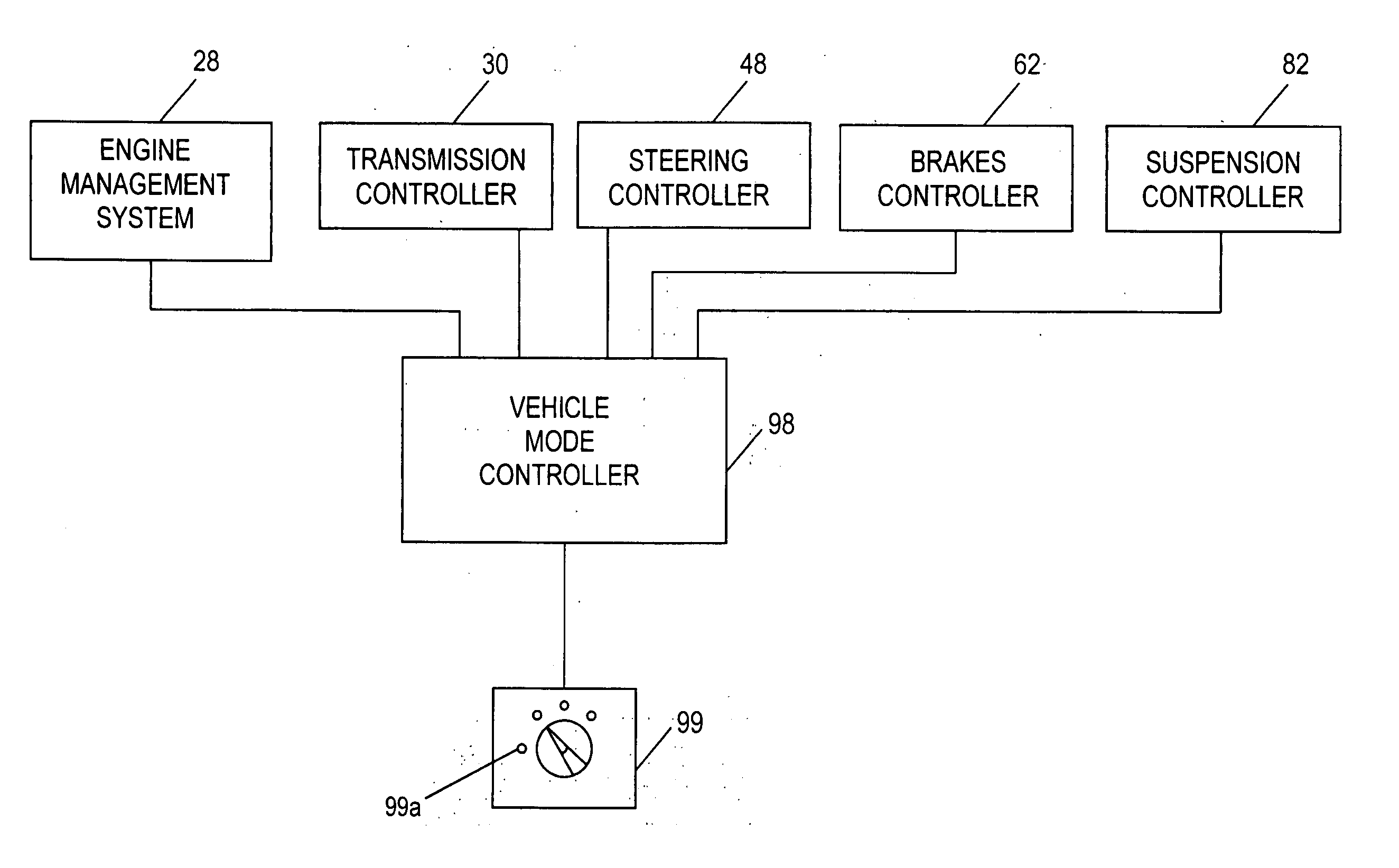

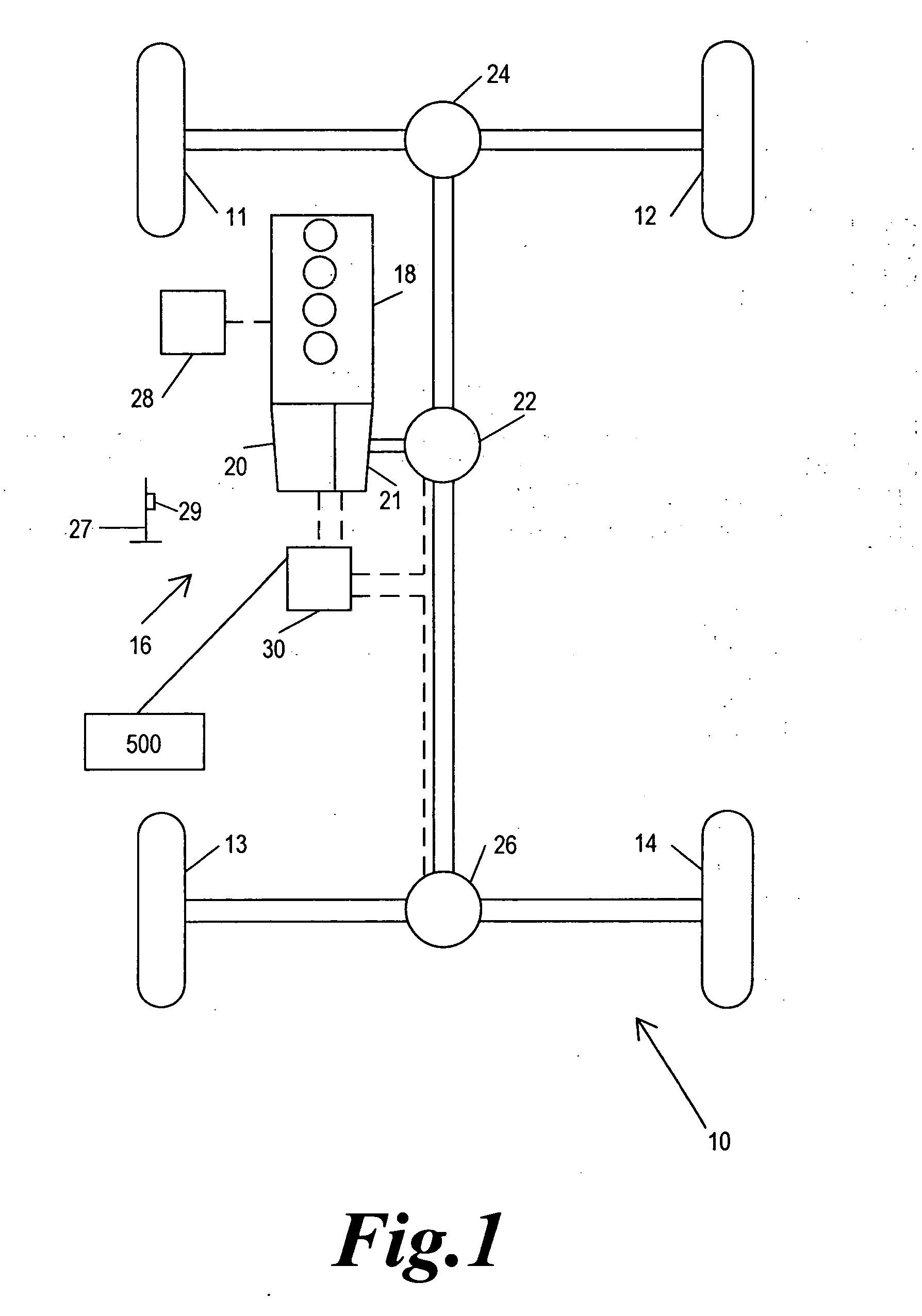

Vehicle control method and apparatus

ActiveUS20050004732A1Minimizes combinationMaximize controlVehicle body stabilisationDigital data processing detailsTerrainMode control

A vehicle mode controller, a driving mode collecting means, and a plurality of subsystem controllers including an engine management system, a transmission controller, a steering controller, a brakes controller and a suspension controller, provide an improved system and method of operating a vehicle control system in a host vehicle in a manner suitable for a respective driving surface in a plurality of different off-road surfaces and terrains such as might be encountered when driving off-road. An improved method is provided for controlling a vehicle control system by avoiding unplanned combinations of subsystem configuration modes and minimizing the transition time when changing between subsystem configuration modes.

Owner:JAGUAR LAND ROVER LTD

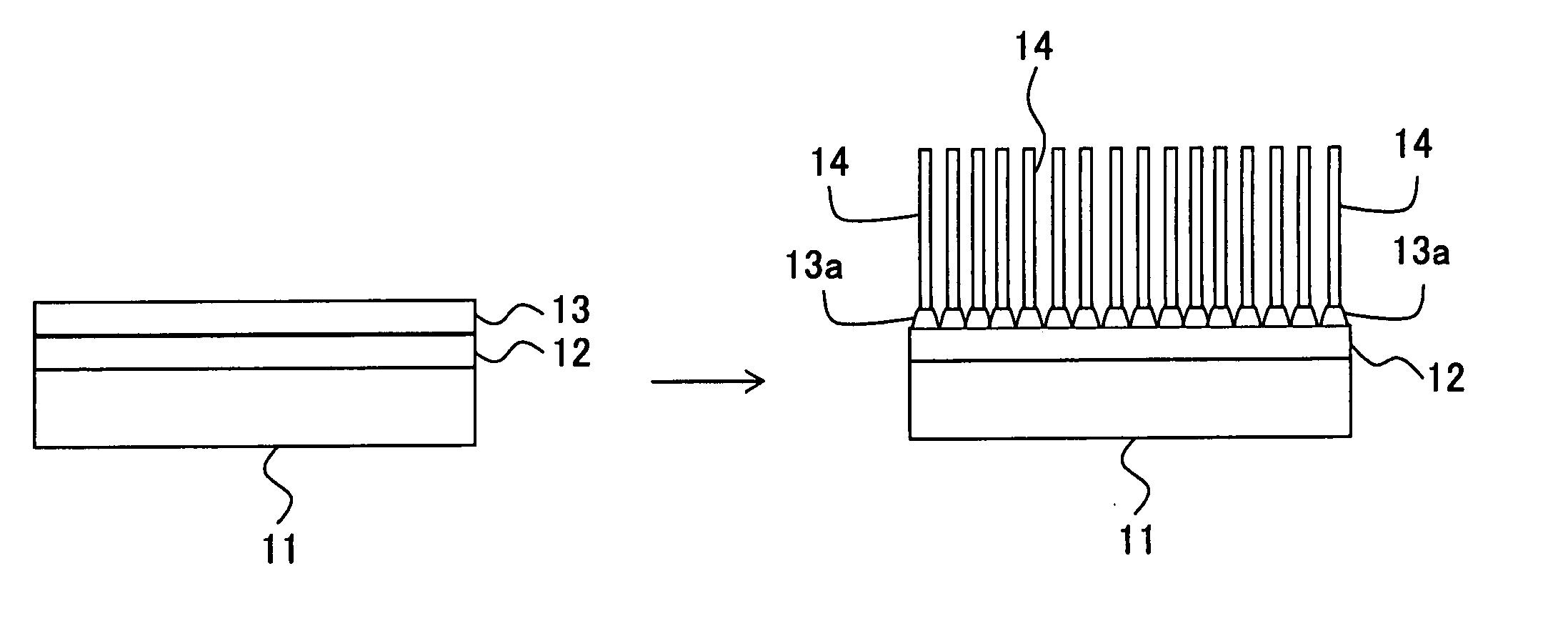

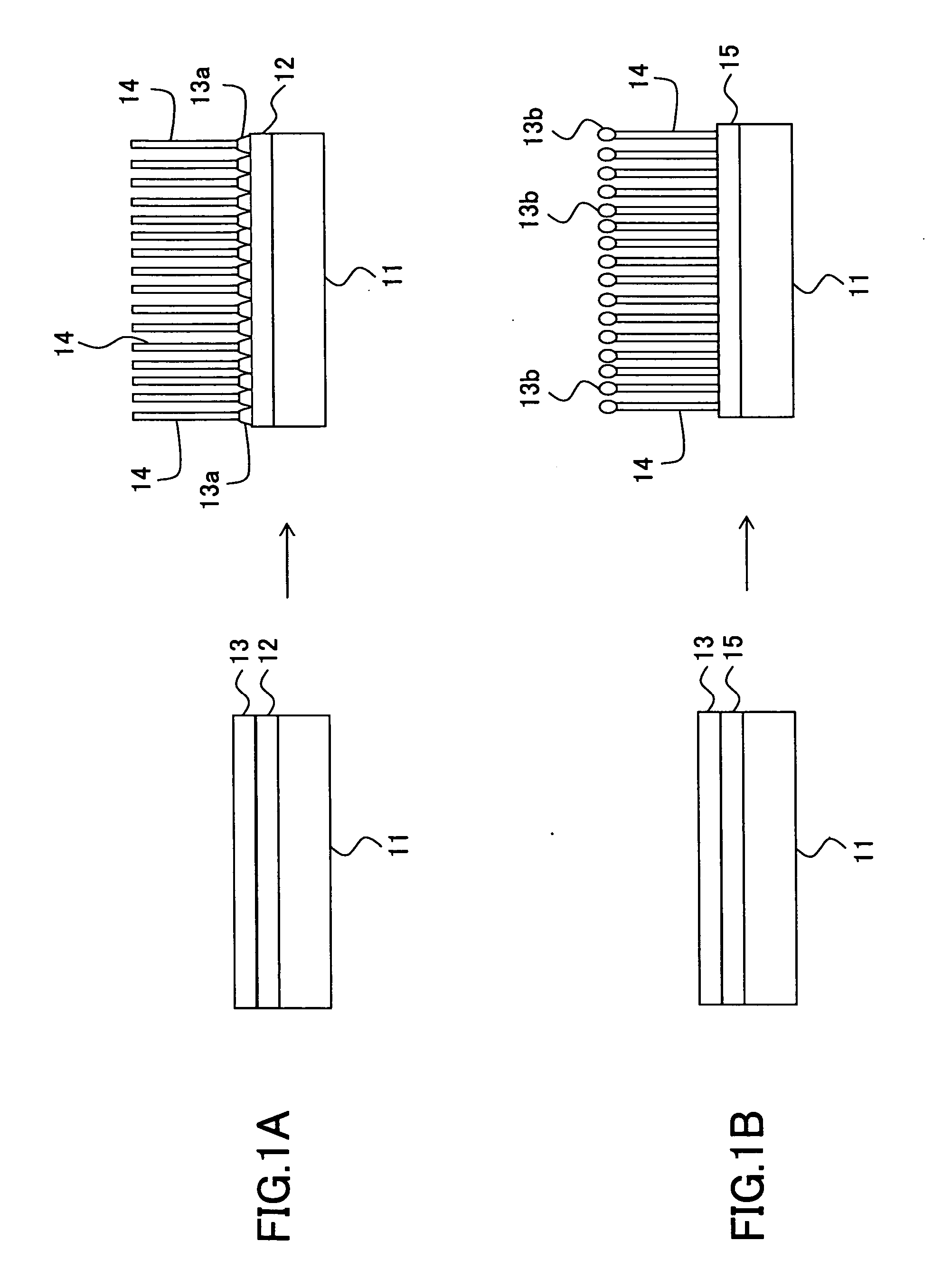

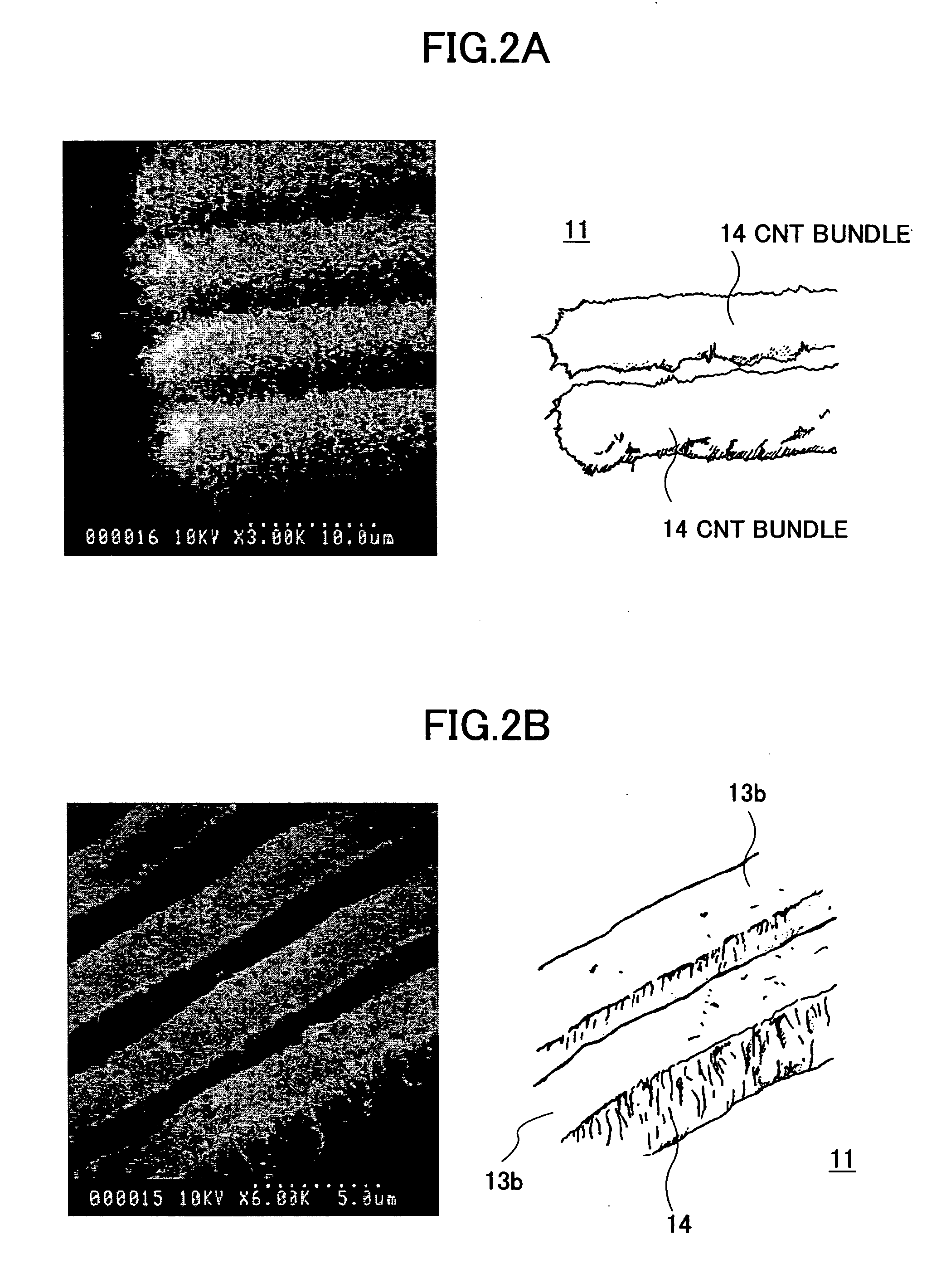

Semiconductor device and method of manufacturing the same

ActiveUS20050215049A1Eliminate disadvantagesSemiconductor/solid-state device detailsNanoinformaticsSputteringDevice material

A method of manufacturing a semiconductor device having an interconnection part formed of multiple carbon nanotubes is disclosed. The method includes the steps of (a) forming a growth mode control layer controlling the growth mode of the carbon nanotubes, (b) forming a catalyst layer on the growth mode control layer, and (c) causing the carbon nanotubes to grow by heating the catalyst layer by thermal CVD so that the carbon nanotubes serve as the interconnection part. The growth mode control layer is formed by sputtering or vacuum deposition in an atmospheric gas, using a metal selected from a group of Ti, Mo, V, Nb, and W. The growth mode is controlled in accordance with a predetermined concentration of oxygen gas of the atmospheric gas.

Owner:FUJITSU LTD

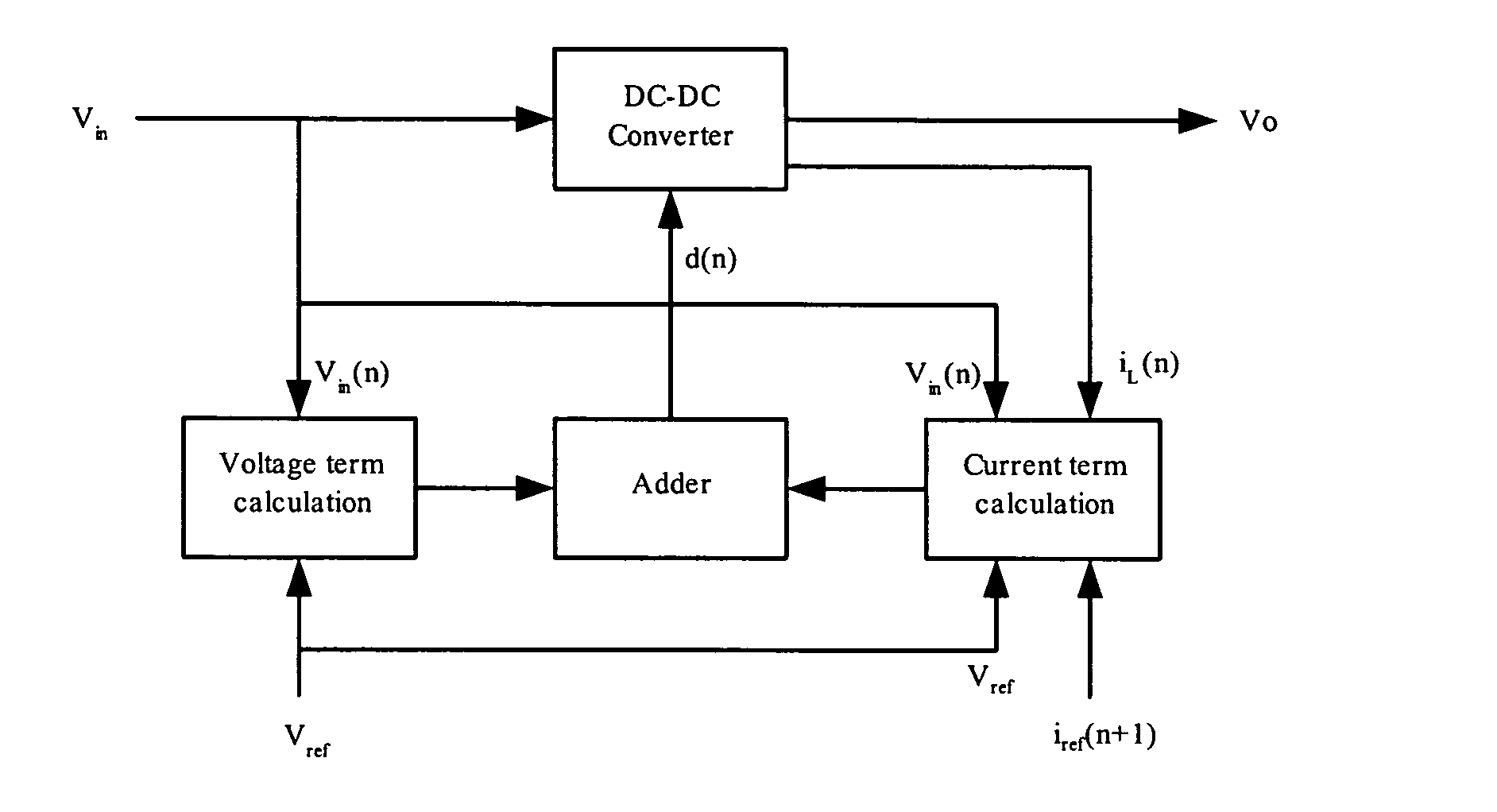

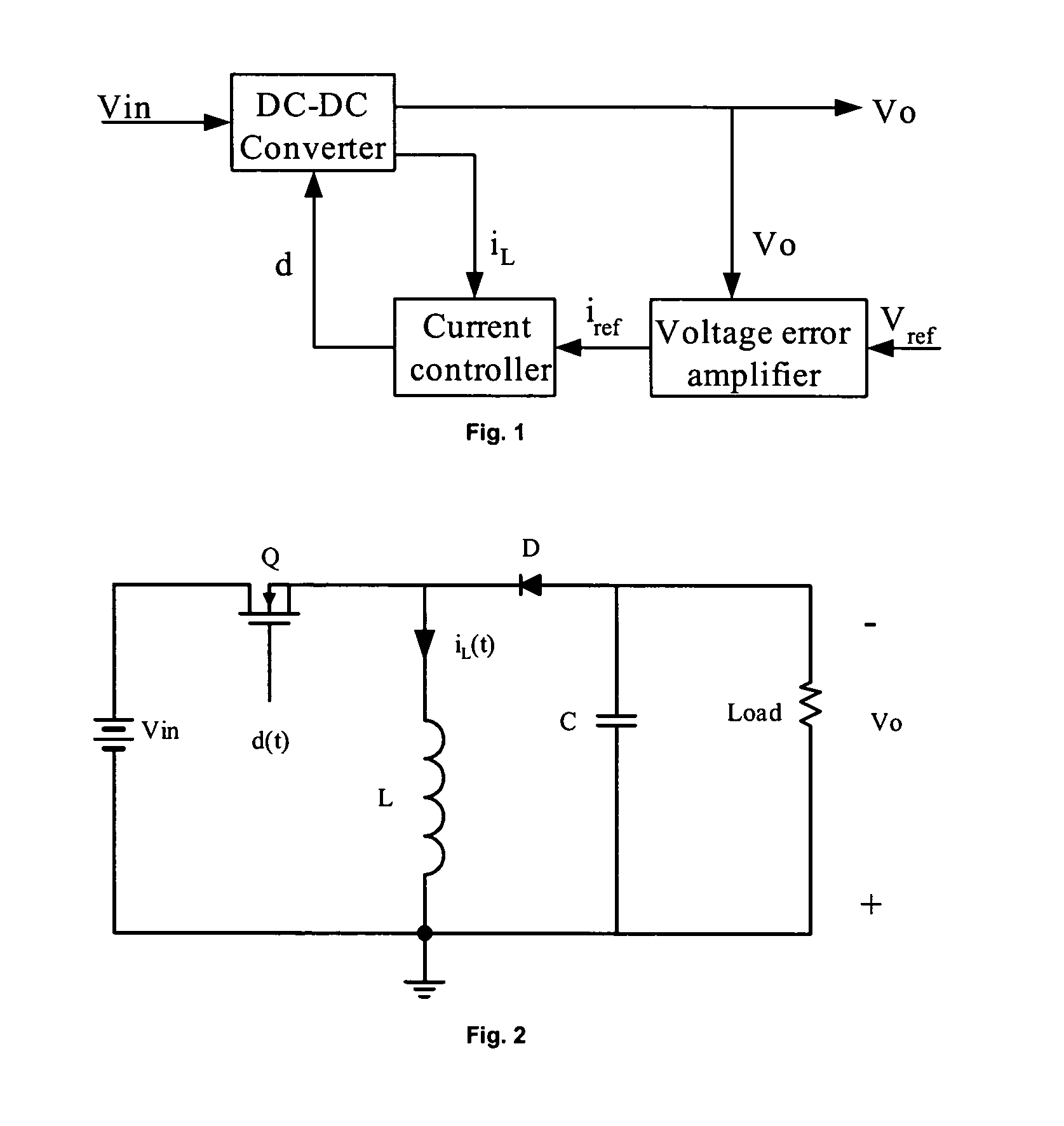

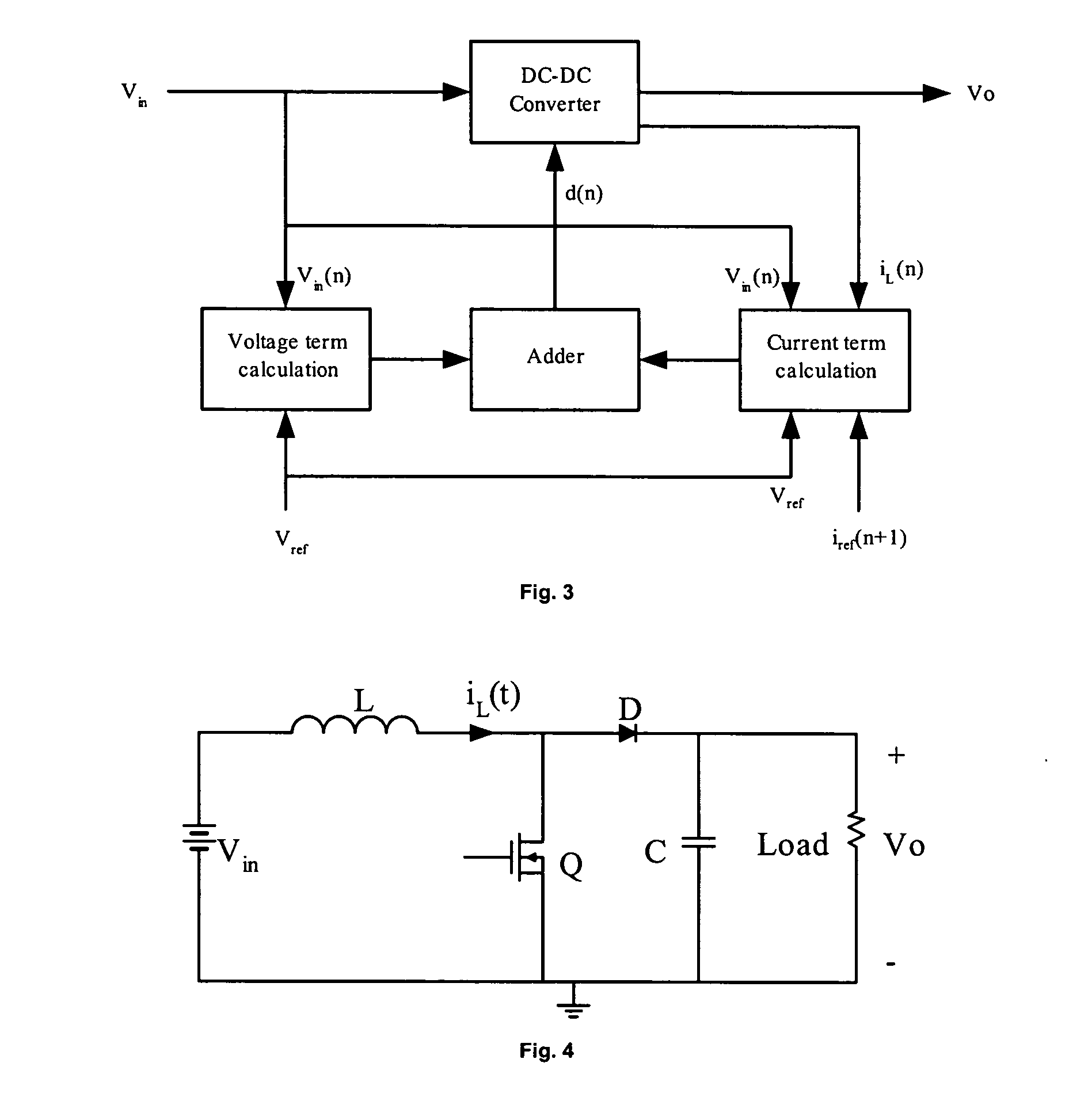

Parallel current mode control

InactiveUS20050270813A1Unity power factor for AC-DC converterLow costAc-dc conversion without reversalEfficient power electronics conversionCurrent mode controlMode control

A method and apparatus to implement parallel current mode control that is suitable for digital and analog implementation. A duty cycle algorithm is composed of a voltage term and a parallel current term which depends on the inductor current change between the inductor current value at the beginning of a switching cycle and the reference inductor current value at the end of that switching cycle. Parallel current mode control can be applied to all DC-DC converters, including both non-isolated and isolated topologies. It can also be applied to AC-DC converters with power factor correction.

Owner:DIALOG SEMICONDUCTOR INC

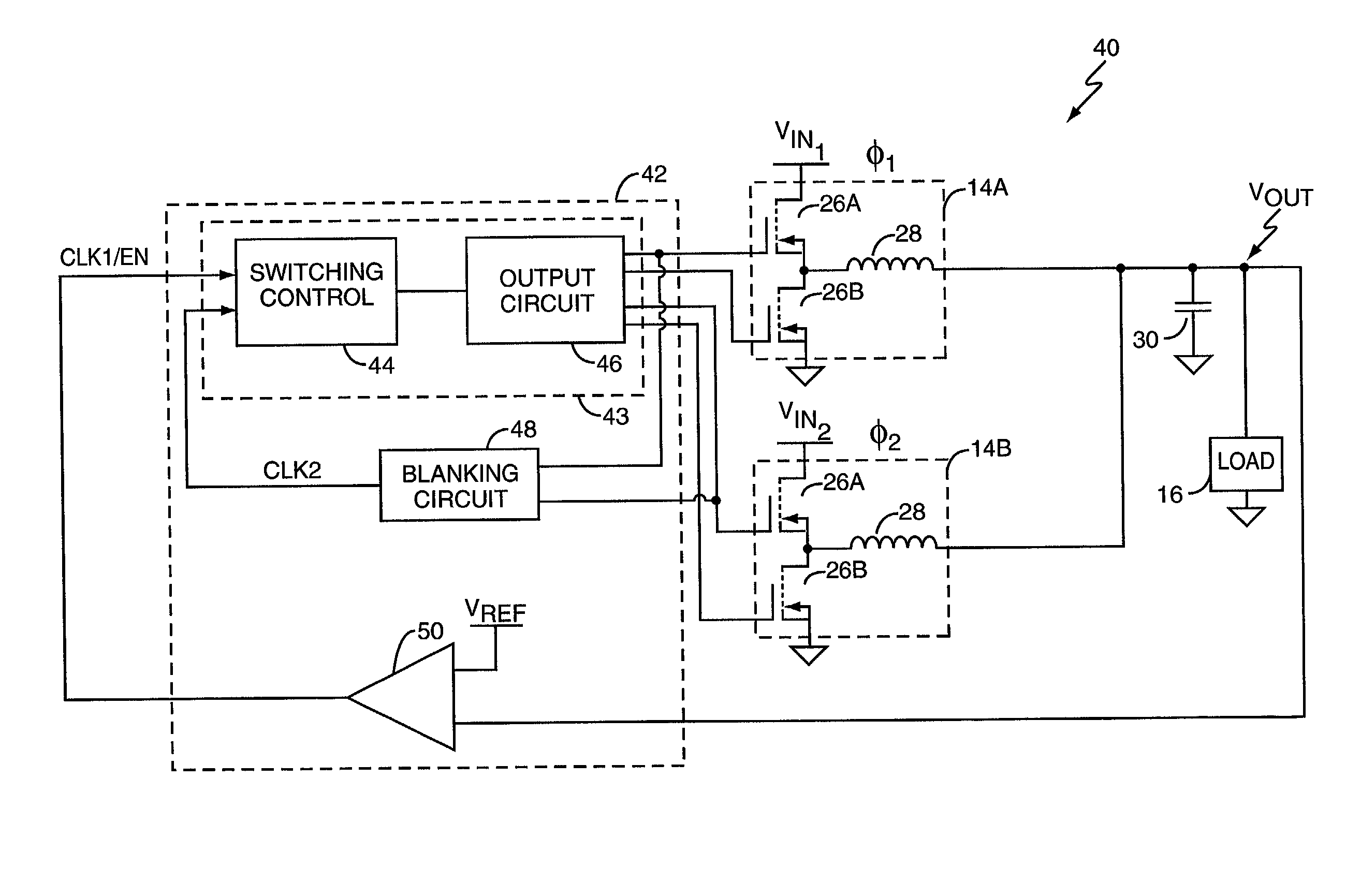

Self-clocking multiphase power supply controller

InactiveUS20020125869A1Improve noise immunityIncrease flexibilityEfficient power electronics conversionDc-dc conversionPower controllerMode control

A ripple-mode controller provides reliable operation in multi-phase power supply circuits, over a variety of operating conditions. Cross-phase blanking allows the controller to preserve the desired phase relationship between the switching pulses its provides to the different output phases, and permits the controller to operate each output phase at nearly 100% duty cycles. Active current sharing compliments blanking operations by adjusting the width of switching pulses the controller provides to one or more of the output phases based on detecting load current imbalances between the different output phases. With active current sharing, the controller prevents one or more output phases from carrying excessive portions of the load current. Further complimenting its operation, the controller may include virtual ripple generation to increase the noise immunity of its ripple-mode regulation.

Owner:SEMTECH CORP

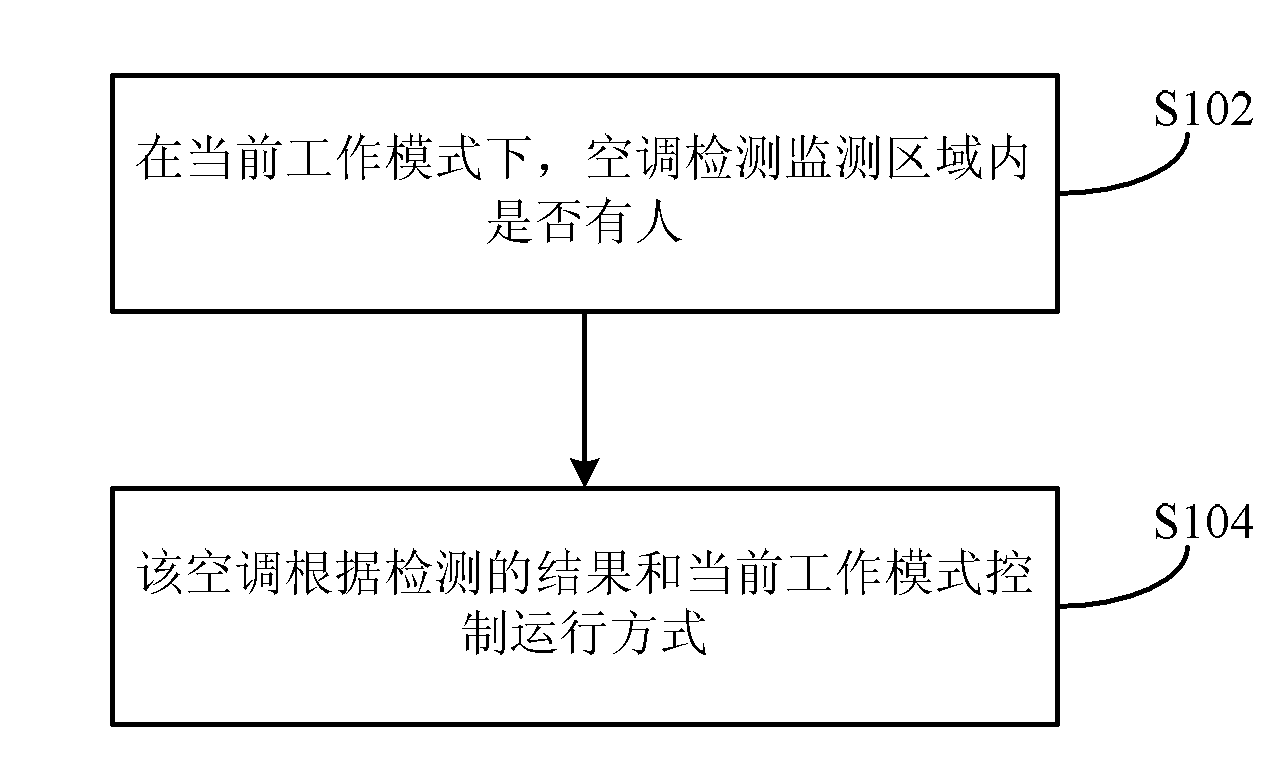

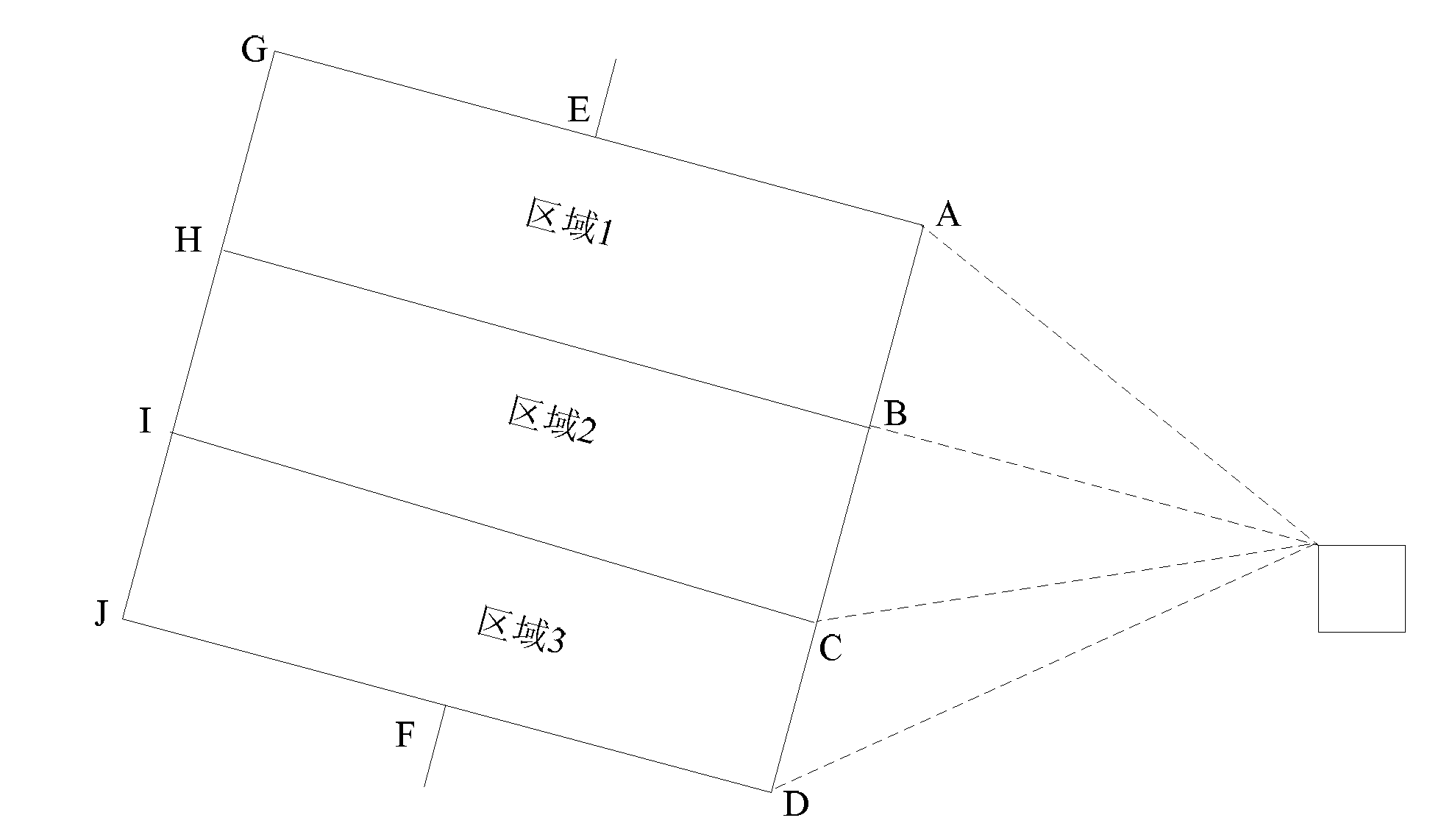

Method for controlling operation mode of air conditioner, and air conditioner

ActiveCN102759173ASolve the comfortSolve environmental problemsSpace heating and ventilation safety systemsLighting and heating apparatusMode controlEngineering

The invention discloses a method for controlling the operation mode of an air conditioner, and the air conditioner, wherein the method comprises the steps of: under a current working mode, detecting whether someone is present in a monitoring area by the air conditioner, wherein the monitoring area comprises a plurality of subareas; and controlling the operation mode by the air conditioner according to a detection result and the current working mode. According to the invention, the problems that the operation mode of the air conditioner influences the comfort level of a human body and is unfavorable for energy saving and environment protection are solved, meanwhile, the control is automatically carried out by the air conditioner according to the detection result, so that the usage by a user is facilitated, and the comfort level of a living environment is promoted.

Owner:GREE ELECTRIC APPLIANCES INC

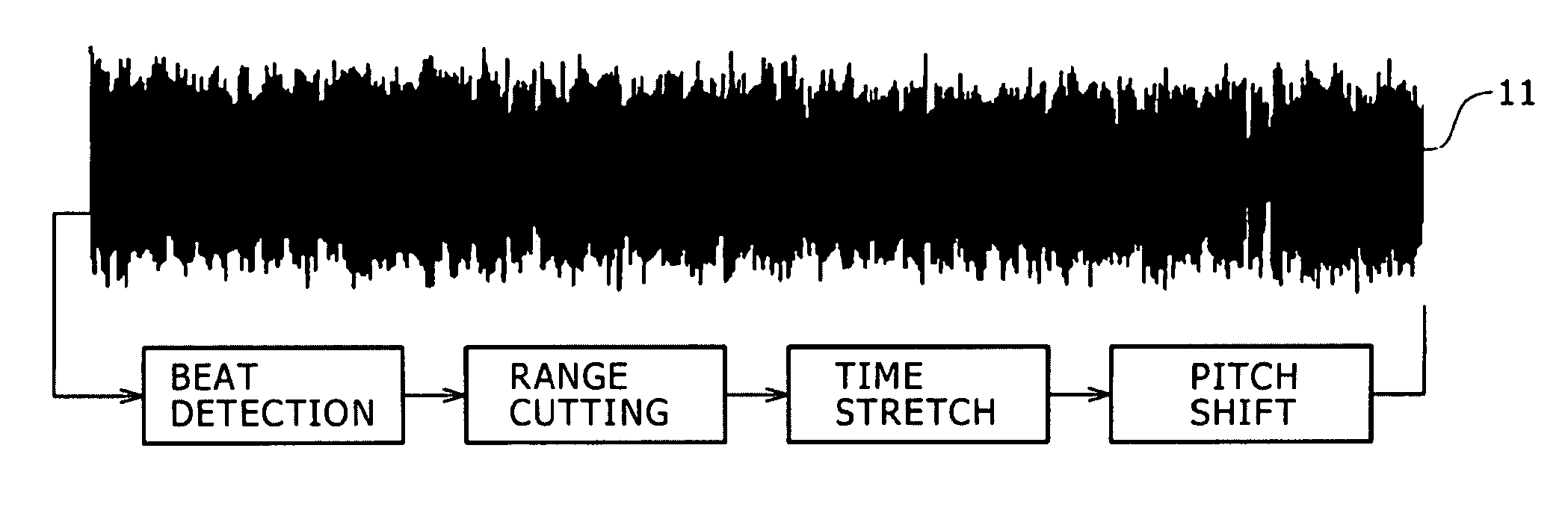

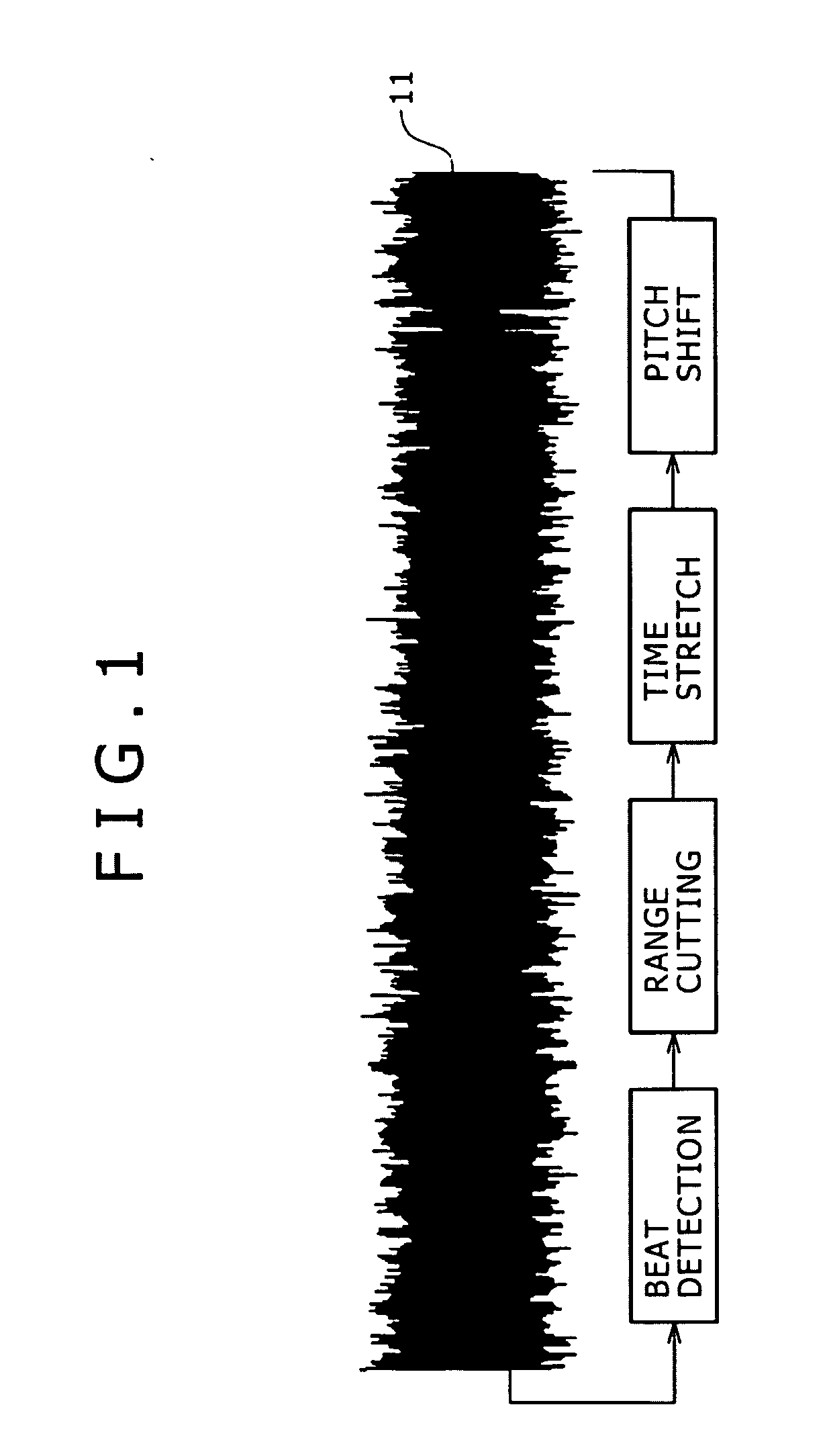

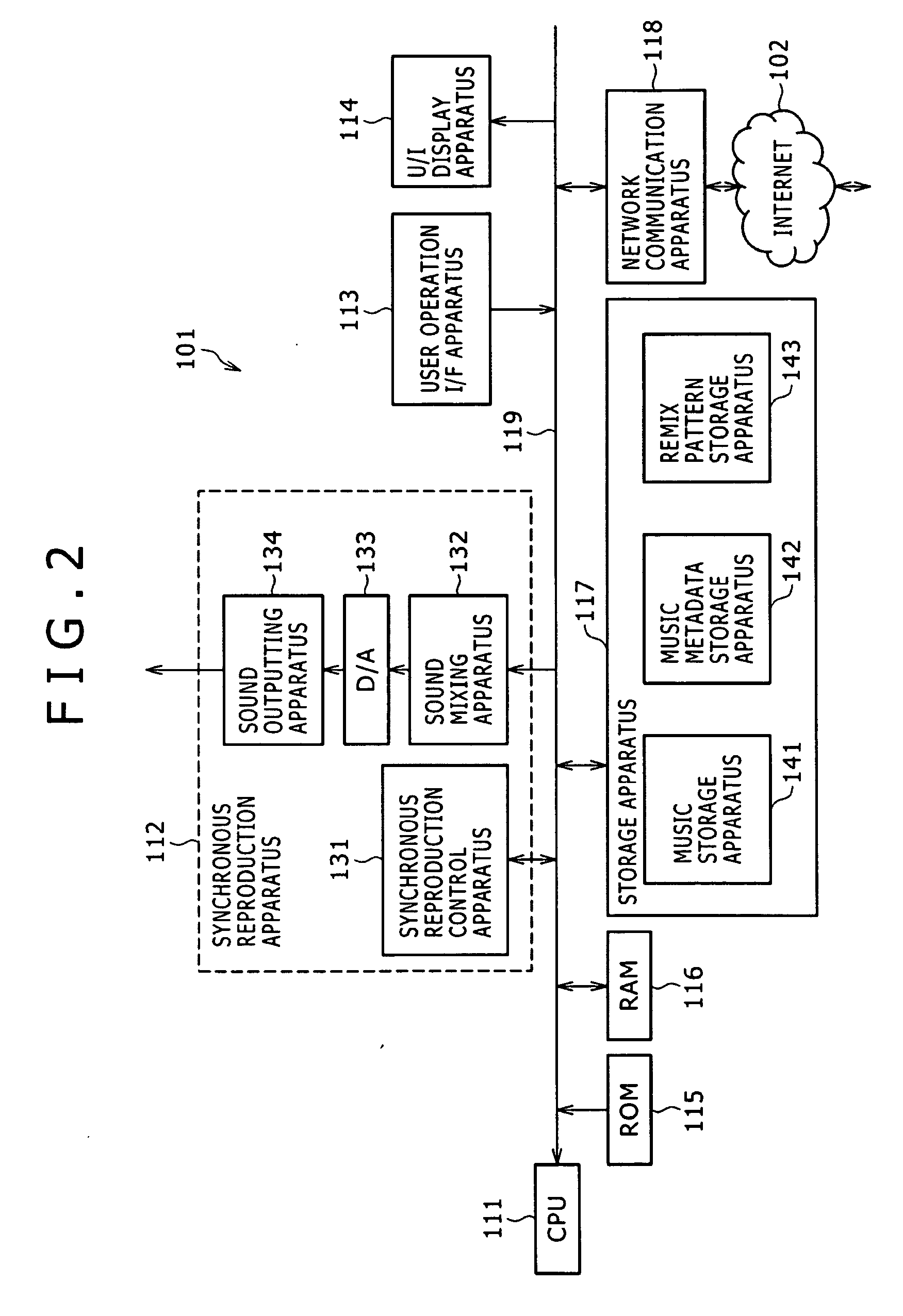

Music Editing Apparatus and Method and Program

InactiveUS20090019995A1High completenessEasy to combineElectrophonic musical instrumentsElectronic editing digitised analogue information signalsMode controlReproduction speed

There is provided a music editing apparatus for remix reproducing a plurality of sound materials, each formed from part or the entirety of a music piece, in combination, including a reproduction pattern control section, a reproduction speed control section; and a pitch control section.

Owner:SONY CORP

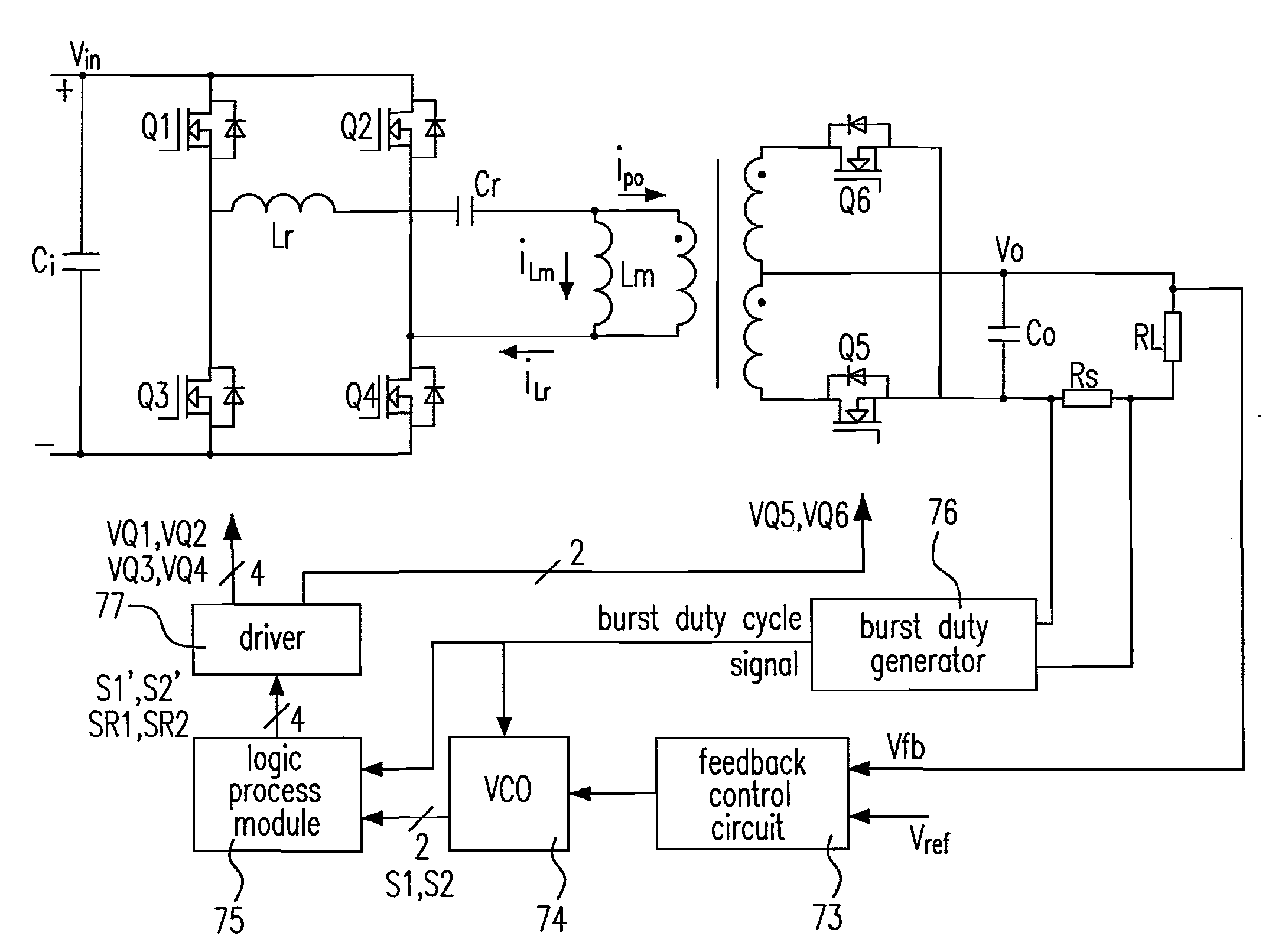

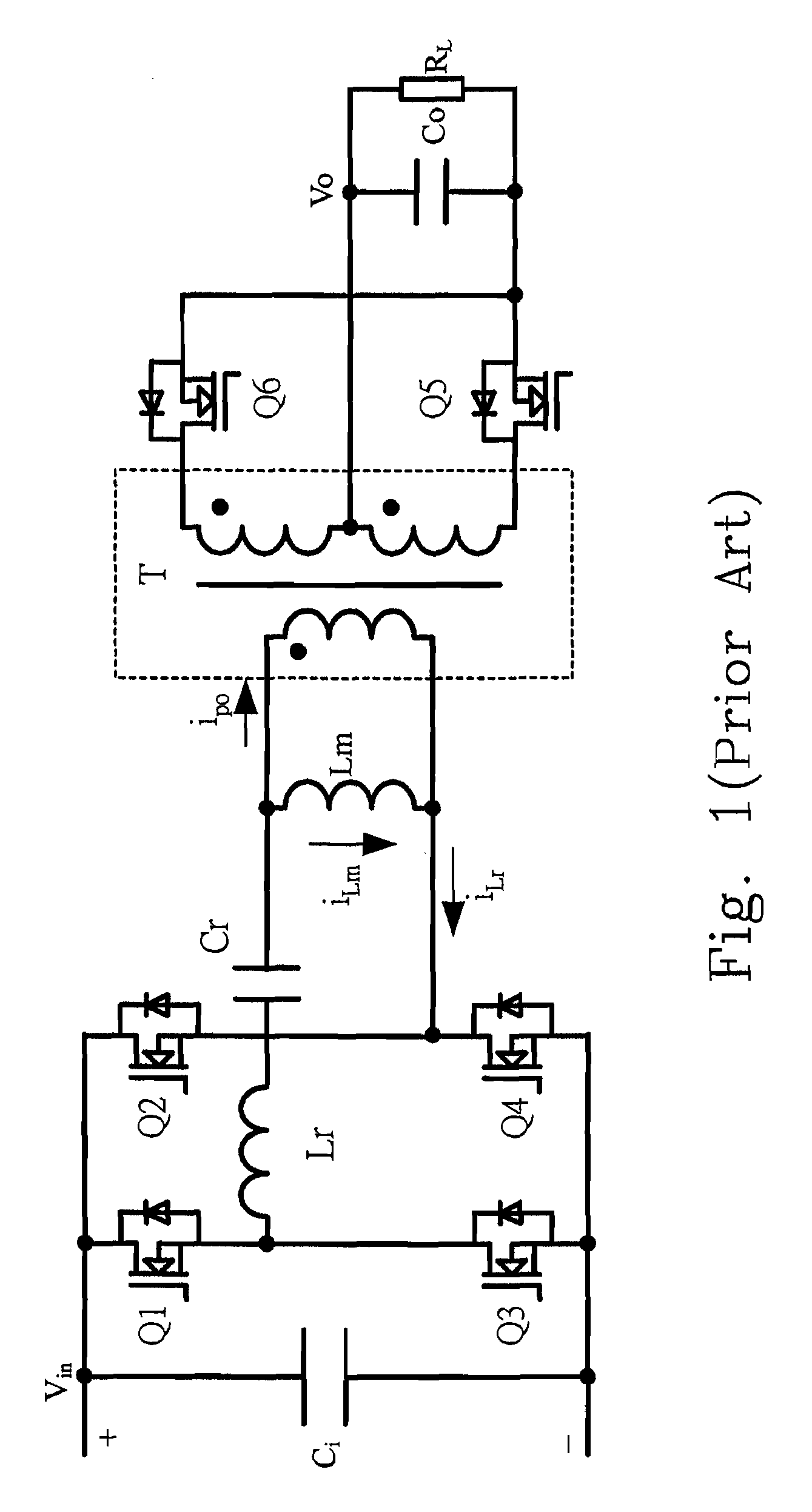

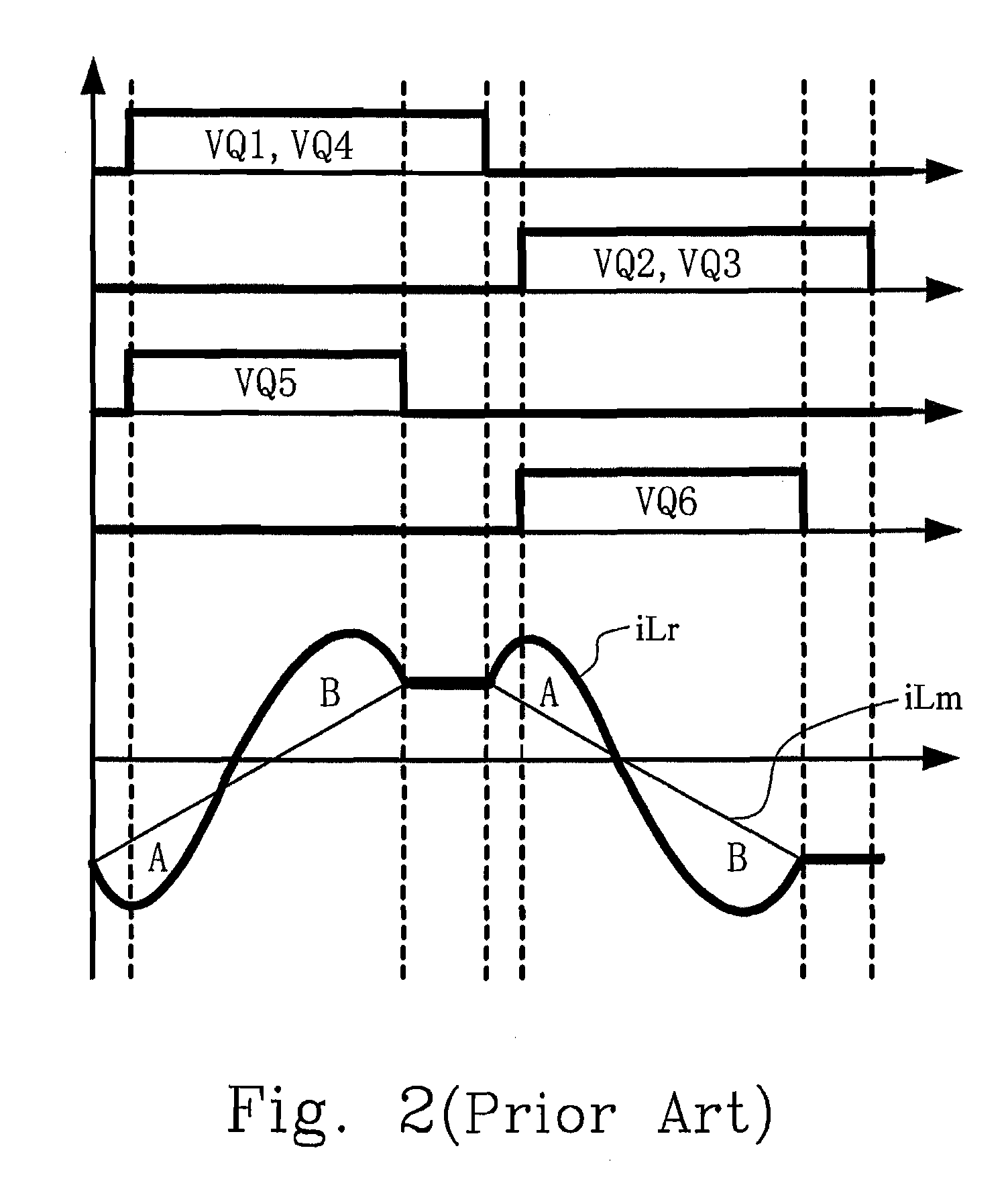

Synchronous rectification circuit having burst mode controller and controlling method thereof

ActiveUS20090244934A1Improve light load efficiencyReduce lossesEfficient power electronics conversionDc-dc conversionProcess moduleMode control

The configuration of a synchronous rectification circuit and a controlling method thereof are provided. The proposed circuit includes a converter including a first switch and a first synchronous rectifier, and a burst mode controller including a logic process module performing one of functions of delaying one of a non-integer and at least one operating periods to generate a synchronous rectification driving signal of the first synchronous rectifier counting from a beginning of a first pulse of a driving signal of the first switch during a working time of a burst period, and turning off the synchronous rectification driving signal of the first synchronous rectifier by one of the non-integer operating period and the at least one operating period ahead of an ending of a last operating period of the driving signal of the first switch during the working time of the burst period.

Owner:DELTA ELECTRONICS INC

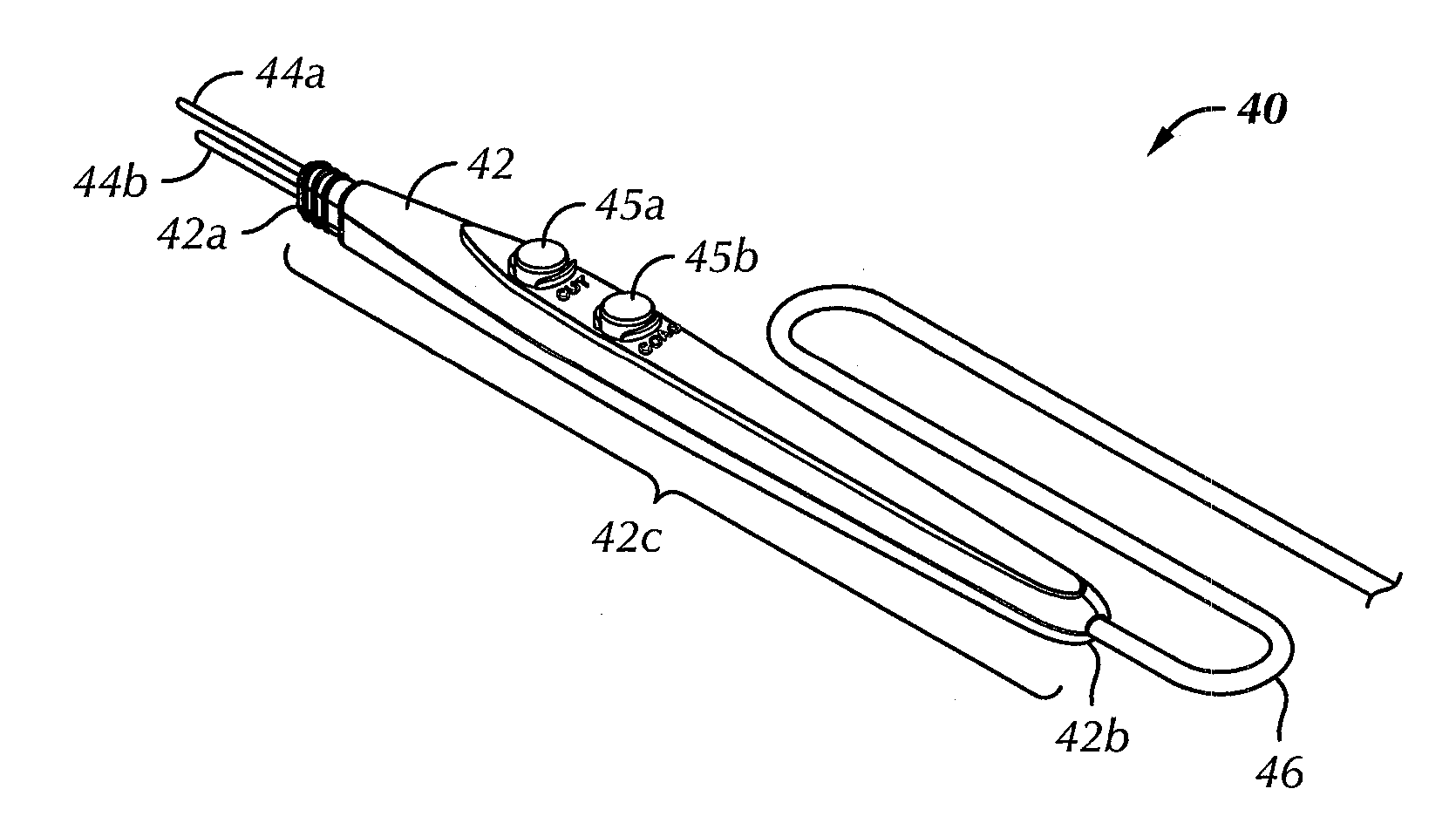

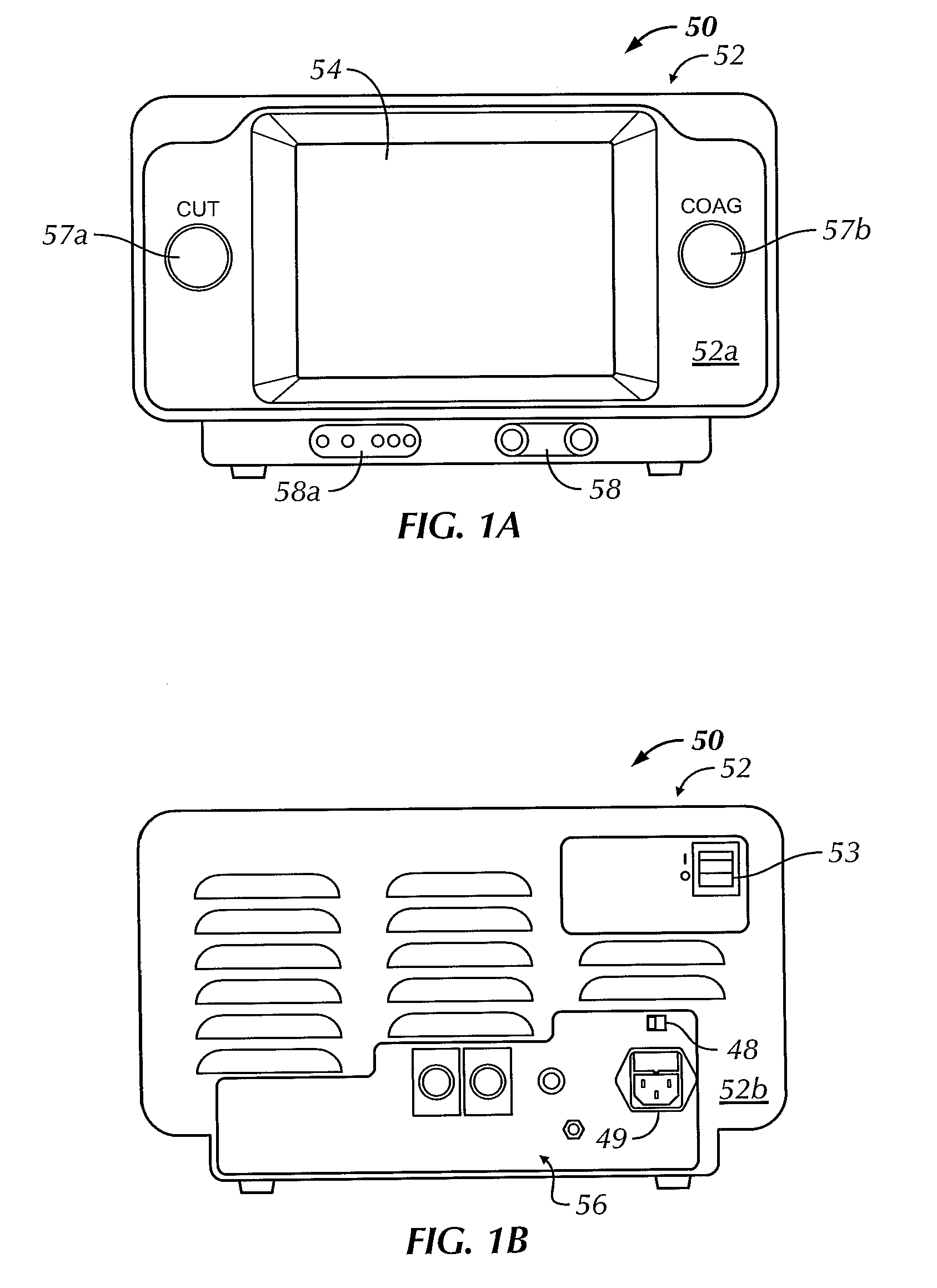

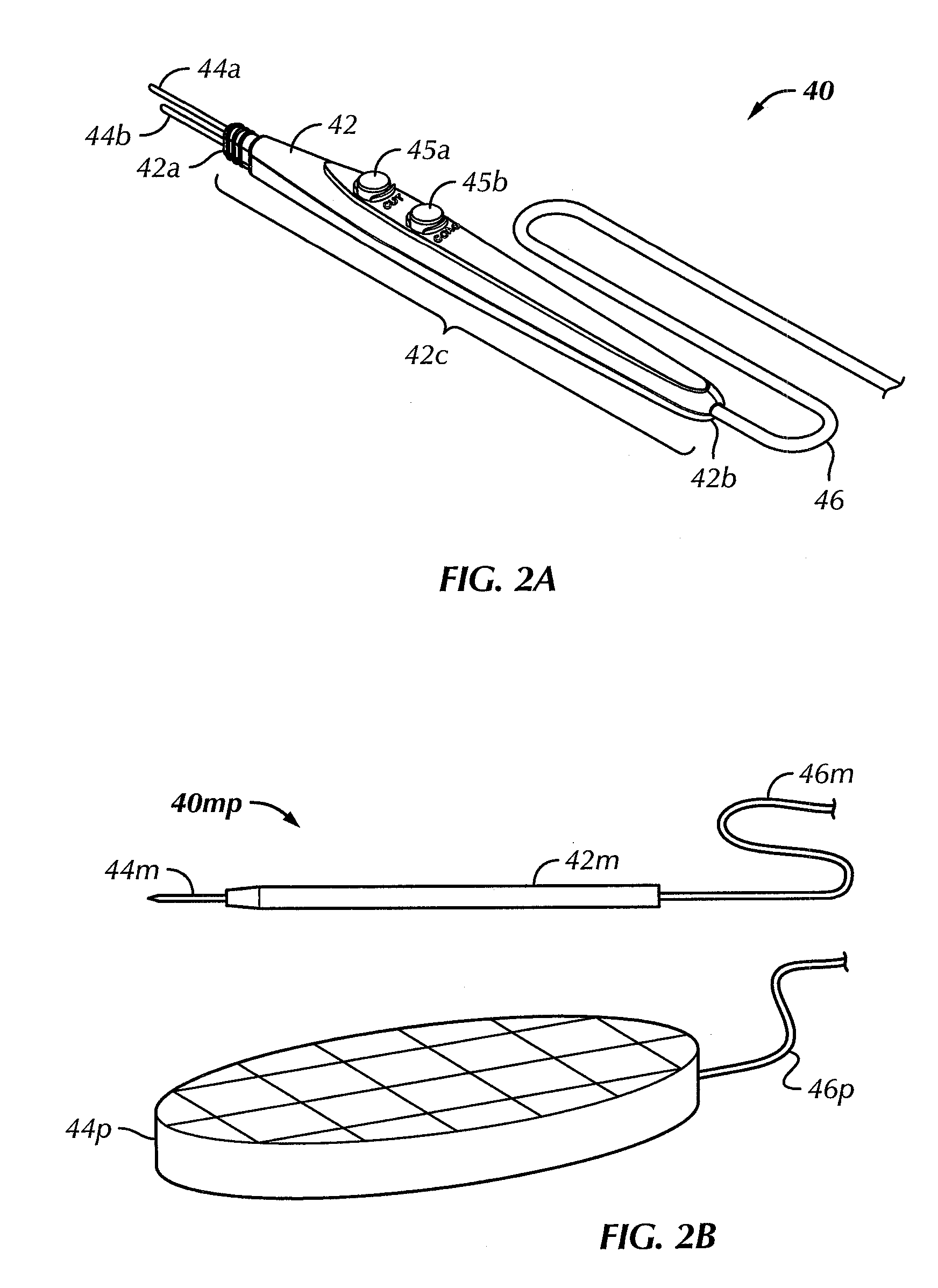

Electrosurgical Generator Having Boost Mode Control Based on Impedance

A method of controlling output power of an electrosurgical generator apparatus that controls a variable output signal to a pair of electrodes includes setting the output power of the generator apparatus to a selected power output level. An impedance is measured across the electrodes when the electrodes are applied to an area of tissue. The output power of the generator apparatus is changed to a boost power output level greater than the selected power output level. The boost power output level corresponds to a calculation based at least in part on the measured impedance. The method further includes applying the output signal to the electrodes at the boost power output level for a first time duration and changing the power output to the selected power output level after the first time duration. An electrosurgical generator apparatus operating in accordance with the method is also described.

Owner:SYNERGETICS USA

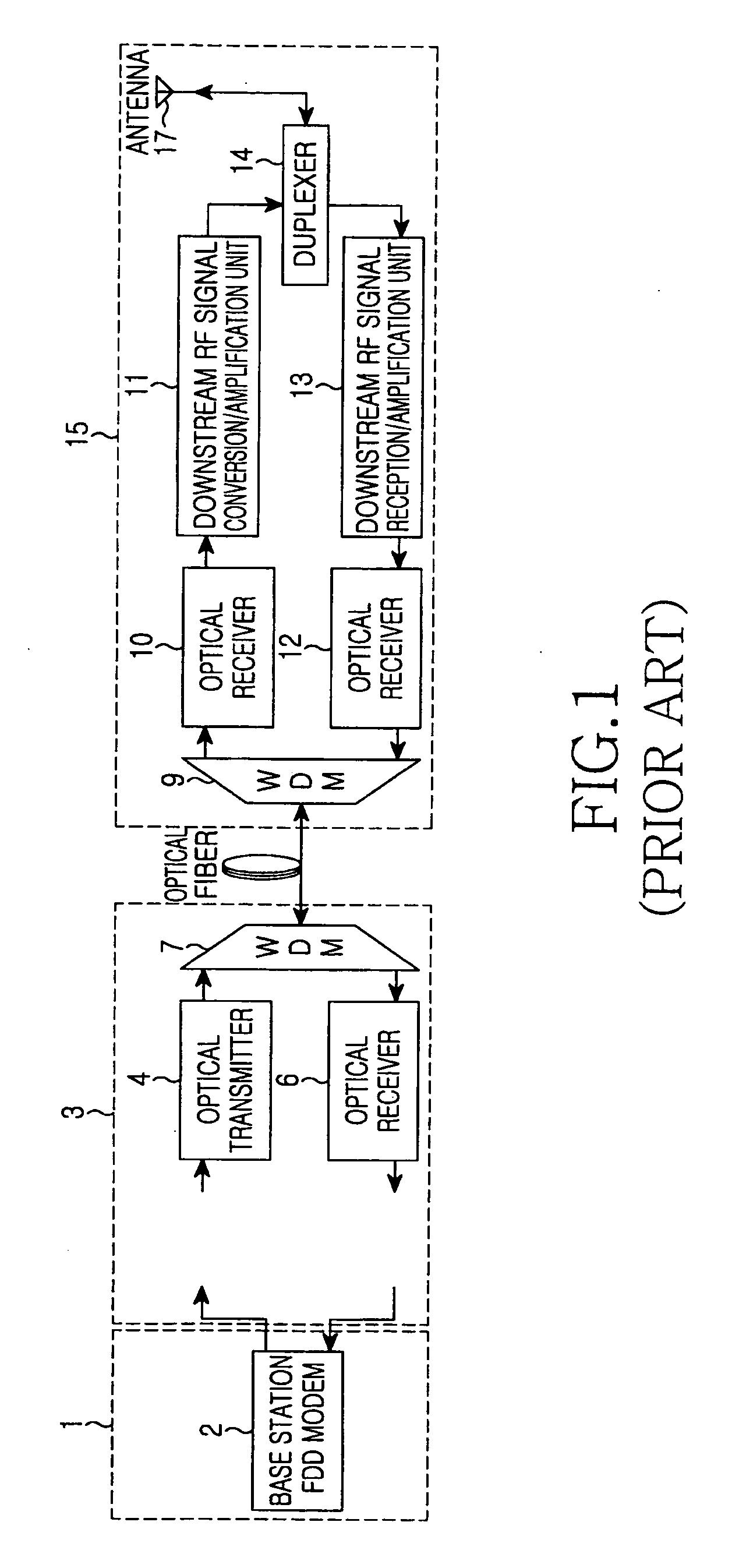

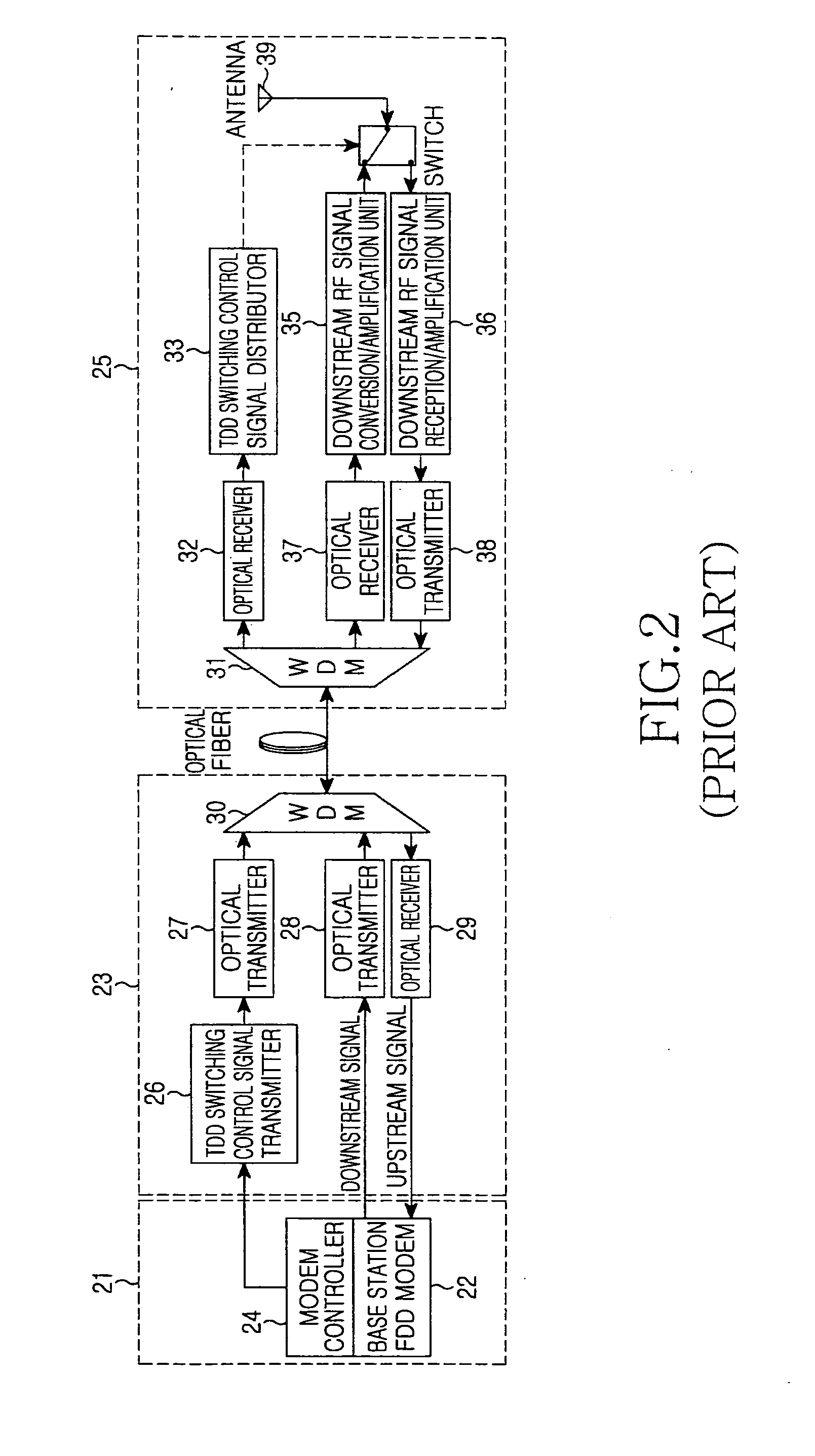

RoF system providing HD wireless communication service and signal control method for the same

Disclosed is an RoF system providing an HD wireless communication service. The RoF system includes the base station for transmitting and receiving each of the TDD / FDD individual signals and TDD / FDD combined signals, channel-combining downstream signals for a TDD scheme with downstream signals for an FDD scheme, and generating TDD / FDD mode control signals; a base station donor for receiving downstream RF signals from the base station, converting the resultant signals into downstream optical signals, outputting the converted signals, and delivering upstream optical signals, which are input to the remote station from the wireless terminals, to the base station; and the remote station for switching a corresponding duplexing mode operation according to wireless service channel states of the wireless terminals, converting the downstream optical signals transmitted from the base station donor into service RF signals, amplifying the converted service RF signals, and providing the amplified service RF signals to the wireless terminals through antennas.

Owner:SAMSUNG ELECTRONICS CO LTD

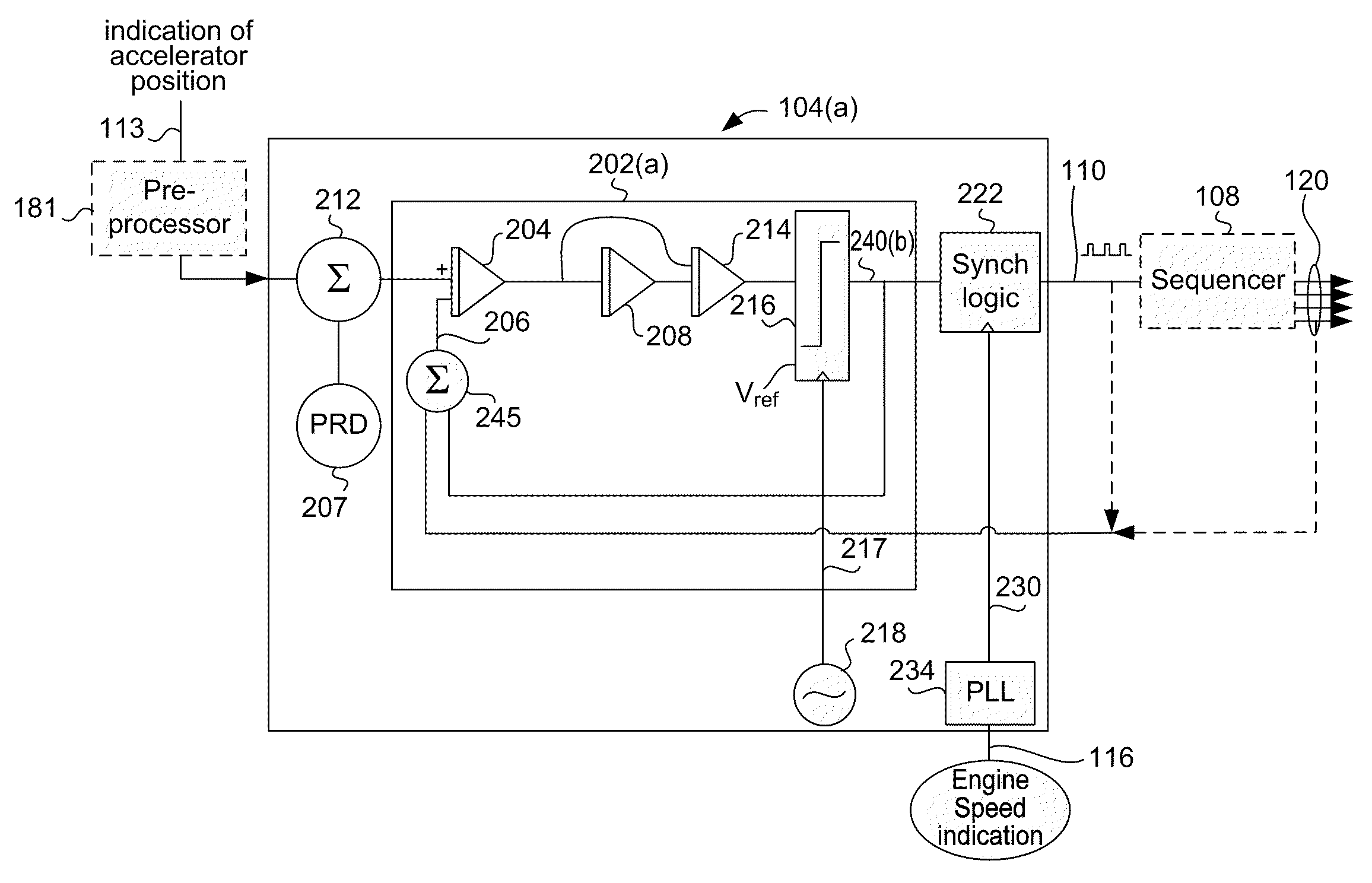

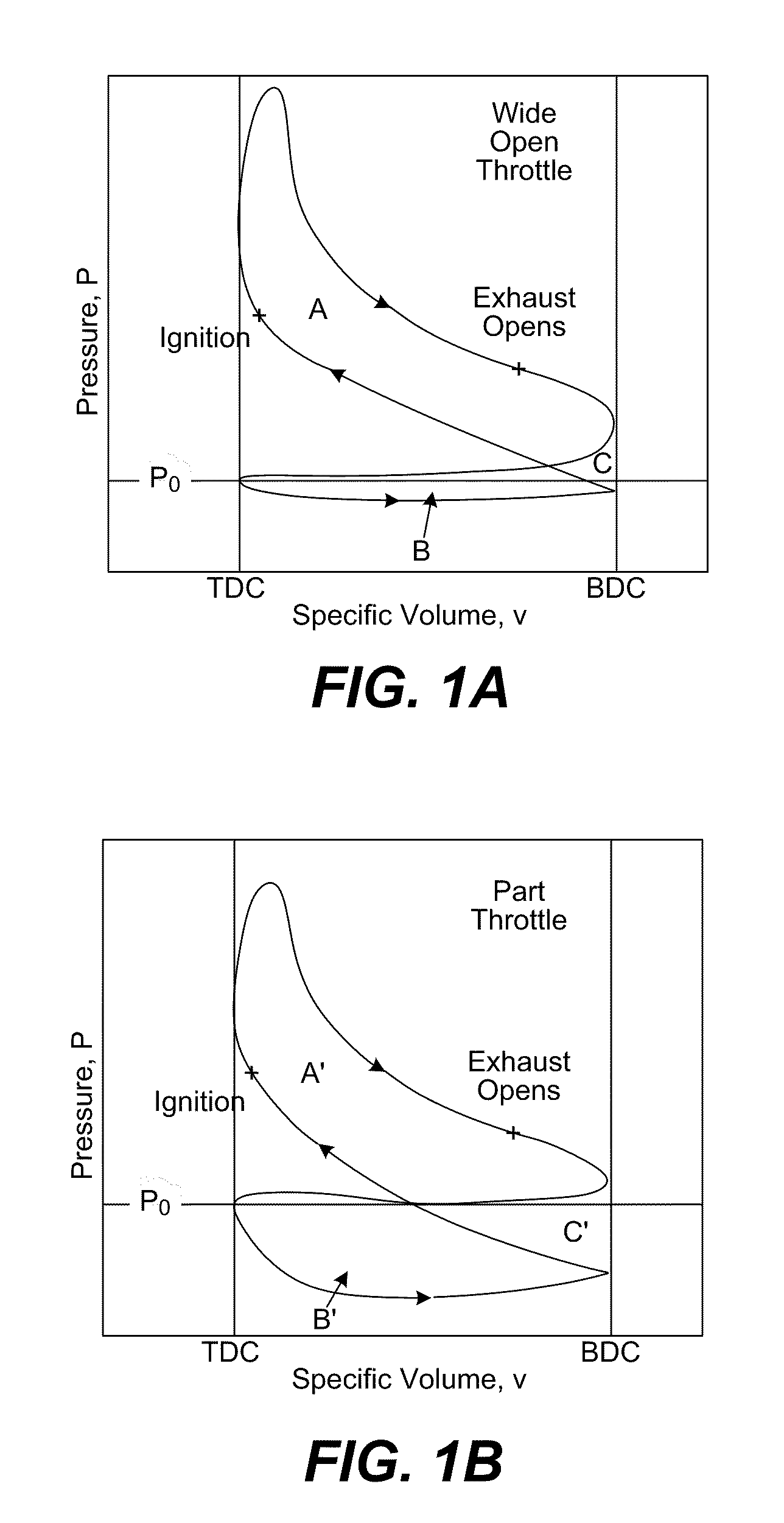

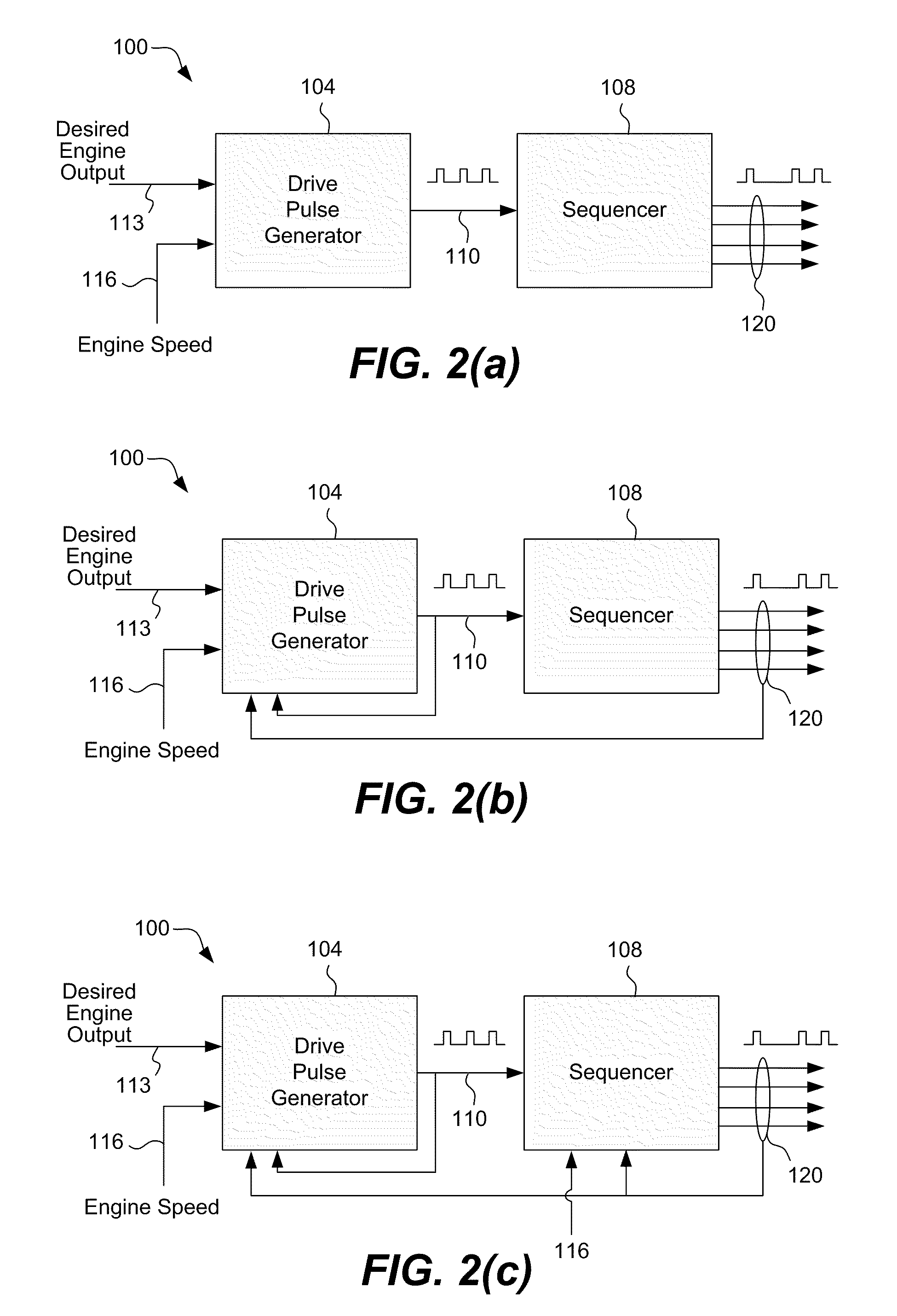

Skip fire engine control

ActiveUS20110030657A1Improve thermodynamic efficiencyReduce wall wetting lossElectrical controlMachines/enginesCombustionMode control

A variety of methods and arrangements for controlling the operation of an internal combustion engine in a skip fire variable displacement mode are described. Generally, an engine is controlled to operate in a skip fire variable displacement mode. In the variable displacement mode, selected combustion events are skipped so that other working cycles can operate at better thermodynamic efficiency. More specifically, selected “skipped” working cycles are not fired while other “active” working cycles are fired. Typically, fuel is not delivered to the working chambers during skipped working cycles. In one aspect of the invention, a firing pattern is determined that is not fixed but the active working cycles are selected to favor the firing of working chambers that have recently been fired at least in part to reduce wall wetting losses. In another aspect of the invention, when an active working cycle follows a skipped working cycle in the same working chamber, the quanta of fuel injected for delivery to the working chamber is increased relative to the quanta of fuel that would be delivered to the working chamber when the active working cycle follows another active working cycle in the same working chamber in order to compensate for wall wetting losses that occur during skipped working cycles.

Owner:TULA TECH INC

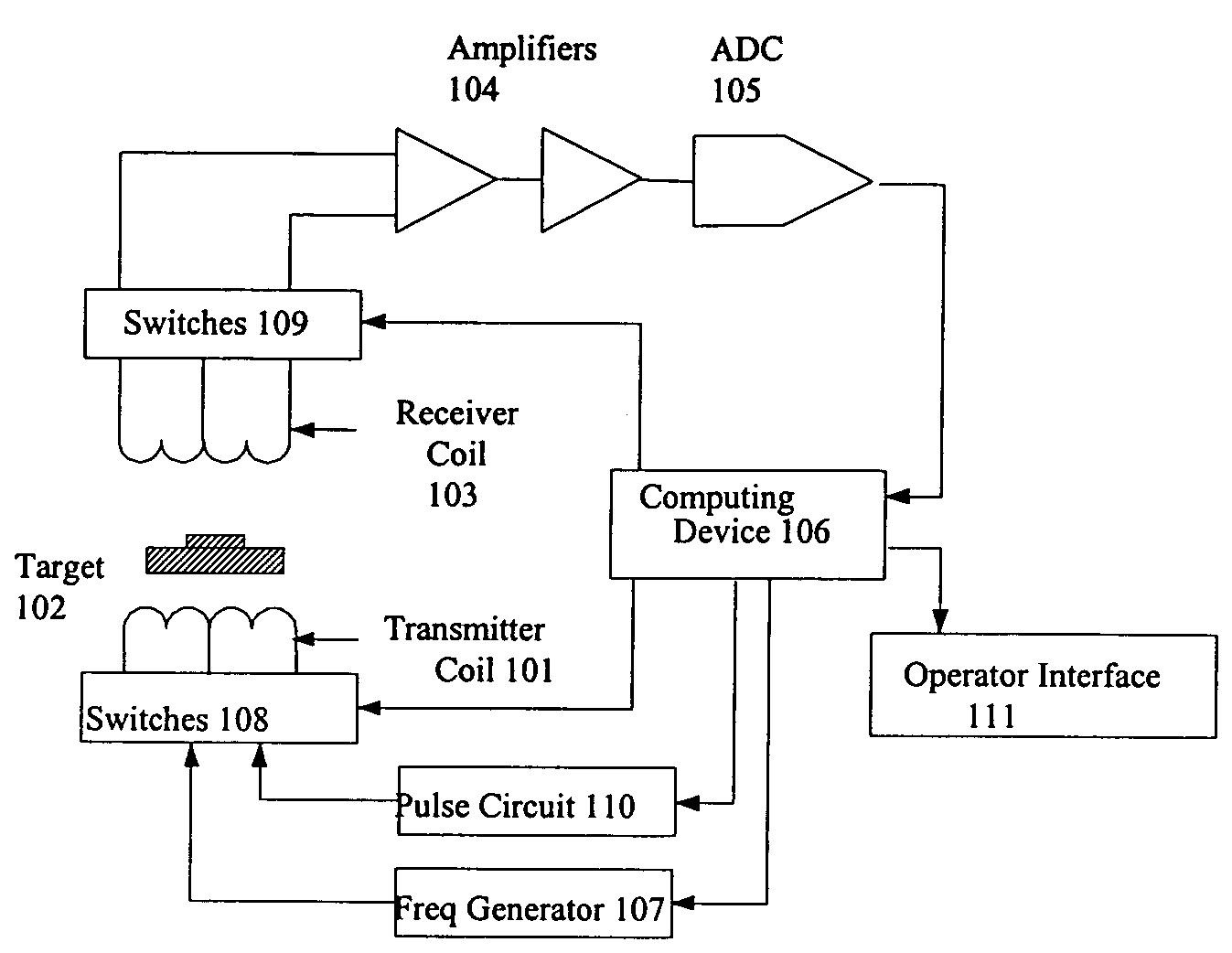

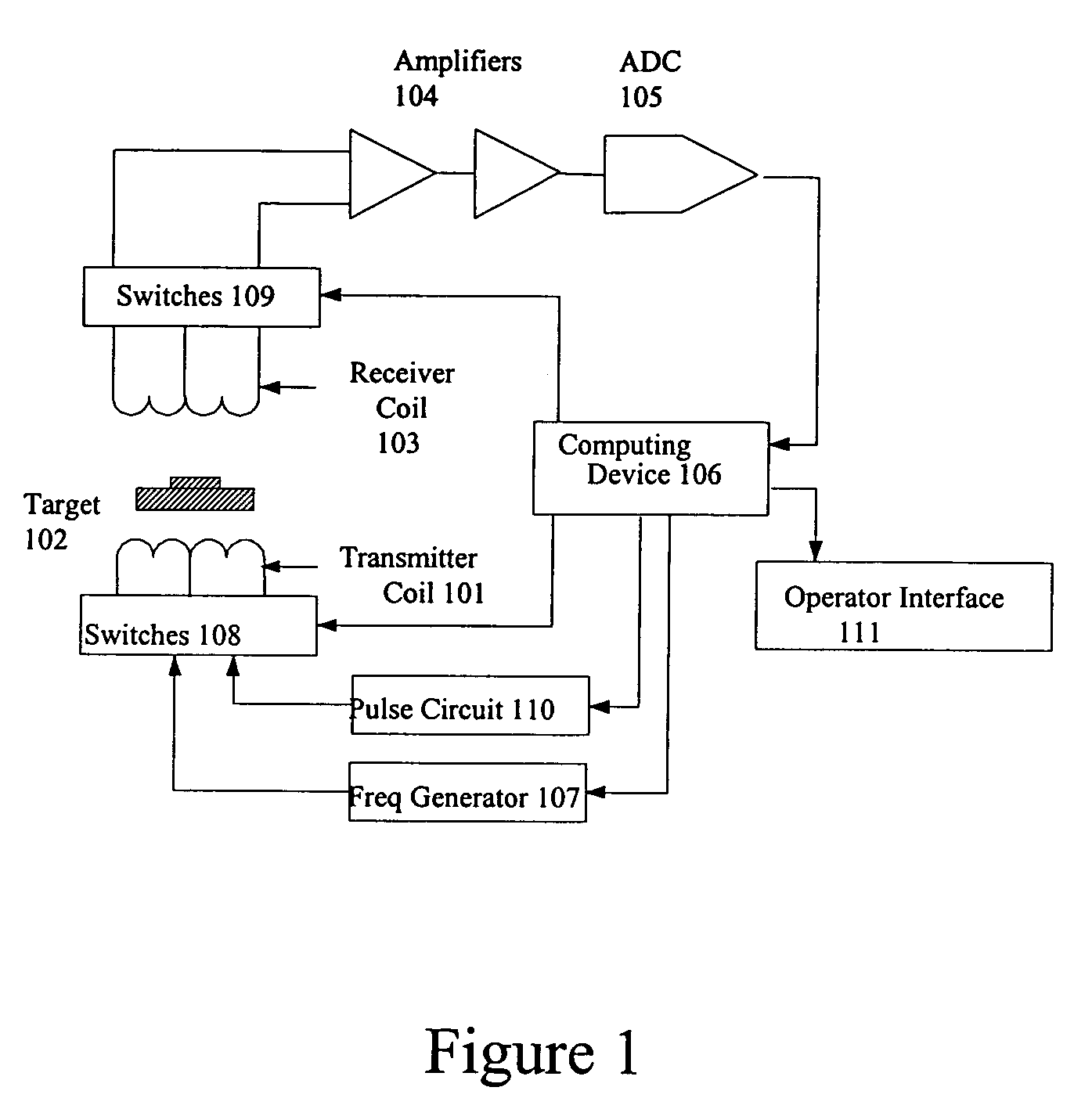

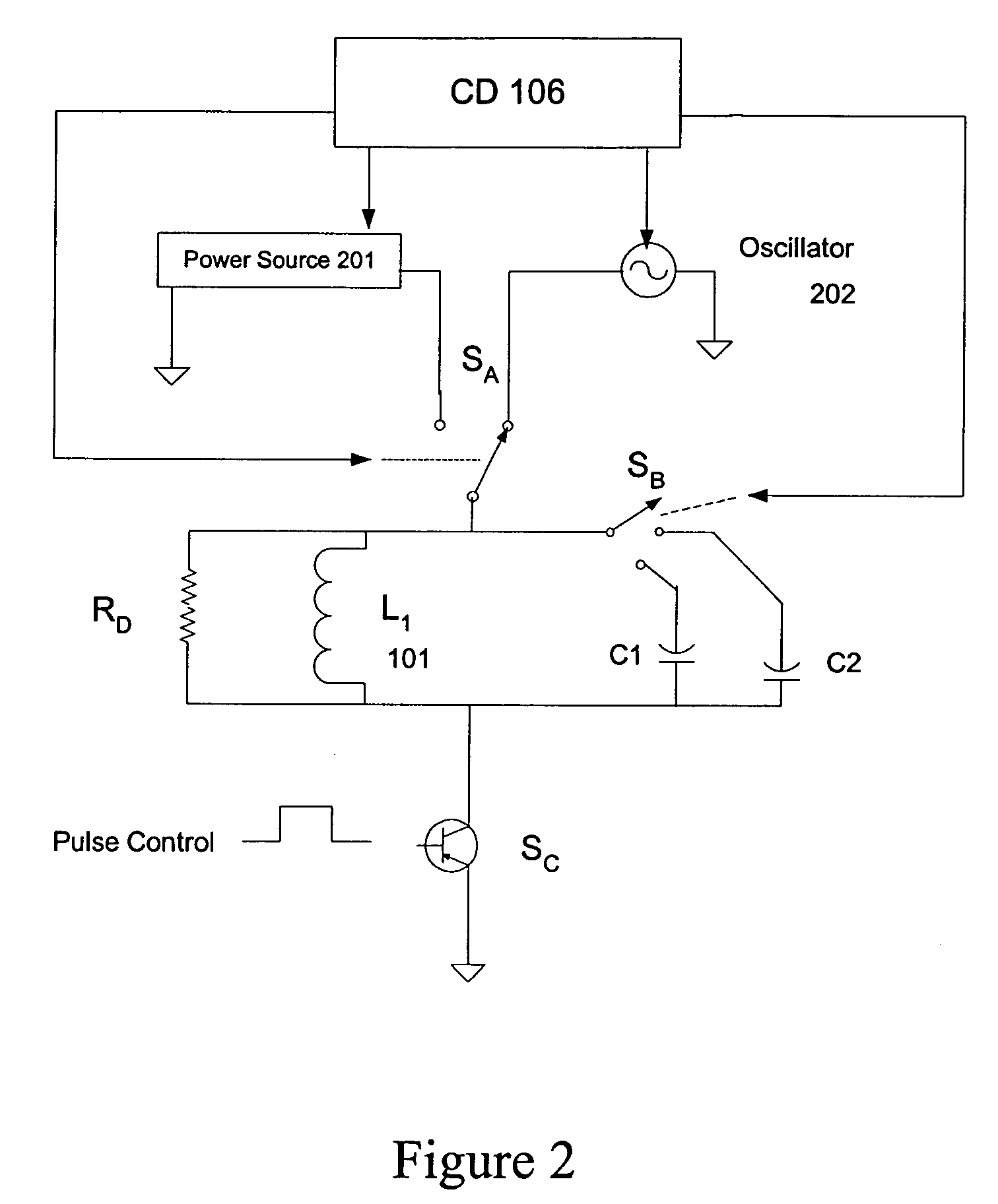

Multi-mode electromagnetic target discriminator sensor system and method of operation thereof

A multi-mode electromagnetic target discrimination sensor system for transmitting an electromagnetic signal and receiving a reflected signal from at least one target is disclosed having a variable inductance antenna having a variable inductance transmitter and a variable inductance receiver for varying at least one of operating bandwidth, sensitivity and size of the antenna, a processor for alternating between a time domain operating mode and a frequency domain operating mode, and controlling the variation of the inductance of the variable inductance antenna based on a current operating mode, and at least one processing algorithm for receiving signals from the receiver, discriminating targets from the received signals, and outputting the discrimination results is disclosed.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

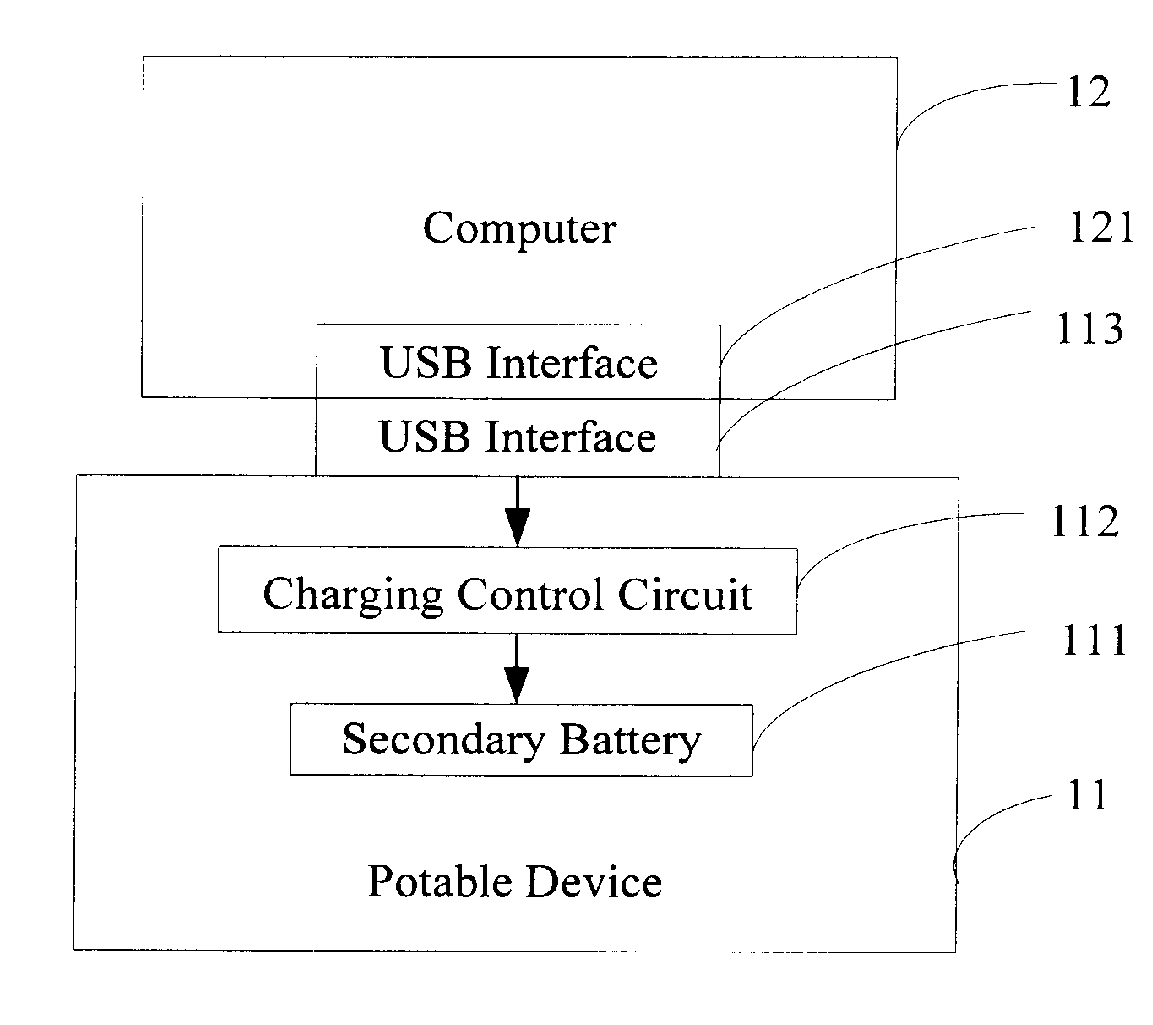

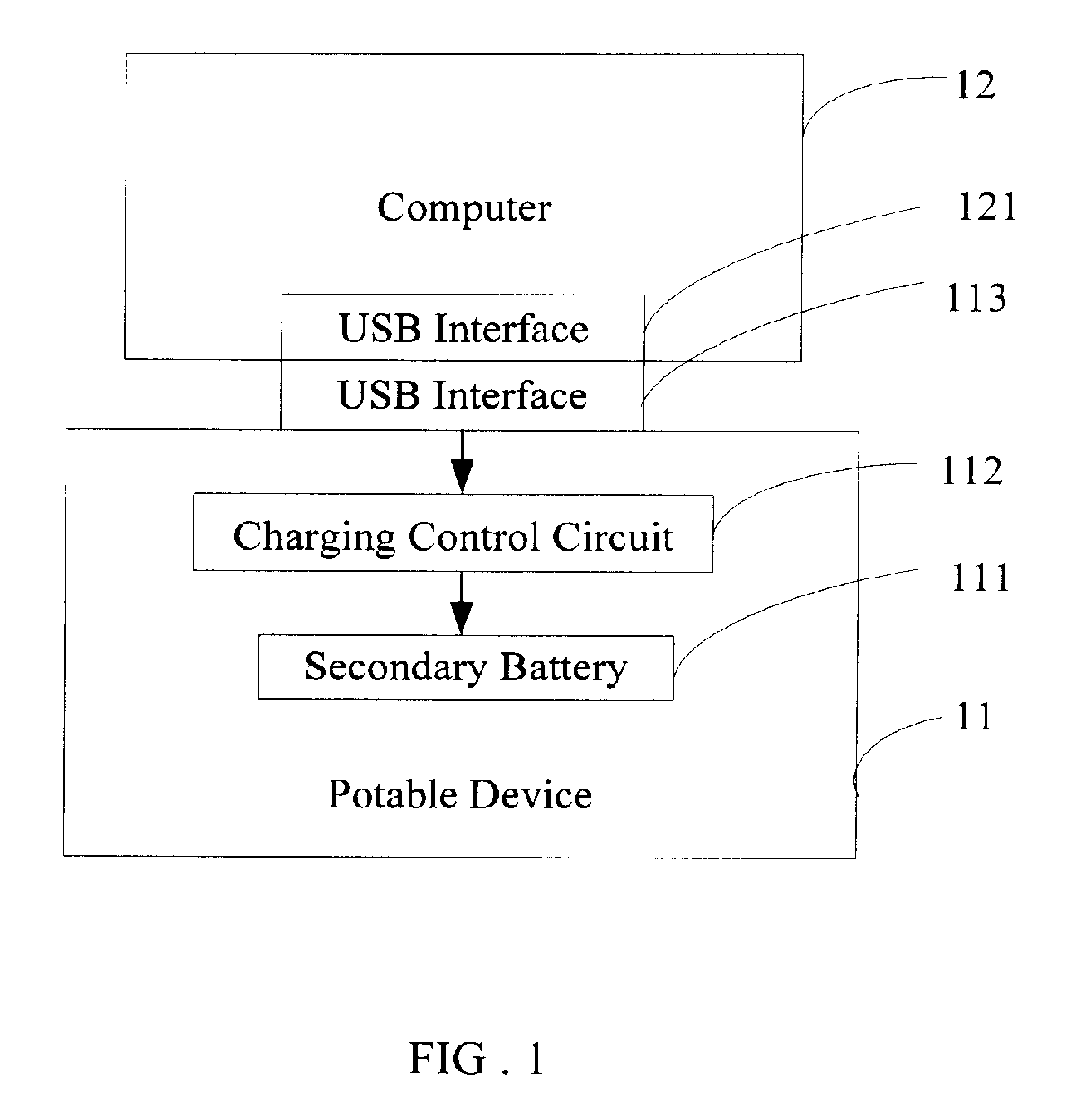

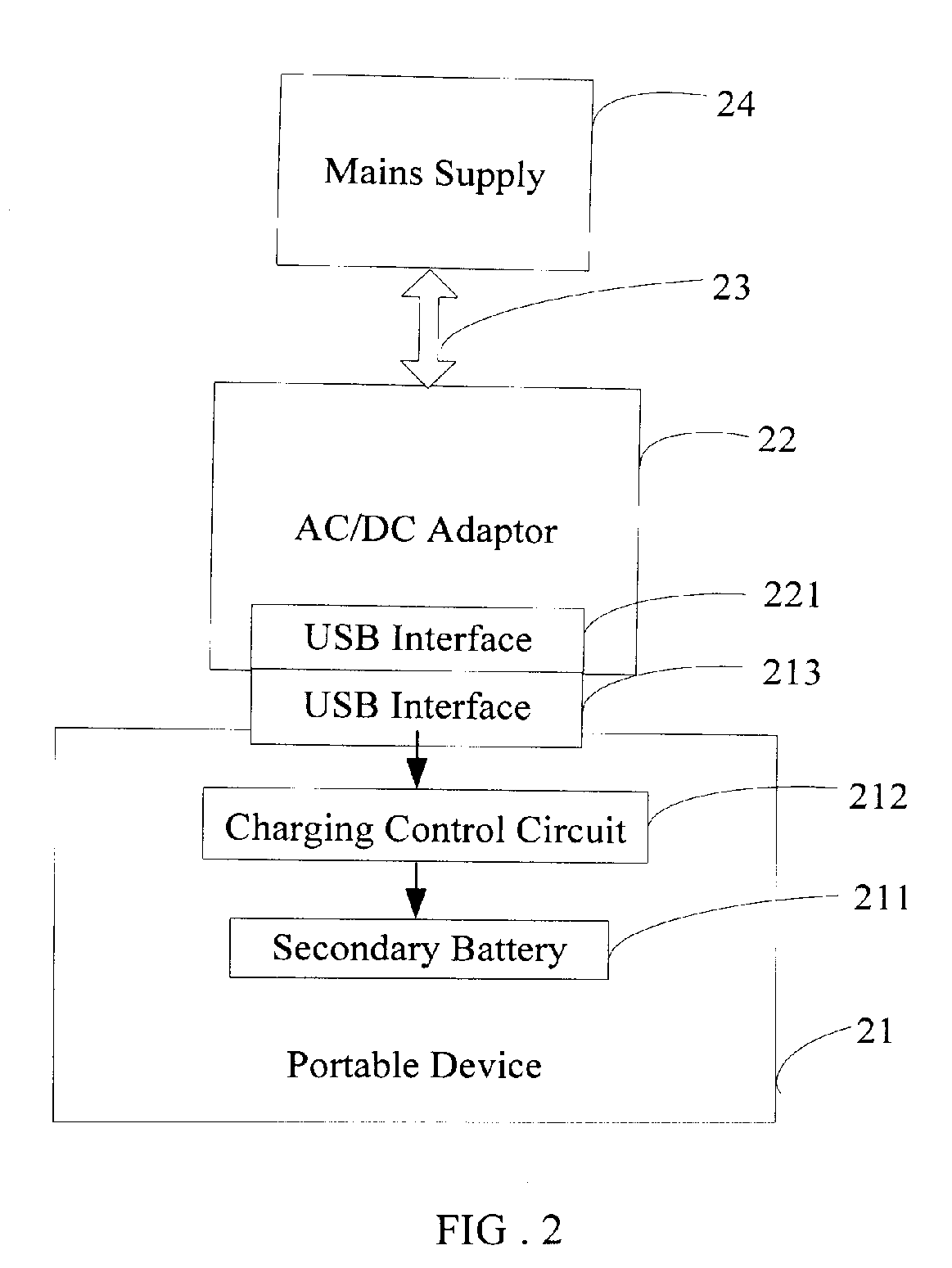

Charging mode control circuit and method

InactiveUS20060284595A1High currentFast chargingBatteries circuit arrangementsElectric powerMode controlFast charging

The present invention provides a charging mode control circuit and method. By utilizing such charging mode control circuit and method, a secondary battery fixed in a portable device can be quickly charged when the portable device communicate with an external computer. The method includes the steps of:a) providing a commutator, the commutator comprising an AC / DC adapter, a first interface, and a second interface, wherein the first interface is connected to the external computer and the second interface is connected to the portable device; b) comparing a charging voltage with a reference voltage, thereby producing a high voltage level signal according to a comparison result, wherein the charging voltage come from the AC / DC adapter; and c) selecting a fast-charging mode on the secondary battery according to the high voltage level signal.

Owner:HON HAI PRECISION IND CO LTD

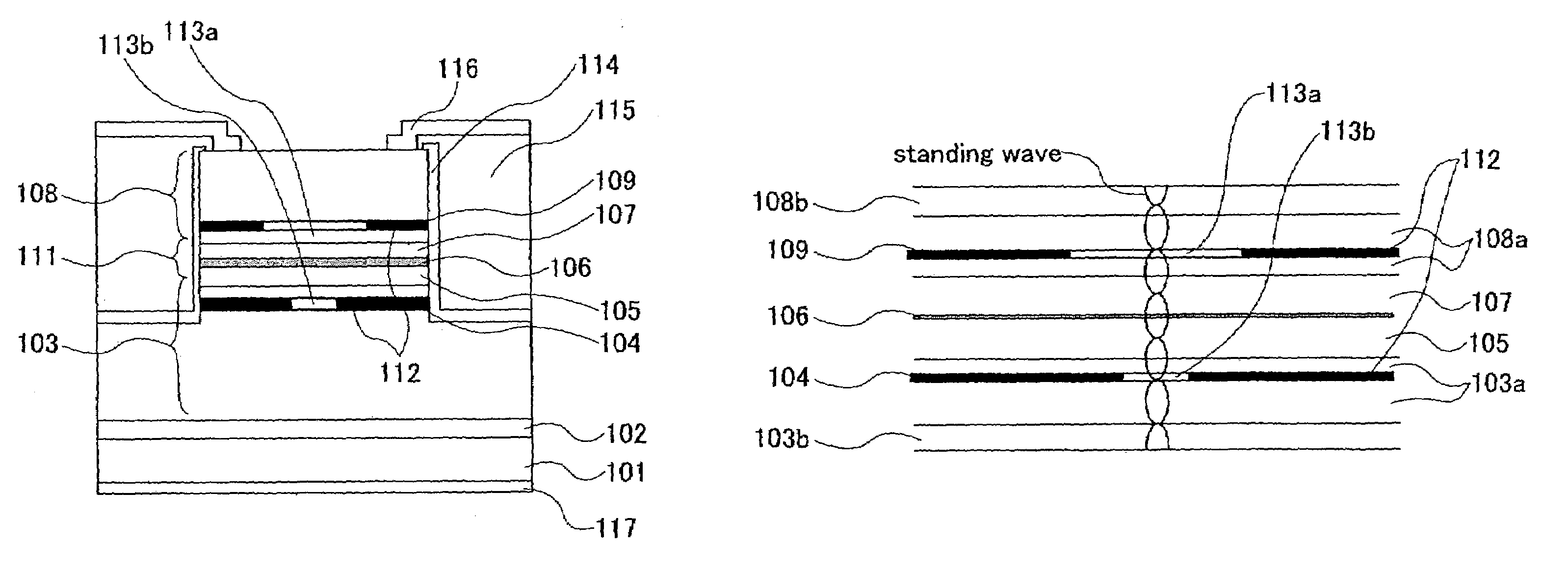

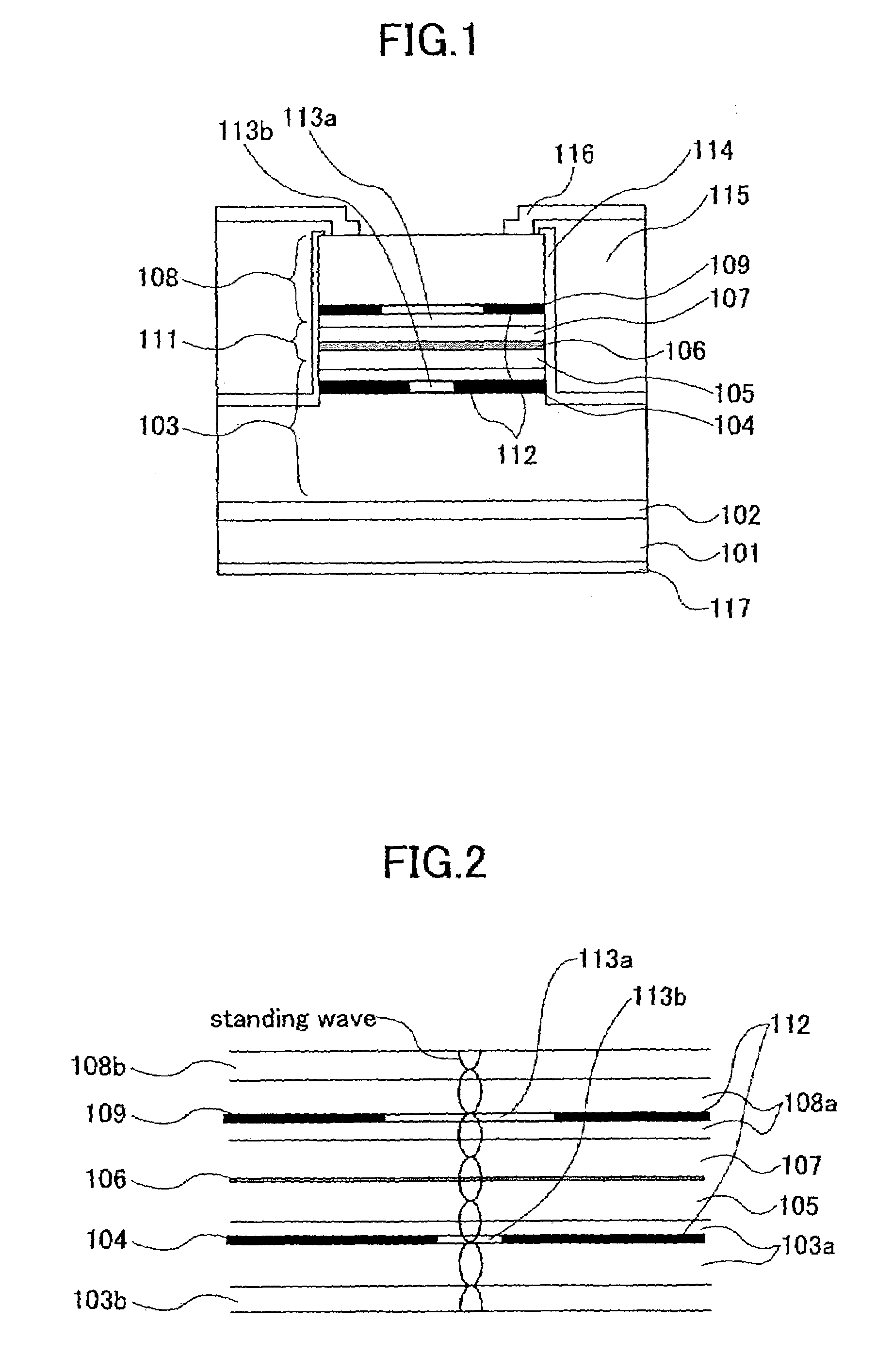

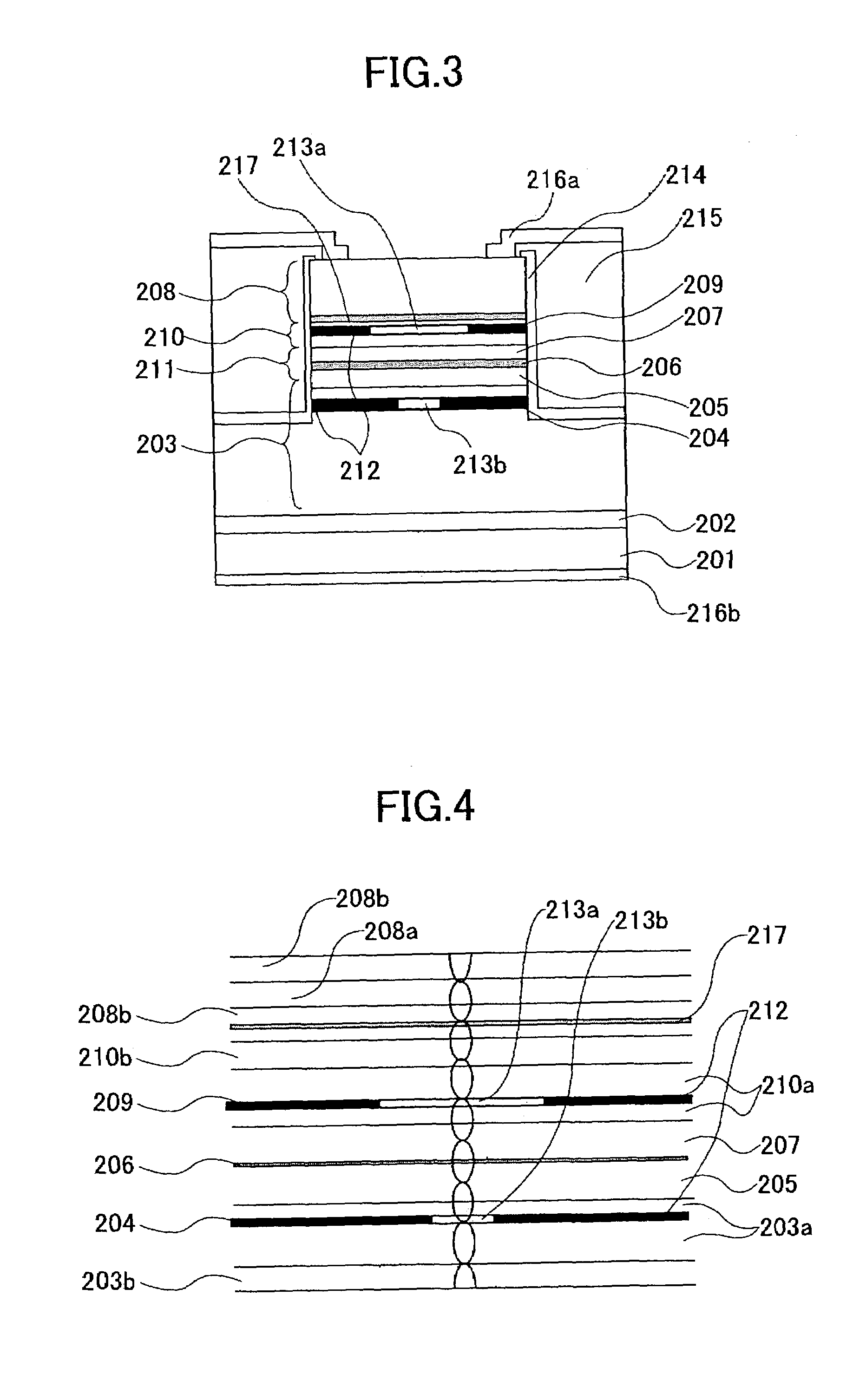

Surface-emitting laser diode having reduced device resistance and capable of performing high output operation, surface-emitting laser diode array, electrophotographic system, surface-emitting laser diode module, optical telecommunication system, optical interconnection system using the surface-emitting laser diode, and method of fabricating the surface-emitting laser diode

ActiveUS6959025B2Lower resistanceHigh-output operationOptical wave guidanceOptical resonator shape and constructionMode controlDistributed Bragg reflector

A surface-emitting laser diode device that oscillates in a direction perpendicular to the substrate is provided. This surface-emitting laser diode device includes: an active layer; a resonator structure including a first distributed Bragg reflector and a second distributed Bragg reflector that face each other and sandwich the active layer; a hole passage that extends from a first electrode to the active layer; an electron passage that extends from a second electrode to the active layer; a hole restricting structure that is located in the hole passage and defines a region for confining holes to the active layer; and an optical mode control structure that includes a non-oxide region provided in the resonator structure and an oxide region surrounding the non-oxide region, each region containing Al as a constituent element. In this surface-emitting laser diode, the area of the non-oxide region is smaller than the area of the hole restricting structure.

Owner:RICOH KK

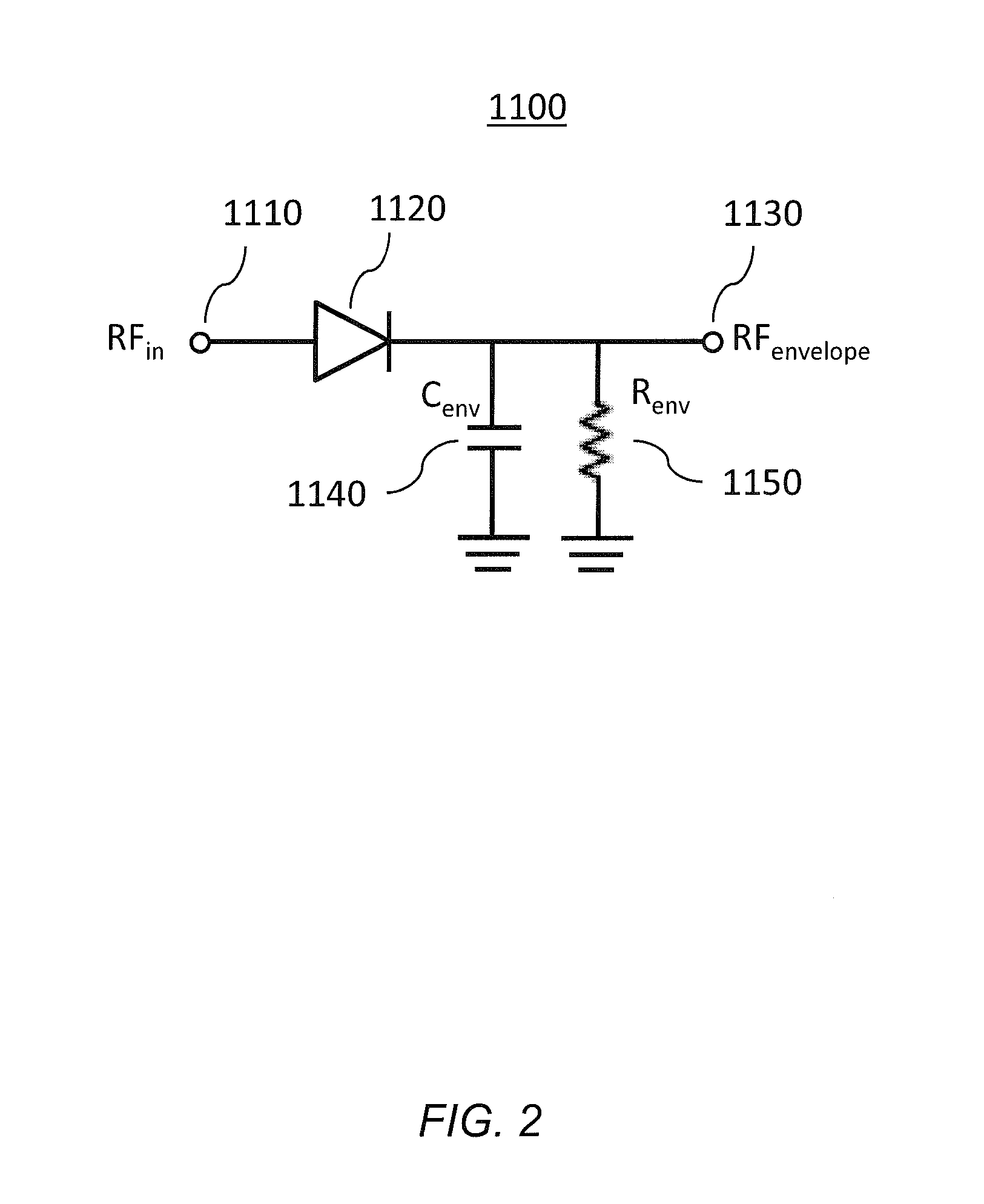

Control Systems and Methods for Power Amplifiers Operating in Envelope Tracking Mode

ActiveUS20140184337A1Improve stabilityReduce oscillationPower amplifiersAmplifier modifications to raise efficiencyAudio power amplifierControl system

Control systems and methods for power amplifiers operating in envelope tracking mode are presented. A set of corresponding functions and modules are described and various possible system configurations using such functions and modules are presented.

Owner:PSEMI CORP

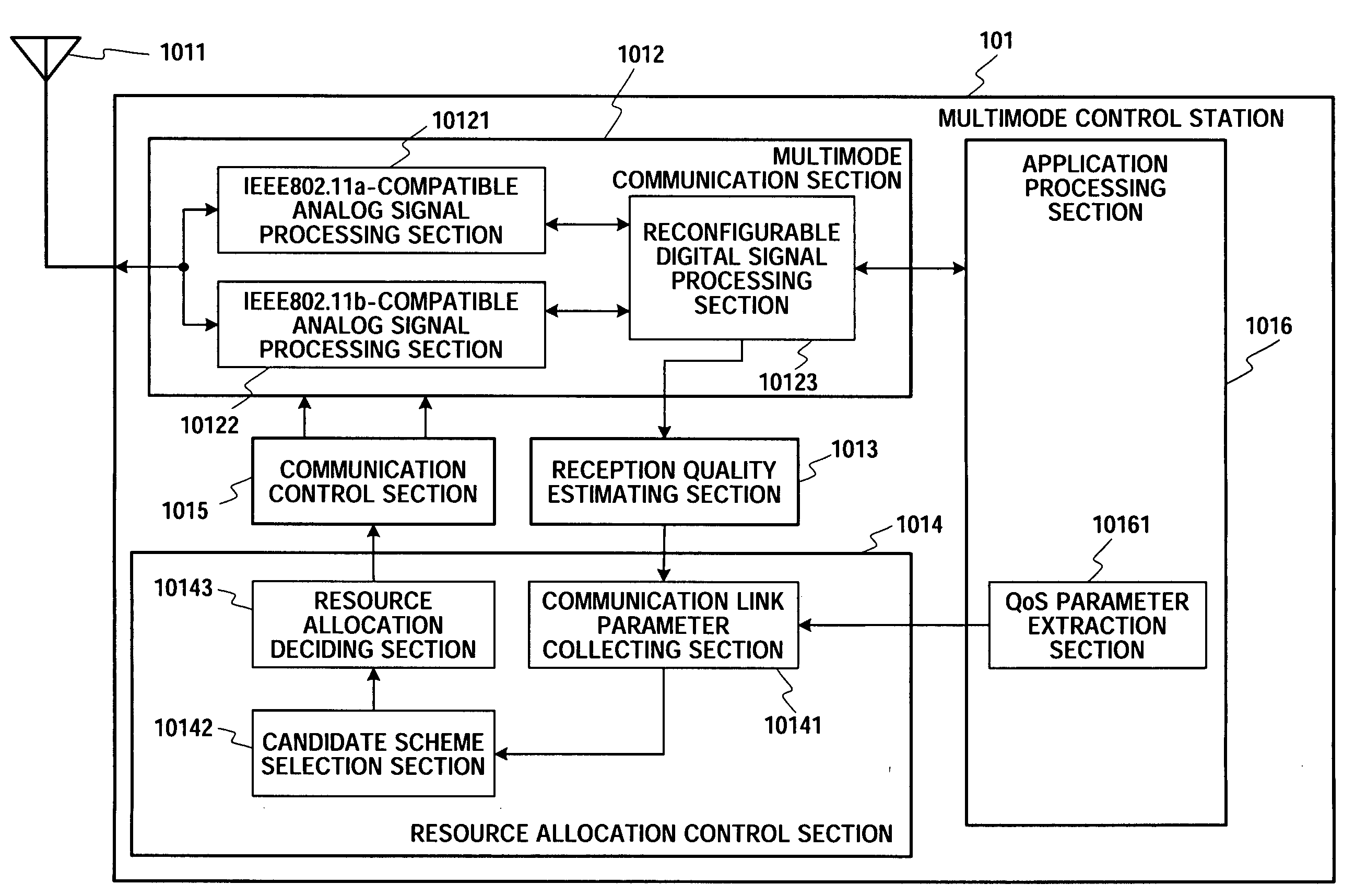

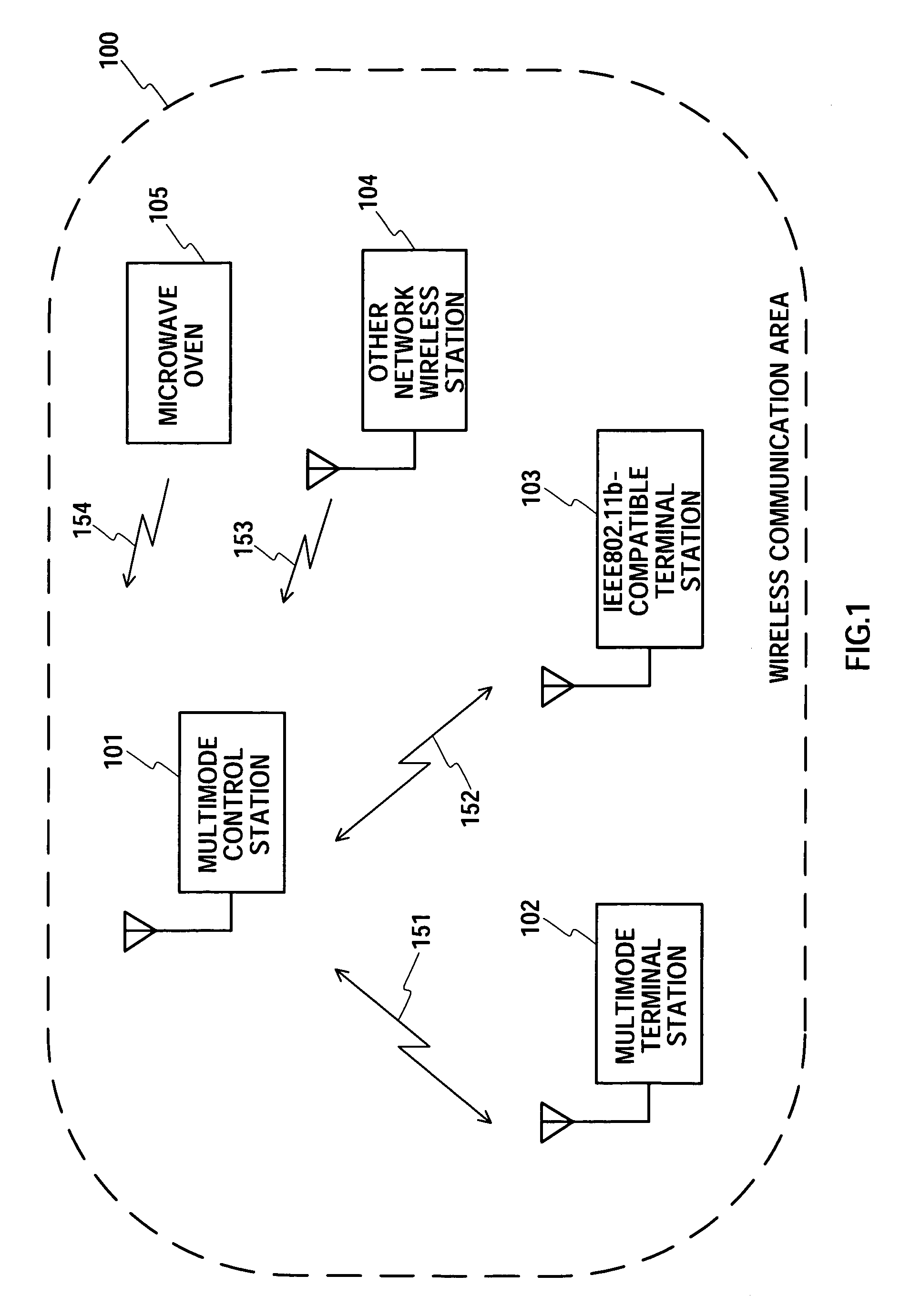

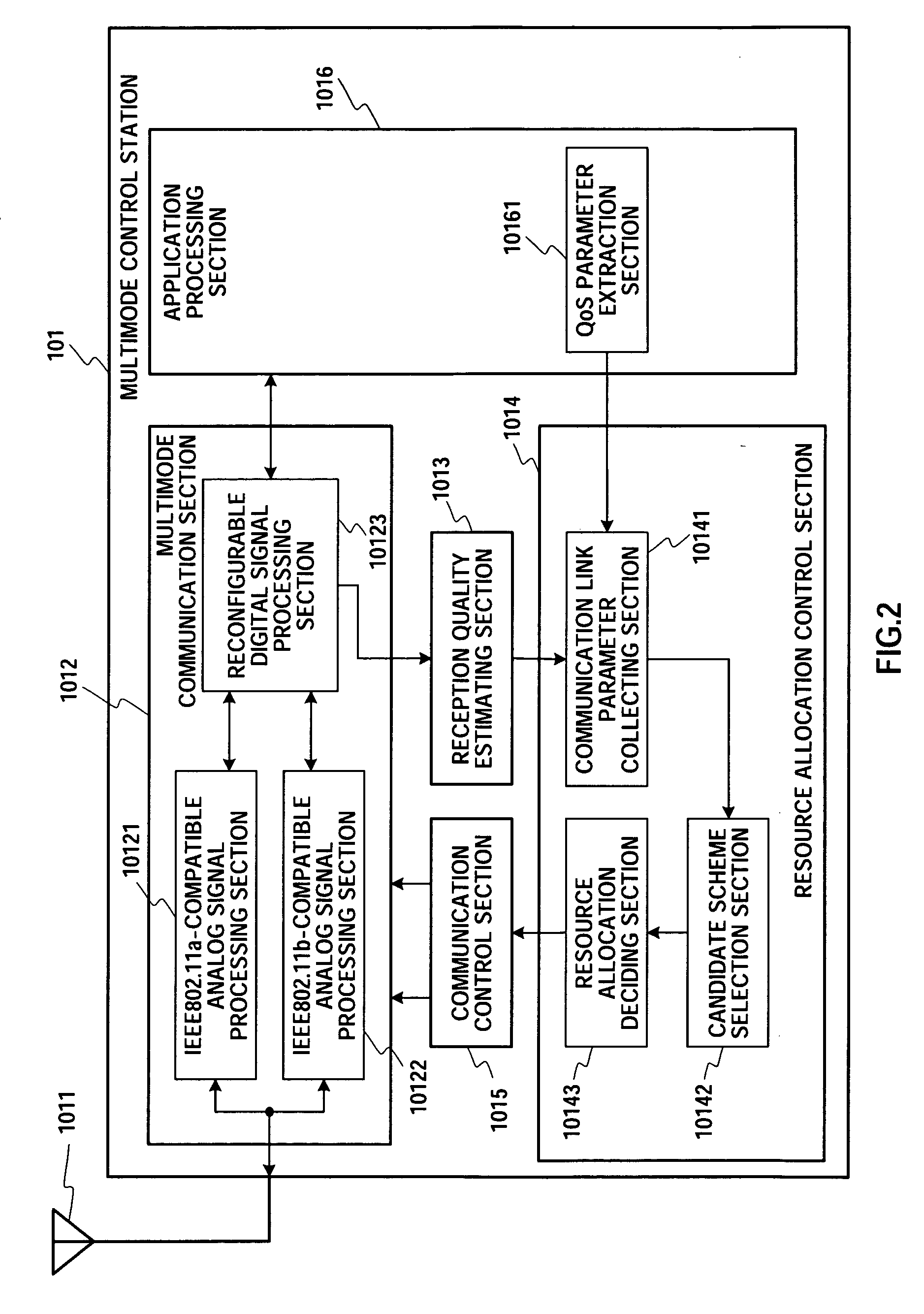

Multi-Mode Control Station, Radio Communication System, Radio Station, and Radio Communication Control Method

InactiveUS20080200195A1Improve system throughputLarge throughputNear-field transmissionTransmission control/equalisingCommunication unitTelecommunications link

The overall throughput of the radio communication traffic in a radio communication area in a radio communication environment where a plurality of types of radio communication systems are mixedly used in a neighboring radio communication area is improved. When a multi-mode control station (101) performs communication with a terminal station in a network through a plurality of types of communication systems, a communication link parameter collecting section (10141) collects parameters indicating the states of the communication links. A resource allocation determining section (10143) determines communication resource allocation for which the throughput is the greatest for each resource allocation period according to the parameters. A communication control section (1015) controls a multi-mode communication unit (1012) according to the result of the determination.

Owner:KOHNO RYUJI +1

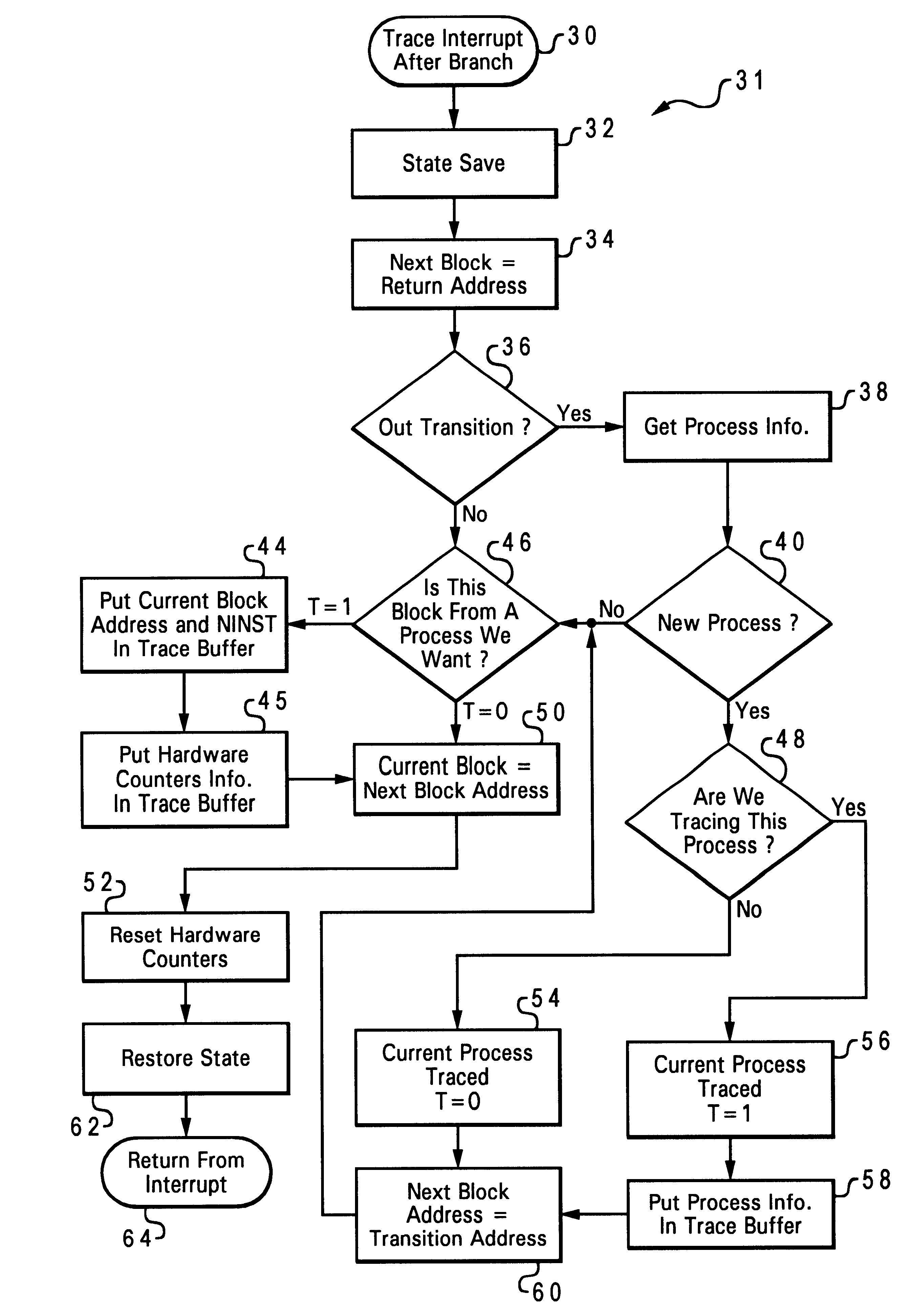

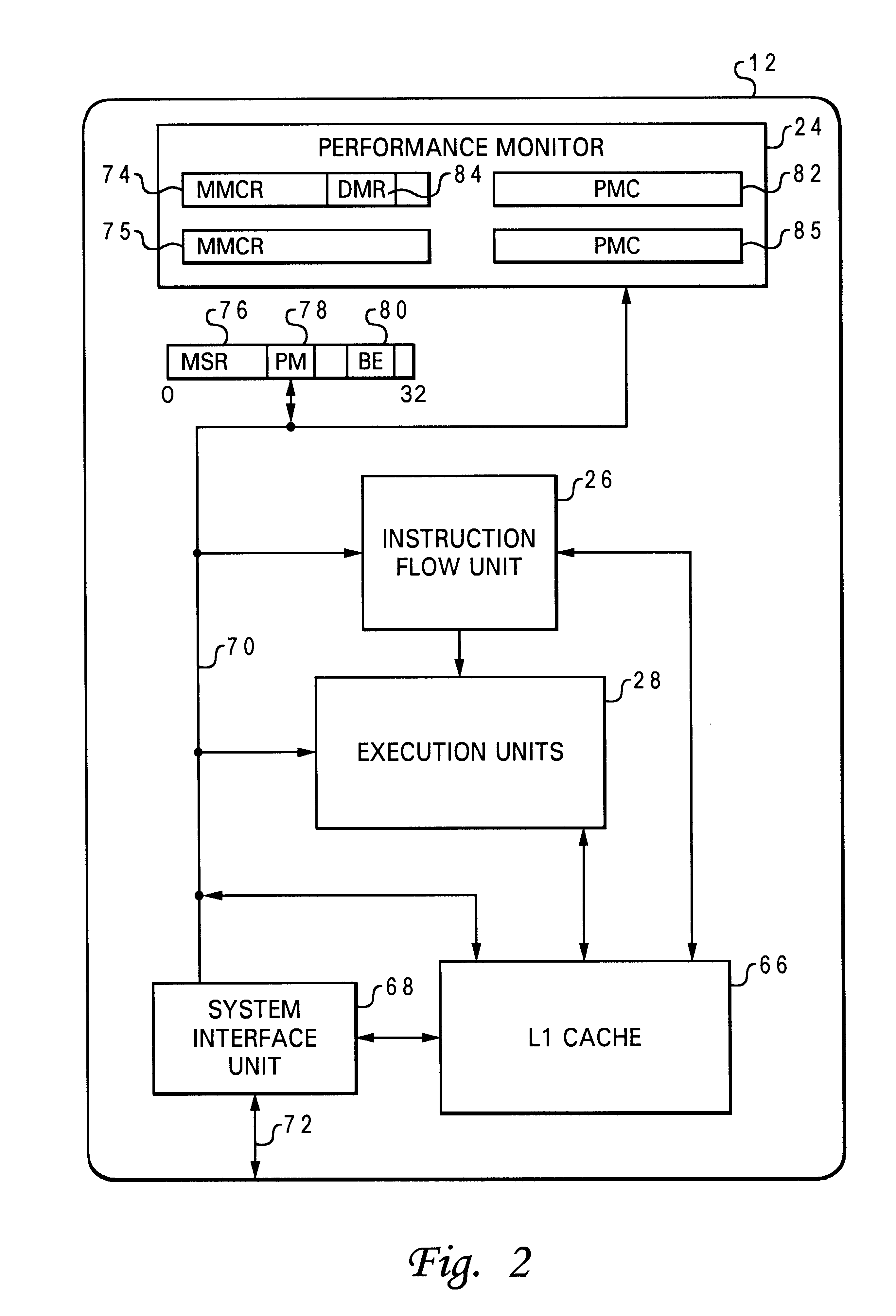

System for tracing hardware counters utilizing programmed performance monitor to generate trace interrupt after each branch instruction or at the end of each code basic block

A method and system within a data processing system or information handling system are disclosed for counting various events from a running program (hereafter called a process) by taking a trace by way of using an interruption. According to the present invention, a performance monitor feature within a data processing system is programmed to generate a trace interrupt after each branch instruction, or at the end of each basic block of code from a currently running program or process. By programming monitor mode control registers within the performance monitor feature, one or more counters are programmed to count various events happening on the data processing system thereby creating tracing information. If the current process is a process to be traced, the tracing information is stored in a trace buffer for post-processing analysis, the counters are reset to zero returning back to the process from the interrupt.

Owner:IBM CORP

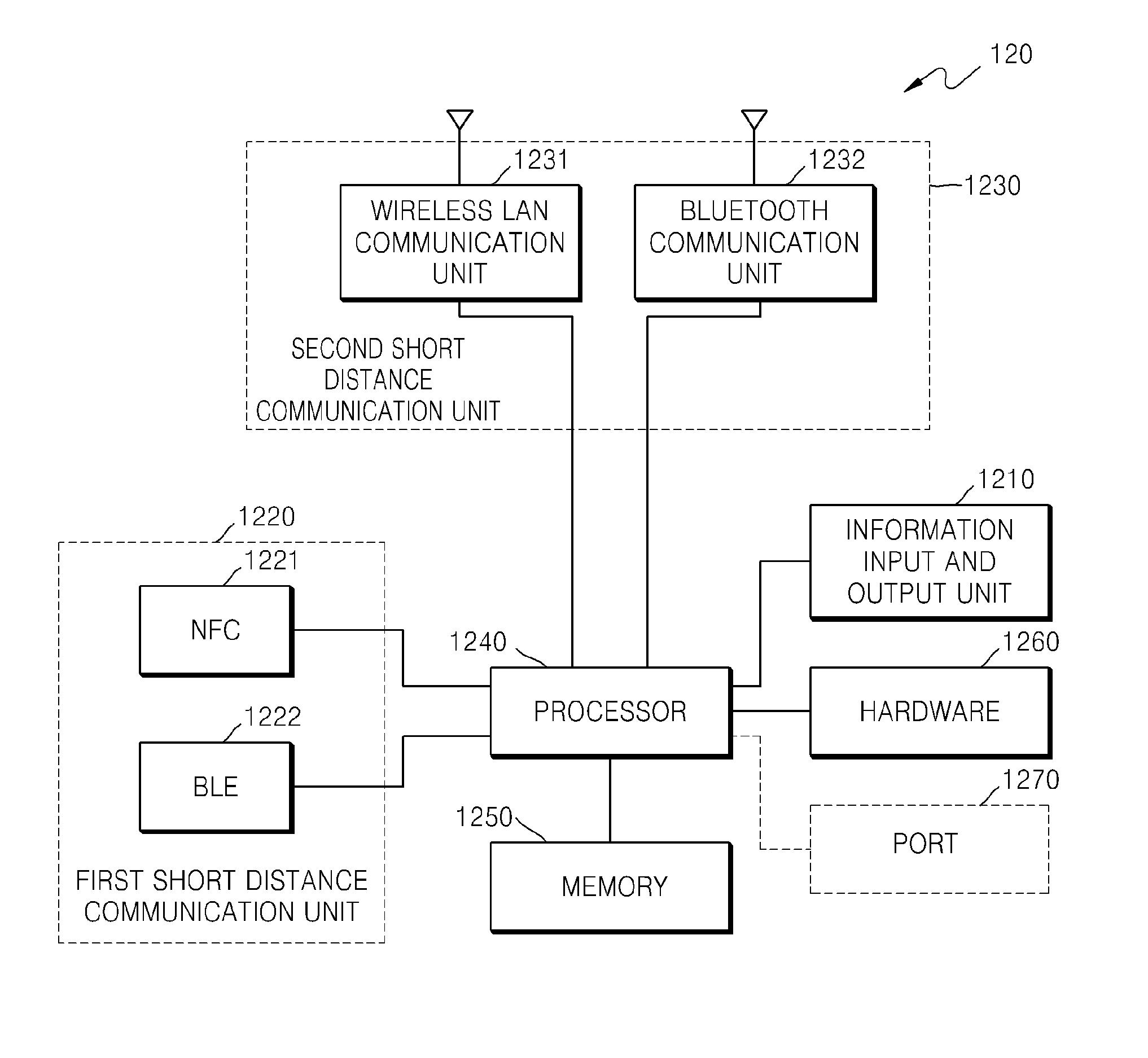

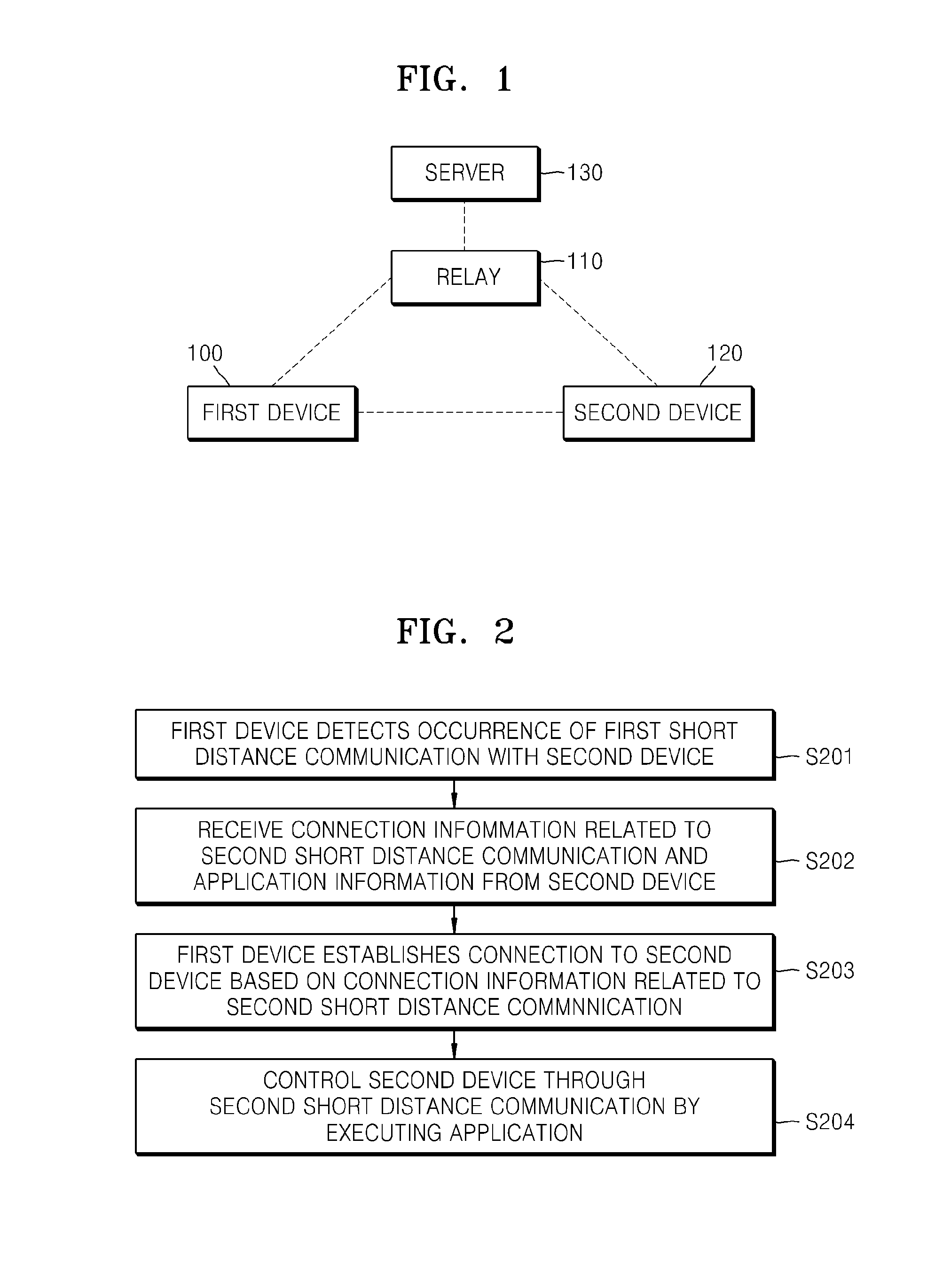

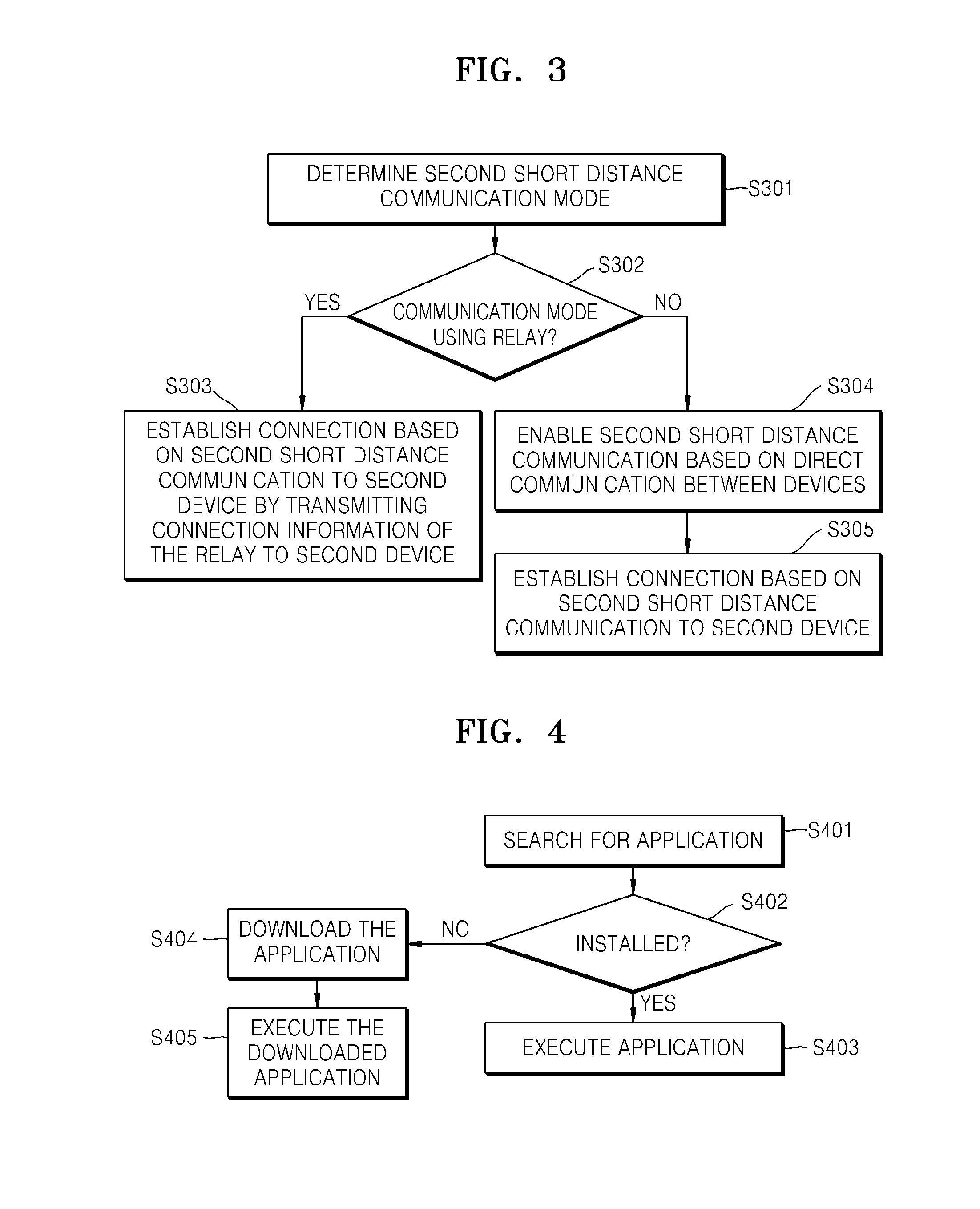

Method and device for executing application

A method for executing an application based on a connection between devices by automatically connecting devices, and a device, are disclosed. The method includes: detecting an occurrence of first short distance communication between at least one external device and the device; receiving connection information which relates to a second short distance communication mode and application information which relates to the at least one external device from the at least one external device via the first short distance communication; establishing a connection based on the second short distance communication mode between the at least one external device and the device based on the received connection information which relates to the second short distance communication mode; and controlling the at least one external device via the second short distance communication mode by using an application which is executable based on the received application information.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com