Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

530results about How to "Good ohmic contact" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

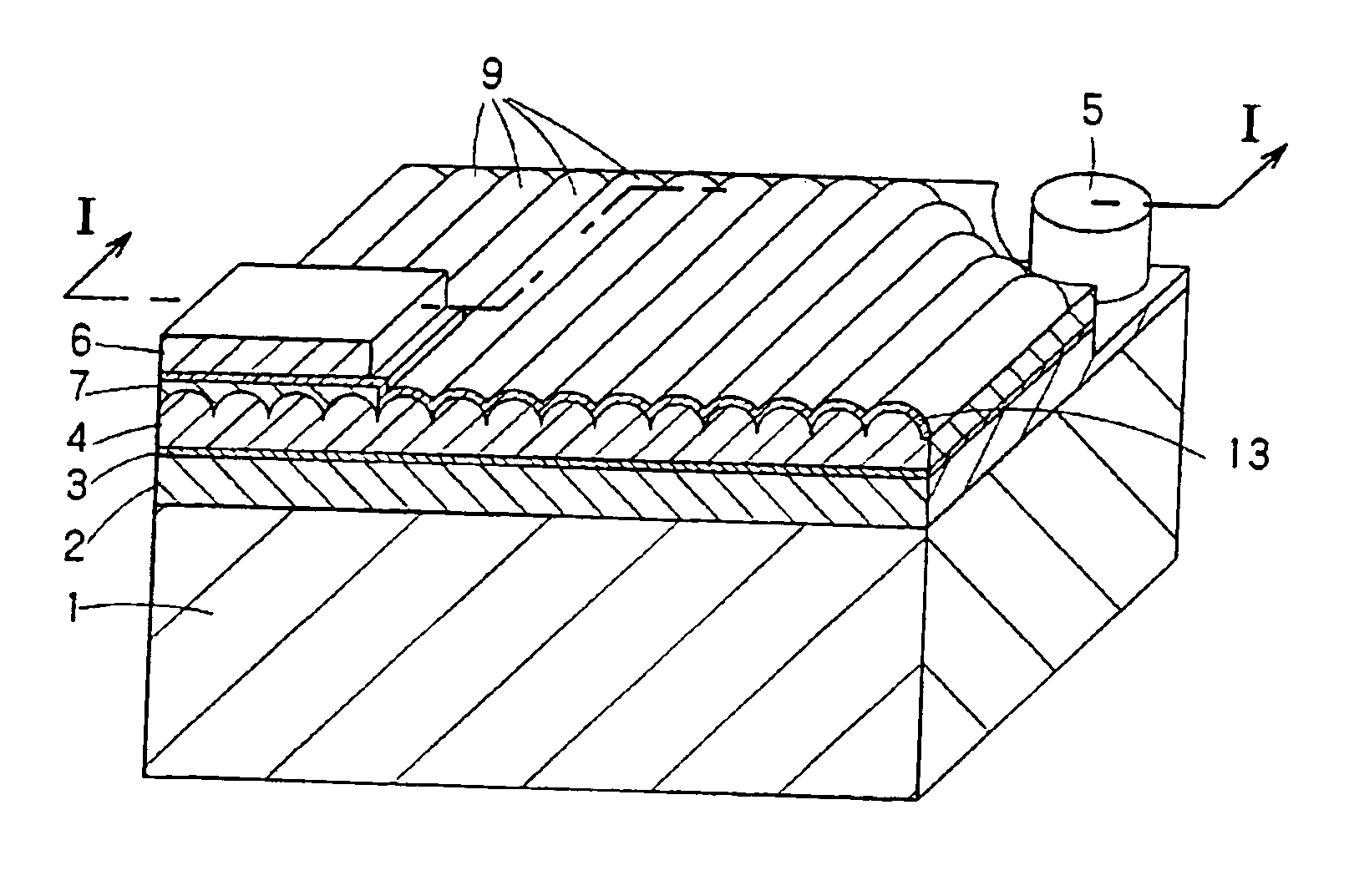

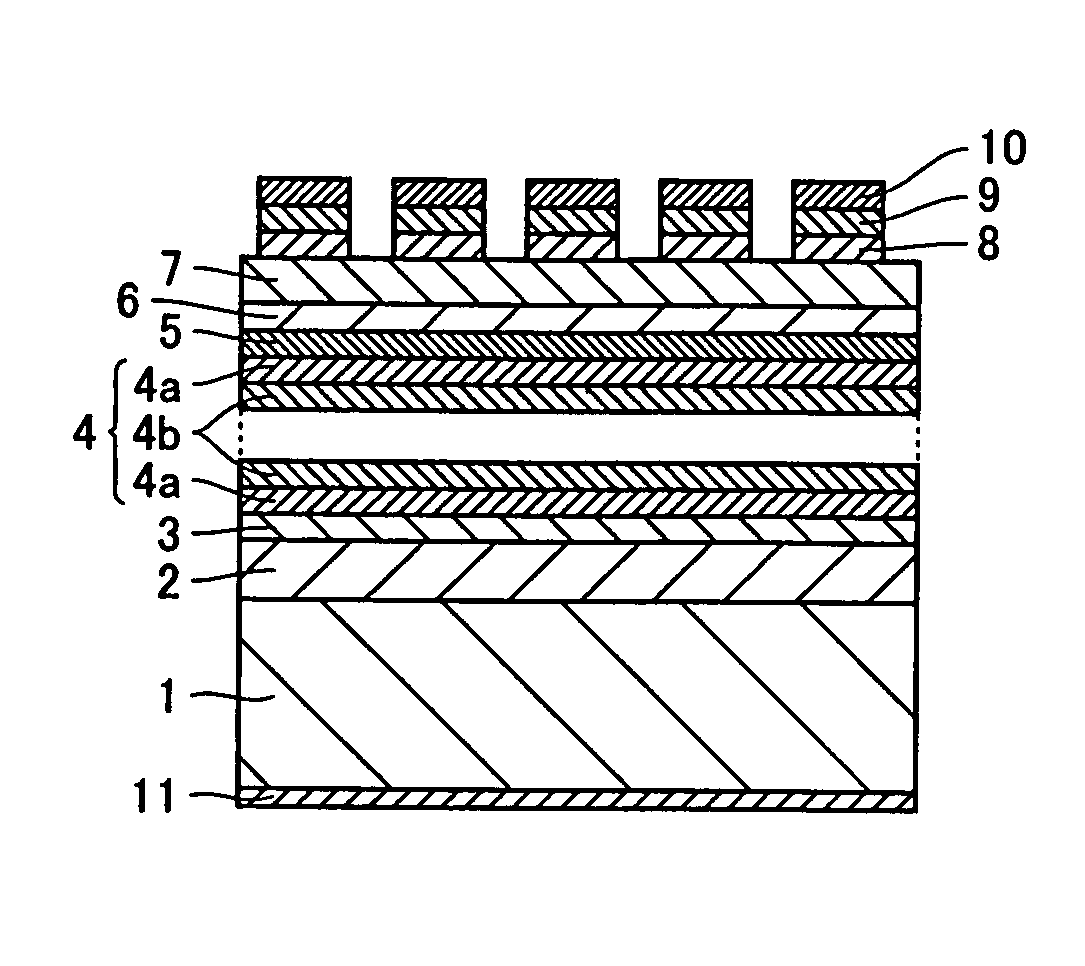

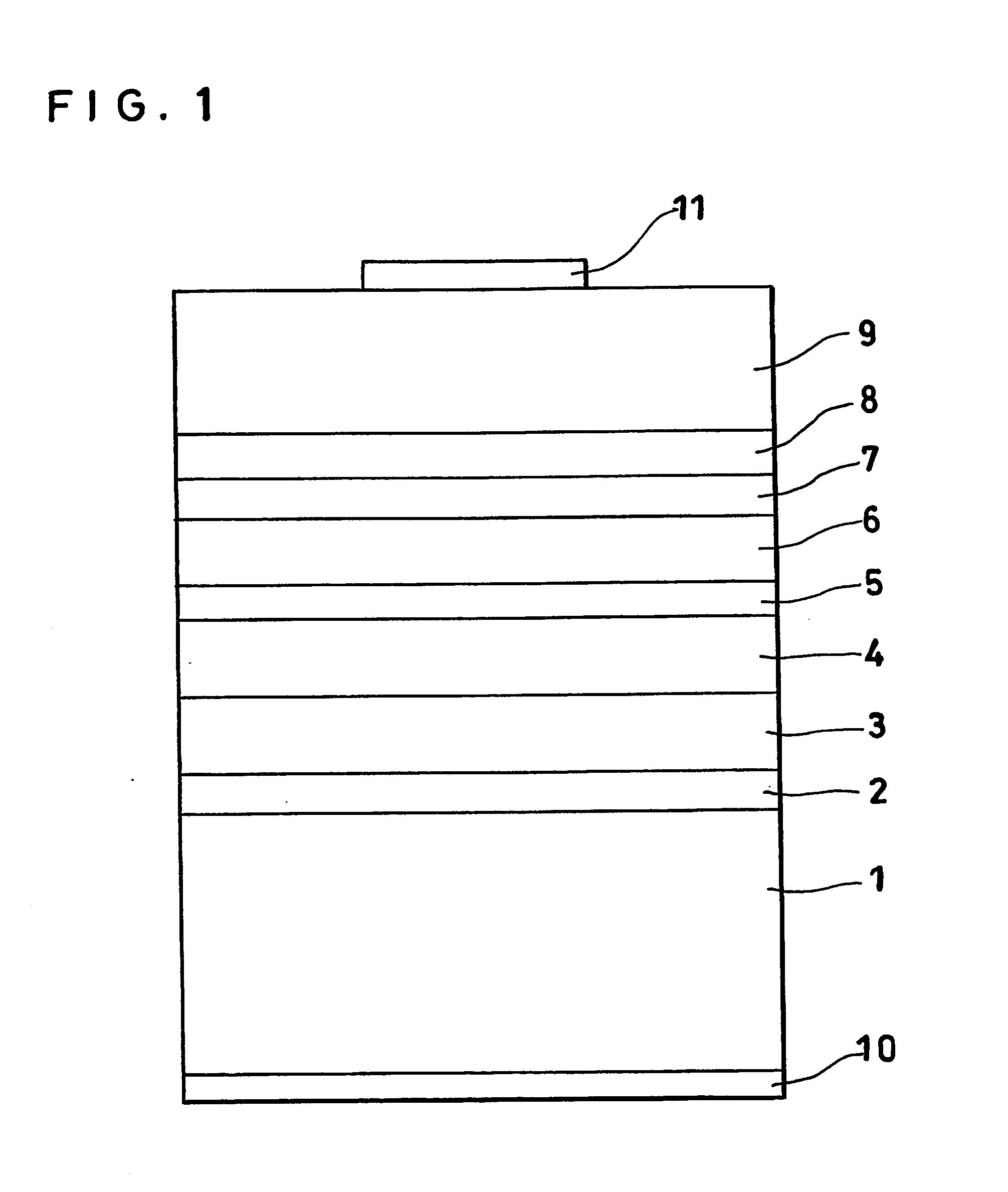

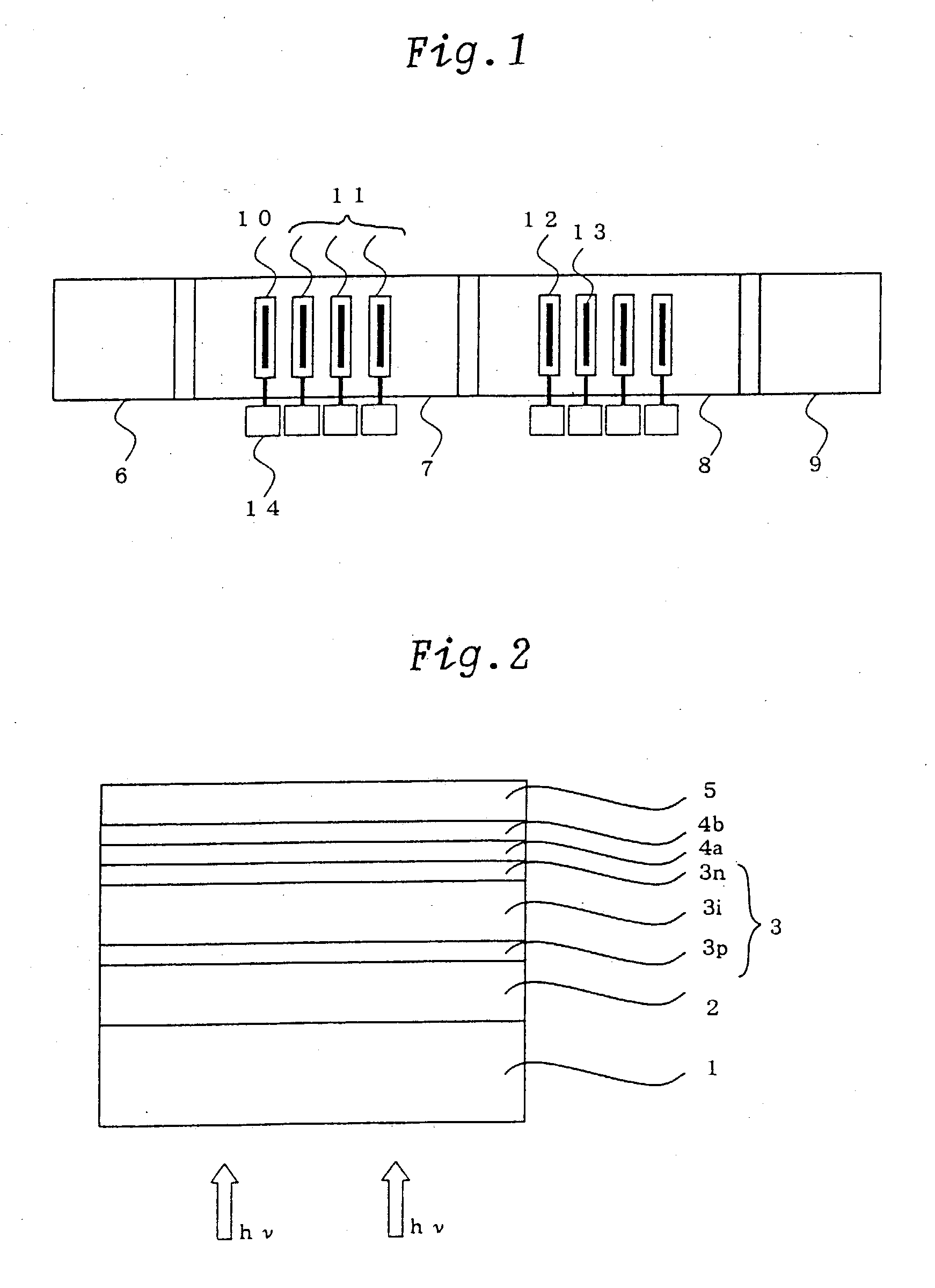

Semiconductor light-emitting device

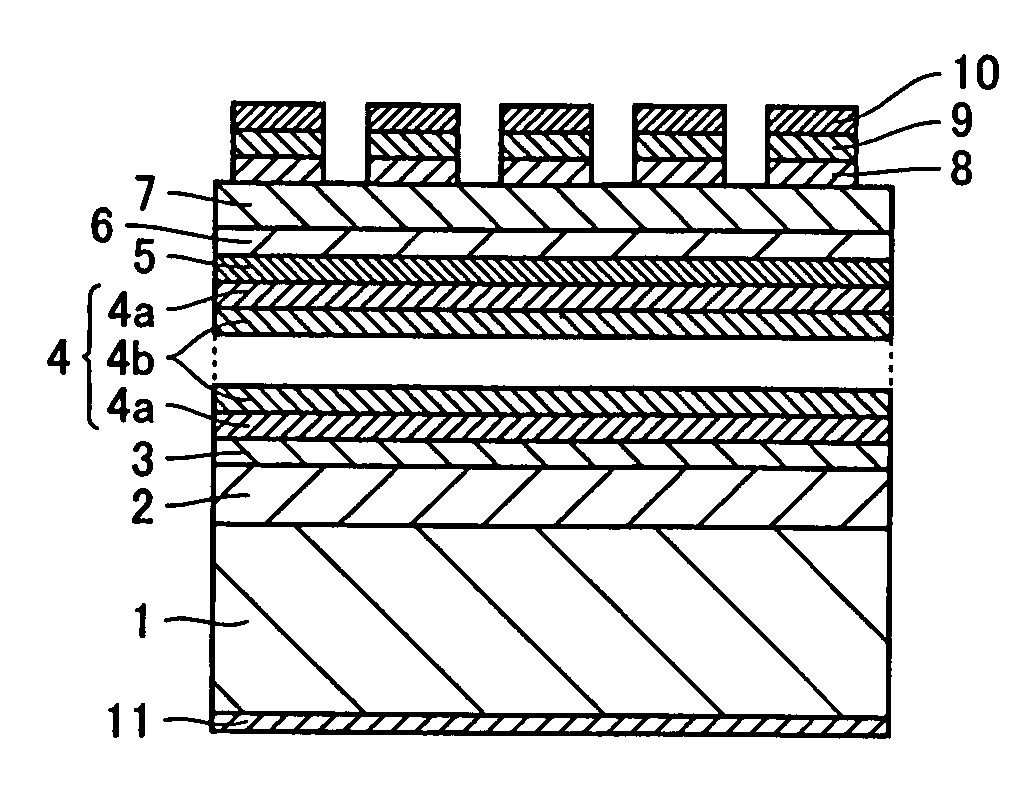

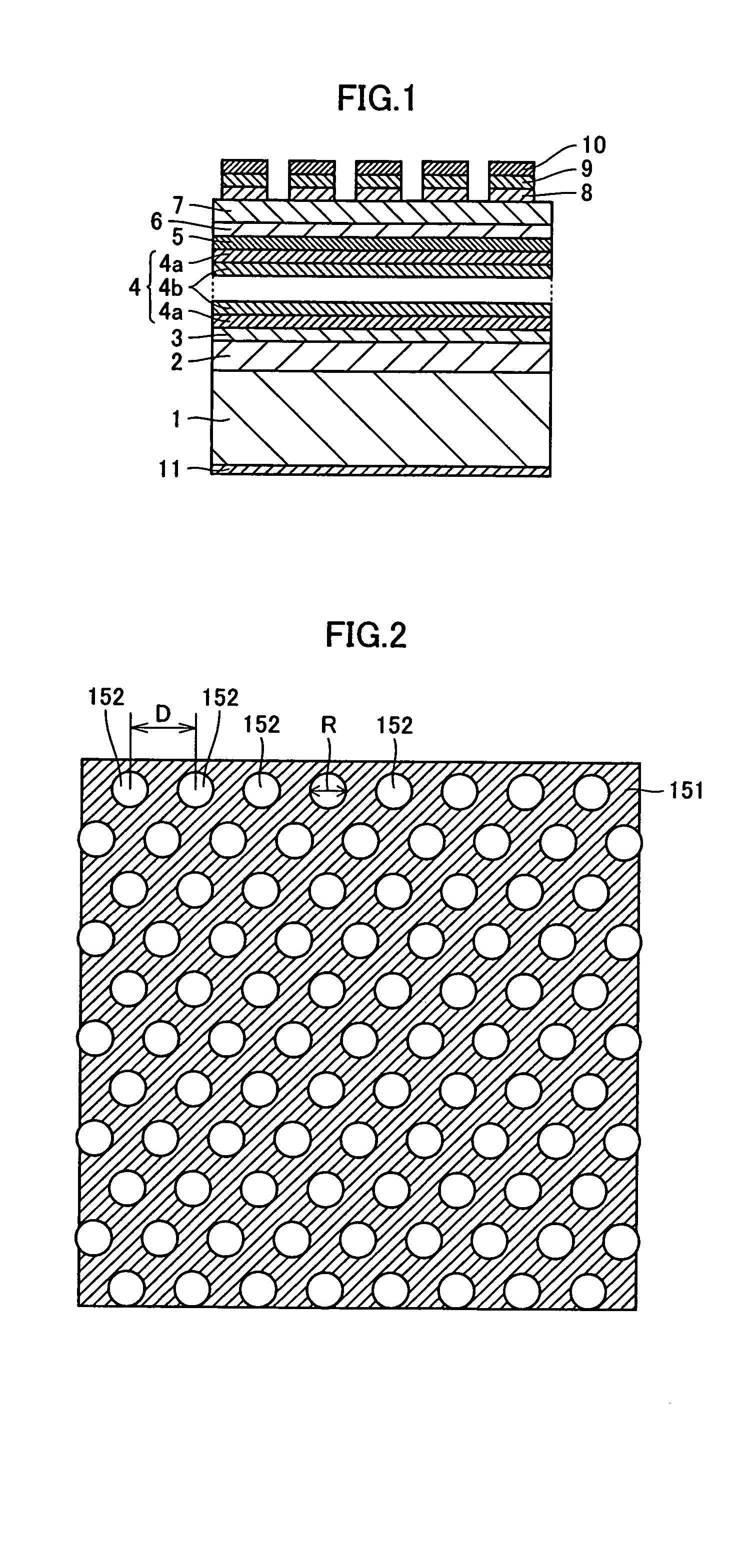

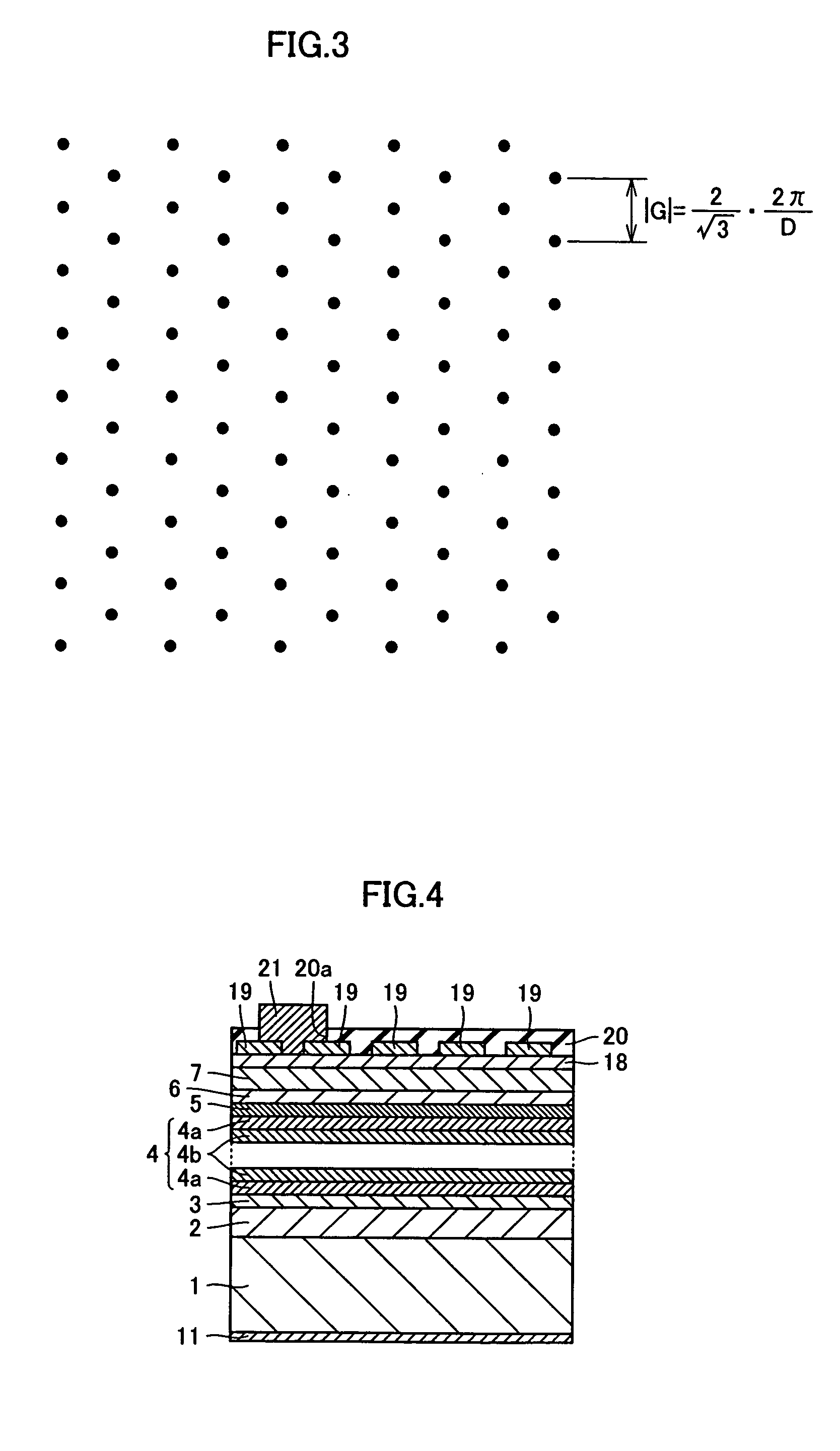

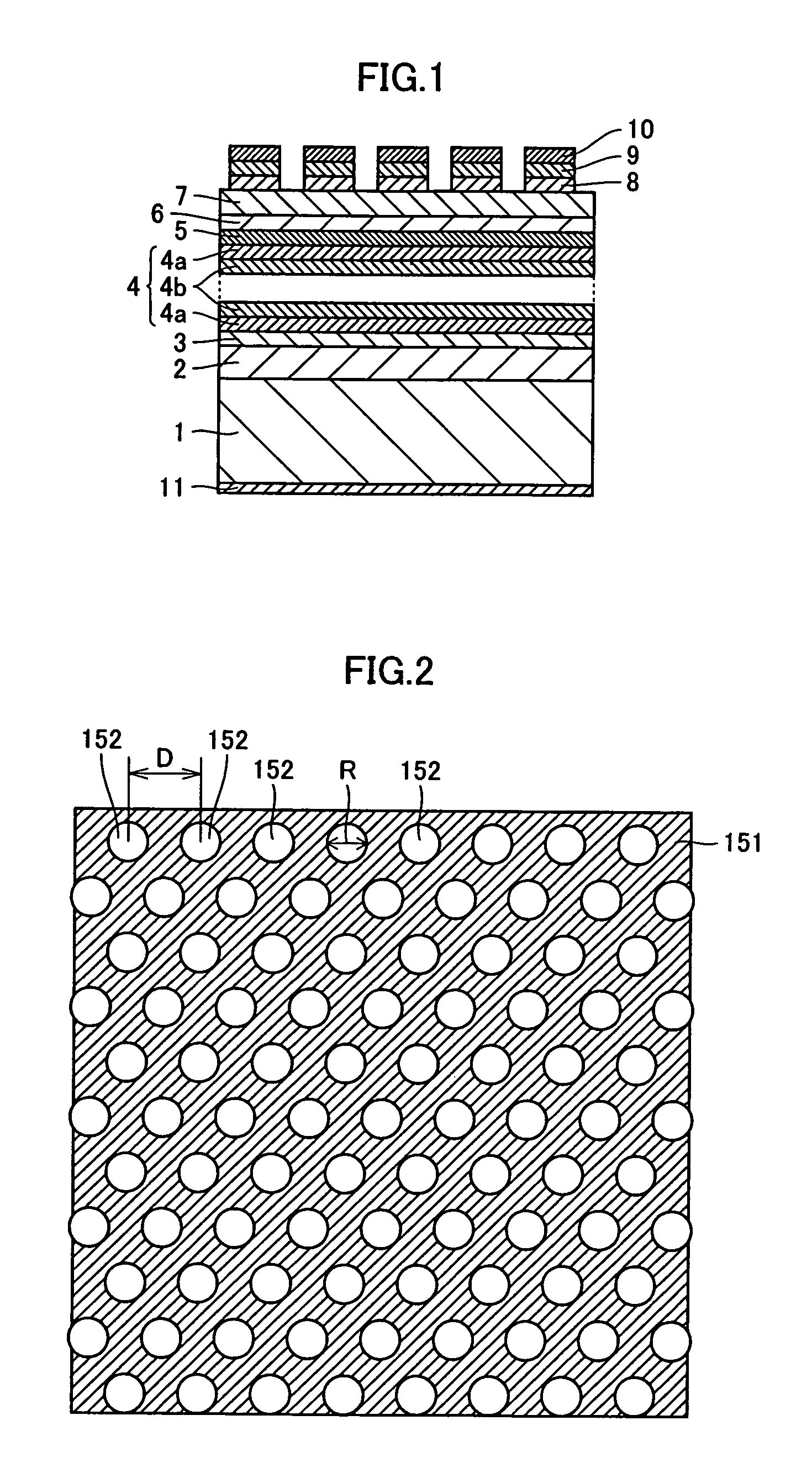

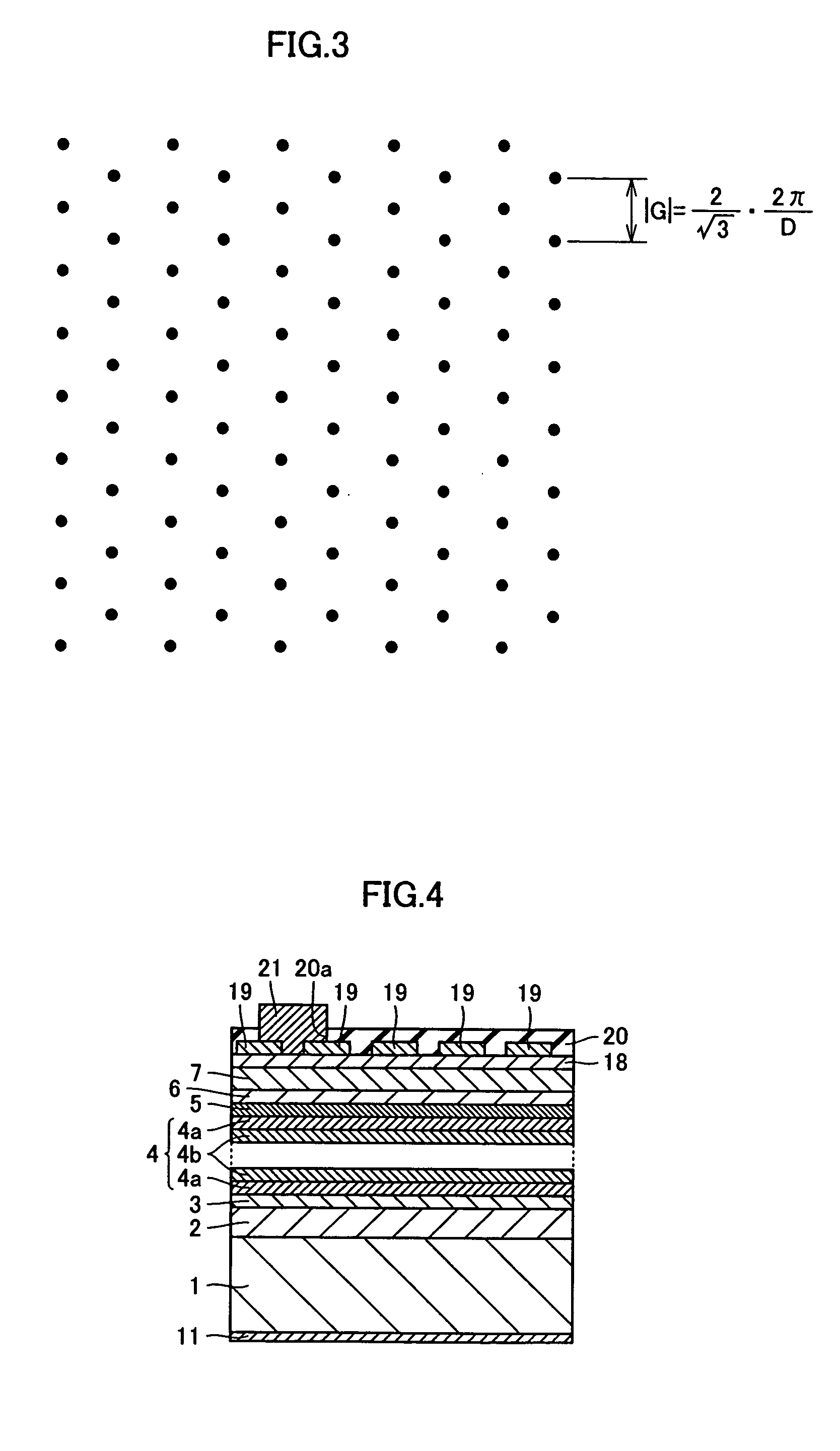

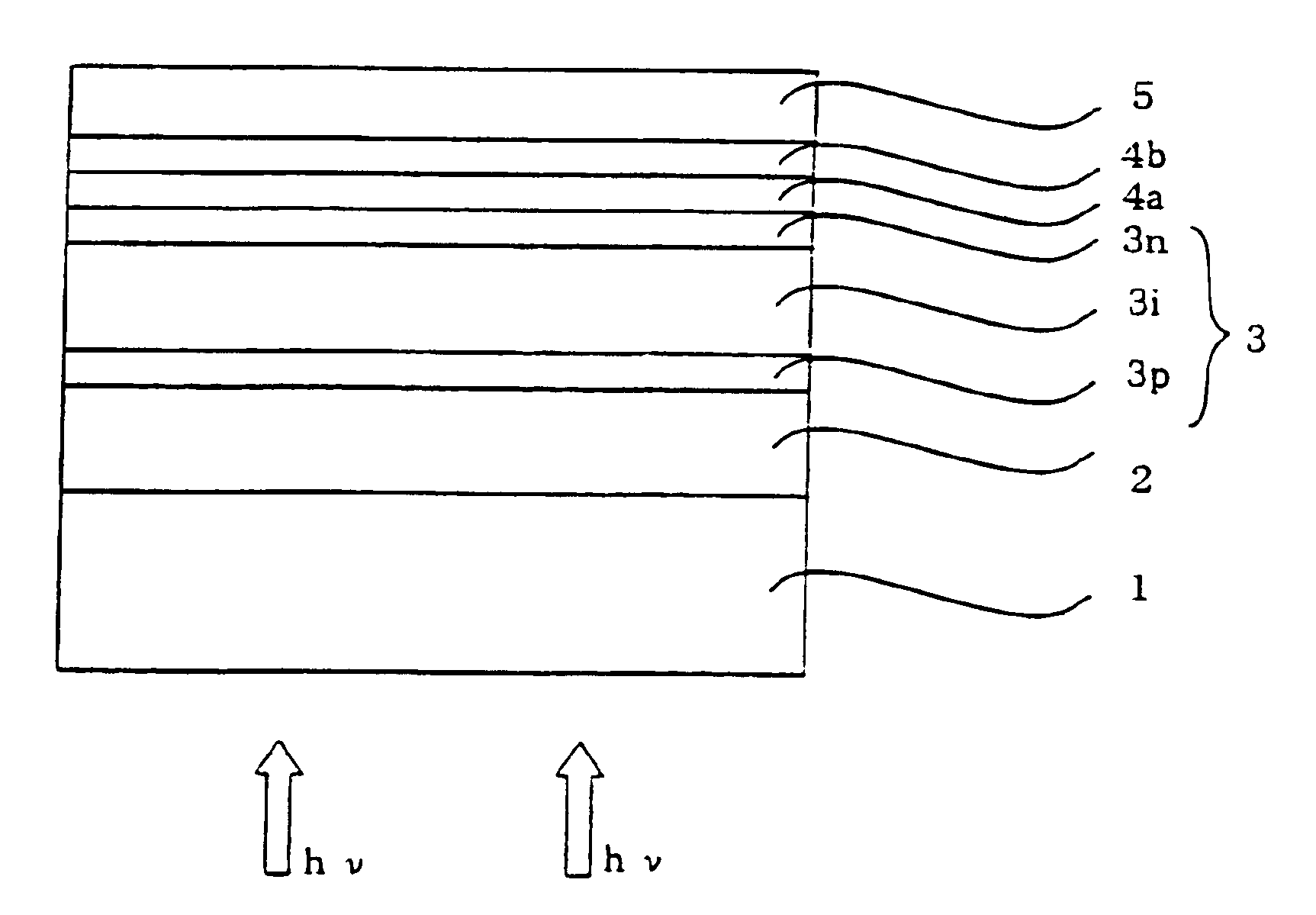

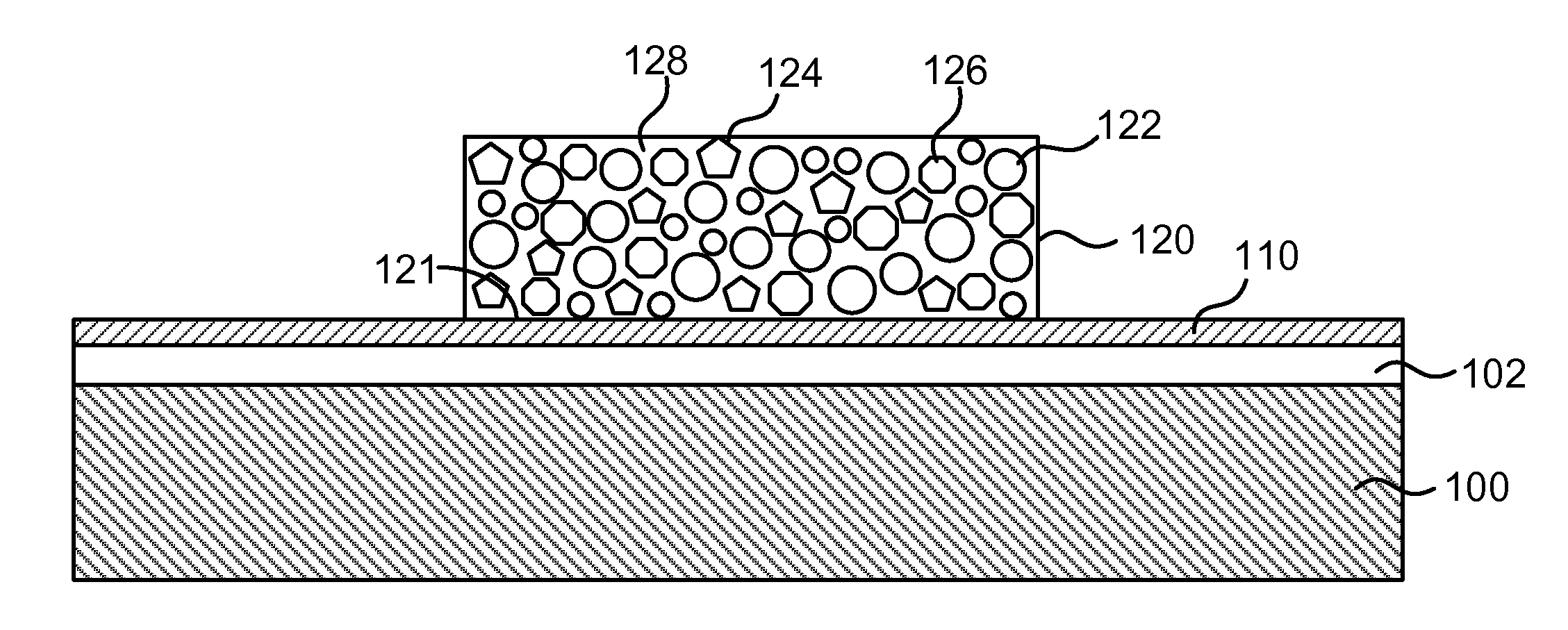

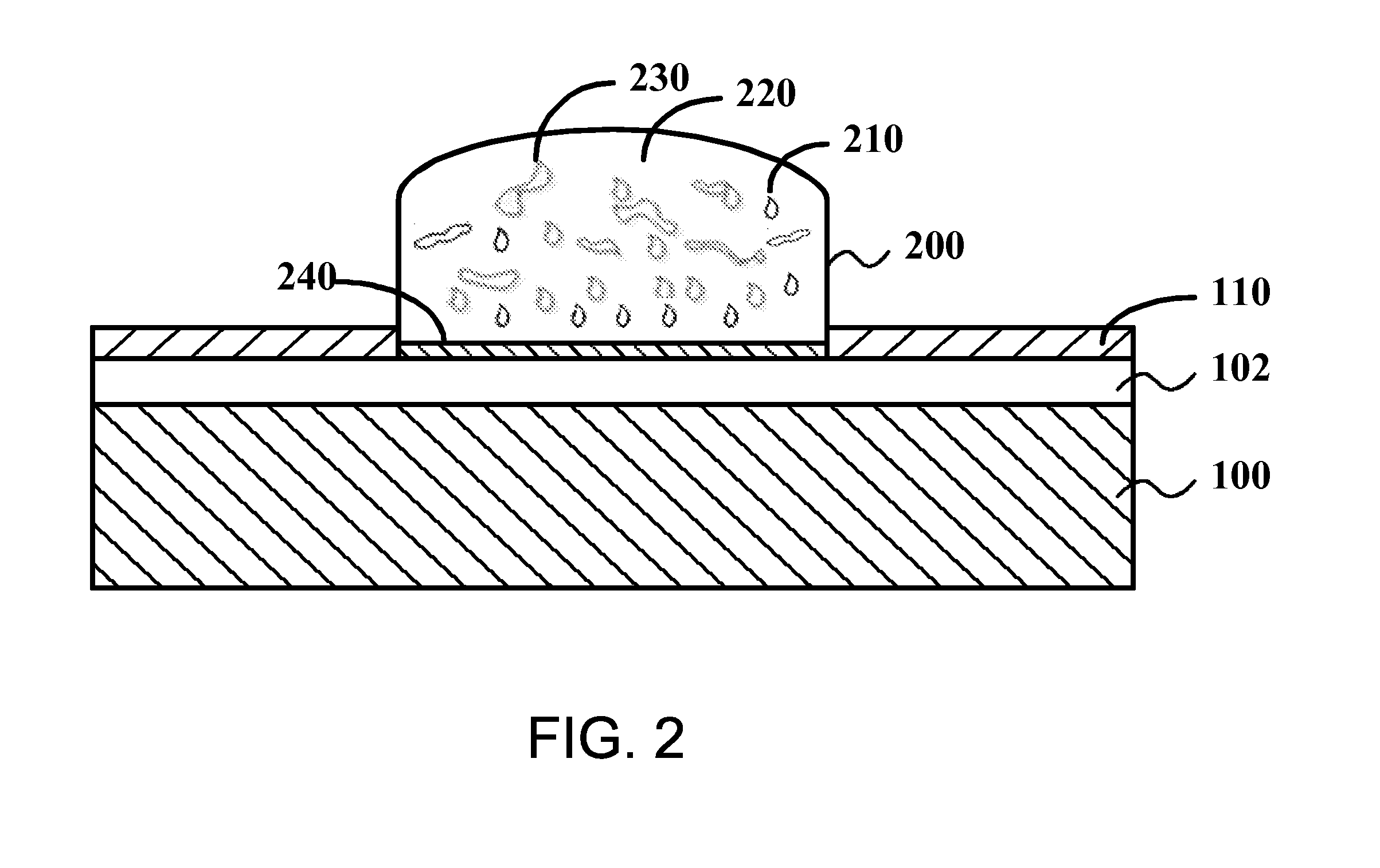

A semiconductor light-emitting device capable of attaining a surface plasmon effect while attaining excellent ohmic contact is provided. This semiconductor light-emitting device comprises a semiconductor layer formed on an emission layer, a first electrode layer formed on the semiconductor layer and a second electrode layer, formed on the first electrode layer, having a periodic structure. The first electrode layer is superior to the second electrode layer in ohmic contact with respect to the semiconductor layer, and the second electrode layer contains a metal exhibiting a higher plasma frequency than the first electrode layer.

Owner:EPISTAR CORP

Semiconductor light emitting device

ActiveUS20060273335A1Good ohmic contactReduce contact resistanceSolid-state devicesSemiconductor devicesOhmic contactLength wave

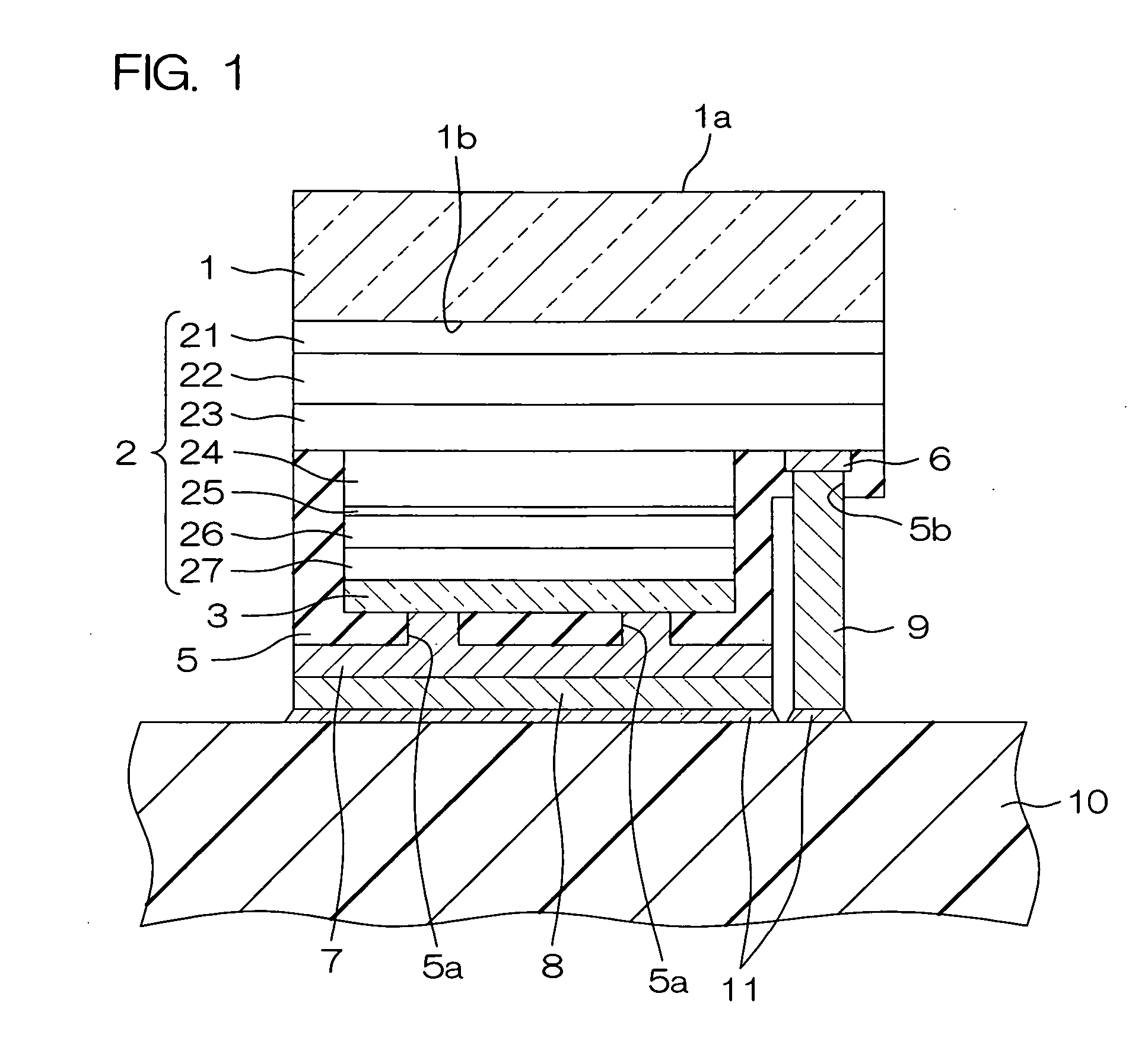

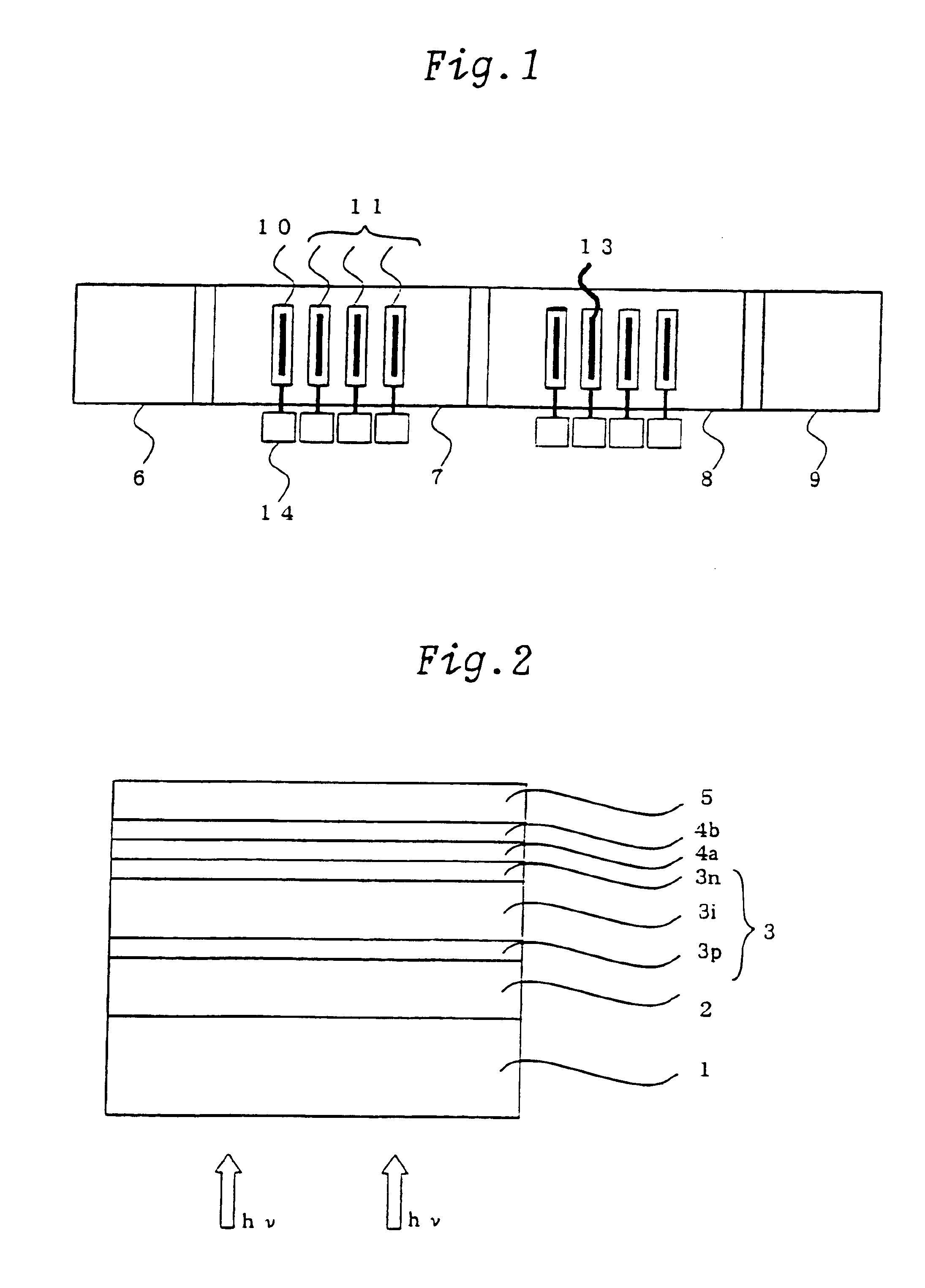

A semiconductor light emitting device includes a semiconductor light emitting portion having a first contact layer of a first conductivity, a second contact layer of a second conductivity and an active layer sandwiched between the first and second contact layers. The device further includes a transparent electrode which substantially entirely covers a surface of the second contact layer in ohmic contact with the surface of the second contact layer and is transparent to a wavelength of light emitted from the semiconductor light emitting portion, and a metal reflection film which is opposed to substantially the entire surface of the transparent electrode and electrically connected to the transparent electrode, and reflects the light emitted from the semiconductor light emitting portion and passing through the transparent electrode toward the semiconductor light emitting portion.

Owner:ROHM CO LTD

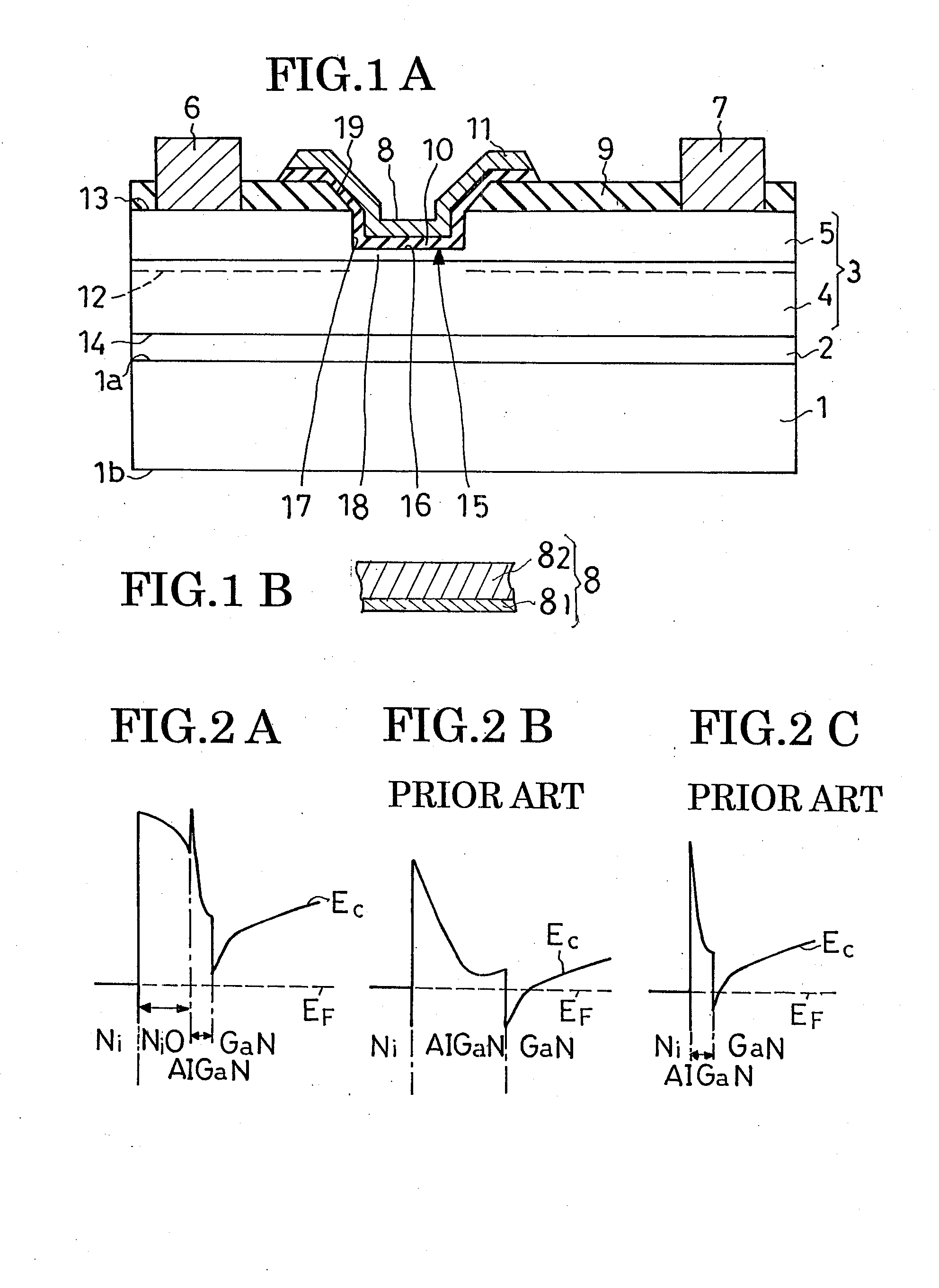

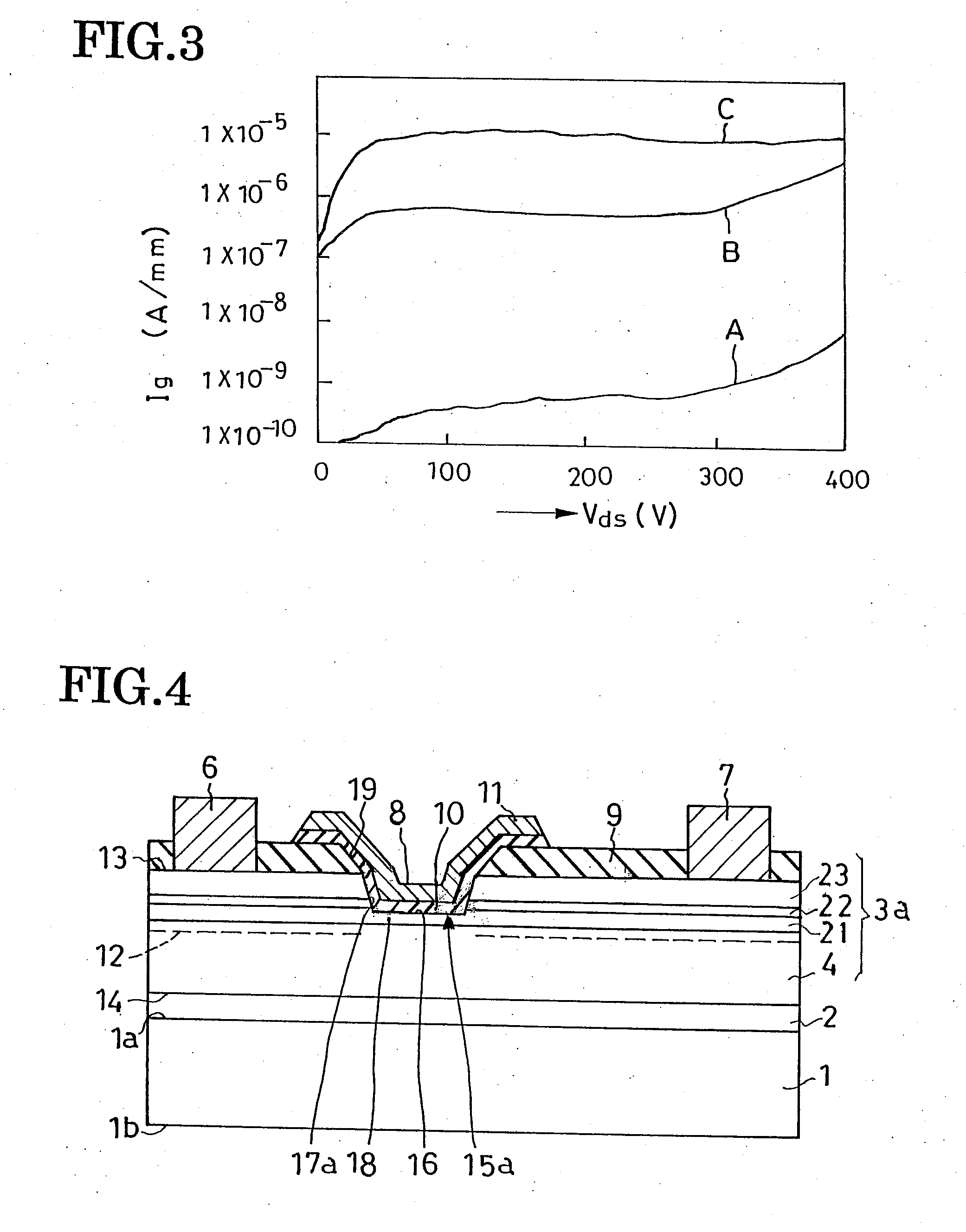

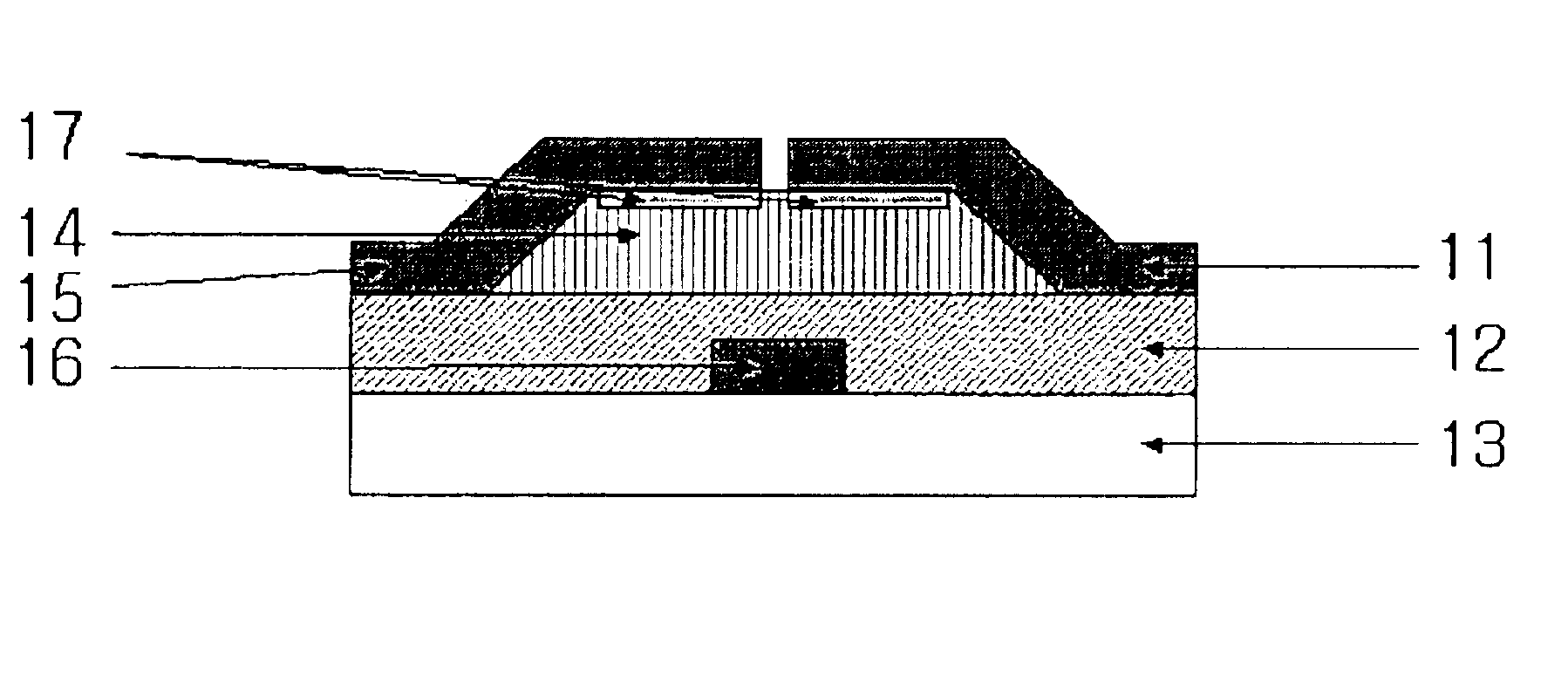

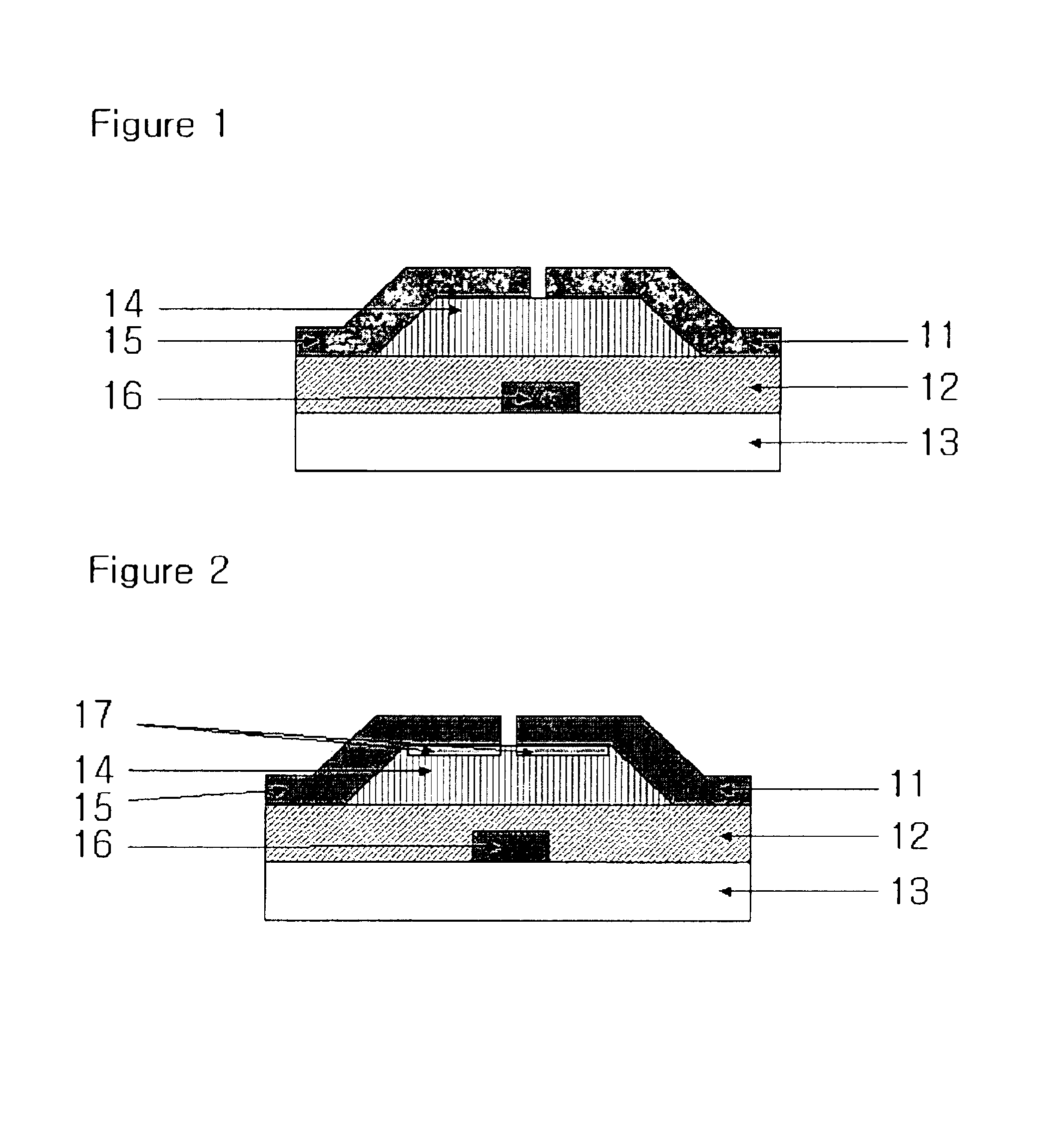

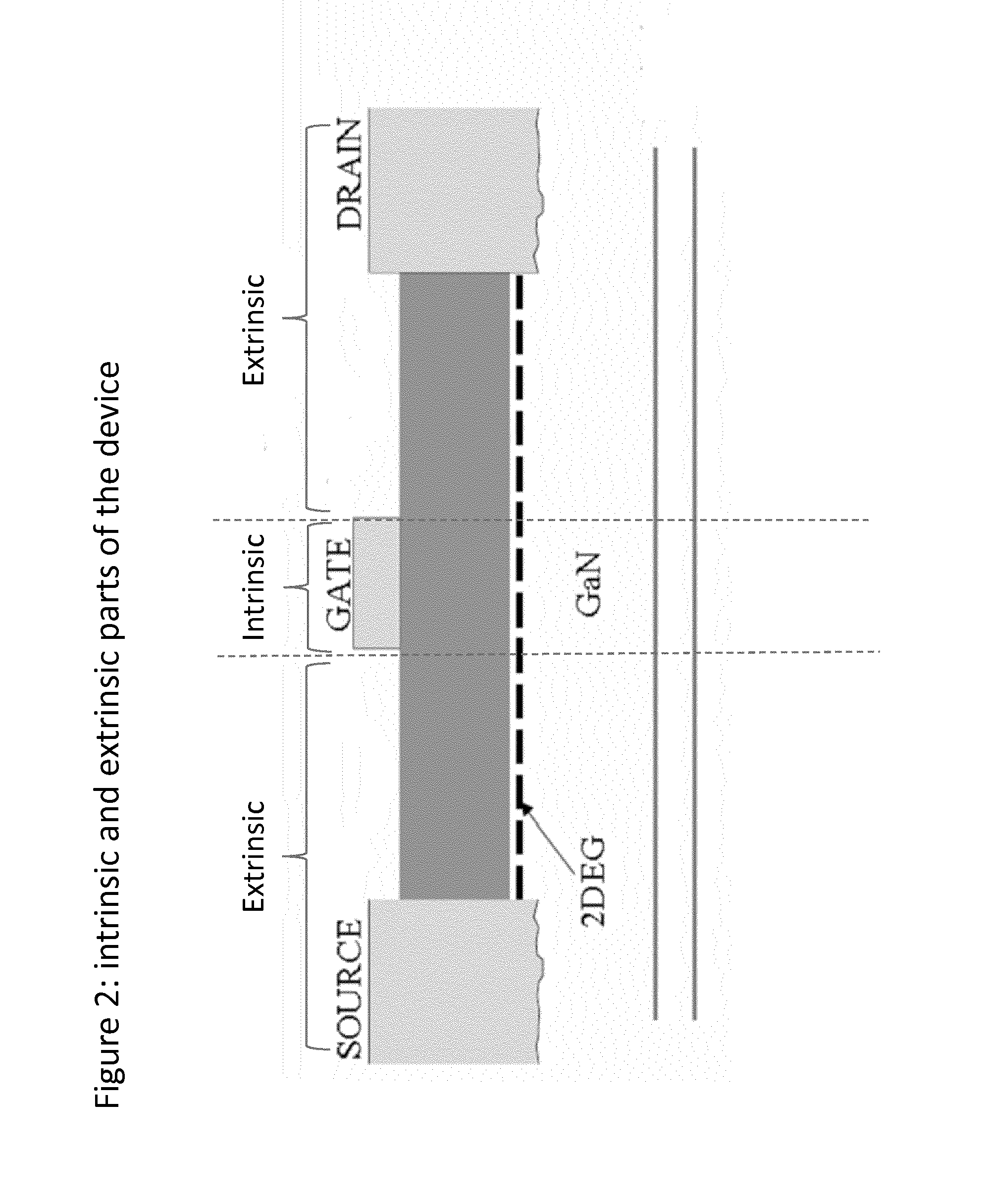

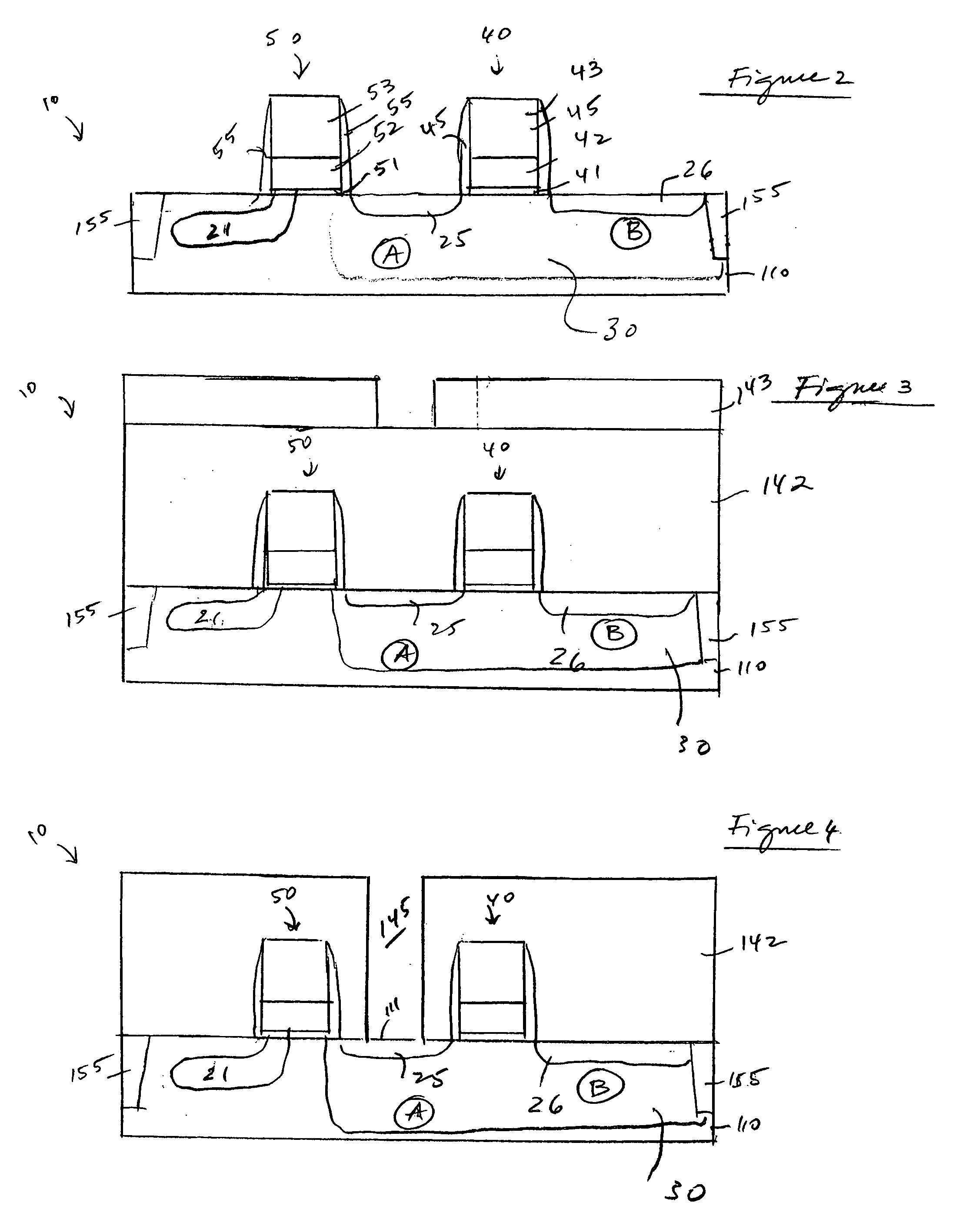

Field-Effect Semiconductor Device, and Method of Fabrication

ActiveUS20090057720A1Reduce leakage currentPreventing current collapseSemiconductor/solid-state device detailsSolid-state devicesHeterojunctionField effect

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film whereby a depletion zone is normally created in the electron gas layer, with a minimum of turn-on resistance and gate leak current.

Owner:SANKEN ELECTRIC CO LTD

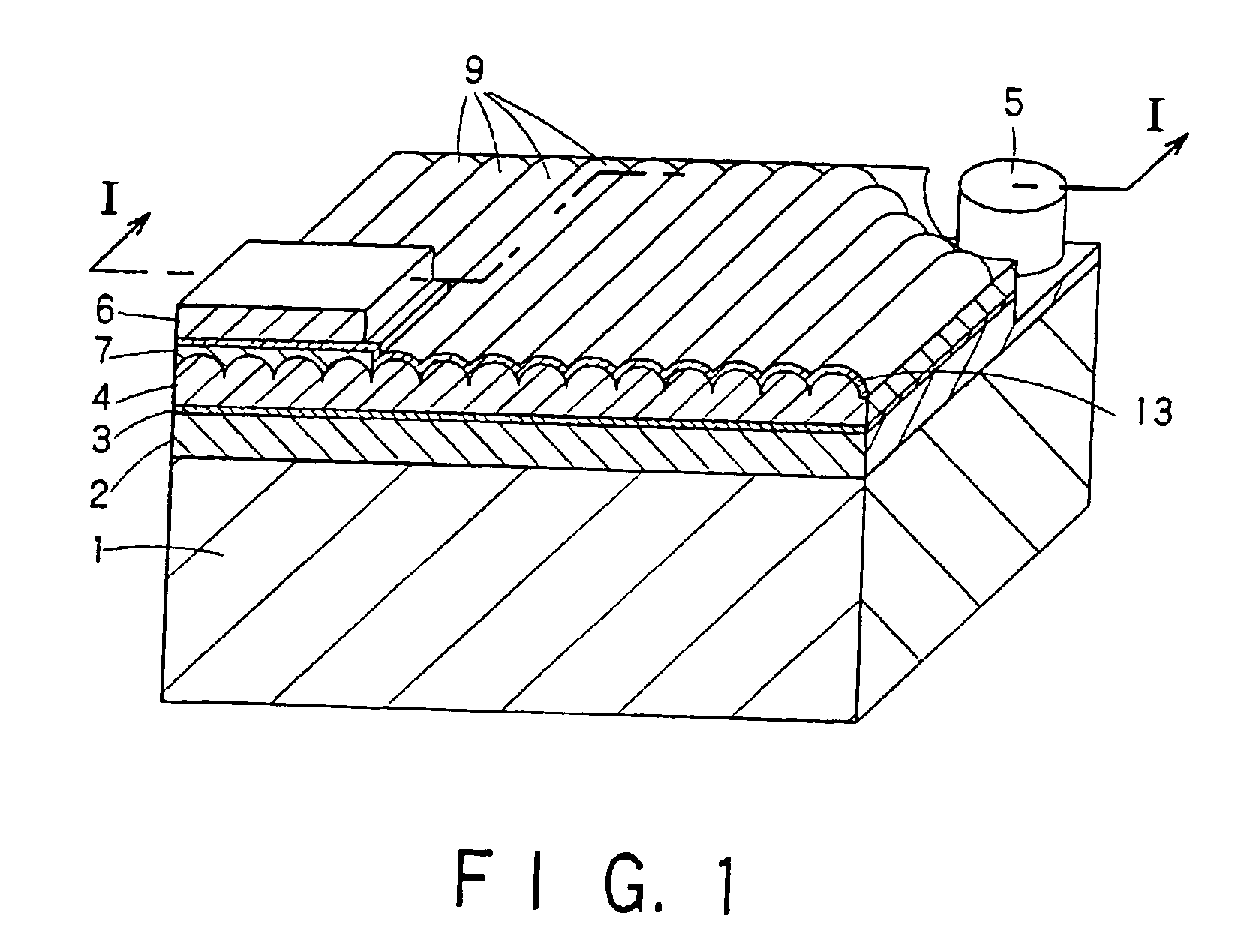

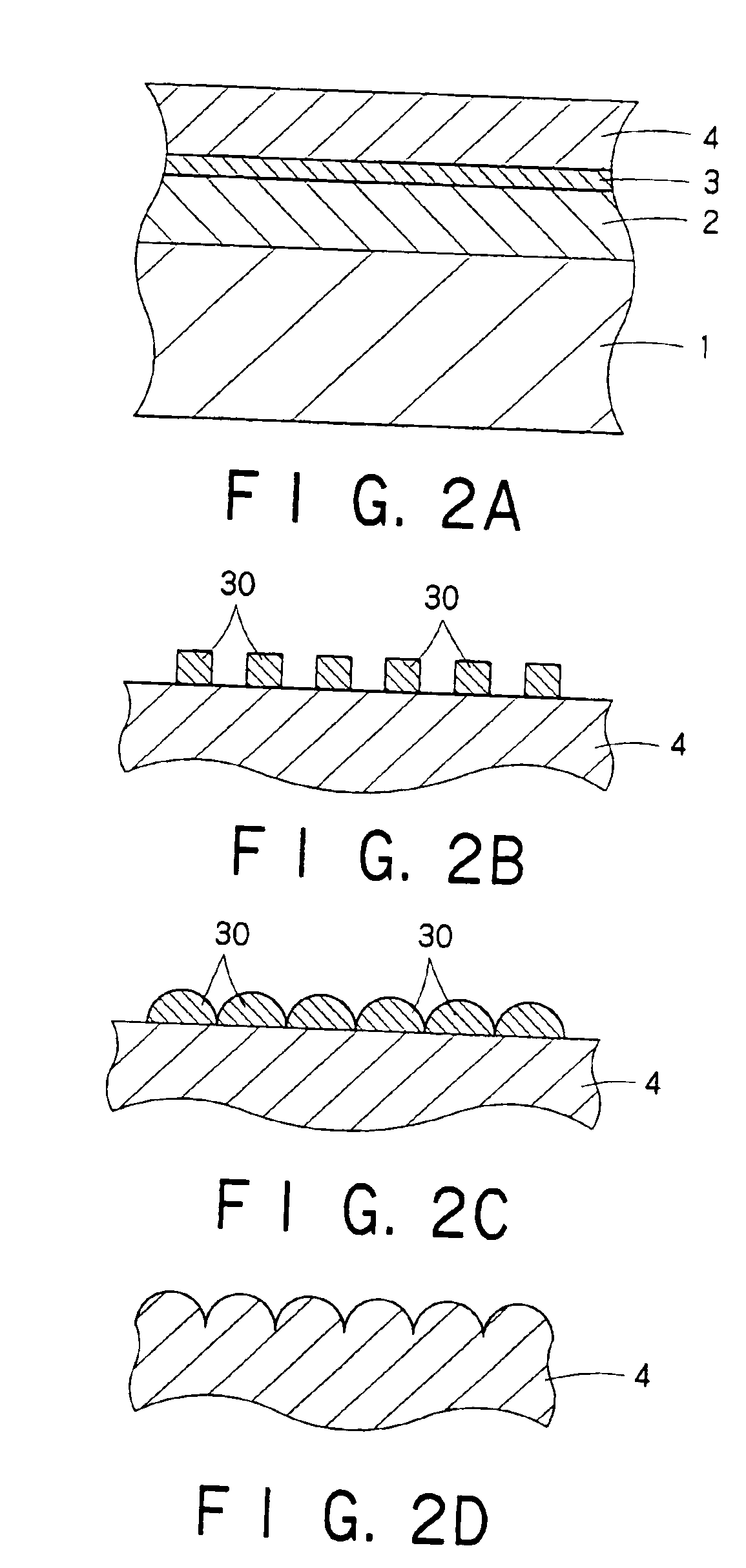

Semiconductor light emitting device and its manufacturing method

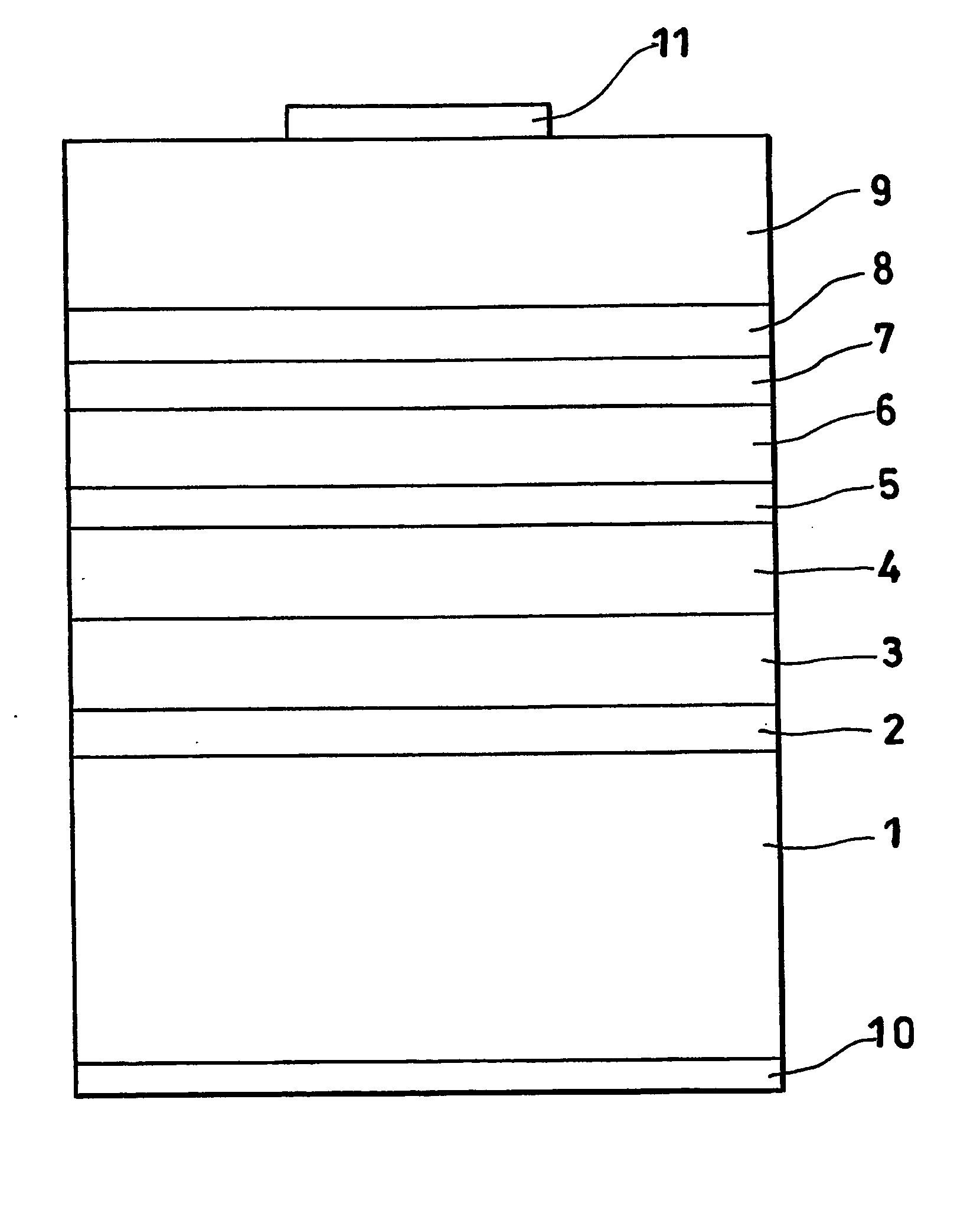

InactiveUS6924163B2Improve lighting efficiencyLow working voltageSolid-state devicesSemiconductor/solid-state device manufacturingMagnesiumOhm

Efficiency of leading out light released from an active layer, i.e. the external quantum efficiency, can be improved remarkably by processing a light lead-out surface to have an embossment. A layer containing a p-type dopant like magnesium (Mg) is deposited near the surface of a p-type GaN layer to diffuse it there, and a p-side electrode is made on the p-type GaN layer after removing the deposited layer. This results in ensuring ohmic contact with the p-side electrode, preventing exfoliation of the electrode and improving the reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

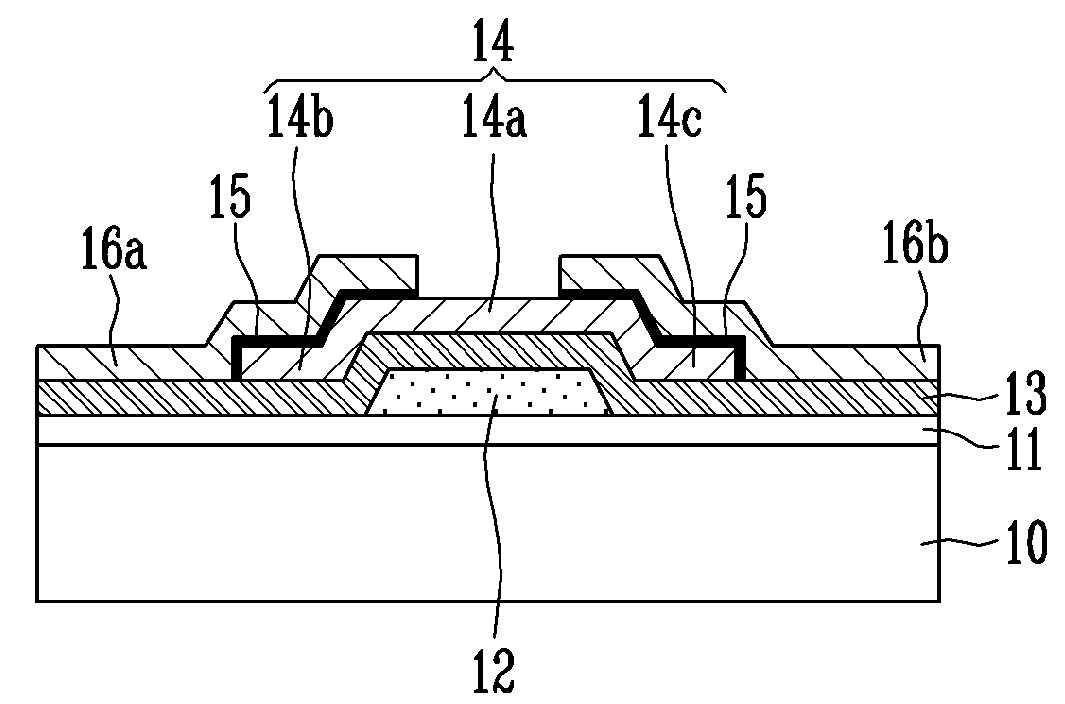

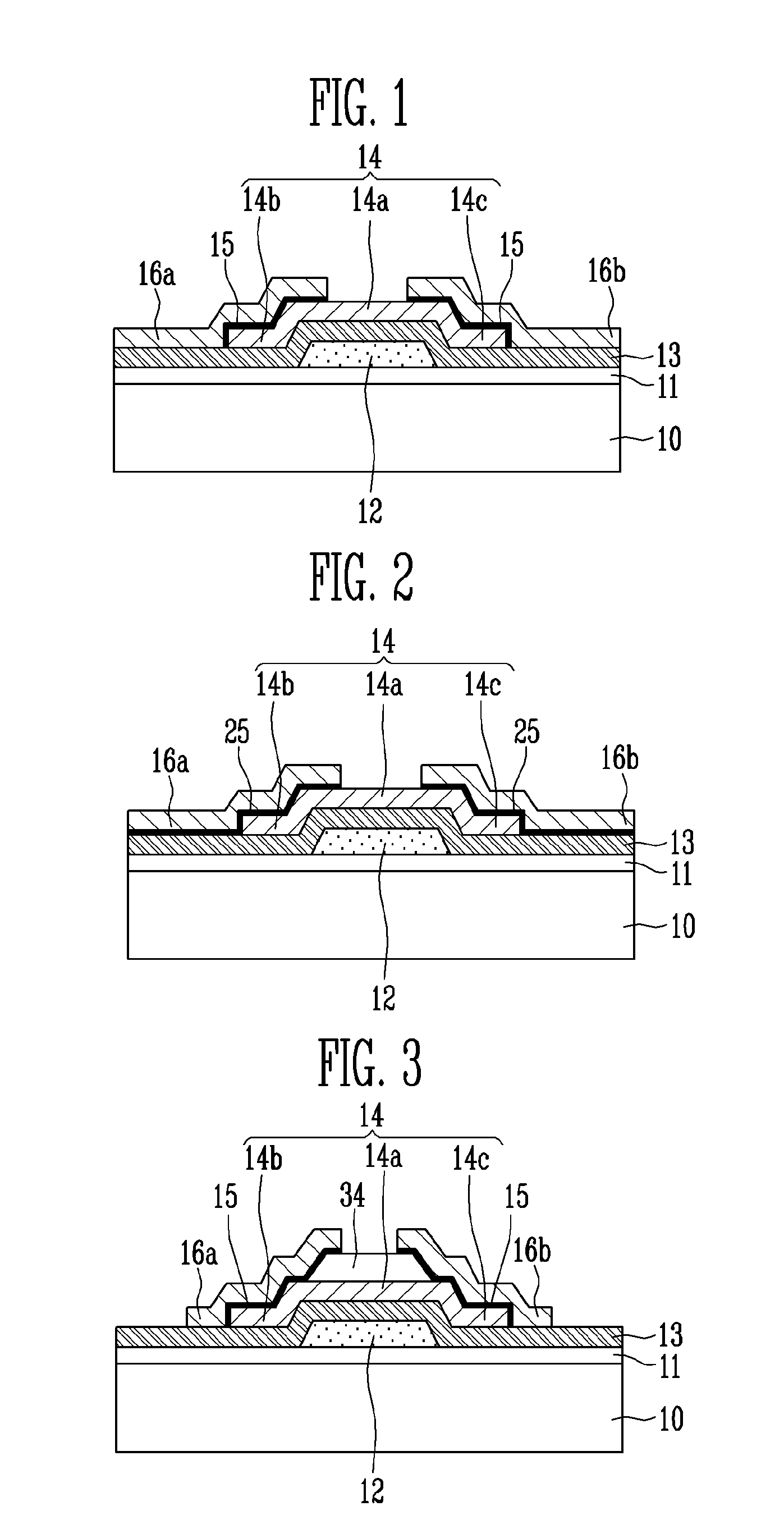

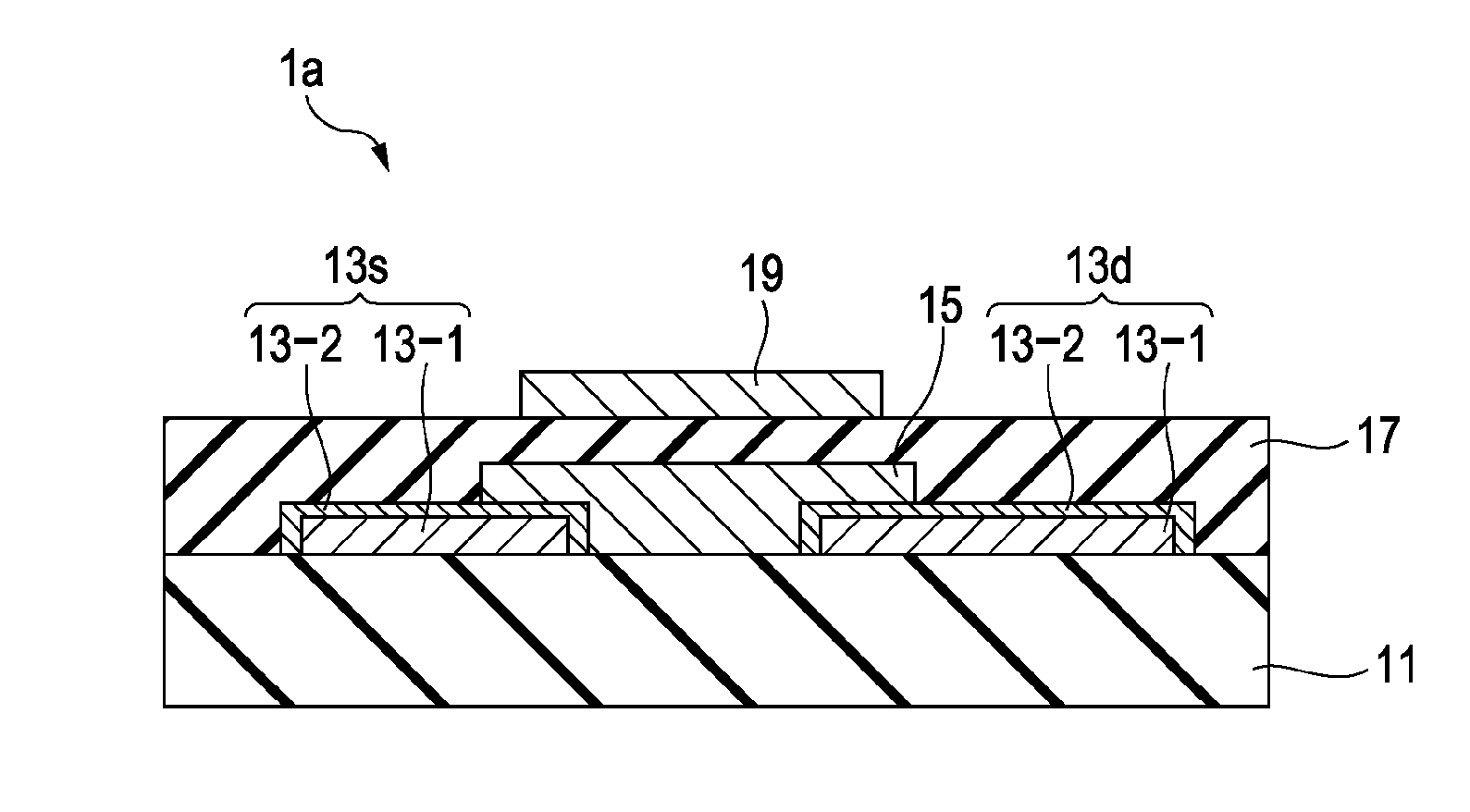

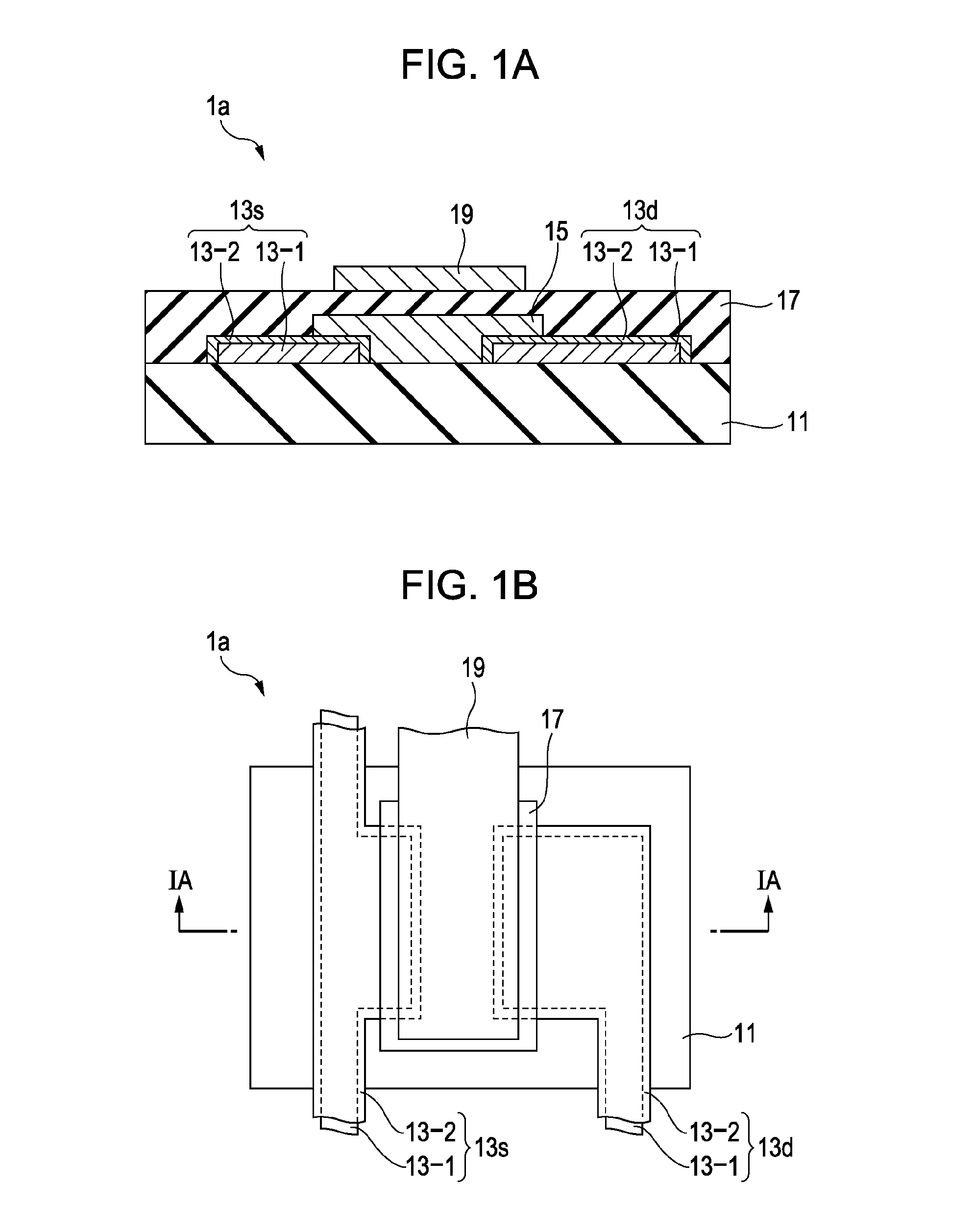

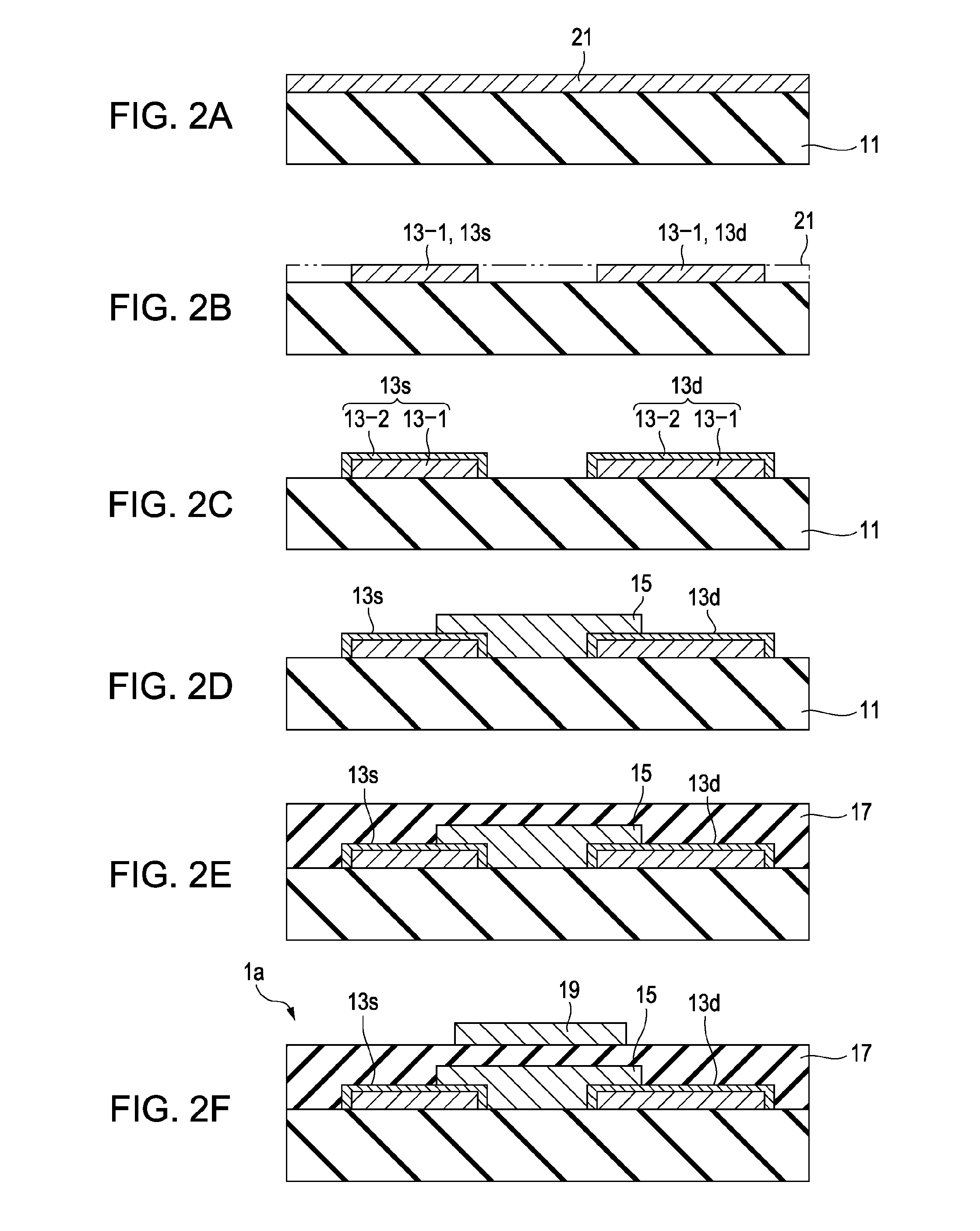

Thin film transistor, method of manufacturing the same, and flat panel display device haviing the same

InactiveUS20090315026A1Good ohmic contactLower Schottky Barrier HeightTransistorNon-linear opticsOhmic contactEngineering

A thin film transistor, a method of manufacturing the same, and a flat panel display device having the same use an oxide semiconductor as an active layer, wherein the thin film transistor includes: an oxide semiconductor layer formed on a substrate and having a channel region, a source region, and a drain region; a gate electrode insulated from the oxide semiconductor layer by a gate insulating layer; an ohmic contact layer formed on the source region and the drain region of the oxide semiconductor layer; and a source electrode and a drain electrode coupled to the source region and the drain region through the ohmic contact layer, the ohmic contact layer being formed of a metal having a lower work function lower than work functions of the source electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

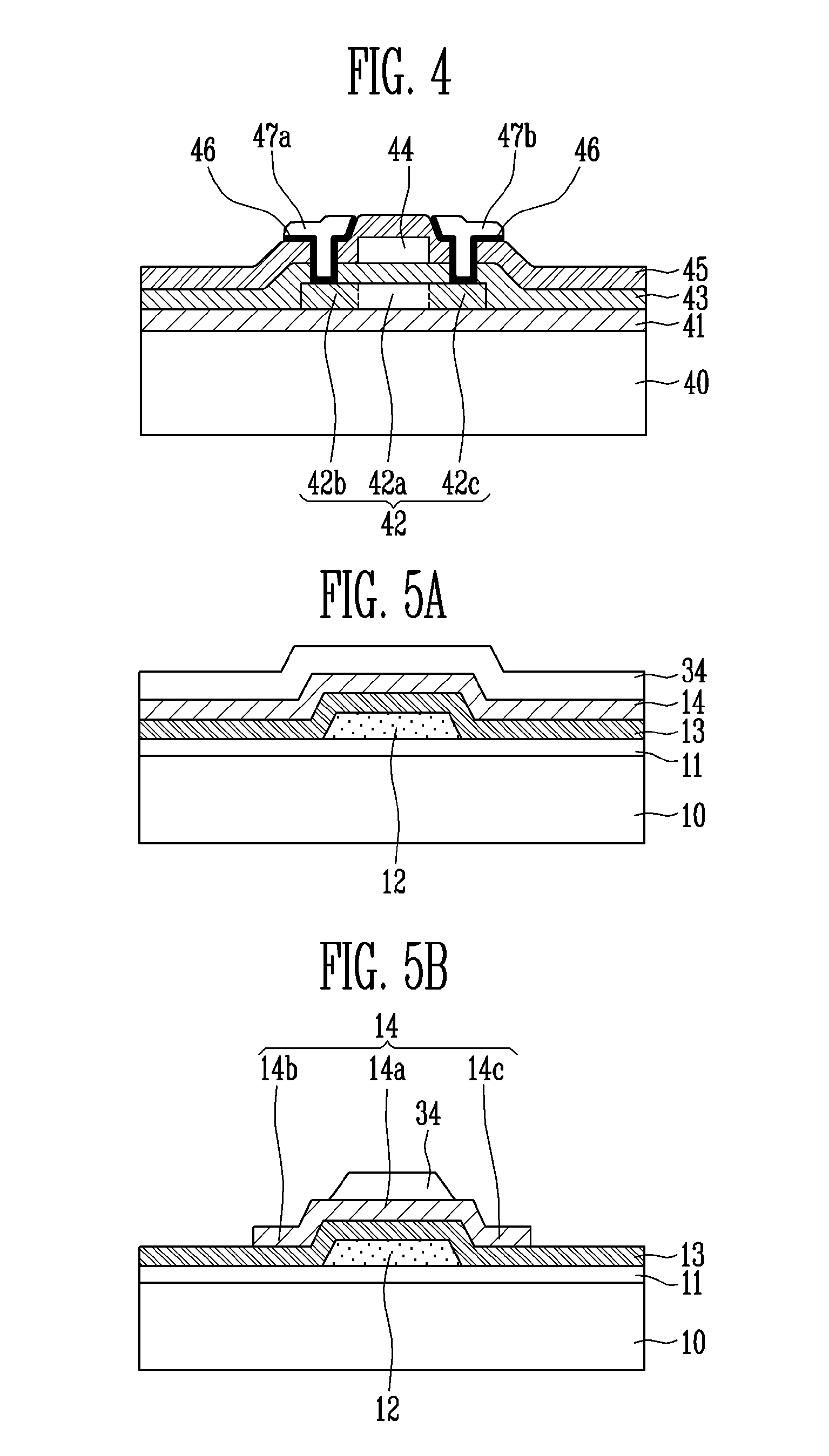

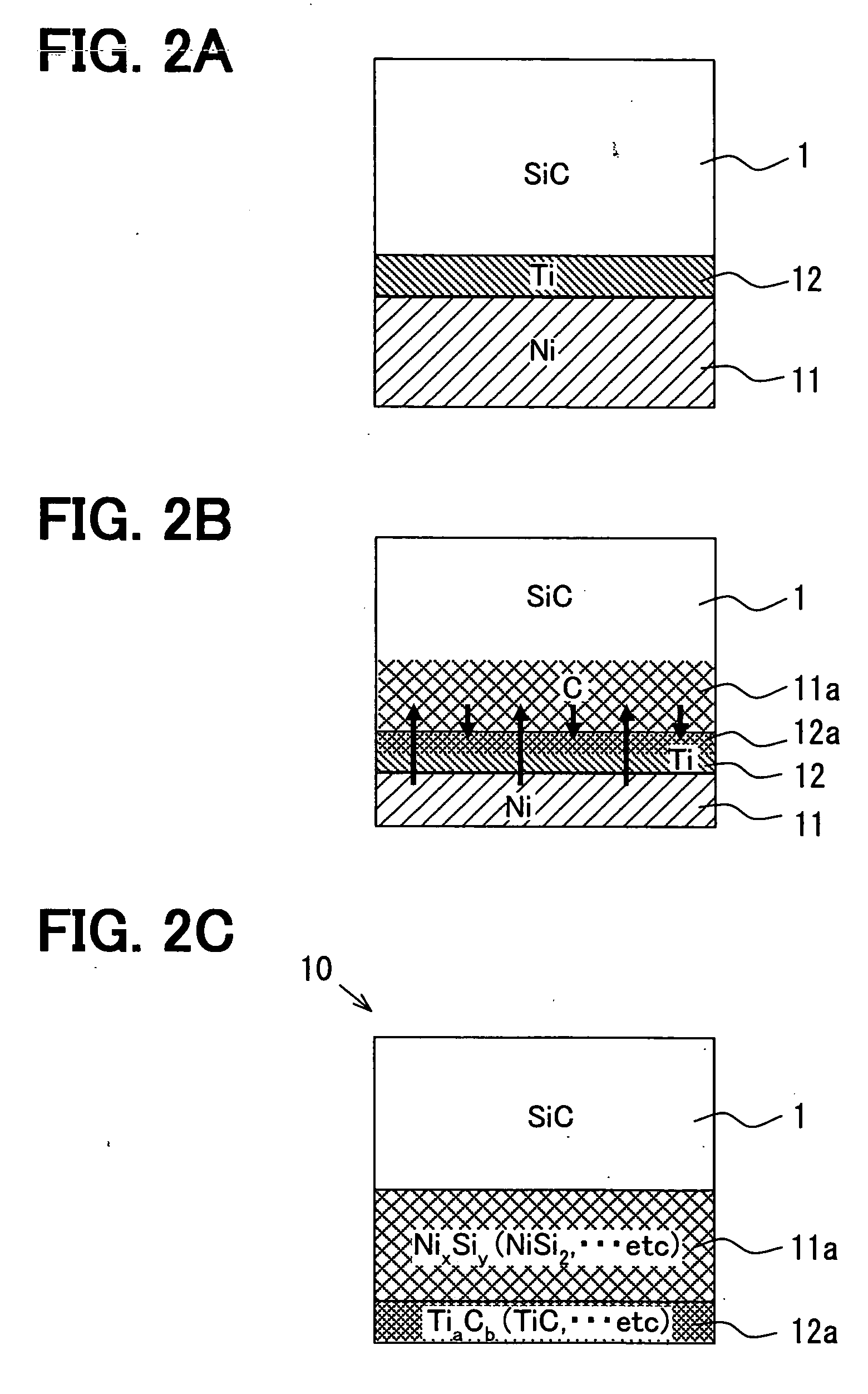

Semiconductor device having SiC substrate and method for manufacturing the same

InactiveUS20060273323A1Good ohmic contactHigh quality surface metallizationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialOhmic contact

A semiconductor device includes: a SiC substrate; a silicide layer disposed on the SiC substrate; and a carbide layer disposed on the silicide layer. The silicide layer includes a first metal, and the carbide layer includes a second metal. The first metal is Ni or Ni alloy, and the second metal is Ti, Ta or W. The device provides excellent ohmic contact and high quality surface metallization construction.

Owner:DENSO CORP +1

Composition and preparation method of silicon solar battery electrode slurry

InactiveCN101651155AEnhanced ohmic contactReduced series resistanceRenewable energy productsSemiconductor devicesBack surface fieldOhm

The invention relates to composition and a preparation method of silicon solar battery electrode slurry. The silicon solar battery electrode slurry comprises silicon solar battery sunny slope grid electrode silver slurry, back surface field silver-aluminium slurry and back surface field aluminium slurry which are used for preparing an ohm contact layer containing silicon alloy powder. In the invention, silver powder, aluminium powder, a simple substance element and the silicon alloy powder are used as raw materials, and an organic bond and an inorganic bond are used as accessories, and after the raw materials and the accessories are evenly mixed, a three-roller rolling mill is utilized to roll the mixture into the silicon solar battery electrode slurry of which the fineness is 20.0-25.0mum and the viscosity is 20000-40000mpa.s.

Owner:谭富彬

Organic thin film transistor

InactiveUS6953947B2Good electrical contactGood ohmic contactOrganic chemistrySolid-state devicesOrganic layerTransistor

An organic transistor including an organic layer is provided. The organic layer includes at least one compound represented by the Chemical Formula I.

Owner:LG CHEM LTD

Graphene/copper nanowire composite electric-conducting material and preparation method thereof

ActiveCN102176338AImprove fill factorSimple processMetal/alloy conductorsCarbon-silicon compound conductorsDiameter ratioConductive materials

The invention provides a composite electric-conducting material, in particular a graphene / copper nanowire composite electric-conducting material which comprises graphene, copper nanowires and a bonding agent, wherein the weight of the copper nanowires accounts for 1-99% of the weight of the graphene, and the weight of the bonding agent accounts for 1-50% of the total weight of the graphene / copper nanowires; the graphene is divided into 1-20 layers and has the area of 1-2500 mum<2>; and the length / diameter ratio of the copper nanowires is 10-10000. The invention further provides a preparation method of the composite electric-conducting material and a back electrode containing the composite electric-conducting material. The composite electric-conducting material provided by the invention has the advantages of low cost and excellent electric performance and can be produced in a large scale.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

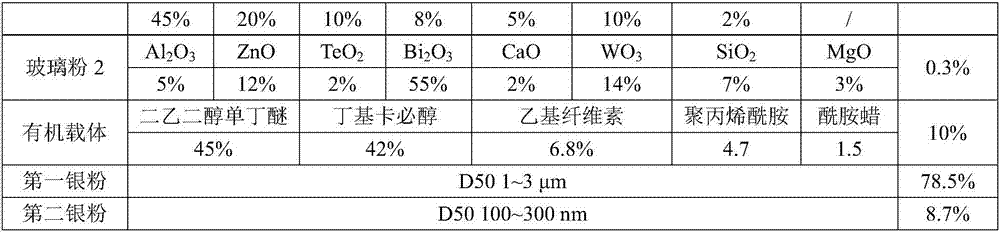

Leadless electronic slurry composition for solar silicon photovoltaic cell and preparation method thereof

InactiveCN101345263AHigh electrical conductivityRefined nanocrystalline structureFinal product manufactureSemiconductor devicesAdhesiveSlurry

The invention discloses a compounding and a preparation method for lead-free electronic slurry used for a solar silicon photocell; according to the mass percentage, the slurry is obtained by preparing 70 to 75 percent of aluminium powders, 20 to 25 percent of organic adhesive, 1 to 5 percent of inorganic glass powders and 1 to 5 percent of additives; the aluminium powder is ball-shaped aluminium powder with the surface covered by an aluminium nitride protection layer, with the purity not less than 99.9 percent and the average grain size of 2 to 6 microns; simultaneously, organic adhesives consisting of ethyl cellulose, resin, hexadecanol, diethyleneglycol monomethyl ether, diethyleneglycol monobutyl ether, terpineol and n-butyl alcohol are added into the aluminium powder; the inorganic glass powder is silicon dioxide, boracic acid, alumina, antimony oxide and zirconia; the additive consists of Span and pump oil. The product prepared by the method of the invention has no dust generation or aluminium peeling phenomenon and achieves the requirement of no lead and environmental protection.

Owner:NANTONG UNIVERSITY

Semiconductor light-emitting device

A semiconductor light-emitting device capable of attaining a surface plasmon effect while attaining excellent ohmic contact is provided. This semiconductor light-emitting device comprises a semiconductor layer formed on an emission layer, a first electrode layer formed on the semiconductor layer and a second electrode layer, formed on the first electrode layer, having a periodic structure. The first electrode layer is superior to the second electrode layer in ohmic contact with respect to the semiconductor layer, and the second electrode layer contains a metal exhibiting a higher plasma frequency than the first electrode layer.

Owner:EPISTAR CORP

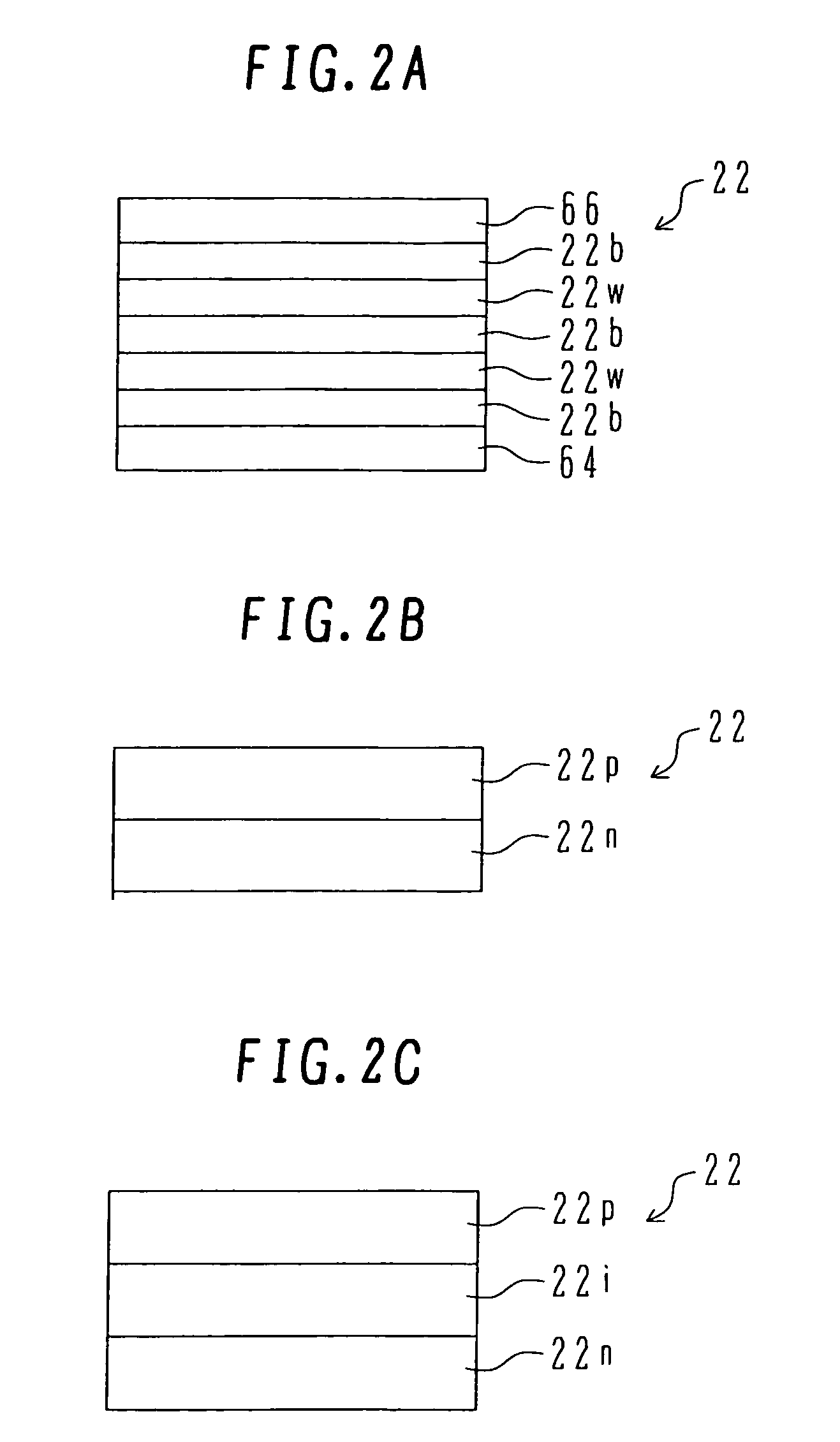

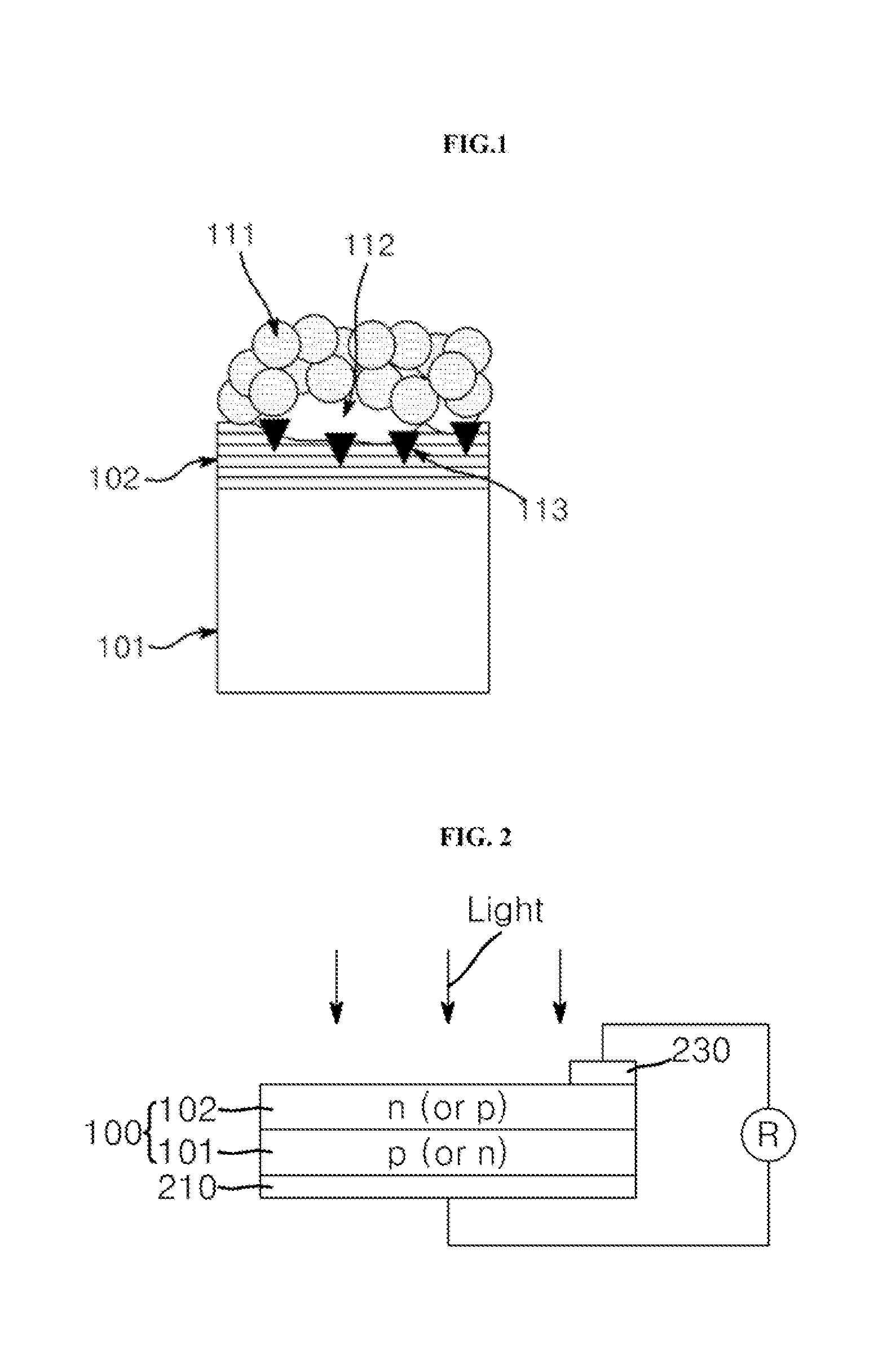

Thin-film solar cell and manufacture method therefor

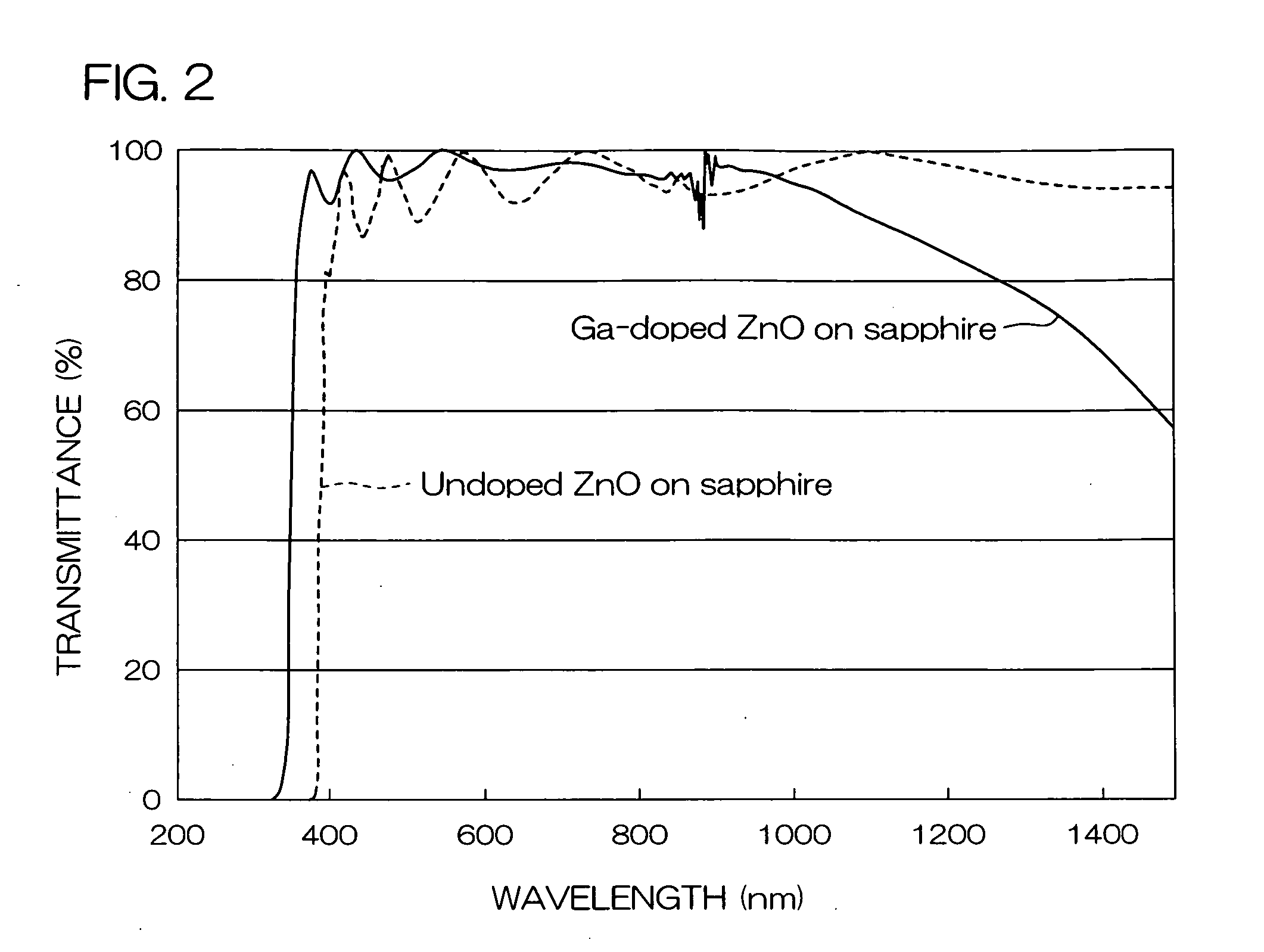

InactiveUS6822158B2Improve film qualityGood ohmic contactCellsVacuum evaporation coatingThin membraneEngineering

A thin-film solar cell including a transparent electrode layer, a semiconductor photovoltaic conversion layer, a rear transparent electrode layer and a rear reflective metal layer, said layers being formed in this order on a transparent substrate, wherein the rear transparent electrode has a two-layer structure of an ITO or ZnO:Ga layer and a ZnO:Al layer formed in this order on the semiconductor photovoltaic conversion layer.

Owner:SHARP KK

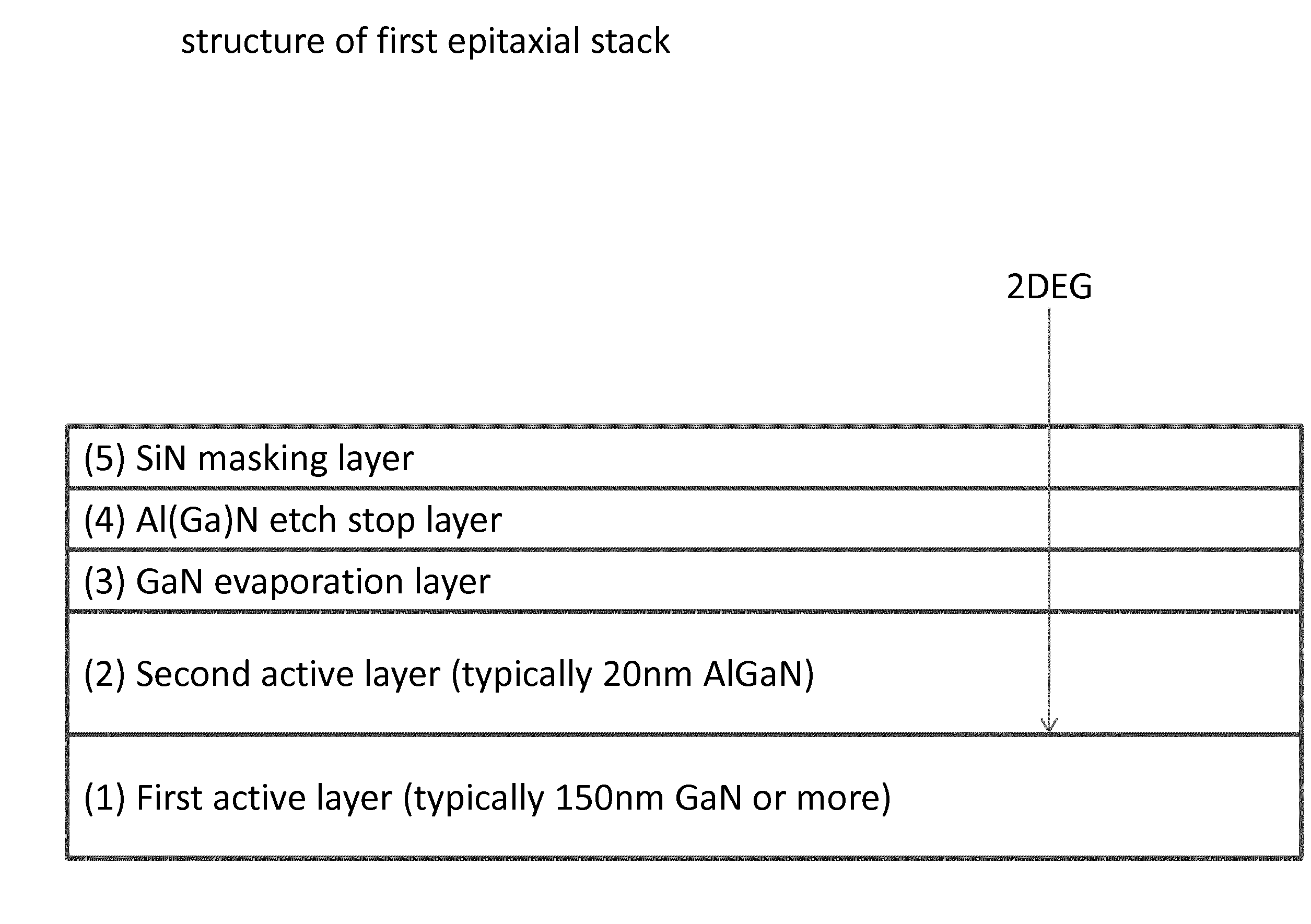

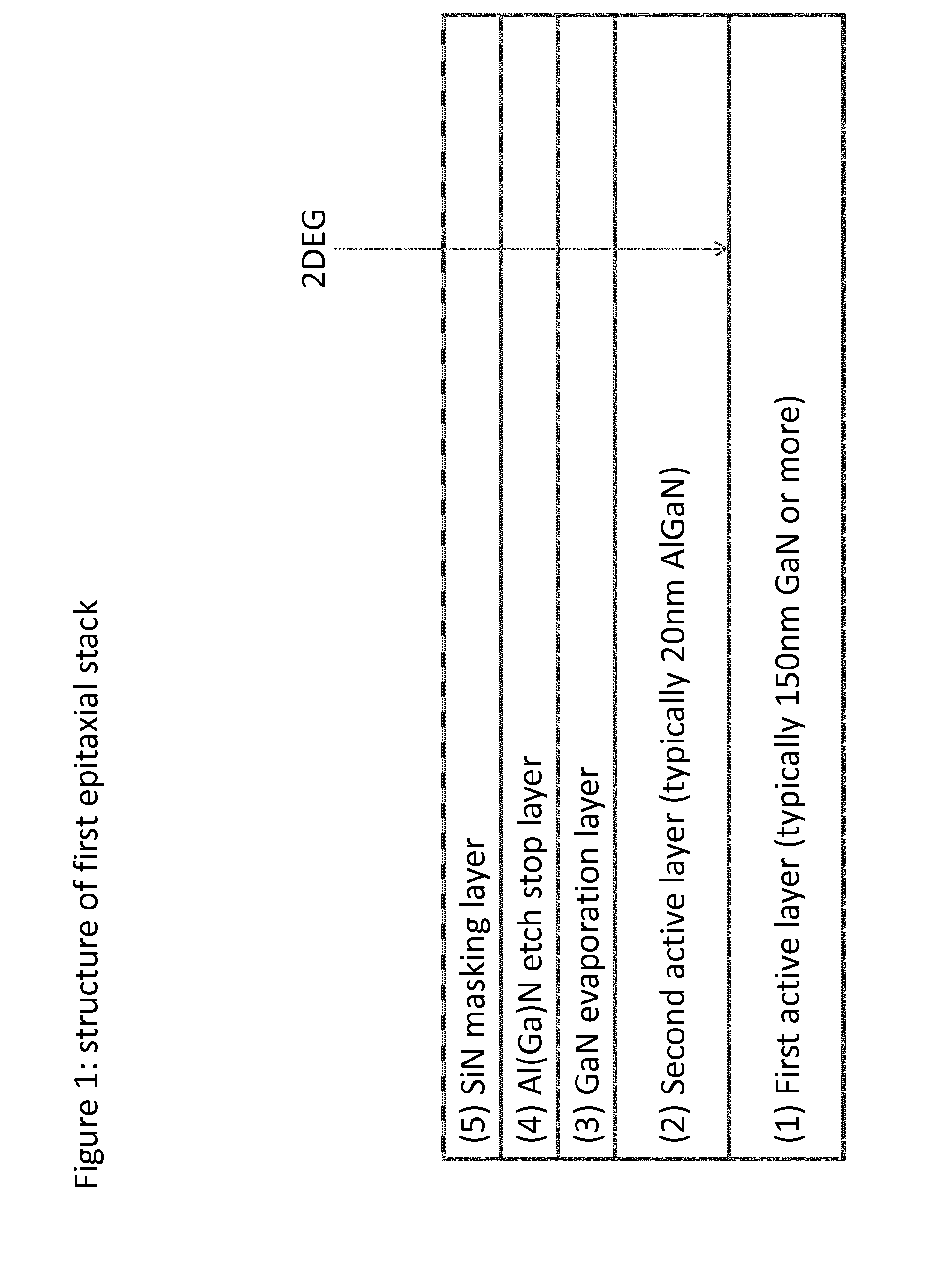

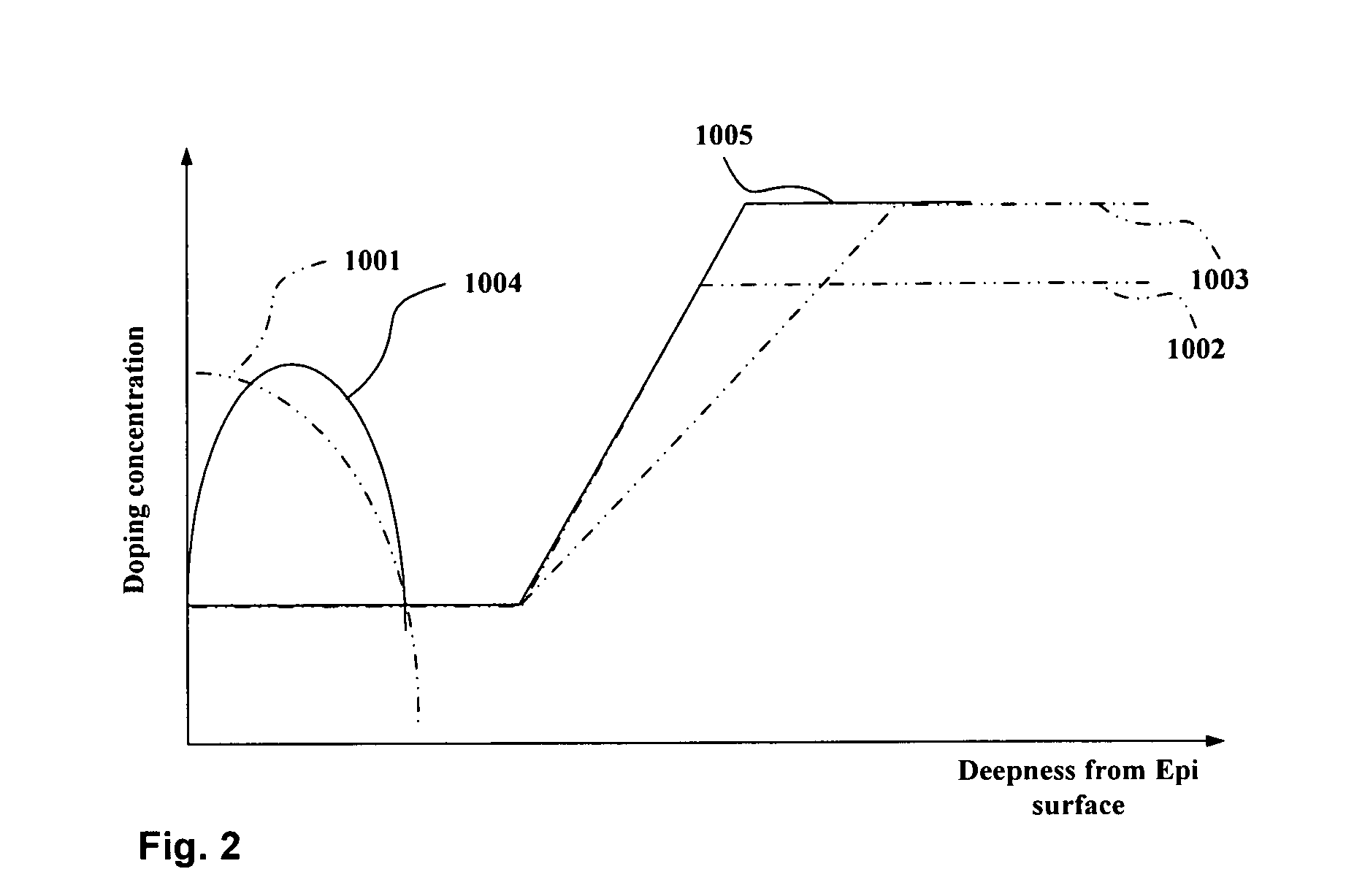

Method for Growing III-V Epitaxial Layers and Semiconductor Structure

ActiveUS20140159119A1Without jeopardizing functionality and advantageGood ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structurePower switching

Disclosed are methods of growing III-V epitaxial layers on a substrate, a semiconductor structure comprising a substrate, a device comprising such a semiconductor structure, and an electronic circuit. Group III-nitride devices, such as, for example, high-electron-mobility transistors, may include a two-dimensional electron gas (2DEG) between two active layers. For example, the 2DEG may be between a GaN layer and a AlGaN layer. These transistors may work in depletion-mode operation, which means the channel has to be depleted to turn the transistor off. For certain applications, such as, for example, power switching or integrated logic, negative polarity gate supply is undesired. Transistors may then work in enhancement mode (E-mode).

Owner:EPIGAN NV

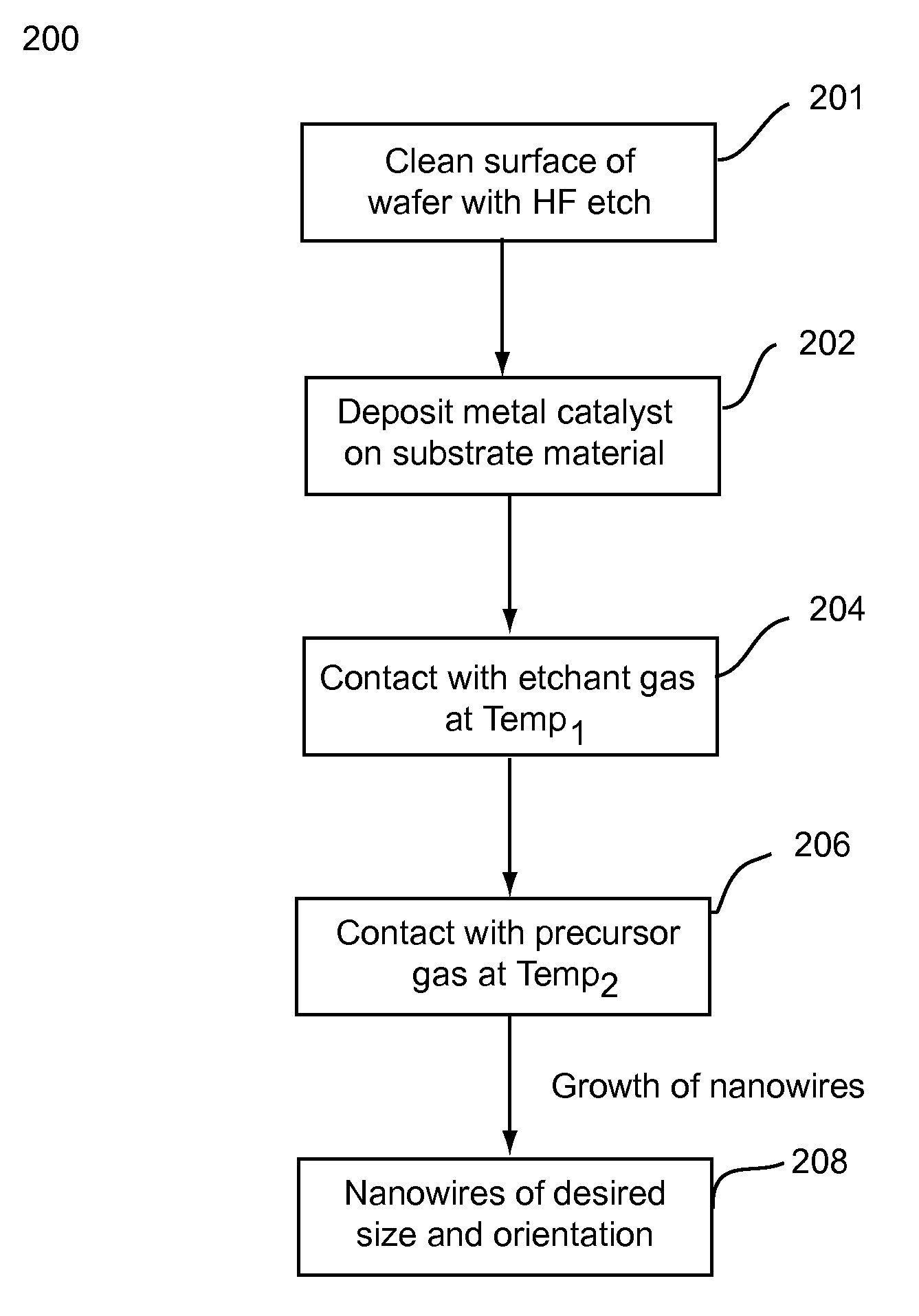

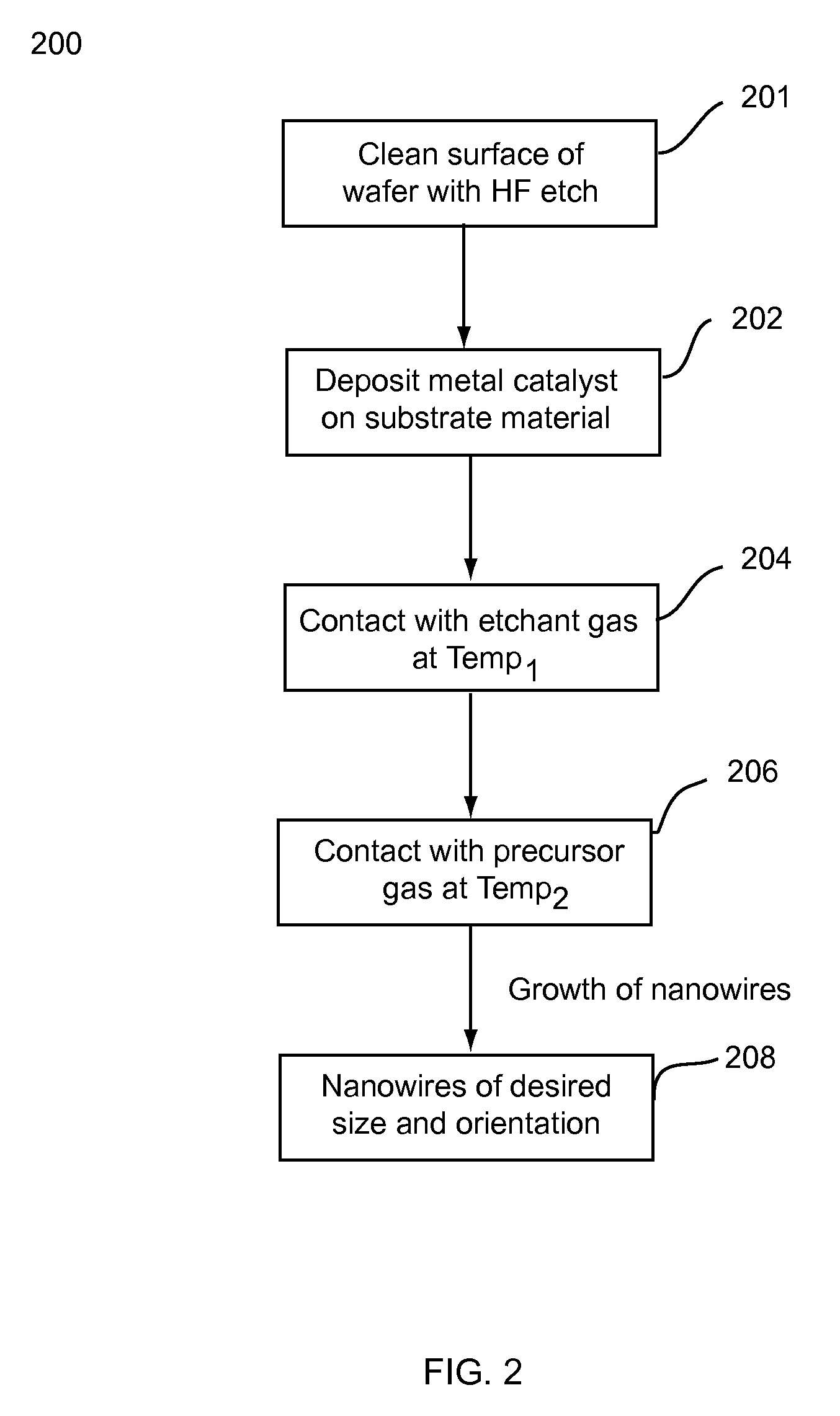

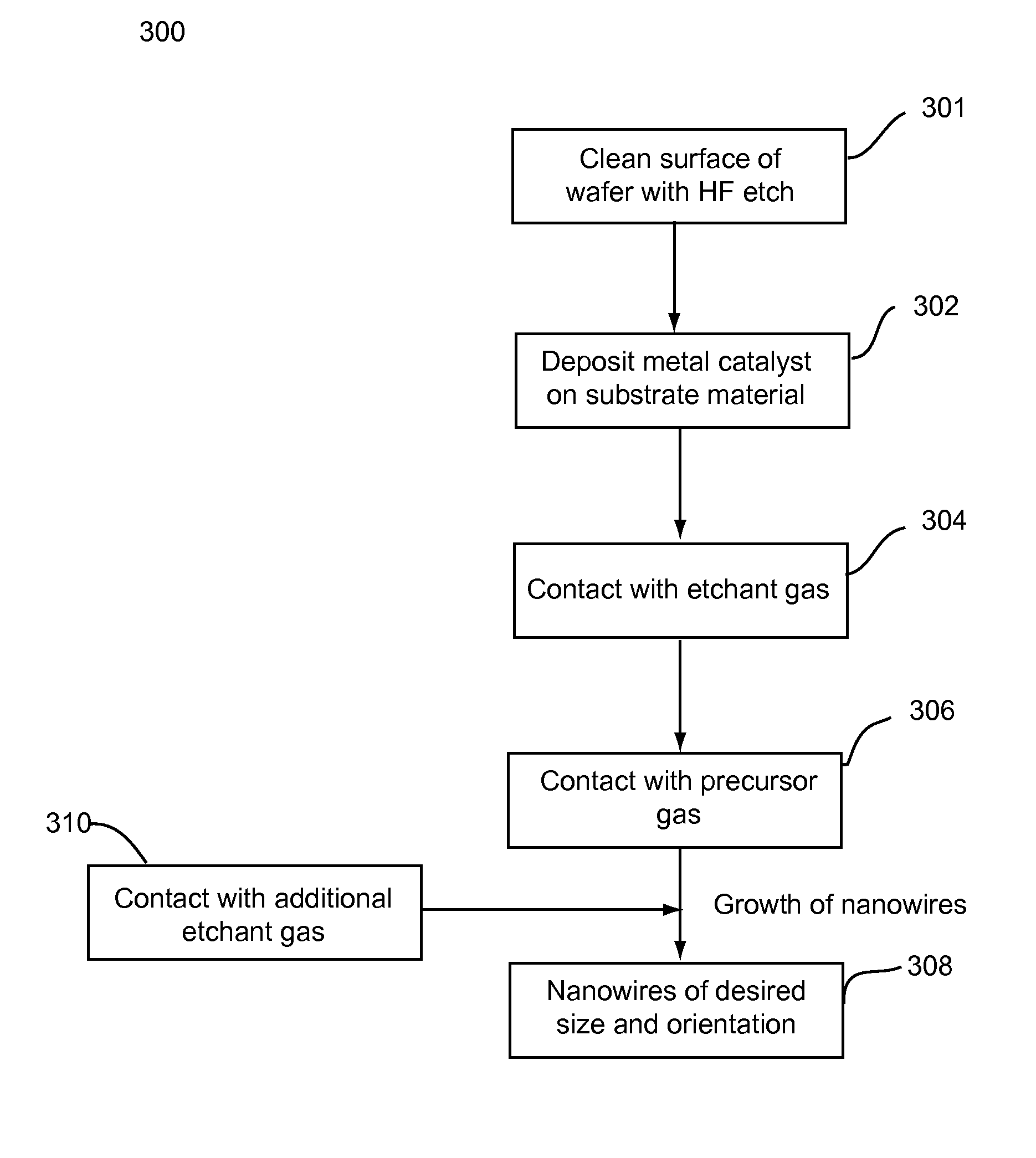

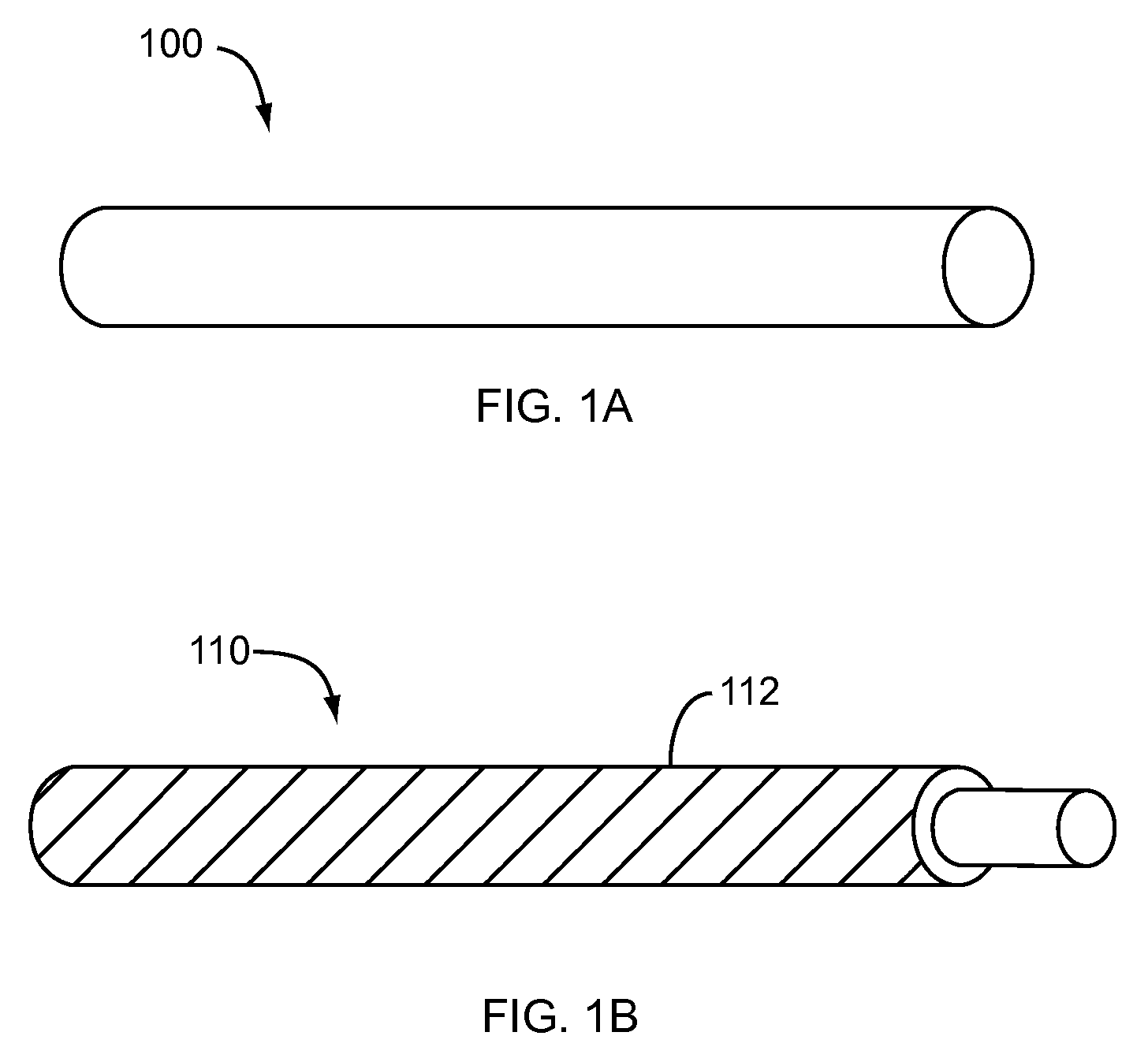

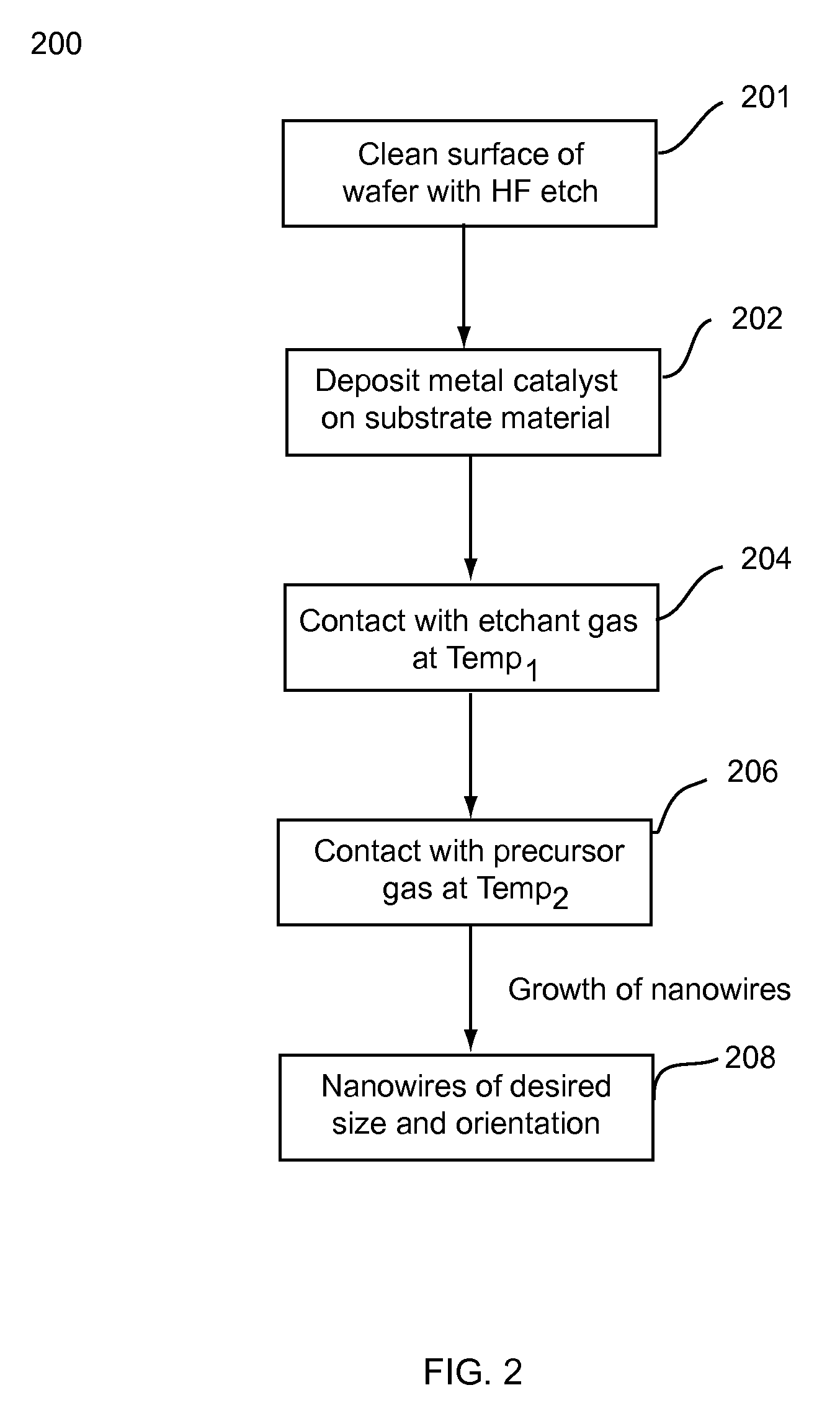

Systems and Methods for Nanowire Growth

ActiveUS20090127540A1Good ohmic contactReduce decomposition ratePolycrystalline material growthIndividual molecule manipulationReaction chamberAlloy

The present invention is directed to systems and methods for nanowire growth. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial vertically oriented nanowire growth including providing a substrate material having one or more nucleating particles deposited thereon in a reaction chamber, introducing an etchant gas into the reaction chamber at a first temperature which gas aids in cleaning the surface of the substrate material, contacting the nucleating particles with at least a first precursor gas to initiate nanowire growth, and heating the alloy droplet to a second temperature, whereby nanowires are grown at the site of the nucleating particles. The etchant gas may also be introduced into the reaction chamber during growth of the wires to provide nanowires with low taper.

Owner:ONED MATERIAL INC

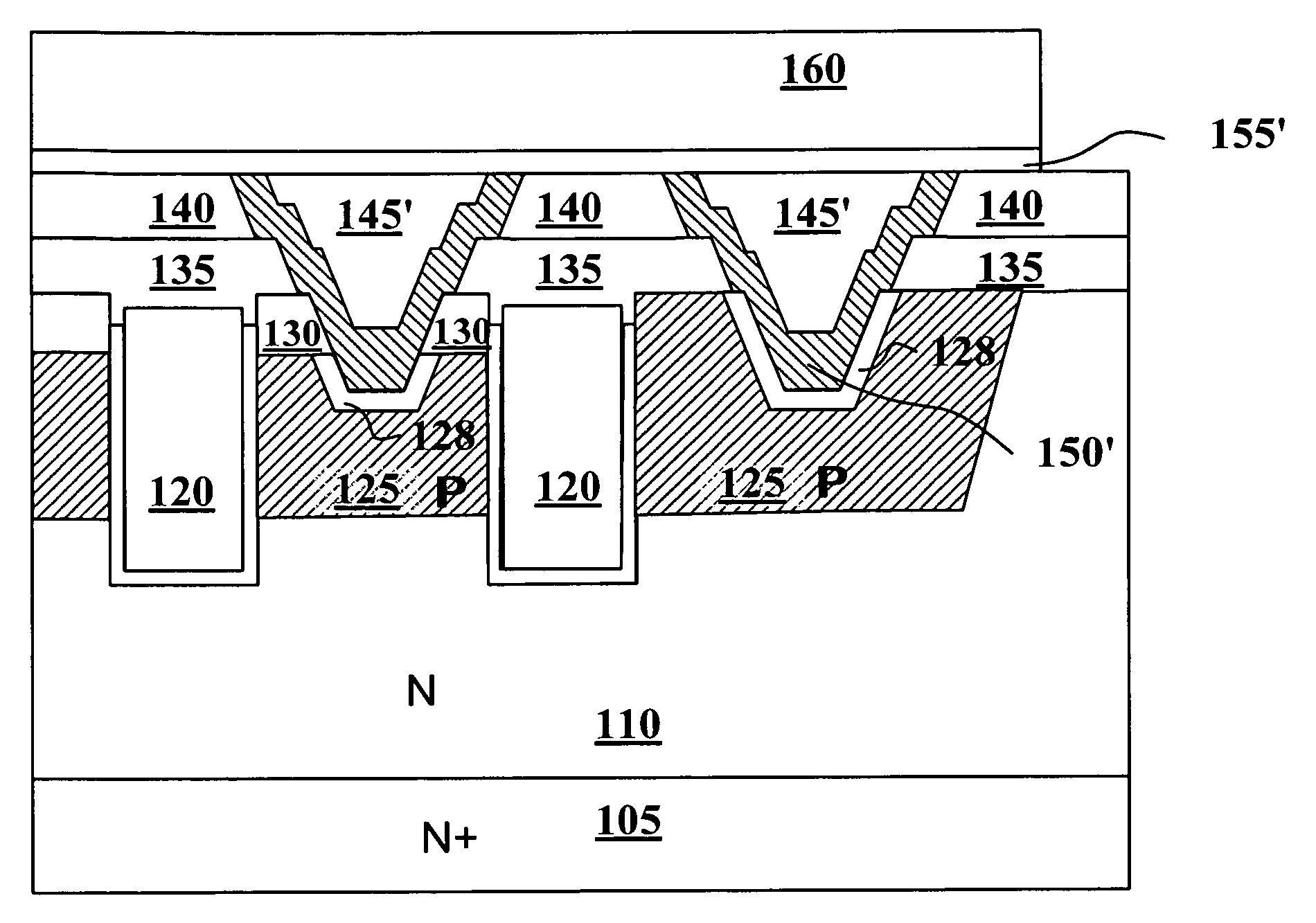

Trench MOSFET with on-resistance reduction

InactiveUS20110006362A1Reducing drain-source resistanceLowering substrate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetInsulation layer

A trench MOSFET with on-resistance reduction comprises a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate, wherein the said MOSFET further comprises a plurality of source-body contact trenches opened relative to a top surface into said source and body regions and each of the source-body contact trenches is filled with a contact metal plug as a source-body contact; a insulation layer covered over the top of the trenched gate, the body region and the source region; a front metal layer formed on a top surface of the MOSFET; wherein a low-resistivity phosphorus substrate and retrograded P-body formed by medium or high energy Ion Implantation to reduce Rds contribution from substrate and drift region.

Owner:FORCE MOS TECH CO LTD

Organic thin film transistor, production method thereof, and electronic device

InactiveUS20100032660A1Improve device characteristicsLow costFinal product manufactureSolid-state devicesOhmic contactMetallic materials

An organic thin film transistor is disclosed, including a substrate formed of an organic insulating layer, a first layer deposited on the substrate using a plating technique to be used for forming a source electrode and a drain electrode, a second layer of a metal material deposited covering the first layer using a further plating technique to be used for forming the source electrode and the drain electrode with the metal material capable of forming an ohmic contact with an organic semiconductor material lower than the first layer, and an organic semiconductor layer over a region between the source electrode and the drain electrode, which are each formed with the first layer and the second layer. Also disclosed is an electric device provided with the organic thin film transistor.

Owner:SONY CORP

Semiconductor device and manufacturing method thereof

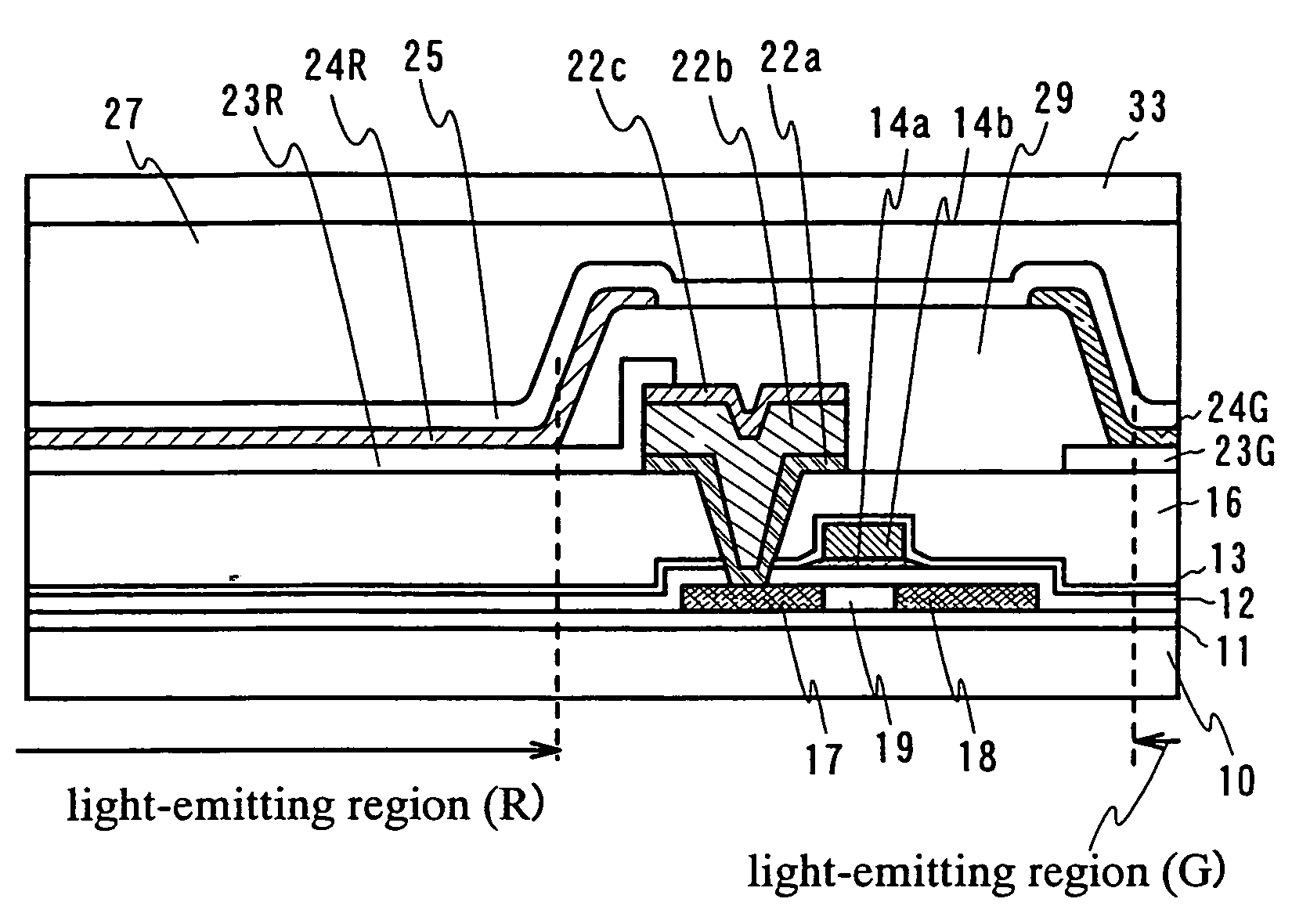

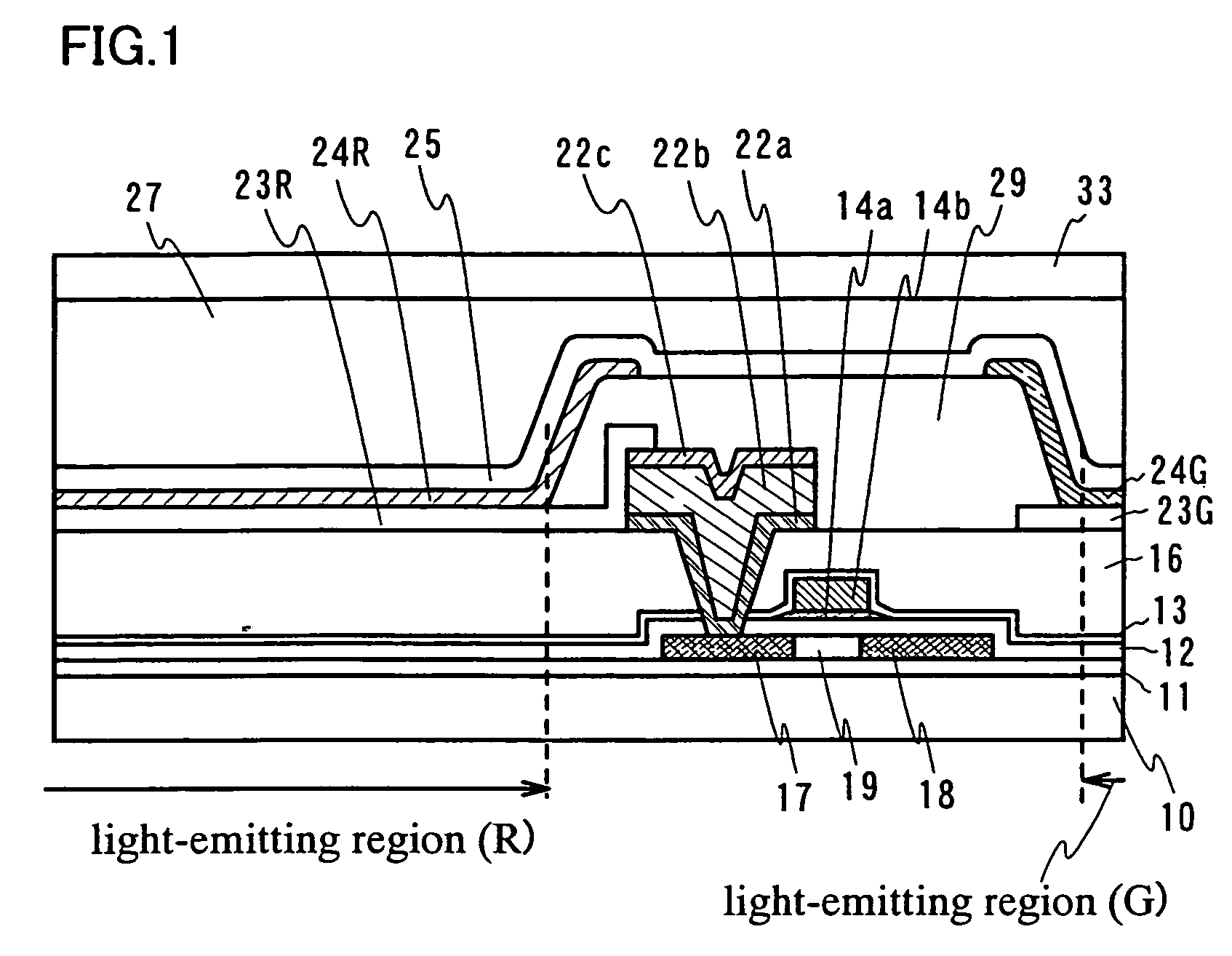

ActiveUS20060038176A1Good ohmic contactSuperior electrodeSolid-state devicesSemiconductor/solid-state device manufacturingActive matrixOhmic contact

According to the present invention, wirings, electrodes or the like formed from two films (an ITO film and an aluminum film) which are incompatible with each other are connected, and low power consumption is realized even if a display screen size is increased in an active matrix display device. A three-layer structure or a two-layer structure is employed to obtain a favorable ohmic contact with ITO. The structure of a wiring or an electrode includes a layer having an aluminum carbon alloy which does not react with ITO. The wiring or an electrode is contacted with ITO.

Owner:SEMICON ENERGY LAB CO LTD

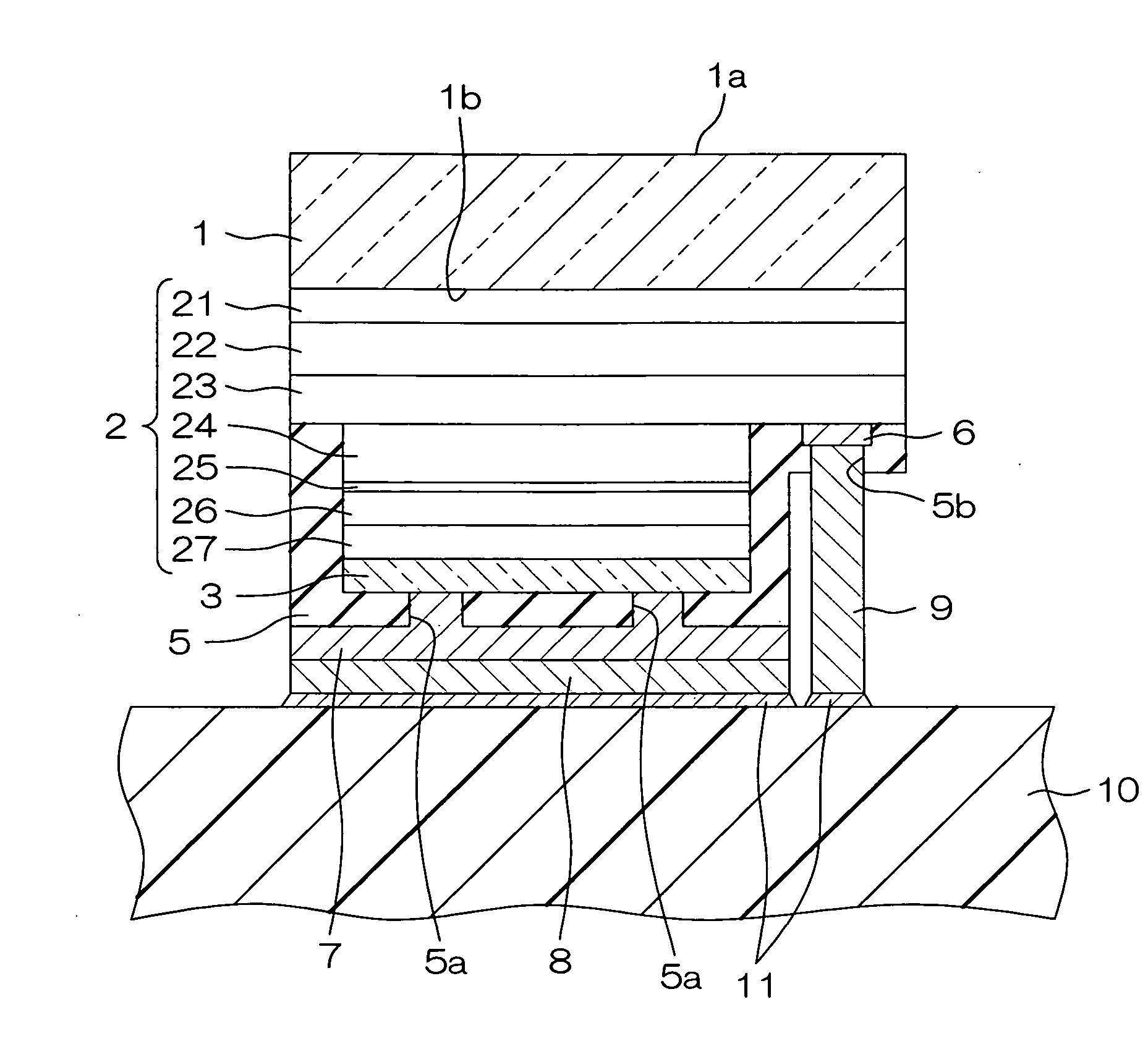

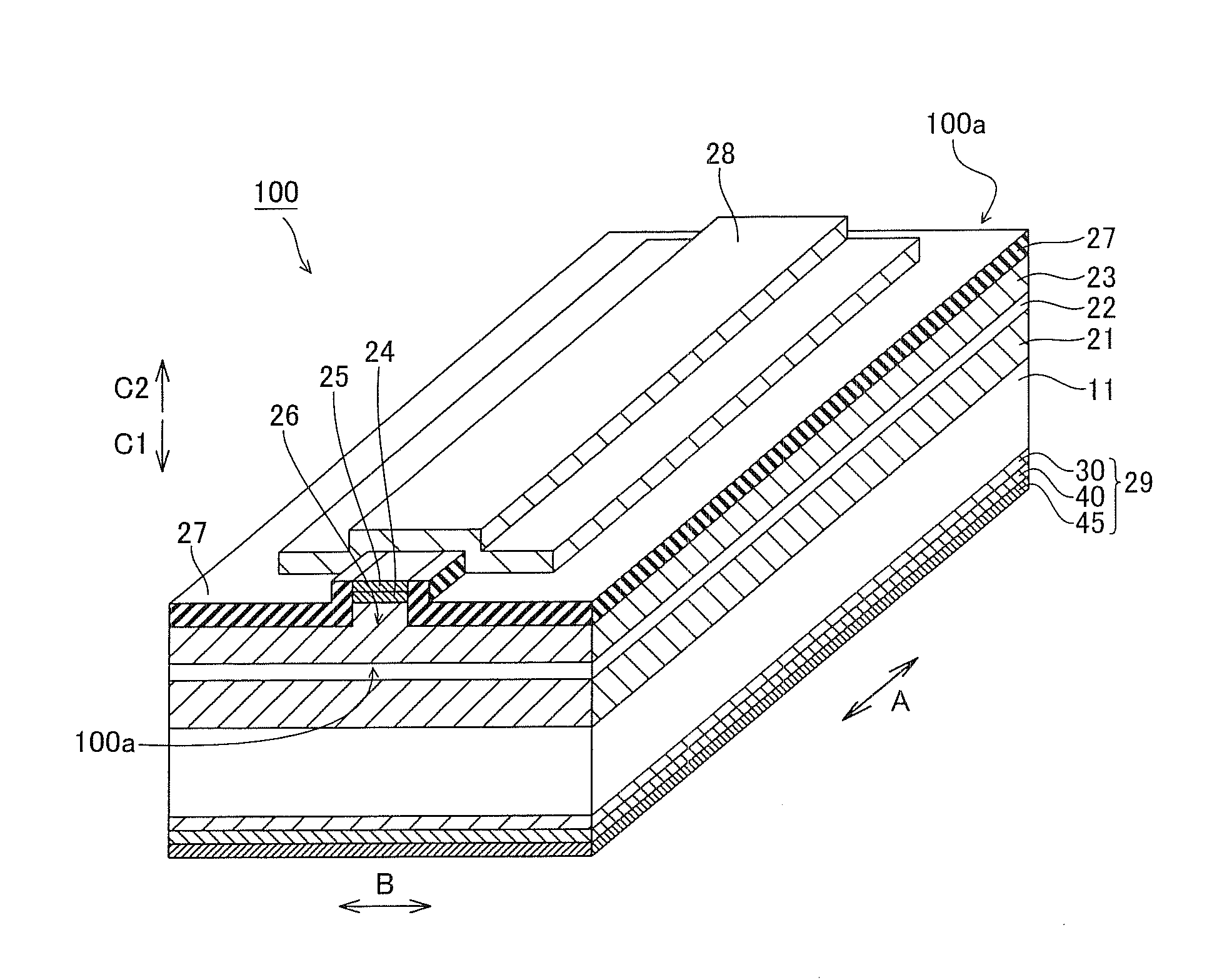

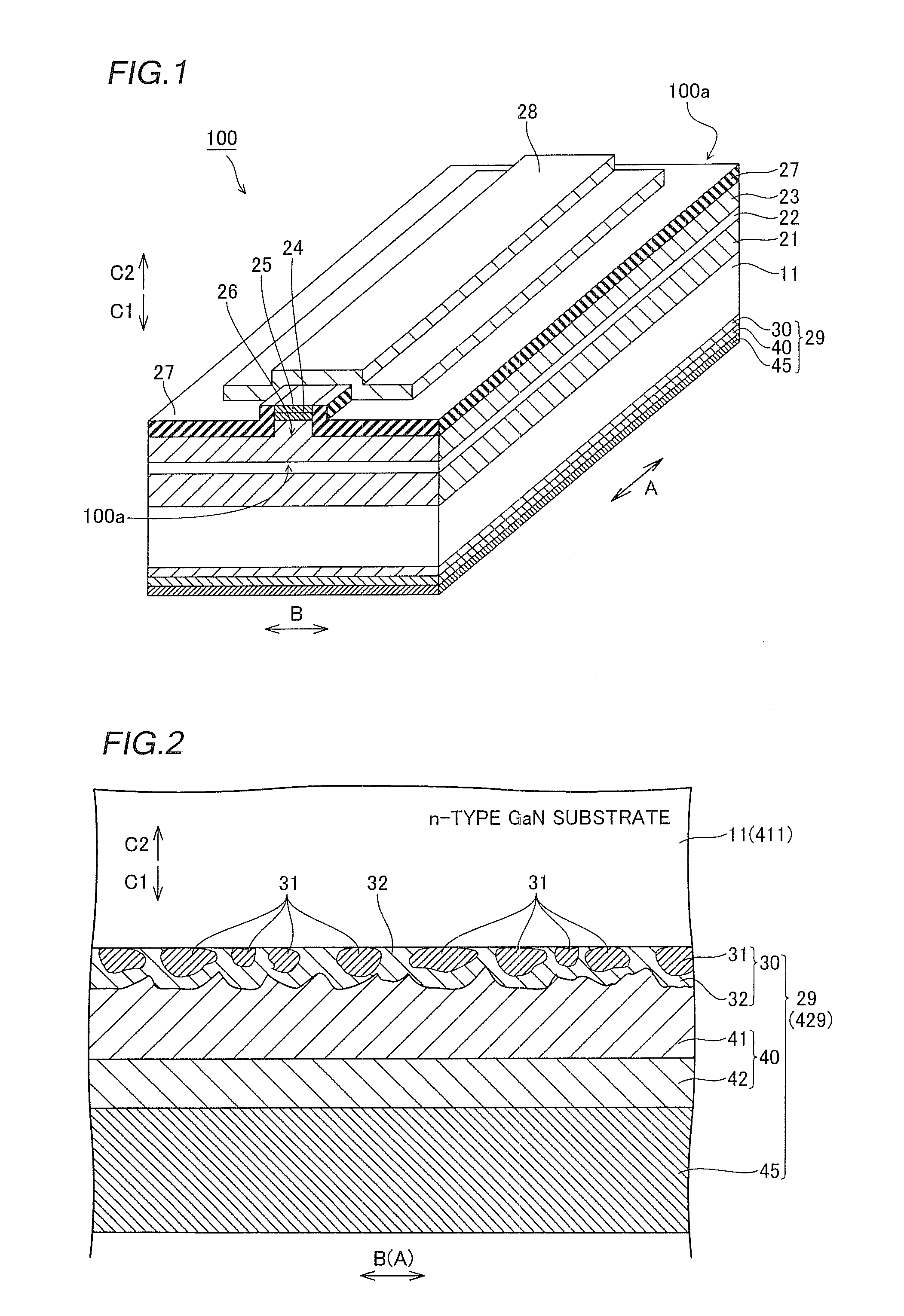

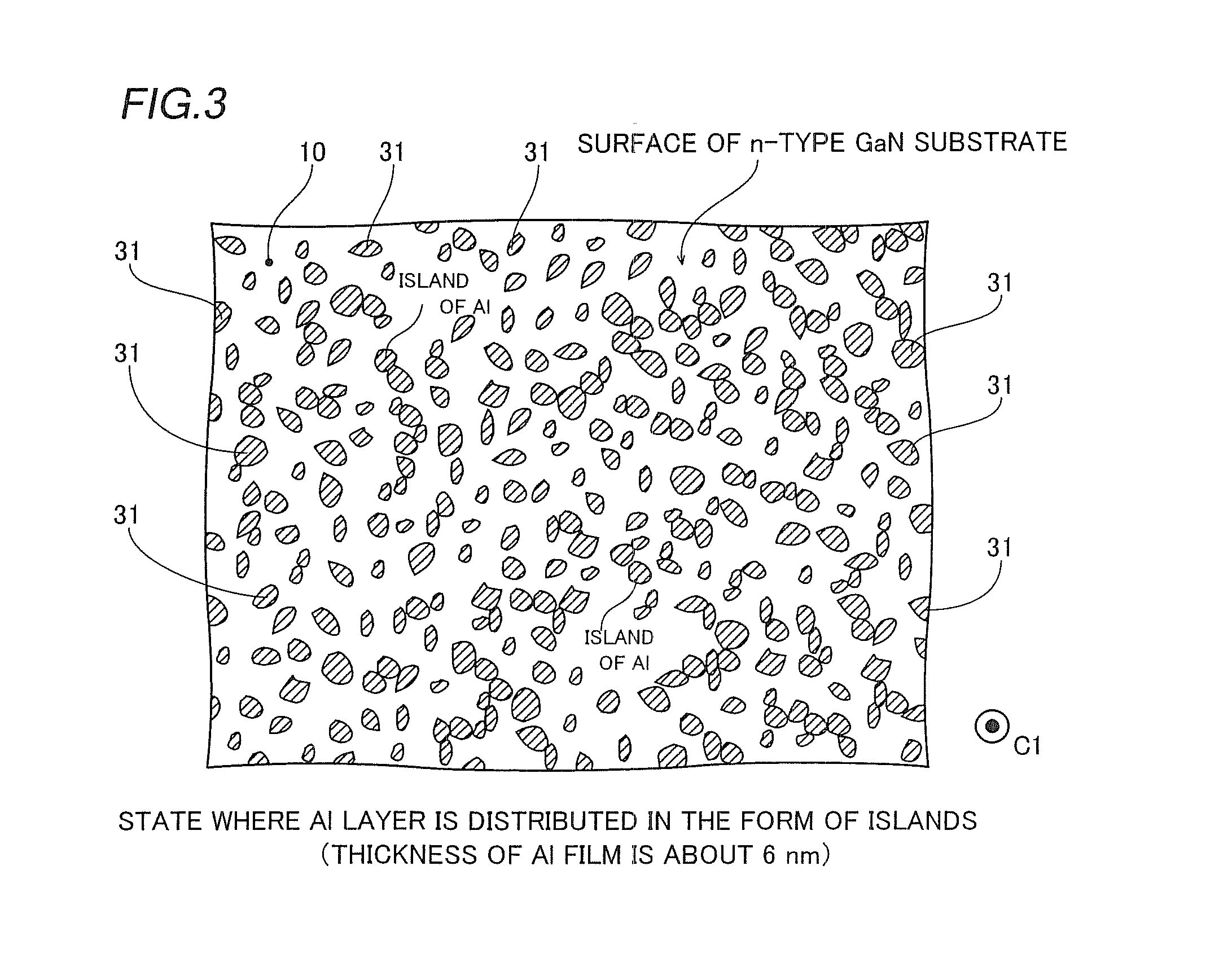

Nitride semiconductor device and method of manufacturing the same

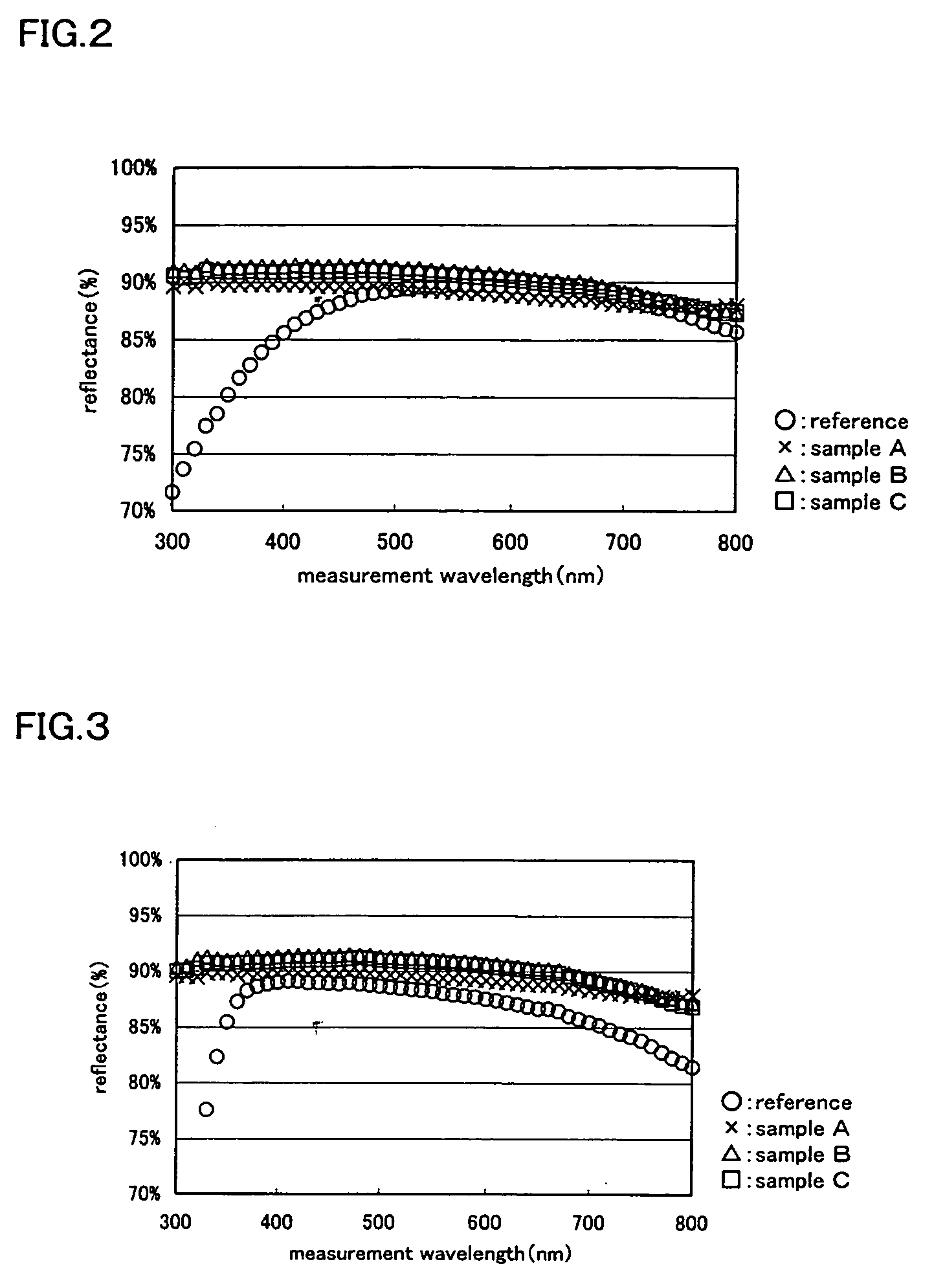

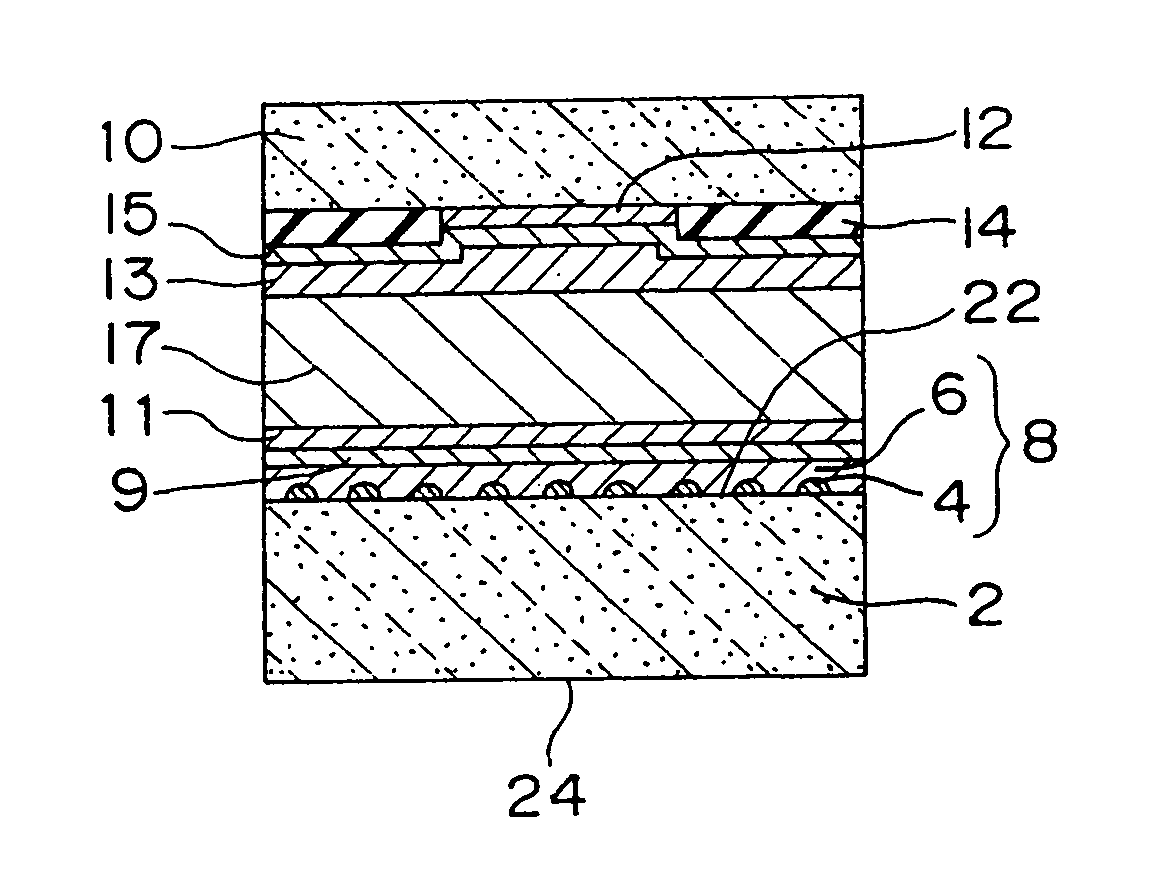

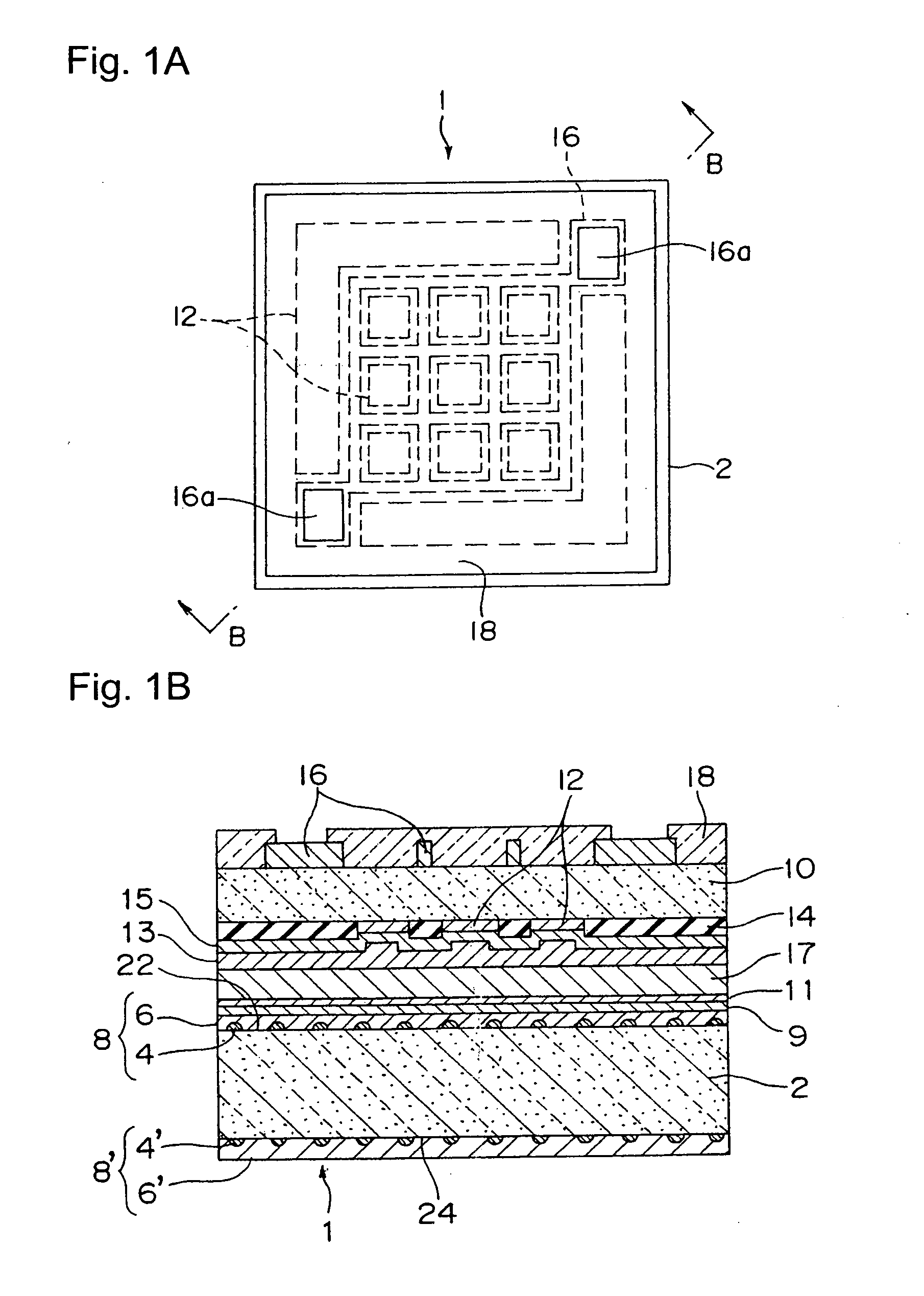

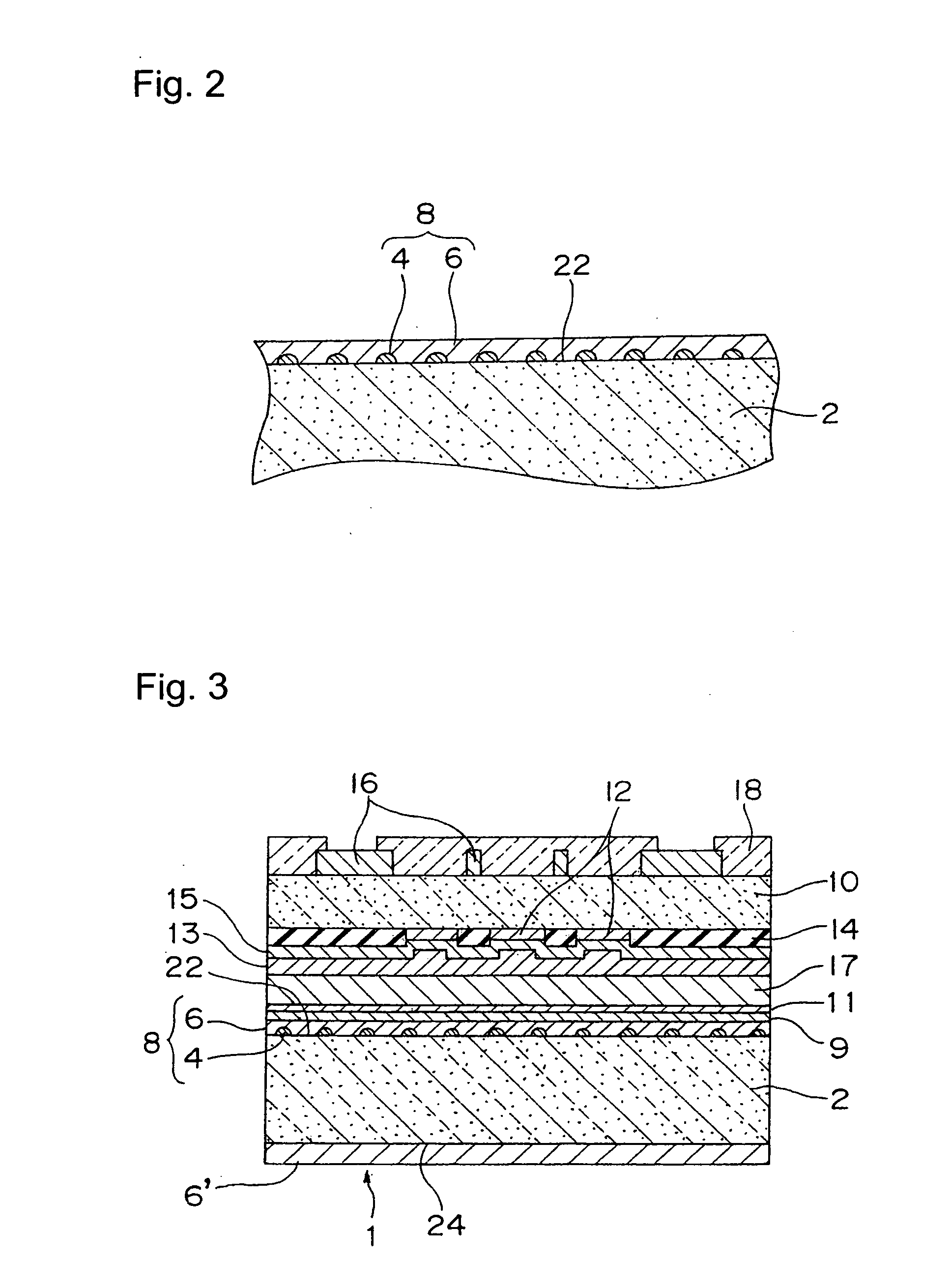

ActiveUS20080296627A1Improve adhesionImproved ohmic contact characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingContact formationOhmic contact

In the nitride semiconductor device using the silicon substrate, the metal electrode formed on the silicon substrate has both ohmic contact property and adhesion, so that the nitride semiconductor device having excellent electric properties and reliability is obtained. The nitride semiconductor device includes a silicon substrate (2), a nitride semiconductor layer (10) formed on the silicon substrate (2), and metal electrodes (8, 8′) formed in contact with the silicon substrate (2). The metal electrodes (8, 8′) has first metal layers (4, 4′) which are formed in a shape of discrete islands and in contact with the silicon substrate (2), and second metal layers (6, 6′) which are in contact with the silicon substrate (2) exposed among the islands of the first metal layers (4, 4′) and are formed to cover the first metal layers (4, 4′). Further, the second metal layers (6, 6′) are made of a metal capable of forming ohmic contact with silicon, and the first metal layers (4, 4′) are made of an alloy containing a metal and silicon, in which the metal is different than that in the second metal layer (6,6′).

Owner:NICHIA CORP

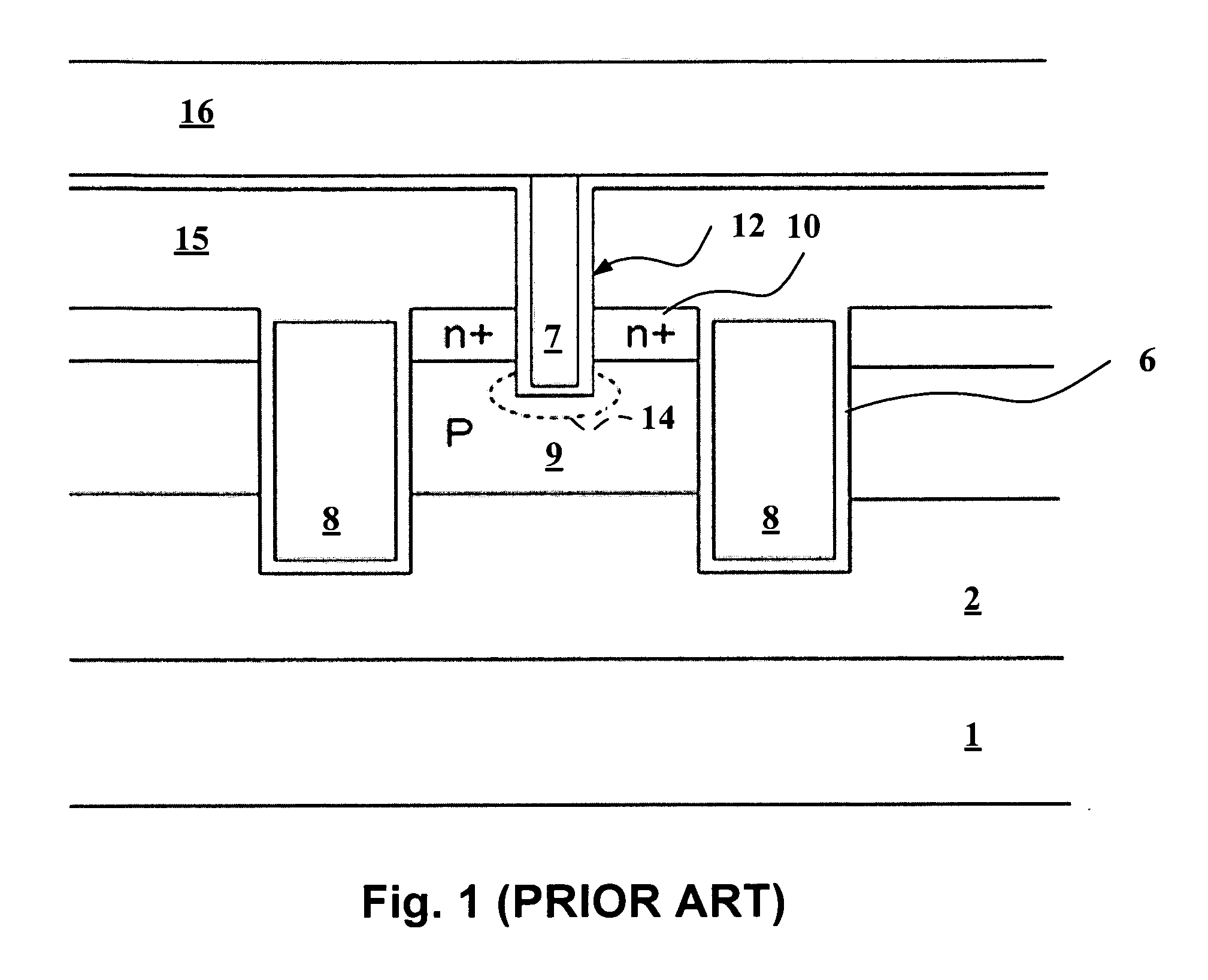

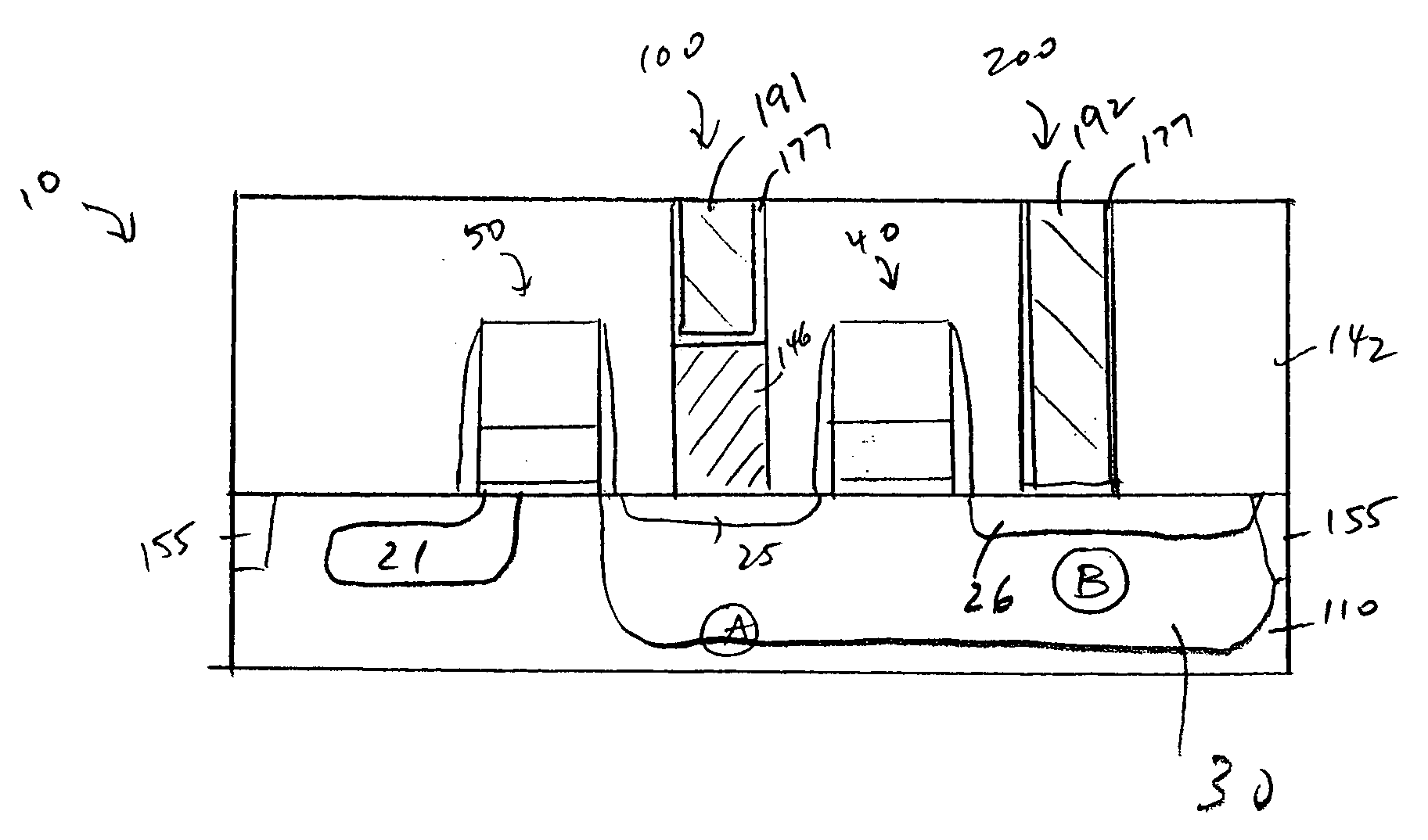

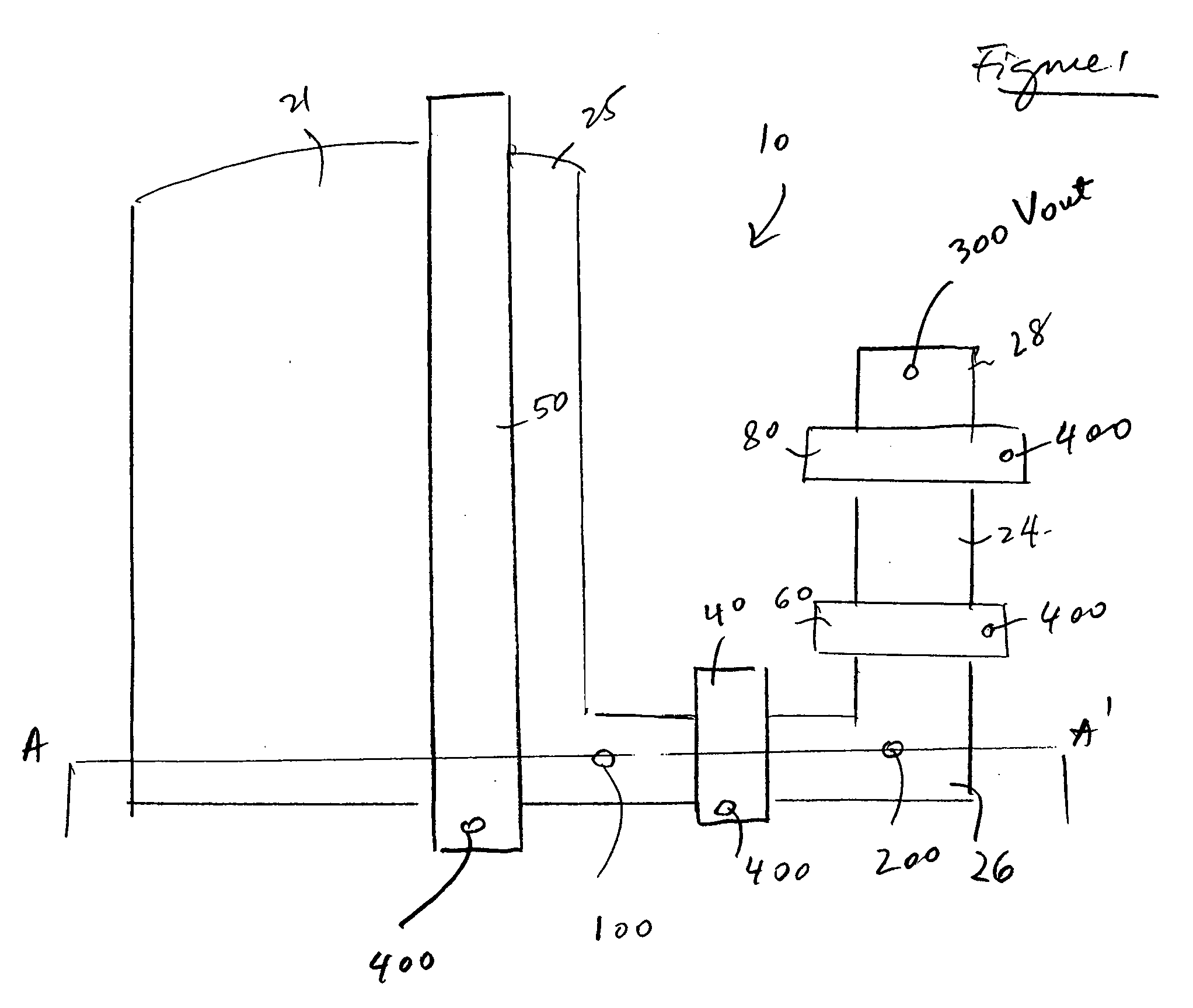

Contacts for CMOS imagers and method of formation

ActiveUS20060043436A1Reduce leakageGood ohmic contactSemiconductor/solid-state device detailsSolid-state devicesCMOSOhmic contact

Low leakage contacts on leakage sensitive areas of a CMOS imager, such as a floating diffusion region or a photodiode, are disclosed. At least one low leakage polysilicon contact is provided over a leakage sensitive area of a CMOS imager. The polysilicon contact comprises a polysilicon region in direct contact with the area of interest (the leakage sensitive area) and a metal region located over the polysilicon region. The polysilicon contact provides an improved ohmic contact with less leakage into the substrate. The polysilicon contact may be provided with other conventional metal contacts, which are employed in areas of the CMOS imager that do not require low leakage.

Owner:APTINA IMAGING CORP

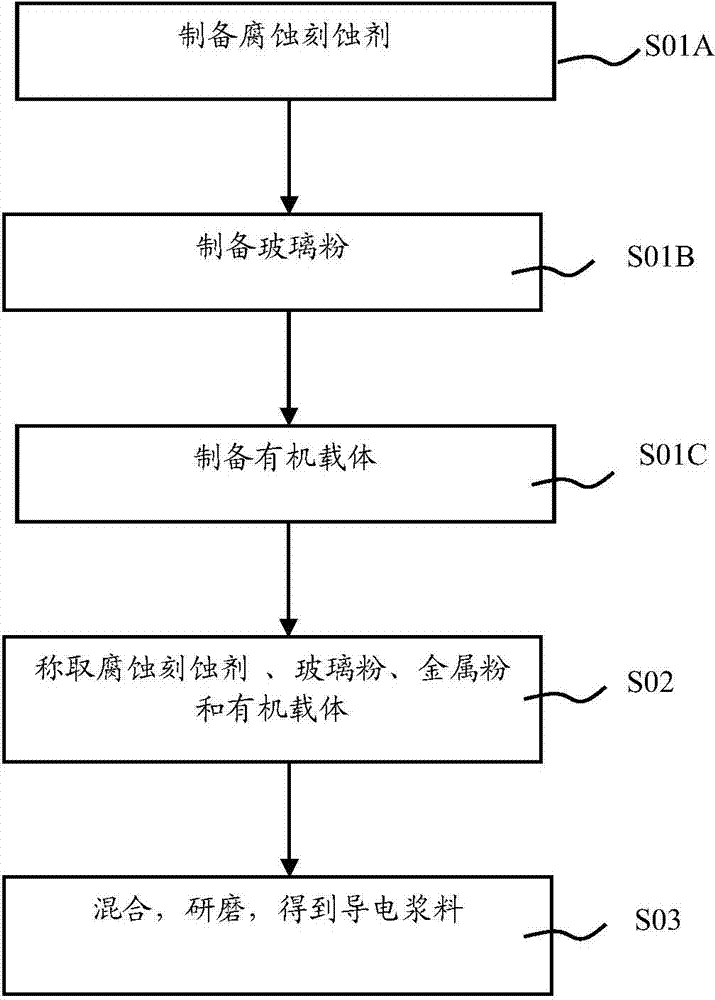

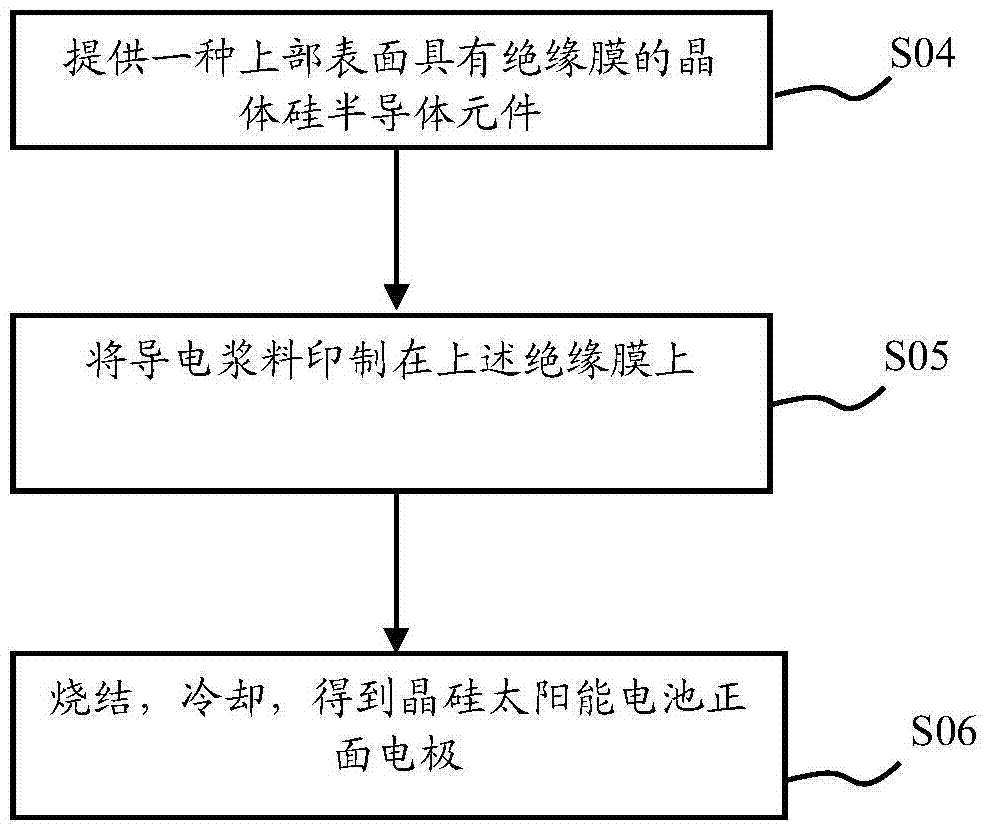

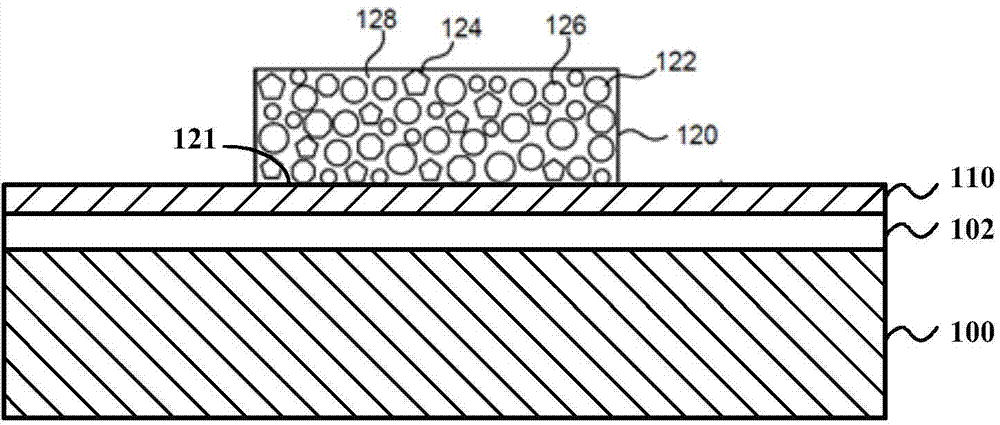

Crystalline silicon solar cell front electrode electrocondution slurry and preparation method thereof

ActiveCN103545016AImprove conductivityEasy to corrode and penetrateFinal product manufactureNon-conductive material with dispersed conductive materialCrystal structureSilicon solar cell

The invention discloses crystalline silicon solar cell front electrode electrocondution slurry and a preparation method of the crystalline silicon solar cell front electrode electrocondution slurry. The crystalline silicon solar cell front electrode electrocondution slurry is composed of a corrosion etching agent, metal powder, an organic carrier and glass powder; the corrosion etching agent is a compound of one or more crystals, and the melting temperature of the corrosion etching agent ranges from 250 DEG C to 760 DEG C; the glass powder is of a non-crystal structure. In the sintering process of the electrode electrocondution slurry, the corrosion etching agent directly turns into a liquid from a solid so that the corrosion etching agent can flow easily; in coordination with the softened glass powder, the corrosion etching agent can easily etch and penetrate through an antireflection insulating layer on the front of a crystalline silicon solar cell so that the conductive metal powder and the crystalline silicon solar cell can form good ohmic contact; moreover, the conductive metal powder can be wetted, contact between the metal powder can be enhanced, and therefore a crystalline silicon solar cell front electrode with excellent conductivity is formed.

Owner:SOLTRIUM ADVANCED MATERIALS TECH LTD SHENZHEN

Nitride-based semiconductor device and method of manufacturing the same

InactiveUS20100059790A1Inhibit deteriorationGood ohmic contactOptical wave guidanceFinal product manufactureNitrideSemiconductor

A nitride-based semiconductor device includes an n-type nitride-based semiconductor layer, and an n-side electrode having a first metal layer made of Al, formed on a surface of the n-type nitride-based semiconductor layer and a second metal layer made of Hf formed so as to cover a surface of the first metal layer on a side opposite to the n-type nitride-based semiconductor layer.

Owner:SANYO ELECTRIC CO LTD

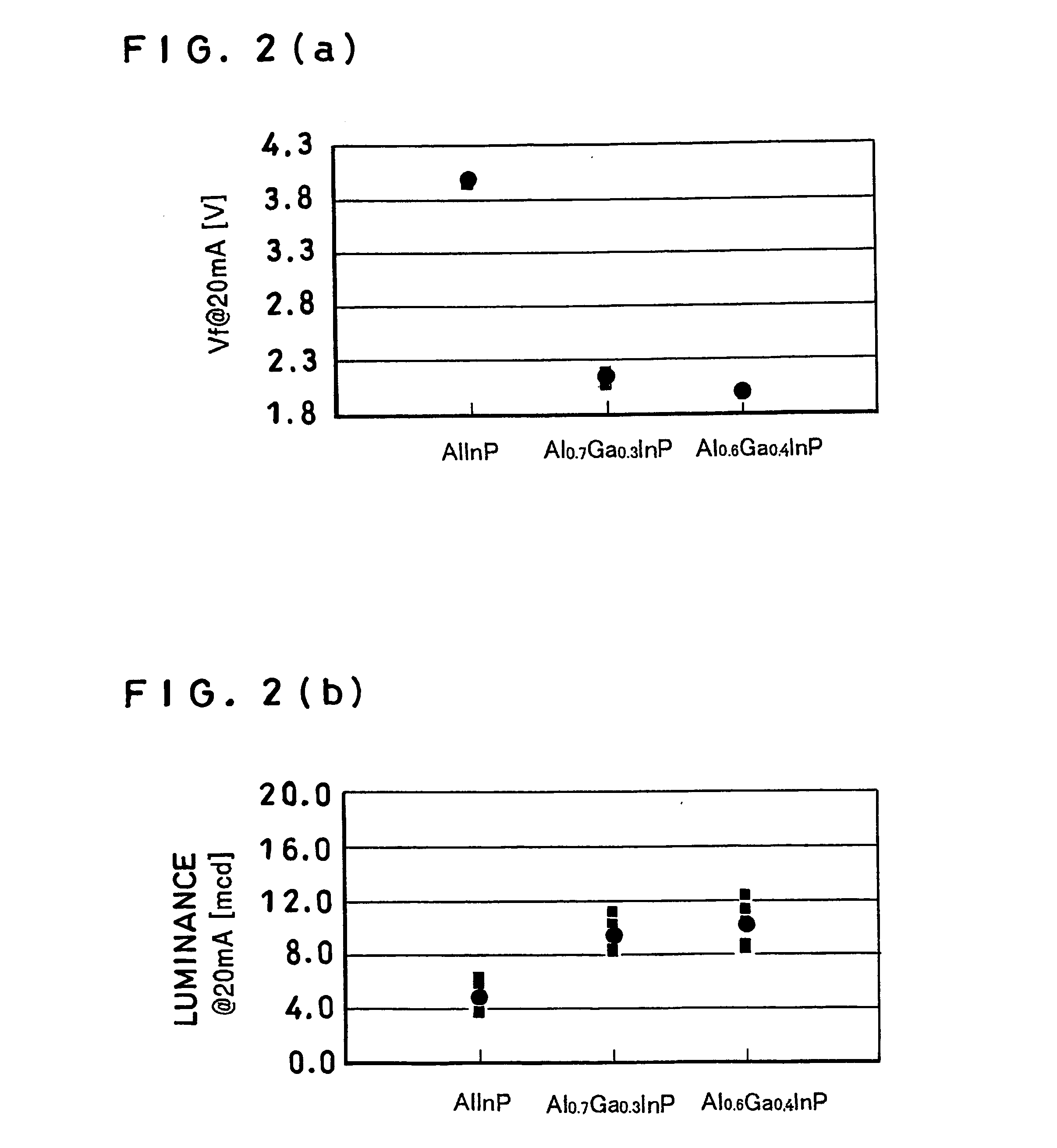

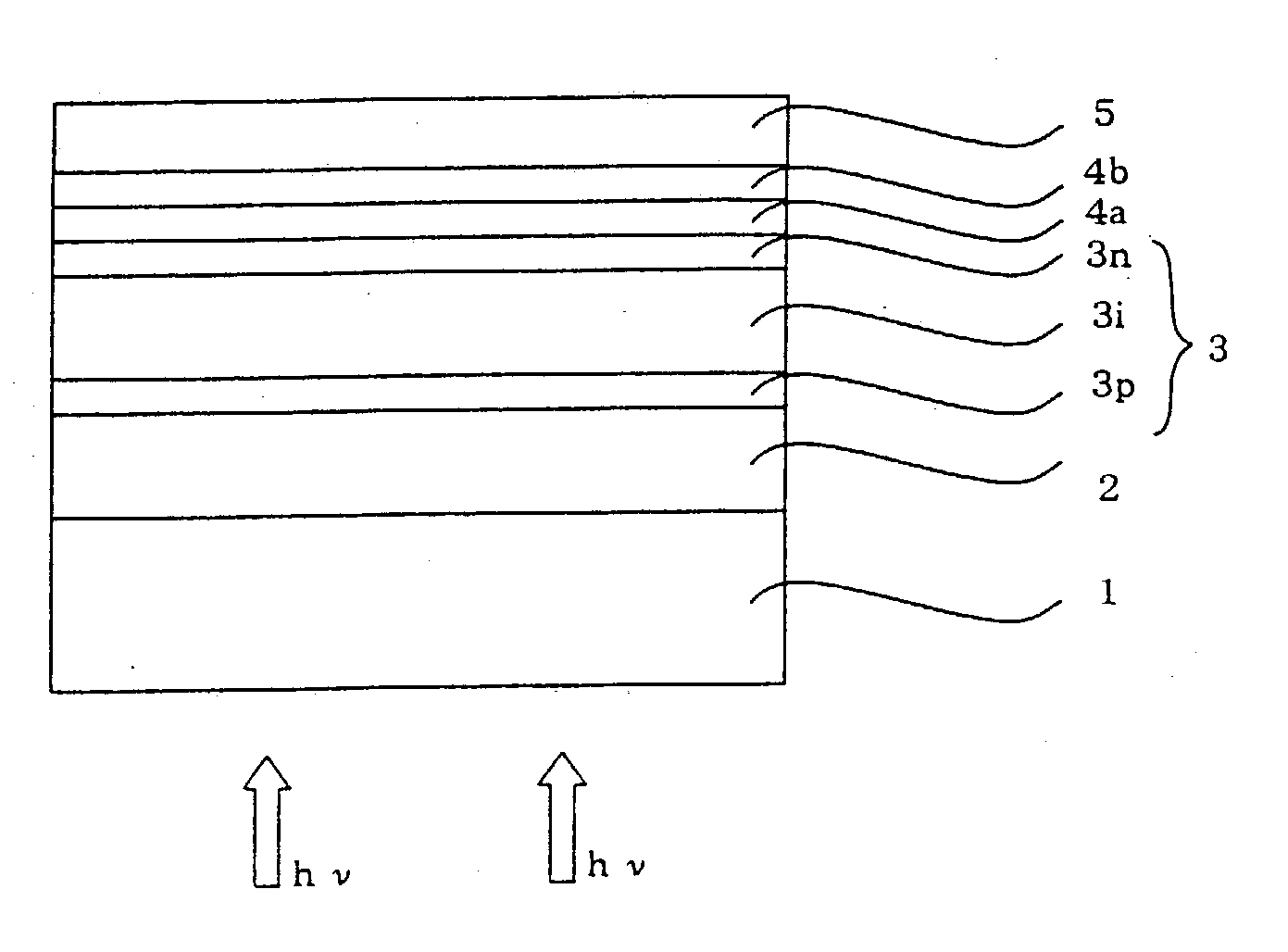

Light-emitting diode device and production method thereof

InactiveUS20060163603A1High precisionHigh crystallinitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystallinityLight-emitting diode

A double hetero structure light-emitting diode device includes an active layer (6), a positive-electrode-side cladding layer, a negative-electrode-side cladding layer (4), a window layer (9) and an undoped AlInP layer. The positive-electrode-side cladding layer includes an undoped AlInP layer (7) grown to have a thickness of 0.5 μm and an intermediate layer (8) doped to assume p-type conductivity and having an intermediate energy band gap value between that of the undoped AlInP layer and that of the window layer. The window layer on the intermediate layer is a GaP layer grown at 730° C. or higher and at a growth rate of 7.8 μm / hour or more in the presence of Ze serving as a dopant. The negative-electrode-side cladding layer is provided with an undoped AlInP layer (5) having a thickness of 0.1 μm or more. With this configuration, there is provided a light-emitting diode device that enhances the crystallinity of a window layer, prevents generation of faults caused by a high-temperature process and attains high luminance at a wavelength falling within a yellow-green band.

Owner:SHOWA DENKO KK

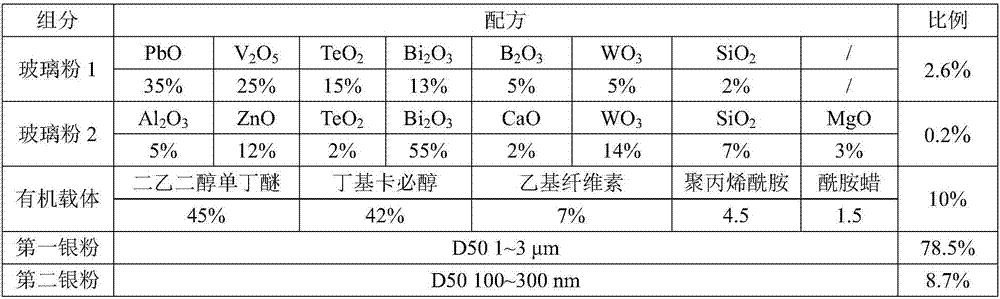

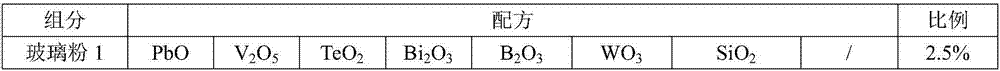

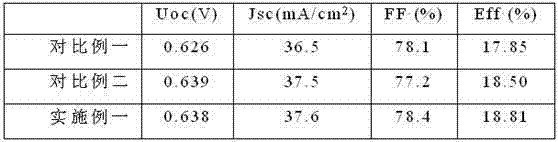

Positive electrode silver paste for back passivation silicon solar cell and preparation method thereof

ActiveCN107195354AHigh sintering activityImprove liquidityNon-conductive material with dispersed conductive materialCable/conductor manufactureSilicon solar cellColloidal particle

The invention discloses positive electrode silver paste for a back passivation silicon solar cell and a preparation method thereof. The positive electrode silver paste comprises, in mass percent, 3%-15% of organic carriers, 80%-95% of silver powders and 1%-5% of inorganic glass materials. The inorganic glass materials are prepared by compounding Pb-V-Te glass and Bi-W-Si glass; and the silver powders are prepared by compounding first silver powders and second silver powders. Through introduction of nanometer silver powders, sintering activity of a silver powder system is improved, and compactness of silver grid lines under low-temperature sintering is improved; by adjusting softening temperature, viscosity and surface tension of the glass materials, liquidity and wetting ability of glass liquid are improved, etching capacity of the glass liquid to a front-surface antireflection layer is ensured and silver powder fusion and reprecipitation capability is improved; precipitation of silver nanometer colloid particles on the surface of a silicon wafer helps to promote the glass layer to form good ohmic contact with the silicon wafer, and thus conversion efficiency is improved; and through introduction of the second component glass powders, bonding strength between the glass layer and a silicon substrate is enhanced.

Owner:GUANGDONG AIKO SOLAR ENERGY TECH CO LTD

Systems and methods for nanowire growth

ActiveUS7776760B2Good ohmic contactReduce decomposition ratePolycrystalline material growthIndividual molecule manipulationNanowireAlloy

Owner:ONED MATERIAL INC

Conductive paste for front electrode of semiconductor device and method of manufacturing thereof

InactiveUS20140220732A1Low viscosityContactConductive materialSemiconductor/solid-state device manufacturingMetallic electrodeDevice material

The present invention provides a conductive paste characterized by a crystal-based corrosion binder being combined with a glass frit and mixed with a metallic powder and an organic carrier. Methods for preparing each components of the conductive paste are disclosed including several embodiments of prepare Pb—Te—O-based crystal corrosion binder characterized by melting temperatures in a range of 440° C. to 760° C. and substantially free of any glass softening transition upon increasing temperature. Method for preparing the conductive paste includes mixture of the components and a grinding process to ensure all particle sizes in a range of 0.1 to 5.0 microns. Method of applying the conductive paste for the formation of a front electrode of a semiconductor device is presented to illustrate the effectiveness of the crystal-based corrosion binder in transforming the conductive paste to a metallic electrode with good ohmic contact with semiconductor surface.

Owner:SOLTRIUM ADVANCED MATERIALS TECH LTD SHENZHEN

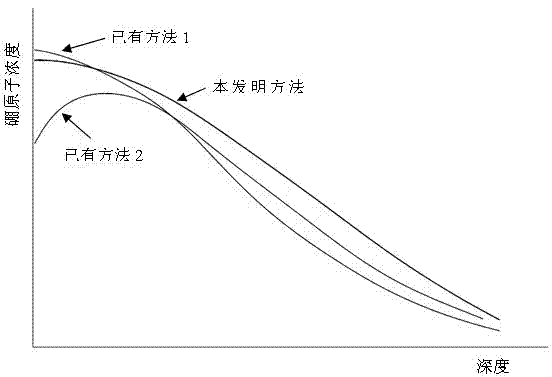

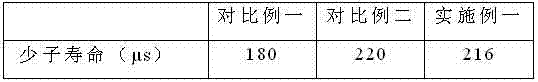

Boron diffusion method of crystalline silicon solar cell

ActiveCN102769069AImprove life expectancyDiffusion avoid or reduceFinal product manufactureDiffusion/dopingHigh surfaceNitrogen gas

The invention discloses a boron diffusion method of a crystalline silicon solar cell. The method comprises the following steps of: (1) putting a silicon chip which is felted and cleaned into a diffusion furnace tube, raising temperature to 800 to 1,000 DEG C, filling oxygen, and oxidizing for 1 to 30 min; (2) keeping the temperature in the step (1), or raising the temperature to 900 to 1,100 DEG C, and filling a boron source, the oxygen and nitrogen for boron diffusion; (3) stopping filling the source, keeping the temperature or reducing the temperature to 800 to 900 DEG C, and keeping the temperature for 5 to 50 min in the nitrogen atmosphere; and (4) reducing the temperature, taking out the silicon chip, and finishing the diffusion process. By adoption of the method, the uniformity of the boron diffusion can be improved, formation of a boron-rich layer is avoided or reduced, and the minority carrier lifetime of the silicon chip is prolonged; and meanwhile, high surface impurity concentration can be kept, and high ohmic contact is formed, so the performance of the cell is improved.

Owner:CSI CELLS CO LTD +1

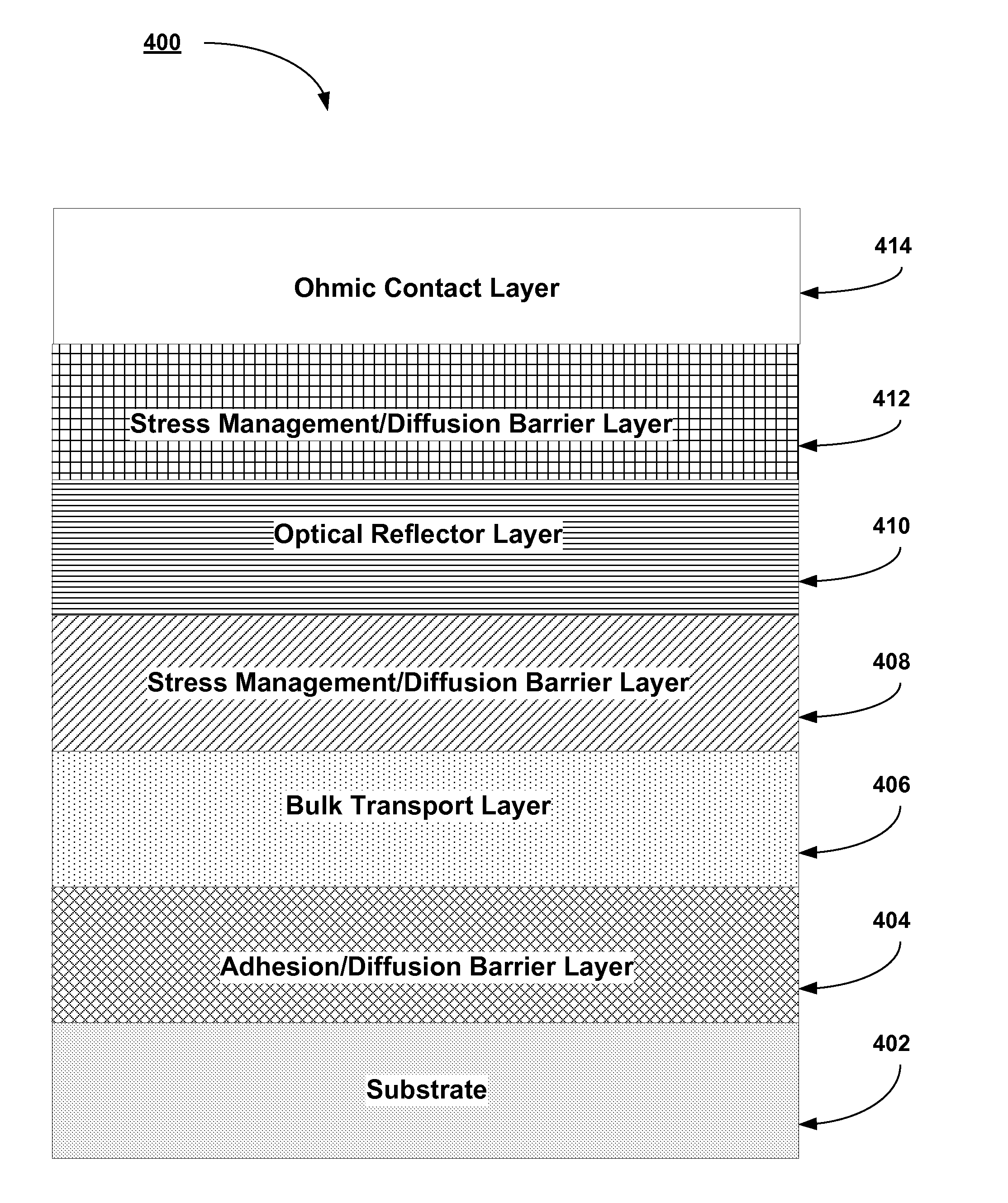

Back contacts for thin film solar cells

InactiveUS20130081688A1Enhanced light absorptionImprove adhesionFinal product manufacturePhotovoltaic energy generationTransport layerOhmic contact

Method for forming back contact stacks for CIGS and CZTS TFPV solar cells are described wherein some embodiments include adhesion promoter layers, bulk current transport layers, stress management / diffusion barrier layers, optical reflector layers, and ohmic contact layers. Other back contact stacks include adhesion promoter layers, bulk current transport layers, diffusion barrier layers, and ohmic contact layers.

Owner:INTERMOLECULAR

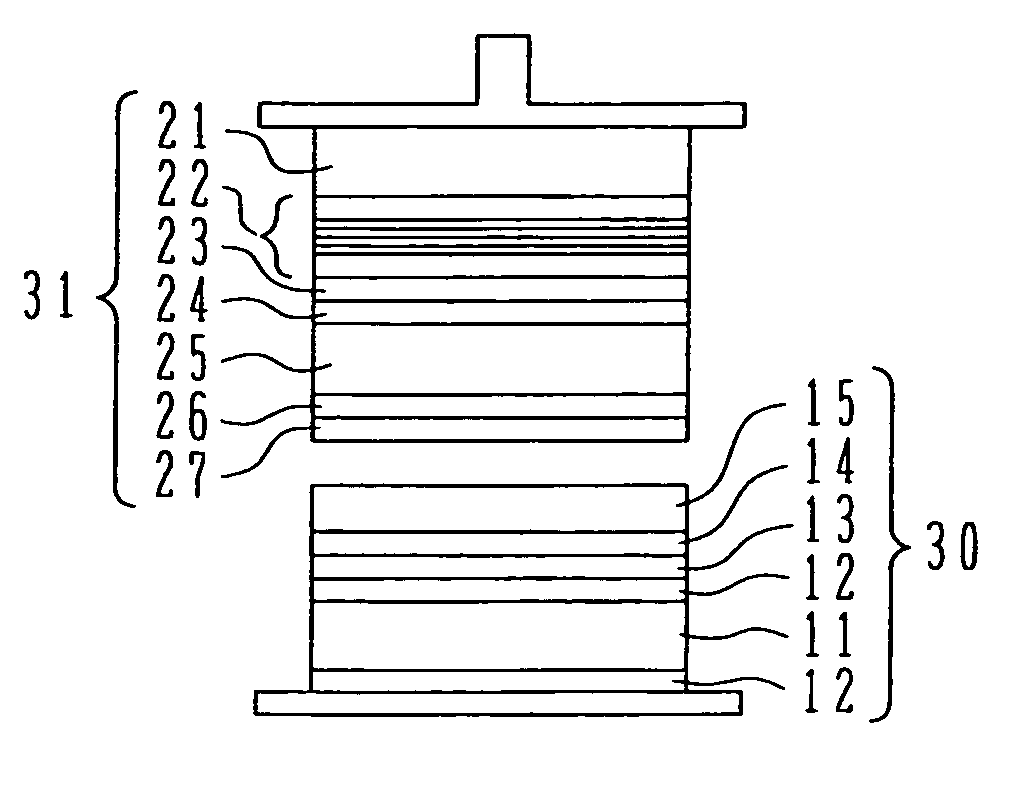

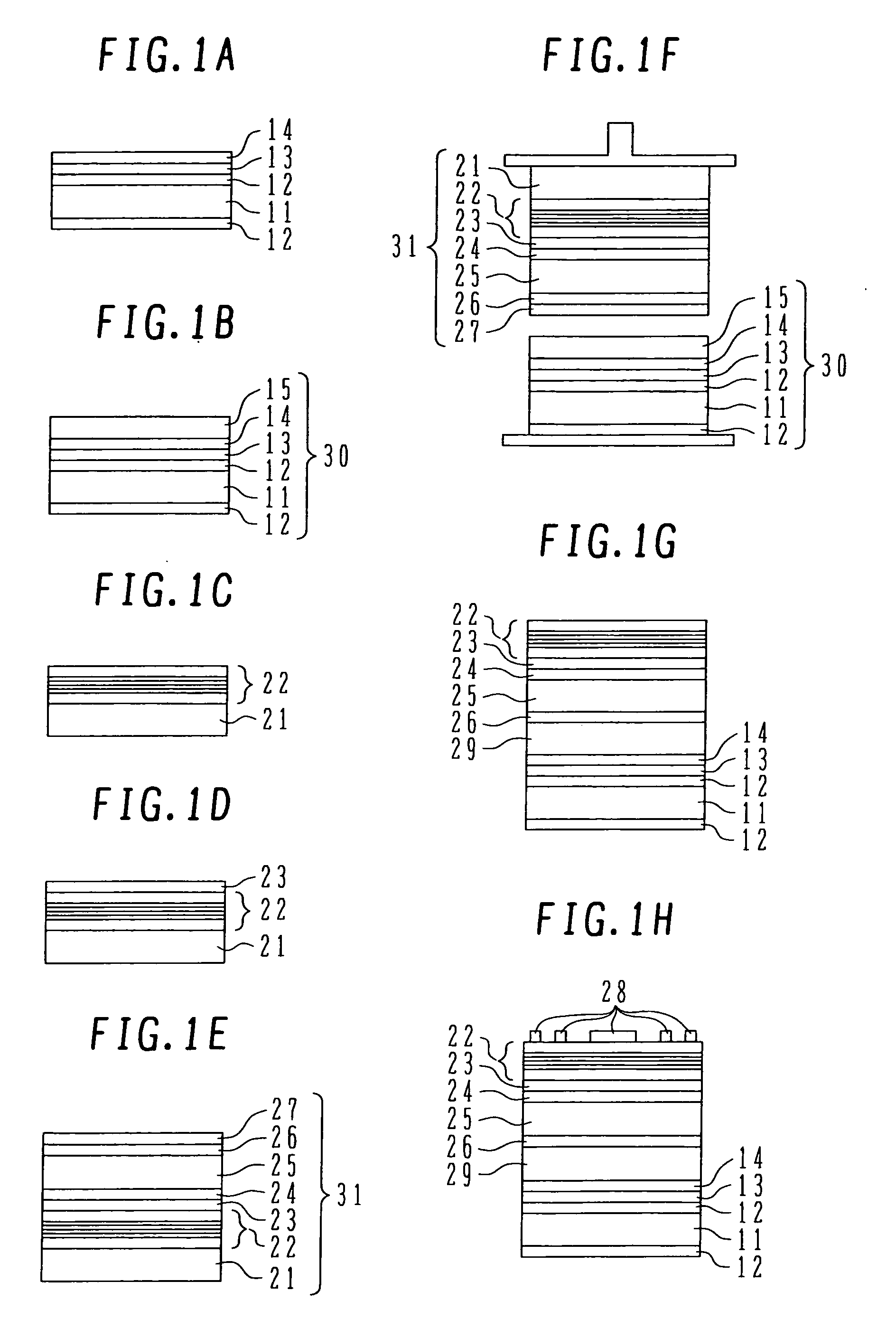

Semiconductor device, its manufacture method and electronic component unit

InactiveUS20060057817A1Quality improvementImprove tight adhesionSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A LED chip having first and second electrodes on opposite principal surfaces, is bonded to a substrate through a composite bonding layer. The composite bonding layer is formed when a support substrate including the substrate and a first bonding layer is bonded to a lamination structure including the LED, the first electrode and a second bonding layer. The first or second bonding layer contains at least part of eutectic composition. At least one of the support substrate and the lamination structure includes a diffusion material layer. The composite bonding layer is formed in such a manner that eutectic material contents are mixed with the other to form a first mixture, and that the first mixture is mixed with diffusion material to form a second mixture having a melting point higher than a melting point of the first mixture.

Owner:STANLEY ELECTRIC CO LTD

Thin-film solar cell and manufacture method therefor

InactiveUS20030168096A1Improve film qualityGood ohmic contactCellsVacuum evaporation coatingSemiconductorMetal

A thin-film solar cell including a transparent electrode layer, a semiconductor photovoltaic conversion layer, a rear transparent electrode layer and a rear reflective metal layer, said layers being formed in this order on a transparent substrate, wherein the rear transparent electrode has a two-layer structure of an ITO or ZnO:Ga layer and a ZnO:Al layer formed in this order on the semiconductor photovoltaic conversion layer.

Owner:SHARP KK

Composition for forming solar cell electrode and electrode produced from same

ActiveUS20150364622A1Good ohmic contactMinimize serial resistanceConductive materialNon-conductive material with dispersed conductive materialFritFill factor

A composition for solar cell electrodes and electrodes fabricated using the same. The composition includes silver powder; fumed silica; a glass frit; and an organic vehicle. The composition has improved contact efficiency between electrodes and a silicon wafer by introducing specific fumed silica. Solar cell electrodes fabricated using the composition exhibit minimized serial resistance, thereby providing excellent fill factor and conversion efficiency.

Owner:CHANGZHOU JUHE NEW MATERIAL CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com