Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70results about How to "Improved ohmic contact characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

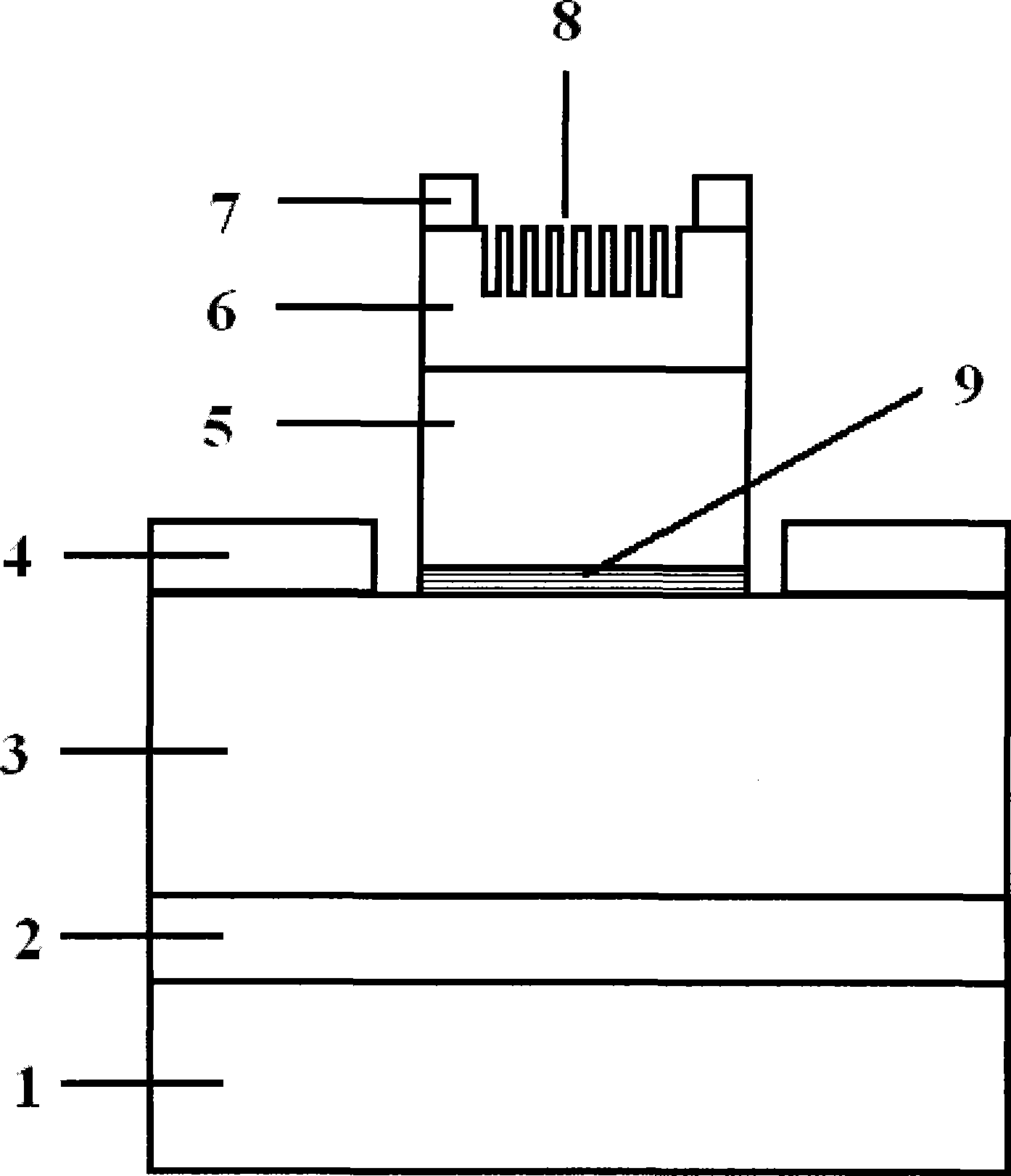

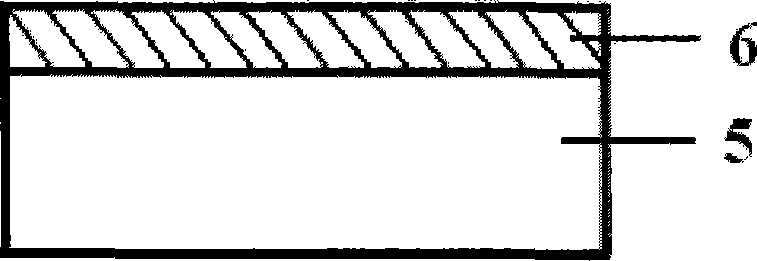

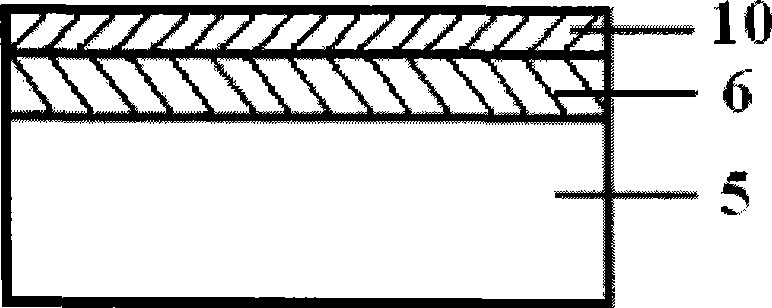

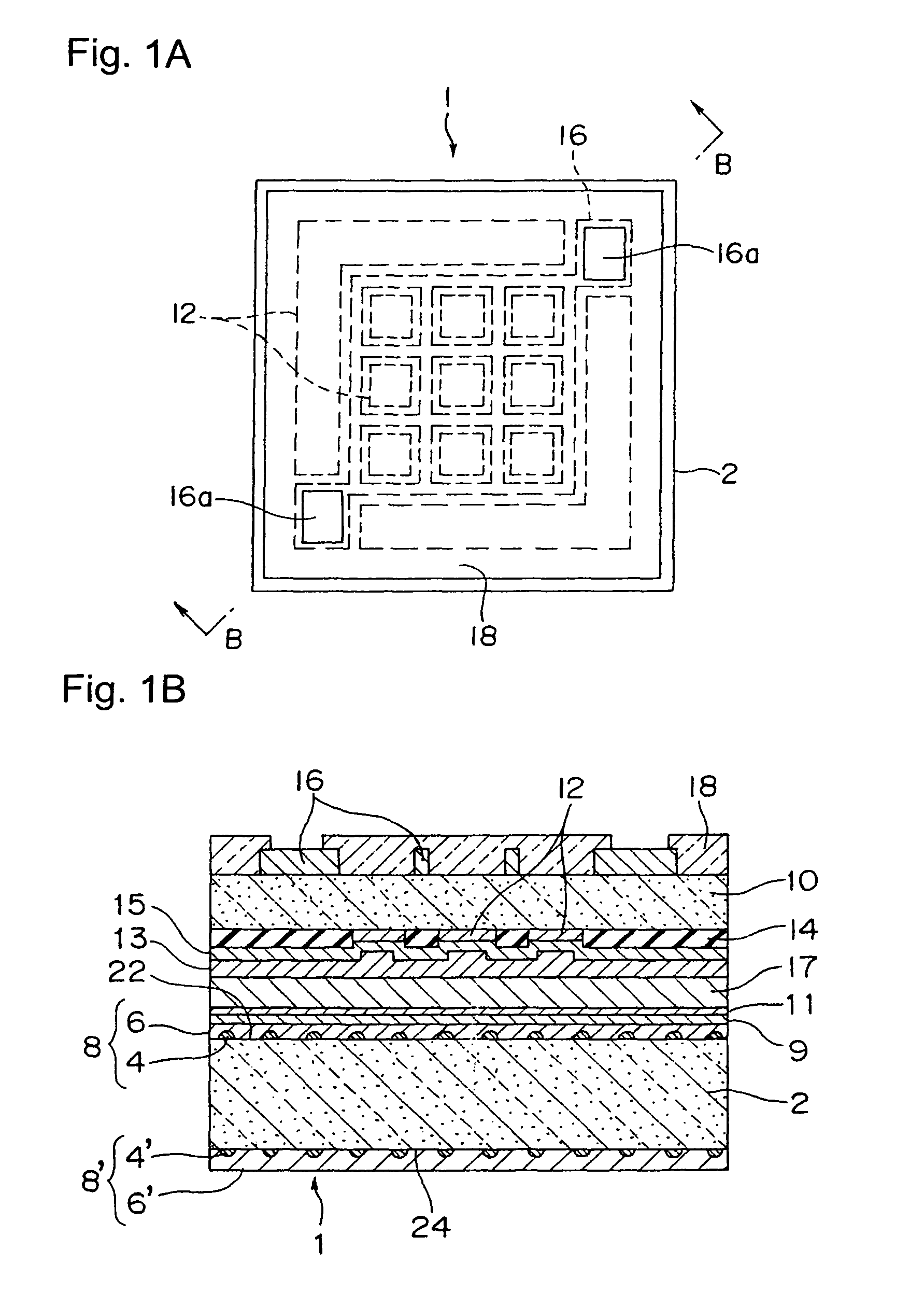

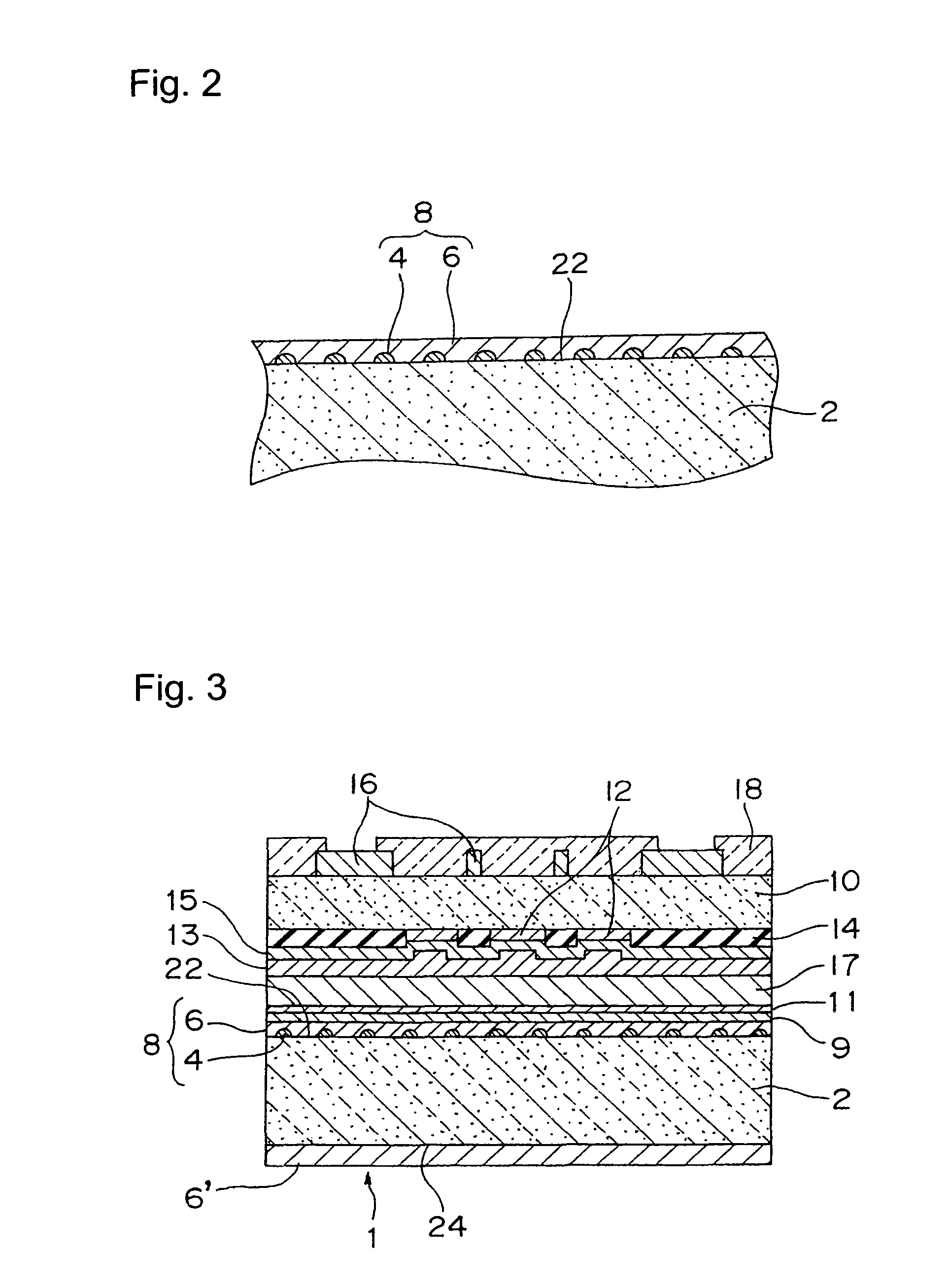

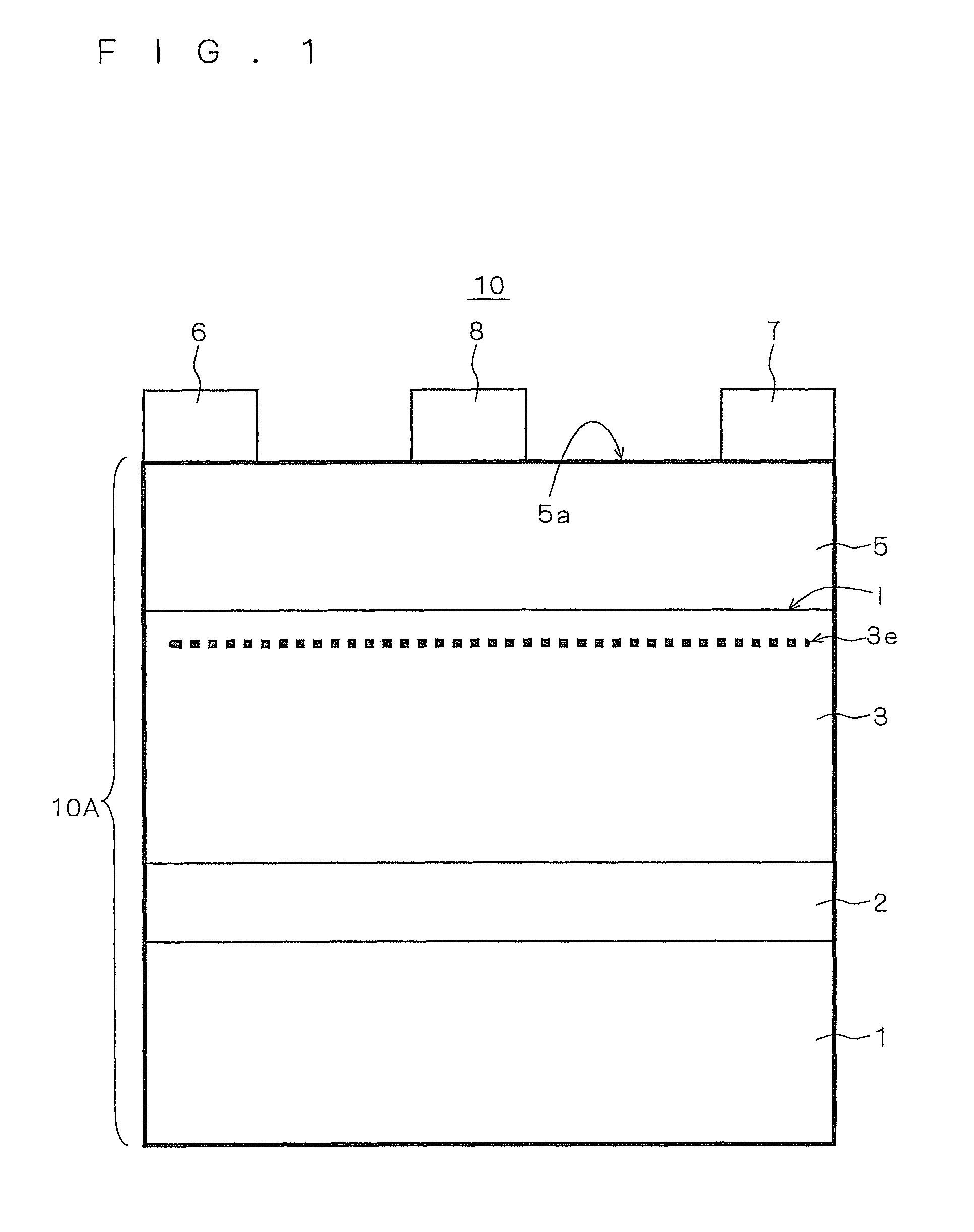

Nitride semiconductor device and method of manufacturing the same

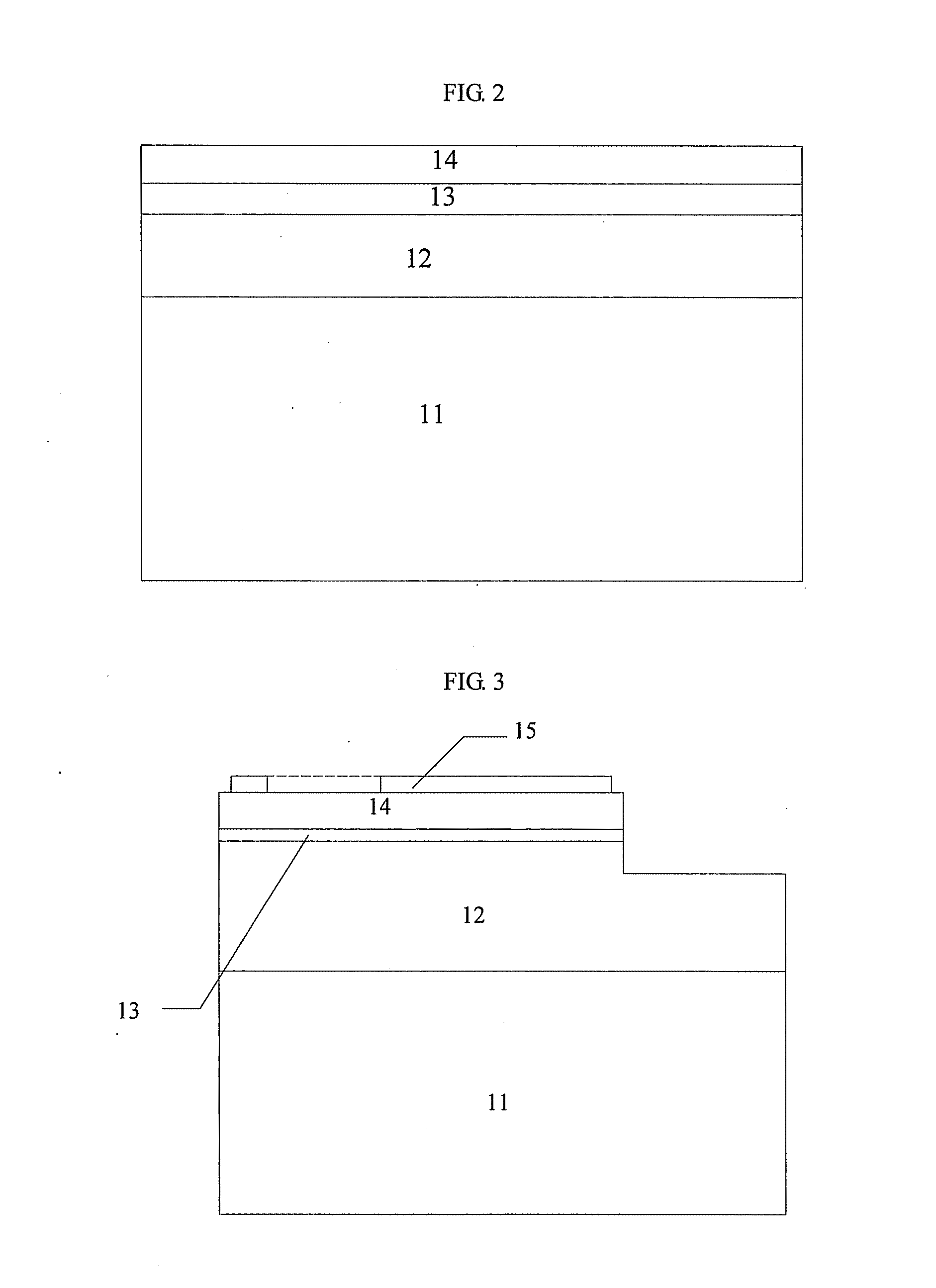

ActiveUS20080296627A1Improve adhesionImproved ohmic contact characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingContact formationOhmic contact

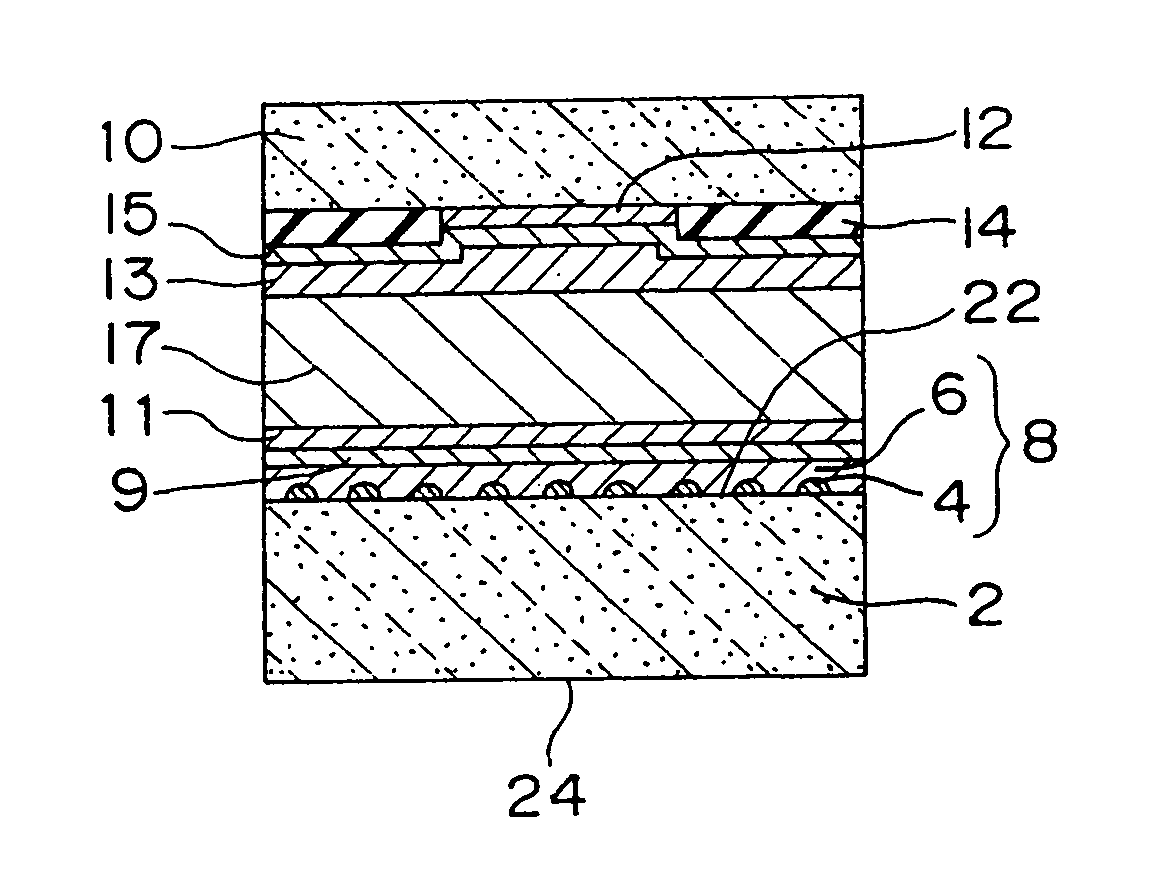

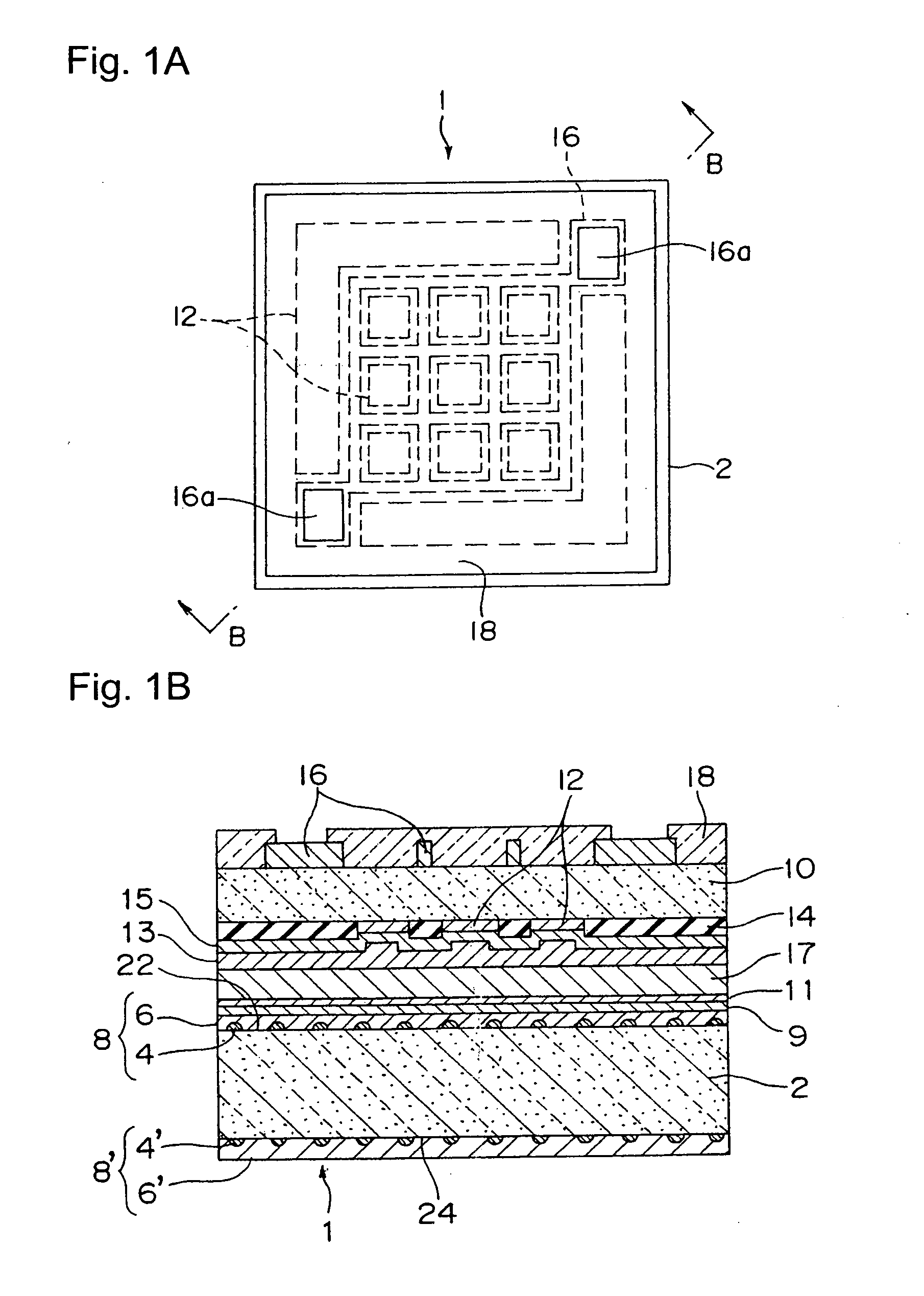

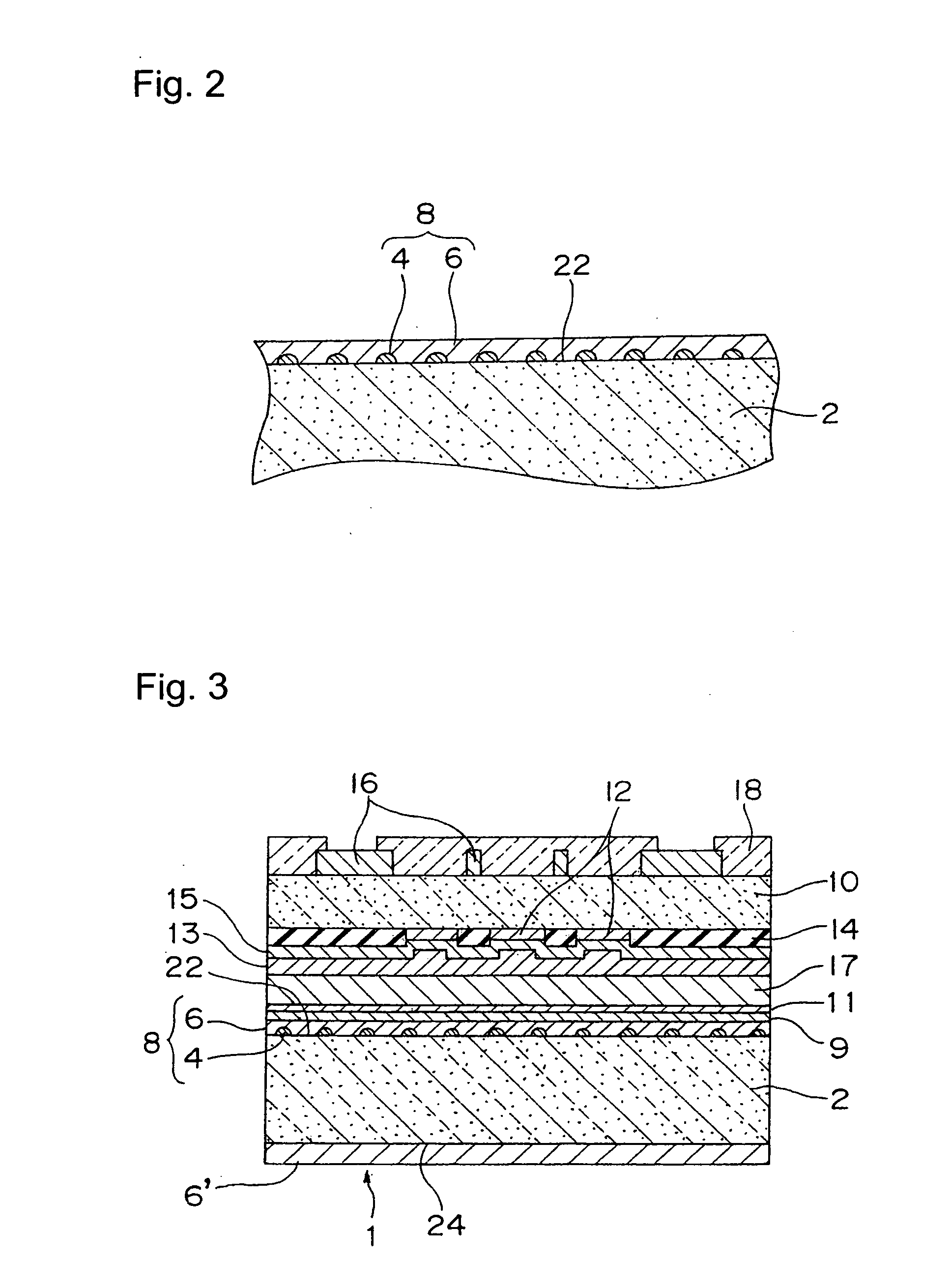

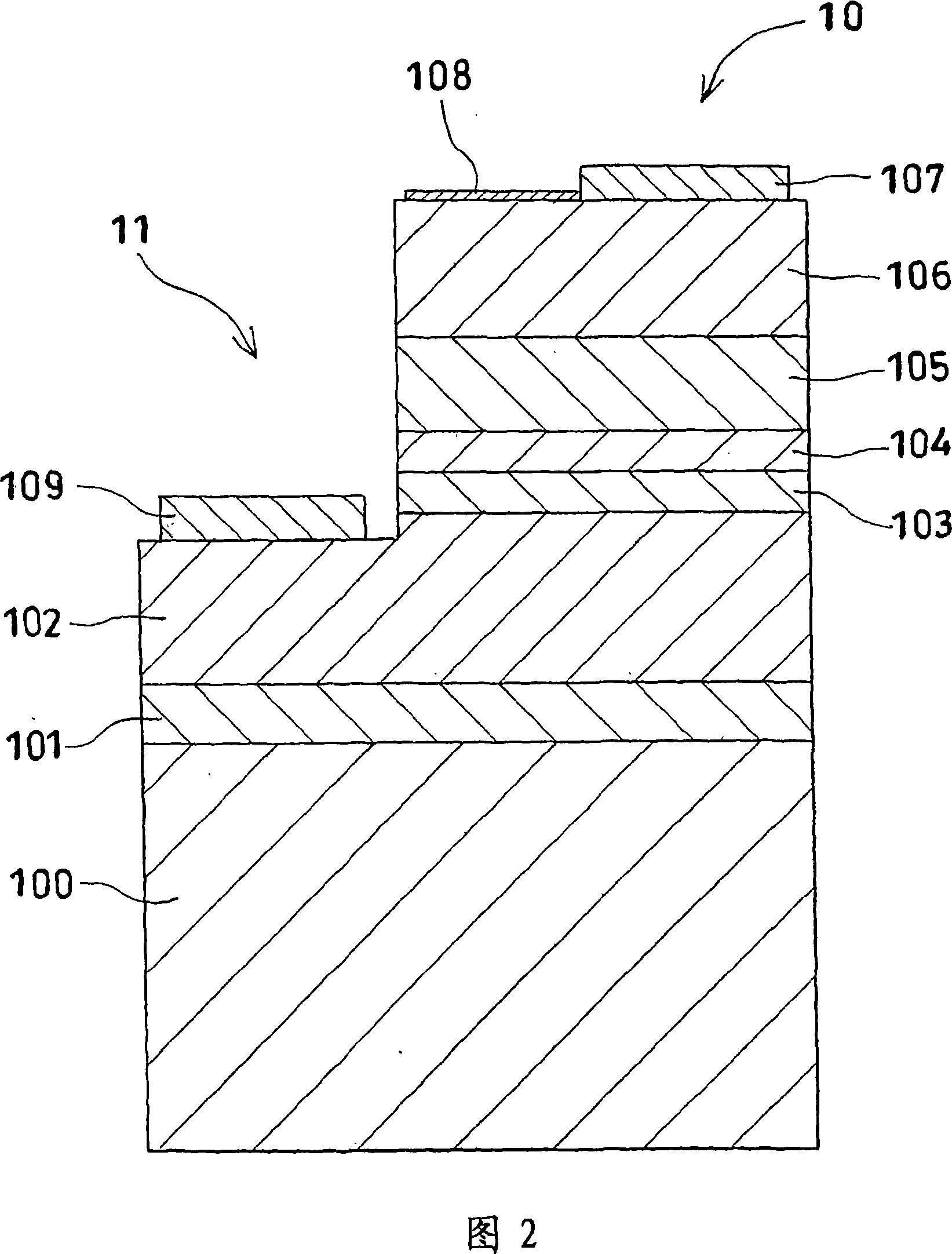

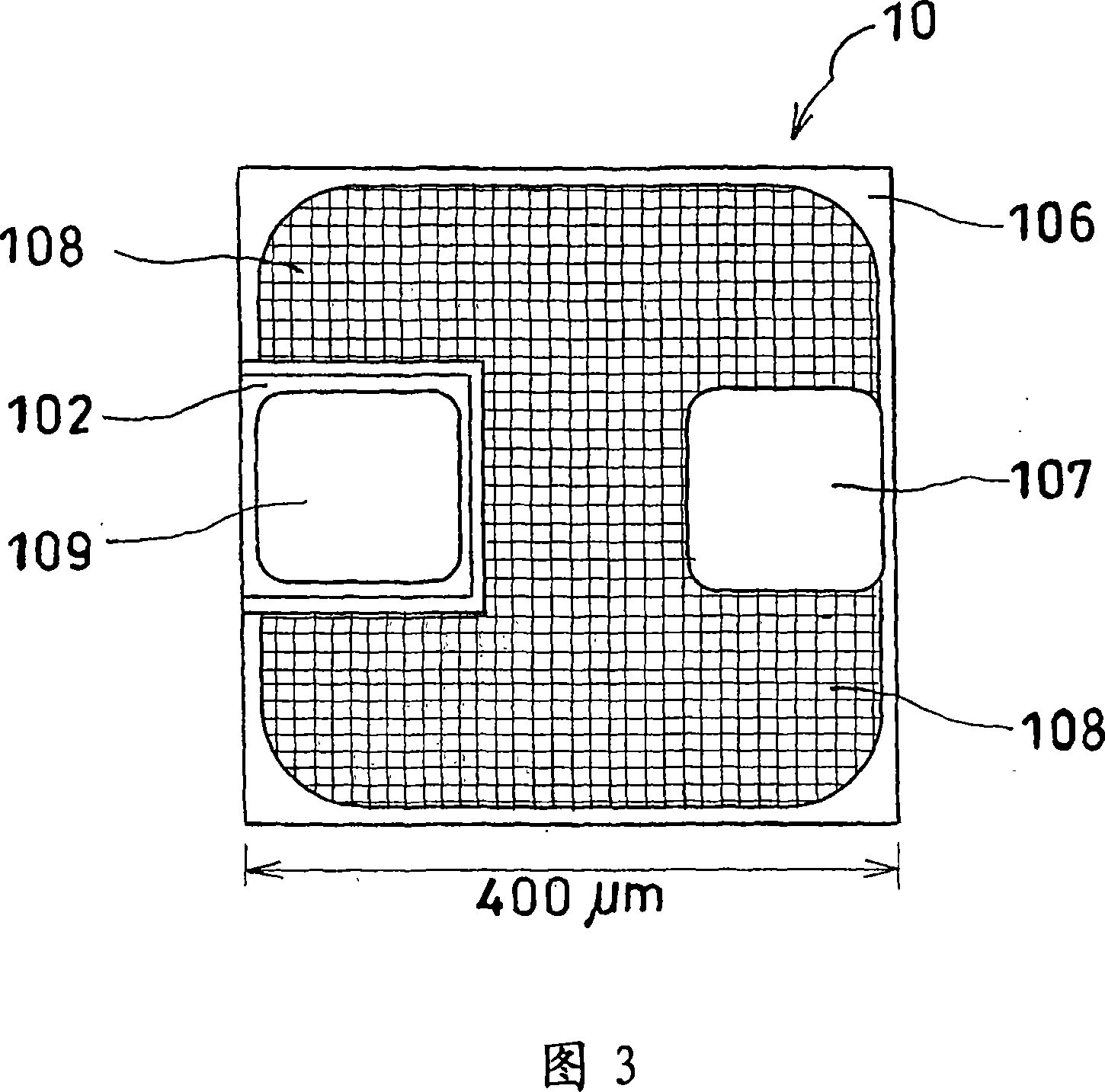

In the nitride semiconductor device using the silicon substrate, the metal electrode formed on the silicon substrate has both ohmic contact property and adhesion, so that the nitride semiconductor device having excellent electric properties and reliability is obtained. The nitride semiconductor device includes a silicon substrate (2), a nitride semiconductor layer (10) formed on the silicon substrate (2), and metal electrodes (8, 8′) formed in contact with the silicon substrate (2). The metal electrodes (8, 8′) has first metal layers (4, 4′) which are formed in a shape of discrete islands and in contact with the silicon substrate (2), and second metal layers (6, 6′) which are in contact with the silicon substrate (2) exposed among the islands of the first metal layers (4, 4′) and are formed to cover the first metal layers (4, 4′). Further, the second metal layers (6, 6′) are made of a metal capable of forming ohmic contact with silicon, and the first metal layers (4, 4′) are made of an alloy containing a metal and silicon, in which the metal is different than that in the second metal layer (6,6′).

Owner:NICHIA CORP

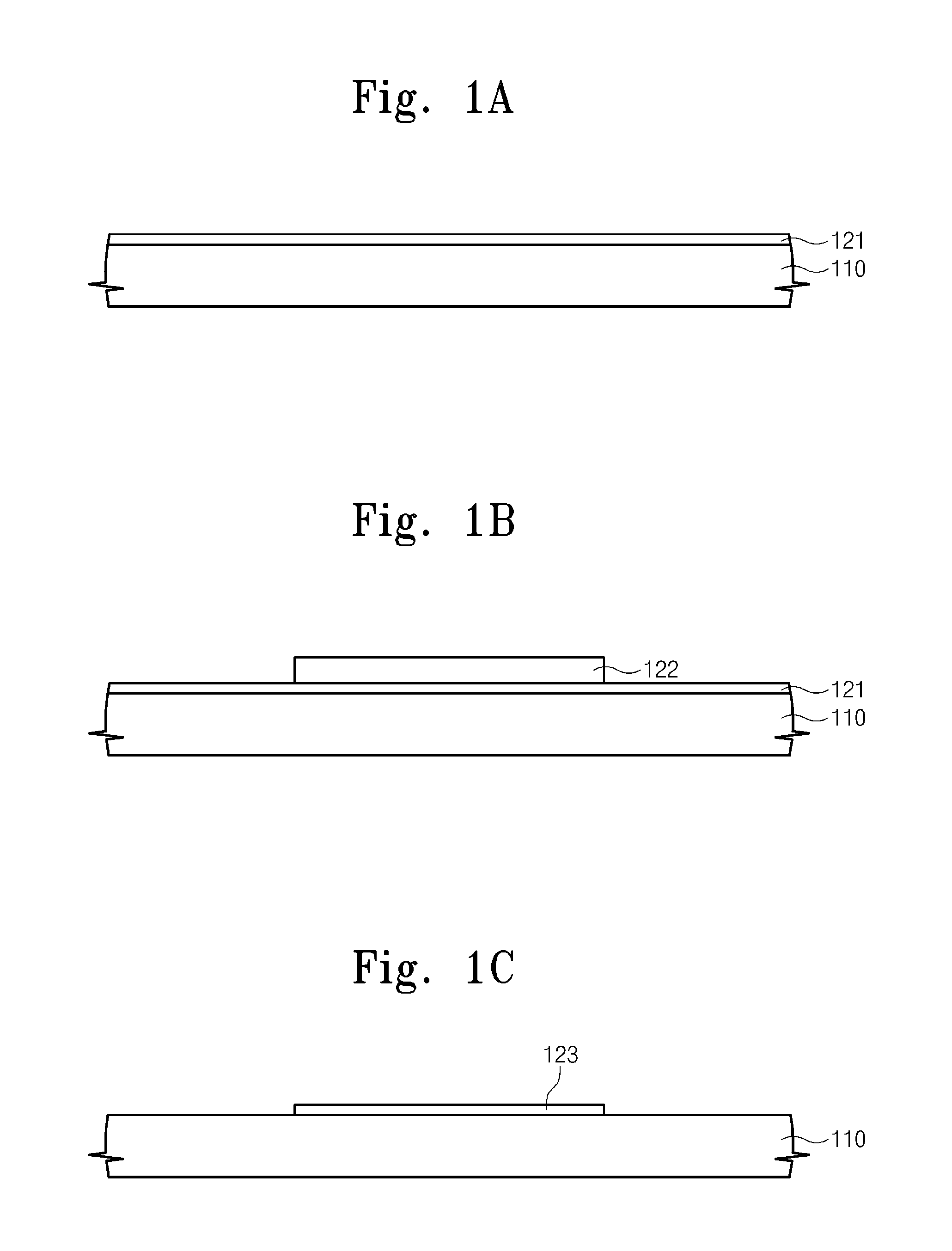

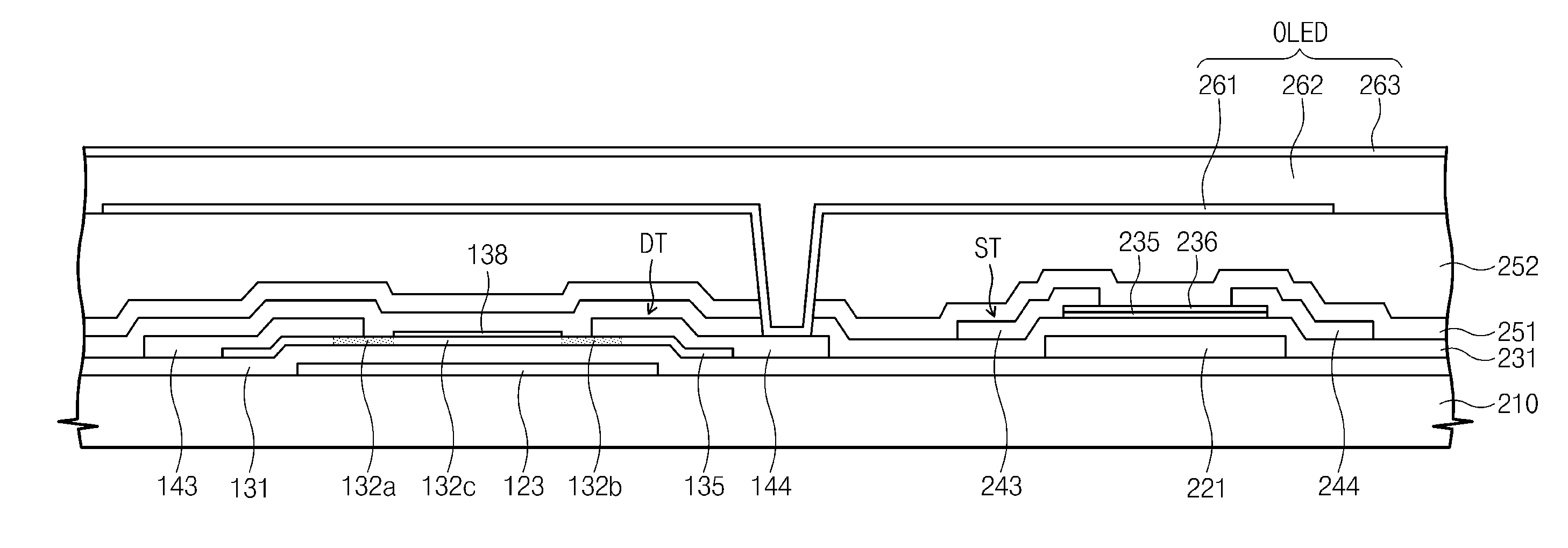

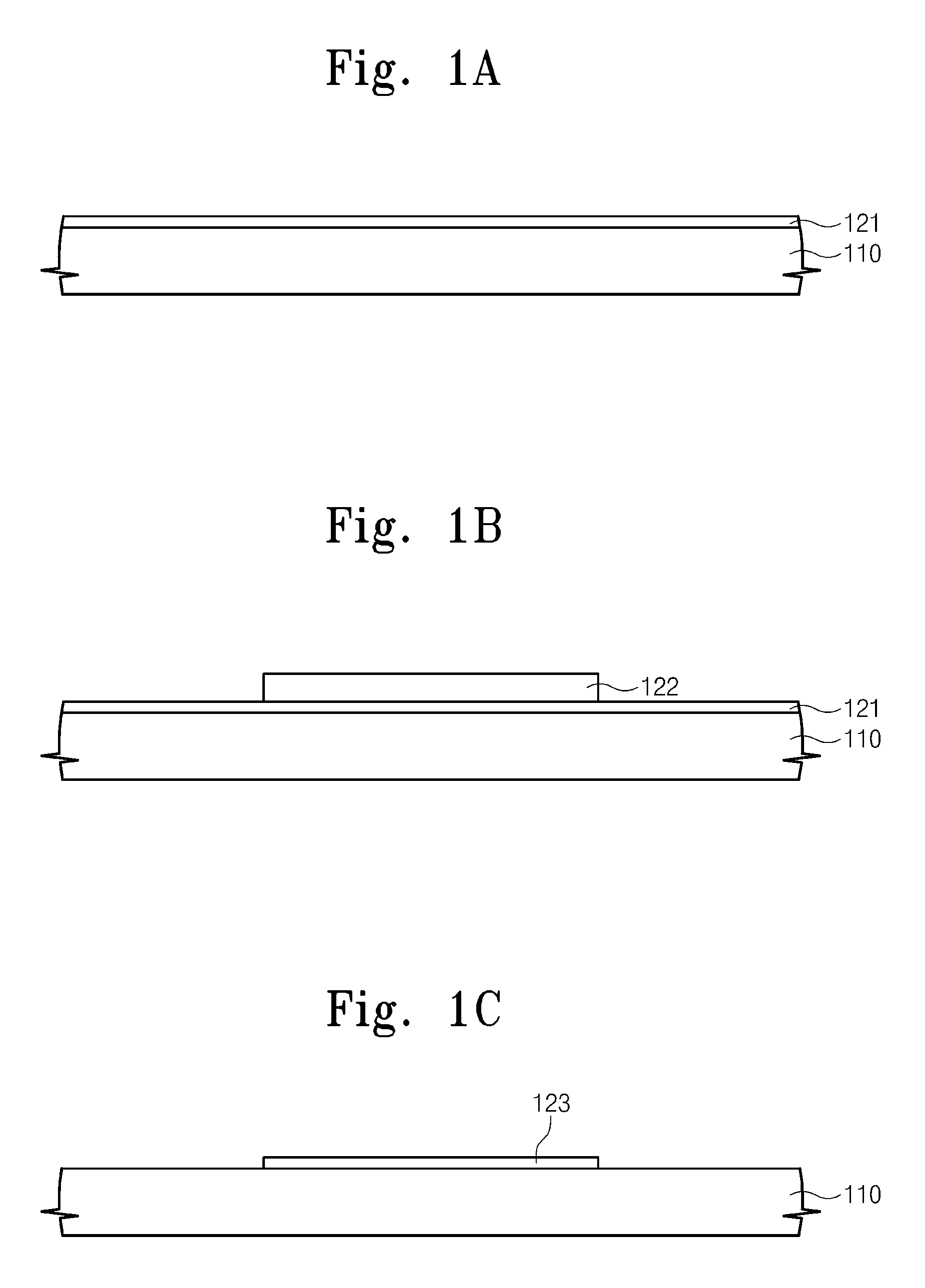

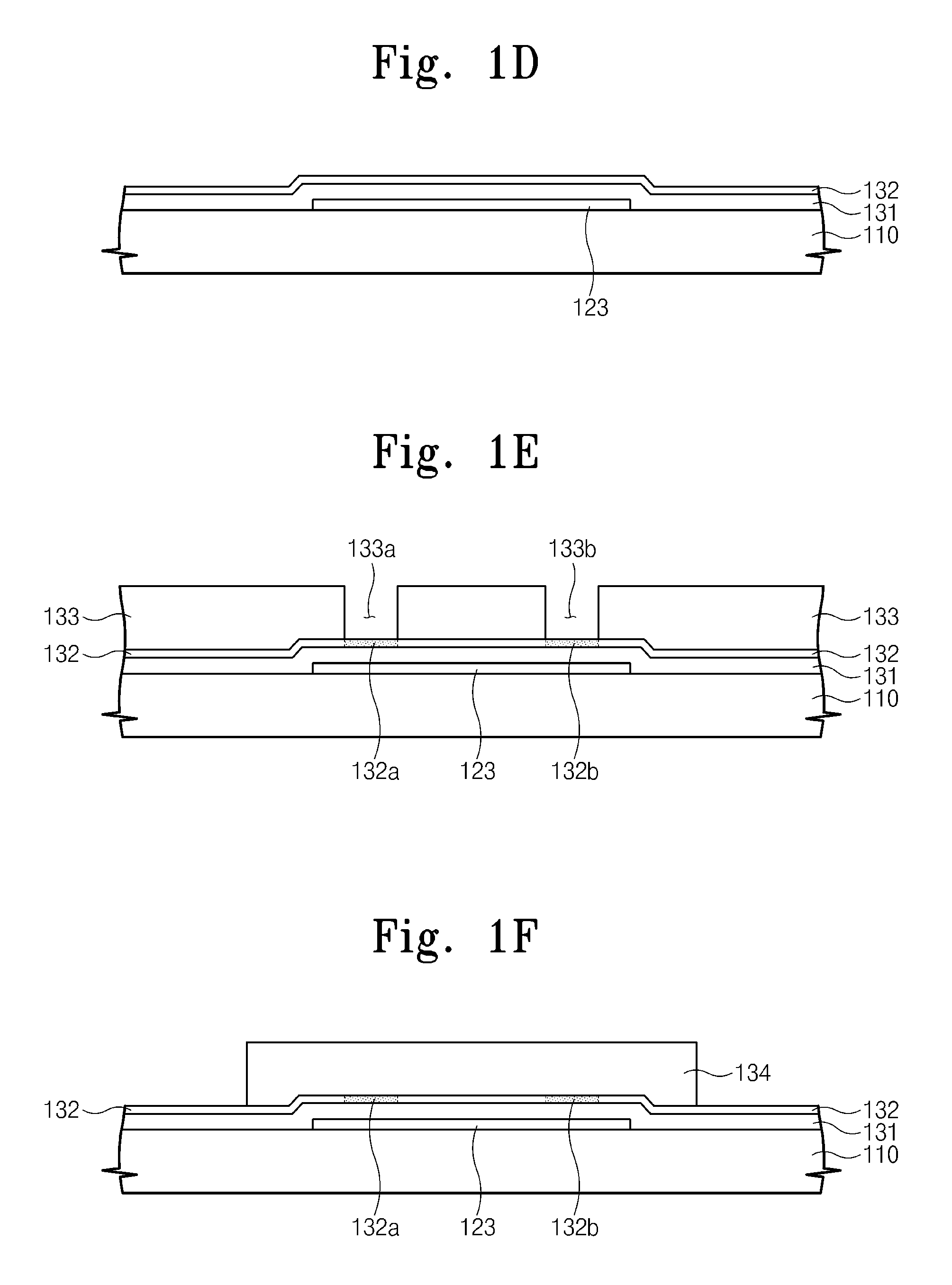

Method of manufacturing transistor and method of manufacturing organic electroluminescence display using the same

InactiveUS20100001284A1Improved ohmic contact characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactDisplay device

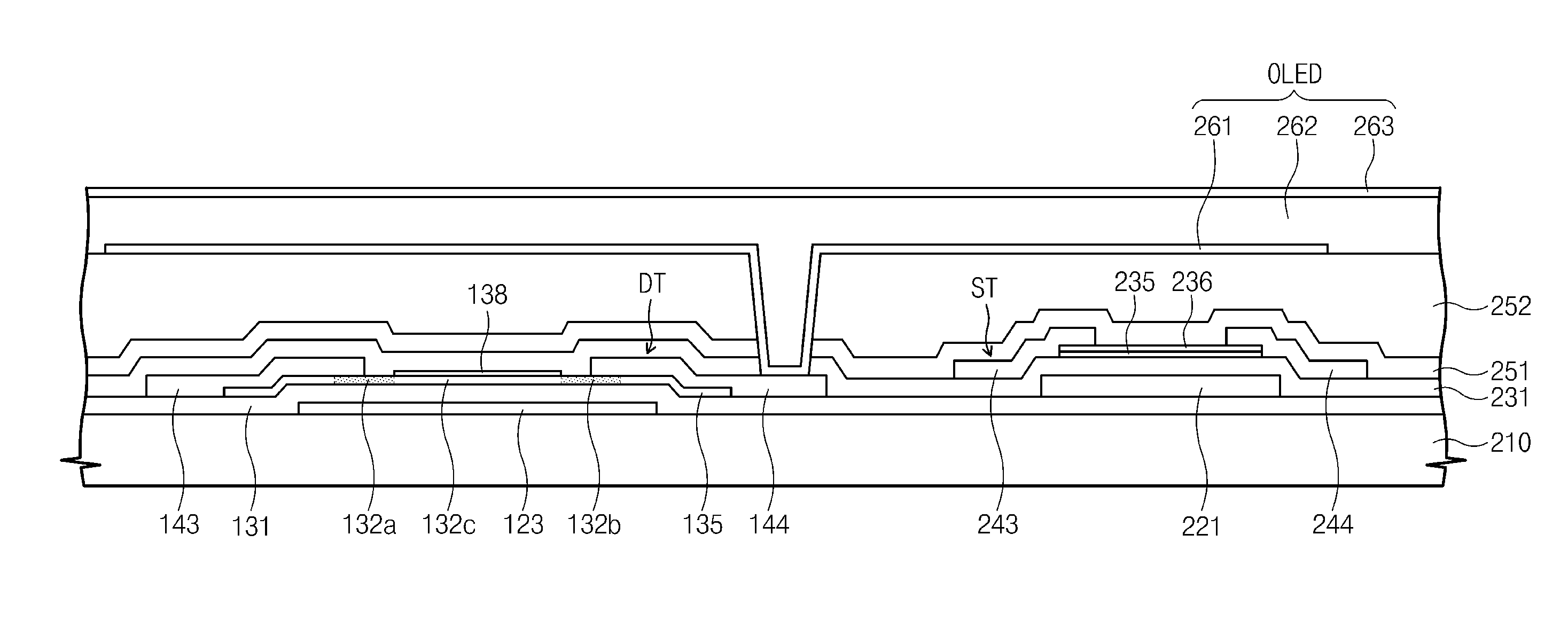

A method of manufacturing a transistor and a method of manufacturing an organic electroluminescence display are disclosed. When an amorphous silicon layer is crystallized, a silicon oxide layer formed on a polysilicon layer is subsequently patterned. Impurity ions are implanted into first and second regions of the amorphous silicon layer to form first and second doped regions. The silicon oxide layer is patterned so that the silicon oxide layer may be removed from an ohmic contact region of the polysilicon layer, and covers only a channel region of the polysilicon layer.

Owner:SAMSUNG DISPLAY CO LTD

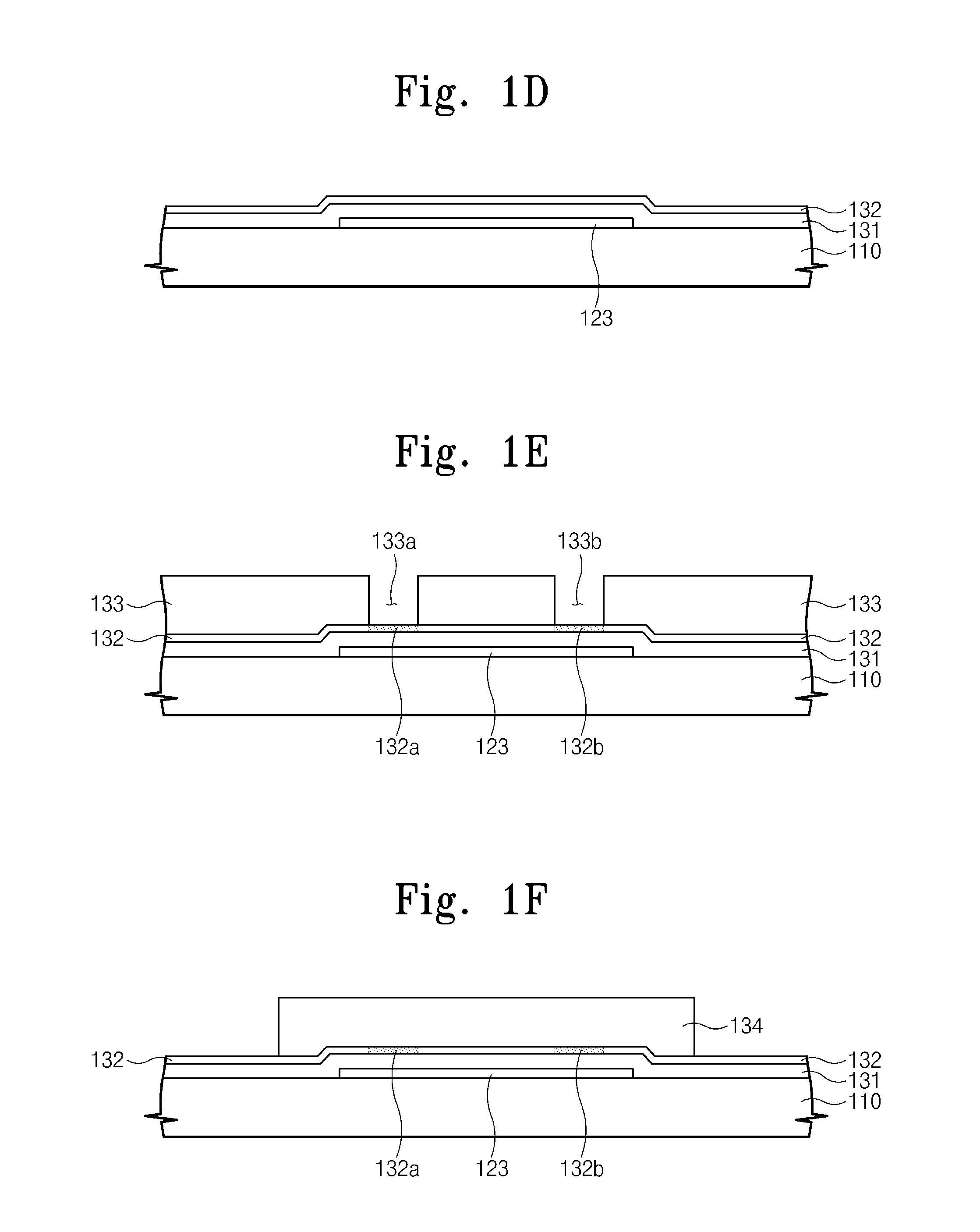

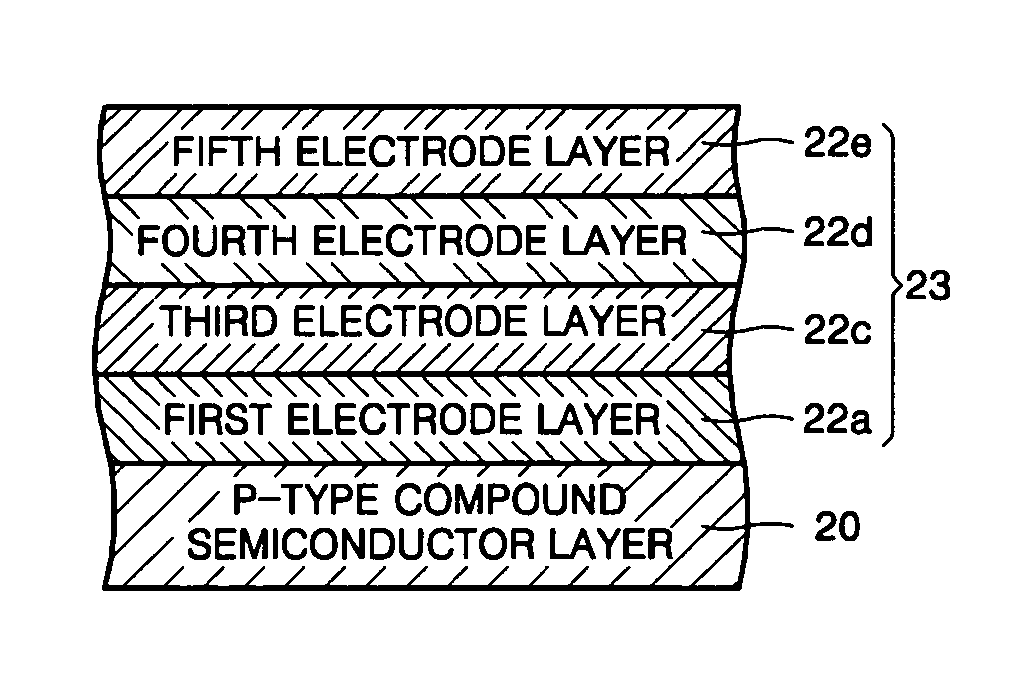

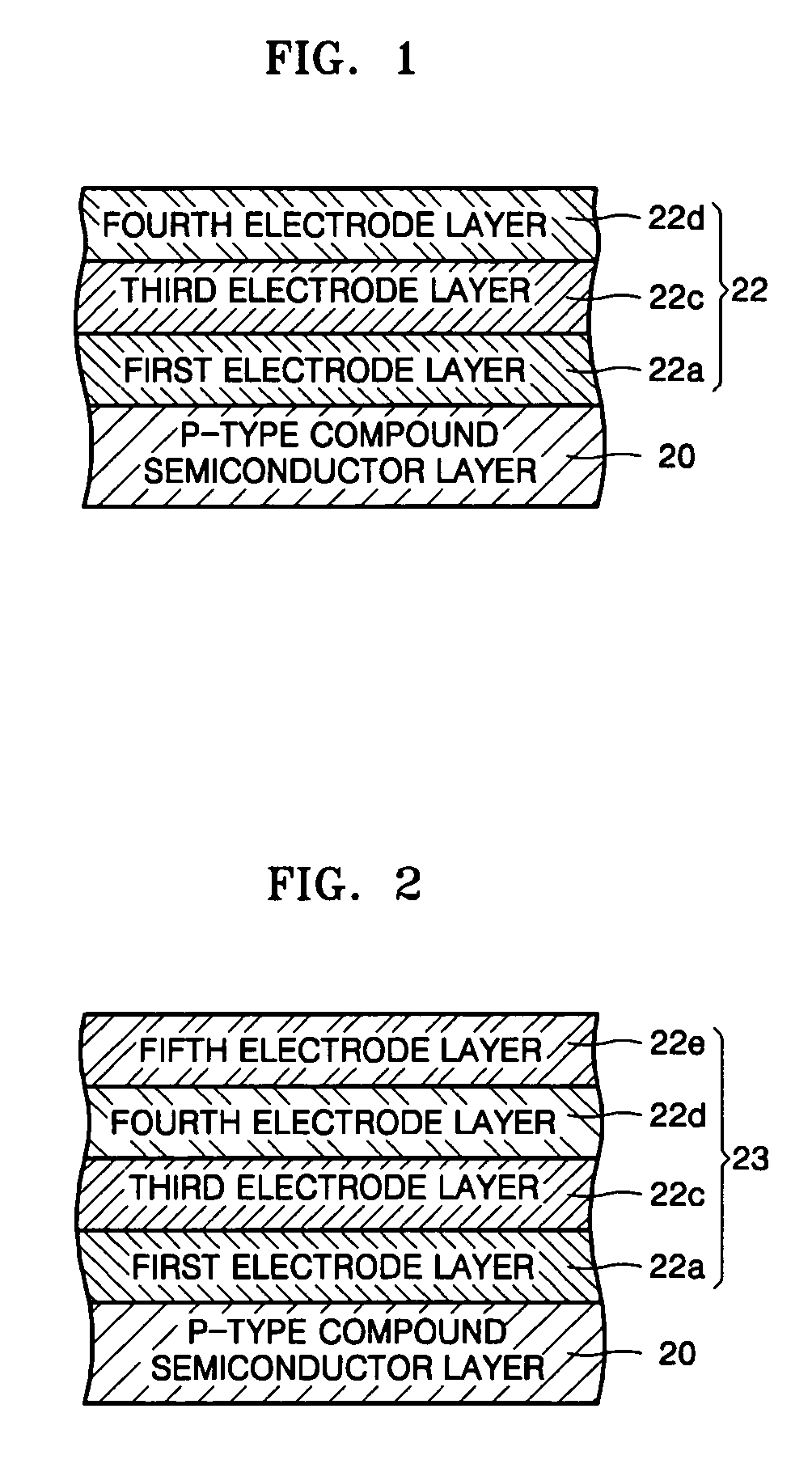

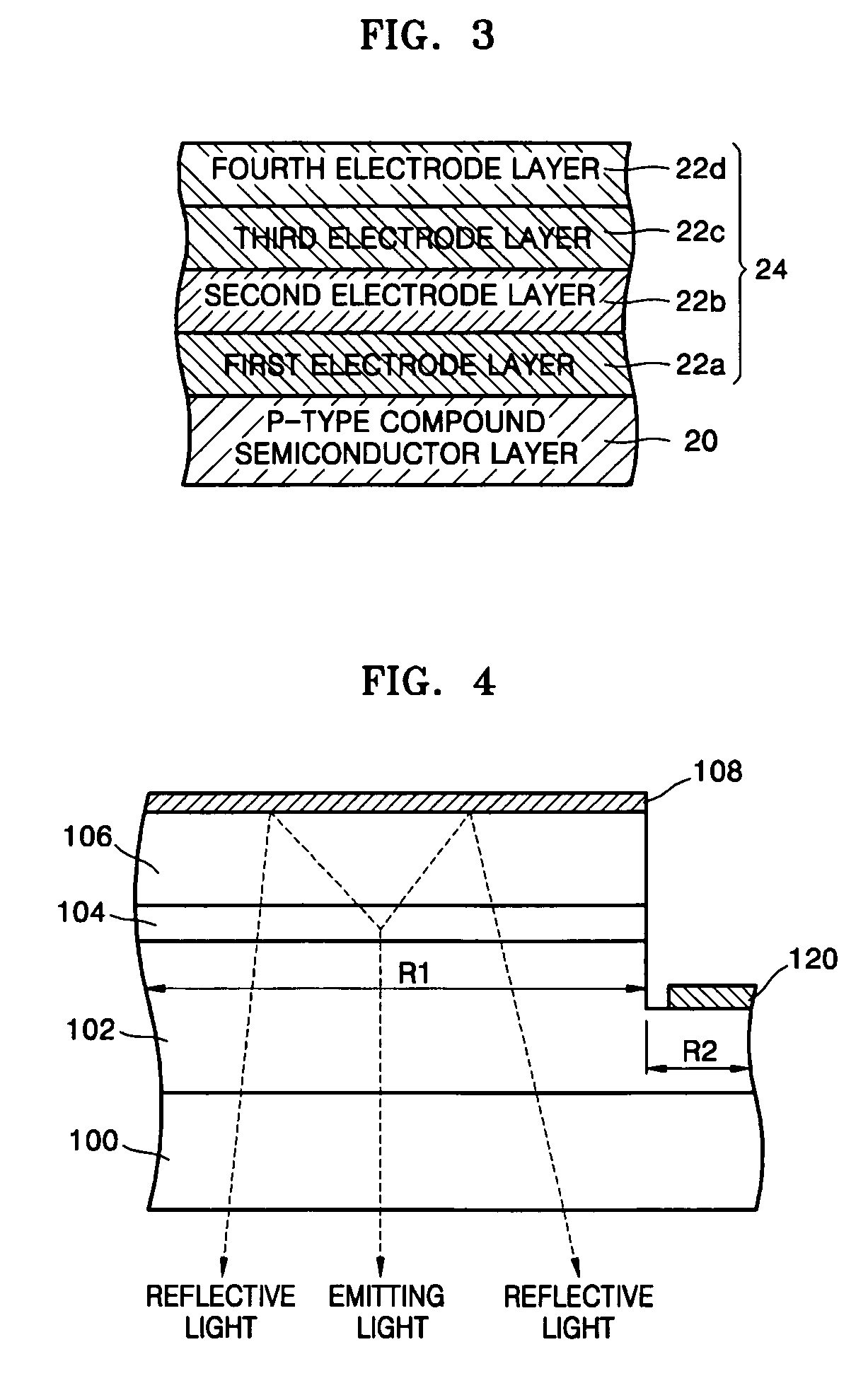

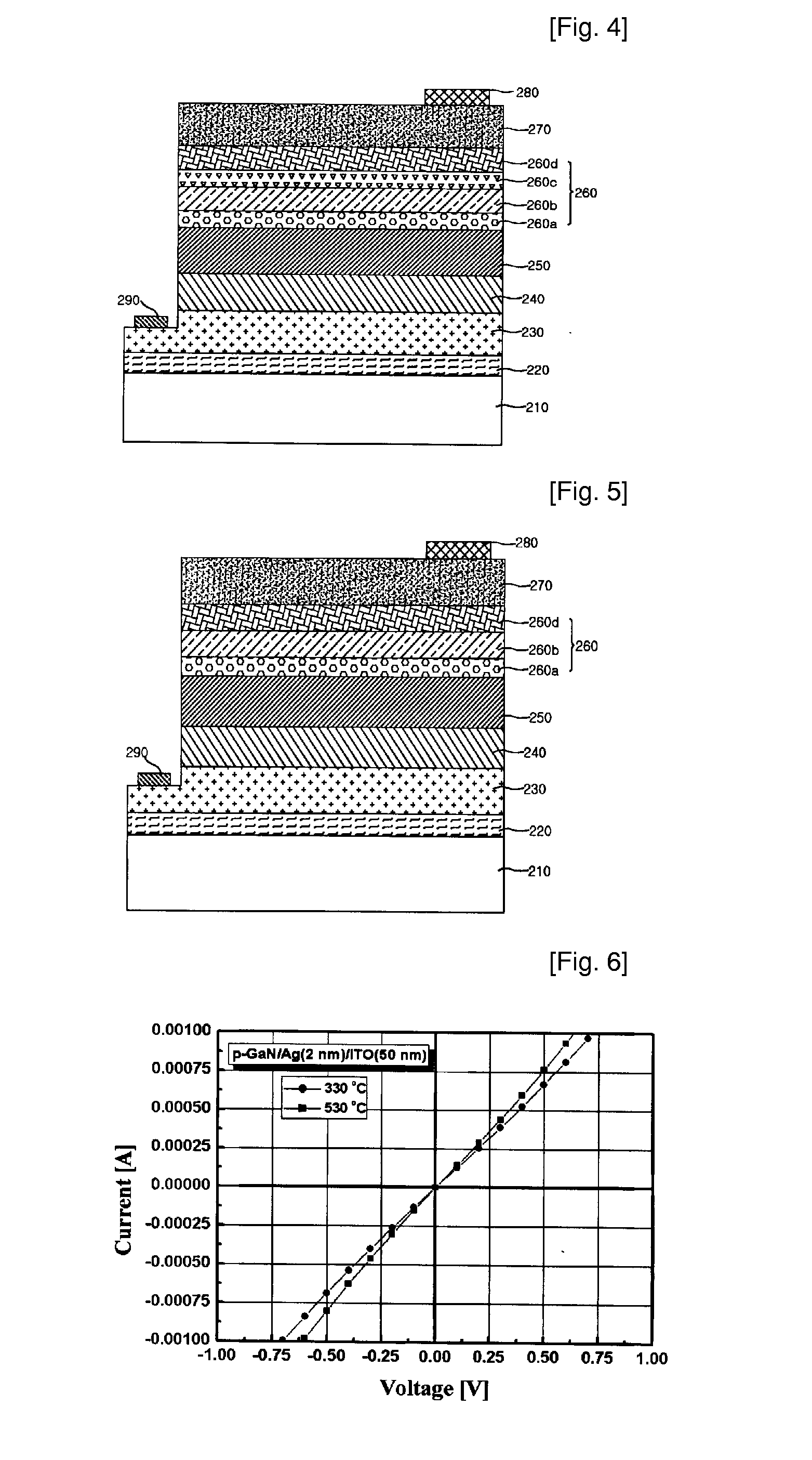

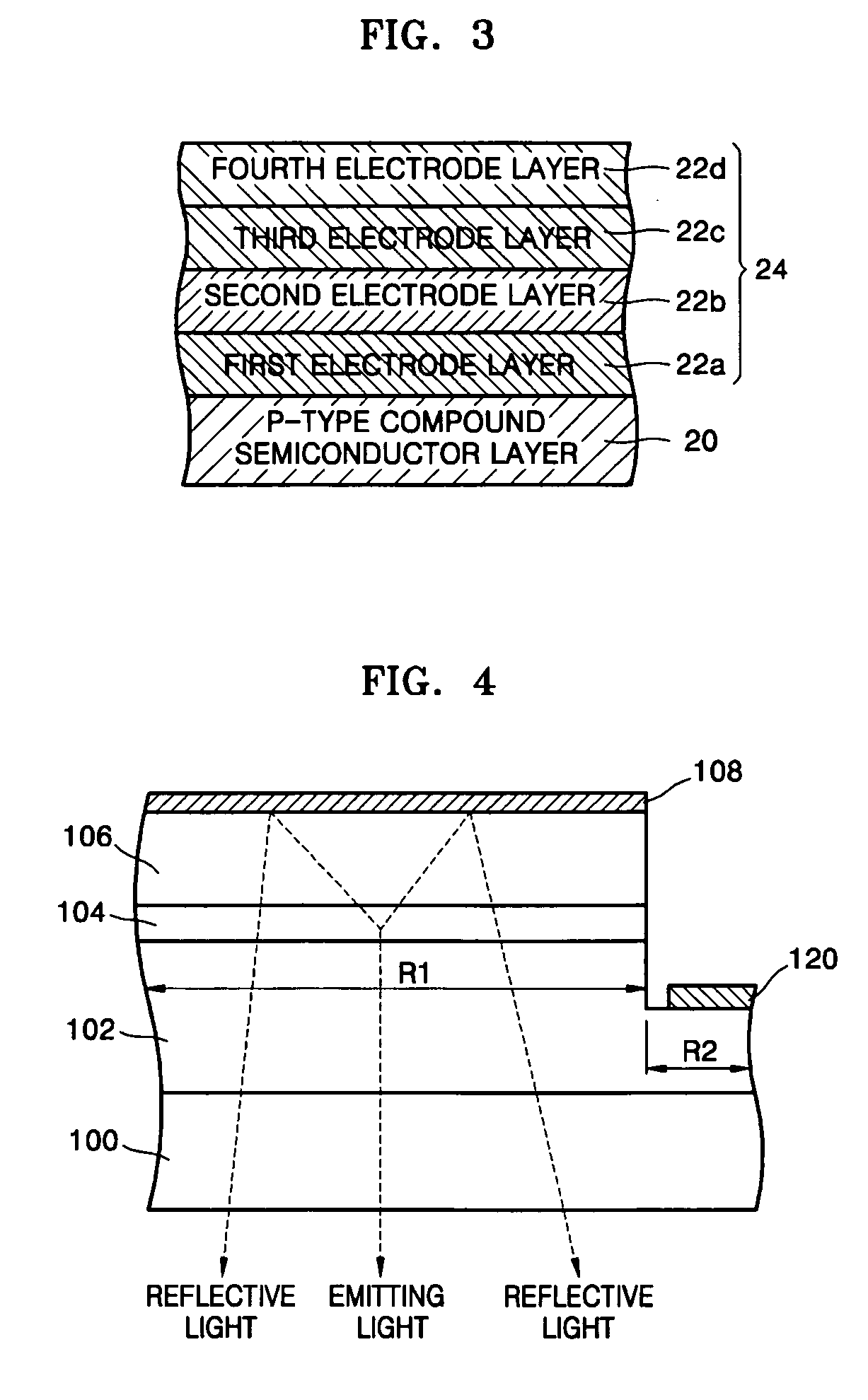

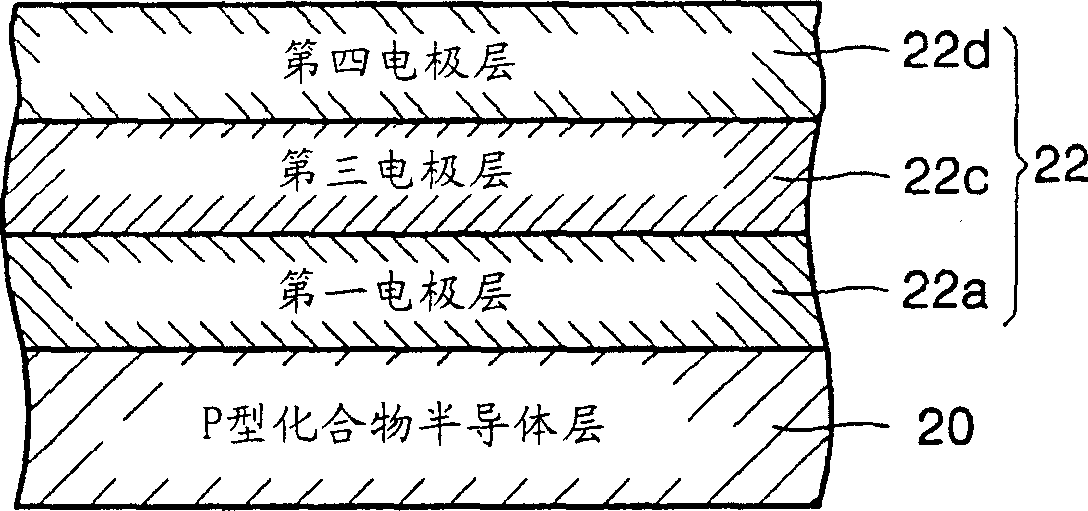

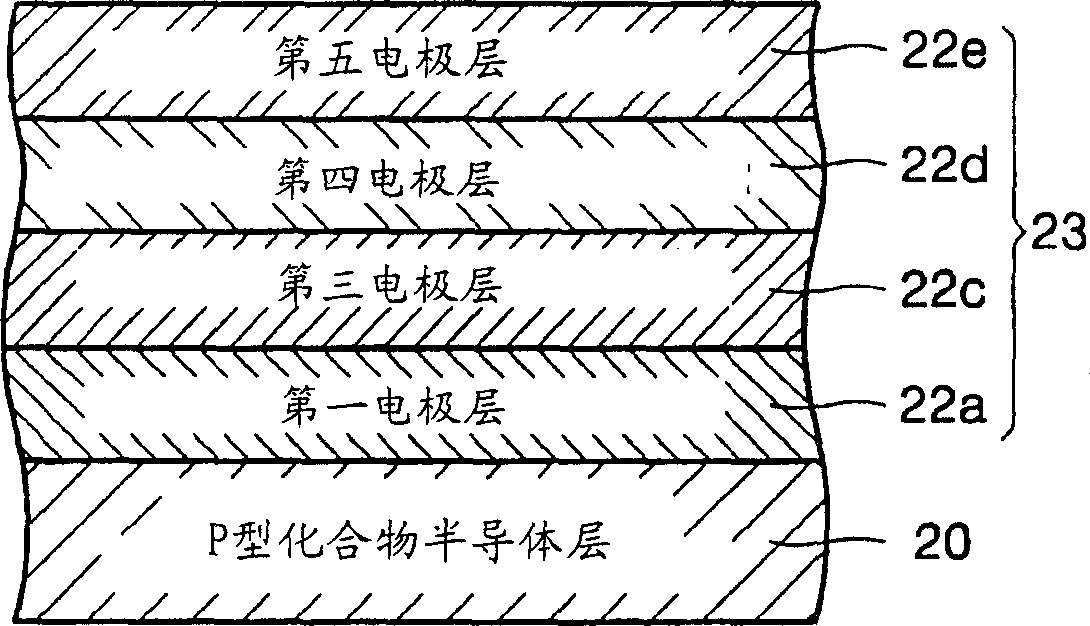

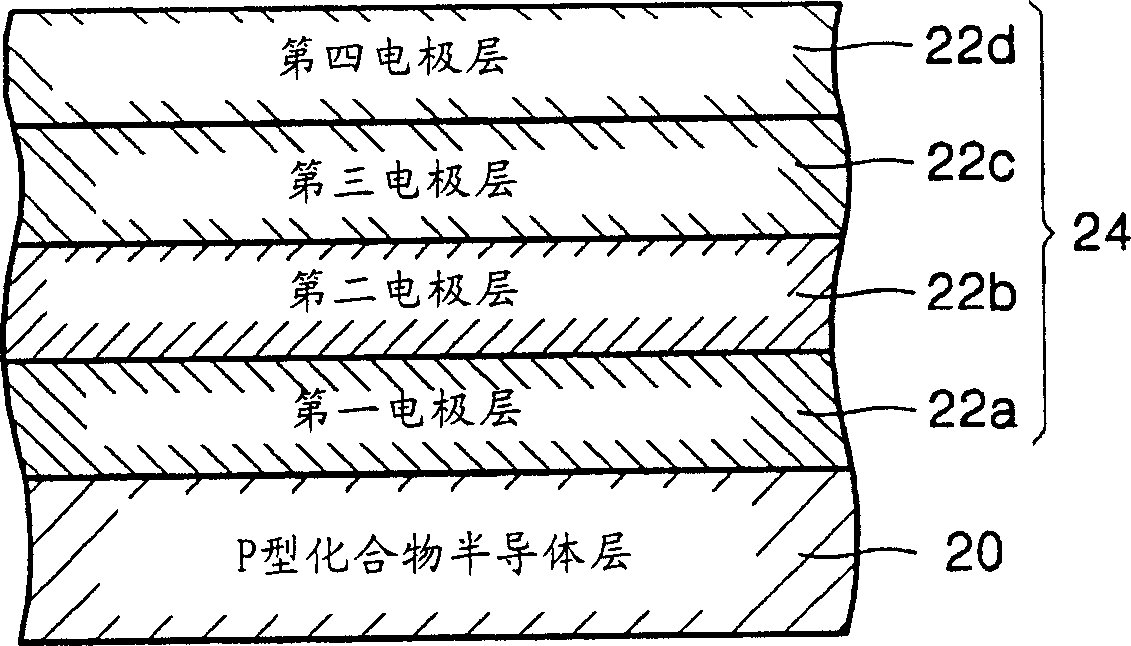

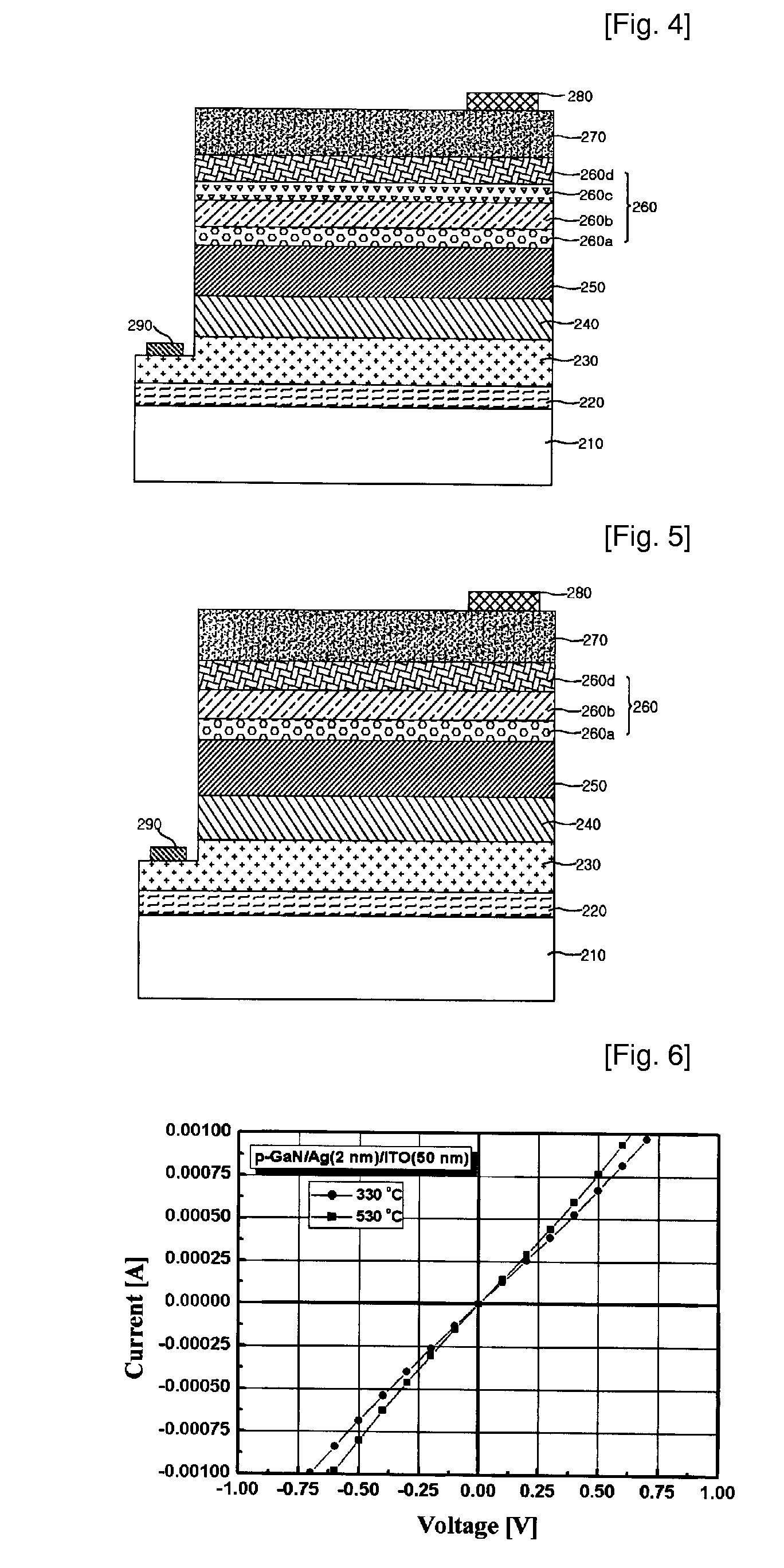

Reflective electrode and compound semiconductor light emitting device including the same

InactiveUS7973325B2Reduce contact resistanceImprove reflectivityLaser optical resonator constructionSemiconductor/solid-state device detailsOhmic contactAlloy

Provided are a reflective electrode and a compound semiconductor light emitting device having the reflective electrode, such as LED or LD is provided. The reflective electrode formed on a p-type compound semiconductor layer of a compound semiconductor light emitting device, comprising a first electrode layer formed one of a Ag and Ag-alloy and forms an ohmic contact with the p-type compound semiconductor layer, a third electrode layer formed of a material selected from the group consisting of Ni, Ni-alloy, Zn, Zn-alloy, Cu, Cu-alloy, Ru, Ir, and Rh on the first electrode layer, and a fourth electrode layer formed of a light reflective material on the third electrode layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Production method for GaN based LED

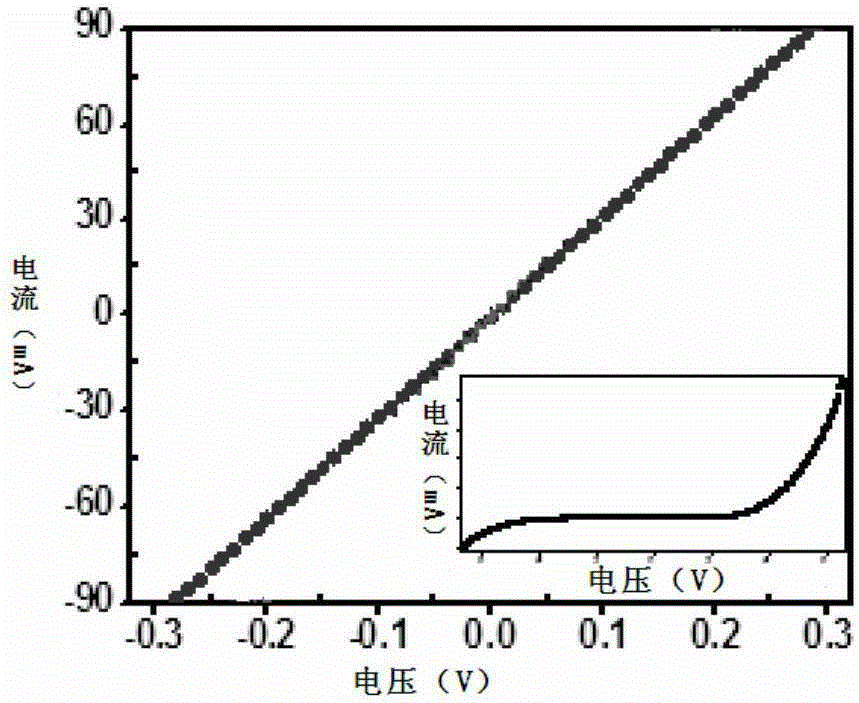

InactiveCN101488551AReasonable selection of electrode materialsThe synthesis process is simple and matureSemiconductor devicesGratingPhotonic crystal

The invention discloses a method for manufacturing GaN-based LED using a CNT thin film as a transparent conducting electrode, comprising growth of epitaxial layers of semiconductors, manufacturing of the transparent conducting electrode of the CNT thin film on the surface of a p-shaped GaN layer, manufacturing of two dimensional CNT thin film photonic crystal, formation of N-shaped metal electrode and manufacturing of P-shaped electrode. The method can effectively improve the light extracting rate of the front of LED and simultaneously solve the problem that the transparent conducting electrode contacts ohm of P-GaN. In terms of technique, materials of electrode are reasonably selected and nano-imprint technique is adopted, therefore, the method is characterized by low manufacturing cost and high production efficiency and grating resolution.

Owner:HUAZHONG UNIV OF SCI & TECH

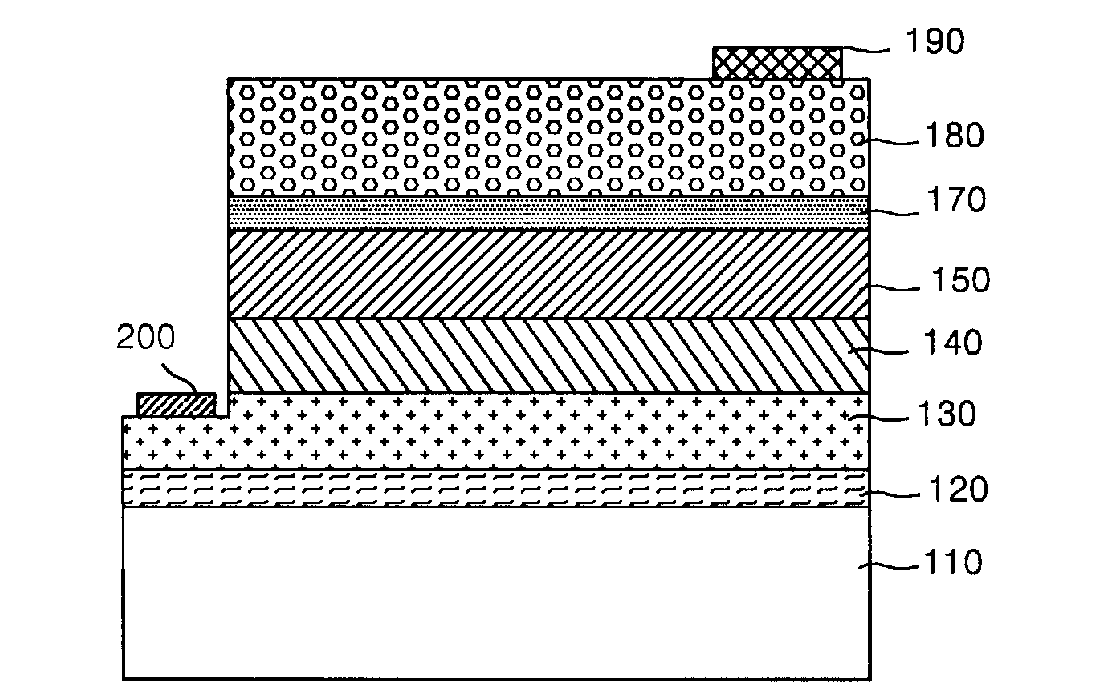

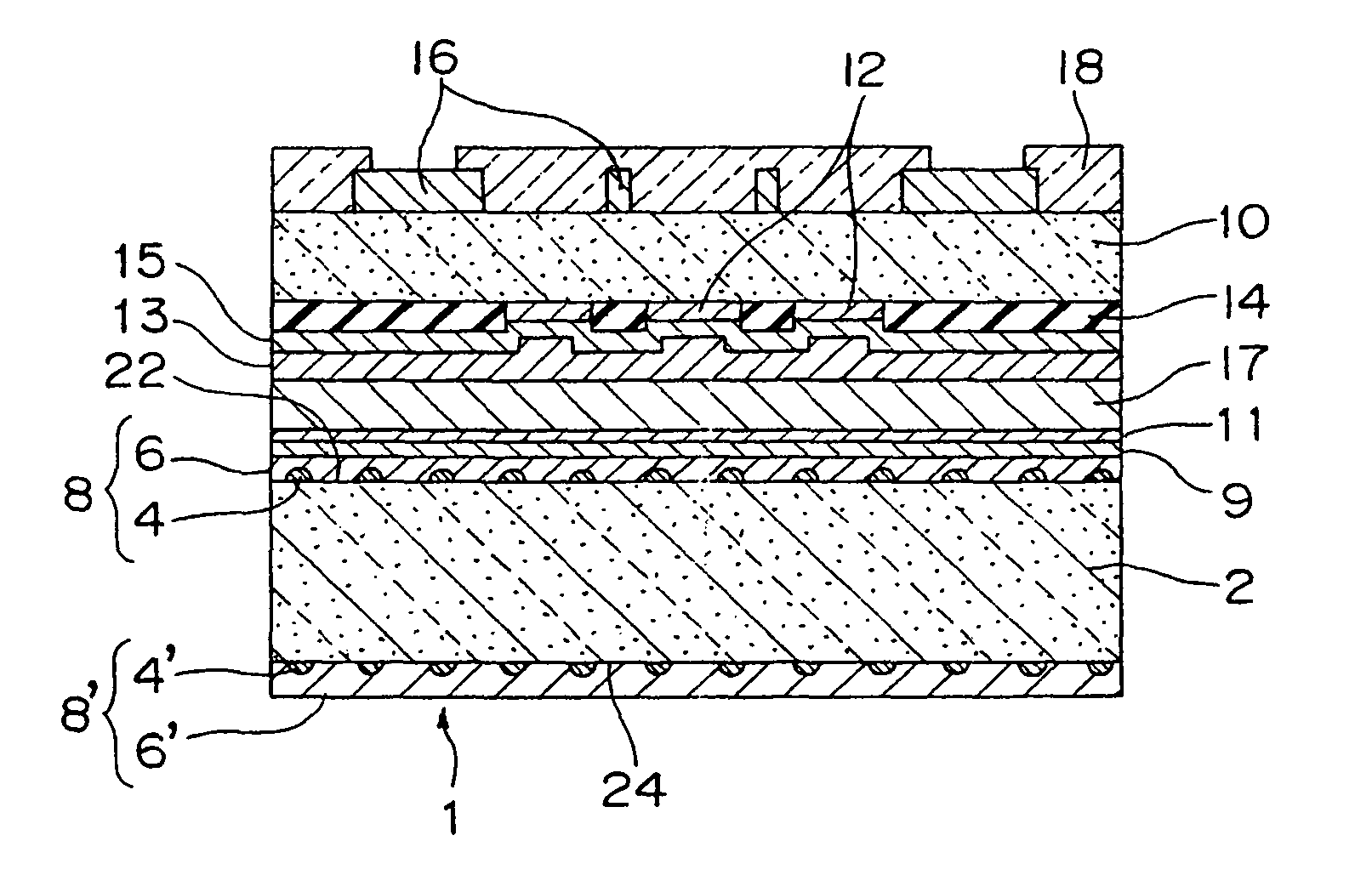

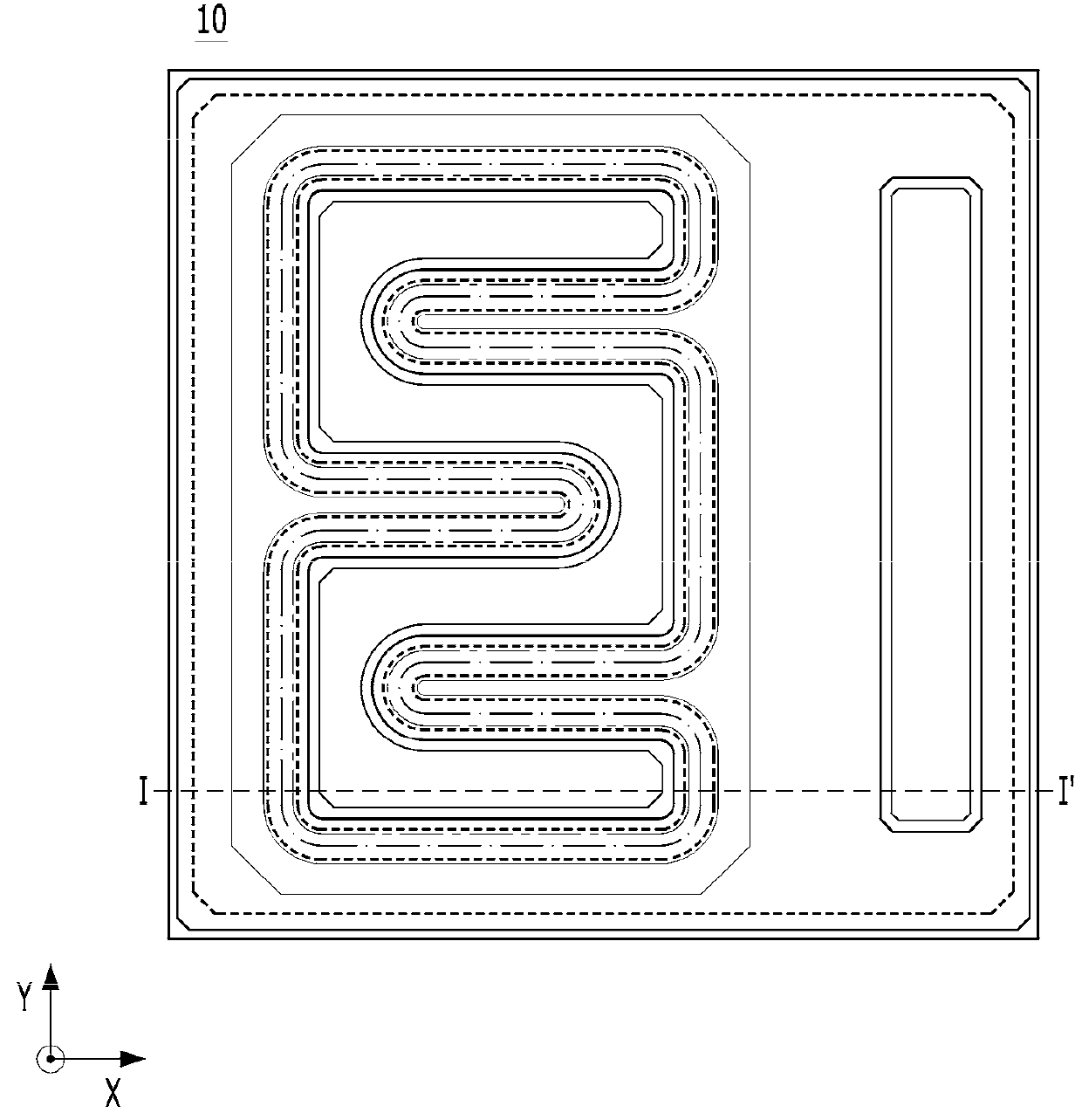

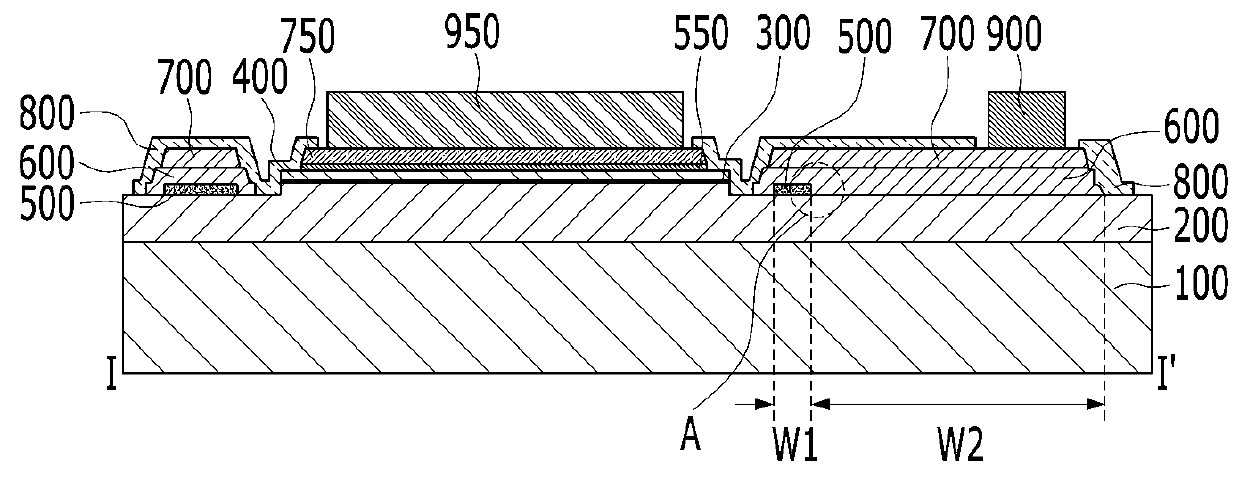

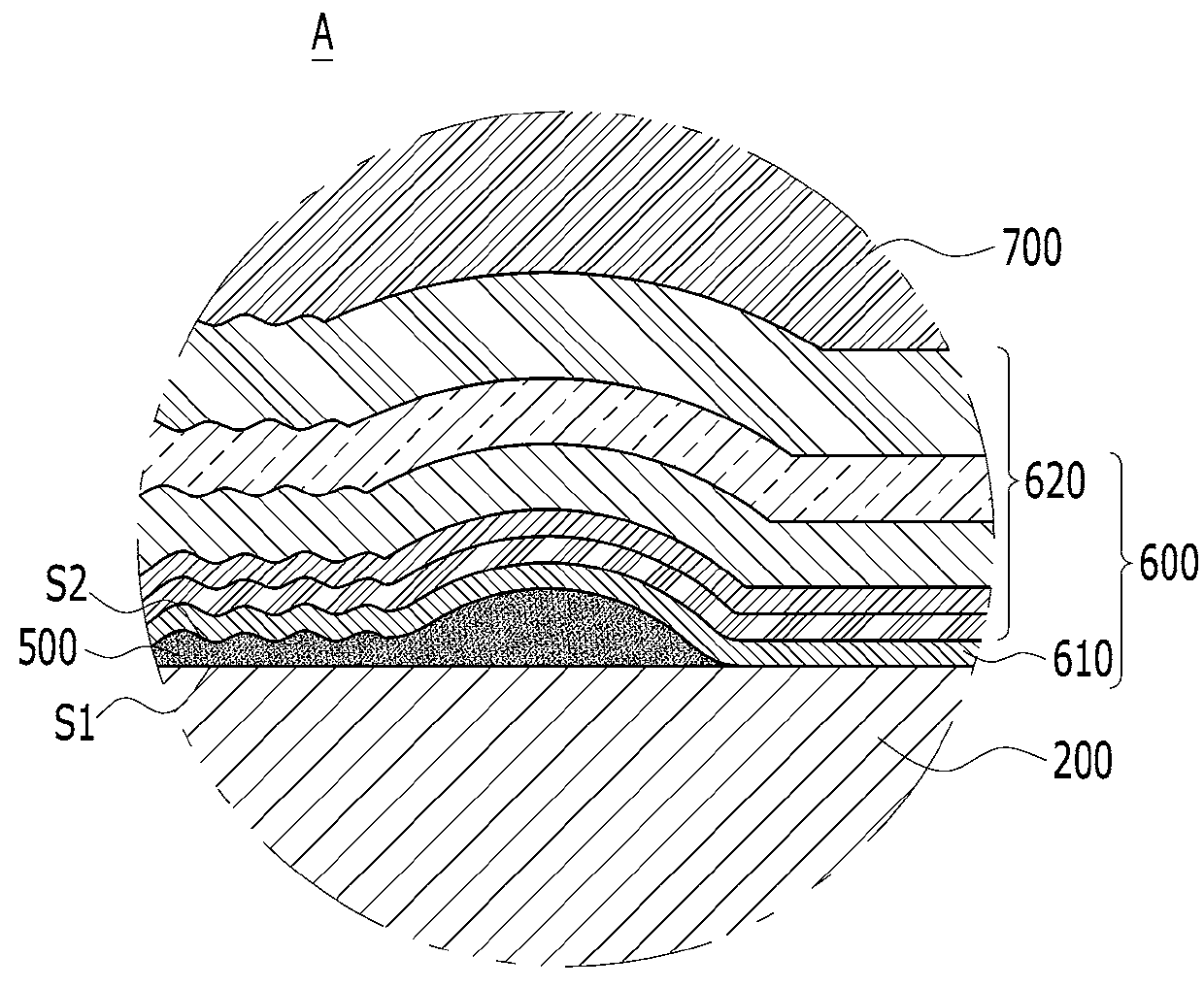

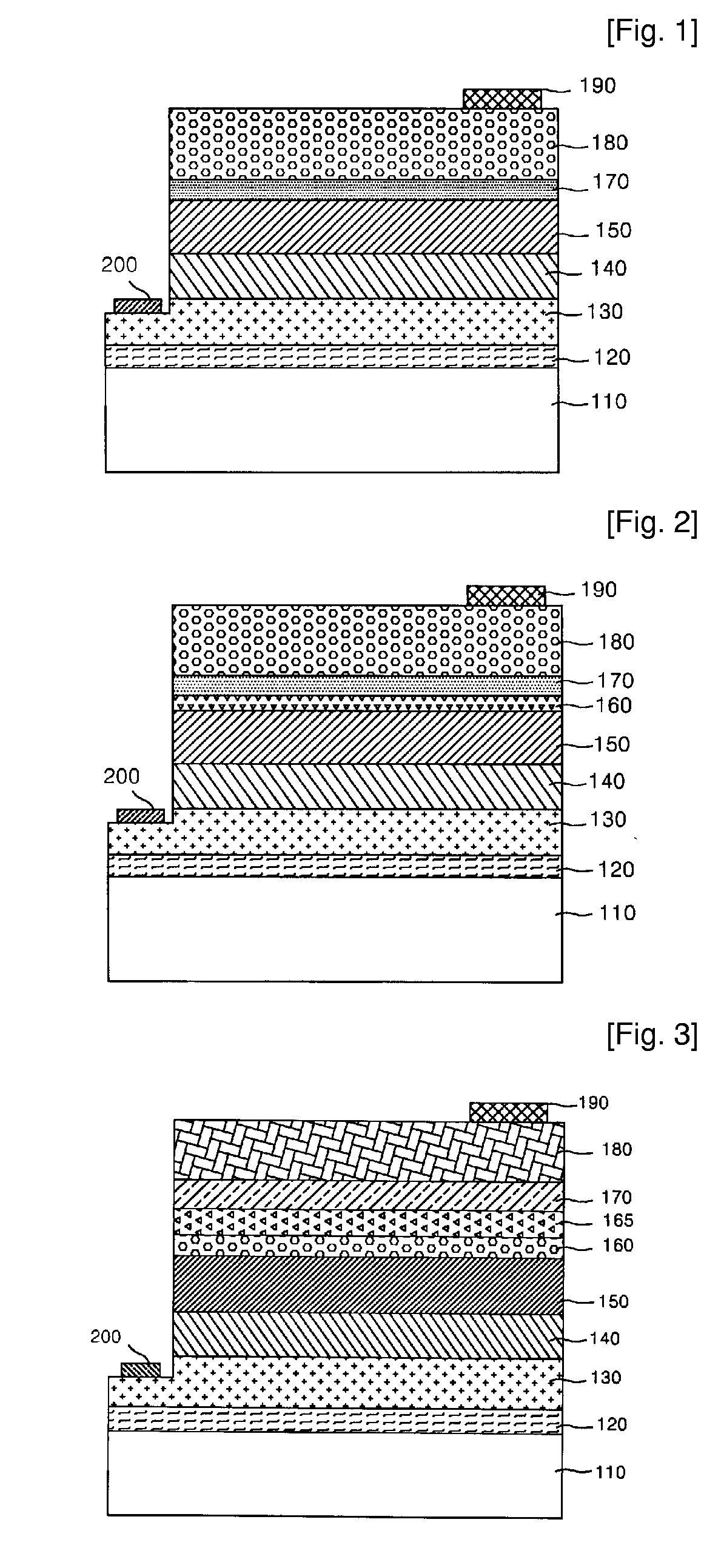

Flip-Chip Light Emitting Diodes and Method of Manufacturing Thereof

ActiveUS20080121914A1Improved ohmic contact characteristicsImprove adhesionSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsLight-emitting diode

Provided are a flip-chip nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising a reflective layer formed on the p-type clad layer and at least one transparent conductive thin film layer made up of transparent conductive materials capable of inhibiting diffusion of materials constituting the reflective layer, interposed between the p-type clad layer and reflective layer; and a process for preparing the same. In accordance with the flip-chip nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact properties with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current-voltage properties.

Owner:SAMSUNG ELECTRONICS CO LTD

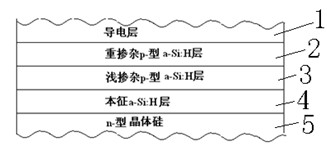

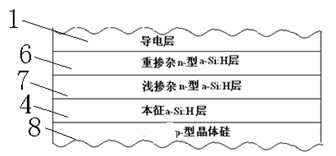

Emitter structure of crystal silicon heterojunction solar battery

InactiveCN102683468AReduce doping concentrationReduce compoundingPhotovoltaic energy generationSemiconductor devicesComposite structureCrystalline silicon

An emitter structure of a crystal silicon heterojunction solar battery is formed by an amorphous silicon film (a-Si:H) with double-layer gradient doping concentration. A composite structure of a heavily-doped p-a-Si:H layer / lightly-doped p-a-Si:H layer or a heavily-doped n-a-Si:H layer / lightly-doped n-a-Si:H layer serves as the emitter of the crystal silicon heterojunction solar battery adopting the a-Si:H / c-Si structure; the heavily-doped layer is connected with a conducting layer; the lightly-doped layer is connected with an intrinsic a-Si:H layer on the surface of crystalline silicon; when the crystalline silicon is n-type, the emitter adopts the heavily-doped p-a-Si:H layer / slightly-doped p-a-Si:H layer structure; and when the crystalline silicon is p-type, the emitter is the heavily-doped n-a-Si:H / slightly-doped n-a-Si:H layer. By adopting the double-layer structure, the open-circuit voltage and short-circuit current of the crystal silicon solar battery can be improved, contact barrier between the amorphous silicon layer and the conducting layer is reduced and the conversion efficiency of the solar battery is improved.

Owner:NANCHANG UNIV

LED (Light Emitting Diode) chip for composite transparent conducting electrode and manufacturing method of LED chip

InactiveCN104505445AImproved ohmic contact characteristicsReduce processing difficultySemiconductor devicesThin membraneGraphite

The invention discloses an LED (Light Emitting Diode) chip for a composite transparent conducting electrode. The LED chip comprises a gallium nitride buffer layer, an N-GaN layer, a quantum well layer, a P-GaN layer and a composite transparent electrode layer which grow on a substrate in sequence. The LED chip is characterized in that an n-type electrode is manufactured on the N-GaN layer; a p-type electrode is manufactured on a graphene layer of the composite transparent electrode layer; the composite transparent electrode layer is formed by compounding a graphene laminar film and ZnO nanorods growing on the graphene laminar film. The invention also discloses a manufacturing method of the chip. The graphene laminar film / ZnO nanorod compounded transparent electrode layer formed by the manufacturing method has the advantages of capability of preventing cracking and good light transmittance performance and is easy to process, so that the contact performance, the current expansion performance and the transmissivity of the chip are greatly improved, and the production cost of the subsequent chip technology can be greatly reduced.

Owner:GUANGDONG DELI PHOTOELECTRIC

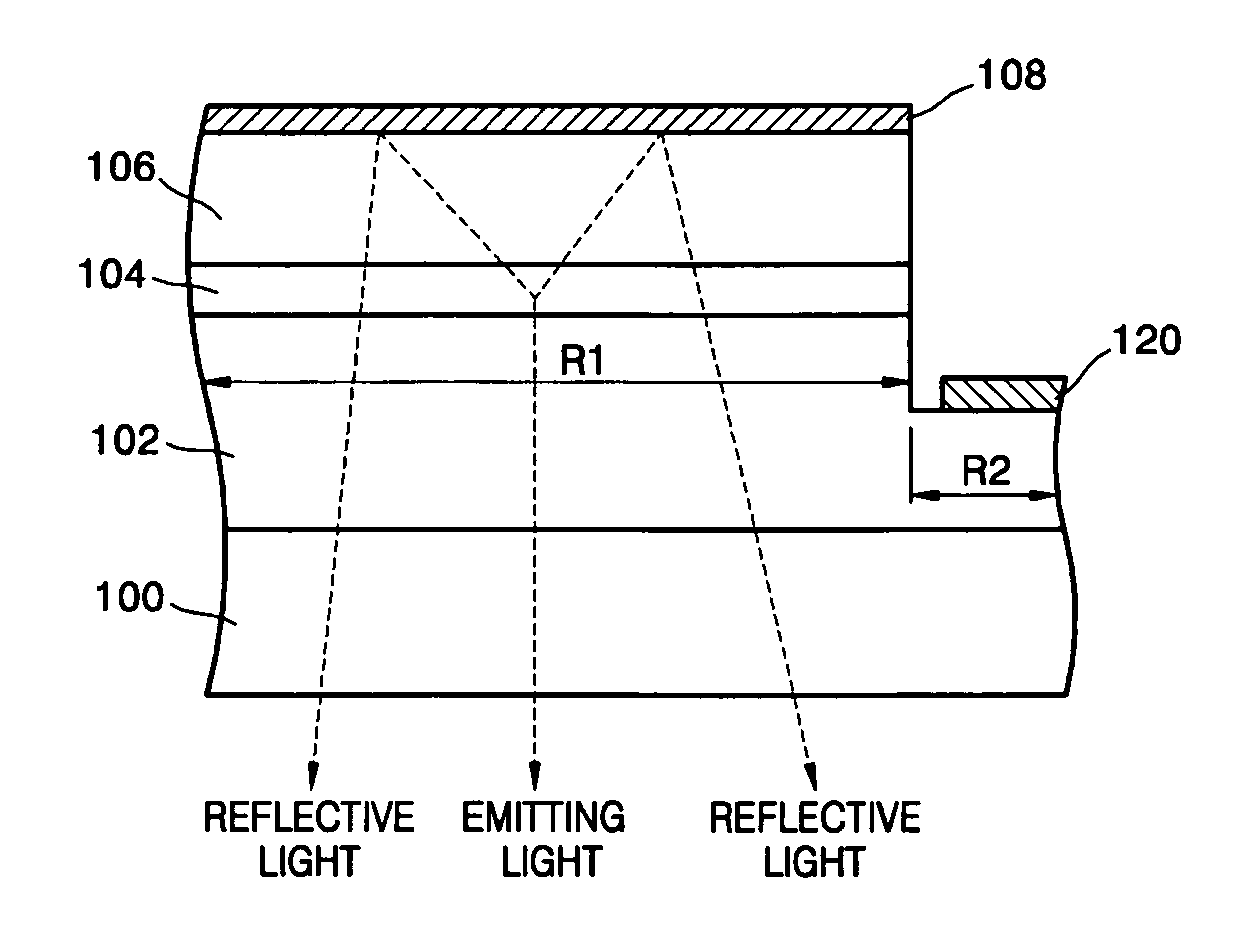

Reflective electrode and compound semiconductor light emitting device including the same

InactiveUS20060081867A1Reduce contact resistanceImprove reflectivityLaser optical resonator constructionSemiconductor/solid-state device manufacturingOhmic contactLight emitting device

Provided are a reflective electrode and a compound semiconductor light emitting device having the reflective electrode, such as LED or LD is provided. The reflective electrode formed on a p-type compound semiconductor layer of a compound semiconductor light emitting device, comprising a first electrode layer formed one of a Ag and Ag-alloy and forms an ohmic contact with the p-type compound semiconductor layer, a third electrode layer formed of a material selected from the group consisting of Ni, Ni-alloy, Zn, Zn-alloy, Cu, Cu-alloy, Ru, Ir, and Rh on the first electrode layer, and a fourth electrode layer formed of a light reflective material on the third electrode layer.

Owner:SAMSUNG ELECTRONICS CO LTD

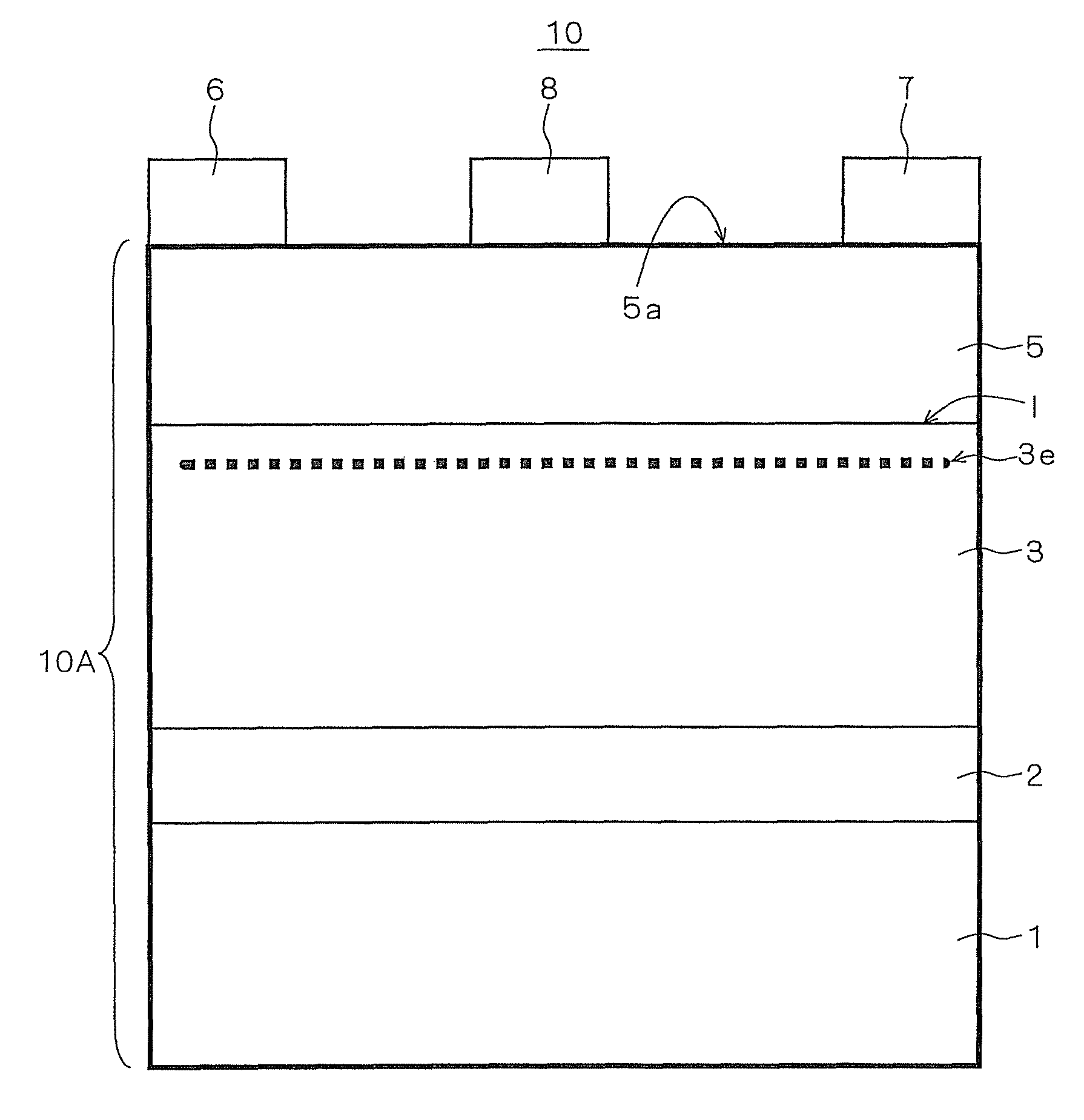

Nitride semiconductor device

ActiveUS8299501B2Excellent reliability and electrical propertyImprove adhesionSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceOhmic contact

In the nitride semiconductor device using the silicon substrate, the metal electrode formed on the silicon substrate has both ohmic contact property and adhesion, so that the nitride semiconductor device having excellent electric properties and reliability is obtained. The nitride semiconductor device includes a silicon substrate (2), a nitride semiconductor layer (10) formed on the silicon substrate (2), and metal electrodes (8, 8′) formed in contact with the silicon substrate (2). The metal electrodes (8, 8′) has first metal layers (4, 4′) which are formed in a shape of discrete islands and in contact with the silicon substrate (2), and second metal layers (6, 6′) which are in contact with the silicon substrate (2) exposed among the islands of the first metal layers (4, 4′) and are formed to cover the first metal layers (4, 4′). Further, the second metal layers (6, 6′) are made of a metal capable of forming ohmic contact with silicon, and the first metal layers (4, 4′) are made of an alloy containing a metal and silicon, in which the metal is different than that in the second metal layer (6,6′).

Owner:NICHIA CORP

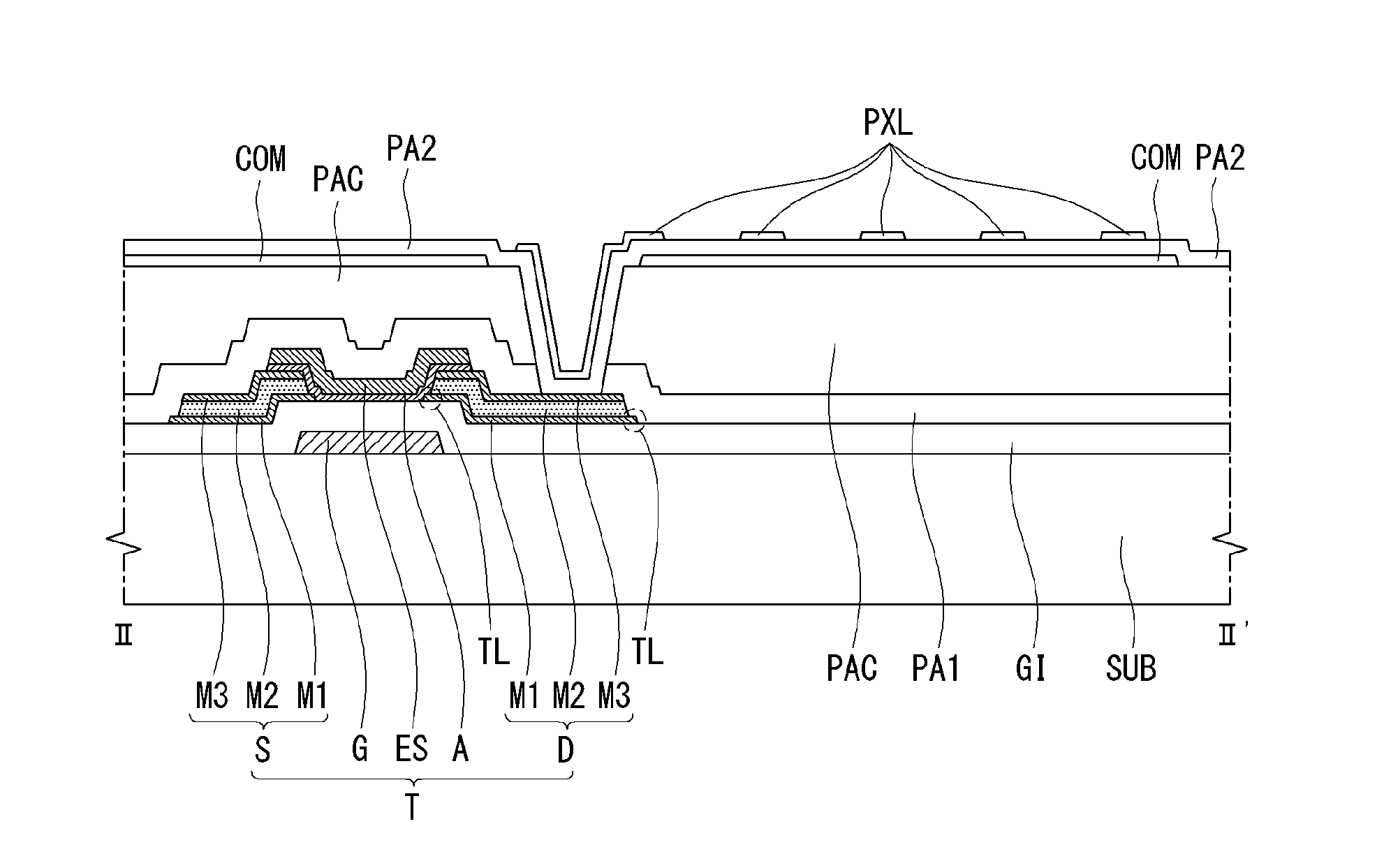

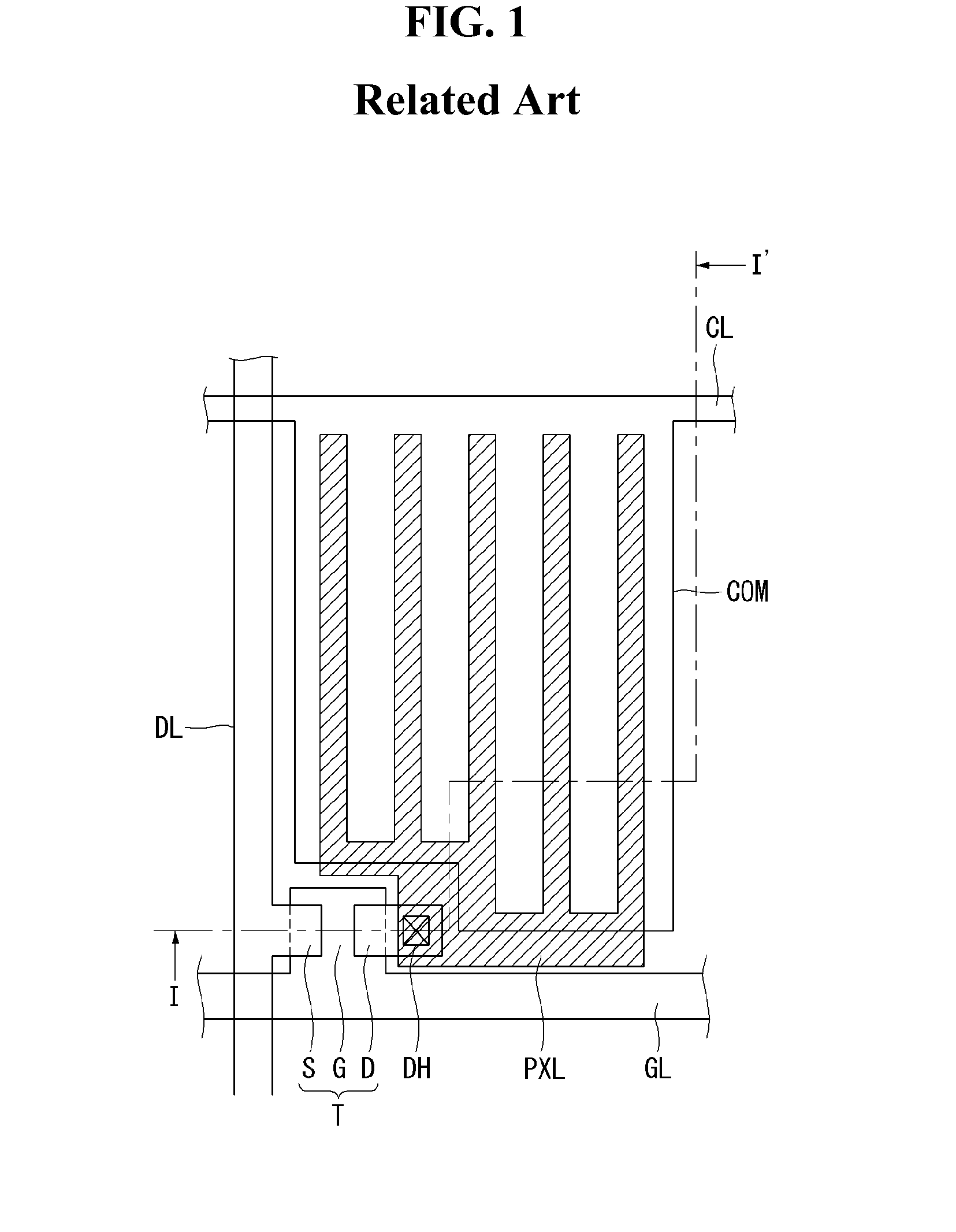

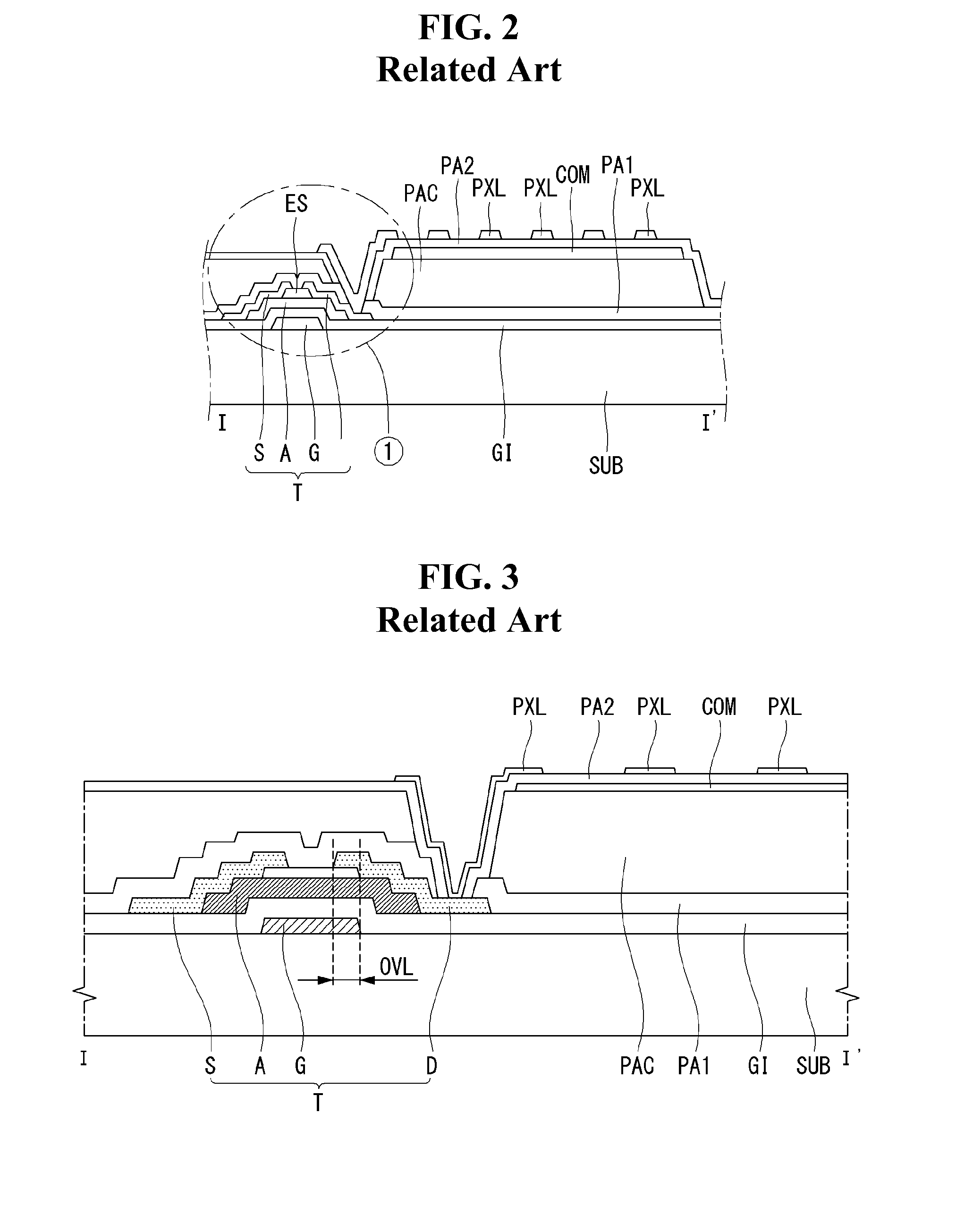

Thin film transistor substrate having metal oxide semiconductor and manufacturing the same

ActiveUS20150155310A1Improved ohmic contact characteristicsLow costTransistorSolid-state devicesDisplay deviceEngineering

The present disclosure relates to a thin film transistor substrate having a metal oxide semiconductor for flat panel displays and a method for manufacturing the same. The present disclosure suggests a thin film transistor substrate including: a gate electrode on a substrate; a gate insulating layer covering the gate electrode; a source electrode overlapping with one side of the gate electrode on the gate insulating layer; a drain electrode being apart from the source electrode and overlapping with other side of the gate electrode on the gate insulating layer; an oxide semiconductor layer contacting an upper surface of the source electrode and the drain electrode, and extending from the source electrode to the drain electrode; and an etch stopper having the same shape with the oxide semiconductor layer, and contacting an upper surface of the oxide semiconductor layer.

Owner:LG DISPLAY CO LTD

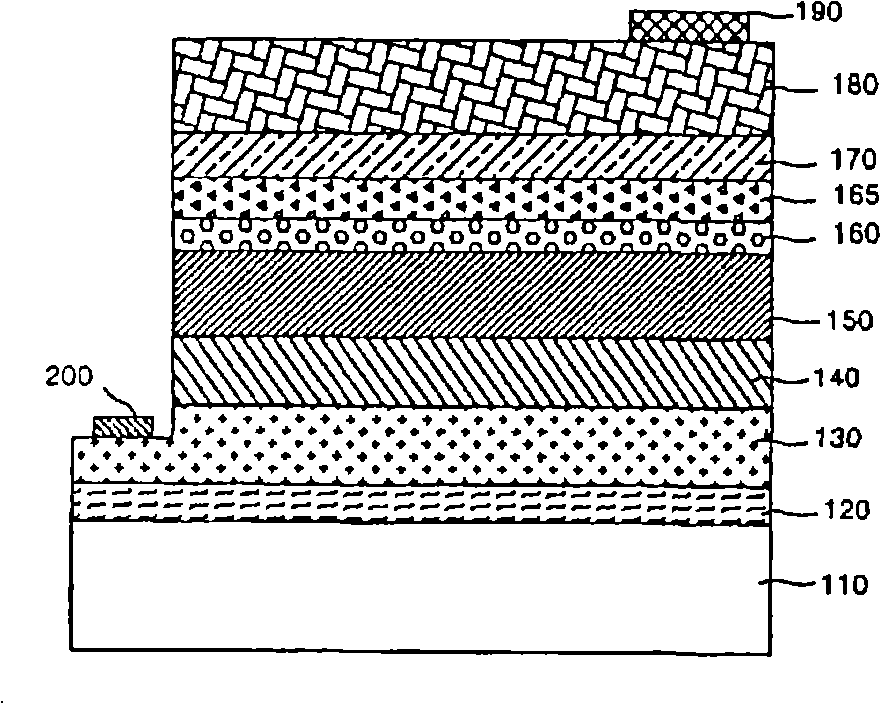

Flip-chip light emitting diodes and method of manufacturing thereof

ActiveCN101278409AImproved ohmic contact characteristicsImprove packaging yieldSemiconductor devicesOhmic contactWire bonding

Provided are a flip-chip nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising a reflective layer formed on the p-type clad layer and at least one transparent conductive thin film layer made up of transparent conductive materials capable of inhibiting diffusion of materials constituting the reflective layer, interposed between the p-type clad layer and reflective layer; and a process for preparing the same. In accordance with the flip-chip nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact properties with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current-voltage properties.

Owner:SAMSUNG ELECTRONICS CO LTD

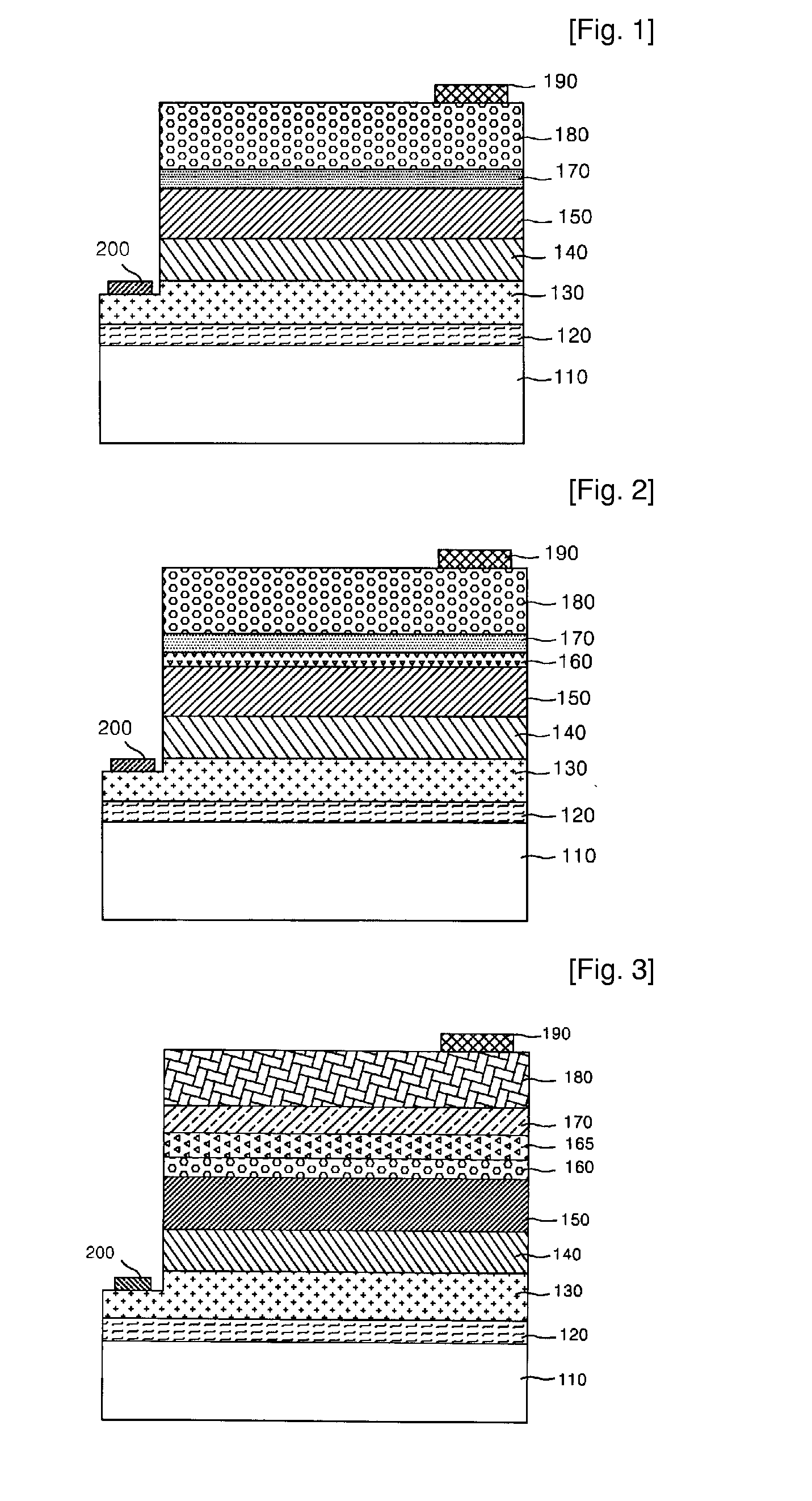

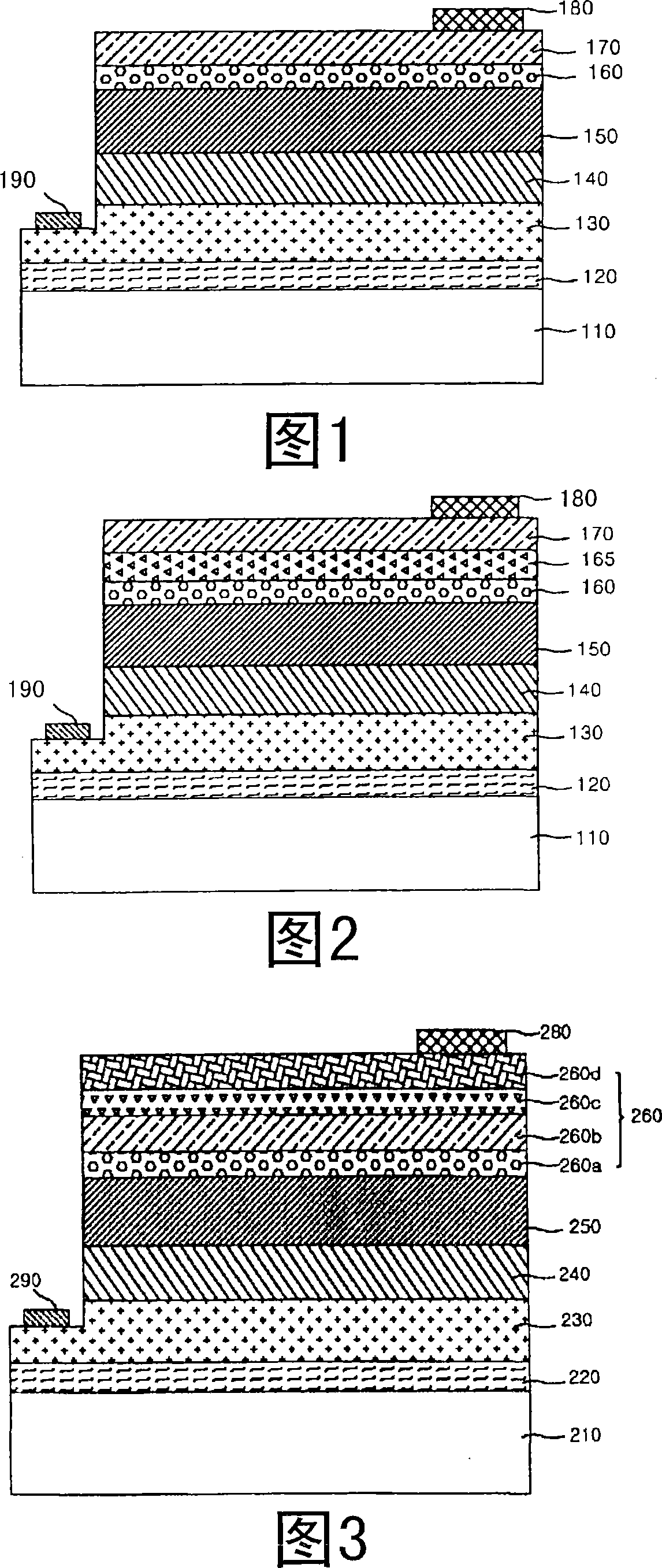

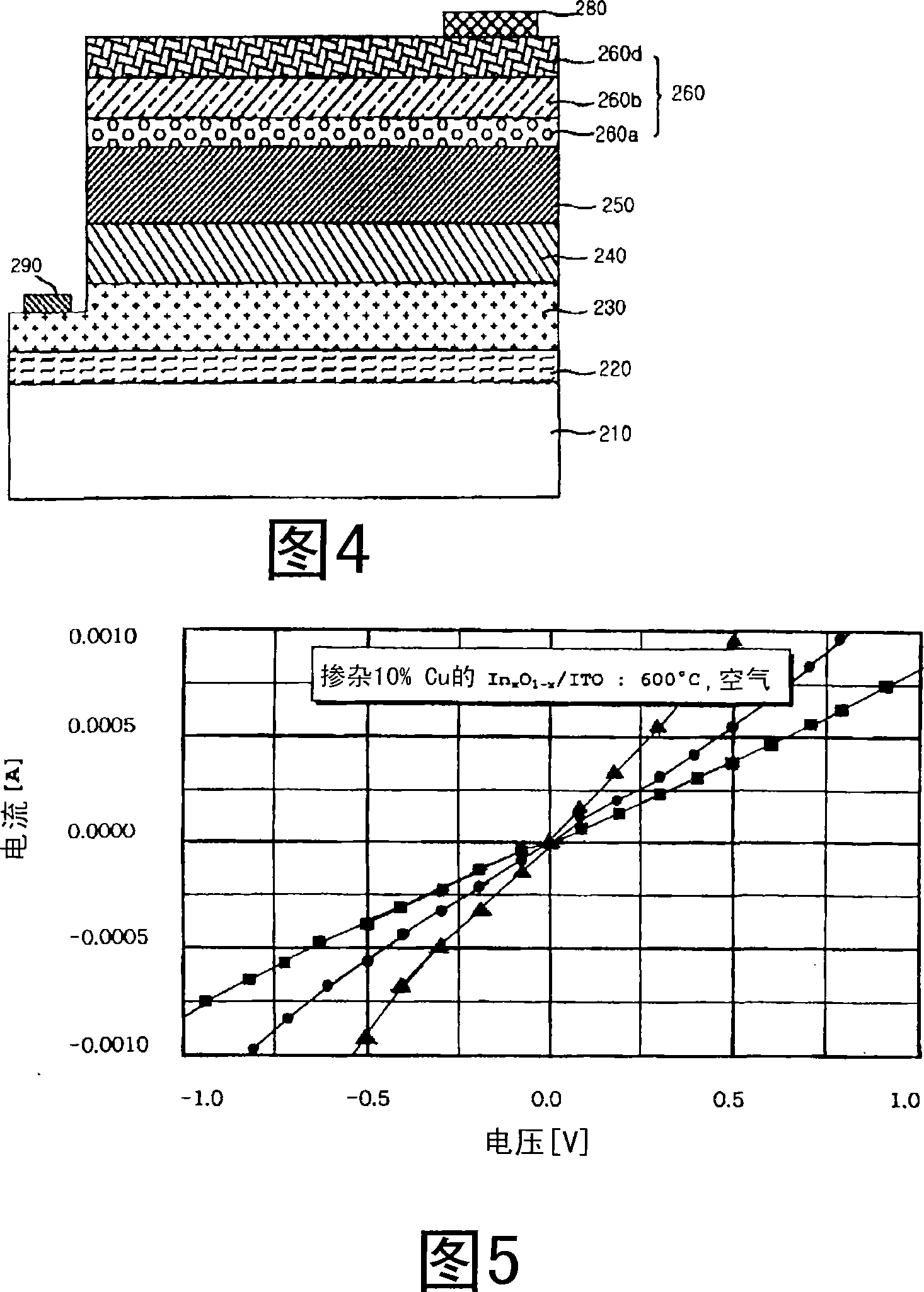

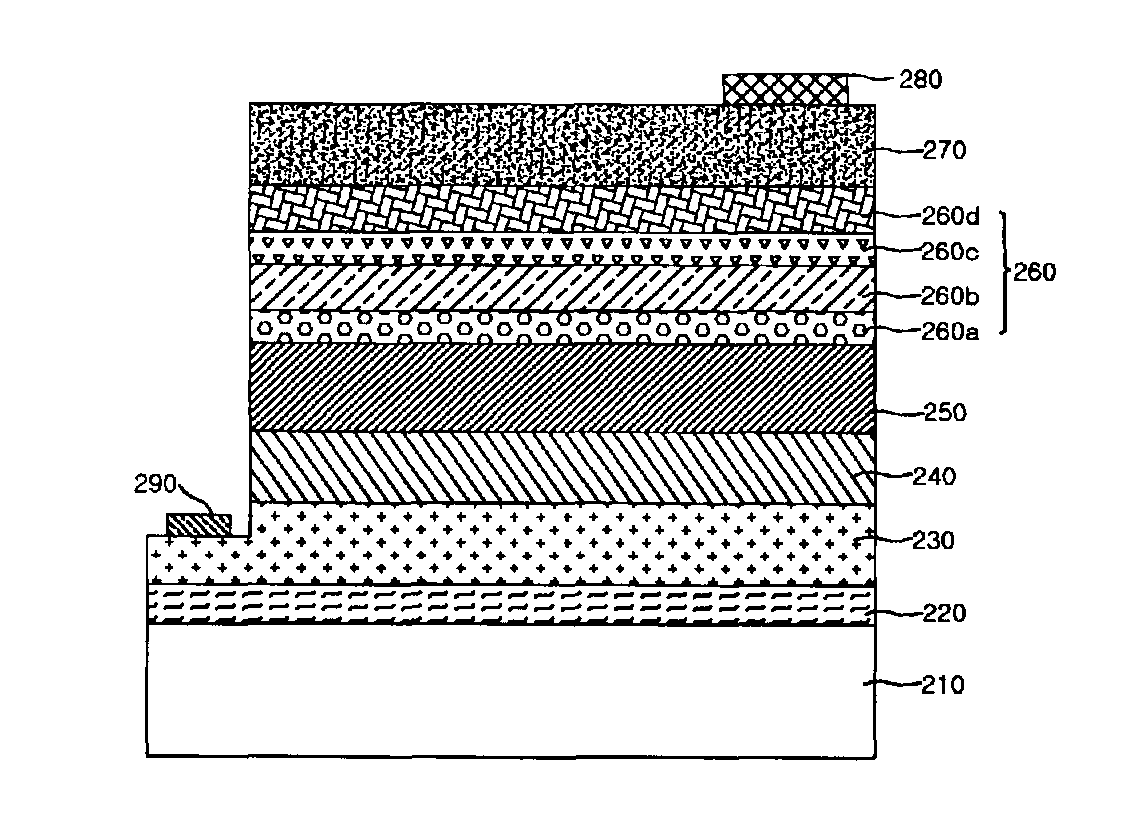

Top-emitting light emitting diodes and method of manufacturing thereof

InactiveCN101027790AImprove packaging yieldImproved ohmic contact characteristicsSemiconductor devicesOhmic contactConductive materials

Provided are a top-emitting nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising an interface modification layer formed on the p-type clad layer and a transparent conductive thin film layer made up of a transparent conductive material formed on the interface modification layer; and a process for preparing the same. In accordance with the top-emitting nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current- voltage properties.

Owner:GWANGJU INST OF SCI & TECH

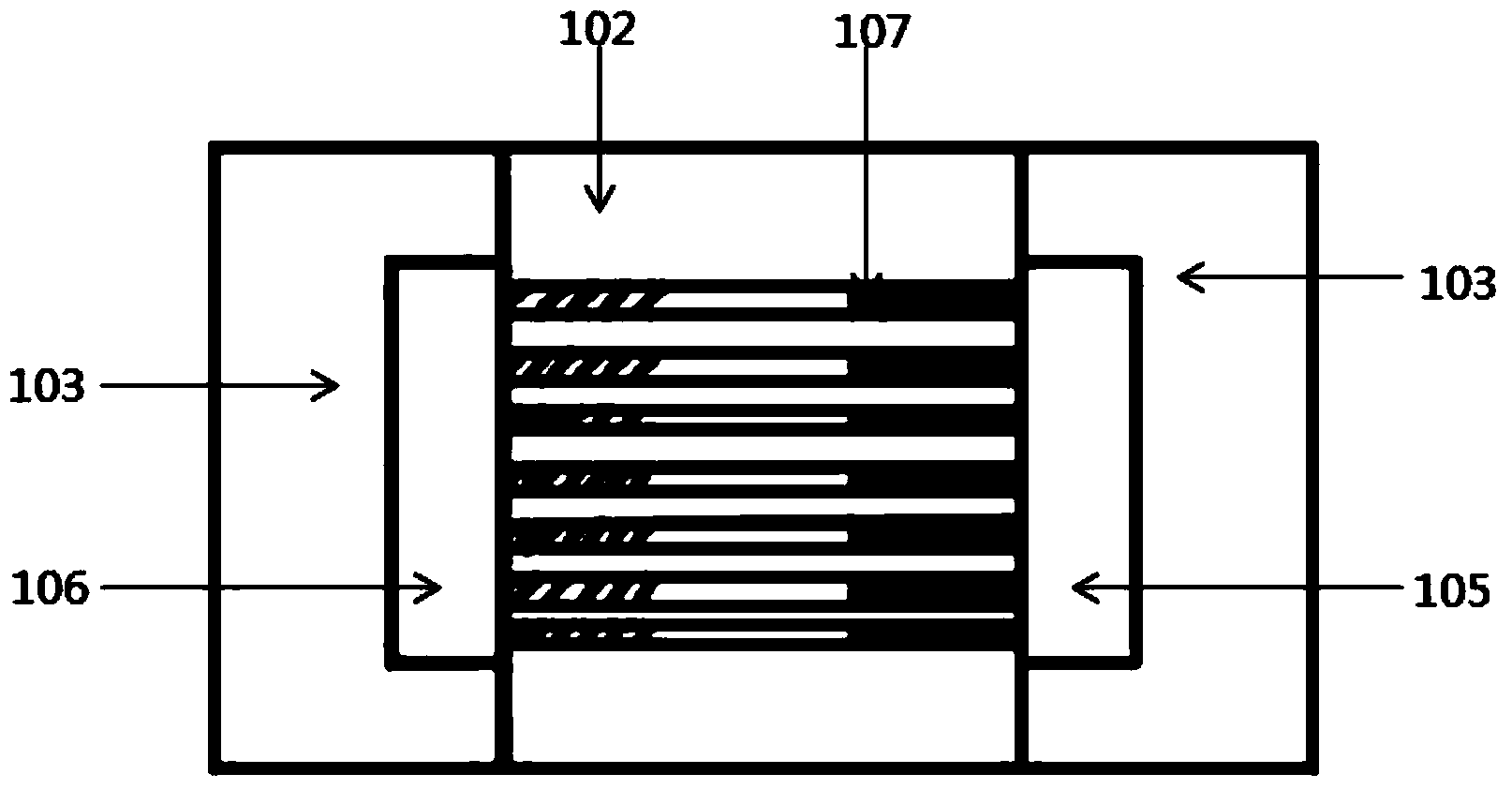

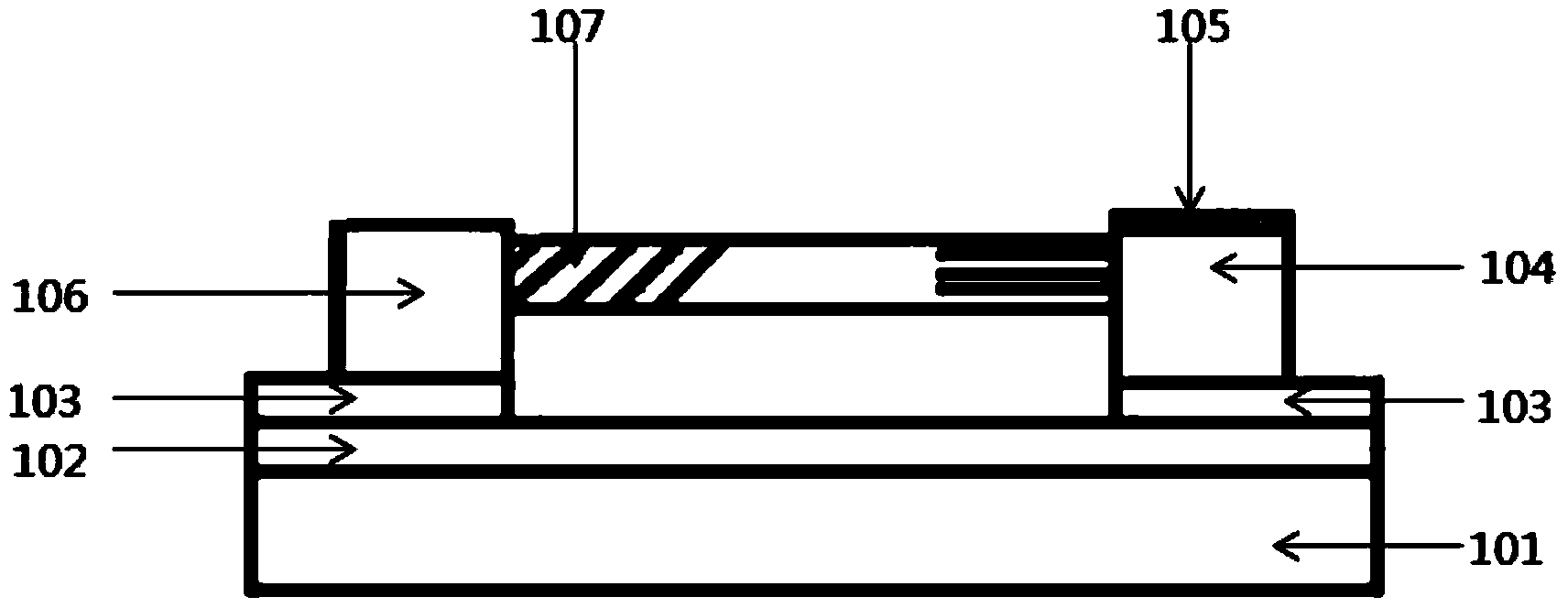

Transverse zinc oxide nanorod array light emitting diode

ActiveCN104051589AHigh light transmittanceImprove optical output powerMaterial nanotechnologySemiconductor devicesElectron injectionEtching

The invention discloses a transverse zinc oxide nanorod array light emitting diode. The transverse zinc oxide nanorod array light emitting diode comprises a sapphire substrate (101), a silicon dioxide insulating layer (102) and a gallium nitride buffer layer (103) which are sequentially arranged from bottom to top. A p-region electrode (106) is arranged on one lateral side of a rectangular etching groove in the gallium nitride buffer layer (103), a piece of blocky n<+>-ZnO (104) is arranged on the other lateral side, opposite to the lateral side, of the rectangular etching groove, and an n-region electrode (105) of an ITO-ZnO film is arranged on the blocky n<+>-ZnO (104). The transverse zinc oxide nanorod array light emitting diode further comprises a ZnO nanorod array (107), an n-type region and a p-type region are arranged at the two ends of the ZnO nanorod array respectively, and meanwhile the ZnO nanorod array is connected with the p-region electrode (106) and the blocky n<+>-ZnO (104) through the p-type region and the n-type region respectively. The transverse zinc oxide nanorod array light emitting diode is high in both light extraction efficiency and electron injection efficiency and meanwhile low in cost.

Owner:SOUTHEAST UNIV

GaN device with mixed polarity

ActiveCN105789281AQuality improvementReduce defectsSemiconductor devicesOhmic contactElectrical polarity

The invention discloses a GaN device with the mixed polarity. The GaN device relates to the technical field of field effect transistors with two-dimensional carrier gas channels. The GaN device comprises a substrate layer, an N-polar GaN buffer layer, a first N-polar Alx GaN layer with a gradually increased Al component x, a second N-polar AlxGaN layer with a constant Al component x, a third N-polar AlxGaN layer with a gradually reduced Al component x, and a Ga-polar GaN channel layer. By virtue of the structure, a GaN based material with higher quality can grow epitaxially and the surface density and migration rate of 2DEG in a channel can be increased; and meanwhile a device with smaller ohmic contact resistance can be fabricated on a material with the mixed polarity by adopting a conventional Ga-polar GaN based device fabrication process.

Owner:SHIJIAZHUANG UNIVERSITY

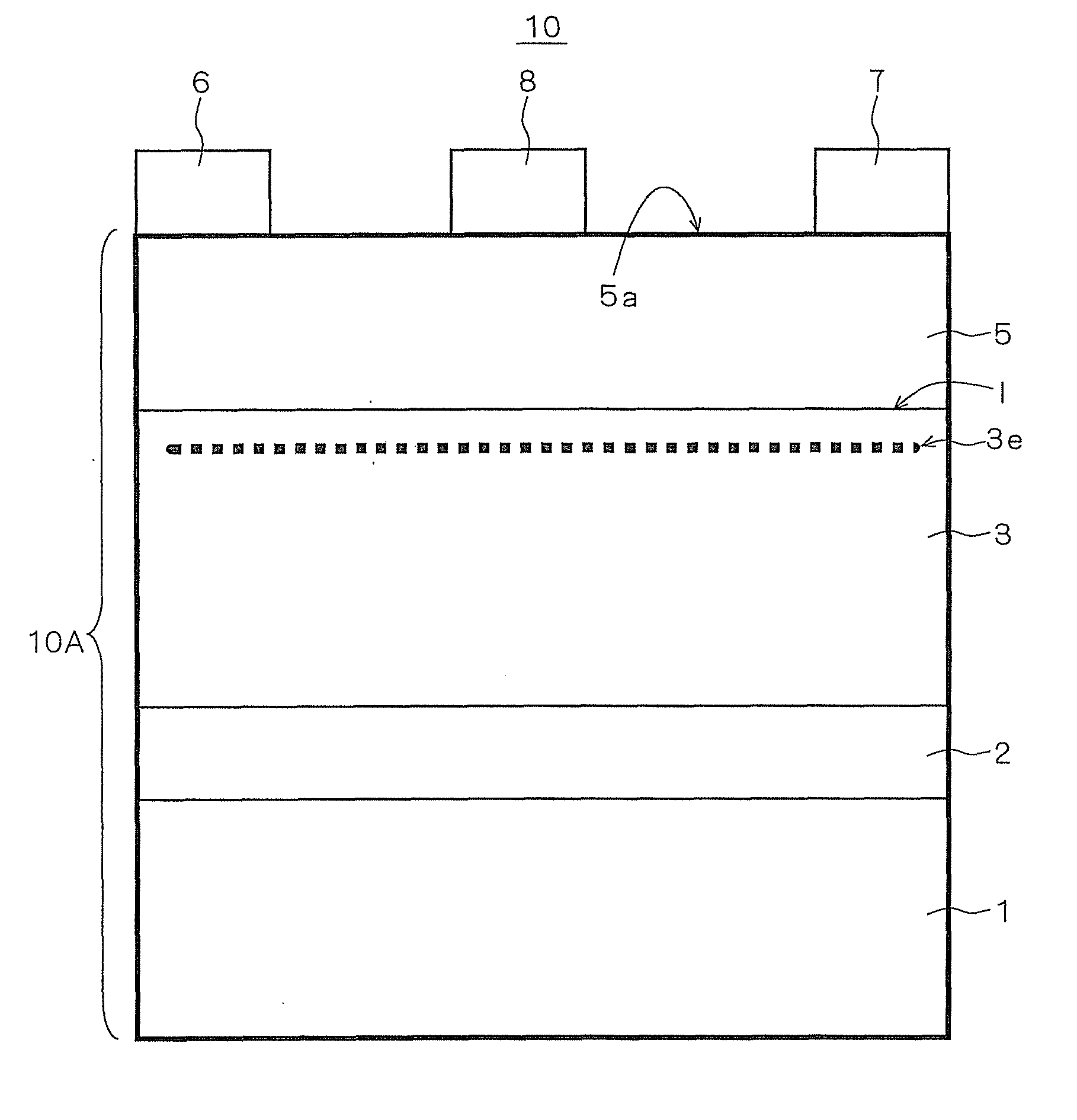

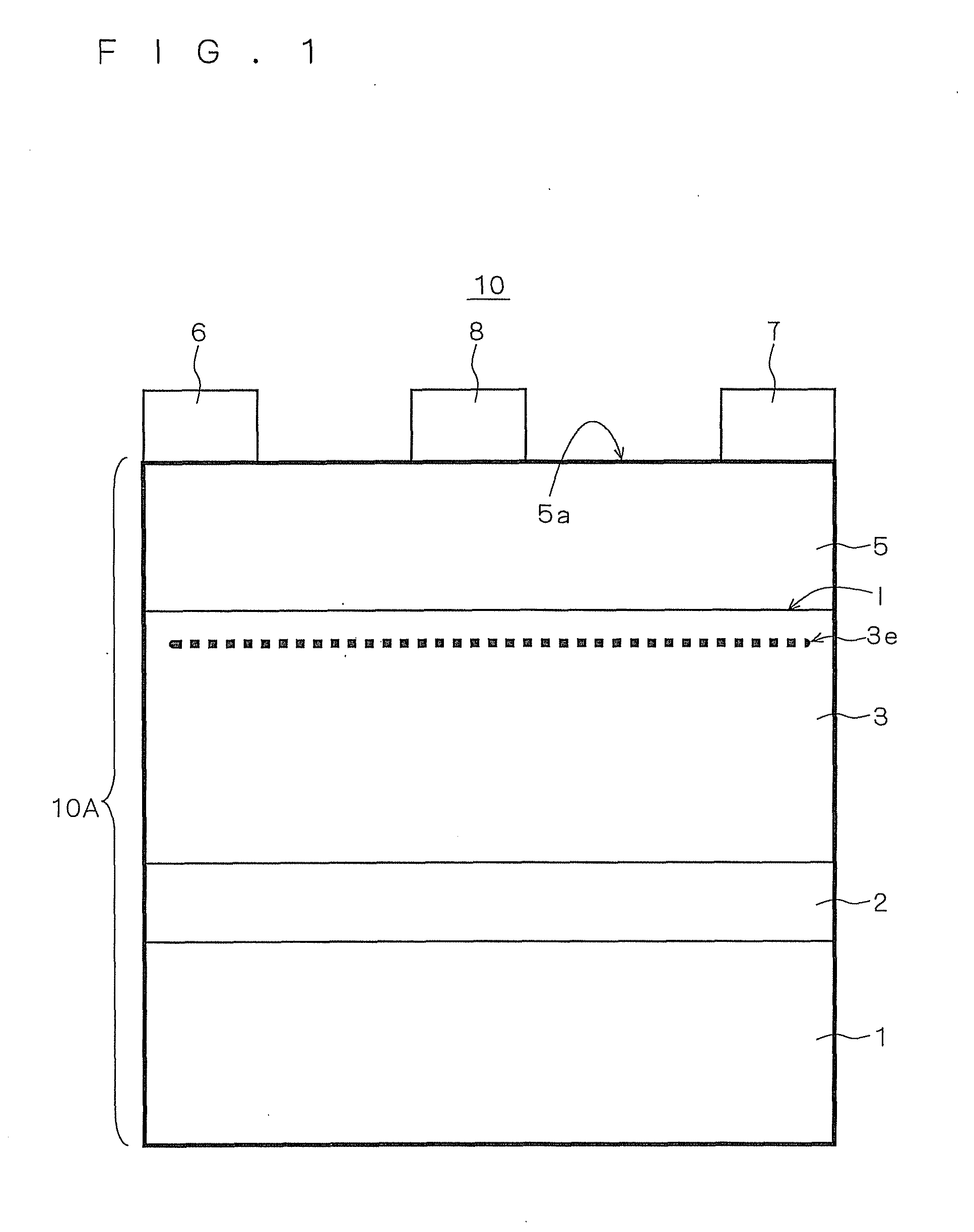

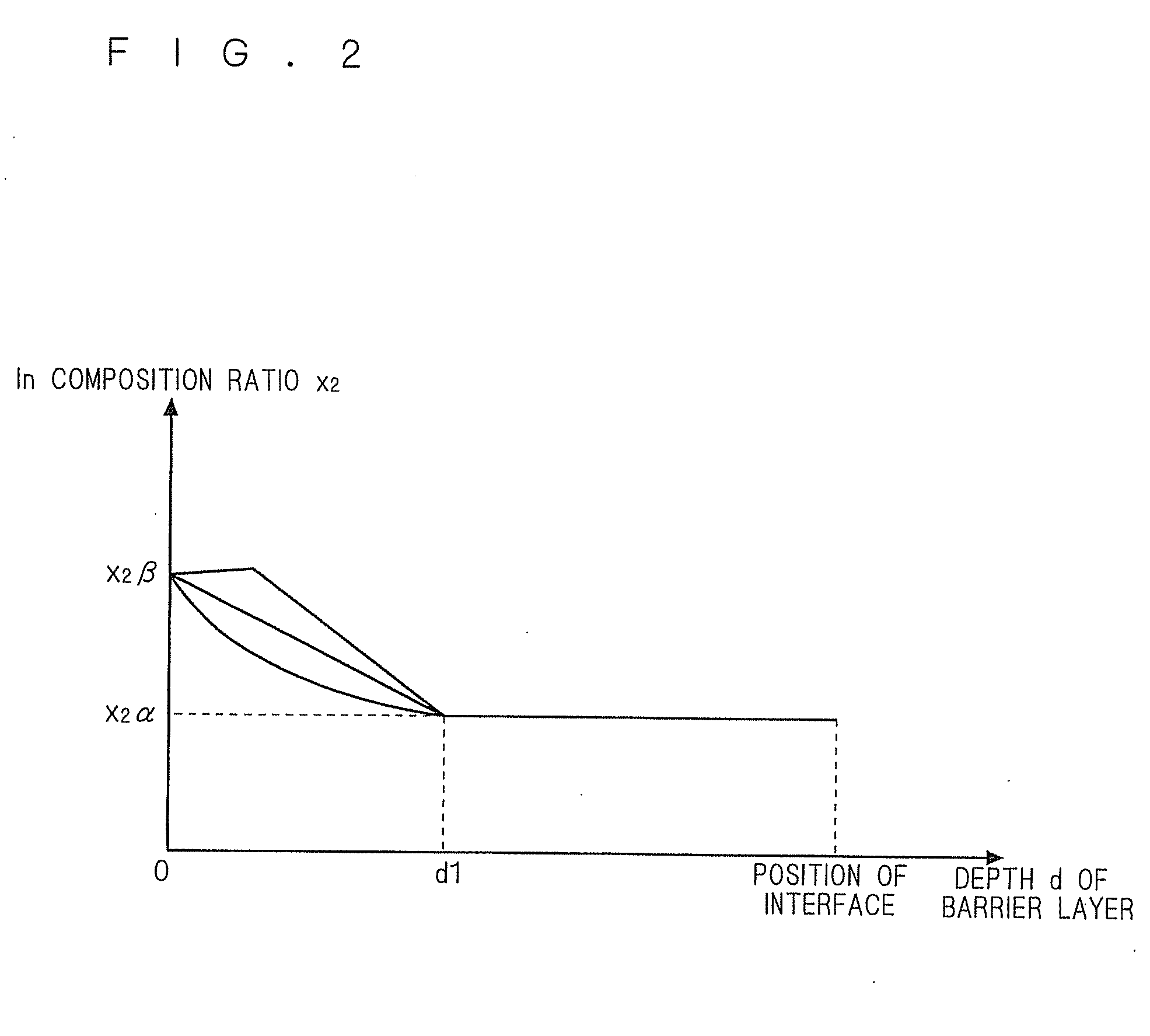

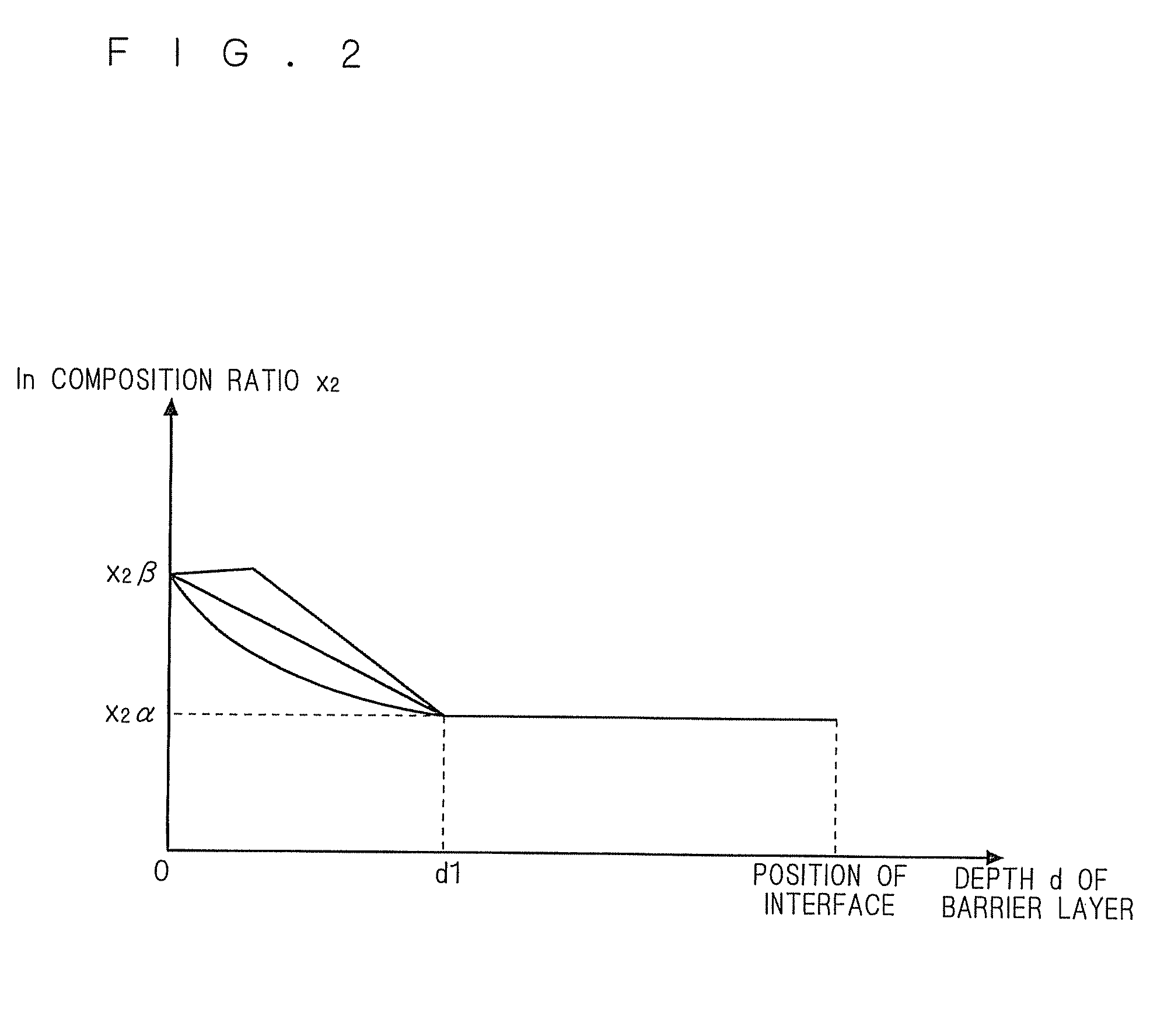

Epitaxial substrate for semiconductor device, semiconductor device, and method of manufacturing epitaxial substrate for semiconductor device

ActiveUS20110049570A1Excellent ohmic contact characteristicSatisfactory device characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesOhmOhmic contact

Provided is an epitaxial substrate capable of achieving a semiconductor device that has excellent ohmic contact characteristics as well as satisfactory device characteristics. On a base substrate, a channel layer formed of a first group III nitride that contains at least Al and Ga and has a composition of Inx1Aly1Gaz1N (x1+y1+z1=1) is formed. On the channel layer, a barrier layer formed of a second group III nitride that contains at least In and Al and has a composition of Inx2Aly2Gaz2N (x2+y2+z2=1) is formed such that an In composition ratio of a near-surface portion is larger than an In composition ratio of a portion other than the near-surface portion.

Owner:NGK INSULATORS LTD

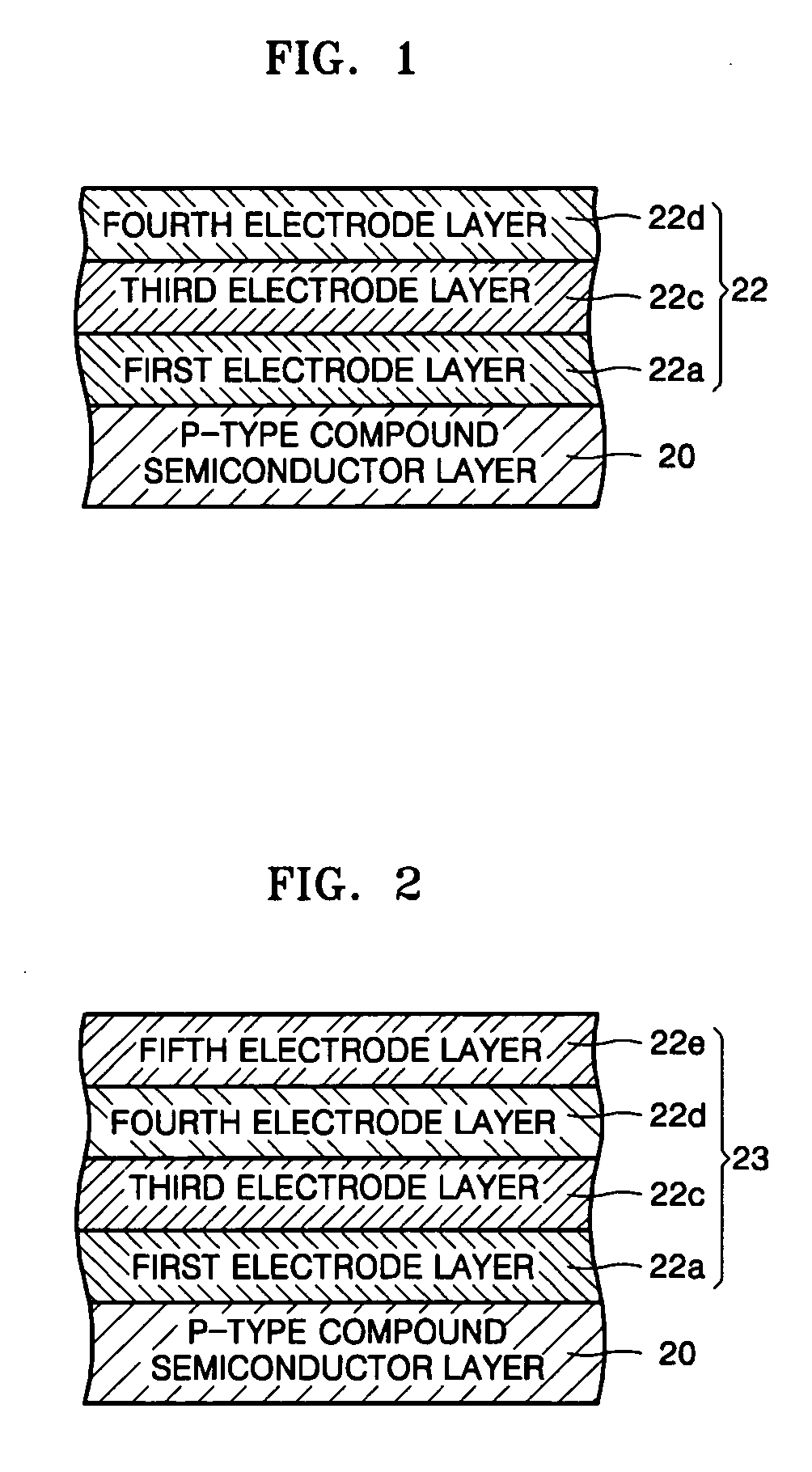

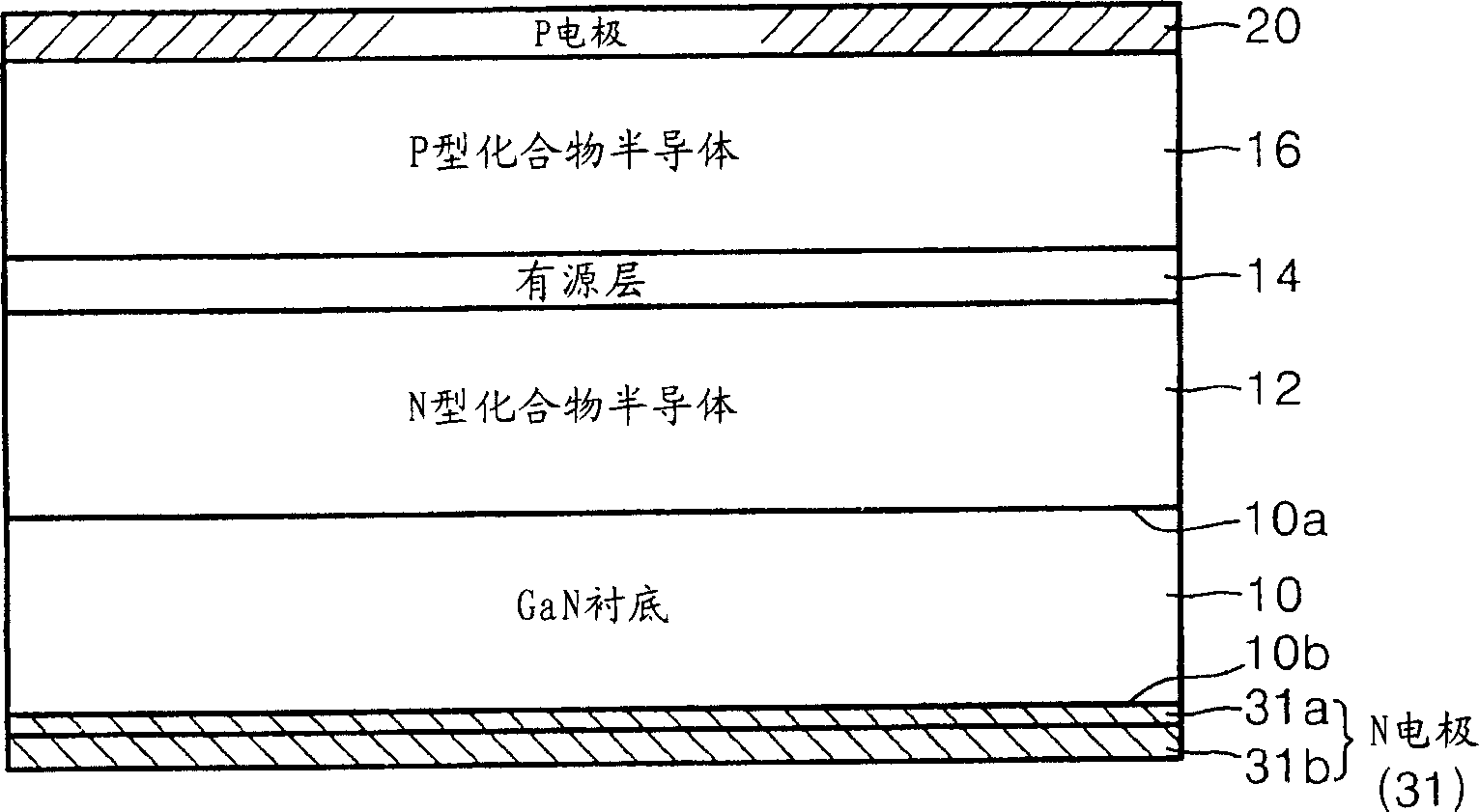

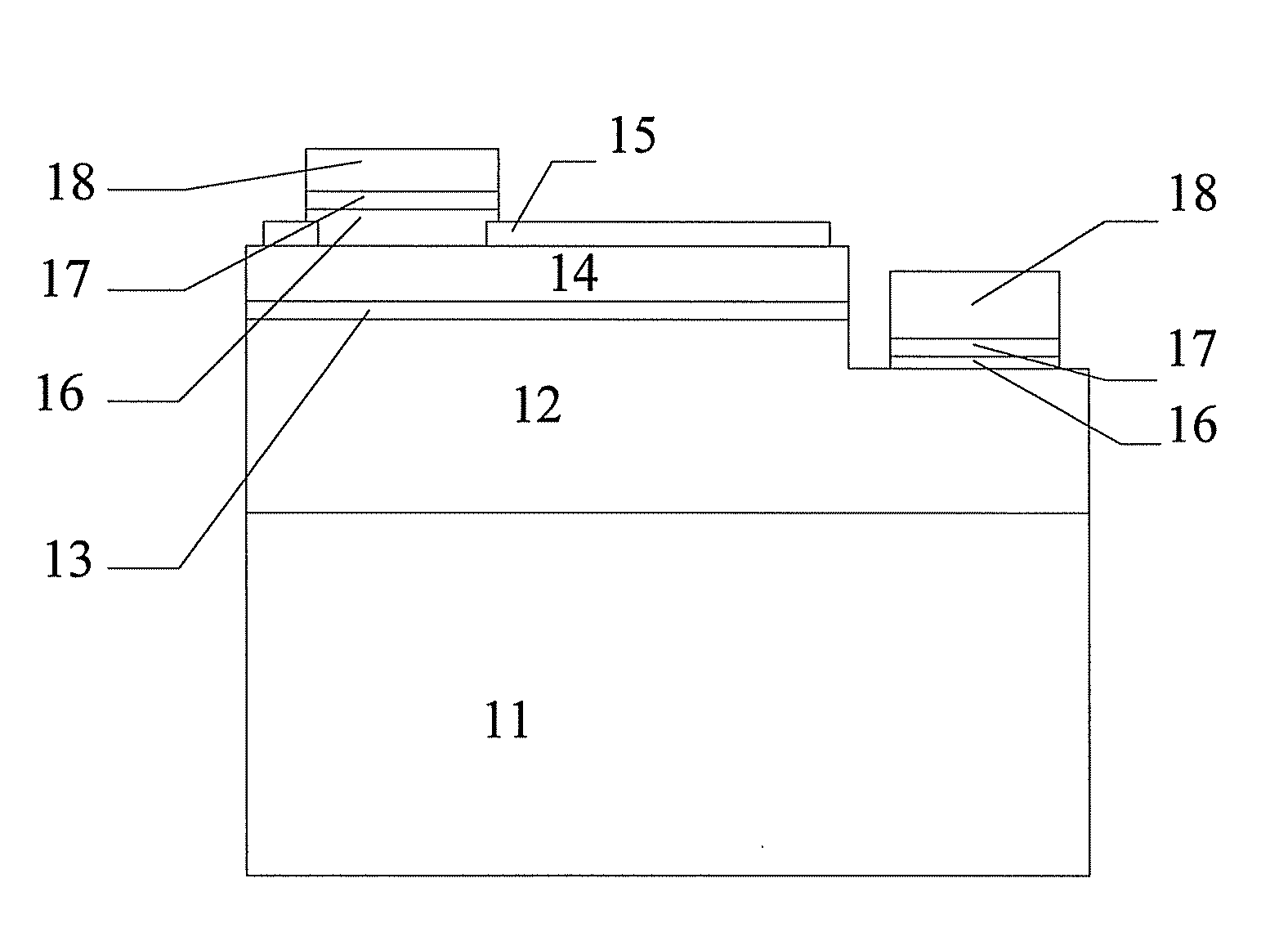

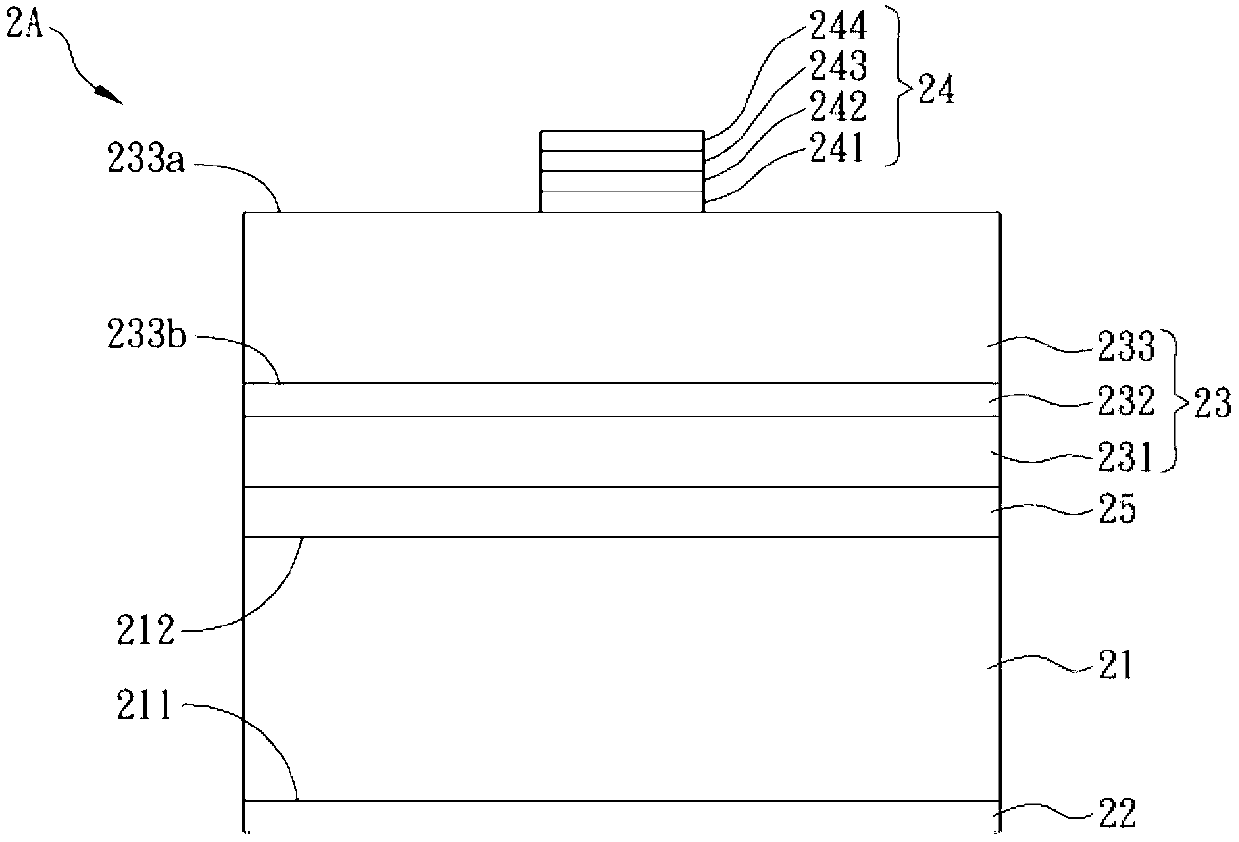

Nitride-based compound semiconductor light emitting device and method of fabricating the same

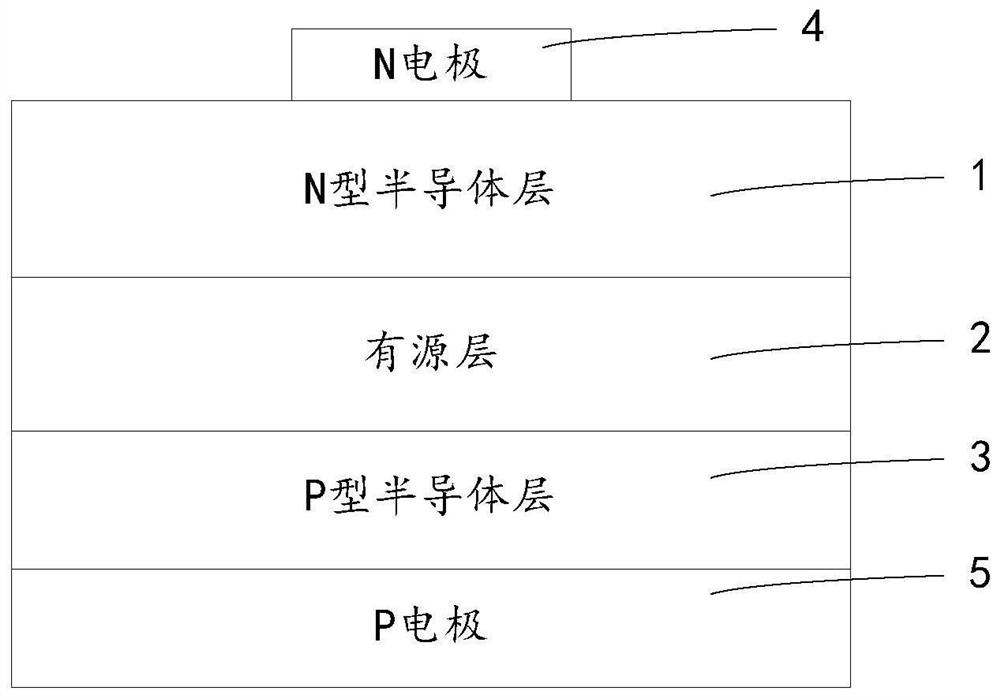

InactiveCN1905225AImproved ohmic contact characteristicsLaser detailsSemiconductor lasersOhmic contactActive layer

The invention discloses a nitride-based semiconductor light-emitting device with improved ohmic contact characteristics for an n-electrode and a manufacturing method thereof. The nitride-based semiconductor light emitting device includes an n-electrode, a p-electrode, and an n-type compound semiconductor layer, an active layer, and a p-type semiconductor layer formed between the n- and p-electrodes. The n-electrode includes a first electrode layer formed of at least one element selected from the group consisting of Pd, Pt, Ni, Co, Rh, Ir, Fe, Ru, Os, Cu, Ag, and Au; Conductivity of at least one element selected from the group consisting of Ti, V, Cr, Zr, Nb, Hf, Ta, Mo, W, Re, Ir, Al, In, Pb, Ni, Rh, Ru, Os, and Au material and form the second electrode layer on the first electrode layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Epitaxial substrate for semiconductor device, semiconductor device, and method of manufacturing epitaxial substrate for semiconductor device

ActiveUS8378386B2Improved ohmic contact characteristicsSatisfactory device characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactNitride

Provided is an epitaxial substrate capable of achieving a semiconductor device that has excellent ohmic contact characteristics as well as satisfactory device characteristics. On a base substrate, a channel layer formed of a first group III nitride that contains at least Al and Ga and has a composition of Inx1Aly1Gaz1N (x1+y1+z1=1) is formed. On the channel layer, a barrier layer formed of a second group III nitride that contains at least In and Al and has a composition of Inx2Aly2Gaz2N (x2+y2+z2=1) is formed such that an In composition ratio of a near-surface portion is larger than an In composition ratio of a portion other than the near-surface portion.

Owner:NGK INSULATORS LTD

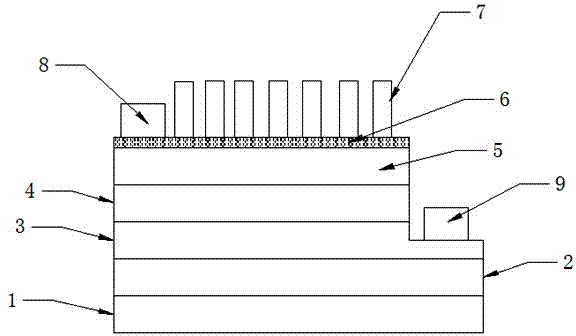

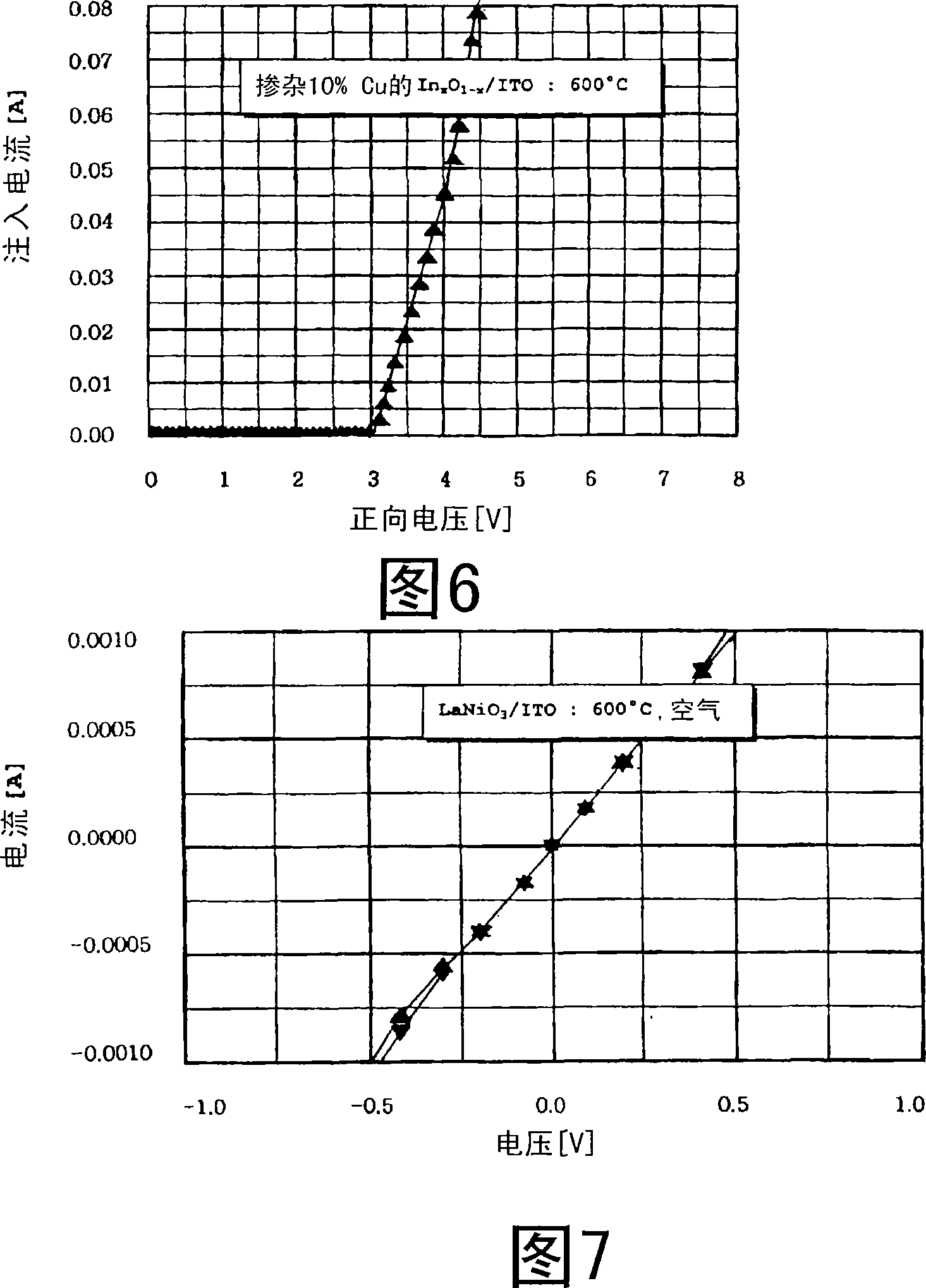

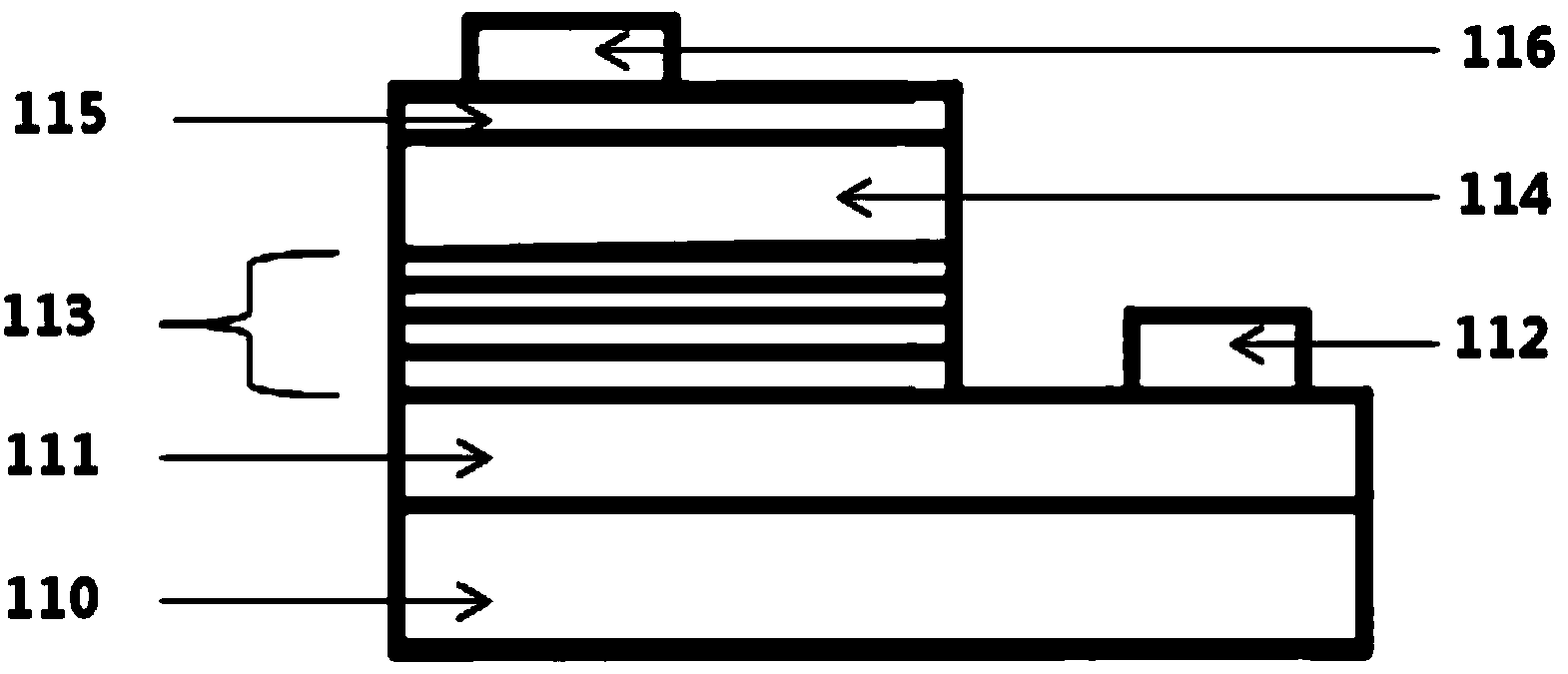

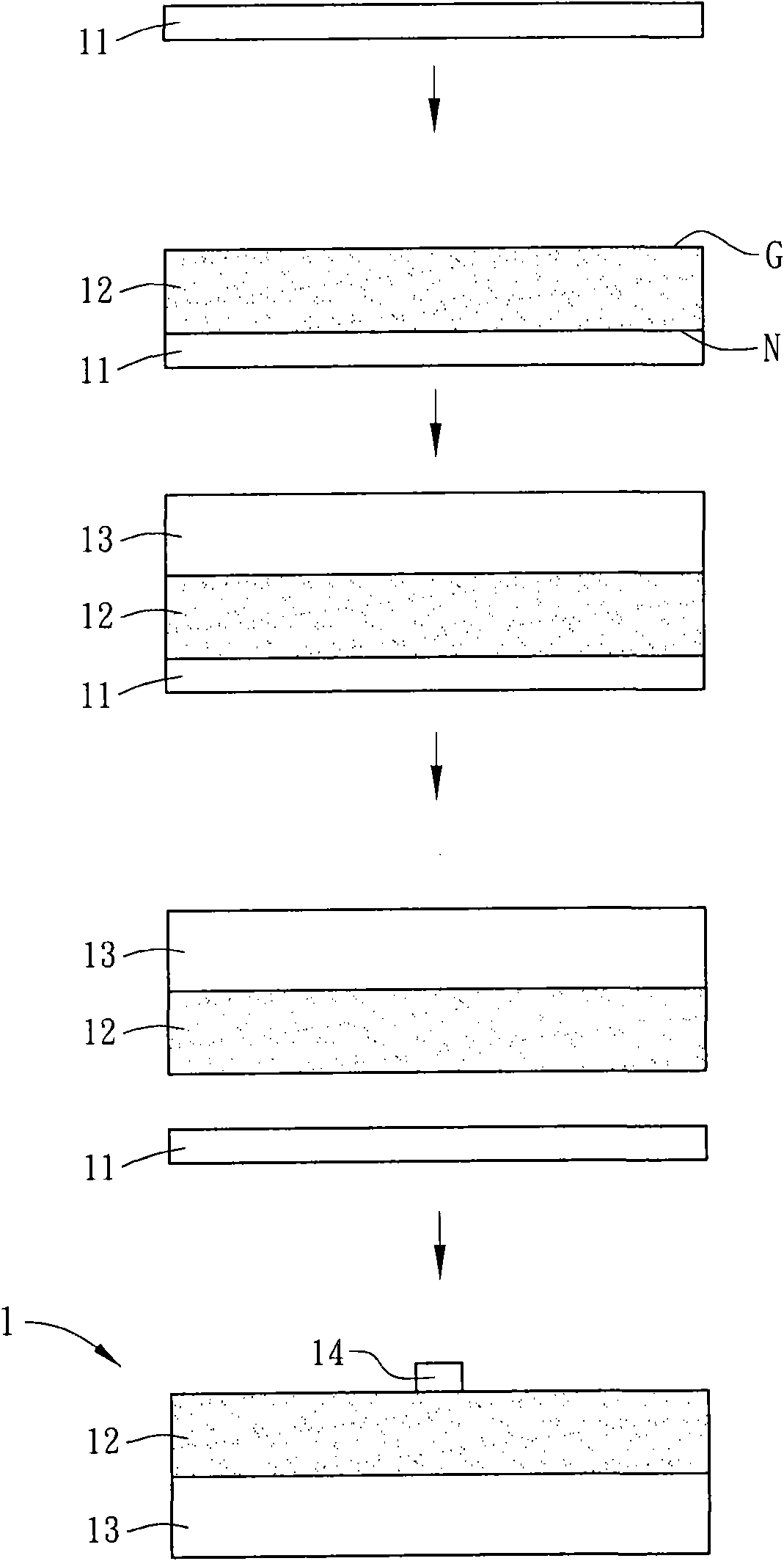

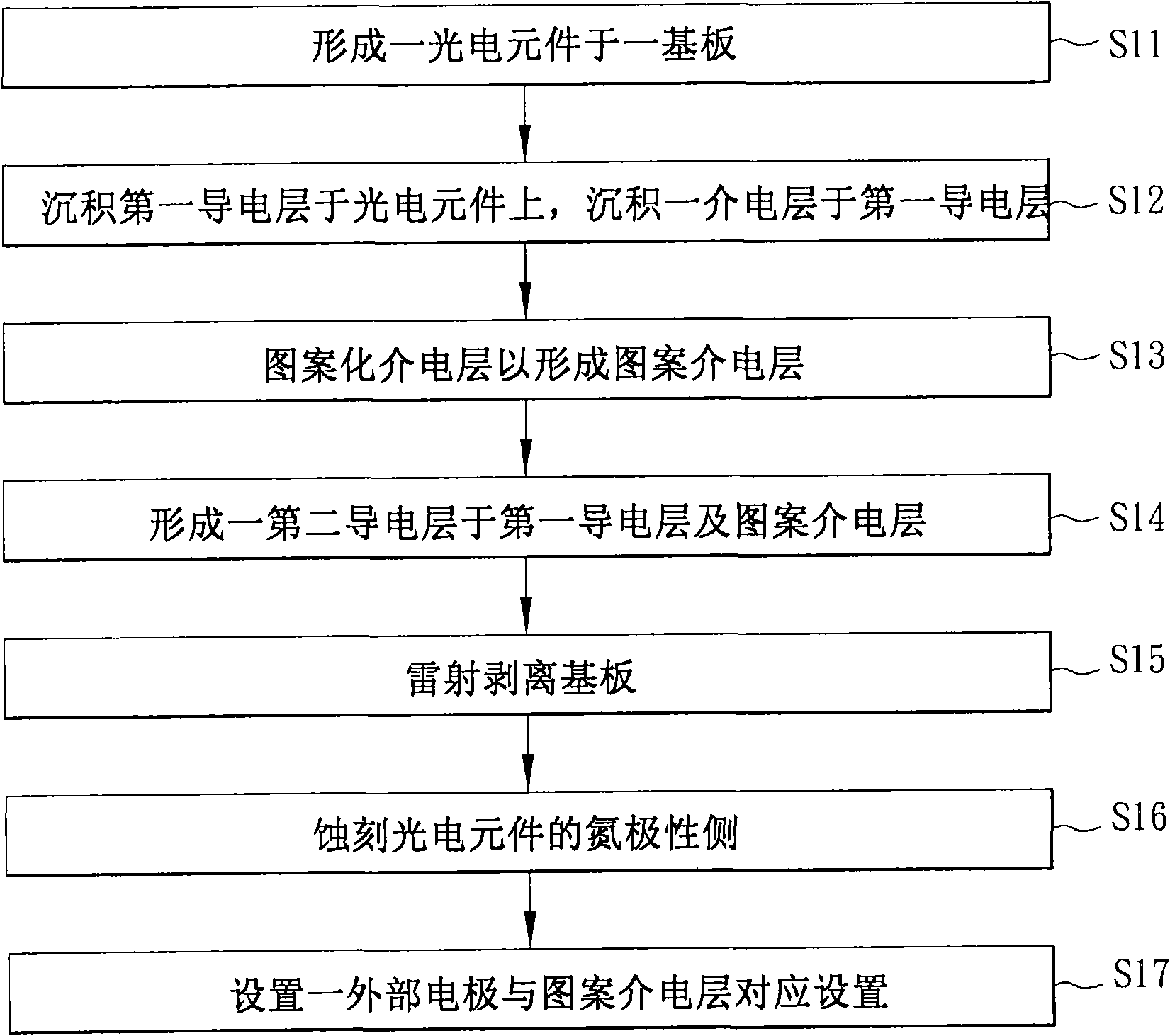

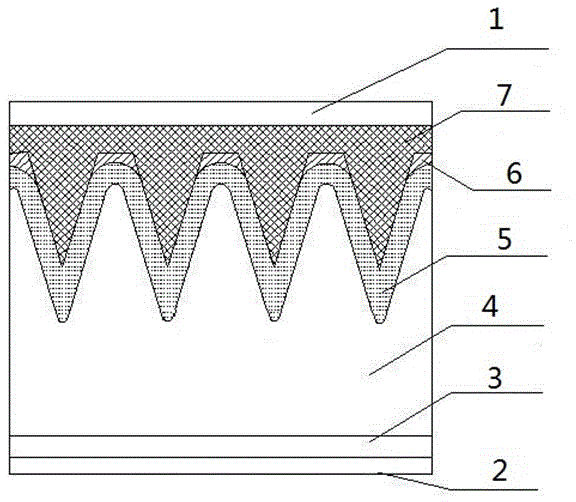

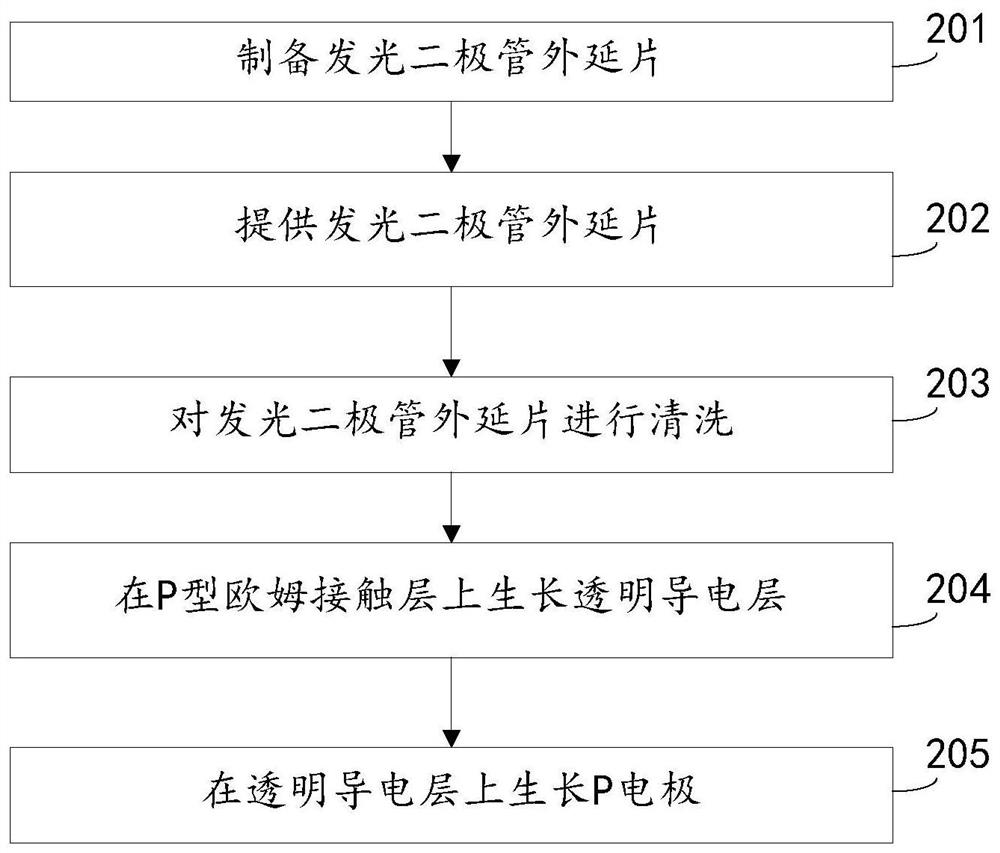

Photoelectronic device and manufacturing method thereof

InactiveCN101621098AImprove luminous efficiencyImproved ohmic contact characteristicsSemiconductor devicesOhmic contactOptoelectronics

A manufacturing method of a photoelectronic device comprises the following steps: forming a photoelectric component on a substrate; forming a reflecting ohmic contact film on the photoelectric component and forming a second conducting layer on the reflecting ohmic contact film; wherein, the reflecting ohmic contact film is provided with a pattern dielectric layer and a first conducting layer; the pattern dielectric layer and the first conducting layer are deposited above the photoelectric component. The invention also discloses the photoelectronic device manufactured by the method.

Owner:TEKCORE CO LTD

Anti-LID black silicon solar high-efficiency cell and production method thereof

ActiveCN106328736APromote absorptionImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationLight energyTrapping

The invention relates to an anti-LID black silicon solar high-efficiency cell and a production method thereof. The anti-LID black silicon solar high-efficiency cell comprises a positive electrode, a negative electrode, an aluminum back surface field, a P-type silicon wafer substrate, and a PN junction, an SiO2 oxide film and an SiNx film located on the P-type silicon wafer substrate sequentially, wherein the thickness of the PN junction is uniform; and the SiNx film coats the surface of the SiO2 oxide film. Through high-light trapping nano column making, first-time diffusion, edge and phosphosilicate glass removal, second-time diffusion, SiNx surface passivation, anti-reflection film deposition, and cell negative electrode and positive electrode and aluminum back surface field making sequentially, the anti-LID black silicon solar cell is made. Thus, the light energy absorption is enhanced, the photoelectric conversion efficiency is improved, the leakage phenomenon of the cell is reduced, and the anti-LID and PID effects are realized.

Owner:镇江市电器设备厂有限公司

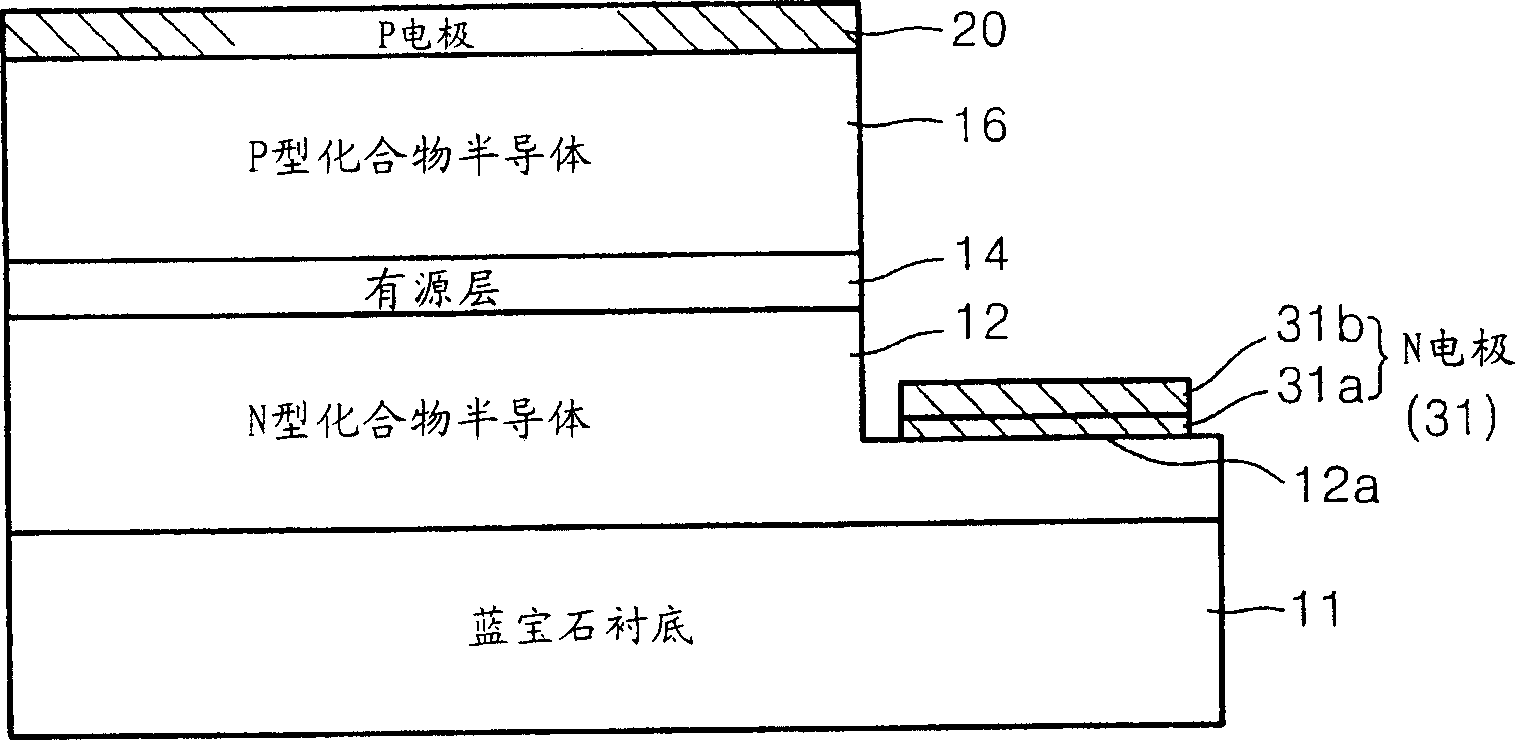

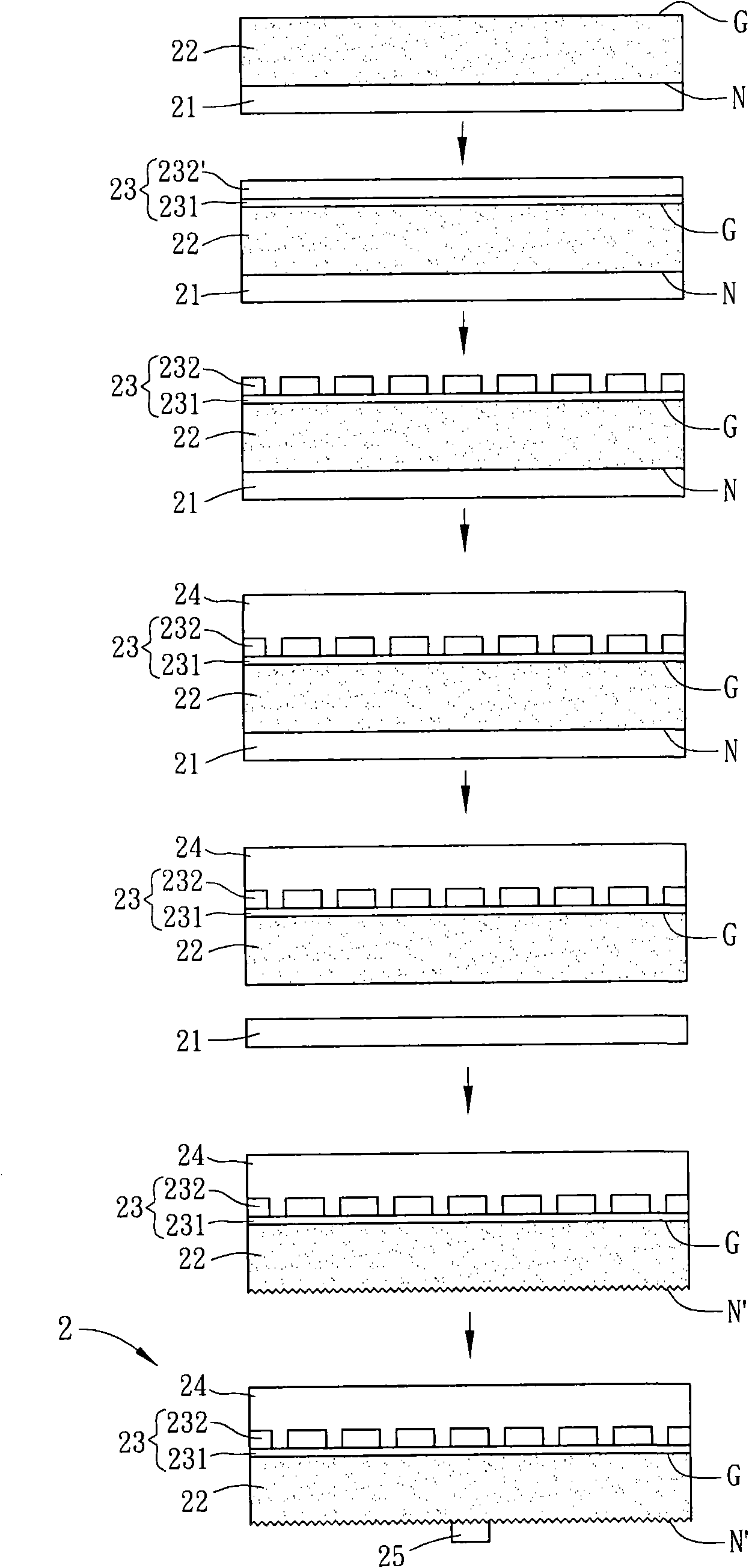

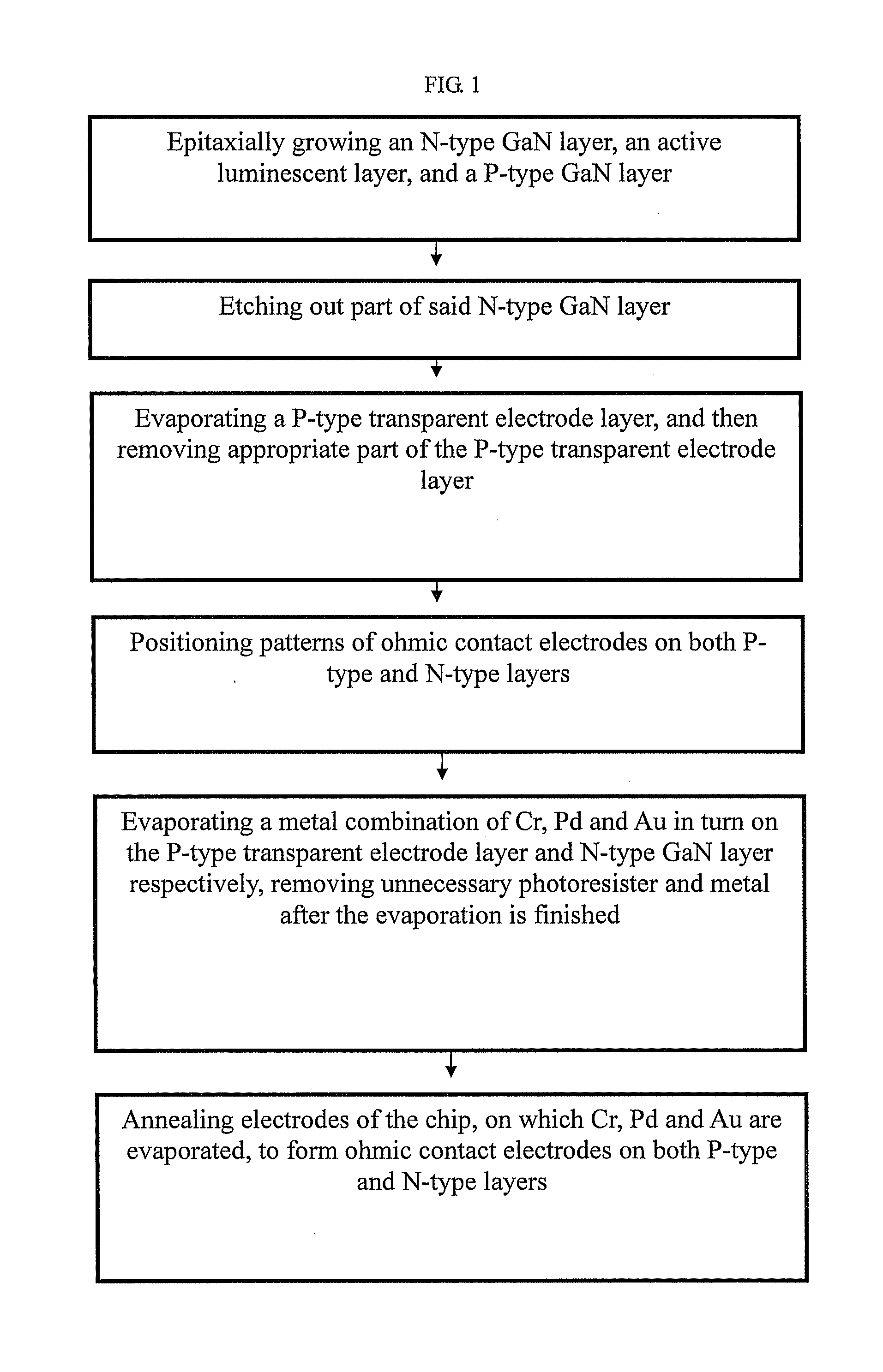

Set of ohmic contact electrodes on both p-type and n-type layers for gan-based LED and method for fabricating the same

InactiveUS20090057706A1Improve reliabilityGood ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactNitrogen atmosphere

The present disclosure relates to set of a ohmic contact electrodes on both P-type and N-type layers of a GaN-based light emitting diode (LED) and a fabricating method thereof. The materials of ohmic contact electrodes on both P-type and N-type layers of a GaN-based LED are a metal combination of Cr / Pd / Au. In one embodiment, the fabricating method comprises etching out an N-type GaN layer on an epitaxial structure on a sapphire substrate, and evaporating a P-type transparent electrode layer on the P-type GaN layer, then positioning patterns of the ohmic contact electrodes on both P-type and N-type layers, and then evaporating a metal combination of a Cr layer 50 Å to 500 Å thick, a Pd layer 300 Å to 1000 Å thick and an Au layer 3000 Å to 20000 Å thick in turn on the P-type transparent electrode layer and N-type GaN layer respectively, and then annealing electrodes of the chip, on which the Cr, Pd and Au layers are evaporated in nitrogen atmosphere for 5 minutes to 20 minutes at a temperature from 200 degrees to 450 degrees. Excellent ohmic contact characteristics and better thermal stability are obtained as well as higher oxidation resistance, thus improving the reliability of diode.

Owner:PODIUM PHOTONICS GUANGZHOU

Light-emitting diode and manufacture method thereof

InactiveCN103325911AUniform current distributionImproved ohmic contact characteristicsSemiconductor devicesOptoelectronicsLight-emitting diode

The invention discloses a light-emitting diode and a manufacture method thereof. The light-emitting diode comprises a substrate, a first electrode, an epitaxial layer and a second electrode. The first electrode is arranged on one surface of the substrate, the epitaxial layer is arranged on the other surface of the substrate, the second electrode is arranged on the epitaxial layer, the second electrode is a composite metal layer including a Ti layer, a TiW layer, a Pt layer and an Au layer in sequence. The second electrode and the substrate are respectively arranged on two sides of the epitaxial layer. The invention also provides the manufacture method thereof.

Owner:CHI MEI LIGHTING TECH +1

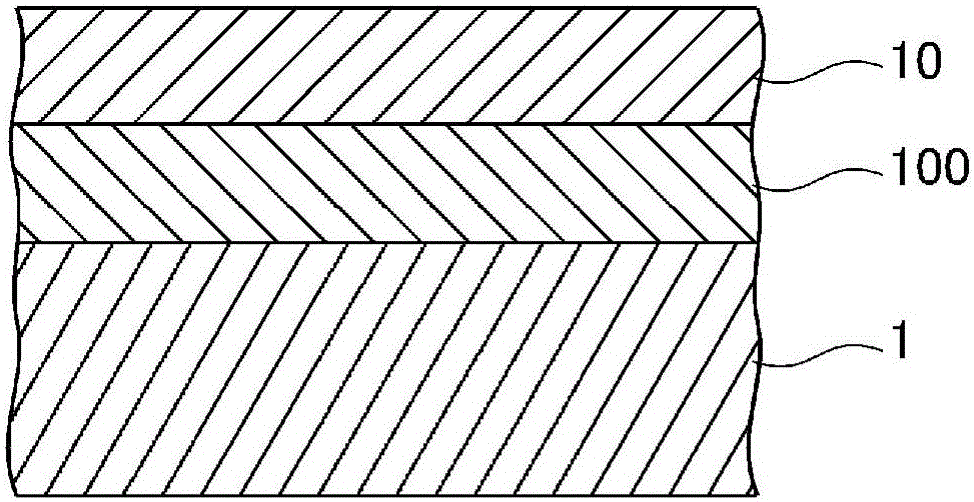

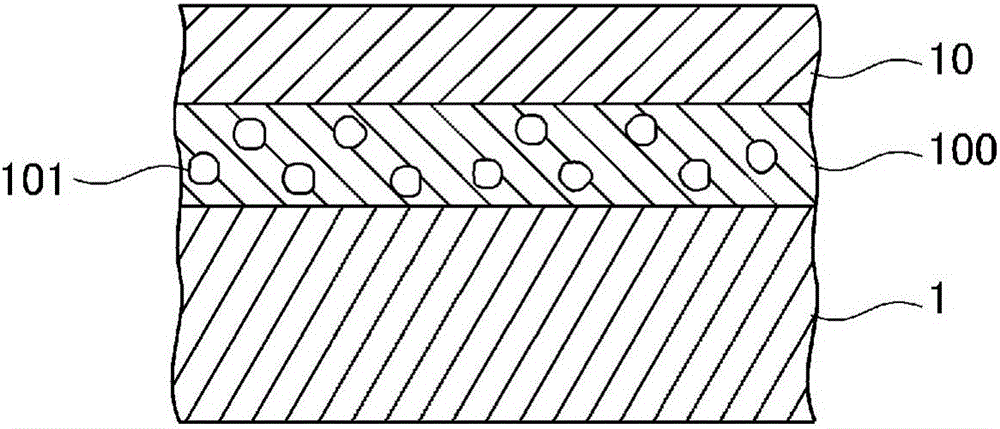

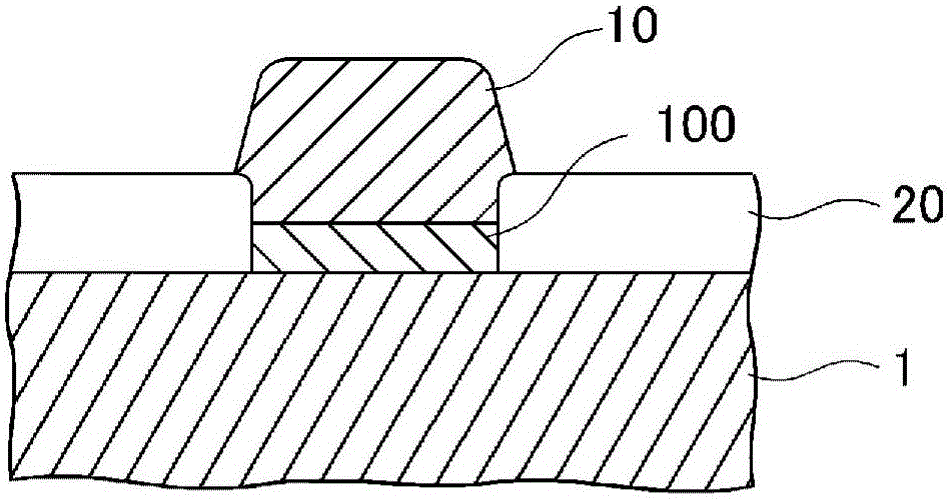

Solar cell and production method therefor

ActiveCN105830227APrevent interdiffusionInhibition of recombinationPhotovoltaic energy generationSemiconductor devicesNiobiumCopper electrode

The present invention is provided with an interface layer that minimizes interdiffusion between a silicon substrate and copper electrode wiring that are used as a solar cell, that improves the adhesive properties of copper wiring, and that is used to obtain ohmic contact characteristics. This silicon solar cell comprises a silicon substrate (1) and is provided with a metal oxide layer (100) that is formed on the silicon substrate and wiring (10) that is formed on the metal oxide layer and that comprises mainly copper. The metal oxide layer contains (a) one of either titanium or manganese, (b) one of vanadium, niobium, tantalum, or silicon, and (c) at least one of copper and nickel. In addition, the metal oxide layer comprises copper or nickel as metal particles that are diffused in the interior of the metal oxide layer.

Owner:MATERIAL CONCEPT

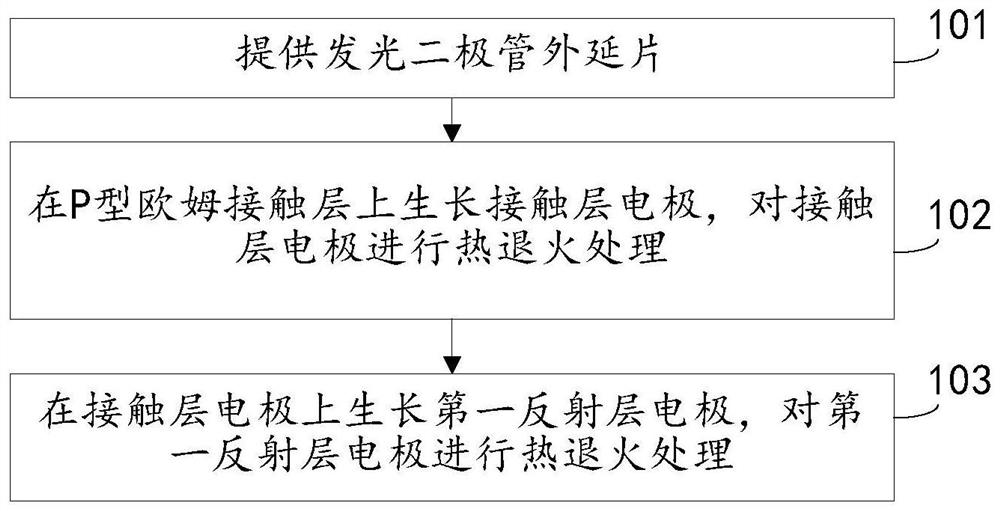

Preparation method of P electrode of light-emitting diode chip with vertical structure

ActiveCN112885937AShorten the annealing timeLow annealing temperatureSemiconductor devicesOhmic contactEngineering

The invention provides a preparation method of a P electrode of a light-emitting diode chip with a vertical structure, and belongs to the field of light-emitting diodes. The method comprises the steps of providing a light-emitting diode epitaxial wafer, wherein the light-emitting diode epitaxial wafer comprises a substrate, and a buffer layer, an undoped GaN layer, an N-type GaN layer, a multi-quantum well layer, an electron barrier layer, a P-type GaN layer and a P-type ohmic contact layer which are stacked on the substrate in sequence, wherein a contact layer electrode is grown on the P-type ohmic contact layer, thermal annealing treatment is conducted on the contact layer electrode, and the contact layer electrode comprises a Ni layer; and a first reflecting layer electrode is grown on the contact layer electrode, thermal annealing treatment is conducted on the first reflecting layer electrode, the first reflecting layer electrode comprises a first Ag layer, the annealing time of the first reflecting layer electrode is shorter than that of the contact layer electrode, and the annealing temperature of the first reflecting layer electrode is lower than that of the contact layer electrode. According to the invention, the P electrode with high reflectivity and low contact resistivity can be obtained.

Owner:HC SEMITEK ZHEJIANG CO LTD

Reflective electrode and compound semiconductor light emitting device including the same

InactiveCN1758455AIncrease optical powerReduce power consumptionLaser detailsLaser optical resonator constructionOhmic contactAlloy

Provided are a reflective electrode and a compound semiconductor light emitting device having the reflective electrode, such as LED or LD is provided. The reflective electrode formed on a p-type compound semiconductor layer of a compound semiconductor light emitting device, comprising a first electrode layer formed one of a Ag and Ag-alloy and forms an ohmic contact with the p-type compound semiconductor layer, a third electrode layer formed of a material selected from the group consisting of Ni, Ni-alloy, Zn, Zn-alloy, Cu, Cu-alloy, Ru, Ir, and Rh on the first electrode layer, and a fourth electrode layer formed of a light reflective material on the third electrode layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor light emitting device

InactiveUS20180182921A1Improve ohmic contact characteristicEasy dischargeSolid-state devicesSemiconductor devicesPhysicsElectrical conductor

A semiconductor light emitting device includes a first semiconductor layer, an active layer disposed on the first semiconductor layer to emit ultraviolet light, a second semiconductor layer disposed on the active layer, and a first electrode disposed on the first semiconductor layer and being in Ohmic contact with a portion of the first semiconductor layer, the first electrode including a contact electrode including aluminum (Al) and at least one other material and having a first region adjacent to the first semiconductor layer and a second region, with each region having an Al composition ratio defined by the amount of Al relative to the amount of the at least one other material, wherein the Al composition ratio of the first region is greater than the Al composition ratio of the second region, and a metal layer disposed on the contact electrode.

Owner:SEOUL VIOSYS CO LTD

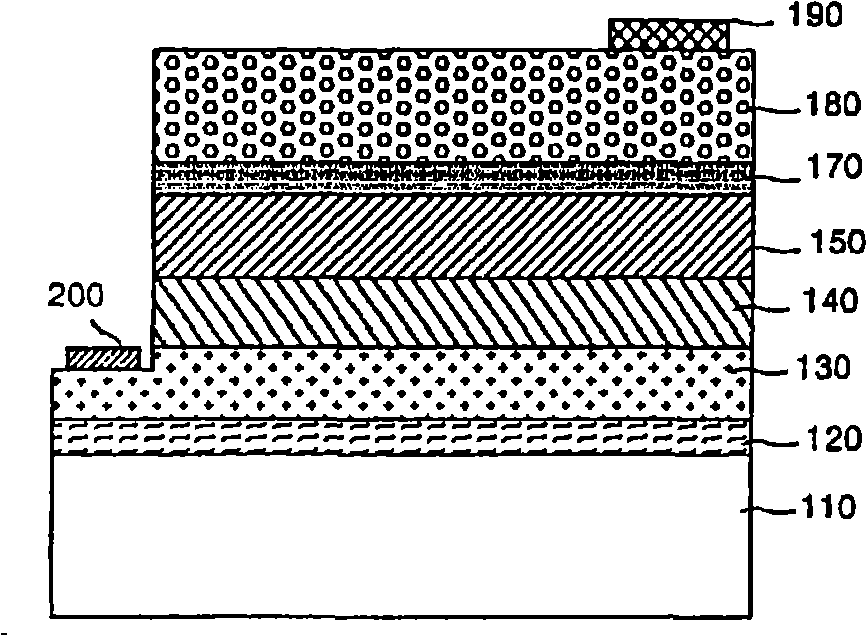

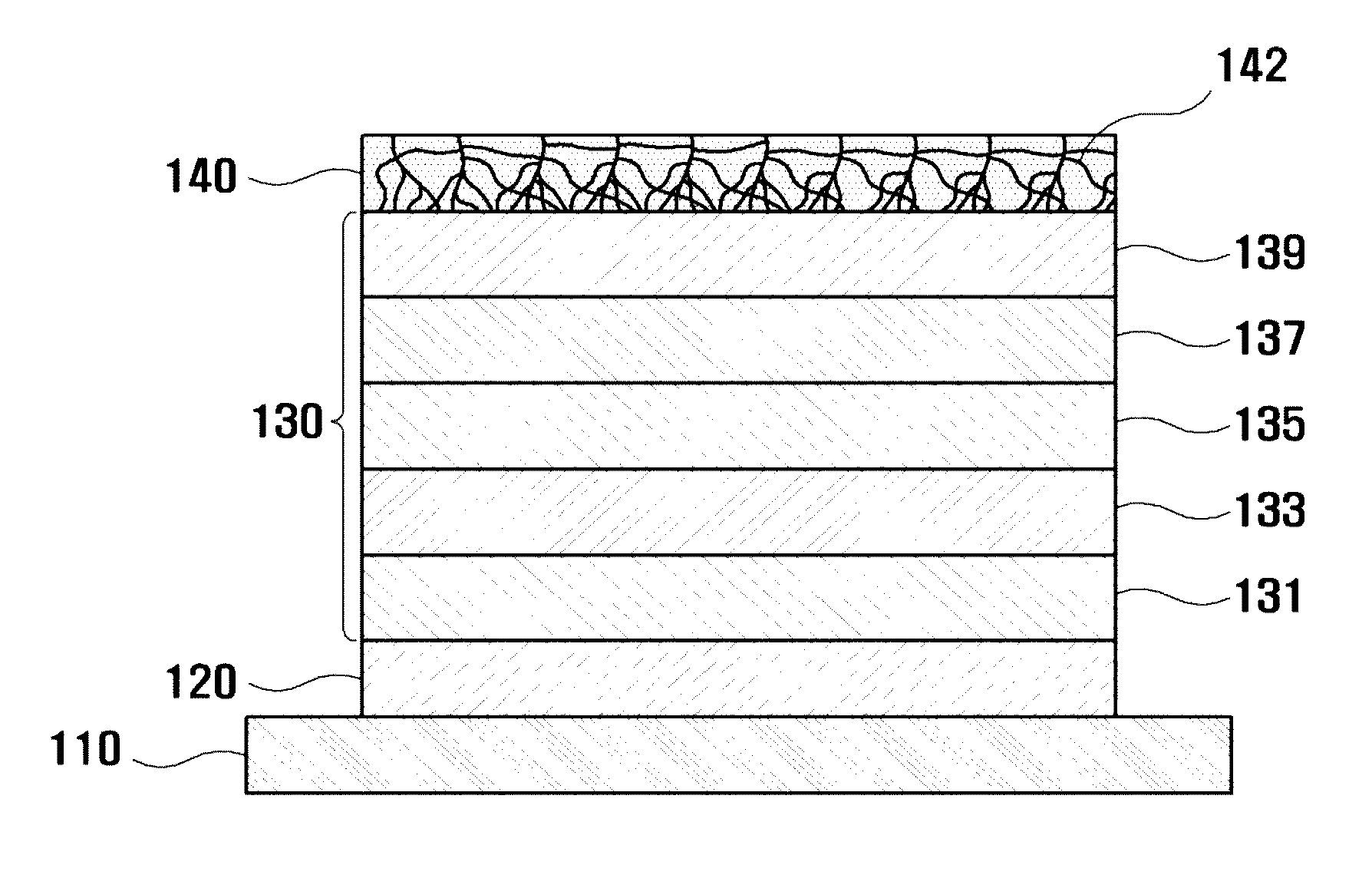

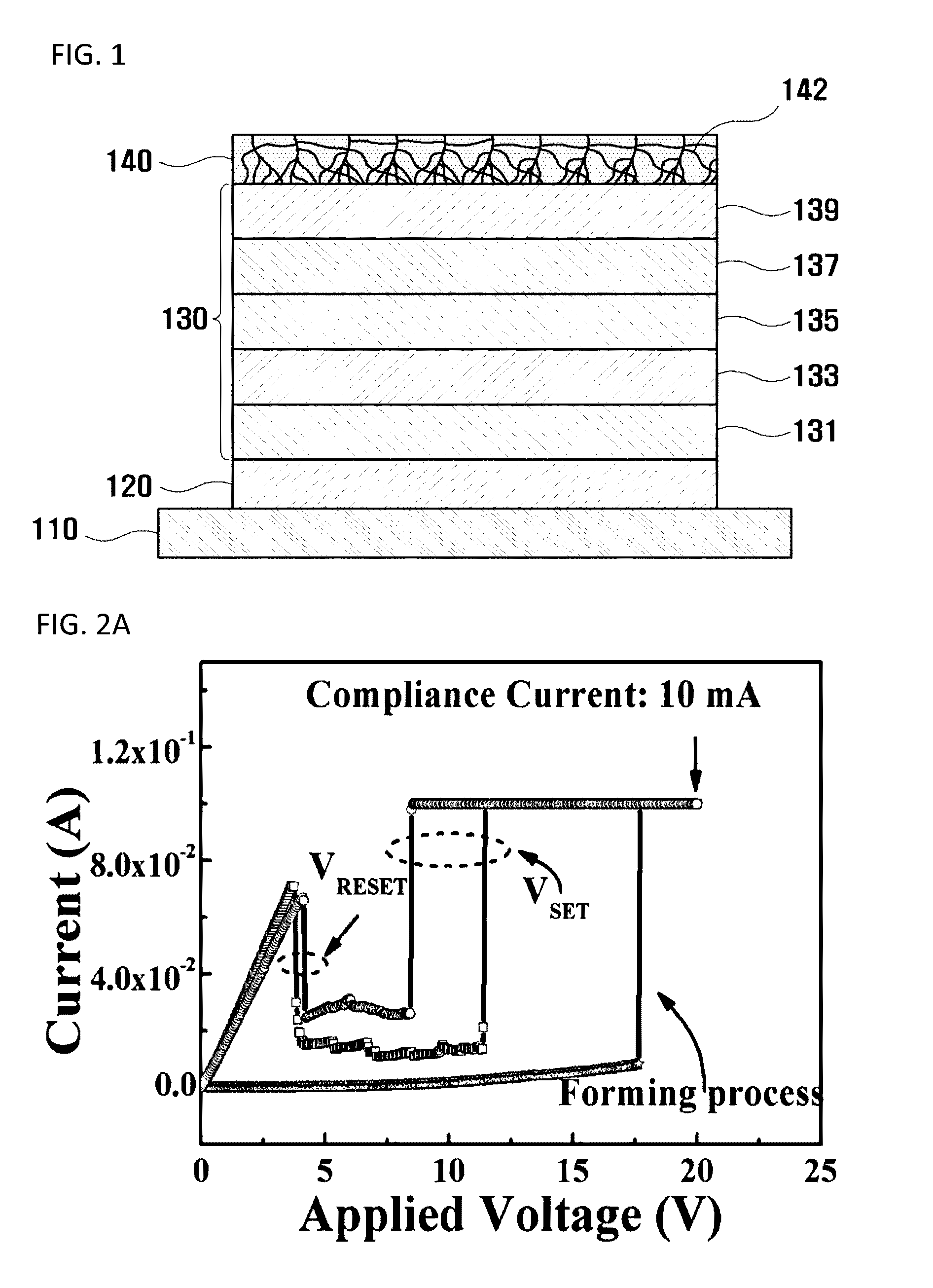

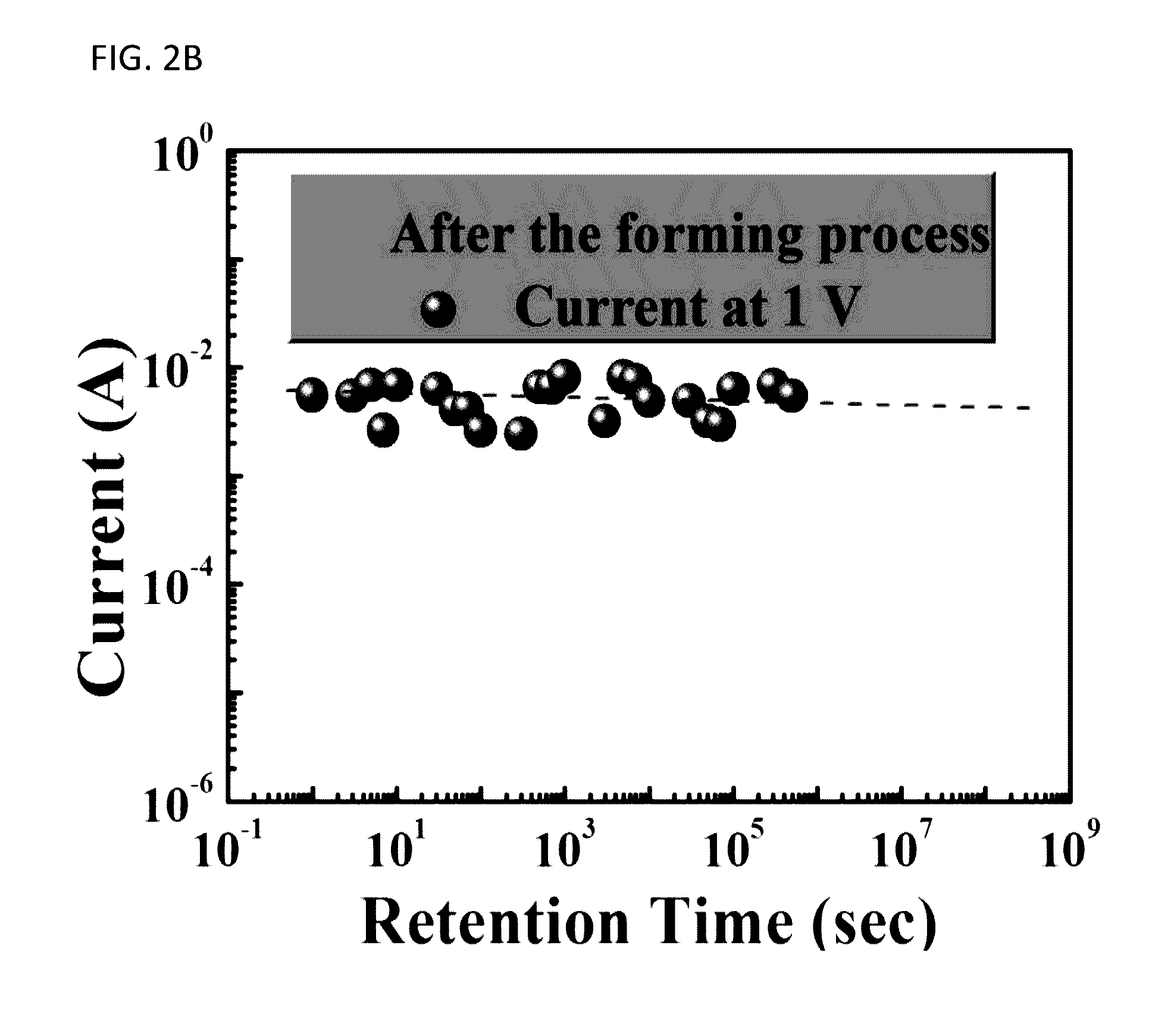

Organic light emitting device having transparent electrode where conducting filaments formed and method of manufacturing the same

ActiveUS9570699B2High light transmittanceImproved ohmic contact characteristicsElectroluminescent light sourcesNanoinformaticsHigh resistanceOrganic light emitting device

Provided is an organic light emitting device including a transparent electrode in which conducting filaments are formed and a method of manufacturing the same. In the organic light emitting device, a transparent electrode of an organic light emitting device is formed by using a resistance change material which has high transmittance with respect to light in a UV wavelength range and of which resistance state is to be changed from a high resistance state into a low resistance state due to conducting filaments, which current can flow through, formed in the material if a voltage exceeding a threshold voltage inherent in a material is applied to the material, so that it is possible to obtain the transparent electrode having high transmittance with respect to light in a UV wavelength range as well as light in a visible wavelength range generated by the organic light emitting device and having high conductivity.

Owner:KOREA UNIV RES & BUSINESS FOUND

P-N junction-type compoud semiconductor light-emitting diode

InactiveCN1969394AIncrease brightnessHigh transparencyLaser detailsLaser active region structureRoom temperatureP–n junction

In a p-n junction-type compound semiconductor light-emitting diode provided on a crystal substrate with at least an n-type active layer formed of a Group III nitride semiconductor as a light emitting layer, and with a Group III nitride semiconductor layer containing a p-type impurity on the n-type active layer, the diode has a boron phosphide-based Group III-V compound semiconductor layer possessing a band gap exceeding that of the Group III nitride semiconductor forming the n-type active layer at room temperature and exhibiting a p-type electroconductivity in an undoped state deposited on the p-type impurity-containing Group Ill nitride semiconductor layer, and has an ohmic positive electrode joined to a surface of the boron phosphide-based Group III-V compound semiconductor layer.

Owner:SHOWA DENKO KK

Silicon carbide PiN device ohmic contact method

ActiveCN105244267AImproved ohmic contact characteristicsSimplify process flowSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactAmorphous silicon

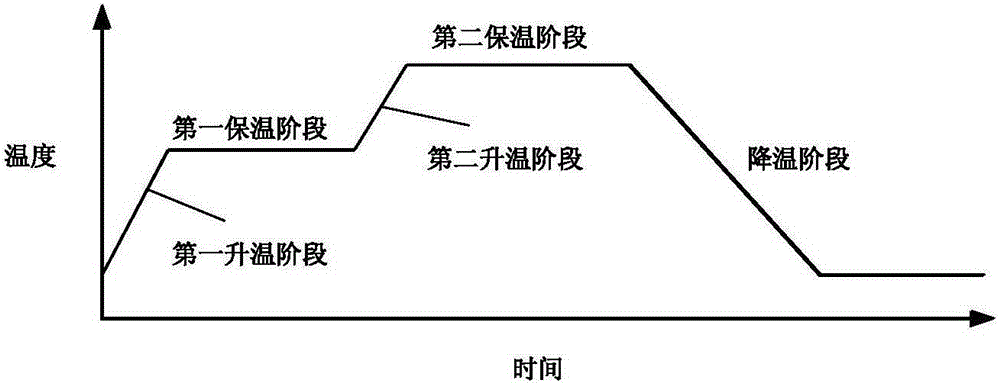

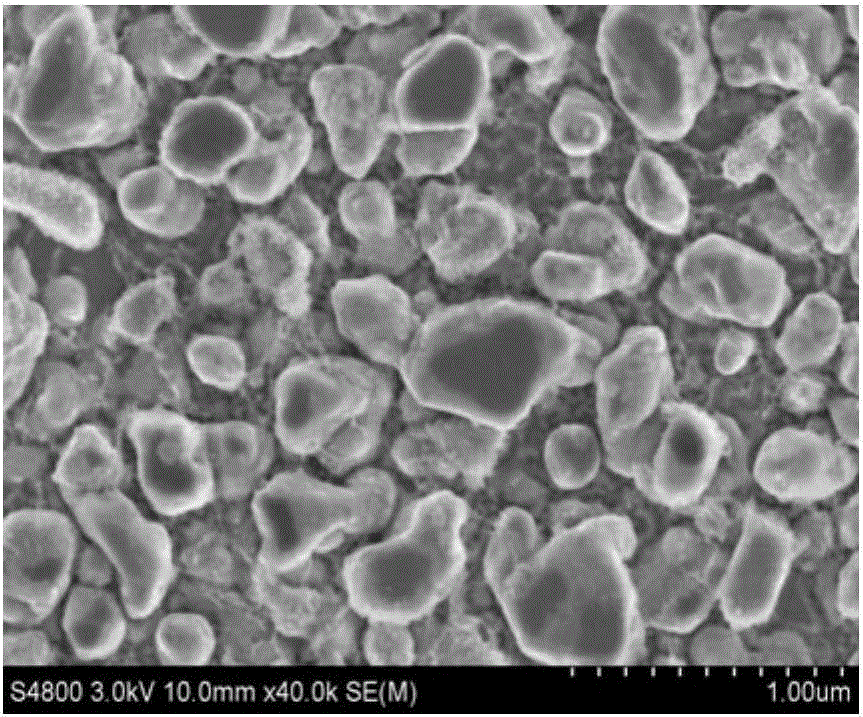

The invention belongs to the field of PiN devices, and particularly relates to a silicon carbide PiN device ohmic contact method. The method comprises the following steps that a) a silicon carbide PiN base body is prepared; b) an amorphous silicon layer is deposited on the surface of the P-type SiC epitaxial layer of the silicon carbide PiN base body; c) a metal layer is respectively deposited on the surface, on which the amorphous silicon layer is deposited, of the SiC substrate of the silicon carbide PiN base body and the surface of the amorphous silicon layer; and d) annealing processing is performed on the silicon carbide PiN base body on which the metal layer is deposited so that a silicon carbide PiN device with formation of ohmic contact is obtained, wherein annealing processing includes a first temperature rising period, a first heat preservation period, a second temperature rising period and a second heat preservation period, and temperature of the first heat preservation period and the second heat preservation period is respectively 450-550 DEG C and 970-1020 DEG C. According to the method, P-type ohmic contact and N-type ohmic contact can be formed on the silicon carbide PiN base body on which the metal layer is deposited through one time of annealing process.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

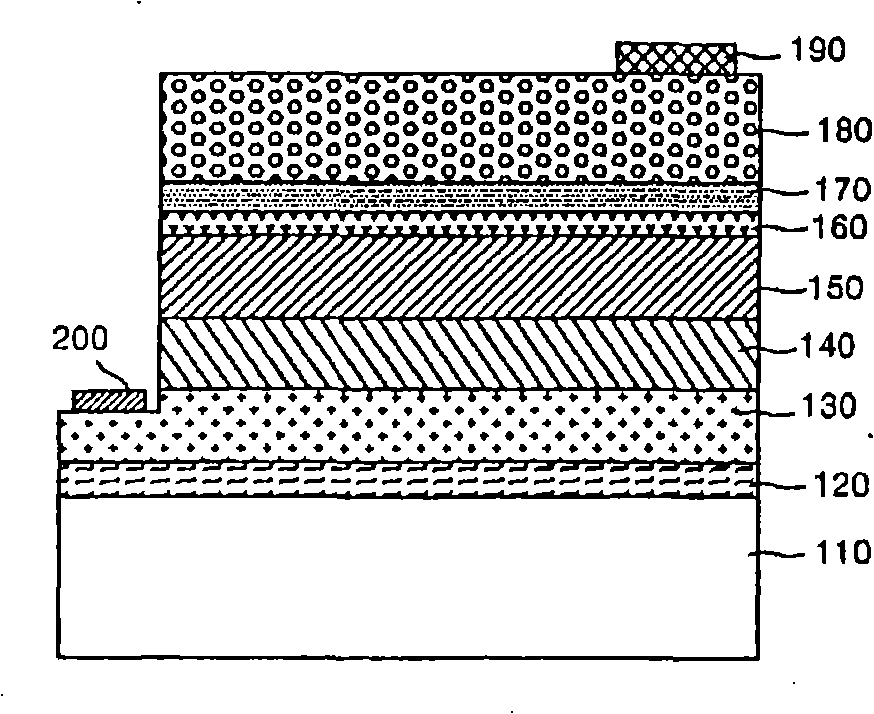

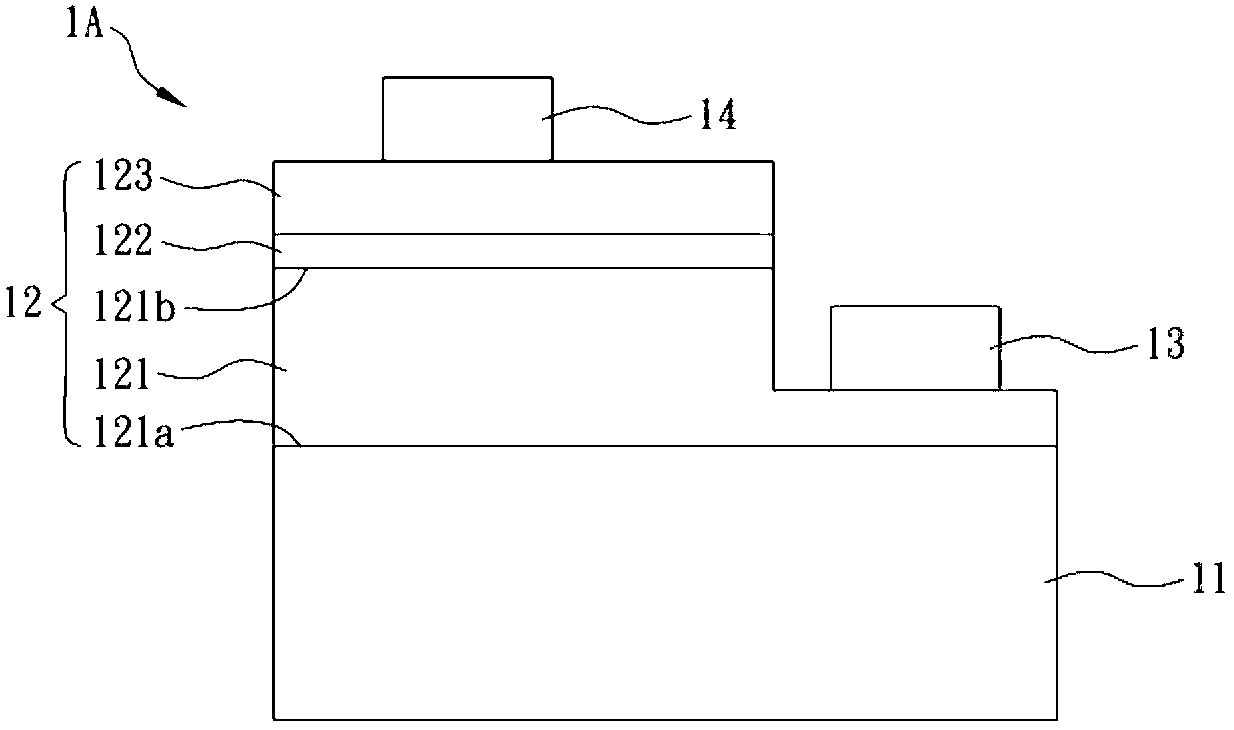

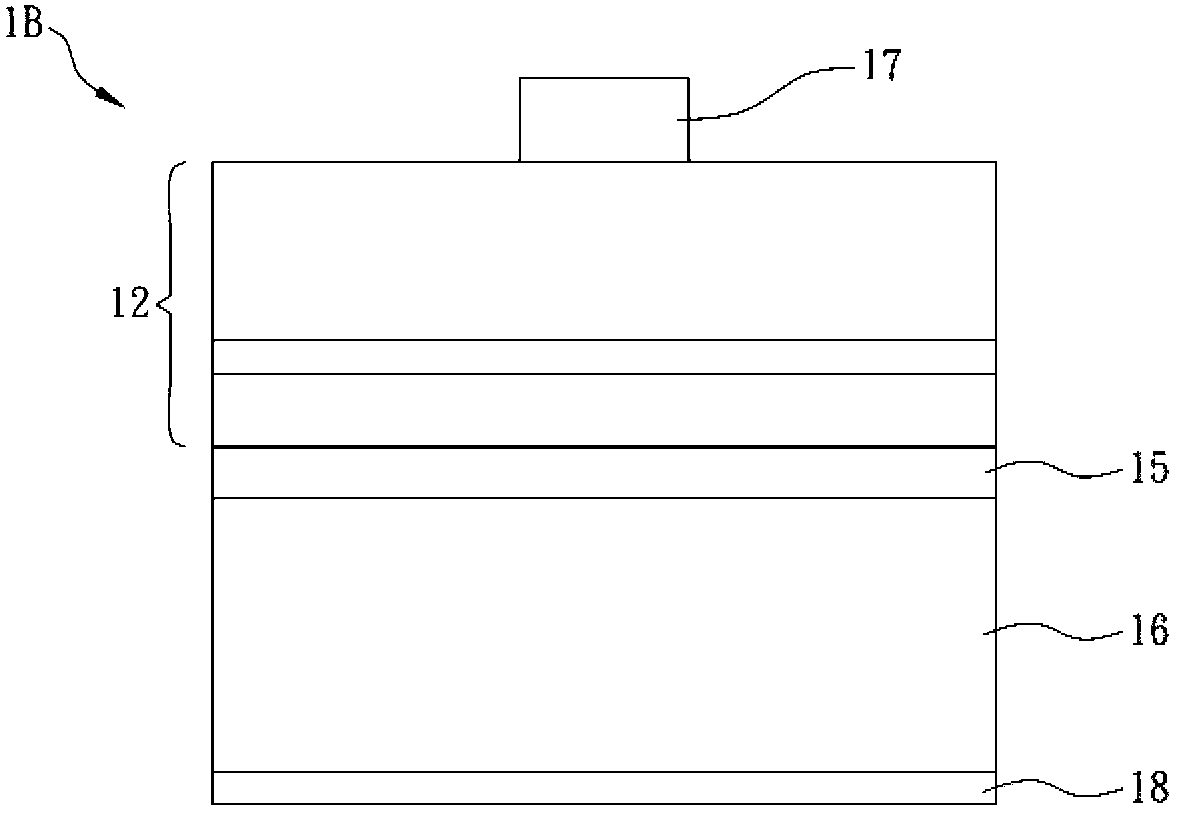

Flip-chip light emitting diodes and method of manufacturing thereof

ActiveUS7872271B2Improved ohmic contact characteristicsImprove adhesionSemiconductor devicesConductive materialsLight emitting device

Provided are a flip-chip nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising a reflective layer formed on the p-type clad layer and at least one transparent conductive thin film layer made up of transparent conductive materials capable of inhibiting diffusion of materials constituting the reflective layer, interposed between the p-type clad layer and reflective layer; and a process for preparing the same. In accordance with the flip-chip nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact properties with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current-voltage properties.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of manufacturing transistor and method of manufacturing organic electroluminescence display using the same

InactiveUS7846787B2Improved ohmic contact characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactAmorphous silicon

A method of manufacturing a transistor and a method of manufacturing an organic electroluminescence display are disclosed. When an amorphous silicon layer is crystallized, a silicon oxide layer formed on a polysilicon layer is subsequently patterned. Impurity ions are implanted into first and second regions of the amorphous silicon layer to form first and second doped regions. The silicon oxide layer is patterned so that the silicon oxide layer may be removed from an ohmic contact region of the polysilicon layer, and covers only a channel region of the polysilicon layer.

Owner:SAMSUNG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com