Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

94 results about "Contact barrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for a multi-use body fluid sampling device with sterility barrier release

Owner:SANOFI AVENTIS DEUT GMBH

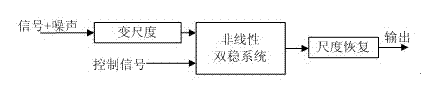

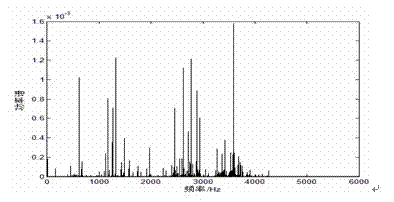

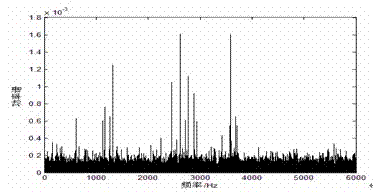

Bearing fault detection method based on manner of controlling stochastic resonance by external periodic signal

InactiveCN102226740AEnhanced spectral valueAccurate detectionMachine bearings testingControl signalEscape rate

The invention discloses a bearing fault detection method based on a manner of controlling stochastic resonance by an external periodic signal. According to the method provided in the invention, after a bearing fault signal is converted by a variable metric method, the converted signal is input in a bistable system; meanwhile, an external single frequency periodic signal is taken as a control signal to act directly on the system; contact barrier height of the bistable system and an escape rate of Kramers are changed by continuously adjusting an amplitude of the control signal. Therefore, stochastic resonance can be generated or increased artificially; a spectral value of an output power spectrum at the position of an input signal frequency can be effectively improved; and thus a characteristic signal of a bearing fault can be detected accurately at last. The detection method provided in the invention enables the effective control of the stochastic resonance to be realized, thereby providing a novel method for early detection of equipment faults.

Owner:CHINA JILIANG UNIV

Nanotube enabled, gate-voltage controlled light emitting diodes

ActiveUS8232561B2Small increase in lifetime of deviceMaterial nanotechnologyNanoinformaticsConductive materialsGate voltage

Owner:UNIV OF FLORIDA RES FOUNDATION INC

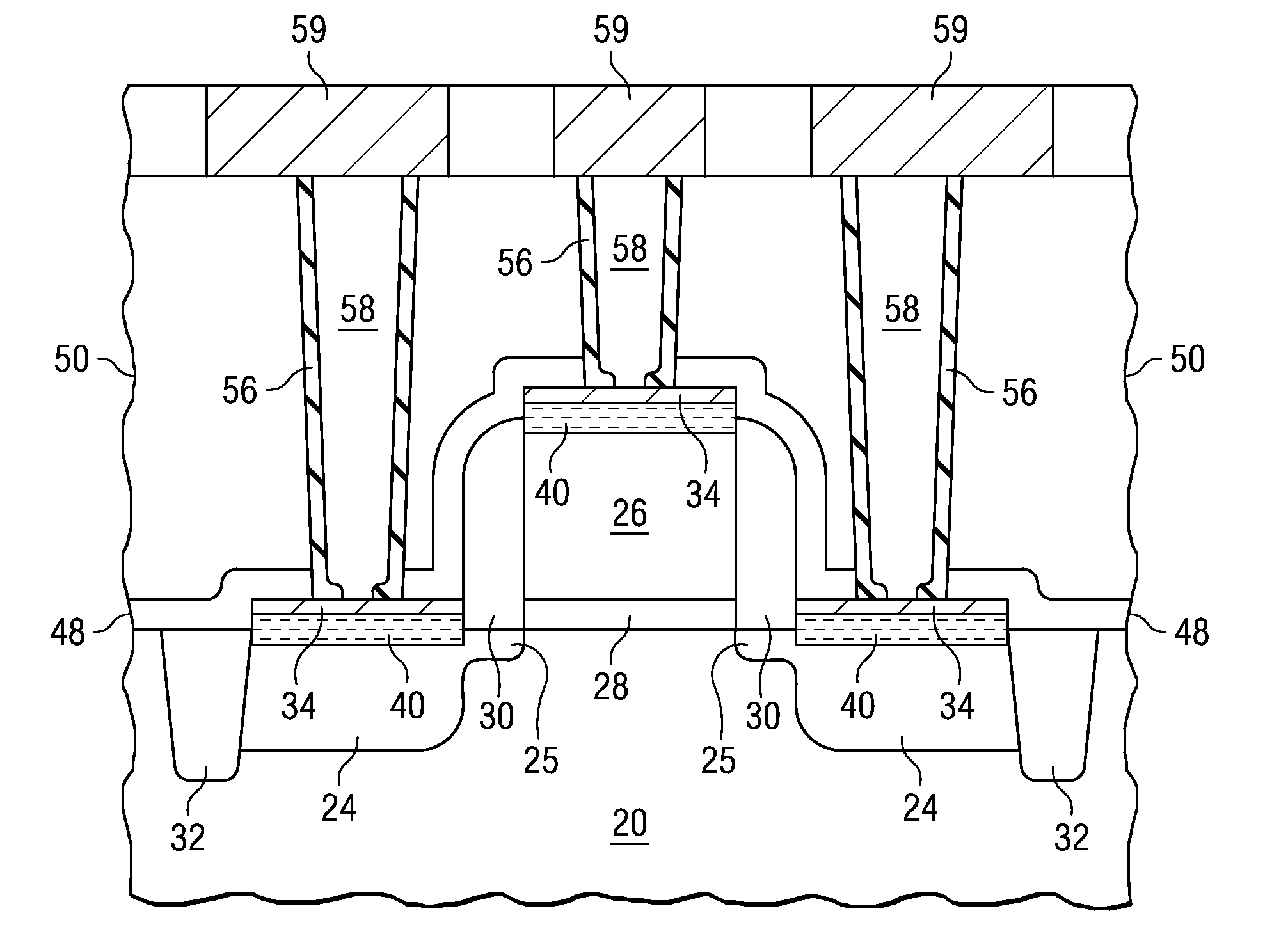

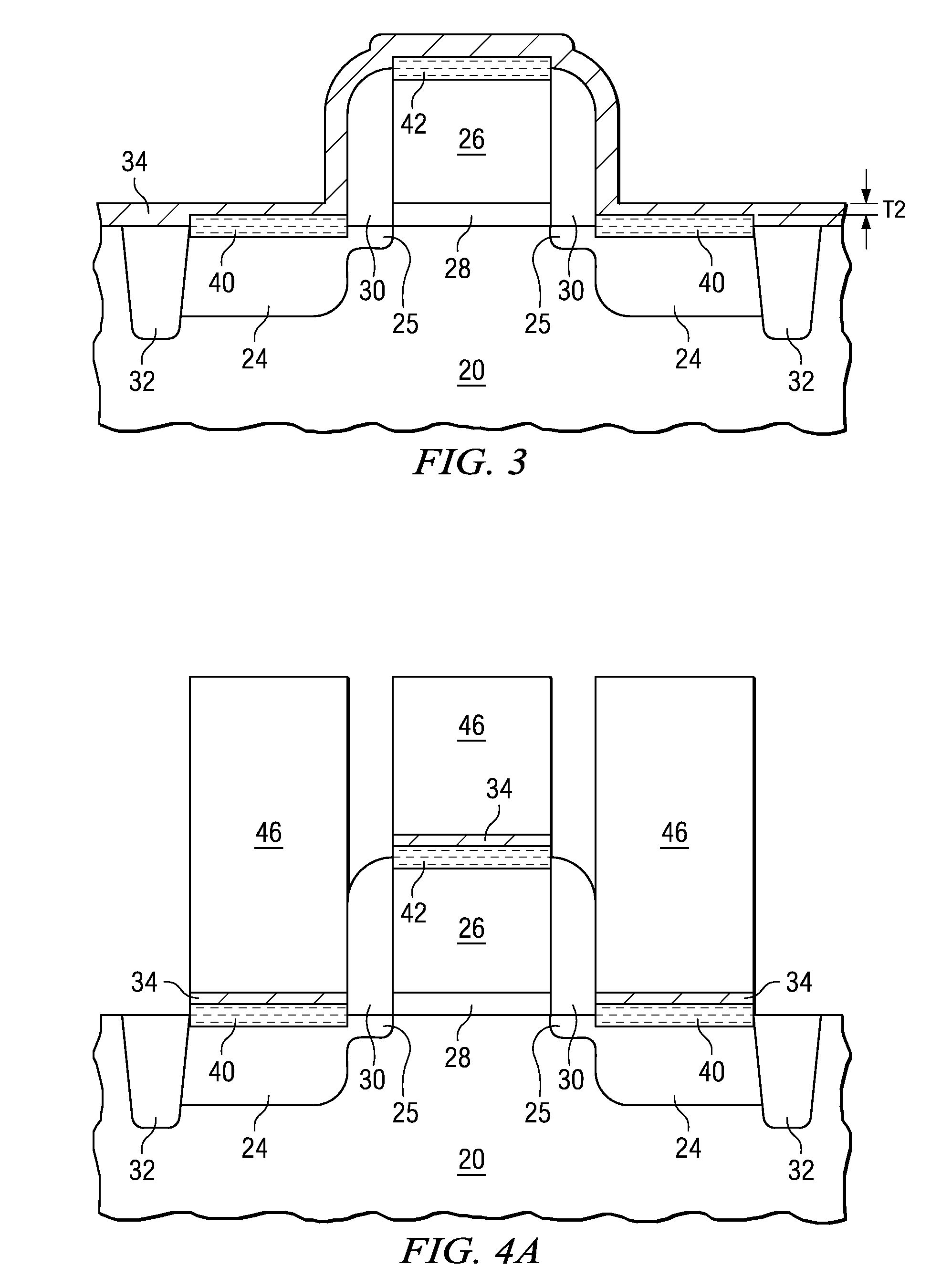

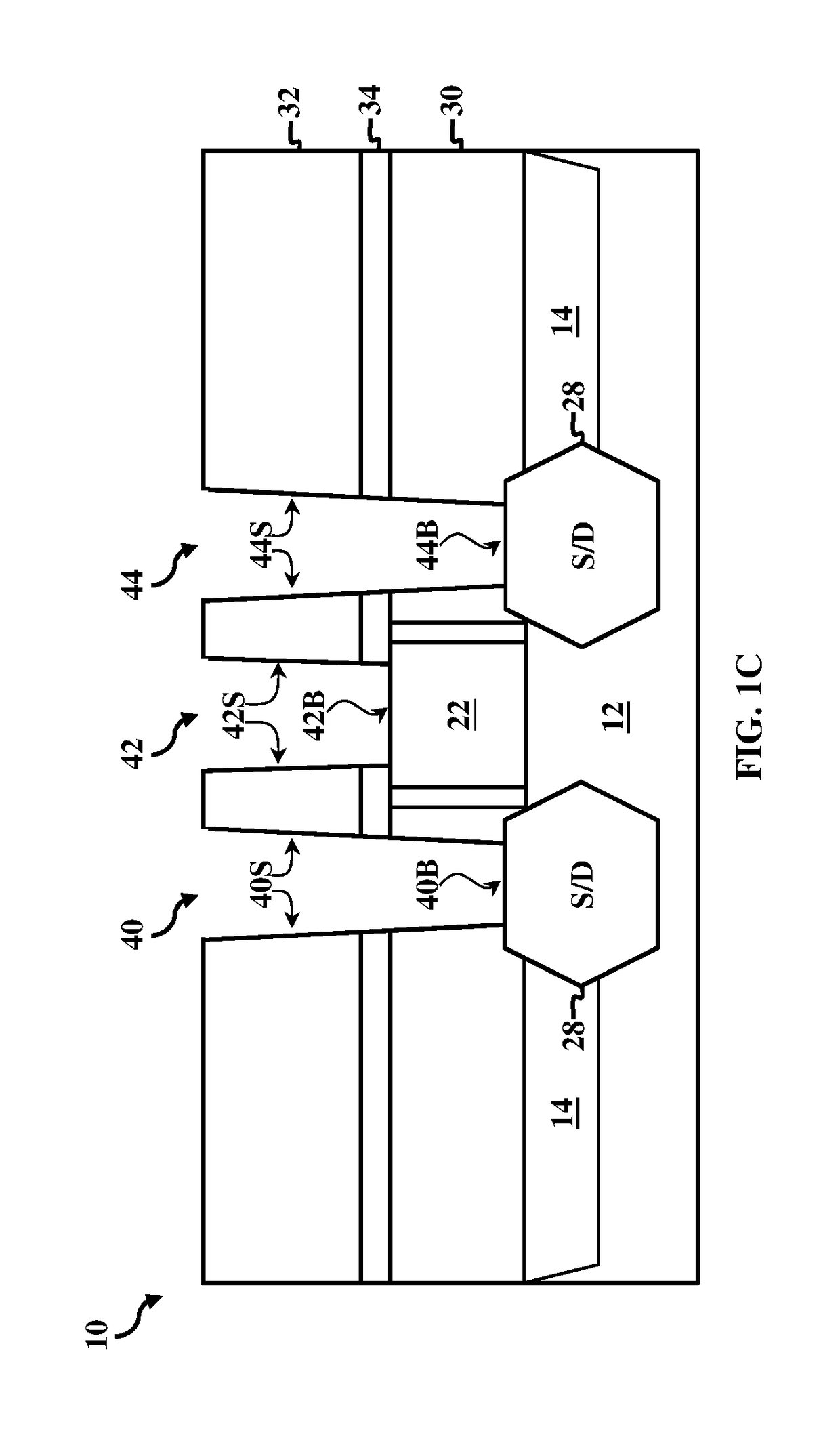

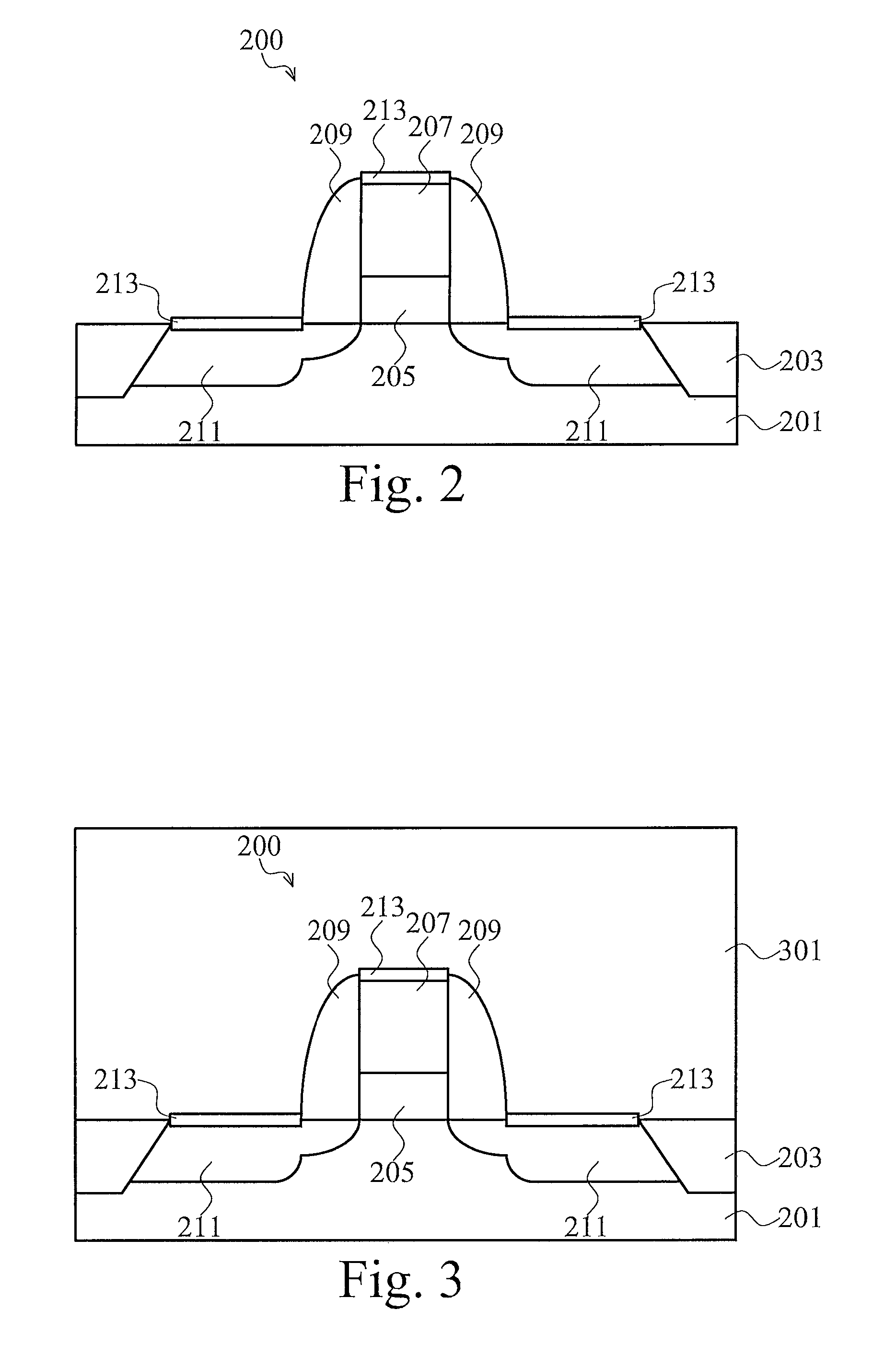

Contact barrier structure and manufacturing methods

ActiveUS20080290421A1Reduce diffuseTransistorSemiconductor/solid-state device detailsSalicideDielectric

A semiconductor structure includes a semiconductor substrate; a gate dielectric over the semiconductor substrate; a gate electrode over the gate dielectric; a source / drain region adjacent the gate dielectric; a silicide region on the source / drain region; a metal layer on top of, and physical contacting, the silicide region; an inter-layer dielectric (ILD) over the metal layer; and a contact opening in the ILD. The metal layer is exposed through the contact opening. The metal layer further extends under the ILD. The semiconductor structure further includes a contact in the contact opening.

Owner:TAIWAN SEMICON MFG CO LTD

Atomic layer deposition based process for contact barrier layer

ActiveUS10170322B1Semiconductor/solid-state device detailsSolid-state devicesNitrogen plasmaTitanium

Interconnect structures and corresponding techniques for forming the interconnect structures are disclosed herein. An exemplary method includes forming a contact opening in a dielectric layer. The contact opening has sidewalls defined by the dielectric layer and a bottom defined by a conductive feature. An ALD-like nitrogen-containing plasma pre-treatment process is performed on the sidewalls (and, in some implementations, the bottom) of the contact opening. An ALD process is performed to form a titanium-and-nitrogen containing barrier layer over the sidewalls and the bottom of the contact opening. A cobalt-containing bulk layer is then formed over the titanium-and-nitrogen-containing barrier layer. A cycle of the ALD-like nitrogen-containing plasma pre-treatment process can include a nitrogen-containing plasma pulse phase and a purge phase. A cycle of the ALD process can include a titanium-containing pulse phase, a first purge phase, a nitrogen-containing plasma pulse phase, and a second purge phase.

Owner:TAIWAN SEMICON MFG CO LTD

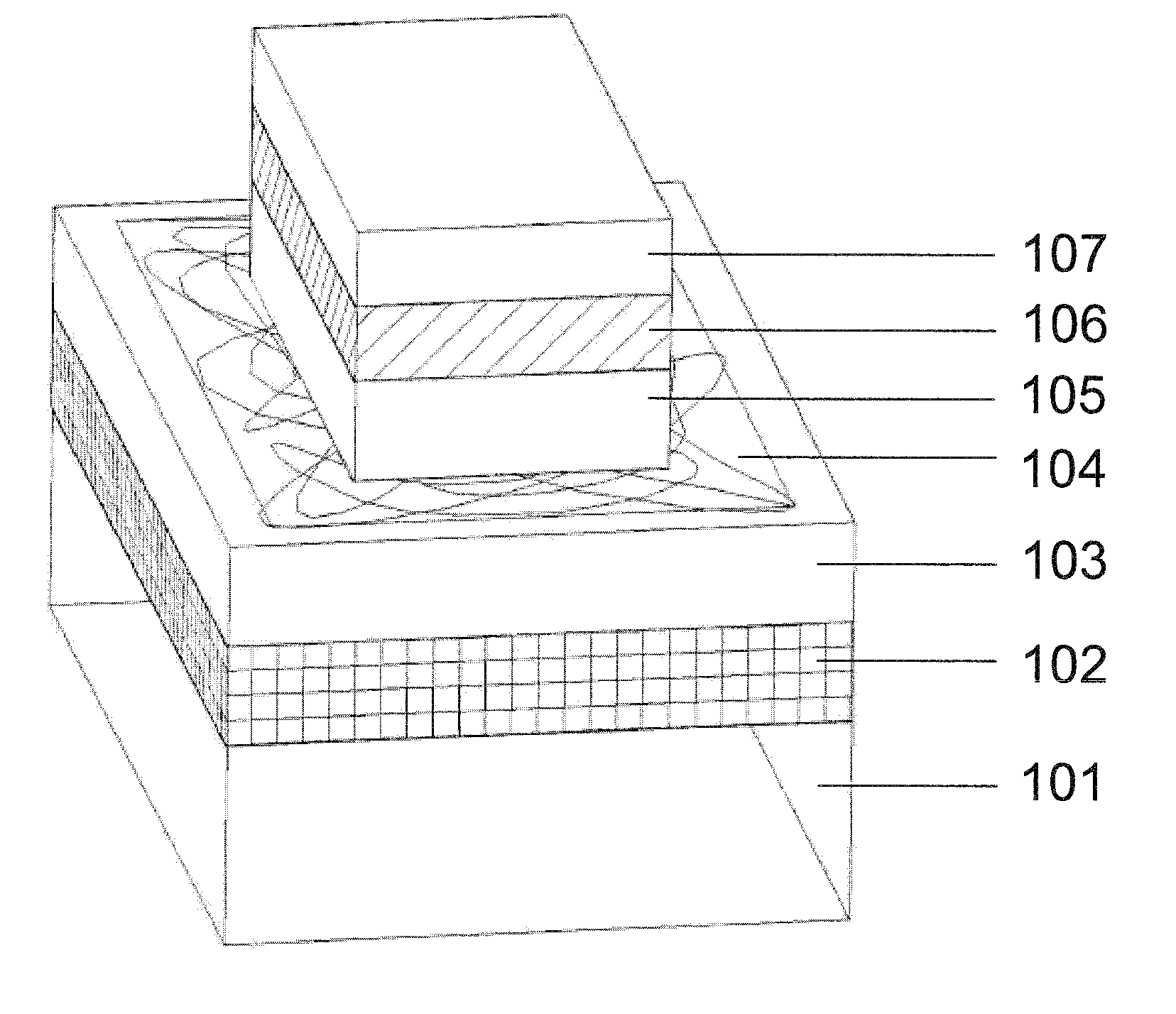

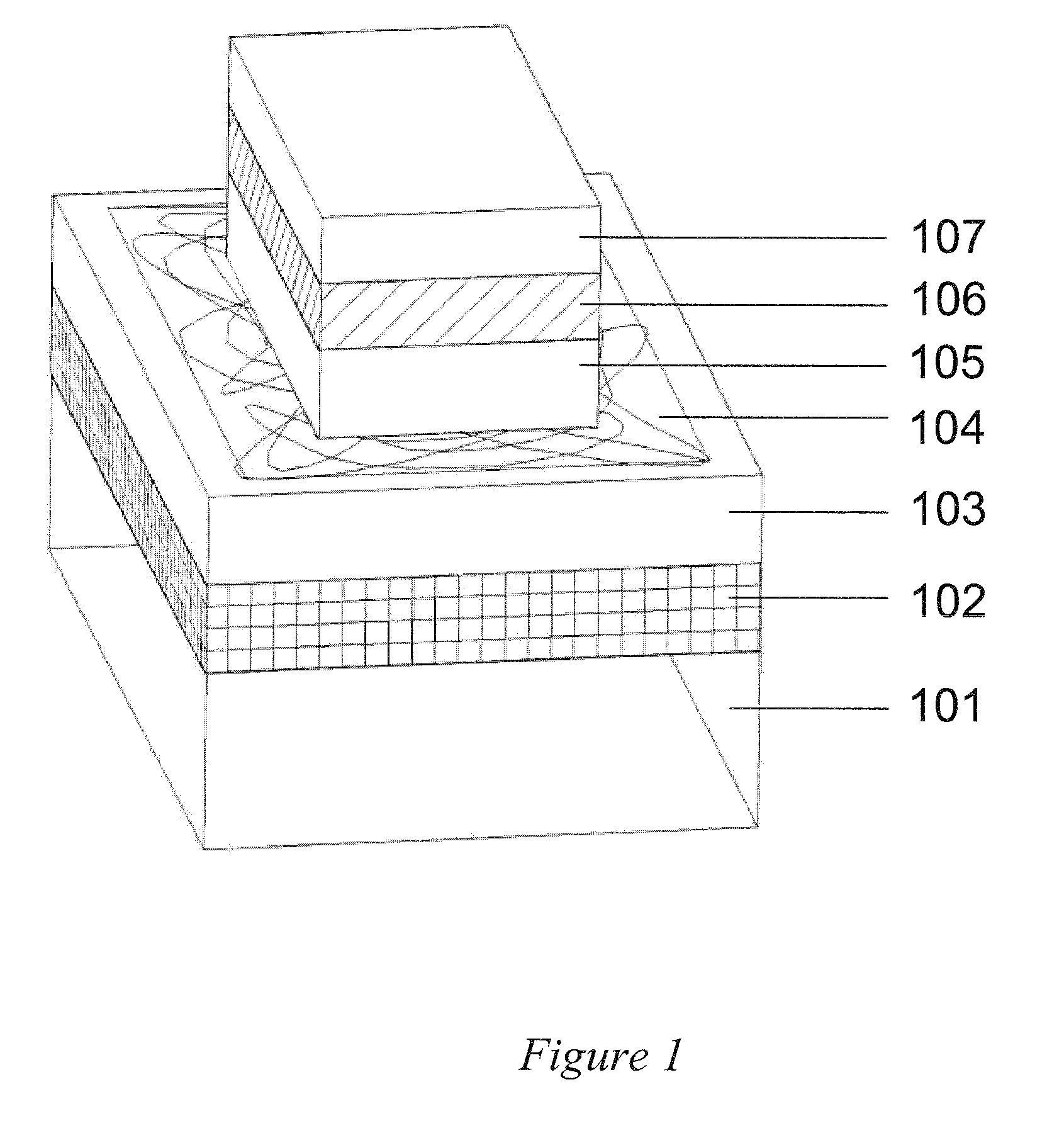

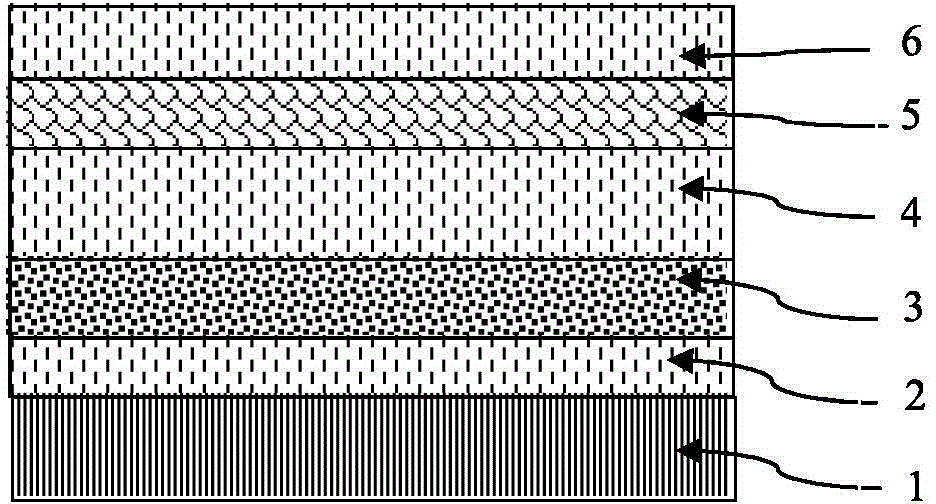

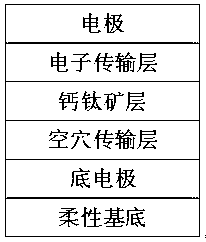

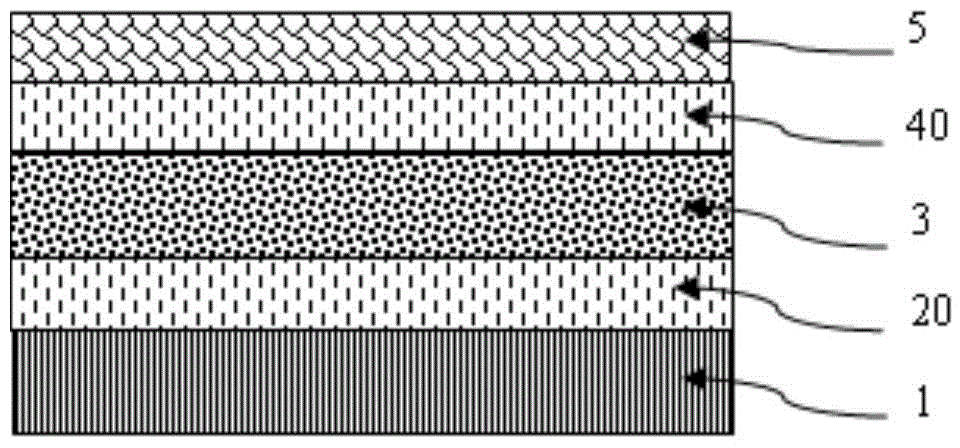

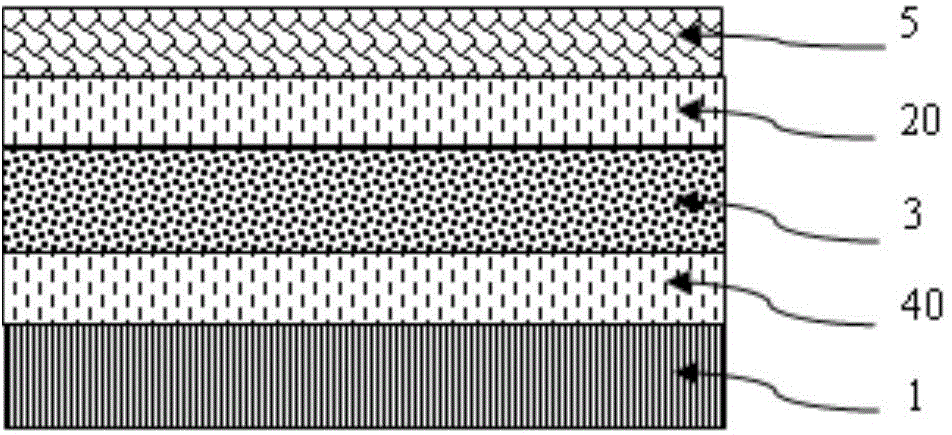

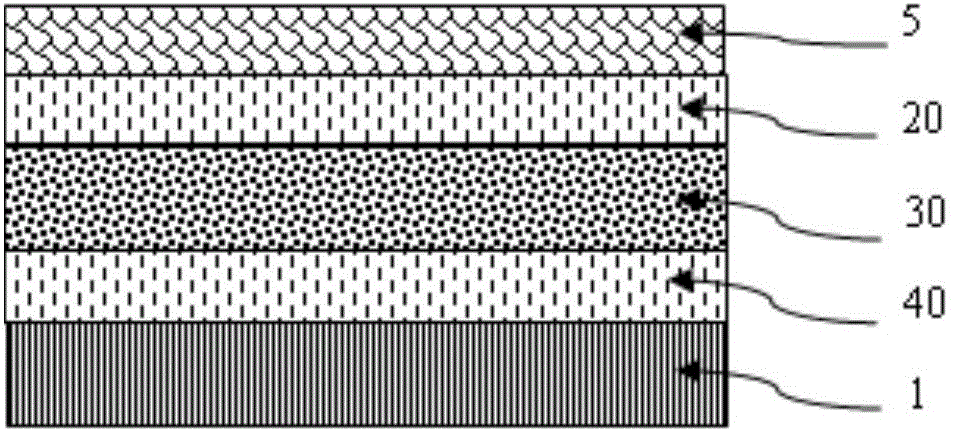

Modified electron transport layer and perovskite solar cell

InactiveCN104638108AImprove efficiencyImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic solar cellPerovskite solar cell

The invention belongs to the field of photoelectric devices, and discloses a modified electron transport layer and a perovskite solar cell, the modified electron transport layer comprises a modified layer capable of decreasing the contact barrier between an electrode and an electron transport layer and the electron transport layer, moreover, the electron transport layer is coated with the modified layer, and the atoms or ions in the modified layer can diffuse to the electron transport layer and enhance the electrical conductivity of the electron transport layer. The invention also discloses the solar cell adopting the modified electron transport layer as an electron transport layer. The invention helps to decrease the series resistance of a perovskite cell and an organic solar cell in order to increase the efficiency of the cells, retards the deterioration of contact performance between the electron transport layer and the electrode, enhances the stability of the cell, and prolongs the life of the cell.

Owner:EAST CHINA NORMAL UNIV +1

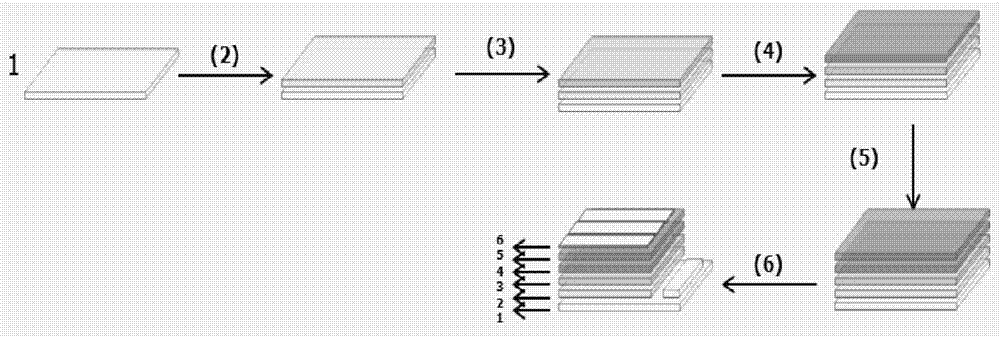

I2-II-IV-VI4 base thin film solar battery

ActiveCN101847669AImprove photoelectric conversion efficiencyImproved charge collection capabilityPhotovoltaic energy generationSemiconductor devicesComposite filmNew energy

The invention relates to an I2-II-IV-VI4 base thin film solar battery, which belongs to the field of new energy resources of solar batteries. The invention uses a p type I2-II-IV-VI4 base semiconductor thin film as a light absorbing layer, uses a thin film homogeneous with the light absorbing layer as a buffer layer, and optimizes the band offsets of the p-n node energy bands. A high-work-function double-layer composite thin film is used as a bottom electrode of the battery, and the contact barrier between the light absorbing layer and the bottom electrode is eliminated. A ZnS semiconductor thin film with wide band gap is used as a window layer, the light utilization efficiency of the battery is improved. The I2-II-IV-VI4 base thin film solar battery provided by the invention has the advantages of rich raw materials and low price, and has excellent device structures.

Owner:山东中科泰阳光电科技有限公司

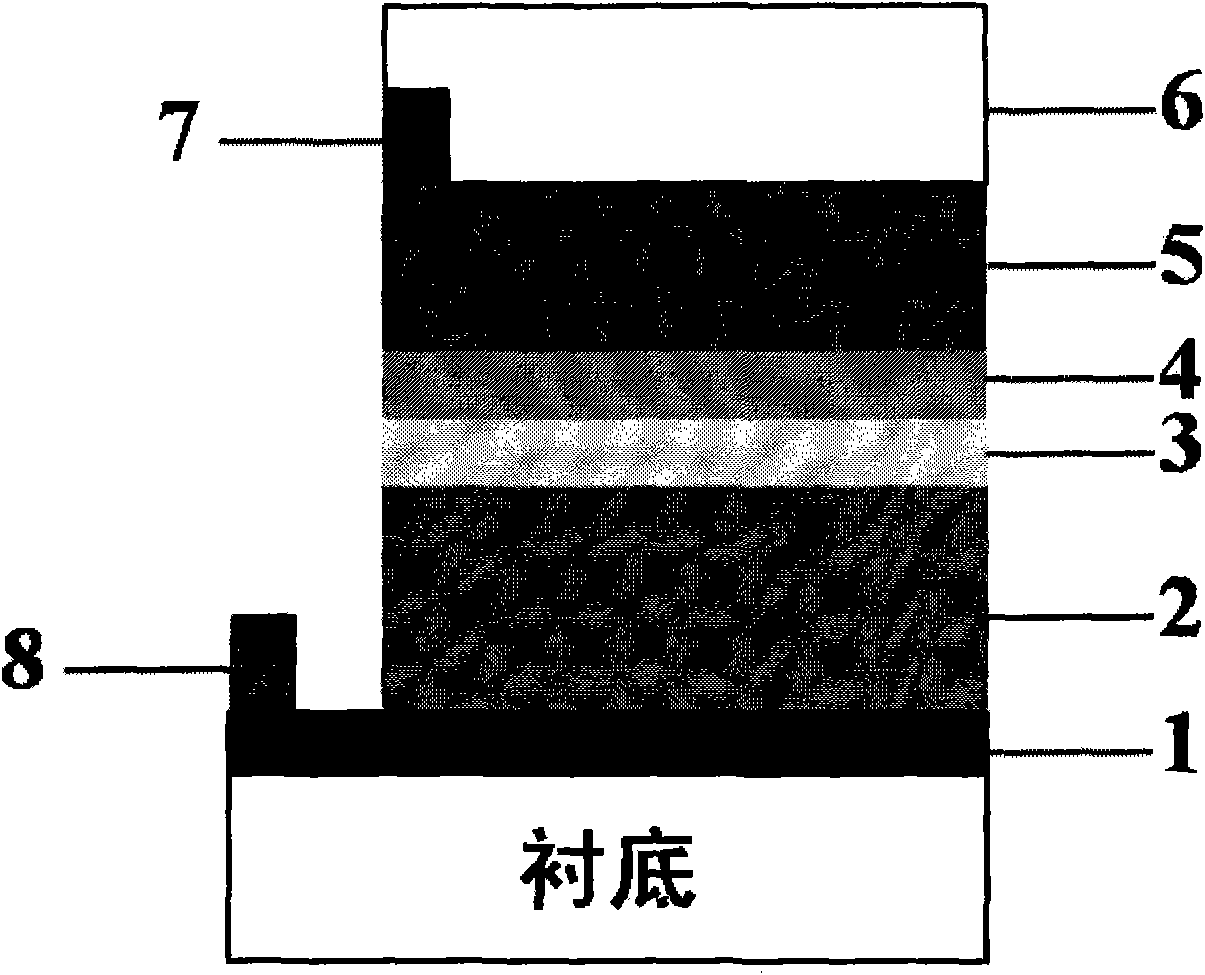

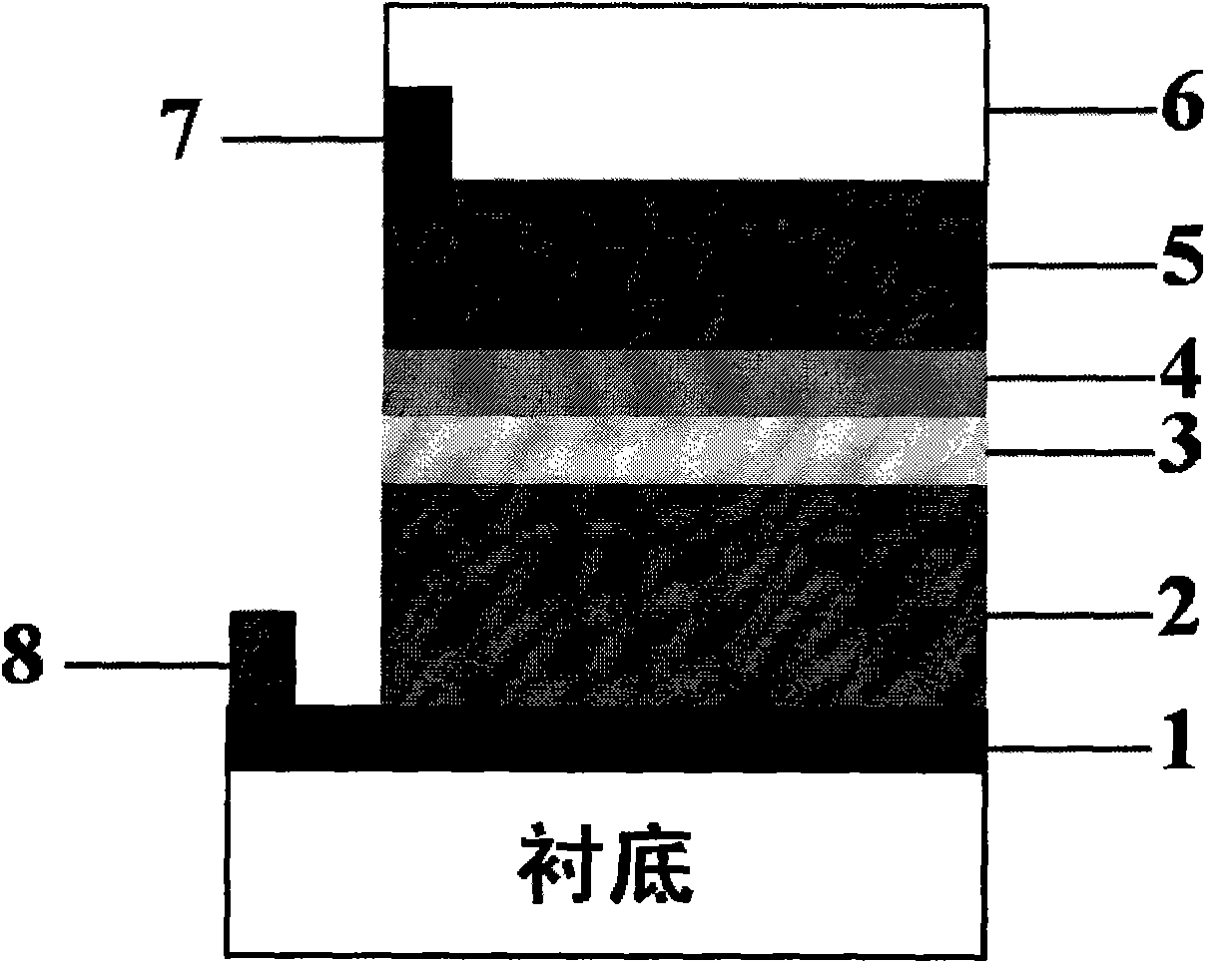

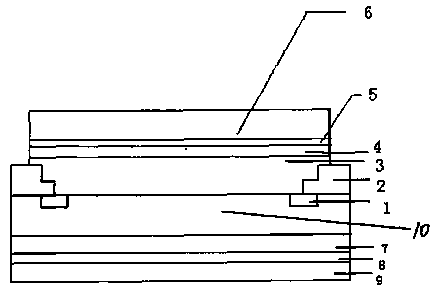

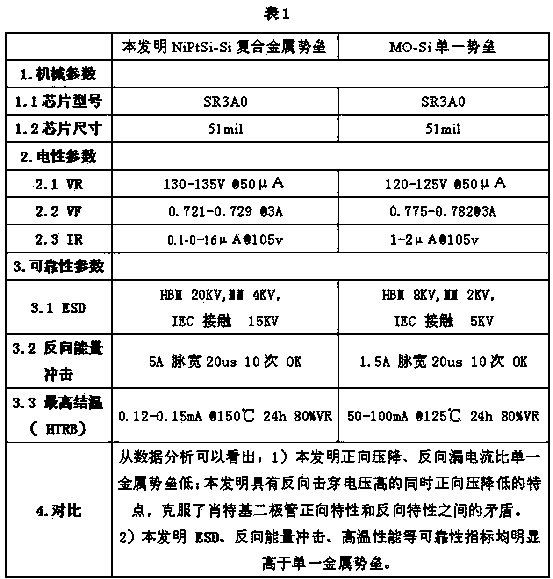

Schottky diode chip, Schottky diode device and manufacturing method for Schottky diode chip-composite barrier

ActiveCN103681885ABlocking mutual expansionImprove fatigue resistanceSemiconductor/solid-state device manufacturingDiodeSchottky barrierMetal silicide

The invention discloses a Schottky diode chip, a Schottky diode device and a manufacturing method for a Schottky diode chip-composite barrier. The Schottky diode chip comprises an N-type silicon semiconductor substrate; the obverse side of the semiconductor substrate is provided with a NiPtSi barrier layer, and the barrier layer makes direct contact with the semiconductor substrate to form a NiPtSi-Si barrier. The manufacturing method is simple, low in cost, practical and effective; NiPt alloy is adopted as Schottky barrier metal, and the composite metal silicide-silicon contact barrier (NiPtSi-Si) is formed; the obtained chip and the device eliminate the contradiction between forward voltage drop and reverse electric leakage with regard to a single-metal barrier, the reverse electric leakage and the forward voltage drop are both low, and meanwhile high-temperature resistant performance, antistatic performance, reverse energy impact performance and the like are well improved.

Owner:济南市半导体元件实验所

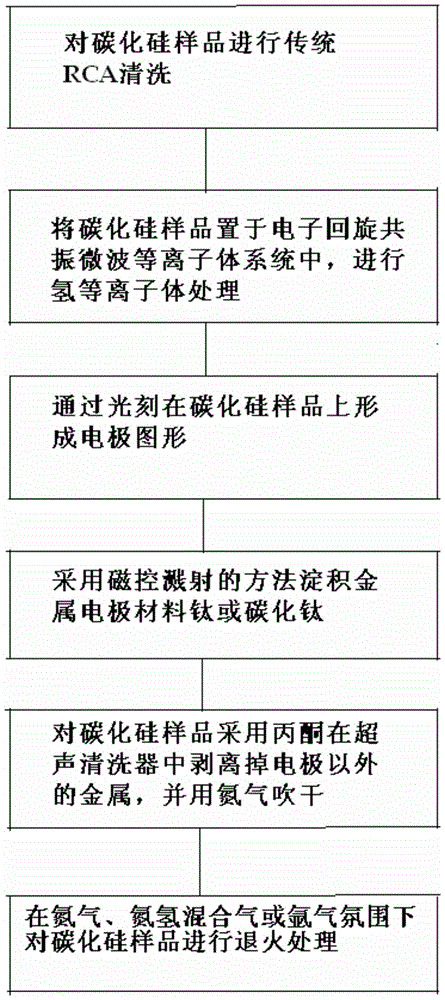

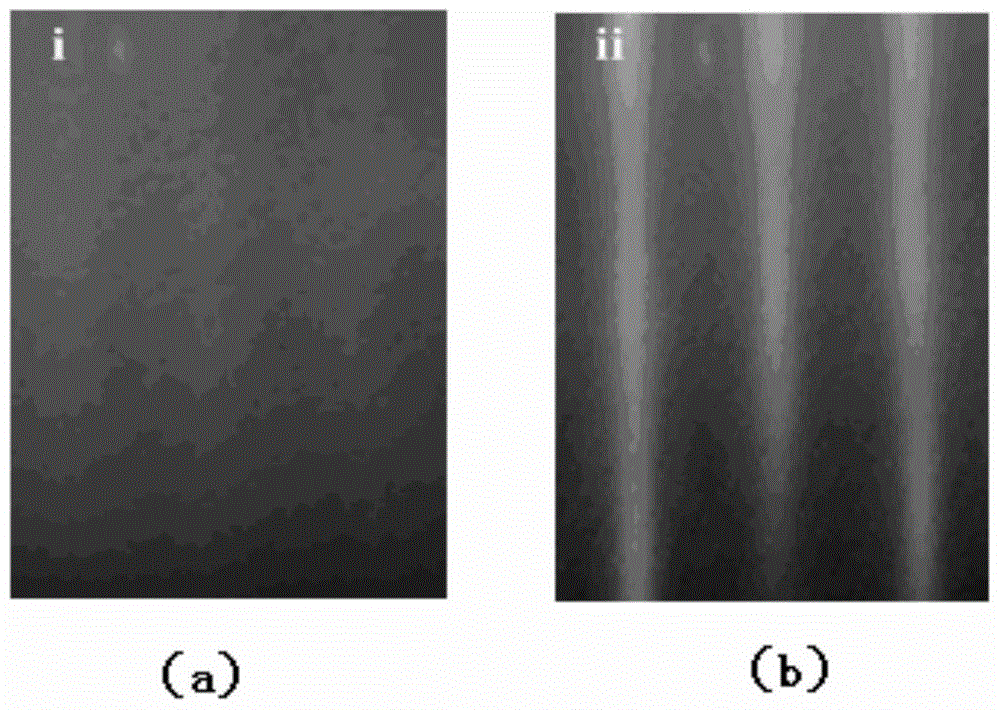

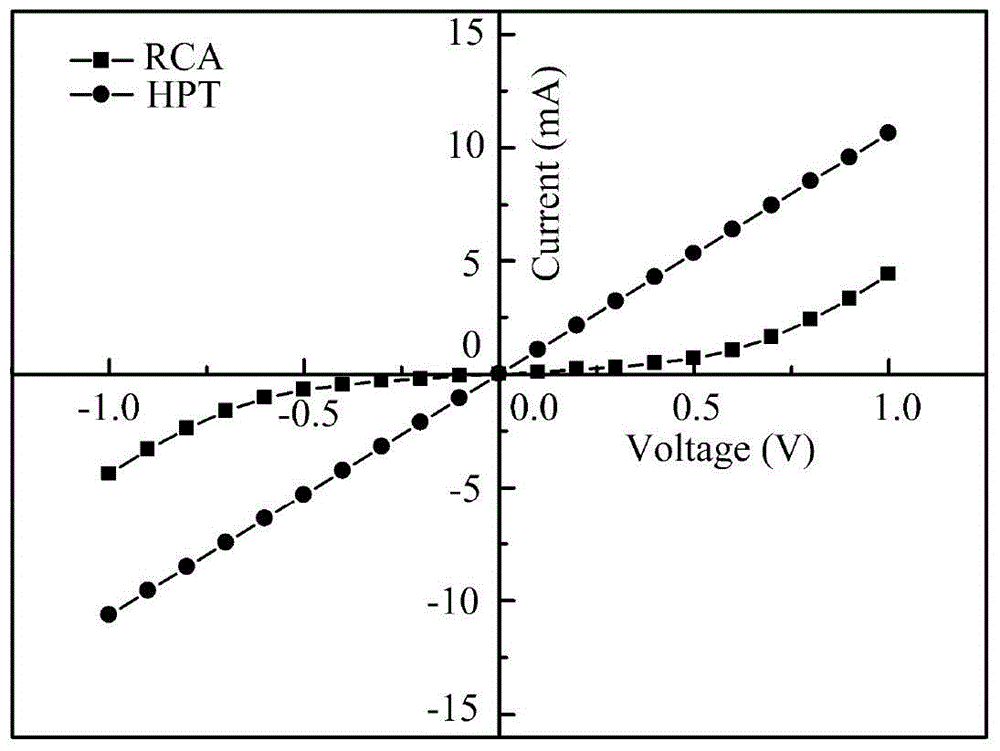

Method for increasing ohmic contact characteristic of silicon carbide semiconductor

InactiveCN105702712AEffective cleaning and passivationDecrease the density of surface statesSemiconductor devicesRCA cleanTitanium carbide

The invention relates to the field of microelectronic technology, a method for improving the ohmic contact characteristics of a silicon carbide semiconductor, comprising the following steps: (1) performing traditional RCA cleaning on a silicon carbide sample; (2) placing the silicon carbide sample in electron cyclotron resonance microwave plasma In the bulk system, hydrogen plasma treatment is carried out; (3) electrode pattern is formed on the silicon carbide sample by photolithography; (4) metal electrode material titanium or titanium carbide is deposited by magnetron sputtering; (5) The silicon sample was stripped of metal other than the electrodes in an ultrasonic cleaner with acetone, and dried with nitrogen; (6) the silicon carbide sample was annealed in a nitrogen atmosphere. In the present invention, after pre-treating the surface of silicon carbide with hydrogen plasma generated by an electron cyclotron resonance system, the surface of silicon carbide is effectively cleaned and passivated, and the surface state density is significantly reduced, and combined with low work function metal titanium or titanium carbide and relatively The silicon carbide substrate with high doping concentration has a low barrier height of Ti / SiC contact, and good ohmic contact can be formed under low temperature annealing conditions.

Owner:DALIAN UNIV OF TECH

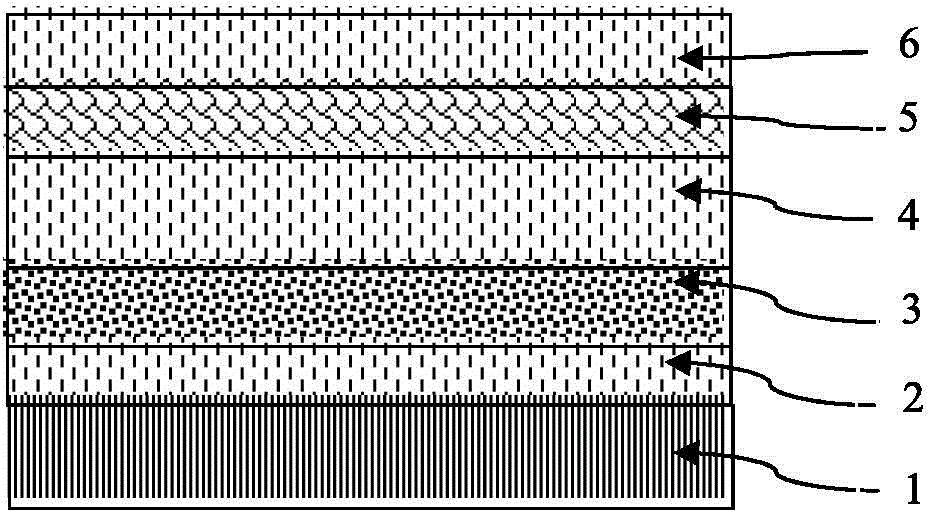

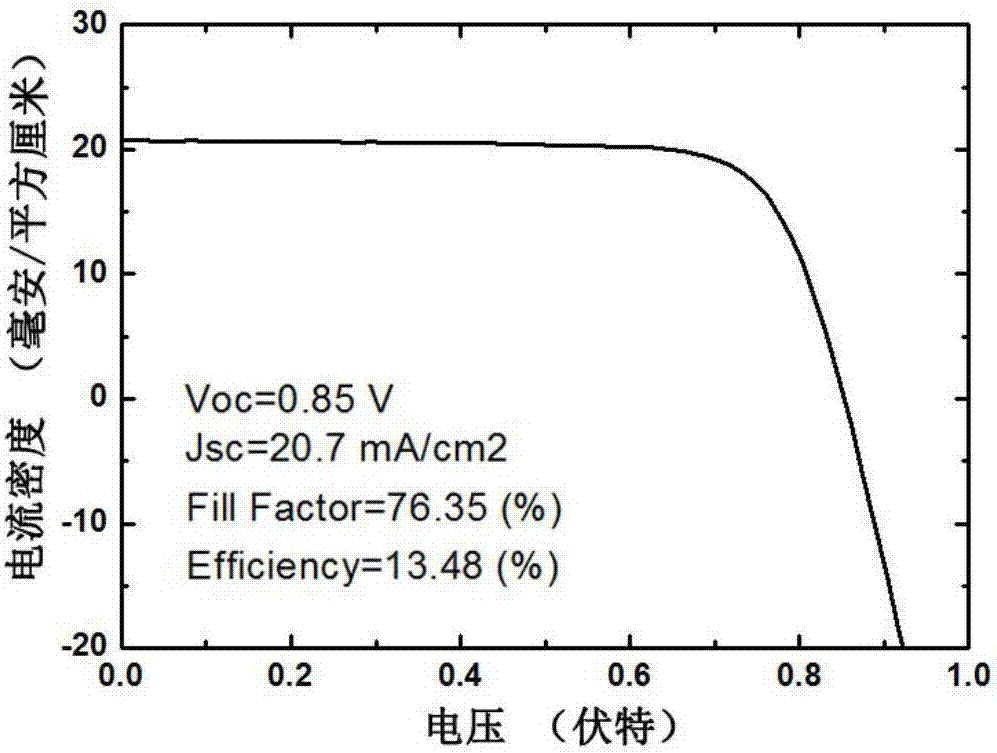

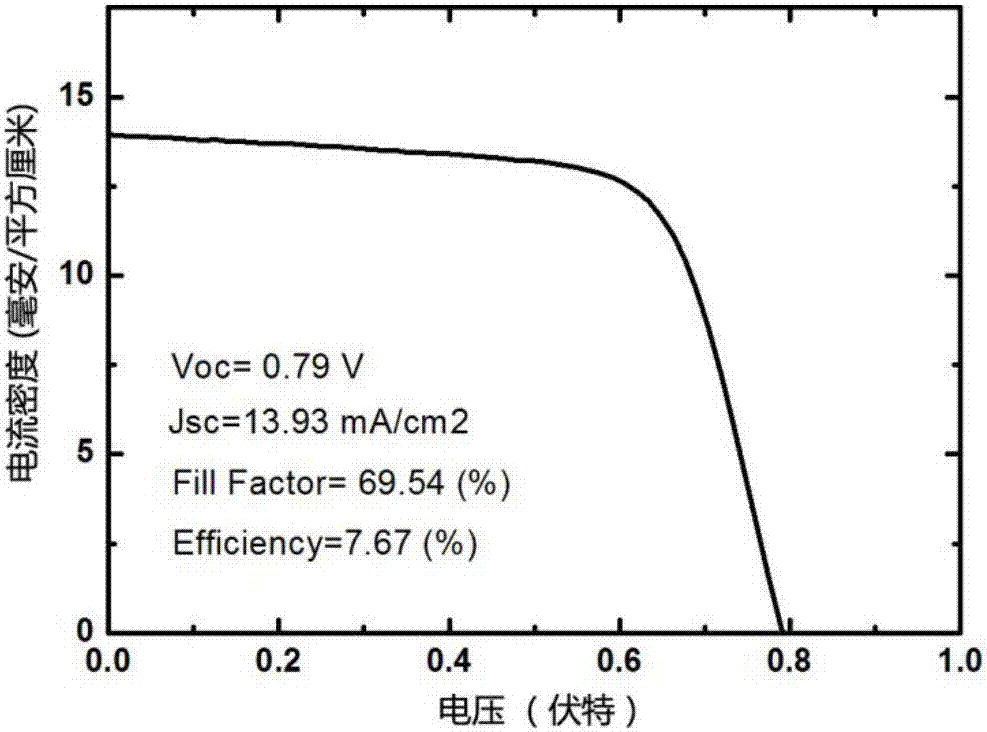

Cathode modified plane perovskite solar energy cell and preparation method thereof

ActiveCN106960908ALower contact barrierReduced series resistanceSolid-state devicesSemiconductor/solid-state device manufacturingEvaporationHole transport layer

The invention discloses a cathode modified plane perovskite solar energy cell and a preparation method thereof; the cathode modified plane perovskite solar energy cell comprises a conductive substrate, a cavity transfer layer, a perovskite layer, an electron transfer layer, a cathode modification layer and a metal counter electrode arranged from bottom to top in order; the cathode modification layer is made of acetylacetone titanium oxide (TOPD) material, and is arranged so as to reduce contact barriers between an cathode metal electrode and the electron transfer layer in certain level, thus reducing series resistances, greatly improving fill factor and current density, and effectively improving the energy conversion efficiency; on the other hand, compared with a method using a thermal evaporation inorganic cathode interface modification layer, the cathode modified plane perovskite solar energy cell preparation method can greatly simplify the production technology, thus reducing the preparation cost. The method employs the low temperature preparation technology in the whole process, thus providing a new path and reliability for the commercialization of the efficient flexible perovskite solar energy cells.

Owner:SOUTH CHINA NORMAL UNIVERSITY

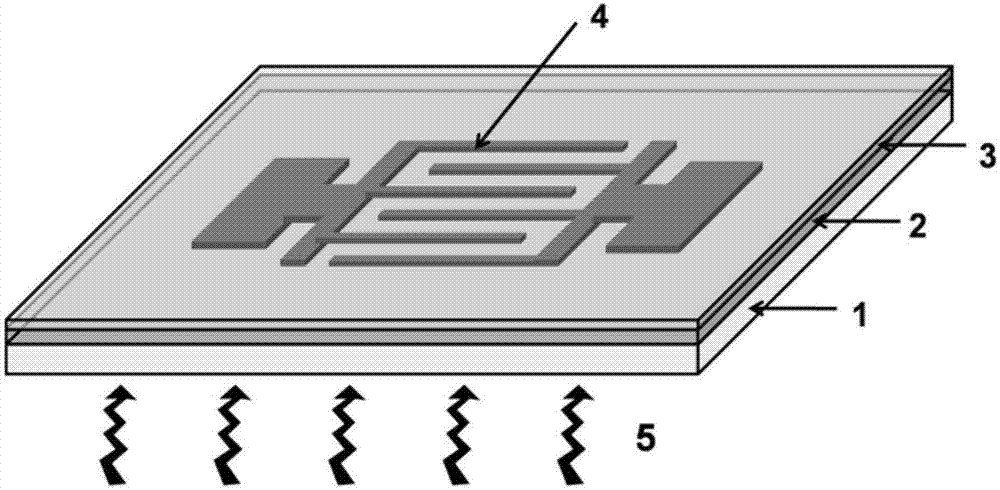

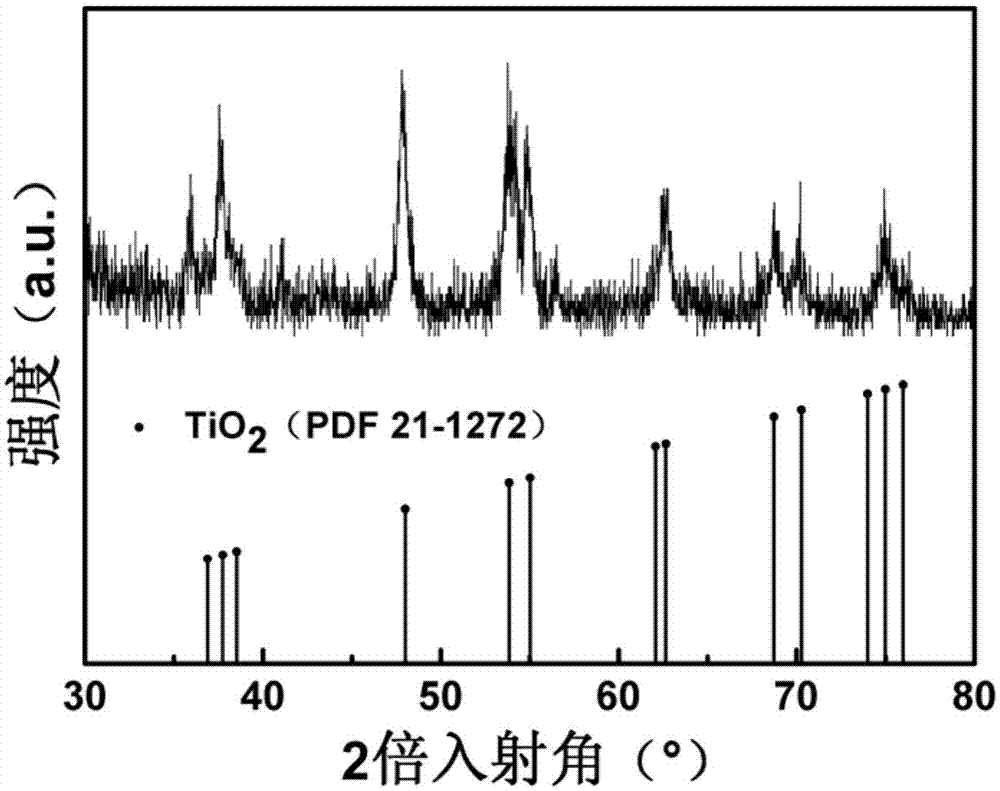

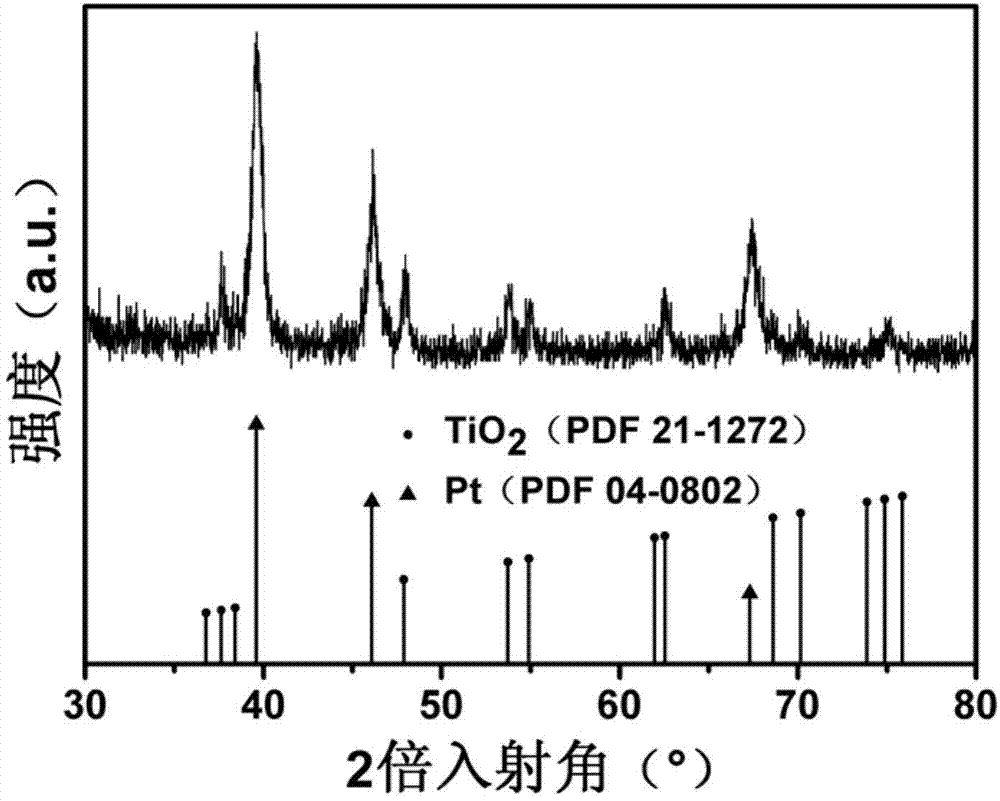

Precious-metal doped TiO2/TiO2 homogeneous-structure ultraviolet detector and preparation method

InactiveCN103887361AImprove photoresponse characteristicsFinal product manufactureSemiconductor devicesUltraviolet detectorsMetal electrodes

The invention relates to a precious-metal doped TiO2 / TiO2 homogeneous-structure ultraviolet detector and a preparation method and belongs to the technical field of semiconductor photoelectric devices. The detector comprises a quartz substrate, a precious-metal doped TiO2 film layer, a pure TiO2 film layer and a metal interdigital electrode. The detector is characterized by being provided with a homogeneous structure formed by the precious-metal doped TiO2 film layer and the pure TiO2 film layer. On one side, by the doping of precious metal, the substrate material has a low Fermi level, and the metal electrode and substrate material contacting barrier height is reduced; on the other side, the built-in electric field direction of the homogeneous structure formed by the precious-metal doped TiO2 film layer and the pure TiO2 film layer is opposite to the built-in electric field direction of metal-semiconductor contact of the detector, and the barrier height is also reduced. The photo-response characteristic of the ultraviolet detector is effectively improved from the material doping modification and the device structure.

Owner:JILIN UNIV

Insulation and reinforcement of individual bonding wires in integrated circuit packages

ActiveUS7202109B1Eliminating mold flow induced short rejectImprove structural rigiditySemiconductor/solid-state device detailsSolid-state devicesCrosstalk interferenceInductance

In an integrated circuit package, a method for insulation and reinforcement of individual bonding wires in an integrated circuit package. Using an airbrush, bonding wires are sprayed and coated with an insulating material prior to the molding process. Mold flow induced short rejects are eliminated as a result of: (a) Electrically insulating the bonding wires by coating them with an insulating mixture; (b) Physically isolating the bonding wires as a result of bead formation around individual bonding wires, with the insulating beads acting as contact barriers between the bonding wires; and (c) Enhancing the structural rigidity of the bonding wires as a result of the coating. Reinforcement and separation of bonding wires also reduces inductive coupling and / or crosstalk interference due to proximity of bonding wires.

Owner:NAT SEMICON CORP

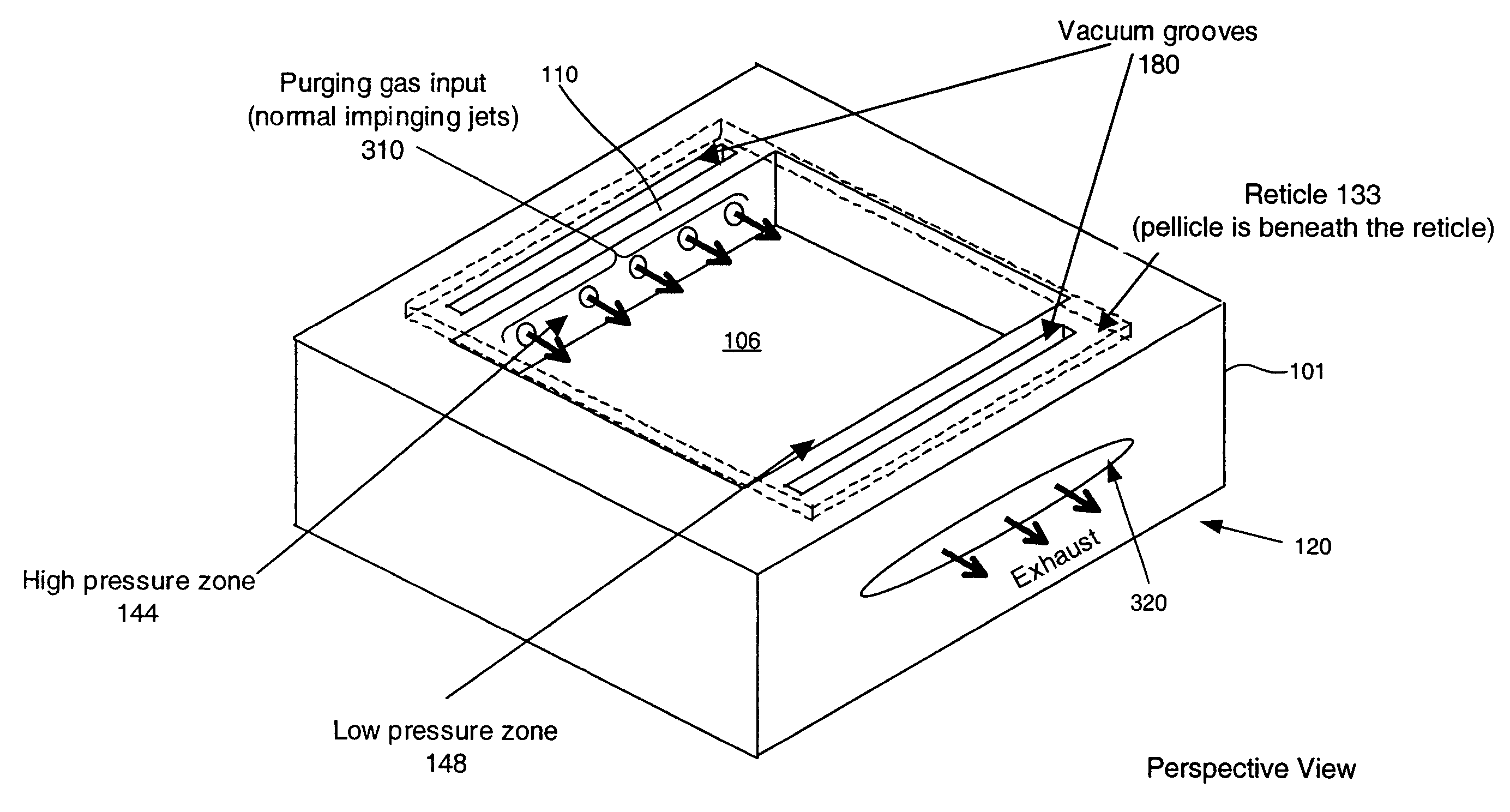

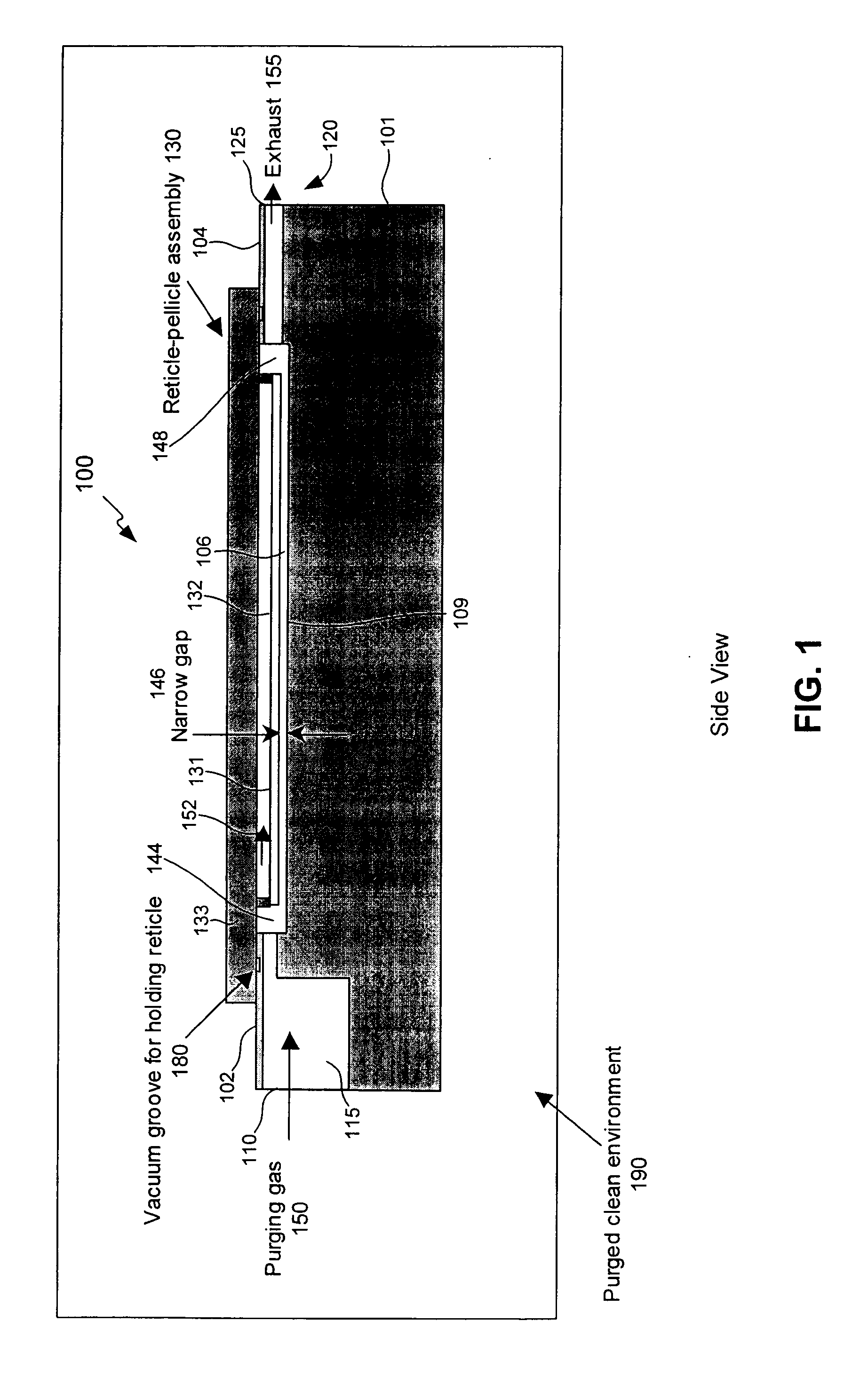

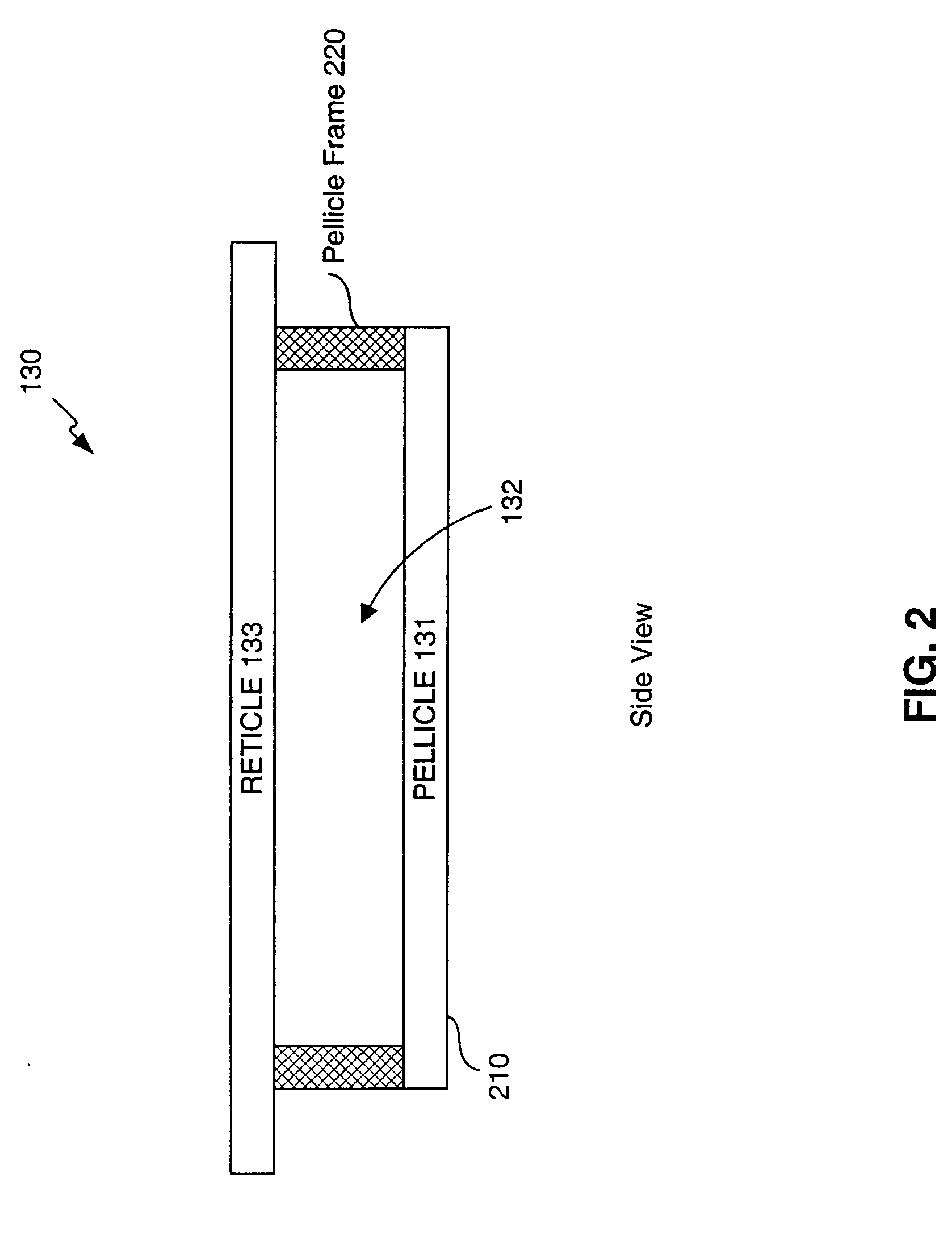

Method and system for active purging of pellice volumes

InactiveUS20050074352A1Increase pressureStress minimizationPositive displacement pump componentsSemiconductor/solid-state device manufacturingEngineeringHigh pressure

The present invention provides methods and systems for fast purging of pellicle volumes. A purge device has a base which is enclosed in a controlled environment filled with purge gas. The base a cavity formed on a surface therein. The cavity receives a reticle-pellicle assembly including a pellicle surface and an enclosed pellicle volume. A first region within the cavity can be formed to hold purging gas at a high pressure. A gap region is formed below the pellicle within the cavity. A displacement force on the pellicle due to a pressure difference between purging gas in the enclosed volume and purging gas in the gap region is kept within a tolerance range of the pellicle. According to further embodiments, a purge device is provided that includes a flow barrier (e.g., non-contacting and / or contacting barriers). A pressure balancing plate and / or flow resistant plates are provided in a purge device.

Owner:ASML HLDG NV

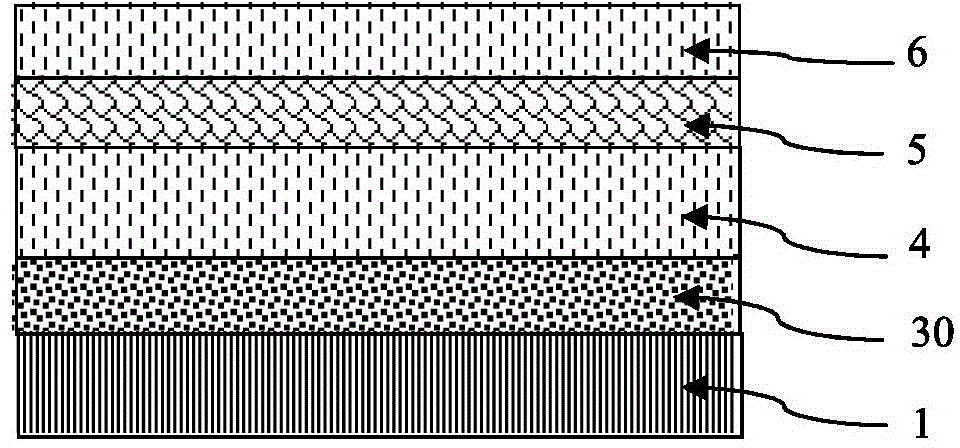

Bottom electrode type flexible perovskite solar cell and preparation method thereof

PendingCN108400242AHigh densityImprove conversion efficiencySolid-state devicesSemiconductor/solid-state device manufacturingPerovskite solar cellConductive polymer

The invention discloses a bottom electrode type flexible perovskite solar cell and a preparation method thereof. The bottom electrode type flexible perovskite solar cell comprises a forward structureand a backward structure; the forward structure comprises a flexible substrate, a bottom electrode, an electron transport layer, a perovskite layer, a hole transport layer and an electrode from the bottom up in sequence; the backward comprises a flexible substrate, a bottom electrode, a hole transport layer, a perovskite layer, an electron transport layer and an electrode from the bottom up in sequence; and the bottom electrode layer adopts a metal nanomaterial and / or a conductive polymer material. On one hand, by virtue of setting of the bottom electrode, the flexibility and bendable propertyof the flexible perovskite solar cell can be improved to a certain degree, so the number of times of bending of the flexible perovskite solar cell can be increased, and a new approach is provided forpracticability of the flexible perovskite solar cell; and on the other hand, by virtue of addition of the bottom electrodes, the contact barrier between the bottom electrodes and the electron transport layer can be lowered, the series resistance is lowered, the filling factor and the current density are improved, the energy conversion efficiency is improved effectively, and feasibility is provided for commercialization of the flexible perovskite solar cell is provided.

Owner:JIMEI UNIV

Semiconductor Contact Barrier

ActiveUS20090191705A1Reduced device resistanceImprove device performanceSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDielectric layerContact resistance

System and method for reducing contact resistance and improving barrier properties is provided. An embodiment comprises a dielectric layer and contacts extending through the dielectric layer to connect to conductive regions. A contact barrier layer is formed between the conductive regions and the contacts by electroless plating the conductive regions after openings have been formed through the dielectric layer for the contact. The contact barrier layer is then treated to fill the grain boundary of the contact barrier layer, thereby improving the contact resistance. In another embodiment, the contact barrier layer is formed on the conductive regions by electroless plating prior to the formation of the dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

Alloy electrode capable of improving efficiency and stability of solar cell

InactiveCN104465804AInhibition of the vulnerability to spreadIncrease parallel resistancePhotovoltaic energy generationSemiconductor devicesAluminiumContact barrier

The invention belongs to the field of photoelectric devices, and discloses an alloy electrode capable of improving the efficiency and the stability of a solar cell. The alloy electrode is a binary or complex alloy electrode formed in the mode that precious metal silver is combined with metal such as aluminum, titanium, zinc, copper and / or magnesium. The invention further discloses the solar cell with the alloy electrode serving as the cathode or the anode of the cell. By means of the alloy electrode and the solar cell, matching between the energy level of the alloy electrode and the energy level of a carrier transport layer is easily improved, the contact barrier is reduced, and the efficiency of the cell is improved; silver atoms in the alloy electrode are slowly diffused to the carrier transport layer and an optical active layer, and therefore the stability of the cell can be improved; the use amount of silver materials in a unit area of the cell is decreased, the cost of the cell is easily controlled, and resources are saved.

Owner:上海纳晶科技有限公司

Method for adjusting Schottky contact barrier height of metal and N-type germanium

InactiveCN101916719ALow requirements for process conditionsLower interface stateSemiconductor devicesSilicon dioxideElectronic process

The invention relates to a method for adjusting the Schottky contact barrier height of metal and N-type germanium. The method comprises the following steps of: cleaning the N-type germanium substrate; putting the cleaned N-type germanium substrate into PECVD to deposit a silicon dioxide layer; photoetching the N-type germanium substrate, and removing the silicon dioxide layer to obtain an N-type germanium substrate with a deposited metal window; and putting the treated N-type germanium substrate into a magnetron sputtering machine, depositing a TaN layer on the front of the N-type germanium substrate, depositing a monomer metal layer on the TaN layer, and preparing metal / TaN / n-Ge contact by adopting a lift-off process. The method is a novel method for adjusting the Schottky contact barrier height of the metal / n-Ge, which is simple and compatible with the micro-electronic process and has low cost.

Owner:XIAMEN UNIV

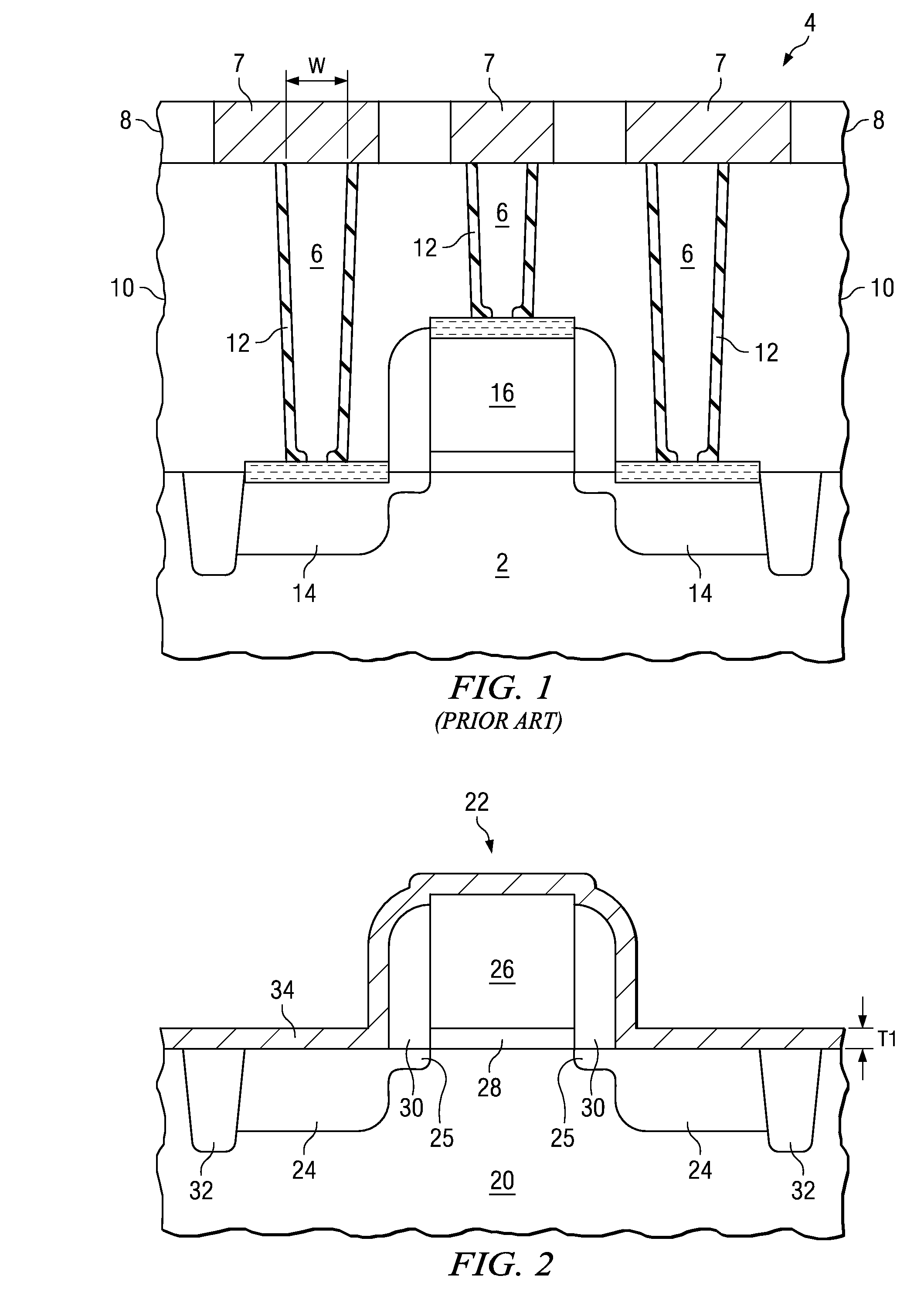

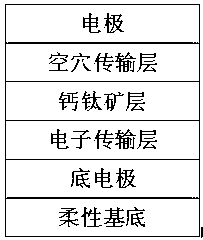

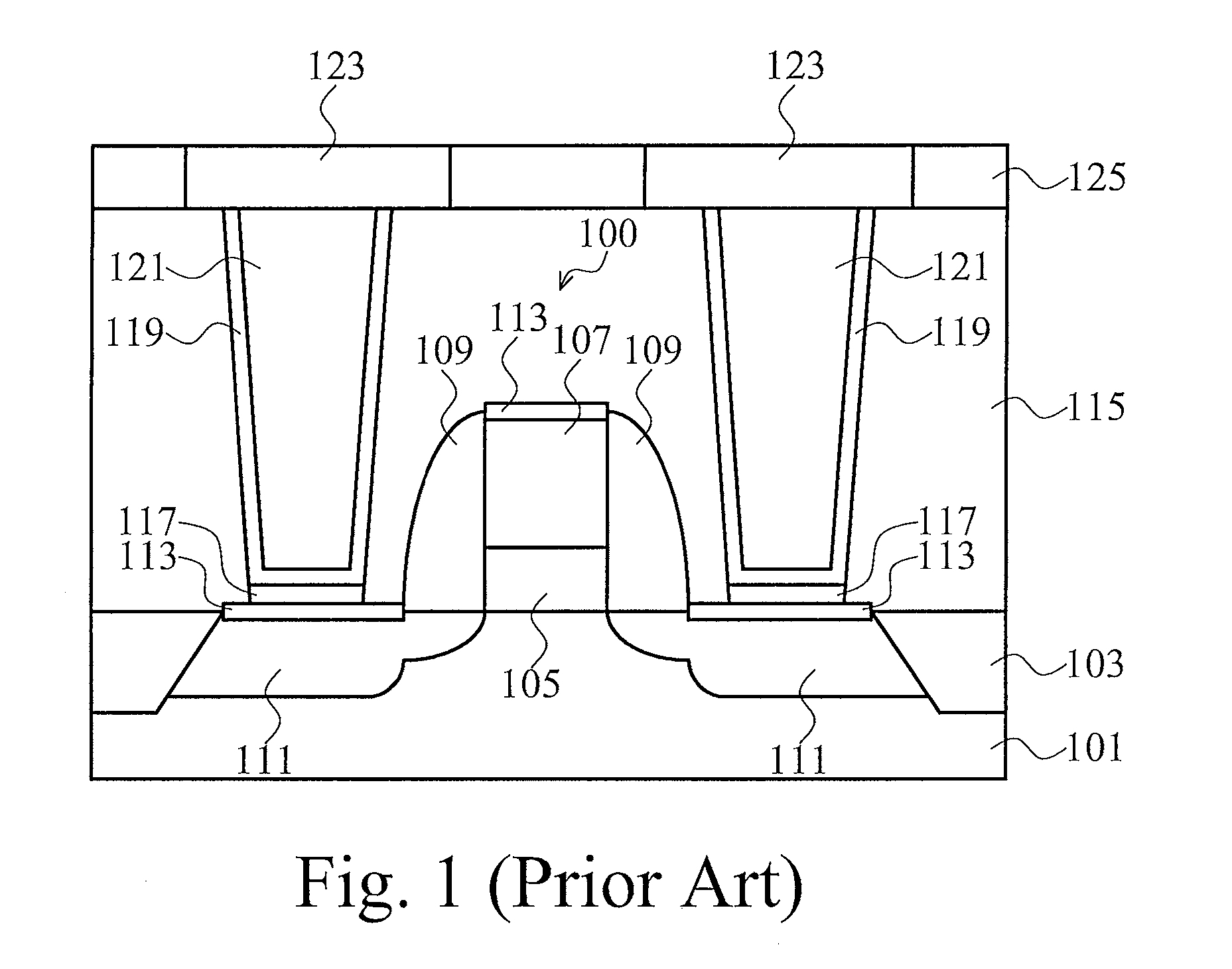

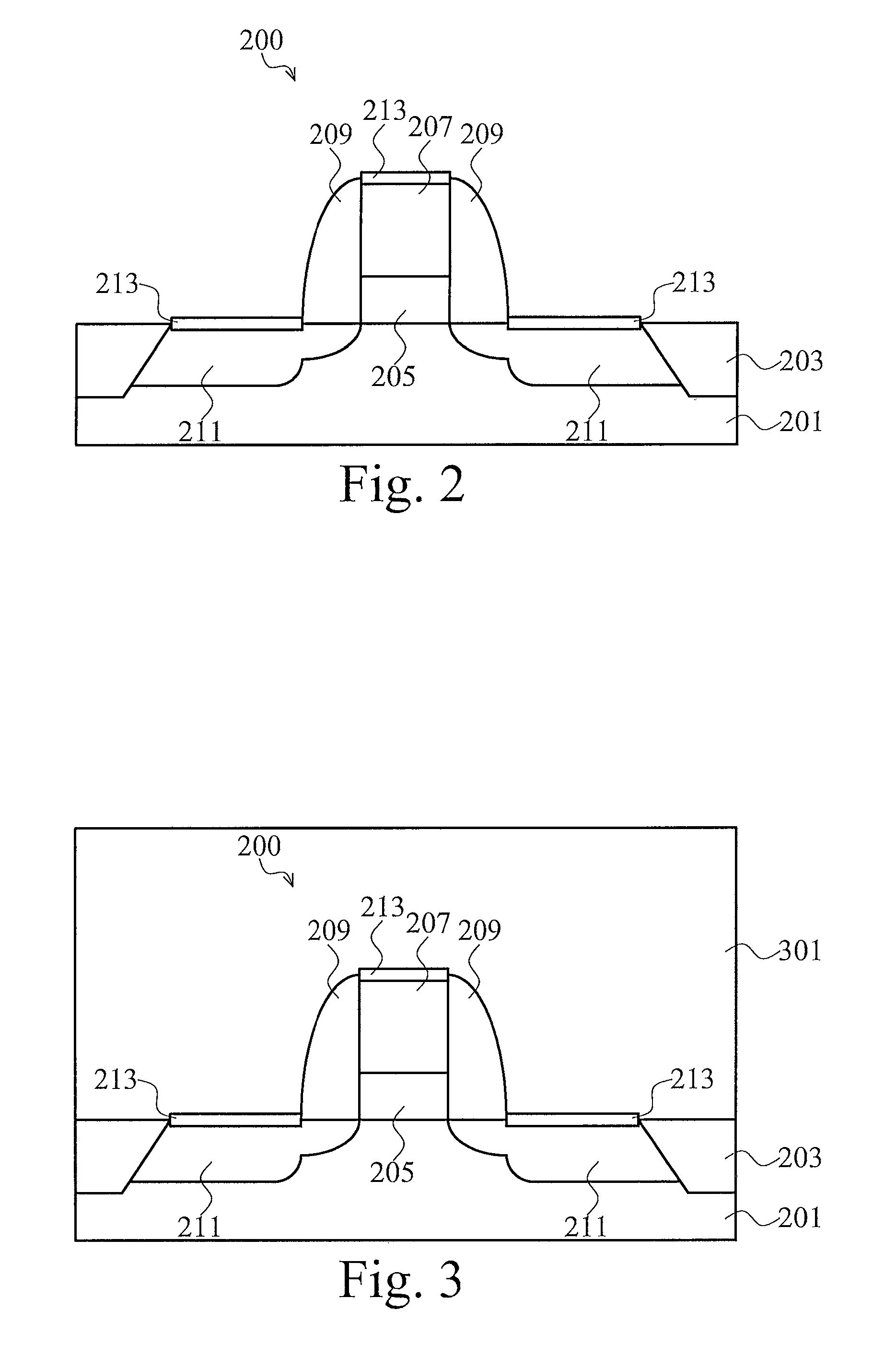

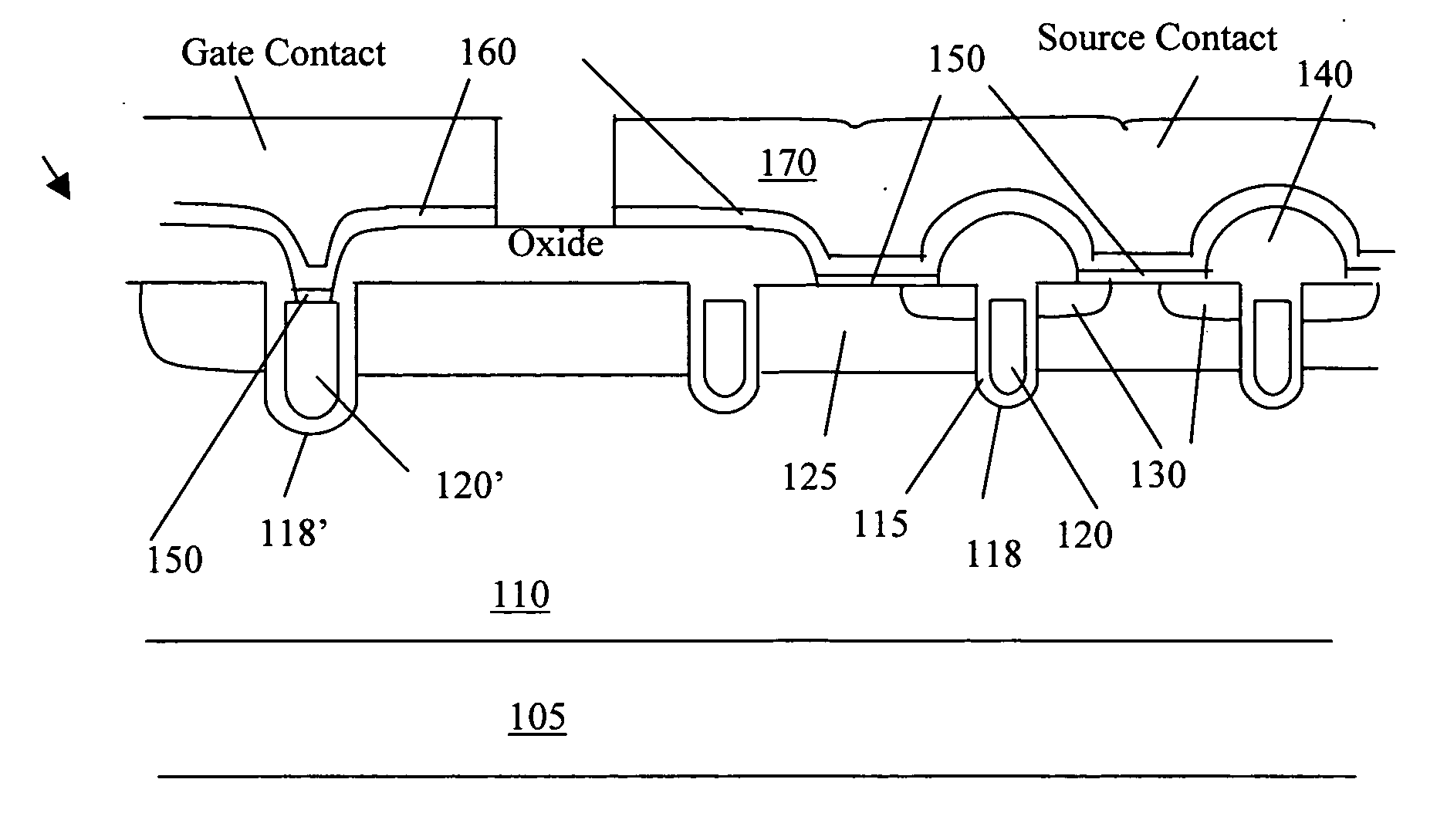

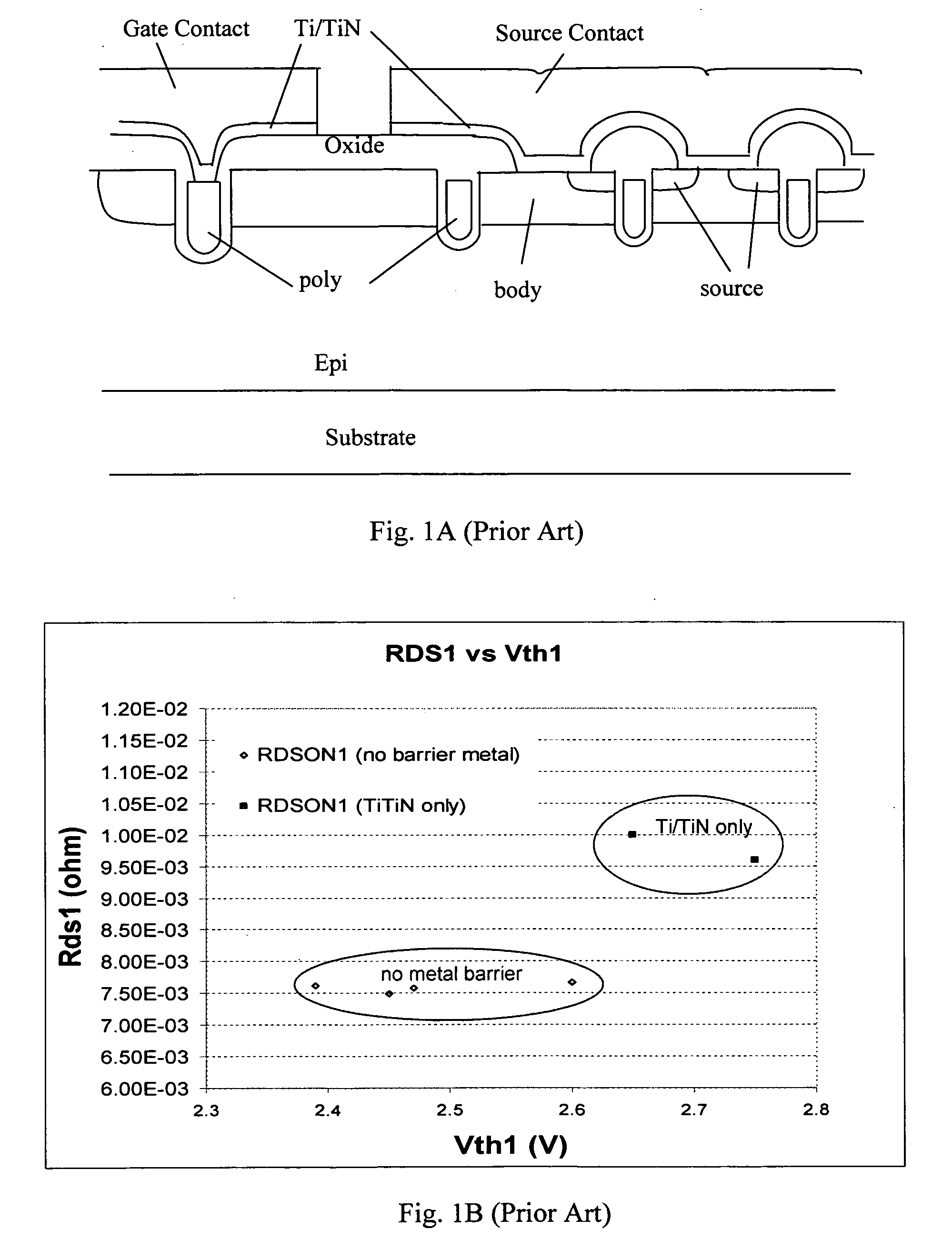

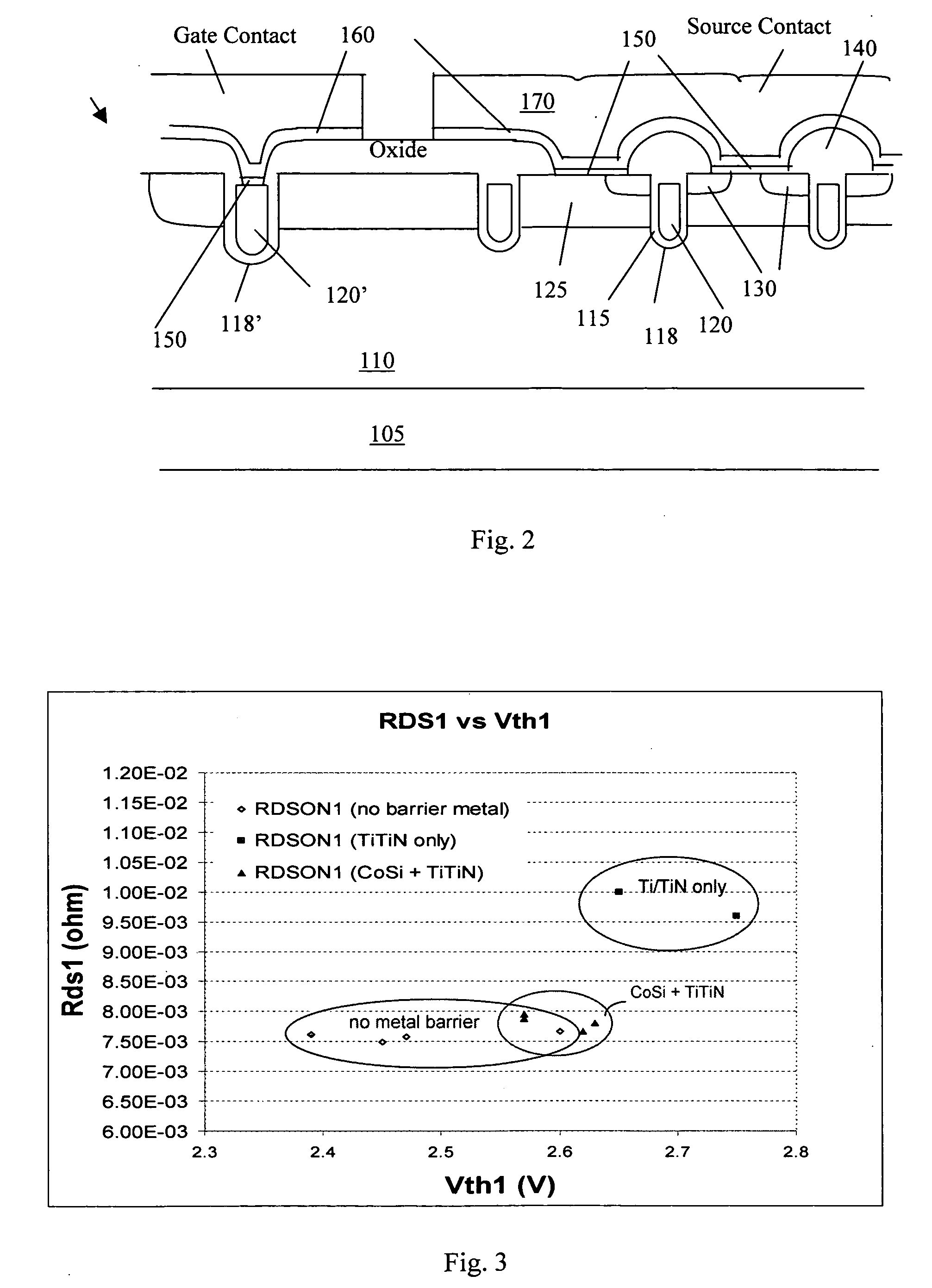

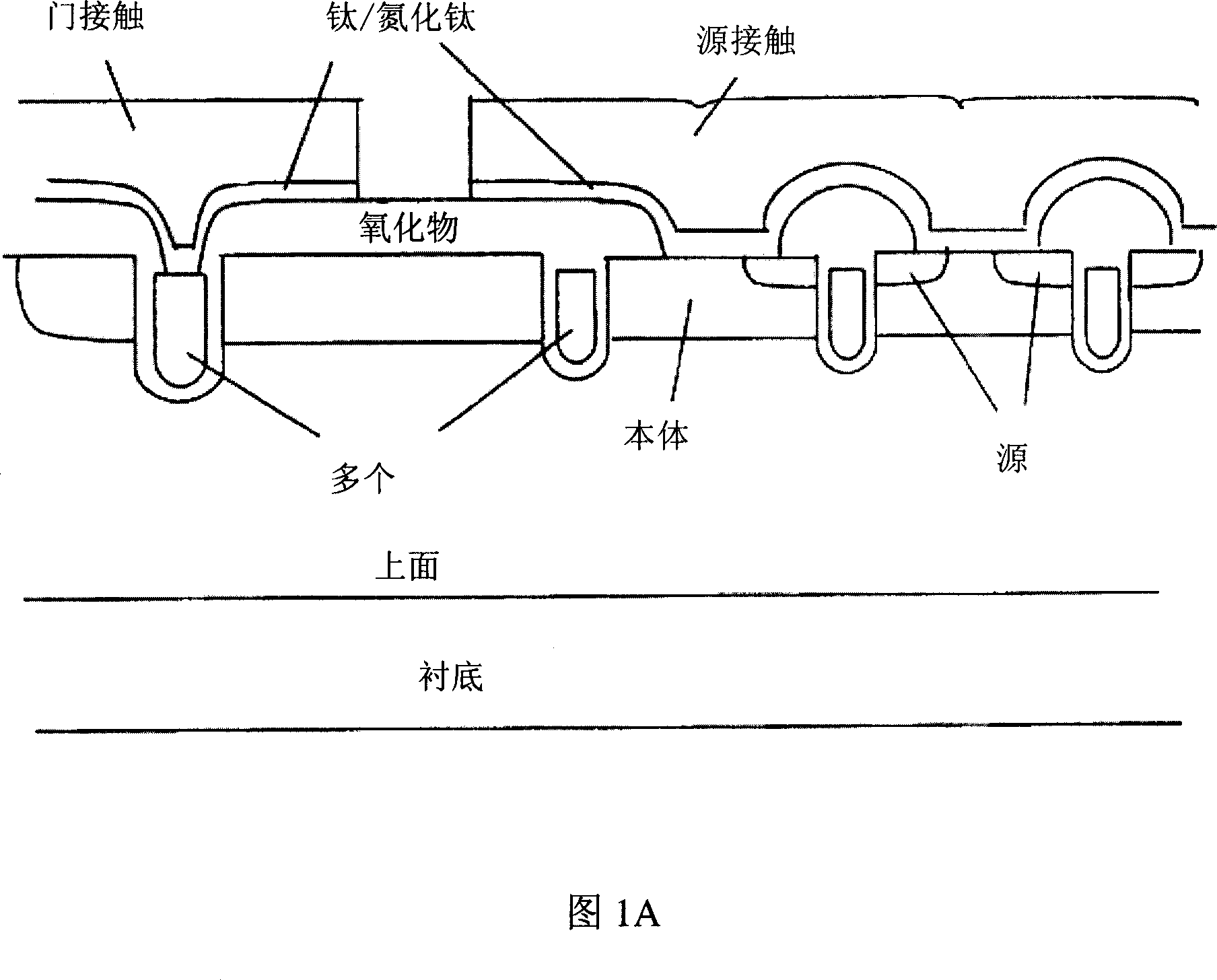

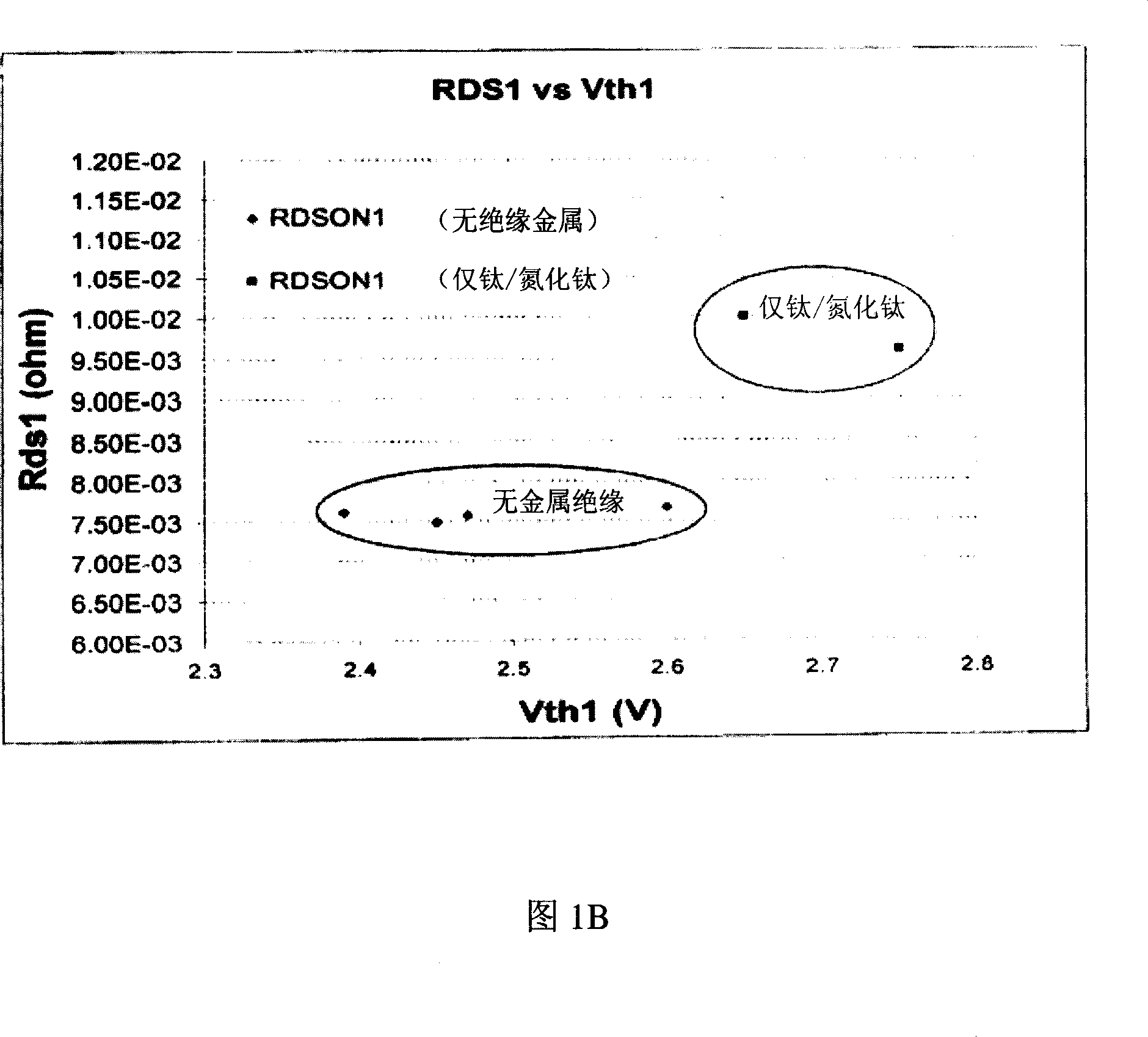

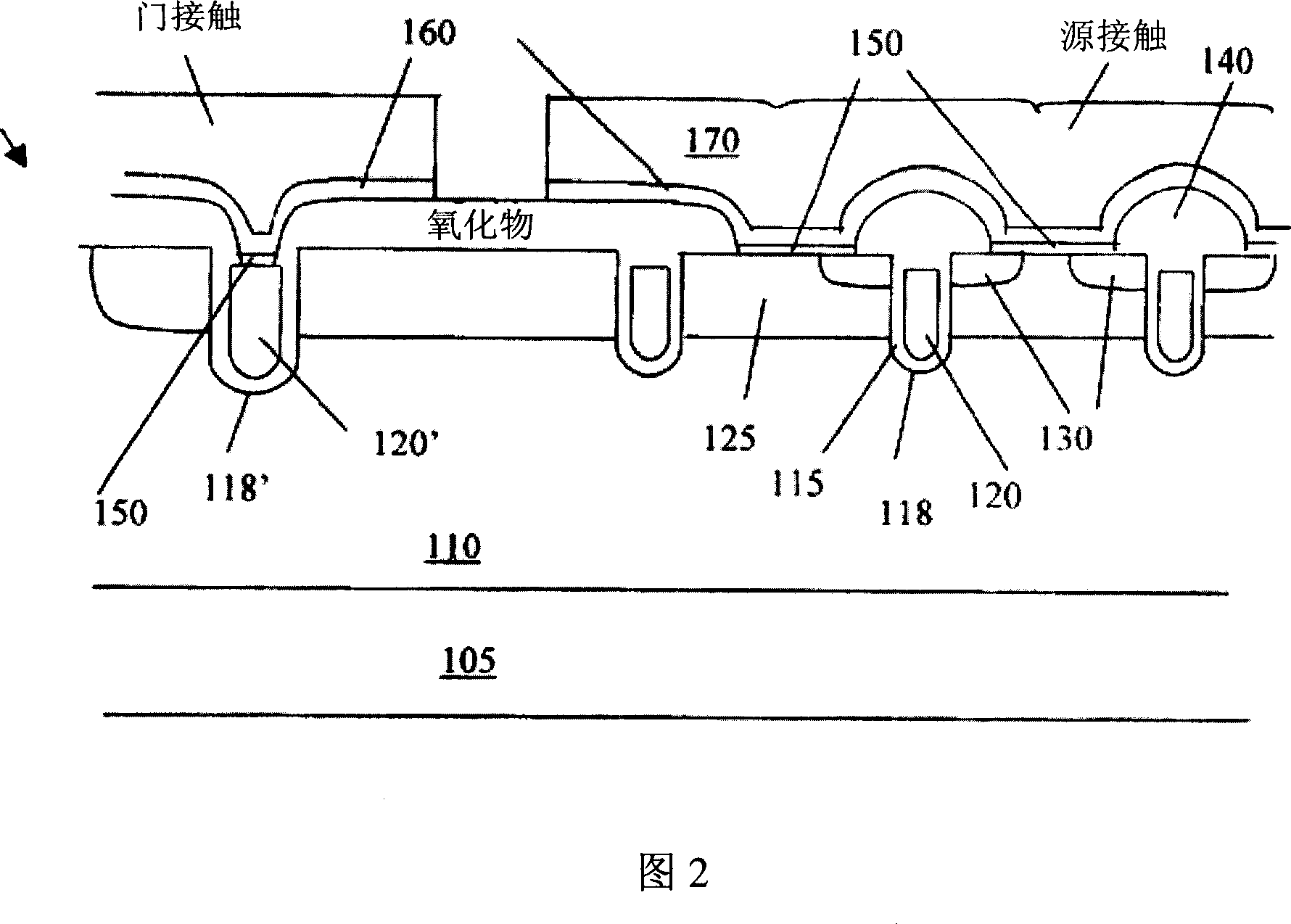

Cobalt silicon contact barrier metal process for high density semiconductor power devices

InactiveUS20070075360A1Loss is particularly problematicSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETInsulation layer

This invention discloses an improved trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a source contact opening opened on top of an area extended over the body region and the source region through a protective insulation layer wherein the area further has a cobalt-silicide layer disposed near a top surface of the substrate. The MOSFET cell further includes a Ti / TiN conductive layer covering the area interfacing with the cobalt-silicide layer over the source contact opening. The MOSFET cell further includes a source contact metal layer formed on top of the Ti / TiN conductive layer ready to form source-bonding wires thereon.

Owner:ALPHA & OMEGA SEMICON LTD

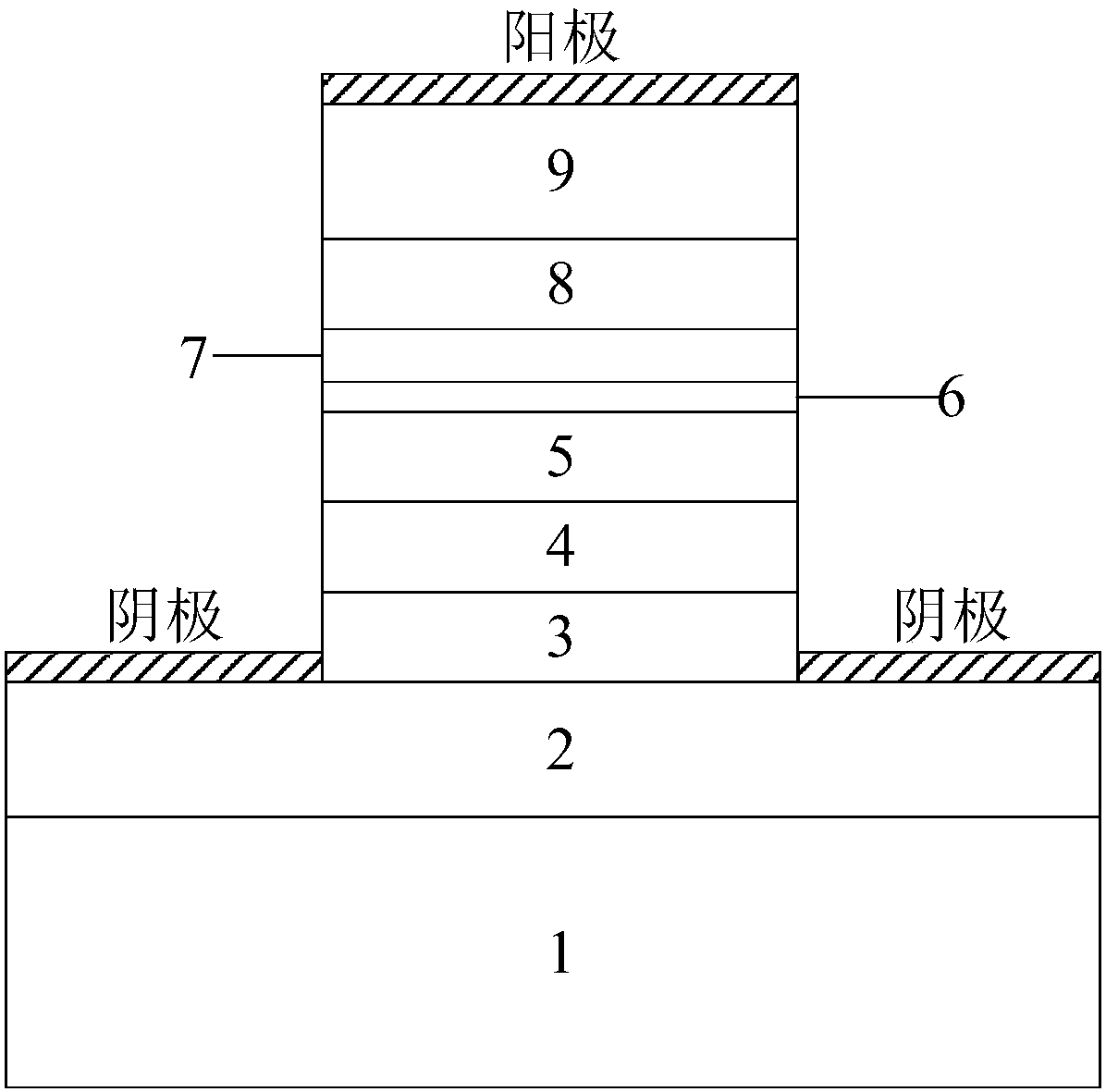

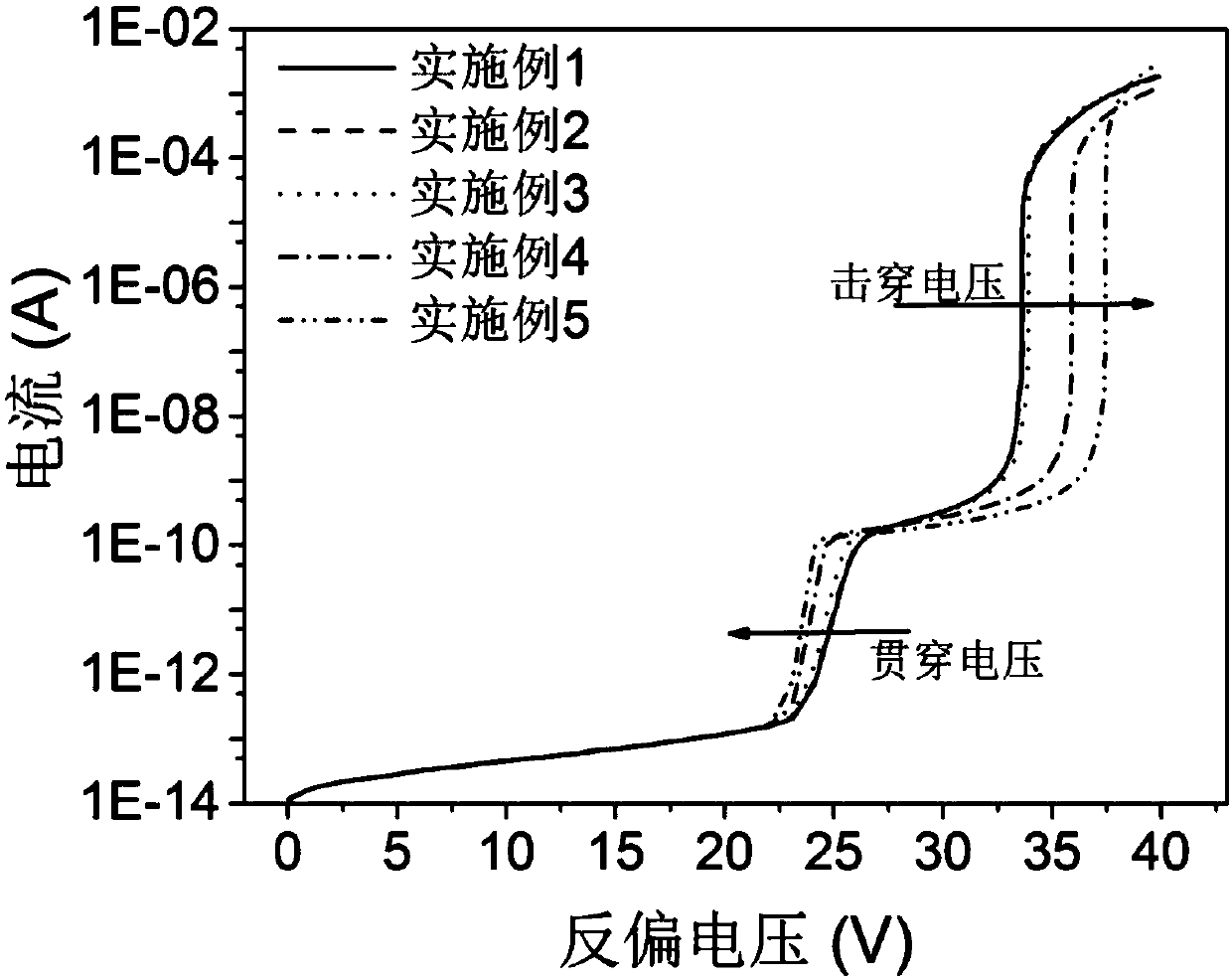

Absorption layer variable doped InGaAs avalanche photodiode and preparation method thereof

InactiveCN107611195ASimple structureWide operating voltage rangeSemiconductor devicesSemiconductor materialsEvaporation

The invention discloses an absorption layer variable doped InGaAs avalanche photodiode and a preparation method thereof. The structure comprises an N+InP substrate, and an N-InP buffer layer, multipleN-In(1-x)GaxAs absorption layers of different doping concentration, an N-In(1-x)GaxAsyP(1-y) gradient layer, an N-InP charge layer, an intrinsic doped InP multiplication layer and a P+-InP contact layer which are arranged on the N+InP substrate from the bottom to the top in turn. The method comprises the steps that the layers are epitaxially grown on the N-type heavily doped InP substrate in turnby using metal organic chemical vapor deposition; silica is downwardly etched by using the plasma enhanced chemical vapor deposition technology with the photoresist acting as the mask, and finally the photoresist is removed; the InGaAs epitaxial structure is etched by using the reactive ion etching technology with the silica acting as the mask; and metal and semiconductor material are enabled toform ohmic contact by using electron beam evaporation and the rapid thermal annealing technology so as to reduce the contact barrier.

Owner:TIANJIN UNIV

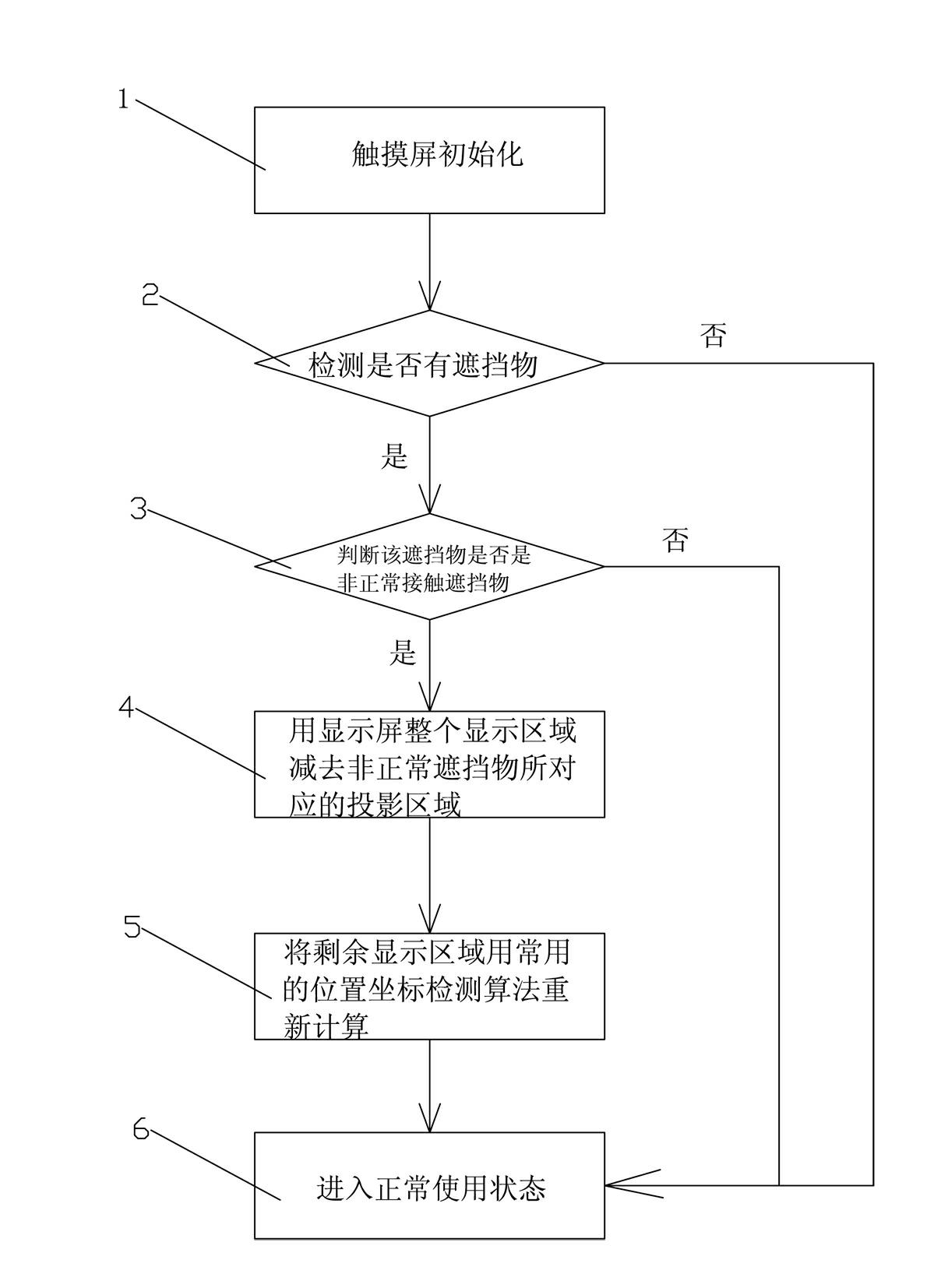

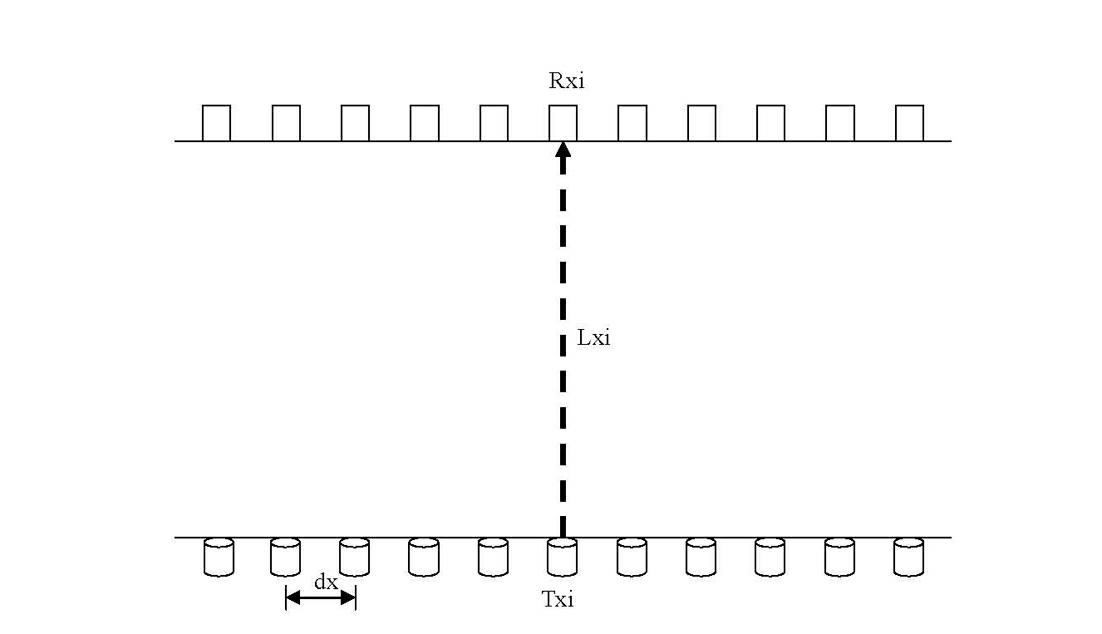

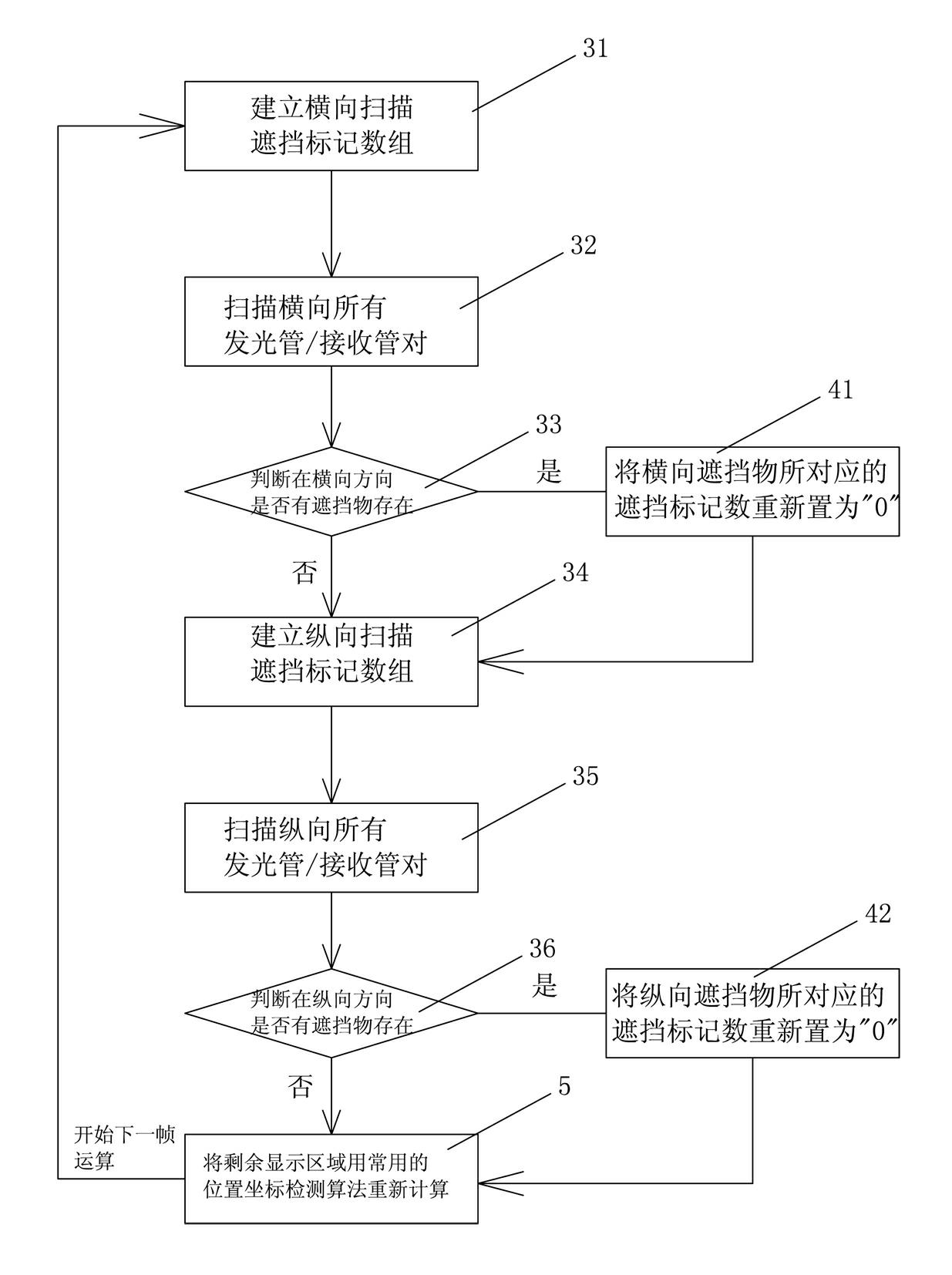

Method for eliminating non-normal contact interference in infrared touch system

ActiveCN102662533AConverting sensor output opticallyInput/output processes for data processingApplication softwareHuman–computer interaction

A method for eliminating non-normal contact interference in an infrared touch system comprises (1) starting up under the condition that a display screen doesn't display any objects, initializing a touch screen, and establishing an environment value; (2) detecting whether a barrier exists on the display screen; (3) judging whether the barrier is a non-normal contact barrier, executing the step (4) if yes, otherwise executing the step (6); (4) subtracting a display region corresponding to the non-normal barrier from a whole display region of the display screen; (5) recalculating the rest display region by using a common position coordinates detection algorithm to obtain a new display region capable of normally operating; and (6) entering a normal operating state. The invention can be realized only by updating software, without redesigning and updating hardware of an infrared touch frame. In addition, only partial program of firmware in a lower computer system belonging to the touch frame is updated, and an upper computer system and application software are not required to change.

Owner:SAMHOO SCI & TECH CO LTD

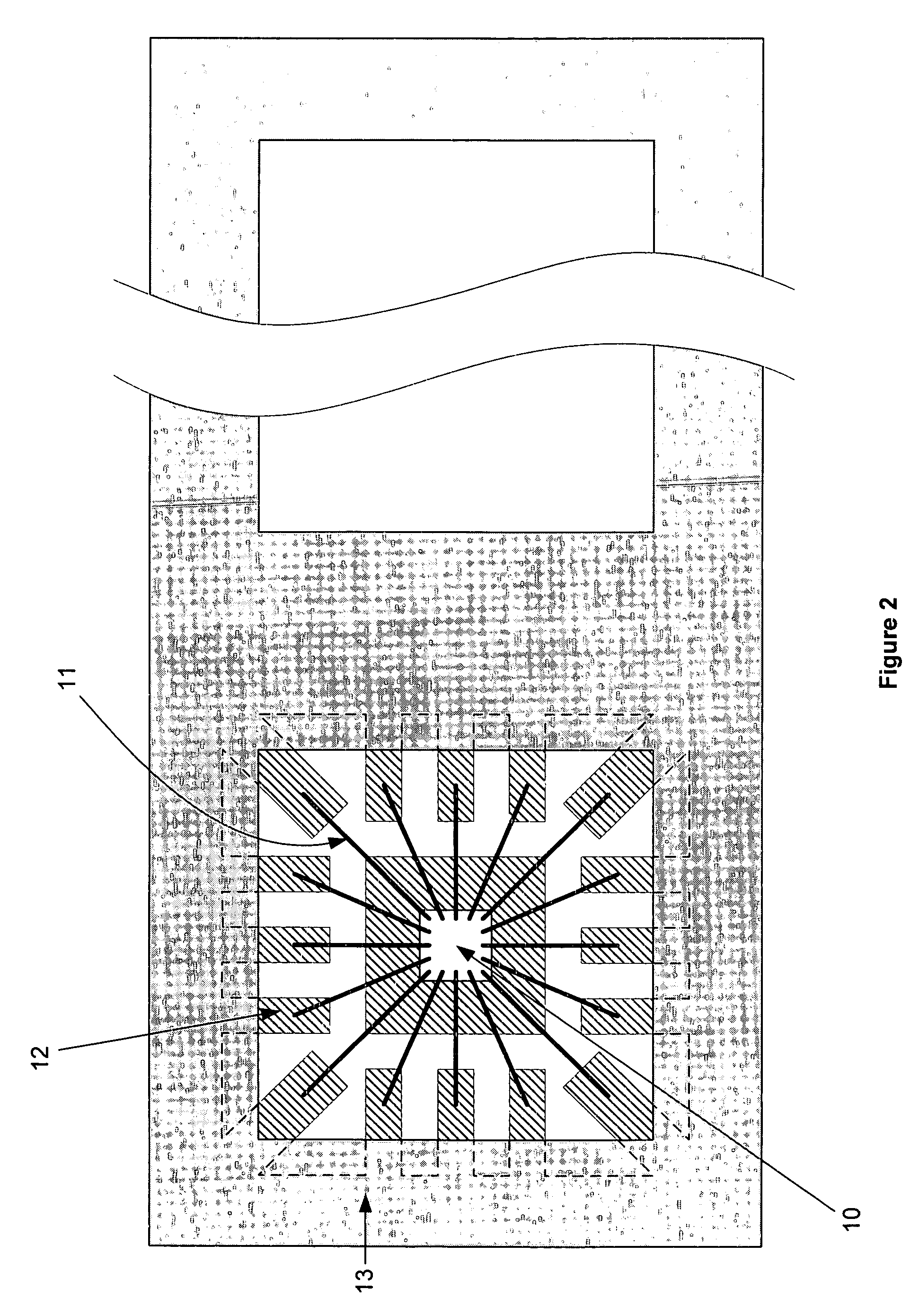

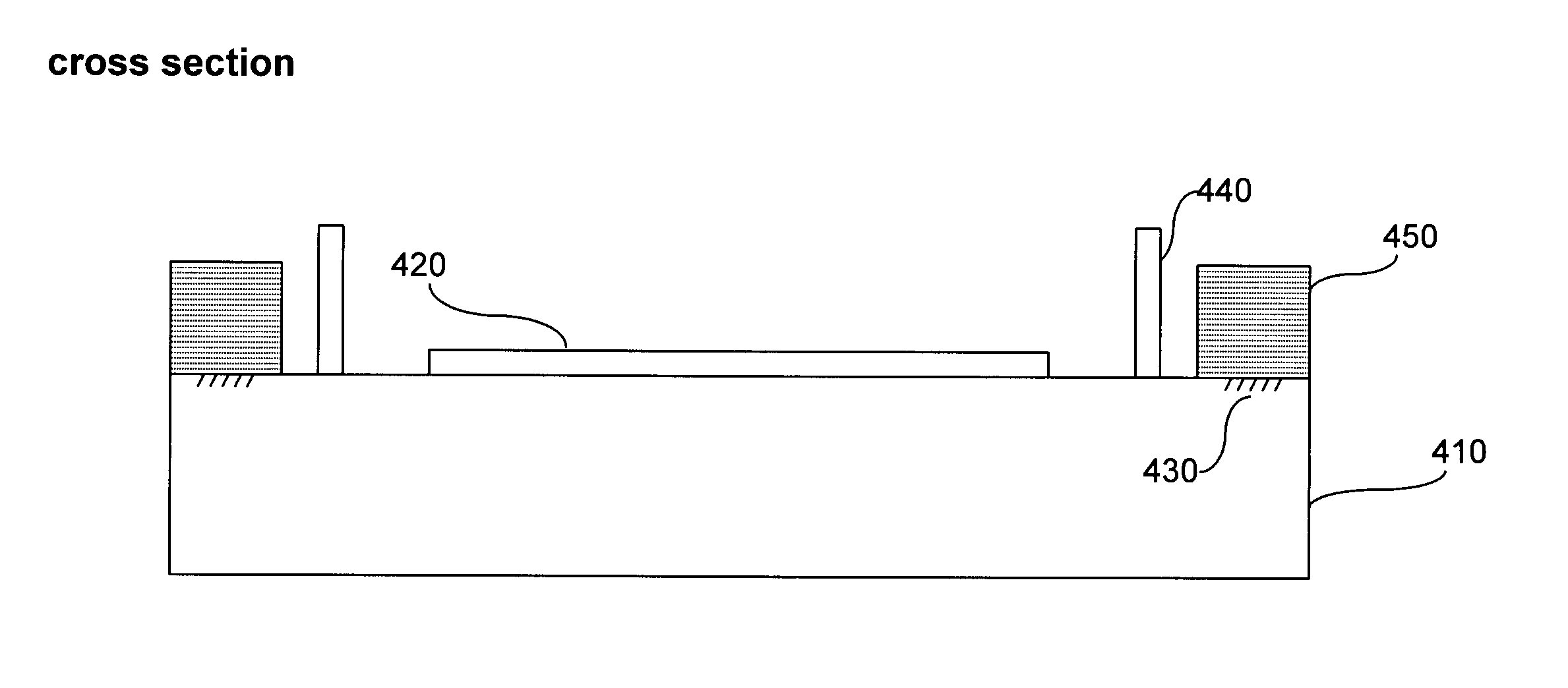

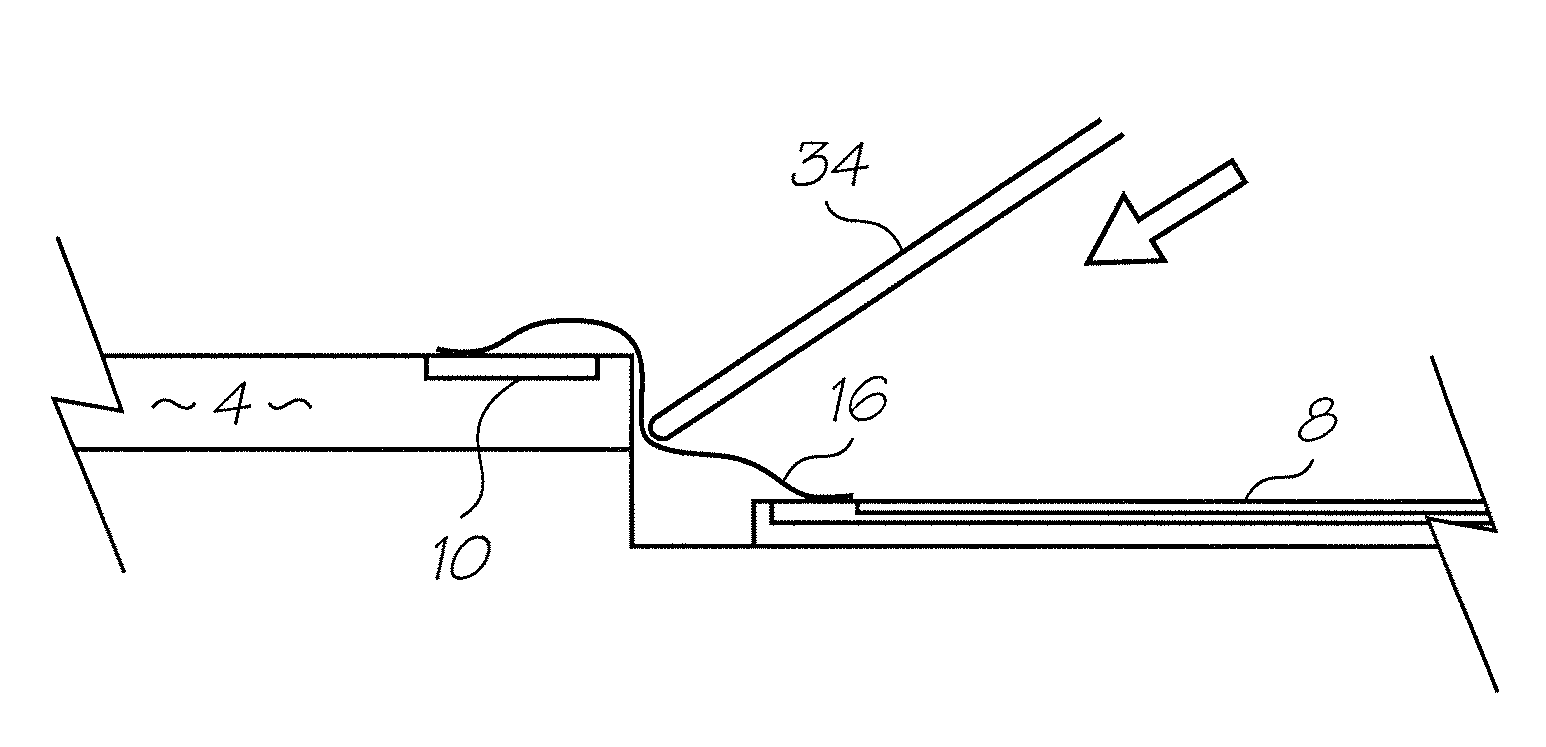

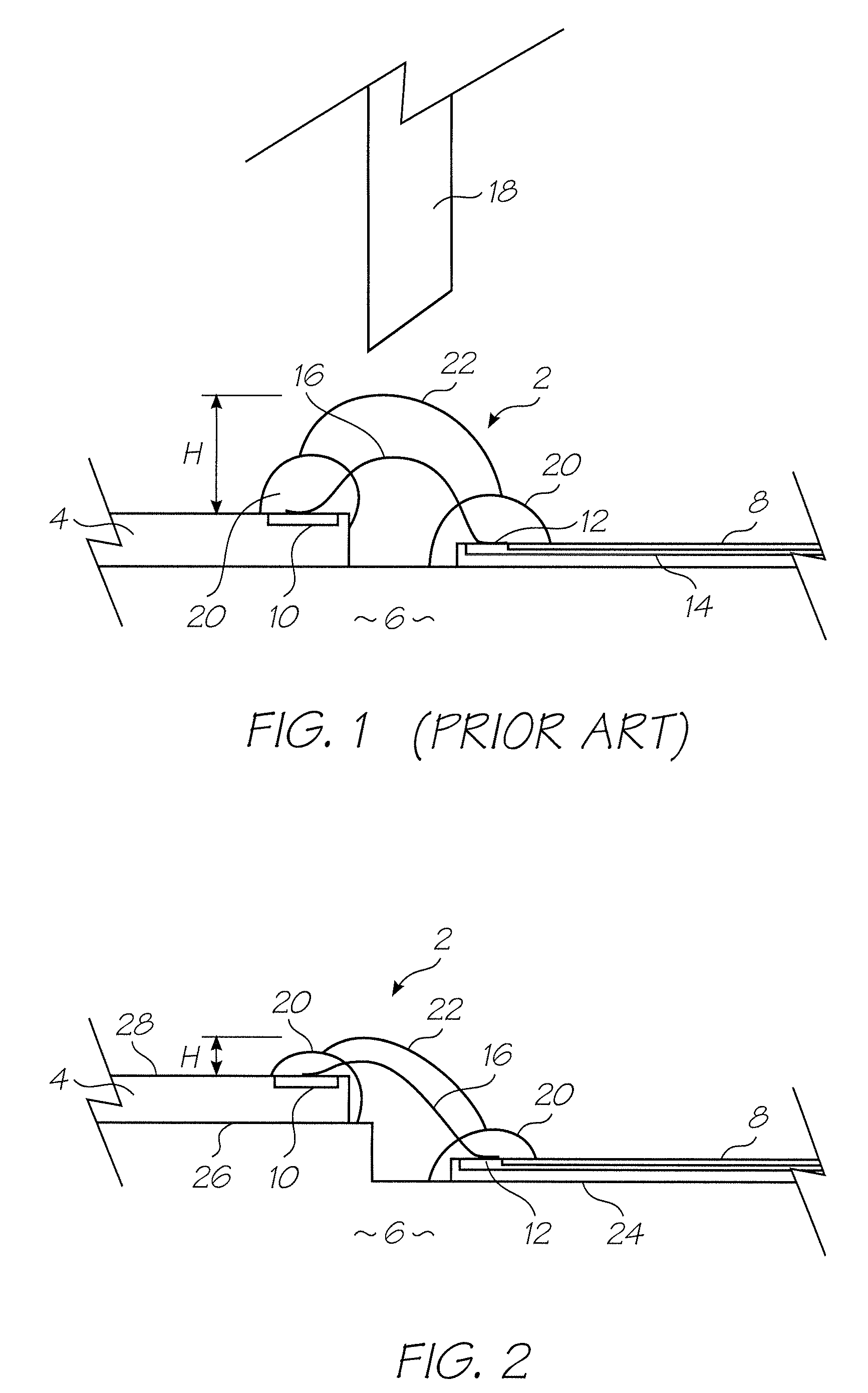

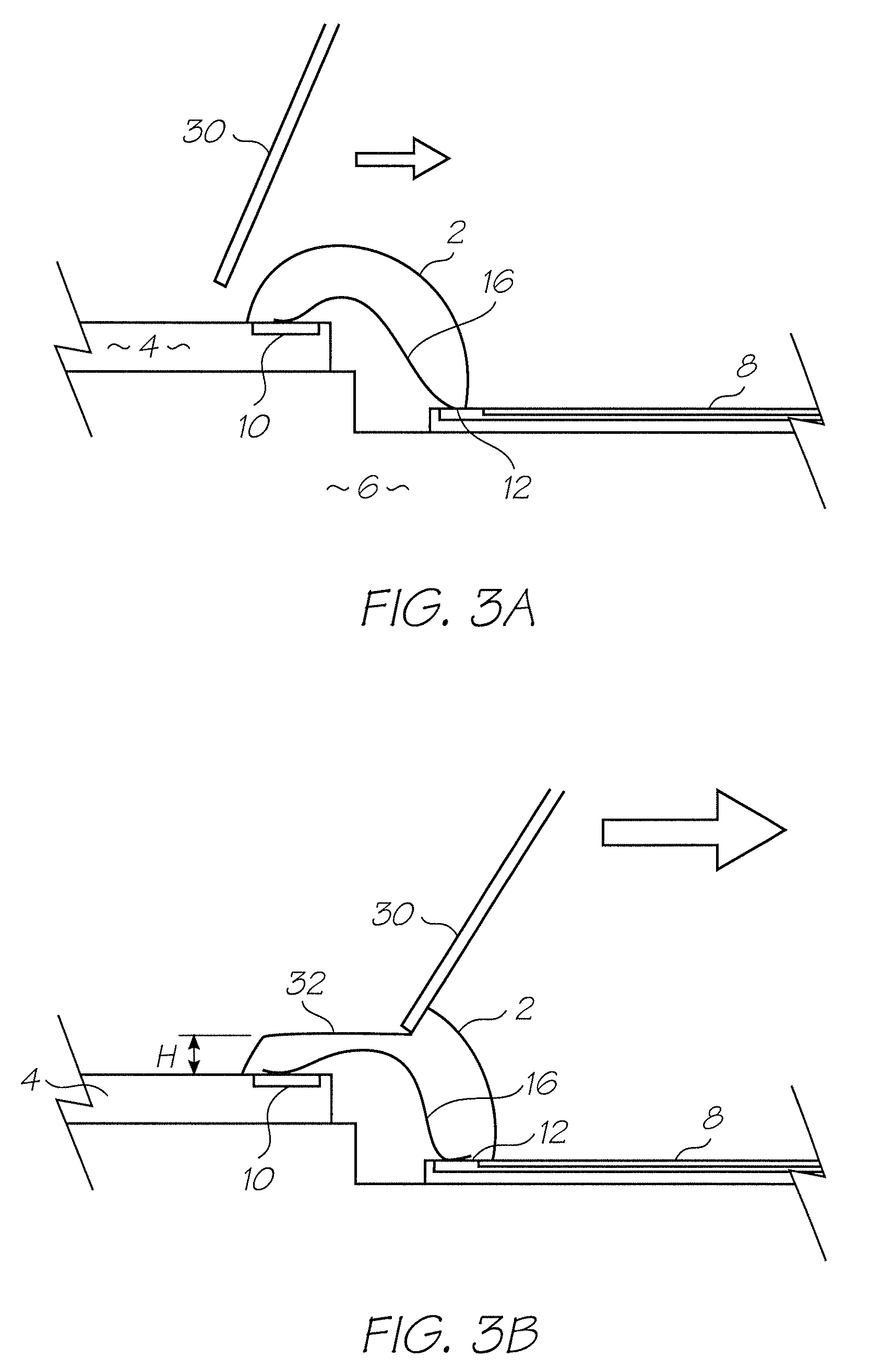

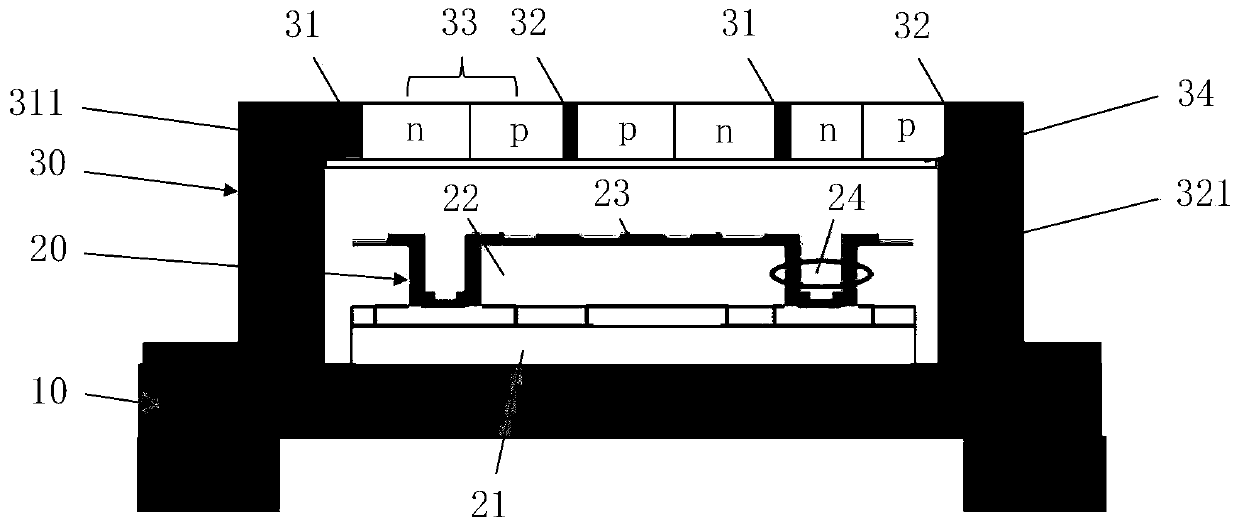

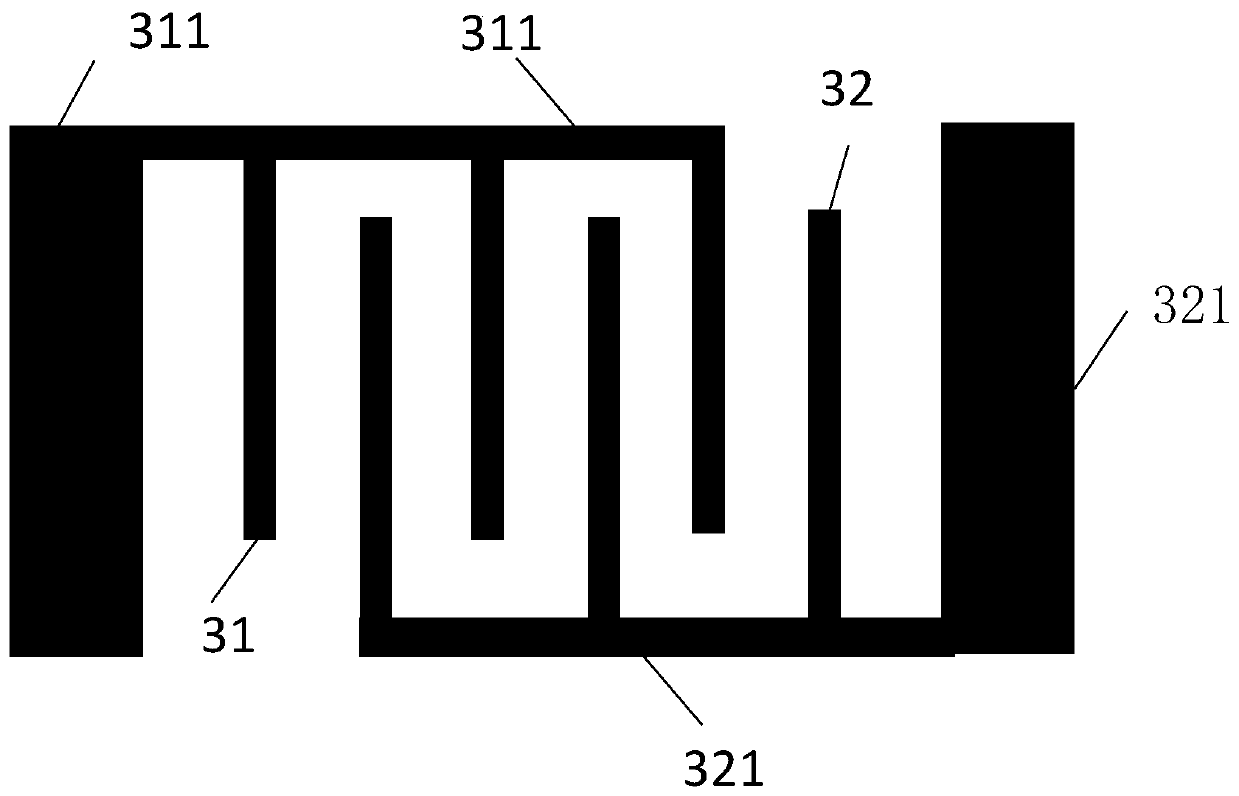

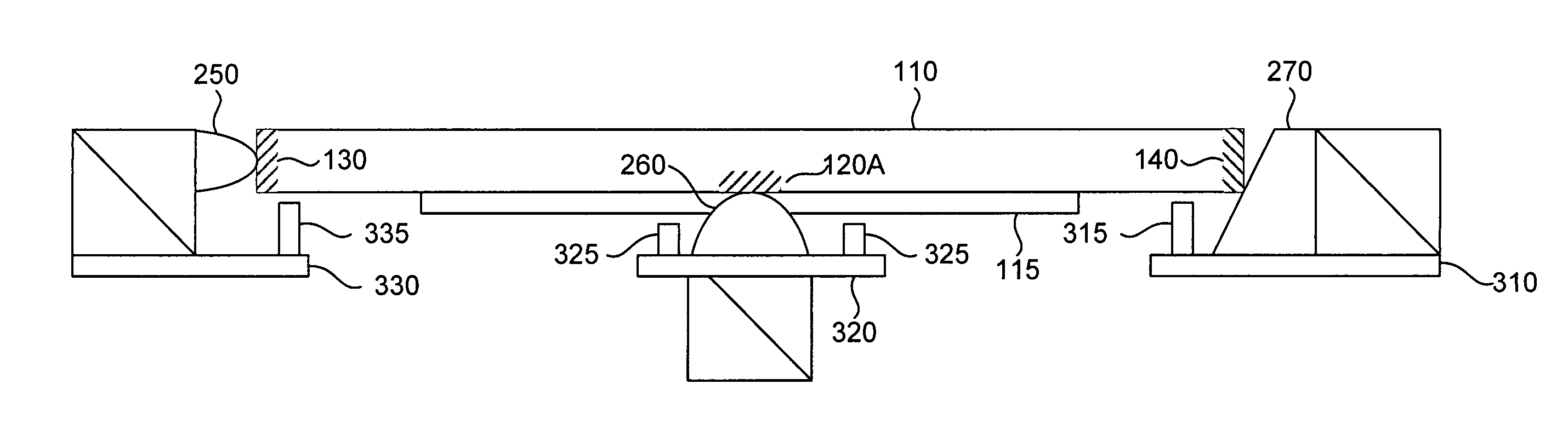

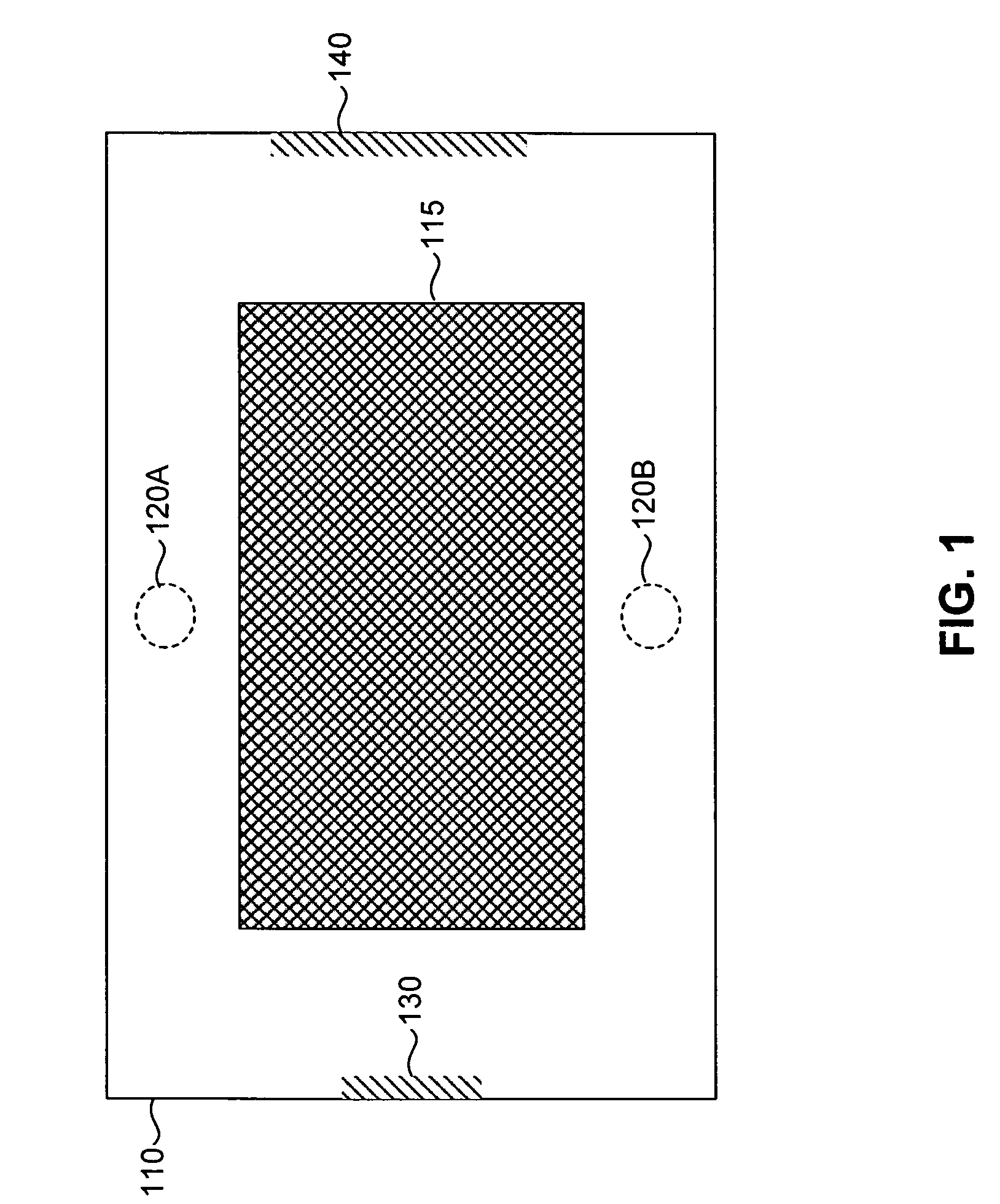

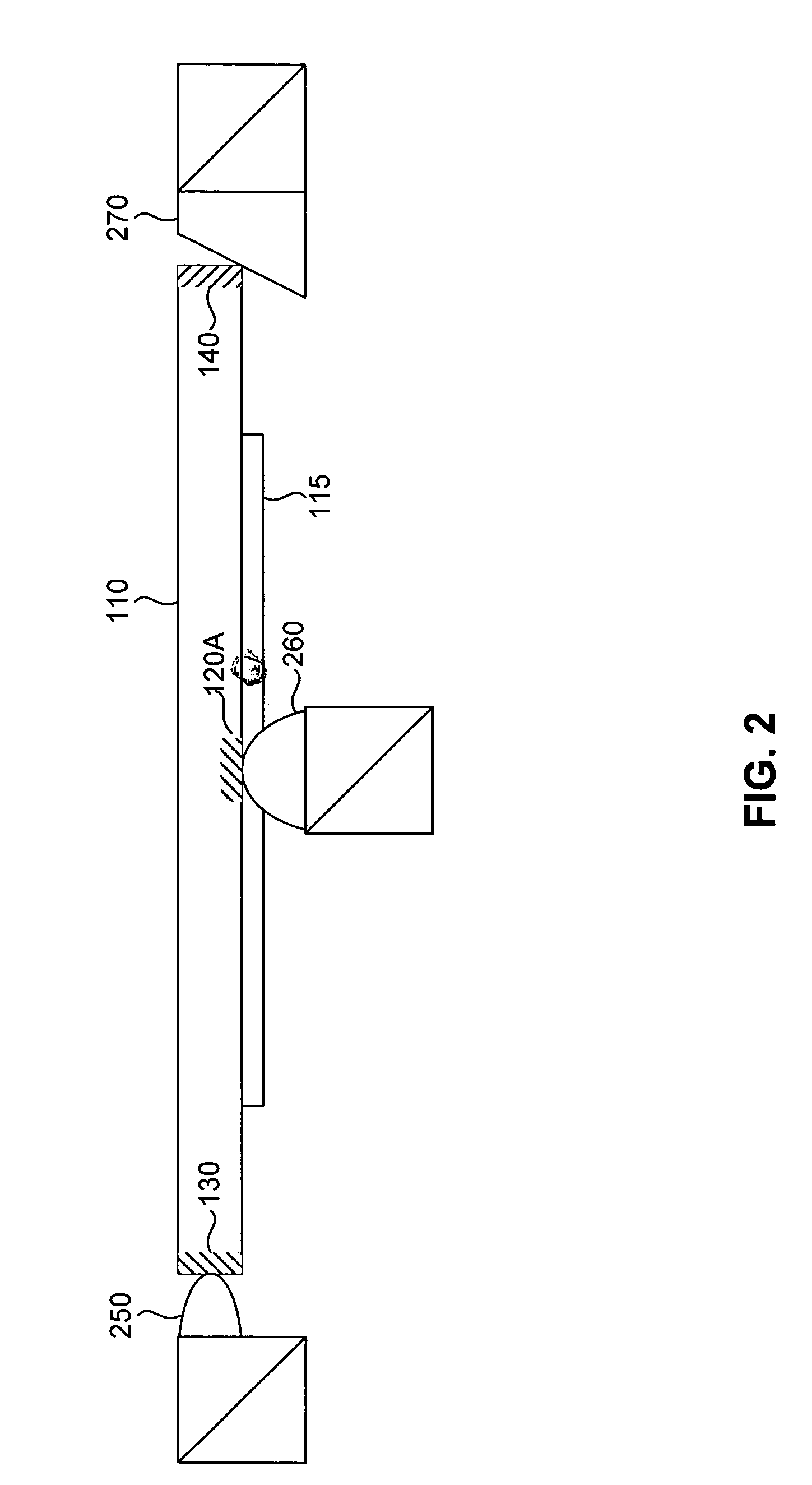

Reticle barrier system for extreme ultra-violet lithography

InactiveUS6984474B2Reduce in quantityAvoid landingPicture framesNanoinformaticsUltravioletSoft lithography

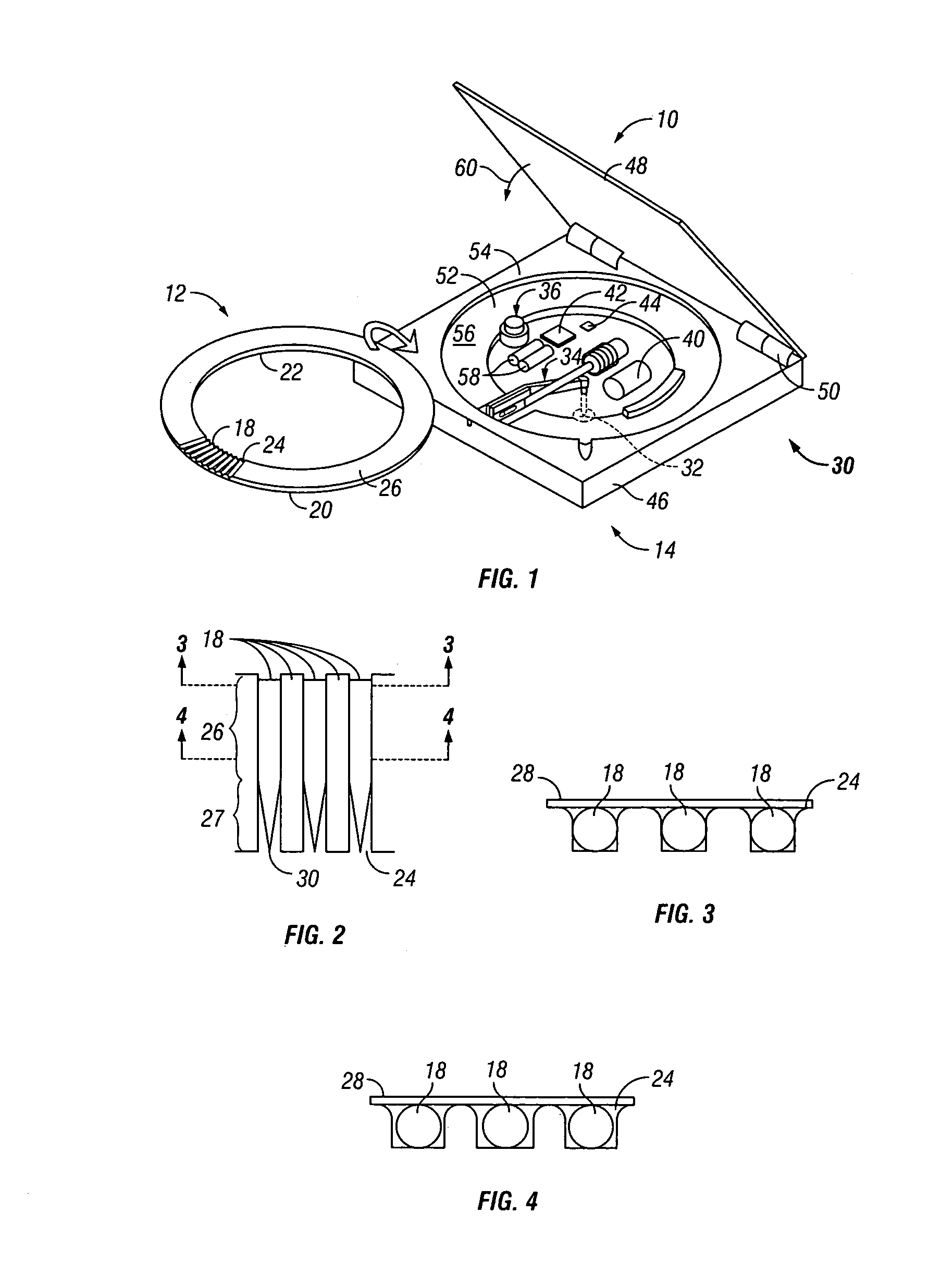

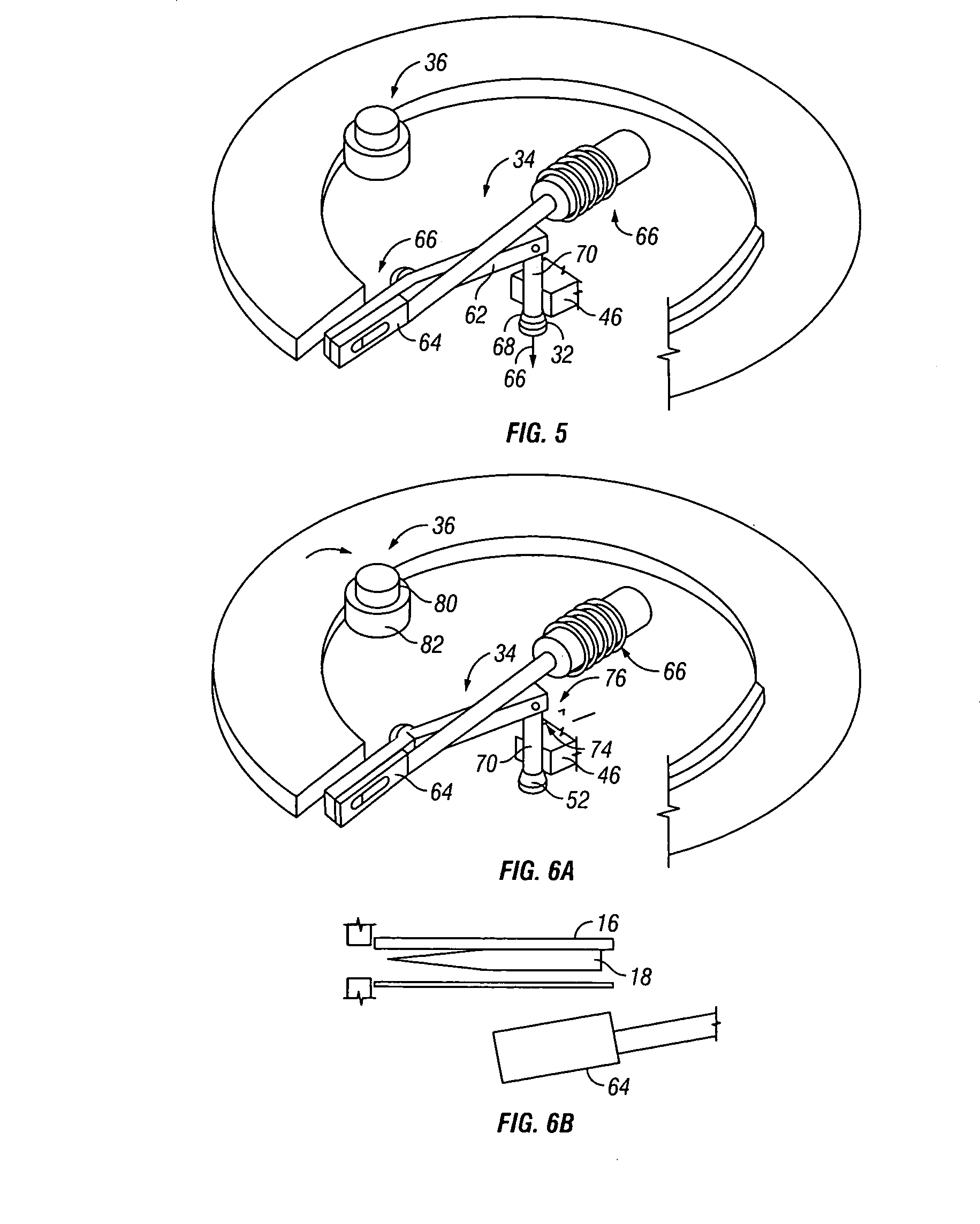

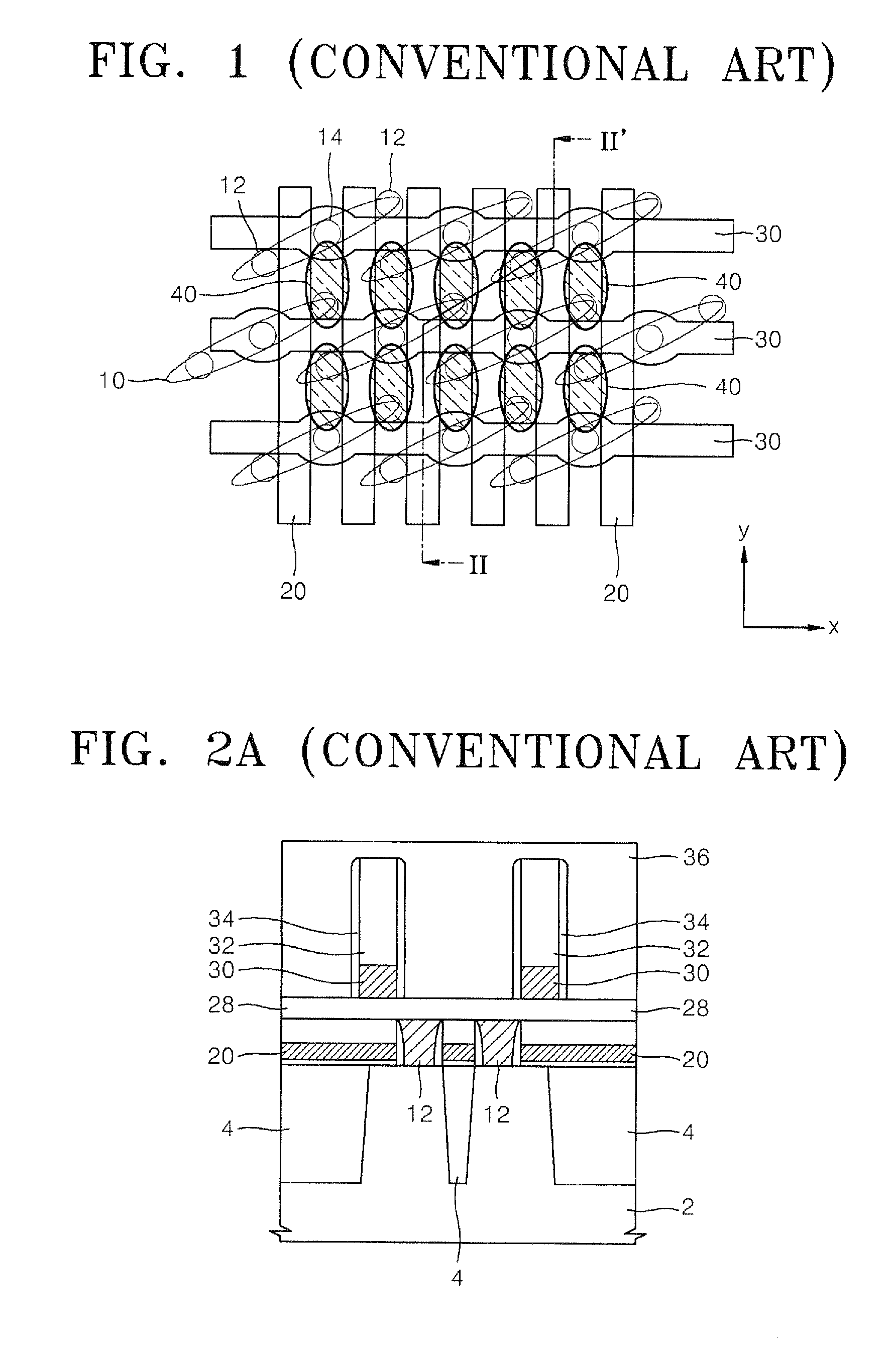

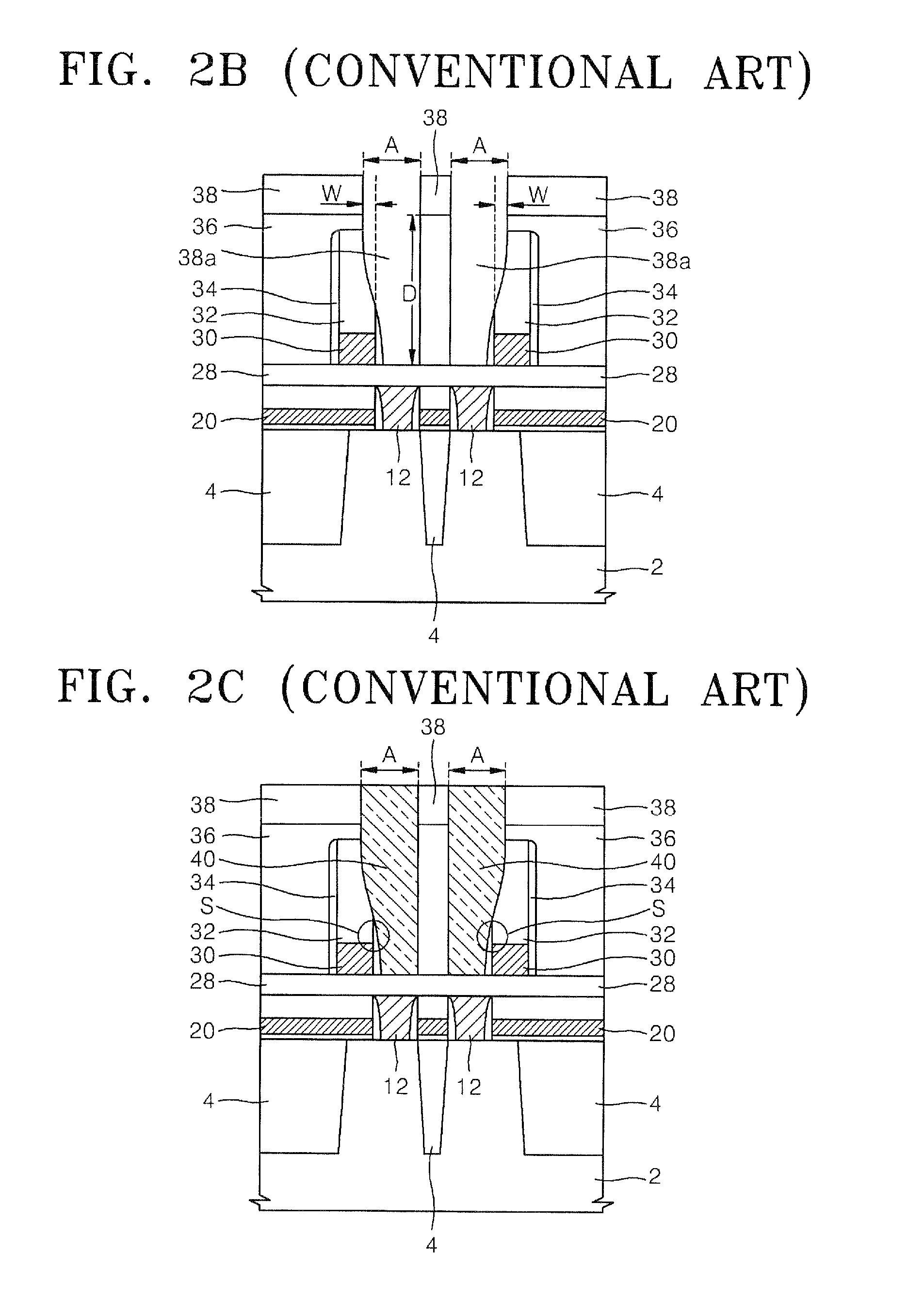

The present invention is directed to a reticle barrier system that prevents contaminants from landing on a mask within lithographic systems using extreme ultra violet light. In particular, a reticle barrier system is provided that consists of a mask barrier and a set of contact barriers. The mask barrier surrounds a mask formed on a reticle, while the contact barriers are affixed between the mask and contact spots on a reticle. The barriers have a height relative to the mask, and different geometries are provided. Collectively, the mask and contact barriers reduce the number of contaminants landing on a mask surface without the use of a pellicle. In an alternate embodiment, the reticle barrier system includes only a mask barrier. Similarly, in another alternate embodiment, the reticle barrier system includes only contact barriers.

Owner:ASML HLDG NV

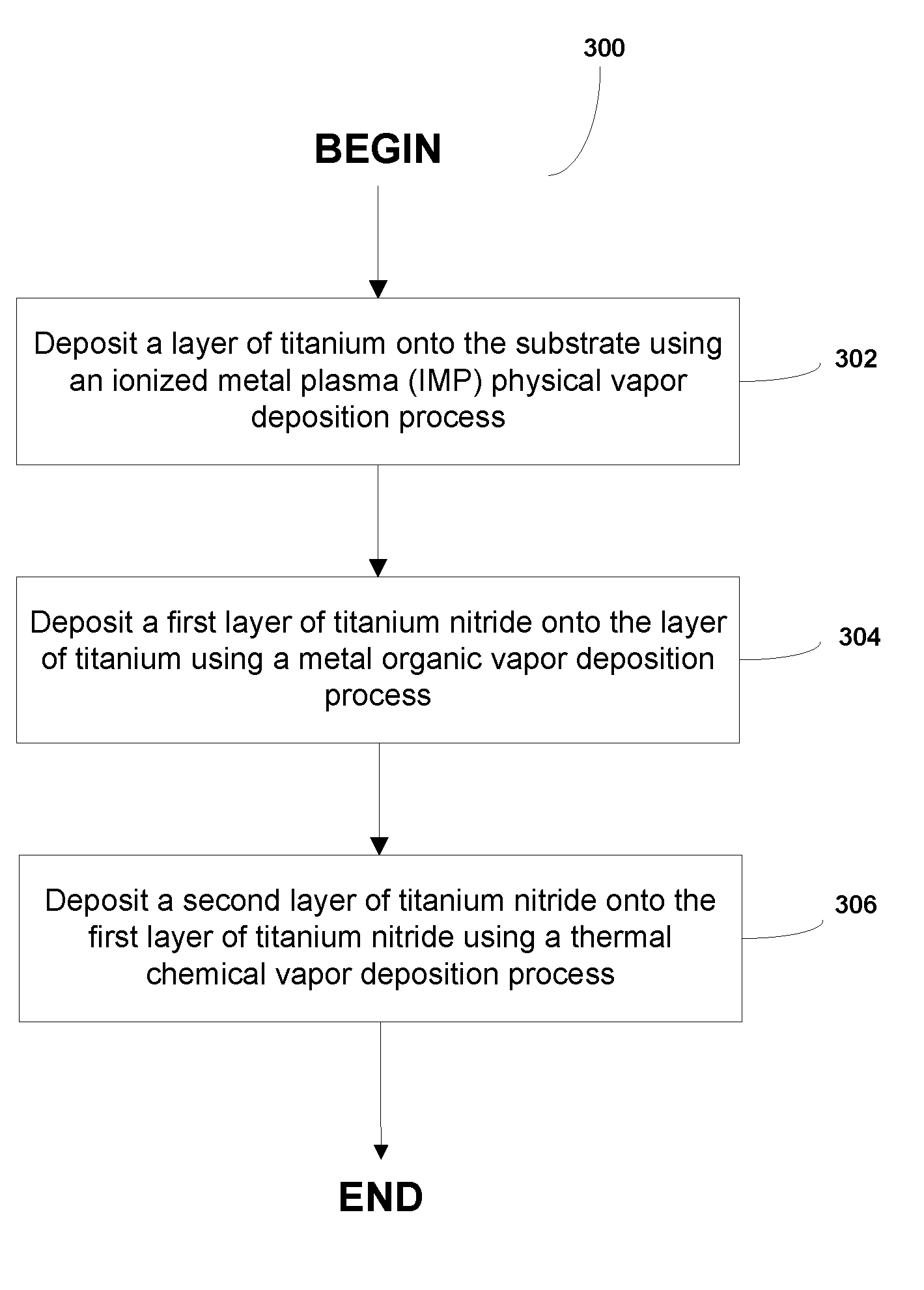

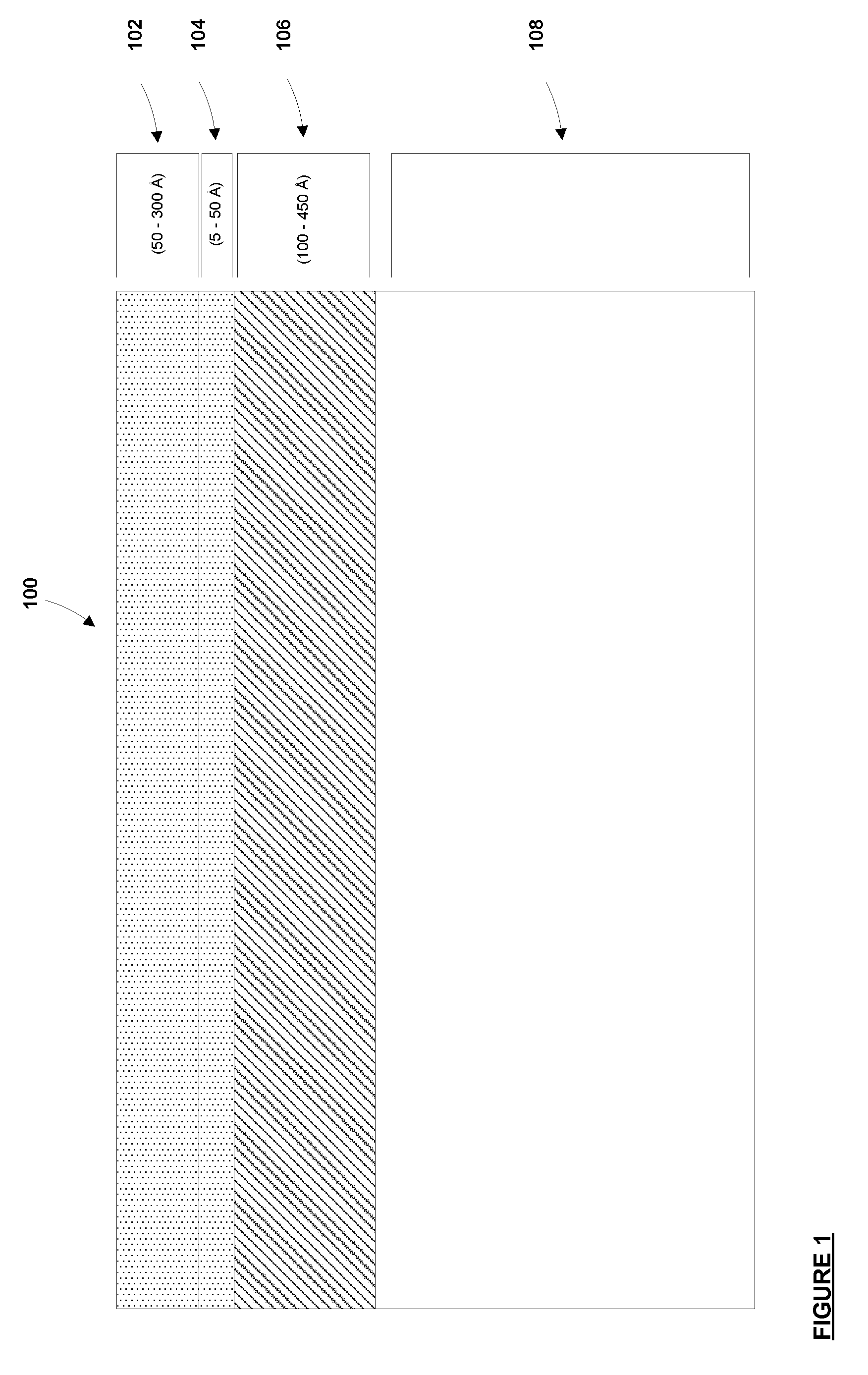

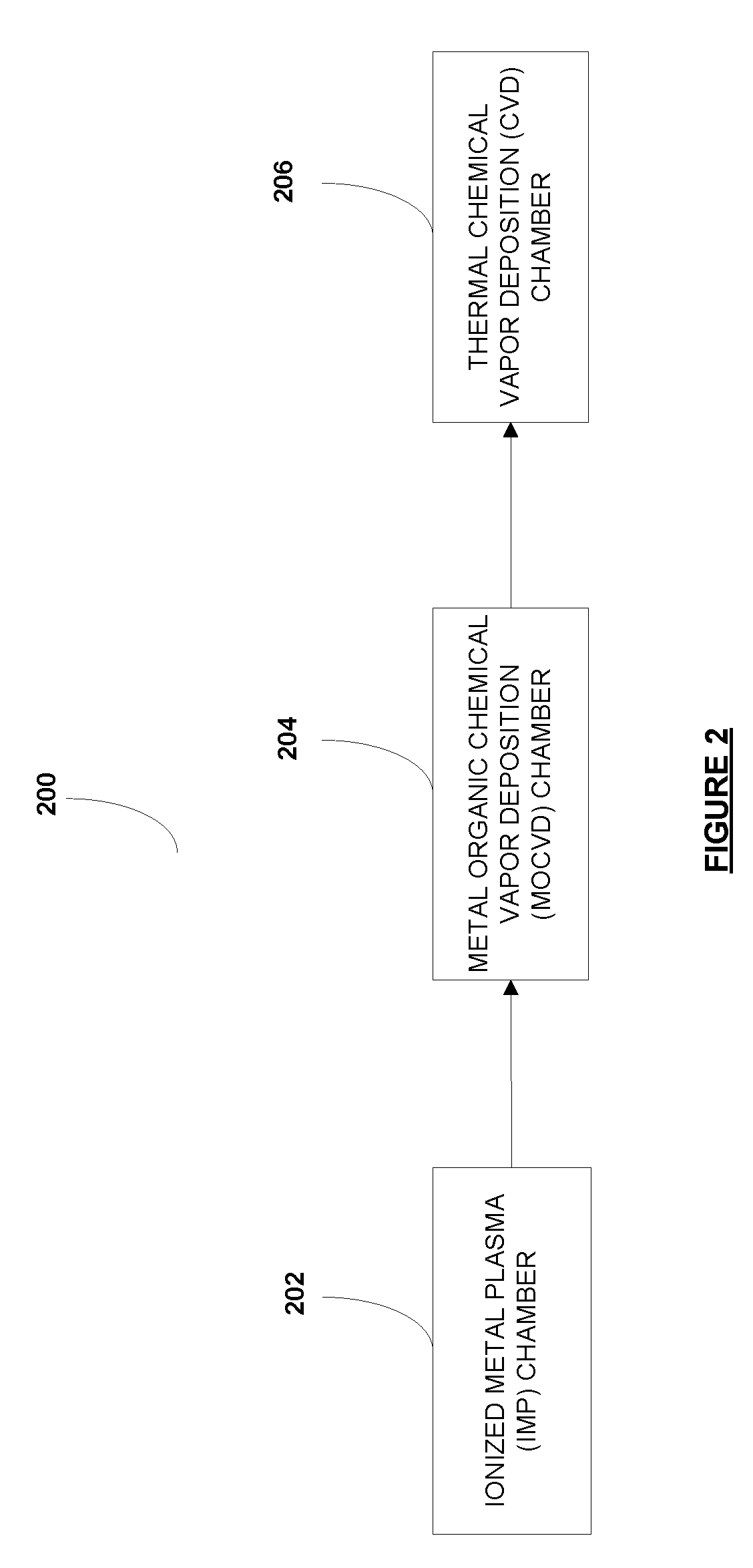

Contact barrier layer deposition process

InactiveUS20080132060A1Semiconductor/solid-state device manufacturingGas phaseThermal chemical vapor deposition

A method for depositing a barrier layer onto a substrate is disclosed. A layer of titanium (Ti) is deposited onto the substrate using an ionized metal plasma physical vapor deposition process, wherein the layer of Ti has a thickness of between about 10 angstroms (Å) and about 1000 Å. A first layer of titanium nitride (TiN) is deposited onto the layer of Ti using a metal organic chemical vapor deposition process, wherein the first layer of TiN has a thickness of between about 1 Å and about 100 Å. A second layer of TiN is deposited onto the first layer of TiN using a thermal chemical vapor deposition process, wherein the second layer of TiN has a thickness of between about 10 Å and about 750 Å.

Owner:MACRONIX INT CO LTD

Wire bond encapsulant application control

InactiveUS7659141B2Reduced strengthEasy to controlSemiconductor/solid-state device detailsSolid-state devicesContact padEffective surface

A method of applying encapsulant to a die mounted to a support structure by providing a die mounted to the support structure, the die having a back surface in contact with the support structure and an active surface opposing the back surface, the active surface having electrical contact pads, positioning a barrier proximate the electrical contact pads and spaced from the active surface to define a gap and, depositing a bead of encapsulant onto the electrical contact pads such that one side of the bead contacts the barrier and a portion of the bead extends into the gap and onto the active surface. Placing a barrier over the active surface so that it defines a narrow gap allows the geometry of the encapsulant front (the line of contact between the encapsulant and the active surface) can be more closely controlled. Any variation in the flowrate of encapsulant from the needle tends to cause bulges or valleys in the height of the bead and or the PCB side of the bead. The fluidic resistance generated by the gap between the barrier and the active surface means that the amount of encapsulant that flows into the gap and onto the active surface is almost constant. The reduced flow variations make the encapsulant front closely correspond to the shape of the barrier. Greater control of the encapsulant front allows the functional elements of the active surface of the die to be closer to the contact pads.

Owner:MEMJET TECH LTD +1

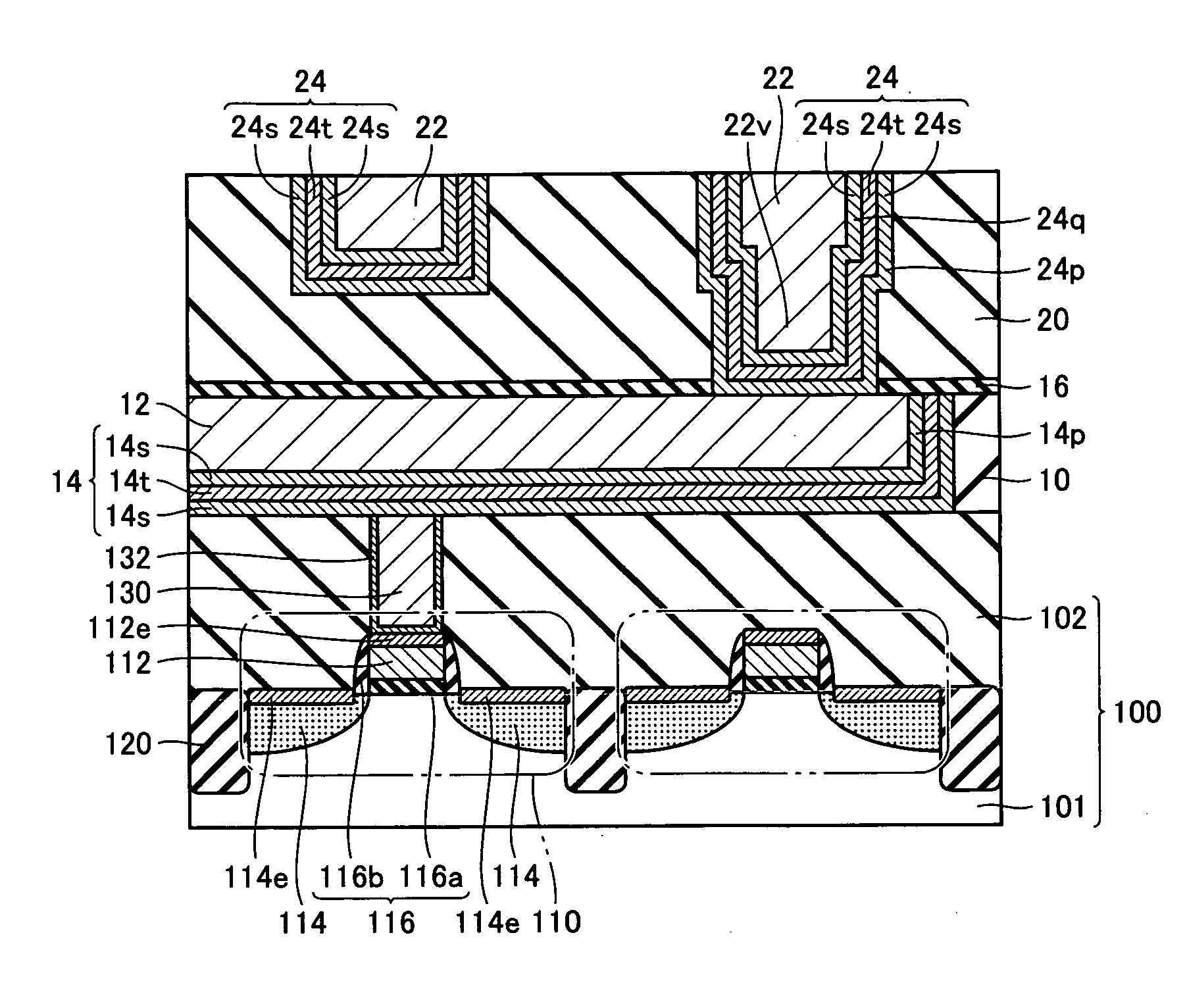

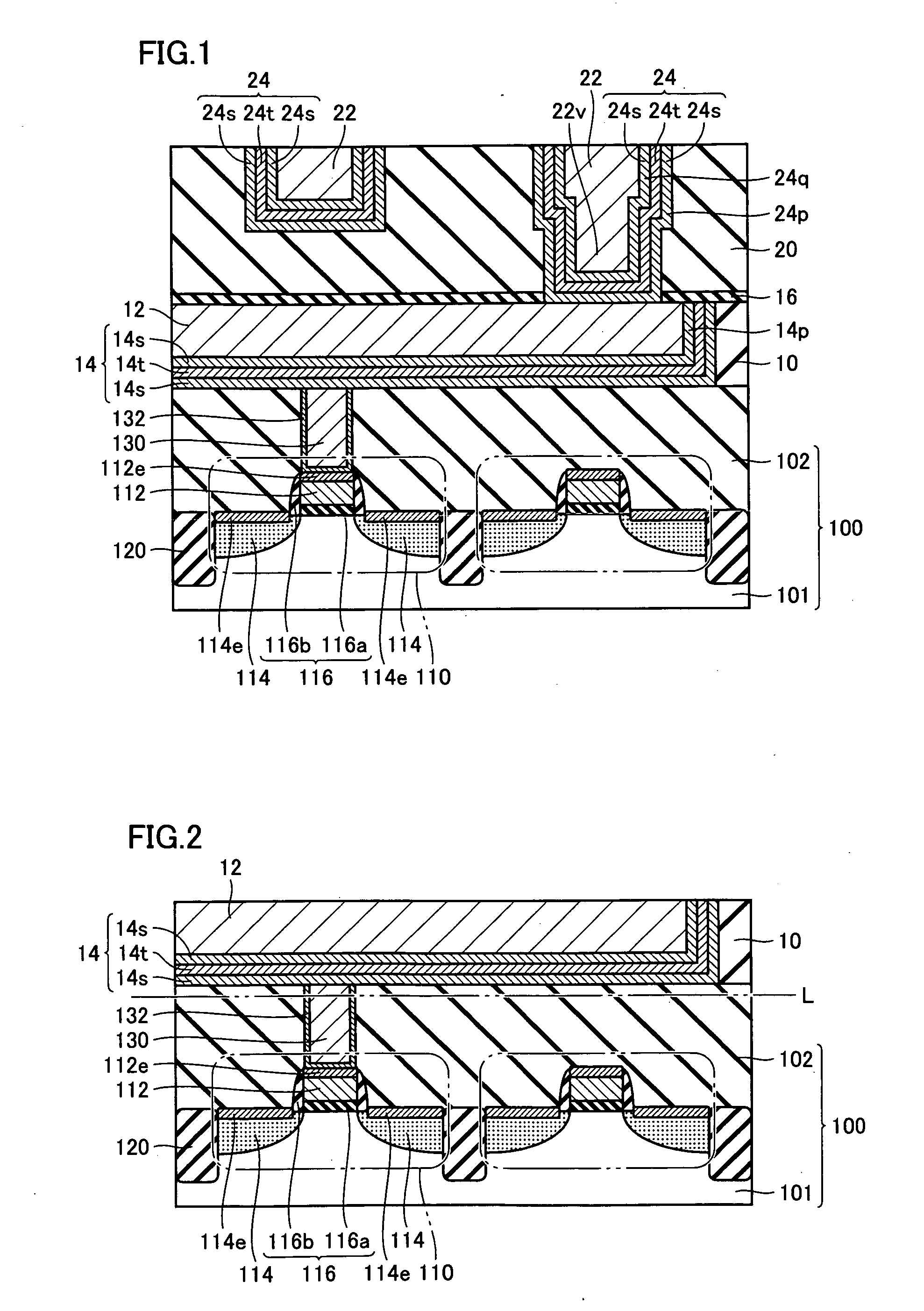

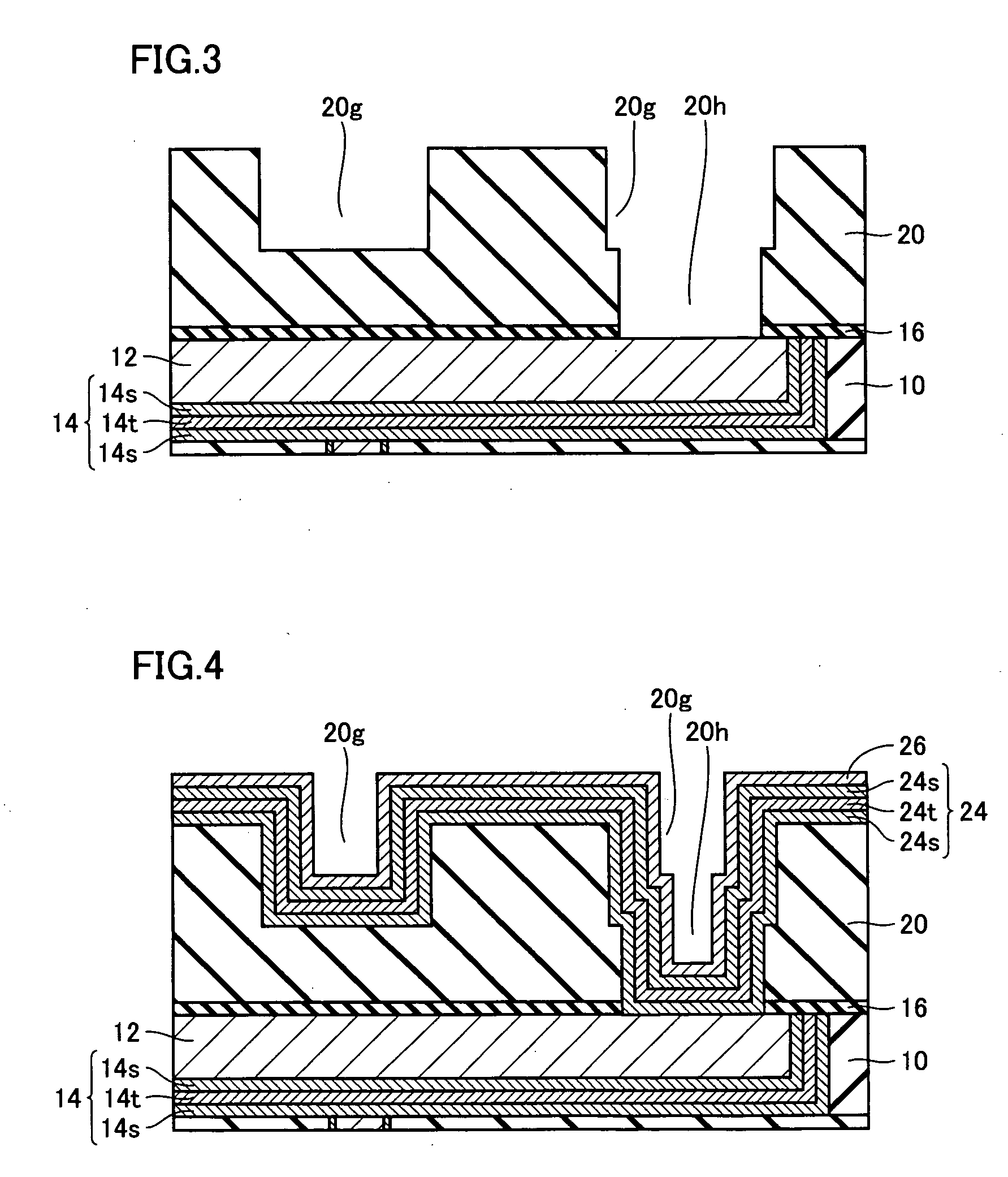

Semiconductor device having at least two layers of wirings stacked therein and method of manufacturing the same

InactiveUS20080197496A1Improve reliabilityLittle changeSemiconductor/solid-state device detailsSolid-state devicesNitrogenSemiconductor

A semiconductor device according to the present invention is a semiconductor device having a first wiring formed in a first insulating layer and a second wiring formed in a second insulating layer formed on the first insulating layer and the first wiring. Here, at least one of the first wiring and the second wiring is a CuAl wiring. The second wiring is electrically connected to the first wiring at its via-plug portion, with a plurality of barrier layers interposed between the second wiring and the first wiring. In the barrier layers, a CuAl-contact barrier layer which is in contact with the CuAl wiring has a nitrogen atom content of less than 10 atomic %. Therefore, the present semiconductor device has high reliability and small variations in initial via resistance value.

Owner:RENESAS ELECTRONICS CORP

Hybrid imaging detector structure

ActiveCN111584530AImprove performanceLow costTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesCMOSResonant cavity

The invention discloses a hybrid imaging detector structure, which comprises a visible light sensor and an infrared sensor which are stacked up and down, and is characterized in that light firstly enters the visible light sensor, is absorbed and filtered, and then further enters the infrared sensor, wherein the visible light sensor is of a sealing cover structure, and the infrared sensor is sealedon a substrate of a single chip in a vacuum mode. According to the invention, a traditional CMOS-MEMS micro-bridge resonant cavity structure is utilized to carry out middle and far infrared detection, and meanwhile, vacuum packaging and visible light detection are realized by using a sealing cover with a pn junction or a metal semiconductor contact barrier device, so that low-cost, high-quality and phase-difference-free single-chip image fusion of visible light and middle and far infrared images is realized.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

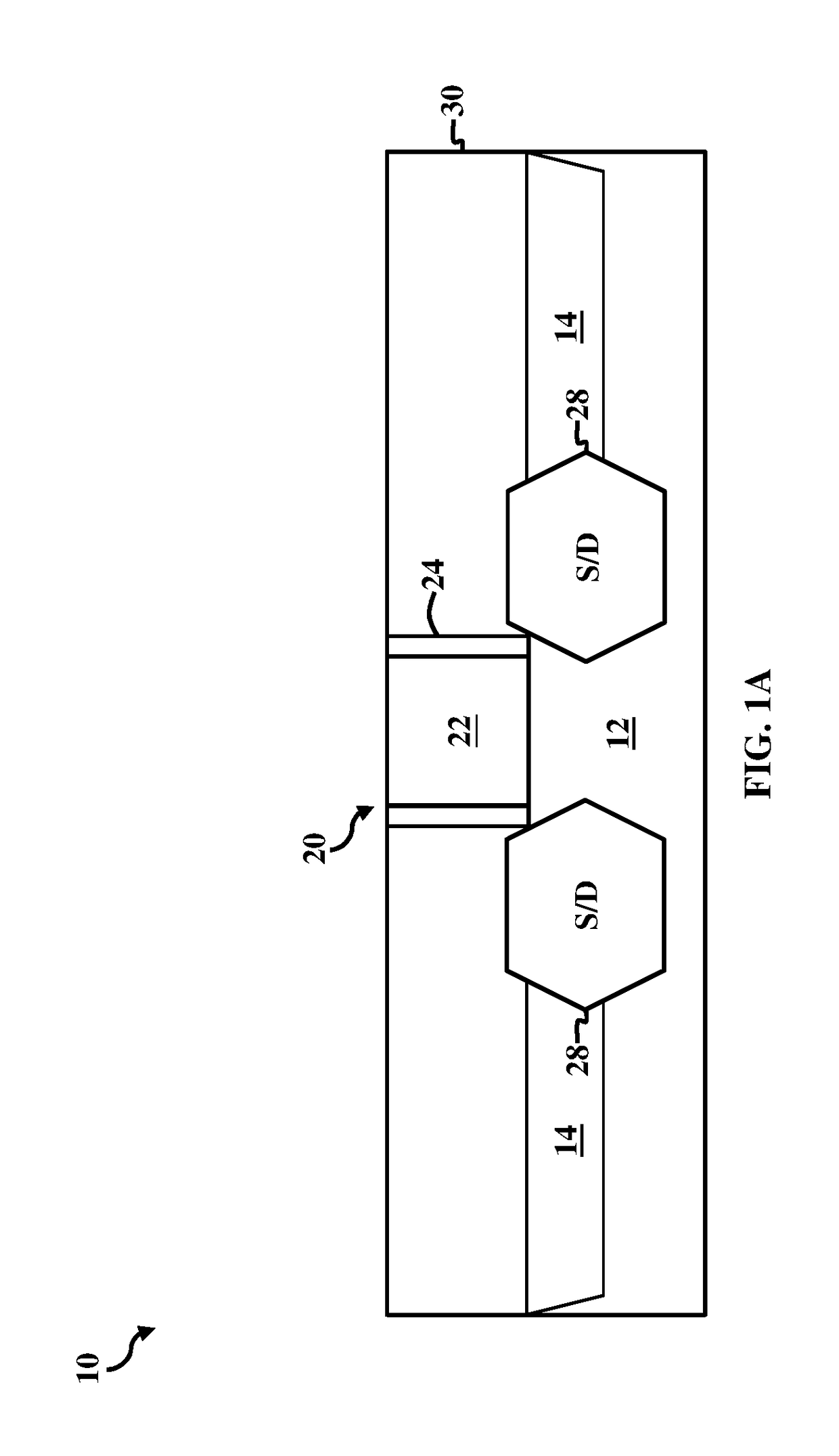

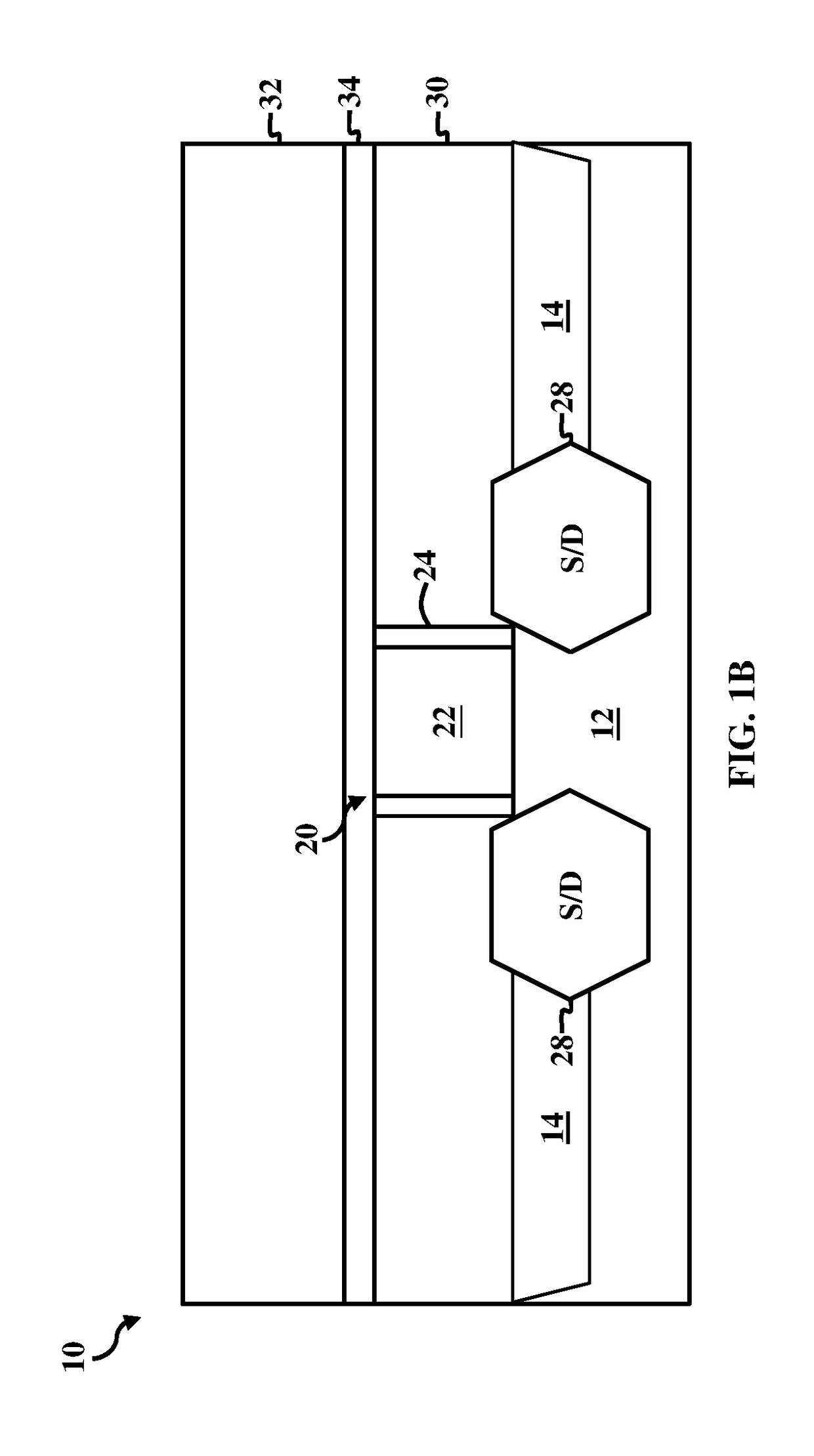

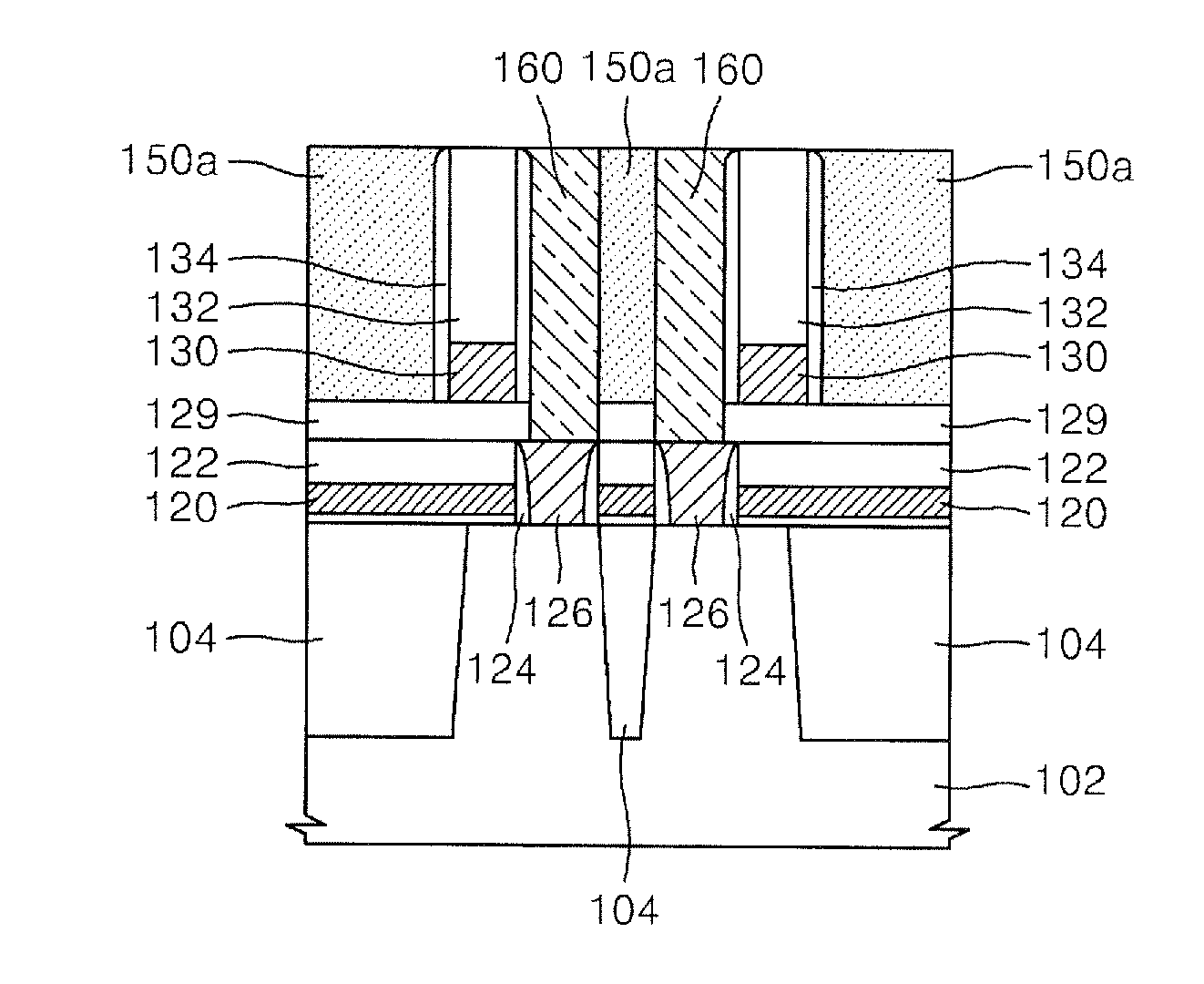

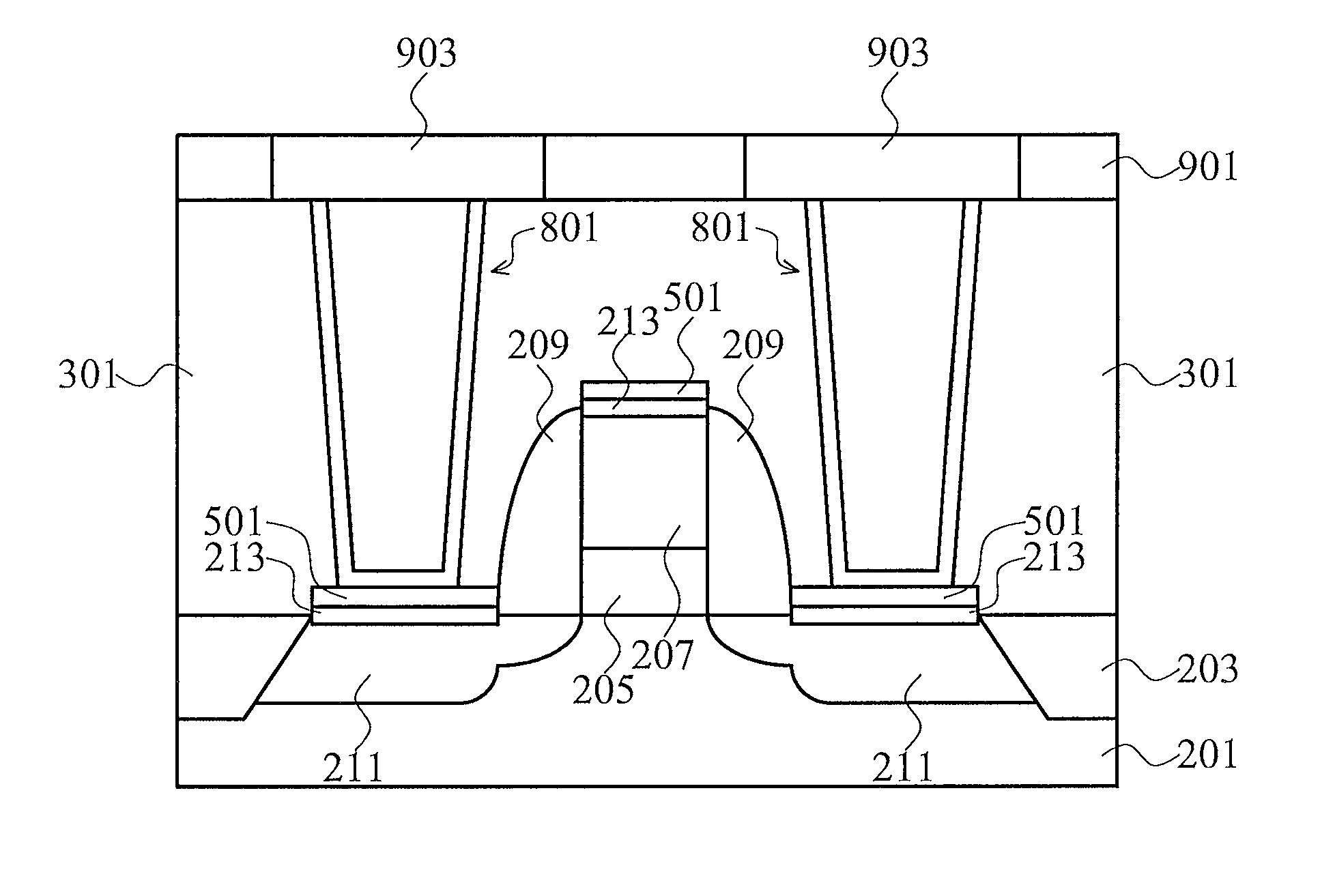

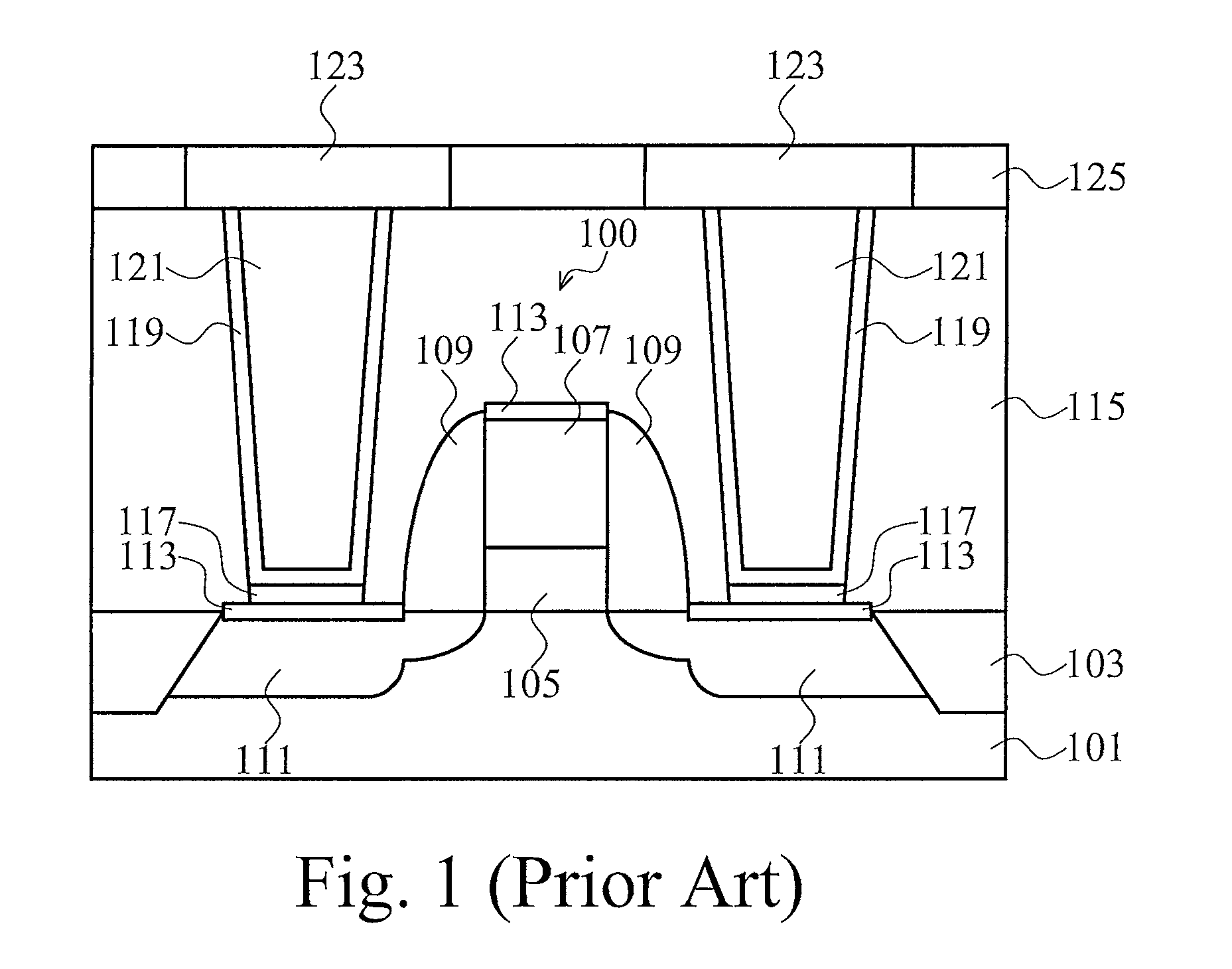

Semiconductor device having contact barrier and method of manufacturing the same

ActiveUS20080088029A1Short circuits can be preventedSemiconductor/solid-state device detailsSolid-state devicesConductive materialsLarge aspect ratio

A semiconductor device having a contact barrier for insulating contacts with a large aspect ratio and having a fine pitch between adjacent conductive lines and a method of manufacturing the same are provided. The semiconductor device includes a buried contact formed in a region between two adjacent first conductive lines and two adjacent second conductive lines. Insulating lines define a width of the buried contact. To form the contact barrier, an interlayer dielectric layer formed on the second conductive lines is patterned to form a space and an insulating line having an etching ratio different from the interlayer dielectric layer is formed in the space. The interlayer dielectric layer is selectively wet etched relative to an insulating layer covering the second conductive line and the first insulating line to form buried contact hole. The buried contact hole is filled with conductive material to form a buried contact.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor contact barrier

ActiveUS7897514B2Reduce resistanceImprove performanceSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

System and method for reducing contact resistance and improving barrier properties is provided. An embodiment comprises a dielectric layer and contacts extending through the dielectric layer to connect to conductive regions. A contact barrier layer is formed between the conductive regions and the contacts by electroless plating the conductive regions after openings have been formed through the dielectric layer for the contact. The contact barrier layer is then treated to fill the grain boundary of the contact barrier layer, thereby improving the contact resistance. In another embodiment, the contact barrier layer is formed on the conductive regions by electroless plating prior to the formation of the dielectric layer.

Owner:TAIWAN SEMICON MFG CO LTD

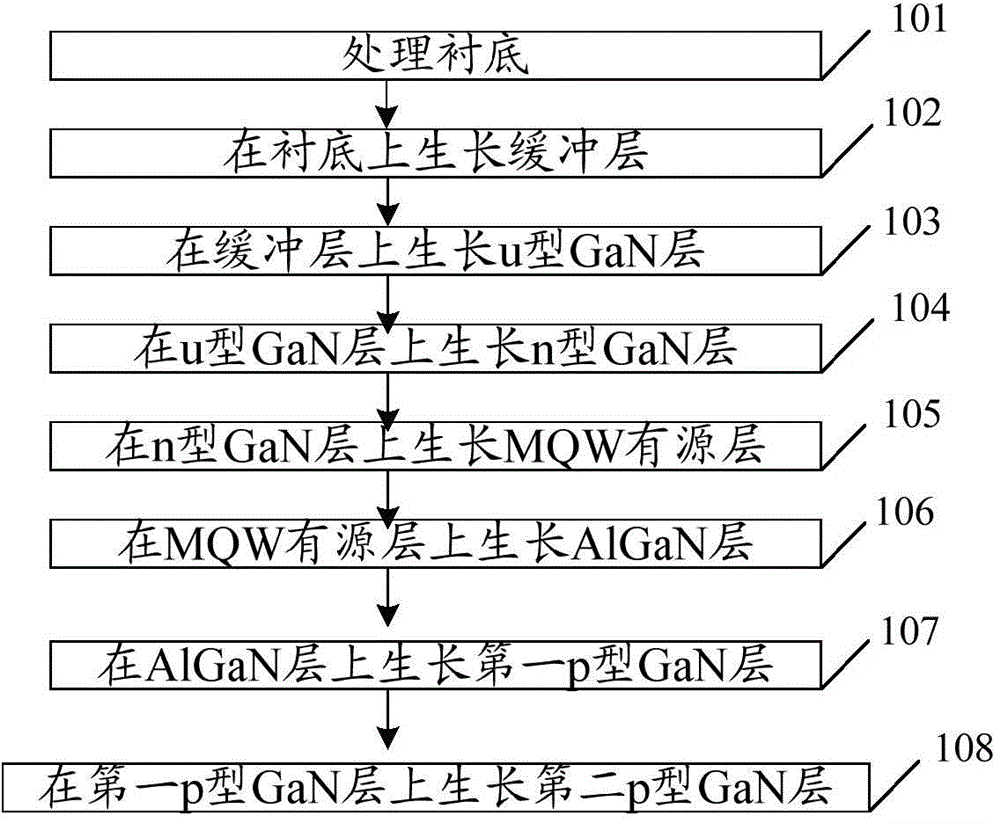

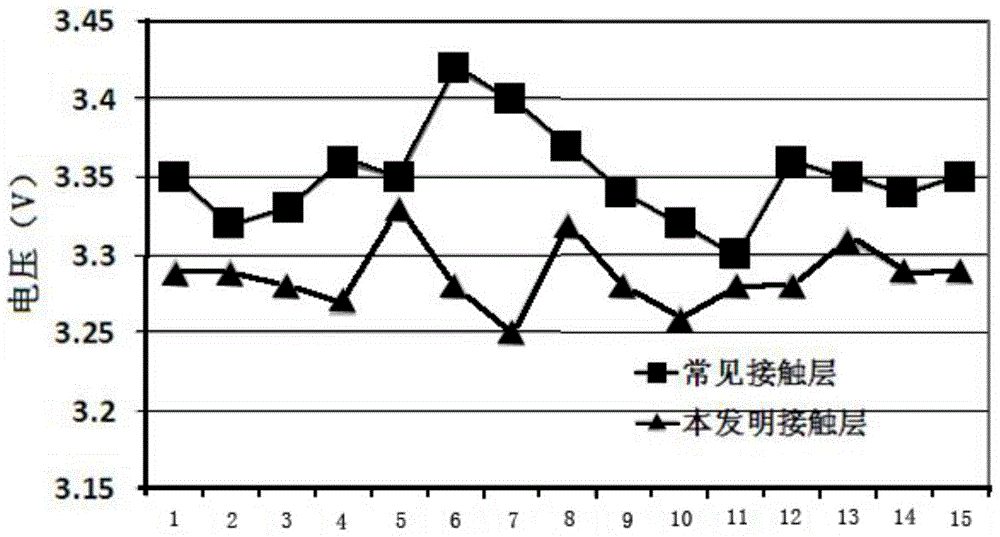

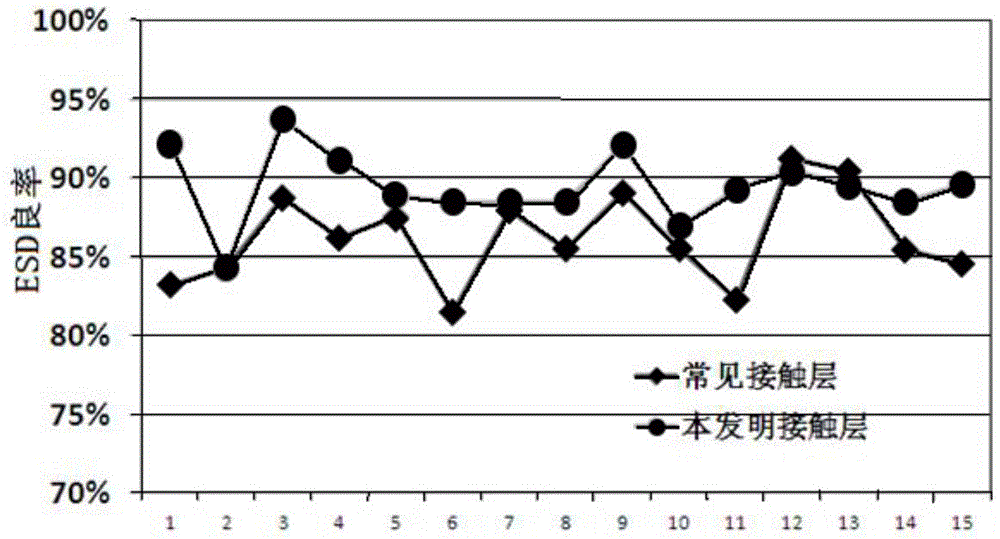

Method for manufacturing p-type GaN low-resistance-value ohmic contact layer

ActiveCN104377278AIncrease hole concentrationReduce contact resistivitySemiconductor devicesOhmic contactCharge carrier

The invention discloses a method for manufacturing a p-type GaN low-resistance-value ohmic contact layer. The method is characterized by sequentially comprising the steps that a substrate is processed, a buffer layer is grown on the substrate, a u-type GaN layer is grown on the buffer layer, an n-type GaN layer is grown on the u-type GaN layer, an MQW active layer is grown on the n-type GaN layer, an AlGaN layer is grown on the MQW active layer, a first p-type GaN layer is grown on the AlGaN layer, and a second p-type GaN layer is grown on the first p-type GaN layer. Compared with the prior art, due to the fact that the second p-type GaN layer has high Mg concentration doping, the hole concentration of the contact layer is high, the contact resistivity of the second p-type GaN layer and metal is reduced, a barrier region generated by the second p-type GaN layer and the metal becomes narrow, the probability that a carrier penetrates through a metal and semiconductor contact barrier region through tunneling is increased, the work voltage of a high-power LED chip is reduced, and therefore the light emitting efficiency of the high-power LED chip is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Cobalt silicon contact barrier metal process for high density semiconductor power devices

ActiveCN1941410ASolve the lossOvercome limitationsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETInsulation layer

The invention provides an improved trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a source contact opening opened on top of an area extended over the body region and the source region through a protective insulation layer, wherein the area further has a cobalt-silicide layer disposed near a top surface of the substrate. The MOSFET cell further includes a Ti / TiN conductive layer covering the area interfacing with the cobalt-silicide layer over the source contact opening. The MOSFET cell further includes a source contact metal layer formed on top of the Ti / TiN conductive layer ready to form source-bonding wires thereon.

Owner:ALPHA & OMEGA SEMICON CAYMAN

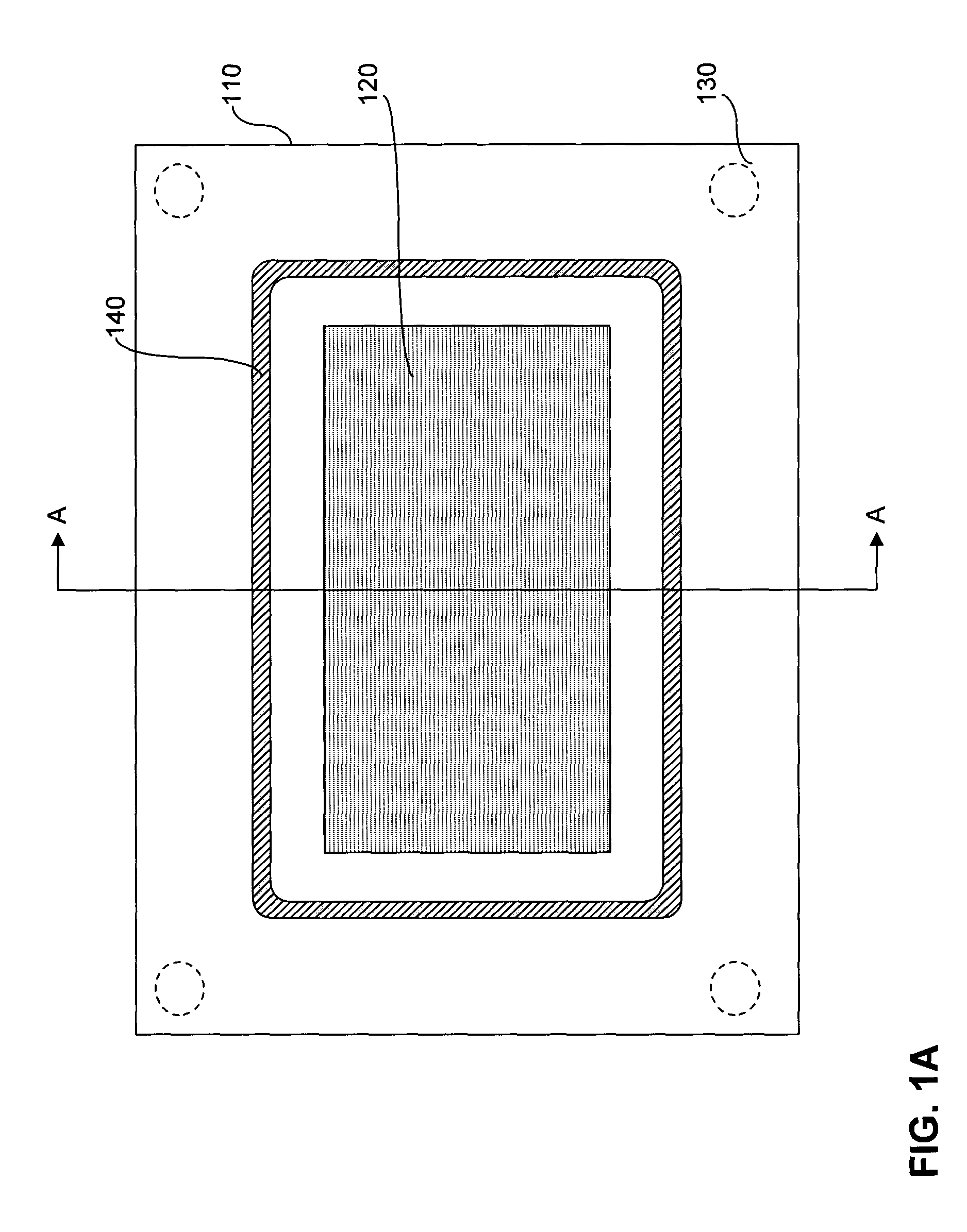

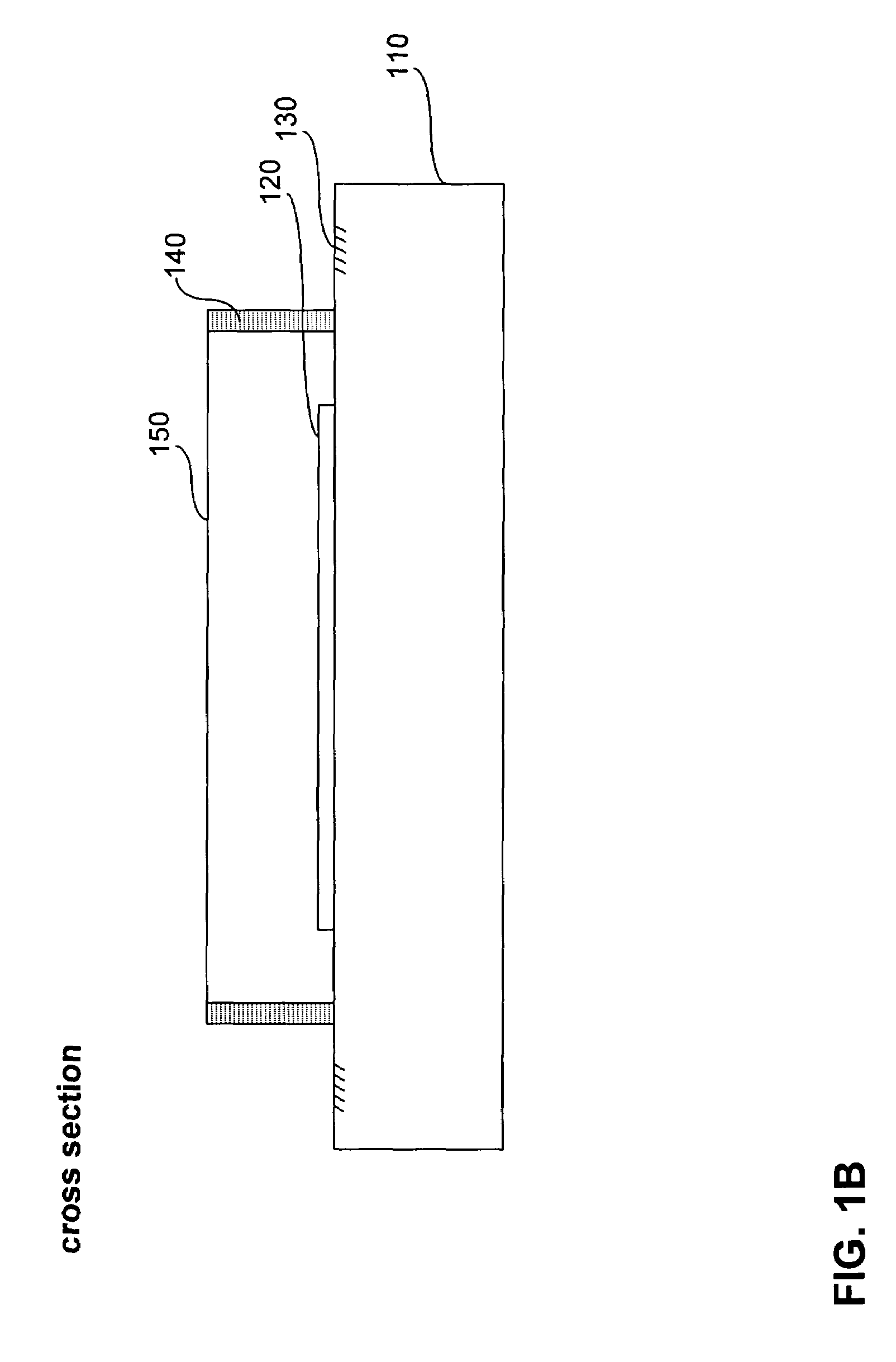

Reticle gripper barrier system for lithography use

InactiveUS7136151B2Improve Wafer QualityReduce in quantityPhotomechanical apparatusOriginals for photomechanical treatmentLithographic artistMechanical engineering

A reticle gripper barrier system for use in concert with a reticle gripper device that contacts a lithographic reticle is presented. In a particular embodiment, a reticle gripper barrier device includes a support plate affixed near or to the reticle gripper device and a gripper barrier or a set of concentric gripper barriers affixed to or near the support plate. A reticle gripper barrier system includes one or more reticle gripper barrier devices that form a complete or partial barrier around the point or points where the reticle gripper device contacts a lithographic reticle. The gripper barriers block contaminants and prevent them from migrating towards the mask and do not contact the lithographic reticle. The gripper barriers can be interleaved with corresponding contact barriers on a lithographic reticle, which the gripper device is contacting.

Owner:ASML HLDG NV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com