Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

389 results about "Vertical field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Vertical Field is specialized in producing natural products integrated with innovative technologies. The lichen is attached in a unique fashion to flexible tiles made of special fabric which can adhere to and implemented on the wall alike regular ceramic, stone tiles or other wall covering materials.

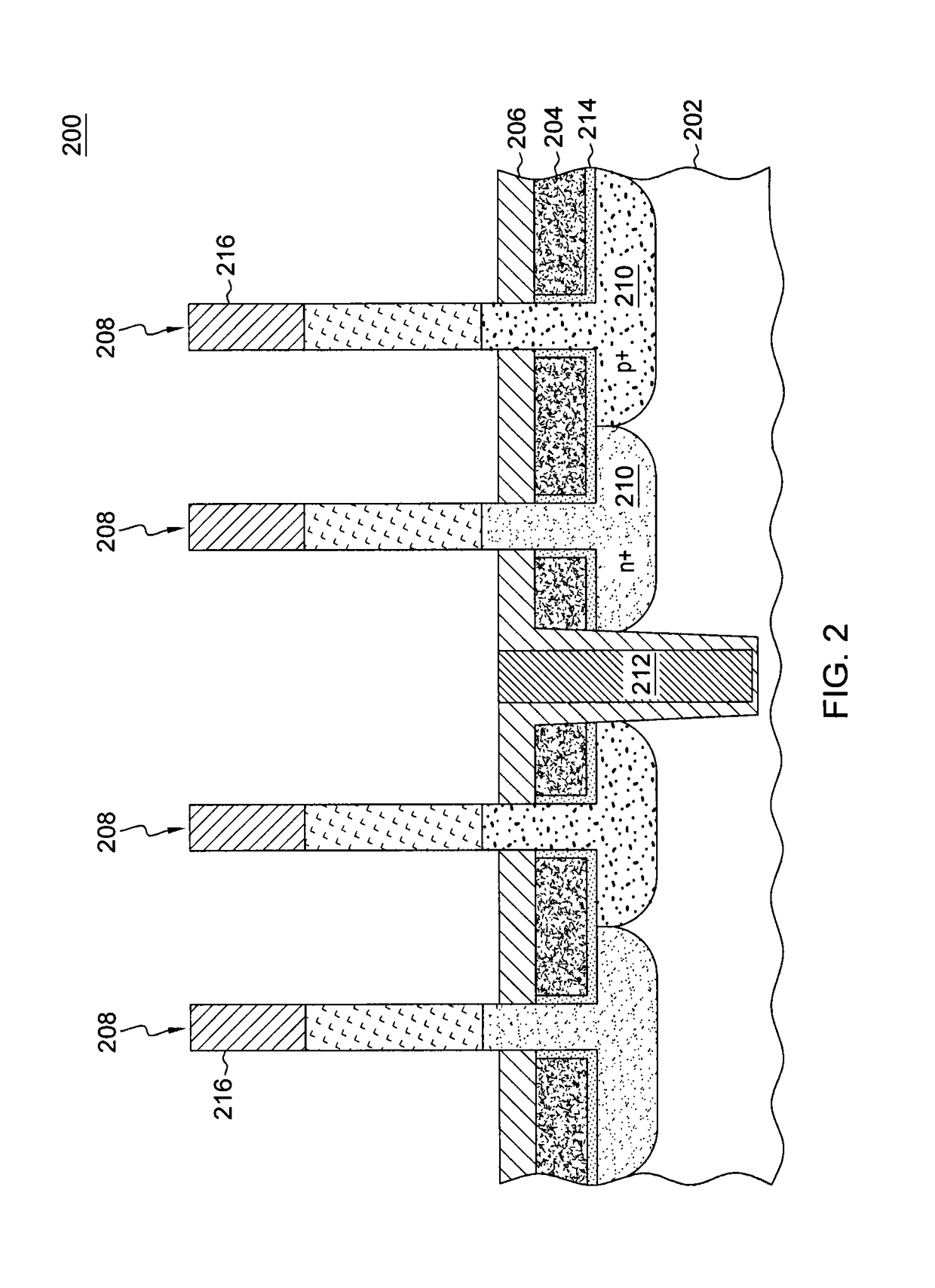

Semiconductor device including a vertical field effect transistor, having trenches, and a diode

Owner:HITACHI LTD +1

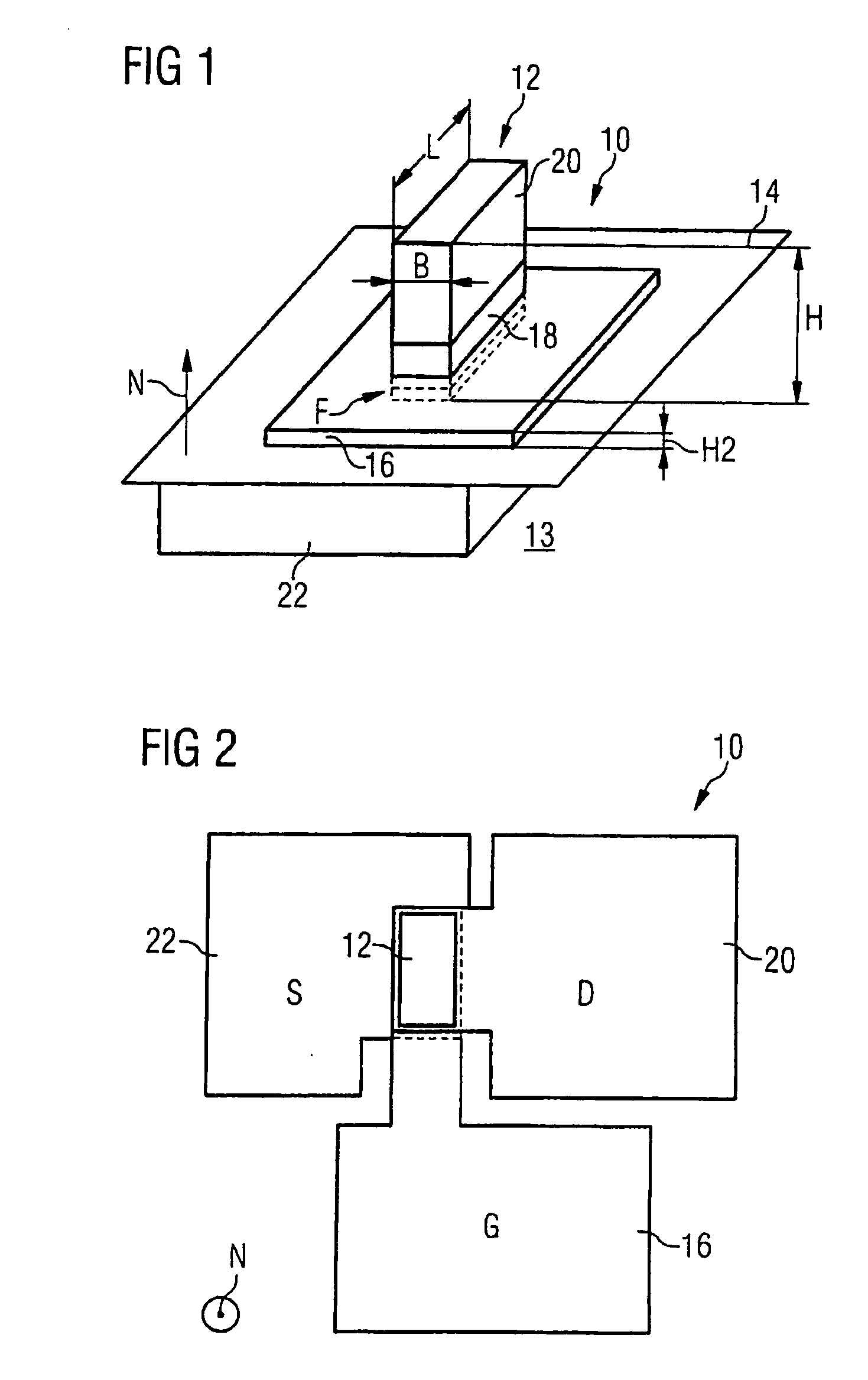

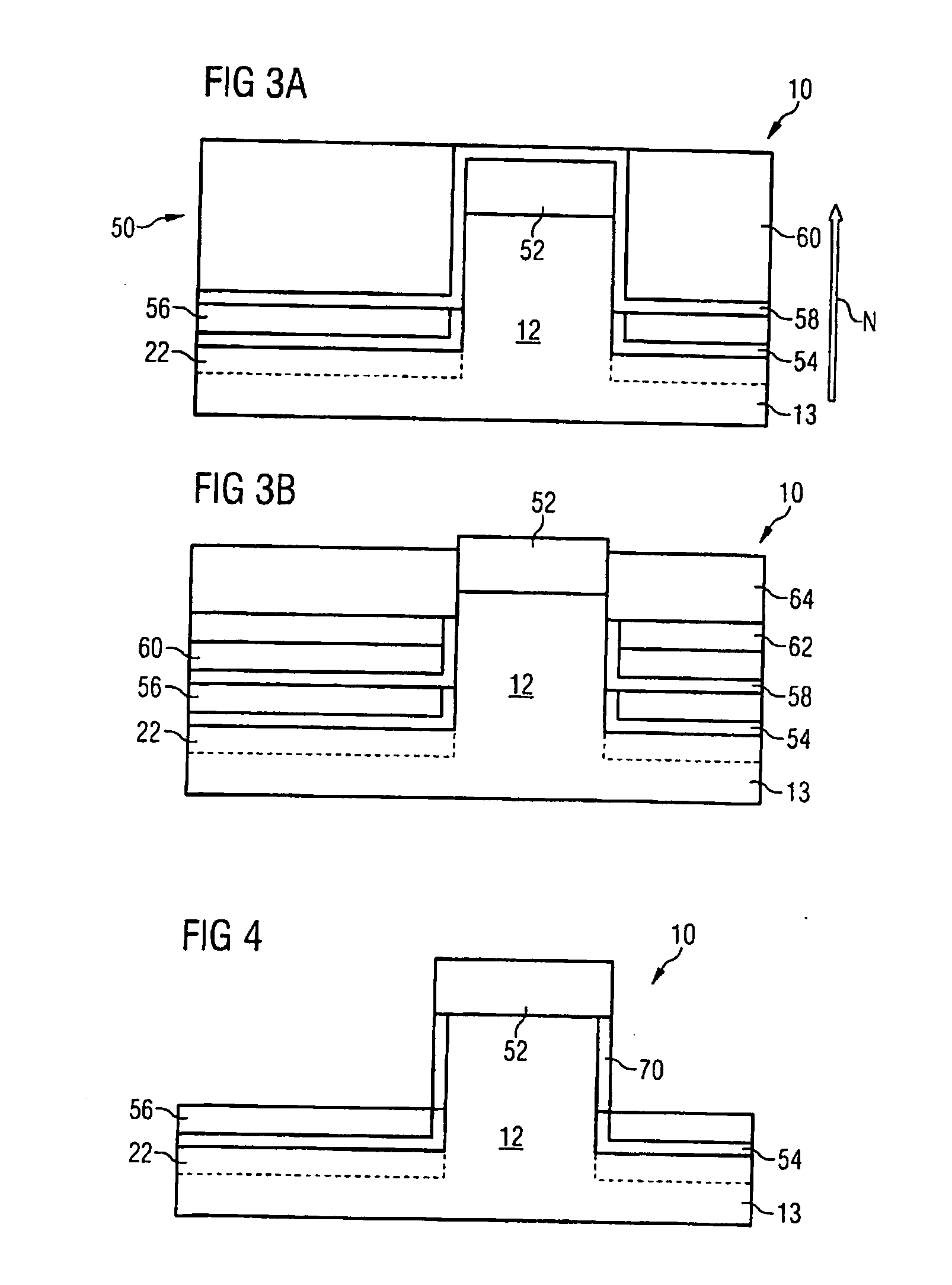

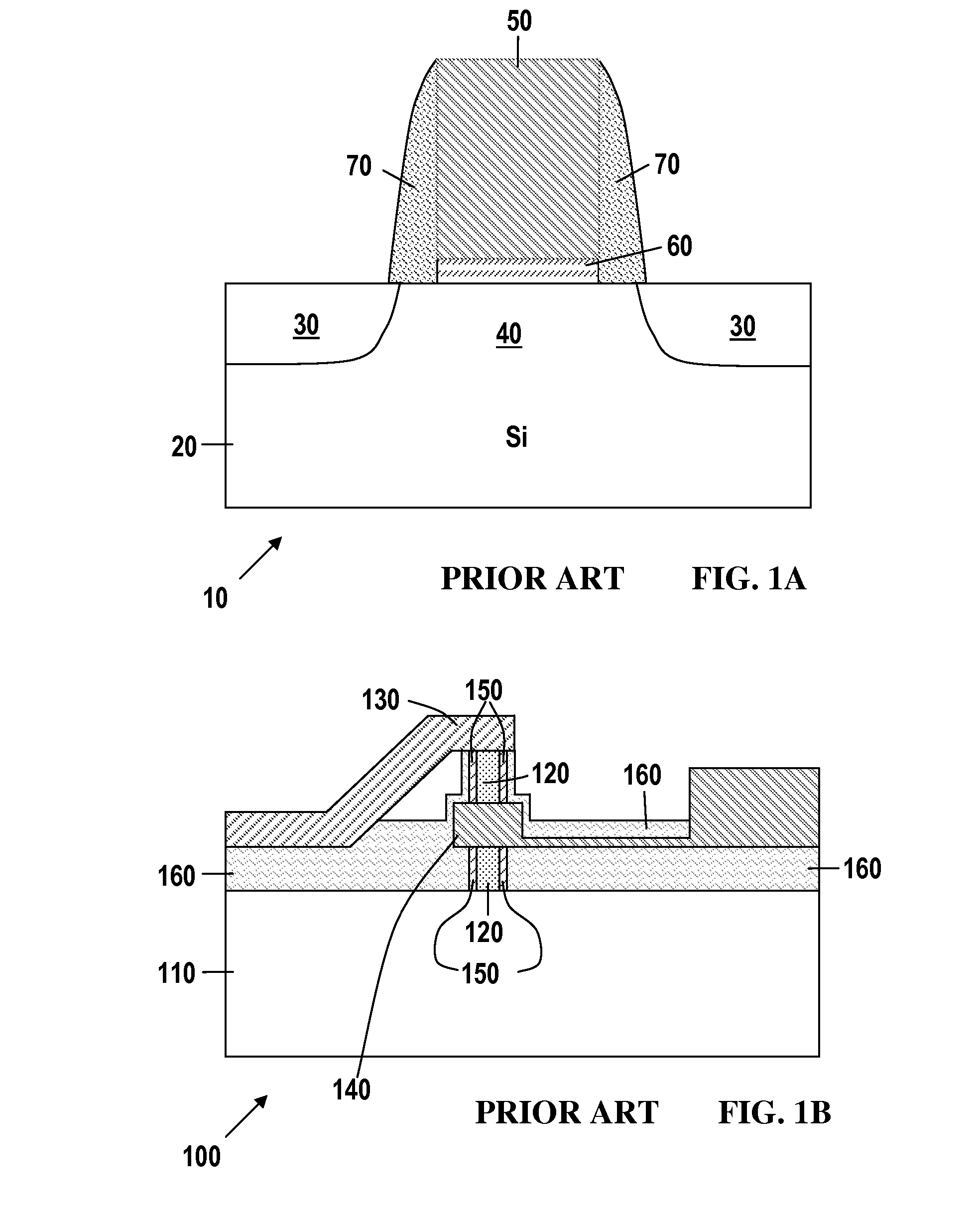

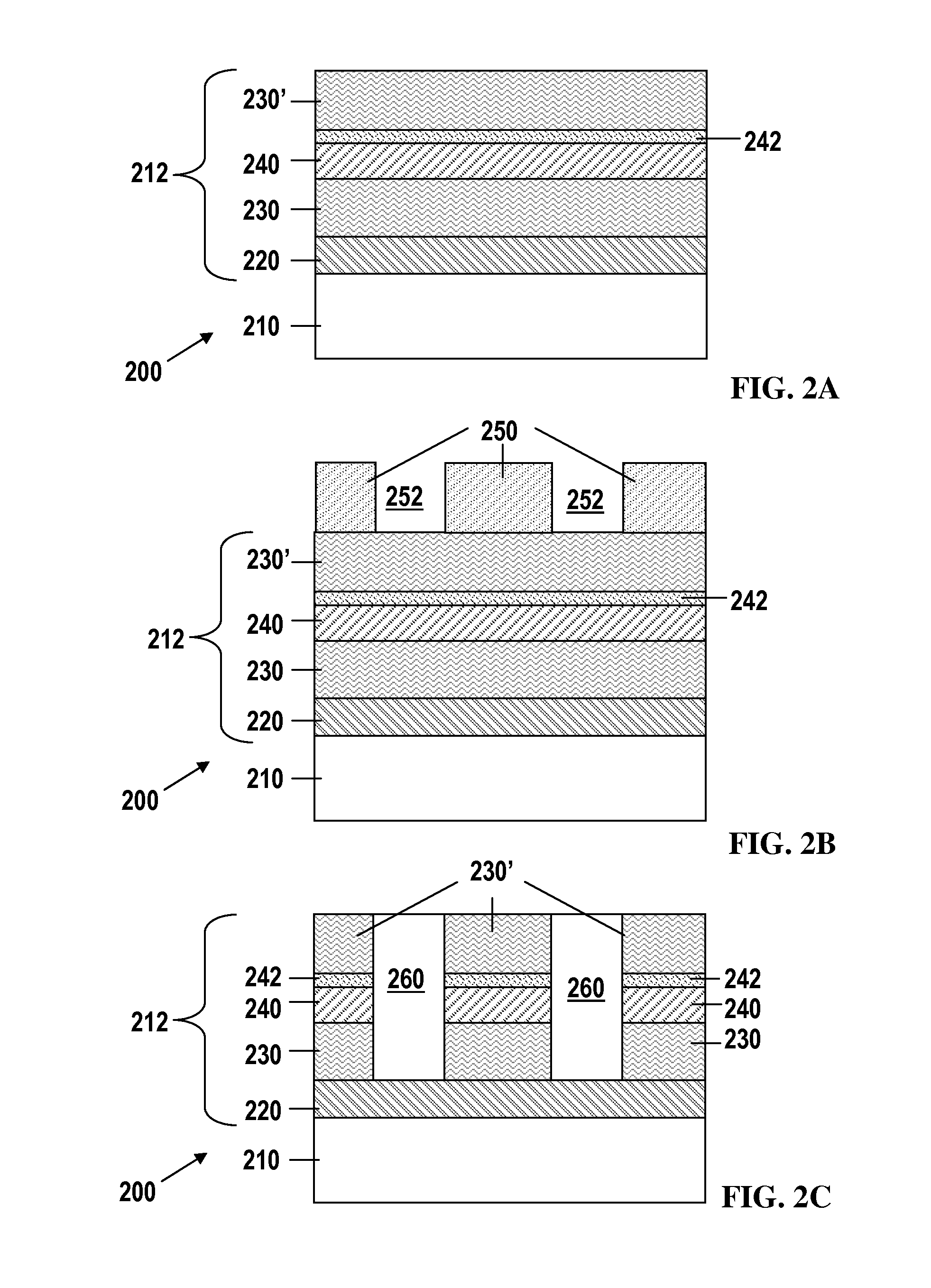

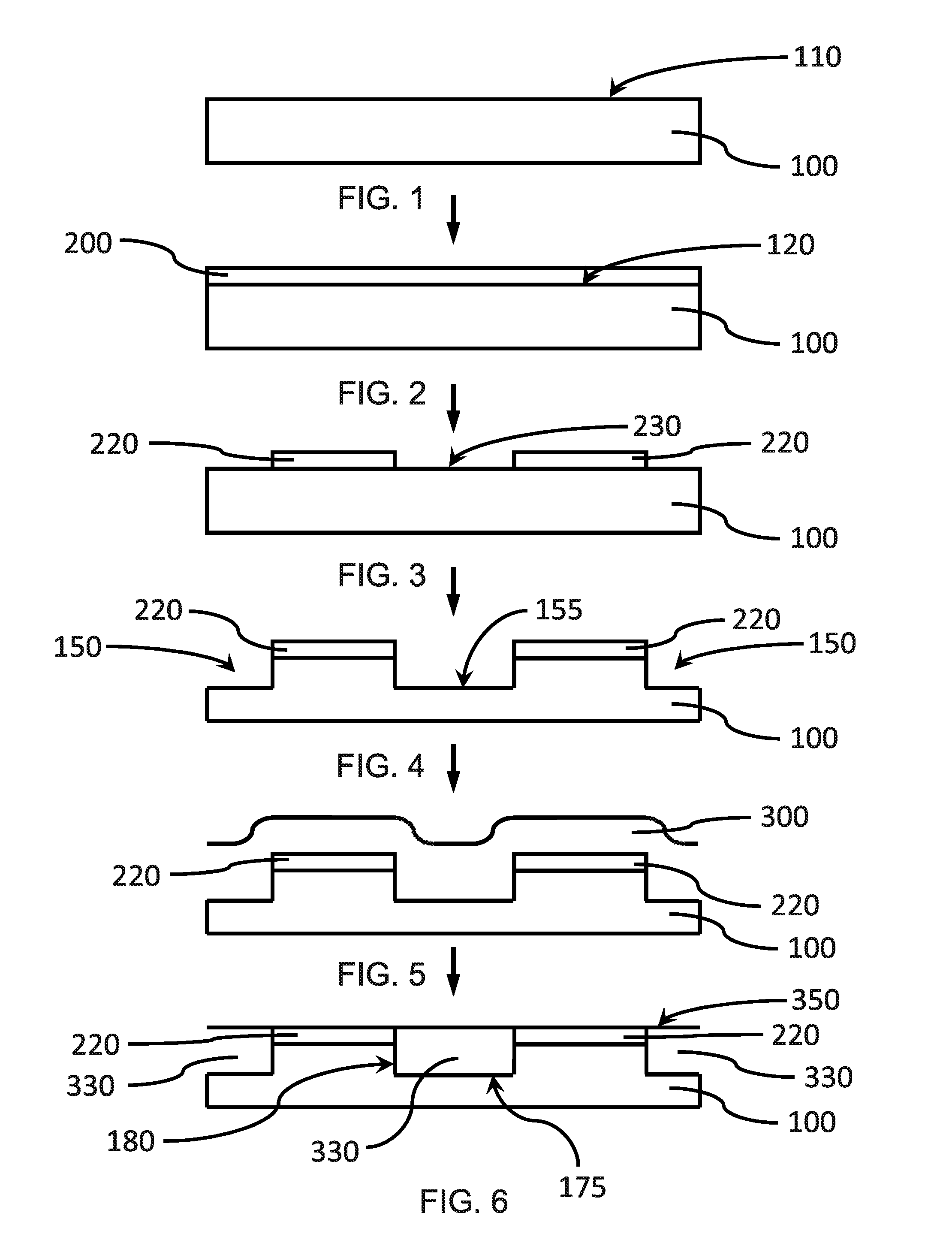

Method for producing a vertical field effect transistor

InactiveUS20070004149A1Improve electrical performanceEasy to produceTransistorSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

A method for producing a field effect transistor, in which a plurality of layers are in each case deposited, planarized and etched back, in particular a gate electrode layer, is disclosed. This method allows the manufacturing of transistors having outstanding electrical properties and having outstanding reproducibility.

Owner:INFINEON TECH AG

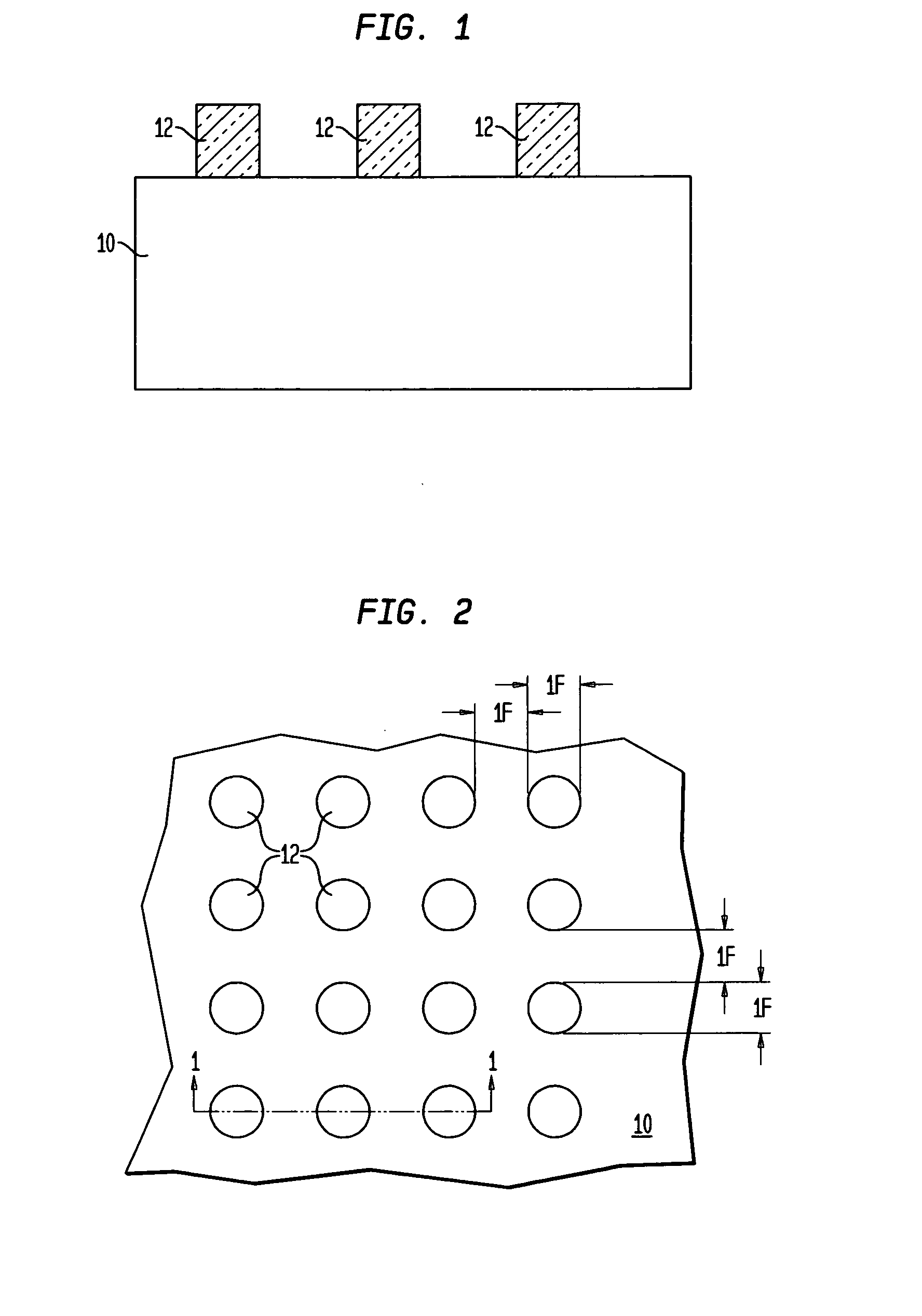

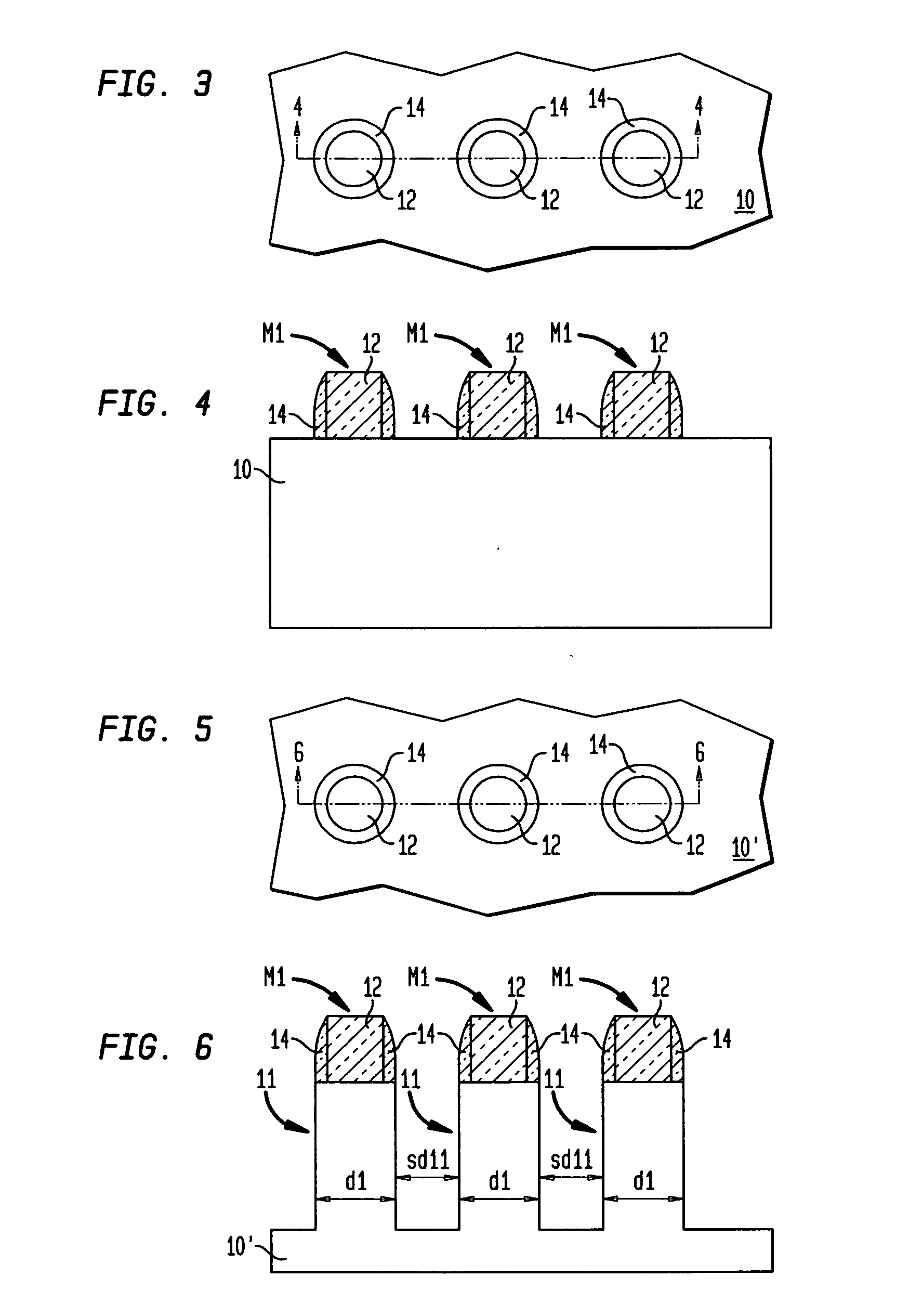

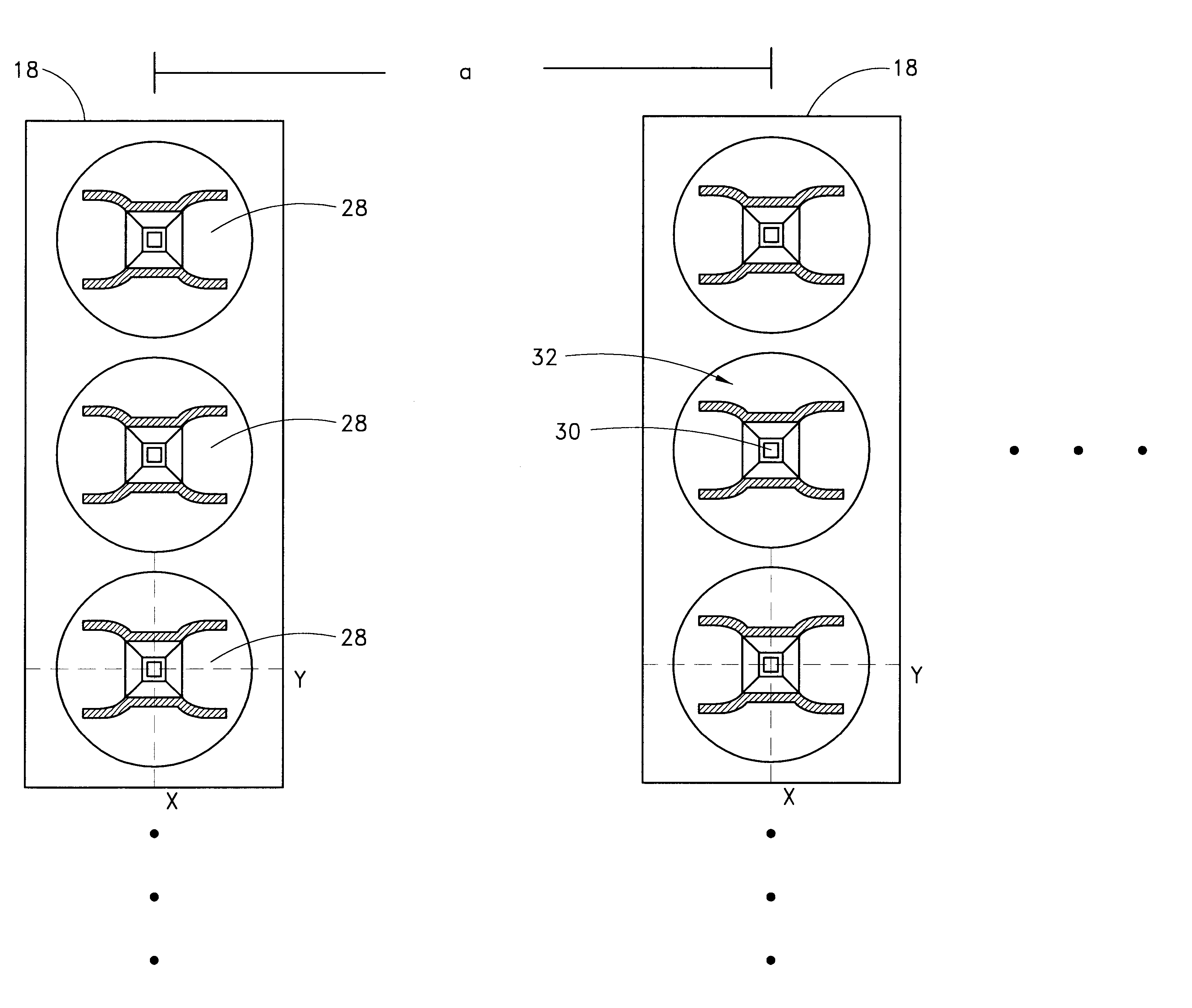

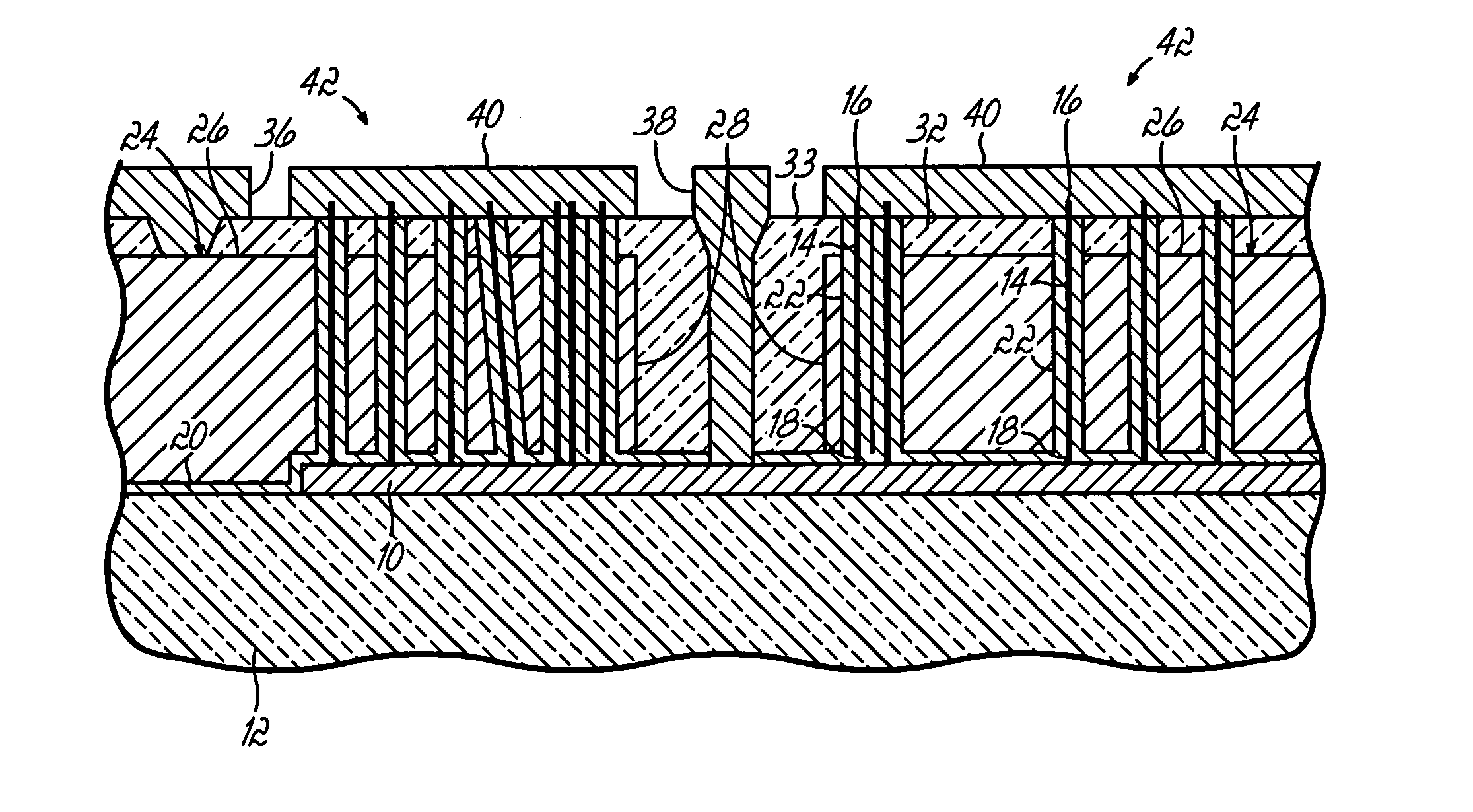

Vertical field effect transistor arrays and methods for fabrication thereof

Vertical field effect transistor semiconductor structures and methods for fabrication of the vertical field effect transistor semiconductor structures provide an array of semiconductor pillars. Each vertical portion of each semiconductor pillar in the array of semiconductor pillars has a linewidth greater than a separation distance to an adjacent semiconductor pillar. Alternatively, the array may comprise semiconductor pillars with different linewidths, optionally within the context of the foregoing linewidth and separation distance limitations. A method for fabricating the array of semiconductor pillars uses a minimally photolithographically dimensioned pillar mask layer that is annularly augmented with at least one spacer layer prior to being used as an etch mask.

Owner:TAIWAN SEMICON MFG CO LTD

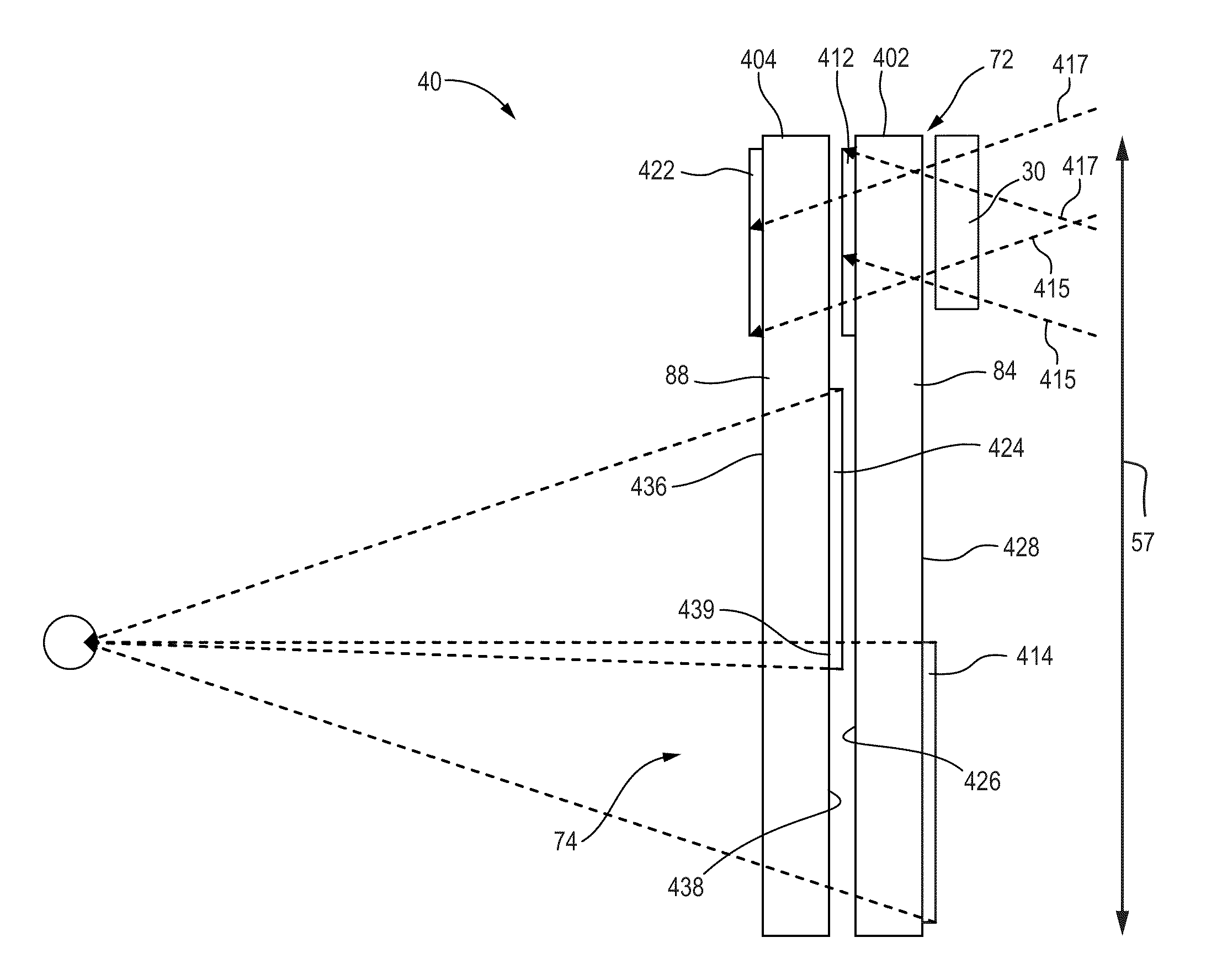

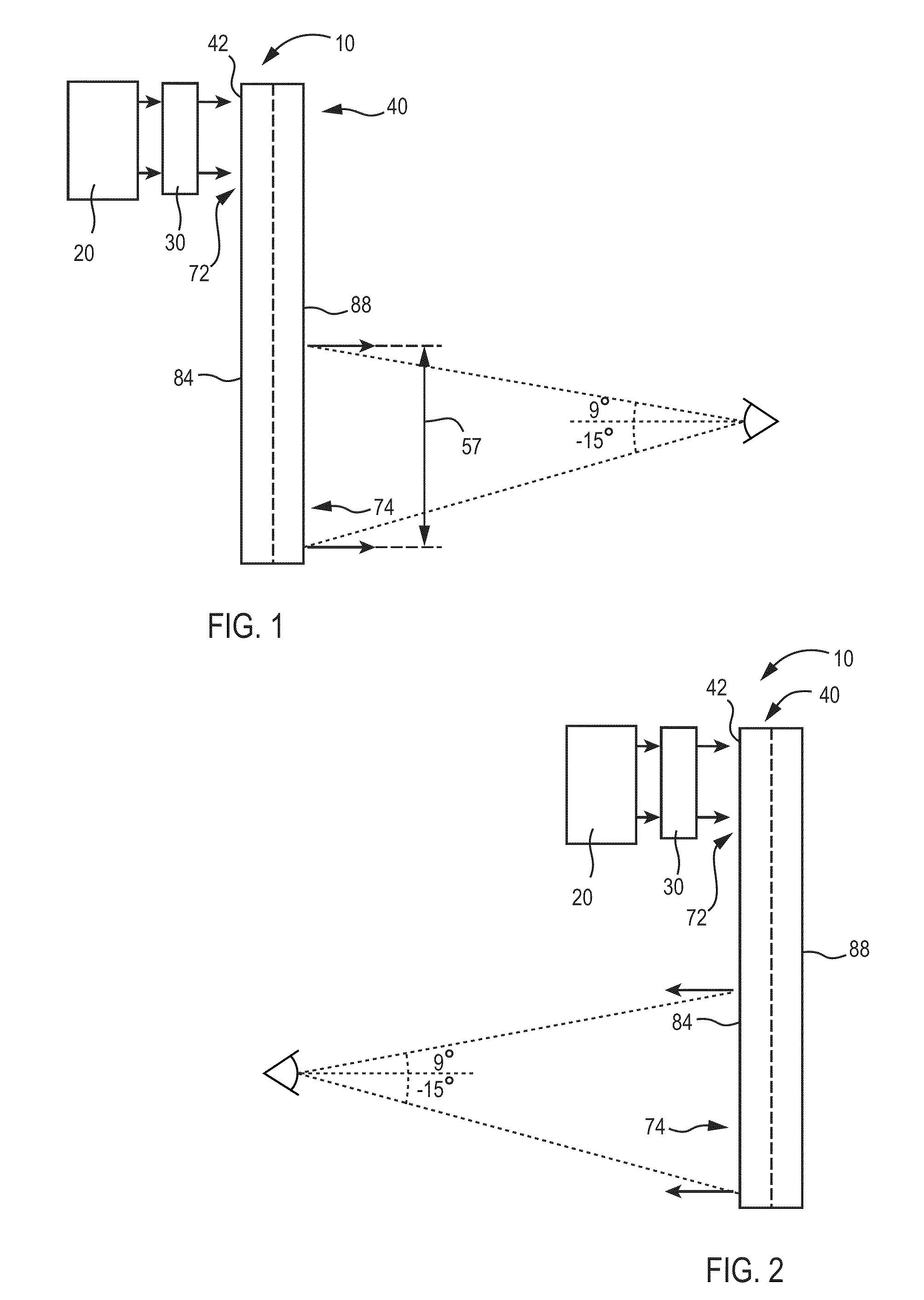

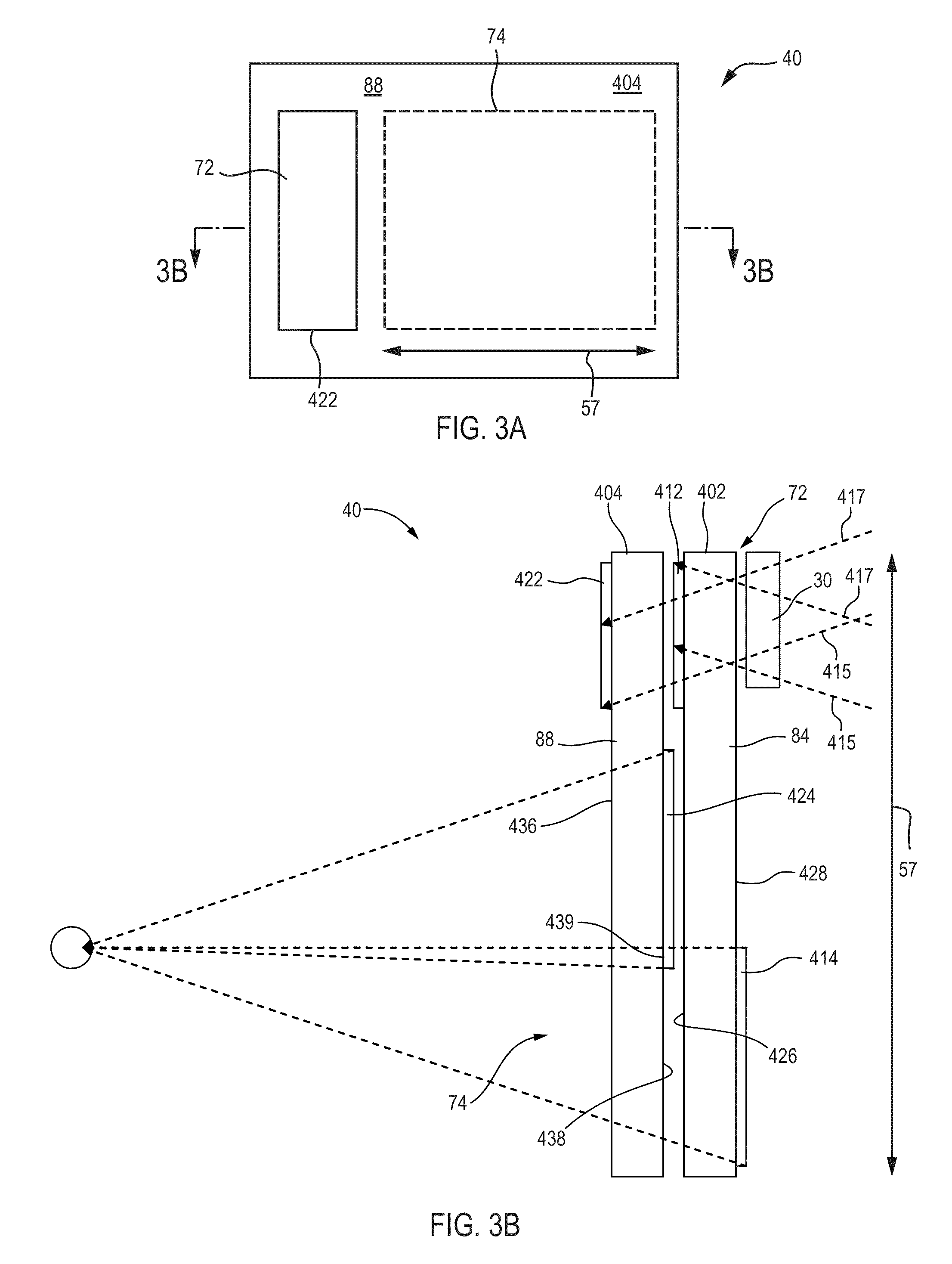

System for and method of extending vertical field of view in head up display utilizing a waveguide combiner

A Head Up Display can be utilized to find light from an energy source. The Head Up Display includes a first waveguide having a first input coupler and a first output coupler. The Head Up Display can also include a second waveguide having a second input coupler and a second output coupler. The first waveguide has a first major surface and the second waveguide has a second major surface, which are disposed approximately parallel to each other. The first waveguide and the second waveguide are positioned as a combiner and allowing viewing an outside feed and information from an image source. The first input coupler diffracts light in the first field of view into the first waveguide and light in a second field of view reaches the second input coupler and is diffracted into the second waveguide.

Owner:ROCKWELL COLLINS INC

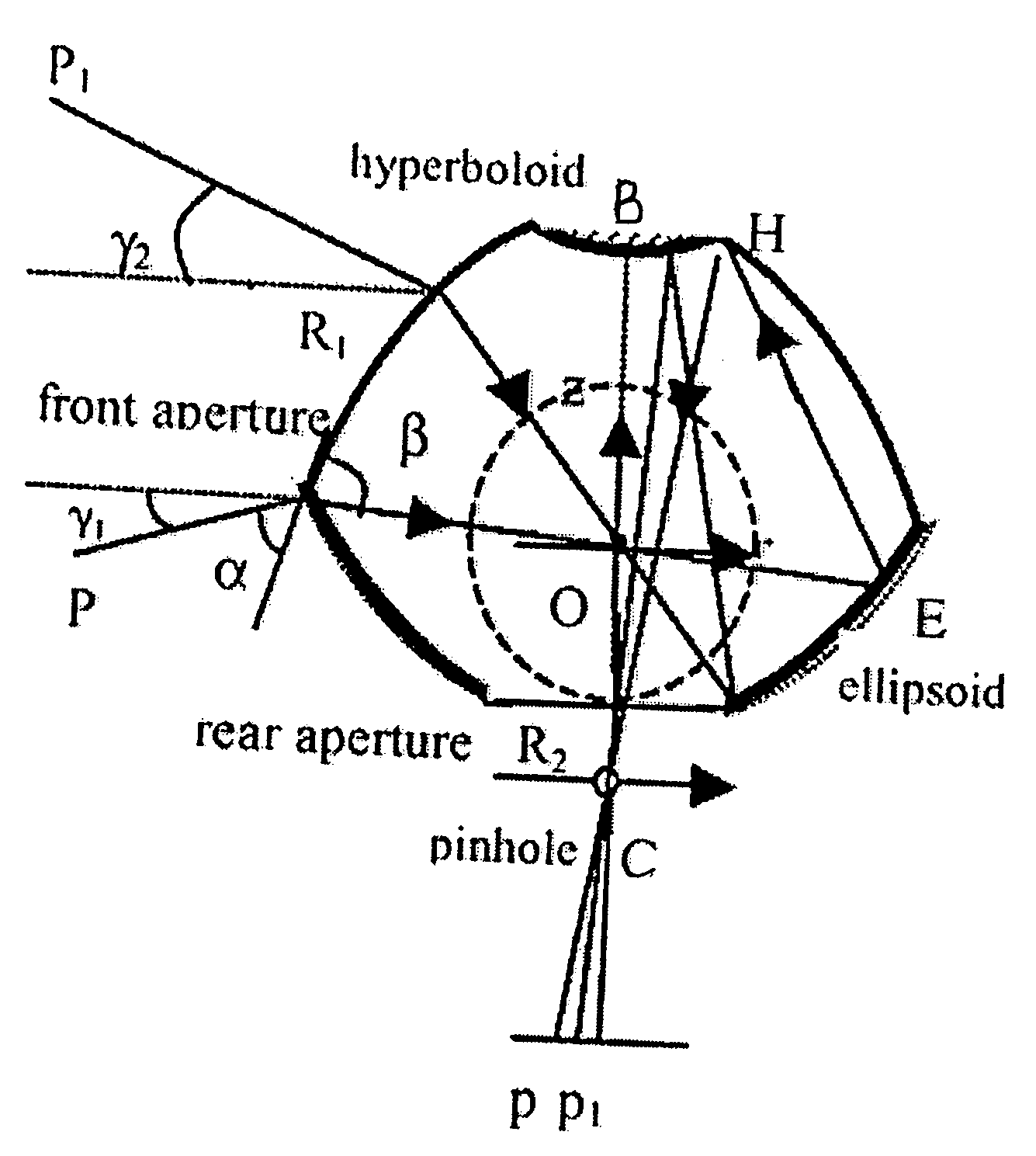

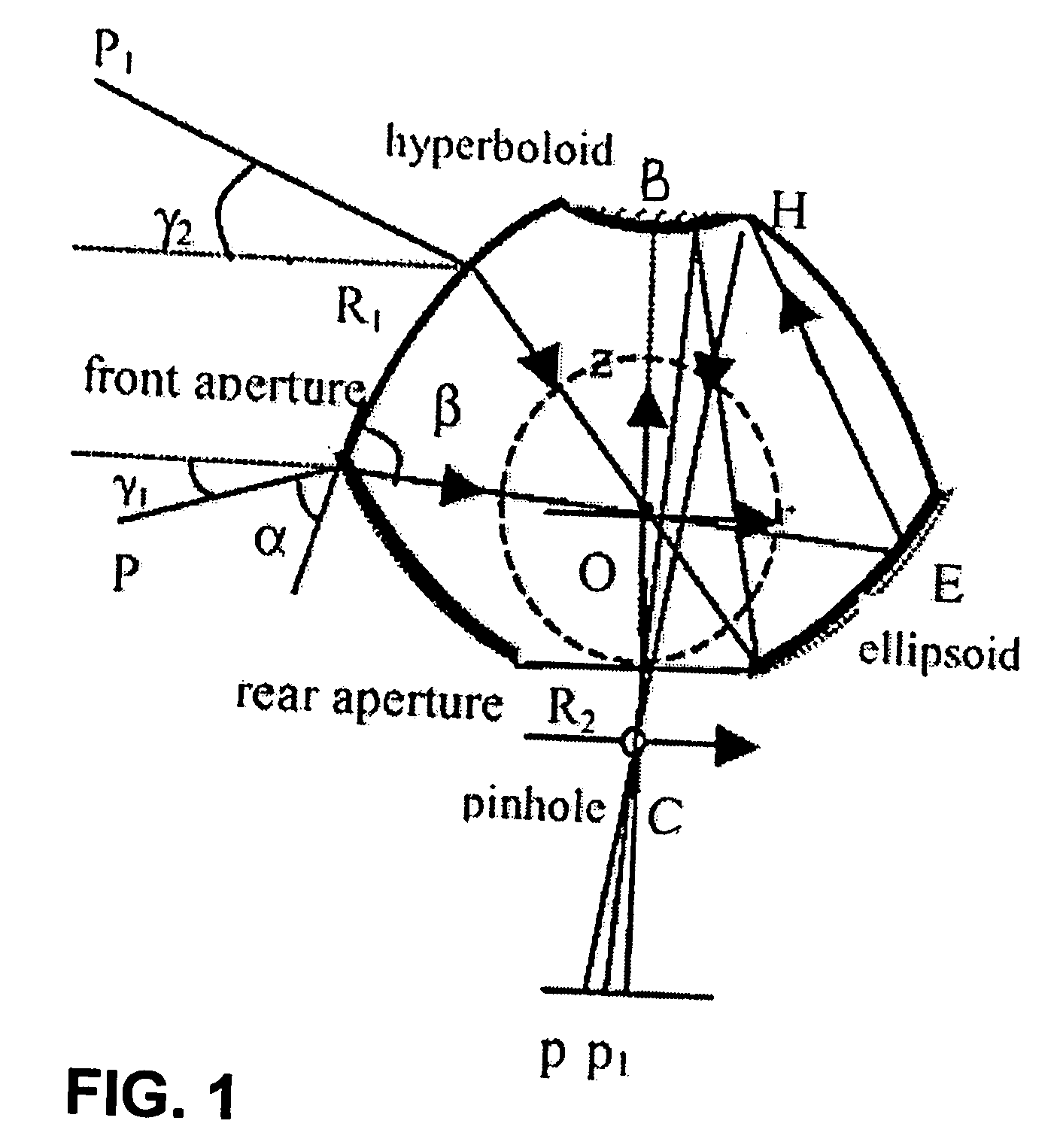

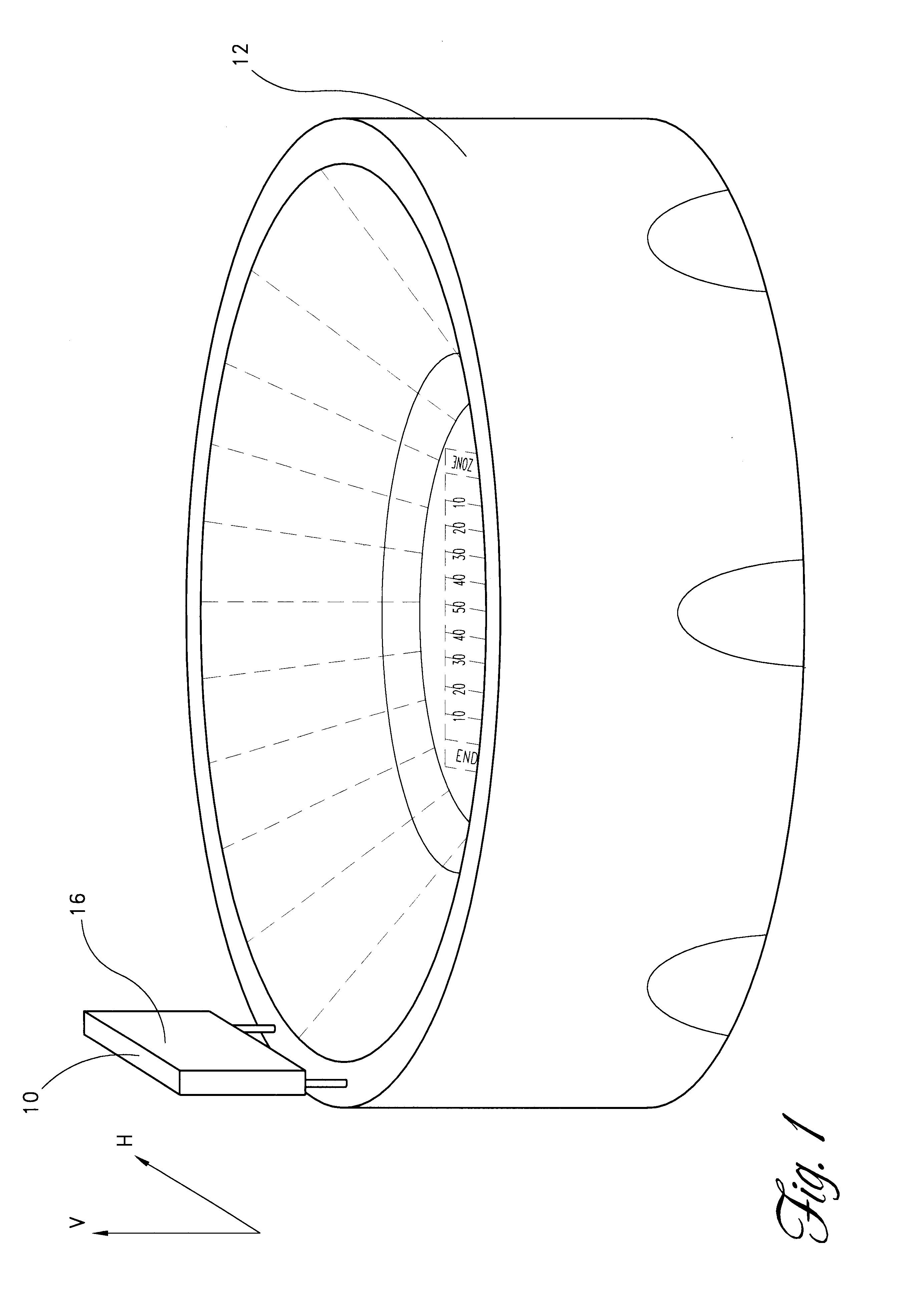

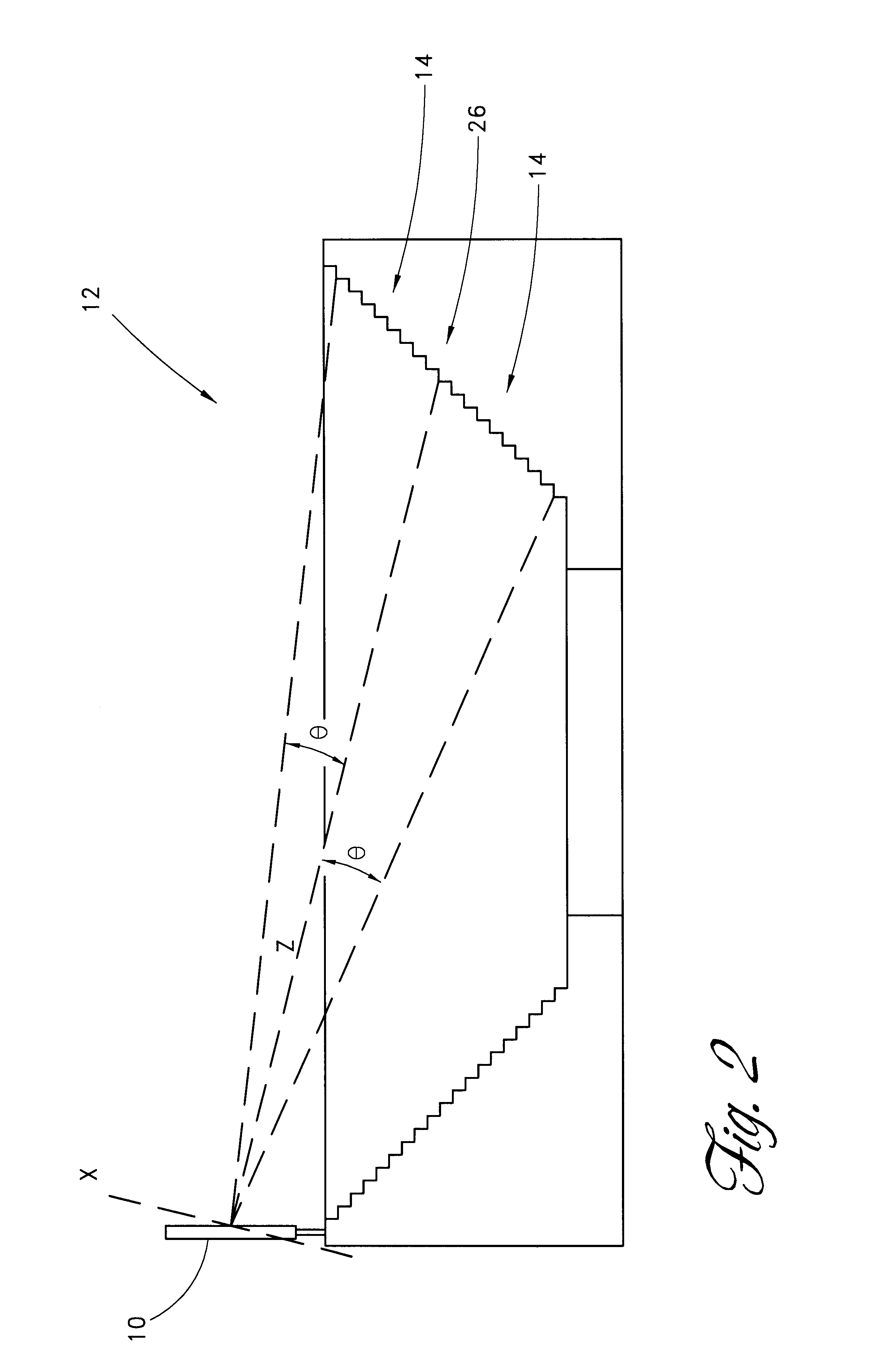

Panoramic video system with real-time distortion-free imaging

ActiveUS20060023105A1Minimizing software overheadHighly efficient regional transformationImage enhancementTelevision system detailsTime distortionGraphic card

A panoramic annular lens system (PAL), a unitary video camera and a PC-based software system that unwraps a 360° video image into a seamless, distortion free horizontal image image in real time. The PAL system of the preferred embodiment has a 360° horizontal field of view and a 90° vertical field of view in a 40 mm diameter compact package. The invention is not limited to any particular type of lens system. In fact, there are numerous lens systems for providing a 360° panoramic view. The video camera may be a CCD or CMOS based device having a pixel resolution of either 1280×1024 (high resolution) or 720×480 (NTSC). The unwrapping system is a radiometric ray tracing program carried out using a computer's graphics card capabilities to produce highly efficient regional transformation while minimizing software overhead. The result is real time, high resolution 30 fps conversion from a spherical distorted image to a flat panoramic image in Cartesian coordinates.

Owner:PHYSICAL OPTICS CORP

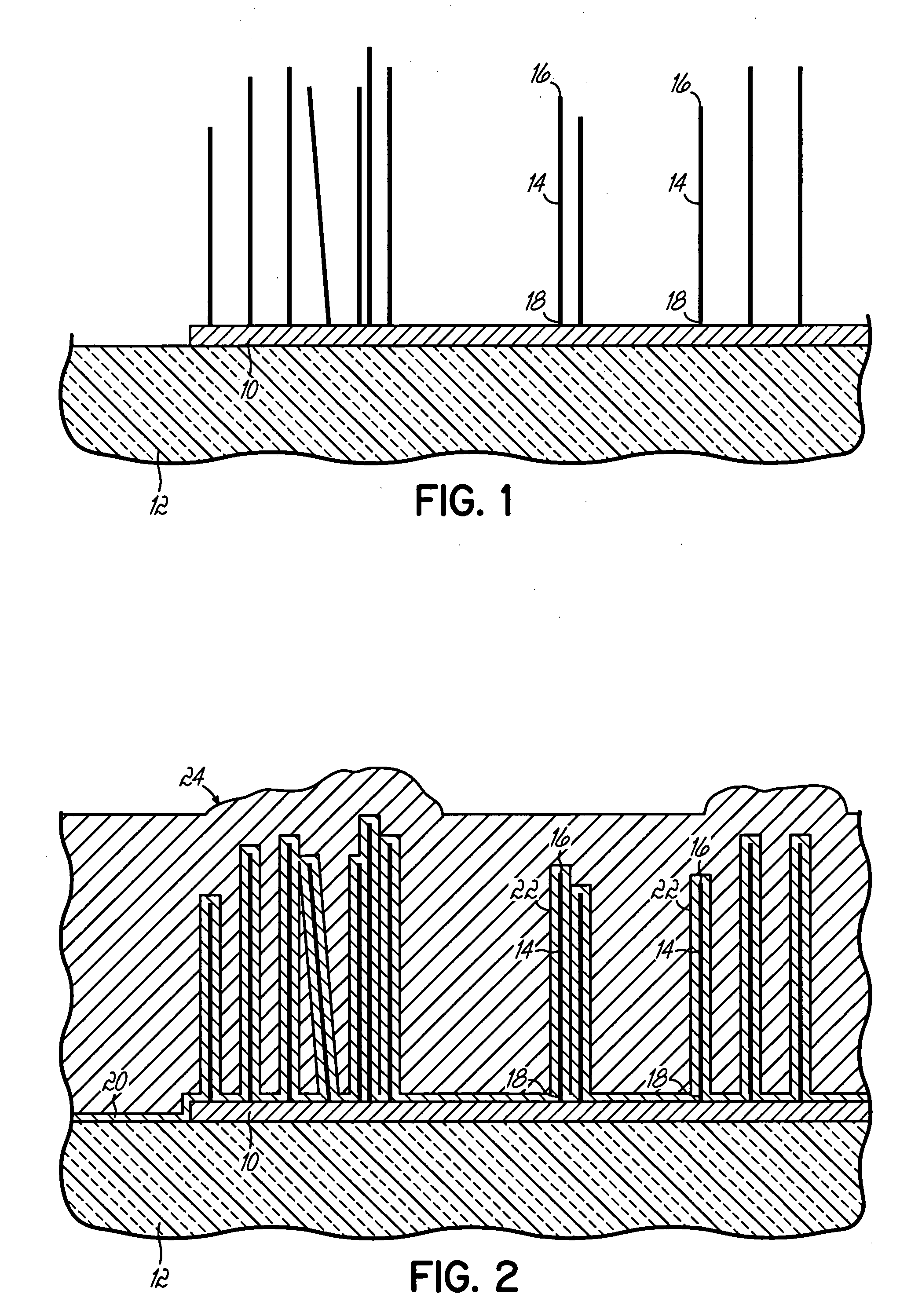

Methods of manufacture of vertical nanowire fet devices

ActiveUS20110012085A1Improve controllabilityIncrease flexibilityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

A vertical Field Effect Transistor (FET) comprising a vertical semiconductor nanowire is formed by the following steps. Create a columnar pore in a bottom dielectric layer formed on a bottom electrode. Fill the columnar pore by plating a vertical semiconductor nanowire having a bottom end contacting the bottom electrode. The semiconductor nanowire forms an FET device with a FET channel region between a source region and a drain region formed in distal ends of the vertical semiconductor nanowire. Form a gate dielectric layer around the channel region of the vertical semiconductor nanowire and then form a gate electrode around the gate dielectric layer. Form a top electrode contacting a top end of the vertical semiconductor nanowire.

Owner:GLOBALFOUNDRIES US INC

LED light source with field-of-view-controlling optics

Pixels for a large video display which employs solid-state emitters, such as colored light emitting diodes, as light source are formed by outfitting each colored solid state emitter within the pixel with an individually tailored miniature intensity-enhancing optical system. Each of these miniature optical systems comprises a set of four wide field-of-view Lambertian reflectors 34, a pair of narrow field-of-view Lambertian reflectors 36, and a beam-shaping lens 38. The miniature intensity-enhancing optical system can be specifically designed to restrict emission in the vertical field-of-view, while providing a Lambertian intensity dependence throughout an unrestricted horizontal view. For example, the field-of-view in the vertical direction may be limited to about .+-.30.degree. while the field-of-view is about .+-.90.degree. in the horizontal direction.

Owner:TELEDYNE LIGHTING & DISPLAY PRODS

Panoramic video system with real-time distortion-free imaging

ActiveUS7336299B2Highly efficient regional transformationMinimize overheadImage enhancementTelevision system detailsTime distortionGraphic card

A panoramic annular lens system (PAL), a unitary video camera and a PC-based software system that unwraps a 360° video image into a seamless, distortion free horizontal image image in real time. The PAL system of the preferred embodiment has a 360° horizontal field of view and a 90° vertical field of view in a 40 mm diameter compact package. The invention is not limited to any particular type of lens system. In fact, there are numerous lens systems for providing a 360° panoramic view. The video camera may be a CCD or CMOS based device having a pixel resolution of either 1280×1024 (high resolution) or 720×480 (NTSC). The unwrapping system is a radiometric ray tracing program carried out using a computer's graphics card capabilities to produce highly efficient regional transformation while minimizing software overhead. The result is real time, high resolution 30 fps conversion from a spherical distorted image to a flat panoramic image in Cartesian coordinates.

Owner:PHYSICAL OPTICS CORP

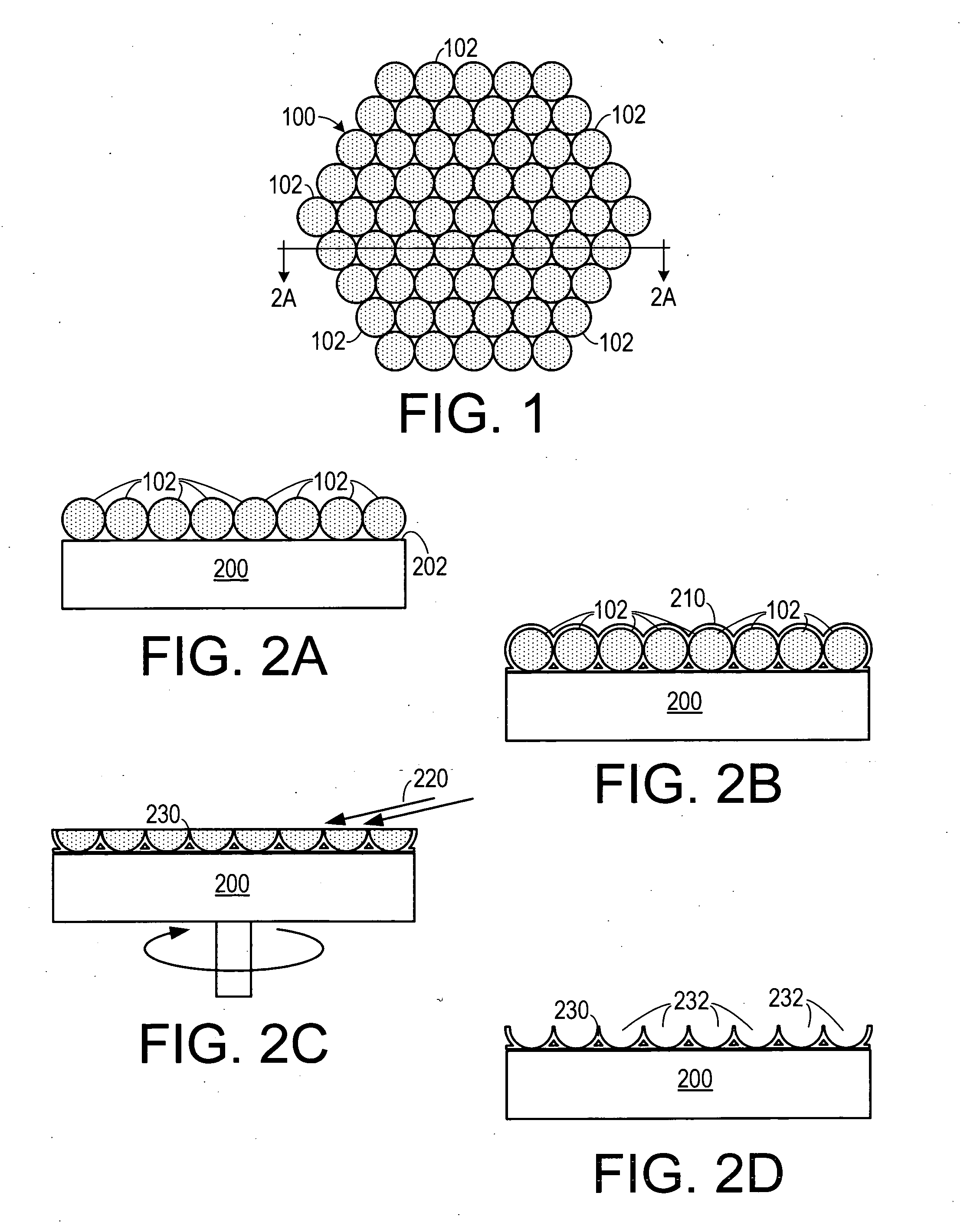

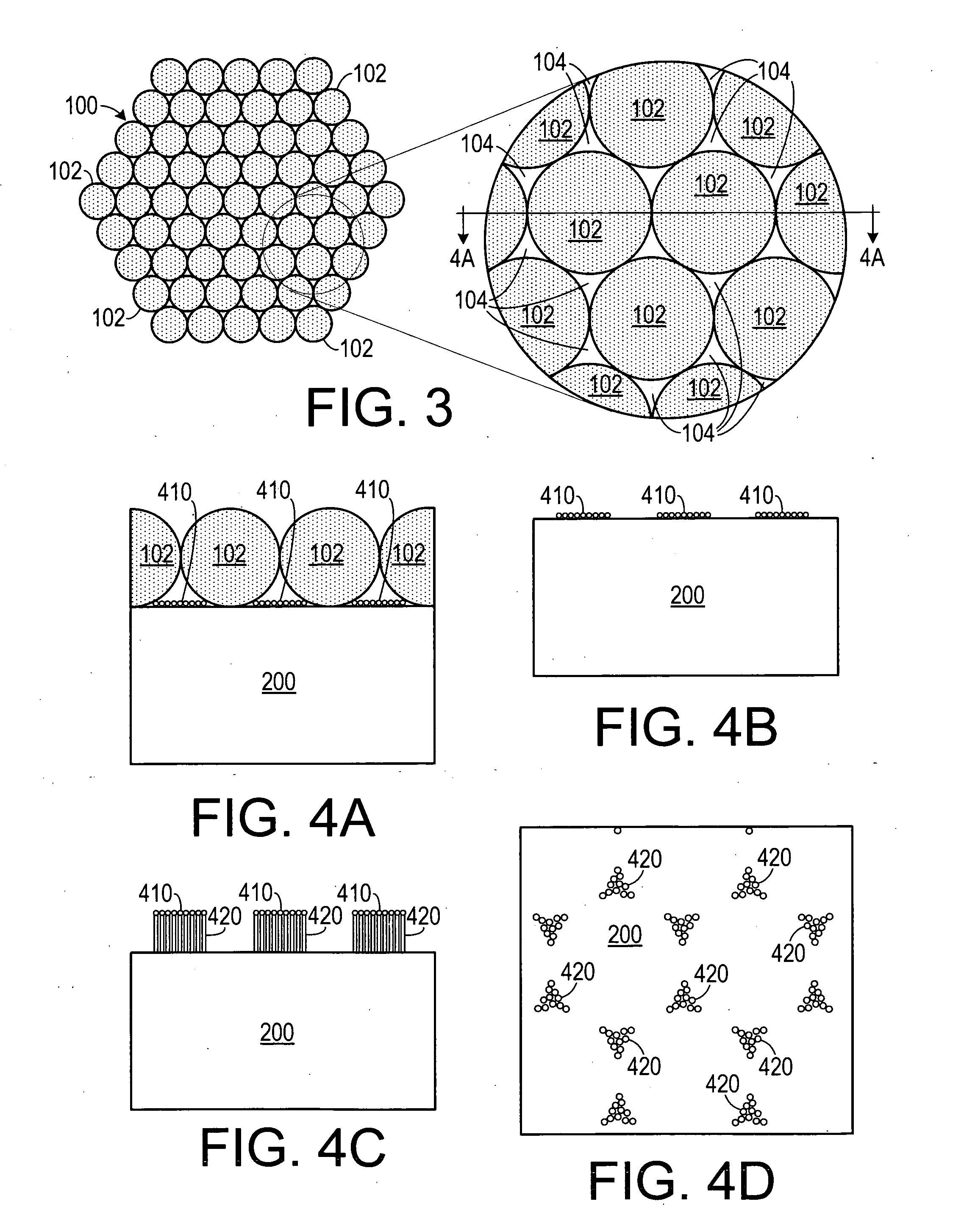

Large scale patterned growth of aligned one-dimensional nanostructures

A method of making nanostructures using a self-assembled monolayer of organic spheres is disclosed. The nanostructures include bowl-shaped structures and patterned elongated nanostructures. A bowl-shaped nanostructure with a nanorod grown from a conductive substrate through the bowl-shaped nanostructure may be configured as a field emitter or a vertical field effect transistor. A method of separating nanoparticles of a desired size employs an array of bowl-shaped structures.

Owner:GEORGIA TECH RES CORP

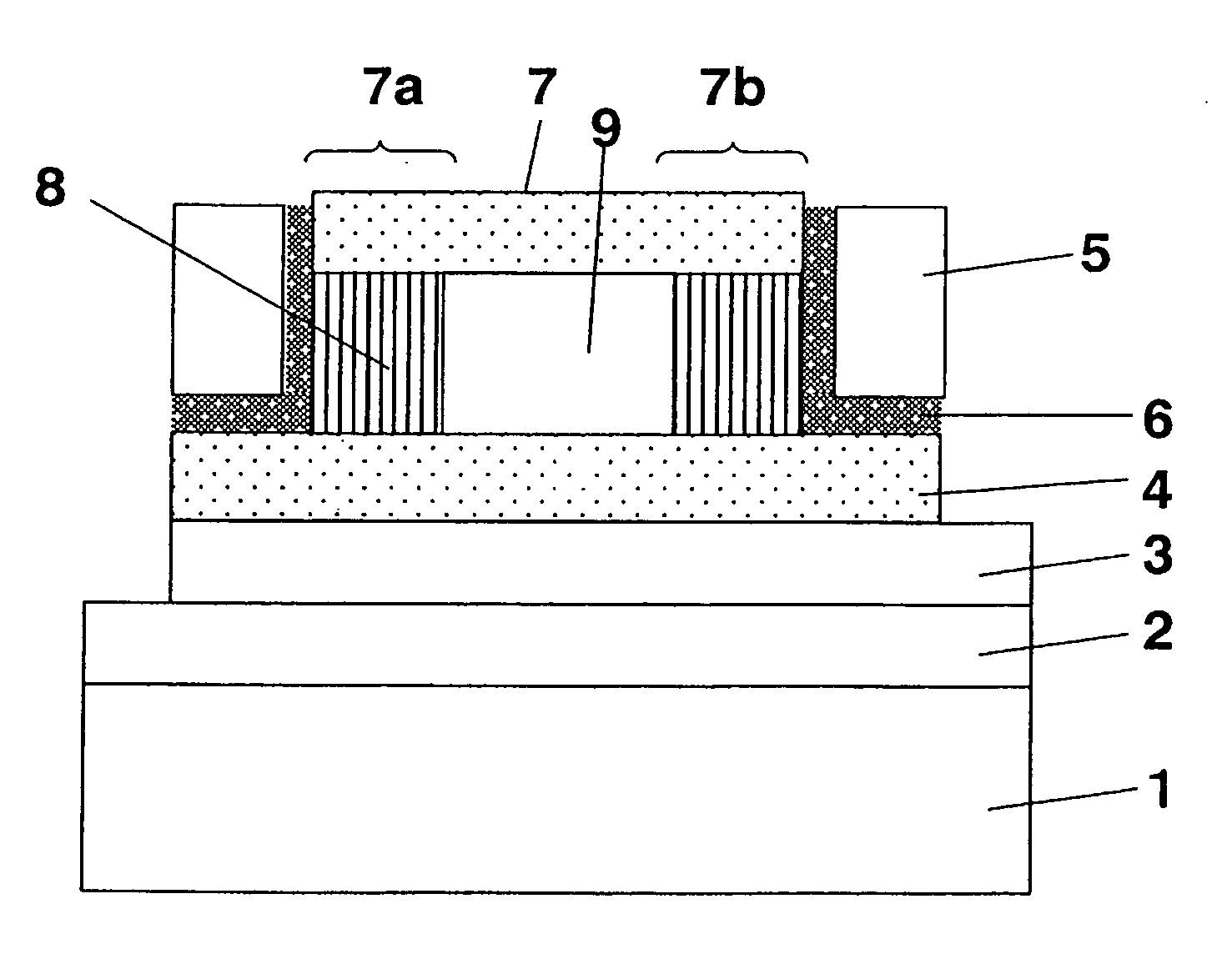

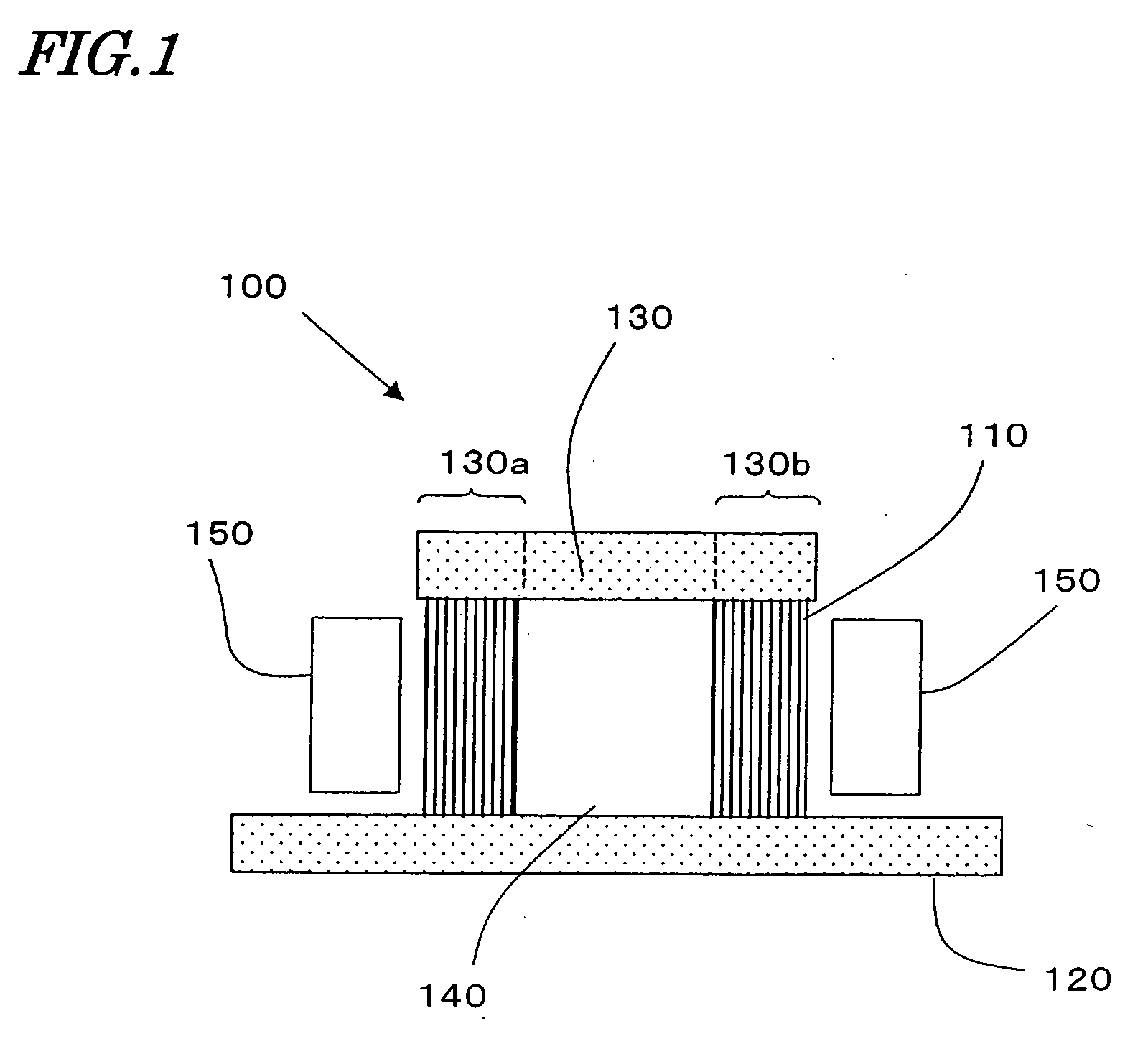

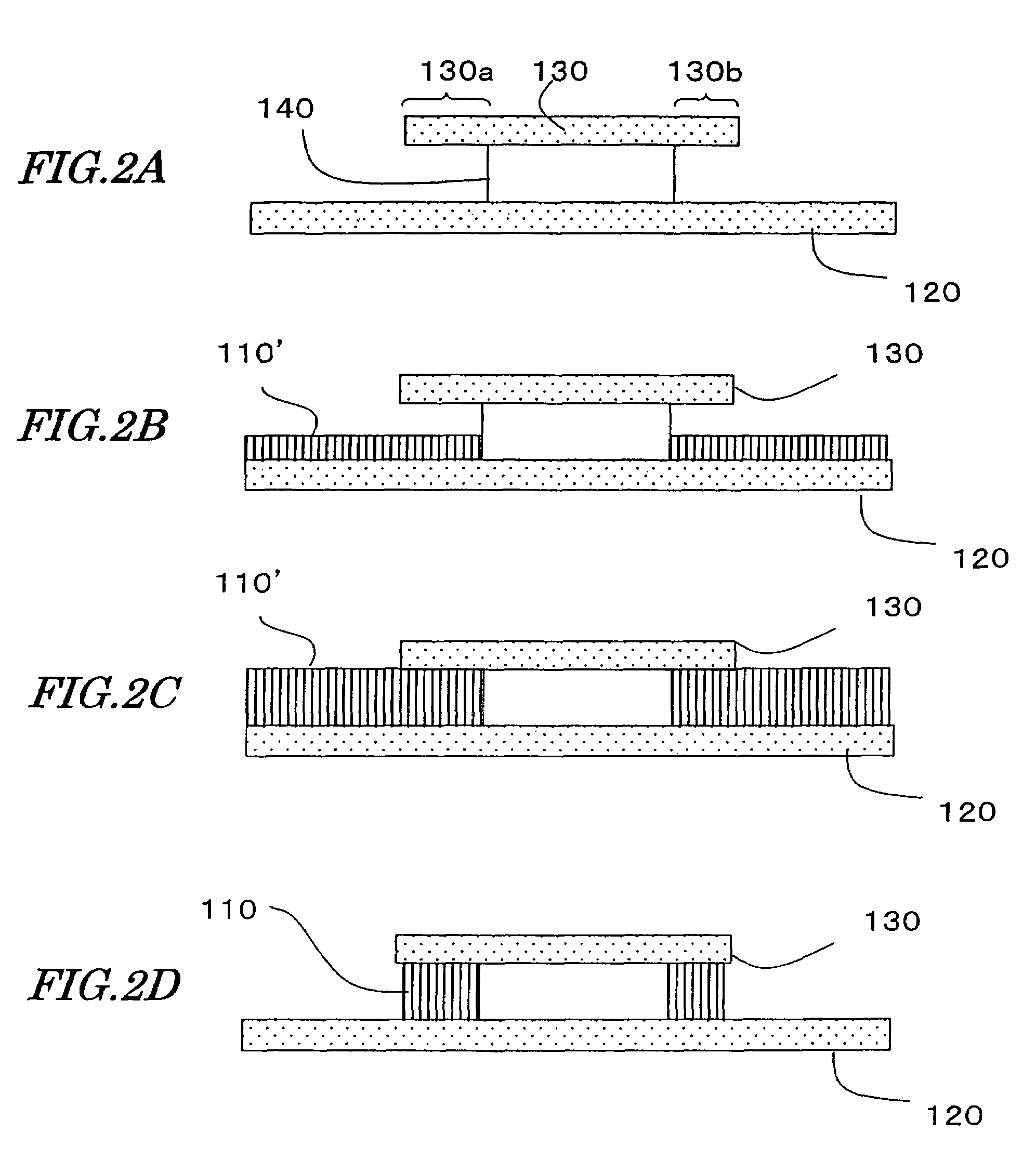

Vertical field effect transistor and method for fabricating the same

A vertical field effect transistor includes: an active region with a bundle of linear structures functioning as a channel region where electric carriers are transported; a lower electrode, connected to the bottom of the active region and functioning as one of source and drain regions; an upper electrode, connected to the top of the active region and functioning as the other of the source and drain regions; a gate electrode for controlling the electric conductivity of at least a portion of the bundle of linear structures included in the active region; and a gate insulating film arranged between the active region and the gate electrode to electrically isolate the gate electrode from the bundle of linear structures. The transistor further includes a dielectric portion between the upper and lower electrodes. The upper electrode is located over the lower electrode with the dielectric portion interposed and includes an overhanging portion that sticks out laterally from over the dielectric portion. The active region is located right under the overhanging portion of the upper electrode.

Owner:JOLED INC

Vertical nanotube semiconductor device structures and methods of forming the same

Vertical device structures incorporating at least one nanotube and methods for fabricating such device structures by chemical vapor deposition. Each nanotube is grown by chemical vapor deposition catalyzed by a catalyst pad and encased in a coating of a dielectric material. Vertical field effect transistors may be fashioned by forming a gate electrode about the encased nanotubes such that the encased nanotubes extend vertically through the thickness of the gate electrode. Capacitors may be fashioned in which the encased nanotubes and the corresponding catalyst pad bearing the encased nanotubes forms one capacitor plate.

Owner:GLOBALFOUNDRIES INC

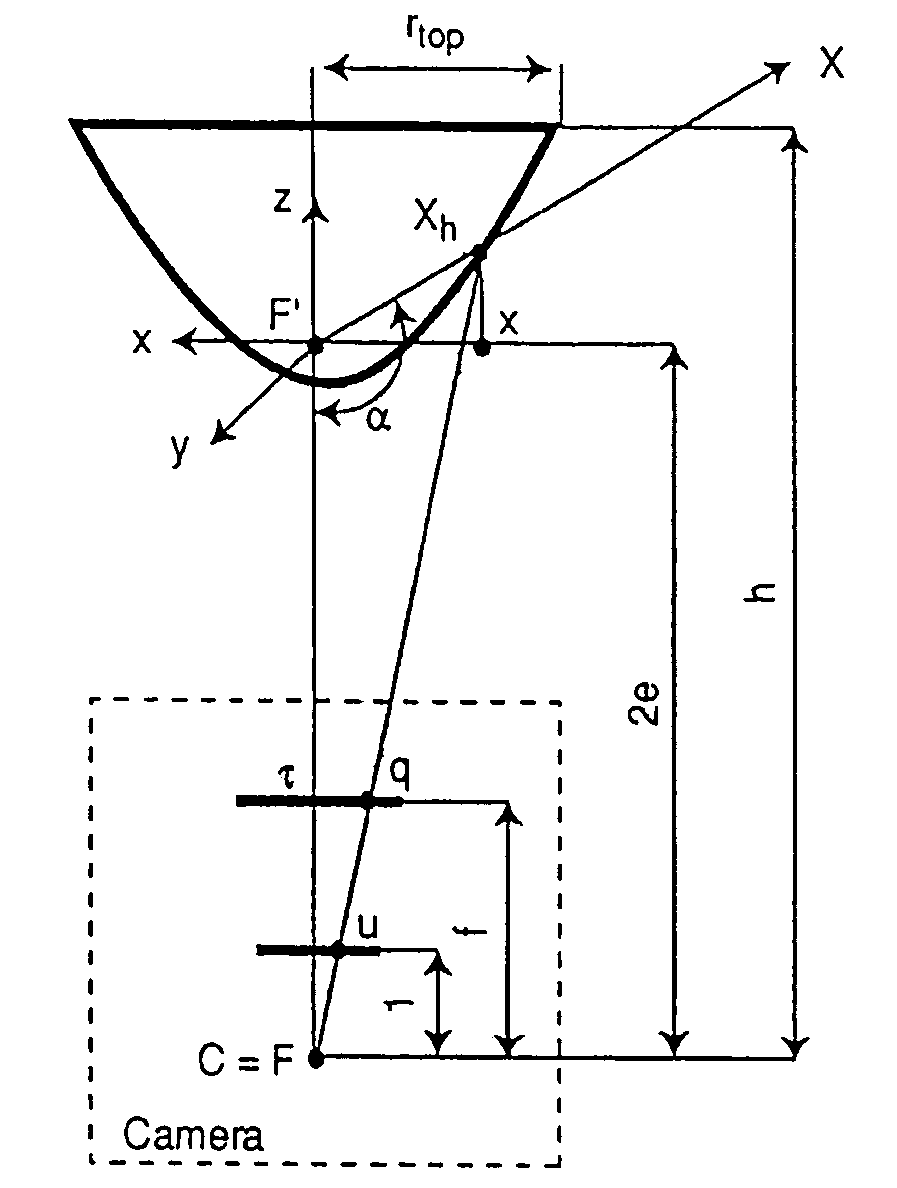

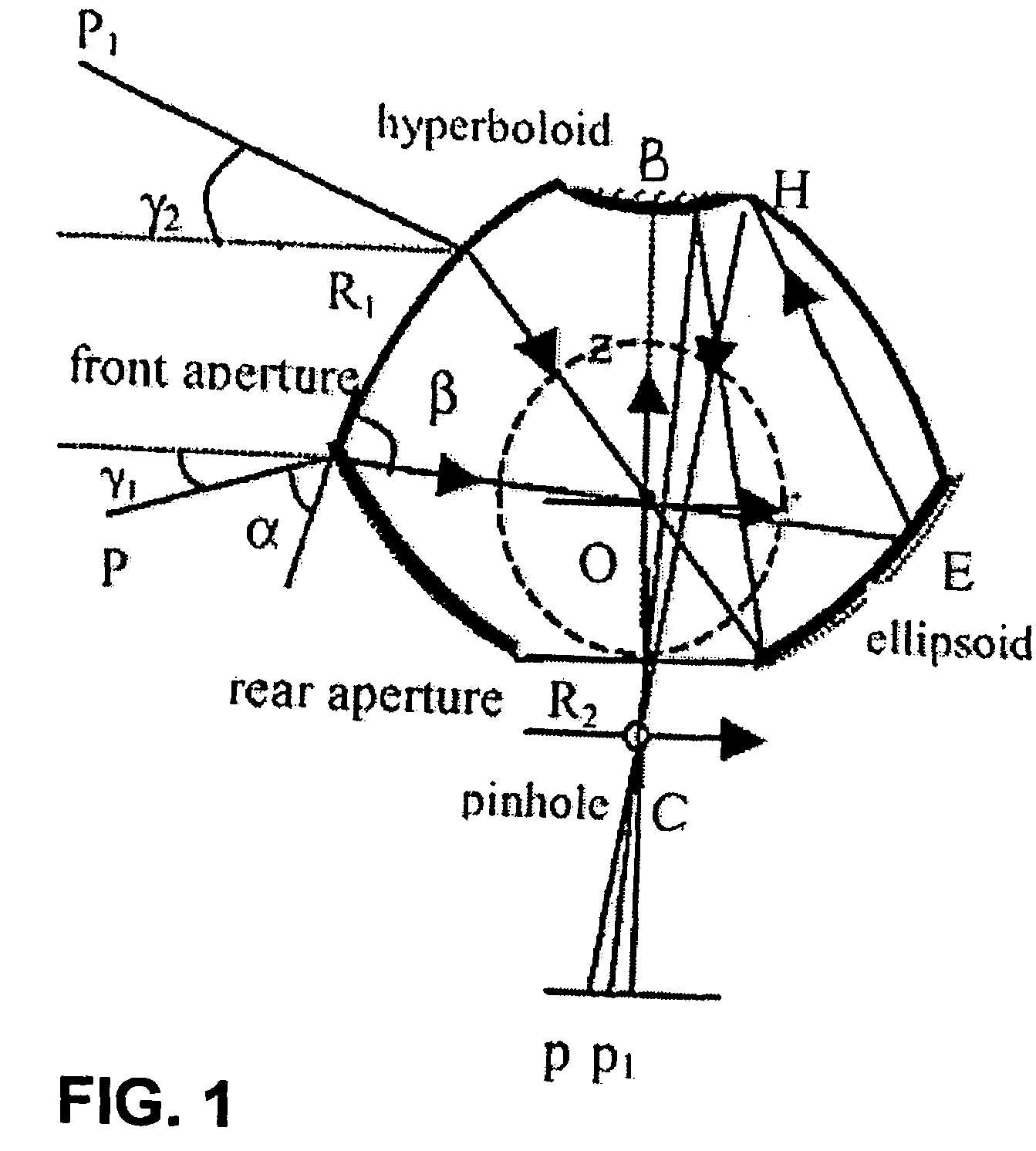

Panoramic mirror and system for producing enhanced panoramic images

InactiveUS6856472B2Improves usable resolutionEnhance the imageGeometric image transformationPanoramic photographyImage resolutionField of view

The present invention relates to providing enhanced panoramic images with an improved panoramic mirror. A panoramic mirror is provided with a controlled vertical field of view. The controlled vertical field of view improves the resolution of a viewable panoramic image by eliminating portions of unwanted images from the viewable panoramic image.

Owner:360AI SOLUTIONS LLC

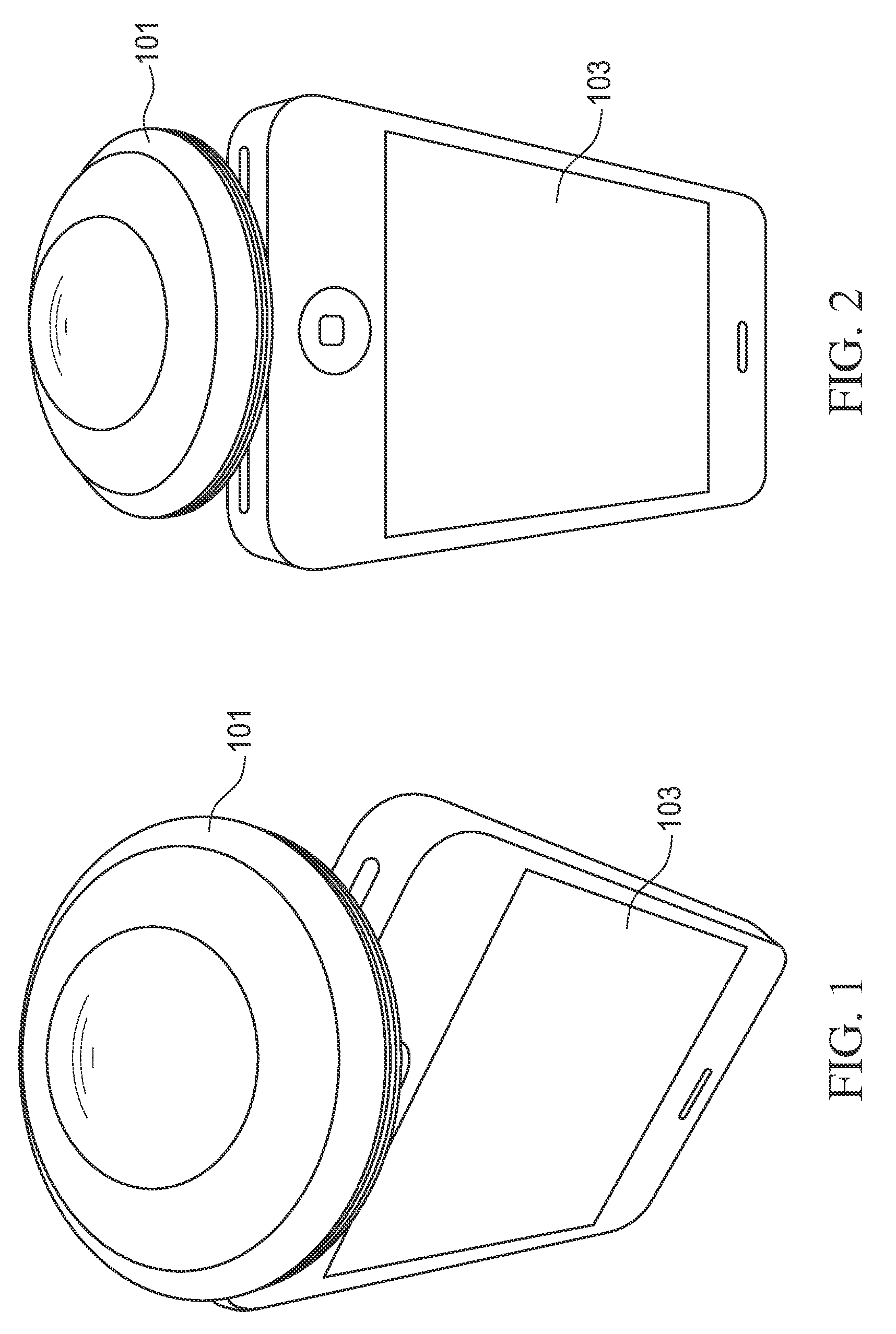

Mobile Device-Mountable Panoramic Camera System and Method of Displaying Images Captured Therefrom

A mobile device-mountable camera apparatus includes a panoramic camera system and a cable-free mounting arrangement. The panoramic camera system includes a panoramic lens assembly and a sensor. The lens assembly provides a vertical field of view in a range of greater than 180° to 360°. The sensor is positioned in image-receiving relation to the lens assembly and is operable to produce image data based on an image received through the lens assembly. The mounting arrangement is configured to removably secure the panoramic camera system to an externally-accessible data port of a mobile computing device to facilitate transfer of the image data to processing circuitry of the mobile device. The mobile device's processing circuitry may produce a video image from the image data and display of the video image may be manipulated based on a change of orientation of the mobile device and / or a touch action of the device user.

Owner:360FLY

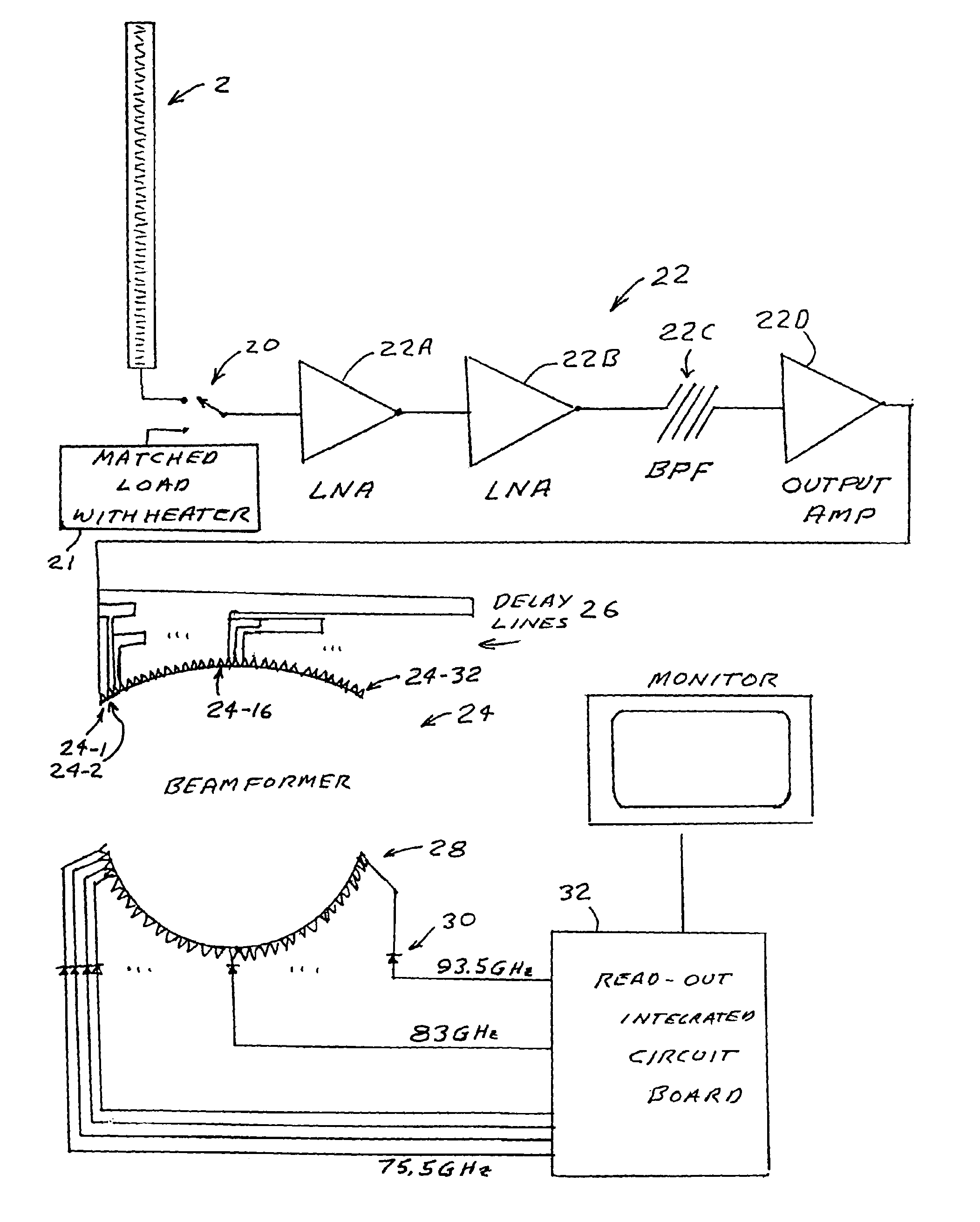

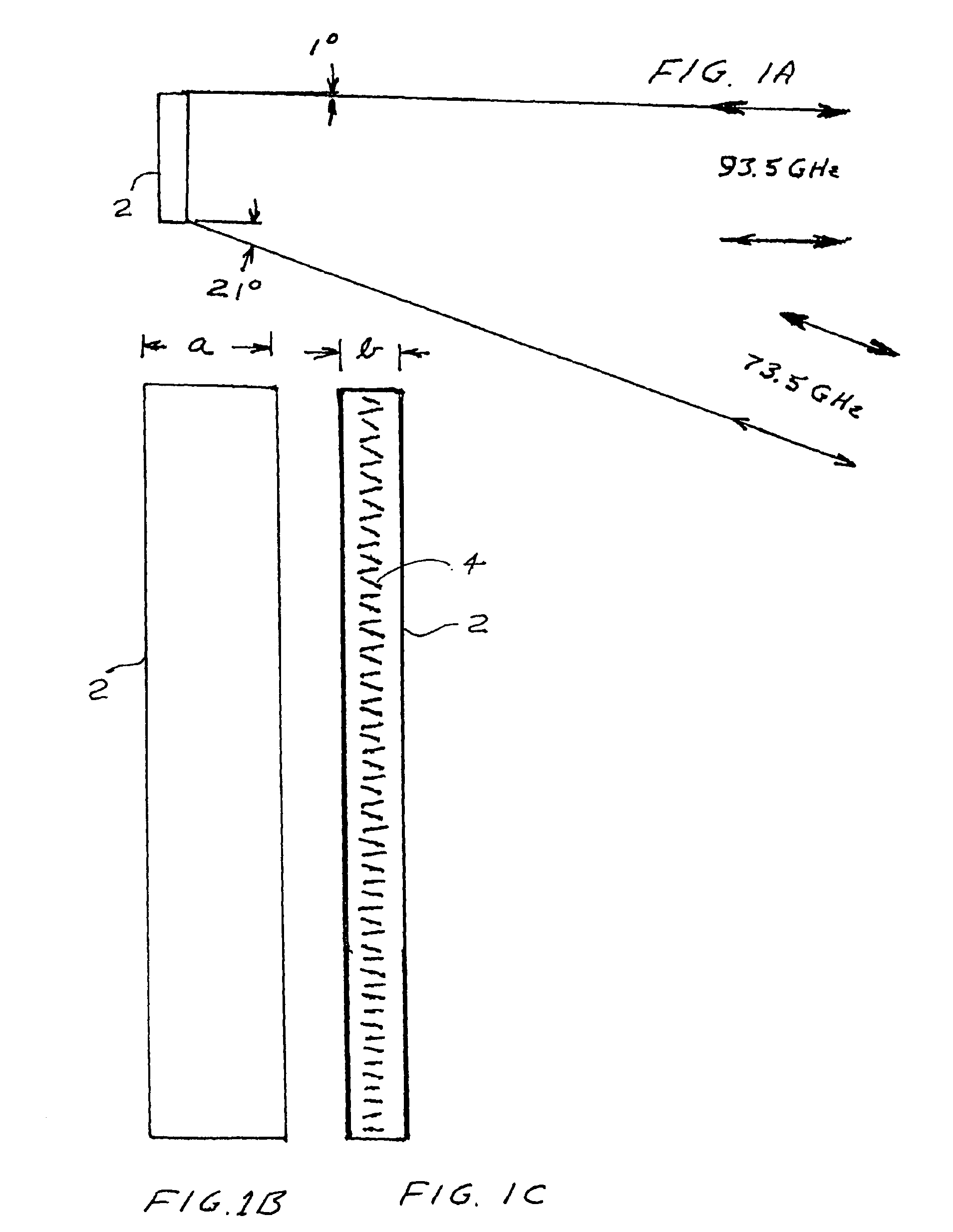

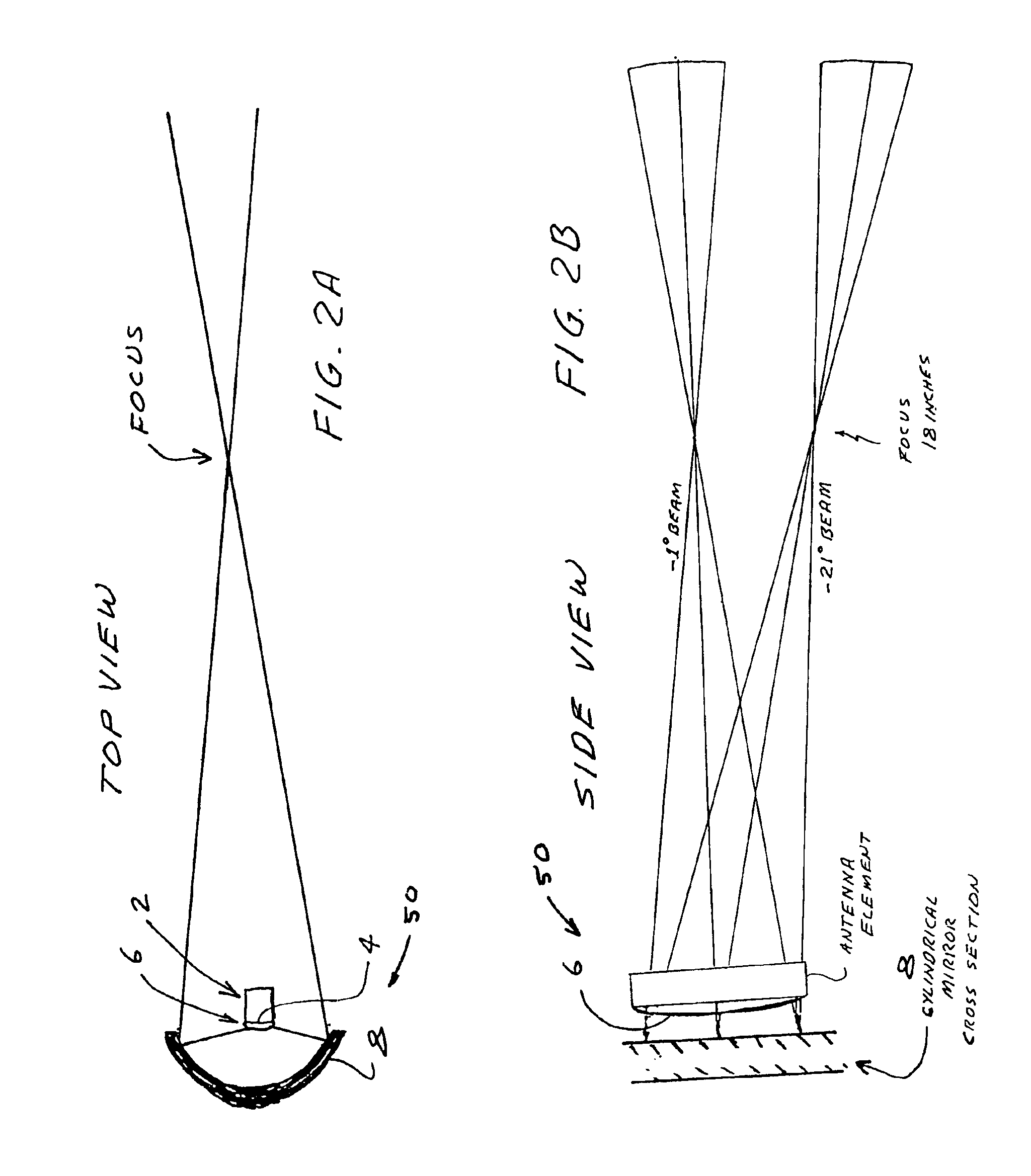

Millimeter wave imaging system

InactiveUS6937182B2Geological detection using milimetre wavesRadio transmissionMillimetre waveAntenna element

A millimeter wave imaging system that includes at least one millimeter wave frequency scanning antenna for collecting frequency dependent beams of millimeter wave radiation from a narrow one-dimensional field of view. The collected radiation is amplified at the collected frequencies and the amplified signals are separated into frequency dependent bins with a tapped-delay beam-former. These bins are then sampled to produce a one-dimensional image of the antenna field of view. A two dimensional image of a target may be obtained by moving the target across the field of view of the scanning antenna. In a preferred embodiment the antenna is only 4.5 inches in length and constructed from WR-10 waveguide with inclined slots cut in one of the narrow walls at 79 mil spacings. This geometry creates a frequency-scanned antenna spanning a 20 degree vertical field of view over a 75.5-93.5 GHz operational band of the sensor, starting at approximately 1 degree below horizontal at 93.5 GHz and ranging to approximately 21 degrees below horizontal at 75.5 GHz. In this embodiment 64 of these antenna elements are arranged in four stacks of 16 antennas focused at about 18 inches to construct a portal contraband screener.

Owner:TREX ENTERPRISE

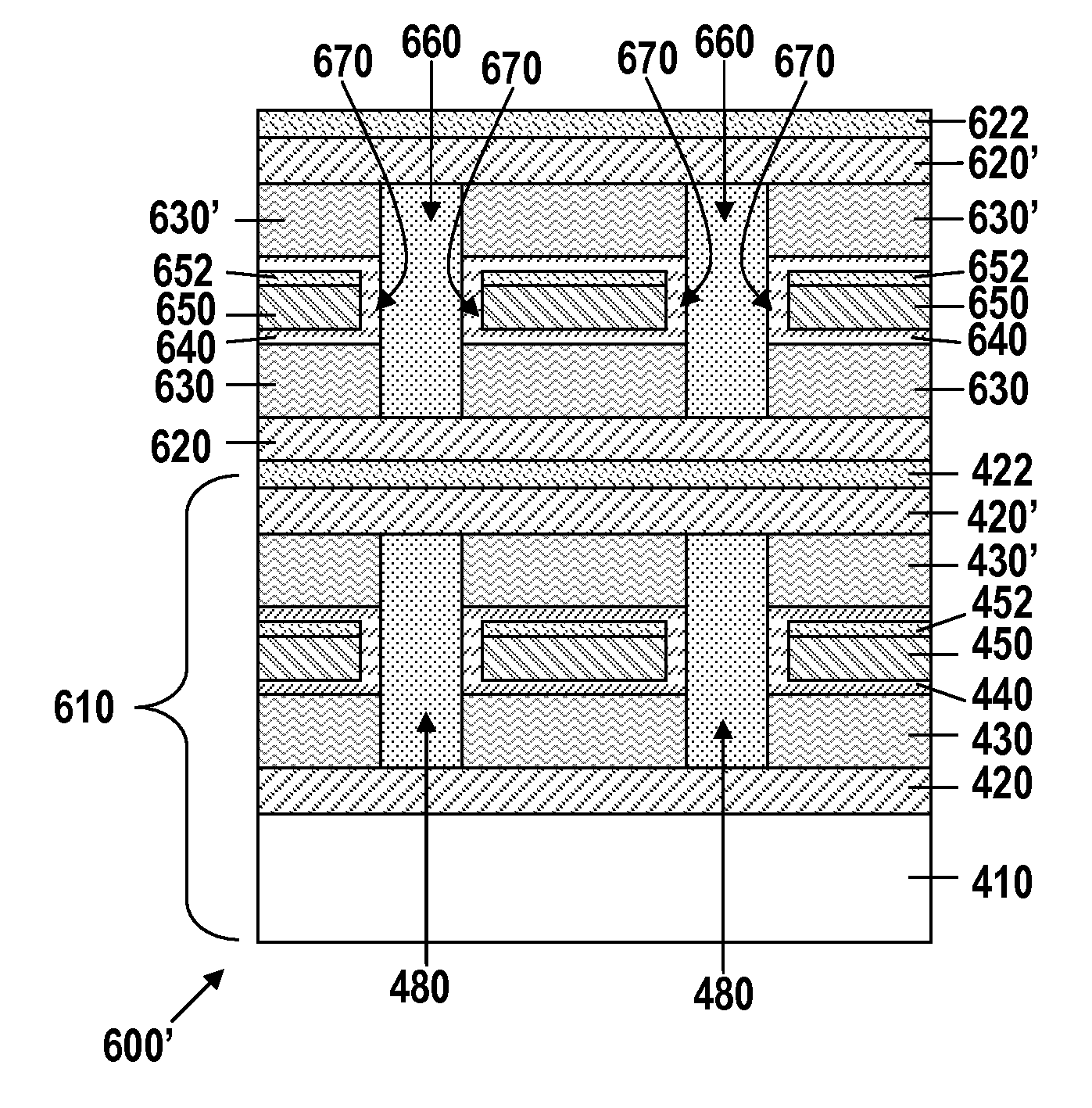

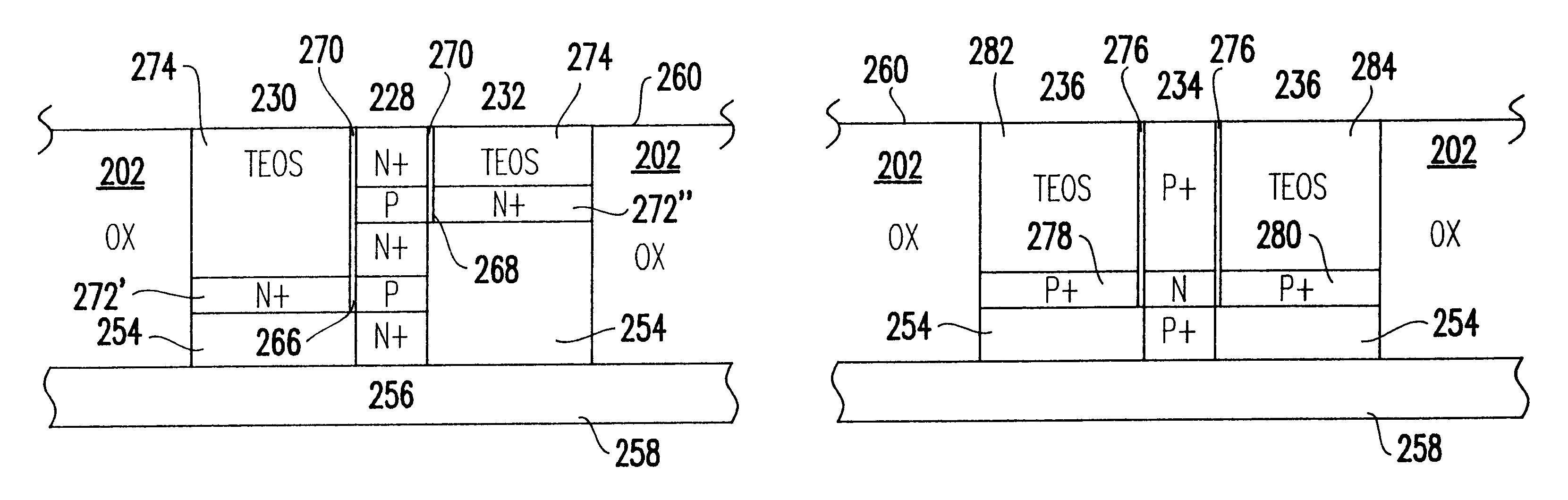

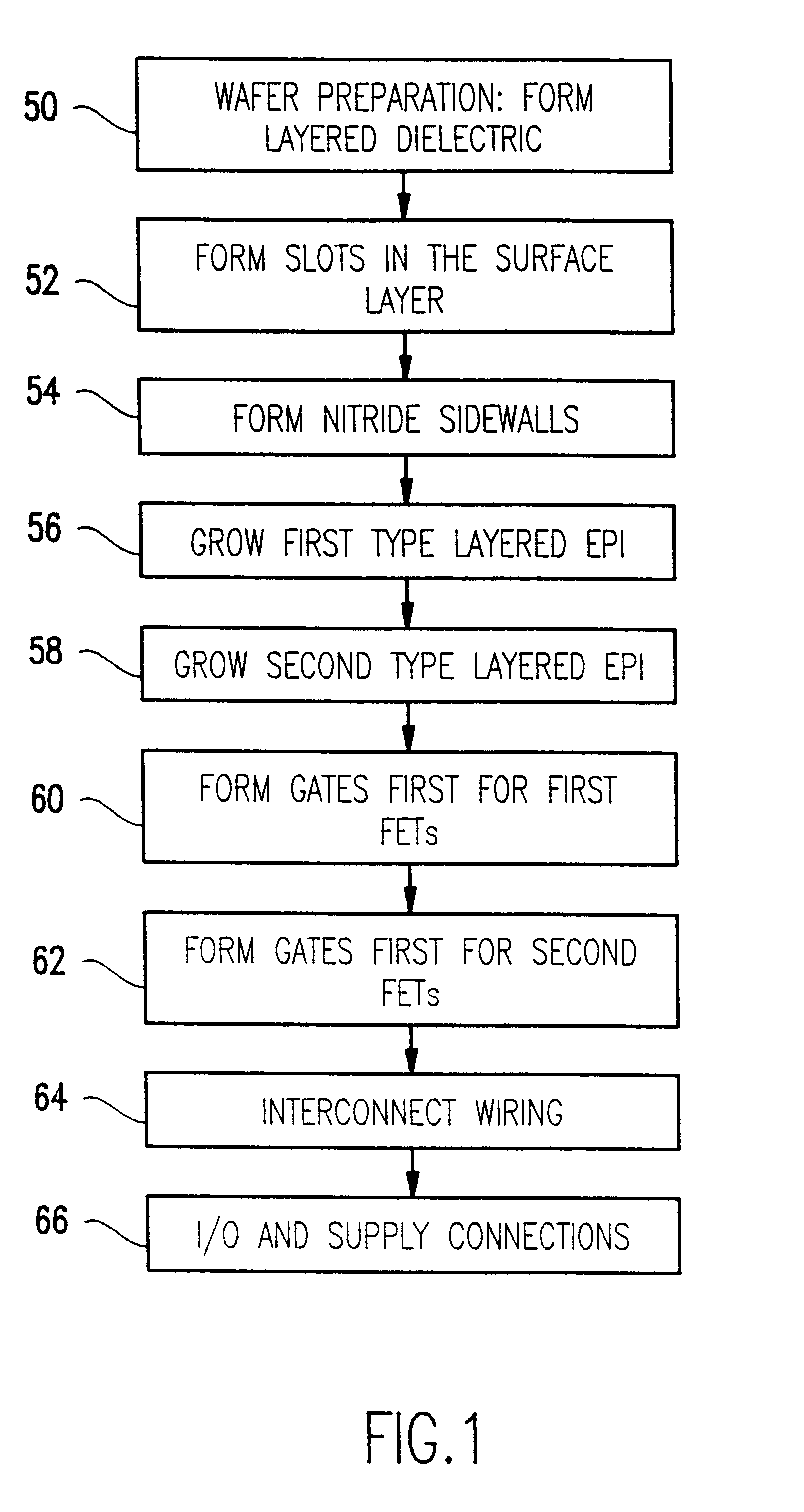

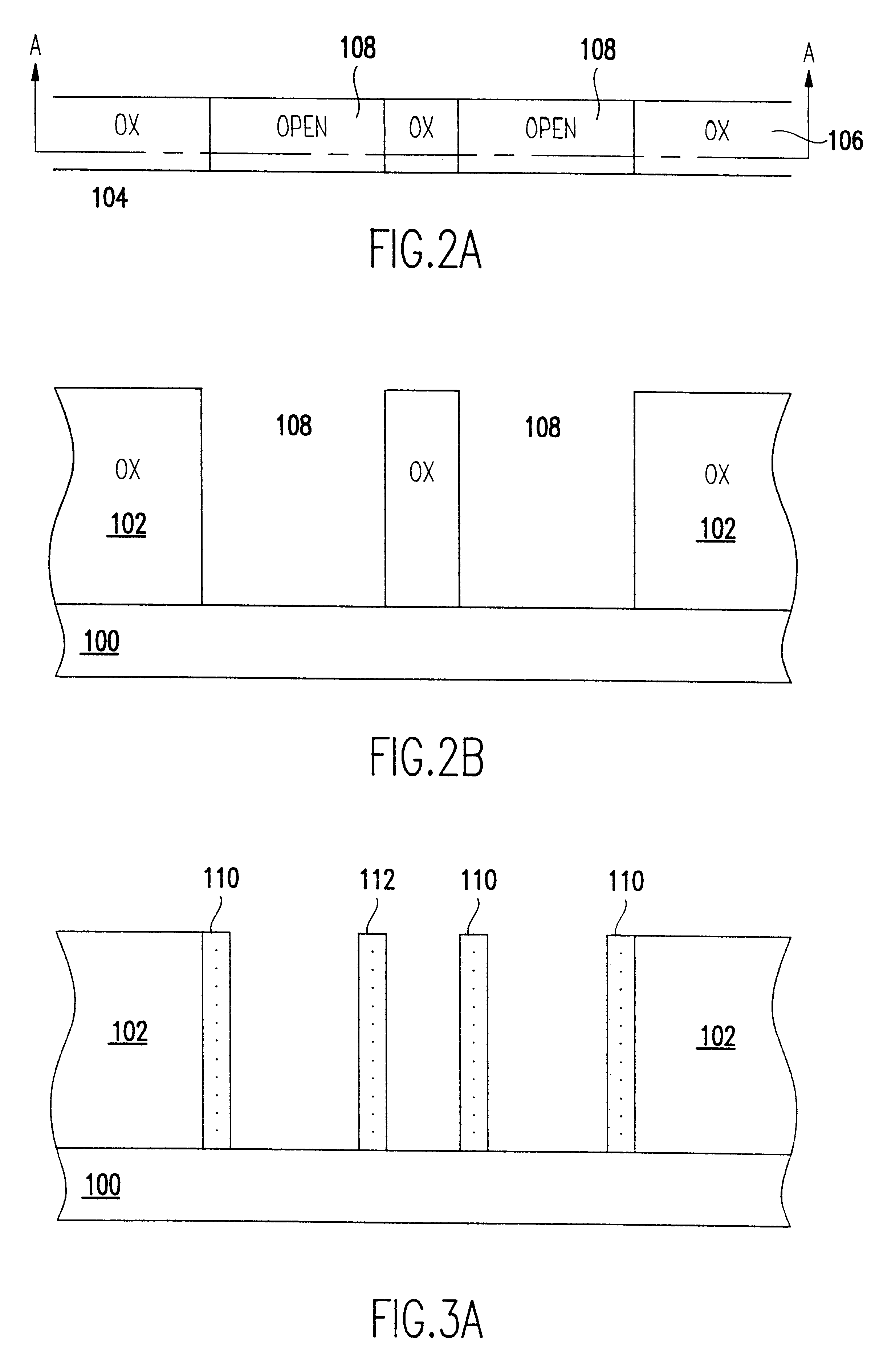

High performance, low power vertical integrated CMOS devices

InactiveUS6297531B2Solid-state devicesSemiconductor/solid-state device manufacturingHigh resistanceCapacitance

Owner:INT BUSINESS MASCH CORP

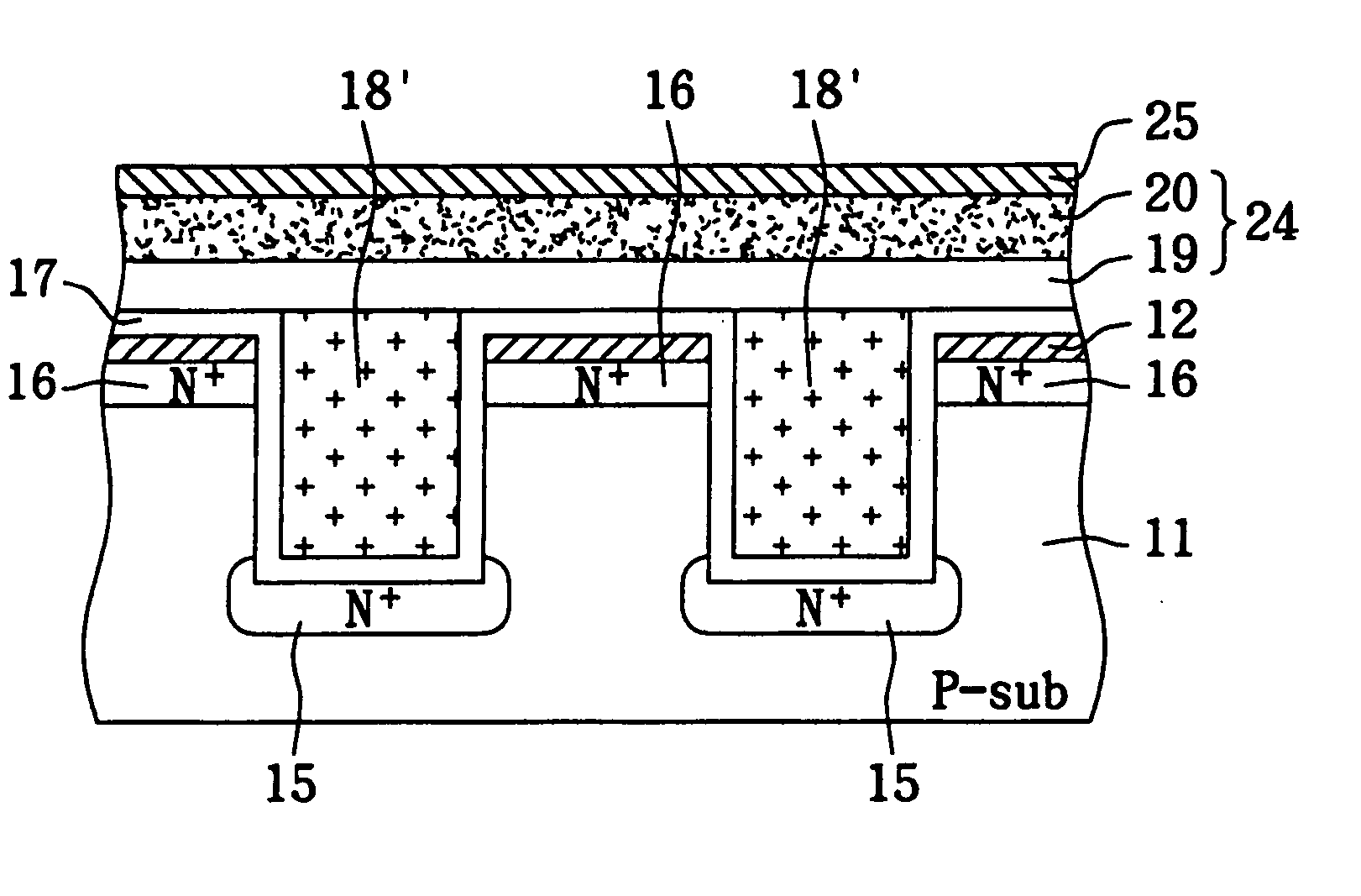

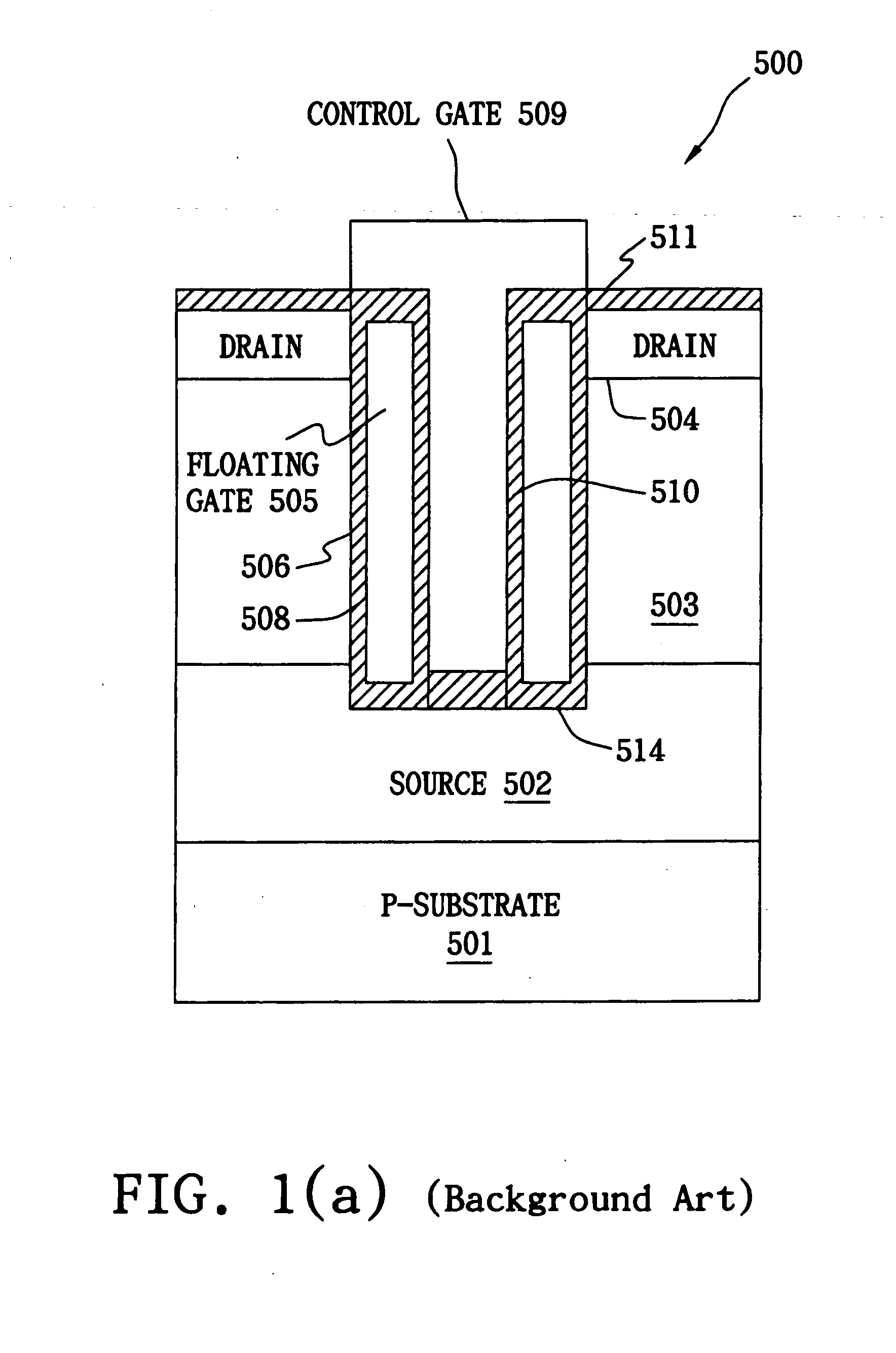

Non-volatile memory array having vertical transistors and manufacturing method thereof

InactiveUS20050148173A1Superior charge storingReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingDopantBit line

A method of manufacturing a non-volatile memory array having vertical field effect transistors is revealed. First, a semiconductor substrate having multiple trenches is provided, and then dopants are implanted into the semiconductor substrate to form first doping regions and second doping regions respectively serving as source and drain bit lines at different heights. Secondly, a gate dielectric including at least one nitride film, e.g., an oxide / nitride / oxide (ONO) layer, is formed onto the surface of the semiconductor substrate, and polysilicon plugs serving as gate electrodes are filled up the multiple trenches afterward. After that, a polysilicon layer and a tungsten silicide (WiSix) layer are sequentially deposited followed by masking and etching processes to form parallel polycide lines serving as word lines, and then an oxide layer is deposited therebetween and planarized for isolation.

Owner:SKYMEDI CORPORATION

Display system for high-definition projectors

A display system is provided to surround a user with an out-the window scene. The system includes a screen structure that is a facetted back-projection dome made up of a polygonal polar top facet surrounded by trapezoidal facets angulated downward from it in an upper facet row. A middle row of facets extends angulated downward therefrom, and a lower row of trapezoidal facets extends down from them. Each facet has video projected thereon by a high definition projector, and to maximize resolution and efficiently use the projector output, the vertical height of each facet makes use of the full vertical field of pixels available from the associated projector. The facets are all tangent to a sphere about a design eyepoint of the dome. The projector resolutions and the size, position and material of the facets are such that the imagery visible on the inside of the dome on the facets is at resolution corresponding to a visual acuity of 20 / 50 or higher, preferably 20 / 20, and at or near eye-limiting resolution.

Owner:L 3 COMM CORP

Methods of manufacture of vertical nanowire FET devices

ActiveUS7892956B2Improve controllabilityIncrease flexibilityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

Owner:GLOBALFOUNDRIES U S INC

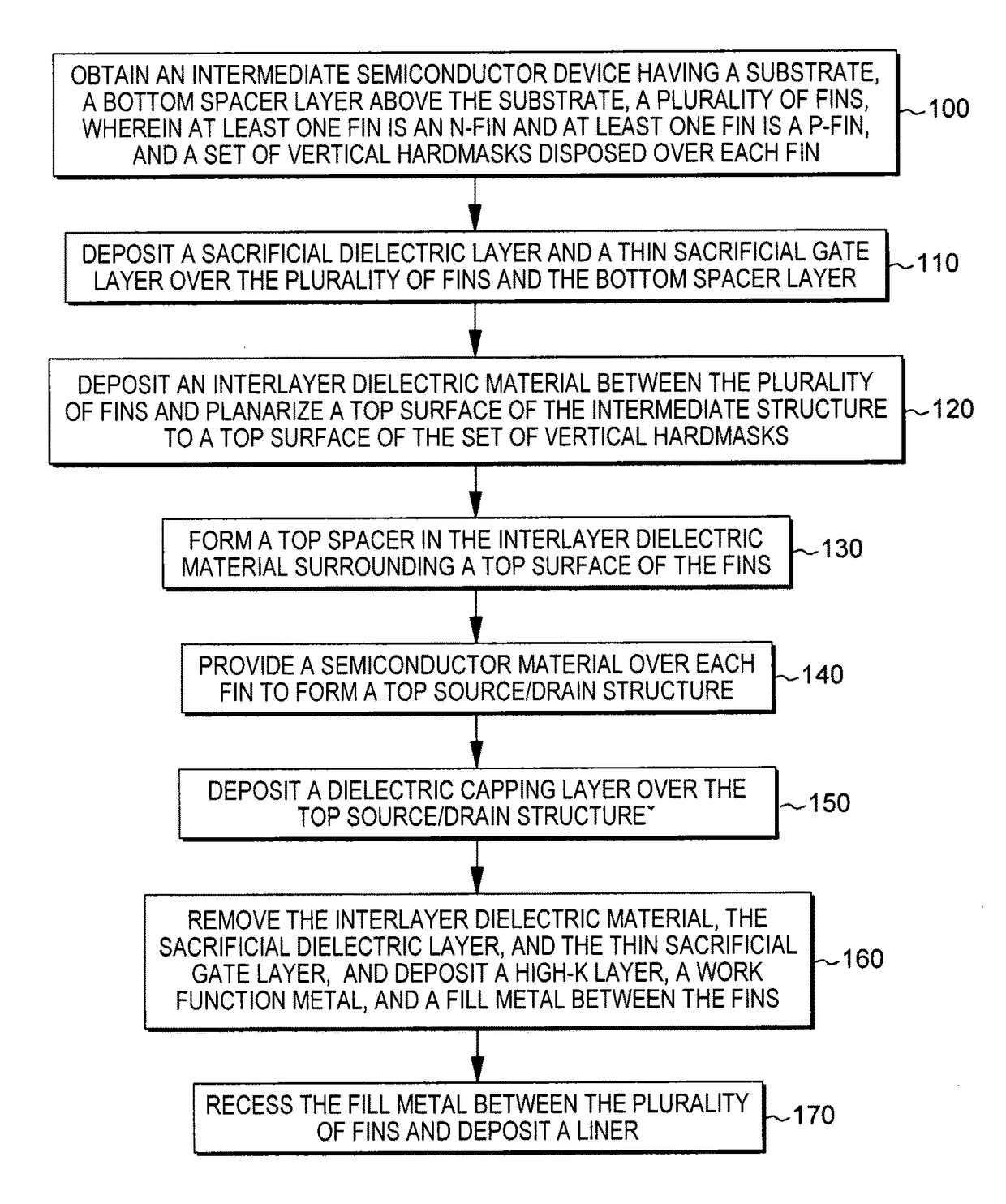

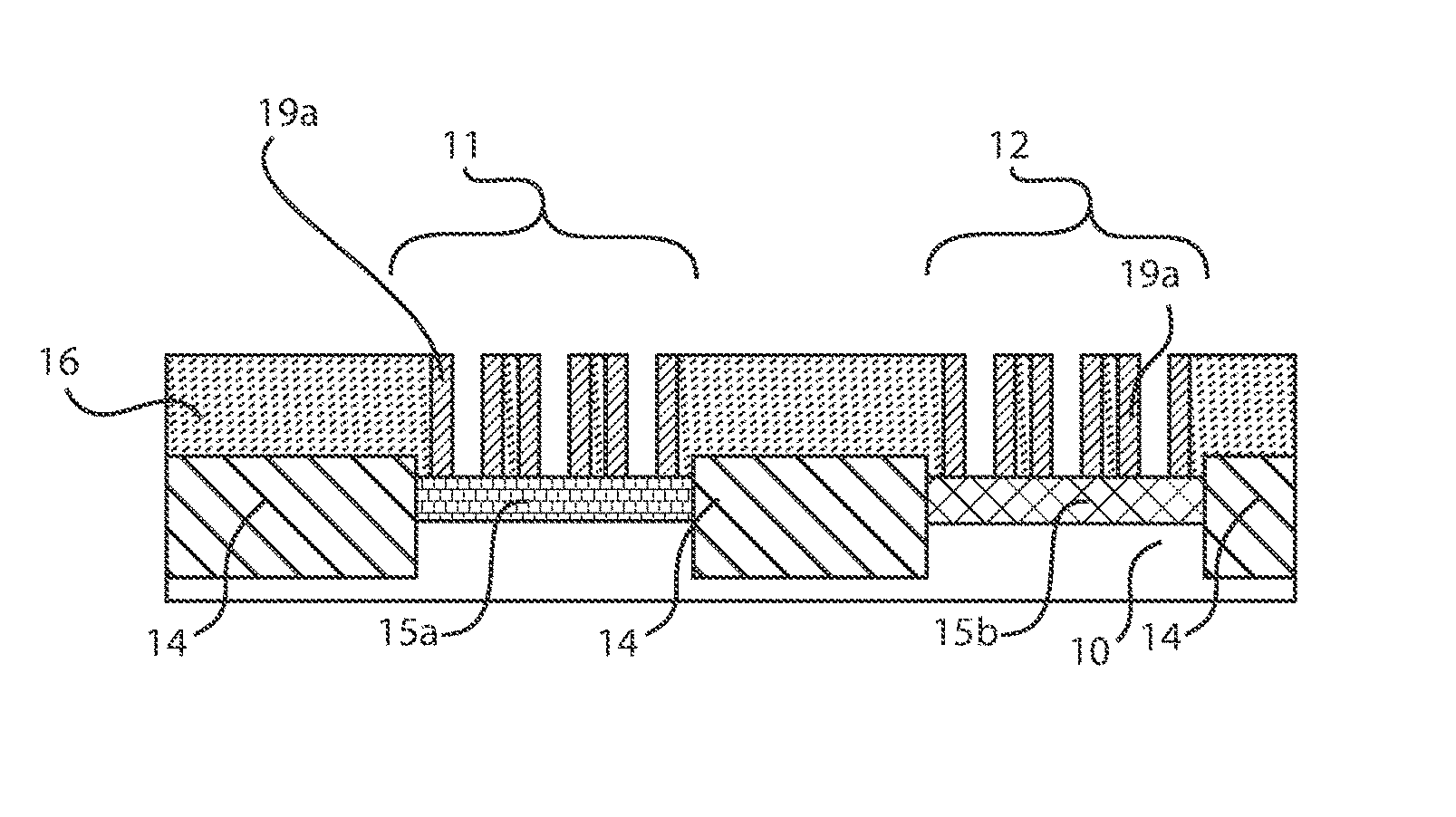

Devices and methods of forming VFET with self-aligned replacement metal gates aligned to top spacer post top source drain EPI

InactiveUS9773708B1Overcomes shortcomingEnhanced advantageTransistorSemiconductor/solid-state device manufacturingWork functionEngineering

Devices and methods of fabricating vertical field effect transistors on semiconductor devices are provided. One intermediate semiconductor includes: a substrate, a bottom spacer layer above the substrate, a plurality of fins, wherein at least one fin is an n-fin and at least one fin is a p-fin; a high-k layer and a work function metal over the bottom spacer layer and around the plurality of fins; a top spacer above the high-k layer and the work function metal and surrounding a top area of the fins; a top source / drain structure over each fin; a dielectric capping layer over the top source / drain structure; a fill metal surrounding the work function metal; and a liner.

Owner:GLOBALFOUNDRIES US INC

Method of fabricating vertical field effect transistors with protective fin liner during bottom spacer recess etch

A method of fabricating a vertical field effect transistor comprising that includes forming openings through a spacer material to provide fin structure openings to a first semiconductor material, and forming an inner spacer liner on sidewalls of the fin structure openings. A channel semiconductor material is epitaxially formed on a surface of the first semiconductor material filling at least a portion of the fin structure openings. The spacer material is recessed with an etch that is selective to the inner spacer liner to form a first spacer. The inner spacer liner is removed selectively to the channel semiconductor material. A gate structure on the channel semiconductor material, and a second semiconductor material is formed in contact with the channel semiconductor material.

Owner:IBM CORP

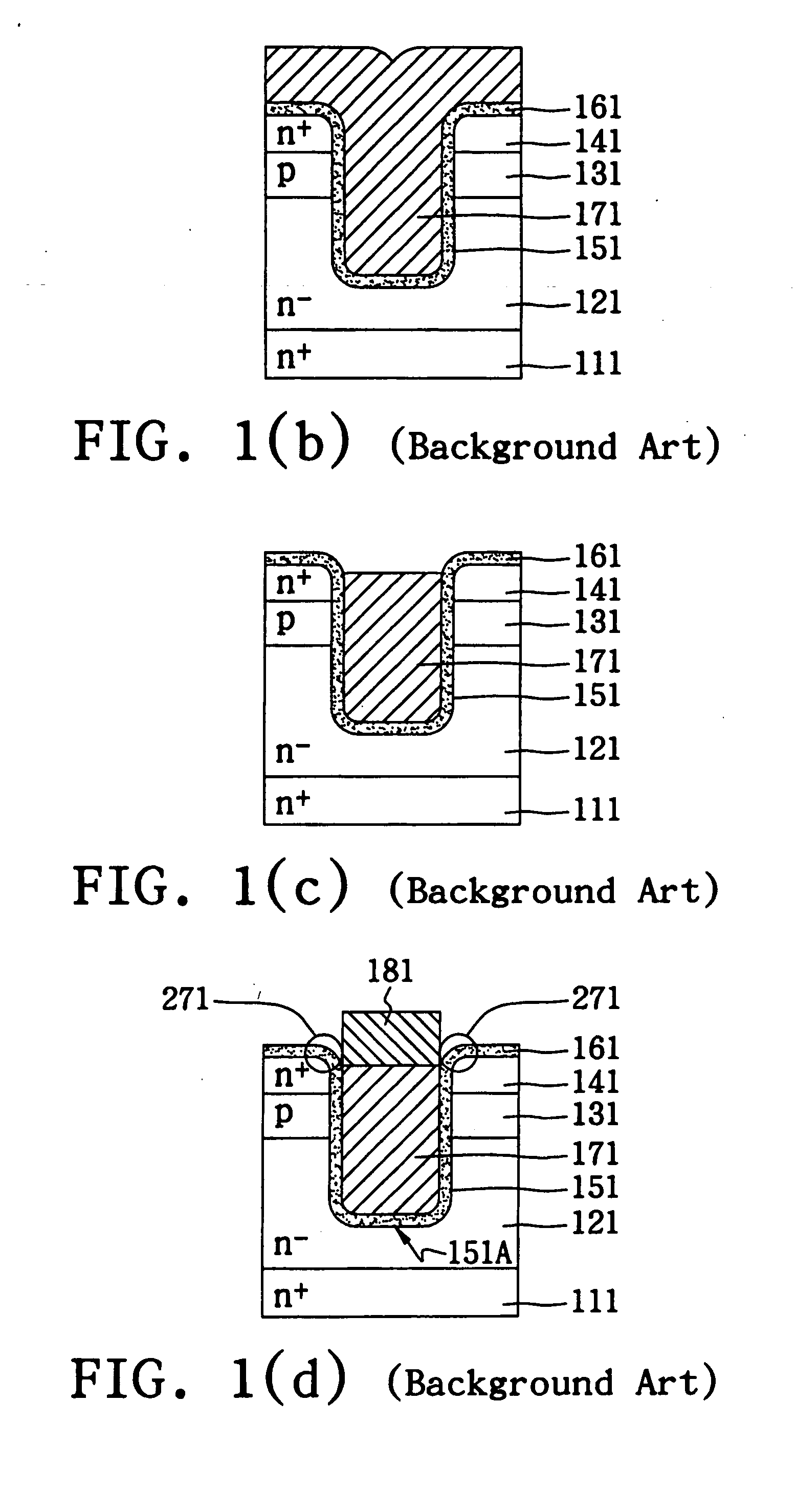

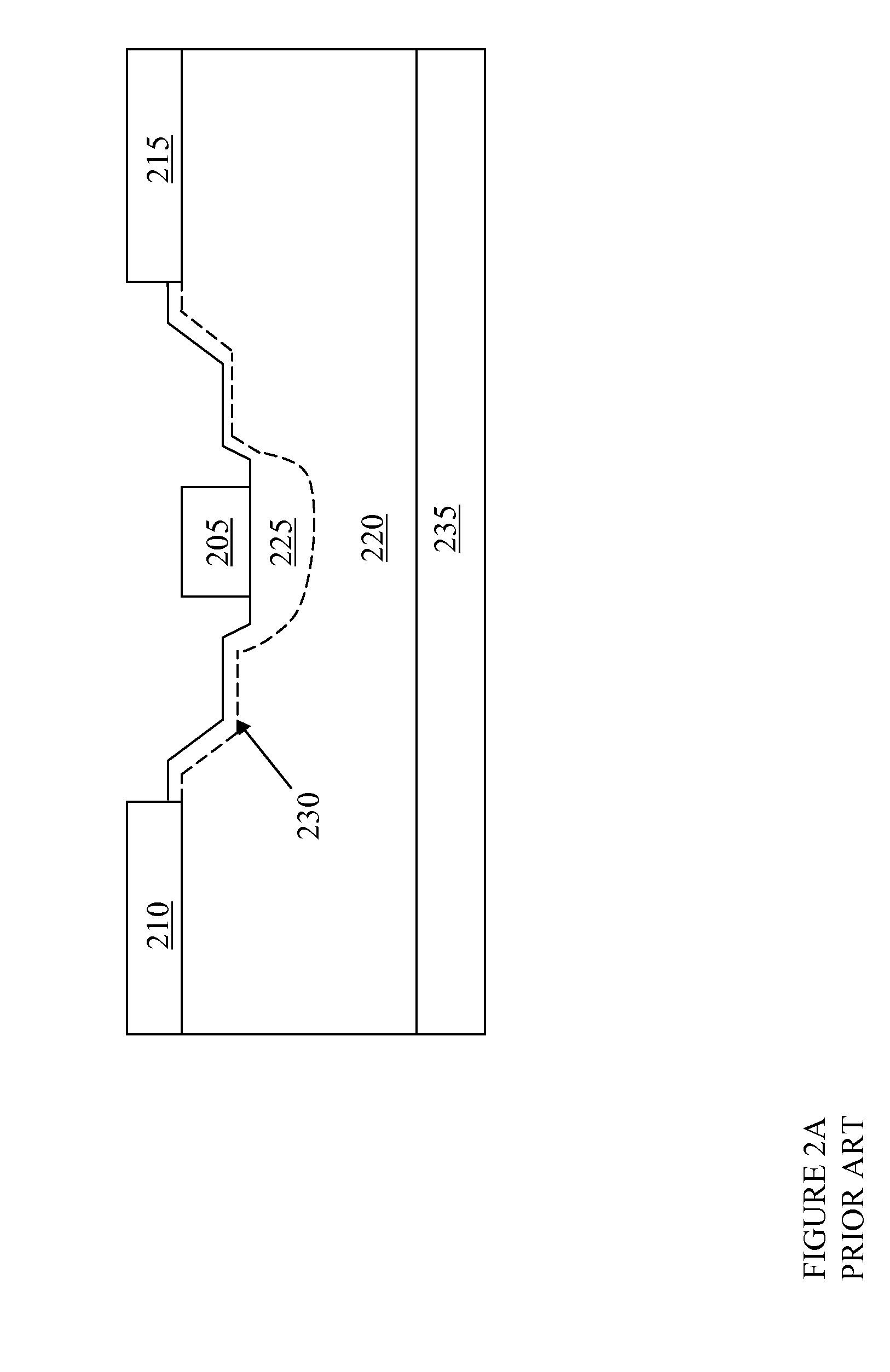

Vertical Field-Effect Transistor and Method of Forming the Same

ActiveUS20070298559A1Semiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorSchottky diode

A semiconductor device, a method of forming the same, and a power converter including the semiconductor device. In one embodiment, the semiconductor device includes a heavily doped substrate, a source / drain contact below the heavily doped substrate, and a channel layer above the heavily doped substrate. The semiconductor device also includes a heavily doped source / drain layer above the channel layer and another source / drain contact above the heavily doped source / drain layer. The semiconductor device further includes pillar regions through the another source / drain contact, the heavily doped source / drain layer, and portions of the channel layer to form a vertical cell therebetween. Non-conductive regions of the semiconductor device are located in the portions of the channel layer within the pillar regions. The semiconductor device still further includes a gate above the non-conductive regions in the pillar regions. The semiconductor device may also include a Schottky diode including the channel layer and a Schottky contact.

Owner:MYPAQ HLDG LTD

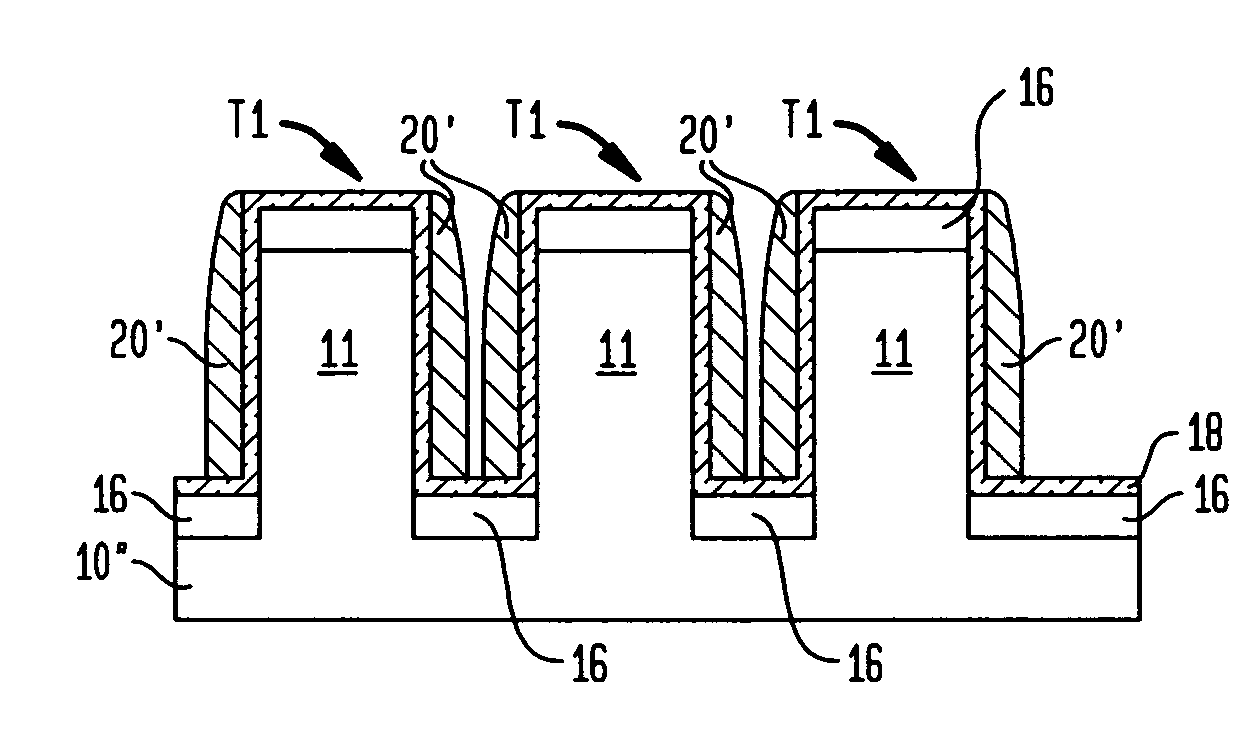

Vertical transistor fabrication and devices

A method of fabricating a vertical field effect transistor including forming a first recess in a substrate; epitaxially growing a first drain from the first bottom surface of the first recess; epitaxially growing a second drain from the second bottom surface of a second recess formed in the substrate; growing a channel material epitaxially on the first drain and the second drain; forming troughs in the channel material to form one or more fin channels on the first drain and one or more fin channels on the second drain, wherein the troughs over the first drain extend to the surface of the first drain, and the troughs over the second drain extend to the surface of the second drain; forming a gate structure on each of the one or more fin channels; and growing sources on each of the fin channels associated with the first and second drains.

Owner:IBM CORP

Vertical Field-Effect Transistor and Method of Forming the Same

ActiveUS20070296028A1Semiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorSchottky diode

A semiconductor device, a method of forming the same, and a power converter including the semiconductor device. In one embodiment, the semiconductor device includes a heavily doped substrate, a source / drain contact below the heavily doped substrate, and a channel layer above the heavily doped substrate. The semiconductor device also includes a heavily doped source / drain layer above the channel layer and another source / drain contact above the heavily doped source / drain layer. The semiconductor device further includes pillar regions through the another source / drain contact, the heavily doped source / drain layer, and portions of the channel layer to form a vertical cell therebetween. Non-conductive regions of the semiconductor device are located in the portions of the channel layer within the pillar regions. The semiconductor device still further includes a gate above the non-conductive regions in the pillar regions. The semiconductor device may also include a Schottky diode including the channel layer and a Schottky contact.

Owner:MYPAQ HLDG LTD

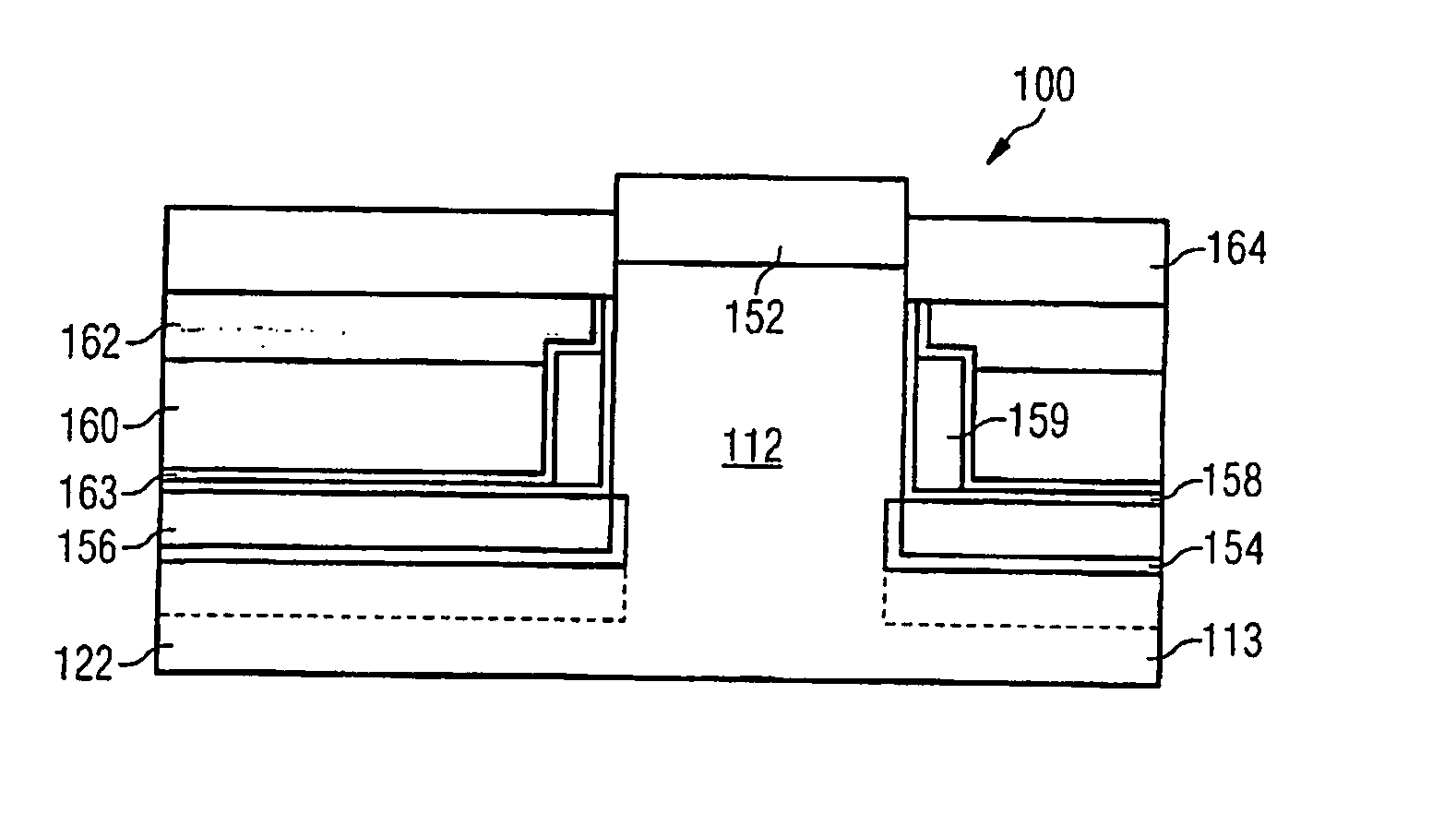

Vertical field effect transistors with controlled overlap between gate electrode and source/drain contacts

ActiveUS9287362B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor structure

An approach to forming a semiconductor structure for a vertical field effect transistor with a controlled gate overlap. The approach includes forming on a semiconductor substrate, a first semiconductor layer, a second semiconductor layer, a third semiconductor layer, a fourth semiconductor layer, a fifth semiconductor layer, and a first dielectric layer. The etched first dielectric layer and a first drain contact are surrounded by a first spacer. The first drain contact is composed of the fifth semiconductor layer. A second drain contact composed of the fourth semiconductor layer, a channel composed of the third semiconductor layer, and a second source contact composed of the second semiconductor layer are formed. Additionally, first source contact composed of the first semiconductor is formed and a gate electrode is formed on a portion of the first source contact layer surrounding a portion of the first pillar and the second pillar.

Owner:IBM CORP

Vertical field-effect transistor and method of forming the same

ActiveUS7663183B2TransistorSemiconductor/solid-state device manufacturingField-effect transistorSchottky diode

A semiconductor device, a method of forming the same, and a power converter including the semiconductor device. In one embodiment, the semiconductor device includes a heavily doped substrate, a source / drain contact below the heavily doped substrate, and a channel layer above the heavily doped substrate. The semiconductor device also includes a heavily doped source / drain layer above the channel layer and another source / drain contact above the heavily doped source / drain layer. The semiconductor device further includes pillar regions through the another source / drain contact, the heavily doped source / drain layer, and portions of the channel layer to form a vertical cell therebetween. Non-conductive regions of the semiconductor device are located in the portions of the channel layer within the pillar regions. The semiconductor device still further includes a gate above the non-conductive regions in the pillar regions. The semiconductor device may also include a Schottky diode including the channel layer and a Schottky contact.

Owner:MYPAQ HLDG LTD

Building method of knowledge map based on vertical field

InactiveCN105956052ARealize self-learningAchieve scalabilitySpecial data processing applicationsText database clustering/classificationKnowledge classificationGraph spectra

The invention provides a building method of a knowledge map based on a vertical field. The method comprises the following steps of (1) extracting the word realization of classes of an on-line encyclopedia and the hyponymy between classes; (2) merging the field knowledge information, defining the data attribute and the relationship attribute of the field, and further setting the statute on the definition domain and the value domain of the attributes; (3) studying an entity layer, i.e., extracting an entity and filling the attribute value of the entity; performing mass processing on structurized and semi-structurized data by D2R or data collecting tools; and for non-structurized text data, defining the classes and the attributes of the upper layer body and the relationship between the classes and the attributes, and recognizing examples according to the relationship between the classes and the attributes. The method has the advantages that by using the method, the built knowledge classification of the vertical field knowledge map is clear; the self study and the automatic expansion of the knowledge map are realized; and the key effects are achieved on the information retrieval and semantic analysis of the vertical field.

Owner:QINGDAO PENGHAI SOFT CO LTD

Vertical field effect transistor on oxide semiconductor substrate

InactiveUS20130043468A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

A transistor, such as a vertical metal field effect transistor, can include a substrate including a ZnO-based material, and a structure disposed on a first side of the substrate comprising of AlGaN-based materials and electrodes disposed on the second side of the substrate. The transistor can also include a plurality of semiconductor layers and a dielectric layer disposed between the plurality of semiconductor layers and electrode materials.

Owner:RAMGOSS

Vertical transistor having an asymmetric gate

InactiveUS20130095623A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricWork function

A transistor structure is formed to include a substrate and, overlying the substrate, a source; a drain; and a channel disposed vertically between the source and the drain. The channel is coupled to a gate conductor that surrounds the channel via a layer of gate dielectric material that surrounds the channel. The gate conductor is composed of a first electrically conductive material having a first work function that surrounds a first portion of a length of the channel and a second electrically conductive material having a second work function that surrounds a second portion of the length of the channel. A method to fabricate the transistor structure is also disclosed. The transistor structure can be characterized as being a vertical field effect transistor having an asymmetric gate.

Owner:IBM CORP

Vertical field effect transistor using linear structure as a channel region and method for fabricating the same

A vertical field effect transistor includes: an active region with a bundle of linear structures functioning as a channel region; a lower electrode, functioning as one of source and drain regions; an upper electrode, functioning as the other of the source and drain regions; a gate electrode for controlling the electric conductivity of at least a portion of the bundle of linear structures included in the active region; and a gate insulating film arranged between the active region and the gate electrode to electrically isolate the gate electrode from the bundle of linear structures. The transistor further includes a dielectric portion between the upper and lower electrodes. The upper electrode is located over the lower electrode with the dielectric portion interposed and includes an overhanging portion sticking out laterally from over the dielectric portion. The active region is located right under the overhanging portion of the upper electrode.

Owner:JOLED INC

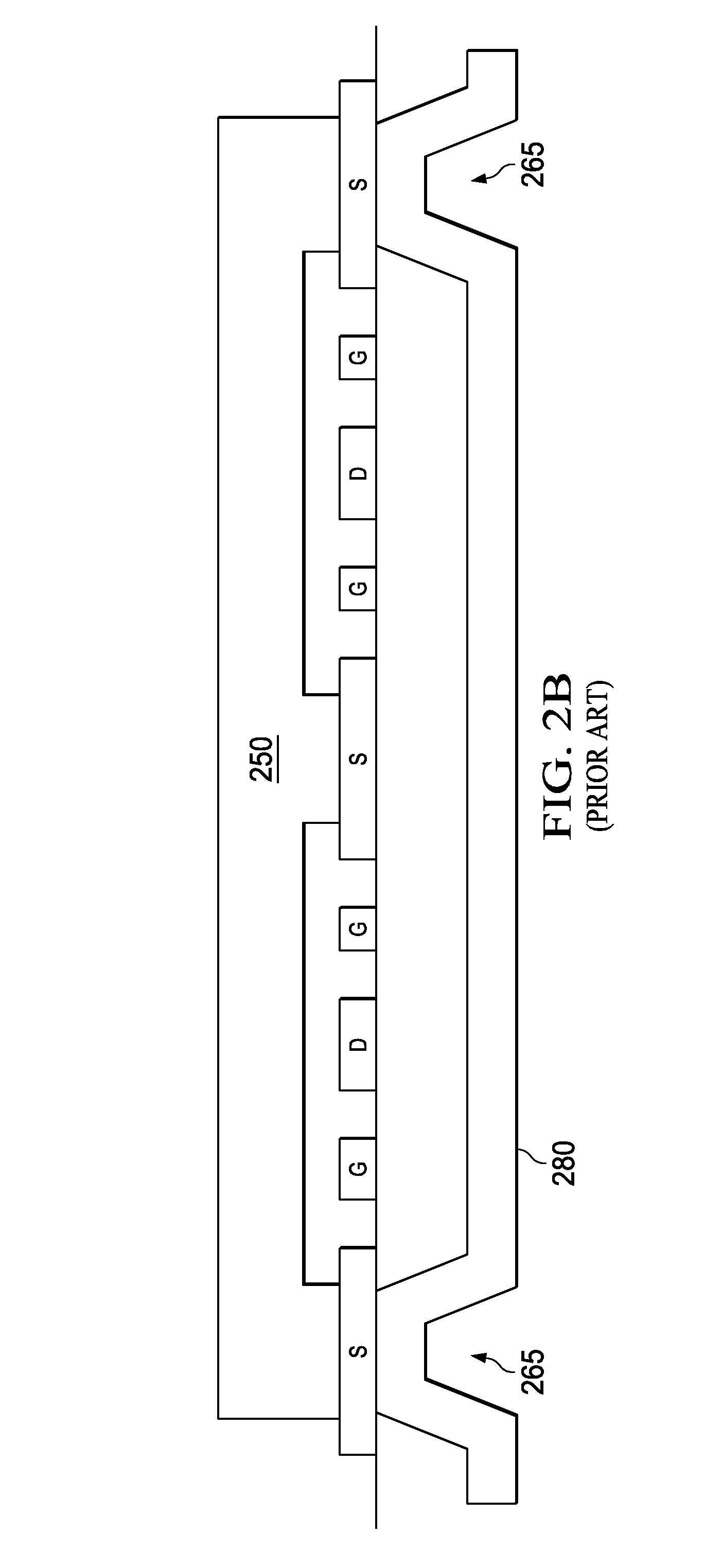

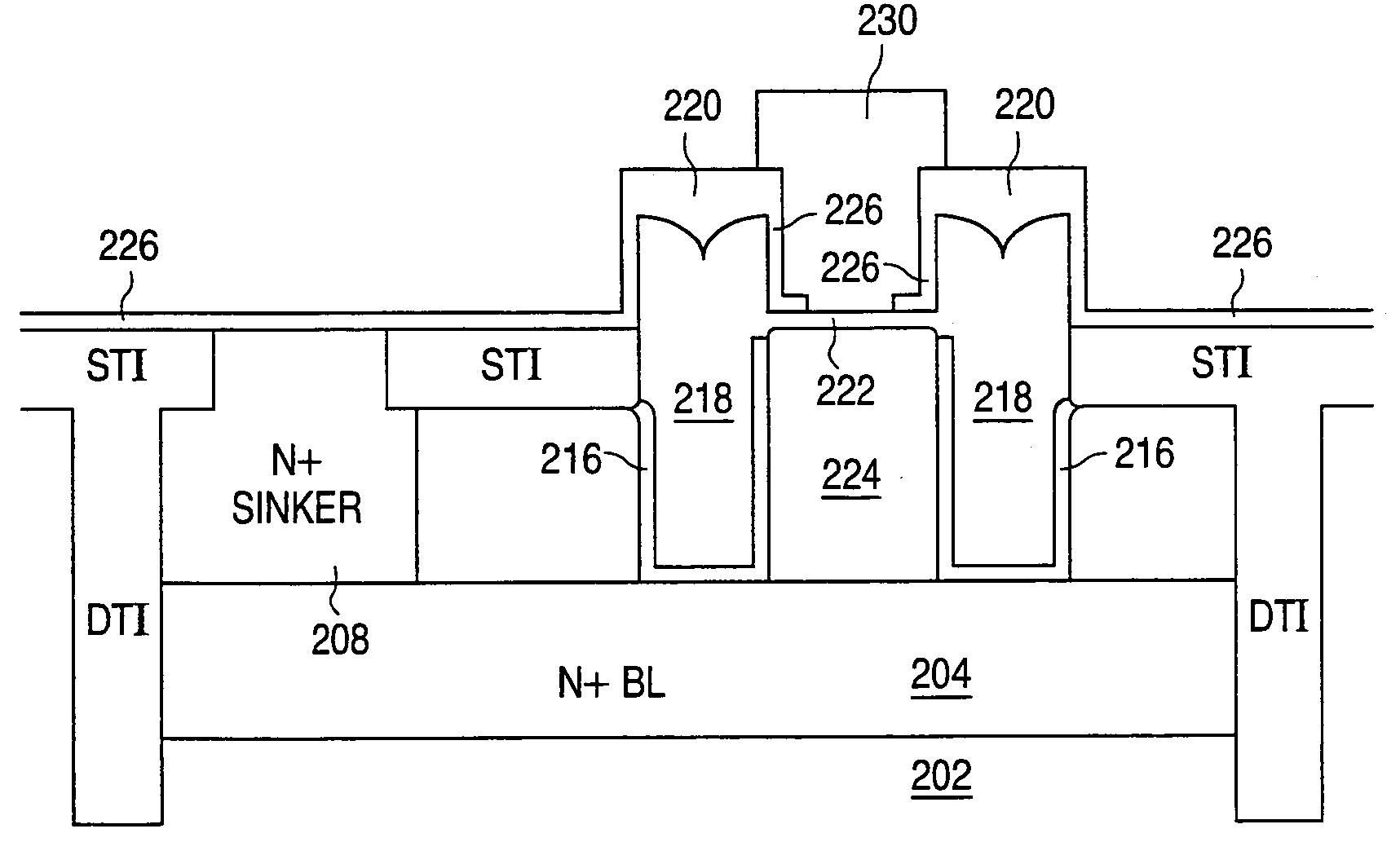

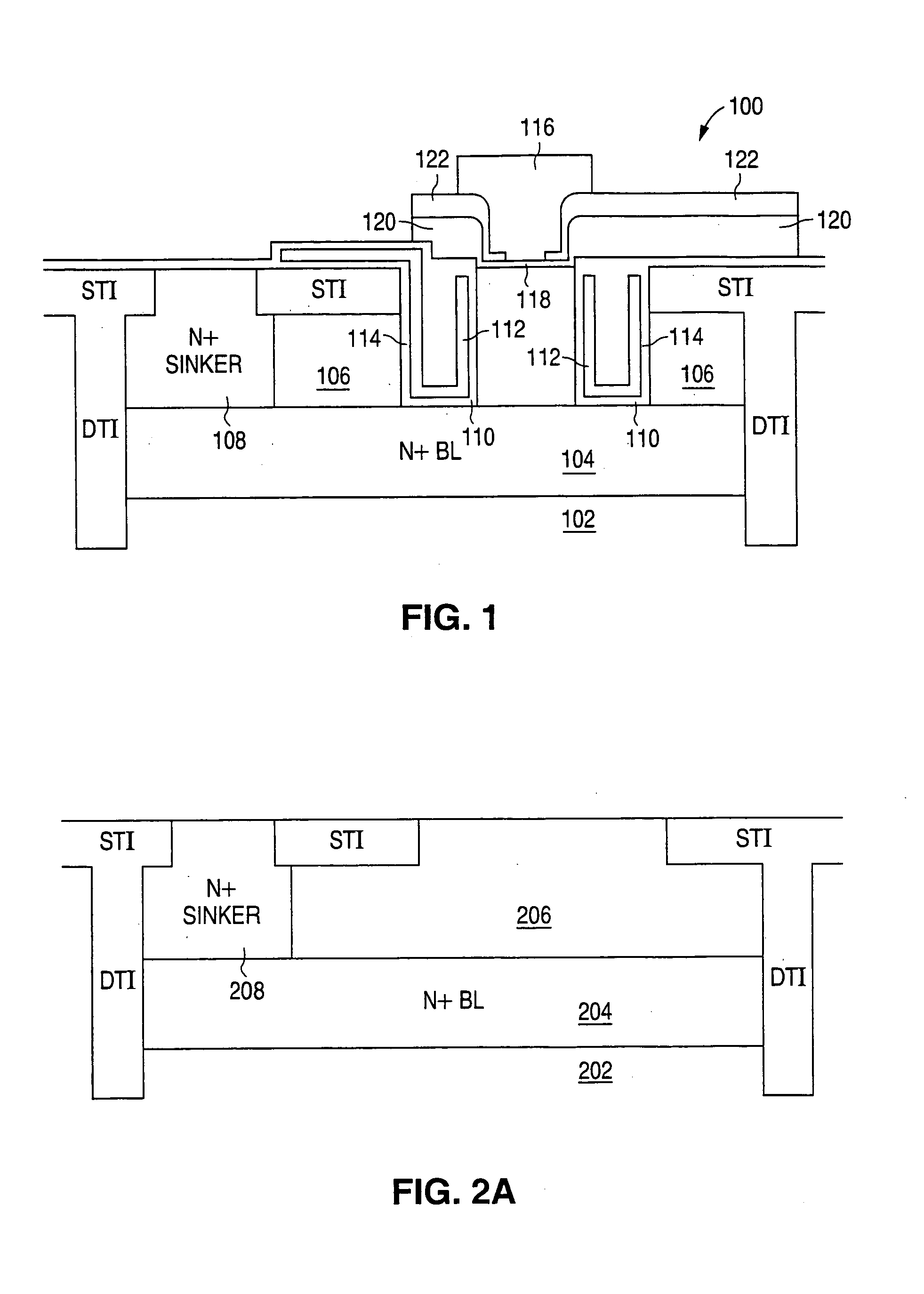

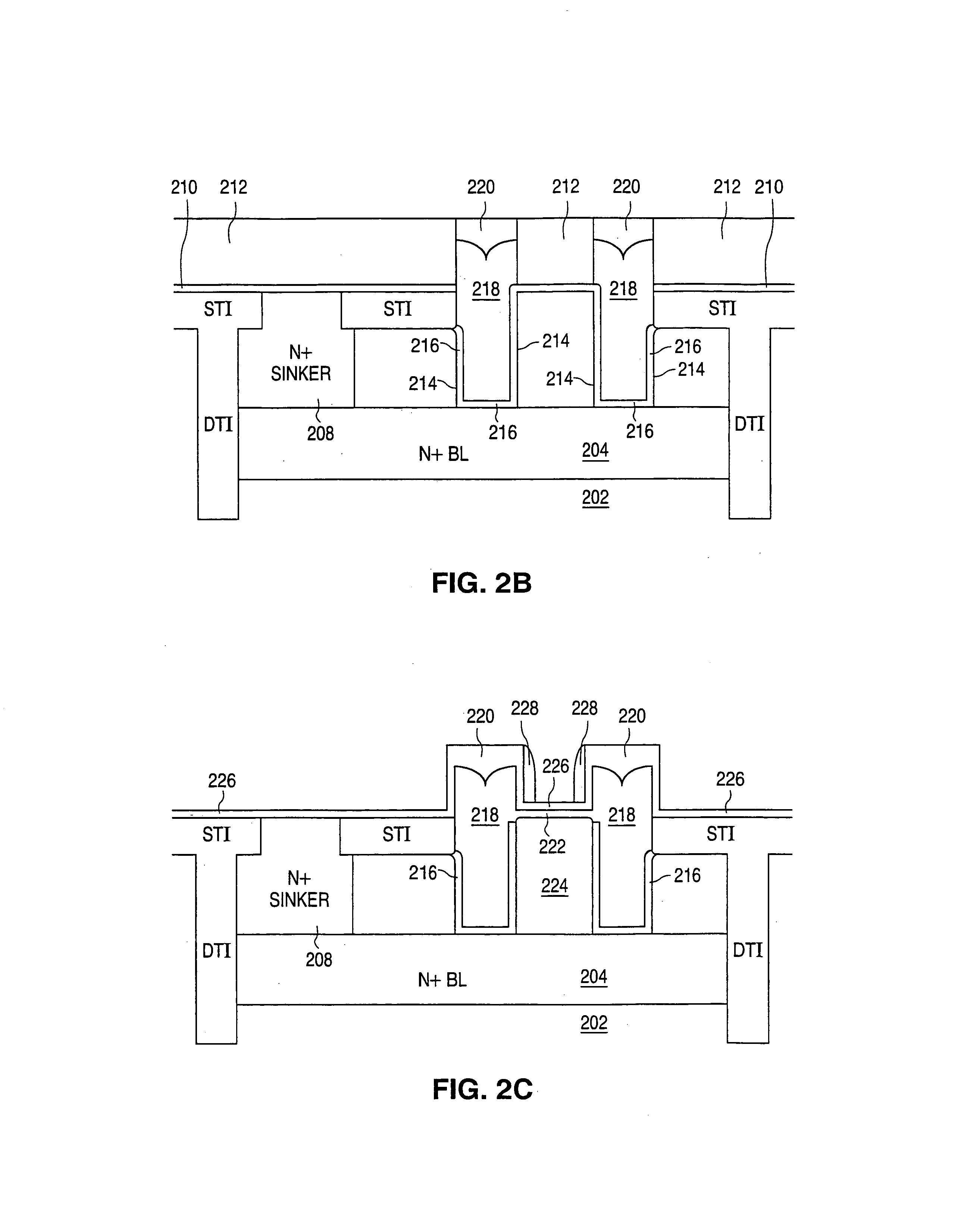

Super self-aligned BJT with base shorted field plate and method of fabricating

ActiveUS7132344B1Raise the ratioSemiconductor/solid-state device manufacturingSemiconductor devicesVertical fieldSubstrate surface

A bipolar junction transistor (BJT) structure and fabrication method are provided in which a doped polysilicon filled trench is utilized to form both the extrinsic base contact region and a vertical field plate. A sacrificial mandrel of dielectric material is formed over regions that will become the BJT active area. This allows the polysilicon filled trench to be extended above the original semiconductor substrate surface. In this way, the base-collector and emitter-base junctions are both self-aligned to the field plate trench. The field plate is utilized to control and shape the electric field in the base-collector depletion region, allowing heavier collector well doping for the same breakdown voltage. This results in improvement in both the breakdown / Ron ratio and the fT*BVcbo product.

Owner:NAT SEMICON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com