Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2831 results about "Metal silicide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Metal silicides were suggested as a candidate for field emitter. Metal silicides have been used as interconnecting materials in the VLSI process because of their high electrical conductivity and thermal stability[6]. In addition, the fabrication of metal silicides has been well established.

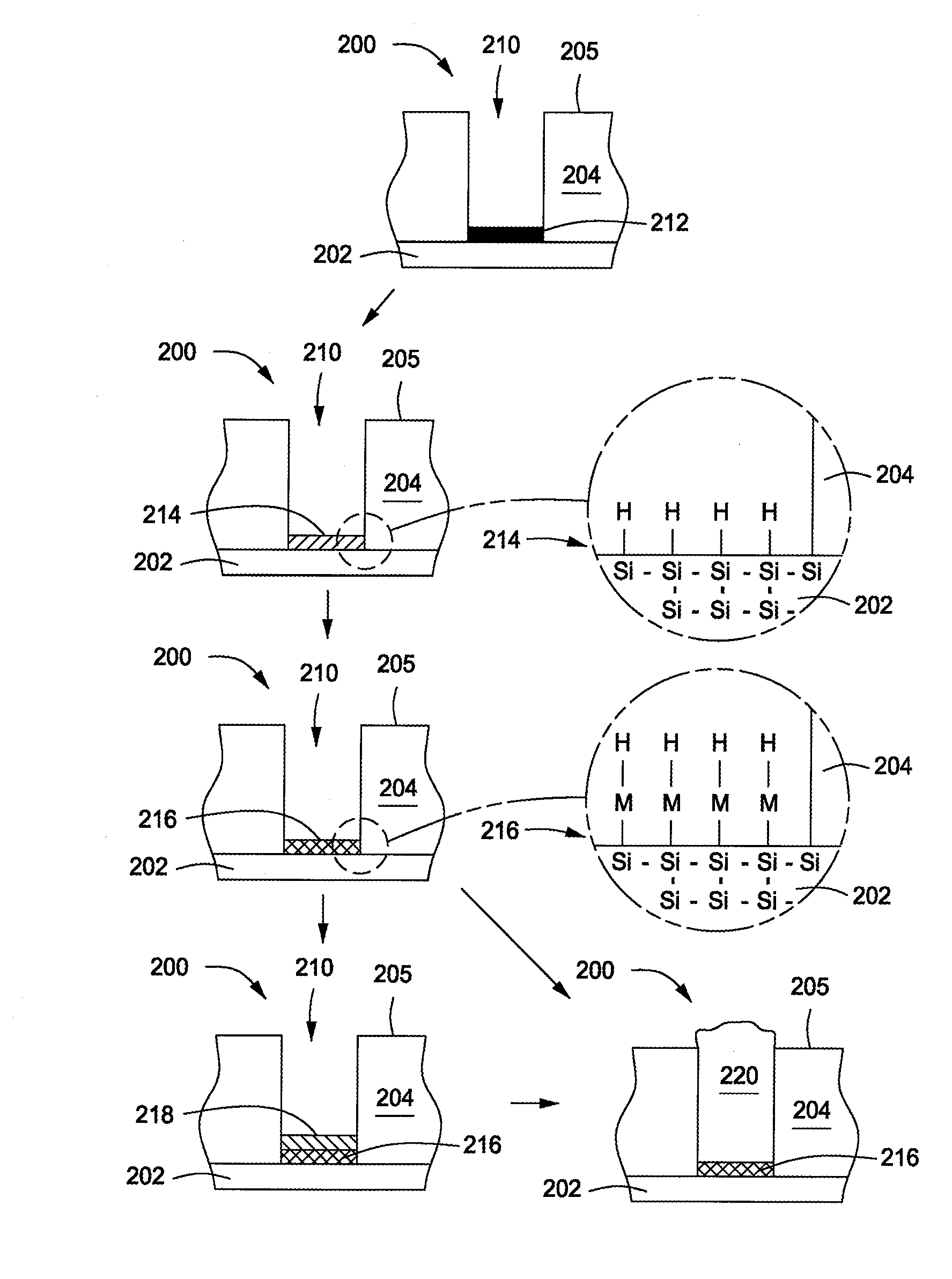

Methods for depositing nickel films and for making nickel silicide and nickel germanide

ActiveUS20130115768A1Semiconductor/solid-state device manufacturingSemiconductor devicesGas phaseMetal silicide

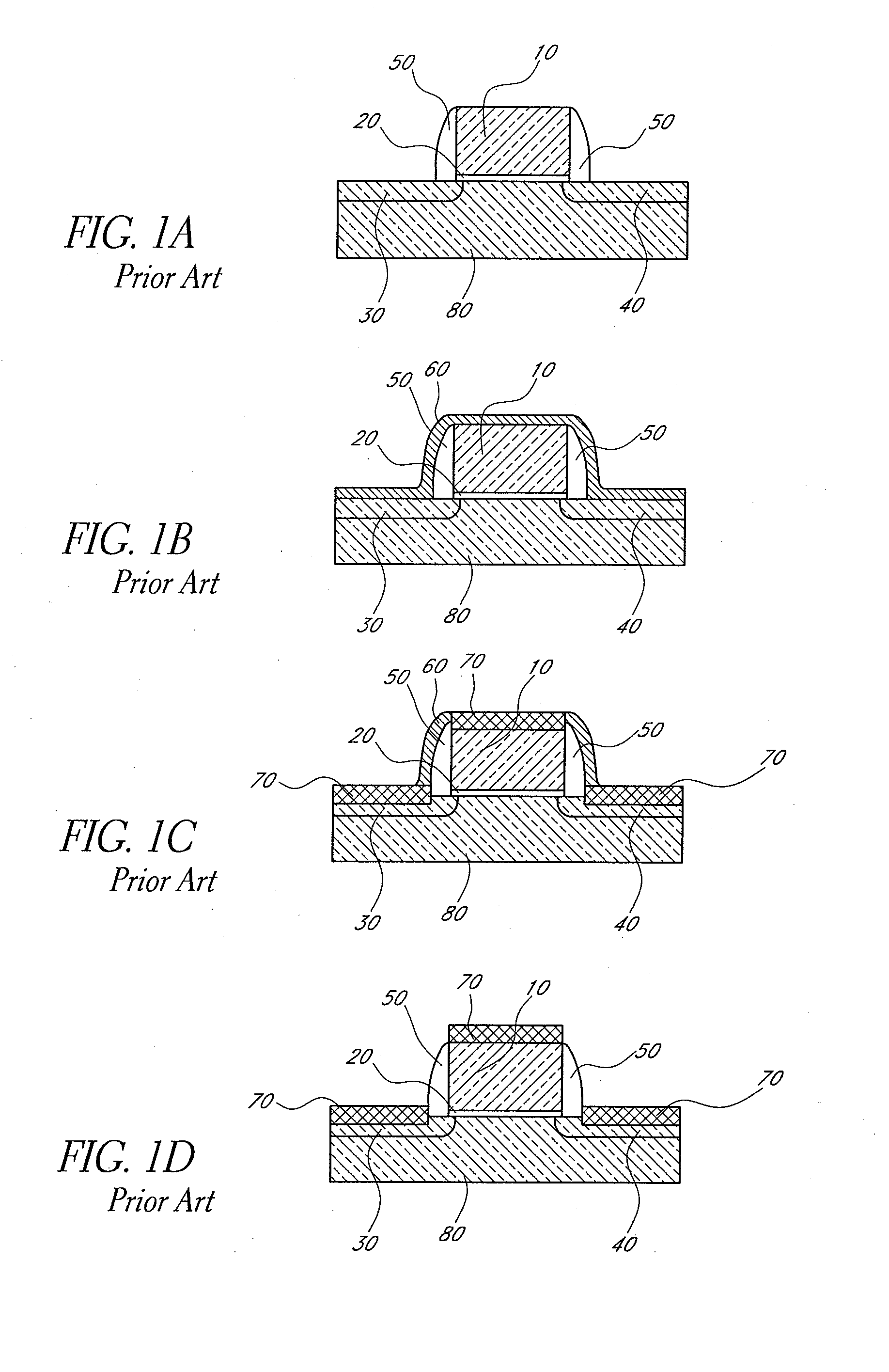

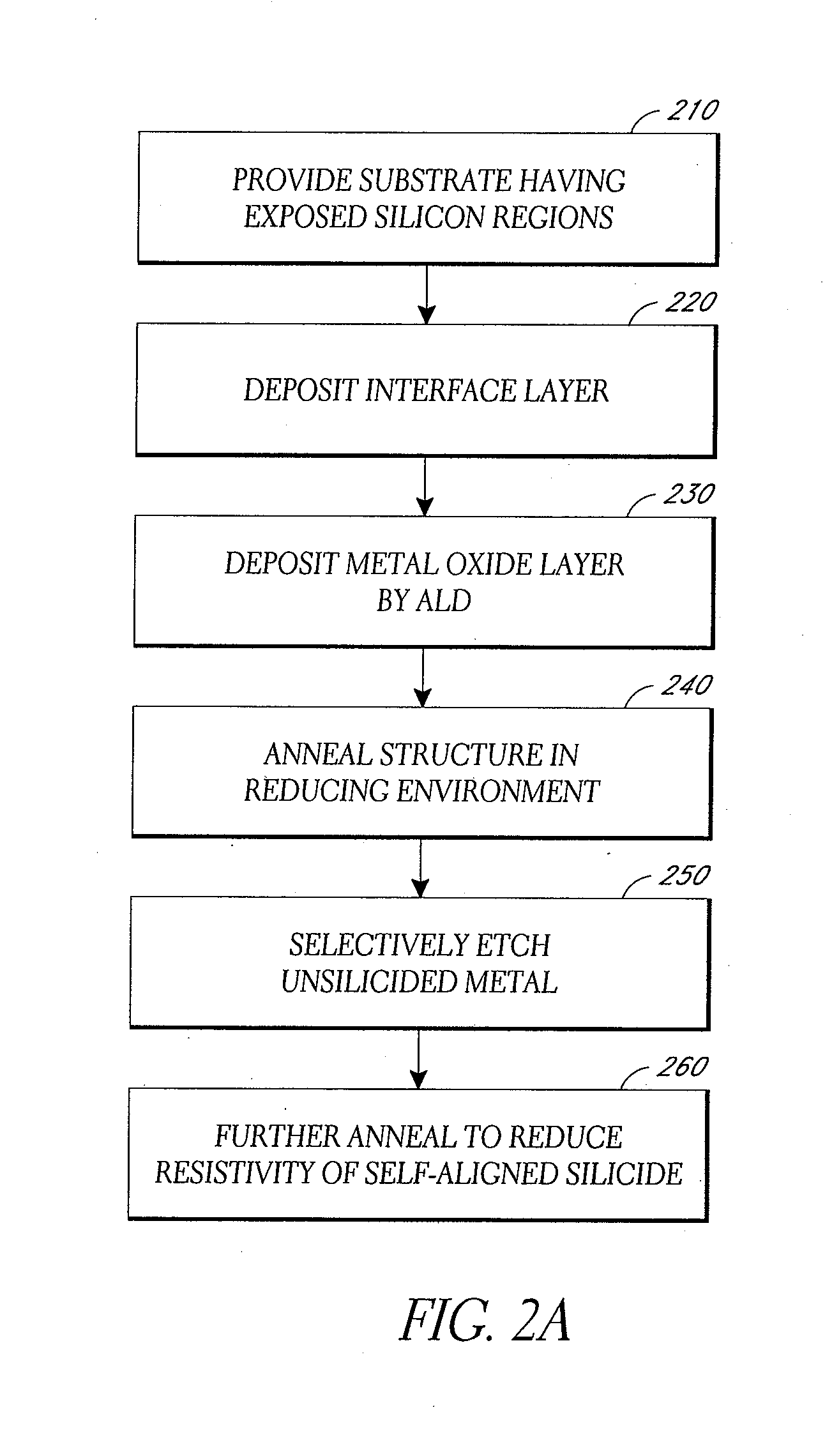

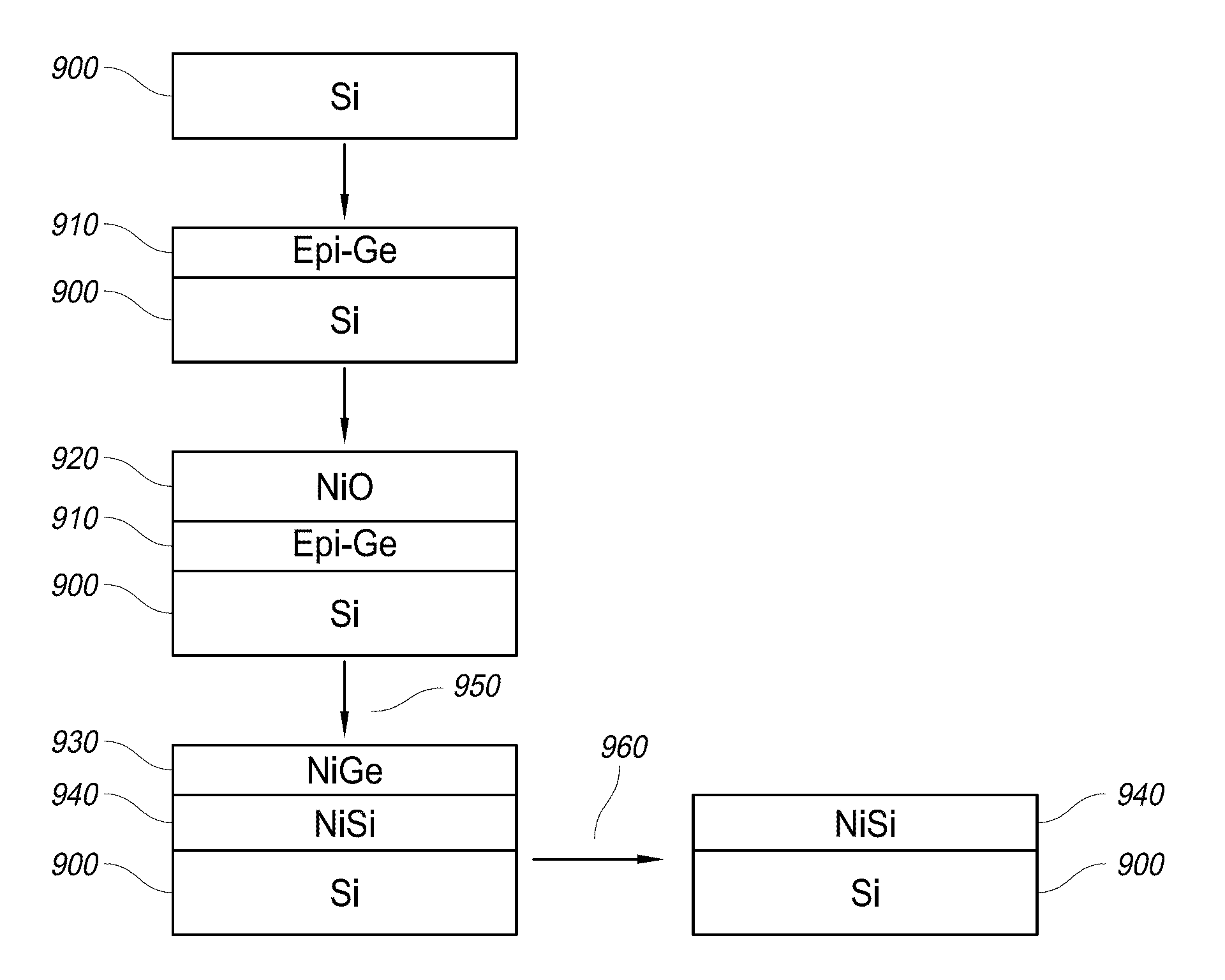

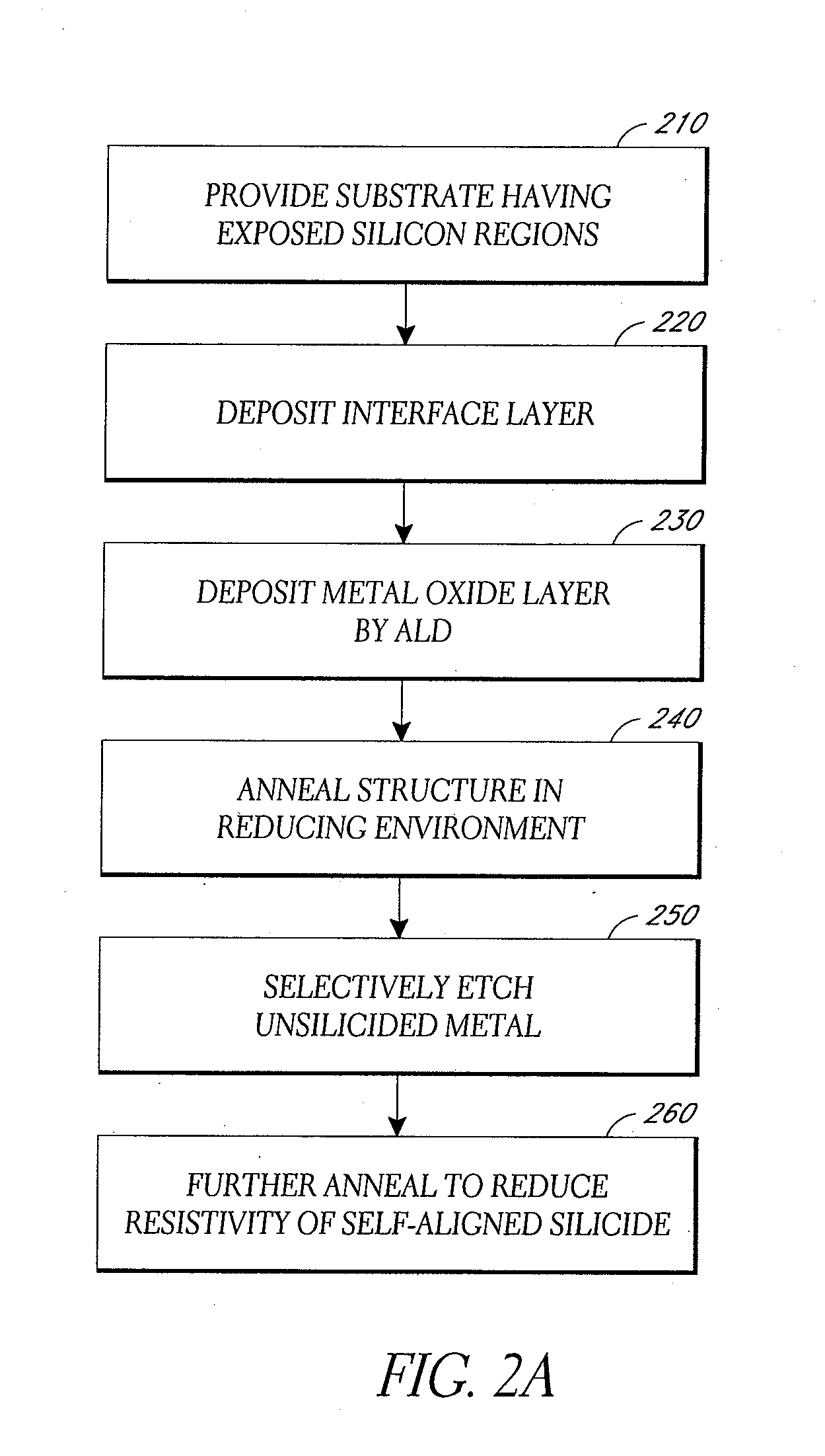

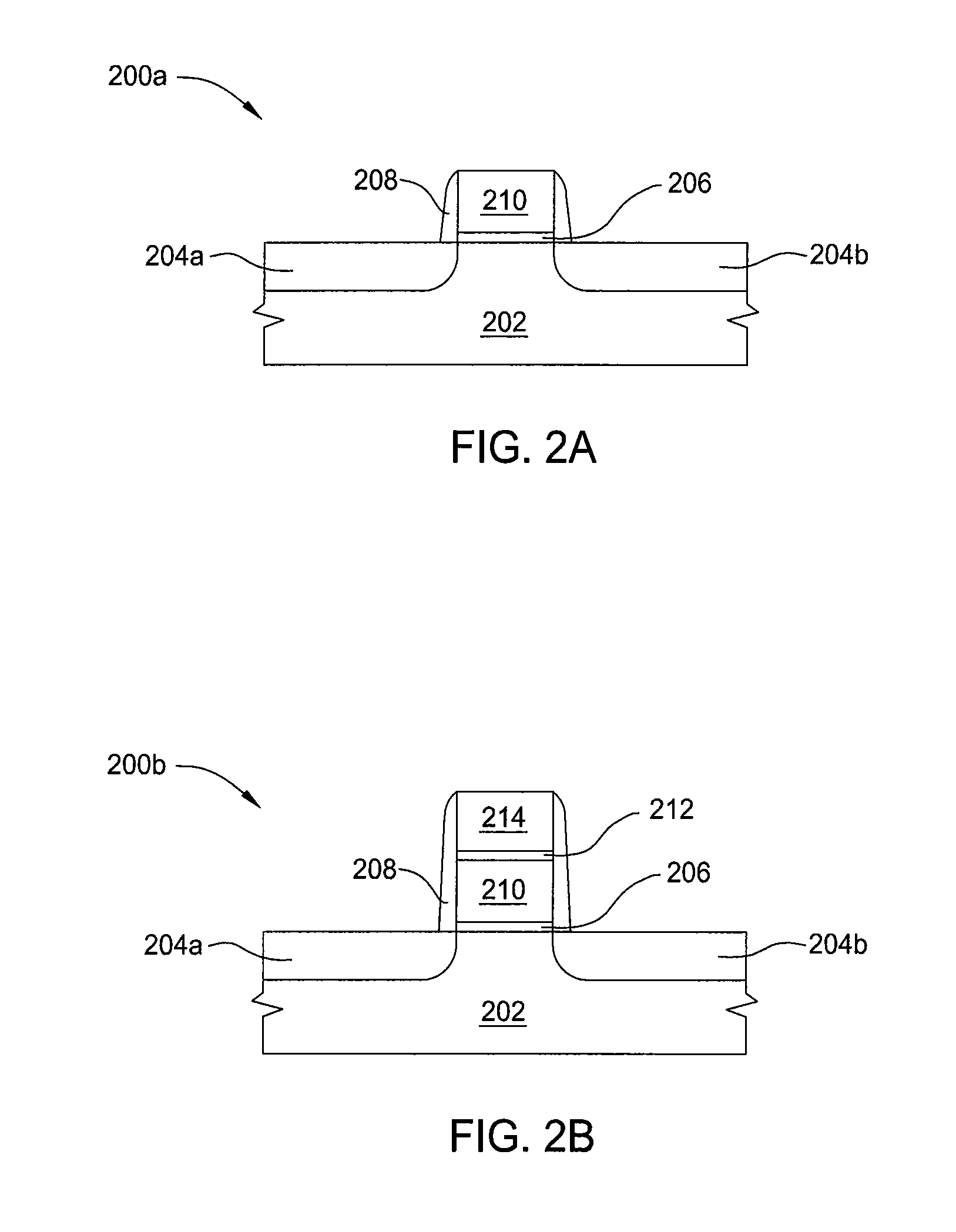

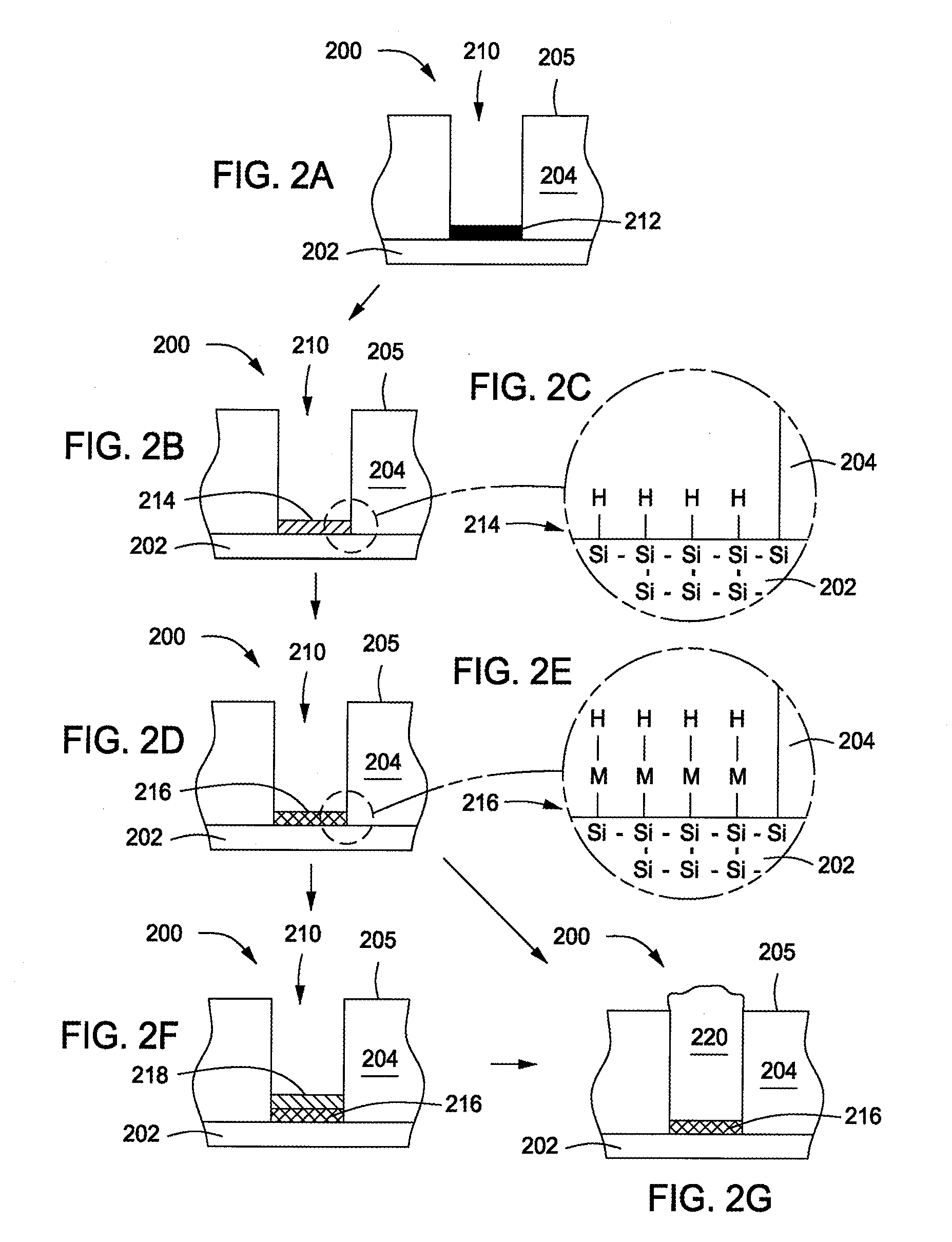

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD. Nickel thin films can be used directly in silicidation and germanidation processes.

Owner:ASM INTERNATIONAL

Metal silicide, metal germanide, methods for making the same

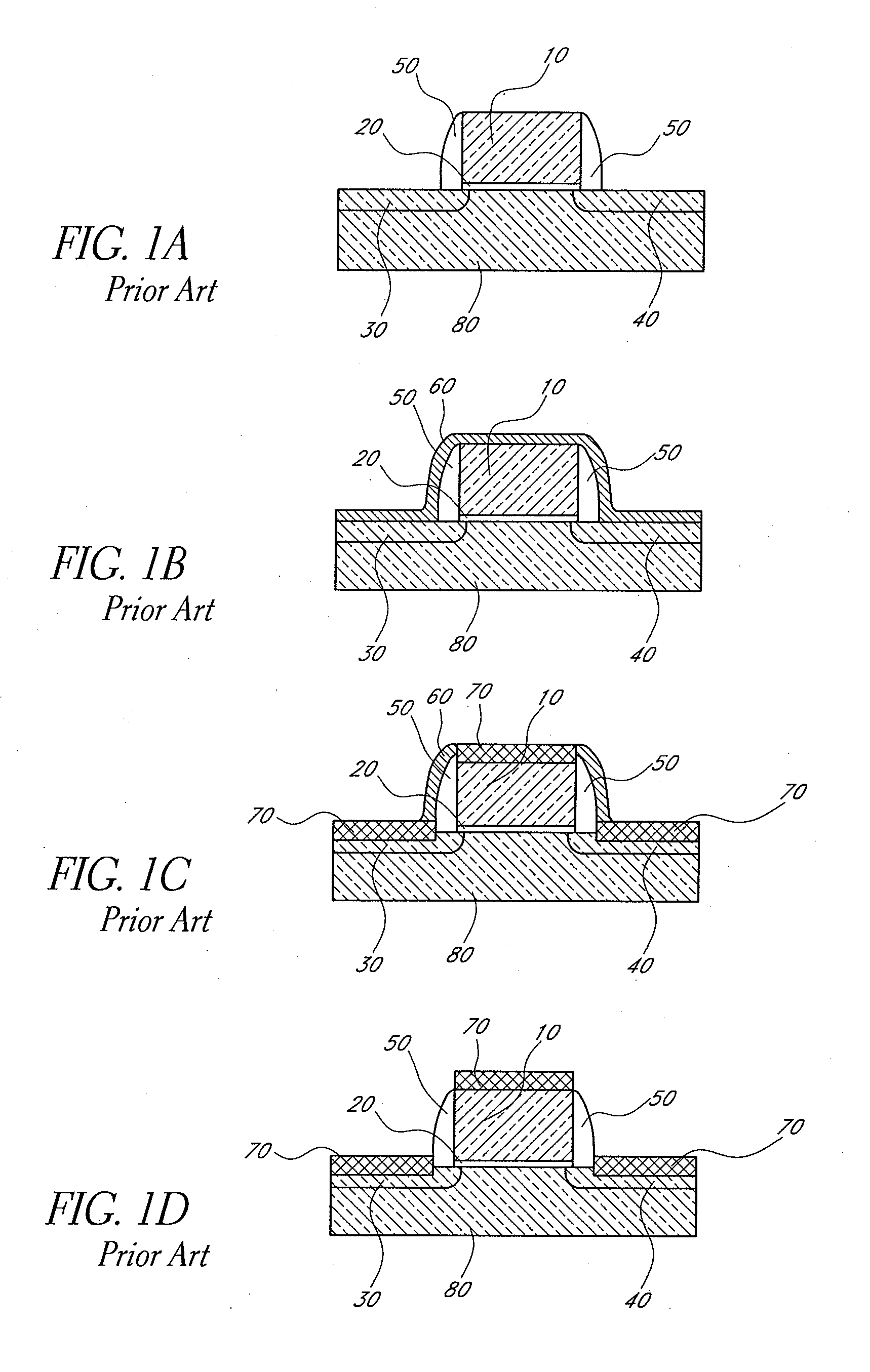

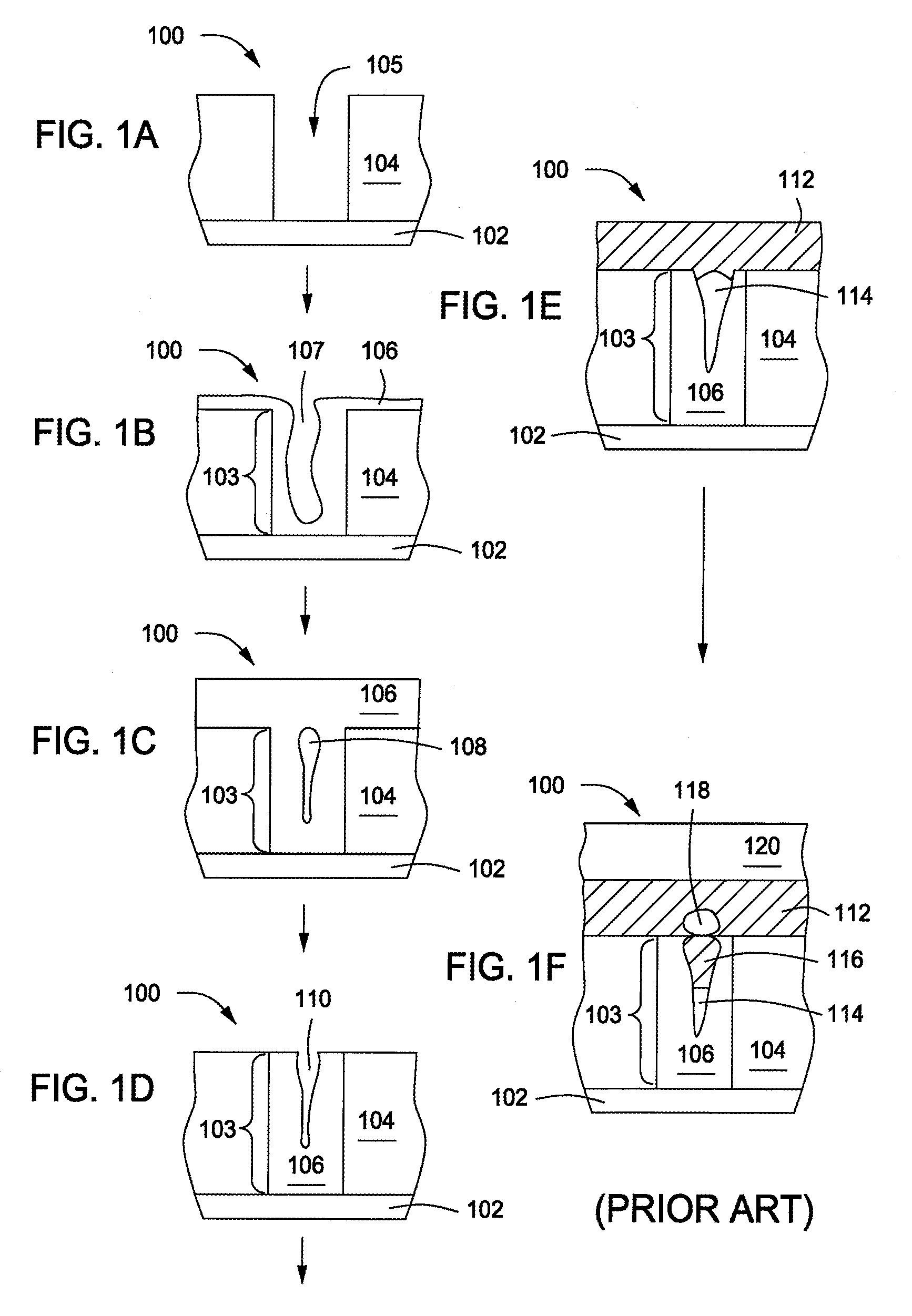

ActiveUS20120270393A1Prevent oxidationSelective silicidationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal silicideGermanide

In one aspect, methods of silicidation and germanidation are provided. In some embodiments, methods for forming metal silicide can include forming a non-oxide interface, such as germanium or solid antimony, over exposed silicon regions of a substrate. Metal oxide is formed over the interface layer. Annealing and reducing causes metal from the metal oxide to react with the underlying silicon and form metal silicide. Additionally, metal germanide can be formed by reduction of metal oxide over germanium, whether or not any underlying silicon is also silicided. In other embodiments, nickel is deposited directly and an interface layer is not used. In another aspect, methods of depositing nickel thin films by vapor phase deposition processes are provided. In some embodiments, nickel thin films are deposited by ALD.

Owner:ASM INTERNATIONAL

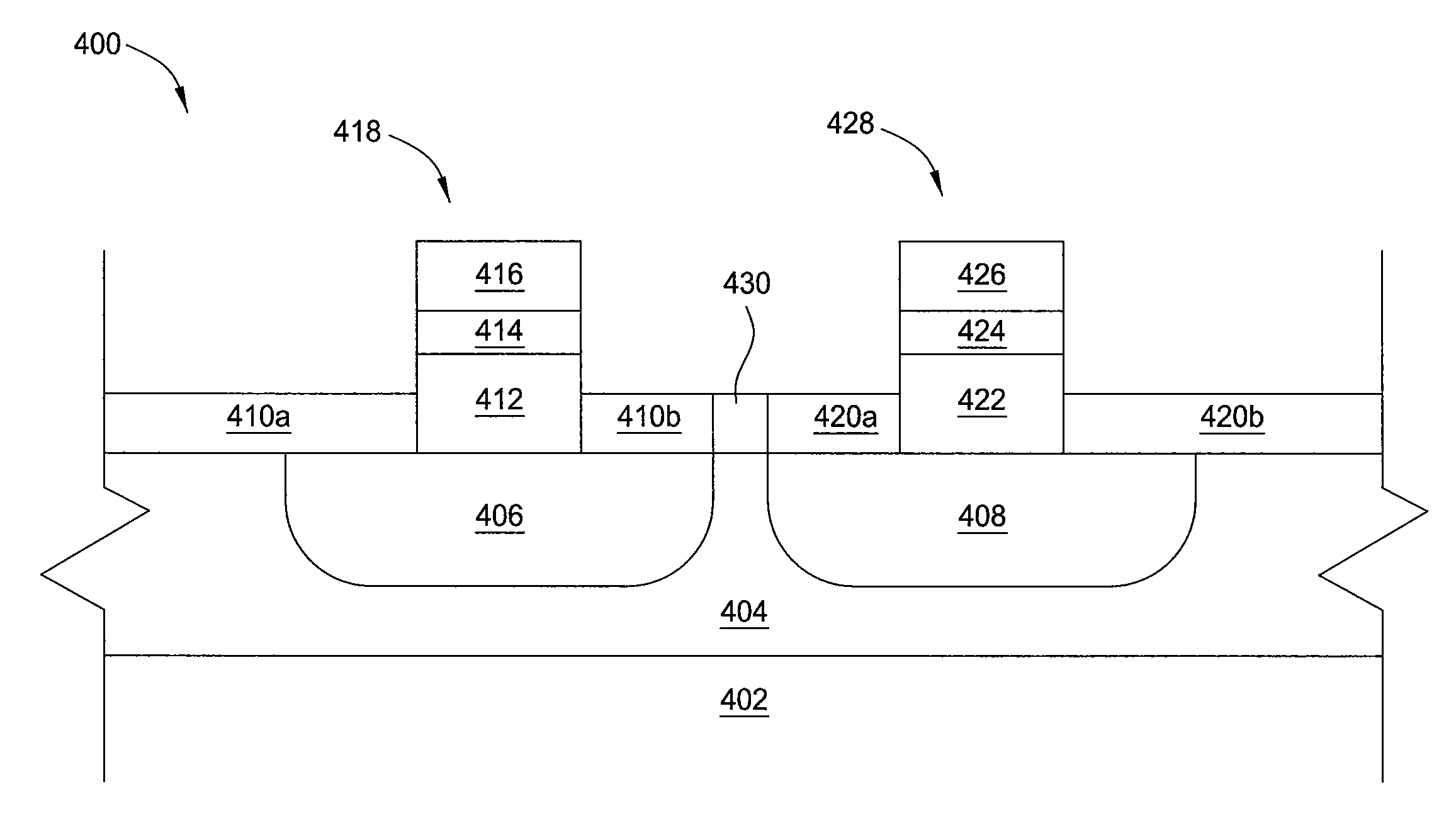

Nmos metal gate materials, manufacturing methods, and equipment using CVD and ald processes with metal based precursors

ActiveUS20110263115A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseMetallic materials

Embodiments of the invention generally provide methods for depositing metal-containing materials and compositions thereof. The methods include deposition processes that form metal, metal carbide, metal silicide, metal nitride, and metal carbide derivatives by a vapor deposition process, including thermal decomposition, CVD, pulsed-CVD, or ALD. In one embodiment, a method for processing a substrate is provided which includes depositing a dielectric material having a dielectric constant greater than 10, forming a feature definition in the dielectric material, depositing a work function material conformally on the sidewalls and bottom of the feature definition, and depositing a metal gate fill material on the work function material to fill the feature definition, wherein the work function material is deposited by reacting at least one metal-halide precursor having the formula MXY, wherein M is tantalum, hafnium, titanium, and lanthanum, X is a halide selected from the group of fluorine, chlorine, bromine, or iodine, and y is from 3 to 5.

Owner:APPLIED MATERIALS INC

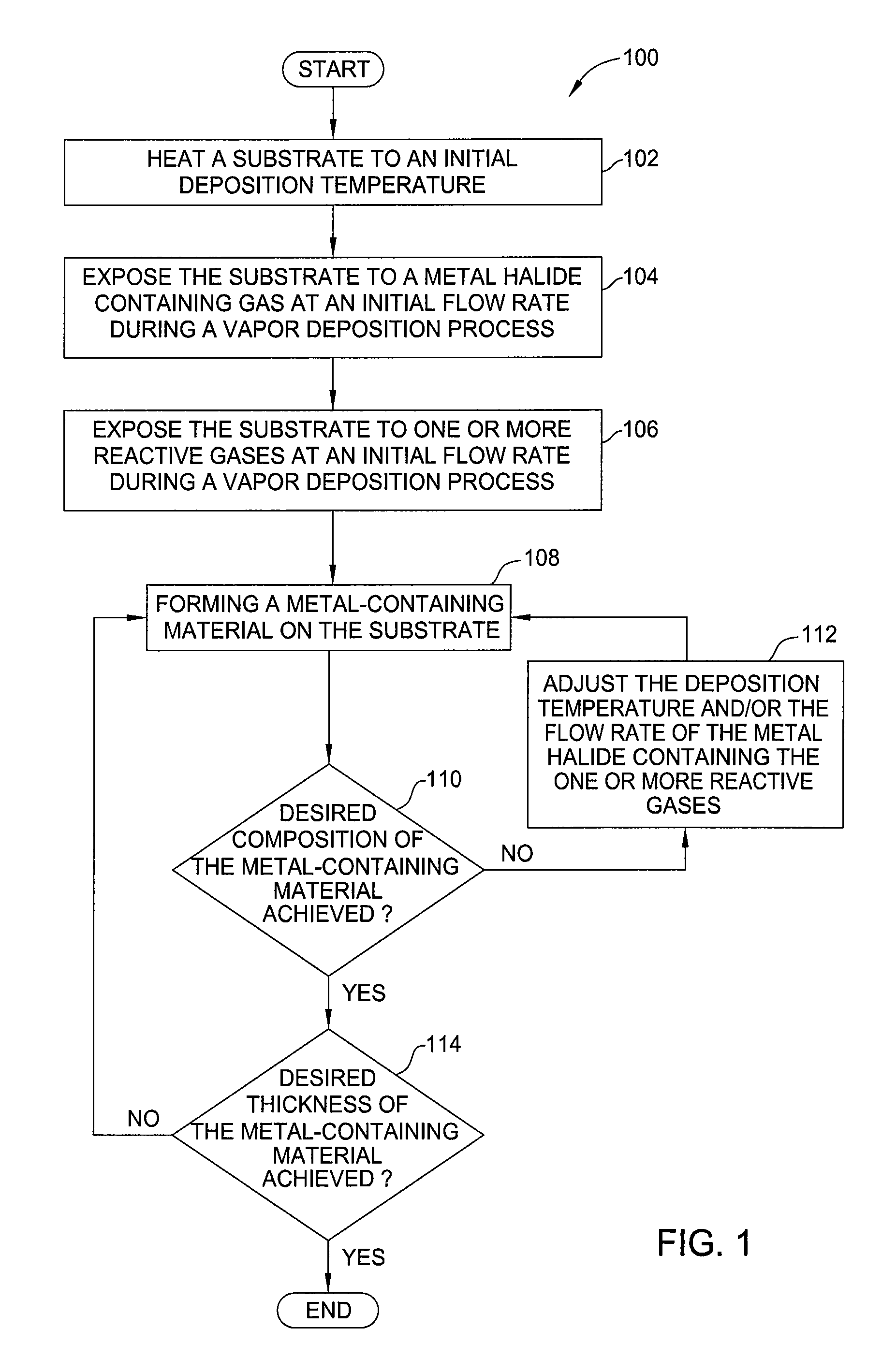

Deposition of metal borides and silicides

ActiveUS20170306479A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal silicideMetal halides

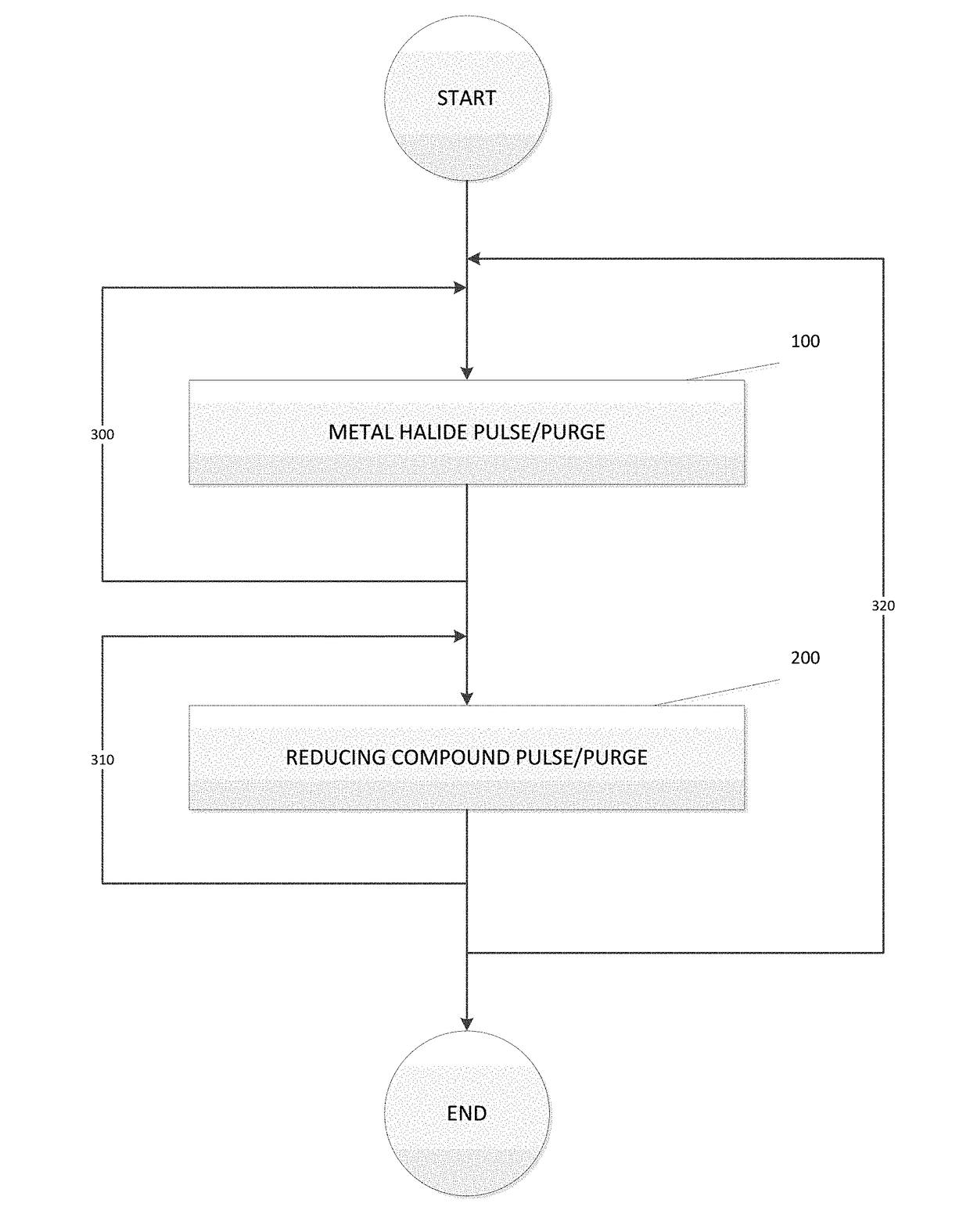

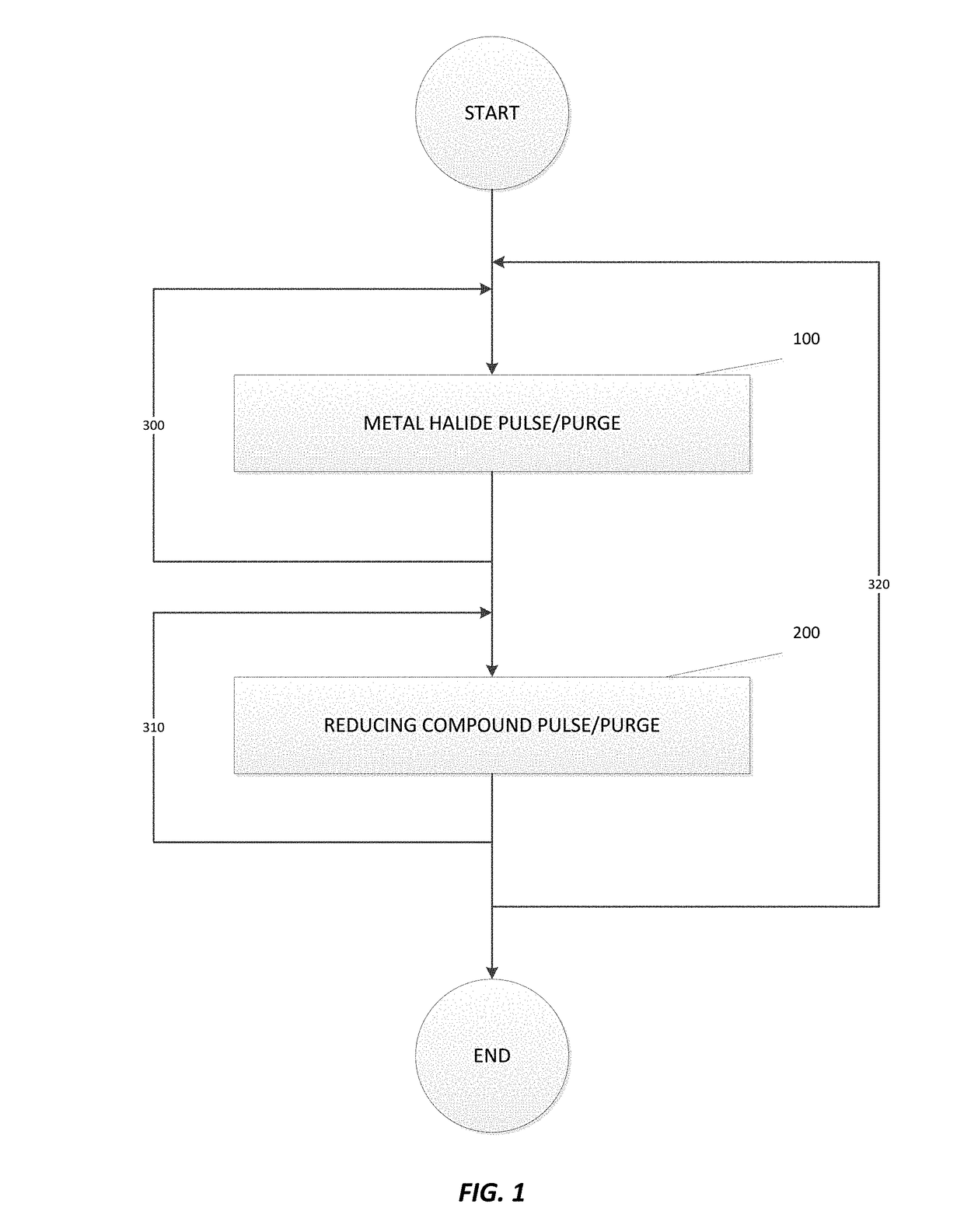

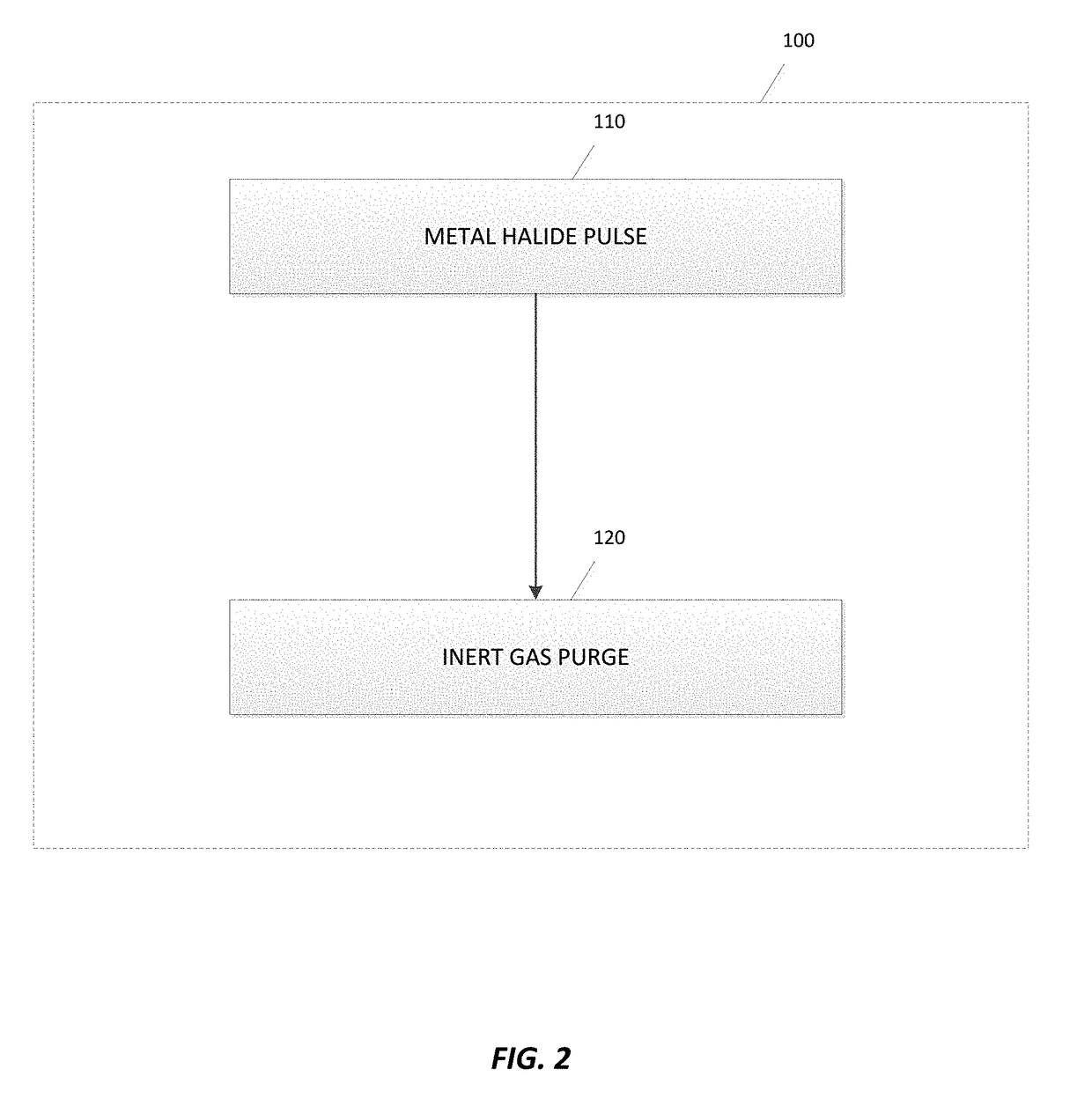

A method for depositing a metal film onto a substrate is disclosed. In particular, the method comprises pulsing a metal halide precursor onto the substrate and pulsing a reducing precursor onto the substrate. A reaction between the metal halide precursor and the reducing precursor forms a metal film. Specifically, the method discloses forming a metal boride or a metal silicide film.

Owner:ASM IP HLDG BV

Method of Manufacturing A Semiconductor Device

ActiveUS20130171818A1Improve thermal stabilityStabilize bonding structureSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

Method of selectively depositing a thin film material at a semiconductor interface

InactiveUS20070108404A1Detergent mixture composition preparationSemiconductor/solid-state device manufacturingDevice formMetal silicide

Embodiments of the invention provide processes to form a high quality contact level connection to devices formed on a substrate. In one embodiment, a method for depositing a material on a substrate is provided which includes exposing the substrate to a buffered oxide etch solution to form a silicon hydride layer during a pretreatment process, depositing a metal silicide layer on the substrate, and depositing a first metal layer (e.g., tungsten) on the metal silicide layer. The buffered oxide etch solution may contain hydrogen fluoride and an alkanolamine compound, such as ethanolamine diethanolamine, or triethanolamine. The metal silicide layer may contain cobalt, nickel, or tungsten and may be deposited by an electroless deposition process. In one example, the substrate is exposed to an electroless deposition solution containing a solvent and a complexed metal compound.

Owner:APPLIED MATERIALS INC

Semiconductor Devices Having Reduced Contact Resistance

ActiveUS20180090583A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialMetal silicide

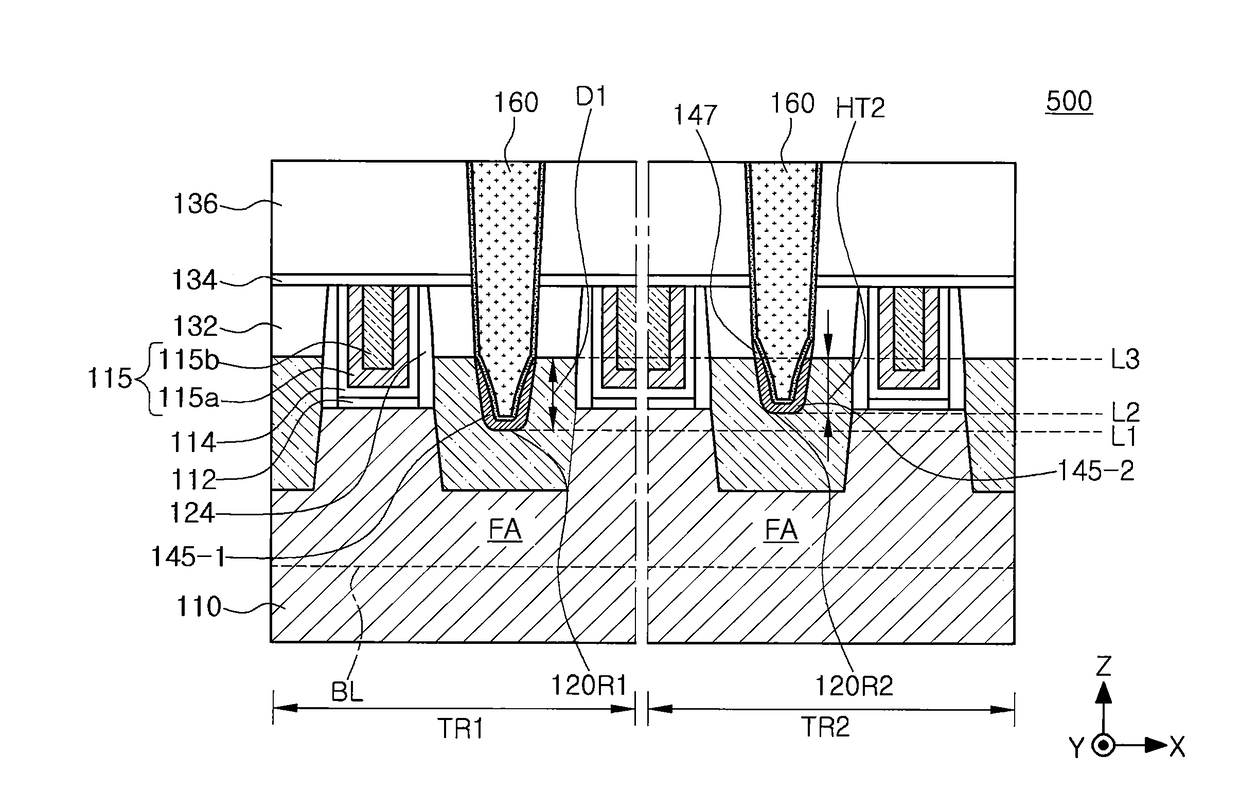

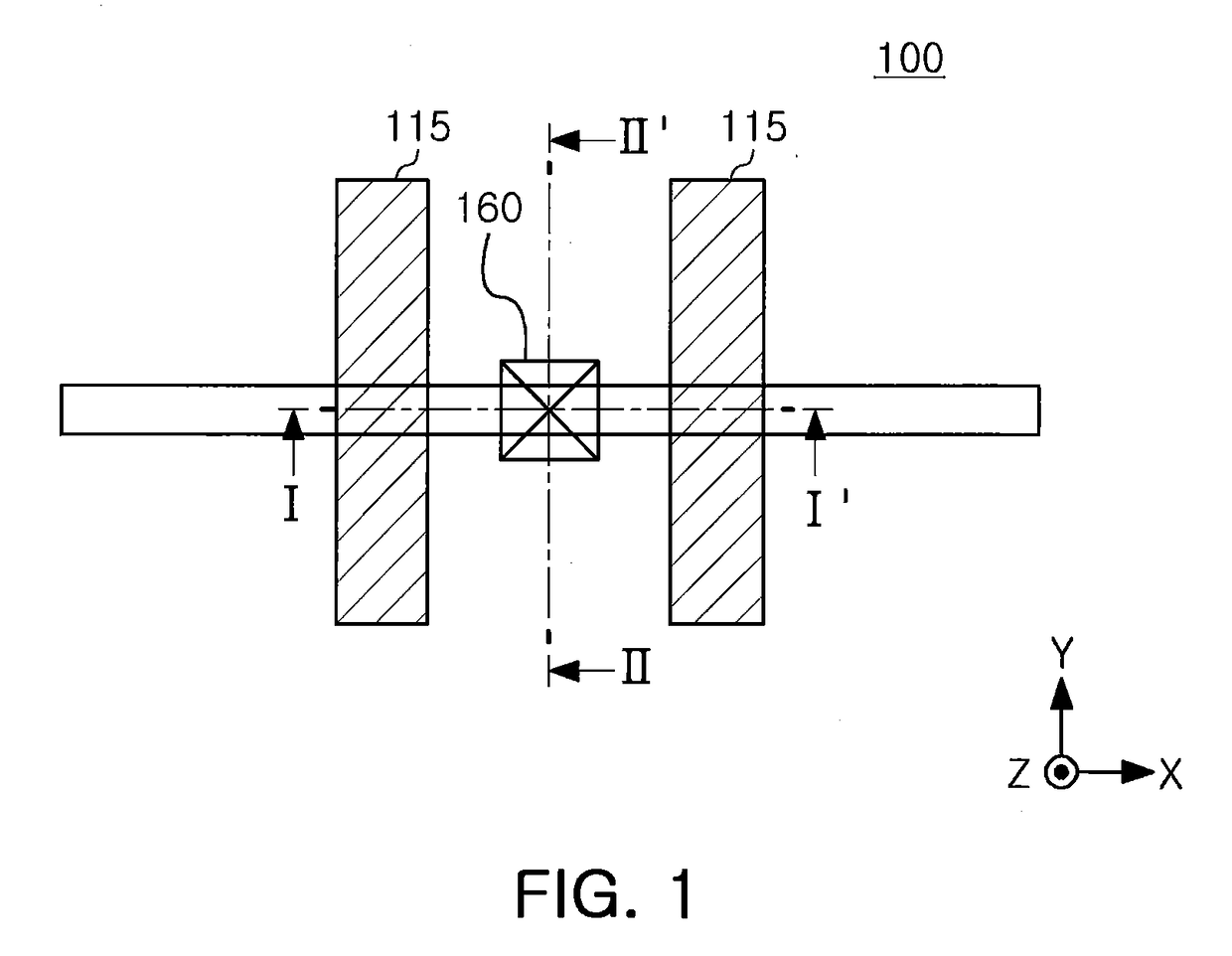

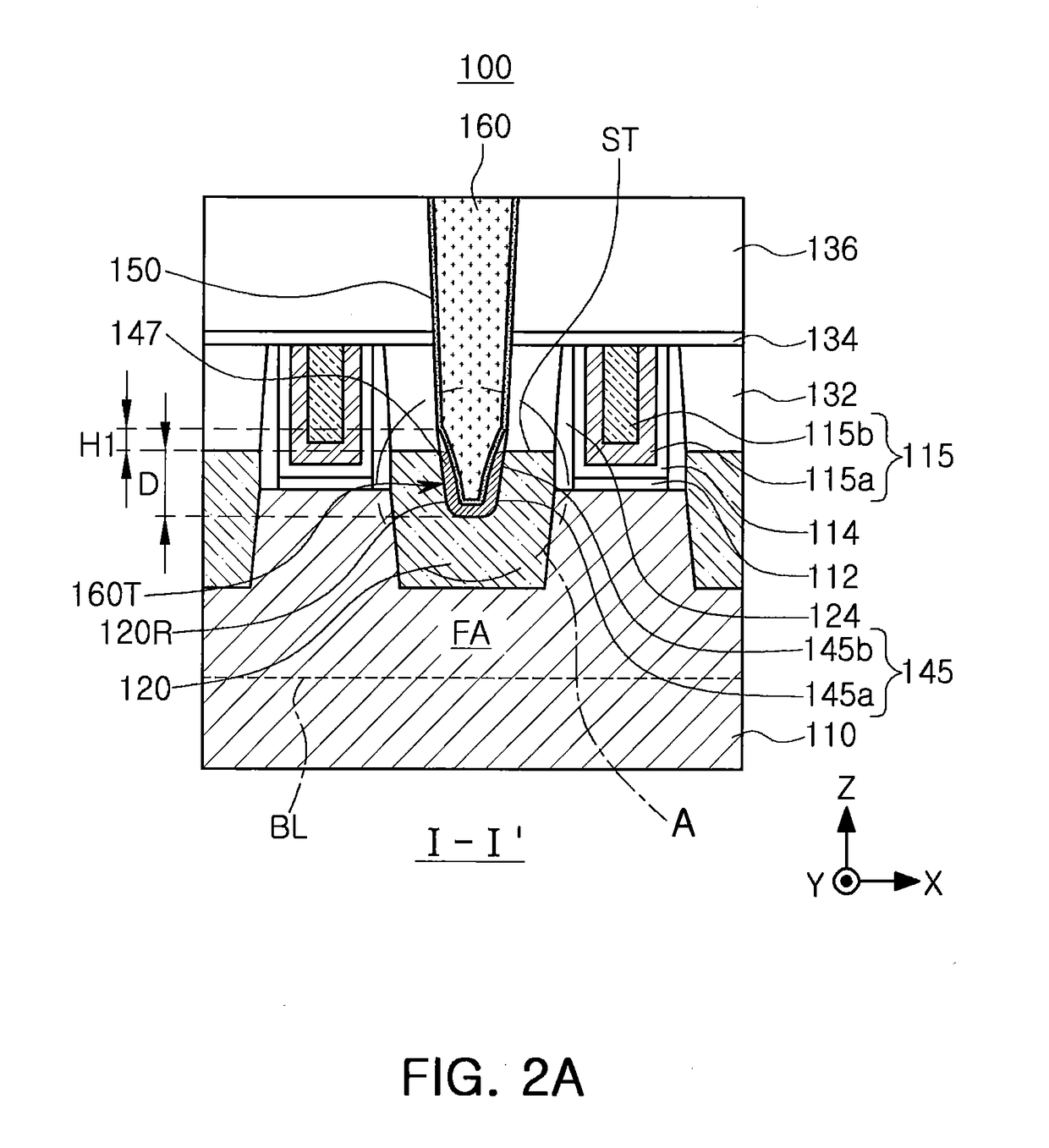

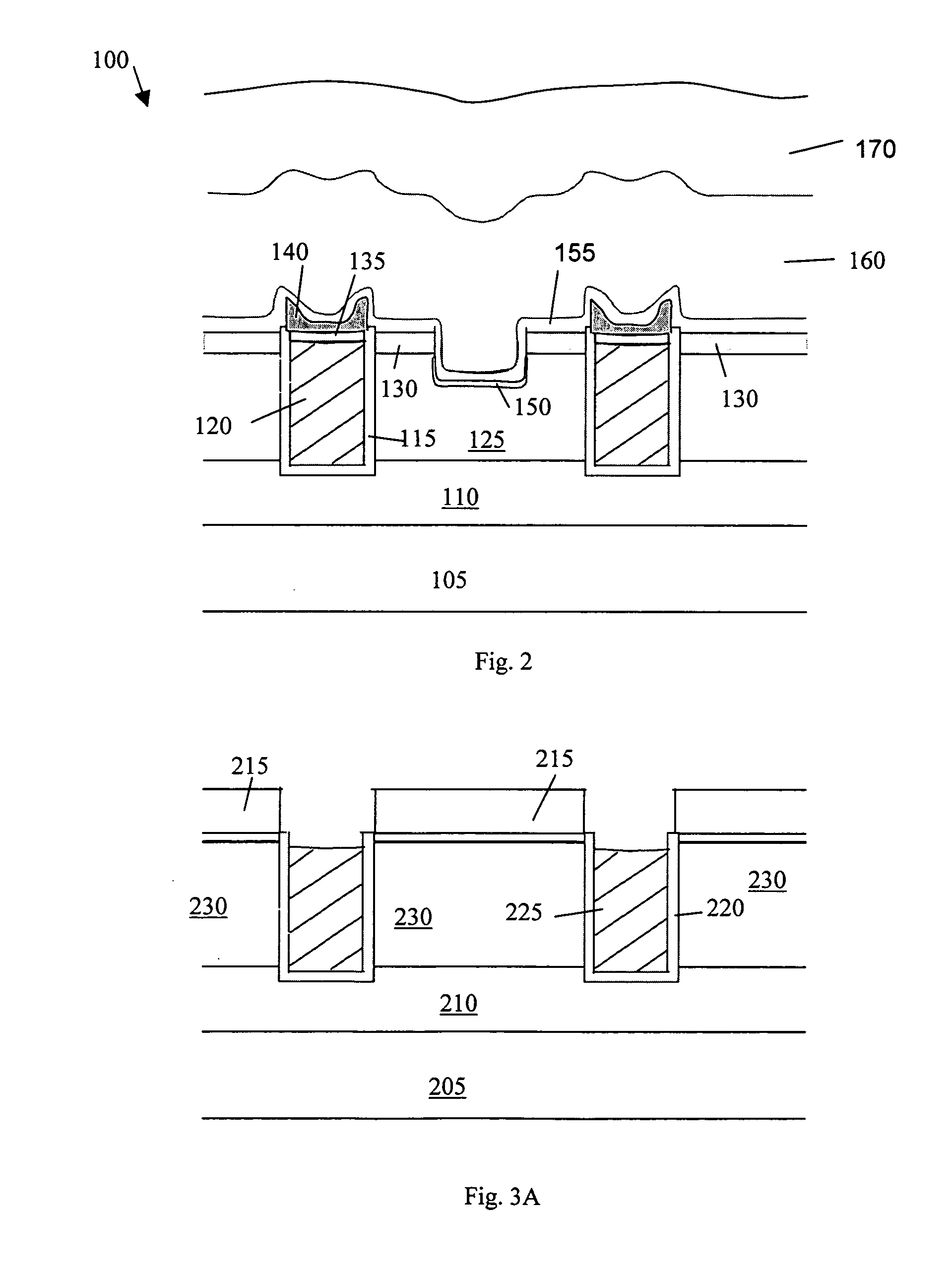

A semiconductor device includes a substrate including an active region, a gate structure, source / drain regions, ones of the source / drain regions having an upper surface in which a recessed region is formed, a contact plug on the source / drain regions and extending in a direction substantially perpendicular to an upper surface of the substrate from an interior of the recessed region, a metal silicide film on an internal surface of the recessed region and including a first portion between a bottom surface of the recessed region and a lower surface of the contact plug and a second portion between a side wall of the recessed region and a side surface of the contact plug, and a metal layer connected to an upper portion of the metal silicide film and on a side surface of a region of the contact plug.

Owner:SAMSUNG ELECTRONICS CO LTD

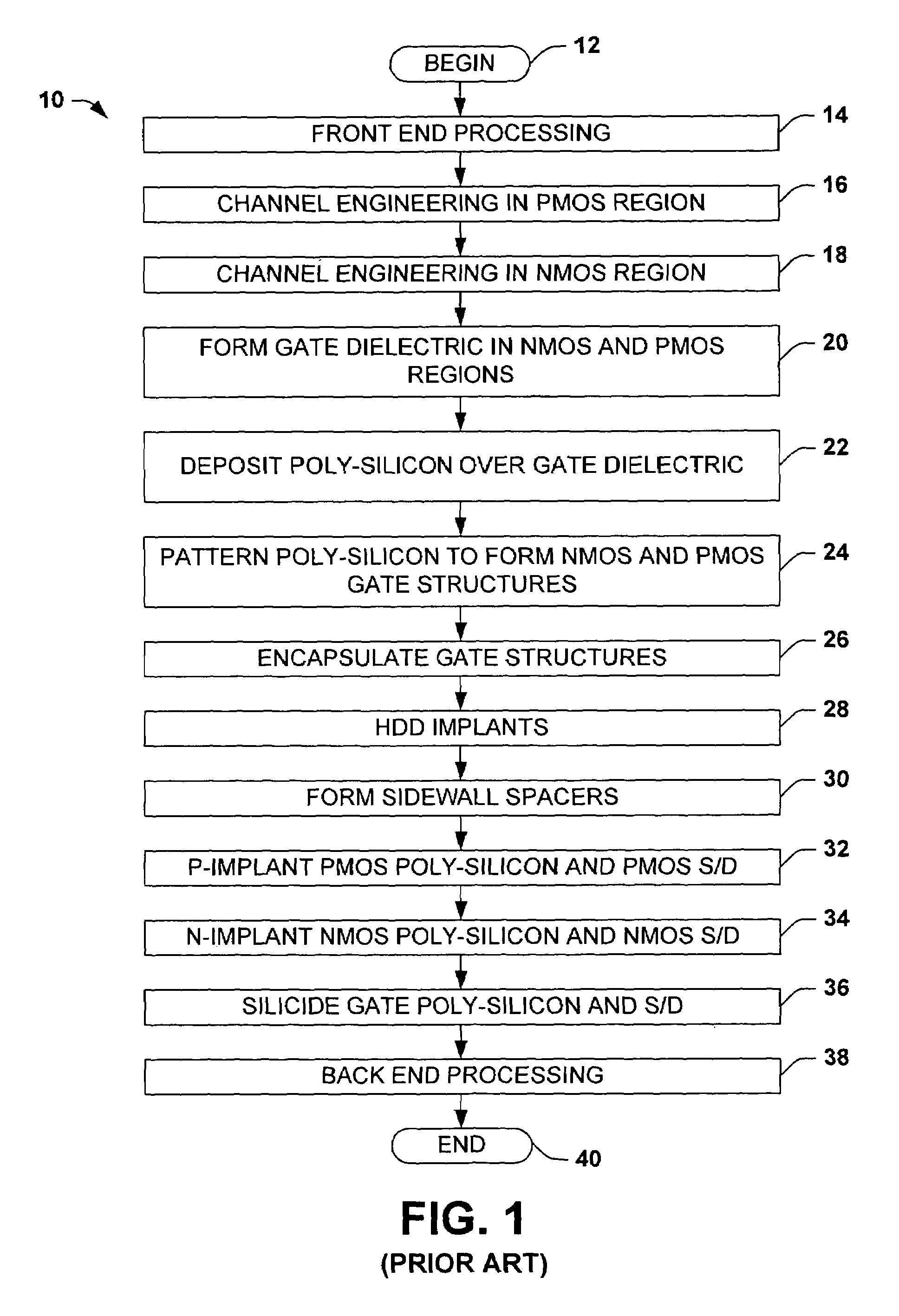

Transistors, integrated circuits, systems, and processes of manufacture with improved work function modulation

ActiveUS20060084247A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantGate dielectric

A process (200) for making integrated circuits with a gate, uses a doped precursor (124, 126N and / or 126P) on barrier material (118) on gate dielectric (116). The process (200) involves totally consuming (271) the doped precursor (124, 126N and / or 126P) thereby driving dopants (126N and / or 126P) from the doped precursor (124) into the barrier material (118). An integrated circuit has a gate dielectric (116), a doped metallic barrier material (118, 126N and / or 126P) on the gate dielectric (116), and metal silicide (180) on the metallic barrier material (118). Other integrated circuits, transistors, systems and processes of manufacture are disclosed.

Owner:TEXAS INSTR INC

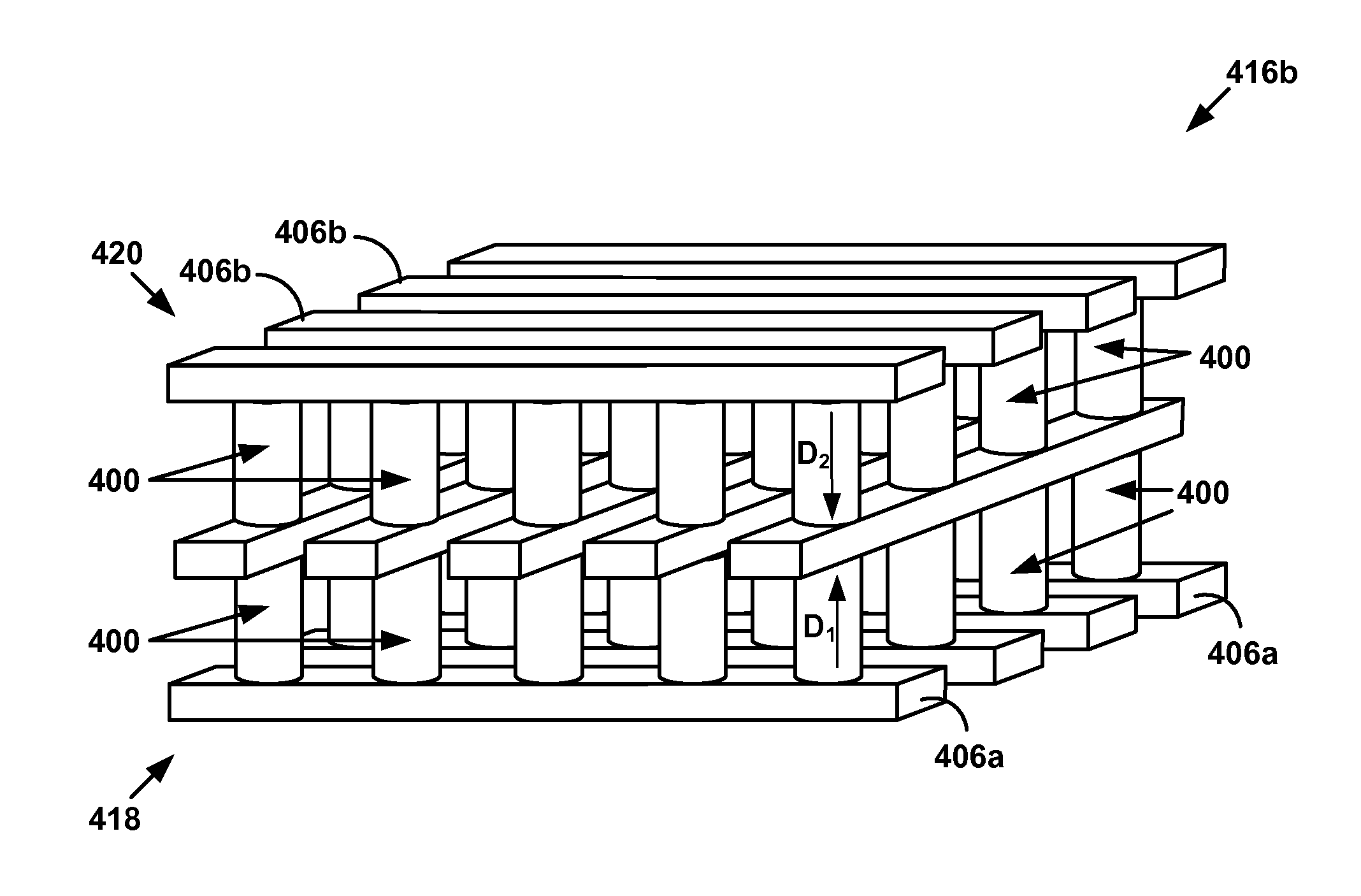

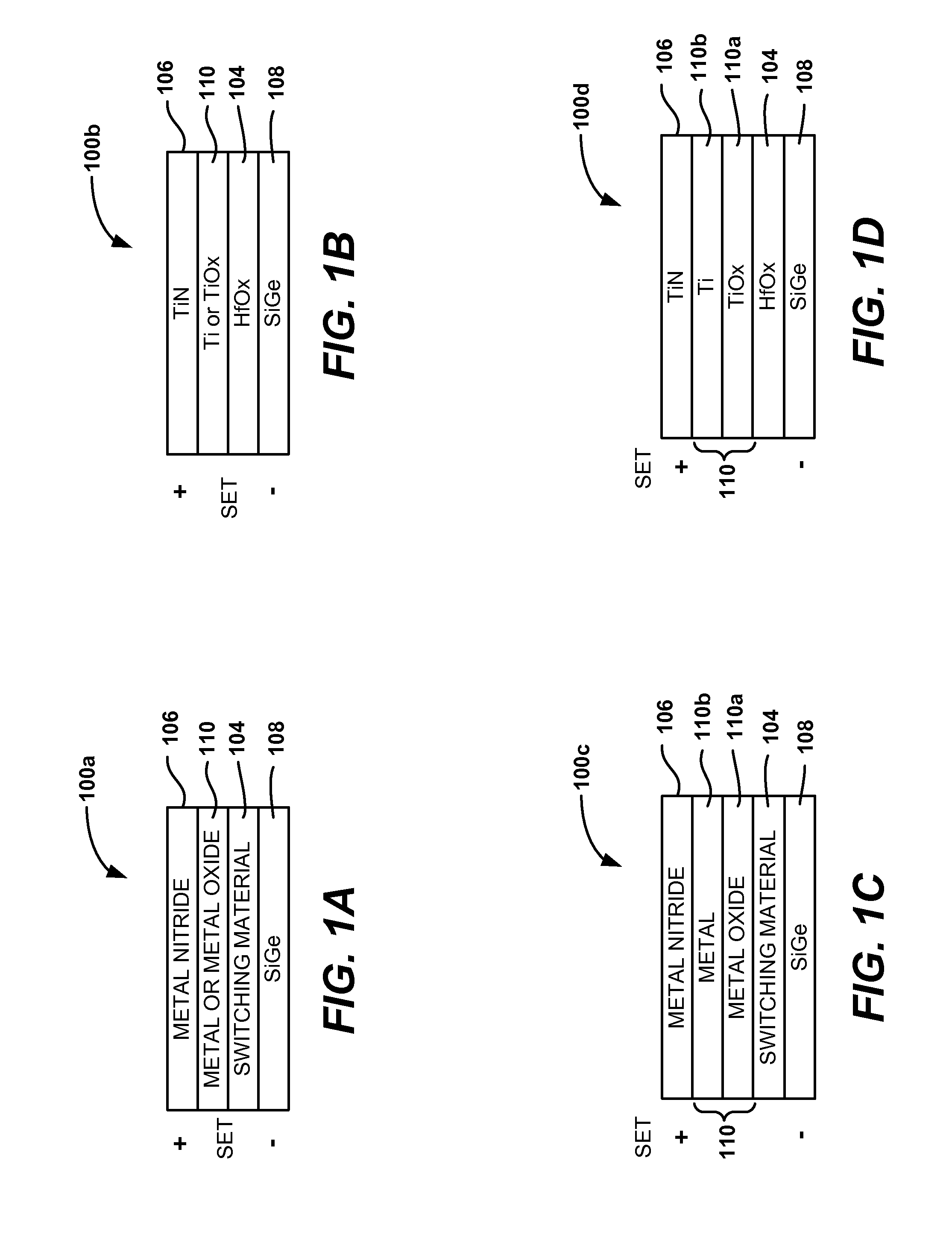

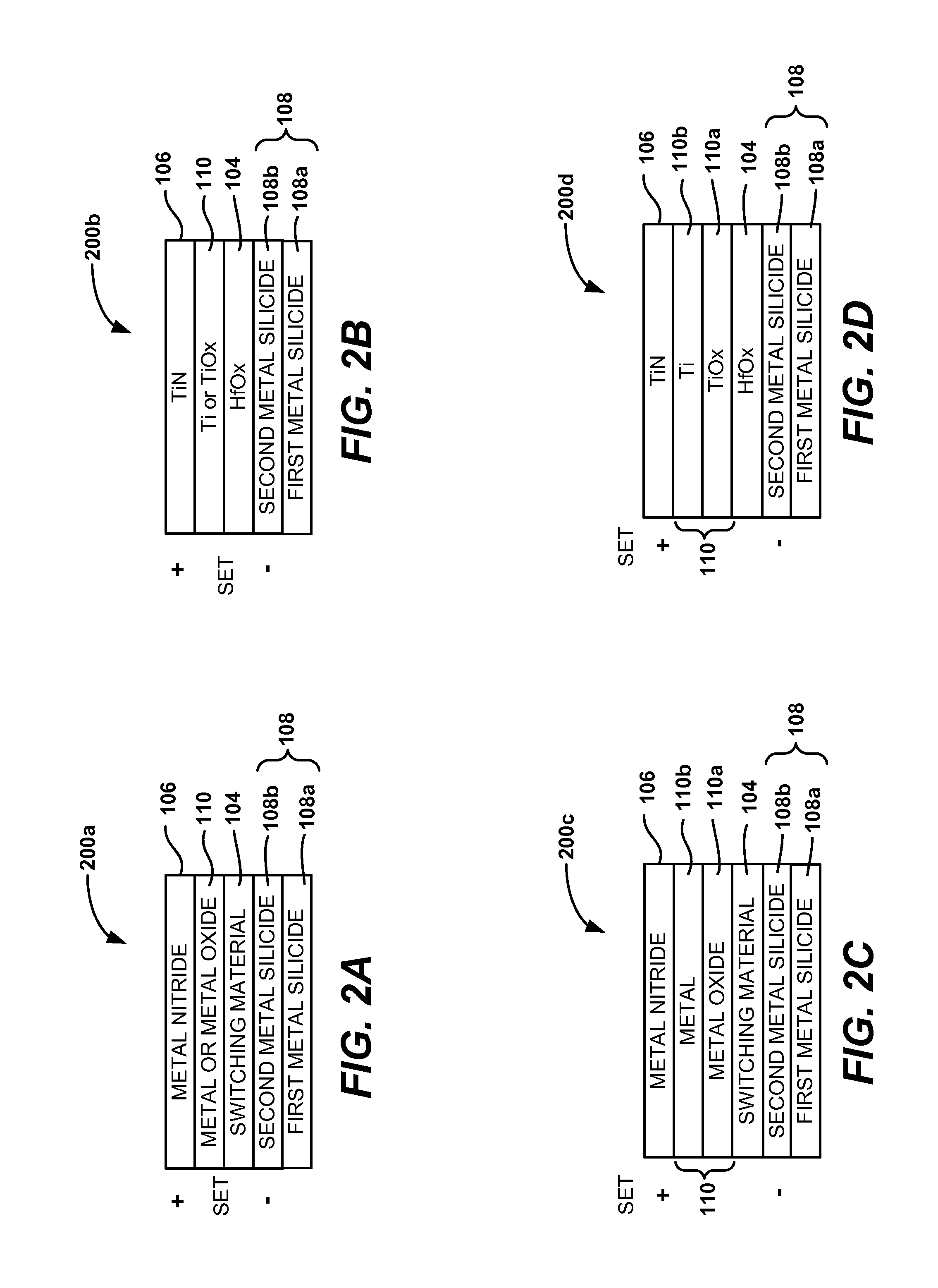

Bottom electrodes for use with metal oxide resistivity switching layers

ActiveUS20110227028A1Solid-state devicesSemiconductor/solid-state device manufacturingMetal silicideOptoelectronics

In a first aspect, an MIM stack is provided that includes (1) a first conductive layer comprising a first metal-silicide layer and a second metal-silicide layer; (2) a resistivity-switching layer comprising a metal oxide layer formed above the first conductive layer; and (3) a second conductive layer formed above the resistivity-switching layer. A memory cell may be formed from the MIM stack. Numerous other aspects are provided.

Owner:SANDISK TECH LLC

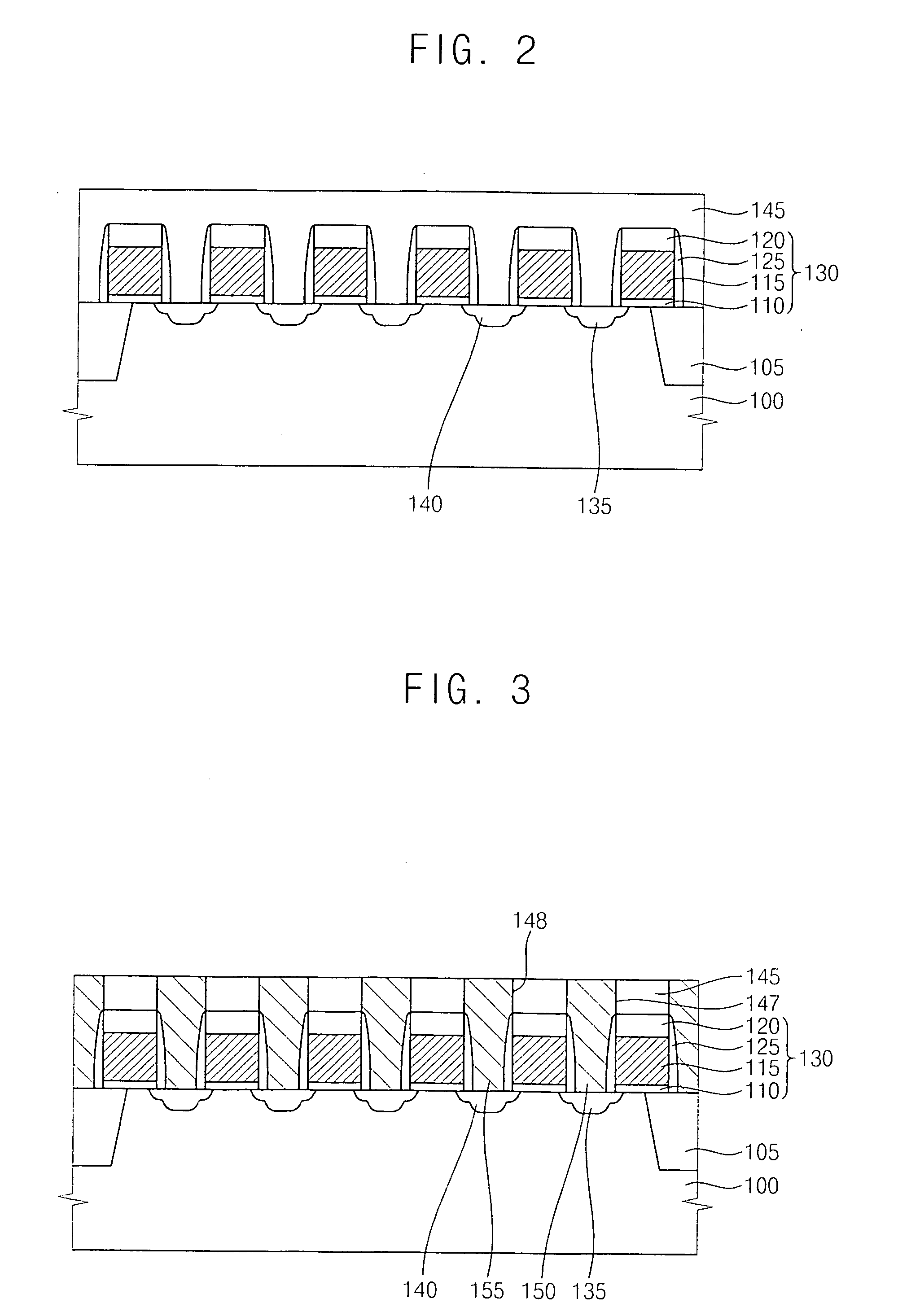

Etching solution for silicon oxide and method of manufacturing a semiconductor device using the same

InactiveUS20070090325A1Efficient removalAvoid damageDecorative surface effectsSolid-state devicesHydrogen fluorideDevice material

An etching solution for silicon oxide may be used in a process for enlarging an opening formed through a silicon oxide layer. The etching solution includes about 0.2 to about 5.0 percent by weight of a hydrogen fluoride solution, about 0.05 to about 20.0 percent by weight of an ammonium fluoride solution, about 40.0 to about 70.0 percent by weight of an alkyl hydroxide solution and remaining water. The etching solution may etch the silicon oxide layer without damage to a metal silicide layer exposed by the opening.

Owner:CONVERSANT INTPROP MANAGEMENT INC

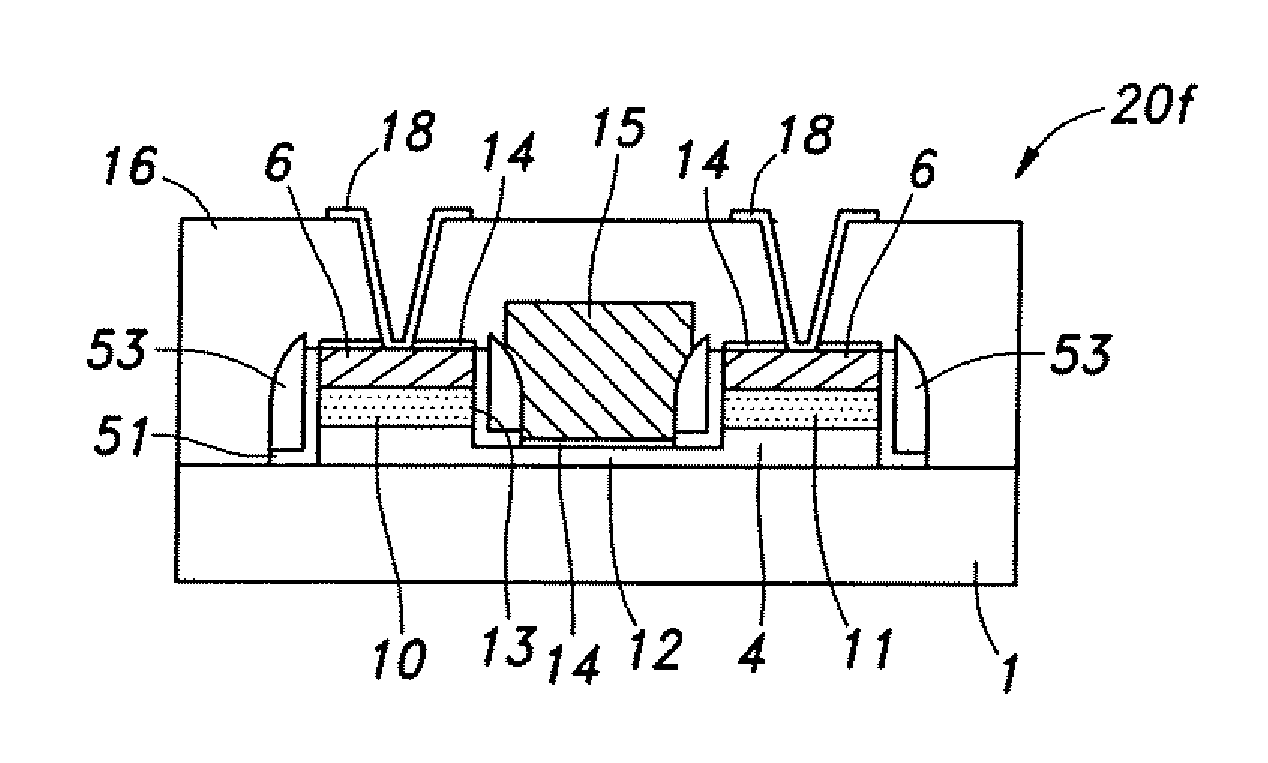

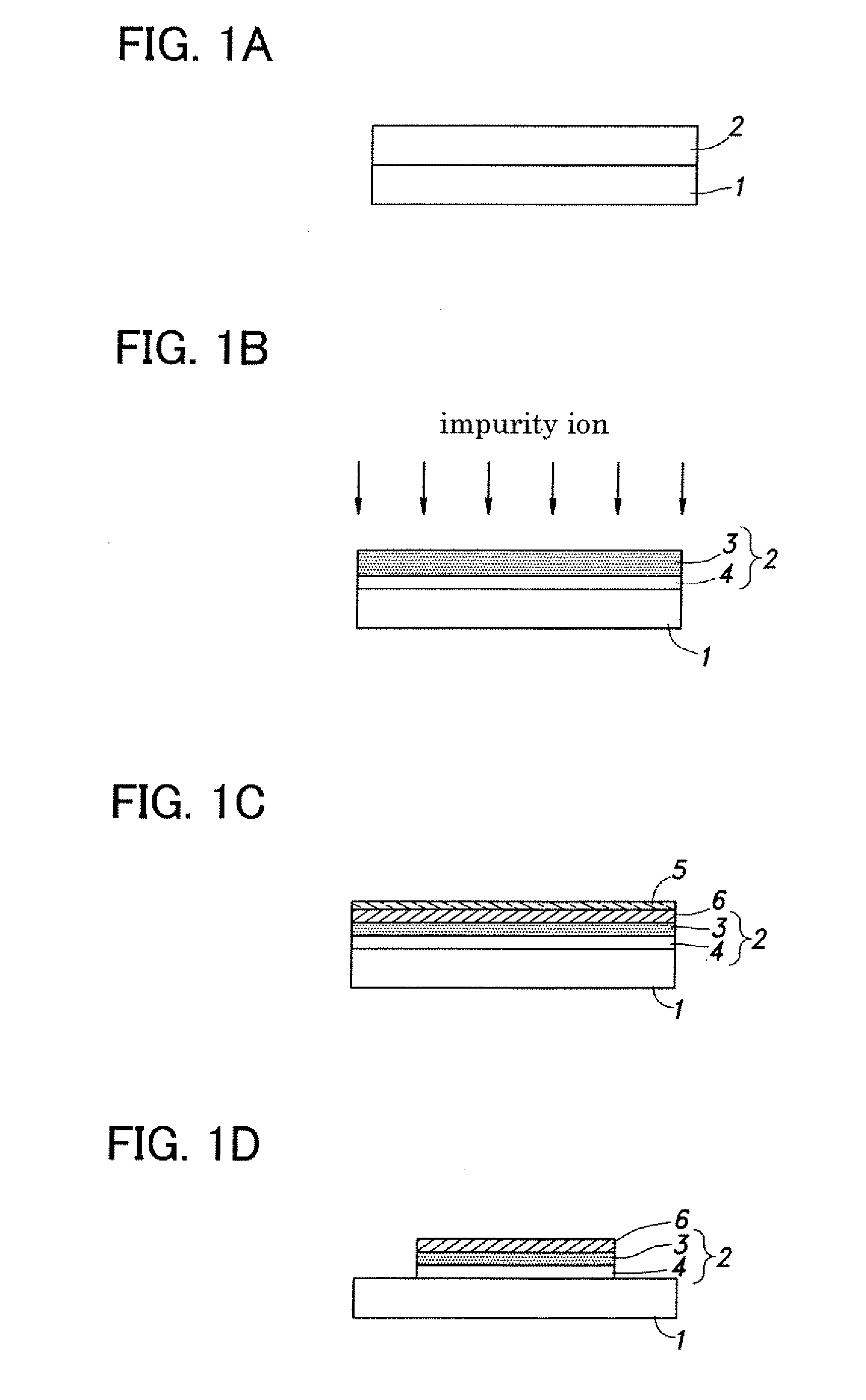

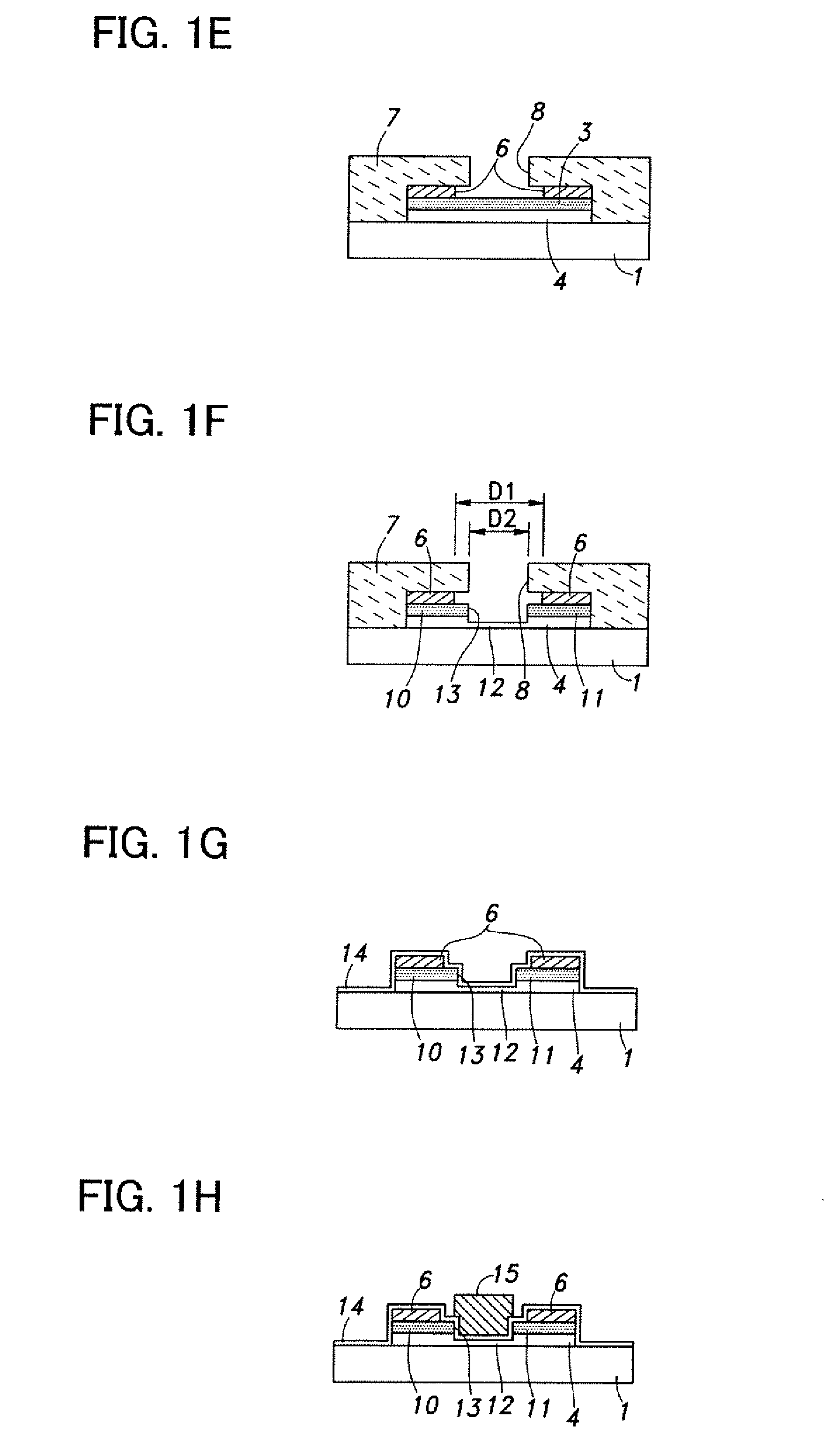

Semiconductor device and manufacturing method thereof

InactiveUS20090096024A1Less heatConsumes less powerSolid-state devicesSemiconductor/solid-state device manufacturingMetal silicideSemiconductor

In a method for manufacturing a semiconductor device, a semiconductor film formed over an insulator is doped with an impurity element to a depth less than the thickness of the semiconductor film, thereby forming an impurity doped layer; a metal silicide layer is formed on the impurity doped layer; the metal silicide layer and the semiconductor film are etched to form a recessed portion; and a layer which is not doped with the impurity element and is located at the bottom of the recessed portion of the semiconductor film is thinned to make a channel formation region. Further, a gate electrode is formed in the recessed portion over the thinned non impurity doped layer, with an insulating film interposed therebetween.

Owner:SEMICON ENERGY LAB CO LTD

Methods for fabricating integrated circuits

ActiveUS20130065371A1Semiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideEngineering physics

Methods are provided for fabricating integrated circuits. One method includes etching a plurality of trenches into a silicon substrate and filling the trenches with an insulating material to delineate a plurality of spaced apart silicon fins. A layer of undoped silicon is epitaxially grown to form an upper, undoped region of the fins. Dummy gate structures are formed overlying and transverse to the plurality of fins and a back fill material fills between the dummy gate structures. The dummy gate structures are removed to expose a portion of the fins and a high-k dielectric material and a work function determining gate electrode material are deposited overlying the portion of the fins. The back fill material is removed to expose a second portion and metal silicide contacts are formed on the second portion. Conductive contacts are then formed to the work function determining material and to the metal silicide.

Owner:GLOBALFOUNDRIES INC

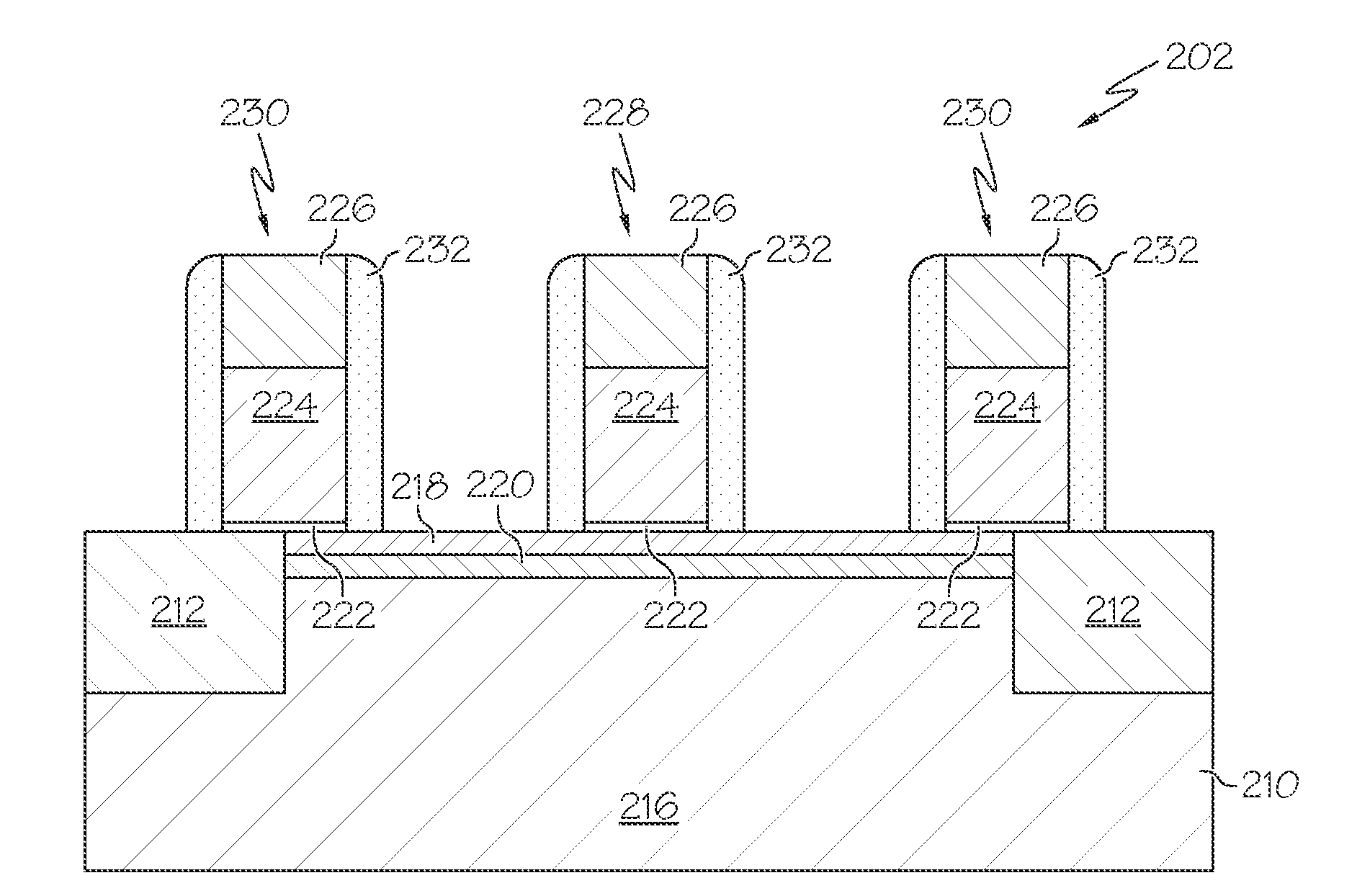

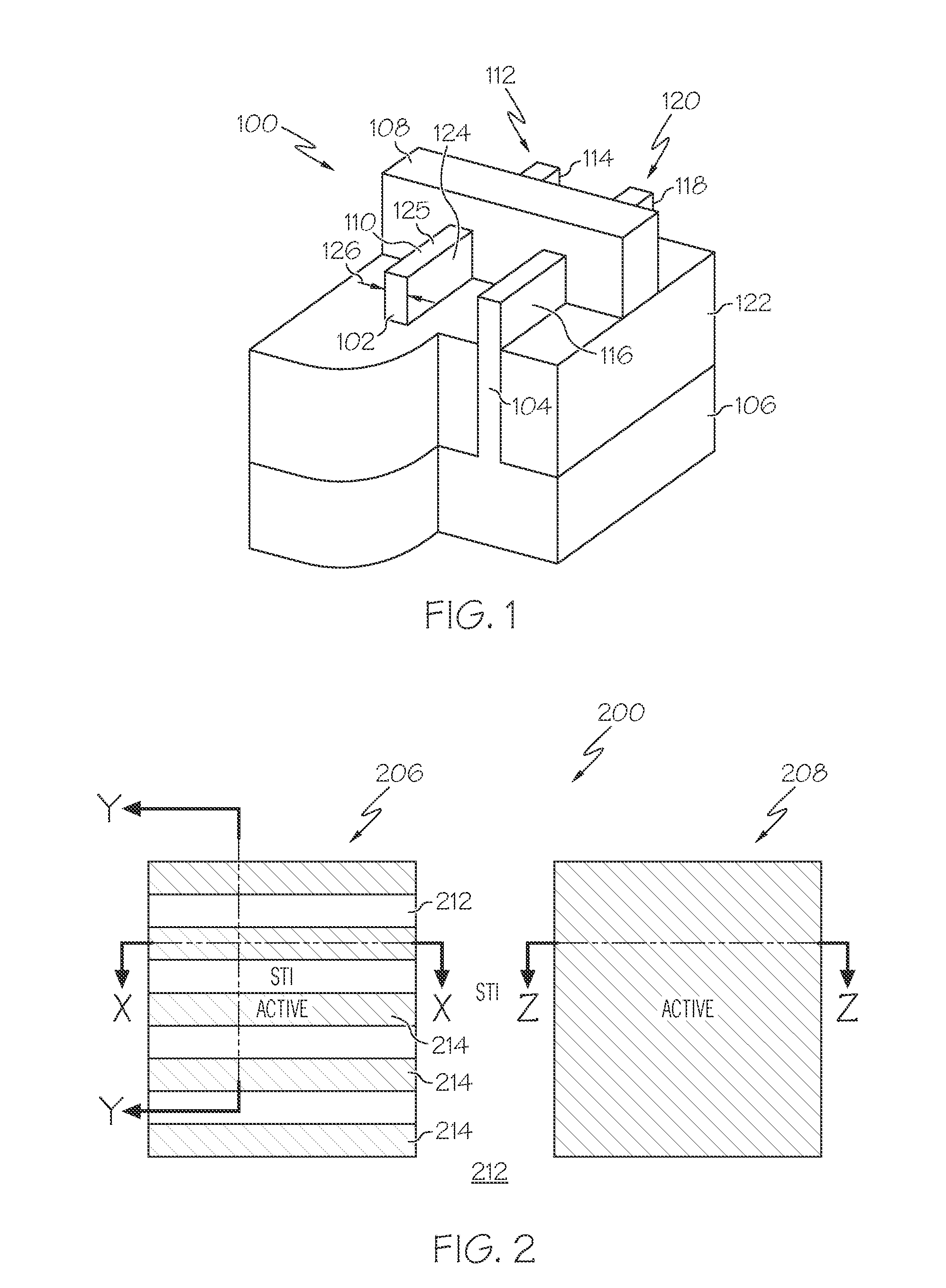

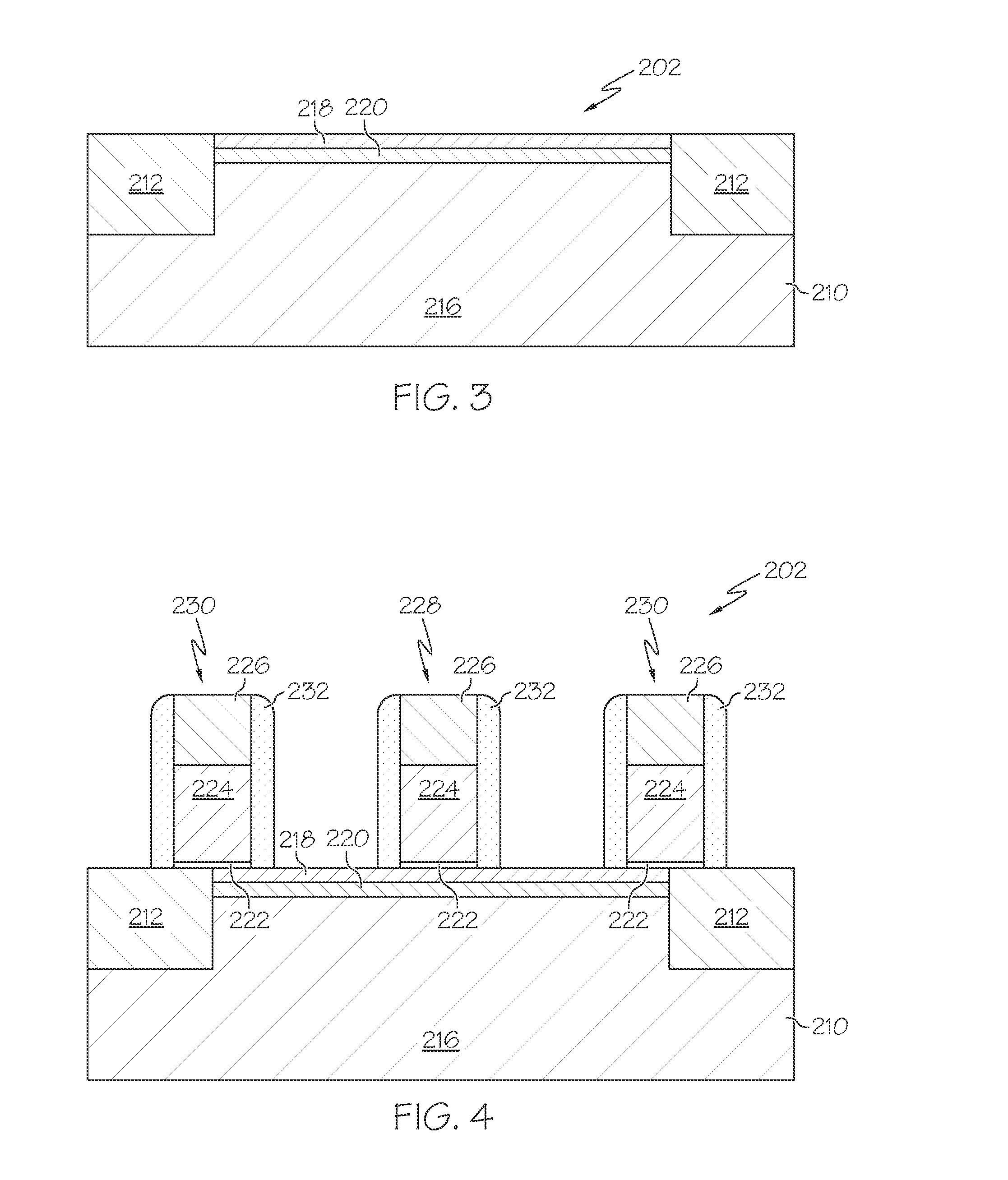

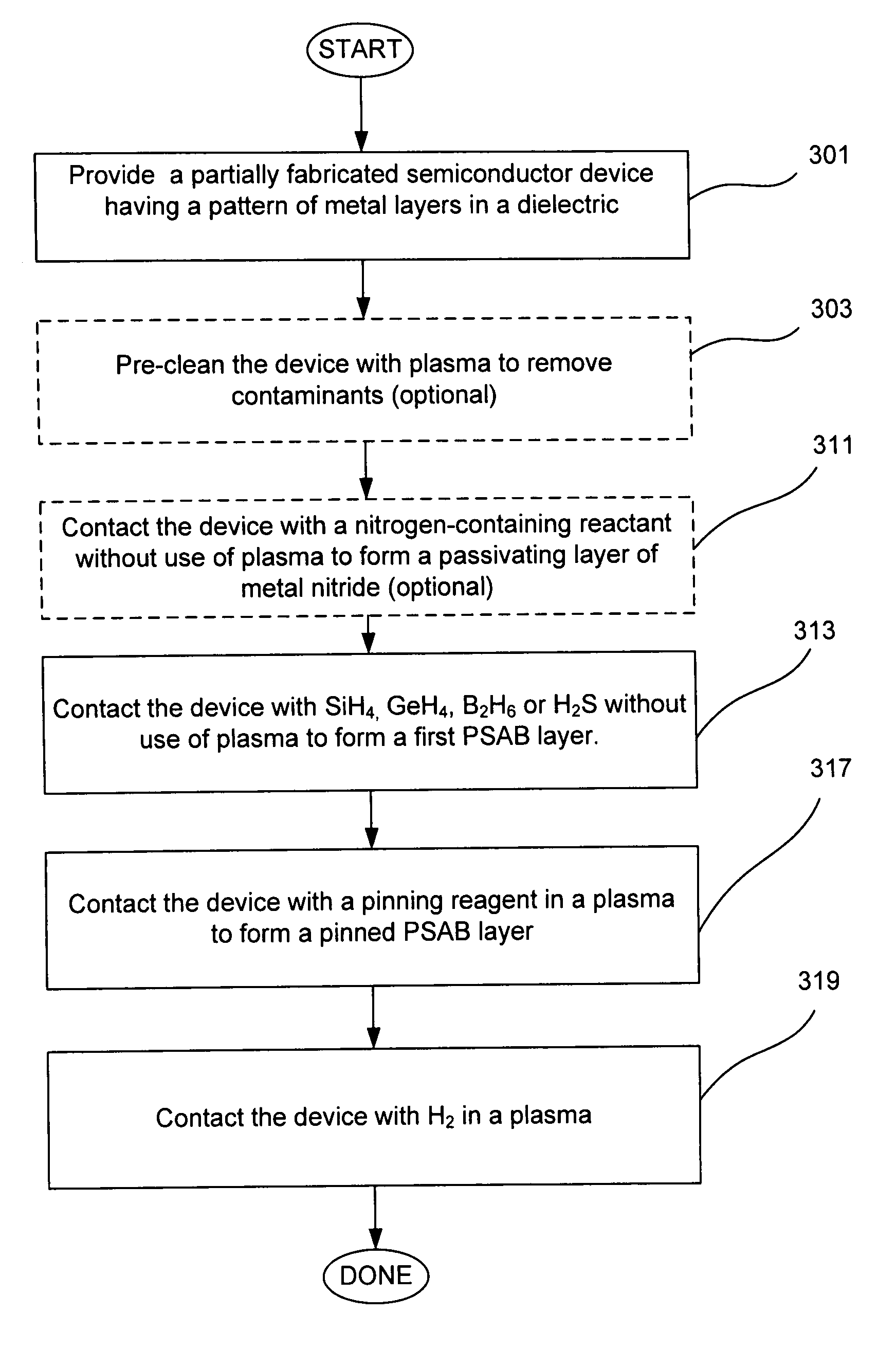

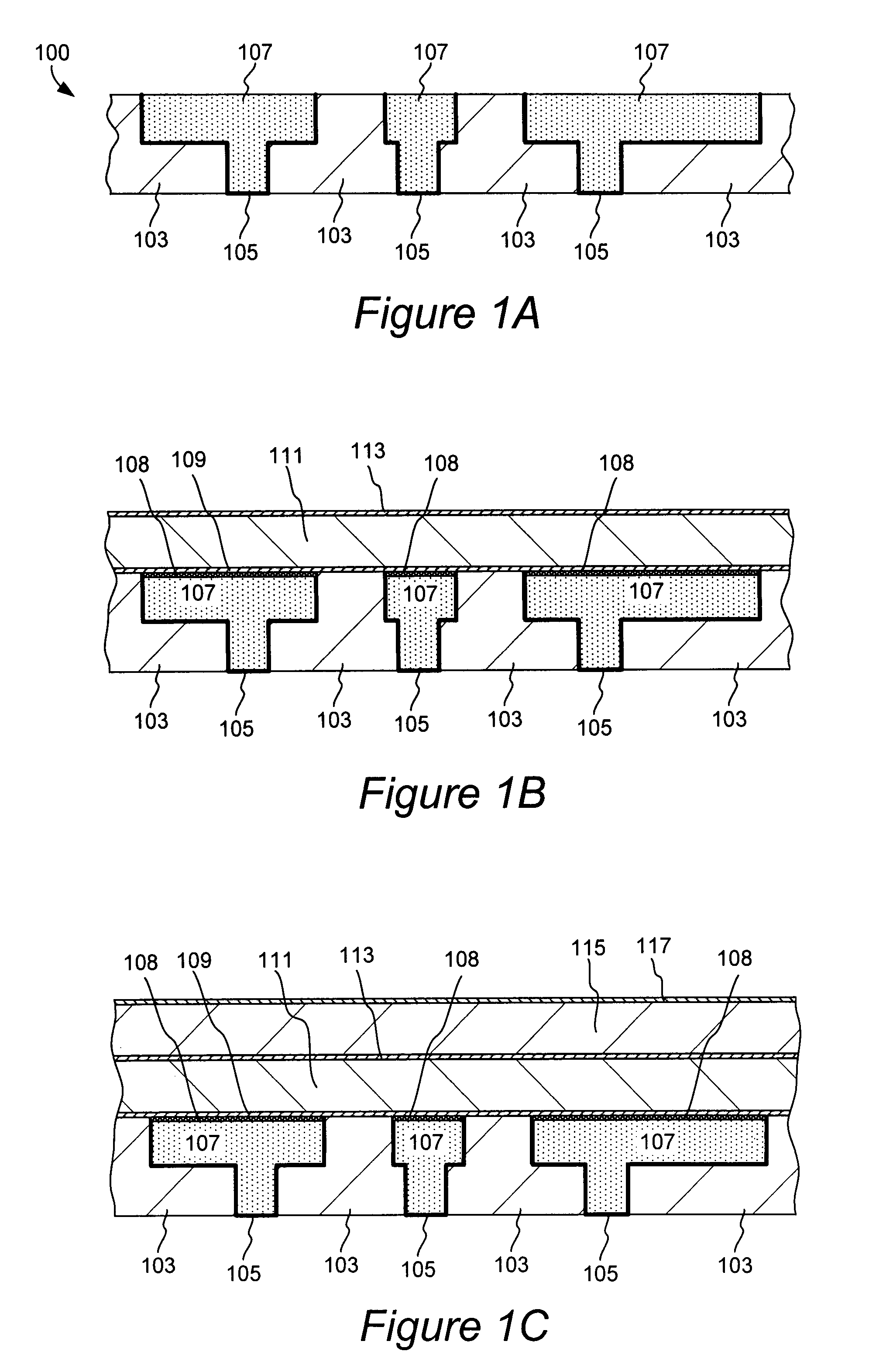

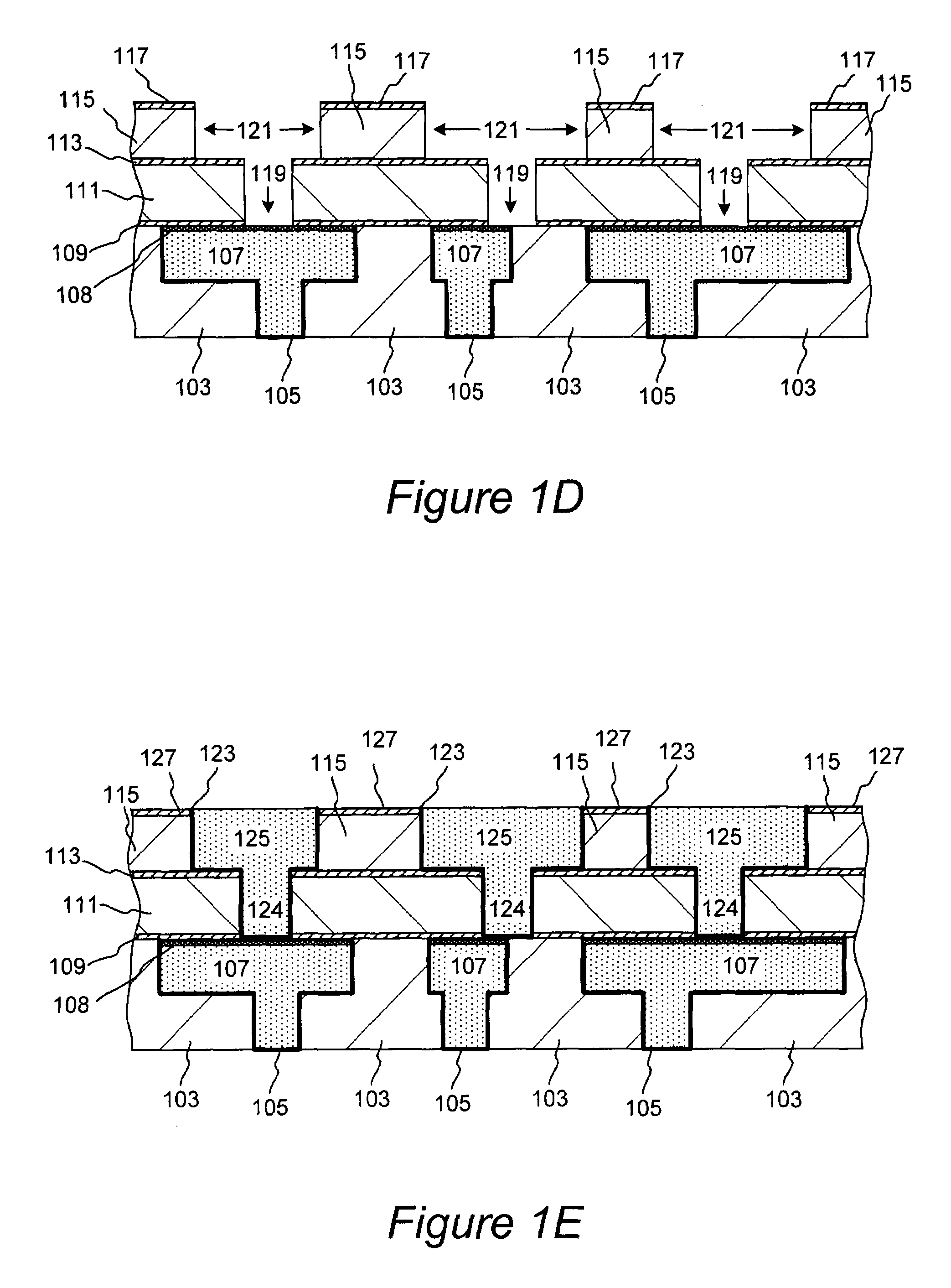

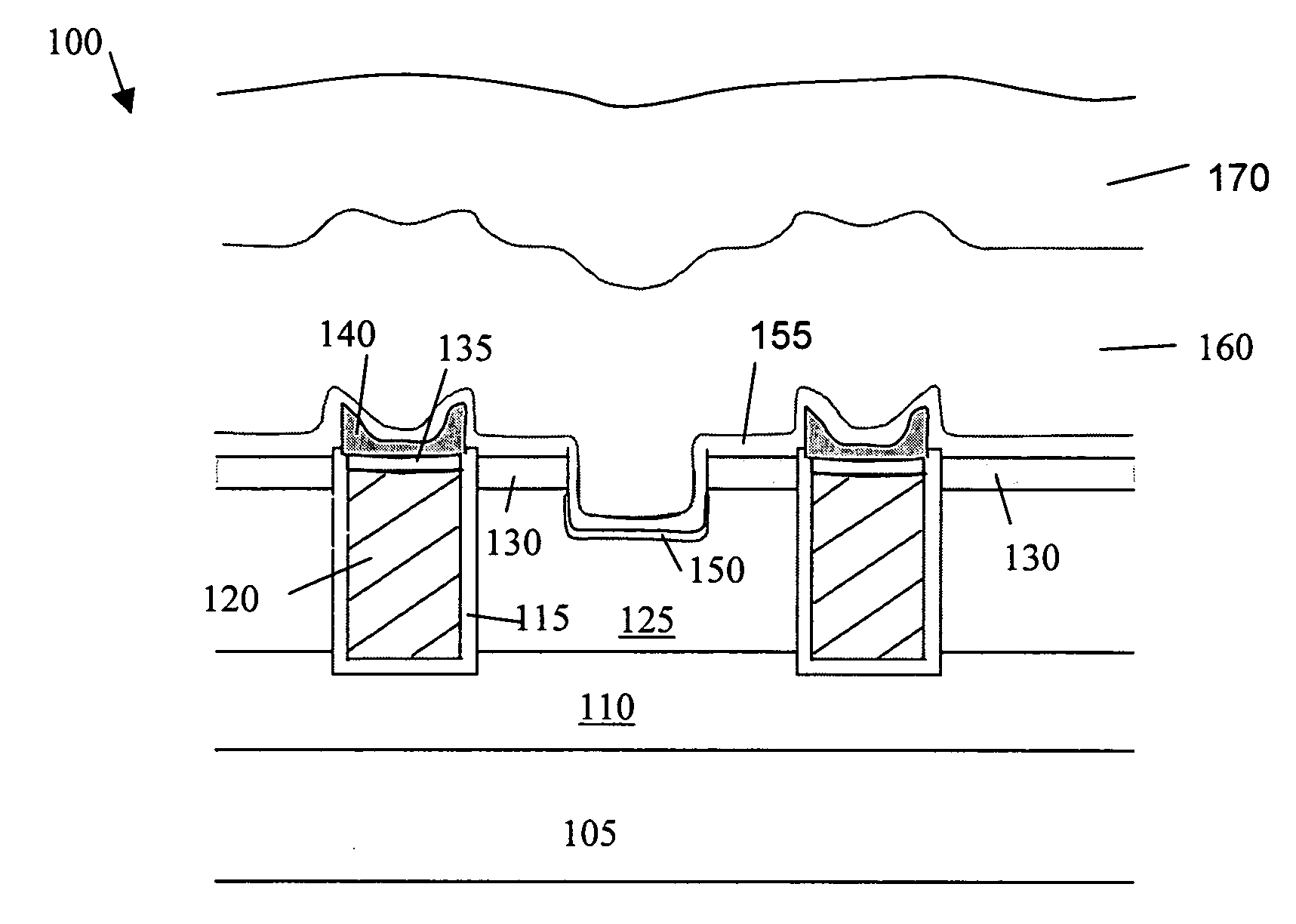

Protective self-aligned buffer layers for damascene interconnects

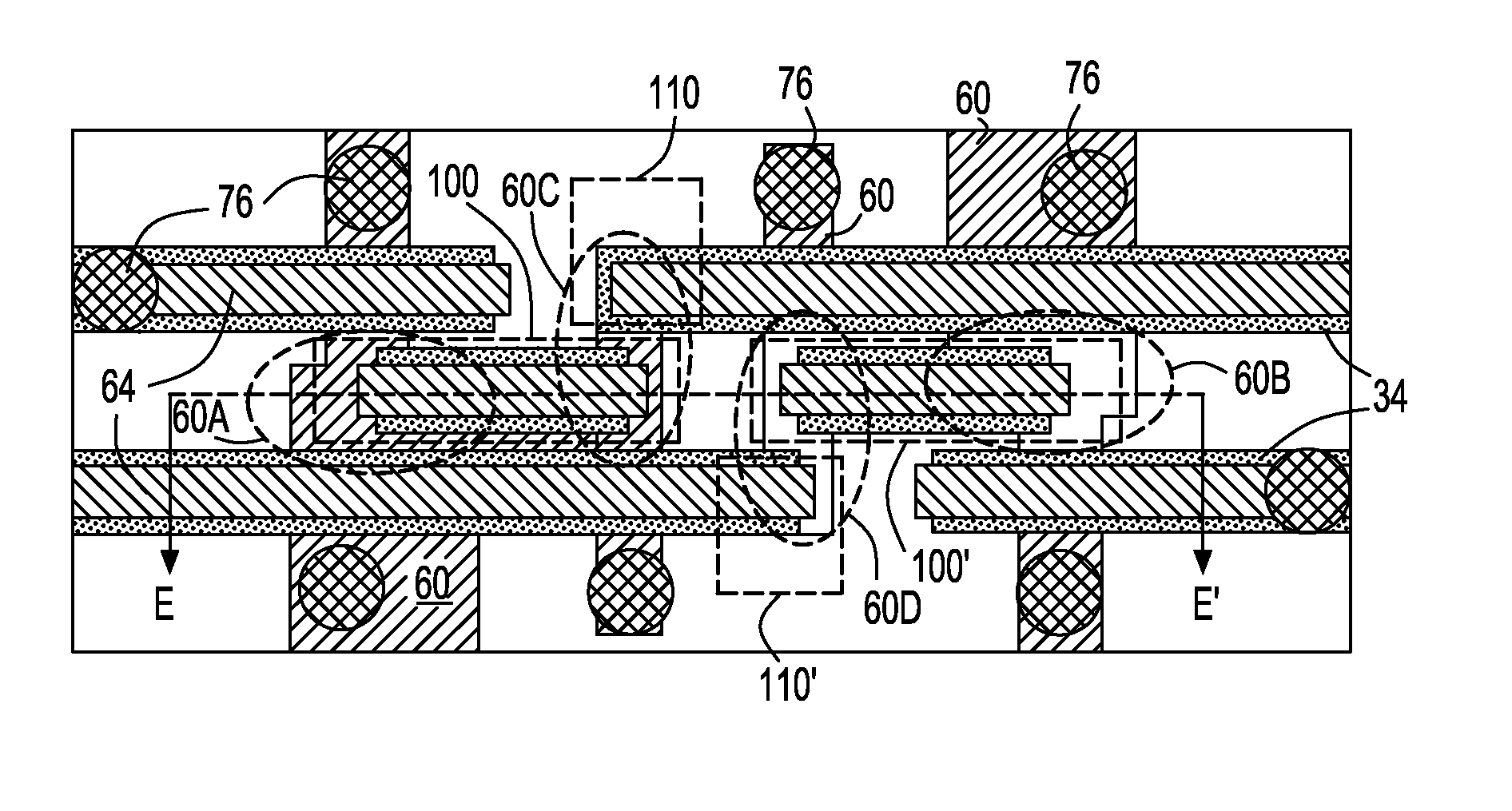

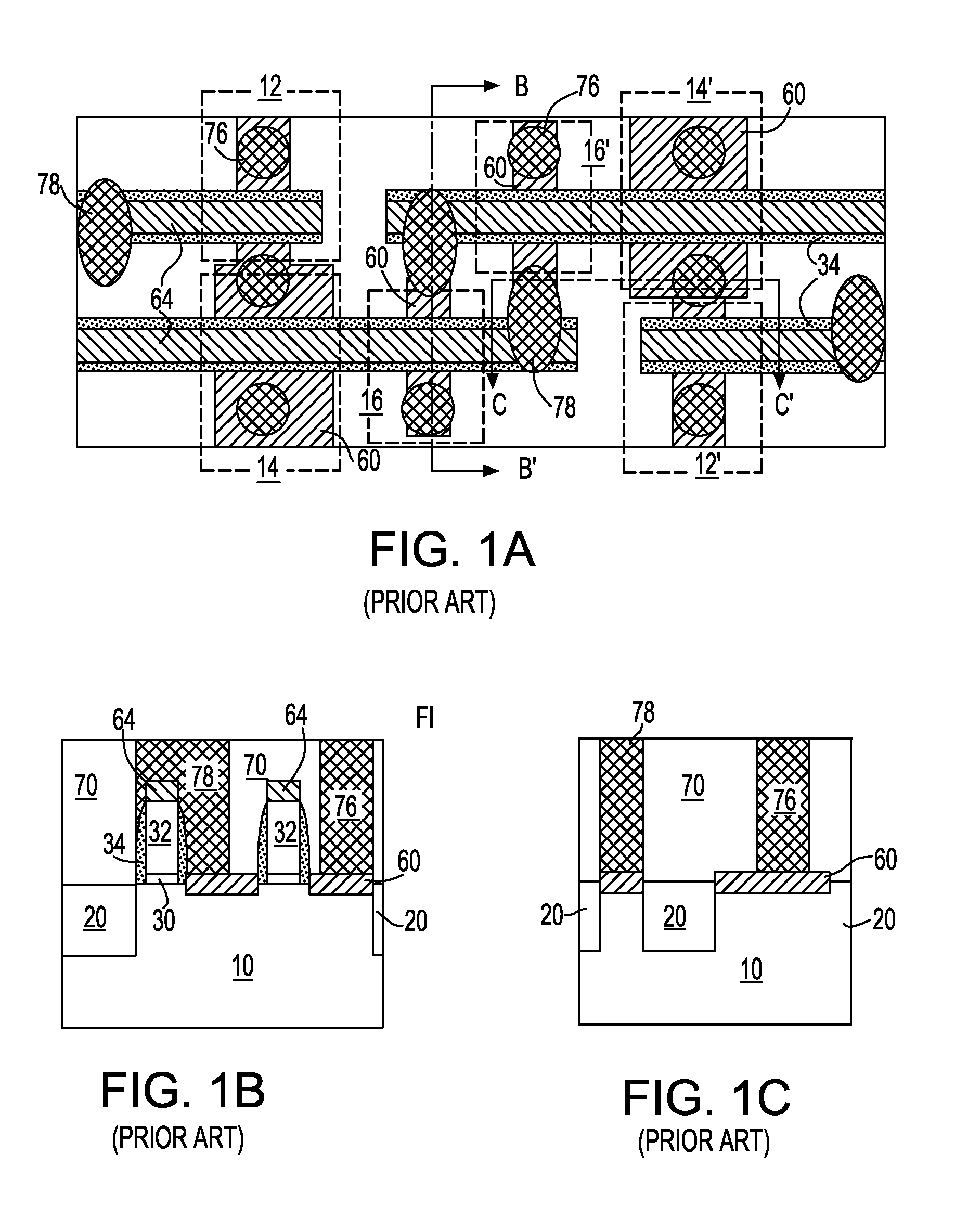

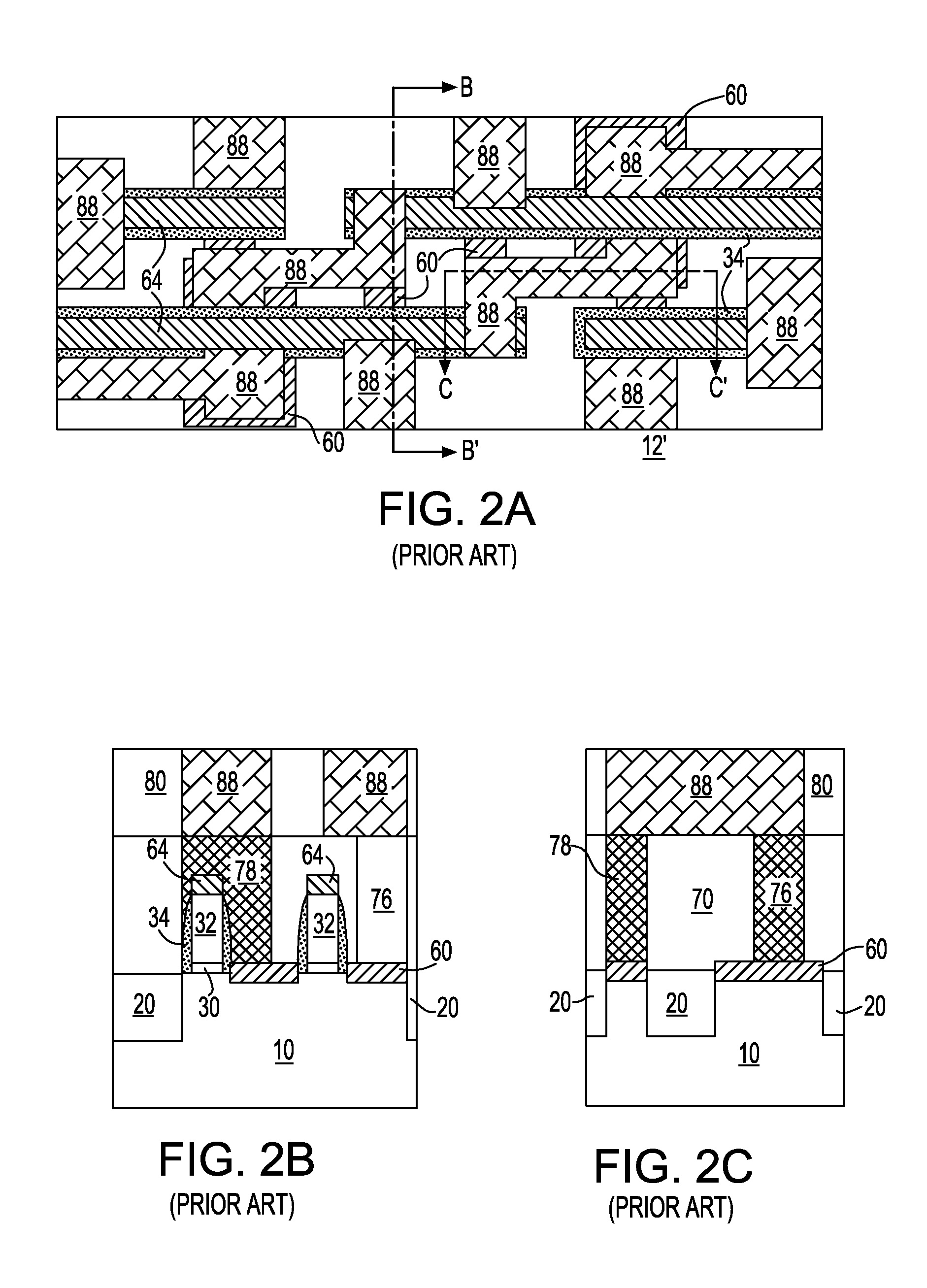

ActiveUS7727880B1Improving several propertyDecrease in metal electromigrationSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

Protective self aligned buffer (PSAB) layers are layers of material that are selectively formed at the surface of metal layers in a partially fabricated semiconductor device. In a Damascene interconnect, PSAB layer typically resides at an interface between the metal layer and a dielectric diffusion barrier layer. PSAB layers promote improved adhesion between a metal layer and an adjacent dielectric diffusion barrier layer. Further, PSAB layers can protect metal surfaces from inadvertent oxidation during fabrication process. A PSAB layer may be formed entirely within the top portion of a metal layer, by, for example, chemically converting metal surface to a thin layer of metal silicide. Thickness of PSAB layers, and, consequently resistance of interconnects can be controlled by partially passivating metal surface prior to formation of PSAB layer. Such passivation can be accomplished by controllably treating metal surface with a nitrogen-containing compound to convert metal to metal nitride.

Owner:NOVELLUS SYSTEMS

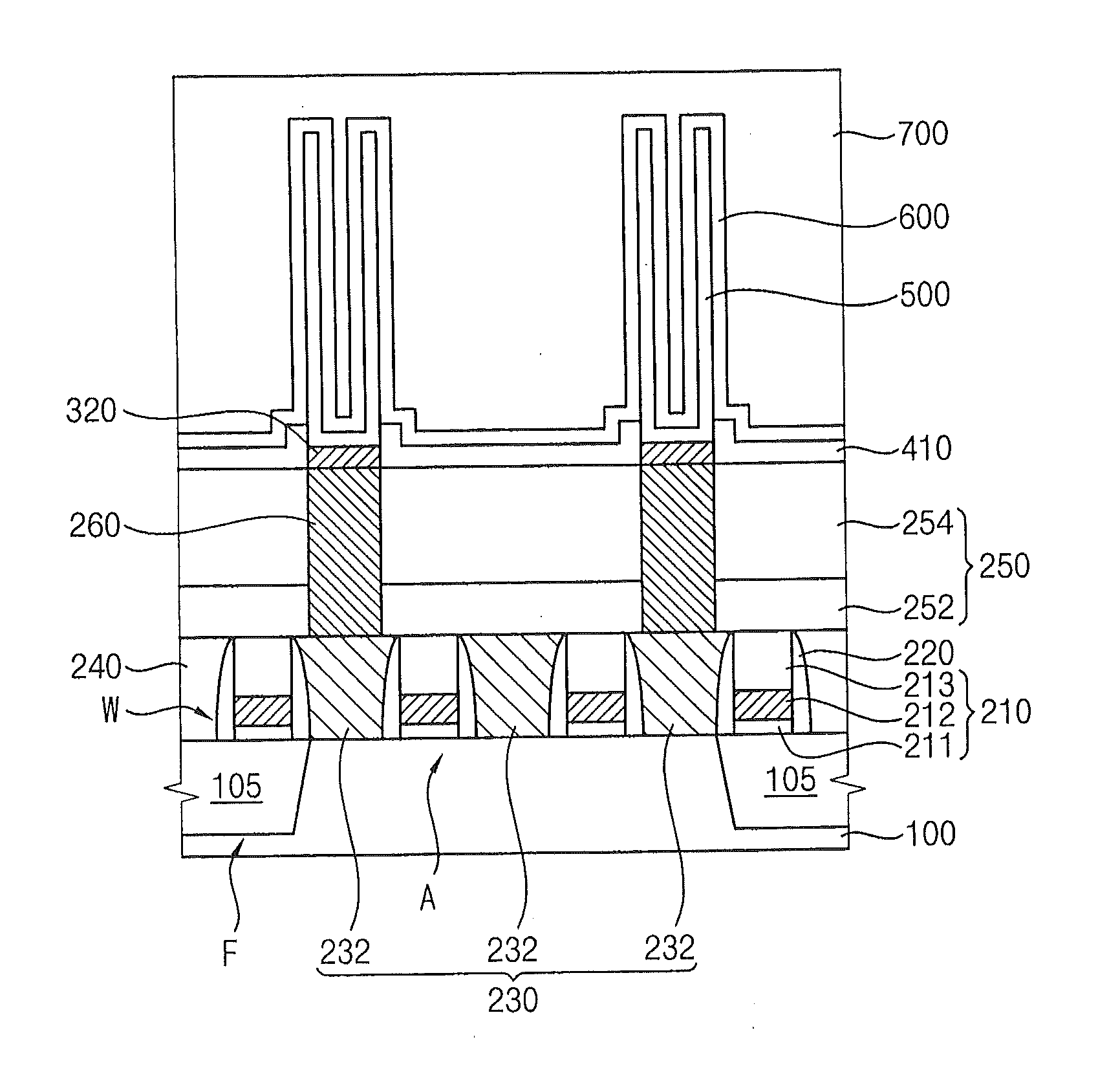

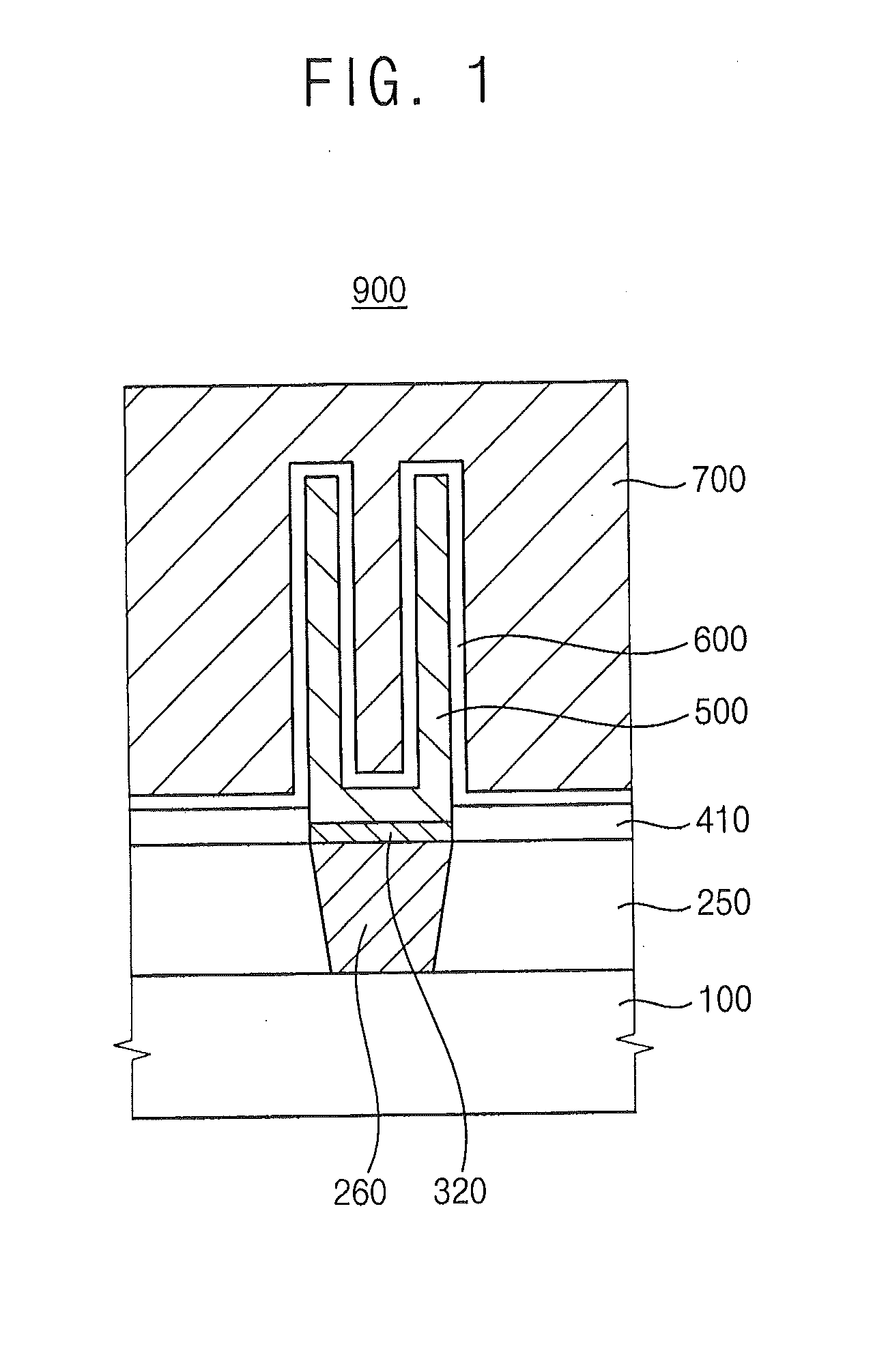

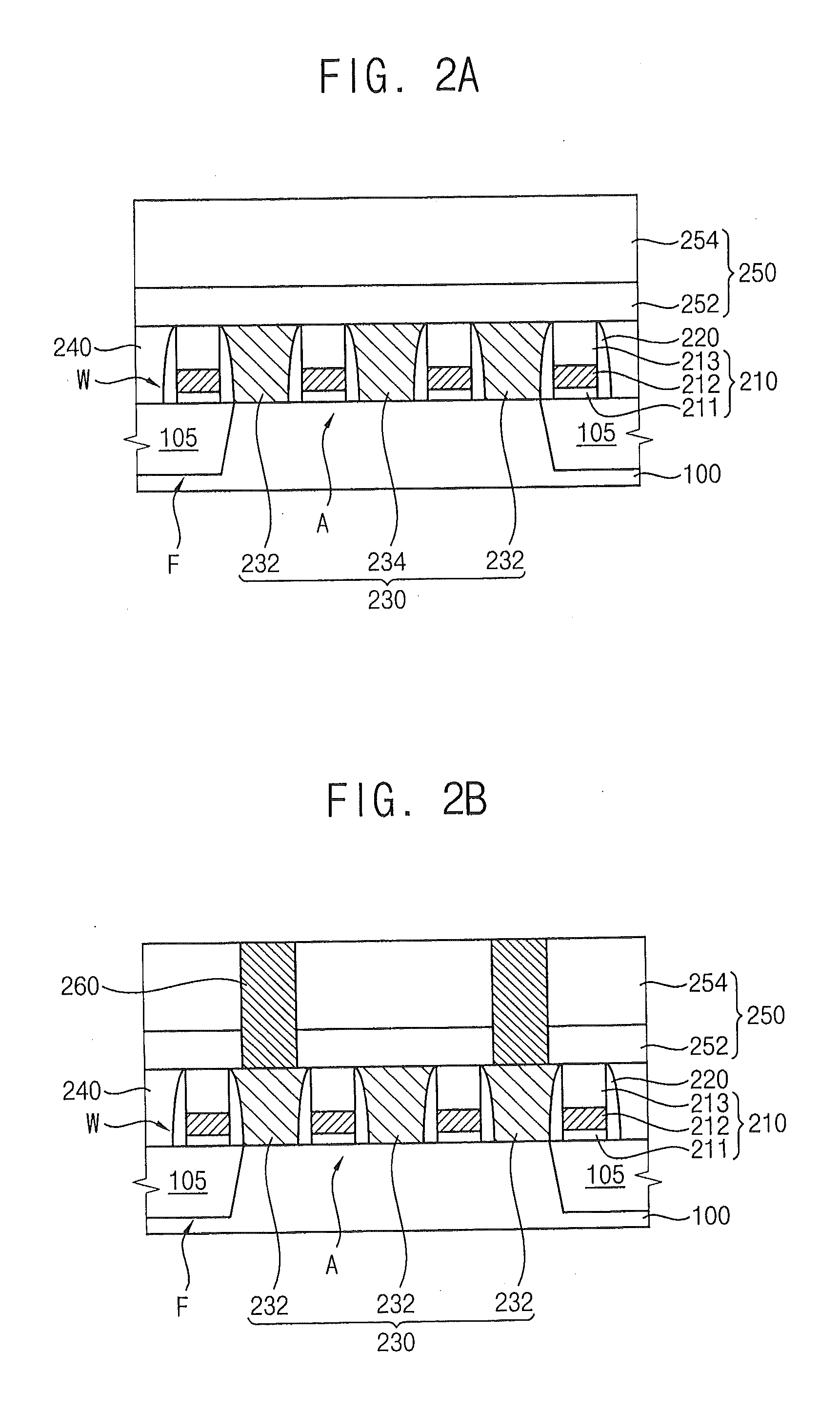

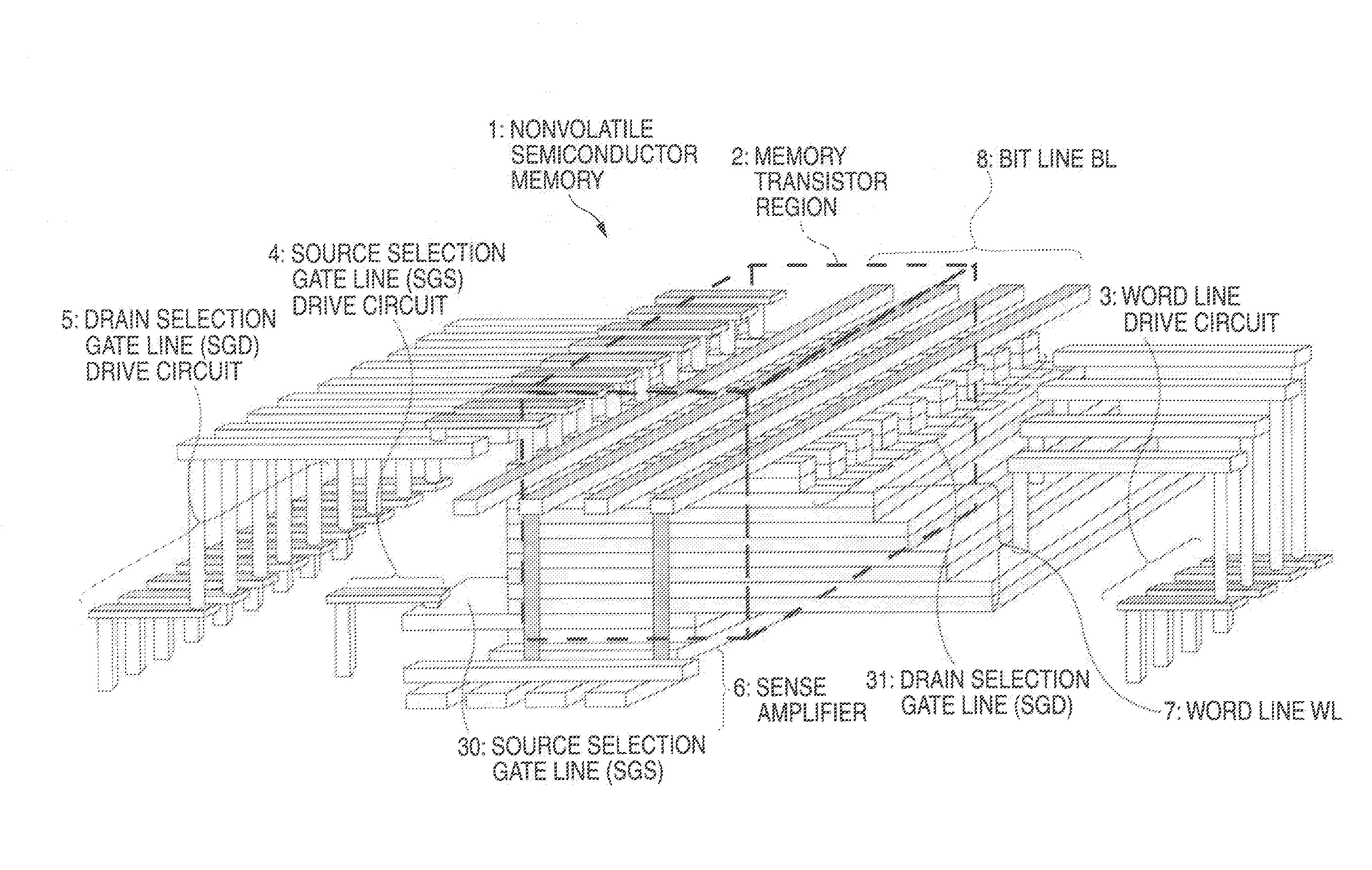

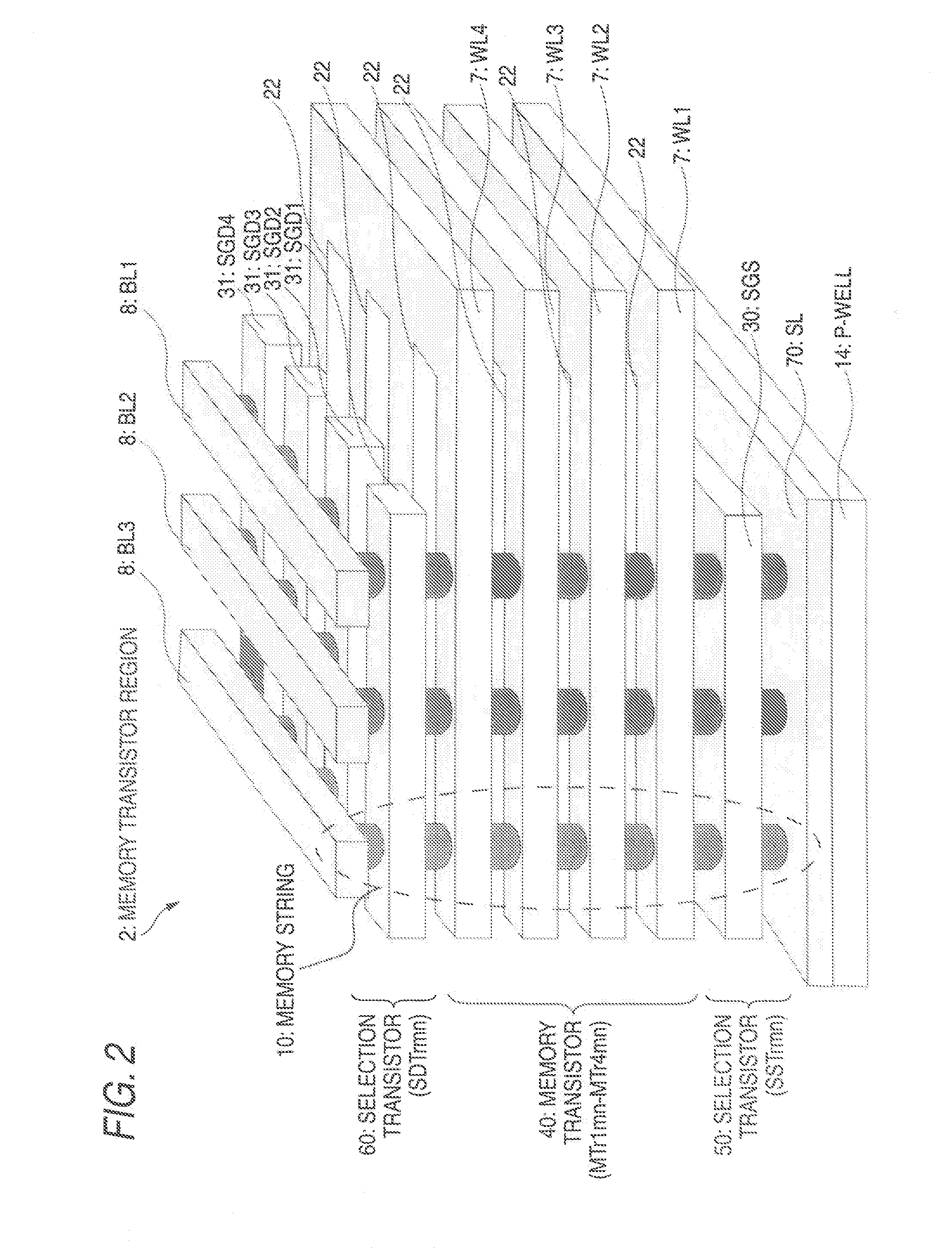

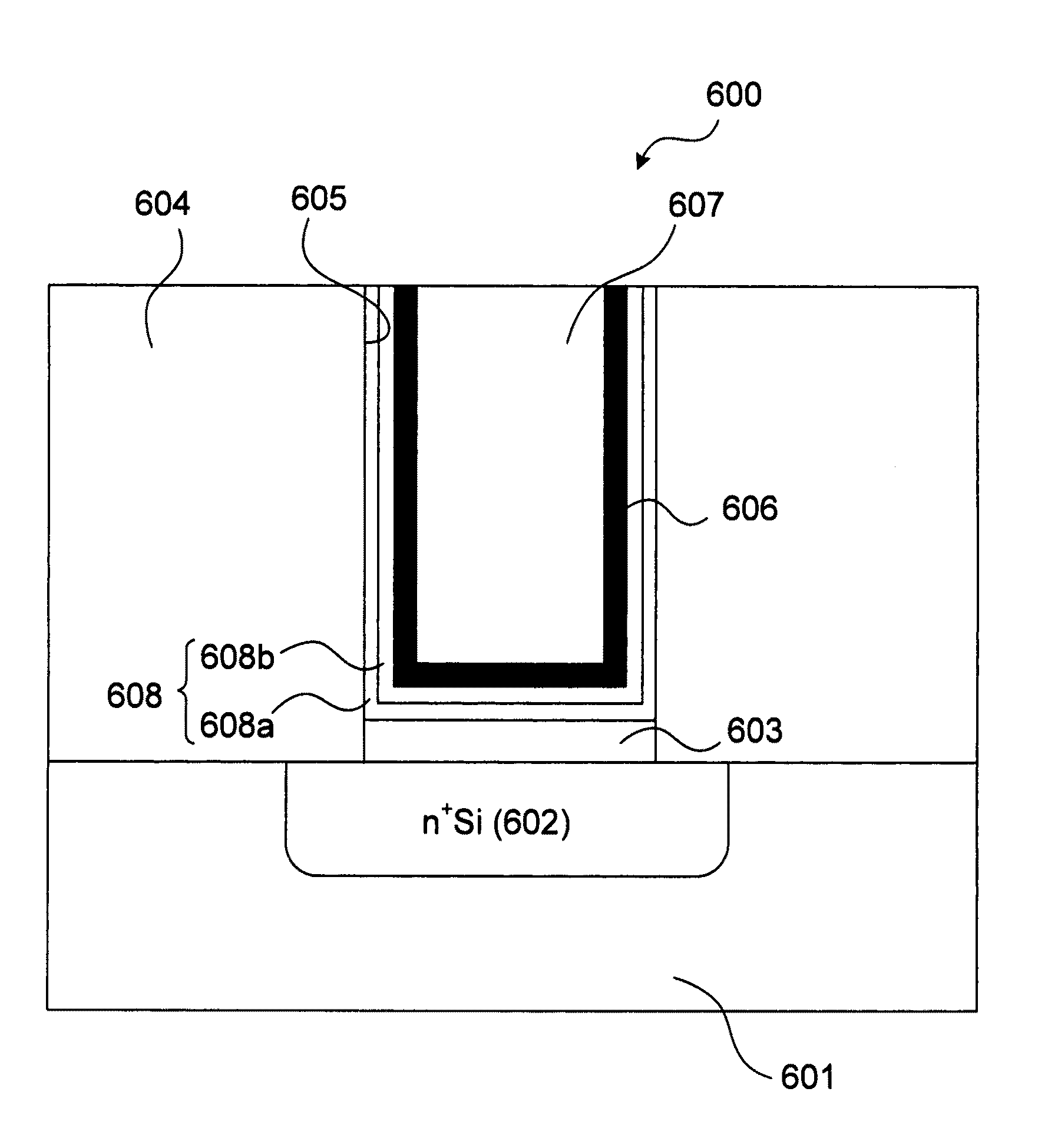

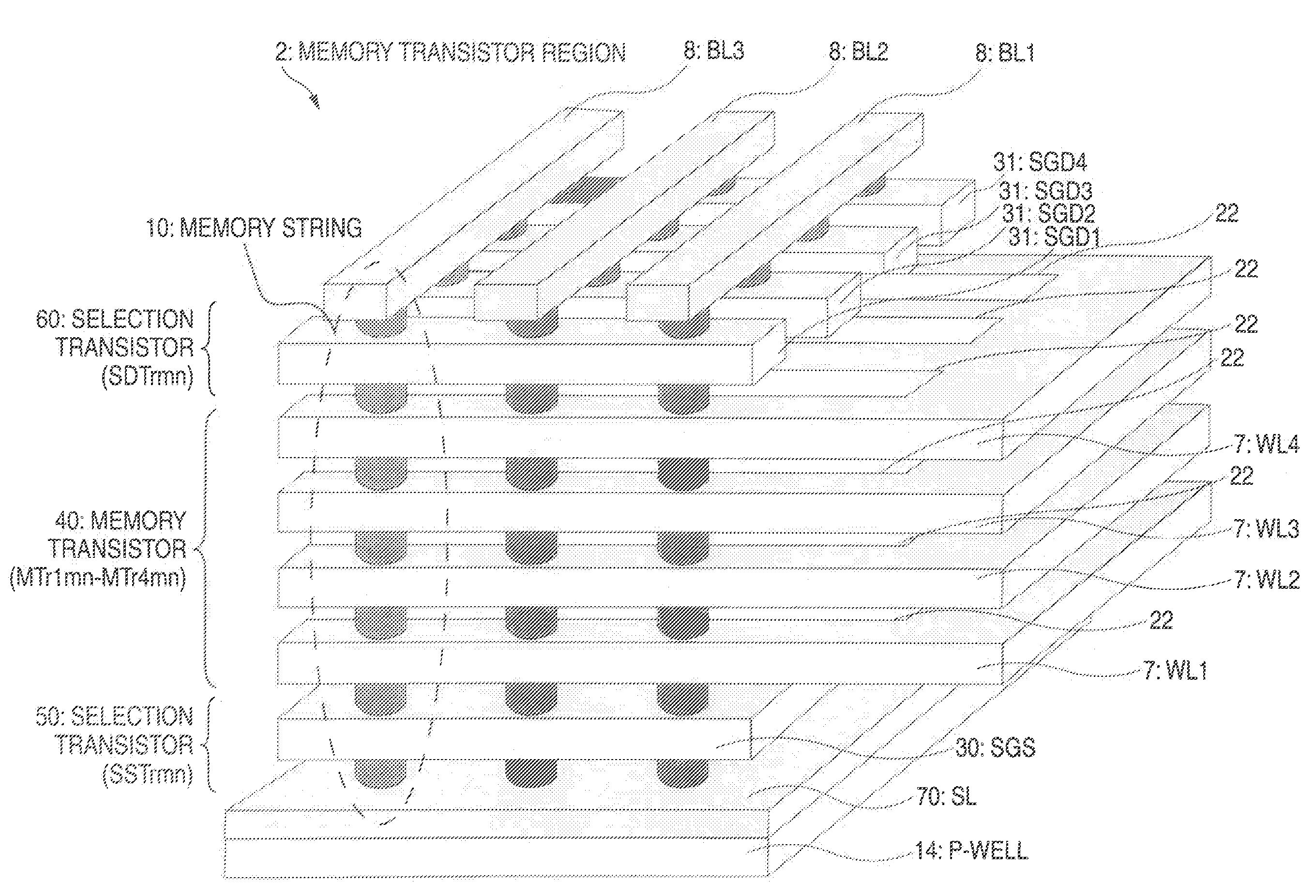

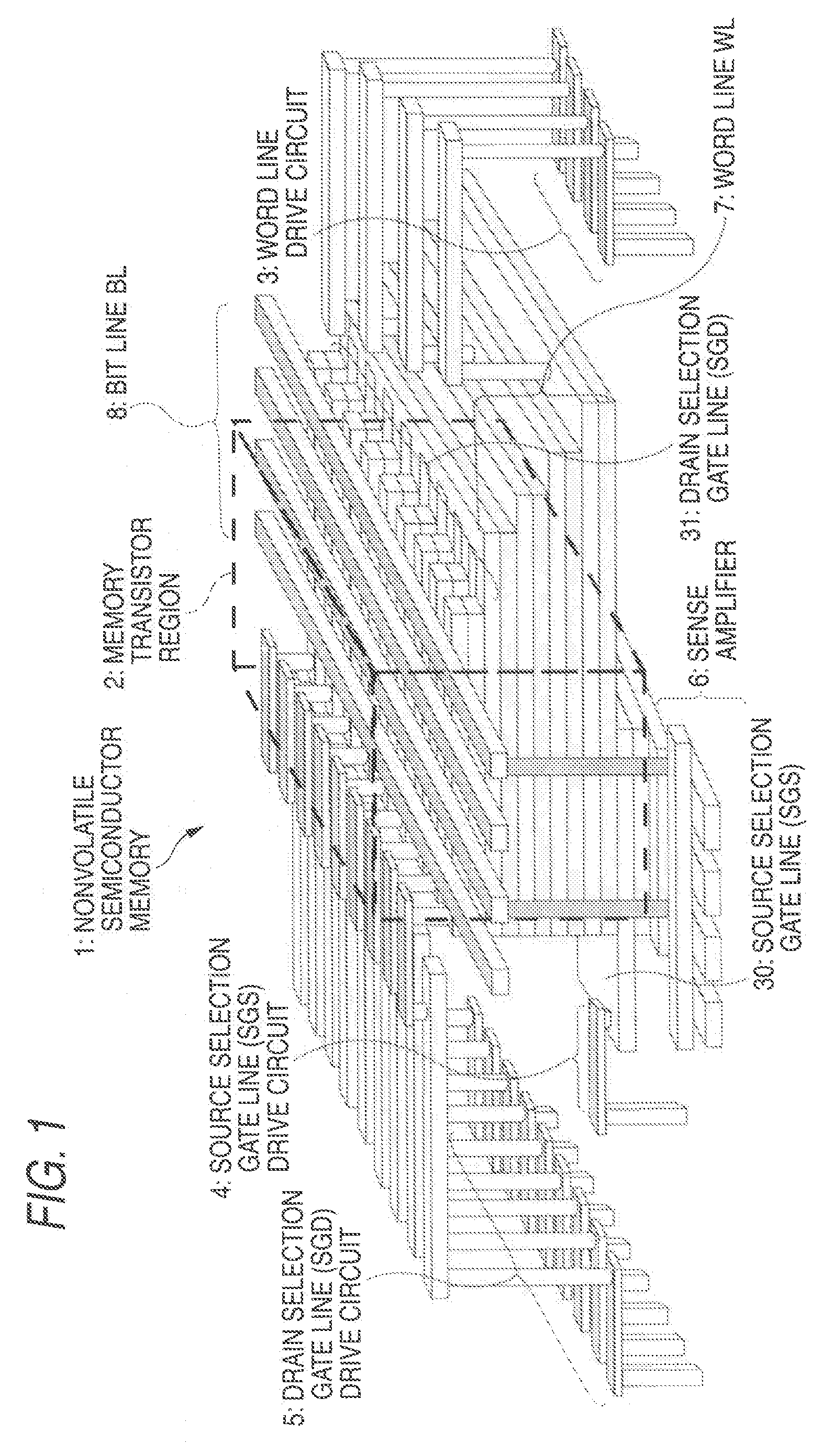

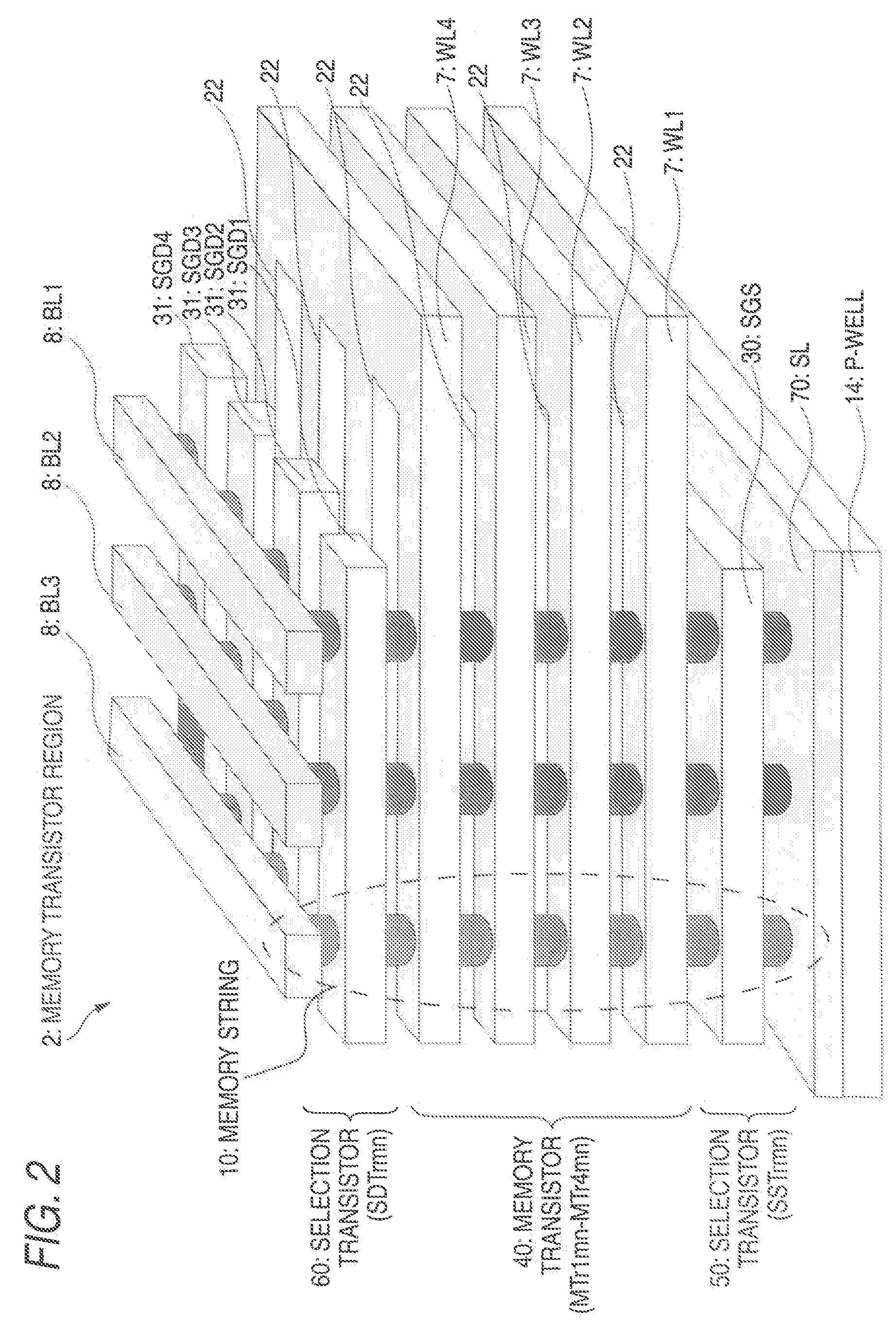

Nonvolatile semiconductor memory and method for manufacturing the same

According to an aspect of the present invention, there is provided a nonvolatile semiconductor memory including: a columnar semiconductor; a charge storage insulating film including: a first insulating film formed around the columnar semiconductor, a charge storage film formed around the first insulating film, and a second insulating film formed around the charge storage film; an electrode extending two-dimensionally to surround the charge storage insulating film, the electrode having a groove; and a metal silicide formed on a sidewall of the groove.

Owner:KIOXIA CORP

Schottky barrier nanowire field effect transistor and method for fabricating the same

InactiveUS20080128760A1Easy to makeEnsure thermal stabilityNanoinformaticsSolid-state devicesSalicideInsulation layer

Provided is a Schottky barrier nanowire field effect transistor, which has source / drain electrodes formed of metal silicide and a channel formed of a nanowire, and a method for fabricating the same. The Schottky barrier nanowire field effect transistor includes: a channel suspended over a substrate and including a nanowire; metal silicide source / drain electrodes electrically connected to both ends of the channel over the substrate; a gate electrode disposed to surround the channel; and a gate insulation layer disposed between the channel and the gate electrode.

Owner:ELECTRONICS & TELECOMM RES INST

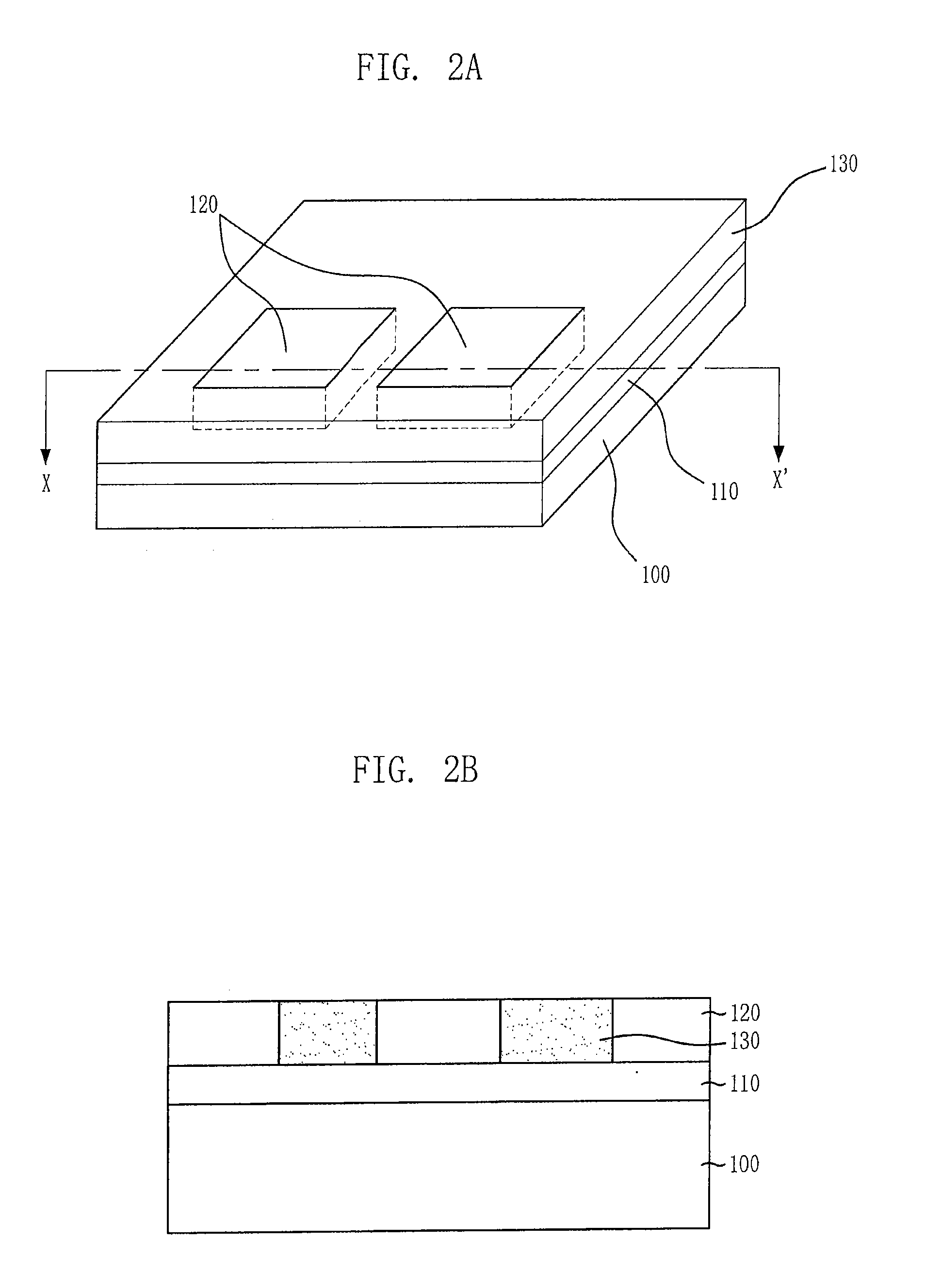

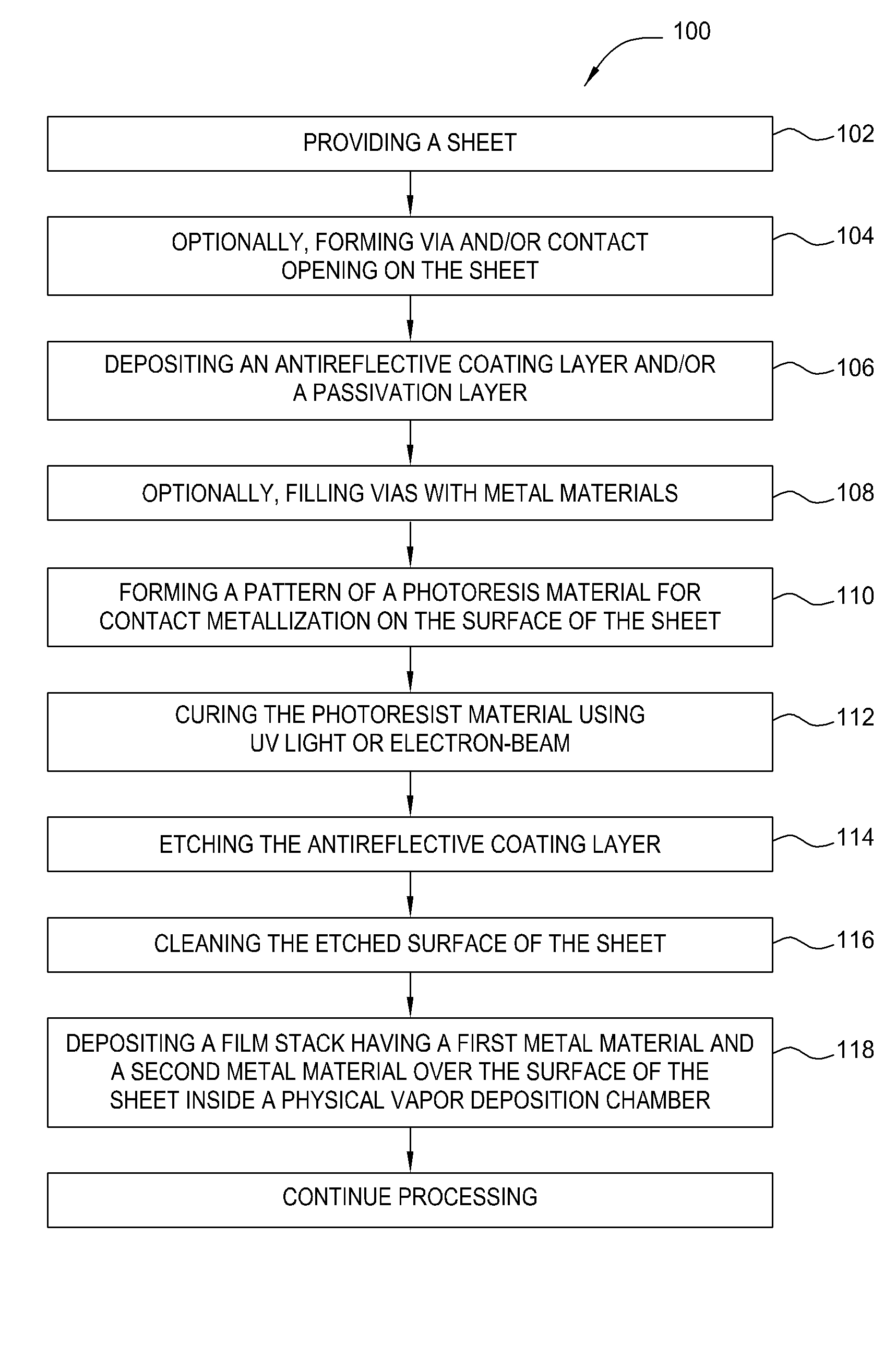

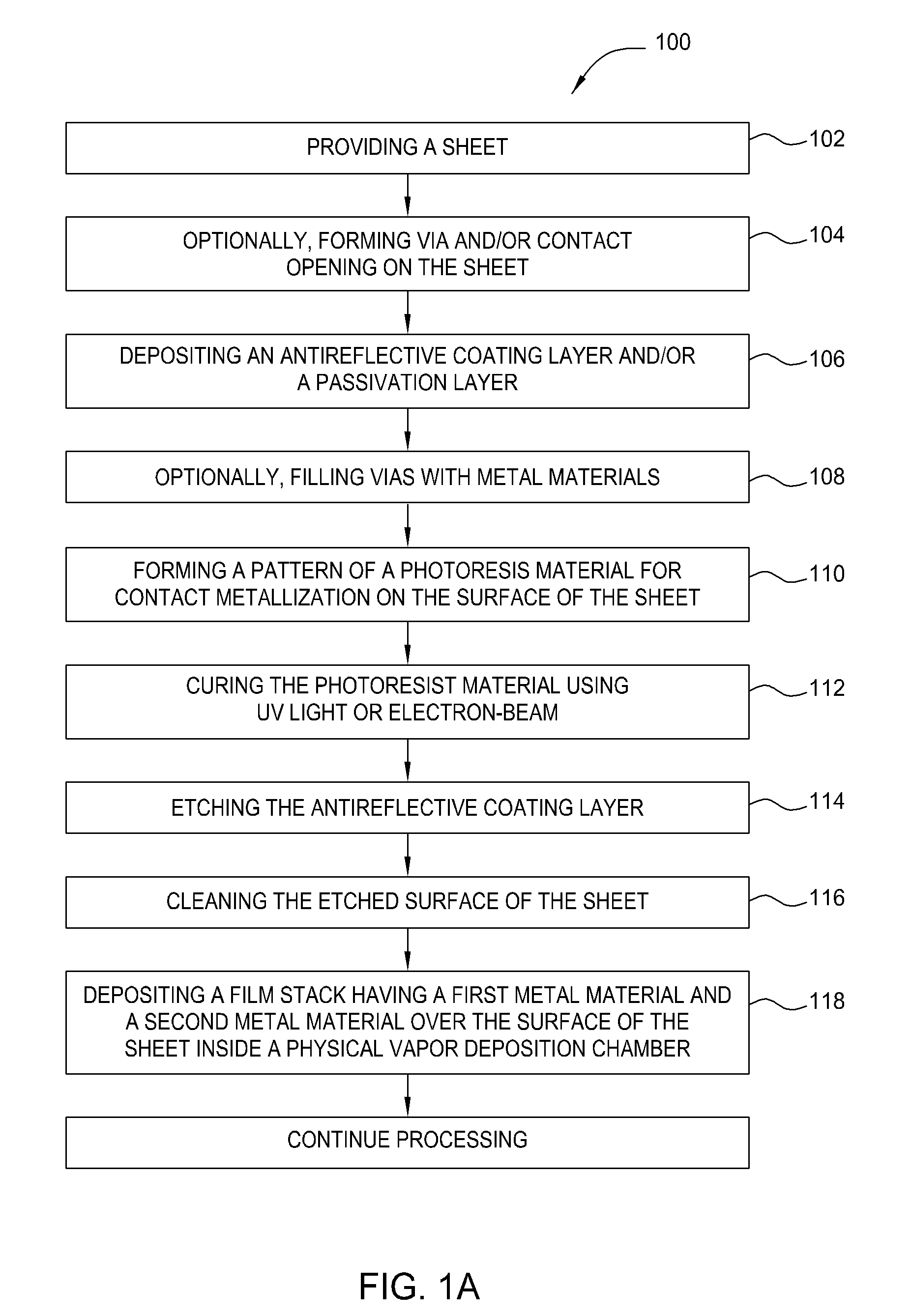

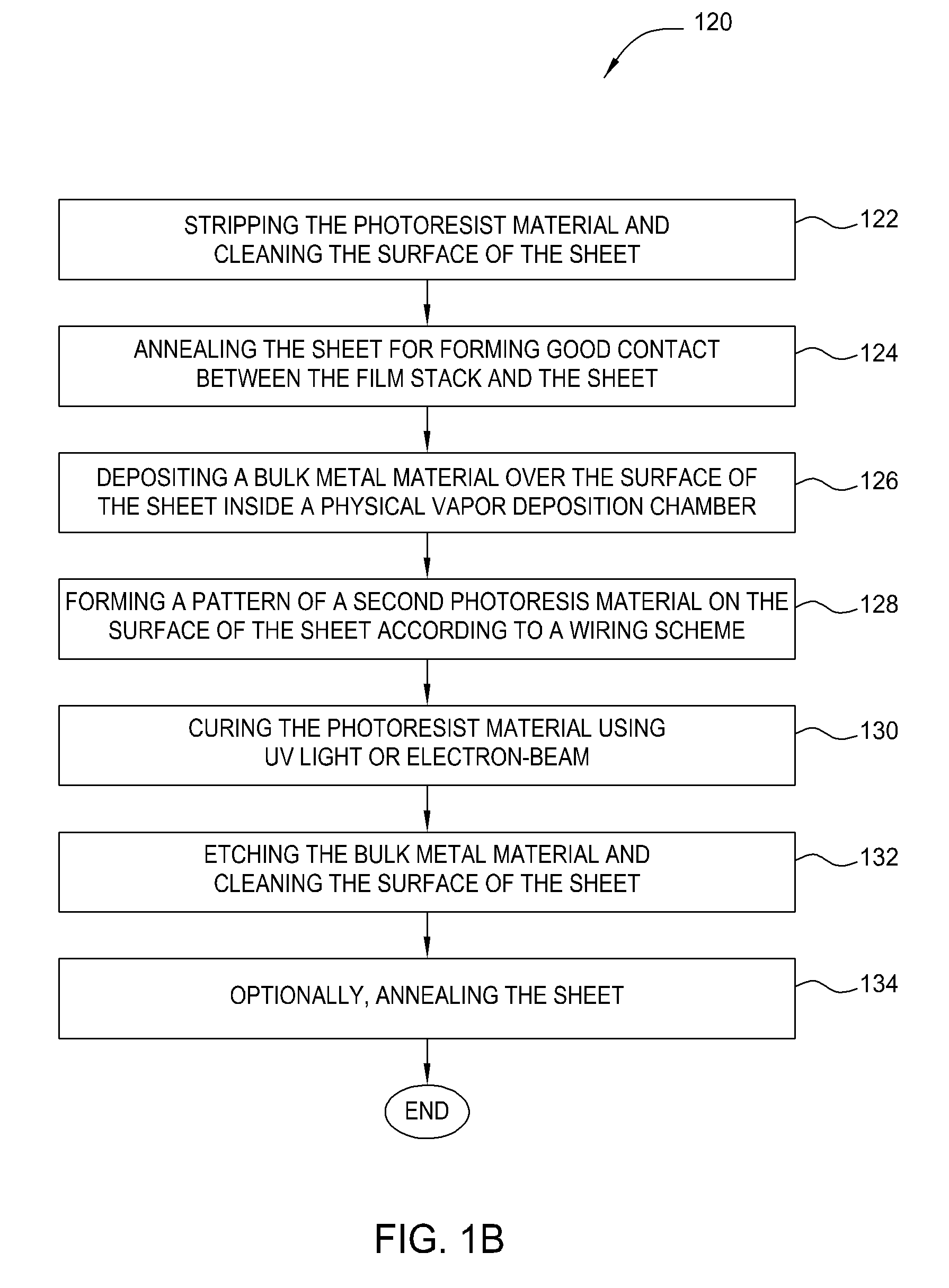

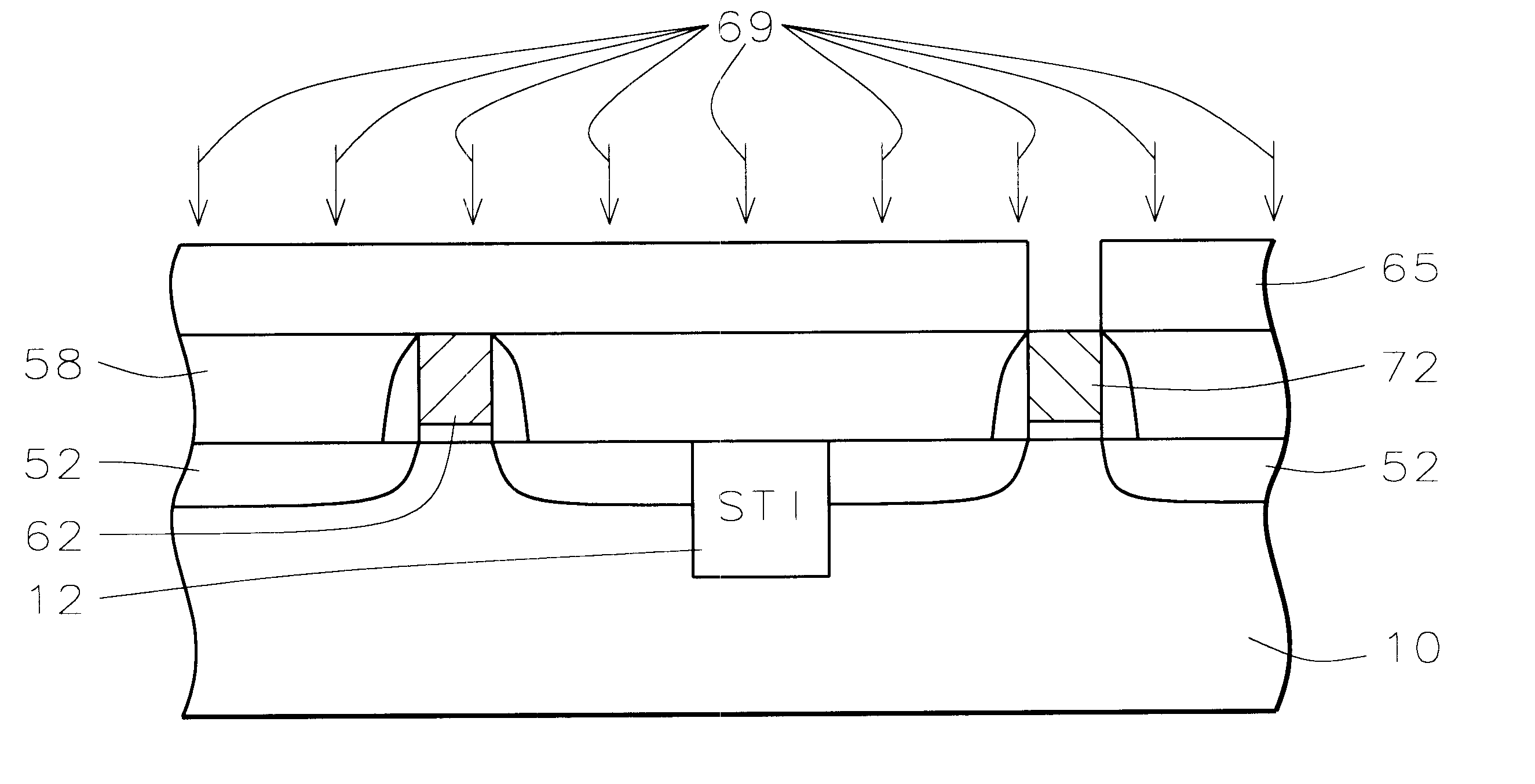

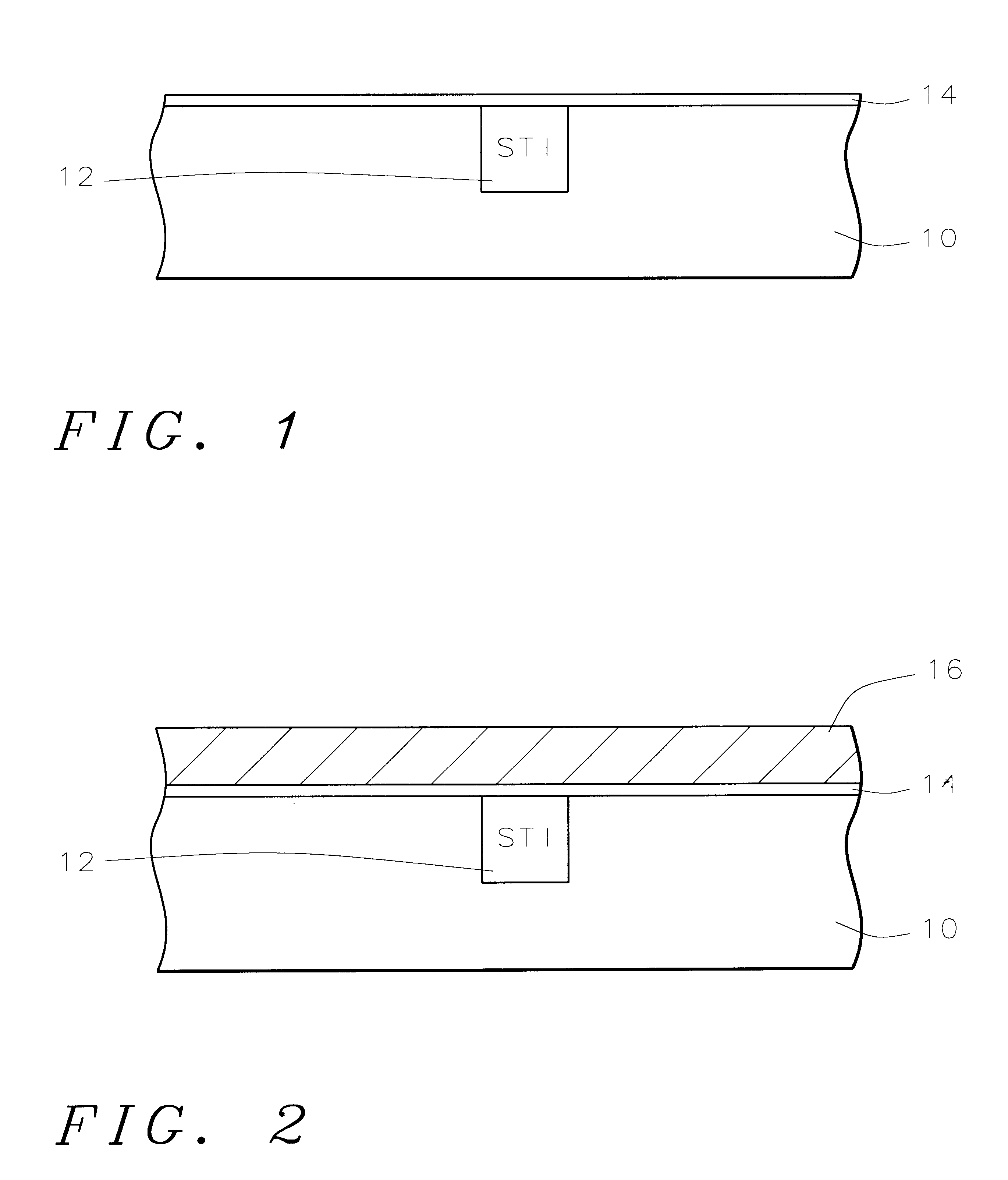

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

Dual metal gate process: metals and their silicides

InactiveUS6475908B1High and work functionImprove work functionOperating chairsSemiconductor/solid-state device manufacturingSalicideCMOS

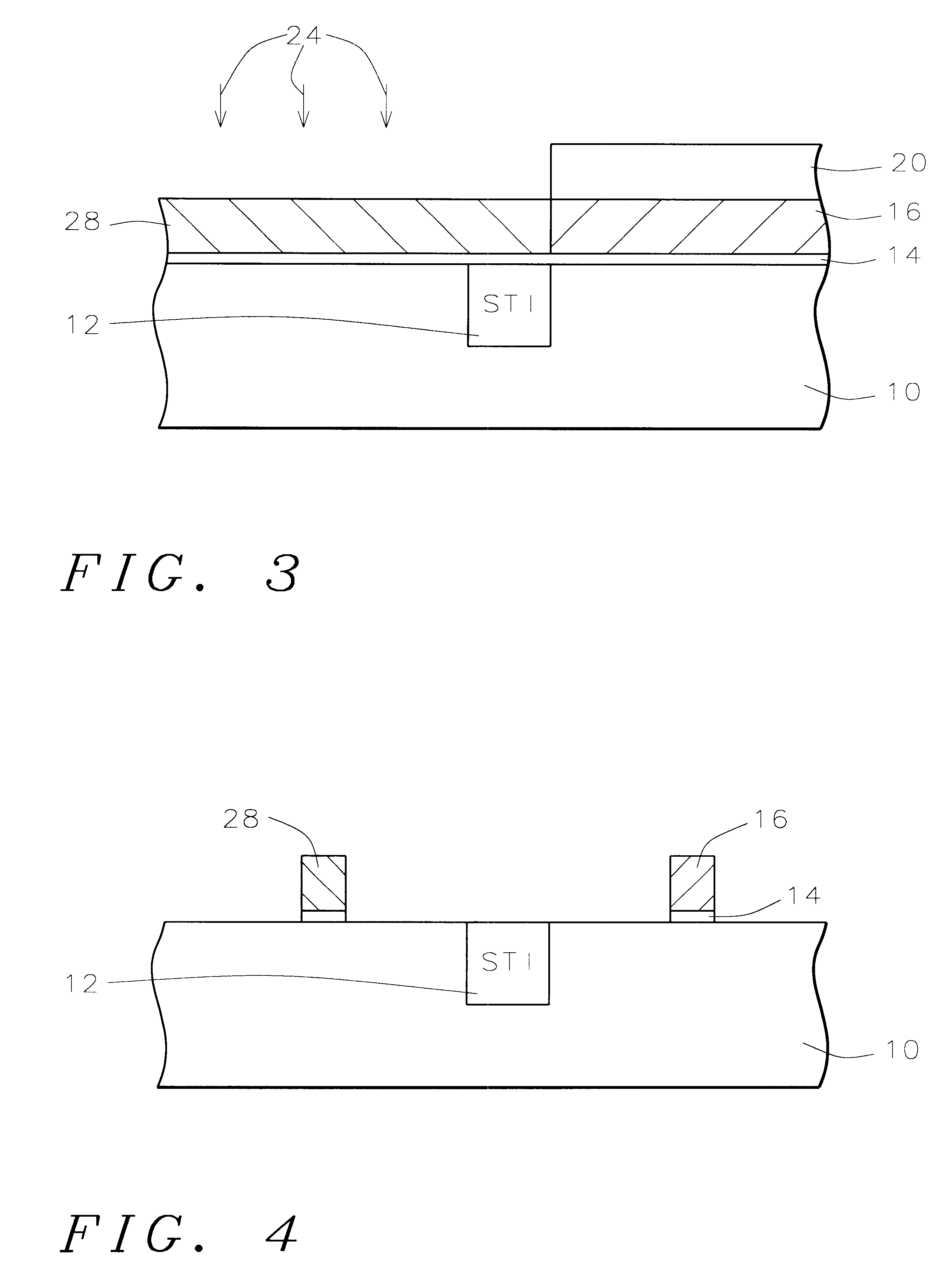

Methods for forming dual-metal gate CMOS transistors are described. An NMOS and a PMOS active area of a semiconductor substrate are separated by isolation regions. A metal layer is deposited over a gate dielectric layer in each active area. Silicon ions are implanted into the metal layer in one active area to form an implanted metal layer which is silicided to form a metal silicide layer. Thereafter, the metal layer and the metal silicide layer are patterned to form a metal gate in one active area and a metal silicide gate in the other active area wherein the active area having the gate with the higher work function is the PMOS active area. Alternatively, both gates may be metal silicide gates wherein the silicon concentrations of the two gates differ. Alternatively, a dummy gate may be formed in each of the active areas and covered with a dielectric layer. The dielectric layer is planarized thereby exposing the dummy gates. The dummy gates are removed leaving gate openings to the semiconductor substrate. A metal layer is deposited over a gate dielectric layer within the gate openings to form metal gates. One or both of the gates are silicon implanted and silicided. The PMOS gate has the higher work function.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Method for manufacturing a semiconductor integrated circuit device circuit device

ActiveUS20100129974A1Increased integration scaleLower gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideField-effect transistor

When a natural oxide film is left at the interface between a metal silicide layer and a silicon nitride film, in various heating steps (steps involving heating of a semiconductor substrate, such as various insulation film and conductive film deposition steps) after deposition of the silicon nitride film, the metal silicide layer partially abnormally grows due to oxygen of the natural oxide film occurring on the metal silicide layer surface. A substantially non-bias (including low bias) plasma treatment is performed in a gas atmosphere containing an inert gas as a main component on the top surface of a metal silicide film of nickel silicide or the like over source / drain of a field-effect transistor forming an integrated circuit. Then, a silicon nitride film serving as an etching stop film of a contact process is deposited. As a result, without causing undesirable cutting of the metal silicide film, the natural oxide film over the top surface of the metal silicide film can be removed.

Owner:RENESAS ELECTRONICS CORP

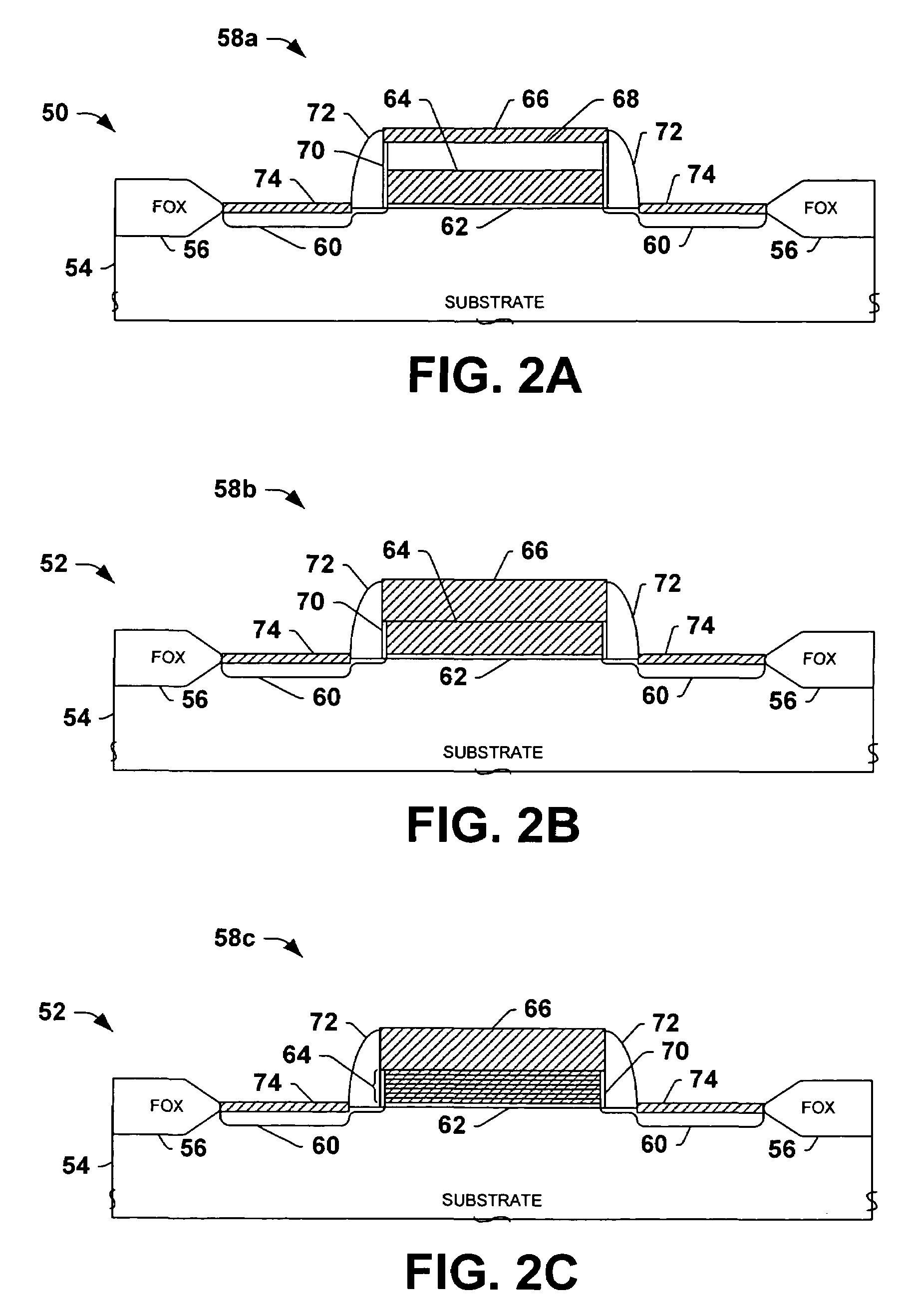

MOS transistor gates with thin lower metal silicide and methods for making the same

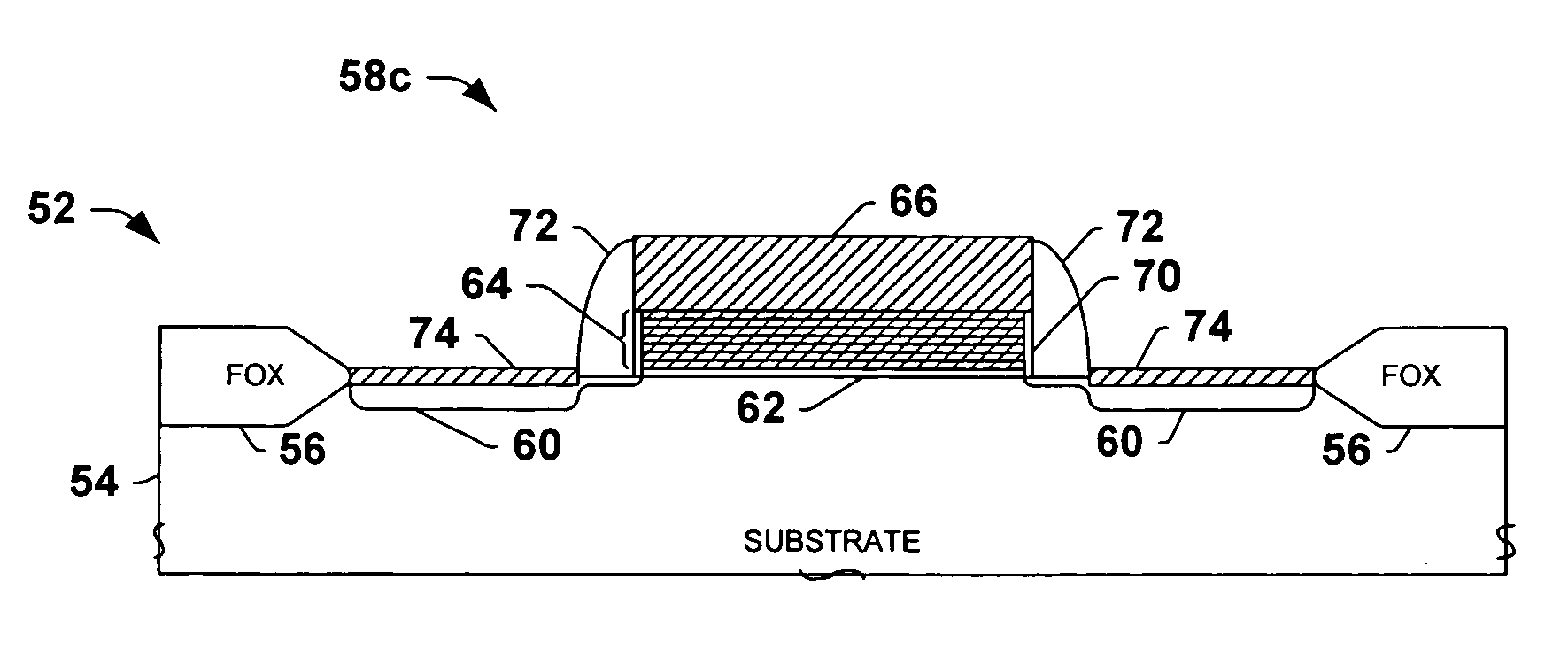

ActiveUS7045456B2Easy to implantEasy to controlTransistorSemiconductor/solid-state device manufacturingSalicideGate dielectric

Methods are presented for fabricating transistor gate structures, wherein upper and lower metal suicides are formed above a gate dielectric. In one example, the lower silicide is formed by depositing a thin first silicon-containing material over the gate dielectric, which is implanted and then reacted with a first metal by annealing to form the lower silicide. A capping layer can be formed over the first metal prior to annealing, to prevent oxidation of the metal prior to silicidation, and a barrier layer can be formed over the lower silicide to prevent reaction with subsequently formed silicon material. In another example, the lower silicide is a multilayer silicide structure including a plurality of metal silicide sublayers.

Owner:TEXAS INSTR INC

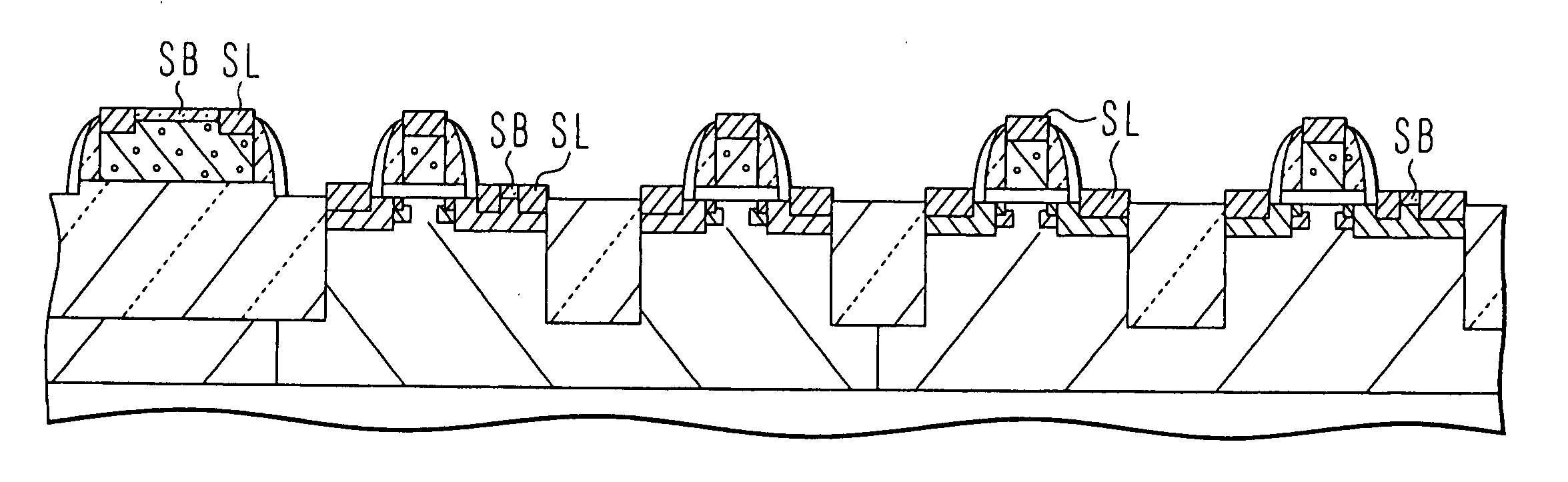

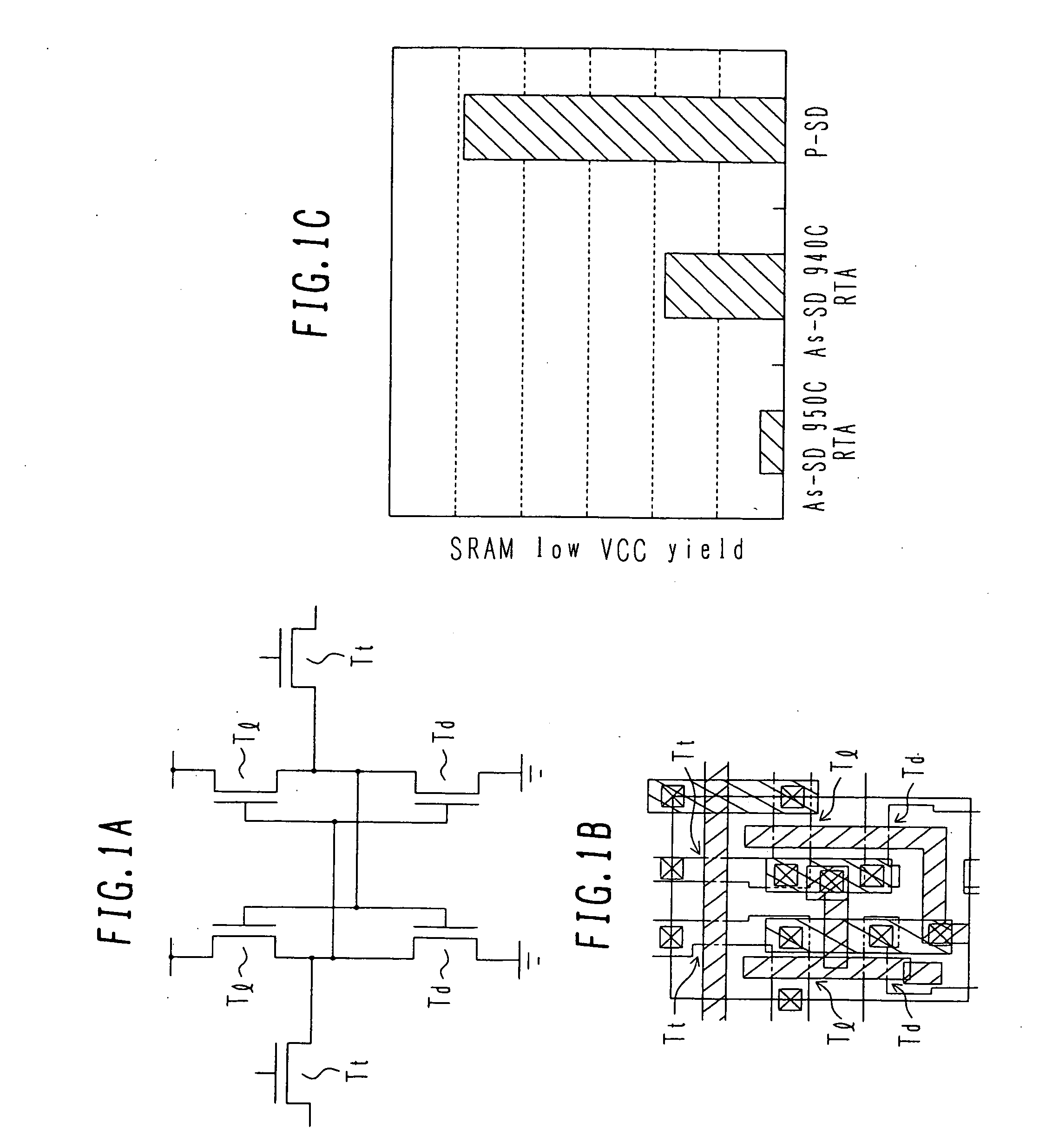

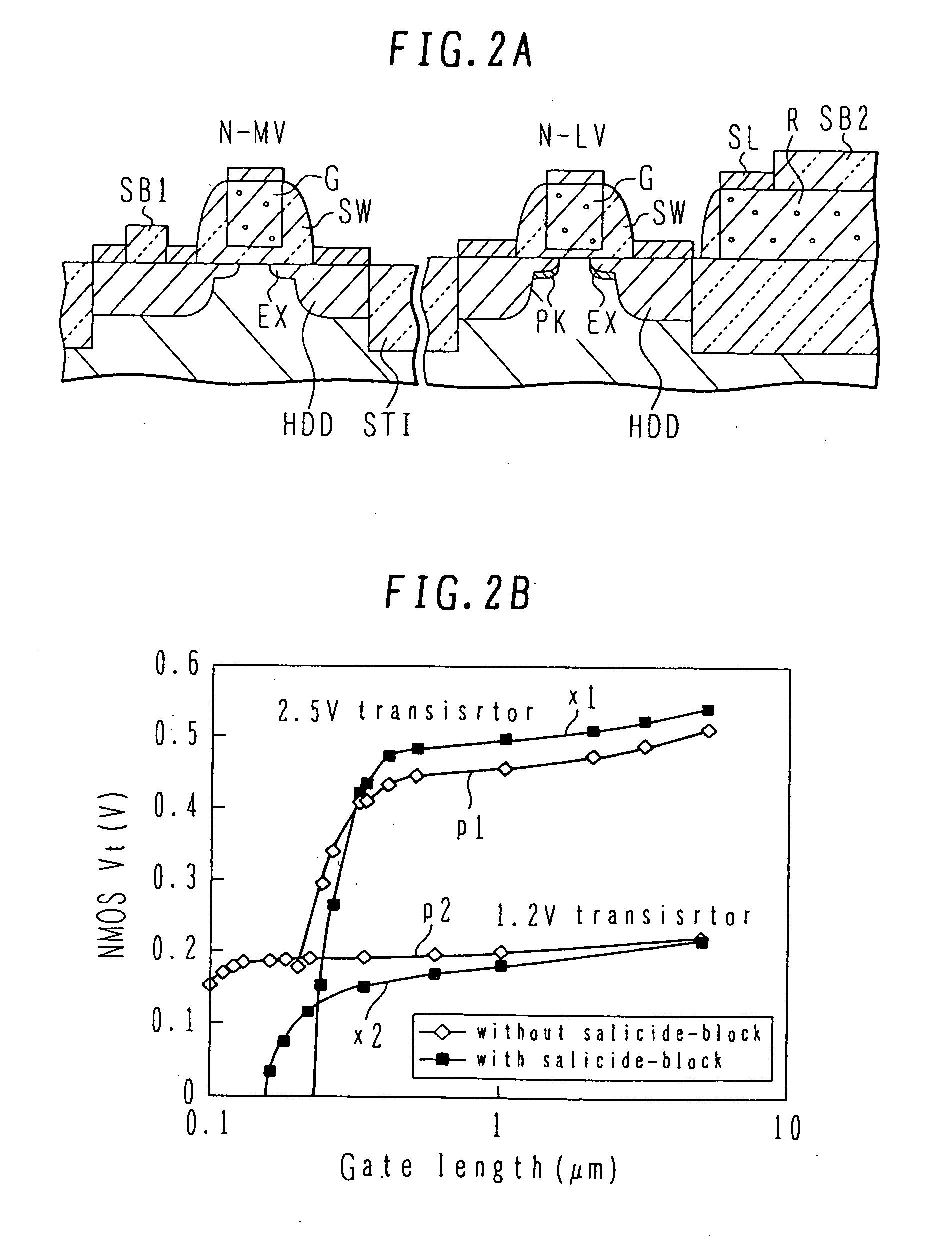

Semiconductor device and its manufacturing method

InactiveUS20050227440A1Simple processEfficient preparation methodTransistorSolid-state devicesDevice materialMetal silicide

A semiconductor device manufacturing method includes, forming isolation region having an aspect ratio of 1 or more in a semiconductor substrate, forming a gate insulating film, forming a silicon gate electrode and a silicon resistive element, forming side wall spacers on the gate electrode, heavily doping a first active region with phosphorus and a second active region and the resistive element with p-type impurities by ion implantation, forming salicide block at 500° C. or lower, depositing a metal layer covering the salicide block, and selectively forming metal silicide layers. The method may further includes, forming a thick and a thin gate insulating films, and performing implantation of ions of a first conductivity type not penetrating the thick gate insulating film and oblique implantation of ions of the opposite conductivity type penetrating also the thick gate insulating film before the formation of side wall spacers.

Owner:FUJITSU LTD

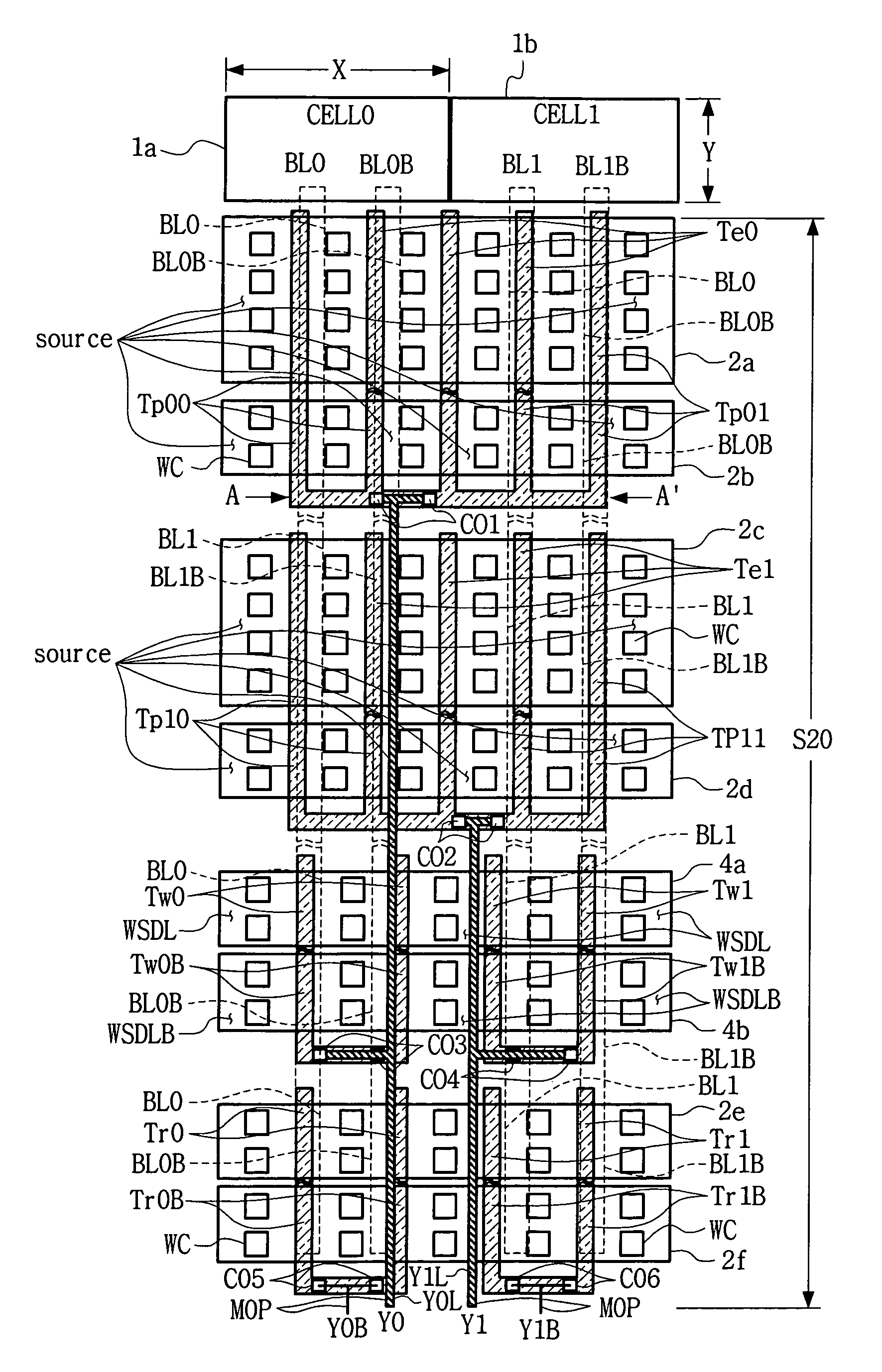

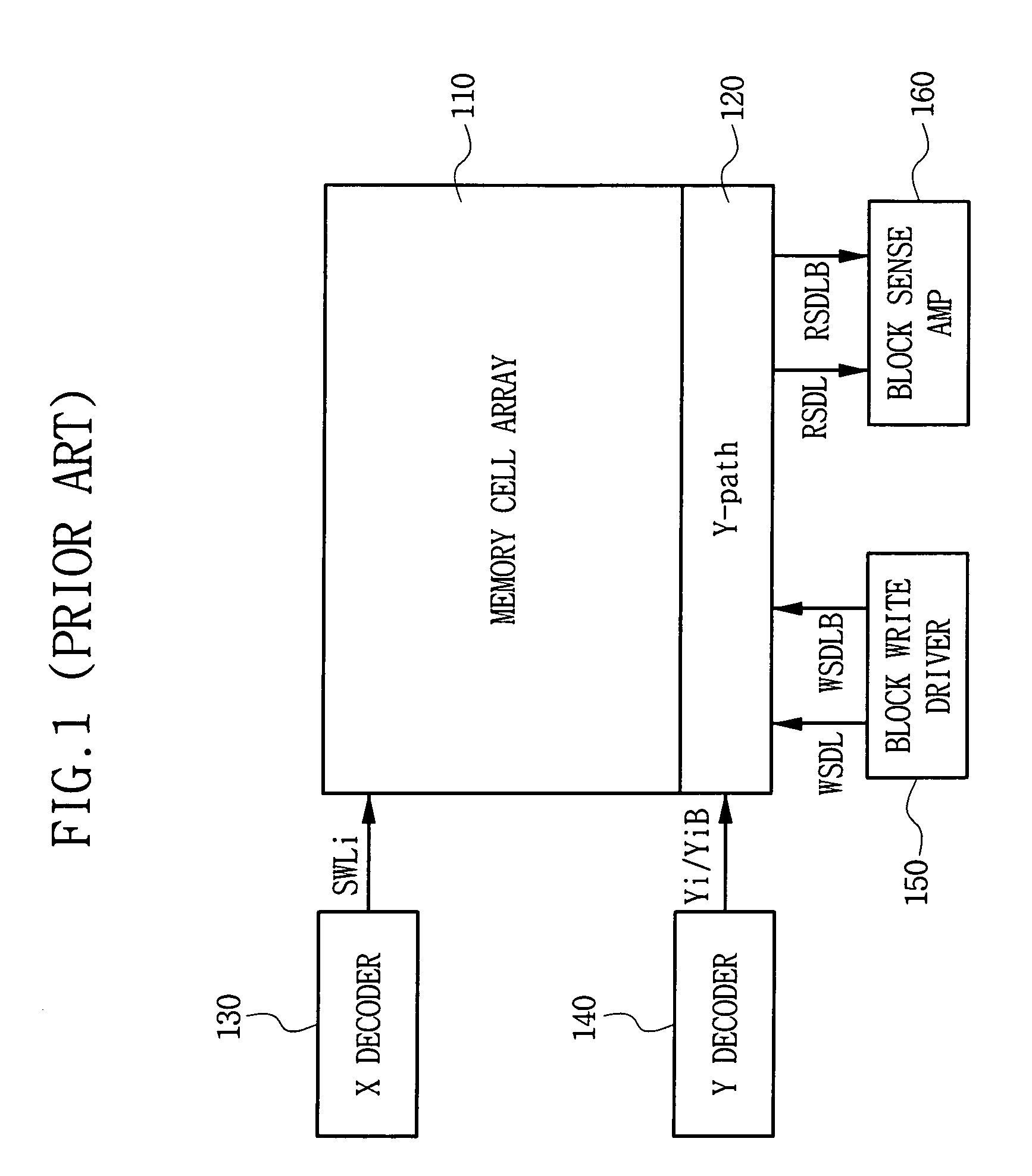

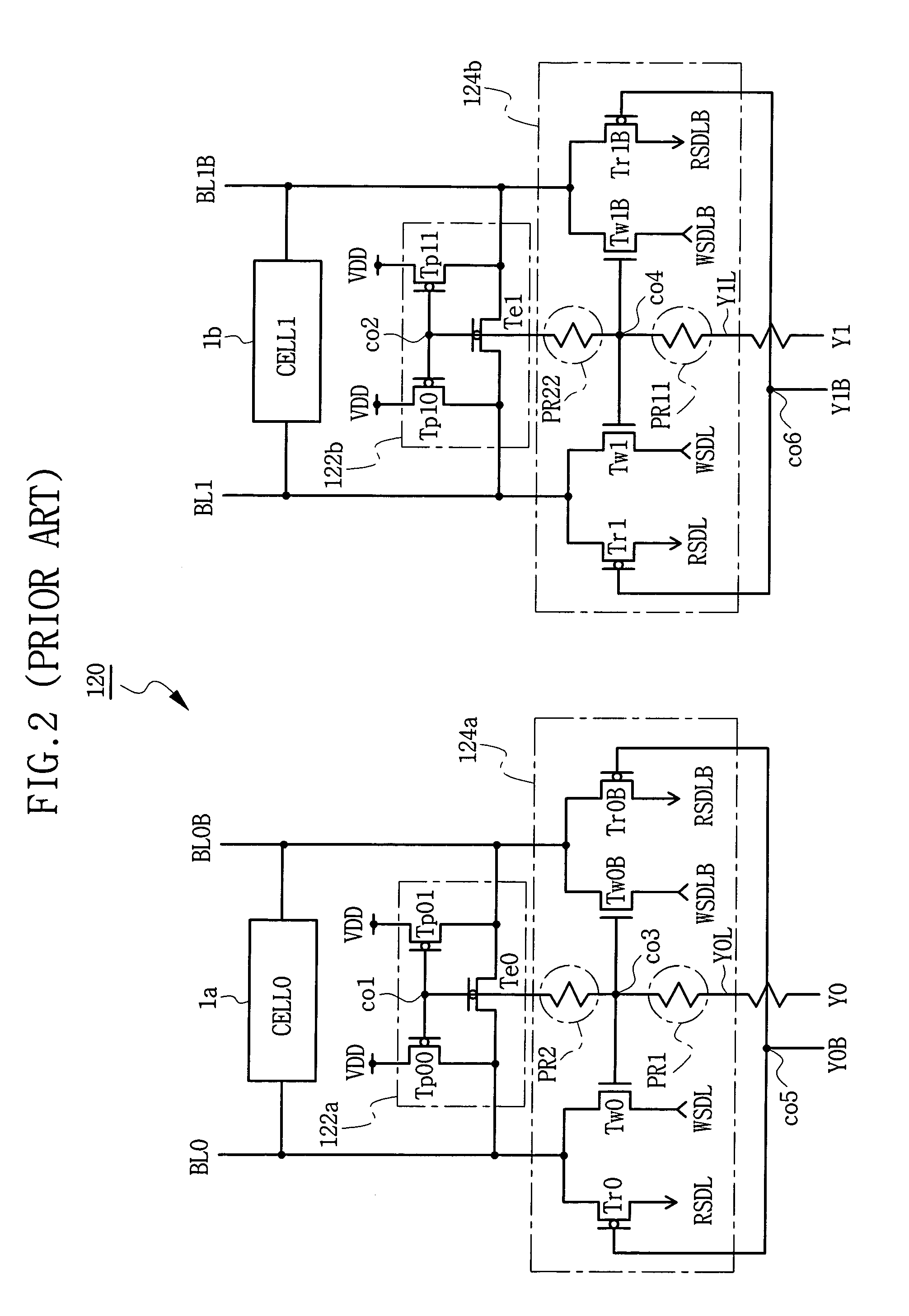

Circuit wiring layout in semiconductor memory device and layout method

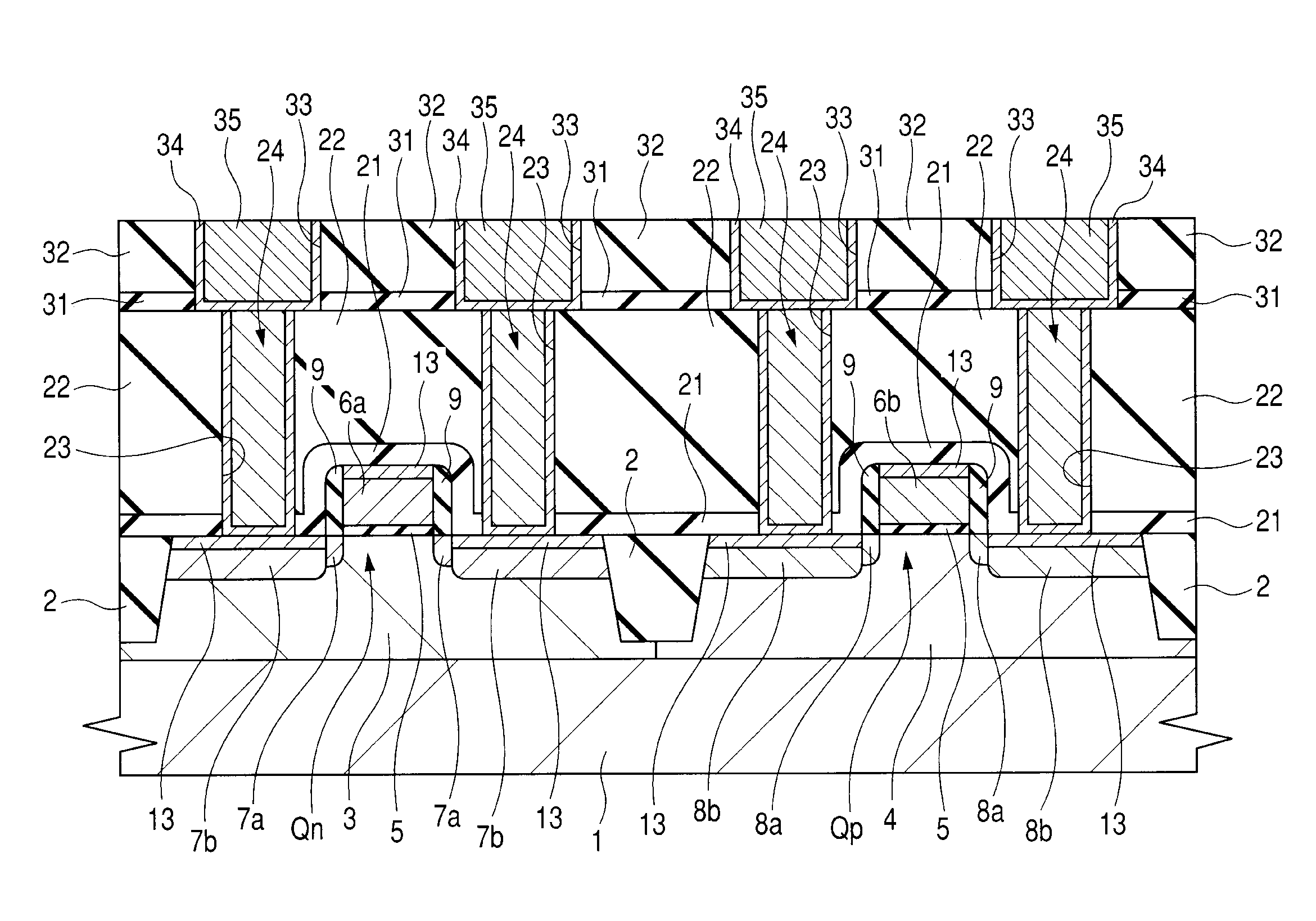

InactiveUS7564134B2Reduced footprintSmooth wiringTransistorSemiconductor/solid-state device detailsMOSFETMetal silicide

An improved circuit wiring layout provides smooth circuit wiring in a peripheral circuit region adjacent to a memory cell region of a semiconductor memory device, and eliminates a write-speed limiting factor. Forming a metal (instead of a metal silicided polysilicon) wiring layer to be connected to a gate layer, to transmit an electrical signal to the gates of FET (e.g., MOSFET (Metal Oxide Semiconductor Field Effect Transistor) transistors formed in the peripheral circuit region; the metal wiring layer is formed (e.g., using one metal damascene process), on a layer different from a word line layer formed on the gate layer (e.g., using another metal damascene process), thereby obtaining a layout of a peripheral circuit region having a reduced area and without using a silicide process.

Owner:SAMSUNG ELECTRONICS CO LTD

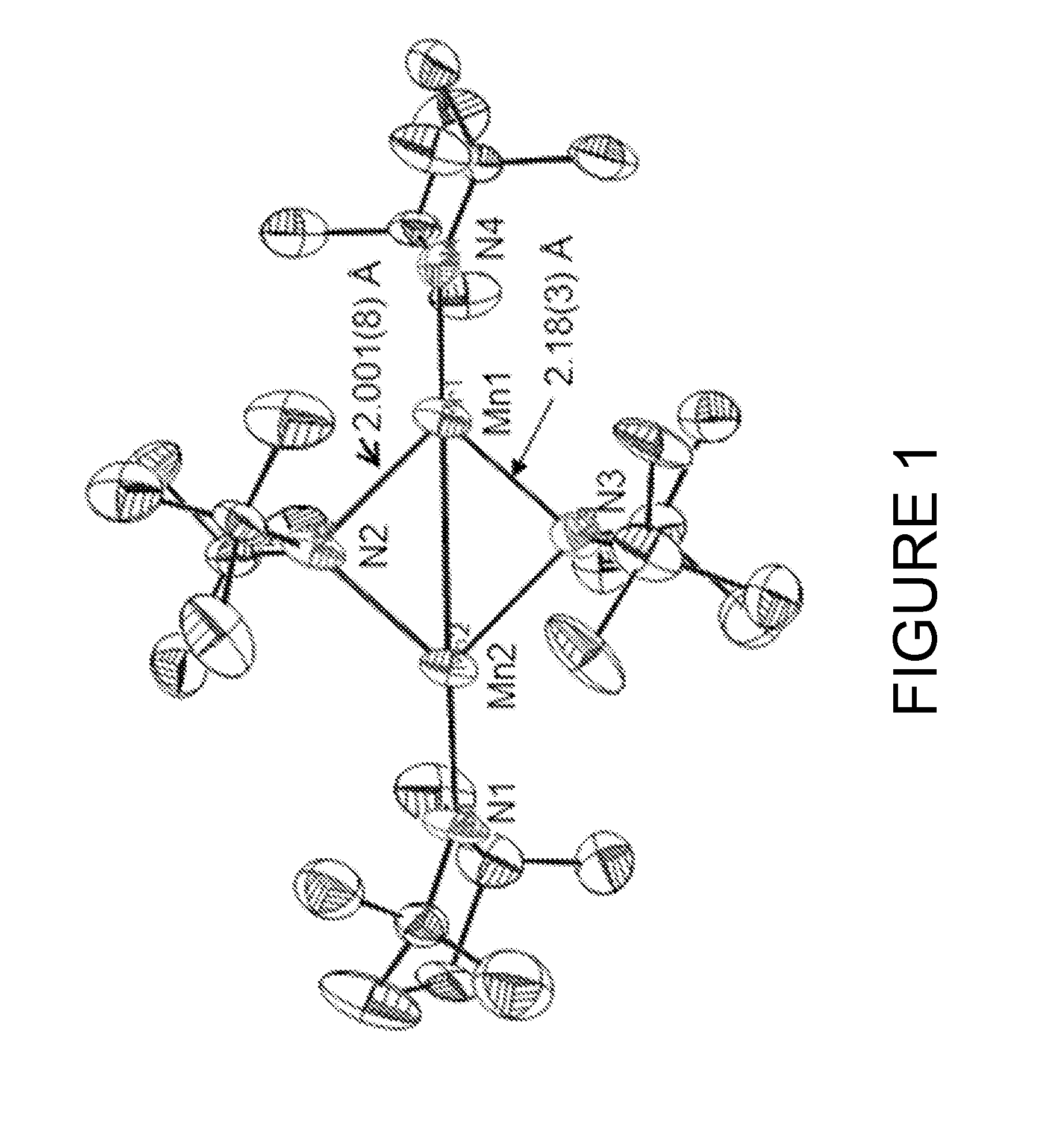

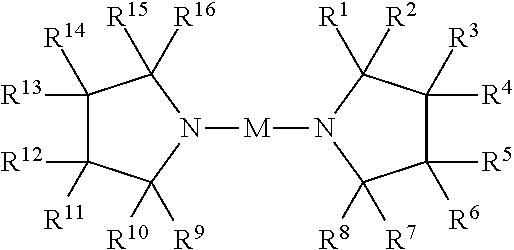

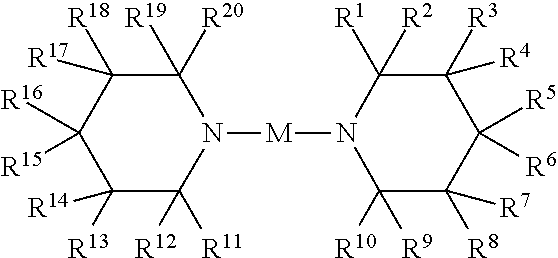

Metal amides of cyclic amines

ActiveUS20160152649A1Improve thermal stabilityImprove conductivityIron group organic compounds without C-metal linkagesNickel organic compoundsGermanideMetal silicide

Compounds, and oligomers of the compounds, are synthesized with cyclic amine ligands attached to a metal atom. These compounds are useful for the synthesis of materials containing metals. Examples include pure metals, metal alloys, metal oxides, metal nitrides, metal phosphides, metal sulfides, metal selenides, metal tellurides, metal borides, metal carbides, metal silicides and metal germanides. Techniques for materials synthesis include vapor deposition (chemical vapor deposition and atomic layer deposition), liquid solution methods (sol-gel and precipitation) and solid-state pyrolysis. Suitable applications include electrical interconnects in microelectronics and magnetoresistant layers in magnetic information storage devices. The films have very uniform thickness and high step coverage in narrow holes.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

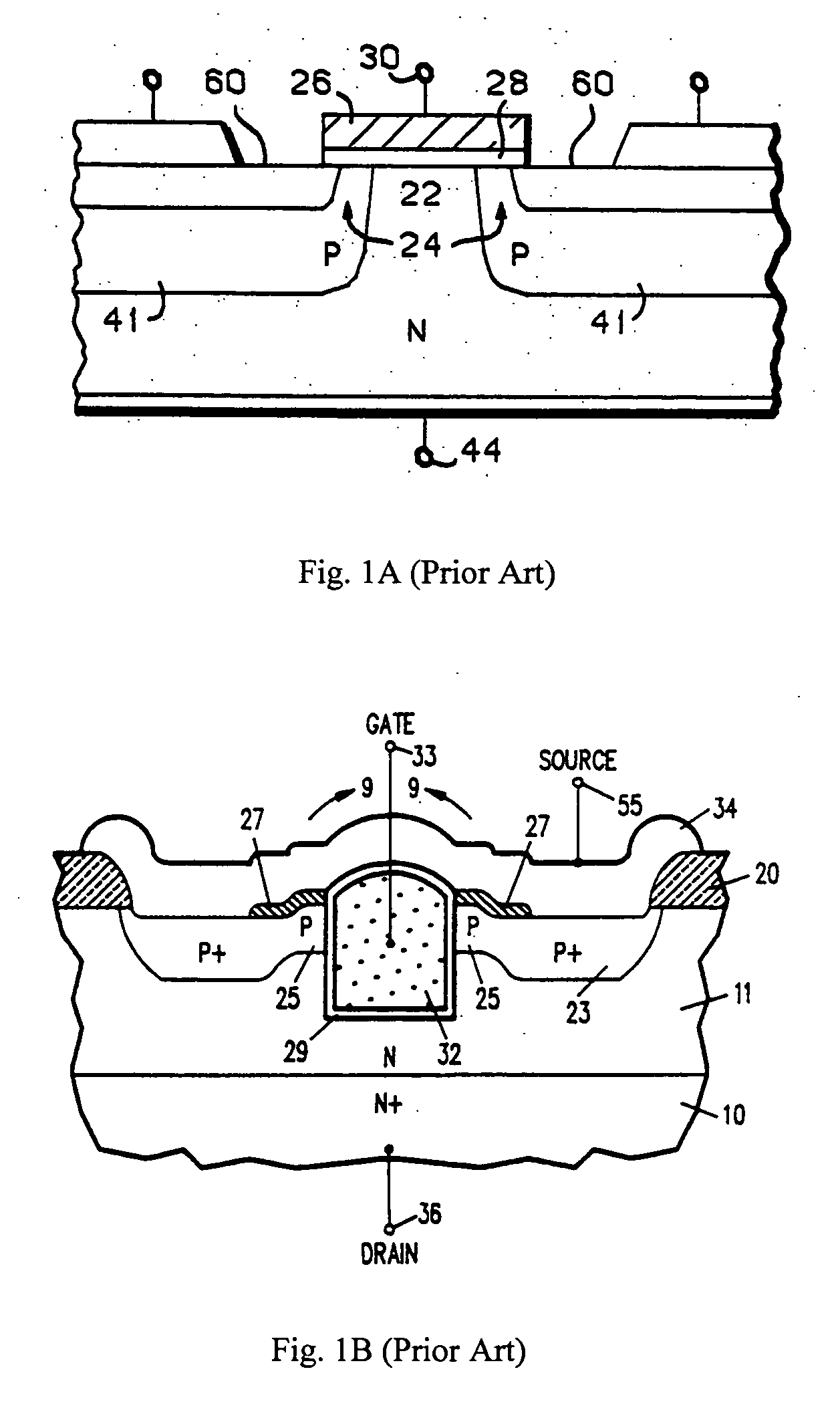

Method of fabrication and device configuration of asymmetrical DMOSFET with Schottky barrier source

ActiveUS20070187751A1Much-reduced contact resistanceTransistorSemiconductor/solid-state device detailsInsulation layerSchottky barrier

A trenched semiconductor power device includes a trenched gate insulated by a gate insulation layer and surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a semiconductor substrate. The source region surrounding the trenched gate includes a metal of low barrier height to function as a Schottky source. The metal of low barrier height further may include a PtSi or ErSi layer. In a preferred embodiment, the metal of low barrier height further includes an ErSi layer. The metal of low barrier height further may be a metal silicide layer having the low barrier height. A top oxide layer is disposed under a silicon nitride spacer on top of the trenched gate for insulating the trenched gate from the source region. A source contact disposed in a trench opened into the body region for contacting a body-contact dopant region and covering with a conductive metal layer such as a Ti / TiN layer. In a preferred embodiment, the semiconductor power device constitutes an asymmetrical double diffusion metal oxide semiconductor field effect transistor (DMOSFET) device.

Owner:ALPHA & OMEGA SEMICON LTD

Metal silicide alloy local interconnect

A local interconnect is formed with a gate conductor line that has an exposed sidewall on an active area of a semiconductor substrate. The exposes sidewall comprises a silicon containing material that may form a silicide alloy upon silicidation. During a silicidation process, a gate conductor sidewall silicide alloy forms on the exposed sidewall of the gate conductor line and an active area silicide is formed on the active area. The two silicides are joined to provide an electrical connection between the active area and the gate conductor line. Multiple sidewalls may be exposed on the gate conductor line to make multiple connections to different active area silicides.

Owner:GLOBALFOUNDRIES INC

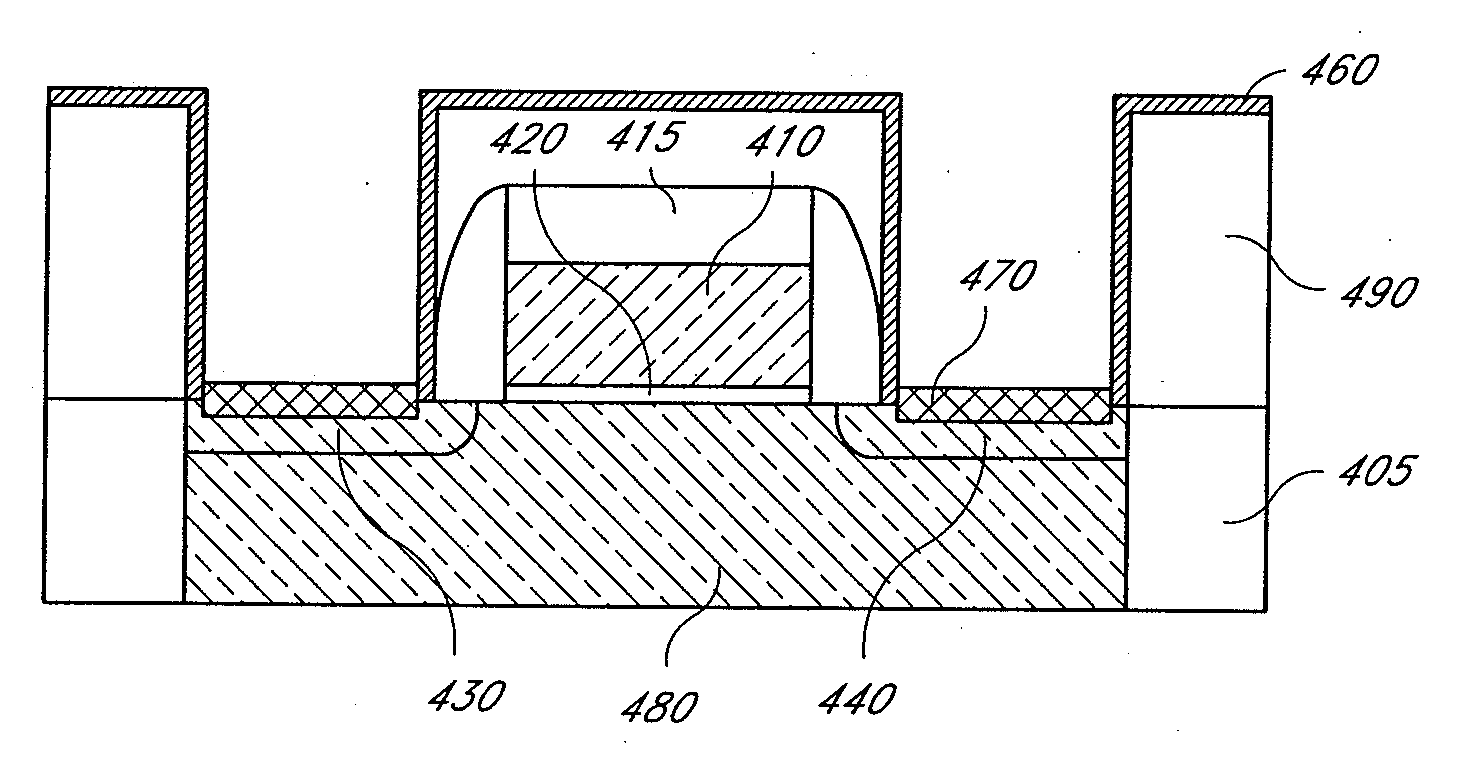

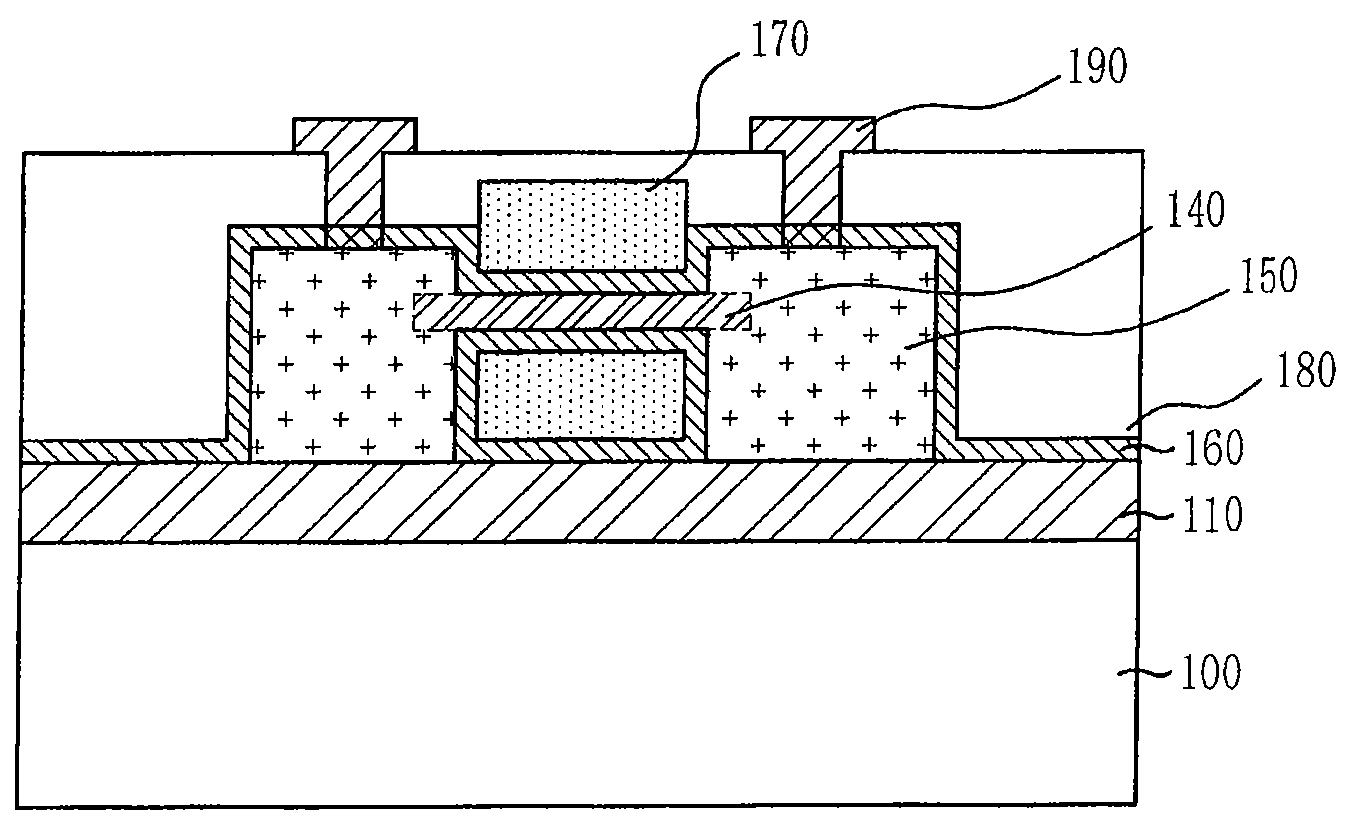

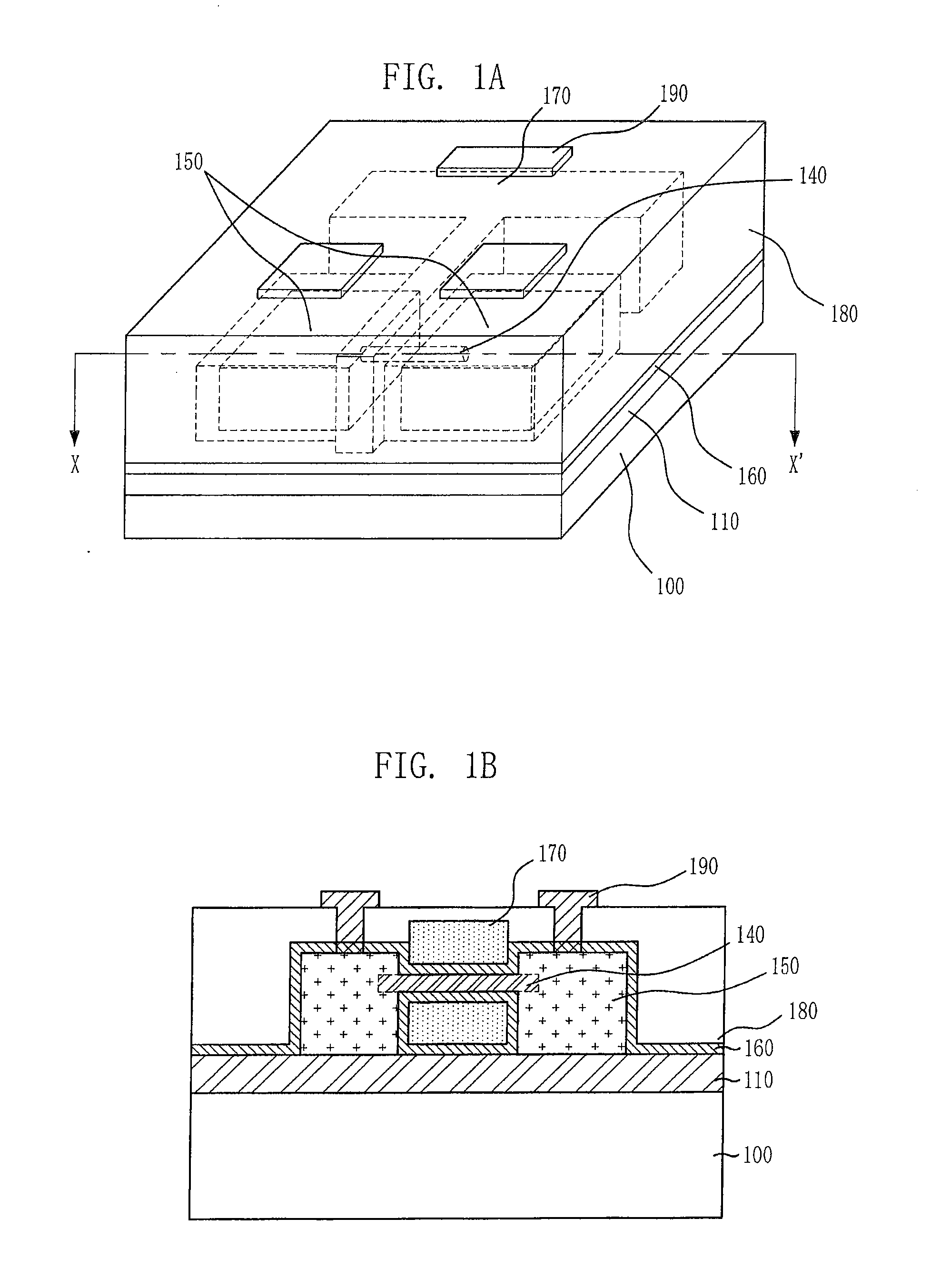

Fin-type field effect transistor structure with merged source/drain silicide and method of forming the structure

ActiveUS7851865B2Increase capacitanceSeries resistance is minimizedSemiconductor devicesMetal silicideParasitic capacitance

Owner:GLOBALFOUNDRIES U S INC

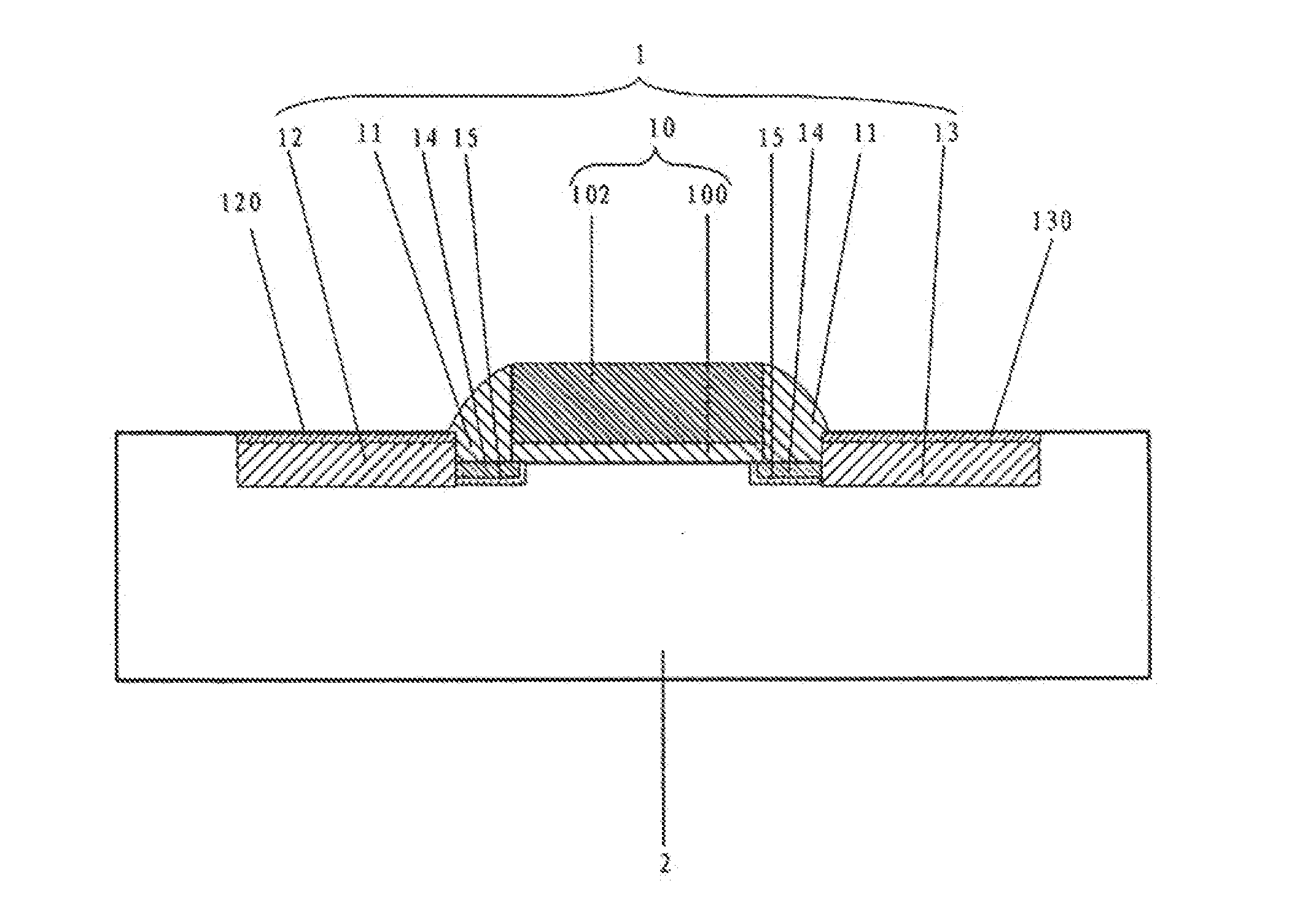

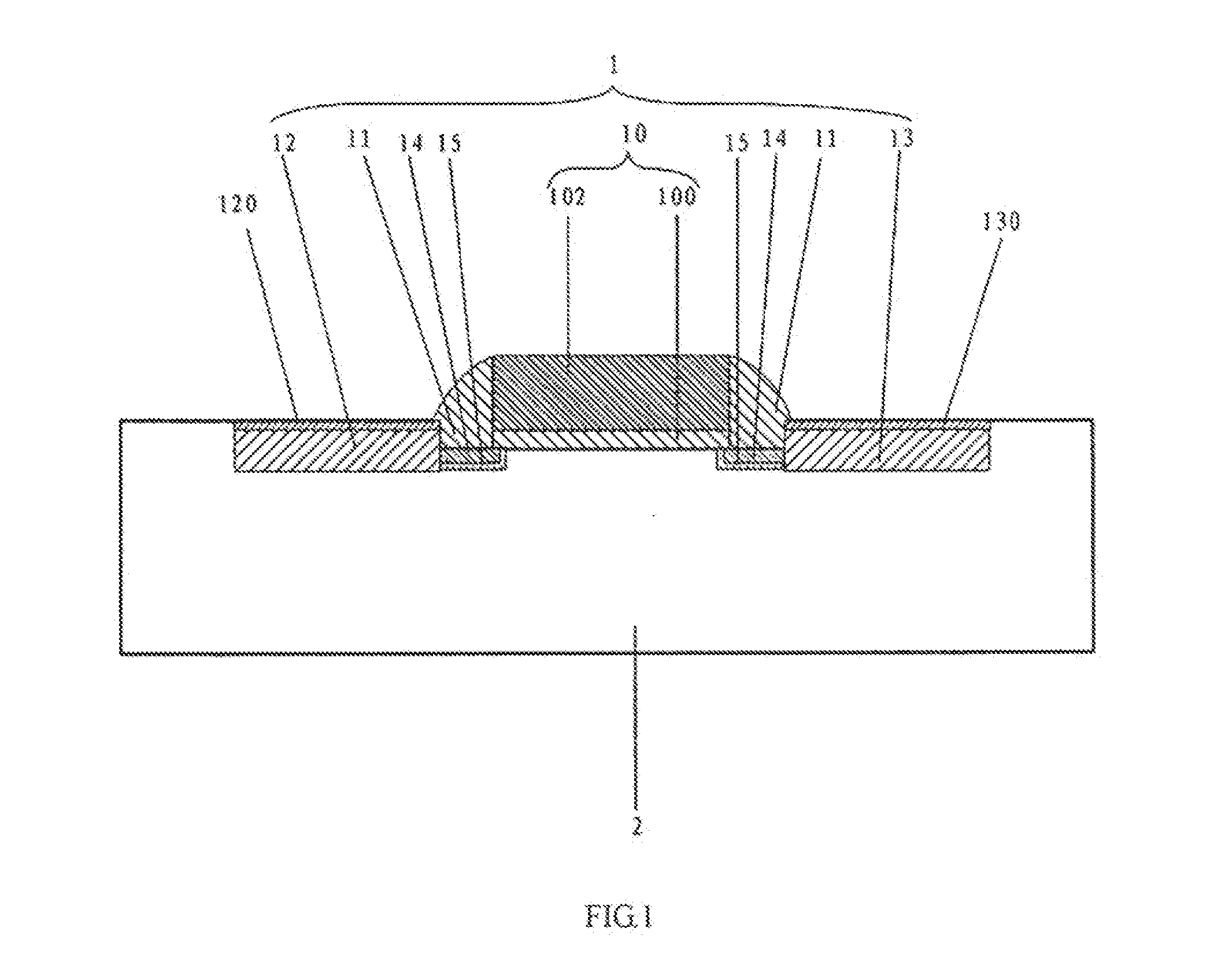

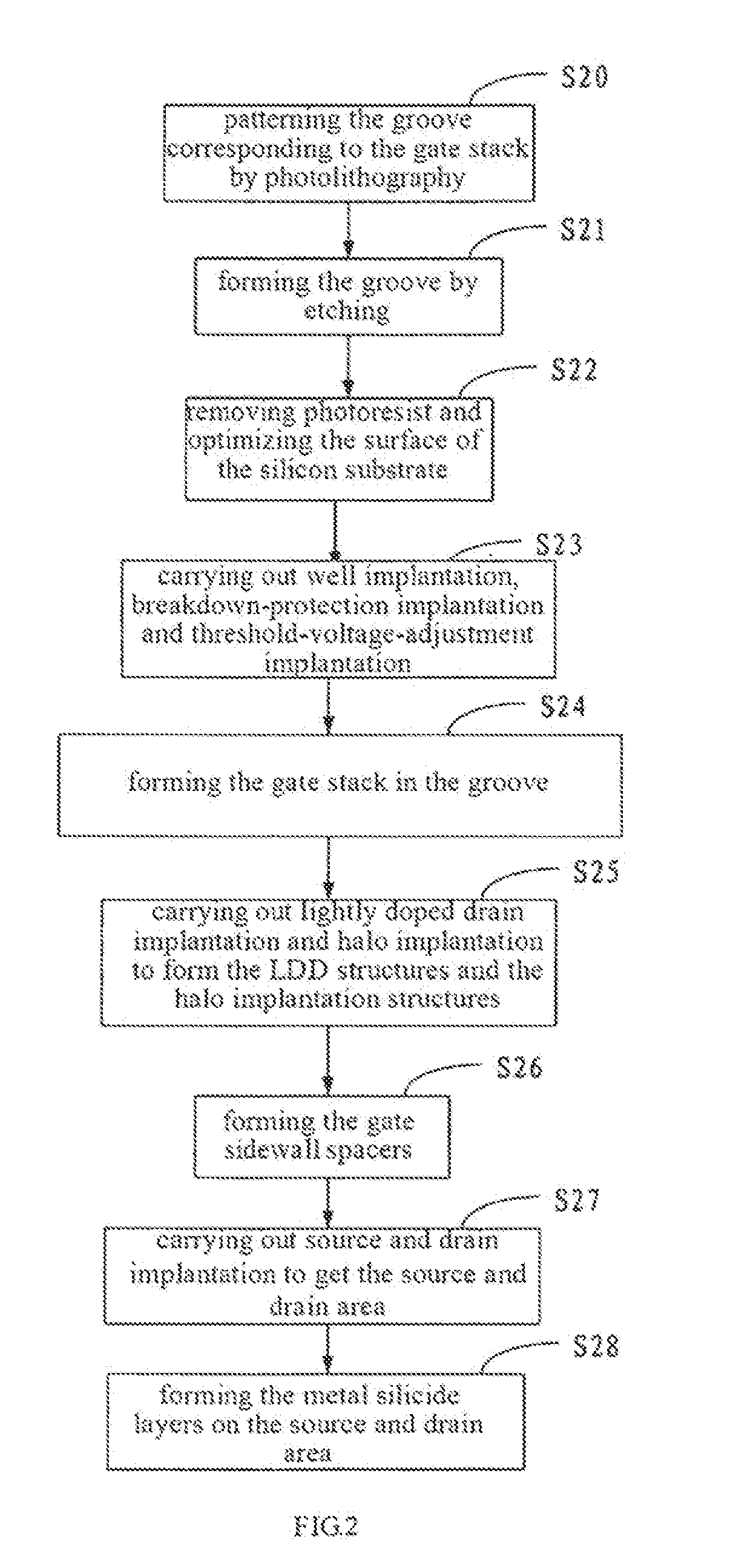

Mos transistor for reducing short-channel effects and its production

ActiveUS20110059588A1Suppression of short channel effectsReduce impactSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideGate stack

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

Contact plug structure, semiconductor device, and method for forming contact plug

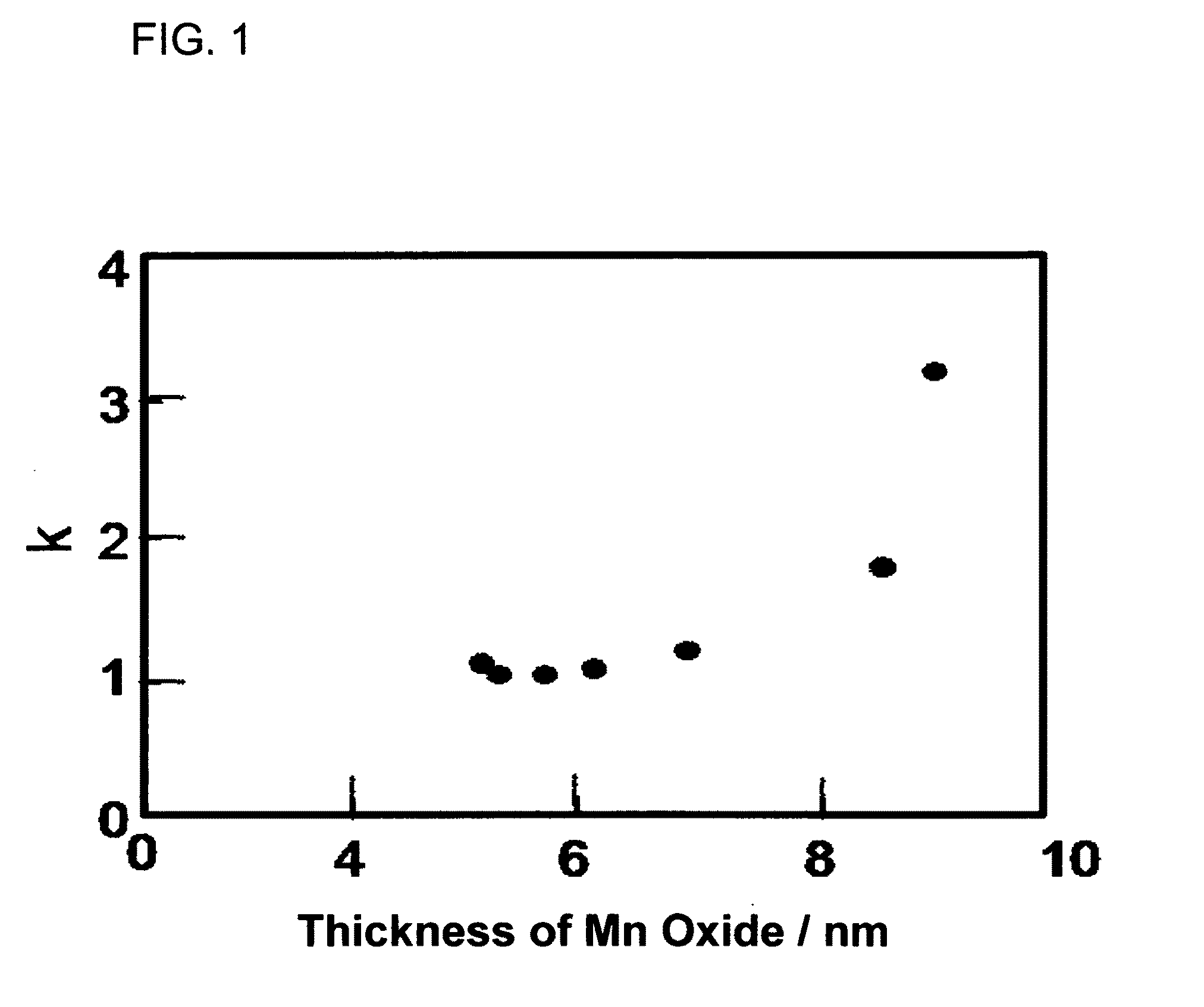

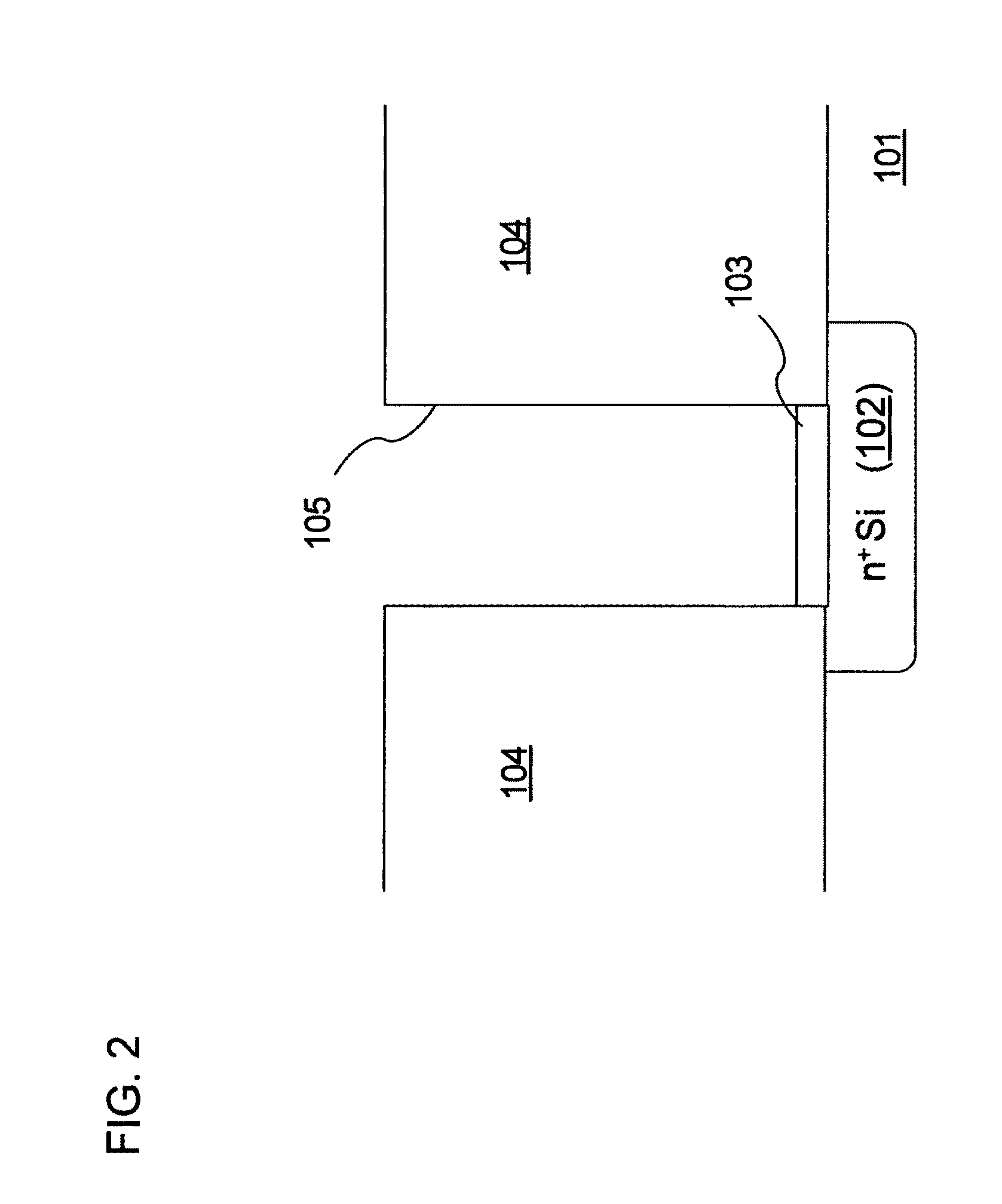

InactiveUS20110057317A1Suppress DiffuseReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesMetal silicideManganese oxide

A contact plug structure formed on a contact hole of an insulating layer of a semiconductor device includes a metal silicide layer formed on a bottom part of the contact hole of the insulating layer, a manganese oxide layer formed on the metal silicide layer in the contact hole, and a buried copper formed on the manganese oxide layer which substantially fills the contact hole.

Owner:ADVANCED INTERCONNECT MATERIAL

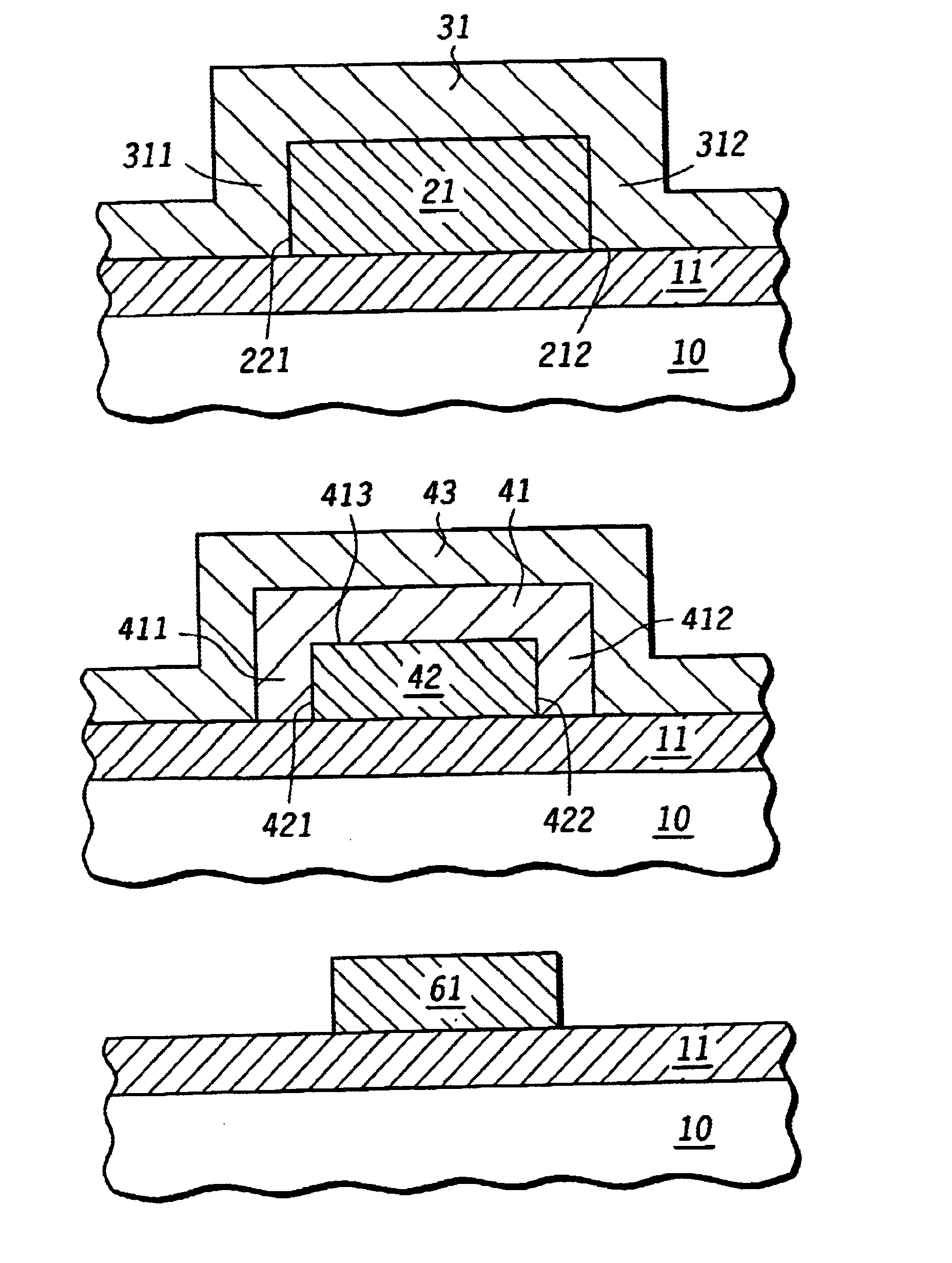

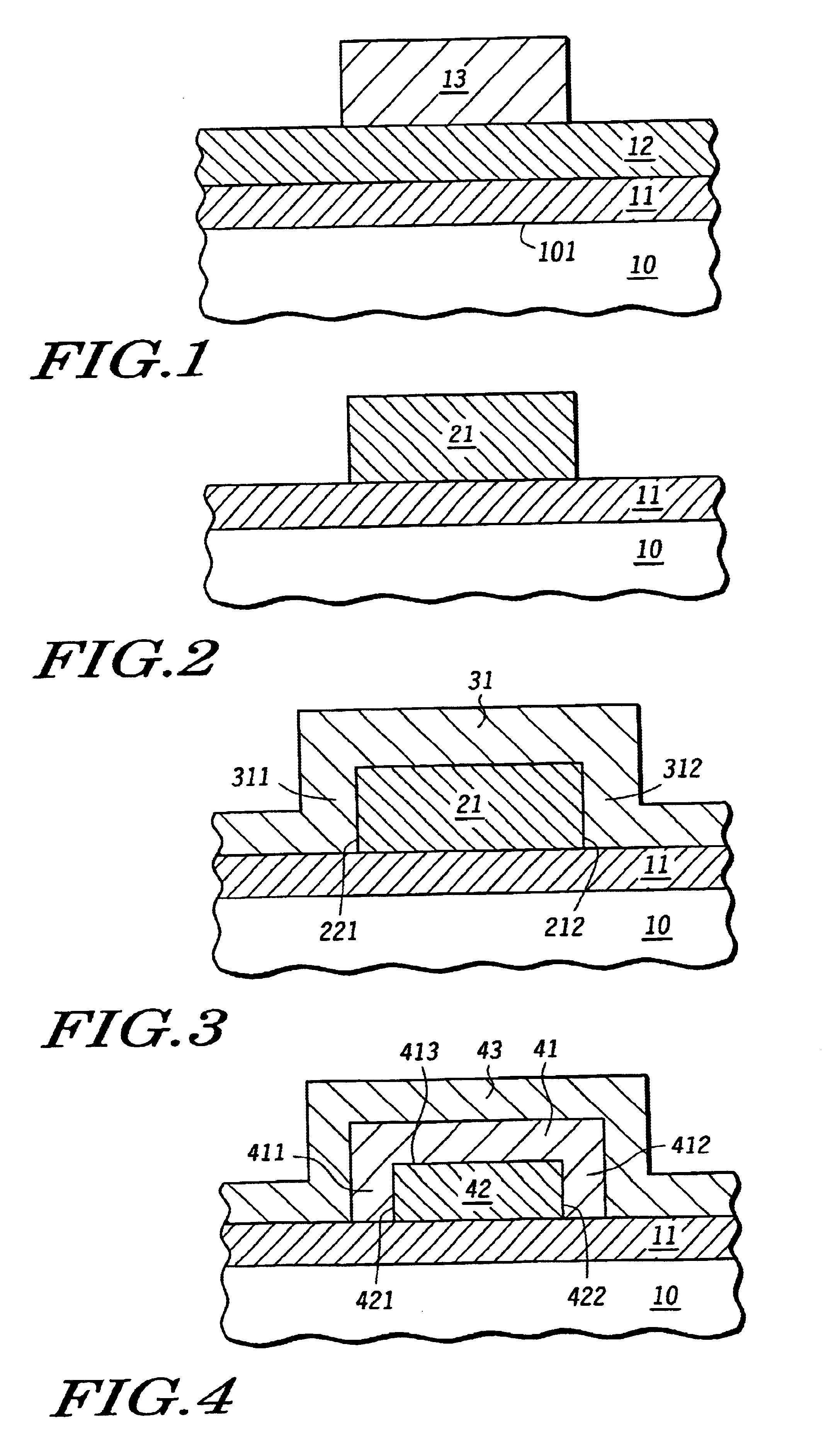

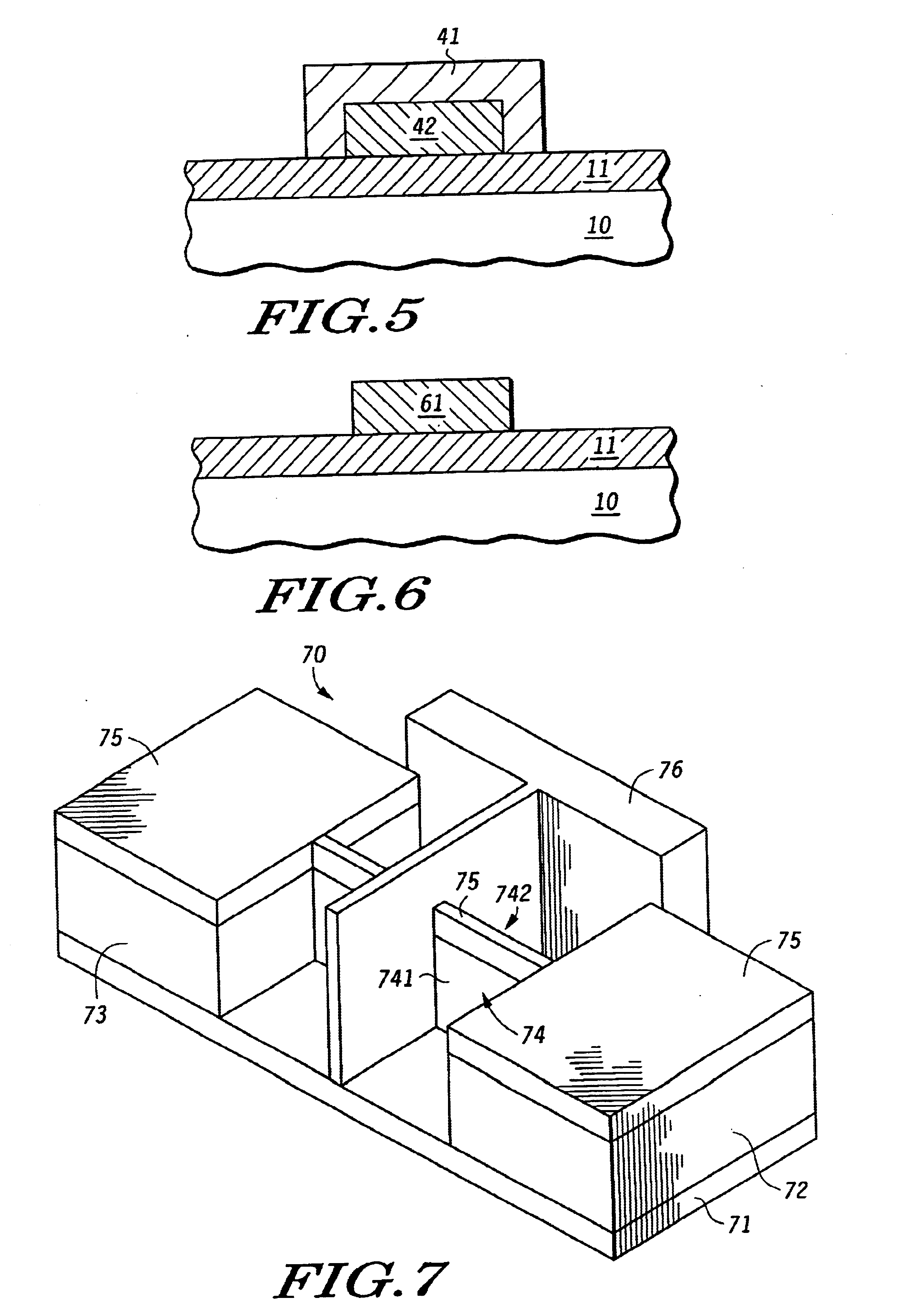

Method for forming an electronic structure using etch

A method of forming a conductive structure having a length that is less than the length define by photolithographic patterning. A silicon layer (12) is formed in a MeOx dielectric layer (11) is photolithographically patterned to a predetermined first length. A metal layer (31) is formed conformally to at least the sidewalls of the silicon layer and then is reacted with the silicon to form a metal silicide (41). In particular, metal silicide abutments (411,412) are formed contiguous to sidewalls (421,422) of a reduced conductor (42). The remaining metal layer and the metal silicide are etched away, resulting in a conductor having predetermined second length that is less than the predetermined first length.

Owner:NORTH STAR INNOVATIONS

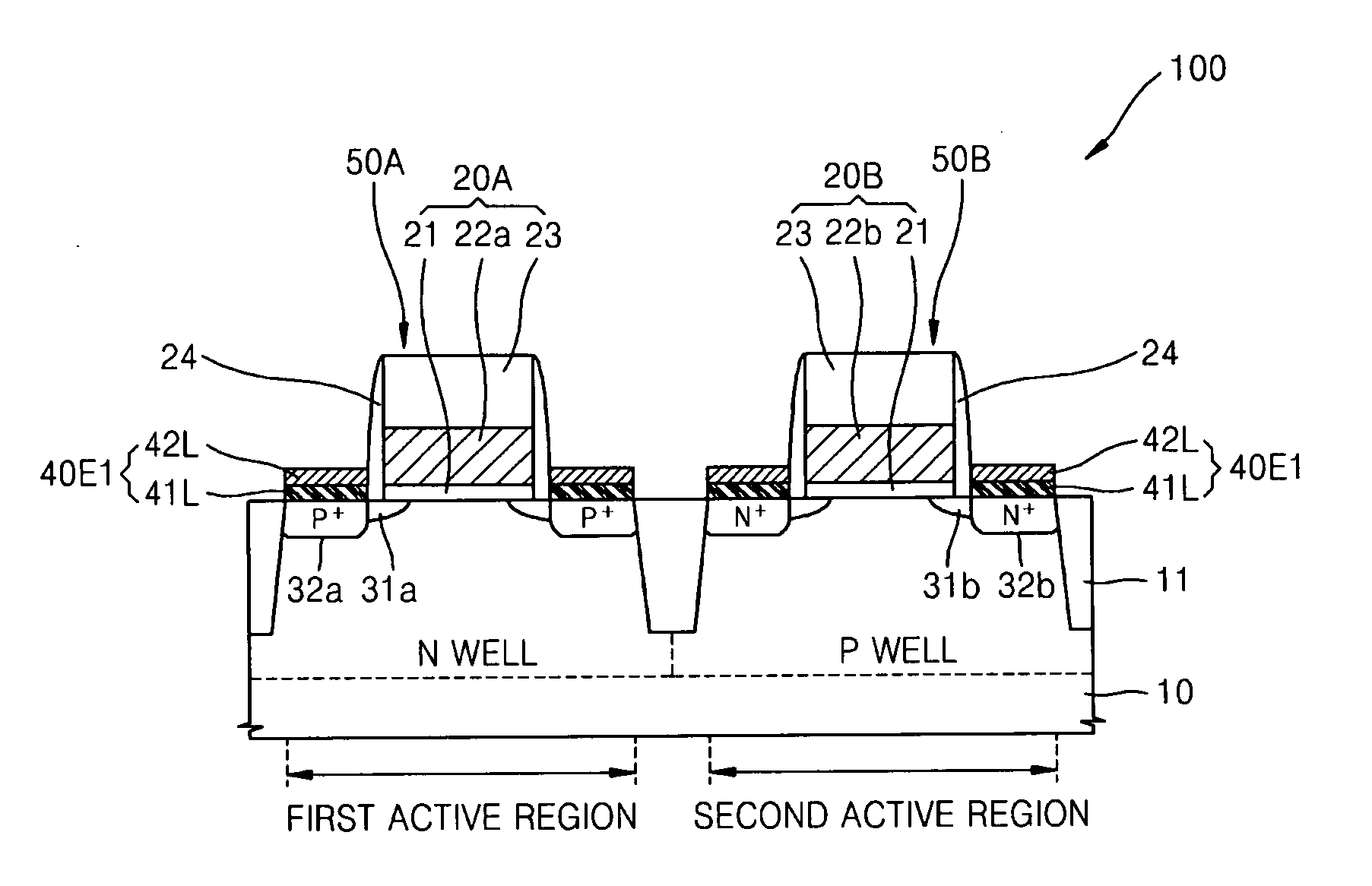

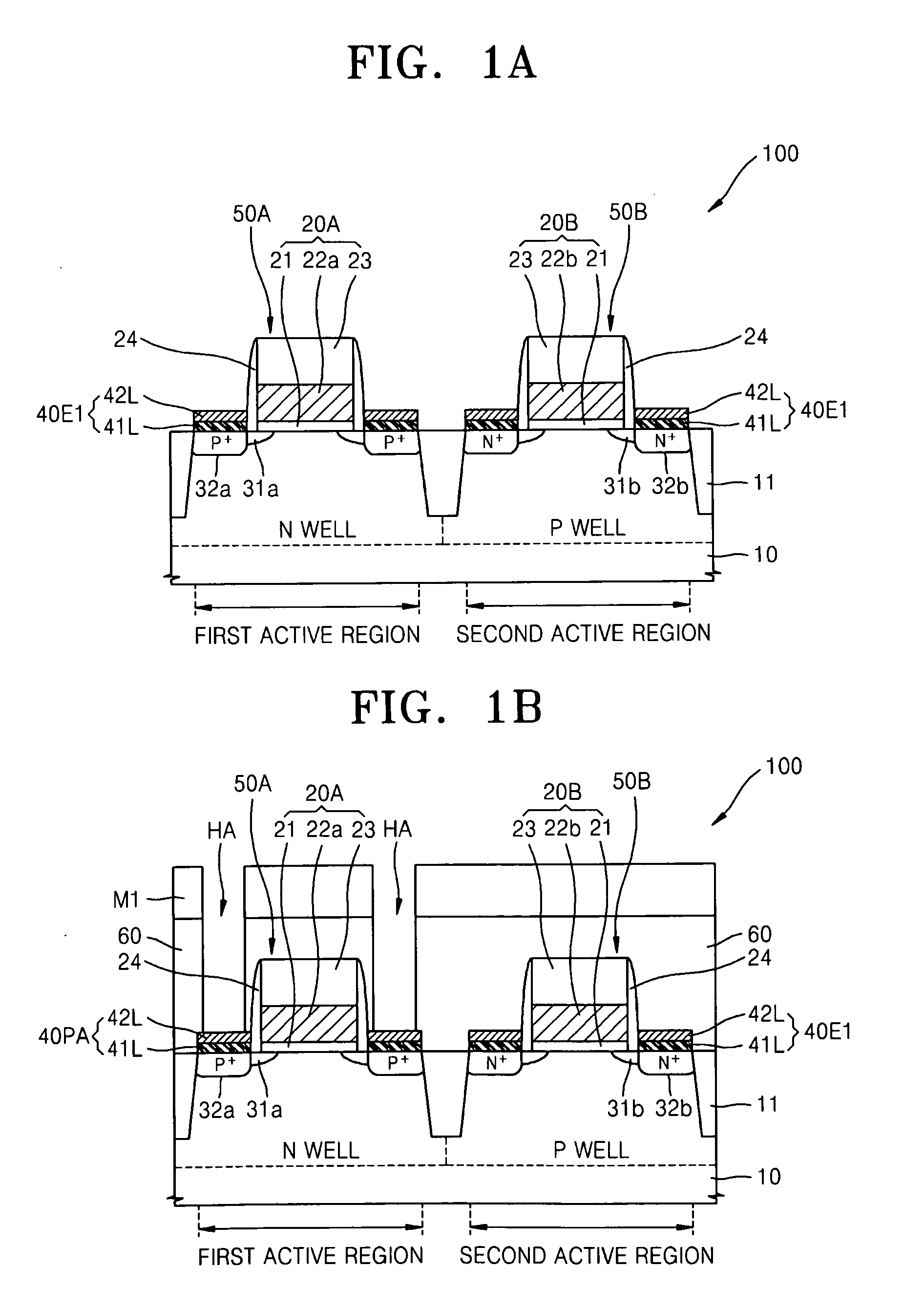

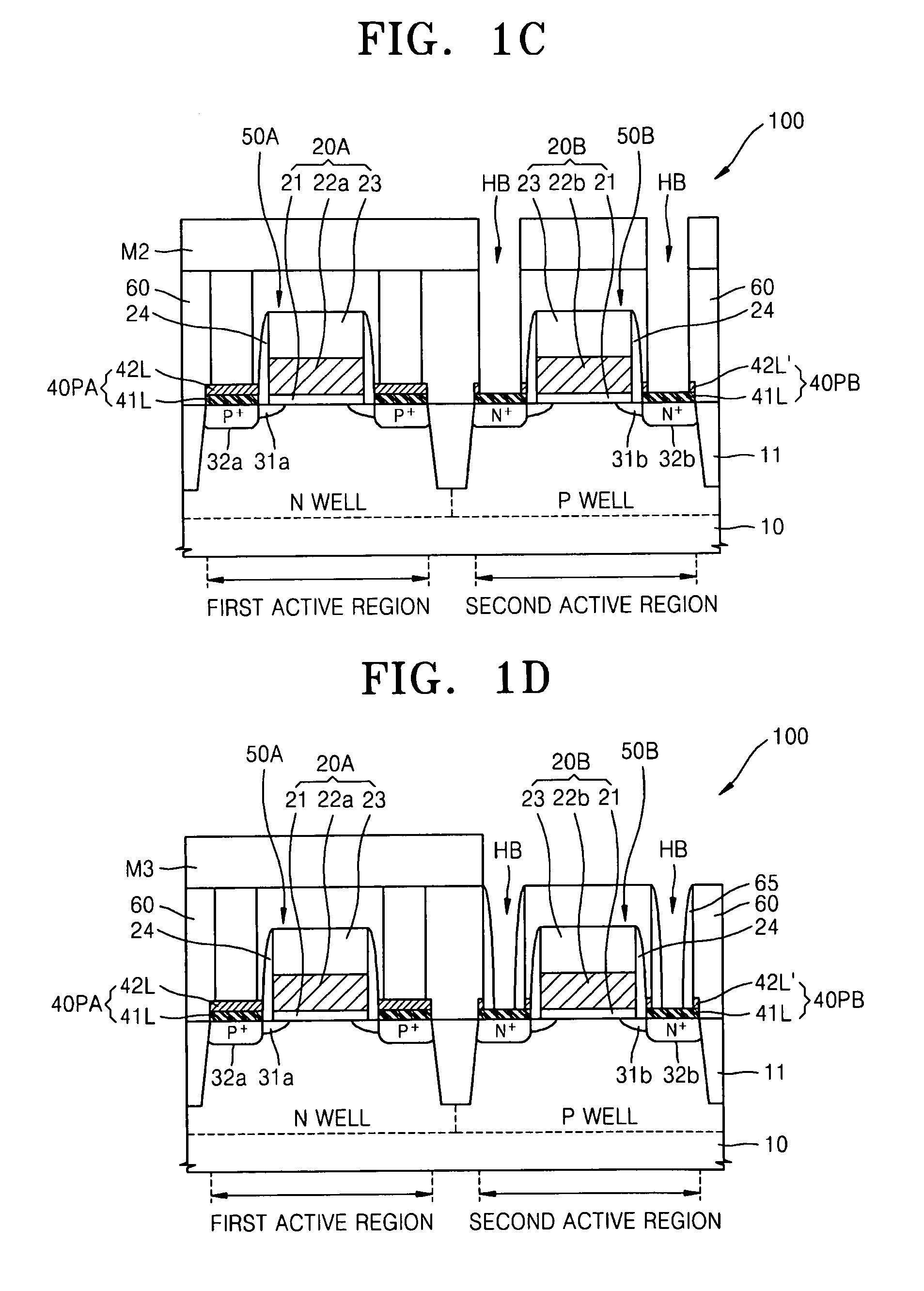

Semiconductor devices and methods of manufacturing the same

ActiveUS20100123198A1Reduce contact resistanceTransistorSemiconductor/solid-state device detailsContact padDevice material

Provided are semiconductor devices having low resistance contacts and methods of manufacturing the same. One or more of the semiconductor devices include a substrate having first and second active regions; a P-channel field-effect transistor associated with the first active region and including at least one of the source and drain regions; a N-channel field-effect transistor associated with the second active region and including at least one of the source and drain regions; a first contact pad layer comprising silicon (Si) and SiGe epitaxial layers on the at least one of the source and drain regions of the P-channel field-effect transistor, the SiGe epitaxial layer being sequentially stacked on the Si epitaxial layer; a second contact pad layer comprising silicon (Si) and SiGe epitaxial layers on the at least one of the source and drain regions of the N-channel field-effect transistor, the SiGe epitaxial layer being sequentially stacked on the Si epitaxial layer; an interlayer insulating film formed on the P-channel and the N-channel field-effect transistors and including first and second contact holes, wherein the first contact hole includes a first lower region that exposes the SiGe epitaxial layer of the first contact pad layer and the second contact hole includes a second lower region that penetrates through the SiGe epitaxial layer of the second contact pad layer to expose the Si epitaxial layer of the second contact pad layer; first and second metal silicide films formed respectively in the first and second lower regions of the contact holes; and contact plugs formed on the first and second metal silicide films and filled in the first and second contact holes.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com