Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Decrease the density of surface states" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

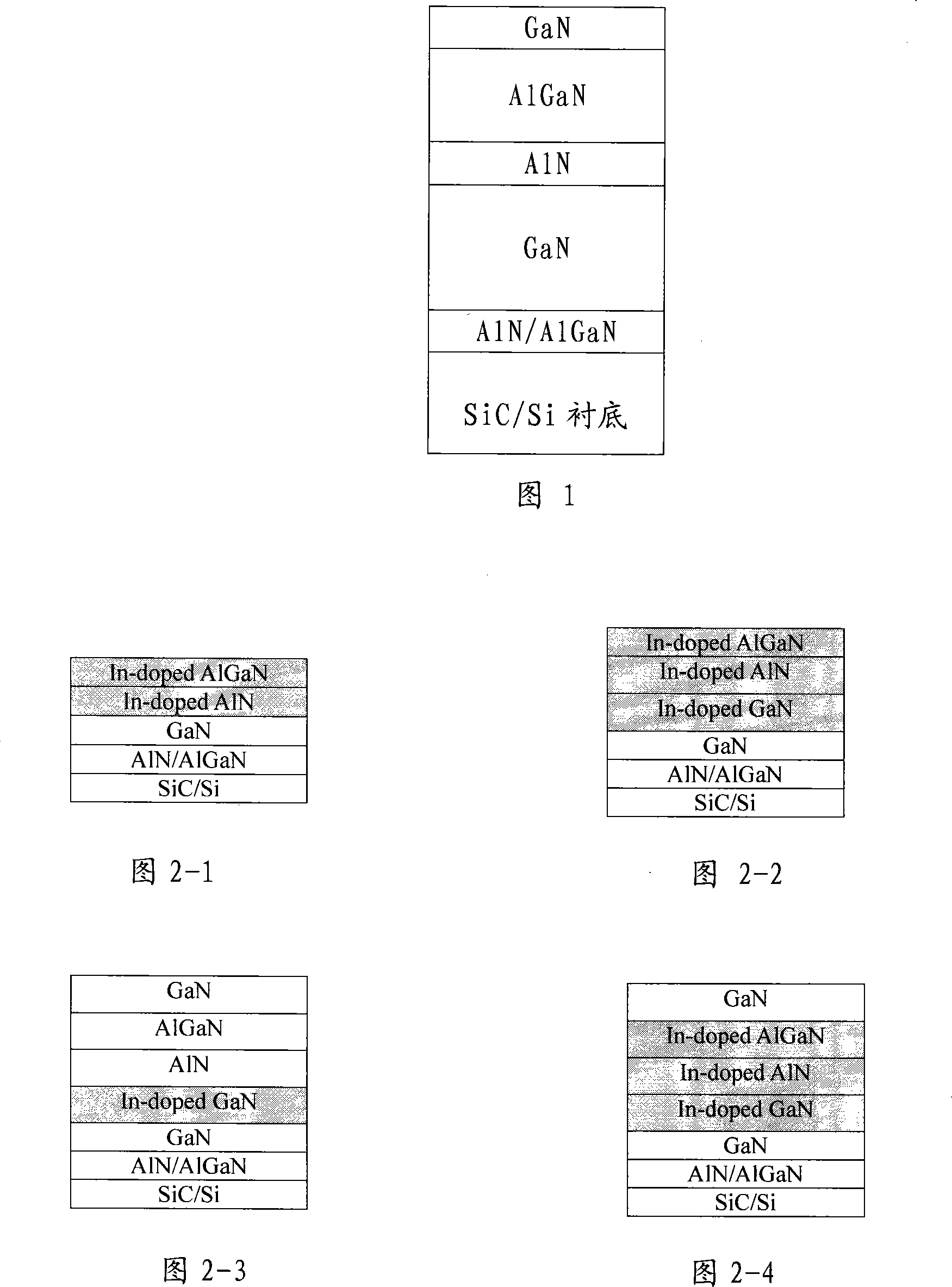

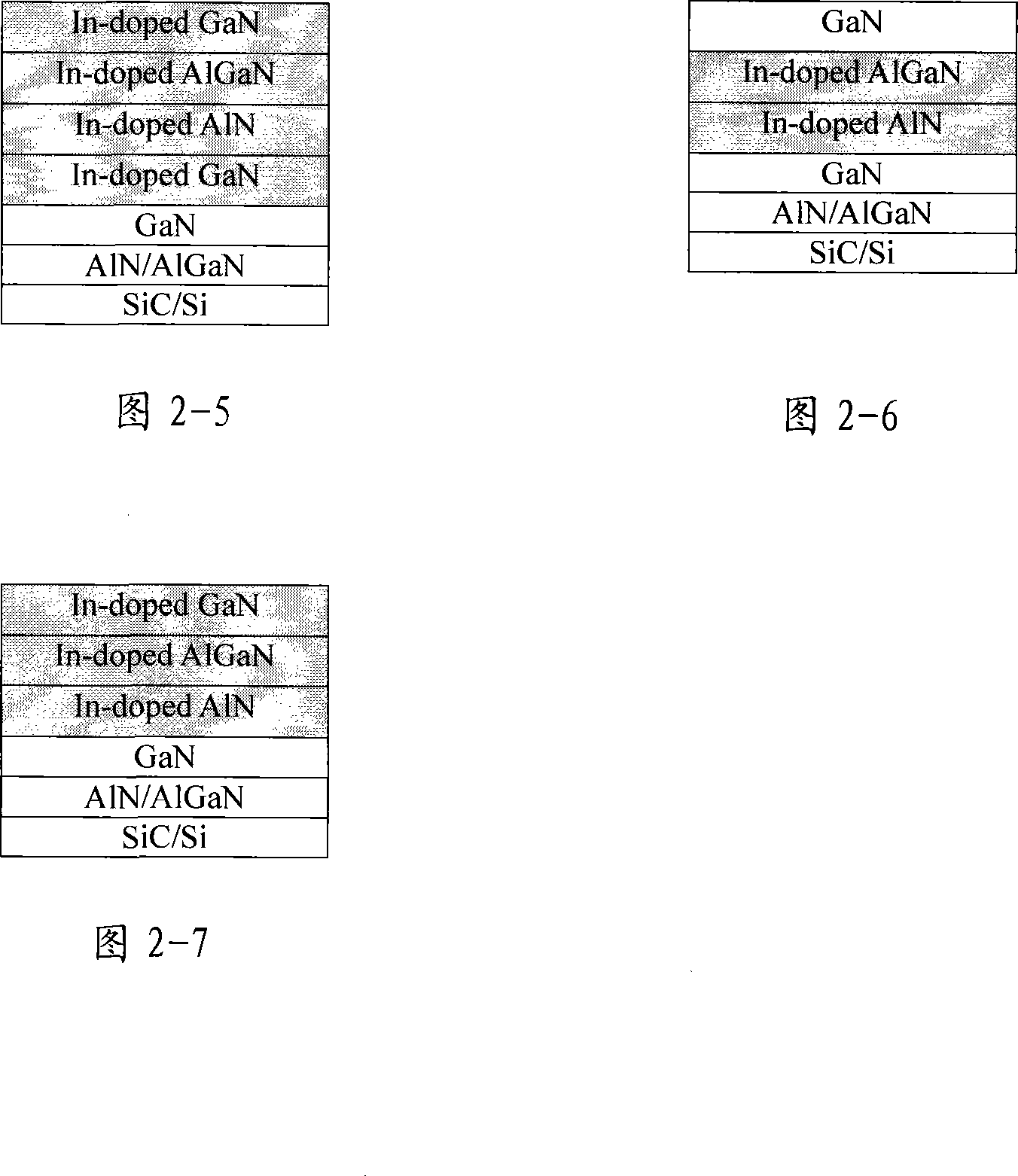

Method for improving gallium nitride based transistor material and device performance using indium doping

ActiveCN101114594AFree diffusionIncrease the diffusion distanceSemiconductor/solid-state device manufacturingGas phaseSingle crystal

The invention discloses a method of increasing the properties of the gallium nitride-based transistor material and device with indium doping and applies in the field of making gallium nitride-based HEMT or HFET materials and devices. The method and process is to form the gallium nitride-based high electron mobility transistor or heterostructure field effect transistor materials on SiC or Si single crystal substrate grown by metal-organic chemical vapor deposition epitaxial growth system. After the AlN or AlGaN nucleating layer and the GaN buffer layer are grown on the SiC or Si single crystal substrate, a GaN channel layer, an AlN insert layer, an AlGaN barrier layer and a GaN capped layer are grown, and trimethyl indium is added in the growth atmosphere to do epitaxial growth with indium doping. The dislocation of the material or device made by the method of the invention is reduced greatly. The invention improves the interfacial smoothness, increases the electron mobility of the material, increases the growth window, ensures the material grow easier, improves the current collapse of the device, reduces the leakage current and increases transconductance and gain and increases the output power of microwave power devices.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

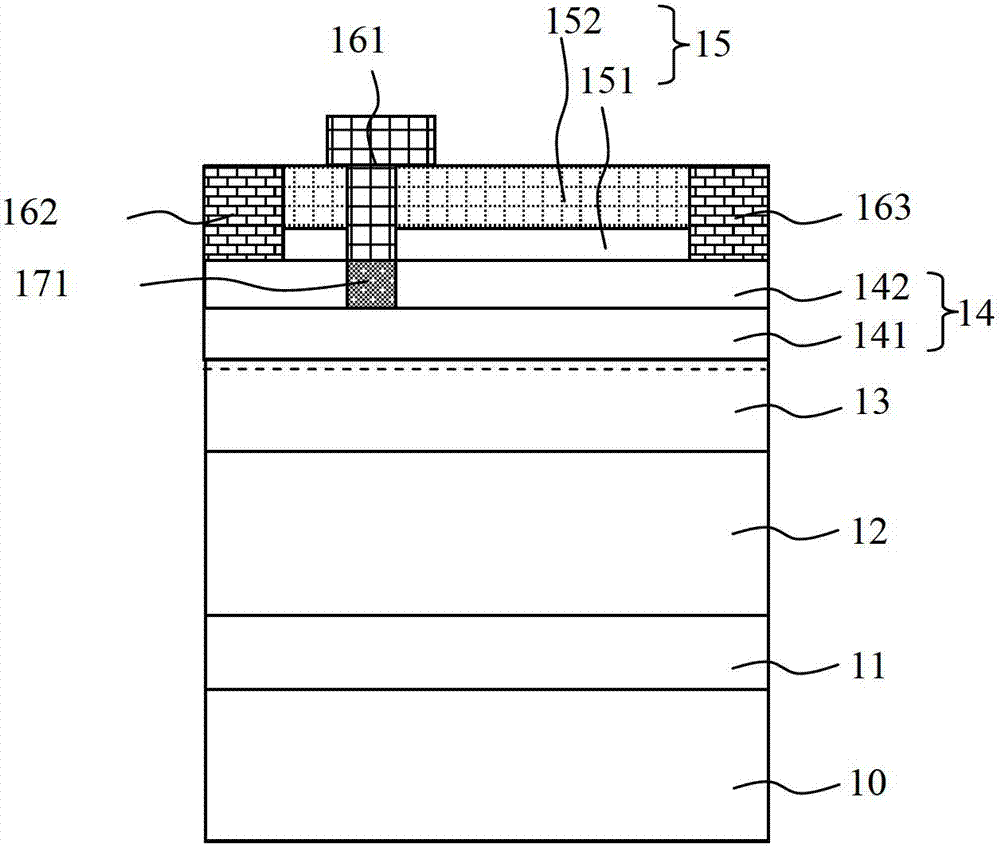

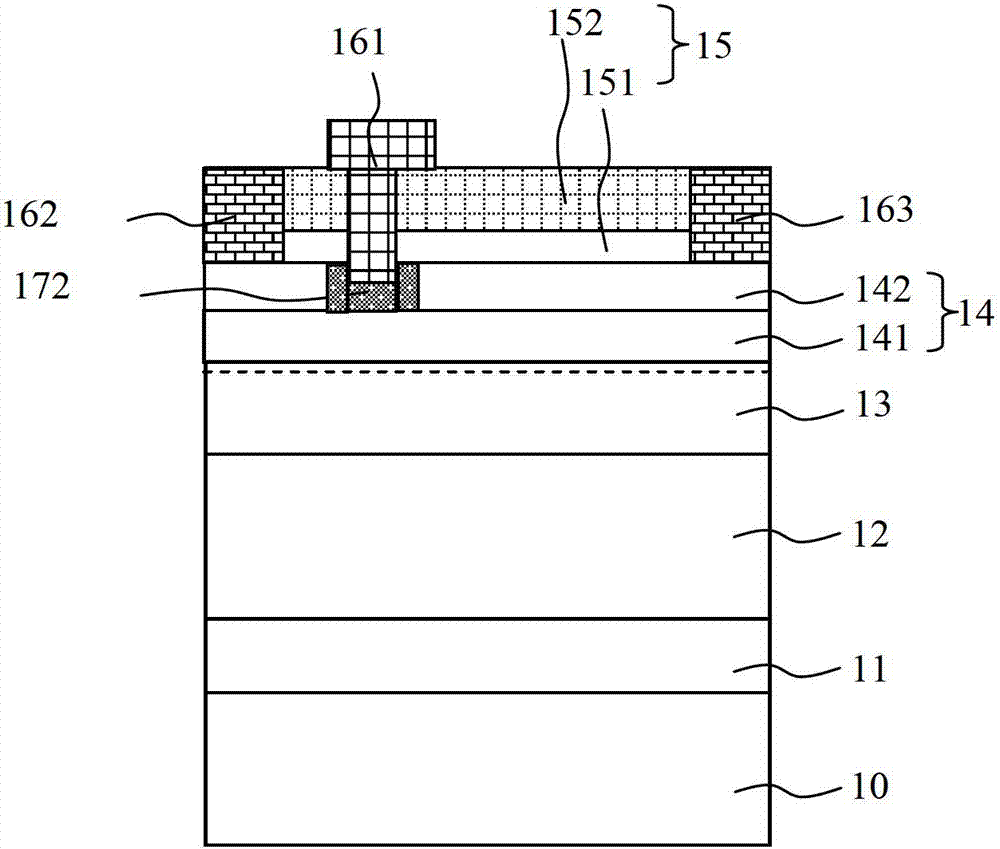

Radio frequency device and manufacturing method thereof

ActiveCN102810564AIncrease contentReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactRadio frequency

The invention discloses a radio frequency device. A nitride barrier layer of the radio frequency device has two layers of aluminum-rich nitride, wherein aluminum content is more than 75 percent. The second nitride layer is silicon-containing nitride, and silicon content is high enough, so that metal electrodes of drain and source electrodes and the second nitride layer are in ohmic contact, and contact resistance of the drain and source electrodes is reduced; and because the silicon-containing nitride can provide more free electrons, concentration of two-dimensional electron gas is further increased, and radio frequency performance of the device is improved. Meanwhile, a dielectric layer used as a passivation layer of the nitride is grown on the silicon-containing nitride in situ, so that surface state intensity is reduced, and stress releasing is reduced. In the manufacturing process of a grid electrode, the passivation layer of a grid region is etched, and the exposed nitride barrier layer is oxidized. Oxide generated on the grid electrode greatly reduces leakage current of the grid electrode and the leakage current between the source and drain electrodes. In addition, the invention also provides a manufacturing method for the radio frequency device.

Owner:DYNAX SEMICON

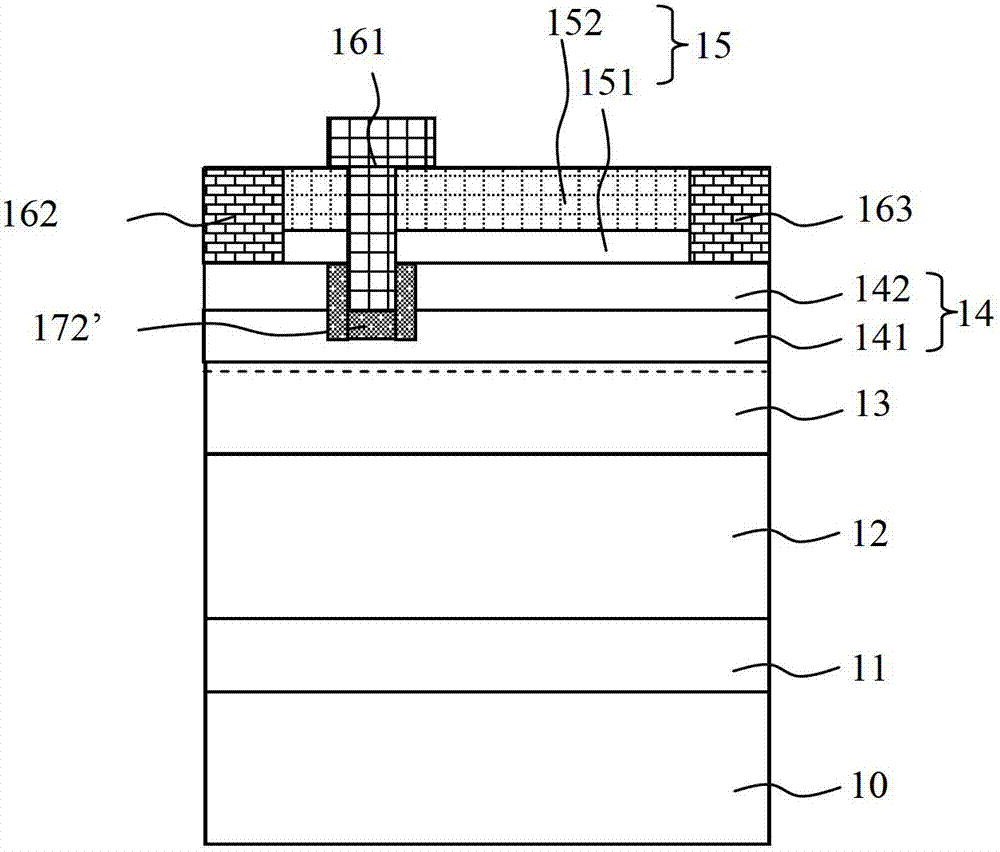

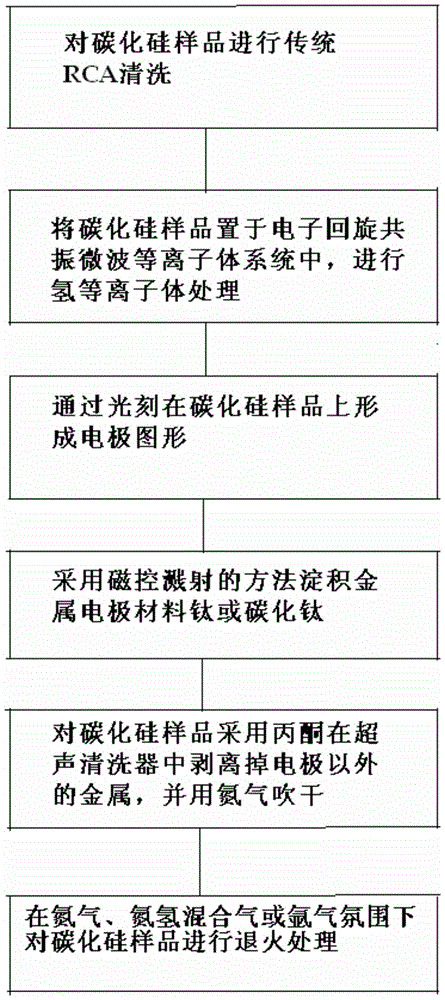

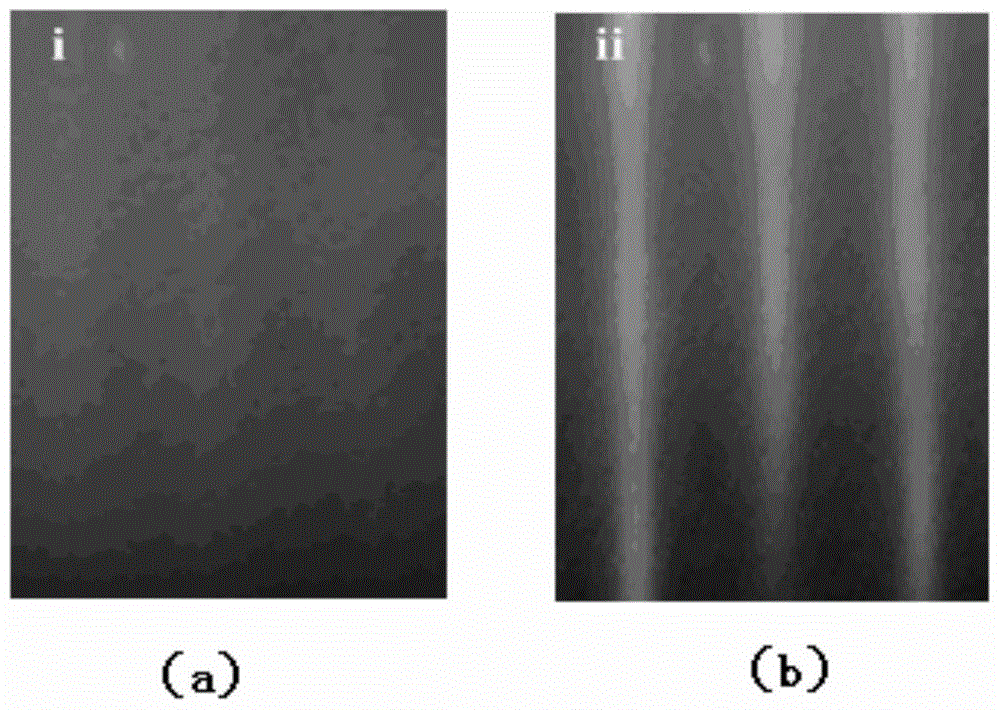

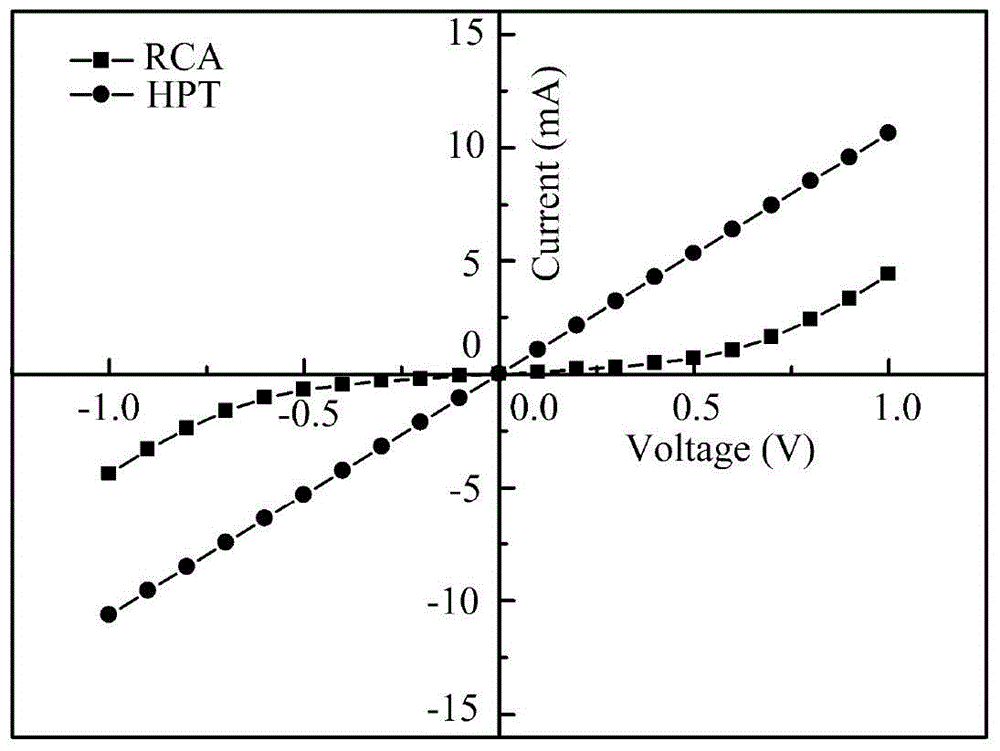

Method for increasing ohmic contact characteristic of silicon carbide semiconductor

InactiveCN105702712AEffective cleaning and passivationDecrease the density of surface statesSemiconductor devicesRCA cleanTitanium carbide

The invention relates to the field of microelectronic technology, a method for improving the ohmic contact characteristics of a silicon carbide semiconductor, comprising the following steps: (1) performing traditional RCA cleaning on a silicon carbide sample; (2) placing the silicon carbide sample in electron cyclotron resonance microwave plasma In the bulk system, hydrogen plasma treatment is carried out; (3) electrode pattern is formed on the silicon carbide sample by photolithography; (4) metal electrode material titanium or titanium carbide is deposited by magnetron sputtering; (5) The silicon sample was stripped of metal other than the electrodes in an ultrasonic cleaner with acetone, and dried with nitrogen; (6) the silicon carbide sample was annealed in a nitrogen atmosphere. In the present invention, after pre-treating the surface of silicon carbide with hydrogen plasma generated by an electron cyclotron resonance system, the surface of silicon carbide is effectively cleaned and passivated, and the surface state density is significantly reduced, and combined with low work function metal titanium or titanium carbide and relatively The silicon carbide substrate with high doping concentration has a low barrier height of Ti / SiC contact, and good ohmic contact can be formed under low temperature annealing conditions.

Owner:DALIAN UNIV OF TECH

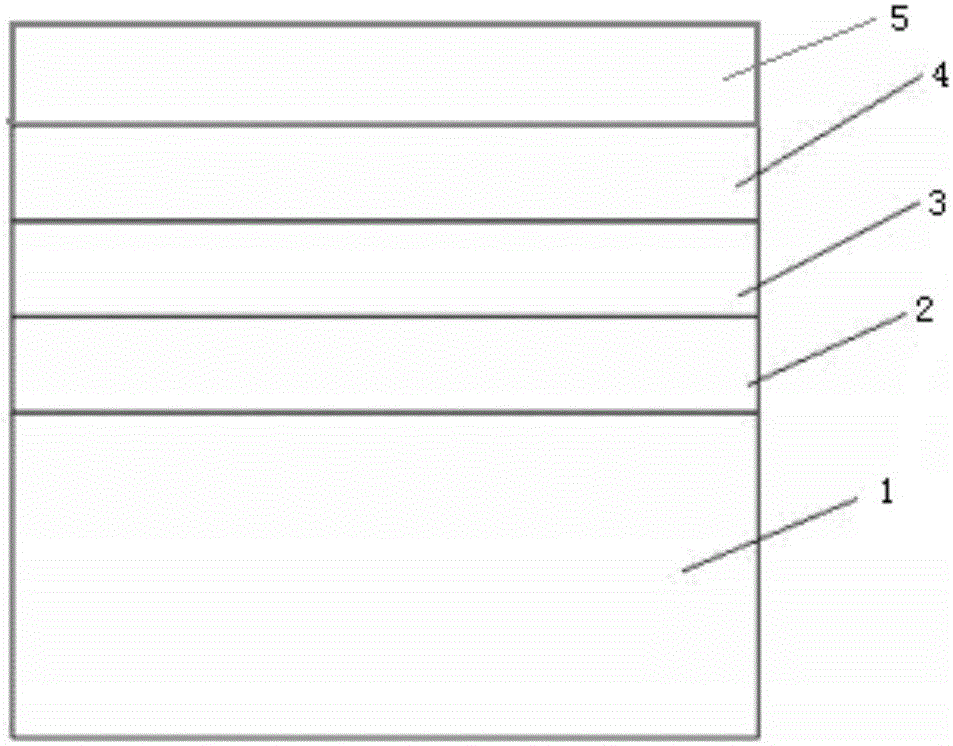

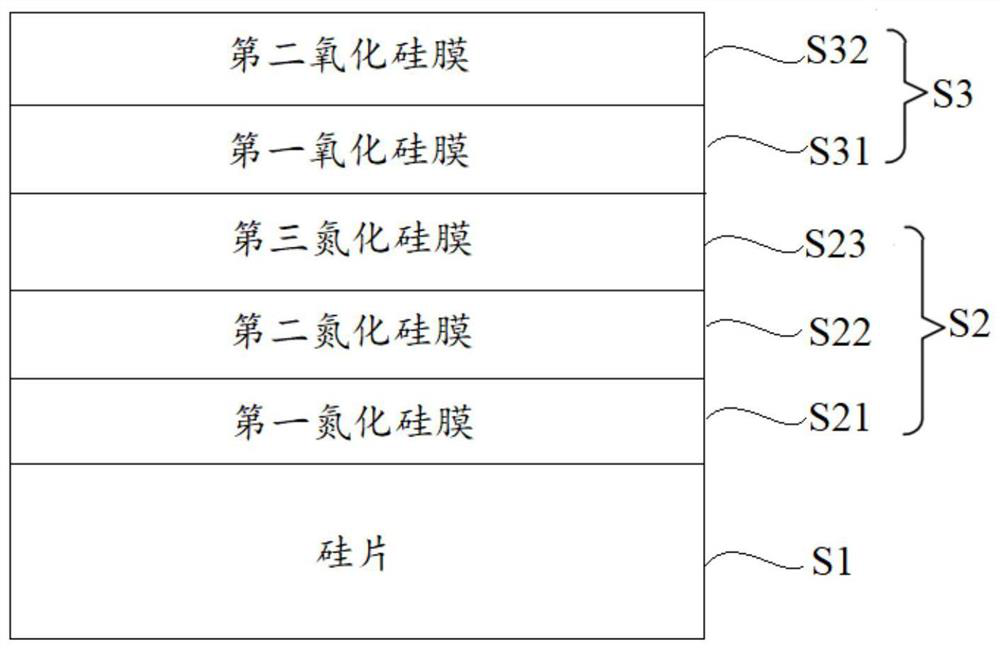

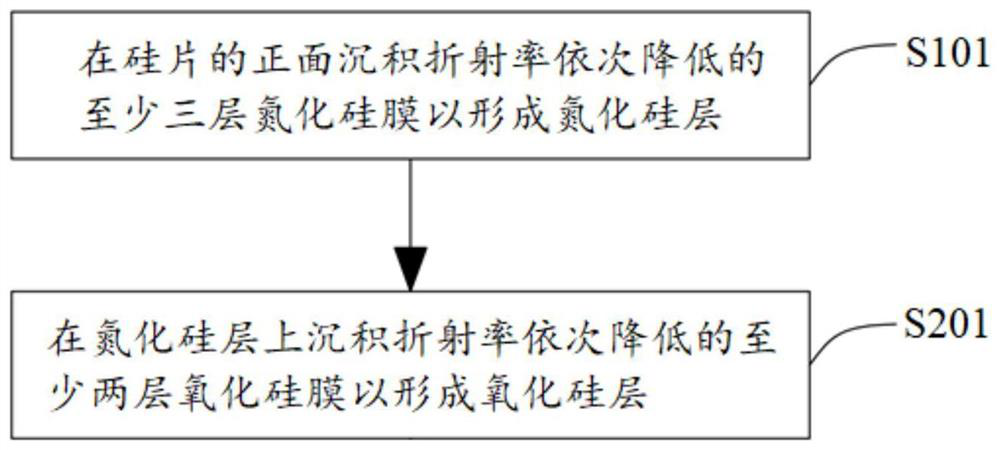

Crystalline silicon battery surface passive film and manufacturing method thereof

InactiveCN103996720AHigh relative permittivityDecrease the density of surface statesFinal product manufactureSemiconductor devicesCrystallographyCharge carrier

The invention discloses a crystalline silicon battery surface passive film and a manufacturing method of the crystalline silicon battery surface passive film. The crystalline silicon battery surface passive film comprises a first silicon oxide film, a silicon nitride film and a second silicon oxide film. The silicon nitride film is deposited on the first silicon oxide film. The second silicon oxide film is deposited on the silicon oxide film. The thickness d1 of the first silicon oxide film is 10 nm-30 nm. The thickness d2 of the silicon nitride film is 30 nm-50 nm. The thickness d3 of the second silicon oxide film is 25 nm-50 nm. The probability of light full reflection is substantially increased, and namely more light enters a silicon wafer, so that more charge carriers are generated, and battery efficiency is improved.

Owner:ALTUSVIA ENERGY TAICANG

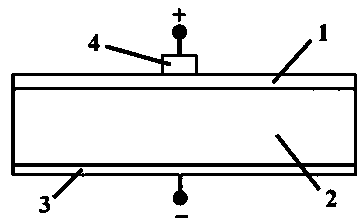

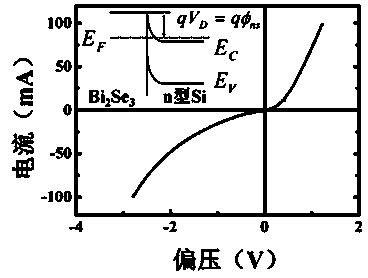

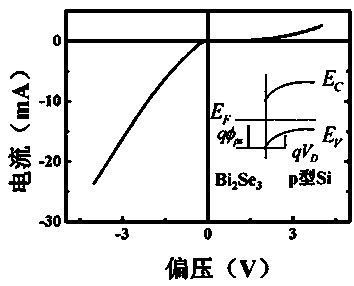

Silicon schottky junction taking Bi2Se3 film as contact layer and preparation method

ActiveCN103390640AExcellent optical and electrical propertiesReduce Si surface state densitySemiconductor devicesPhysicsOhmic contact

The invention discloses a silicon schottky junction taking a Bi2Se3 film as a contact layer and a preparation method. The silicon schottky junction comprises an Si substrate, wherein a Bi2Se3 schottky contact layer is arranged at the upper part of the Si substrate; an ohmic contact back electrode is arranged at the bottom of the Si substrate; an ohmic contact electrode is arranged on the Bi2Se3 schottky contact layer; and a bonding layer is arranged between the Bi2Se3 schottky contact layer and the ohmic contact electrode, and is made of Cr or Ti. With the adoption of the structure, the stable schottky junction can be formed between Bi2Se3 and n-type Si; in addition, the bonding layer can allow a Bi2Se3 single crystal sheet and an Si sheet to be pasted together effectively; the schottky junction is suitable for scale production; and the quality of a heterojunction interface can be ensured.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Preparation method of concentrating solar cell chip capable of preventing edge leakage

ActiveCN101969086AQuality improvementIncrease reflectionSemiconductor/solid-state device manufacturingPhotovoltaic energy generationCompound (substance)Engineering

The invention relates to a preparation method of a concentrating solar cell chip capable of preventing edge leakage and the method adopts the accurate half-cutter cutting method. The method comprises the following steps: the half-cutter cutting blade of which cutting edge has an inclined side is used to cut a groove along the cutting street of the battery chip, wherein the side wall of the groove also has a certain angle of inclination; chemical polishing is performed to the side wall of the groove; a transparent insulation material used as the anti-reflection film is covered on the surface of the battery chip, the surface of battery chip is passivated to avoid current leakage; and a conventional blade of which edge width is less than that of the half-cutter cutting blade is used to scratch the chip and form a single solar battery chip. The cutting blade of which edge has an angle of inclination is used to perform half-cutter cutting to the chip so that the side wall of the cutting street has the same angle of inclination, the chip can be prevented from damaging during the scratching process and a passivating film with high quality and reflecting property can be prepared on the chip; the width of the blade used for scratching the chip is less than that of the half-cutter cutting blade, thus preventing that the passivating film is damaged during the scratching process; and good passivation edge of the solar battery chip can be obtained and the edge leakage can be prevented.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

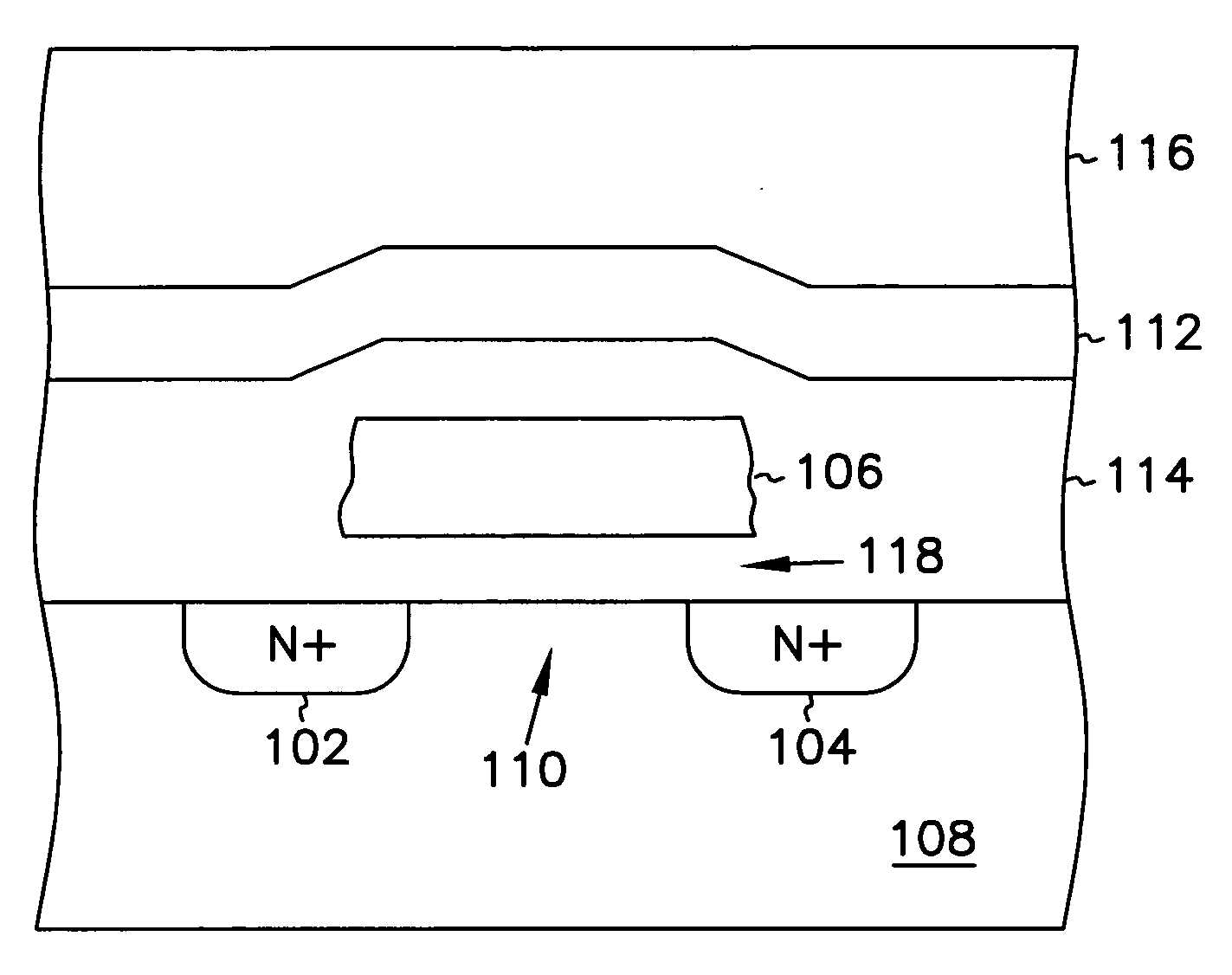

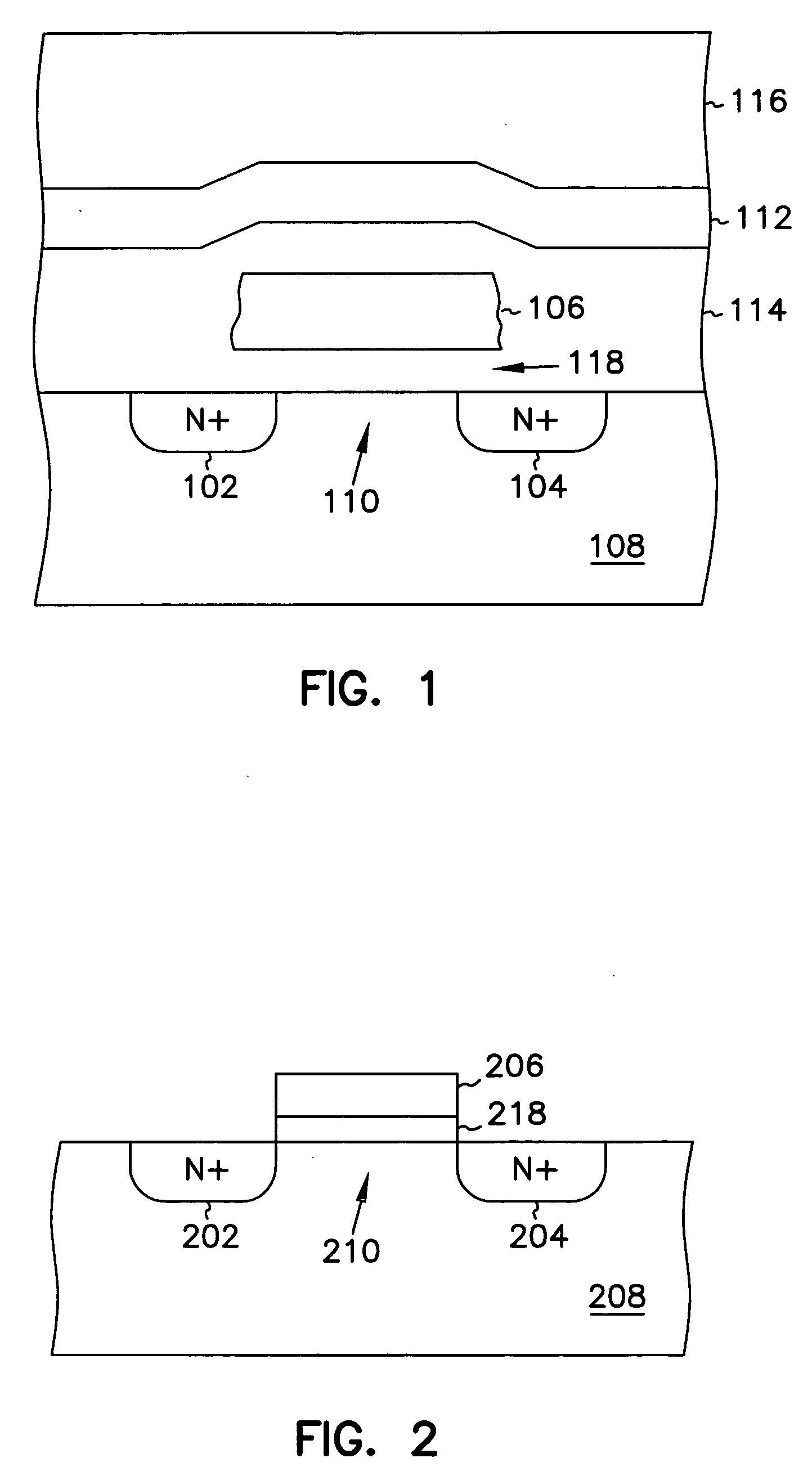

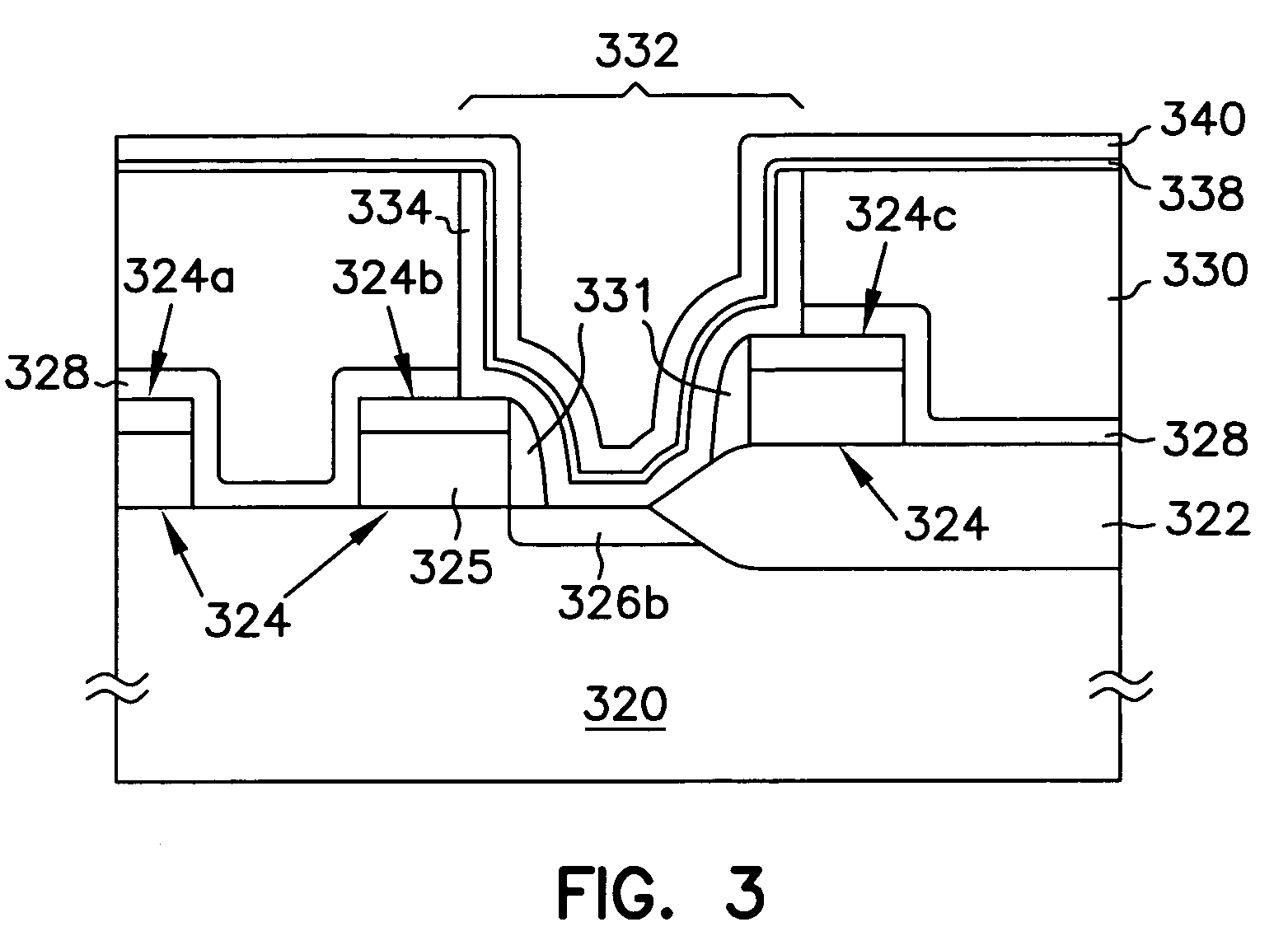

Carburized silicon gate insulators for integrated circuits

InactiveUS20060017095A1Decrease the density of surface statesTunneling barrierTransistorSolid-state devicesPhysicsIntegrated circuit

Silicon carbide films are grown by carburization of silicon to form insulative films. In one embodiment, the film is used to provide a gate insulator for a field effect transistor. The film is grown in a microwave-plasma-enhanced chemical vapor deposition (MPECVD) system. A silicon substrate is first etched in dilute HF solution and rinsed. The substrate is then placed in a reactor chamber of the MPECVD system in hydrogen along with a carbon containing gas. The substrate is then inserted into a microwave generated plasma for a desired time to grow the film. The microwave power varies depending on substrate size. The growth of the film may be continued following formation of an initial film via the above process by using a standard CVD deposition of amorphous SiC. The film may be used to form gate insulators for FET transistors in DRAM devices and flash type memories. It may be formed as dielectric layers in capacitors in the same manner.

Owner:MICRON TECH INC

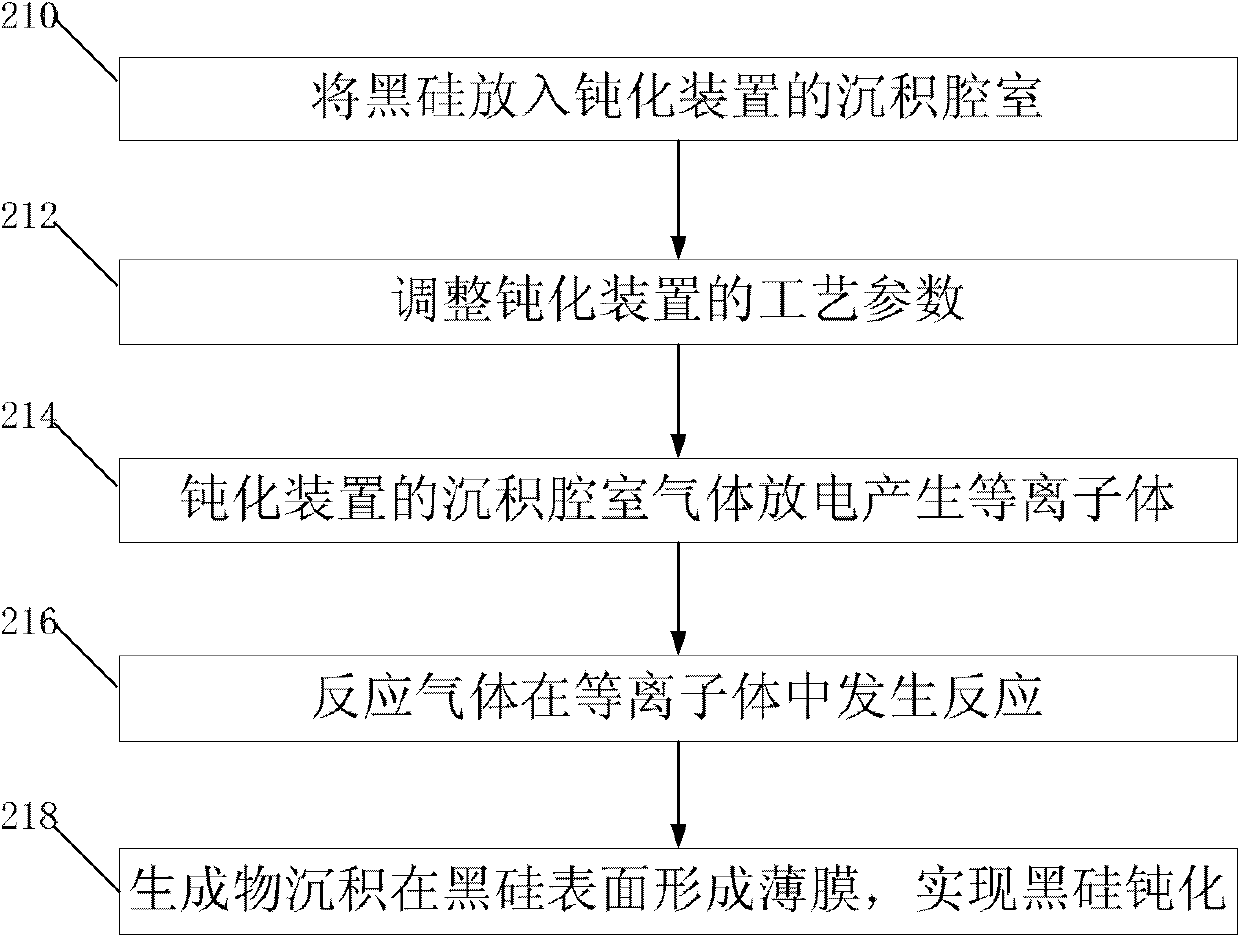

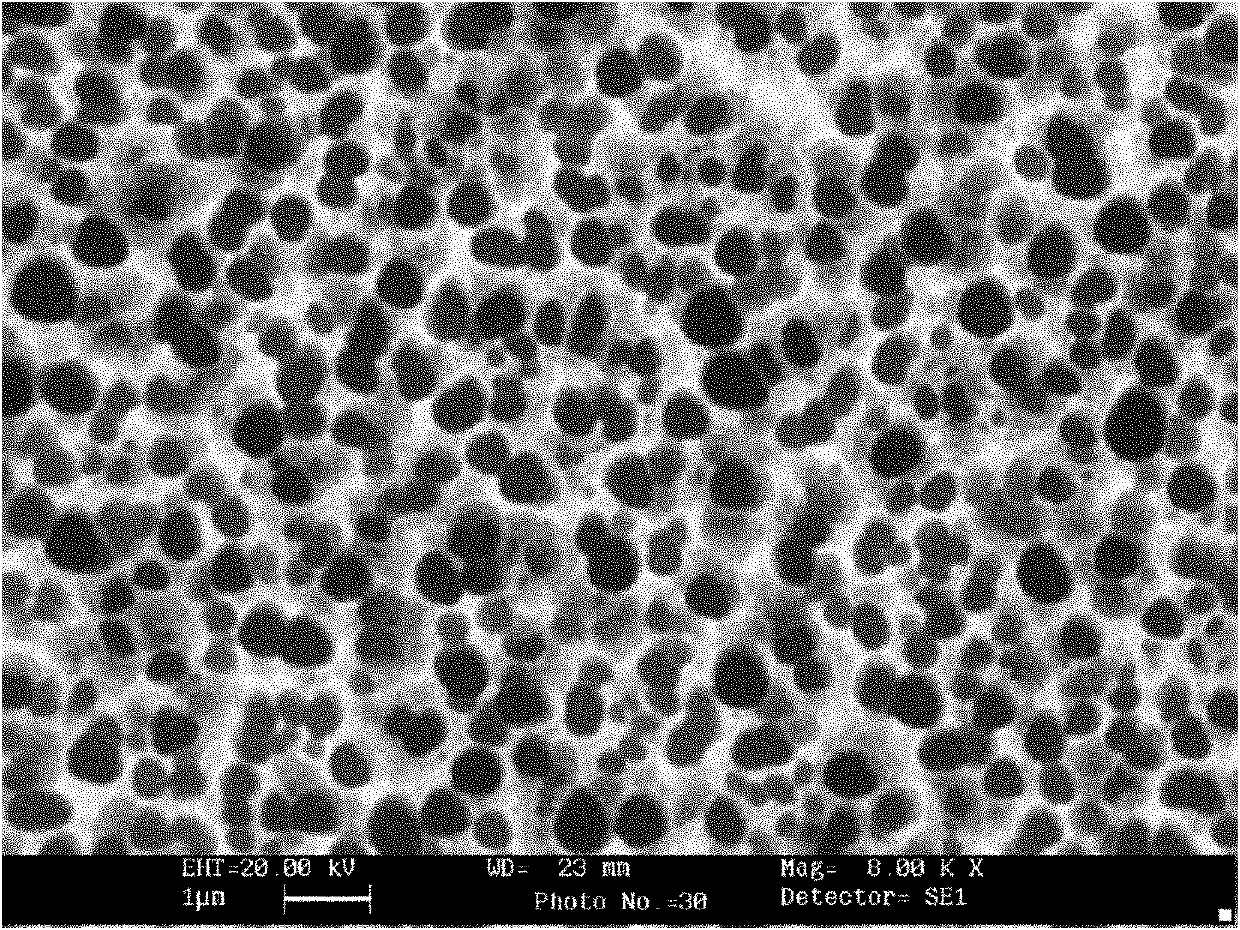

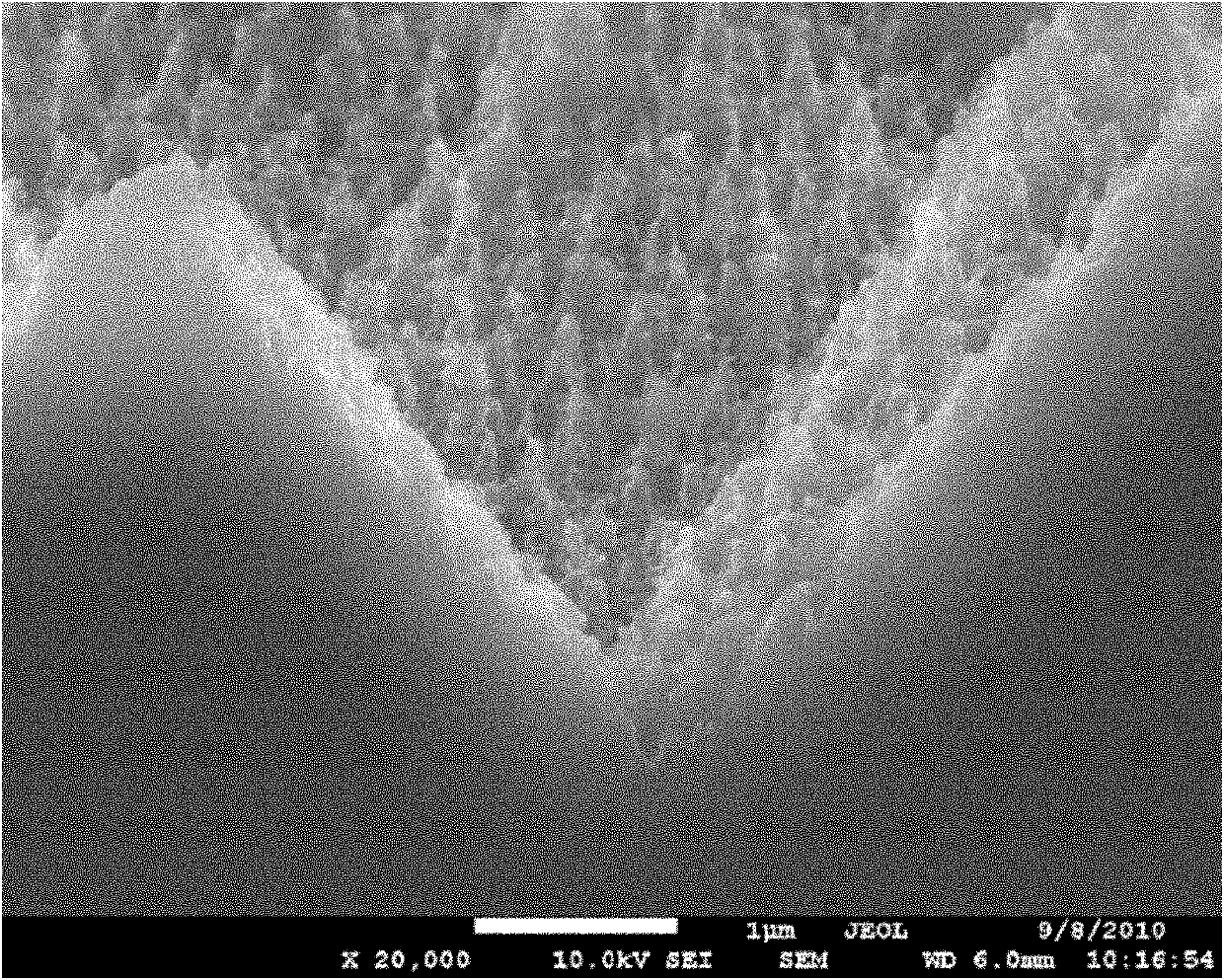

Black silicon passivation method

InactiveCN101993081ADecrease the density of surface statesReduced surface state densityFinal product manufactureChemical vapor deposition coatingManufacturing technologyThermal chemical vapor deposition

The invention relates to the technical field of photoelectron device manufacture, in particular to a black silicon passivation method. The method comprises the following steps of: putting black silicon into the chamber of a passivation device; adjusting the process parameters of the passivation device to a preset working range, and introducing mixed gas into the passivation device, wherein the mixed gas comprises reaction gases; and depositing a passivation film on the surface of the black silicon by using plasma enhanced chemical vapor deposition. The method reduces the surface state density of the black silicon so as to improve the conversion efficiency of a solar cell prepared by using the black silicon.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

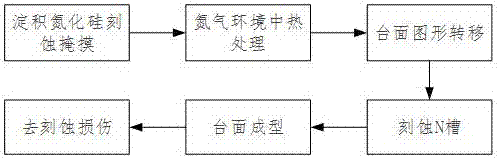

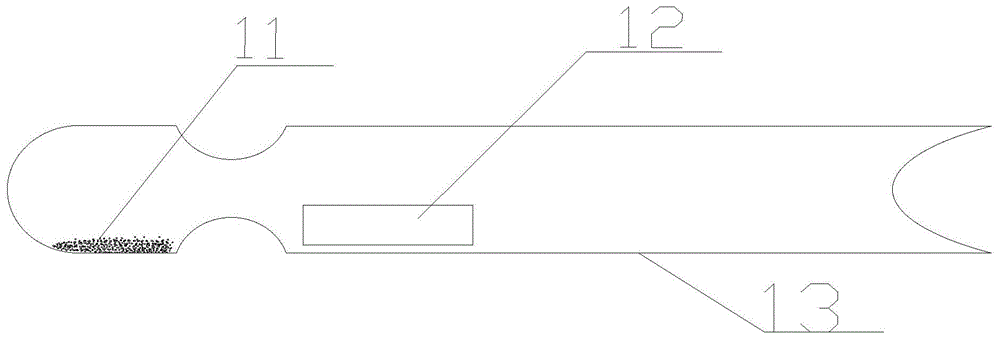

Method for improving extended wavelength gallium indium arsenide detector etching damage

InactiveCN107994094ARepair damageQuality improvementFinal product manufactureSemiconductor devicesIndium arsenideMaterial quality

The invention discloses a method for improving extended wavelength gallium indium arsenide detector etching damage which is provided with a whole set of chip preparation etching processes. The methodincludes the steps: (1) depositing a mask etched by silicon nitride; (2) performing heat treatment in the nitrogen environment; (3) transferring table top images; (4) etching an N groove; (5) forminga table top; (6) removing etching damage. The method has the advantages that the mask etched by the silicon nitride is deposited, the heat treatment is performed in the nitrogen environment, materialdamage can be repaired, complex center density is reduced, material quality is improved, dark current of devices is reduced, hole carrier density can be increased, P-electrode ohmic contact stabilityis facilitated, resistance is reduced, a table top forming process includes gas is etched by the aid of chlorine methane, hydrogen decomposed by the methane in the plasma etching process can passivatedangling bonds formed by etching, and non-radiative recombination center density in materials is reduced. According to an etching damage removing process, damage layers of etching surfaces can be removed, the non-radiative recombination center density is reduced, subsequent passivation effects are enhanced, and the method is applicable to preparation of a high-performance short wave infrared gallium indium arsenide detector.

Owner:GUIZHOU ZHENHUA FENGGUANG SEMICON

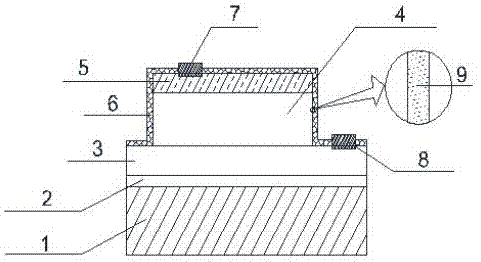

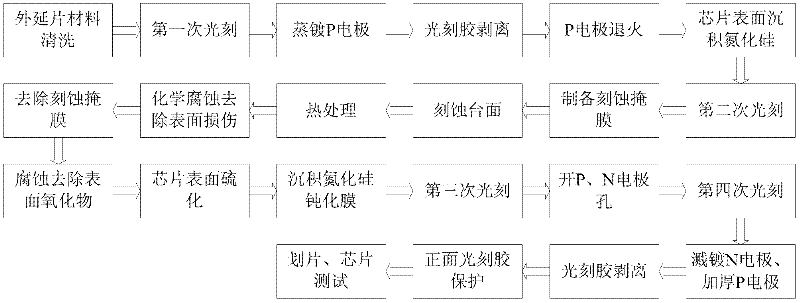

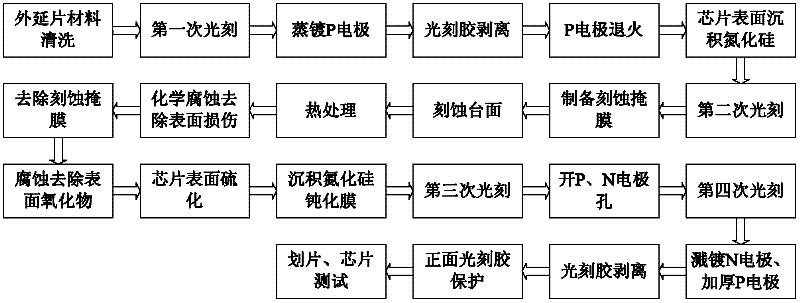

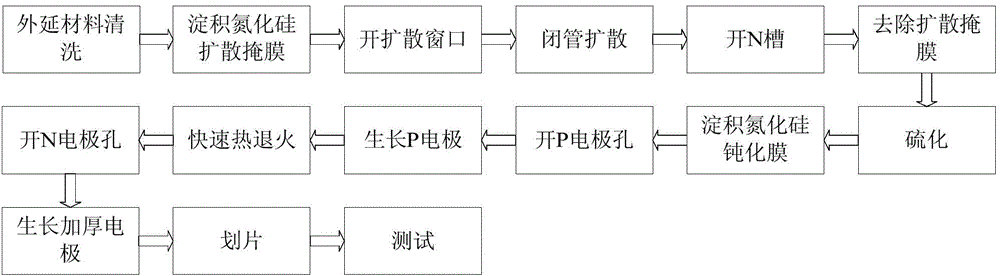

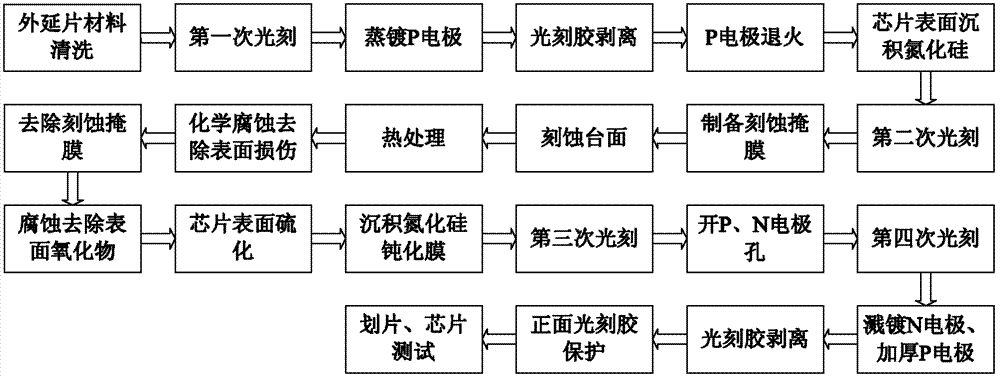

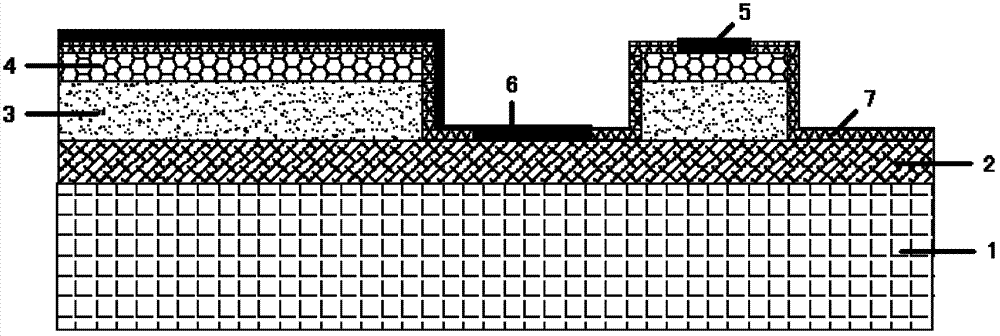

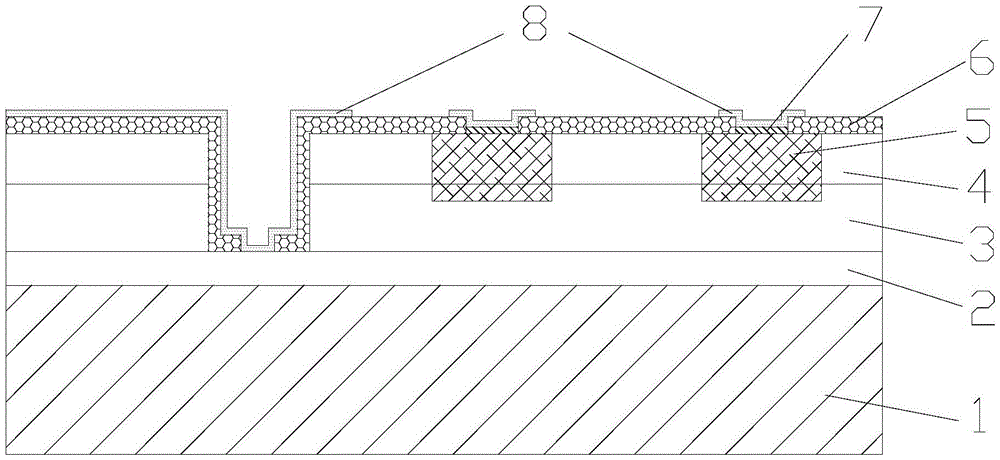

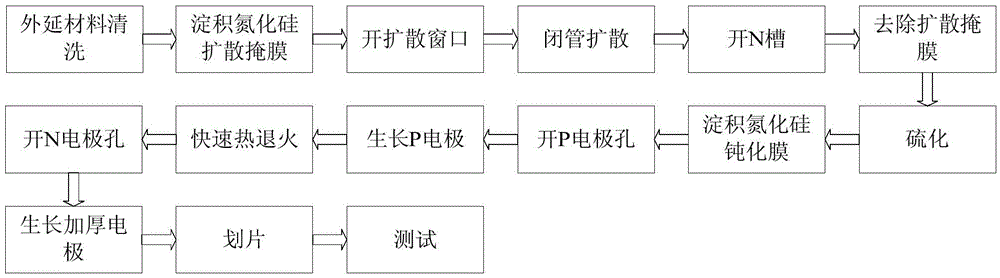

Manufacture method of table surface type indium gallium arsenic detector

ActiveCN102376824AAvoid damageImprove yieldFinal product manufactureSemiconductor devicesVulcanizationIndium

The invention discloses a manufacture method of a table surface type indium gallium arsenic detector, which comprises the step of performing the step of evaporating a P-InP contact electrode and the step of high-temperature quick annealing in advance of the step of passivating silicon nitride. The manufacture method has the advantages that a silicon nitride passivating film is damaged since the surface of a material is polluted or remained with a plurality of particles in the process of high-temperature quick annealing can be avoided, the yield for manufacturing the detector can be improved, the manufacture method is particularly suitable for researching and manufacturing a long linear detector and a plane array detector, and the influence of the process of high-temperature quick annealing to the contact status between the passivating film and the surface of the material can be eliminated; and as a thermal treatment technology is introduced after ion etching, the surface fixed charge introduced into the surface of the material by etching ions can be effectively reduced, the surface oxide can be removed and the crystal lattice damage and the dangling bond of the surface caused by ion etching can be reduced by adopting a chemical corrosion and vulcanization method, the surface state density can be reduced, and the surface composite dark current can be effectively reduced.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

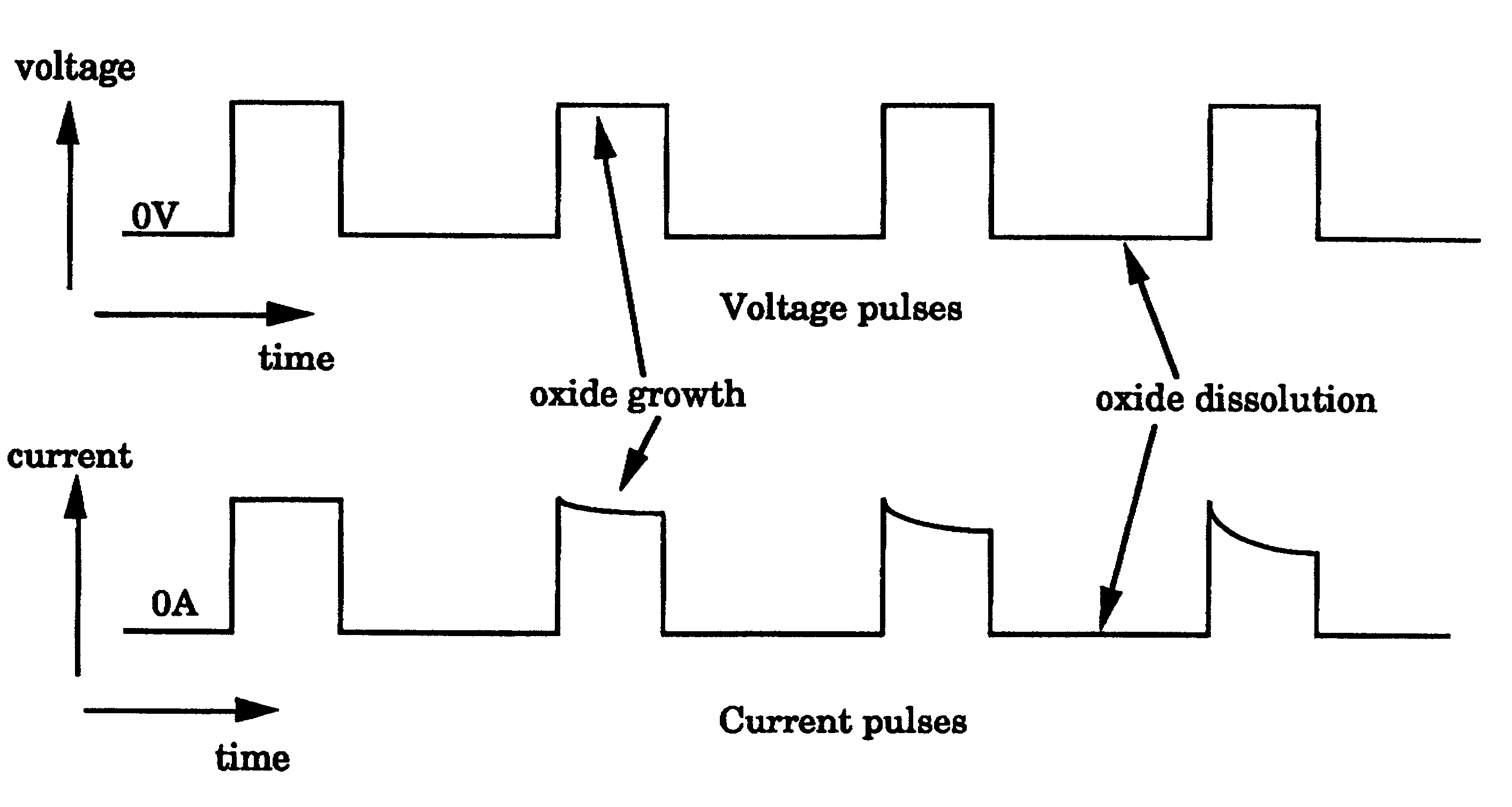

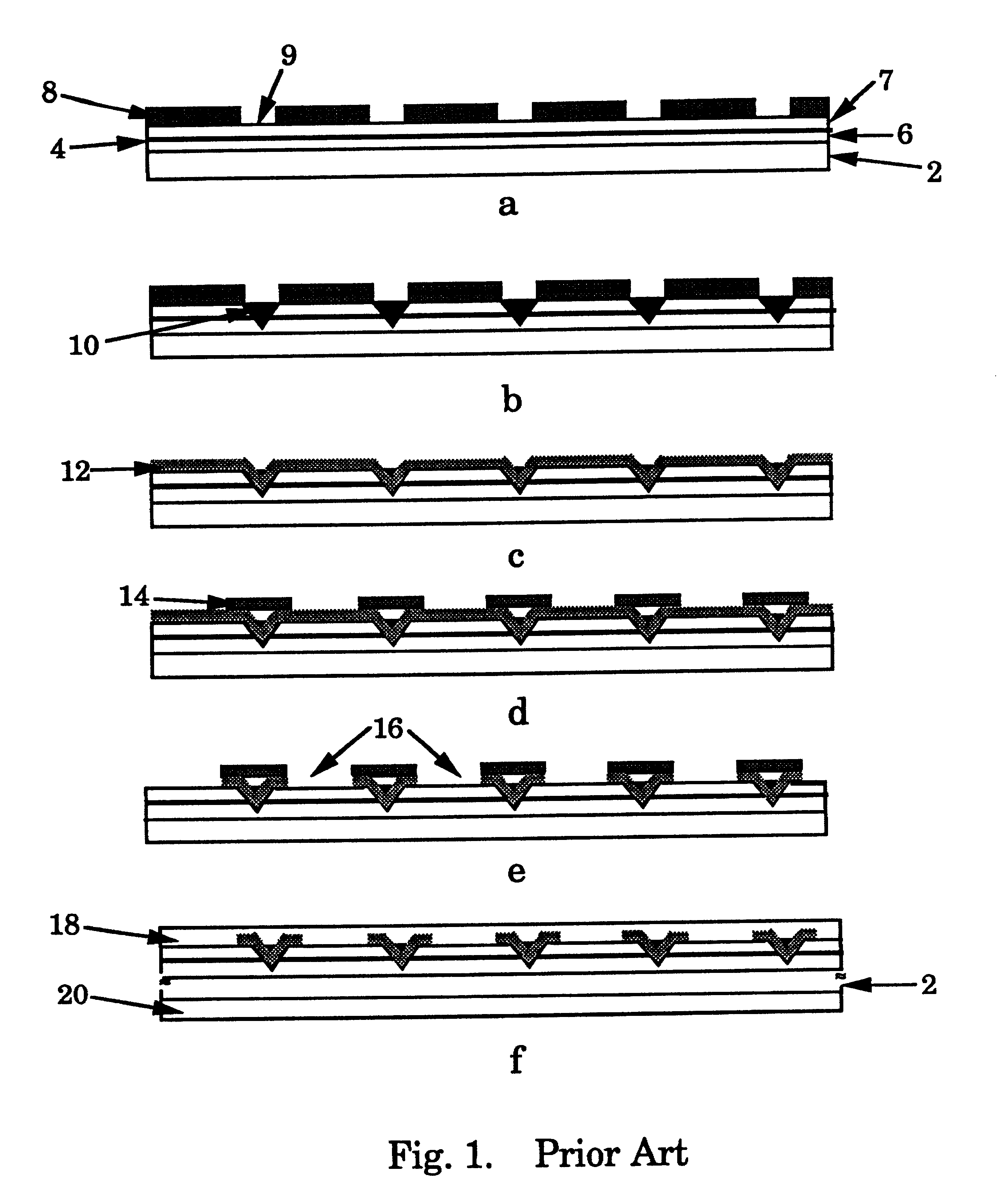

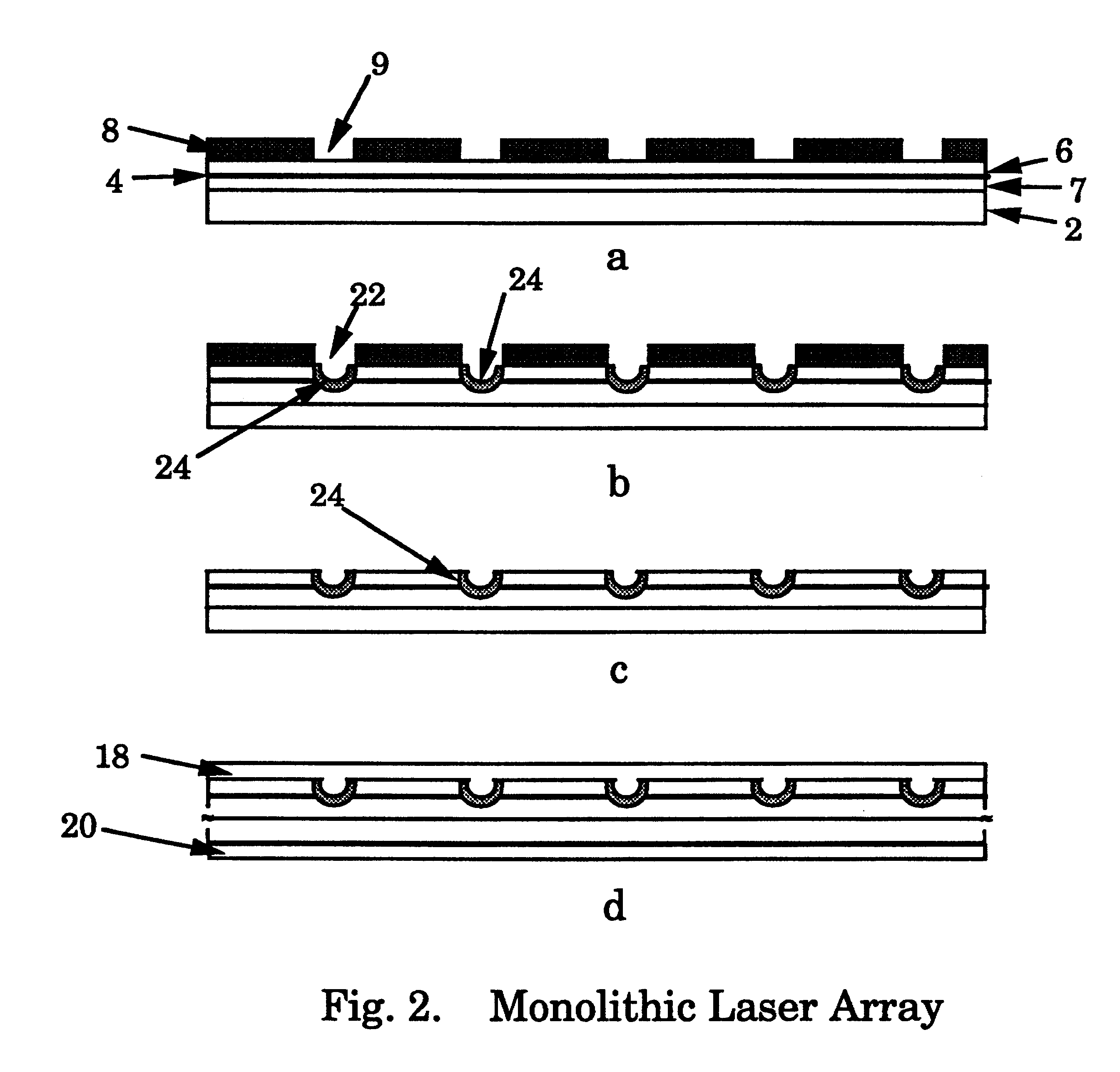

Method for etching multilayer compound semiconductor material

InactiveUS6306674B1Improve the immunityDecrease the density of surface statesAnodisationSemiconductor/solid-state device testing/measurementCondensed matter physicsElectrical current

A multilayer compound semiconductor is contacted with an electrically conducting fluid, and a current is passed between the semiconductor and the fluid. The current passes is monitored, and the current is controlled in response to the monitoring.

Owner:ZORY JR PETER S

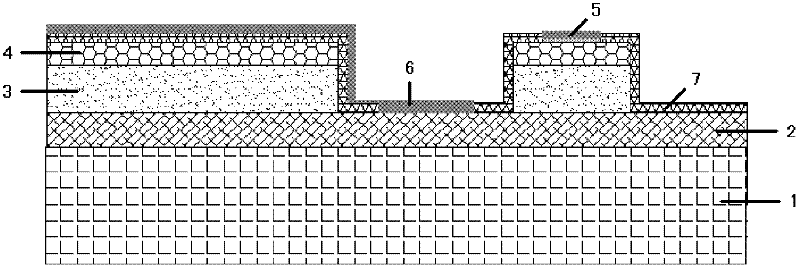

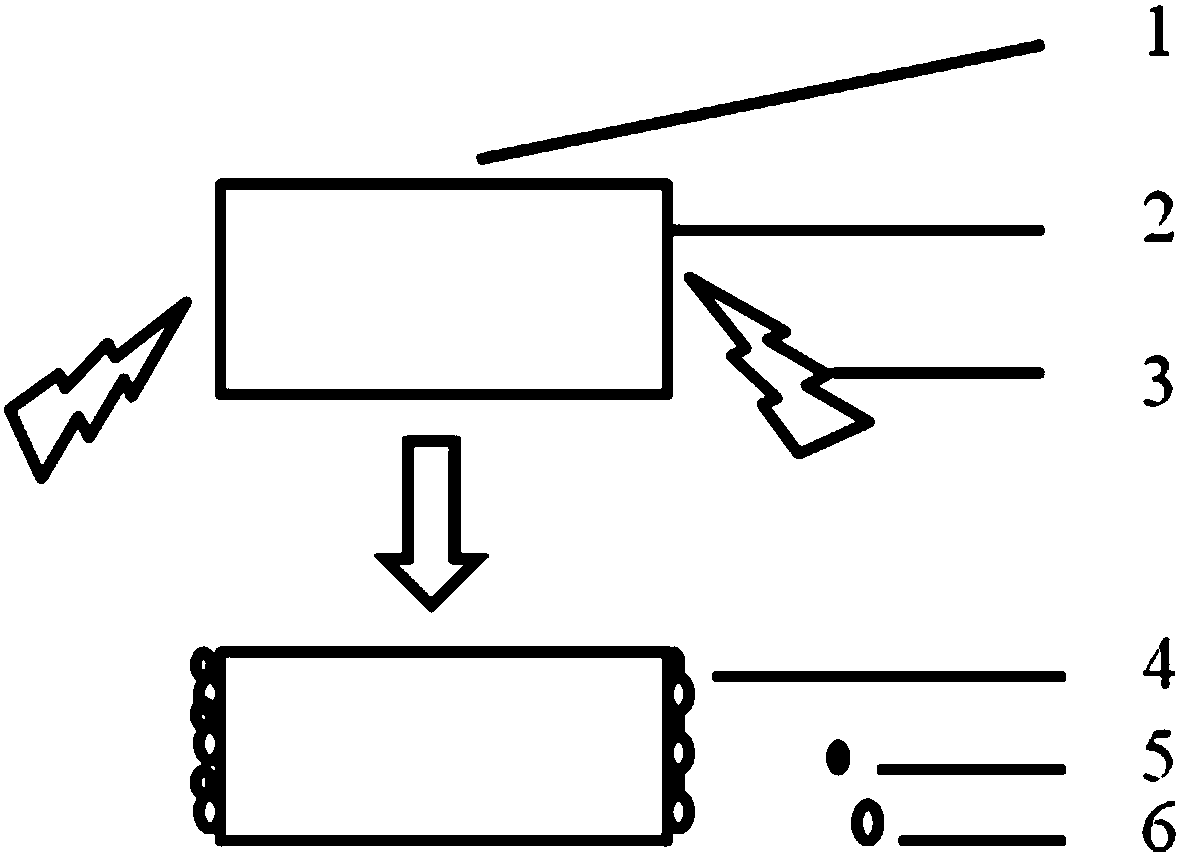

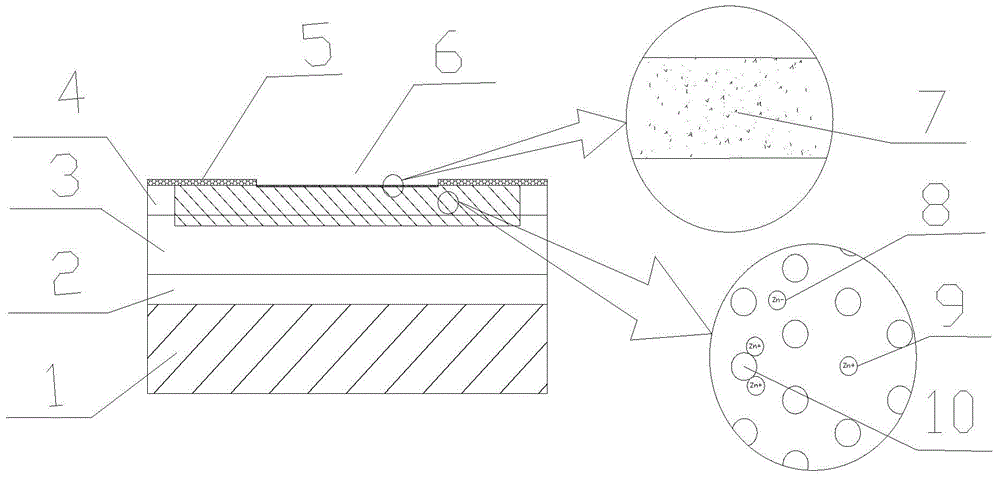

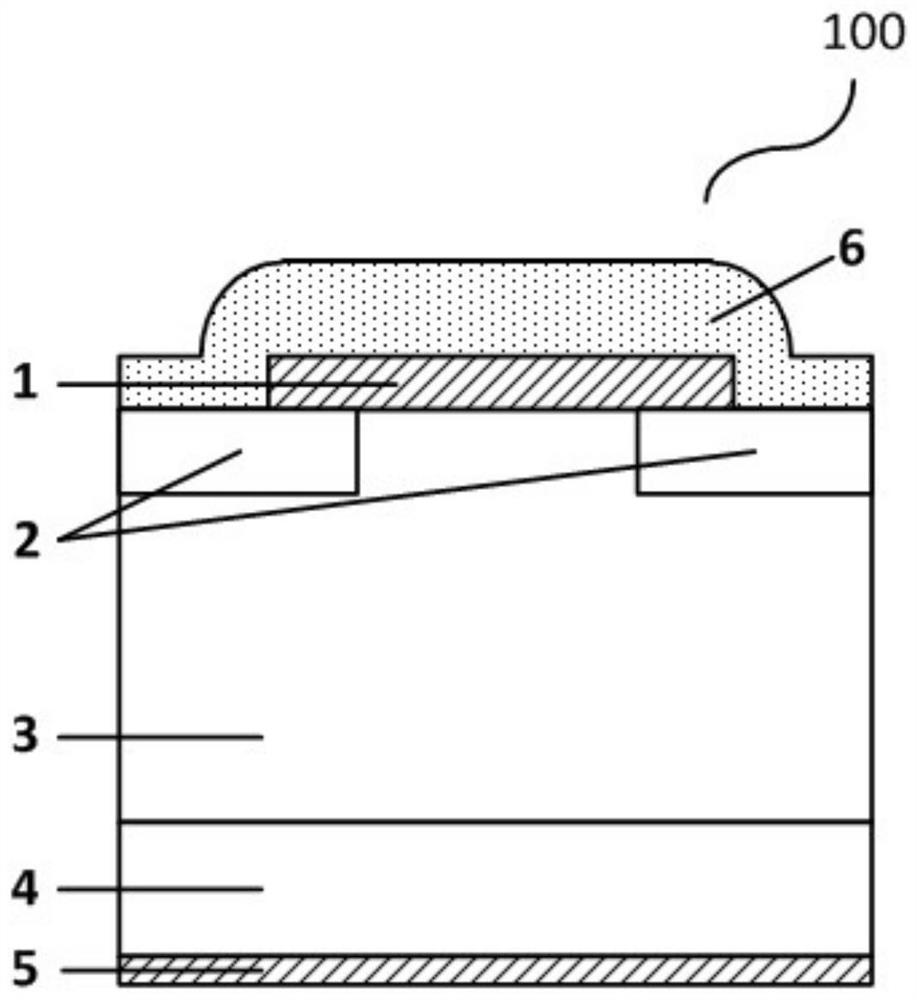

Planar indium gallium arsenic light-sensitive chip with surface passivation improved and manufacturing method

ActiveCN104538463AImprove passivation effectWon't hurtFinal product manufactureSemiconductor devicesVulcanizationIndium

The invention discloses a planar indium gallium arsenic light-sensitive chip with surface passivation improved and a manufacturing method. According to the structure of the planar indium gallium arsenic light-sensitive chip, an N-type InP layer, an indium gallium arsenic intrinsic absorption layer, an N-type InP cap layer, a SiNx passivation layer, a P-electrode and a thickened electrode (8) are grown on a semi-insulating InP substrate in sequence. The manufacturing process is improved on the basis of an original process, and comprises removal and vulcanization of a diffusion mask and silicon nitride passive film growing through an inductive coupling plasma chemical vapor deposition (ICPCVD) technology. The planar indium gallium arsenic light-sensitive chip with surface passivation improved and the manufacturing method have the advantages the passivation layer of the chip is even in structure; the surface state density of a device is effectively reduced, and the surface can be prevented from being oxidized again through a vulcanization film formed on the surface; damage of the process to the surface of materials is small, the film is compact and is in stress fit with the substrate, the element bonding state is good, and the passivaition effect is excellent.

Owner:无锡中科德芯感知科技有限公司

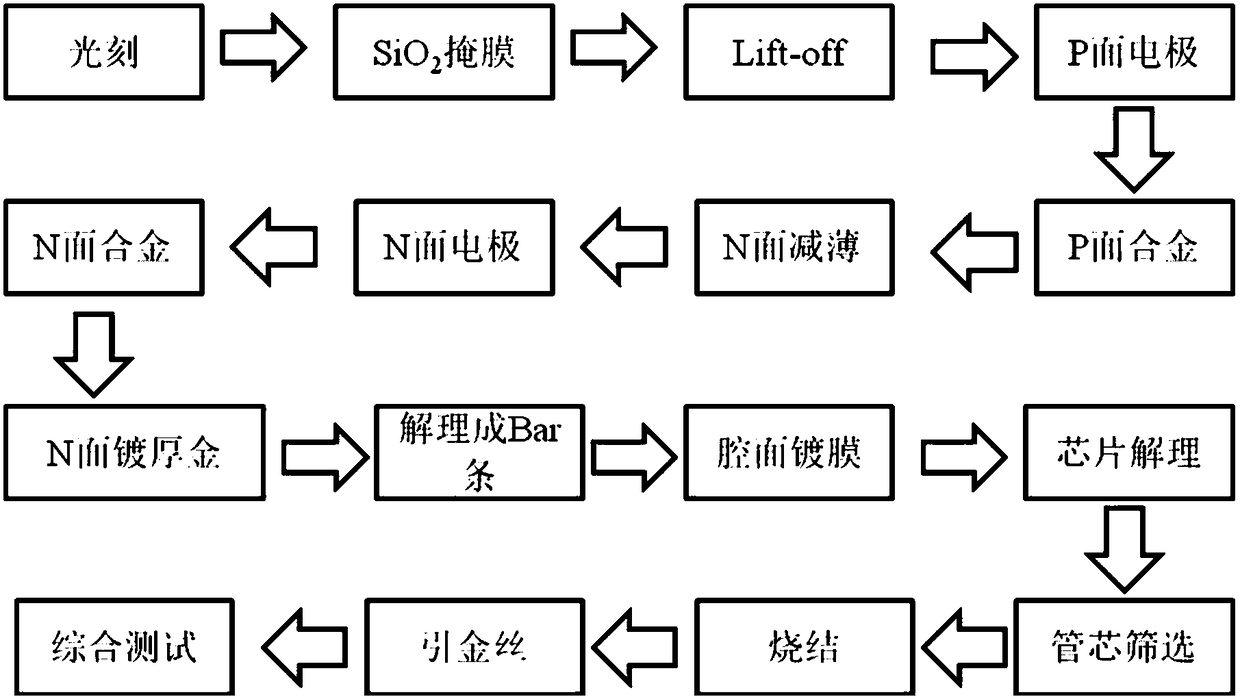

Semiconductor laser material passivation method

PendingCN108288816AGood optical performanceWon't hurtLaser detailsSemiconductor lasersLow temperature depositionResonant cavity

The invention discloses a semiconductor laser material passivation method. The method is applicable to passivation treatment of a cavity surface material of a semiconductor laser resonant cavity; themethod specifically comprises the steps of performing bombardment cleaning on the cavity surface material of the semiconductor laser resonant cavity by adopting ion beams, and depositing an AlN passivation layer on the cavity surface of the semiconductor laser resonant cavity by adopting an ALD technology. According to the semiconductor laser material passivation method disclosed in the invention,the surface of the resonant cavity is bombarded by the ion beams in a vacuum environment to effectively remove an oxide layer form the cavity surface, cavity surface pollutants, surface state, surface material dislocation and surface material dangling bond to obtain a clean semiconductor laser resonant cavity surface, and then low-temperature deposition in an ALD apparatus is realized in a plasmaauxiliary condition to obtain the AlN passivation layer for protecting the cavity surface of the resonant cavity. By virtue of the method disclosed in the invention, by performing process treatment on the resonant cavity surface, the cavity surface damage threshold value of the semiconductor laser is improved, and improvement of the output power, the service life and performance stability of thedevice is realized.

Owner:CHANGCHUN UNIV OF SCI & TECH

Multilayer passivation film of crystalline-silicon battery and manufacturing method thereof

InactiveCN106409926ADecrease the density of surface statesImprove shortwave responseFinal product manufacturePhotovoltaic energy generationCrystalline siliconSilicon oxide

The invention discloses a multilayer passivation film of a crystalline-silicon battery and a manufacturing method thereof. The multilayer passivation film comprises a first silicon oxide film, a silicon nitride film, a second silicon oxide film and a silicon oxynitride film. The silicon nitride film is deposited on the first silicon oxide film; the second silicon oxide film is deposited on the silicon nitride film; and the silicon oxynitride film is deposited on the second silicon oxide film. The thickness of the first silicon oxide film is 5 to 9 nm, the thickness of the silicon nitride film is 60 to 90 nm, the thickness of the second silicon oxide film is 10 to 20nm, and the thickness of the silicon oxynitride film is 15 to 30nm. According to the invention, the probability of total reflection of light is improved substantially and thus more light enters a silicon wafer to generate more carriers, so that the battery efficiency is enhanced.

Owner:庞倩桃

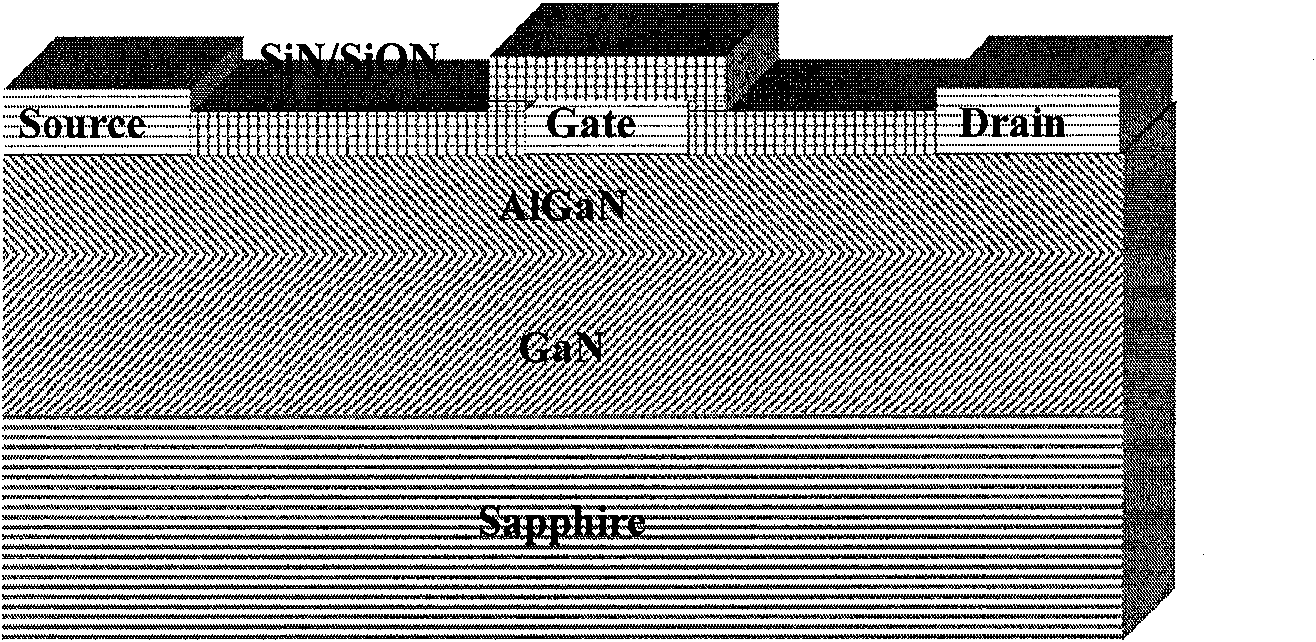

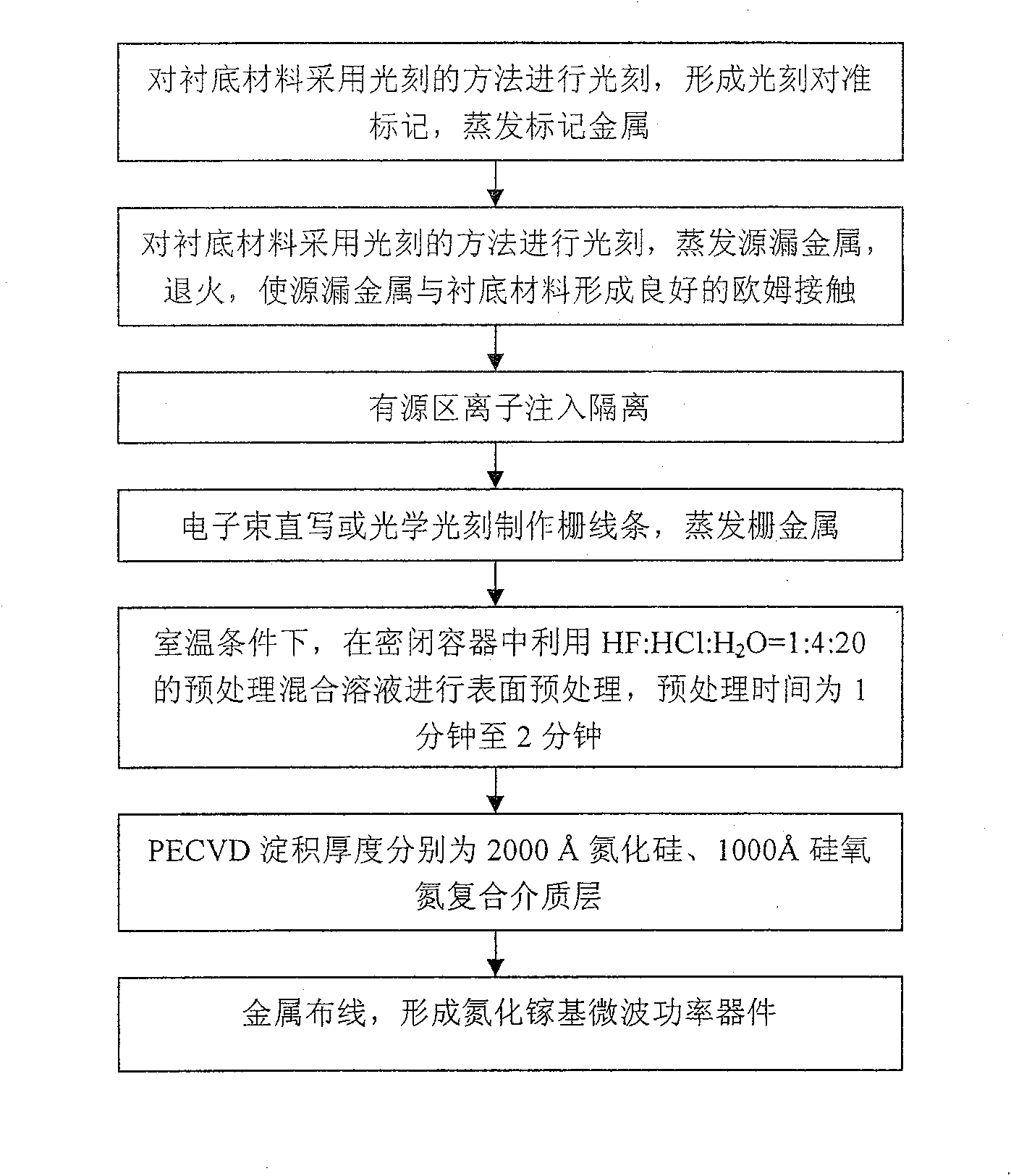

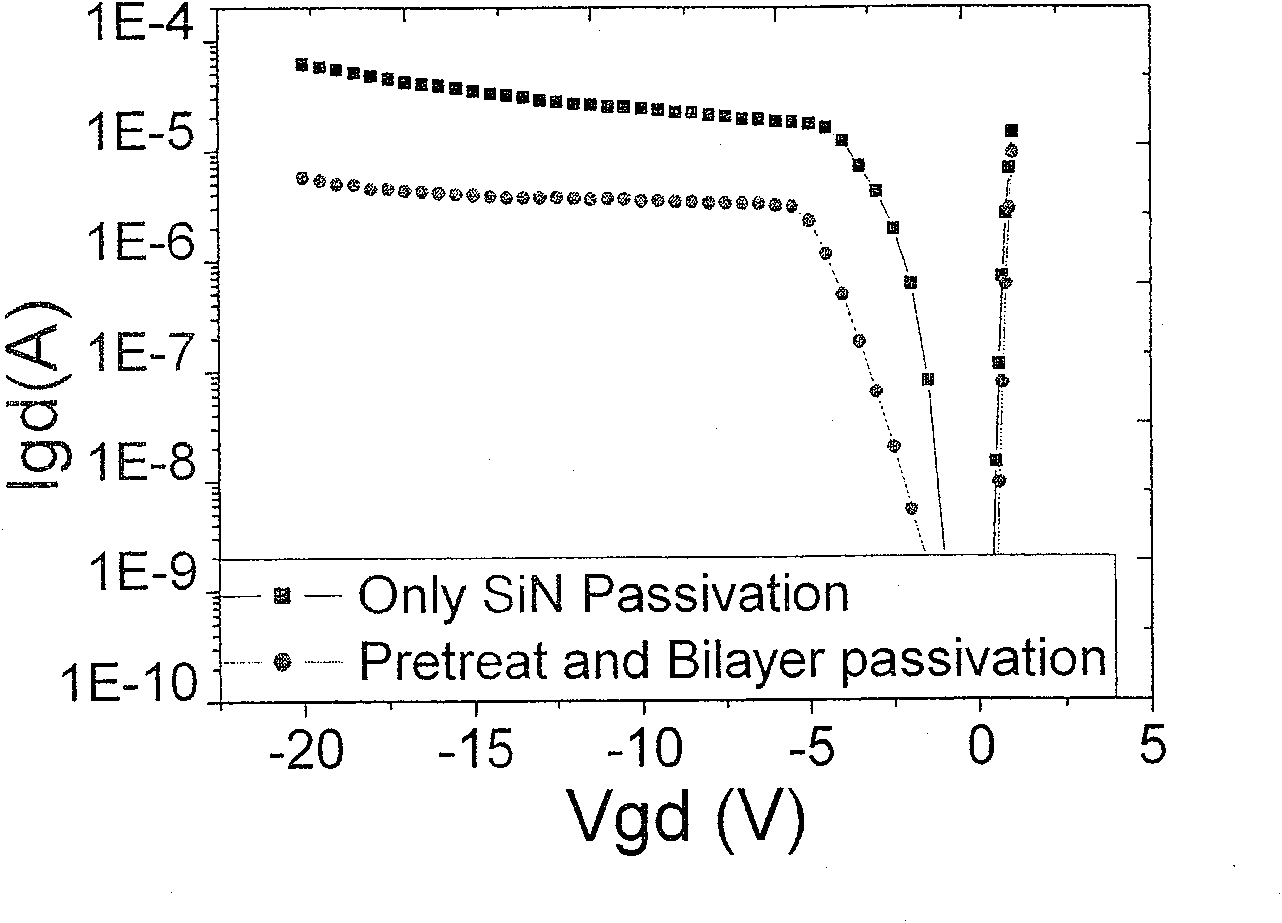

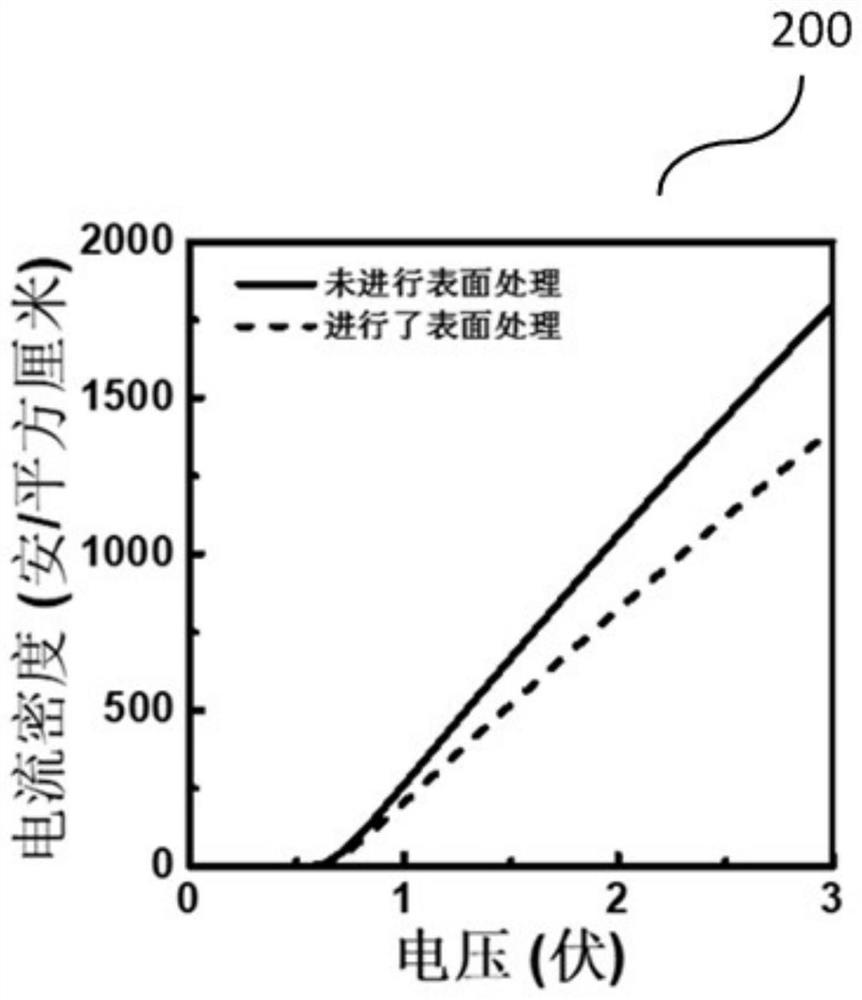

Method for improving the performance of gallium nitride based field effect transistor

InactiveCN100594591CSolve the current collapse effectSolve the collapse effectSemiconductor/solid-state device manufacturingSemiconductor materialsSurface oxidation

The invention relates to the technical field of production of wide bandgap semiconductor materials and devices and discloses a method for improving the performance of a GaN-based field-effect transistor, the method comprises: mixed pre-treatment solution is adopted to carry out the surface pre-treatment of the surface of a device before the passivation of the GaN-based field-effect transistor during the production process of the GaN-based field-effect transistor, then a compound dielectric layer of silicon nitride and oxygen-rich silicon nitride is deposited on the surface of the device afterthe surface pre-treatment, and the GaN-based field-effect transistor is passivated. The use of the method can solve a surface original oxide layer which is existed on the surface of AlGaN for a long time, eliminate the AlGaN surface state which is induced by the surface oxide layer, solve the surface state existing in an AlGaN and silicon nitride interface, the current collapse effect which is induced by the surface original oxide layer and the significant increase of the reverse gate leakage current caused by the conventional passivation and improve the stability and the reliability of GaN-based HEMT.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method improving manufacturing process of crystalline silicon solar cell through arsenic ion implantation

ActiveCN102683504AExtend your lifeDecrease the density of surface statesFinal product manufactureSemiconductor devicesCell fabricationHigh doses

The invention discloses a method improving a manufacturing process of a crystalline silicon solar cell through arsenic ion implantation. On one hand, an N-type area is formed on the surface of the crystalline silicon solar cell through arsenic ion implantation, the crystalline silicon solar cell has high doping and shallow junction functions simultaneously, the open-circuit voltage and cell efficiency are improved, high-dose arsenic does not cause too many defects to the surface of silicon after annealing in contrast with phosphorus, reduction of the surface state density of a silicon chip is facilitated, and the service lives of minority carriers are prolonged; and on the other hand, metal of the silicon chip is in ohmic contact with the silicon chip in a traditional diffusion junction mode, the method is completely compatible with the conventional diffusion junction and screen printing sintering technology in the field of manufacture of photovoltaic cell, new parameters do not need exploring, and mass production can be achieved.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Shallow trench separation structure, formation method thereof and image sensor

InactiveCN108550550AImprove diffusion abilitySuppressed surface stateSolid-state devicesSemiconductor/solid-state device manufacturingPower flowEngineering

The invention discloses a shallow trench separation structure, a formation method thereof and an image sensor. The formation method comprises steps of providing a semiconductor substrate, and forminga grinding stopping layer on the semiconductor substrate; successively etching the grinding stopping layer and the semiconductor substrate, and shallow trenches in the grinding stopping layer and thesemiconductor substrate; forming oxide layers on the surface of the grinding stopping layer, side walls of the shallow trenches and the bottom; forming a fluorine-doped medium layer on the surface ofeach oxide layer; filling the interiors of the shallow trench with insulation media, wherein the insulation media fill the shallow trench and cover the fluorine-doped medium layer; and carrying out annealing technology. According to the invention, through the planarization technology, by removing the insulation media, the fluorine-doped medium layer and the oxide layers on the grinding stopping layer, a shallow trench separation structure is formed. Through the shallow trench separation structure, dark current of the image sensor can be reduced.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

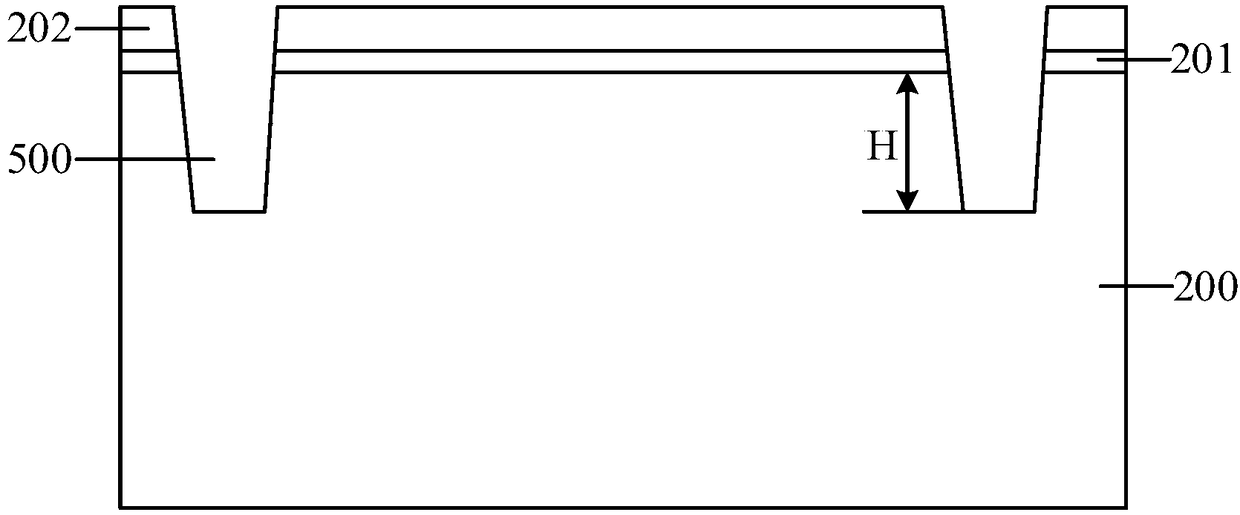

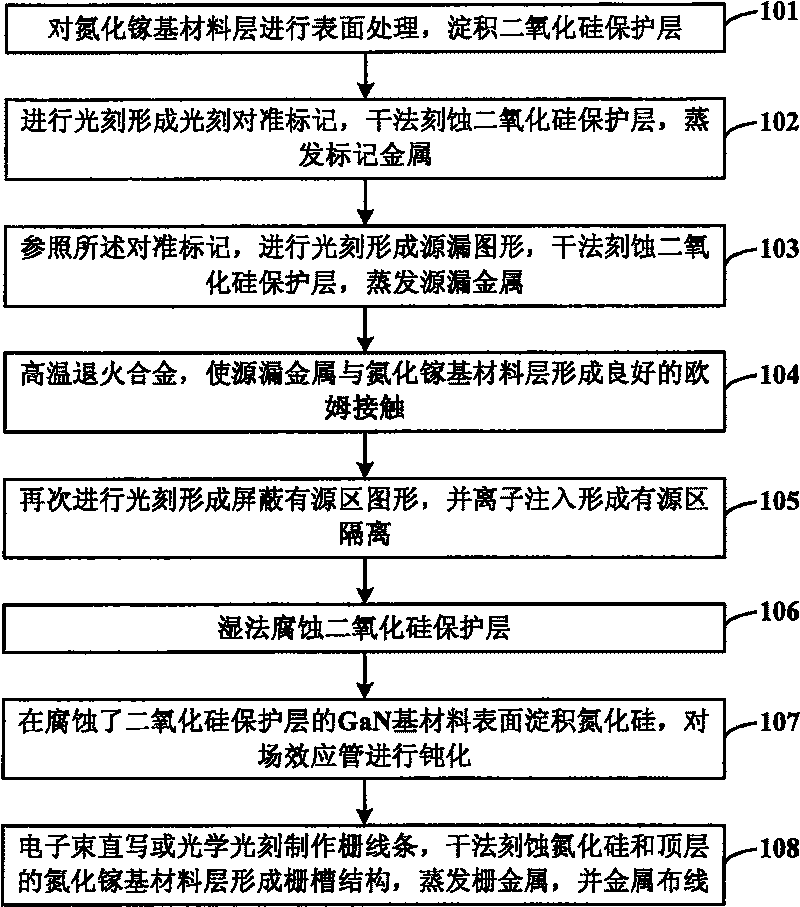

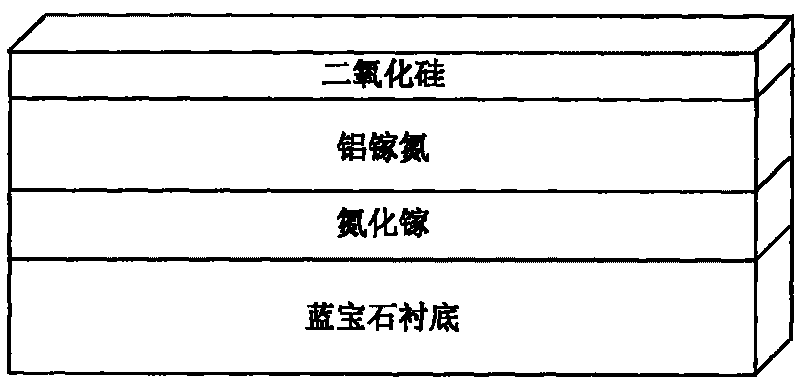

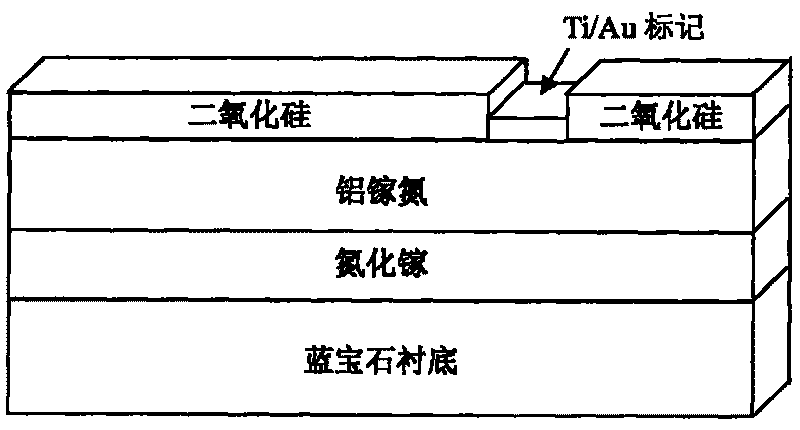

Method for preparing gallium nitride based field-effect transistor

ActiveCN101459080BDecrease the density of surface statesEliminate surface statesSemiconductor/solid-state device manufacturingSilicon oxideAlloy

The invention discloses a method of manufacturing GaN-based field-effect transistors, which includes steps of surface-finishing a GaN-based material layer, depositing a silicon oxide protective layer,forming lithographic alignment marks via lithography, dry-etching the silicon oxide protective layer, evaporating marked metal, forming source-drain patterns via lithography, dry-etching the siliconoxide protective layer, evaporating source-drain metal, annealing alloy at high temperature, forming shielding active region patterns via lithography, forming active region isolation via ion implantation, then wet-etching the silicon oxide protective layer, depositing silicon nitride on the surface of the GaN-based material, passivating field effect transistors, forming grids via electron-beam direct writing or optical lithography, dry-etching the silicon nitride and the GaN-based material layer at the top to form a gate-recessed structure, evaporating gate metal and metal wiring. The method of manufacturing GaN-based field-effect transistors avoids the surface of the GaN-based material being exposed in air, prevents the surface of the GaN-based material from being polluted during fabrication process, and inhibits current collapse effect of AlGaN / GaN HEMTs.

Owner:中科芯未来微电子科技成都有限公司

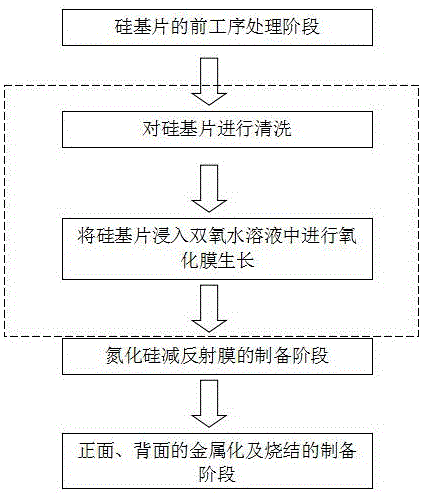

Manufacturing method of crystalline silicon solar cell resistant to PID effect

InactiveCN106611807AAnti-reflection effectsThickness can be adjustedFinal product manufacturePhotovoltaic energy generationEtchingSilicon oxide

The invention discloses a manufacturing method of a crystalline silicon solar cell resistant to a PID effect. In the crystalline silicon solar cell resistant to the PID effect, a silicon dioxide layer is formed between a silicon substrate layer and a silicon nitride film. The manufacturing method comprises the following specific steps: carrying out front process treatment on the silicon substrate, wherein the treatment comprises the steps of affected layer removal and cleaning, texturing, diffusion and etching; carrying out phosphorosilicate glass removal and cleaning on the treated silicon substrate; soaking the cleaned silicon substrate into a hydrogen peroxide solution with certain concentration and temperature for oxidation treatment, taking out the silicon substrate after a certain period of time, drying after rinsing with deionized water to obtain the silicon dioxide layer; depositing a silicon nitride layer on the surface of a silicon oxide layer; and carrying out metallization and sintering on the front face and the back face of the silicon substrate. A silicon oxide film obtained by adopting a hydrogen peroxide oxidation technology is compact and has a relatively low surface state density, and the passivation effect for surface defects of base silicon is improved, so that the photoelectric conversion efficiency of the solar cell is improved.

Owner:JIANGSU FOCUS NEW ENERGY TECH

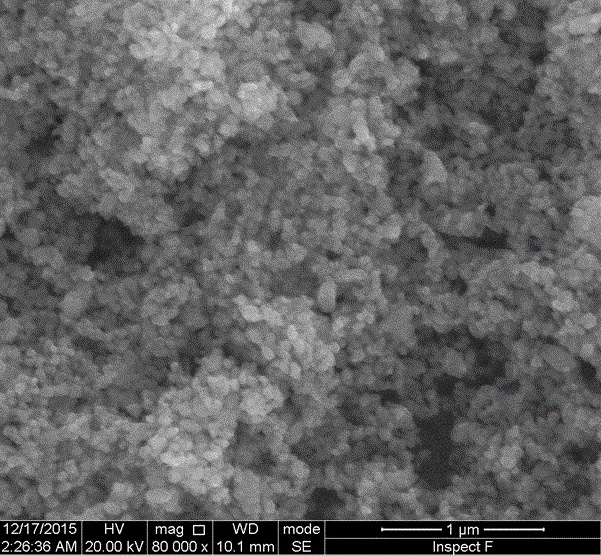

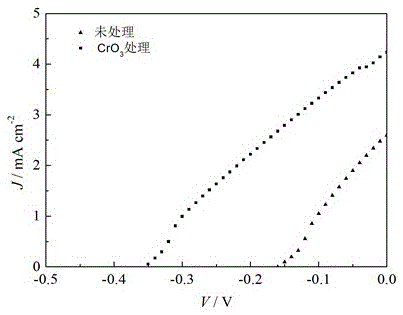

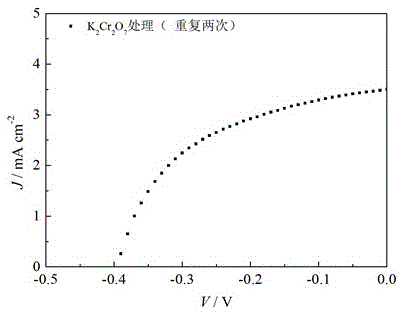

Surface modification method for SnO<2>-based photo-anode

InactiveCN105609310AImprove performanceDecrease the density of surface statesLight-sensitive devicesCapacitor electrodesHydrophilizationThin membrane

The invention discloses a surface modification method for an SnO<2>-based photo-anode, and belongs to the field of photoelectrochemistry. The surface modification method comprises the following implementation steps: (1) dissolving soluble chromic acid or chromate containing high-valent chromium into water to prepare a chromic acid or chromate solution a containing the high-valent chromium; (2) preparing a water solution b of a non-oxidizing acid with certain concentration; (3) soaking an SnO<2> mesoporous thin film of which the surface is subjected to hydrophilizing treatment into the solution a for a certain period of time, taking out and soaking the SnO<2> mesoporous thin film into deionized water or washing the SnO<2> mesoporous thin film with the deionized water, soaking the SnO<2> mesoporous thin film into the solution b for a certain period of time, taking out and soaking the SnO<2> mesoporous thin film into the deionized water or washing the SnO<2> mesoporous thin film with the deionized water, and drying the SnO<2> mesoporous thin film at a certain temperature; and (4) repeating the step (3) for a plurality of times, drying and burning the SnO<2> mesoporous thin film to obtain the SnO<2>-based photo-anode subjected to CrO<x> surface modification. The effect improvement of the SnO<2>-based photo-anode prepared by the method disclosed by the invention is obvious; and the method is simple to operate and easy to implement.

Owner:XIANGTAN UNIV

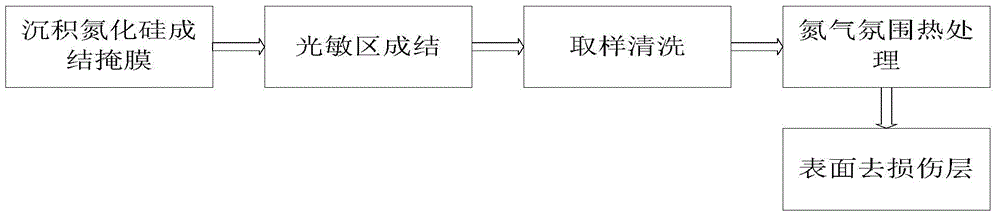

Low-damage indium gallium arsenic detector p+n junction preparation method

ActiveCN104916731AIncreased hole carrier concentrationReduced series resistanceFinal product manufactureSemiconductor devicesIndiumSurface oxidation

The invention discloses a low-damage indium gallium arsenic detector p+n junction preparation method. The method comprises the following specific steps that: 1) silicon nitride junction formation mask deposition; 2) photosensitive area junction formation; 3) sampling and cleaning; 4) nitrogen atmosphere thermal treatment; and 5) surface damage layer removal. The nitrogen atmosphere thermal treatment, one the one hand, can restore lattice damage introduced in a junction formation process, reduce the density of recombination centers, and reduce the dark current of a detector, and on the other hand, can activate acceptor ions, decrease a donor compensation effect, increase hole carrier concentration in a P area, benefit the stability of P electrode ohmic contact and decrease series resistance; the surface damage layer removal, on the one hand, can effectively remove a surface oxidation layer, reduce recombination centers on a surface, benefit surface passivation, and improve the performance of the detector, and on the other hand, can remove an ion enrichment layer and a surface damage layer which are formed on the surface.

Owner:无锡中科德芯感知科技有限公司

Plasma processing method and application thereof

PendingCN112186031AAchieve modulationHigh surfaceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsOhmic contact

The invention provides a plasma processing method which is applied to manufacturing of barrier modulation or manufacturing of III-V nitride P-type ohmic contact of a III-V nitride power device, the surface of the power device is processed, an atomic structure and a corresponding electronic structure of a semiconductor material on the surface layer of the device are changed, dangling bonds are passivated, vacancies are compensated, and therefore, the surface or interface quality is improved, the surface state density is reduced, the surface natural oxide layer is removed, and lattice defects such as nitrogen vacancy can be repaired.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT +1

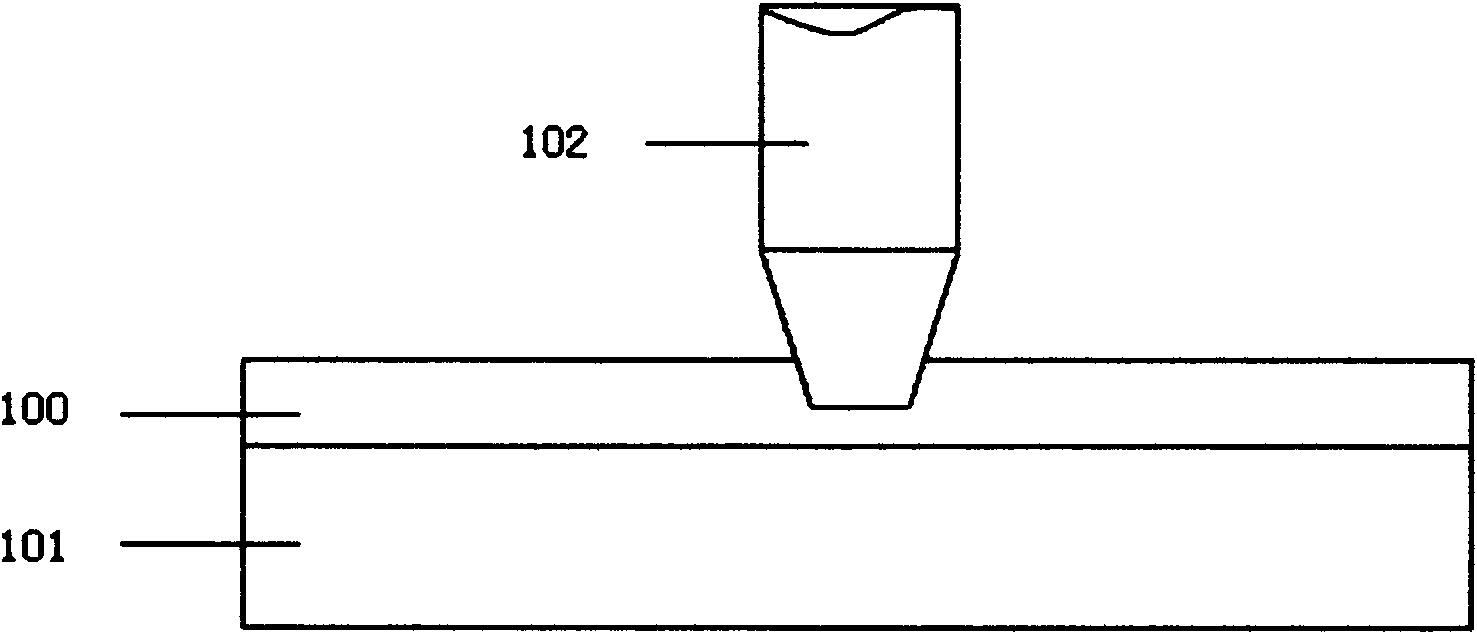

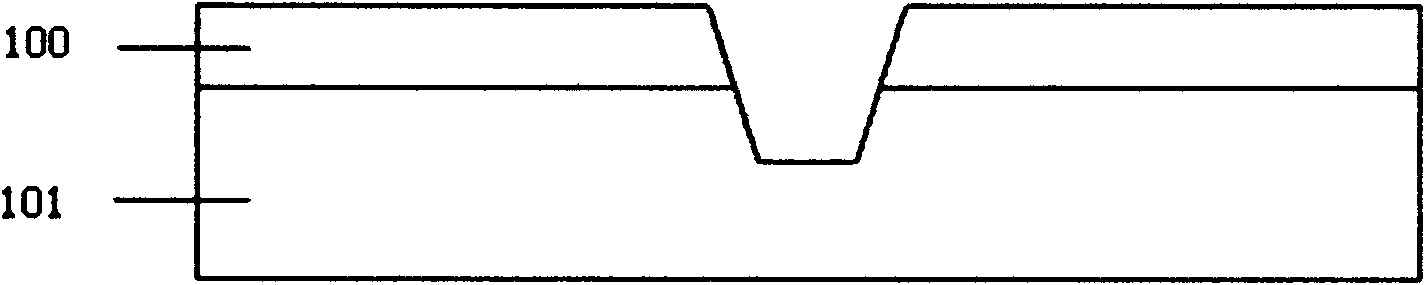

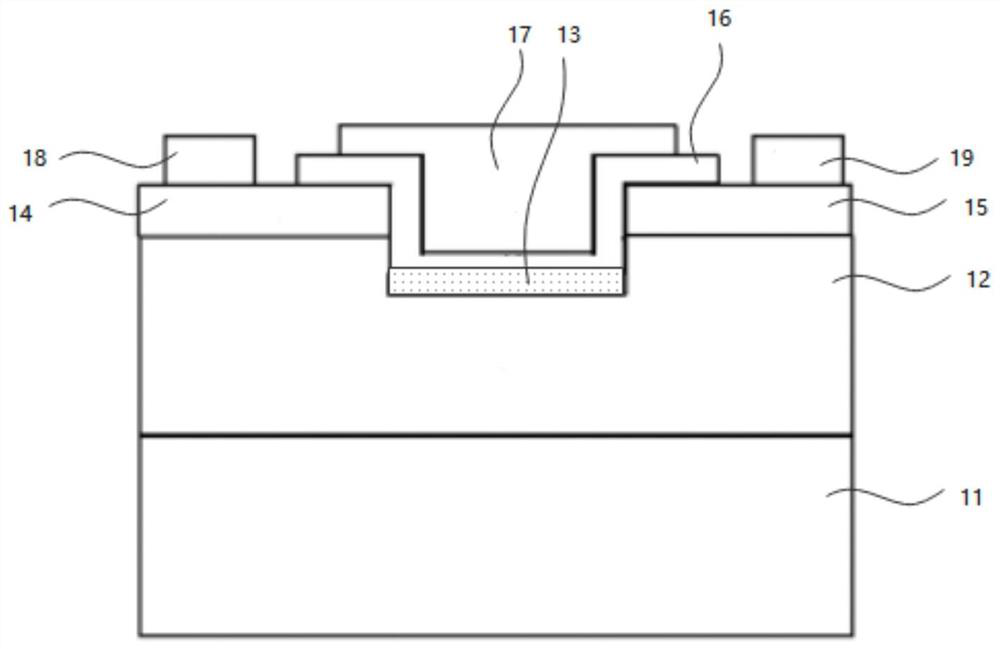

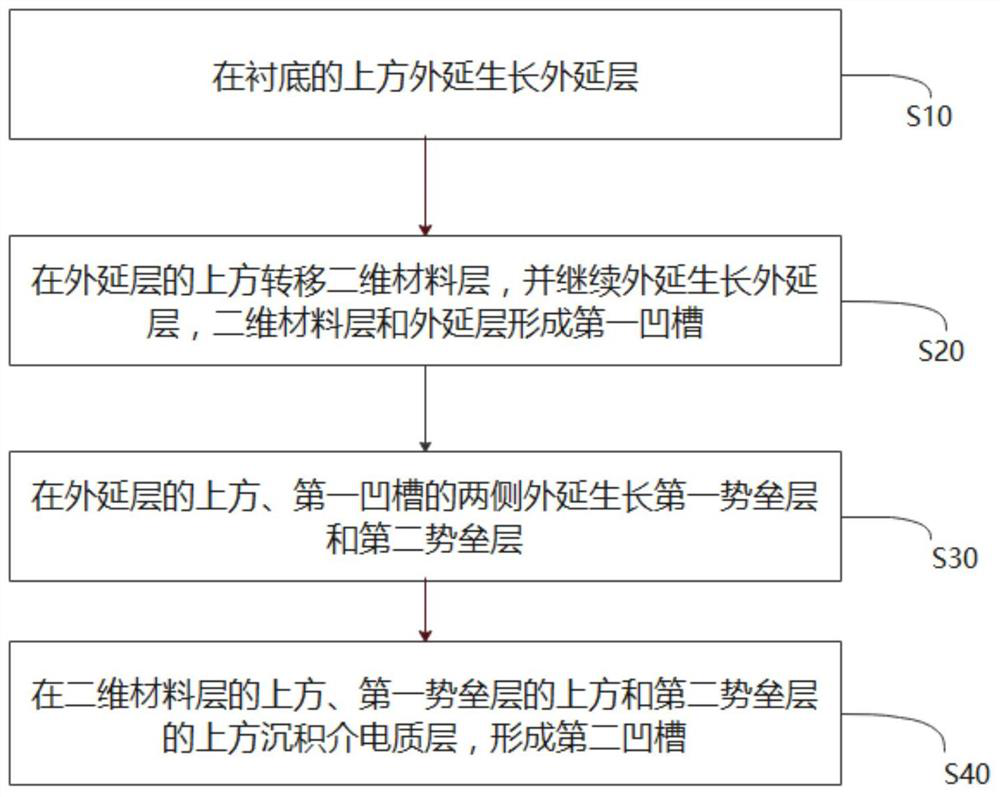

Transistor groove manufacturing method and transistor

ActiveCN111952175ADecrease the density of surface statesAvoid introducingFinal product manufactureNanoinformaticsEngineeringDielectric layer

The invention provides a transistor groove manufacturing method and a transistor. The method comprises the following steps: epitaxially growing an epitaxial layer above a substrate; transferring the two-dimensional material layer above the epitaxial layer, continuing to epitaxially grow the epitaxial layer, and forming a first groove by the two-dimensional material layer and the epitaxial layer; epitaxially growing a first barrier layer and a second barrier layer above the epitaxial layer and on two sides of the first groove; and depositing a dielectric layer above the two-dimensional materiallayer, the first barrier layer and the second barrier layer to form a second groove. According to the groove system of the transistor manufactured through the method, the surface of the groove is smoother, and the surface state density is lower.

Owner:深圳市红与蓝企业管理中心(有限合伙)

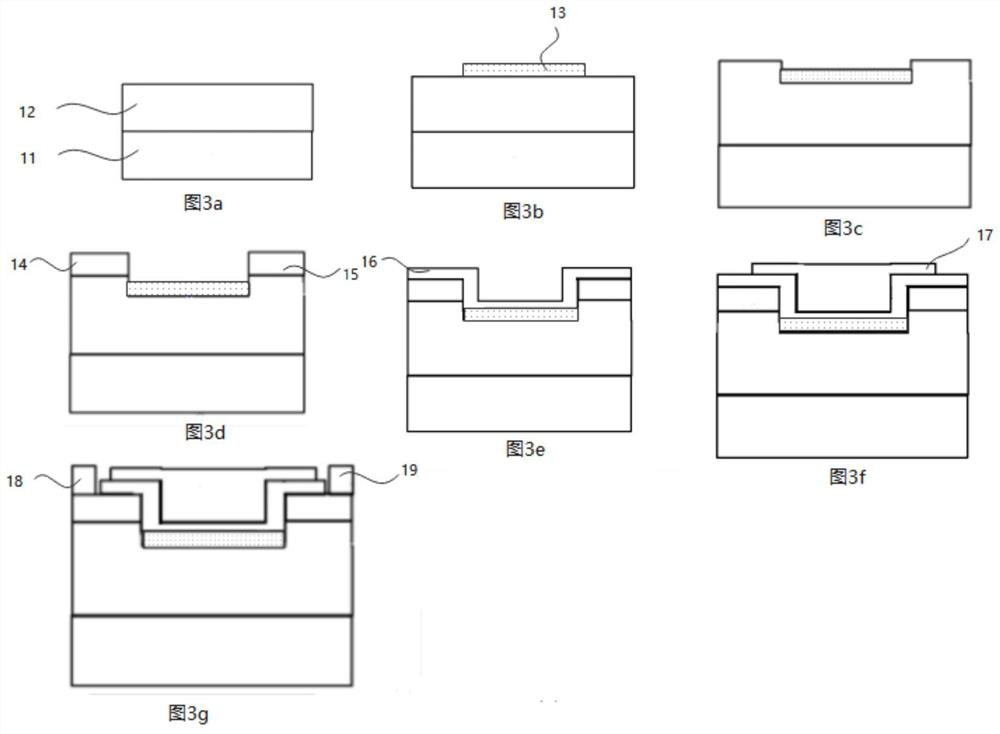

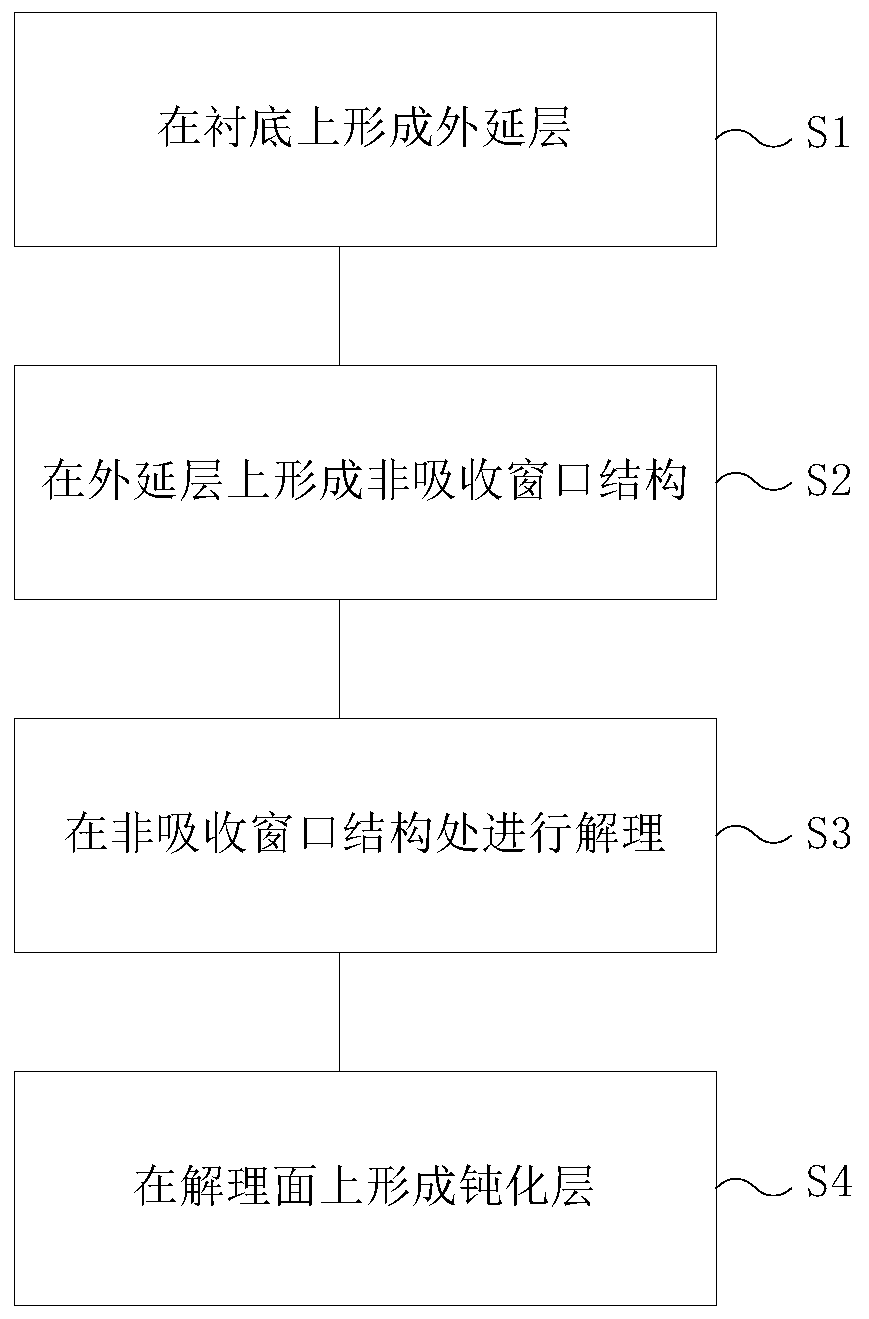

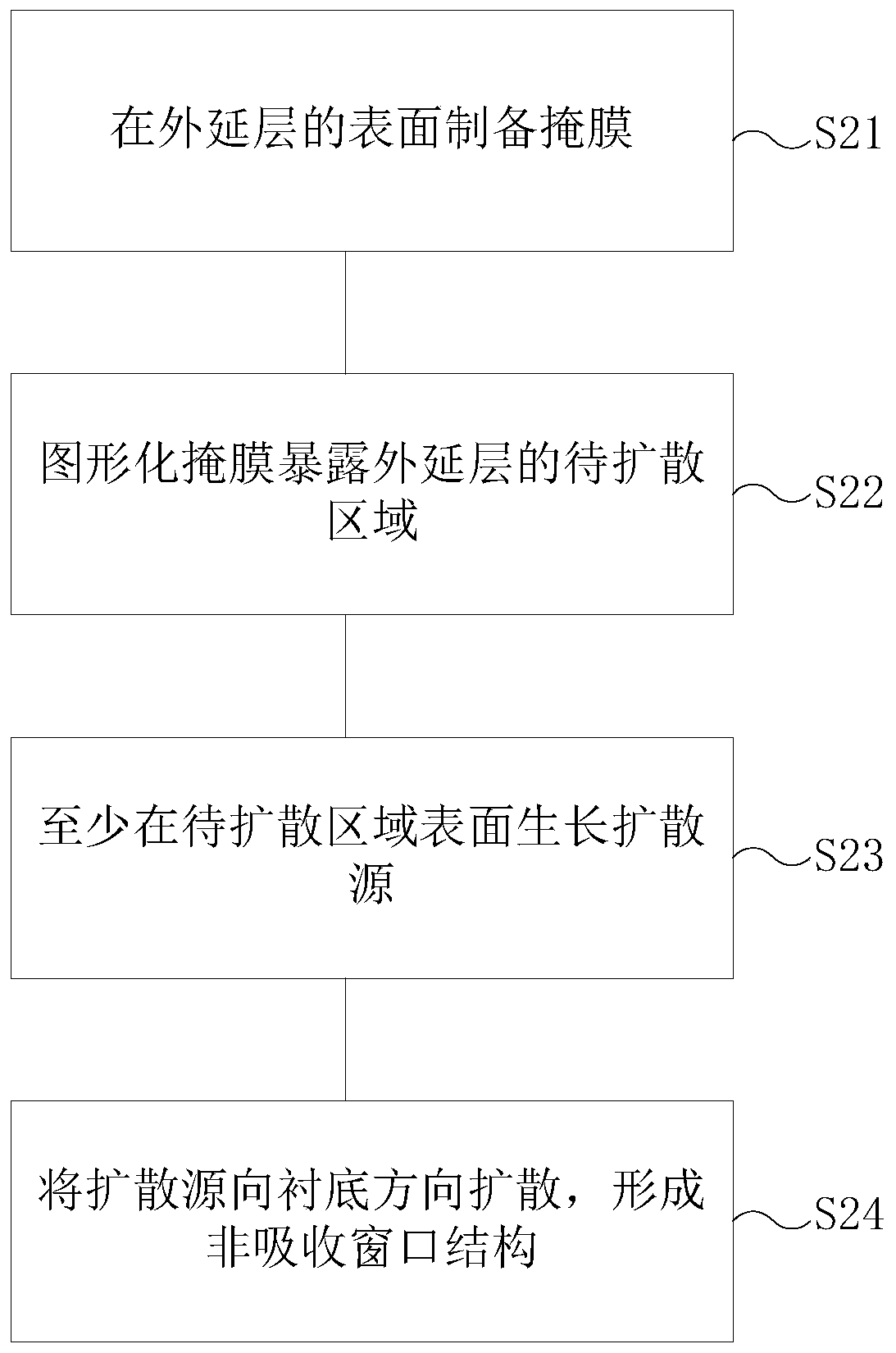

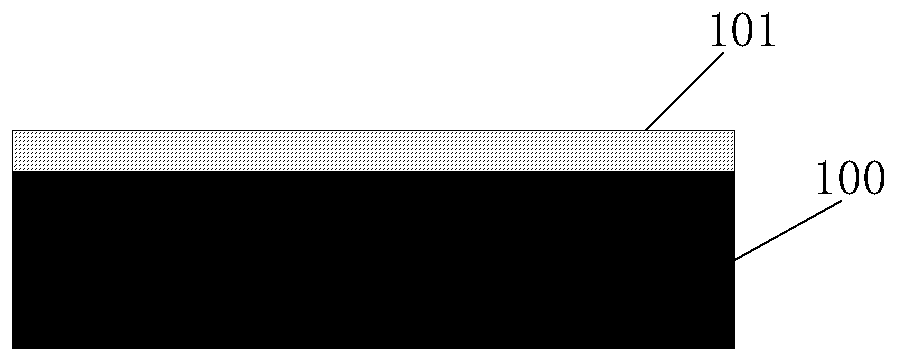

Method for eliminating semiconductor laser COMD and semiconductor laser

InactiveCN109921277AIncreased surface state densityIncrease COMD ThresholdLaser detailsSemiconductor laser structural detailsNon-radiative recombinationSemiconductor laser theory

The invention discloses a method for eliminating a semiconductor laser COMD and a semiconductor laser, wherein the method for eliminating the semiconductor laser COMD comprises the following steps: forming an epitaxial layer on a substrate; forming a non-absorption window structure on the epitaxial layer; cleaving at the non-absorbing window structure; and forming a passivation layer on the cleavage plane. By adopting the method for eliminating the semiconductor laser COMD disclosed by the invention, the forbidden bandwidth of the non-absorption window structure is large, and photons cannot beabsorbed; and since the non-absorption window structure is passivated by vacuum cleavage coating, the surface state density of the non-absorption window structure is low, and the non-radiative recombination of carriers is effectively inhibited, so that the heat productivity of the cavity surface position is extremely low, and the COMD is completely eliminated. Moreover, when the non-absorption window structure is subjected to vacuum cleavage passivation, even if the vacuum degree is reduced moderately, the non-radiative recombination at the cavity surface position can still be ignored in theworking state of the laser, and the COMD threshold value of the laser is not influenced.

Owner:SUZHOU EVERBRIGHT PHOTONICS

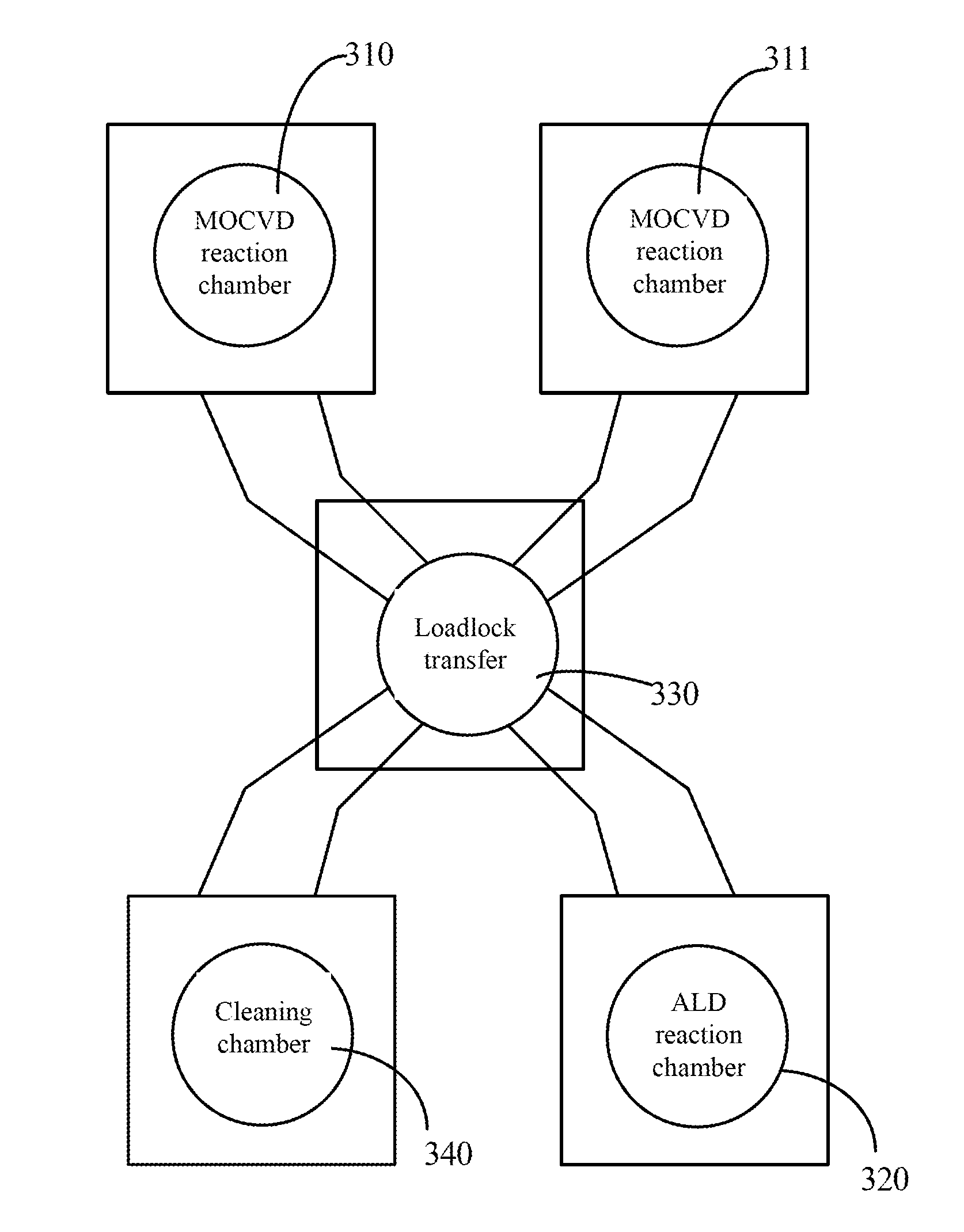

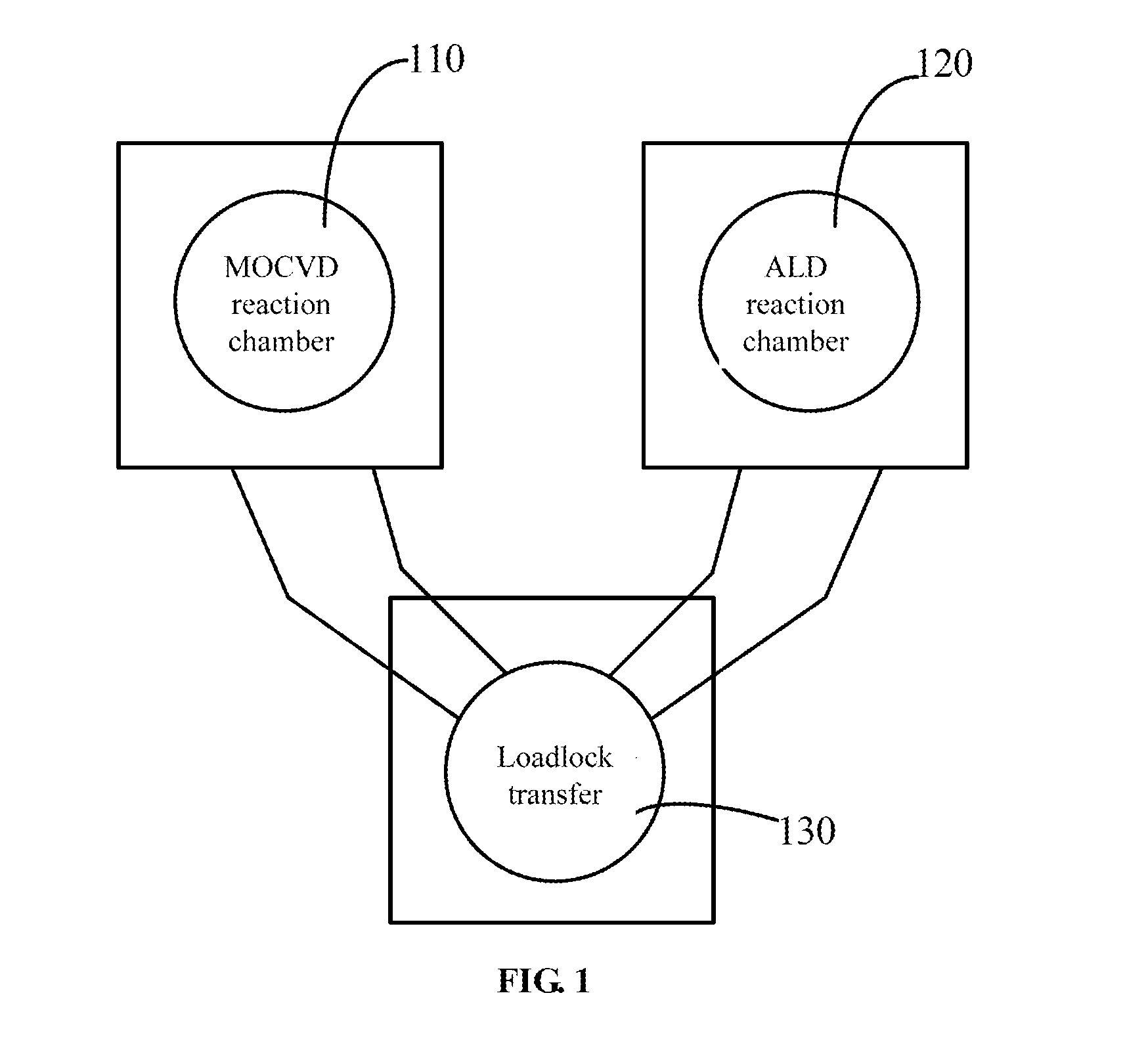

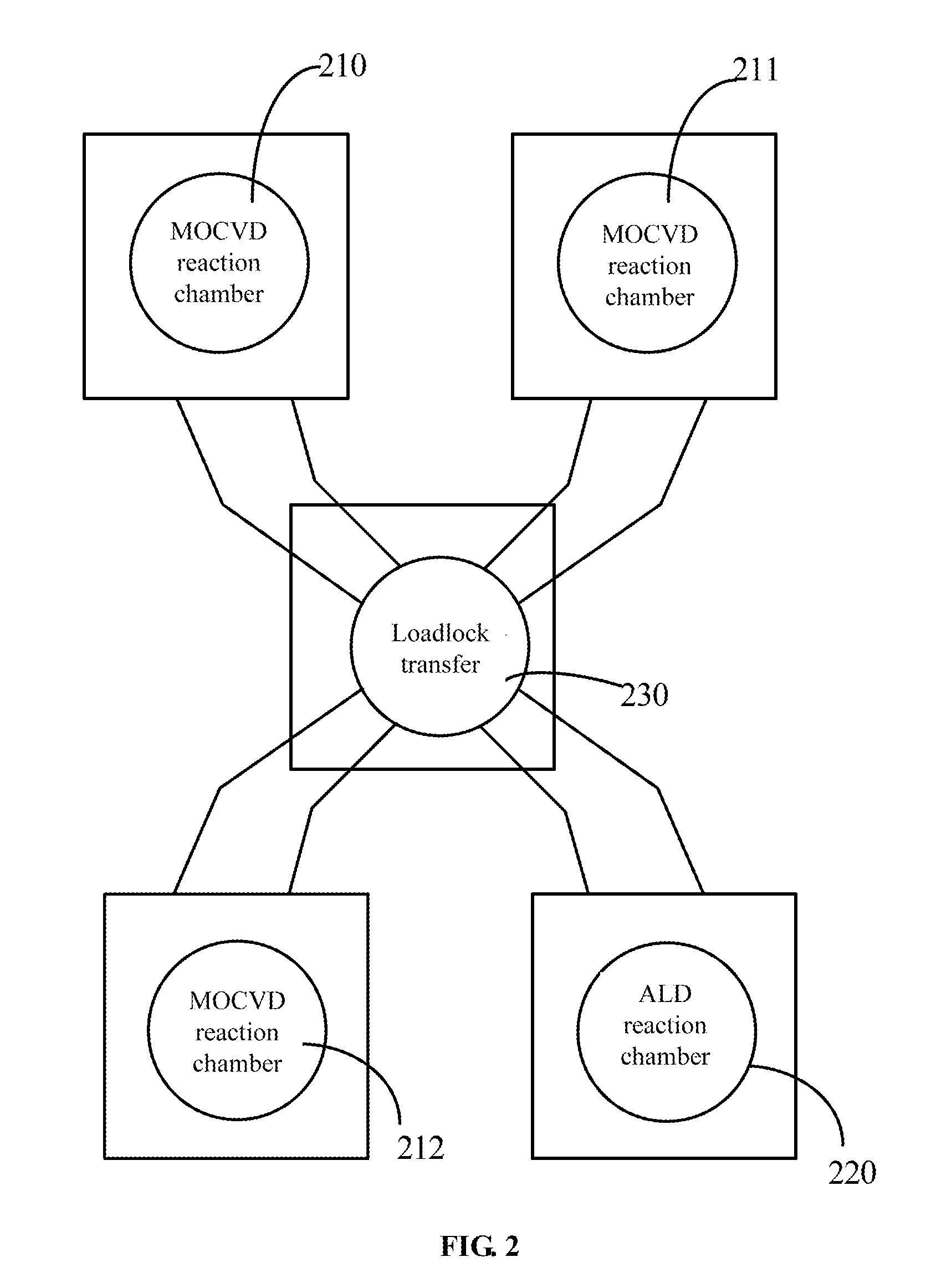

System and method for forming gan-based device

InactiveUS20150187618A1Good performanceQualityPolycrystalline material growthSemiconductor/solid-state device manufacturingChemistryIntegrated systems

A system and a method for forming a GaN based device are provided. The system may include: at least one MOCVD reaction chamber; at least one ALD or CVD reaction chamber; and a loadlock transfer connecting with the MOCVD reaction chamber and the ALD or CVD reaction chamber. The MOCVD reaction chamber may be a standard chamber for nitride growth. The ALD or CVD reaction chamber may be used for growing nitride and oxide dielectric layers, which may have a highest growth temperature no less than about 500° C., such that nitride and oxide may have better qualities. The system may include a cleaning chamber for cleaning the substrate and the nitride films. Using the integrated system, cleaning processes and growing processes for epitaxial layers and dielectric layers can be implemented in a same system, which may avoid contaminations in the air. Device performance may be improved.

Owner:ENKRIS SEMICON

Manufacture method of table surface type indium gallium arsenic detector

ActiveCN102376824BAvoid damageImprove yieldRenewable energy productsSemiconductor devicesIndiumVulcanization

The invention discloses a manufacture method of a table surface type indium gallium arsenic detector, which comprises the step of performing the step of evaporating a P-InP contact electrode and the step of high-temperature quick annealing in advance of the step of passivating silicon nitride. The manufacture method has the advantages that a silicon nitride passivating film is damaged since the surface of a material is polluted or remained with a plurality of particles in the process of high-temperature quick annealing can be avoided, the yield for manufacturing the detector can be improved, the manufacture method is particularly suitable for researching and manufacturing a long linear detector and a plane array detector, and the influence of the process of high-temperature quick annealing to the contact status between the passivating film and the surface of the material can be eliminated; and as a thermal treatment technology is introduced after ion etching, the surface fixed charge introduced into the surface of the material by etching ions can be effectively reduced, the surface oxide can be removed and the crystal lattice damage and the dangling bond of the surface caused by ion etching can be reduced by adopting a chemical corrosion and vulcanization method, the surface state density can be reduced, and the surface composite dark current can be effectively reduced.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Planar indium gallium arsenic photosensitive chip with improved surface passivation and preparation method thereof

ActiveCN104538463BImprove passivation effectWon't hurtFinal product manufactureSemiconductor devicesVulcanizationIndium

The invention discloses a planar indium gallium arsenic light-sensitive chip with surface passivation improved and a manufacturing method. According to the structure of the planar indium gallium arsenic light-sensitive chip, an N-type InP layer, an indium gallium arsenic intrinsic absorption layer, an N-type InP cap layer, a SiNx passivation layer, a P-electrode and a thickened electrode (8) are grown on a semi-insulating InP substrate in sequence. The manufacturing process is improved on the basis of an original process, and comprises removal and vulcanization of a diffusion mask and silicon nitride passive film growing through an inductive coupling plasma chemical vapor deposition (ICPCVD) technology. The planar indium gallium arsenic light-sensitive chip with surface passivation improved and the manufacturing method have the advantages the passivation layer of the chip is even in structure; the surface state density of a device is effectively reduced, and the surface can be prevented from being oxidized again through a vulcanization film formed on the surface; damage of the process to the surface of materials is small, the film is compact and is in stress fit with the substrate, the element bonding state is good, and the passivaition effect is excellent.

Owner:无锡中科德芯感知科技有限公司

Solar cell, front film layer structure of solar cell, preparation method of front film layer structure, assembly and system

PendingCN113921619APromote absorptionImprove utilizationFinal product manufacturePhotovoltaic energy generationPotential induced degradationEngineering

The invention is suitable for the technical field of solar cells, and provides a solar cell, a front film layer structure of the solar cell, a preparation method of the front film layer structure, an assembly and a system. According to the solar cell front film layer structure provided by the embodiment of the invention, at least three silicon nitride layers and at least two silicon oxide film layers are arranged in the front film layer; compared with an existing front surface film layer structure, light absorption of short wavelength is increased, light reflection back to an incident interface is reduced, reflection loss of light on the front surface is reduced, light absorption and utilization of a silicon wafer are increased, the conversion efficiency of the front surface of the solar cell is improved, and the efficiency of the front surface is improved by more than 0.05%; compared with the prior art, the invention has the advantages of improving the contact with the silicon wafer, improving the compactness and passivation effect of the front surface of the battery, effectively reducing the state density of the silicon surface and reducing the non-radiative recombination of carriers, thereby effectively improving the potential induced degradation resistance of the battery assembly, delaying the attenuation of the battery assembly and prolonging the service life of the battery assembly.

Owner:TIANJIN AIKO SOLAR ENERGY TECH CO LTD +3

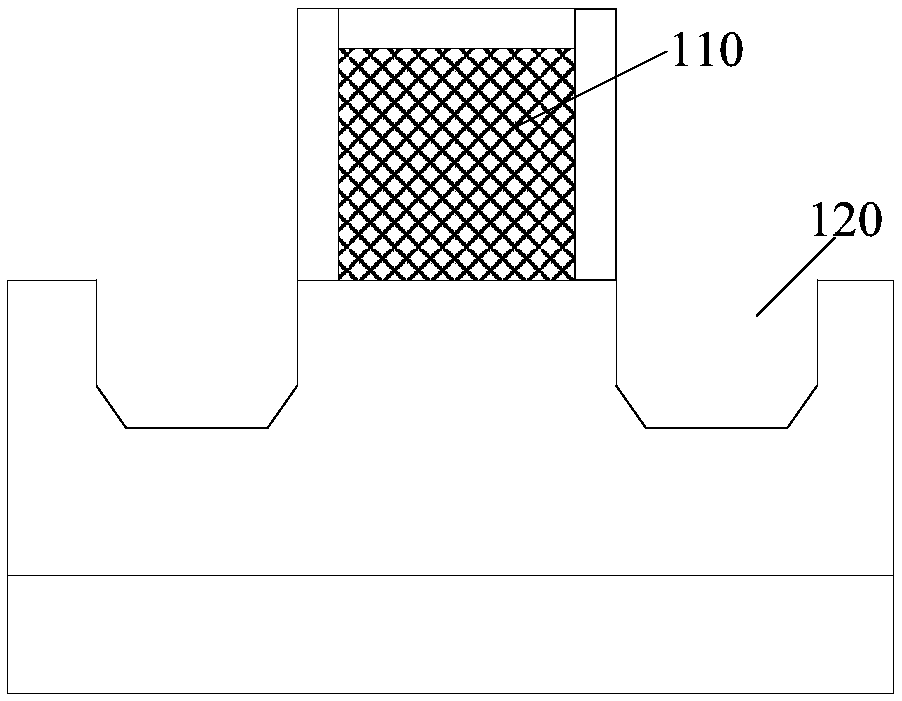

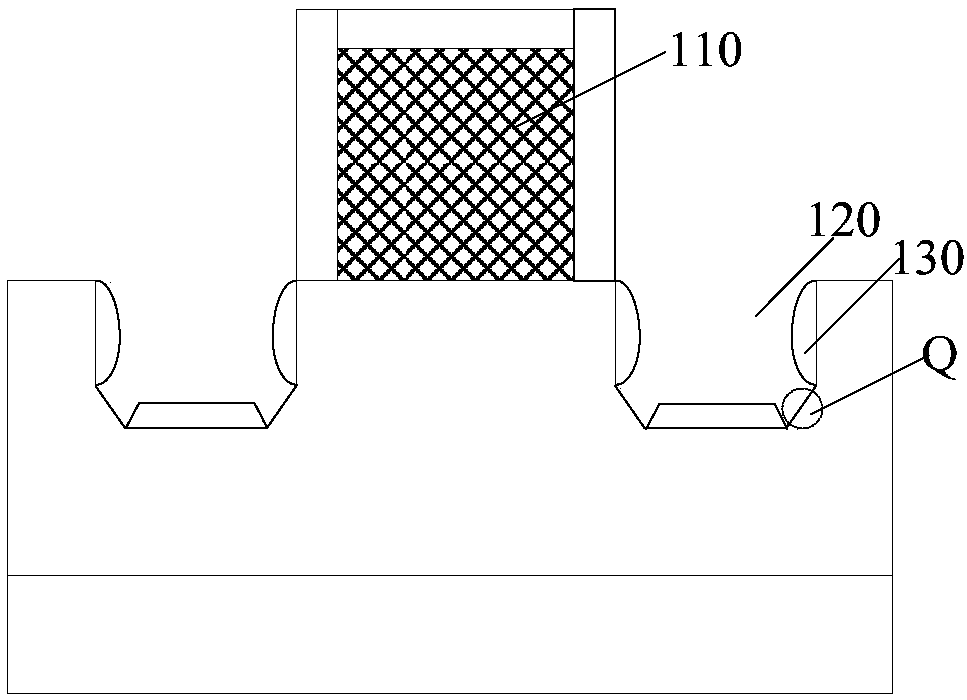

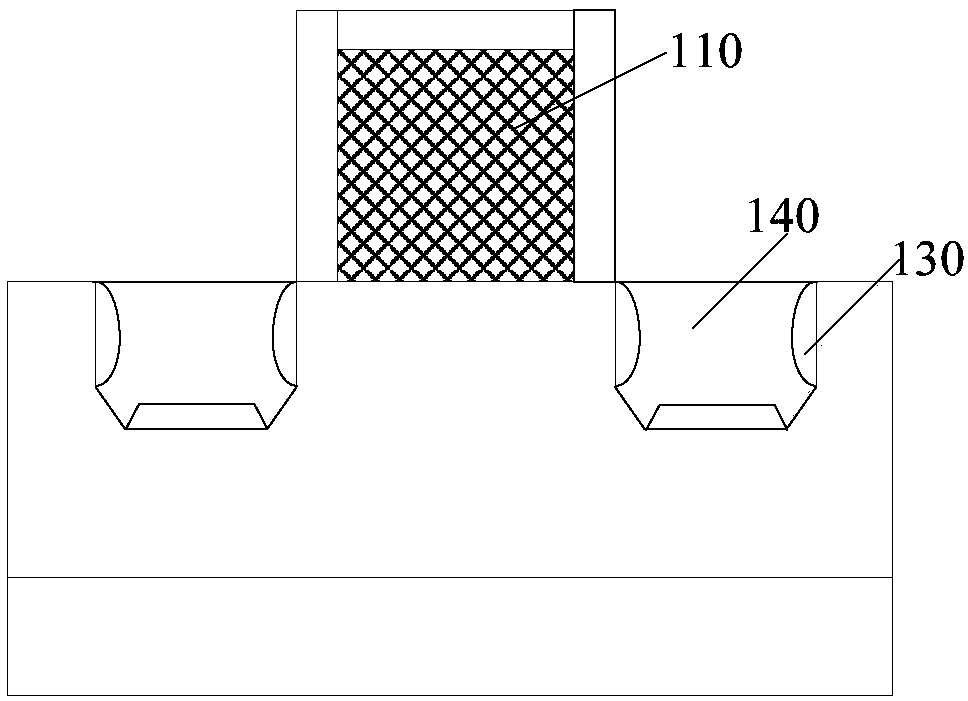

Semiconductor device and forming method thereof

ActiveCN109817713AImprove performanceDecrease the density of surface statesSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention discloses a semiconductor device and a forming method thereof. The method comprises the steps: providing a substrate which is provided with a gate structure; respectively forming initialgrooves in the substrate at two sides of the gate structure; carrying out surface smoothing treatment on the inner walls of the initial grooves to enable the initial grooves to form grooves, and enabling a corner between the bottom surface and the side wall of each groove to be a round corner; forming a seed layer on the inner wall of each groove, wherein each seed layer covers the whole inner wall of the corresponding groove; and forming a source-drain body layer on the surface of each seed layer in the groove. The method improves the performance of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

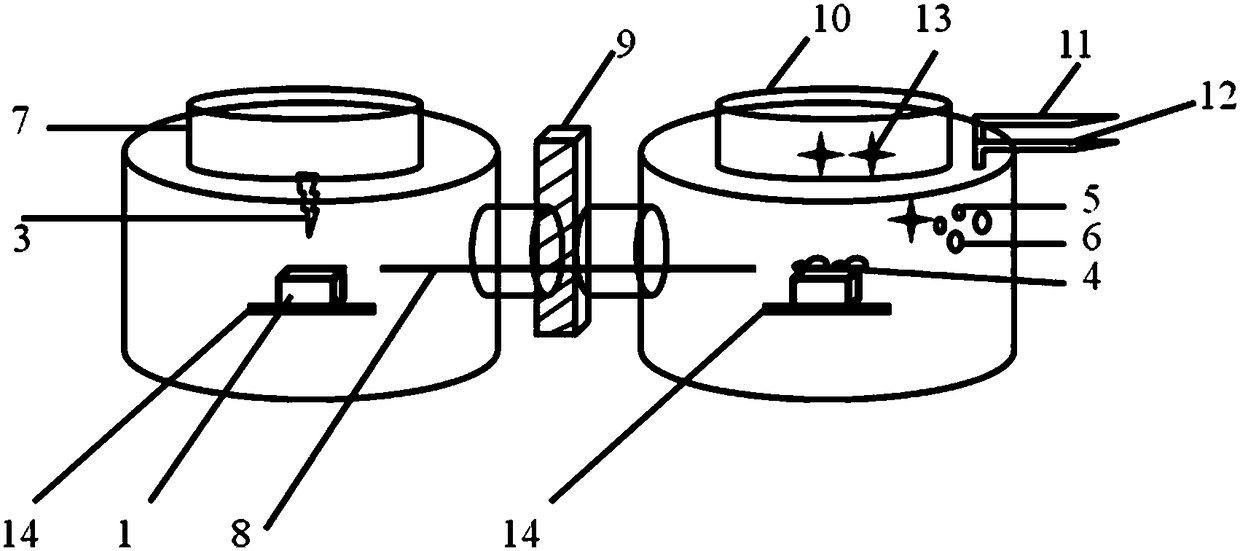

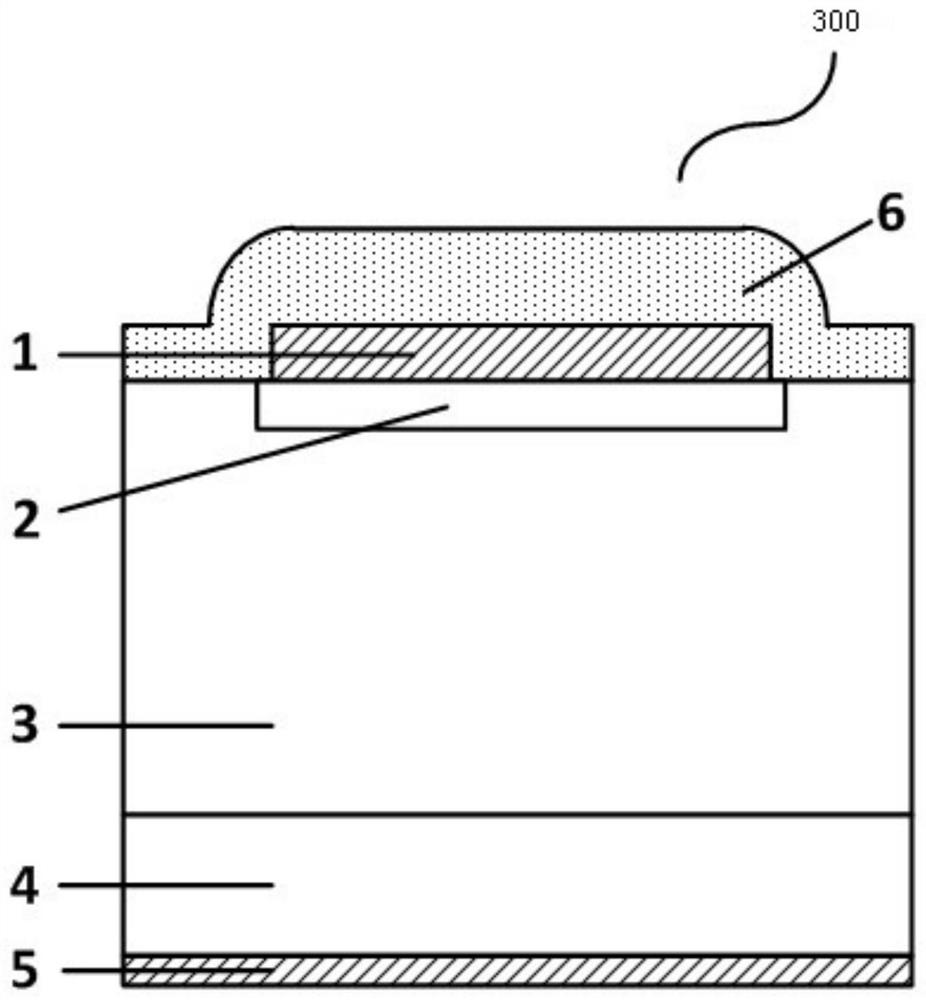

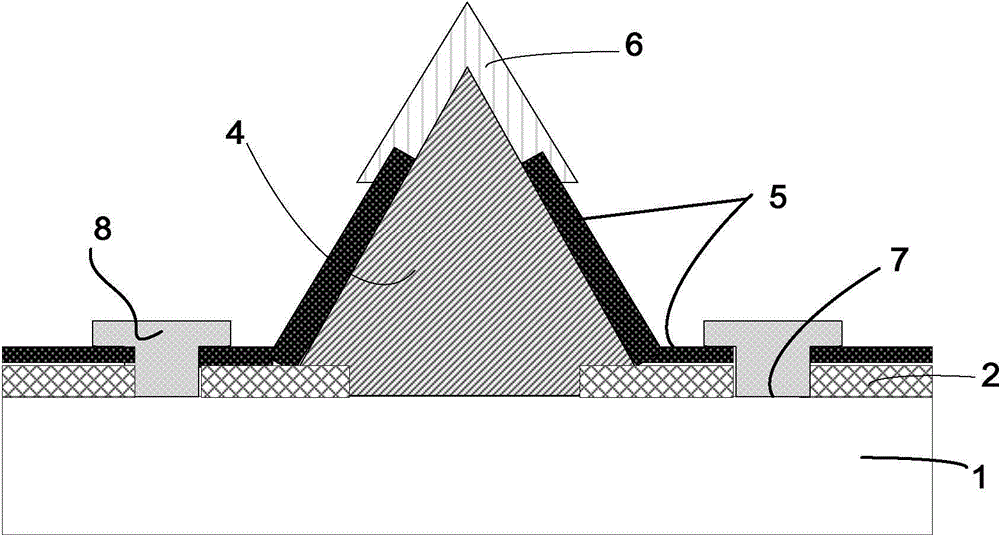

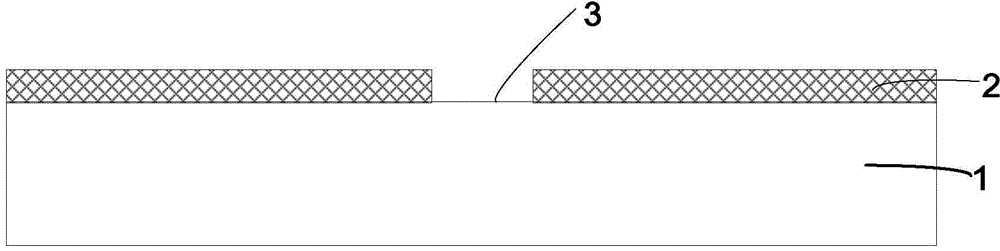

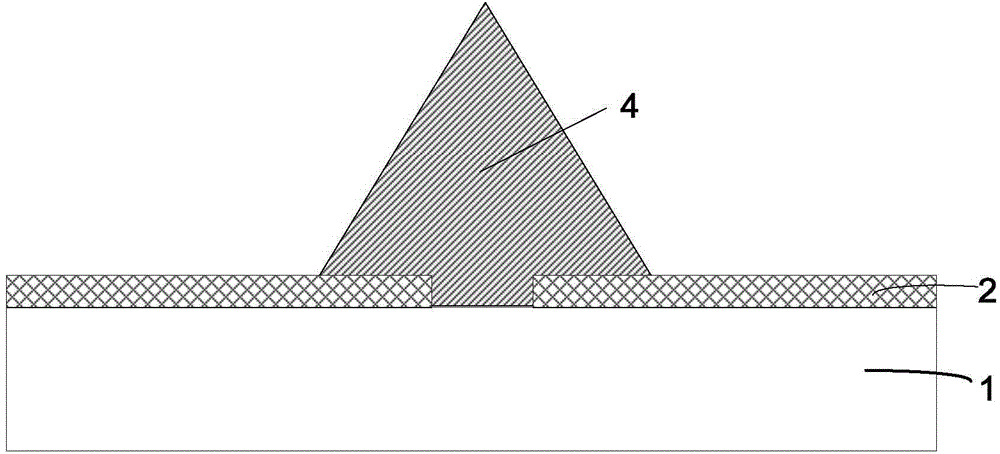

Method for growth and preparation of III-nitride Schottky barrier diode

InactiveCN104795324AReduce reverse leakage currentImprove reverse breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowOhmic contact

The invention discloses a method for preparing a III-nitride Schottky barrier diode (SBD) which is provided with a thick film and is low in defect density and high in pressure resistance. A method of selection region epitaxial growth is utilized for the III-nitride SBD. The III-nitride SBD structurally sequentially comprises a bottom layer substrate, a dielectric layer, a III-nitride three-dimensional structure, a side wall barrier layer, a Schottky contact layer and an Ohmic contact layer from bottom to top, wherein the dielectric layer is provided with a selection region growth window; the III-nitride three-dimensional structure is obtained by utilizing the selective epitaxial growth; and the side wall barrier layer is used for preventing electric leakage. The three-dimensional III-nitride structure obtained through the selective epitaxial growth method is large in thickness and lower in defect density, the SBD has a lower reverse leakage current and higher reverse breakdown voltage; the III-nitride SBD is simple in structure, the parallel connection packaging of multiple devices is achieved easily, and the method has wide prospect in the aspect of high-current high-voltage resistant SBD devices.

Owner:SUN YAT SEN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com