Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

202results about How to "Prevent interdiffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

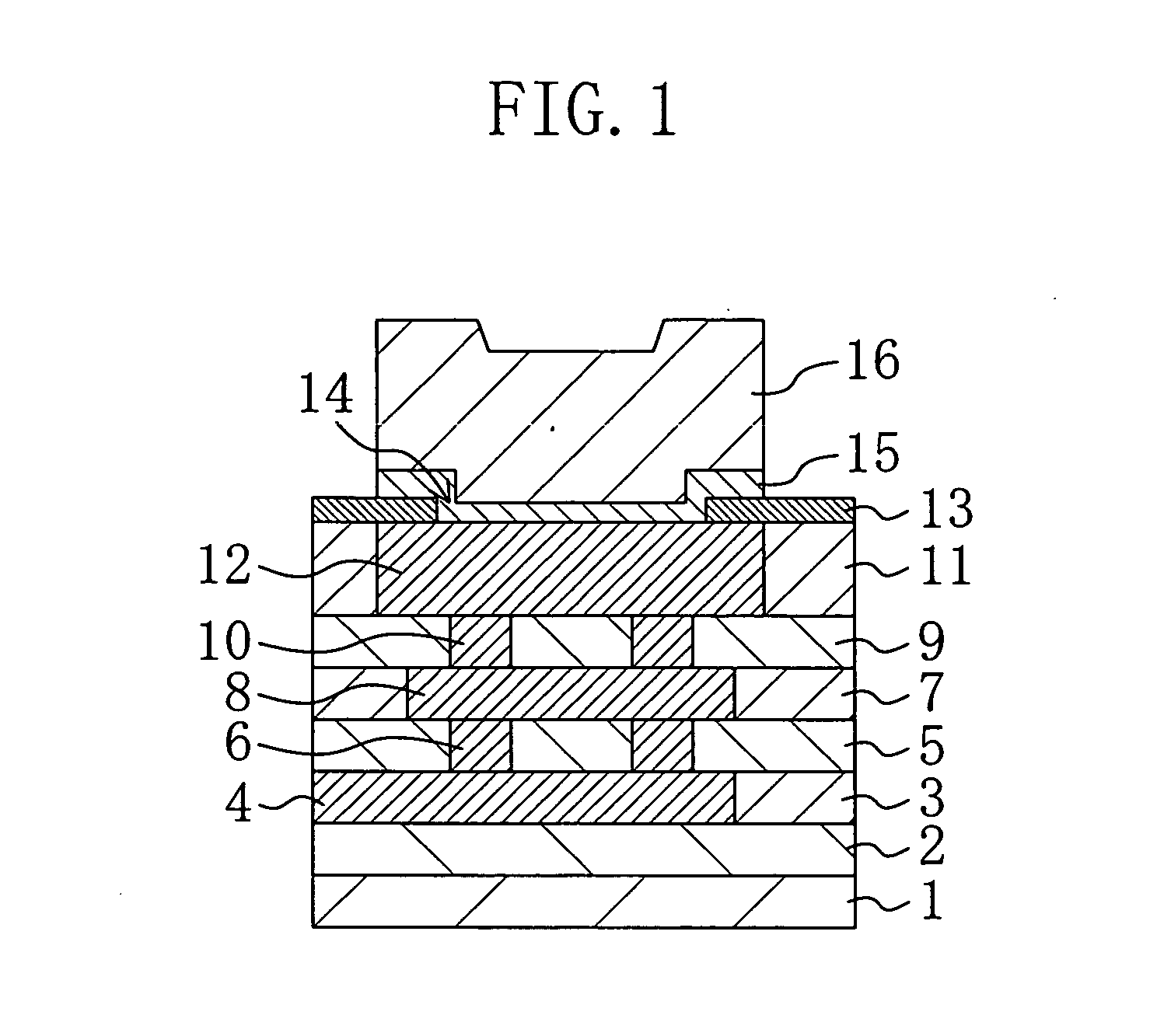

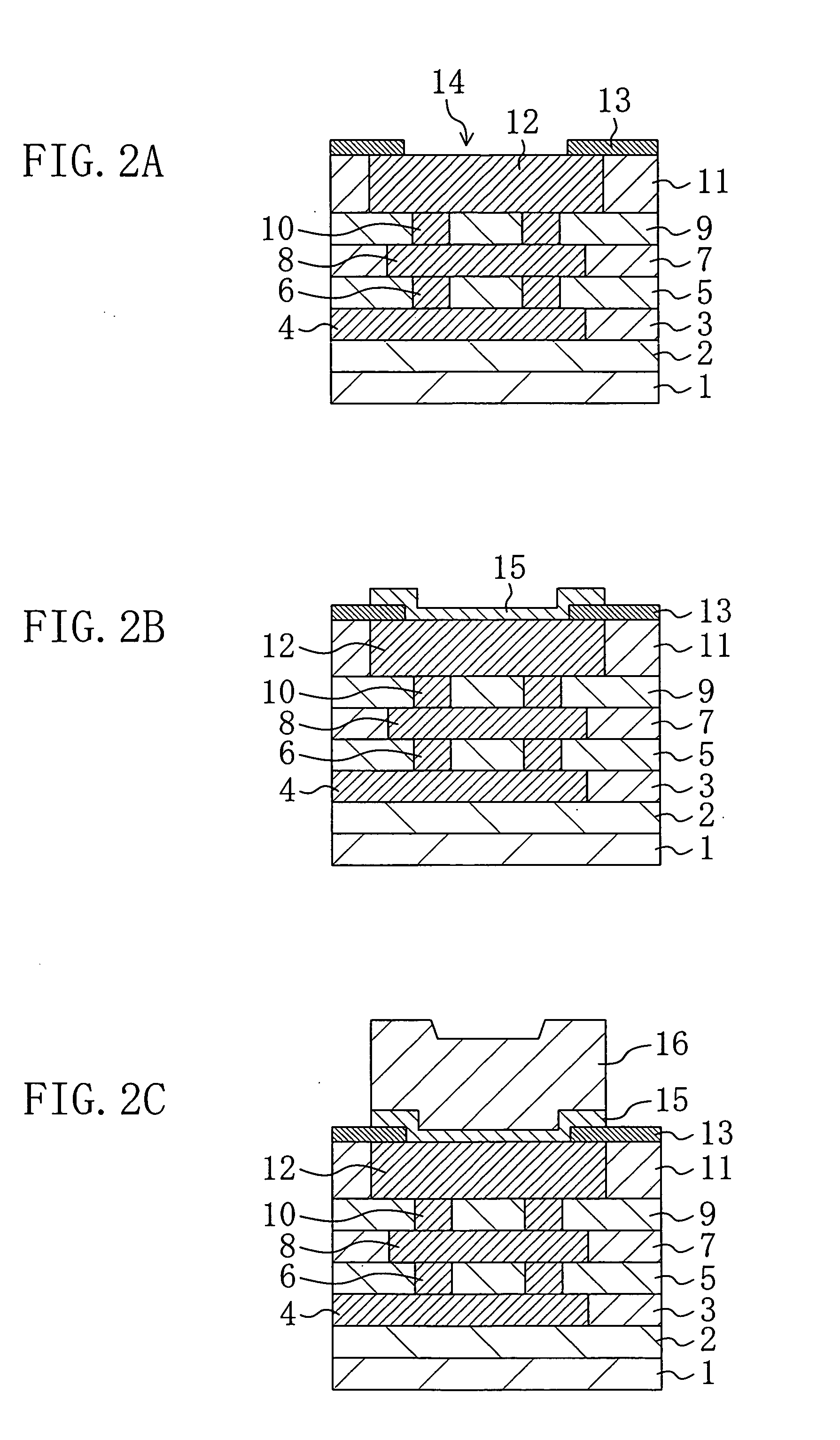

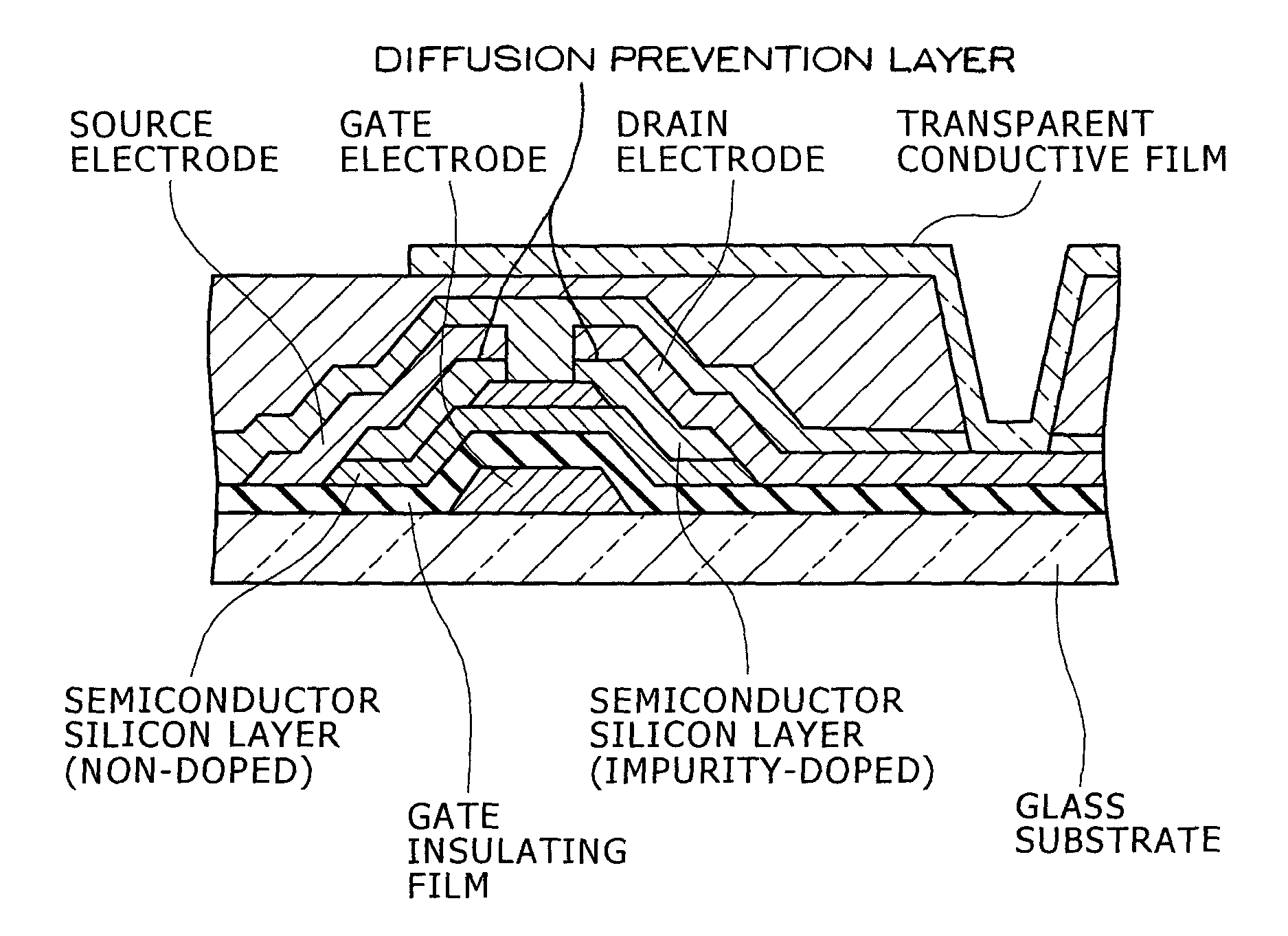

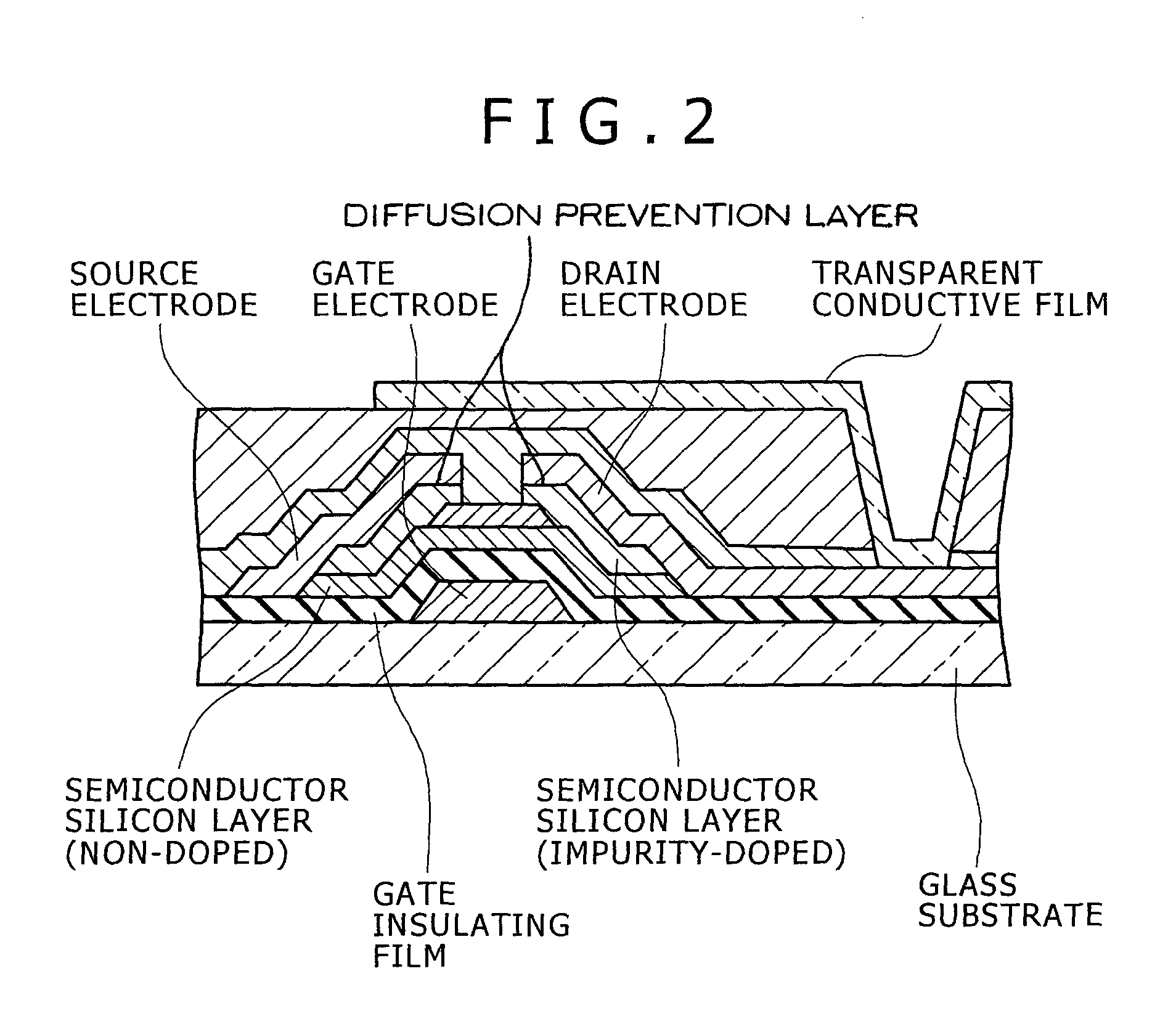

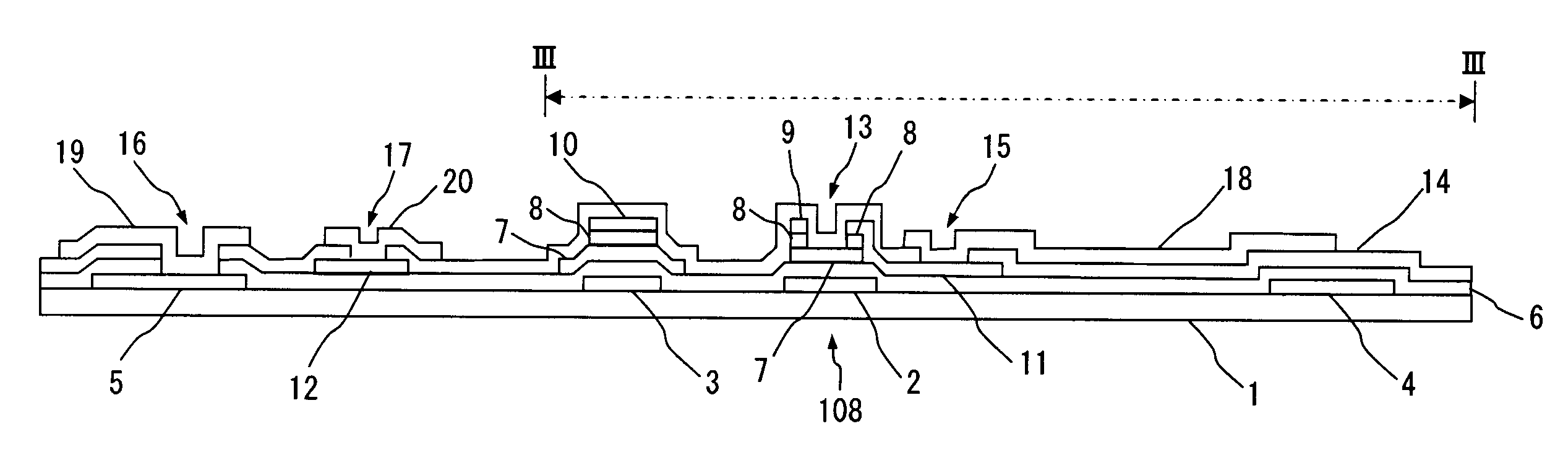

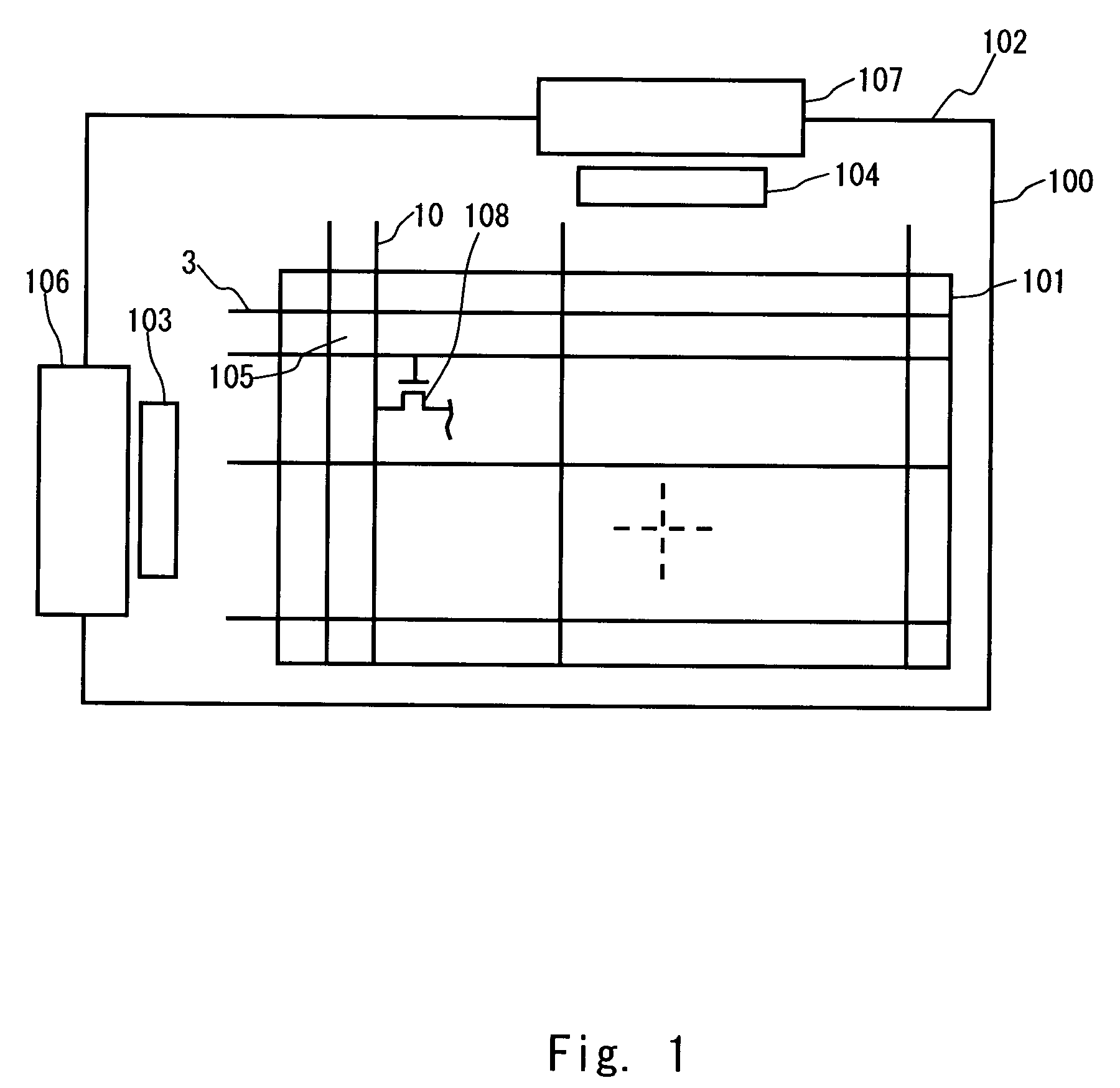

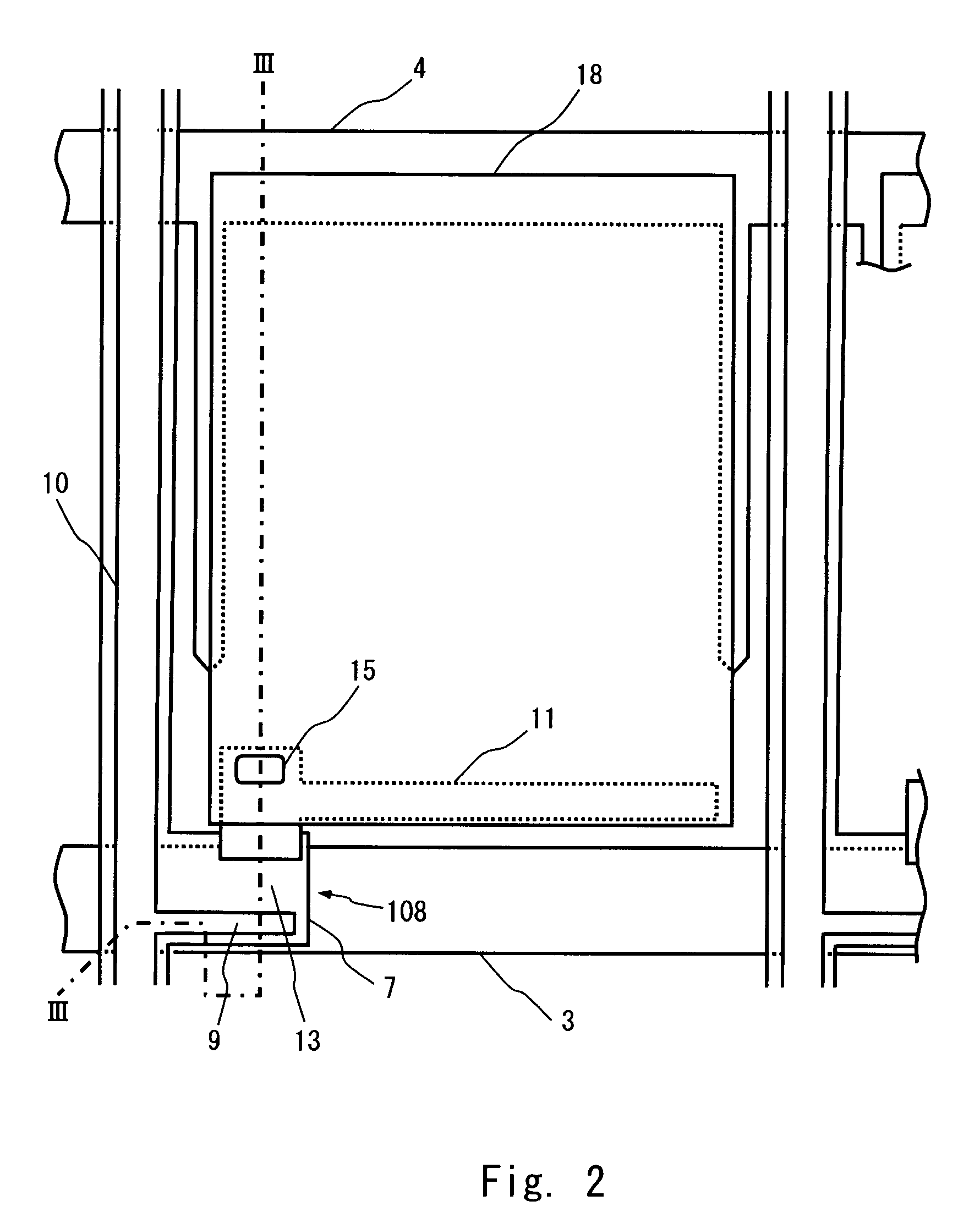

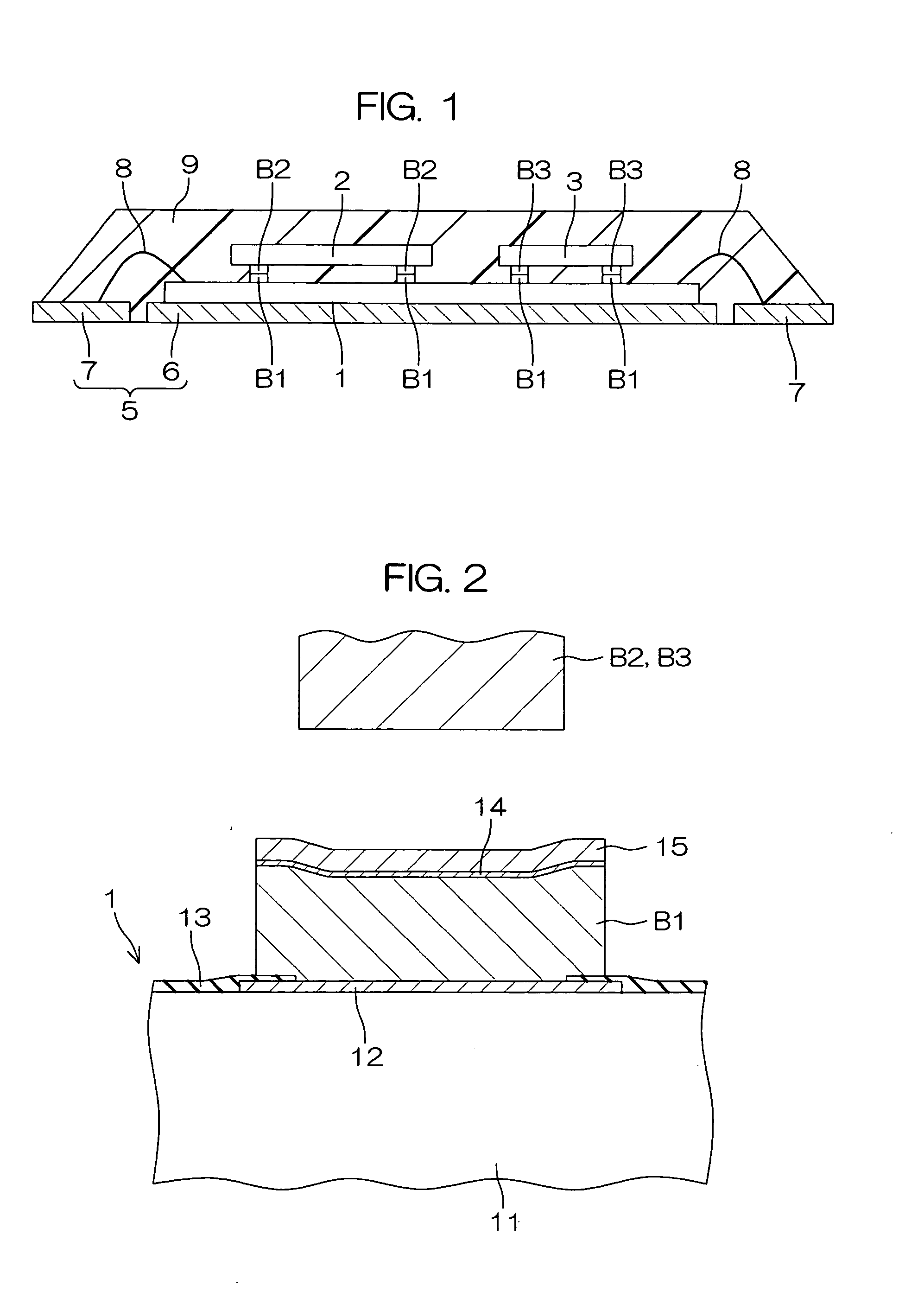

Thin film transistor substrate and display device

InactiveUS20070278497A1Reduce adverse effectsDesired switching performanceSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceAlloy thin film

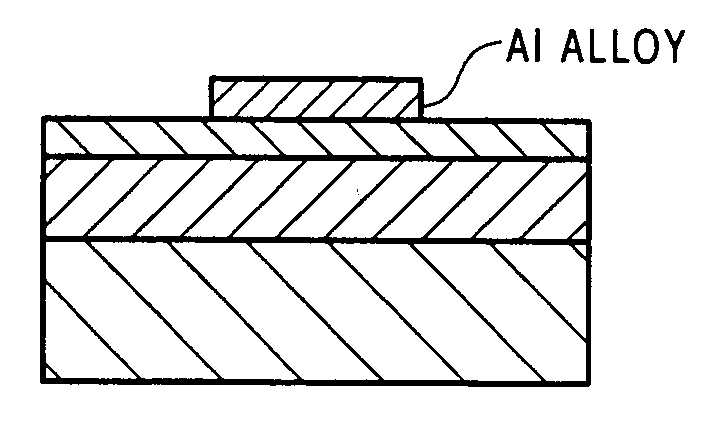

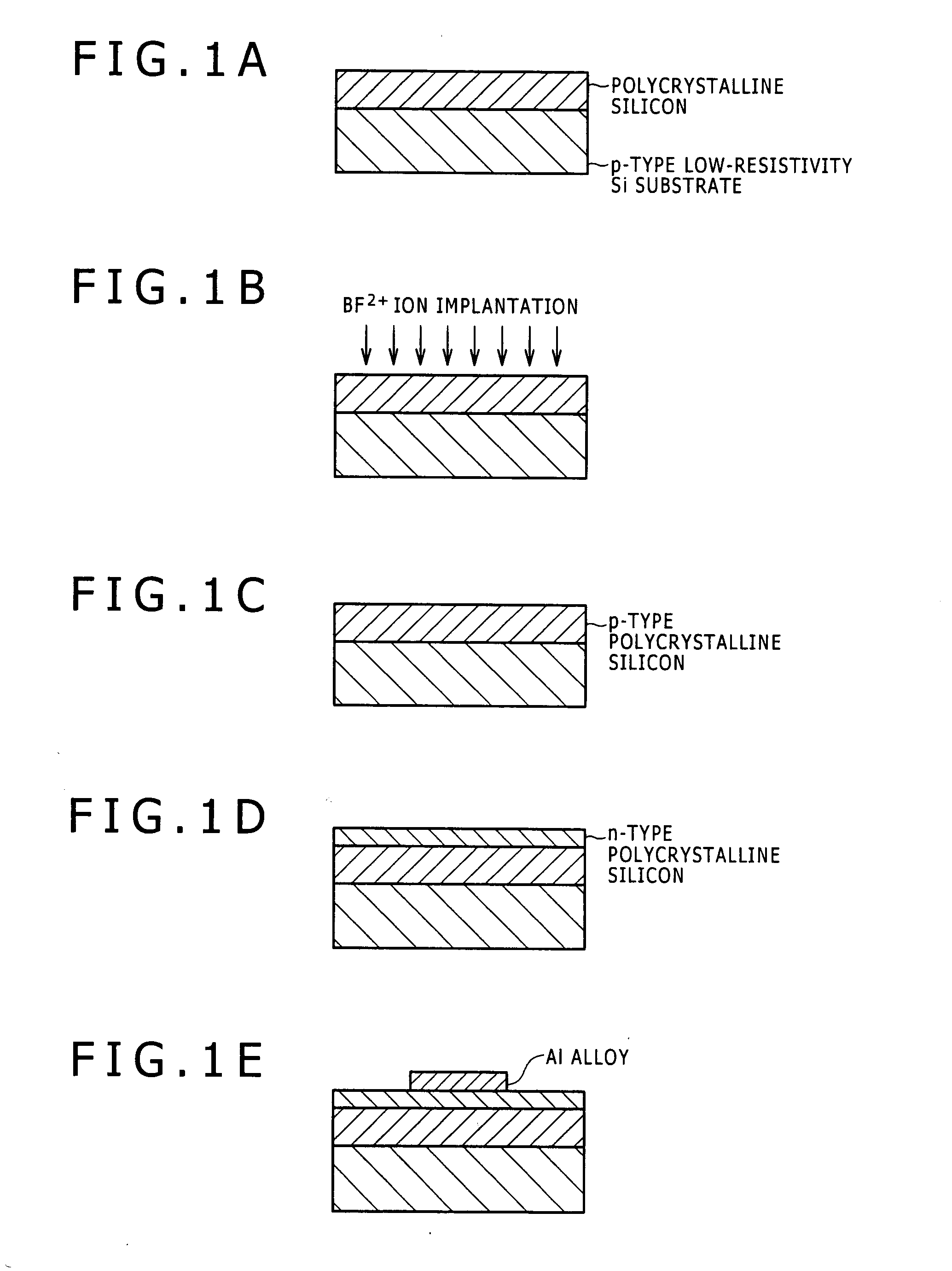

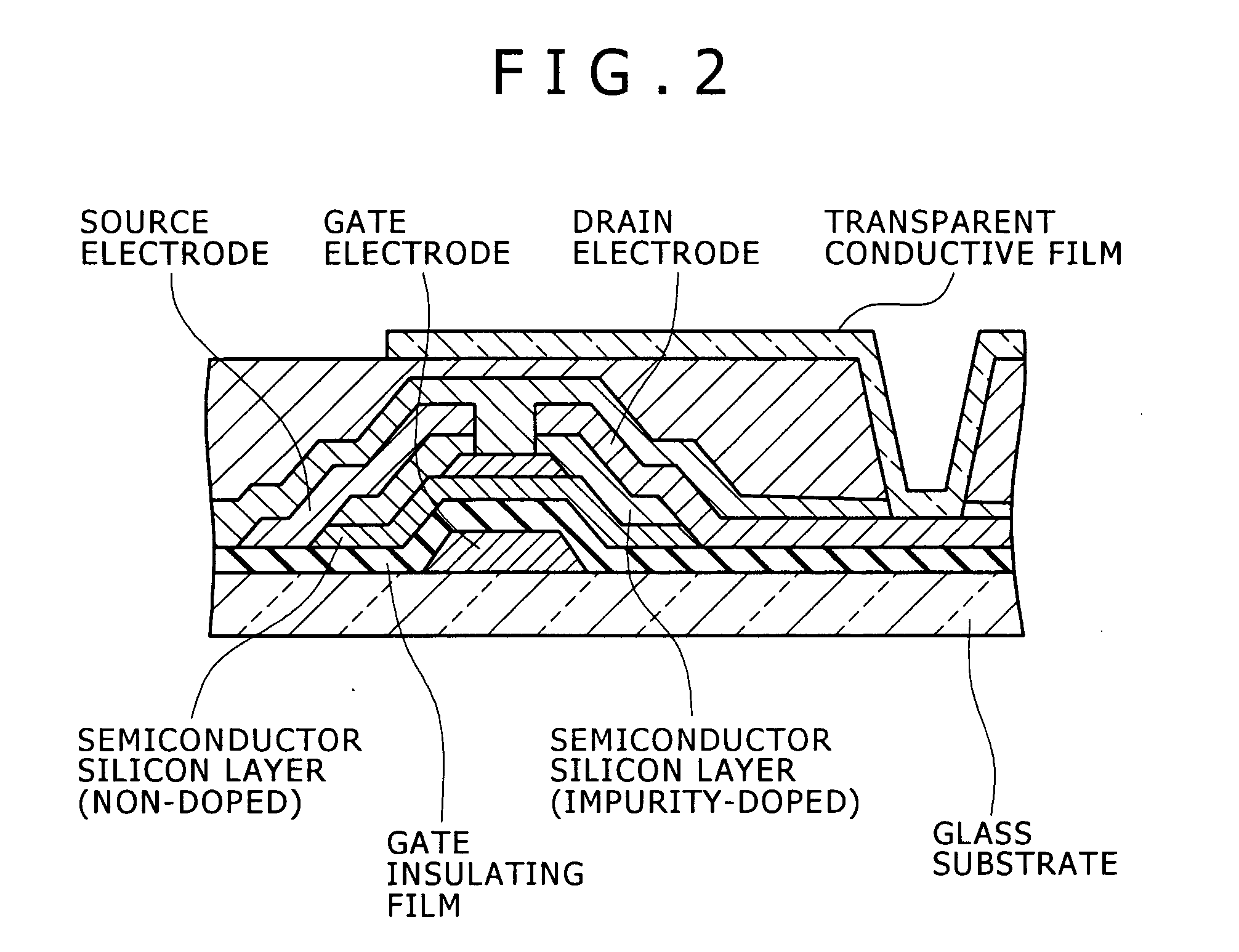

Disclosed are a thin film transistor substrate where barrier metal can be omitted to be formed between a semiconductor layer of a thin film transistor and source and drain electrodes (barrier metal need not be formed between the semiconductor layer of the thin film transistor and the source and drain electrodes), and a display device. (1) A thin film transistor substrate has a semiconductor layer of a thin film transistor, a source electrode, a drain electrode, and a transparent conductive film, wherein the substrate has a structure in which the source and drain electrodes are directly connected to the semiconductor layer of the thin film transistor, and the source and drain electrodes include an Al alloy thin film containing Ni of 0.1 to 6.0 atomic percent, La of 0.1 to 1.0 atomic percent, and Si of 0.1 to 1.5 atomic percent. (2) A display device has the thin film transistor substrate.

Owner:KOBE STEEL LTD

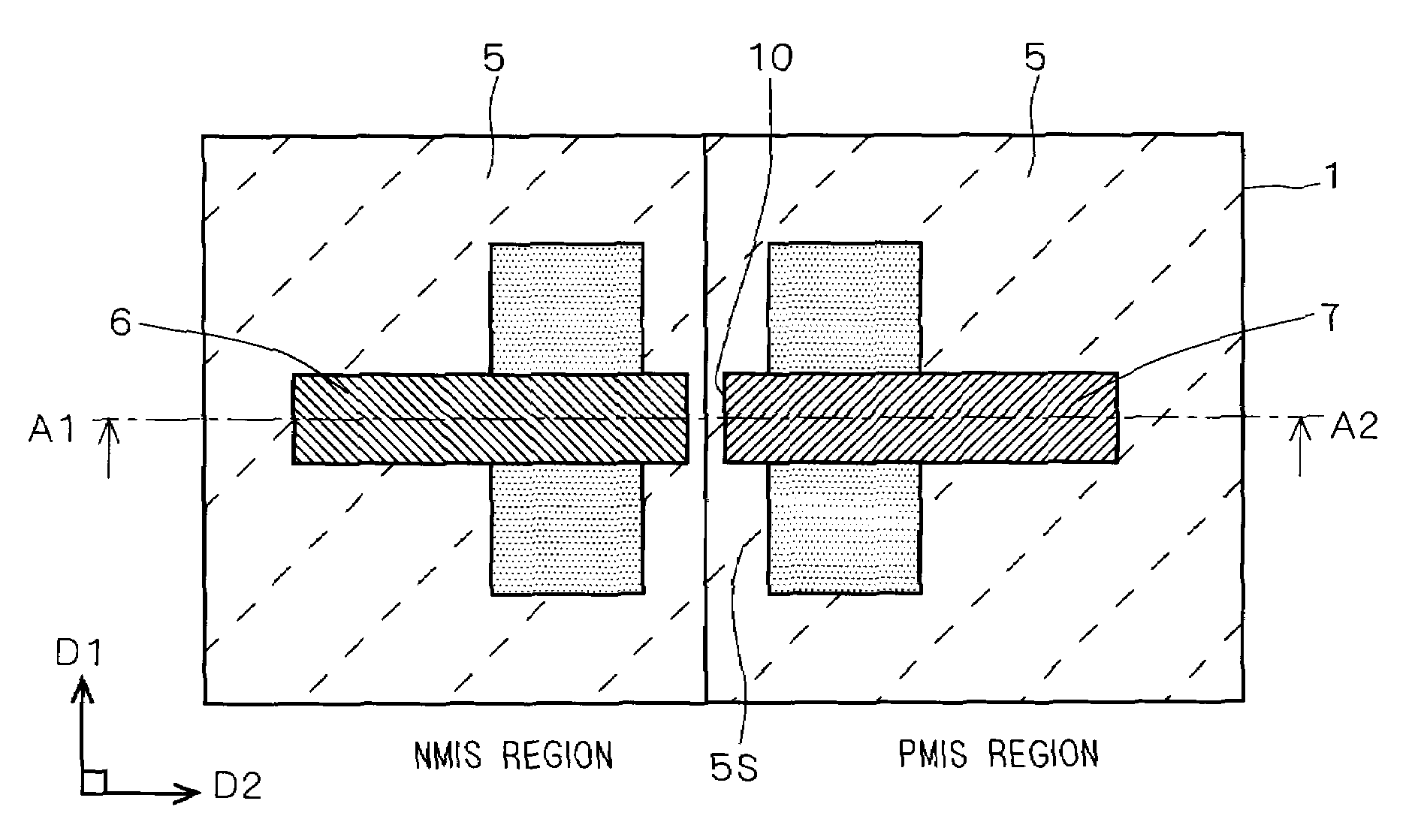

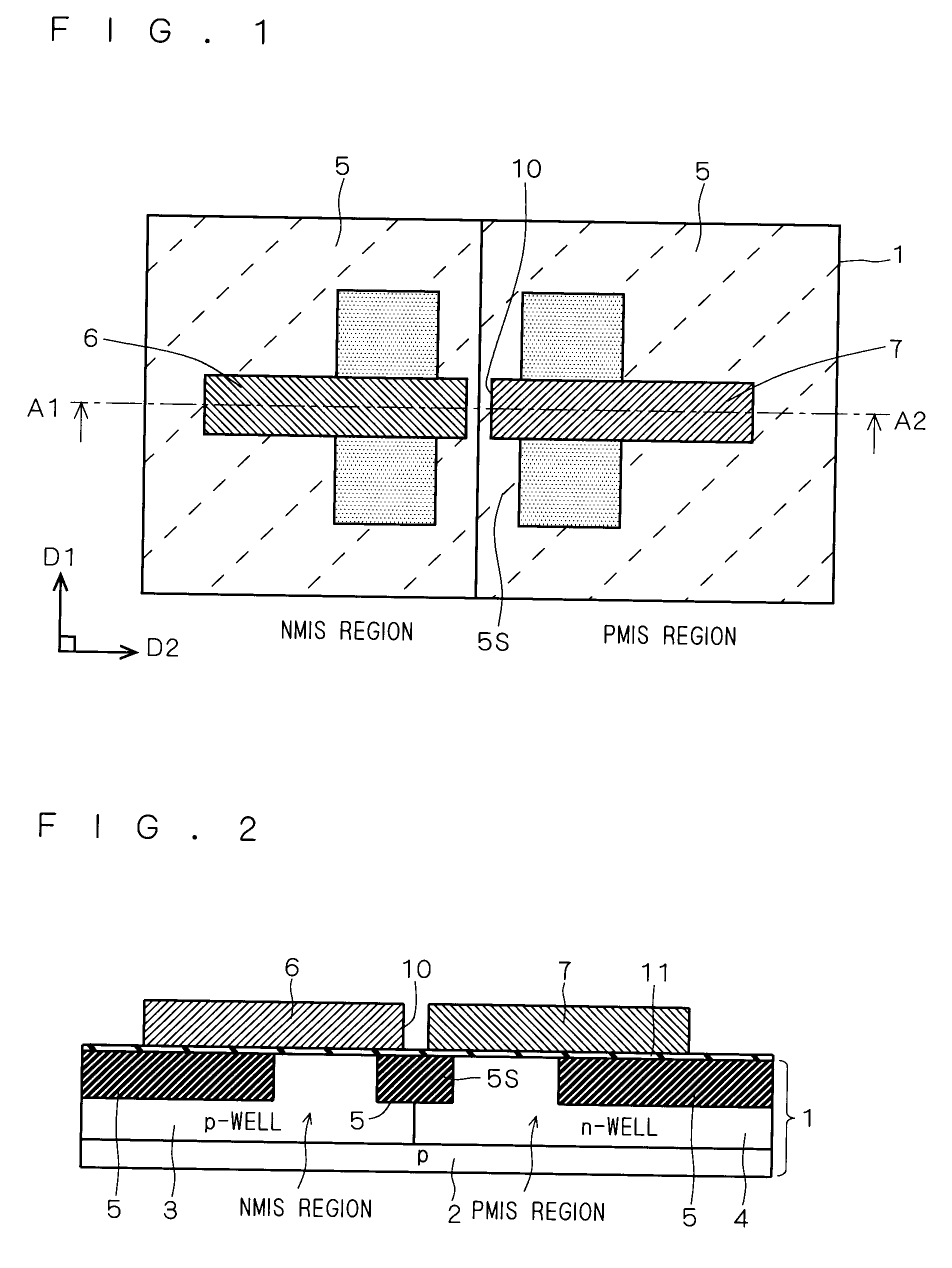

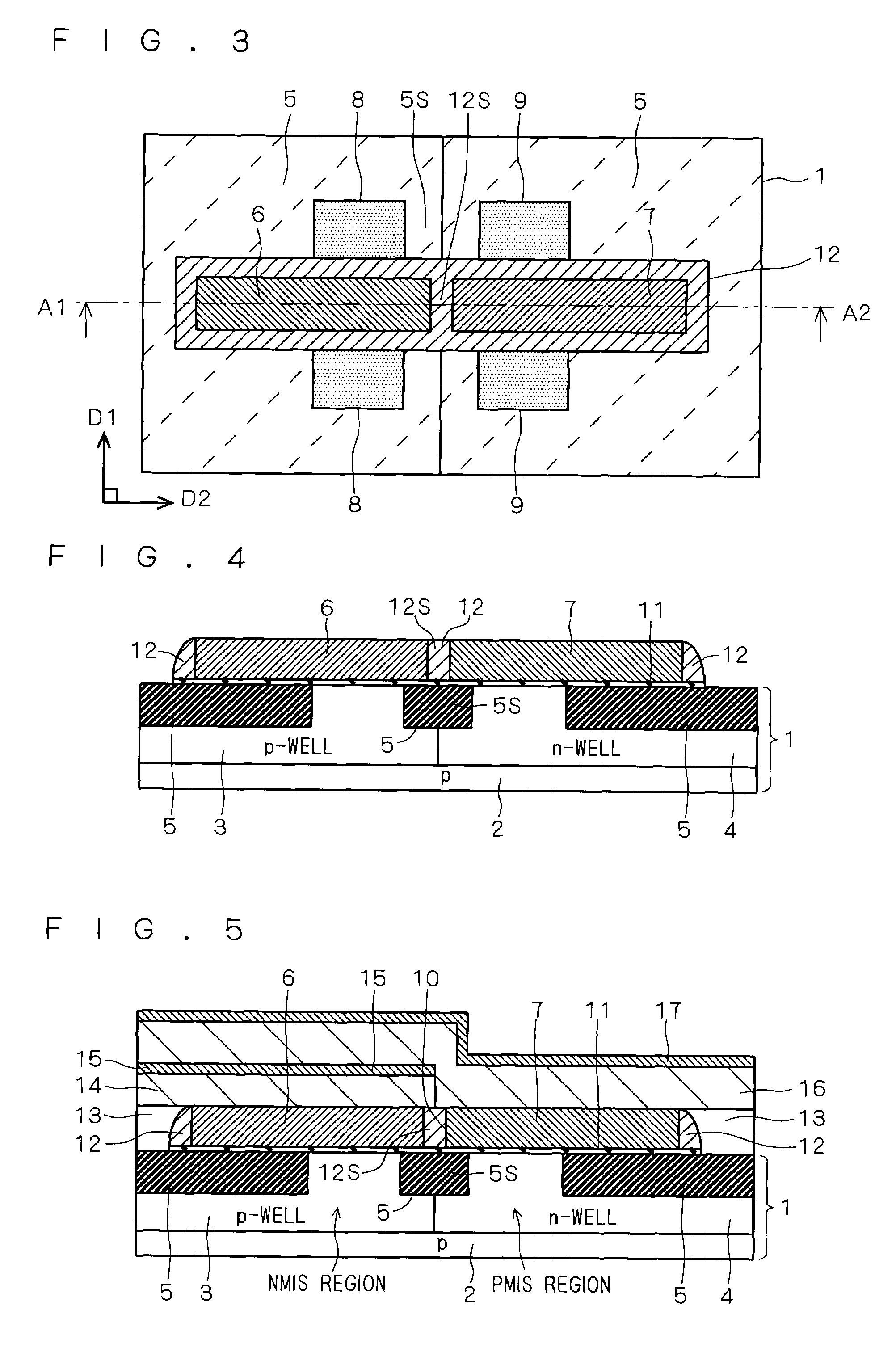

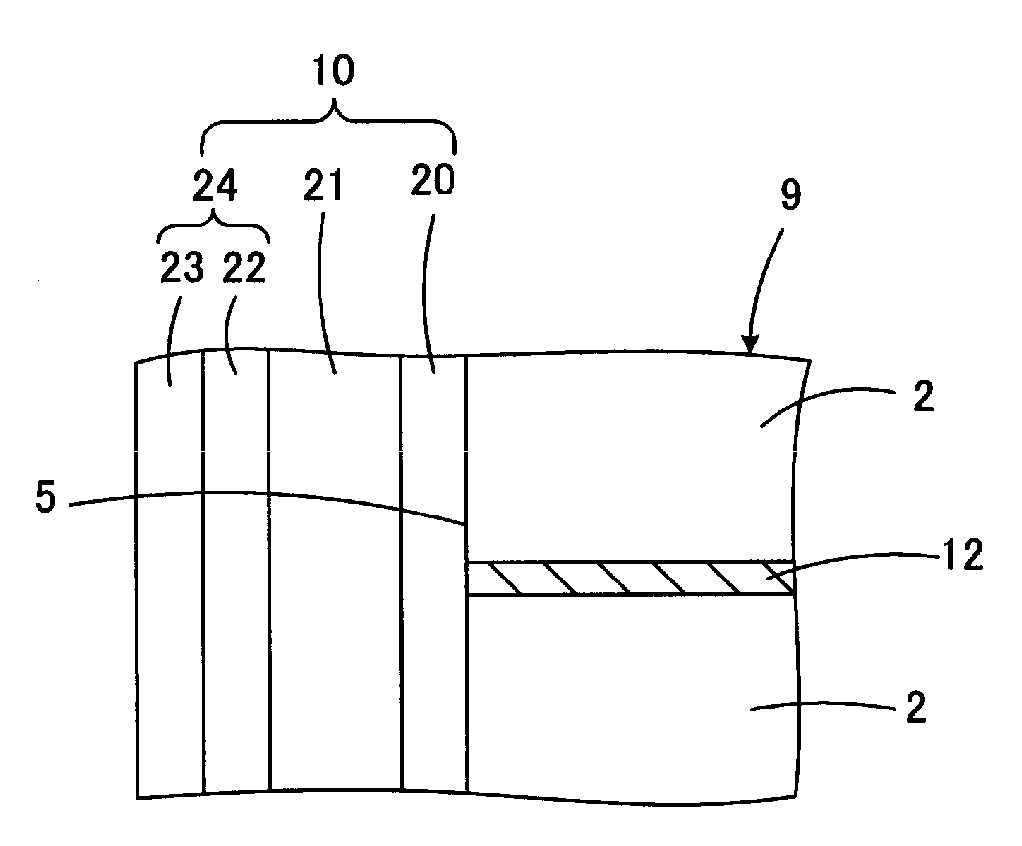

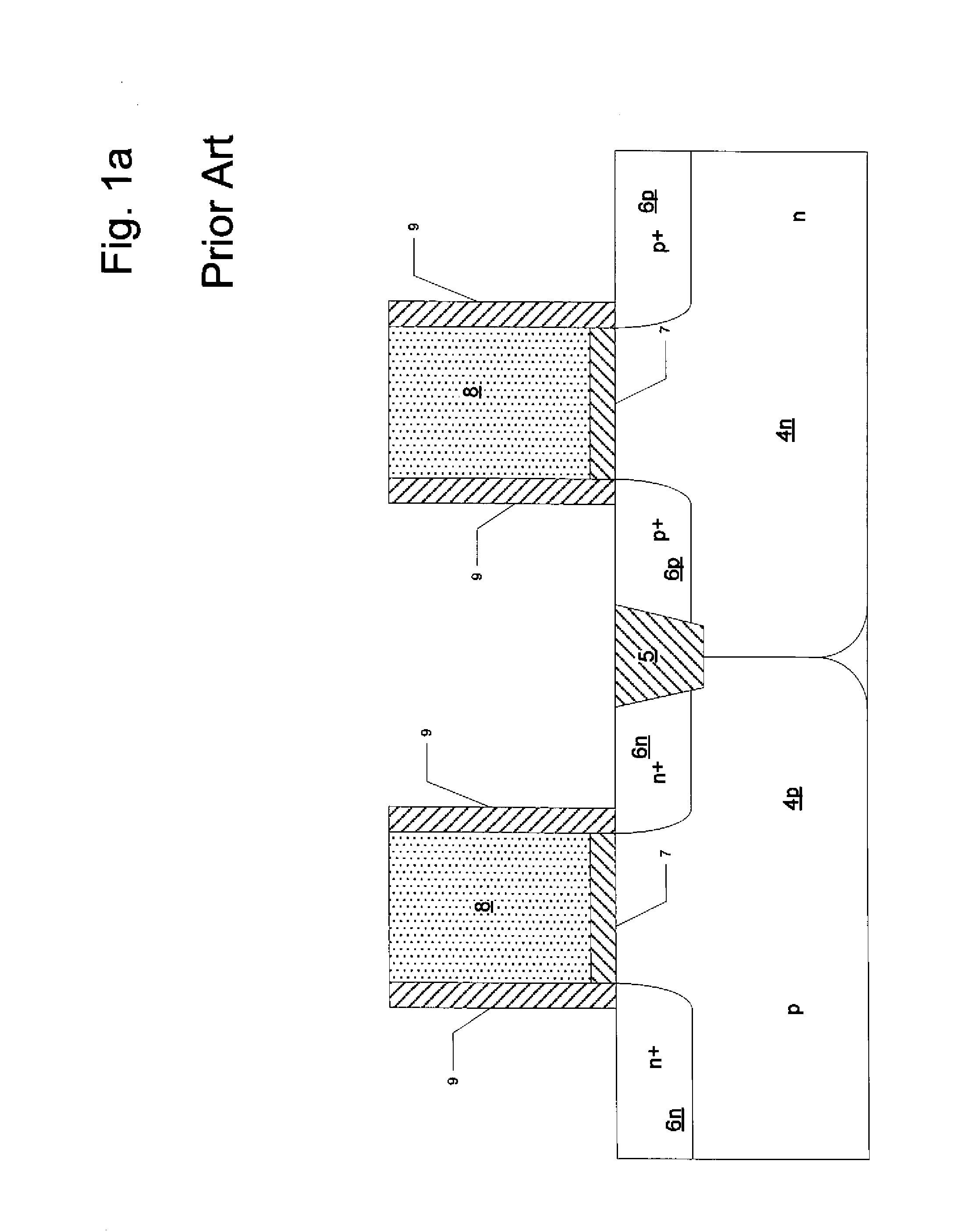

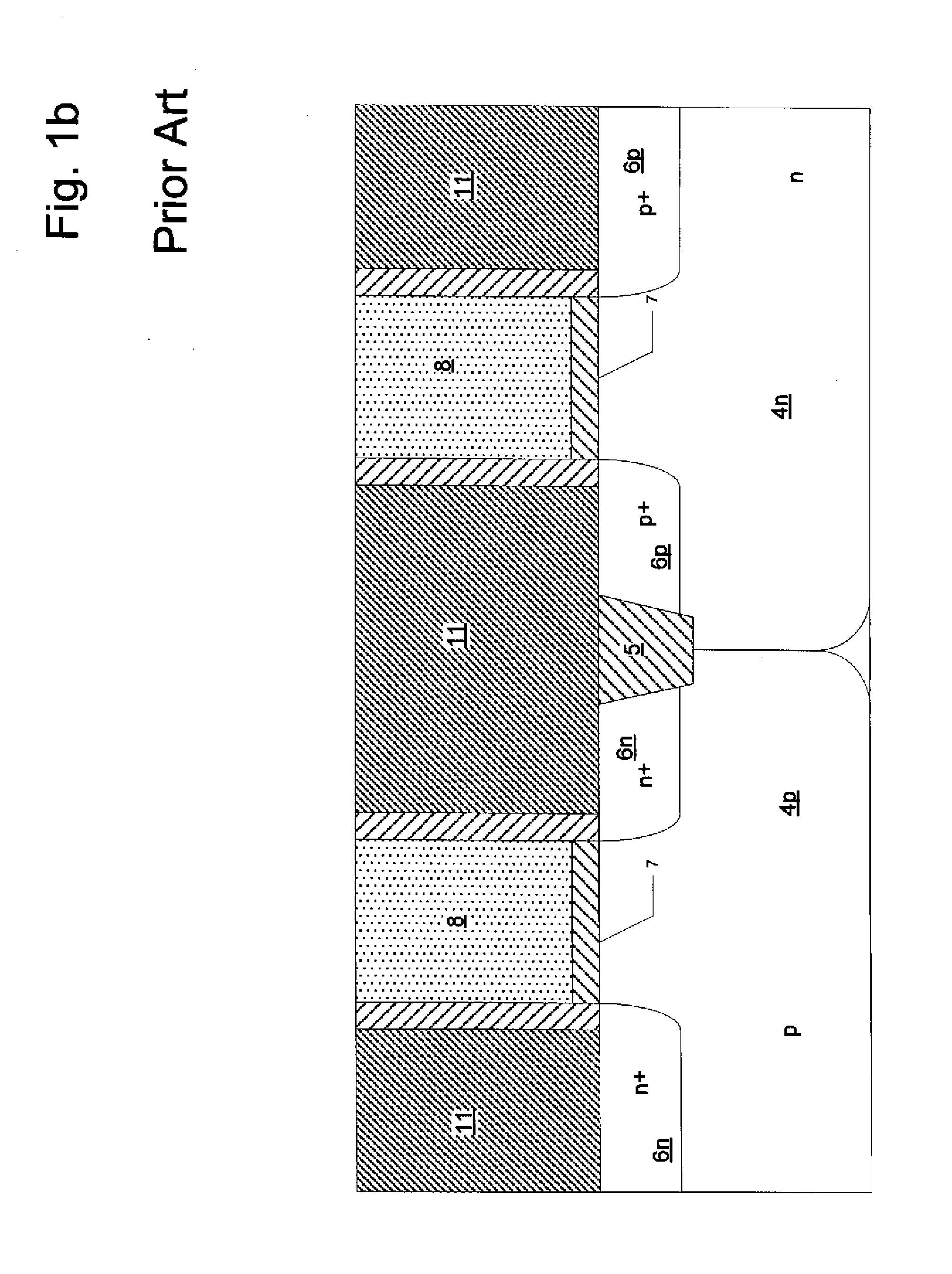

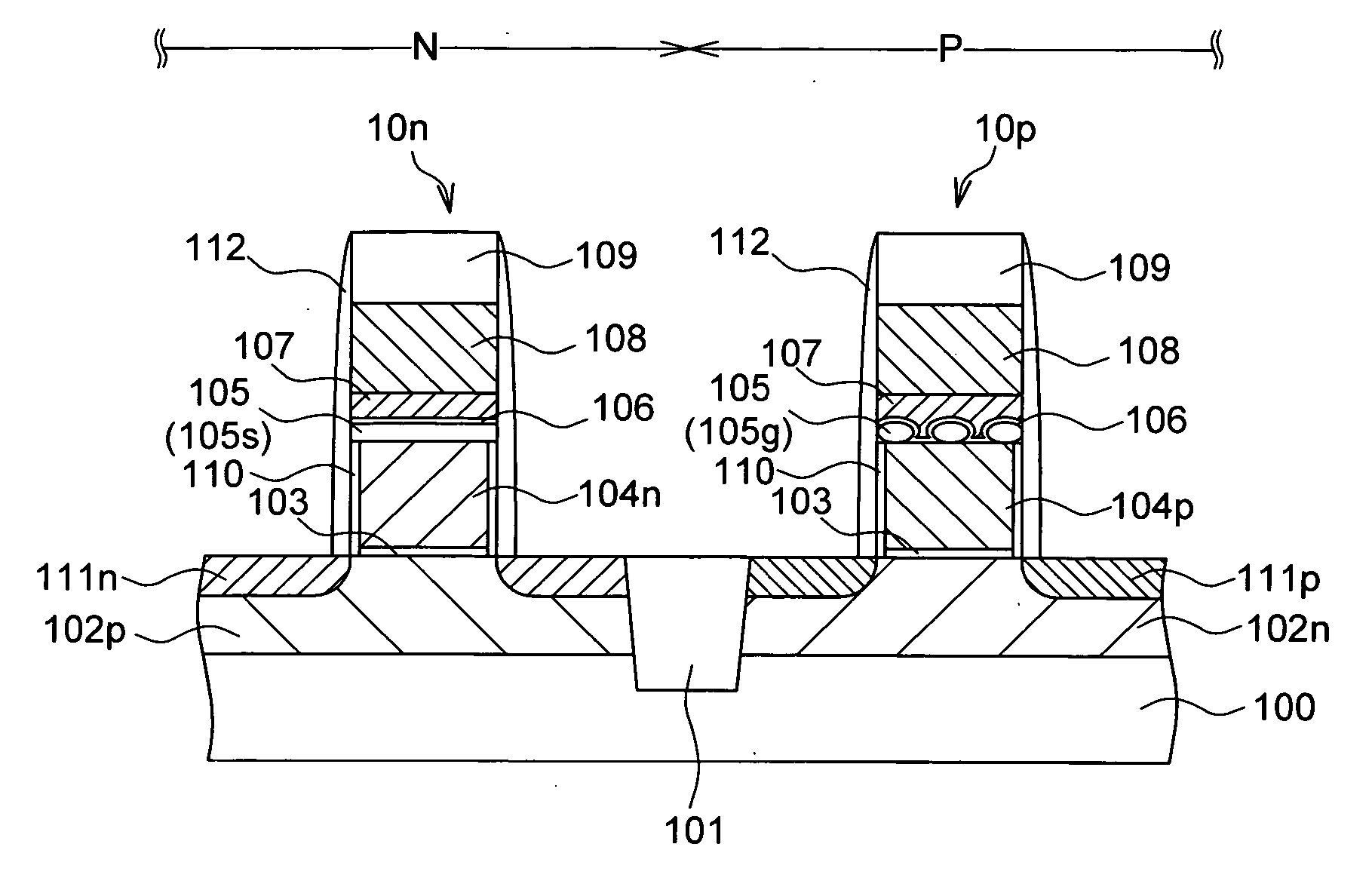

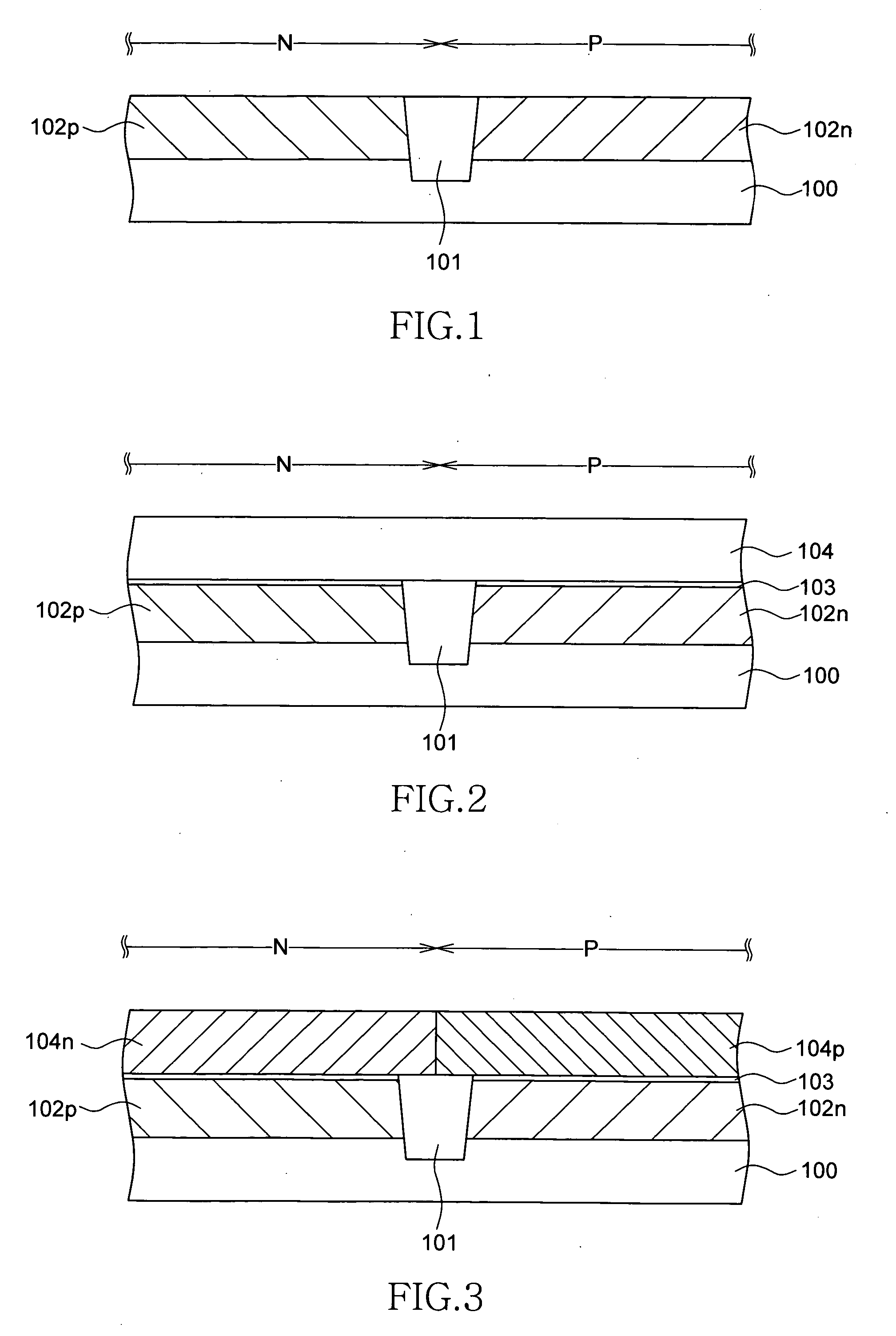

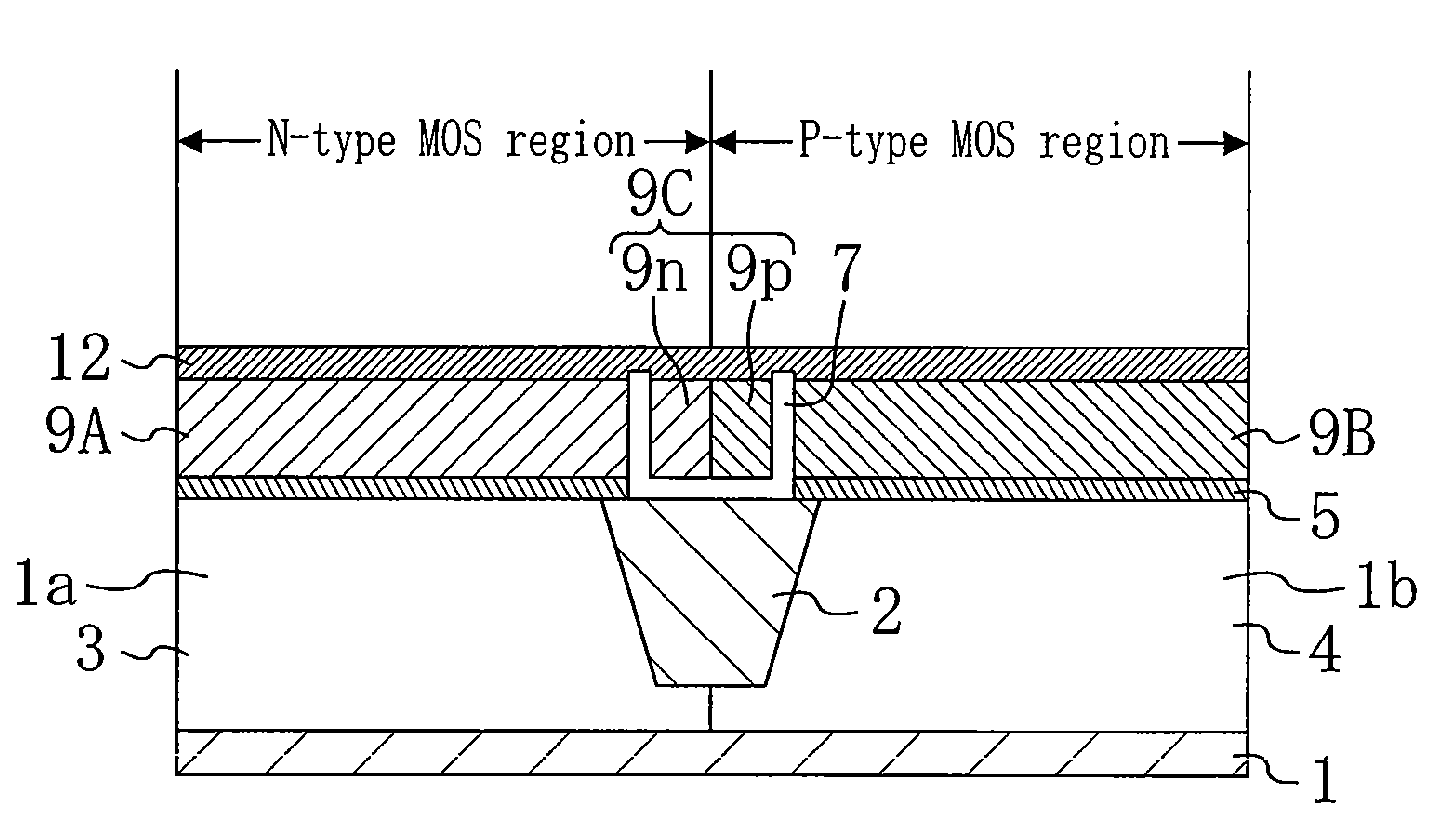

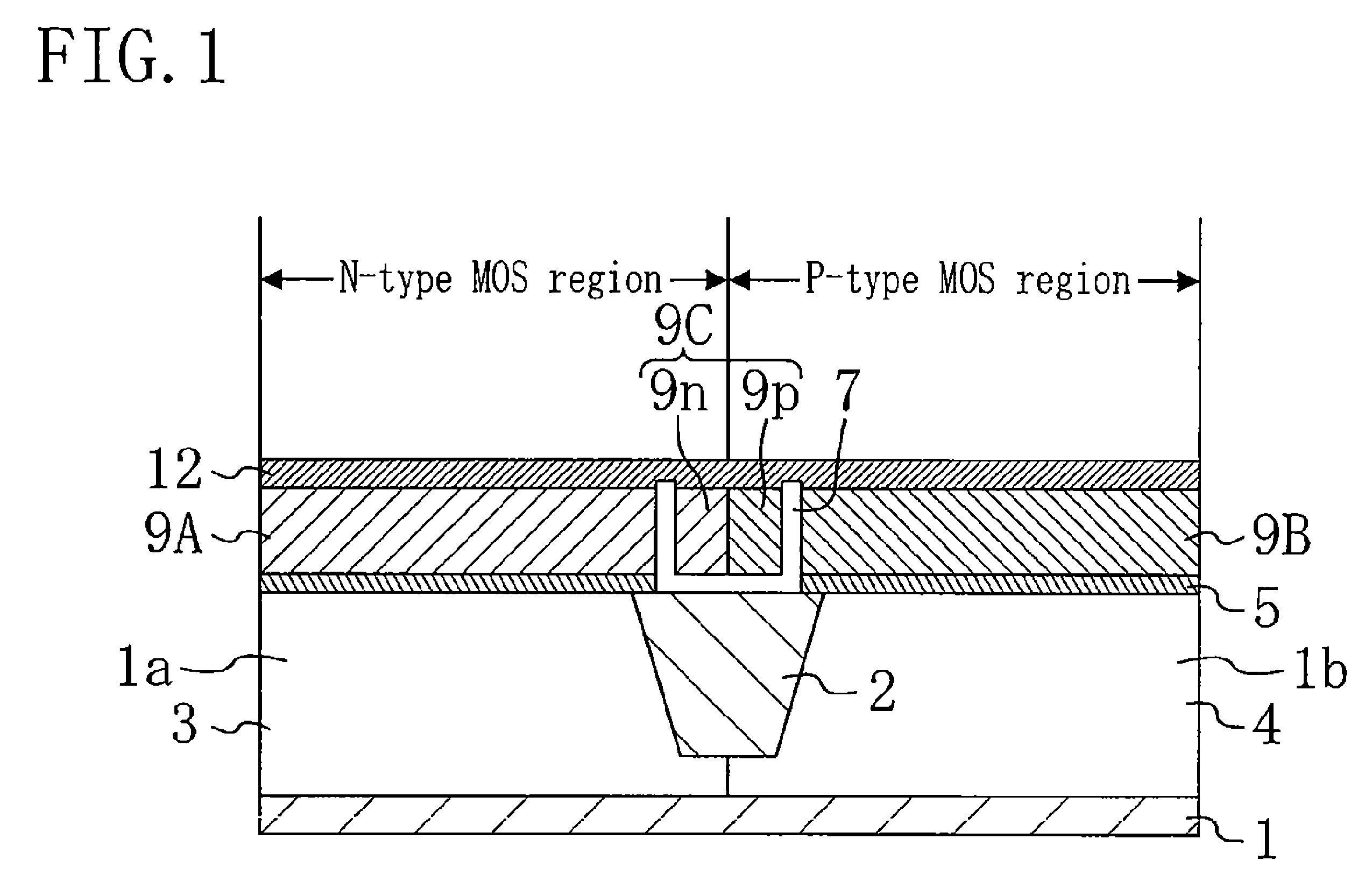

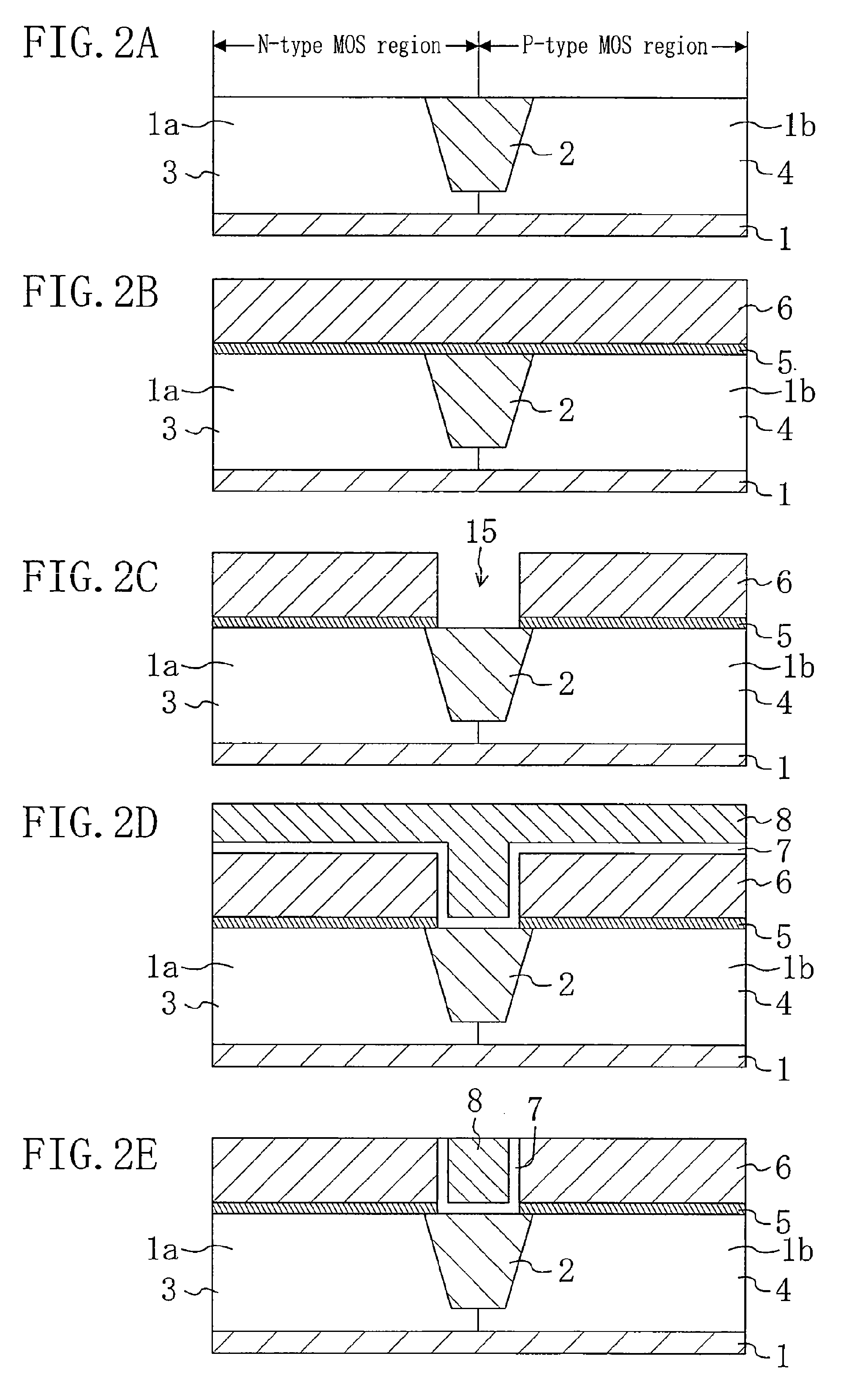

Semiconductor device including cmis transistor

InactiveUS20070284671A1Prevent interdiffusionReduce yieldTransistorSolid-state devicesSalicideMetal silicide

Gate electrodes made of polysilicon film are isolated and face each other by way of a side wall spacer portion that fills a gap formed above an isolation insulating film at the boundary of NMIS region and PMIS region. A first metal film is formed on one of the gate electrodes, and an inhomogeneous second metal film is formed on the other of the gate electrodes. The both gate electrodes become inhomogeneous metal silicide gates through the promotion of silicide reaction by heat treatment. The mutual diffusion of metal atoms from the metal film to the gate electrode is suppressed by the interposition of the side wall spacer portion being an insulating film.

Owner:RENESAS TECH CORP

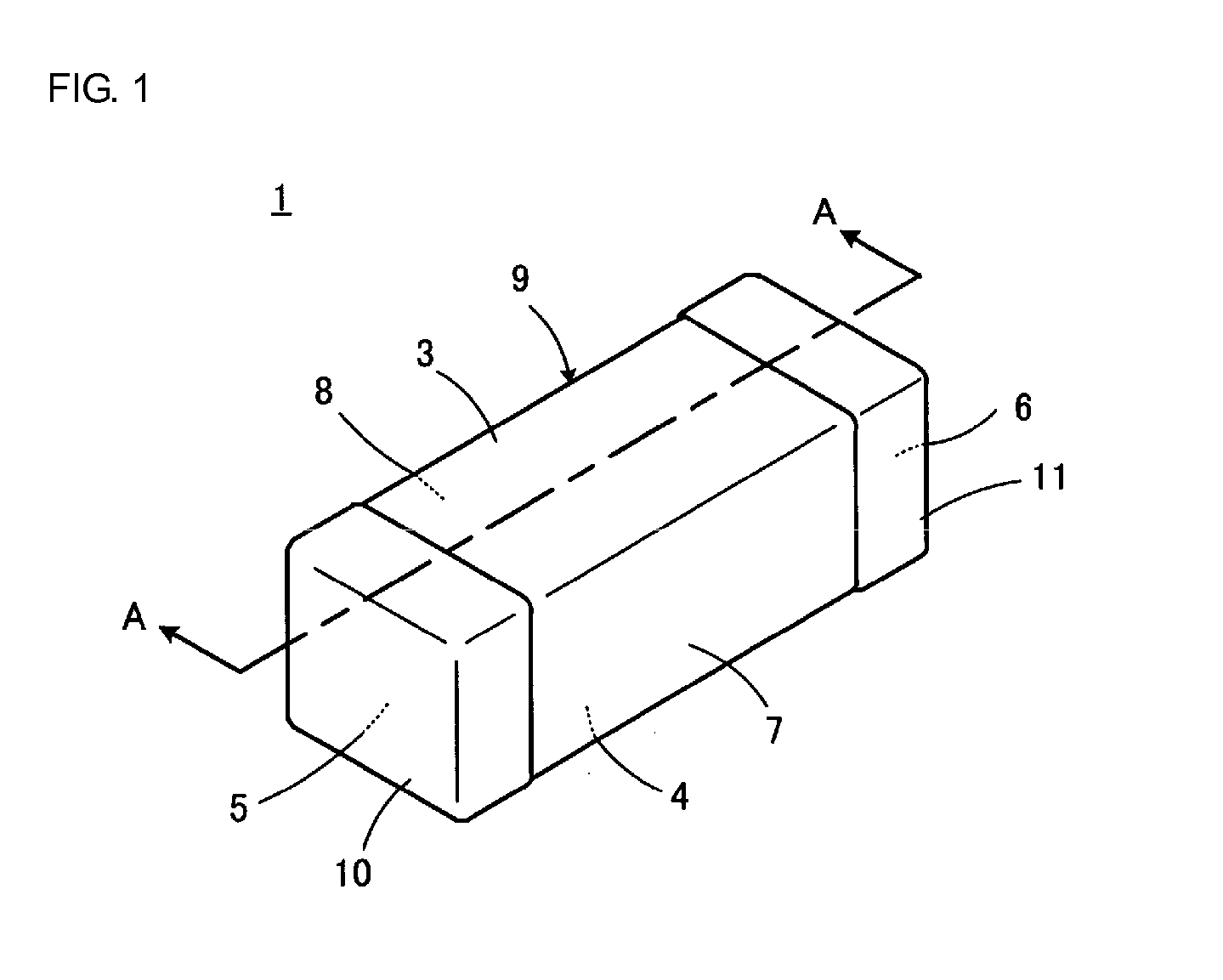

Multilayer ceramic electronic component and method for making the same

ActiveUS20090310277A1Prevent penetrationPrevent interdiffusionFixed capacitor electrodesFixed capacitor dielectricElectrical conductorElectronic component

A multilayer ceramic electronic component includes a ceramic body including a plurality of ceramic layers, the ceramic body having a first main surface and a second main surface and a plurality of side surfaces that connect the first main surface to the second main surface, an internal conductor including nickel, the internal conductor being disposed in the ceramic body and having an exposed portion exposed at least one of the side surfaces, and an external terminal electrode disposed on at least one of the side surfaces of the ceramic body, the external terminal electrode being electrically connected to the internal conductor. The external terminal electrode includes a first conductive layer including a Sn—Cu—Ni intermetallic compound, the first conductive layer covering the exposed portion of the internal conductor at least one of the side surfaces of the ceramic body.

Owner:MURATA MFG CO LTD

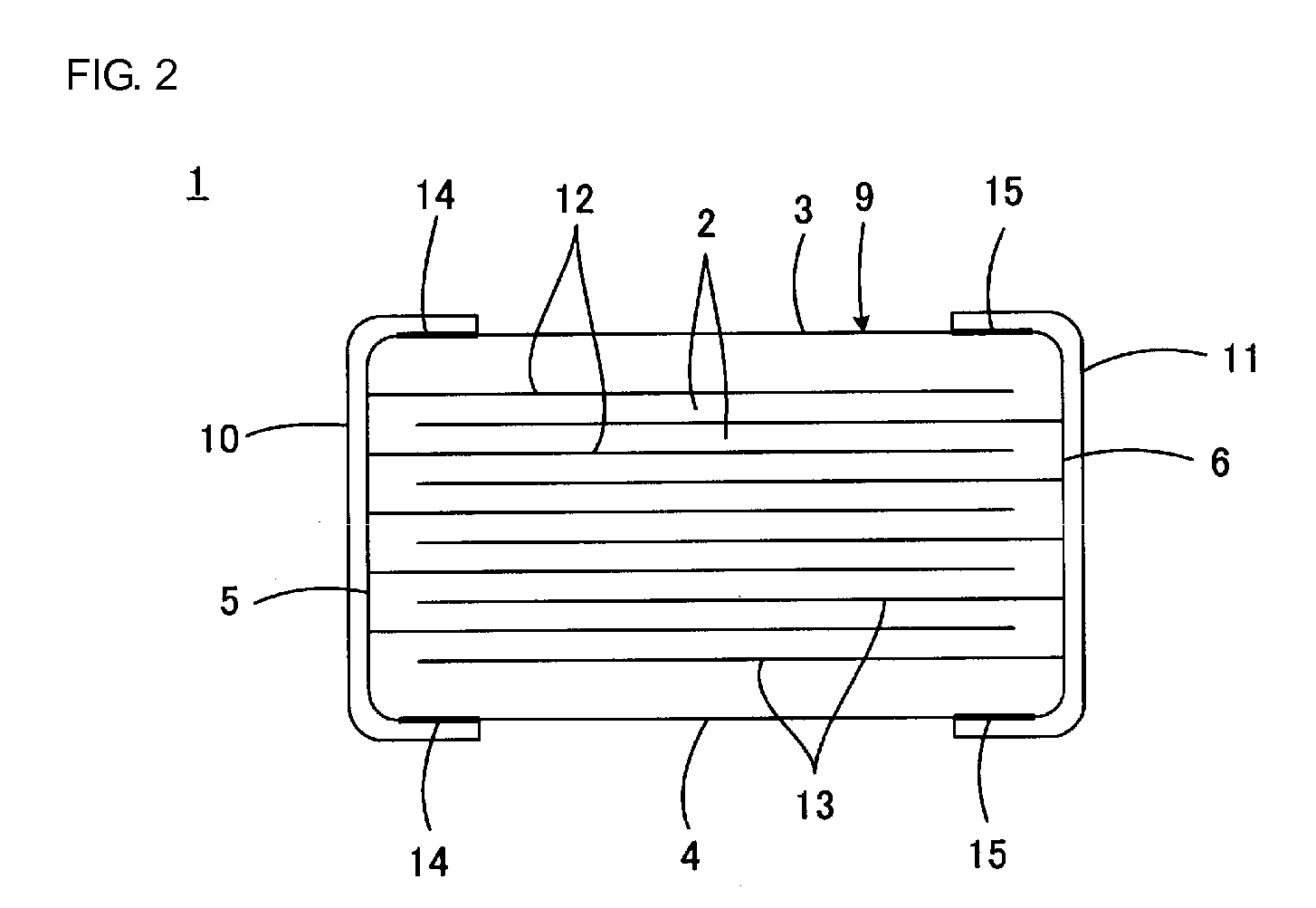

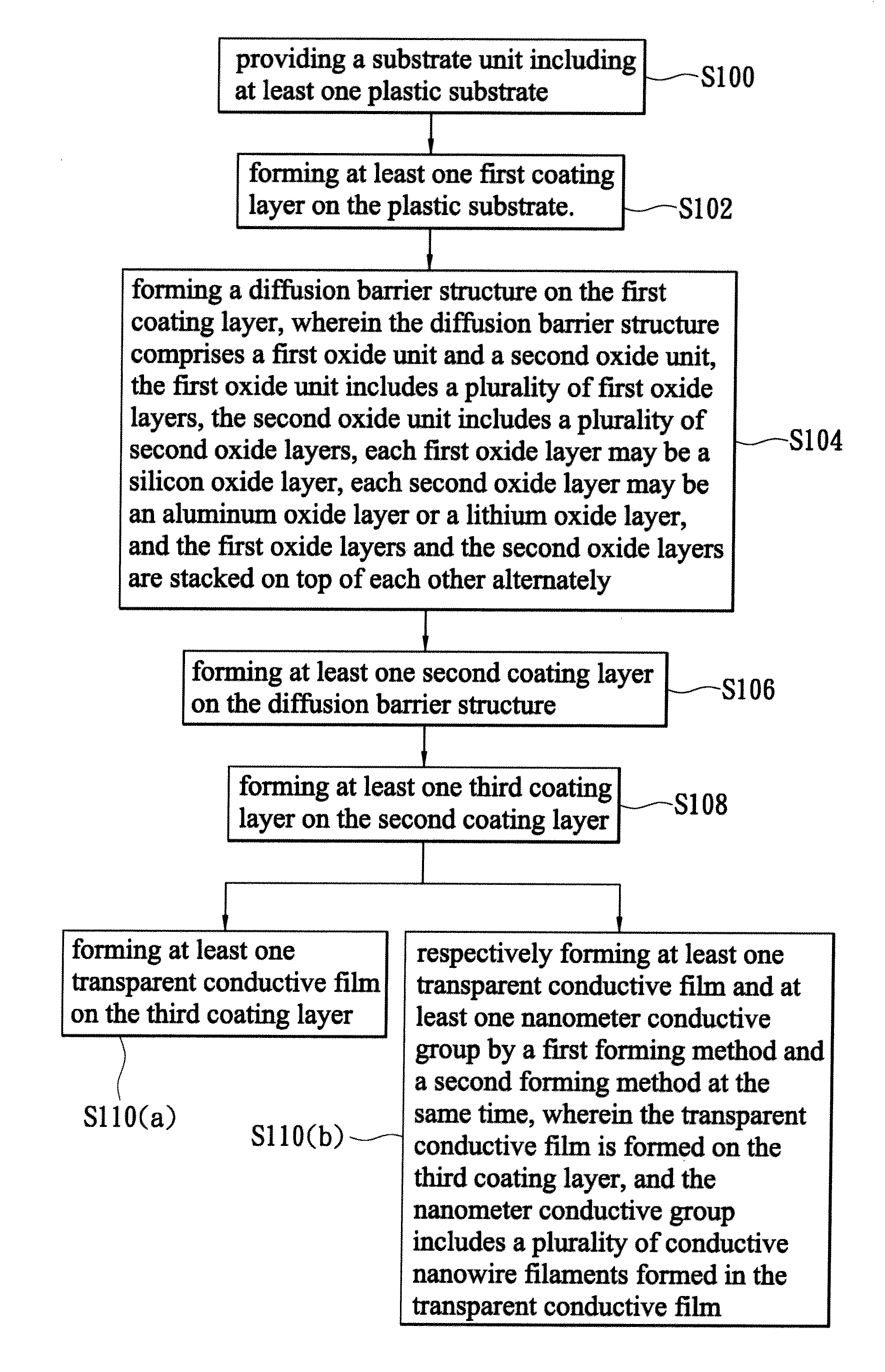

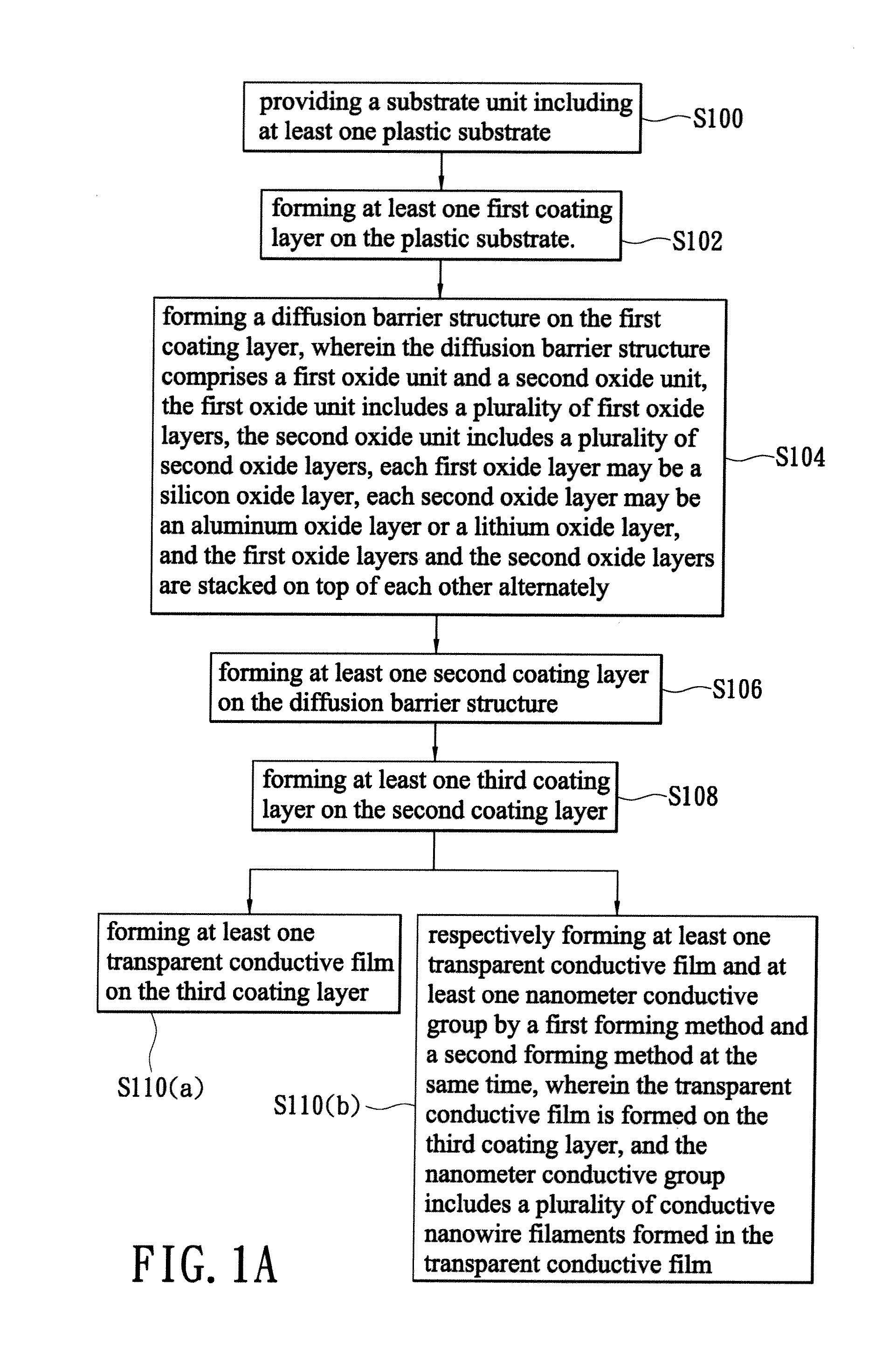

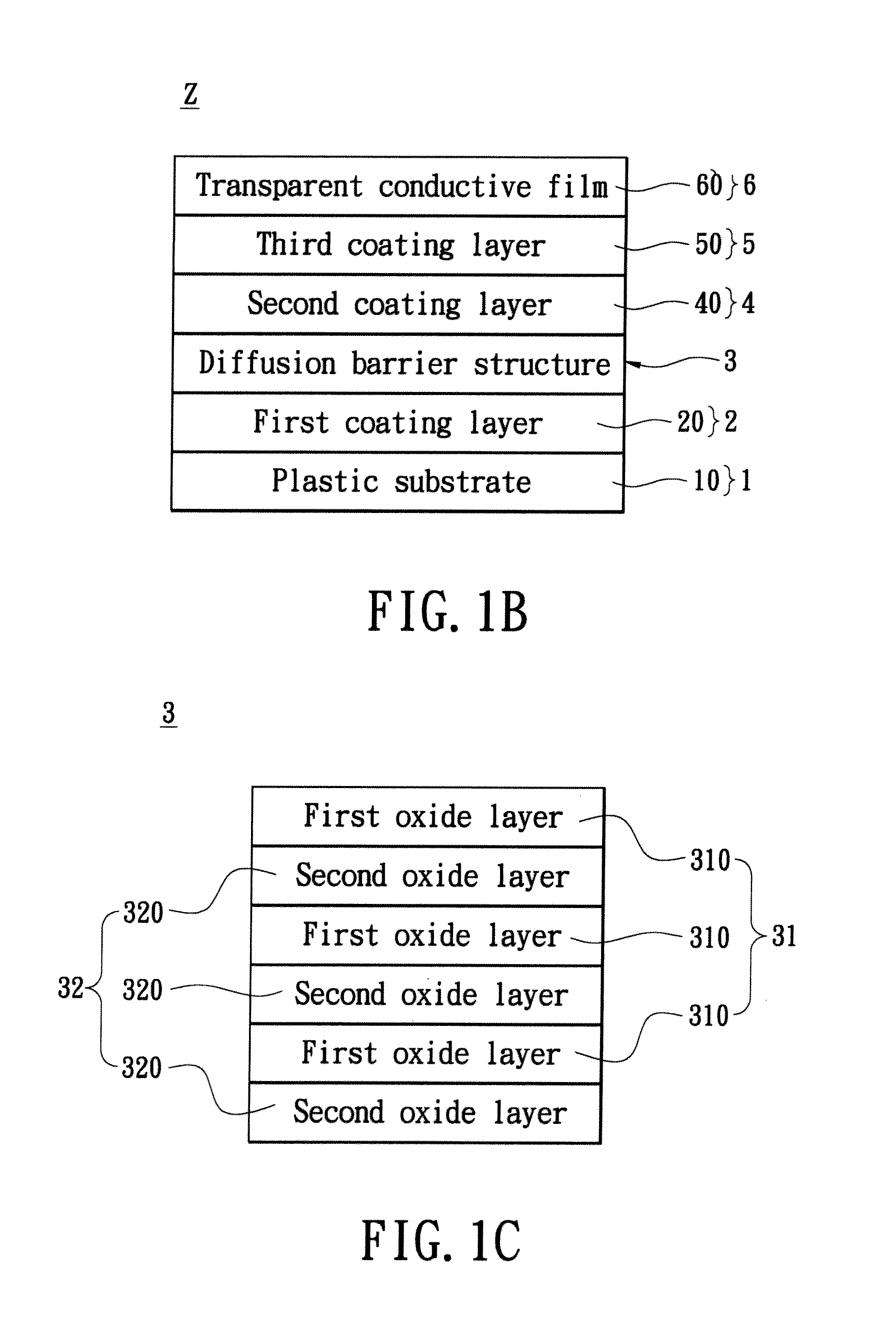

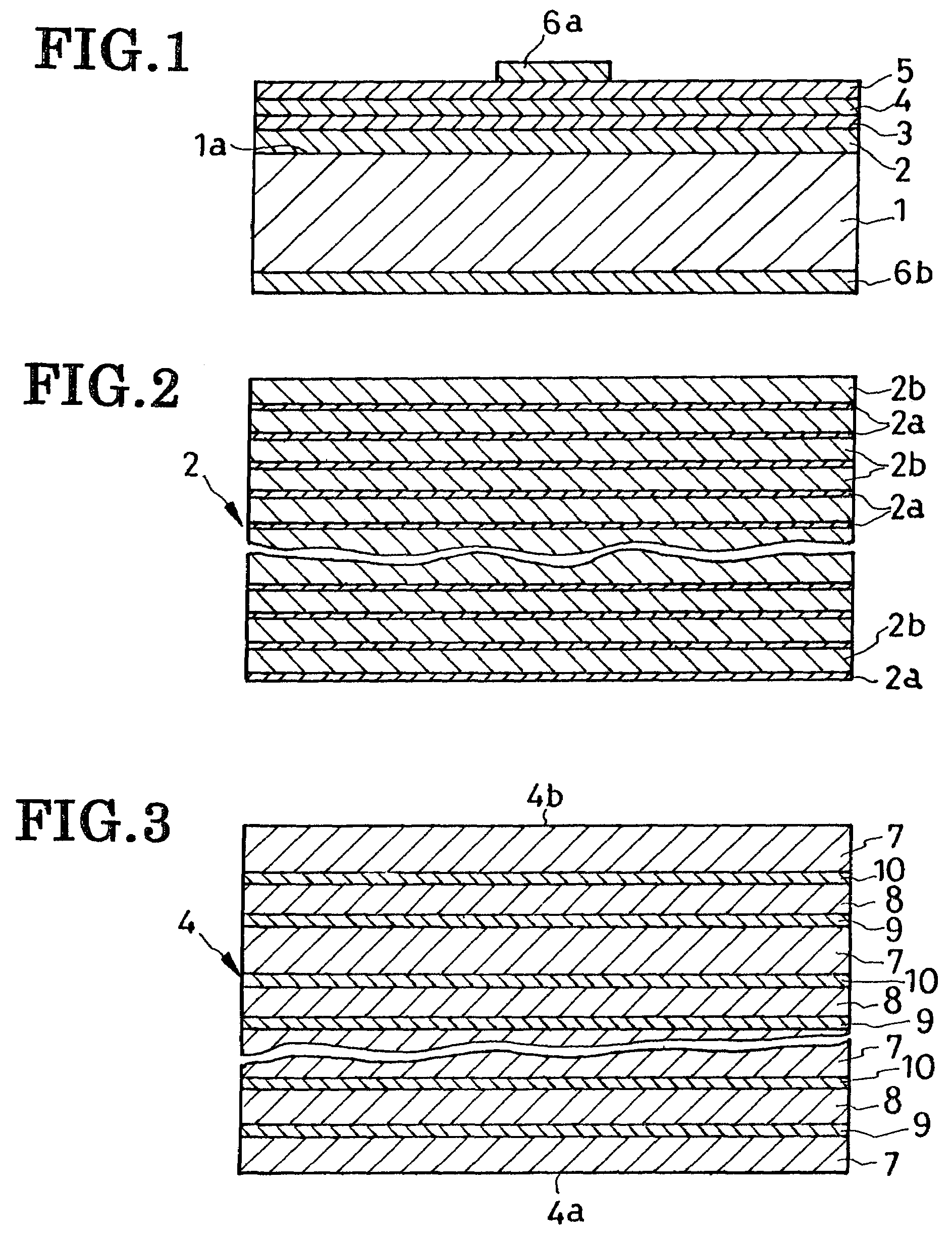

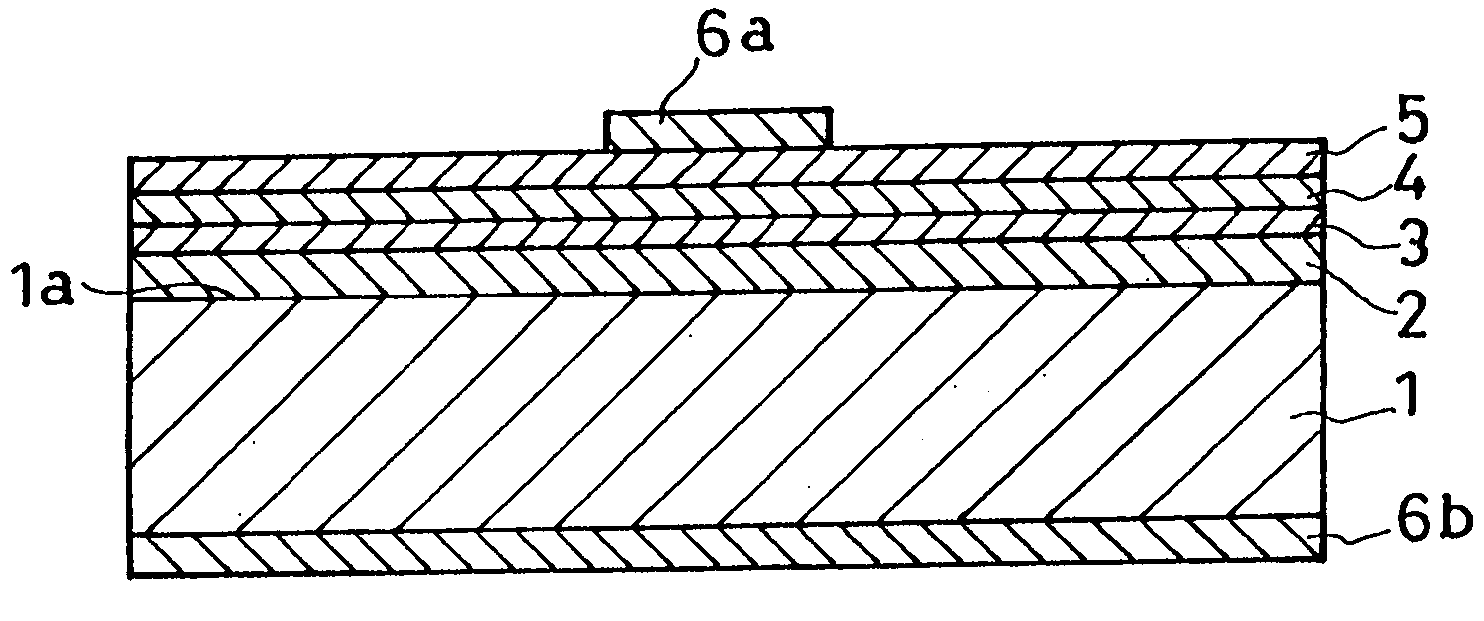

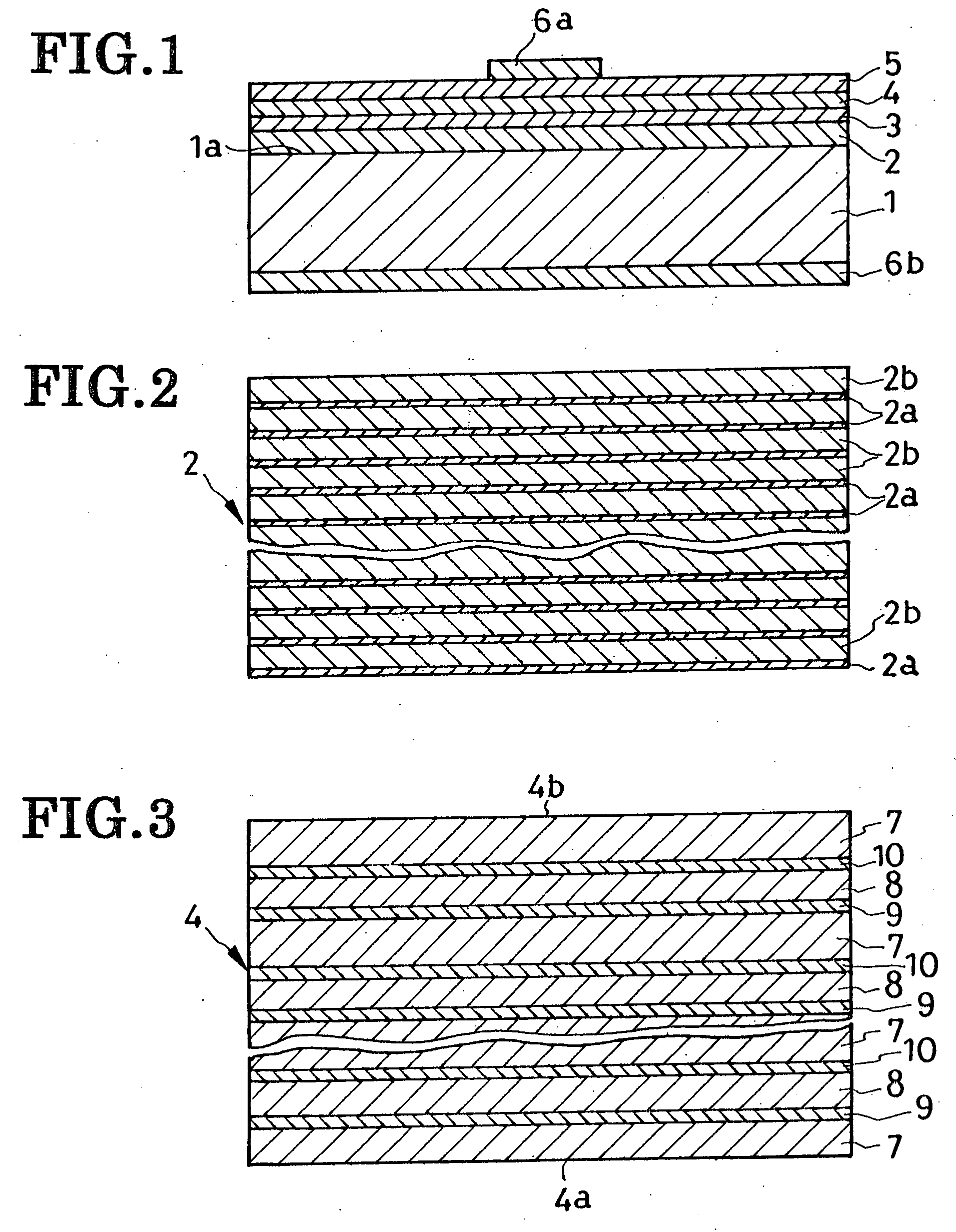

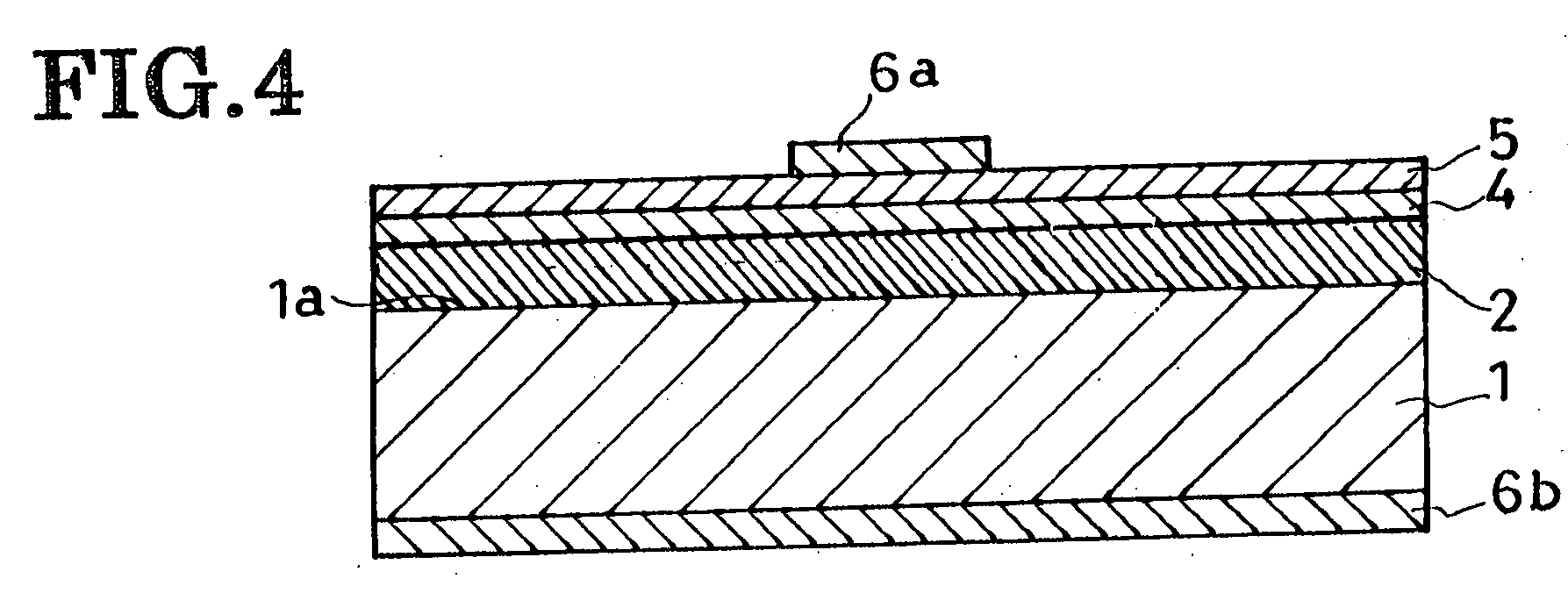

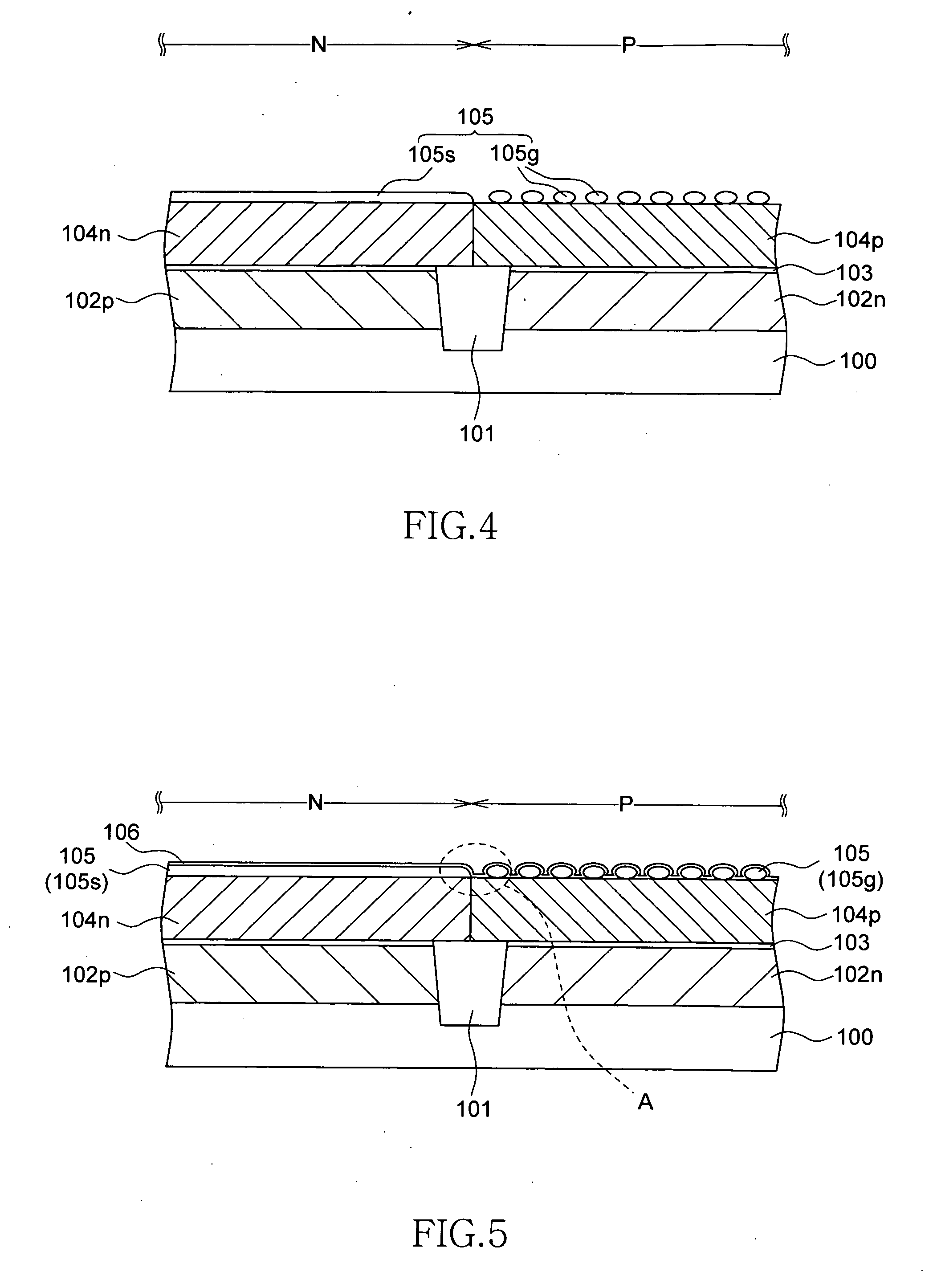

Diffusion barrier structure, transparent conductive structure and method for making the same

InactiveUS20120156458A1High crystallinityLower the resistance valueMaterial nanotechnologyLiquid surface applicatorsTransparent conducting filmDiffusion barrier

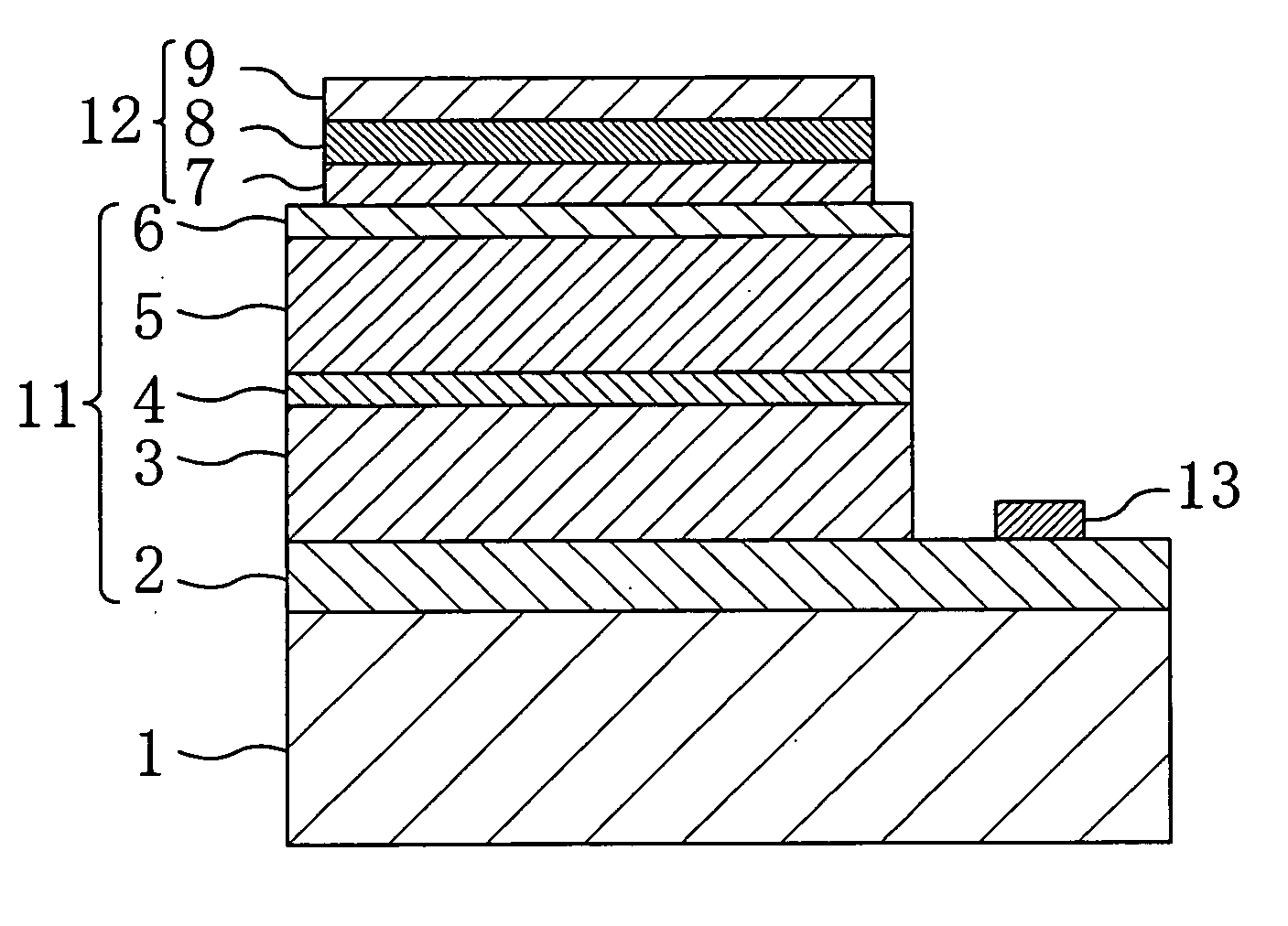

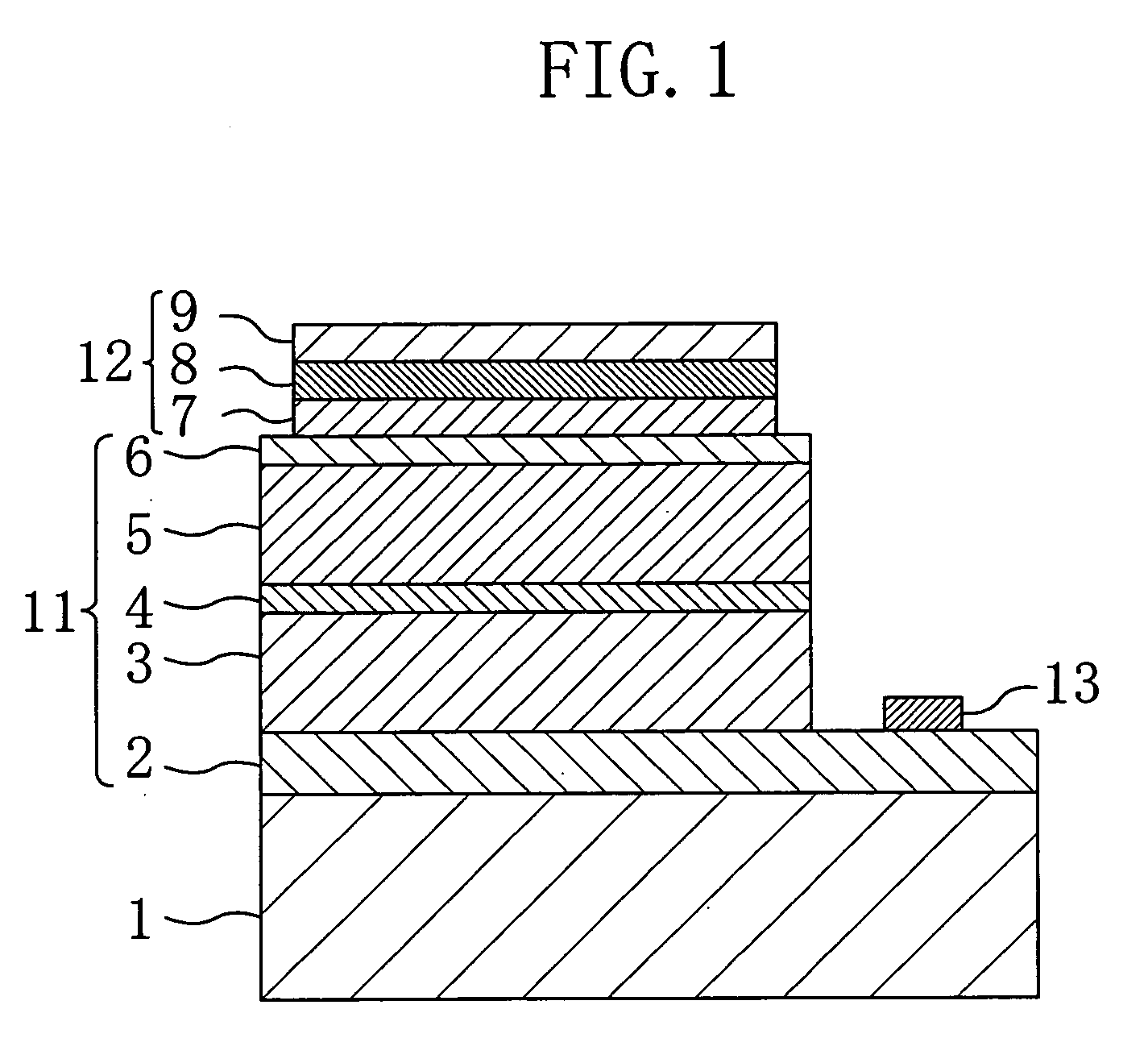

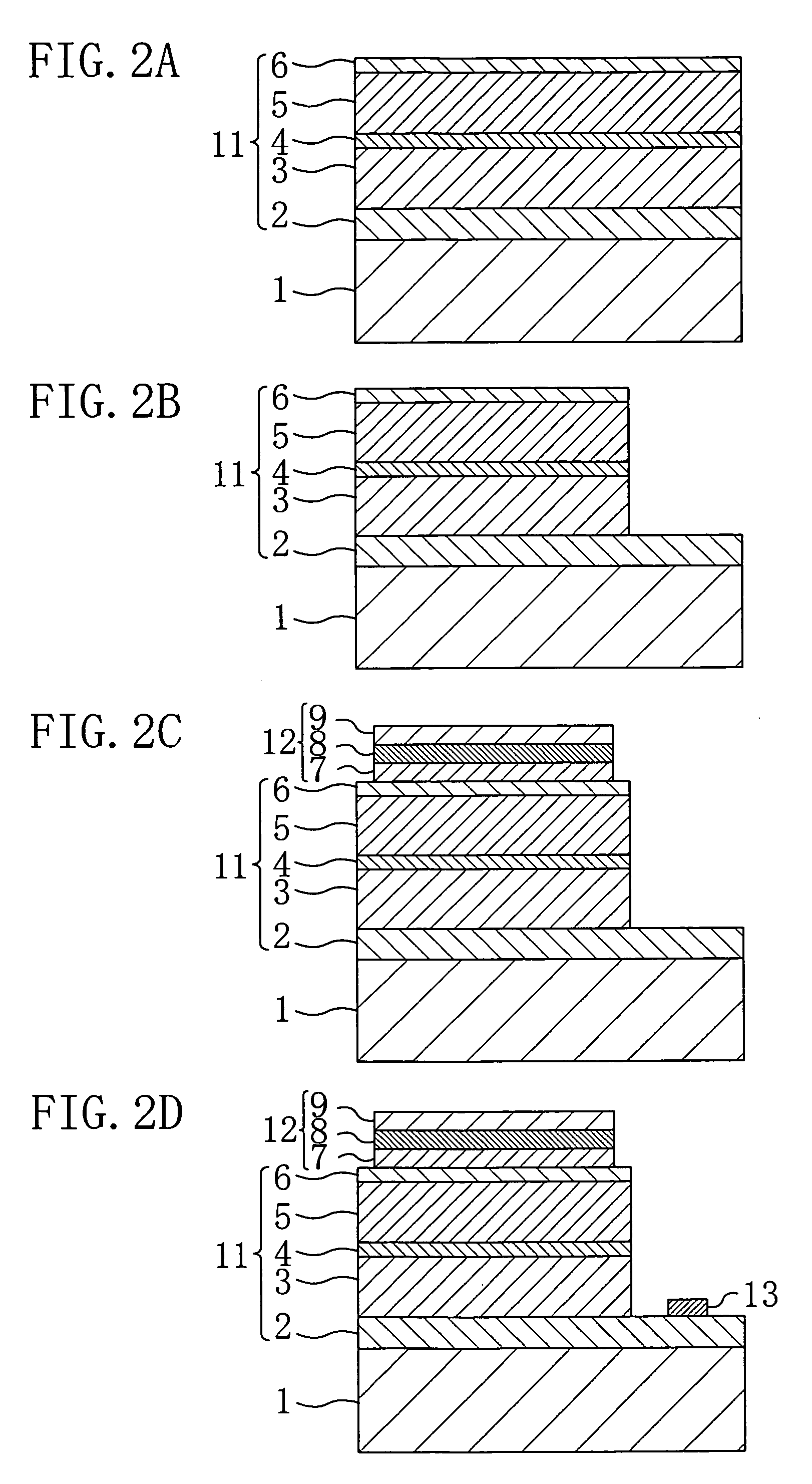

A transparent conductive structure includes a substrate unit, a first coating unit, a diffusion barrier structure, a second coating unit, a third coating unit and a conductive unit. The substrate unit includes a plastic substrate. The first coating unit includes a first coating layer formed on the plastic substrate. The diffusion barrier structure is formed on the first coating layer. The diffusion barrier structure includes a first oxide unit having a plurality of first oxide layers and a second oxide unit having a plurality of second oxide layers. The first oxide layers and the second oxide layers are stacked on top of each other alternately. The second coating unit includes a second coating layer formed on the diffusion barrier structure. The third coating unit includes a third coating layer formed on the second coating layer. The conductive unit includes a transparent conductive film formed on the third coating layer.

Owner:INNOVATION & INFINITY GLOBAL

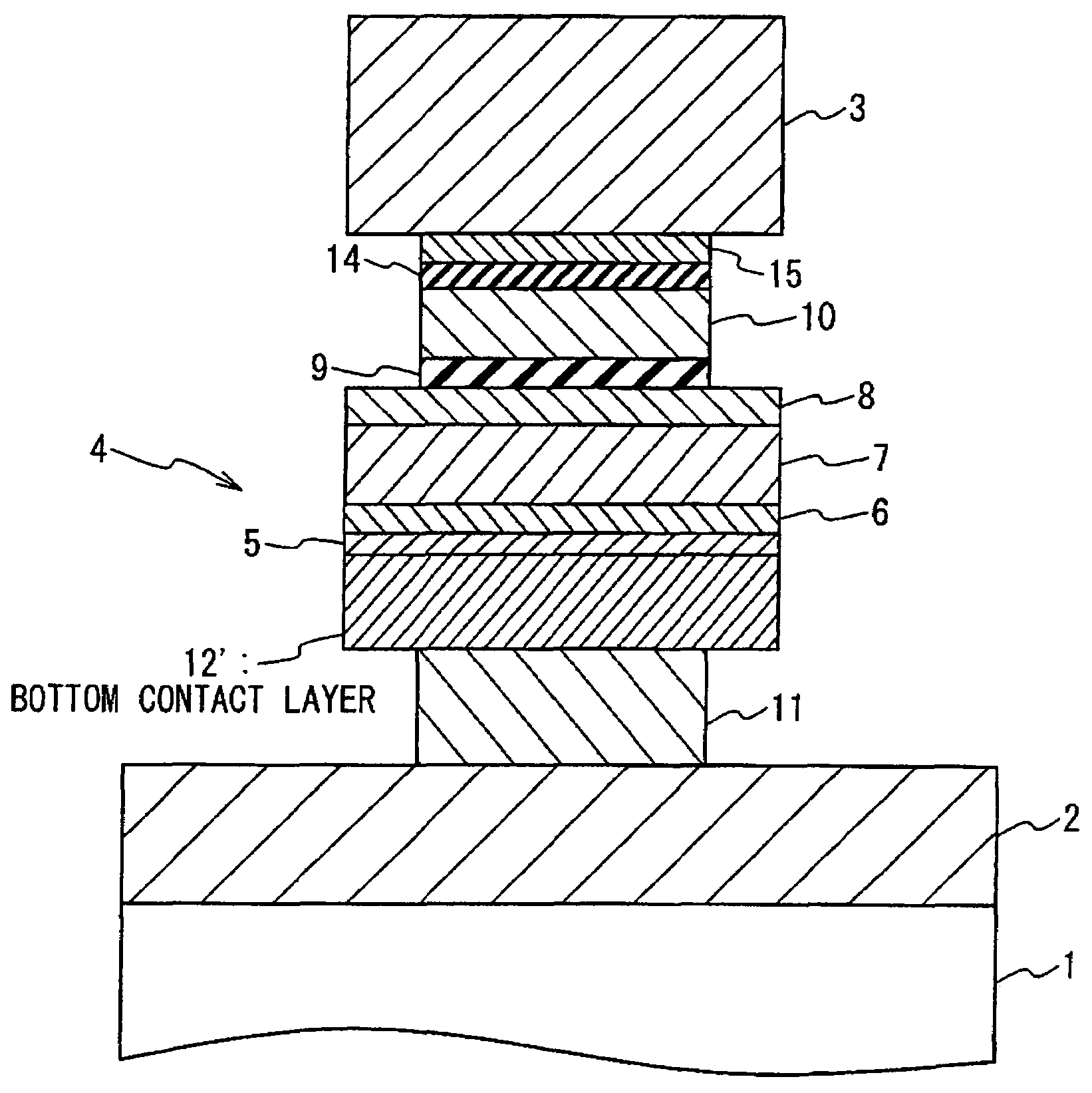

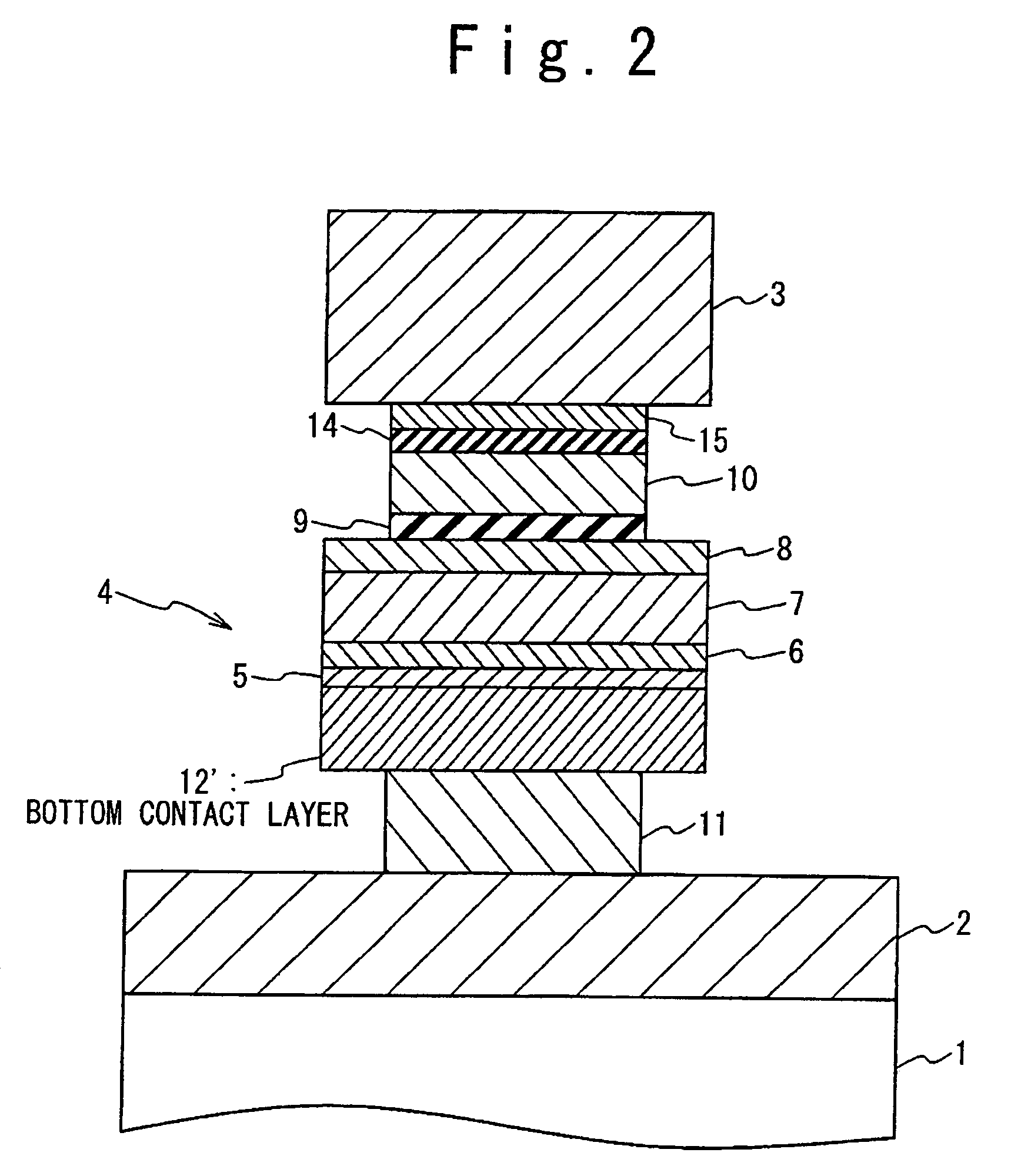

Magnetoresistance device with a diffusion barrier between a conductor and a magnetoresistance element and method of fabricating the same

ActiveUS7394626B2Improve thermal stabilityPrevent interdiffusionNanostructure applicationNanomagnetismElectrical conductorMagnetic reluctance

Owner:NEC CORP

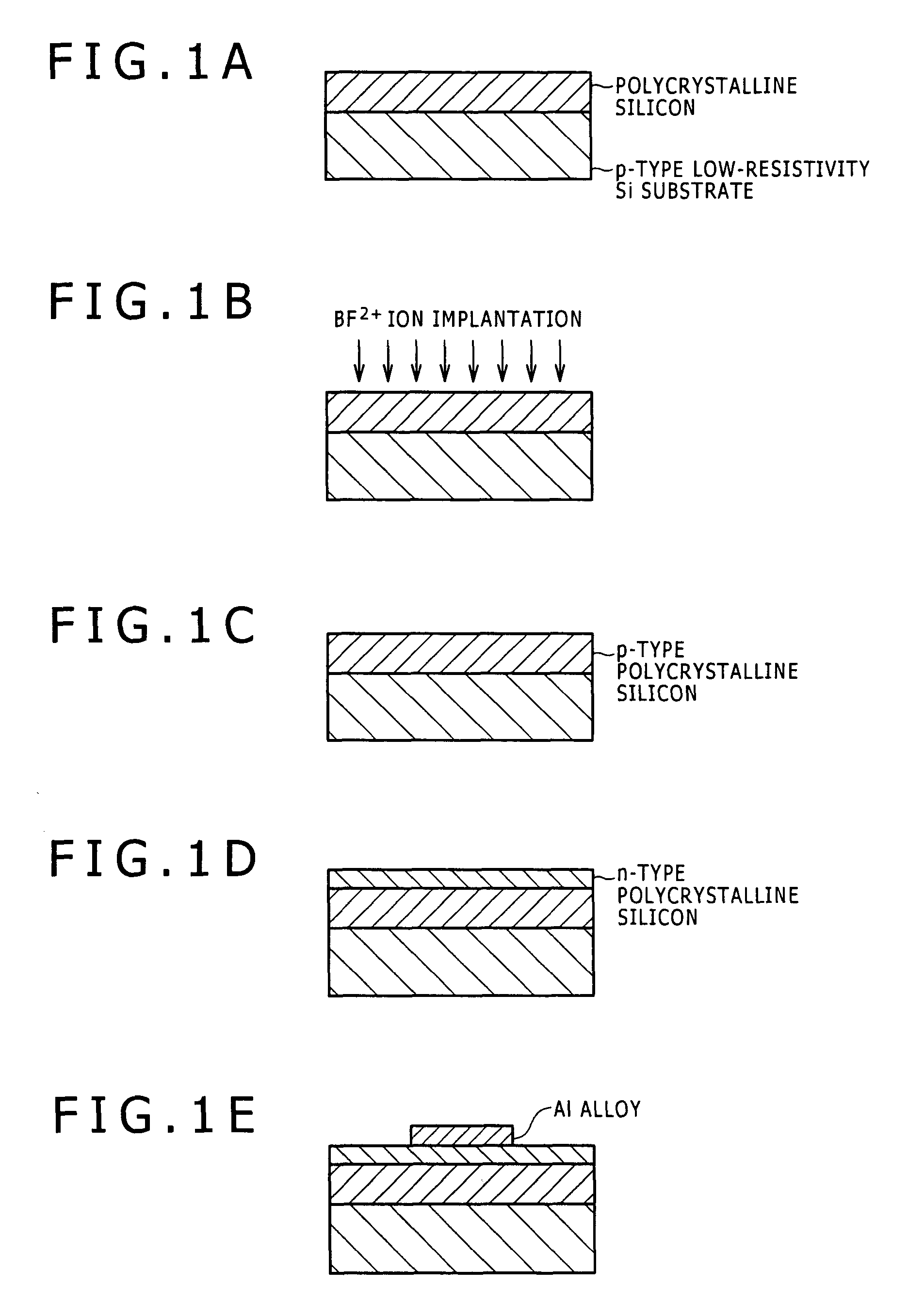

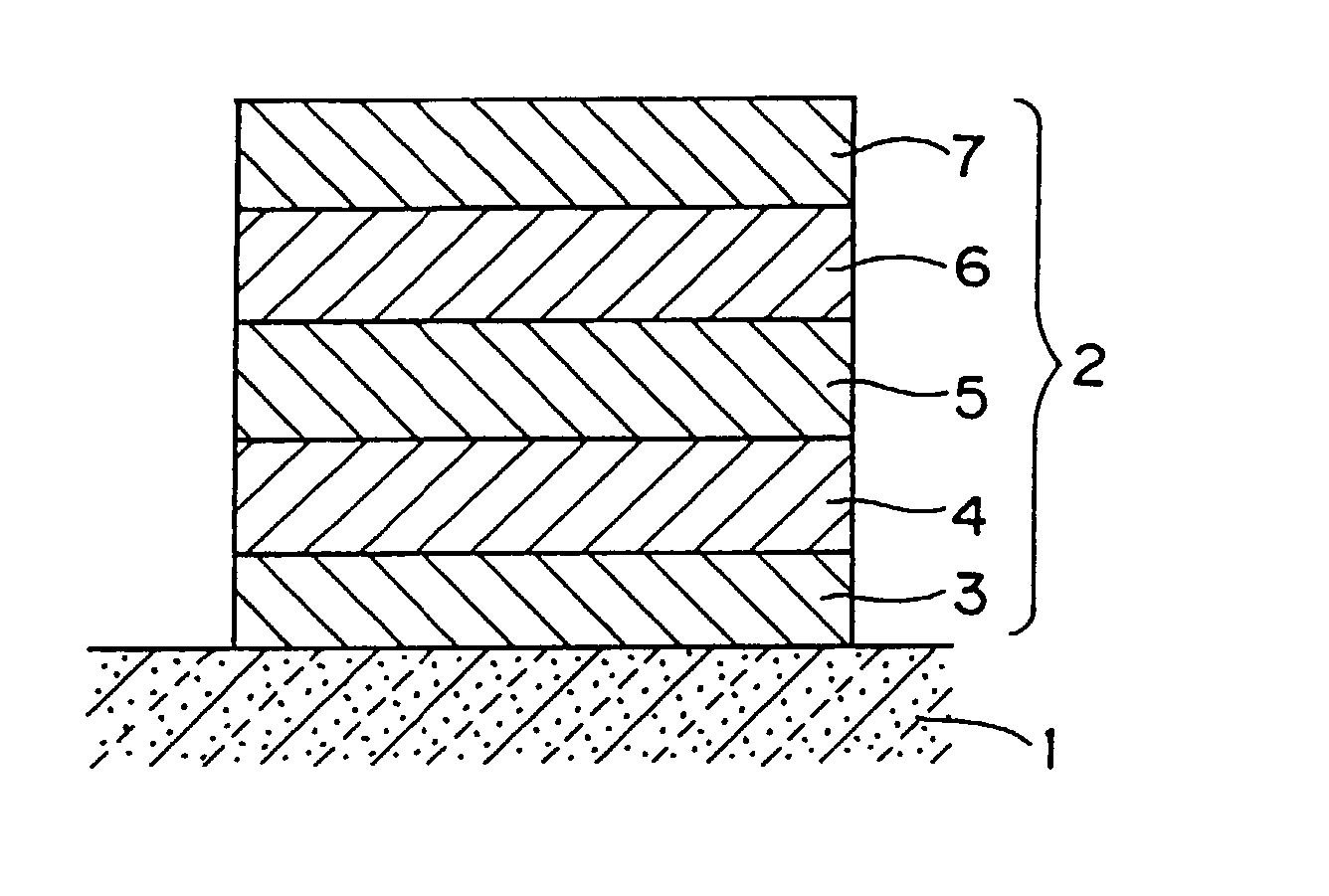

Light-emitting semiconductor device having a quantum well active layer, and method of fabrication

InactiveUS7176480B2High crystallinityPrevent evaporationSemiconductor/solid-state device manufacturingSemiconductor devicesIndiumEvaporation

Owner:SANKEN ELECTRIC CO LTD

Light-emitting semiconductor device having a quantum well active layer, and method of fabrication

InactiveUS20050191778A1Prevent indium evaporationInhibited DiffusionSemiconductor/solid-state device manufacturingSemiconductor devicesMultiple quantumIndium

A light-emitting diode has a low-resistivity silicon substrate on which there are laminated a buffer layer, an n-type lower confining layer, an active layer of multiple quantum well configuration, and a p-type upper confining layer. The active layer is constituted of cyclic alternations of a barrier sublayer of InGaN, a first complementary sublayer of AlGaInN, a well sublayer of InGaN, and a second complementary sublayer of AlGaInN. The proportions of the noted ingredients of the active sublayers are all specified. The first and the second complementary sublayers prevent the evaporation or diffusion of indium from the neighboring sublayers.

Owner:SANKEN ELECTRIC CO LTD

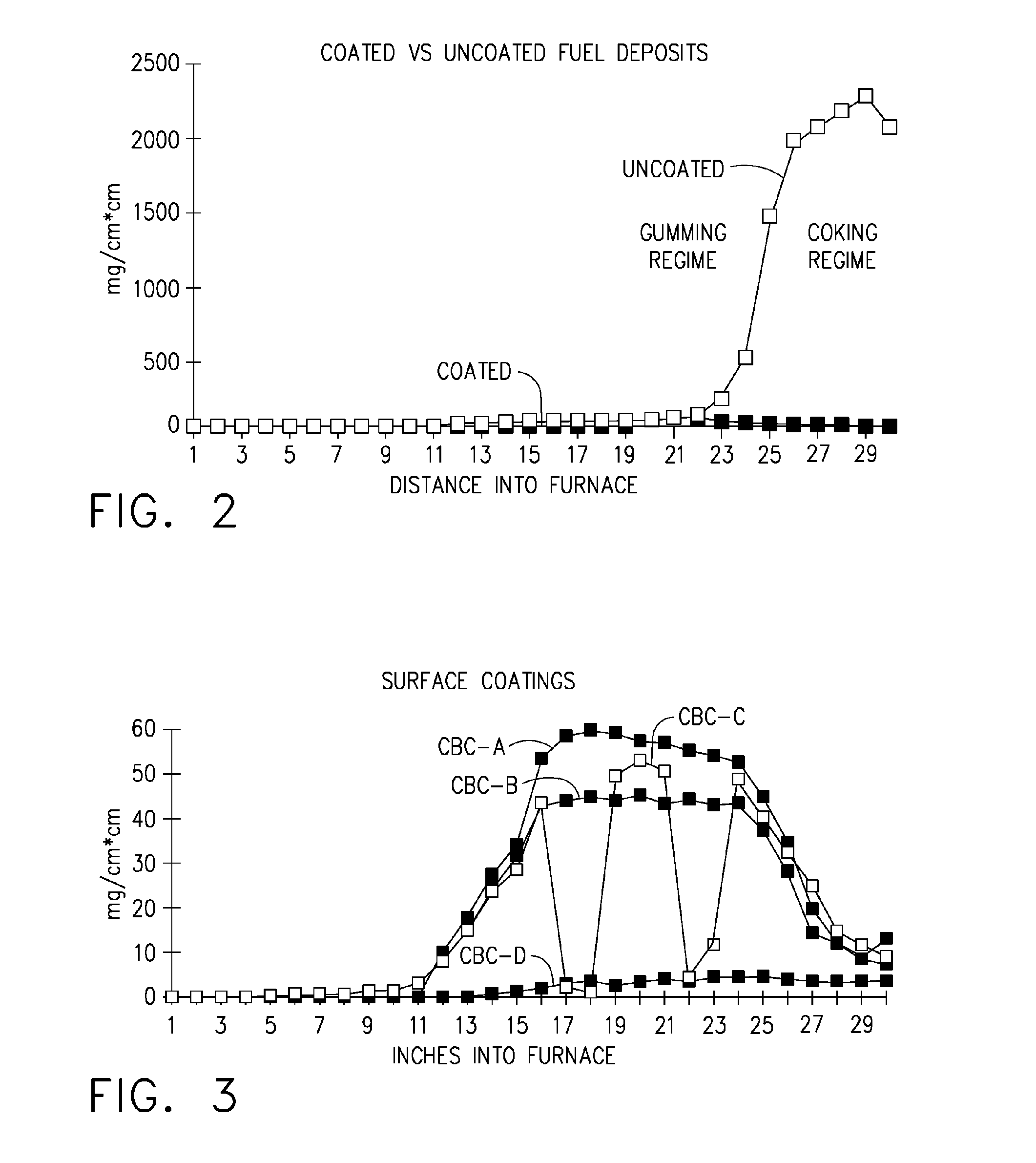

Method and coating system for reducing carbonaceous deposits on surfaces exposed to hydrocarbon fuels at elevated temperatures

InactiveUS20050019593A1Reduce formationReduce adhesionPropellersRecord information storagePlatinumCoating system

A coating system and method for reducing the tendency for hydrocarbon fluids, such as fuels and oils, to form carbonaceous deposits that adhere to a wall of a containment article. Of particular concern are carbonaceous deposits that form at temperatures below about 650° F. (about 345° C.). The coating system combines an outermost layer of platinum with a ceramic barrier layer. The coating system significantly reduces the formation of carbonaceous deposits and the adhesion of such deposits. To further reduce wall and hydrocarbon fluid temperatures and formation of carbonaceous deposits, the coating system is preferably applied to the surface of the wall wetted by the fluid, as well as the opposite surface of the wall exposed to a surrounding environment. The outermost layers serve as radiation shields to reduce heat transfer from the surrounding environment to the wall, and from the wall to the hydrocarbon fluid.

Owner:GENERAL ELECTRIC CO

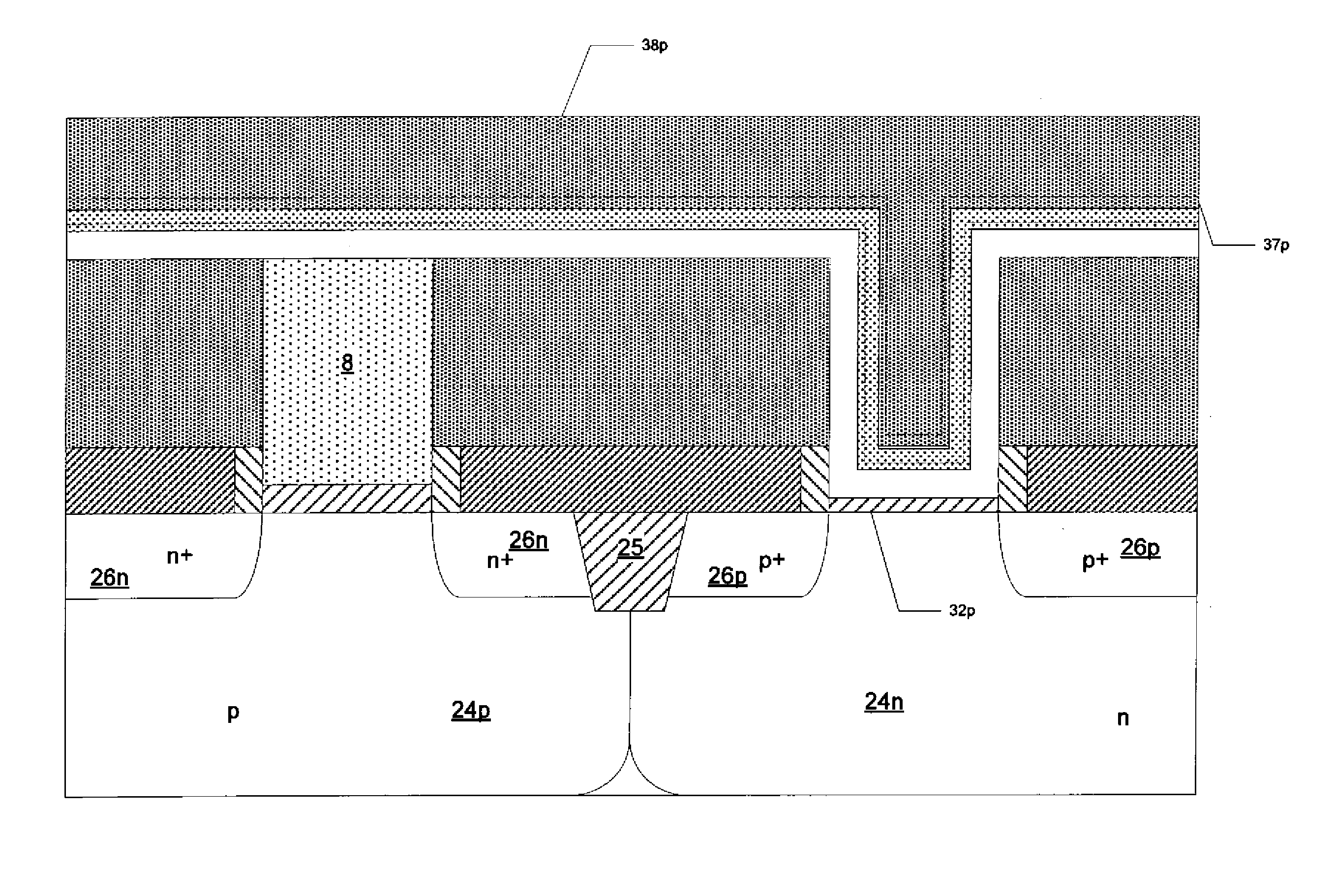

Replacement Metal Gate Process for CMOS Integrated Circuits

ActiveUS20140070327A1Good filling characteristicGood step coverageTransistorSolid-state devicesCMOSGate dielectric

A complementary metal-oxide-semiconductor (CMOS) integrated circuit structure, and method of fabricating the same according to a replacement metal gate process. P-channel and n-channel MOS transistors are formed with high-k gate dielectric material that differ from one another in composition or thickness, and with interface dielectric material that differ from one another in composition or thickness. The described replacement gate process enables construction so that neither of the p-channel or n-channel transistor gate structures includes the metal gate material from the other transistor, thus facilitating reliable filling of the gate structures with fill metal.

Owner:TEXAS INSTR INC

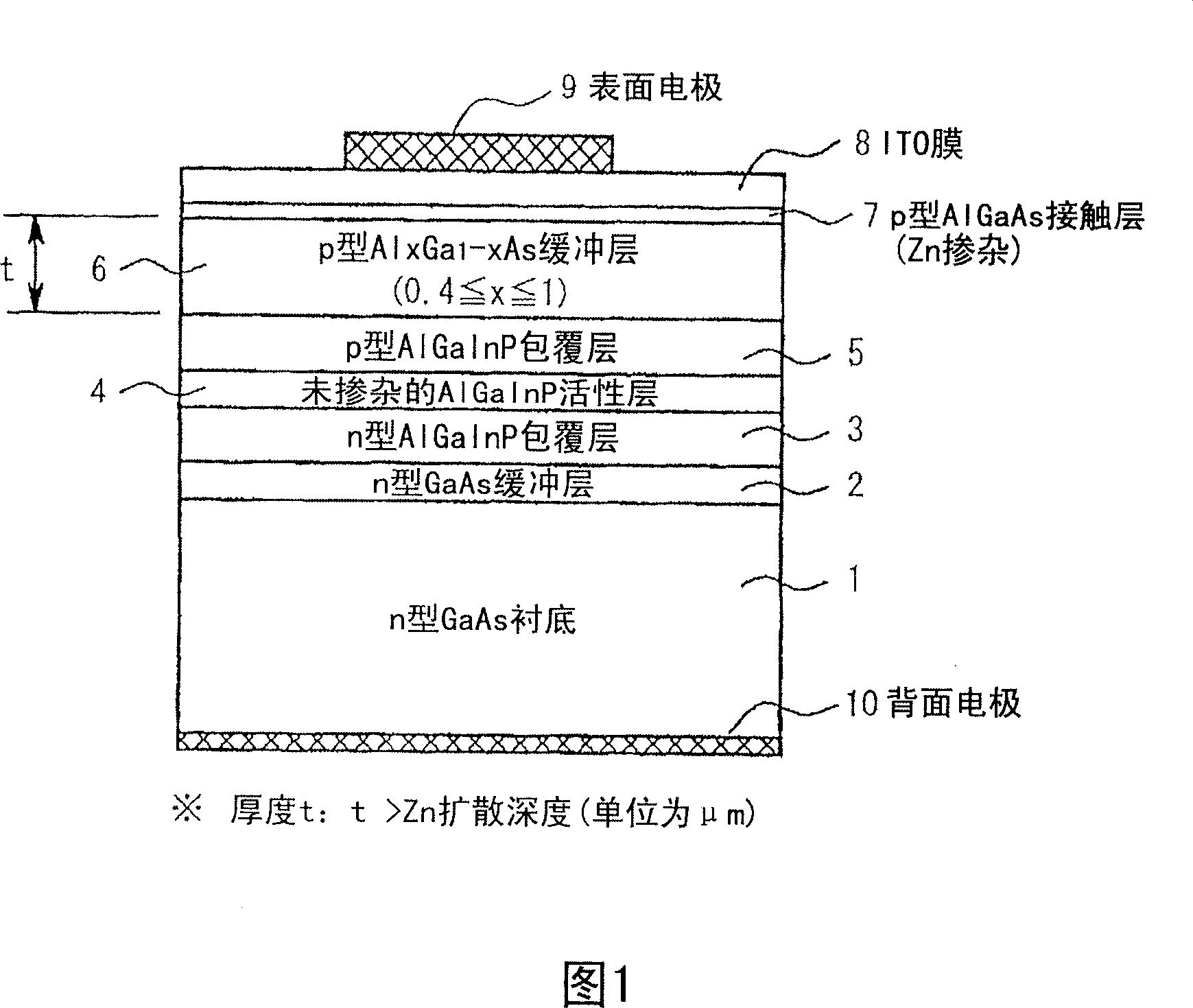

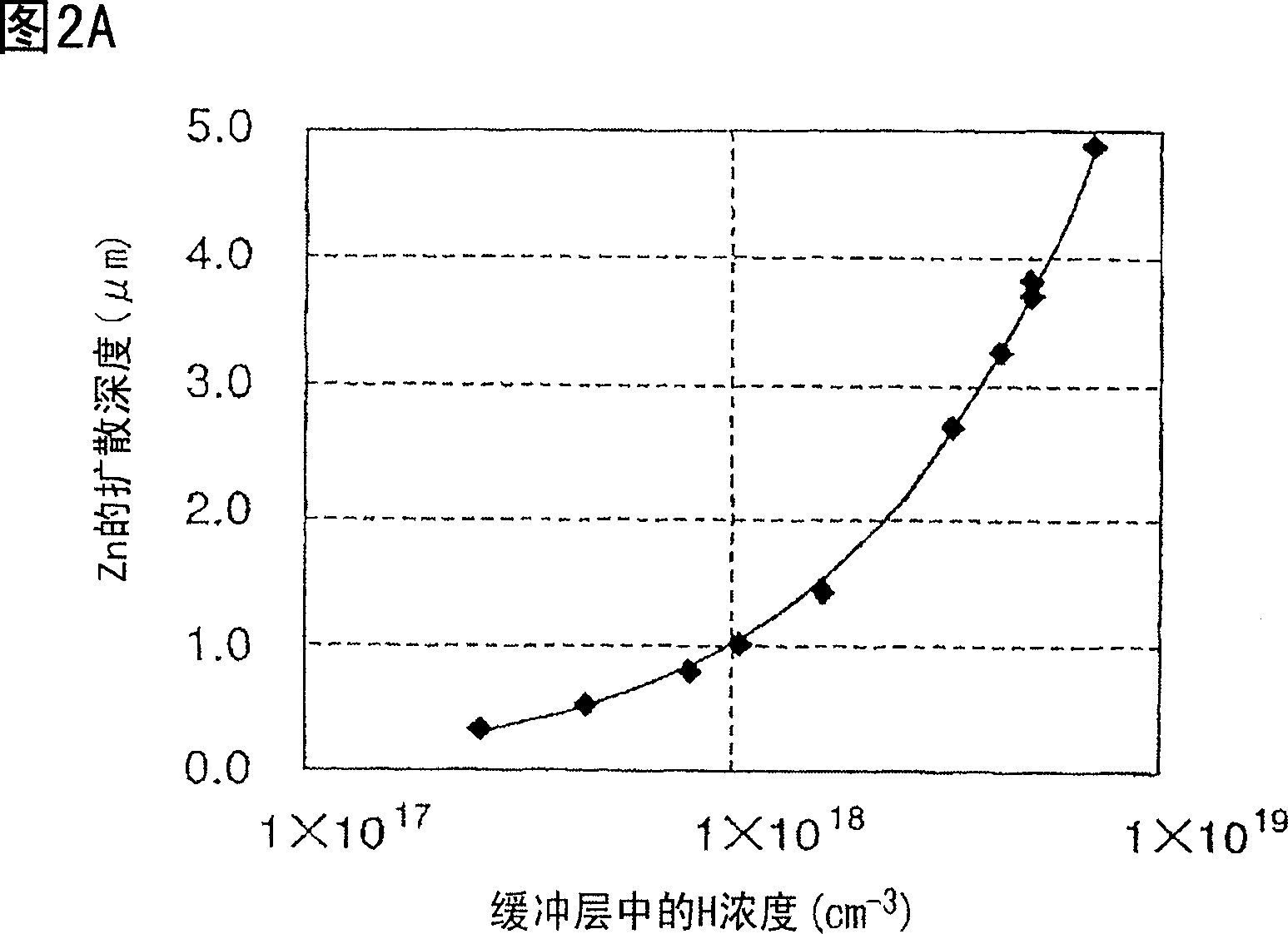

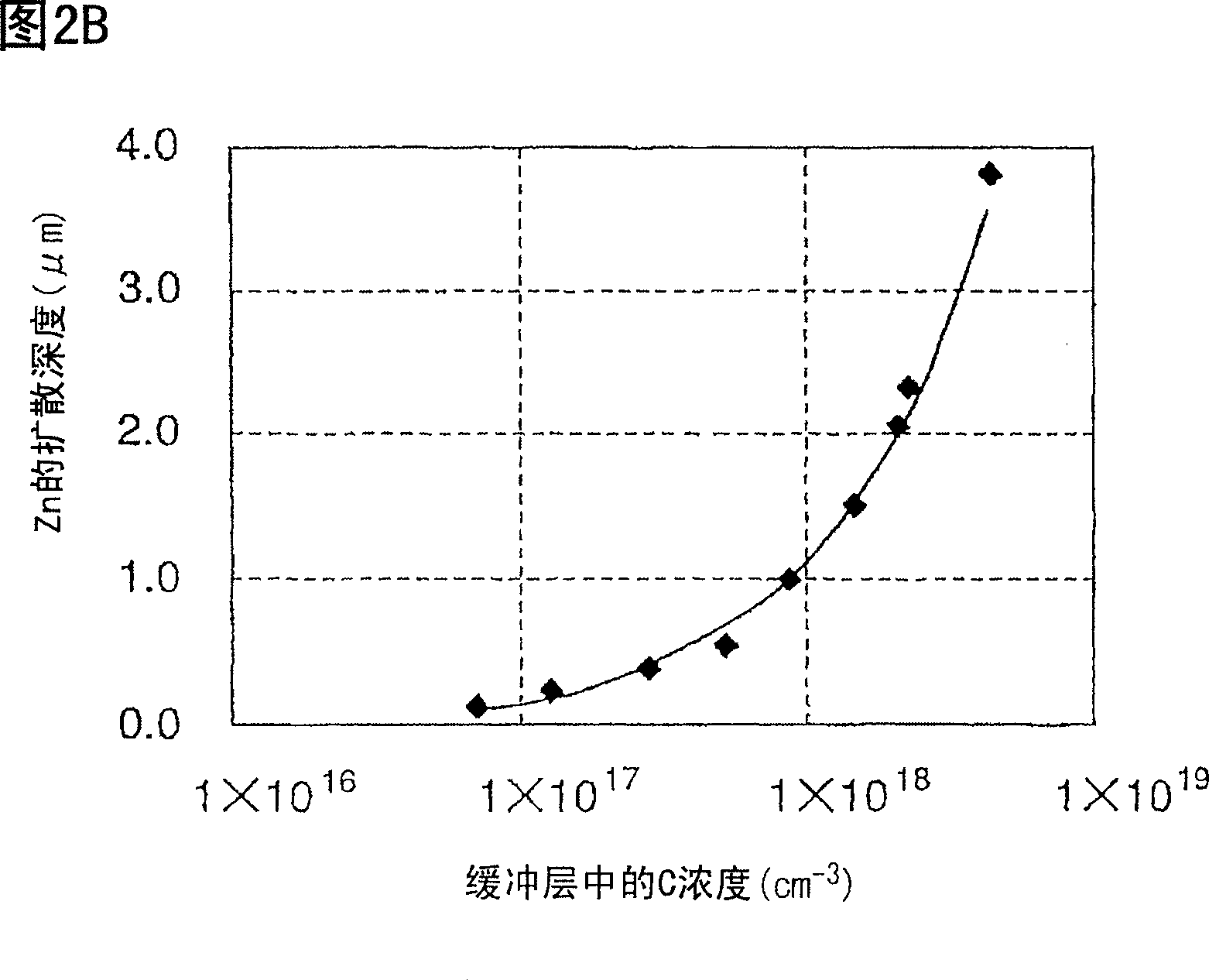

Semiconductor light-emitting device

A semiconductor light emitting device comprises: a light-emitting portion formed on a semiconductor substrate, an As-based p-type contact layer formed thereon, a current spreading layer formed thereon of a metal oxide material, and a buffer layer formed between the p-type cladding layer and the p-type contact layer. The buffer layer has a group III / V semiconductor with a p-type conductivity and hydrogen or carbon included intentionally or unavoidably therein, and the buffer layer has a thickness equal to or greater than a diffusion length L of a dopant doped into the p-type contact layer.

Owner:HITACHI CABLE

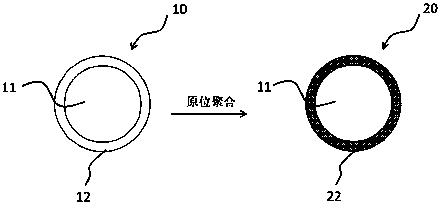

Positive electrode material with low internal resistance for solid state lithium battery and preparation method of positive electrode material

InactiveCN108232138ALower internal resistancePrevent interdiffusionCell electrodesSecondary cellsInternal resistanceConductive materials

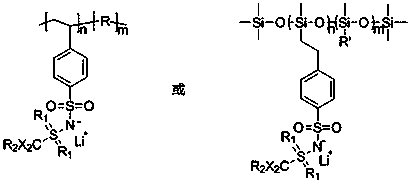

The invention provides a positive electrode material with low internal resistance and particularly relates to a positive electrode material with low internal resistance for a solid state lithium battery and a preparation method of the positive electrode material. The positive electrode material with low internal resistance is prepared from a positive electrode active material core and a surface composite material layer covering the positive electrode active material core, wherein the surface composite material layer is mainly prepared from a nano long-range conducting material and a single ionconductor polymer material. The positive electrode material with low internal resistance, provided by the invention, has higher electronic conductivity and lithium ion conductivity and can effectively reduce the internal resistance of the solid state lithium battery; because the positive electrode active material core and the surface composite material layer have strong interaction, the phenomenaof granule cracking and grinding caused by volume deformation of the positive electrode active material core in repeated charging and discharging process can be effectively inhibited so as to ensurethe structural integrity of the positive electrode active material core and good interface stability; and furthermore, the technical scheme provided by the invention is simple and easy, low in production cost and suitable for performing large-scale production.

Owner:QINGDAO INST OF BIOENERGY & BIOPROCESS TECH CHINESE ACADEMY OF SCI

Light emitting element and method for manufacturing the same

InactiveUS20060214574A1Reduce contact resistanceImprove reflectivityDischarge tube luminescnet screensLamp detailsRheniumOptical reflection

A light emitting element including: a semiconductor layer stack including a light emitting layer; a metal optical reflection film which is formed on the surface of the semiconductor layer stack opposite to the surface from which light emitted from the light emitting layer is taken out of the semiconductor layer stack to reflect the emitted light; a metal cover film which is formed above the metal optical reflection film to prevent the metal optical reflection film from coming off; and a metal anti-diffusion film which is formed between the metal optical reflection film and the metal cover film to prevent interdiffusion between the metal optical reflection film and the metal cover film. The metal anti-diffusion film is a single layer film made of any one of tungsten, rhenium and tantalum or a layered film made of two or more of tungsten, rhenium and tantalum.

Owner:PANASONIC CORP

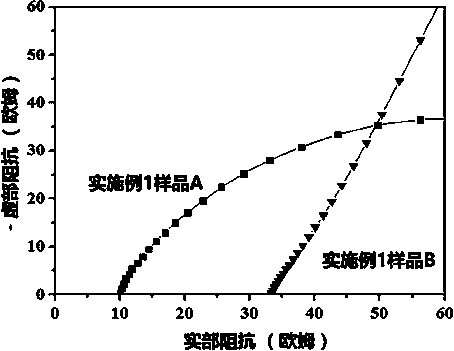

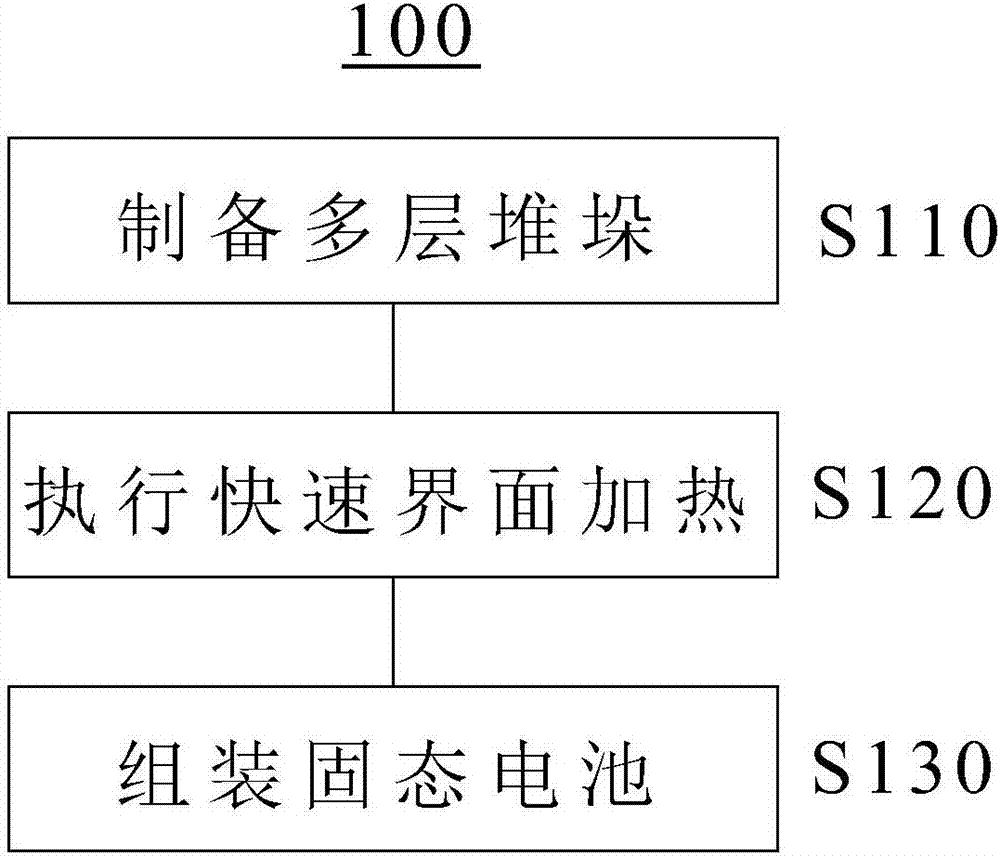

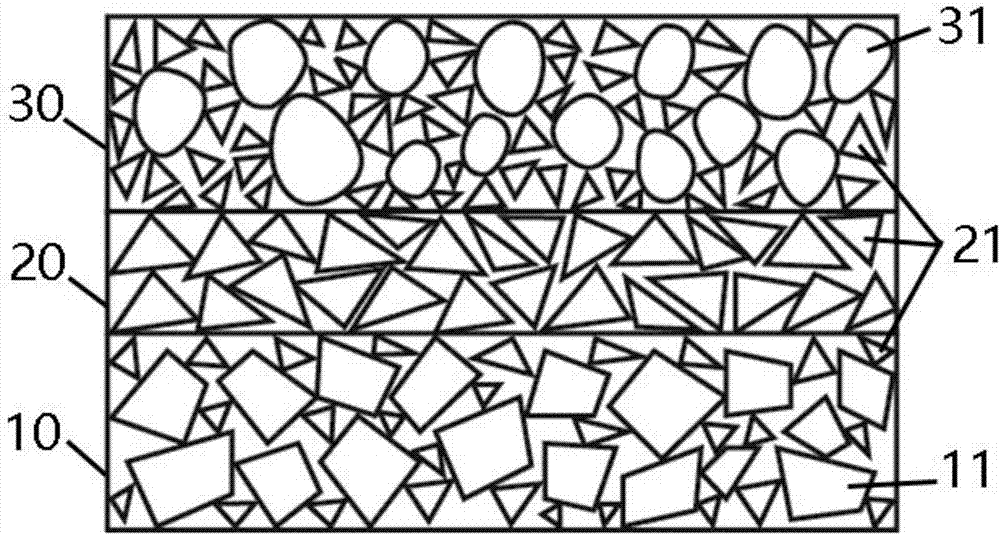

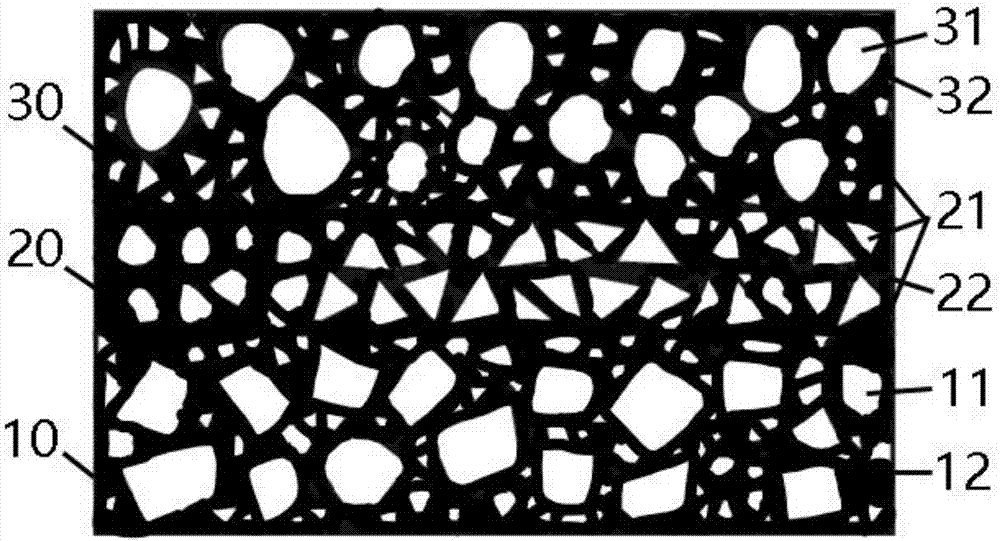

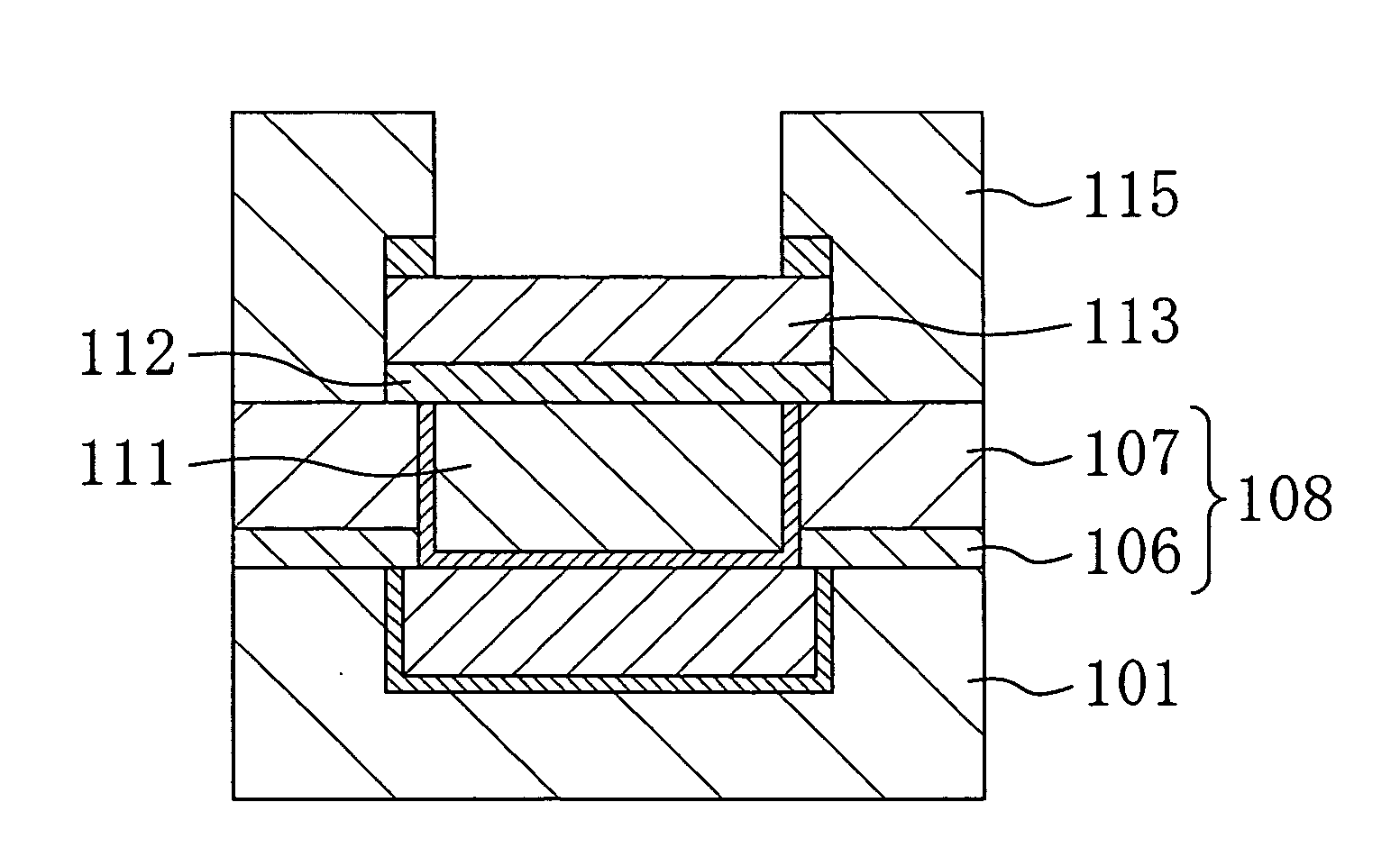

Solid-state battery and preparation method therefor

ActiveCN107240718AIncrease contactEasy transferFinal product manufactureElectrolyte accumulators manufactureSolid state electrolyteEngineering

The invention relates to a solid-state battery and a preparation method therefor. The preparation method for the solid-state battery comprises the steps of preparing a stacking structure, wherein the stacking structure at least comprises a positive electrode layer and a solid-state electrolyte layer arranged on the positive electrode layer; the positive electrode layer comprises positive electrode active material granules and solid-state electrolyte granules; and performing quick interface heating on the stacking structure to enable the interface of at least one kind of the positive electrode active material granules and the solid-state electrolyte granules in the positive electrode layer to be fused to generate an interface fused phase, so as to directly connect the positive electrode active material granules and the solid-state electrolyte granules.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Semiconductor device

ActiveUS20070096320A1Improve stabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesAlloyCopper

Owner:PANNOVA SEMIC

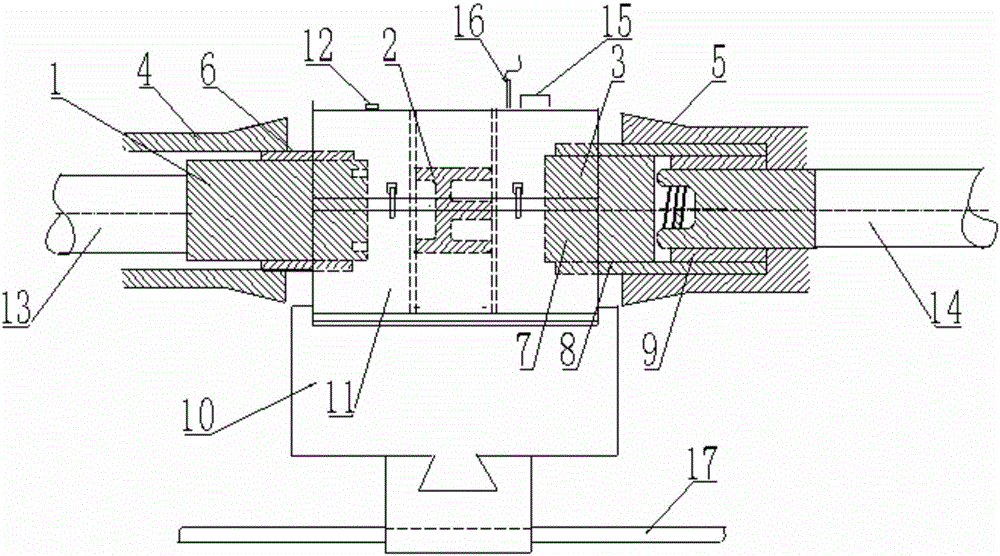

Dissimilar material composite welding method

ActiveCN106735969AImprove welding qualityGood quality jointsWelding/soldering/cutting articlesWelding apparatusFriction weldingTransition layer

The invention discloses a dissimilar material composite welding method. The dissimilar material composite welding method comprises the following steps: firstly, a welding device is obtained; secondly, a to-be-welded part a and a to-be-welded part c which are each made of dissimilar materials and wholly in a columnar shape are obtained, and the dissimilar material composite welding method is characterized in that the welding device in the first step further comprises a heater; thirdly, a middle transition layer and a top pressure bar are obtained; fourthly, the middle transition layer and the to-be-welded part a are in diffusion welding; fifthly, friction pre-welding clamping is carried out; sixthly, friction pre-welding preheating is carried out; seventhly, inertia friction welding connection of a material with the middle transition layer is carried out; and eighthly, after-welding treatment is carried out. The dissimilar material composite welding method has the beneficial effects of being higher in welding efficiency and better in welding quality.

Owner:CHONGQING UNIV OF TECH

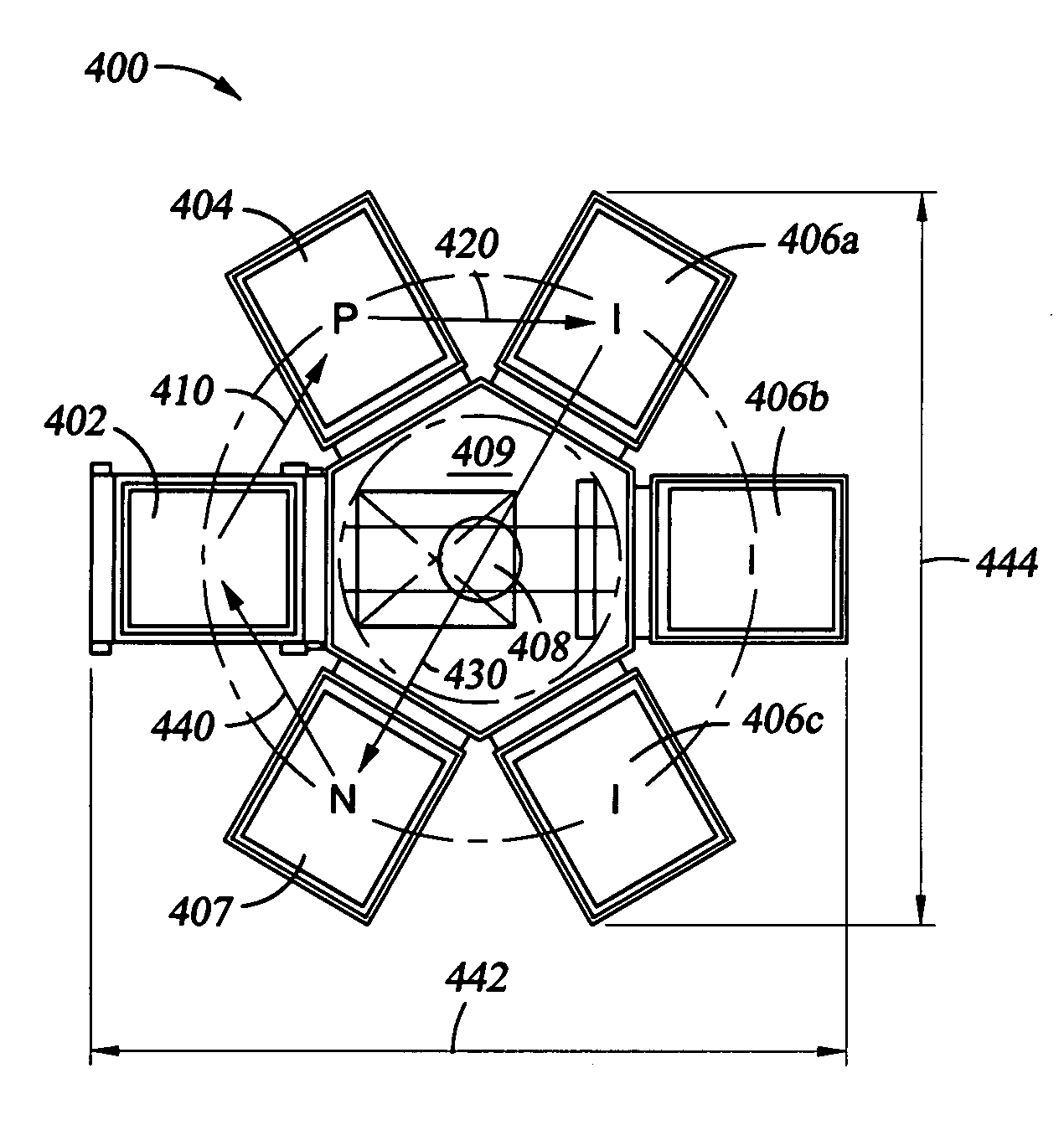

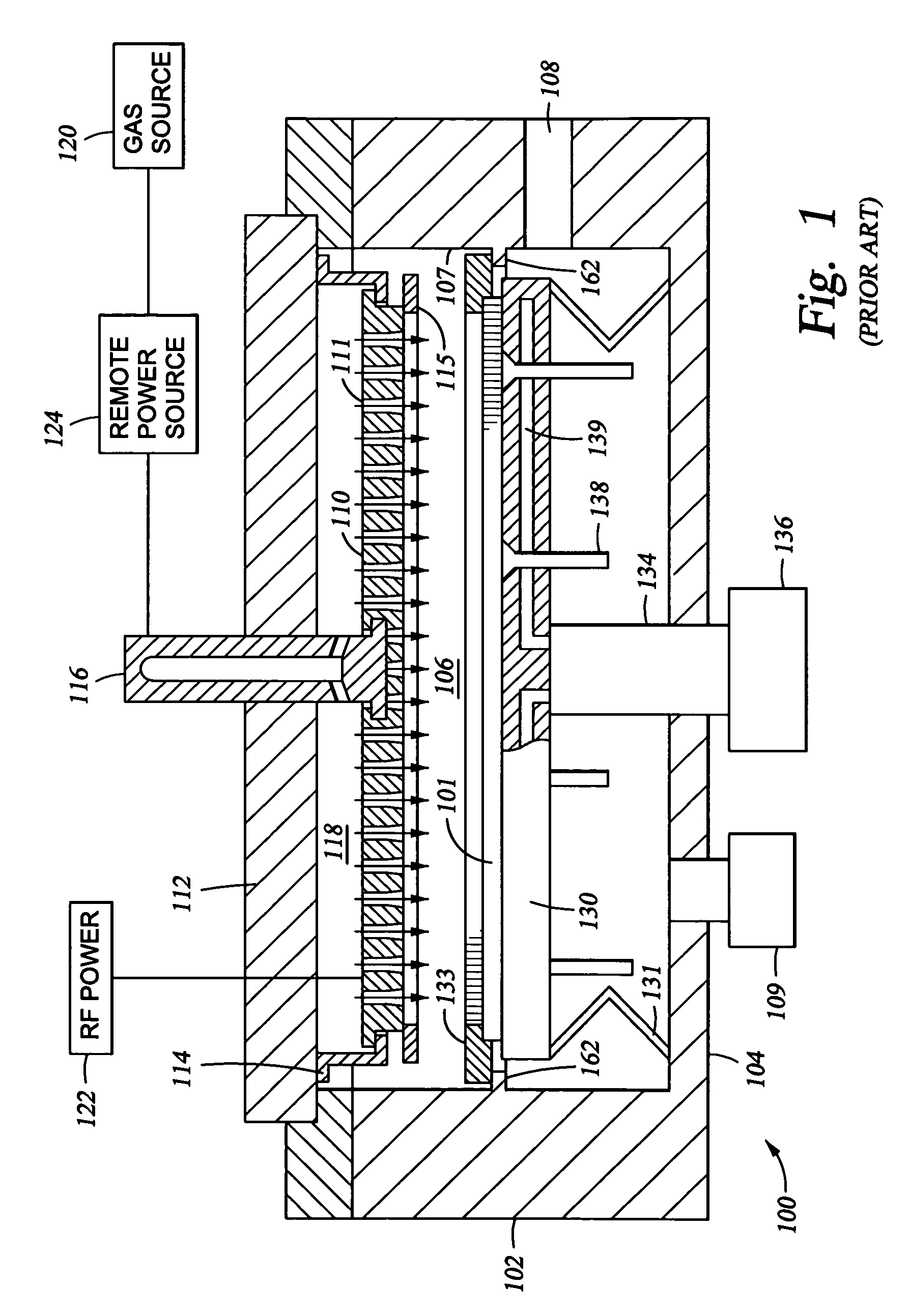

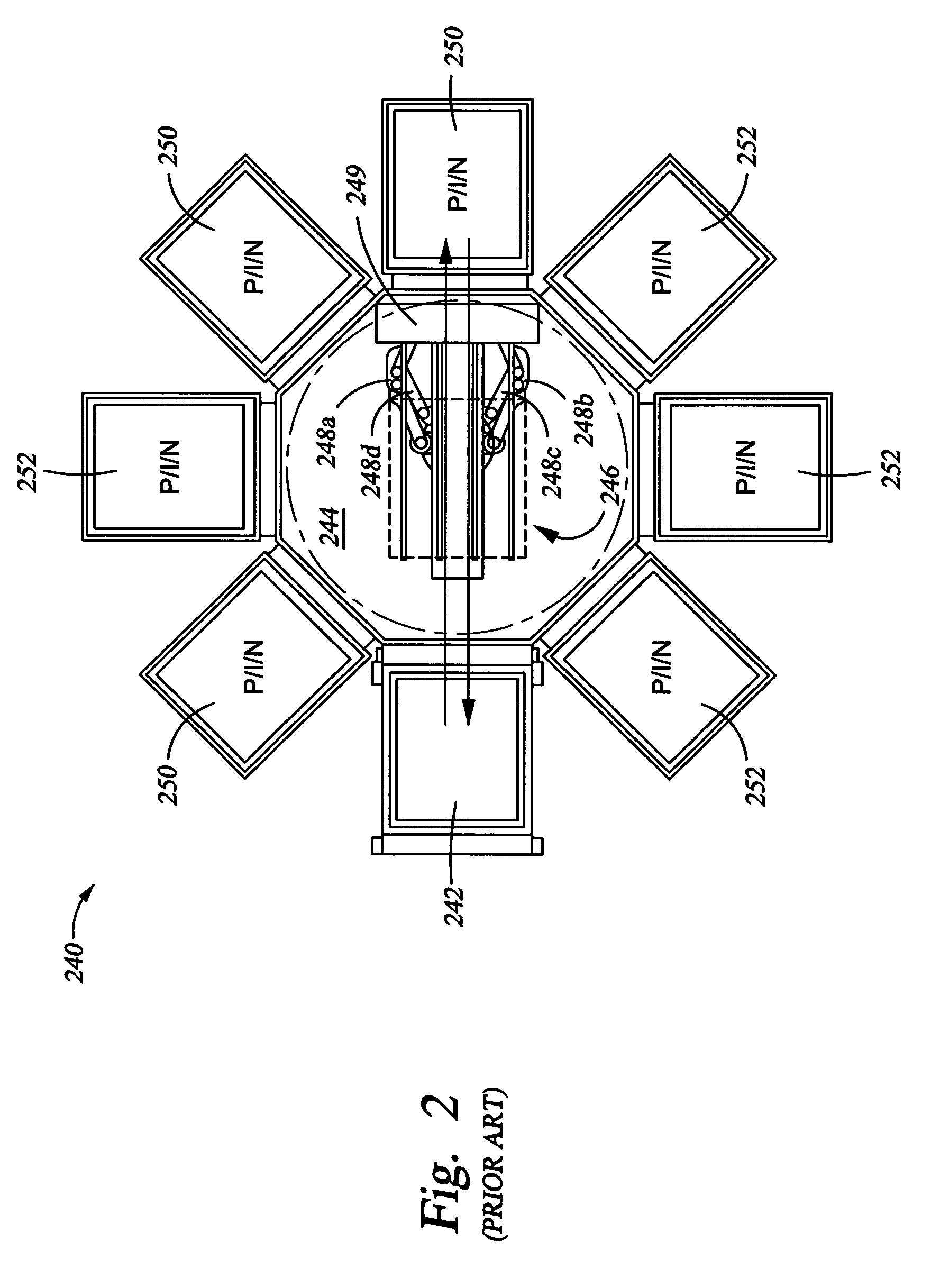

Formation of clean interfacial thin film solar cells

InactiveUS20090208668A1Extended production timeLess riskSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringHandling system

A “three” chamber design multi-chamber cluster processing system which is used in the fabrication of a solar cell-comprising substrate. The processing system includes at least one PECVD processing chamber configured to deposit a p-doped layer, at least three PECVD processing chambers configured to deposit an i-layer, and at least one PECVD processing chamber configured to deposit an n-doped layer. The processing system also includes at least one central substrate transferring chamber which is typically located substantially equidistant from each of the PECVD processing chambers, and a transfer robot present in the central transferring chamber which is capable of paired transfer of substrates. An apparatus which provides a source of fluorine-comprising reactive species is in communication with each of said PECVD processing chambers.

Owner:APPLIED MATERIALS INC

Thin film transistor substrate and display device

InactiveUS7781767B2Desired switching performancePerformance of semiconductor will deteriorateSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceAlloy thin film

Owner:KOBE STEEL LTD

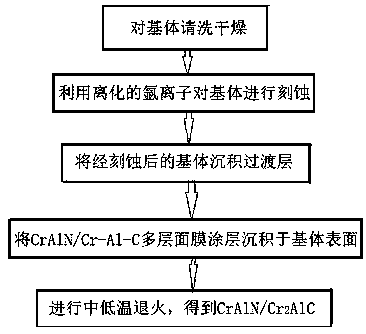

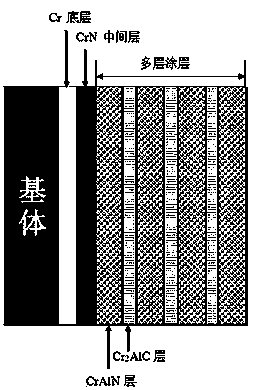

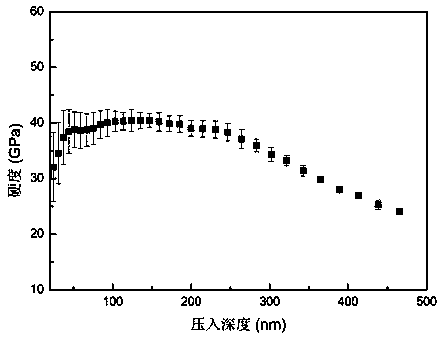

High-toughness anticorrosion CrAlN/Cr2AlC multilayer film coating and preparation method thereof

ActiveCN108728793AReduce coating stressImprove toughnessVacuum evaporation coatingSputtering coatingIonCorrosion

The invention provides a high-toughness anticorrosion CrAlN / Cr2AlC multilayer coating and a preparation method thereof. The preparation method comprises the steps that a matrix is cleaned and dried, etching is conducted on the matrix with argon ions, a transition layer is deposited on the matrix, the CrAlN / Cr-Al-C multilayer film coating is deposited on the surface of the matrix, and low temperature annealing is conducted to obtain CrAlN / Cr2AlC. The transition layer is arranged between the matrix and the CrAlN / Cr2AlC multilayer coating, and according to the multilayer coating, CrAlN hard filmsand Cr2AlC MAX phase films are alternately stacked to form periodic arrangement. The multilayer film coating has high hardness, low internal stress and the high anticorrosion characteristic, and abrasion resistant and anticorrosion lives of the matrix can be prolonged. The problems that a single CrAlN coating is high in hardness but insufficient in toughness, and a single Cr2AlC coating is good in toughness and corrosion resistance but low in hardness are solved. According to the provided preparation method of the multilayer film coating, the multilayer film coating is obtained through the combination of periodic control over the flow of N2 and CH4 reaction gases, with subsequent low temperature heat treatment, the process is simple and easy to control, industrialized production can be achieved, and the prepared multilayer film coating is stable in performance and is suitable for abrasion-resistant anticorrosion protection of tool molds or other moving parts in different environments.

Owner:INST OF APPLIED PHYSICS JIANGXI ACADEMY OF SCI

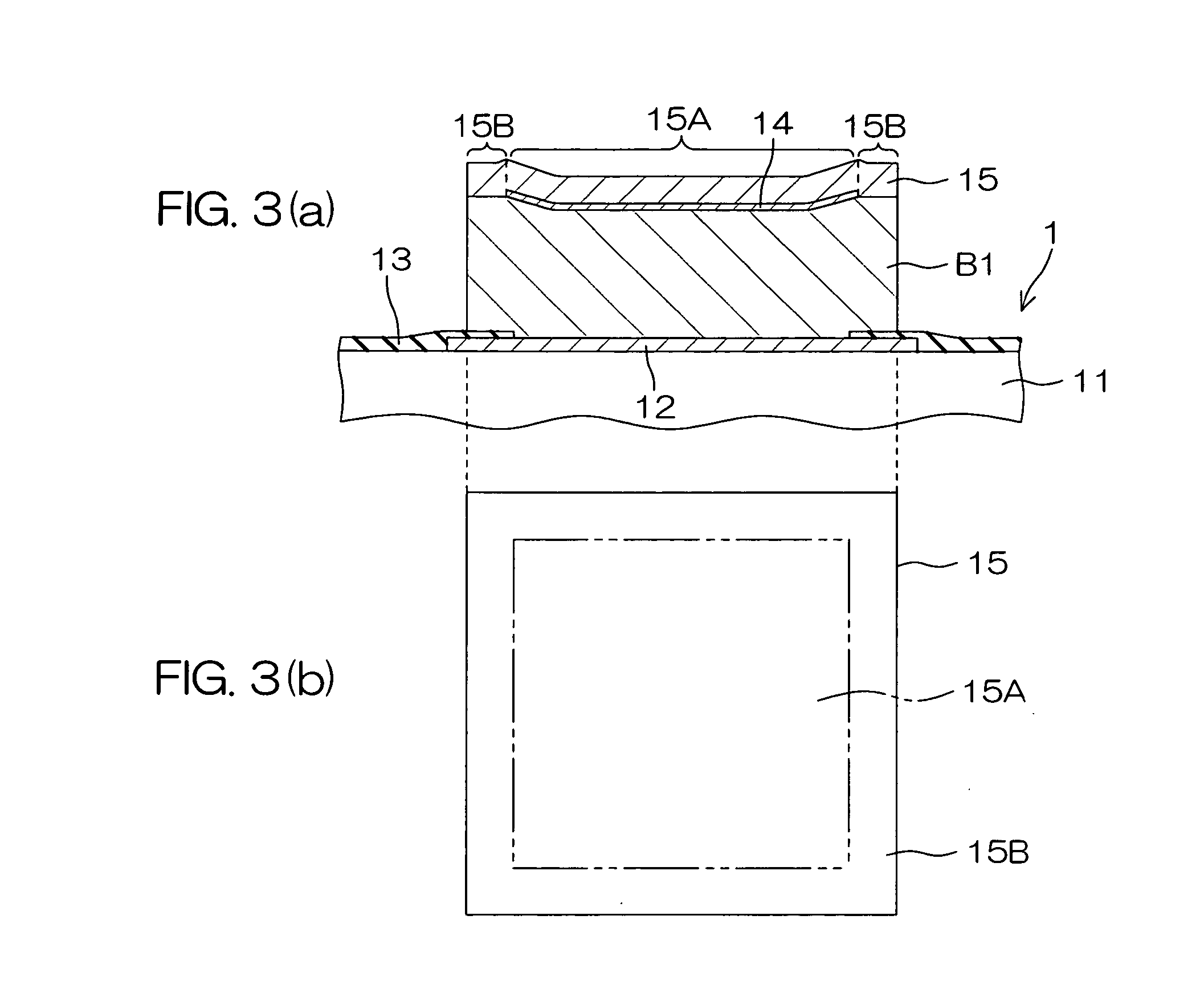

TFT array substrate and method of manufacturing the same

ActiveUS20070295963A1Improve electrical contact characteristicsPrevent interdiffusionSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactOptoelectronics

A TFT array substrate includes a TFT having an ohmic contact film and a source electrode and a drain electrode formed on the ohmic contact film. It also includes a pixel electrode electrically connected with the drain electrode. The source electrode and the drain electrode are made of an Al alloy containing Ni as an additive.

Owner:TRIVALE TECH

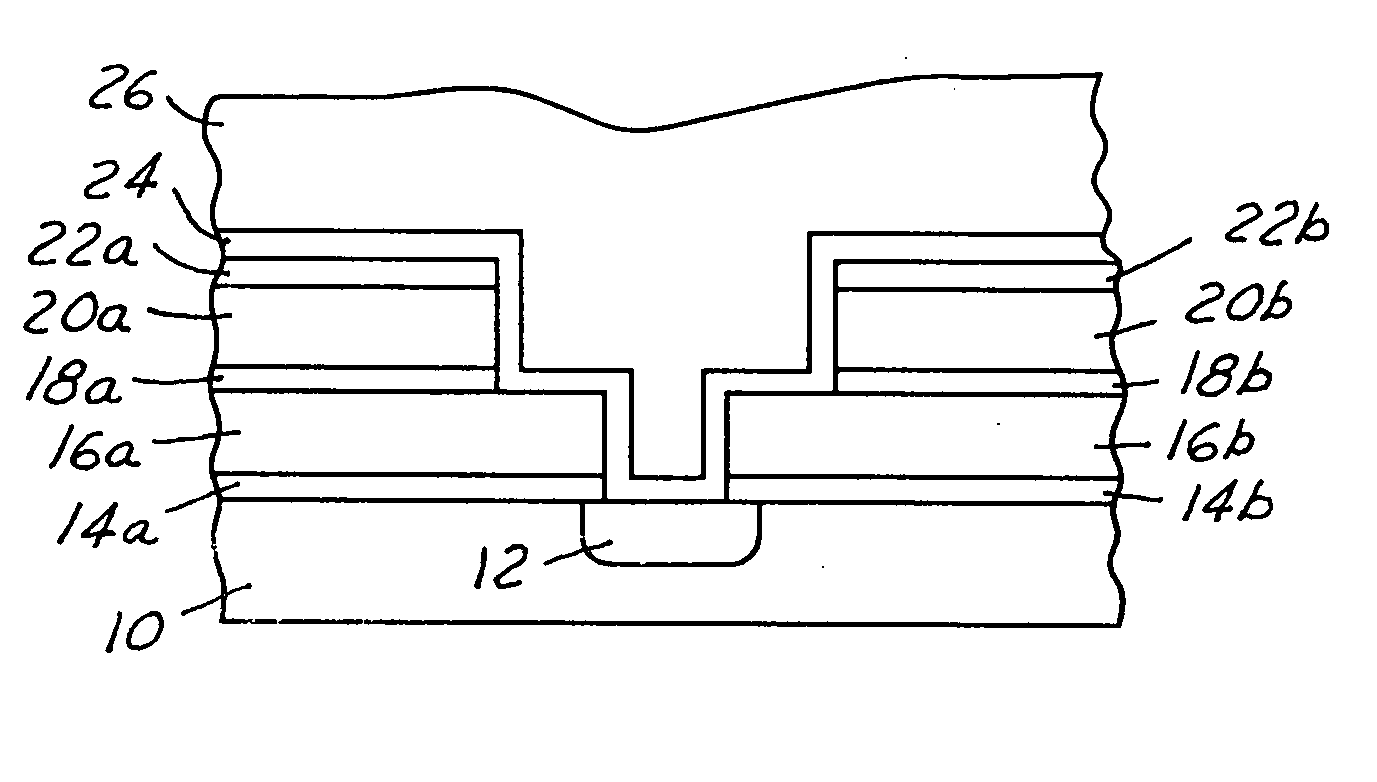

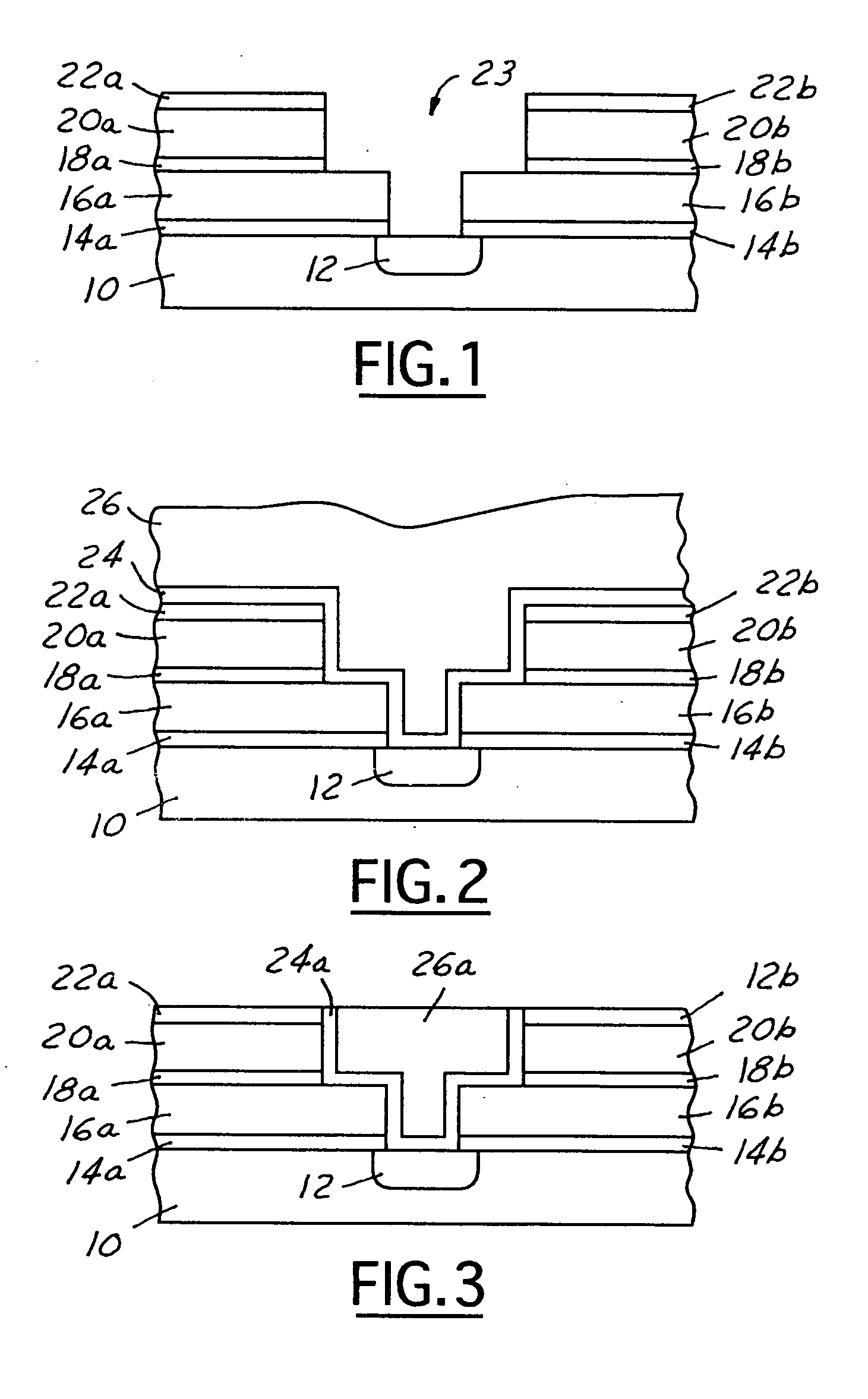

Semiconductor device and manufacturing method thereof

InactiveUS20060284264A1Prevent interdiffusionReduce sheet resistanceTransistorSolid-state devicesDevice materialEngineering

A semiconductor device and a manufacturing method thereof that can prevent mutual diffusion of impurity in a silicide layer and can decrease sheet resistance of an N-type polymetal gate electrode and a P-type polymetal gate electrode, respectively in the semiconductor device having gate electrodes of a polymetal gate structure and a dual gate structure are provided. The P-type polymetal gate electrode includes a P-type silicon layer containing P-type impurity, a silicide layer formed on the P-type silicon layer and having a plurality of silicide grains which are discontinuously disposed in a direction substantially parallel with the surface of the semiconductor substrate, a silicon film continuously formed on the surface of the P-type silicon layer exposed on the discontinuous part of the silicide layer and on the surface of the silicide layer, a second metal nitride layer formed on the silicon film, and a metal layer formed on the metal nitride layer.

Owner:SEMICON PATENT

Semiconductor device

InactiveUS20030034485A1Prevent interdiffusionInhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

The semiconductor device has a backside electrode disposed on a backside of the semiconductor substrate and including multiple layers of metal. The backside electrode includes, on the semiconductor substrate, a first layer of aluminum, a second layer of barrier metal, a third layer of nickel, a fourth layer of silver and a fifth layer of gold which are disposed in this order.

Owner:MITSUBISHI ELECTRIC CORP

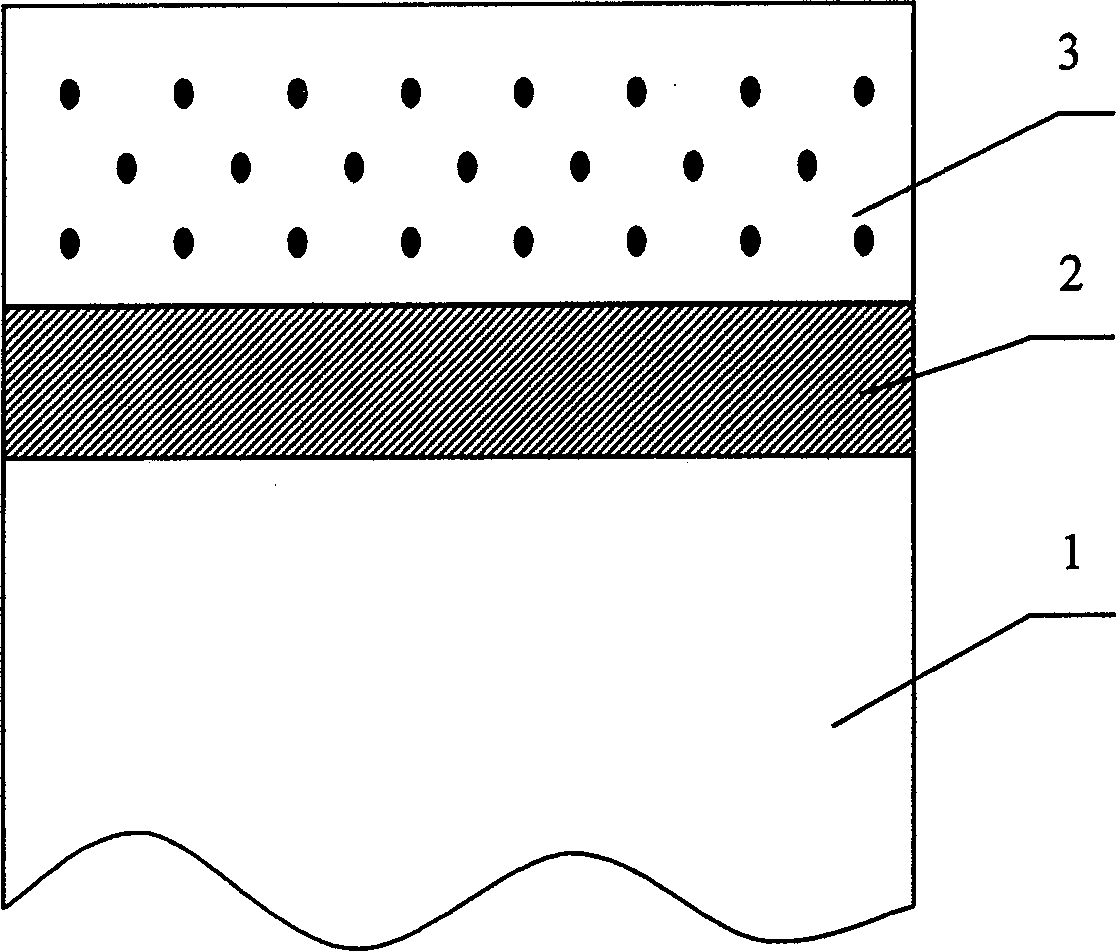

Phase change memory and manufacturing method thereof

InactiveCN110335942ALow thermal conductivityHigh thermal efficiencySolid-state devicesSemiconductor devicesPhase-change memoryHigh density

The invention provides a phase change memory and a manufacturing method thereof. The phase change memory comprises a substrate, a plurality of phase change memory units and isolation material layers.The phase change memory units are discretely arranged on the substrate. Each phase change memory unit comprises a first electrode material layer, a first transition material layer, a threshold gate tube material layer, a second transition material layer, a second electrode material layer, a third transition material layer, a phase change material layer, a fourth transition material layer and a third electrode material layer in turn from bottom to top. The isolation material layers are located on the substrate and surround the sides of the phase change memory units, and the phase change memoryunits are isolated from one another through the isolation material layers. In the phase change memory of the invention, the phase change material and the OTS material are limited in the same space bythe isolation material, and the transition material layers are located between the phase change material and the electrode material, between the phase change material and the OTS material and betweenthe OTS material and the electrode material, so that the phase change memory has the characteristics of high density, high speed, low power consumption and long life.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

High temperature alloy protective technology

InactiveCN1858304AReduce corrosion rateAccelerated corrosionSuperimposed coating processAlloy substrateSuperalloy

The high temperature alloy protecting technology includes the first forming binding layer in the same components as the substrate on the surface of the high temperature alloy substrate and the subsequent baking composite oxide coating on the surface. The composite oxide coating consists of basic enamel material and added Al2O3 or MgO in 10-40 wt% and Y2O3 in 1-5 wt%; and the basic enamel material consists of ZrO2 3-6 wt%, Al2O3 3-6 wt%, ZnO 8-12 wt%, CaO 3-6 wt%, B2O3 3-6 wt%, Na2O 3-6 wt%, K2O 5-8 wt%, TiO2 1-4 wt% and SiO2 for the rest. The present invention raises the high temperature oxidation resistance and heat corrosion resistance of the substrate and raise the stripping-off resistance of the coating and avoids the mutual diffusion between elements.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

Semiconductor device and method for fabricating the same

ActiveUS7825482B2Avoid impuritiesSuppress mutationTransistorSolid-state devicesMetal silicideSemiconductor

A semiconductor device includes: an isolation region formed in a semiconductor substrate; a first active region and a second active region surrounded by the isolation region; an n-type gate electrode and a p-type gate electrode formed on gate insulating films; an insulating film and a silicon region formed on the isolation region and isolating the n-type gate electrode and the p-type gate electrode from each other; and a metal silicide film formed on the upper surfaces of the n-type gate electrode, the silicon region, the p-type gate electrode, and part of the insulating film formed therebetween. The n-type gate electrode is electrically connected to the p-type gate electrode through the metal silicide film.

Owner:PANNOVA SEMIC

Electronic device, semiconductor device using same, and method for manufacturing semiconductor device

ActiveUS20070075422A1Shorten the timeInhibition effectSemiconductor/solid-state device detailsSolid-state devicesDevice materialMetallic materials

Disclosed is an electronic device comprising a substrate, a bump formed on a substrate surface and composed of a first metal material, a junction film for connection with an electrical connecting portion of another device which is formed on the top face of the bump and composed of a second metal material, the melting point of which second metal material itself is lower than the melting point of an alloy thereof with the first metal material, and a diffusion-preventing film which is so arranged between the top face of the bump and the junction film as to cover at least a part of the top face of the bump and composed of a third metal material whose diffusion coefficient in the first metal material is lower than that of the second metal material.

Owner:TAIWAN SEMICON MFG CO LTD

Refractory metal nitride barrier layer with gradient nitrogen concentration

InactiveUS20050156316A1Improve performanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesNitrogenNitride

Owner:TAIWAN SEMICON MFG CO LTD

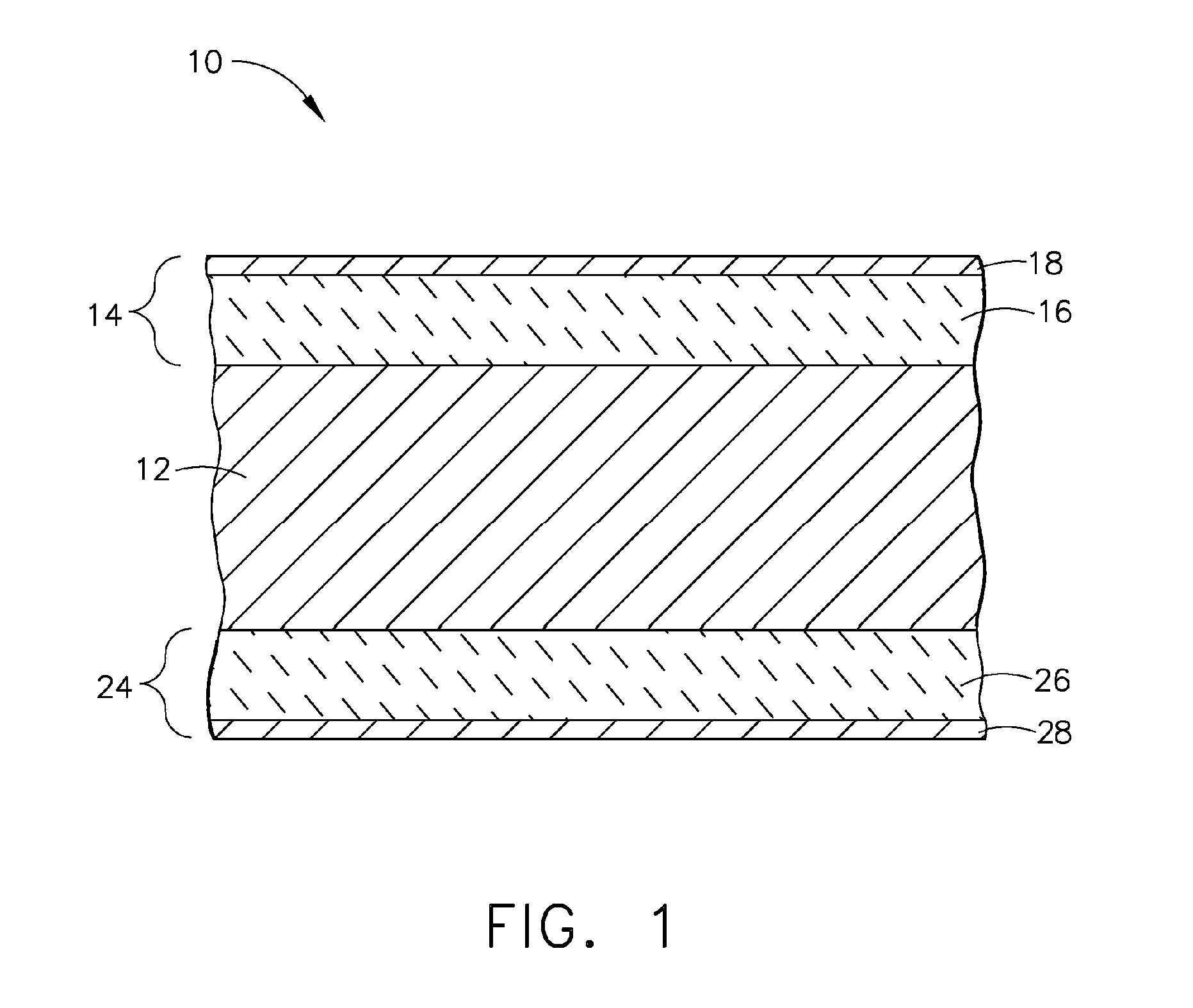

Coating system and process and apparatus for depositing a coating system

A coating system for reducing the tendency for hydrocarbon fluids, such as fuels and oils, to form carbonaceous deposits that adhere to fluid containment surfaces. The coating system combines an outermost layer of platinum with an inner ceramic barrier layer of silica and / or tantala. The platinum layer catalyzes the hydrocarbon fluid to form particles of carbonaceous gum substances, and the ceramic barrier layer seals the containment surface from the hydrocarbon fluid to eliminate attachments points for deposits and inhibit interdiffusion between the platinum layer and the containment surface. The invention also encompasses a coating apparatus and process for depositing the coating system.

Owner:GENERAL ELECTRIC CO

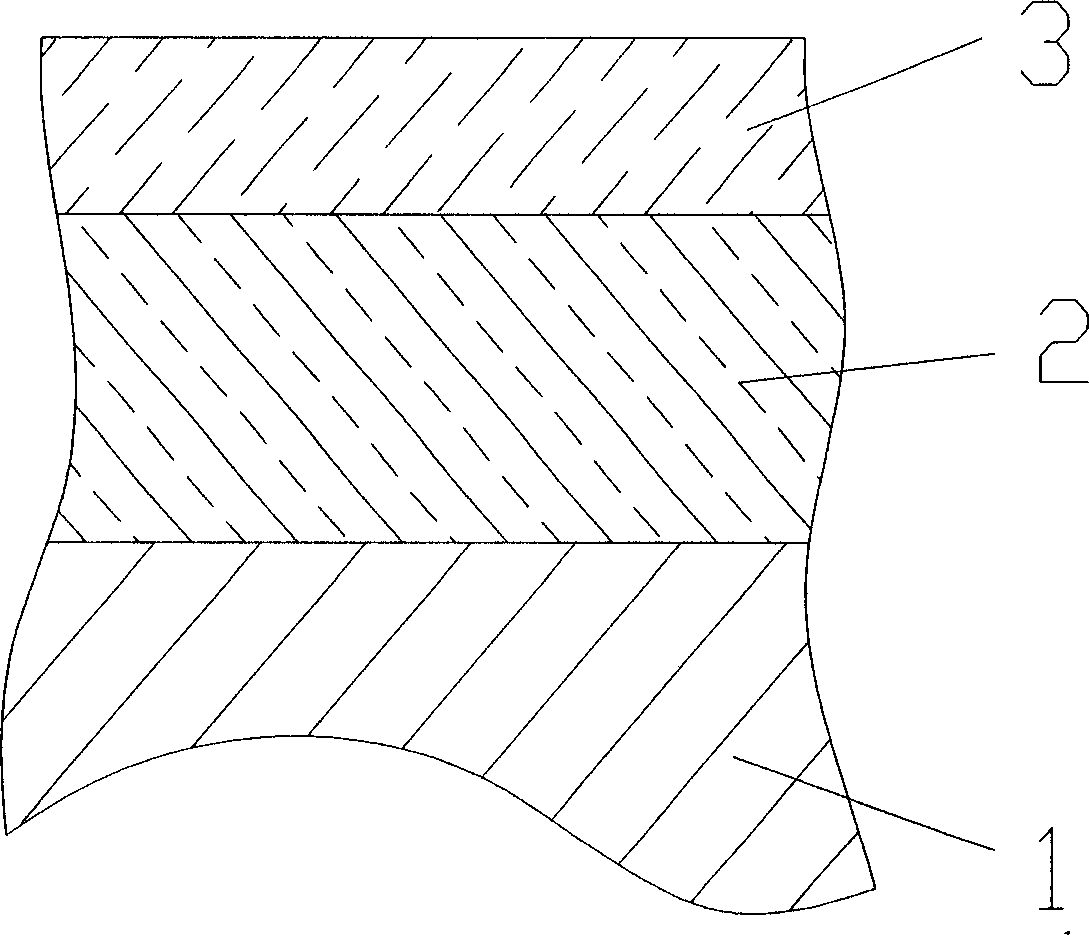

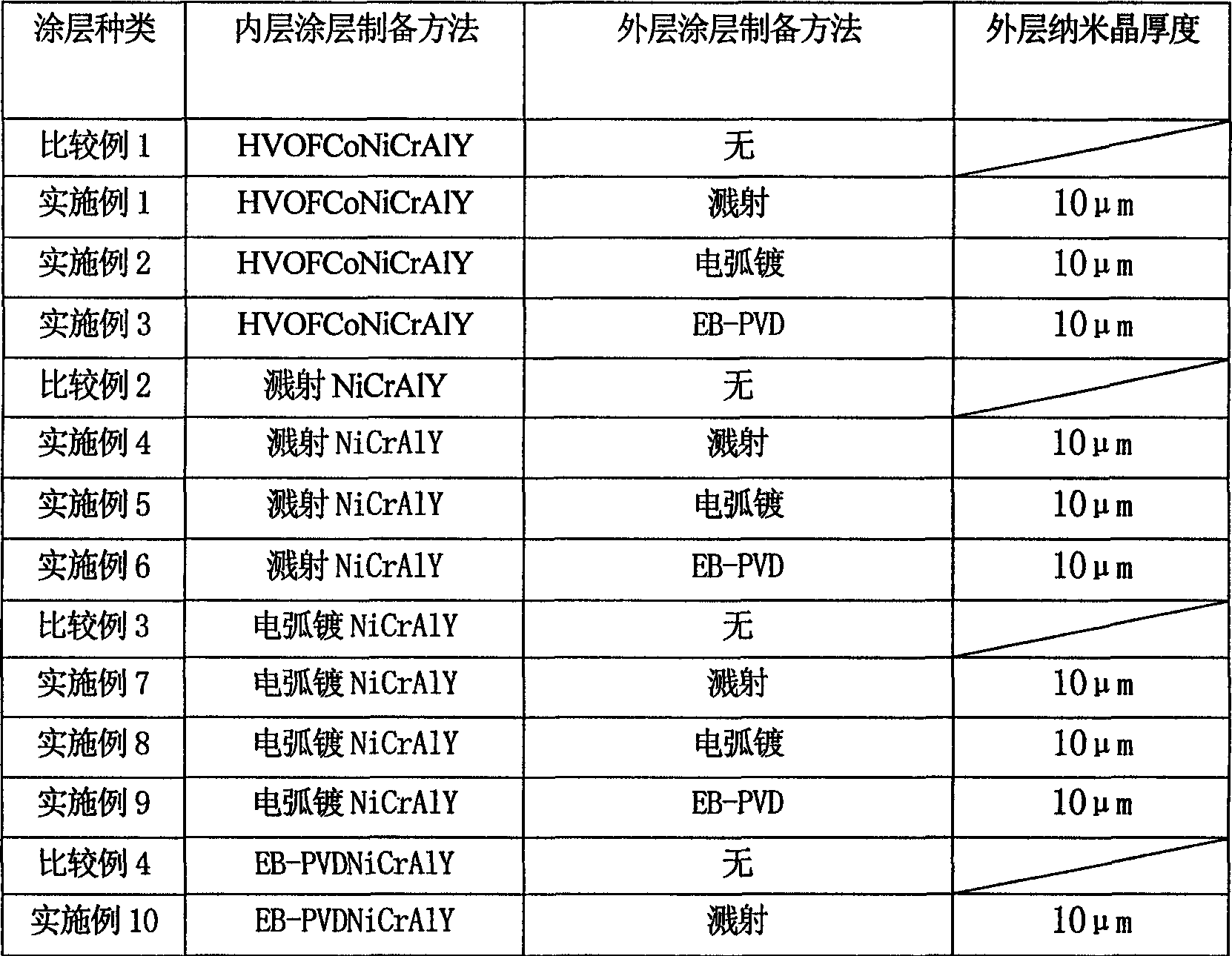

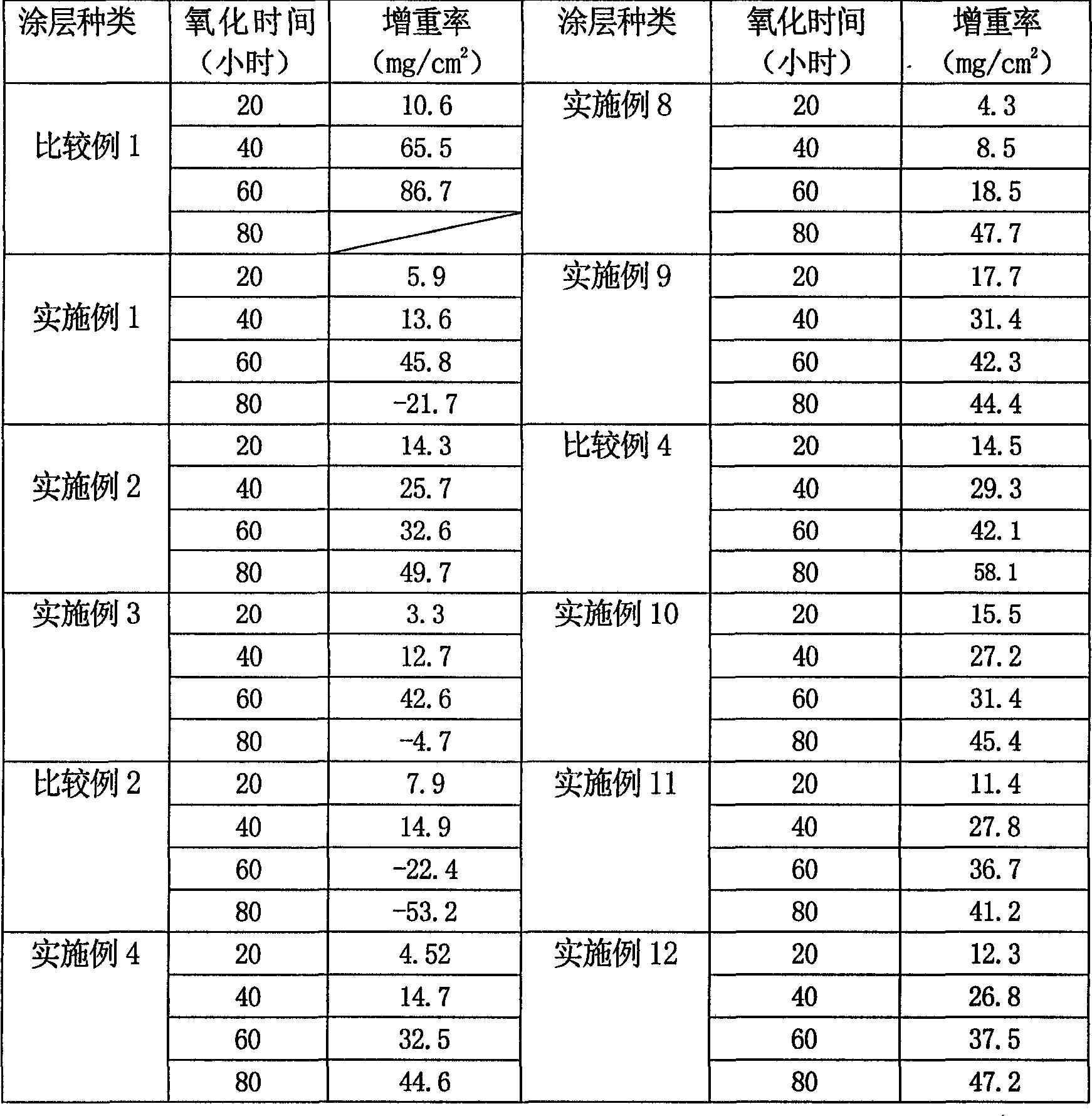

Nanometer crystalline compound coating and its prepn process

InactiveCN1846985AQuality assuranceGuaranteed service lifeMetal layered productsCoating systemHigh heat

The nanometer crystalline compound coating includes one inner MCrAlY layer, with M being mixture of Ni and / or Co, and one outer nanometer crystalline layer of Al, Cr, Y and other material in certain weight proportion. The preparation process of the nanometer crystalline compound coating includes the first preparation of the MCrAlY layer on the surface of the substrate, and the subsequent preparation of the nanometer crystalline layer on the surface of the MCrAlY layer. The present invention has low preparation cost and simple preparation process, and the nanometer crystalline compound coating has excellent heat resisting and anticorrosive performance and long service life.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

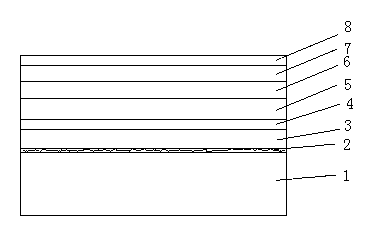

Film system structure of moderate and high temperature solar energy selective absorption coating and production method thereof

ActiveCN103234294AHigh bonding strengthNo cracking and falling offSolar heat devicesVacuum evaporation coatingTitanium nitrideDiffusion barrier

The invention discloses a production method of a film system structure of a moderate and high temperature solar energy selective absorption coating. The film system structure is characterized in that an ion etching layer, an aluminum infrared reflection film layer, a titanium nitride thermal diffusion barrier film layer, a titanium oxynitride absorbing film layer with high metal content, a titanium oxynitride absorbing film layer with low metal content, a silicon nitride antireflection film layer and a silicon dioxide antireflection film layer are sequentially arranged on one surface of a substrate. The production method of the film system structure is characterized in that firstly the surface of the metal copper substrate is etched, and then the aluminum infrared reflection film layer, the titanium nitride thermal diffusion barrier film layer, the titanium oxynitride absorbing film layer with high metal content, the titanium oxynitride absorbing film layer with low metal content, the silicon nitride antireflection film layer and the silicon dioxide antireflection film layer are sequentially plated. The production method has the advantages of being simple, easy to control, good in product quality, suitable for industrial mass production and the like.

Owner:JIANGSU DOCTORXIA SOLAR ENERGY

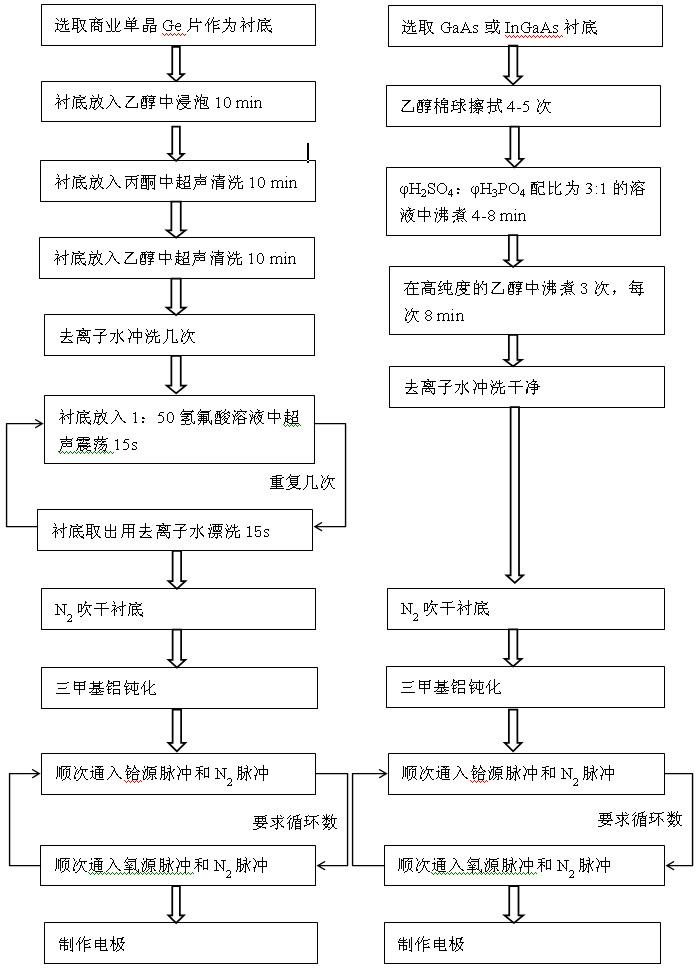

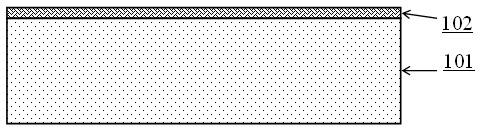

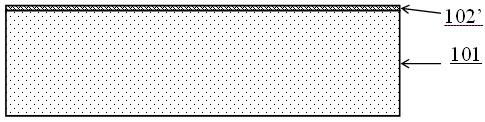

High-mobility MOS (Metal Oxide Semiconductor) capacitor and manufacturing method thereof

InactiveCN102403367APrevent interdiffusionReduce defect charge and interface state densitySemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorState density

The invention belongs to the technical field of a semiconductor and particularly relates to a high-mobility MOS (Metal Oxide Semiconductor) capacitor and a manufacturing method thereof. The MOS capacitor structure is in sequence provided with a mobility substrate, a trimethyl aluminum purification layer, an HfO2 grid medium layer and an electrode. The manufacturing method for the high-mobility MOS capacitor comprises the following steps of: washing the high-mobility substrate; forming the trimethyl aluminum purification layer on the surface of the substrate; depositing the HfO2 grid medium by ALD; and making the electrode. The trimethyl aluminum purification layer can reduce residual oxide content on the surface of the substrate to reduce interfacial state density with the grid medium material so as to improve interface properties. The deposited HfO2 medium layer has accurate controllability of film thickness, excellent conformality, good interface control capability and wonderful large area uniformity, so that electric properties of the MOS capacitor are greatly improved, thereby improving the performance of the MOS transistor.

Owner:FUDAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com