Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

567 results about "Trench mosfet" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

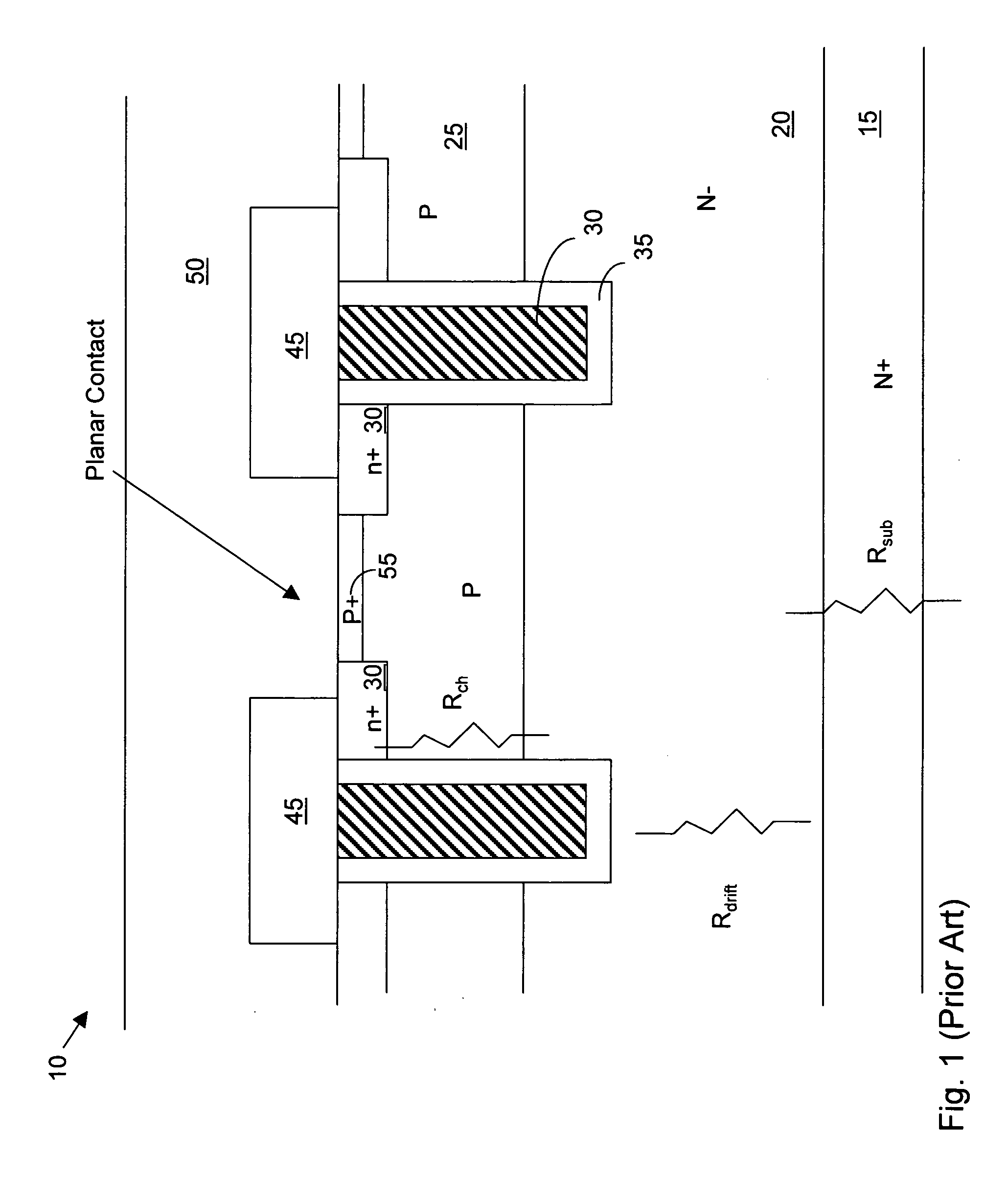

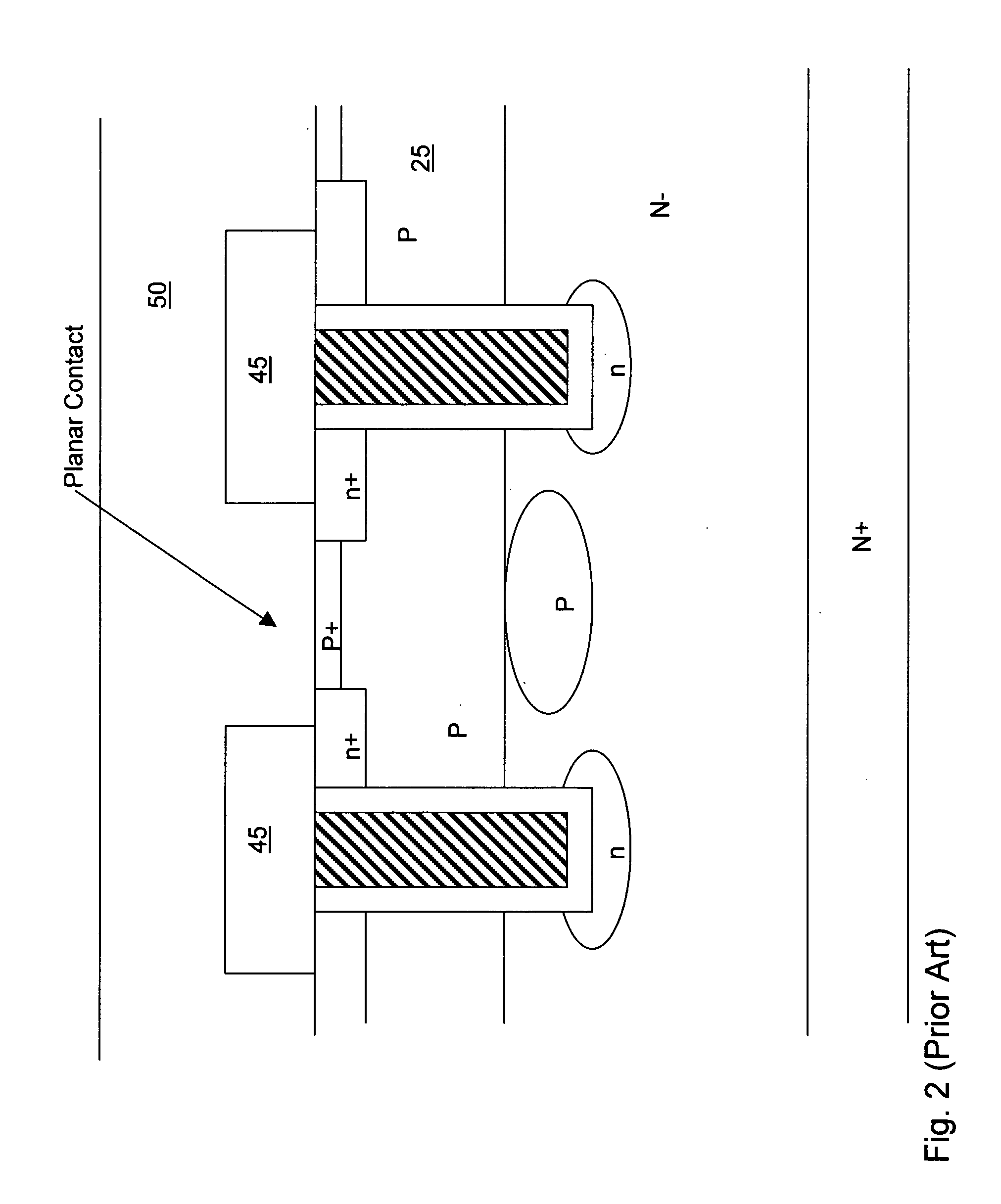

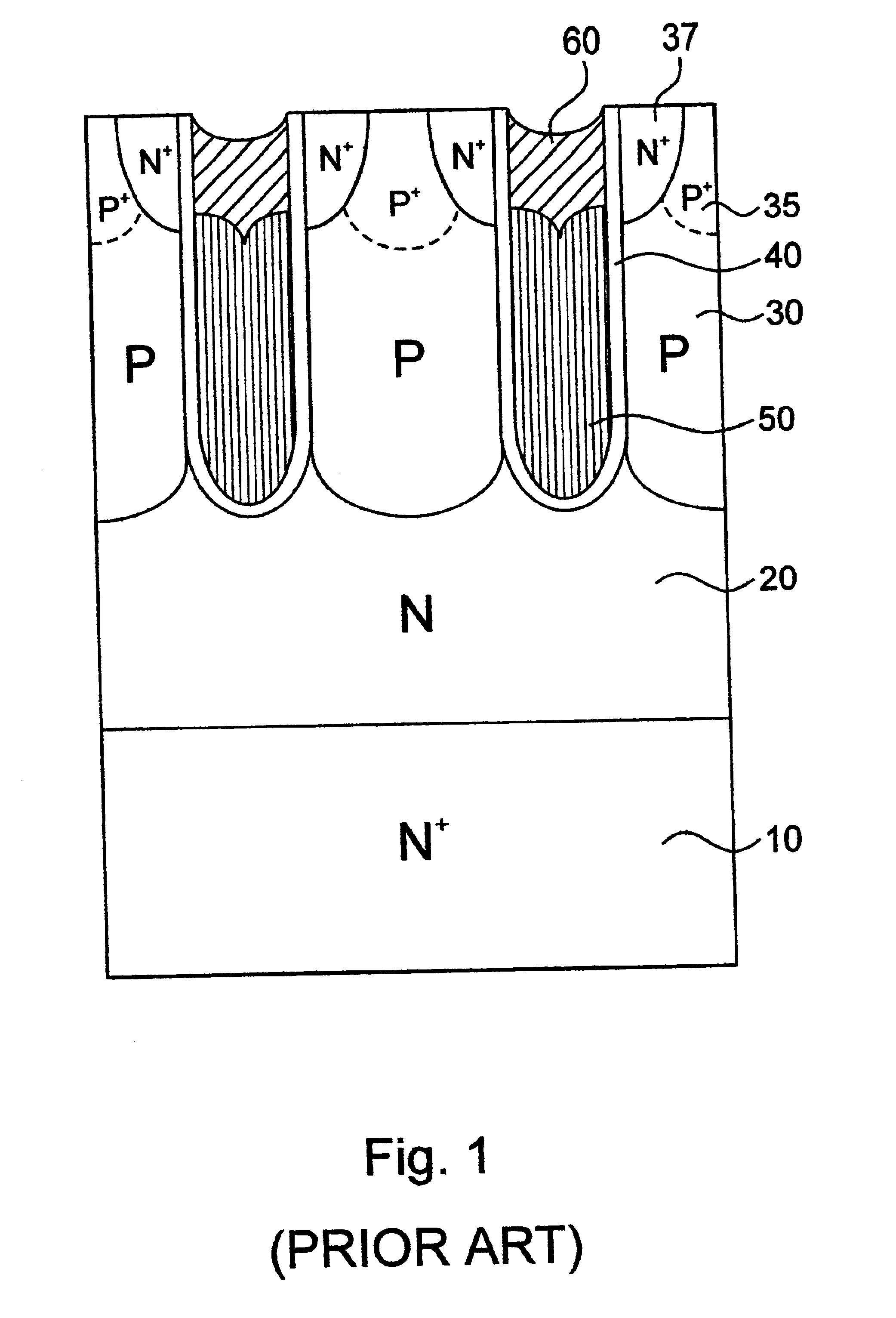

The Trench MOSFET has a field plate that extends into the drift region which is electrically coupled with the source. This arrangement helps to deplete the drift region when the MOSFET turns off. Unlike other planar Power MOSFETS, trench MOSFET is used in low voltage applications.

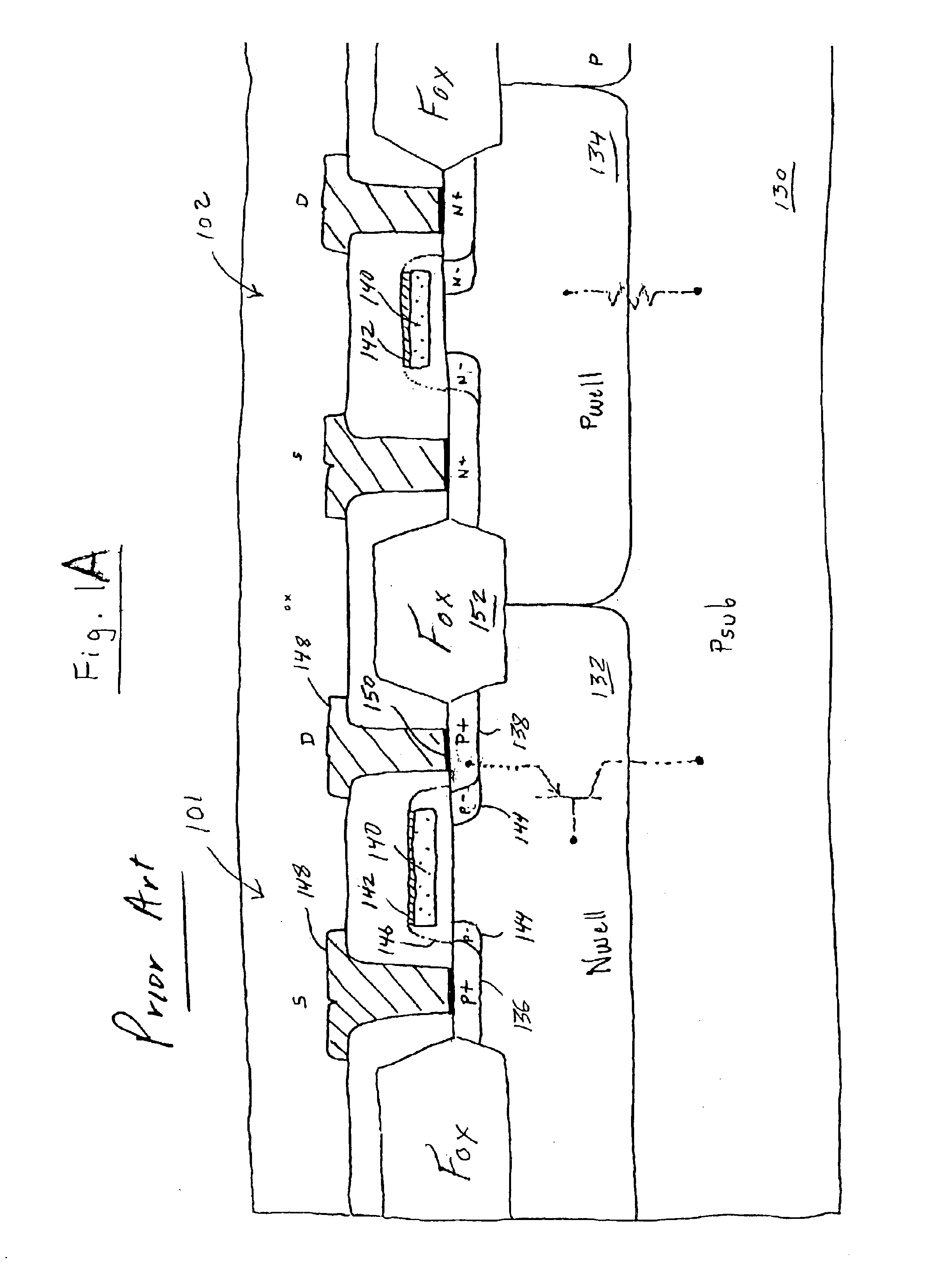

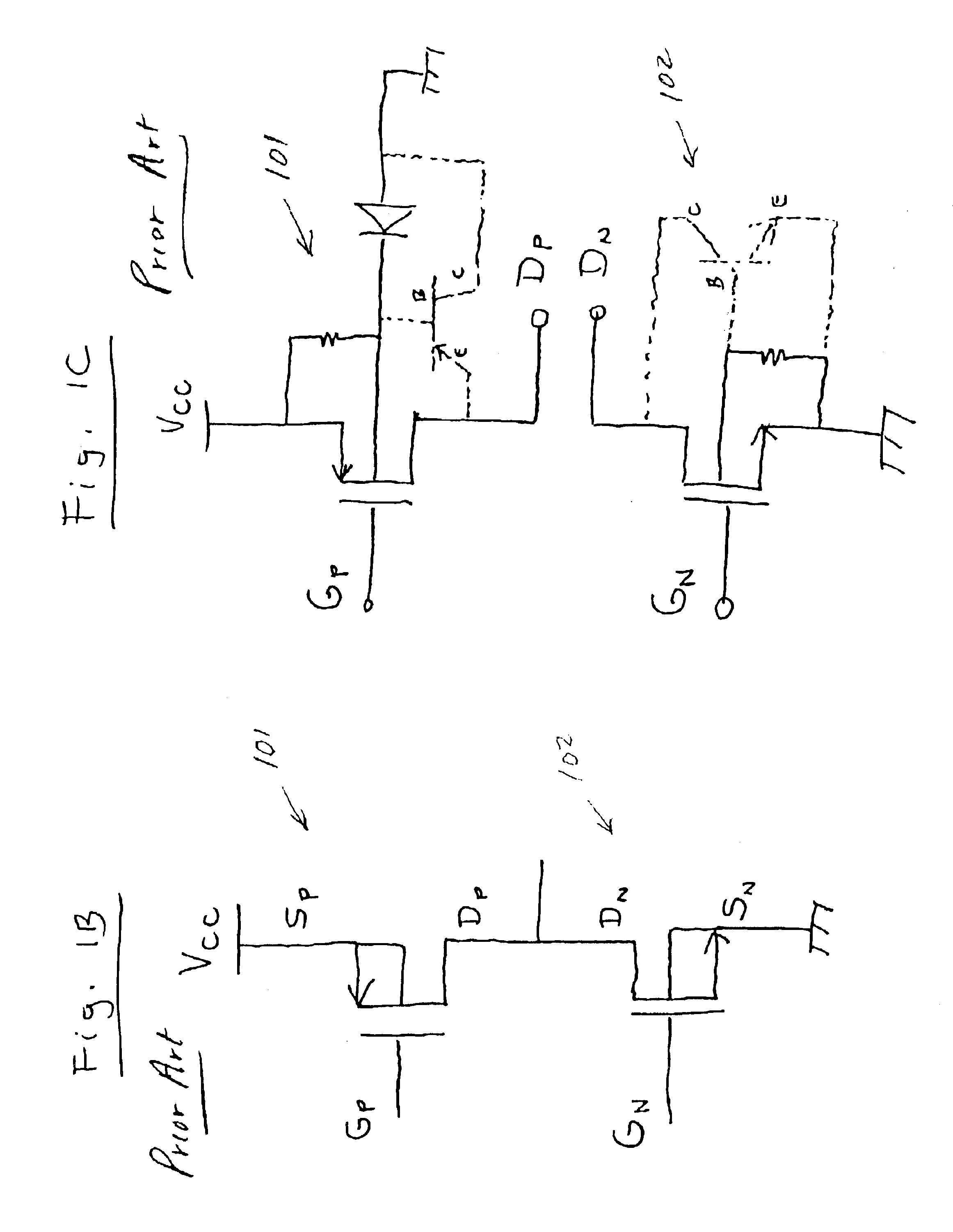

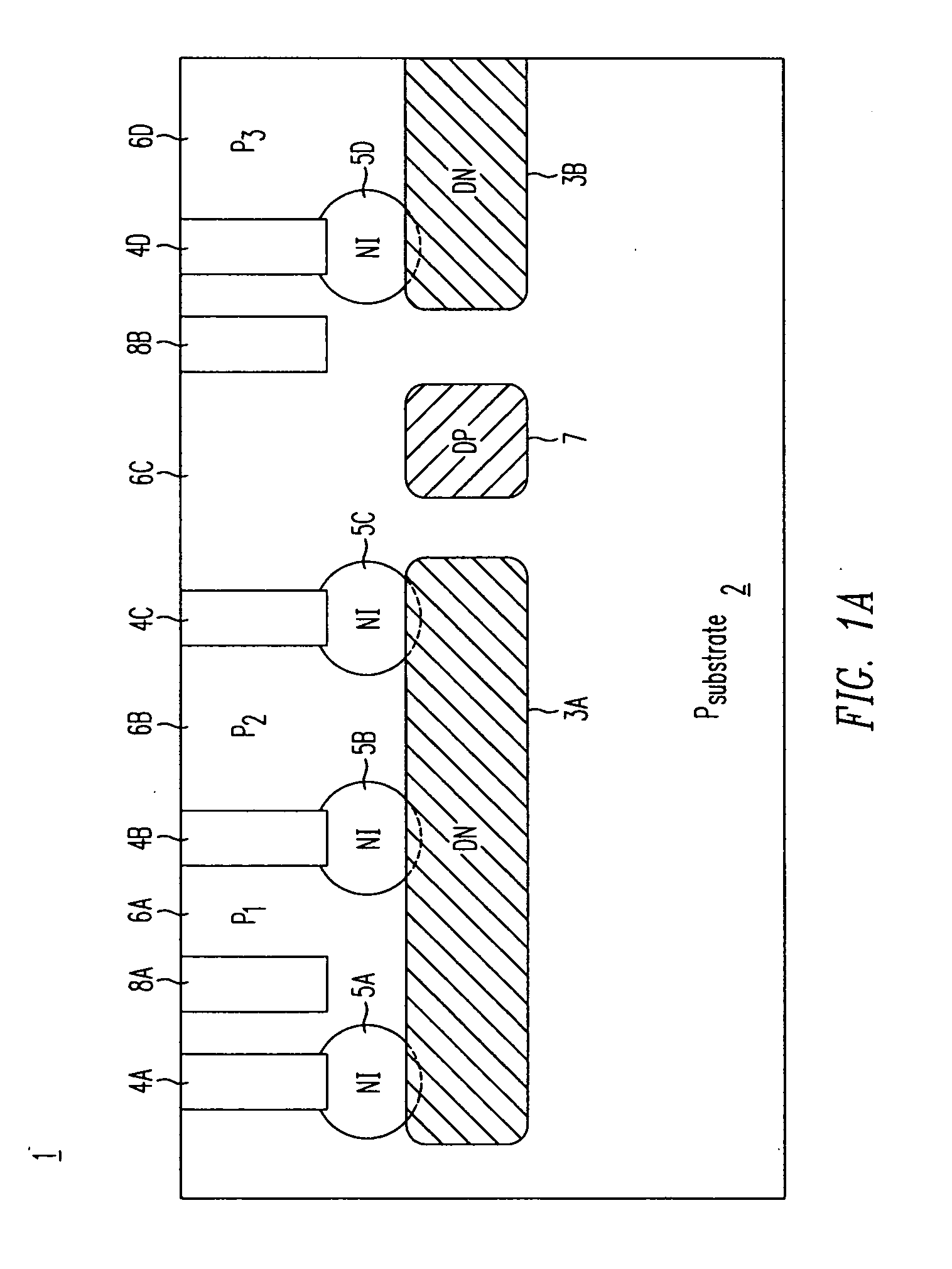

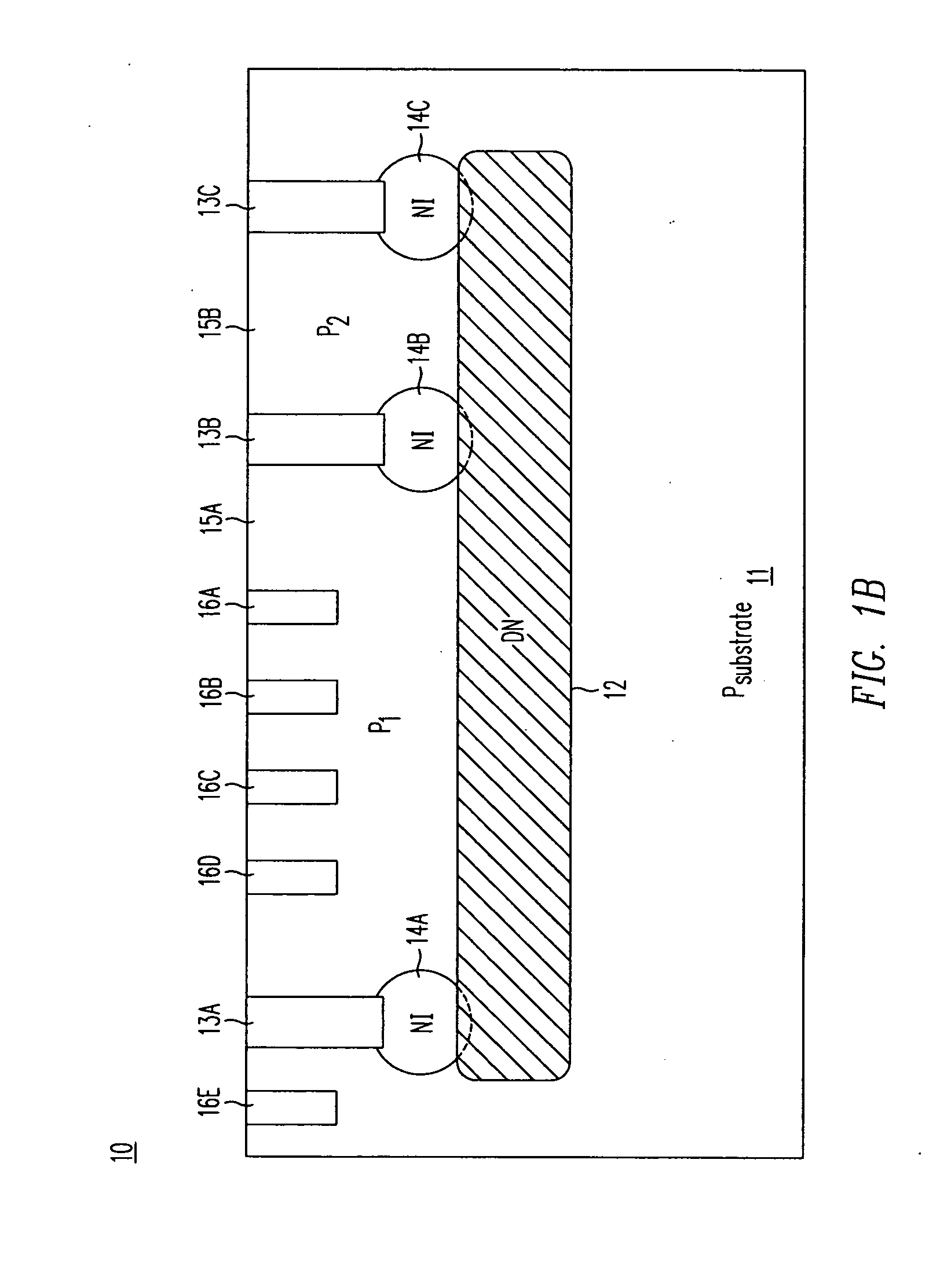

Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology

A family of semiconductor devices is formed in a substrate that contains no epitaxial layer. In one embodiment the family includes a 5V CMOS pair, a 12V CMOS pair, a 5V NPN, a 5V PNP, several forms of a lateral trench MOSFET, and a 30V lateral N-channel DMOS. Each of the devices is extremely compact, both laterally and vertically, and can be fully isolated from all other devices in the substrate.

Owner:ADVANCED ANALOGIC TECH (HONG KONG) LTD +1

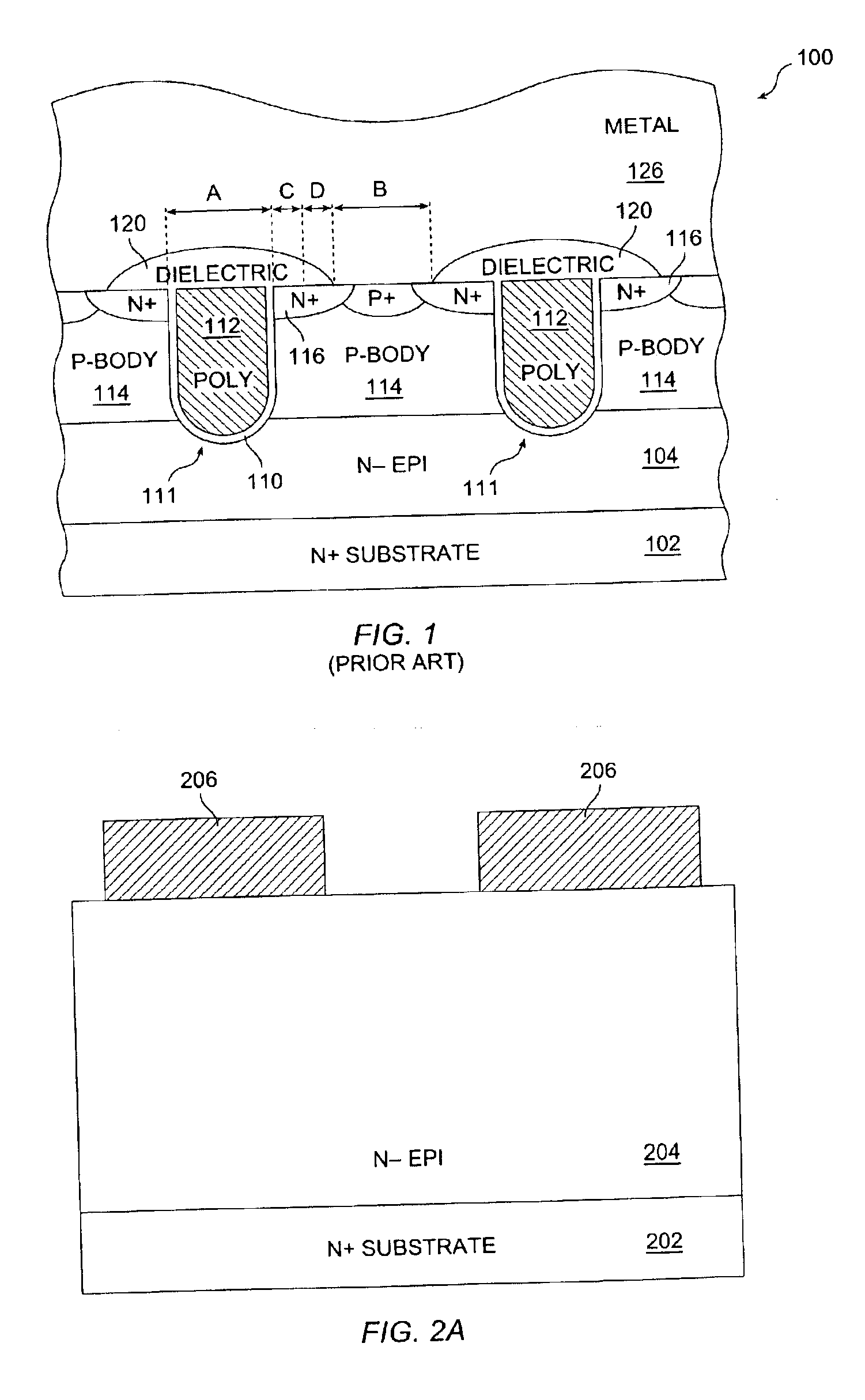

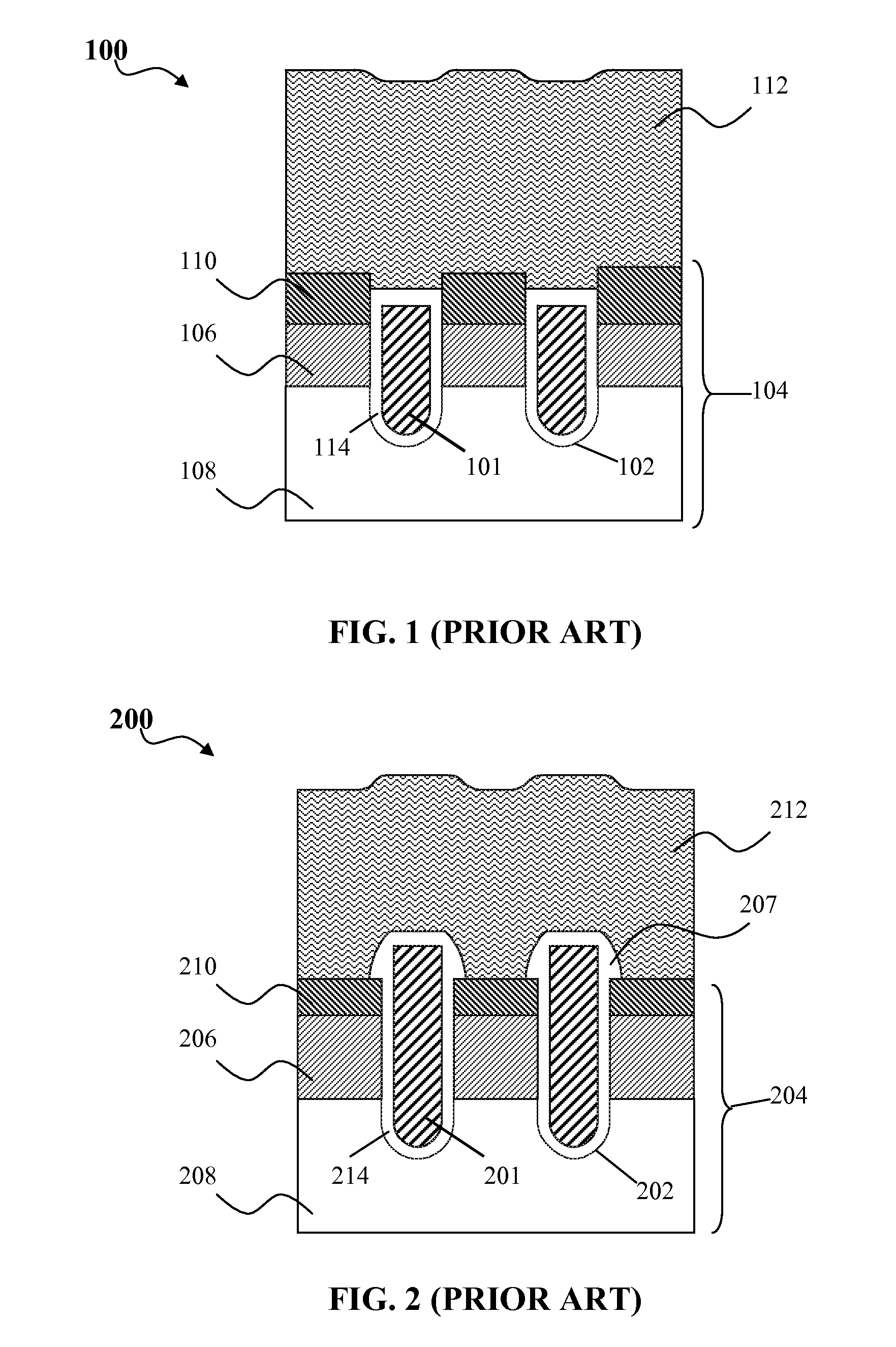

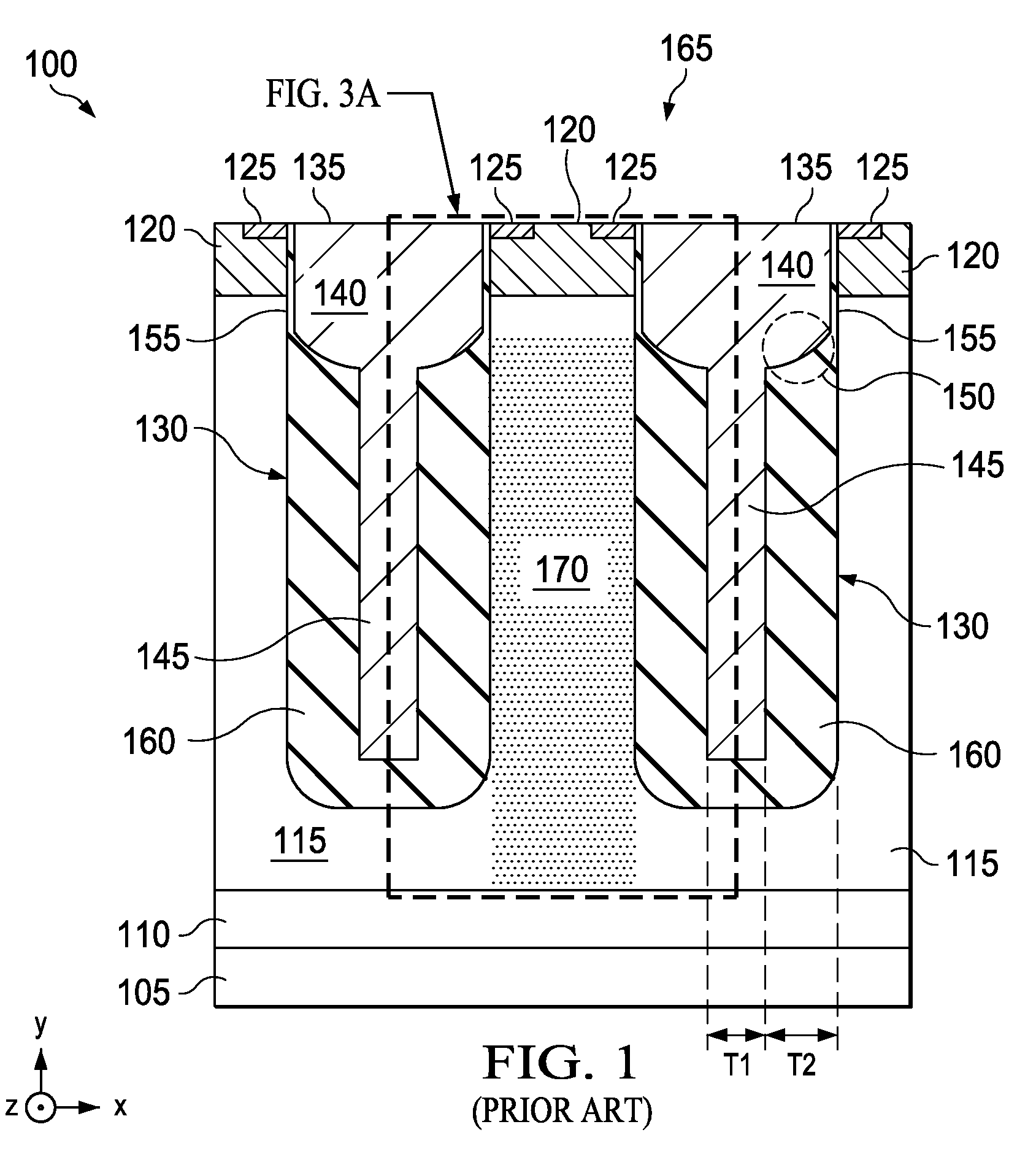

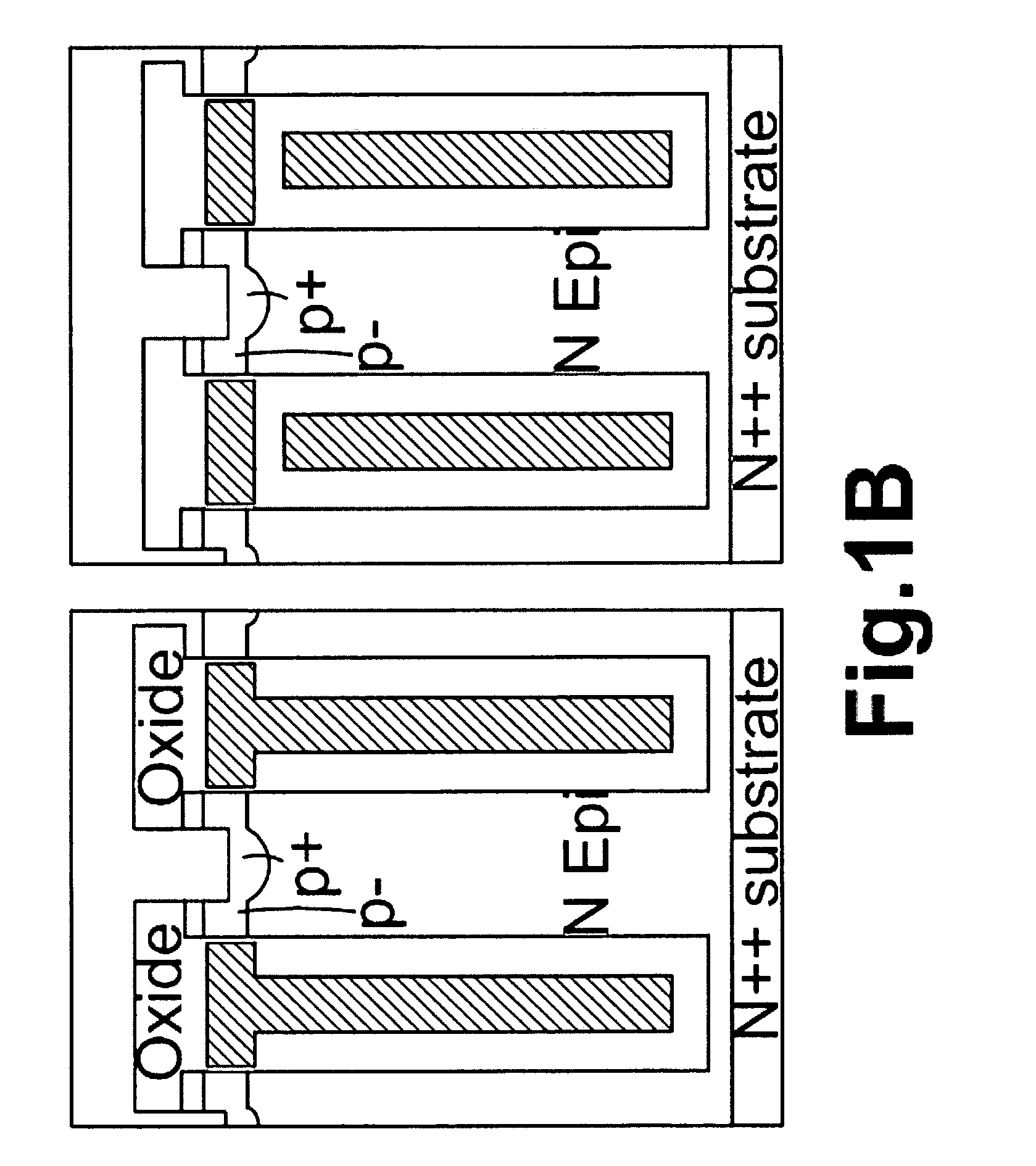

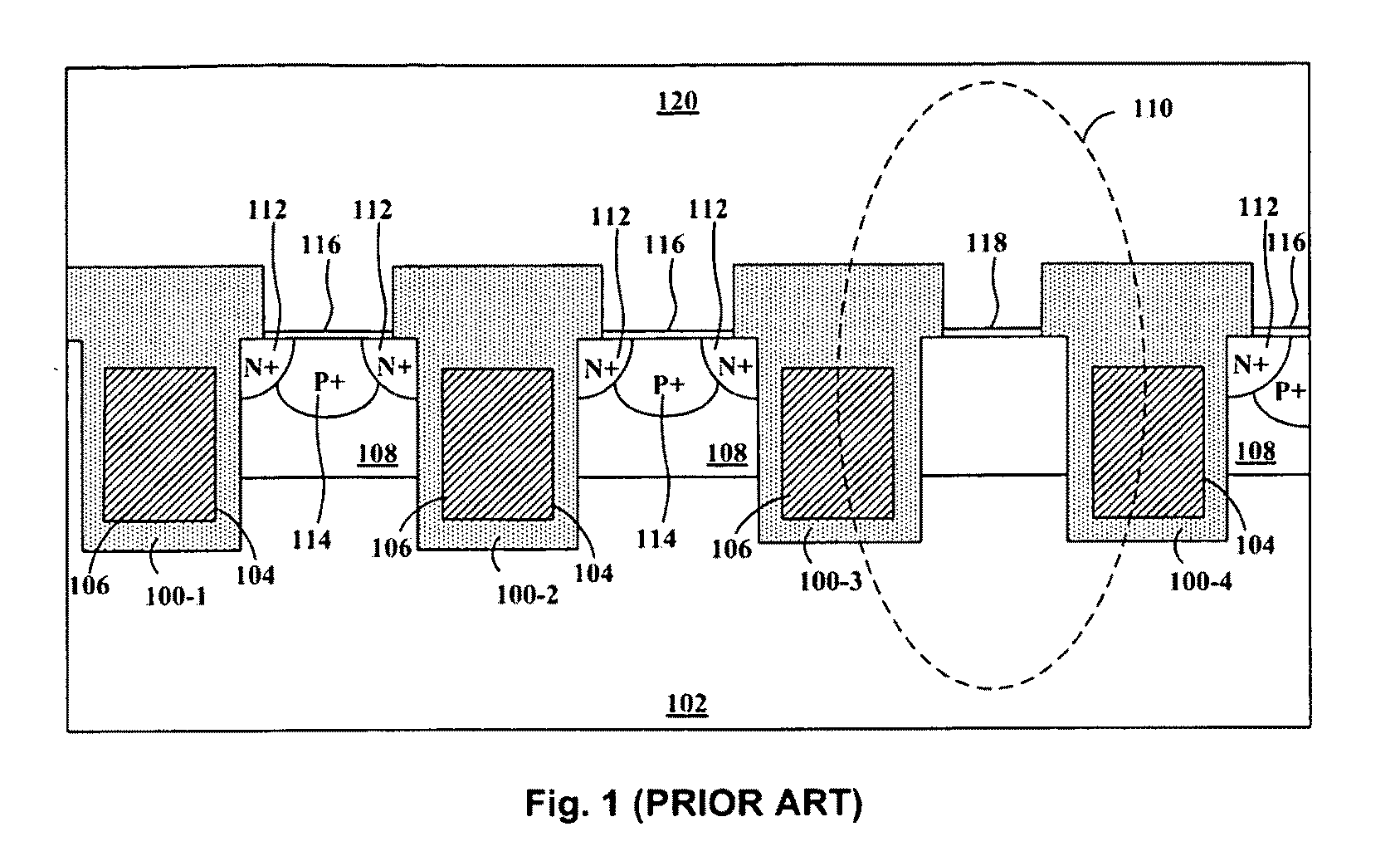

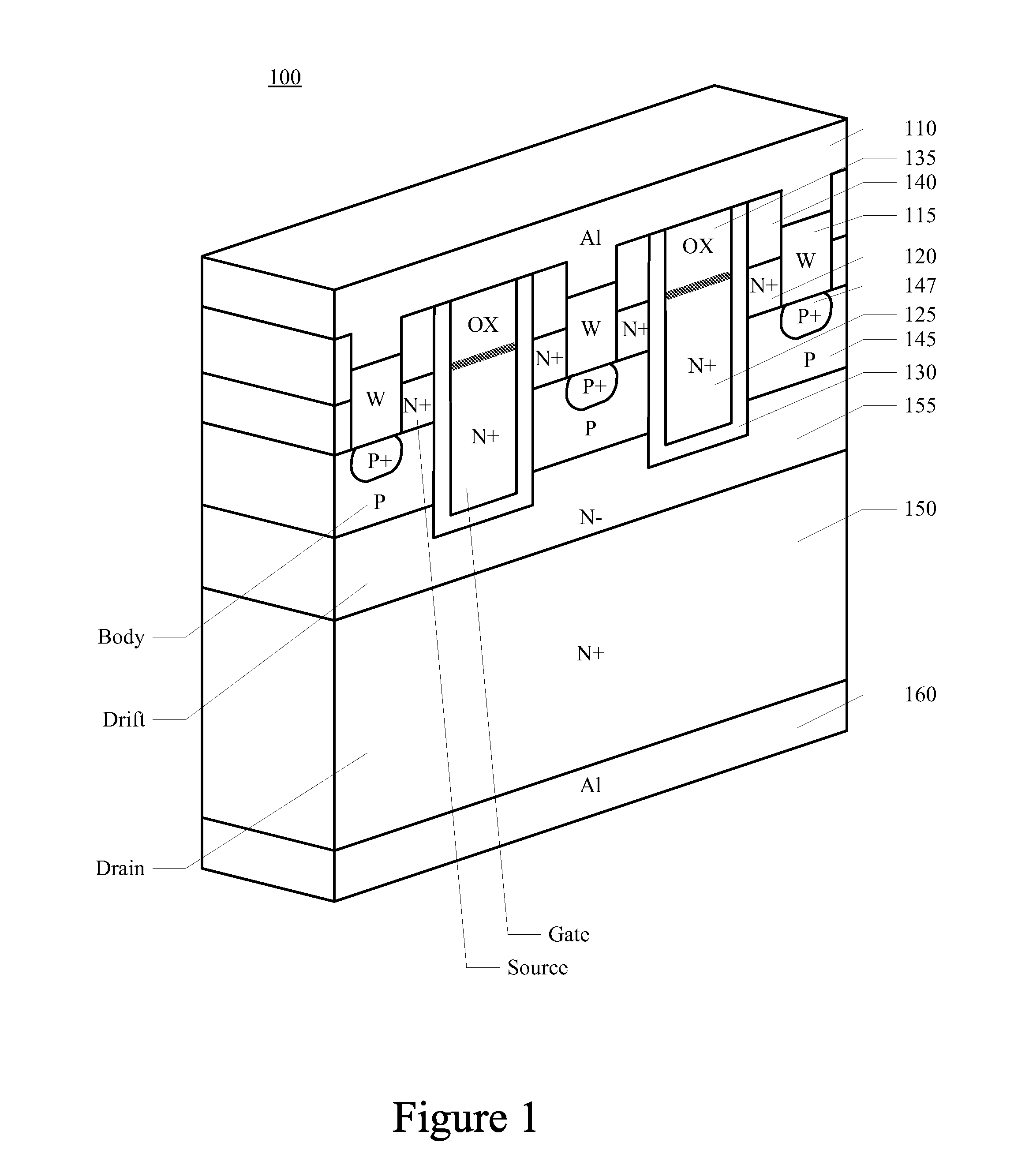

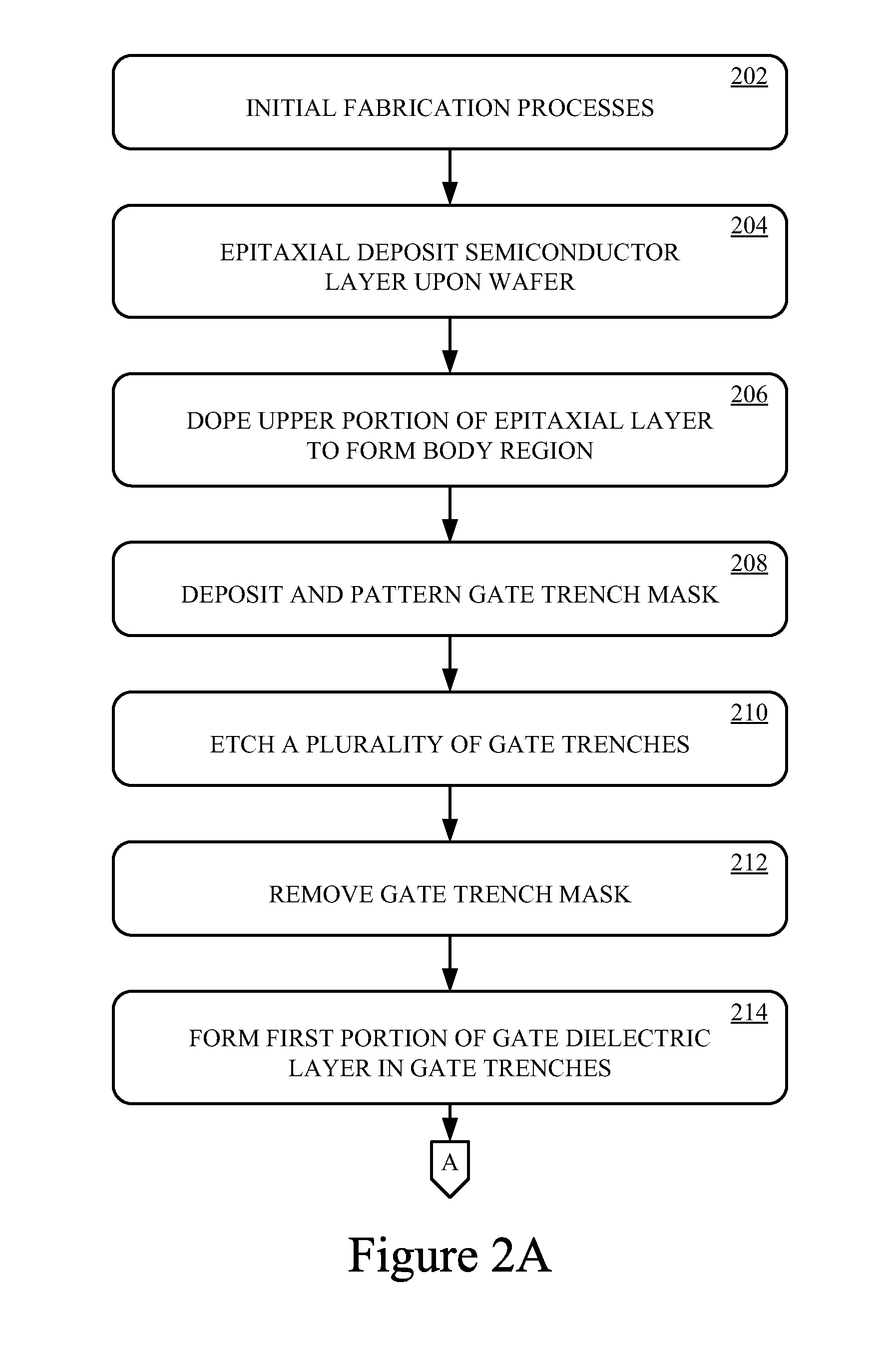

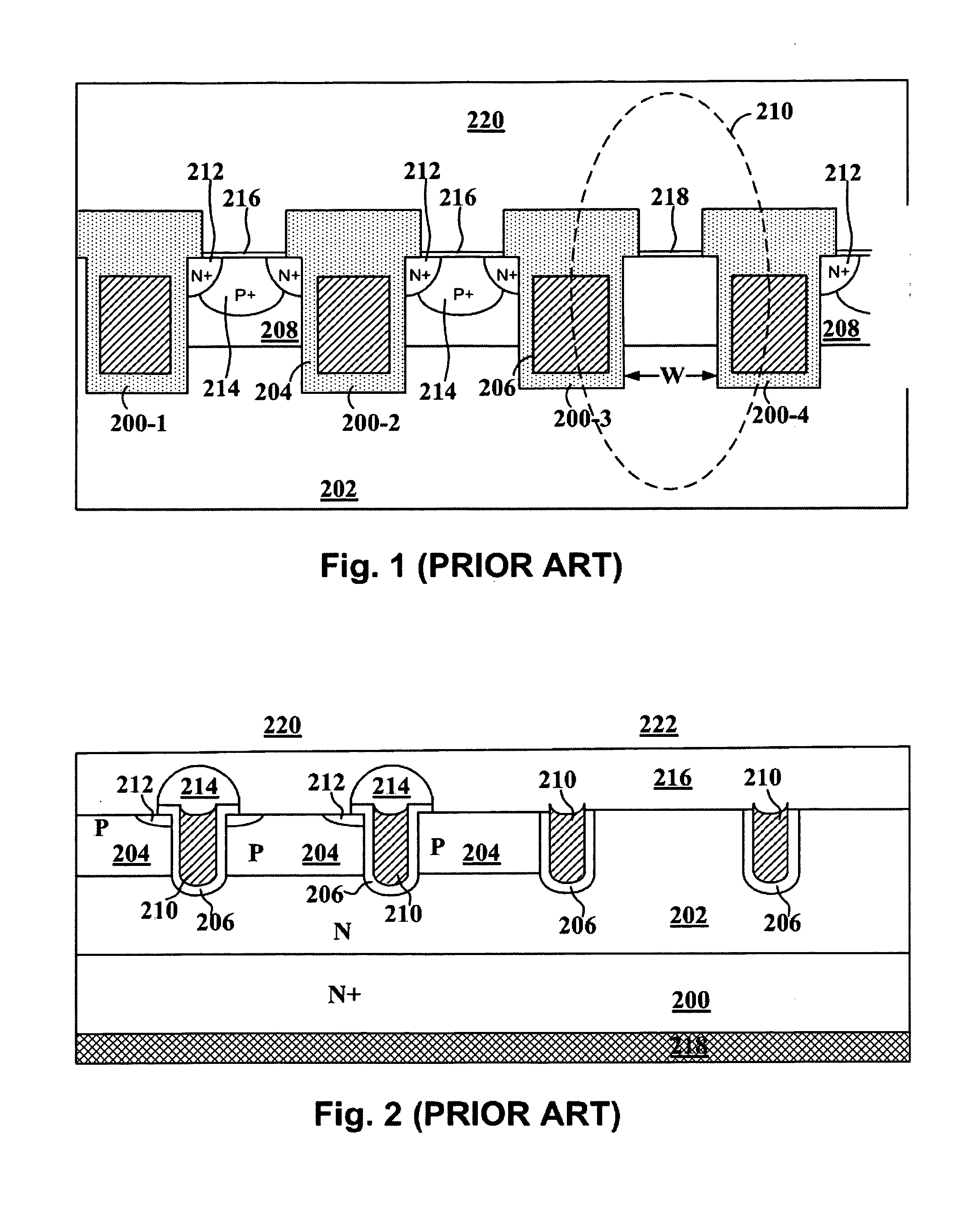

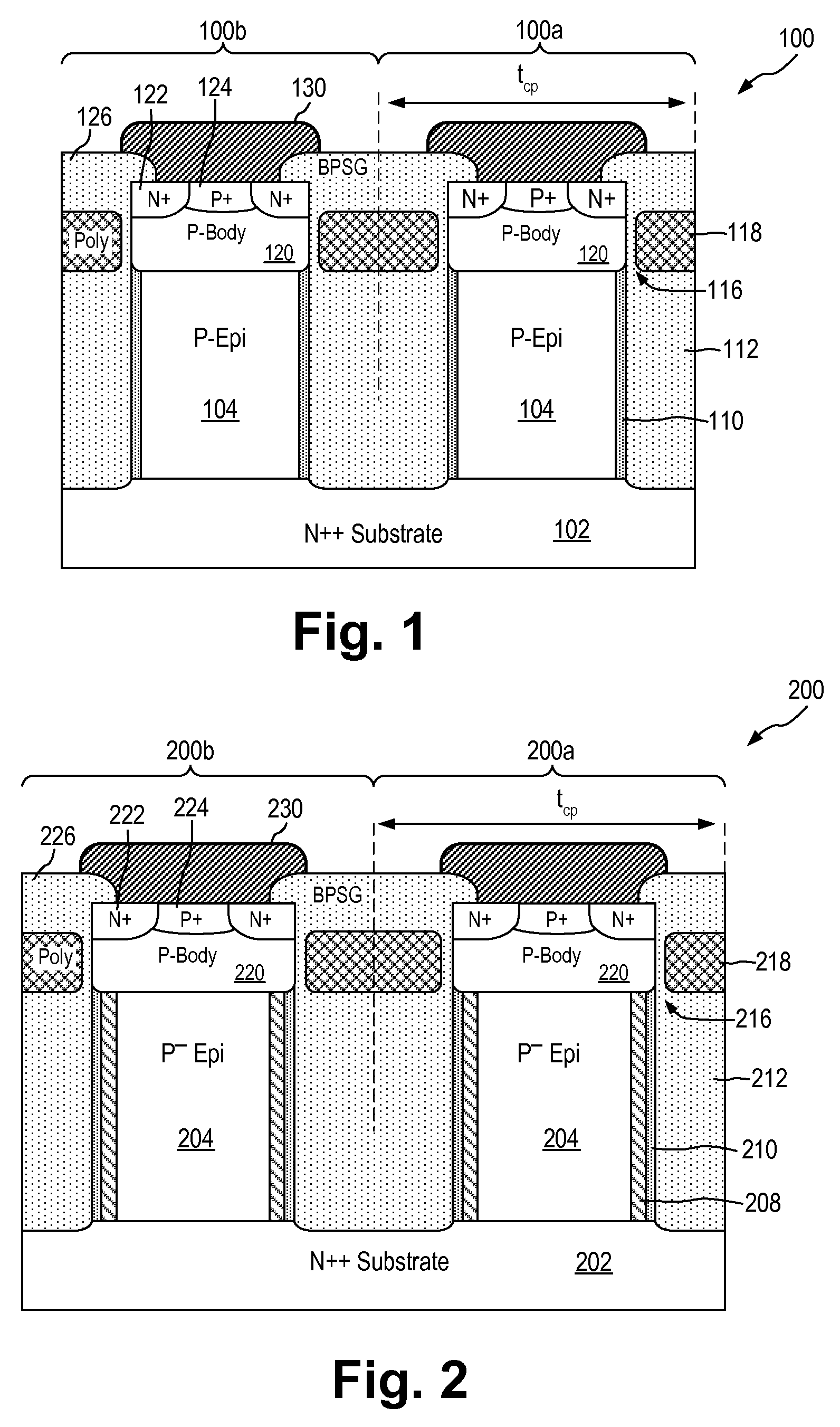

High density trench MOSFET with reduced on-resistance

InactiveUS20070114599A1Reduce resistanceImprove breakdown voltageSemiconductor devicesInsulation layerBody contact

Owner:M MOS SEMICON

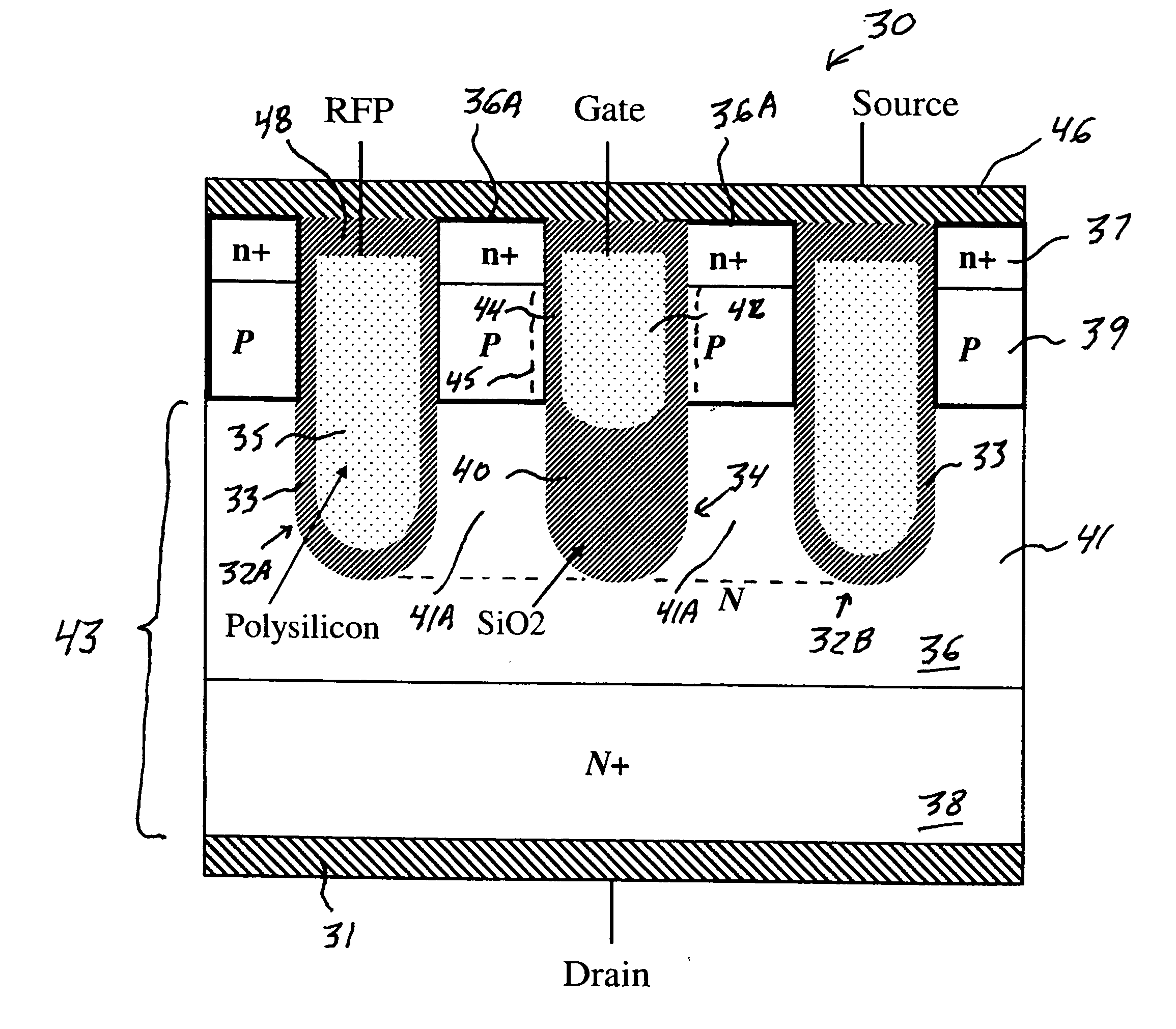

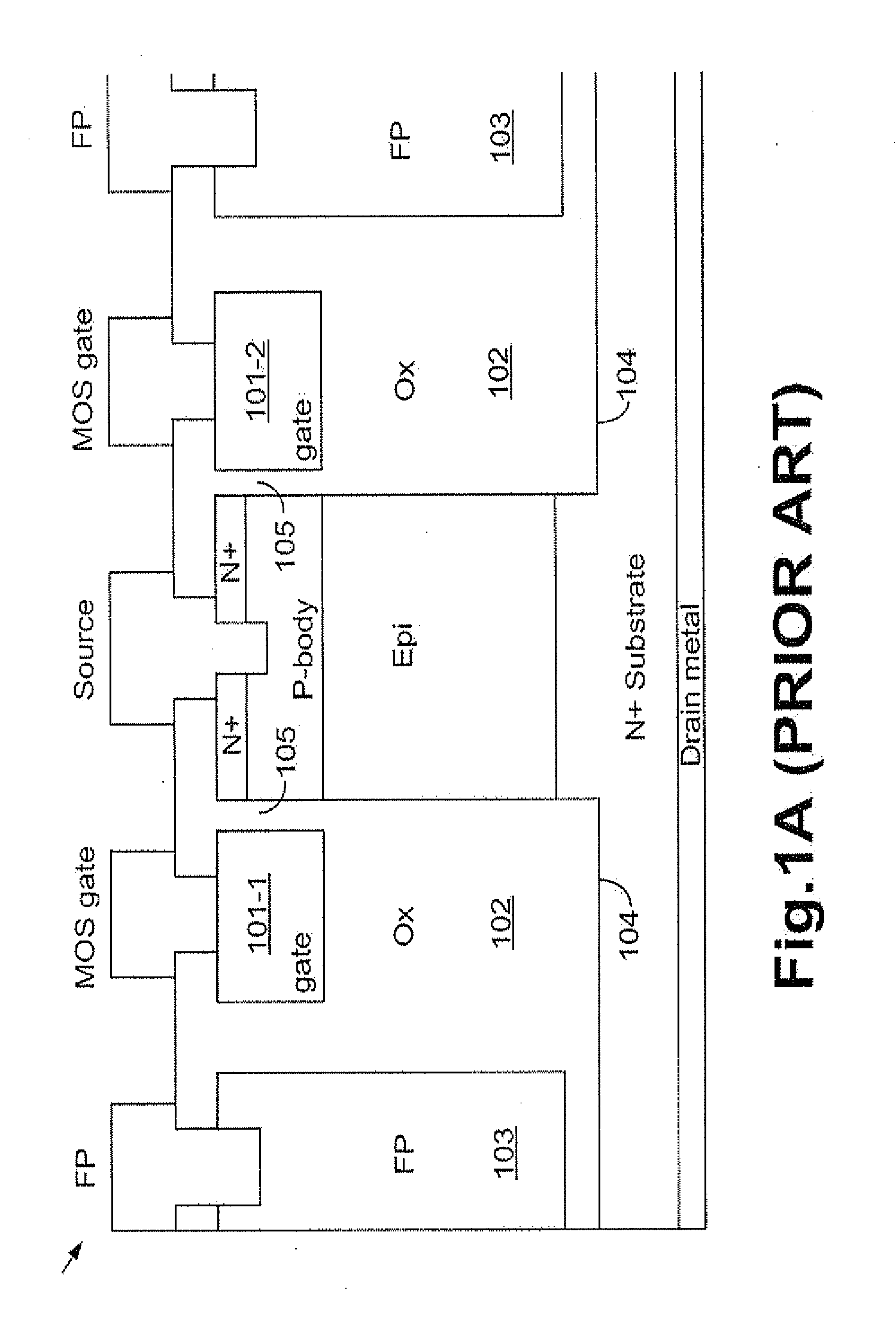

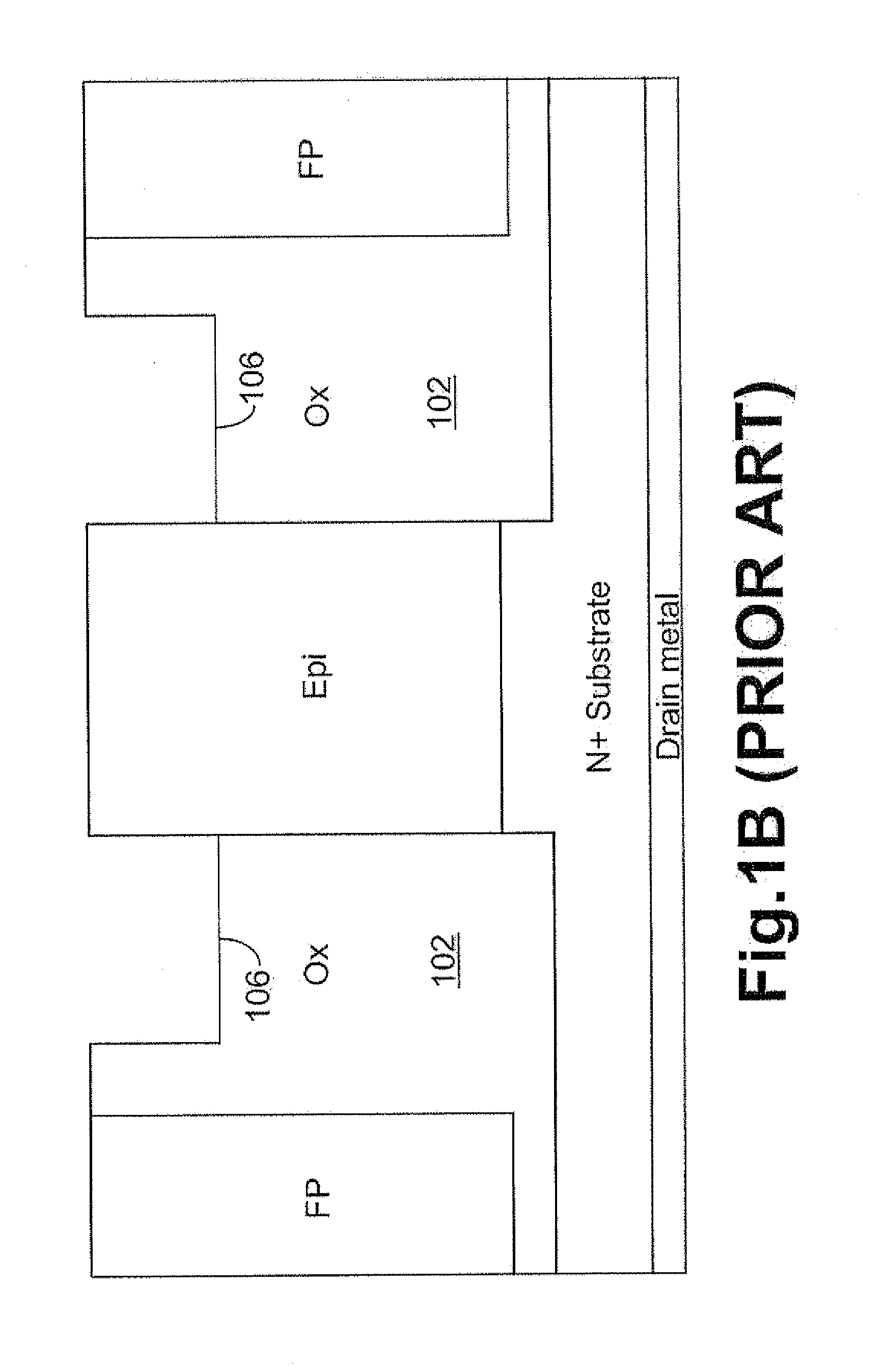

Power MOSFET with recessed field plate

ActiveUS20080073707A1Solid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetReverse recovery

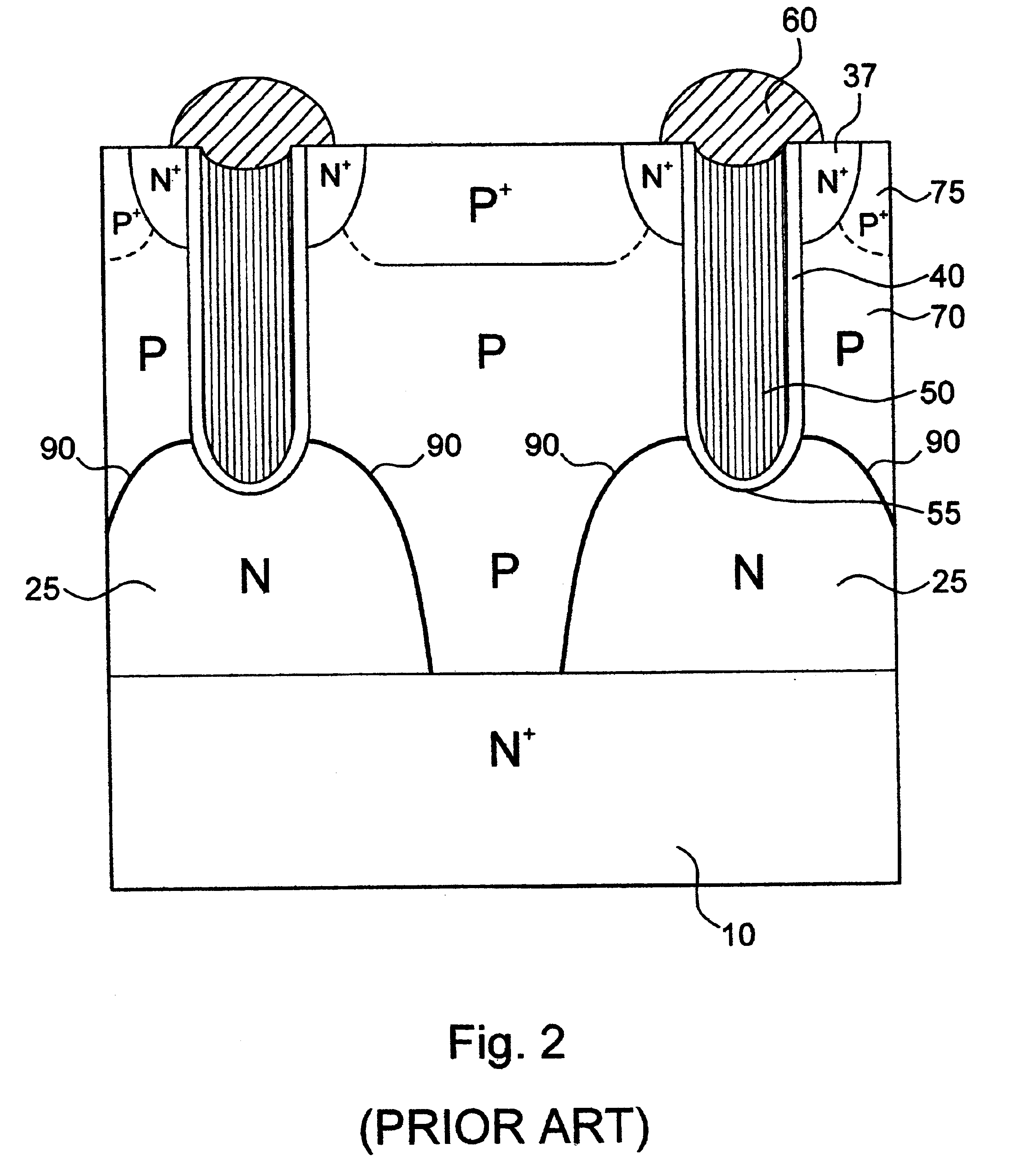

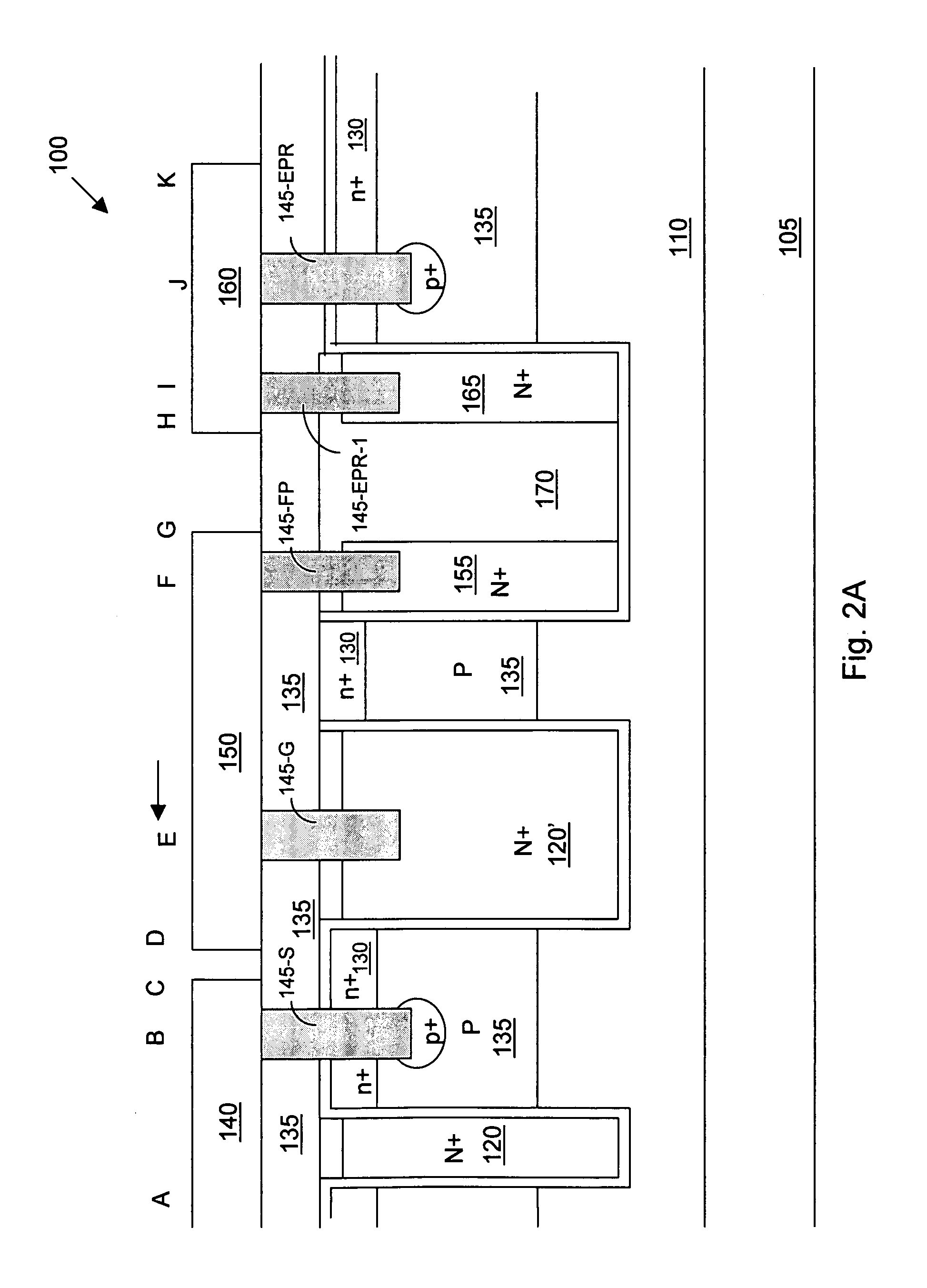

A trench MOSFET contains a recessed field plate (RFP) trench adjacent the gate trench. The RFP trench contains an RFP electrode insulated from the die by a dielectric layer along the walls of the RFP trench. The gate trench has a thick bottom oxide layer, and the gate and RFP trenches are preferably formed in the same processing step and are of substantially the same depth. When the MOSFET operates in the third quadrant (with the source / body-to-drain junction forward-biased), the combined effect of the RFP and gate electrodes significantly reduces in the minority carrier diffusion current and reverse-recovery charge. The RFP electrode also functions as a recessed field plates to reduce the electric field in the channel regions when the MOSFET source / body to-drain junction reverse-biased.

Owner:MAXPOWER SEMICON INC

Semiconductor device and manufacturing method of the same

InactiveUS20090140327A1Increase impurity concentrationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetElectrode Contact

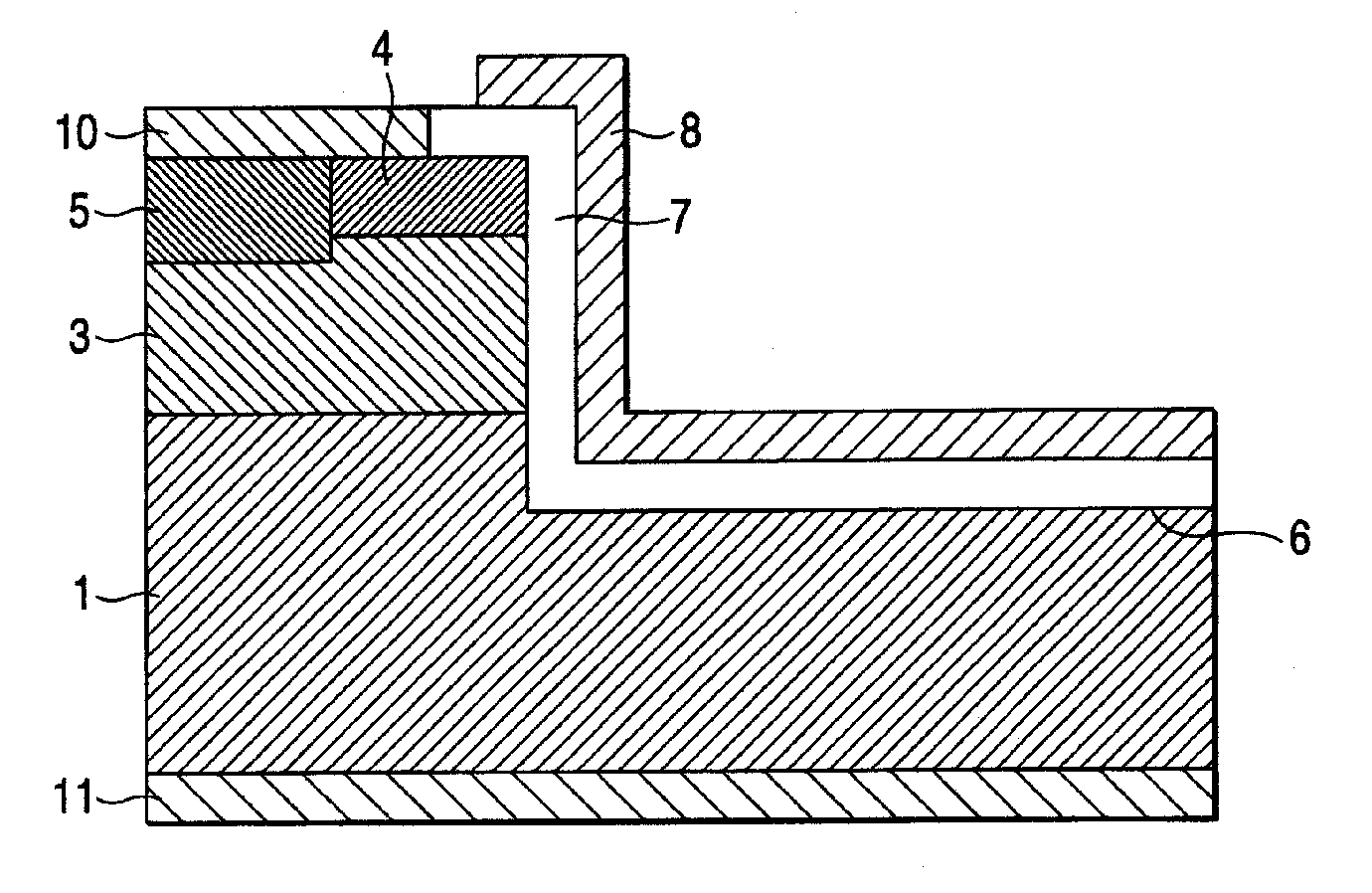

The vertical trench MOSFET comprises: an N type epitaxial region formed on an upper surface of an N+ type substrate having a drain electrode on a lower surface thereof; a gate trench extending from a front surface into the N type epitaxial region; a gate electrode positioned in the gate trench so as to interpose an insulator; a channel region formed on the N type epitaxial region; a source region formed on the channel region; a source electrode formed on the source region; a source trench extending from the front surface into the N type epitaxial region; and a trench-buried source electrode positioned in the source trench so as to interpose an insulator, wherein the source electrode contacts with the trench-buried source electrode.

Owner:RENESAS ELECTRONICS CORP

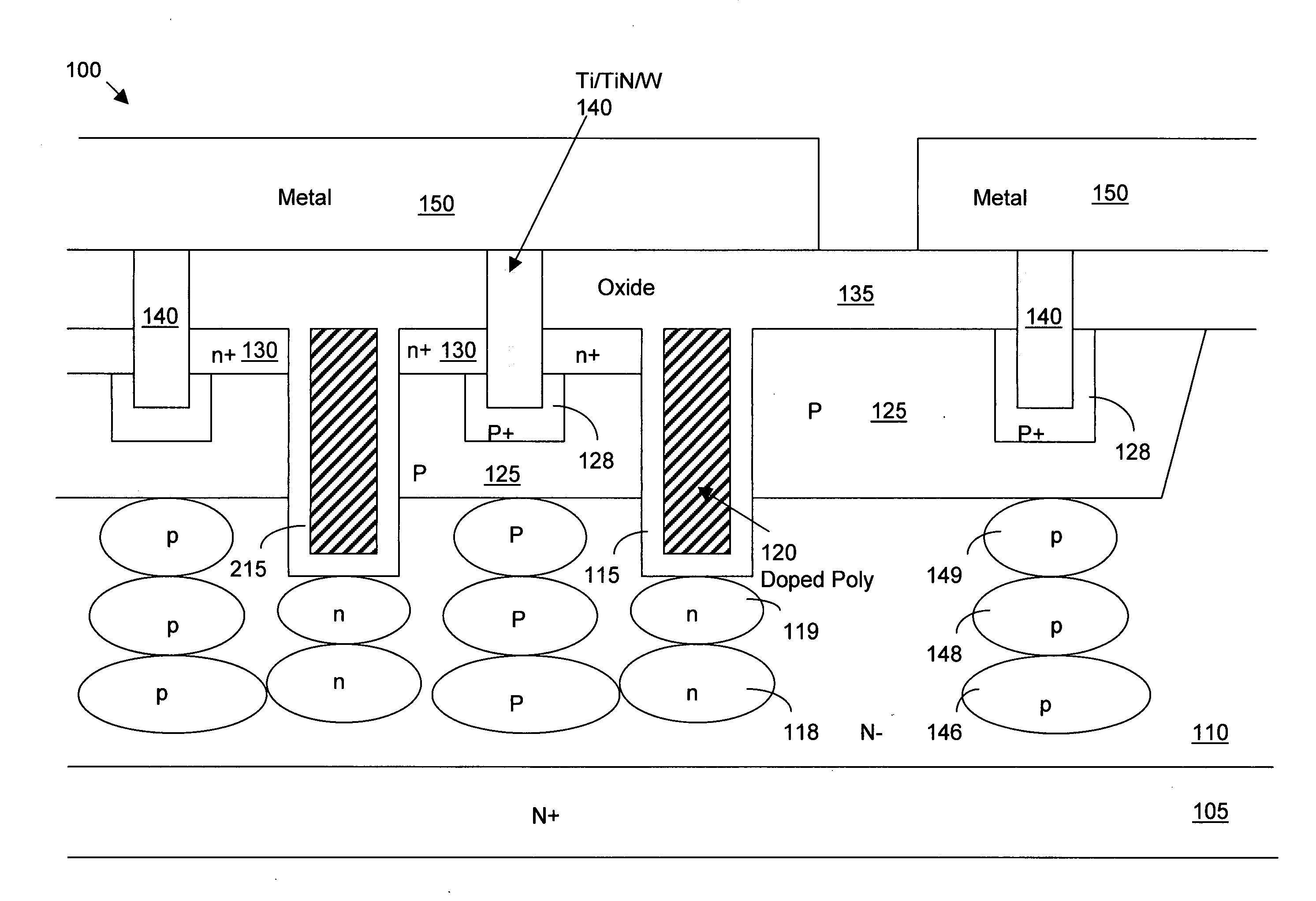

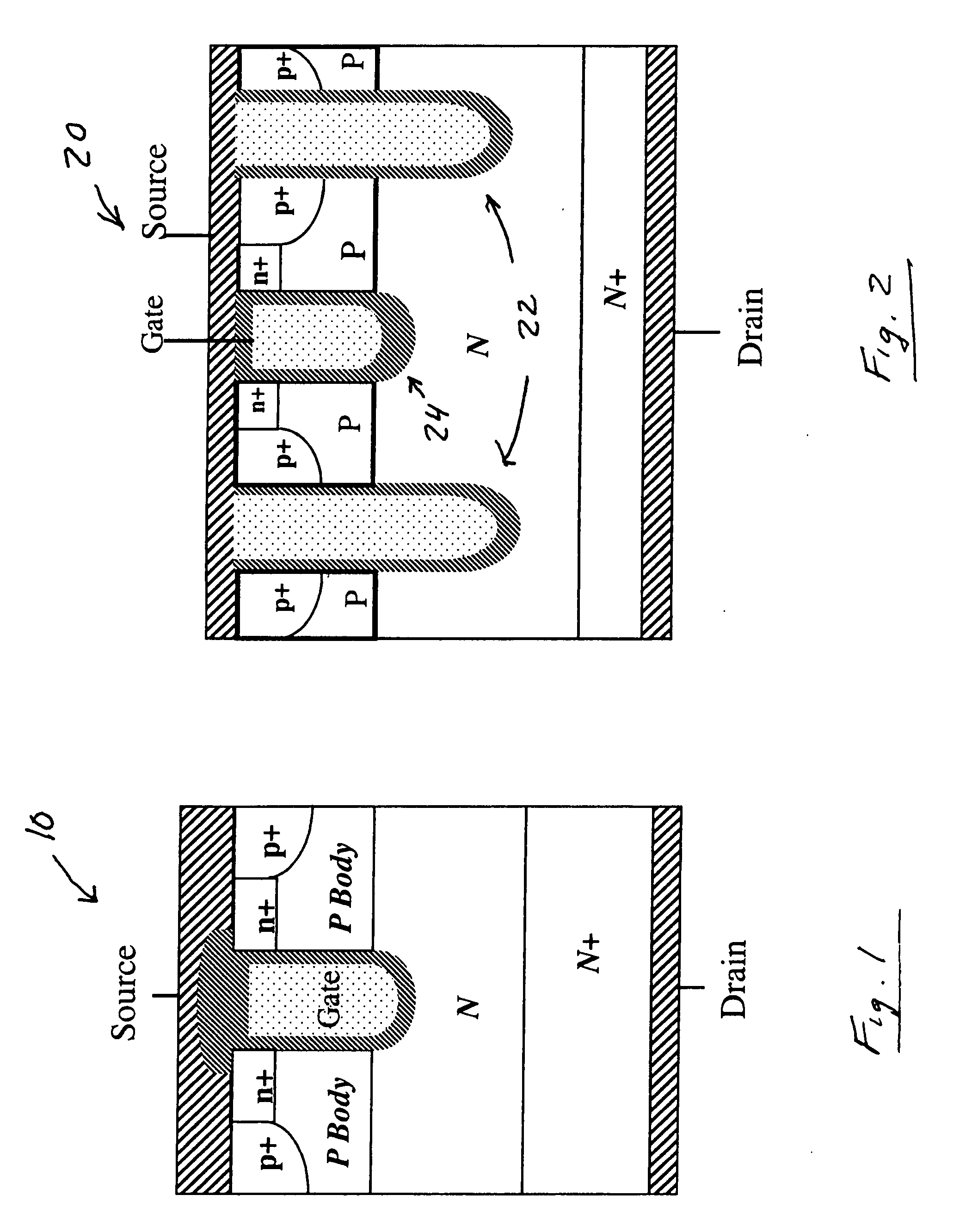

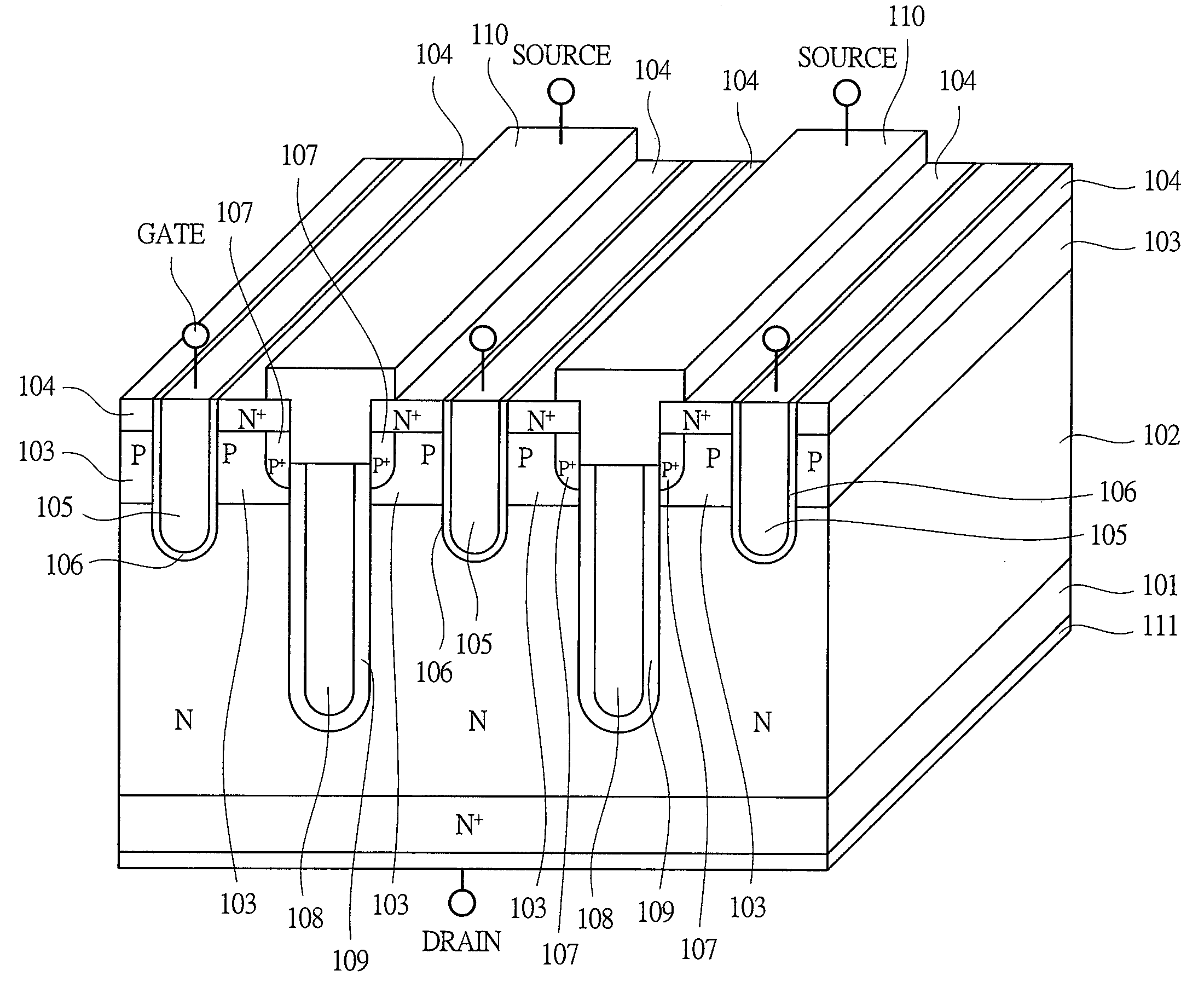

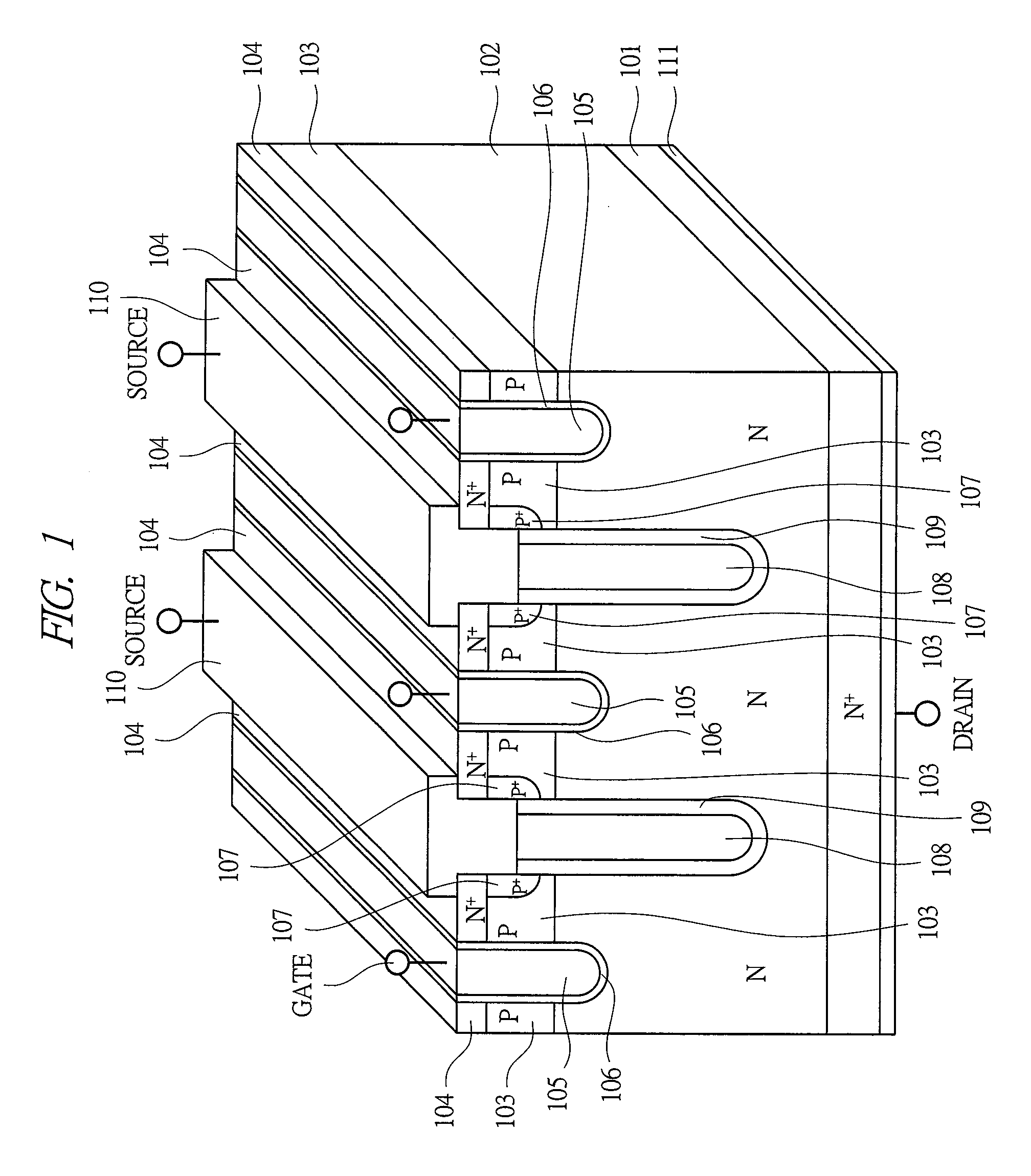

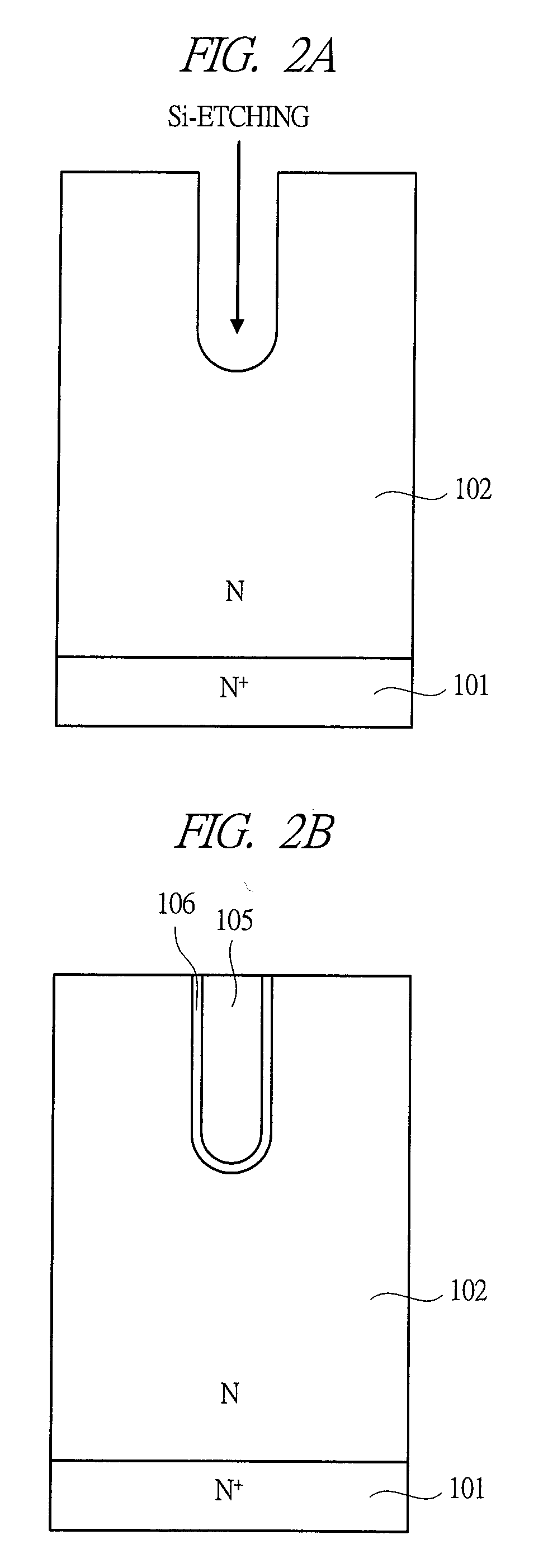

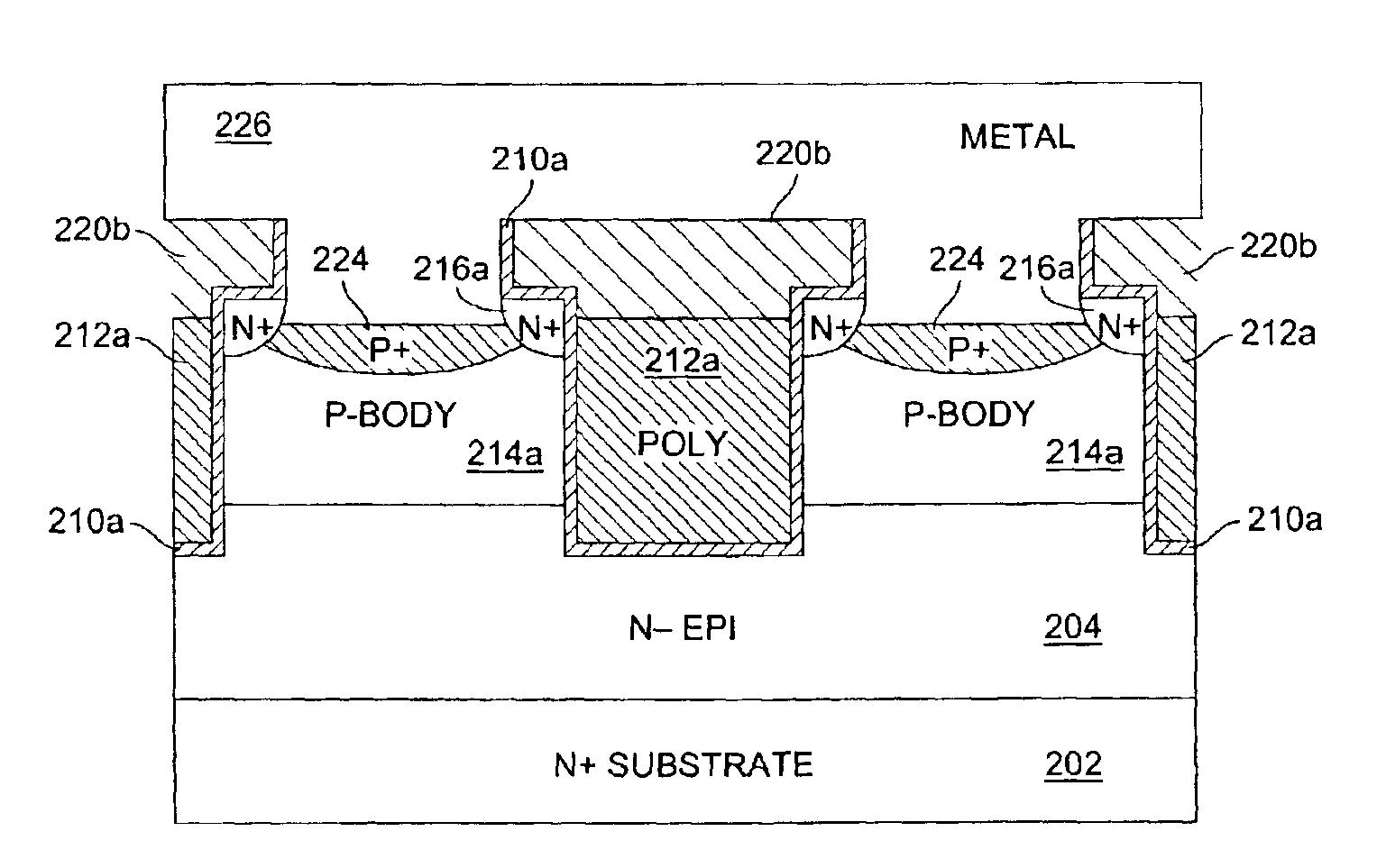

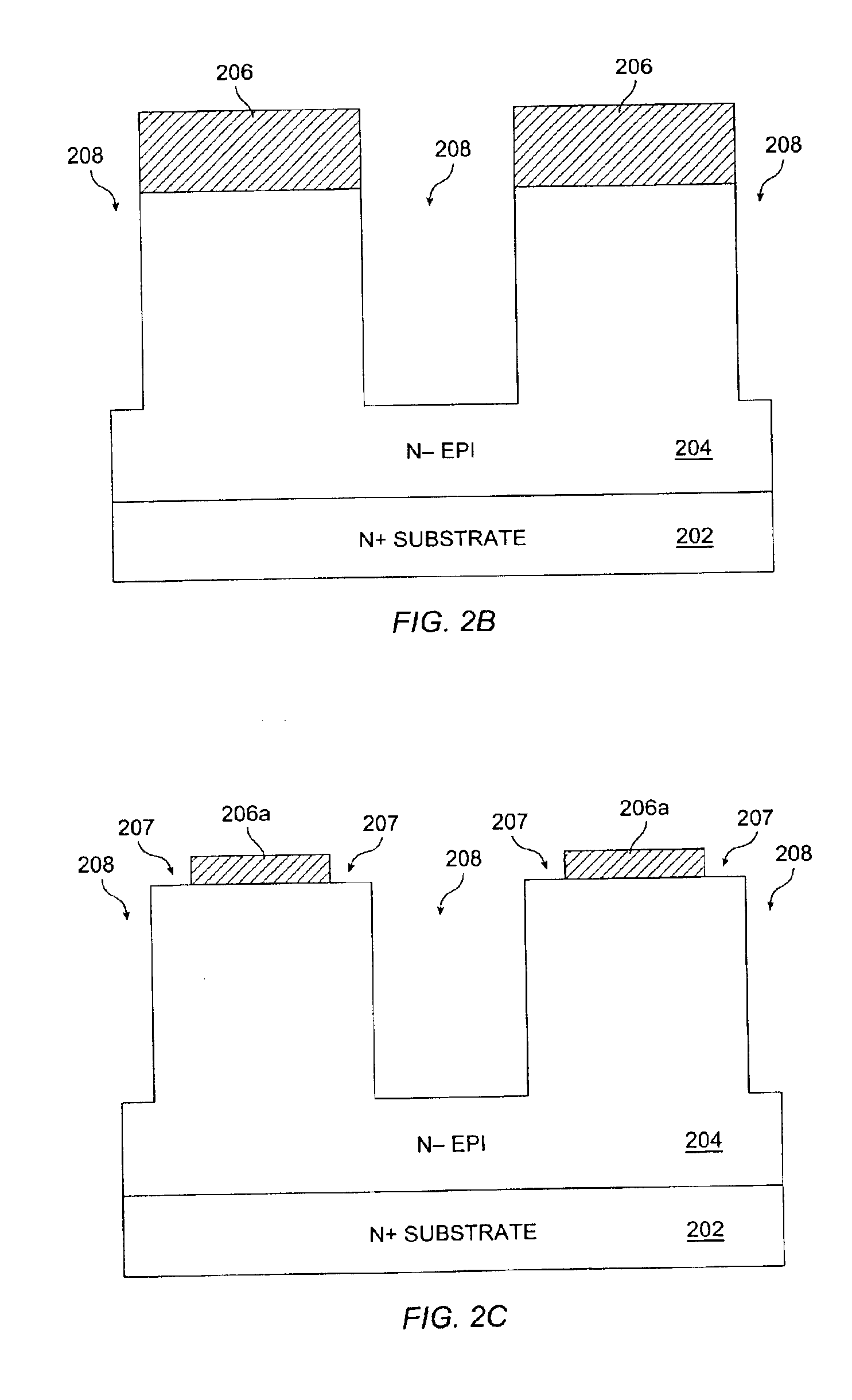

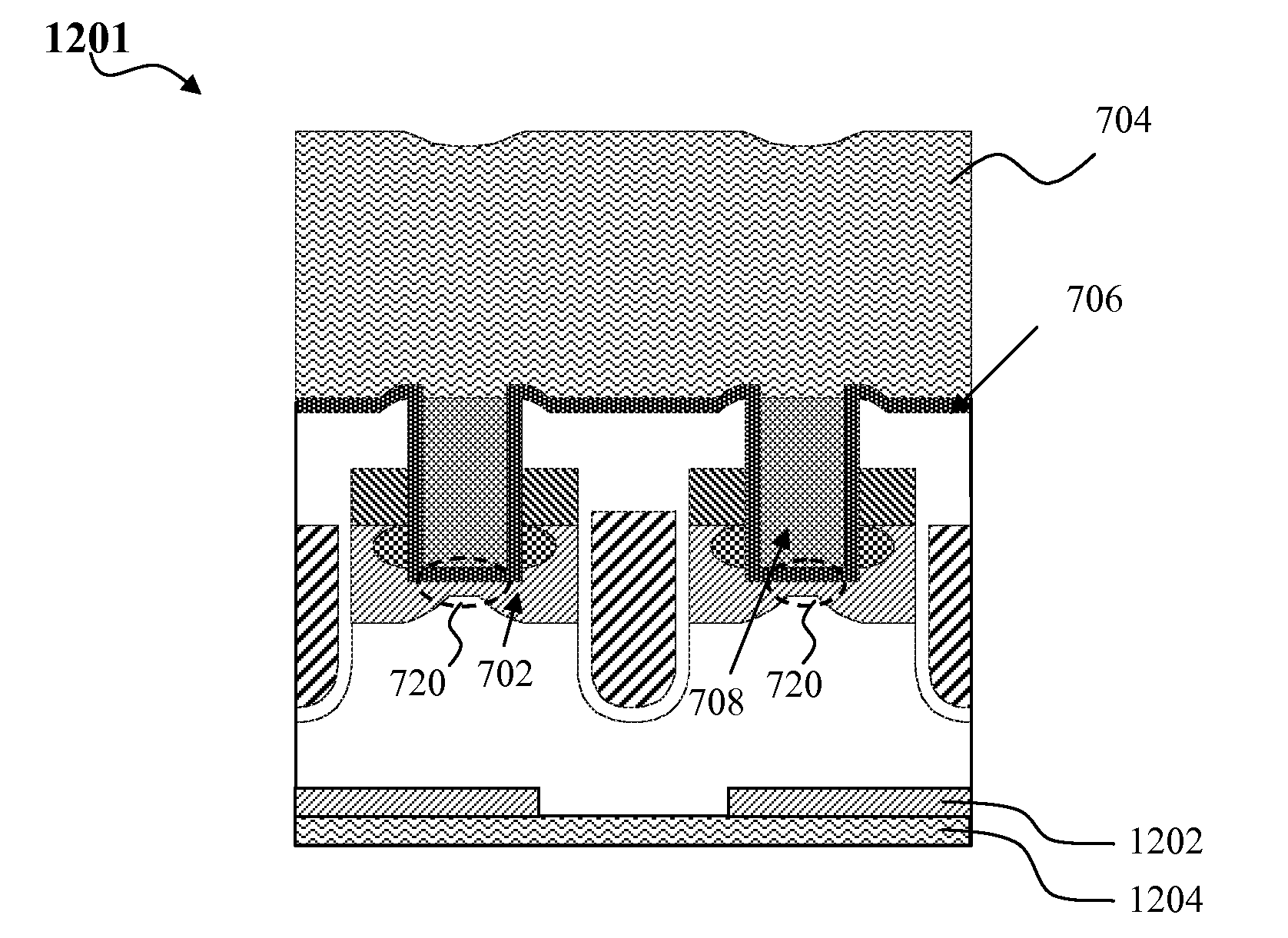

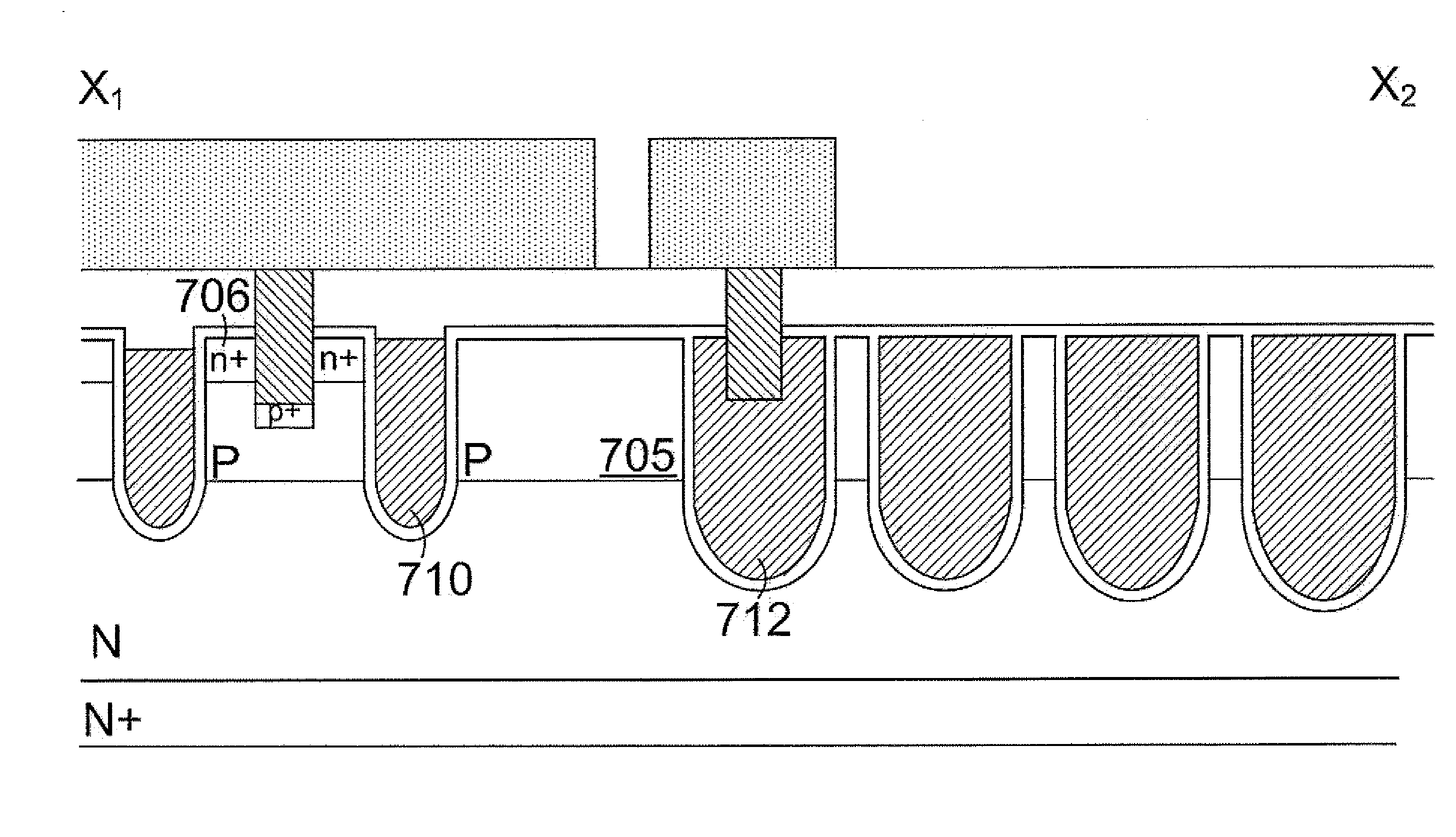

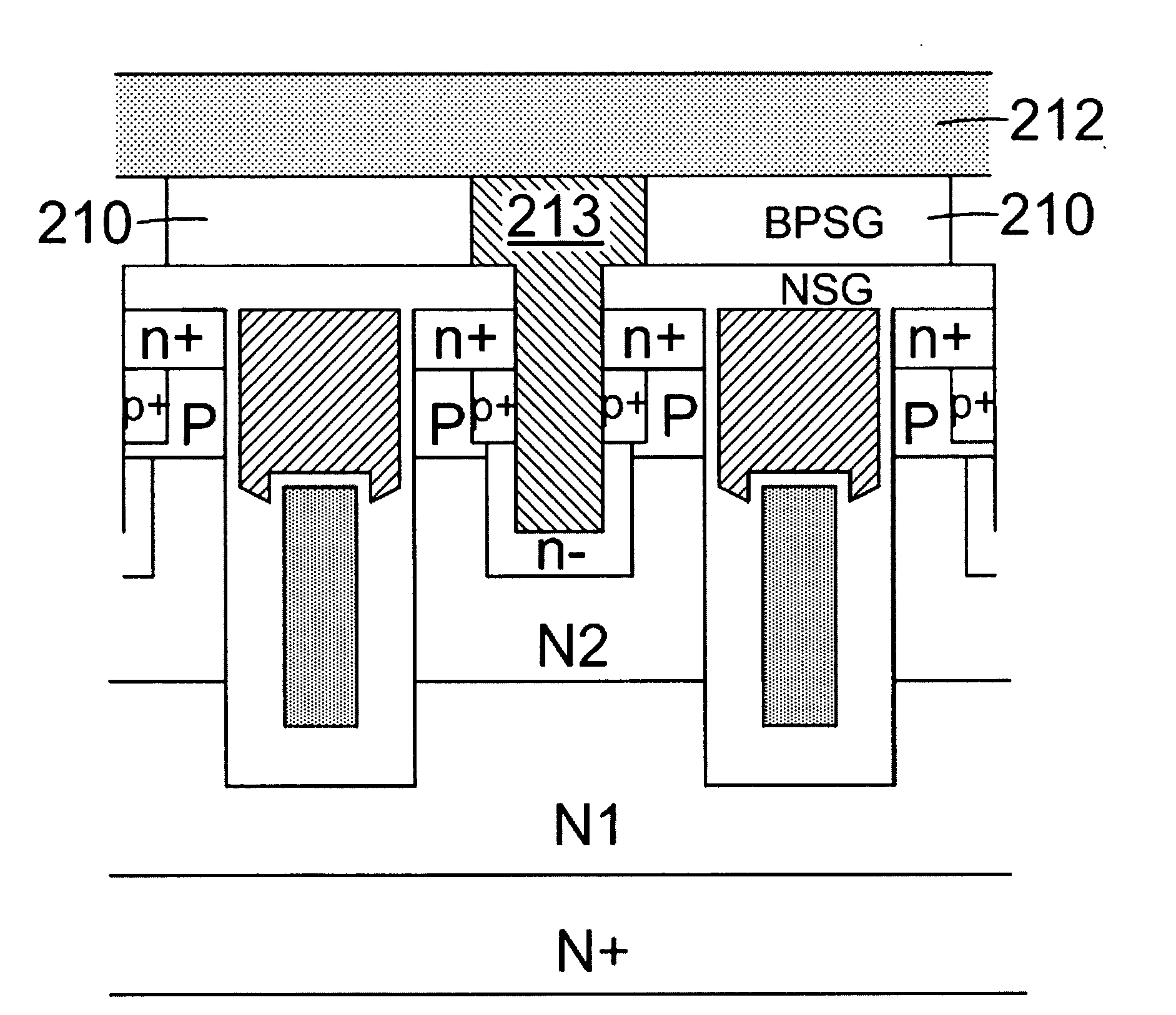

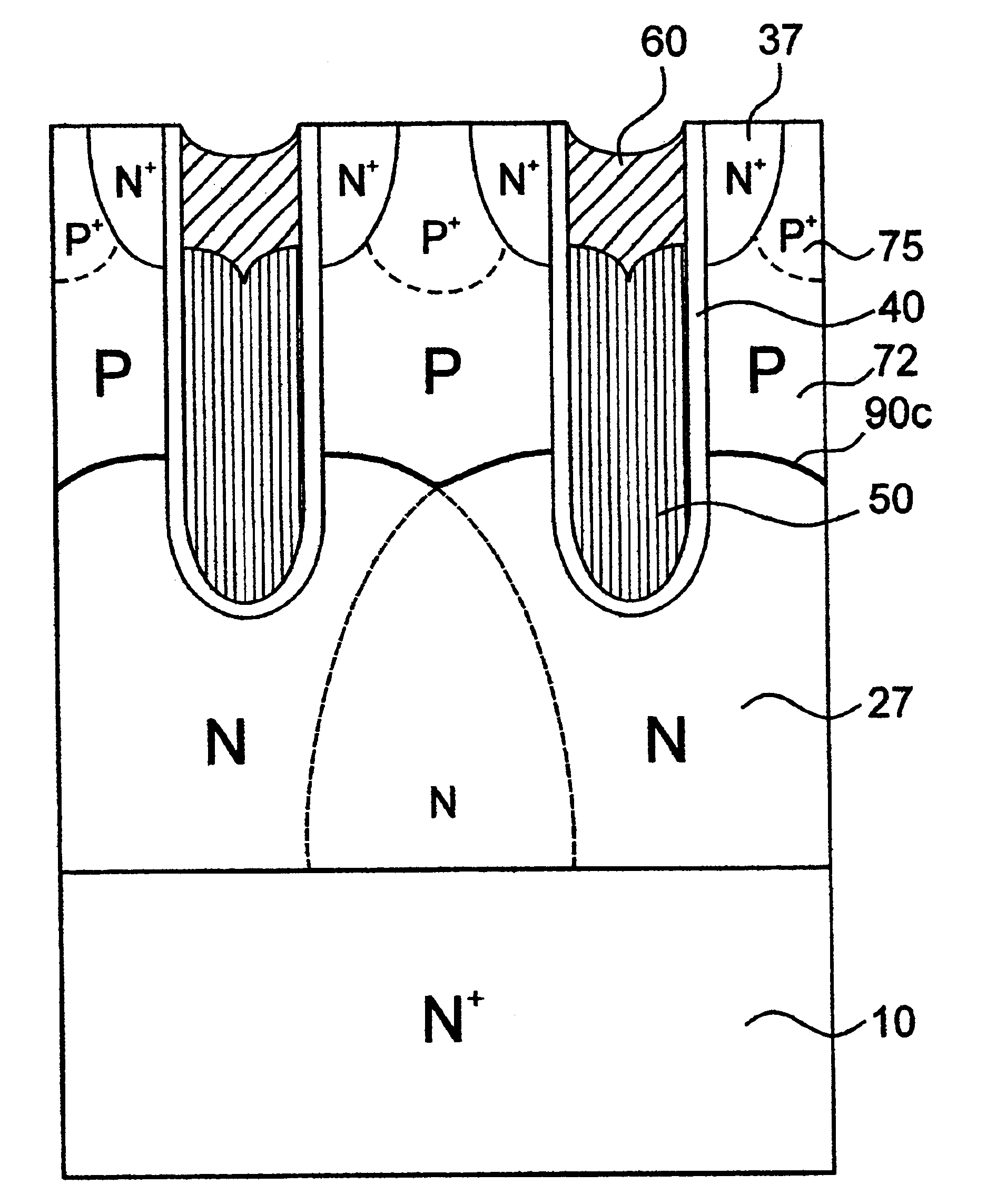

Super trench MOSFET including buried source electrode and method of fabricating the same

InactiveUS7183610B2Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

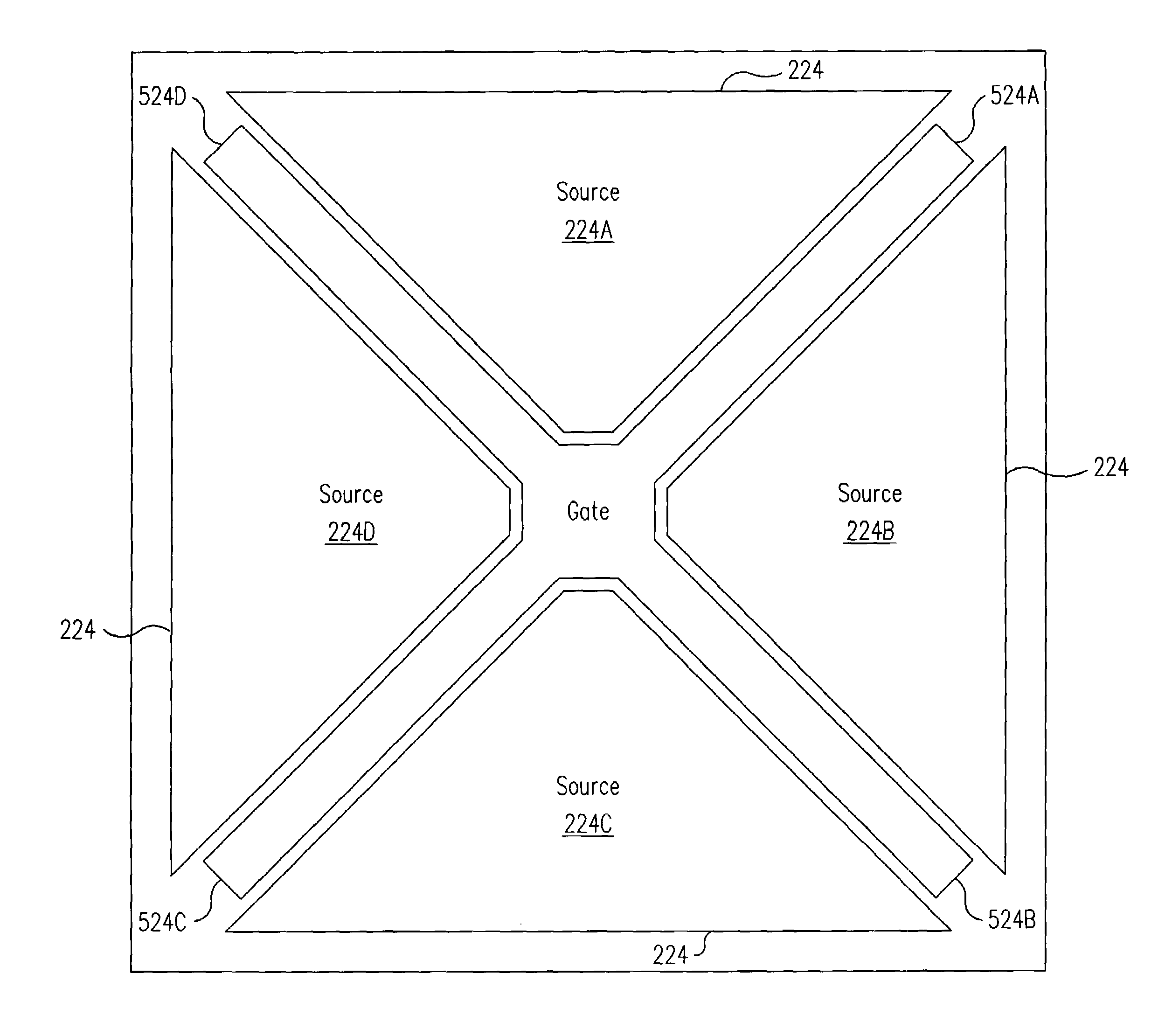

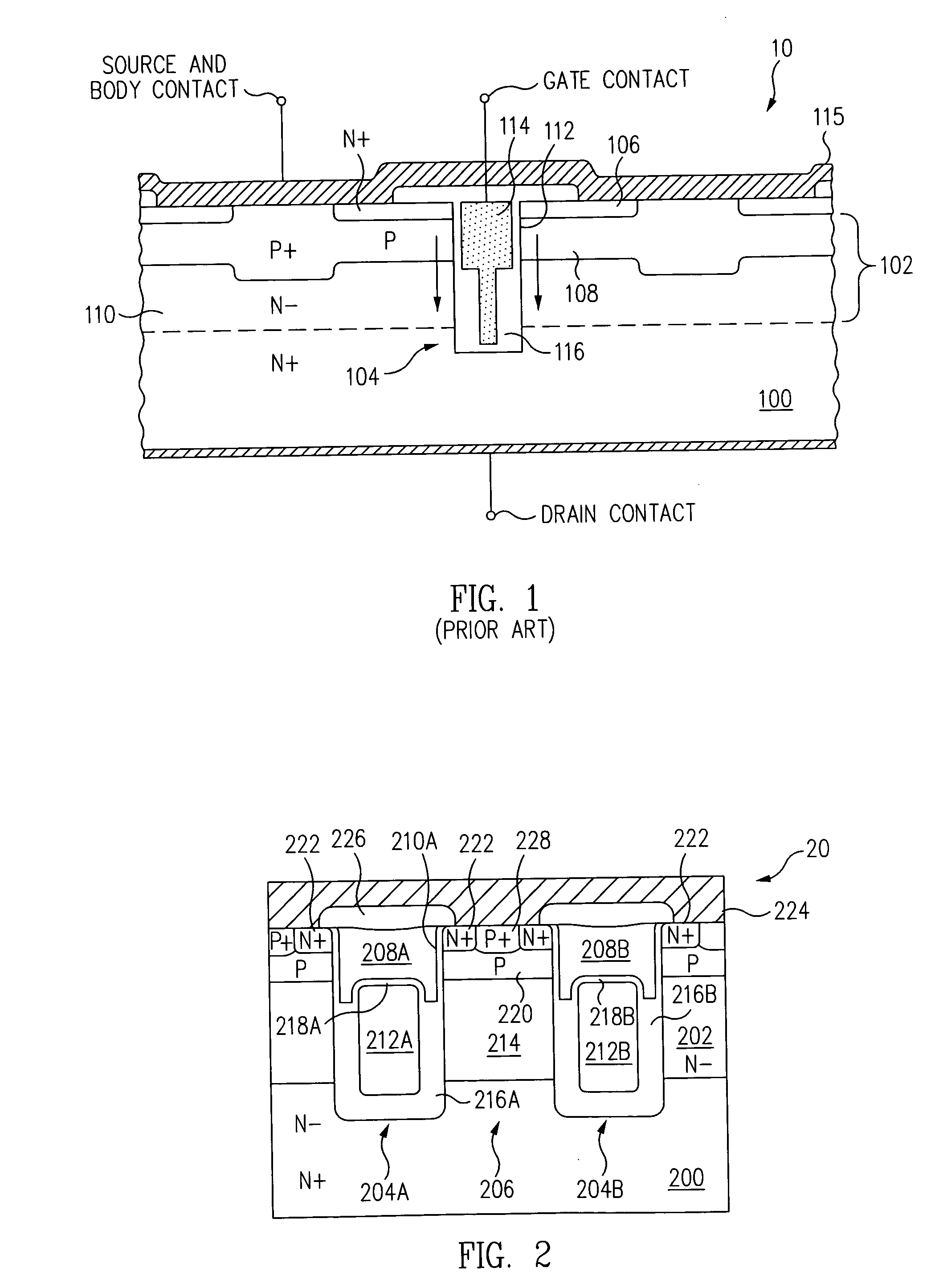

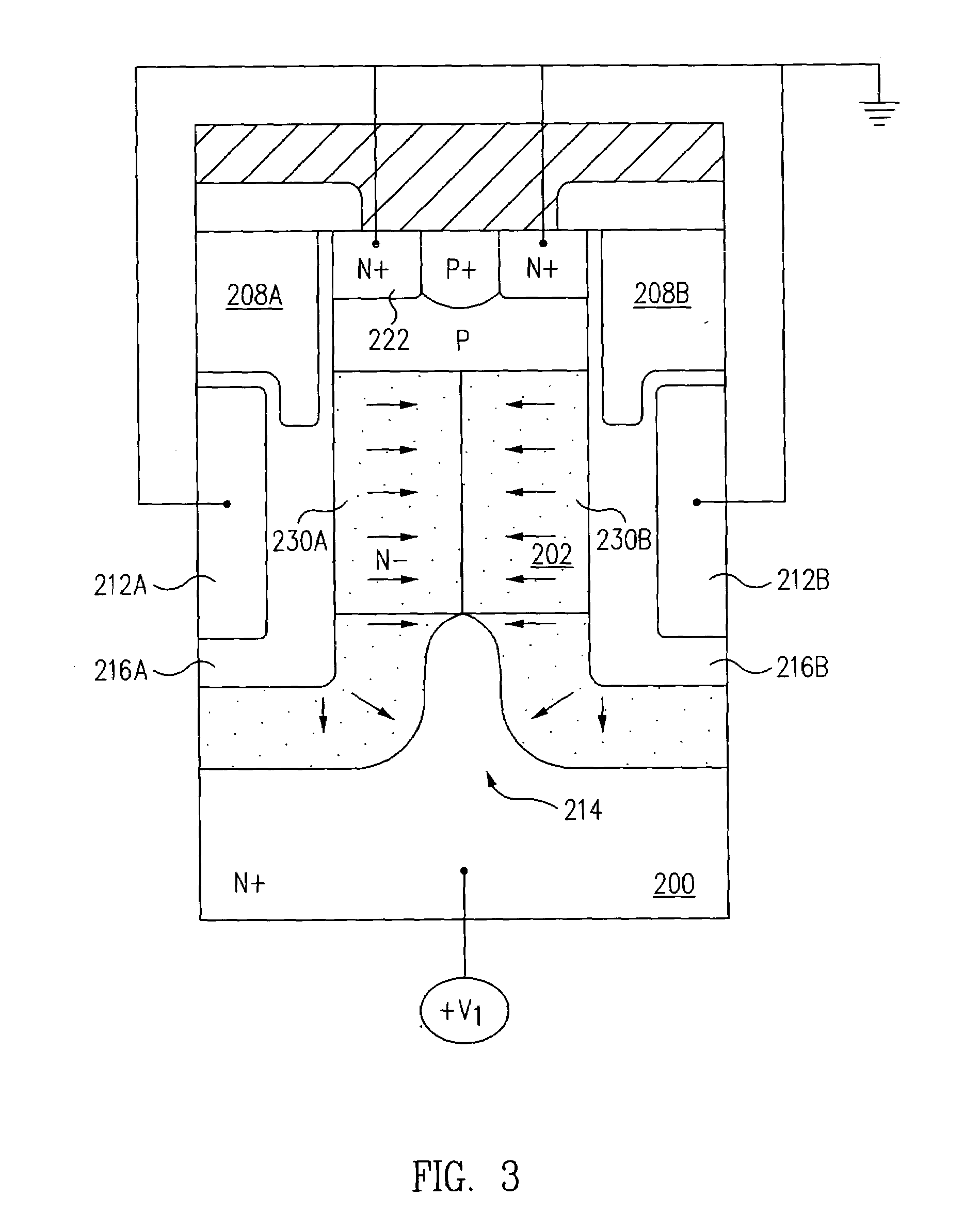

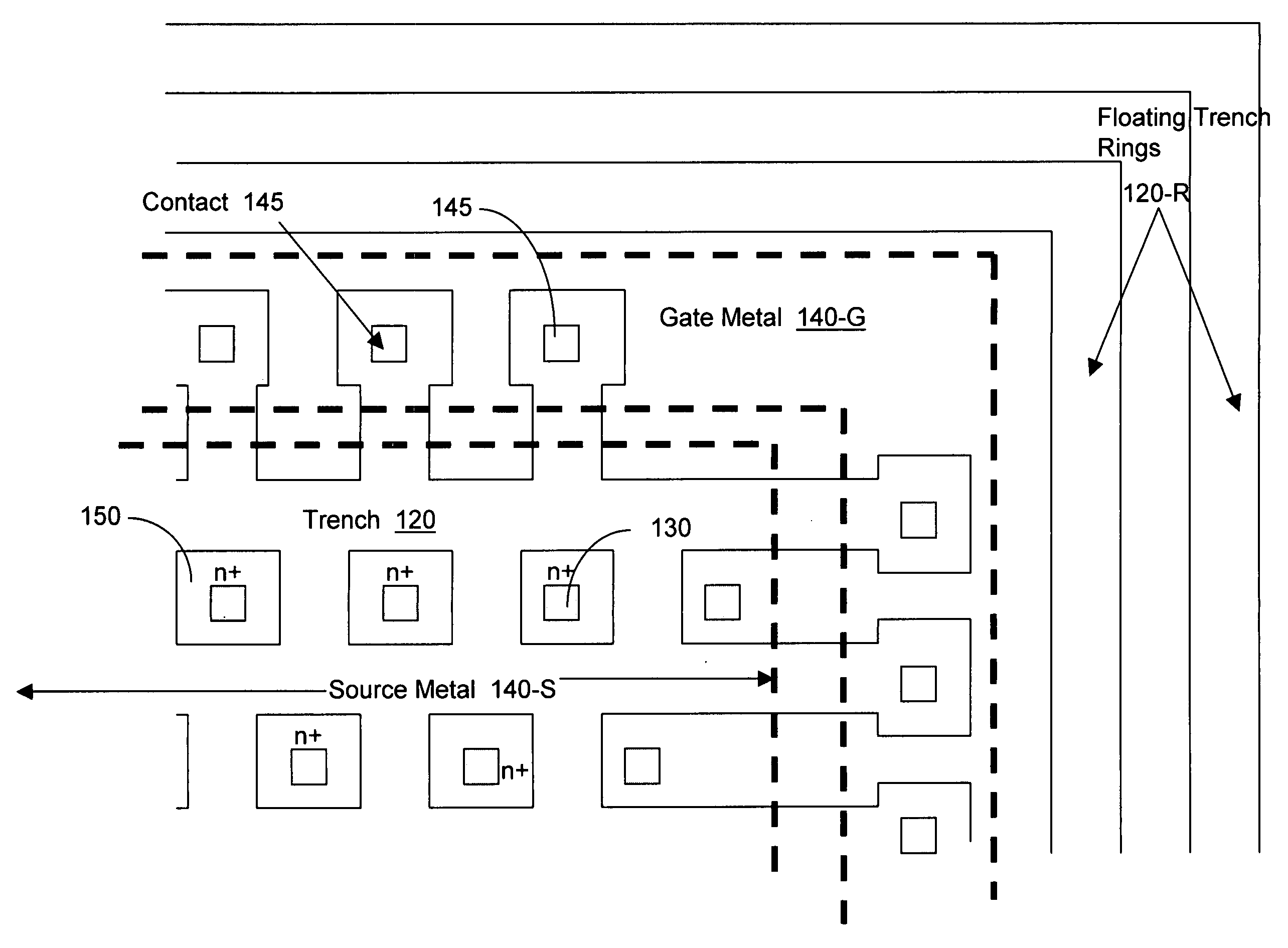

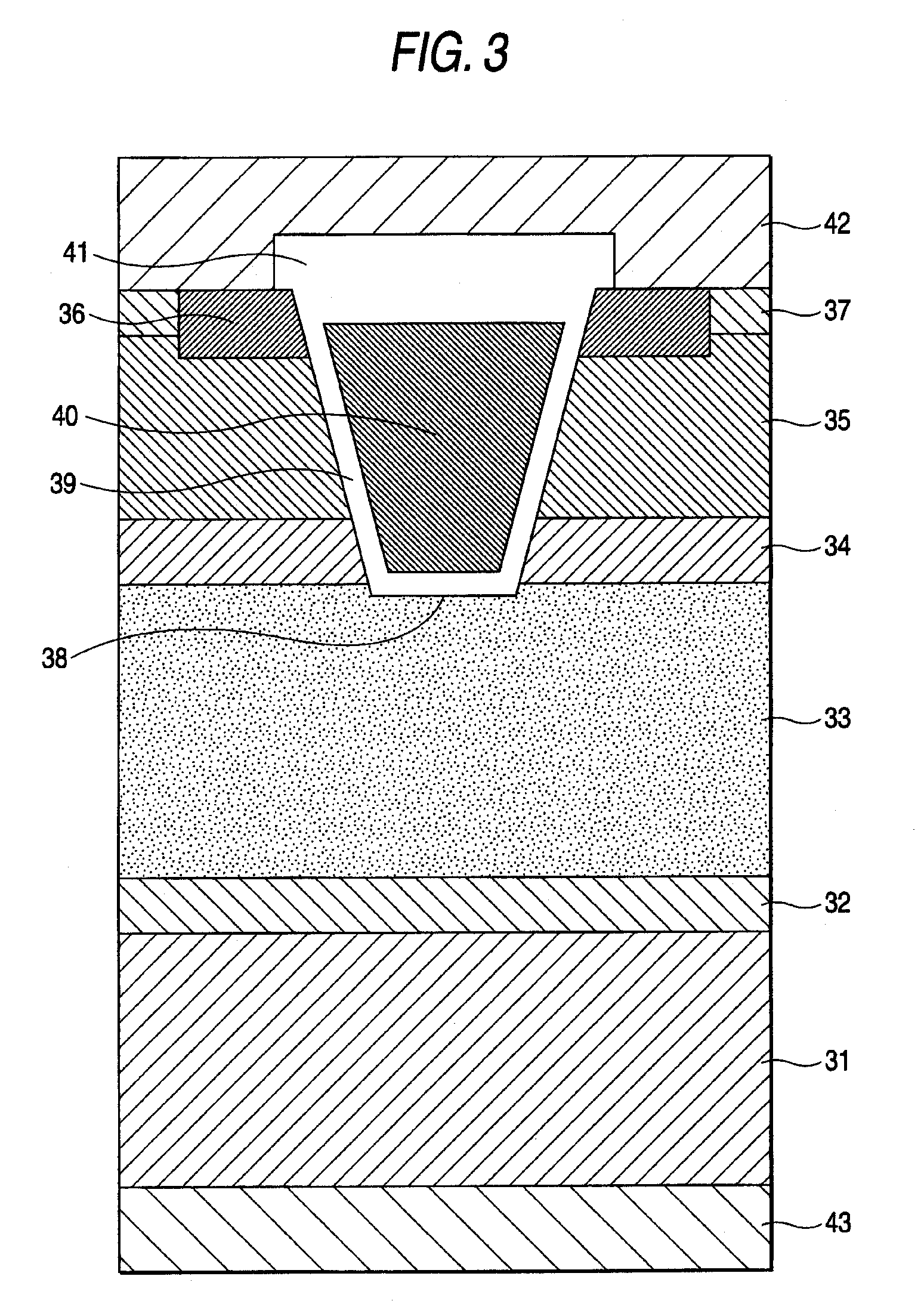

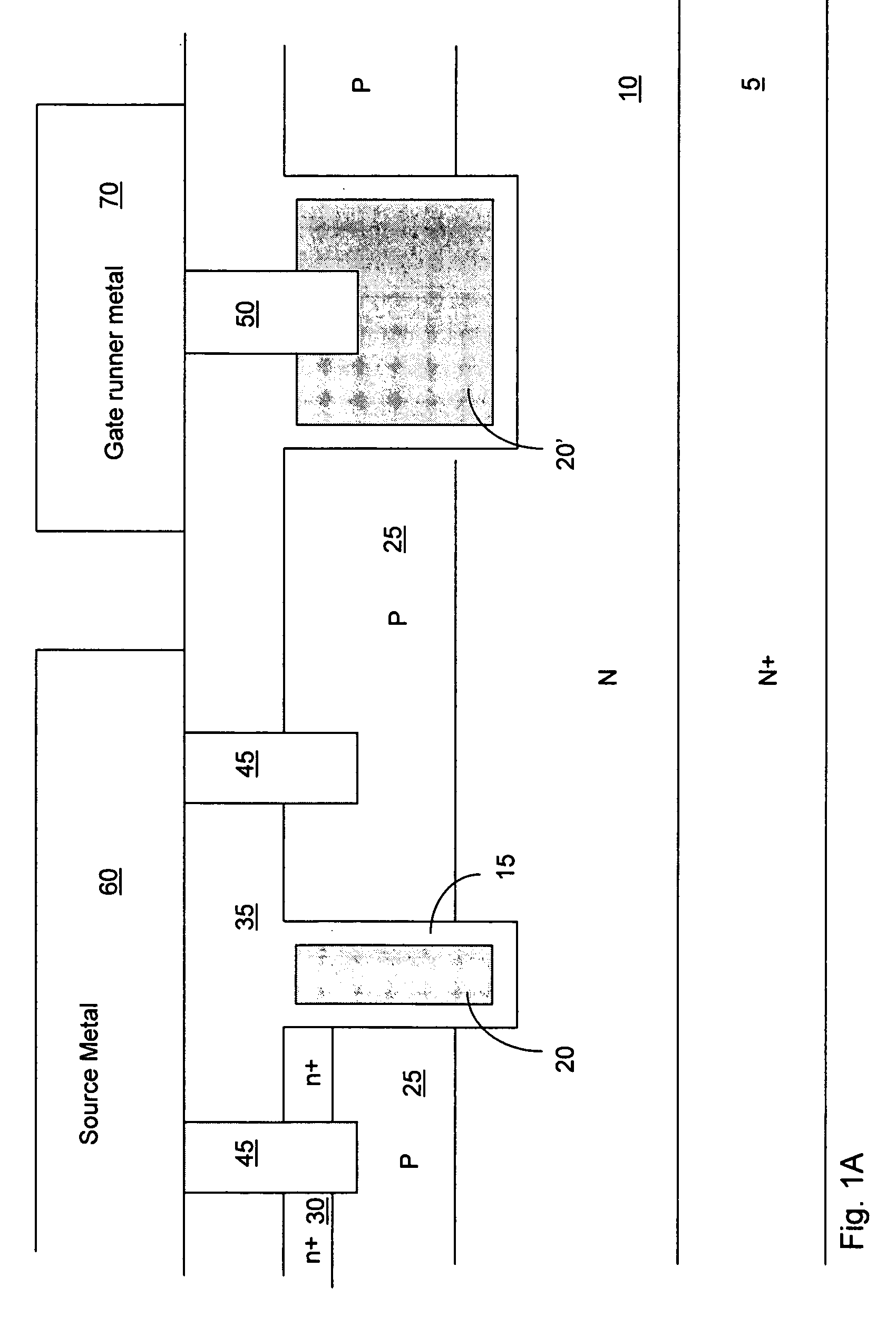

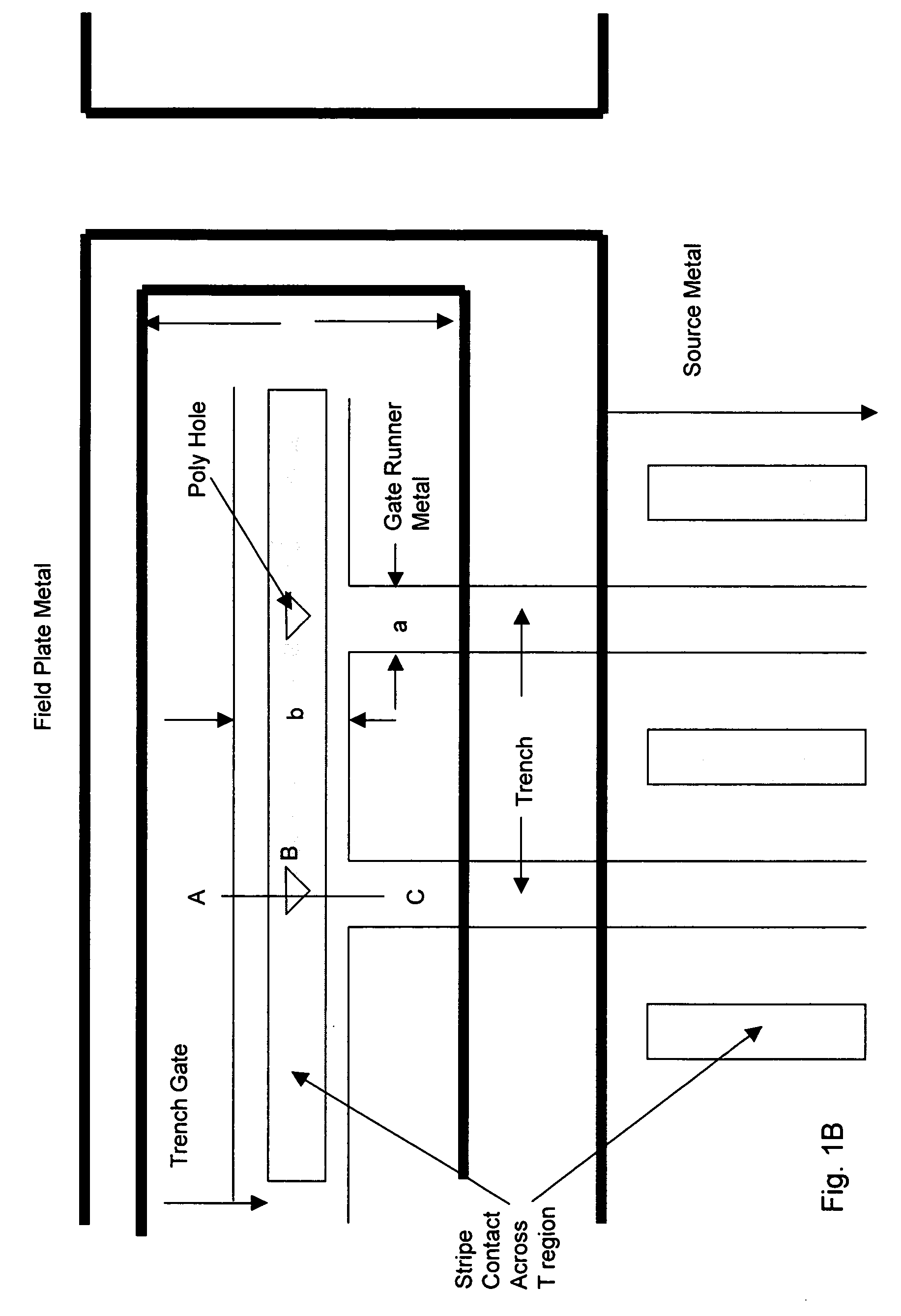

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

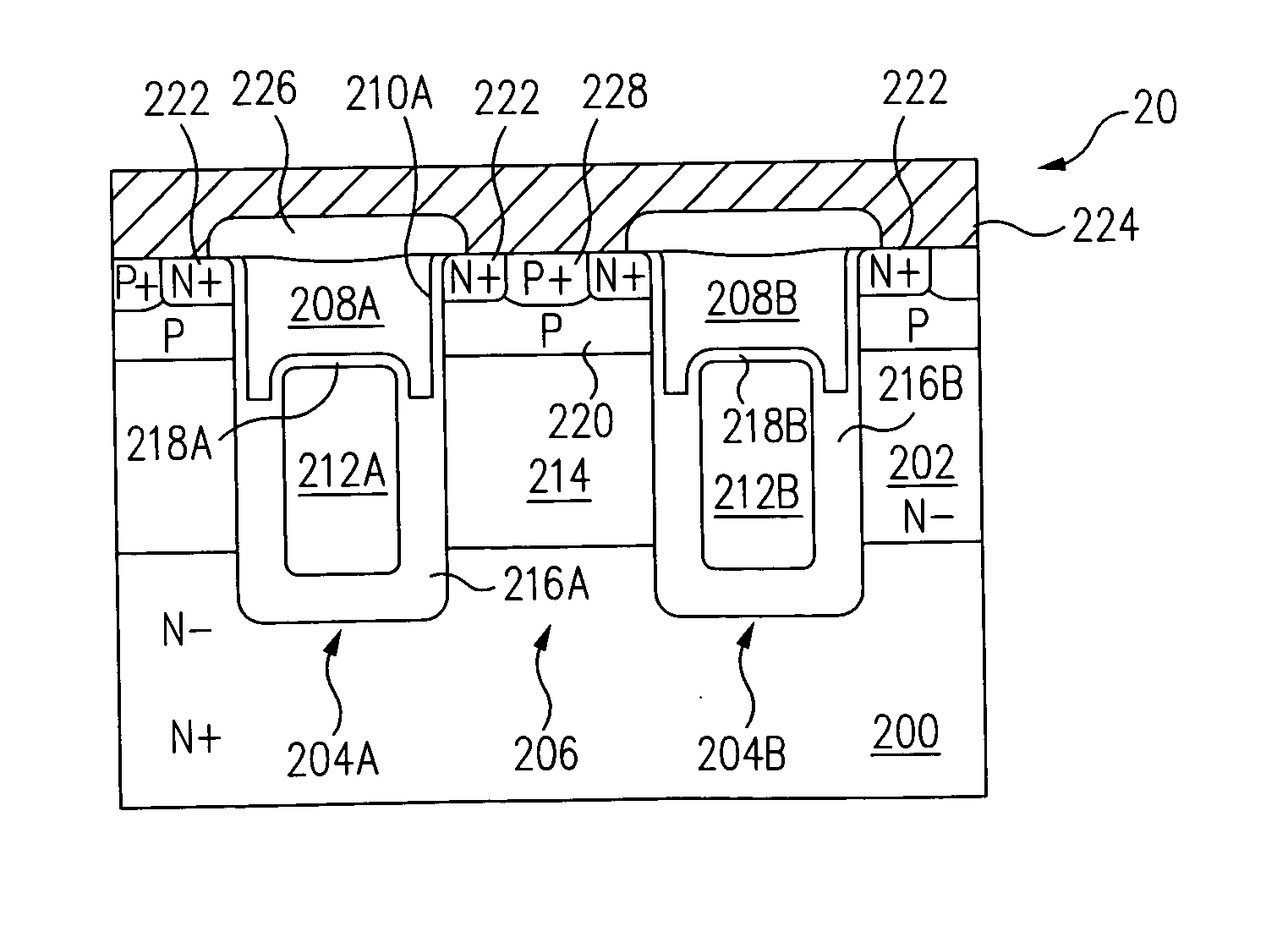

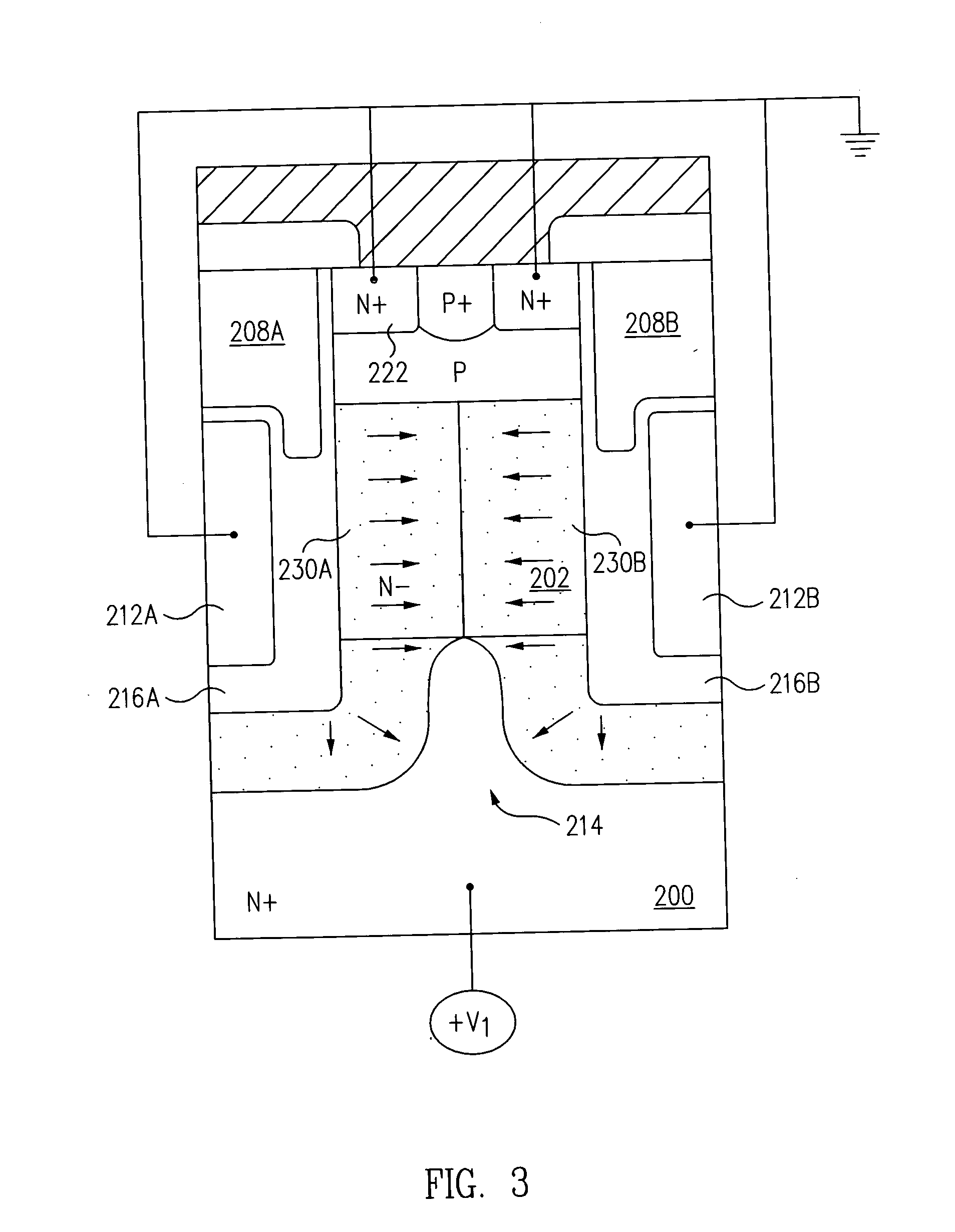

Isolated trench MOSFET

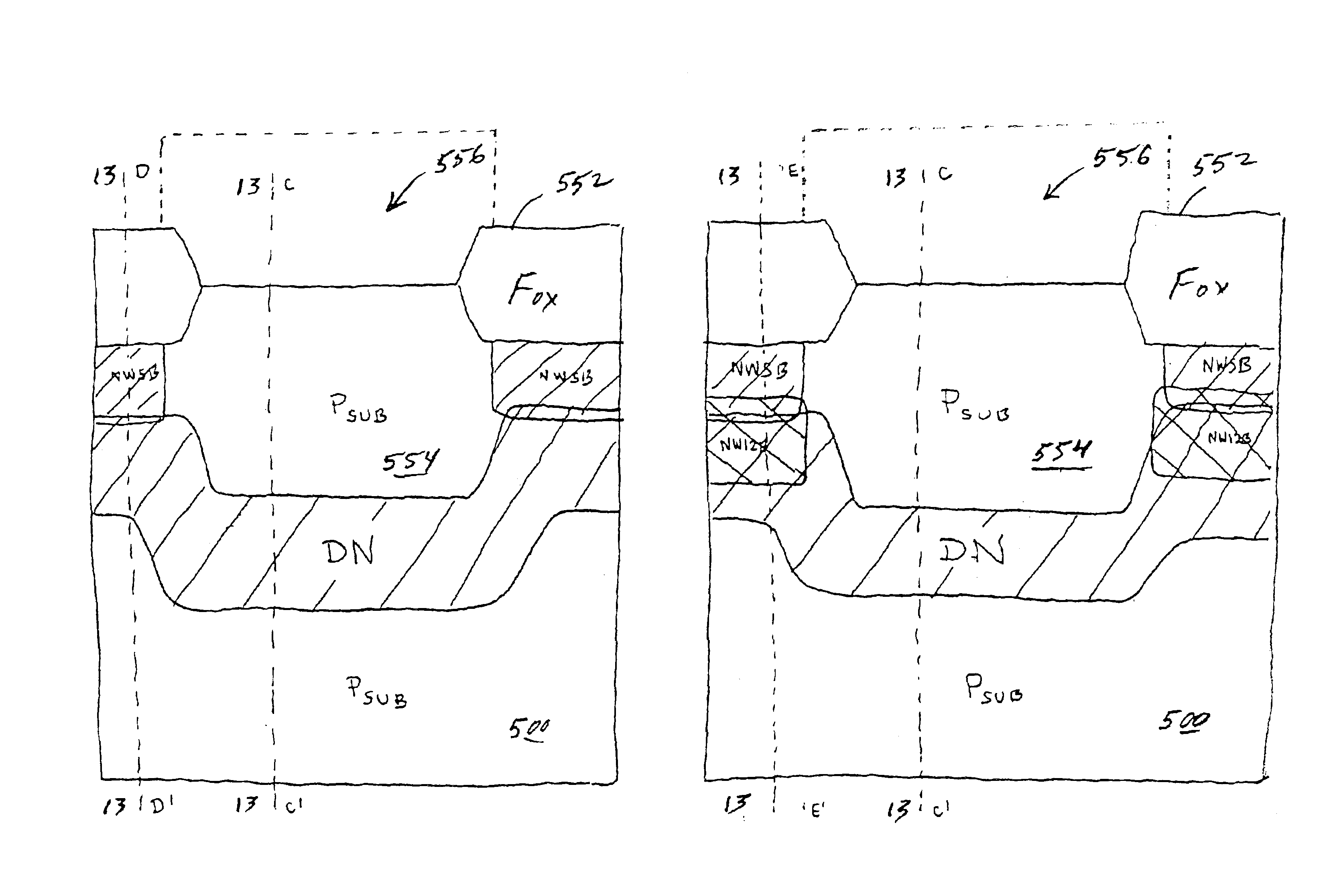

An isolation structure for a semiconductor device comprises a floor isolation region, a dielectric filled trench above the floor isolation region and a sidewall isolation region extending downward from the bottom of the trench to the floor isolation region. This structure provides a relatively deep isolated pocket in a semiconductor substrate while limiting the depth of the trench that must be etched in the substrate. A MOSFET is formed in the isolated pocket.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

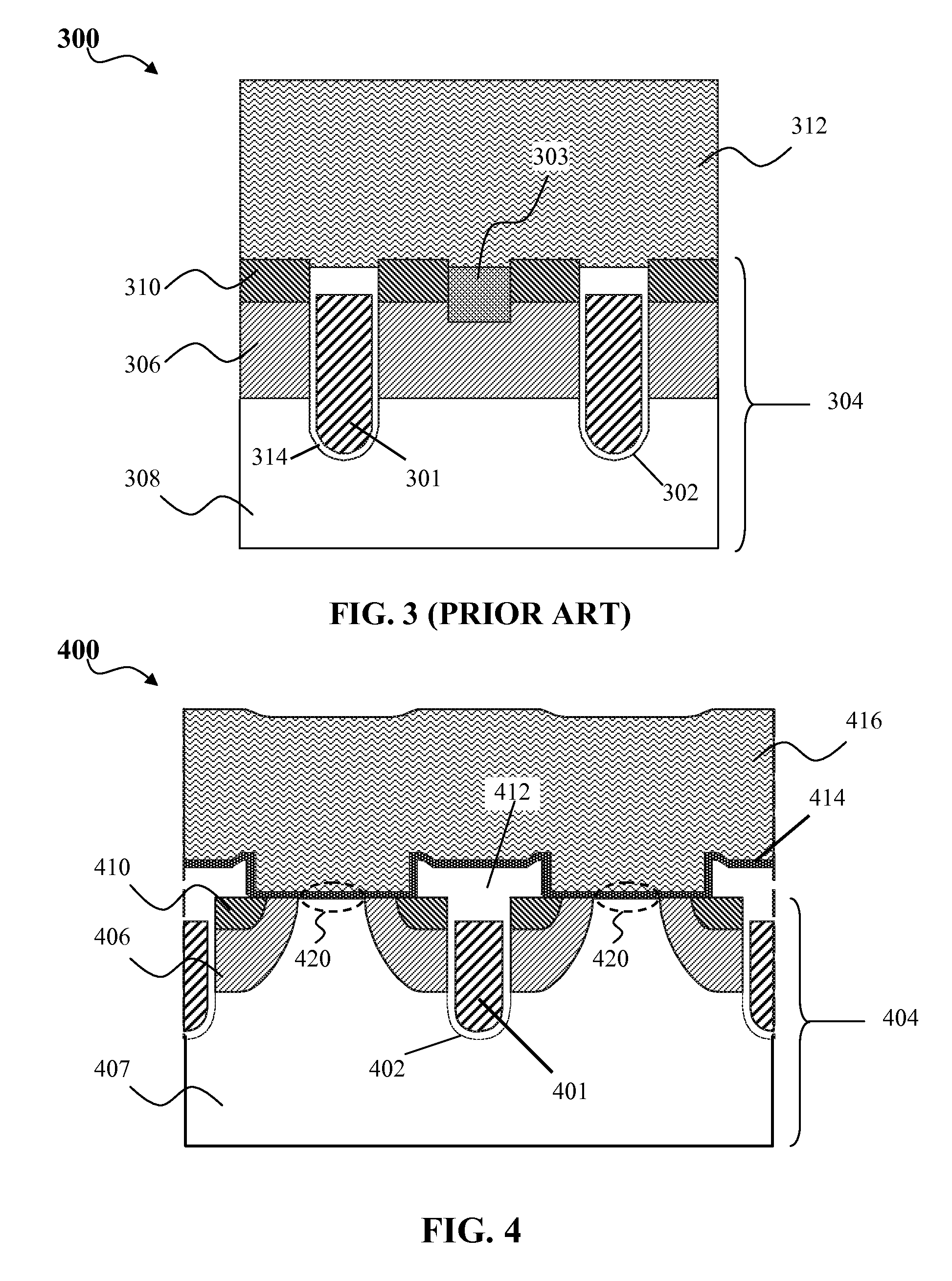

Structure and method for forming a trench MOSFET having self-aligned features

In accordance with an embodiment of the present invention, a semiconductor device is formed as follows. An exposed surface area of a silicon layer where silicon can be removed is defined. A portion of the silicon layer is removed to form a middle section of a trench extending into the silicon layer from the exposed surface area of the silicon layer. Additional exposed surface areas of the silicon layer where silicon can be removed are defined. Additional portions of the silicon layer are removed to form outer sections of the trench such that the outer sections of the trench extend into the silicon layer from the additional exposed surface areas of the silicon layer. The middle section of the trench extends deeper into the silicon layer than the outer sections of the trench.

Owner:SEMICON COMPONENTS IND LLC

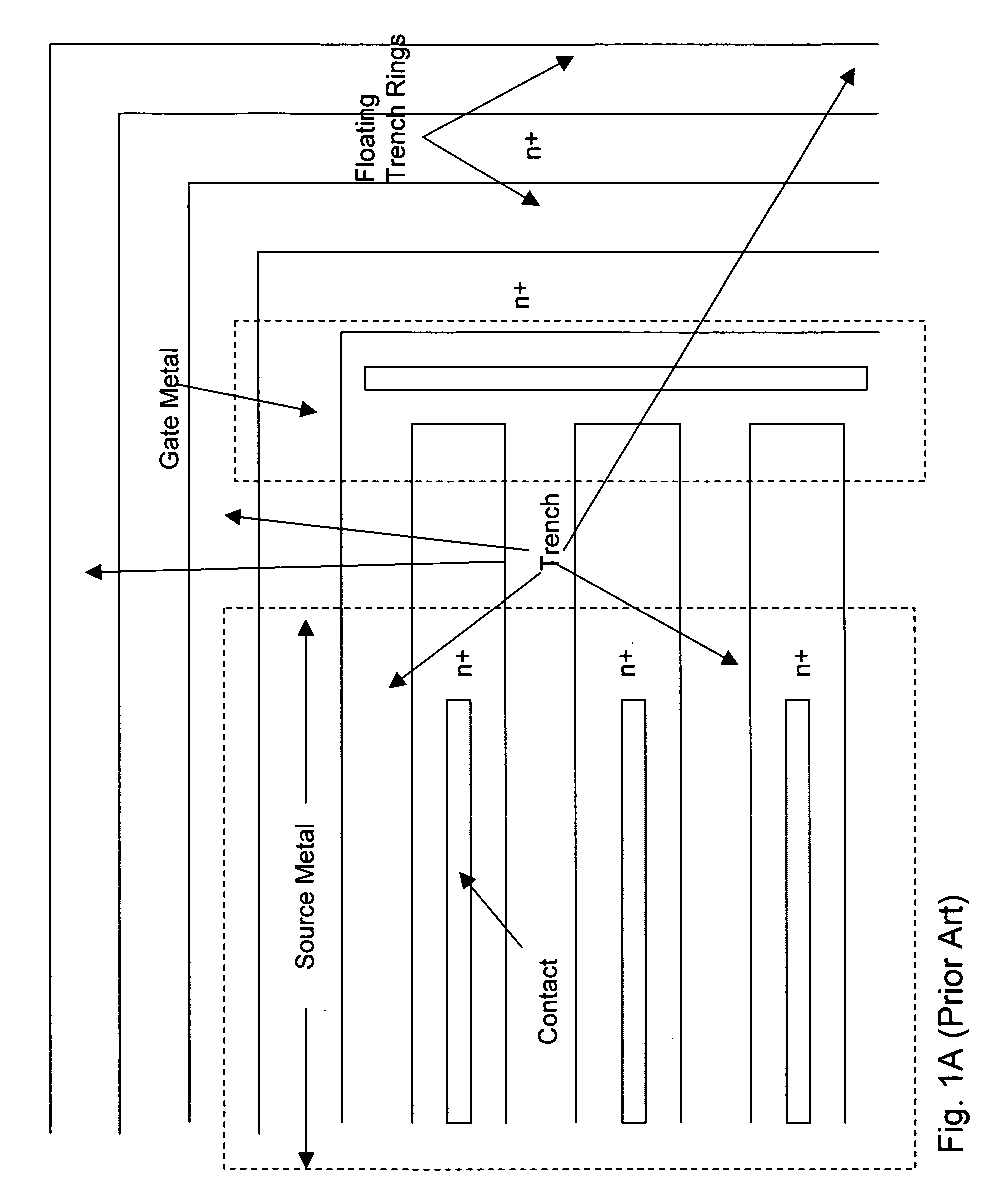

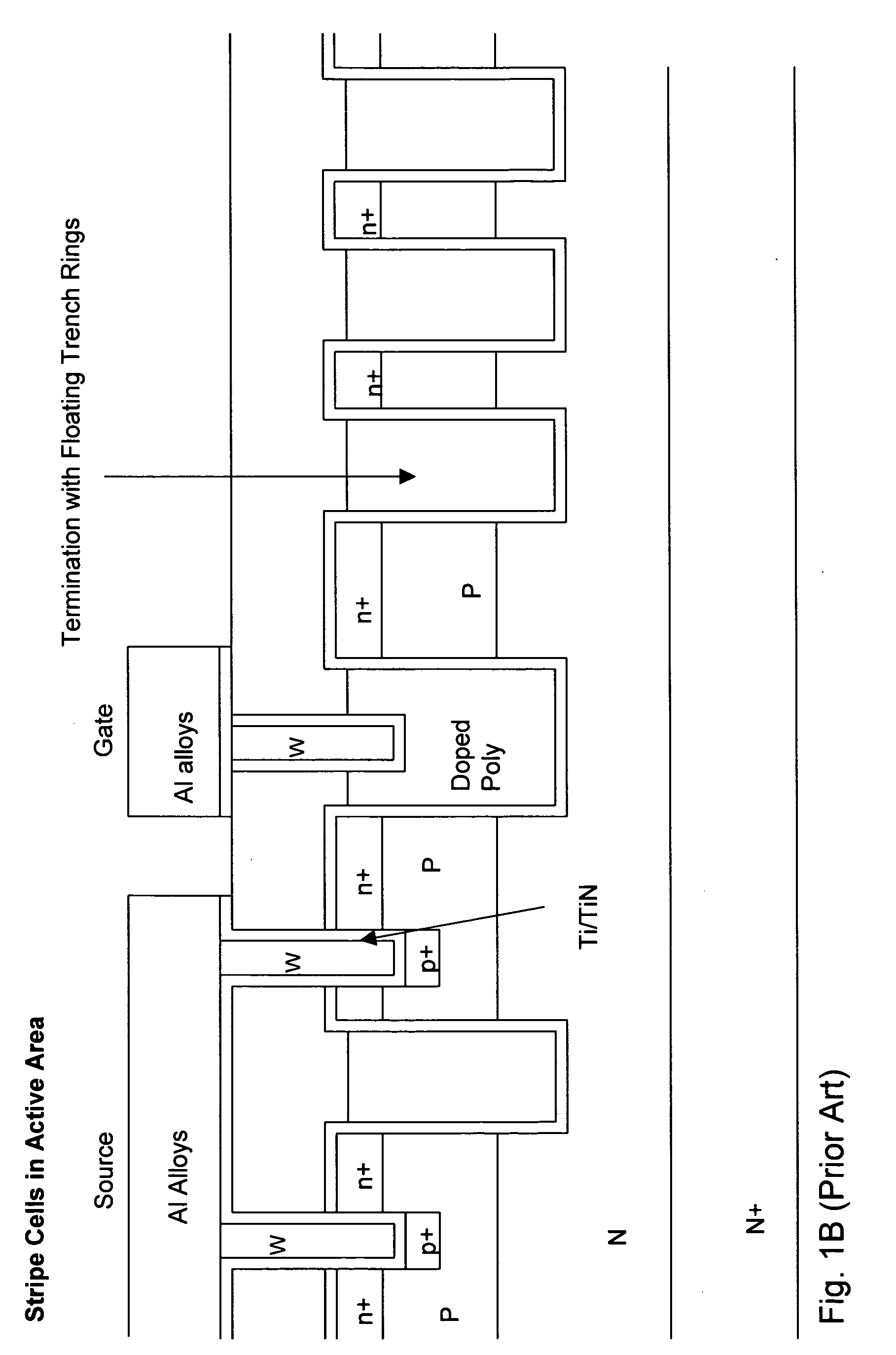

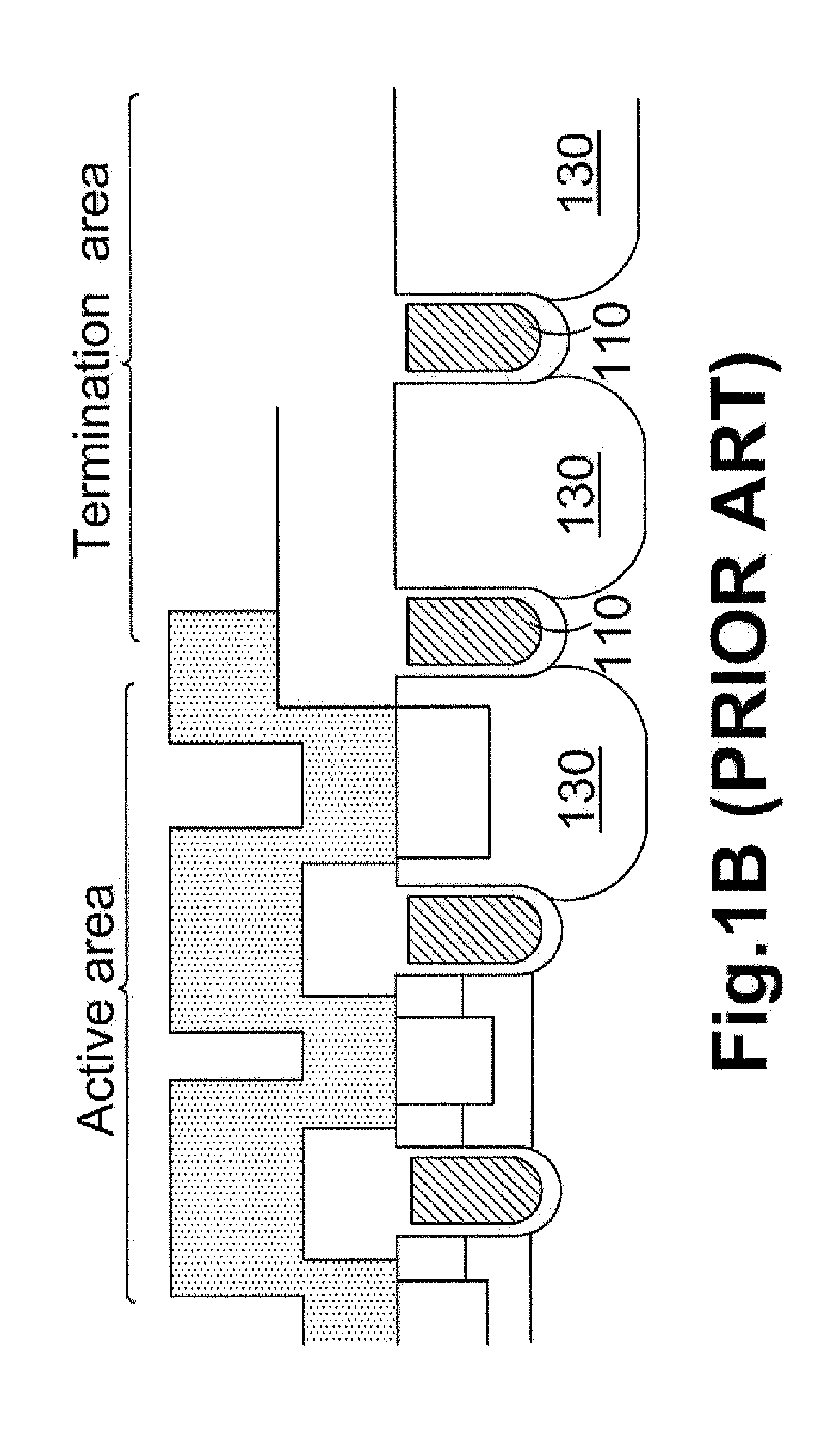

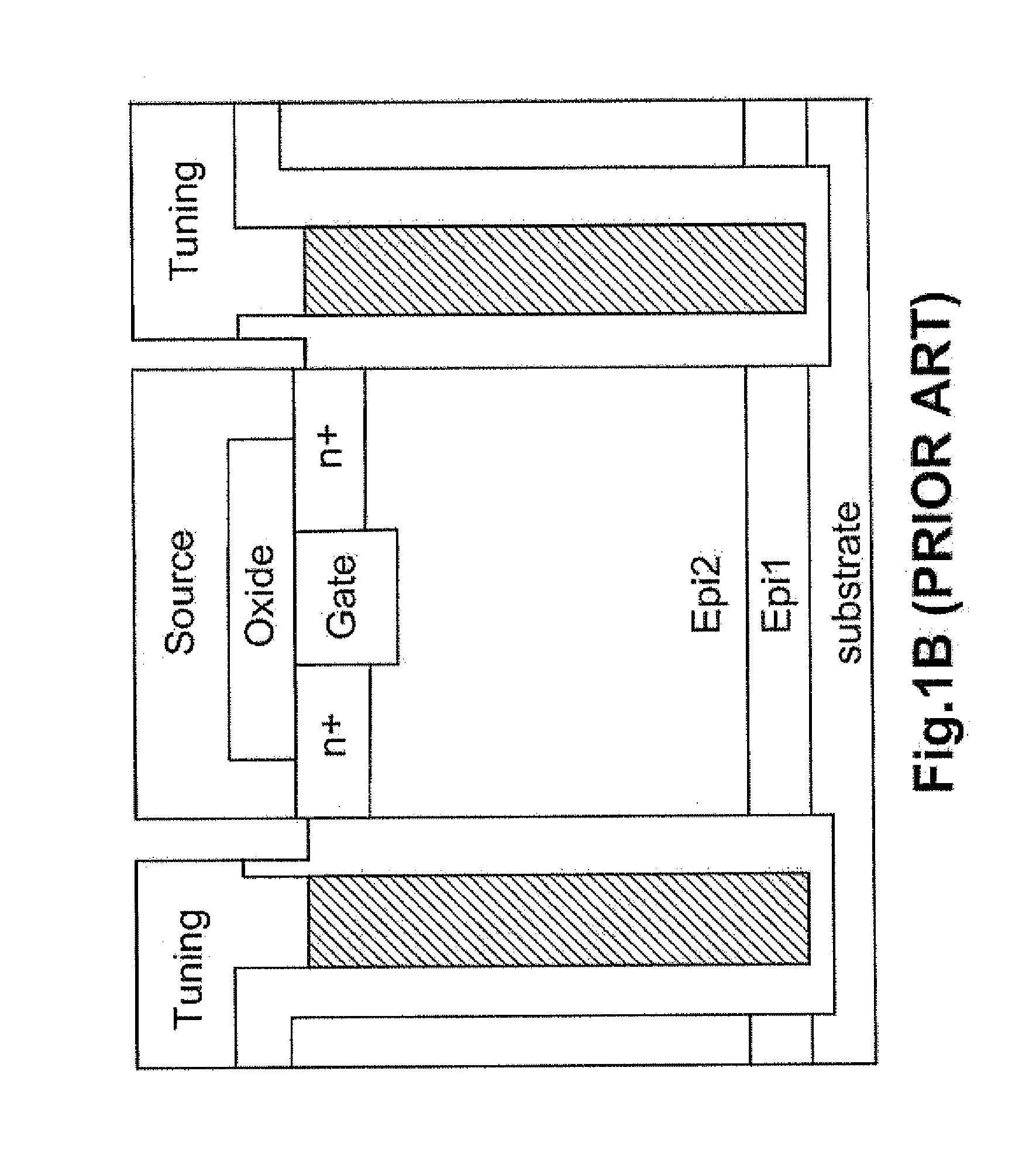

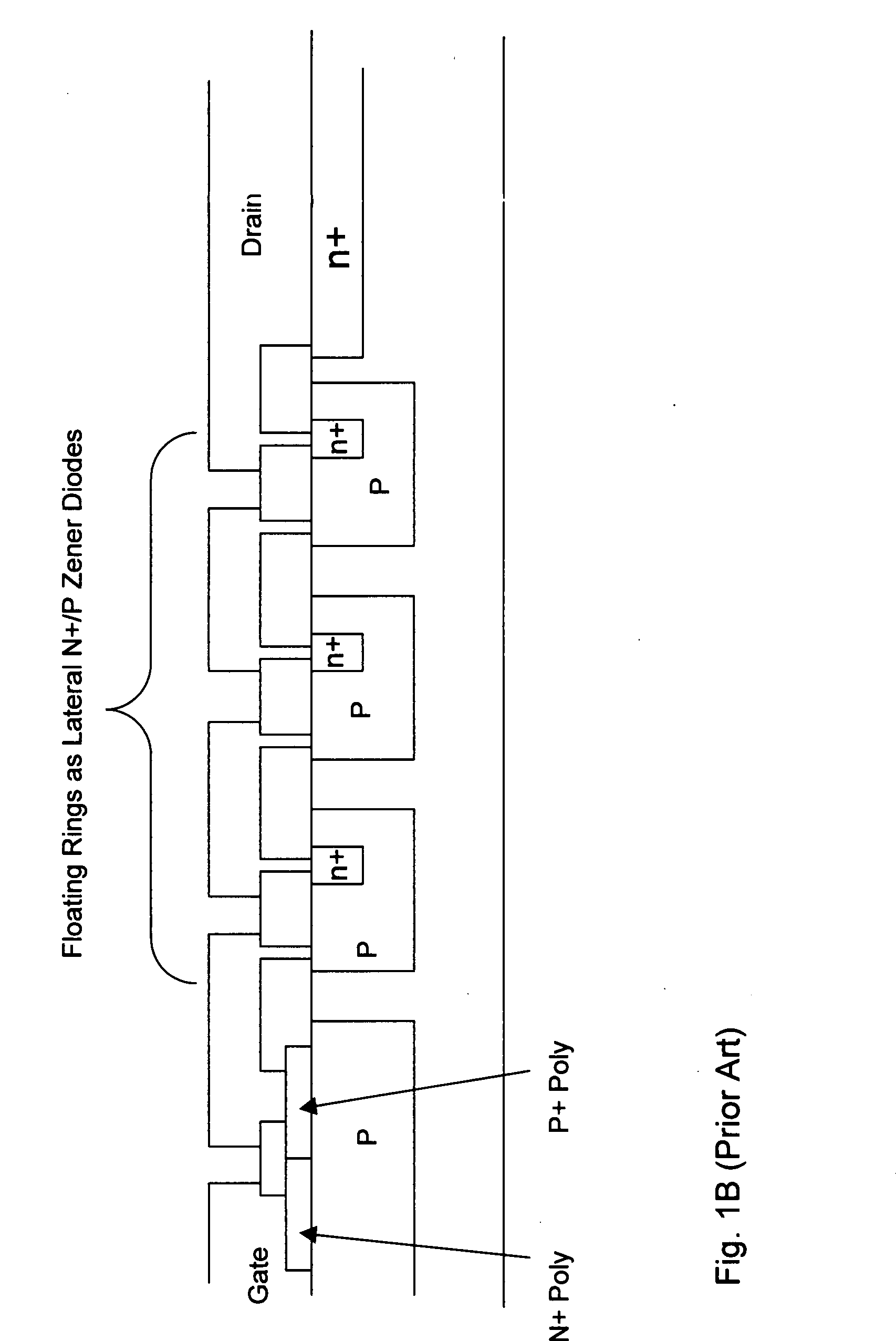

Closed trench MOSFET with floating trench rings as termination

ActiveUS20080179662A1Increased durabilityImprove breakdown voltageTransistorSolid-state devicesTrench mosfetTrench gate

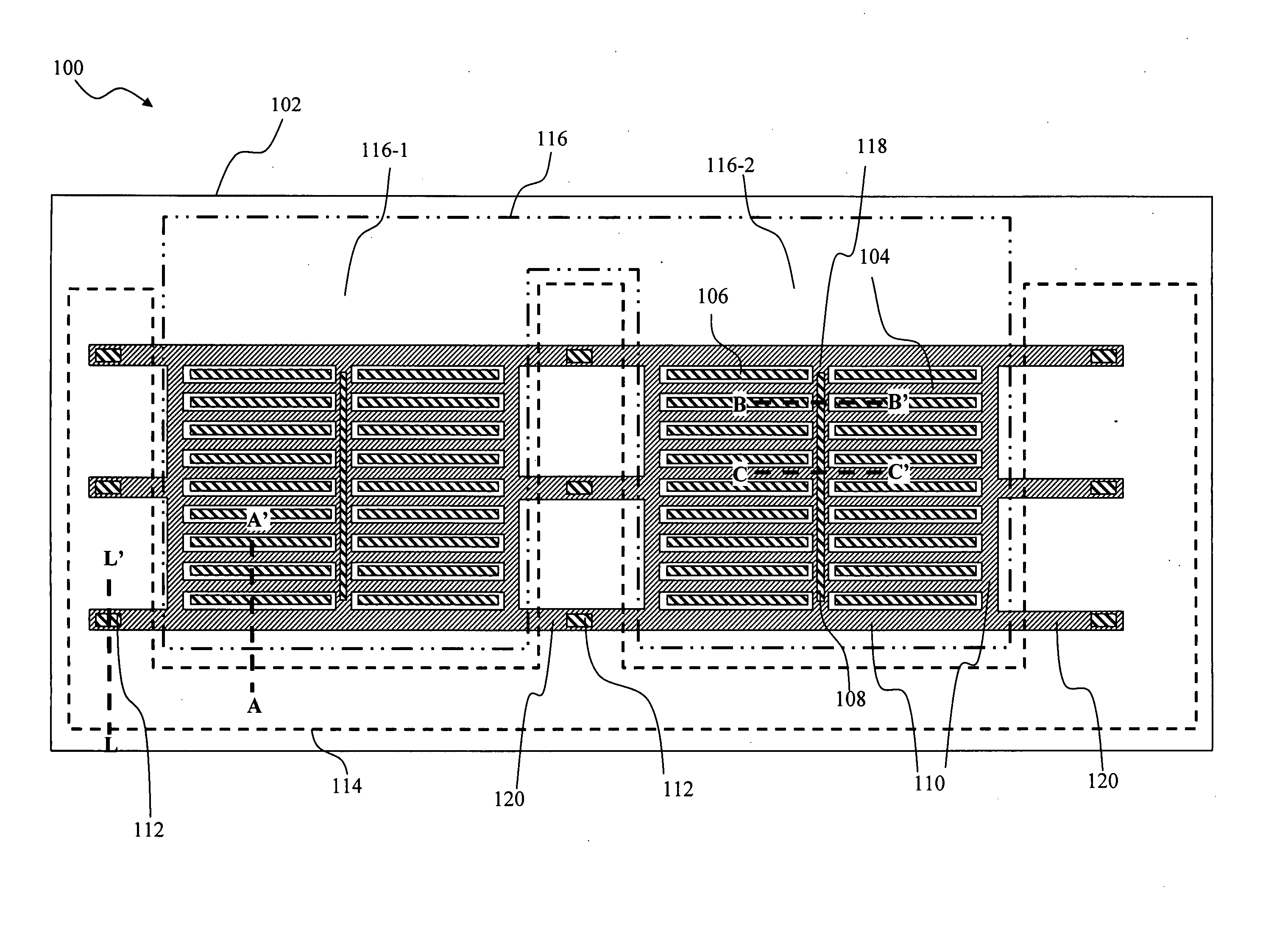

A semiconductor power device includes a plurality of closed N-channel MOSFET cells surrounded by trenched gates constituting substantially a square or rectangular cell. The trenched gates are further extended to a gate contact area and having greater width as wider trenched gates for electrically contacting a gate pad wherein the semiconductor power device further includes a source region disposed only in regions near the trenched gates in the closed N-channel MOSFET cells and away from regions near the wider trenched gate whereby a device ruggedness is improved. The source region is further disposed at a distance away from a corner or an edge of the semiconductor power device and away from a termination area. The semiconductor device further includes multiple trenched rings disposed in a termination area opposite the active area and the trenched rings having a floating voltage. The closed N-channel MOSFET cells are further supported on a red phosphorous substrate.

Owner:FORCE MOS TECH CO LTD

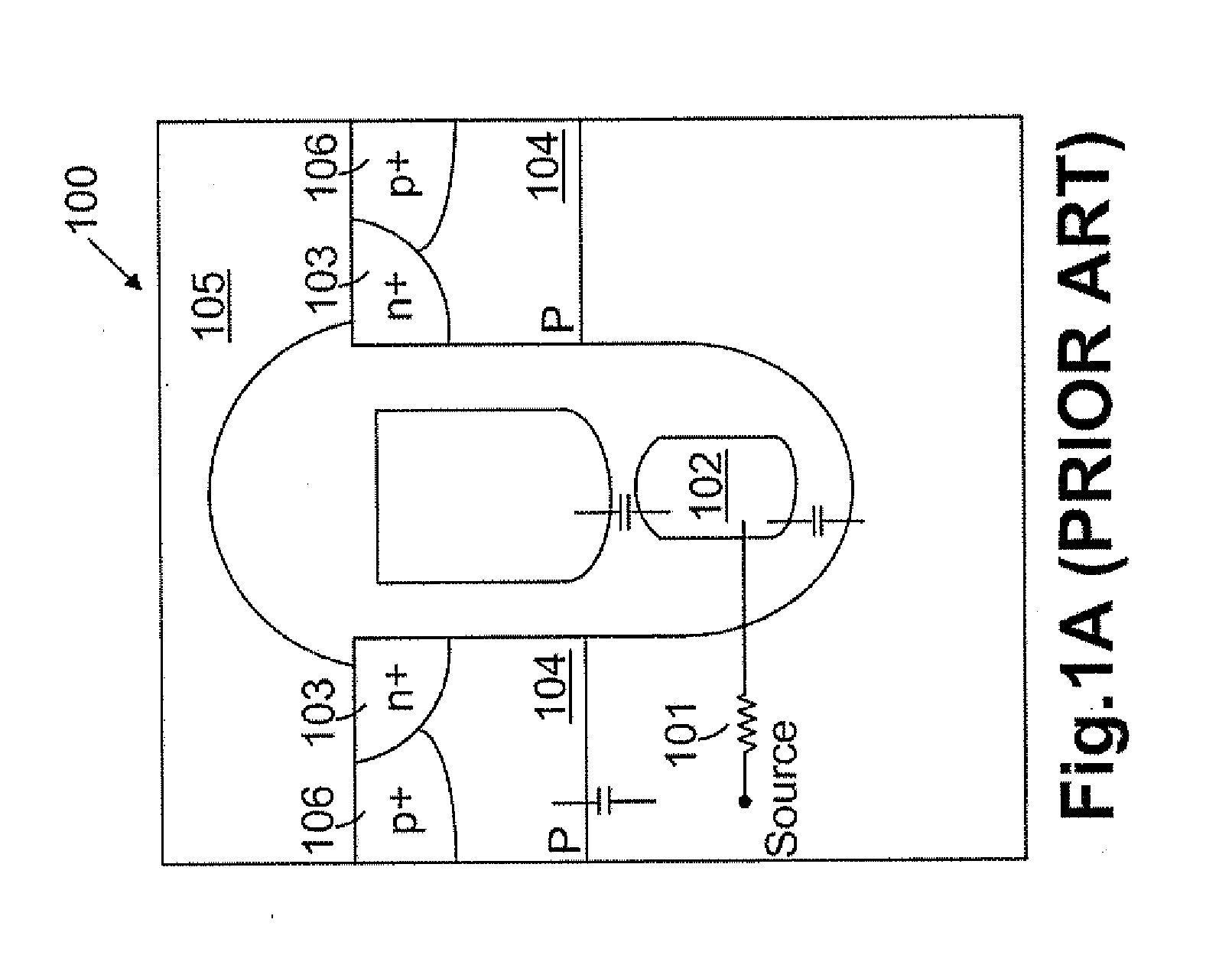

Self aligned trench mosfet with integrated diode

Transistor devices can be fabricated with an integrated diode using a self-alignment. The device includes a doped semiconductor substrate having one or more electrically insulated gate electrodes formed in trenches in the substrate. One or more body regions are formed in a top portion of the substrate proximate each gate trench. One or more source regions are formed in a self-aligned fashion in a top portion of the body regions proximate each gate trench. One or more thick insulator portions are formed over the gate electrodes on a top surface of the substrate with spaces between adjacent thick insulator portions. A metal is formed on top of the substrate over the thick insulator portions. The metal forms a self-aligned contact to the substrate through the spaces between the thick insulator portions. An integrated diode is formed under the self-aligned contact.

Owner:ALPHA & OMEGA SEMICON INC

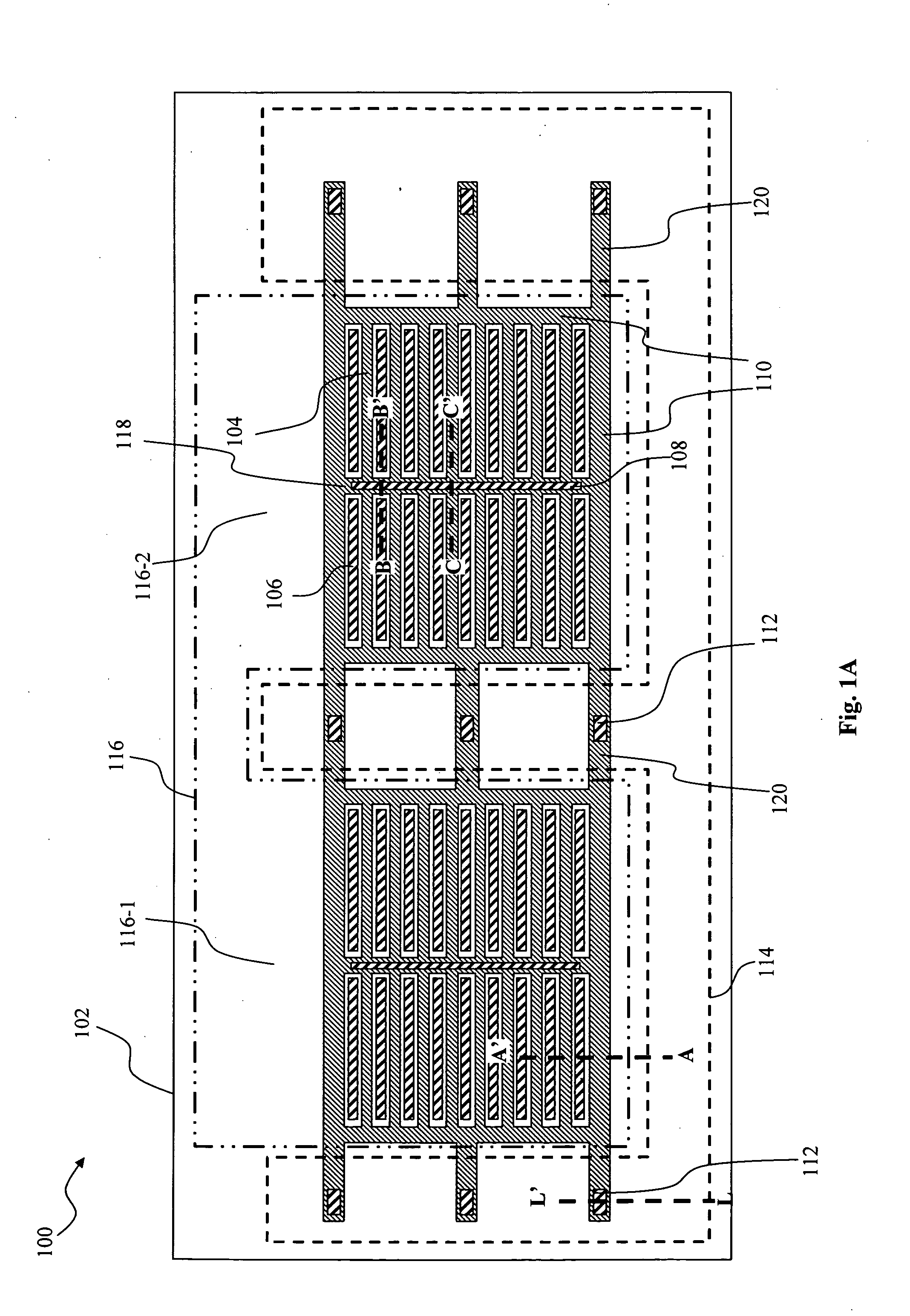

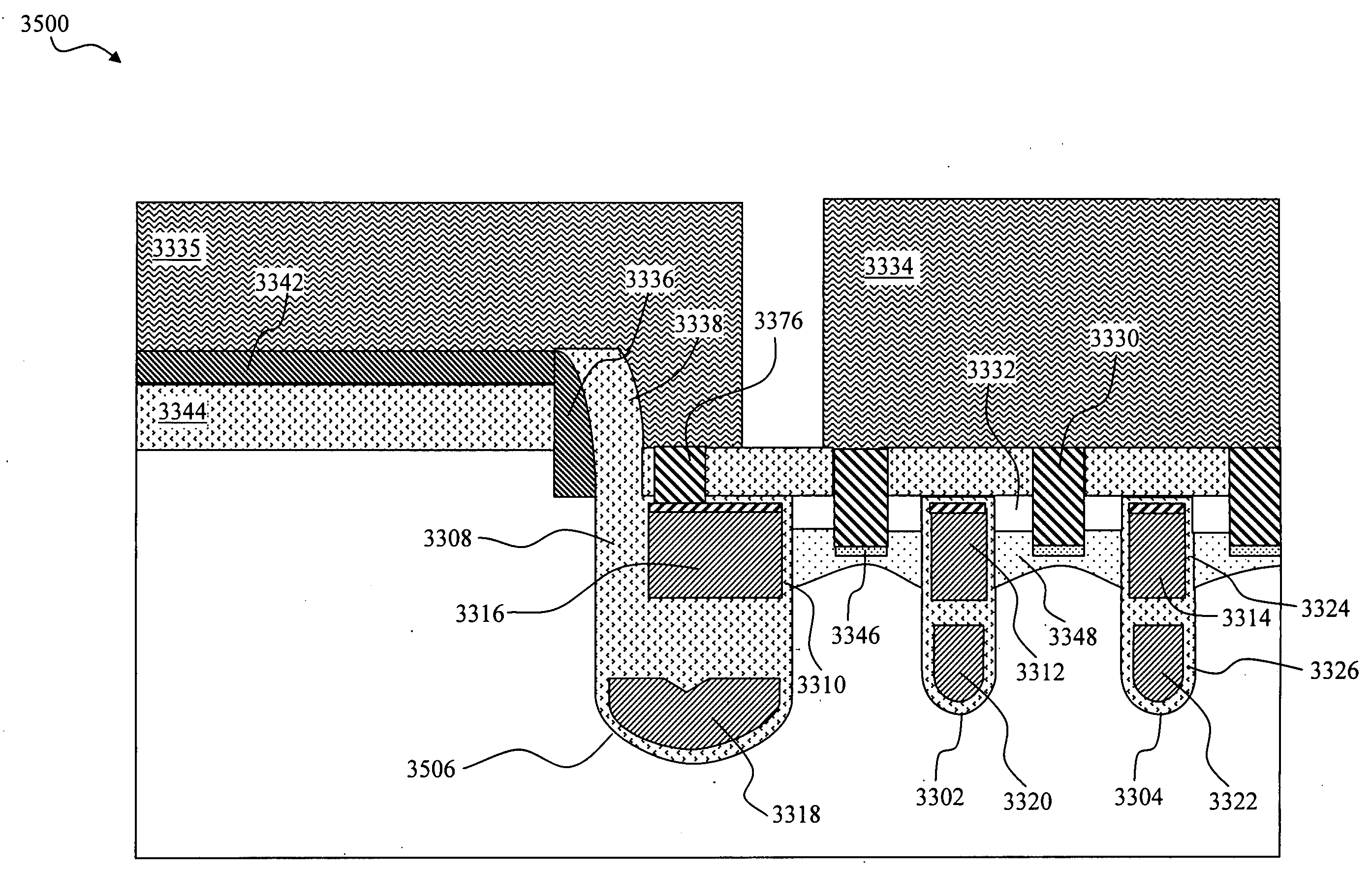

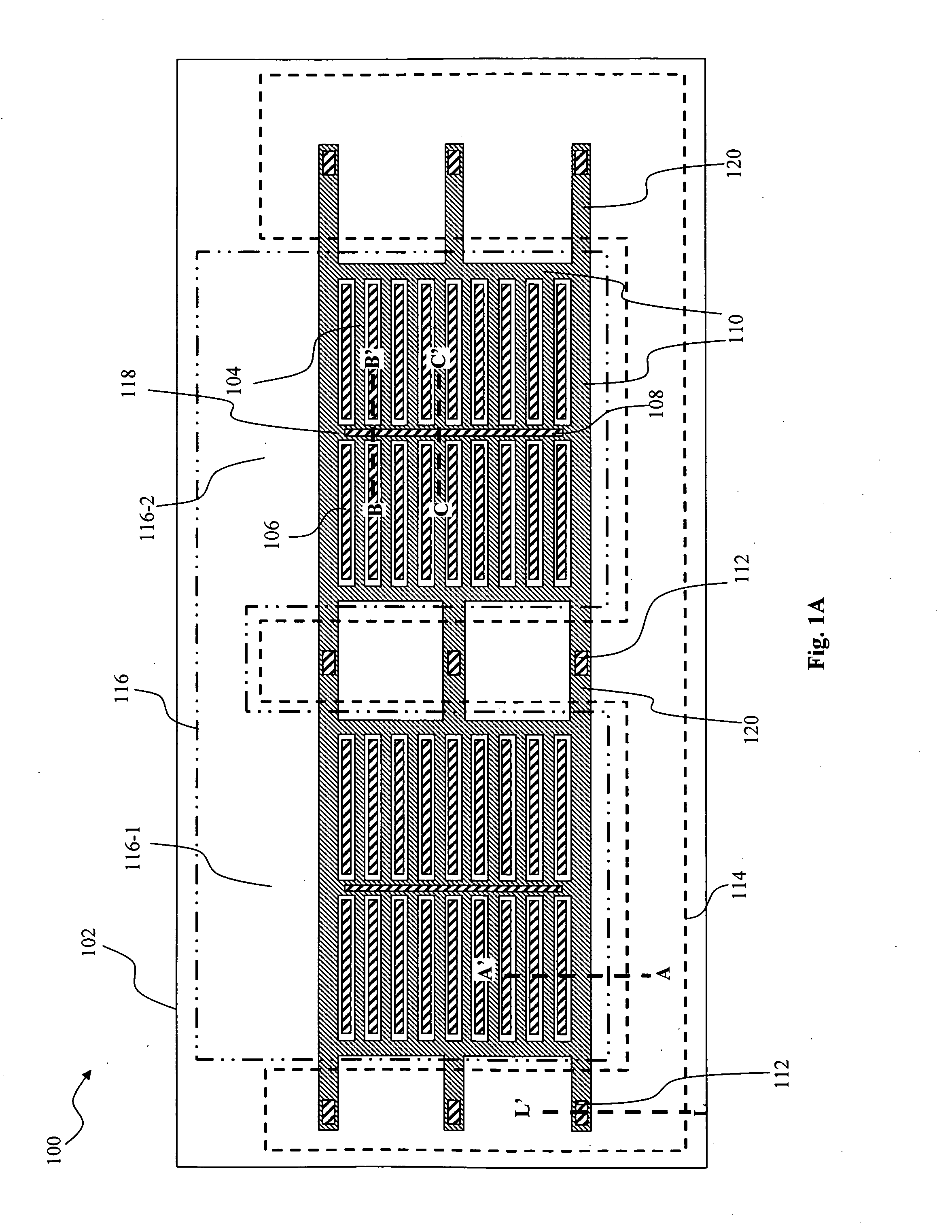

Super trench MOSFET including buried source electrode and method of fabricating the same

InactiveUS20050242392A1Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

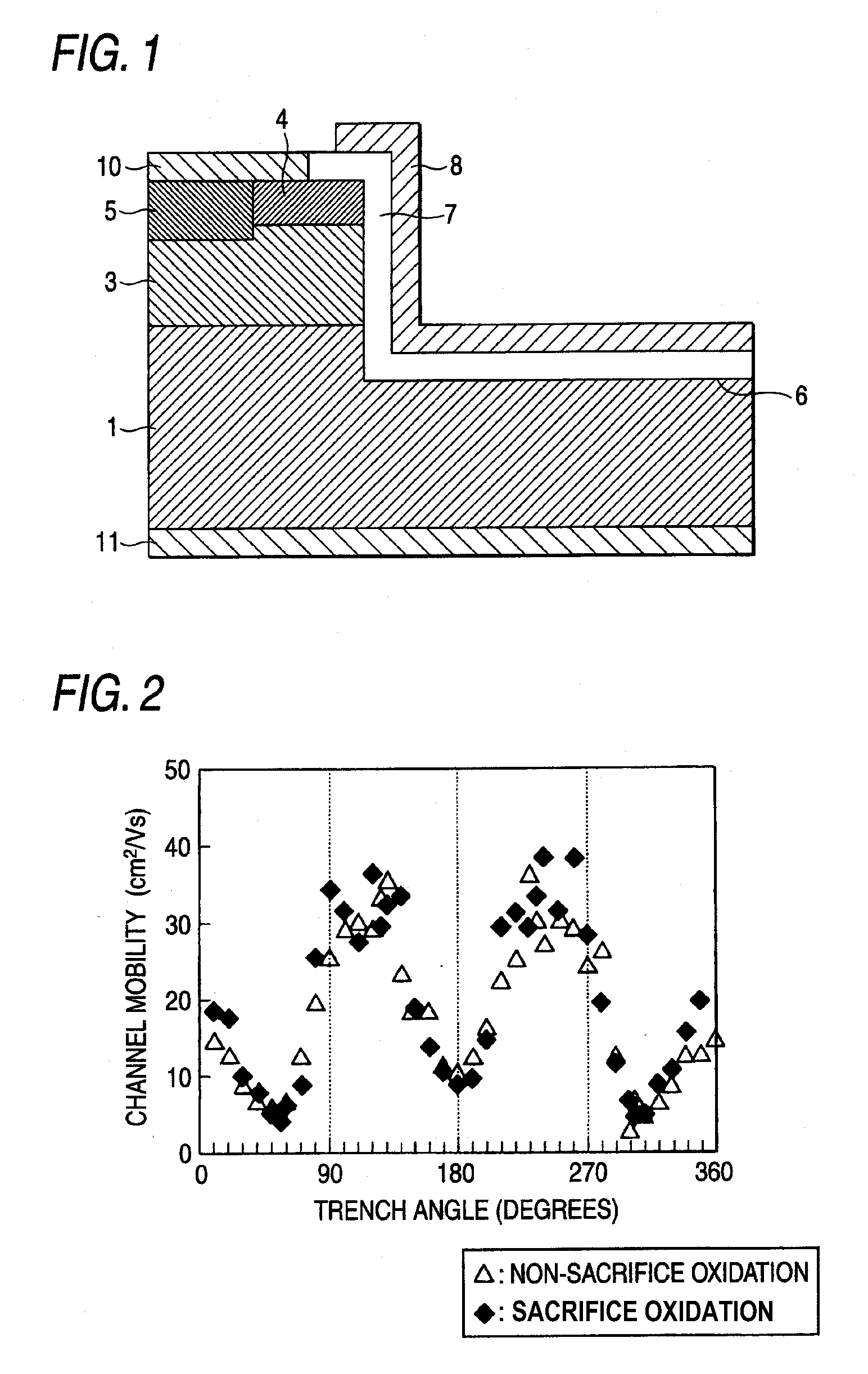

Semicoductor device and manufacturing method thereof

InactiveUS20070057262A1Semiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetSic substrate

In a semiconductor device having SiC vertical trench MOSFETs, it is aimed to prevent the generation of large scattering in the channel resistance without largely increasing the average value of channel resistance. A 4H-SiC substrate having a major face thereof that is generally a {0001} face and having an off angle α. The trench is formed with the standard deviation σ in scattering of the angle formed by a trench side wall face and a substrate major face within a wafer face. By setting the designed value of the angle formed by the trench side wall face and the substrate major face at an any angle ranging from [(60 degrees)+2σ] to [(90 degrees)−tan−1 (0.87×tan α)−2σ] in forming the trench in the SiC substrate, a semiconductor device in which the angle formed by the trench side wall face and the substrate major face is 60 degrees or more but not more than [(90 degrees)−tan−1 (0.87×tan α)] can be obtained.

Owner:FUJI ELECTRIC HLDG CO LTD

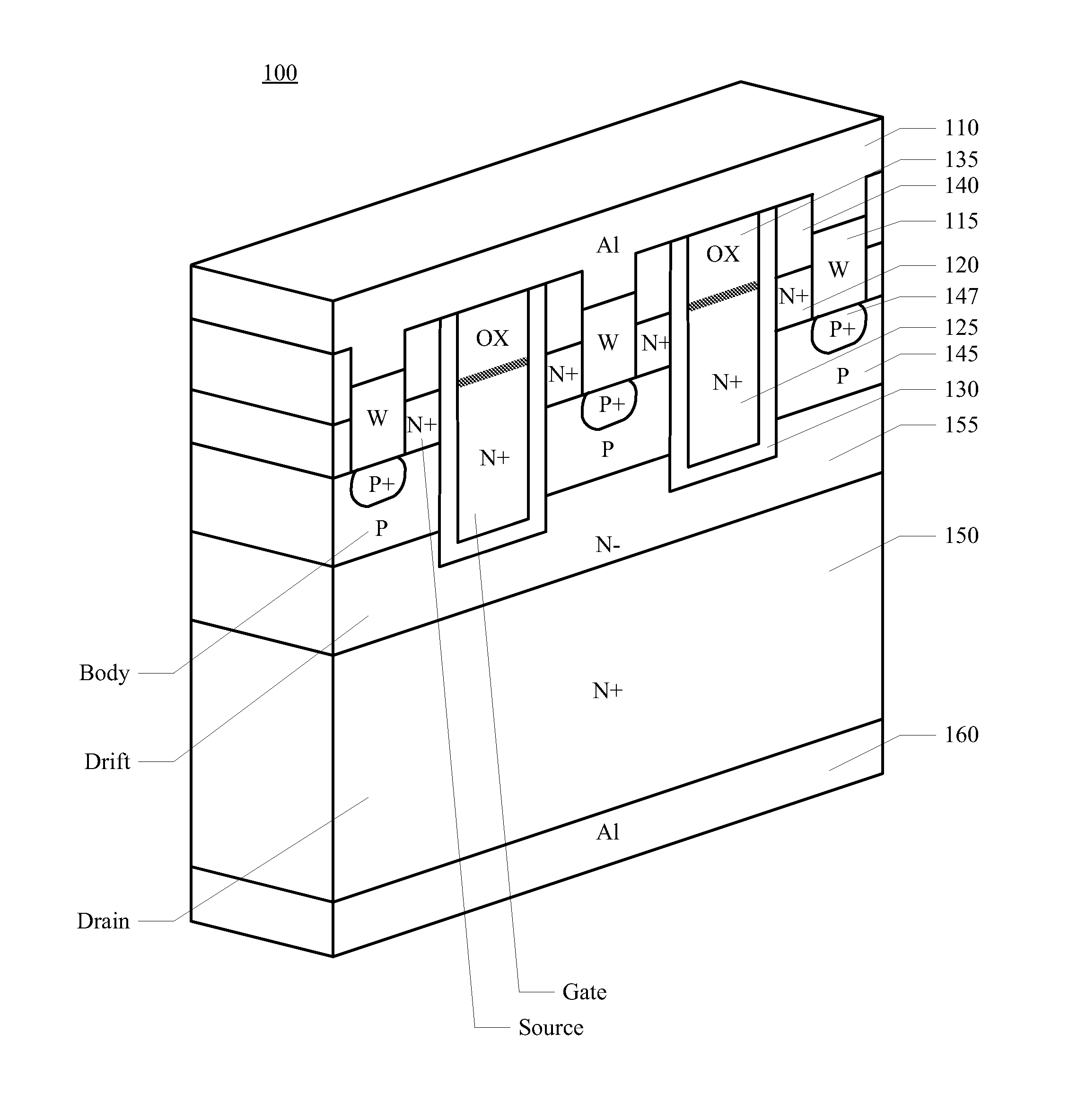

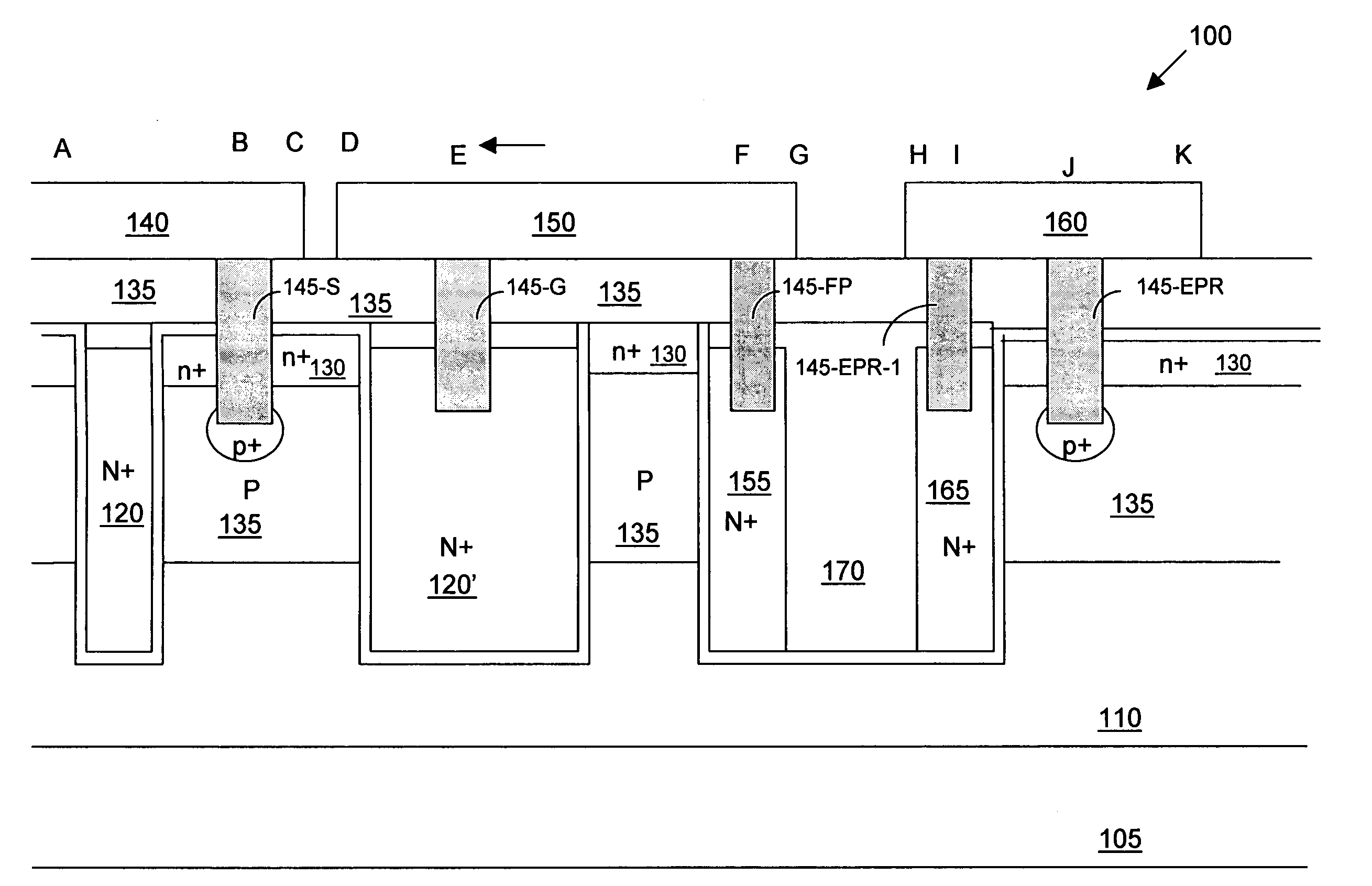

Shielded gate trench MOSFET device and fabrication

A semiconductor device embodiment includes a substrate, an active gate trench in the substrate, and an asymmetric trench in the substrate. The asymmetric trench has a first trench wall and a second trench wall, the first trench wall is lined with oxide having a first thickness, and the second trench wall is lined with oxide having a second thickness that is different from the first thickness. Another semiconductor device embodiment includes a substrate, an active gate trench in the substrate; and a source polysilicon pickup trench in the substrate. The source polysilicon pickup trench includes a polysilicon electrode, and top surface of the polysilicon electrode is below a bottom of a body region. Another semiconductor device includes a substrate, an active gate trench in the substrate, the active gate trench has a first top gate electrode and a first bottom source electrode, and a gate runner trench comprising a second top gate electrode and a second bottom source electrode. The second top gate electrode is narrower than the second bottom source electrode.

Owner:ALPHA & OMEGA SEMICON INC

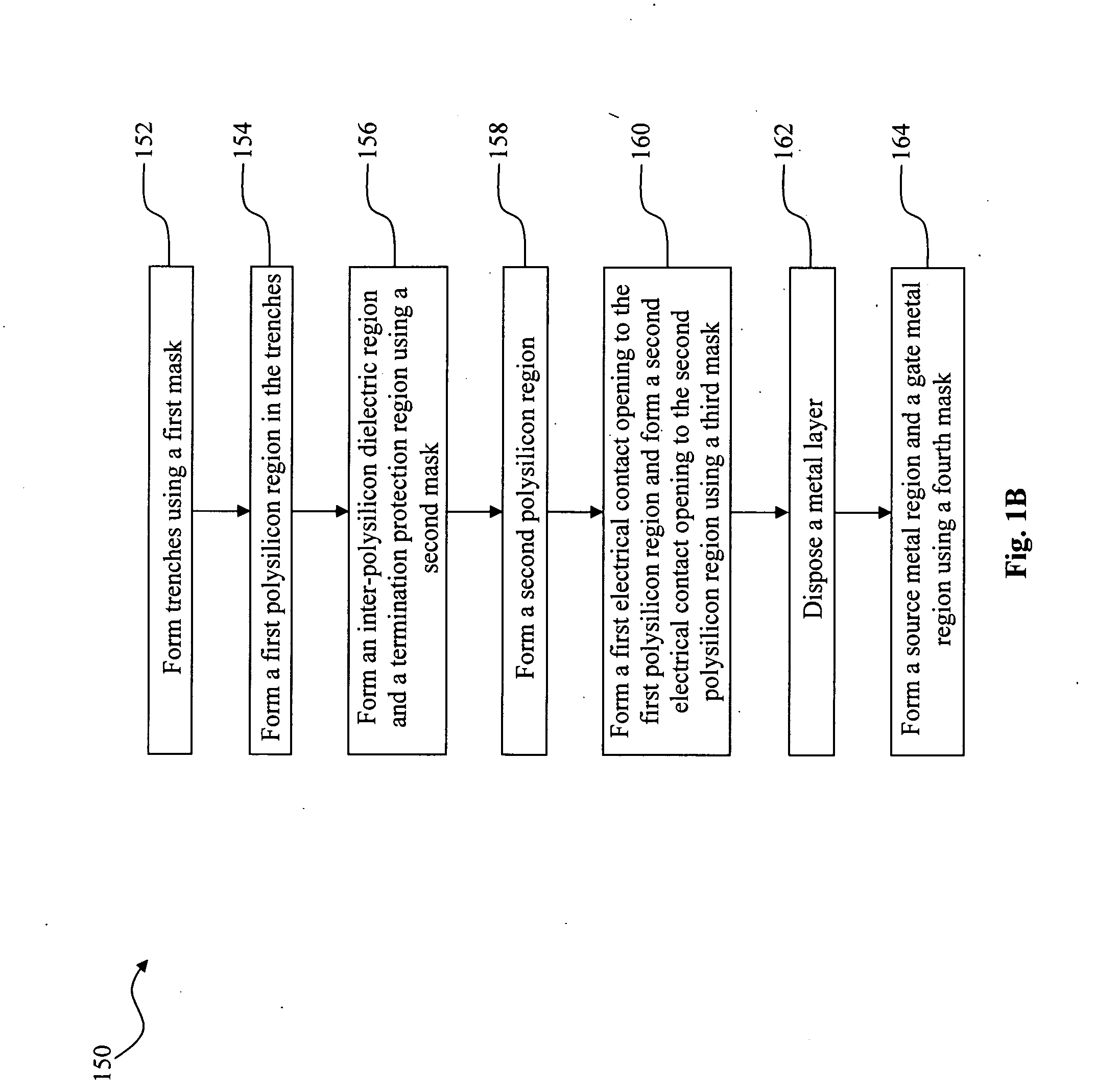

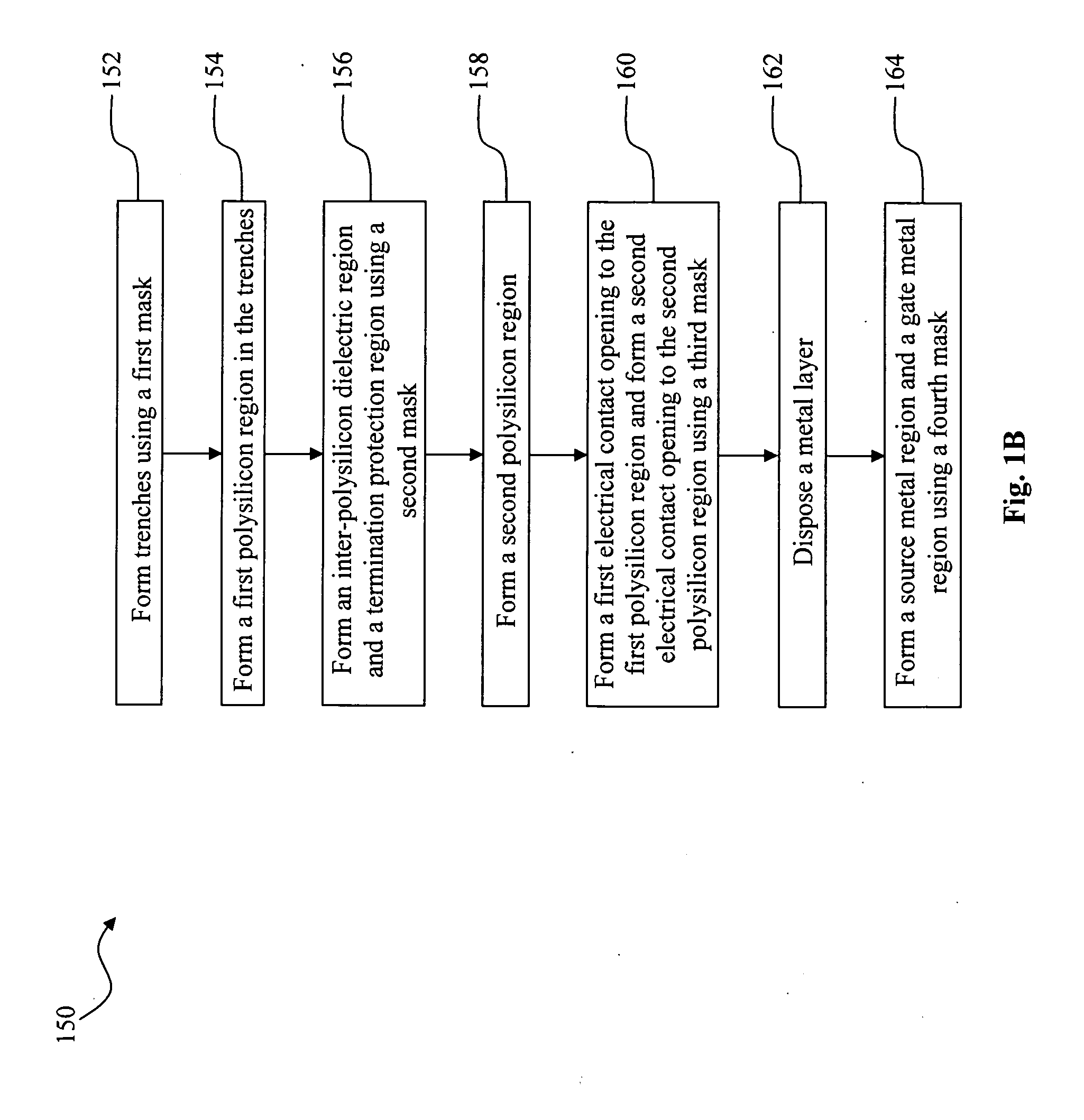

Shielded gate trench MOSFET device and fabrication

ActiveUS20110039383A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricTrench mosfet

A method for fabricating a semiconductor device includes forming a plurality of trenches, including applying a first mask, forming a first polysilicon region in at least some of the plurality of trenches, forming a inter-polysilicon dielectric region and a termination protection region, including applying a second mask, forming a second polysilicon region in the at least some of the plurality of trenches, forming a first electrical contact to the first polysilicon region and forming a second electrical contact to the second polysilicon region, including applying a third mask, disposing a metal layer, and forming a source metal region and a gate metal region, including applying a fourth mask.

Owner:ALPHA & OMEGA SEMICON INC

Field plate trench mosfet transistor with graded dielectric liner thickness

InactiveUS20100264486A1Add dimensionSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricVertical drift

An electronic device has a plurality of trenches formed in a semiconducting layer. A vertical drift region is located between and adjacent the trenches. An electrode is located within each trench, the electrode having a gate electrode section and a field plate section. A graded field plate dielectric is located between the field plate section and the vertical drift region.

Owner:TEXAS INSTR INC

Super-junction trench MOSFET with resurf step oxide and the method to make the same

ActiveUS8067800B2Minimize impactImprove rendering capabilitiesSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetEngineering

A super-junction trench MOSFET with Resurf Stepped Oxide is disclosed. The inventive structure can apply additional freedom for better optimization and manufacturing capability by tuning thick oxide thickness to minimize influence of charge imbalance, trapped charges, etc. . . . . Furthermore, the fabrication method can be implemented more reliably with lower cost.

Owner:FORCE MOS TECH CO LTD

Trench mosfet with resurf stepped oxide and diffused drift region

ActiveUS20130168760A1Super cost-effectiveEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetEngineering

A trench MOSFET with split gates and diffused drift region for on-resistance reduction is disclosed. Each of the split gates is symmetrically disposed in the middle of the source electrode and adjacent trench sidewall of a deep trench. The inventive structure can save a mask for definition of the location of the split gate electrodes. Furthermore, the fabrication method can be implemented more reliably with lower cost.

Owner:FORCE MOS TECH CO LTD

Shielded trench mosfet with multiple trenched floating gates as termination

ActiveUS20110254086A1Semiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetBody region

A trench MOSFET comprising a plurality of transistor cells having shielded trenched gates and multiple trenched floating gates as termination region is disclosed. The trenched floating gates have trench depth equal to or deeper than body junction depth of body regions in termination area. In some preferred embodiments, the trenched floating gates in the termination area are implemented by using shielded electrode structure.

Owner:FORCE MOS TECH CO LTD

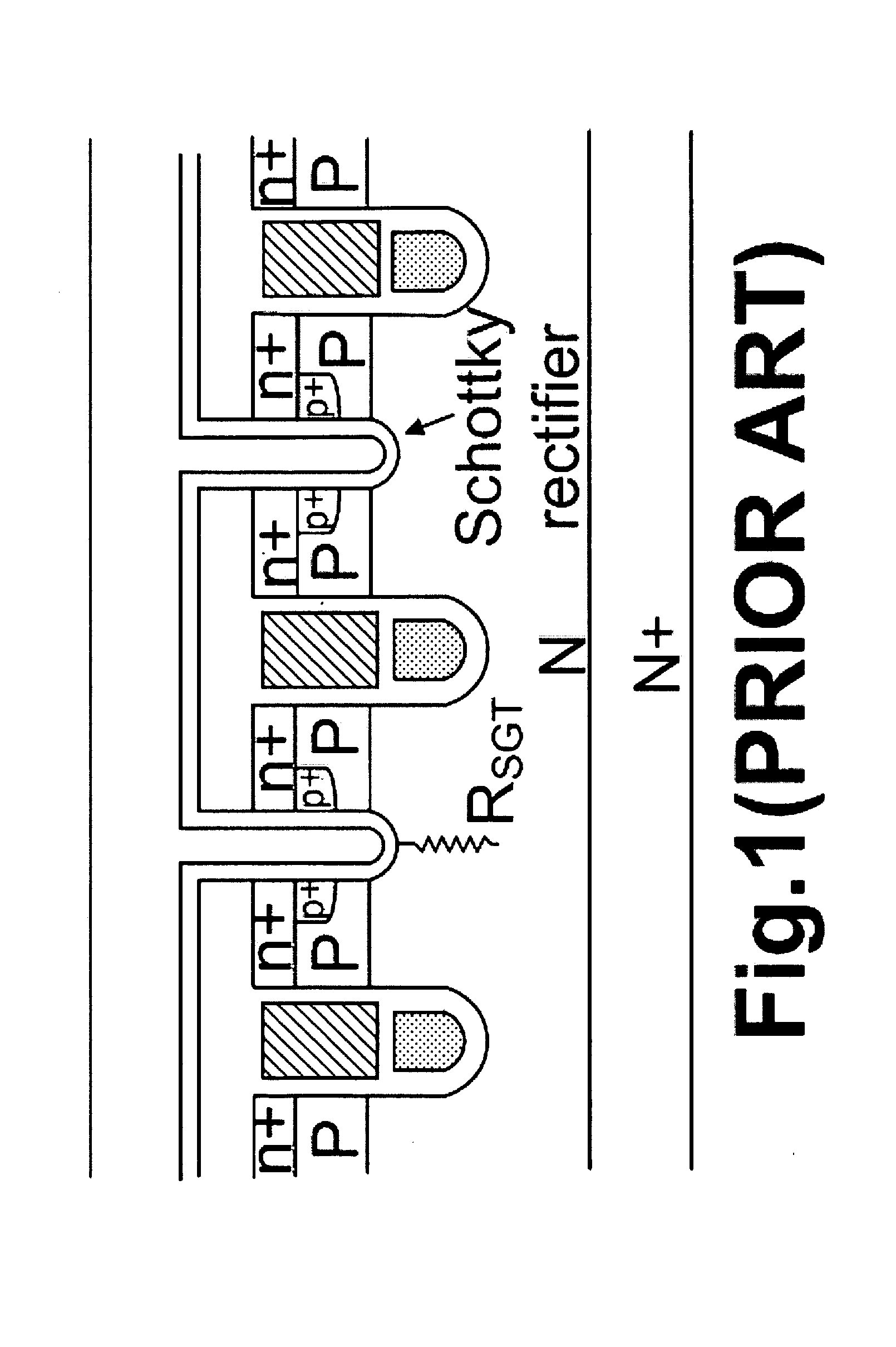

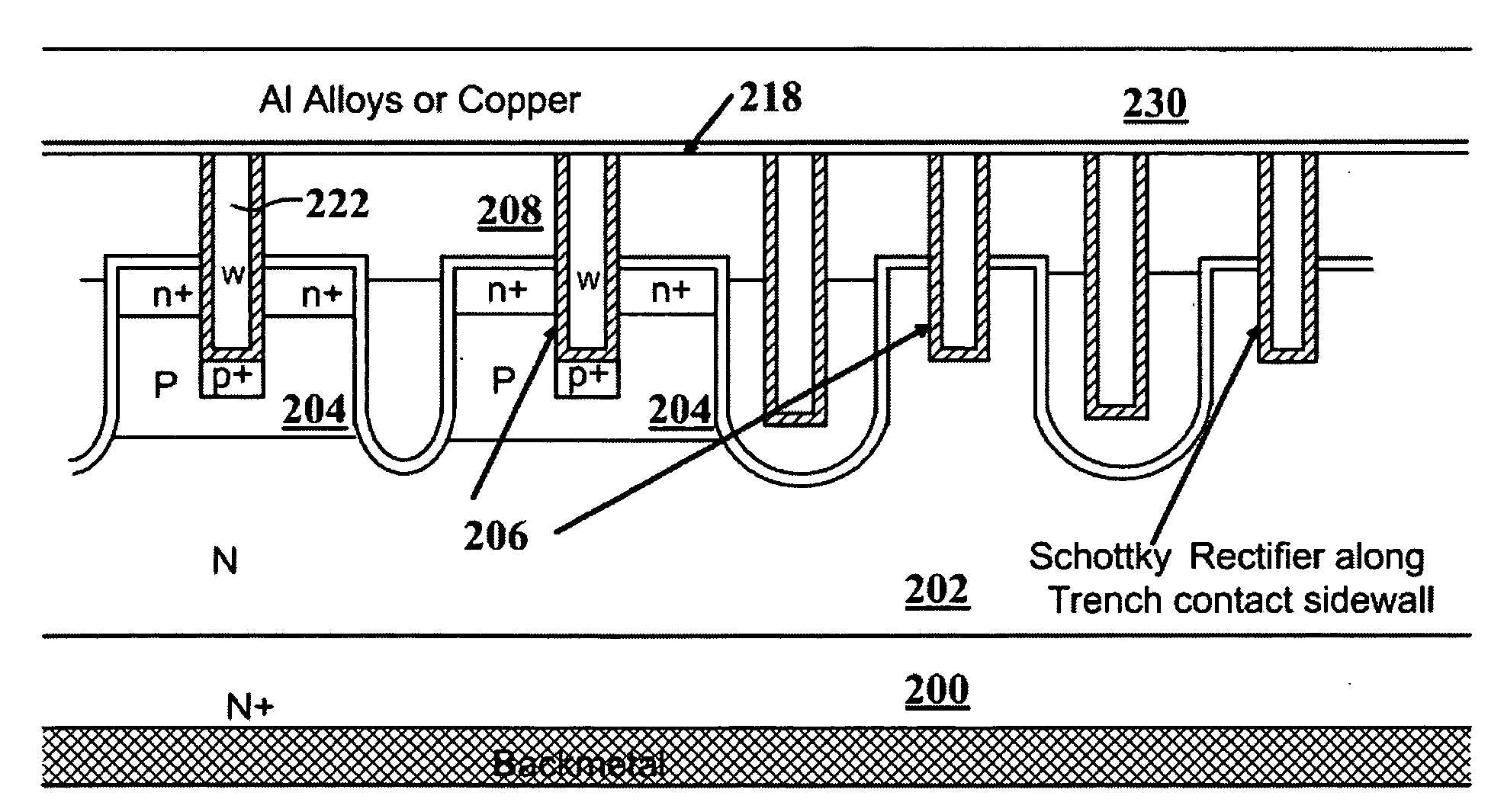

Trench mosfet with integrated schottky rectifier in same cell

InactiveUS20120037983A1Reduce parasitic resistanceReduce concentrationTransistorSemiconductor/solid-state device manufacturingTrench mosfetSchottky barrier

A semiconductor power device comprising a plurality of trench MOSFETs integrated with Schottky rectifier in same cell is disclosed. The invented semiconductor power device comprises a tilt-angle implanted drift region having higher doping concentration than epitaxial layer to reduce Vf in Schottky rectifier portion and to reduce Rds in trench MOSFET portion while maintaining a higher breakdown voltage by implementation of thick gate oxide in trench bottom of trenched gates. Furthermore, the invented semiconductor power device further comprises a Schottky barrier height enhancement region to enhance the barrier layer covered in trench bottom of trenched source-body-Schottky contact in Schottky rectifier portion.

Owner:FORCE MOS TECH CO LTD

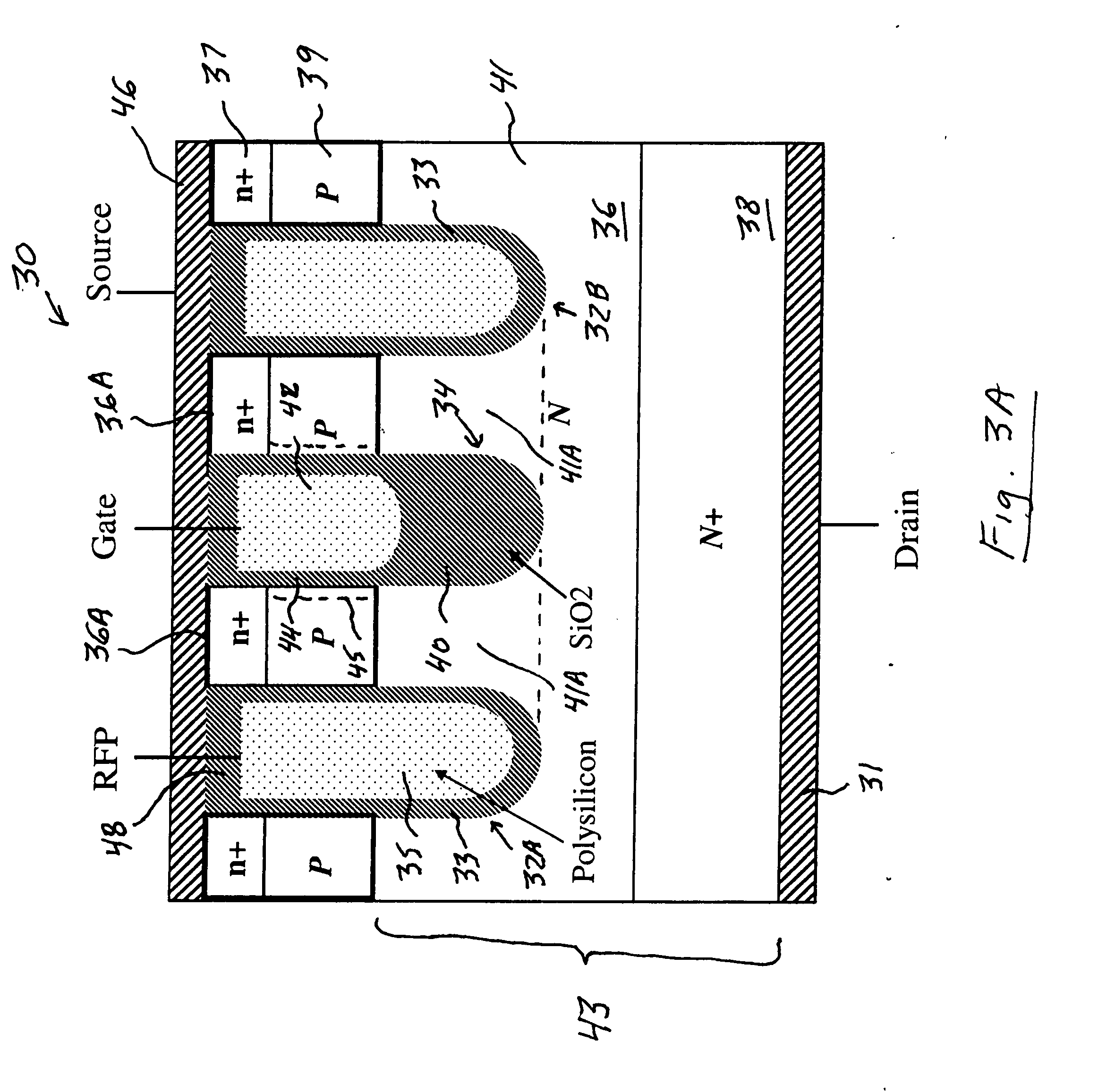

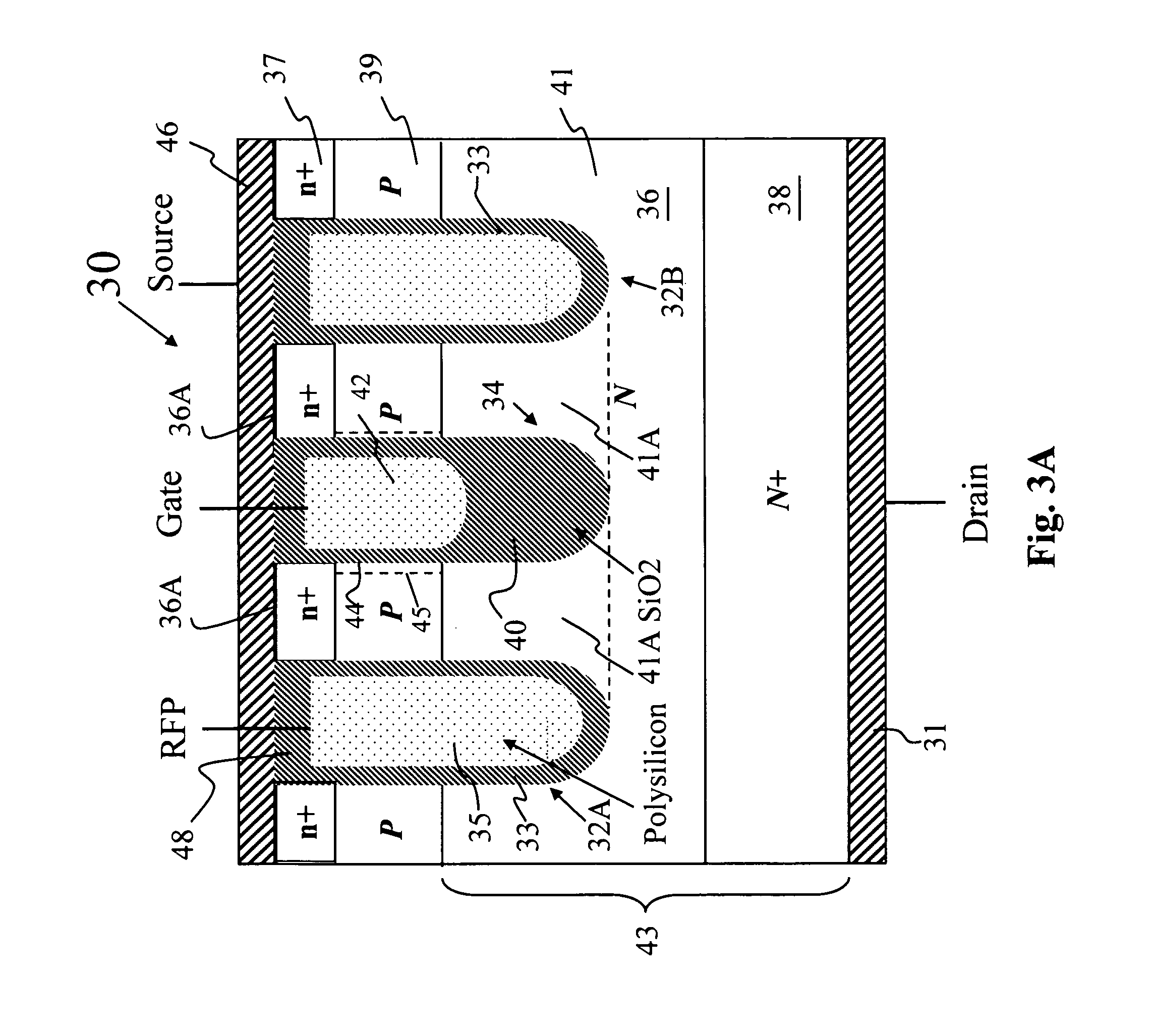

Power MOSFET with recessed field plate

ActiveUS7843004B2Solid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetReverse recovery

A trench MOSFET contains a recessed field plate (RFP) trench adjacent the gate trench. The RFP trench contains an RFP electrode insulated from the die by a dielectric layer along the walls of the RFP trench. The gate trench has a thick bottom oxide layer, and the gate and RFP trenches are preferably formed in the same processing step and are of substantially the same depth. When the MOSFET operates in the third quadrant (with the source / body-to-drain junction forward-biased), the combined effect of the RFP and gate electrodes significantly reduces in the minority carrier diffusion current and reverse-recovery charge. The RFP electrode also functions as a recessed field plates to reduce the electric field in the channel regions when the MOSFET source / body to-drain junction reverse-biased.

Owner:MAXPOWER SEMICON INC

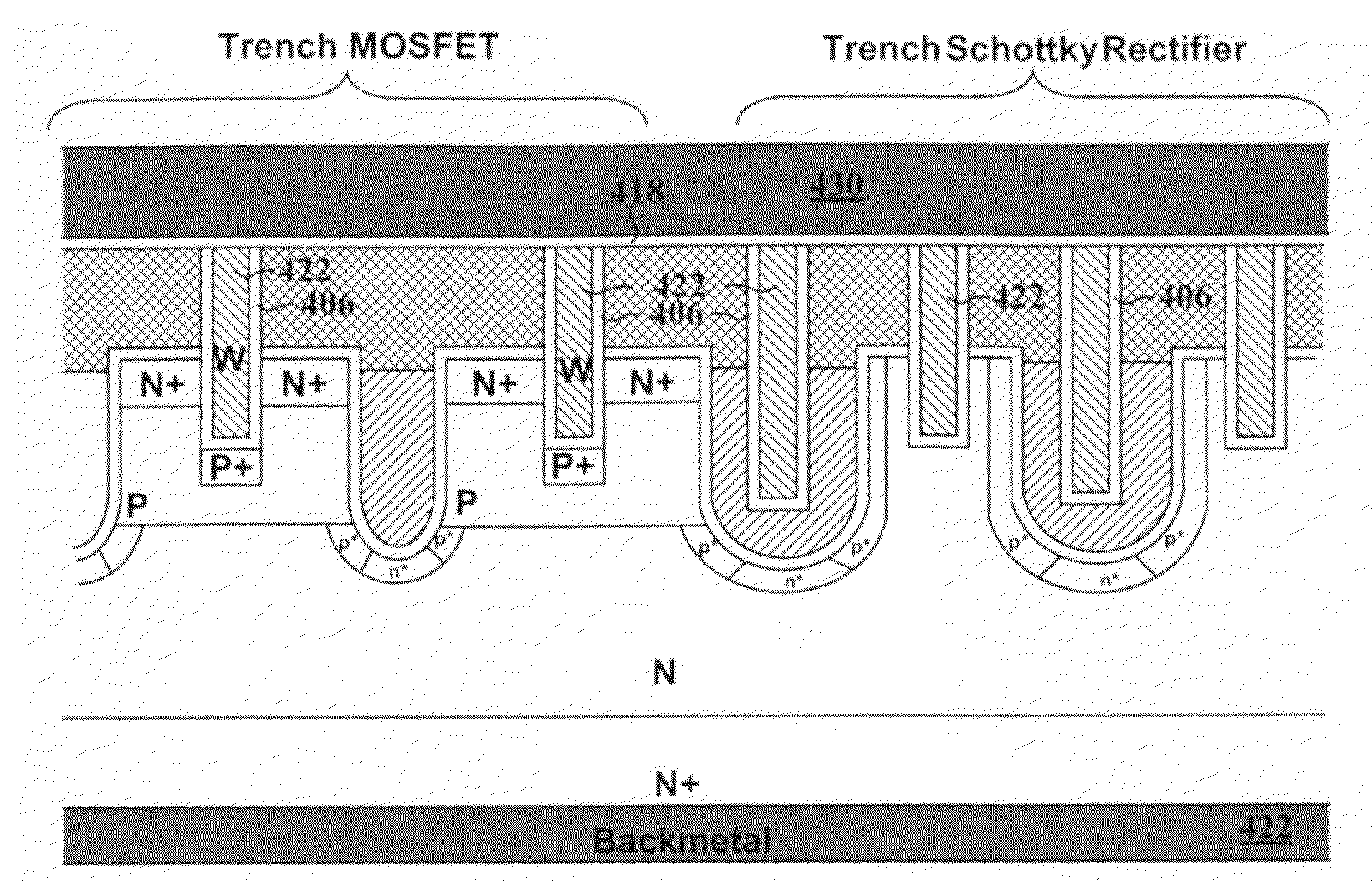

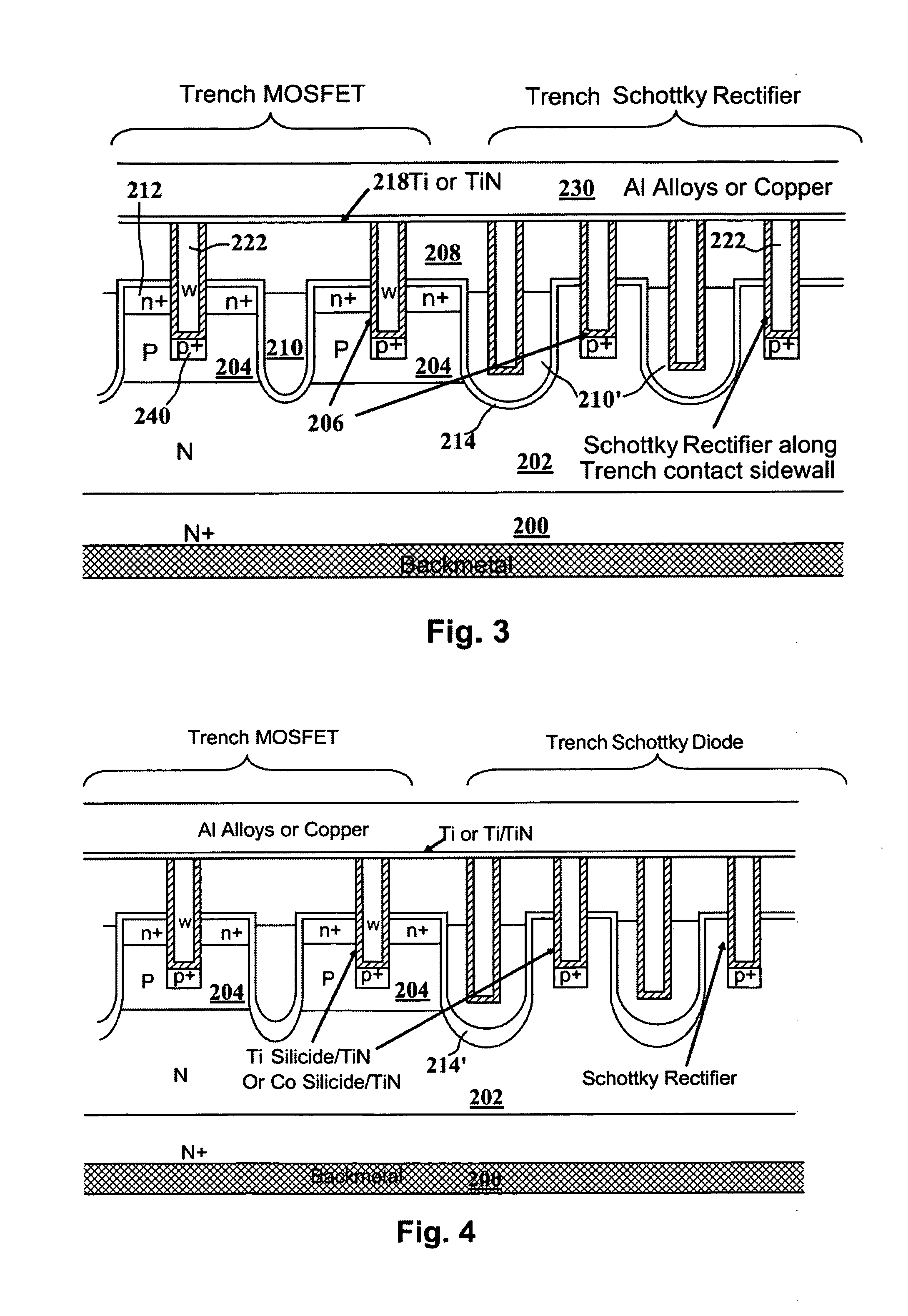

Low Qgd trench MOSFET integrated with schottky rectifier

InactiveUS20100264488A1Coupling chargeReducing coupling chargeSemiconductor/solid-state device manufacturingDiodeDopantTrench mosfet

An integrated circuit includes a plurality of trench MOSFET and a plurality of trench Schottky rectifier. The integrated circuit further comprises: tilt-angle implanted body dopant regions surrounding a lower portion of all trench gates sidewalls for reducing Qgd; a source dopant region disposed below a bottom surface of all trench gates for functioning as a current path for preventing a resistance increased caused by the body dopant regions.

Owner:FORCE MOS TECH CO LTD

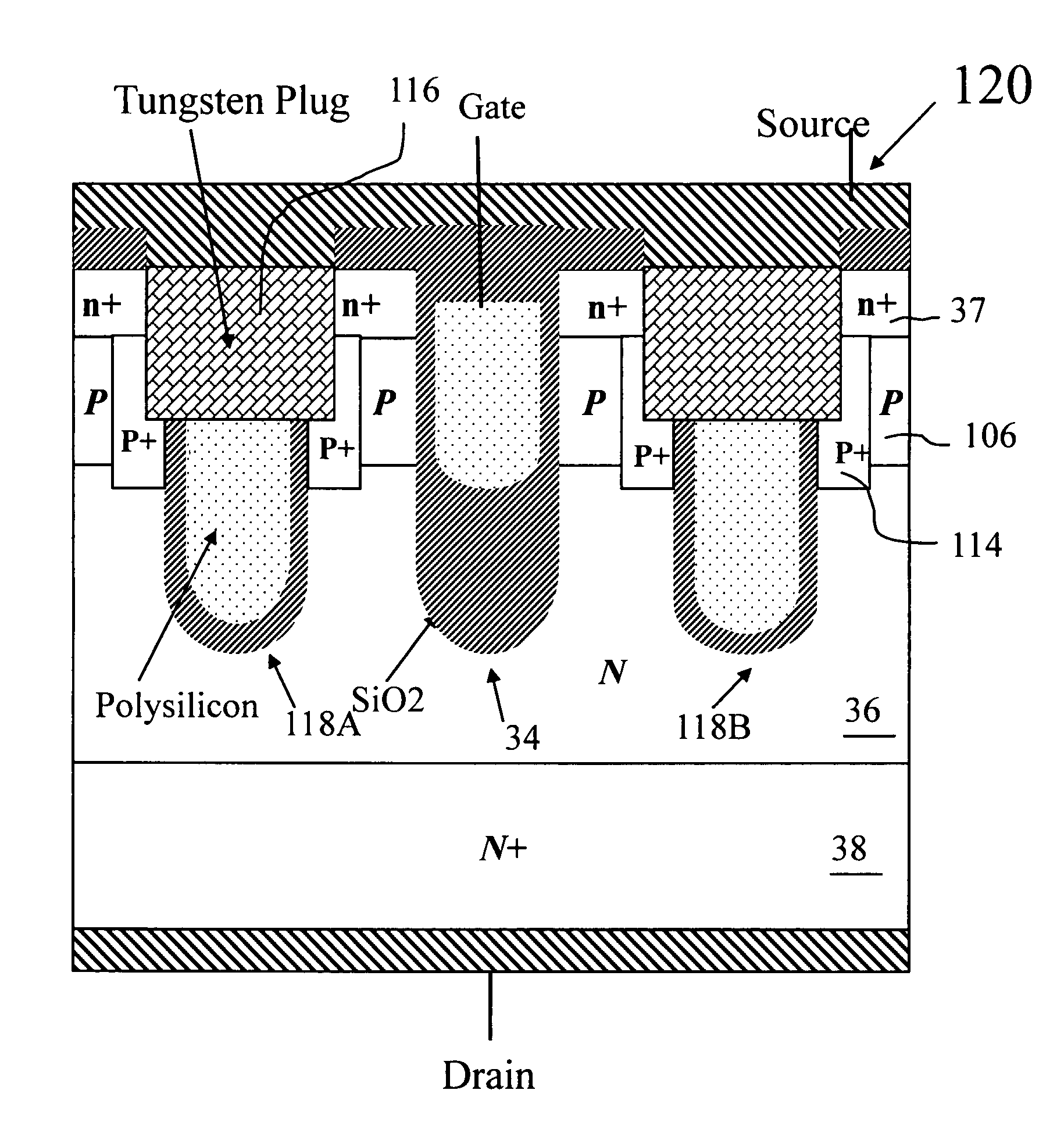

Trenched MOSFET device with contact trenches filled with tungsten plugs

InactiveUS20060273385A1Simple processSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetInsulation layer

A trenched semiconductor power device that includes a trenched gate disposed in an extended continuous trench surrounding a plurality of transistor cells in an active cell area and extending as trench-gate fingers to intersect with a trenched gate under the gate metal runner at a termination area. At least one of the trench-gate fingers intersects with the trenched gate under the gate metal runner near the termination area having trench intersection regions vulnerable to have a polysilicon void developed therein. At least a gate contact trench opened through an insulation layer covering the semiconductor power device wherein the gate contact trench penetrating from the insulation layer and extending into the gate polysilicon and the gate contact trench is opened in an area away from the trench intersection regions.

Owner:M MOS SEMICON

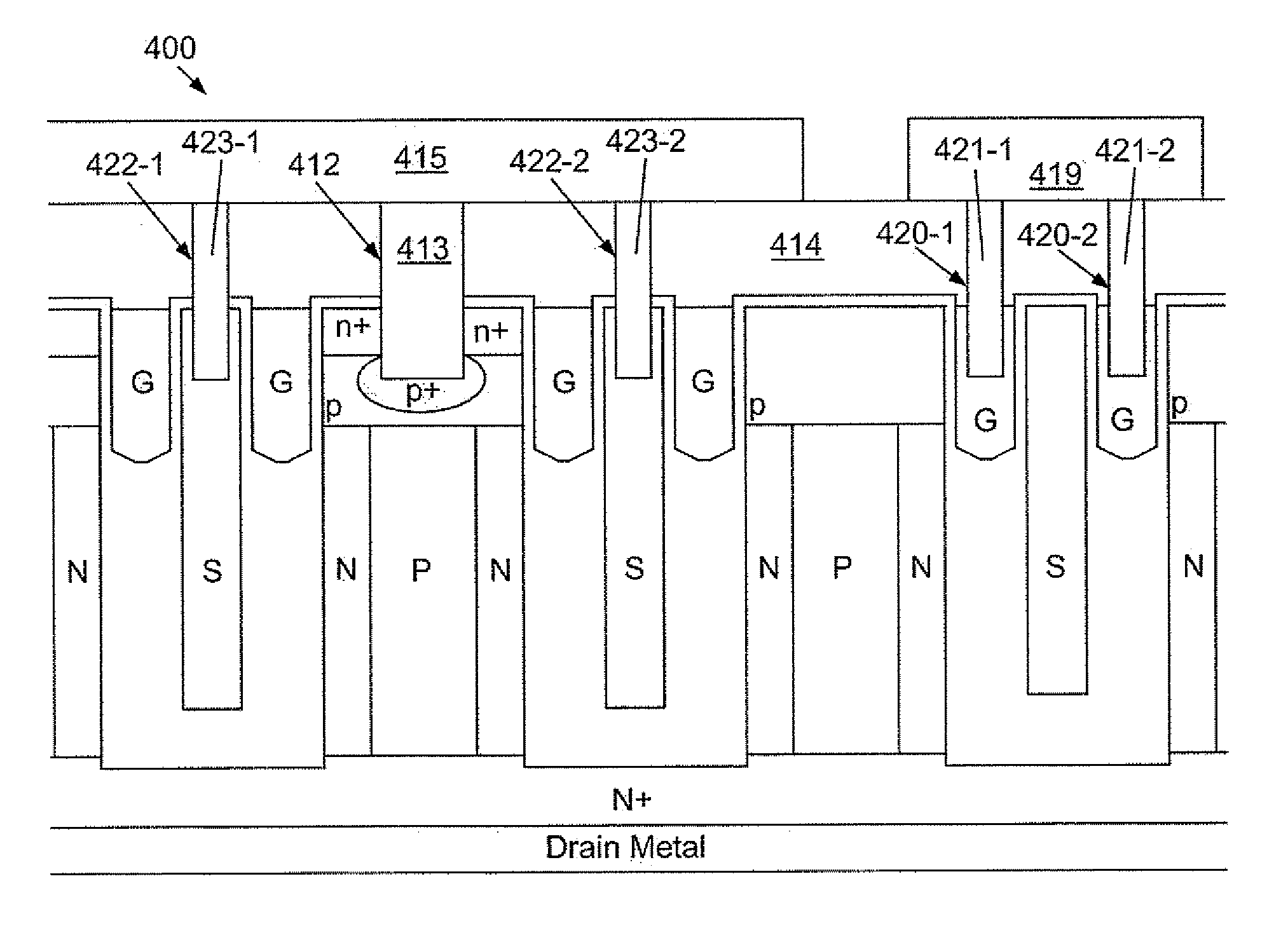

Self-Aligned Trench MOSFET and Method of Manufacture

ActiveUS20080246081A1Semiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetBody contact

A trench metal-oxide-semiconductor field effect transistor (MOSFET), in accordance with one embodiment, includes a drain region, a plurality of gate regions disposed above the drain region, a plurality of gate insulator regions each disposed about a periphery of a respective one of the plurality of gate regions, a plurality of source regions disposed in recessed mesas between the plurality of gate insulator regions, a plurality of body regions disposed in recessed mesas between the plurality of gate insulator regions and between the plurality of source regions and the drain region. The MOSFET also includes a plurality of body contact regions disposed in the each body region adjacent the plurality of source regions, a plurality of source / body contact spacers disposed between the plurality of gate insulator regions above the recessed mesas, a source / body contact disposed above the source / body contact spacers, and a plurality of source / body contact plugs disposed between the source / body contact spacers and coupling the source / body contact to the plurality of body contact regions and the plurality of source regions.

Owner:VISHAY SILICONIX LLC

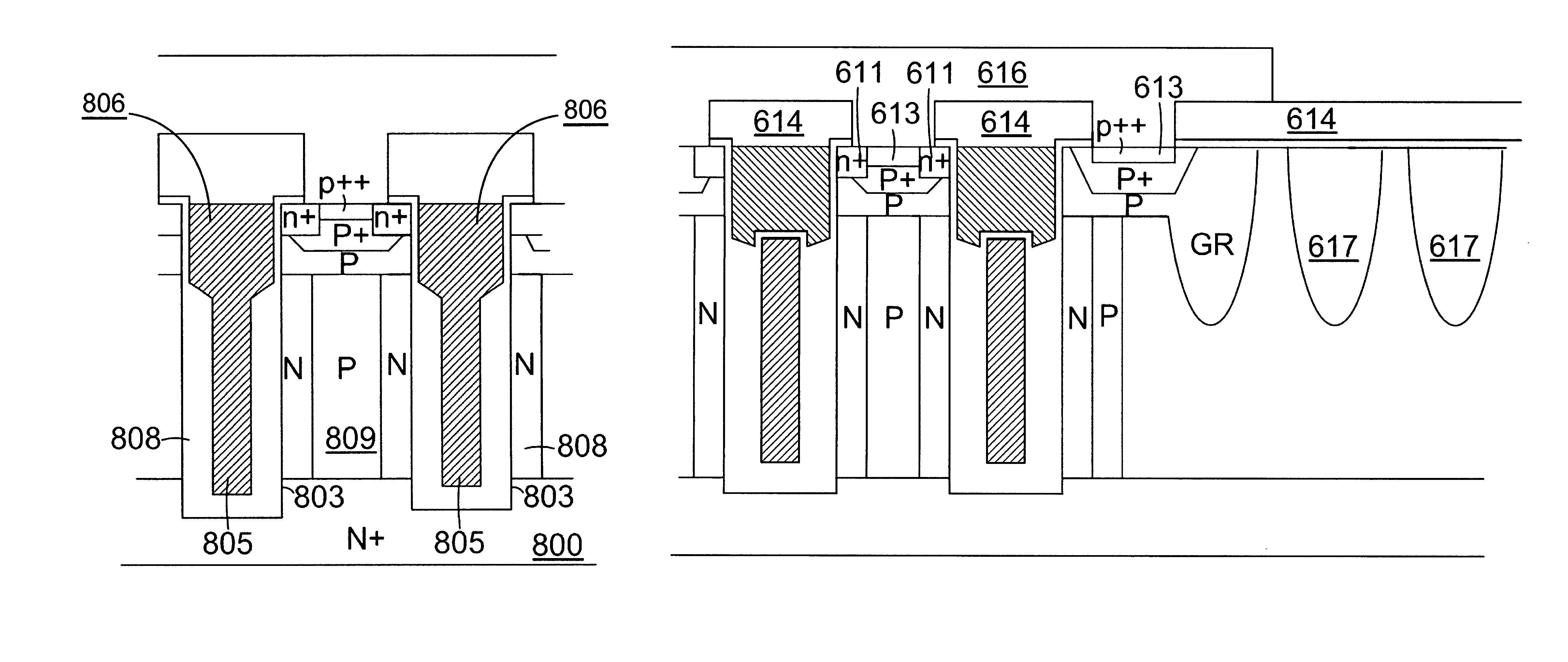

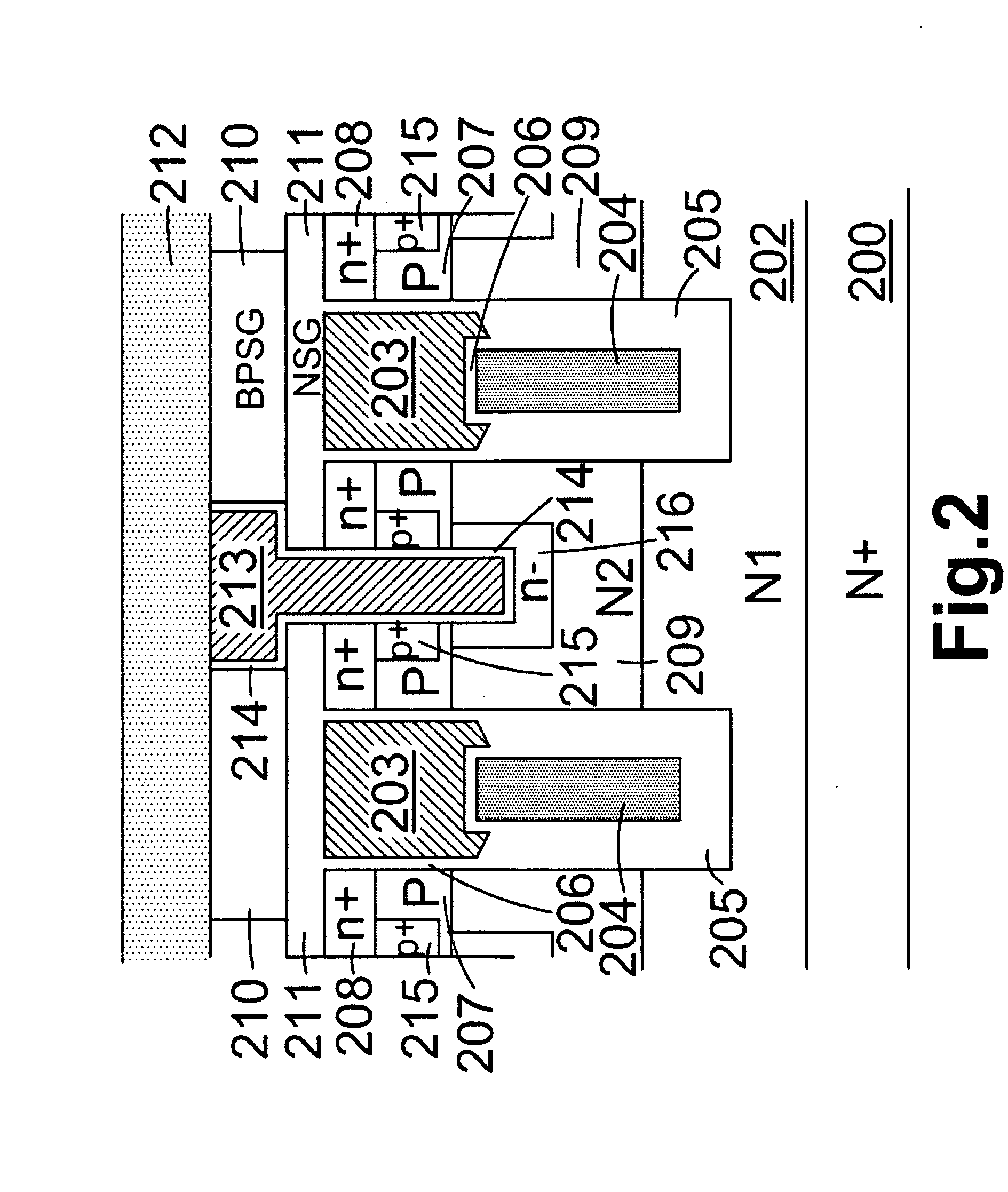

Super-junction trench mosfet with multiple trenched source-body contacts

ActiveUS20120187477A1Good performance optimizationGood manufacturing capabilitySemiconductor devicesTrench mosfetBody contact

A super-junction trench MOSFET with split gate electrodes is disclosed for high voltage device by applying multiple trenched source-body contacts with narrow CDs in unit cell. Furthermore, source regions are only formed along channel regions near the gate trenches, not between adjacent trenched source-body contacts for UIS (Unclamped Inductance Switching) current enhancement

Owner:FORCE MOS TECH CO LTD

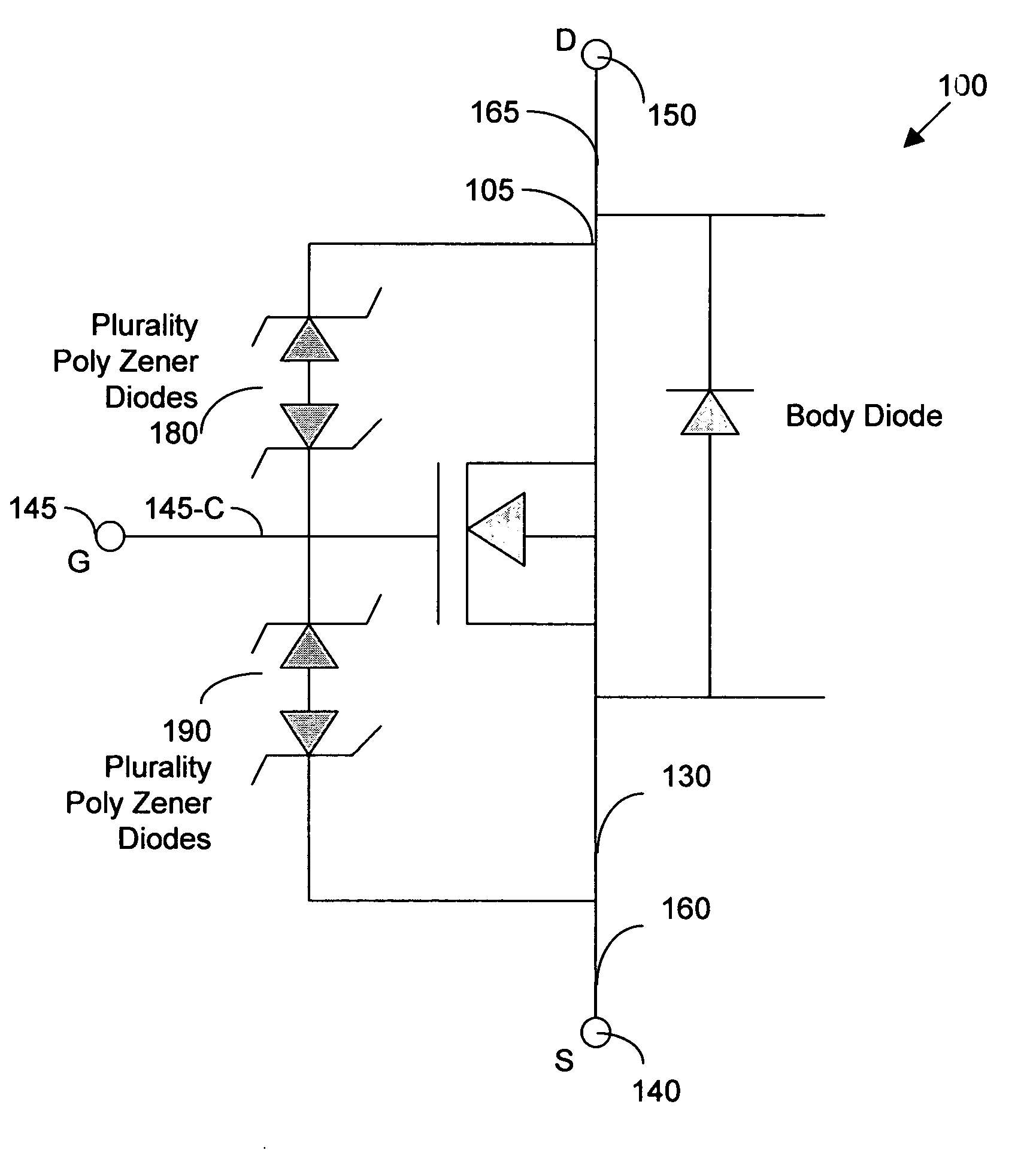

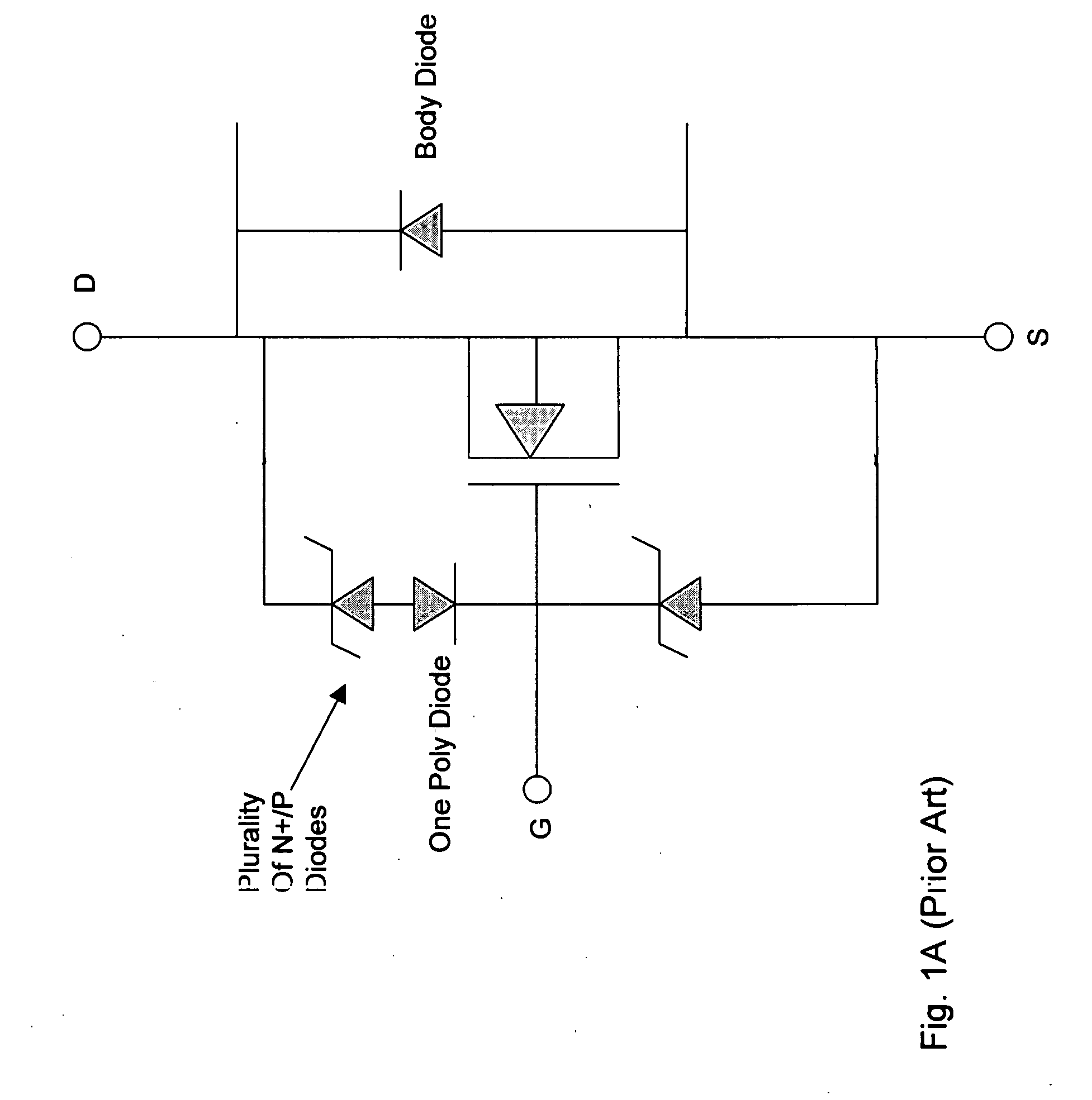

Trenched MOSFETs with improved gate-drain (GD) clamp diodes

ActiveUS20080258224A1Prevent channelingLower breakdown voltageTransistorSemiconductor/solid-state device detailsDopantInsulation layer

A MOSFET device that includes a first Zener diode connected between a gate metal and a drain metal of said semiconductor power device for functioning as a gate-drain (GD) clamp diode. The GD clamp diode includes multiple back-to-back doped regions in a polysilicon layer doped with dopant ions of a first conductivity type next to a second conductivity type disposed on an insulation layer above the MOSFET device, having an avalanche voltage lower than a source / drain avalanche voltage of the MOSFET device wherein the Zener diode is insulated from a doped region of the MOSFET device for preventing a channeling effect. The MOSFET device further includes a second Zener diode connected between a gate metal and a source metal of the MOSFET device for functioning as a gate-source (GS) clamp diode, wherein the GD clamp diode includes multiple back-to-back doped regions in the polysilicon layer doped with dopant ions of a first conductivity type next to a second conductivity type disposed on the insulation layer above the MOSFET device having a lower breakdown voltage than a gate oxide rupture voltage of the MOSFET device.

Owner:FORCE MOS TECH CO LTD

Integrated trench Mosfet and Schottky Rectifier with trench contact structure

InactiveUS20090315106A1Lower on-resistanceLow VfTransistorSolid-state devicesTrench mosfetReverse leakage current

A trench MOSFET in parallel with trench Schottky barrier rectifier is formed on a single substrate. The present invention solves the constrains brought by planar contact of Schottky, for example, the large area occupied by planar structure. As the size of present device is getting smaller and smaller, the trench Schottky structure of this invention is able to be shrink and, at the same time, to achieve low specific on-resistance. By applying a double epitaxial layer in trench Schottky barrier rectifier, the device performance is enhanced for lower Vf and lower reverse leakage current Ir is achieved.

Owner:FORCE MOS TECH CO LTD

High switching trench mosfet

ActiveUS20120292694A1Improve performanceIncrease costSemiconductor/solid-state device manufacturingSemiconductor devicesHigh cellTrench mosfet

A shielded gate trench metal oxide semiconductor filed effect transistor (MOSFET) having high switching speed is disclosed. The inventive shielded gate trench MOSFET includes a shielded electrode spreading resistance placed between a shielded gate electrode and a source metal to enhance the performance of the shielded gate trench MOSFET by adjusting doping concentration of poly-silicon in gate trenches to a target value. Furthermore, high cell density is achieved by employing the inventive shielded gate trench MOSFET without requirement of additional cost.

Owner:FORCE MOS TECH CO LTD

Method for forming nanotube semiconductor devices

ActiveUS7910486B2NanoinformaticsSemiconductor/solid-state device manufacturingPower semiconductor deviceTrench mosfet

A method for forming a semiconductor device includes forming a nanotube region using a thin epitaxial layer formed on the sidewall of a trench in the semiconductor body. The thin epitaxial layer has uniform doping concentration. In another embodiment, a first thin epitaxial layer of the same conductivity type as the semiconductor body is formed on the sidewall of a trench in the semiconductor body and a second thin epitaxial layer of the opposite conductivity type is formed on the first epitaxial layer. The first and second epitaxial layers have uniform doping concentration. The thickness and doping concentrations of the first and second epitaxial layers and the semiconductor body are selected to achieve charge balance. In one embodiment, the semiconductor body is a lightly doped P-type substrate. A vertical trench MOSFET, an IGBT, a Schottky diode and a P-N junction diode can be formed using the same N-Epi / P-Epi nanotube structure.

Owner:ALPHA & OMEGA SEMICON INC

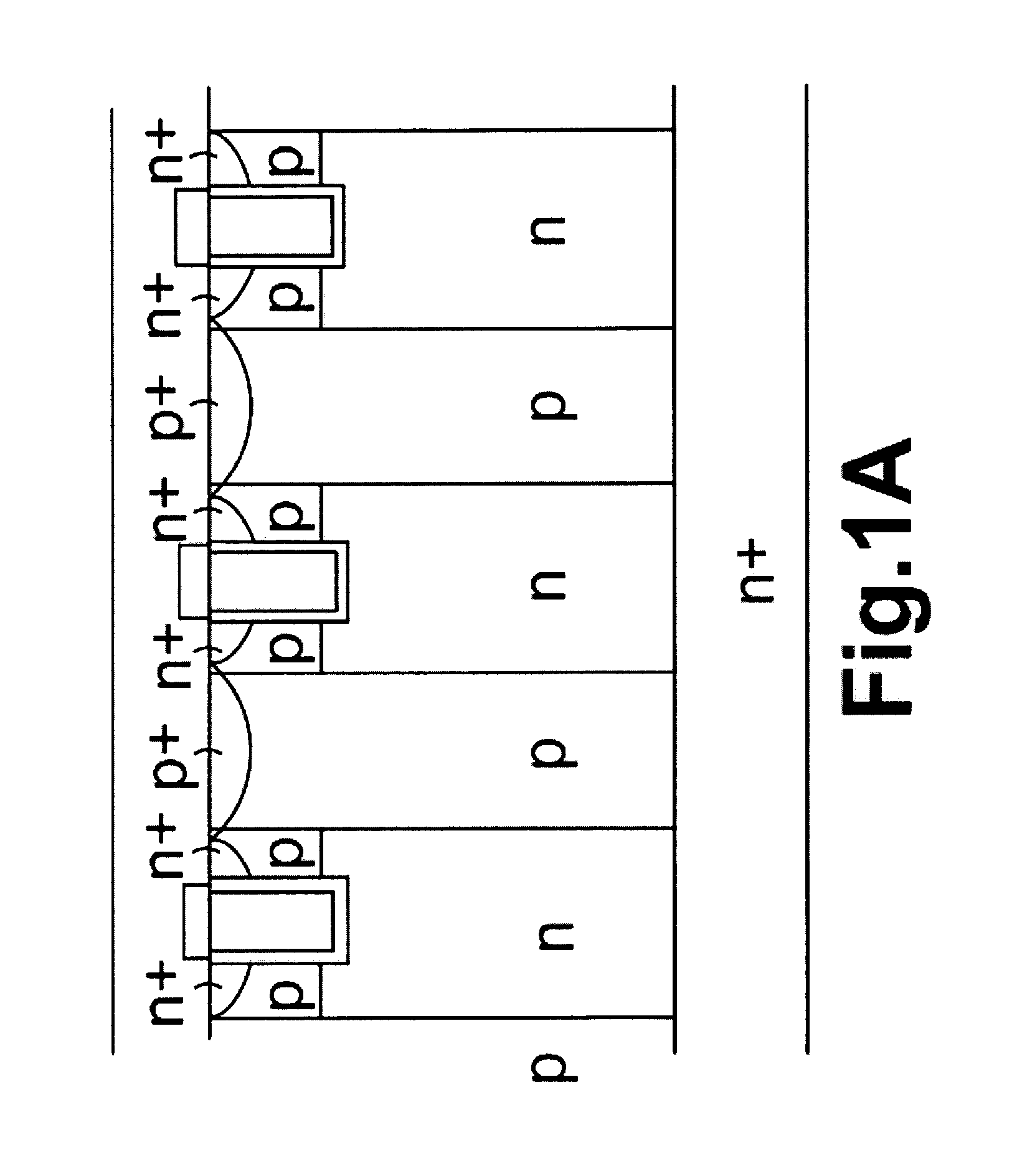

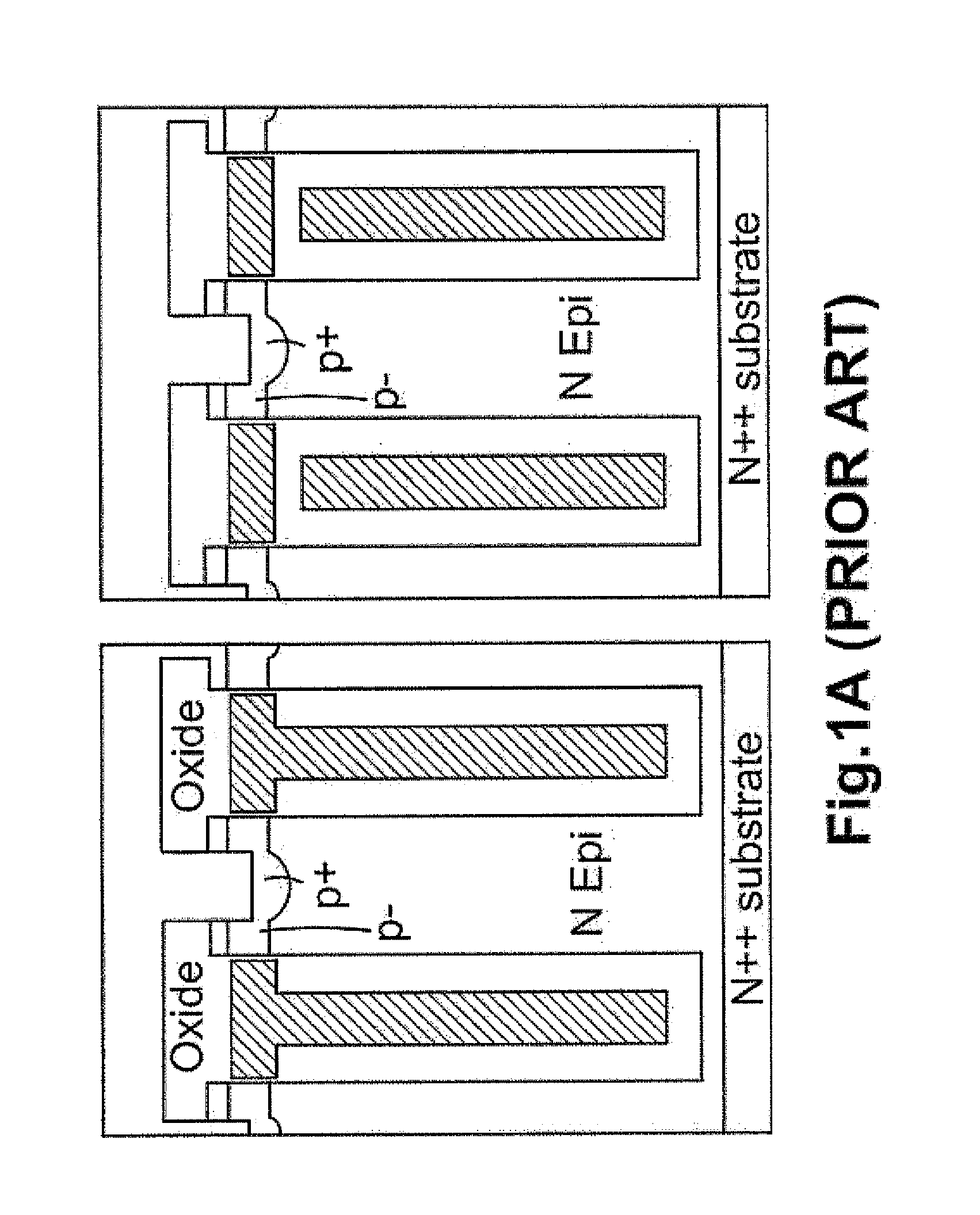

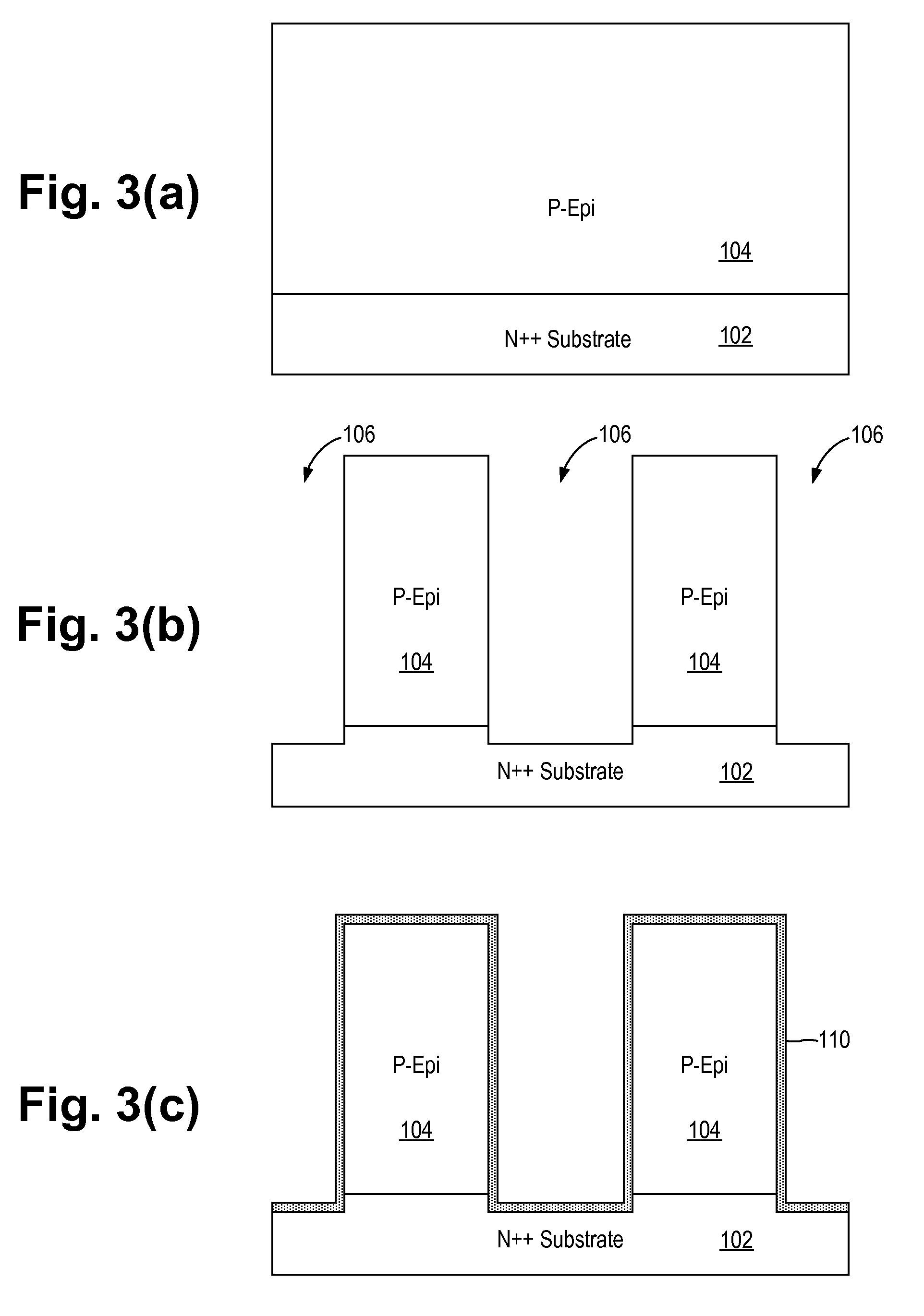

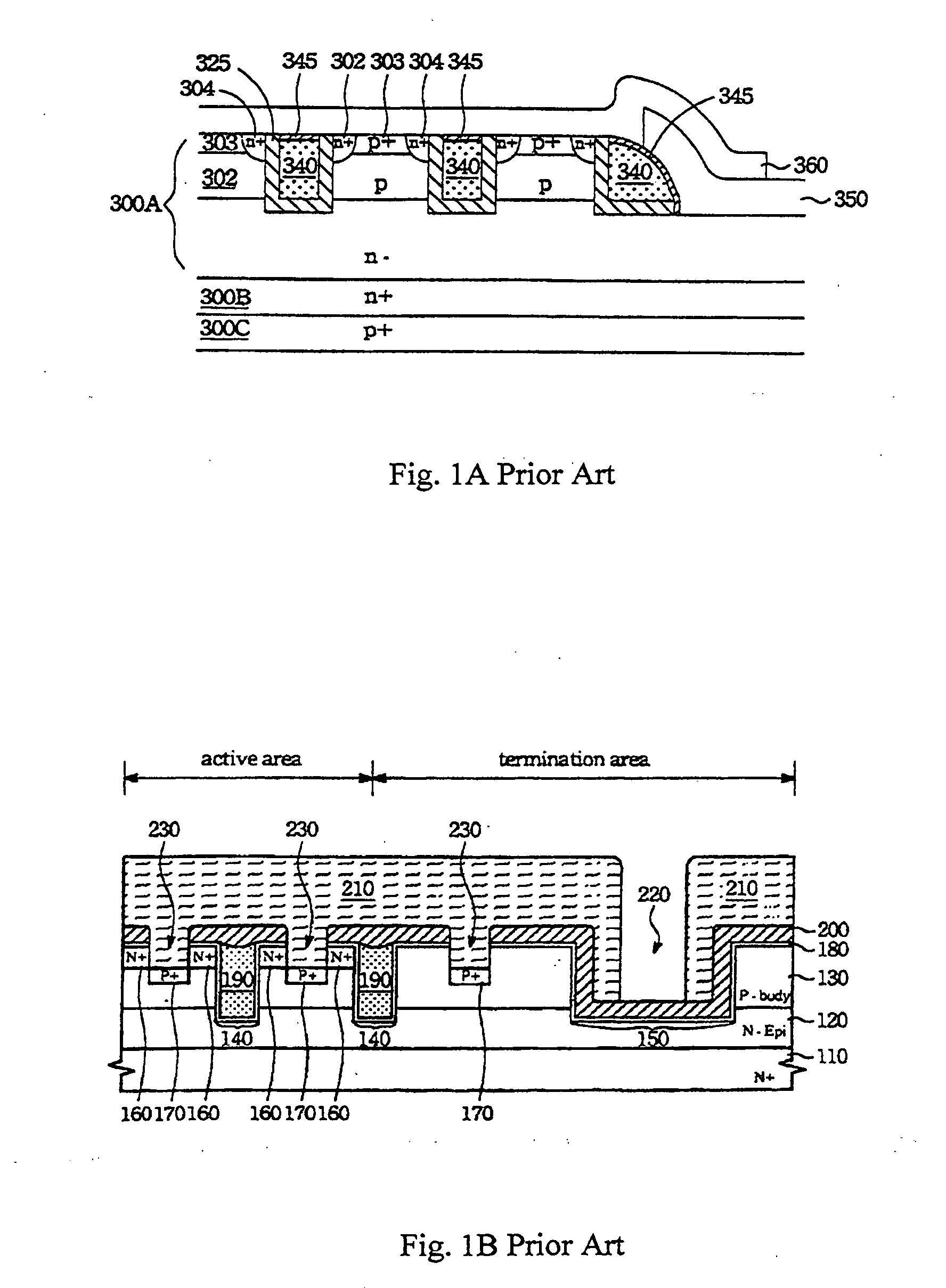

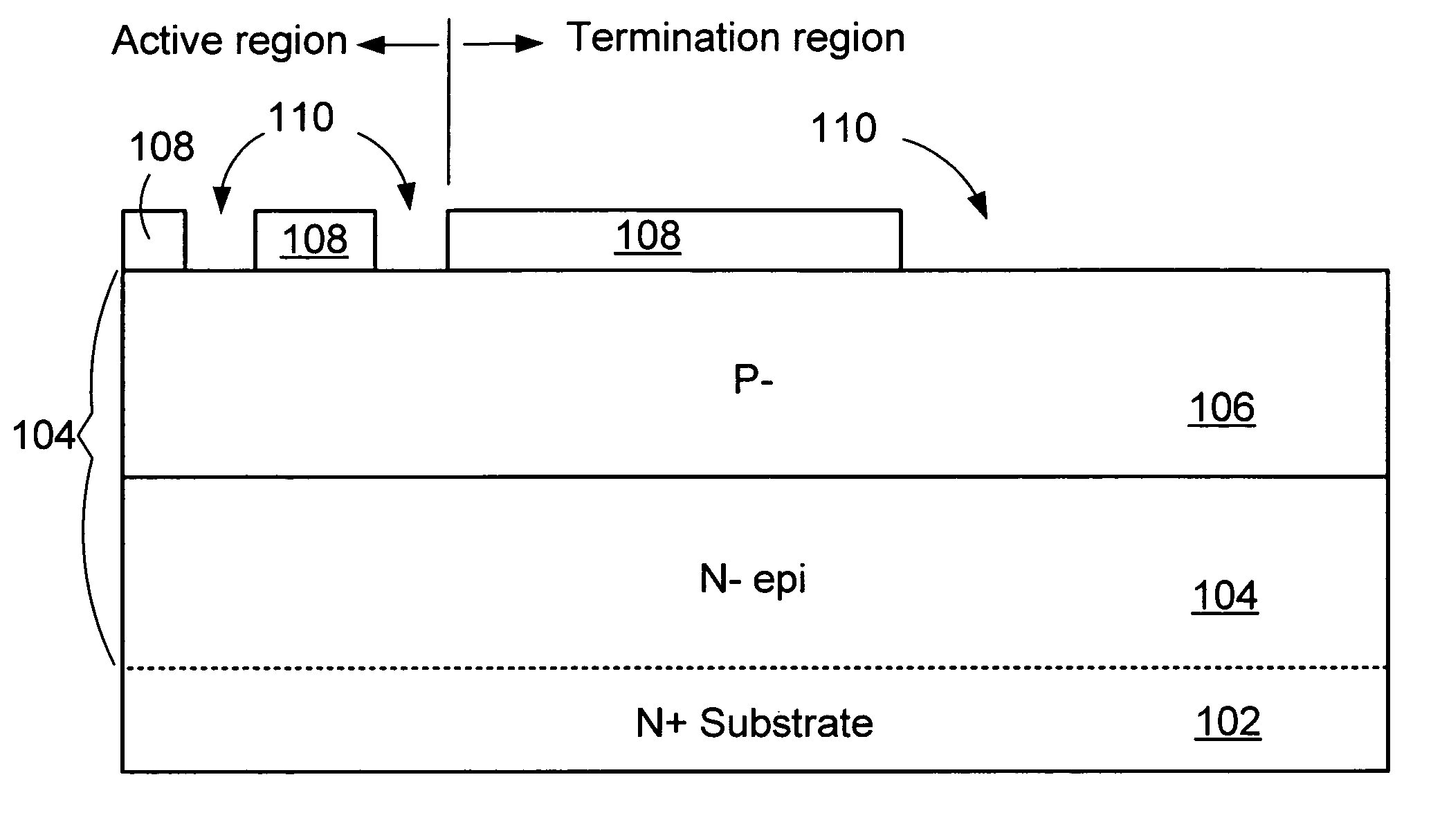

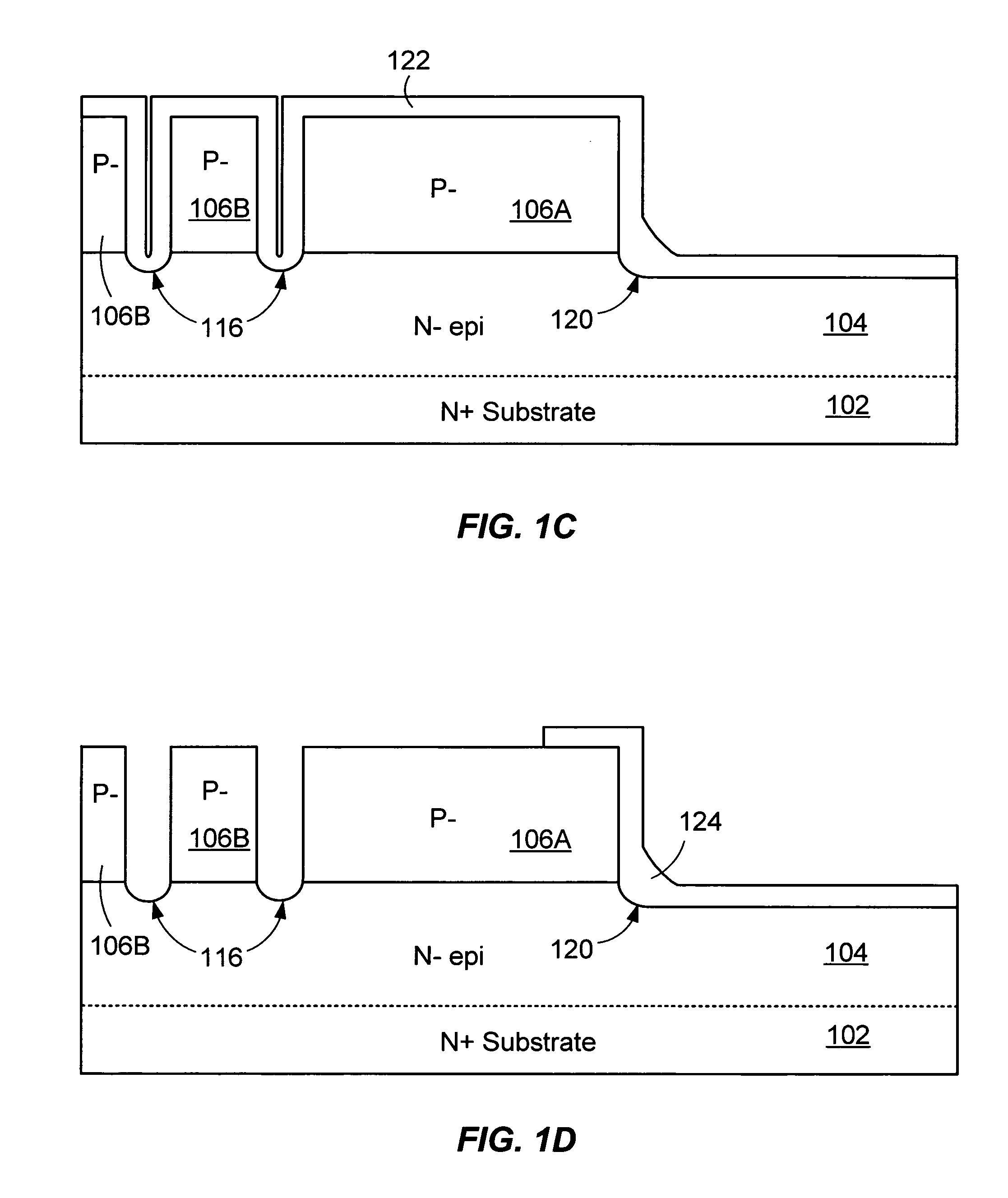

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS6784505B2Increase reverse voltageLow densityTransistorSolid-state devicesDopantChannel density

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

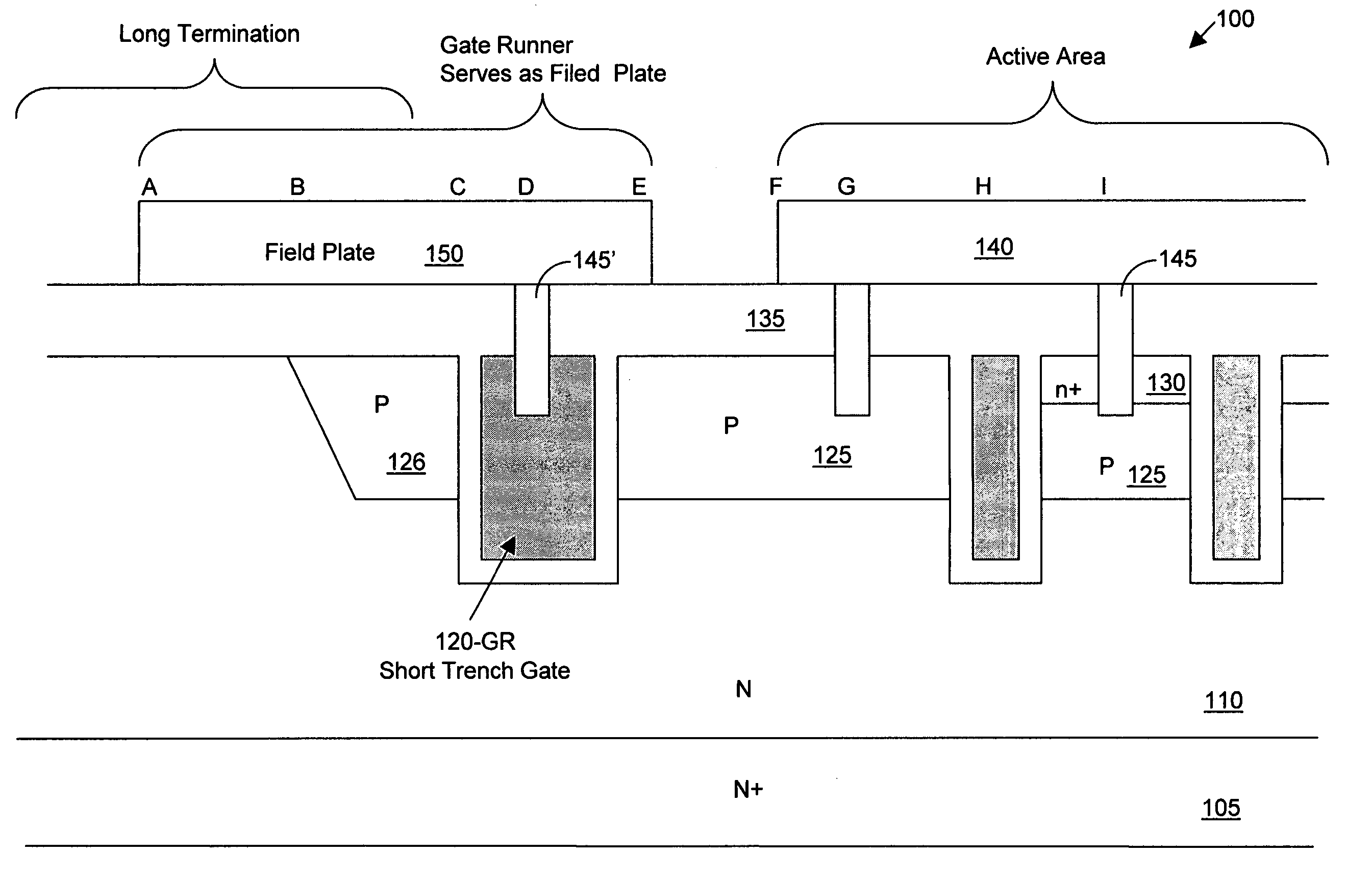

Trenched mosfet device configuration with reduced mask processes

A semiconductor power device comprising a termination area that includes a trenched gate runner electrically connected to a trenched gate of said semiconductor power device. The semiconductor power device further includes a trenched field plate disposed in a trench opened in the termination area and the trenched field plate is electrically connected to the trenched gate runner. A gate runner contact trench and a field plate contact trench opened through an insulation layer covering the gate runner and the trenched field plate for extending into a doped gate dielectric filling in the trenched gate runner and the field plate wherein the gate runner contact trench and the field plate contact trench filled with a gate runner contact plug and a field plate contact plug respectively. A gate metal disposed on top of the insulation layer to electrically contact the gate runner contact plug and the field plate contact plug for electrically interconnecting the trenched gate runner and the trenched field plate.

Owner:FORCE MOS TECH CO LTD

Self-aligned trench MOSFET structure and method of manufacture

ActiveUS20070173021A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantTrench mosfet

PATENT A trench gate FET is formed as follows. A well region is formed in a silicon region. A plurality of active gate trenches and a termination trench are simultaneously formed in an active region and a termination region of the FET, respectively, such that the well region is divided into a plurality of active body regions and a termination body region. Using a mask, openings are formed over the termination body region and the active body region. Dopants are implanted into the active body regions and the termination body region through the openings thereby forming a first region in each active and termination body region. Exposed surfaces of all first regions are recessed so as to form a bowl-shaped recess having slanted walls and a bottom protruding through the first region such that remaining portions of the first region in each active body region form source regions that are self-aligned to the active gate trenches.

Owner:SEMICON COMPONENTS IND LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com