Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3490 results about "N channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

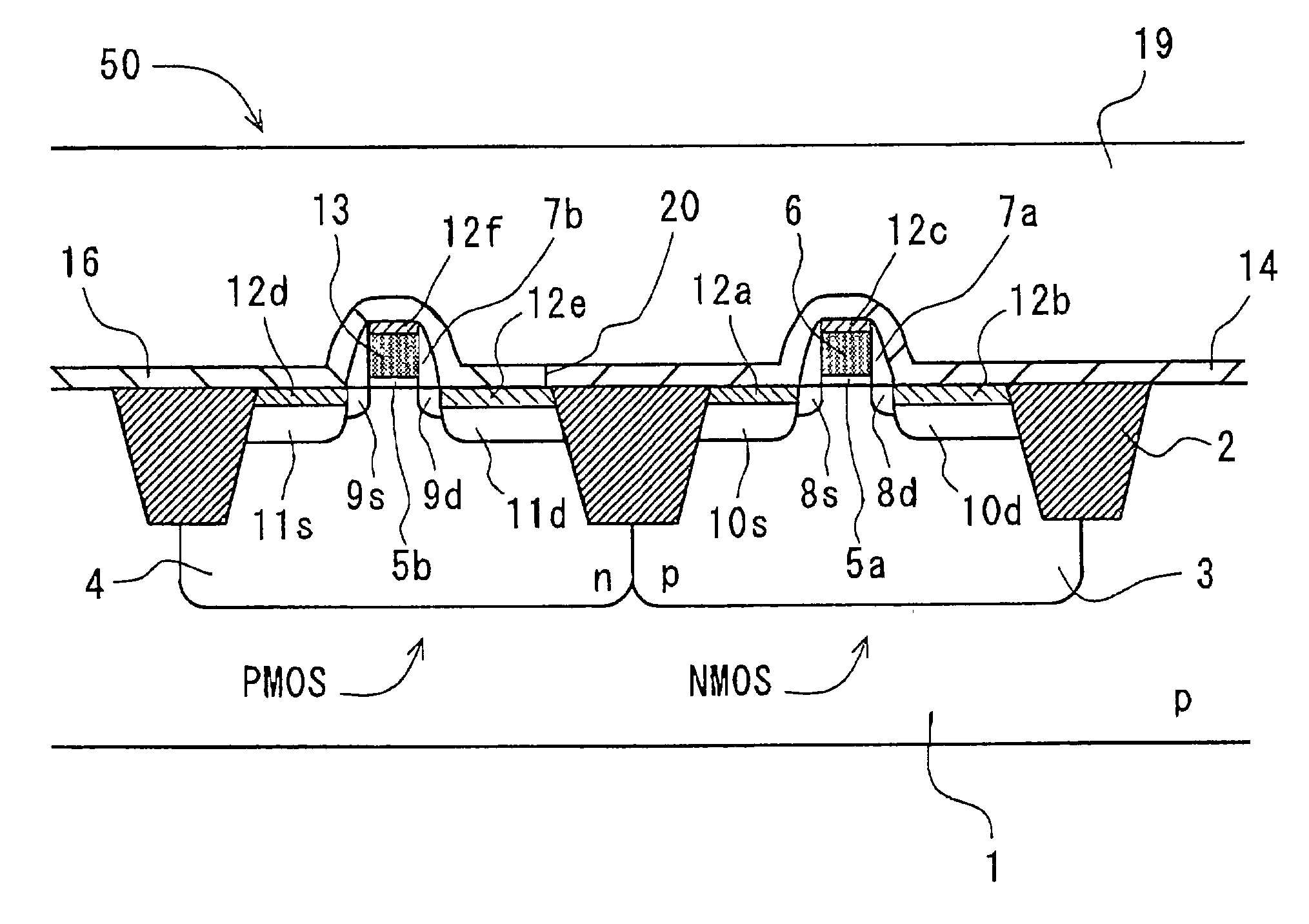

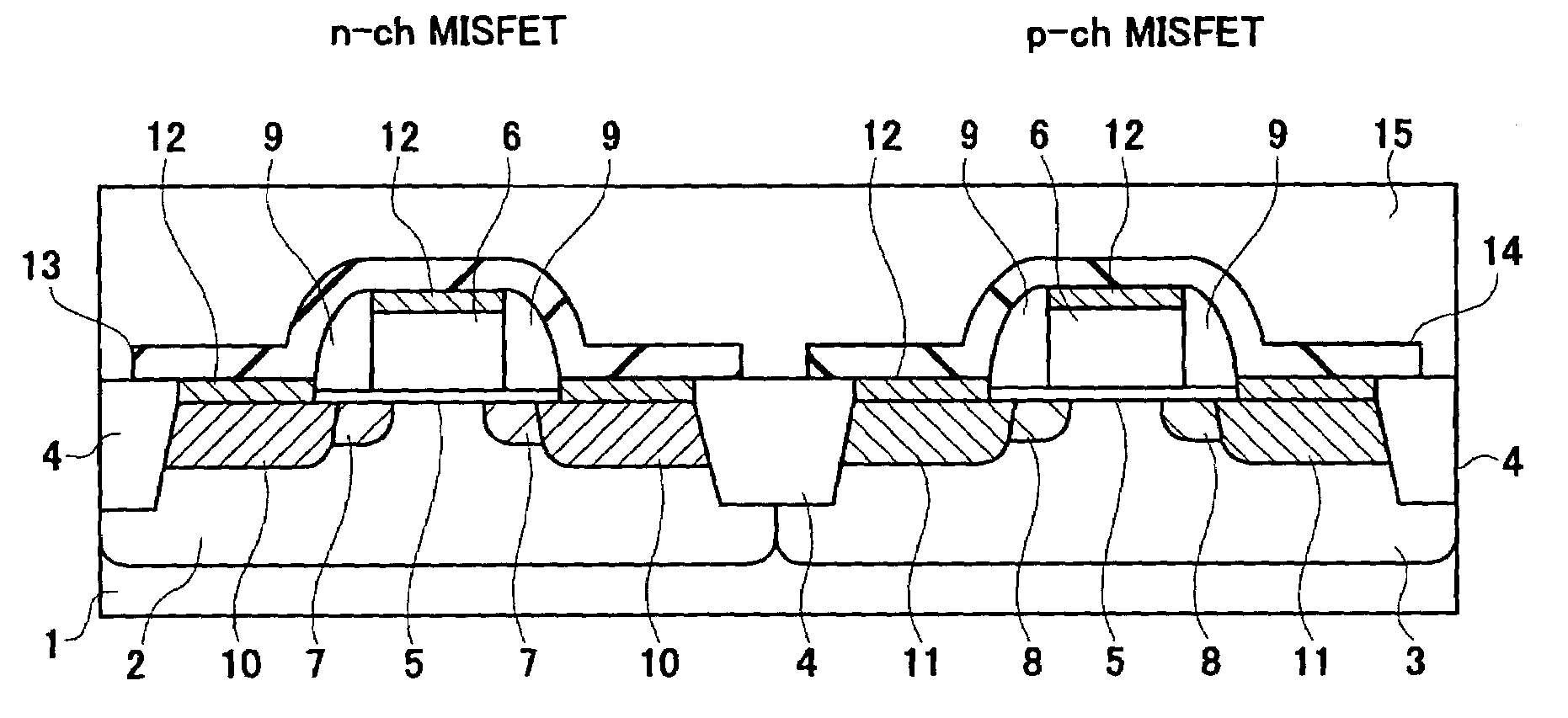

Semiconductor device and method of fabricating the same

InactiveUS20030040158A1TransistorSemiconductor/solid-state device manufacturingMOSFETElectron mobility

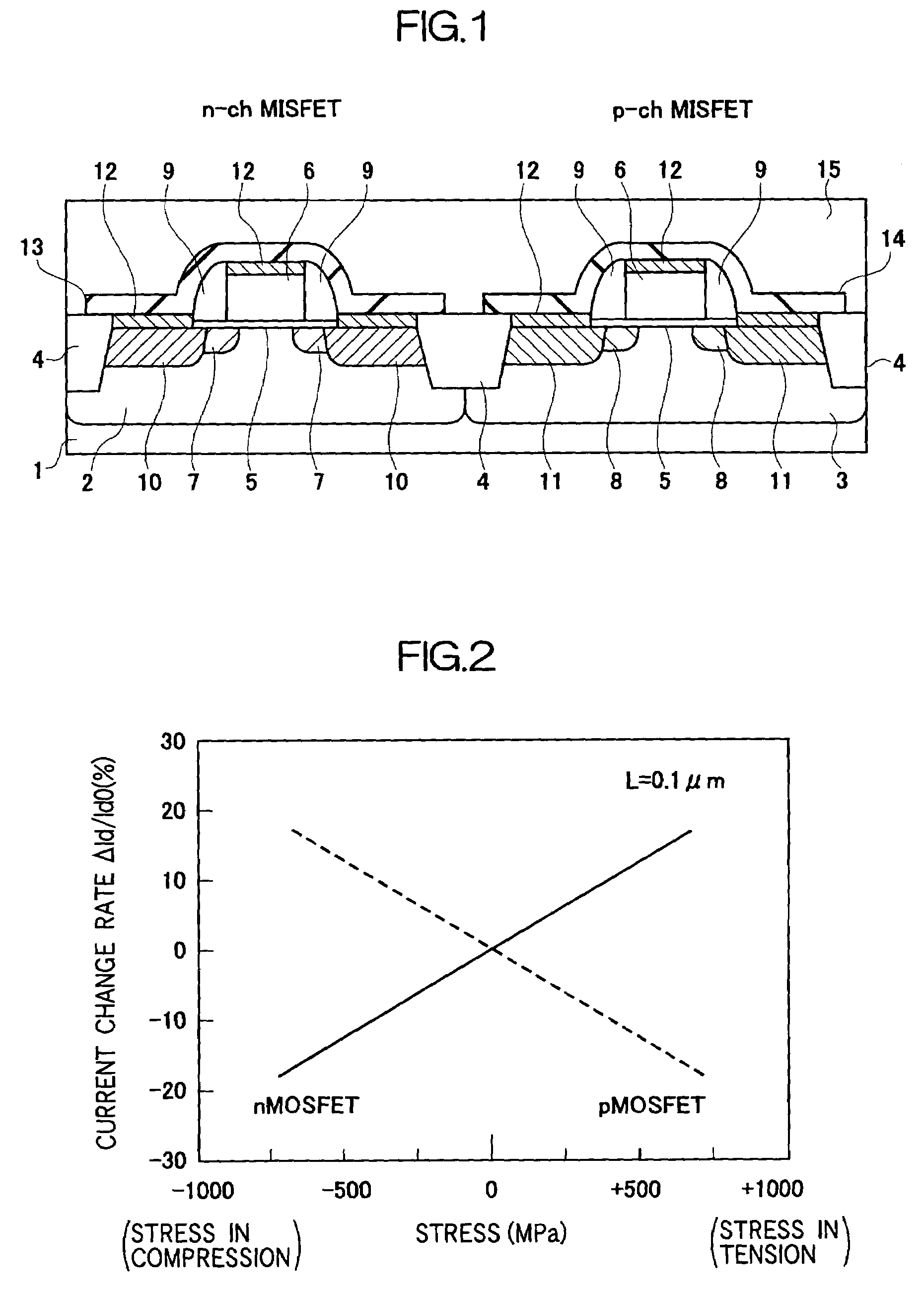

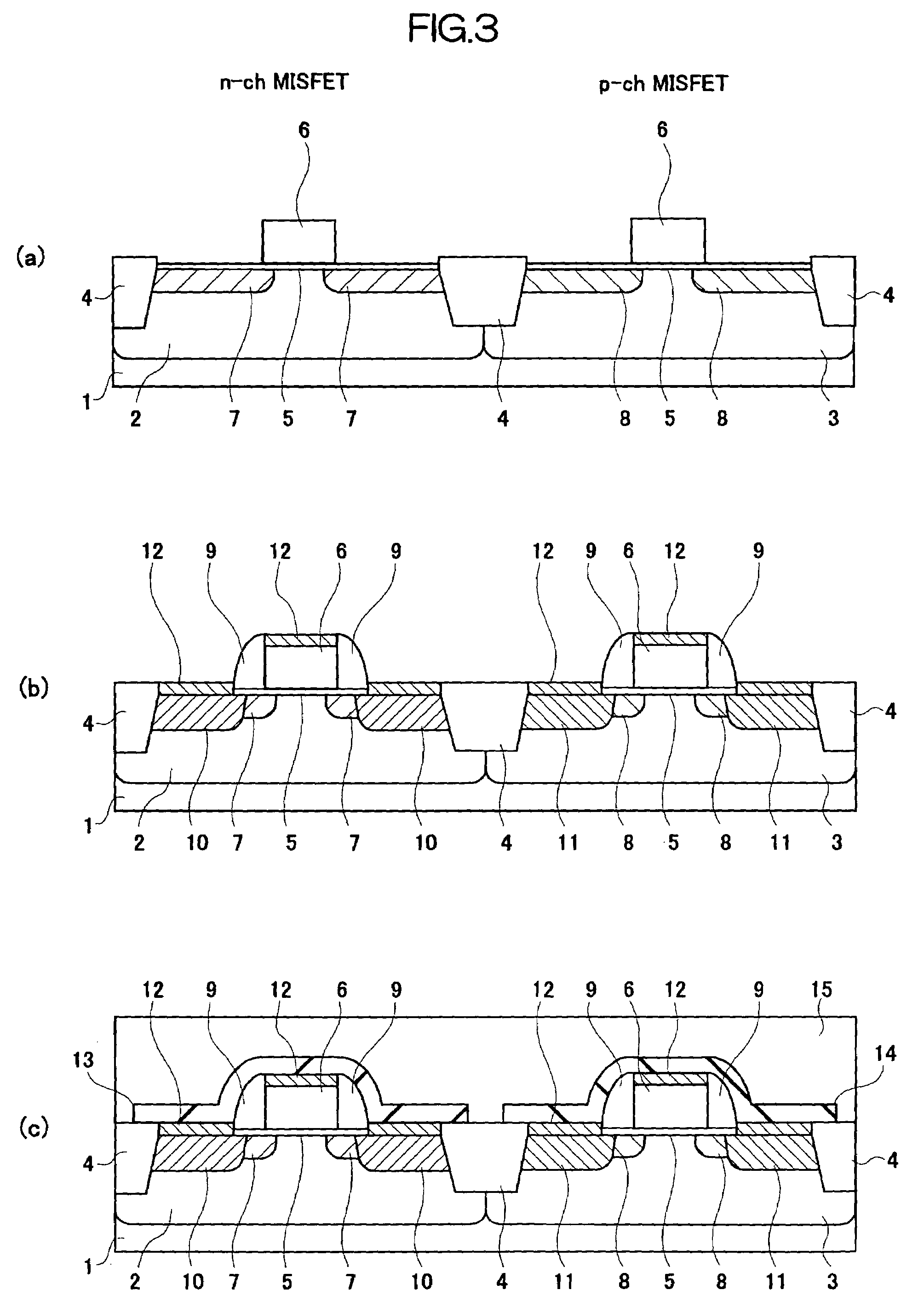

A semiconductor device improves the electron mobility in the n-channel MOSFET and reduces the bend or warp of the semiconductor substrate or wafer. The fist nitride layer having a tensile stress is formed on the substrate to cover the n-channel MOSFET. The tensile stress of the first nitride layer serves to relax a compressive stress existing in the channel region. The second nitride layer having an actual compressive stress is formed on the substrate to cover the p-channel MOSFET. The first and second nitride layers serve to decrease bend or warp of the substrate. Preferably, the first nitride layer is a nitride layer of Si formed by a LPCVD process, and the second nitride layer is a nitride layer of Si formed by a PECVD process.

Owner:NEC ELECTRONICS CORP

Semiconductor device

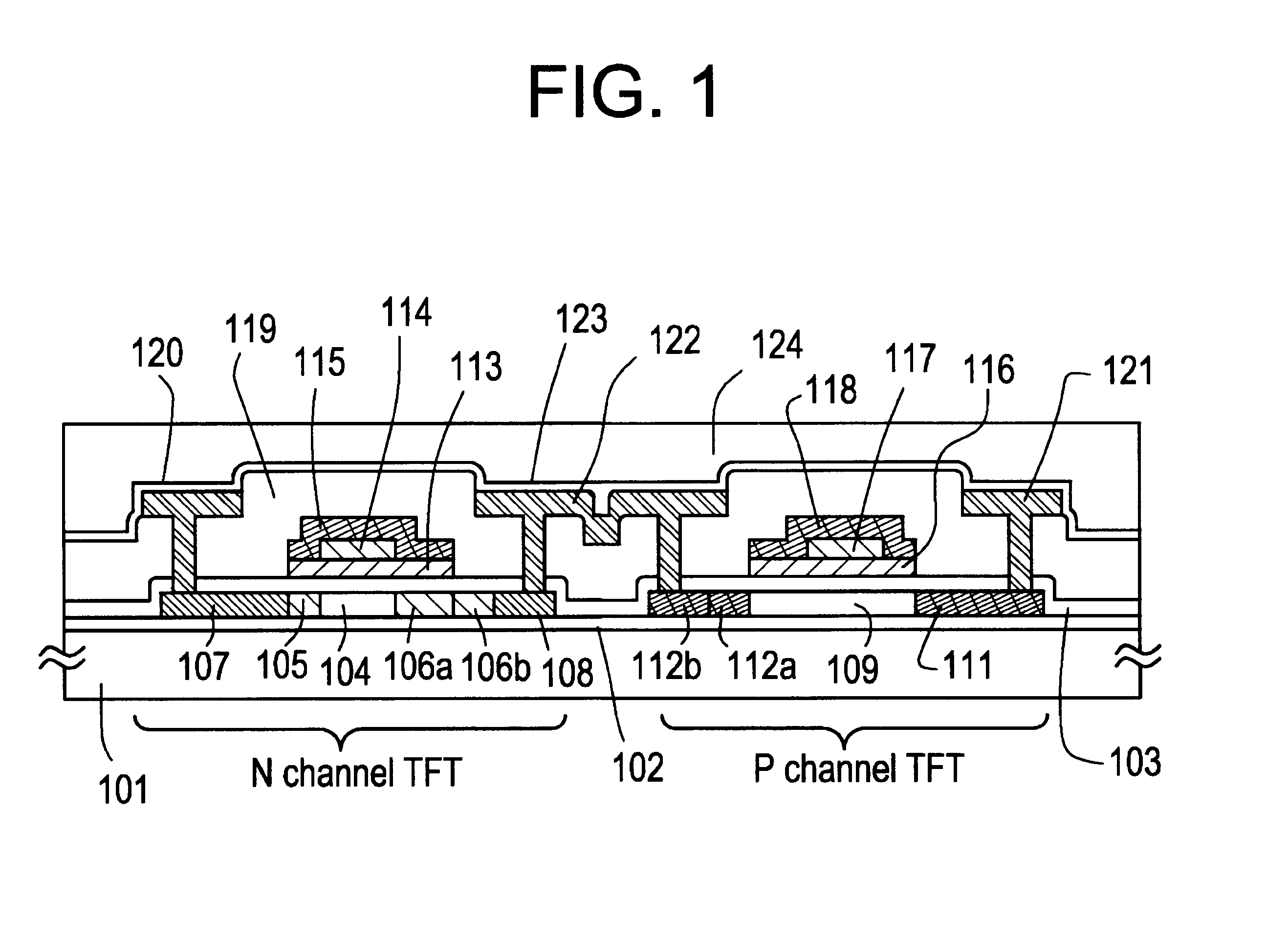

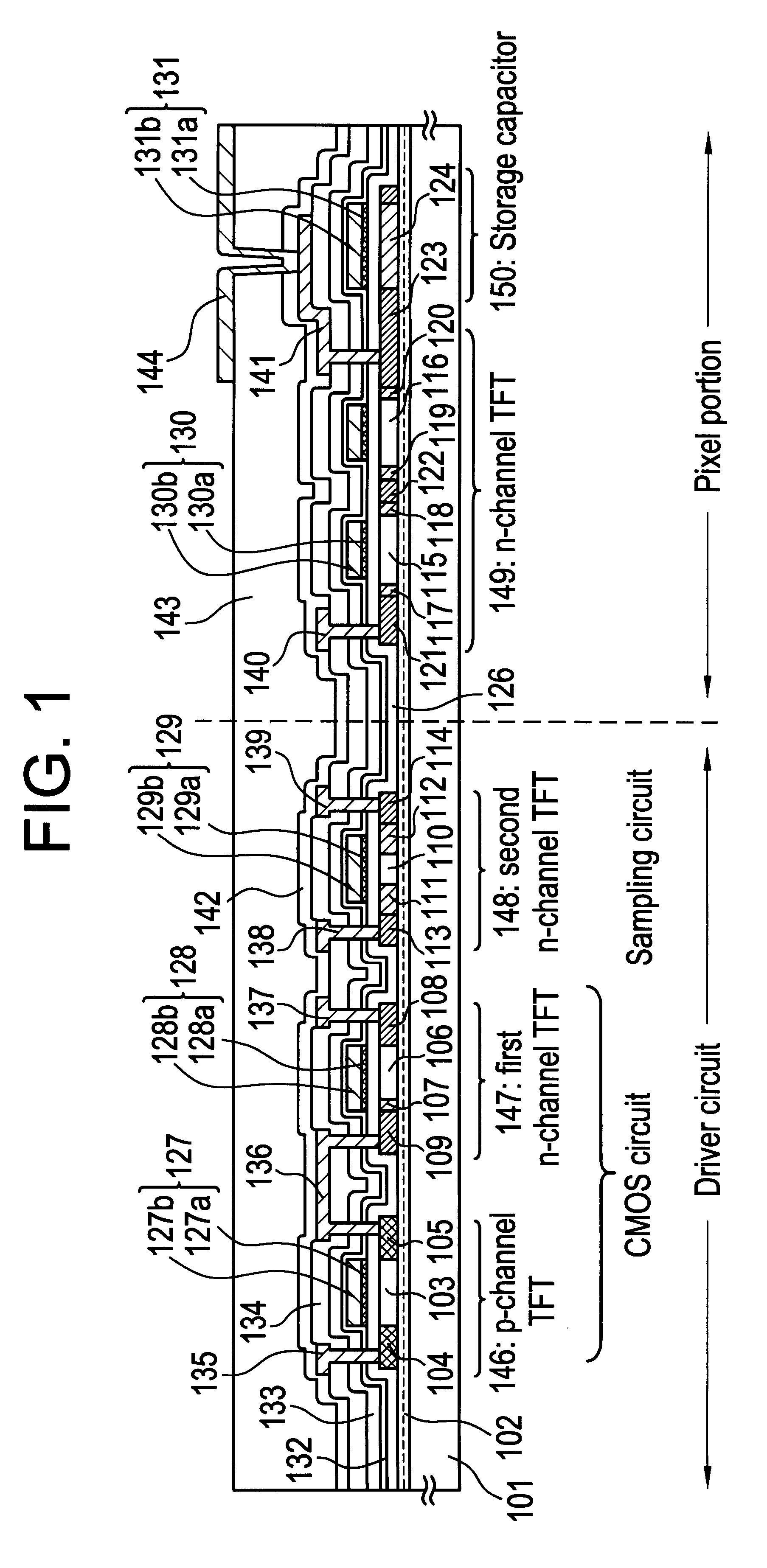

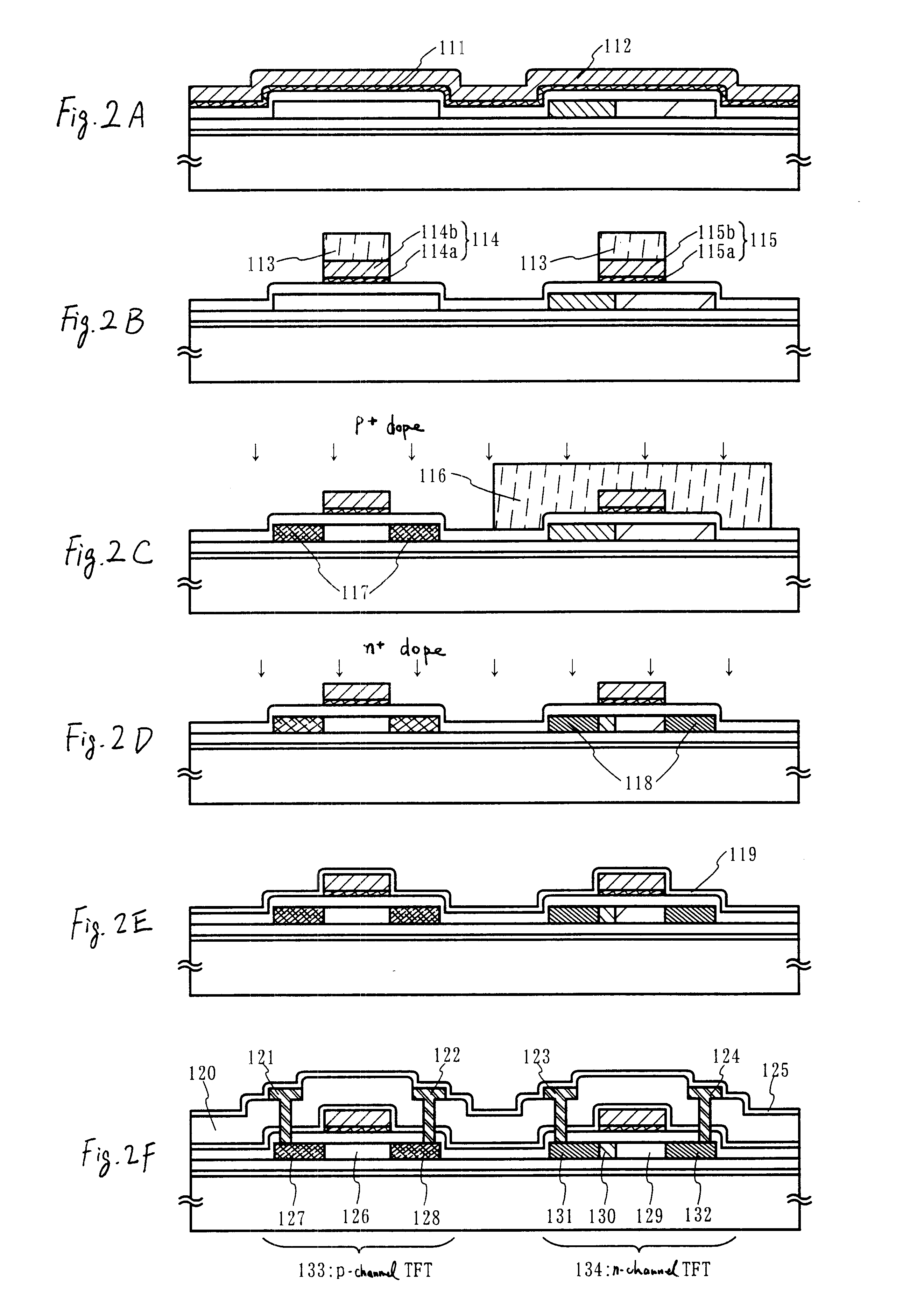

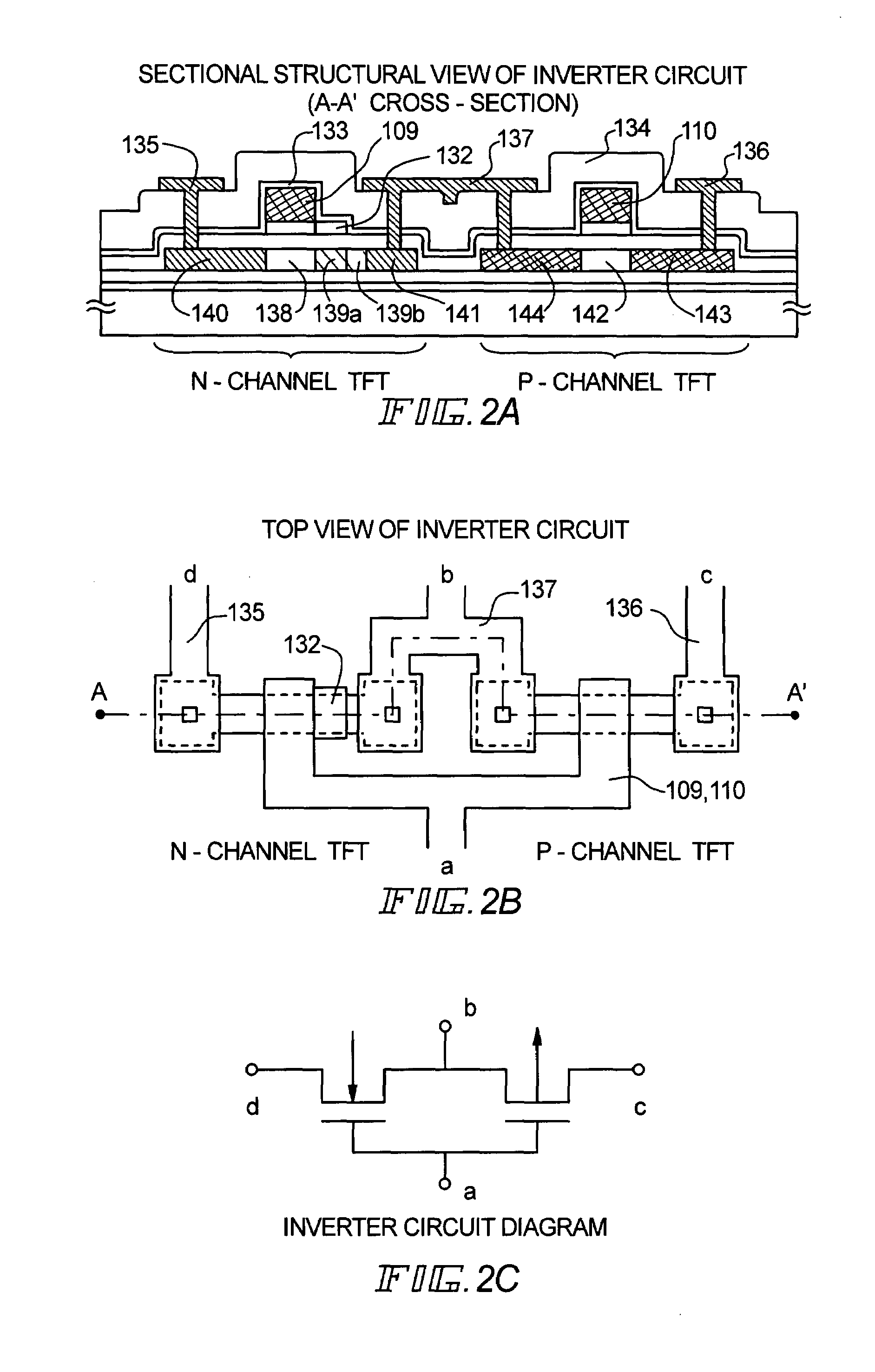

The gate electrode of a crystalline TFT is constructed as a clad structure which consists of a first gate electrode, a second gate electrode and a third gate electrode, thereby to enhance the thermal resistance of the gate electrode. Besides, an n-channel TFT is provided with a low-concentration impurity region which adjoins a channel forming region, and which includes a subregion overlapped by the gate electrode and a subregion not overlapped by the gate electrode, thereby to mitigate a high electric field near the drain of the TFT and to simultaneously prevent the OFF current of the TFT from increasing.

Owner:SEMICON ENERGY LAB CO LTD

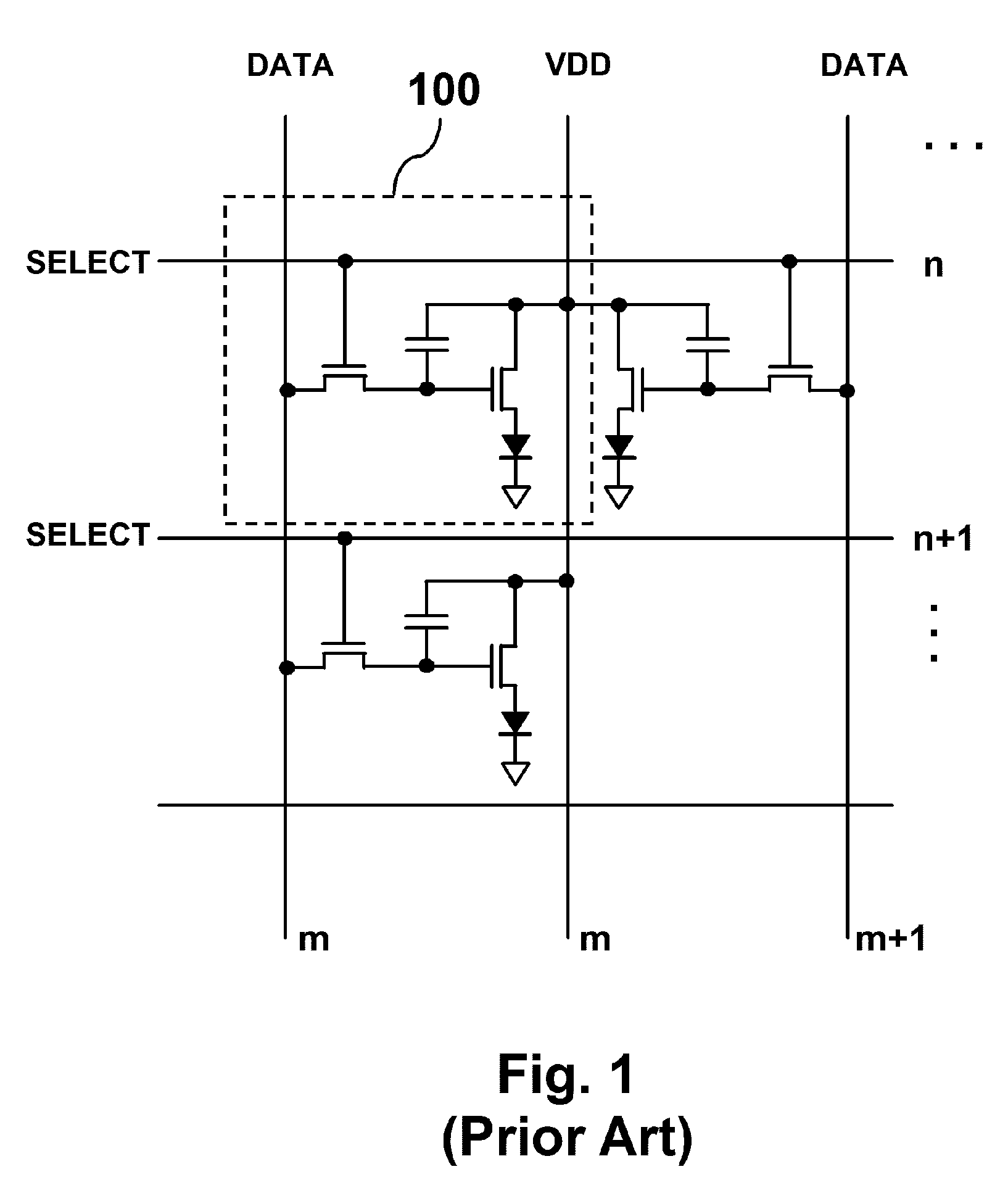

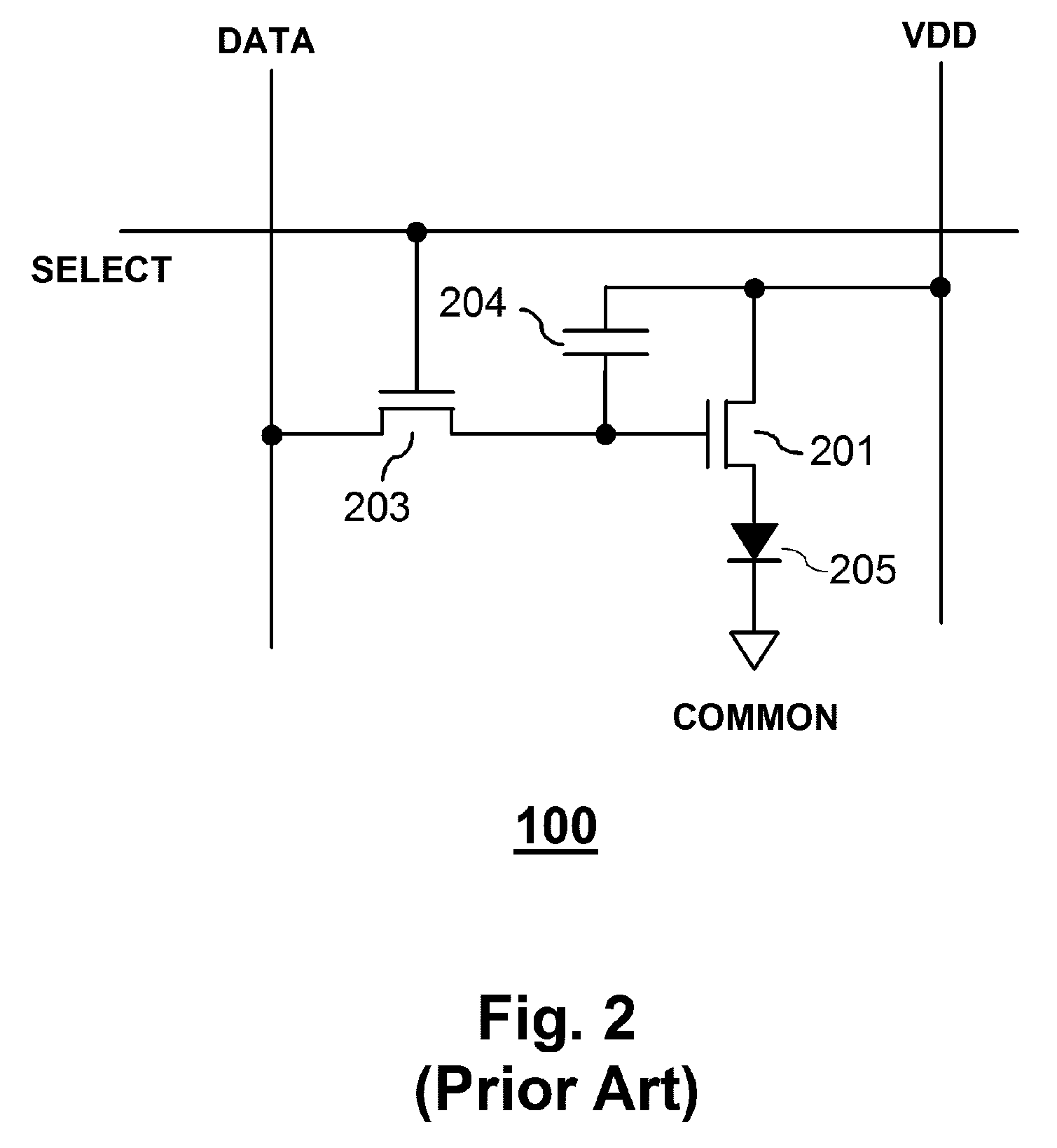

Pixel circuit, active matrix apparatus and display apparatus

ActiveUS20050269959A1Low costLuminance of light emission can be fixedStatic indicating devicesSolid-state devicesElectricityActive matrix

A pixel circuit having a function of compensating for characteristic variation of an electro-optical element and threshold voltage variation of a transistor is formed from a reduced number of component elements. The pixel circuit includes an electro-optical element, a holding capacitor, and five N-channel thin film transistors including a sampling transistor, a drive transistor, a switching transistor, and first and second detection transistors. The sampling transistor samples and supplies an input signal from a signal line so as to be held into the holding capacitor. The driving transistor drives the electro-optical element with current in response to the held signal potential. The first and second detection transistors detect a threshold voltage of the drive transistor and supply the detected voltage into the holding capacitor in order to cancel an influence of the threshold voltage in advance.

Owner:SONY CORP

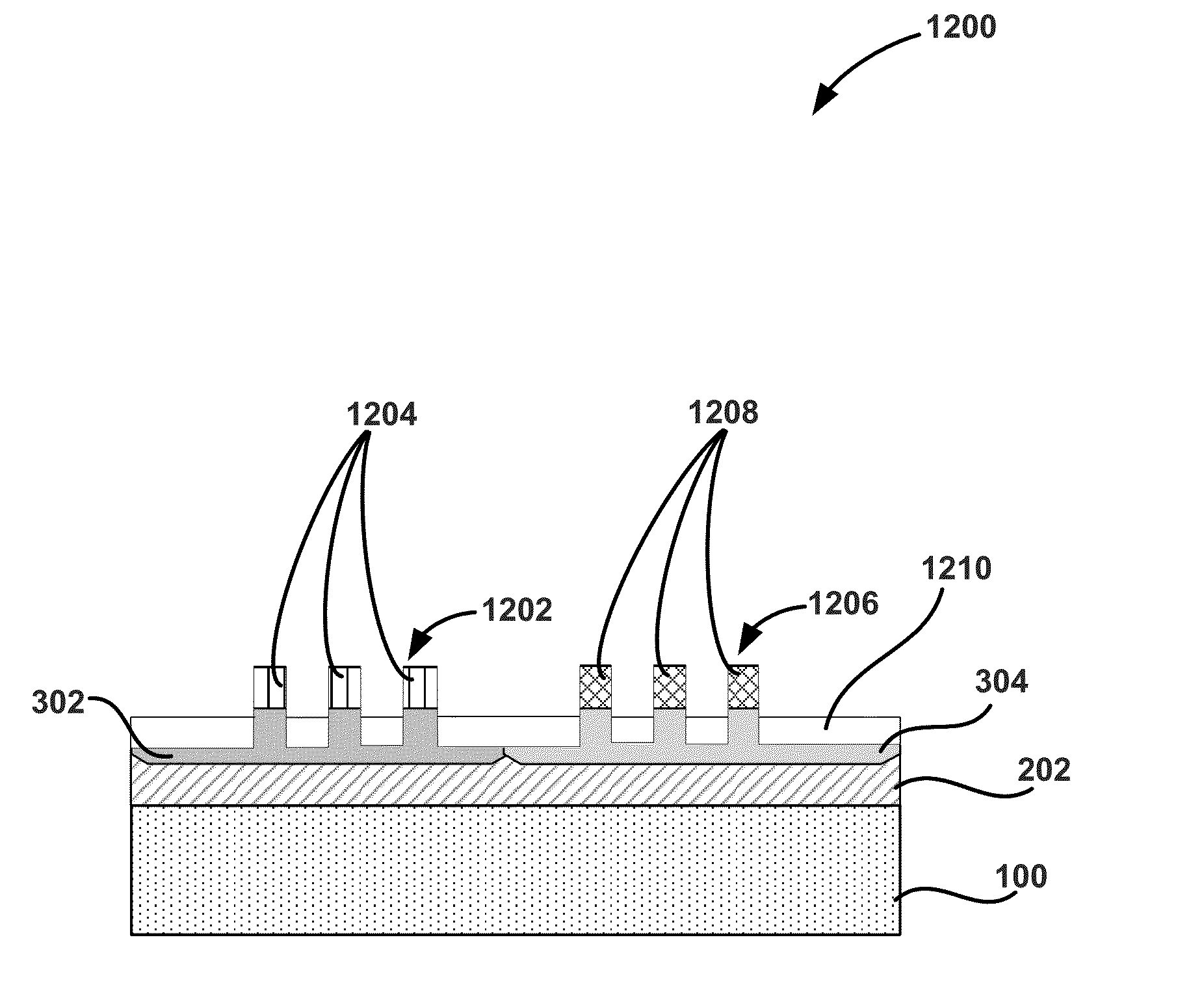

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both n-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Field effect transistor having an interlayer dielectric material having increased intrinsic stress

InactiveUS20080203487A1Optimization mechanismImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentField-effect transistor

By providing a highly stressed interlayer dielectric material, the performance of at least one type of transistor may be increased due to an enhanced strain-inducing mechanism. For instance, by providing a highly compressive silicon dioxide of approximately 400 Mega Pascal and more as an interlayer dielectric material, the drive current of the P-channel transistors may be increased by 2% and more while not unduly affecting the performance of the N-channel transistors.

Owner:ADVANCED MICRO DEVICES INC

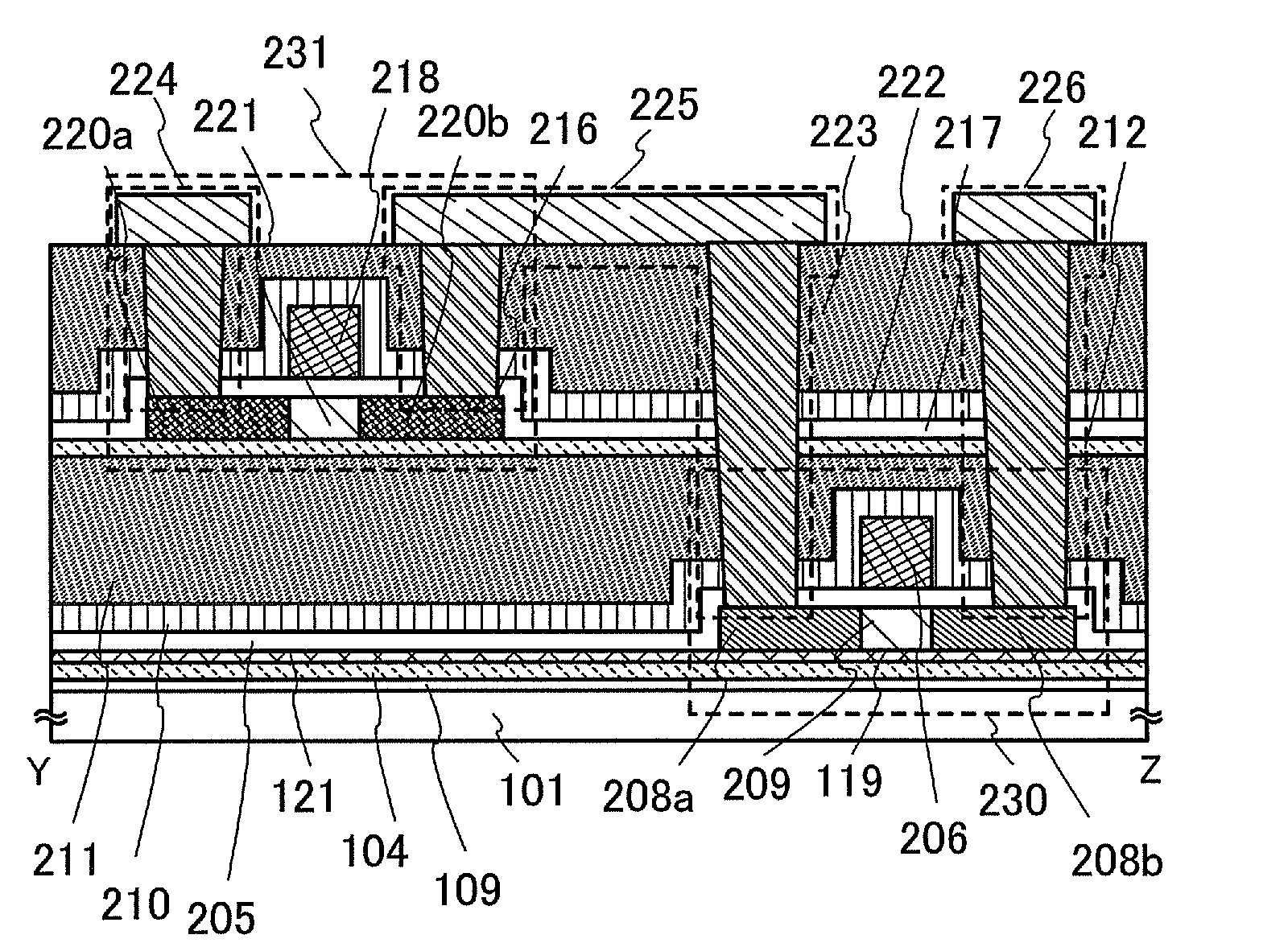

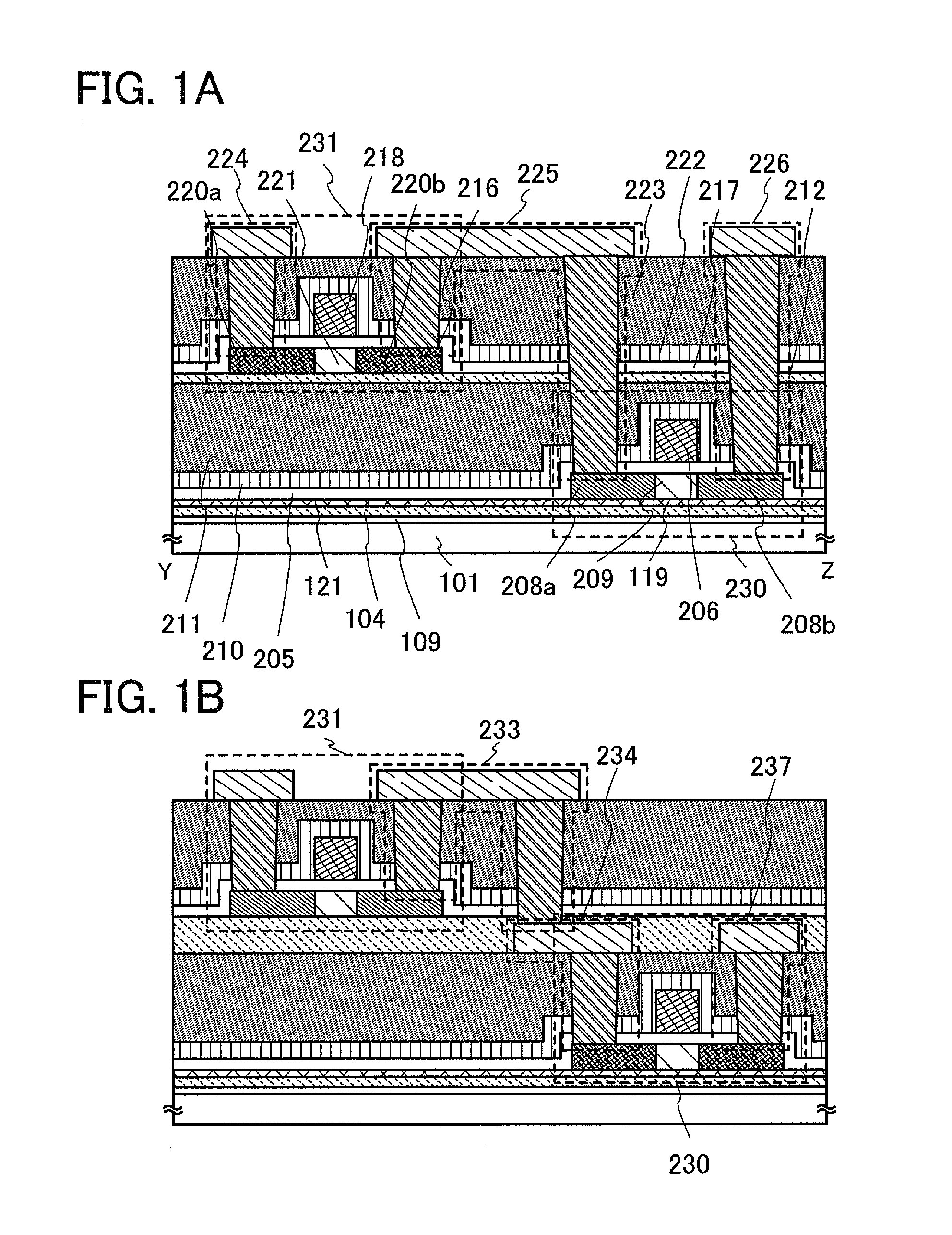

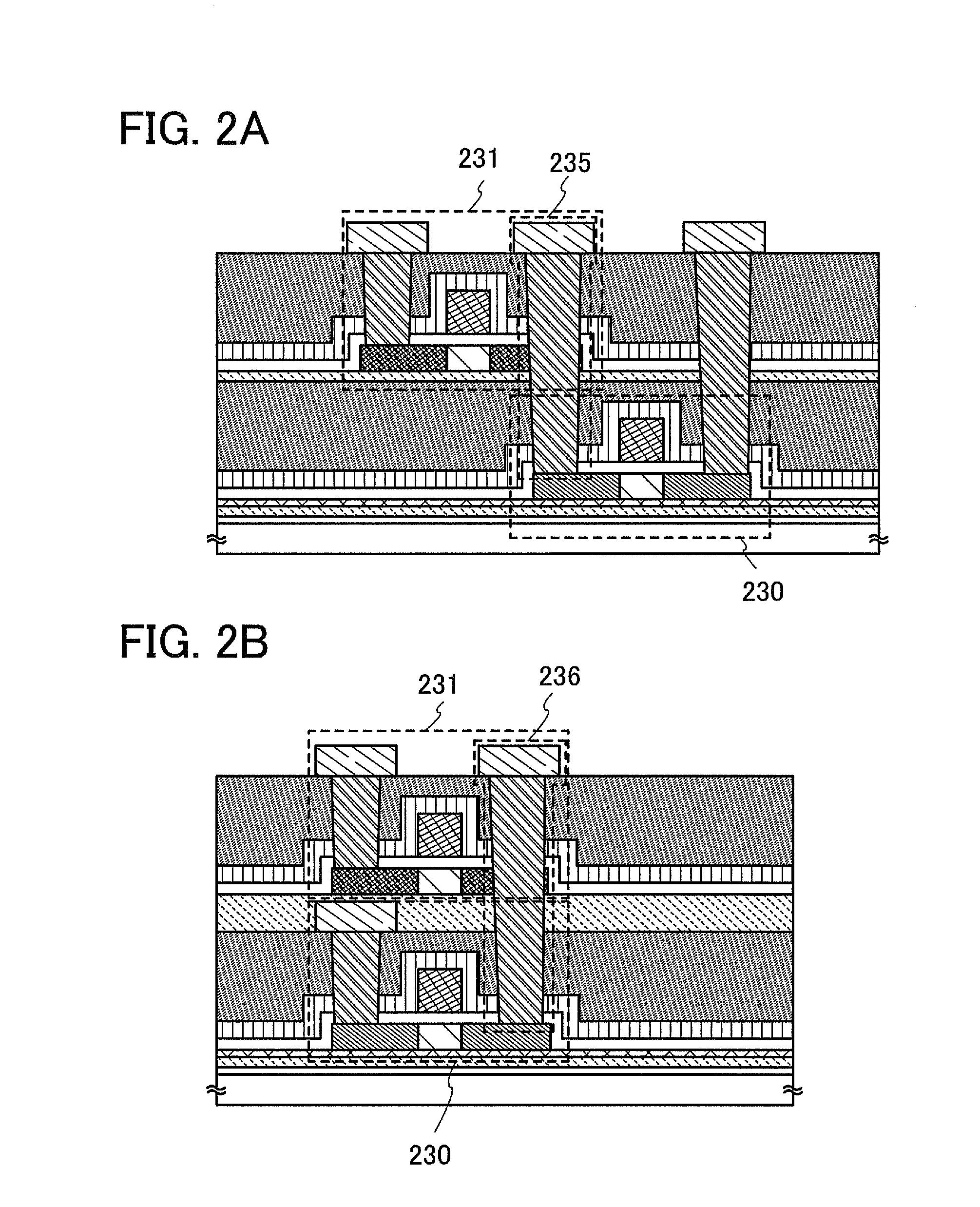

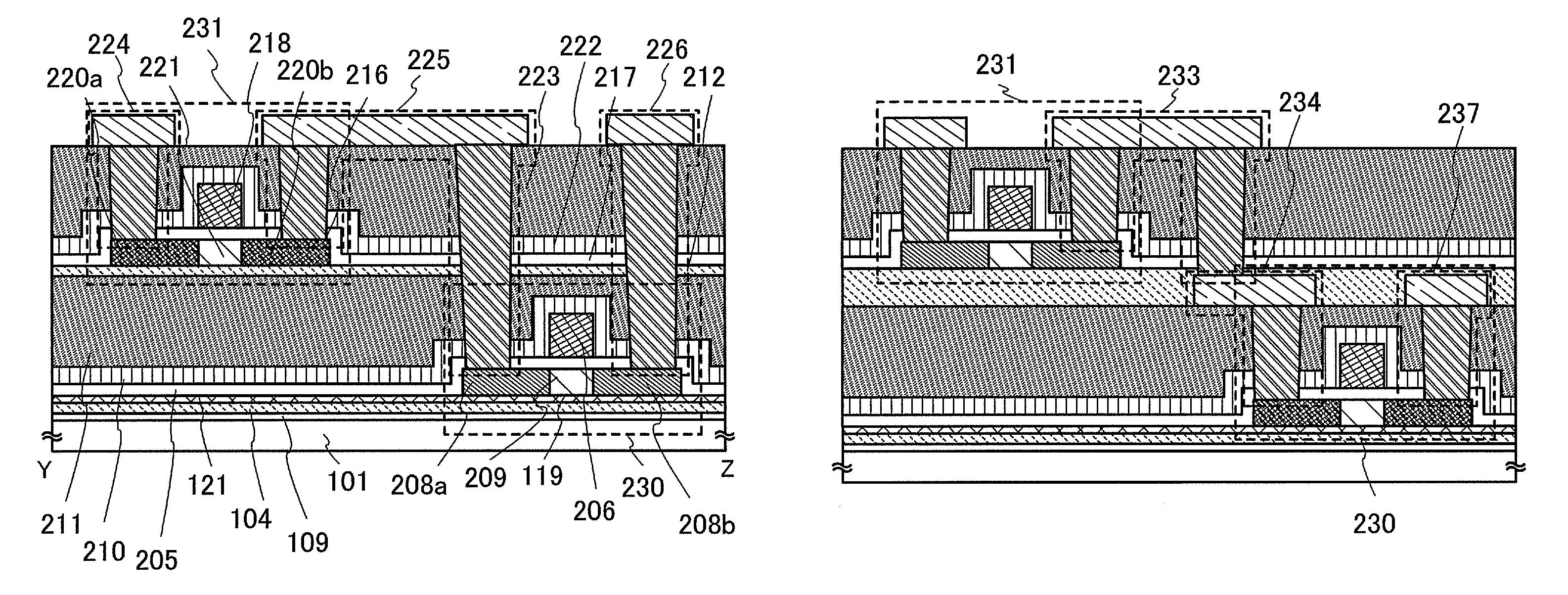

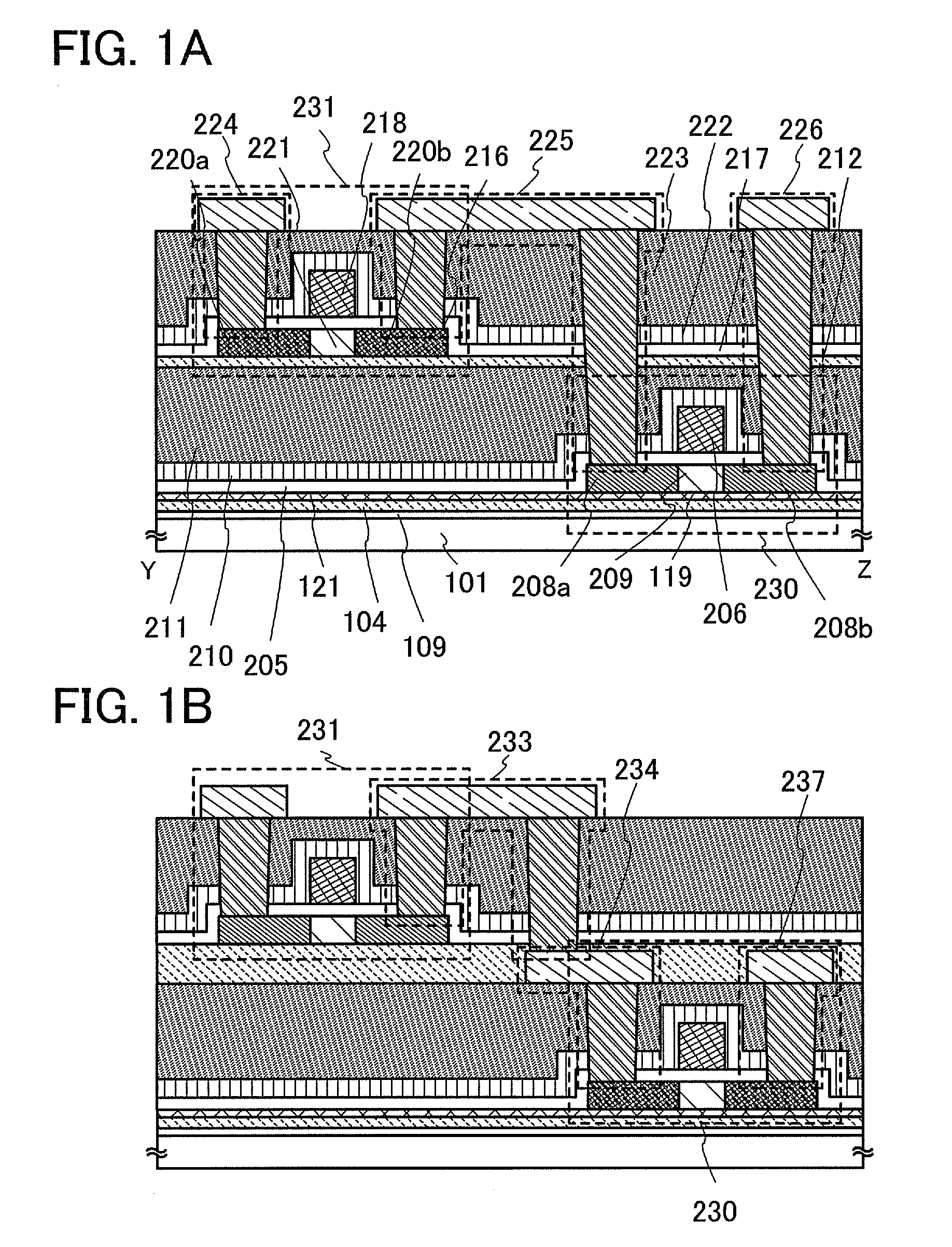

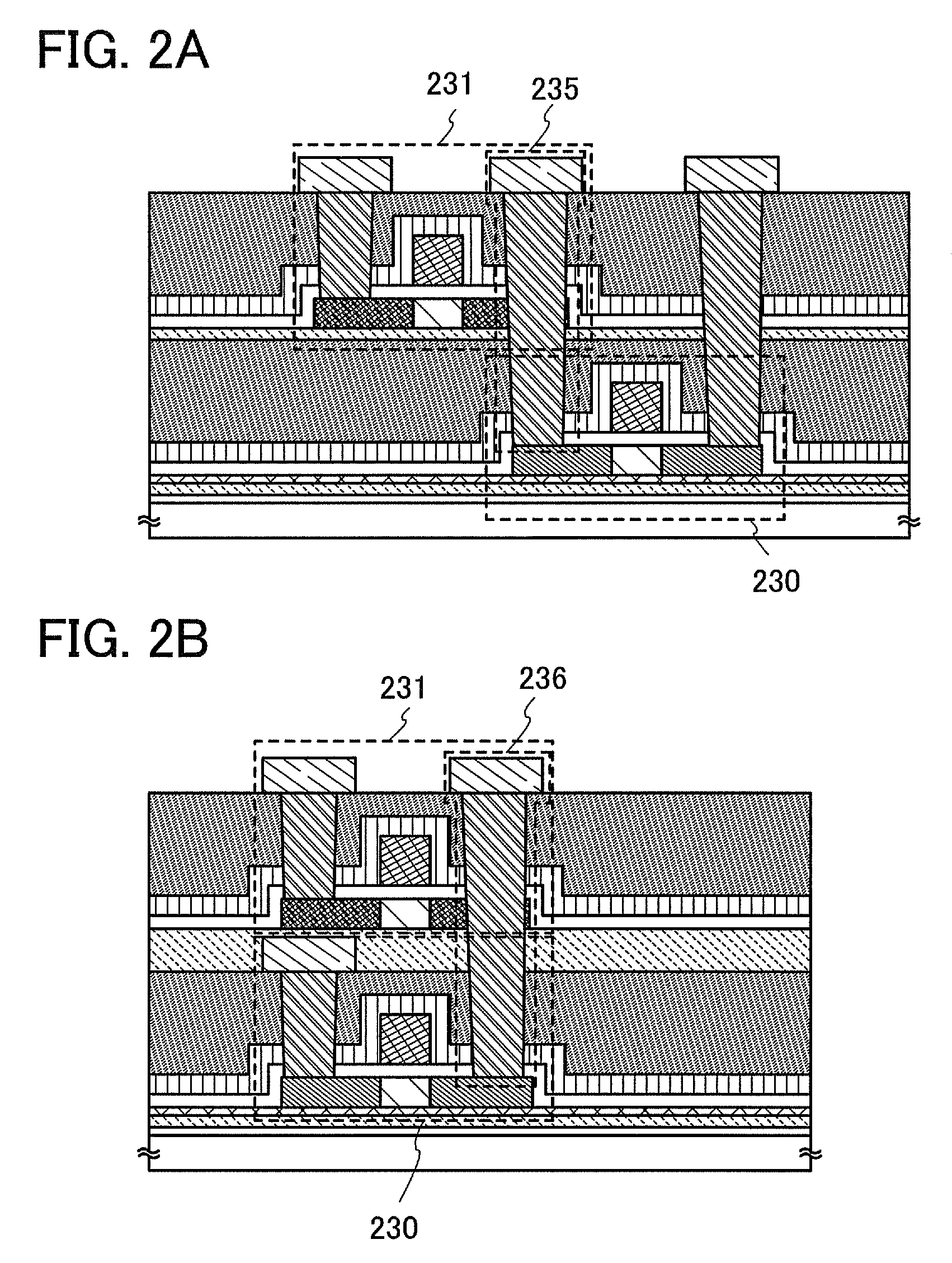

Semiconductor device

ActiveUS20090079000A1Difference in mobilityReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesDevice materialPlane orientation

An object is to realize high performance and low power consumption in a semiconductor device having an SOI structure. In addition, another object is to provide a semiconductor device having a high performance semiconductor element which is more highly integrated. A semiconductor device is such that a plurality of n-channel field-effect transistors and p-channel field-effect transistors are stacked with an interlayer insulating layer interposed therebetween over a substrate having an insulating surface. By controlling a distortion caused to a semiconductor layer due to an insulating film having a stress, a plane orientation of the semiconductor layer, and a crystal axis in a channel length direction, difference in mobility between the n-channel field-effect transistor and the p-channel field-effect transistor can be reduced, whereby current driving capabilities and response speeds of the n-channel field-effect transistor and the p-channel field-effect can be comparable.

Owner:SEMICON ENERGY LAB CO LTD

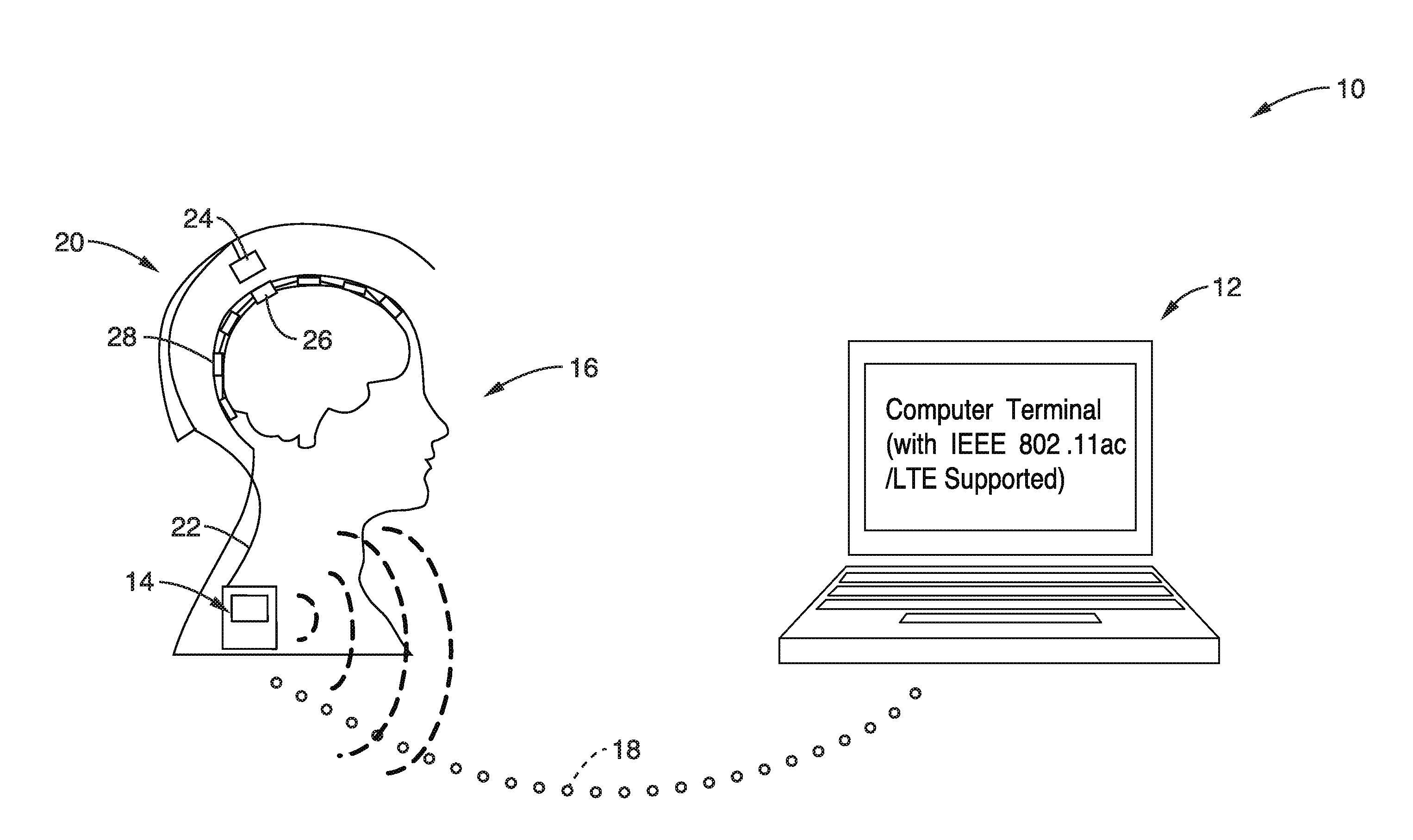

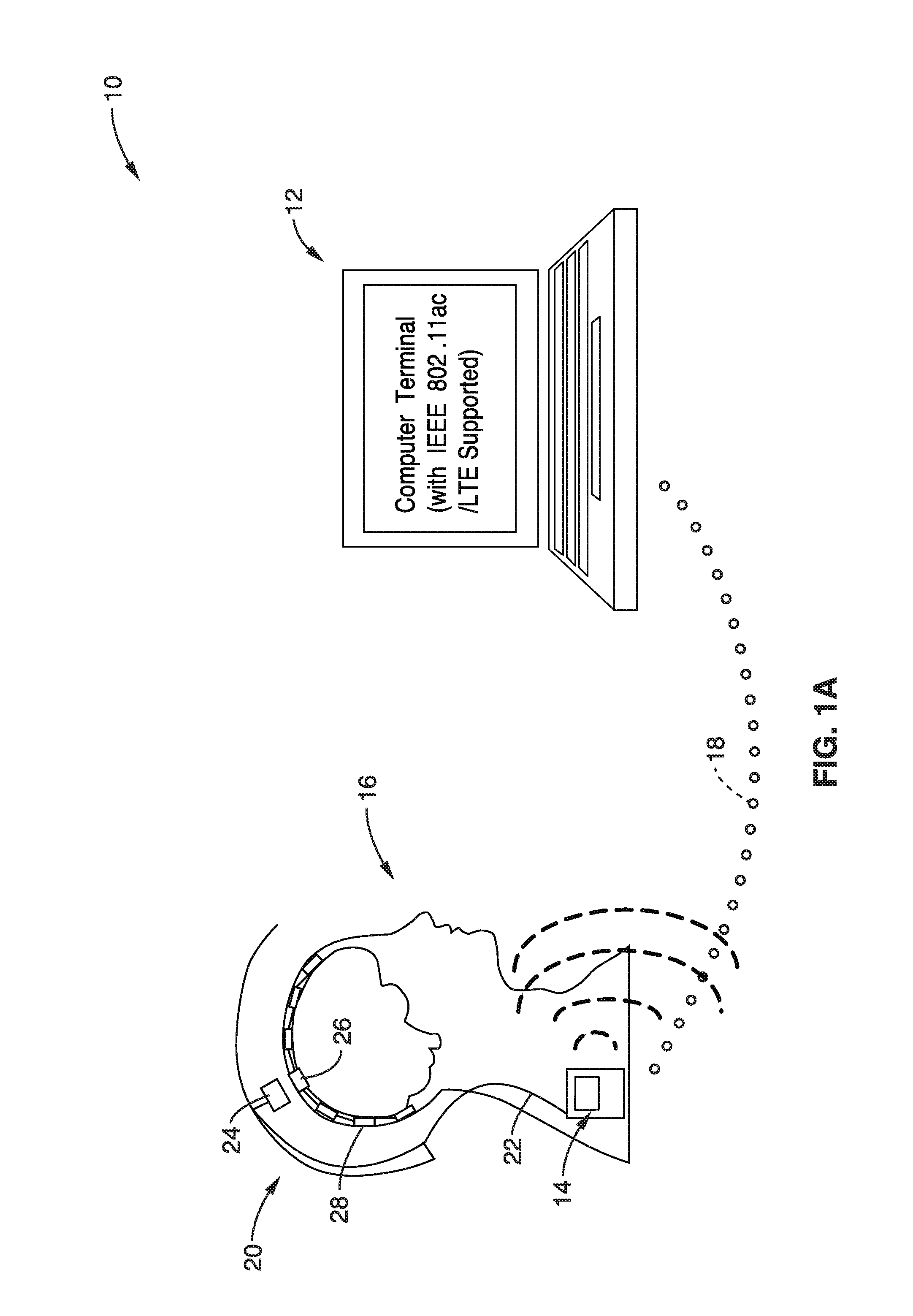

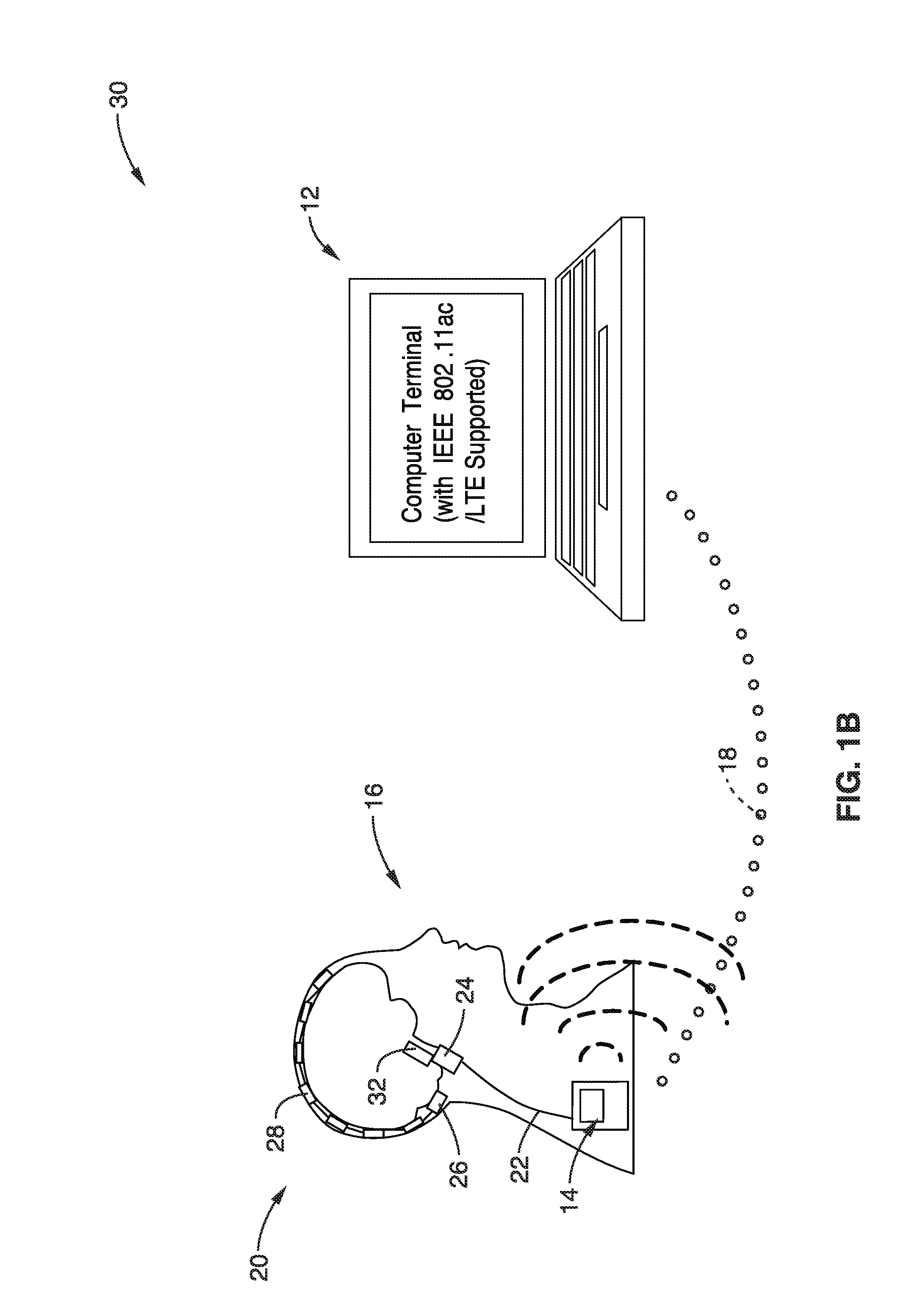

Wireless wearable big data brain machine interface

ActiveUS20160323000A1Circuit arrangementsDiagnostic recording/measuringComputer hardwareShortest distance

A wireless wearable high data throughput (big data) brain machine interface apparatus is presented. An implanted recording and transmitting module collects neural data from a plurality of implanted electrodes and wirelessly transmits this over a short distance to a wearable (not implanted) receiving and forwarding module, which communicates the data over a wired communication to a mobile post processing device. The post processing device can send this neural data to an external display or computer enabled device for viewing and / or manipulation. High data throughput is supported by aggregating multiple groups of electrodes by multiple n-channel recording elements, which are multiplexed and then modulated into high frequency wireless communications to the wearable module. Embodiments include use of multiple radiators (multiple polarizations and / or spatially distributed), with beam alignment adjustment.

Owner:RGT UNIV OF CALIFORNIA

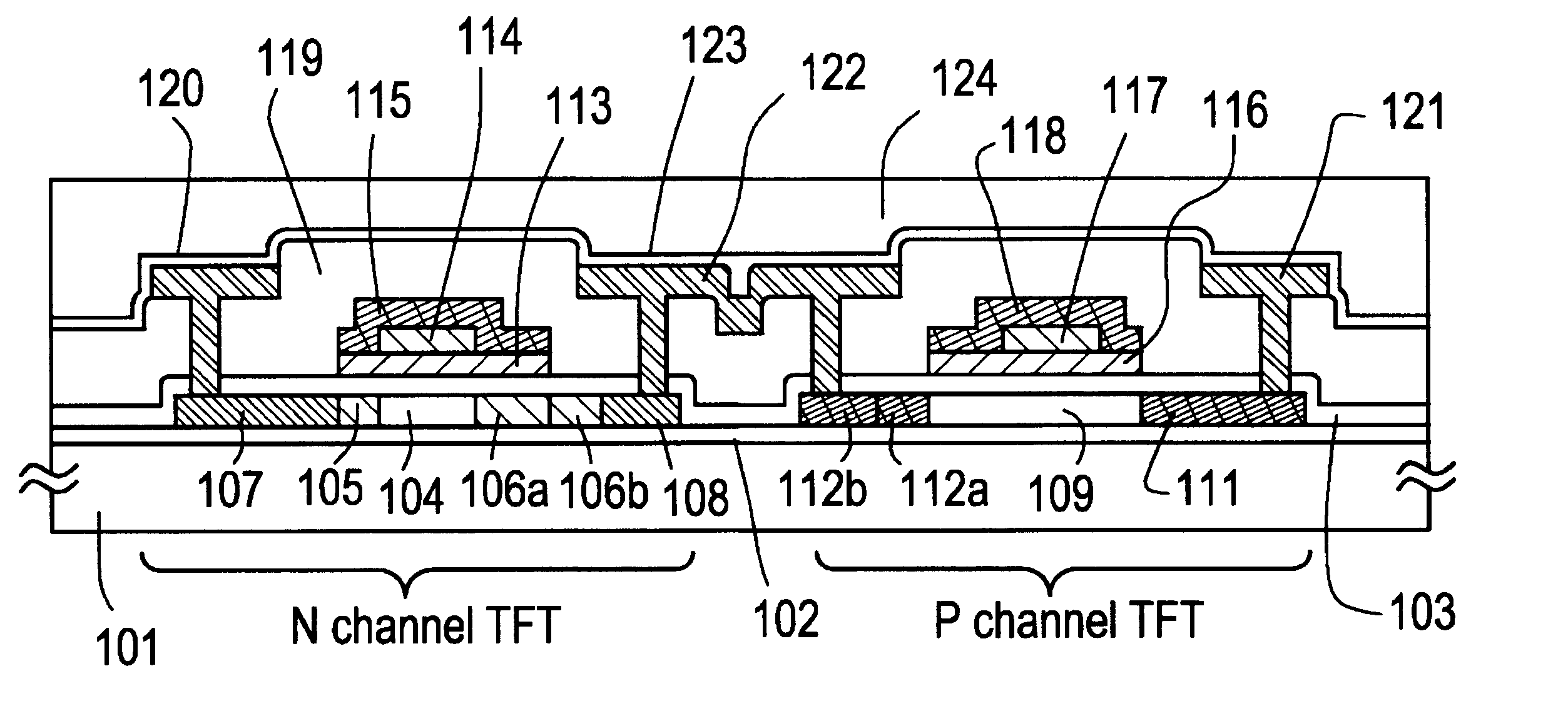

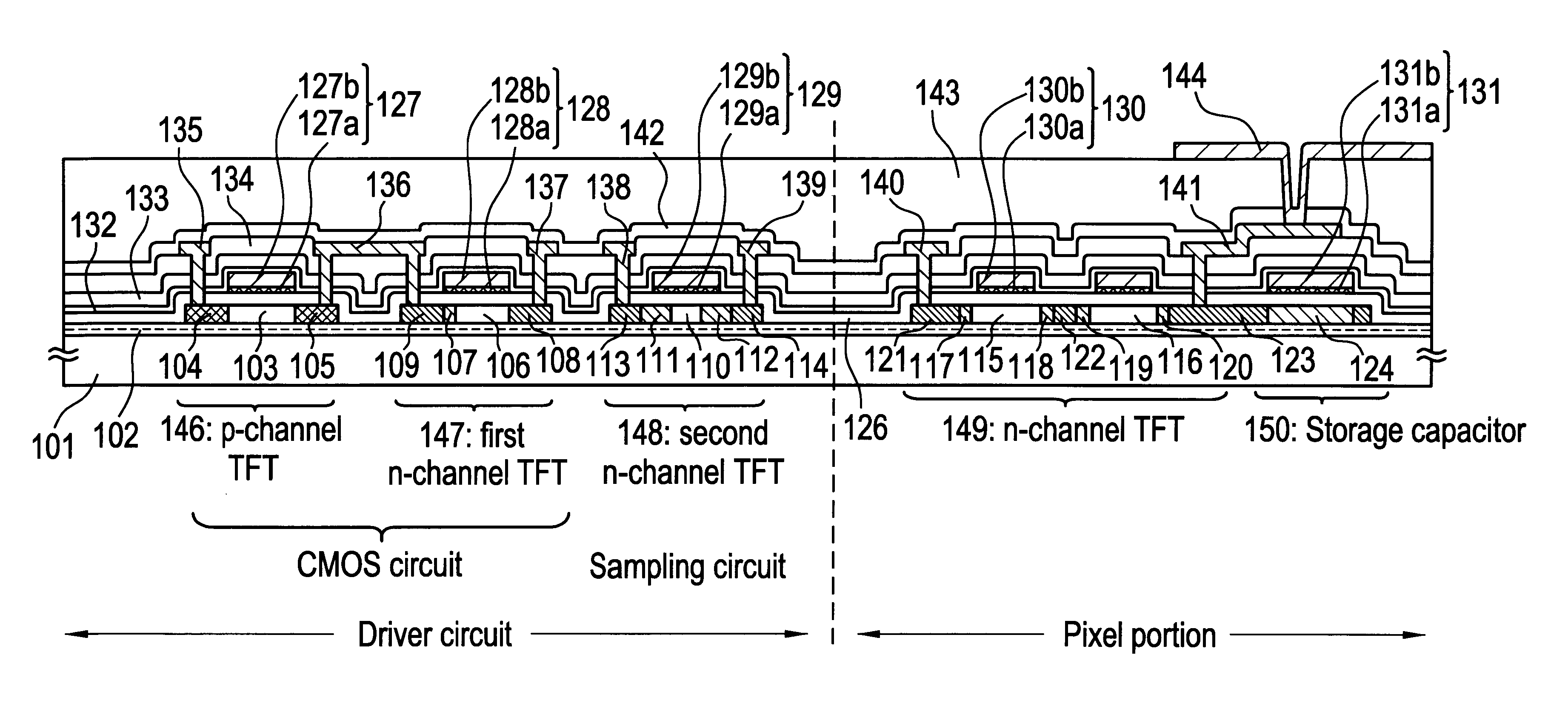

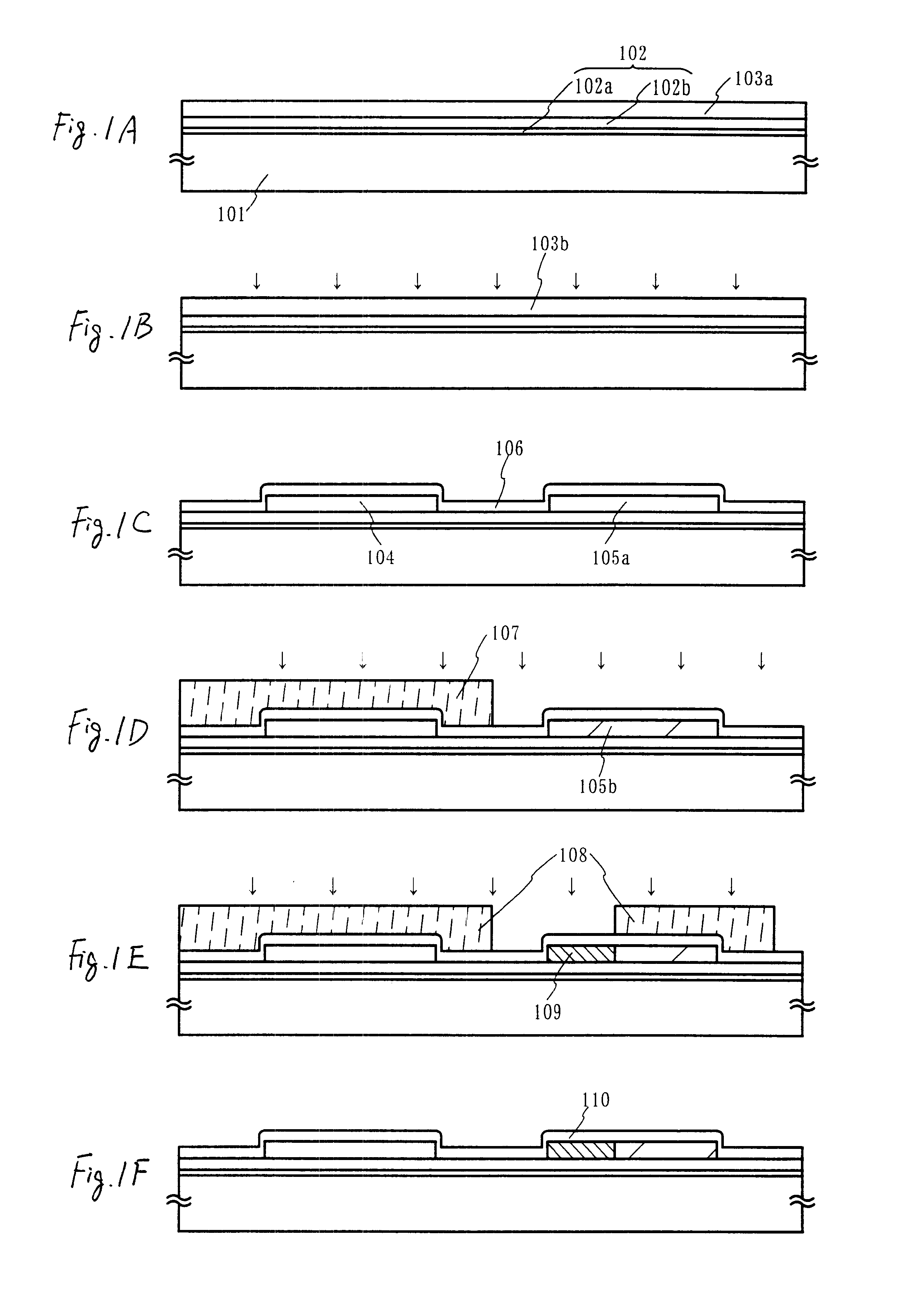

Thin film transistor having lightly doped regions

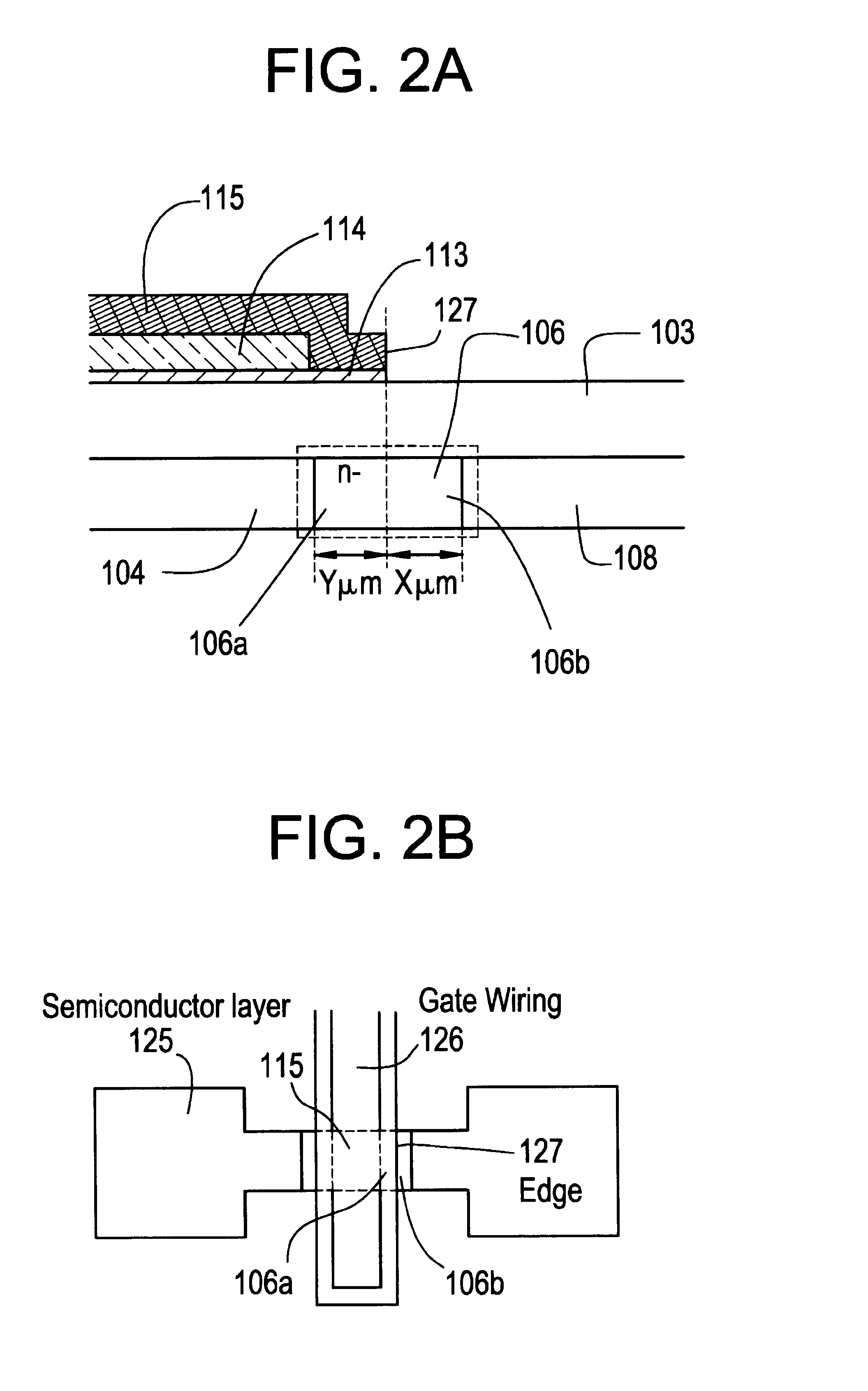

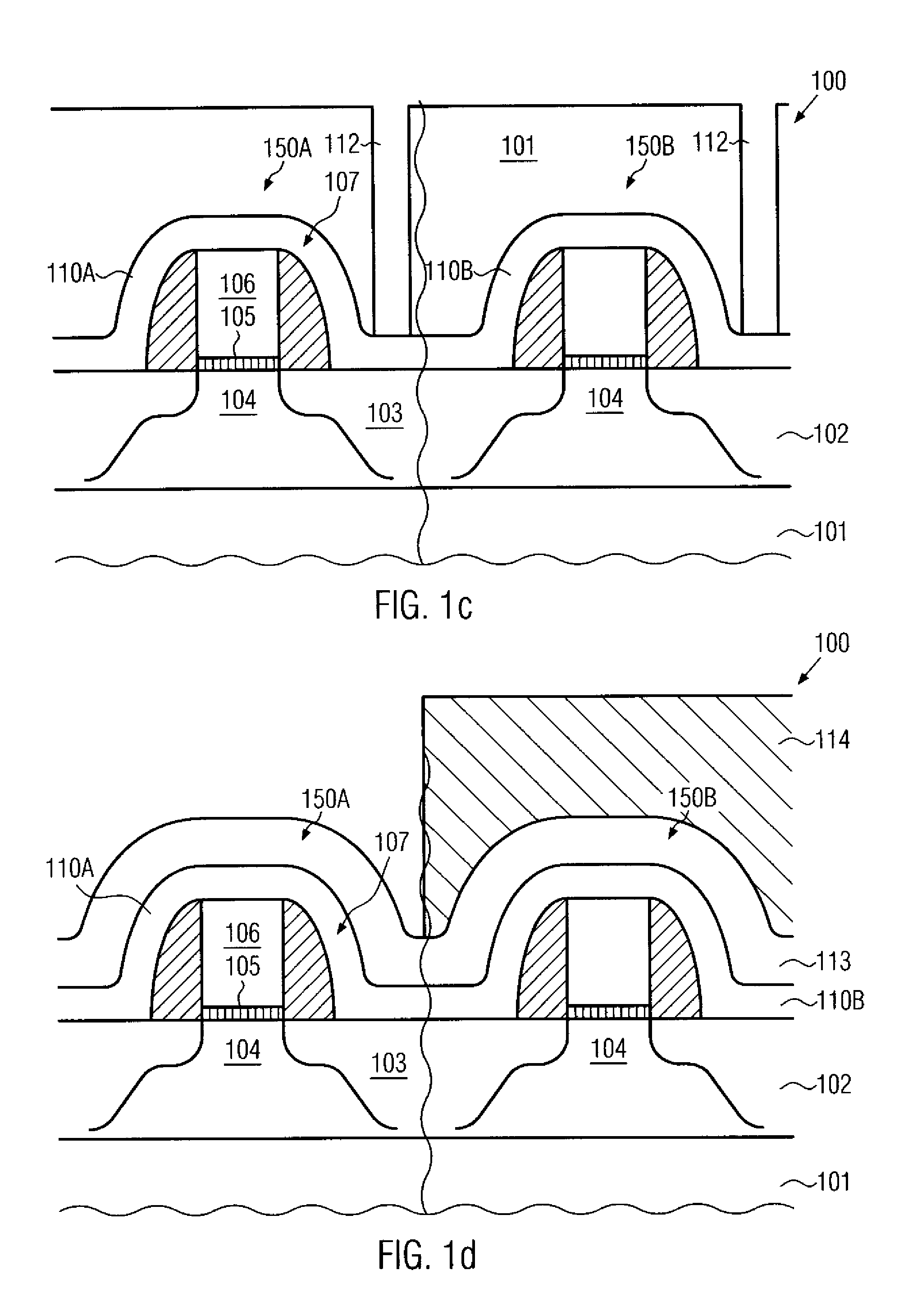

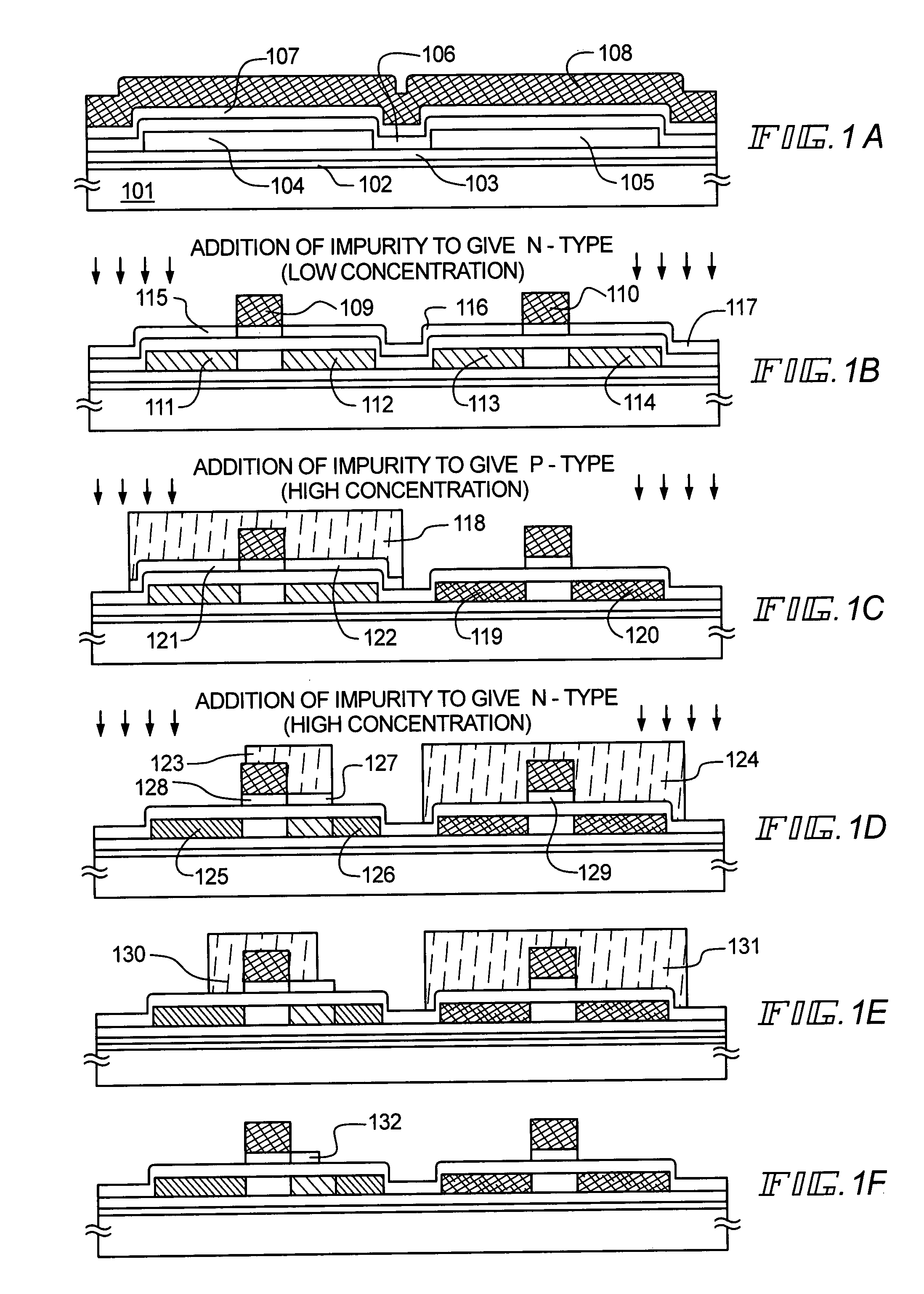

By appropriately selecting the structure of top gate type or staggered type TFTs disposed in the respective circuits of a semiconductor device depending on the function of the circuits, the operating characteristics and the reliability of the semiconductor device is improved. An LDD region (107) the whole of which overlaps a gate electrode is provided in a first n-channel type TFT of a controlling circuit. LDD regions (111) and (112) at least part of which overlaps a gate electrode are provided in a second n-channel type TFT of the control circuit. LDD regions (117) to (120) which do not overlap a gate electrode through offset regions are provided in an n-channel type TFT of a pixel matrix circuit. By making different the concentration of LDD regions of the control circuit and the concentration of the pixel matrix circuit, optimized circuit operation is obtained.

Owner:SEMICON ENERGY LAB CO LTD

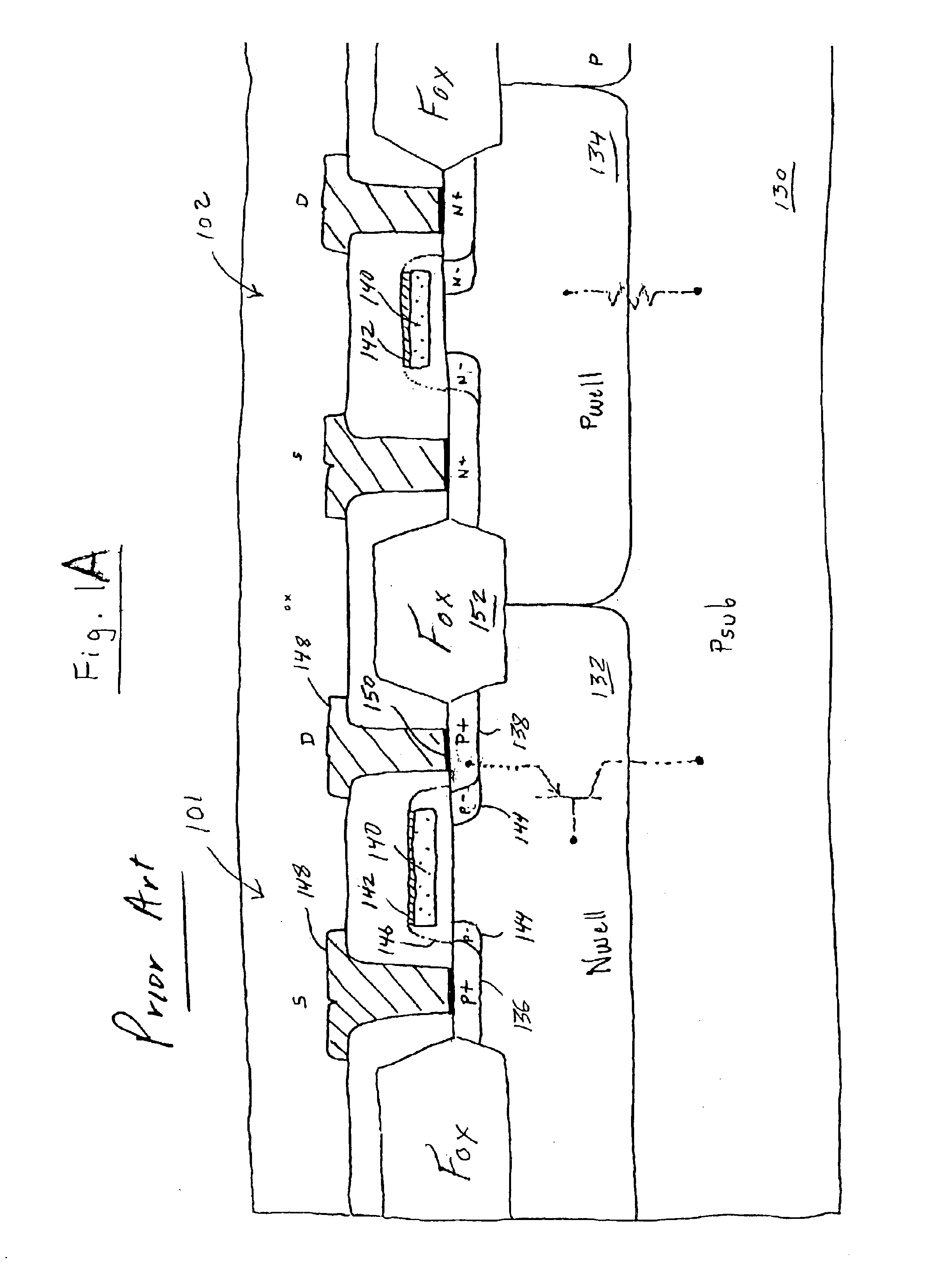

Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology

A family of semiconductor devices is formed in a substrate that contains no epitaxial layer. In one embodiment the family includes a 5V CMOS pair, a 12V CMOS pair, a 5V NPN, a 5V PNP, several forms of a lateral trench MOSFET, and a 30V lateral N-channel DMOS. Each of the devices is extremely compact, both laterally and vertically, and can be fully isolated from all other devices in the substrate.

Owner:ADVANCED ANALOGIC TECH (HONG KONG) LTD +1

Semiconductor device

InactiveUS8044464B2Guaranteed high speed operationReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packagePlane orientation

Owner:SEMICON ENERGY LAB CO LTD

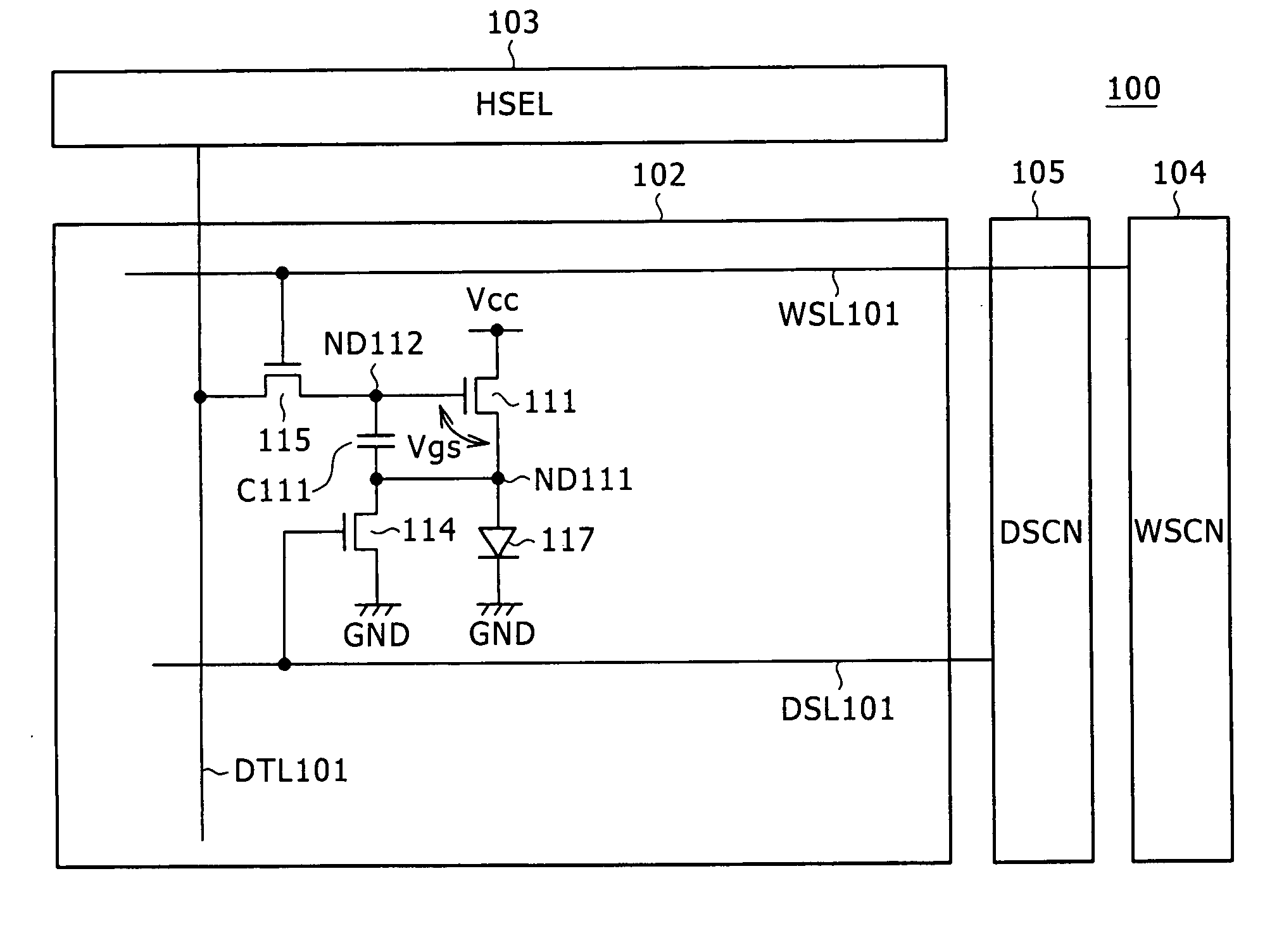

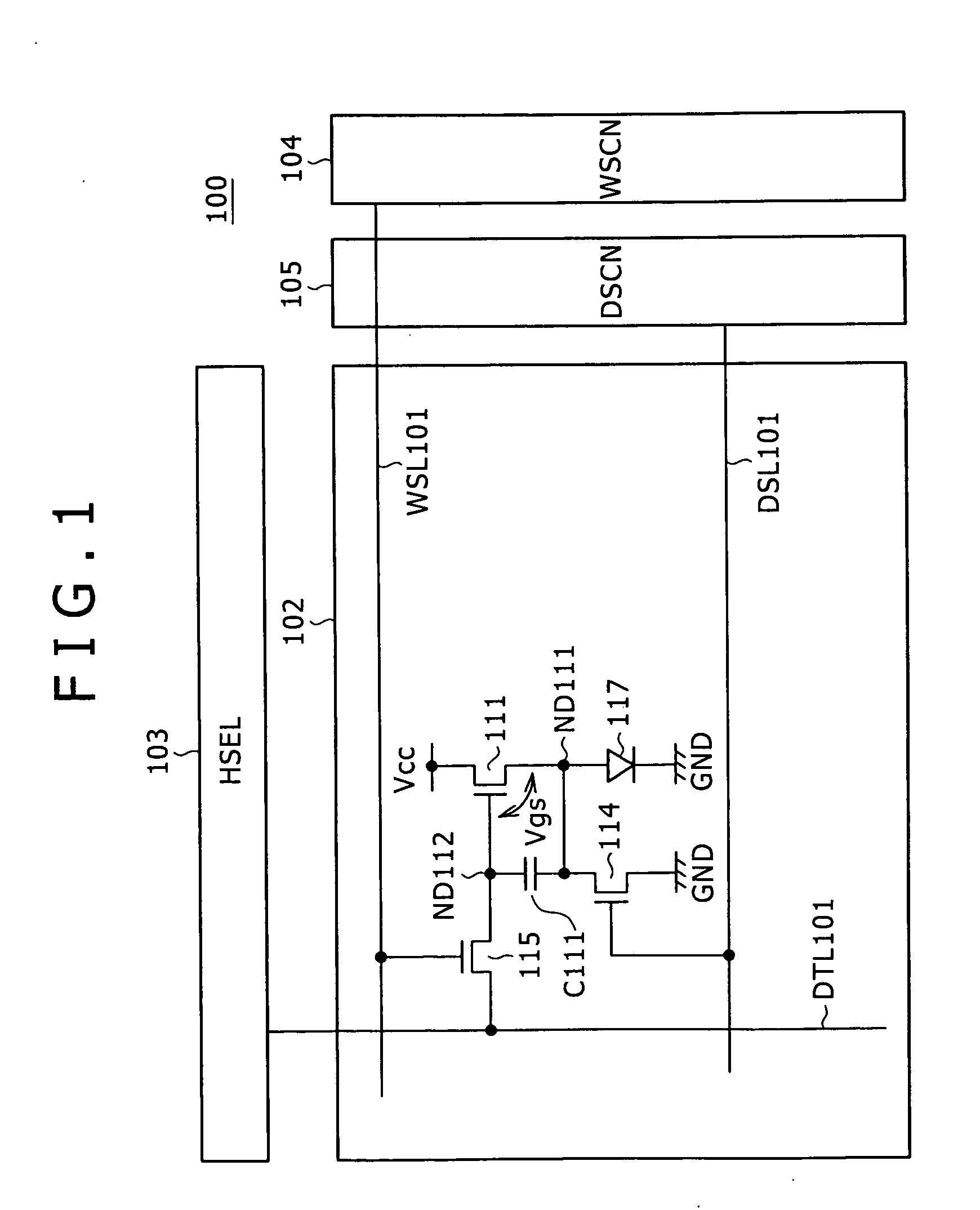

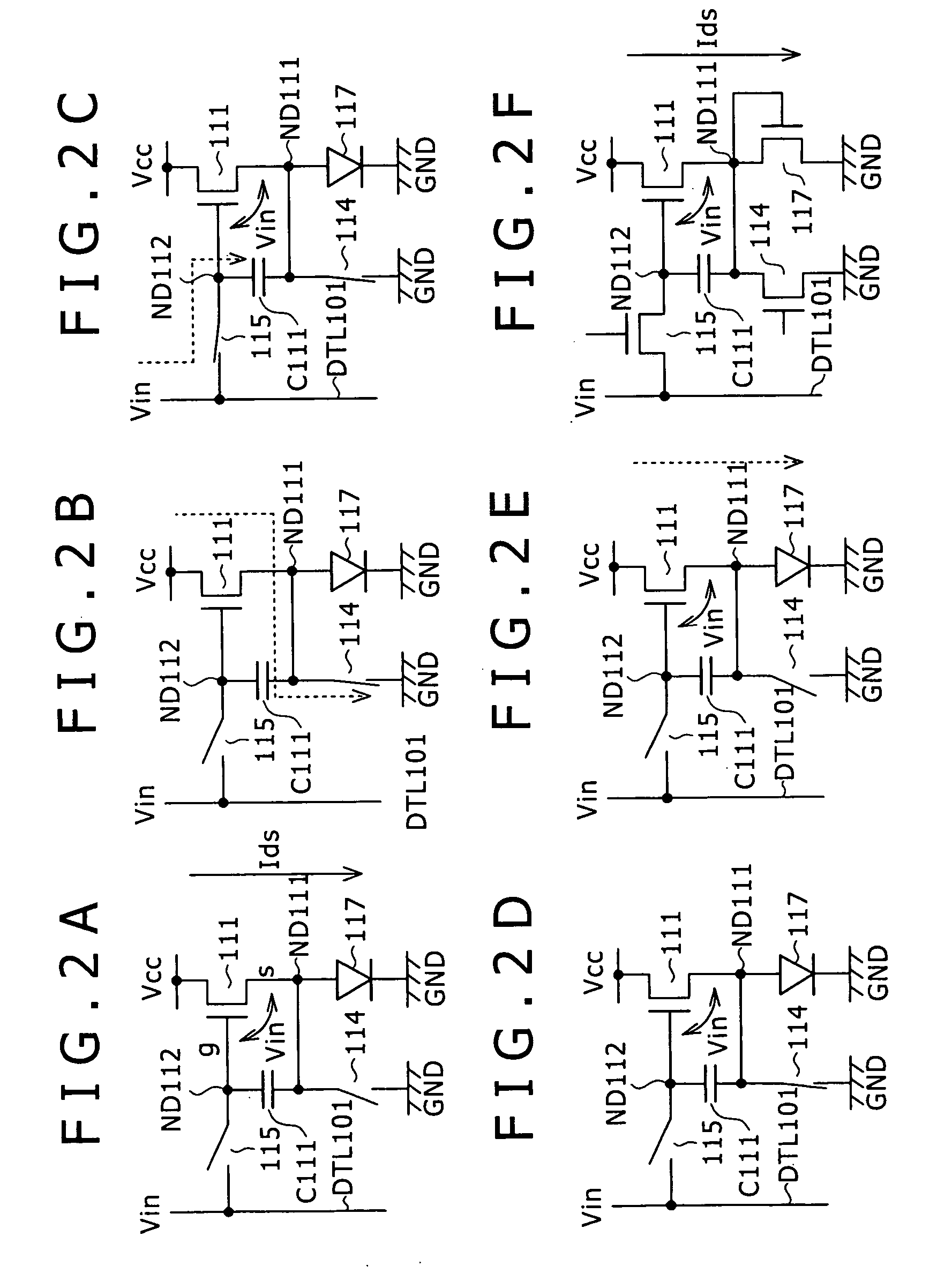

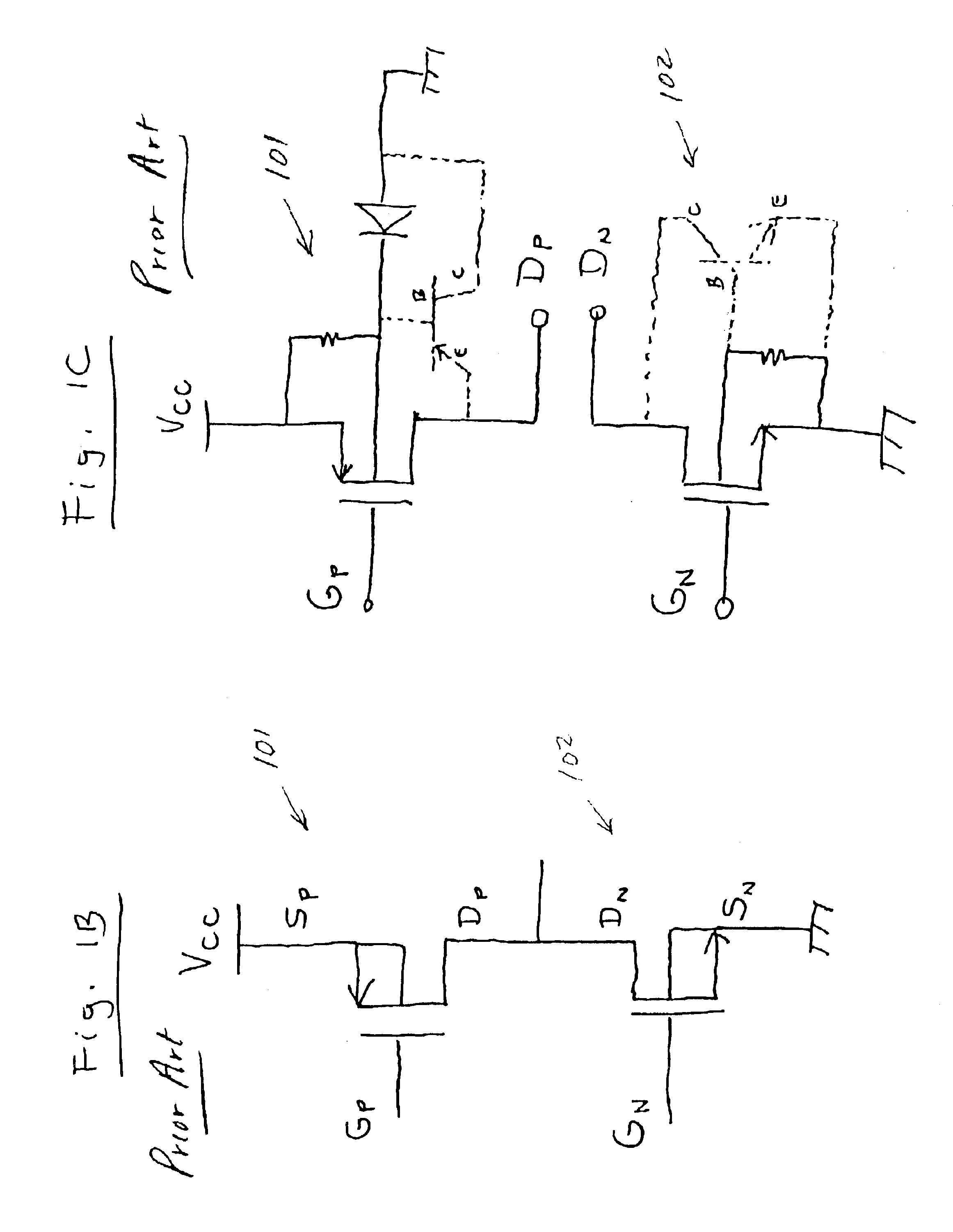

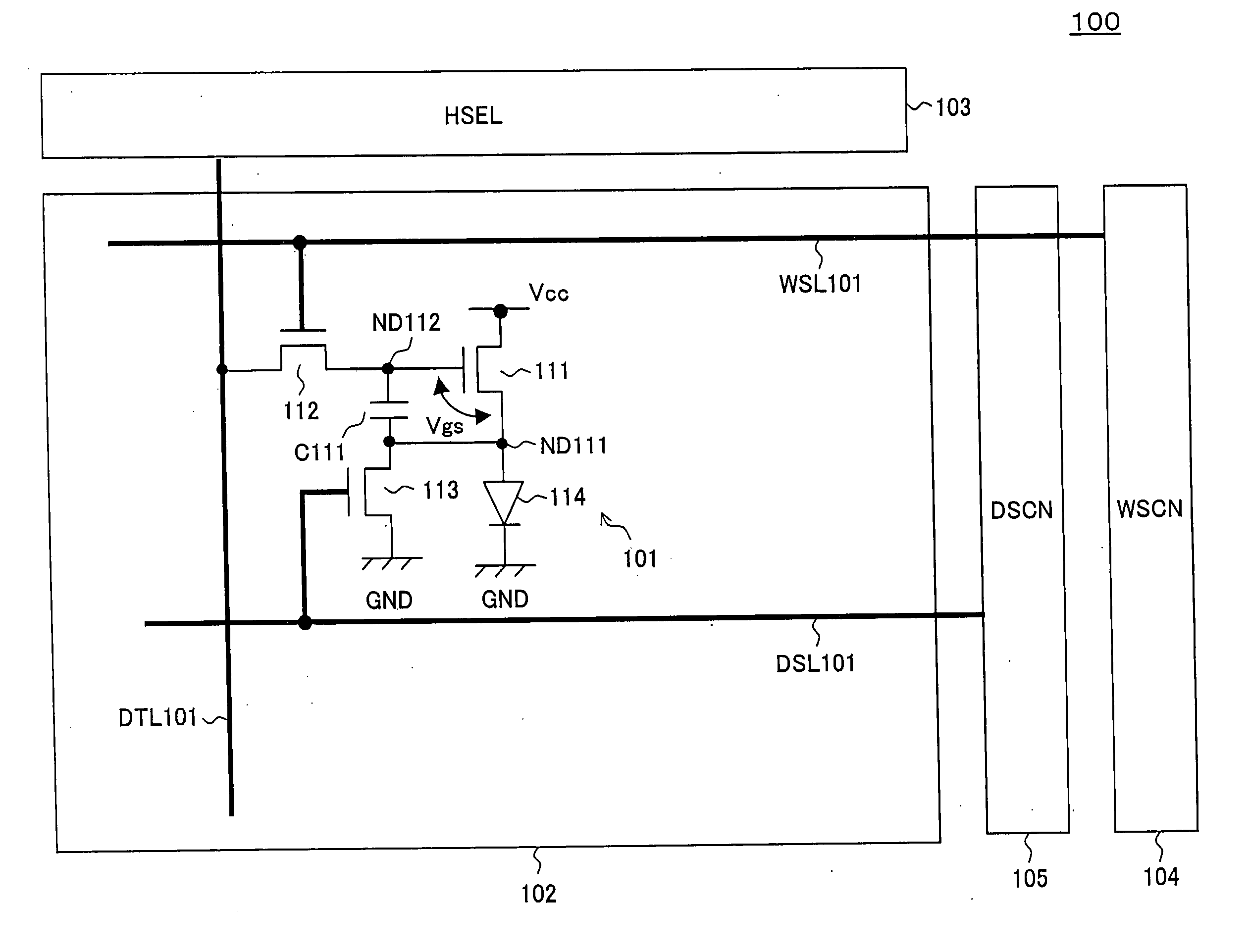

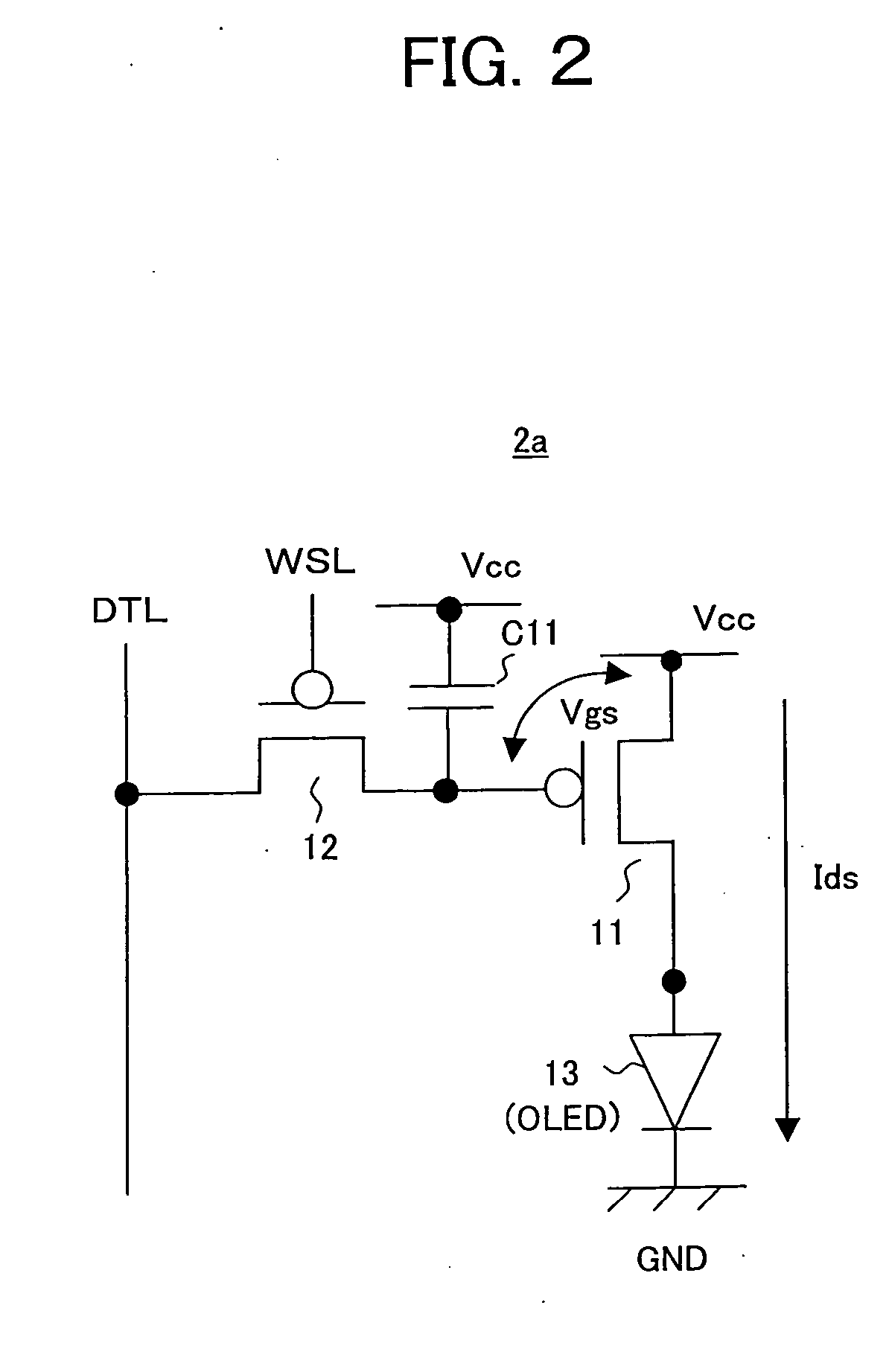

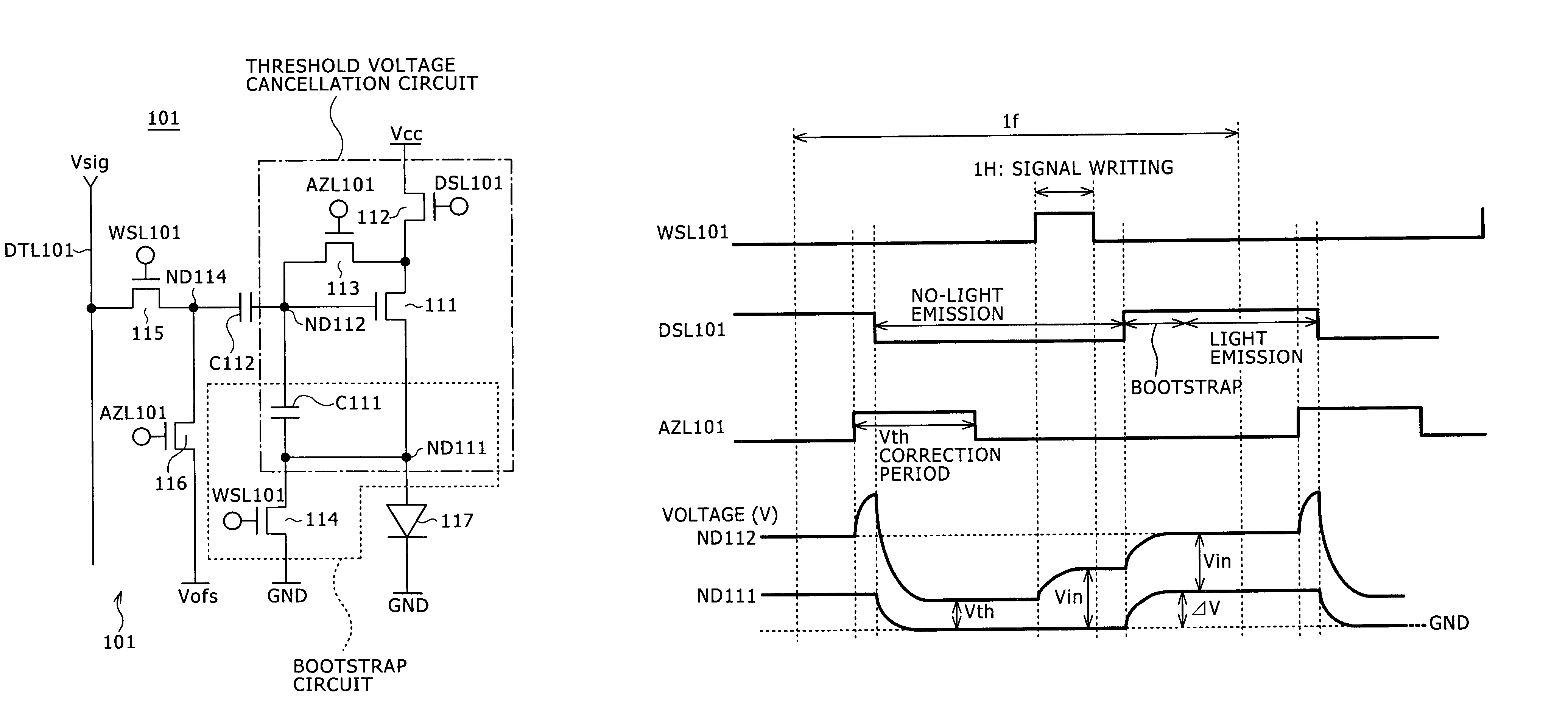

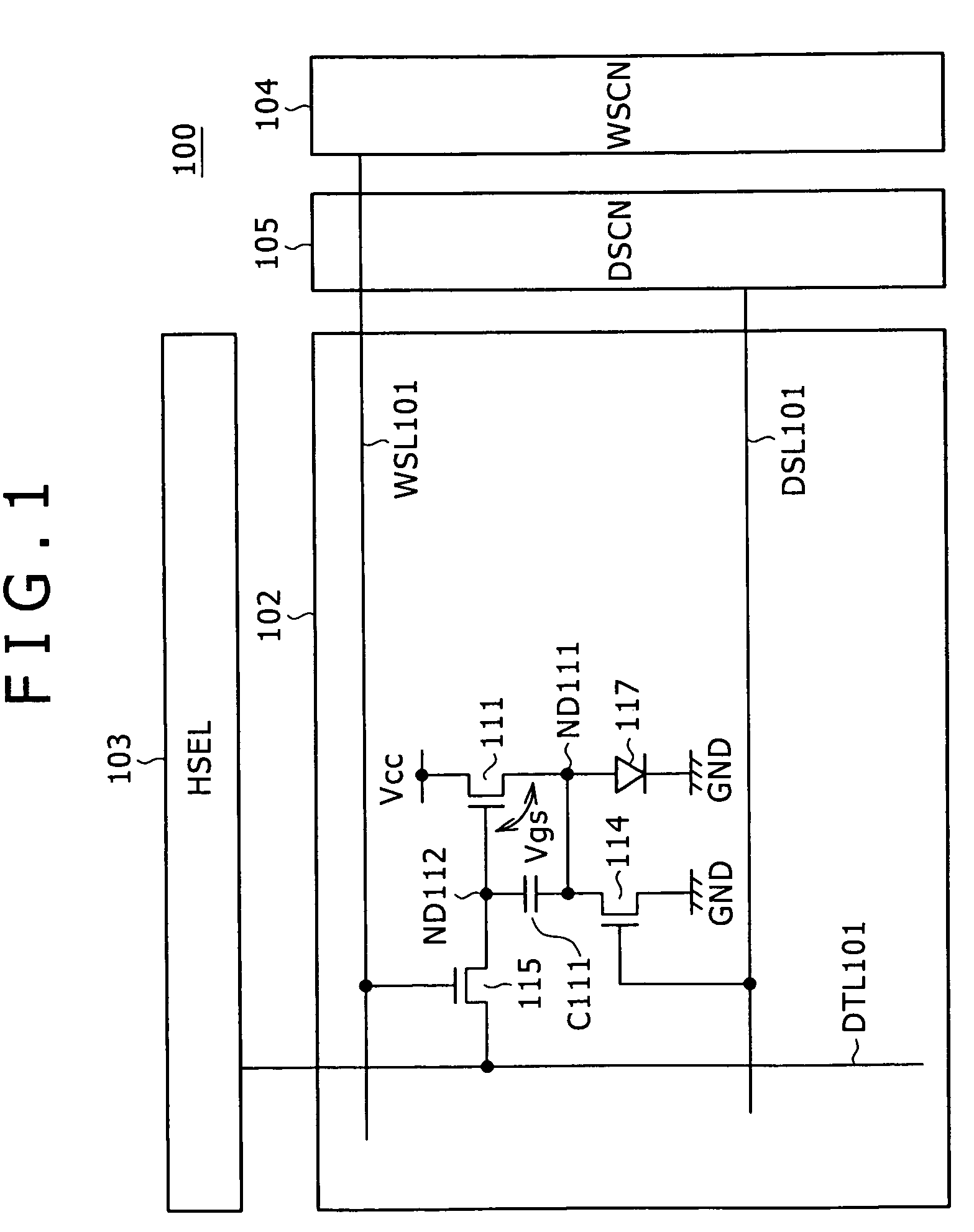

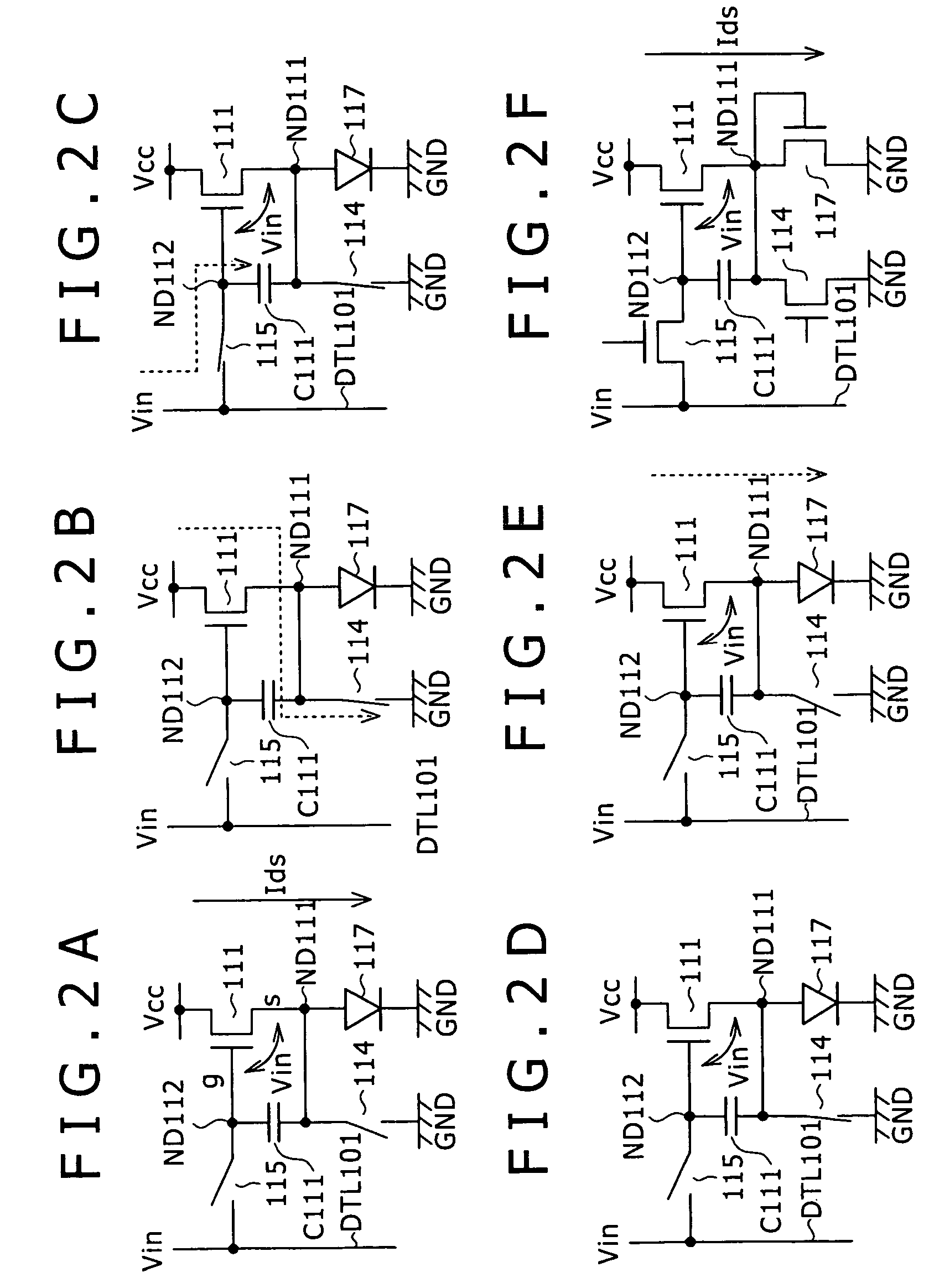

Pixel circuit, display unit, and pixel circuit drive method

ActiveUS20070057873A1No deterioration of luminanceNo deteriorationTransistorStatic indicating devicesDisplay deviceCapacitor

A pixel circuit, display device, and method of driving a pixel circuit enabling source-follower output with no deterioration of luminance even with a change of the current-voltage characteristic of the light emitting element along with elapse, enabling a source-follower circuit of n-channel transistors, and able to use an n-channel transistor as an EL drive transistor while using current anode-cathode electrodes, wherein a source of a TFT 111 as a drive transistor is connected to an anode of a light emitting element 114, a drain is connected to a power source potential VCC, a capacitor C111 is connected between a gate and source of the TFT 111, and a source potential of the TFT 111 is connected to a fixed potential through a TFT 113 as a switching transistor.

Owner:SONY CORP

Semiconductor integrated circuit device

InactiveUS7016214B2Reduced footprintSuppress relative deviation of operation characteristicsTransistorSolid-state devicesMOSFETGate insulator

A semiconductor integrated circuit device capable of achieving higher integration and simplification of manufacturing processes is provided. Circuitry is provided which includes a first N-channel MOSFET and a first p-channel MOSFET each having a gate insulating dielectric film with a first film thickness, wherein a poly-silicon layer making up a gate electrode is doped with an N-type impurity. The circuitry also includes a second N-channel MOSFET having a gate insulator film with a second film thickness thinner than the first thickness, wherein an N-type impurity is doped into a polysilicon layer making up a gate electrode, and a second P-channel MOSFET with a P-type impurity being doped into a polysilicon layer making up a gate electrode. The gate electrodes of the first N-channel MOSFET and first P-channel MOSFET are integrally formed and mutually connected together.

Owner:HITACHI LTD

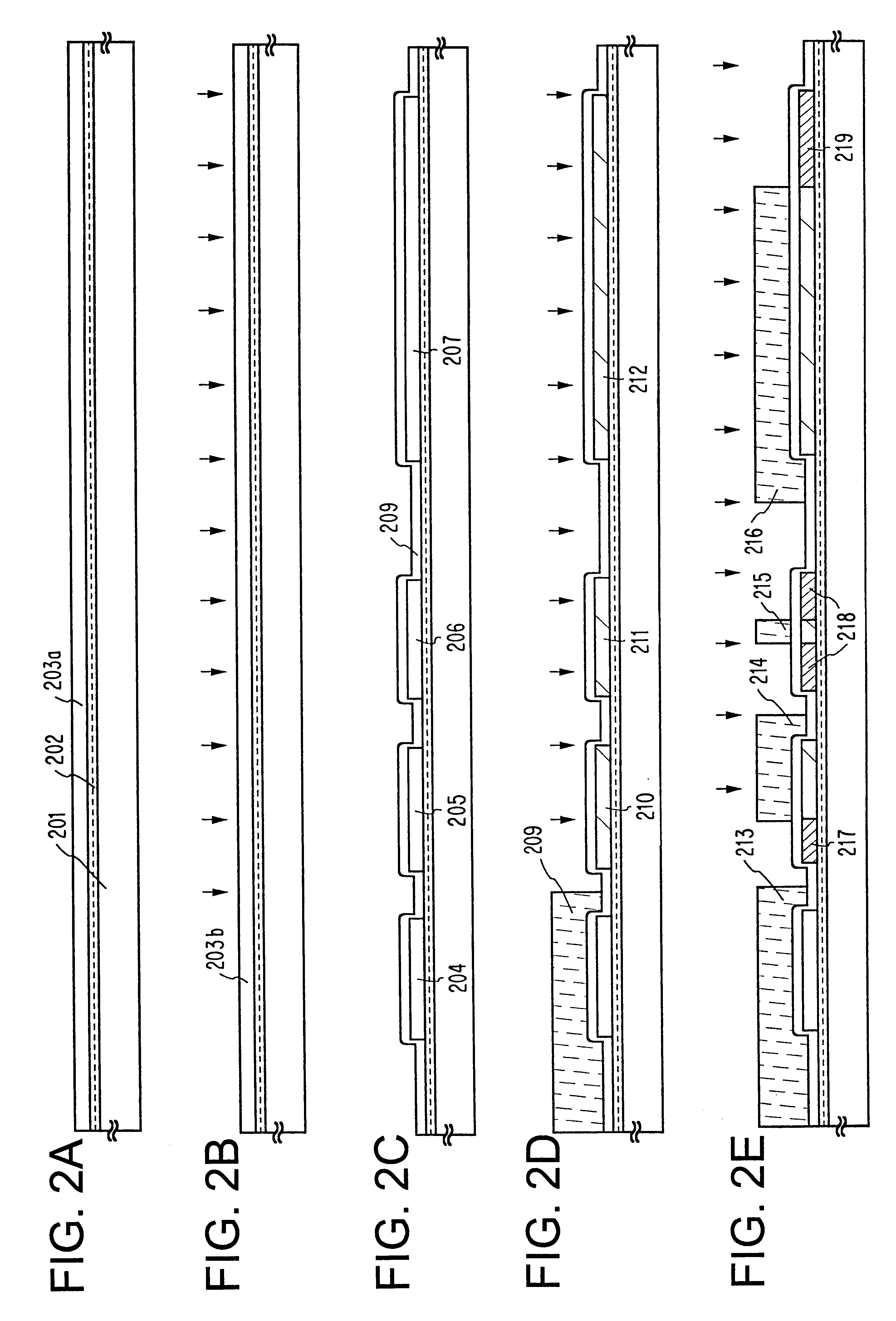

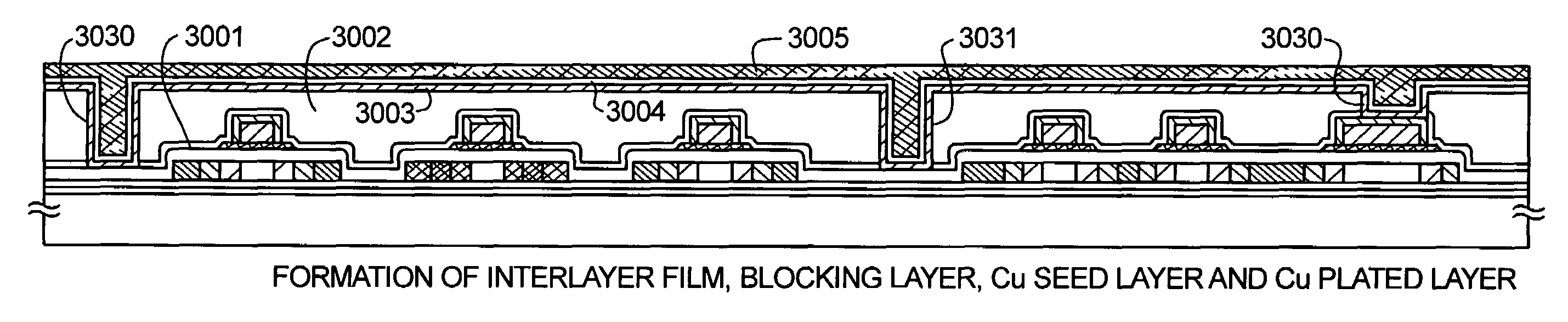

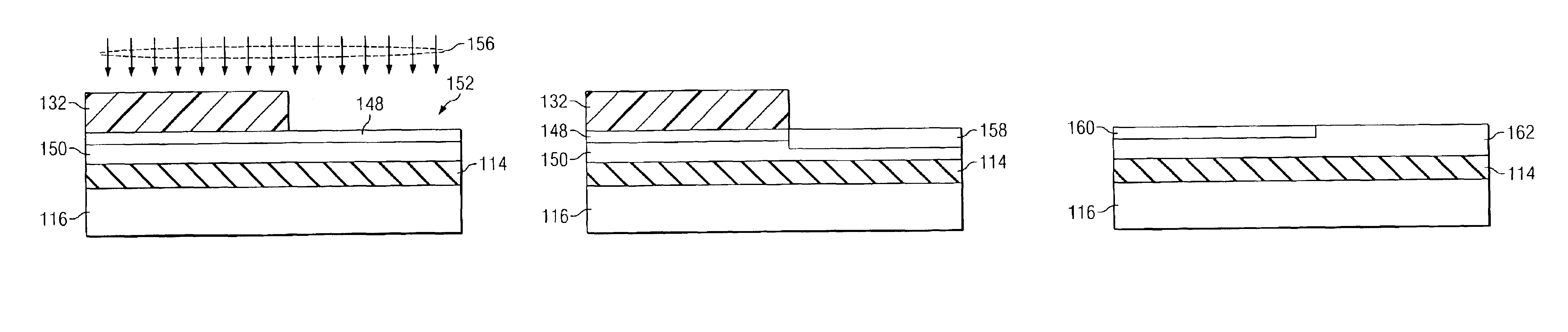

Oxynitride laminate "blocking layer" for thin film semiconductor devices

Channel doping is an effective method for controlling Vth, but if Vth shifts to the order of -4 to -3 V when forming circuits such as a CMOS circuit formed from both an n-channel TFT and a P-channel TFT on the same substrate, then it is difficult to control the Vth of both TFTs with one channel dope. In order to solve the above problem, the present invention forms a blocking layer on the back channel side, which is a laminate of a silicon oxynitride film (A) manufactured from SiH4, NH3, and N2O, and a silicon oxynitride film (B)manufactured from SiH4and N2O. By making this silicon oxynitride film laminate structure, contamination by alkaline metallic elements from the substrate can be prevented, and influence by stresses, caused by internal stress, imparted to the TFT can be relieved.

Owner:SEMICON ENERGY LAB CO LTD

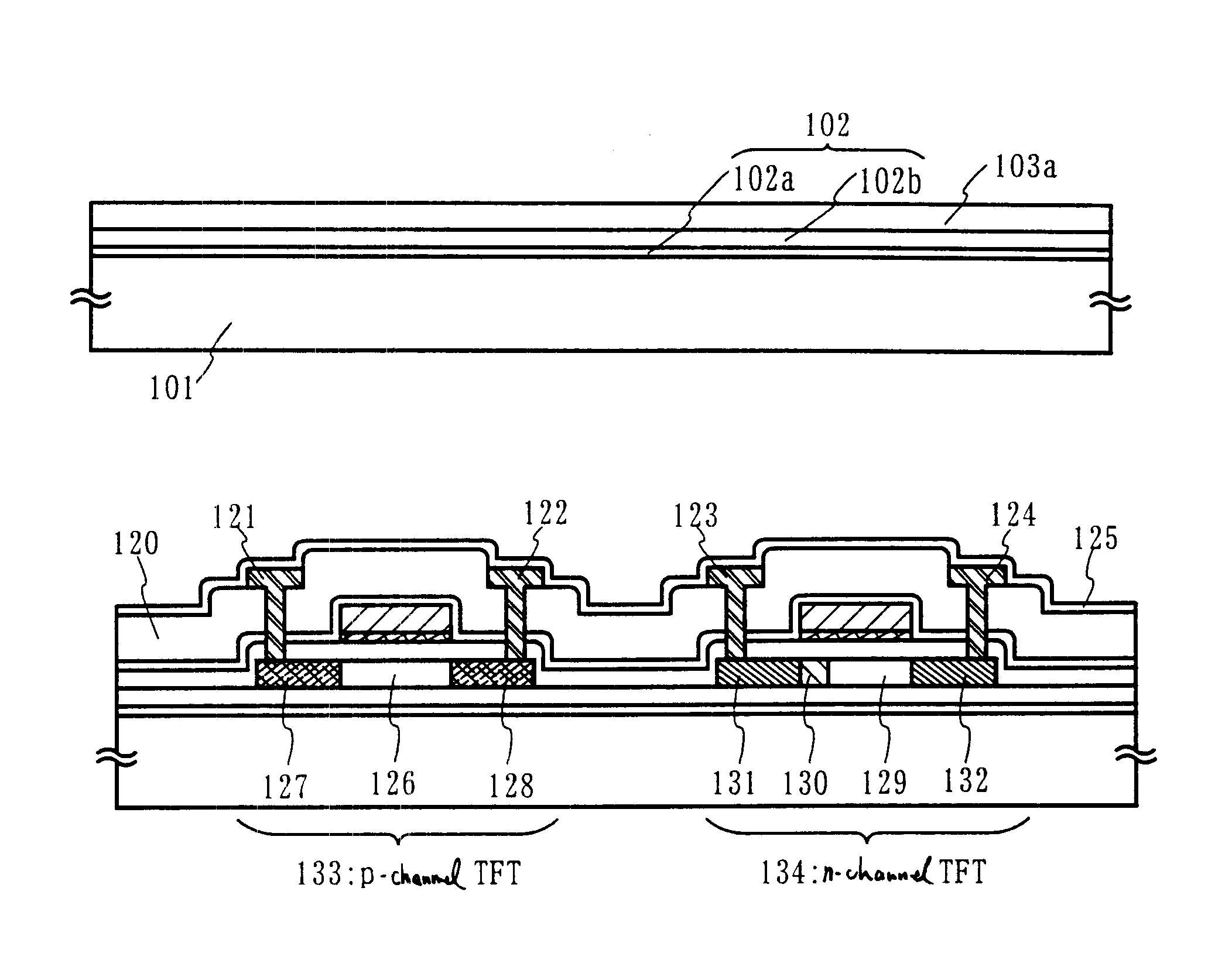

Semiconductor device and method of fabricating the same

InactiveUS7235810B1Suppress deterioration of on currentOff-current can be reducedTransistorSolid-state devicesSemiconductor materialsMetallic materials

There is provided a crystalline TFT in which reliability comparable to or superior to a MOS transistor can be obtained and excellent characteristics can be obtained in both an on state and an off state. A gate electrode of the crystalline TFT is formed of a laminate structure of a first gate electrode made of a semiconductor material and a second gate electrode made of a metal material. An n-channel TFT includes an LDD region, and a region overlapping with the gate electrode and a region not overlapping with the gate electrode are provided, so that a high electric field in the vicinity of a drain is relieved, and at the same time, an increase of an off current is prevented.

Owner:SEMICON ENERGY LAB CO LTD

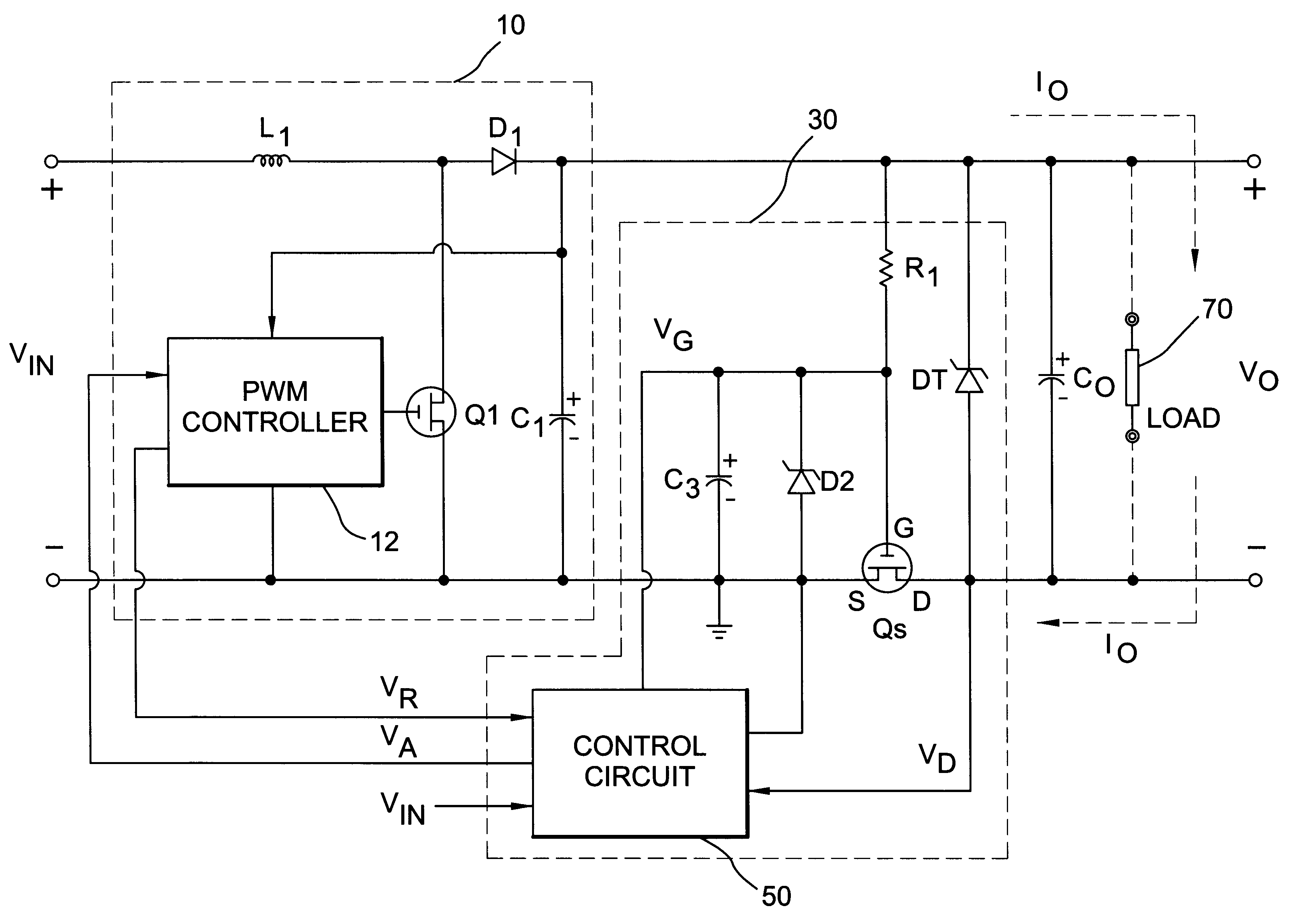

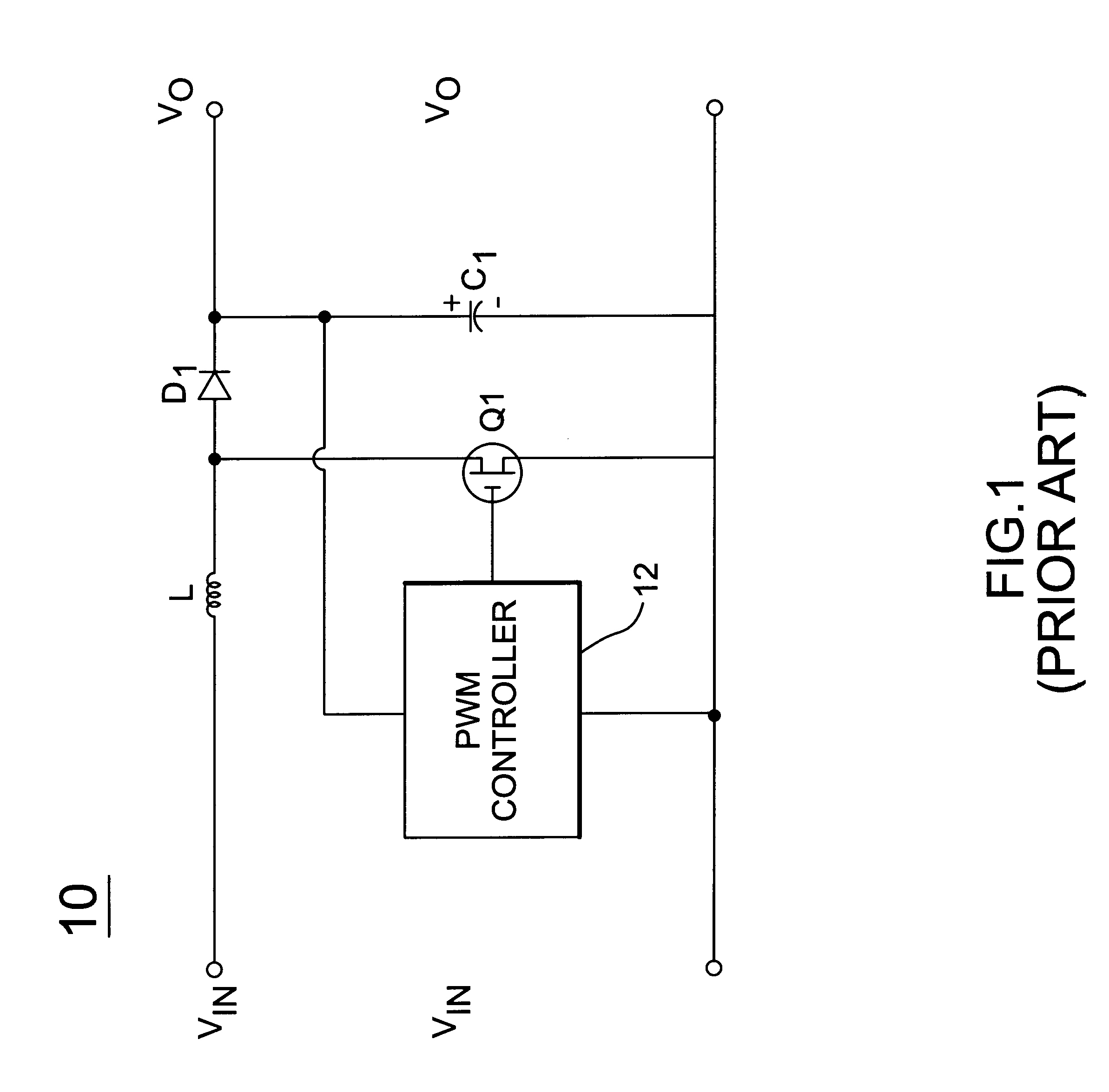

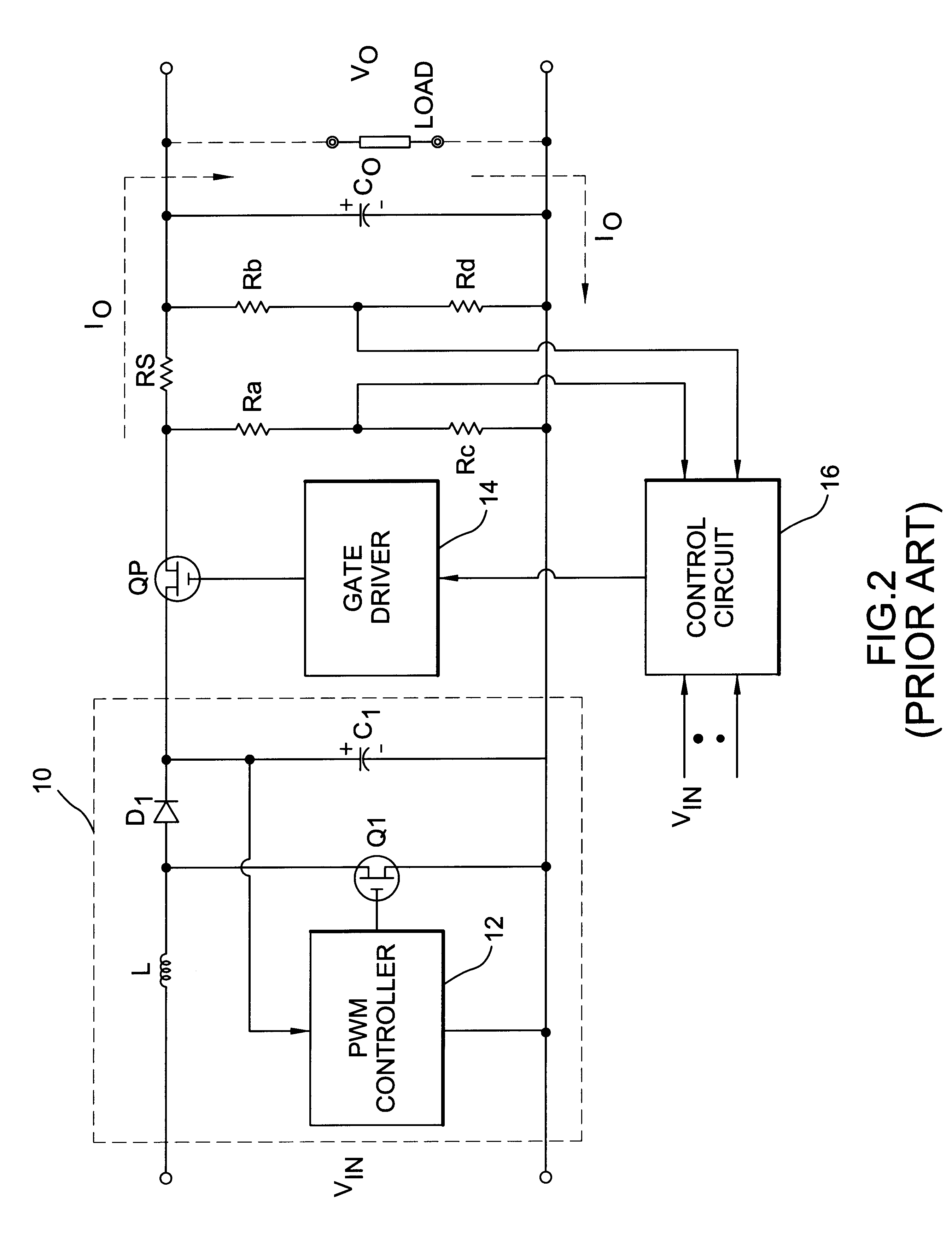

Protection circuit for a boost power converter

InactiveUS6185082B1Apparatus without intermediate ac conversionArrangements responsive to excess currentCurrent limitingTime delays

A protection circuit for a boost power converter provides input under-voltage protection and output over-voltage and over-current protection. The protection circuit includes a control power MOSFET connected in series between the ground of the boost power converter and the ground of the load. The arrangement of the circuit makes it easy to drive the gate of an N-channel power MOSFET and is ideal for current-limiting control, which utilizes the Rds-on of the MOSFET as a current sensing element. Neither a specific gate-driver nor a current sensing resistor is required, and thus high efficiency can be achieved. Furthermore, the slow slew-rate at the gate of the MOSFET provides a soft-start to the load. The protection circuit includes a temperature compensation circuitry to offset the variation of the Rds-on. A time delay circuit prevents the switching elements and protection elements from overload damage.

Owner:SEMICON COMPONENTS IND LLC

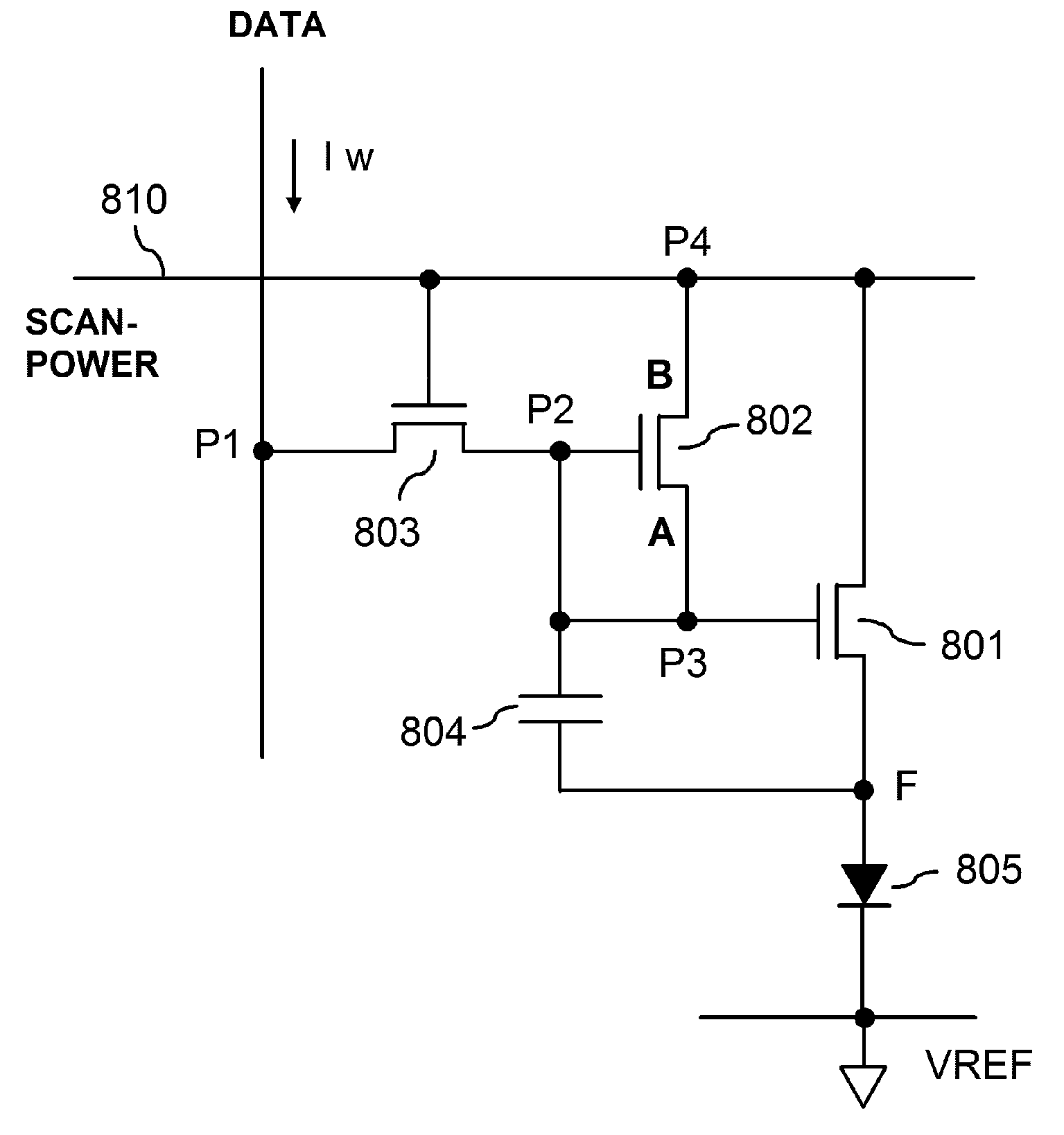

Active matrix light emitting device display pixel circuit and drive method

InactiveUS7589707B2Cathode-ray tube indicatorsInput/output processes for data processingActive matrixDisplay device

Display pixel circuits and a drive scheme utilizing a switching element operating in reverse direction in a data scan period to provide voltage reference are provided. Preferred embodiments and operation method leading to three-transistor solutions in current-control mode, common-cathode, and n-channel transistor drive configuration for light emitting device display are described.

Owner:CHOU CHEN JEAN

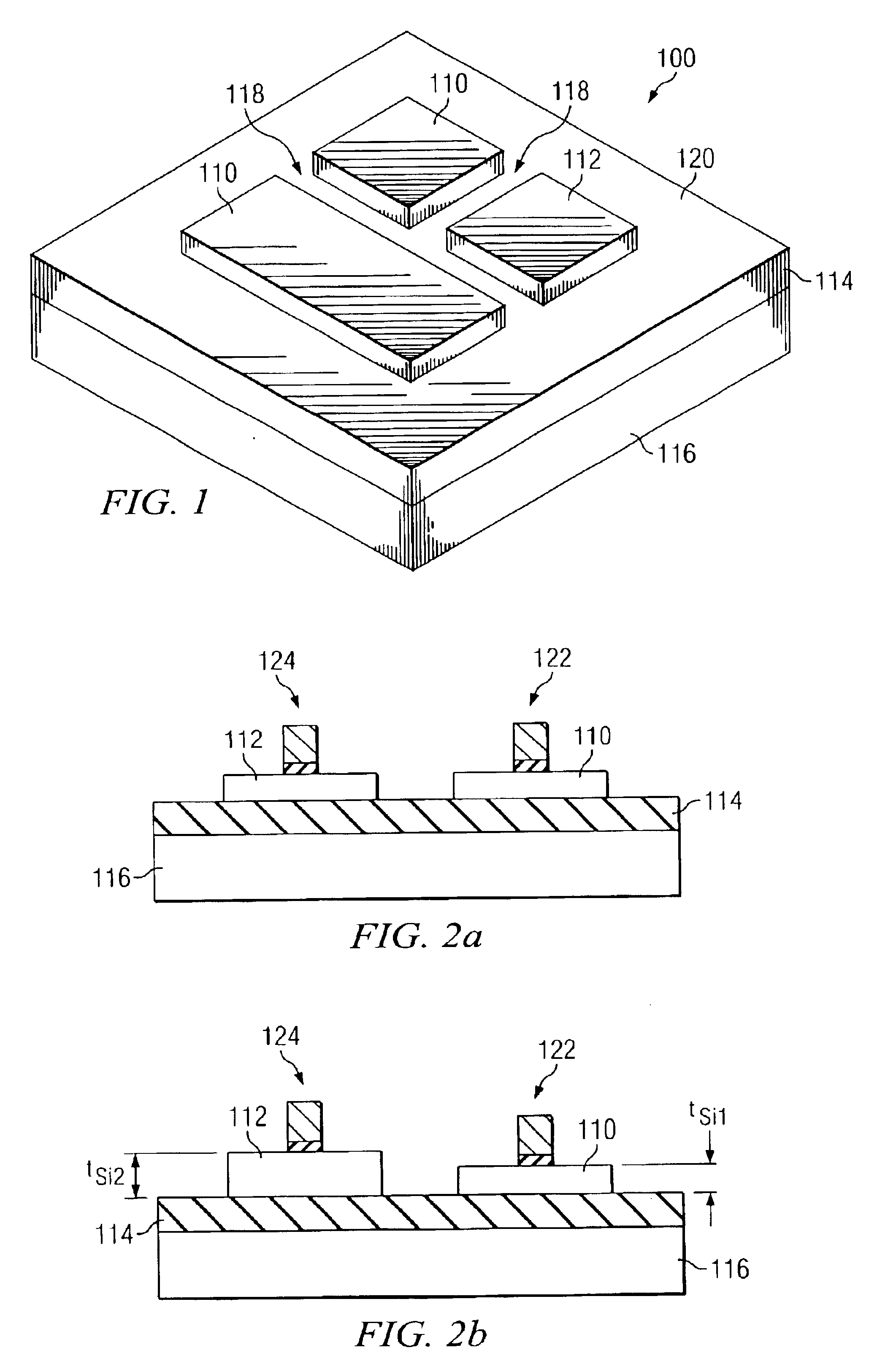

Silicon-on-insulator chip with multiple crystal orientations

A silicon-on-insulator chip includes an insulator layer, typically formed over a substrate. A first silicon island with a surface of a first crystal orientation overlies the insulator layer and a second silicon island with a surface of a second crystal orientation also overlies the insulator layer. In one embodiment, the silicon-on-insulator chip also includes a first transistor of a first conduction type formed on the first silicon island, and a second transistor of a second conduction type formed on the second silicon island. For example, the first crystal orientation can be (110) while the first transistor is a p-channel transistor, and the second crystal orientation can be (100) while the second transistor is an n-channel transistor.

Owner:TAIWAN SEMICON MFG CO LTD

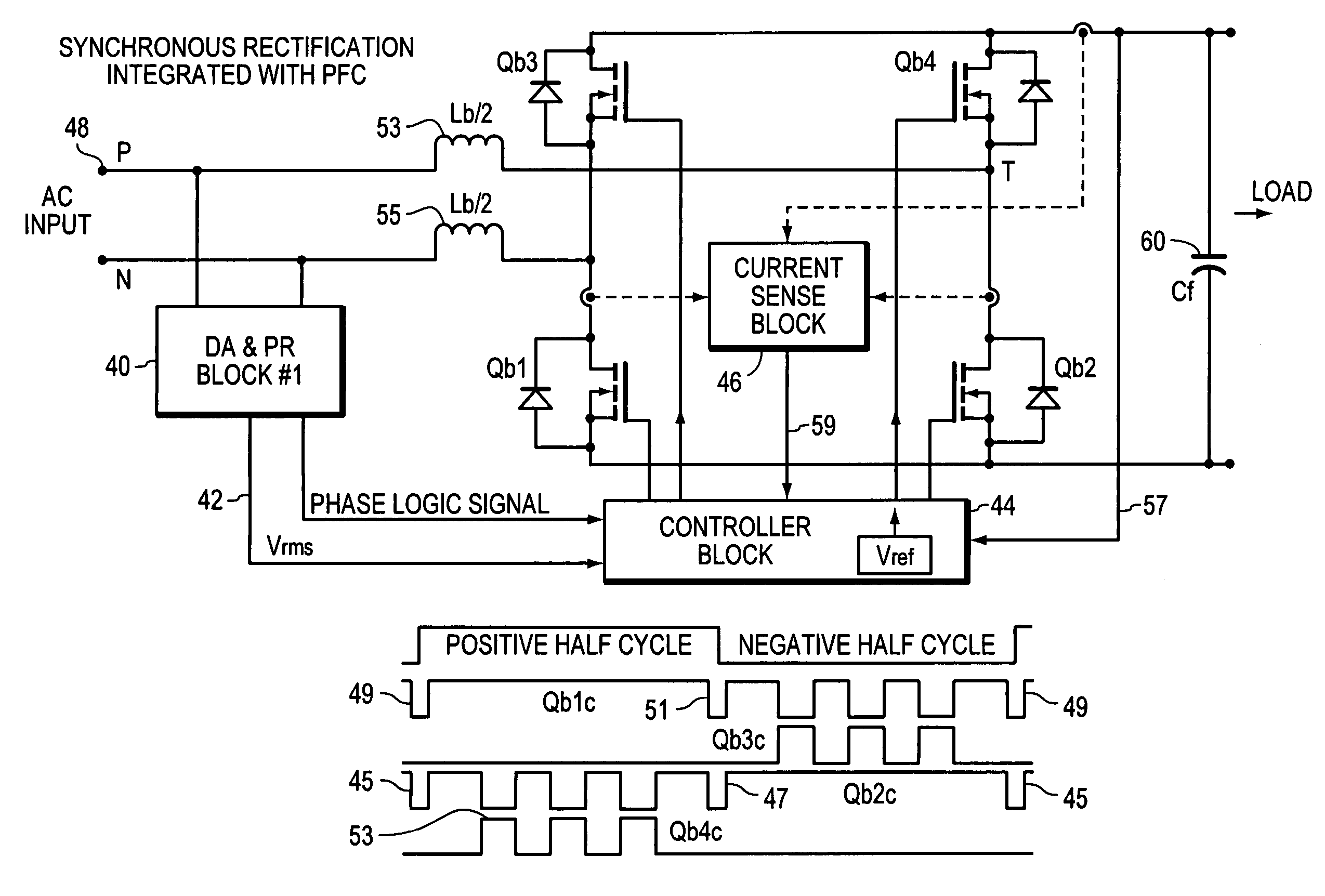

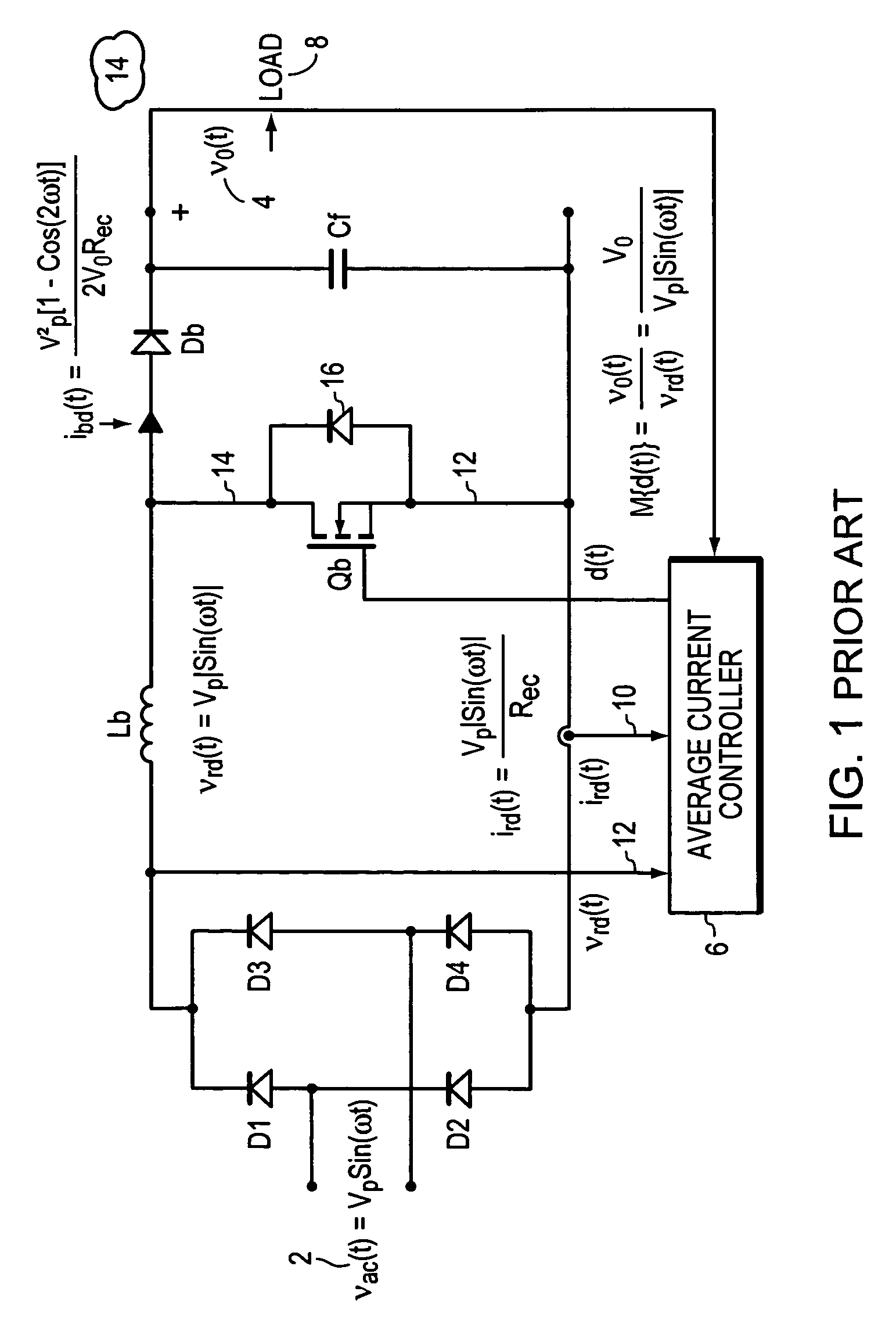

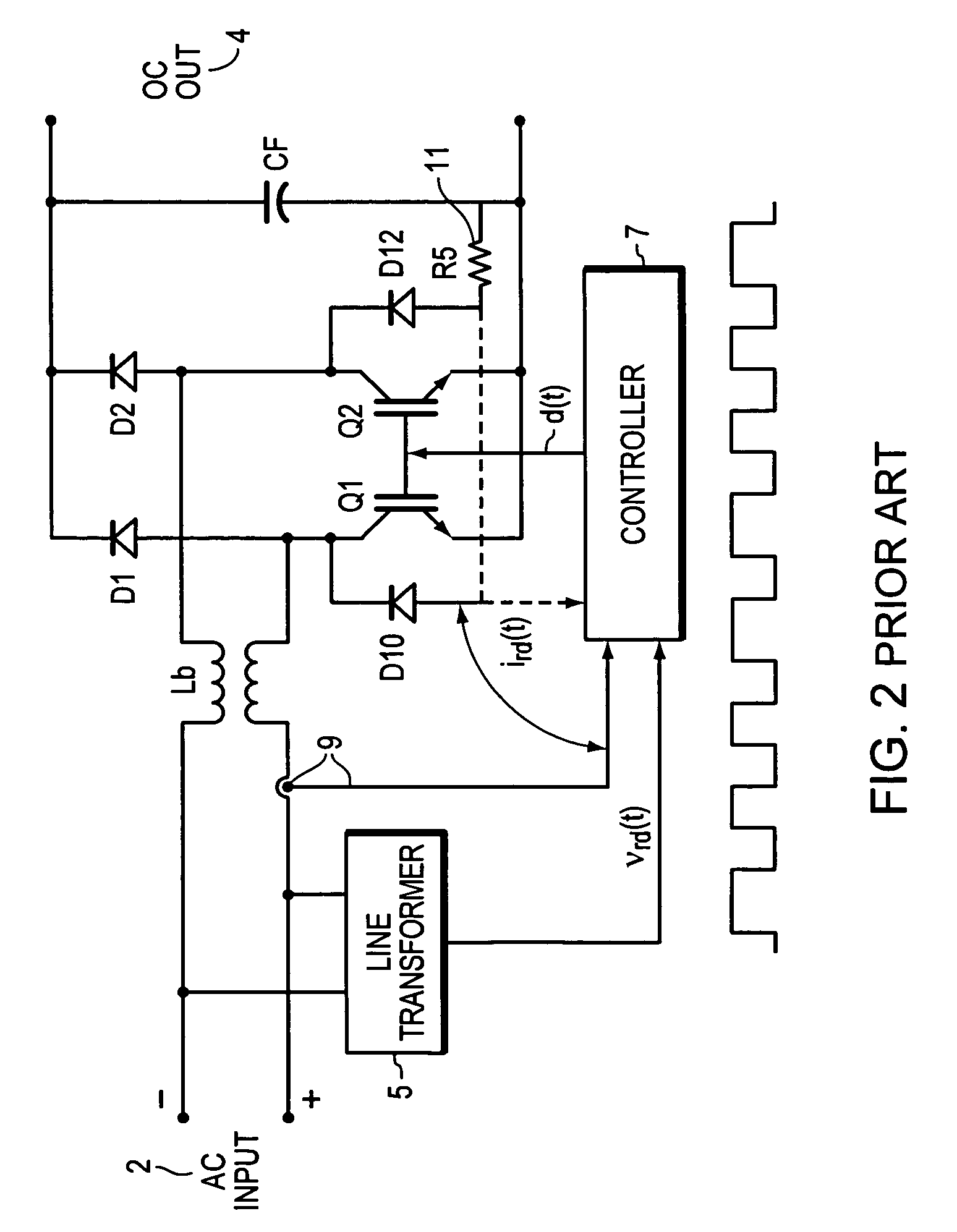

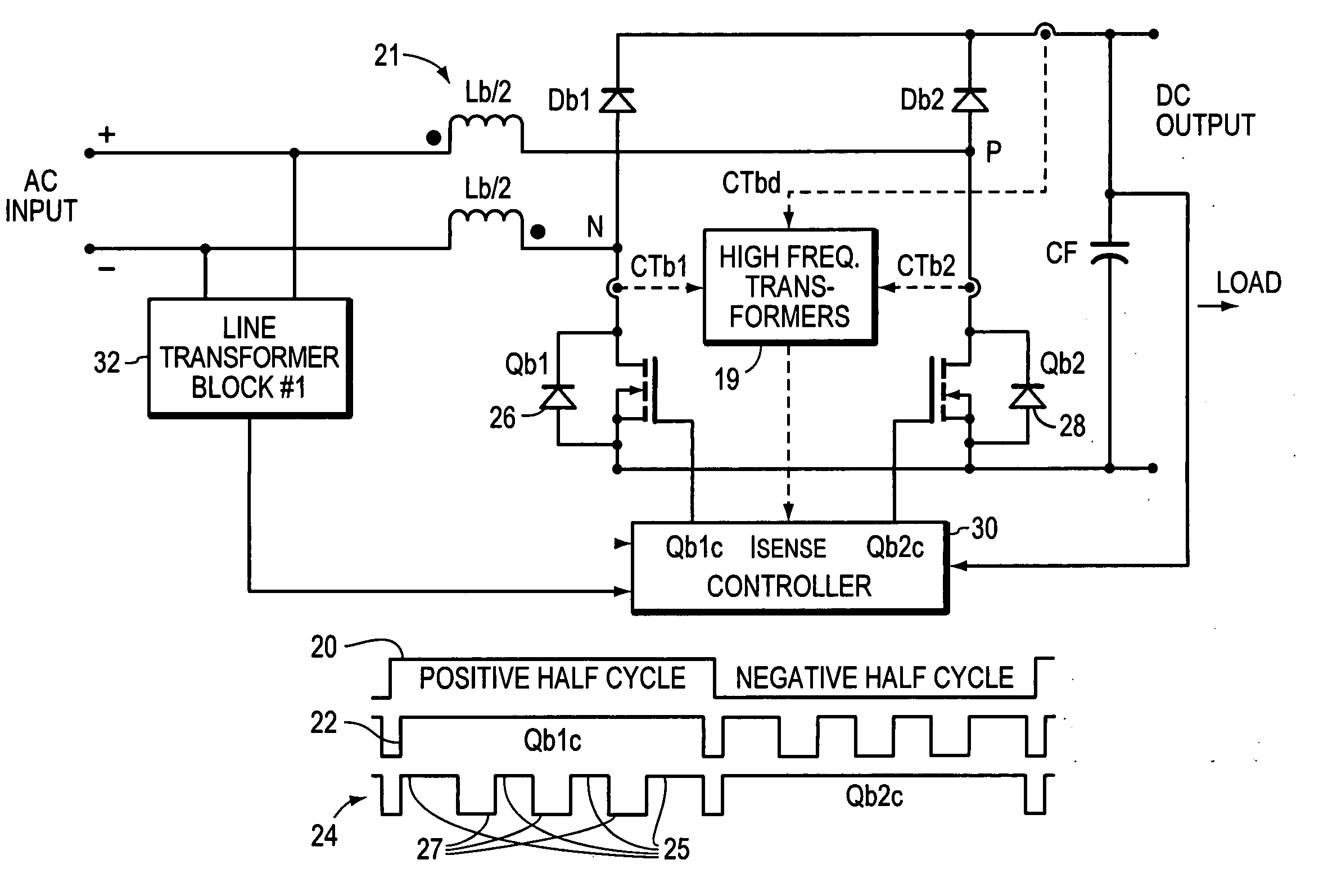

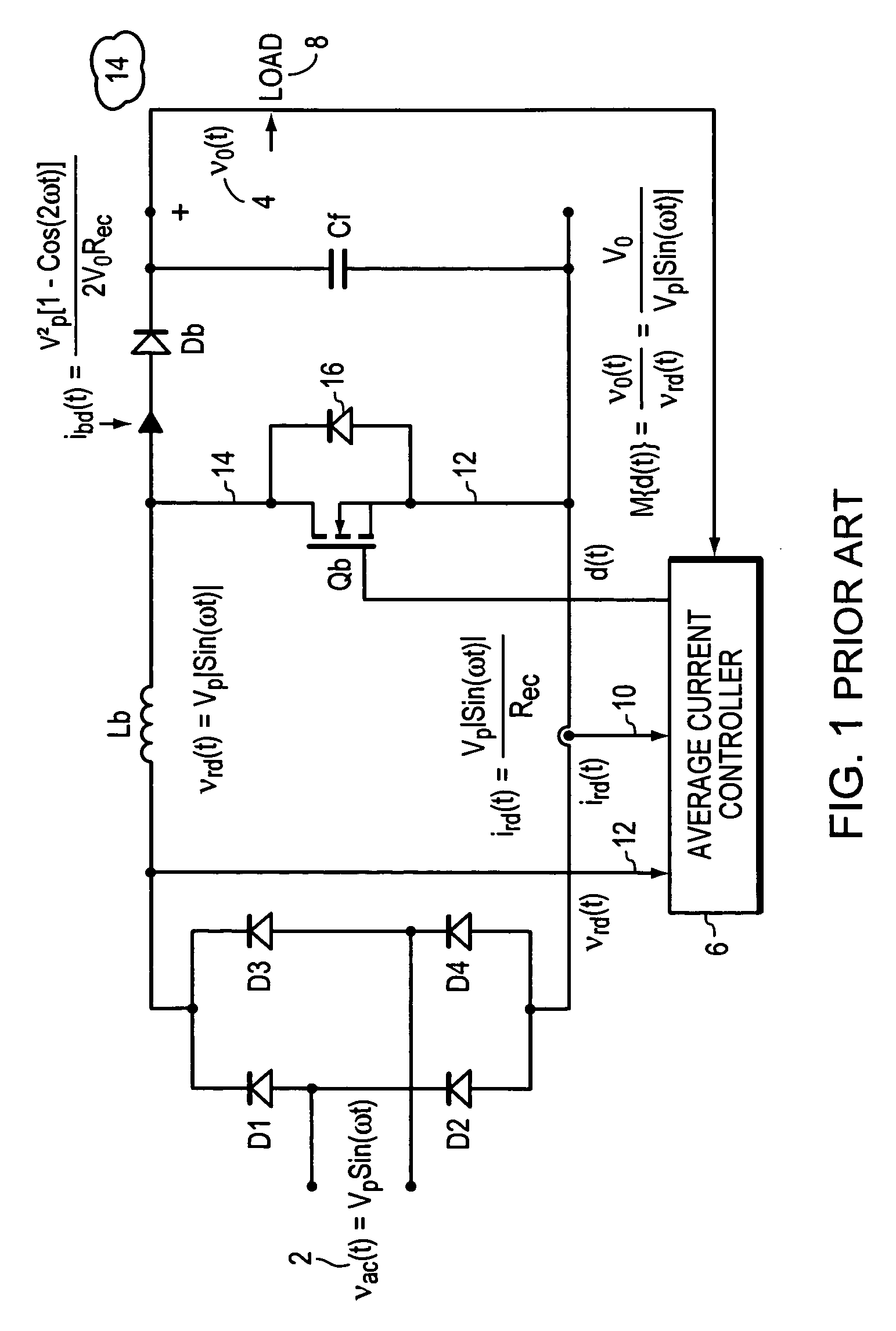

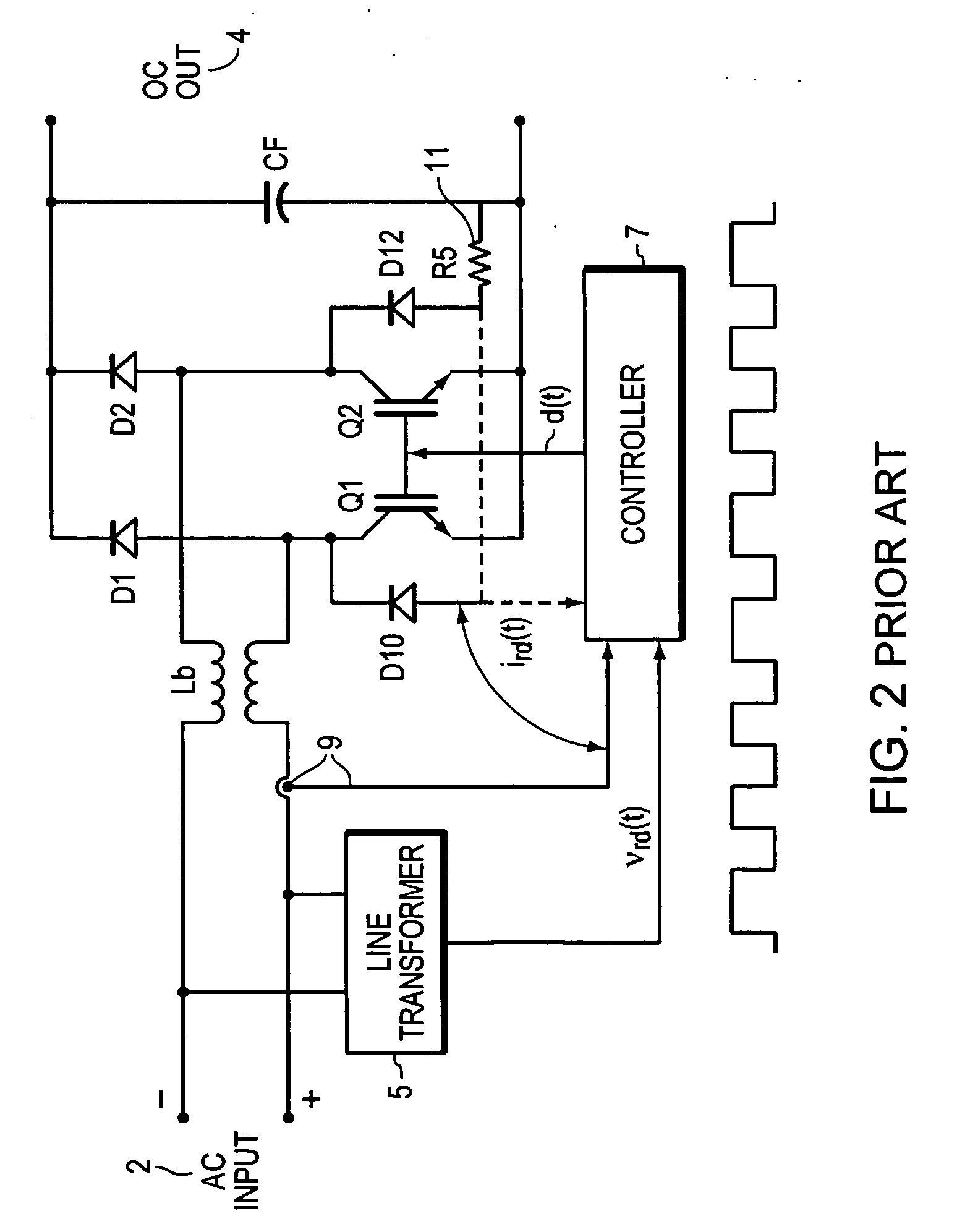

Vrms and rectified current sense full-bridge synchronous-rectification integrated with PFC

ActiveUS7269038B2Ac-dc conversion without reversalEfficient power electronics conversionMOSFETFull bridge

A synchronous full bridge rectifier is controlled to provide a power factor near unity. The full bridge rectifiers are transistors each with a controlling input. The AC input signal and currents within the circuit are sensed and sent to a controller. In response, the controller output control signals to turn on / off the rectifying MOSFETS on a timely basis to form a power factor of near one with respect to the AC input signal. The full wave rectifier is made of N-channel MOSFET's, some with fast body diodes. The MOSFET's are rectifiers and PFC control elements. The result is a one stage synchronous rectifier with PFC. A solid state precision analog differential amplifier senses the AC line waveform and high frequency current transformers sense the currents. The controller accepts the inputs of the amplifier and the sensed currents and outputs control signals that turn on and off the four MOSFET's. The timing of turning on / off is arranged so that the current drawn from the AC source is sinusoidal and matches the phase of the sinusoidal AC source.

Owner:SEMICON COMPONENTS IND LLC

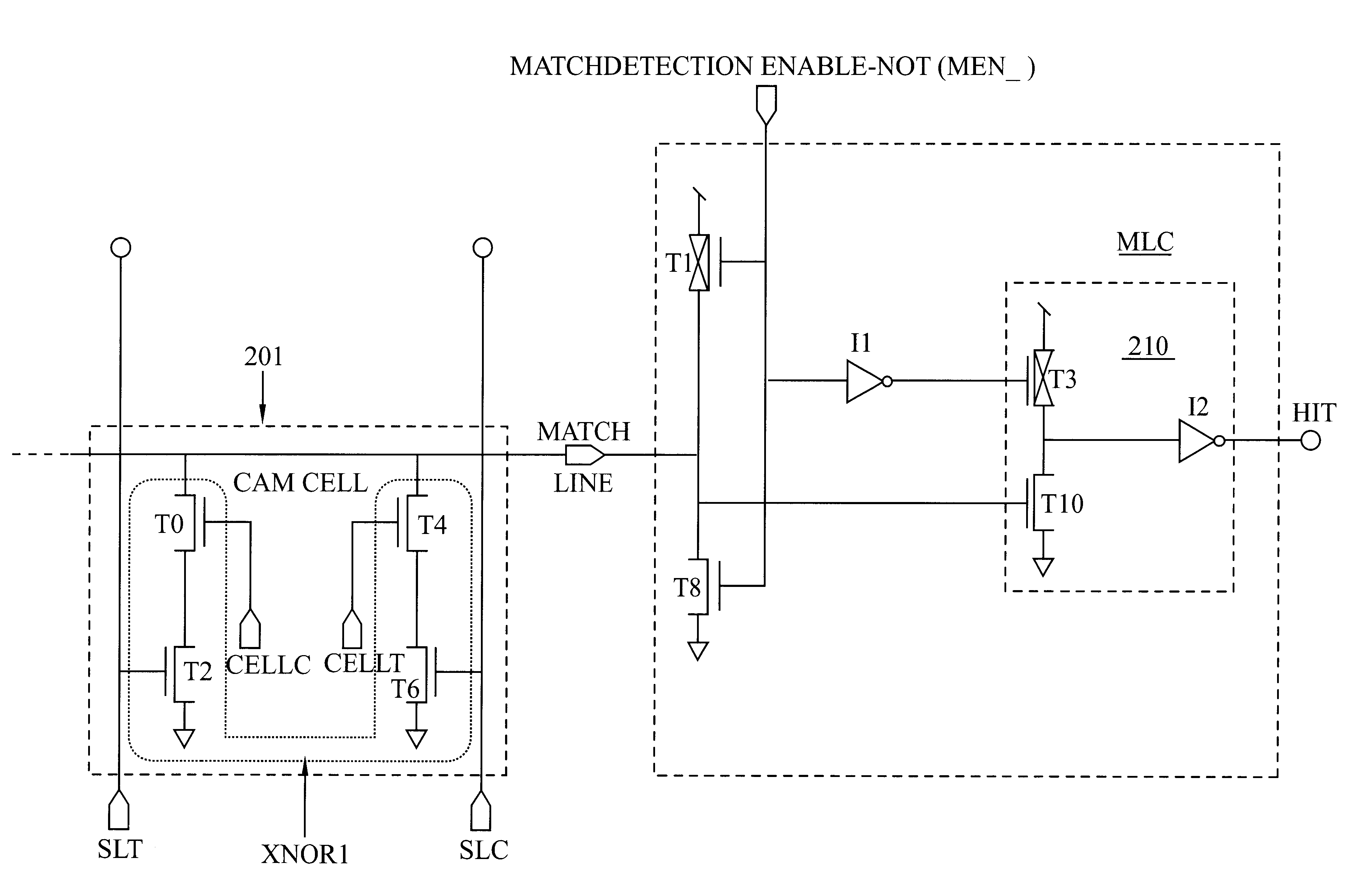

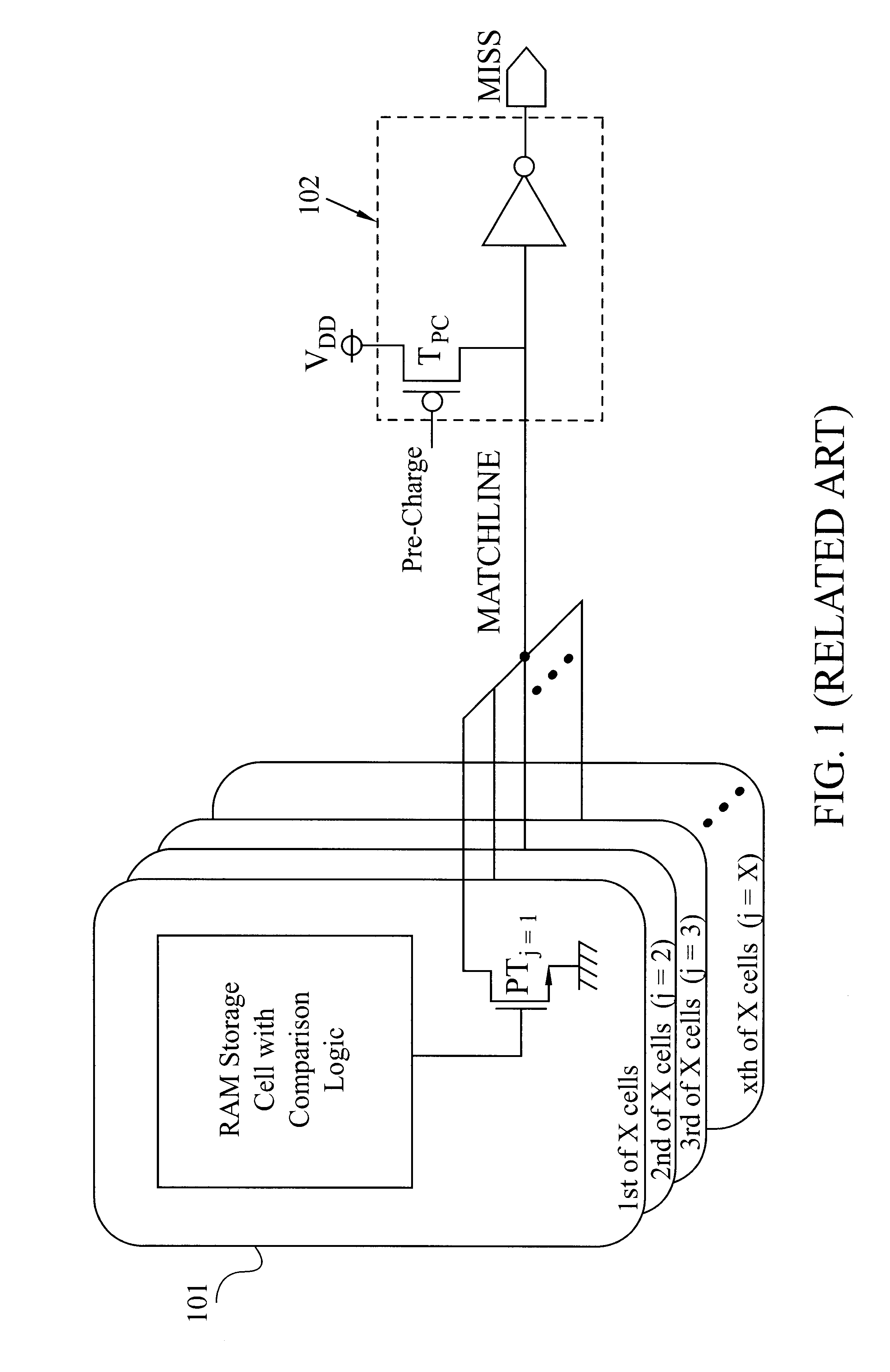

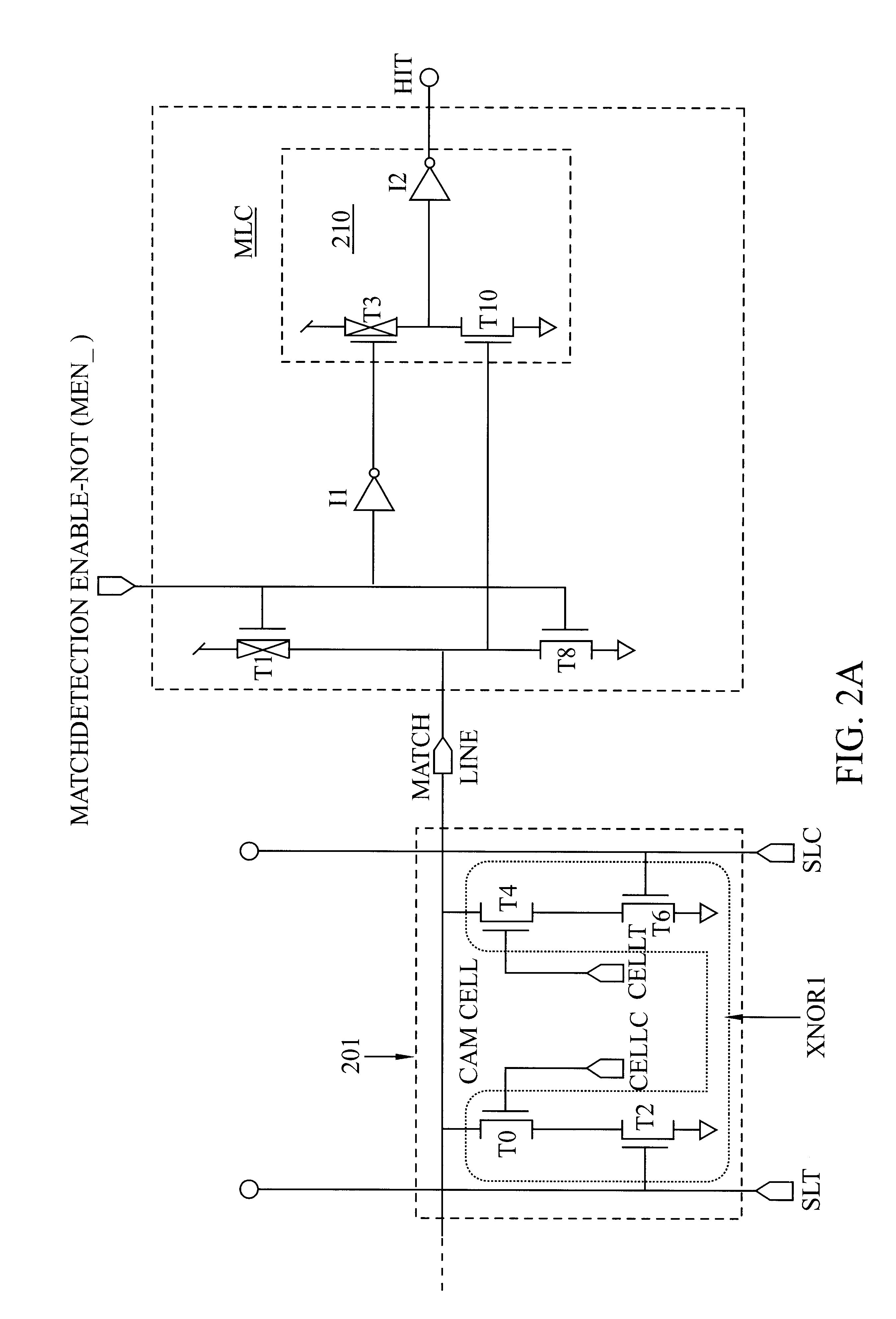

Low power CAM match line circuit

A Match-Detection Circuit and Match-Detection method, for low-power-consuming searches in a Content Addressable Memory. A HIT is output when the Match Line rises from a Low voltage level to a higher Match Detection Voltage. The Match Detection Voltage is approximately the conducting threshold voltage of an N-channel Field Effect Transistor (FET), and is normally less than One Half of the Power Supply Voltage. Circuits and methods to turn of the through-current in each MISS-ing entry by a carefully timed control signal at the end of a brief Match Detection Period, are disclosed.

Owner:IBM CORP

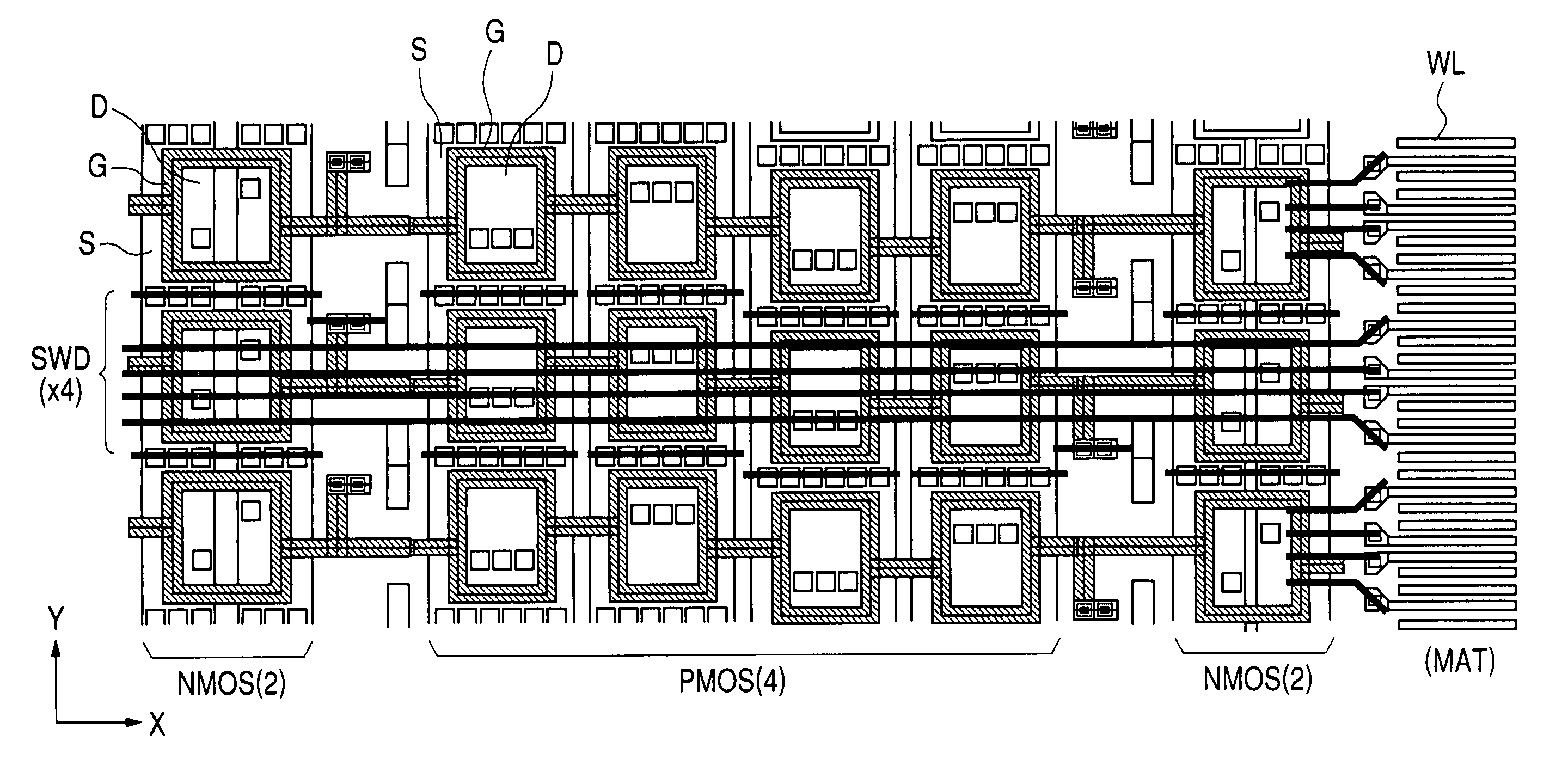

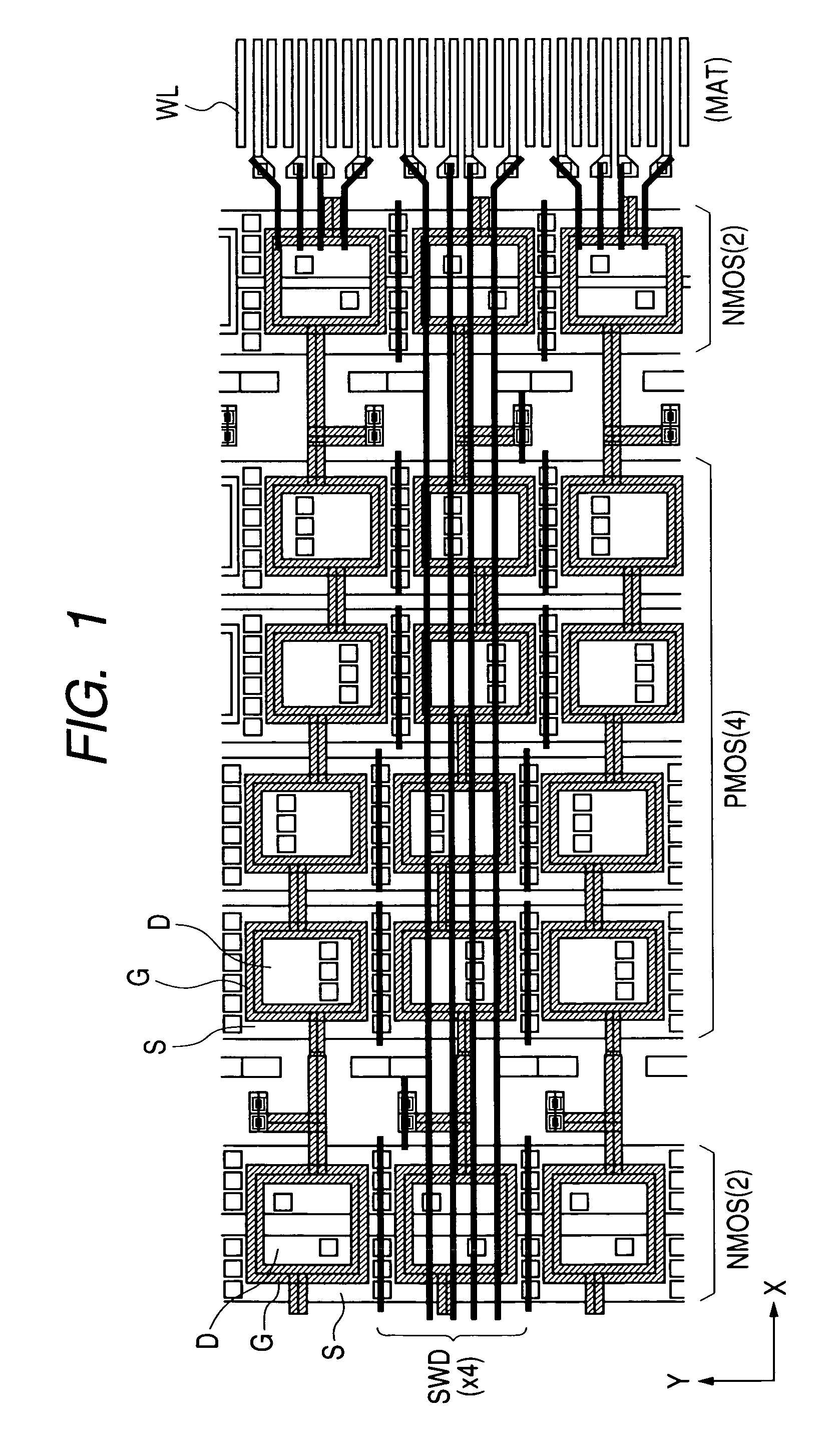

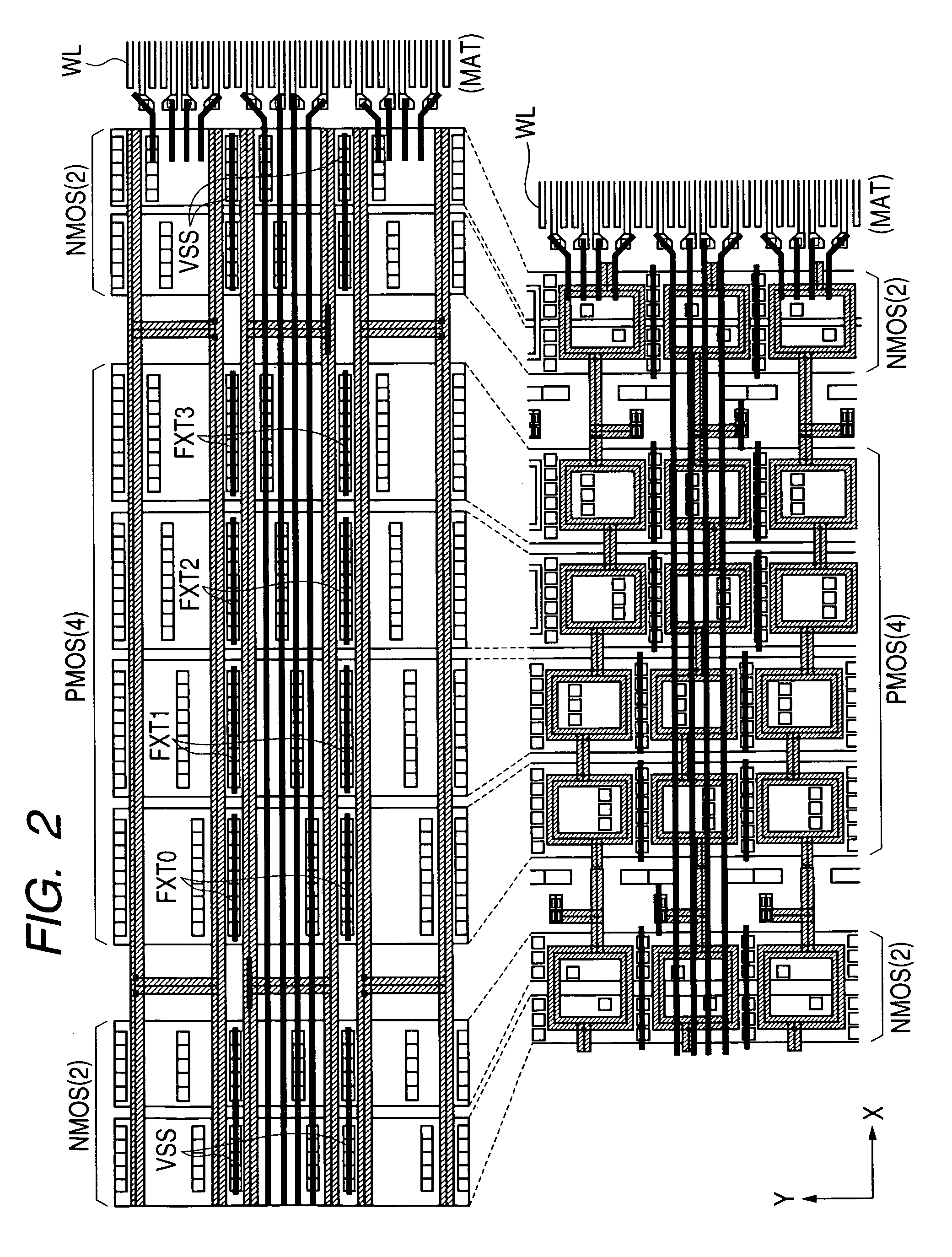

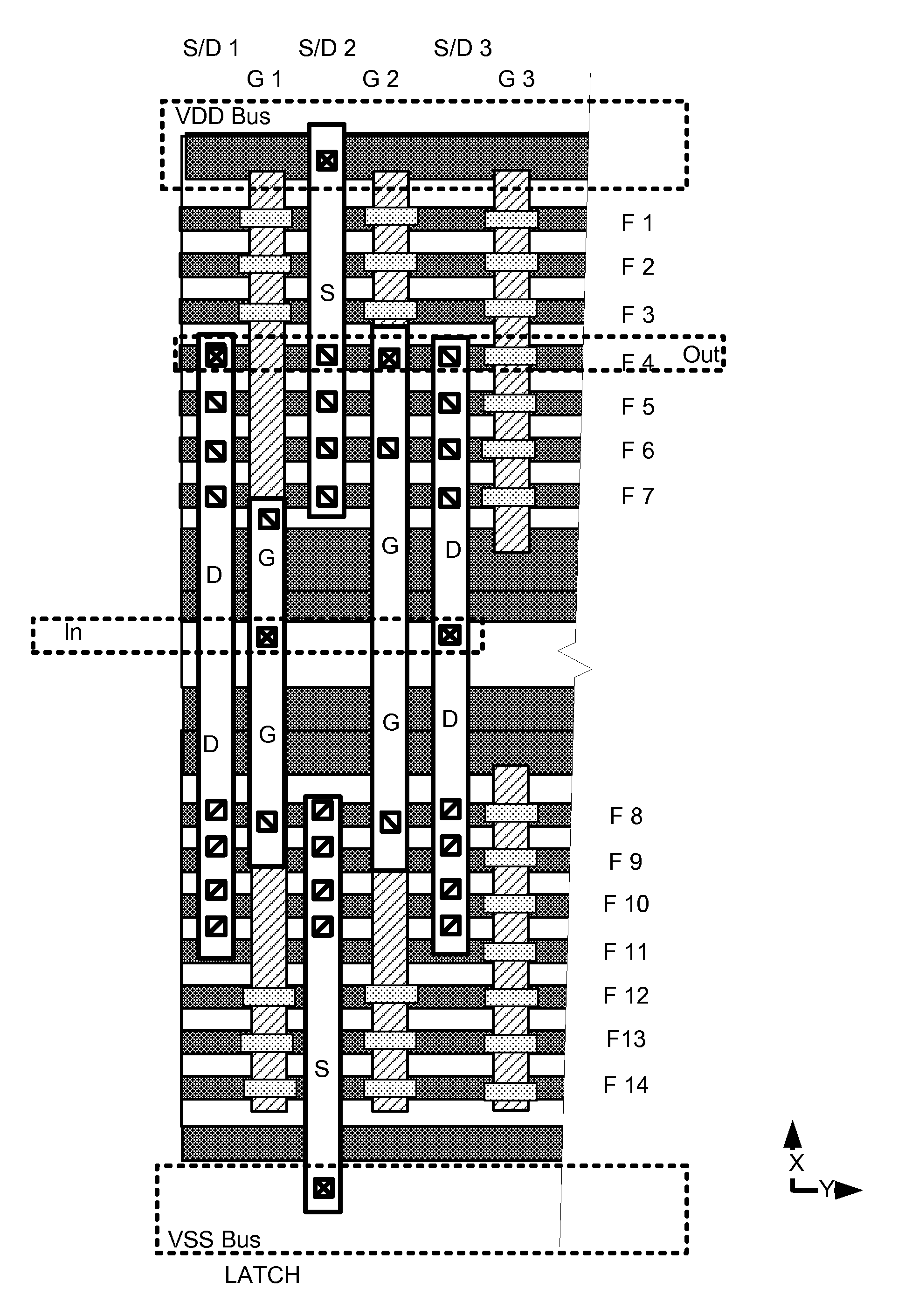

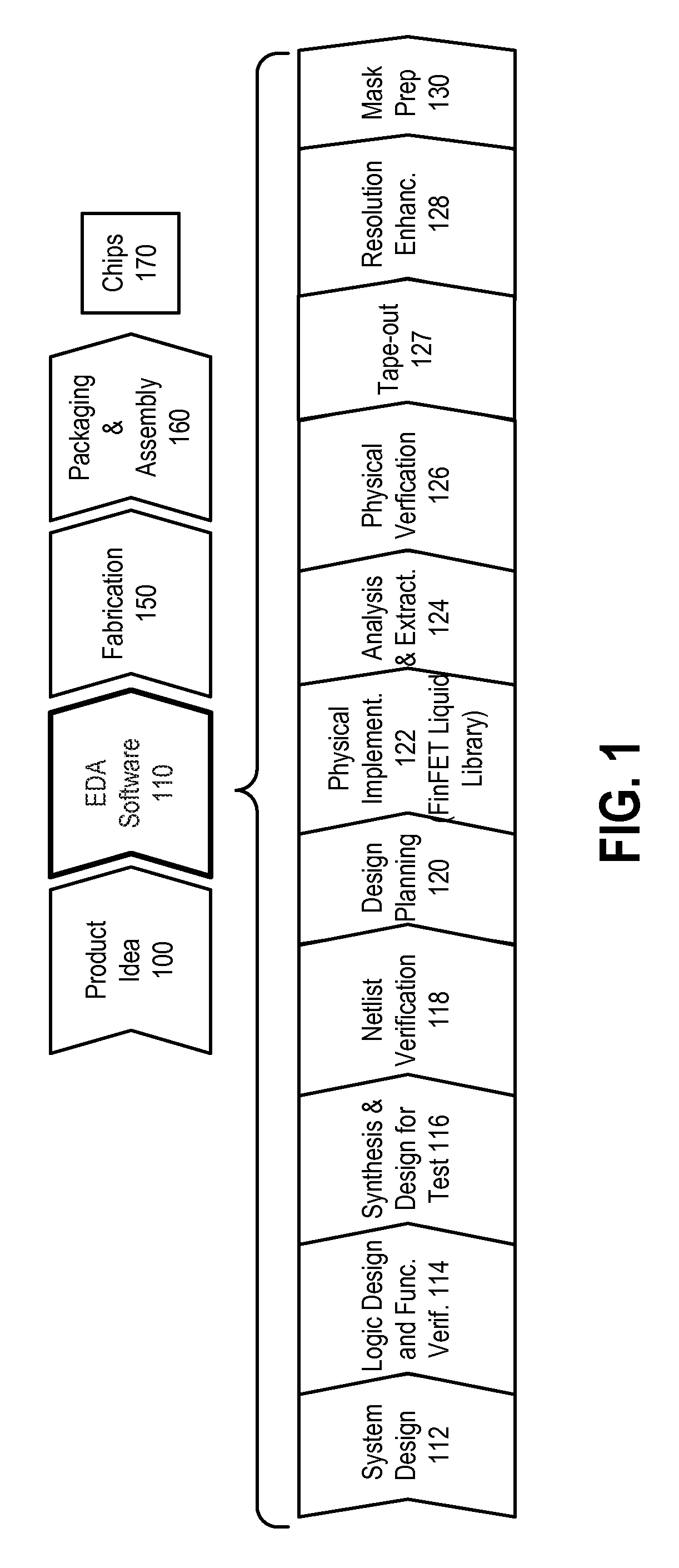

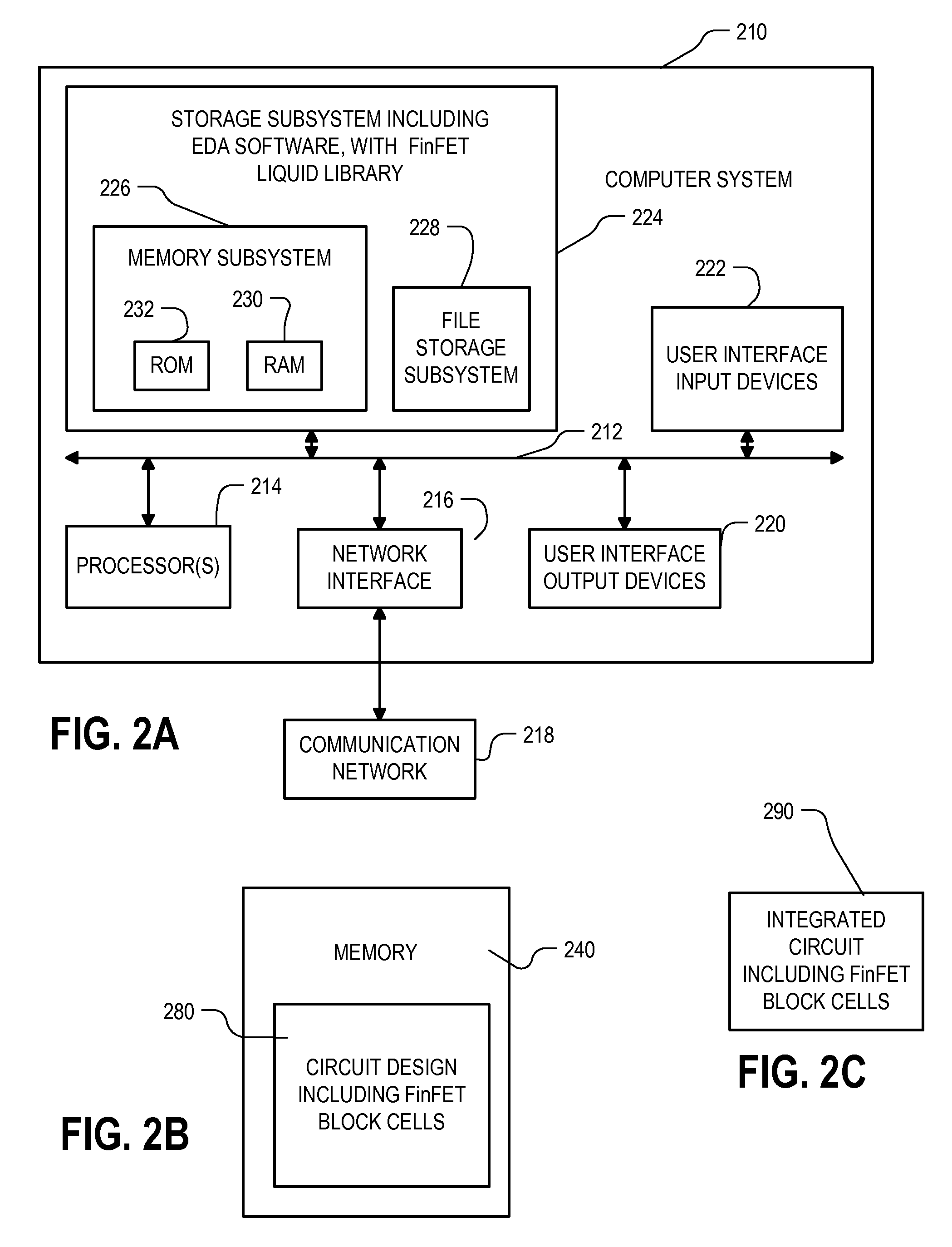

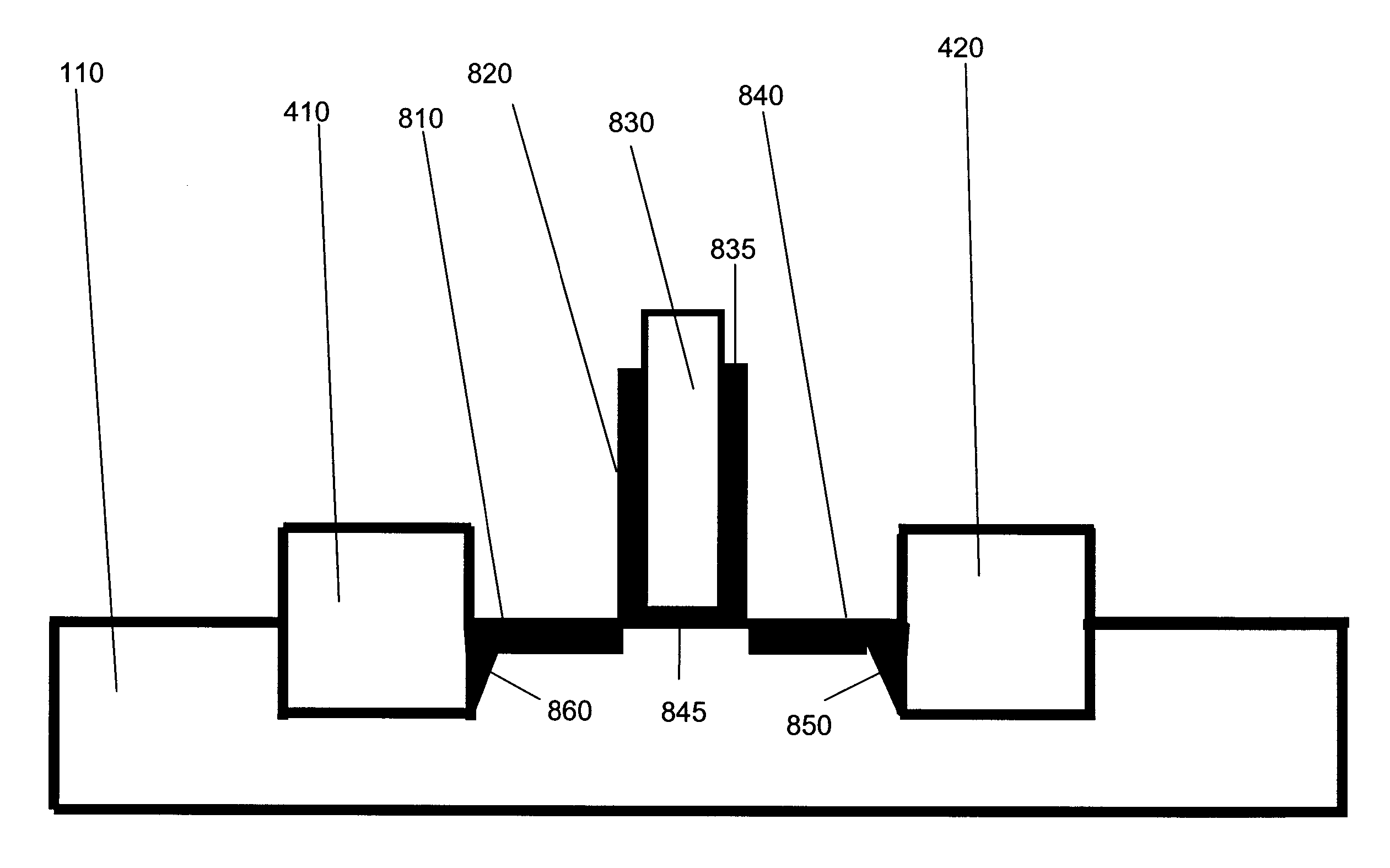

N-channel and p-channel finfet cell architecture

ActiveUS20130026572A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorP channel

A finFET block architecture suitable for use of a standard cell library, is based on an arrangement including a first set of semiconductor fins in a first region of the substrate having a first conductivity type, and a second set of semiconductor fins in a second region of the substrate, the second region having a second conductivity type. A patterned gate conductor layer including gate traces in the first and second regions, arranged over channel regions of the first and second sets of semiconductor fins is used for transistor gates. Patterned conductor layers over the gate conductor layer are arranged in orthogonal layout patterns, and can include a plurality of floating power buses over the fins in the first and second regions.

Owner:SYNOPSYS INC

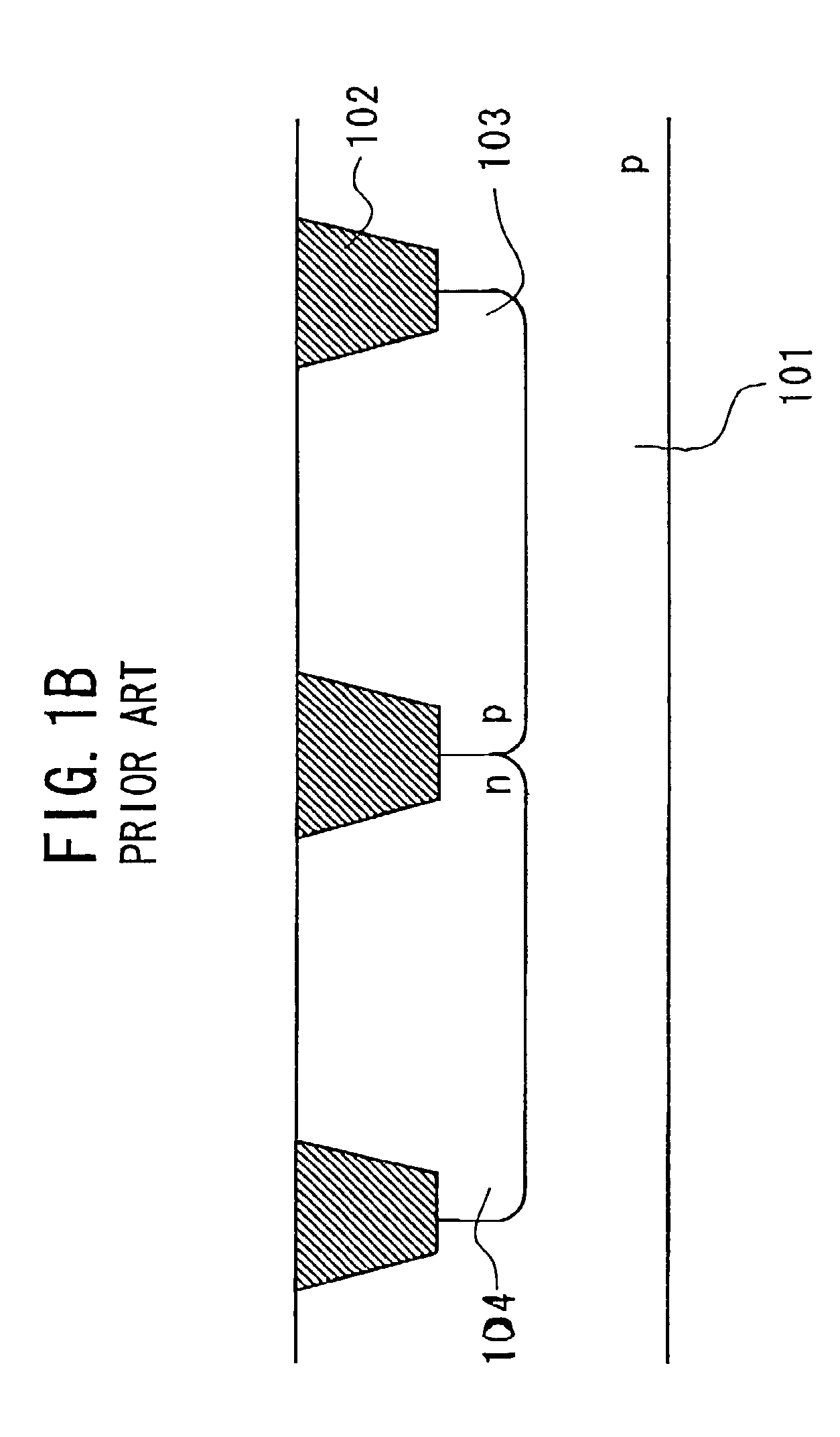

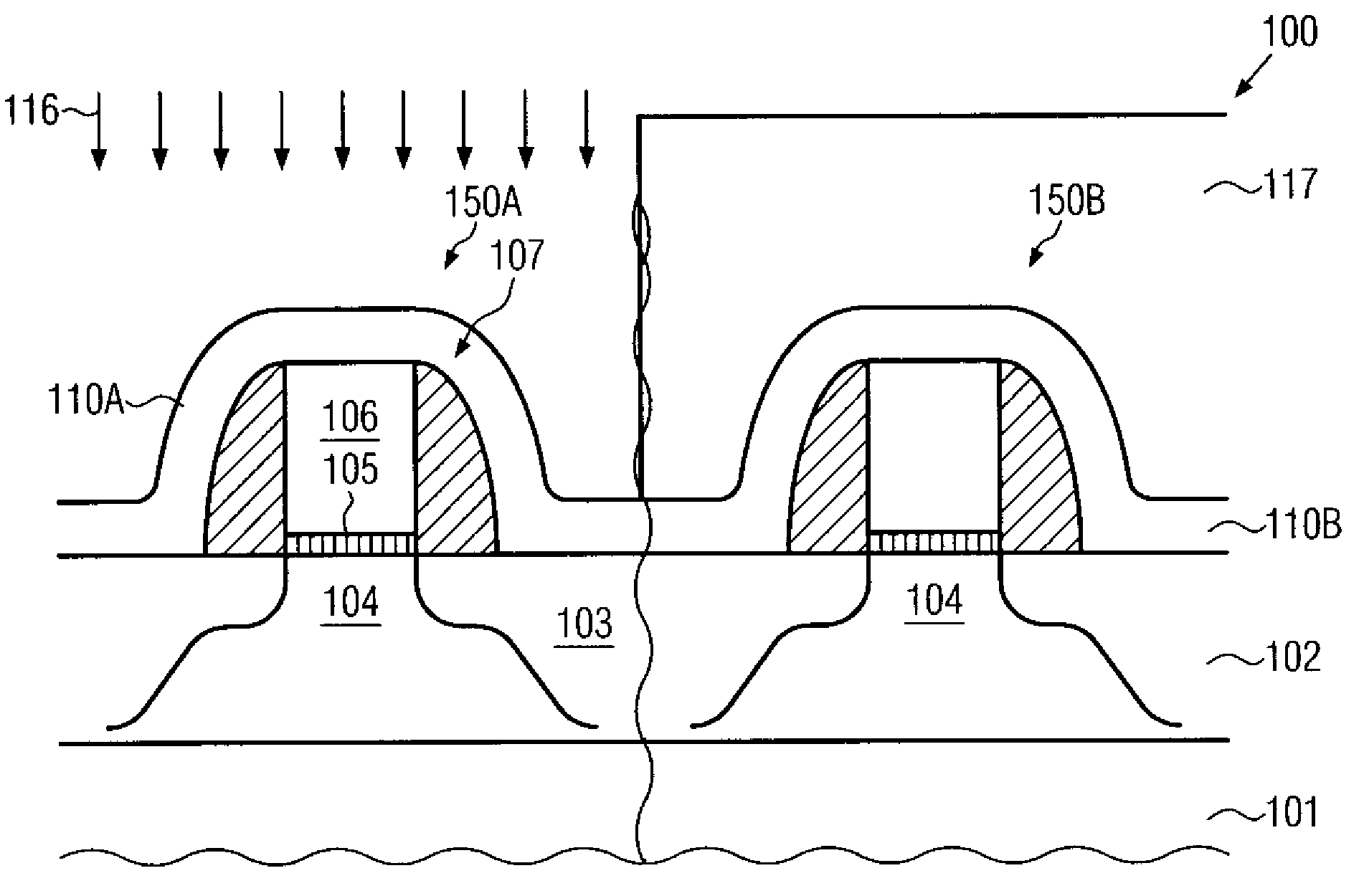

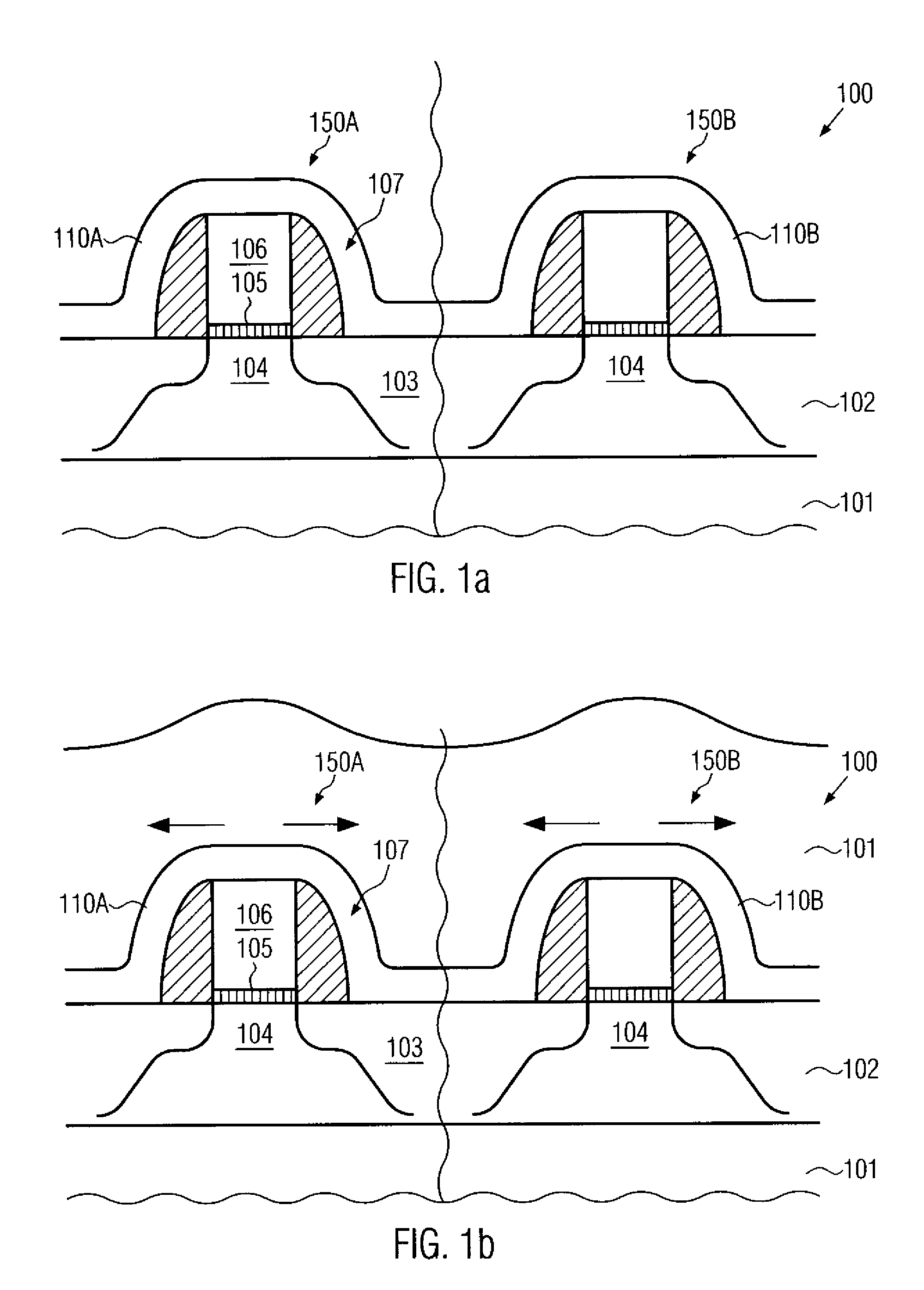

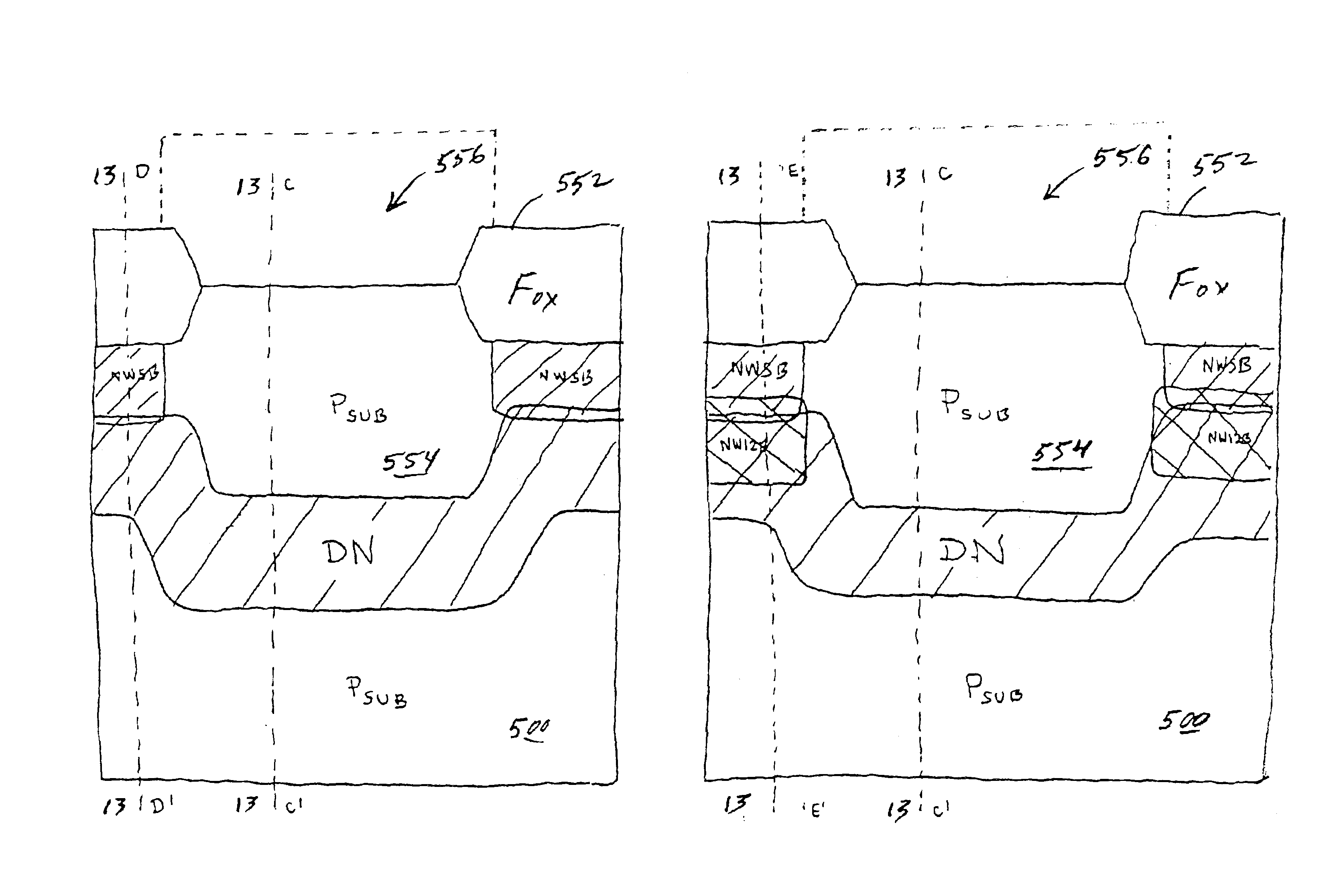

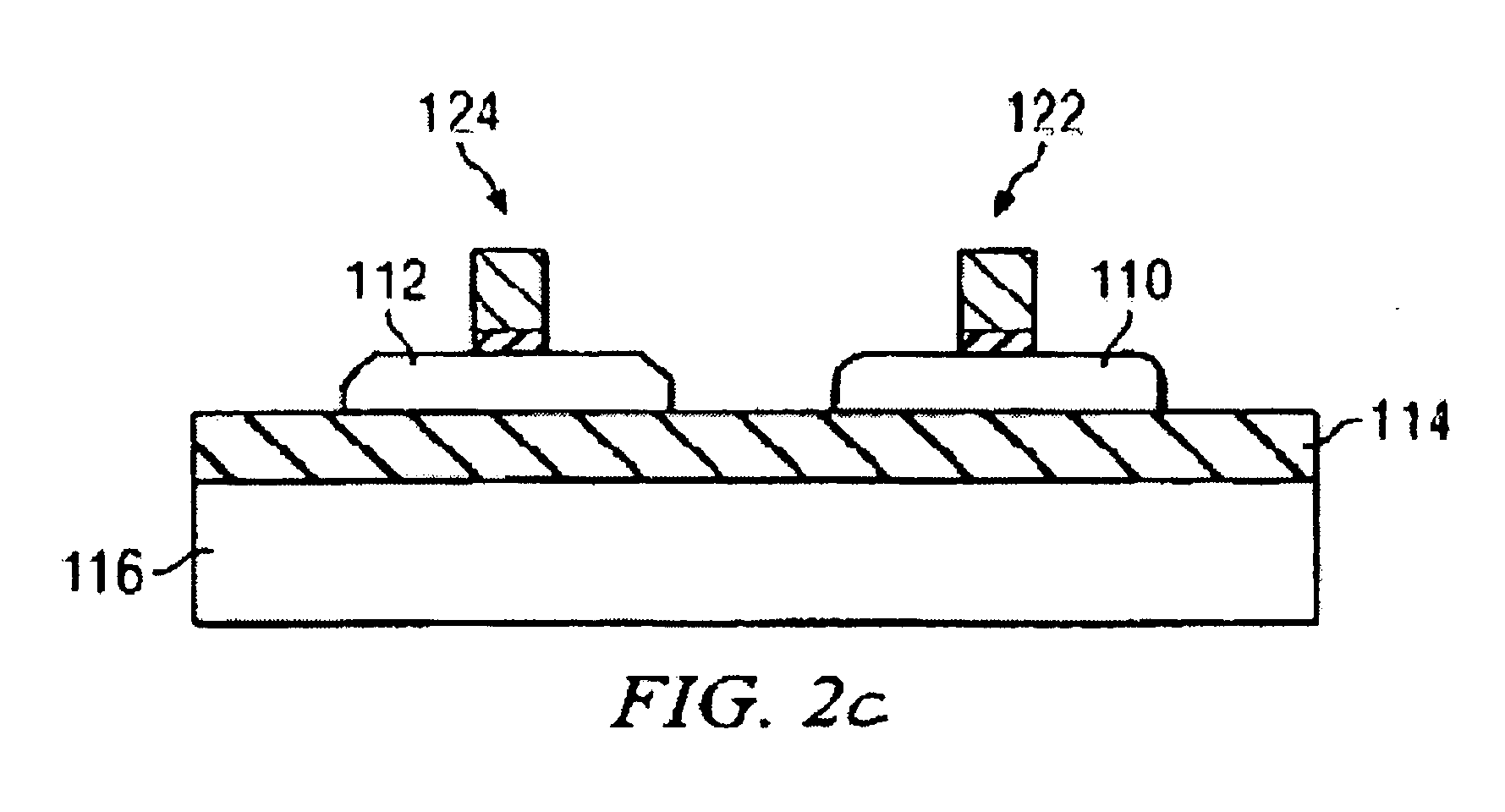

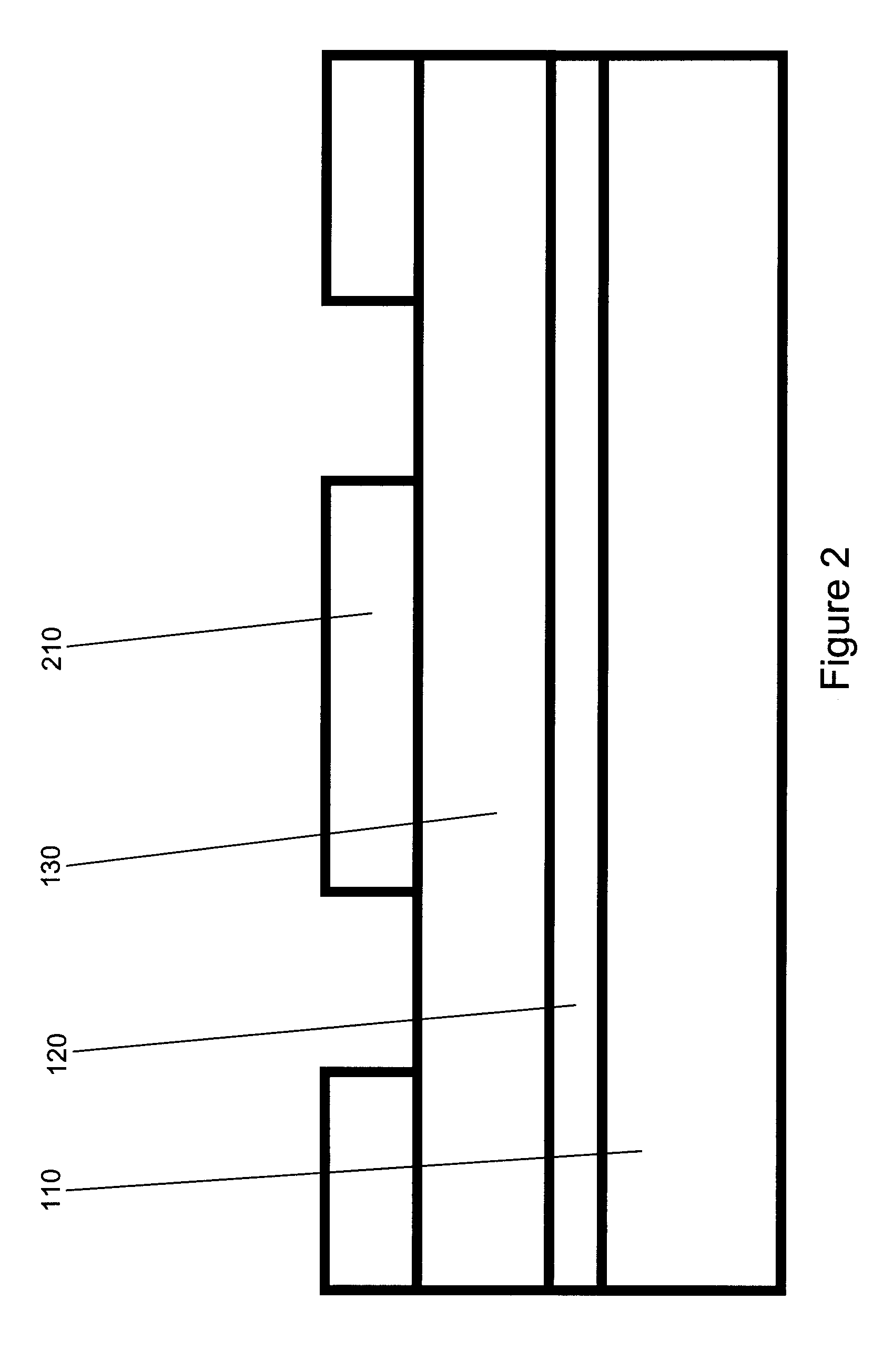

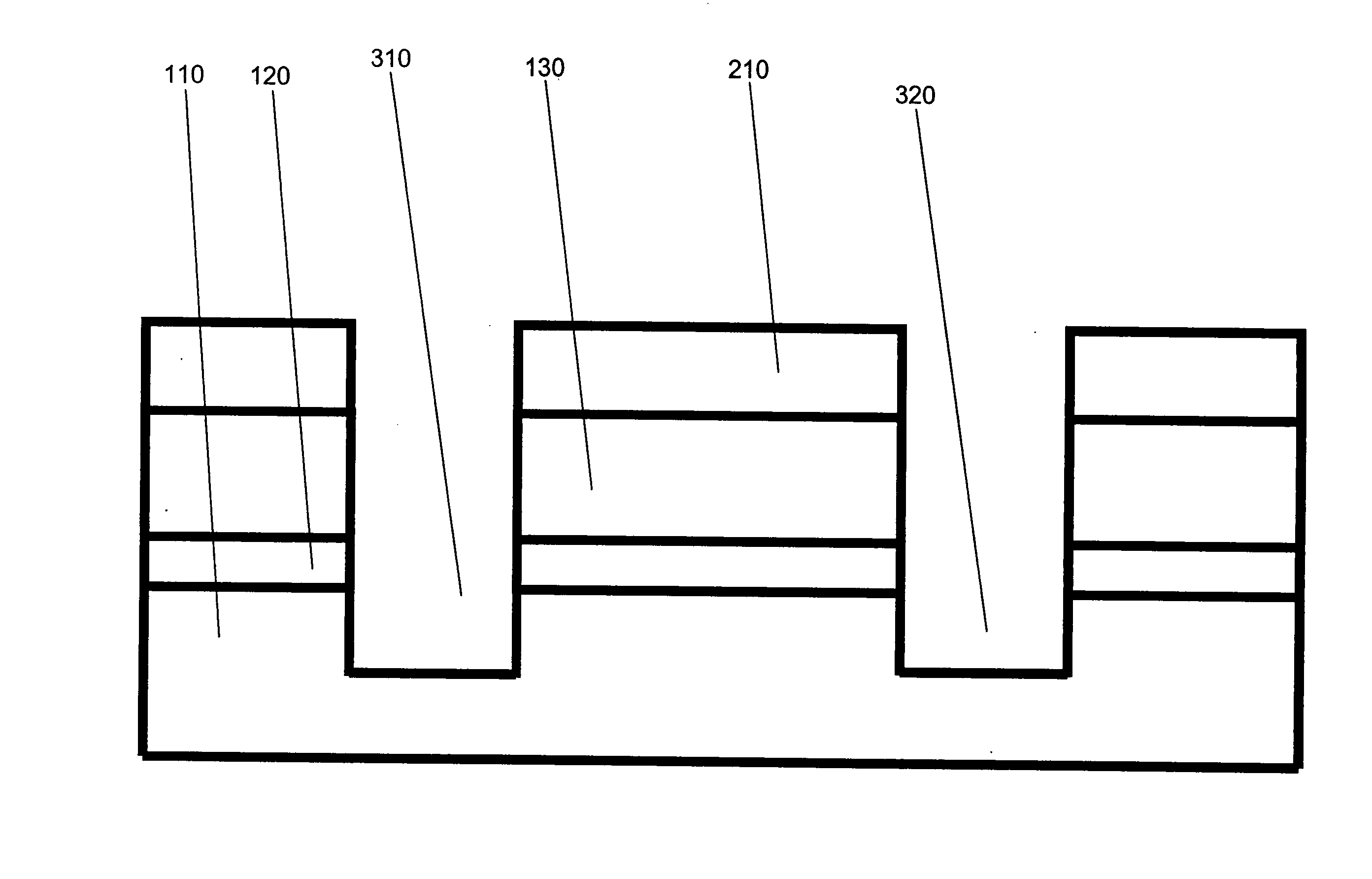

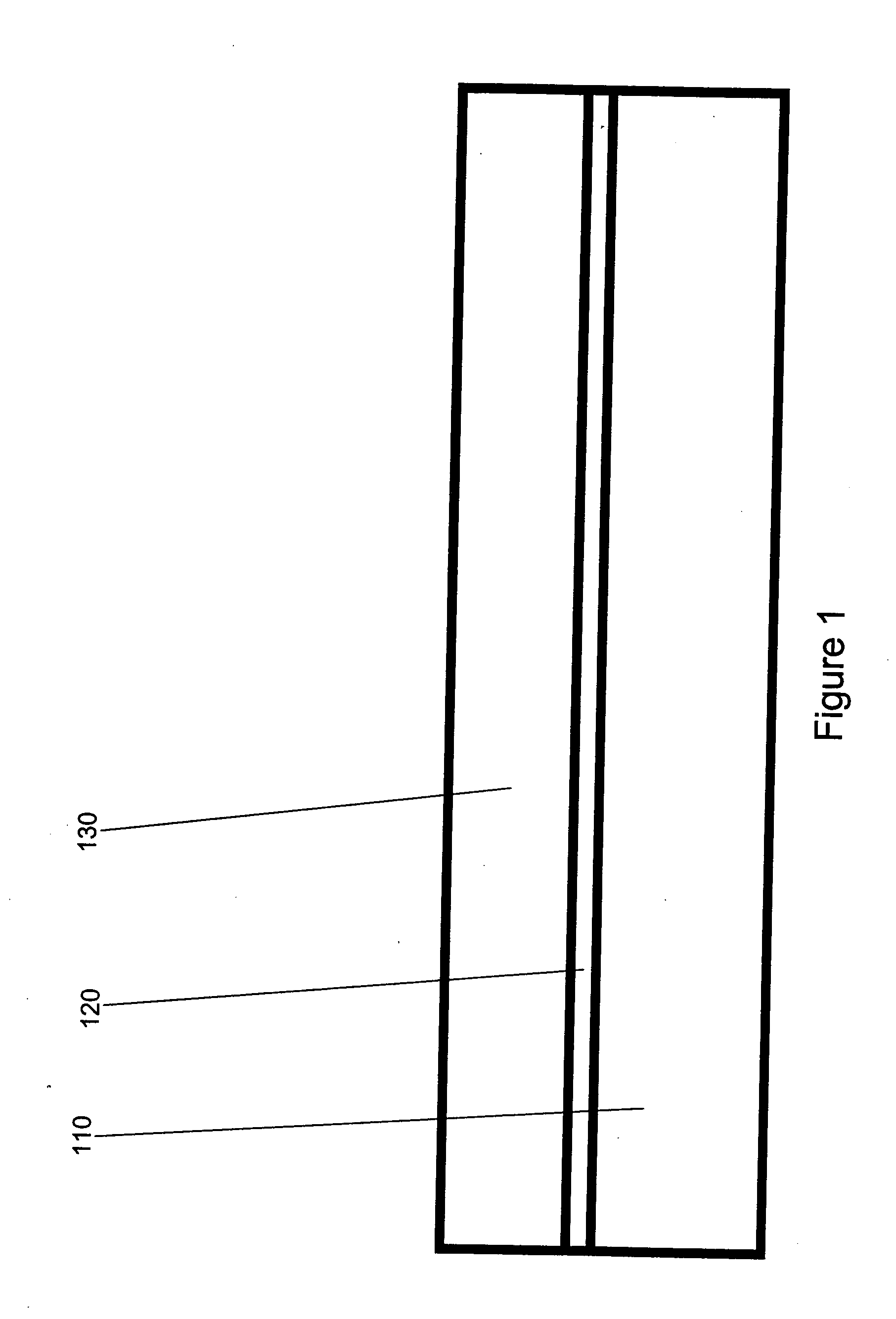

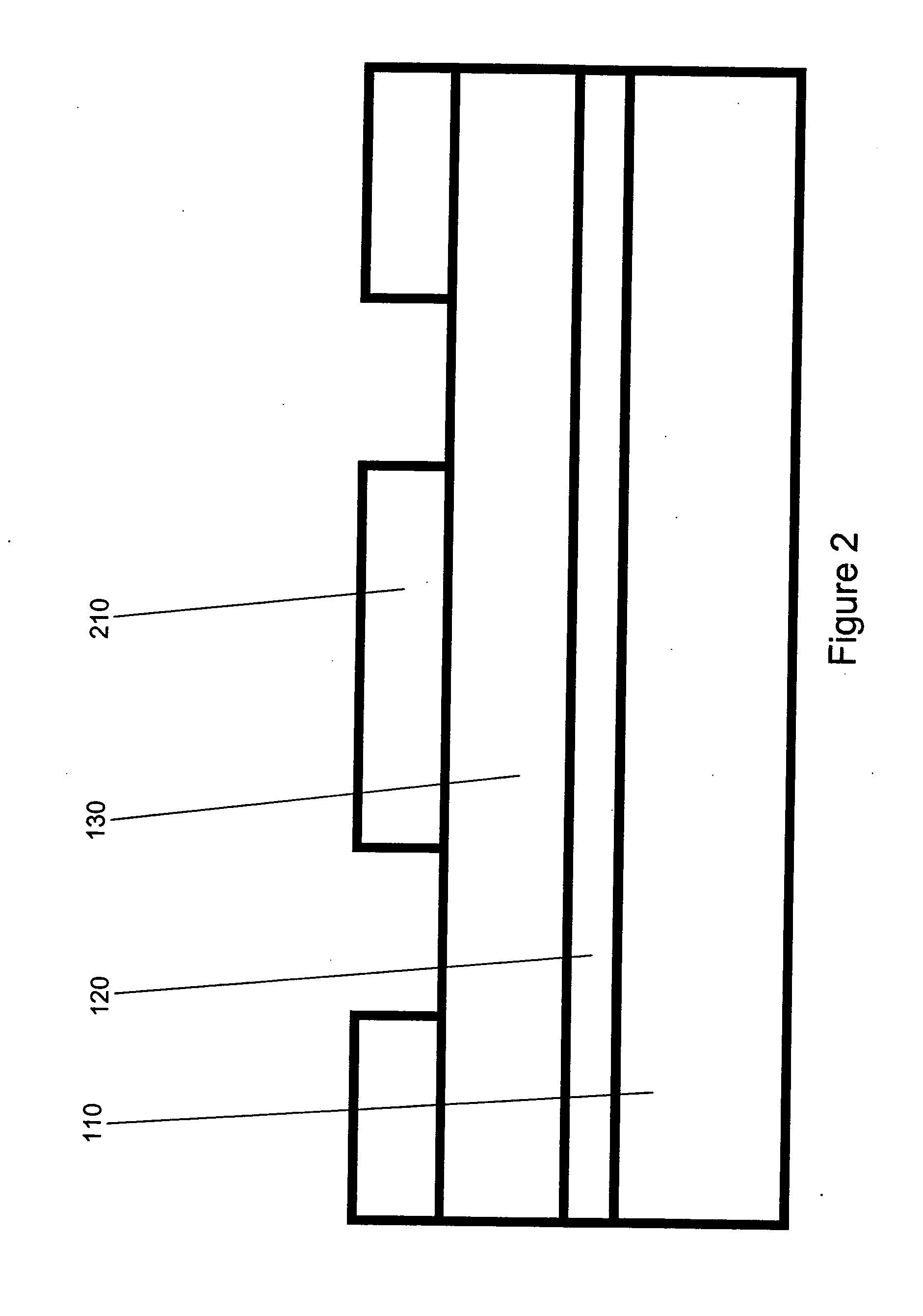

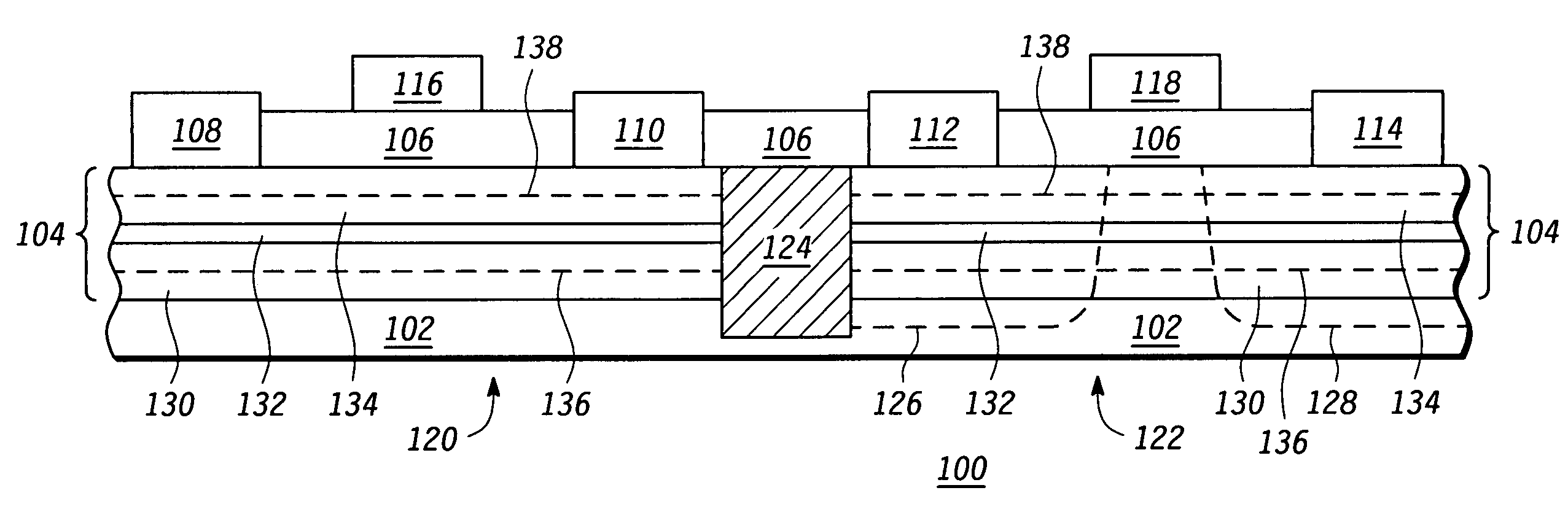

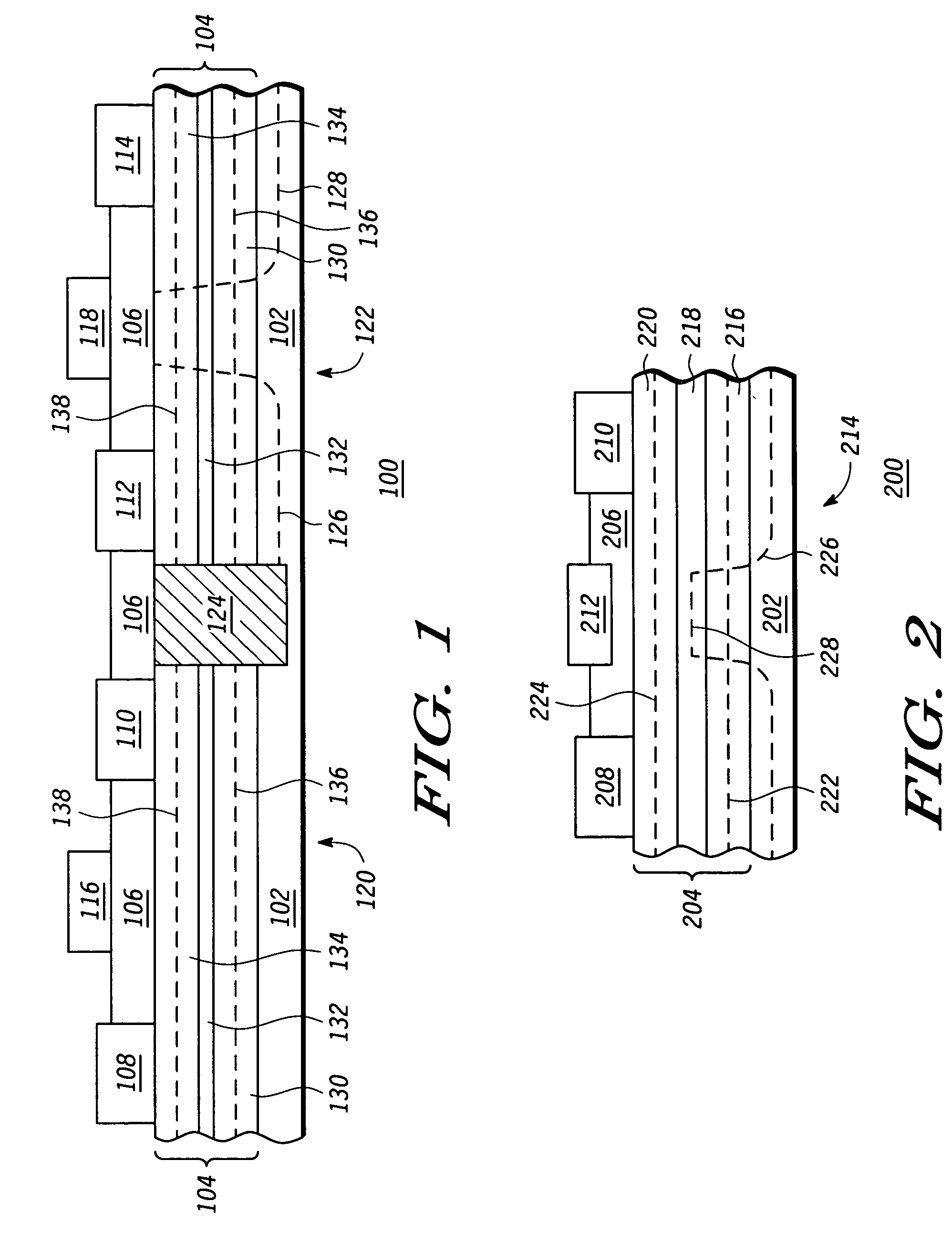

High performance strained CMOS devices

ActiveUS20050082634A1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSN channel

A semiconductor device and method of manufacture provide an n-channel field effect transistor (nFET) having a shallow trench isolation with overhangs that overhang Si-SiO2 interfaces in a direction parallel to the direction of current flow and in a direction transverse to current flow. The device and method also provide a p-channel field effect transistor (pFET) having a shallow trench isolation with an overhang that overhangs Si-SiO2 interfaces in a direction transverse to current flow. However, the shallow trench isolation for the pFET is devoid of overhangs, in the direction parallel to the direction of current flow.

Owner:GLOBALFOUNDRIES US INC

High performance strained CMOS devices

InactiveUS20050148146A1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

A semiconductor device and method of manufacture provide an n-channel field effect transistor (nFET) having a shallow trench isolation with overhangs that overhang Si—SiO2 interfaces in a direction parallel to the direction of current flow and in a direction transverse to current flow. The device and method also provide a p-channel field effect transistor (pFET) having a shallow trench isolation with an overhang that overhangs Si—SiO2 interfaces in a direction transverse to current flow. However, the shallow trench isolation for the pFET is devoid of overhangs, in the direction parallel to the direction of current flow.

Owner:GLOBALFOUNDRIES INC

Vrms and rectified current sense full-bridge synchronous-rectification integrated with PFC

ActiveUS20070058402A1Ac-dc conversion without reversalEfficient power electronics conversionMOSFETPower factor

A synchronous full bridge rectifier is controlled to provide a power factor near unity. The full bridge rectifiers are transistors each with a controlling input. The AC input signal and currents within the circuit are sensed and sent to a controller. In response, the controller output control signals to turn on / off the rectifying MOSFETS on a timely basis to form a power factor of near one with respect to the AC input signal. The full wave rectifier is made of N-channel MOSFET's, some with fast body diodes. The MOSFET's are rectifiers and PFC control elements. The result is a one stage synchronous rectifier with PFC. A solid state precision analog differential amplifier senses the AC line waveform and high frequency current transformers sense the currents. The controller accepts the inputs of the amplifier and the sensed currents and outputs control signals that turn on and off the four MOSFET's. The timing of turning on / off is arranged so that the current drawn from the AC source is sinusoidal and matches the phase of the sinusoidal AC source.

Owner:SEMICON COMPONENTS IND LLC

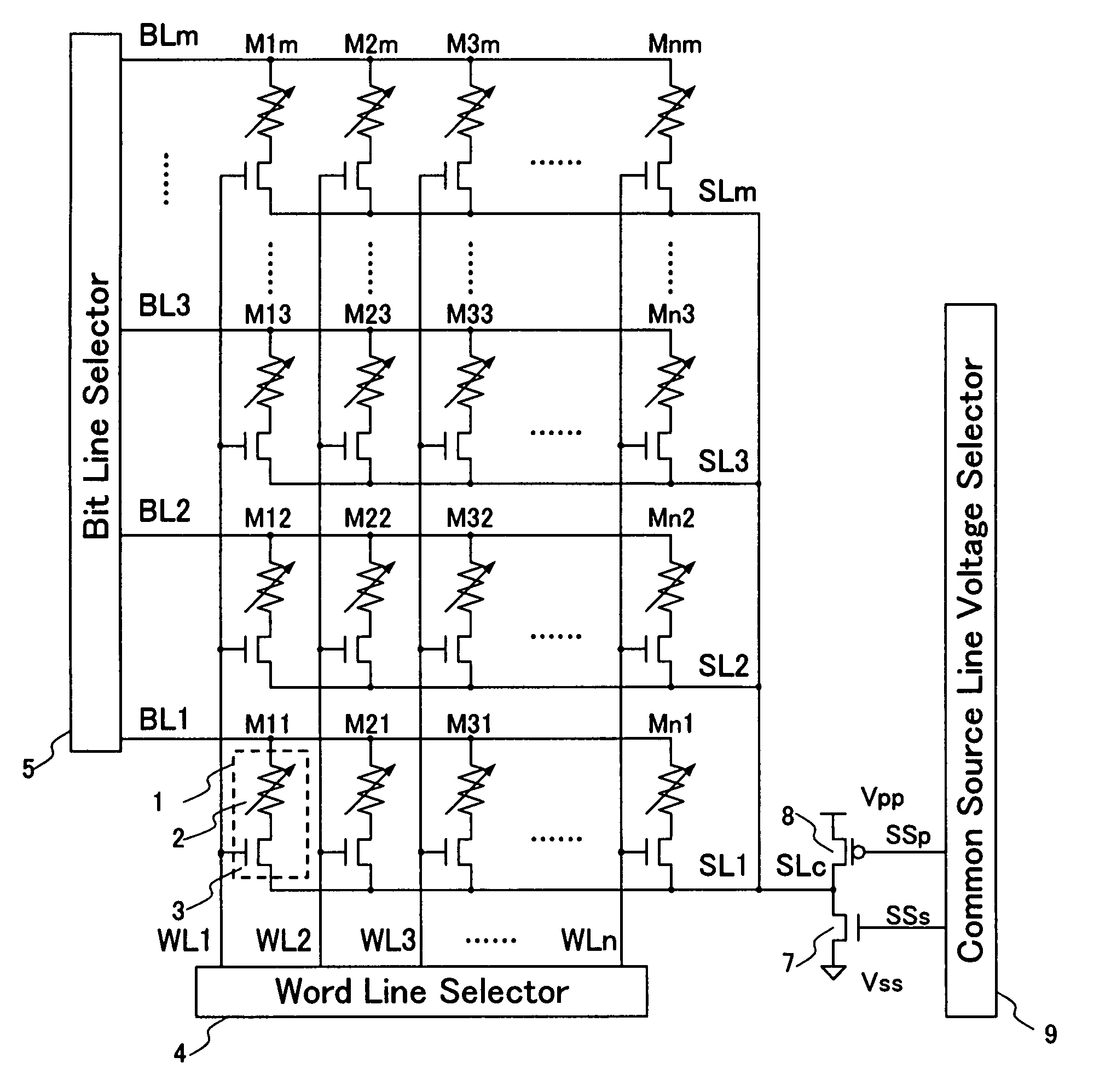

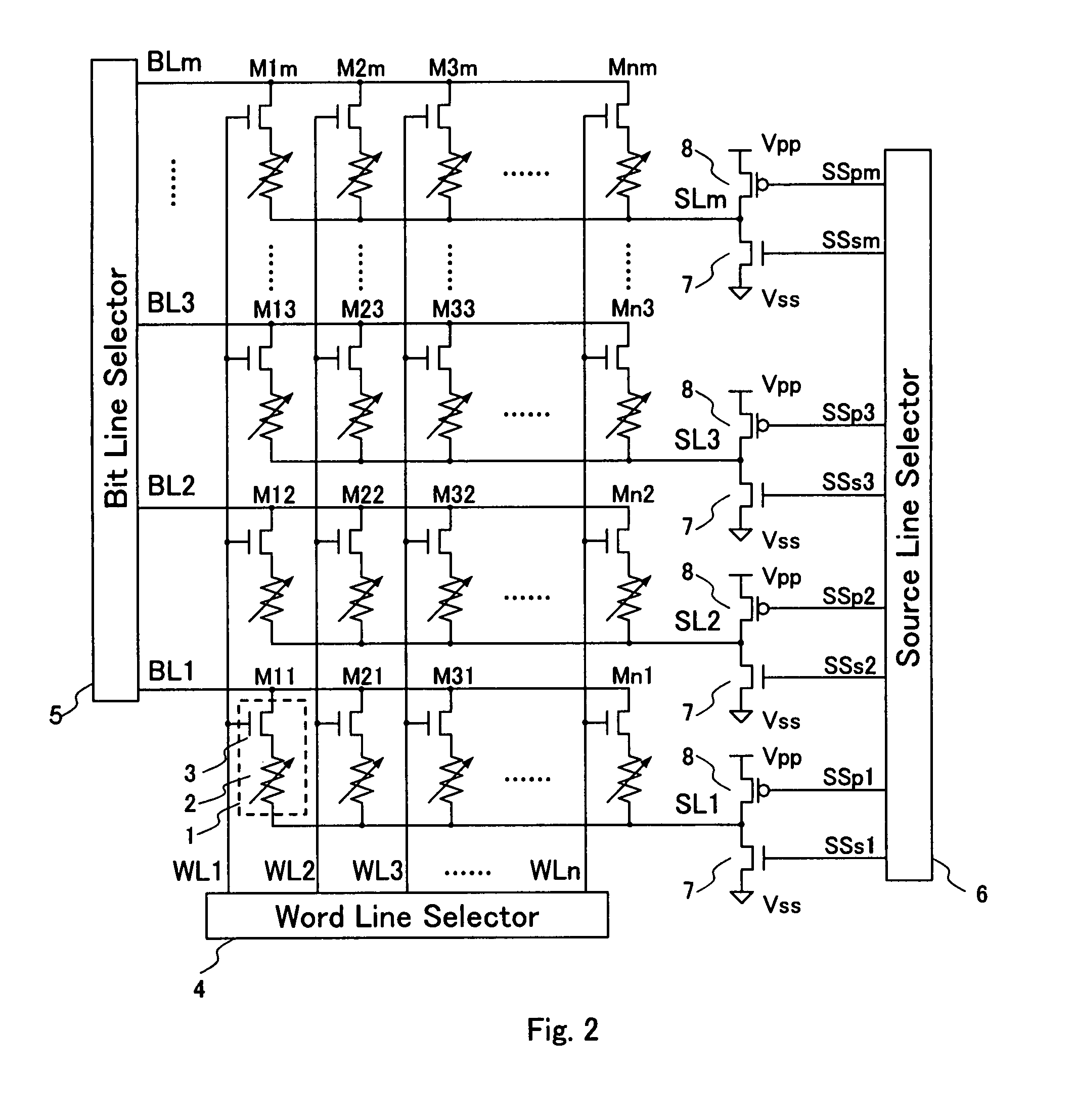

Semiconductor memory device

A semiconductor memory device comprises an array of memory cells each comprising a variable resistance element and a cell access transistor, and a voltage supplying means for applying the first voltage between the bit and source lines connected to the selected memory cell, the third voltage to the word line to apply the first write voltage between the two ports of the variable resistance element for shifting the resistance from the first state to the second state, and the second voltage opposite in polarity to the first voltage between the bit and source lines, the third voltage to the word line to apply the second write voltage opposite in polarity to and different in the absolute value from the first write voltage between the two ports for shifting the resistance from the second state to the first state, the voltage supplying means comprising an n-channel MOSFET and a p-channel MOSFET.

Owner:SAMSUNG ELECTRONICS CO LTD

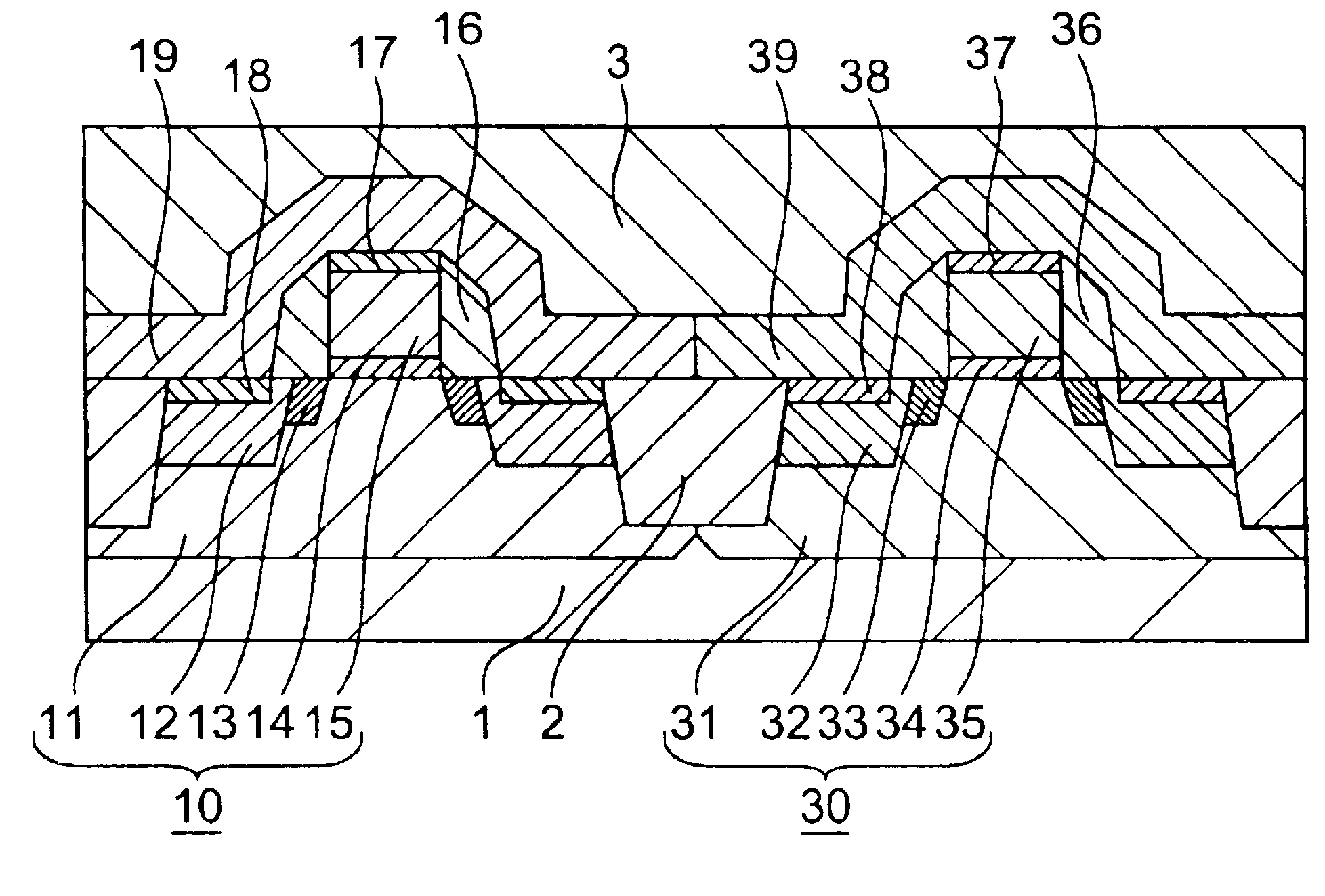

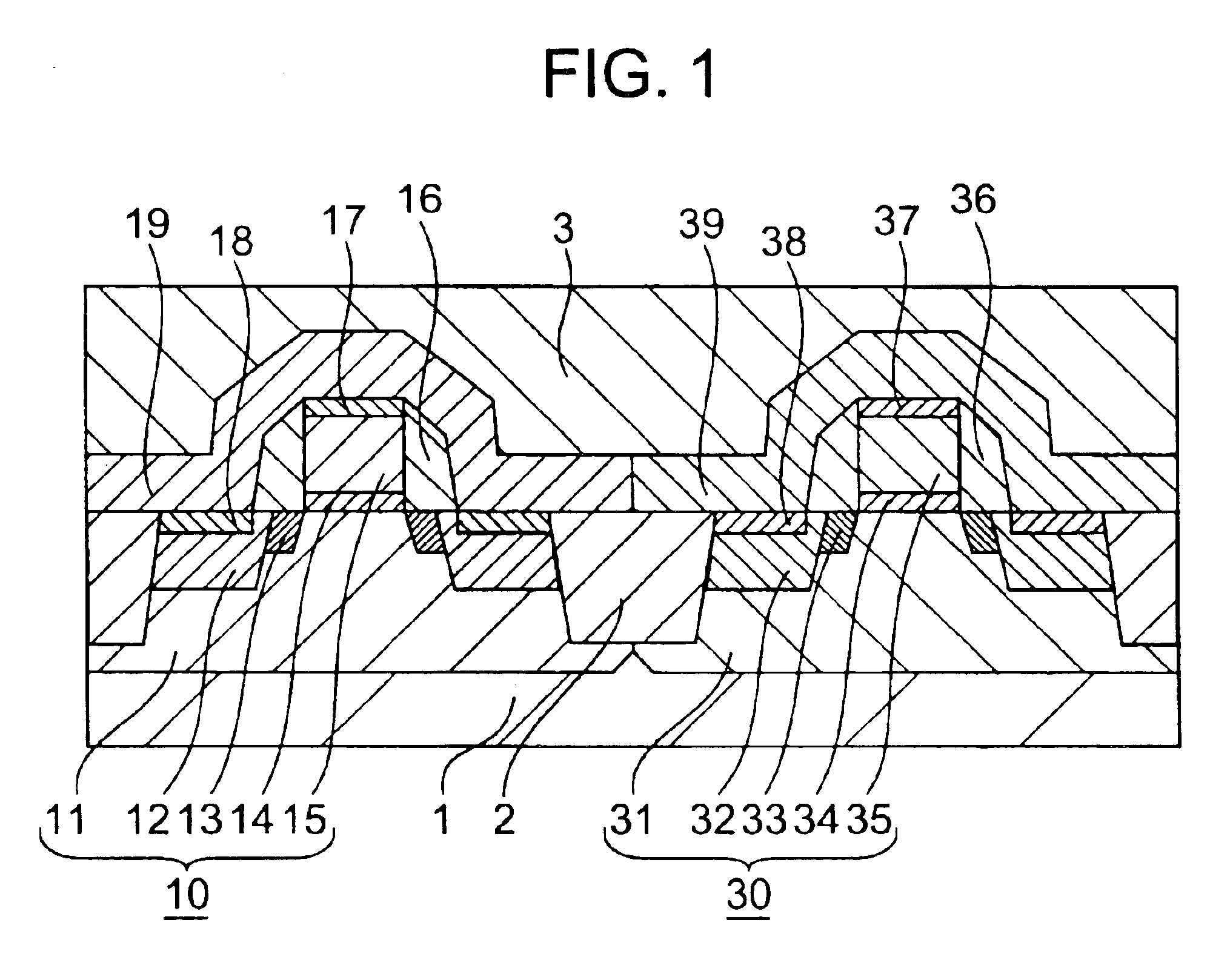

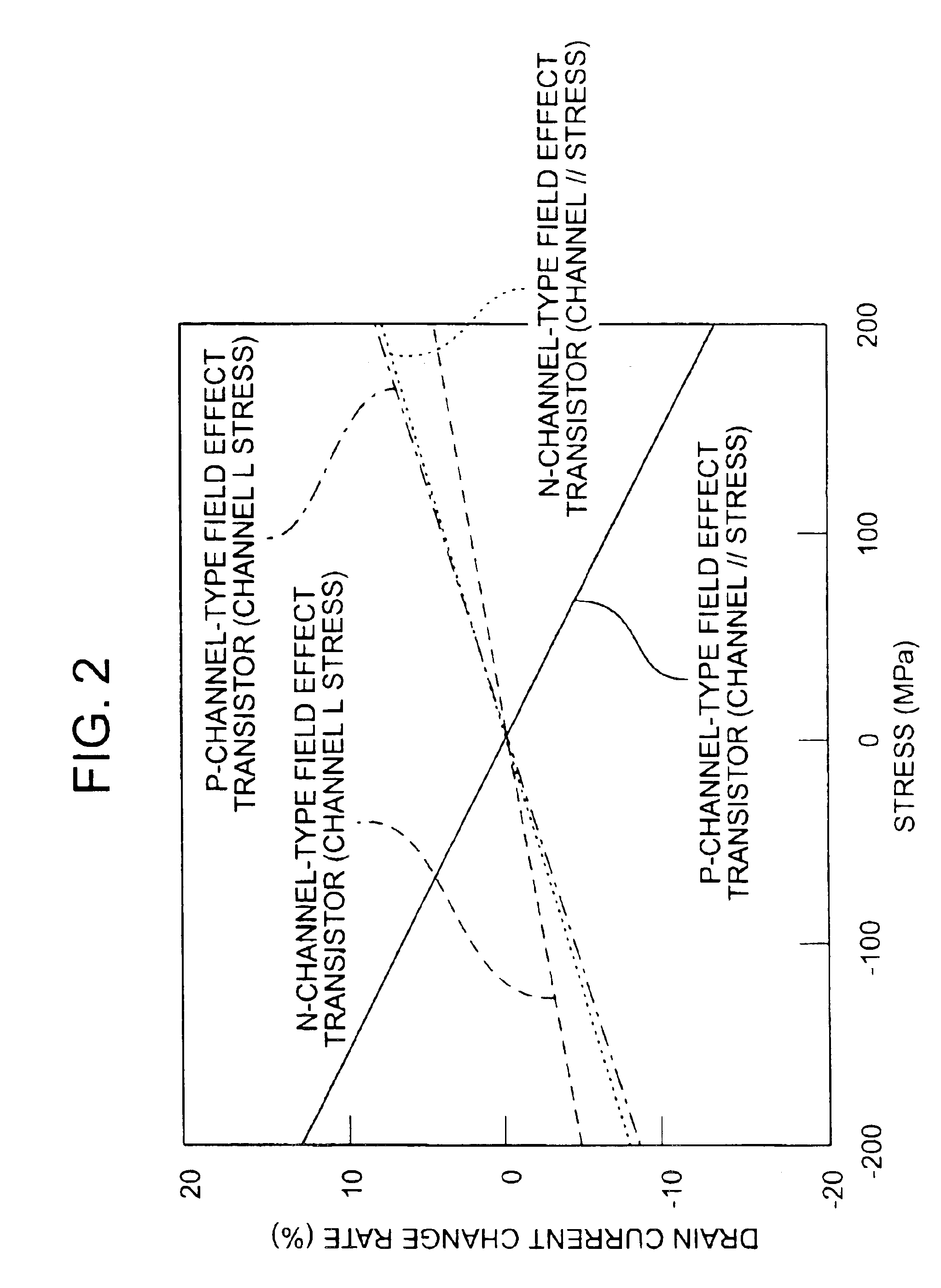

Semiconductor device with CMOS-field-effect transistors having improved drain current characteristics

InactiveUS6982465B2High speedImprove mobilityTransistorSemiconductor/solid-state device detailsCMOSField-effect transistor

The present invention provides a semiconductor device including n-channel field effect transistors and p-channel field effect transistors all of which have excellent drain current characteristics.In a semiconductor device including an n-channel field effect transistor 10 and a p-channel field effect transistor 30, a stress control film 19 covering a gate electrode 15 of the n-channel field effect transistor 10 undergoes film stress mainly composed of tensile stress. A stress control film 39 covering a gate electrode 15 of the p-channel field effect transistor 30 undergoes film stress mainly caused by compression stress compared to the film 19 of the n-channel field effect transistor 10. Accordingly, drain current is expected to be improved in both the n-channel field effect transistor and the p-channel field effect transistor. Consequently, the characteristics can be generally improved.

Owner:RENESAS ELECTRONICS CORP

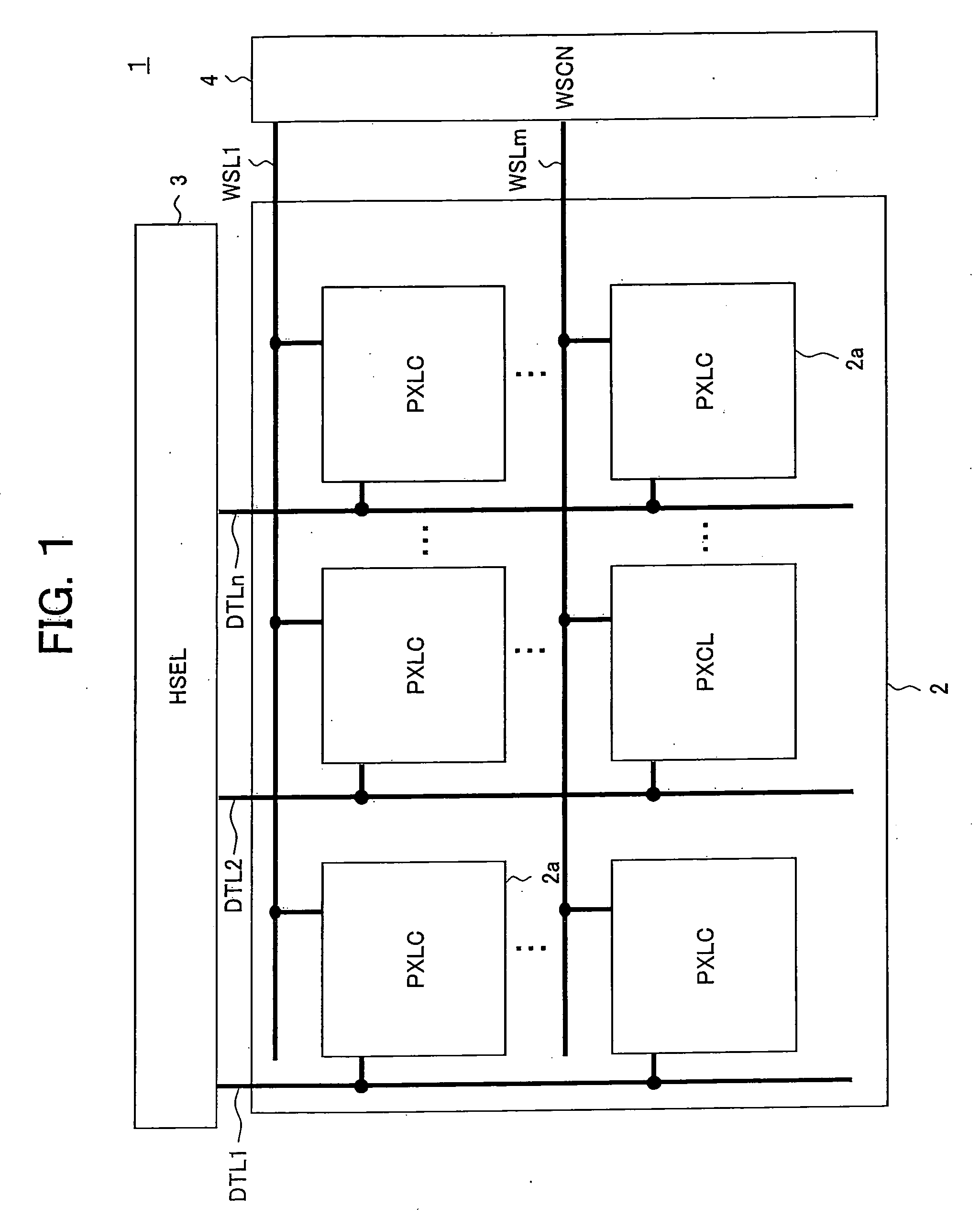

Pixel circuit, active matrix apparatus and display apparatus

ActiveUS7173590B2Low costLuminance of light emission can be fixedStatic indicating devicesSolid-state devicesElectricityActive matrix

A pixel circuit having a function of compensating for characteristic variation of an electro-optical element and threshold voltage variation of a transistor is formed from a reduced number of component elements. The pixel circuit includes an electro-optical element, a holding capacitor, and five N-channel thin film transistors including a sampling transistor, a drive transistor, a switching transistor, and first and second detection transistors. The sampling transistor samples and supplies an input signal from a signal line so as to be held into the holding capacitor. The driving transistor drives the electro-optical element with current in response to the held signal potential. The first and second detection transistors detect a threshold voltage of the drive transistor and supply the detected voltage into the holding capacitor in order to cancel an influence of the threshold voltage in advance.

Owner:SONY CORP

Semiconductor device including stress inducing films formed over n-channel and p-channel field effect transistors and a method of manufacturing the same

InactiveUS7115954B2Improve driving abilityImprove current drive capabilityTransistorSemiconductor/solid-state device detailsStress inducedField-effect transistor

A semiconductor device has an n channel conductivity type field effect transistor having a channel formation region formed in a first region on one main surface of a semiconductor substrate and a p channel conductivity type field effect transistor having a channel formation region formed in a second region on the main surface of the semiconductor substrate, which second region is different from the first region. An internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is different from an internal stress generated in the channel formation region of the p channel conductivity type field effect transistor. The internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is a tensile stress, while the internal stress generated in the channel formation region of the p channel conductivity type field effect transistor is a compressive stress.

Owner:RENESAS ELECTRONICS CORP

Complementary metal-oxide-semiconductor field effect transistor structure having ion implant in only one of the complementary devices

Owner:NORTH STAR INNOVATIONS

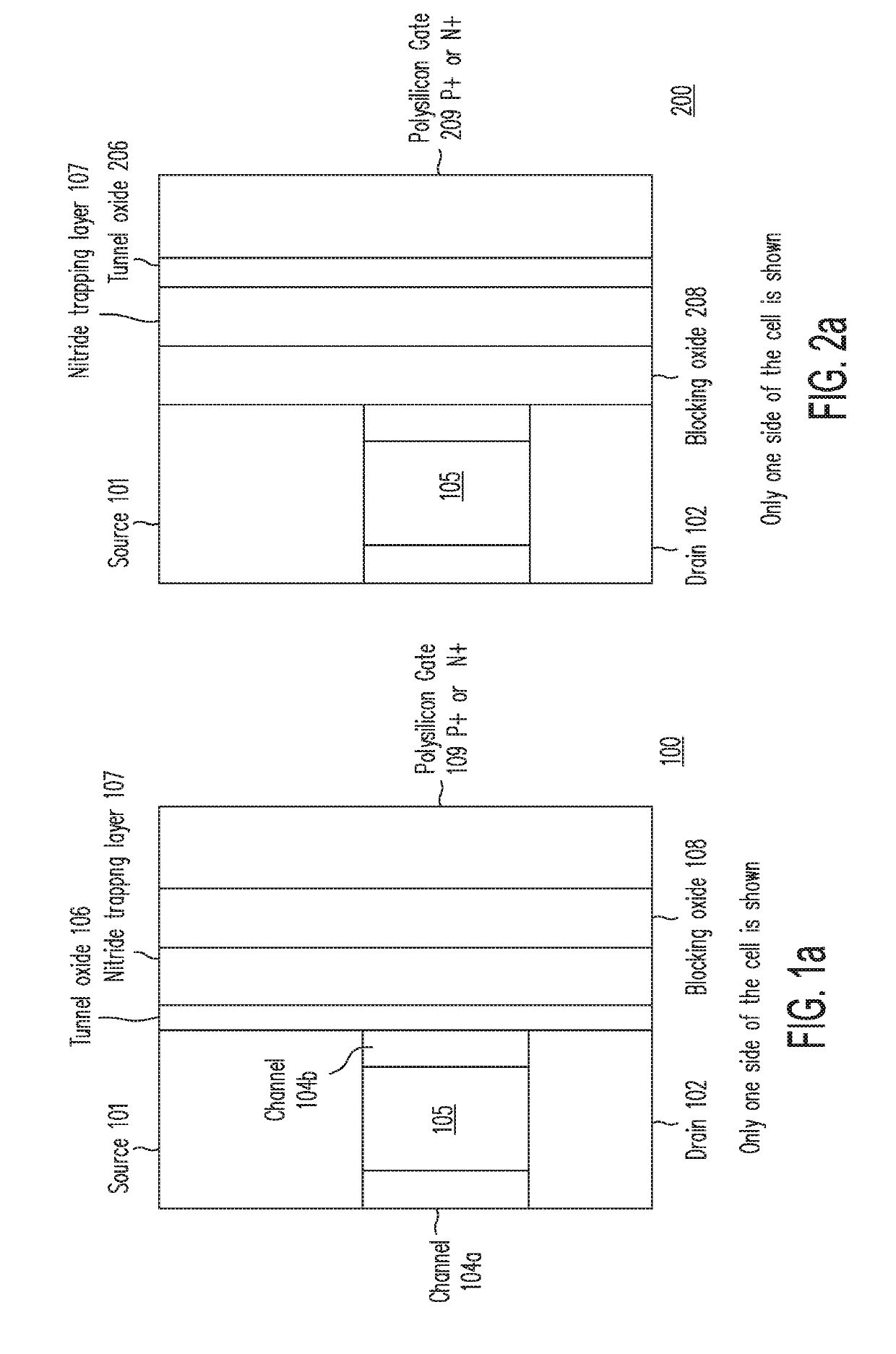

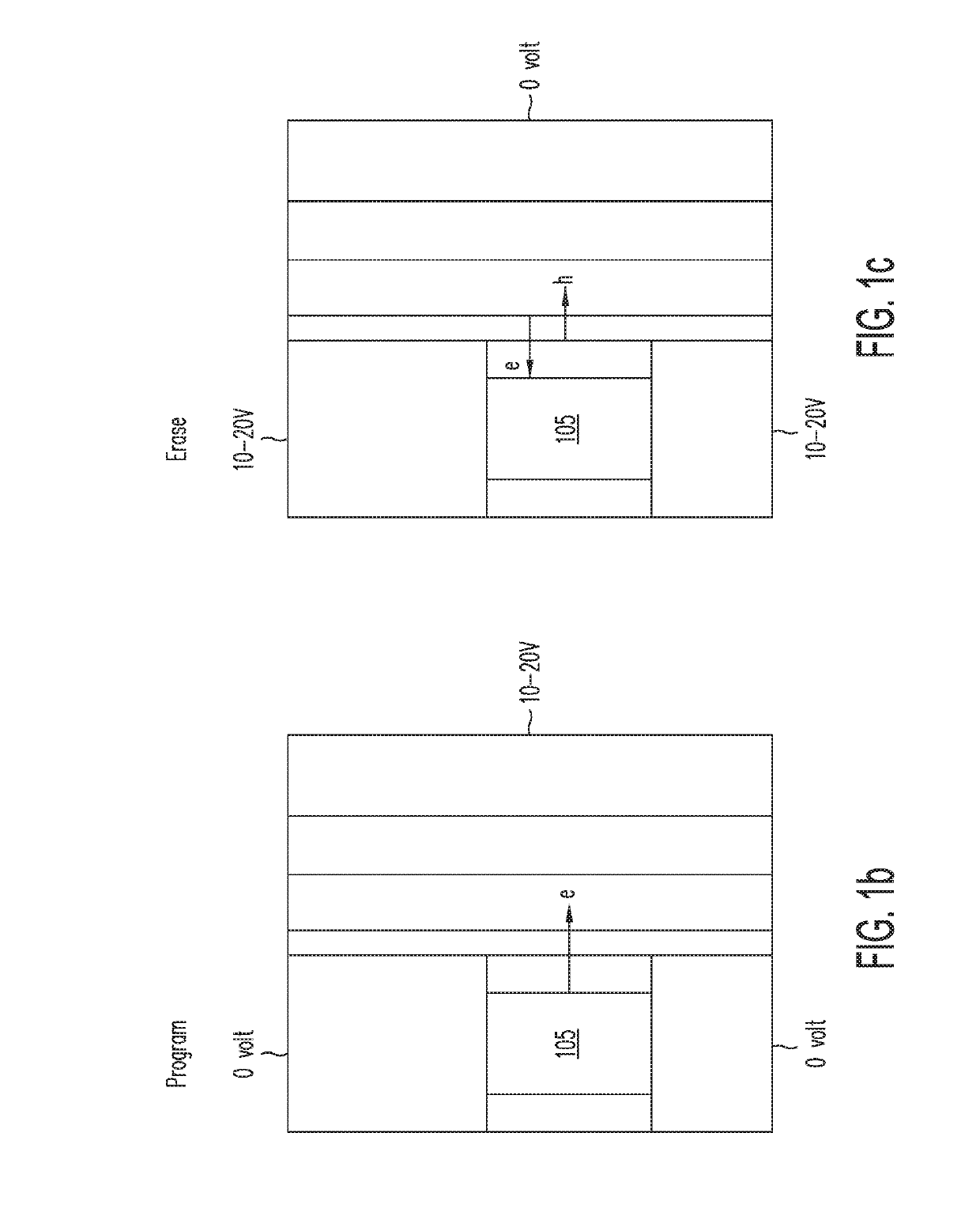

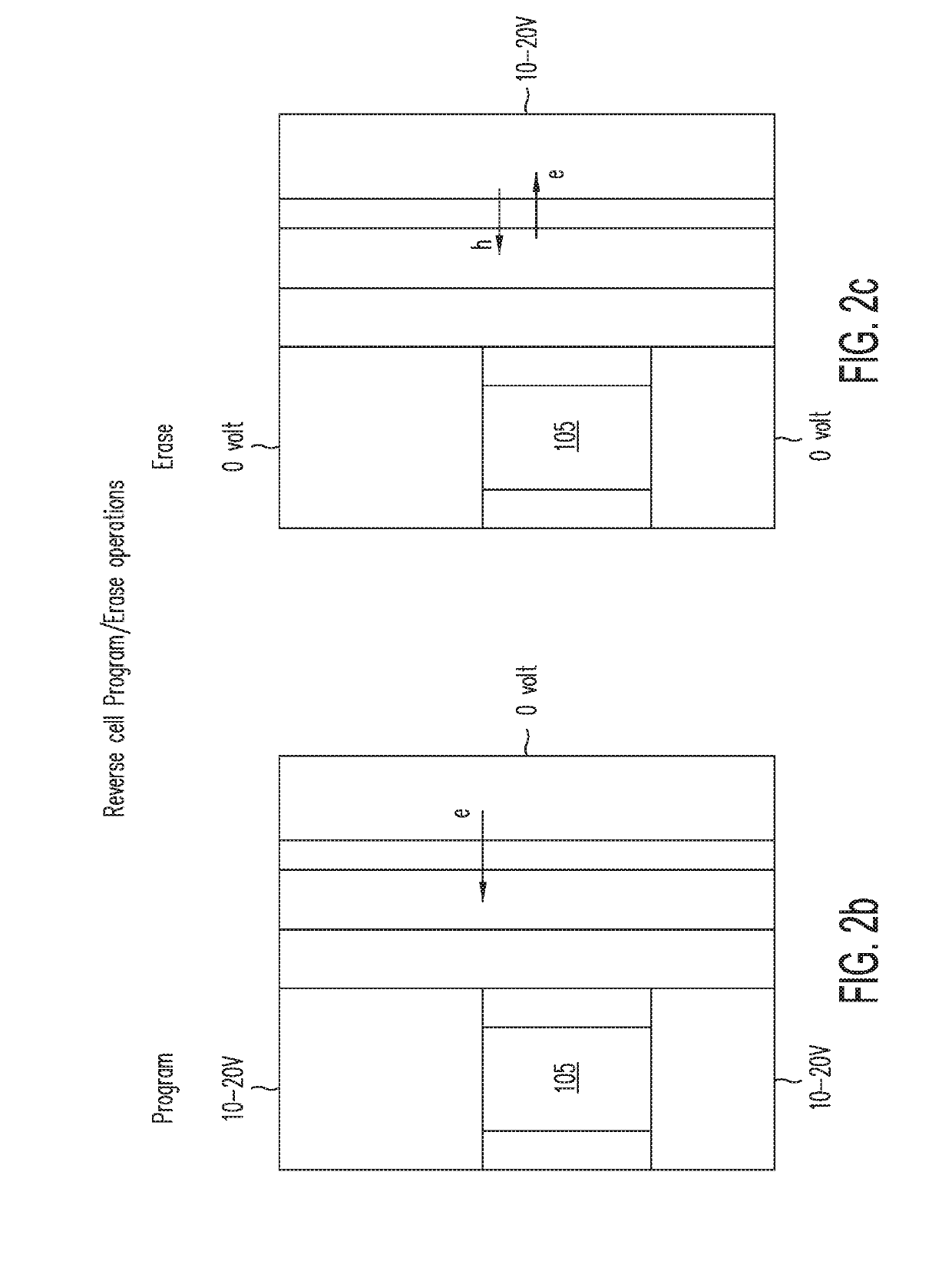

Reverse memory cell

A non-volatile “reverse memory cell” suitable for use as a building block for a 3-dimensional memory array includes a charge-trapping layer which is programmed or charged through gate-injection, rather than channel-injection. Such a reverse cell may be implemented as either an n-channel memory cell or a p-channel memory cell, without incurring design or process penalties, or any complexity in programming or erase operations. Furthermore, all reading, programming, erase, program-inhibiting operations may be carried out in the reverse memory cell using only positive or only negative voltages, thereby simplifying both the design and the power management operations.

Owner:SUNRISE MEMORY CORP

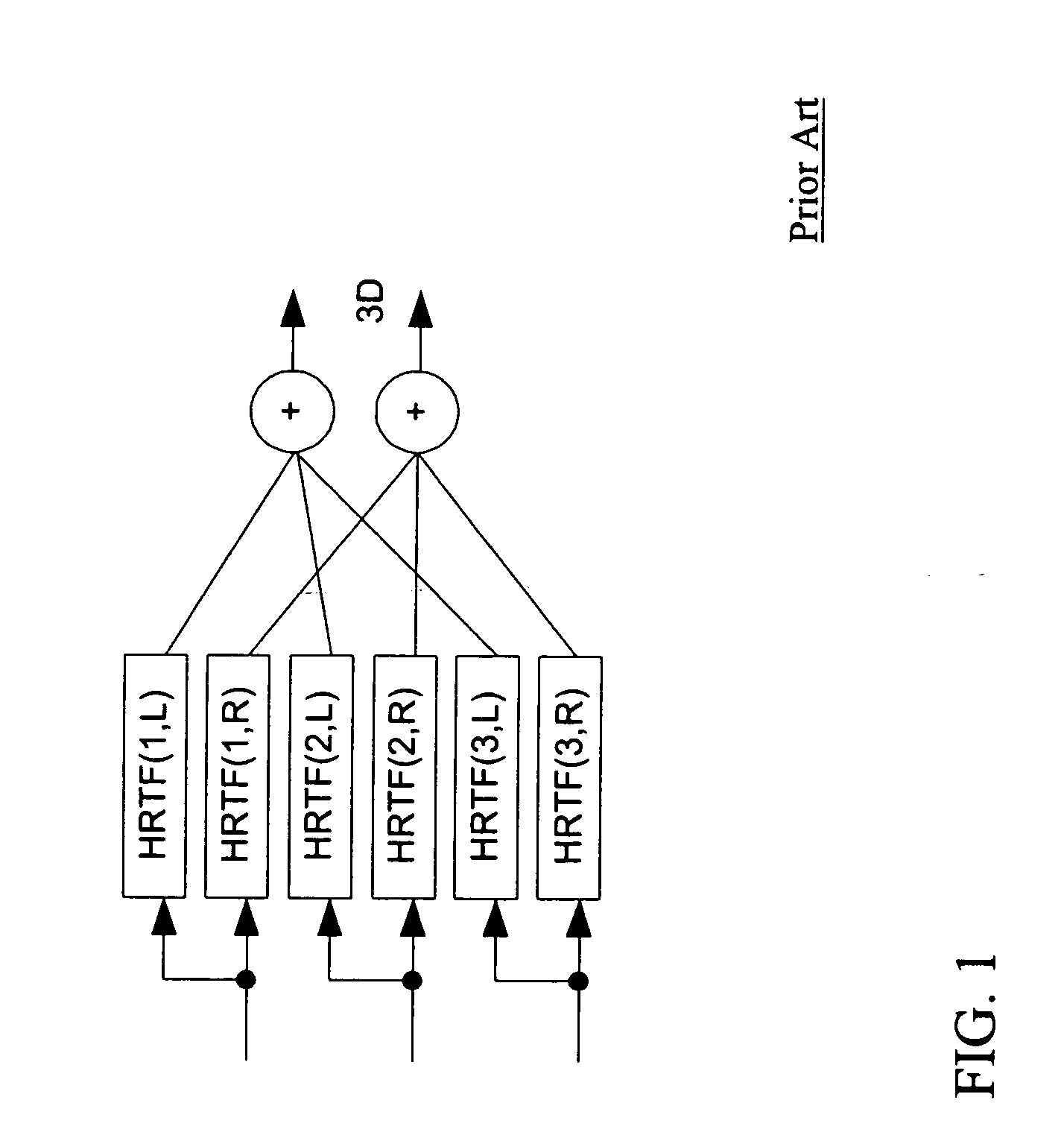

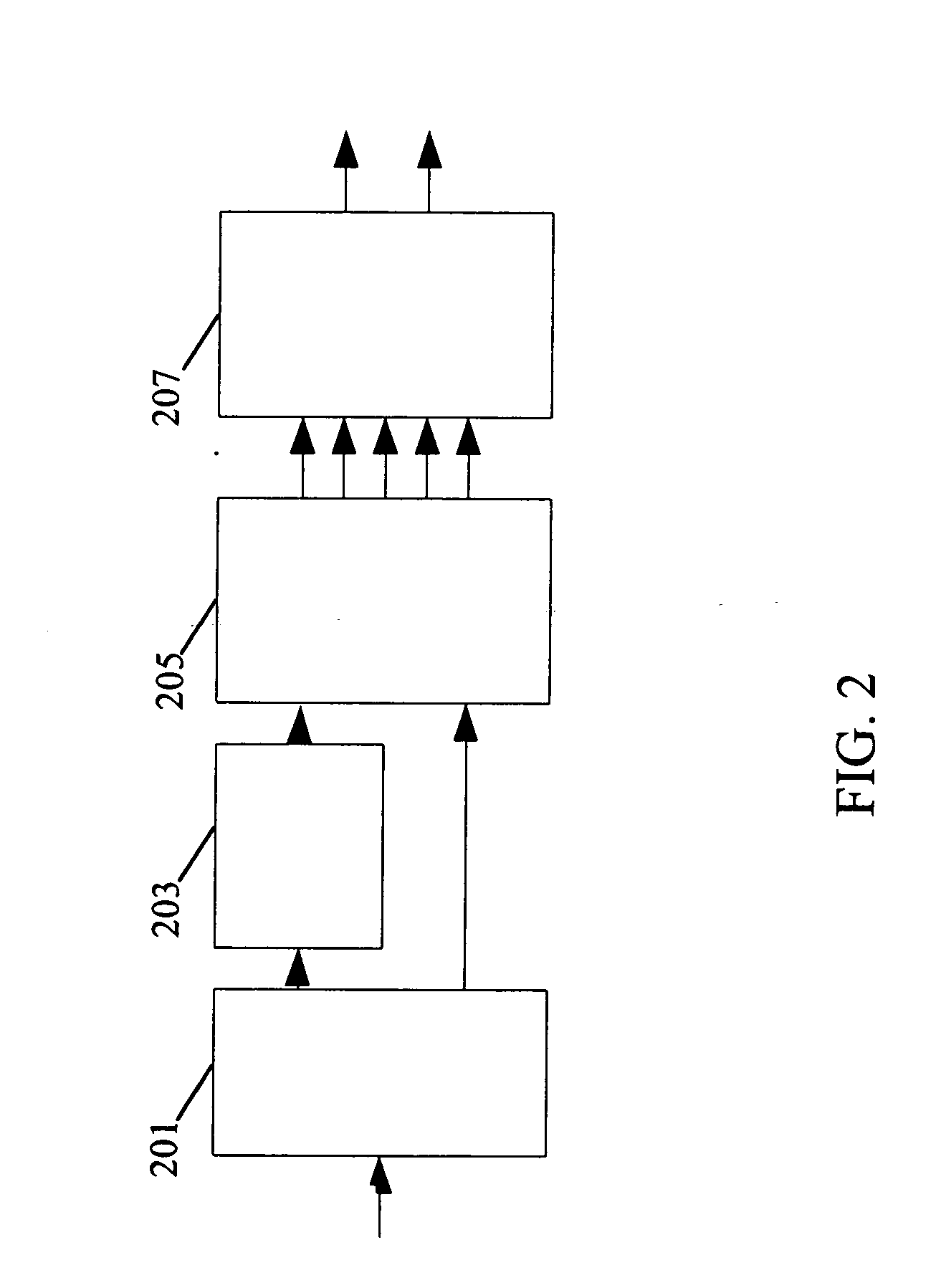

Method and apparatus for generating a binaural audio signal

ActiveUS20100246832A1Improved binauralReduce complexitySpeech analysisStereophonic systemsMultiplexerAudio frequency

An apparatus for generating a binaural audio signal includes a de-multiplexer and decoder which receives audio data comprising an audio M-channel audio signal which is a downmix of an N-channel audio signal and spatial parameter data for upmixing the M-channel audio signal to the N-channel audio signal. A conversion processor converts spatial parameters of the spatial parameter data into first binaural parameters in response to at least one binaural perceptual transfer function. A matrix processor converts the M-channel audio signal into a first stereo signal in response to the first binaural parameters. A stereo filter generates the binaural audio signal by filtering the first stereo signal. The filter coefficients for the stereo filter are determined in response to the at least one binaural perceptual transfer function by a coefficient processor. The combination of parameter conversion / processing and filtering allows a high quality binaural signal to be generated with low complexity.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com