Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2953 results about "P channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An P-Channel MOSFET is made up of a P channel, which is a channel composed of a majority of hole current carriers. The gate terminals are made up of N-type material. Depending on the voltage quantity and type (negative or positive) determines how the transistor operates and whether it turns on or off.

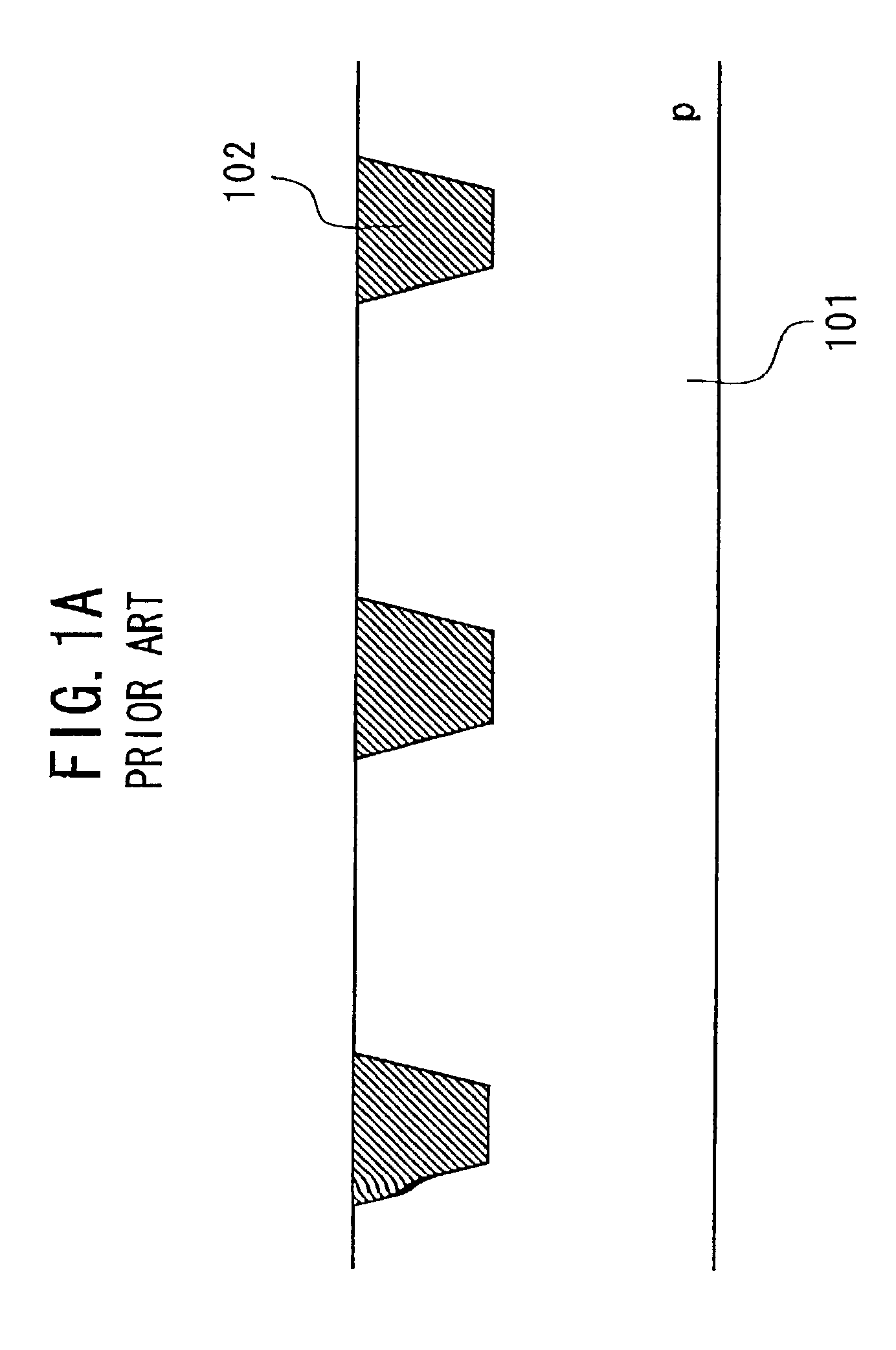

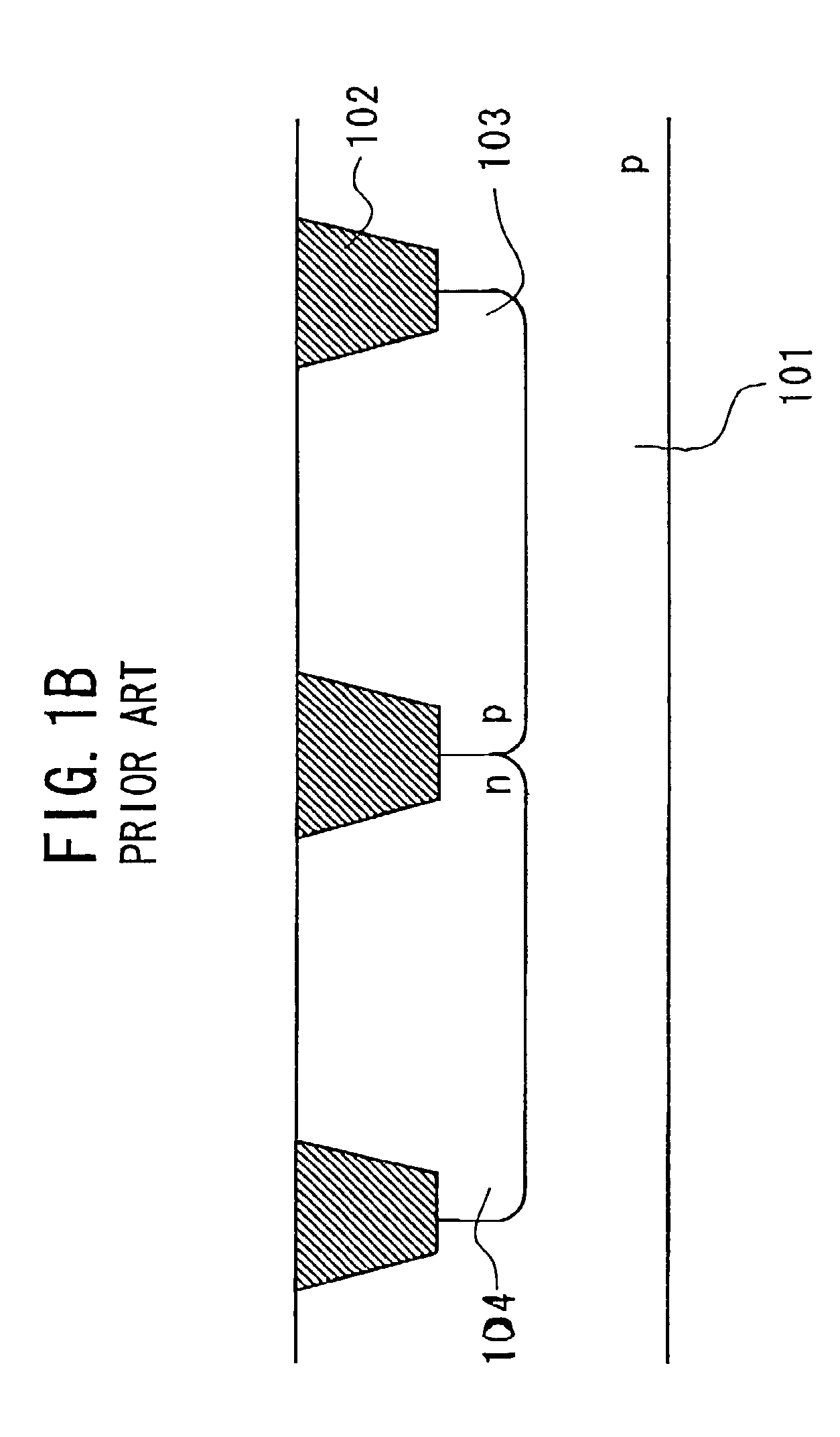

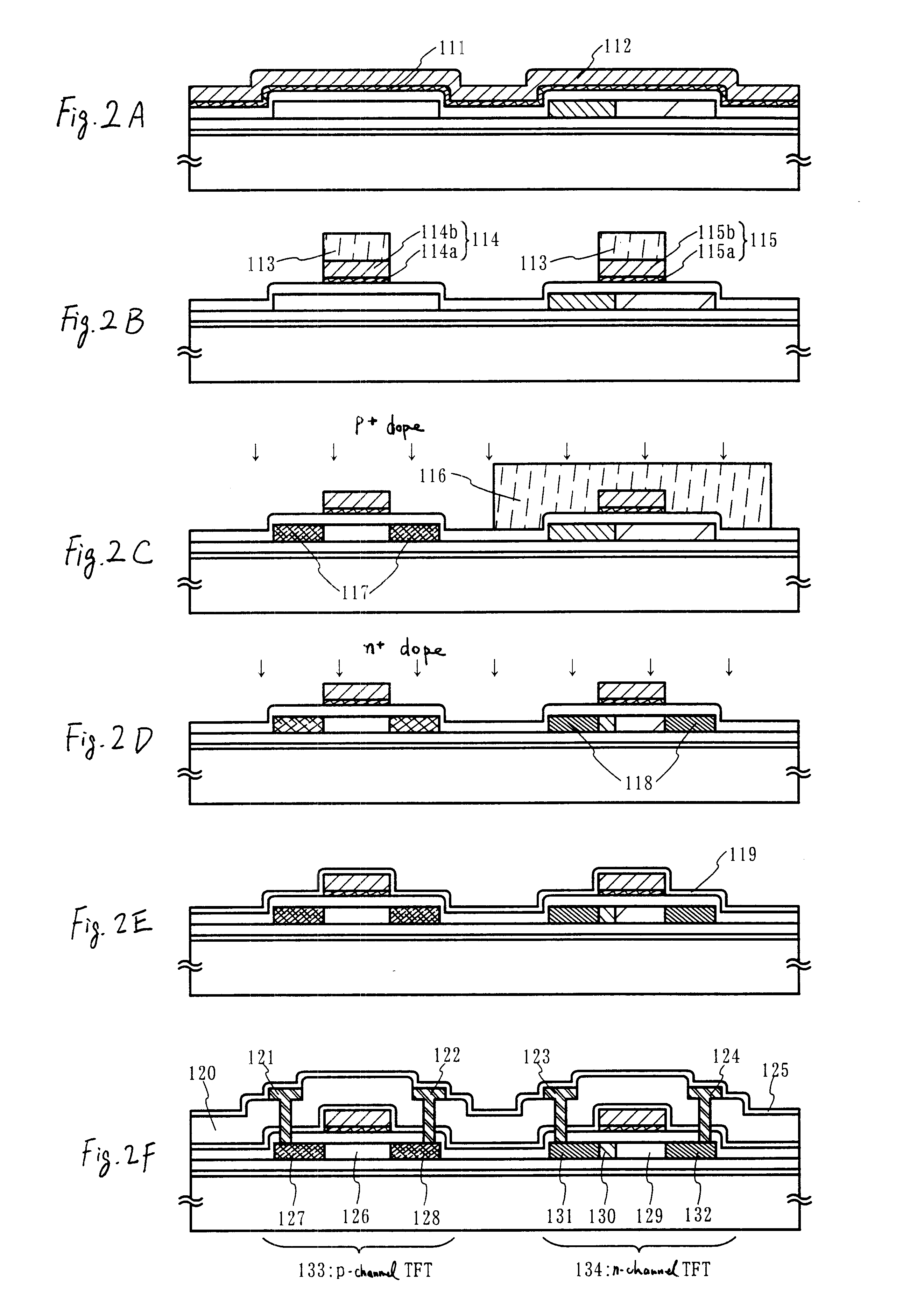

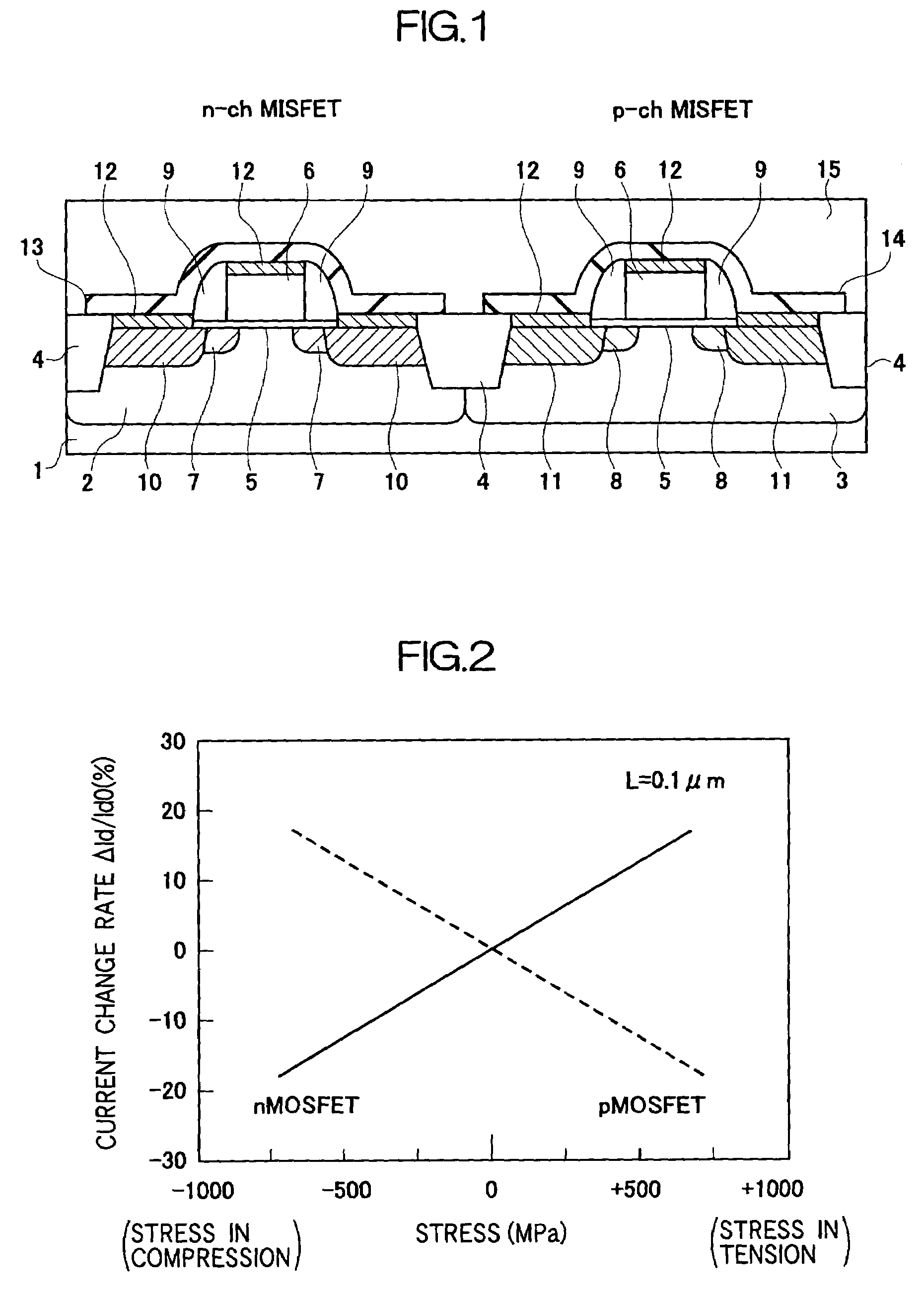

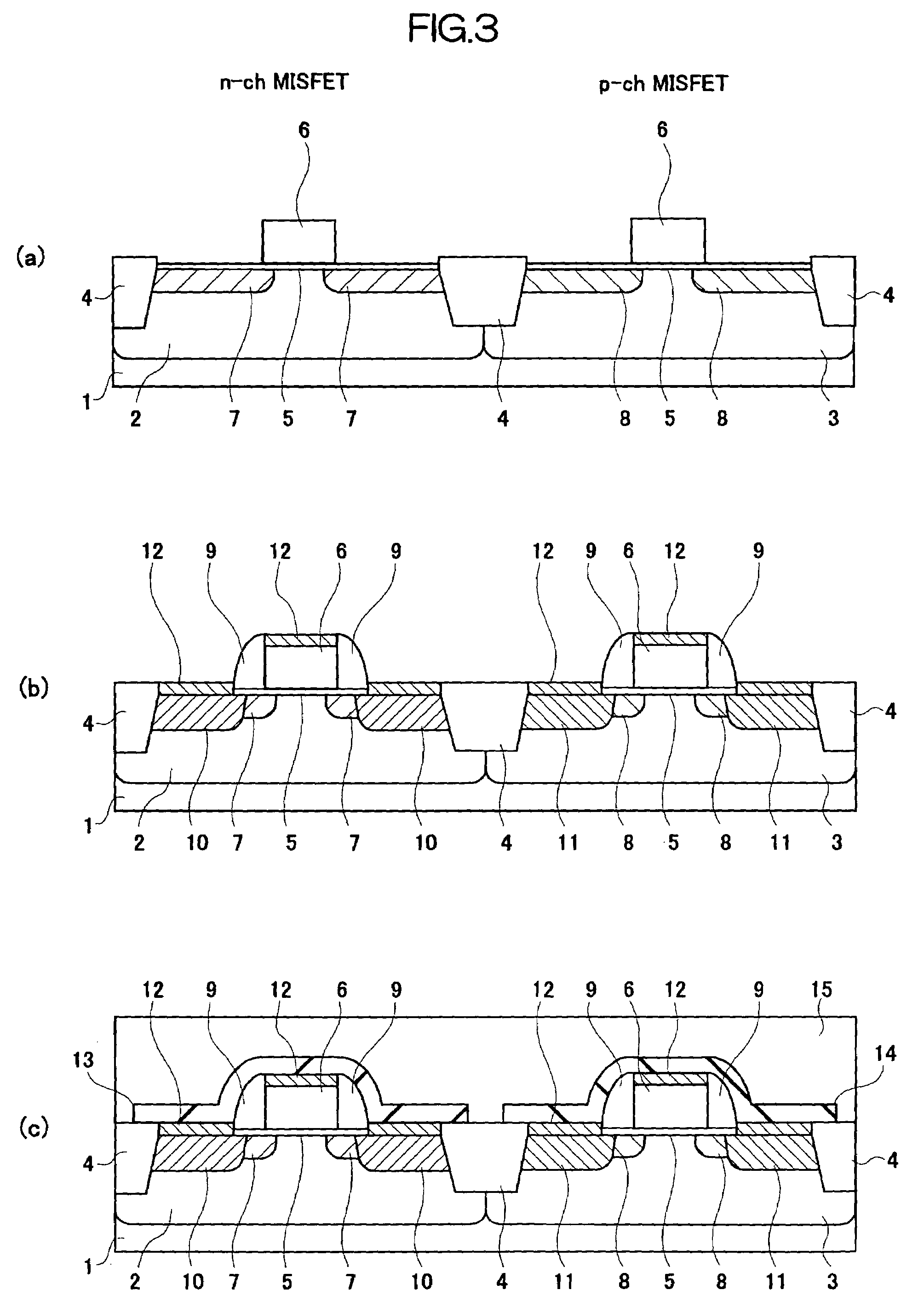

Semiconductor device and method of fabricating the same

InactiveUS20030040158A1TransistorSemiconductor/solid-state device manufacturingMOSFETElectron mobility

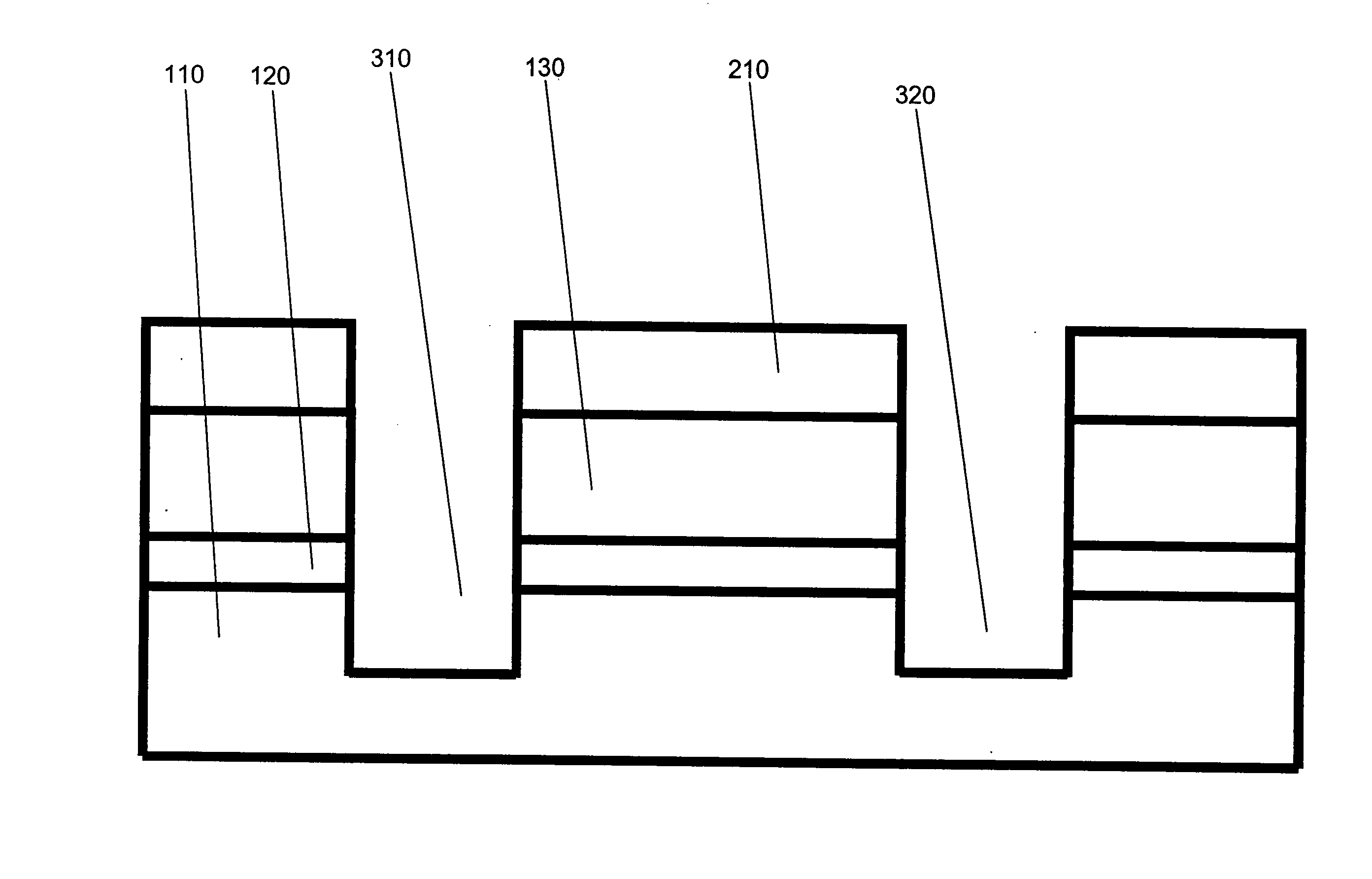

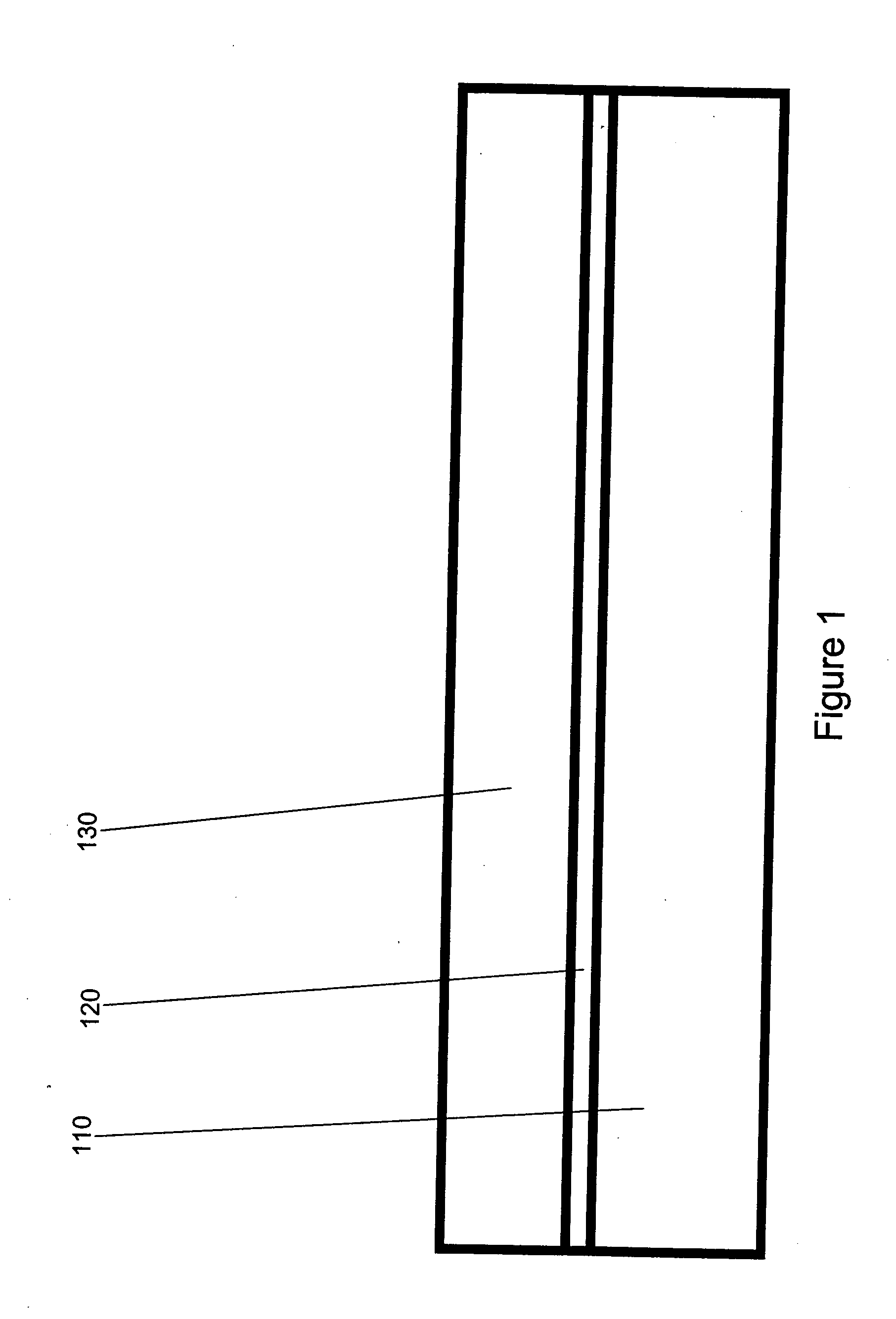

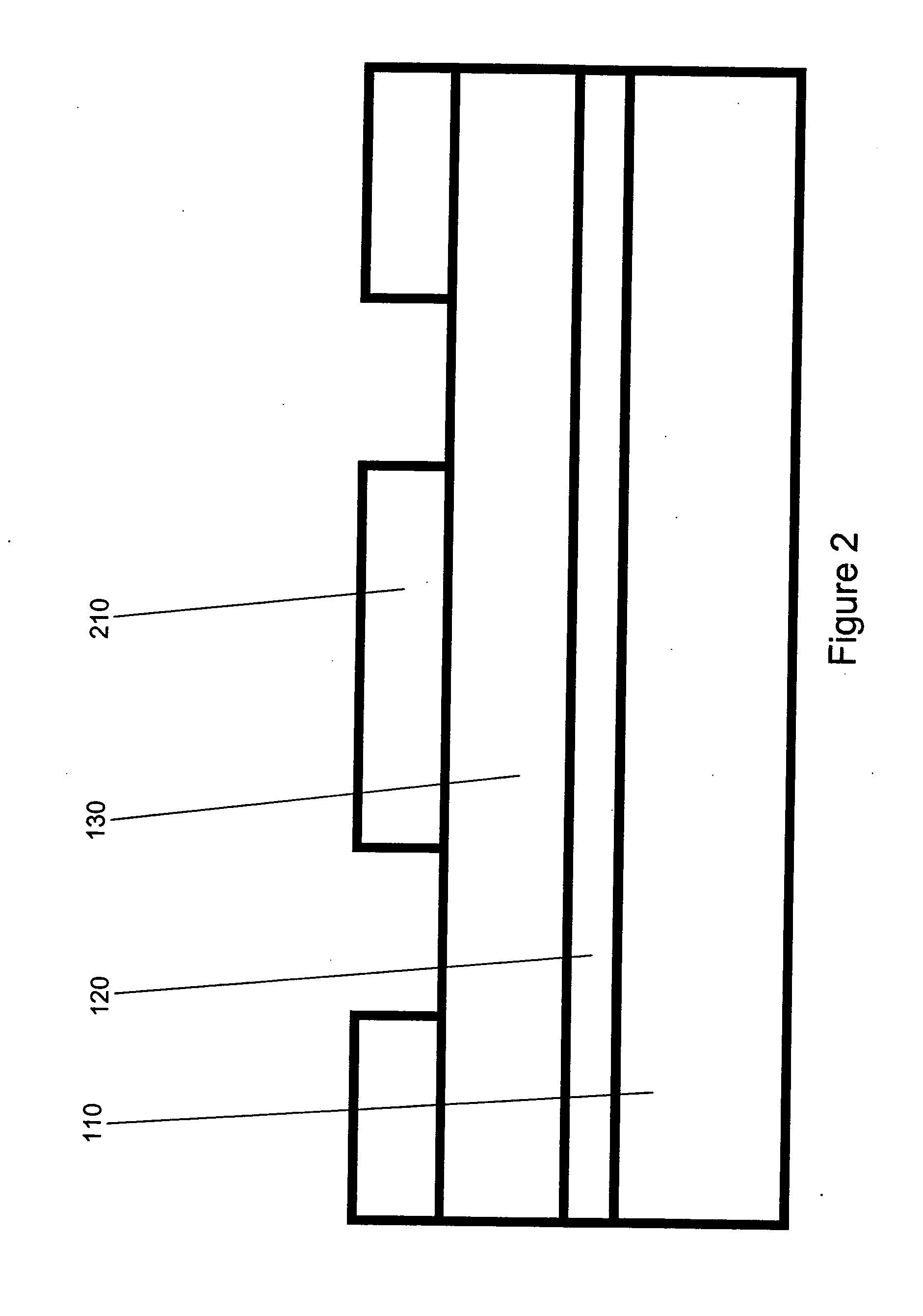

A semiconductor device improves the electron mobility in the n-channel MOSFET and reduces the bend or warp of the semiconductor substrate or wafer. The fist nitride layer having a tensile stress is formed on the substrate to cover the n-channel MOSFET. The tensile stress of the first nitride layer serves to relax a compressive stress existing in the channel region. The second nitride layer having an actual compressive stress is formed on the substrate to cover the p-channel MOSFET. The first and second nitride layers serve to decrease bend or warp of the substrate. Preferably, the first nitride layer is a nitride layer of Si formed by a LPCVD process, and the second nitride layer is a nitride layer of Si formed by a PECVD process.

Owner:NEC ELECTRONICS CORP

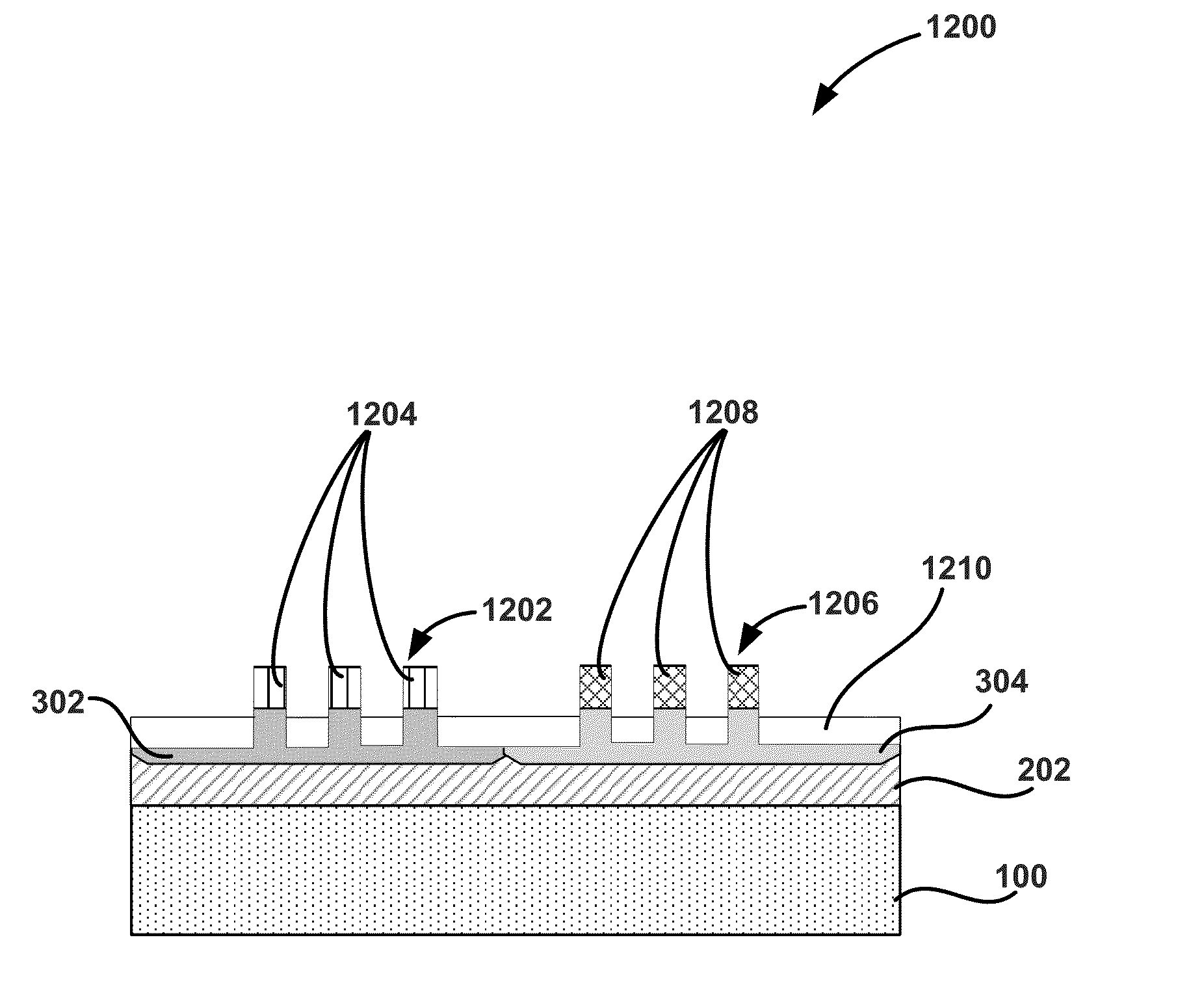

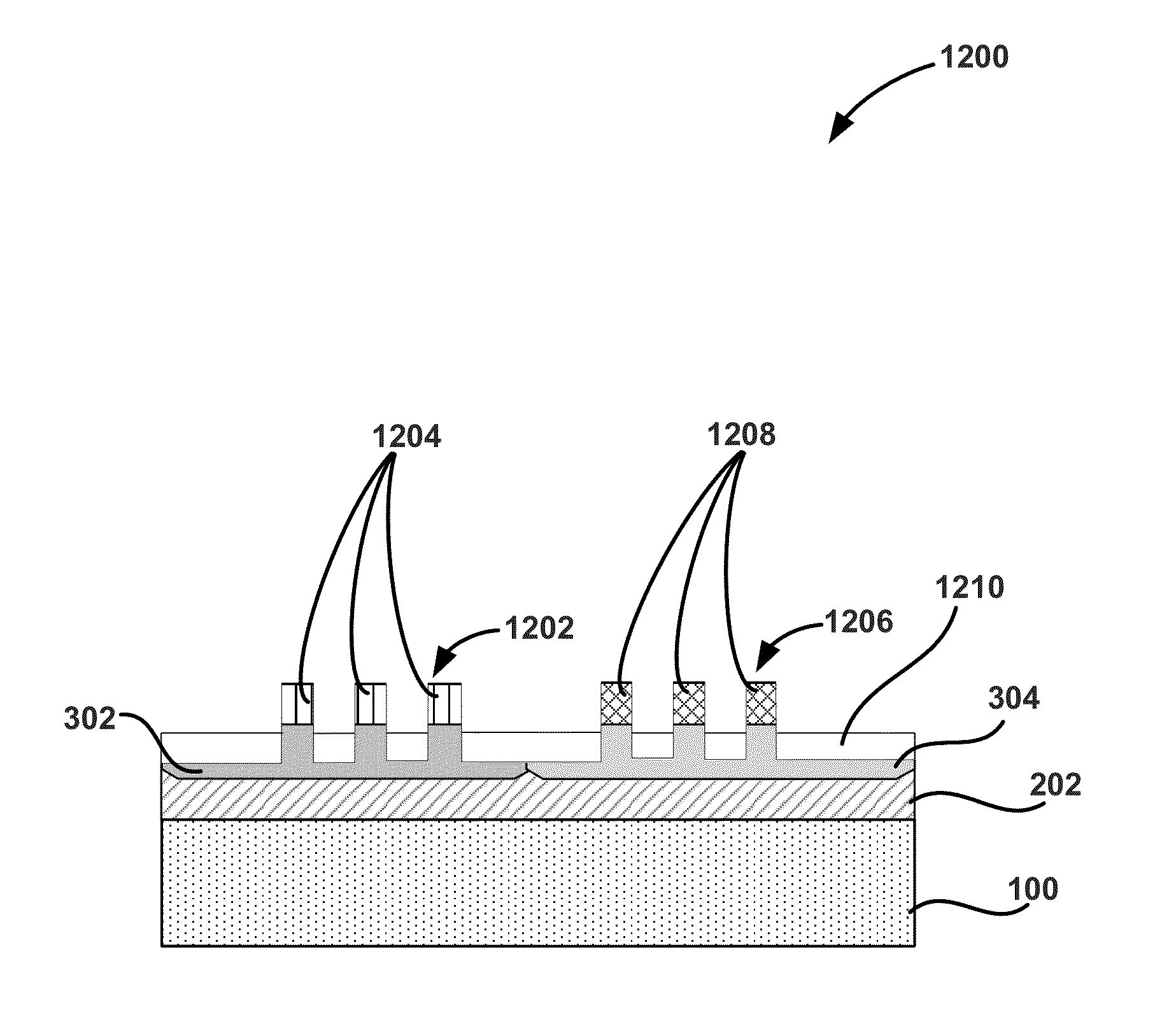

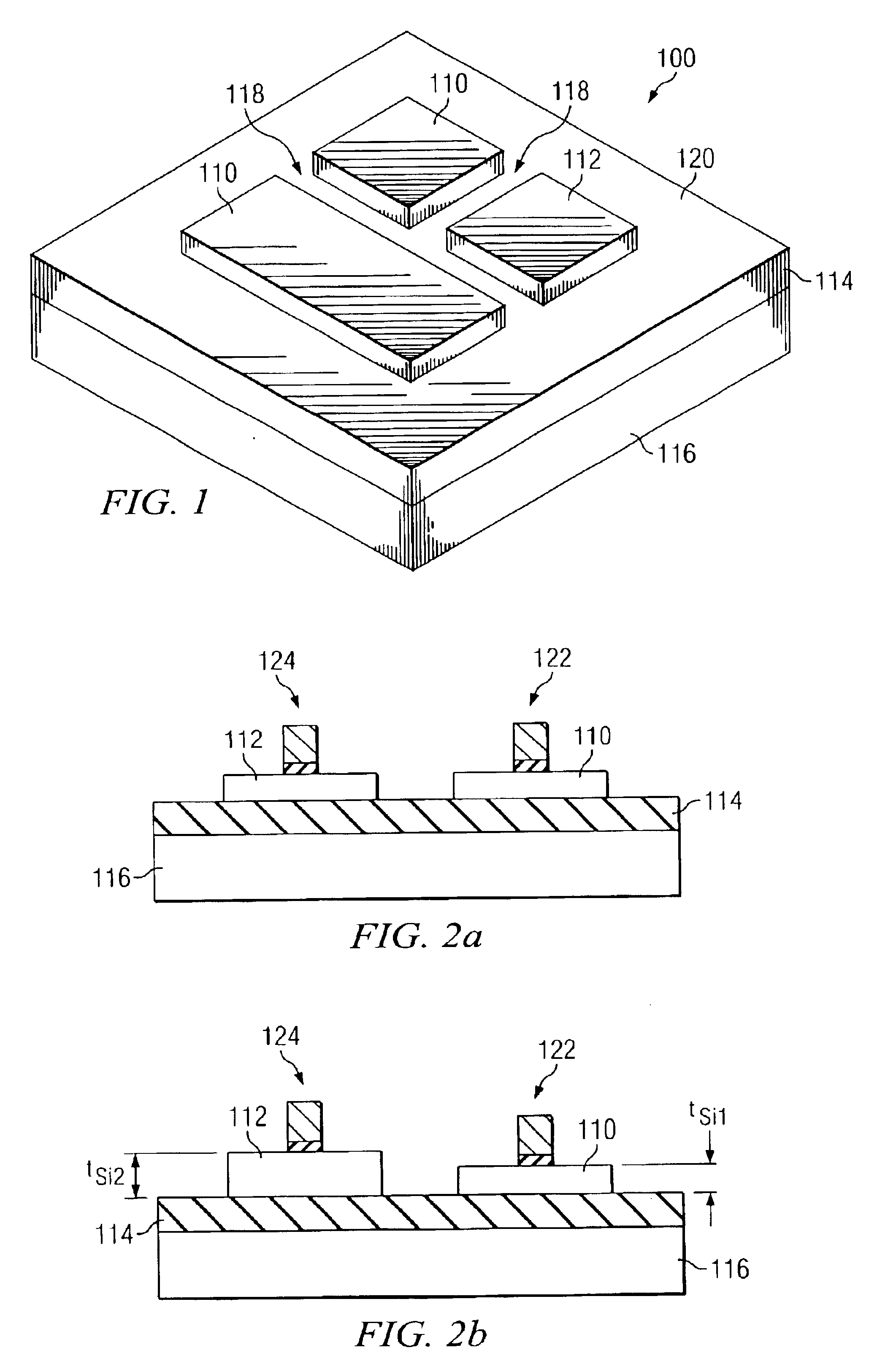

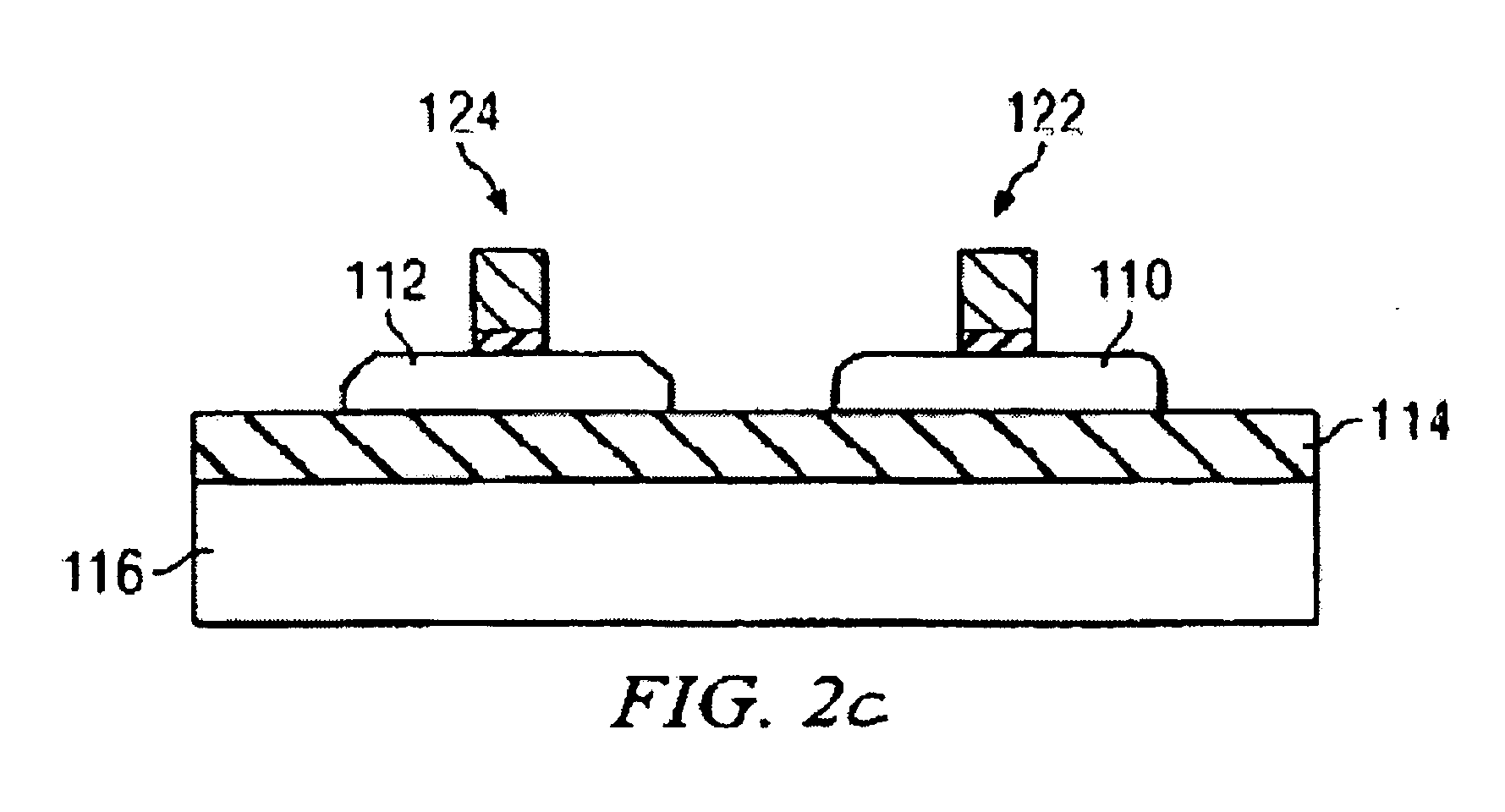

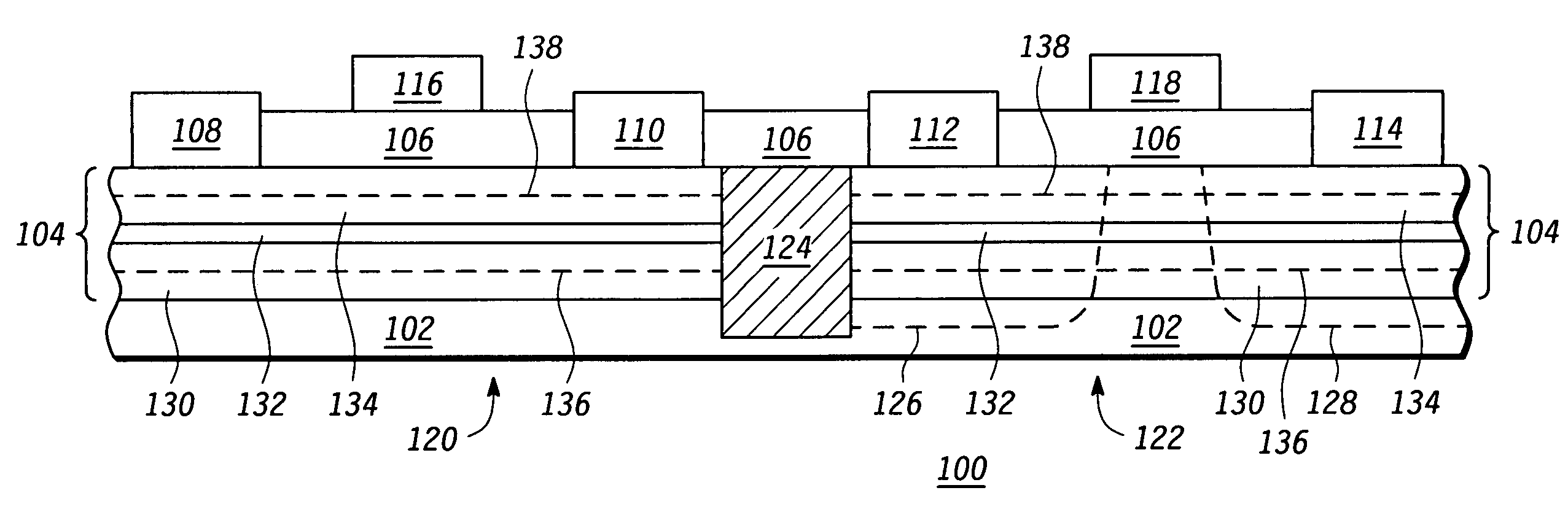

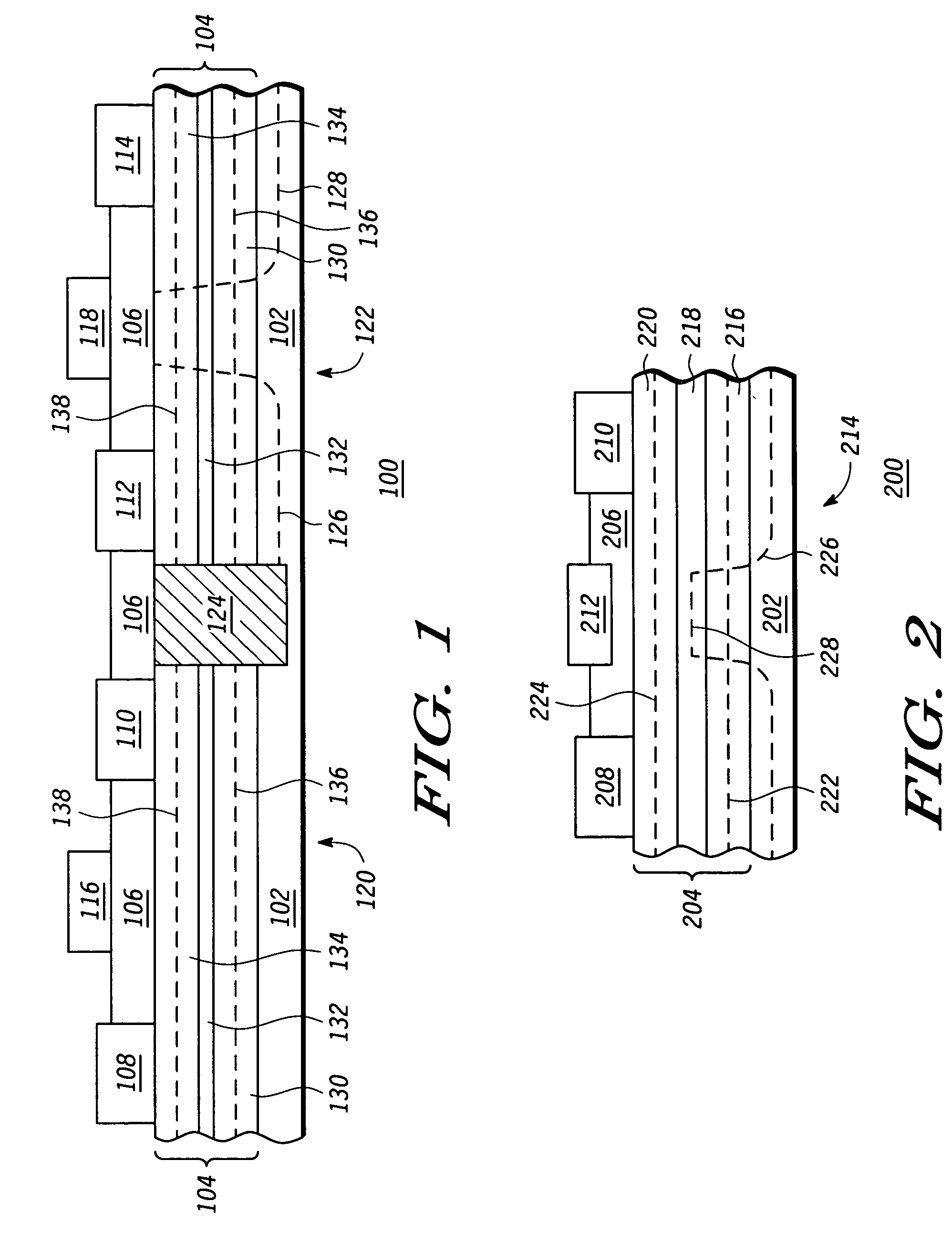

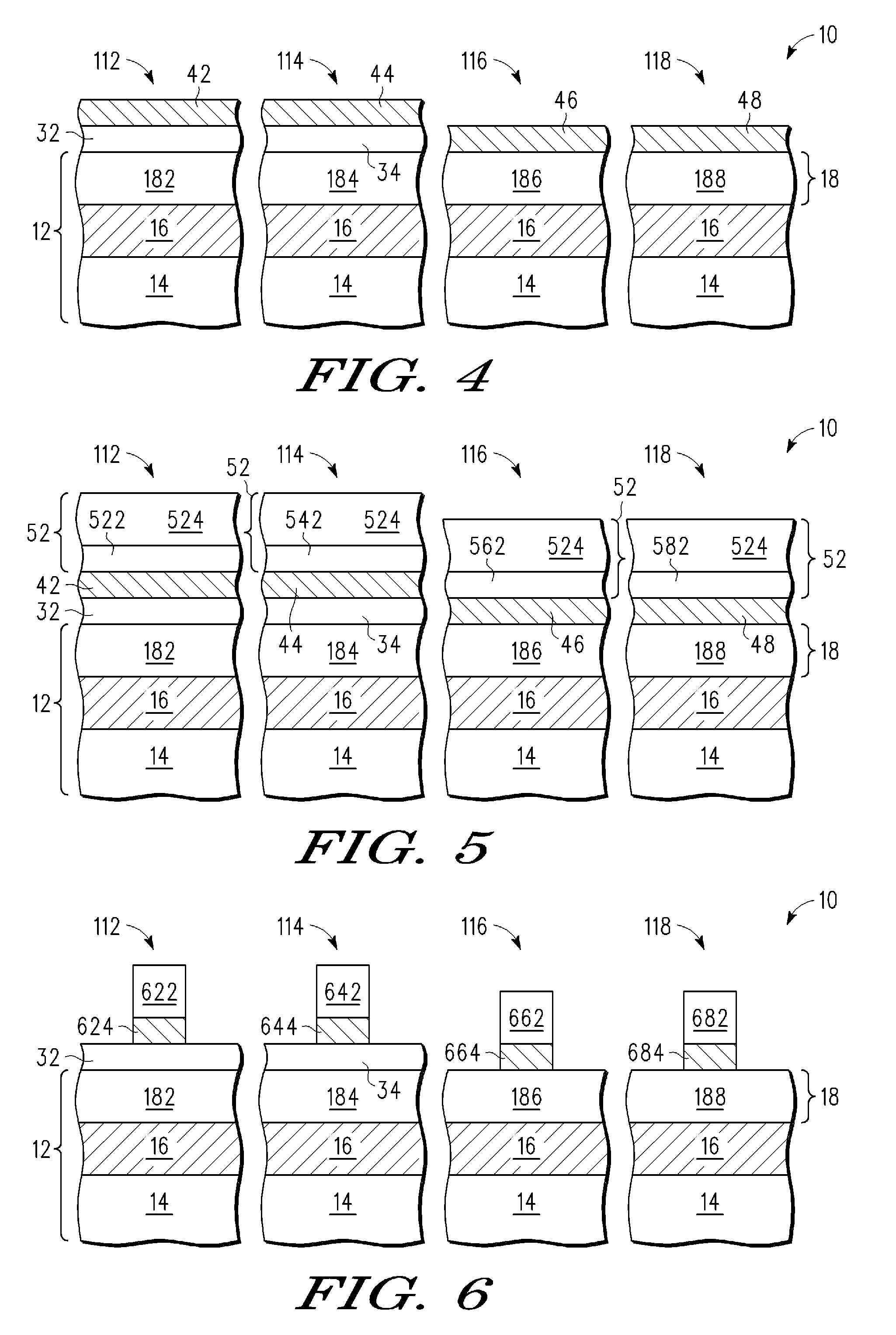

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both n-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both re-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

Field effect transistor having an interlayer dielectric material having increased intrinsic stress

InactiveUS20080203487A1Optimization mechanismImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentField-effect transistor

By providing a highly stressed interlayer dielectric material, the performance of at least one type of transistor may be increased due to an enhanced strain-inducing mechanism. For instance, by providing a highly compressive silicon dioxide of approximately 400 Mega Pascal and more as an interlayer dielectric material, the drive current of the P-channel transistors may be increased by 2% and more while not unduly affecting the performance of the N-channel transistors.

Owner:ADVANCED MICRO DEVICES INC

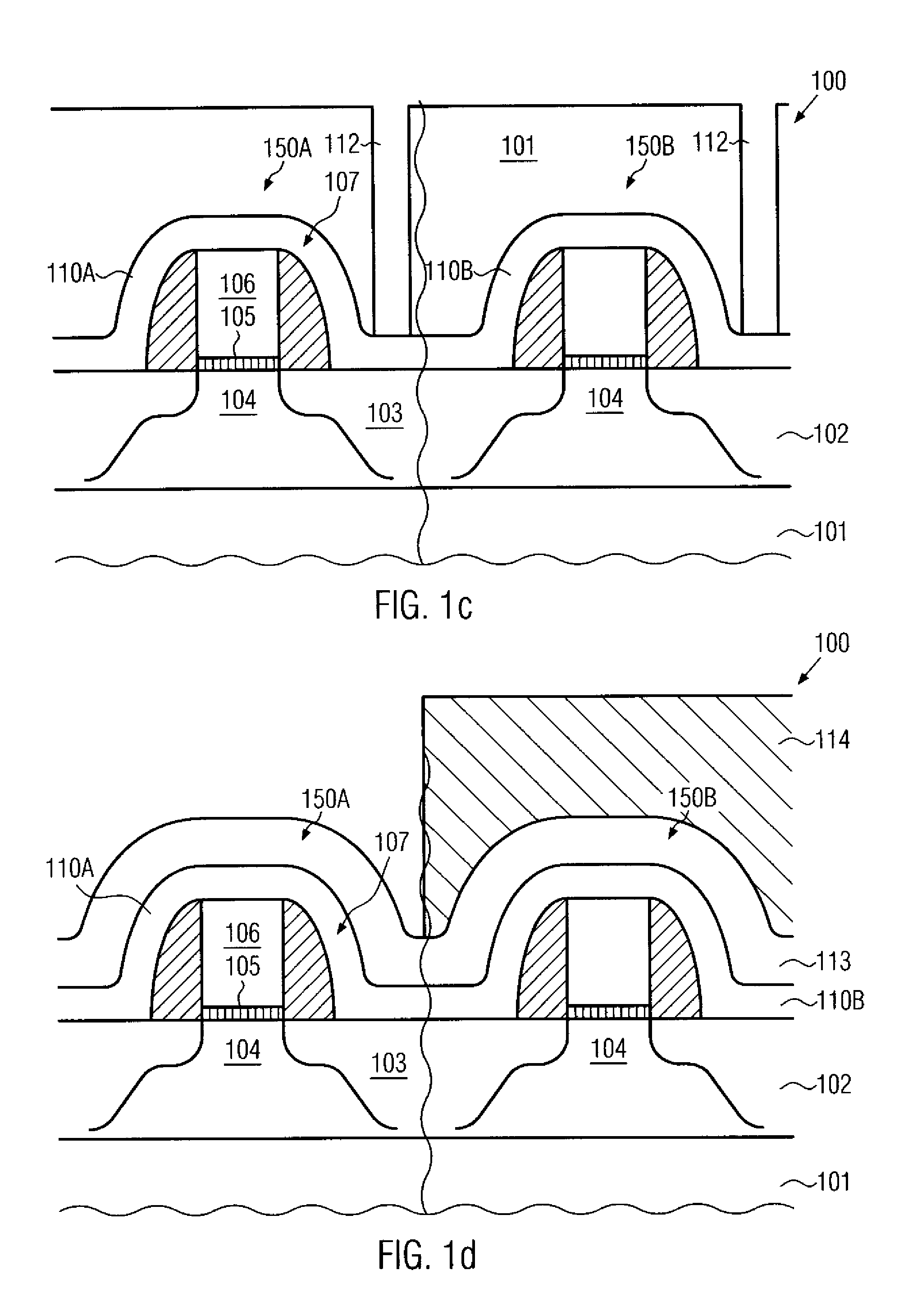

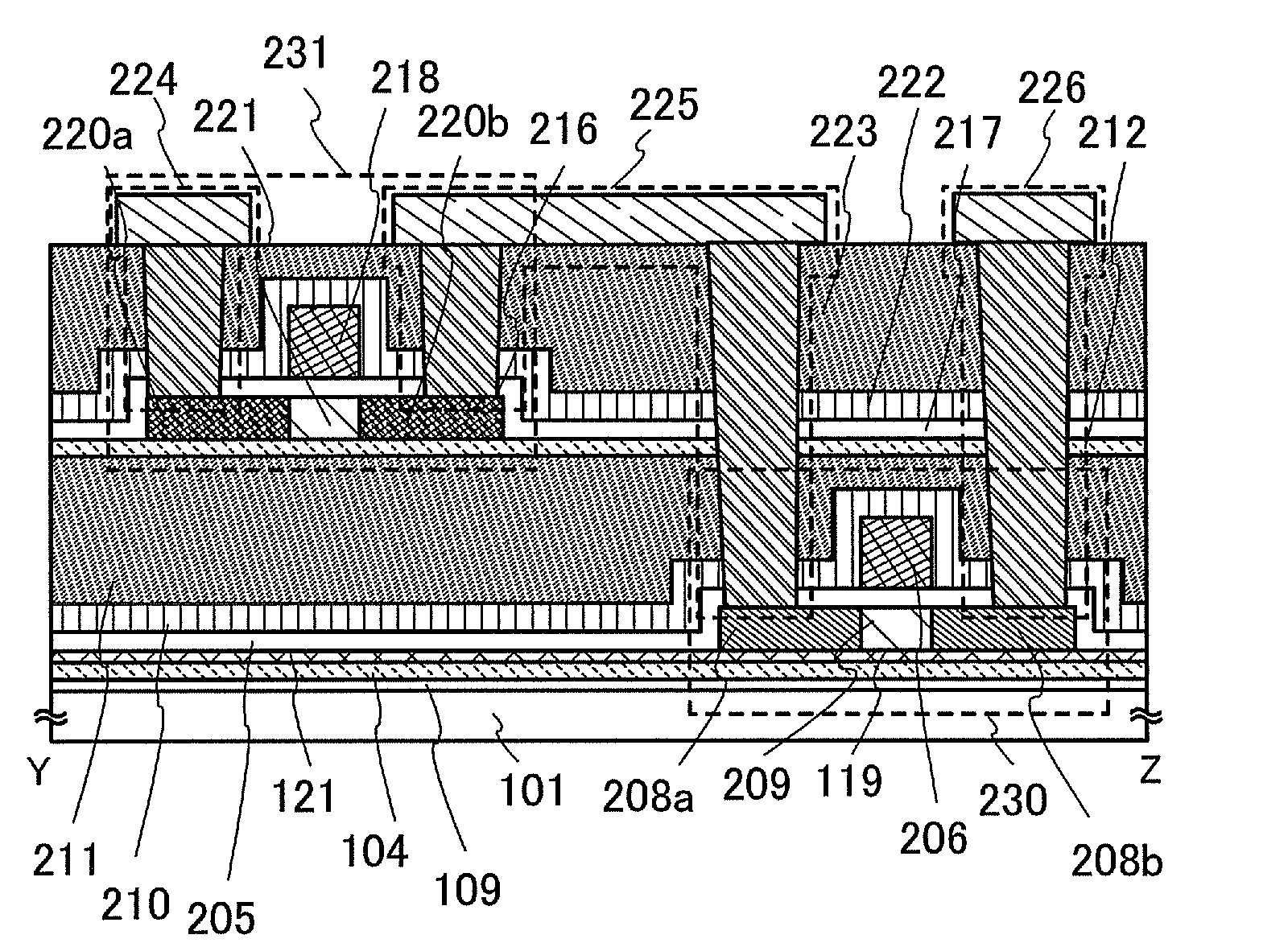

Semiconductor device

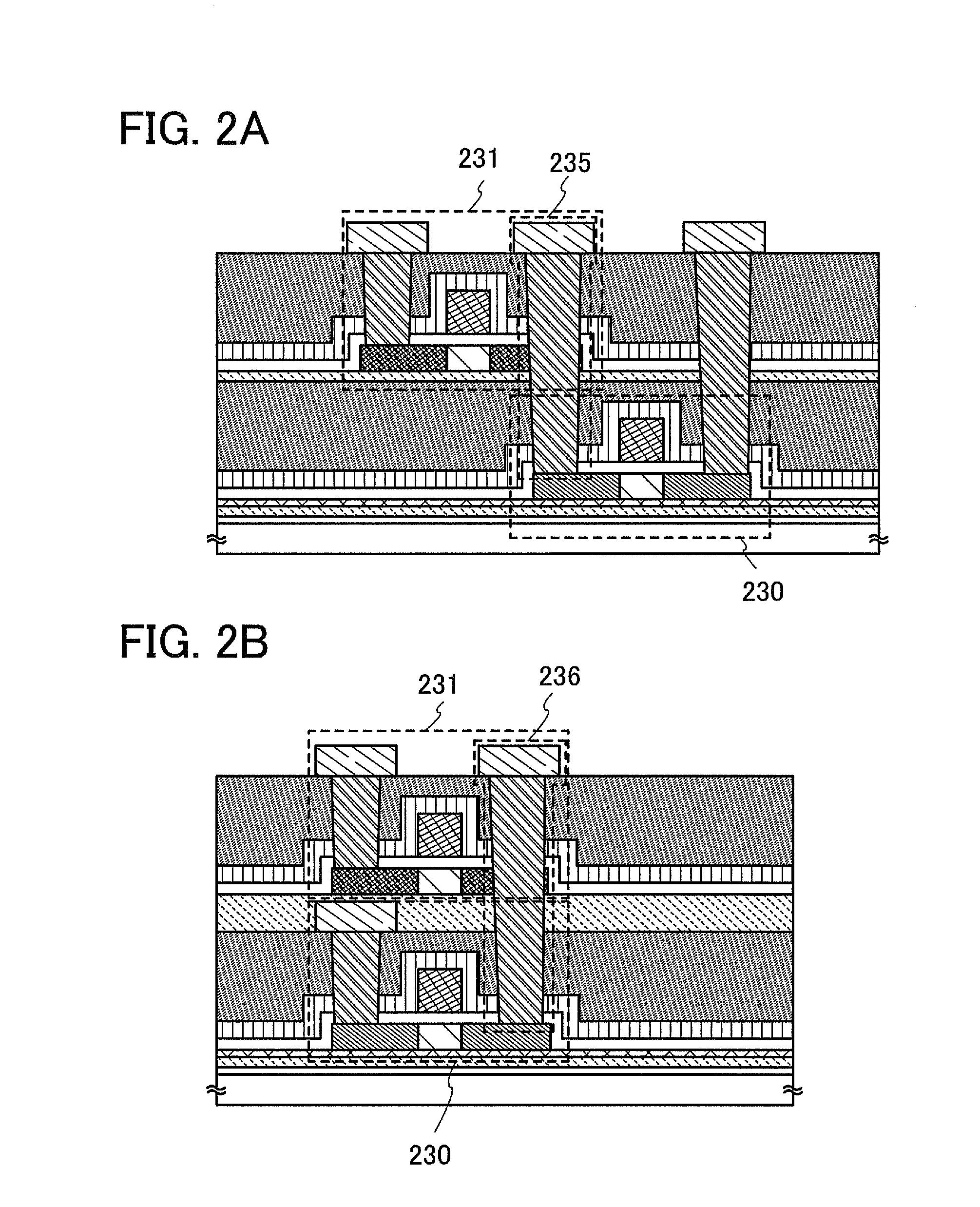

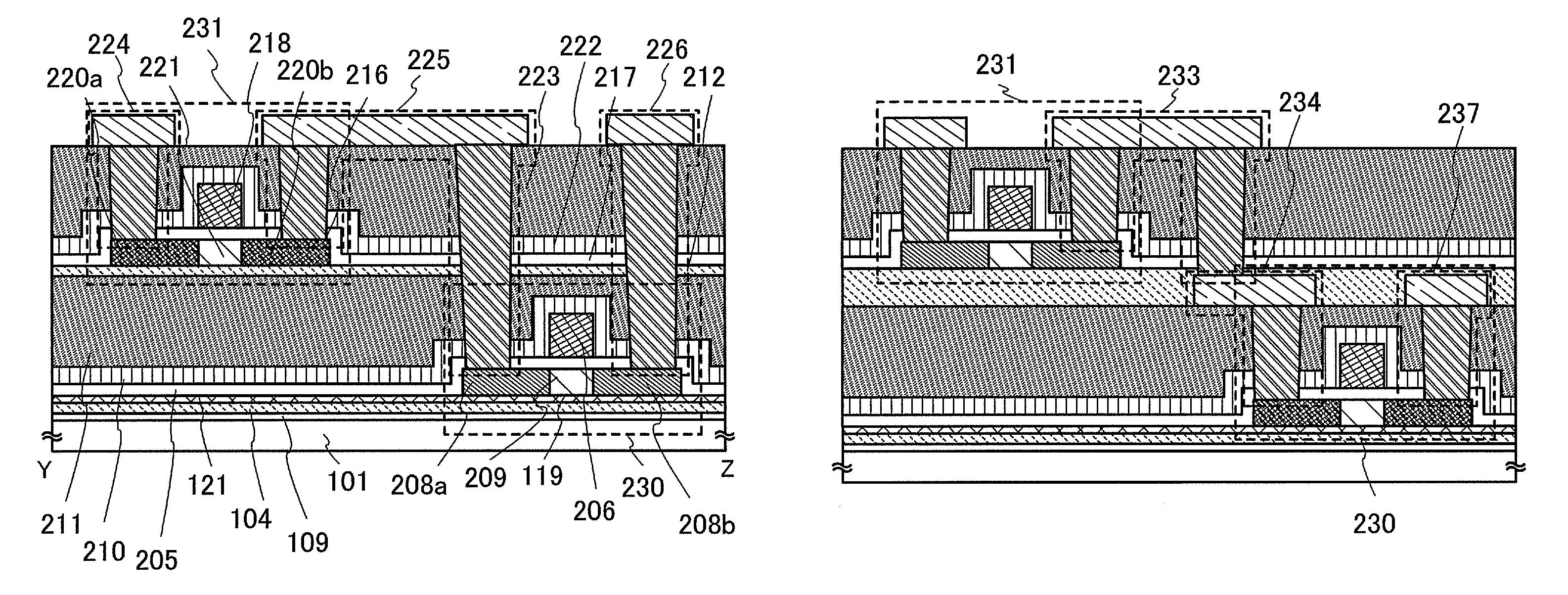

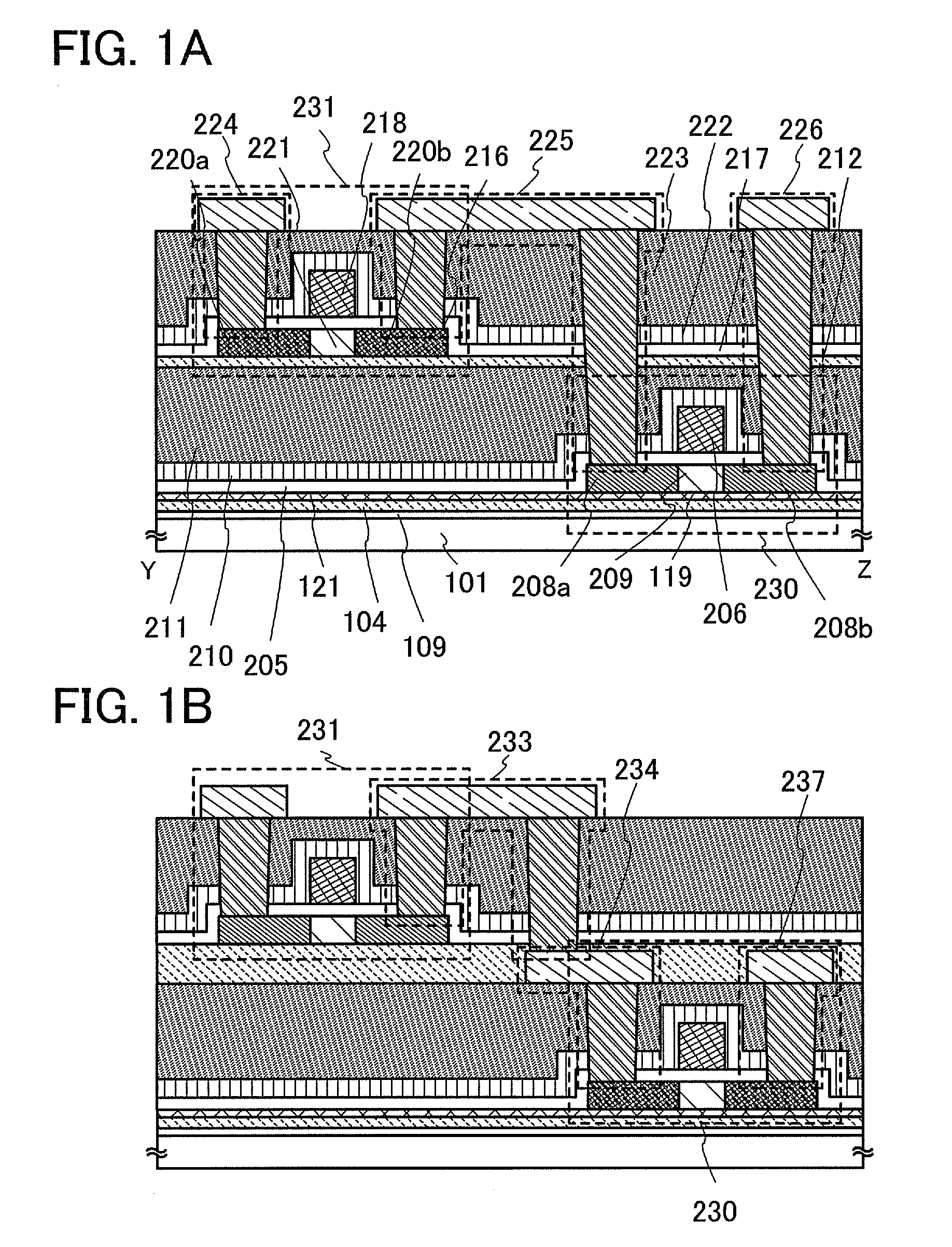

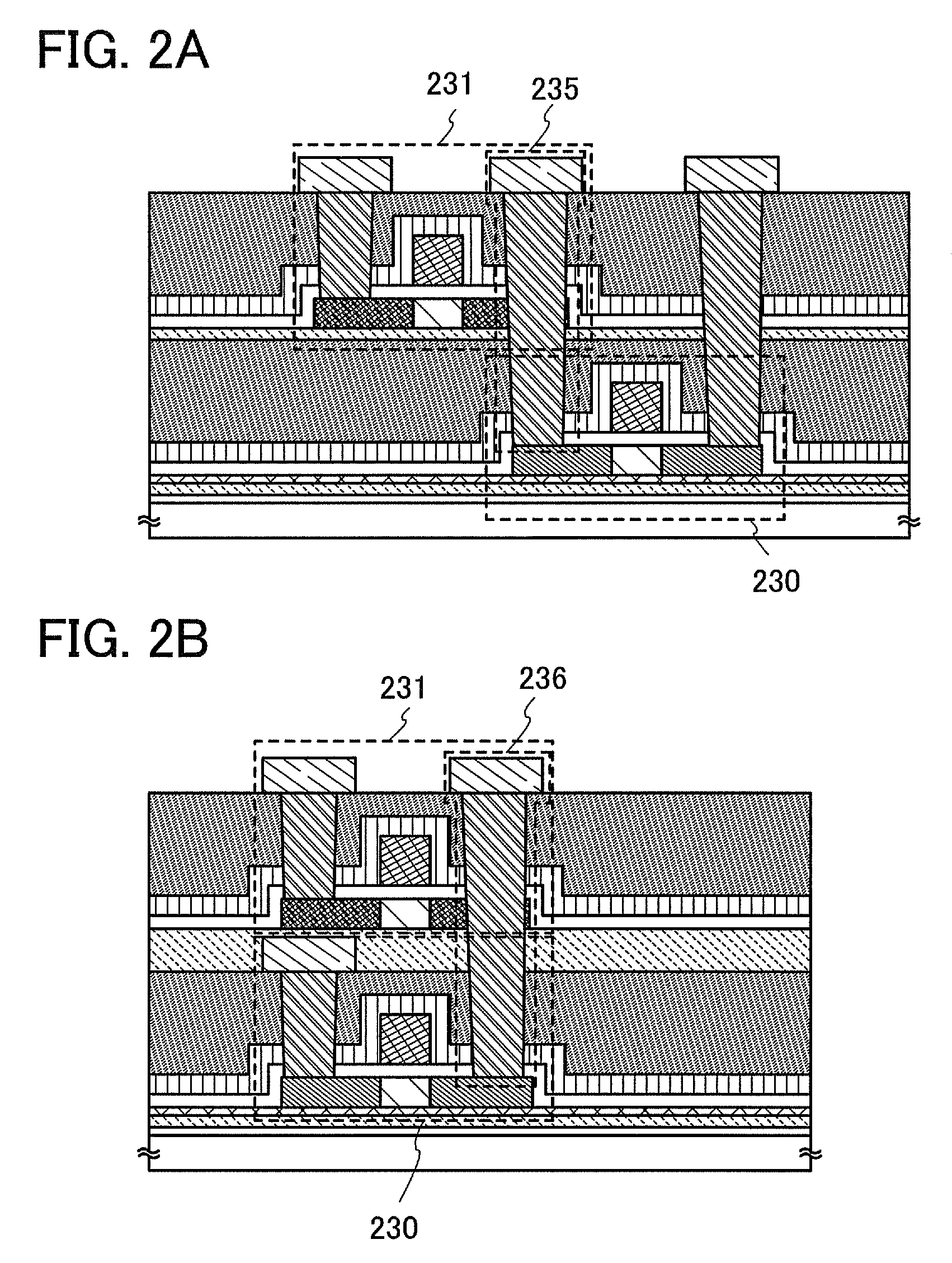

ActiveUS20090079000A1Difference in mobilityReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesDevice materialPlane orientation

An object is to realize high performance and low power consumption in a semiconductor device having an SOI structure. In addition, another object is to provide a semiconductor device having a high performance semiconductor element which is more highly integrated. A semiconductor device is such that a plurality of n-channel field-effect transistors and p-channel field-effect transistors are stacked with an interlayer insulating layer interposed therebetween over a substrate having an insulating surface. By controlling a distortion caused to a semiconductor layer due to an insulating film having a stress, a plane orientation of the semiconductor layer, and a crystal axis in a channel length direction, difference in mobility between the n-channel field-effect transistor and the p-channel field-effect transistor can be reduced, whereby current driving capabilities and response speeds of the n-channel field-effect transistor and the p-channel field-effect can be comparable.

Owner:SEMICON ENERGY LAB CO LTD

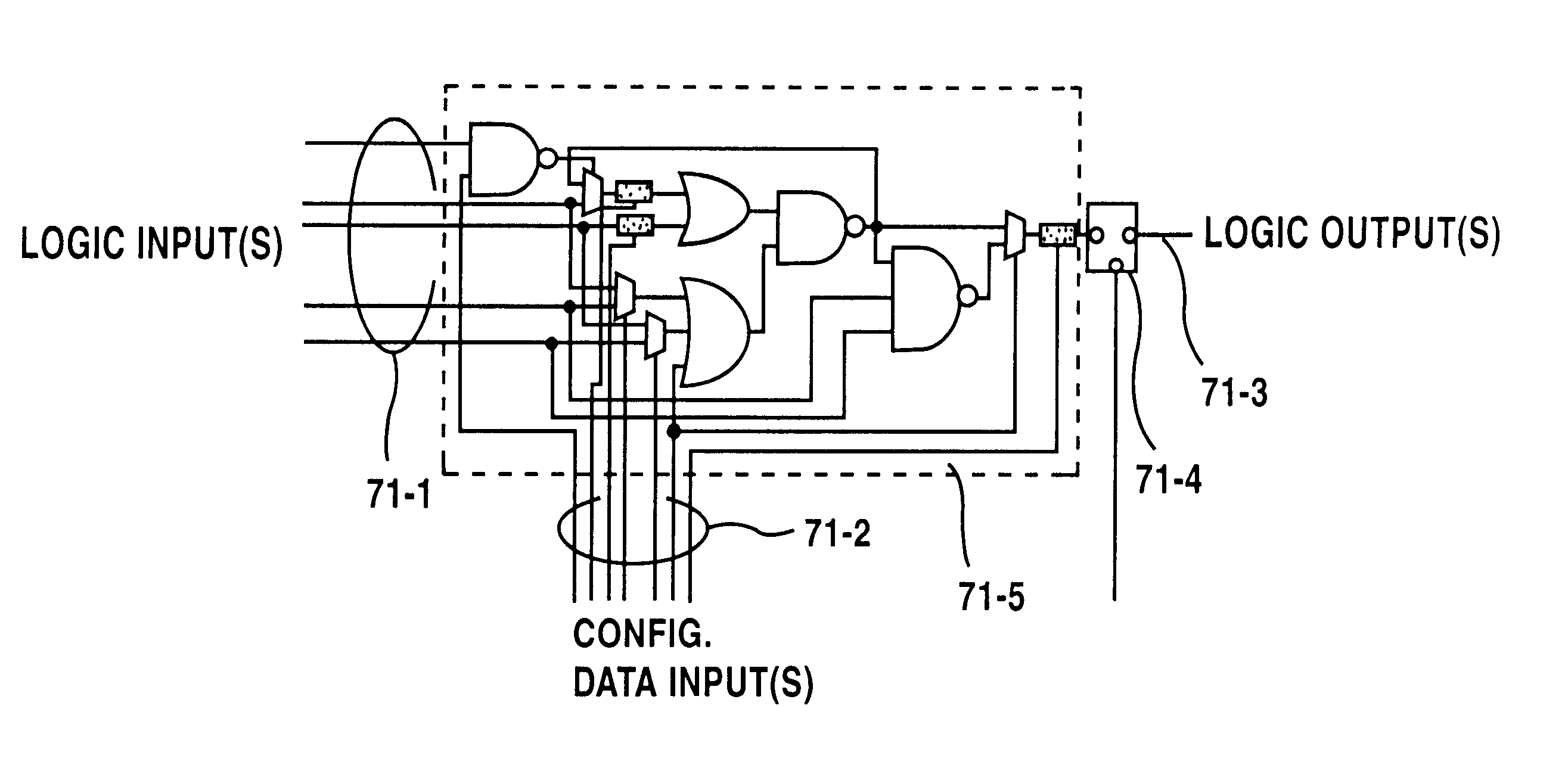

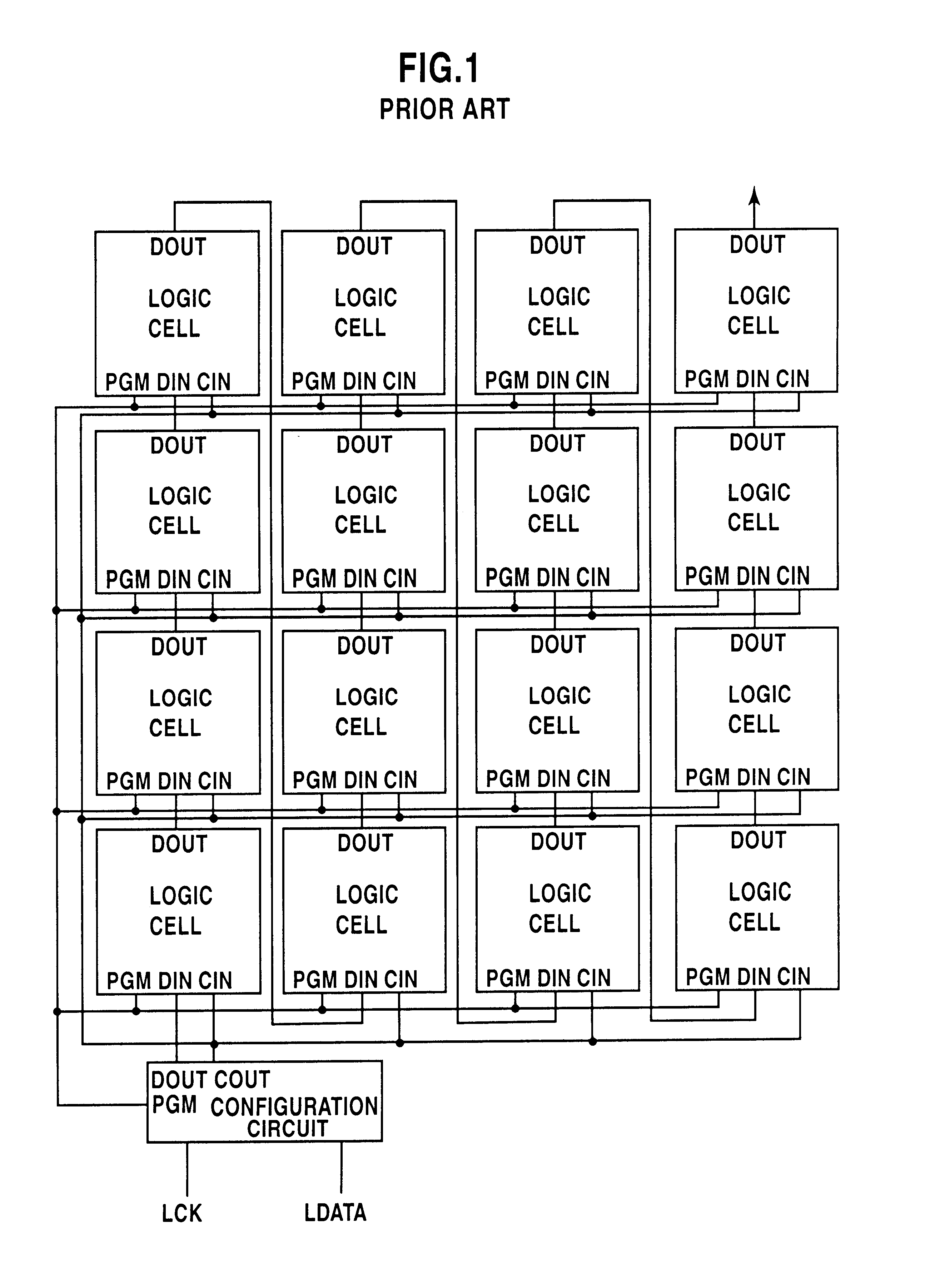

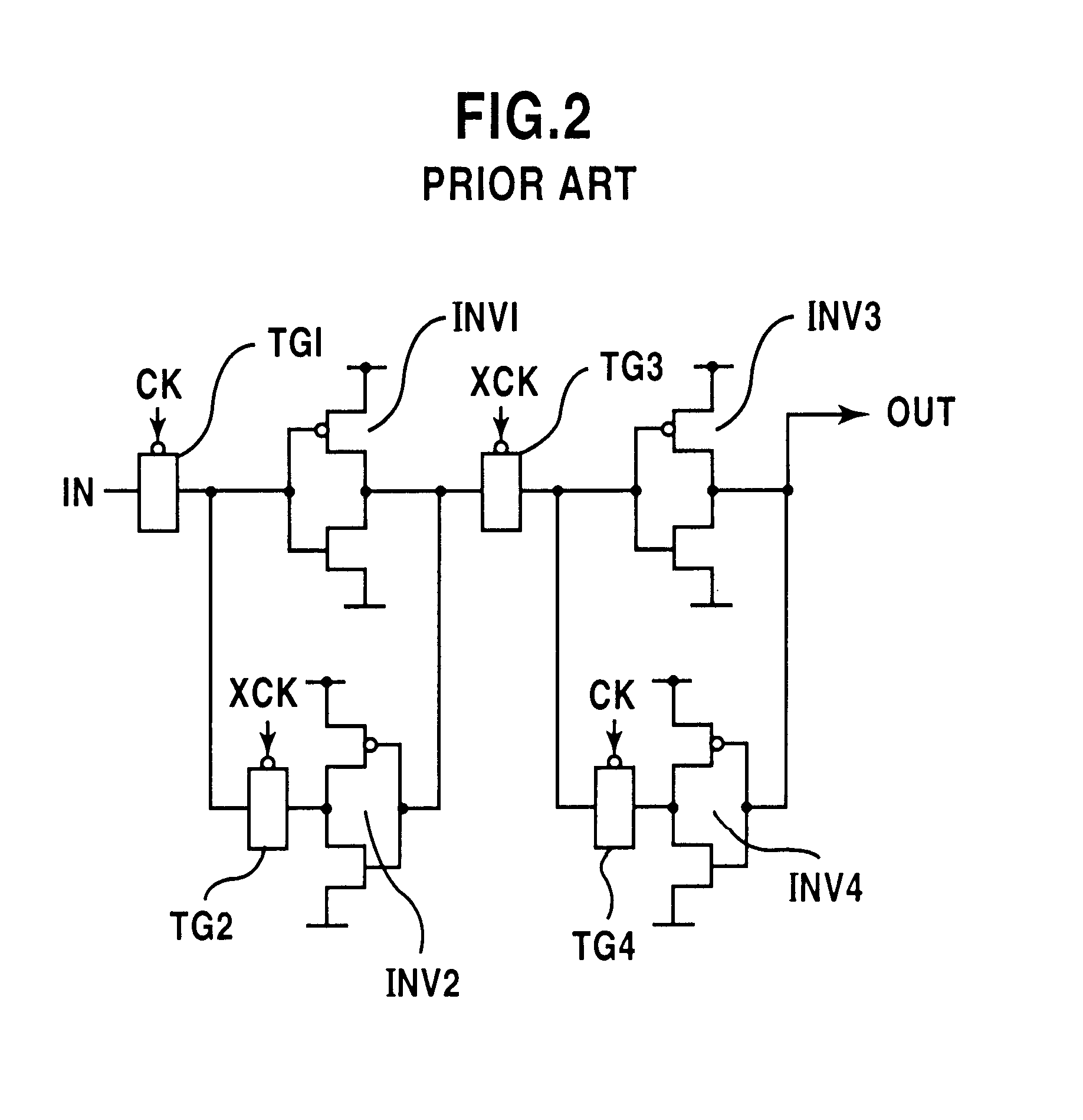

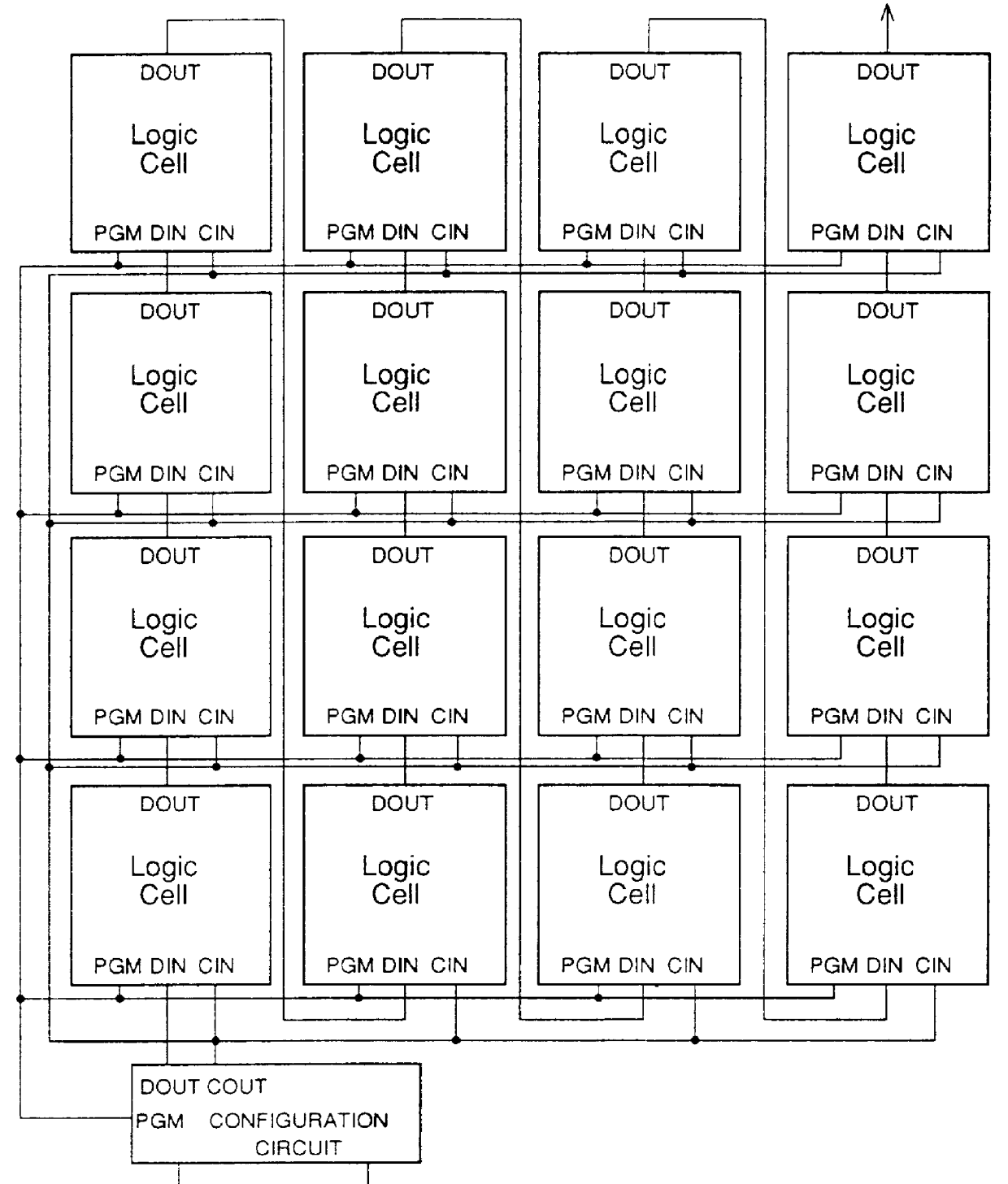

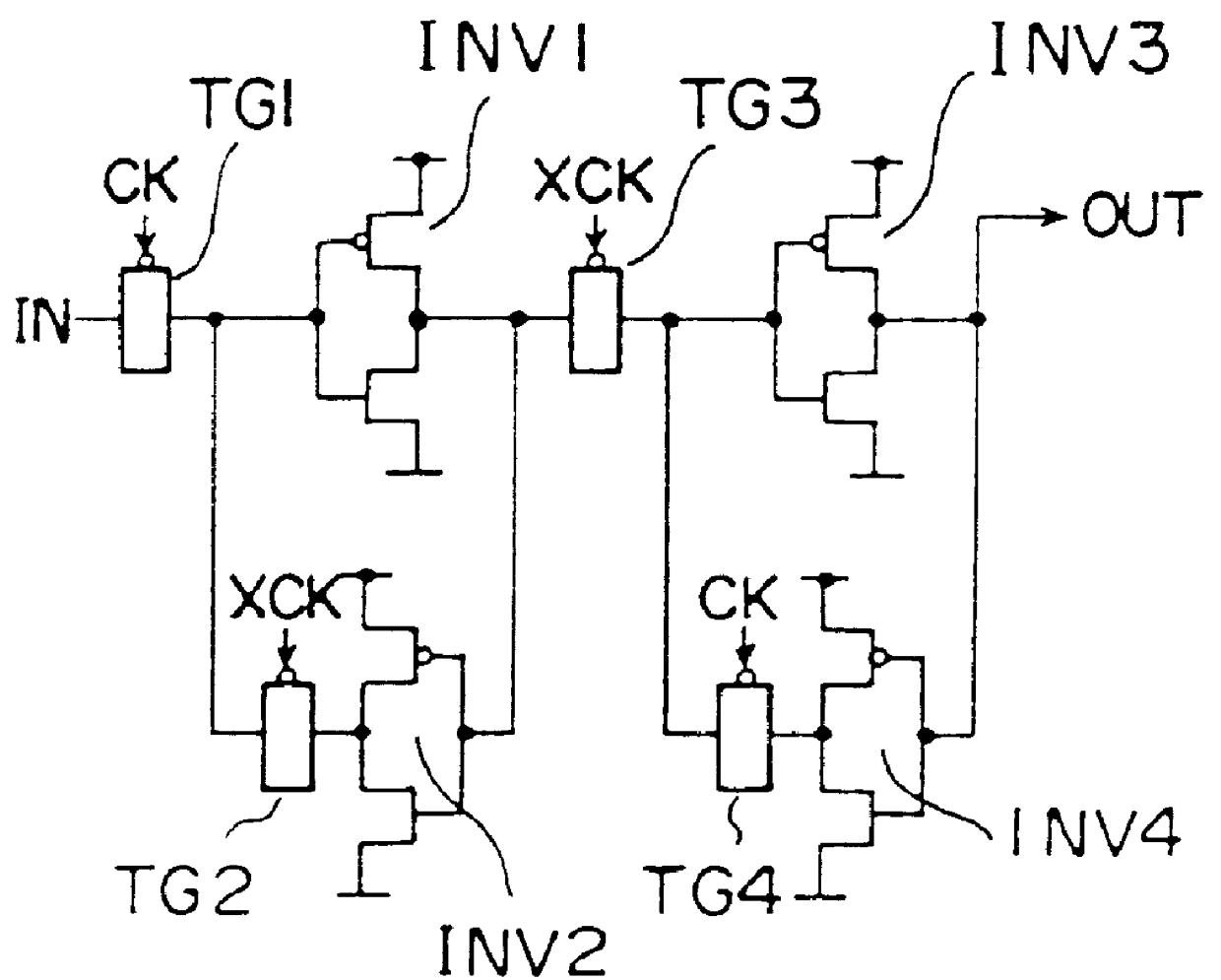

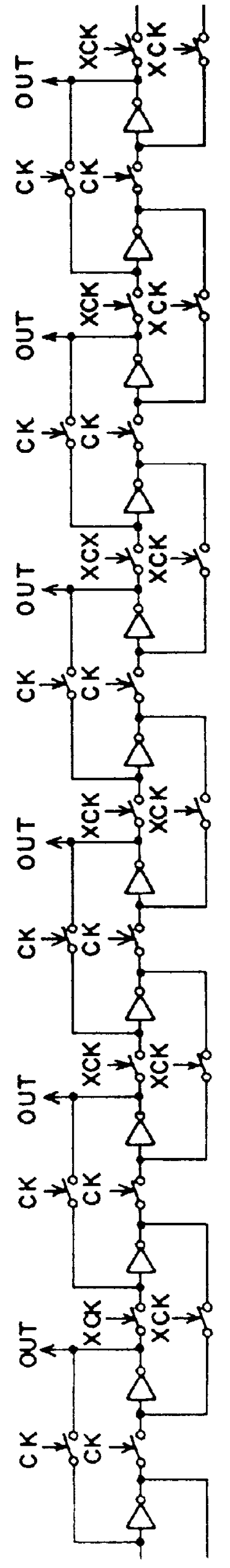

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

Semiconductor device

InactiveUS8044464B2Guaranteed high speed operationReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packagePlane orientation

Owner:SEMICON ENERGY LAB CO LTD

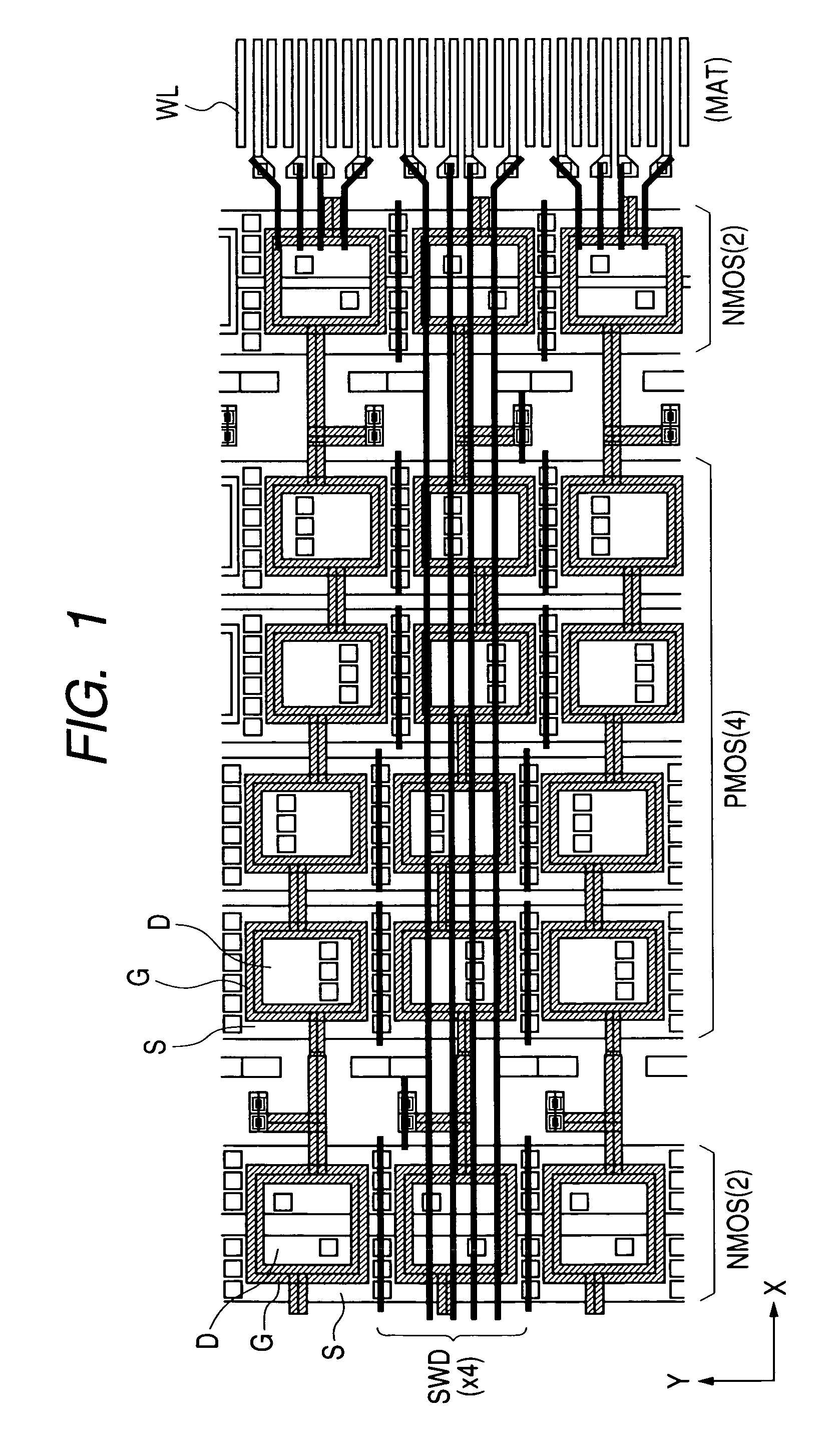

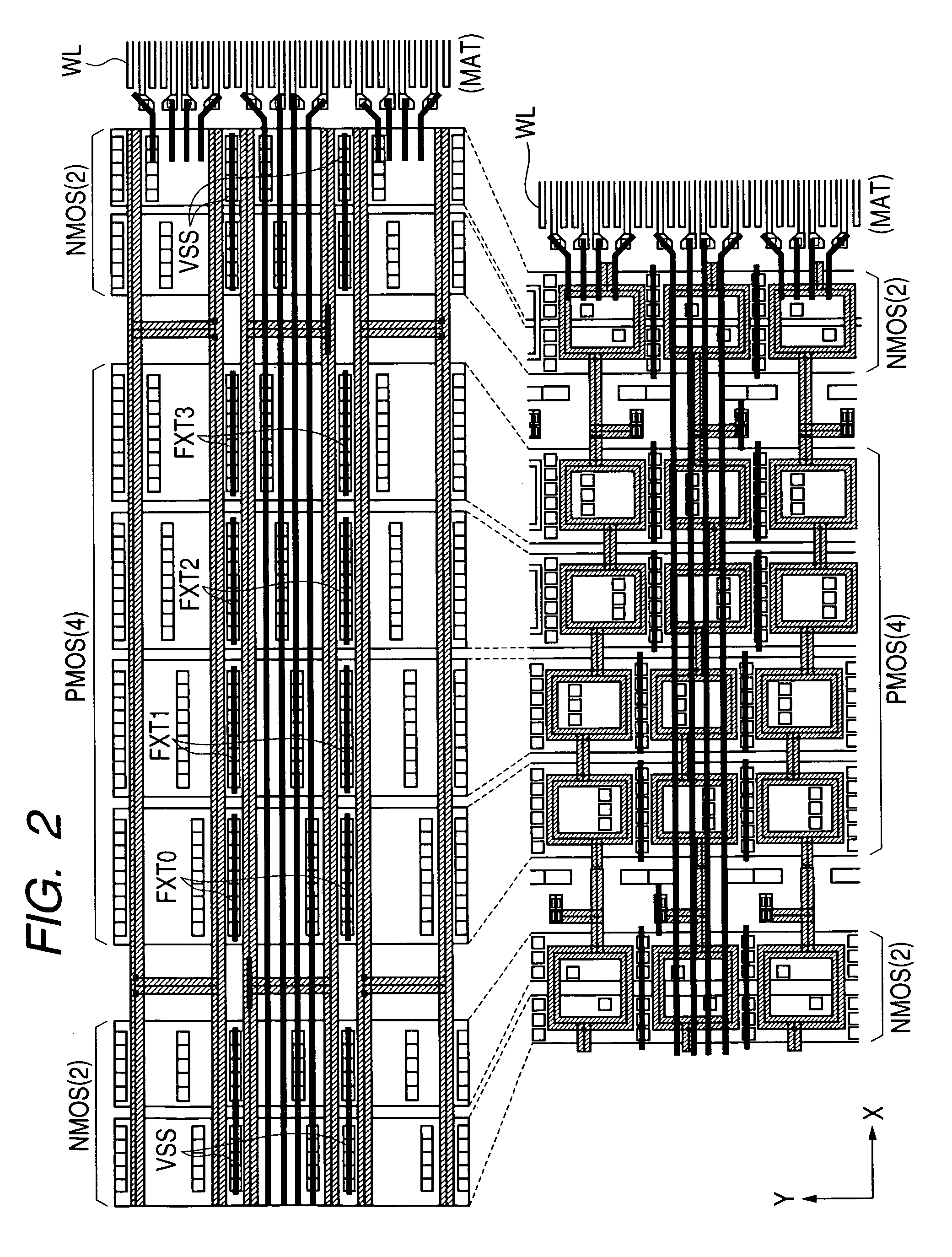

Semiconductor integrated circuit device

InactiveUS7016214B2Reduced footprintSuppress relative deviation of operation characteristicsTransistorSolid-state devicesMOSFETGate insulator

A semiconductor integrated circuit device capable of achieving higher integration and simplification of manufacturing processes is provided. Circuitry is provided which includes a first N-channel MOSFET and a first p-channel MOSFET each having a gate insulating dielectric film with a first film thickness, wherein a poly-silicon layer making up a gate electrode is doped with an N-type impurity. The circuitry also includes a second N-channel MOSFET having a gate insulator film with a second film thickness thinner than the first thickness, wherein an N-type impurity is doped into a polysilicon layer making up a gate electrode, and a second P-channel MOSFET with a P-type impurity being doped into a polysilicon layer making up a gate electrode. The gate electrodes of the first N-channel MOSFET and first P-channel MOSFET are integrally formed and mutually connected together.

Owner:HITACHI LTD

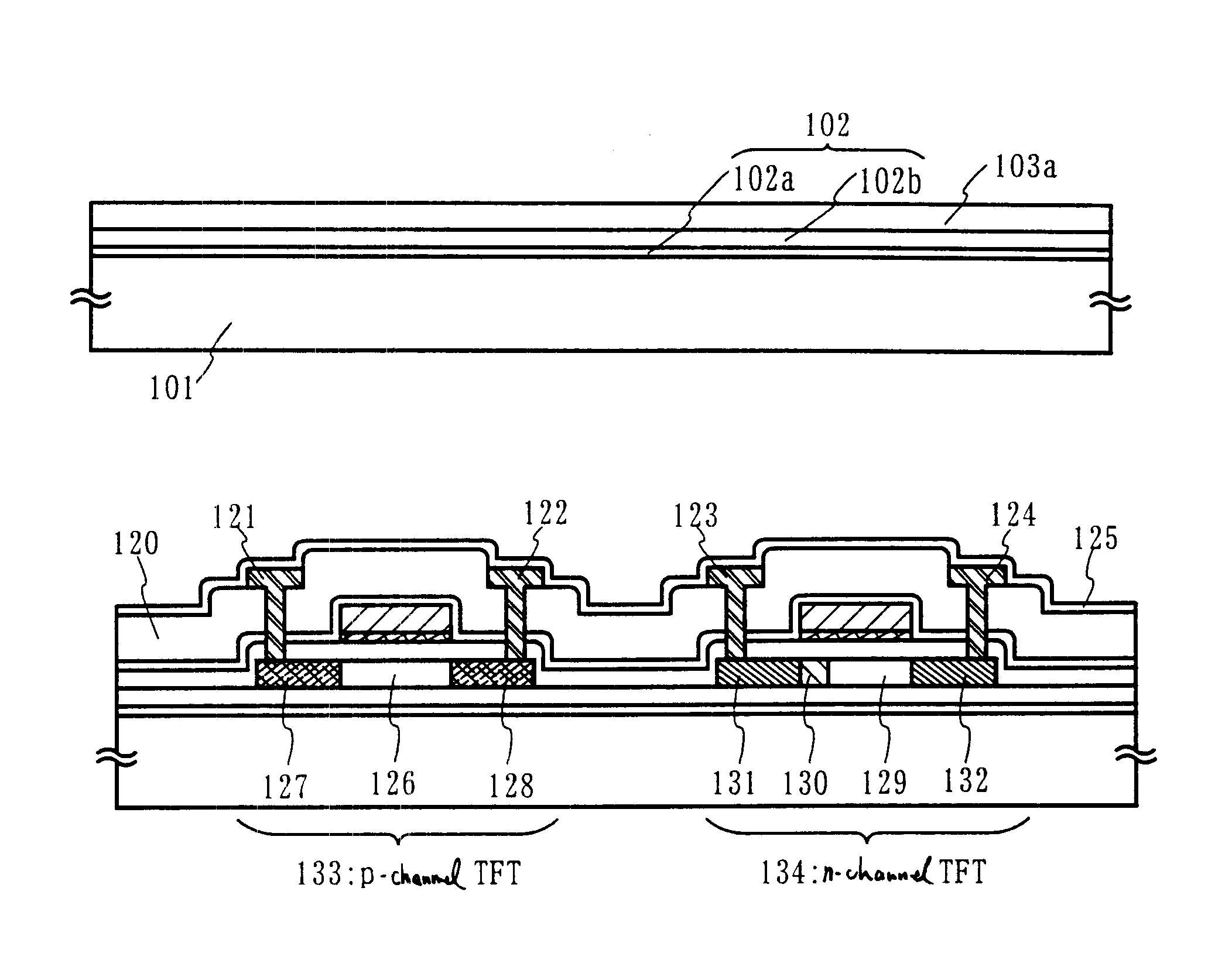

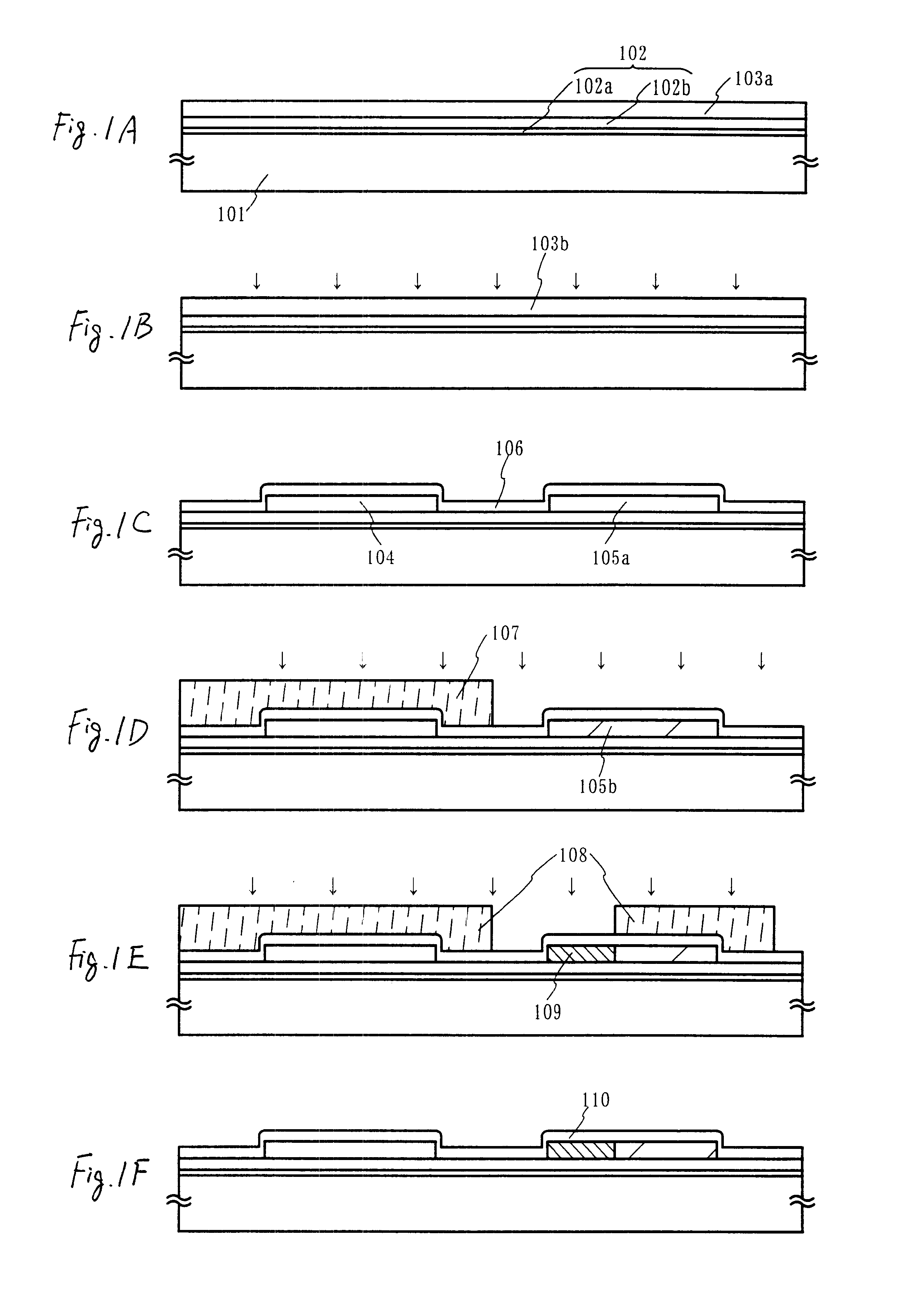

Oxynitride laminate "blocking layer" for thin film semiconductor devices

Channel doping is an effective method for controlling Vth, but if Vth shifts to the order of -4 to -3 V when forming circuits such as a CMOS circuit formed from both an n-channel TFT and a P-channel TFT on the same substrate, then it is difficult to control the Vth of both TFTs with one channel dope. In order to solve the above problem, the present invention forms a blocking layer on the back channel side, which is a laminate of a silicon oxynitride film (A) manufactured from SiH4, NH3, and N2O, and a silicon oxynitride film (B)manufactured from SiH4and N2O. By making this silicon oxynitride film laminate structure, contamination by alkaline metallic elements from the substrate can be prevented, and influence by stresses, caused by internal stress, imparted to the TFT can be relieved.

Owner:SEMICON ENERGY LAB CO LTD

Chain-connected shift register and programmable logic circuit whose logic function is changeable in real time

InactiveUS6018559ADigital storageLogic circuits using elementary logic circuit componentsShift registerTransmission gate

A shift register having a plurality of circuit cells successively connected in a chain formation is proposed. Each of the circuit cells includes a first inversion gate, a first transmission gate, connected to an output of the first inversion gate, being switched by a clock, and a second inversion gate connected to an output of the first transmission gate. The circuit cell further includes a first P-channel transistor, connected between an output of the second inversion gate and an input of the first inversion gate, being switched by the clock, a second transmission gate, connected to the output of the second inversion gate, being switched by an inversion clock, and a second P-channel transistor, connected to the output of the first transmission gate, being switched by the inversion clock. In the shift register, the plurality of circuit cells are successively connected such that the input of the first inversion gate of the circuit cell is connected to an output of a second transmission gate of a former-stage circuit cell, and the output of the first inversion gate of the circuit cell is connected to an output of a second P-channel transistor of the former-stage circuit cell.

Owner:FUJITSU LTD

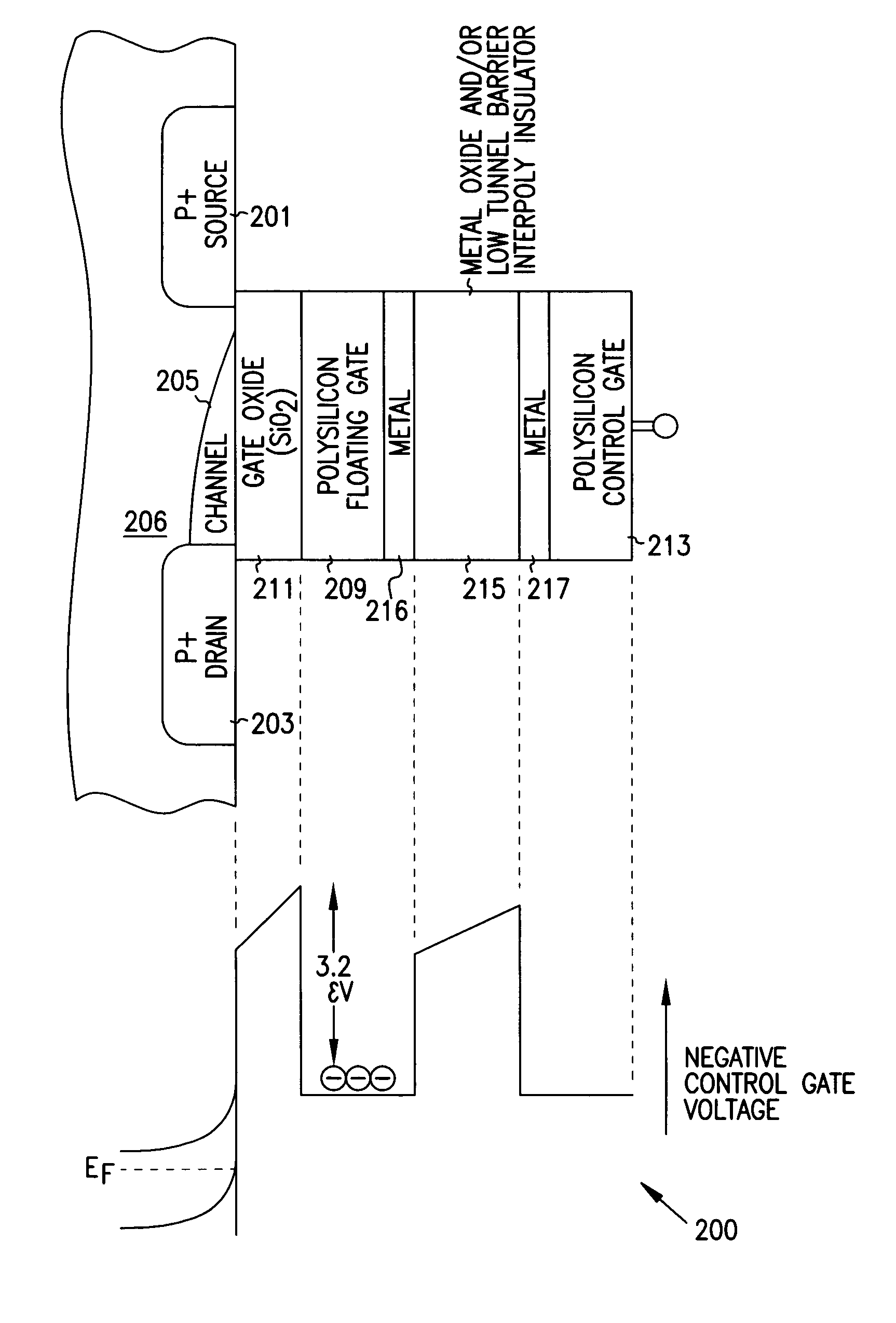

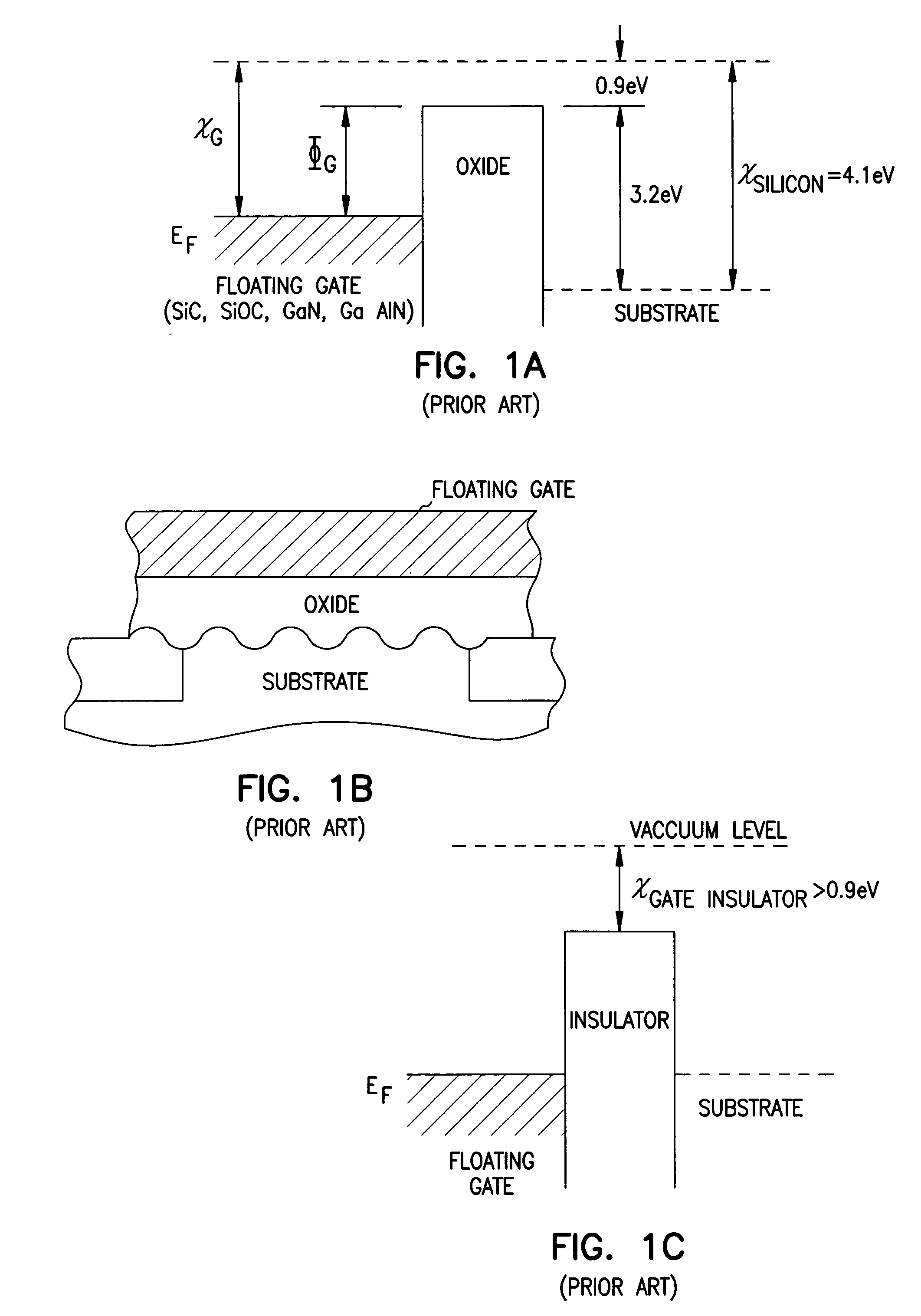

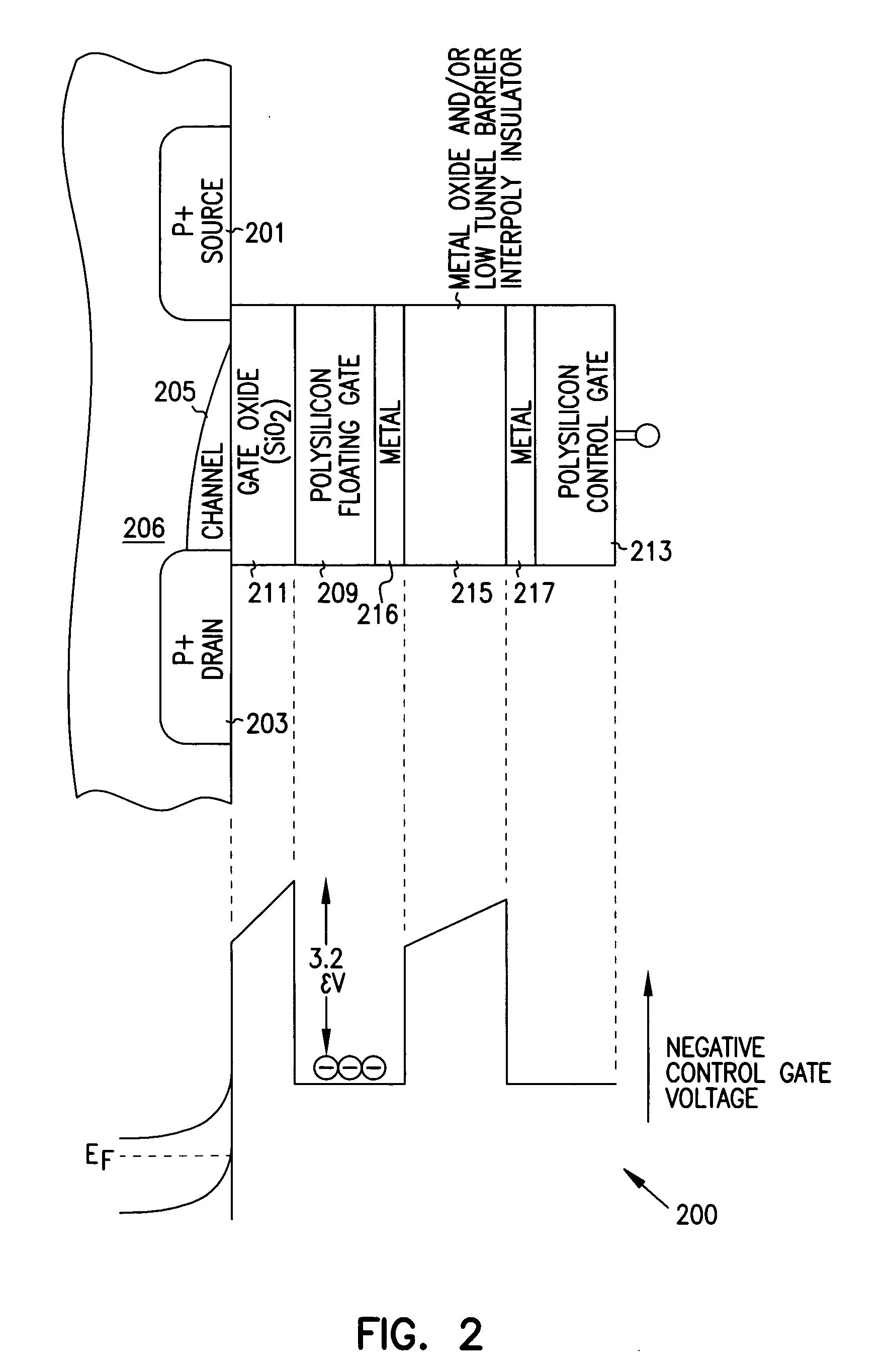

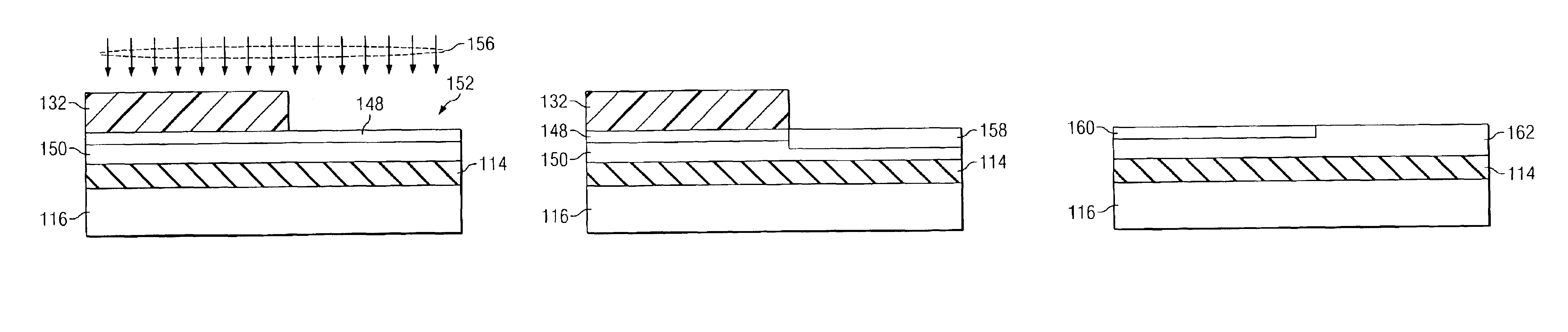

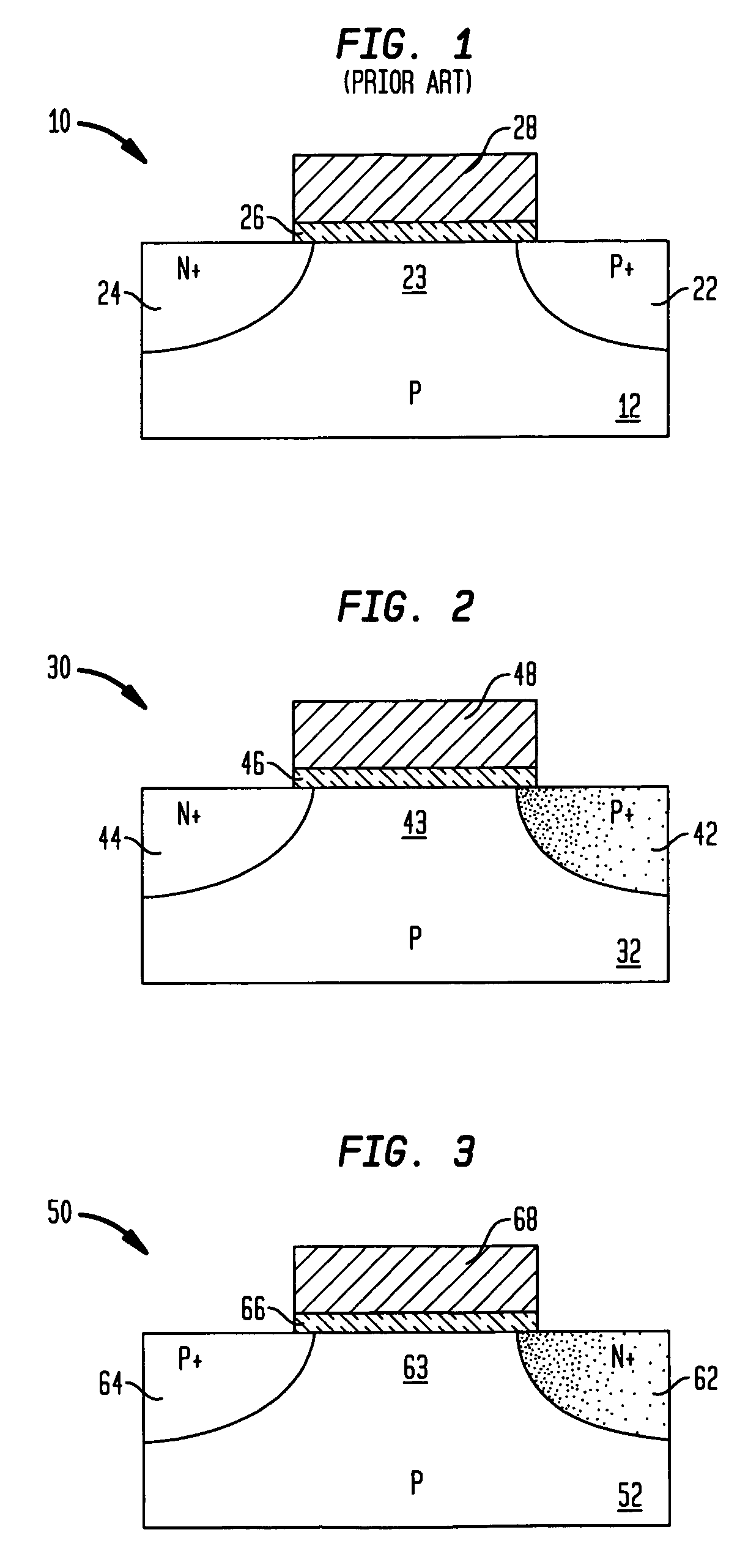

Programmable array logic or memory with p-channel devices and asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory with p-channel devices and asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include p-channel non-volatile memory which has a first source / drain region and a second source / drain region separated by a p-type channel region in an n-type substrate. A floating gate opposing the p-type channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Silicon-on-insulator chip with multiple crystal orientations

A silicon-on-insulator chip includes an insulator layer, typically formed over a substrate. A first silicon island with a surface of a first crystal orientation overlies the insulator layer and a second silicon island with a surface of a second crystal orientation also overlies the insulator layer. In one embodiment, the silicon-on-insulator chip also includes a first transistor of a first conduction type formed on the first silicon island, and a second transistor of a second conduction type formed on the second silicon island. For example, the first crystal orientation can be (110) while the first transistor is a p-channel transistor, and the second crystal orientation can be (100) while the second transistor is an n-channel transistor.

Owner:TAIWAN SEMICON MFG CO LTD

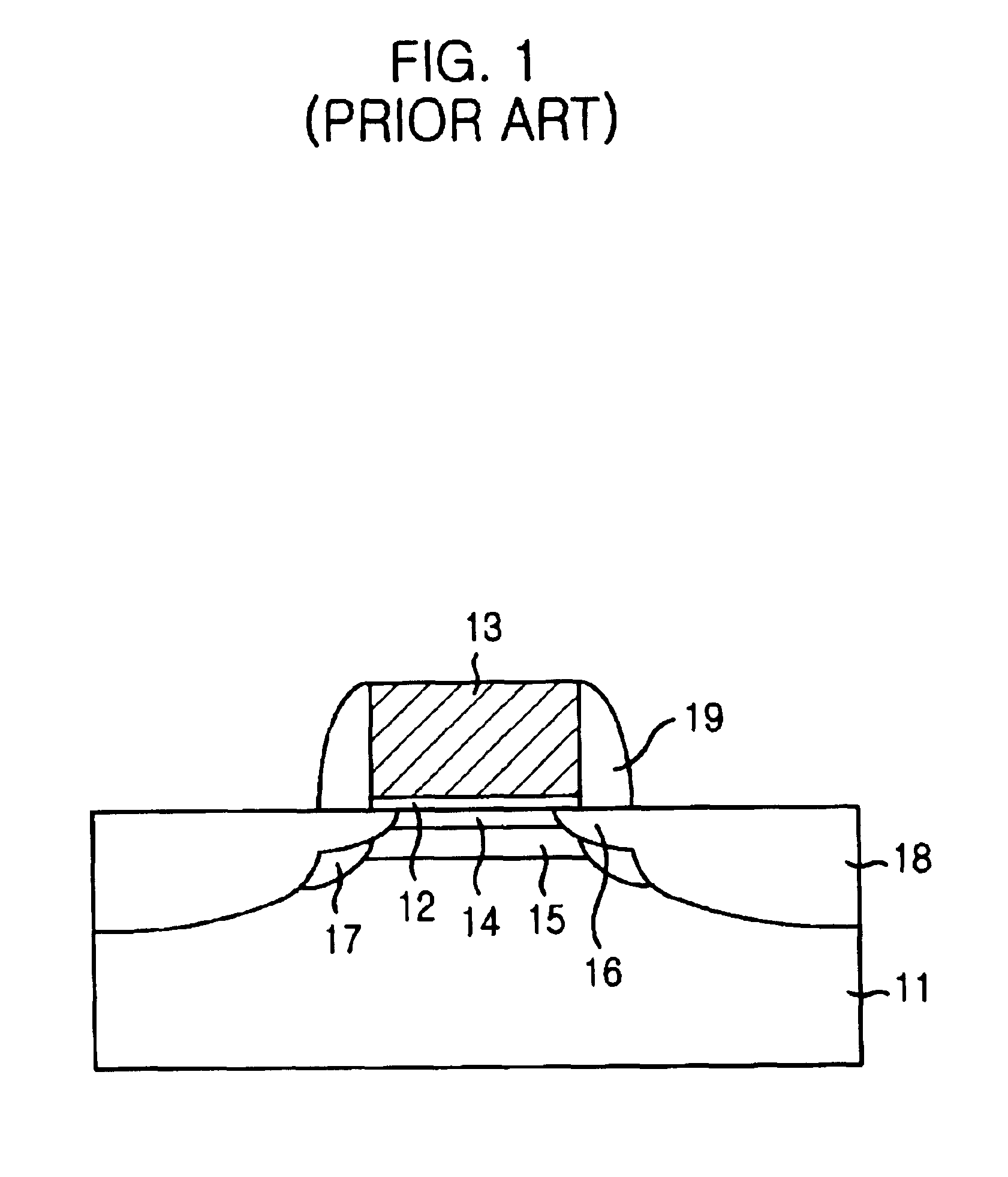

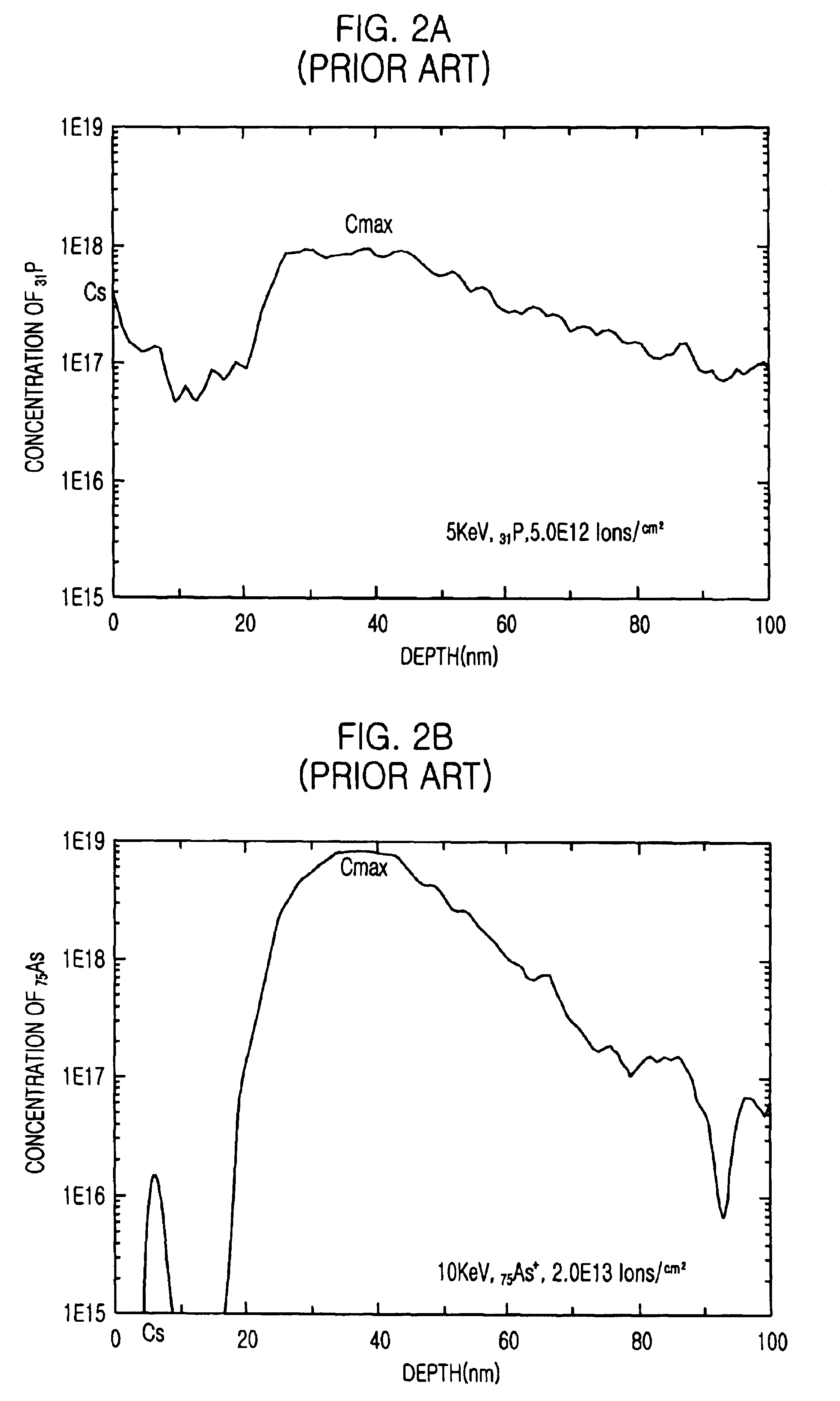

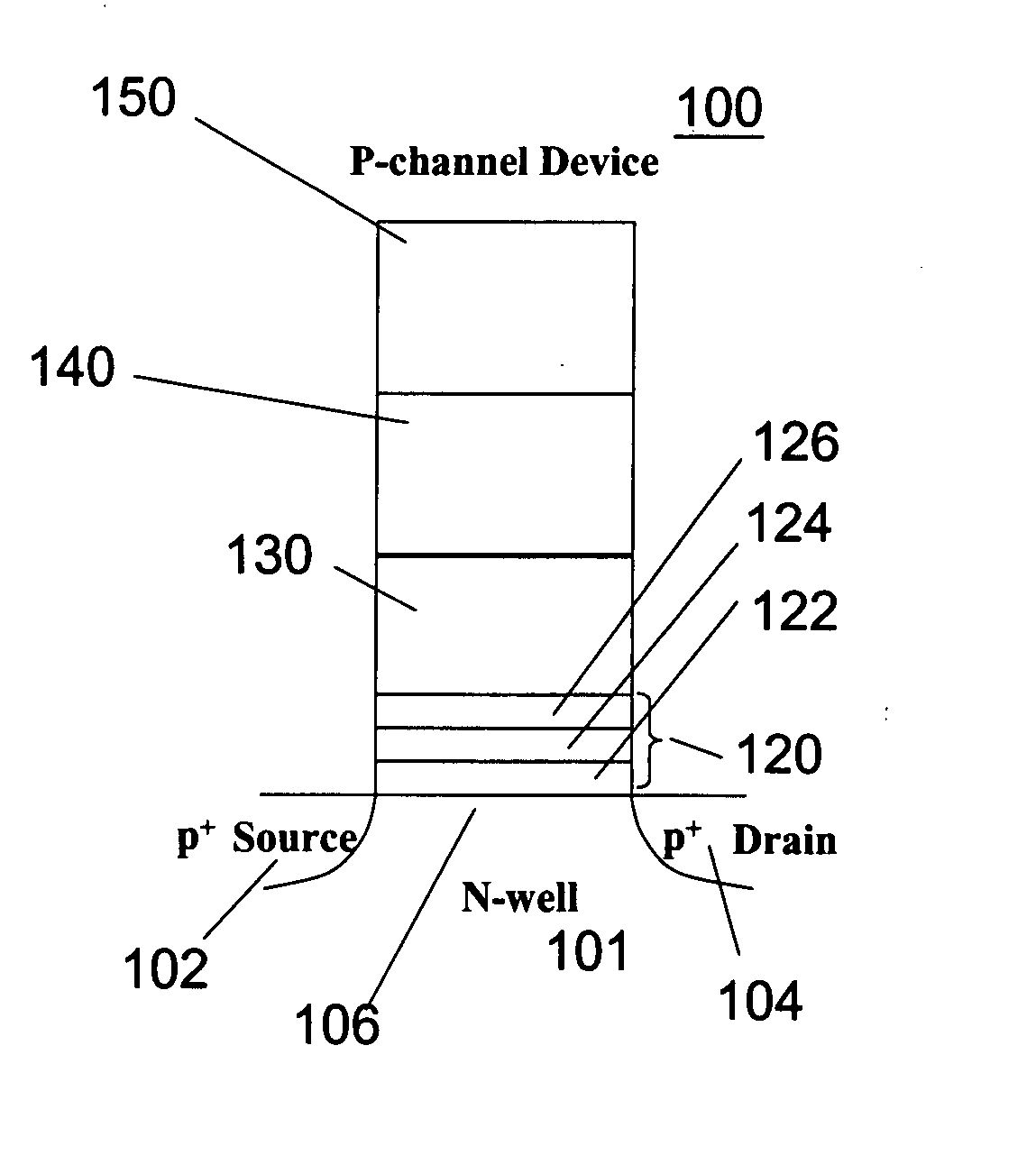

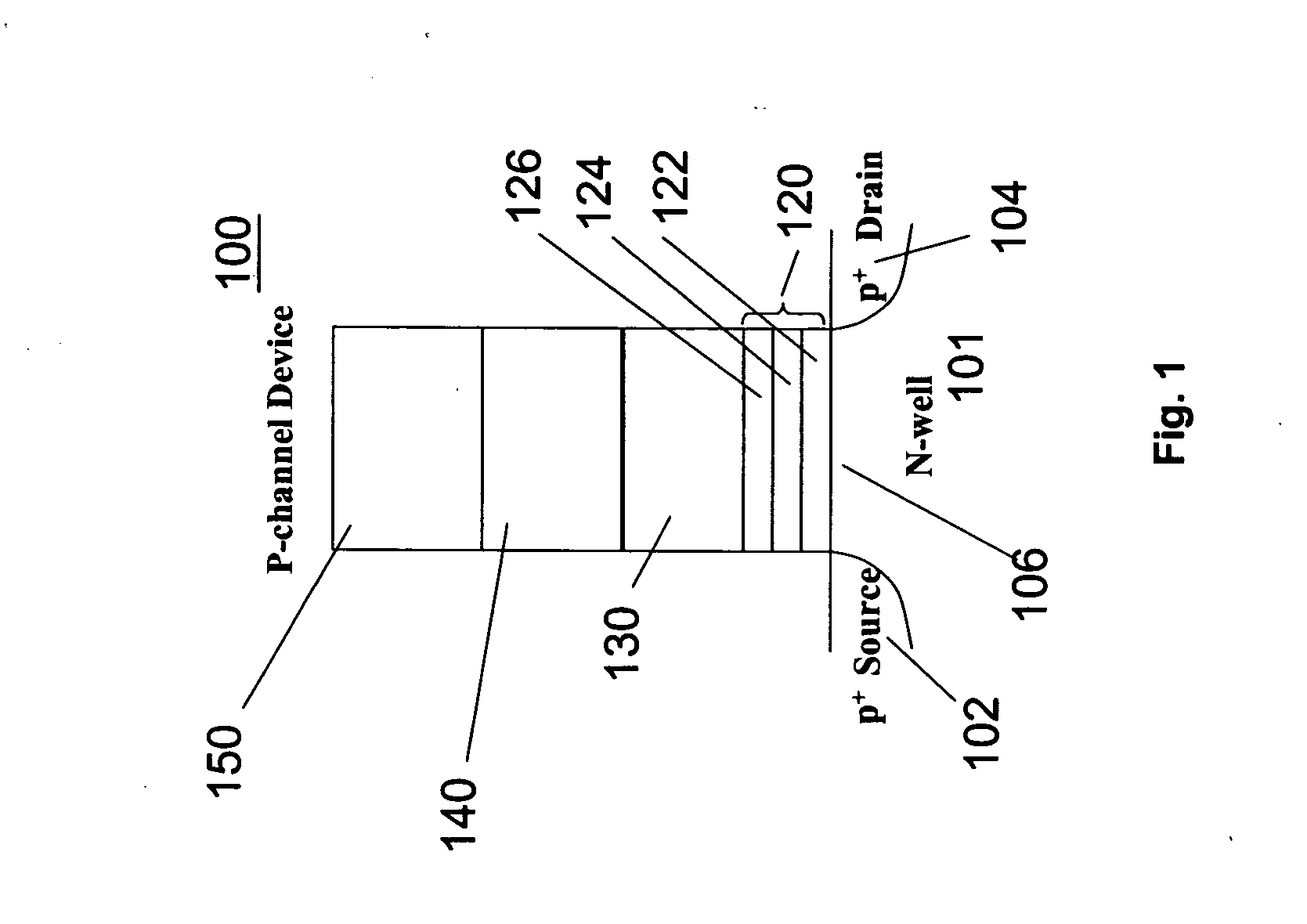

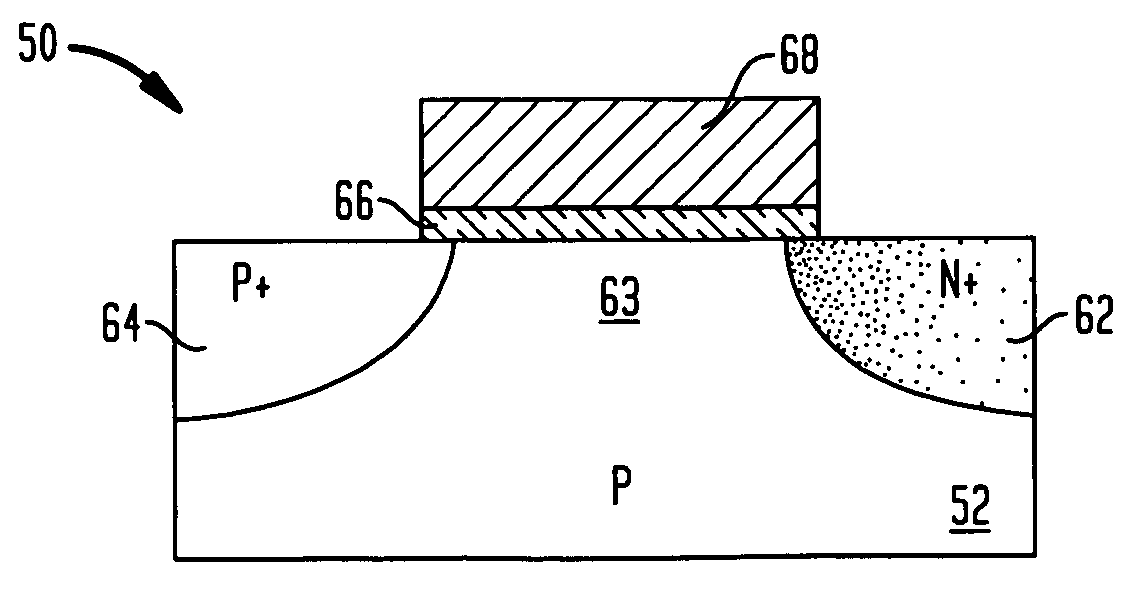

pMOS device having ultra shallow super-steep-retrograde epi-channel with dual channel doping and method for fabricating the same

InactiveUS6881987B2Semiconductor/solid-state device manufacturingSemiconductor devicesDopantP channel

The present invention provides a p-channel metal-oxide-semiconductor (pMOS) device having an ultra shallow epi-channel satisfying a high doping concentration required for a device of which gate length is about 30 nm even without using a HALO doping layer and a method for fabricating the same. The pMOS device includes: a semiconductor substrate; a channel doping layer being formed in a surface of the semiconductor substrate and being dually doped with dopants having different diffusion rates; a silicon epi-layer being formed on the channel doping layer, whereby constructing an epi-channel along with the channel doping layer; a gate insulating layer formed on the silicon epi-layer; a gate electrode formed on the gate insulating layer; a source / drain extension region highly concentrated and formed in the semiconductor substrate of lateral sides of the epi-channel; and a source / drain region electrically connected to the source / drain extension region and deeper than the source / drain region.

Owner:SK HYNIX INC

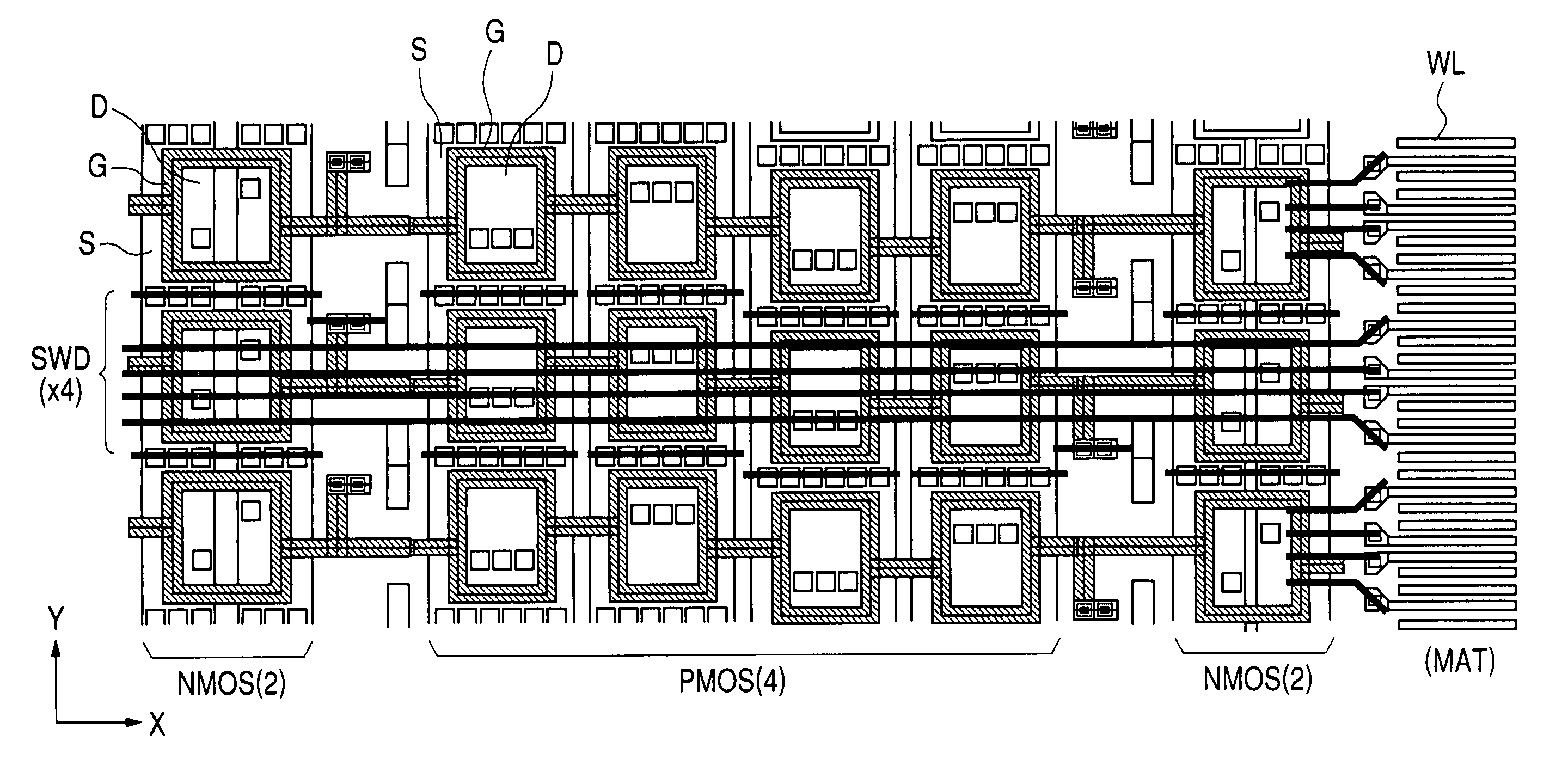

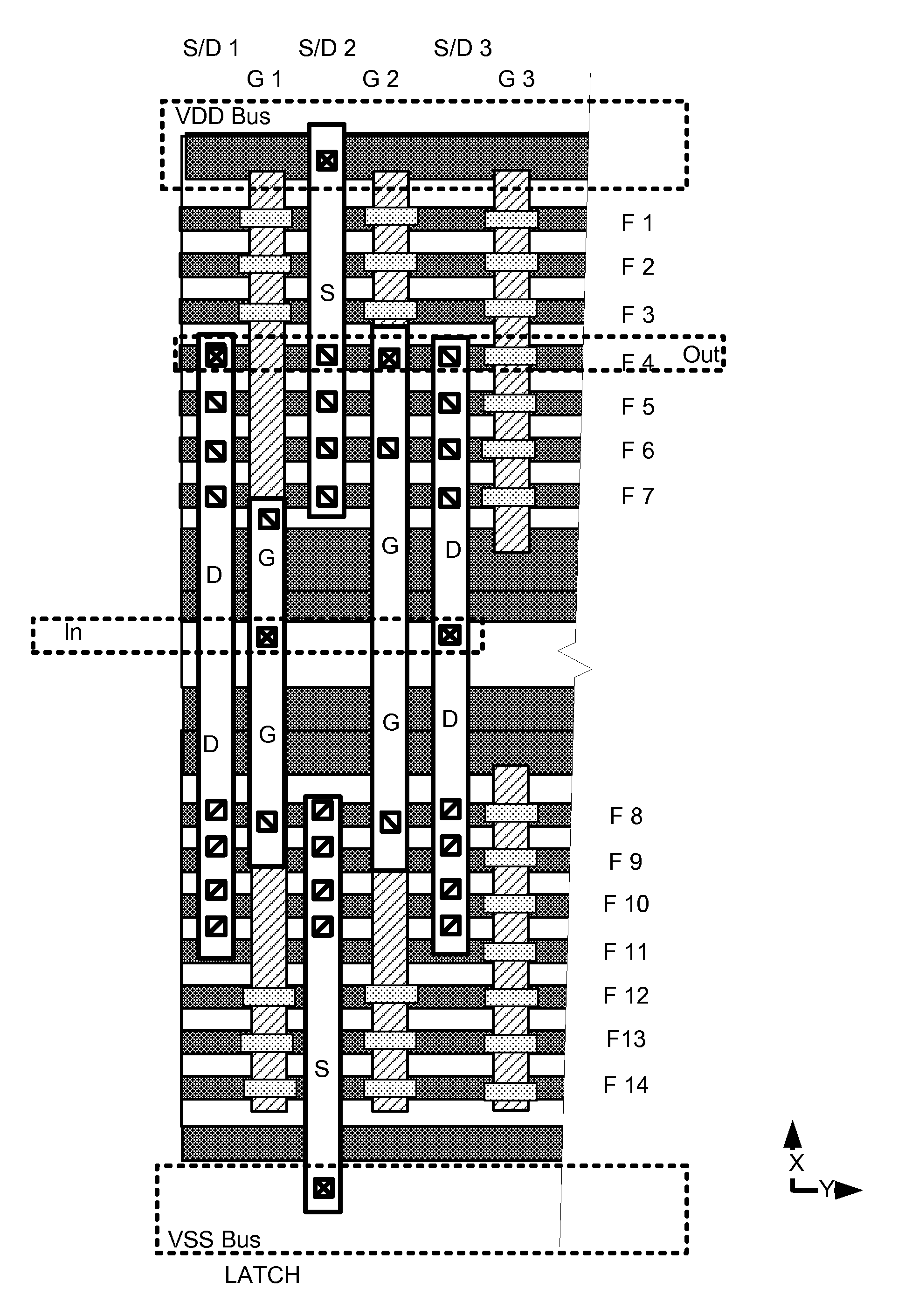

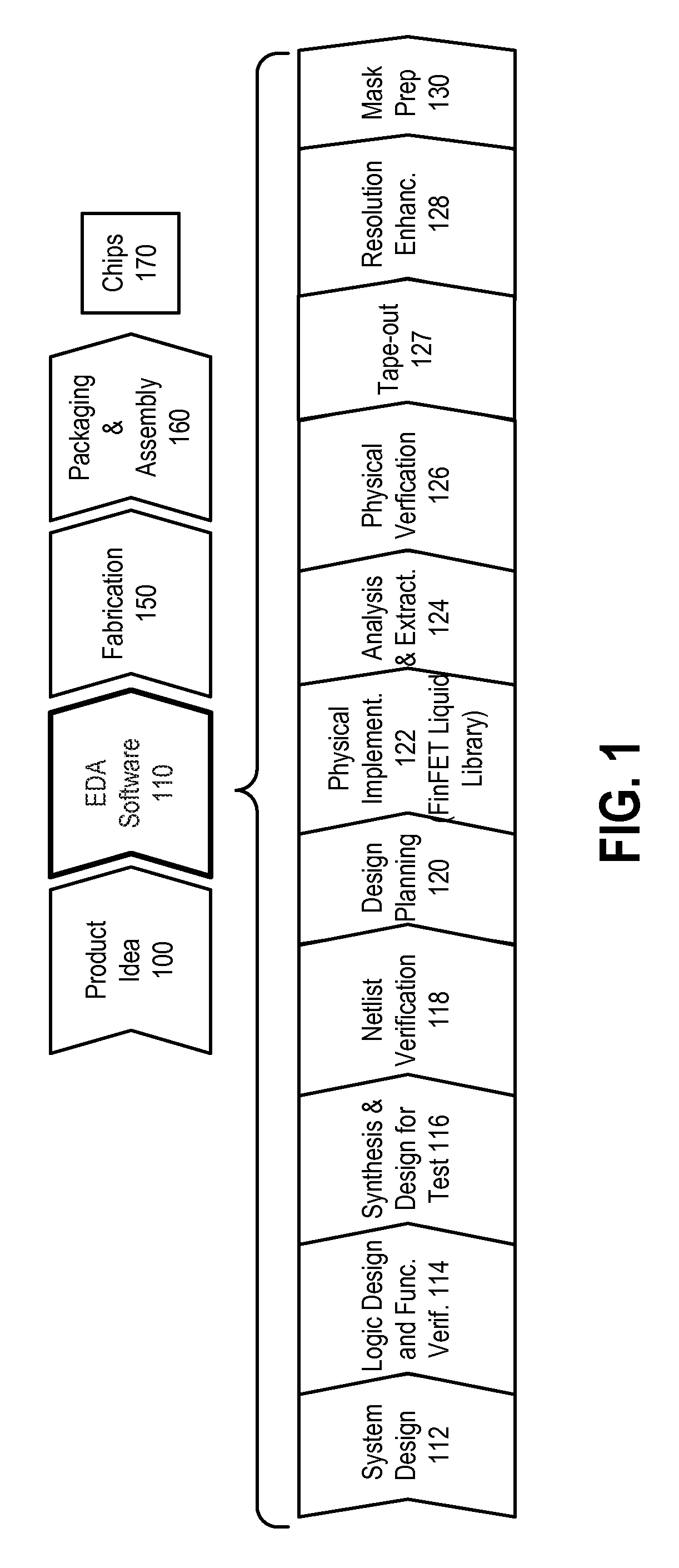

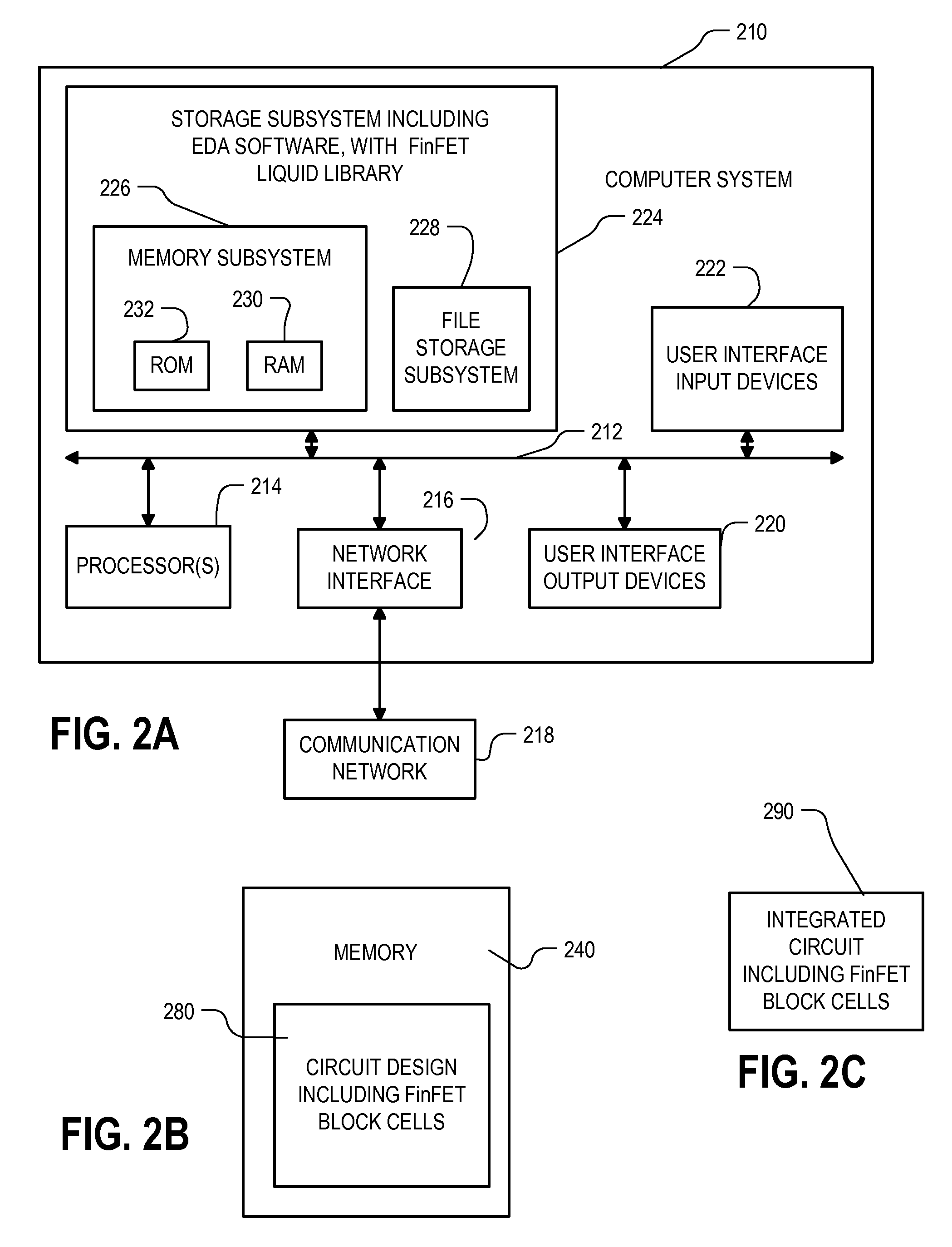

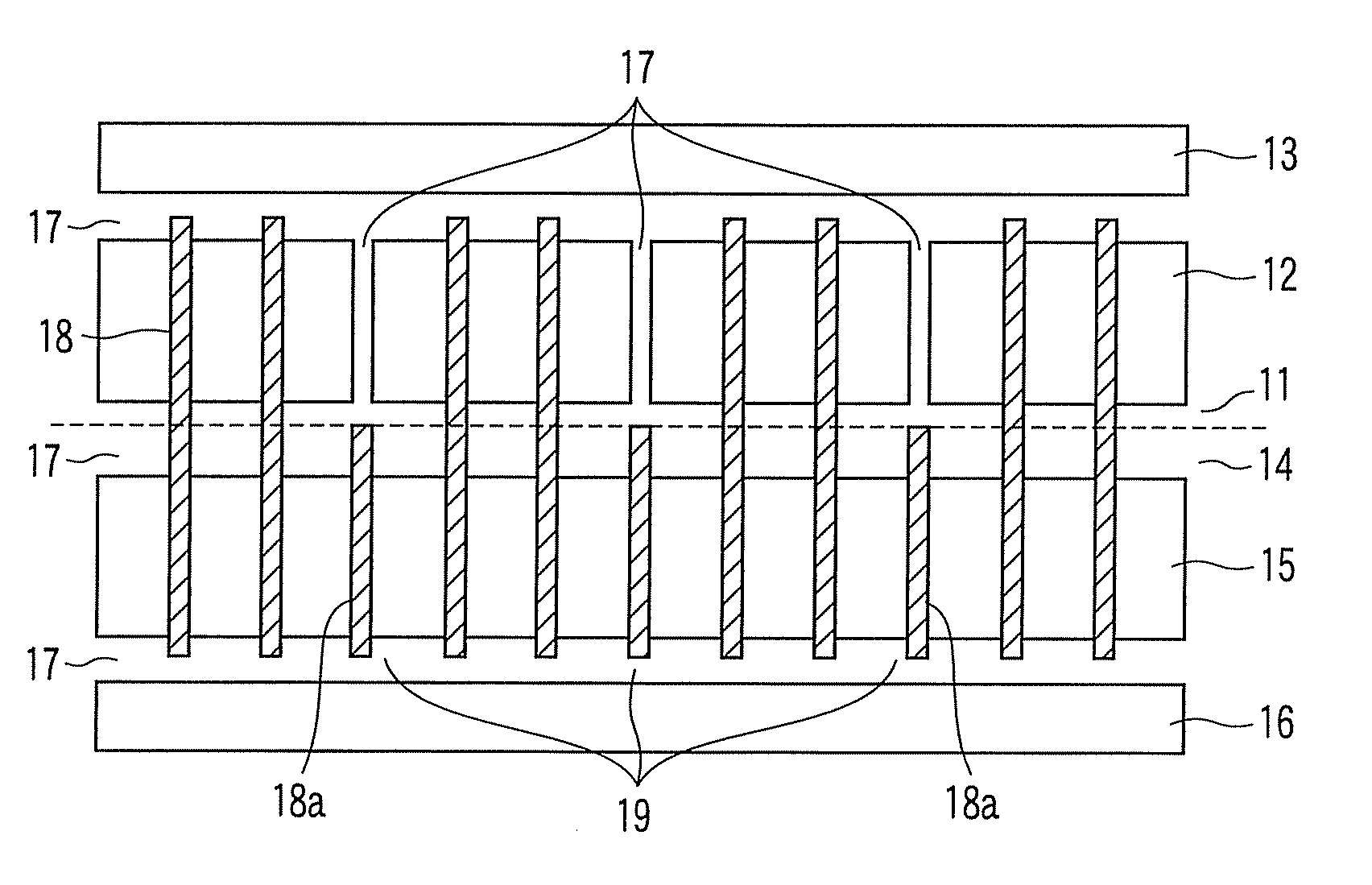

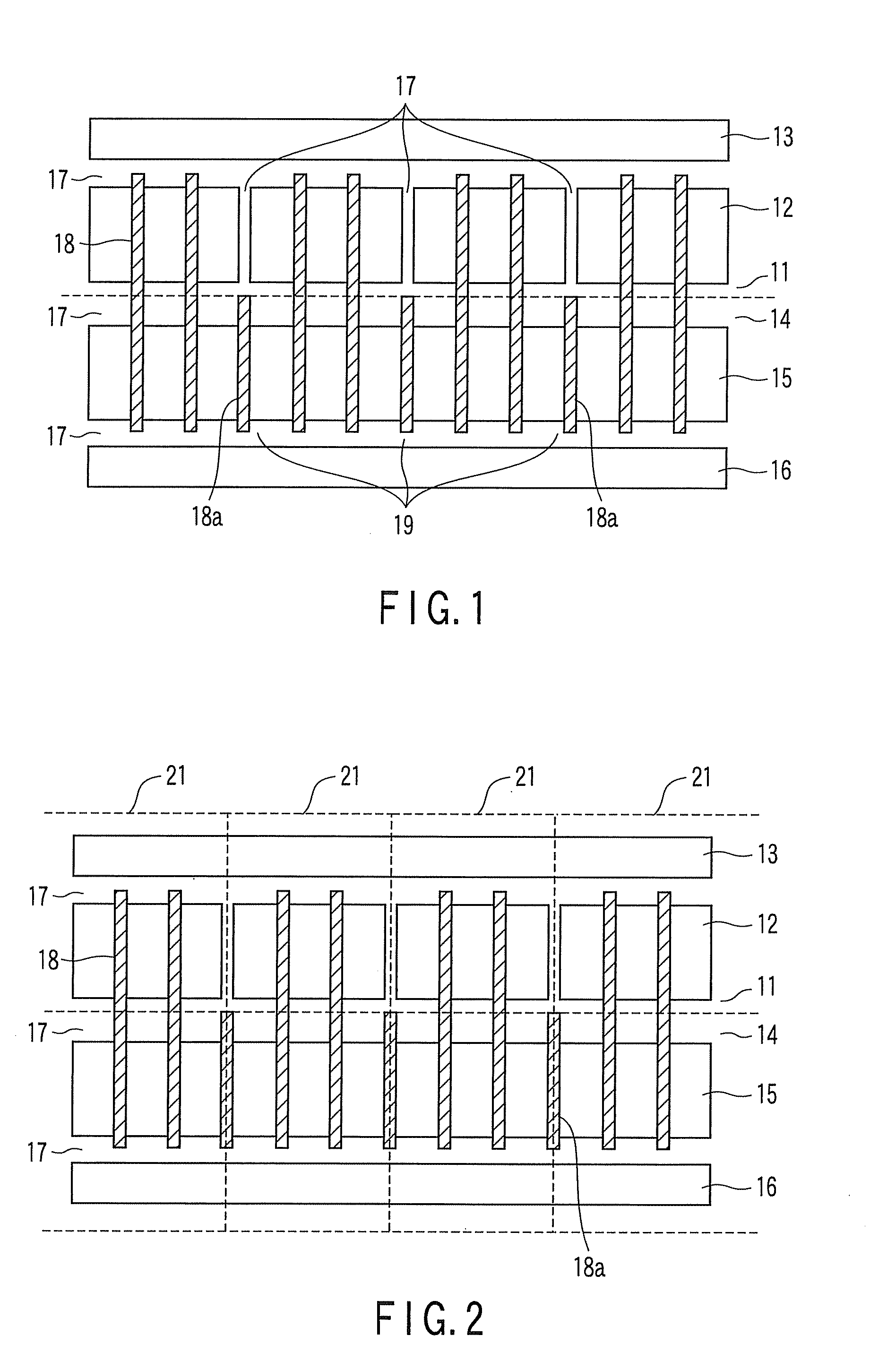

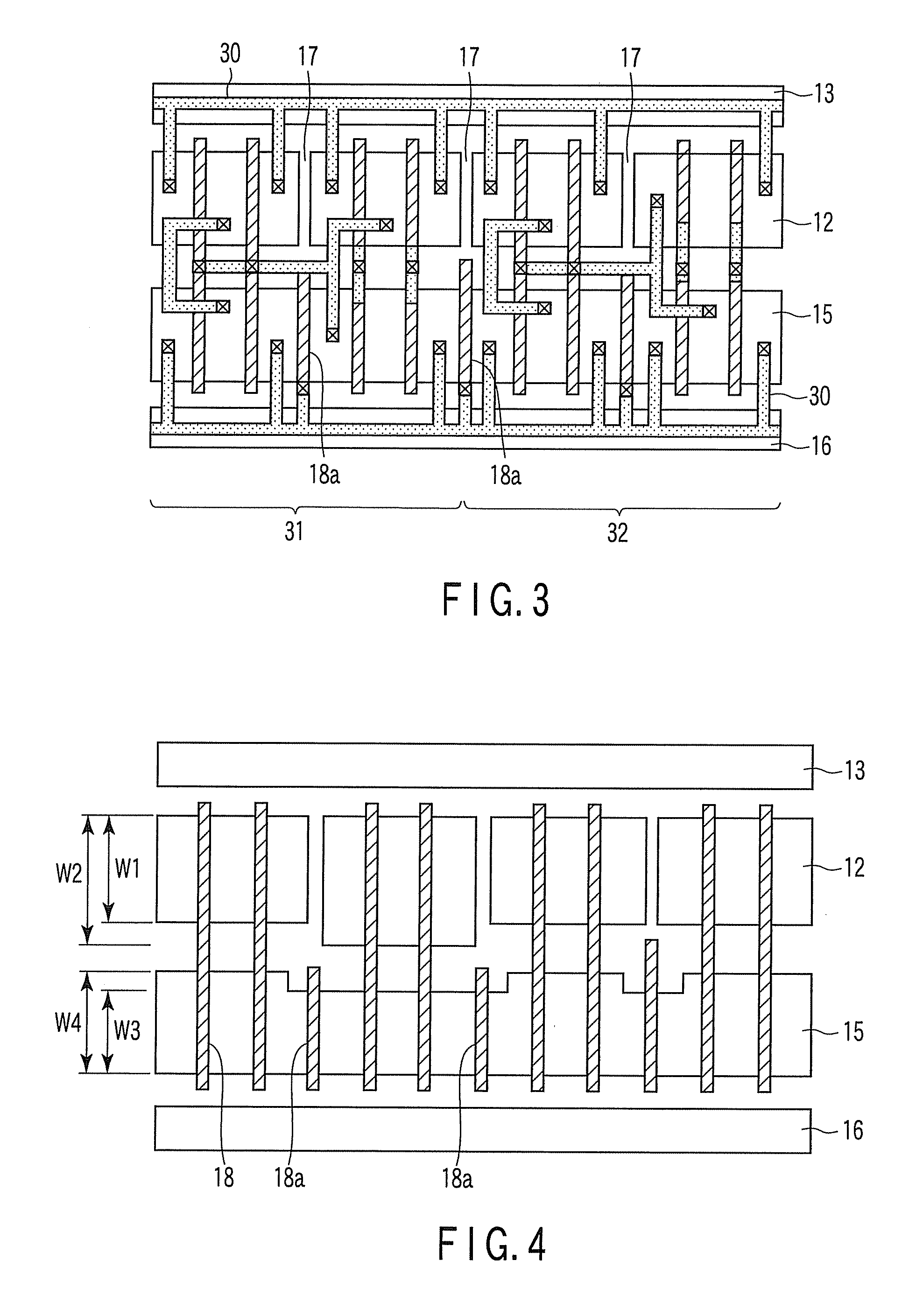

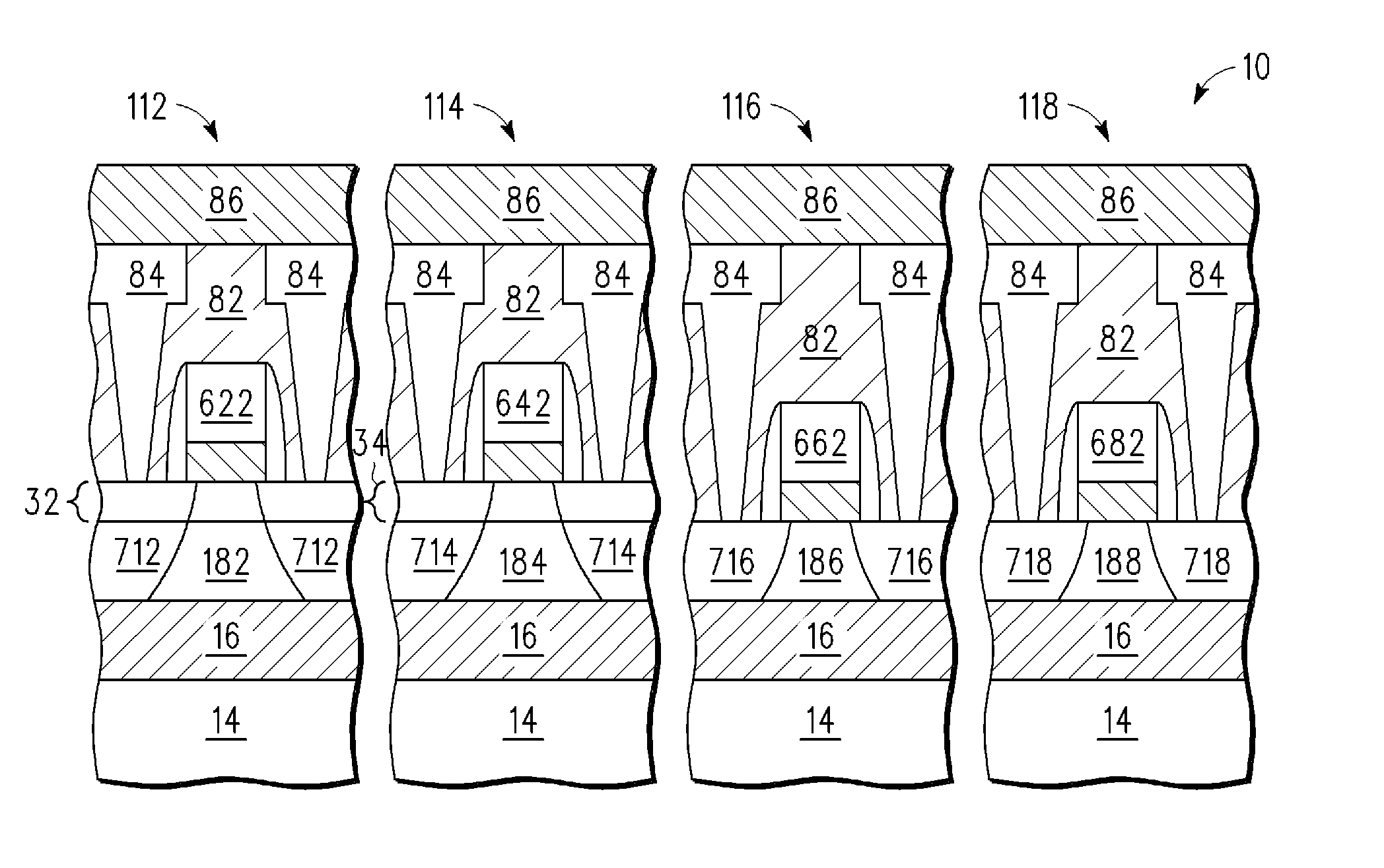

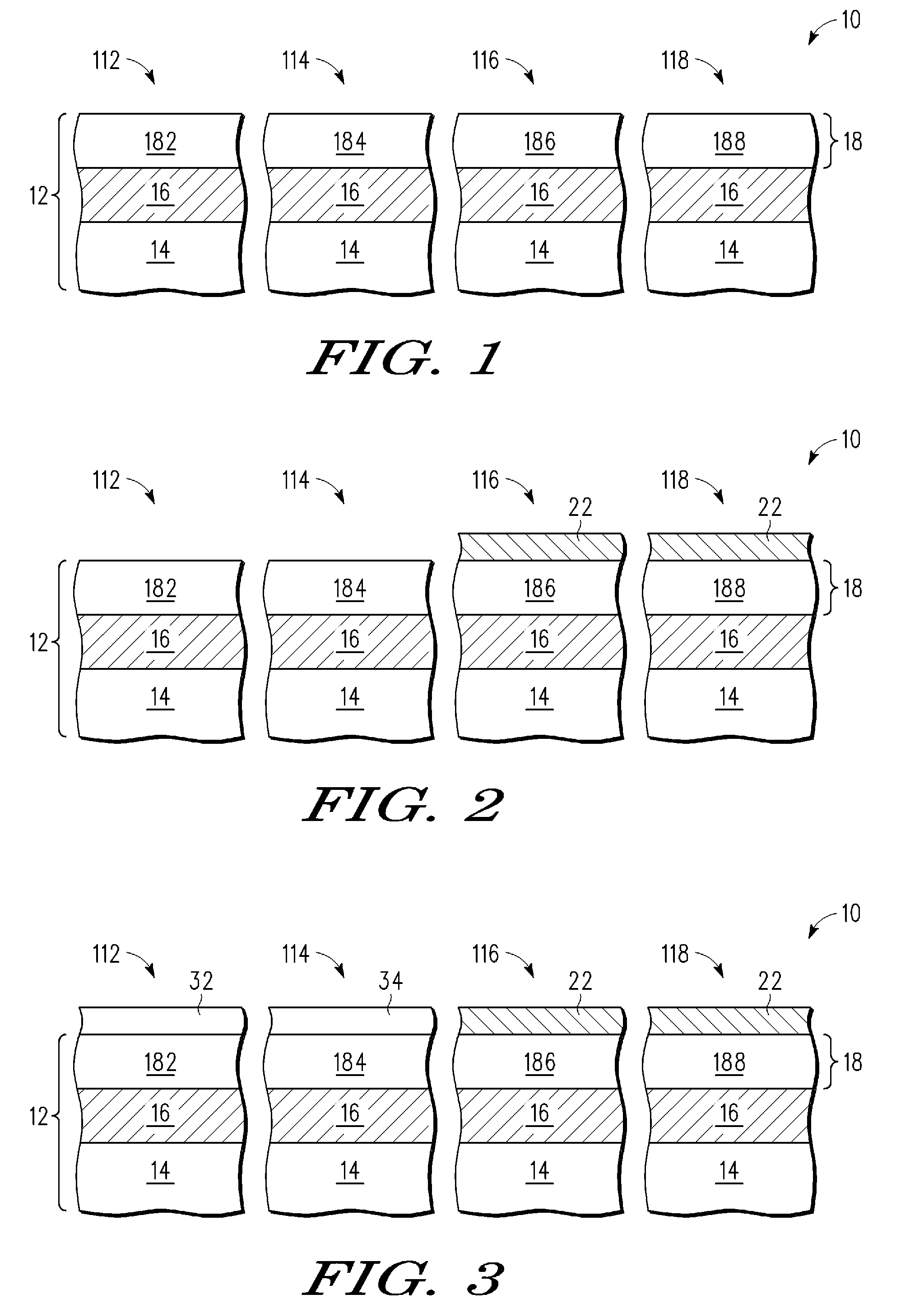

N-channel and p-channel finfet cell architecture

ActiveUS20130026572A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorP channel

A finFET block architecture suitable for use of a standard cell library, is based on an arrangement including a first set of semiconductor fins in a first region of the substrate having a first conductivity type, and a second set of semiconductor fins in a second region of the substrate, the second region having a second conductivity type. A patterned gate conductor layer including gate traces in the first and second regions, arranged over channel regions of the first and second sets of semiconductor fins is used for transistor gates. Patterned conductor layers over the gate conductor layer are arranged in orthogonal layout patterns, and can include a plurality of floating power buses over the fins in the first and second regions.

Owner:SYNOPSYS INC

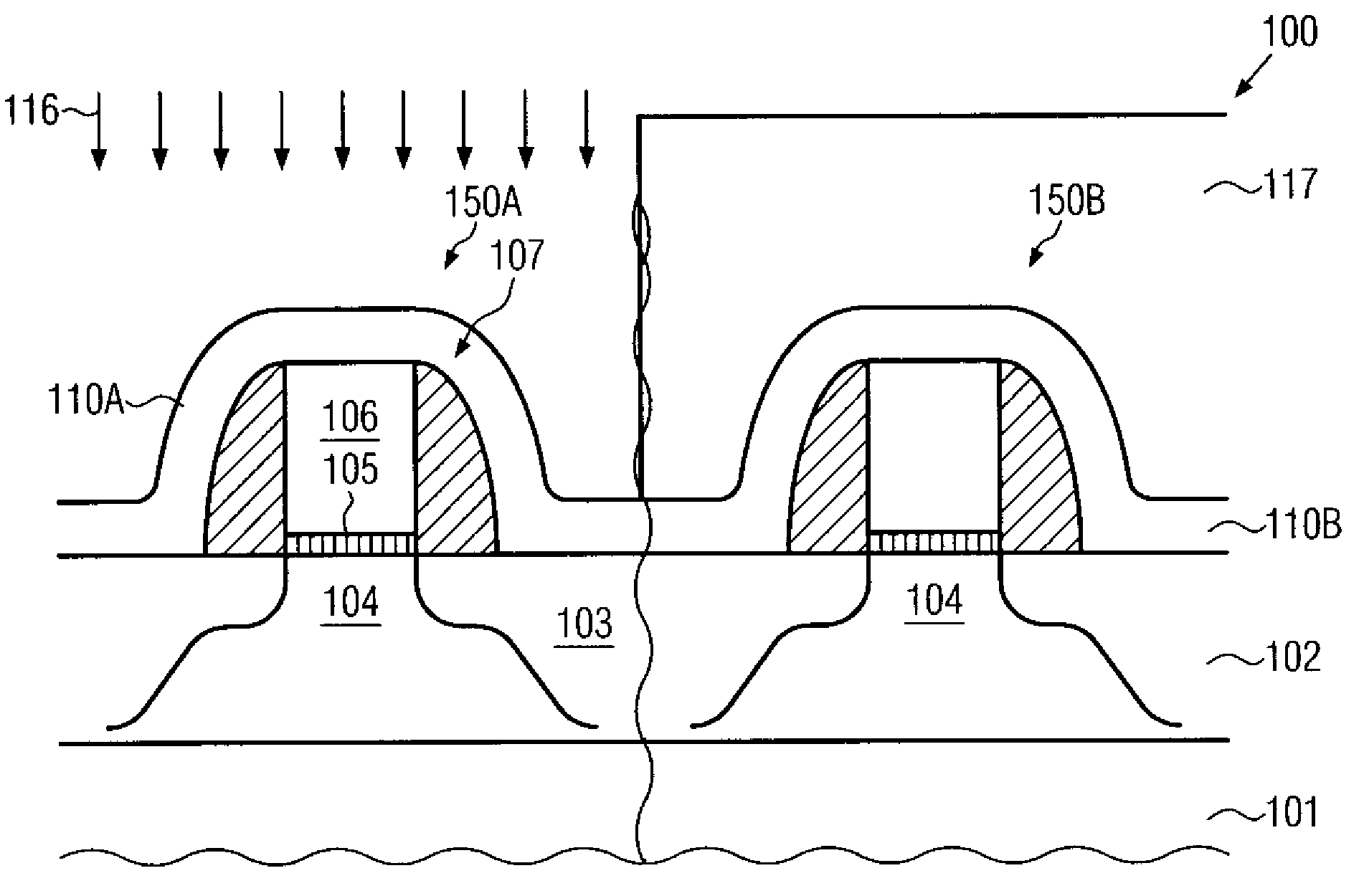

High performance strained CMOS devices

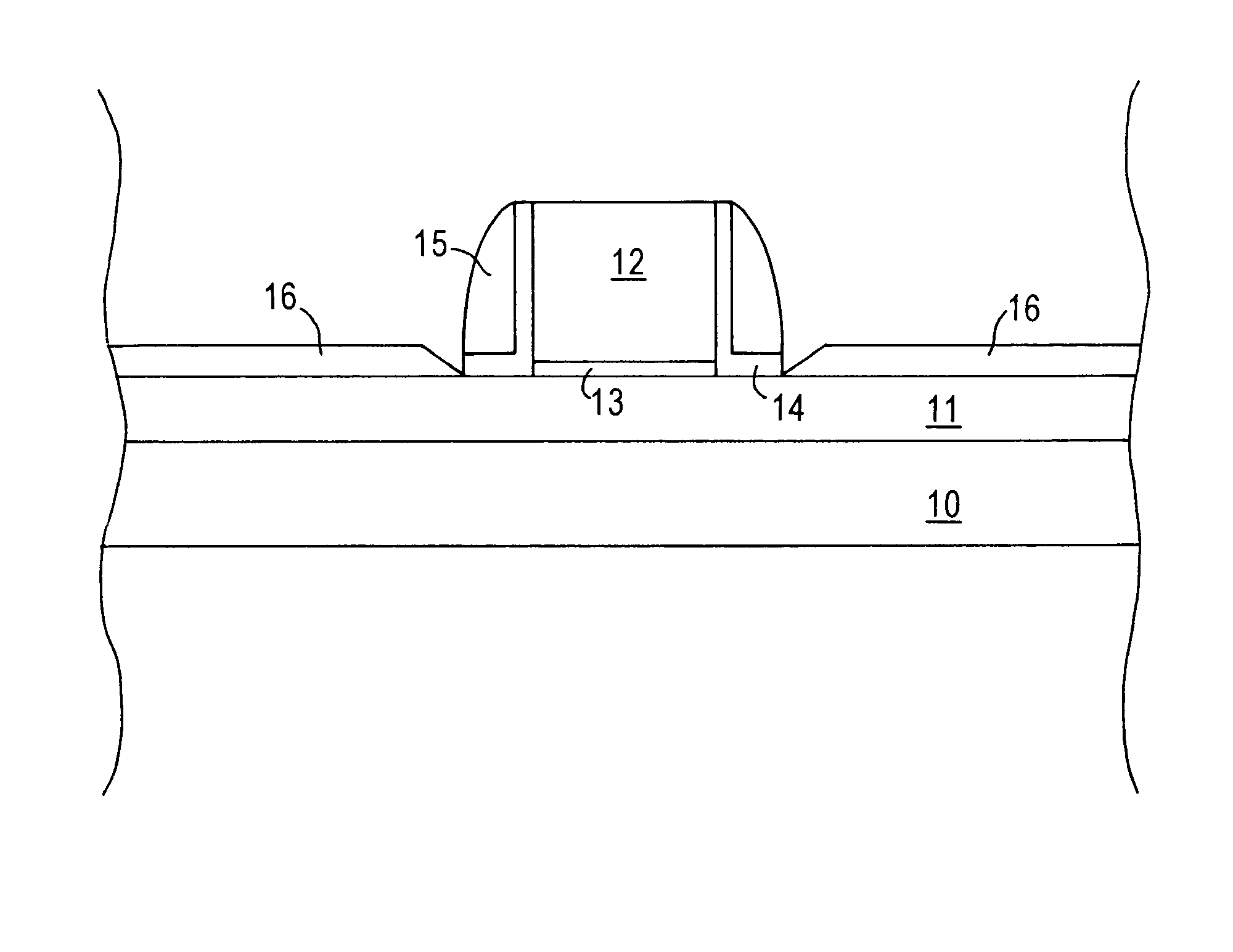

InactiveUS20050148146A1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

A semiconductor device and method of manufacture provide an n-channel field effect transistor (nFET) having a shallow trench isolation with overhangs that overhang Si—SiO2 interfaces in a direction parallel to the direction of current flow and in a direction transverse to current flow. The device and method also provide a p-channel field effect transistor (pFET) having a shallow trench isolation with an overhang that overhangs Si—SiO2 interfaces in a direction transverse to current flow. However, the shallow trench isolation for the pFET is devoid of overhangs, in the direction parallel to the direction of current flow.

Owner:GLOBALFOUNDRIES INC

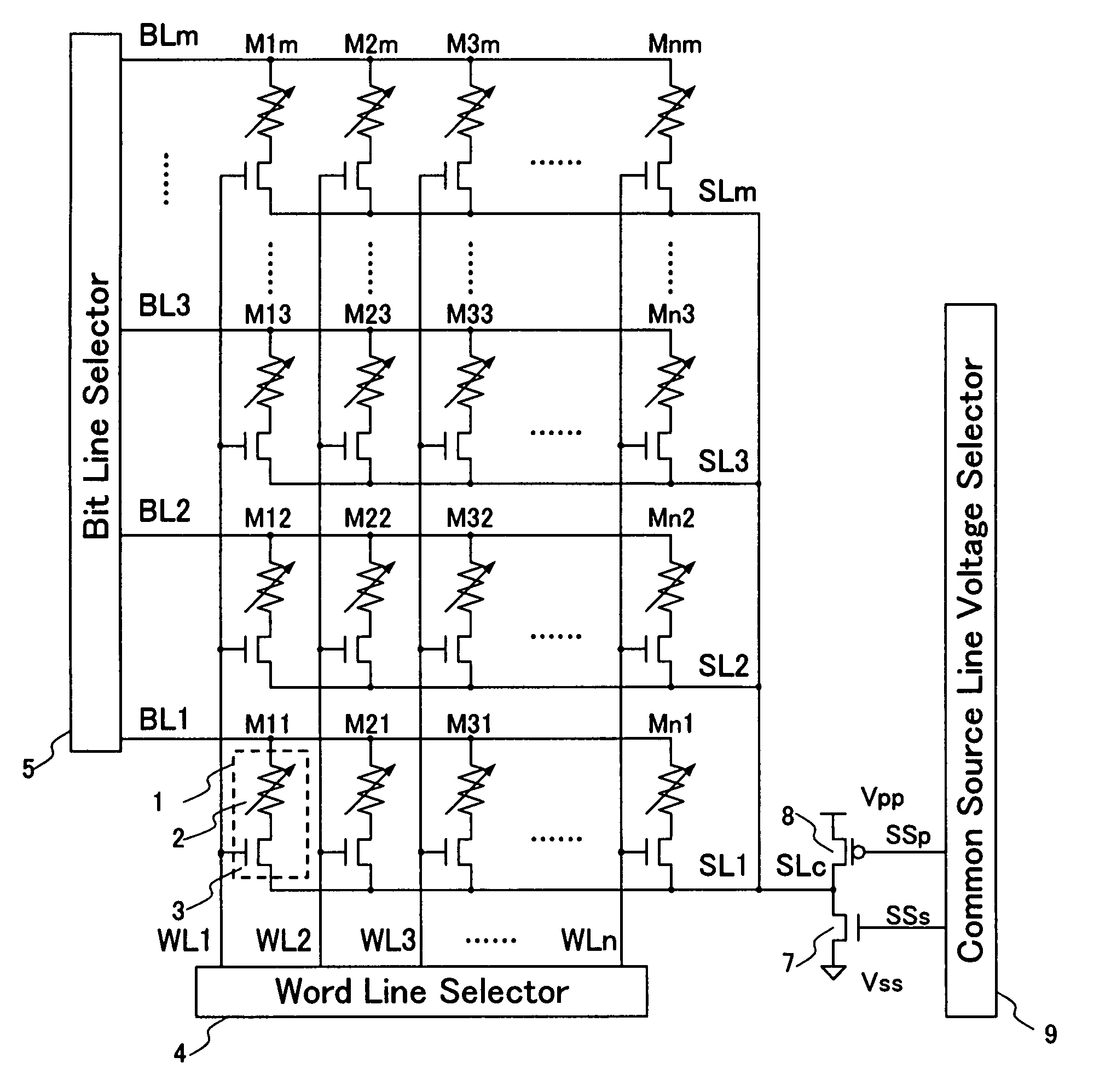

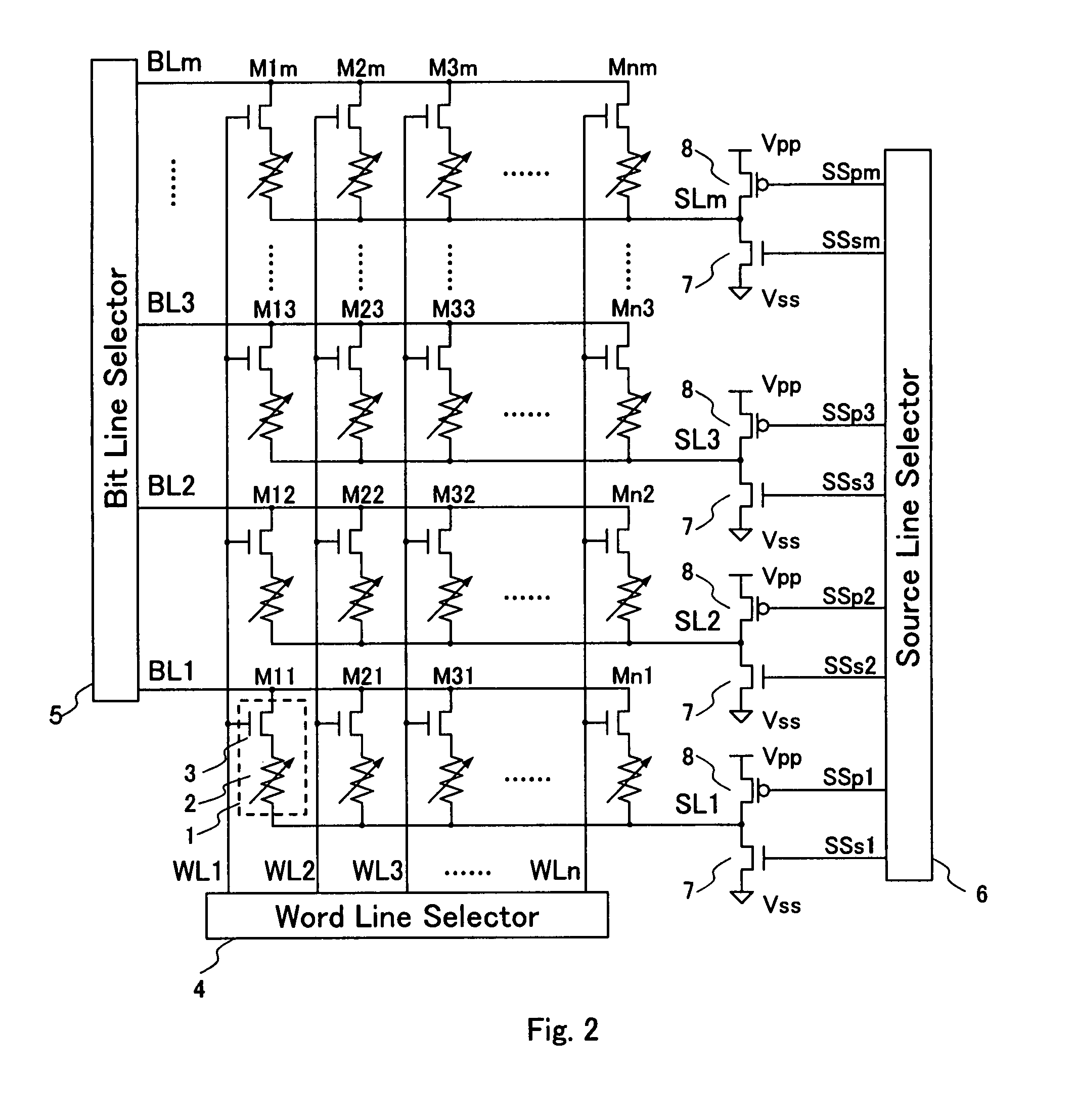

Semiconductor memory device

A semiconductor memory device comprises an array of memory cells each comprising a variable resistance element and a cell access transistor, and a voltage supplying means for applying the first voltage between the bit and source lines connected to the selected memory cell, the third voltage to the word line to apply the first write voltage between the two ports of the variable resistance element for shifting the resistance from the first state to the second state, and the second voltage opposite in polarity to the first voltage between the bit and source lines, the third voltage to the word line to apply the second write voltage opposite in polarity to and different in the absolute value from the first write voltage between the two ports for shifting the resistance from the second state to the first state, the voltage supplying means comprising an n-channel MOSFET and a p-channel MOSFET.

Owner:SAMSUNG ELECTRONICS CO LTD

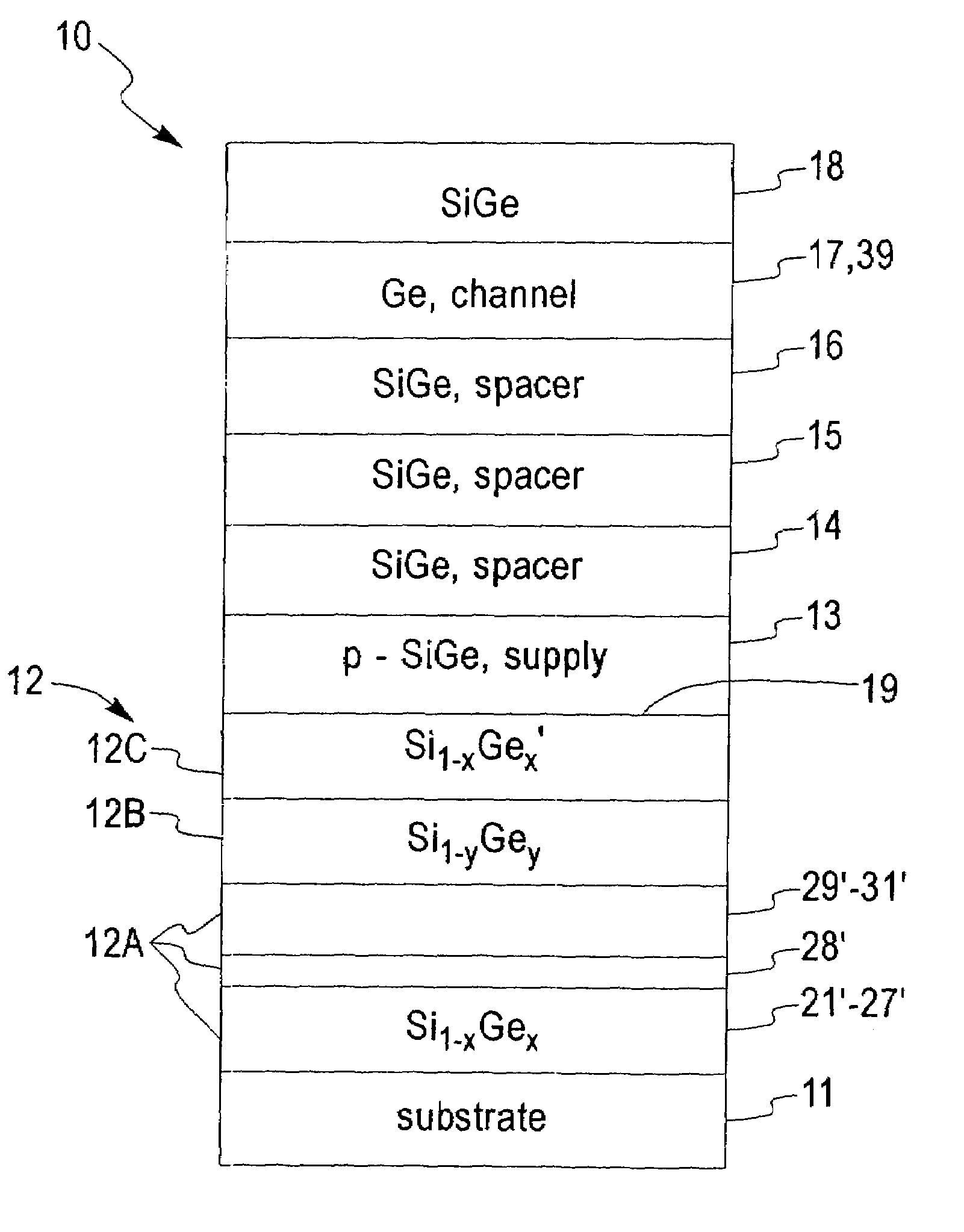

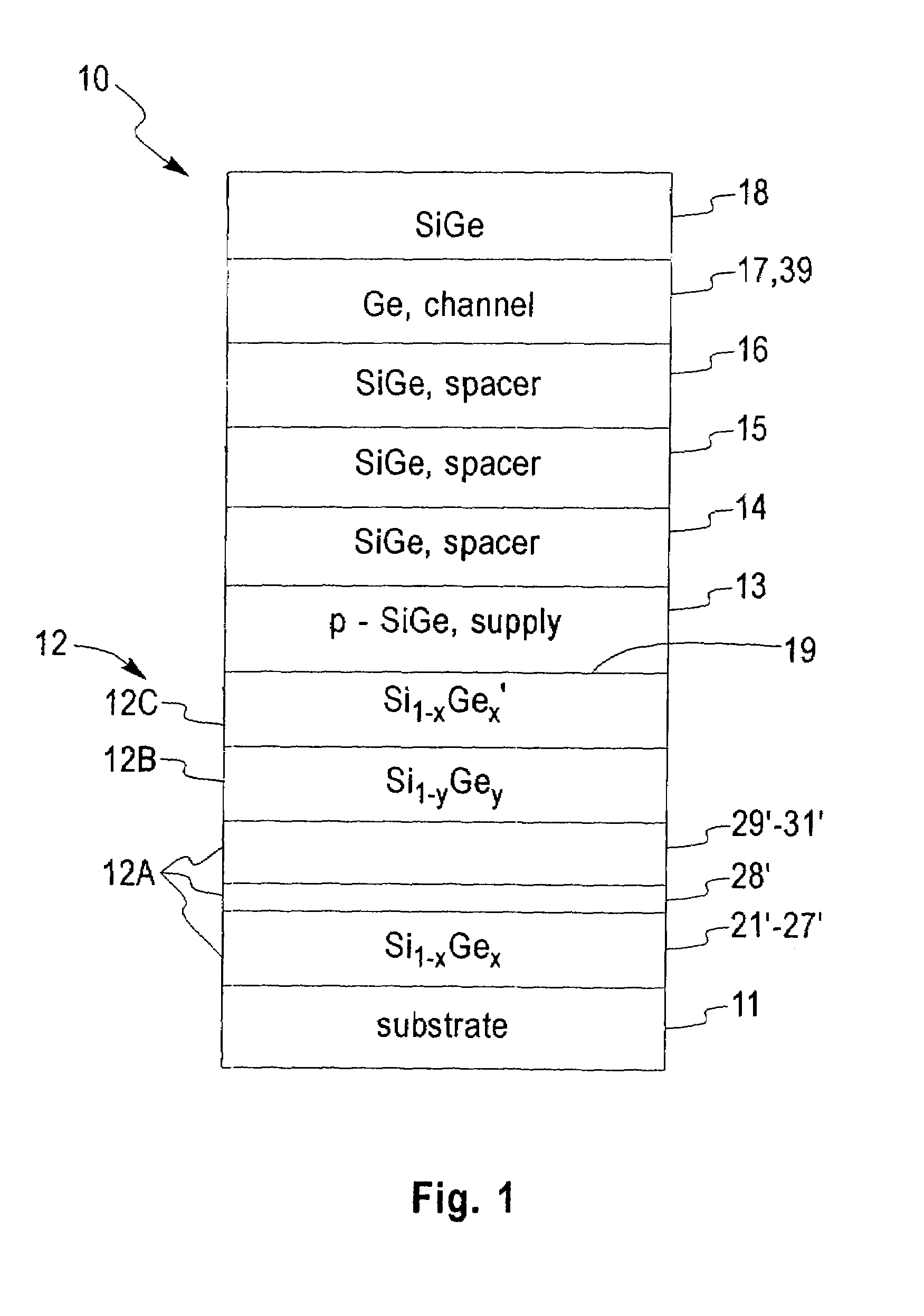

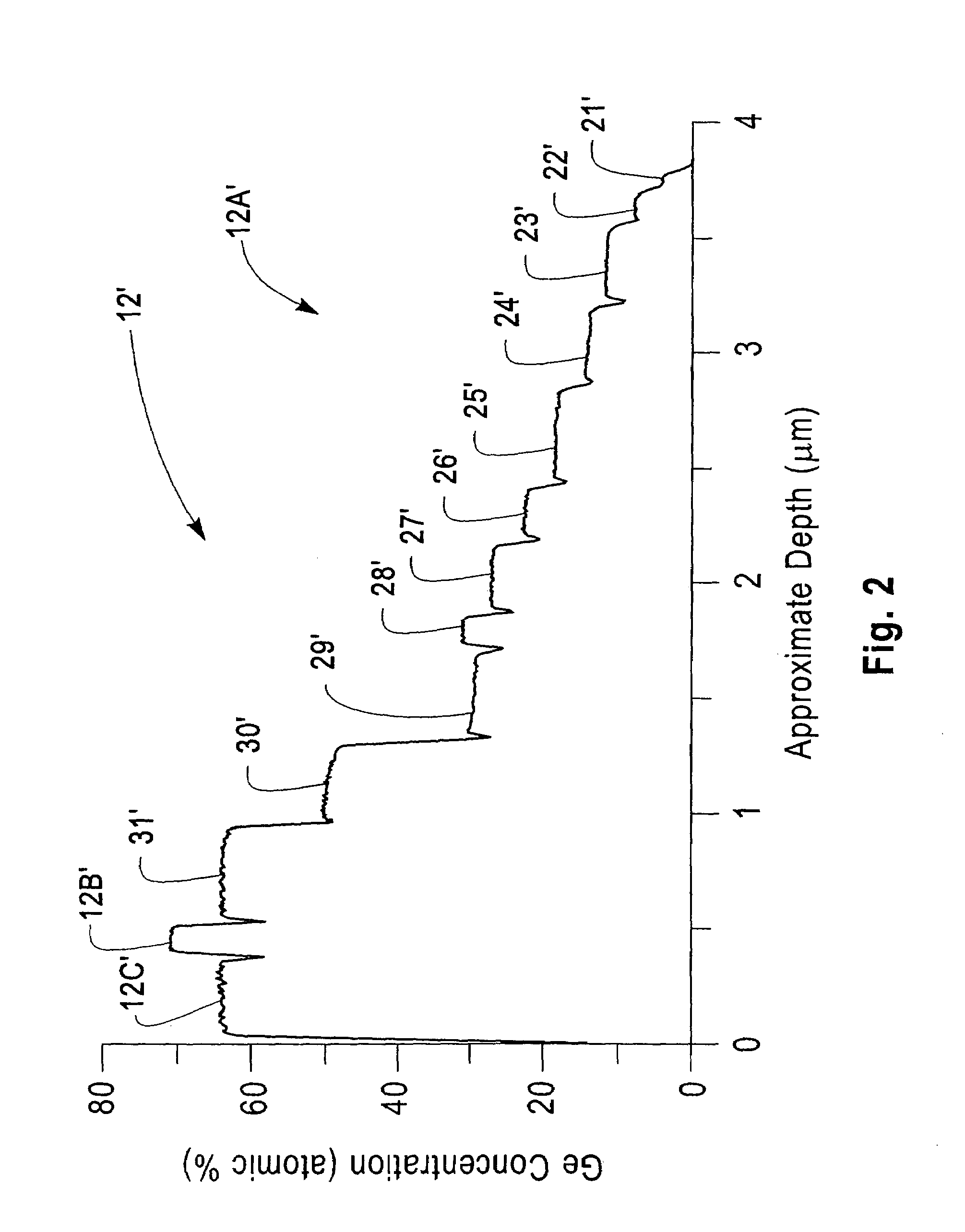

High speed Ge channel heterostructures for field effect devices

InactiveUS7145167B1High hole mobilityHigh compressive strainTransistorSemiconductor/solid-state device manufacturingMOSFETAlloy scattering

A method and a layered heterostructure for forming high mobility Ge channel field effect transistors is described incorporating a plurality of semiconductor layers on a semiconductor substrate, and a channel structure of a compressively strained epitaxial Ge layer having a higher barrier or a deeper confining quantum well and having extremely high hole mobility for complementary MODFETs and MOSFETs. The invention overcomes the problem of a limited hole mobility due to alloy scattering for a p-channel device with only a single compressively strained SiGe channel layer. This invention further provides improvements in mobility and transconductance over deep submicron state-of-the art Si pMOSFETs in addition to having a broad temperature operation regime from above room temperature (425 K) down to cryogenic low temperatures (0.4 K) where at low temperatures even high device performances are achievable.

Owner:ELPIS TECH INC

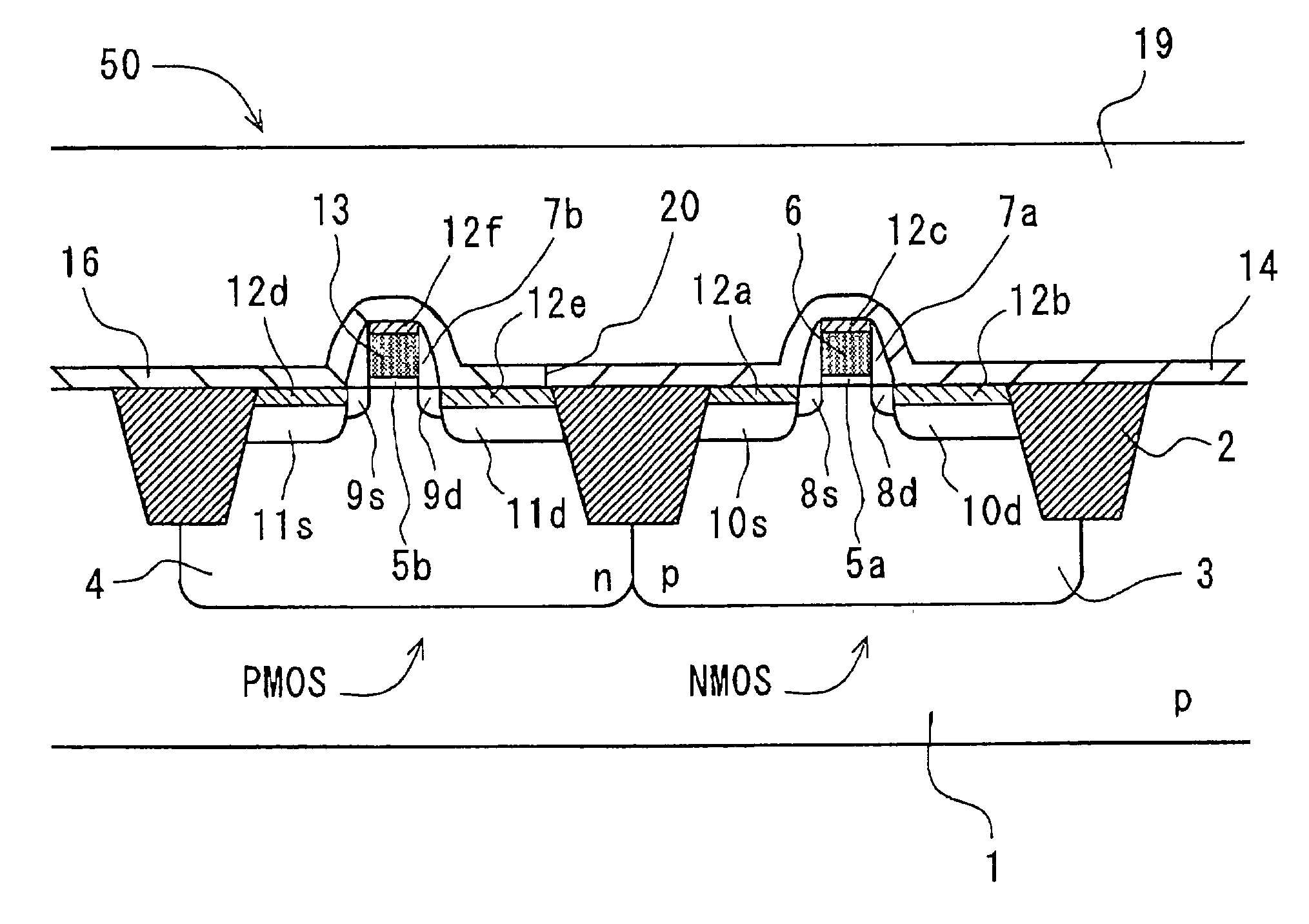

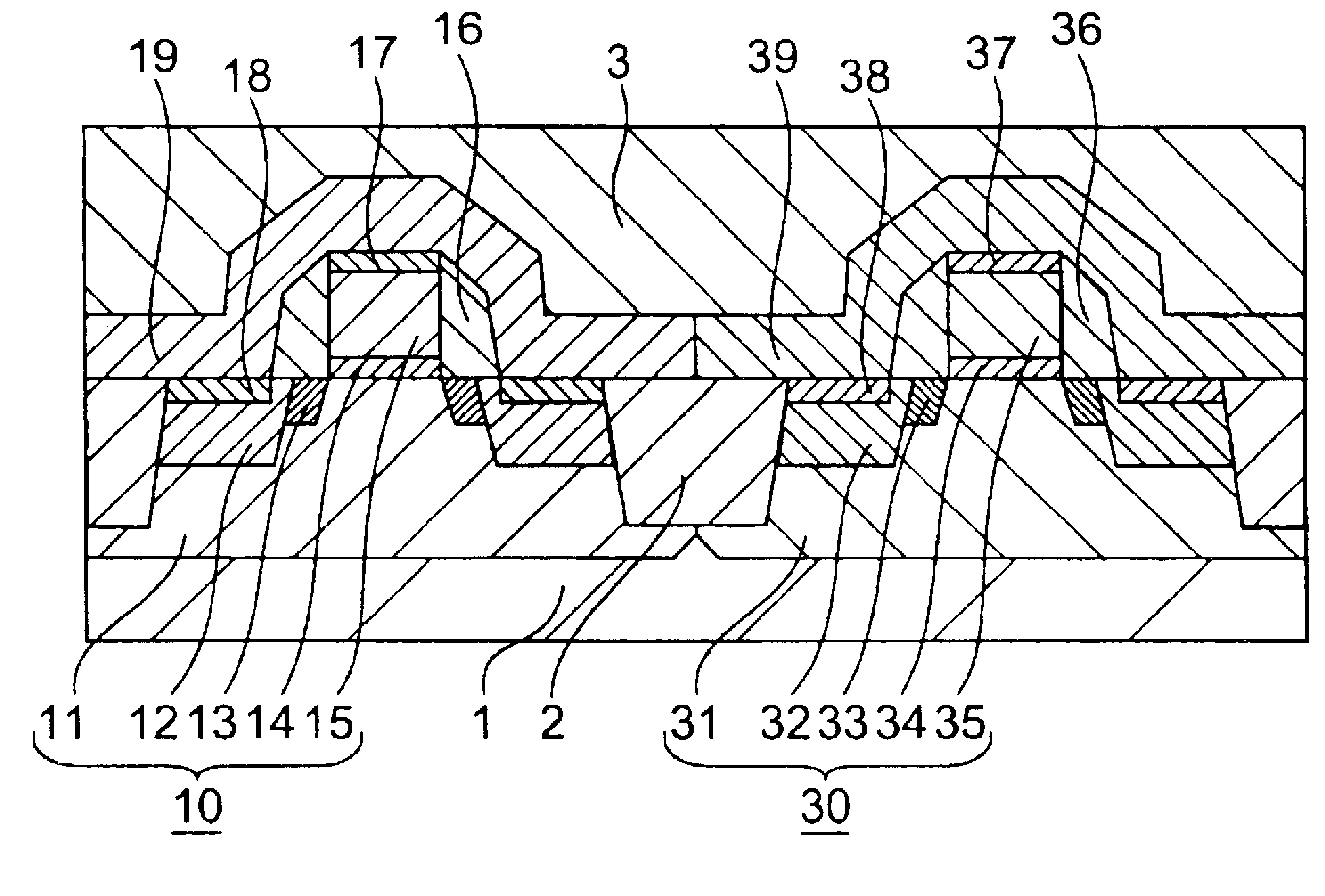

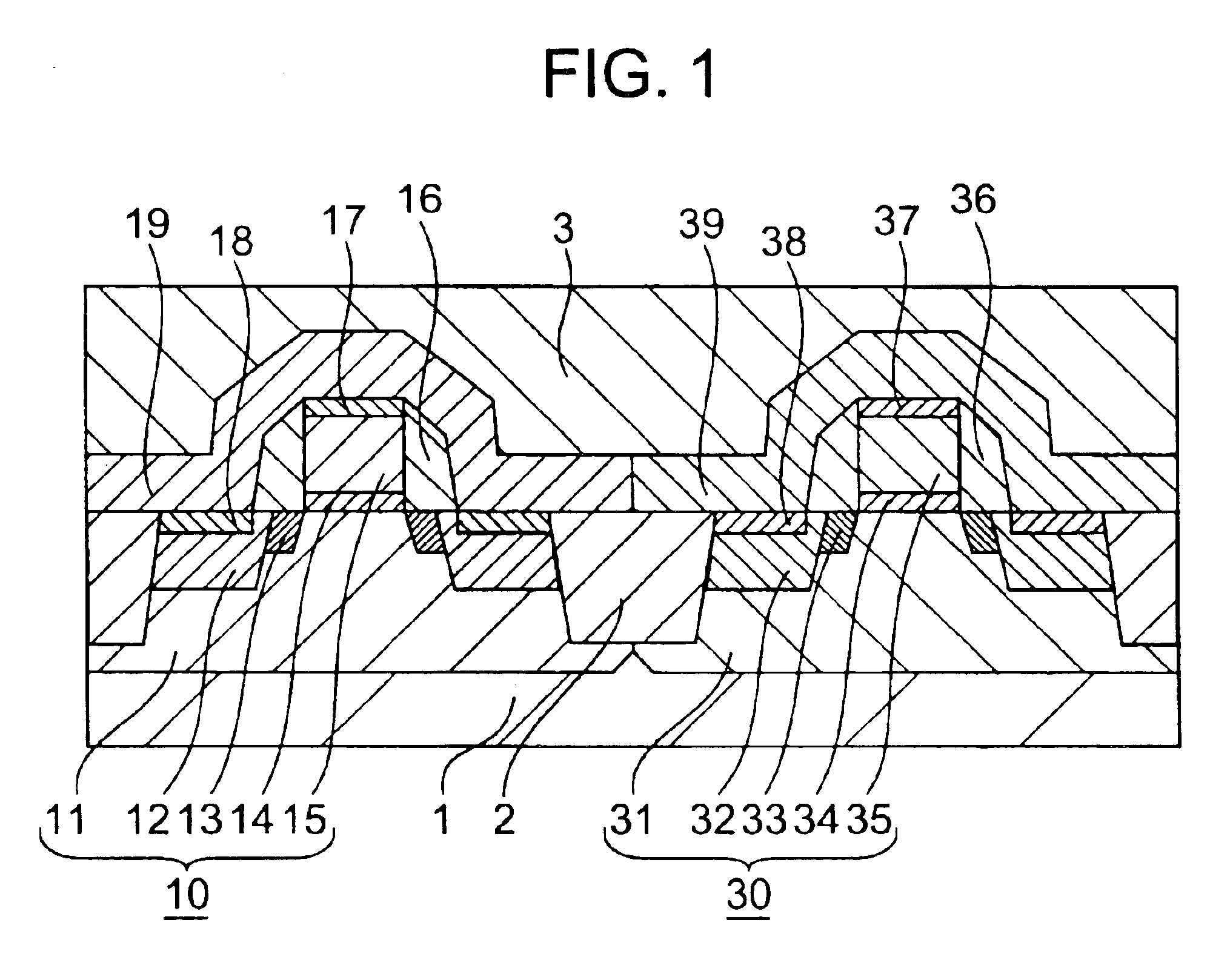

Semiconductor device with CMOS-field-effect transistors having improved drain current characteristics

InactiveUS6982465B2High speedImprove mobilityTransistorSemiconductor/solid-state device detailsCMOSField-effect transistor

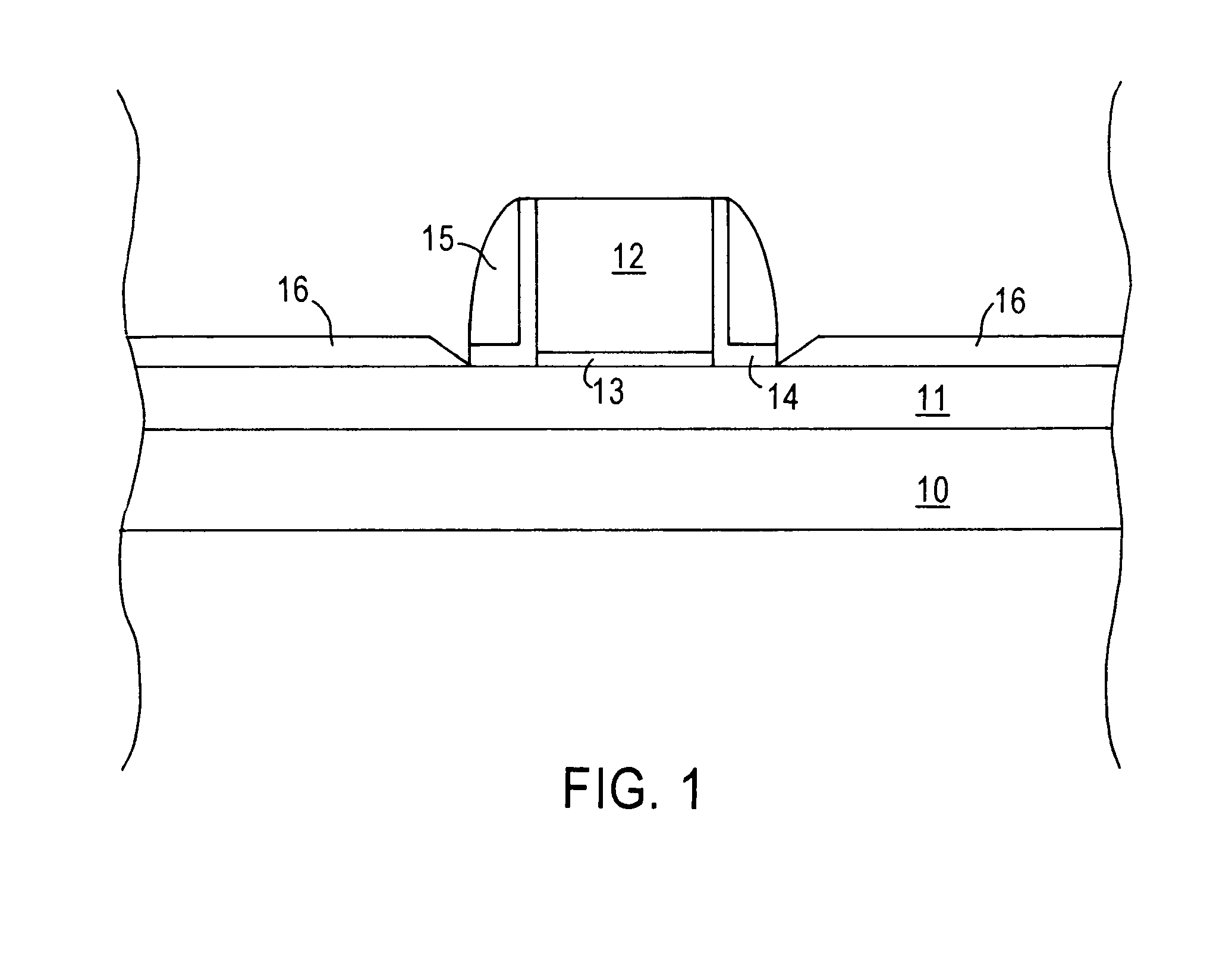

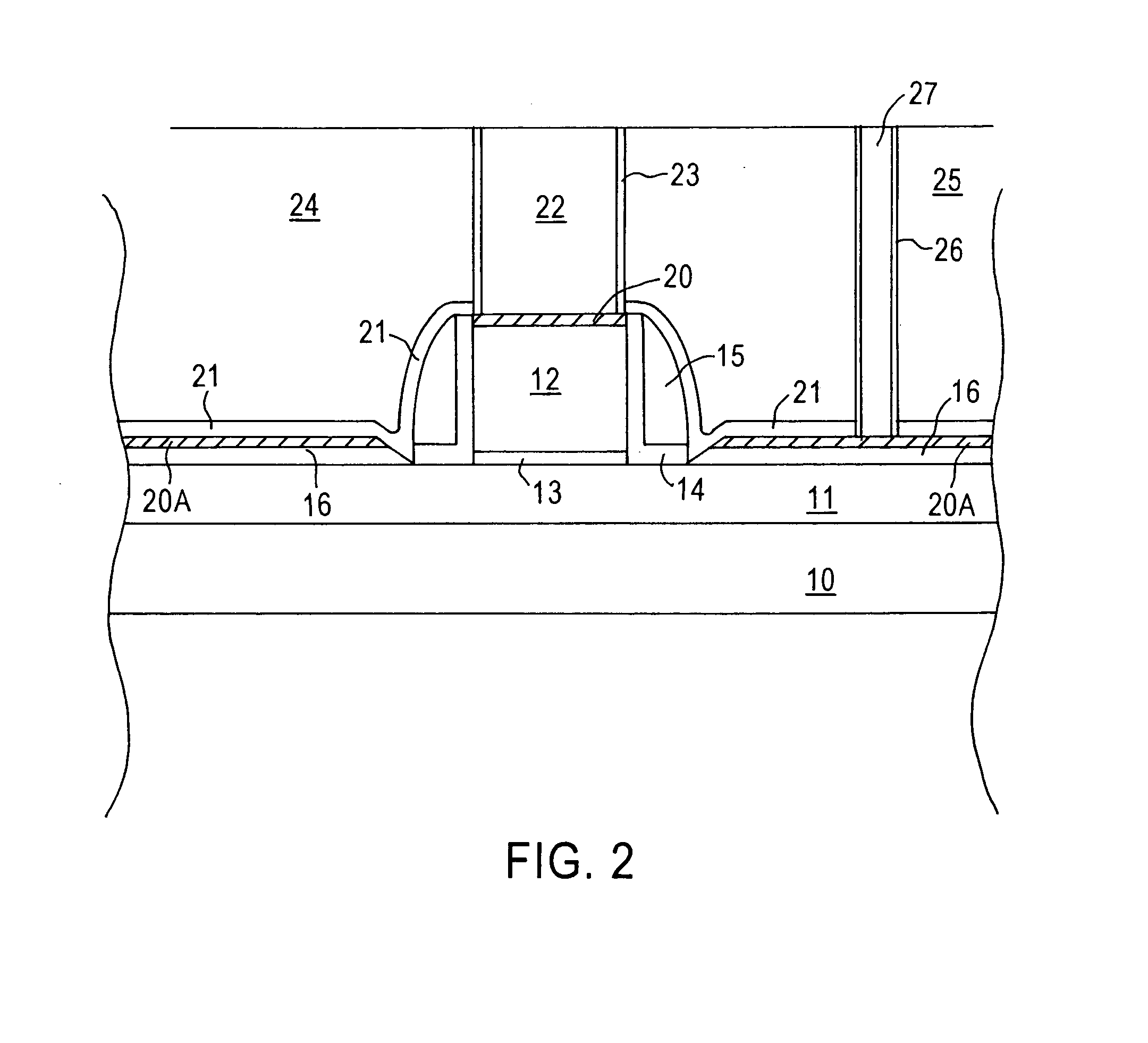

The present invention provides a semiconductor device including n-channel field effect transistors and p-channel field effect transistors all of which have excellent drain current characteristics.In a semiconductor device including an n-channel field effect transistor 10 and a p-channel field effect transistor 30, a stress control film 19 covering a gate electrode 15 of the n-channel field effect transistor 10 undergoes film stress mainly composed of tensile stress. A stress control film 39 covering a gate electrode 15 of the p-channel field effect transistor 30 undergoes film stress mainly caused by compression stress compared to the film 19 of the n-channel field effect transistor 10. Accordingly, drain current is expected to be improved in both the n-channel field effect transistor and the p-channel field effect transistor. Consequently, the characteristics can be generally improved.

Owner:RENESAS ELECTRONICS CORP

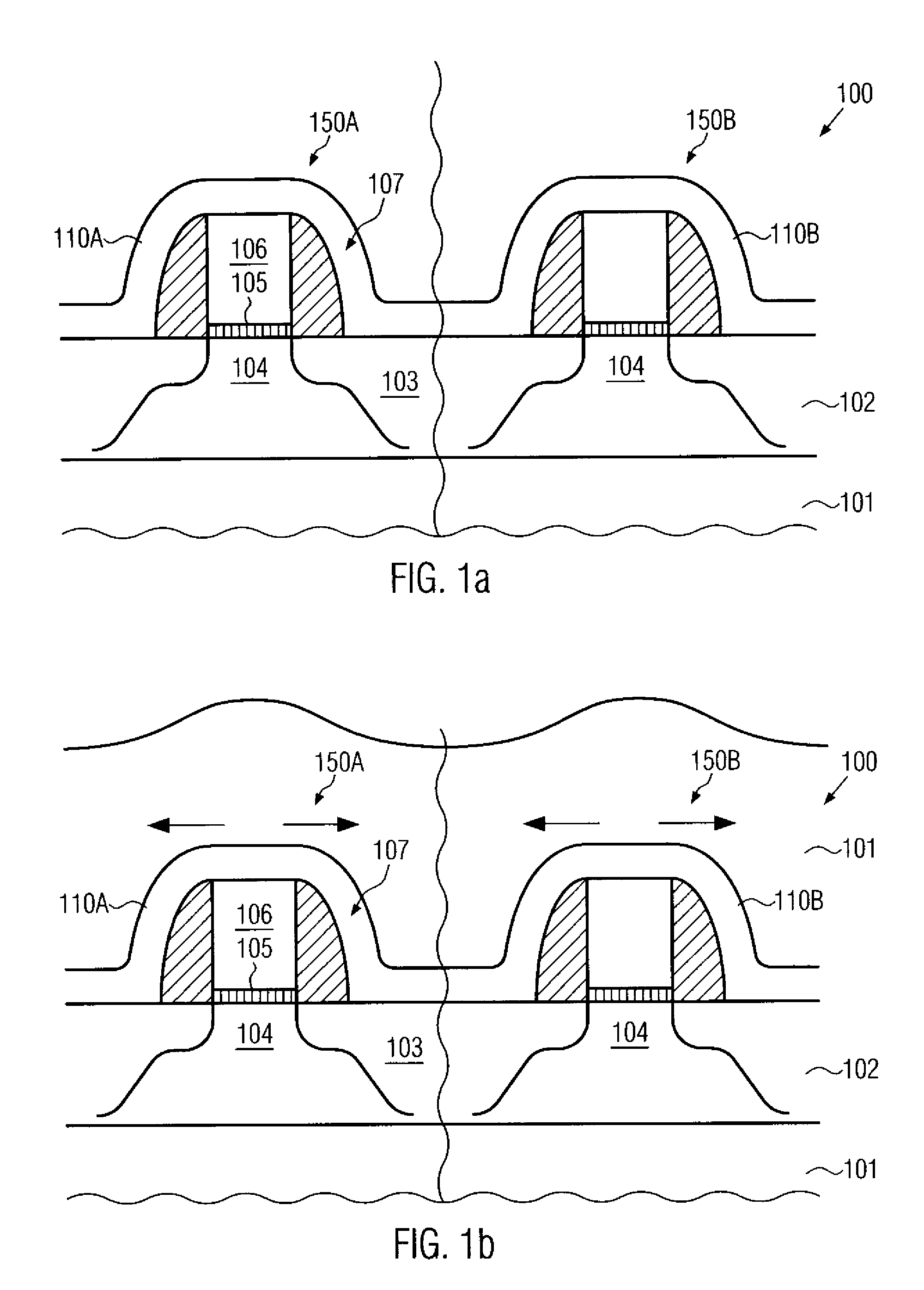

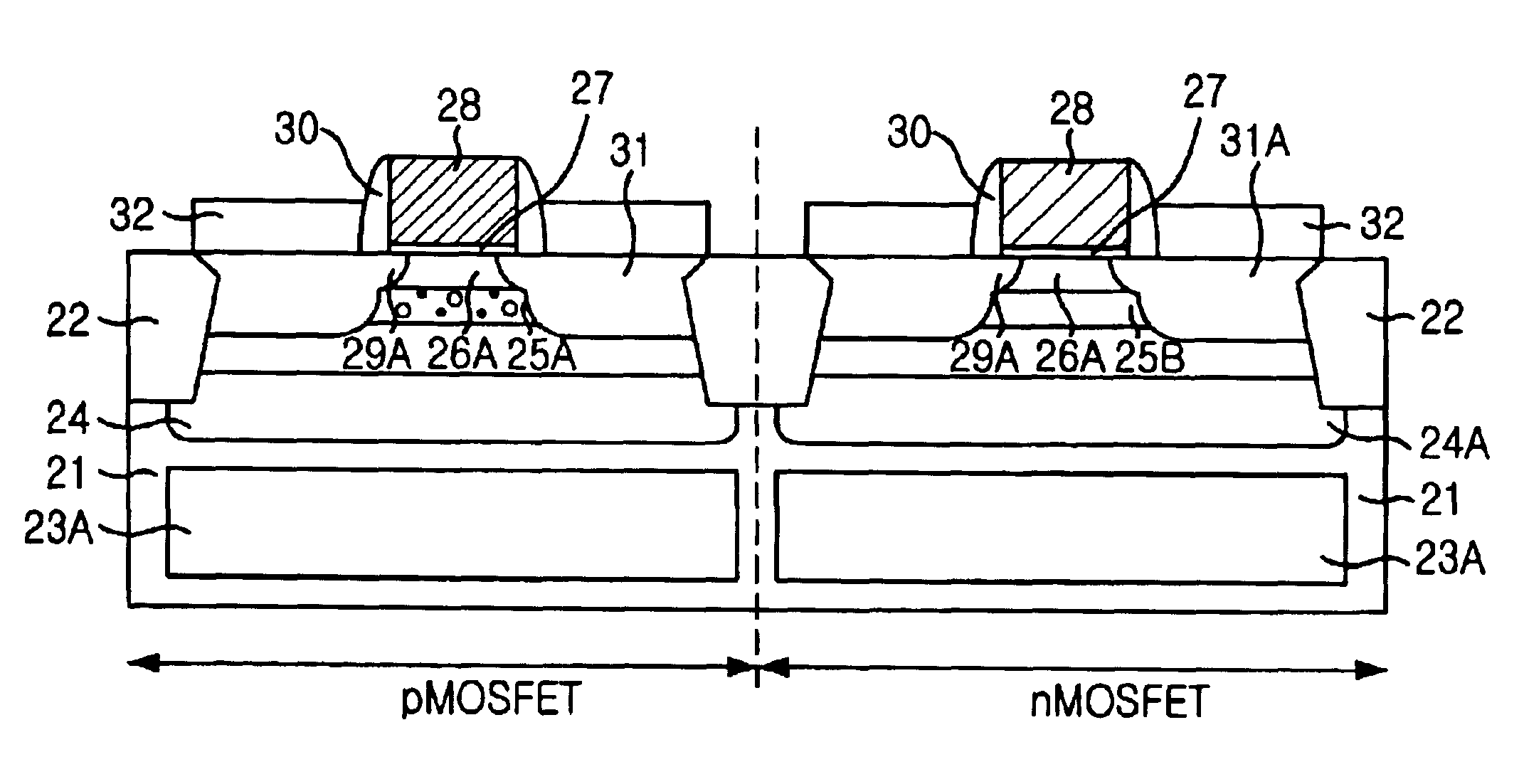

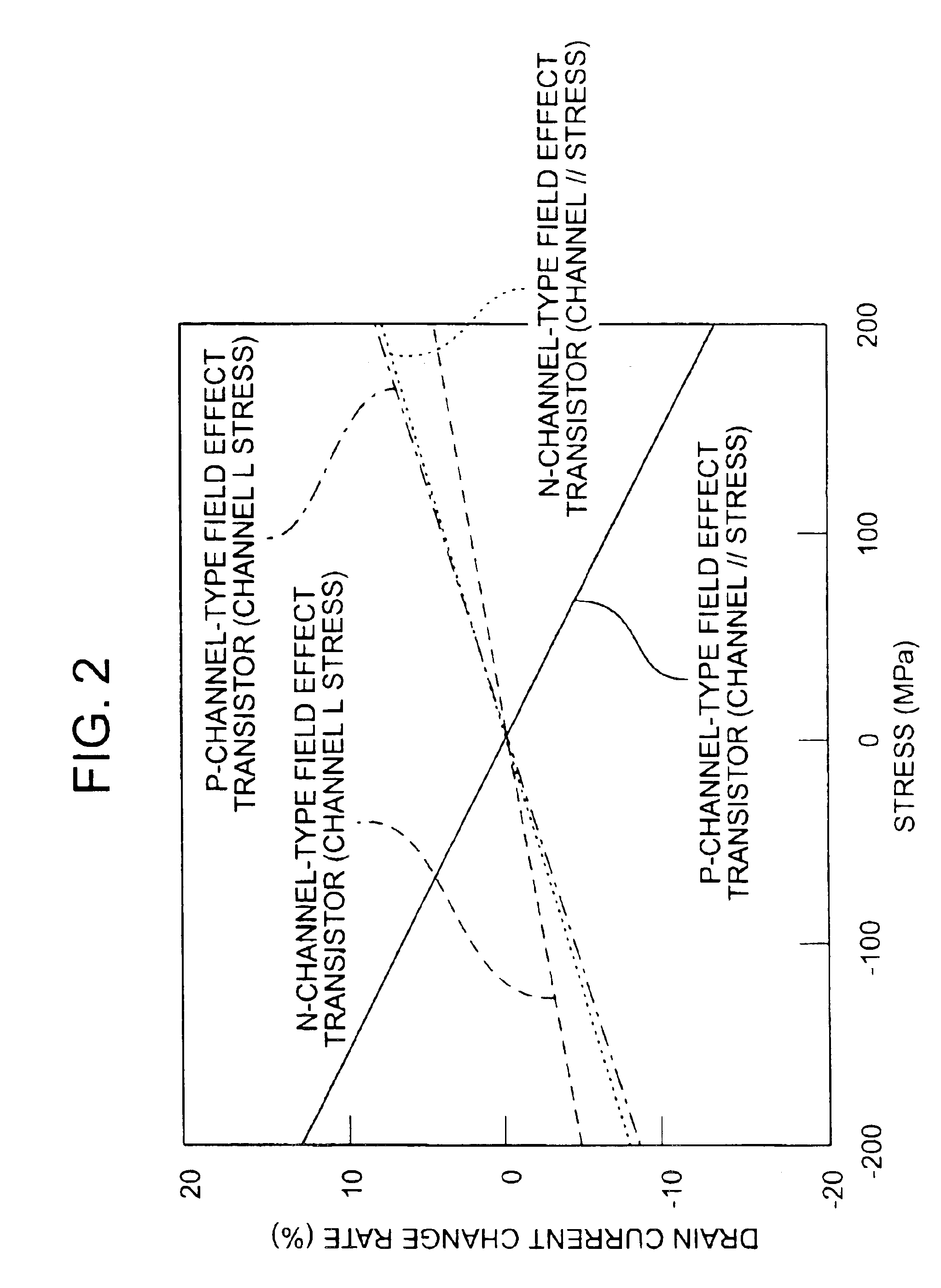

Semiconductor device including stress inducing films formed over n-channel and p-channel field effect transistors and a method of manufacturing the same

InactiveUS7115954B2Improve driving abilityImprove current drive capabilityTransistorSemiconductor/solid-state device detailsStress inducedField-effect transistor

A semiconductor device has an n channel conductivity type field effect transistor having a channel formation region formed in a first region on one main surface of a semiconductor substrate and a p channel conductivity type field effect transistor having a channel formation region formed in a second region on the main surface of the semiconductor substrate, which second region is different from the first region. An internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is different from an internal stress generated in the channel formation region of the p channel conductivity type field effect transistor. The internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is a tensile stress, while the internal stress generated in the channel formation region of the p channel conductivity type field effect transistor is a compressive stress.

Owner:RENESAS ELECTRONICS CORP

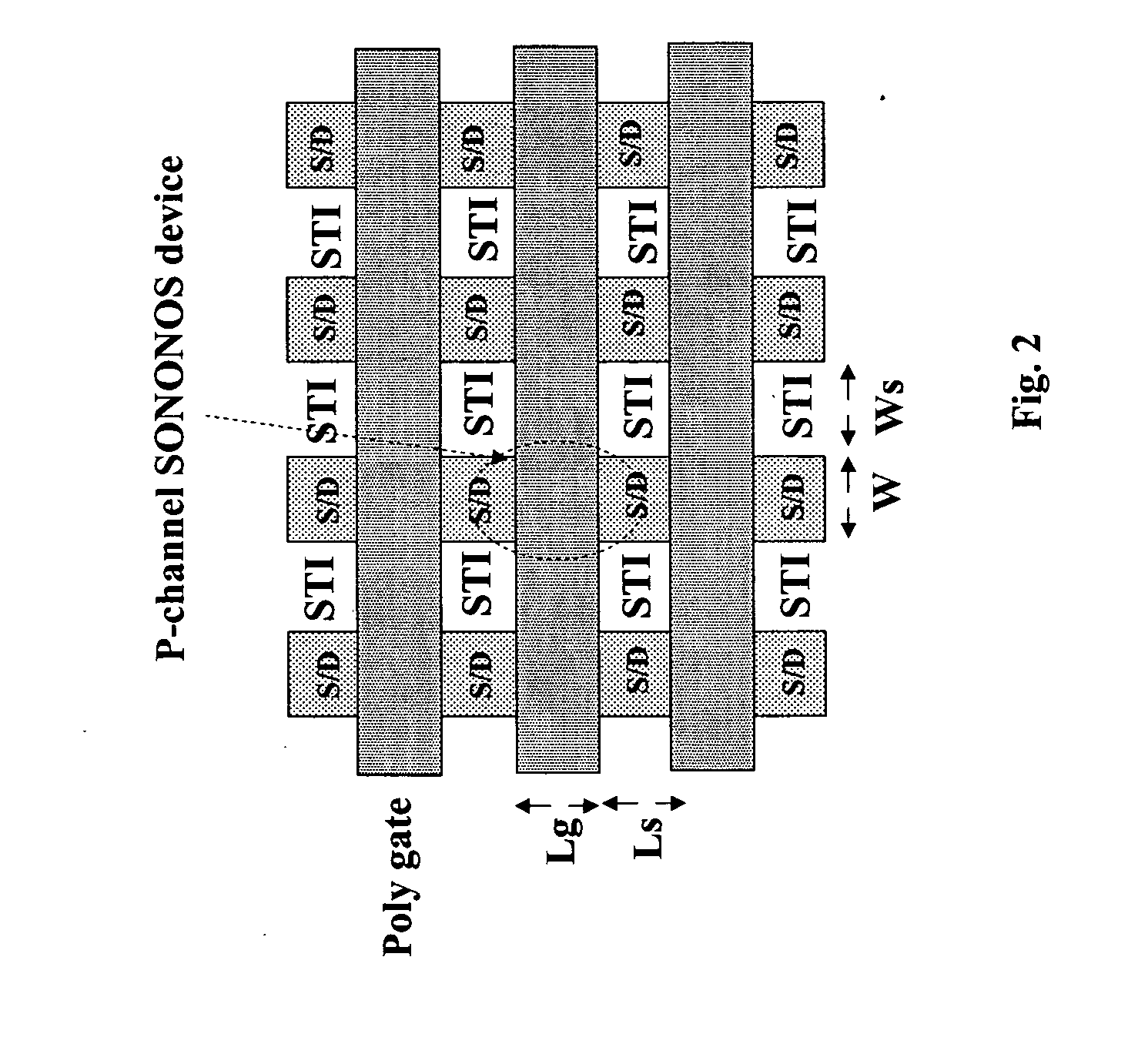

Methods of operating p-channel non-volatile memory devices

ActiveUS20060281260A1Disturbing effectNegative biasSolid-state devicesRead-only memoriesBit lineEngineering

Methods of operating non-volatile memory devices are described. The memory devices comprise memory cells having an n-type semiconductor substrate and p-type source and drain regions disposed below a surface of the substrate and separated by a channel region. A tunneling dielectric layer is disposed above the channel region. A charge storage layer is disposed above the tunneling dielectric layer. An upper insulating layer is disposed above the charge storage layer, and a gate is disposed above the upper insulating multi-layer structure. A positive bias is applied to a word lines of the memory device in a selected memory cell and a negative bias is applied to a bit line in the selected cell.

Owner:MACRONIX INT CO LTD

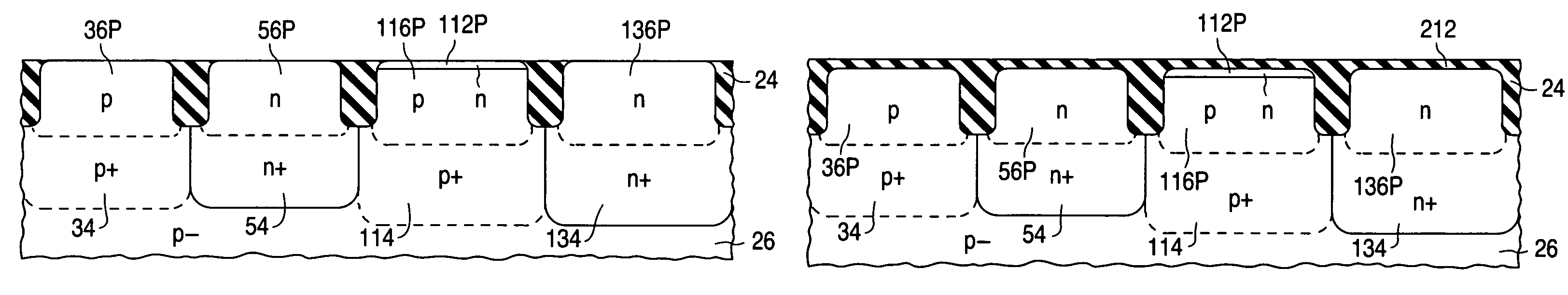

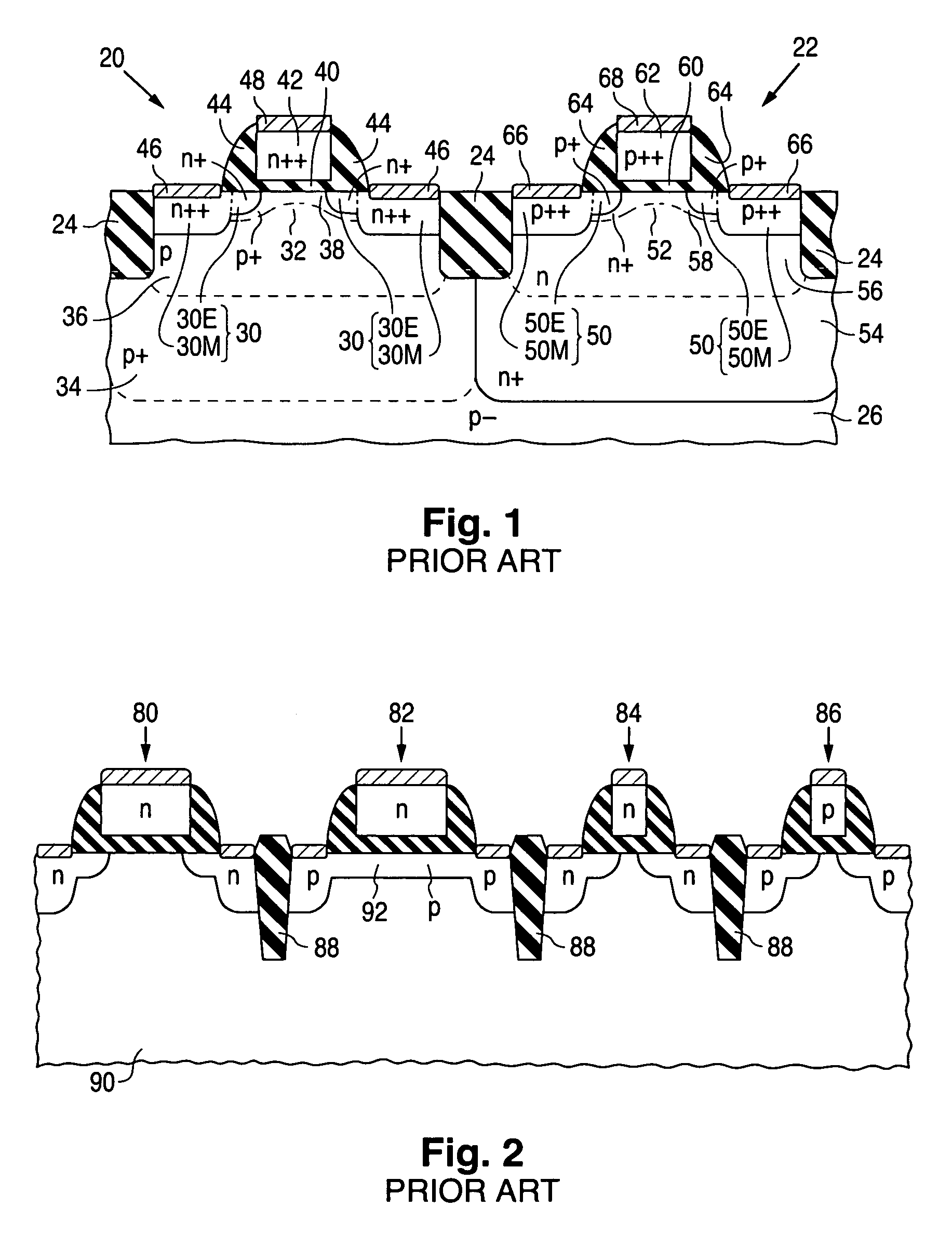

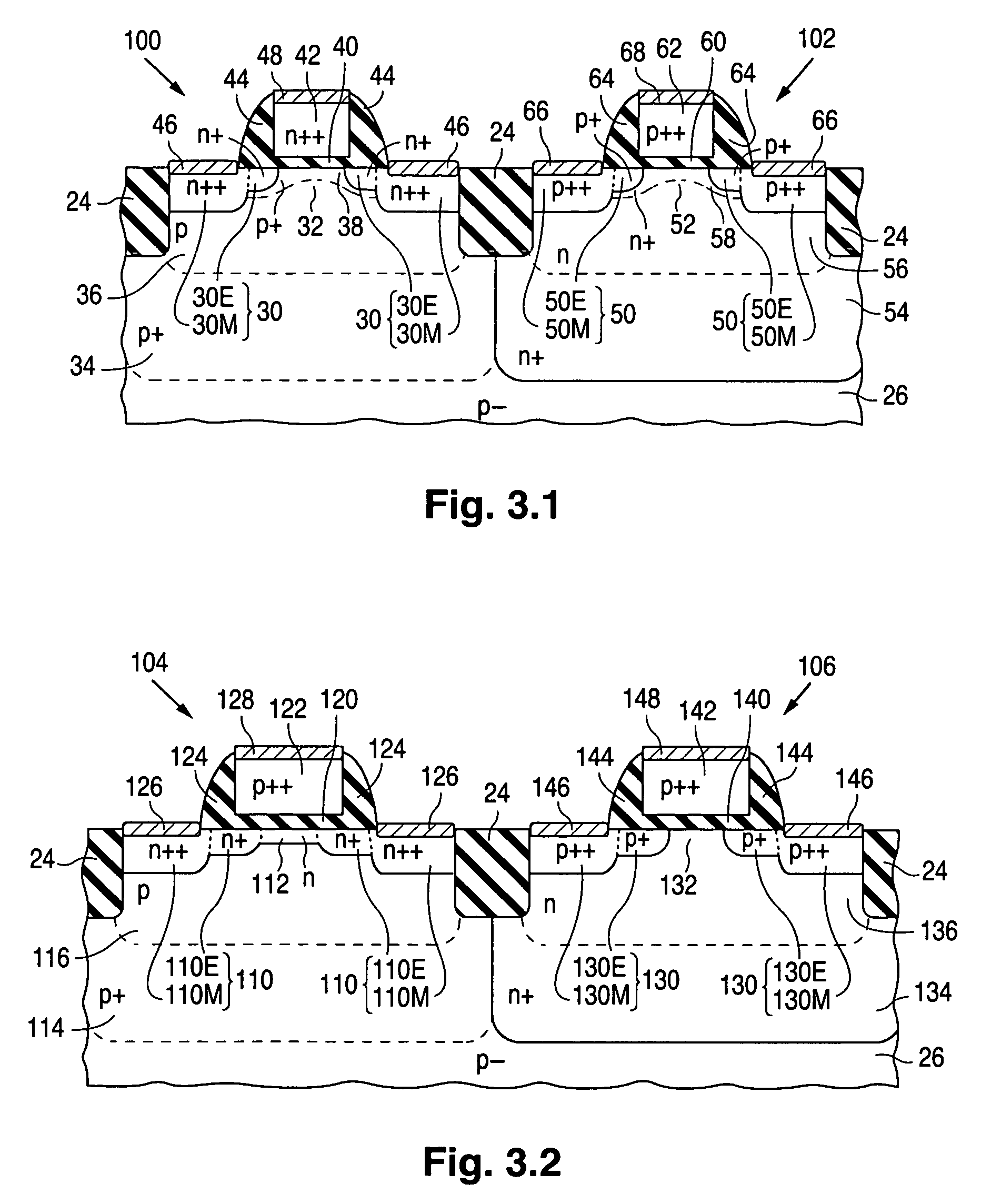

Complementary metal-oxide-semiconductor field effect transistor structure having ion implant in only one of the complementary devices

Owner:NORTH STAR INNOVATIONS

Fabrication of semiconductor structure having N-channel channel-junction field-effect transistor

ActiveUS7595243B1Performance characteristicHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally fabricated to be of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. A p-channel surface-channel IGFET (102 or 162), which is typically fabricated to be of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically fabricated to be of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

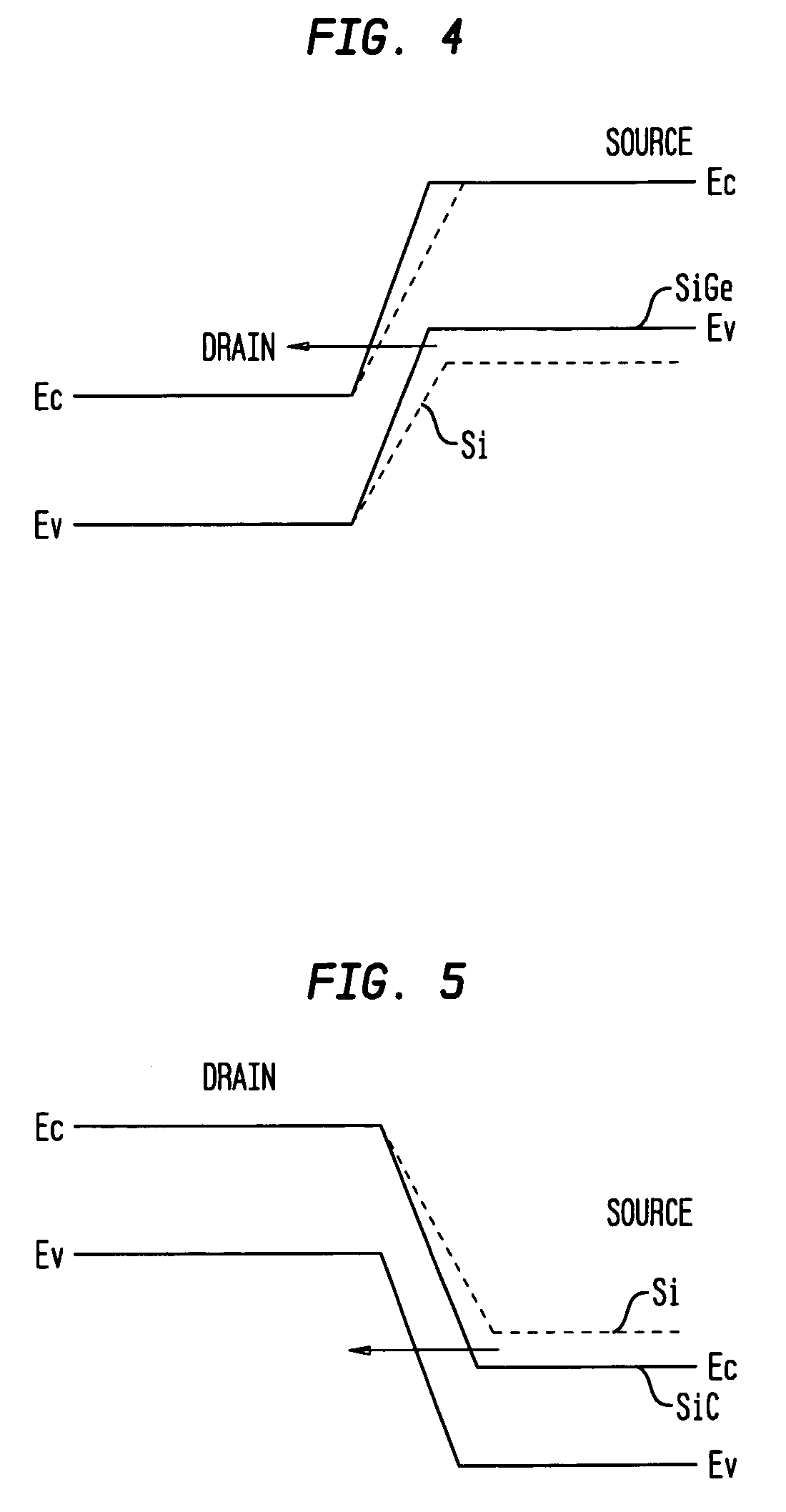

Heterojunction tunneling field effect transistors, and methods for fabricating the same

InactiveUS20070178650A1Increase currentEnhance junction currentSemiconductor/solid-state device manufacturingDiodeHeterojunctionDopant

The present invention relates to a heterojunction tunneling effect transistor (TFET), which comprises spaced apart source and drain regions with a channel region located therebetween and a gate stack located over the channel region. The drain region comprises a first semiconductor material and is doped with a first dopant species of a first conductivity type. The source region comprises a second, different semiconductor material and is doped with a second dopant species of a second, different conductivity type. The gate stack comprises at least a gate dielectric and a gate conductor. When the heterojunction TFET is an n-channel TFET, the drain region comprises n-doped silicon, while the source region comprises p-doped silicon germanium. When the heterojunction TFET is a p-channel TFET, the drain region comprises p-doped silicon, while the source region comprises n-doped silicon carbide.

Owner:IBM CORP

Semiconductor integrated circuit device

A semiconductor integrated circuit device contains a CMOS circuit that includes a plurality of N-channel transistors and a plurality of P-channel transistors. The plurality of N-channel transistors is provided with device isolation by one of a gate isolation structure and a shallow trench isolation structure. The plurality of P-channel transistors are provided with device isolation by the other of the gate isolation structure and the shallow trench isolation structure.

Owner:KK TOSHIBA

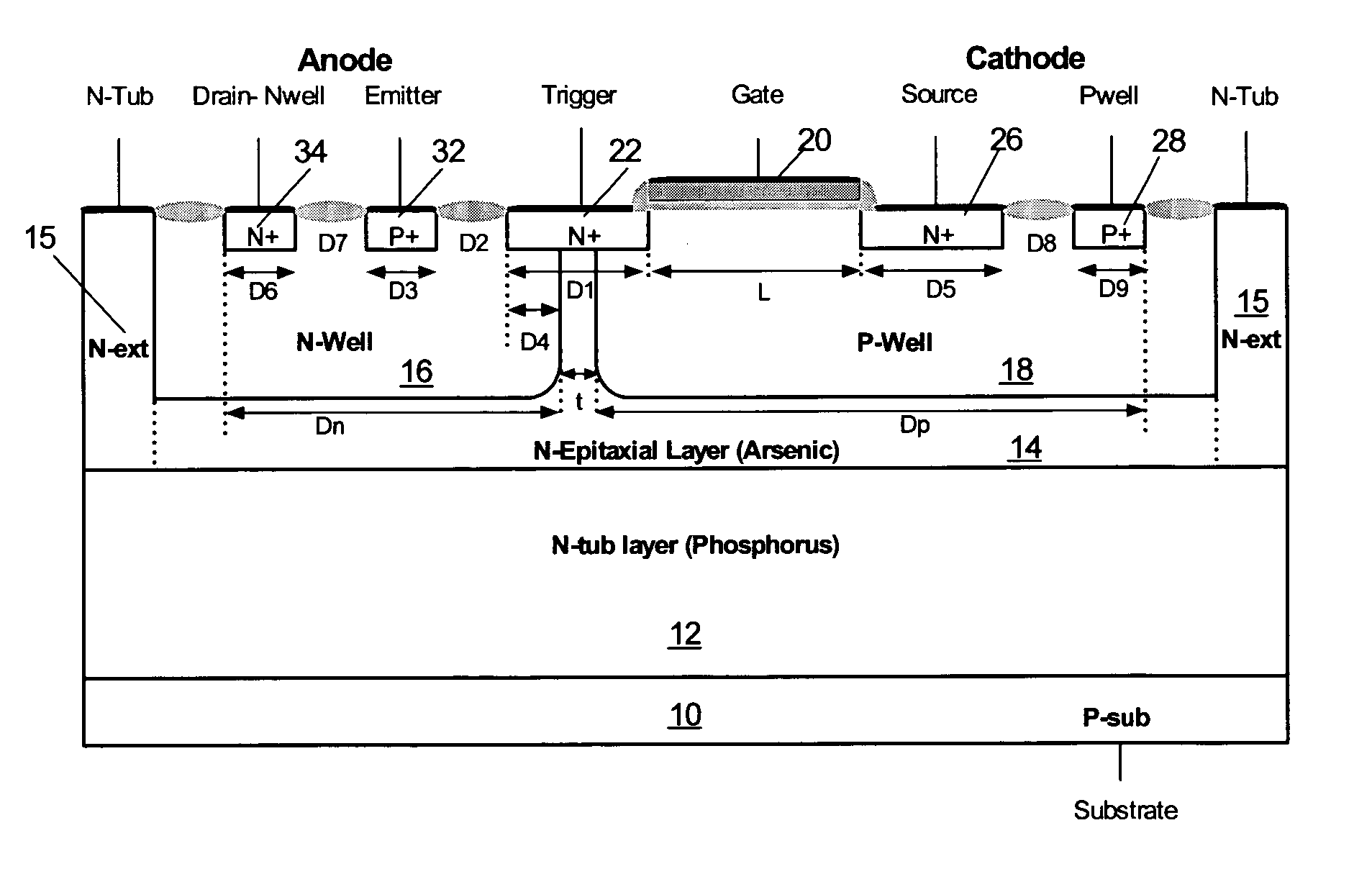

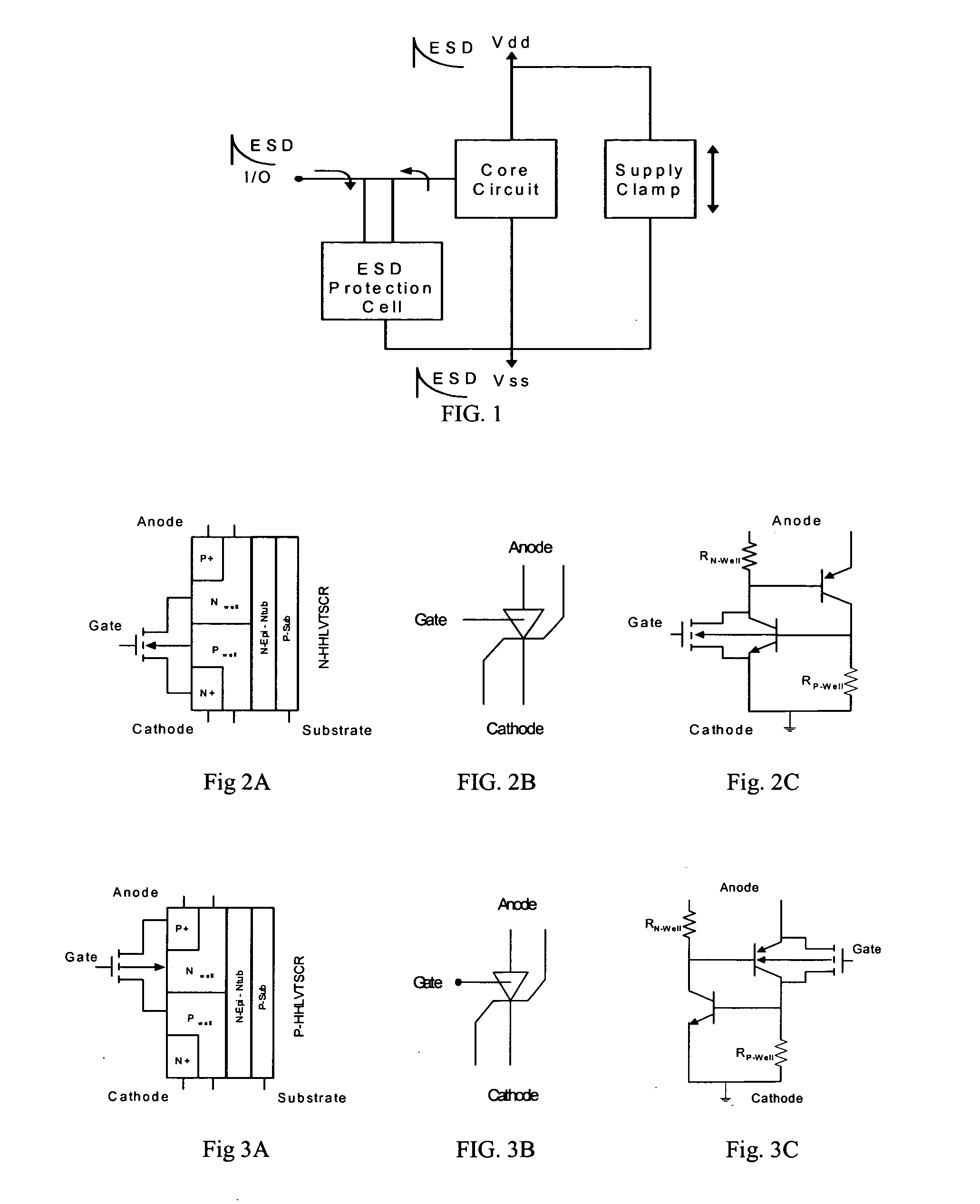

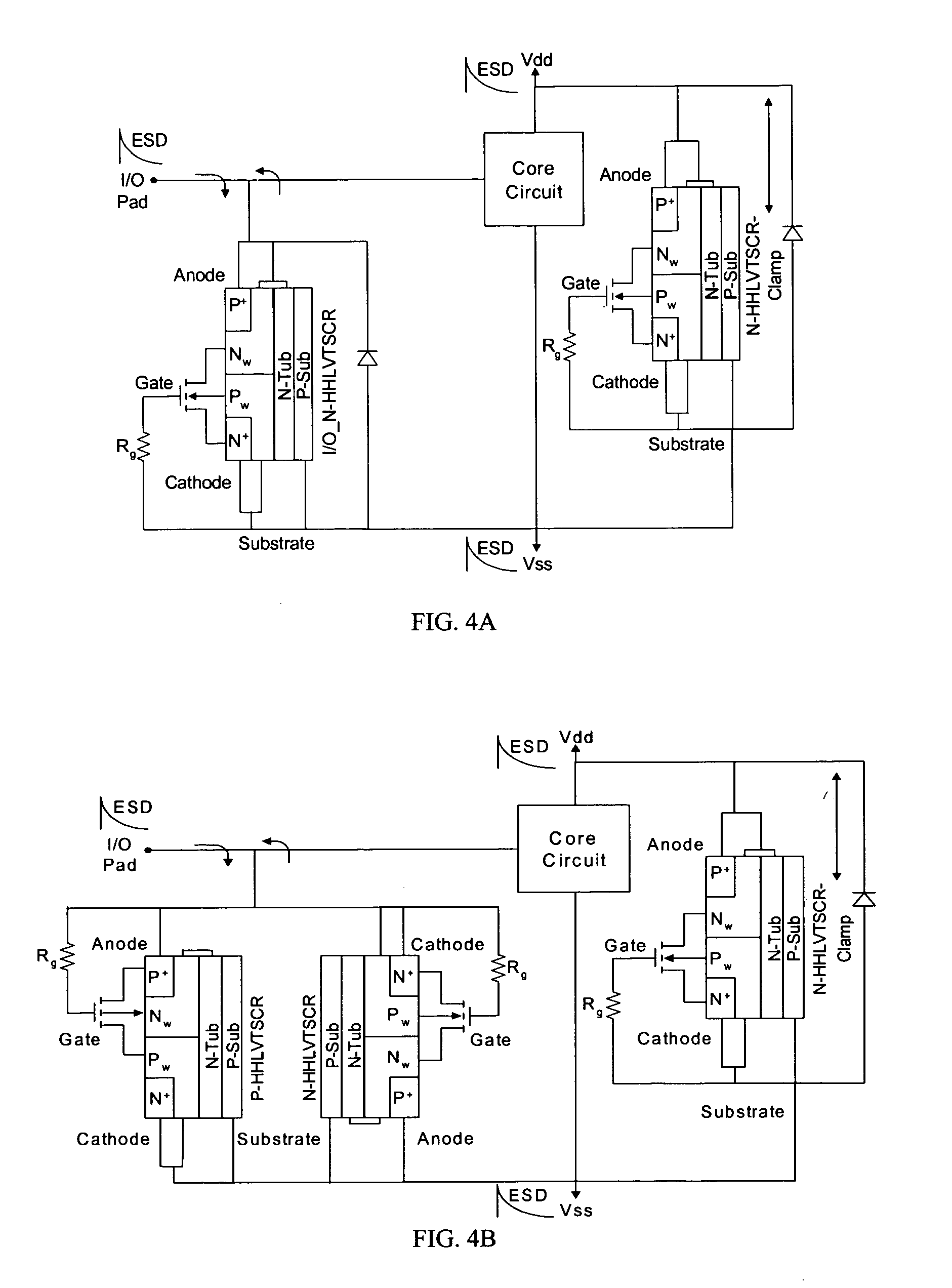

On-chip structure for electrostatic discharge (ESD) protection

InactiveUS20050151160A1Efficient and reliableRobust and ESD protectionTransistorSemiconductor/solid-state device detailsCMOSLow voltage

A complementary SCR-based structure enables a tunable holding voltage for robust and versatile ESD protection. The structure are n-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (N-HHLVTSCR) device and p-channel high-holding-voltage low-voltage-trigger silicon controller rectifier (P-HHLVTSCR) device. The regions of the N-HHLVTSCR and P-HHLVTSCR devices are formed during normal processing steps in a CMOS or BICMOS process. The spacing and dimensions of the doped regions of N-HHLVTSCR and P-HHLVTSCR devices are used to produce the desired characteristics. The tunable HHLVTSCRs makes possible the use of this protection circuit in a broad range of ESD applications including protecting integrated circuits where the I / O signal swing can be either within the range of the bias of the internal circuit or below / above the range of the bias of the internal circuit.

Owner:INTERSIL INC

Semiconductor device based on Si-Ge with high stress liner for enhanced channel carrier mobility

ActiveUS20050247926A1Increase drive currentIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCharge carrier mobility

The carrier mobility in transistor channel regions of Si—Ge devices is increased by employing a stressed liner. Embodiments include applying a high compressive or tensile stressed film overlying relaxed source / drain regions. Other embodiments include applying a high compressively or high tensilely stressed film, after post silicide spacer removal, over gate electrodes and strained Si source / drain regions of P-channel or N-channel transistors, respectively.

Owner:ADVANCED MICRO DEVICES INC

Process for forming an electronic device including a transistor having a metal gate electrode

An electronic device includes an n-channel transistor and a p-channel transistor. The p-channel transistor has a first gate electrode with a first work function and a first channel region including a semiconductor layer immediately adjacent to a semiconductor substrate. In one embodiment, the first work function is less than the valence band of the semiconductor layer. In another embodiment, the n-channel transistor has a second gate electrode with a second work function different from the first work function and closer to a conduction band than a valence band of a second channel region. A process of forming the electronic device includes forming first and second gate electrodes having first and second work functions, respectively. First and second channel regions having a same minority carrier type are associated with the first and second gate electrodes, respectively.

Owner:NORTH STAR INNOVATIONS

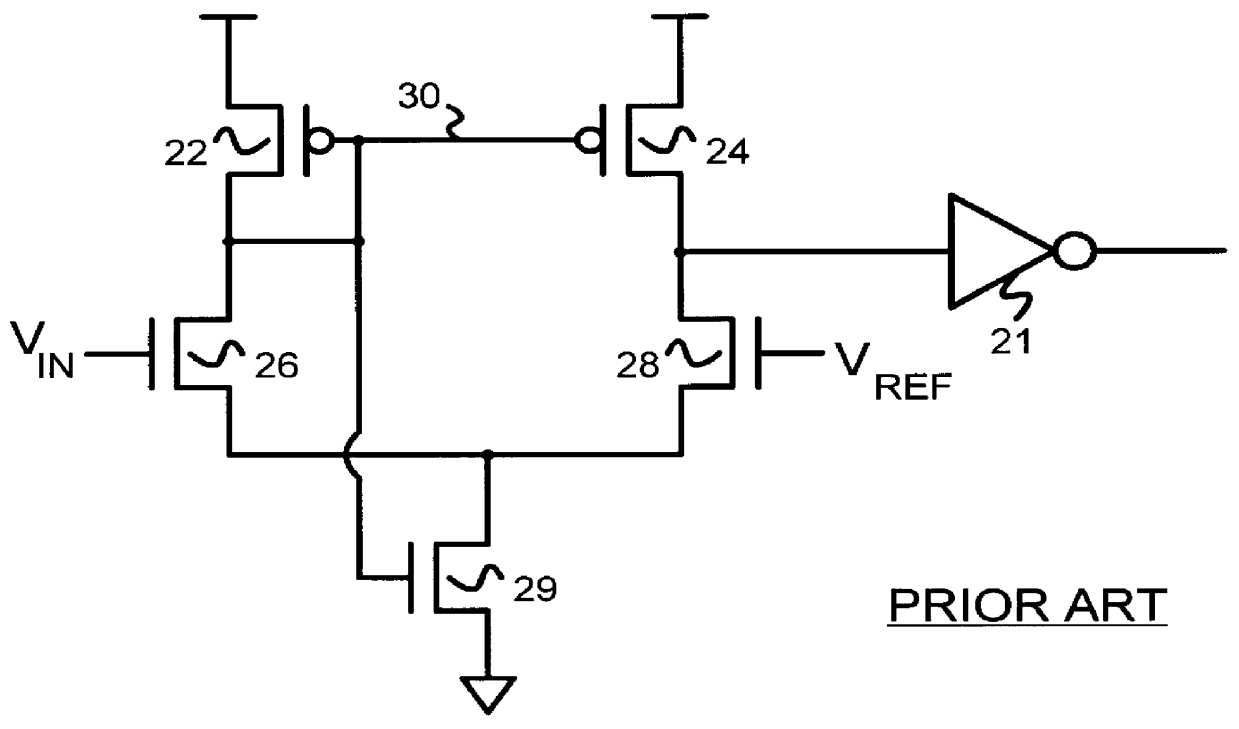

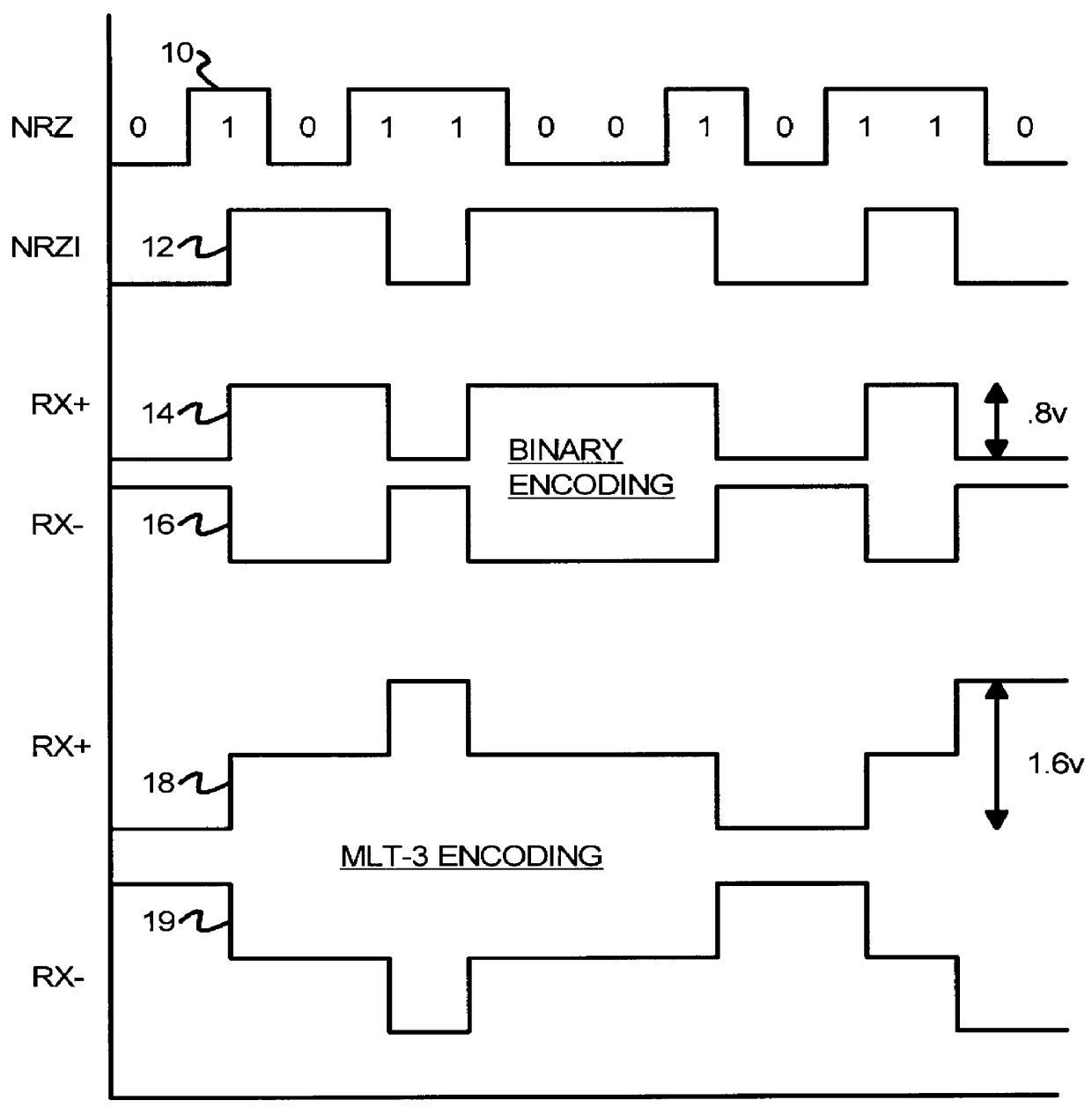

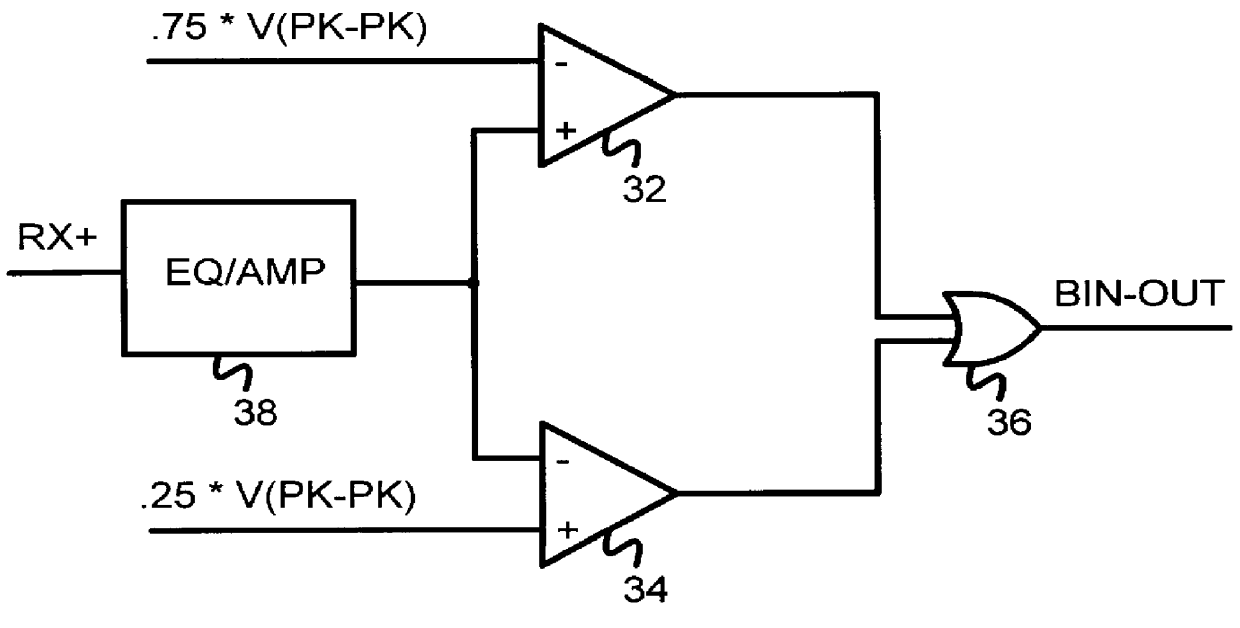

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

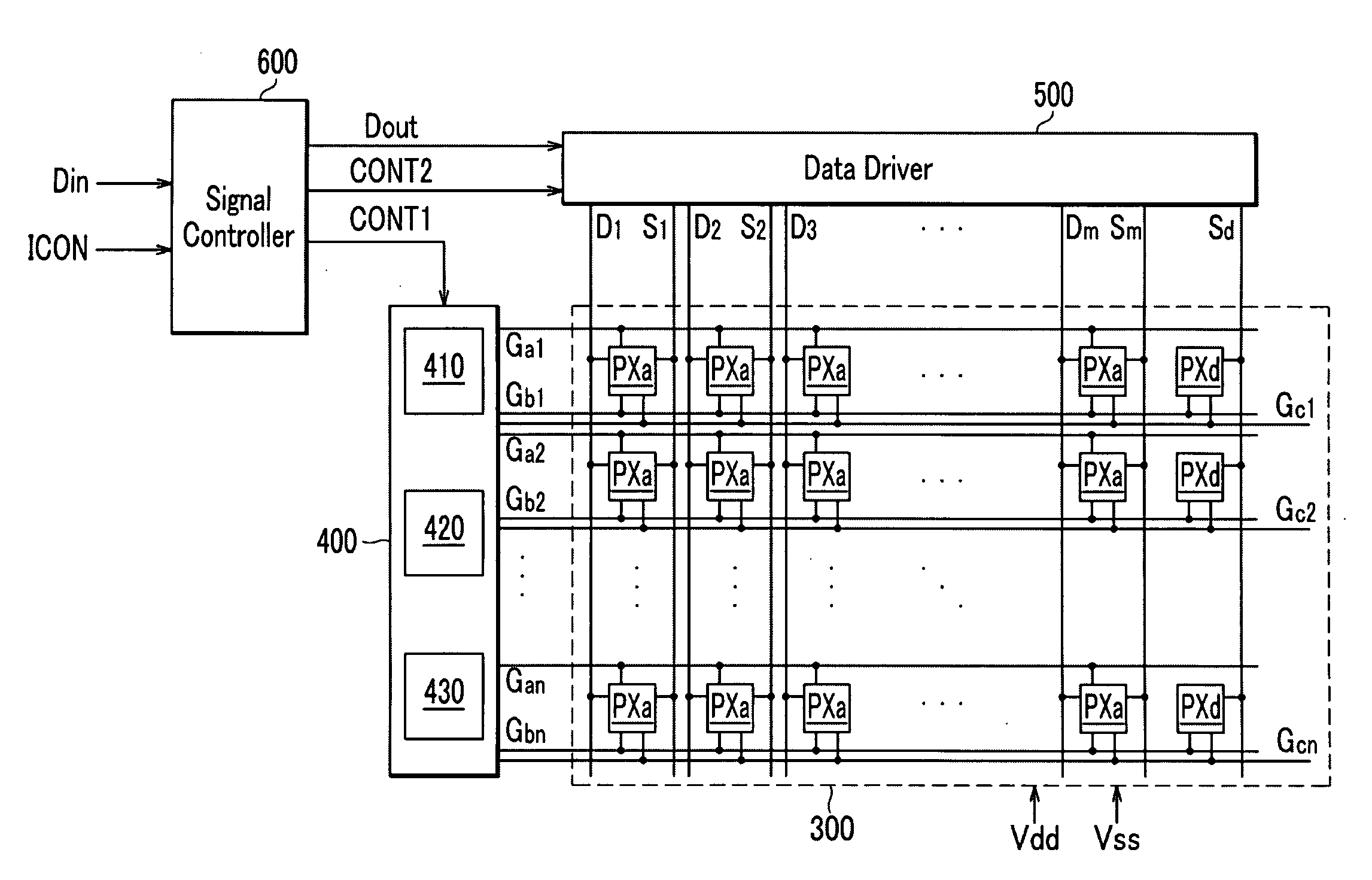

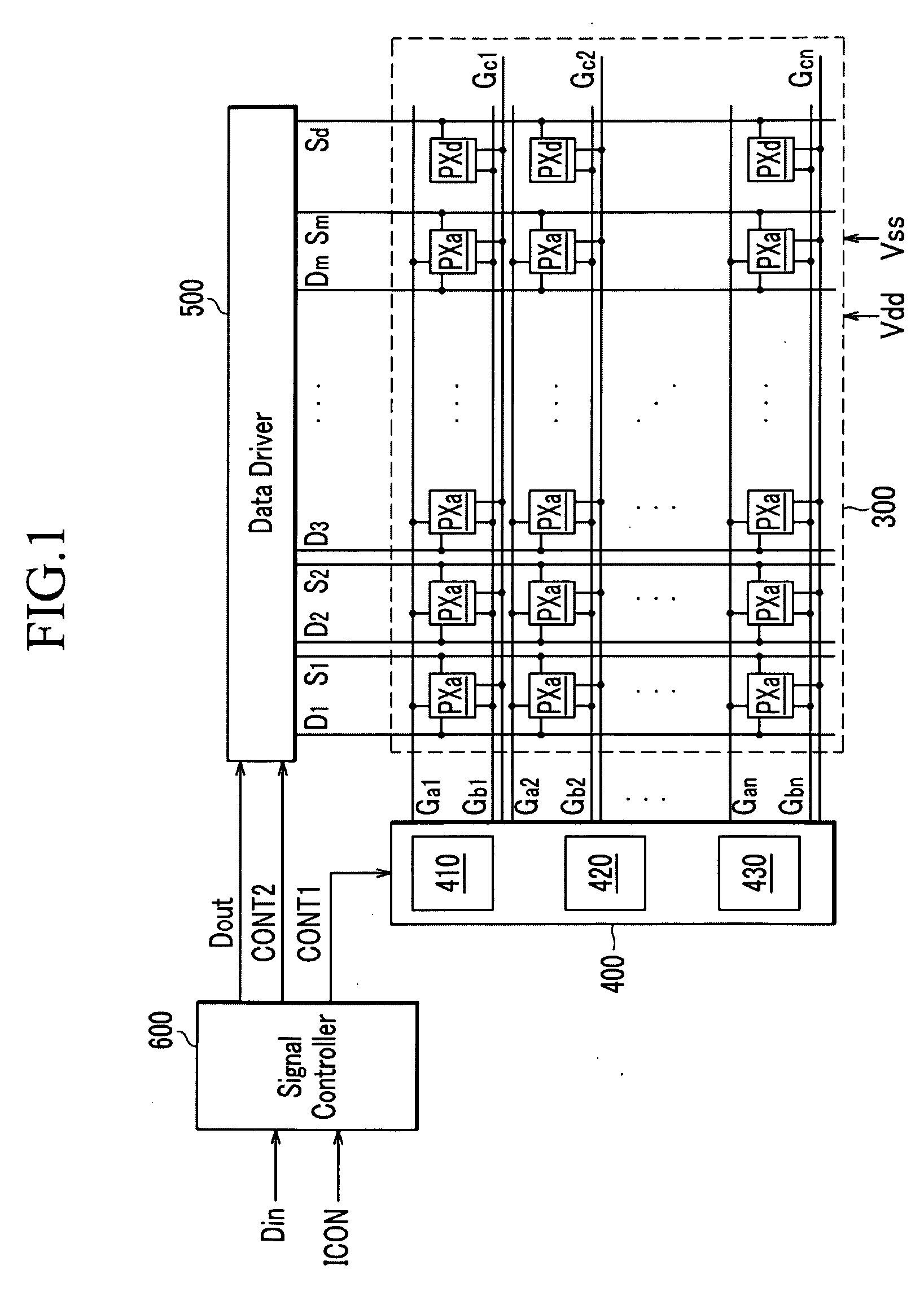

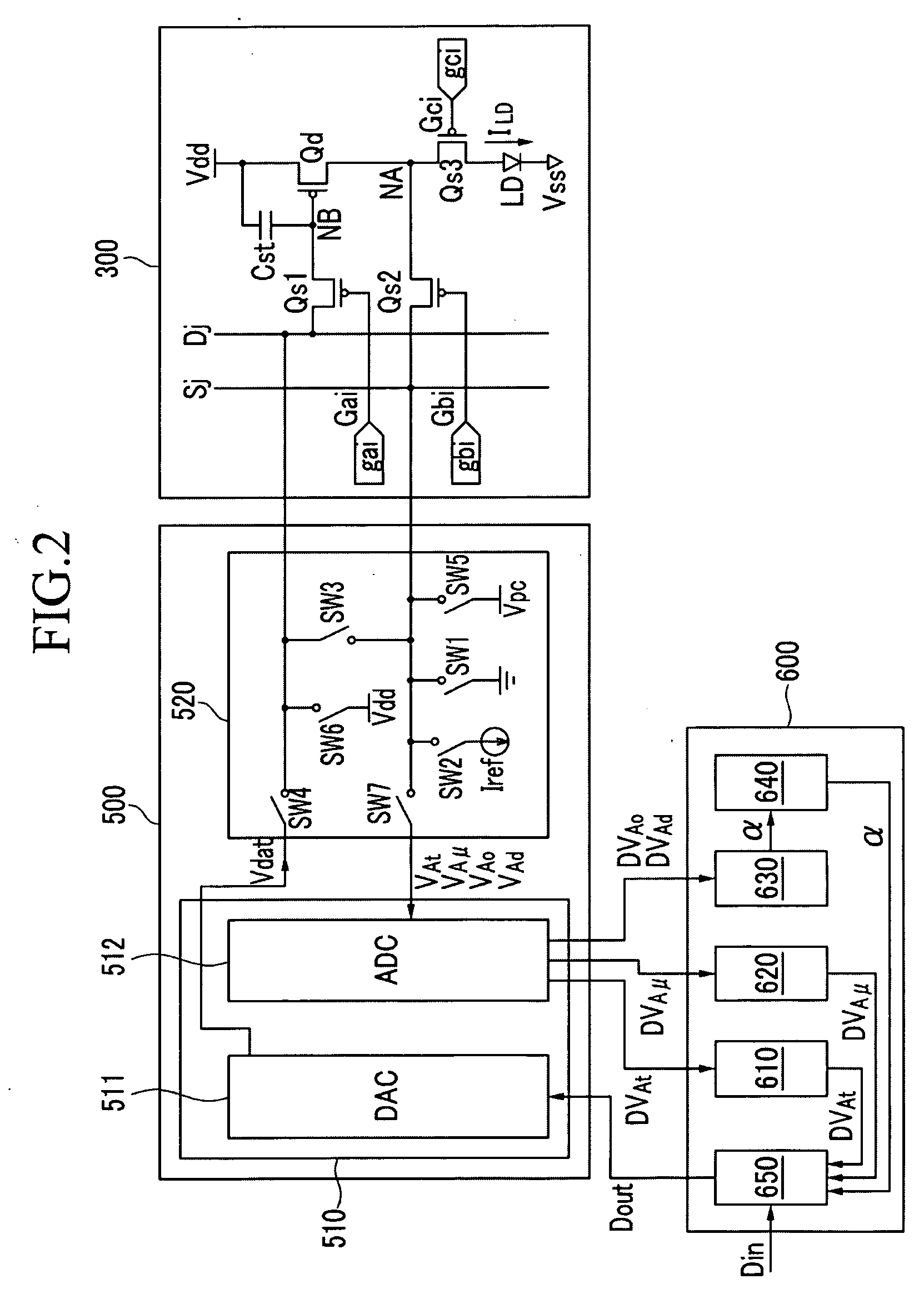

Display device and method of driving the same

The present invention provides a display device and a method of driving the same. The display device includes a plurality of display pixels to display an image, a plurality of data lines connected to the display pixel, and a plurality of sensing lines connected to the display pixel. Each display pixel includes: a driving transistor including a control terminal, an input terminal, and an output terminal; a capacitor connected to the control terminal of the driving transistor; a first switching transistor connected to the data line and the control terminal of the driving transistor; a light-emitting element to receive a driving current from the driving transistor, the light-emitting element to emit light; a second switching transistor connected between the sensing line and the output terminal of the driving transistor; and a third switching transistor connected between the output terminal of the driving transistor and the light-emitting element, wherein the driving transistor is a p-channel electric field effect transistor.

Owner:SAMSUNG DISPLAY CO LTD +1

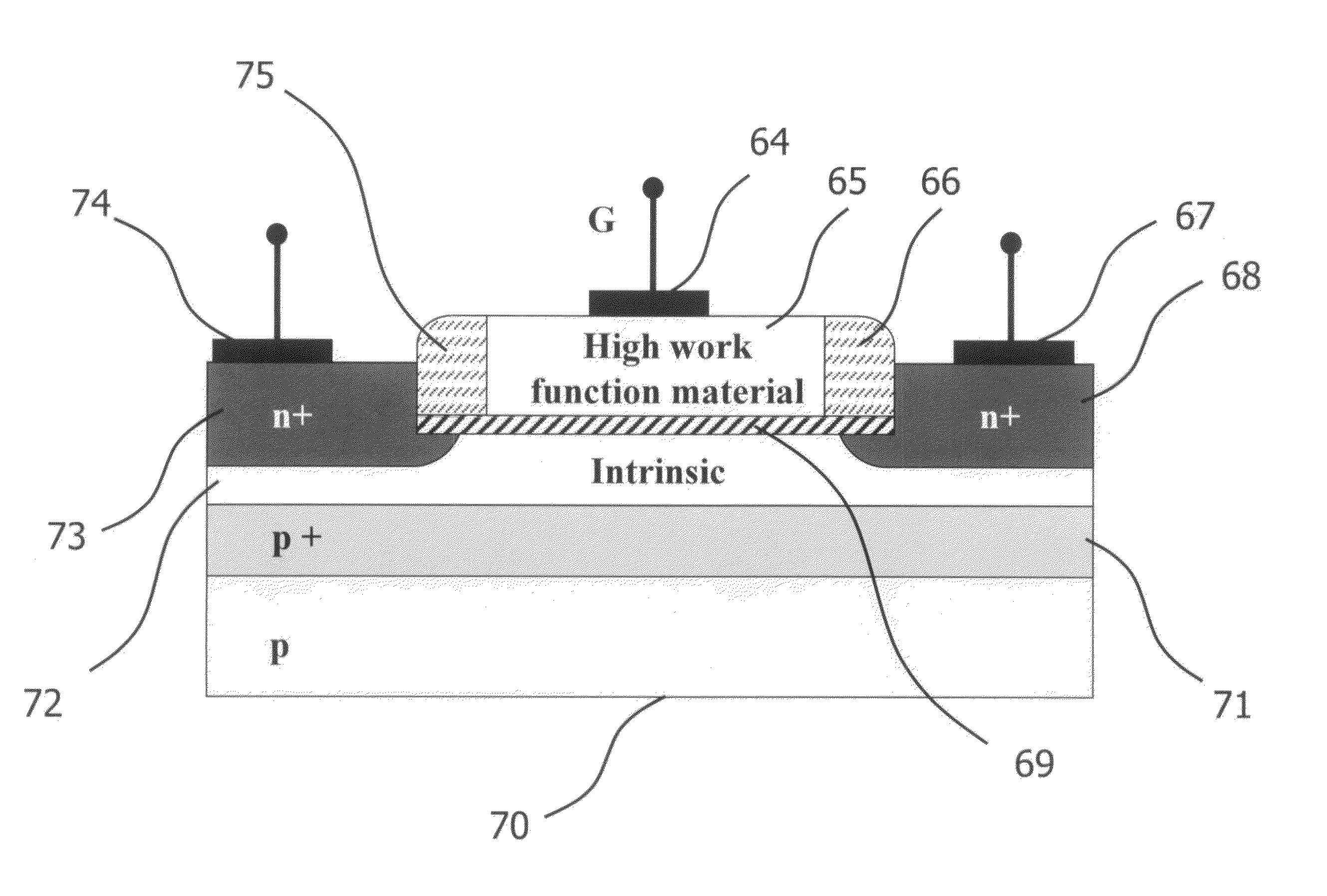

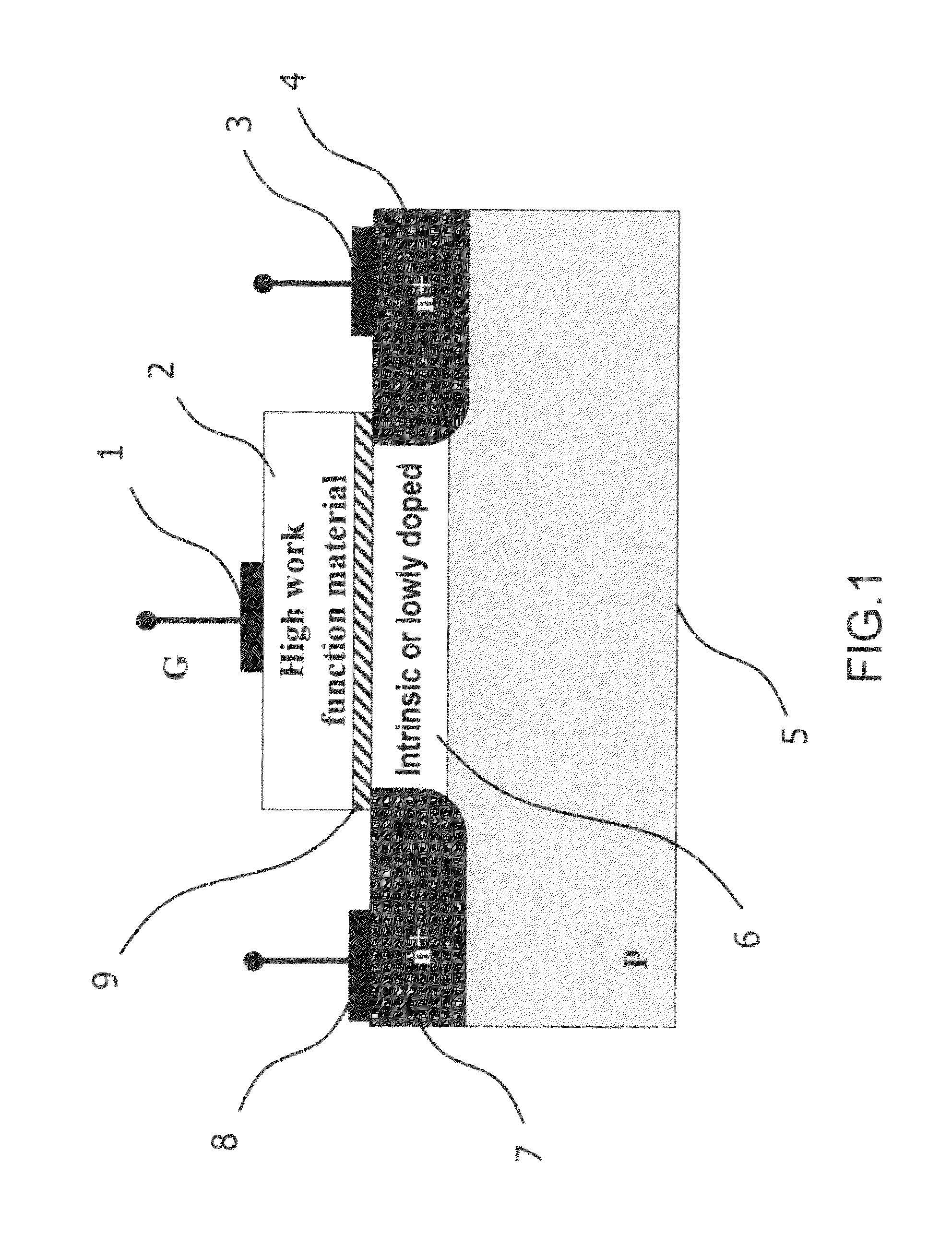

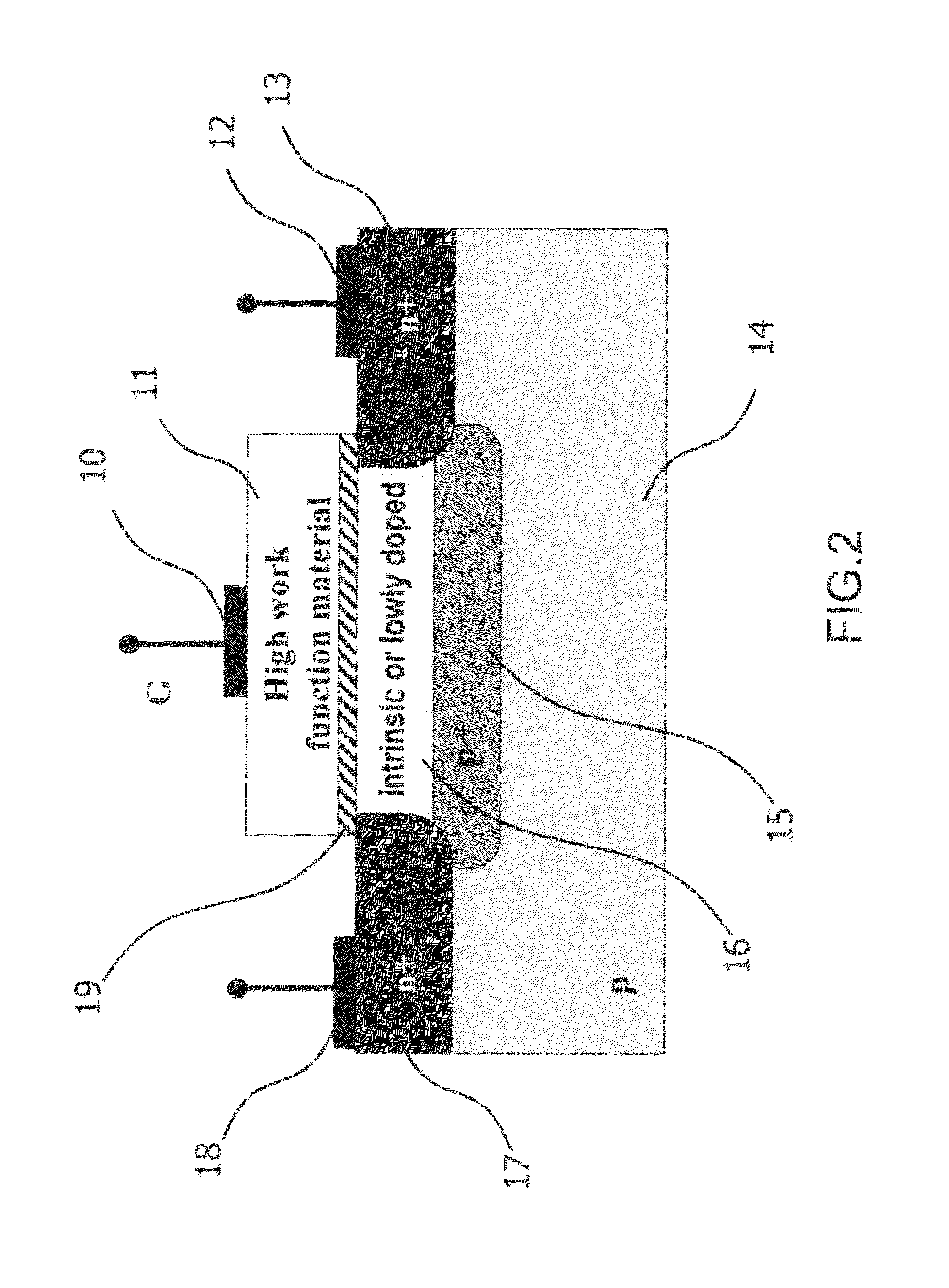

High mobility enhancement mode FET

ActiveUS8803242B2Reduce variationReduce impurityTransistorSolid-state devicesMOSFETSemiconductor structure

A novel semiconductor transistor is presented. The semiconductor structure has a MOSFET like structure, with the difference that the device channel is formed in an intrinsic region, so as to effectively decrease the impurity and surface scattering phenomena deriving from a high doping profile typical of conventional MOS devices. Due to the presence of the un-doped channel region, the proposed structure greatly reduces Random Doping Fluctuation (RDF) phenomena decreasing the threshold voltage variation between different devices. In order to control the threshold voltage of the device, a heavily doped poly-silicon or metallic gate is used. However, differently from standard CMOS devices, a high work-function metallic material, or a heavily p-doped poly-silicon layer, is used for a n-channel device and a low work-function metallic material, or heavily n-doped poly-silicon layer, is used for a p-channel FET.

Owner:QUALCOMM INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com